Patents

Literature

283 results about "Generative Design" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

Generative design is an iterative design process that involves a program that will generate a certain number of outputs that meet certain constraints, and a designer that will fine tune the feasible region by changing minimal and maximal values of an interval in which a variable of the program meets the set of constraints, in order to reduce or augment the number of outputs to choose from. The program doesn't need to be run on a machine like a digital computer, it can be run by a human for example with pen and paper. The designer doesn't need to be a human, it can be a test program in a testing environment or an artificial intelligence, for example a generative adversarial network. The designer learns to refine the program (usually involving algorithms) with each iteration as his design goals become better defined over time.

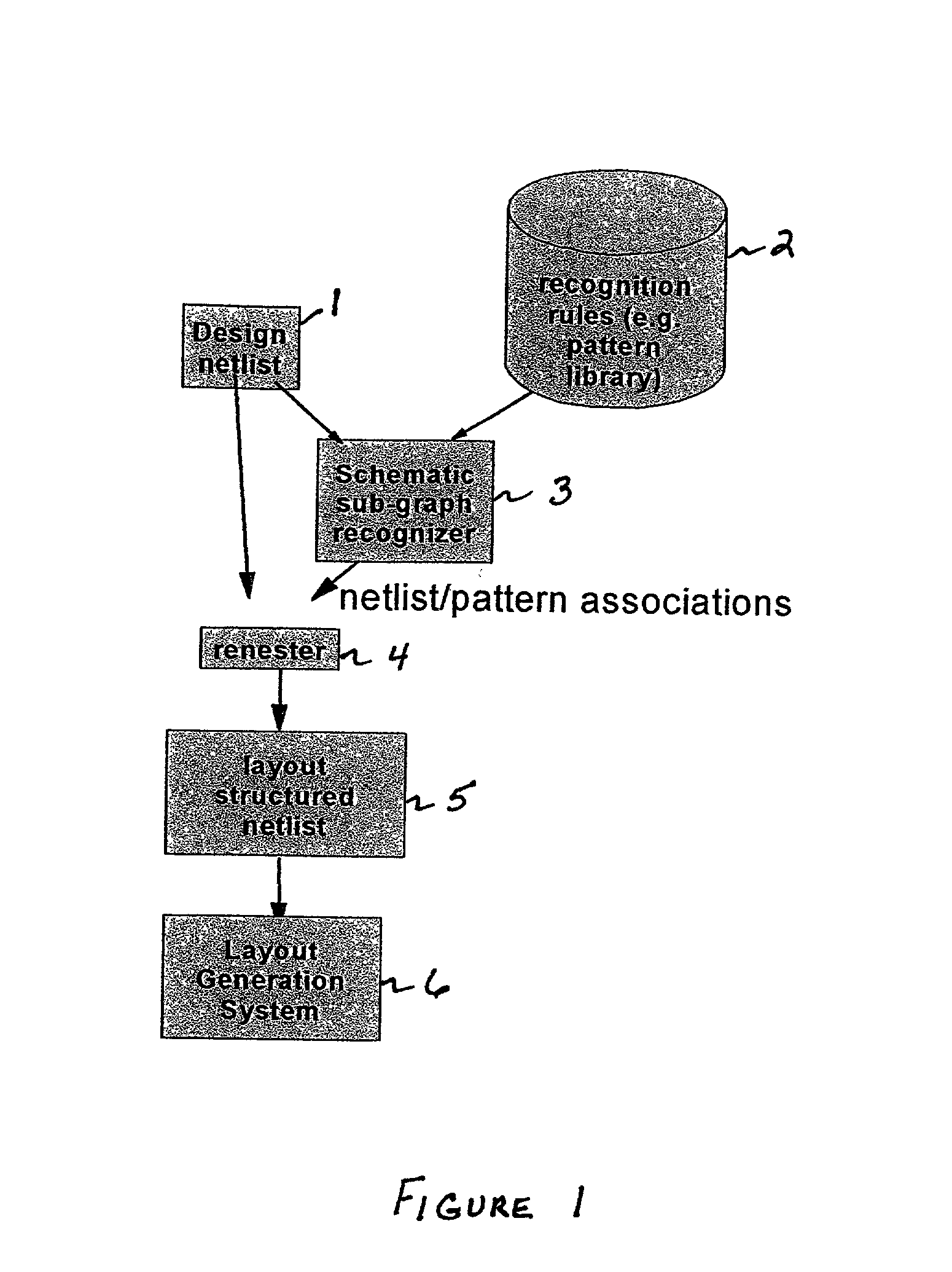

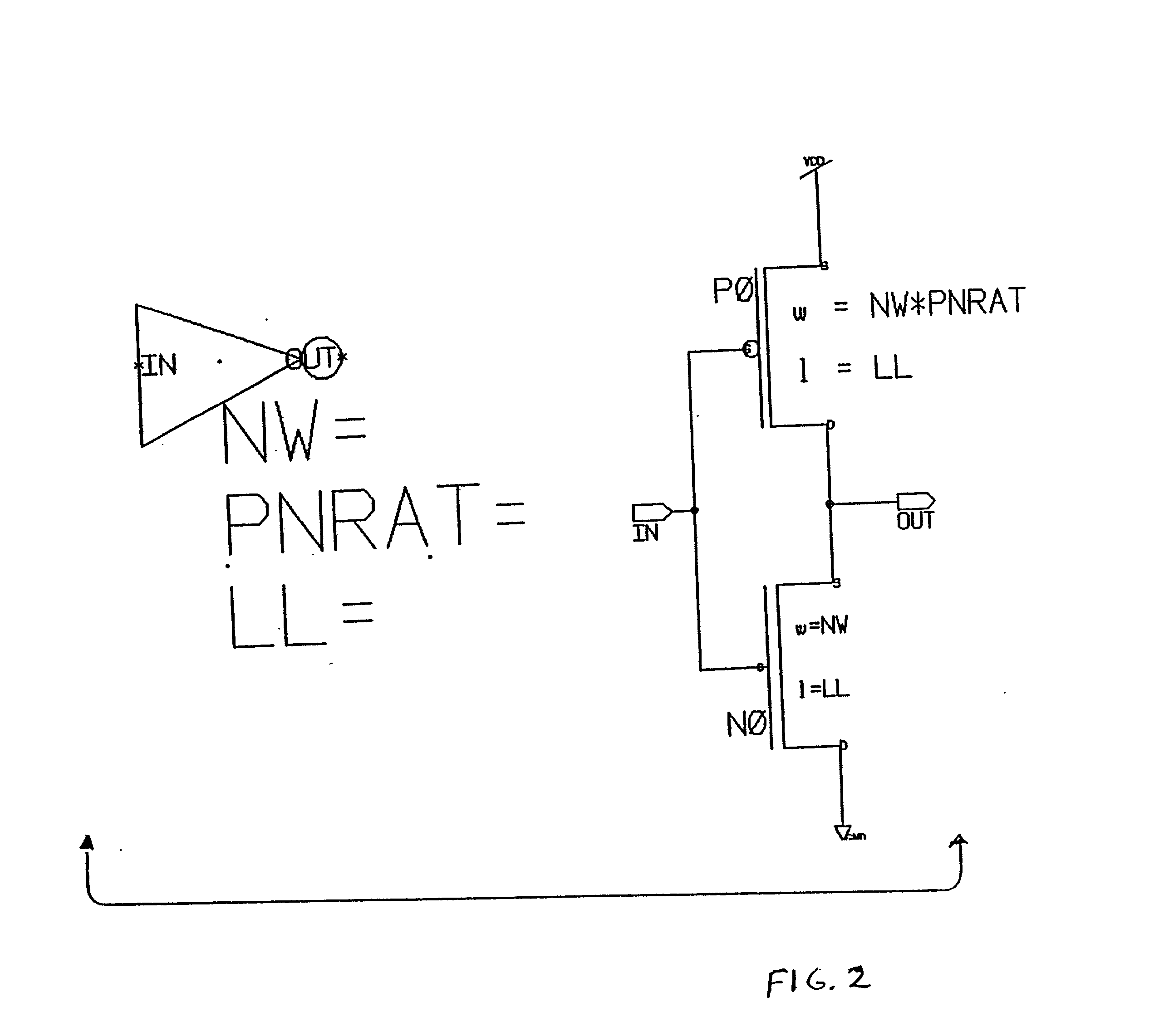

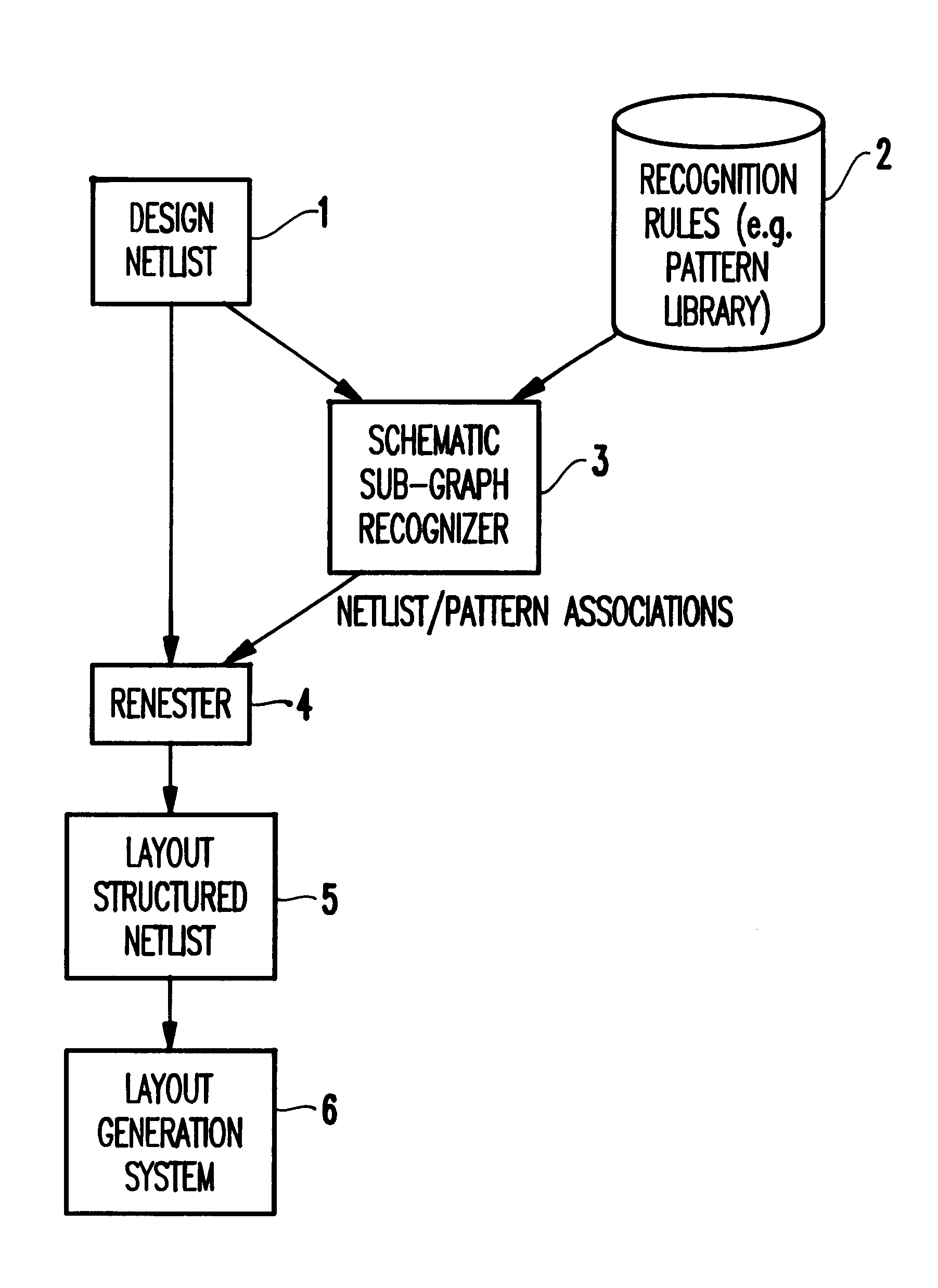

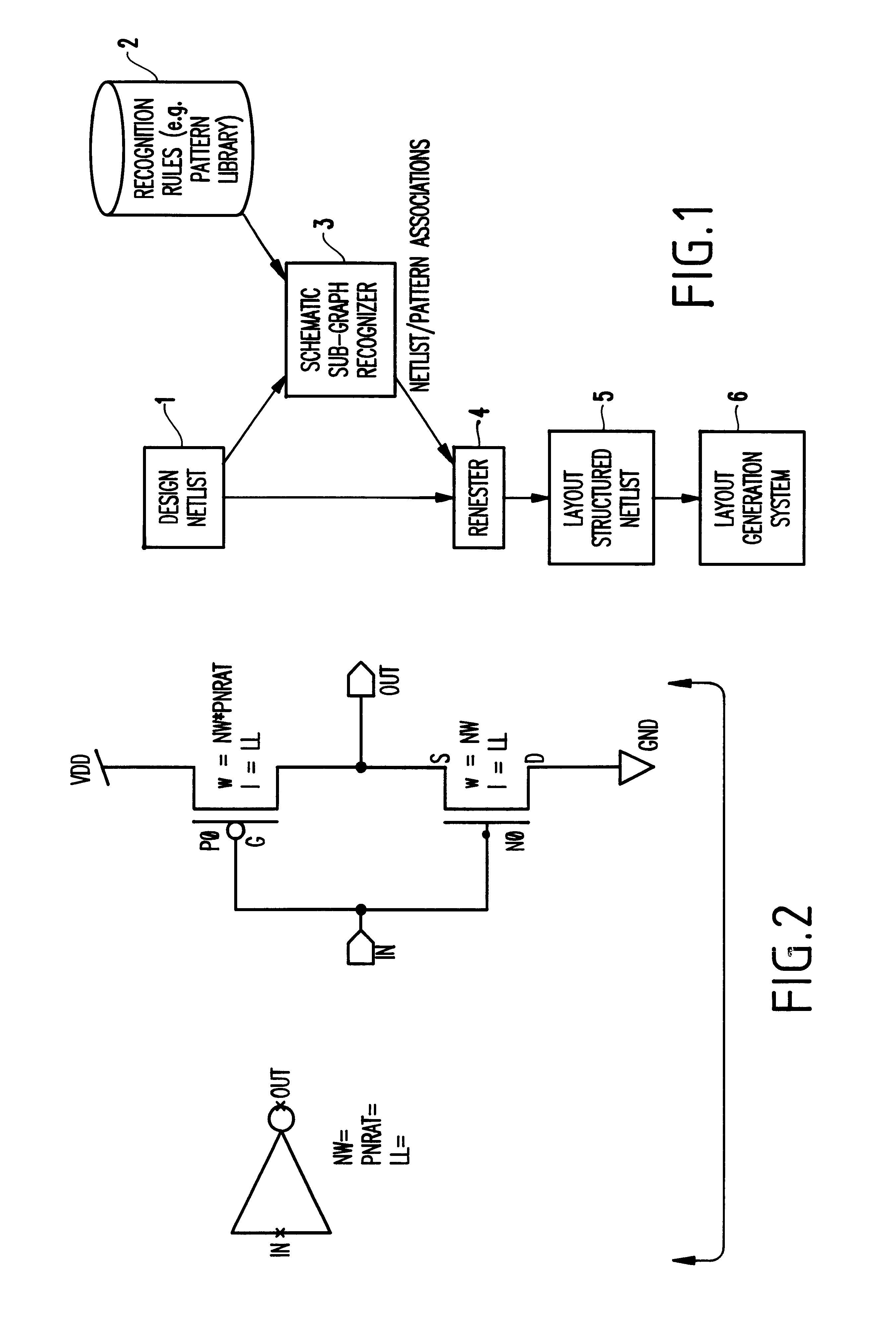

Hierarchical layout method for integrated circuits

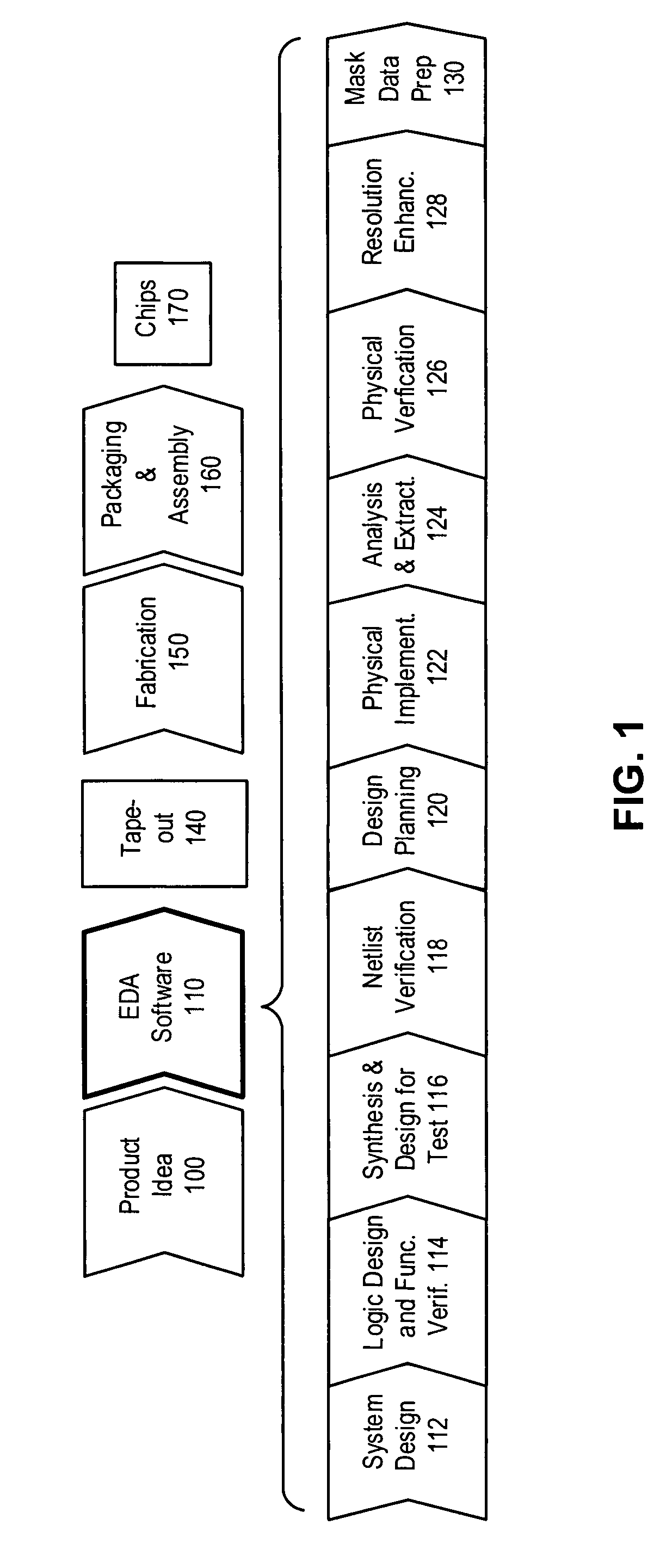

InactiveUS20020194575A1Easy to modifyIncrease production capacityCAD circuit designProgram controlComputer architectureGenerative Design

A method for hierarchical layout of an electronic design using an electronic computer aided design system, wherein the method includes generating a parameterized pattern library and using an existing netlist and analyze in a pattern recognizer, from which a list of associations between the pattern library and the netlist is created. Renesting then occurs wherein the netlist using the list of associations is used for generating a hierarchical layout of the electronic components in the design.

Owner:IBM CORP

Hierarchical layout method for integrated circuits

InactiveUS6574779B2Easy to modifyIncrease production capacityCAD circuit designProgram controlComputer architectureGenerative Design

Owner:INT BUSINESS MASCH CORP

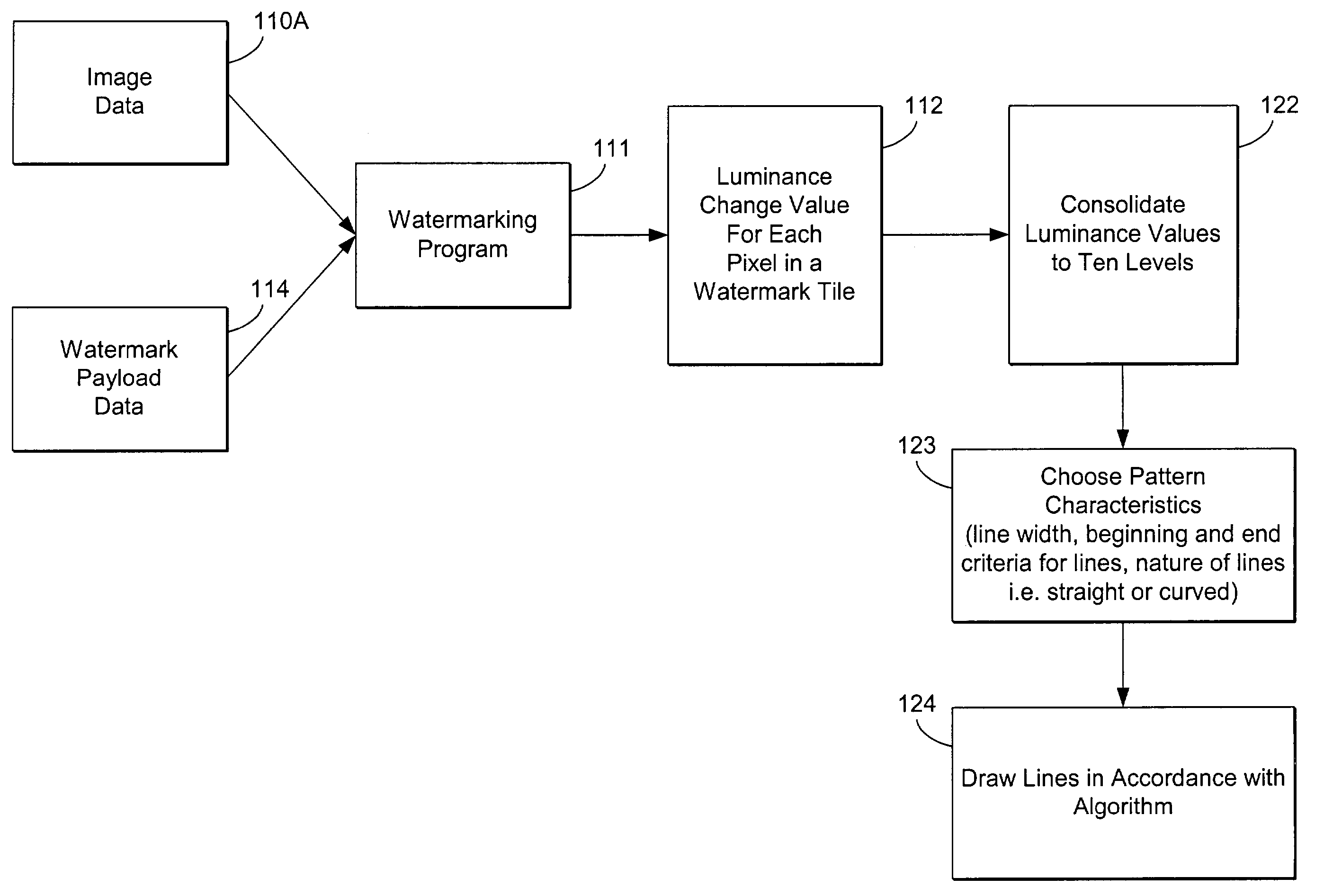

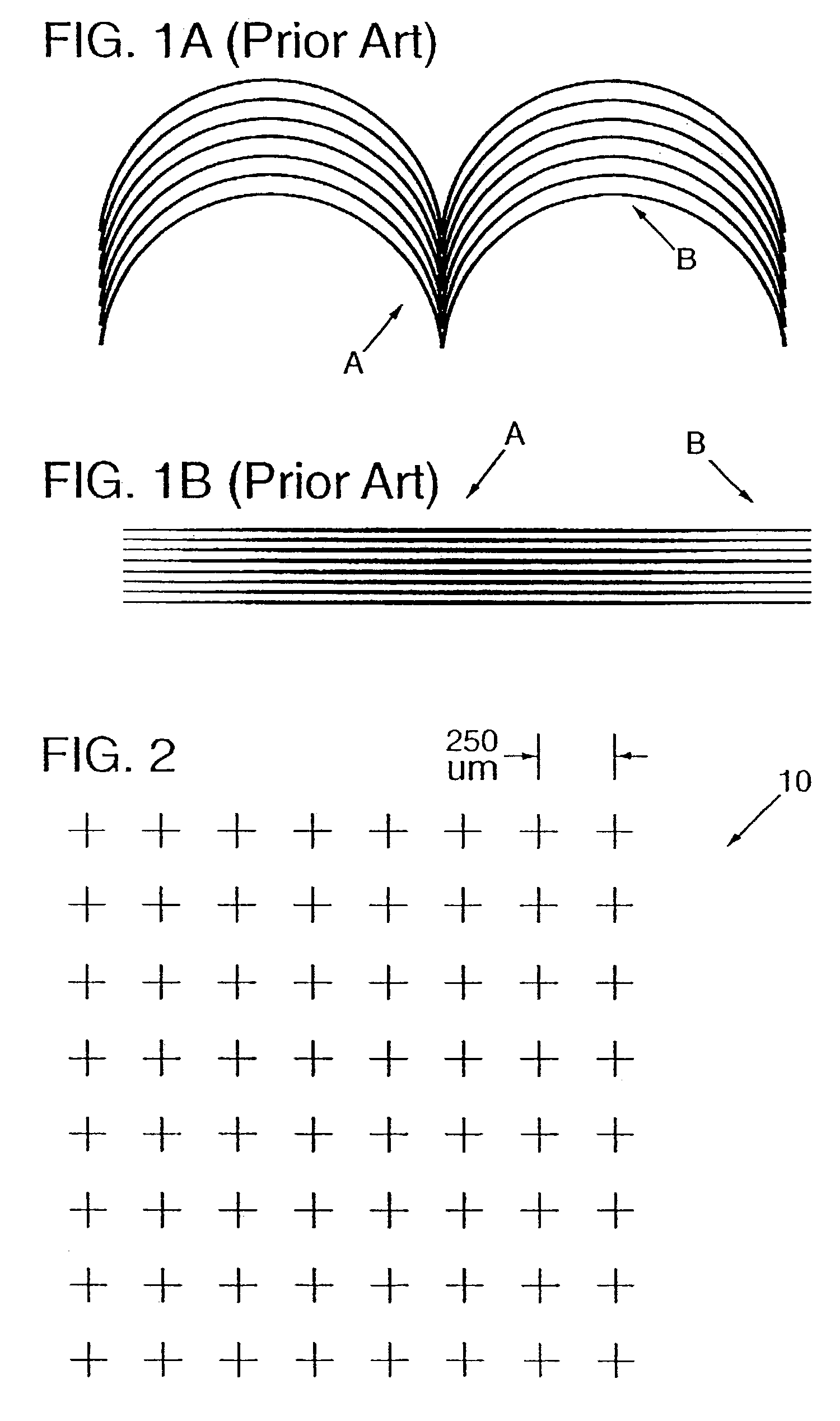

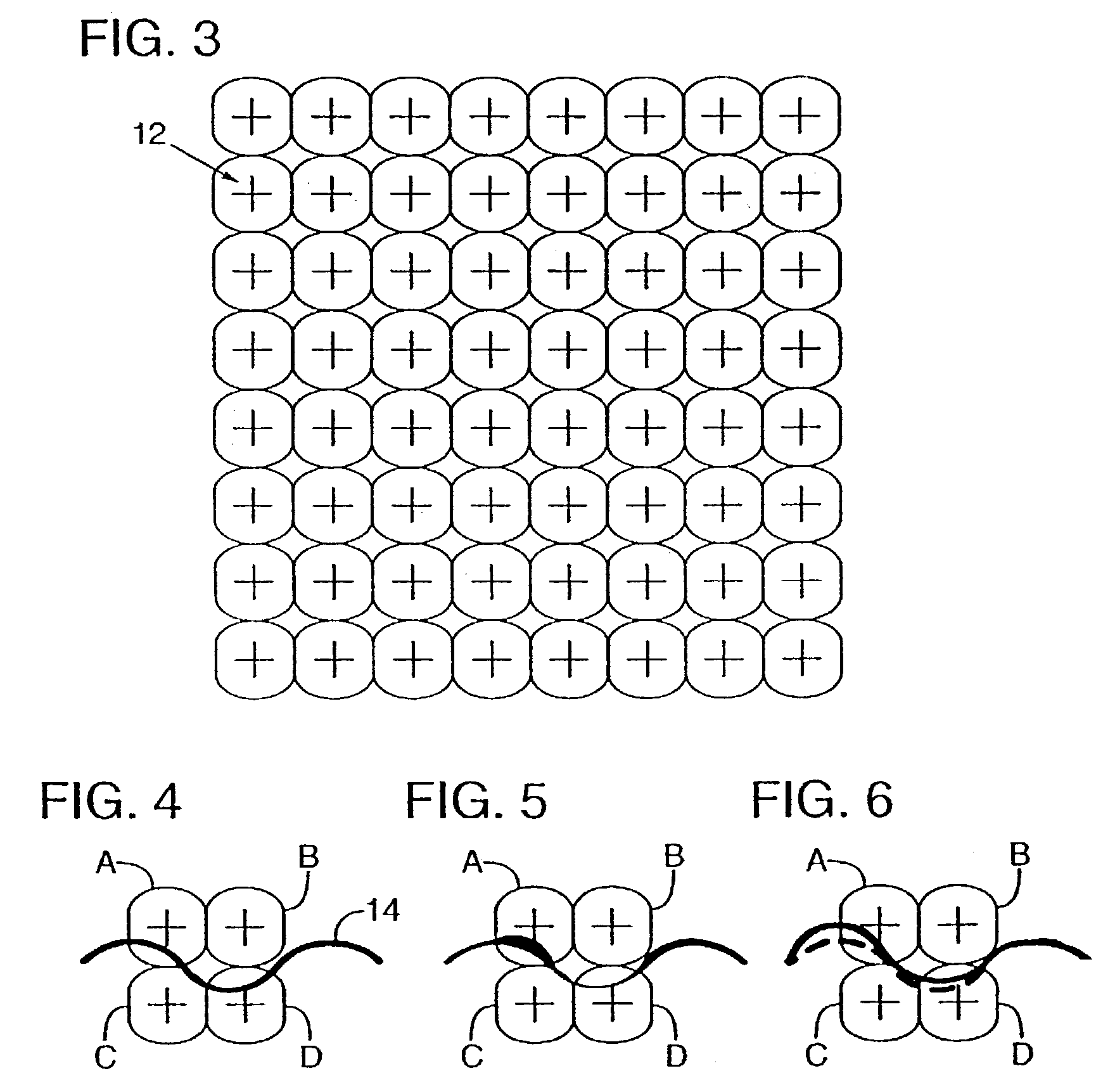

Secure document design carrying auxiliary machine readable information

InactiveUS7286684B2Easy to detectTelevision system detailsRecord information storageComputer graphics (images)Generative Design

A two dimensional pattern design for secure documents serves as both a machine readable code and an aesthetic part of the documents' design. A method for generating the design generates a variable auxiliary message comprising message values and maps the message values to a two dimensional pattern of areas on the document. The areas each comprise an arrangement of pixels on the printed document. Depending on a value of the message mapped to a corresponding area, the method assigns a visible structure to the corresponding area. Different visible structures are assignable to a single value of the message to create a visible design having a desired aesthetic appearance.

Owner:DIGIMARC CORP (FORMERLY DMRC CORP)

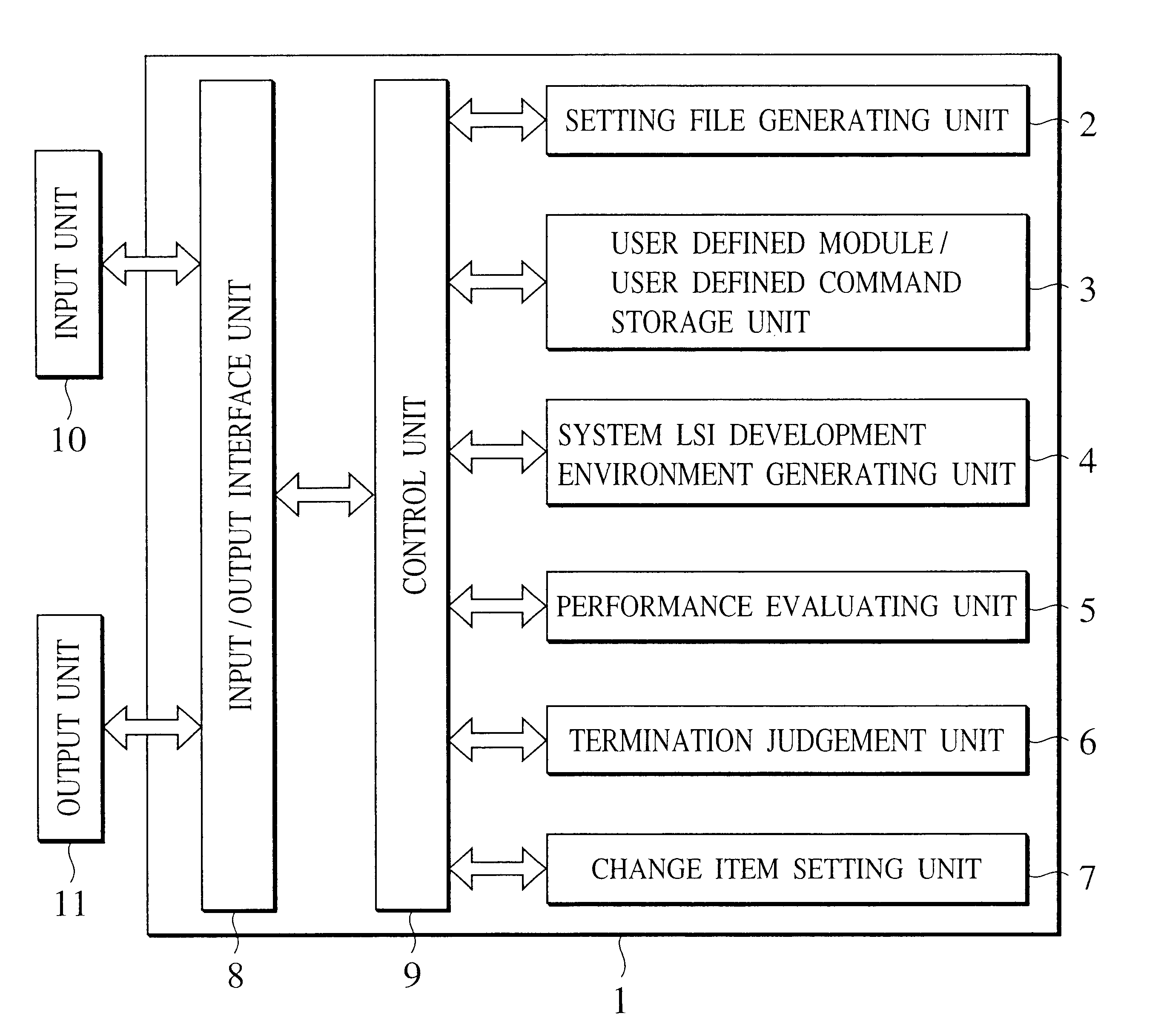

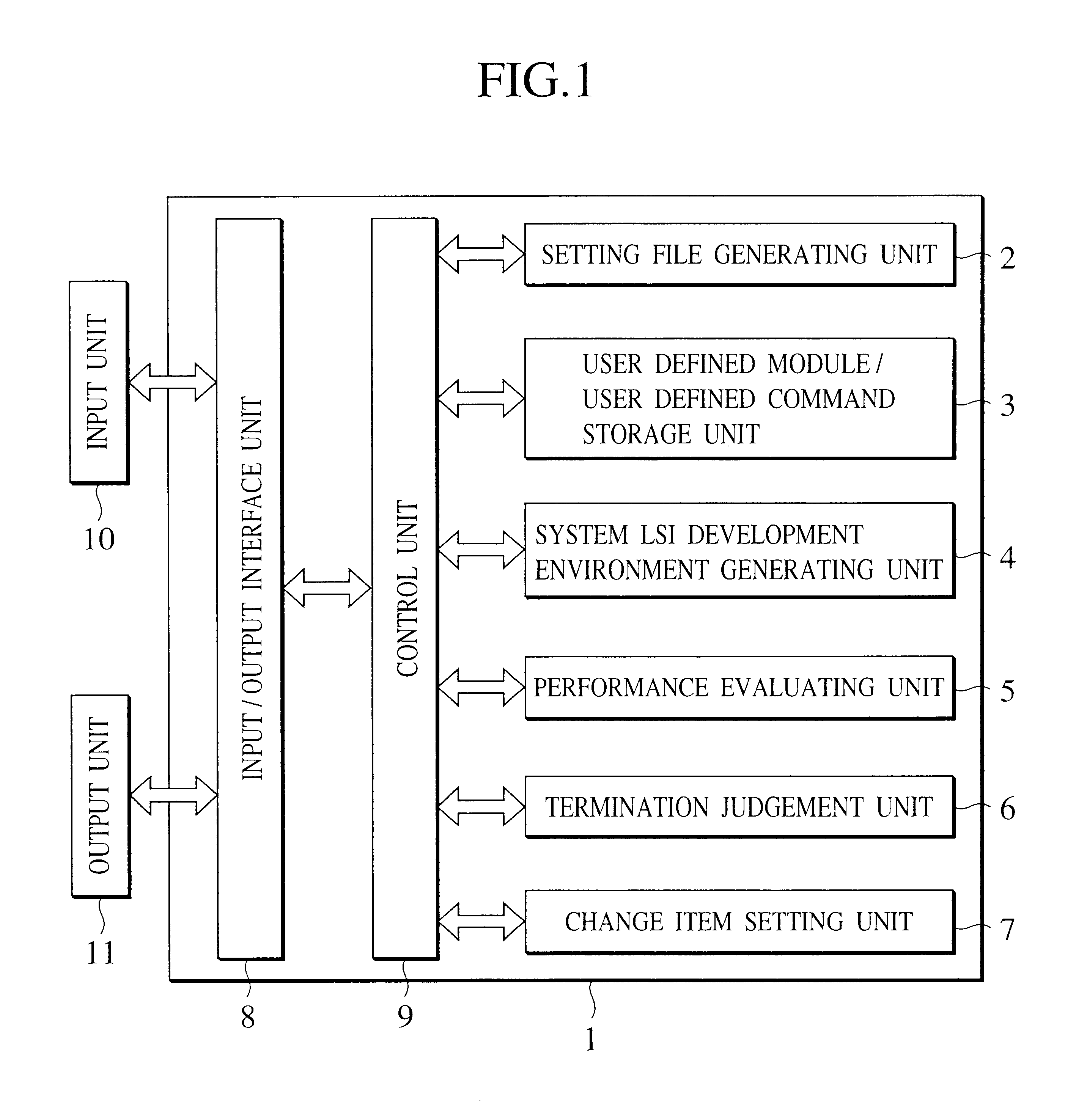

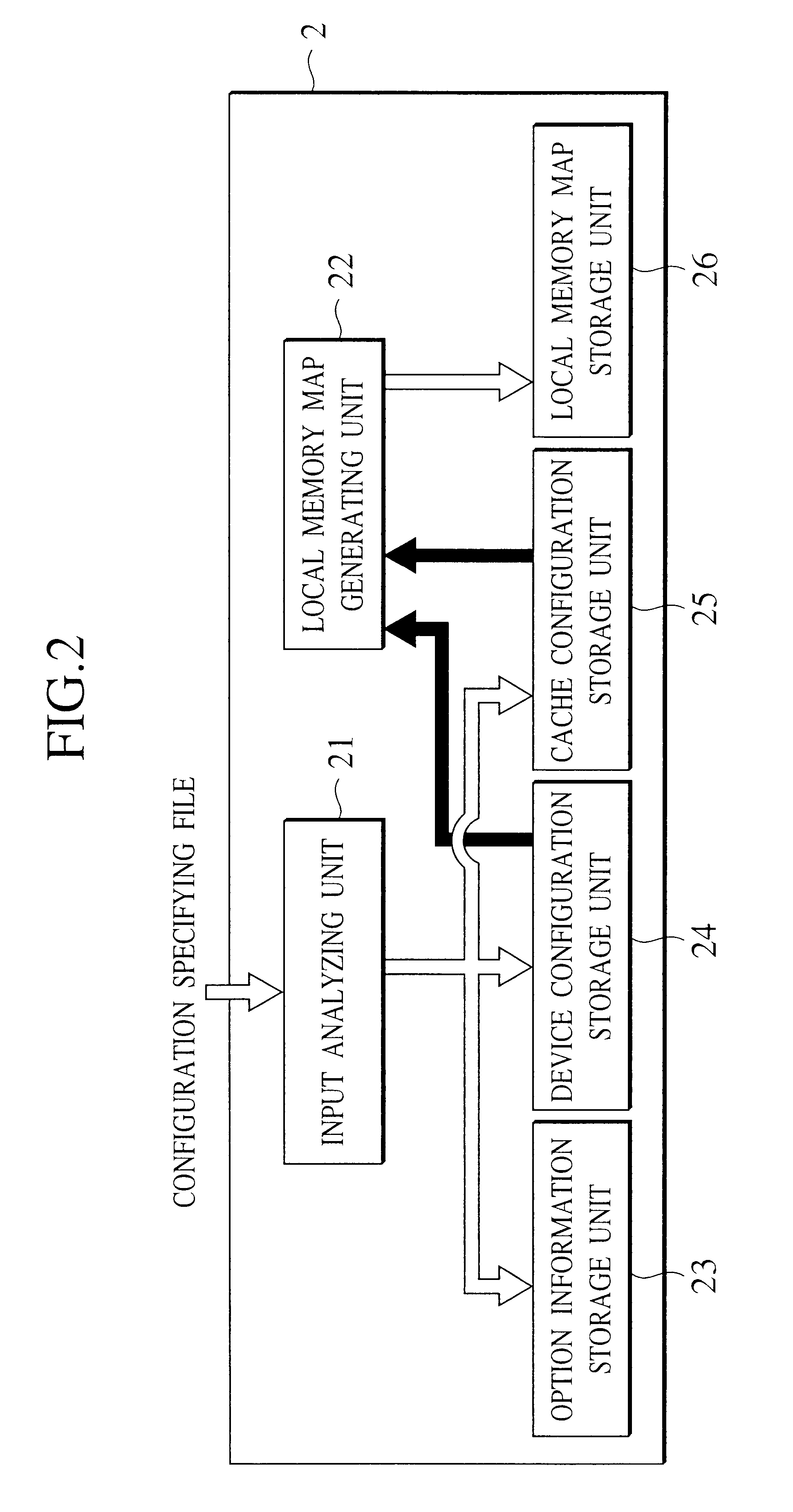

System LSI development apparatus and the method thereof for developing a system optimal to an application

In this disclosure, based on change item definition information concerning system LSI development and design, software used for development and design of a system LSI that contains a processor having optional instructions defined therein is operated, and system LSI hardware description, verification environment and a development and design tools are generated, thus making it possible to develop a system LSI optimal to an application within a short period.< / PTEXT>

Owner:KK TOSHIBA

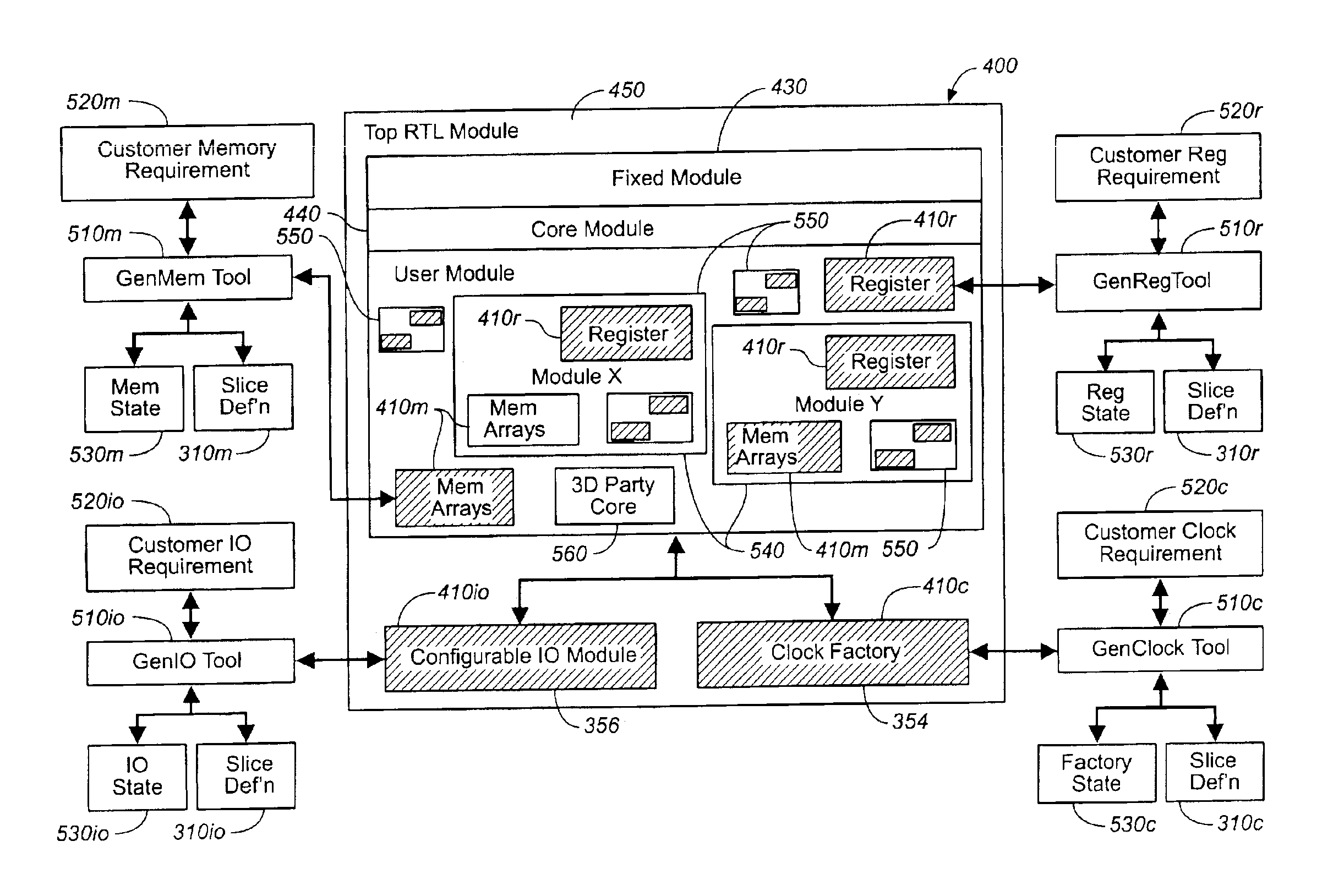

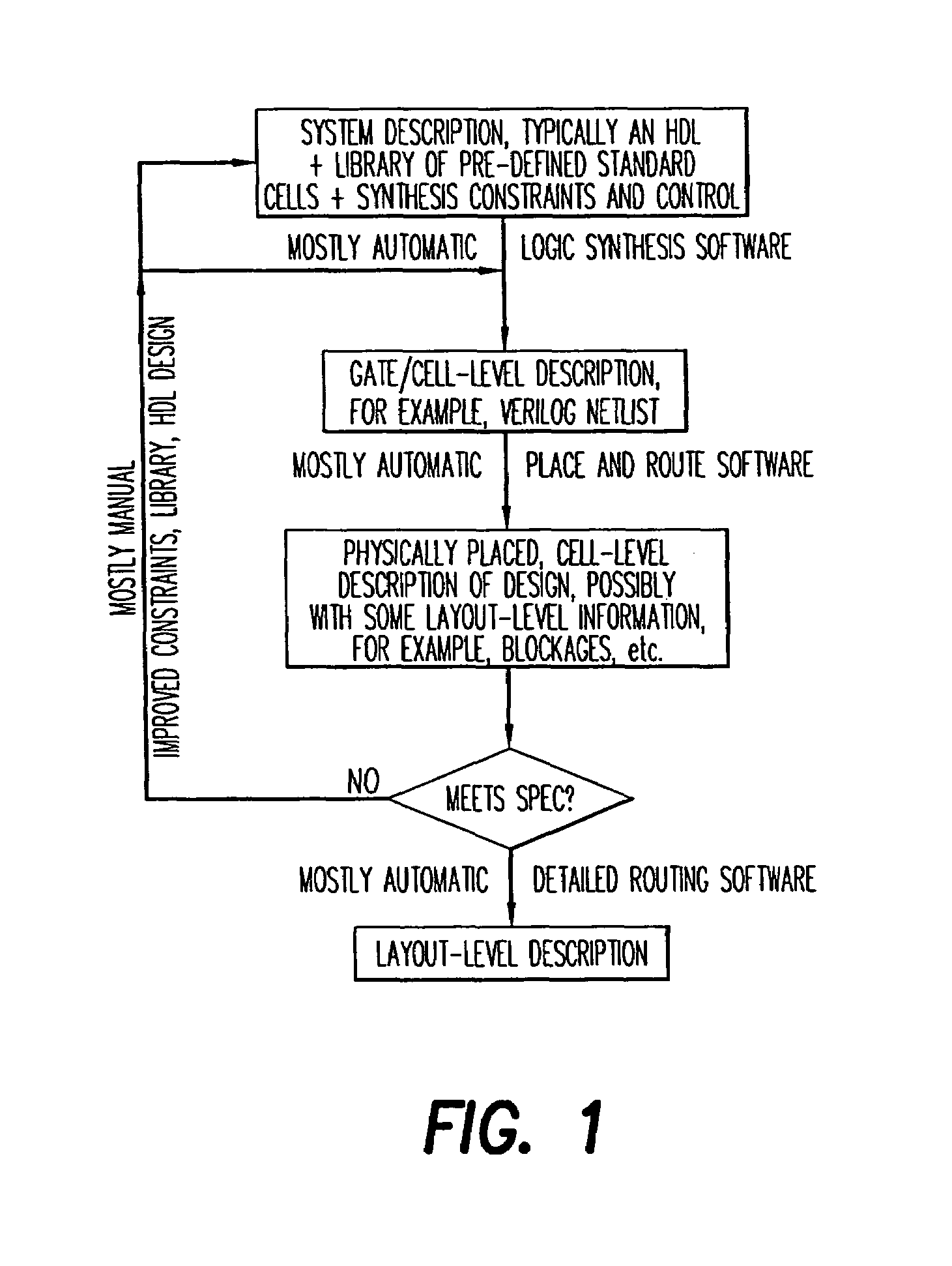

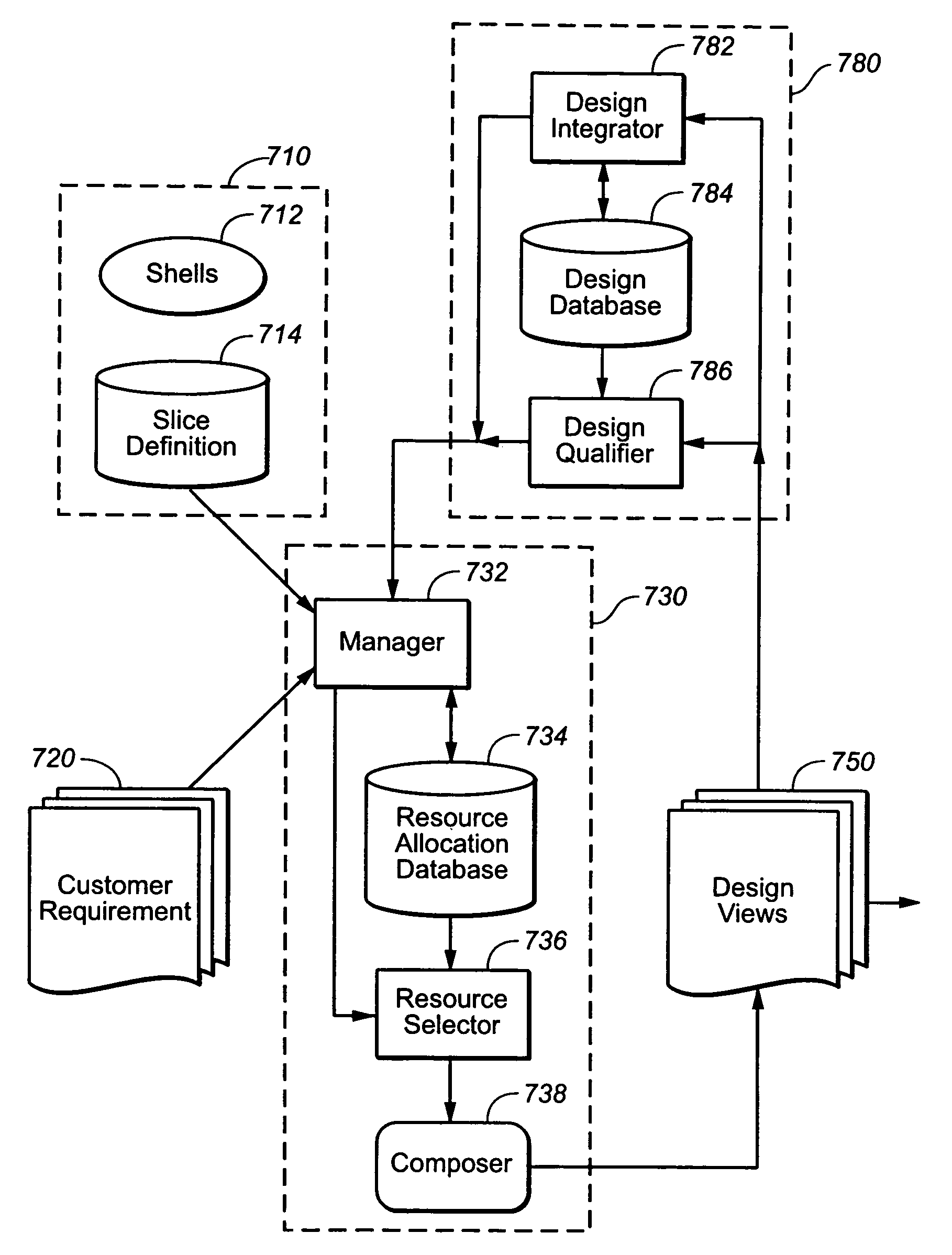

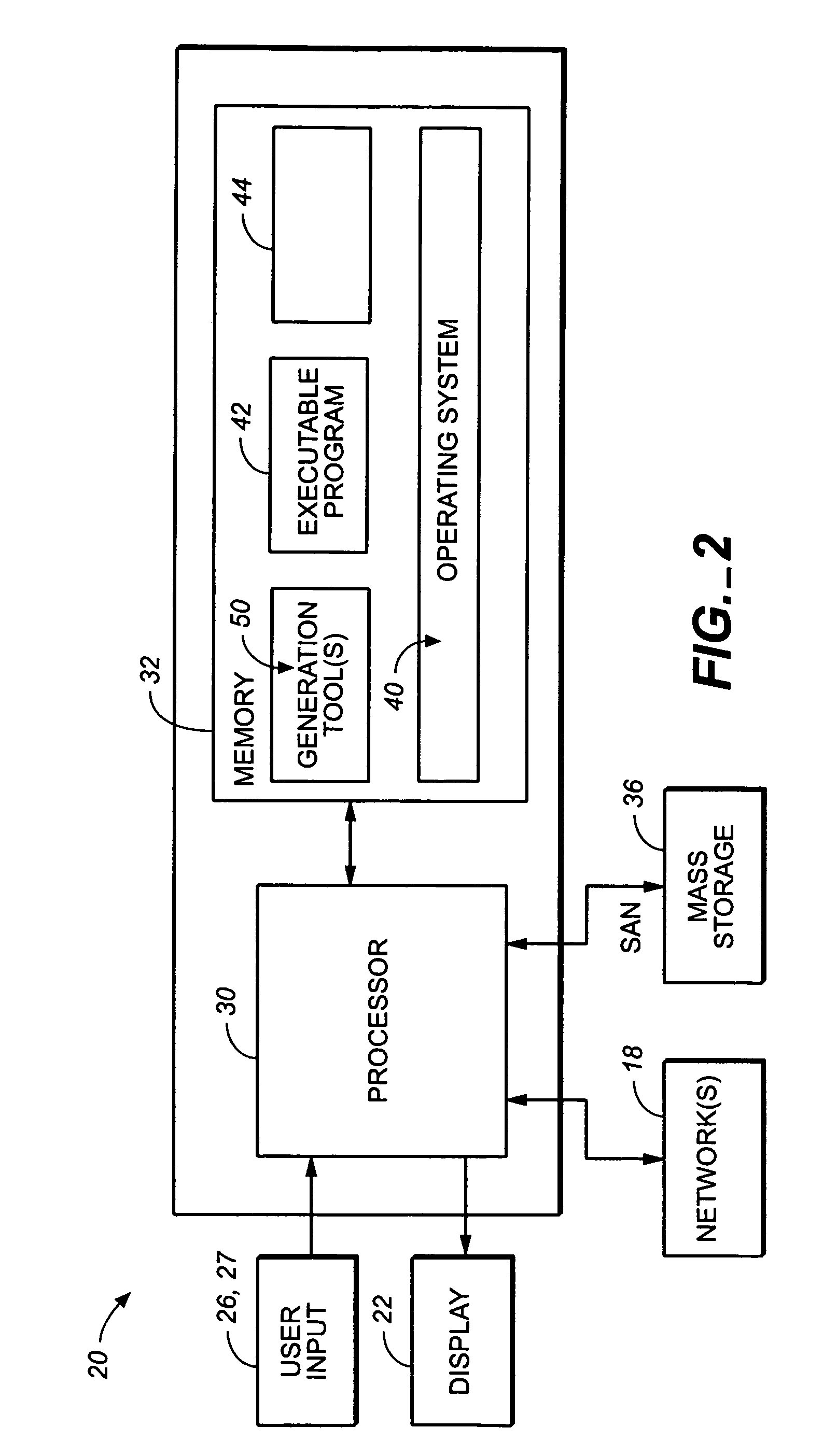

Simplified process to design integrated circuits

ActiveUS7055113B2Computer aided designSoftware simulation/interpretation/emulationCustomer requirementsFoundry

A set of tools is provided herein that produces useful, proven, and correct integrated semiconductor chips. Having as input either a customer's requirements for a chip, or a design specification for a partially manufactured semiconductor chip, the tools generate the RTL for control plane interconnect; memory composition, test, and manufacture; embedded logic analysis, trace interconnection, and utilization of spare resources on the chip; I / O qualification, JTAG, boundary scan, and SSO analysis; testable clock generation, control, and distribution; interconnection of all of the shared logic in a testable manner from a transistor fabric and / or configurable blocks in the slice. The input customer requirements are first conditioned by RTL analysis tools to quickly implement its logic. The slice definition and the RTL shell provides the correct logic for a set of logic interfaces for the design specification to connect. The tools share a common database so that logical interactions do not require multiple entries. The designs are qualified, tested, and verified by other tools. The tools further optimize the placement and timing of the blocks on the chip with respect to each other and with respect to placement on a board. The suite may be run as batch processes or can be driven interactively through a common graphical user interface. The tools also have an iterative mode and a global mode. In the iterative mode, one or more of the selected tools can generate the blocks or modify a design incrementally and then look at the consequences of the addition, or change. In the global mode, the semiconductor product is designed all at once in a batch process as above and then optimized altogether. This suite of generation tools generates design views including a qualified netlist for a foundry to manufacture.

Owner:BELL SEMICON LLC

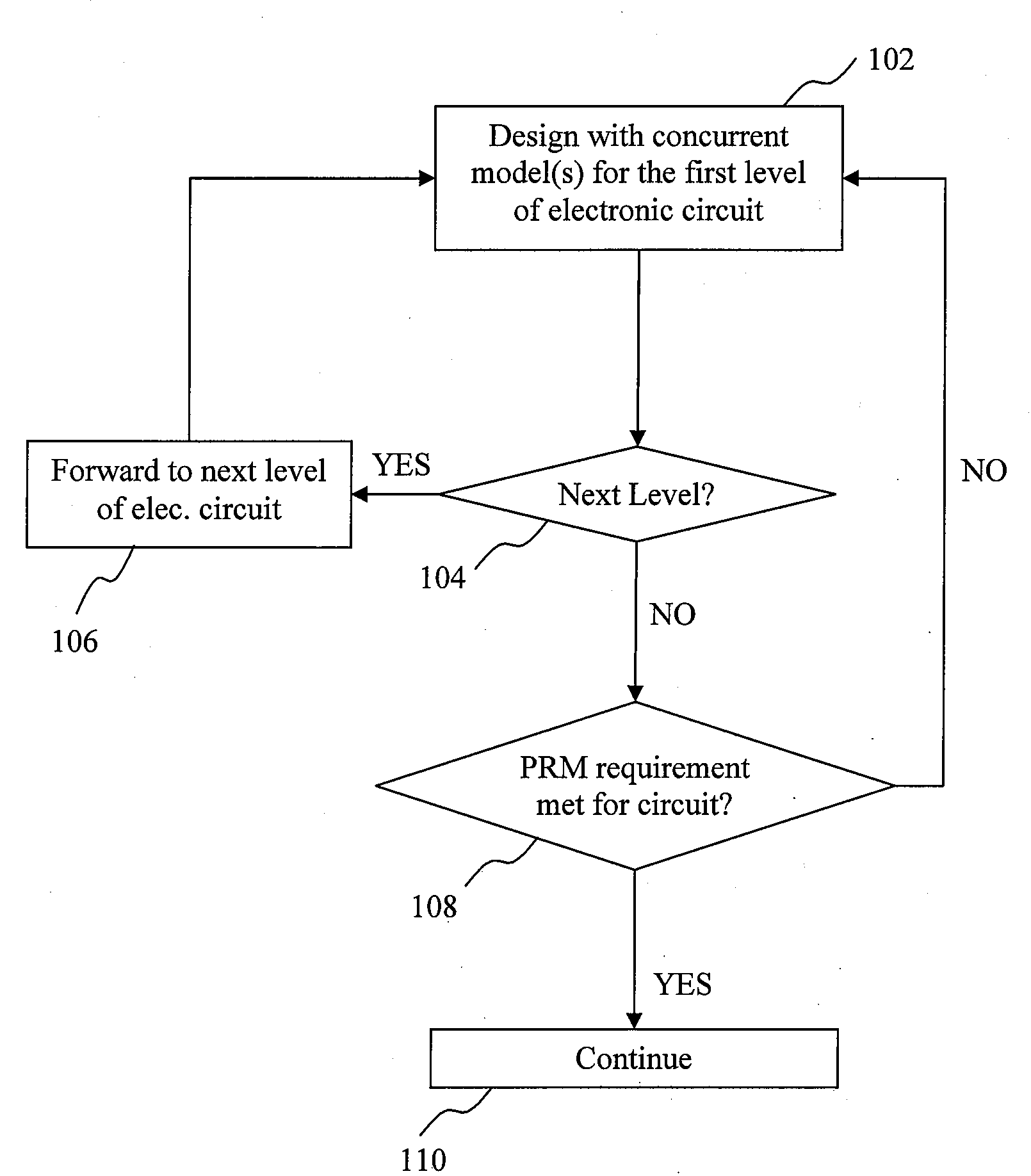

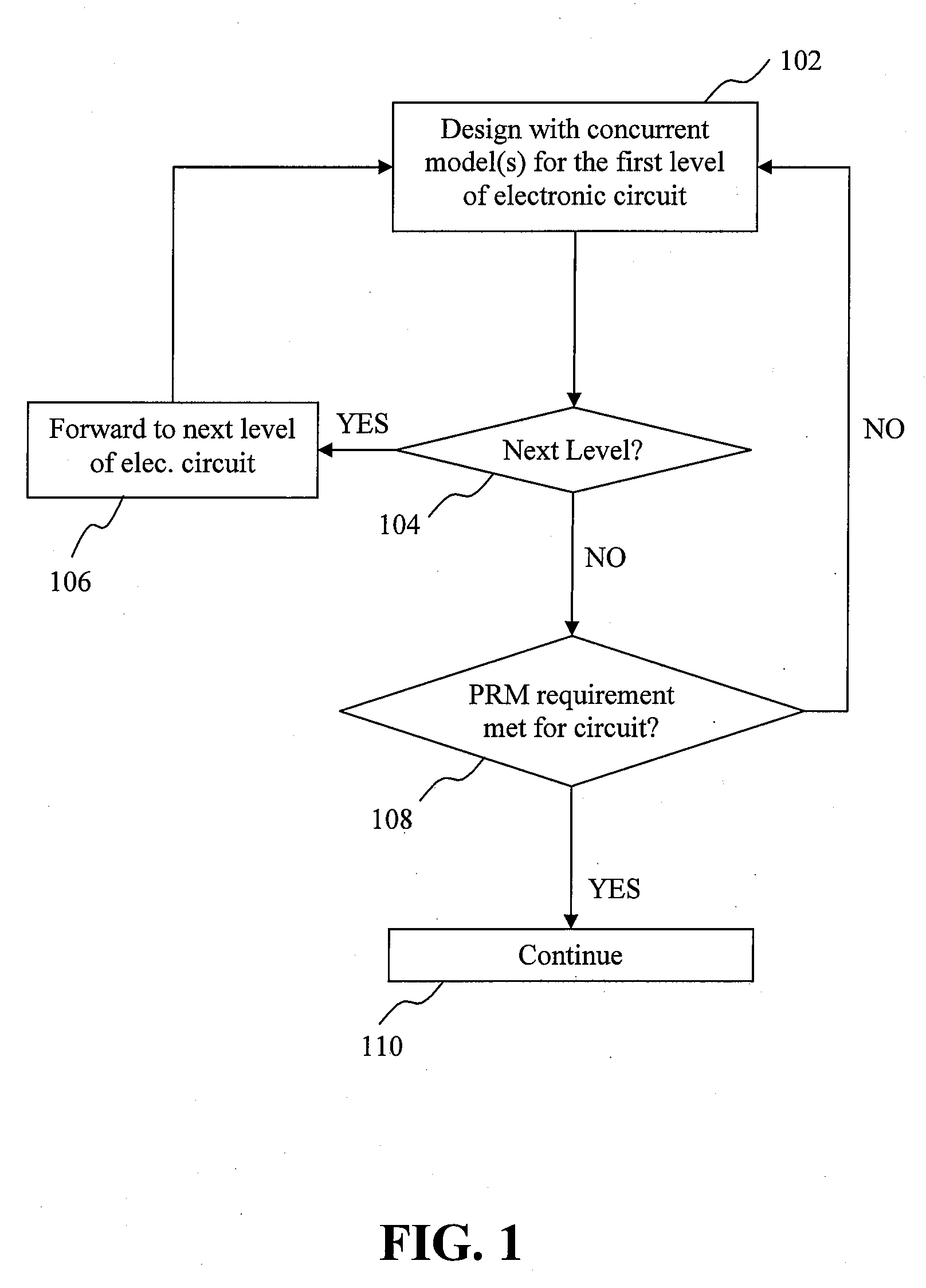

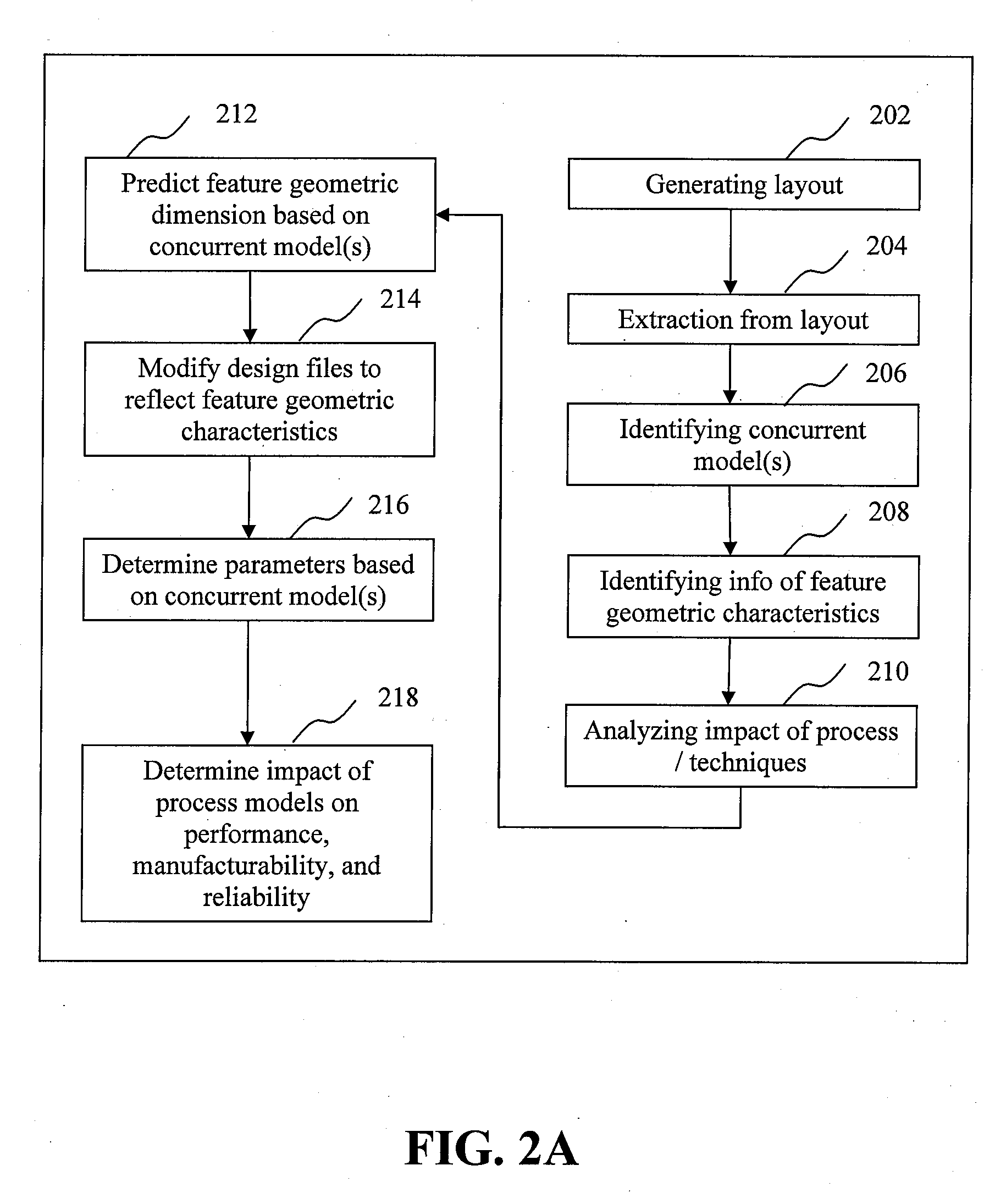

Method, system, and computer program product for concurrent model aided electronic design automation

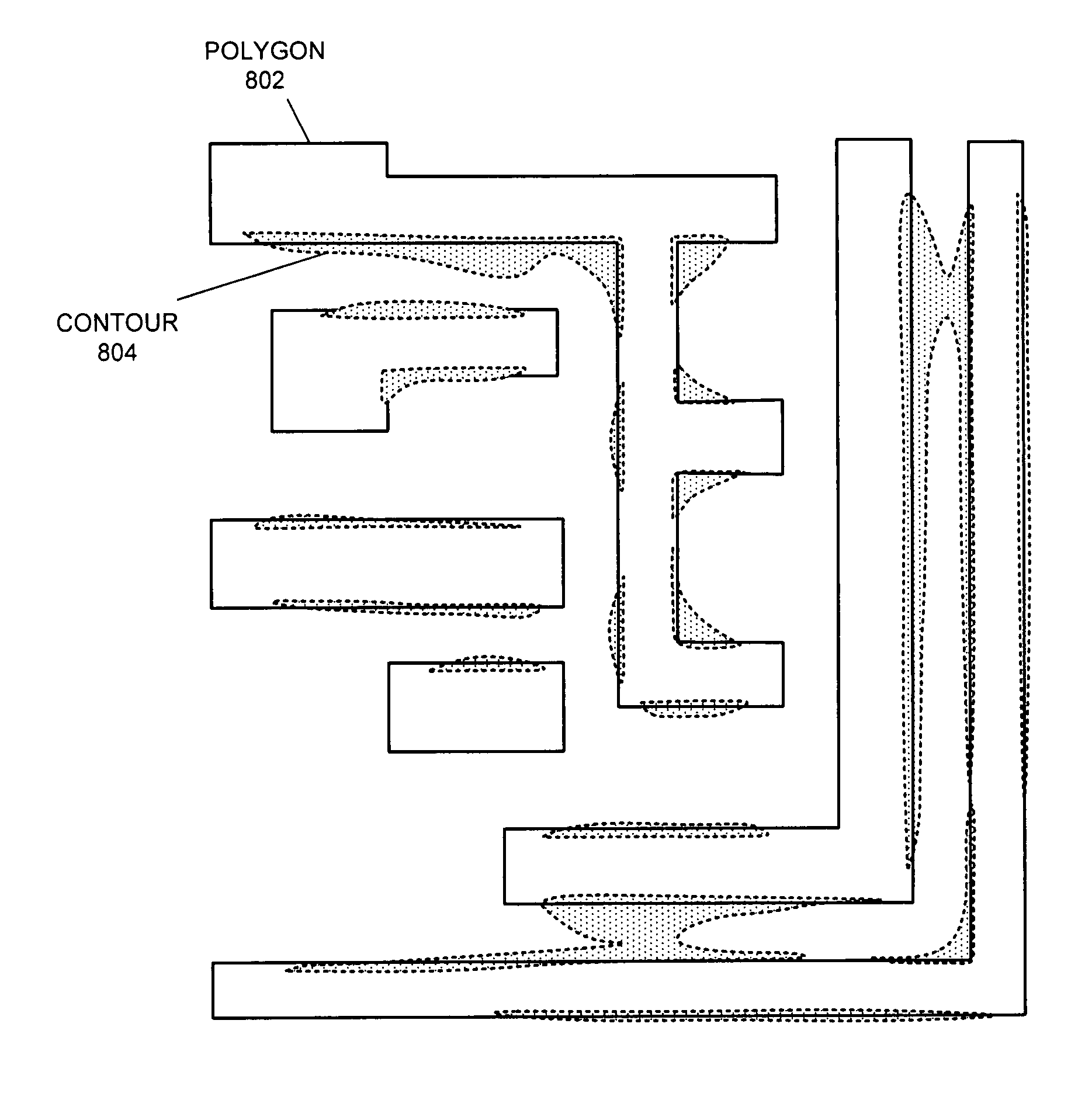

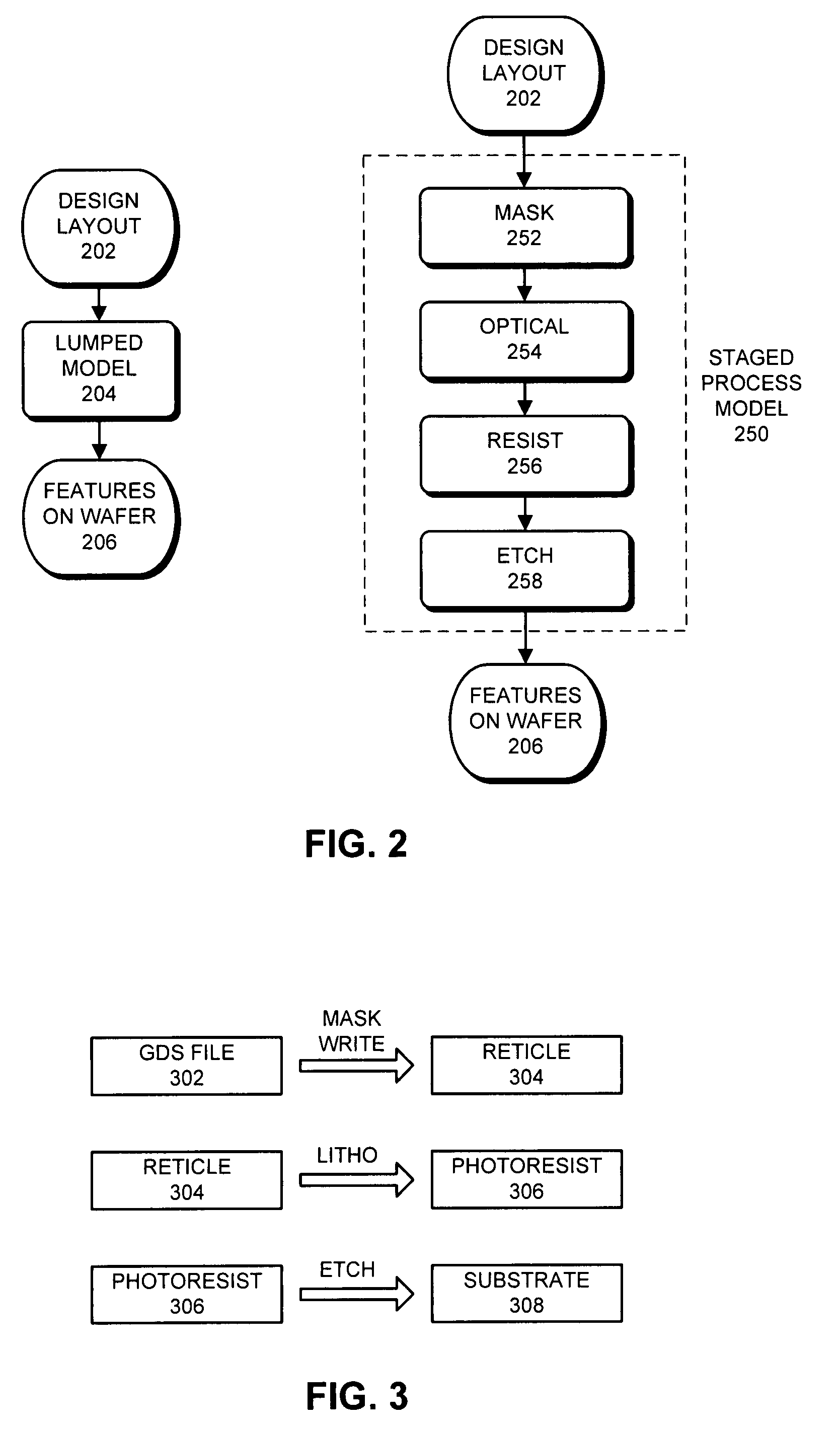

InactiveUS20080162103A1Effective and accurate methodologyAccurate predictionAnalogue computers for electric apparatusPhotomechanical apparatusComputer architectureGenerative Design

Disclosed are improved methods, systems, and computer program products for predicting performance, manufacturability, and reliability (PMR) using concurrent model analyses for electronic designs. Various embodiments of the present invention disclose a method for predicting PMR with concurrent process model analysis in which a method with concurrent model(s) generate a design for the one or more layers in the electronic circuit. The method then analyzes the impact of the processes or techniques for feature geometric characteristic predictions or PMR evaluations, based upon the concurrent models. Results may be reported to the users, or the method may modify the designs to accommodate the variations and determines one or more parameters based upon the concurrent models. One embodiment determines the impact of concurrent model on one or more of performance, manufacturability, and reliability criteria.

Owner:CADENCE DESIGN SYST INC

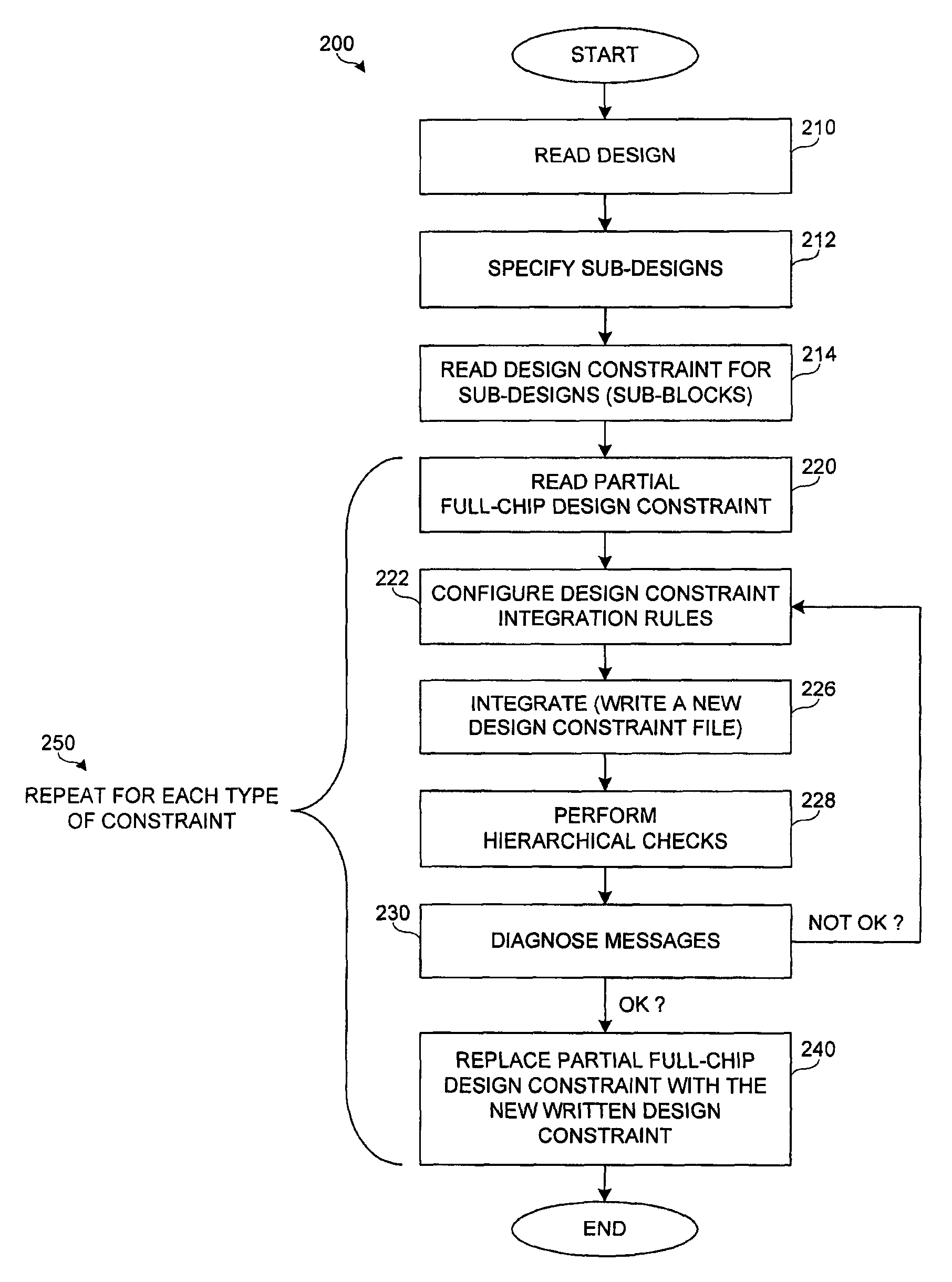

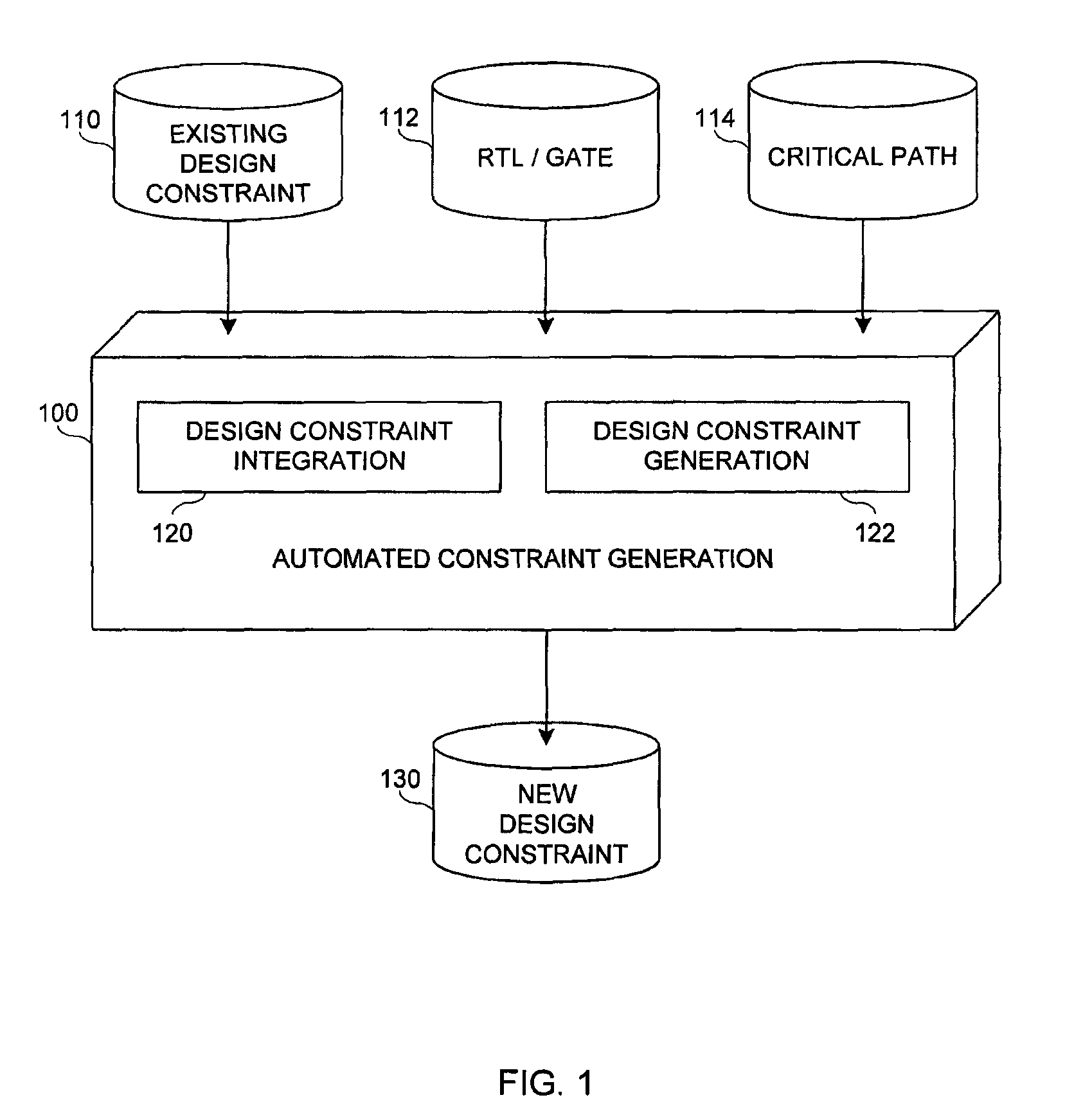

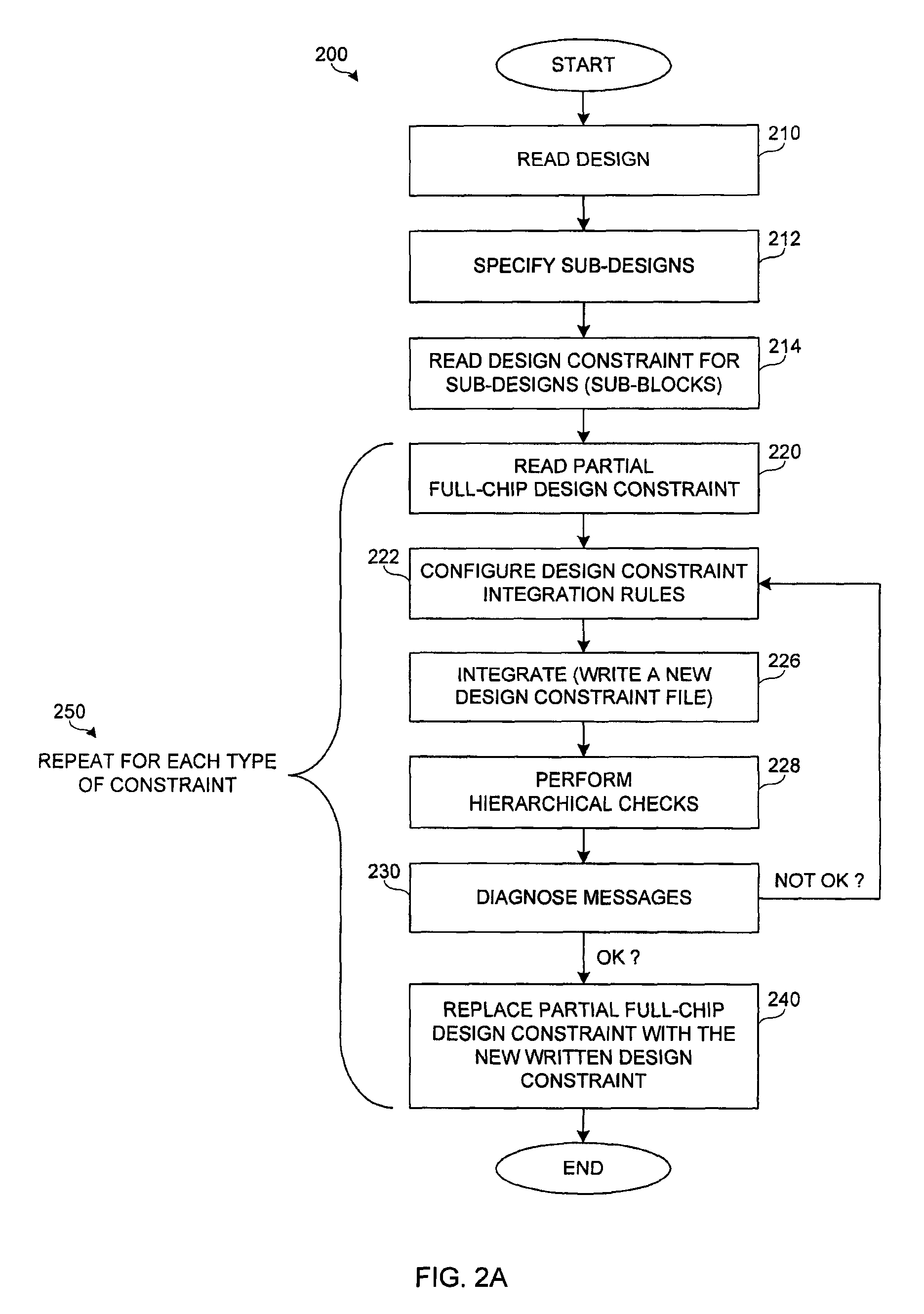

Method and system for generating design constraints

ActiveUS7962886B1Consistency issuesConstraint issuesDetecting faulty computer hardwareCAD circuit designConfiguration designIntegration rule

A method and system for generating design constraints for an electronic circuit design is disclosed. The method and system include reading a design description and an existing design constraint file, configuring design constraint integration rules, writing a new design constraint file, evaluating results of the new design constraint file, and replacing existing design constraint file with the new design constraint file.

Owner:CADENCE DESIGN SYST INC

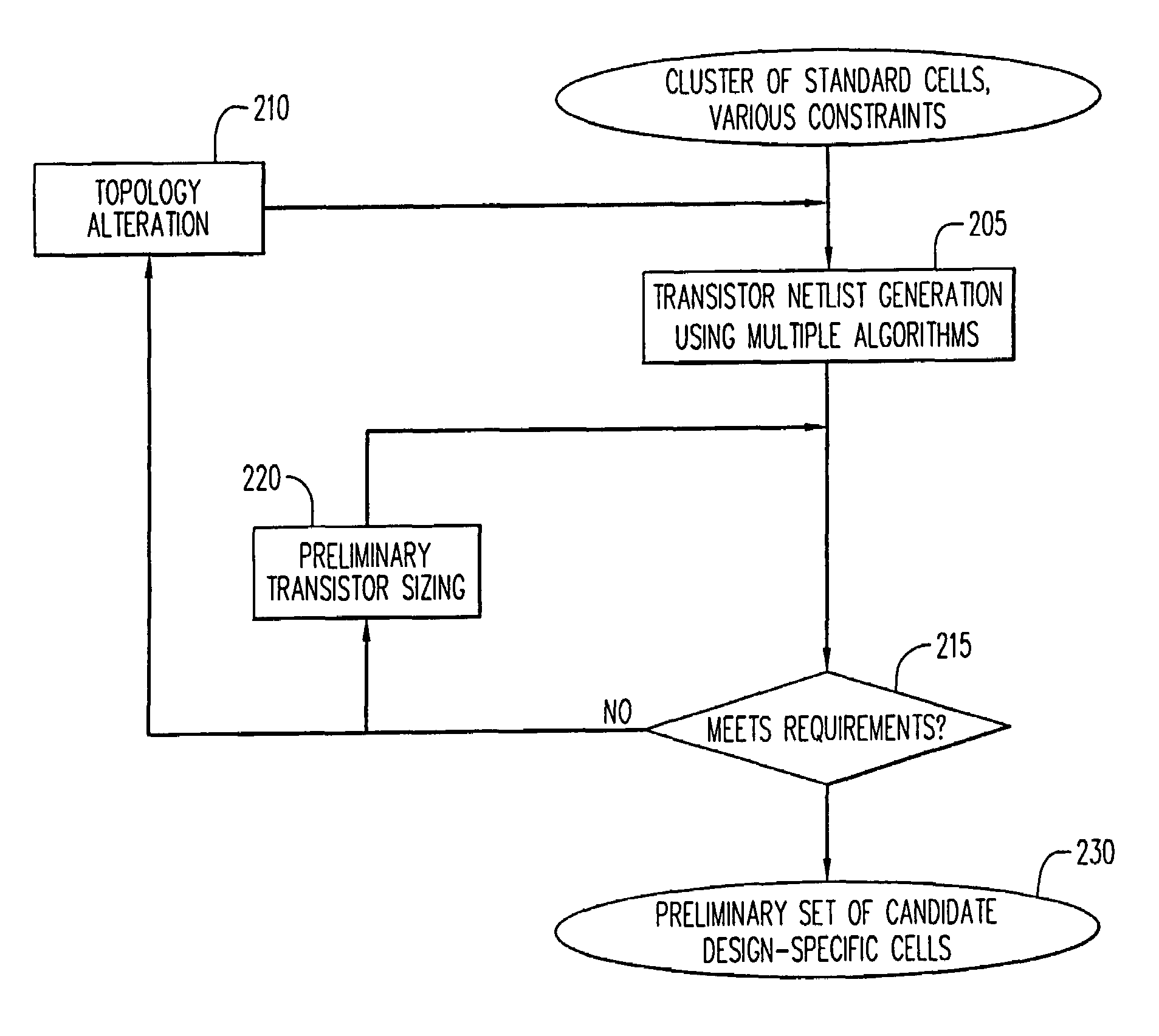

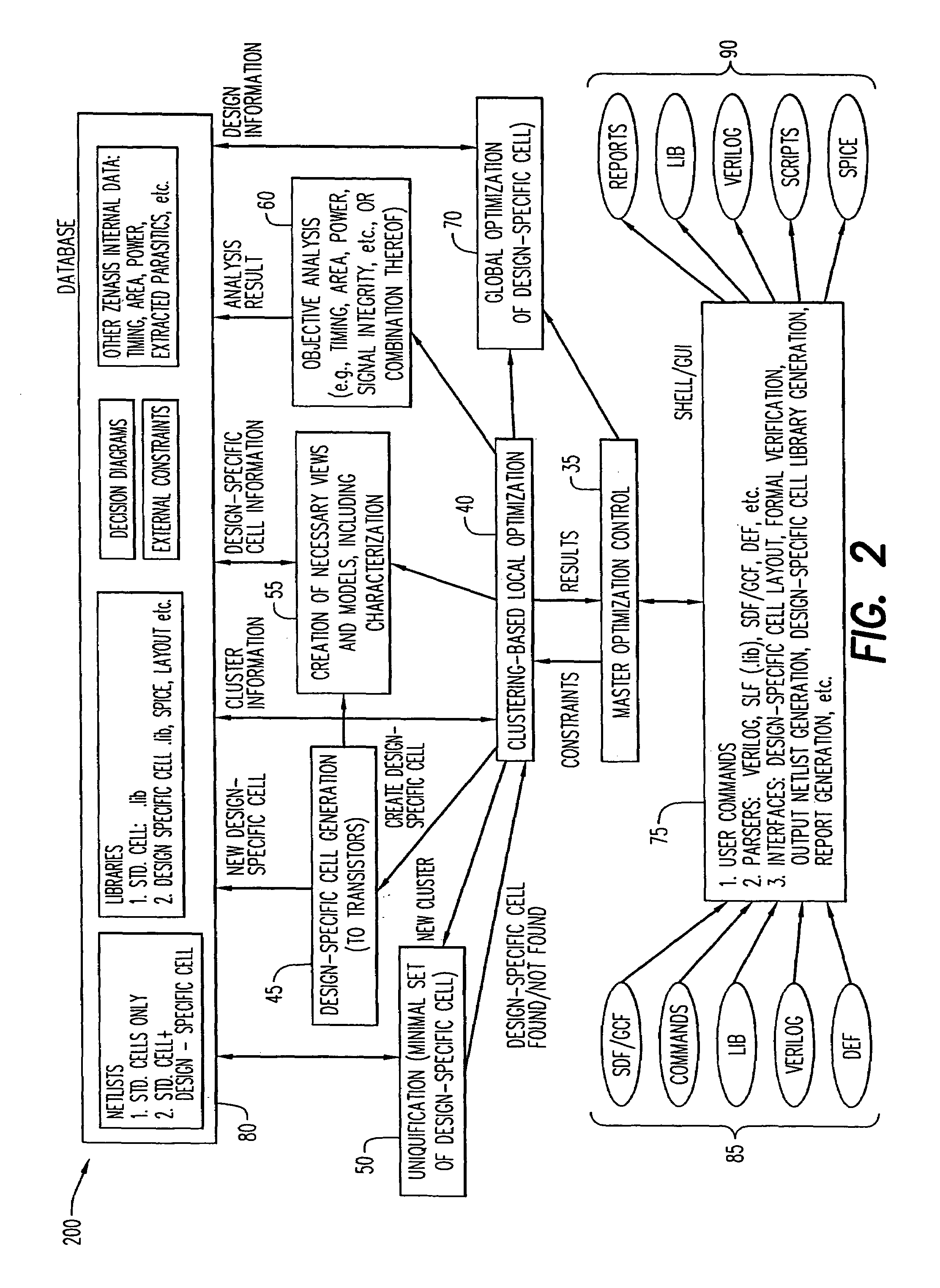

Process for automated generation of design-specific complex functional blocks to improve quality of synthesized digital integrated circuits in CMOS using altering process

InactiveUS7003738B2Small sizeCAD circuit designSoftware simulation/interpretation/emulationCMOSGenerative Design

The present invention pertains to an automated method for designing a integrated circuit (IC) design-specific cell, the method includes the steps of receiving a design specification for the design-specific cell, mapping a transistor-level representation of the design-specific cell, wherein the mapping is based on at least one, but perhaps plural design specifications, and evaluating the transistor-level representation of the design-specific cell for satisfaction of the design specification.

Owner:OPEN-SILICON

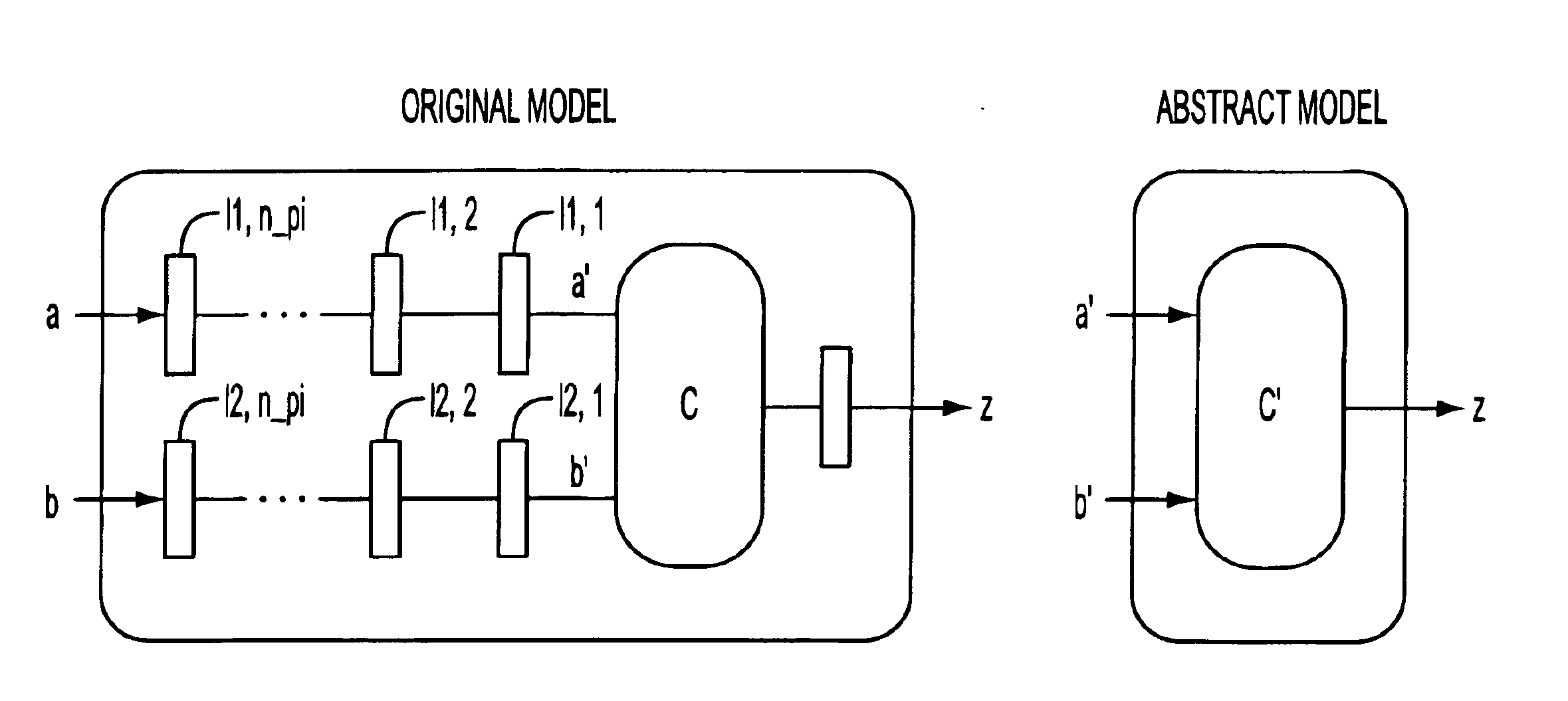

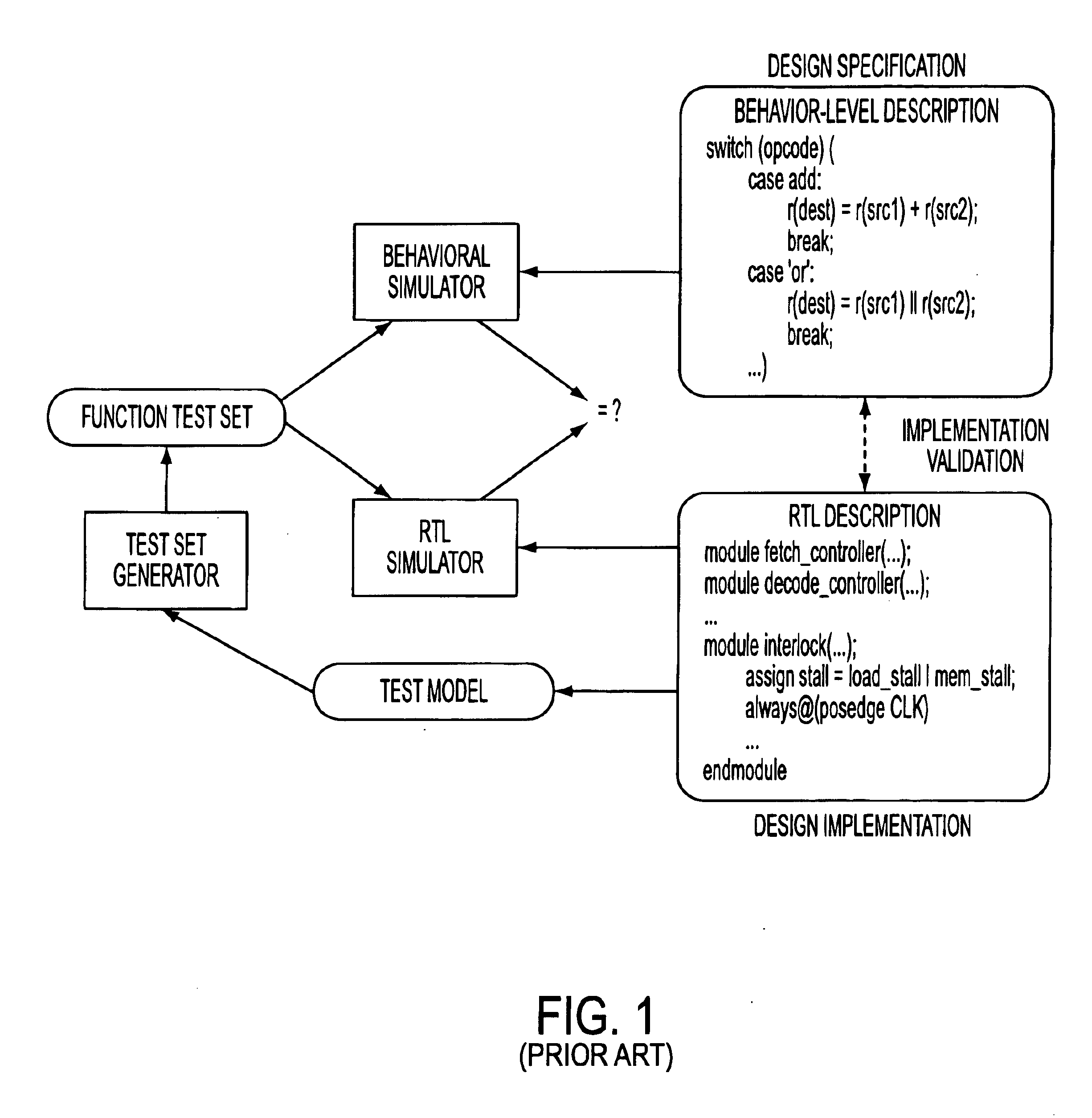

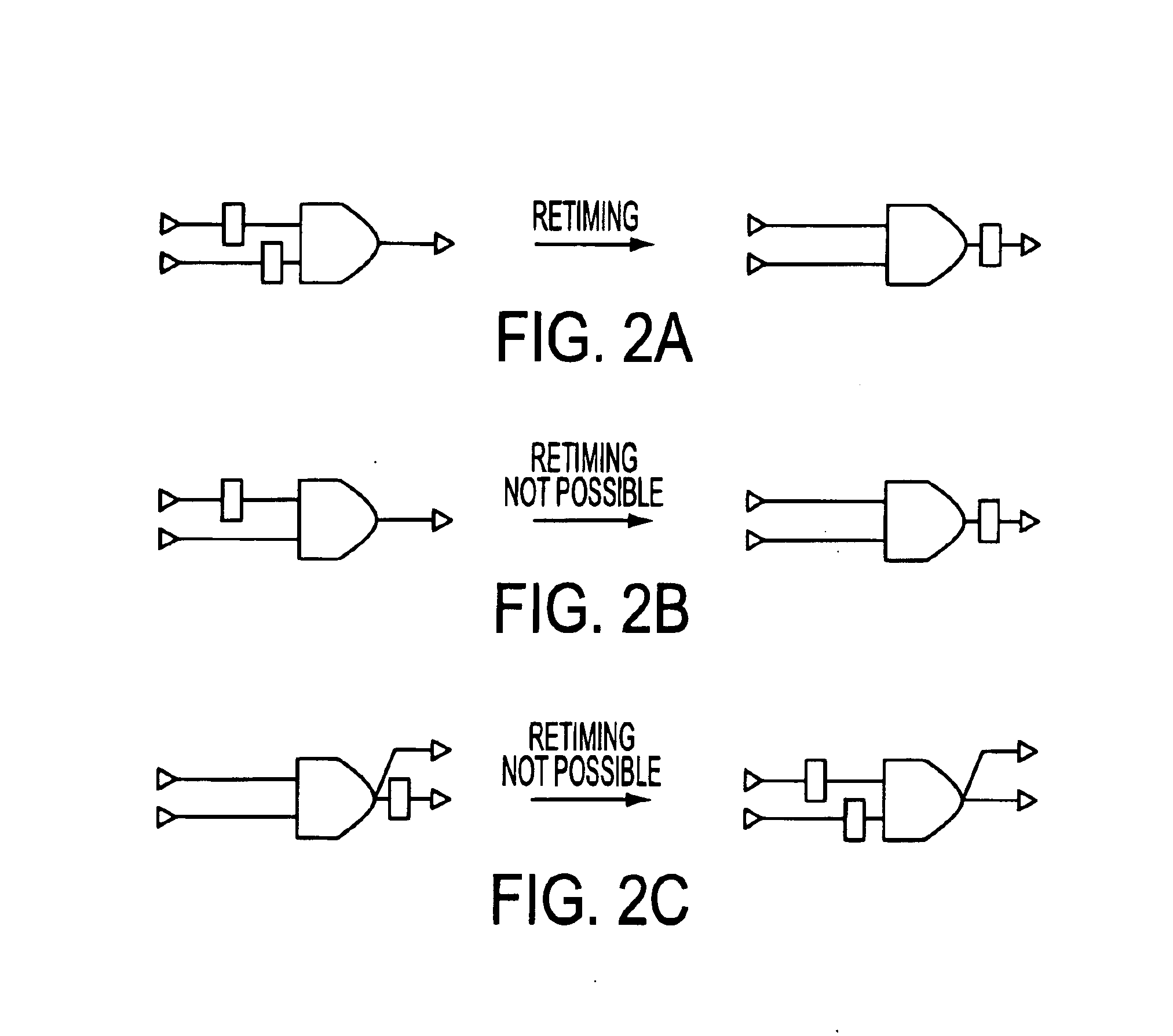

Method for design validation using retiming

InactiveUS6874135B2Minimize the numberReduce complexityDetecting faulty computer hardwareCAD circuit designDesign testingTest sequence

A method for derivation and abstraction of test models for validation of industrial designs using guided simulation is described. The method employs automatic abstractions for the test model which reduce its complexity while preserving the class of errors that can be detected by a transition tour. A method for design validation comprising generating a state-based test model of the design. The test model is abstracted by retiming and latch removal. Finally, a validation technique is applied on the abstracted test model. First, the number of internal (non-peripheral) latches in a design is minimized via retiming using a method of Maximal Peripheral Retiming (MPR). According to the MPR method, internal latches are retimed to the periphery of the circuit. Subsequently, all latches that can be retimed to the periphery are automatically abstracted in the test model. The validation technique may comprise of model checking, invariant checking or simulation using test sequences generated from the abstracted test model.

Owner:NEC CORP

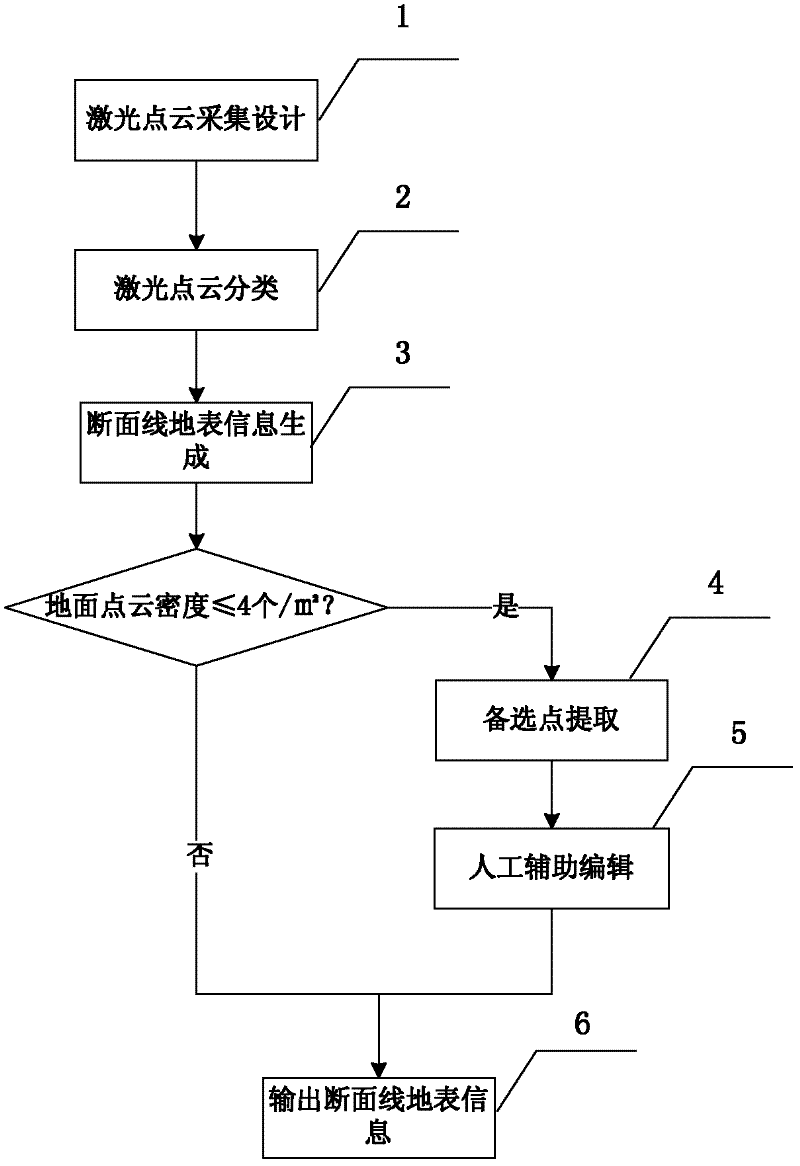

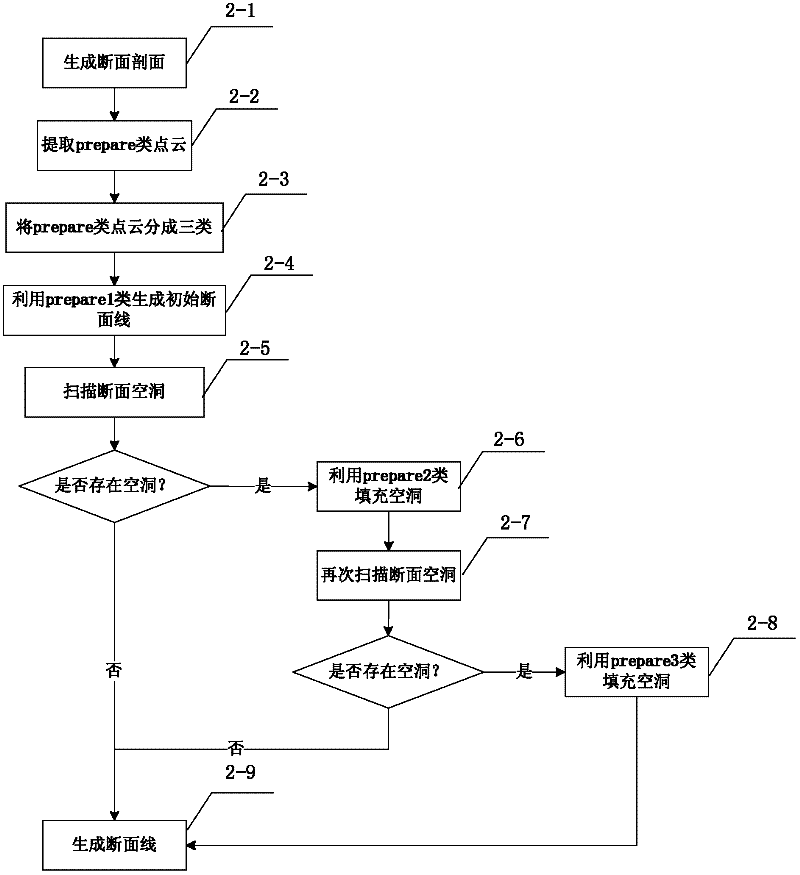

Method for generating road design surface information by laser radar scan

ActiveCN102445186AHigh precisionImprove efficiencySpecial data processing applicationsProfile tracingJet aeroplaneData acquisition

The invention discloses a method for generating road design surface information by laser radar scan, which comprises the following steps: a, an airplane or automobile is used for collecting data for a platform-carried laser scanner; b, original laser point cloud is classified to a ground point type and a non-ground point type; c, the point cloud data of the classified ground point types can be used for generating road surface information required by design; d, for regions with the point cloud density of the ground point type less than 4 / m<2>, an alternative point is automatically extracted from the non-ground point type point cloud; e, a sectional profile is taken as a projection surface, the extracted section point, ground point, non-ground point and alternative point are stacked for displaying, artificial auxiliary edit is carried out, in the section ground line, the alternative point is added, or an abrupt abnormal point is removed; and f, accurate section ground line surface information after editing is output according to a format required by the road design. The method of the invention has the advantages of rapidity, high efficiency and high stability; and is suitable for collecting information of construction, reconstruction and extension of various complex road surfaces.

Owner:中交和美环境生态建设有限公司

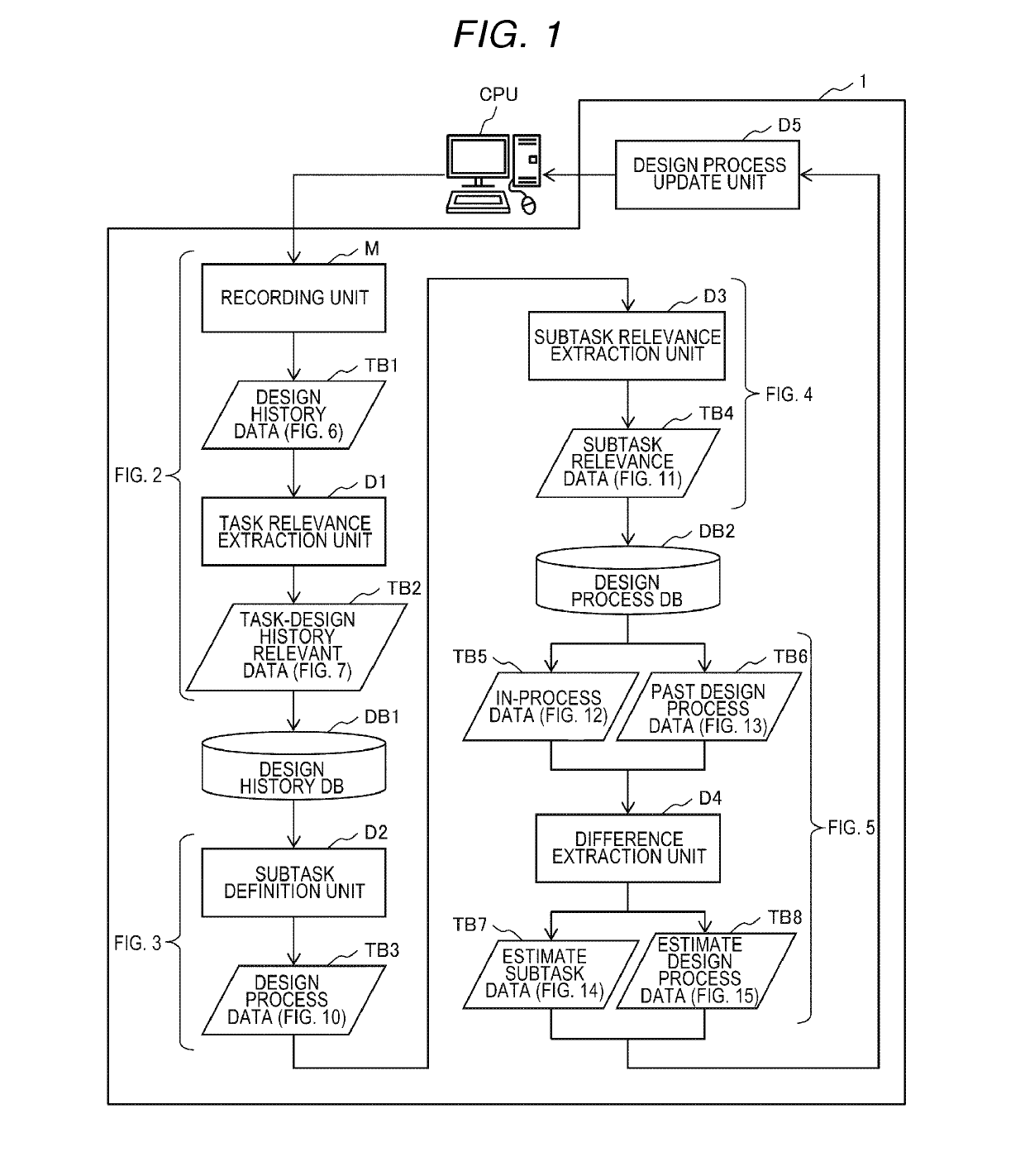

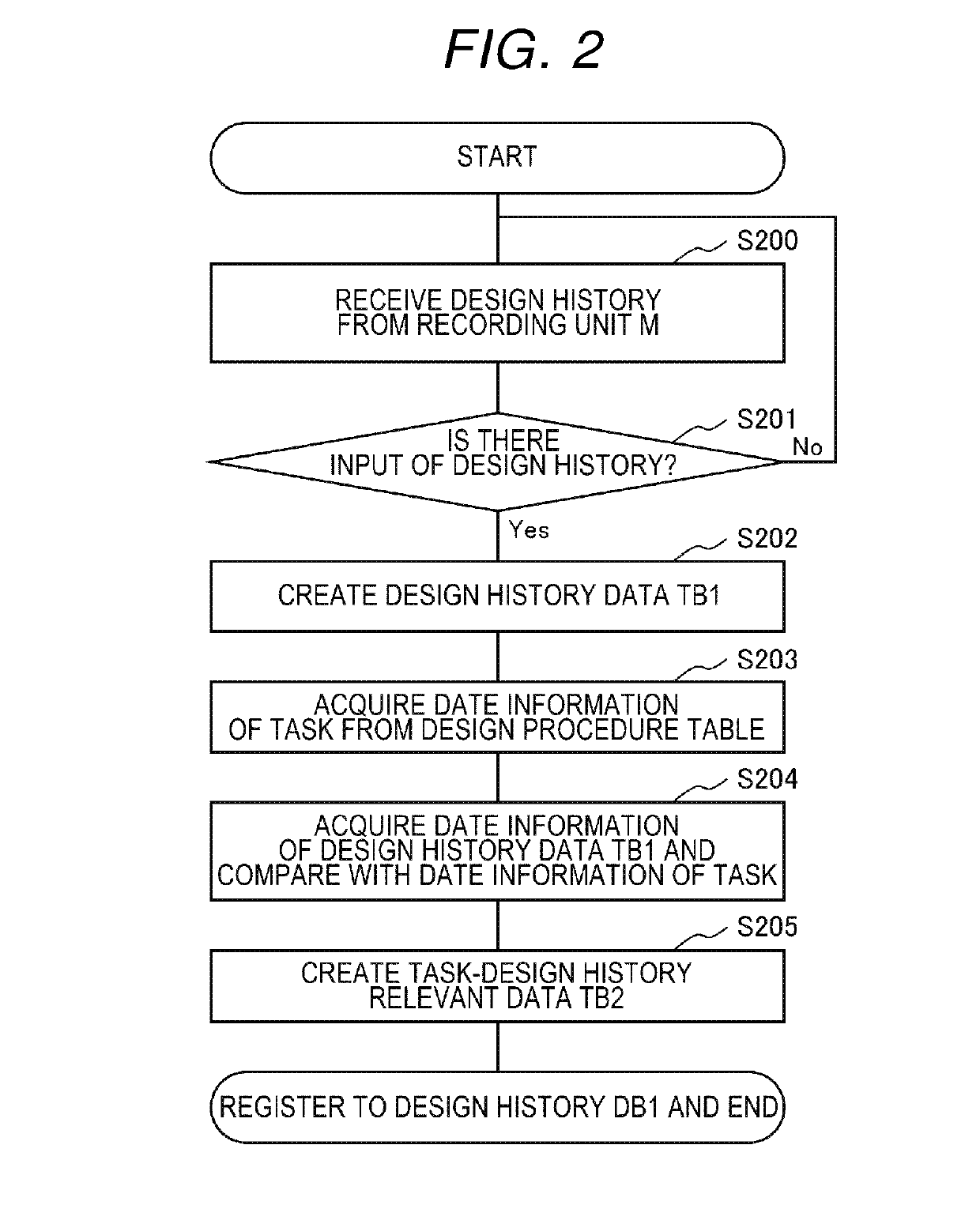

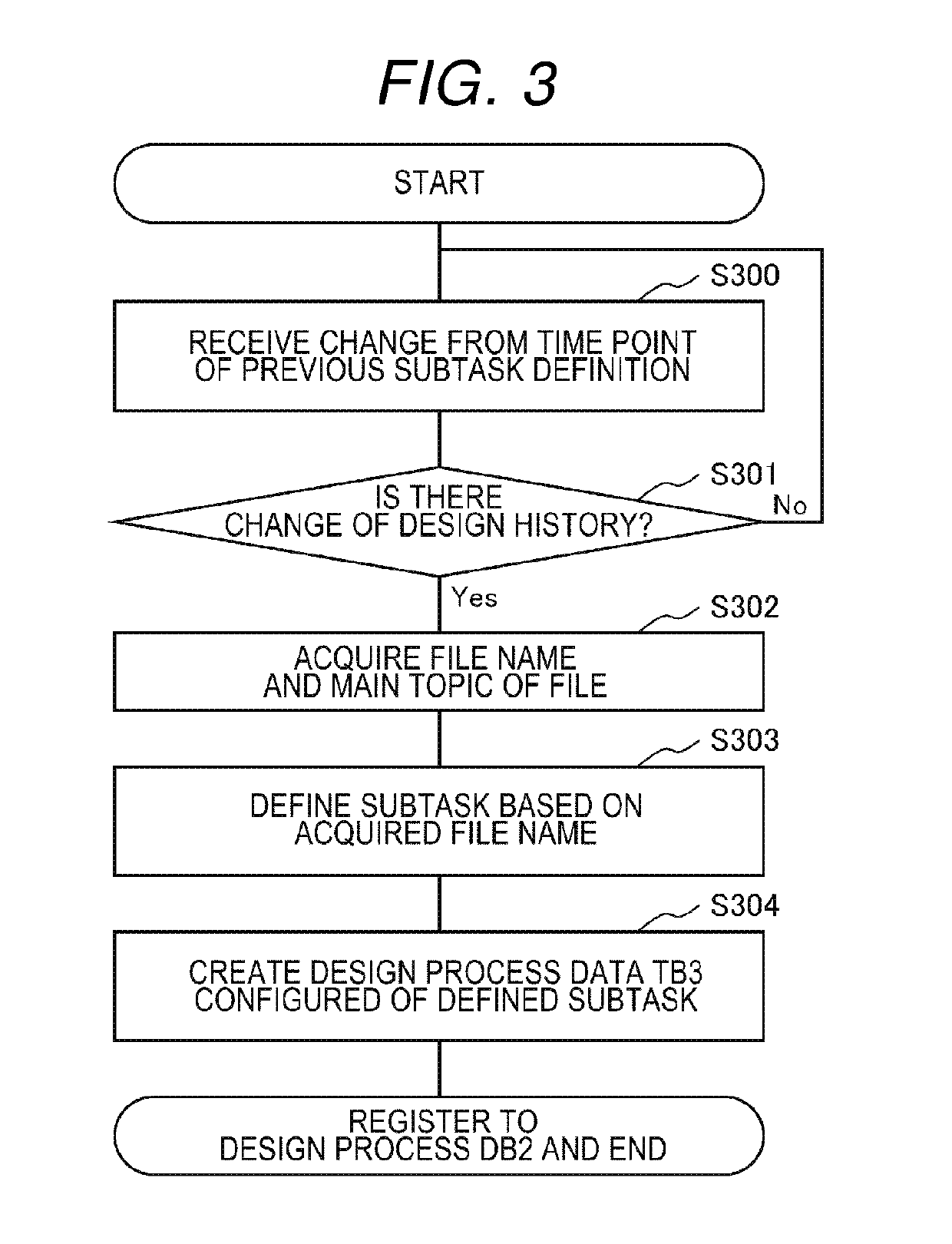

Design support device and design support method

InactiveUS20190095839A1Maintain qualityAvoid reworkResourcesSpecial data processing applicationsDesign supportGenerative Design

A design support device supports a design project achieved by executing a plurality of tasks including subtasks. The design history data of the design performed by a designer is sequentially stored and associated with a task to sequentially generate task-design history relevant data. A subtask is defined with respect to the task-design history relevant data to sequentially generate design process data. Subtask relevant data indicating a relevance between subtasks with respect to the plurality of pieces of design process data is generated, and a subtask to be performed in a later design work is estimated with respect to an in-process design work from a difference between past design process data of a project performed in the past and in-process data in a project performed currently to obtain an estimate subtask. An optimal execution order is calculated to obtain estimate design process data and the estimate design process data is output.

Owner:HITACHI LTD

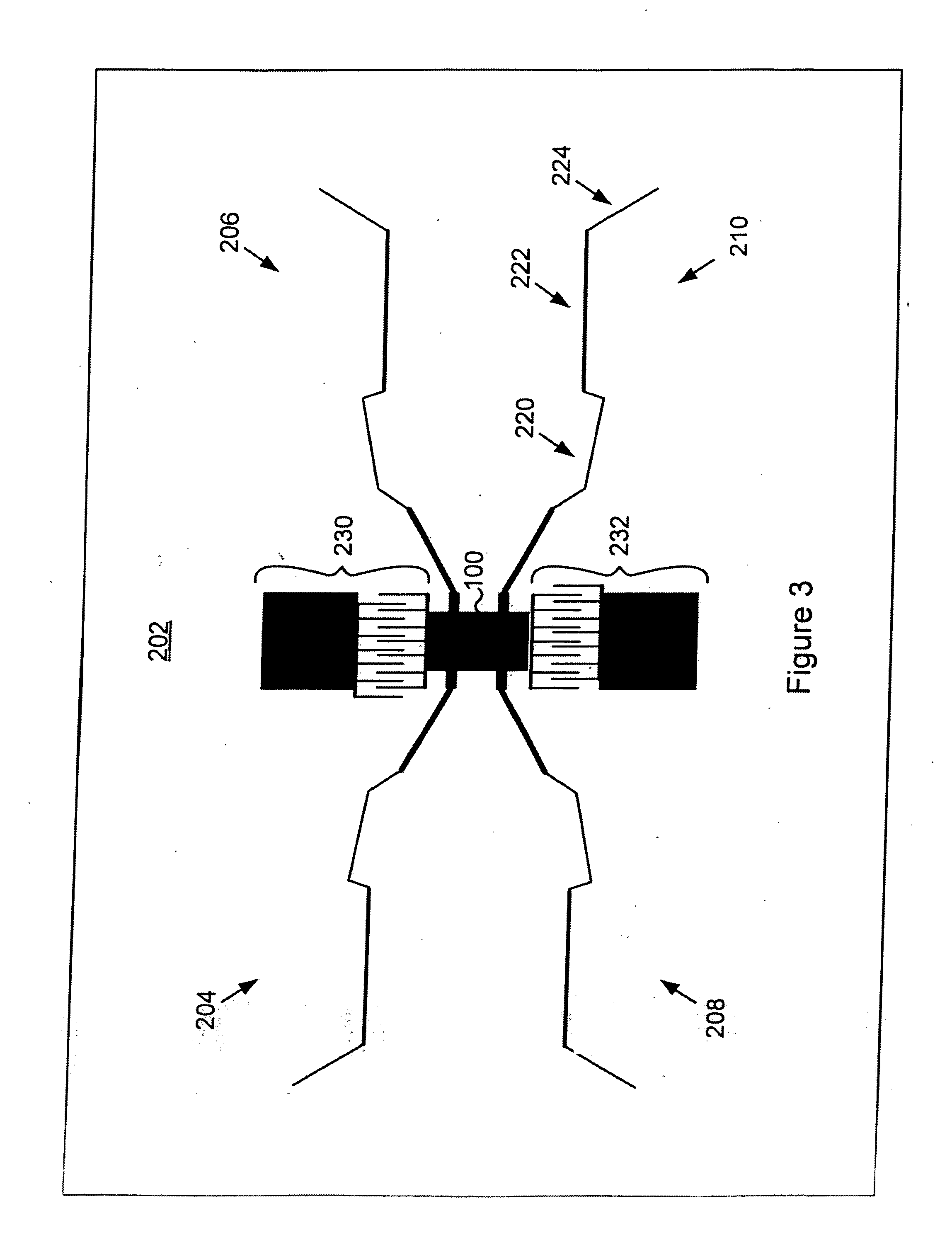

Method and apparatus to determine if a pattern is robustly manufacturable

ActiveUS7739651B2Originals for photomechanical treatmentSpecial data processing applicationsGenerative DesignEngineering

One embodiment provides a method to determine if a pattern is robustly manufacturable. During operation, the system may receive a first pattern and a design intent, wherein the first pattern is intended to generate the design intent. Next, the system may determine a second pattern using the design intent, wherein subjecting the second pattern to a second manufacturing process is expected to generate a third pattern that is substantially similar to the design intent. The system may then determine if a first semiconductor manufacturing process is capable of robustly manufacturing the second pattern. If the second pattern is not robustly manufacturable, the system may generate an indicator that indicates that the first pattern is not robustly manufacturable.

Owner:SYNOPSYS INC

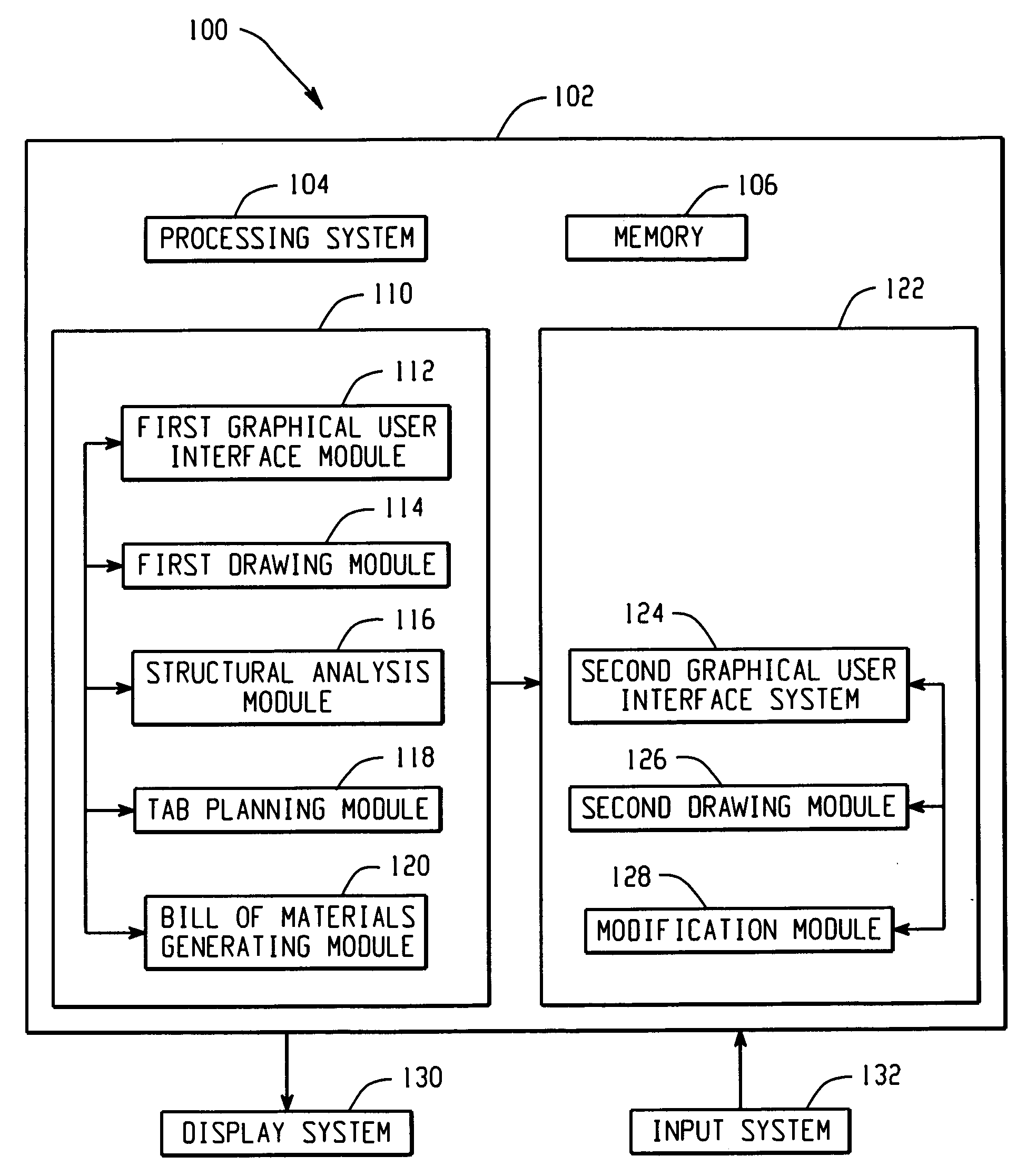

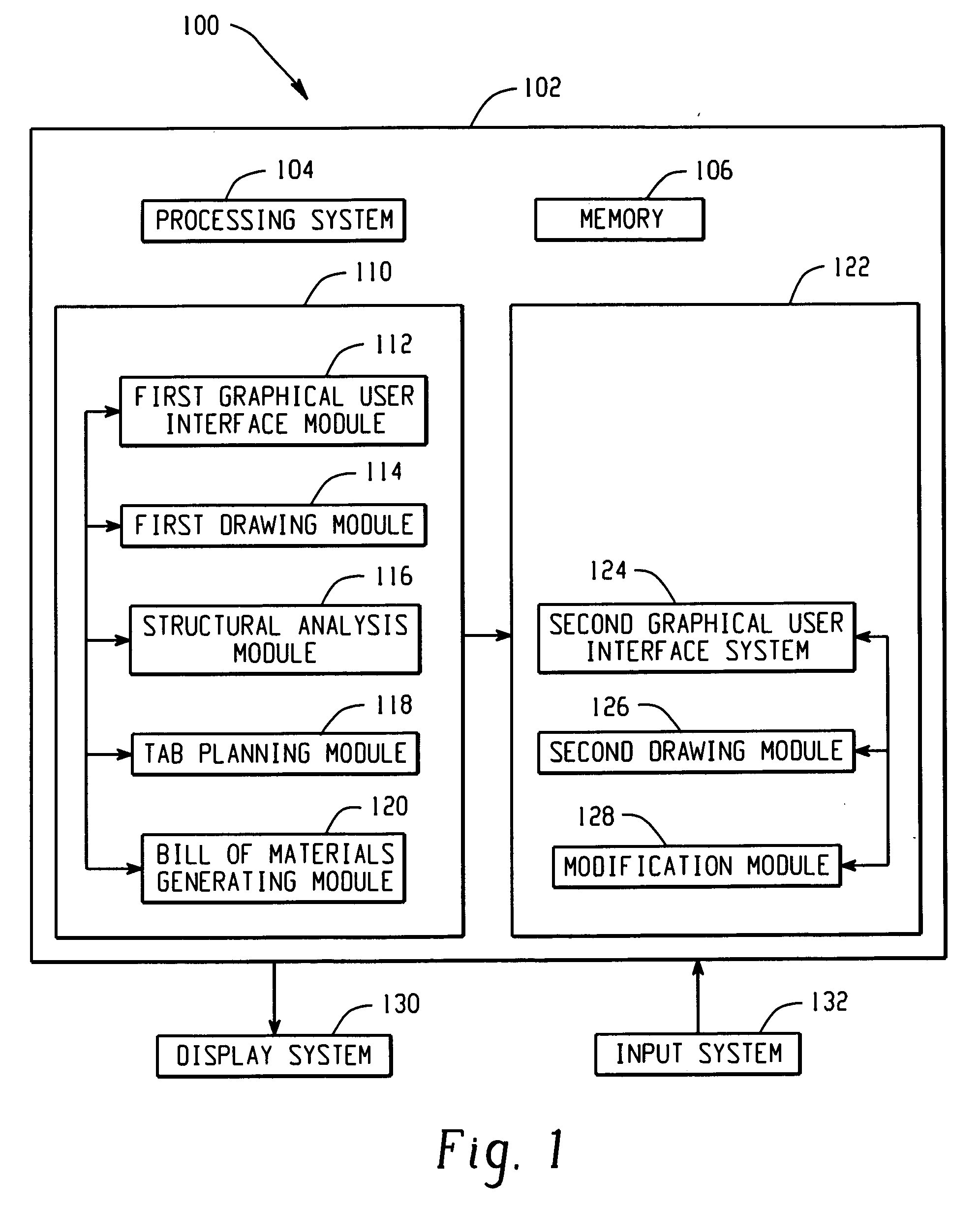

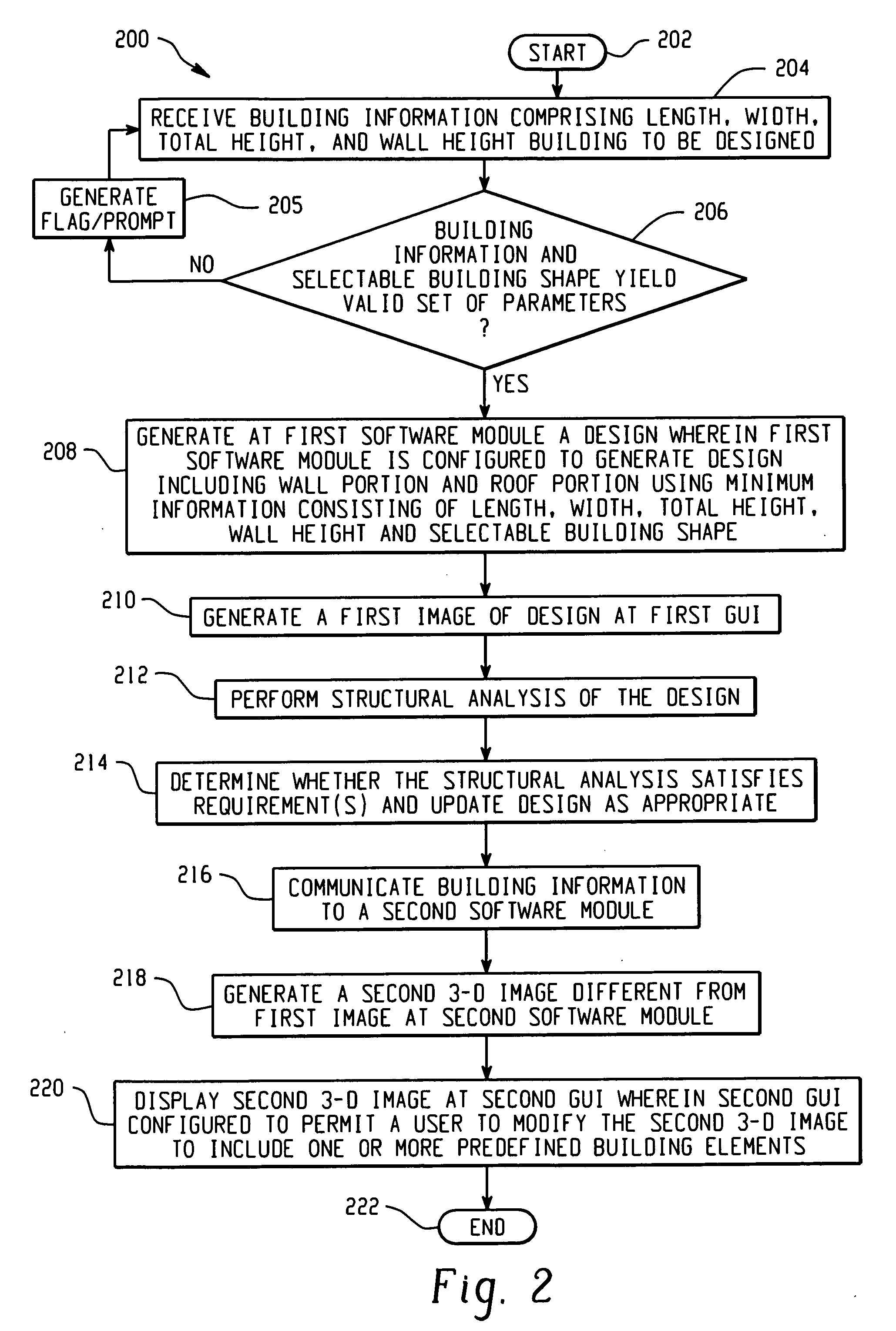

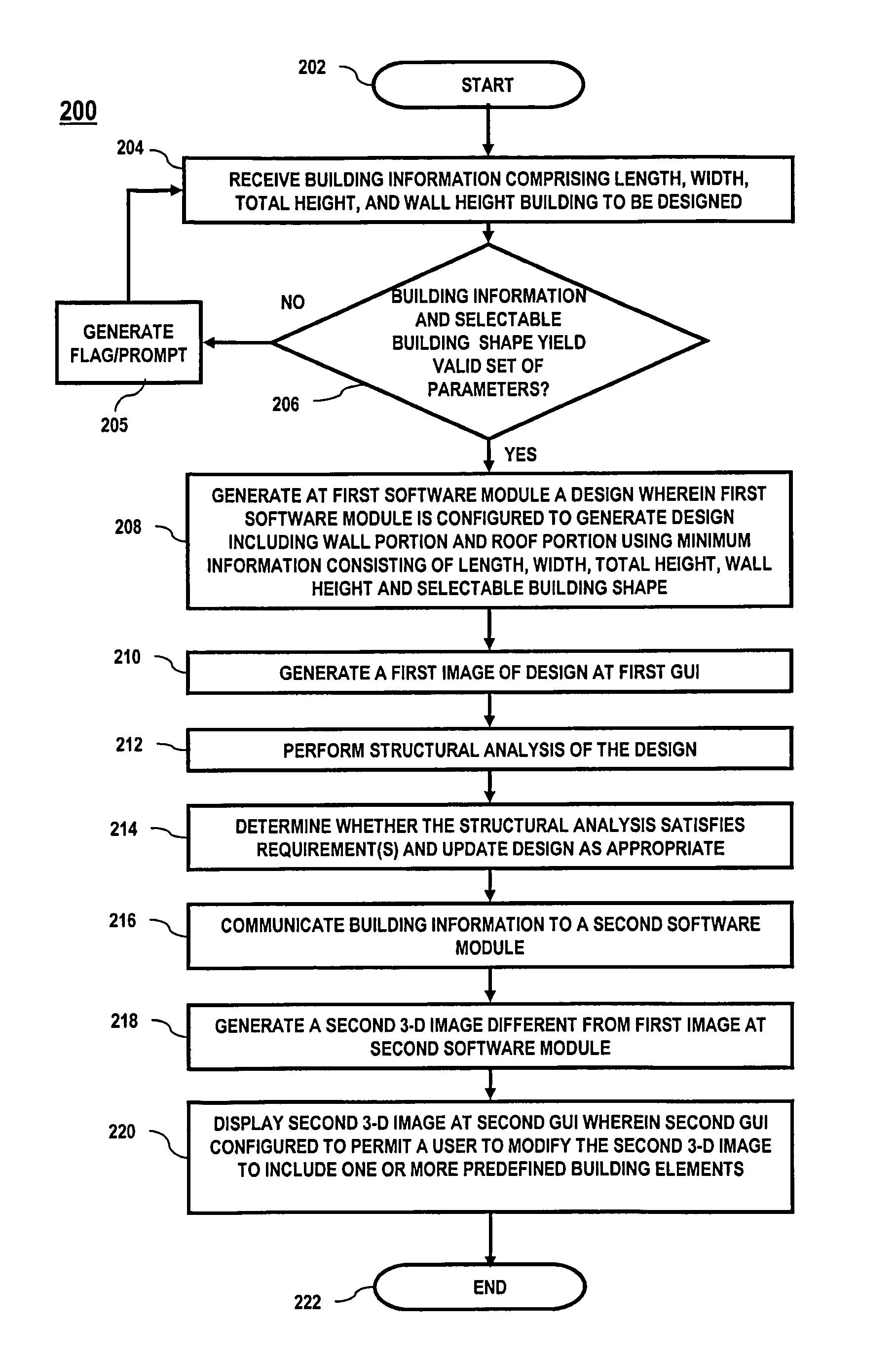

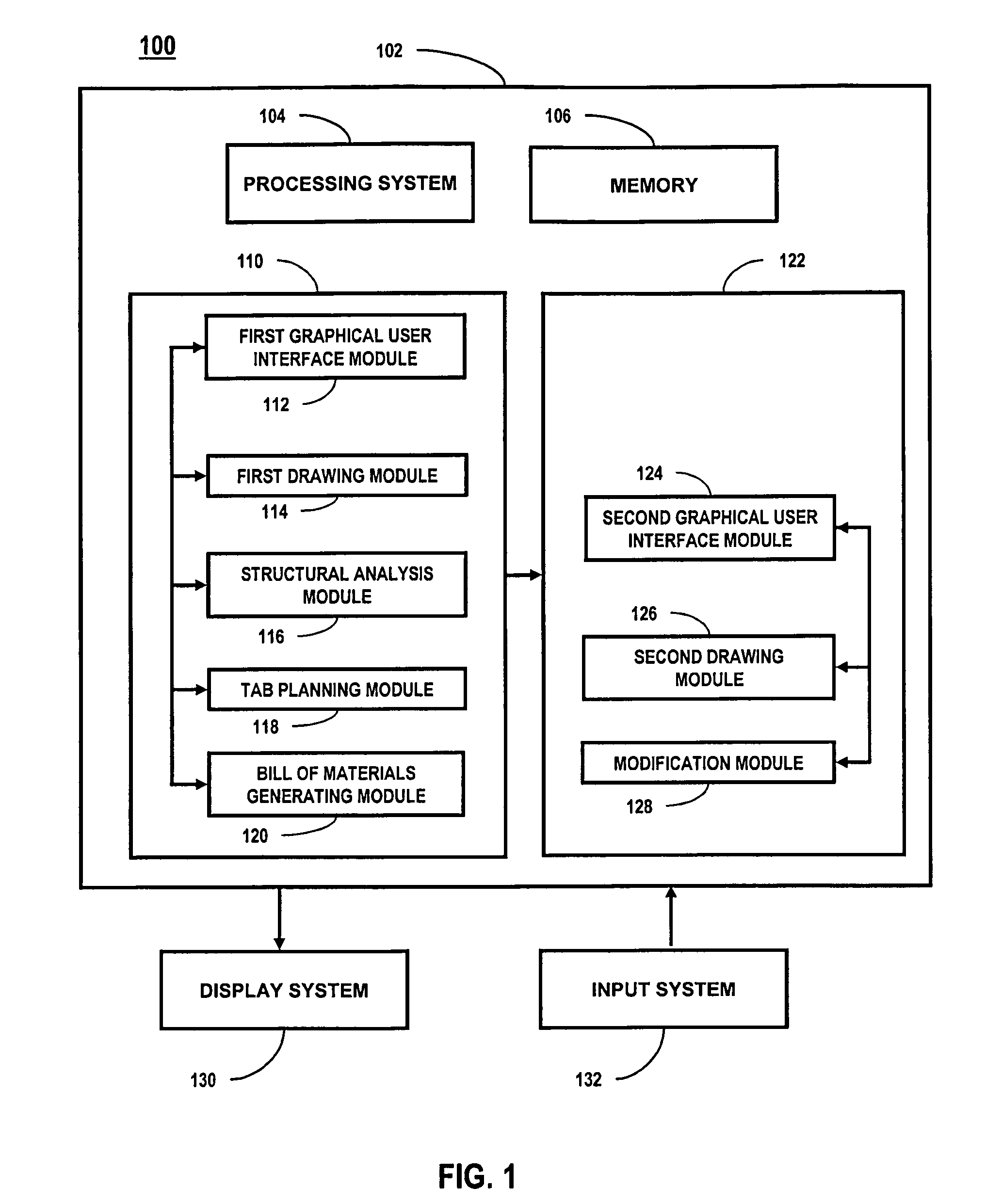

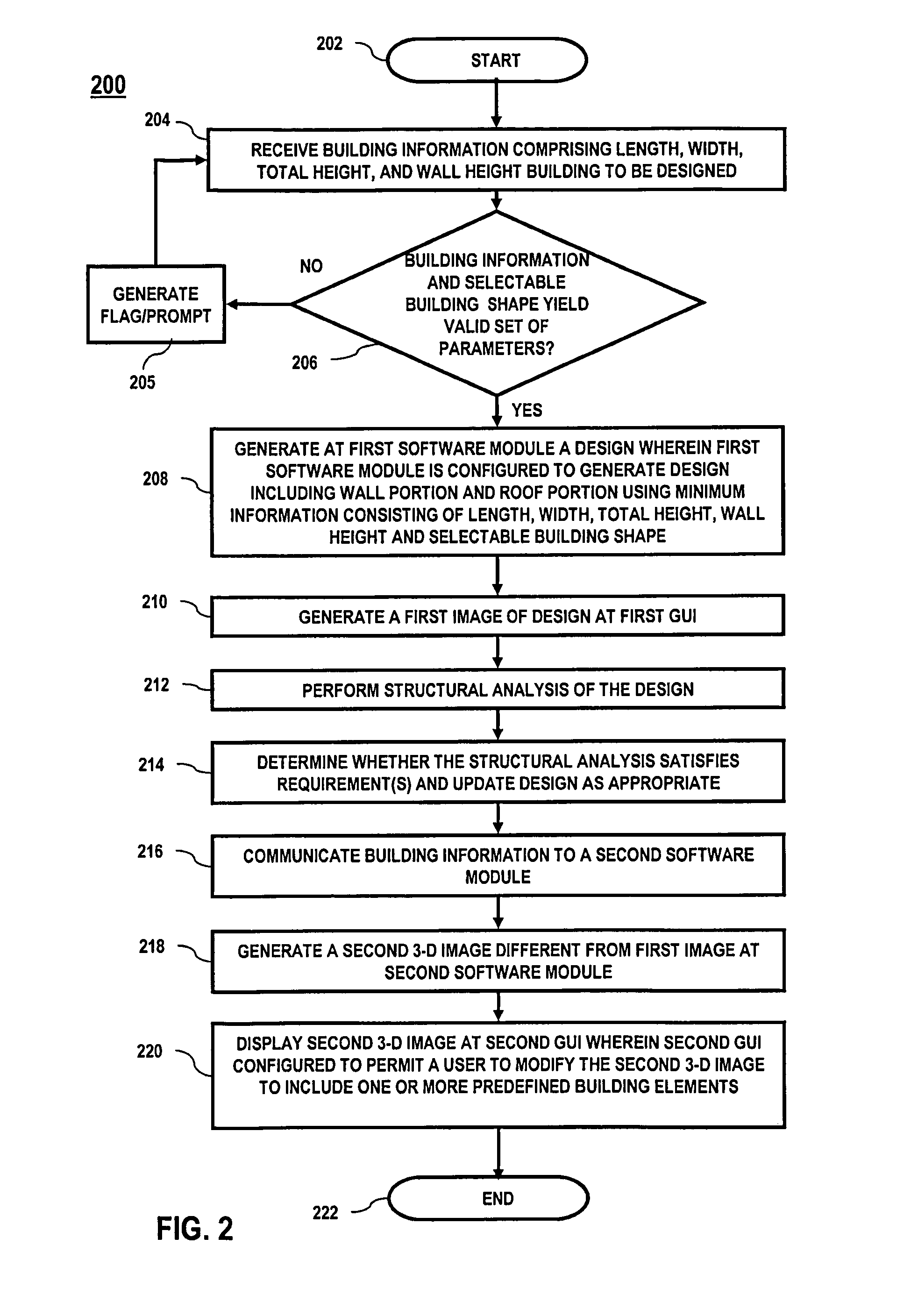

Systems and methods for computational design and modeling of buildings

A method and system generates a building design and a three-dimensional image thereof. First building information comprising a length, width, total height and wall height of a building is received via a first graphical user interface. If the length, width, total height, wall height, and a selectable building shape yield a valid set of building parameters, a design of said building is generated at a first software module, which is configured to generate the design, including wall portions and a roof portion, using minimum information consisting of the length, width, total height, wall height, and selectable building shape. A first image and a structural analysis of the design are generated. A second software module generates a second three-dimensional image of the building, which is different from the first image. A second graphical user interface permits a user to modify the second image to include predefined building elements.

Owner:MIC IND INC

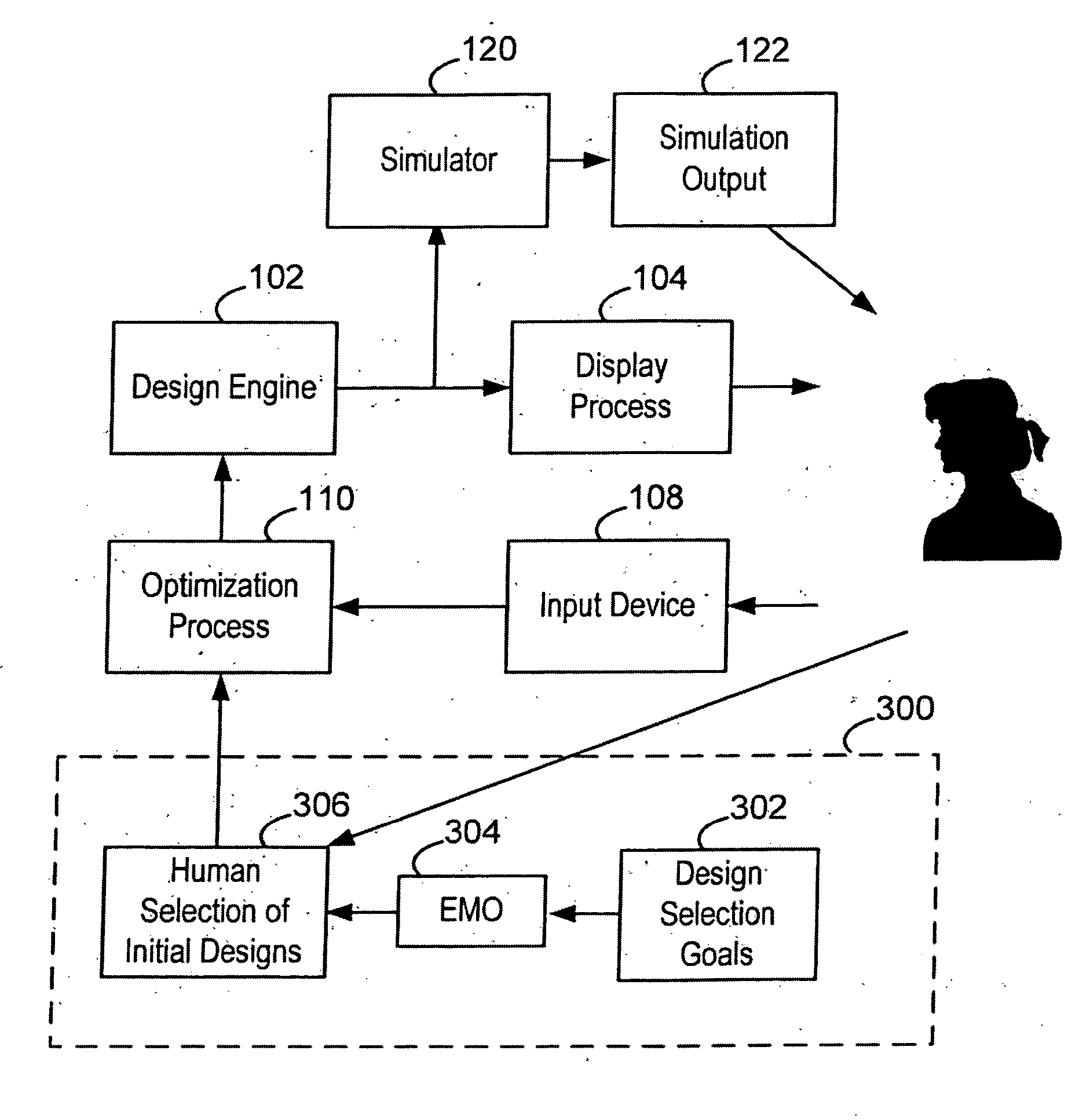

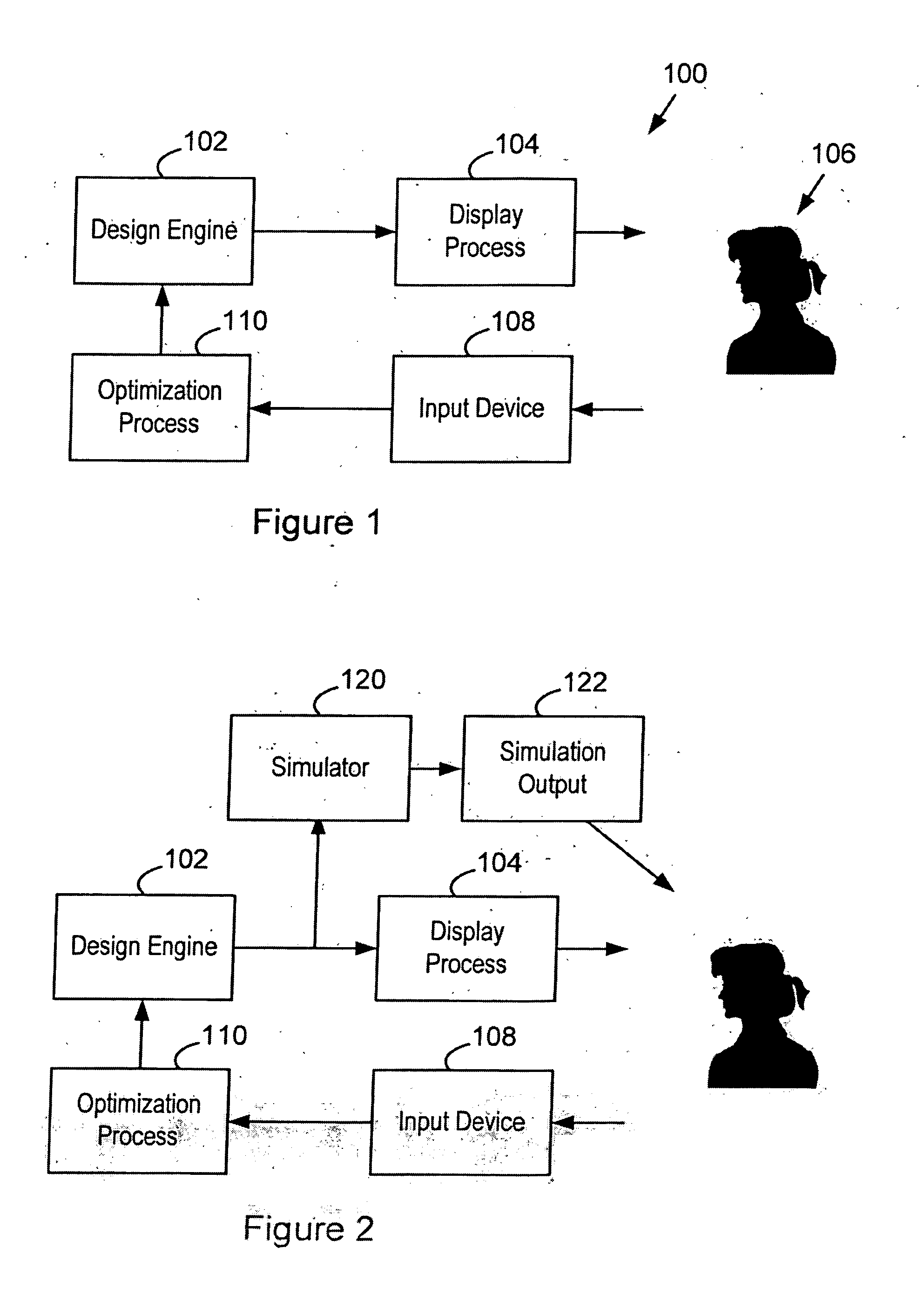

Engineering design system using human interactive evaluation

InactiveUS20060225003A1Detecting faulty computer hardwareComputer programmed simultaneously with data introductionGenerative DesignEngineering design process

A design system includes a design engine for generating designs, an evaluation process for evaluating the generated designs based on human visual inspection and / or domain knowledge, and an optimization process for pruning based at least in part on the evaluation. Generation of additional designs is performed based on optimization. Newly-generated designs are then subjected to the same iterative steps. In one embodiment a simulator is also used to evaluate the generated designs, in part, with numerically designed specification. Subjective human evaluation is used fully or at least in part of an optimization process to obtain final designs. Human visual inspection and domain knowledge is used to evaluate and rate key designs at different points in the evolution of a design.

Owner:RGT UNIV OF CALIFORNIA +1

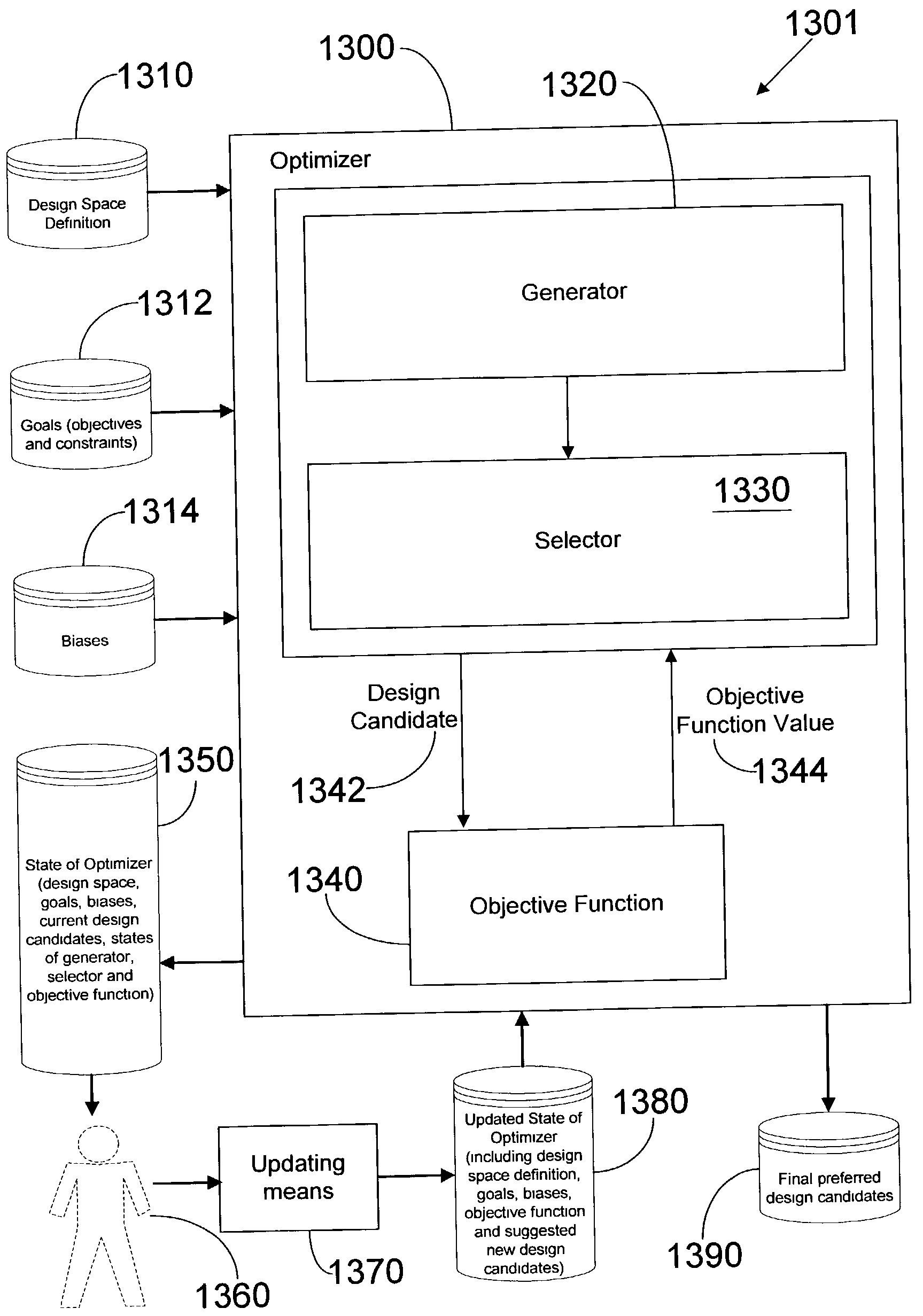

Method of interactive optimization in circuit design

InactiveUS6968517B2Easy to understandDone more quicklyData processing applicationsAnalogue computers for electric apparatusCurrent meterGenerative Design

A method of interactively determining at least one optimized design candidate using an optimizer, the optimizer having a generation algorithm and an objective function, the optimized design candidate satisfying a design problem definition, comprises generating design candidates based on the generation algorithm. The generated design candidates are added to a current set of design candidates to form a new set of design candidates. The design candidates are evaluated based on the objective function so that design candidates can be selected for inclusion in a preferred set of design candidates. The current state of the optimizer is presented to a designer for interactive examination and input is received from the designer for updating the current state of the optimizer. These steps are repeated until a stopping criterion is satisfied.

Owner:SYNOPSYS INC

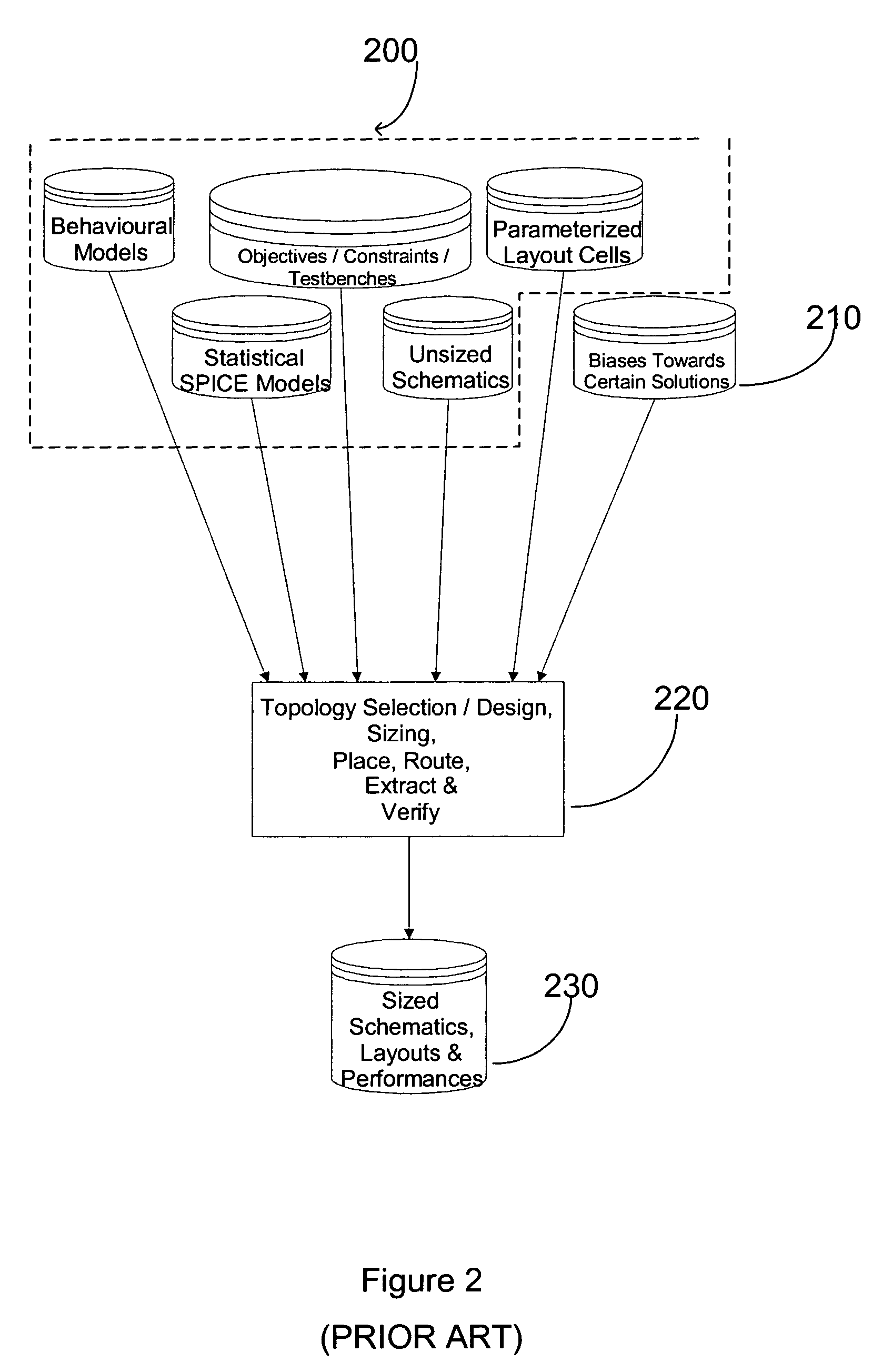

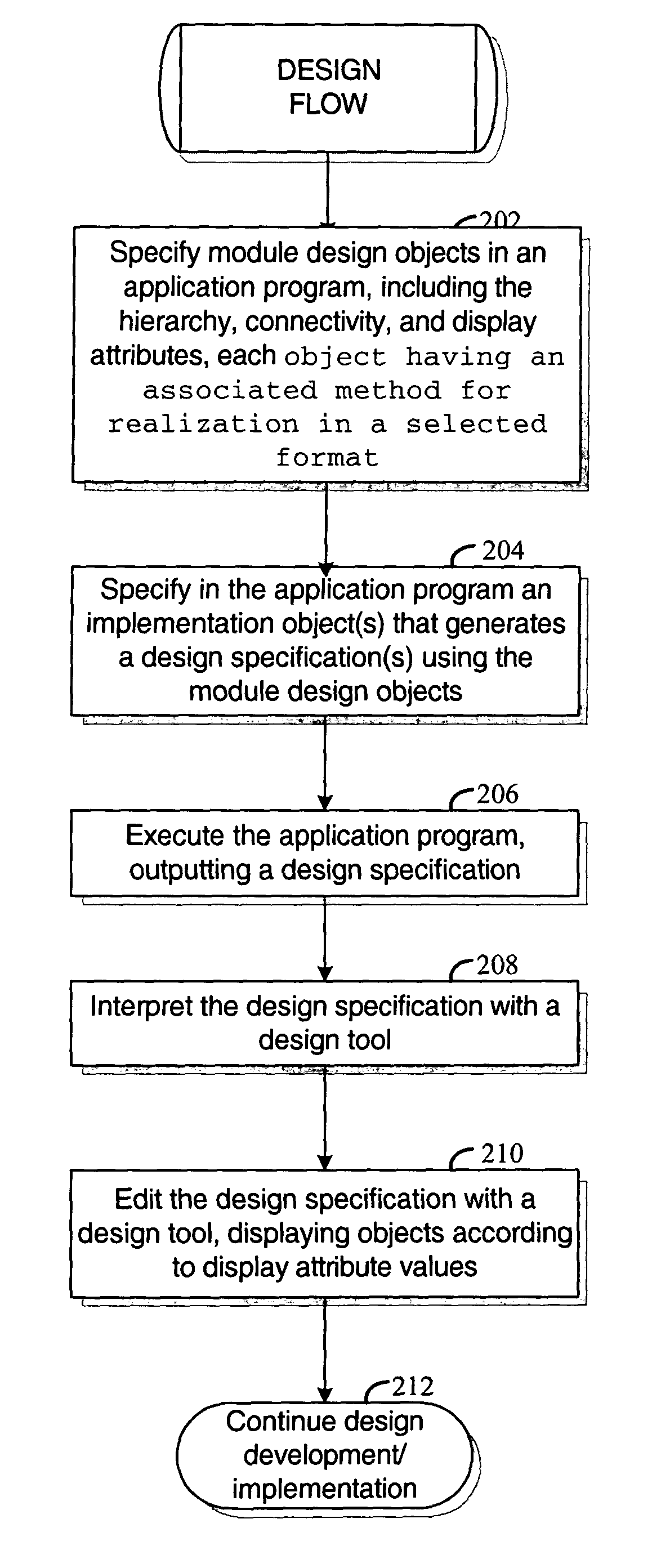

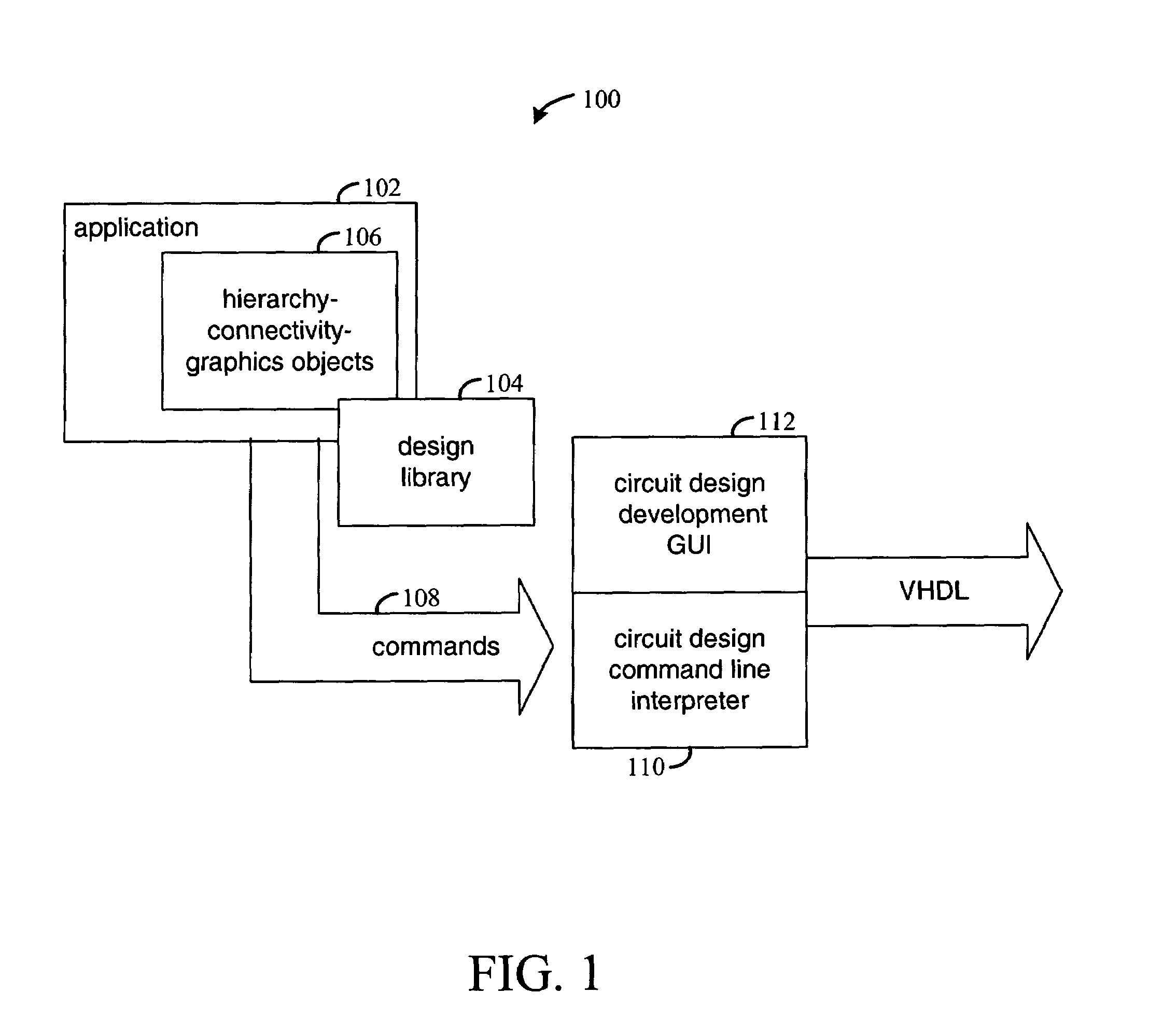

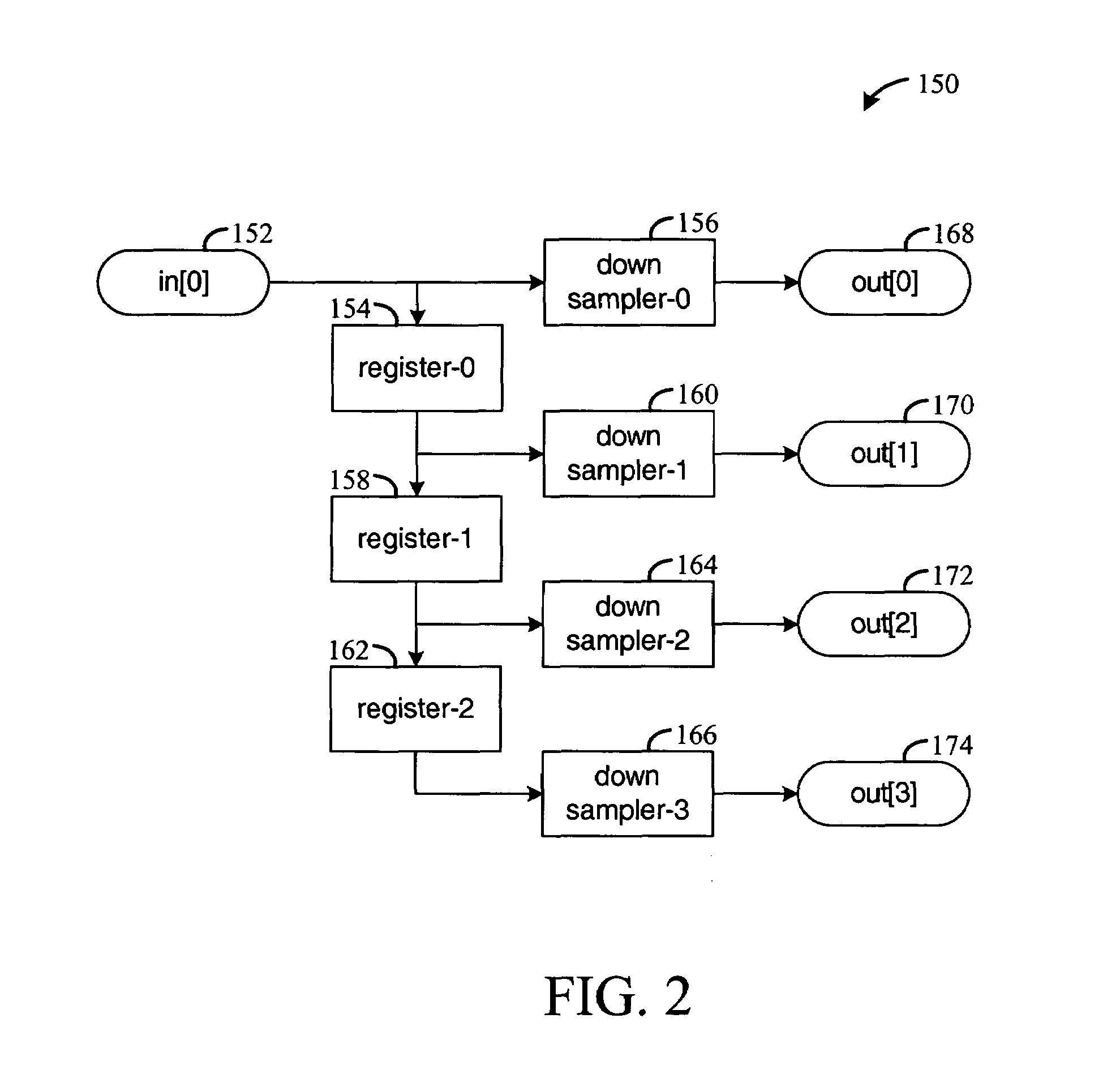

Specification of the hierarchy, connectivity, and graphical representation of a circuit design

Method and apparatus for creating a circuit design. An object-oriented program instantiates a plurality of objects that model a circuit design. The objects have hierarchy attributes, connectivity attributes, and display attributes that describe a plurality of modules. The hierarchy attributes define parent-child relationships between modules, the connectivity attributes define input-output connections between modules, and the display attributes define a layout of the modules for viewing. Each of the objects has an associated method for generating a design specification in a selected format. When the program is executed, the design specification is generated from the set of objects. Depending on the capabilities of the available tools, the modules and logic elements are displayed in accordance with the display attributes either from the object-oriented program or from the design specification.

Owner:XILINX INC

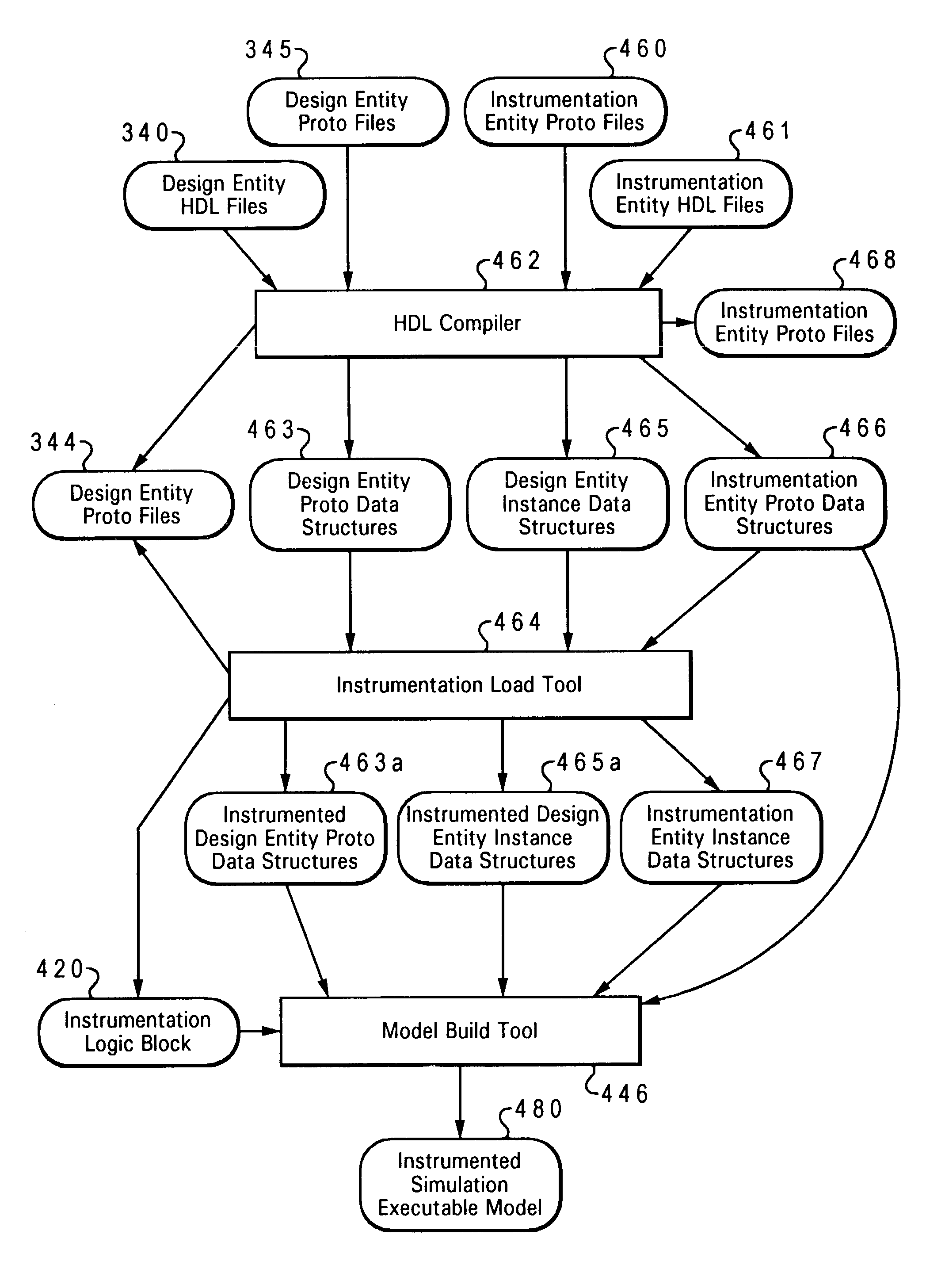

Dynamic loading of C-API HDL model instrumentation

InactiveUS7158924B2Error detection/correctionAnalogue computers for electric apparatusCode moduleTheoretical computer science

A method and system for tracking instances of a testcase execution event within a hardware description language (HDL) model using a simulation control program. In accordance with the method of the present invention, a design entity list is generated within the HDL model, wherein the design entity list identifies all design entities instantiated within the HDL model. One or more instrumentation code modules are dynamically loaded into the simulation control program, wherein the instrumentation code modules generate and process testcase execution events associated with at least one of the identified design entities.

Owner:IBM CORP

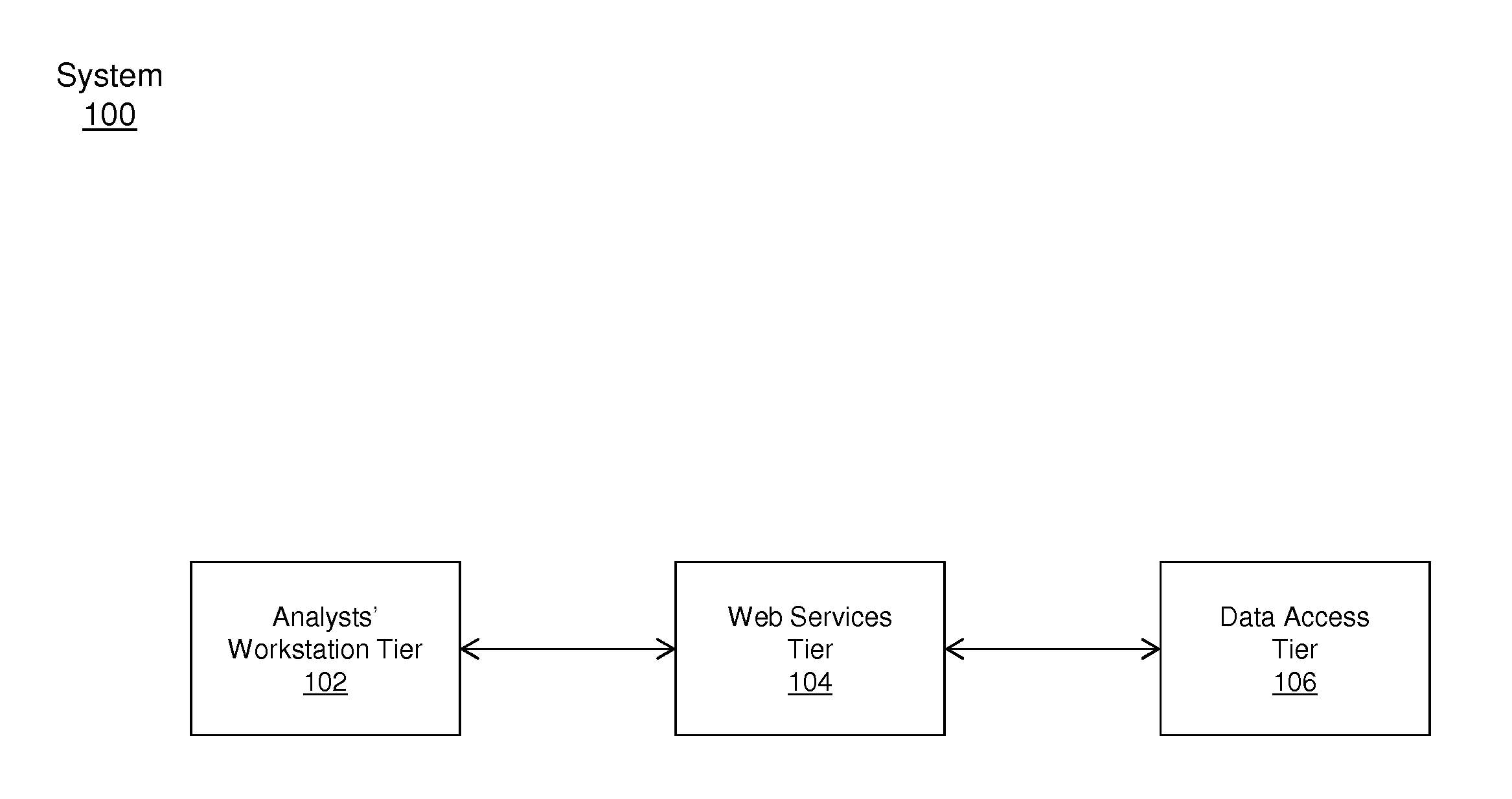

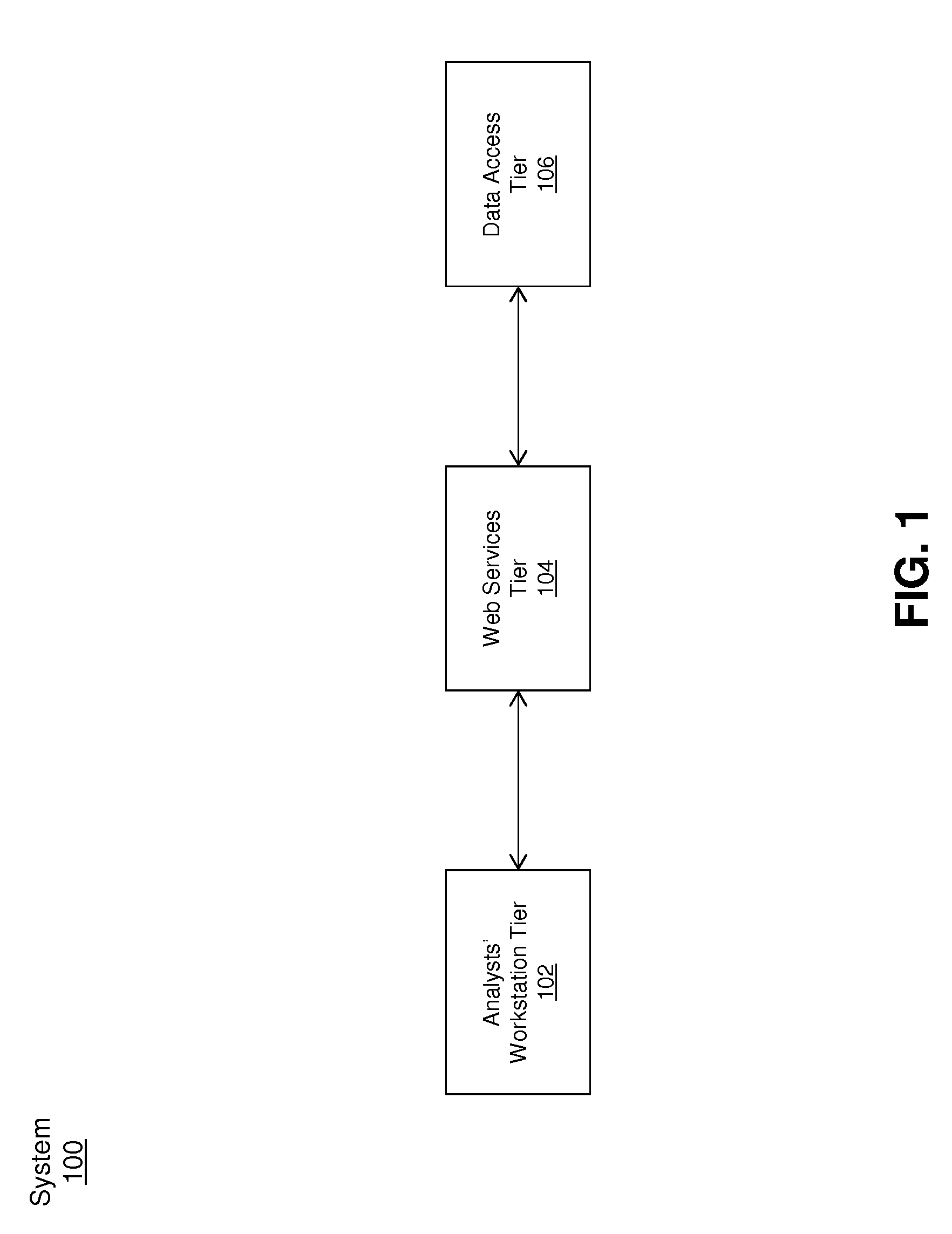

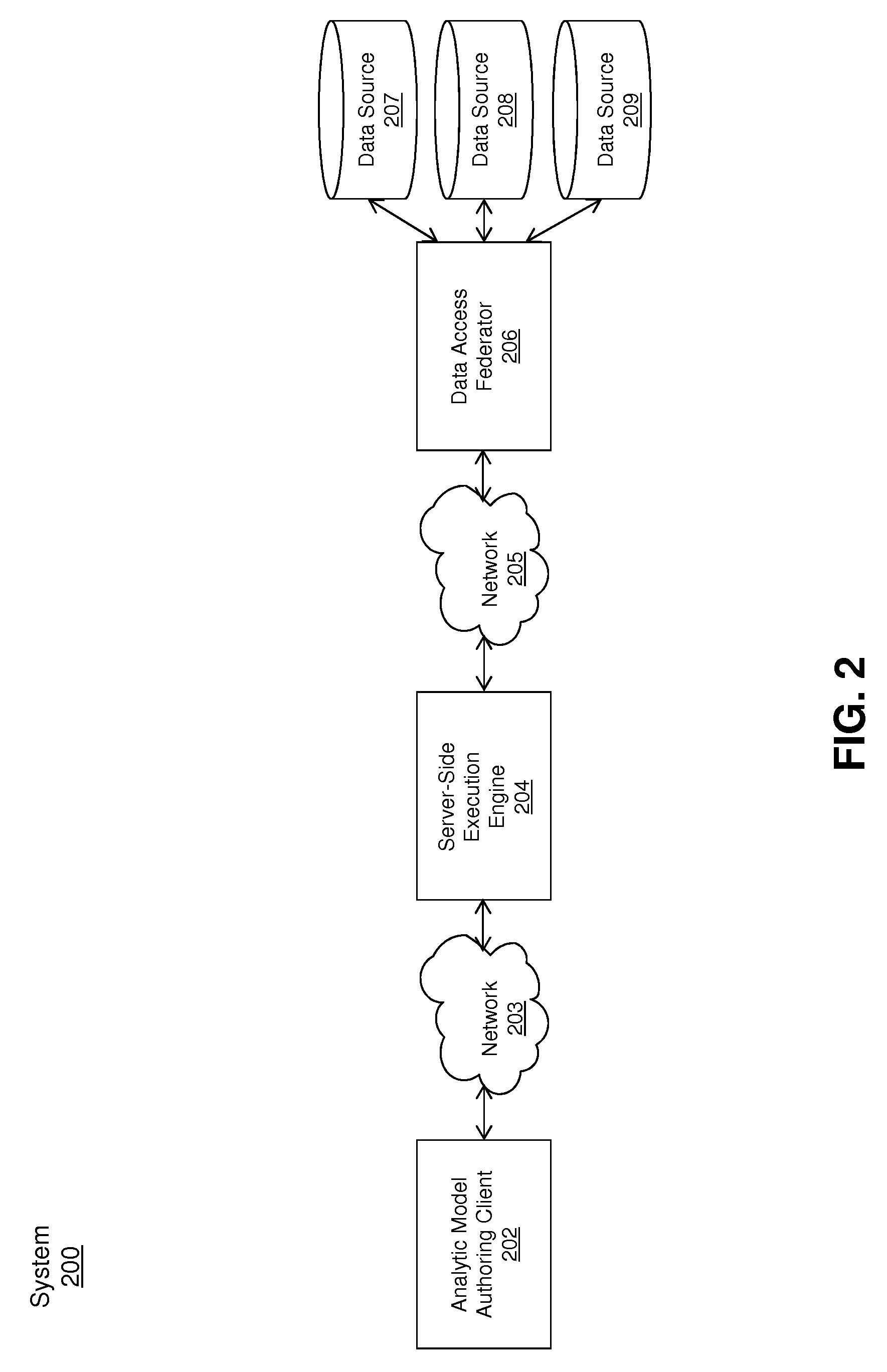

Enterprise-scalable model-based analytics

Enterprise-scalable model-based analytics systems are disclosed. One example system may organize an analytic process in the form of an analytic model containing interconnected functional components, with each functional component containing a specific algorithm or analysis technique for fetching, manipulating, or analyzing data. A user may generate an analytic model designed to perform a desired analytic process by placing sub-analytic models and / or functional components in a particular configuration within a graphical user interface by dragging and dropping the sub-analytic models and / or functional components. The resulting process represented by the analytic model may depend on the sub-analytic models and / or functional components within the analytic model and the way they are interconnected. The resulting analytic model may be saved and distributed to other users for use and / or modification.

Owner:KEYW

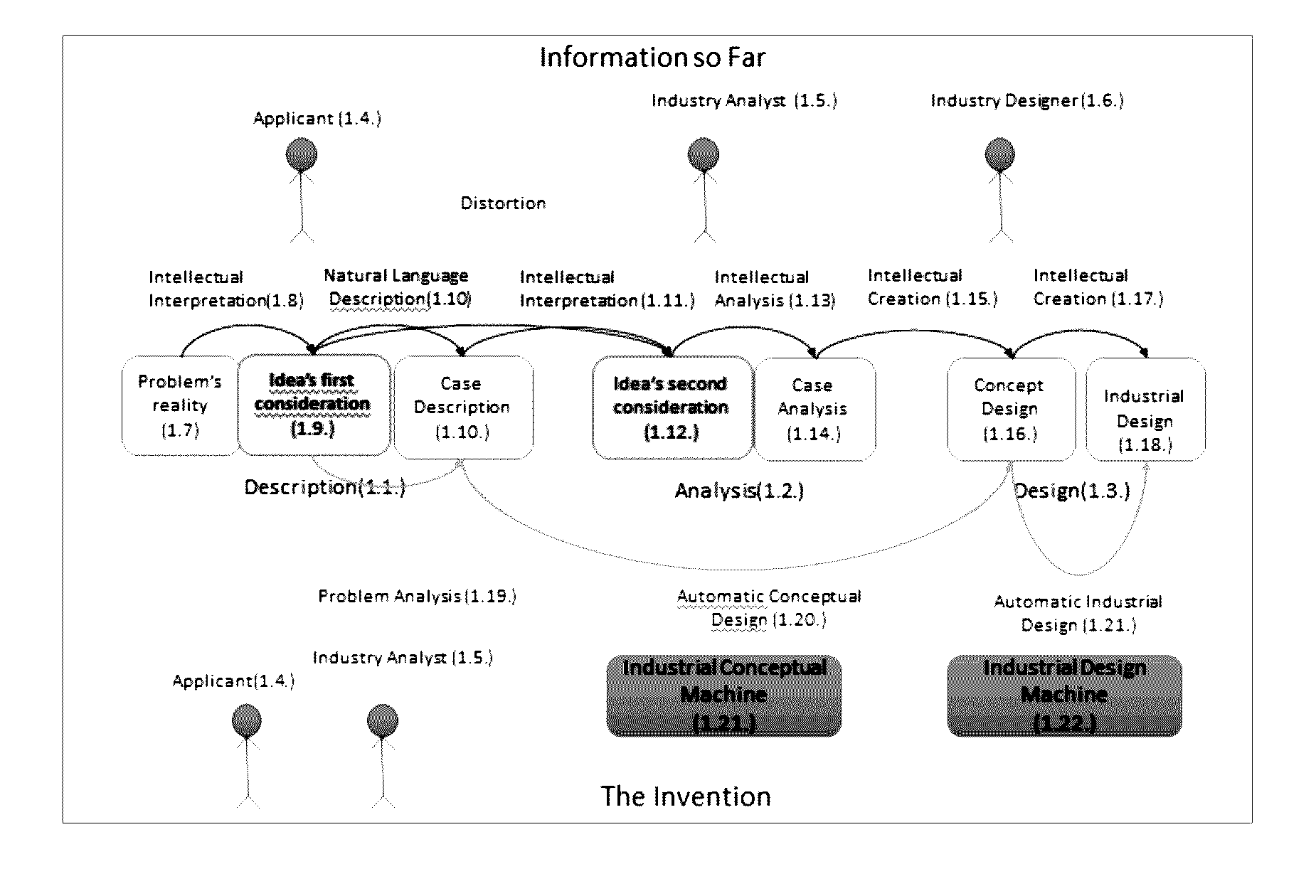

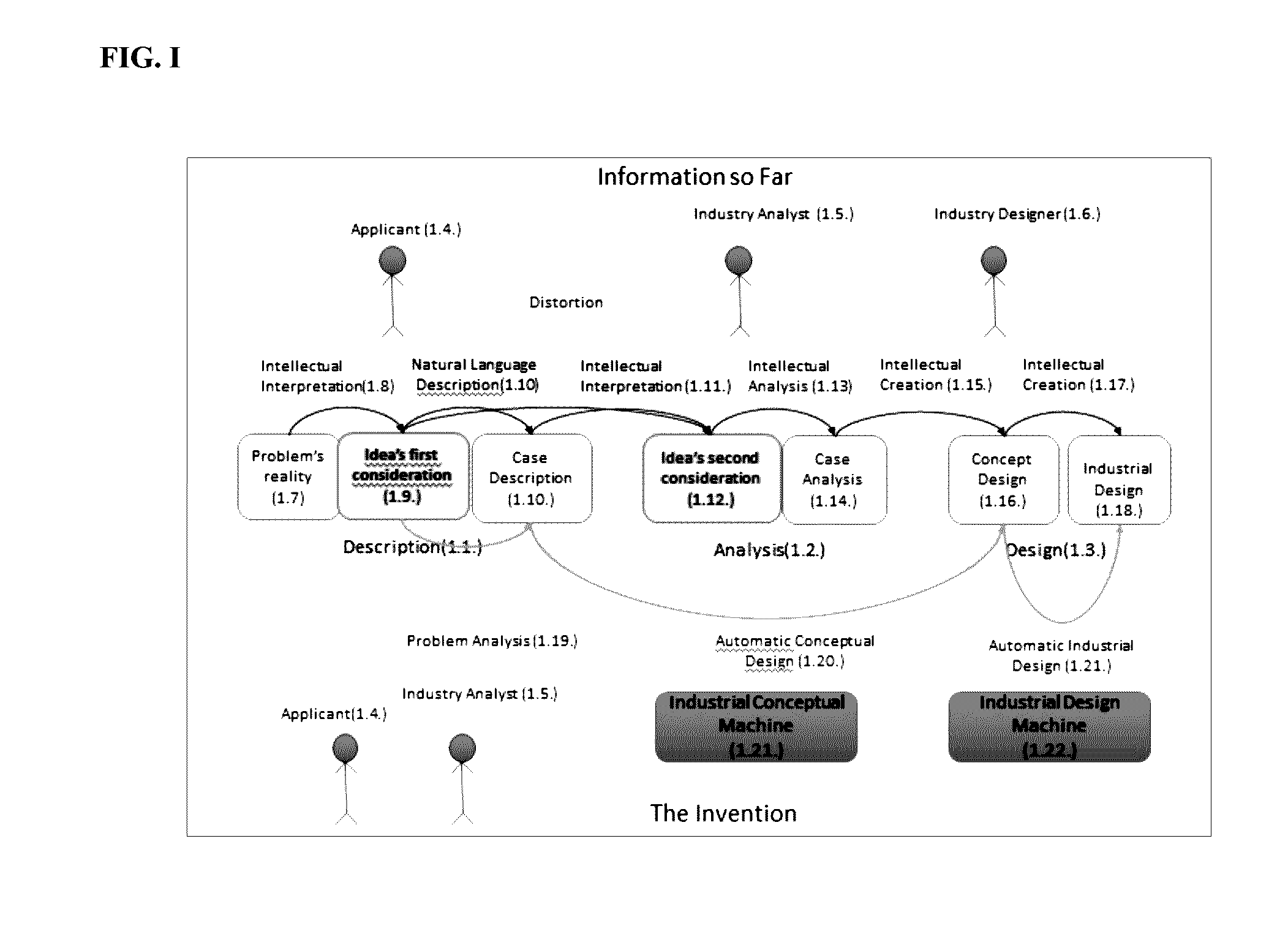

Process and system for automatic generation of functional architecture documents and software design and analysis specification documents from natural language

ActiveUS20170003937A1Accurate understandingReduce designProgram documentationNatural language data processingDocumentation procedureSpecification document

The present invention is a computer-implemented system and method for automatic generation of Functional Architecture, business, analysis and software design documents based on phrases expressed in natural language.Eligible languages and their syntactic and grammatical features can be entered into the system. The system receives the description of the case in natural language, in one of the eligible languages, through an input / output device. The processor automatically analyses the description, automatically extracts the functional components from its morphosyntactic structure and automatically generates functional architecture documents for use in industry. Based on the functional components of the text, the processor automatically generates design components in order to produce business, analysis, and software design specification documents.

Owner:HUEBRA NADIA ANALIA

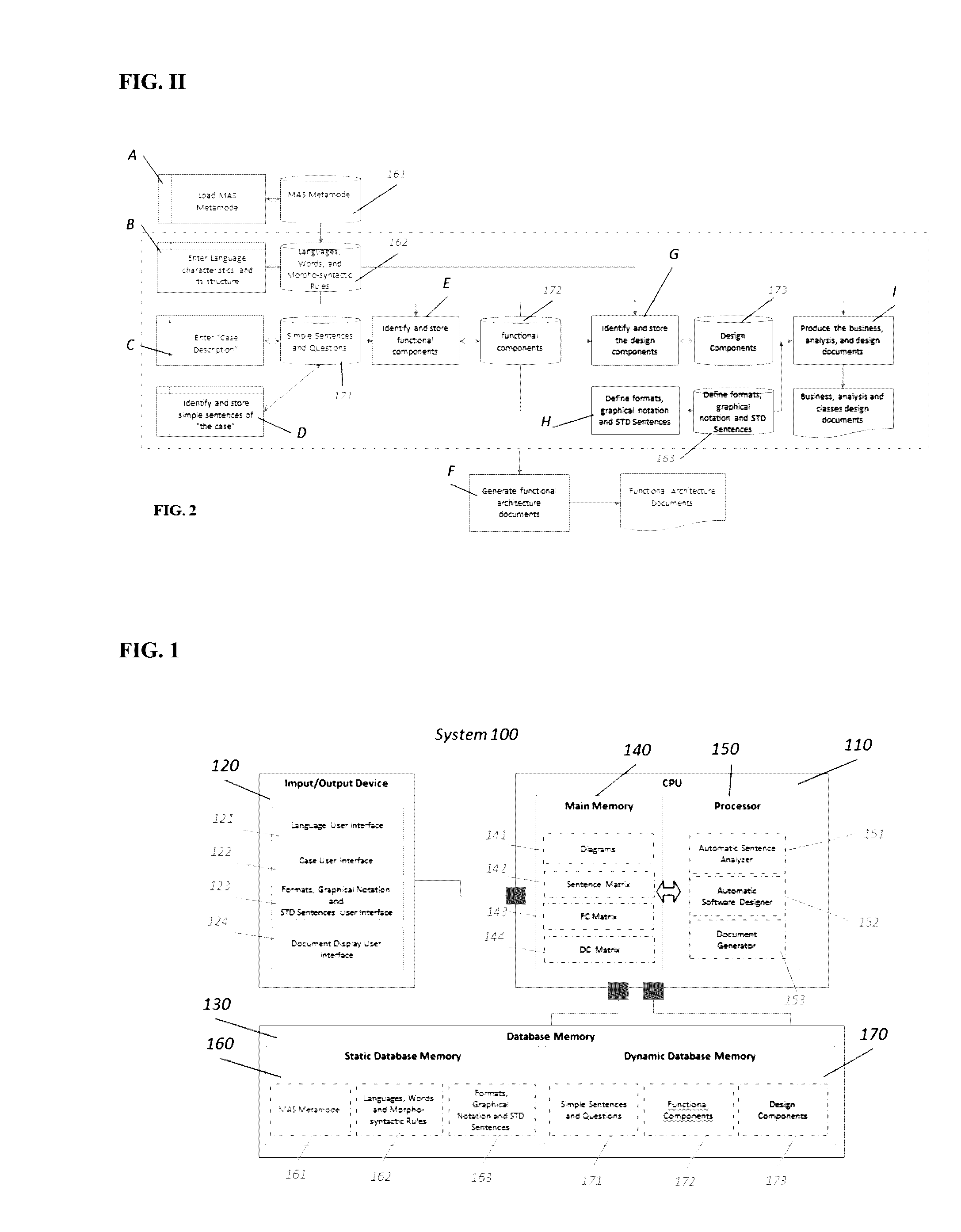

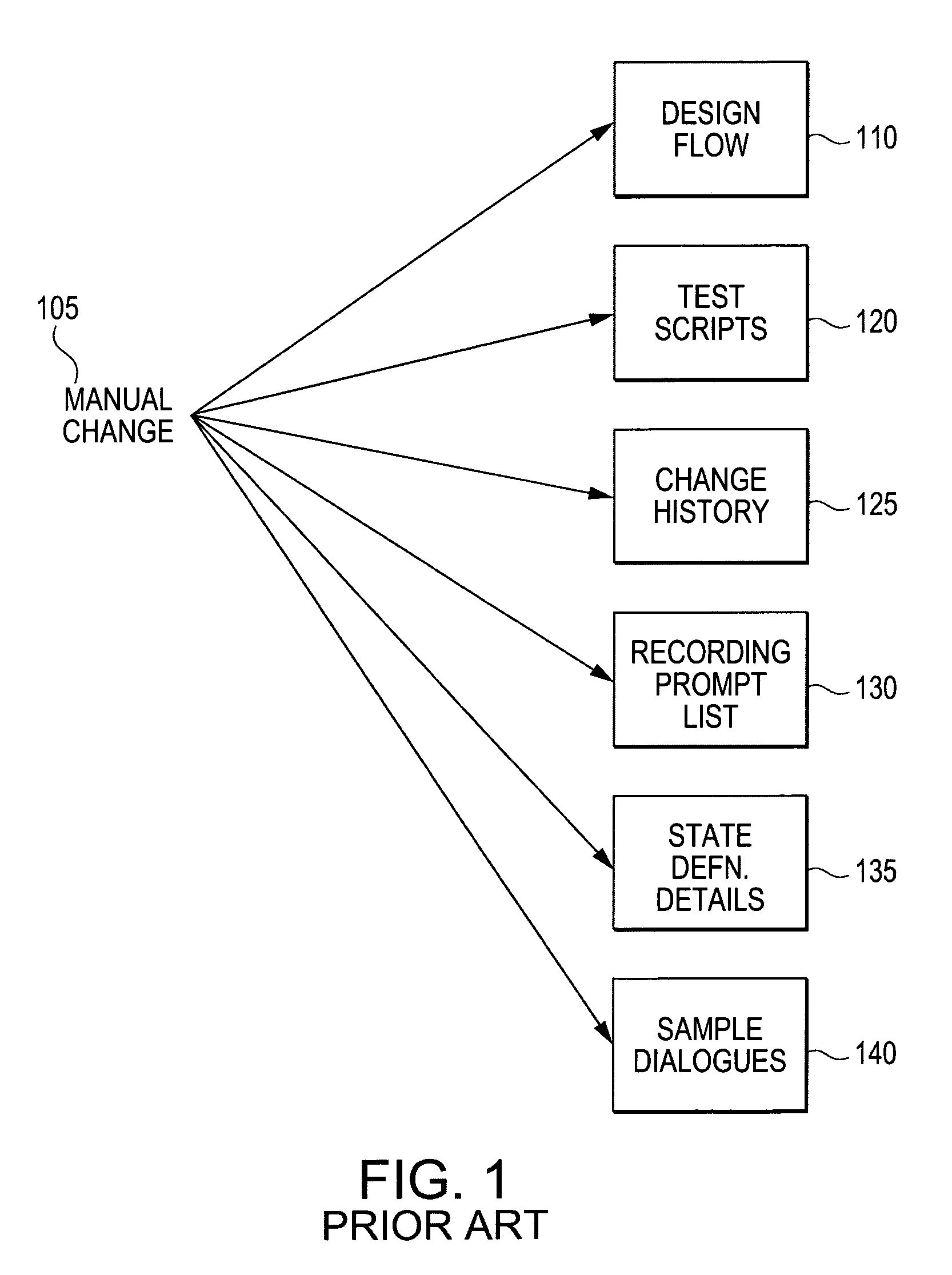

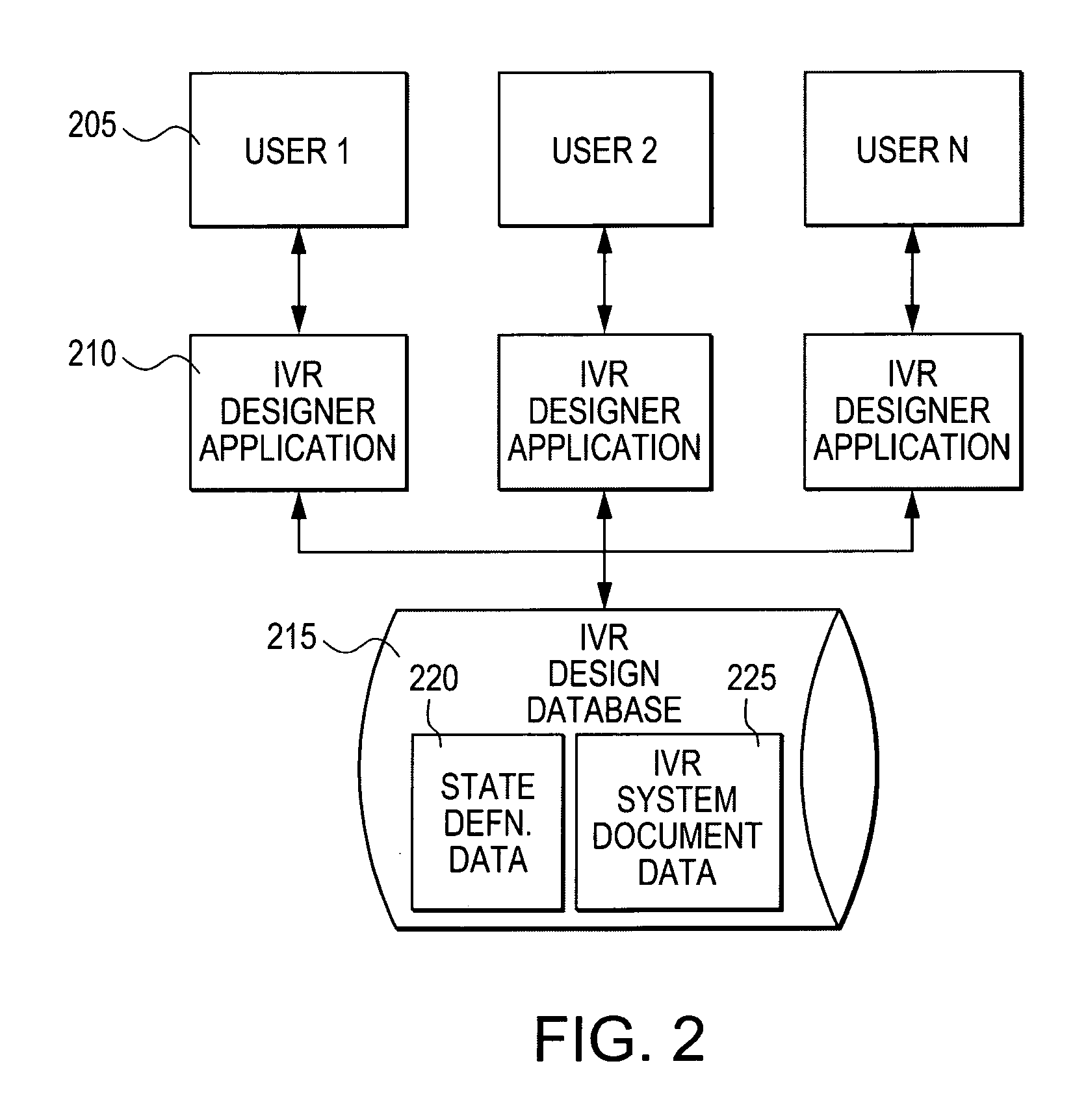

IVR system manager

InactiveUS20070192113A1Automatic call-answering/message-recording/conversation-recordingSpeech analysisSystems designTest script

An IVR system designer receives design specification data (which may be either state definition data or IVR system document data) and stores it in a database. A design specification report can be generated based on the stored design specification data. The report may correspond to a chosen period of time or it may correspond to chosen version of the IVR system. It may provide one or more of the following: a summary of a state within the IVR system, a listing of the previous states that lead to the current state, prompts for the state, inputs for the state, a listing of decision outcomes, key performance indicator triggers for the state, global commands that are active in the state, business units for which the state is applicable, a sample dialogues listing, test scripts listing for testing the IVR system, a change history listing for the system, a design flow diagram for the system, or pseudo-code listing for a portion of the system.

Owner:ACCENTURE GLOBAL SERVICES LTD

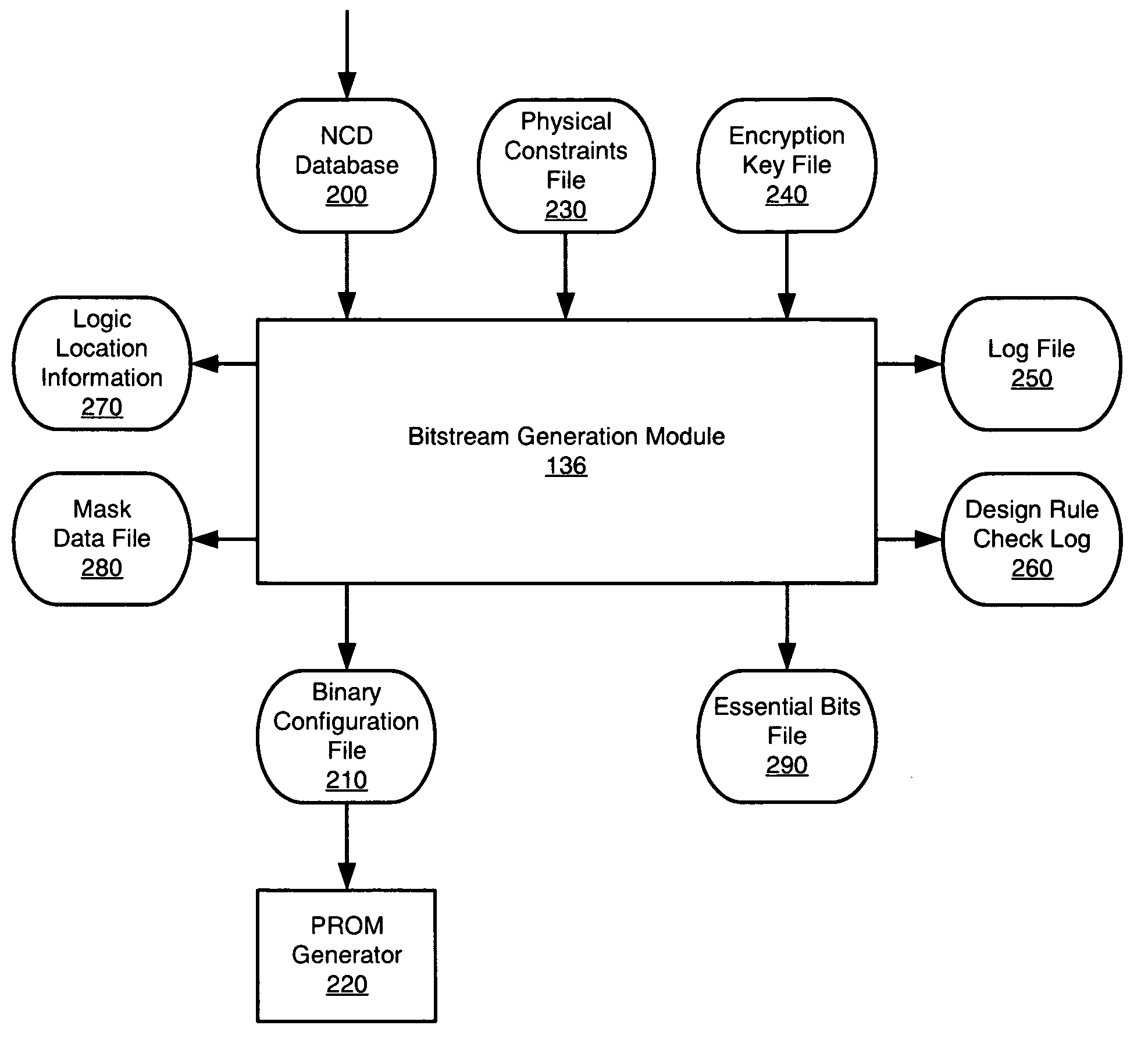

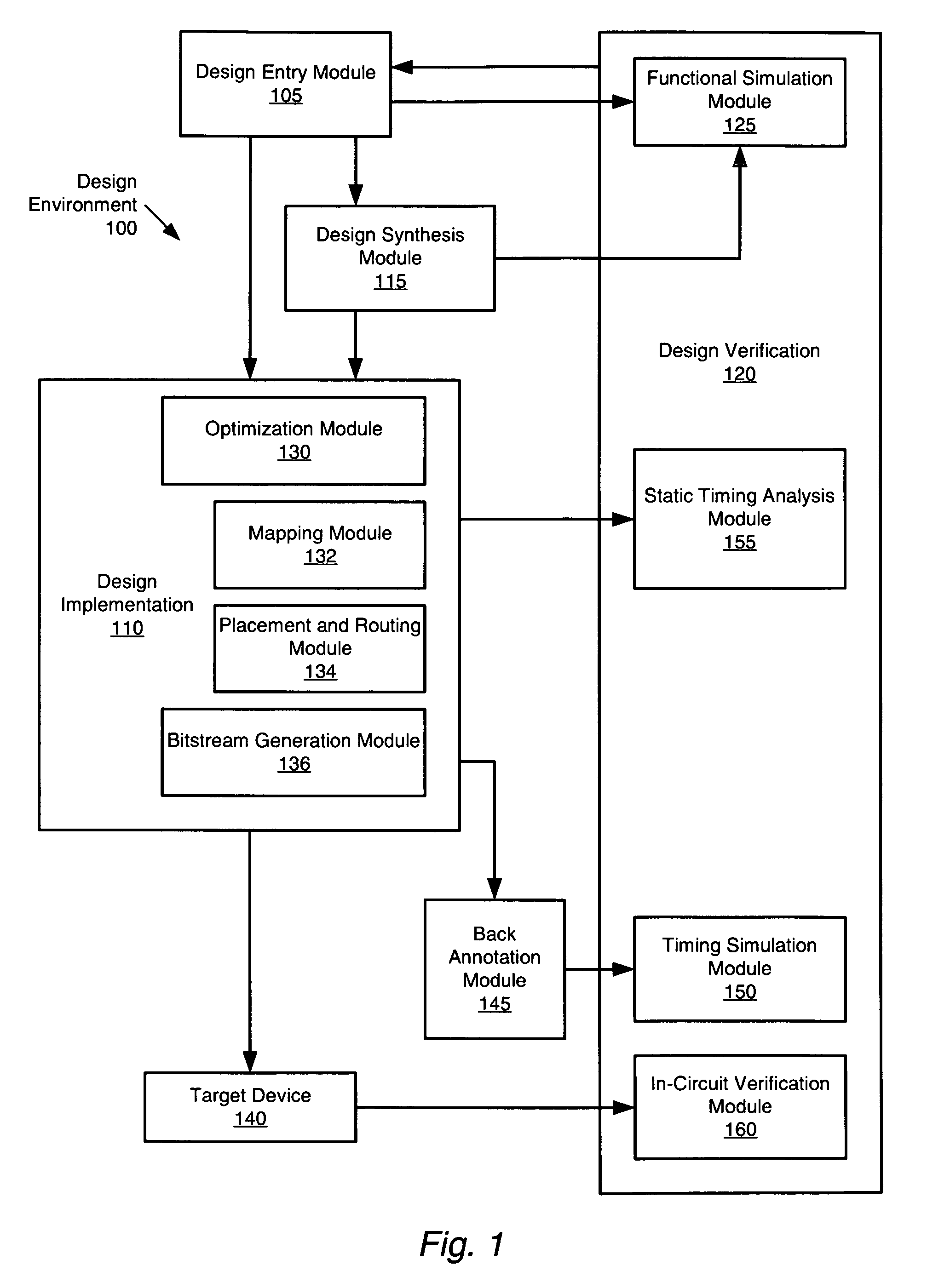

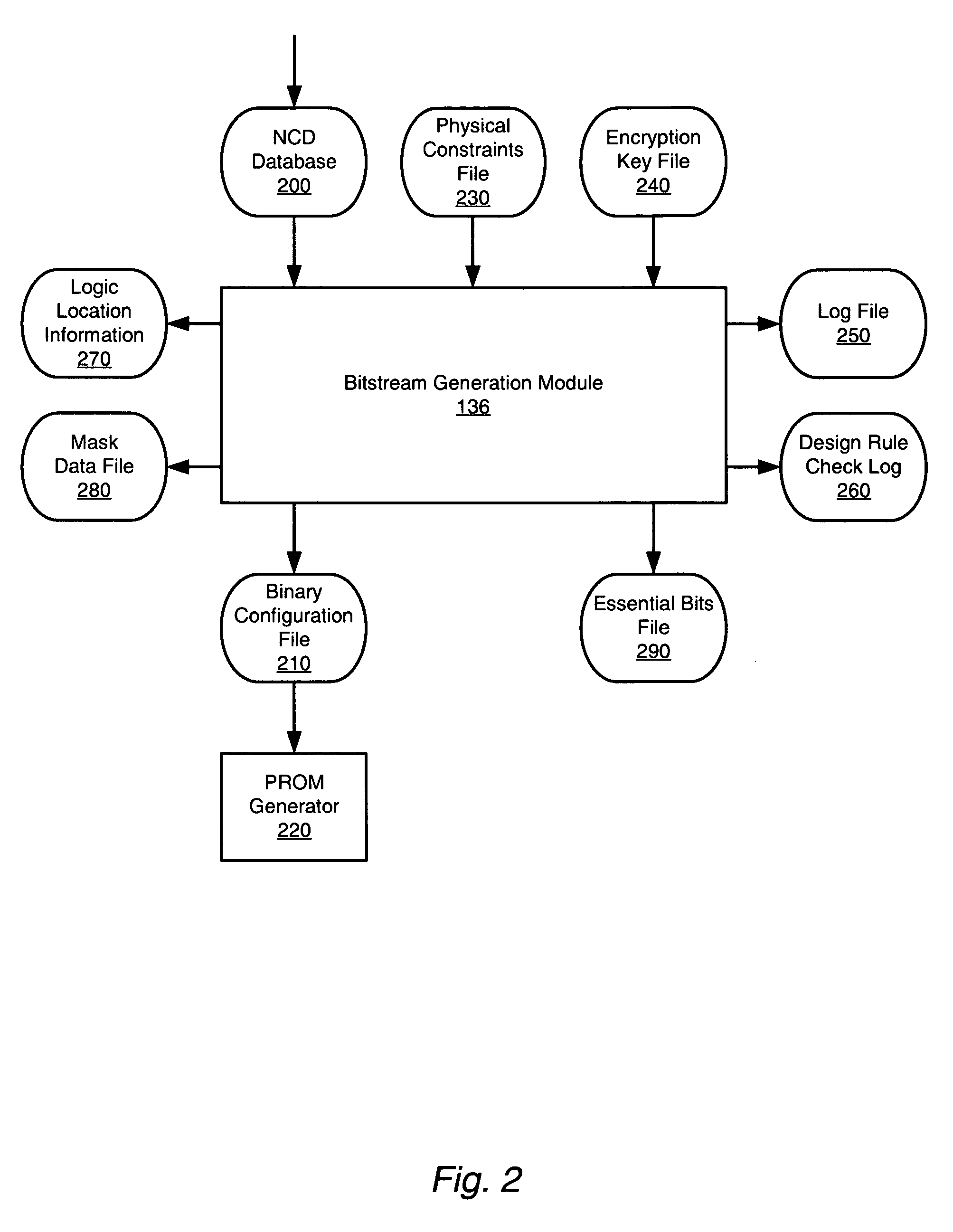

Method and system for generating a bitstream view of a design

ActiveUS7343578B1CAD circuit designSpecial data processing applicationsLogical elementComputer architecture

A method and system for generating a bitstream view of a programmable logic device (PLD) design are disclosed. The present invention allows for the correlation of a physical circuit description (e.g., one or more of a PLD design's essential configuration bits) and a logical circuit description (e.g., one or more of the logic elements that make up a PLD design), which can also be viewed as correlating one or more of the physical elements of the design's implementation in the PLD with one or more of the design's logical elements.

Owner:XILINX INC

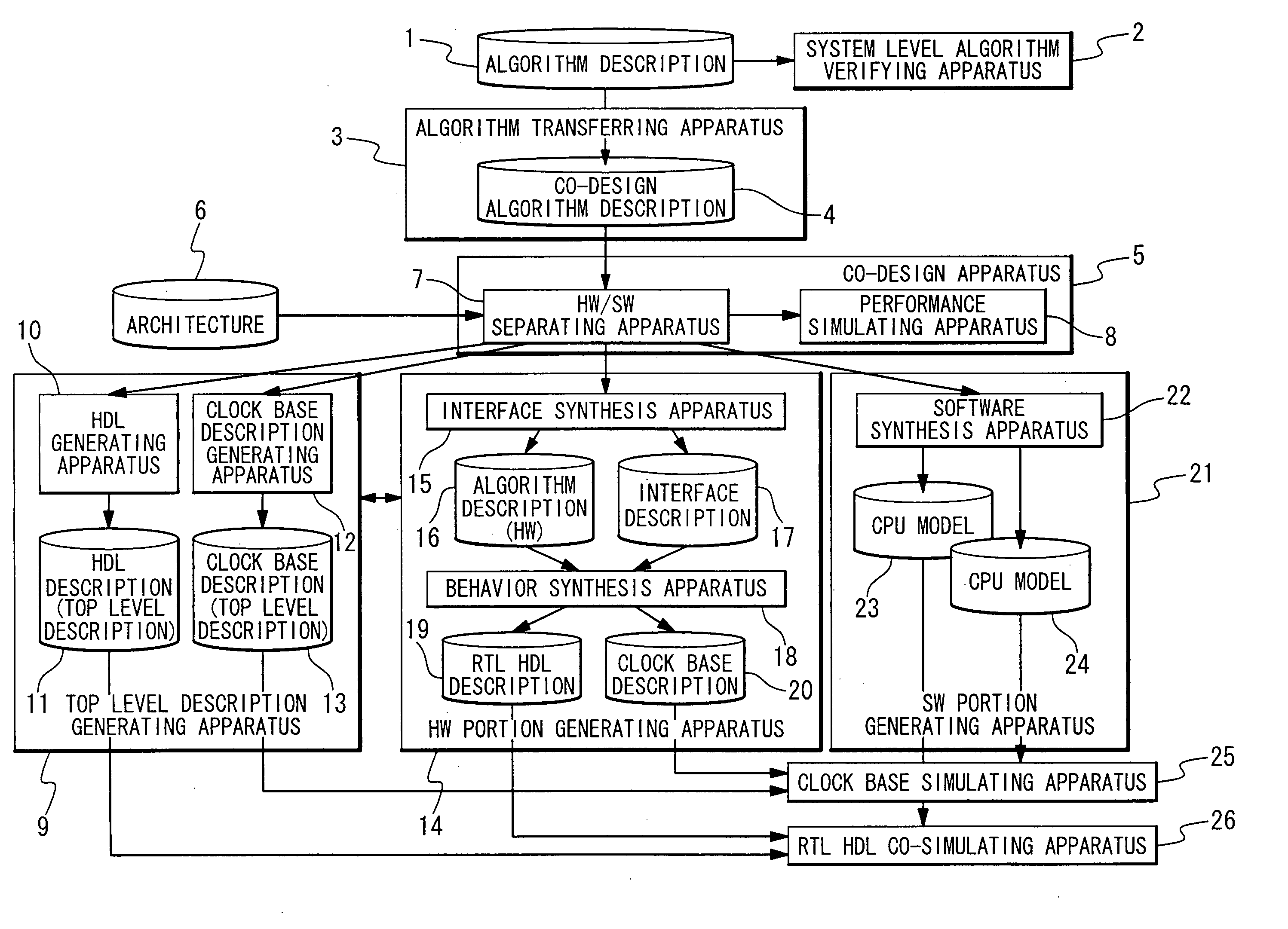

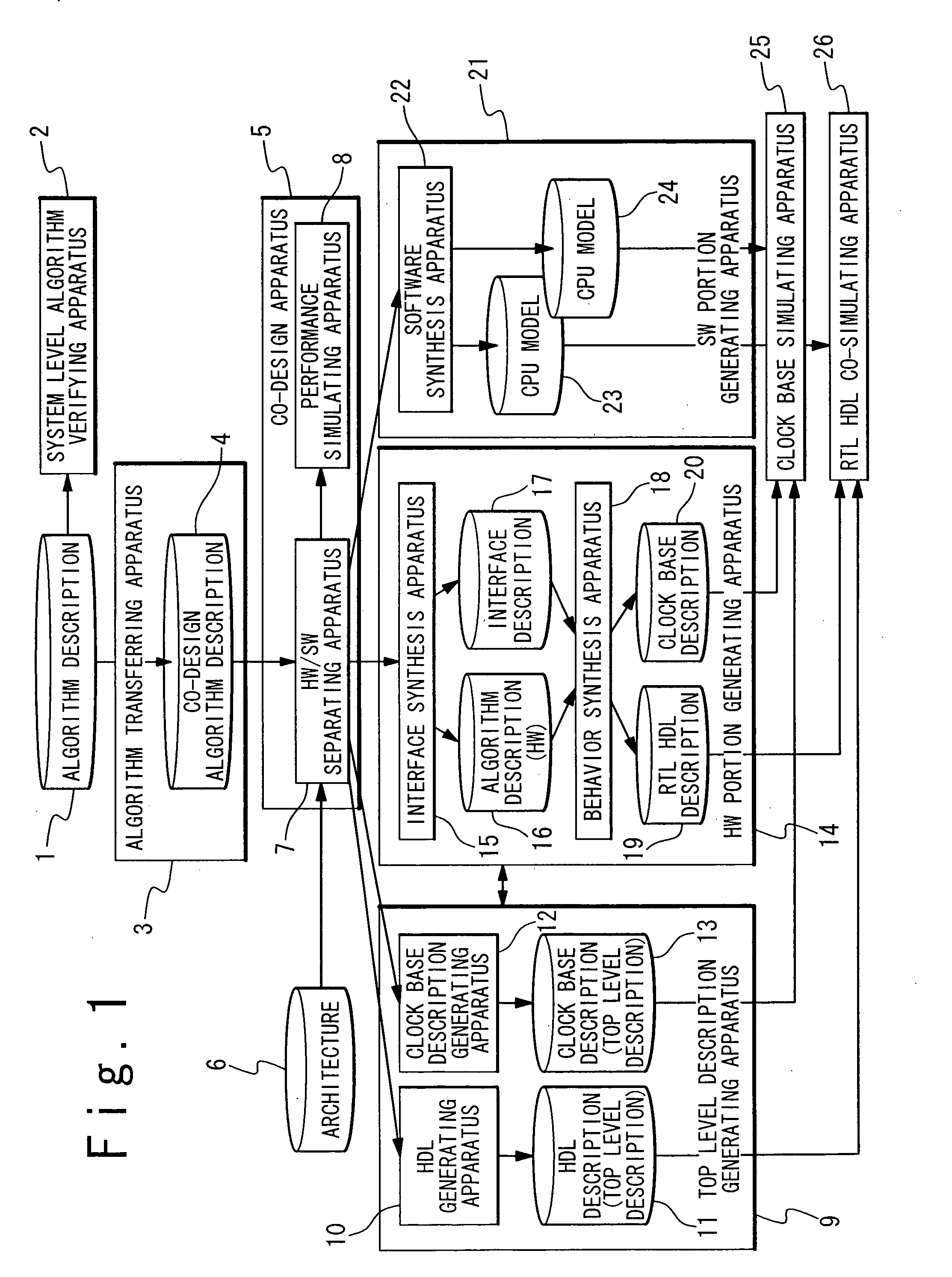

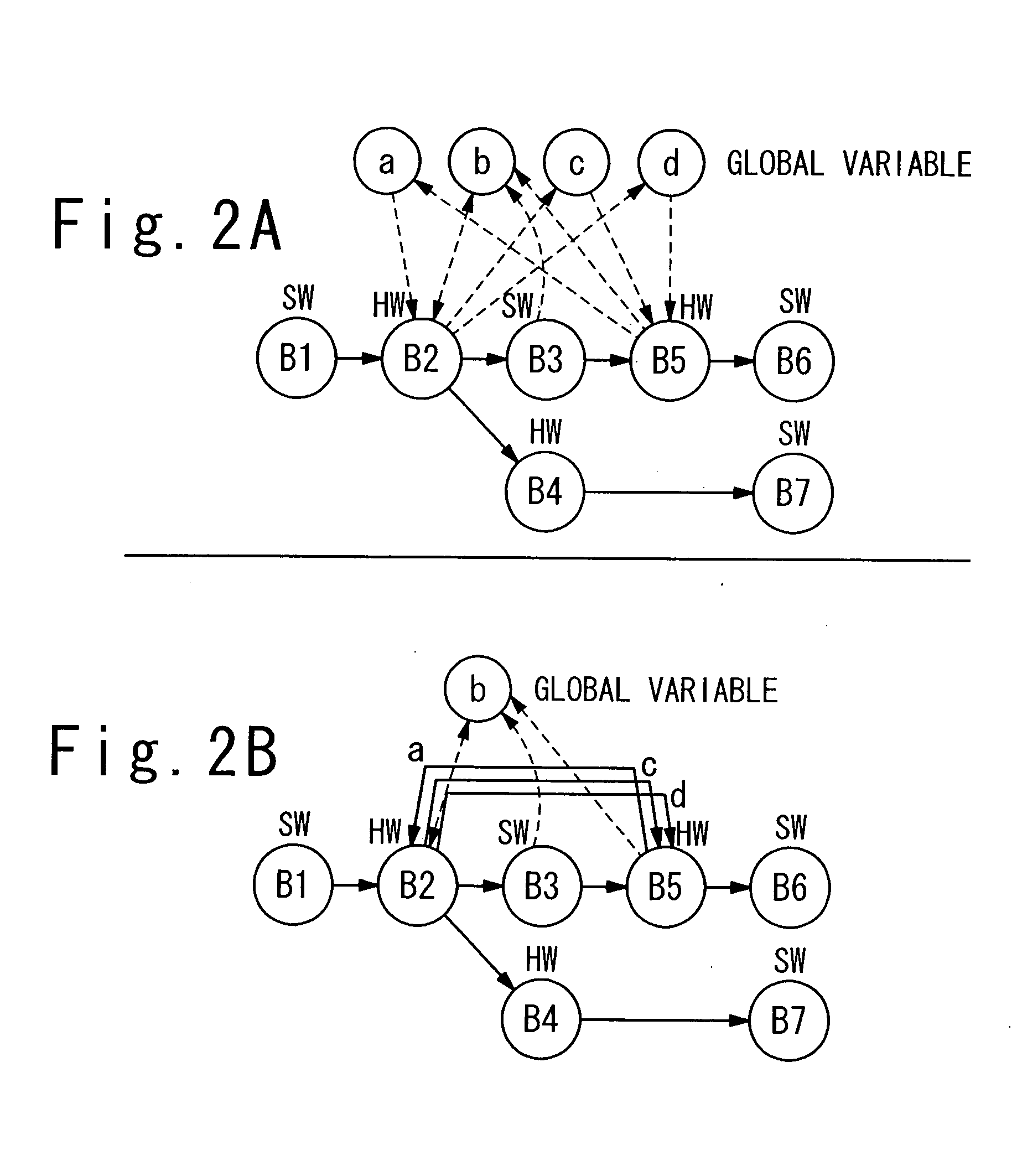

Circuit designing method and a circuit designing system

InactiveUS20050034090A1Reduce circuit sizeAnalogue computers for electric apparatusCAD circuit designGenerative DesignTheoretical computer science

A circuit designing method includes steps (a) to (d). The step (a) separates a first algorithm description for a simulation into a hardware portion describing hardware and a software portion describing software, and generating a design data automatically, wherein the design data includes behavior data, architecture data, mapping data and address data. The step (b) generates a first clock base description automatically based on the design data, wherein the first clock base description describes relation between the hardware portion and the software portion. The step (c) generates a second clock base description automatically based on the design data, wherein the second clock base description describes the hardware portion. The step (d) generates a first CPU model automatically based on the design data, wherein the first CPU model describes the software portion. Here, the first clock base description, the second clock base description and the first CPU model are used for verifying the design data.

Owner:NEC ELECTRONICS CORP

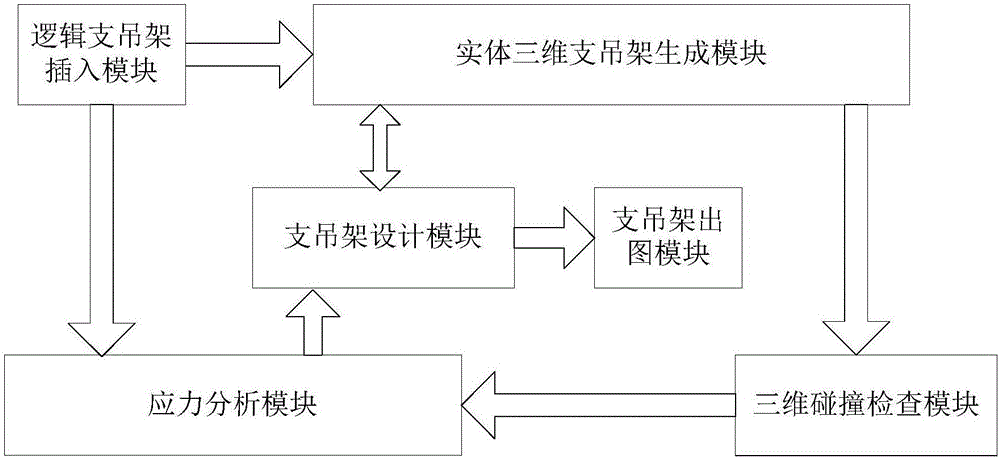

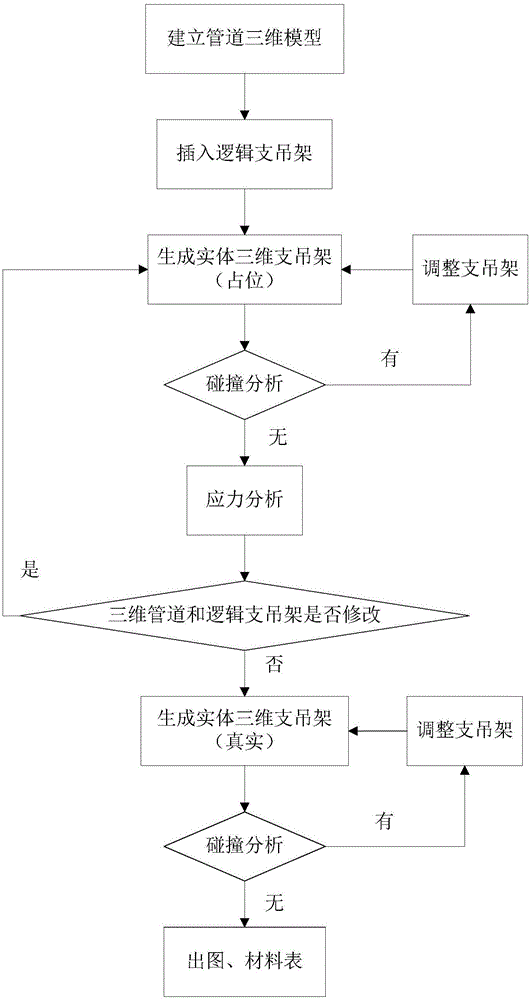

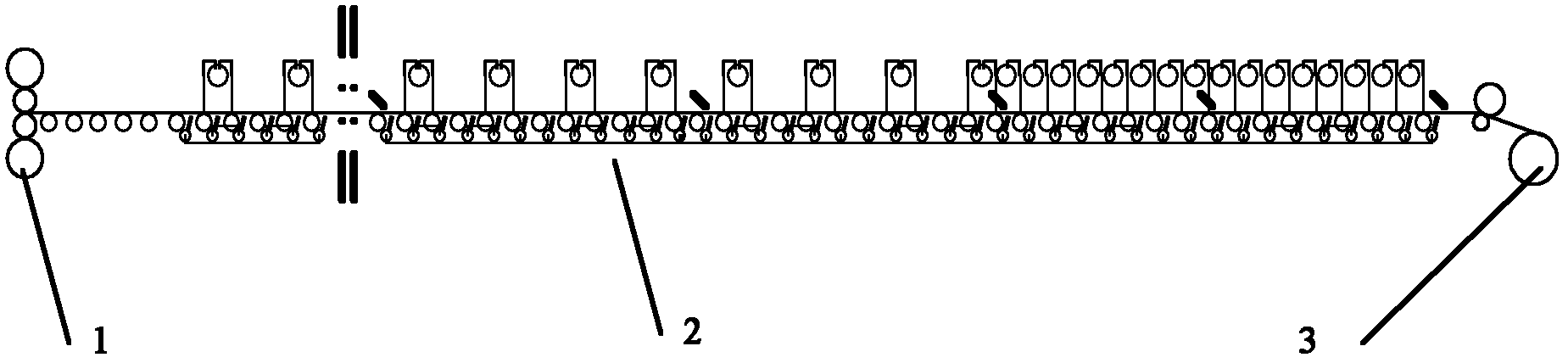

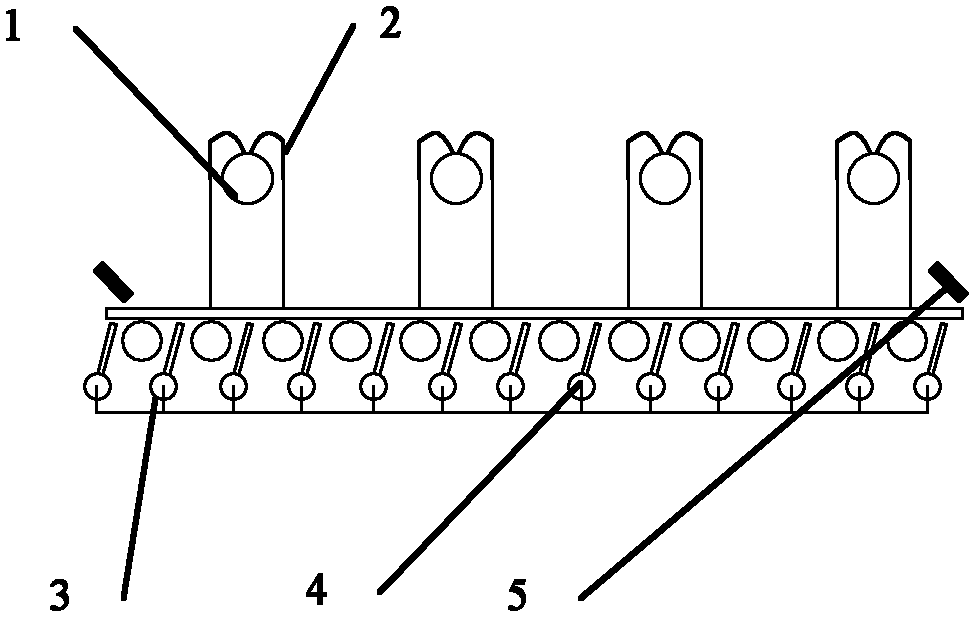

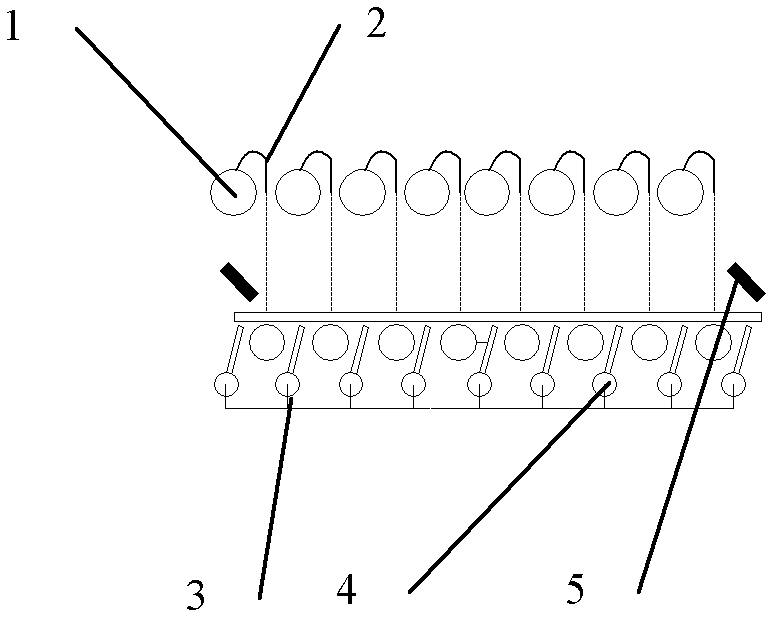

System and method for design of pipe support hanger

ActiveCN106446409ARealize two-way mutual conductionReduce two-way mutual conductionGeometric CADSpecial data processing applicationsAnalysis dataCollision analysis

The invention relates to a system and method for the design of a pipe support hanger. The pipe support hanger includes a logic support hanger insertion module, a solid three-dimensional support hanger generating module, a stress analysis module, a support hanger design module and a three-dimensional collision check module, wherein a logic support hanger is allowed to be inserted in logic support hanger insertion module, the solid three-dimensional support hanger generating module is used for generating a three-dimensional support hanger used for occupying space and a real three-dimensional support hanger, the stress analysis module is used for conducting stress analysis and the corresponding three-dimensional model modification, the support hanger design module is used for generating a data file required by the design, and the three-dimensional collision check module is used for conducting collision analysis. According to the system and method for the design of the pipe support hanger, rapid automatic insertion of the logical support hanger is achieved; the solid three-dimensional model of the support hanger can be generated and the collision analysis of the support hanger can be conducted before the stress analysis is conducted; the follow-up inspection and analysis processes are greatly simplified, redesign and recalculation caused by collision are greatly reduced, bi-directional mutual conductance among three-dimensional design data, stress analysis data and support hanger design software data is achieved, repeated inputting of the data is avoided, and probability of errors caused by manual input is greatly reduced.

Owner:四川电力设计咨询有限责任公司

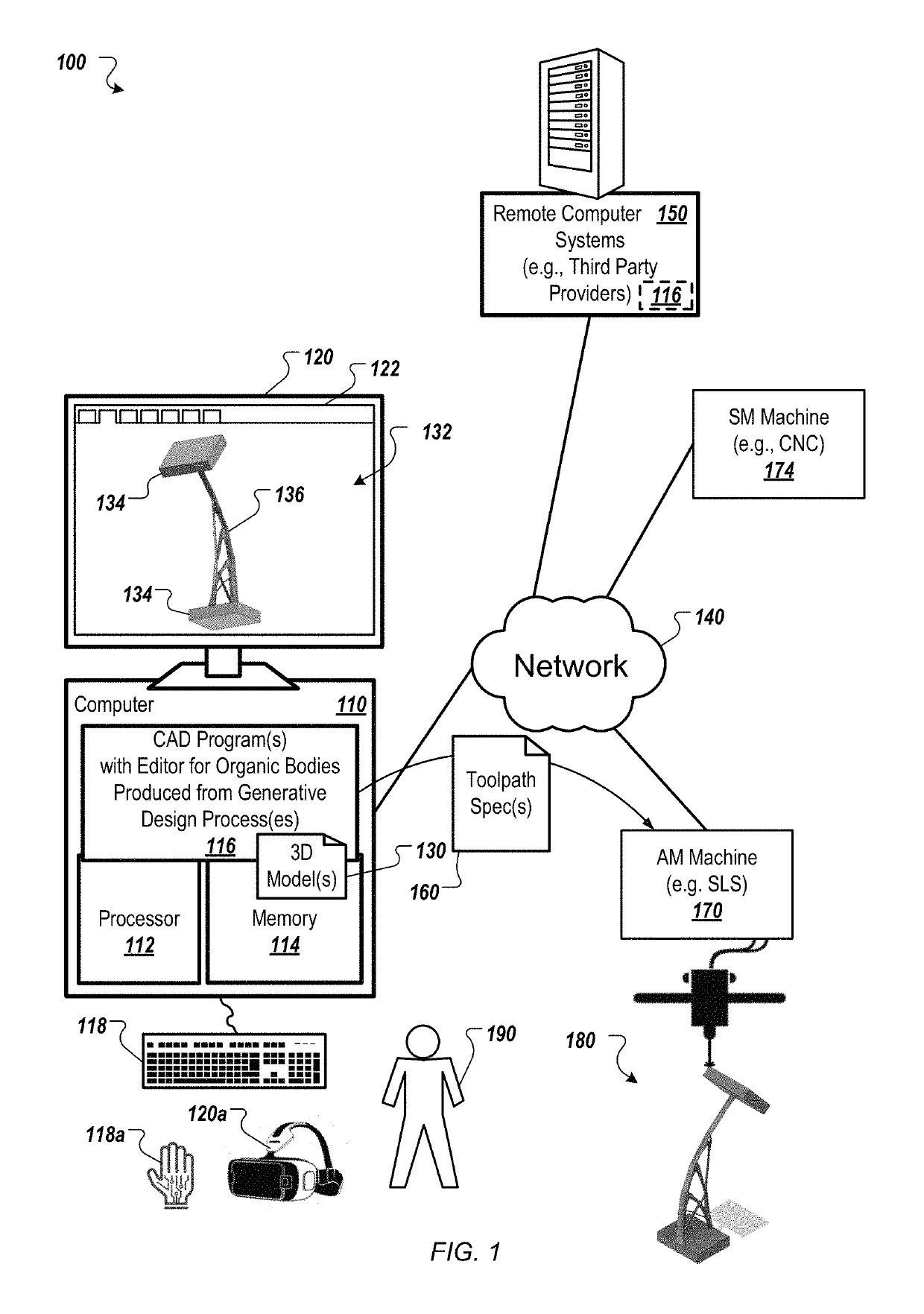

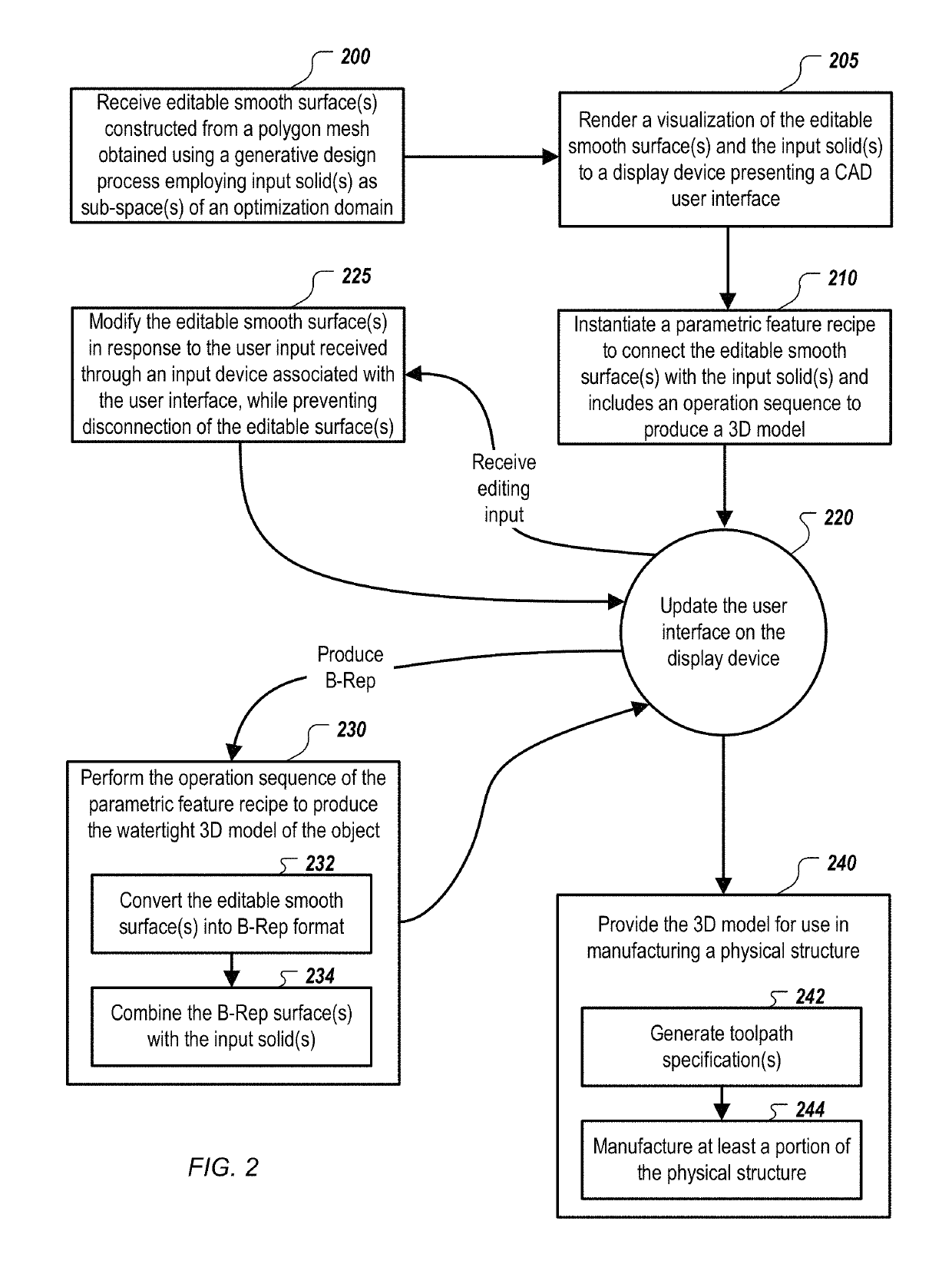

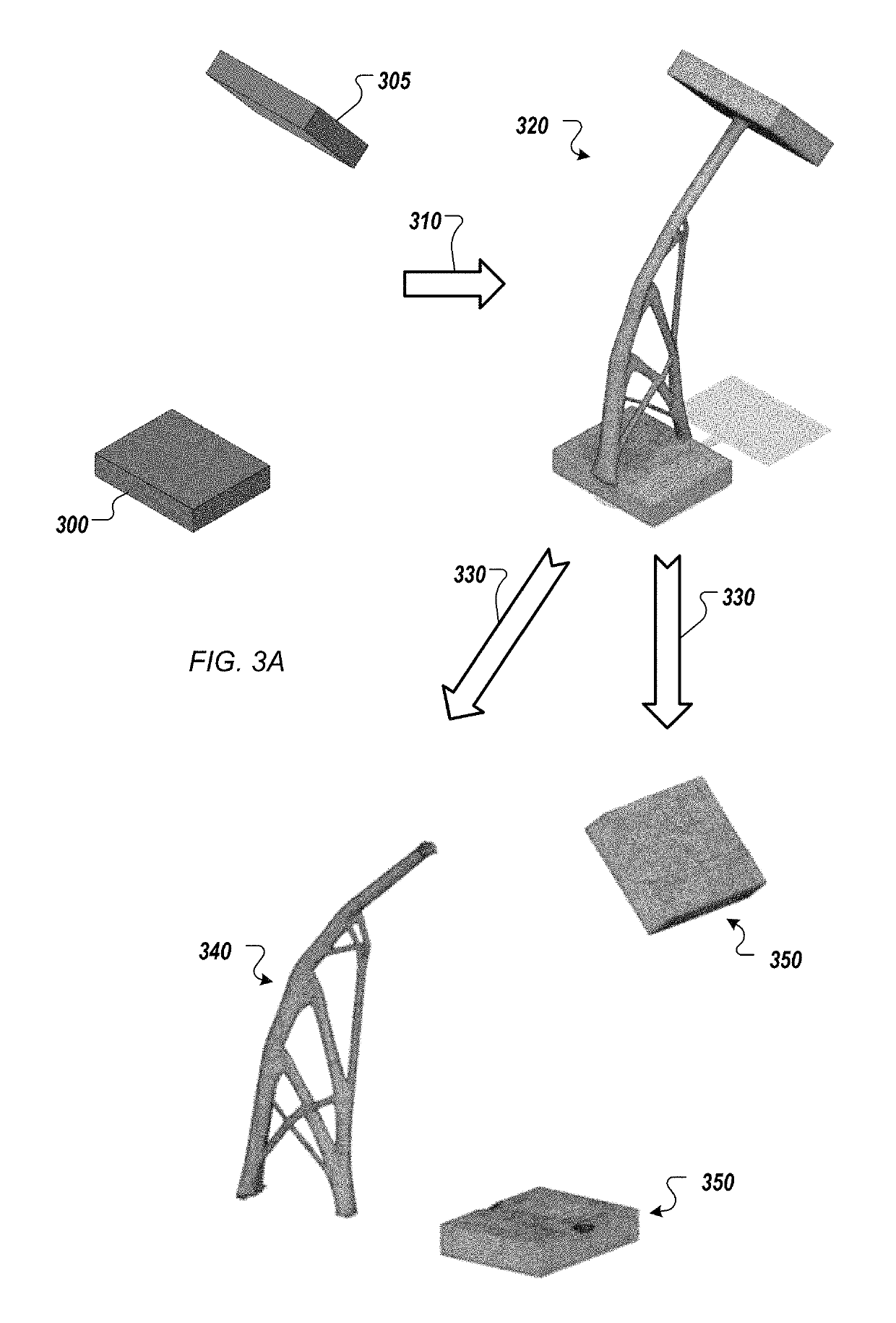

Facilitated editing of generative design geometry in computer aided design user interface

ActiveUS10467807B1Easy to editShorten the timeGeometric CADAdditive manufacturing apparatusComputer Aided DesignGenerative Design

Methods, systems, and apparatus, including medium-encoded computer program products, for facilitating editing of generative design geometry of physical structures, include a method including: receiving editable smooth surface(s), e.g., a T-Spline, constructed from a mesh obtained using a generative design process; instantiating a parametric feature recipe to connect the editable smooth surface(s) with input solid(s), wherein the parametric feature recipe includes an operation sequence that (i) converts the editable smooth surface(s) into boundary representation format and (ii) combines the boundary representation formatted smooth surface(s) with the input solid(s) to produce a watertight three dimensional model of an object; modifying the editable smooth surface(s) in response to input, while preventing disconnection of the editable smooth surface(s) from the input solid(s); updating a visualization thereof in a user interface; and performing the operation sequence of the parametric feature recipe to produce the watertight three dimensional model of the object.

Owner:AUTODESK INC

Design method of hot-rolling strip steel rolled cooling line

InactiveCN102513385AClear designShort design cycleWork treatment devicesMetal rolling arrangementsEngineeringVolumetric Mass Density

The invention discloses a design method of a hot-rolling strip steel rolled cooling line. The design method comprises the following steps of: determining the header arrangement mode of the cooling line; calculating the upper header flow rate; calculating the lower header flow rate; calculating the side-spraying header flow rate; calculating the hot flow density; calculating the cooling capability of a single upper header and a single lower header; calculating the total water quantity; checking the flow rate; drawing a cooling line equipment arrangement diagram; simulating the cooling process; and generating the design information report. In the design, the method of combining the rolling procedure and the equipment structure is adopted, so the whole design process is very clear. The design method can adopt the computer program for calculation, so the design period is short. The design method adopts the calculation method of combining the theoretical model and the field actual data, so the equipment parameter calculation is accurate. The design method has the advantages that the calculation result practicability is fully considered, and the complete one-package service can be provided from the cooling line design and the process calculation to bidding document making and the like.

Owner:DALIAN DESIGN INST CO LTD CHINA FIRST HEAVY IND +1

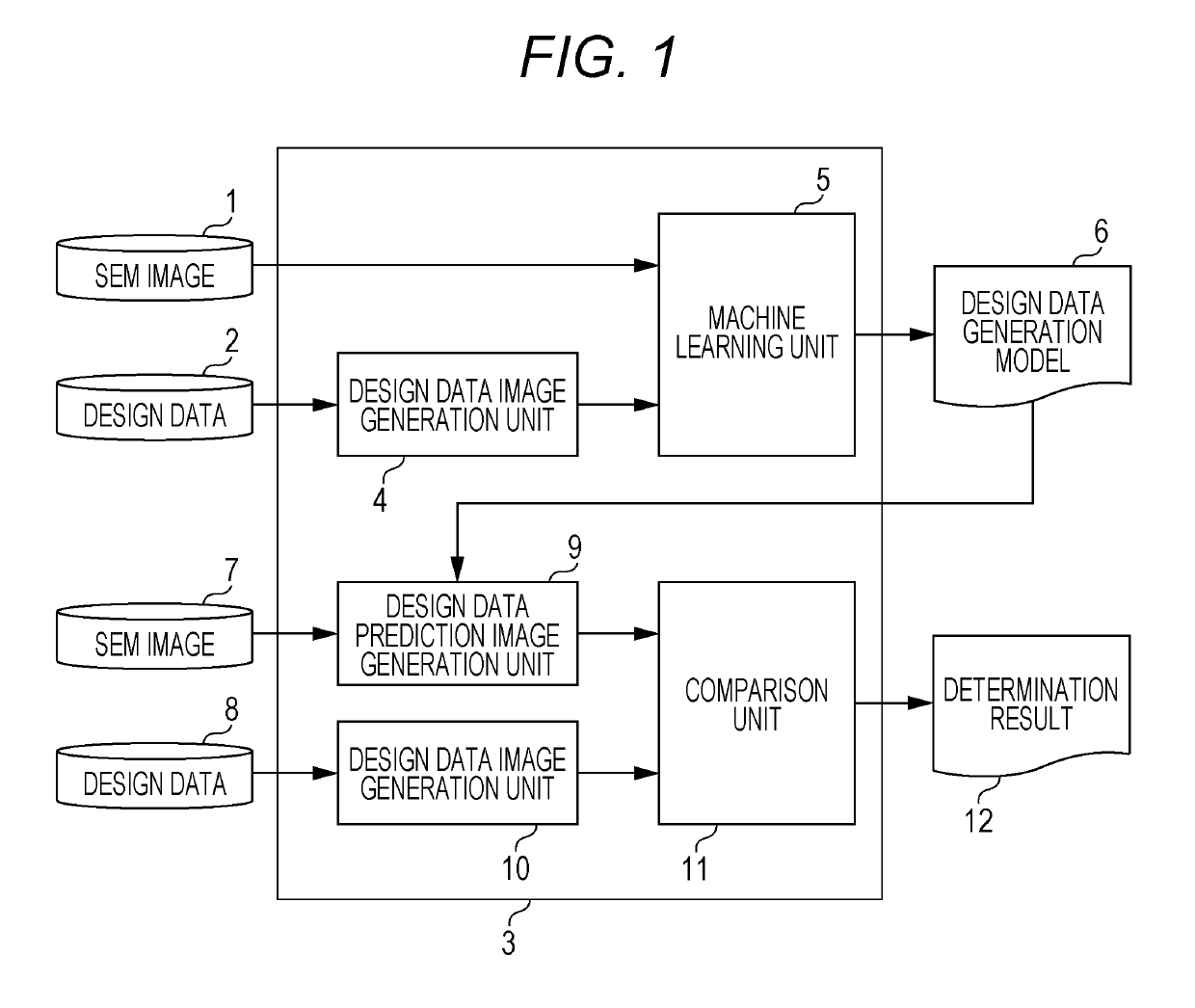

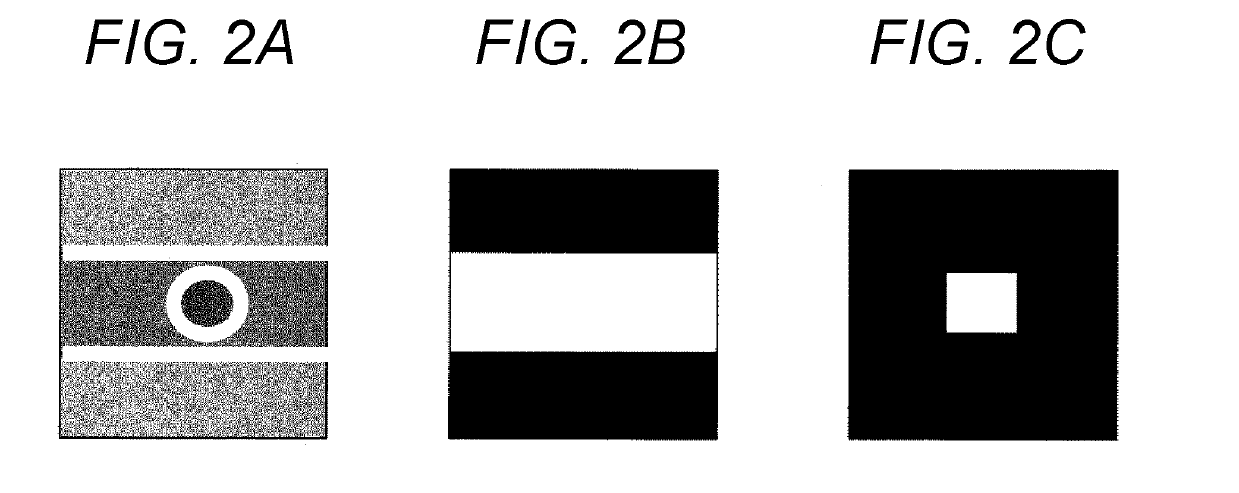

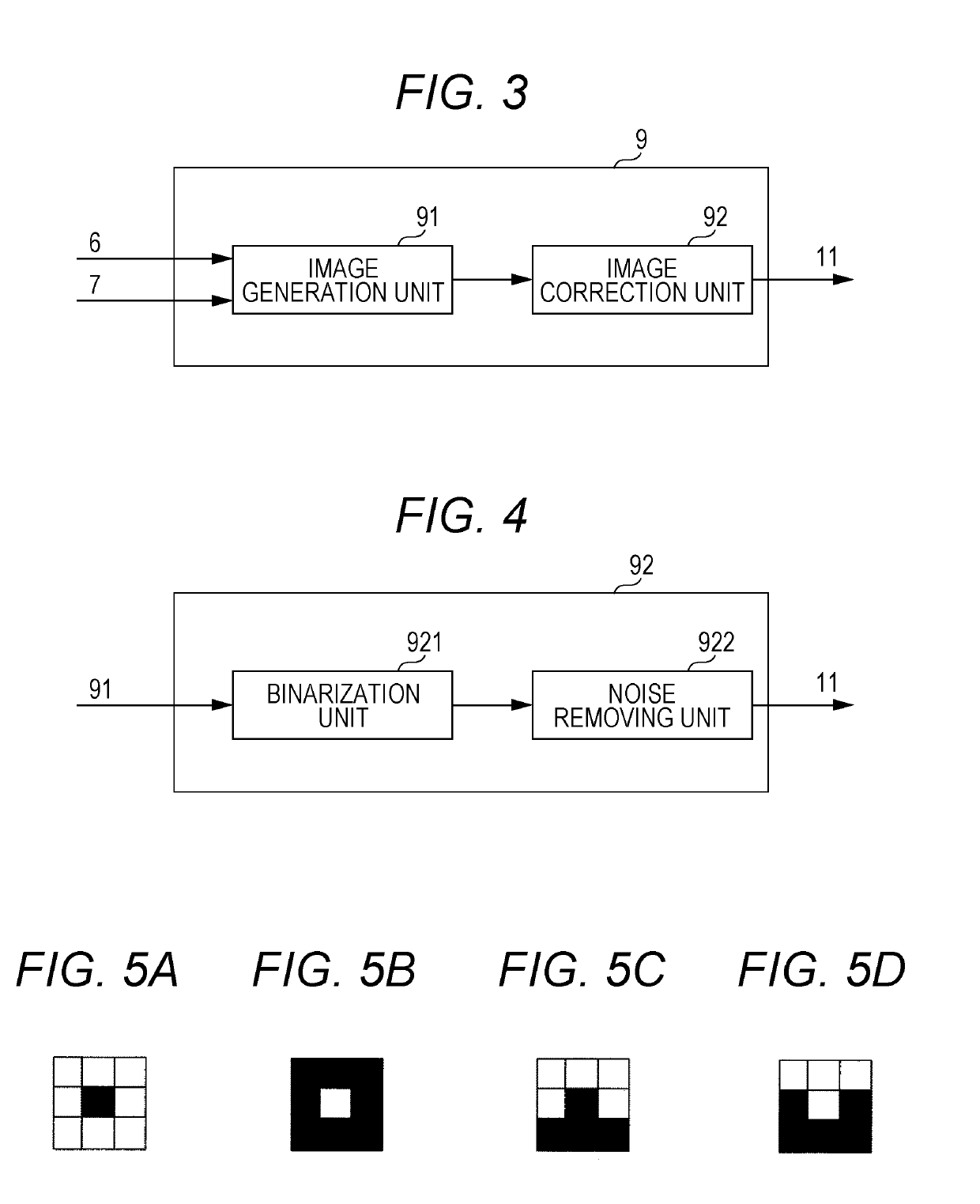

Image Evaluation Method and Image Evaluation Device

The image evaluation device includes a design data image generation unit that images design data; a machine learning unit that creates a model for generating a design data image from an inspection target image, using the design data image as a teacher and using the inspection target image corresponding to the design data image; a design data prediction image generation unit that predicts the design data image from the inspection target image, using the model created by the machine learning unit; a design data image generation unit that images the design data corresponding to the inspection target image; and a comparison unit that compares a design data prediction image generated by the design data prediction image generation unit and the design data image. As a result, it is possible to detect a systematic defect without using a defect image and generating misinformation frequently.

Owner:HITACHI HIGH-TECH CORP

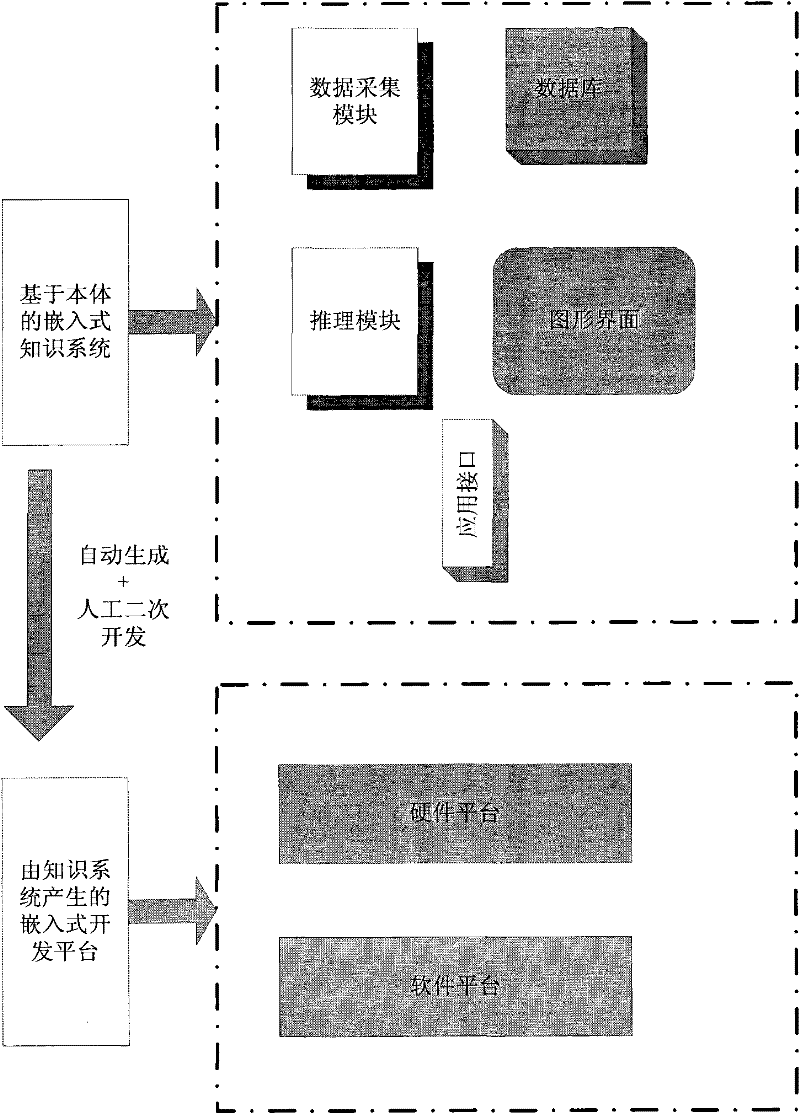

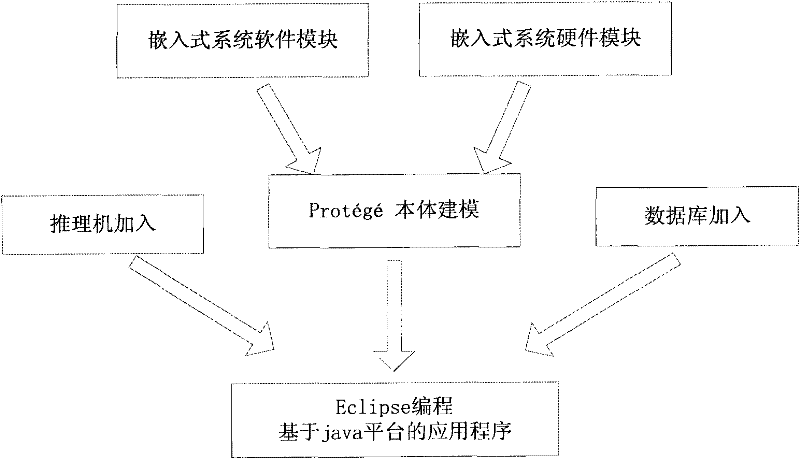

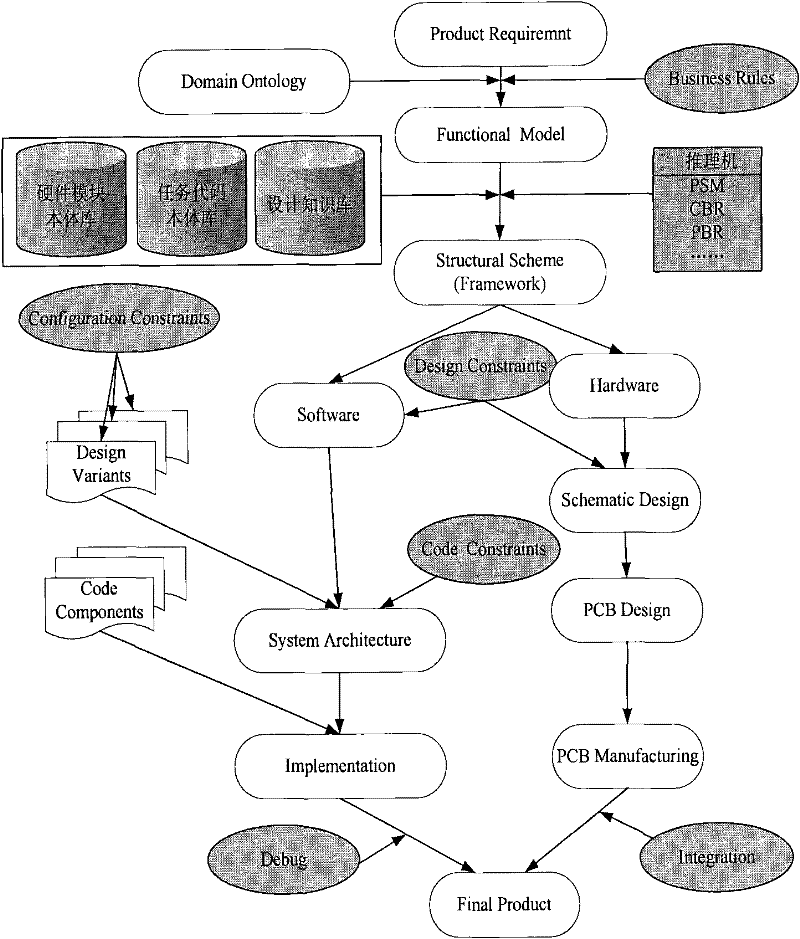

Design method of reconfigurable embedded system based on ontology and system

InactiveCN102054087AAchieve reuseShorten the design cycleSpecial data processing applicationsDesign planGenerative Design

The invention relates to a design method of a reconfigurable embedded system based on the ontology and a system. The method comprises the specific steps as follows: the design method is implemented by a noumenon-based knowledge system which is designed for the application in the embedded system field and an embedded type development platform which is specially developed for the embedded system design. The invention has the advantages that the method greatly shortens the design period, achieves the reuse of design knowledge and solves the problems of the prior art, such as long design period and failure in reuse of design knowledge; the noumenon-based embedded type knowledge system is developed, and the knowledge system is established based on the ontology; the knowledge system has updating and self-learning characteristics and can collect the up-to-date information on the Web network by adding a data acquisition module during the development process of the knowledge system; the embedded type system platform is developed under the guidance of the knowledge system; and according to the design purpose, the knowledge system generates the design plan, and then the design details are manually completed to make the system prefect.

Owner:EAST CHINA UNIV OF SCI & TECH

Systems and methods for computational design and modeling of buildings

A method and system generates a building design and a three-dimensional image thereof. First building information comprising a length, width, total height and wall height of a building is received via a first graphical user interface. If the length, width, total height, wall height, and a selectable building shape yield a valid set of building parameters, a design of said building is generated at a first software module, which is configured to generate the design, including wall portions and a roof portion, using minimum information consisting of the length, width, total height, wall height, and selectable building shape. A first image and a structural analysis of the design are generated. A second software module generates a second three-dimensional image of the building, which is different from the first image. A second graphical user interface permits a user to modify the second image to include predefined building elements.

Owner:MIC IND INC

Suite of tools to design integrated circuits

InactiveUS7430725B2Detecting faulty computer hardwareComputer programmed simultaneously with data introductionComputer architectureBatch processing

A set of tools is provided herein that produces useful, proven, and correct integrated semiconductor chips. Having as input either a customer's requirements for a chip, or a design specification for a partially manufactured semiconductor chip, the tools generate the RTL for control plane interconnect; memory composition, test, and manufacture; embedded logic analysis, trace interconnection, and utilization of spare resources on the chip; I / O qualification, JTAG, boundary scan, and SSO analysis; testable clock generation, control, and distribution; interconnection of all of the shared logic in a testable manner from a transistor fabric and / or configurable blocks in the slice. The input customer requirements are first conditioned by RTL analysis tools to quickly implement its logic. The slice definition and the RTL shell provides the correct logic for a set of logic interfaces for the design specification to connect. The tools share a common database so that logical interactions do not require multiple entries. The designs are qualified, tested, and verified by other tools. The tools further optimize the placement and timing of the blocks on the chip with respect to each other and with respect to placement on a board. The suite may be run as batch processes or can be driven interactively through a common graphical user interface. The tools also have an iterative mode and a global mode. In the iterative mode, one or more of the selected tools can generate the blocks or modify a design incrementally and then look at the consequences of the addition, or change. In the global mode, the semiconductor product is designed all at once in a batch process as above and then optimized altogether. This suite of generation tools generates design views including a qualified netlist for a foundry to manufacture.

Owner:BELL SEMICON LLC

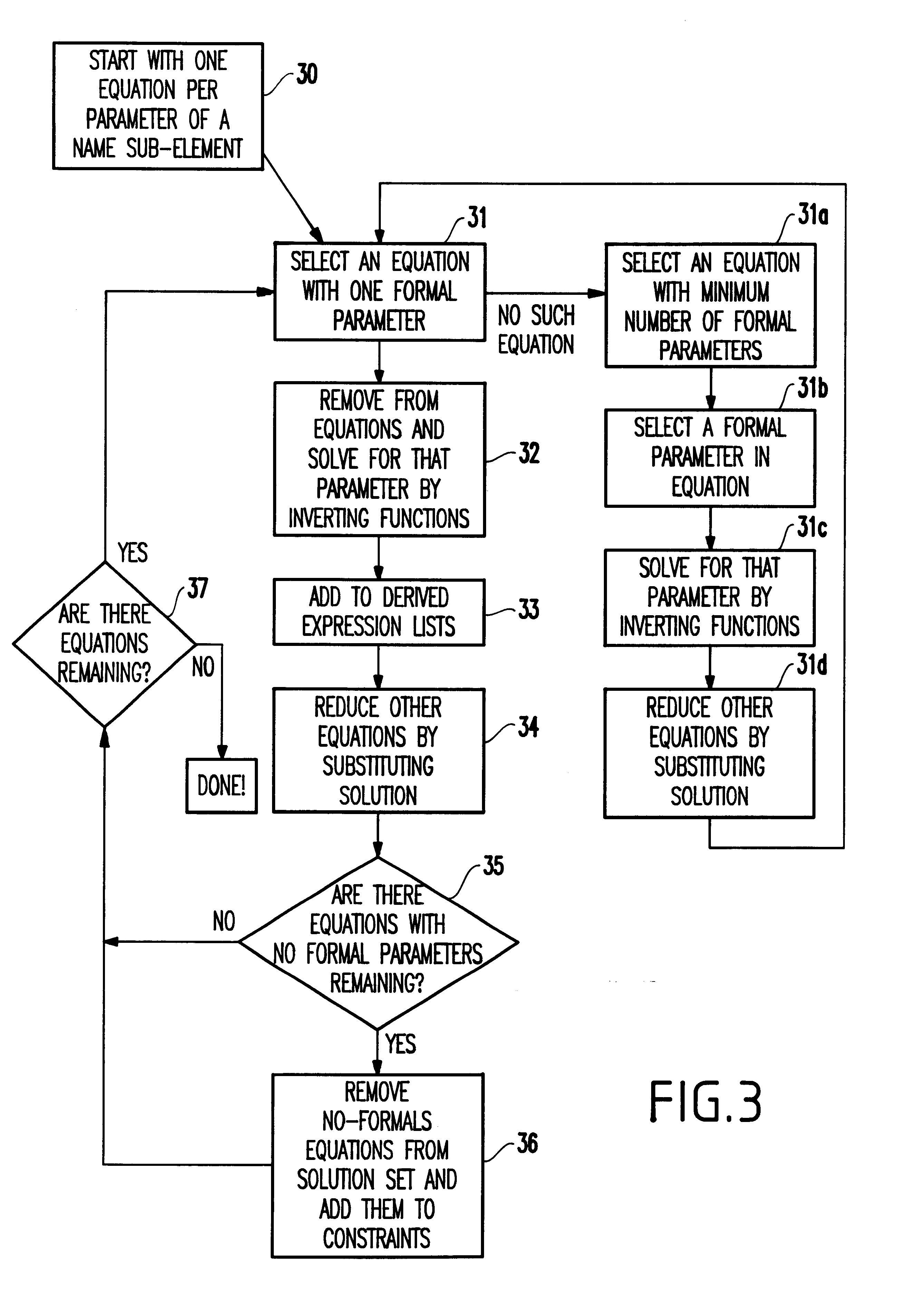

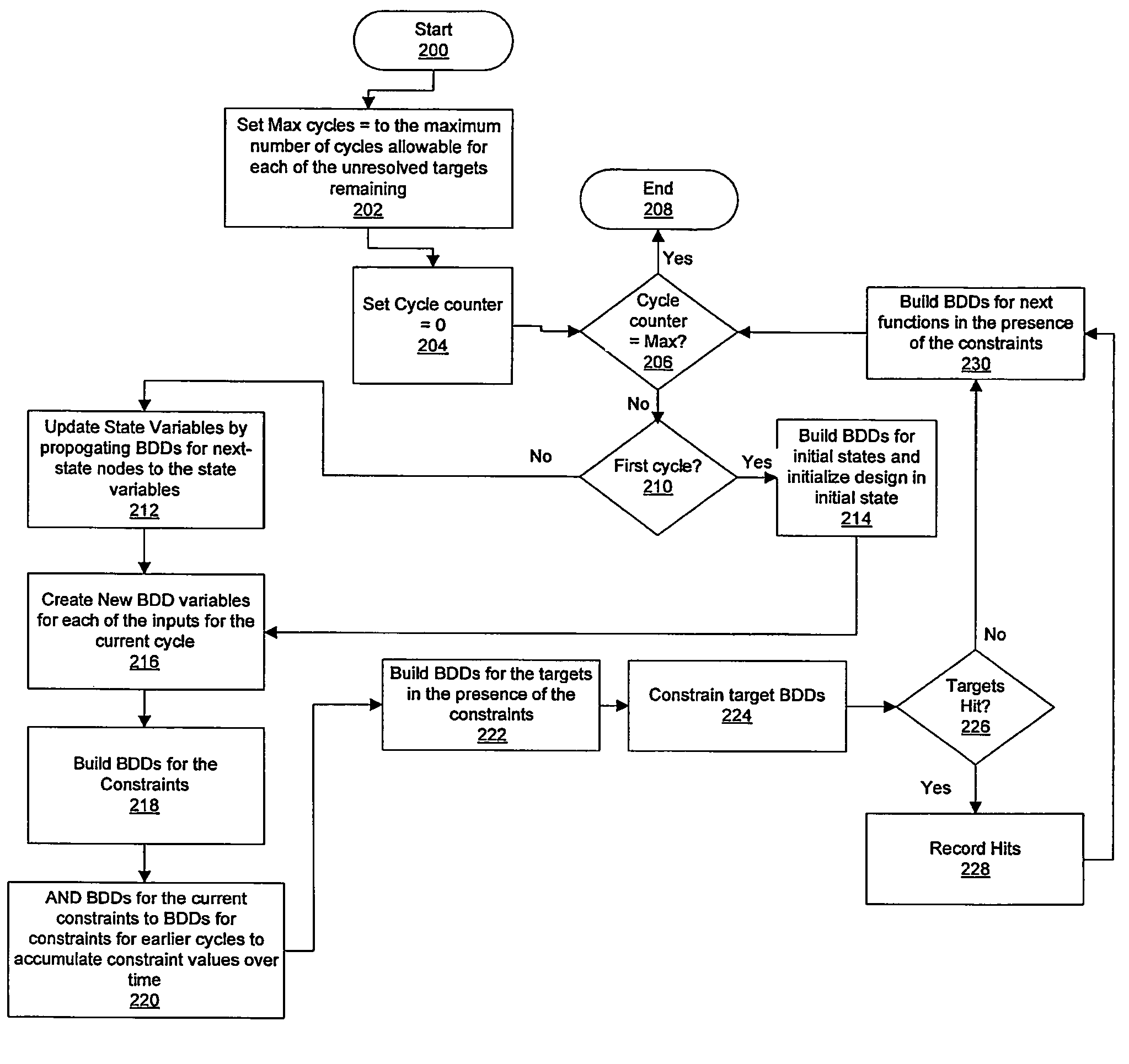

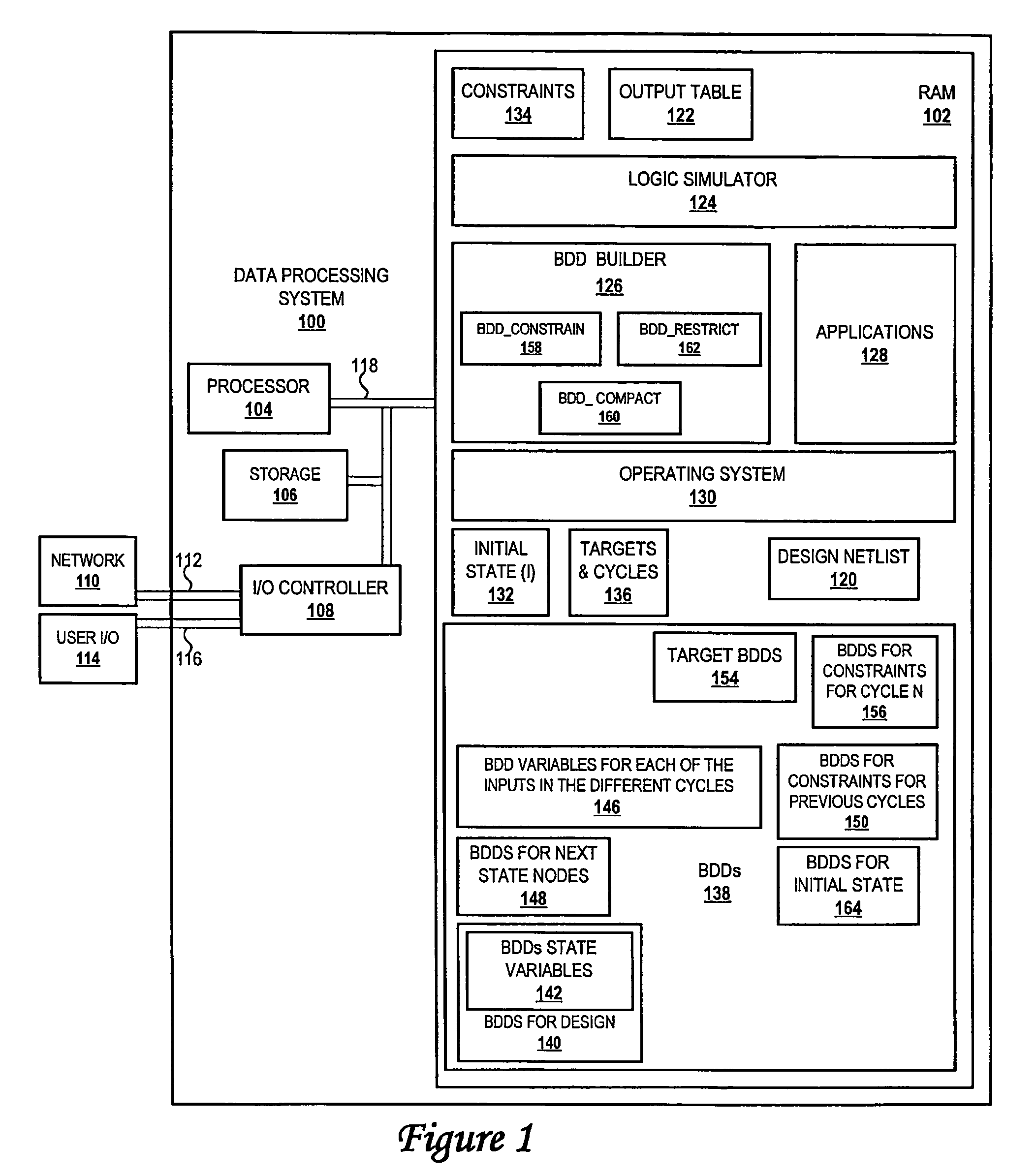

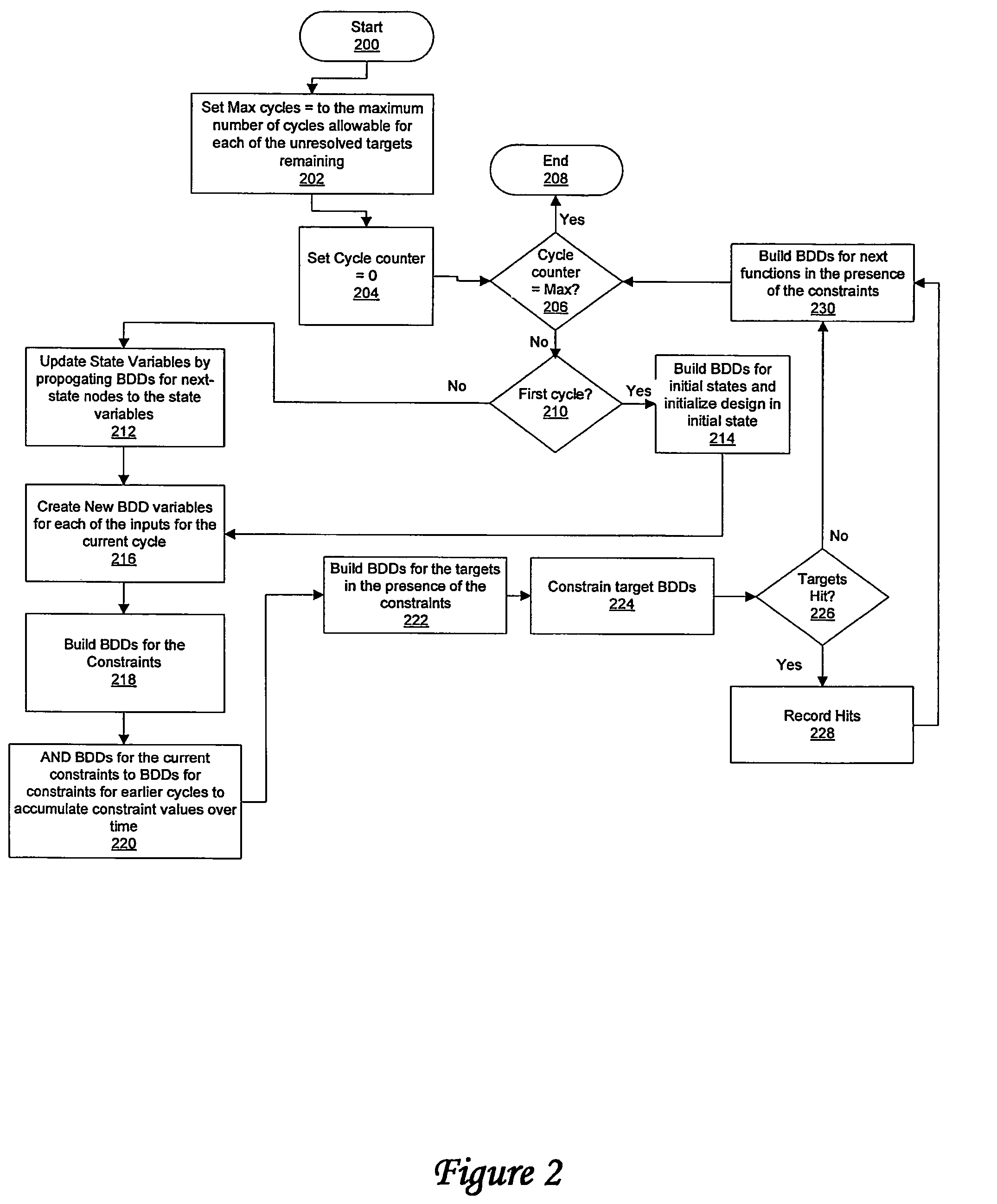

Method and system for optimized handling of constraints during symbolic simulation

InactiveUS7290229B2Computer aided designSoftware simulation/interpretation/emulationSymbolic simulationState variable

A method for verifying a design through symbolic simulation is disclosed. The method comprises creating one or more binary decision diagram variables for one or more inputs in a design containing one or more state variables and building a binary decision diagram for a first node of one or more nodes of the design. A binary decision diagram for the initial state function of one or more state variables of the design is generated and the design is subsequently initialized. Binary decisions diagrams for one or more constraints are synthesized. A set of constraint values is accumulated over time by combining the binary decision diagrams for the one or more constraints with a set of previously generated binary decision diagrams for a set of constraints previously used in one or more previous time-steps. A binary decision diagram for the next state function of the one or more state variables in the design is constructed in the presence of the constraints. The one or more state variables in the design are updated by propagating the binary decision diagram for the next state function to the one or more state variables and a set of binary decision diagrams for the one or more targets in the presence of the one or more constraints is calculated. The set of binary decision diagrams for one or more targets is constrained and the design is verified by determining whether the one or more targets were hit.

Owner:GLOBALFOUNDRIES INC