Patents

Literature

71 results about "Design Validation" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

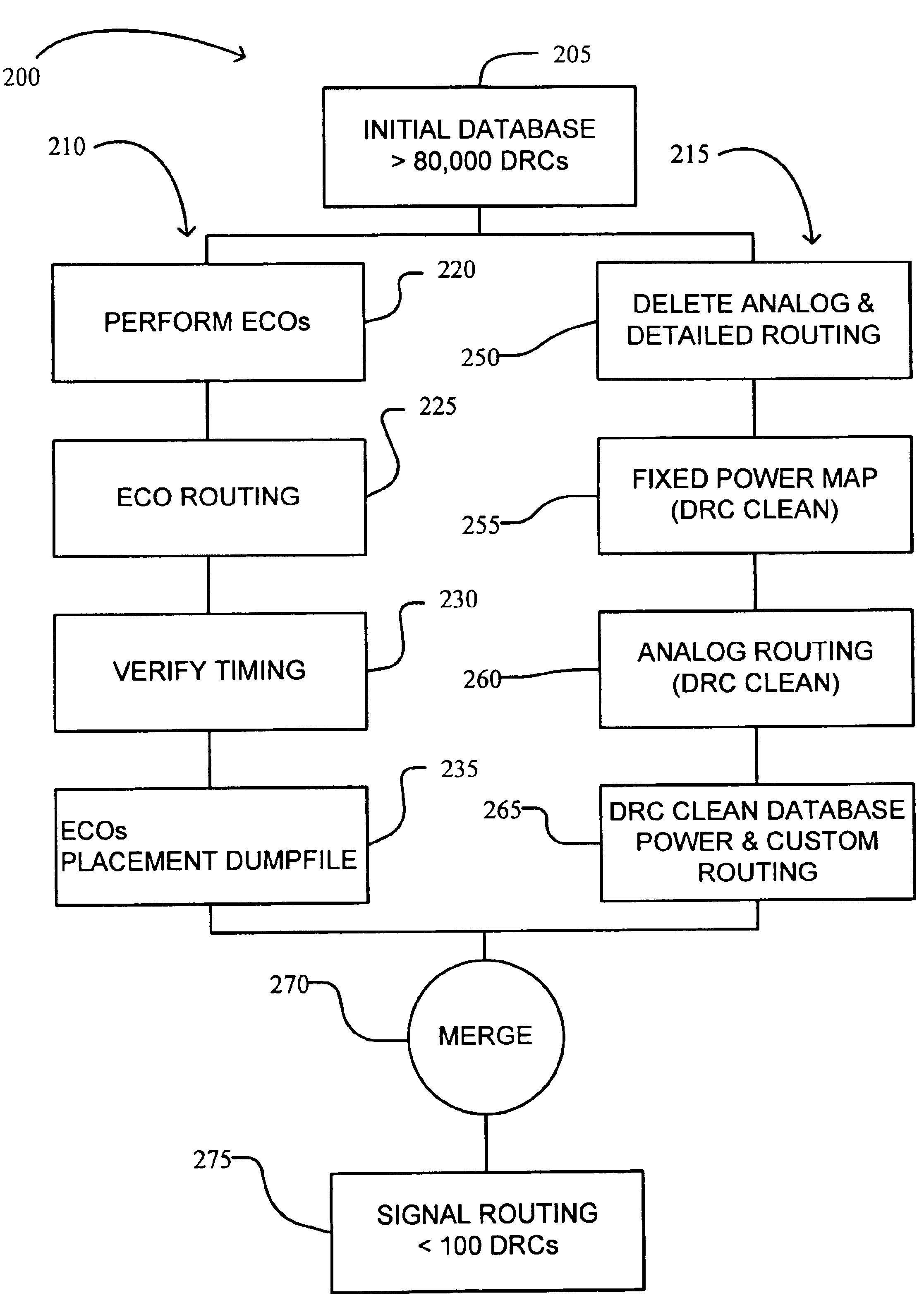

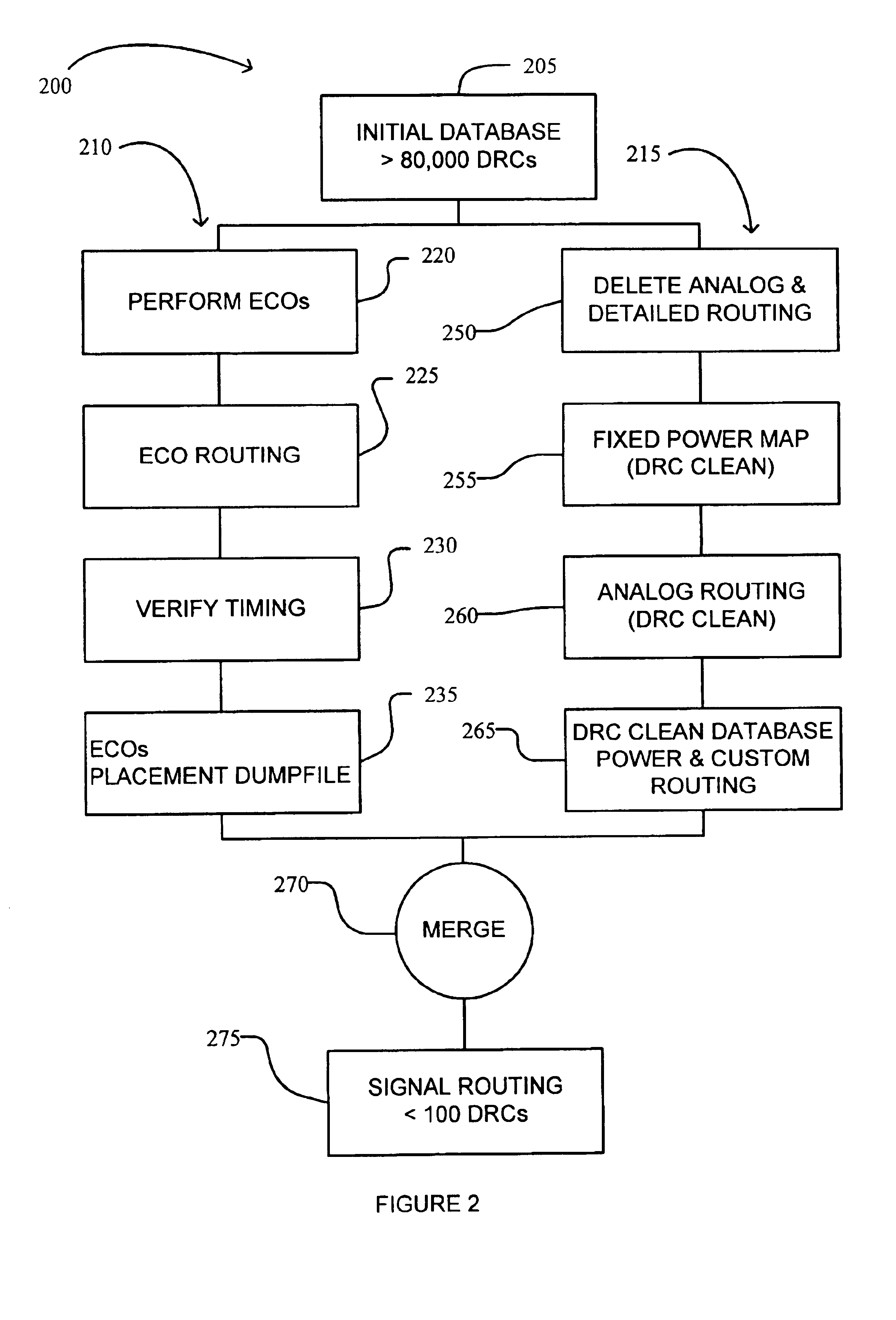

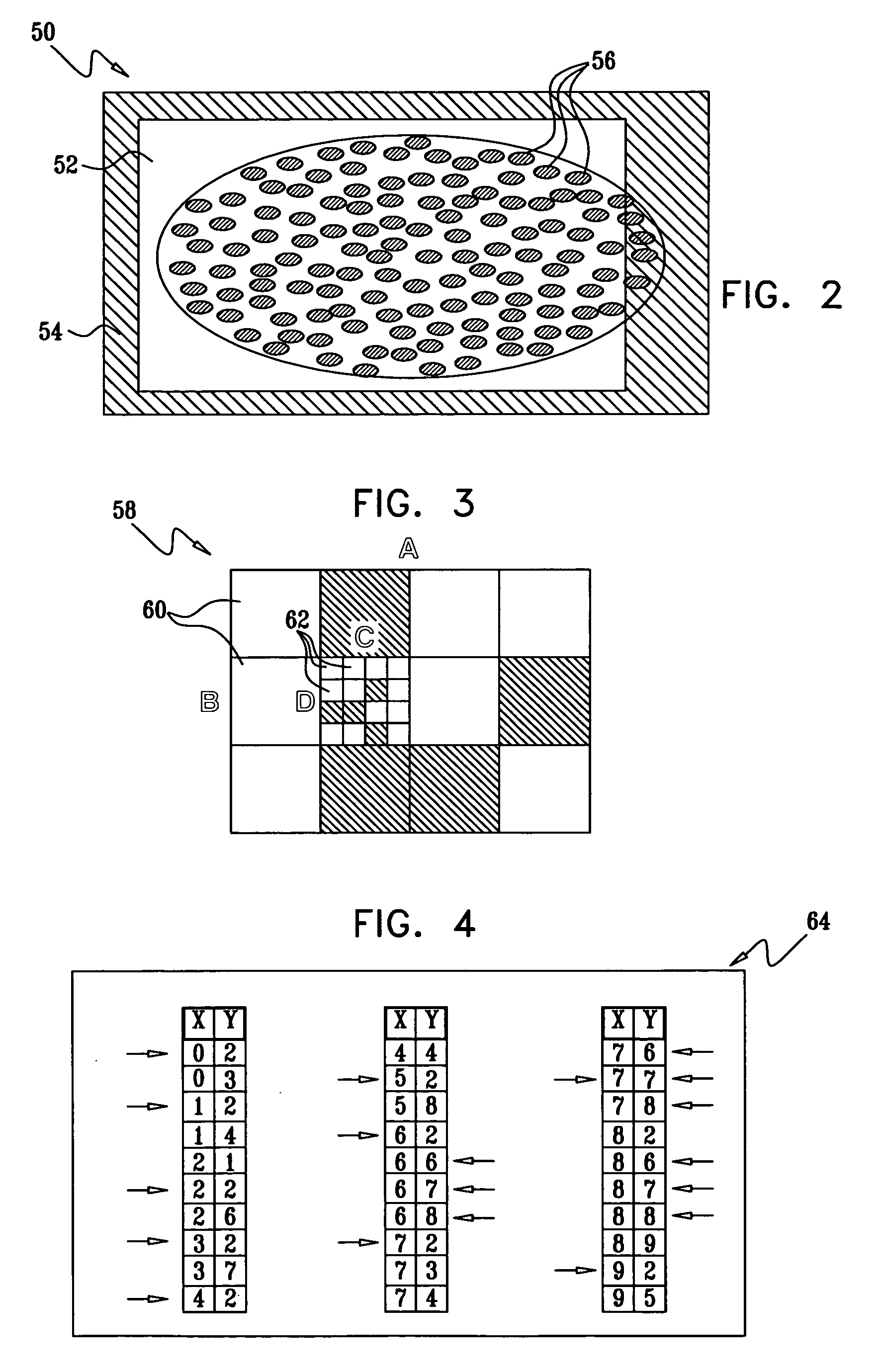

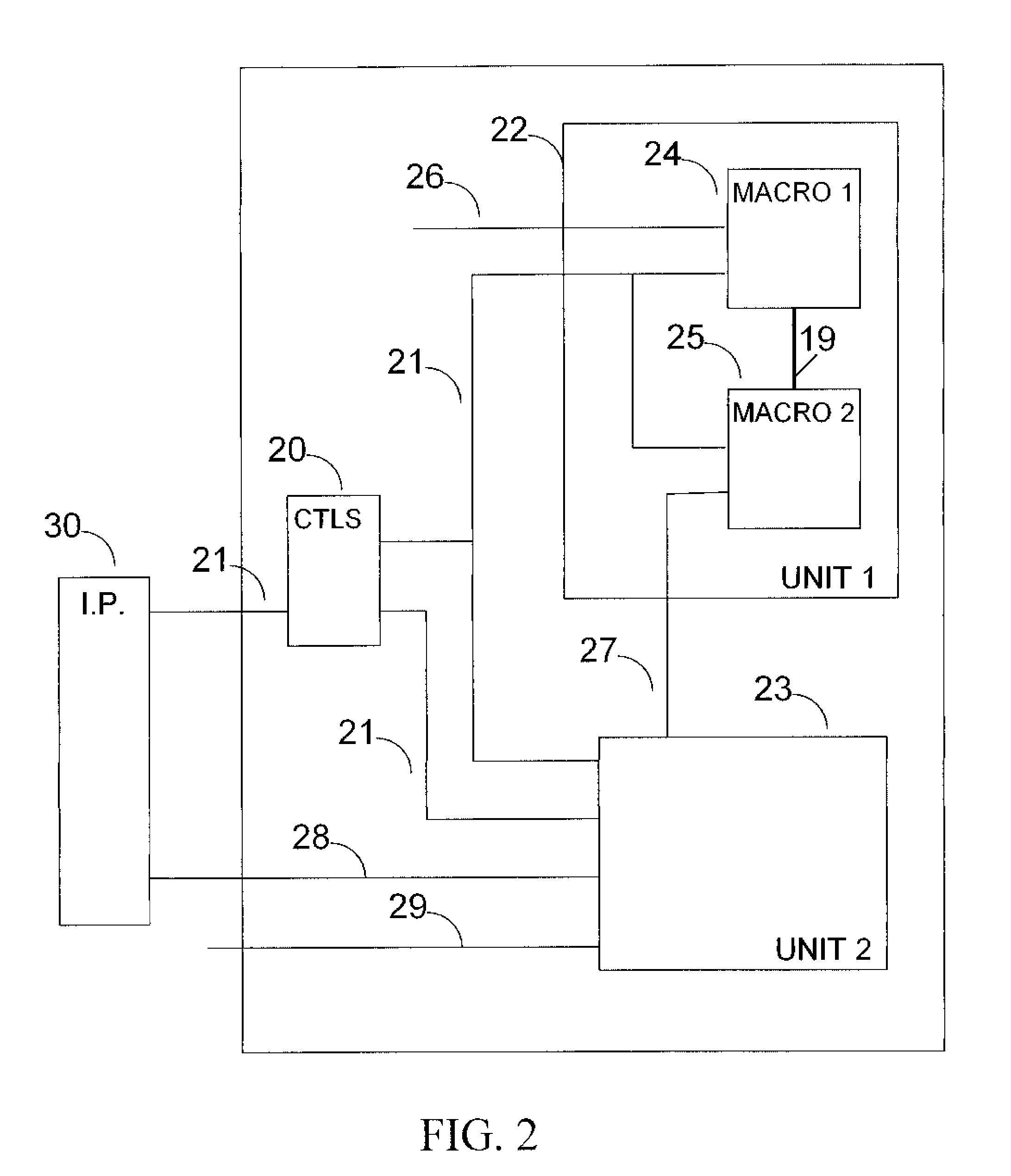

Split and merge design flow concept for fast turnaround time of circuit layout design

ActiveUS6898770B2Increase turnaround timeAccurate verificationComputer aided designSoftware simulation/interpretation/emulationSufficient timeTurnaround time

A method and system is disclosed to improve the turnaround time to provide adequate time to meet project schedules in the event that adjustments or modifications to the design are necessary. A method for improving a turnaround time for design verification of a process database representing a semiconductor design includes the steps of (a) deriving a timing database and a (DNE) database from the process database; (b) performing, using the timing database, one or more design changes and one or more timing verifications and corrections to generate a modified timing database; (c) initiating, using the process database, physical validation of the semiconductor design prior to completion of step (b) to generate a modified DNE database; (d) merging the modified timing database with the modified DNE database to form a modified process database; and (e) performing, using the modified process database, one or more design verification checks of the semiconductor design.

Owner:BELL SEMICON LLC

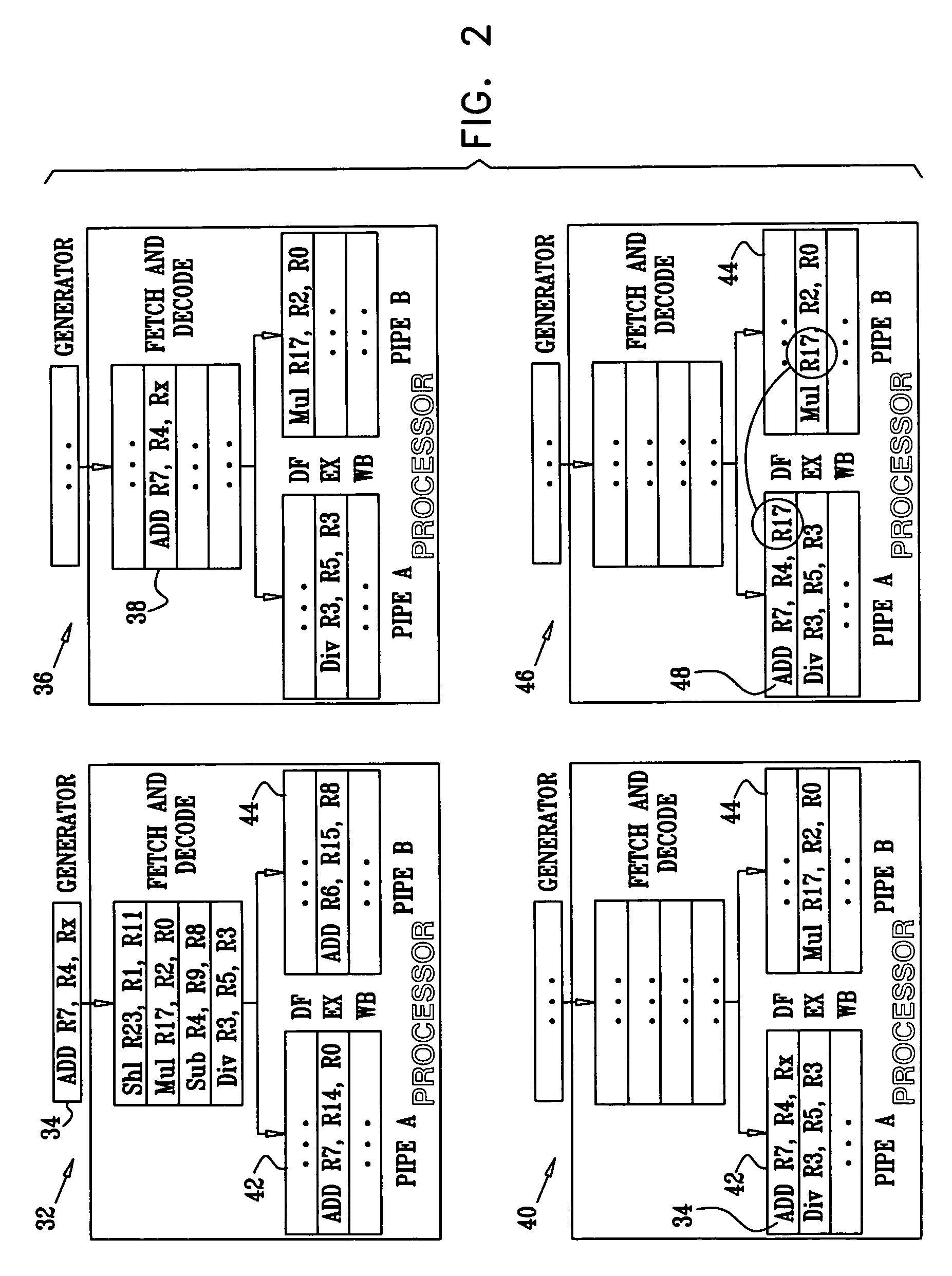

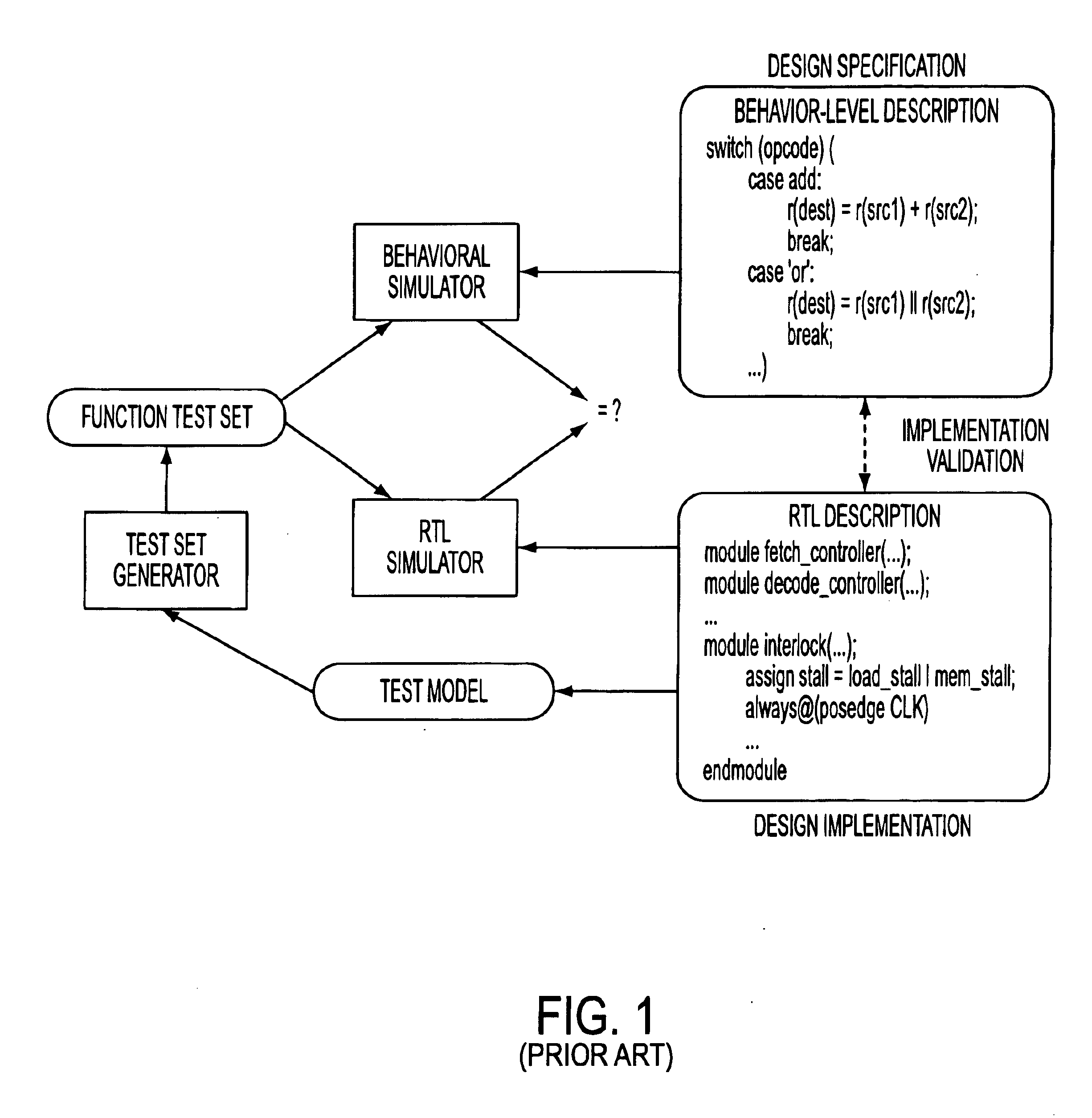

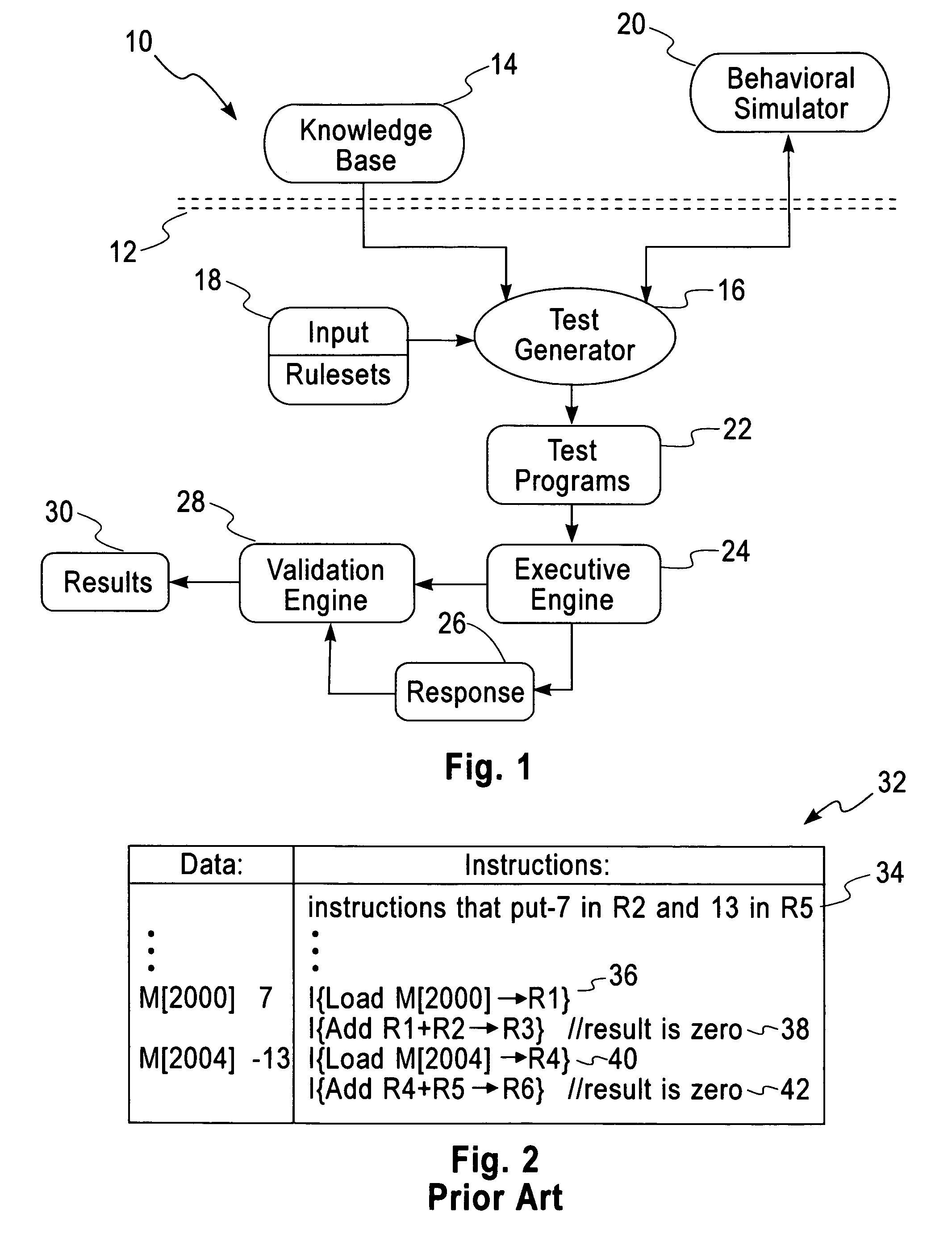

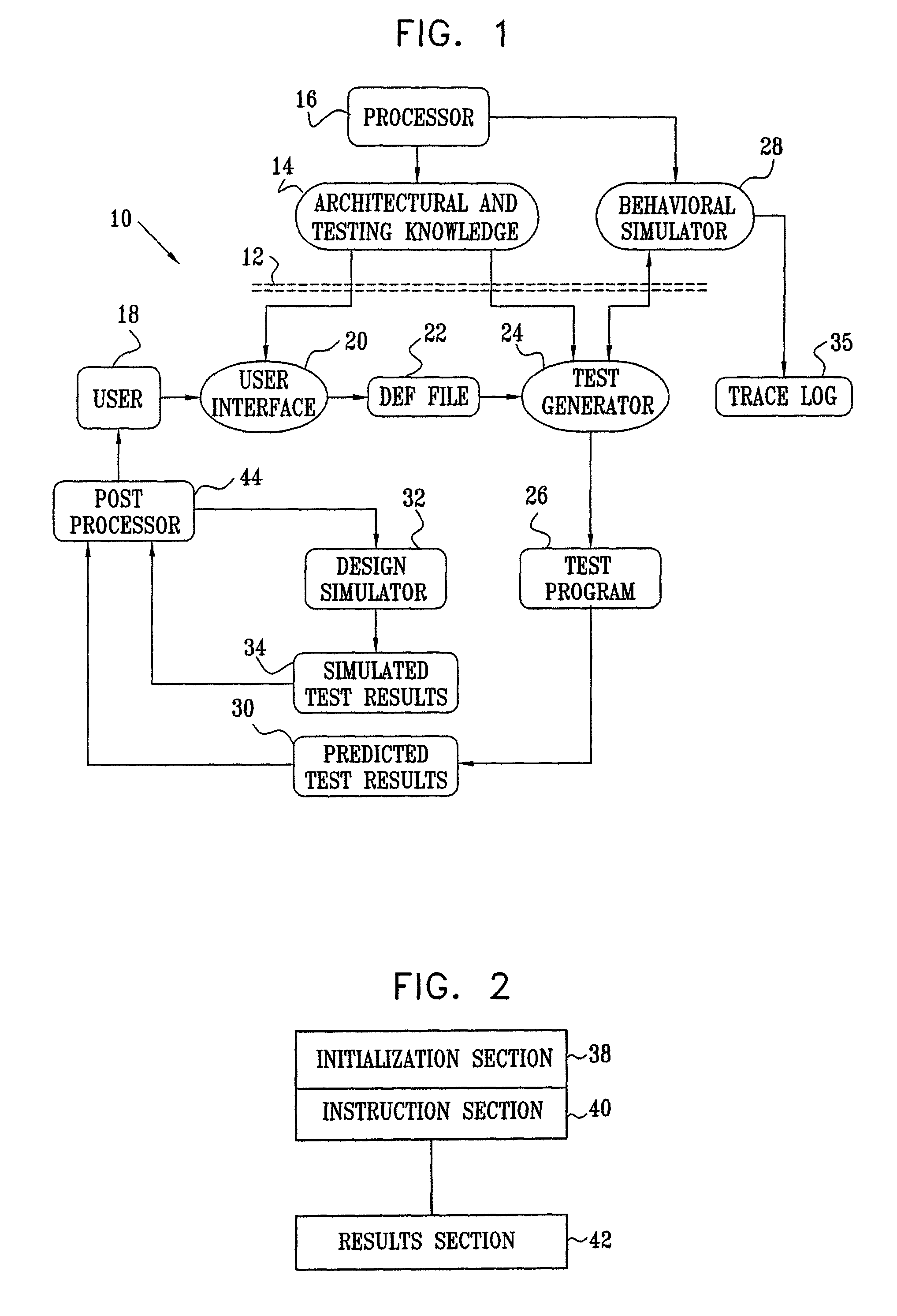

Late binding of variables during test case generation for hardware and software design verification

InactiveUS7003420B2Improves quality and rapidityPerformance penaltyResistance/reactance/impedenceCAD circuit designSoftware designTheoretical computer science

Methods and systems are provided that improve design verification by test generators by delaying assignment of values in the generated stimuli until these values are used in the design. Late binding allows the generator to have a more accurate view of the state of the design, and in order to choose correct values. Late binding can significantly improve test coverage with a reasonable performance penalty as measured by simulation time.

Owner:IBM CORP

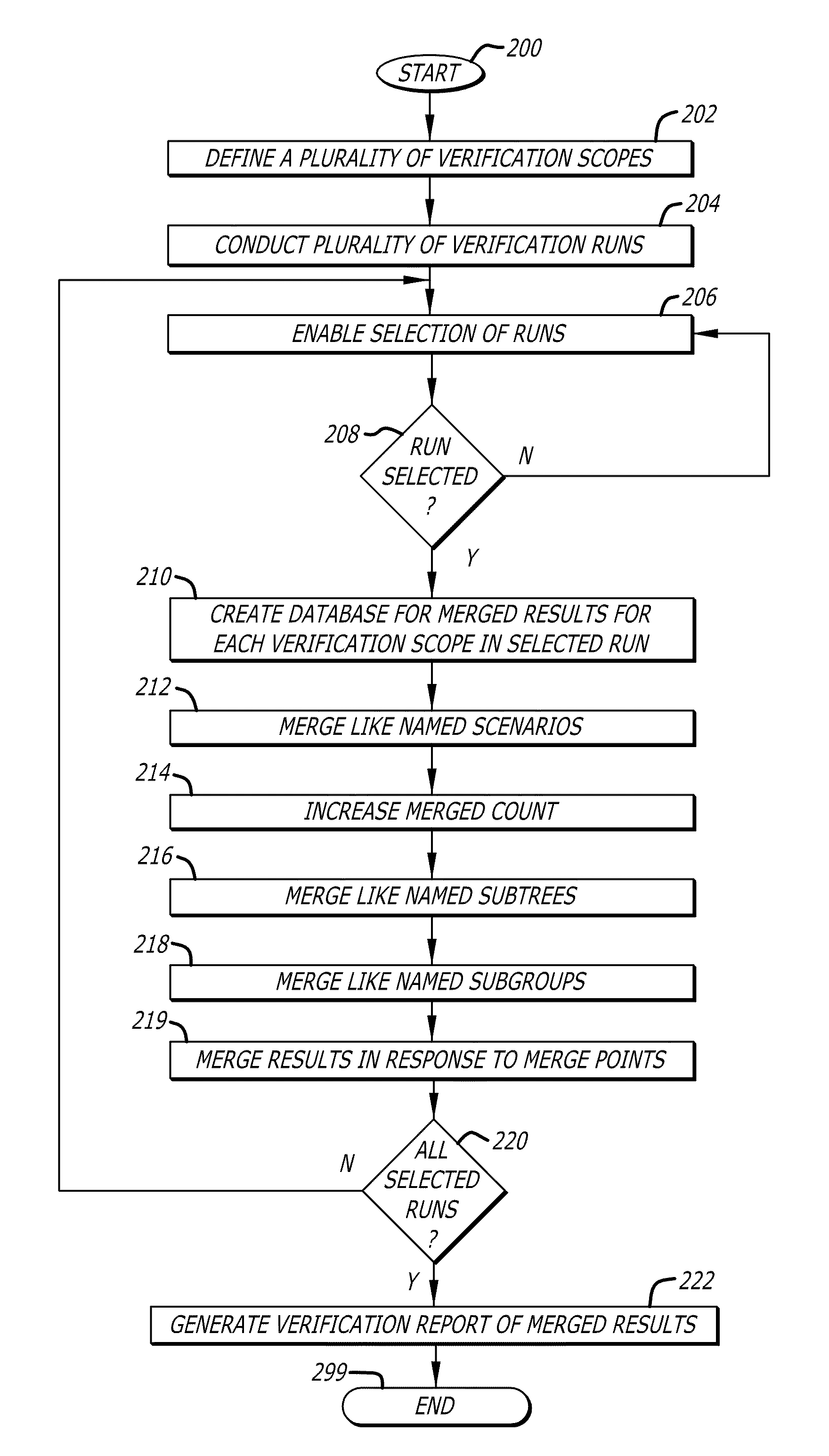

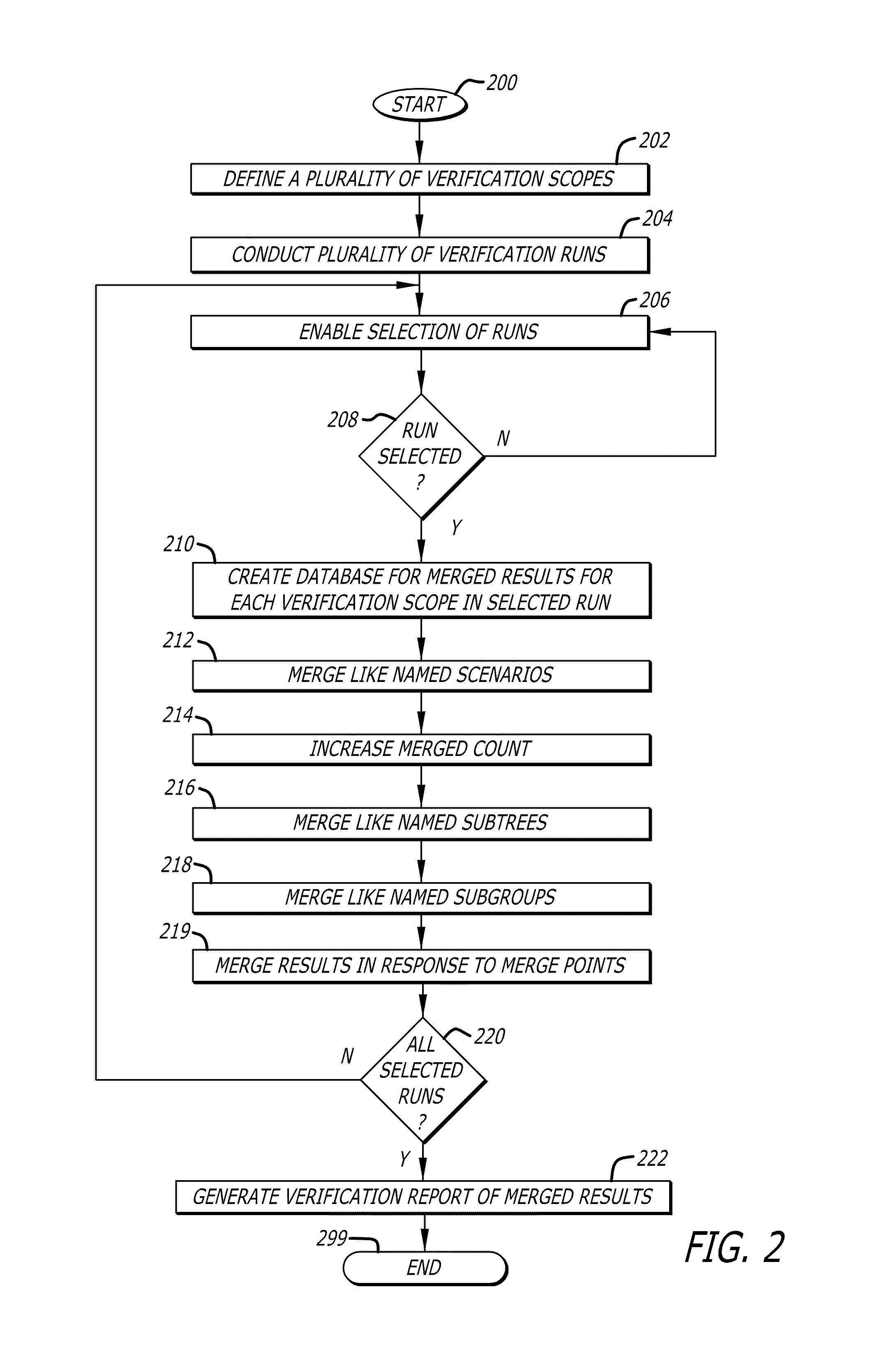

Verification plans to merging design verification metrics

ActiveUS8413088B1Flexible controlAccurate progress measurementElectrical testingCAD circuit designComputer architectureProgram planning

A method and apparatus for producing a verification of digital circuits are provided. In an exemplary embodiment on the invention, a plurality of verification scopes of an integrated circuit design as defined as part of a verification plan. A plurality of verification runs are executed within two or more verification scopes defined by the verification plan. At least two verification runs are selected to merge verification results together. Like named scenarios are merged together for each verification scope to generate merged verification results that are then stored into a merge database. A verification report is generated for the integrated circuit design from the merged verification results. A merge point may be specified so like named subtrees and subgroups may be merged across different verification scopes of selected verification runs. The merge point may combine check and coverage results obtained during simulation with check and coverage results obtained during formal verification.

Owner:CADENCE DESIGN SYST INC

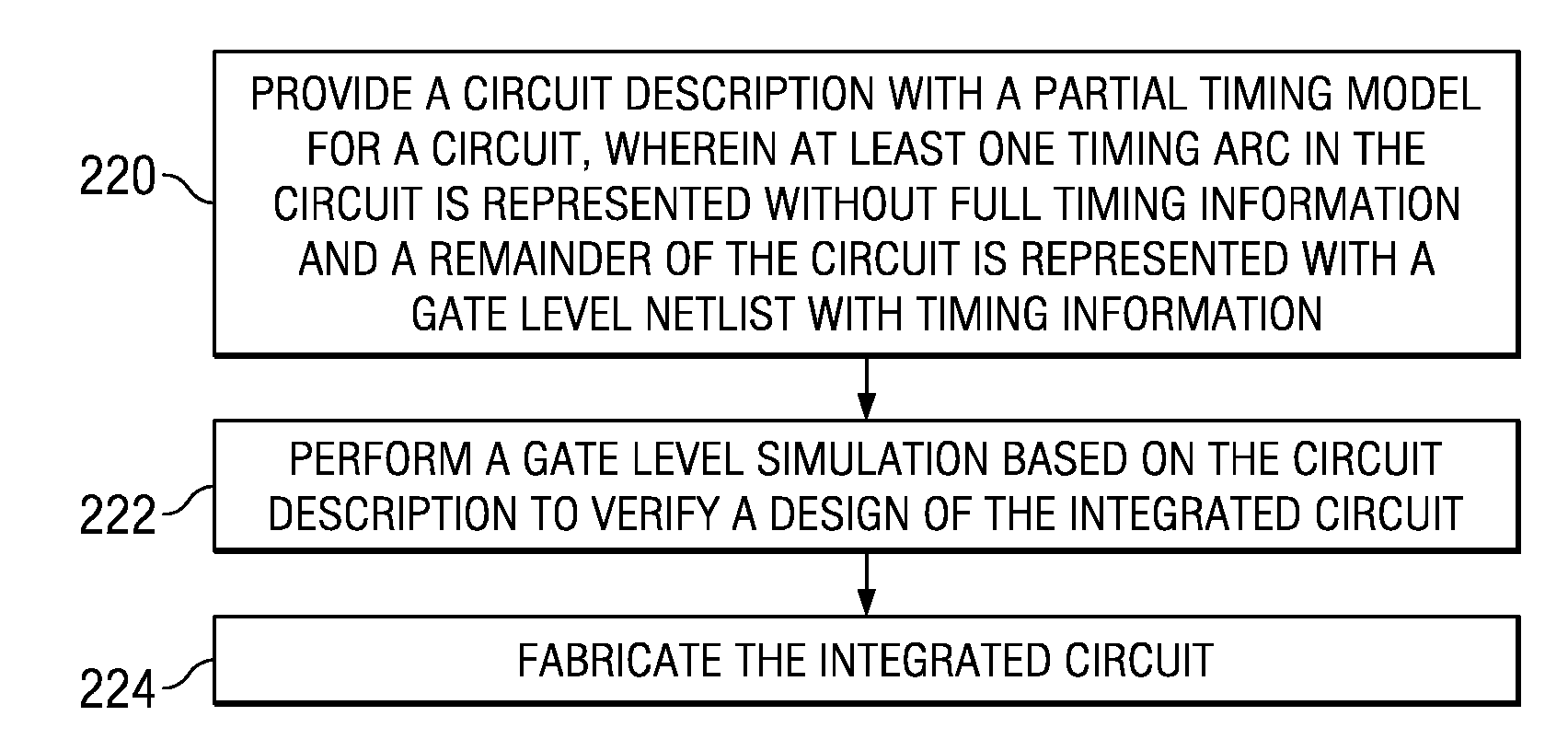

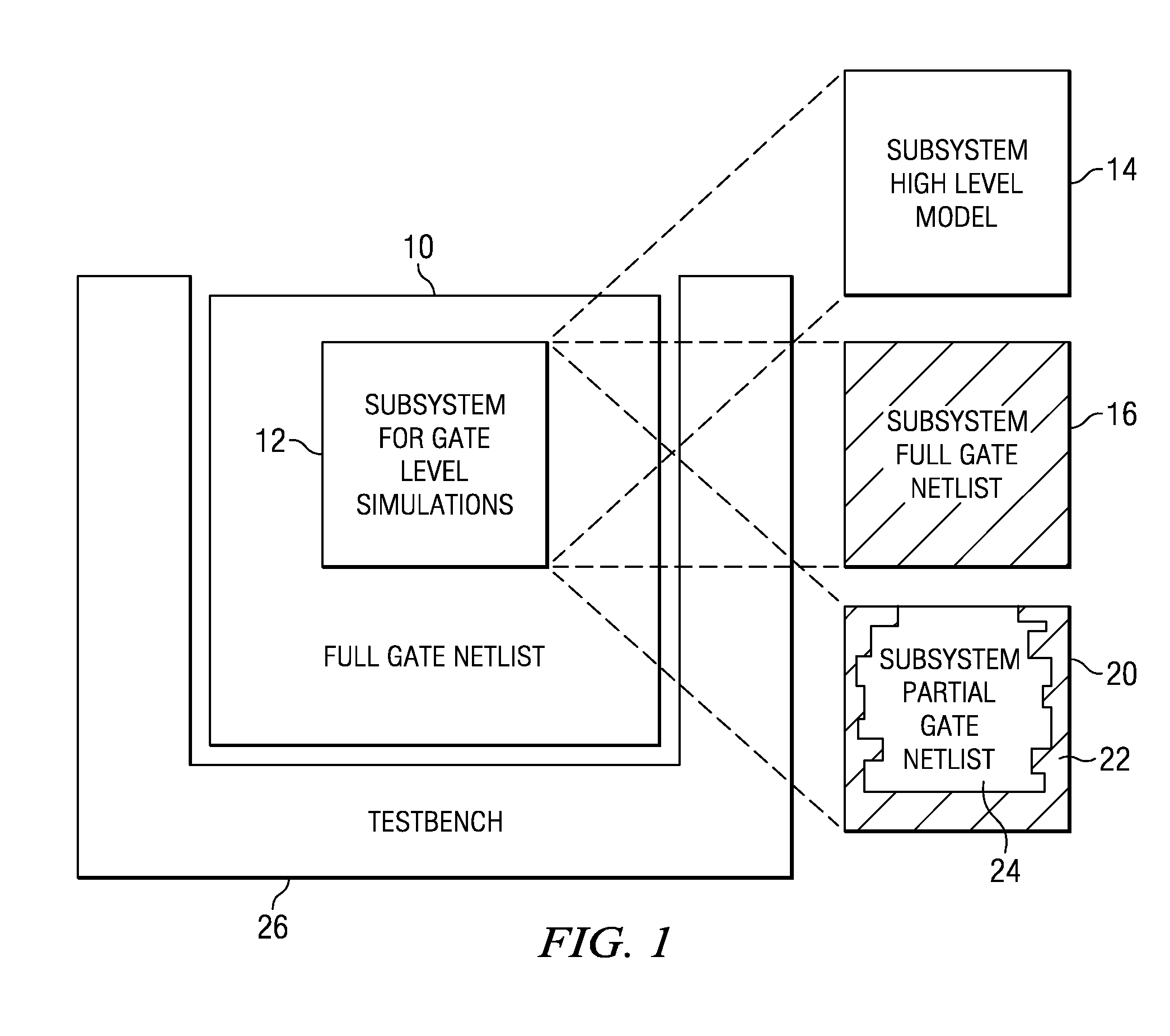

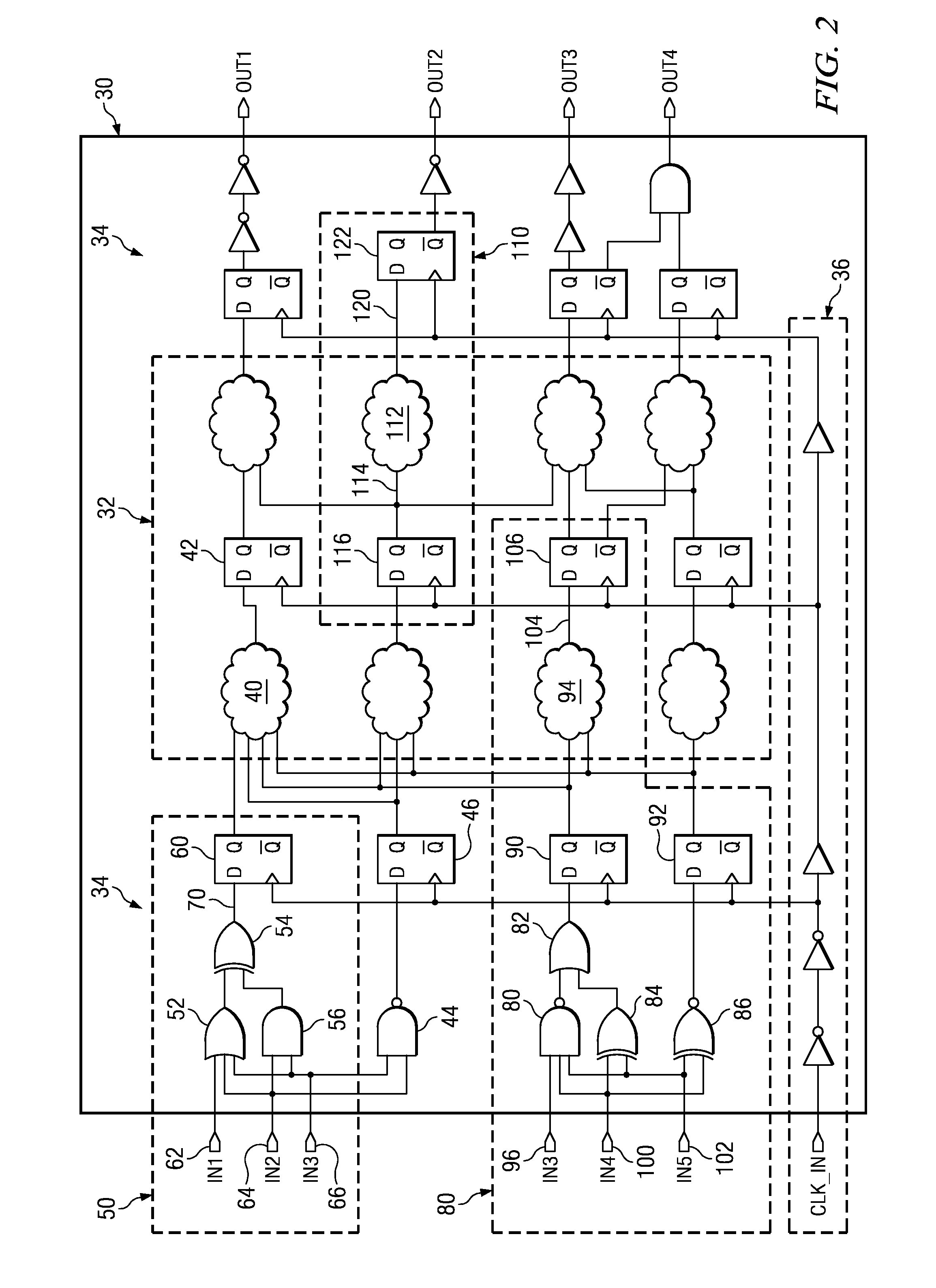

Partial Timing Modeling for Gate Level Simulation

ActiveUS20100031209A1Computer aided designSoftware simulation/interpretation/emulationComputer architectureComputerized system

Various apparatuses, methods and systems for creating an integrated circuit and performing a gate level simulation of a circuit are disclosed herein. For example, some embodiments of the present invention provide a system for performing a gate level simulation of a circuit including a computer system, a design verification tool and an output device. The design verification tool, executable on the computer system, includes a simulator and a partial timing model generator. The partial timing model generator is operable to generate a representation of the circuit for simulation by cutting a first portion of a circuit out of a full gate level netlist for the circuit and leaving a second portion of the circuit represented by the full gate level netlist, and to overlay a simplified representation of the first portion of the circuit over the representation of the circuit. The first portion of the circuit is cut out at timing paths. The simulator is operable to perform a gate level simulation of the circuit based on the representation of the circuit. The output device is connected to the computer system and is operable to provide an indication of a result of the gate level simulation of the circuit.

Owner:TEXAS INSTR INC

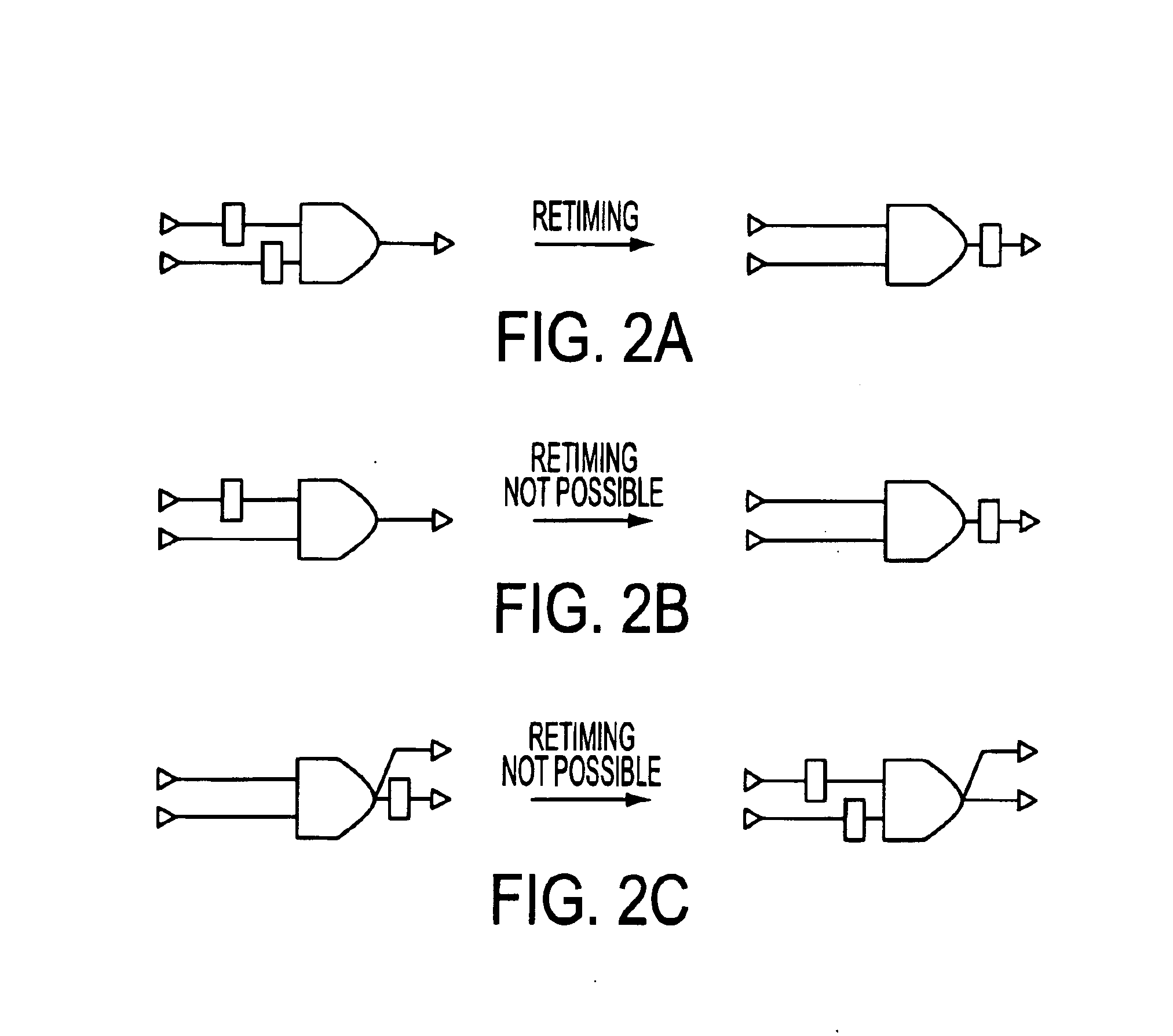

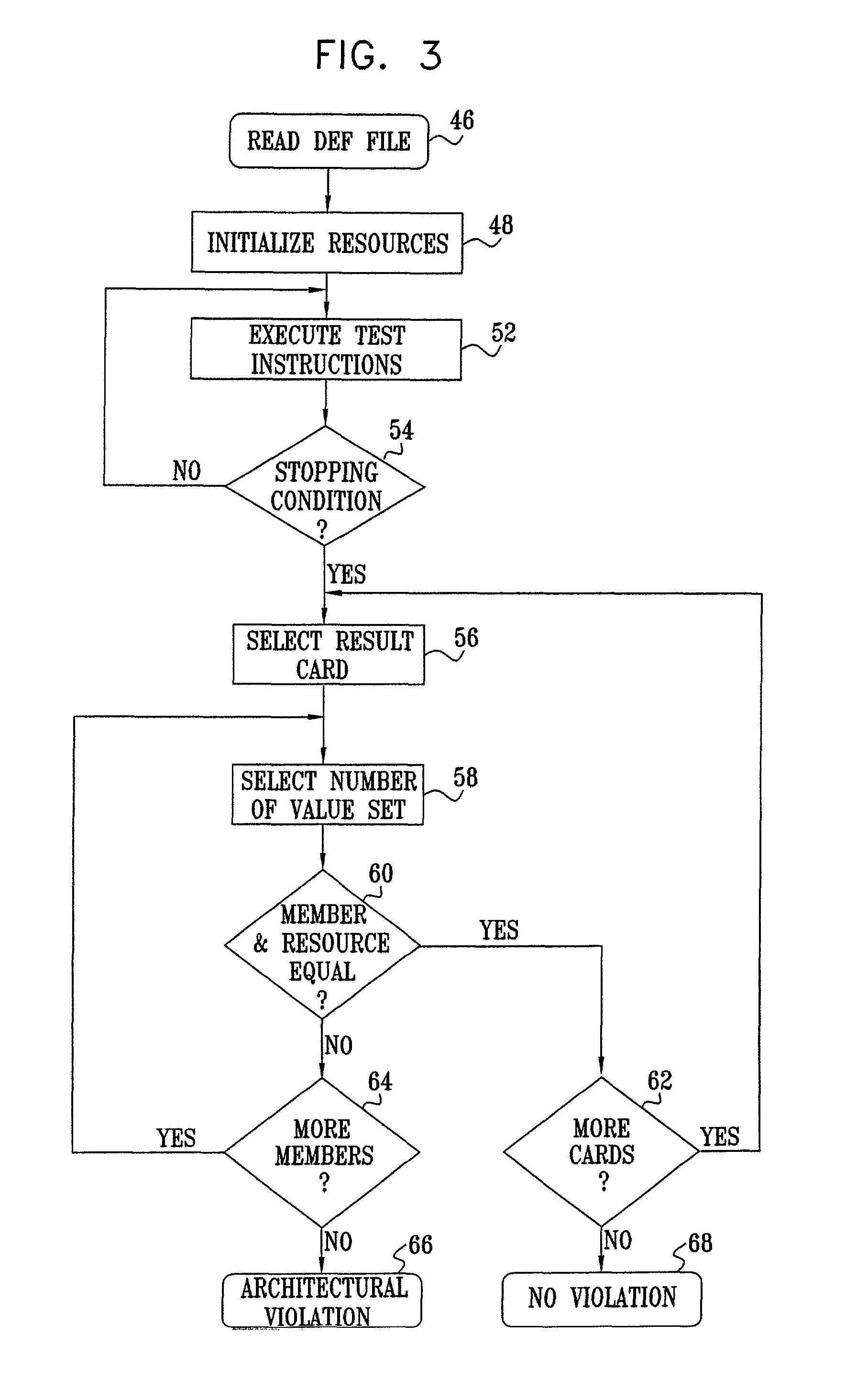

Method for design validation using retiming

InactiveUS6874135B2Minimize the numberReduce complexityDetecting faulty computer hardwareCAD circuit designDesign testingTest sequence

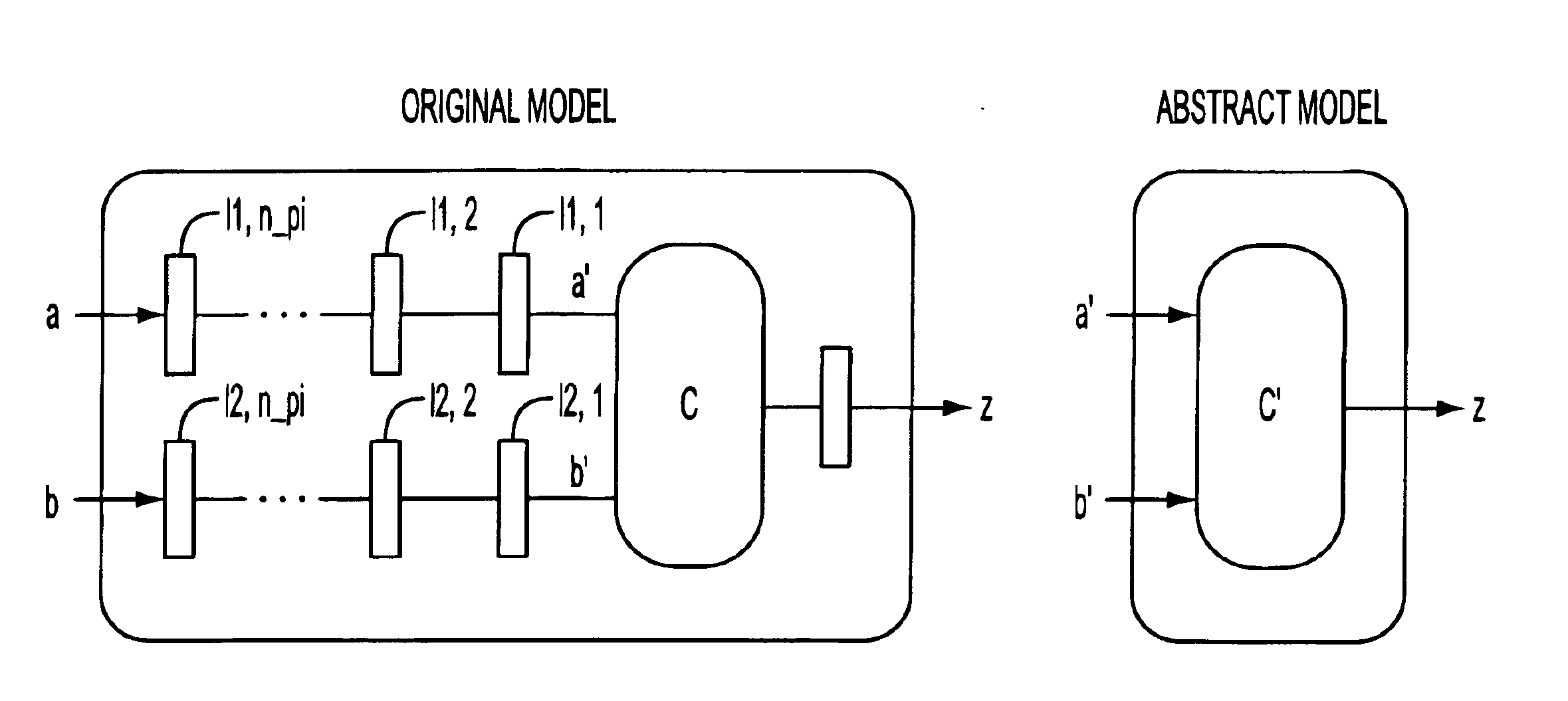

A method for derivation and abstraction of test models for validation of industrial designs using guided simulation is described. The method employs automatic abstractions for the test model which reduce its complexity while preserving the class of errors that can be detected by a transition tour. A method for design validation comprising generating a state-based test model of the design. The test model is abstracted by retiming and latch removal. Finally, a validation technique is applied on the abstracted test model. First, the number of internal (non-peripheral) latches in a design is minimized via retiming using a method of Maximal Peripheral Retiming (MPR). According to the MPR method, internal latches are retimed to the periphery of the circuit. Subsequently, all latches that can be retimed to the periphery are automatically abstracted in the test model. The validation technique may comprise of model checking, invariant checking or simulation using test sequences generated from the abstracted test model.

Owner:NEC CORP

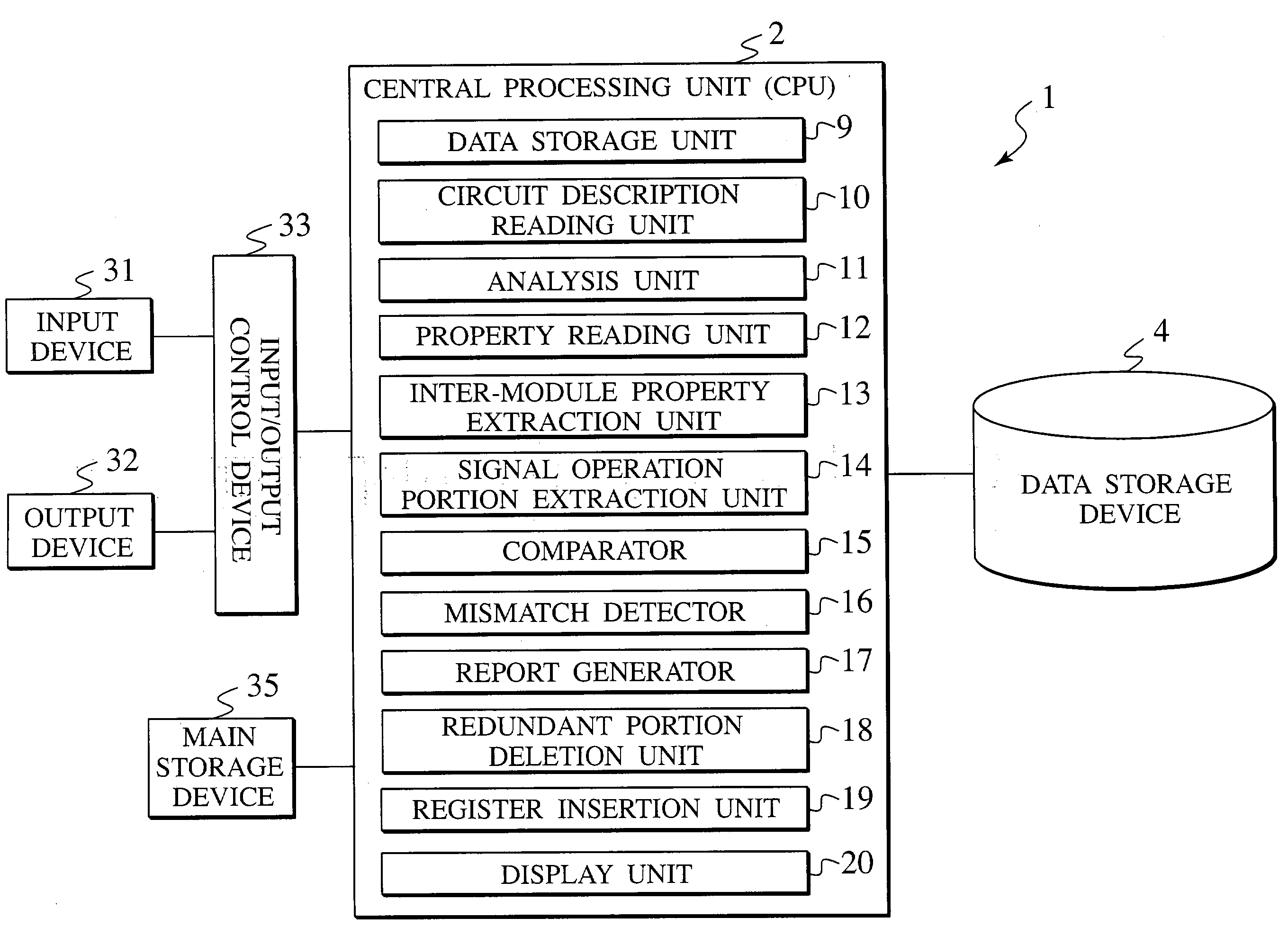

LSI design verification apparatus, LSI design verification method, and LSI design verification program

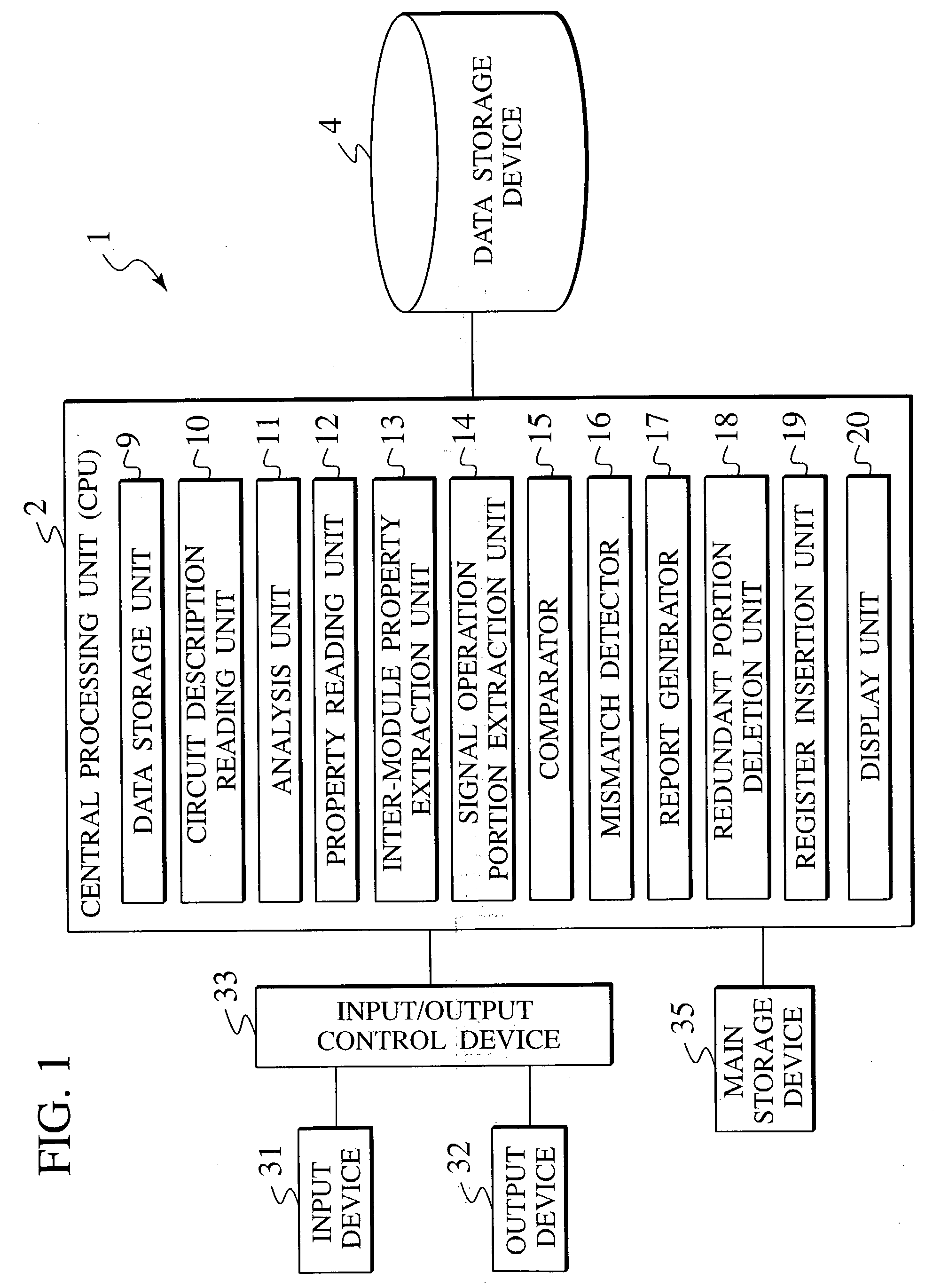

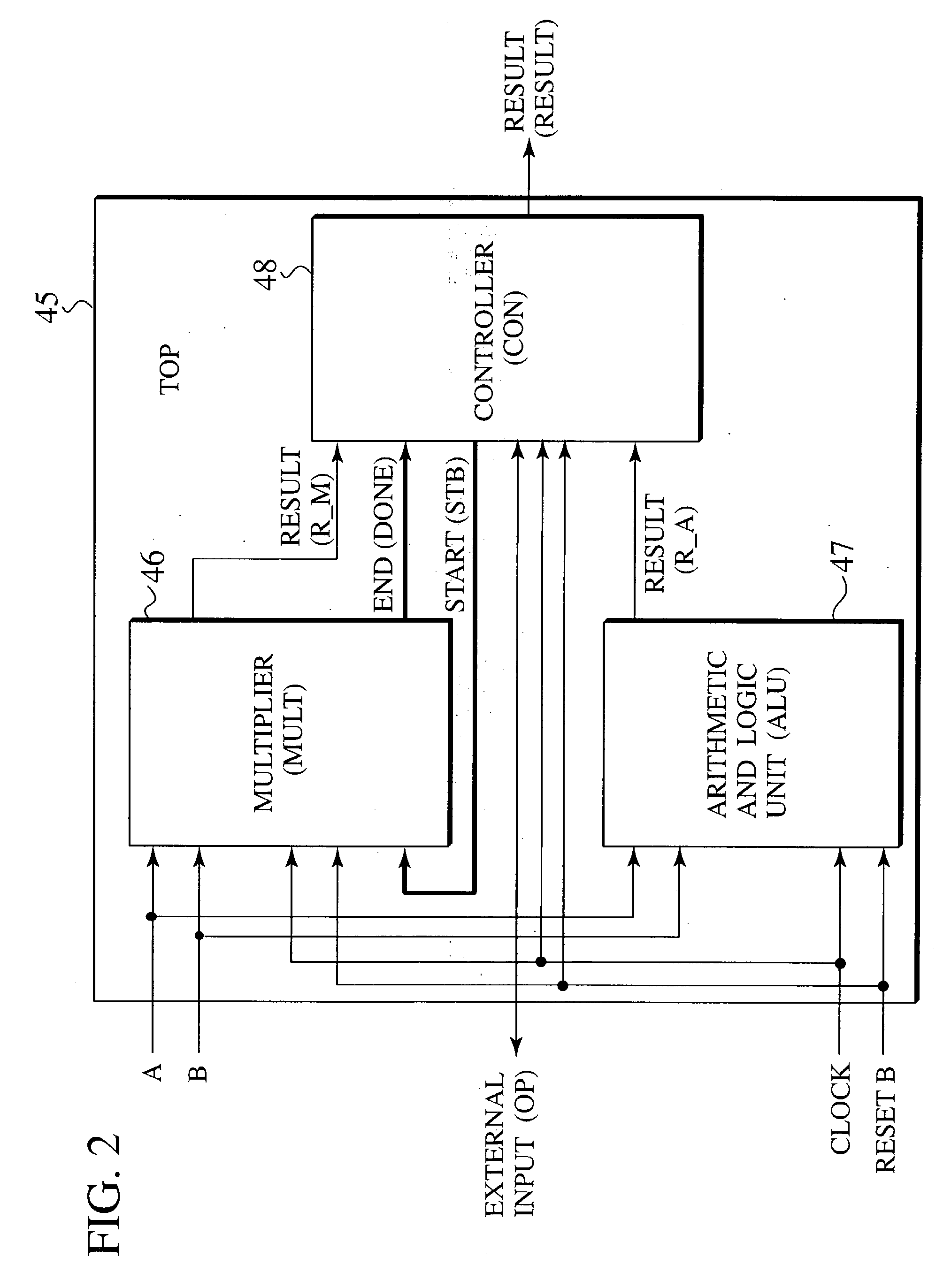

InactiveUS20030125920A1Electronic circuit testingSemiconductor/solid-state device manufacturingComputer architectureValidation methods

A computer implemented method for design verification using logical simulation of a circuit description having a plurality of hierarchies from top to bottom in accordance with abstraction of circuit components, which have an arithmetic and logic function, reads the circuit description and analyzes signal connection topologies between the hierarchies of the circuit description from top to bottom. The method stores the data of the signal connection topologies. The method reads properties of target modules implemented by the circuit components in the circuit description. The method extracts a property part having a signal communicating between the target modules. The method extracts an output operation property, defining output operation of an output side module, and an expecting operation property, defining an expecting operation of an input side module among the properties of the target modules. The method compares the output operation properties with the expecting operation properties.

Owner:KK TOSHIBA

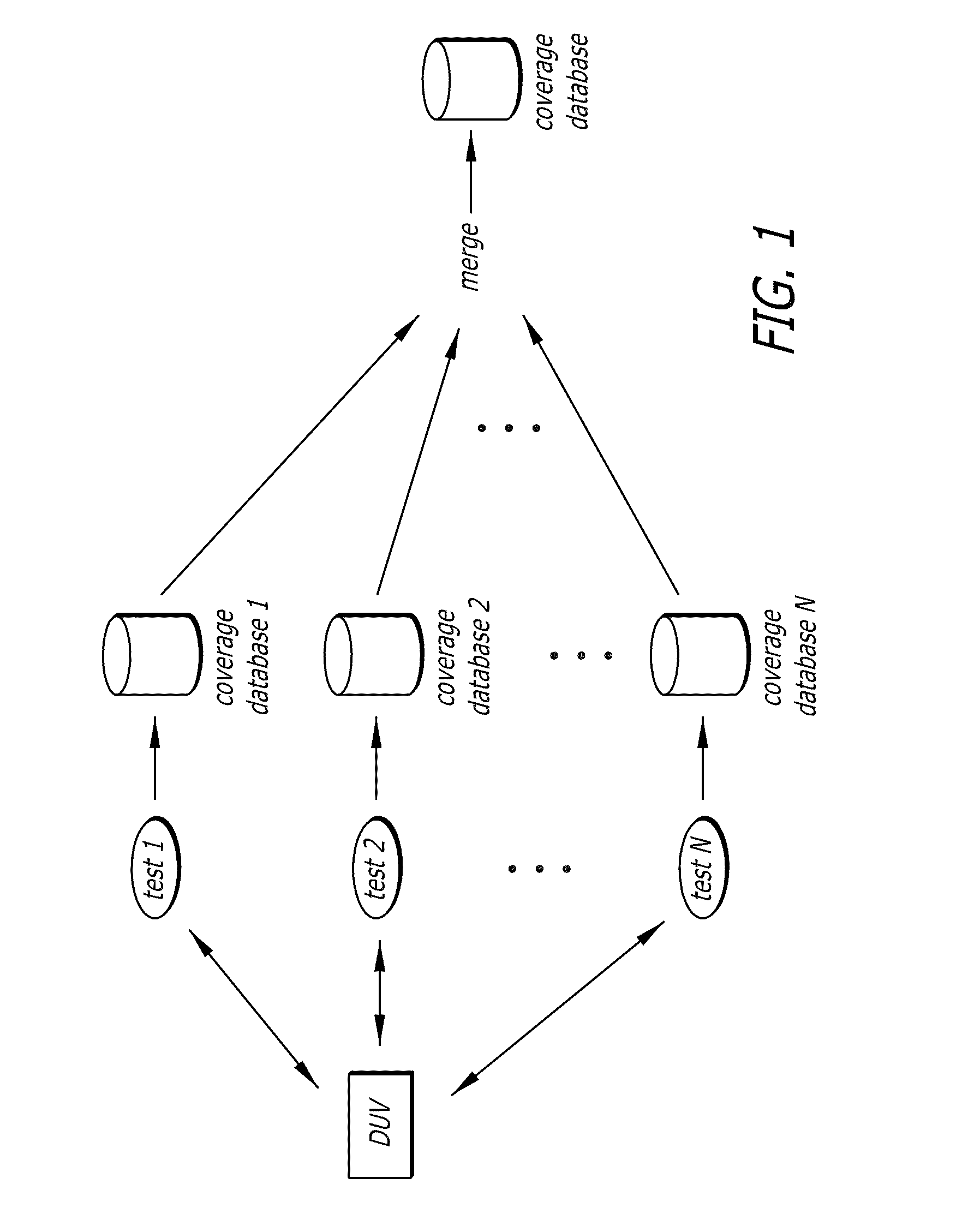

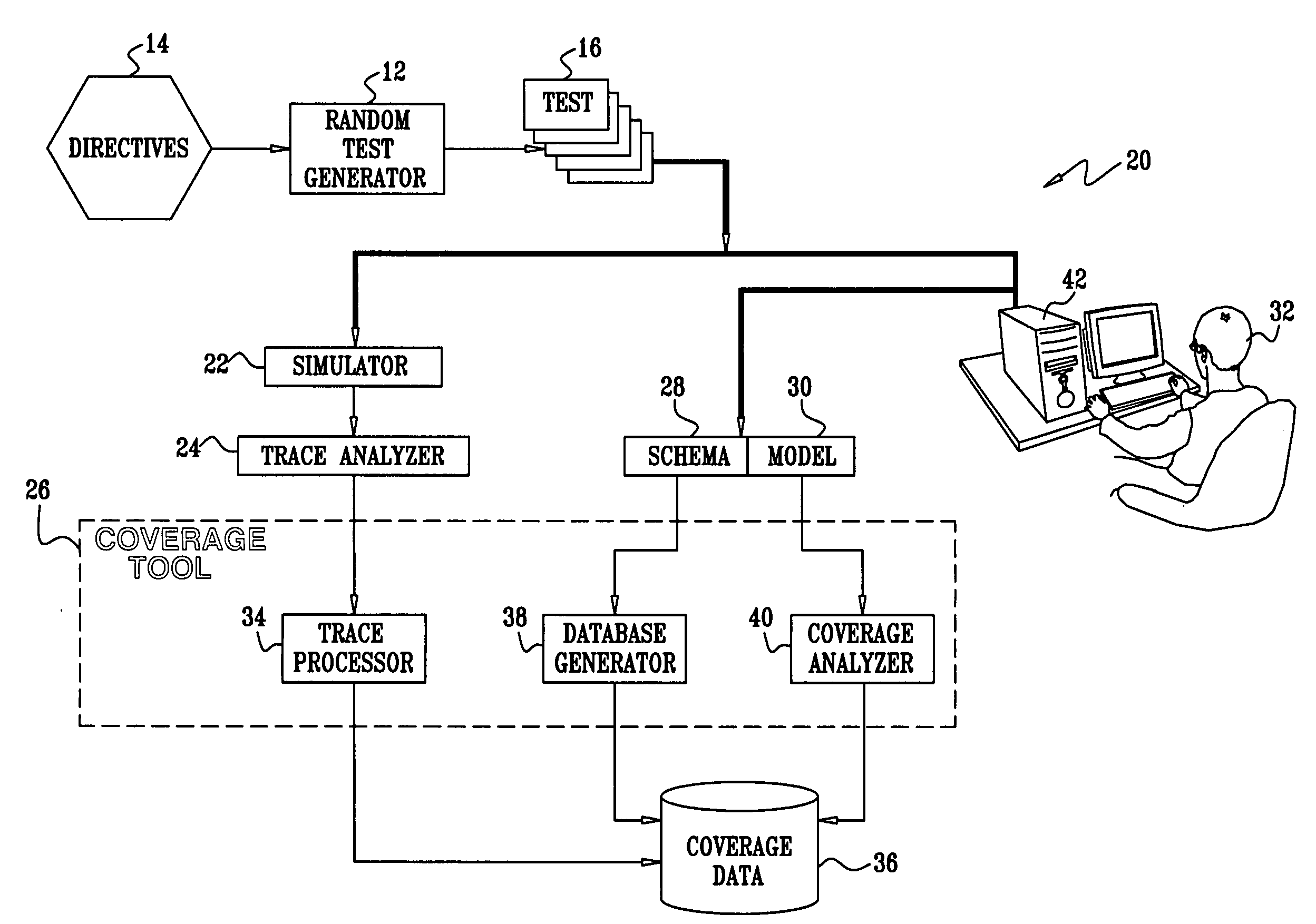

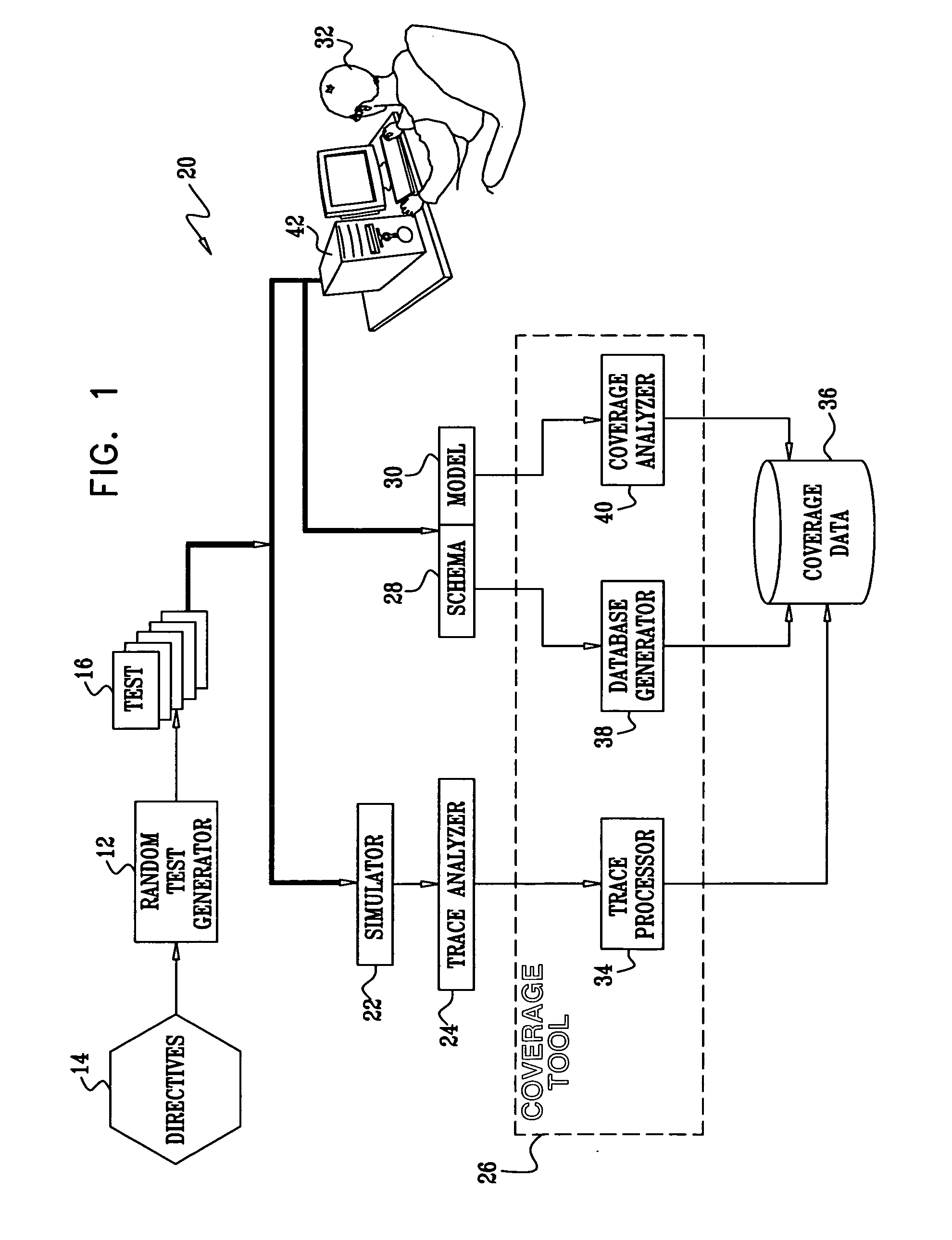

Hole query for functional coverage analysis

ActiveUS20070168727A1Simplify the viewing processDetecting faulty computer hardwareElectrical testingTest suiteData mining

Functional coverage techniques during design verification using cross-product coverage models and hole analysis are enhanced by the use of coverage queries. After running a test suite, a core set of non-covered events is specified. A coverage query is then automatically constructed and executed on the test results to identify a hole in the functional coverage that satisfies conditions of the coverage query and includes the core set. The results of the query are presented as a simplified view of the coverage of the events in the cross-product space. Use of coverage queries allows a verification team to focus on specific areas of interest in the coverage space and to deal practically with highly complex coverage models. It also avoids the burden of producing and evaluating complete hole analysis reports.

Owner:SAP AG

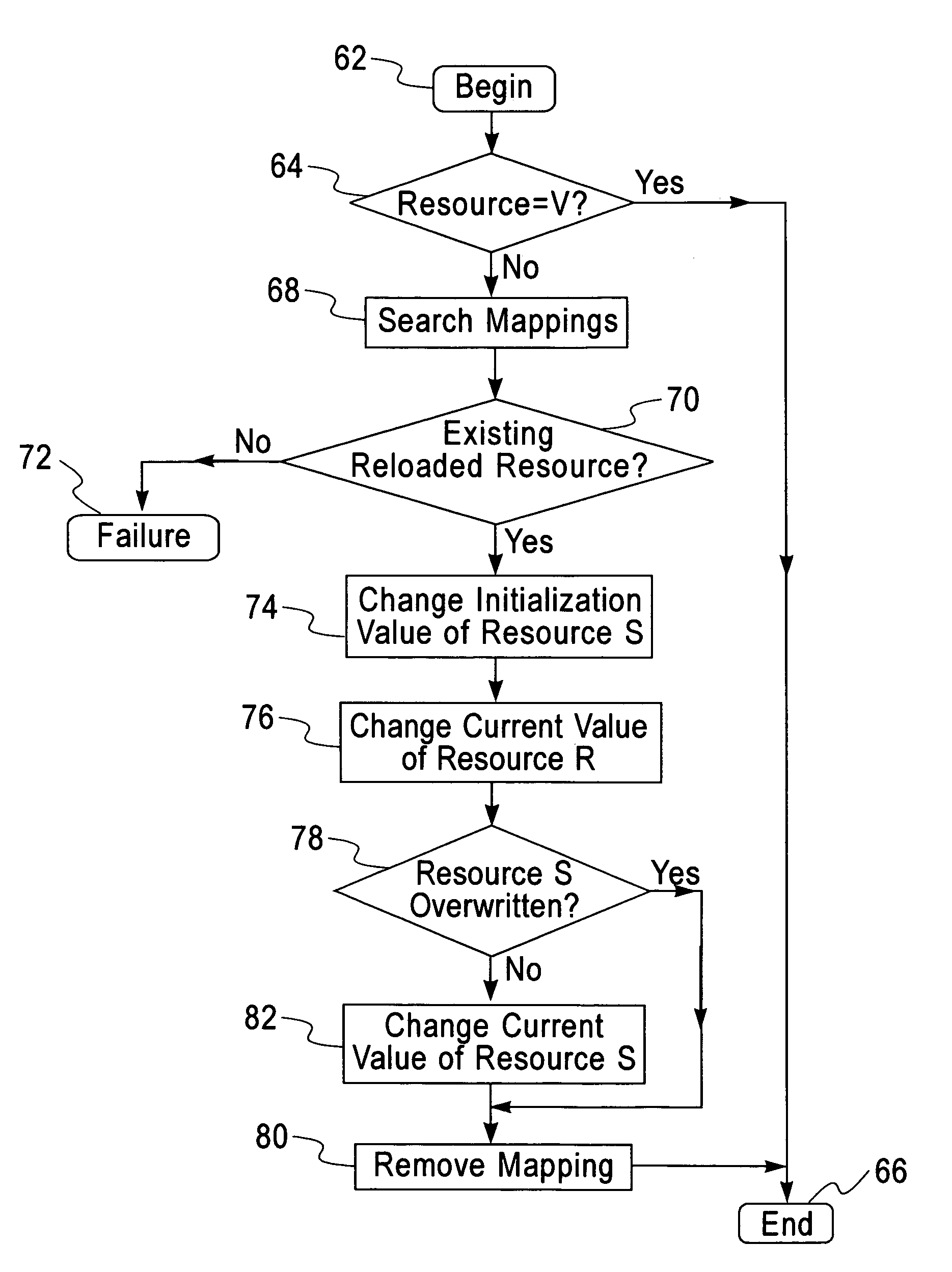

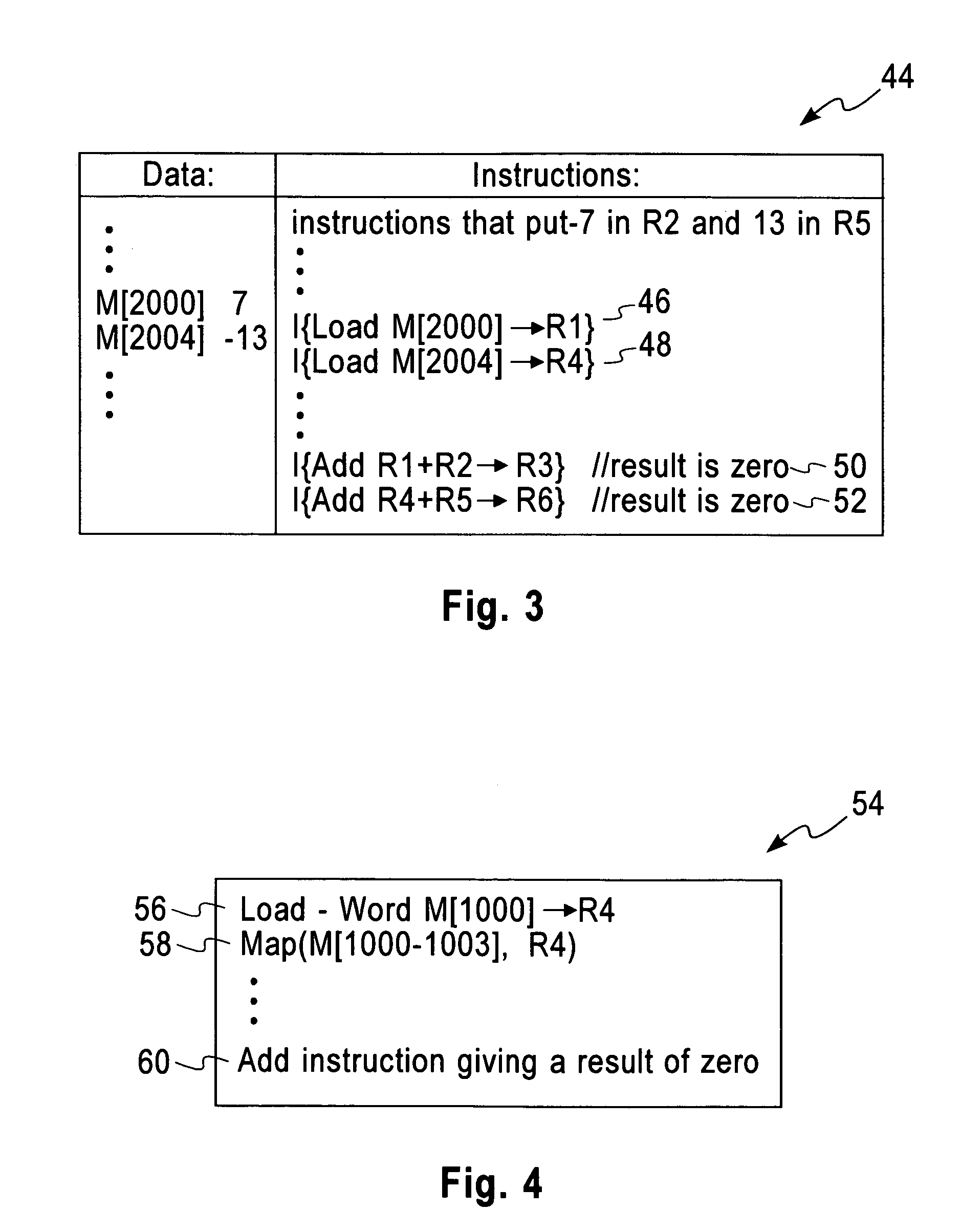

Test quality through resource reallocation

InactiveUS7133816B2Less resourcesInterference minimizationError detection/correctionEmergency protective arrangements for automatic disconnectionProgramming languageLoad instruction

A preemptive reloading technique is employed in a test program generator. Initialized resources are reset with needed values by reloading instructions. The actual reloaded value is chosen later, when the instruction that actually needs the value is generated. The test program generator distances the reloading instruction from the instruction that actually needs the value, thus making it possible to avoid fixed test patterns and to generate interference-free test segments during design verification.

Owner:IBM CORP

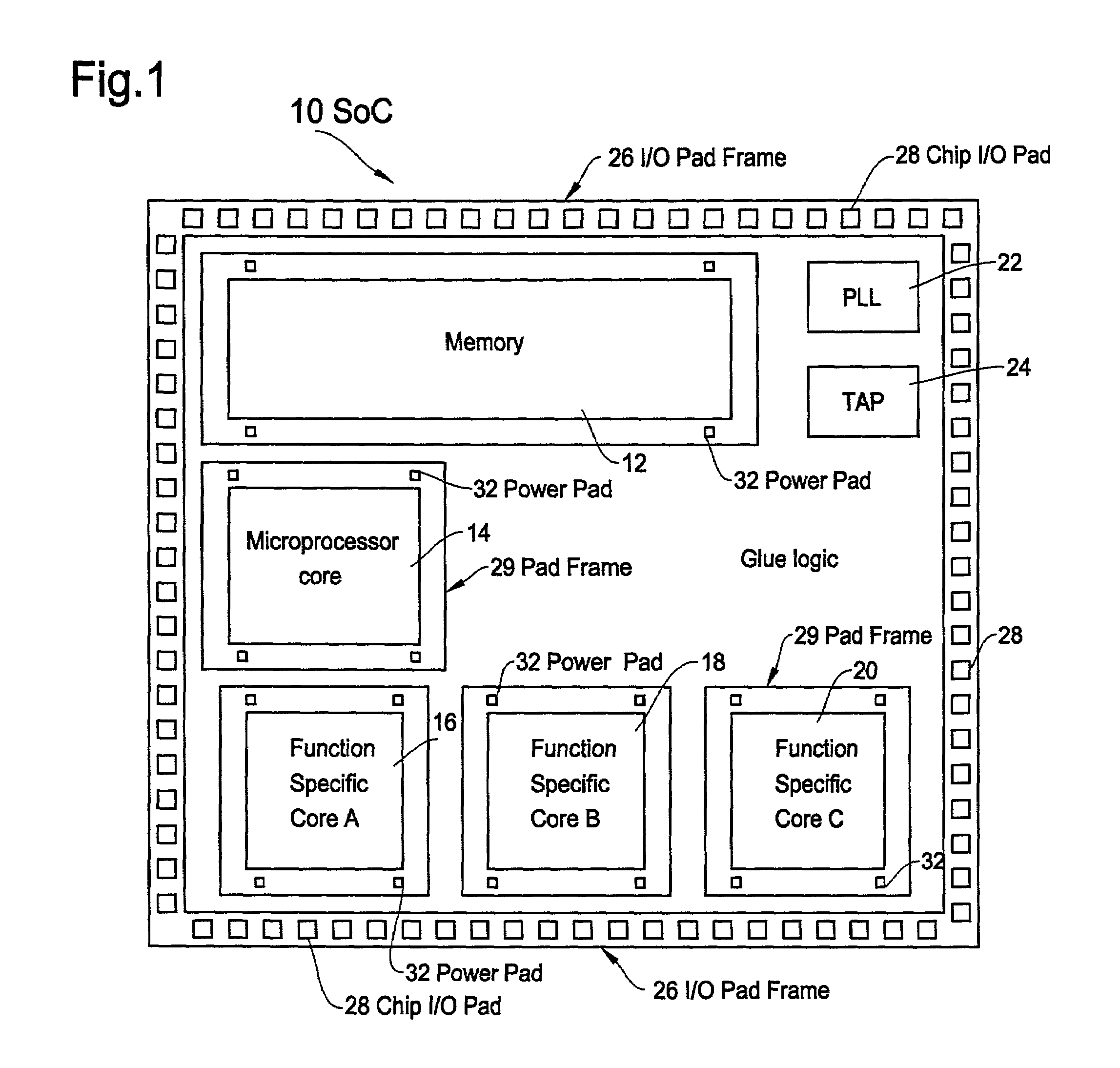

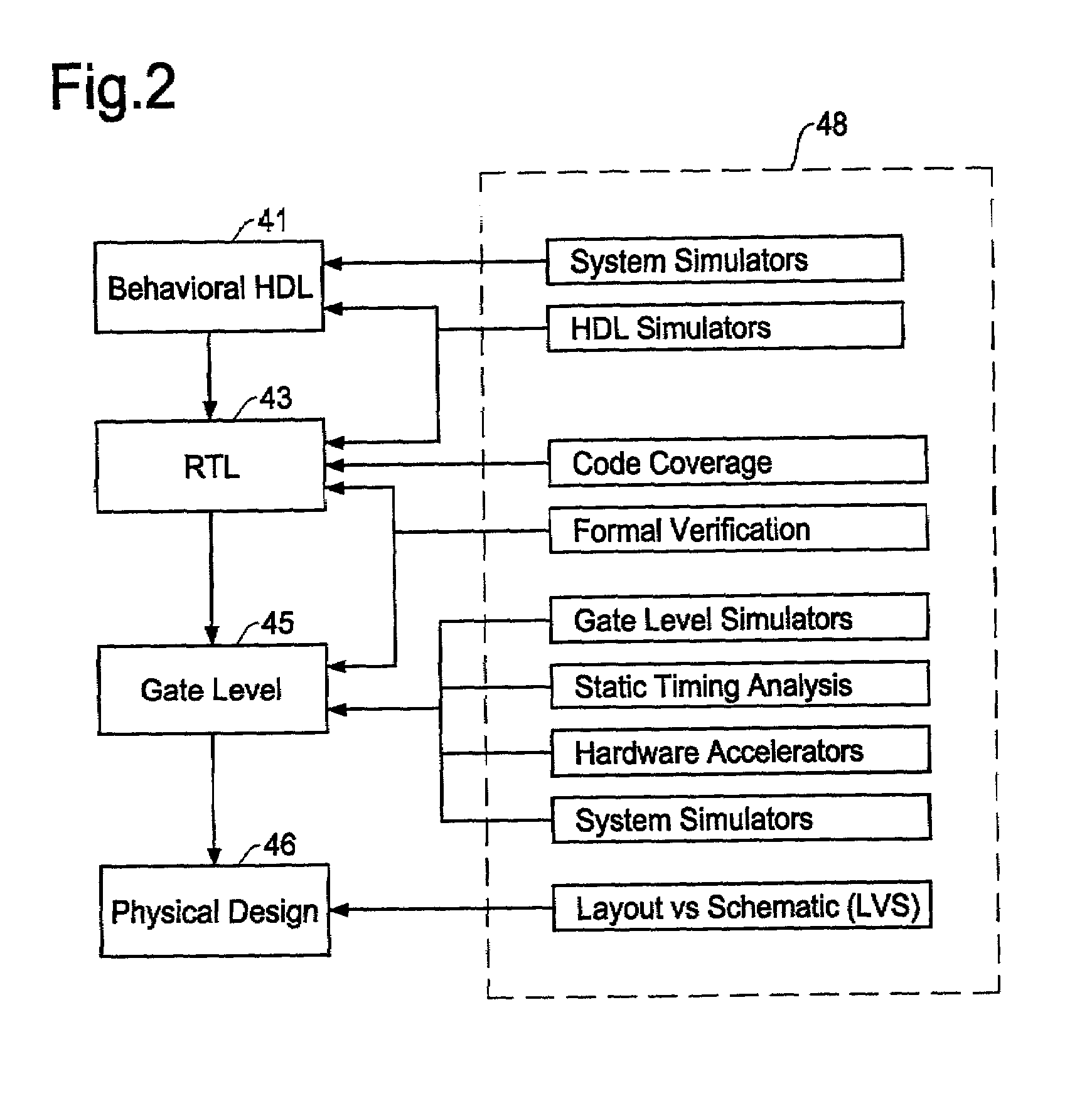

Method for design validation of complex IC

InactiveUS7089517B2Design errorSatisfied with the resultElectronic circuit testingAnalogue computers for electric apparatusComputer architectureDesign testing

A method for design validation of complex IC with use of a combination of electronic design automation (EDA) tools and a design test station at high speed and low cost. The EDA tools and device simulator are linked to the event based test system to execute the original design simulation vectors and testbench and make modifications in the testbench and event based test vectors until satisfactory results are obtained. The event based test vectors are test vectors in an event format in which an event is any change in a signal which is described by its timing and the event based test system is a test system for testing an IC by utilizing the event based test vectors. Because EDA tools are linked with the event based test system, these modifications are captured to generate a final testbench that provides satisfactory results.

Owner:ADVANTEST CORP

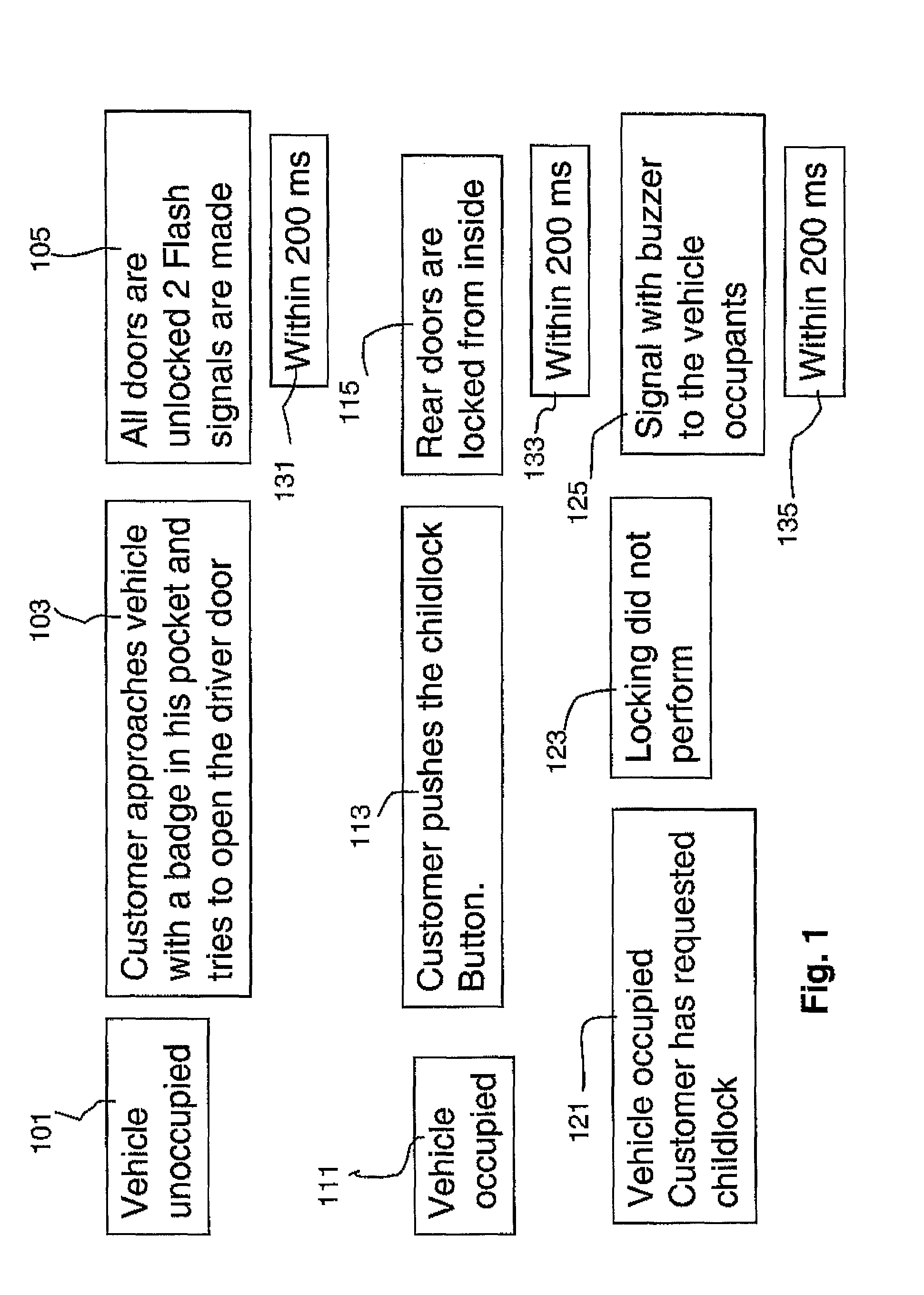

Validation method for embedded systems

InactiveUS20070192076A1Improve test coverageShorten the timeAdditive manufacturing apparatusAnalogue computers for electric apparatusControl flowValidation methods

A method of designing a validation environment for a service implemented by an embedded electrical system. In the method one or more user requests and system responses are assigned. Next, a behavioral automata is assigned to the service, which fixes the allowed sequencing of the user requests and system responses. Then, a skeleton validation environment is automatically generated for the service. The skeleton validation environment includes testing automata produced from a traversal of the behavioral automata, a model of initial conditions, models of user requests, models of system response accuracy, an environmental model, and the dataflow and control flow assembling these models together. The skeleton validation environment covers all user requests and resultant system responses of the service. The skeleton validation environment is then recorded in a computer readable memory device for use by a design validation tool.

Owner:RENAULT SA

FPGA (filed programmable gate array) fault automatic diagnosing method based on knowledge database

InactiveCN103473409AImprove scalabilitySolve the problem of poor matchingSpecial data processing applicationsGate arrayFpga design

The invention discloses an FPGA (filed programmable gate array) fault automatic diagnosing method based on a knowledge database. The method includes: structuralizing fault information during storage FPGA design and verification; performing fault search according to feature information a new fault case, matching most related and similar fault information according to information such as fault generation and fault feature, and displaying detailed contents and fault solutions to solve the new fault. Acquired fault experience and methods during FPGA design verification are used to build a knowledge database system, detailed fault information and solutions are displayed visually, faults can be positioned accurately, conveniently and fast, and fault debugging and solving efficiency of FPGA design verification staff is increased greatly.

Owner:ZHEJIANG UNIV

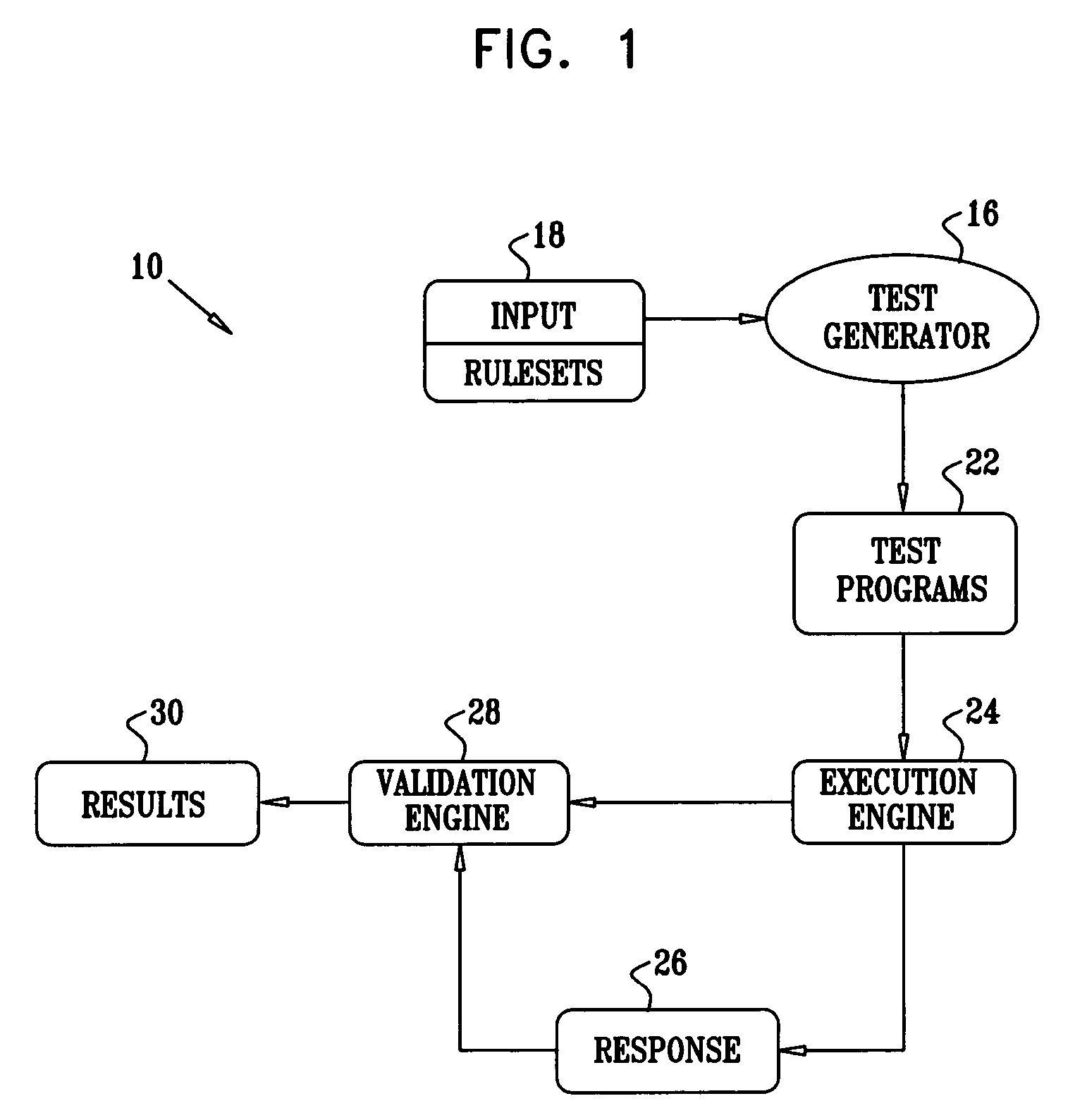

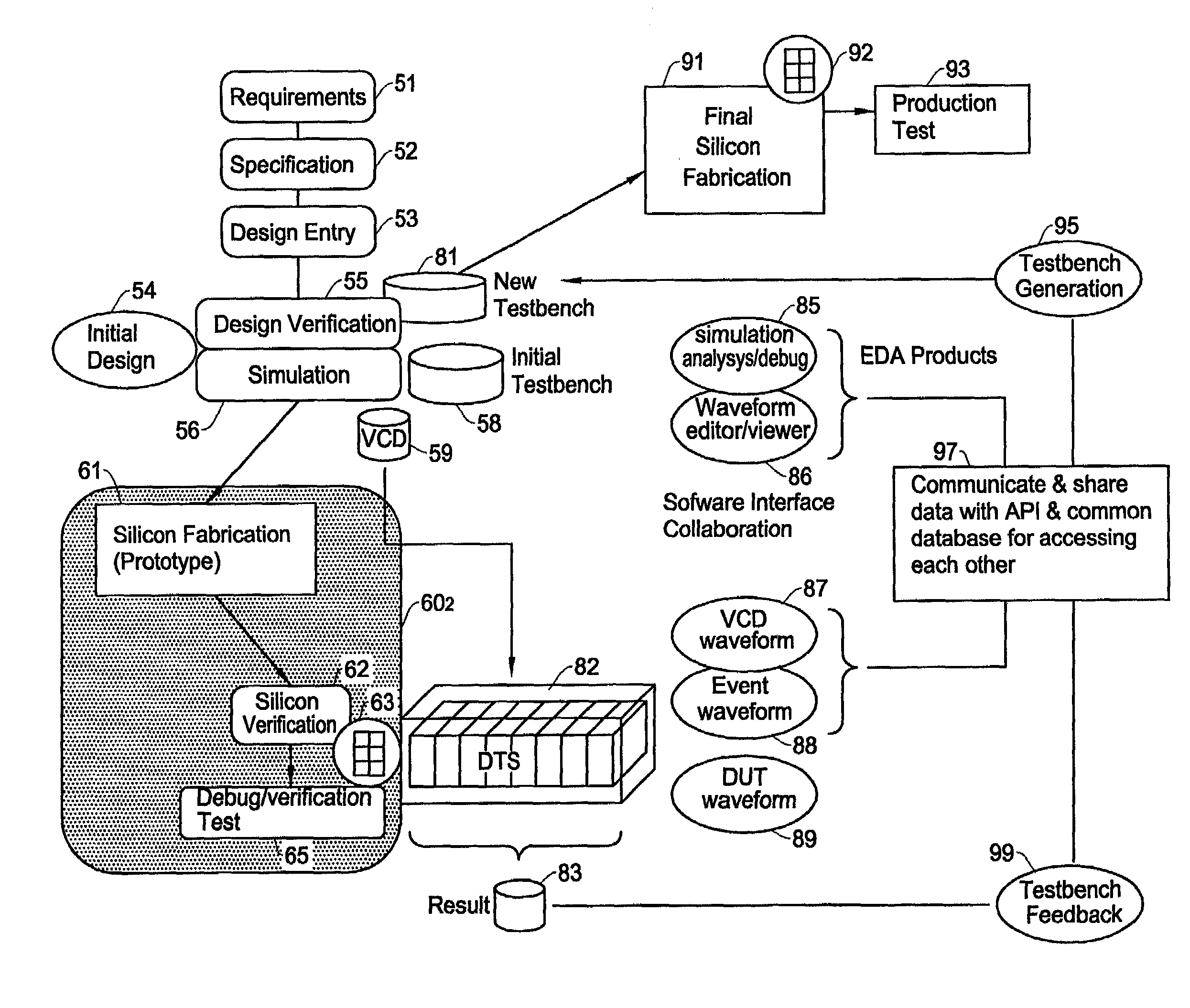

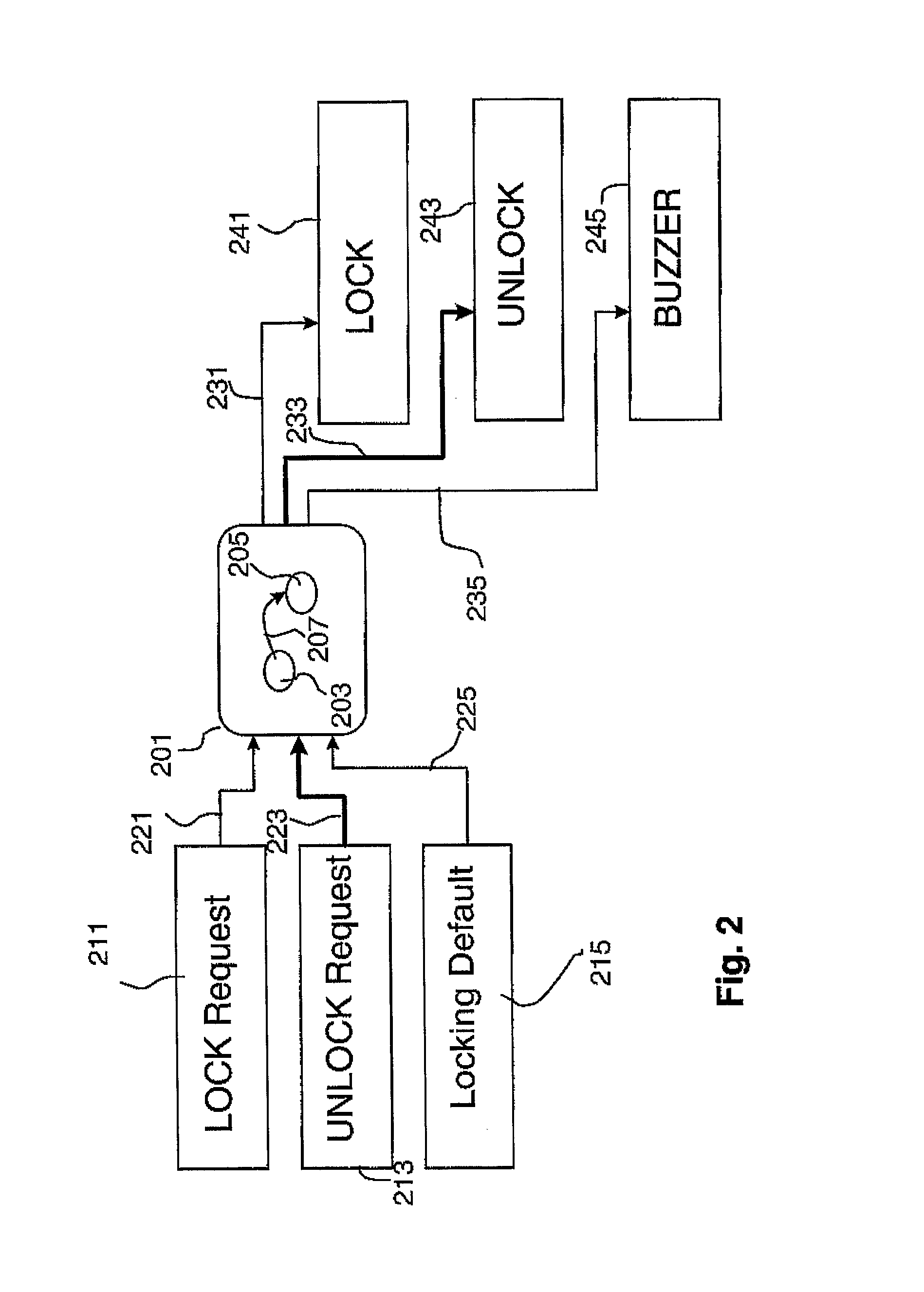

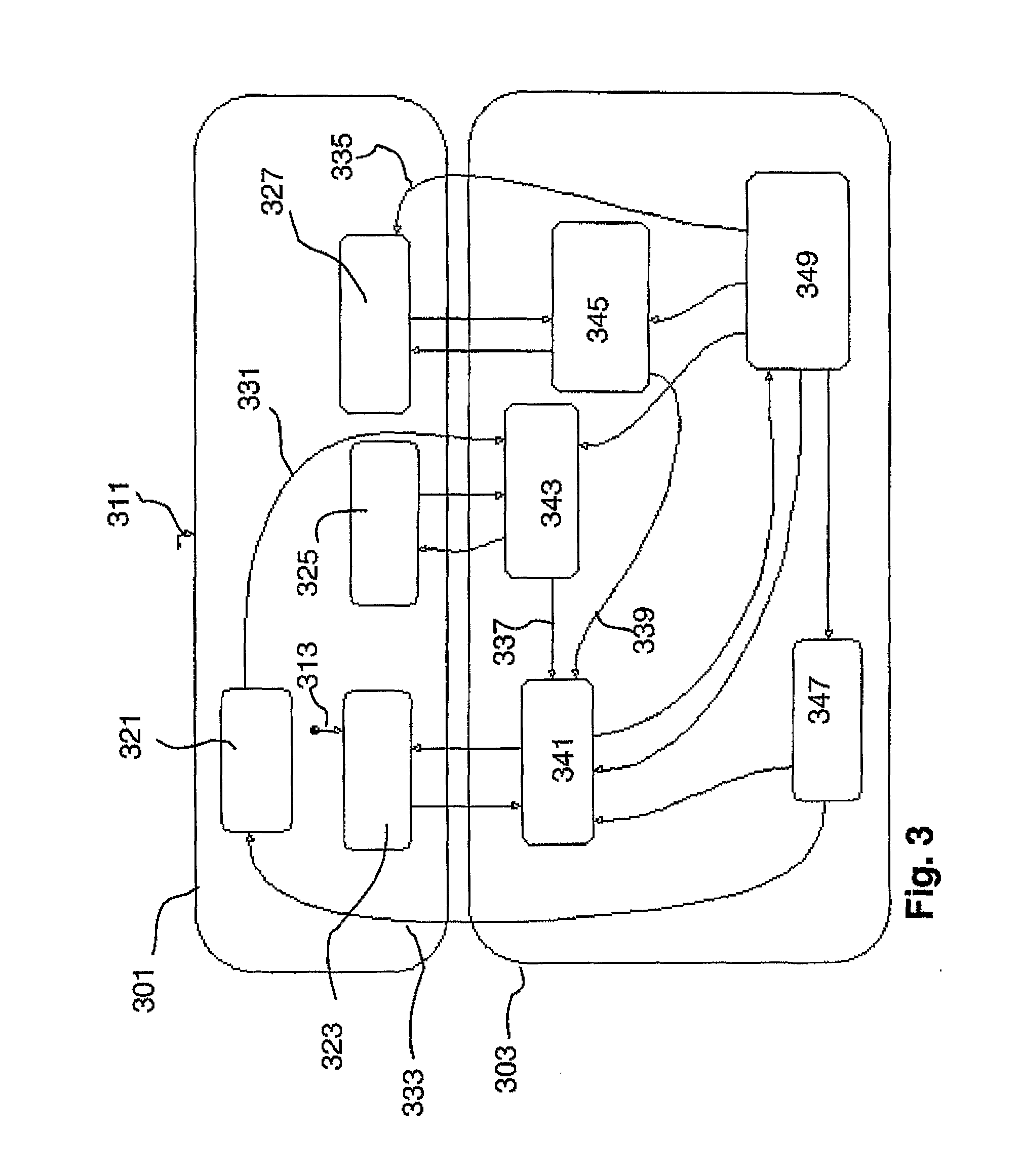

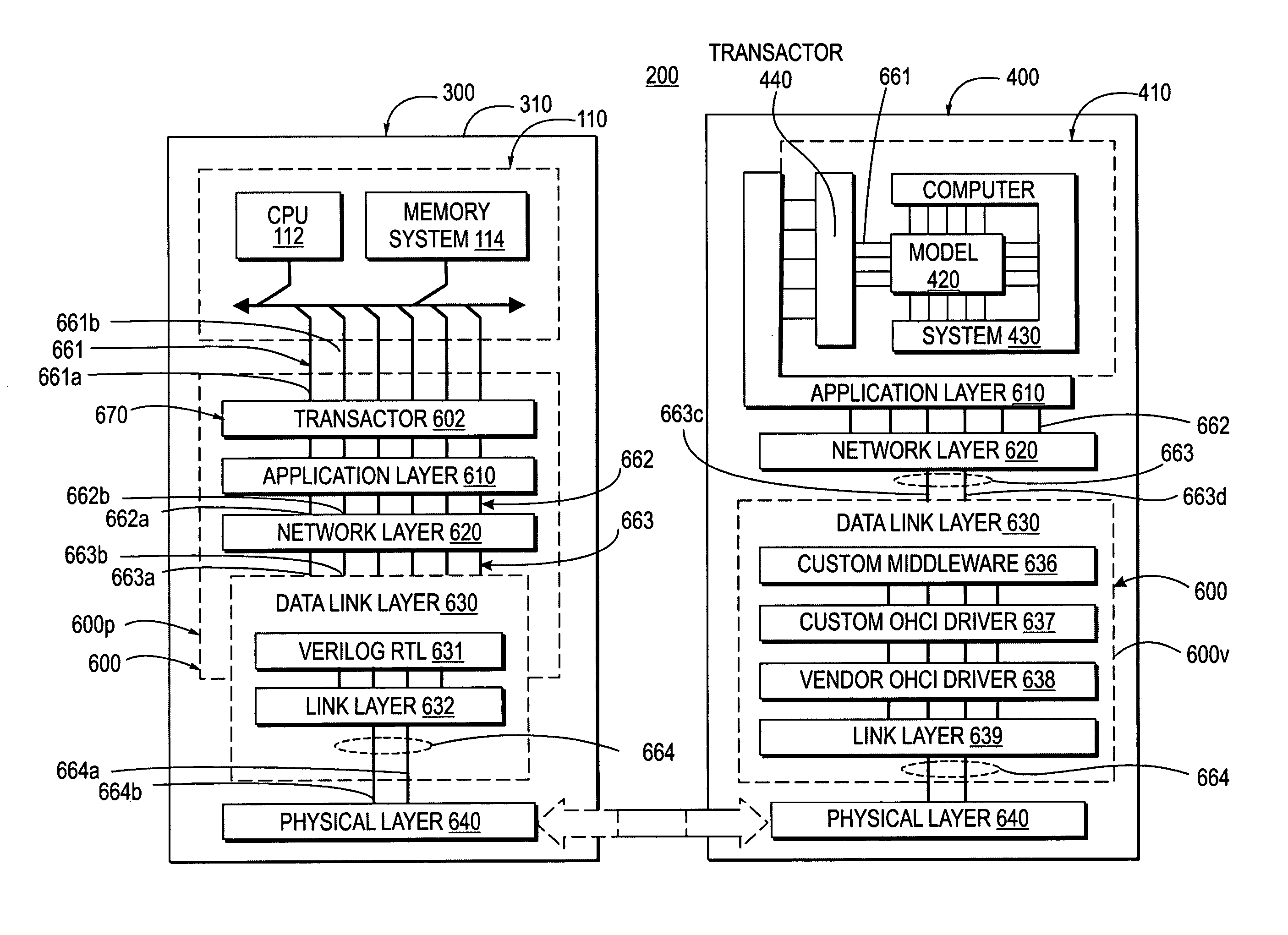

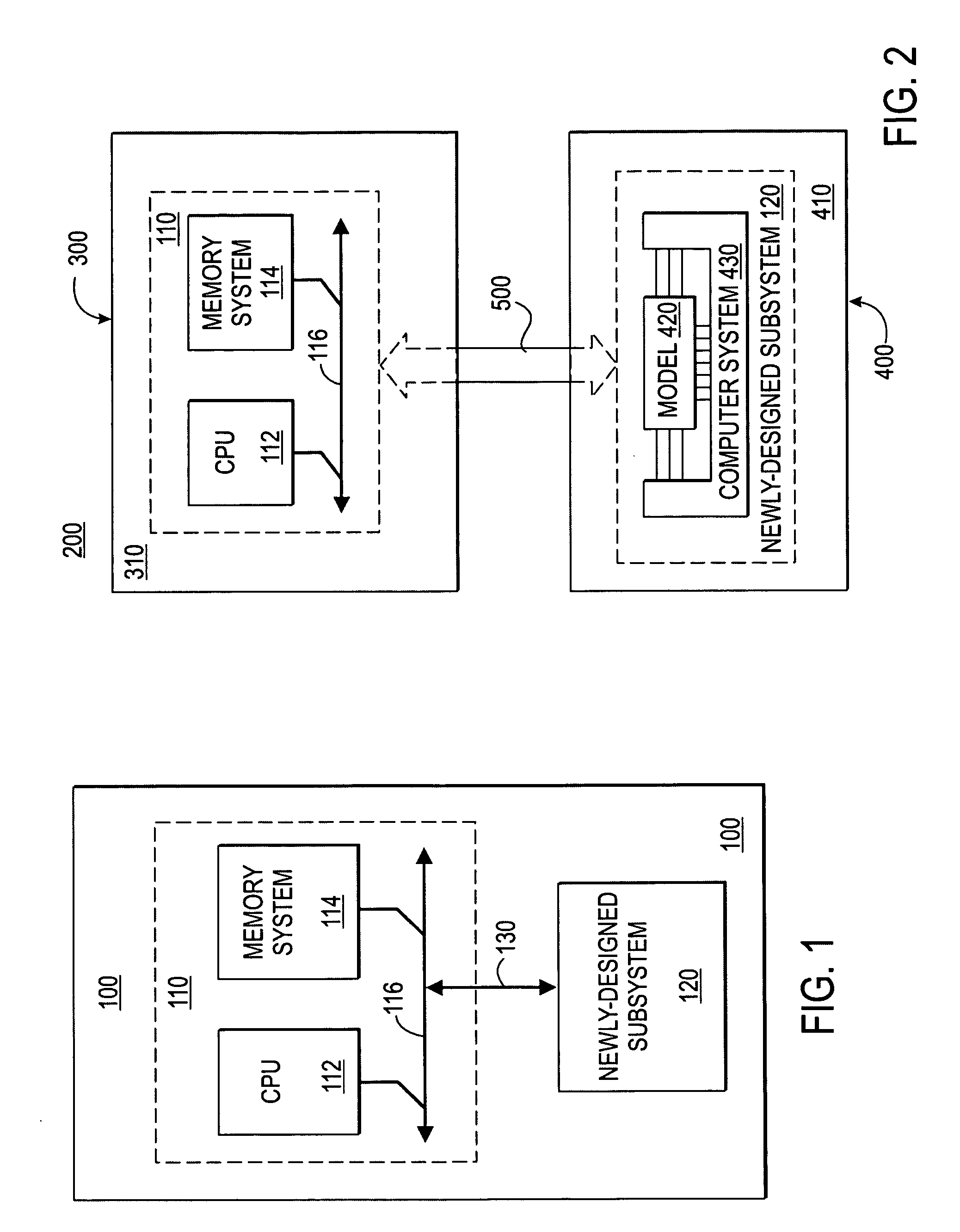

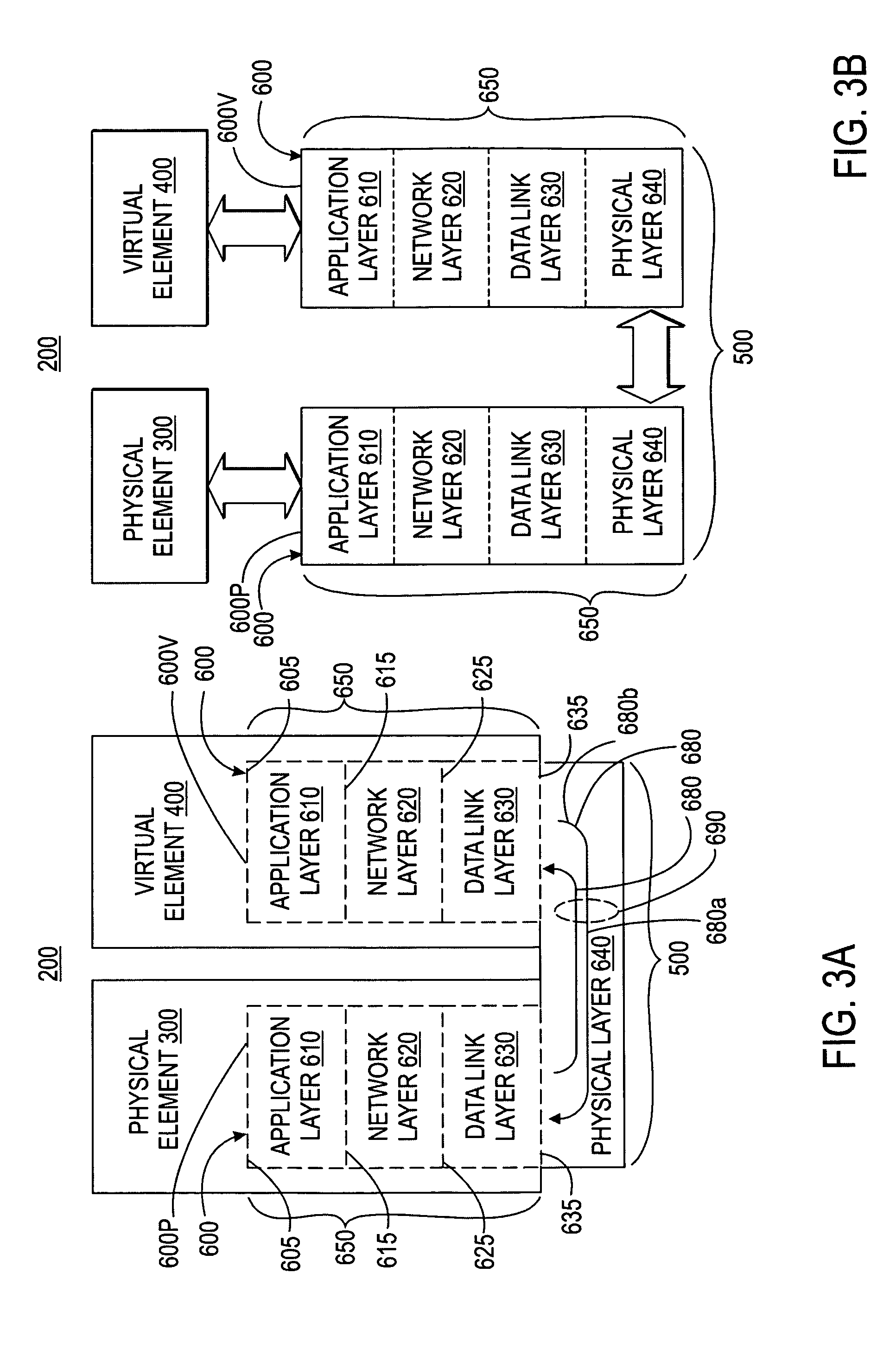

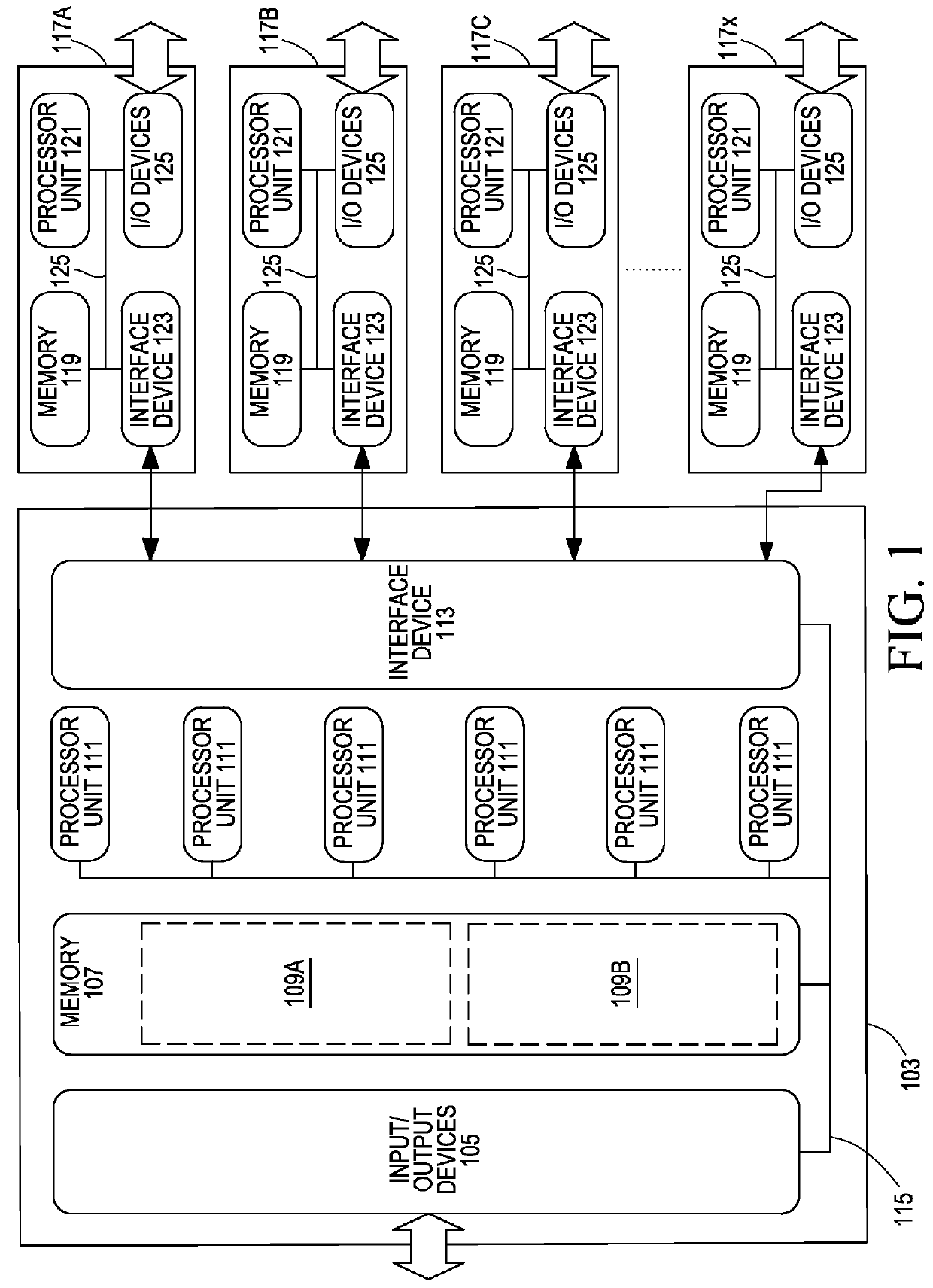

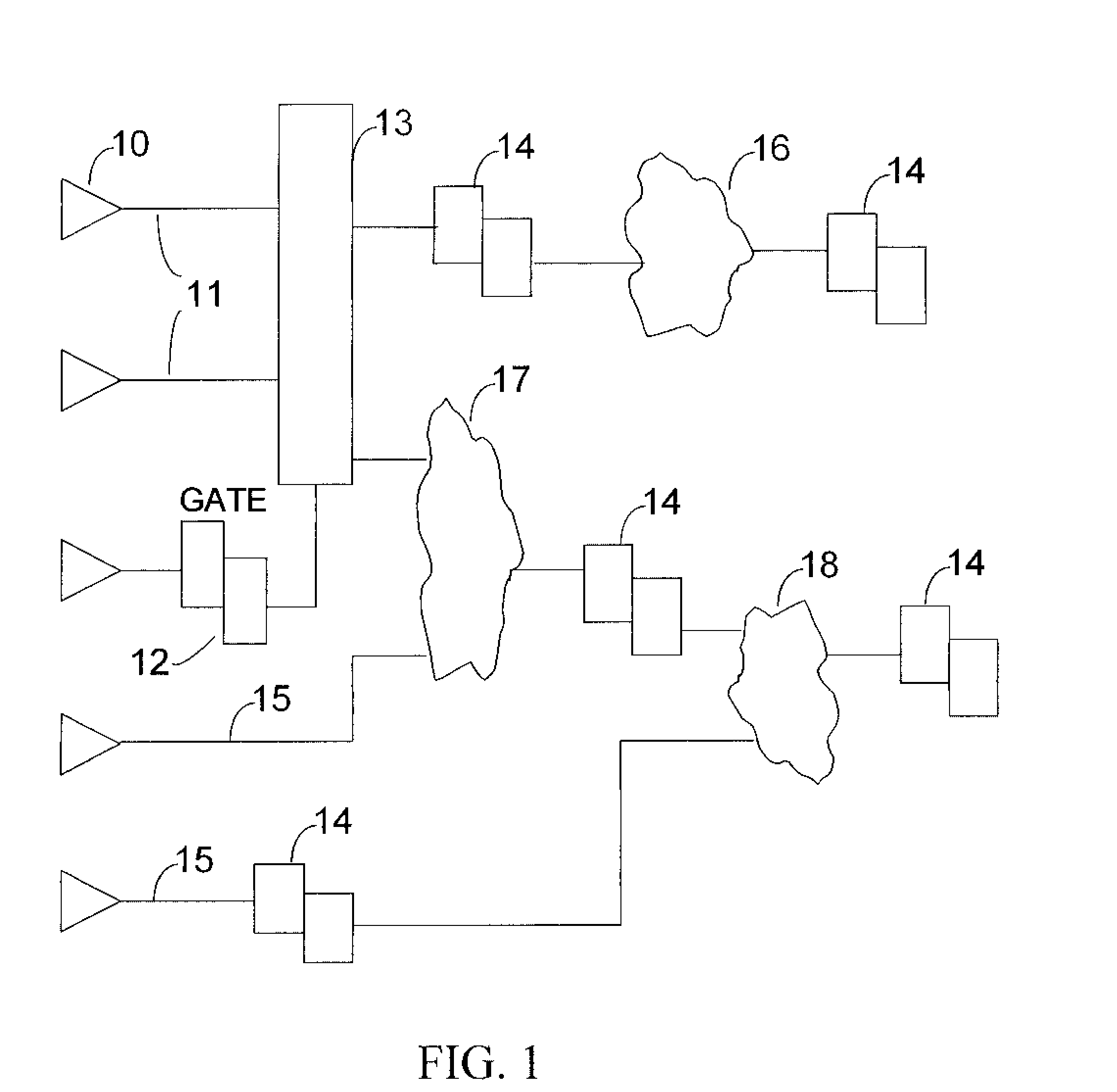

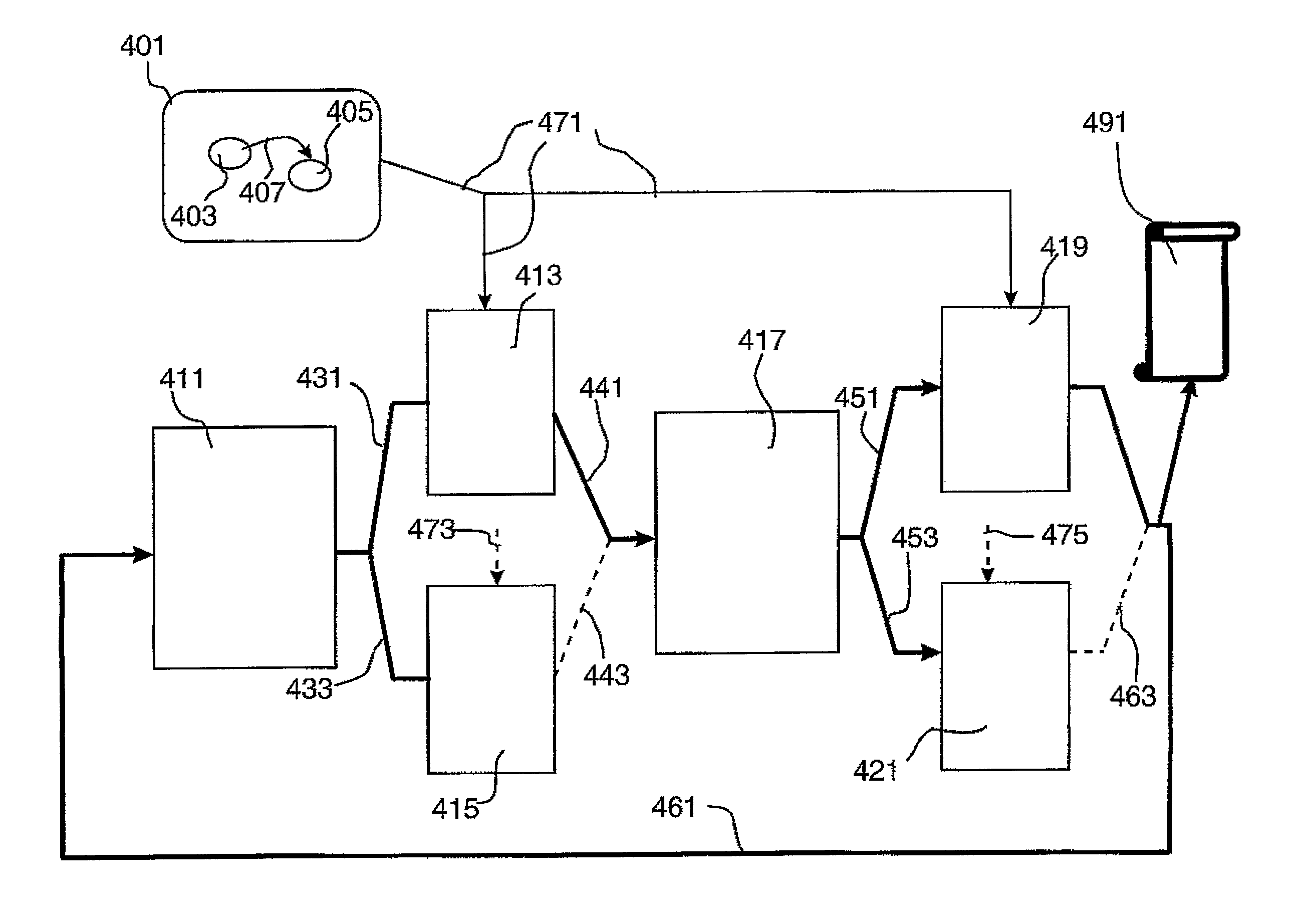

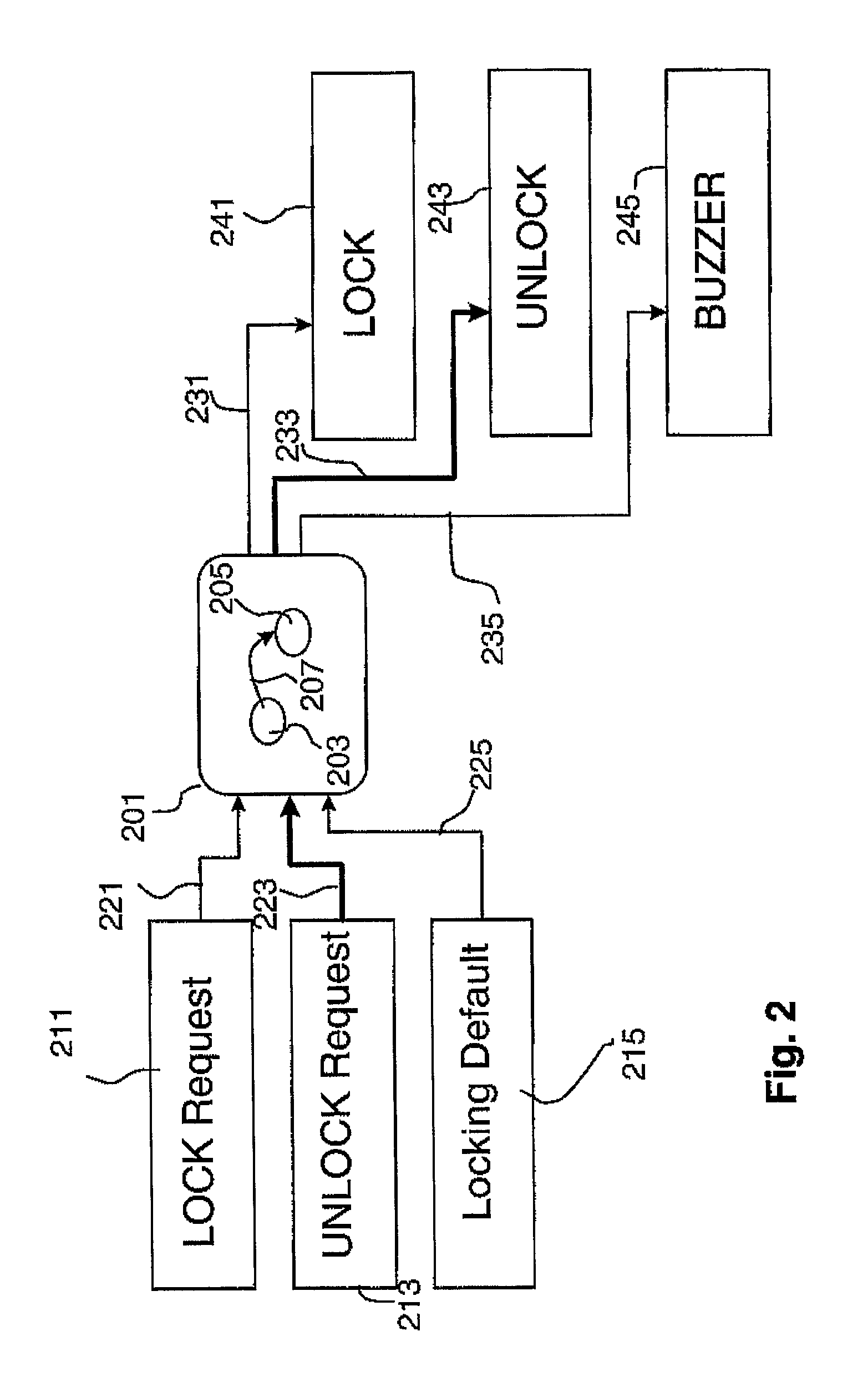

System and method for performing design verification

ActiveUS7792933B2Facilitate communicationAssure flexibilityDigital computer detailsCAD circuit designElectronic systemsCommunications system

A design verification system for developing electronic systems and methods for manufacturing and using same. The design verification system comprises a plurality of system elements, including at least one physical (or hardware) element and / or at least one virtual (or software) element, which are coupled, and configured to communicate, via a general communication system. Since the system elements may be provided on dissimilar development platforms, each system element is coupled with the communication system via a co-verification interface, which is provided as a layered protocol stack to assure portability and flexibility. Through use of the co-verification interface, the design verification system can be configured to support a wide variety of mixed physical / virtual systems.

Owner:CADENCE DESIGN SYST INC

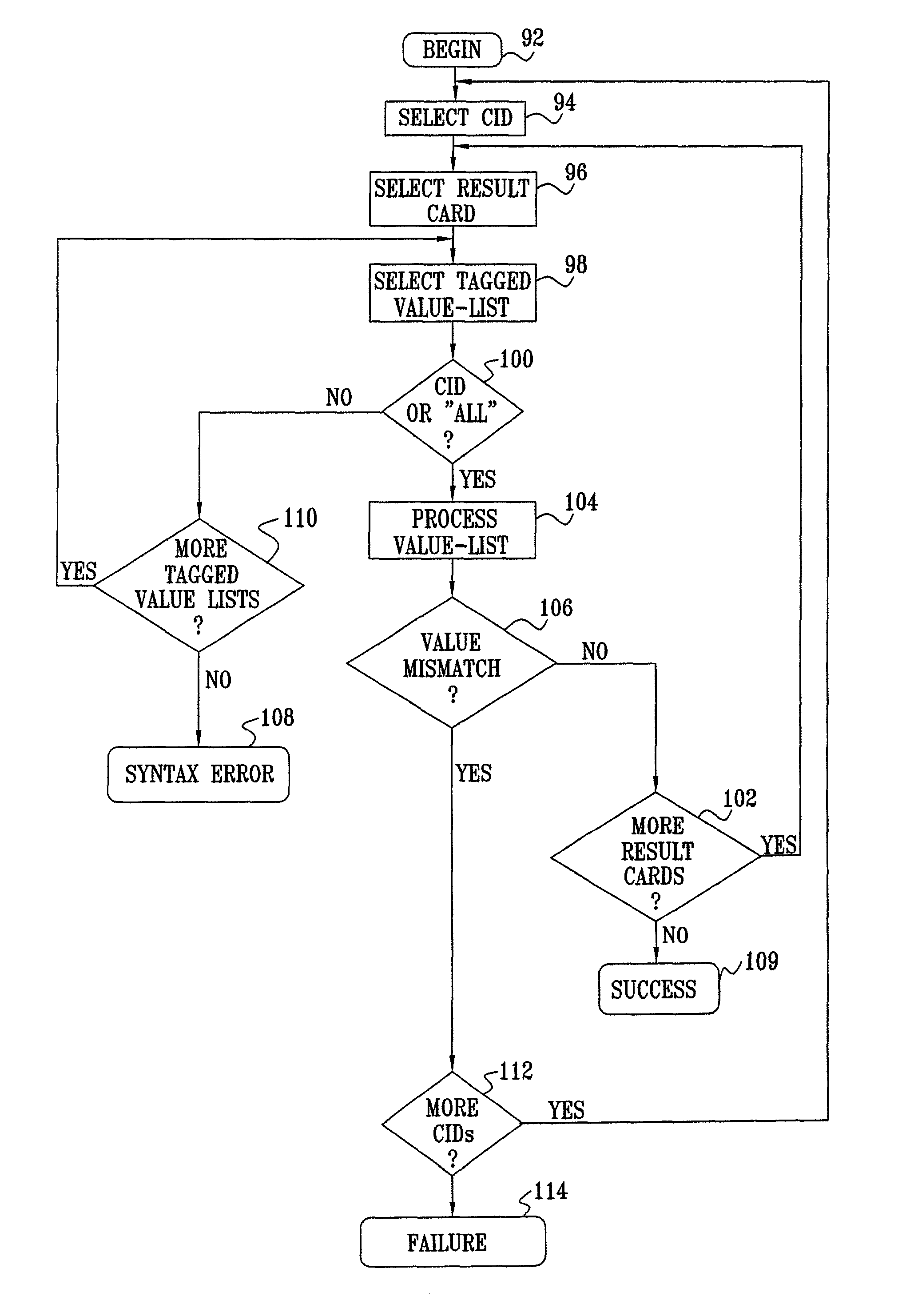

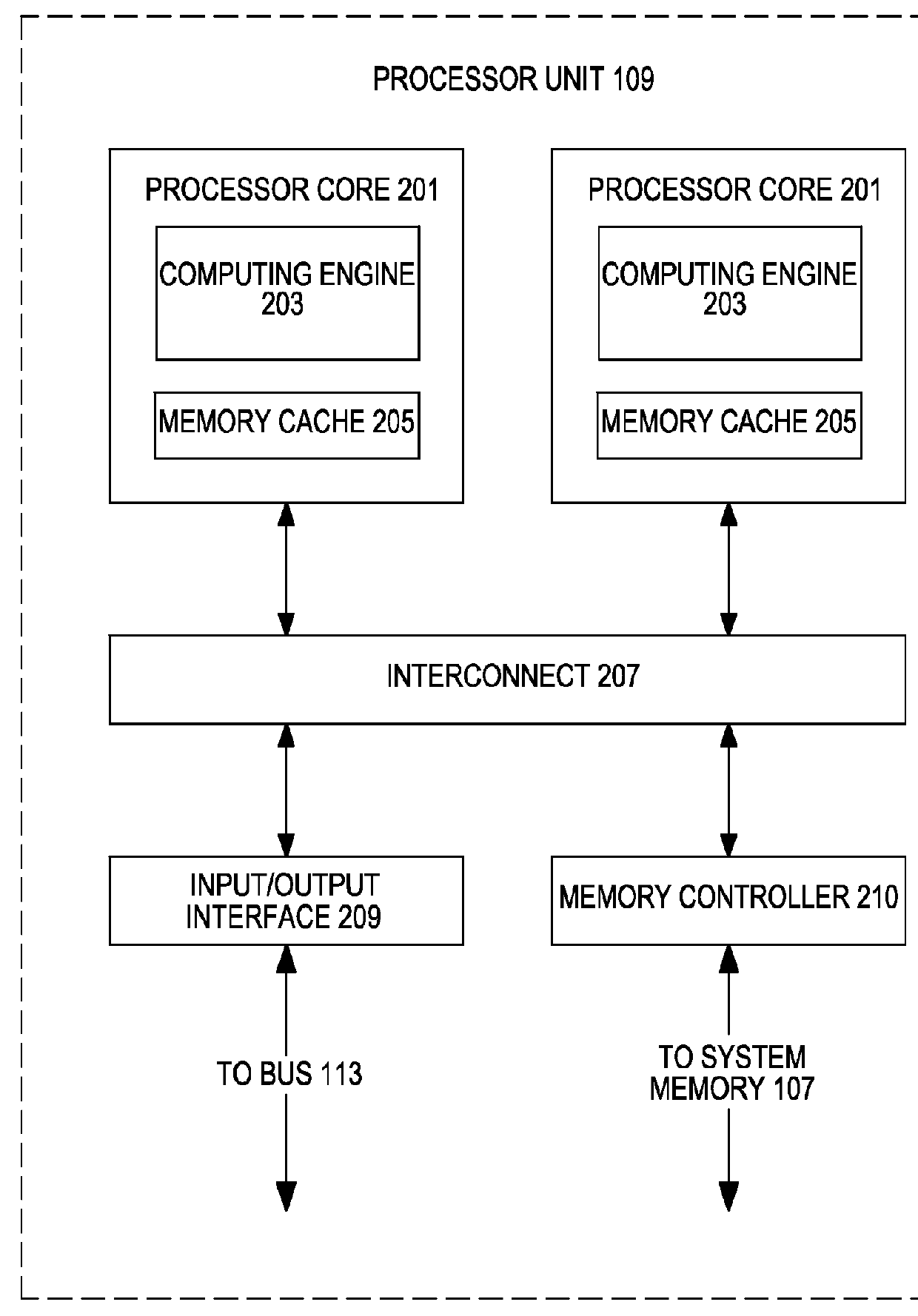

Non-unique results in design verification by test programs

InactiveUS8055492B2Accurate predictionDetecting faulty computer hardwareAnalogue computers for electric apparatusProgramming languageMulti processor

A design verification system that verifies the operation of multi-processor architecture by generating test programs in which the behavior of the processor, when executing the test program, is evaluated against the behavior required by the design specification. The test program generator produces scenarios for a multi-processor design in which non-unique results may occur. The system is provided with facilities to report expected outcomes, and to evaluate the validity of non-unique results in multiple resources under conditions of non-unique result propagation and dependencies among adjacent and non-adjacent resources.

Owner:GLOBALFOUNDRIES INC

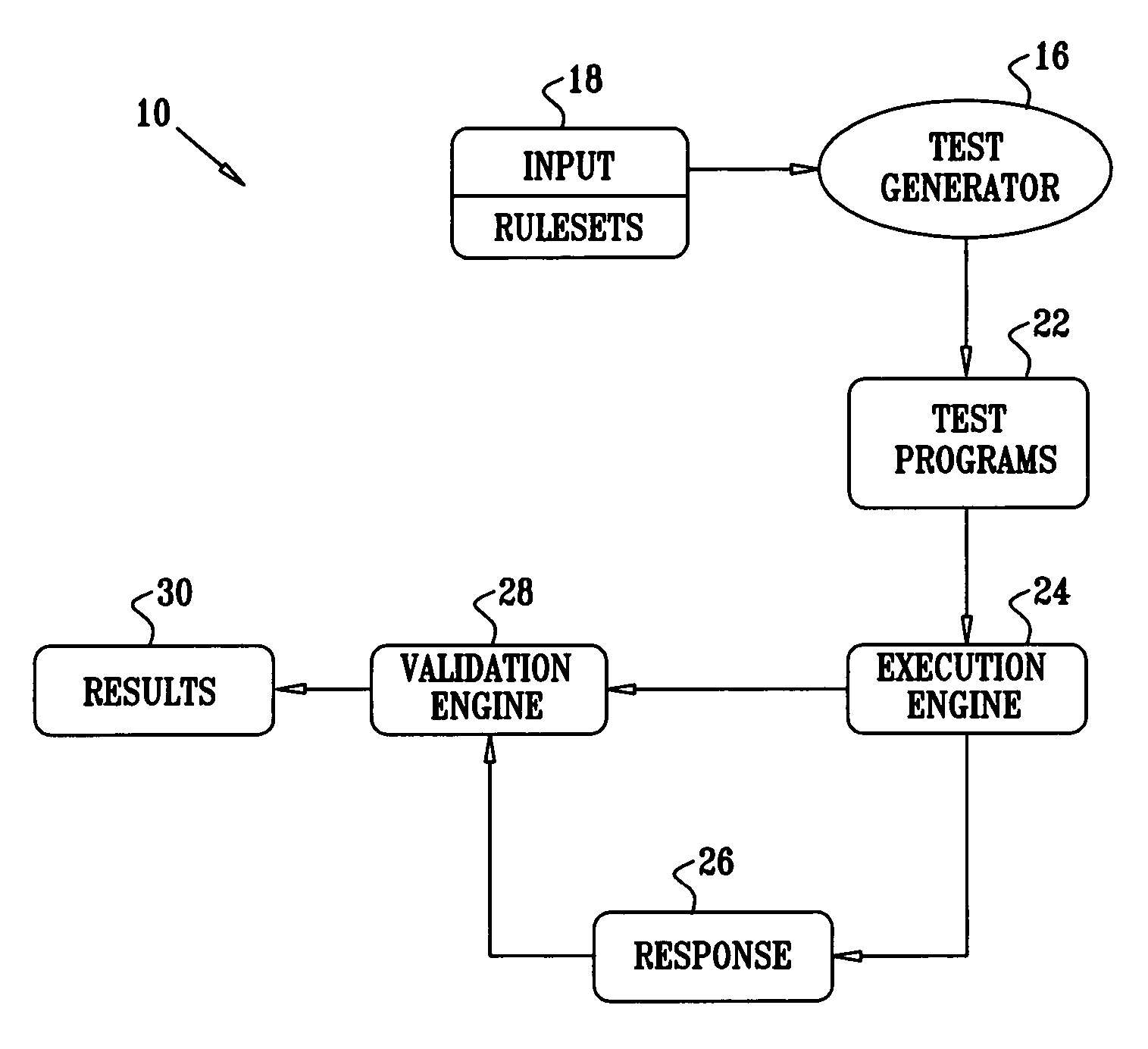

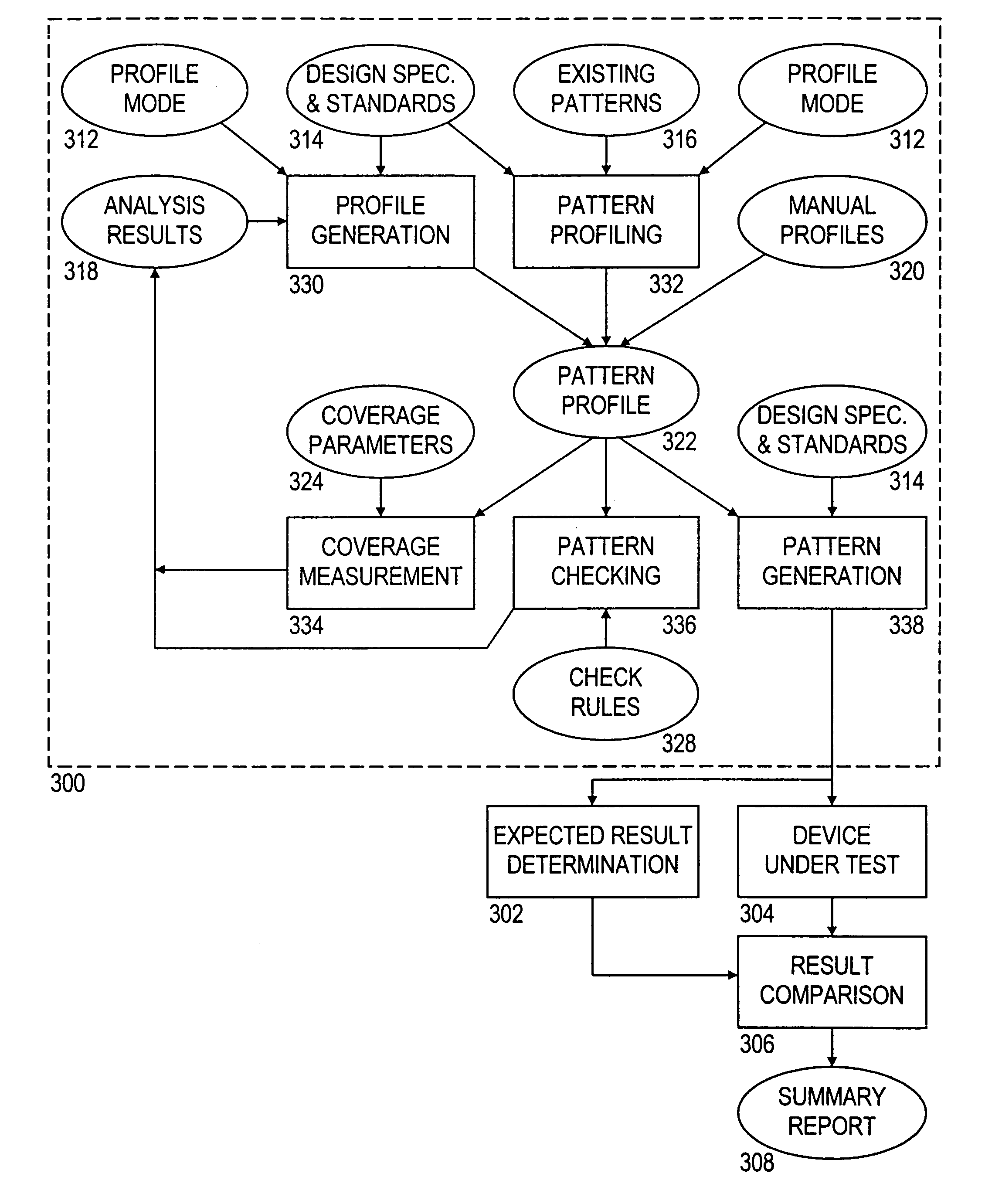

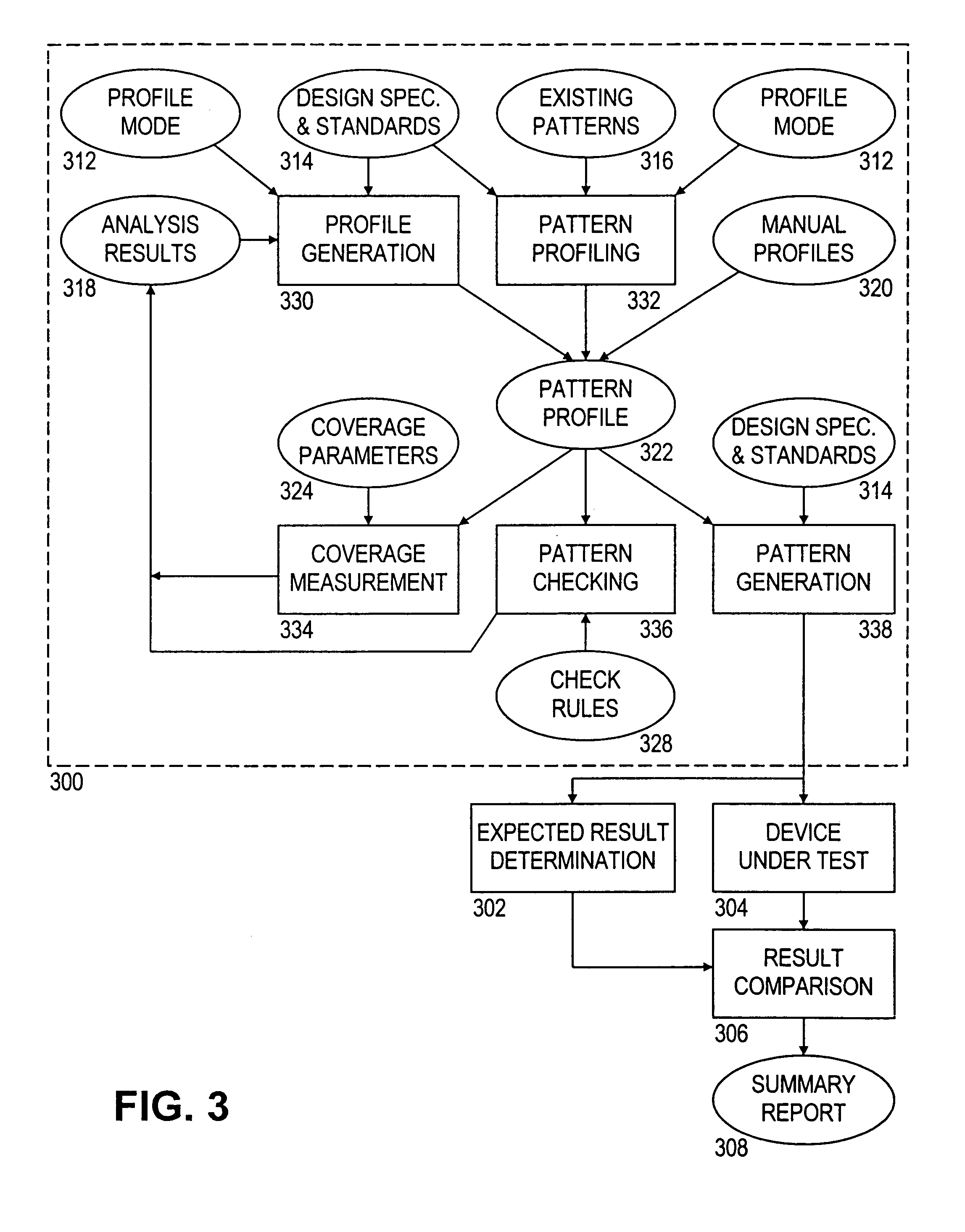

Functional-pattern management system for device verification

InactiveUS6968286B1Easy to understandIncrease coverageError detection/correctionSpecial data processing applicationsPattern generationManagement system

A profile-based system is described for verifying the functionality of a device design. In one embodiment, the system includes a profile generation module, a coverage measurement module, and a pattern generation module. The profile generation module operates from a rule set that represents the design specification and any applicable standards, and a profile mode that specifies “interesting” aspects of test patterns for device design verification. The profile generation module determines an ordered set of variable values that specify a test pattern, and produces a profile that intelligibly describes the interesting aspects of the test pattern. The coverage measurement module analyzes the profile to determine coverage, and the analysis results may be operated on by the profile generation module to determine a profile for an improved test pattern. The pattern generation module converts the profile into a test pattern having the interesting aspects specified in the profile.

Owner:BELL SEMICON LLC

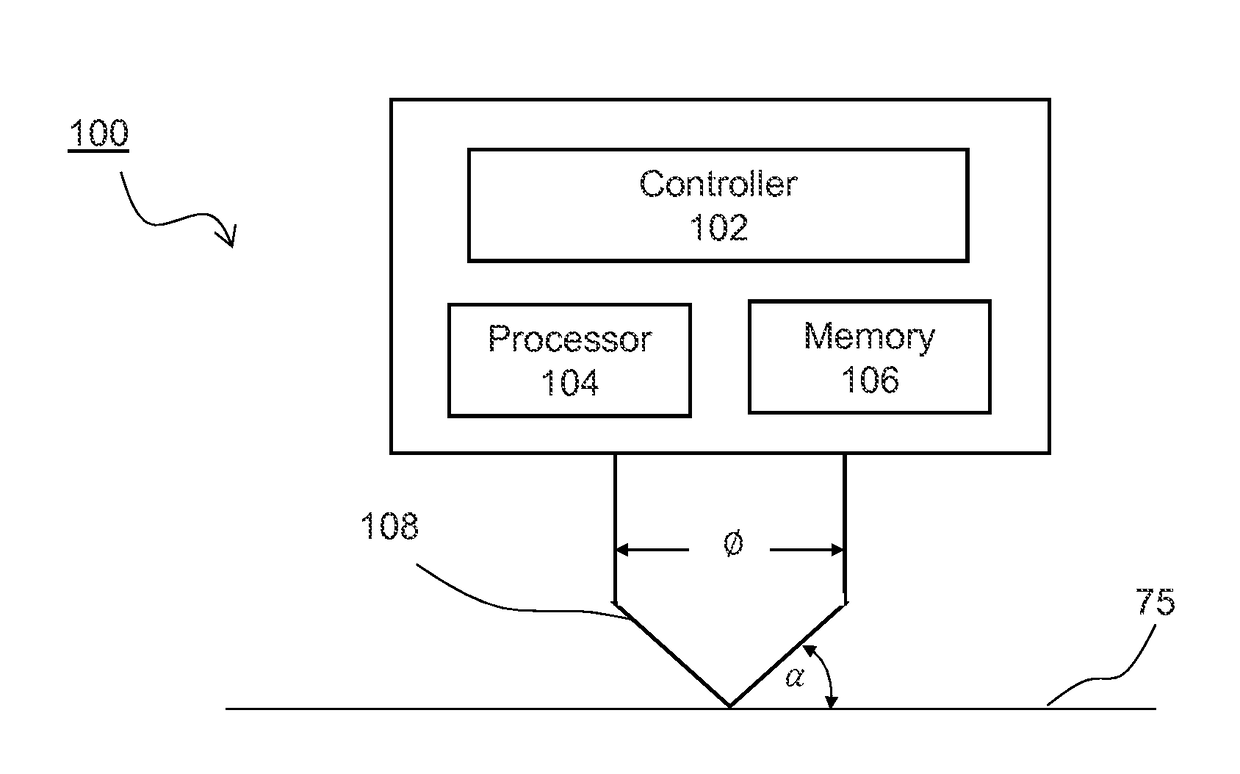

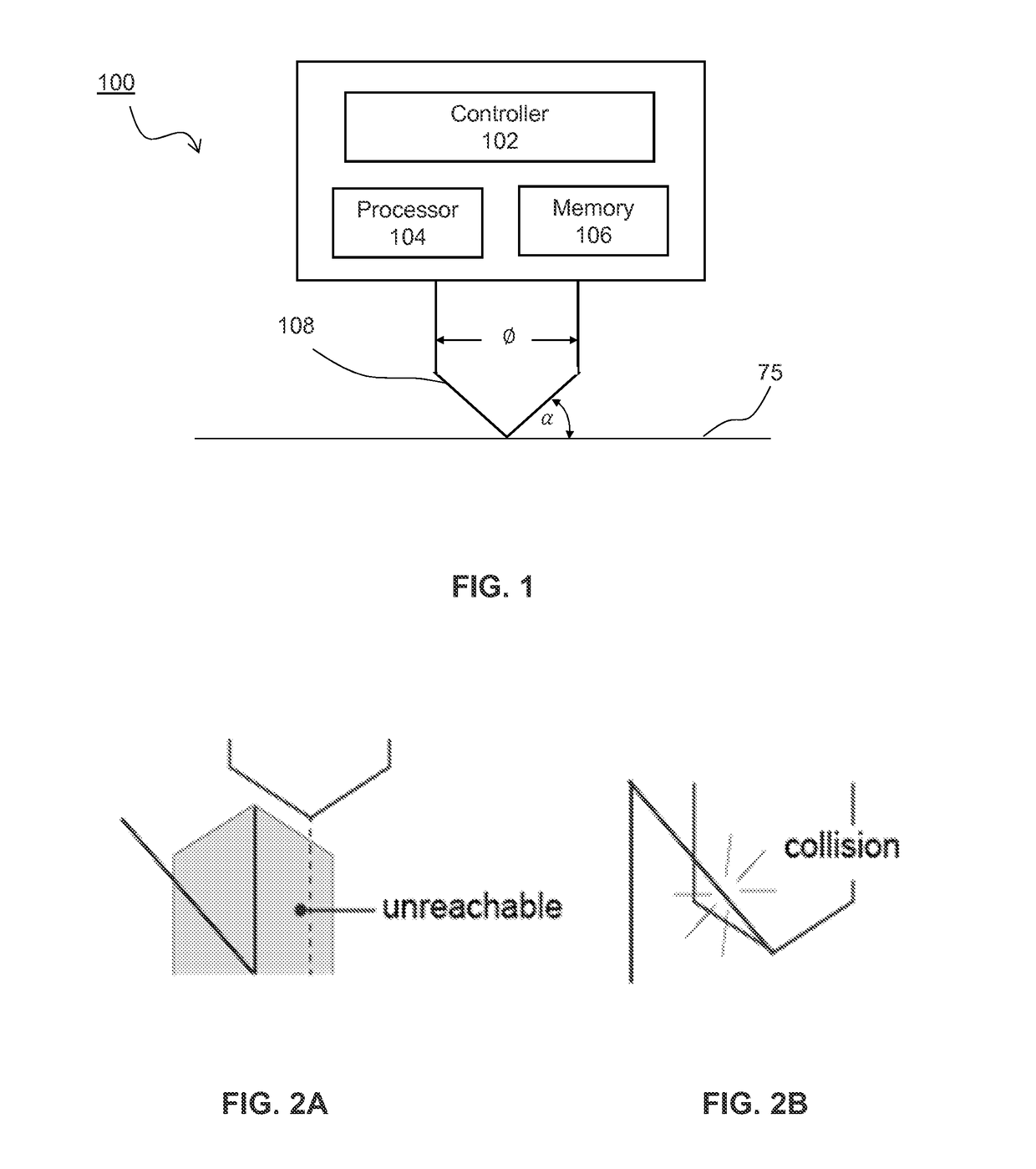

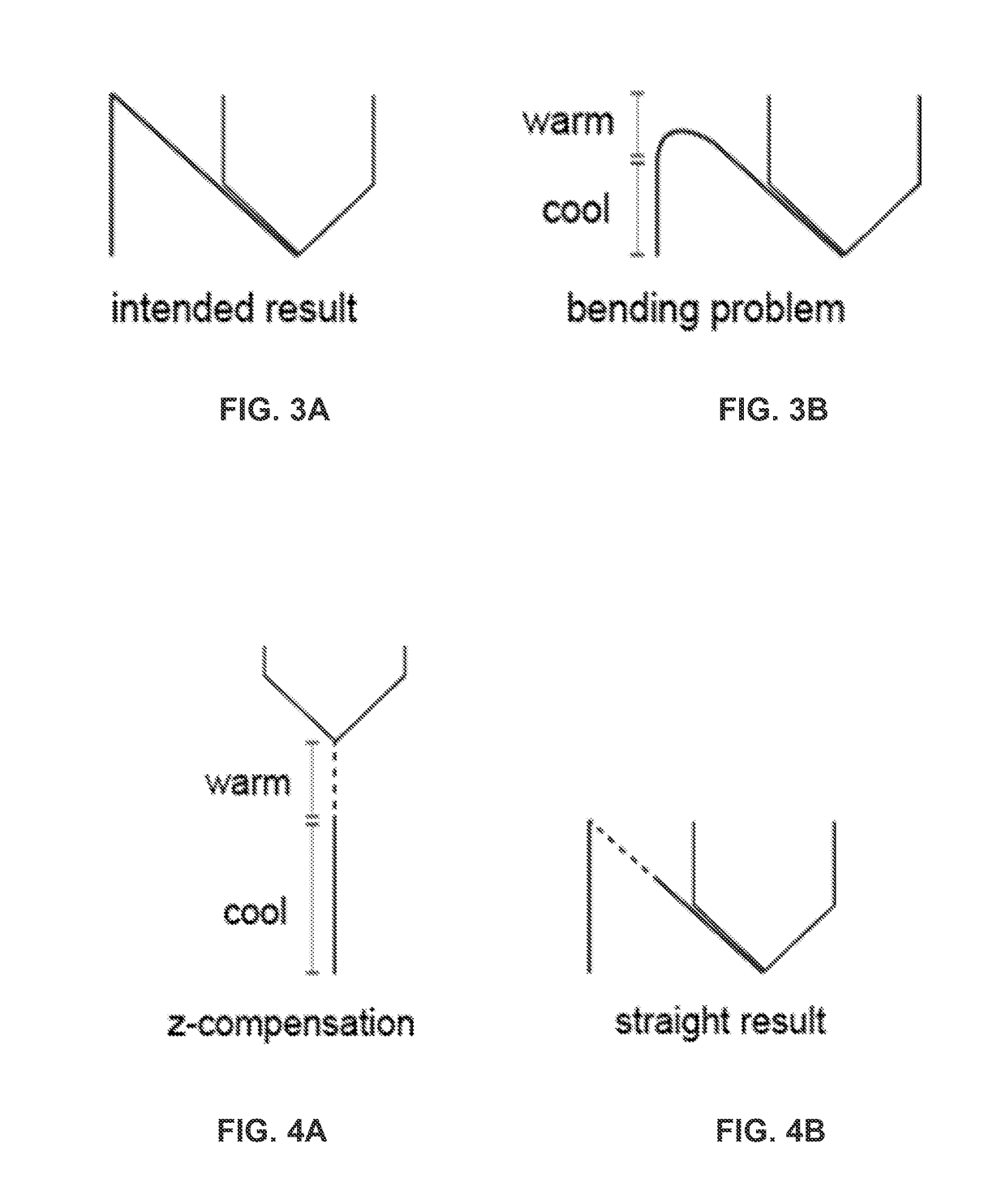

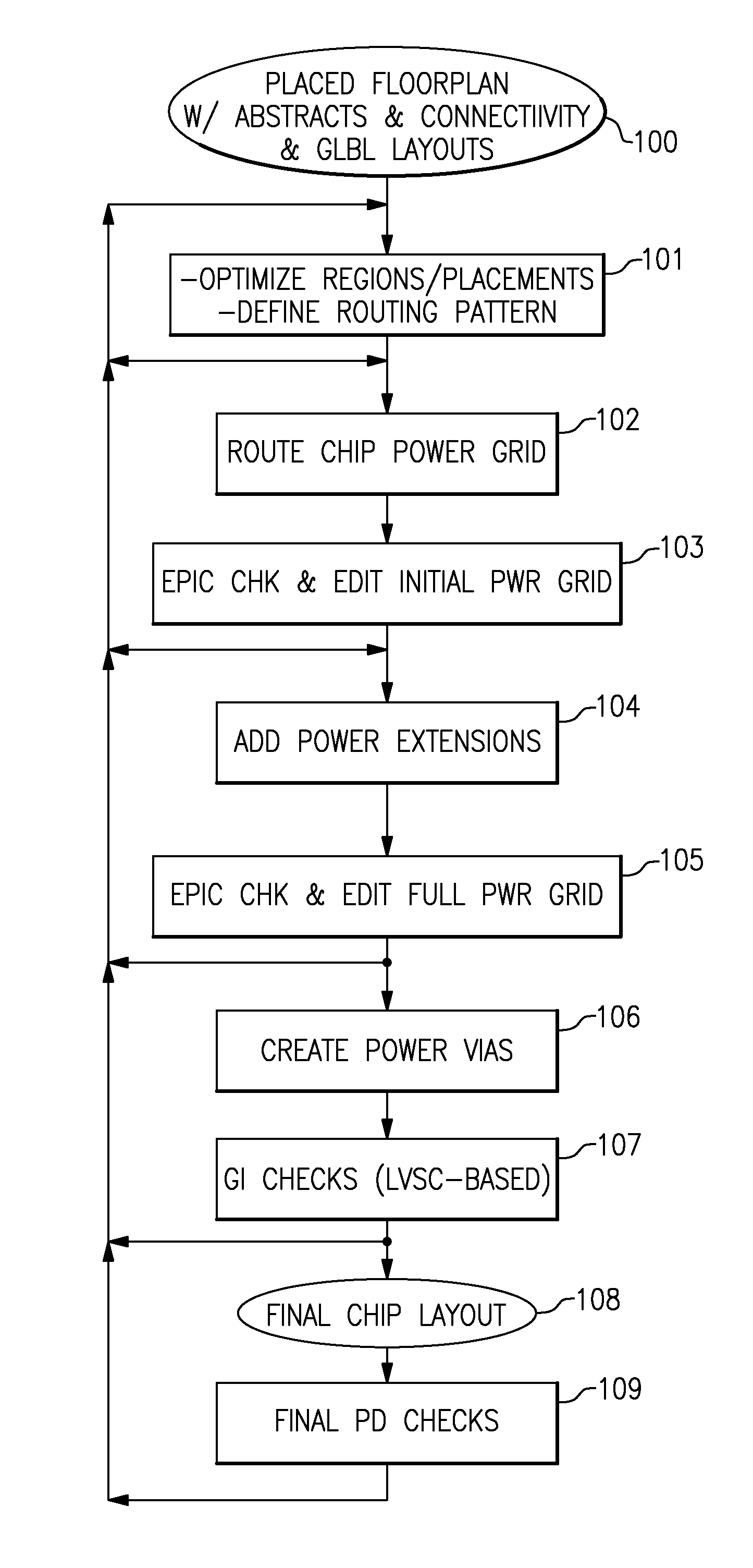

System and methods for three-dimensional printing

ActiveUS20170248937A1Lower the volumeLess supportingProgramme controlAdditive manufacturing apparatusEngineeringRapid prototyping

A fast and economical system and methods directed to low-fidelity fabrication of three-dimensional (3D) objects using 3D printing. The invention facilitates rapid prototyping by providing a wireframe structure in the form of the underlying design structure of a 3D model, which may be useful for a variety of reasons including to provide a prototype preview that may be used for design validation of a 3D model.

Owner:CORNELL UNIVERSITY

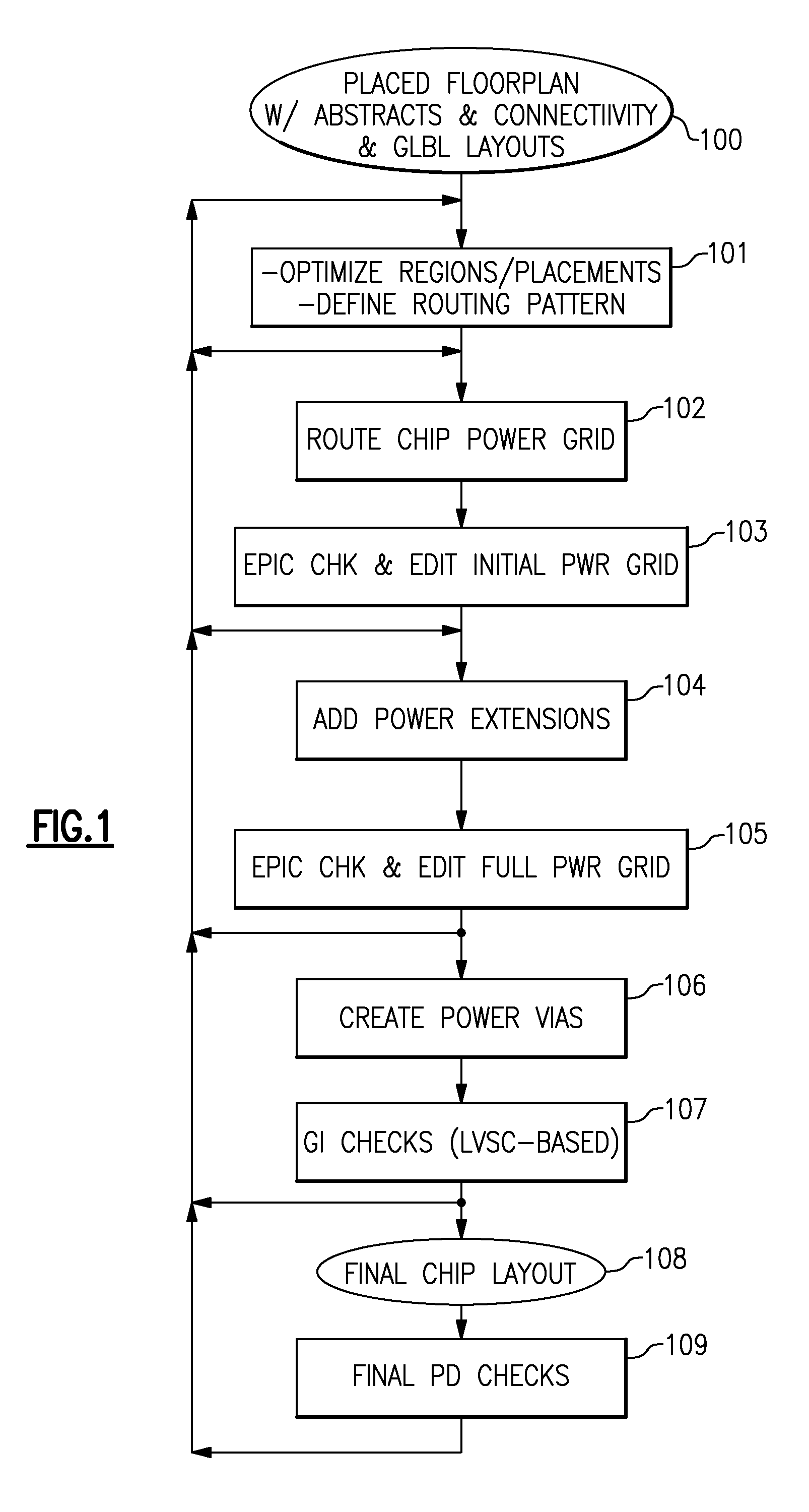

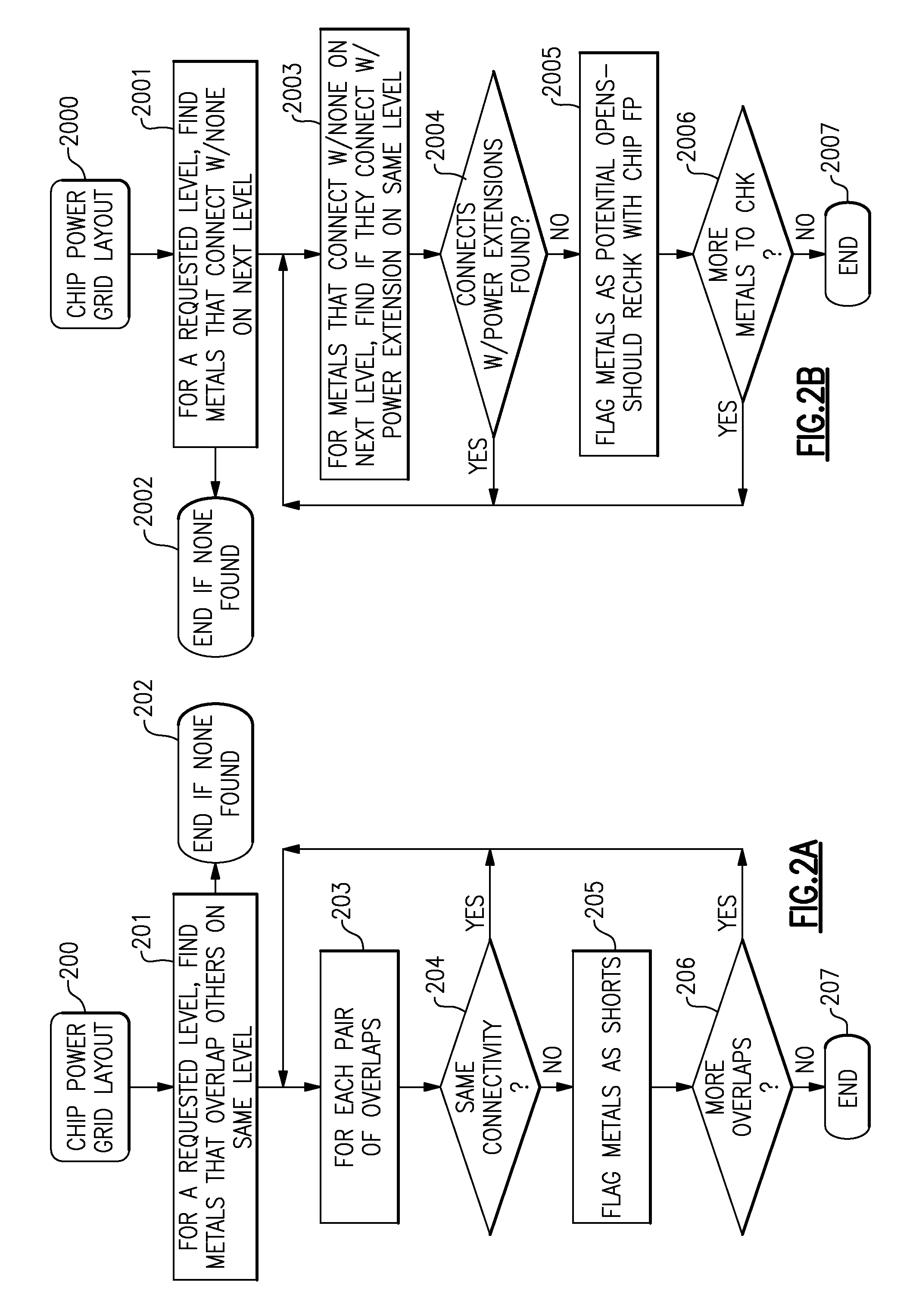

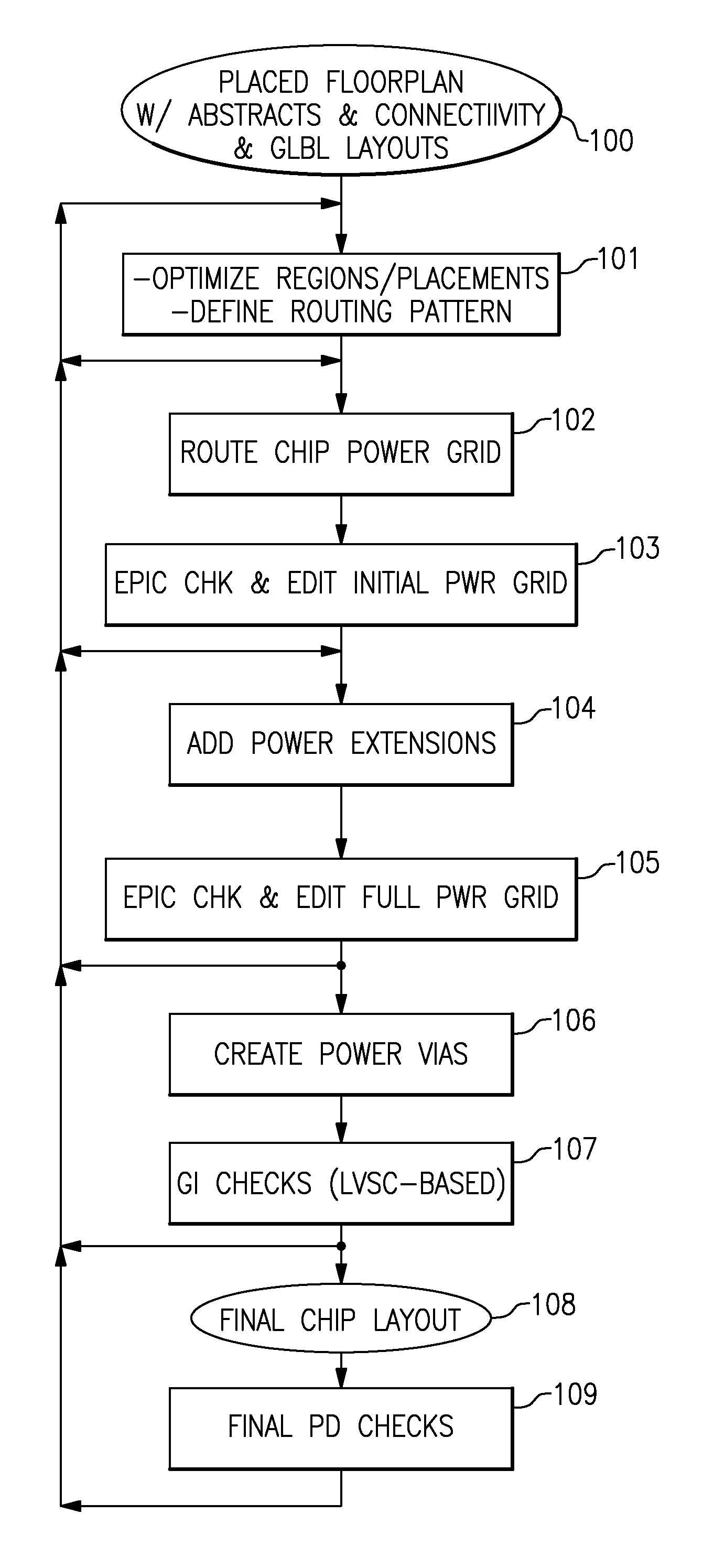

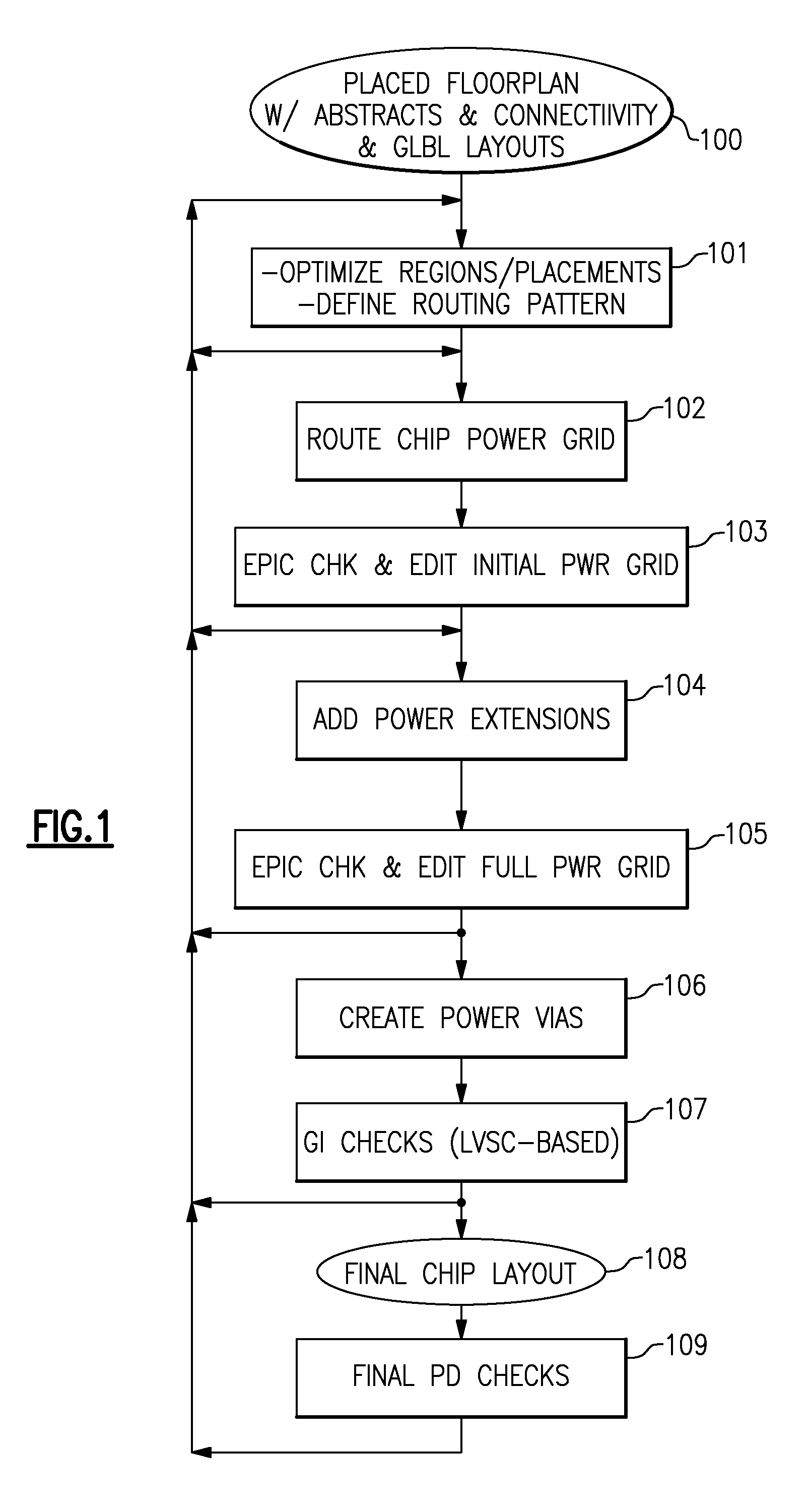

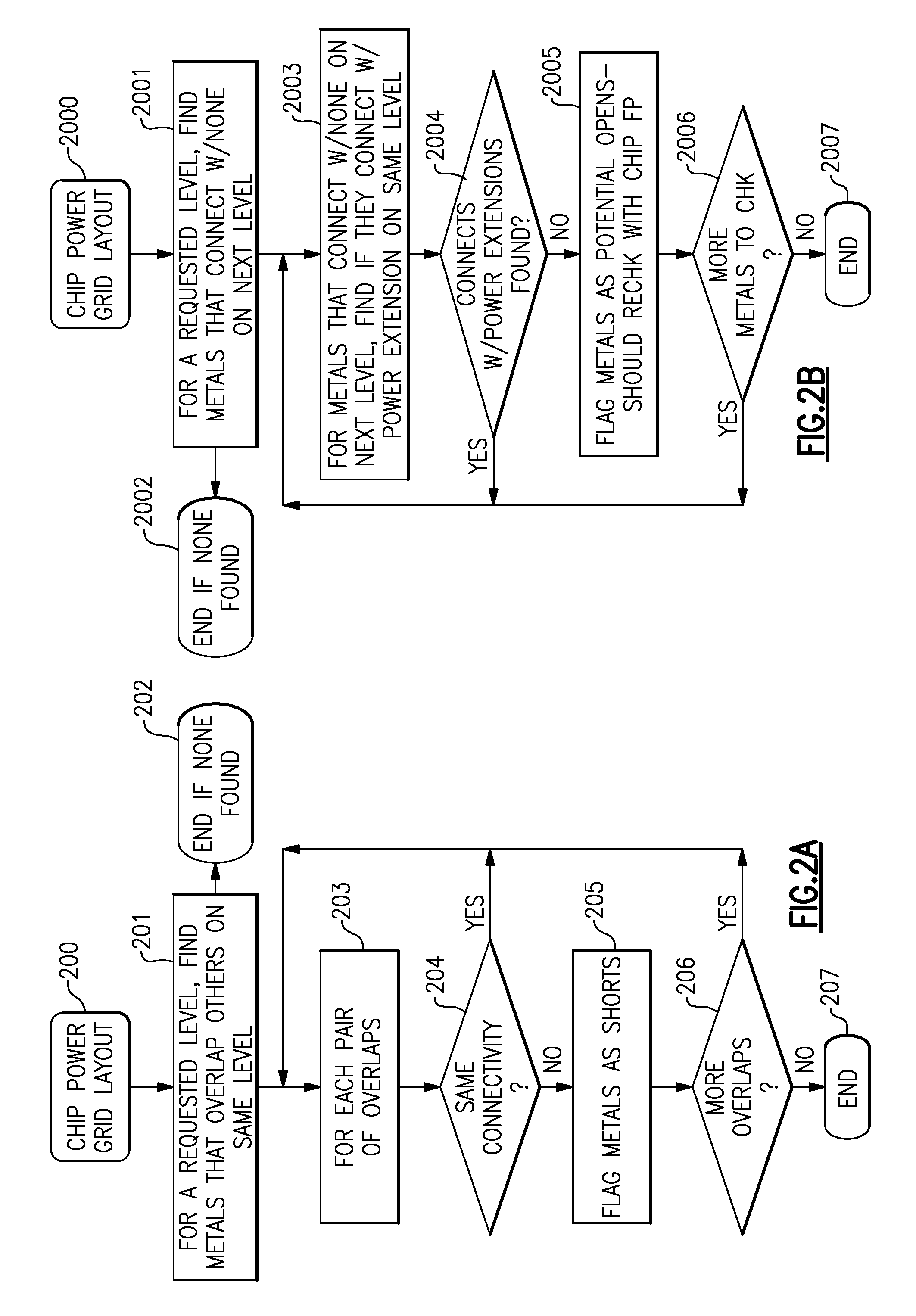

Automated method and apparatus for very early validation of chip power distribution networks in semiconductor chip designs

InactiveUS8028259B2Computer aided designSoftware simulation/interpretation/emulationEffective solutionDesign cycle

Validation of full-chip power distribution networks can be performed very early, and continuously throughout the design cycle, to detect real physical power connection problems and enable early correction of power grid designs using early floor plan and power grid design data. Common power connection and distribution errors are automatically addressed as an integral part of the early chip floor planning and chip power build processes providing efficient solutions requiring no extra wiring resource to be implemented and reducing the runtime of required final full-chip physical design checks, and the overall design cycle.

Owner:GLOBALFOUNDRIES INC

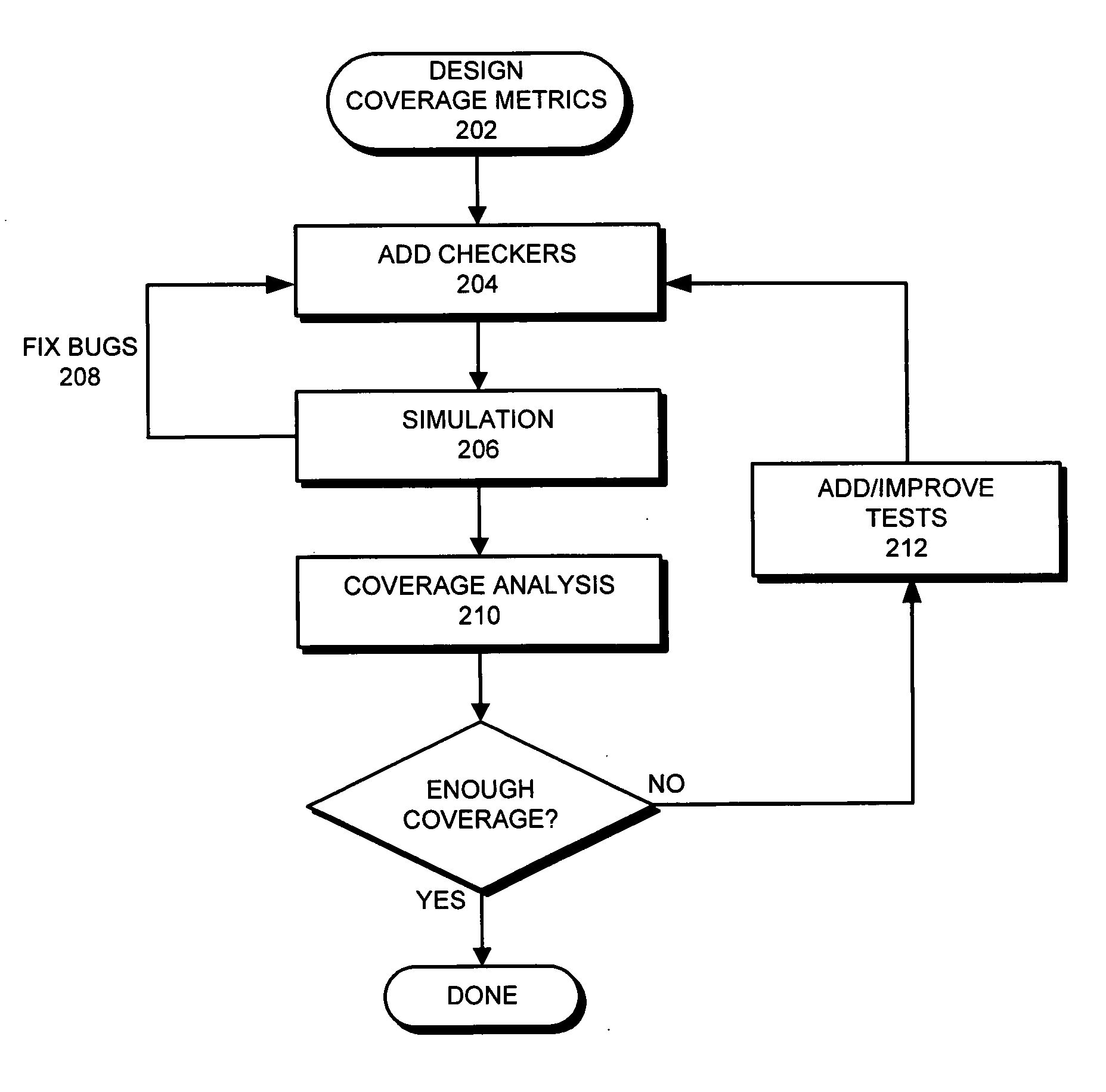

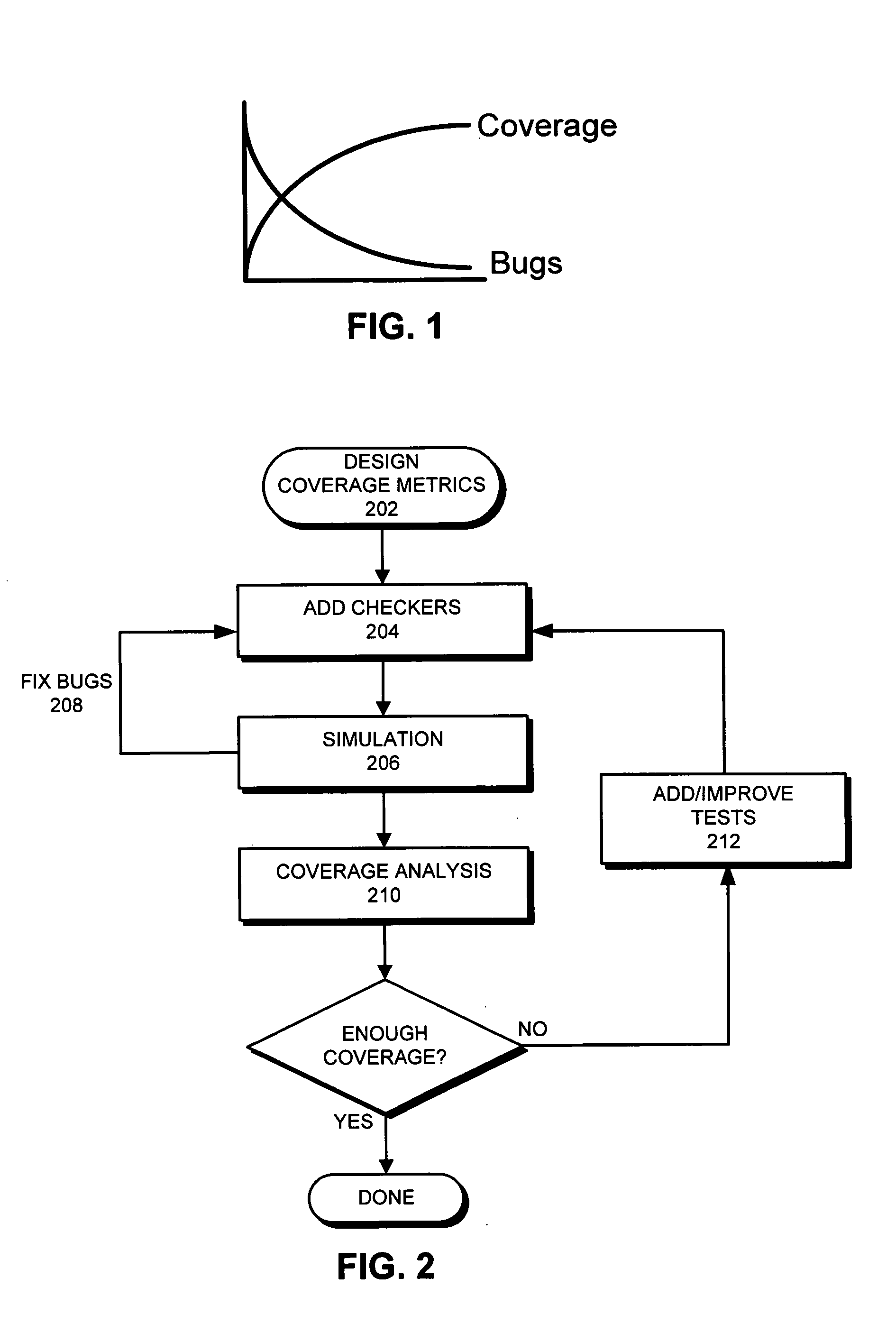

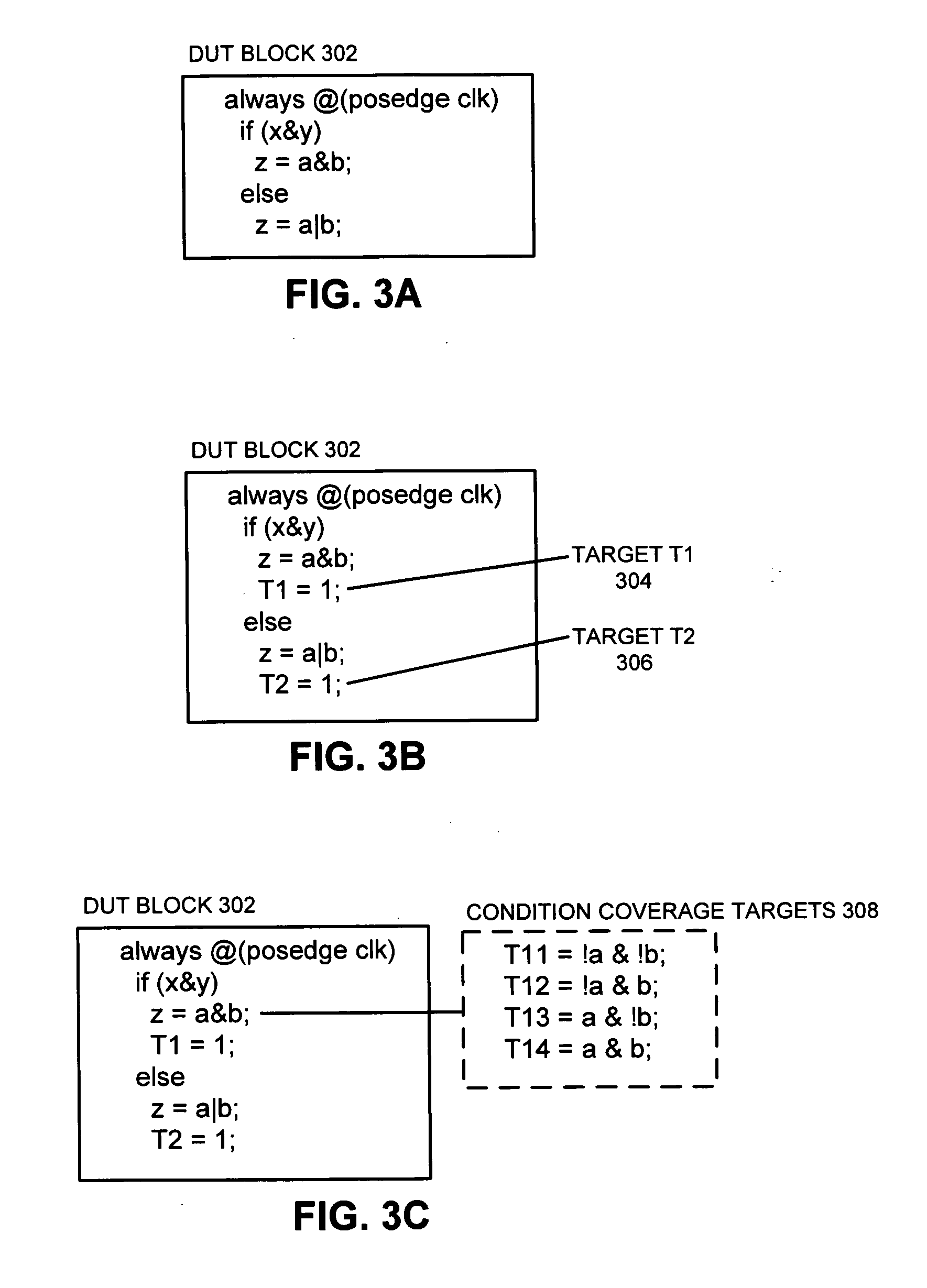

Facilitating structural coverage of a design during design verification

ActiveUS20070180414A1Convenient verificationCAD circuit designSoftware simulation/interpretation/emulationControl flowFormal methods

One embodiment of the present invention provides a method and a system that facilitates structural coverage of a design during a design verification process. During operation, the system receives a hardware description of the design, which contains one or more module instances and a set of structural coverage targets for a set of structures in the design. The system then extracts a control flow, the set of structural coverage targets, and a set of structural coverage metrics for the hardware description, and creates a shadow module with the same control flow as the hardware description. This shadow module contains a set of parallel structures that correspond to the set of structural coverage targets in the control flow of the hardware description and serve as targets for formal methods used to analyze the design. The system also generates a set of cross-module references to link the set of parallel structures in the shadow module with signals from the set of structures in the hardware description. The system then applies a formal verification tool to the design, including the shadow module and the cross-module references in an attempt to achieve the desired structural coverage.

Owner:SYNOPSYS INC

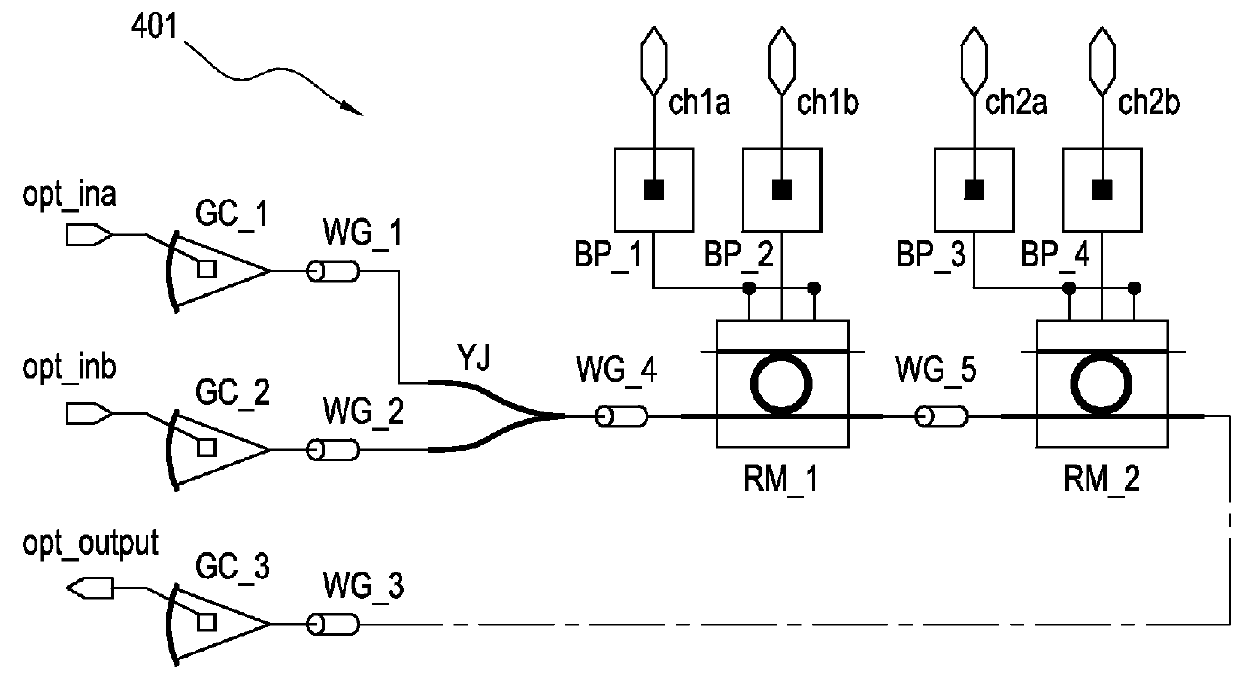

Verification Of Photonic Integrated Circuits

ActiveUS20160055289A1Computer aided designSoftware simulation/interpretation/emulationLayout Versus SchematicAnalysis tools

Techniques and mechanisms for the use of layout-versus-schematic (LVS) design tools to validate photonic integrated circuit designs. Various implementations employ alternate analysis techniques with LVS analysis tools to perform one or more LVS analysis processes on photonic integrated circuits. These analysis processes may include curvilinear design validation and the associated flow implementations.

Owner:SIEMENS PROD LIFECYCLE MANAGEMENT SOFTWARE INC

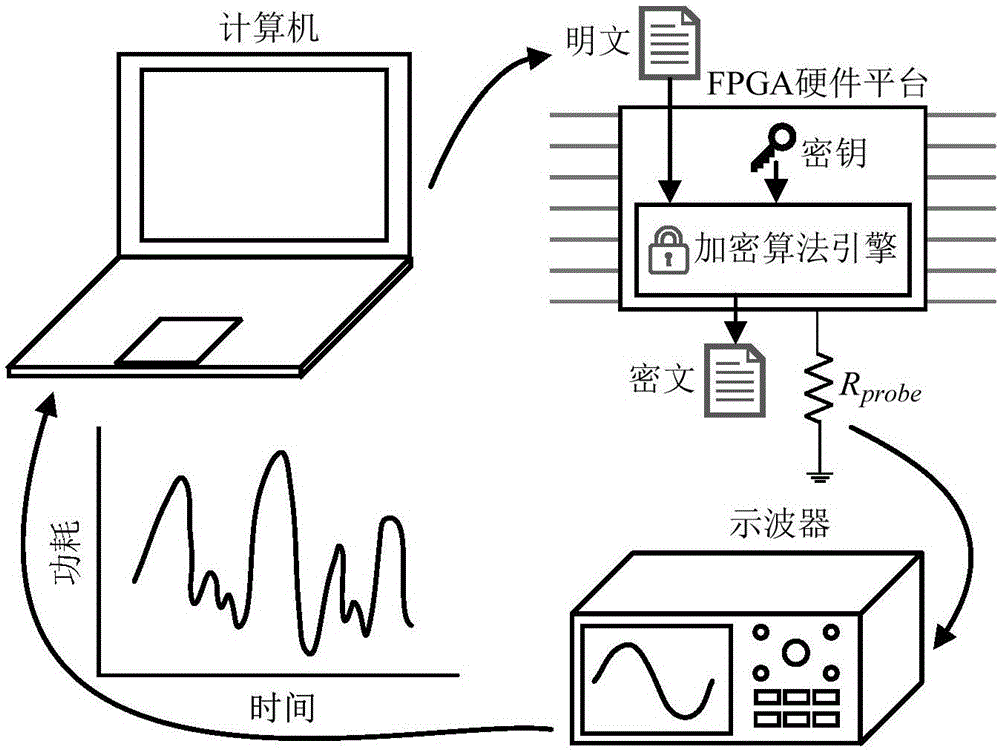

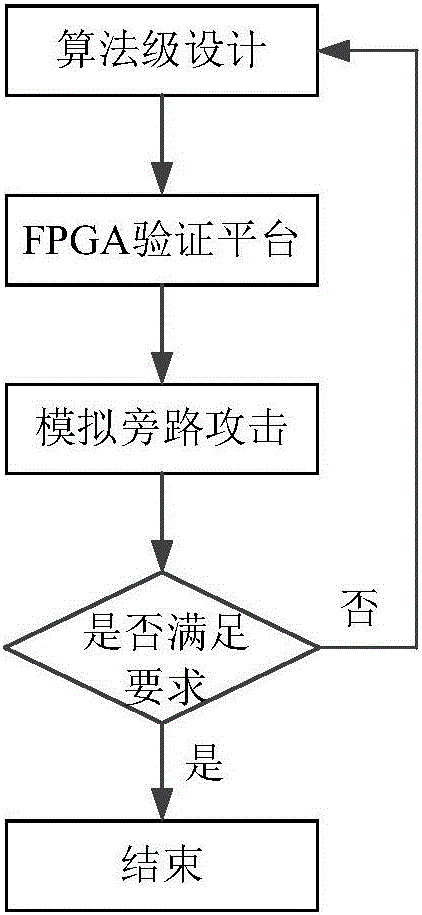

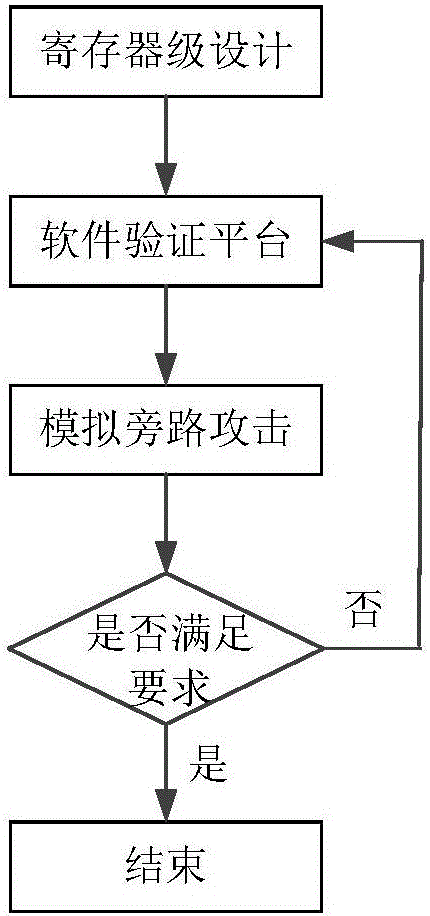

On-chip power supply network verification method for side channel attack

ActiveCN106817215AIntuitive and usable attack defense capability evaluation resultsLow costEncryption apparatus with shift registers/memoriesPlaintextValidation methods

The invention discloses an on-chip power supply network verification method for a side channel attack. The method comprises: logical synthesis and physical design processing is carried out on a register transmission level netlist file of a chip to obtain a transistor level netlist file; according to the obtained transistor level netlist file, a circuit model including a power supply network and a load is established; according to a generated plaintext-ciphertext data pair and a corresponding secret key, a logic process for encryption operation execution on the chip is simulated to obtain a current waveform file of the load; on the basis of the circuit model and the current waveform file of the load, a physical process for encryption operation execution on the chip is simulated to obtain a power consumption curve of the chip; according to the obtained power consumption curve, a side channel attack is carried out on the chip to obtain a guess secret key of the attack; and on the basis of the obtained guess secret key, a side channel attack result is analyzed and an anti-side channel attack capability of the power supply network is verified. The method has advantages of low cost, high accuracy, and reduced design verification period.

Owner:TSINGHUA UNIV

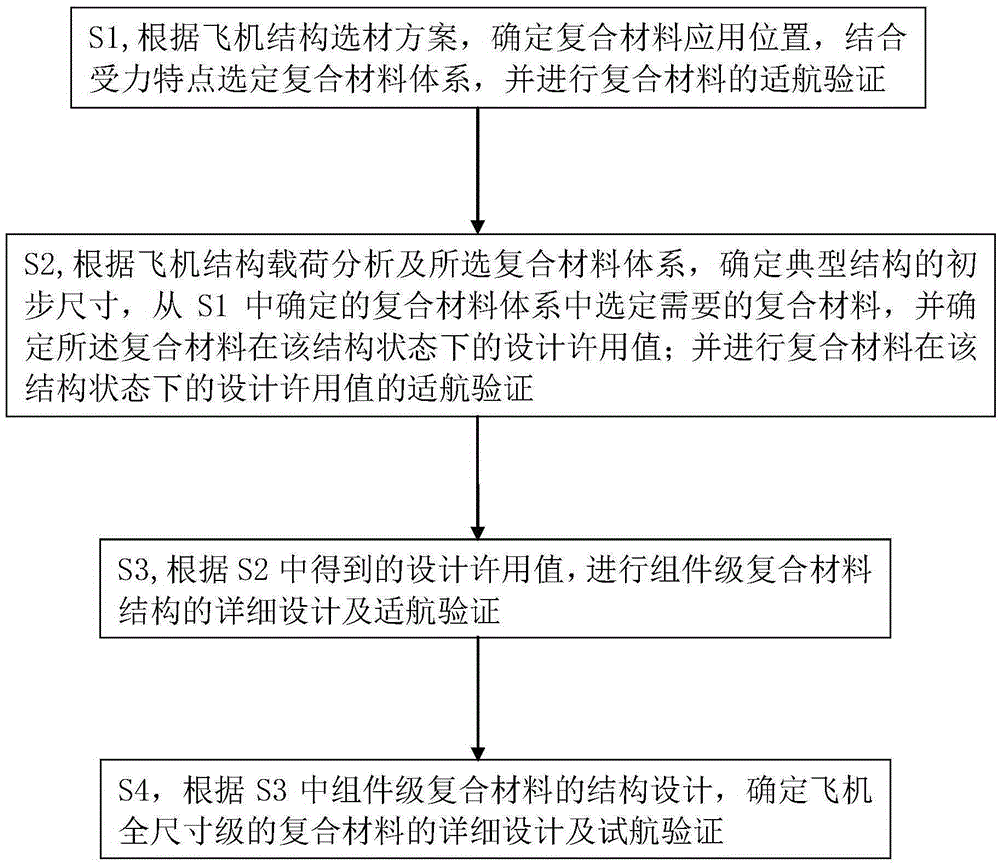

Composite material structural design verification method for airworthiness certification

InactiveCN105426631ALow experience requirementHigh confidence in the resultGeometric CADSpecial data processing applicationsJet aeroplaneValidation methods

The invention discloses a composite material structural design verification method for airworthiness certification. The composite material structural design verification method for airworthiness certification comprises the following steps that 1, the application positions of composite materials are determined, and airworthiness verification of the composite materials is performed; 2, the preliminary dimension of the typic structure is determined, the needed composite material is selected from the composite material system determined in the first step, and airworthiness verification is performed on design allowable values of the composite material in the structural state; 3, according to the design allowable values obtained in the second step, assembly-level detailed design and airworthiness verification of the composite material structure are performed; 4, according to the structural design of the assembly-level composite material in the third step, the detailed design and trial trip verification of the composite material of full-scale-level of an airplane are determined. The composite material structural design verification method has the advantages that the confidence coefficient of a result obtained through the experimental verification method is high, the requirement for experience of designers is low, different persons can follow the same verification method, the certification time is shortened, and the product development period is shortened.

Owner:XIAN AIRCRAFT DESIGN INST OF AVIATION IND OF CHINA

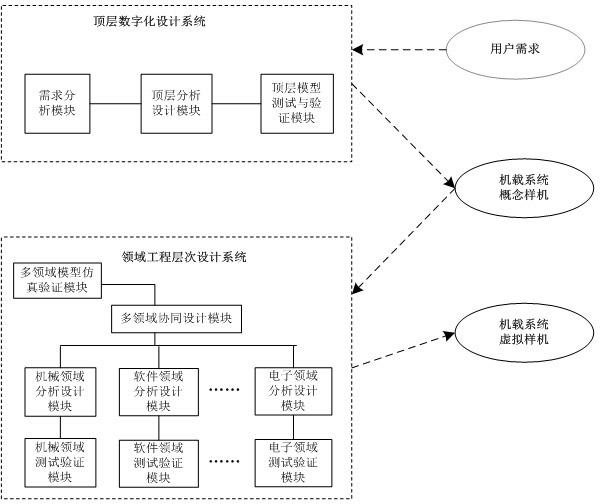

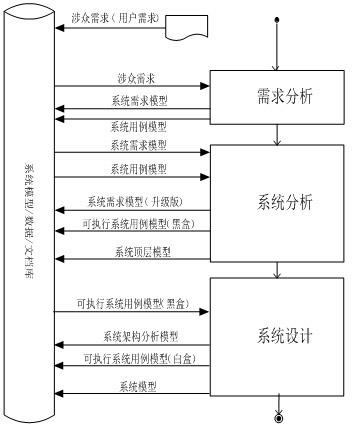

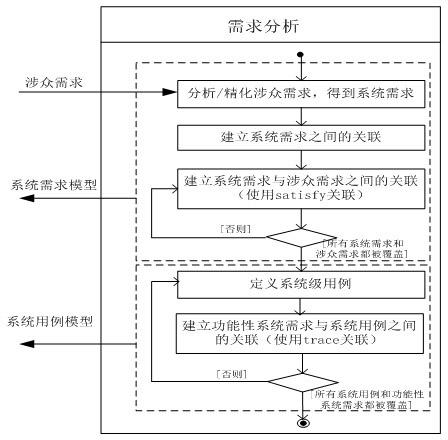

Airborne system digital design verification system and method

The invention discloses an airborne system digital design verification system and method and belongs to the technical field of system engineering. The system disclosed by the invention comprises a top-layer digital design system and a domain engineering layered digital design system, wherein the top-layer digital design system comprises a demand analysis module, a top-layer analysis design module and a top-layer model test and verification module; and the domain engineering layered design system comprises a single-domain analysis design module, a single-domain test and verification module, multi-domain collaborative design module and a multi-domain model simulation verification module. The method disclosed by the invention comprises the following two steps: concept model machine design of an airborne system and virtual model machine design of the airborne system, wherein the former step comprises the following three sub-steps: demand analysis of the airborne system, system analysis of the airborne system and system design of the airborne system. The system and method disclosed by the invention can be used for supporting the digital analysis, design and verification of the airborne system, realizing 'design and verification first, implementation later' of the airborne system, avoiding the problems of long period, high cost, great risk and the like caused by the 'design and implementation first, verification later' of the traditional design method.

Owner:NANJING UNIV OF AERONAUTICS & ASTRONAUTICS

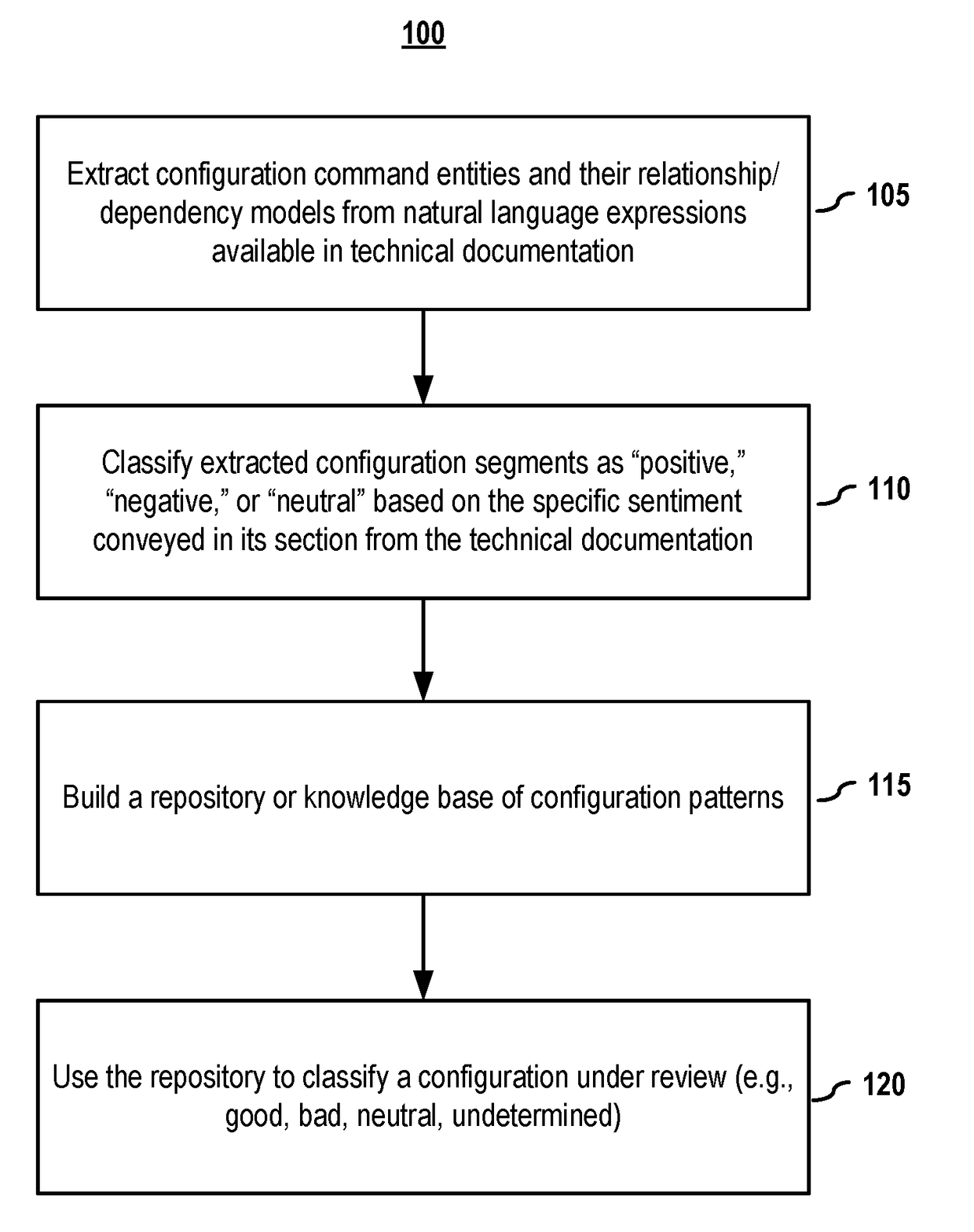

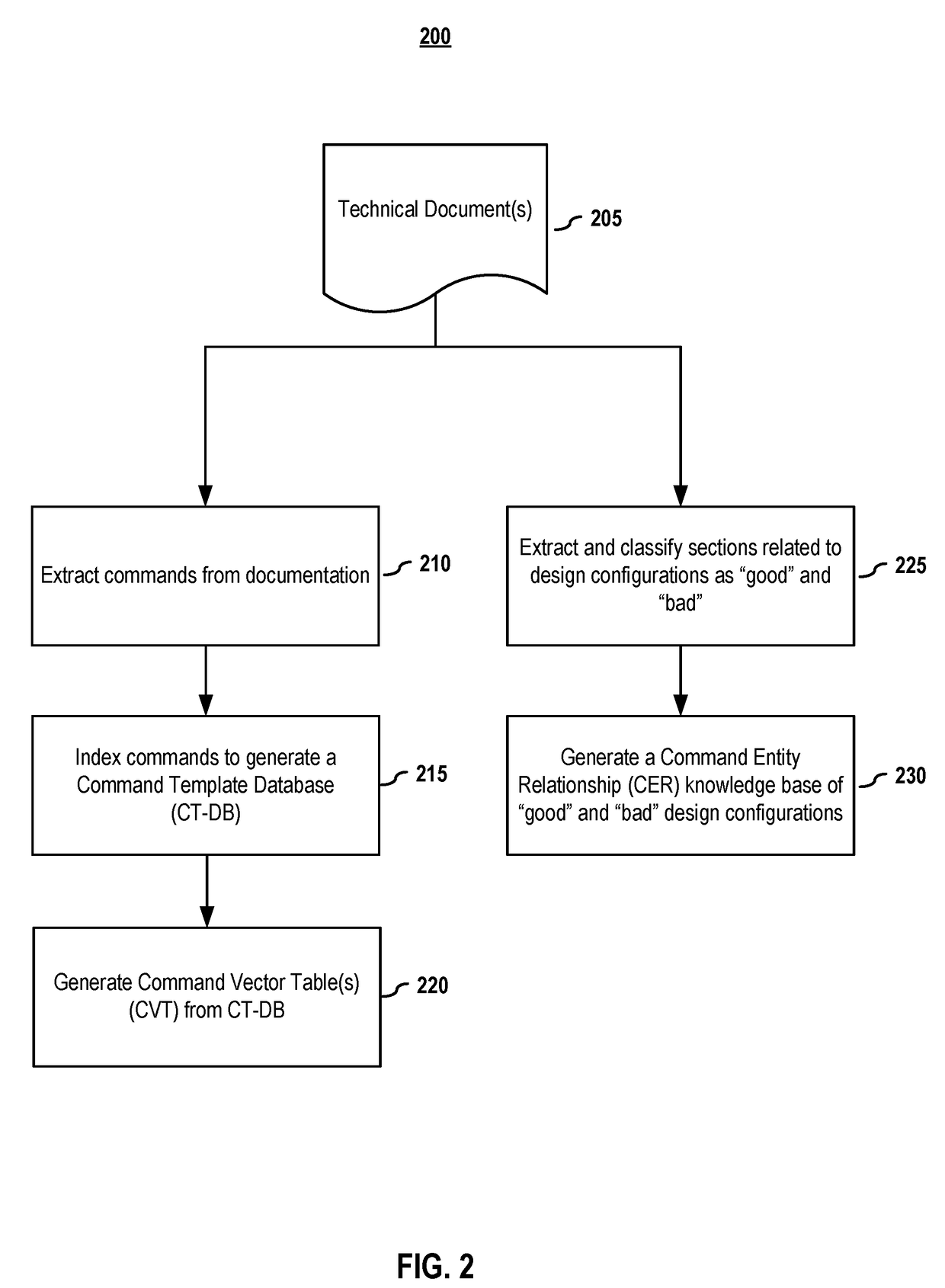

Design validation using natural language processing

Aspects of the present disclosure relate to systems and methods that help automate the validation of a configuration of a functional product. Every functional product, be it a service, device, or combination thereof, has one or more documents associated with it. These documents may include such documentation as: (1) Release Notes; (2) Configuration Guides; (3) command line interfaces (CLIs) / application program interfaces (APIs); (4) Data Sheets; (5) Installation Guides; (6) User Manuals; (7) Errata notices; and (8) other documentation. In embodiments, datatset used for validating a configuration setting may be extracted using natural language processing from technical documentation. In embodiments, this extracted information is used to validate a design vector representing a configuration setting.

Owner:DELL PROD LP

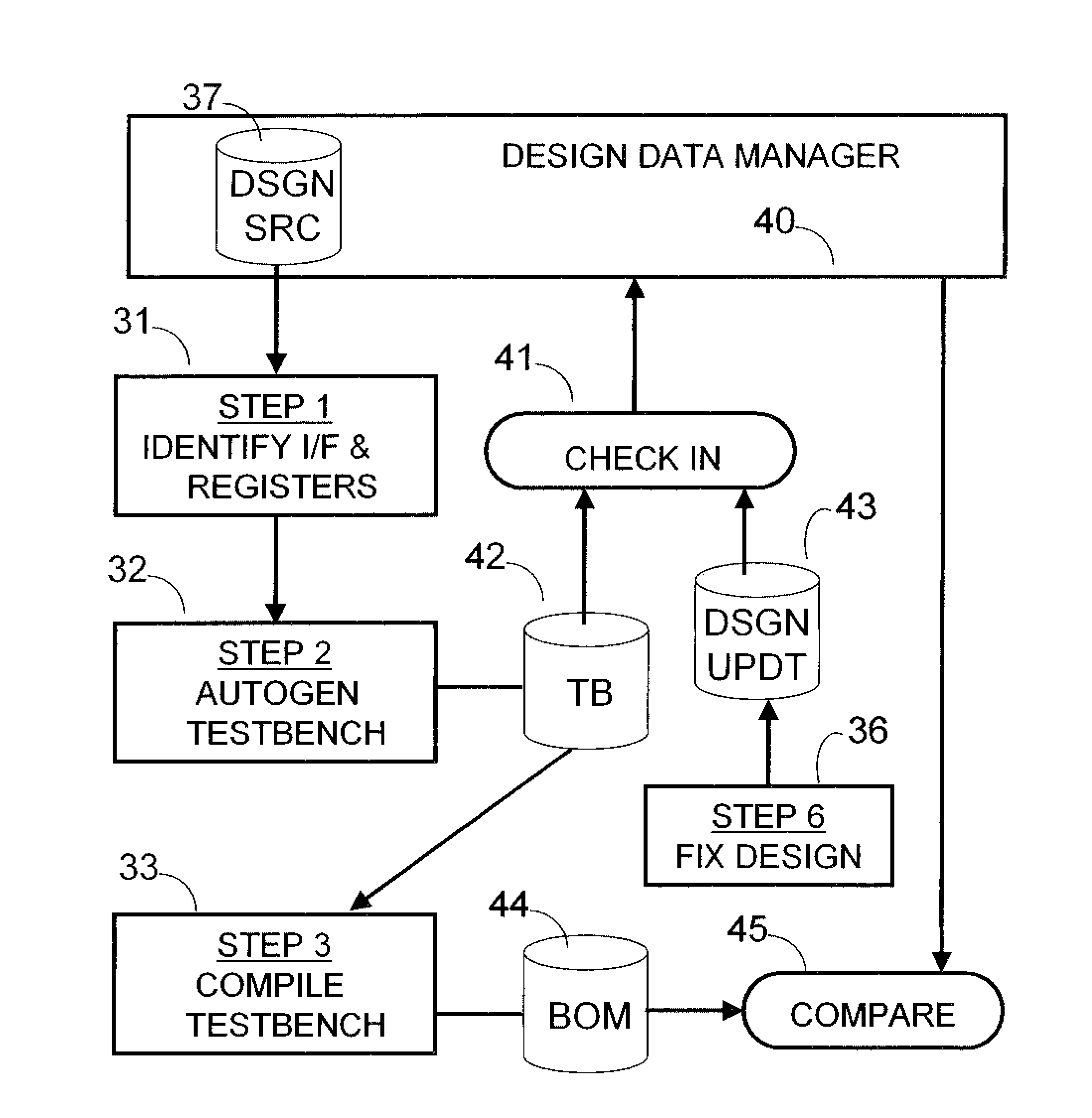

Method, System, and Program Product for Automated Verification of Gating Logic Using Formal Verification

InactiveUS20080059925A1Improve rendering capabilitiesExpand coverageComputer aided designSoftware simulation/interpretation/emulationValidation methodsTest bench

As described herein the automated verification methodology parsing scripts auto generate test bench hardware design langaue, such as VHDL or Verilog, from the design source VHDL or Verilog. A formal verification model is then built comprising the testbench VHDL and the design under test. The resulting design verification tool then provides proofs and counterexamples for all of the rules, e.g., auto-generated rules, in the test bench.

Owner:GLOBALFOUNDRIES INC

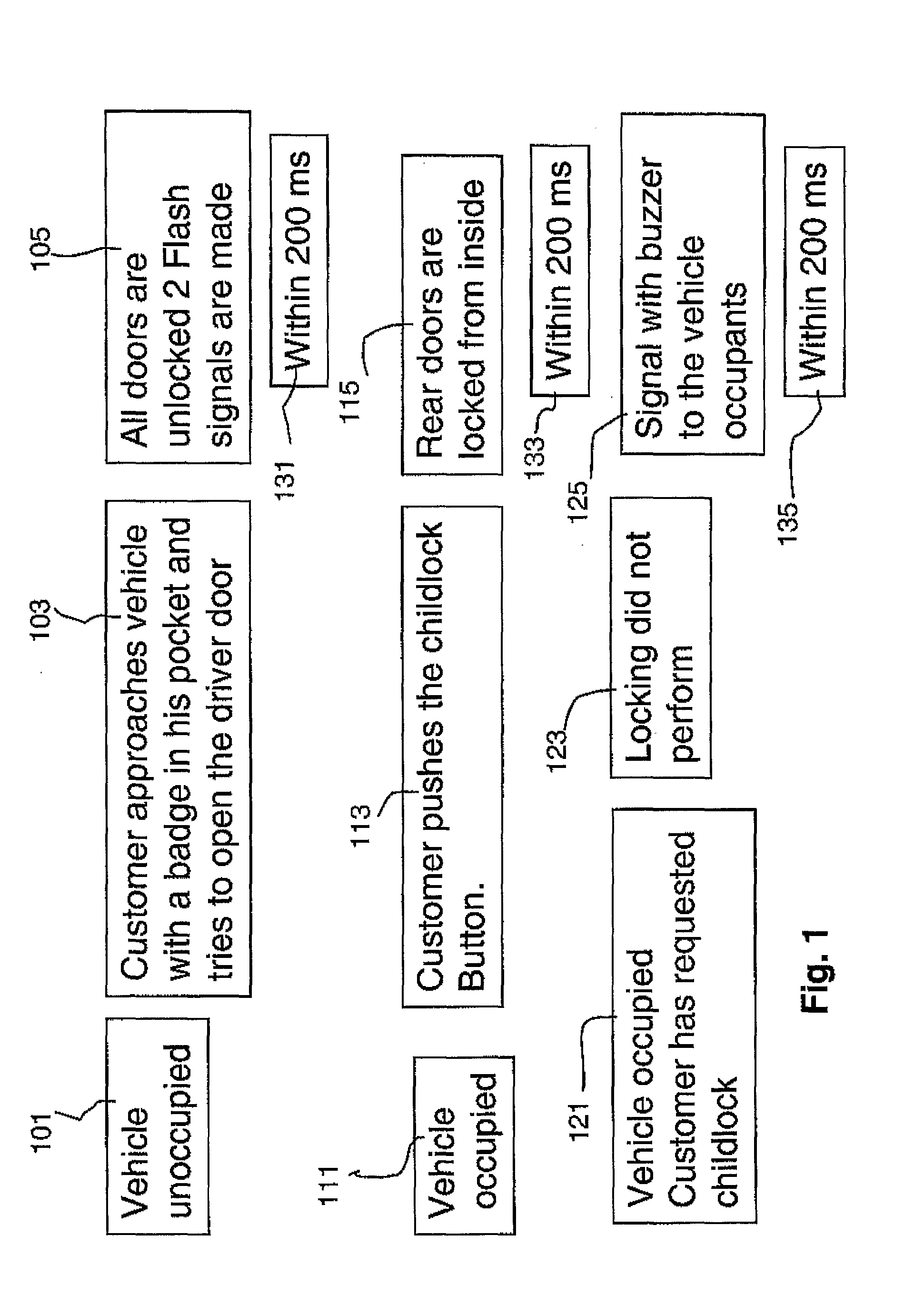

Validation method for embedded systems

InactiveUS7895025B2Shorten the timeImprove test coverageAdditive manufacturing apparatusAnalogue computers for electric apparatusControl flowData stream

A method of designing a validation environment for a service implemented by an embedded electrical system. In the method one or more user requests and system responses are assigned. Next, a behavioral automata is assigned to the service, which fixes the allowed sequencing of the user requests and system responses. Then, a skeleton validation environment is automatically generated for the service. The skeleton validation environment includes testing automata produced from a traversal of the behavioral automata, a model of initial conditions, models of user requests, models of system response accuracy, an environmental model, and the dataflow and control flow assembling these models together. The skeleton validation environment covers all user requests and resultant system responses of the service. The skeleton validation environment is then recorded in a computer readable memory device for use by a design validation tool.

Owner:RENAULT SA

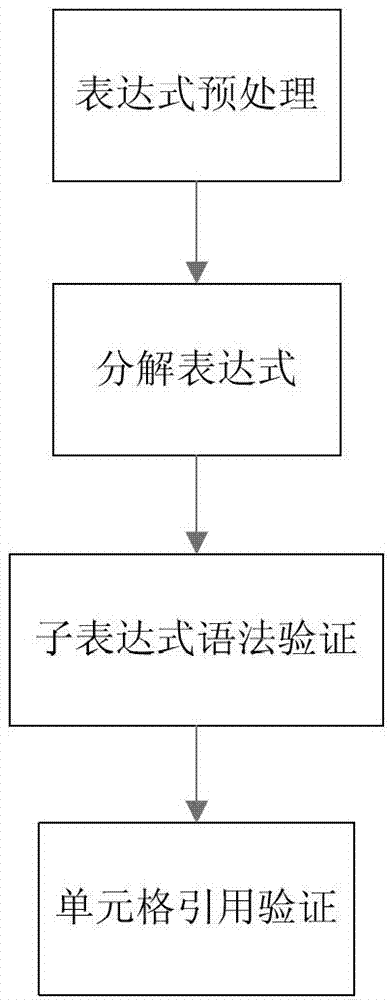

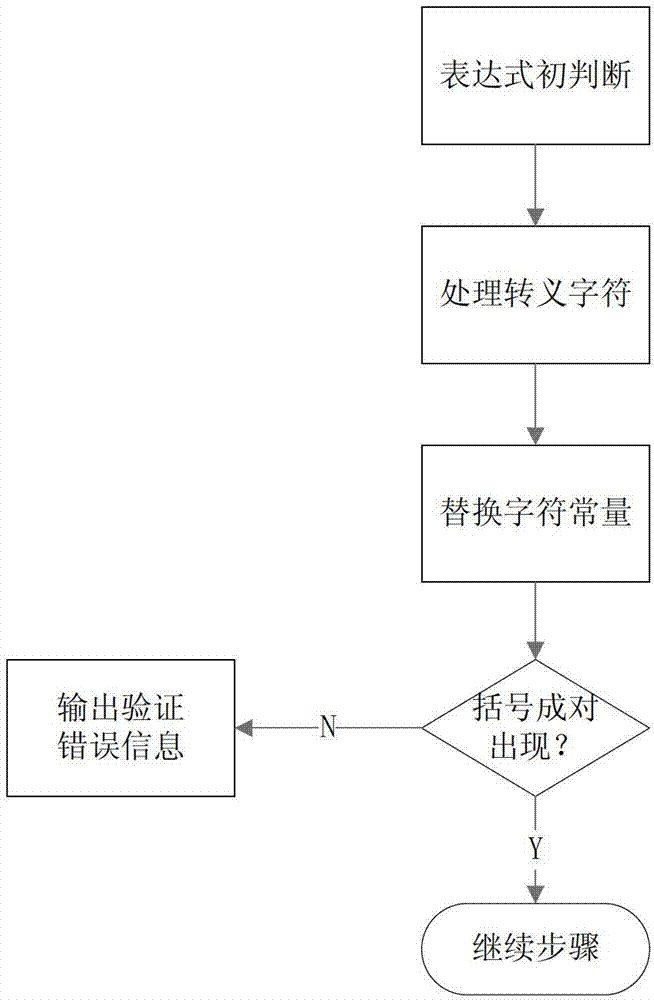

Intelligent verification algorithm, method and device for report designer

The invention relates to an intelligent verification algorithm, an intelligent verification method and an intelligent verification device for a report designer. The method comprises the following steps of: verifying according to a data source, function parameters, a calculation and display expression, a statistical chart expression, cell cross-reference dependence and the like configured in a report designer template rule, after completing configuration of one item for the report designer automatically triggering verification whether the specifications or requirements of a verification algorithm are met or not, i.e., automatically verifying a design expression or other functions and the like after the design expression or a function is completed, so that the conditions that sending all verification requests to a background for verifying one by one during click storage after the design of an entire report sheet is completed, and causing unnecessary background service pressure are eliminated, and the rapidness and friendliness of report design verification are realized. Verification comprises data source verification, expression verification, function parameter verification, cell verification and the like.

Owner:XIAMEN GREAT POWER GEO INFORMATION TECH +2

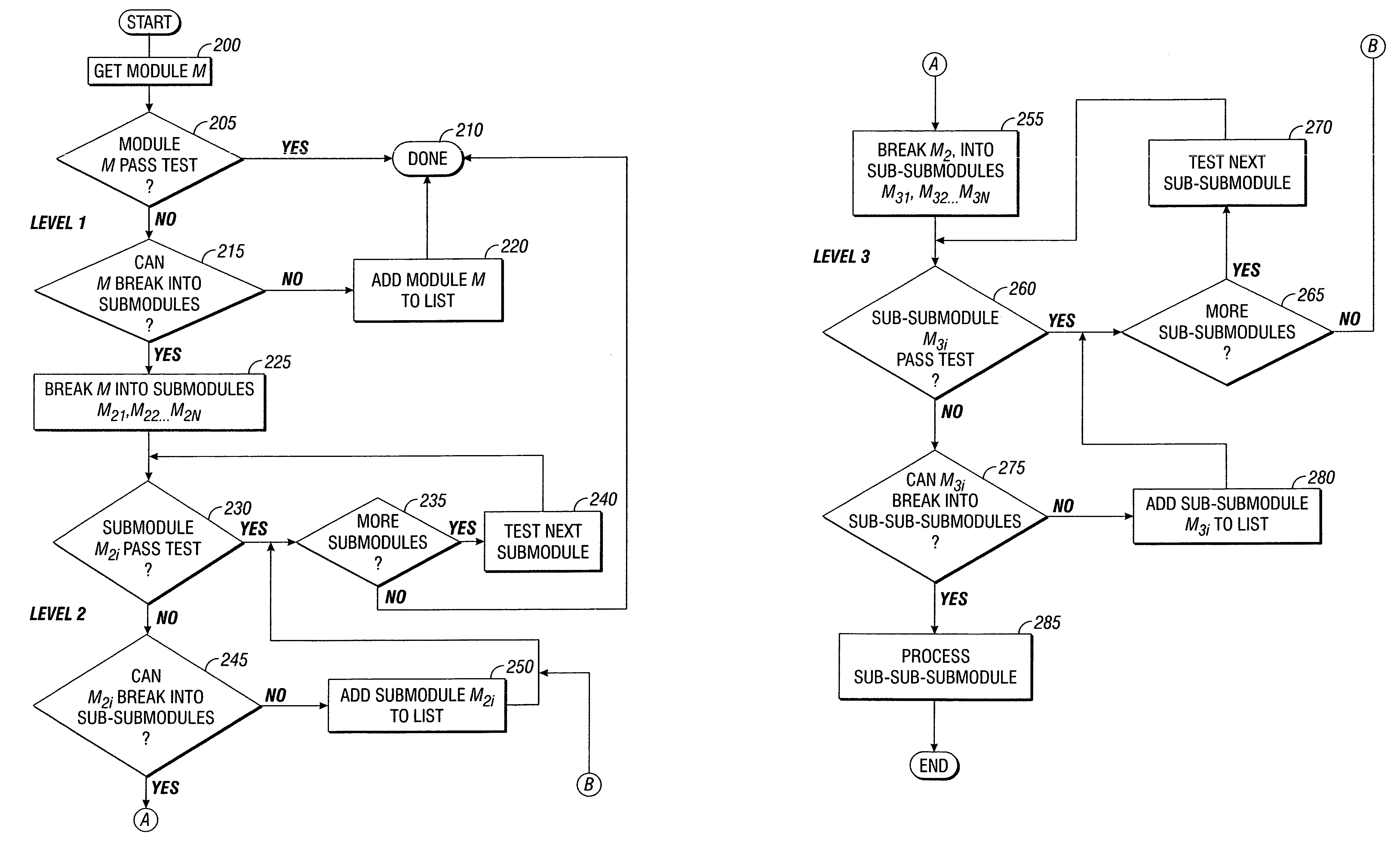

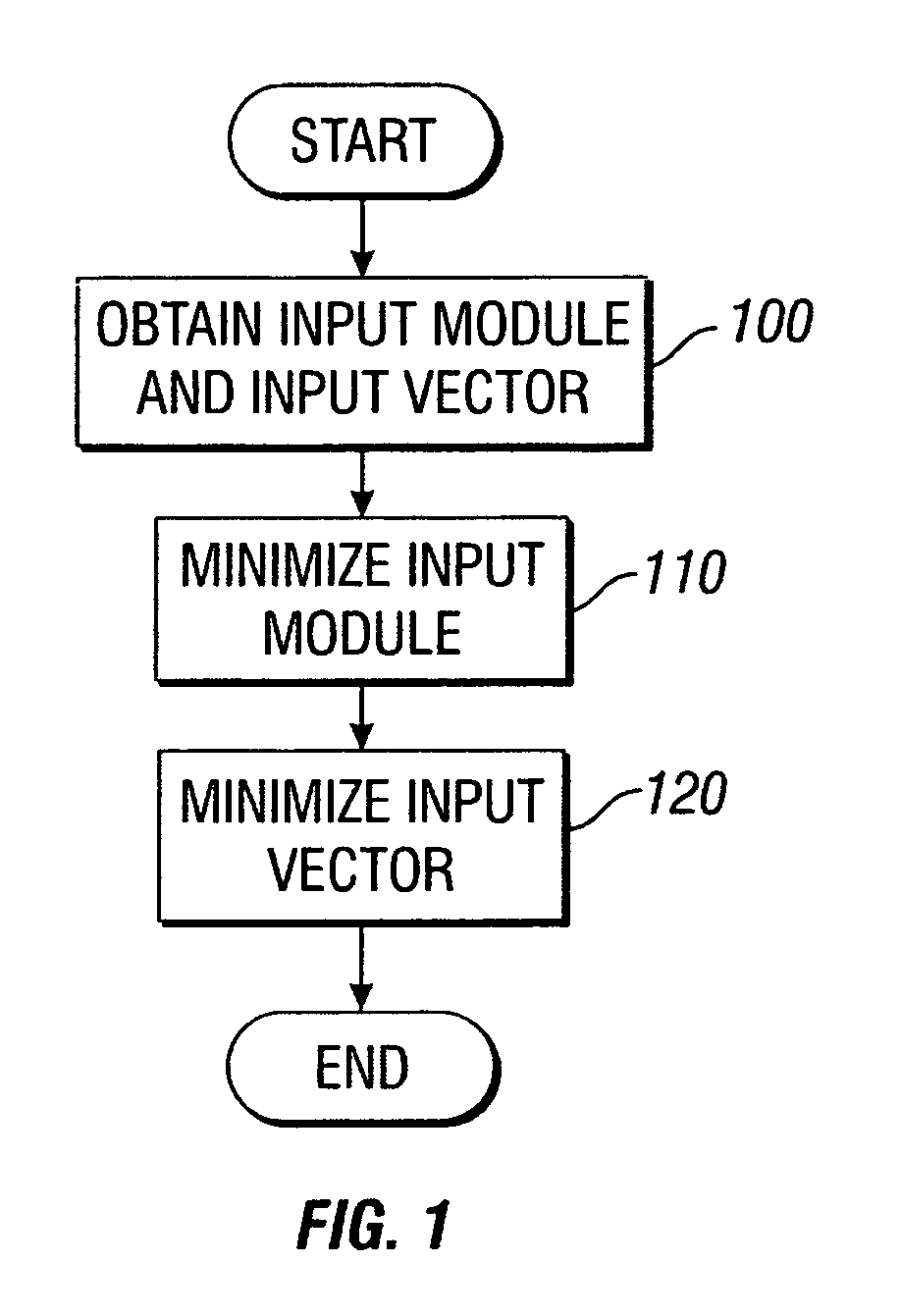

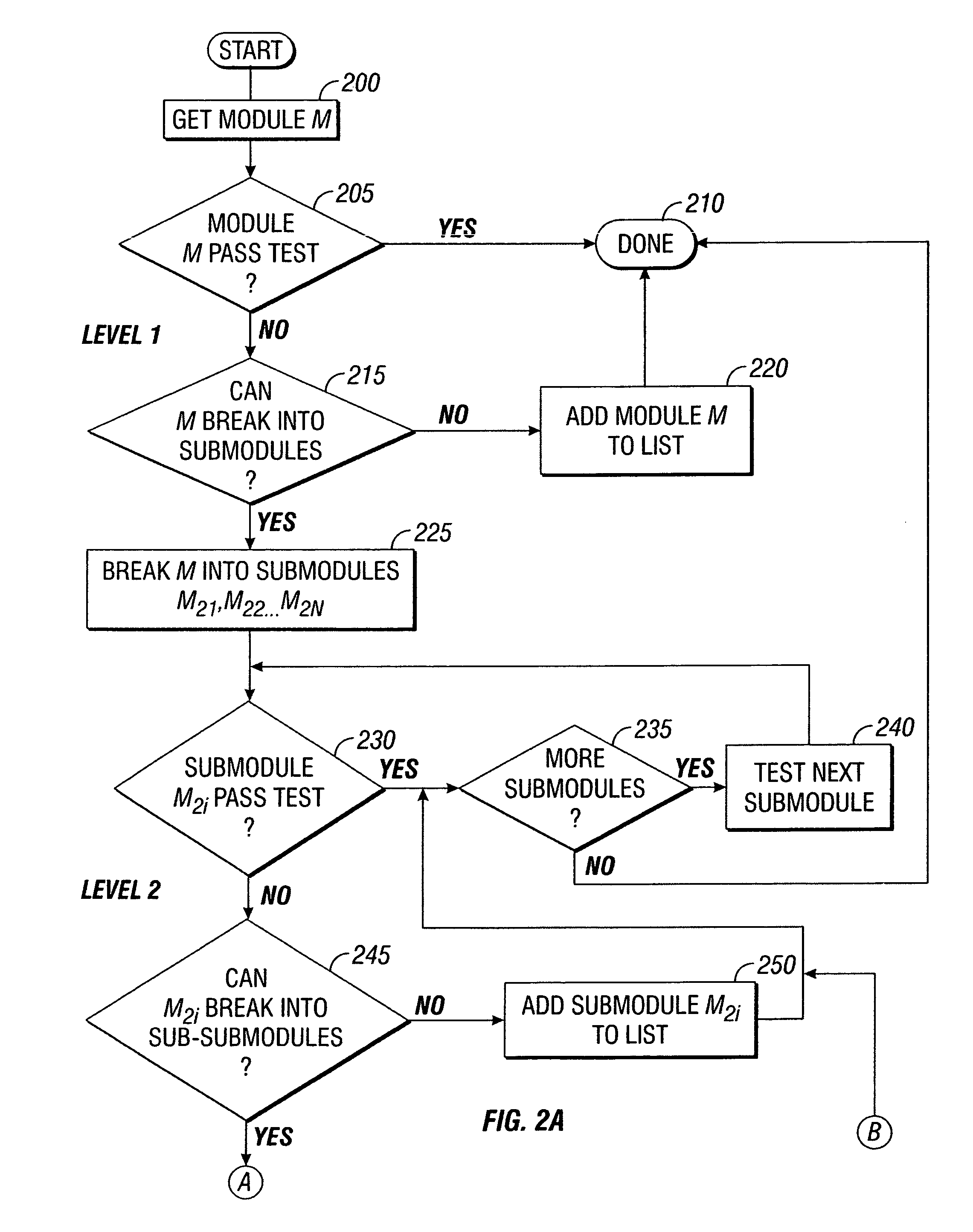

Method and apparatus for automatically isolating minimal distinguishing stimuli in design verification and software development

InactiveUS7017150B2Software testing/debuggingSpecific program execution arrangementsSoftware development processSoftware bug

The invention provides a method for detecting and isolating software bugs and generating a minimal set of stimuli to reproduce the bugs. The present invention utilizes a recursive algorithm to compare the output of successively smaller software blocks of a program in development to a verified output sample. The smallest software blocks which are found to contain a bug are isolated. For each of these isolated blocks, the smallest input vector is determined such that the application of this vector to the block expresses the bug. The present invention utilizes a separate recursive algorithm to determine these minimal vectors.

Owner:ORACLE INT CORP

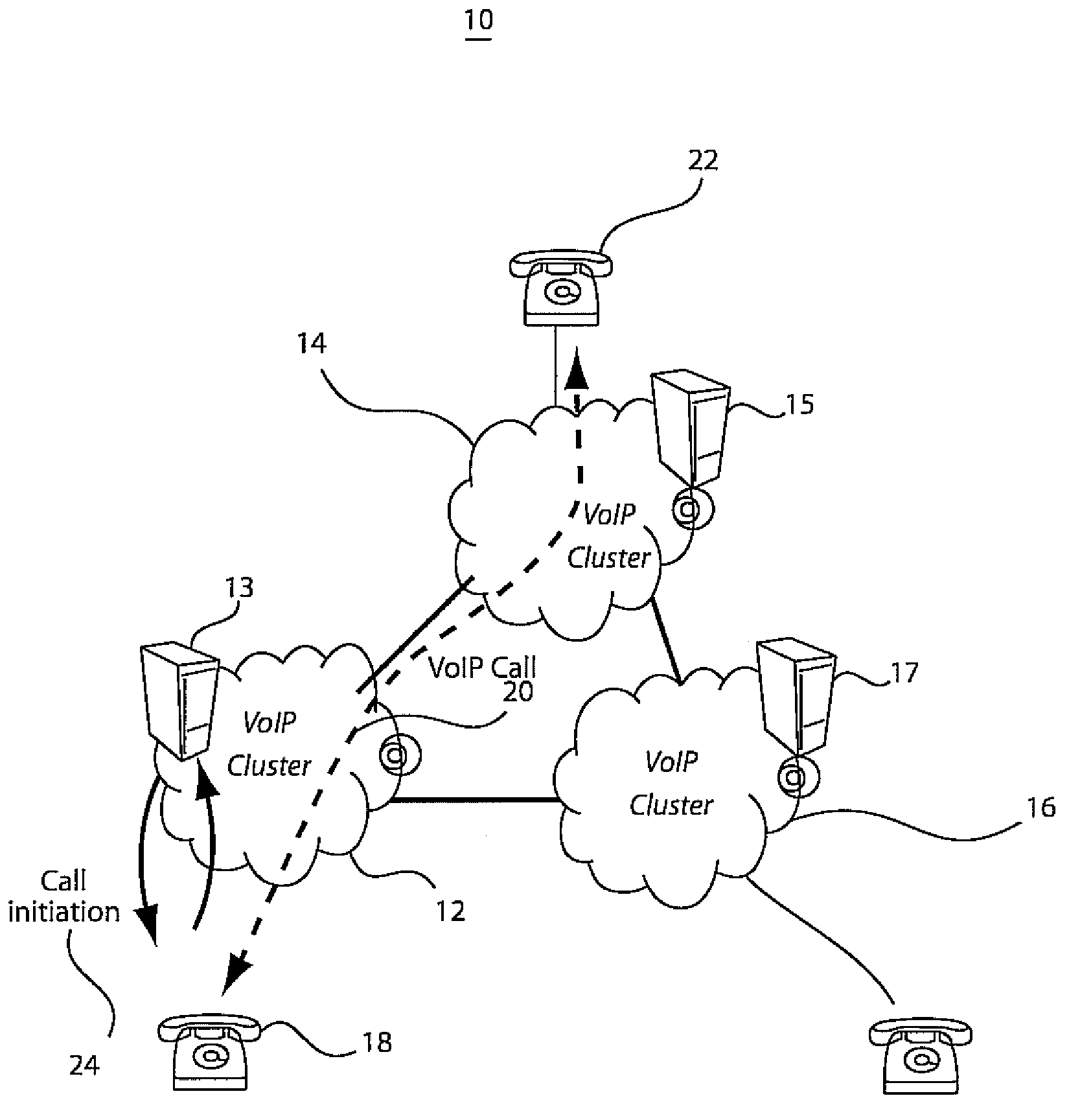

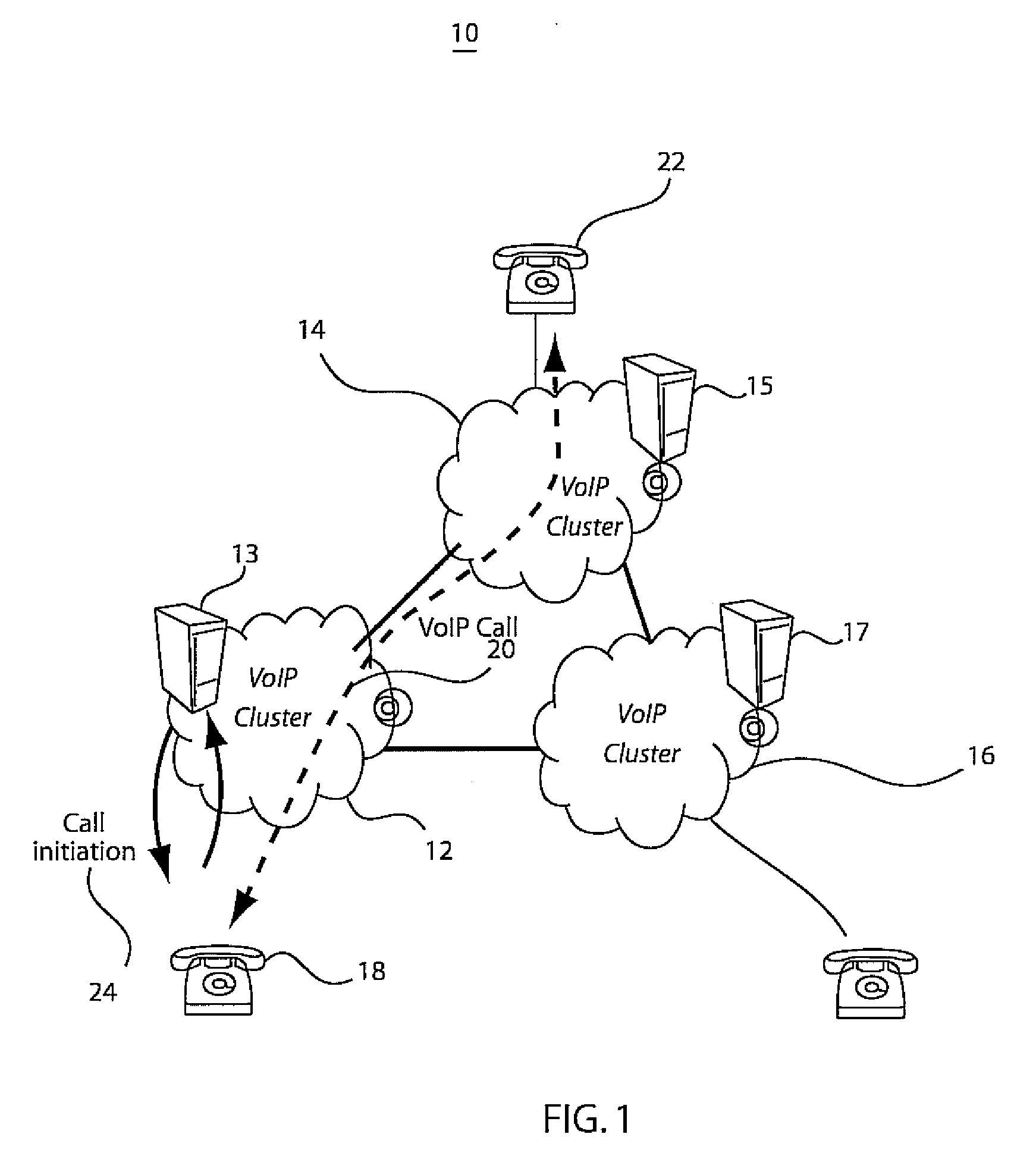

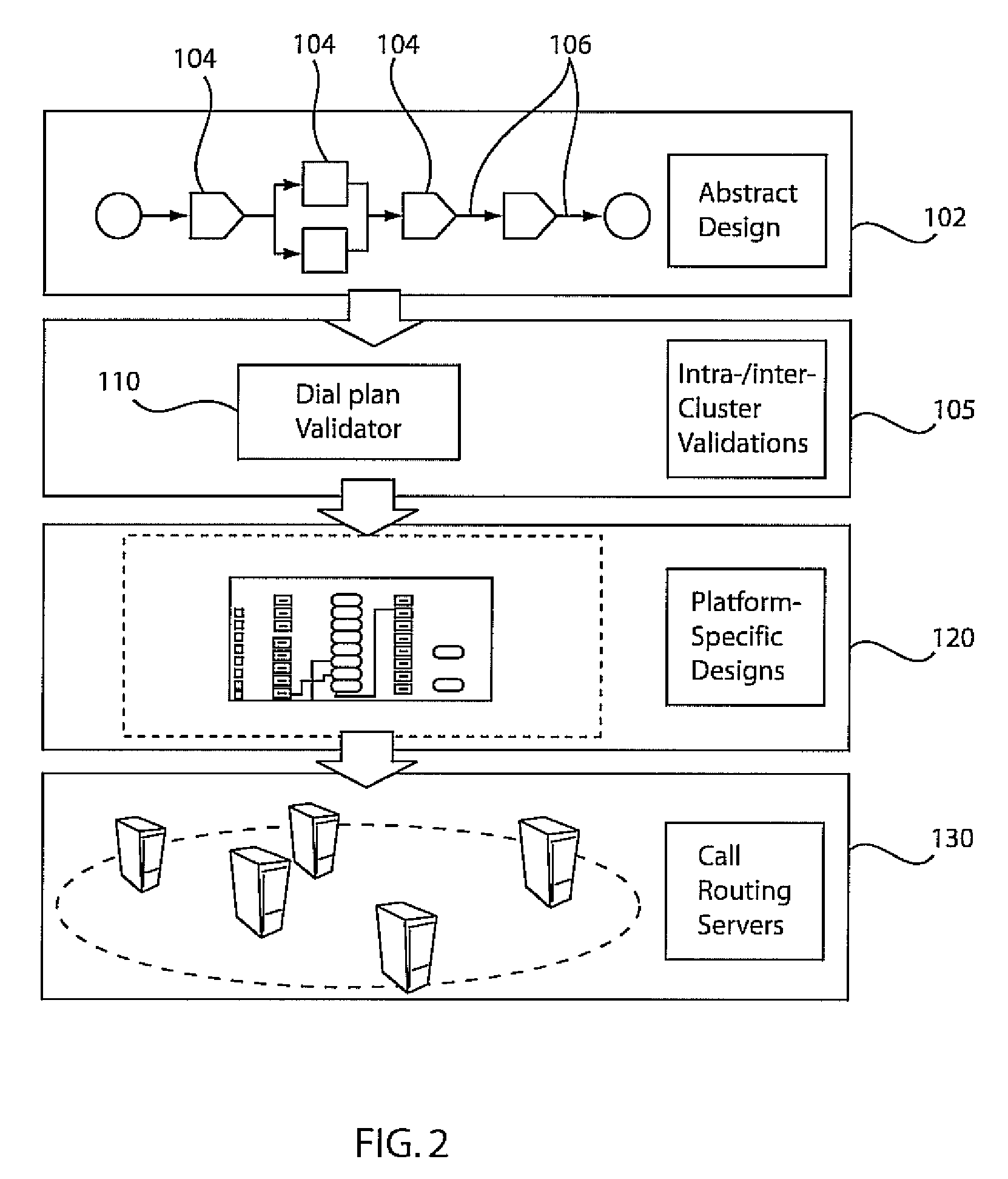

Method and system for platform-independent VOIP dial plan design, validation, and deployment

ActiveUS20110051715A1Network connectionsSelection arrangementsVoice over internet protocol voipProgram planning

A system and method for designing a dial plan for Voice over Internet Protocol (VoIP) systems includes generating an abstract dial plan design which is platform independent, the dial plan including rules for routing communications in a VoIP network structure. The dial plan is validated through simulations prior to deployment to evaluate the dial plan performance under simulated conditions. The dial plan design is translated to provide compatibility with a deployed network using platform specific configuration adaptors.

Owner:IBM CORP

Automated Method and Apparatus for Very Early Validation of Chip Power Distribution Networks in Semiconductor Chip Designs

InactiveUS20090210836A1Speed up checking algorithmQuick identificationComputer aided designSoftware simulation/interpretation/emulationEffective solutionDesign cycle

Validation of full-chip power distribution networks can be performed very early, and continuously throughout the design cycle, to detect real physical power connection problems and enable early correction of power grid designs using early floor plan and power grid design data. Common power connection and distribution errors are automatically addressed as an integral part of the early chip floor planning and chip power build processes providing efficient solutions requiring no extra wiring resource to be implemented and reducing the runtime of required final full-chip physical design checks, and the overall design cycle.

Owner:GLOBALFOUNDRIES INC

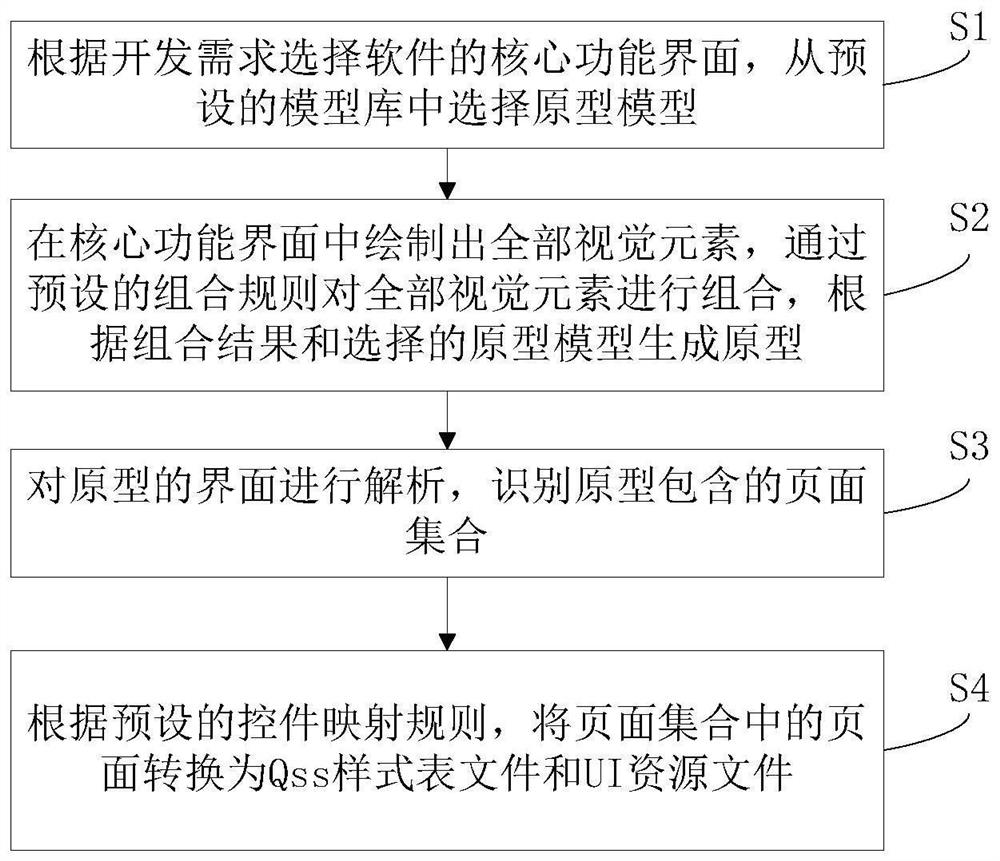

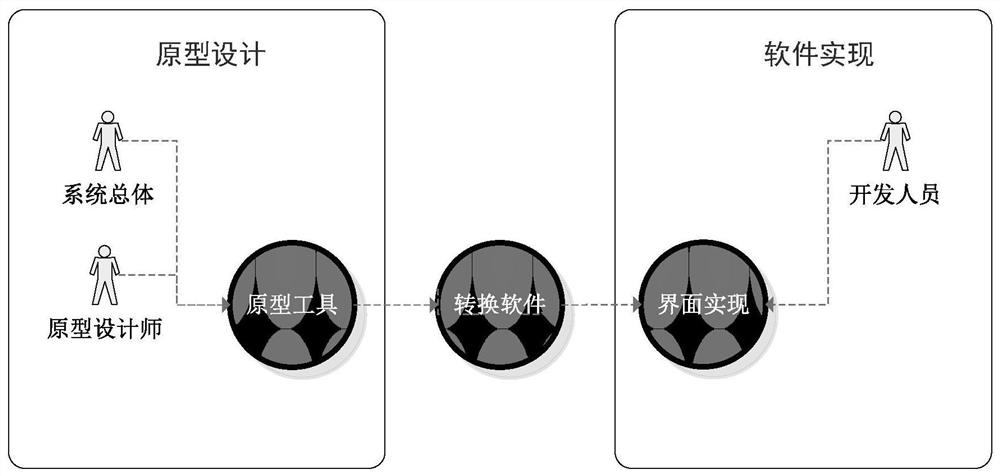

Prototype-based human-computer interaction design implementation method and system

ActiveCN111625226AImprove development efficiencyAccurate Cost EstimationSoftware designEnergy efficient computingCore functionInteraction design

The invention discloses a prototype-based human-computer interaction design implementation method and system, and relates to the field of software development. The method comprises the steps of drawing all visual elements in a core function interface, combining all the visual elements through a preset combination rule, and generating a prototype according to a combination result and a selected prototype model; analyzing an interface of the prototype, and identifying a page set contained in the prototype; and converting the pages in the page set into a Qss style sheet file and a UI resource file according to a preset control mapping rule. Demand verification and design verification can be conveniently carried out at any time; the cost of a development system is estimated more accurately, research and development control points are moved forwards, development risks are reduced, a model library is automatically generated by using a software conversion tool according to a prototype system,the model library in the corresponding field is continuously created, accumulated and perfected, and subsequent inheritance and use of new research models can be facilitated.

Owner:BEIJING INST OF RADIO MEASUREMENT

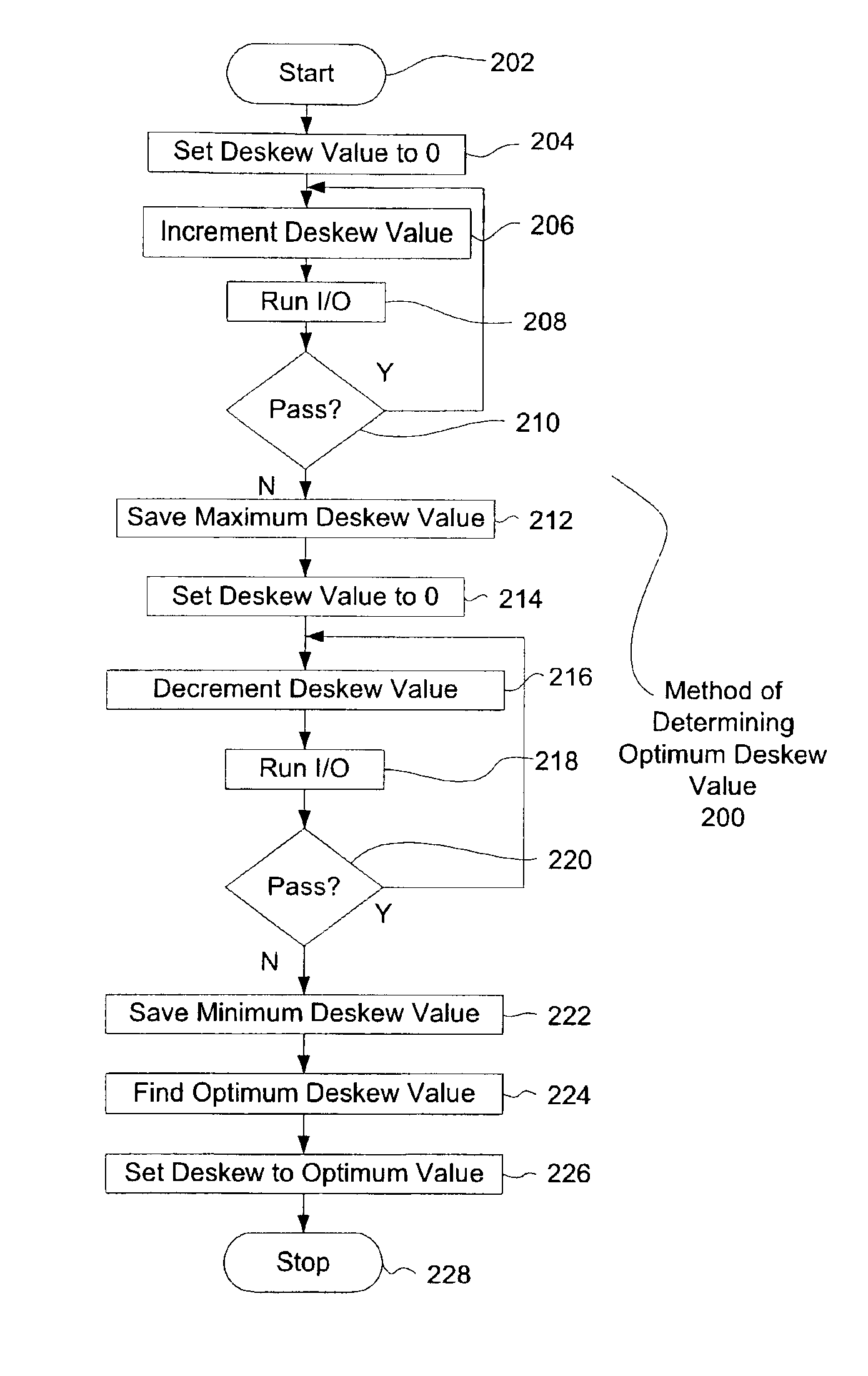

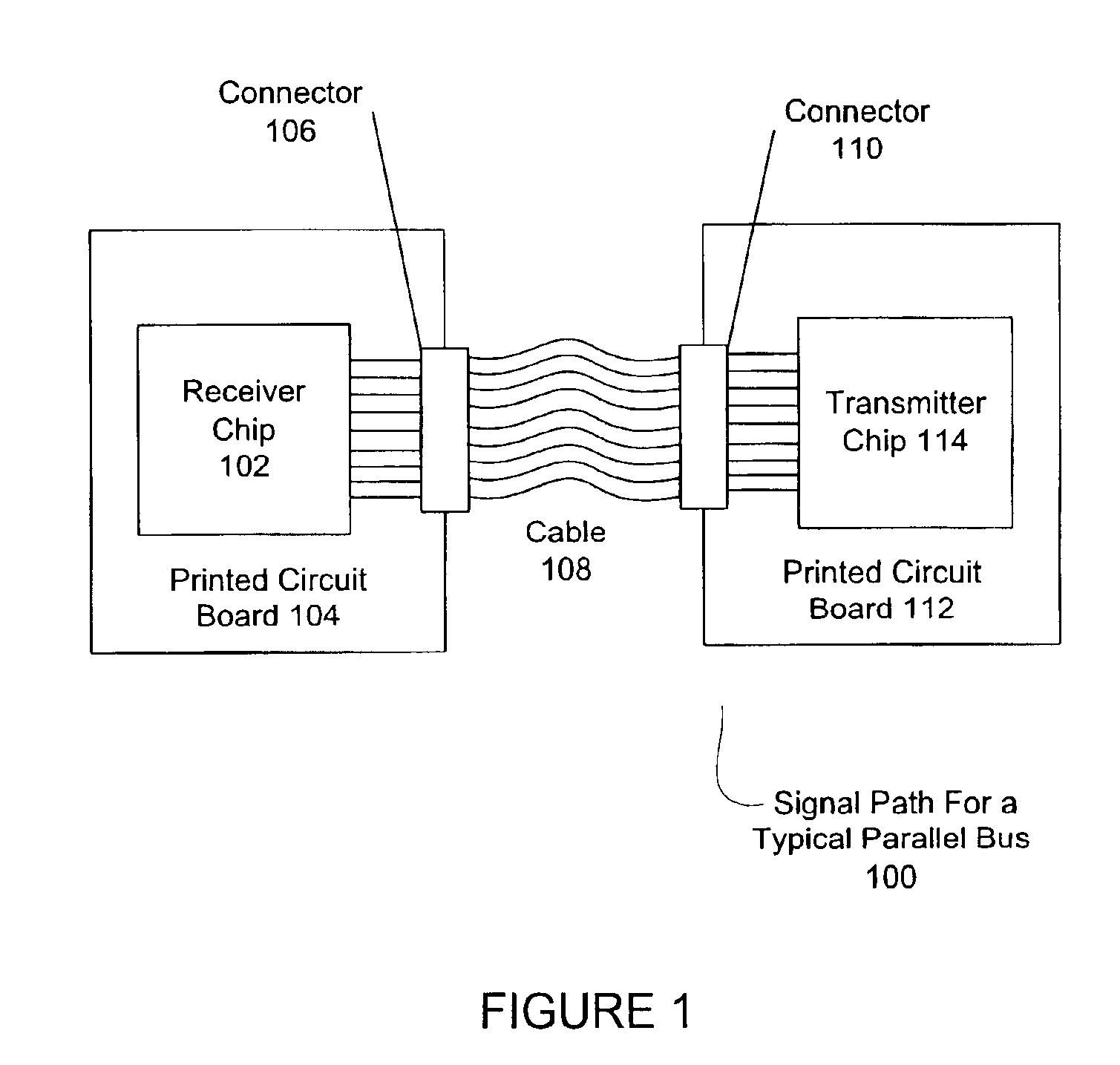

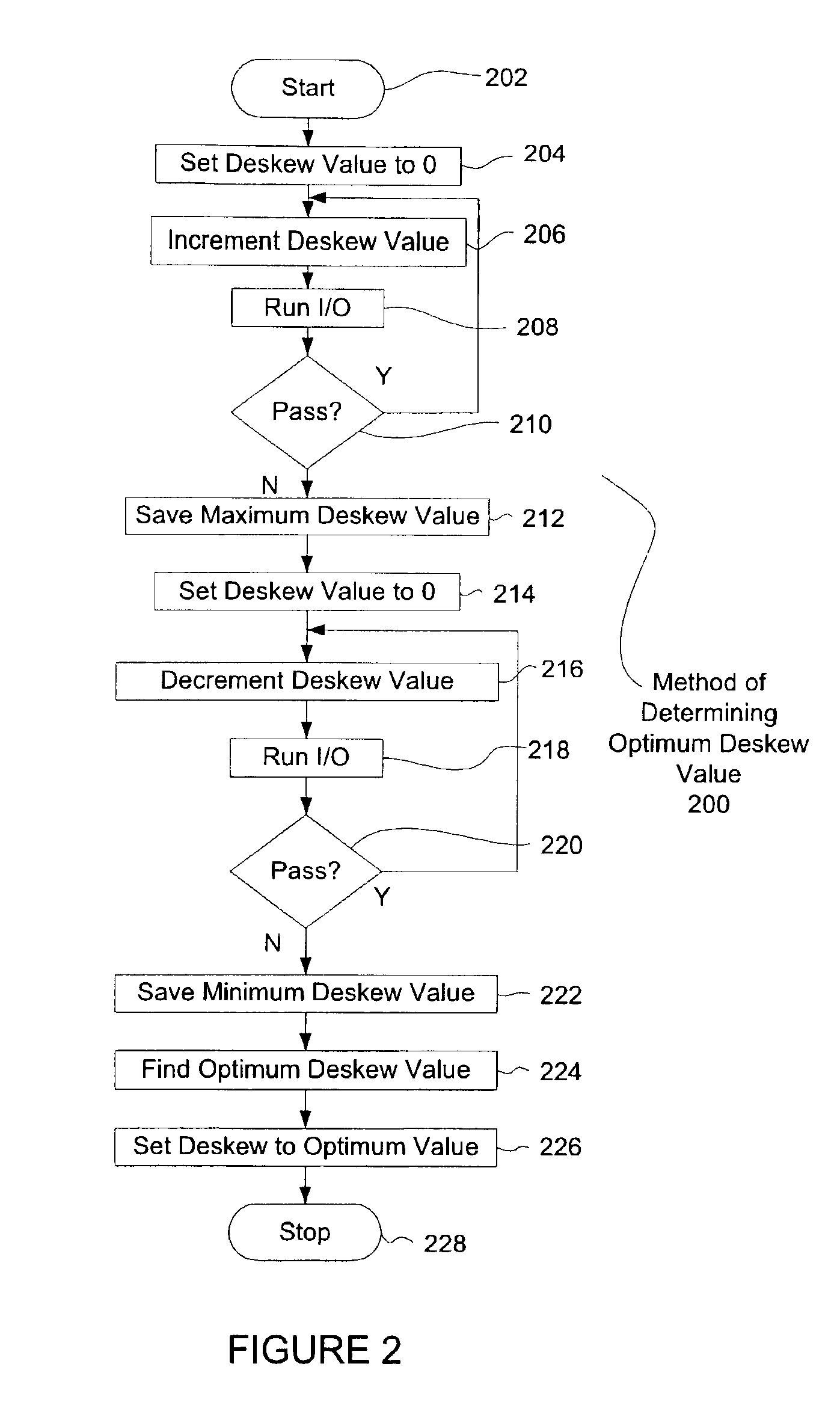

Method for determining deskew margins in parallel interface receivers

InactiveUS6892334B2Improve performanceImprove system performanceError detection/correctionTime-division multiplexLower limitData interface

Disclosed is a method for automatically testing the deskew setting for the clock in a parallel data interface. The deskew value is varied to a high and a low limit to the point where errors occur when transmissions occur. After determining the high and low operable limits of the deskew values, an optimum deskew setting may be determined and set for the system. The present invention may be used as a design verification technique, for optimizing a system after integration, or for further optimization of the deskew value after performing a training pattern for optimizing transmission performance.

Owner:NETWORK APPLIANCE INC