Patents

Literature

330 results about "Design testing" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

Design for testing or design for testability (DFT) consists of IC design techniques that add testability features to a hardware product design. The added features make it easier to develop and apply manufacturing tests to the designed hardware.

Correlation of electrical test data with physical defect data

ActiveUS6950771B1Improve yield analysisEasy to analyzeResistance/reactance/impedenceElectronic circuit testingData setDesign testing

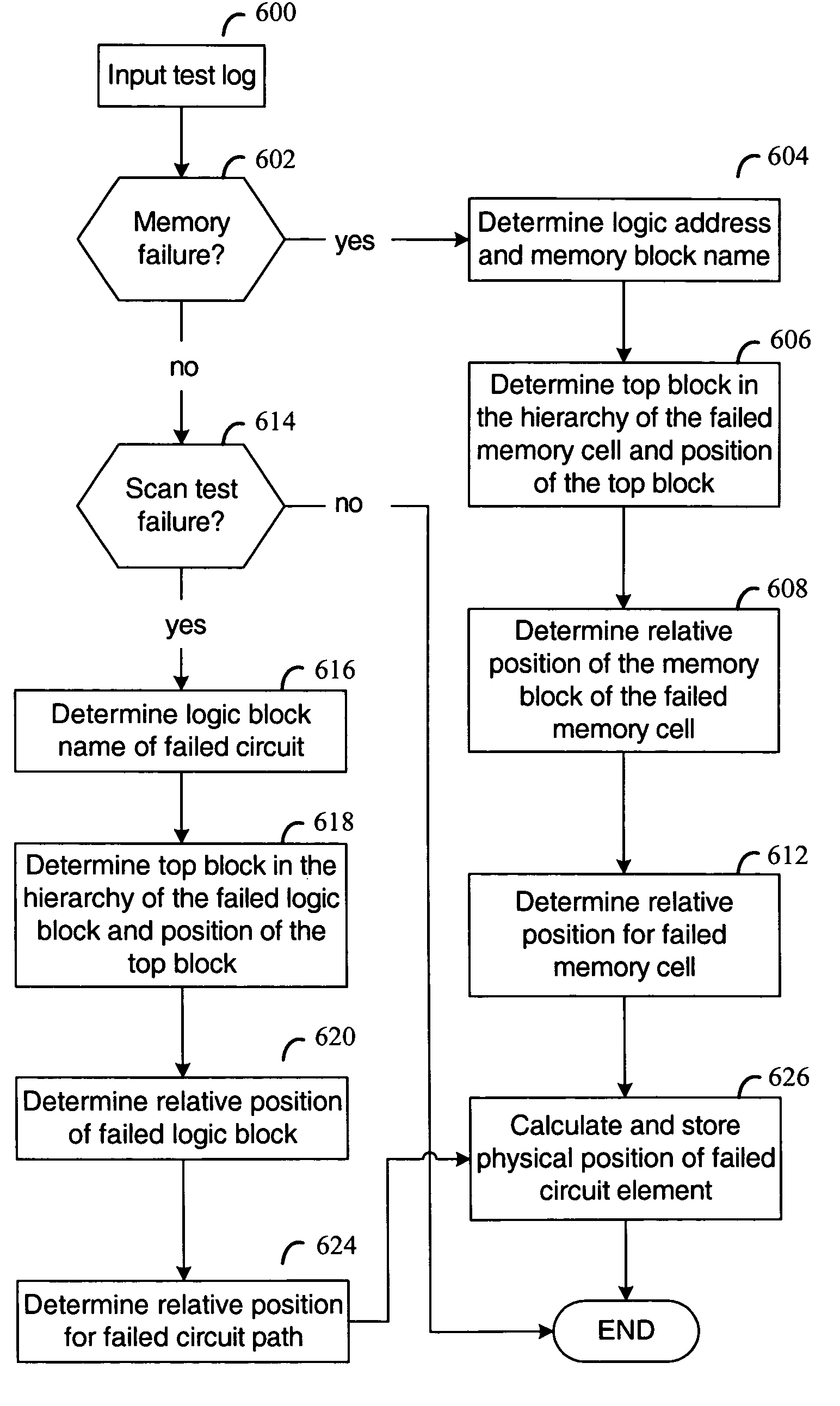

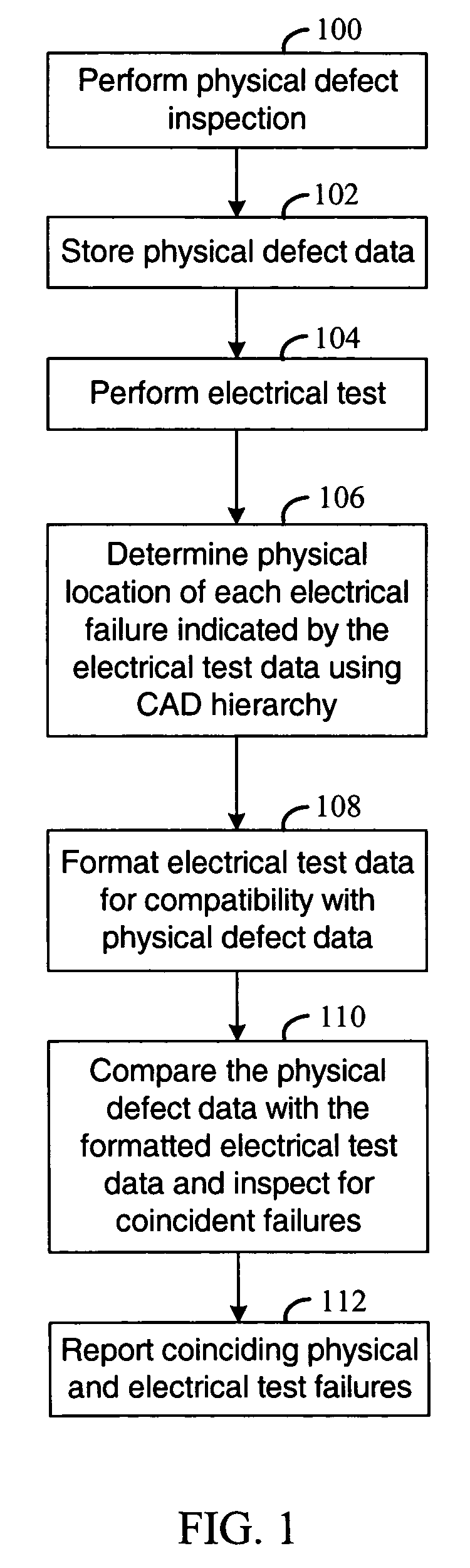

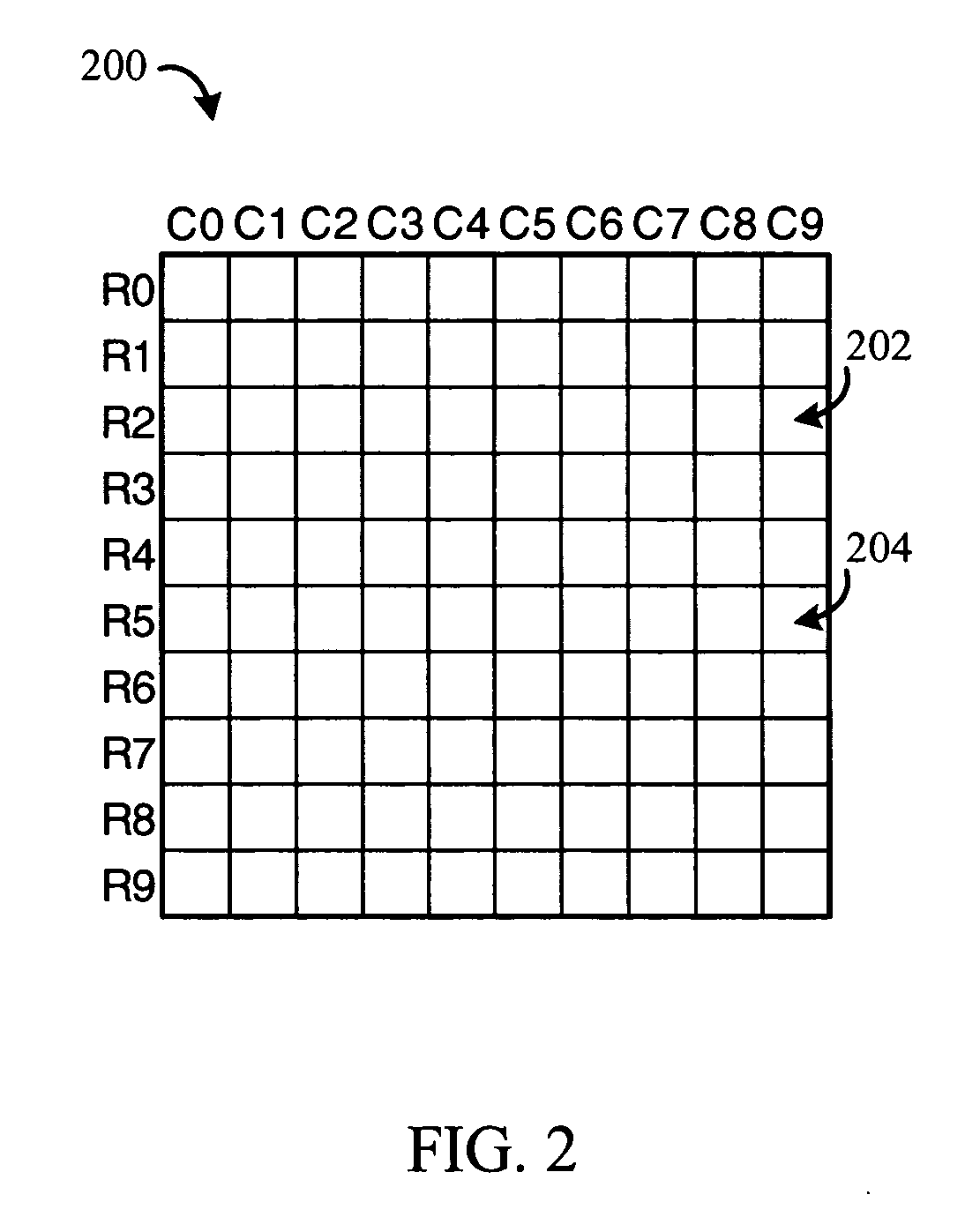

Method and apparatus are disclosed for analyzing defect data produced in testing a semiconductor chip from a logic design. In various embodiments, input for processing is a first inspection data set that identifies a first set of physical locations that are associated with defects detected during fabrication of the chip. Also input is a second test data set that includes one or more identifiers associated with failing circuitry in the chip. A second set of physical locations is determined from the one or more identifiers of failing circuitry, hierarchical relationships between blocks of the design, and placement information associated with the blocks. Each of the one or more identifiers is associated with at least one of the blocks. Correspondences are identified between physical locations in the first inspection data set and the second set of physical locations.

Owner:XILINX INC

Modelling network to assess security properties

ActiveUS20070136788A1Random number generatorsUser identity/authority verificationRich modelReachability

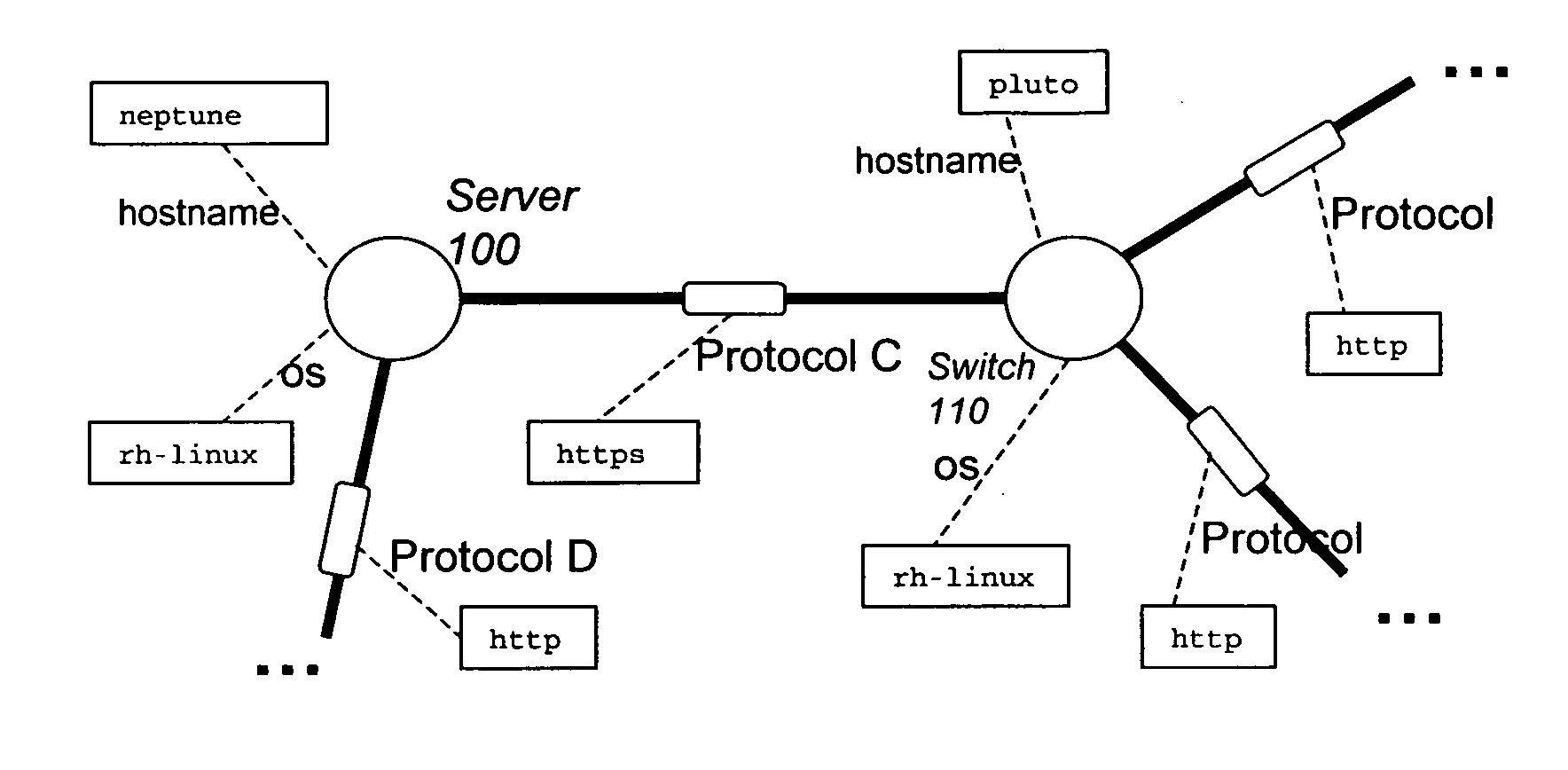

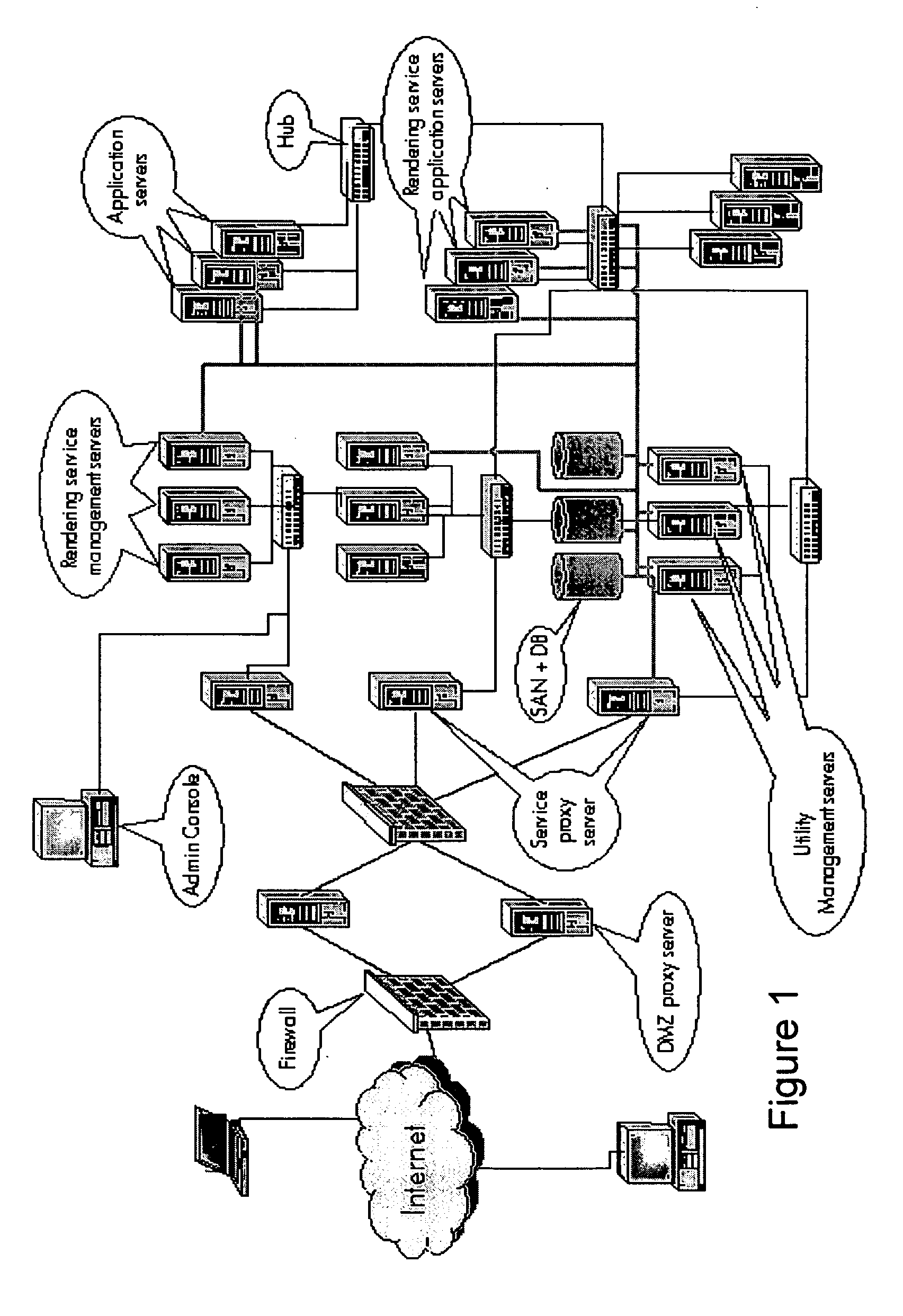

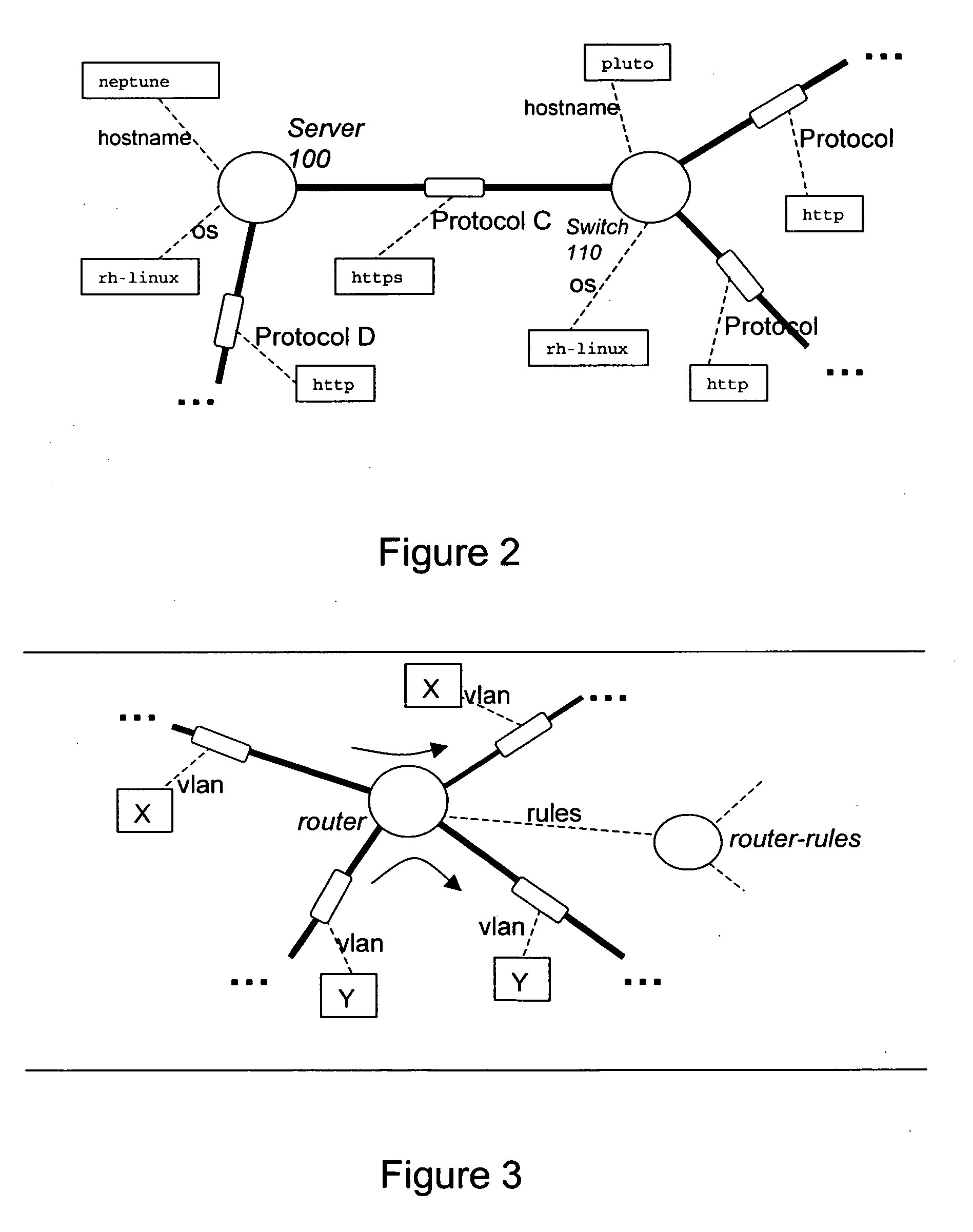

A method of assessing a network uses a model (450) having nodes (100, 110) to represent parts of the network infrastructure and the application services, and having links to represent how the nodes influence each other. Dependencies or effects of the application services are found by determining paths through the nodes and links of the model (530). Such assessment can be useful for design, test, operations, and diagnosis, and for assessment of which parts of the infrastructure are critical to given services, or which services are dependent on, or could have an effect on a given part of the infrastructure. The dependencies or effects can encompass reachability information. The use of a model having links and nodes can enable more efficient processing, to enable larger or richer models. What changes in the dependencies or effects result from a given change in the network can be determined (830).

Owner:HEWLETT-PACKARD ENTERPRISE DEV LP

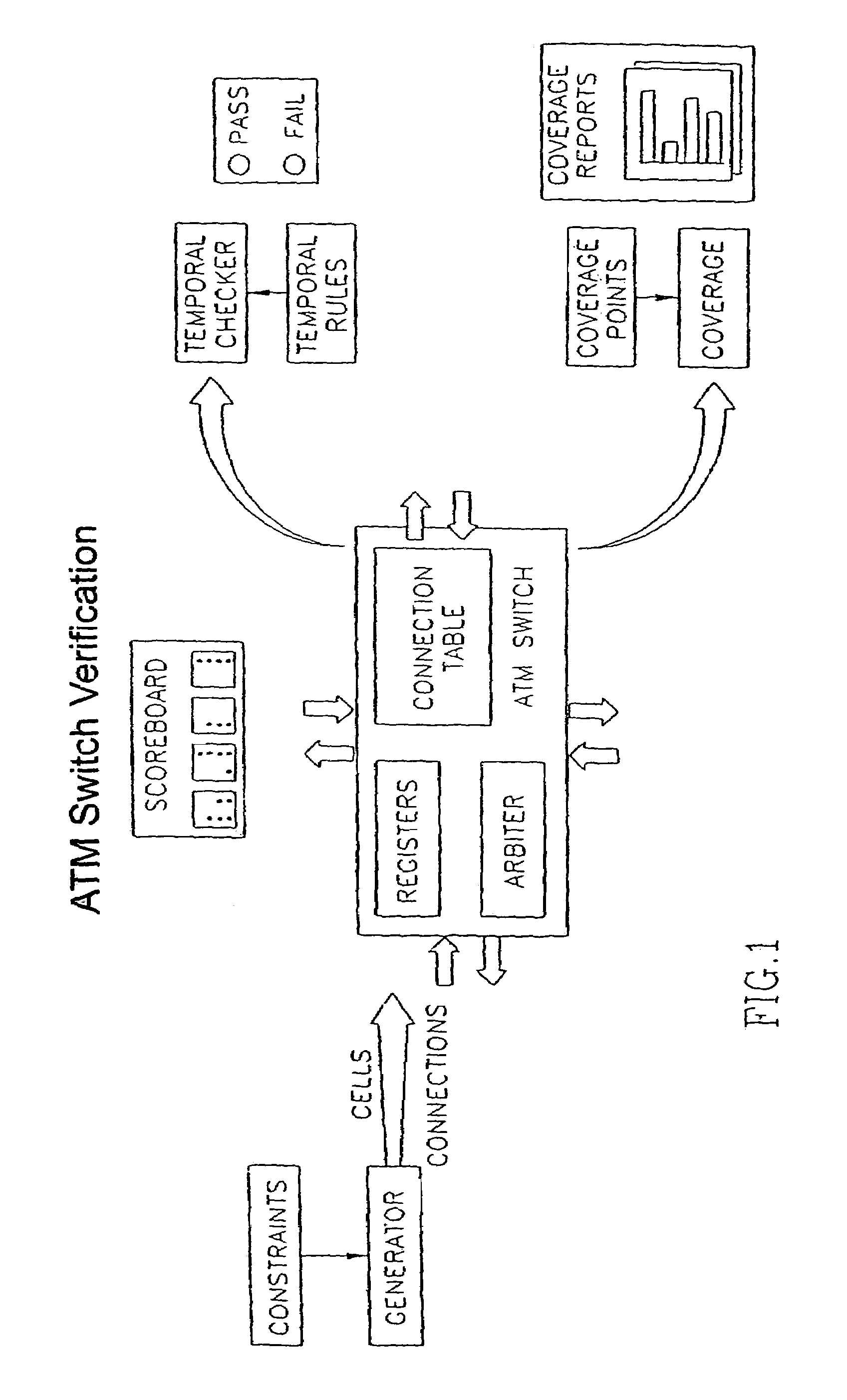

Integrated circuit test coverage evaluation and adjustment mechanism and method

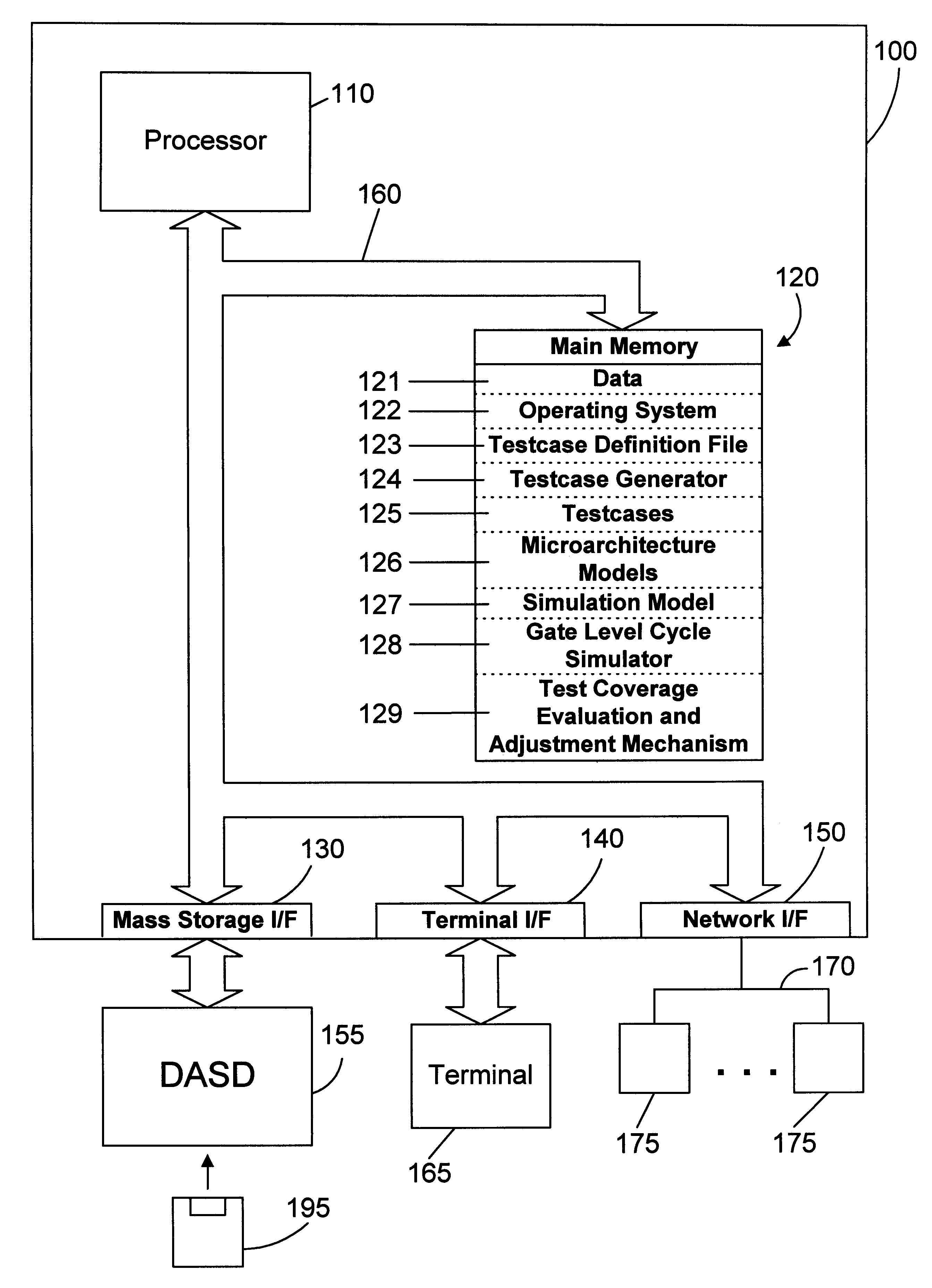

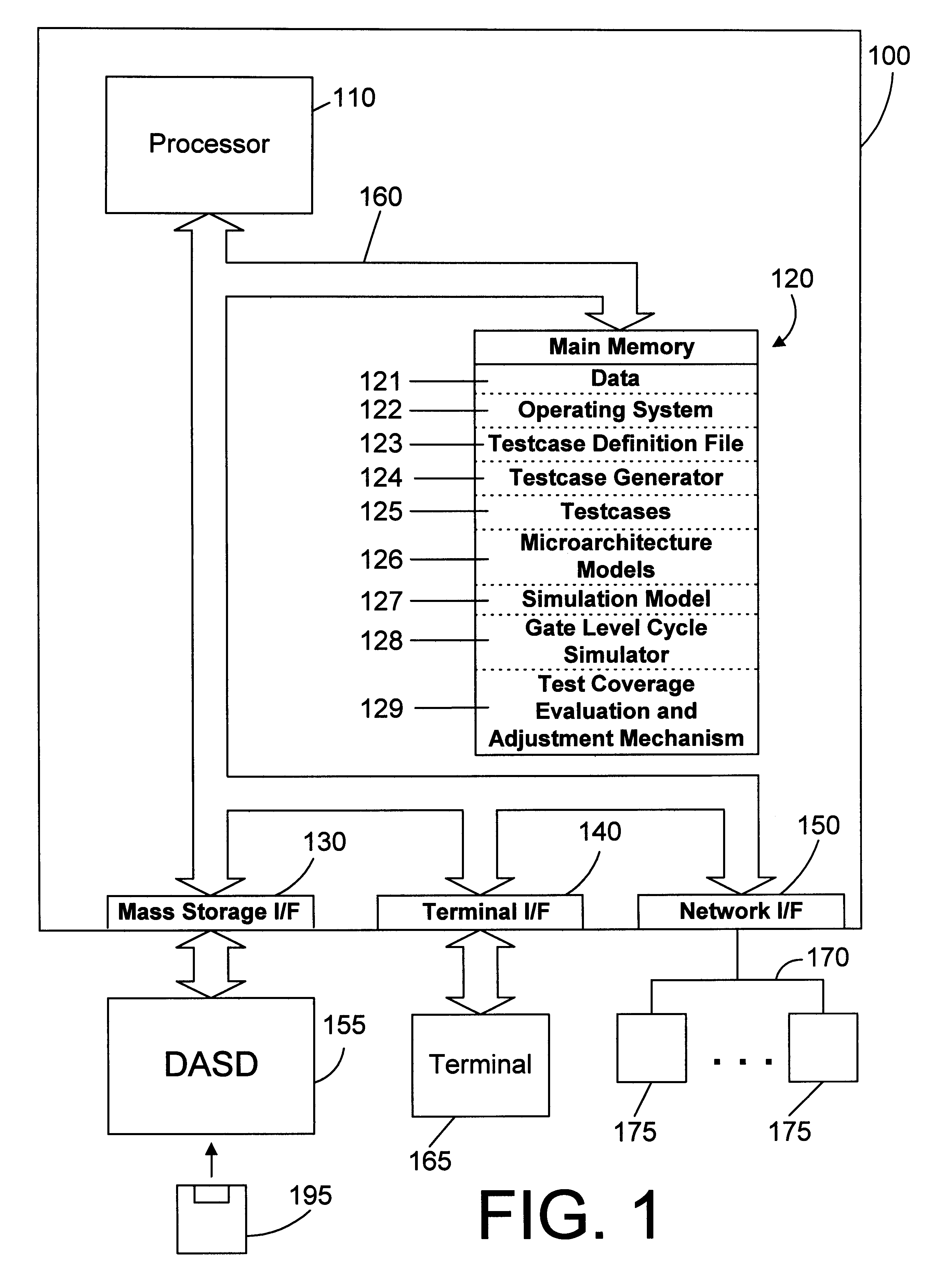

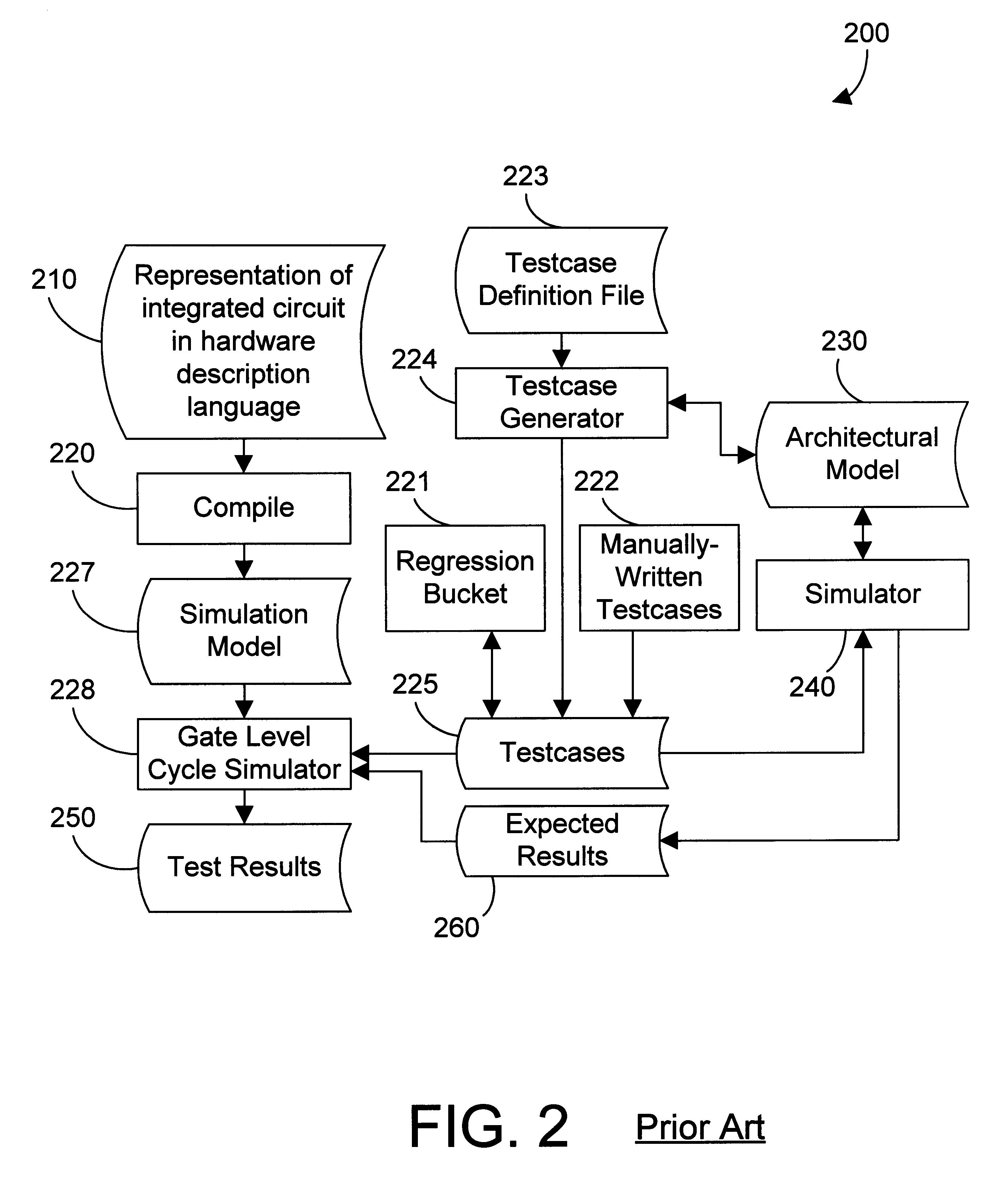

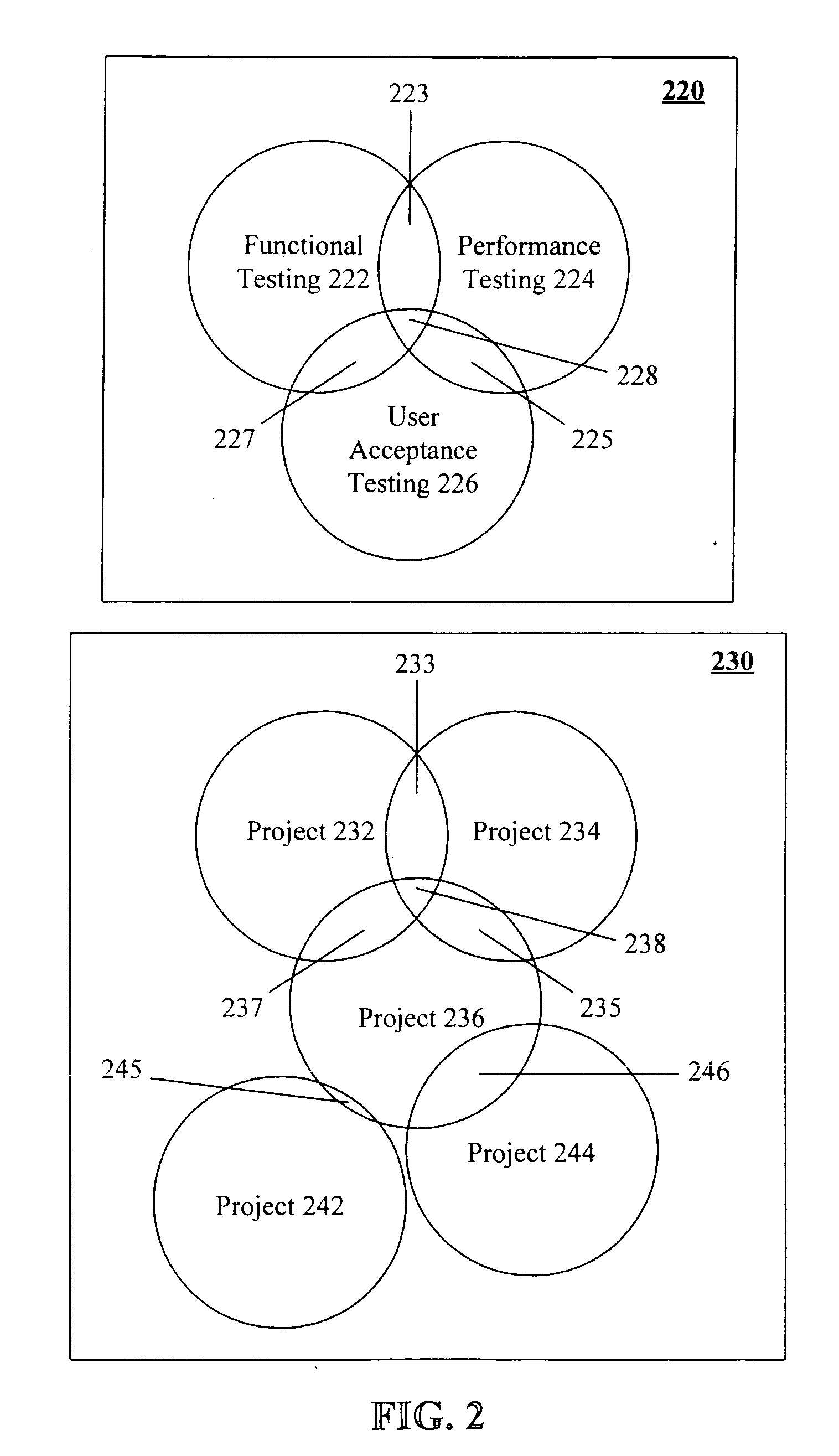

InactiveUS6212667B1Reduce decreaseElectronic circuit testingDetecting faulty computer hardwareDesign testingMicroarchitecture

Testcases are run to test the design of an integrated circuit. The coverage of the testcases is evaluated and compared against one or more microarchitecture models that define the behavior of a portion of the integrated circuit. If the coverage of the testcases is not adequate, new testcases are generated to test the previously untested behavior specified in the microarchitecture models.

Owner:GLOBALFOUNDRIES INC

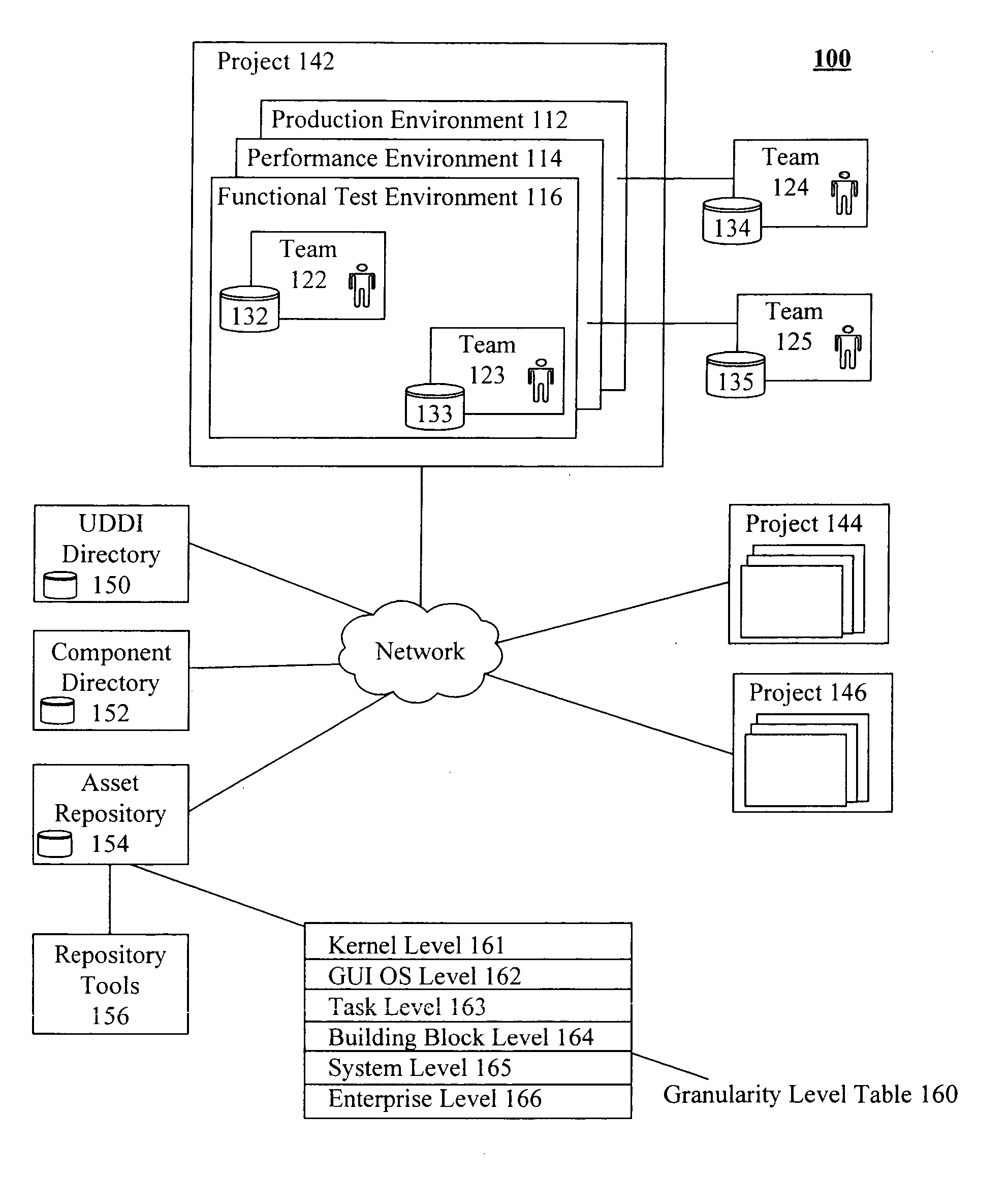

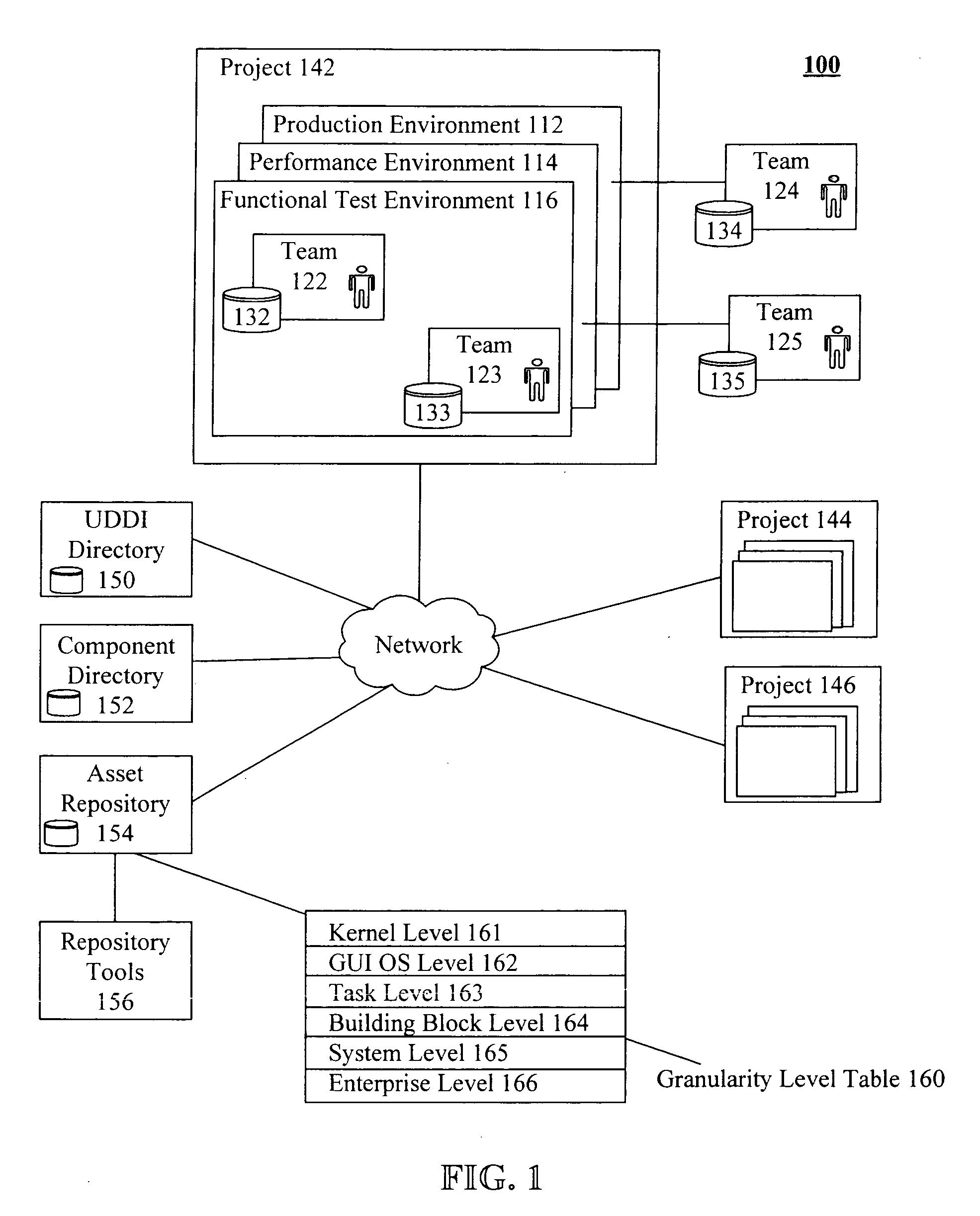

Software development tool for sharing test and deployment assets

InactiveUS20070240102A1Facilitate utilizationFacilitate acceptanceError detection/correctionSoftware reuseGranularityDesign testing

A solution for sharing assets associated with componentized software units (software components) having a set of well defined interfaces. Each software component can be associated with a particular level of granularity and can be formed from one or more other lower-level software components. Each software components can be associated with one or more test assets as well as one or more deployment assets. The software components and associated assets can be stored in one or more shared asset repositories. Solutions and / or solution templates can be rapidly developed using automated tools associated with the shared asset repository, as previous design, test, and deployment efforts are able to be strongly leveraged.

Owner:IBM CORP

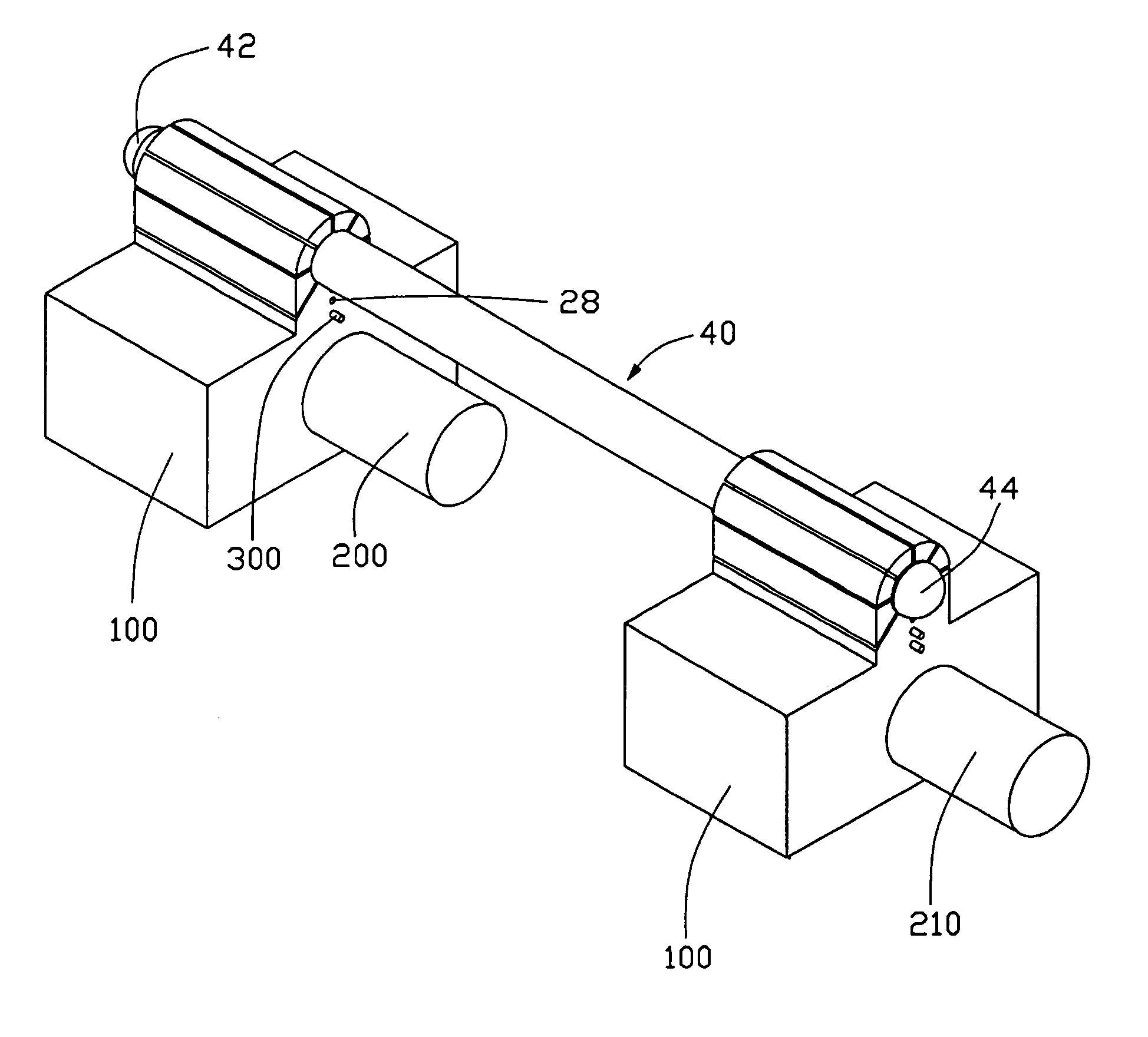

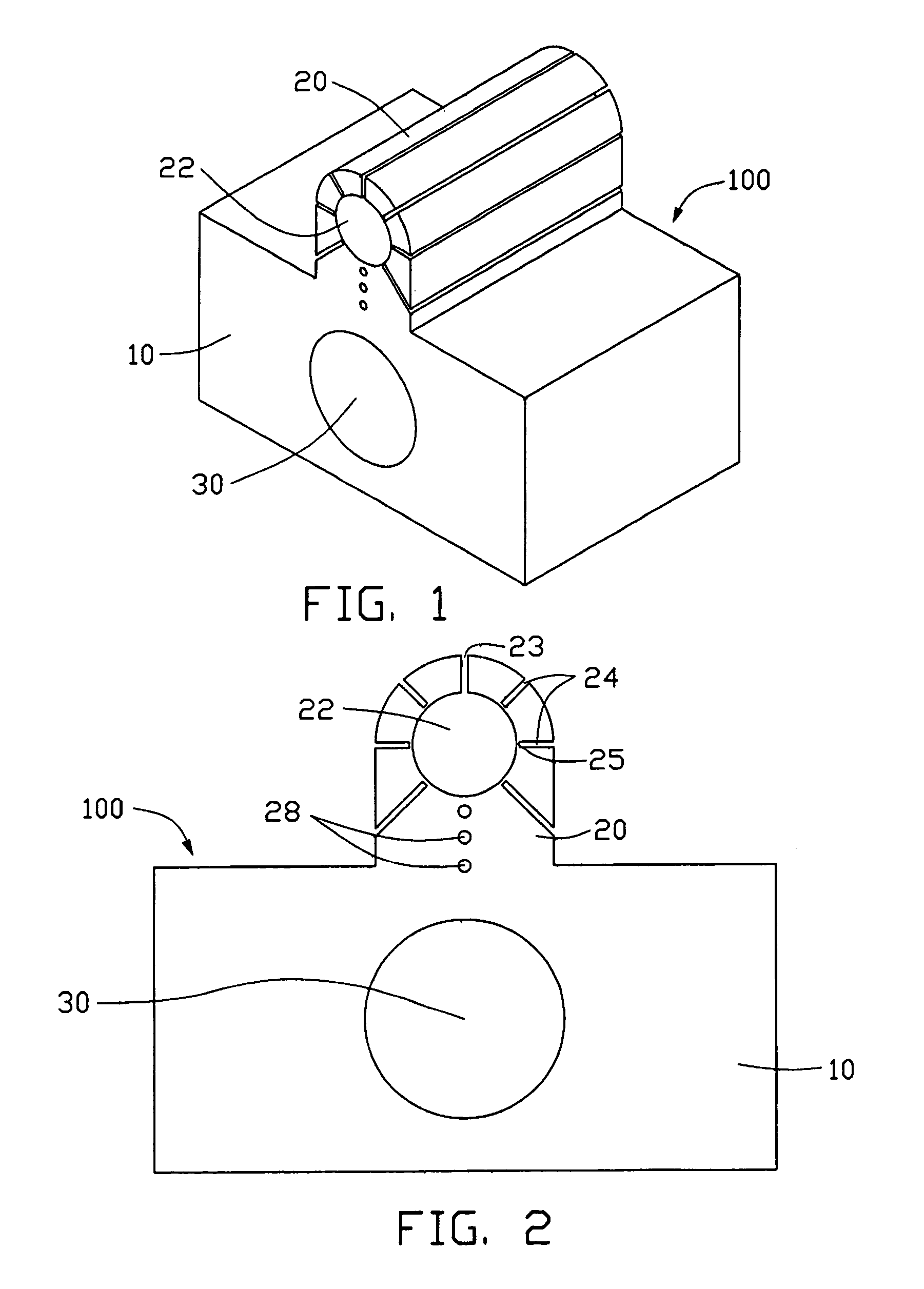

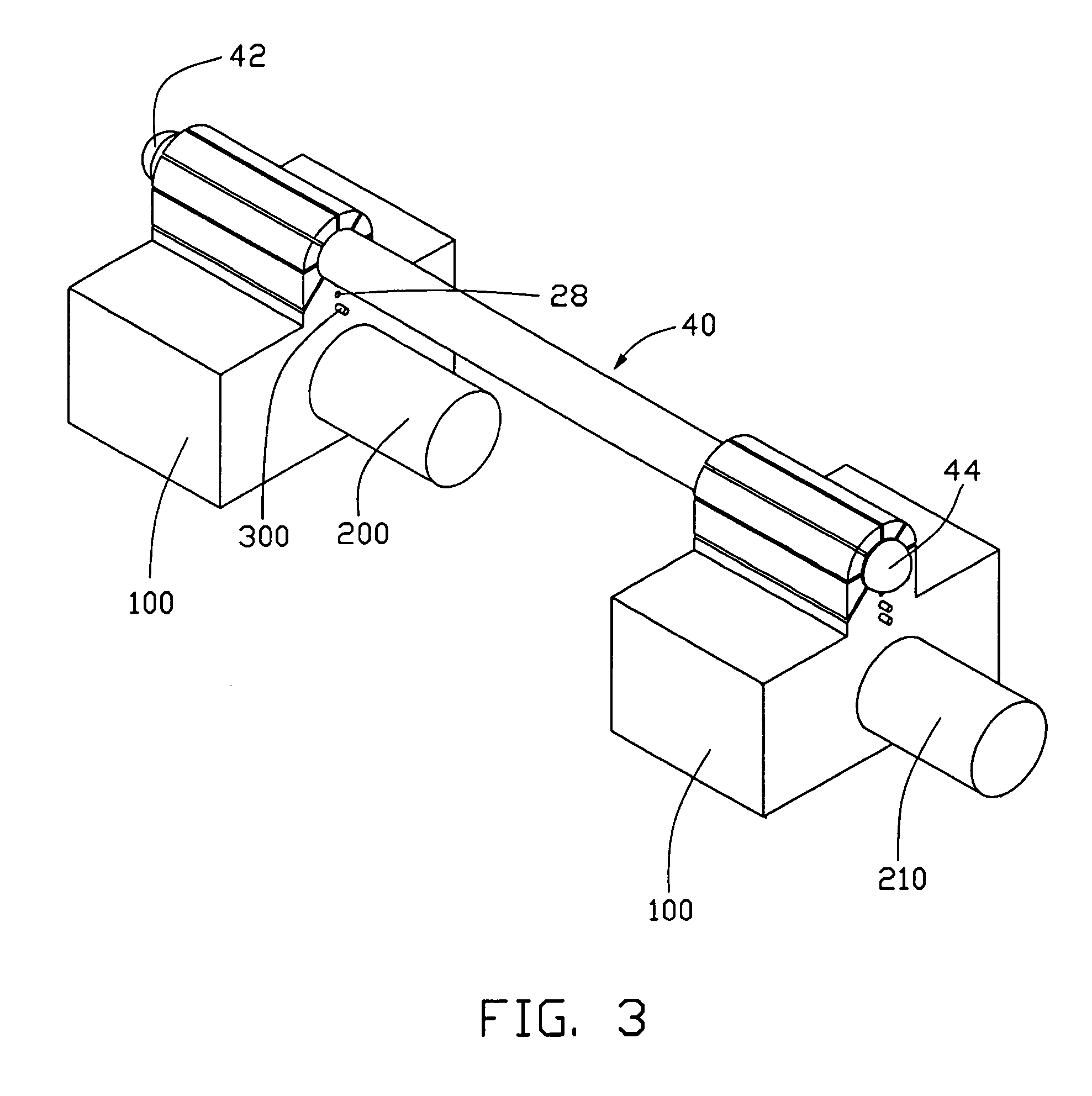

Measuring device for heat pipe

InactiveUS7147368B2Accurate transferLow thermal conductivityThermometer detailsMaterial thermal conductivityWorking fluidDesign testing

Owner:HON HAI PRECISION IND CO LTD

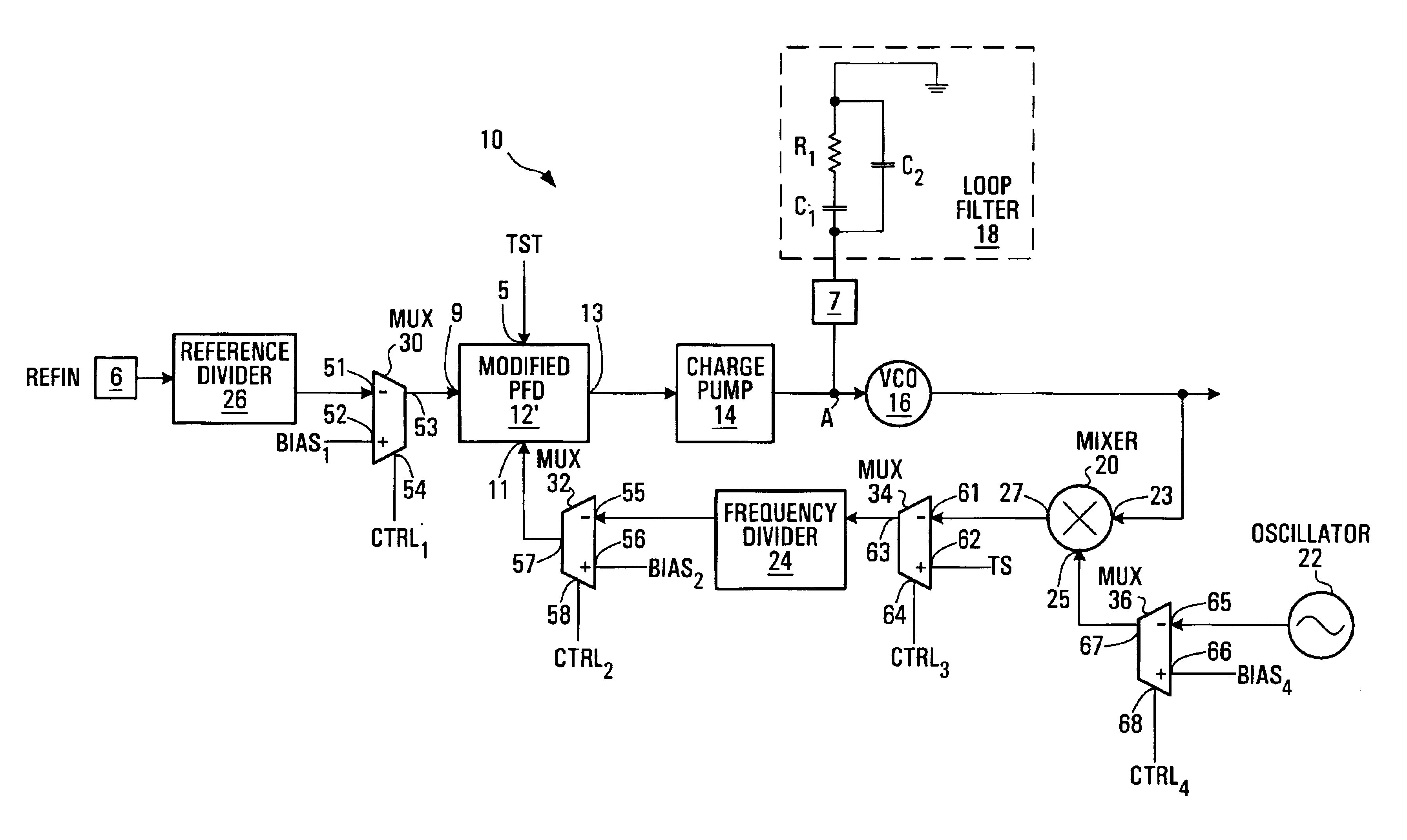

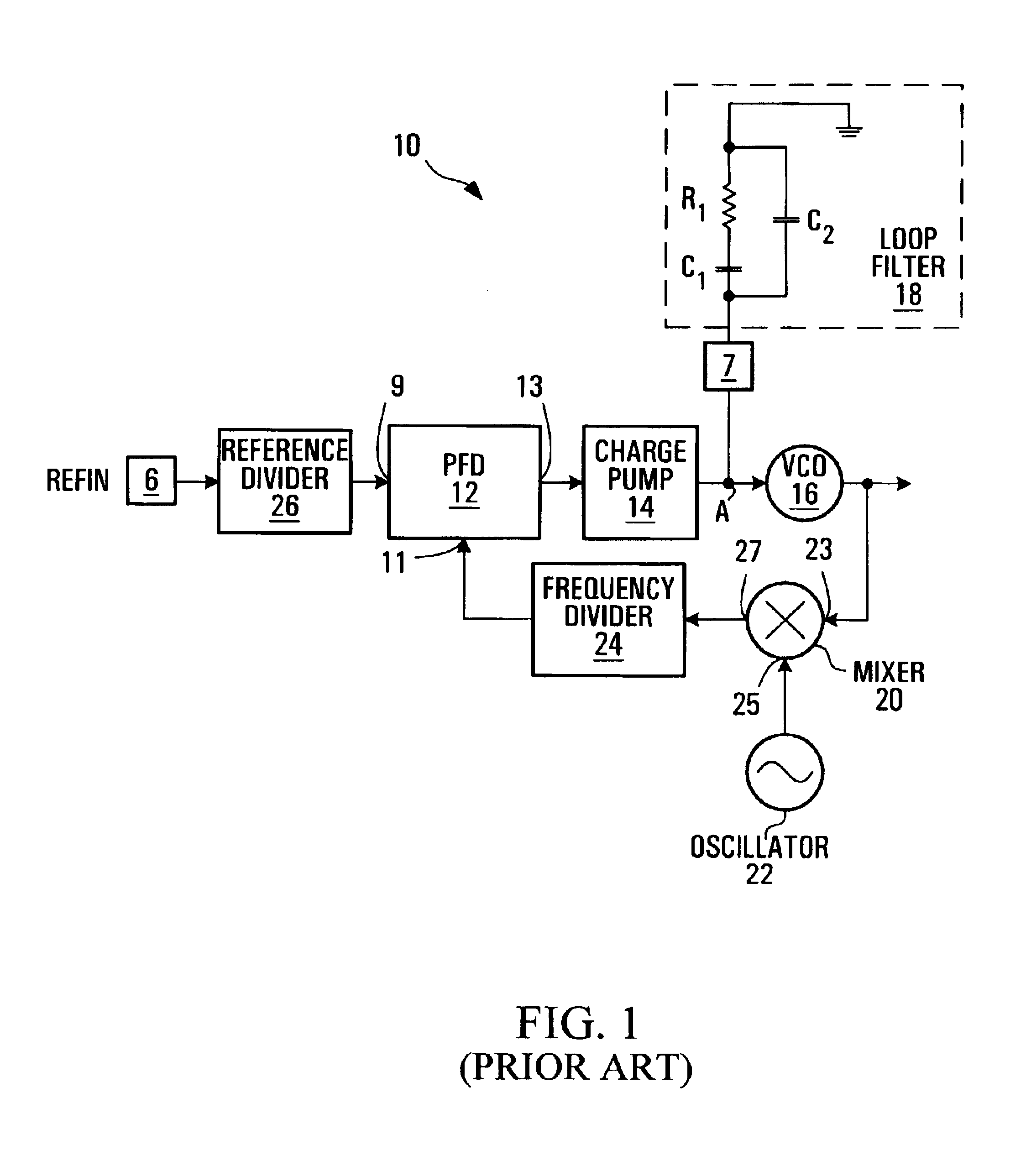

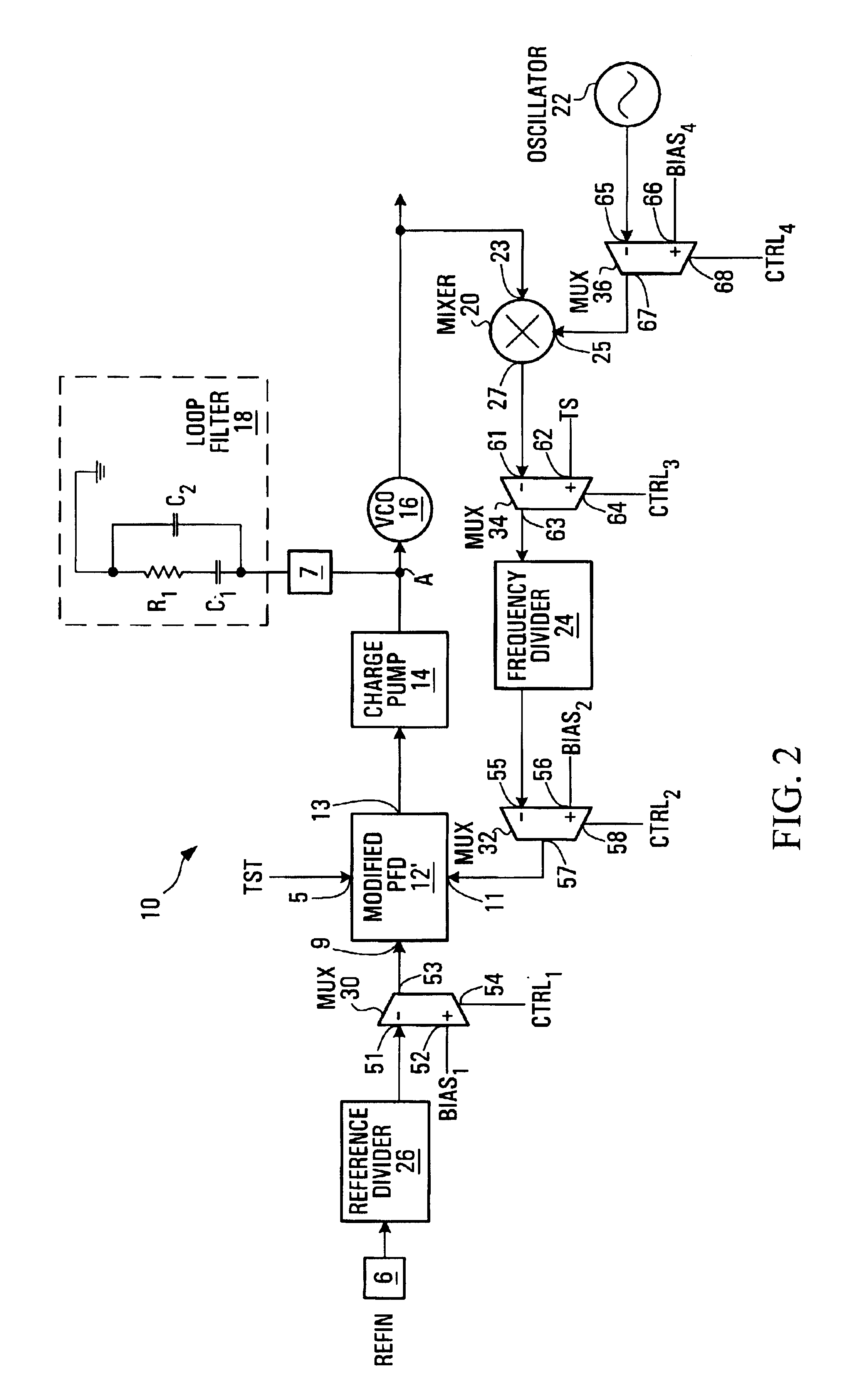

Design-for-test modes for a phase locked loop

There is a desire to provide a testing method and apparatus that can be successfully integrated into a PLL and PLL-like circuits (e.g. frequency synthesizers, delay lock loops, etc.). It is desirable that the PLL or PLL-like circuit integrated with testing apparatus does not suffer from performance degradations during nominal (mission mode) operation. Furthermore, it is desirable that the PLL and the testing apparatus share the same interface. In order to produce a PLL having integrated testing apparatus, without having the PLL suffer severe performance degradations during nominal operation nor having the combination of the PLL and testing apparatus be unnecessarily large, a modified PLL integrated with testing apparatus is provided.

Owner:INTELLECTUAL VENTURES HOLDING 81 LLC

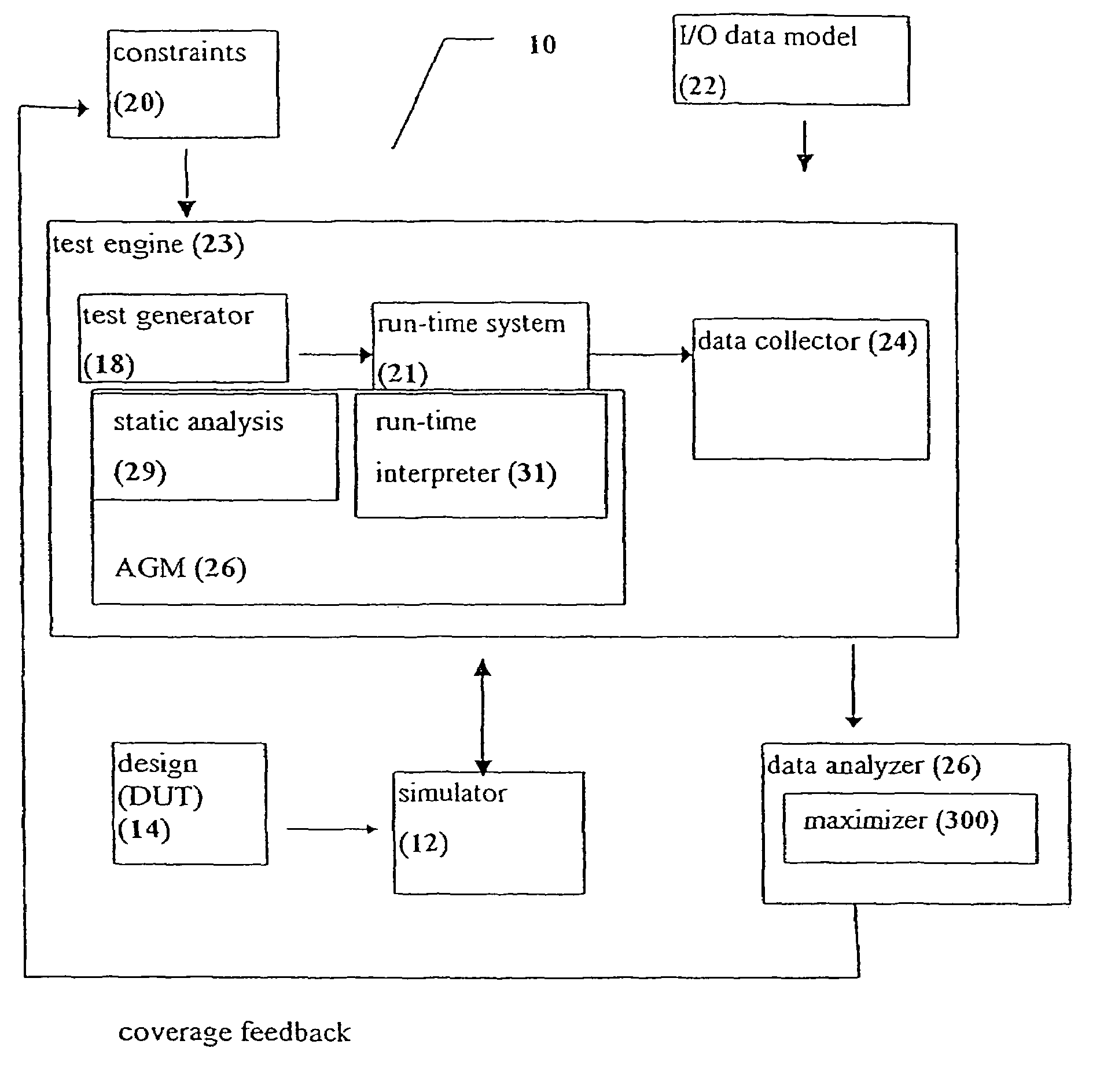

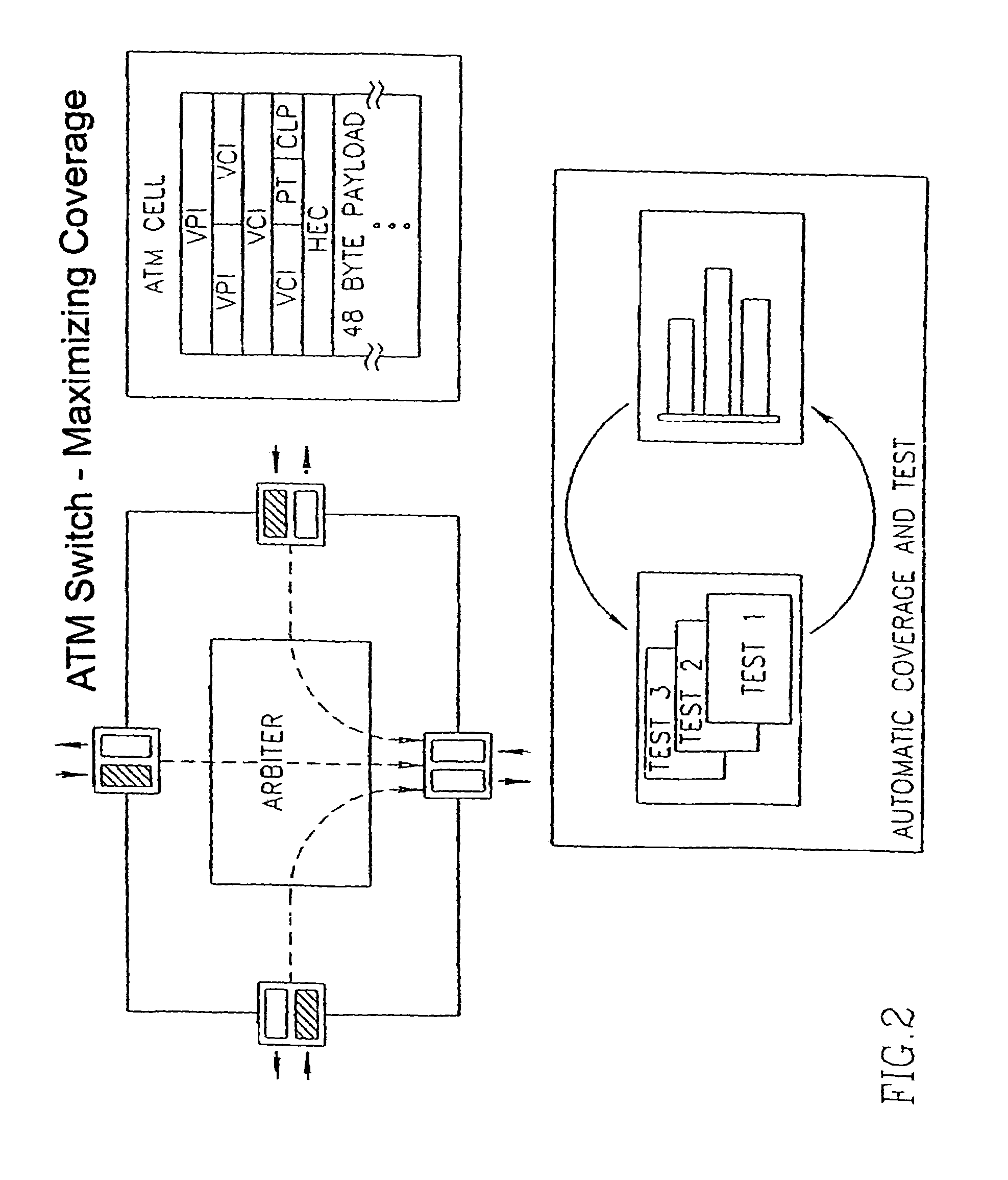

Method and apparatus for maximizing test coverage

InactiveUS7114111B2Improve test coverageDigital circuit testingDetecting faulty computer hardwareDesign testingEngineering

A method and an apparatus for determining functional coverage of a design for a device under test (DUT), the design being encapsulated in a DUT circuit design specification, in a test environment during a design test verification process.The method and apparatus utilize a coverage metric constructed from a plurality of coverage items. A first step involves obtaining a coverage group from the DUT design, for examining during the design test verification process. The coverage group includes at least one functional coverage item. Then, a set of input values is provided to the design test verification process. Next, design test verification process is performed with the set of input test values to obtain a value for each coverage item.Next step involves examining obtained coverage by comparing the value obtained from each coverage item with a coverage goal. Finally, the set of input test value is automatically altered in accordance with the examination of the obtained coverage.

Owner:CADENCE DESIGN ISRAEL II

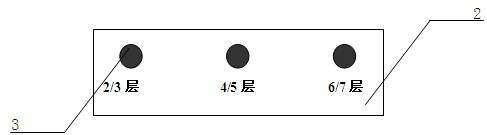

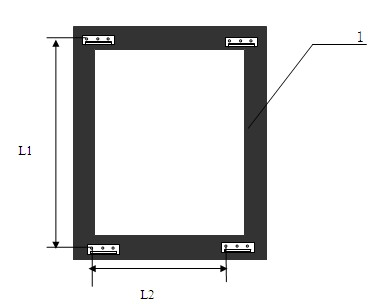

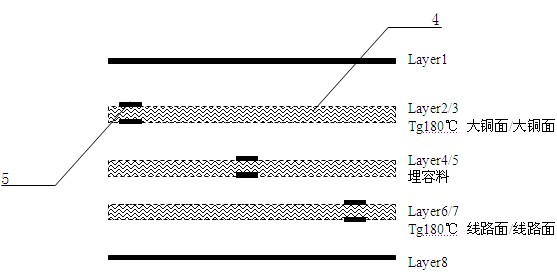

Method for classifying and compensating nonlinear variation of core boards for manufacturing multilayer circuit boards

InactiveCN102036511AHigh dimensional accuracyEasy alignmentMultilayer circuit manufactureDesign testingMultiple layer

The invention discloses a method for classifying and compensating nonlinear variation of core boards for manufacturing multilayer circuit boards, which comprises the following steps of: A. classifying factors affecting the deformation of core board materials; B. designing a test pattern on an inner negative film; C. measuring the distance of the test pattern on the inner negative film; D. transferring the test pattern on the inner negative film to an inner core board; E. blackening and browning multiple layers of circuit boards; F. laminating the circuit boards, and measuring the distance of the test pattern on the inner core board after the lamination; G. calculating the expansion and shrinkage distance of the inner core board of the multilayer circuit boards; H. creating a compensation database in accordance with the classification of the step A, and optimizing the design dimension of the inner core board of the multilayer circuit boards. By using the technical scheme described in the invention, problems of deviation between layers and out-of-tolerance of expansion and shrinkage dimension appear during the lamination of the multilayer circuit boards can be solved, the dimension accuracy of the finished product and alignment accuracy between core board layers are improved, and the reliability of the product is improved.

Owner:ZHUZHOU CSR TIMES ELECTRIC CO LTD

Automatically connecting remote network equipment through a graphical user interface

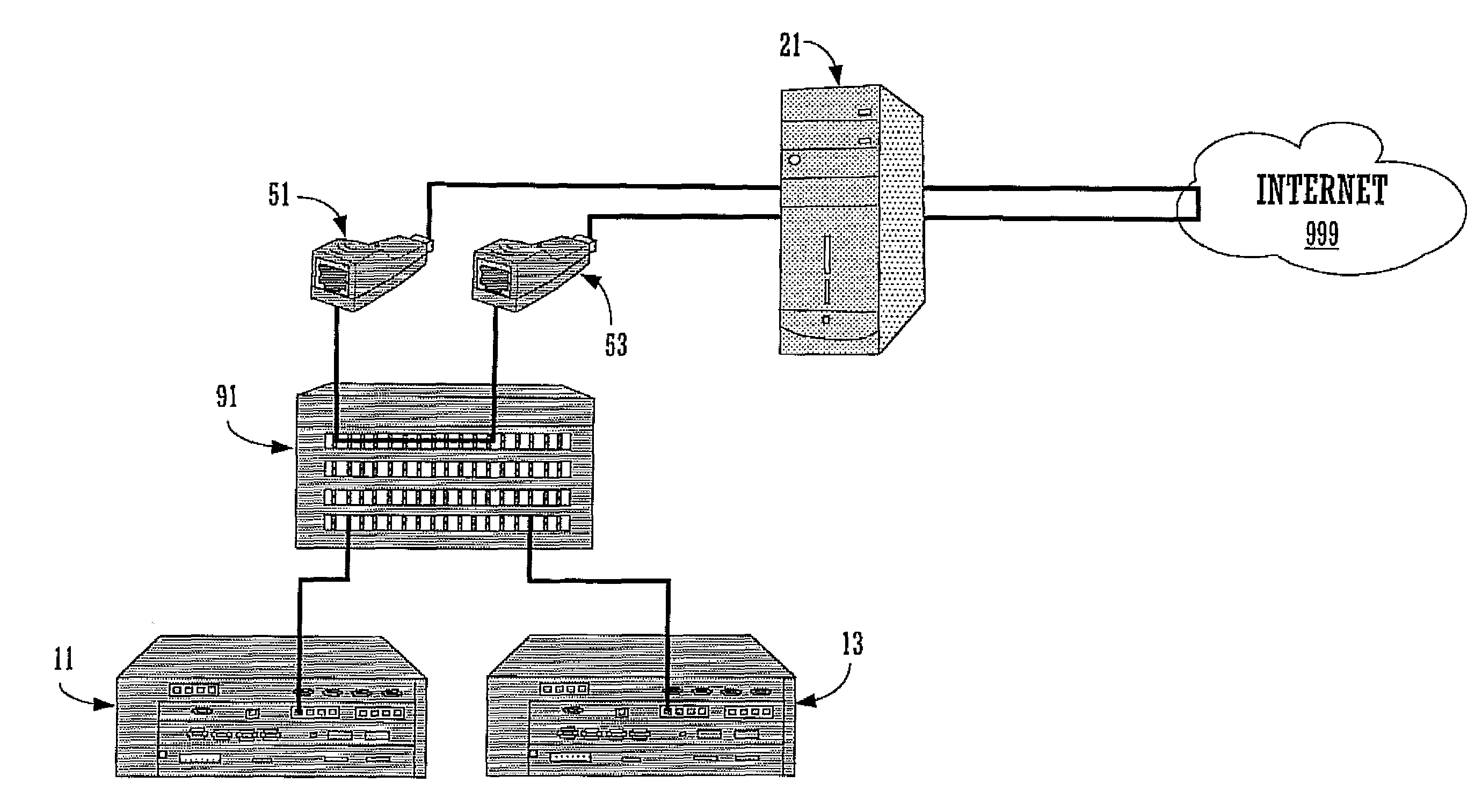

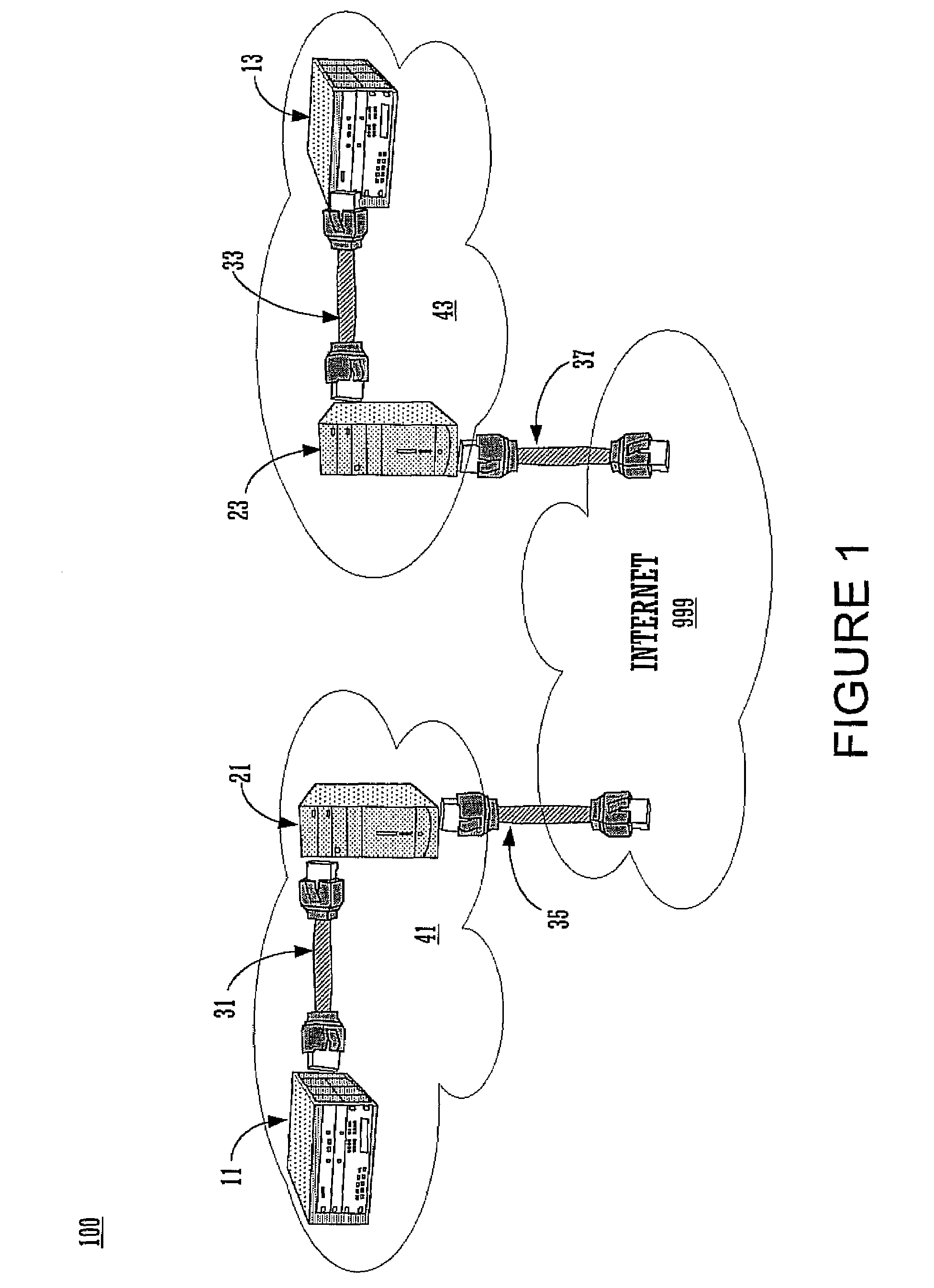

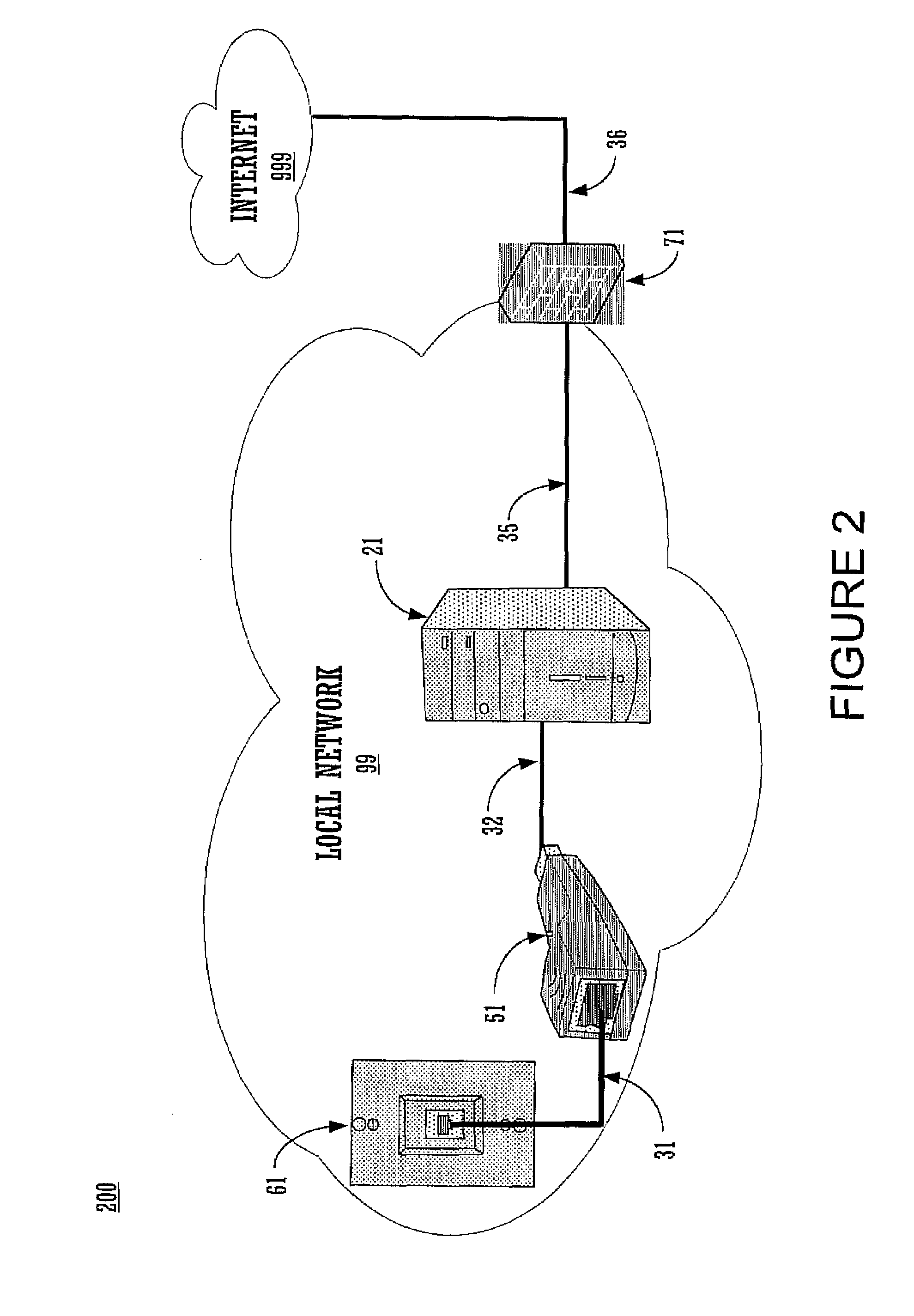

ActiveUS20100100767A1Well formedError detection/correctionData switching networksGraphicsAuto-configuration

Embodiments of the present invention provide a method and system for designing a test network in an integrated application, and configuring remote network devices through a network design application to test a network design. One embodiment of the present claimed subject matter is provided as a system for automatically configuring remote network devices to simulate a network connection. The system includes a plurality of computing devices which are physically coupled to one or more network devices, wherein the network devices are automatically configured to comprise a test network corresponding to a remote test network topology design.

Owner:ACCENTURE GLOBAL SERVICES LTD

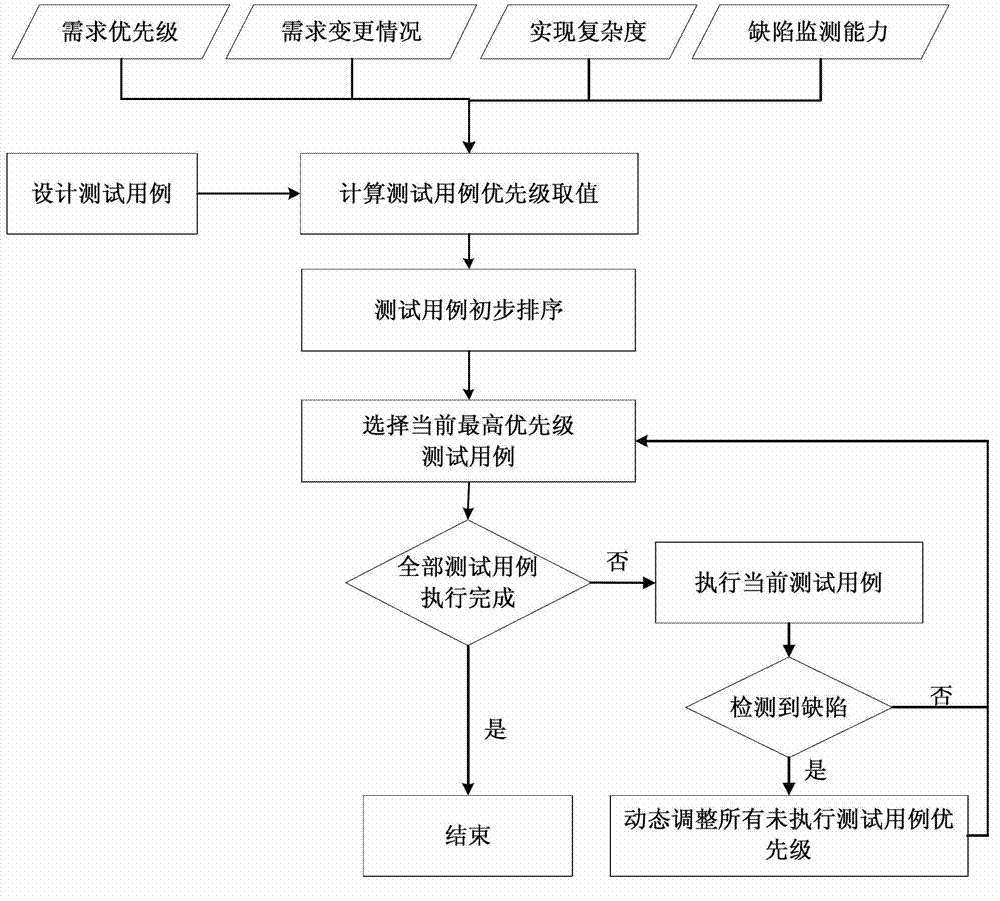

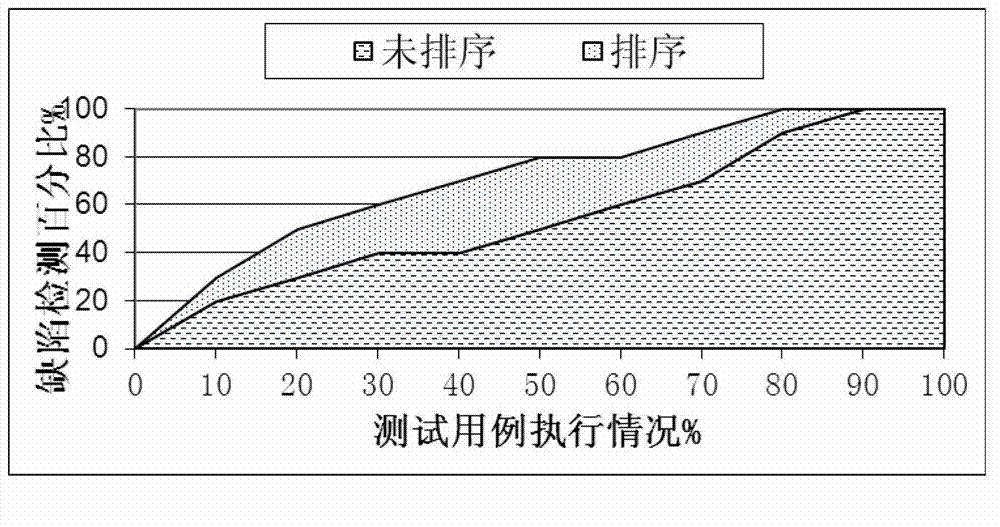

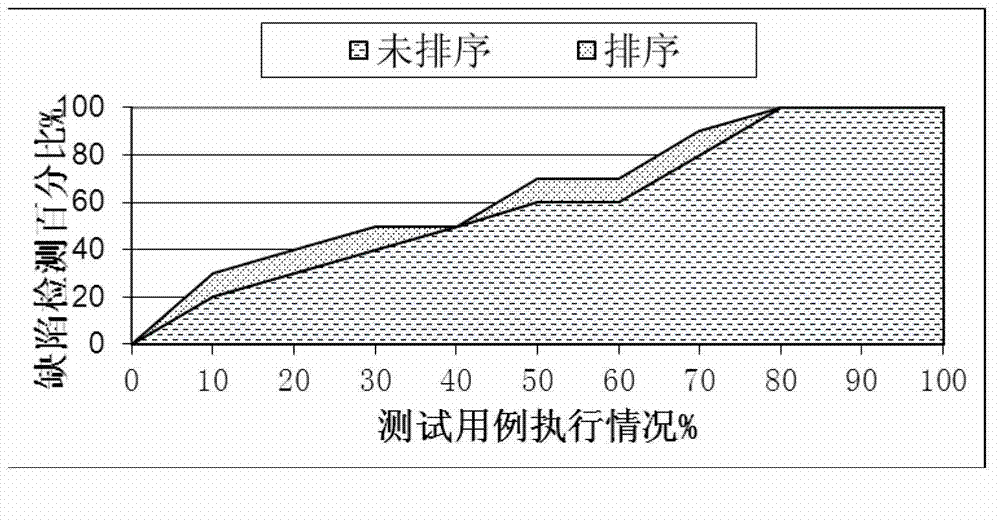

Method for dynamically adjusting priority sequence of test cases

InactiveCN102880545AThe test effect is goodAdjust execution strategySoftware testing/debuggingDesign testingTest execution

The invention provides a method for dynamically adjusting a priority sequence of test cases. The method comprises the following steps of: designing the test cases; calculating priority values of the test cases; and sequencing and dynamically adjusting the test cases. By dynamically adjusting the priority of the test cases in the test execution process, a plurality of system defects can be found in short time, and the using efficiency of the test cases is improved.

Owner:中国人民解放军63928部队

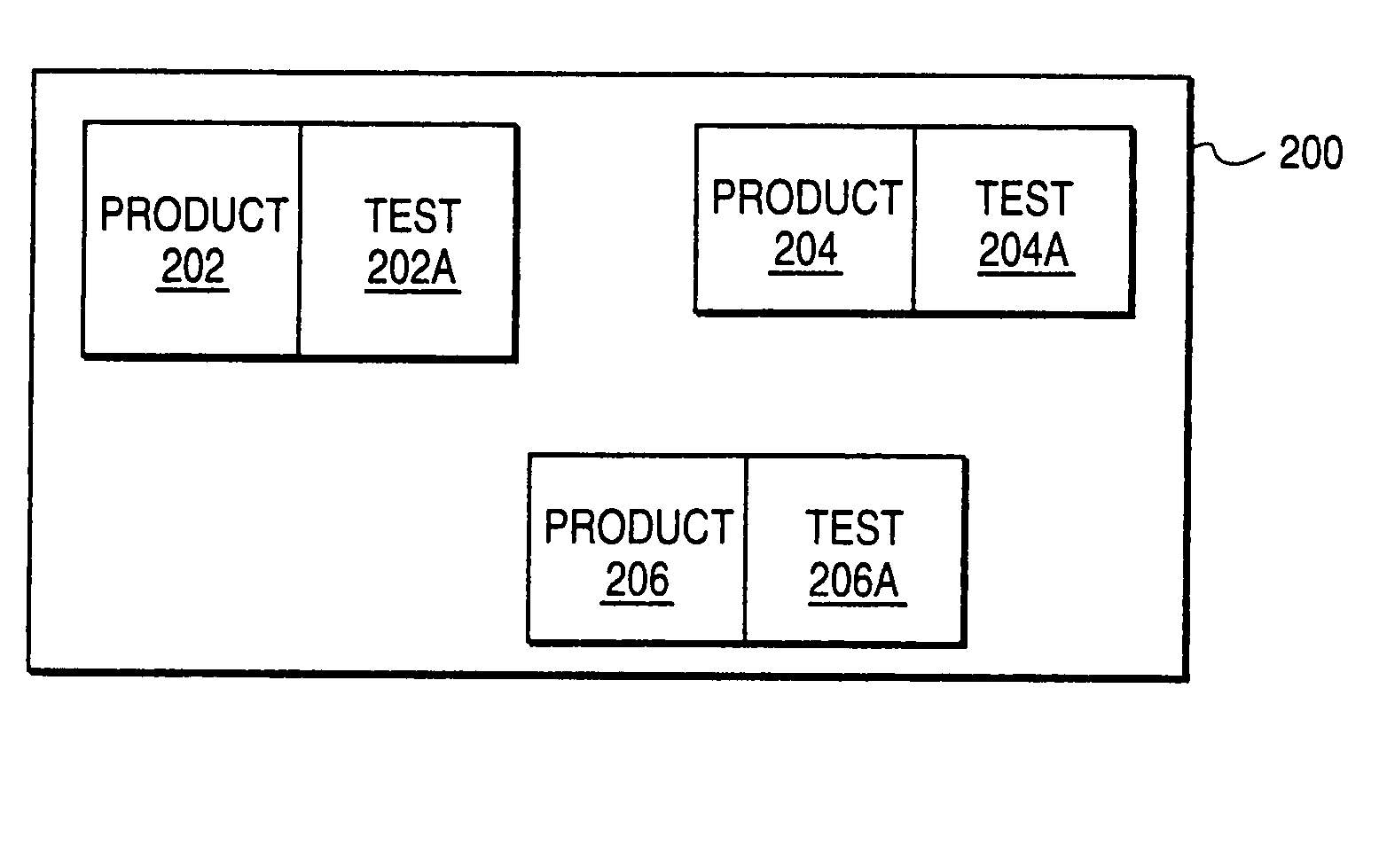

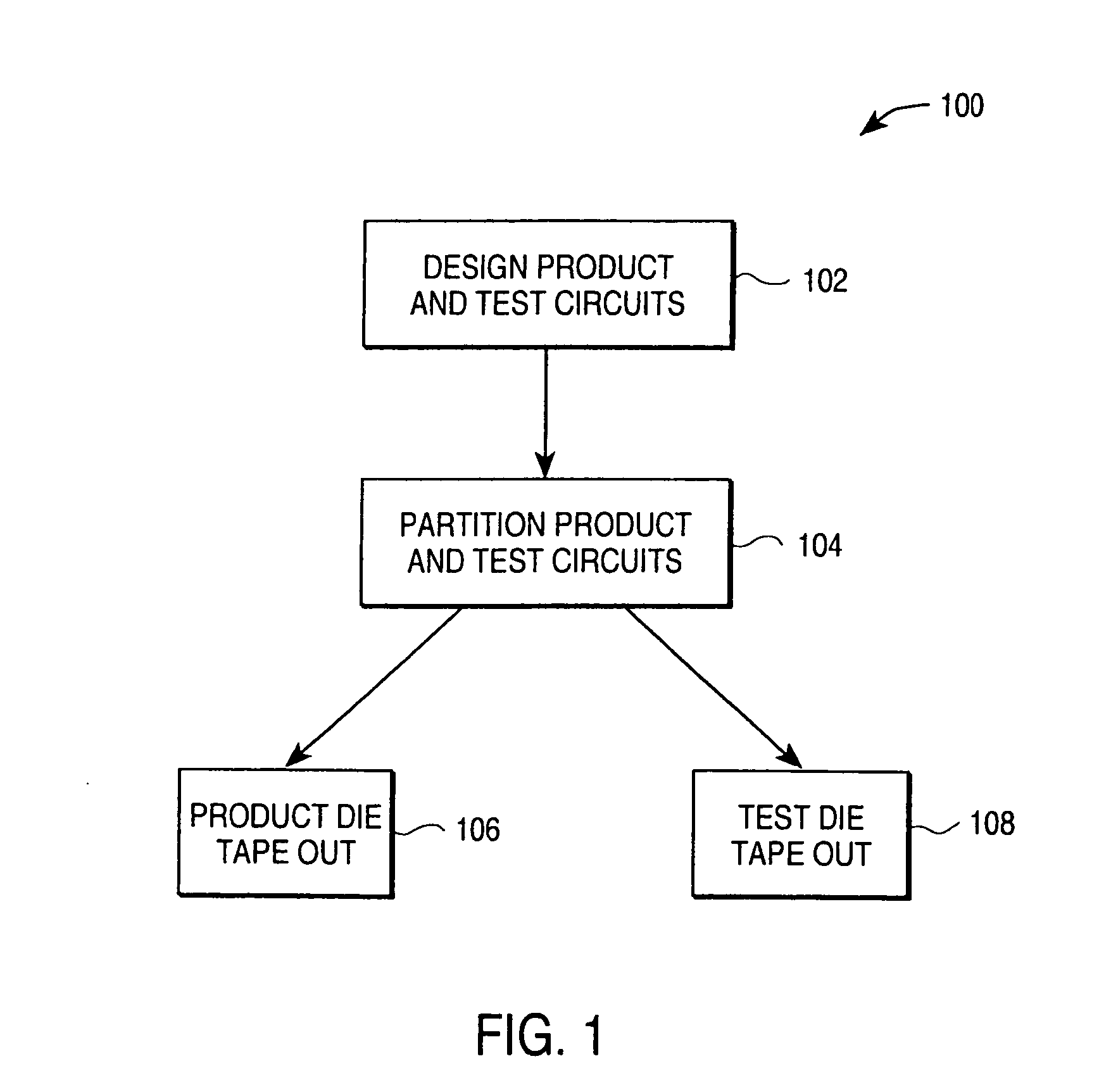

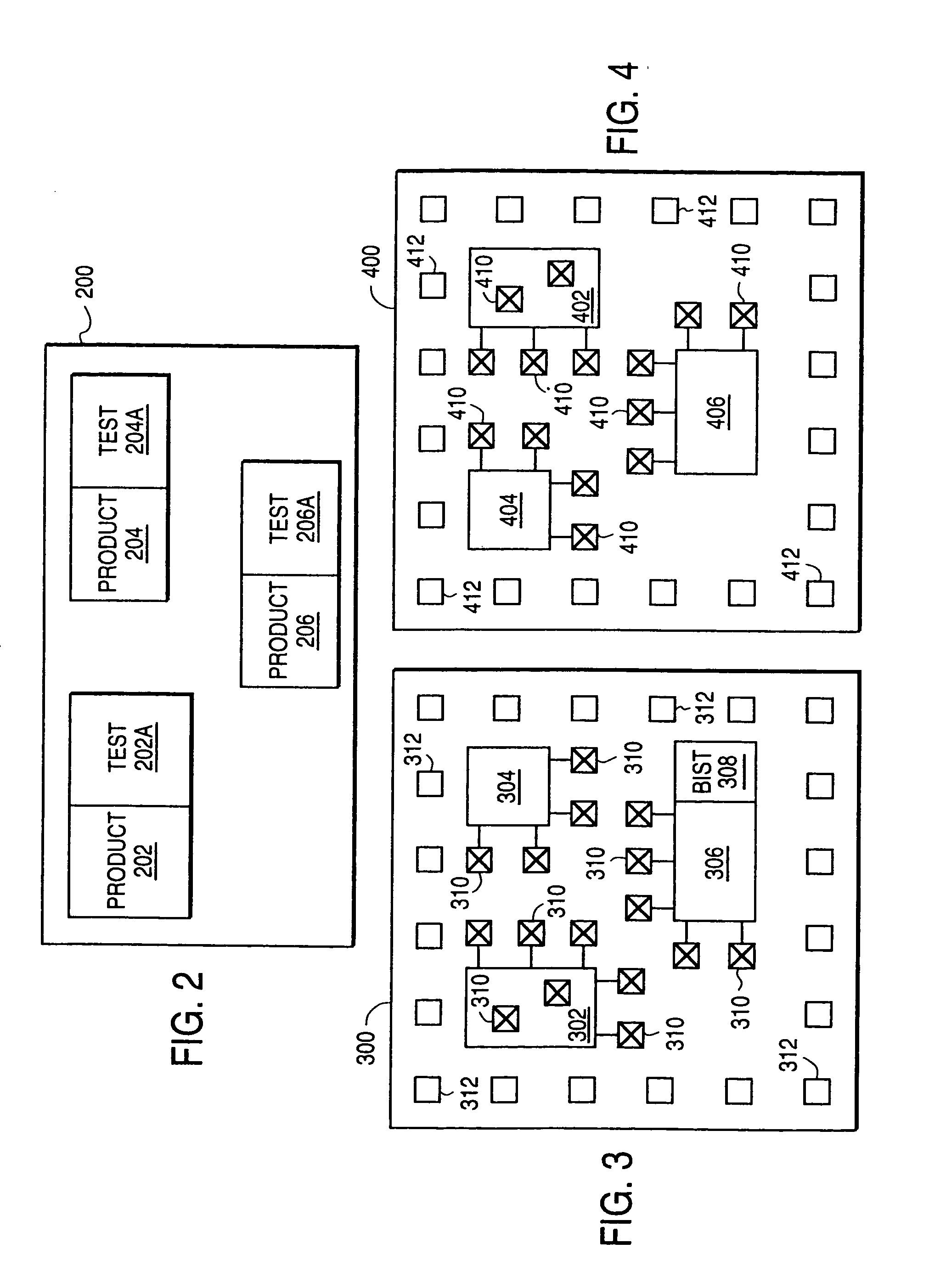

Test assembly including a test die for testing a semiconductor product die

InactiveUS20050156165A1High degreeSmall sizePrinted circuit assemblingSemiconductor/solid-state device testing/measurementFault coverageUniform design

One embodiment of the present invention concerns a test assembly for testing product circuitry of a product die. In one embodiment, the test assembly includes at test die and an interconnection substrate for electrically coupling the test die to a host controller that communicates with the test die. The test die may be designed according to a design methodology that includes the step of concurrently designing test circuitry and a product circuitry in a unified design. The test circuitry can be designed to provide a high degree of fault coverage for the corresponding product circuitry generally without regard to the amount of silicon area that will be required by the test circuitry. The design methodology then partitions the unified design into the test die and the product die. The test die includes the test circuitry and the product die includes the product circuitry. The product and test die may then be fabricated on separate semiconductor wafers. By partitioning the product circuitry and test circuitry into separate die, embedded test circuitry can be either eliminated or minimized on the product die. This will tend to decrease the size of the product die and decrease the cost of manufacturing the product die while maintaining a high degree of test coverage of the product circuits within the product die. The test die can be used to test multiple product die on one or more wafers.

Owner:FORMFACTOR INC

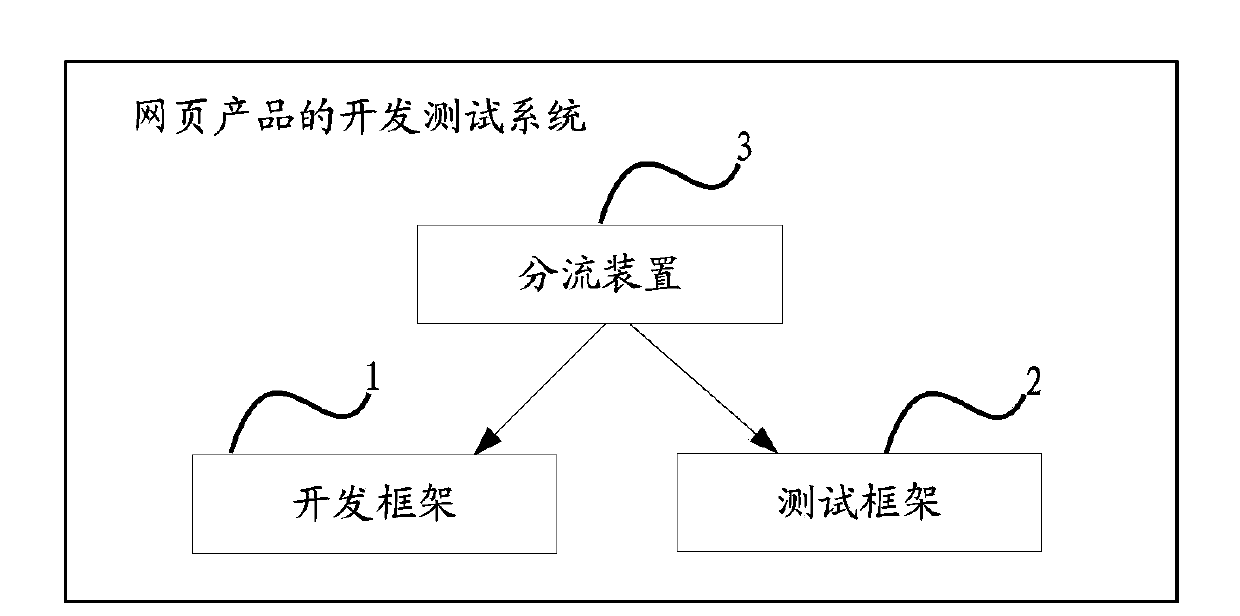

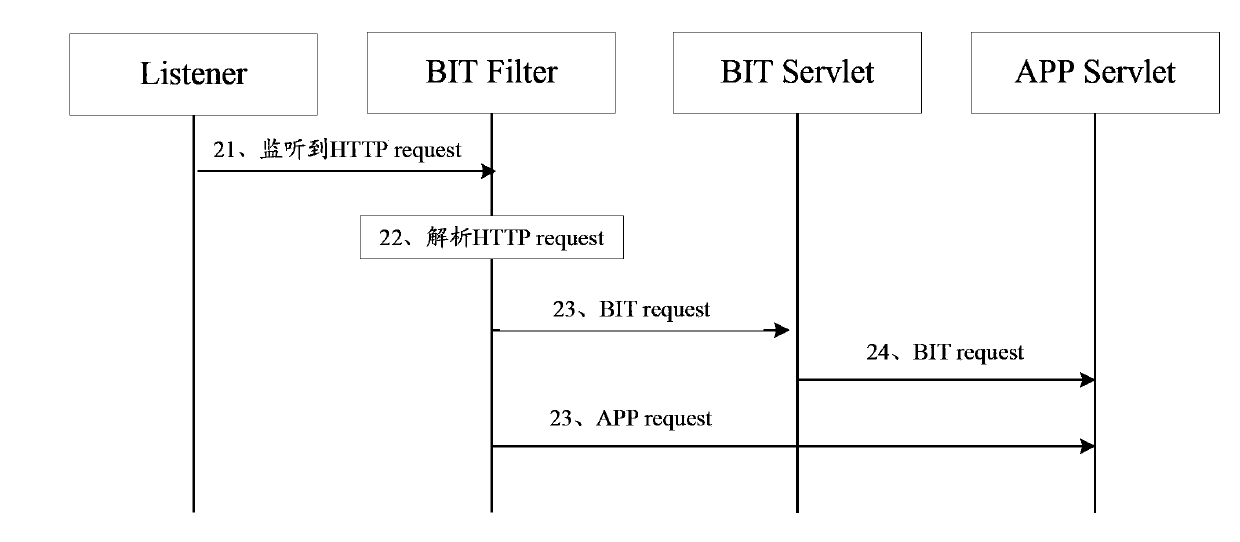

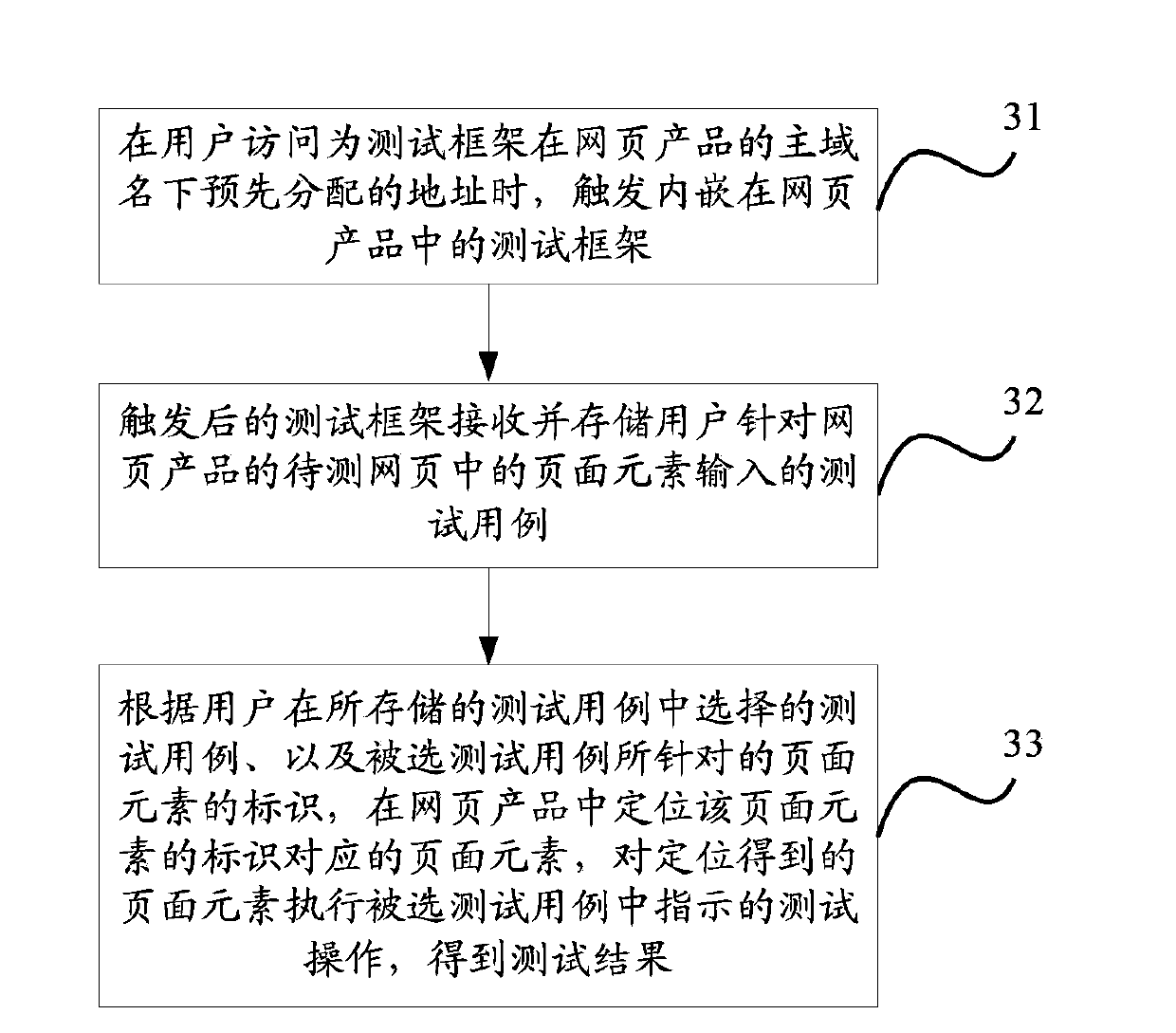

Development testing system, testing method and device for webpage product

ActiveCN103377127ATest in timeSpeed upSoftware testing/debuggingSpecific program execution arrangementsTest efficiencyDesign testing

The invention discloses a development testing system, a testing method and a device for a webpage product. According to the technical scheme of an embodiment of the invention, a testing case inputted by a user for page elements is received and stored by a testing frame embedded into the webpage product, the page elements are tested according to the testing case selected by the user to obtain a testing result, testing and development for the webpage product can be integrated on the same resource platform, testing progress can be accelerated, testing period can be shortened, a developer can perform testing only by designing the testing case without specially writing testing codes for the testing case, testing complexity can be reduced, and testing efficiency can be improved, so that the problems that development and testing for the webpage product are separated, the testing progress is backward, testing efficiency is low and development requirements cannot be met in the prior art can be solved.

Owner:ALIBABA GRP HLDG LTD

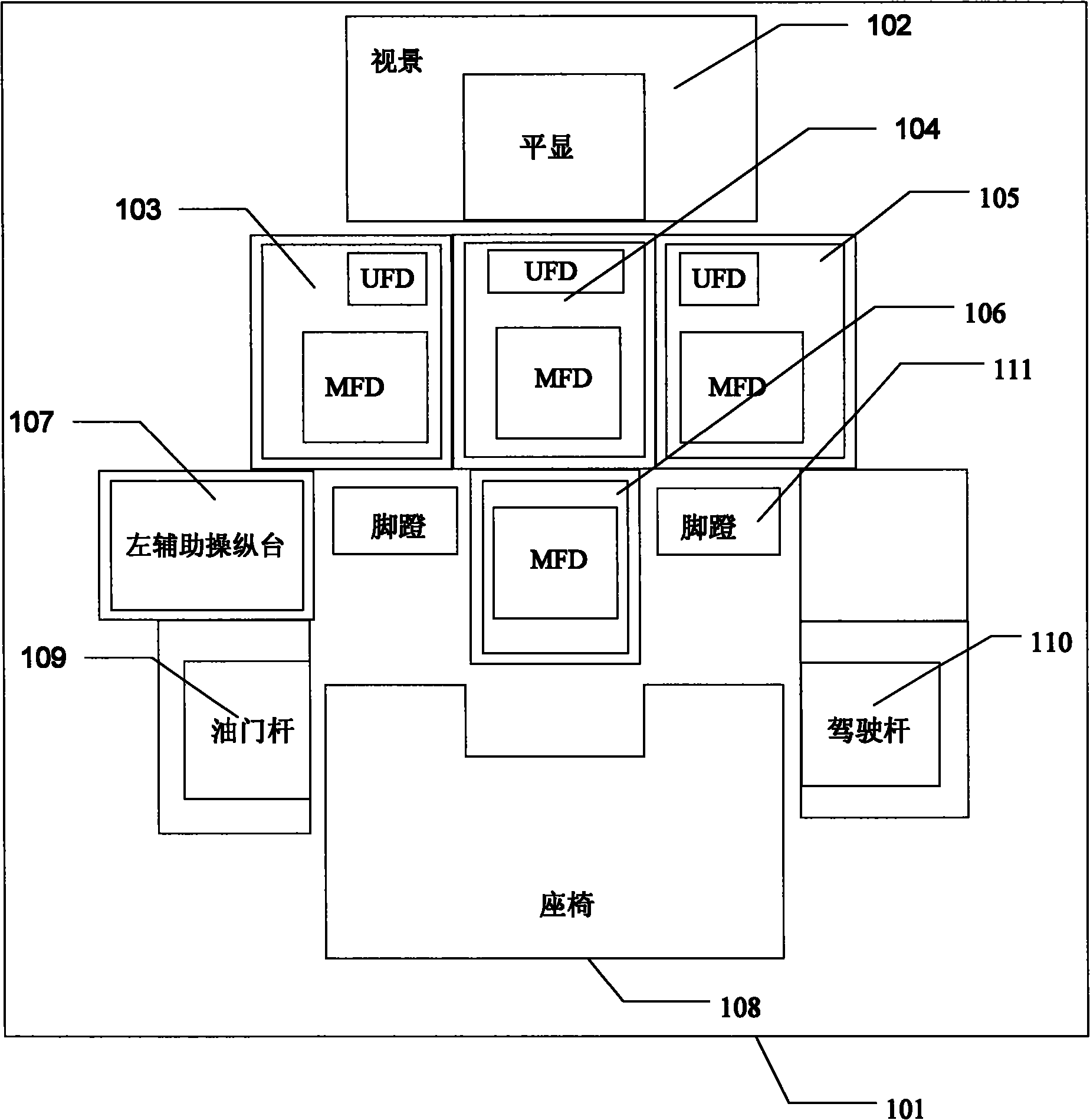

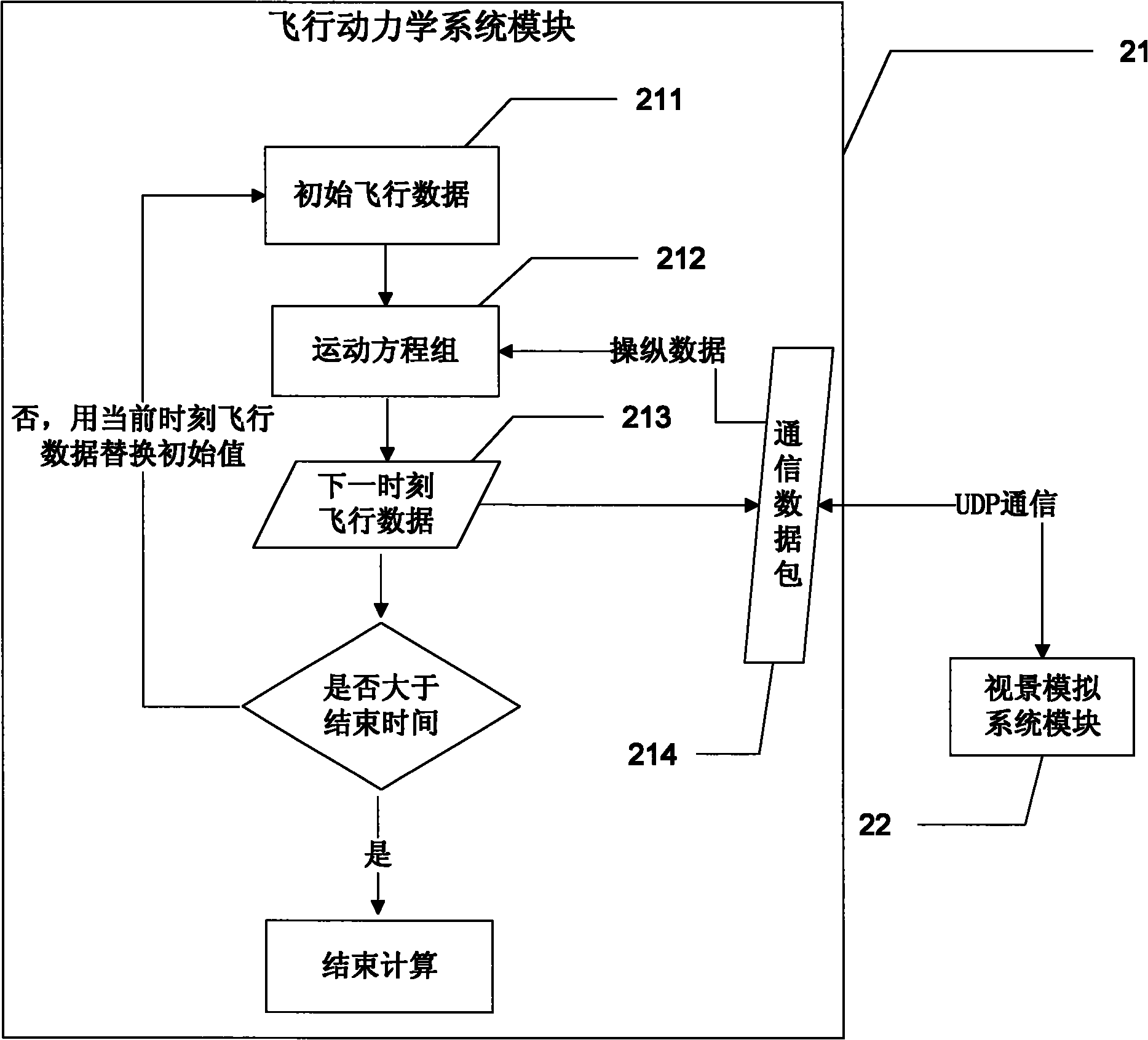

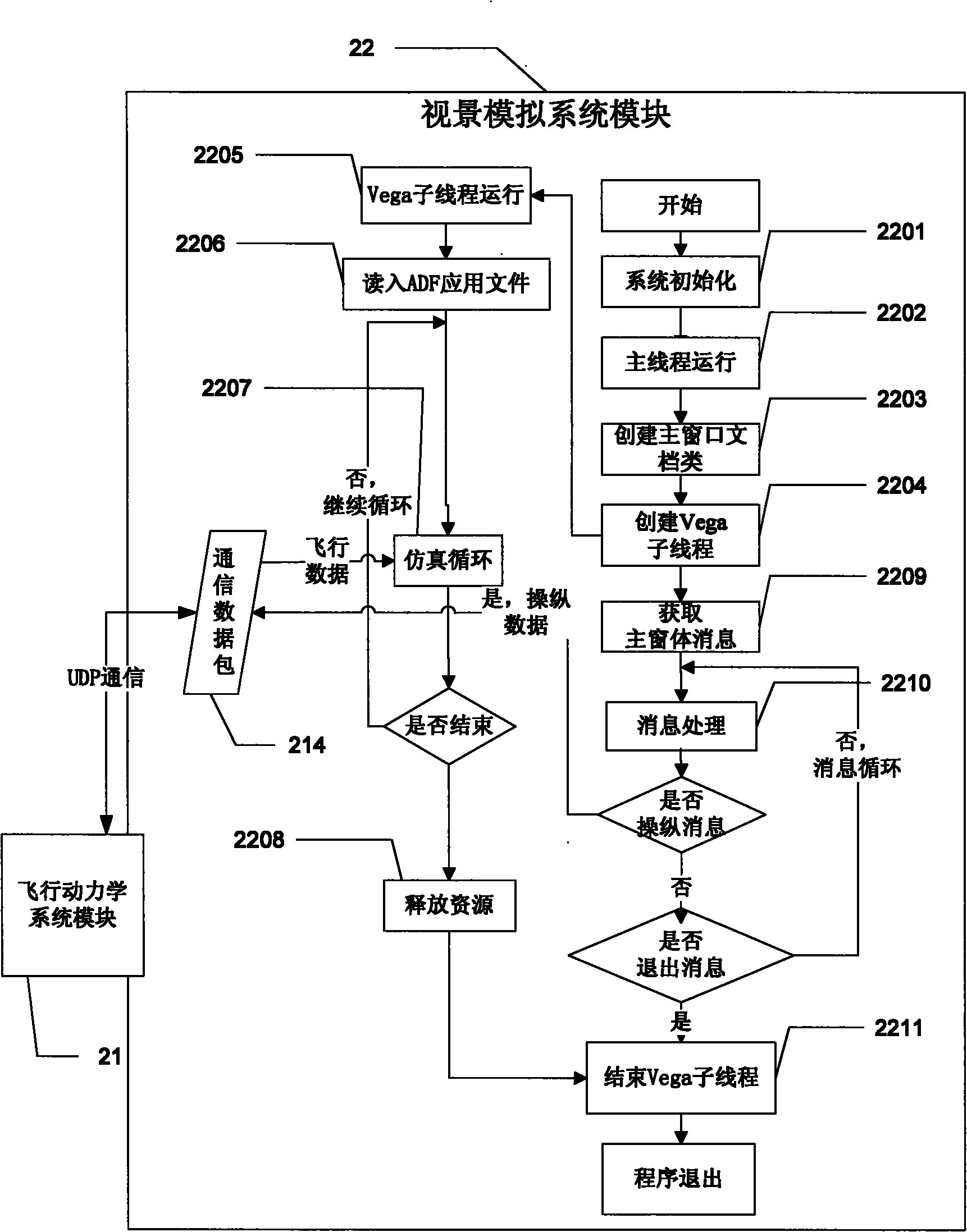

Flight simulation system with design and test functions of information display interface

The invention discloses a fight simulation system. An experiment table of the fight simulation system comprises a navigation bridge hardware system, a fight task simulation system and a human-machine work efficiency assessment system. The human-machine work efficiency assessment experiment table integrates the work efficiency assessment of the information display interface with the traditional fight task simulation. By loading the design scheme of the information display interface of the aviation cockpit into the fight simulation system, the design scheme of the information display interface is assessed by using the human-machine work efficiency assessment system after a tester simulates the fight, thereby assessing the human suitability of the information display interface of the aviation cockpit. By using the human-machine work efficiency assessment experiment table, the design quality of the information display interface of the aviation cockpit can be improved, the development period can be shortened and the development cost can be reduced.

Owner:BEIHANG UNIV

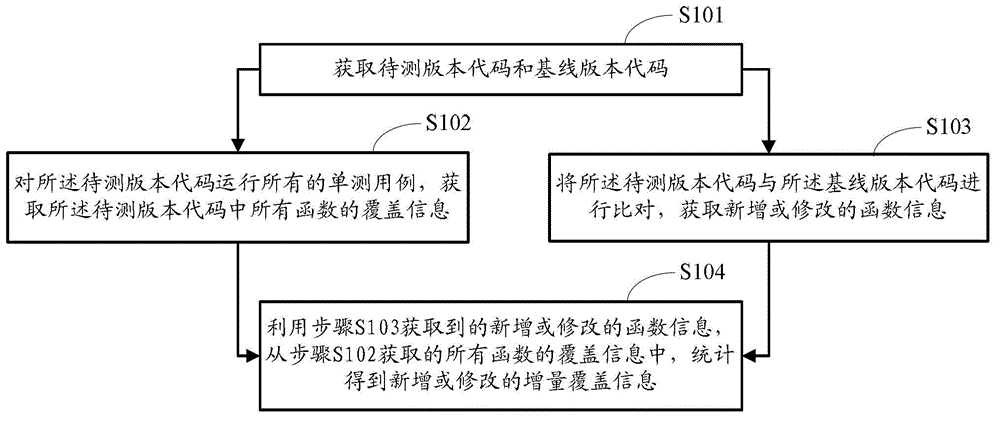

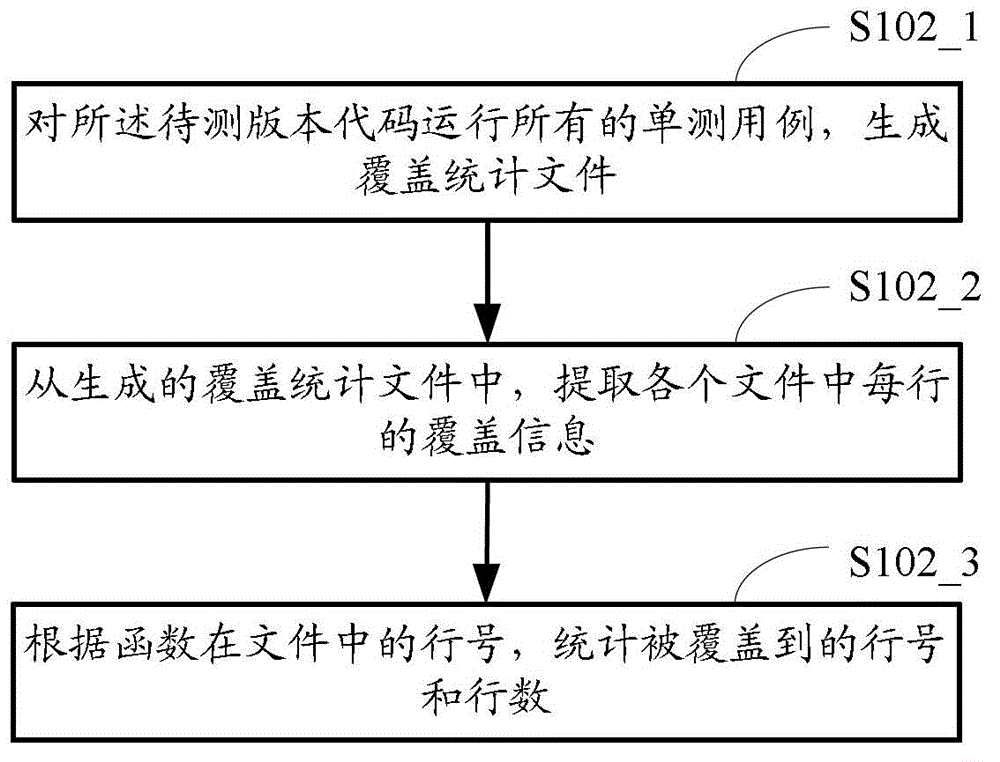

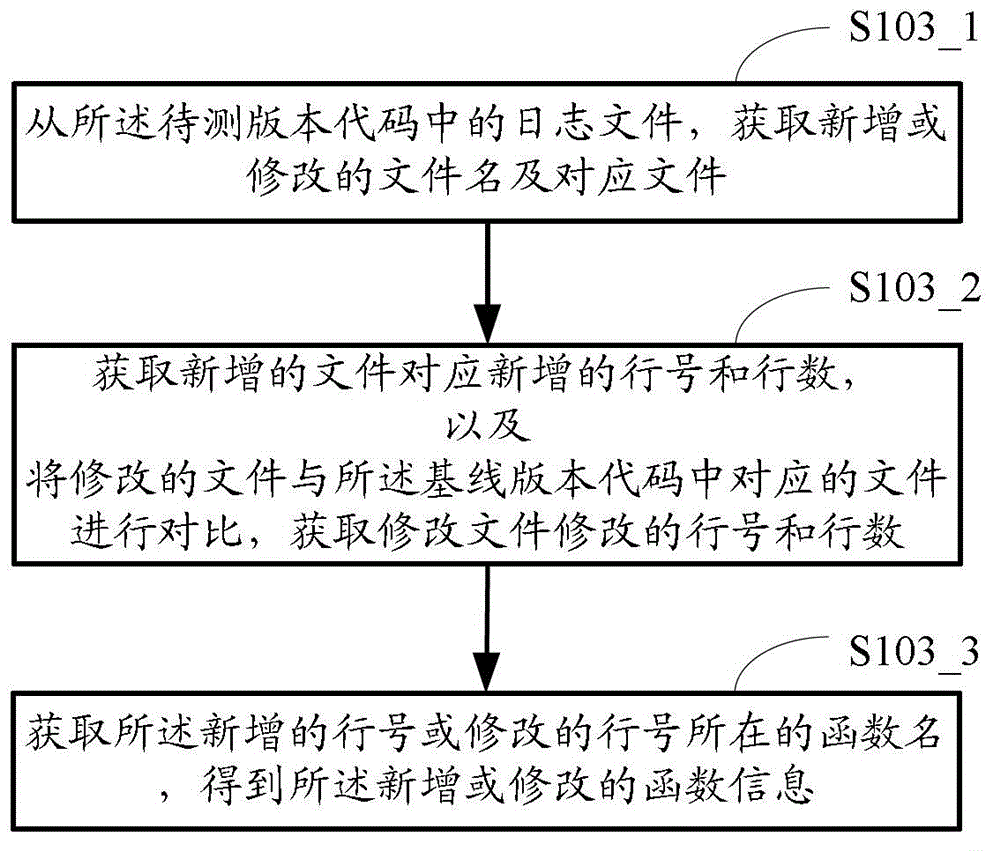

Statistical method and device for incremental coverage information

ActiveCN102722436AEasy accessImprove work efficiencySoftware testing/debuggingTest efficiencyDesign testing

The invention provides a statistical method and a statistical device for incremental coverage information. The statistical method comprises the following steps: S1, acquiring a test version code and a baseline version code; S2, running all single test cases for the test version code, acquiring coverage information of all functions in the test version code, and comparing the test version code and the baseline version code so as to obtain newly-added or modified function information; and S3, acquiring newly-added or modified incremental coverage information from the coverage information of all the functions according to the newly-added or modified function information. Compared with the prior art, the statistical method and the statistical device can automatically count the incremental information of a test version, so that a tester can quickly acquire the incremental coverage information and pertinently design a test case according to the incremental coverage information, thus improving the test efficiency and the test accuracy and reducing the missing test.

Owner:BAIDU ONLINE NETWORK TECH (BEIJIBG) CO LTD

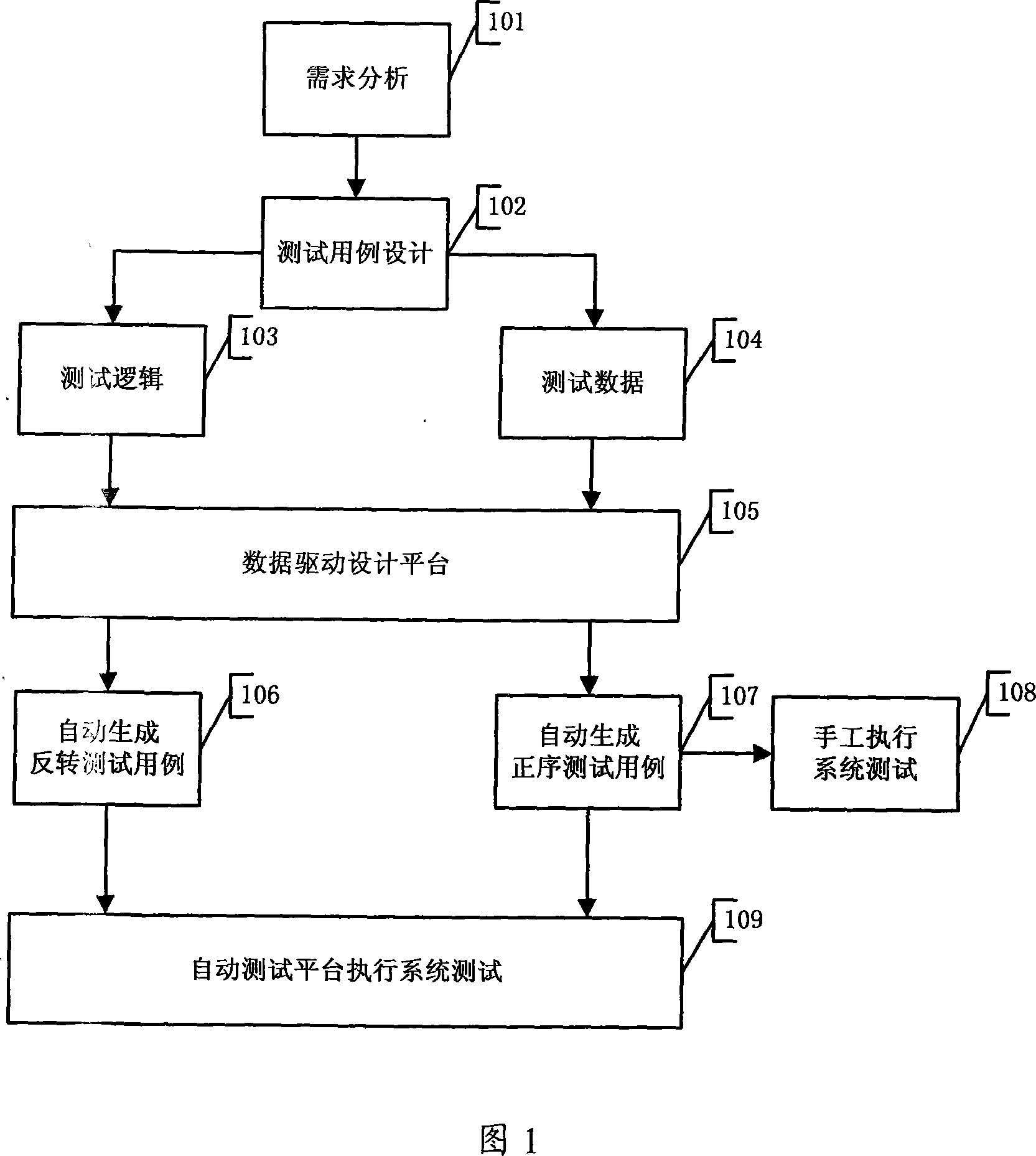

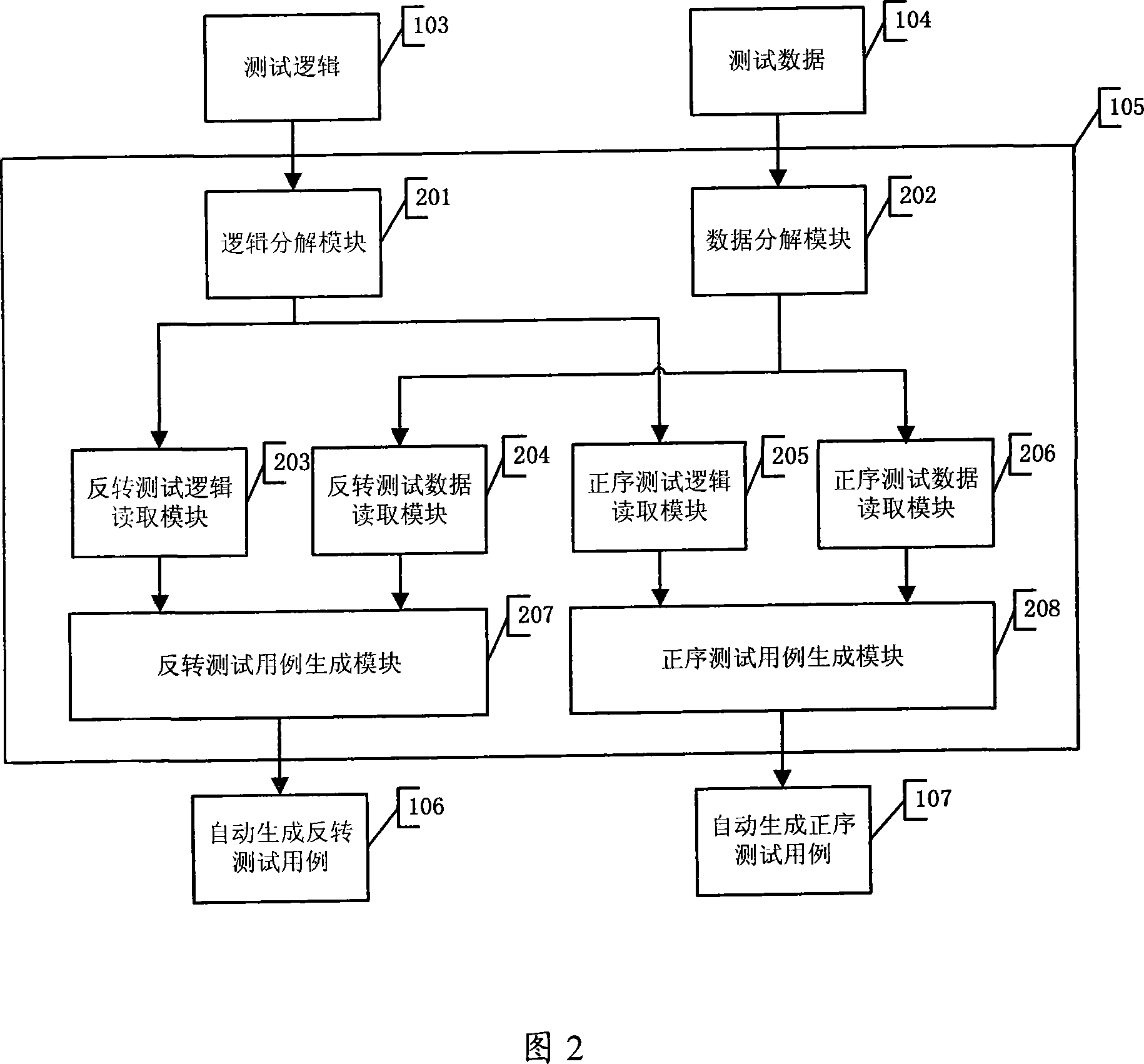

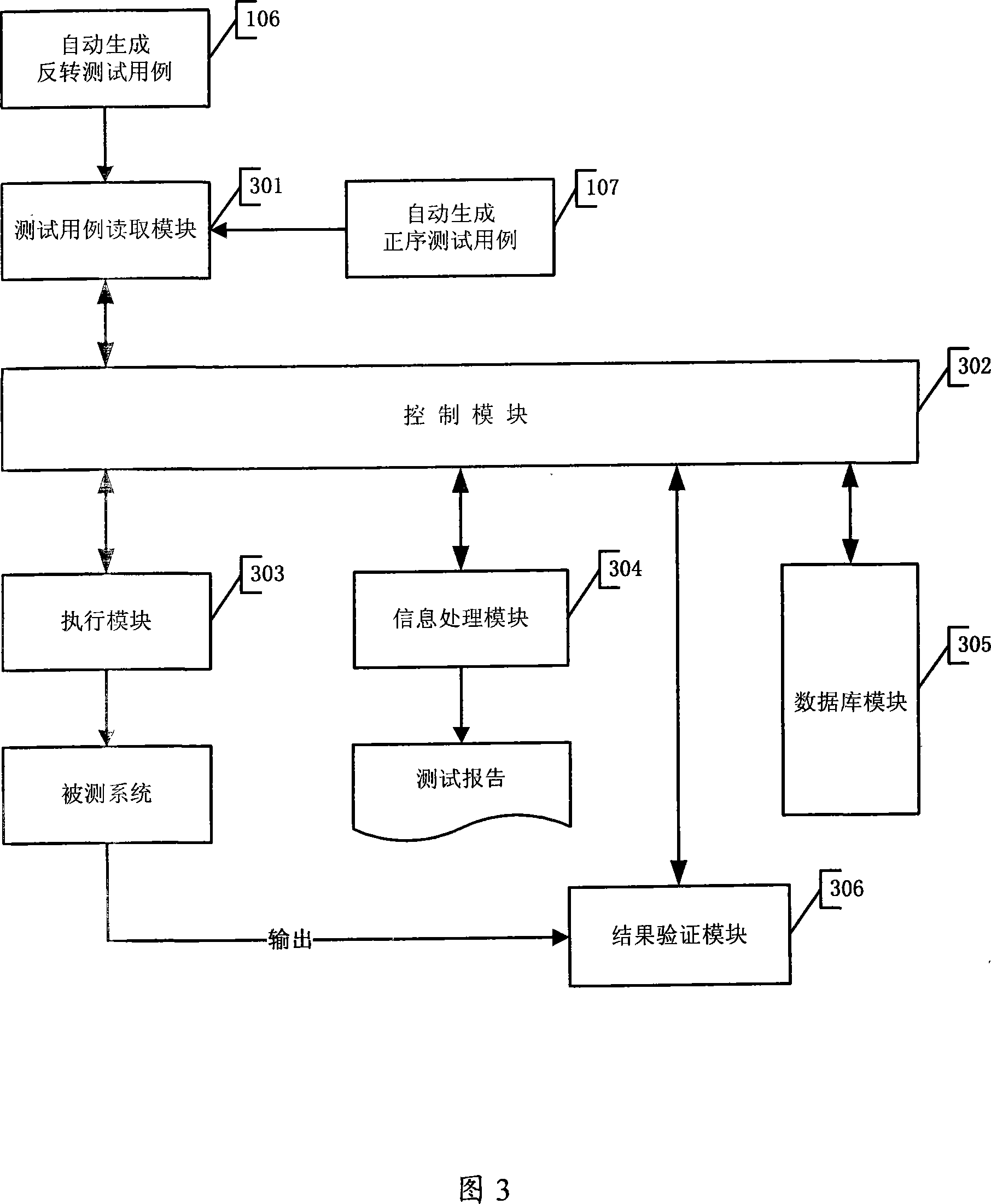

Example design test method for testing based on data driving and automatically testing platform

InactiveCN101162426AImprove test efficiencyReduce testing costsSoftware testing/debuggingSpecific program execution arrangementsTest designTest efficiency

The invention discloses a data driven-based test case design test method and an automatic test platform; the method includes: based on the requirement analysis, the test logic and the test data are designed respectively; based on the test logic and the test data, the automatic test platform automatically generates the positive sequence test case and the reverse test case which certainly has the positive sequence test case corresponding to the reverse test case; based on the reverse test case, the automatic test platform acquires the positive sequence test case, the positive sequence test case and the reverse test case which are in pairs are stored in a database and undergo the automatic test. The data driven-based test case design test method and the automatic test platform of the invention effectively utilize the data driven theory to design test cases and automatically test the test cases, thereby the invention has the advantages of providing a systematic resolving proposal for test designers, offering a shortcut for switching between the system test and the automatic test, improving test efficiency and lowering test cost.

Owner:ZTE CORP

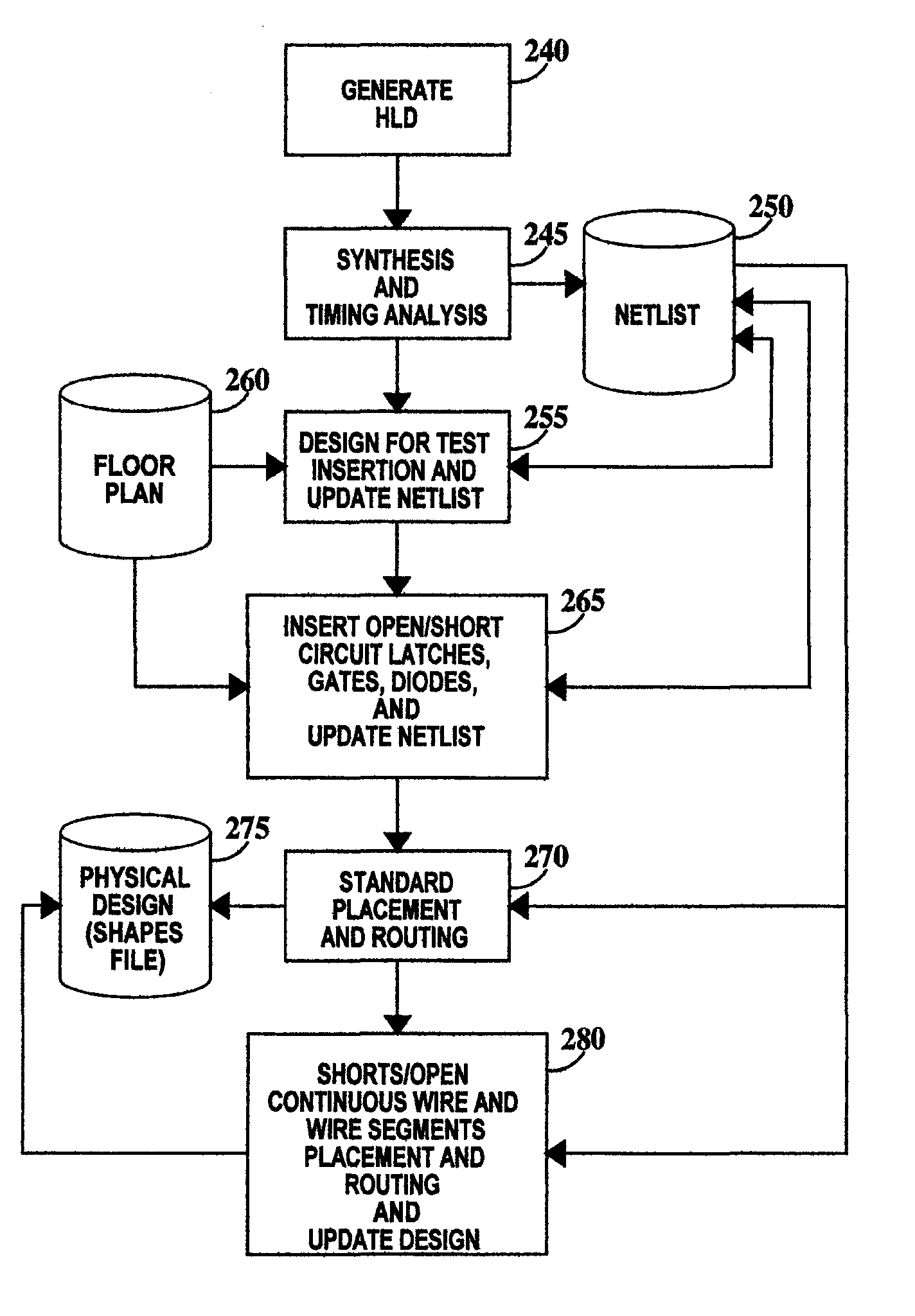

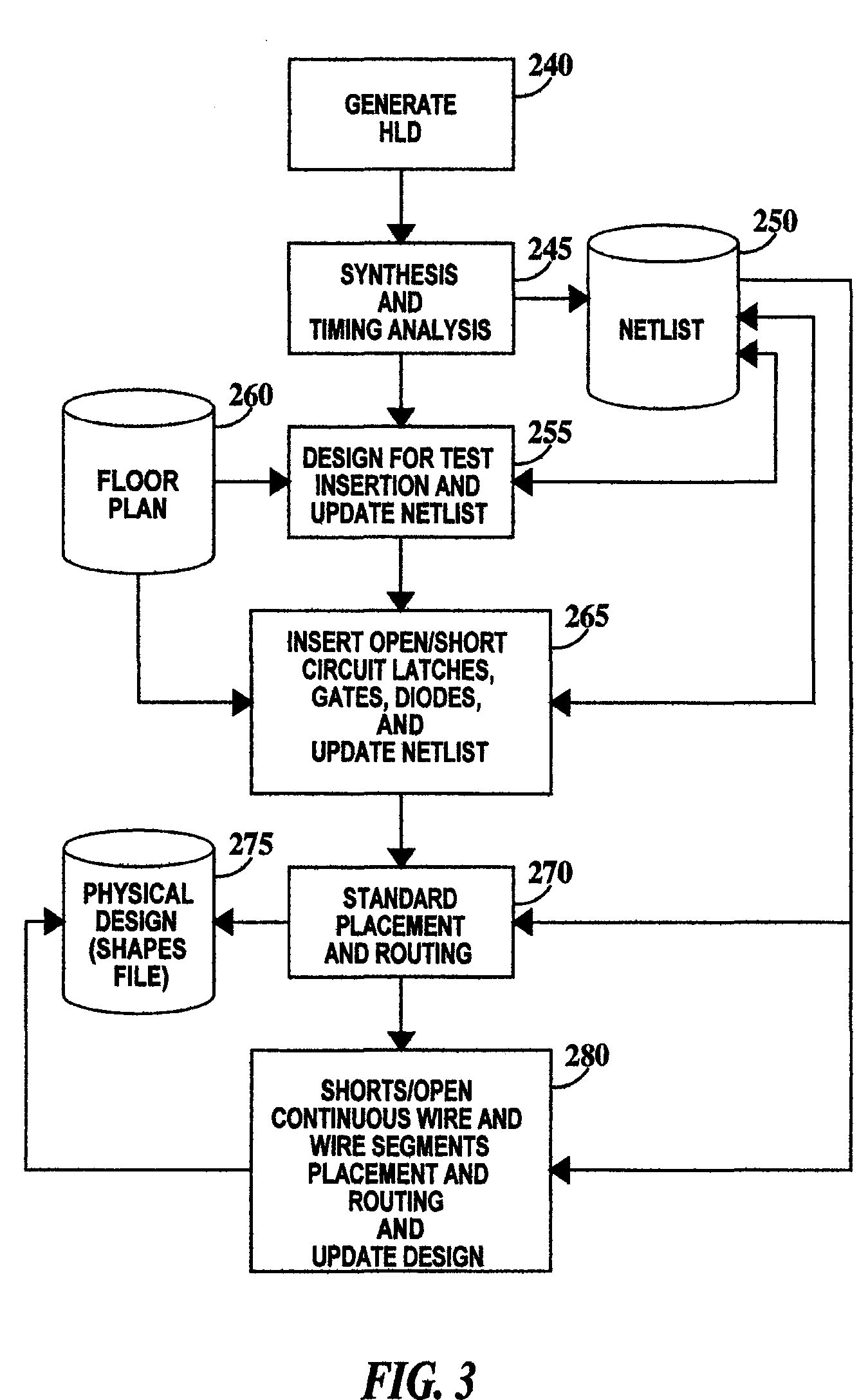

Method for designing an integrated circuit defect monitor

A method and system for designing a test structure. The method including: defining and placing test circuit pins in an integrated circuit design; routing one or more fat wires, each fat wire routed between a set of the test circuit pins; processing each fat wire into a continuous wire and one or more corresponding wire segments adjacent to the continuous wire, the continuous wire separated from the one or more corresponding wire segments by a space; and connecting the continuous wire and the one or more wire segments to circuit elements of a defect monitor scan chain, the circuit elements previously inserted into the integrated circuit design.

Owner:IBM CORP

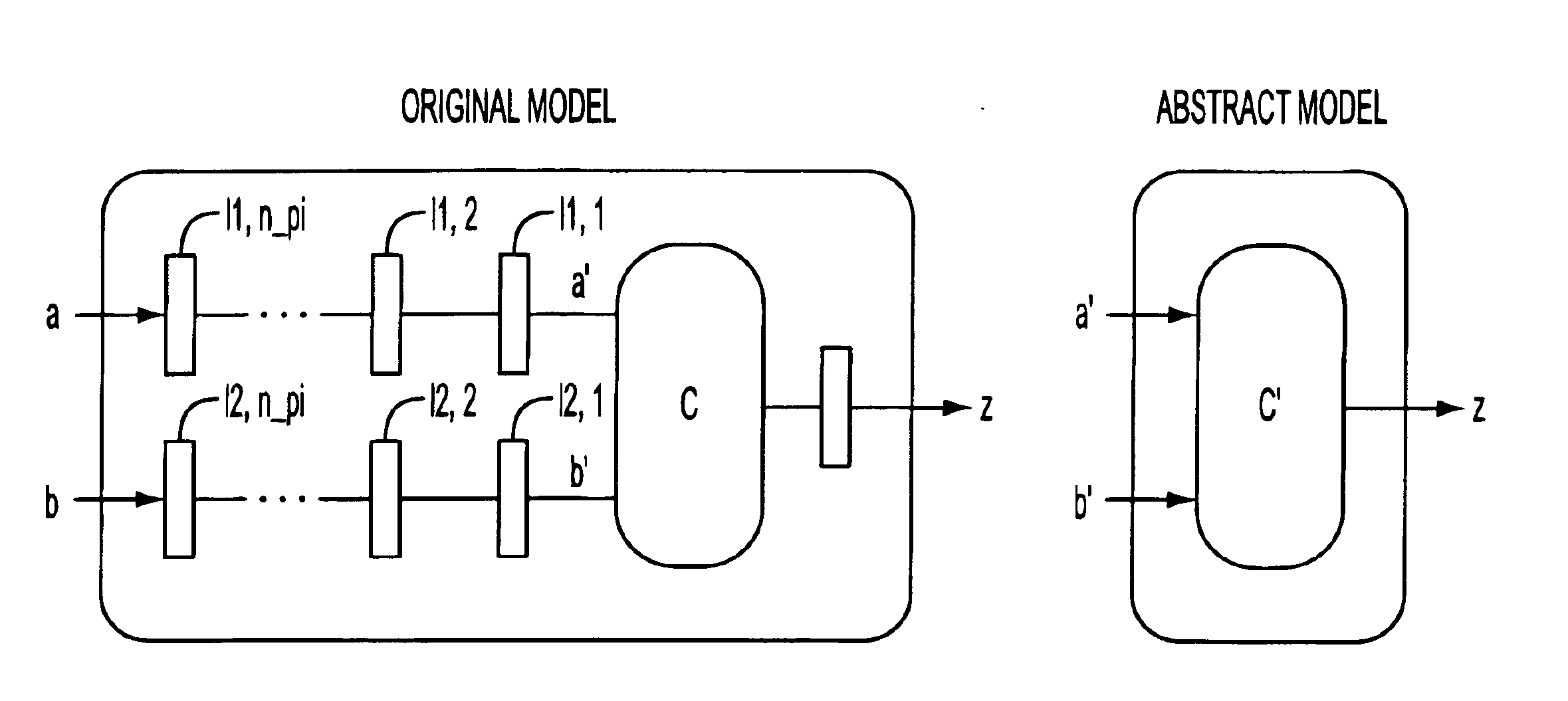

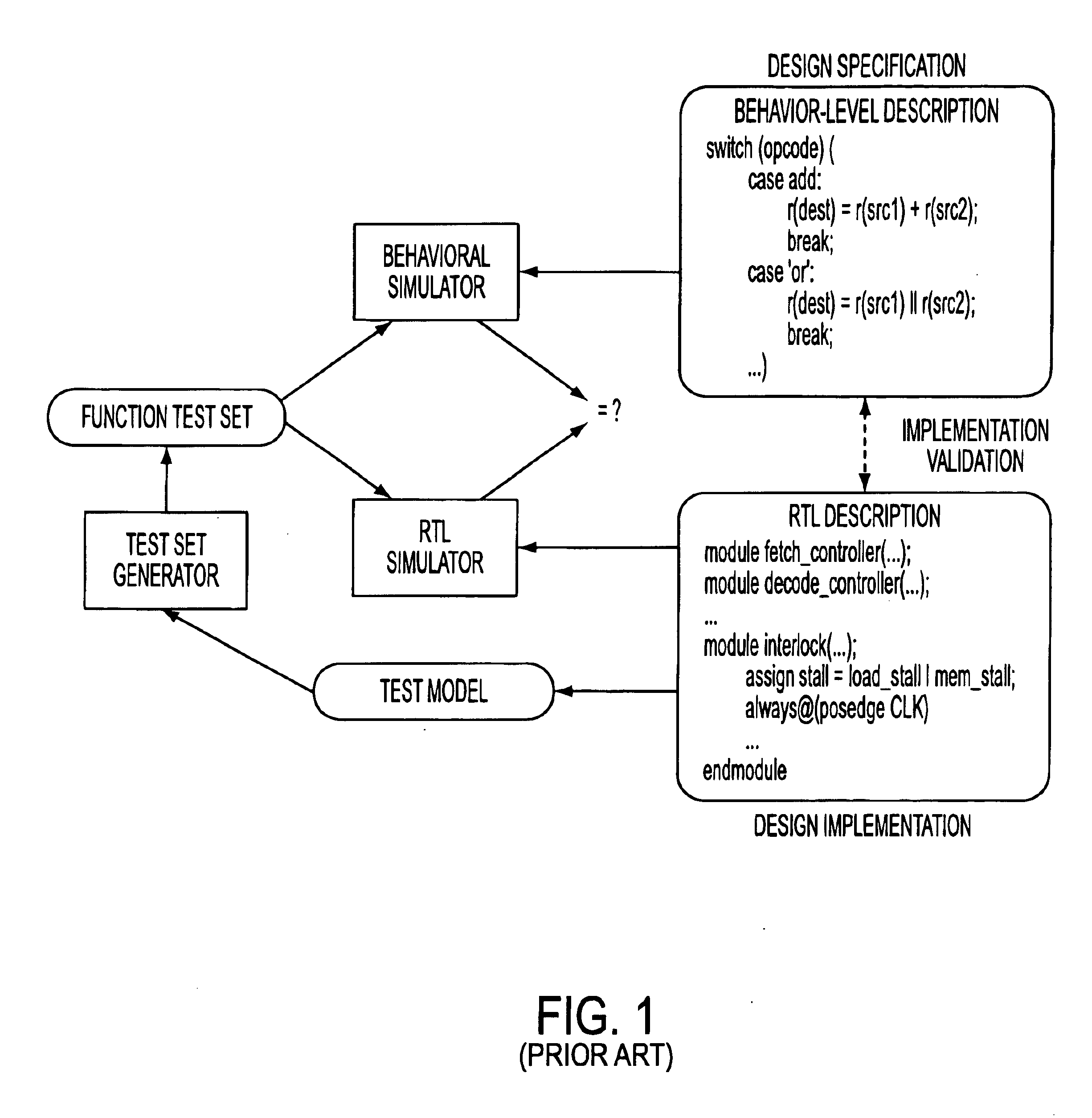

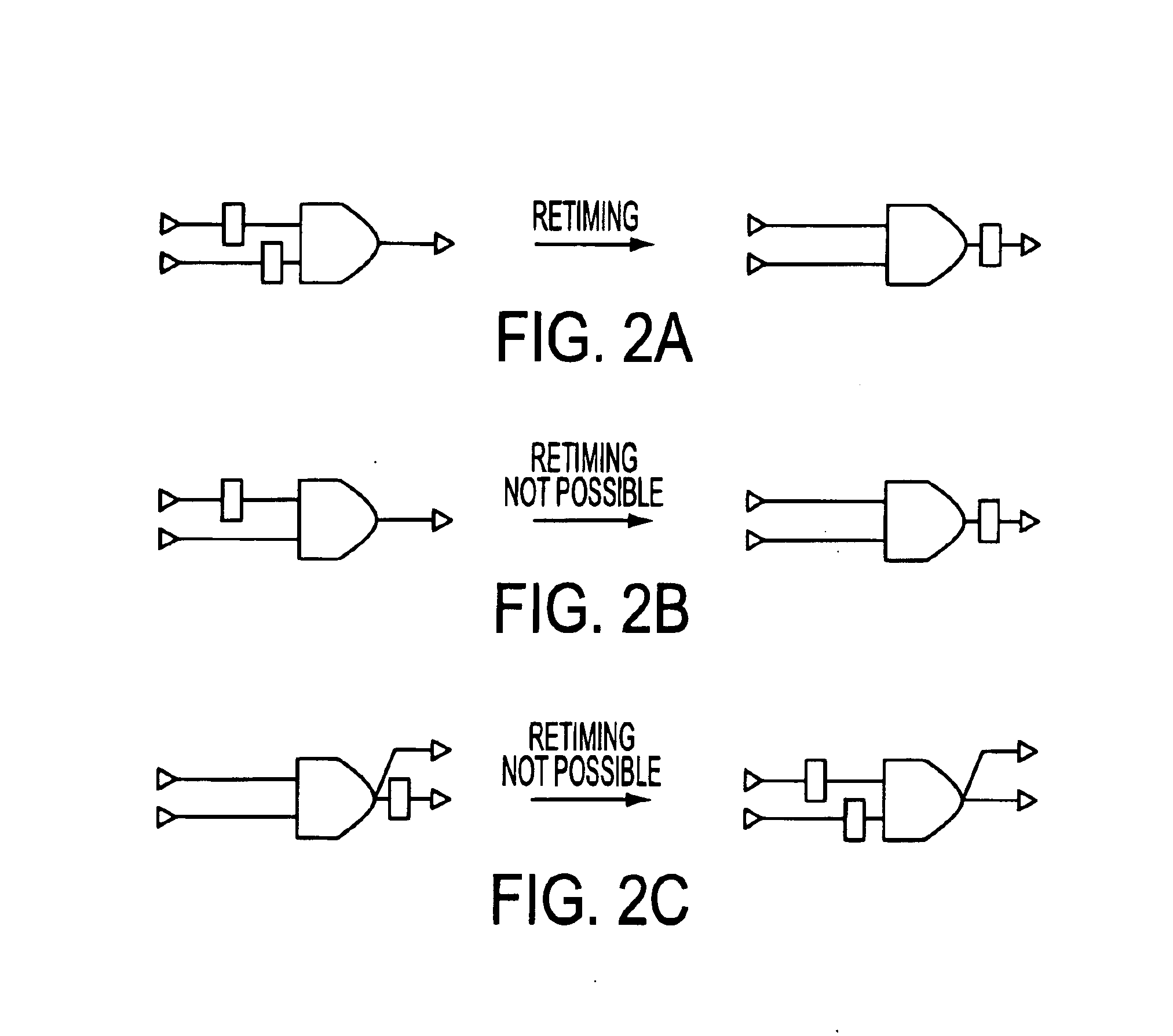

Method for design validation using retiming

InactiveUS6874135B2Minimize the numberReduce complexityDetecting faulty computer hardwareCAD circuit designDesign testingTest sequence

A method for derivation and abstraction of test models for validation of industrial designs using guided simulation is described. The method employs automatic abstractions for the test model which reduce its complexity while preserving the class of errors that can be detected by a transition tour. A method for design validation comprising generating a state-based test model of the design. The test model is abstracted by retiming and latch removal. Finally, a validation technique is applied on the abstracted test model. First, the number of internal (non-peripheral) latches in a design is minimized via retiming using a method of Maximal Peripheral Retiming (MPR). According to the MPR method, internal latches are retimed to the periphery of the circuit. Subsequently, all latches that can be retimed to the periphery are automatically abstracted in the test model. The validation technique may comprise of model checking, invariant checking or simulation using test sequences generated from the abstracted test model.

Owner:NEC CORP

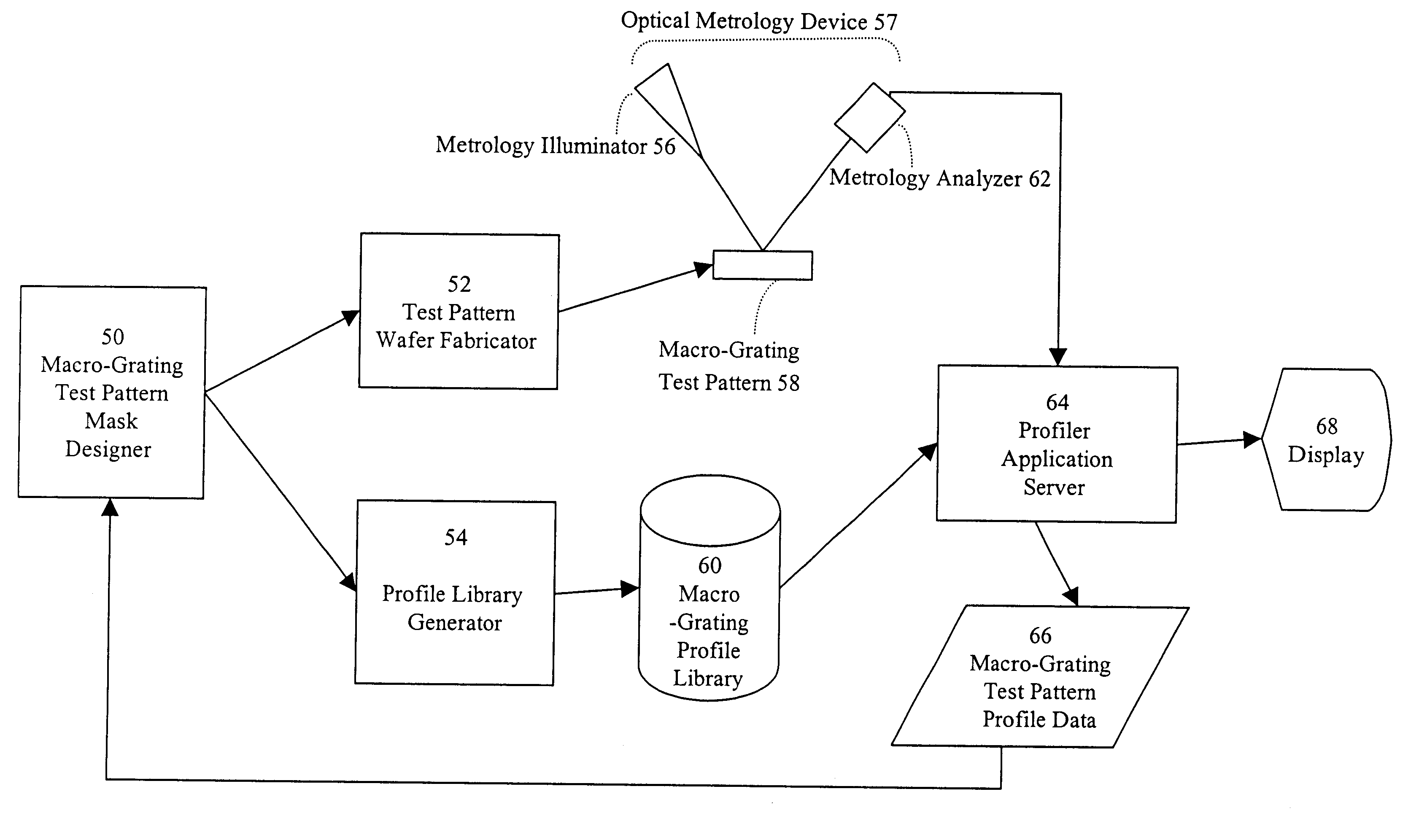

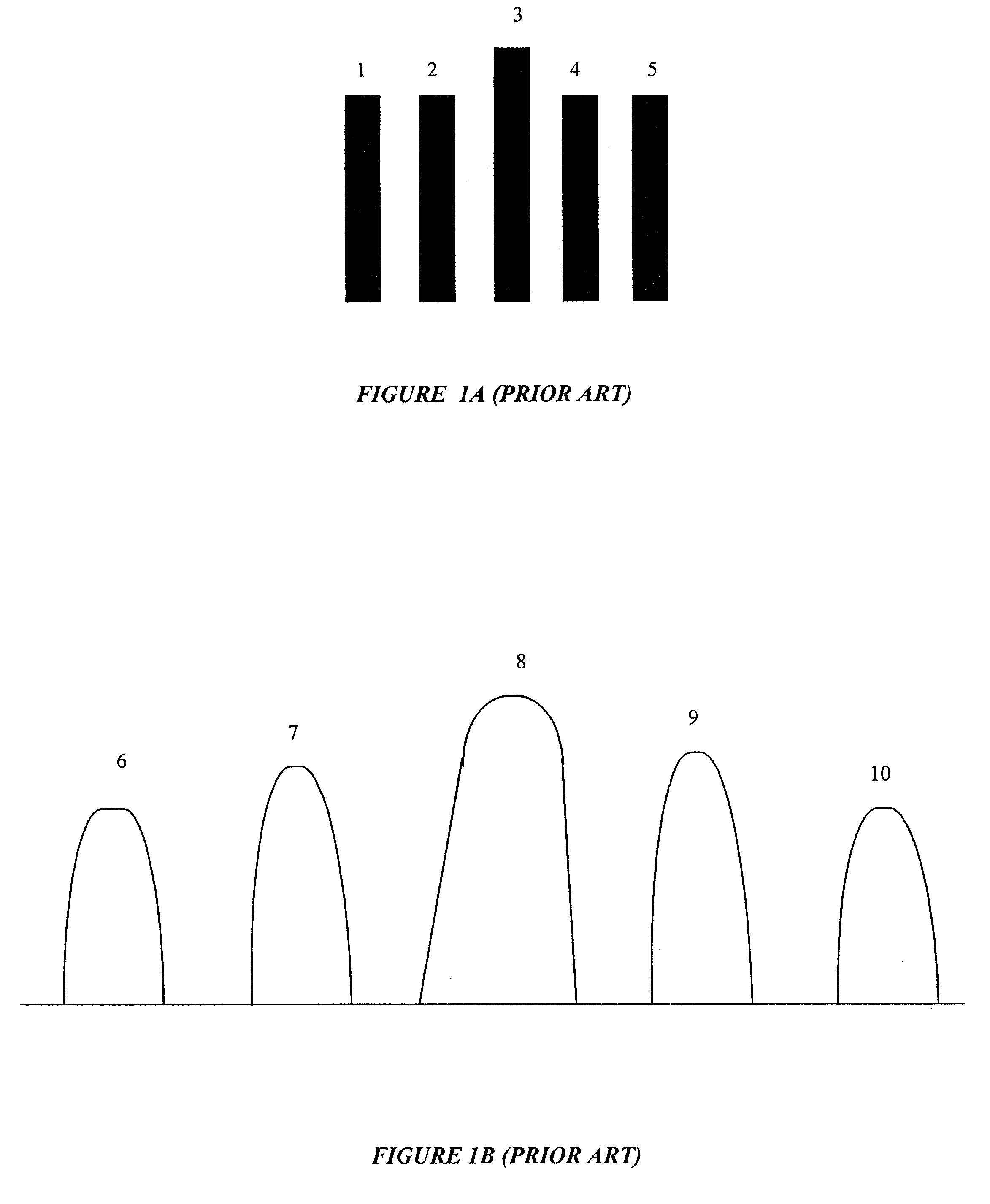

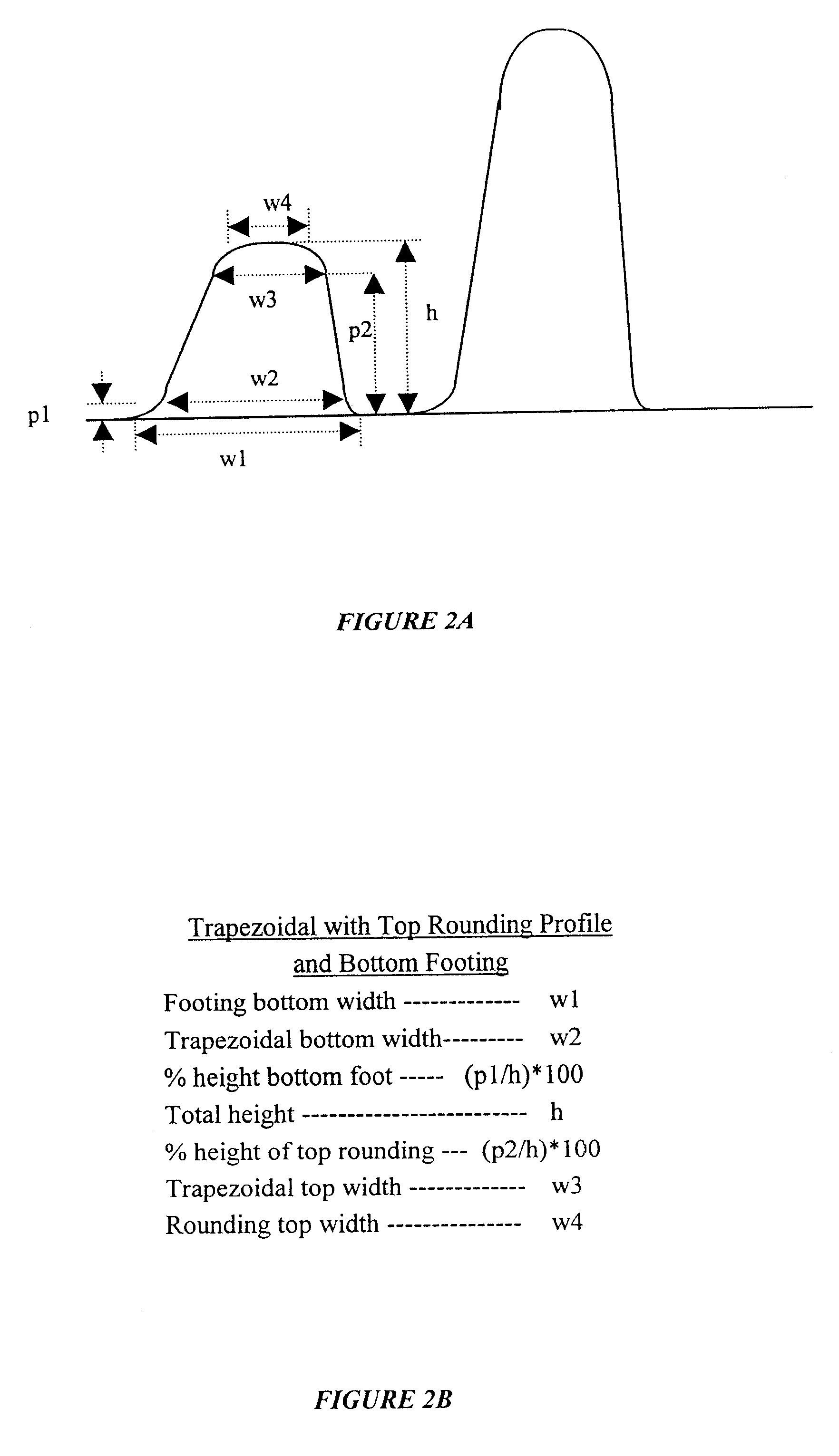

System and method for characterizing macro-grating test patterns in advanced lithography and etch processes

InactiveUS6538731B2Semiconductor/solid-state device testing/measurementScattering properties measurementsNon destructiveGrating

Owner:TIMBRE TECH INC

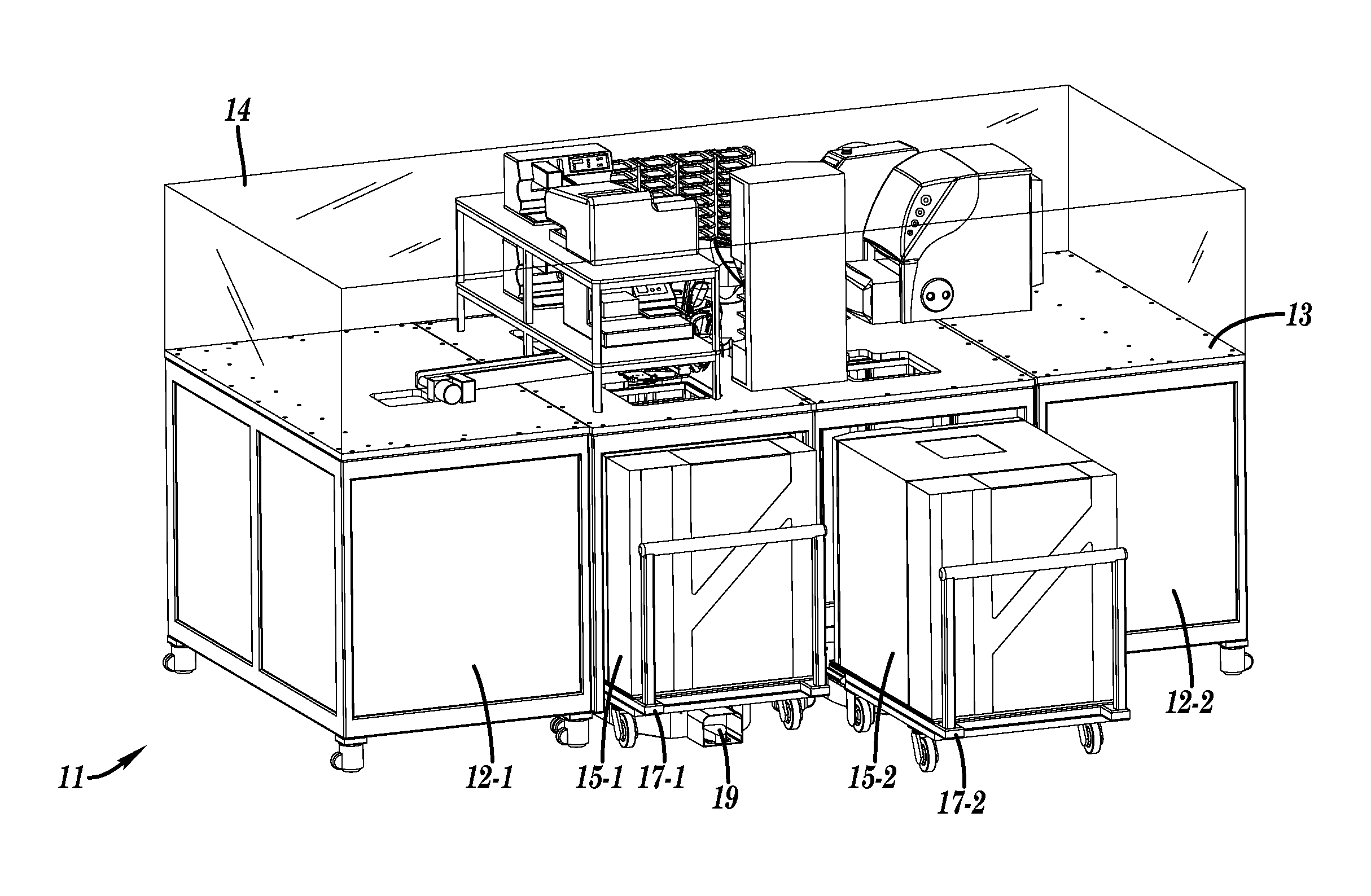

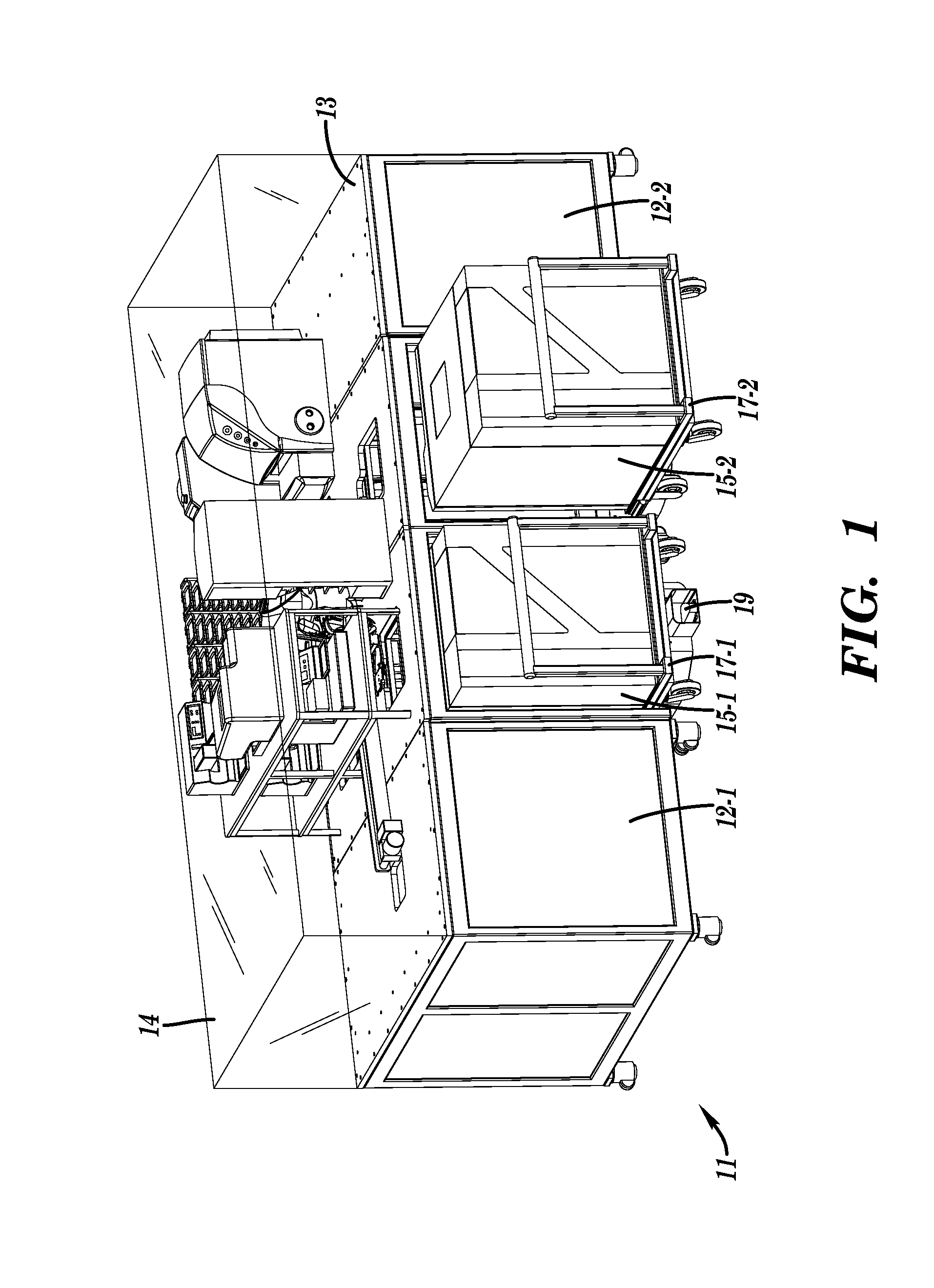

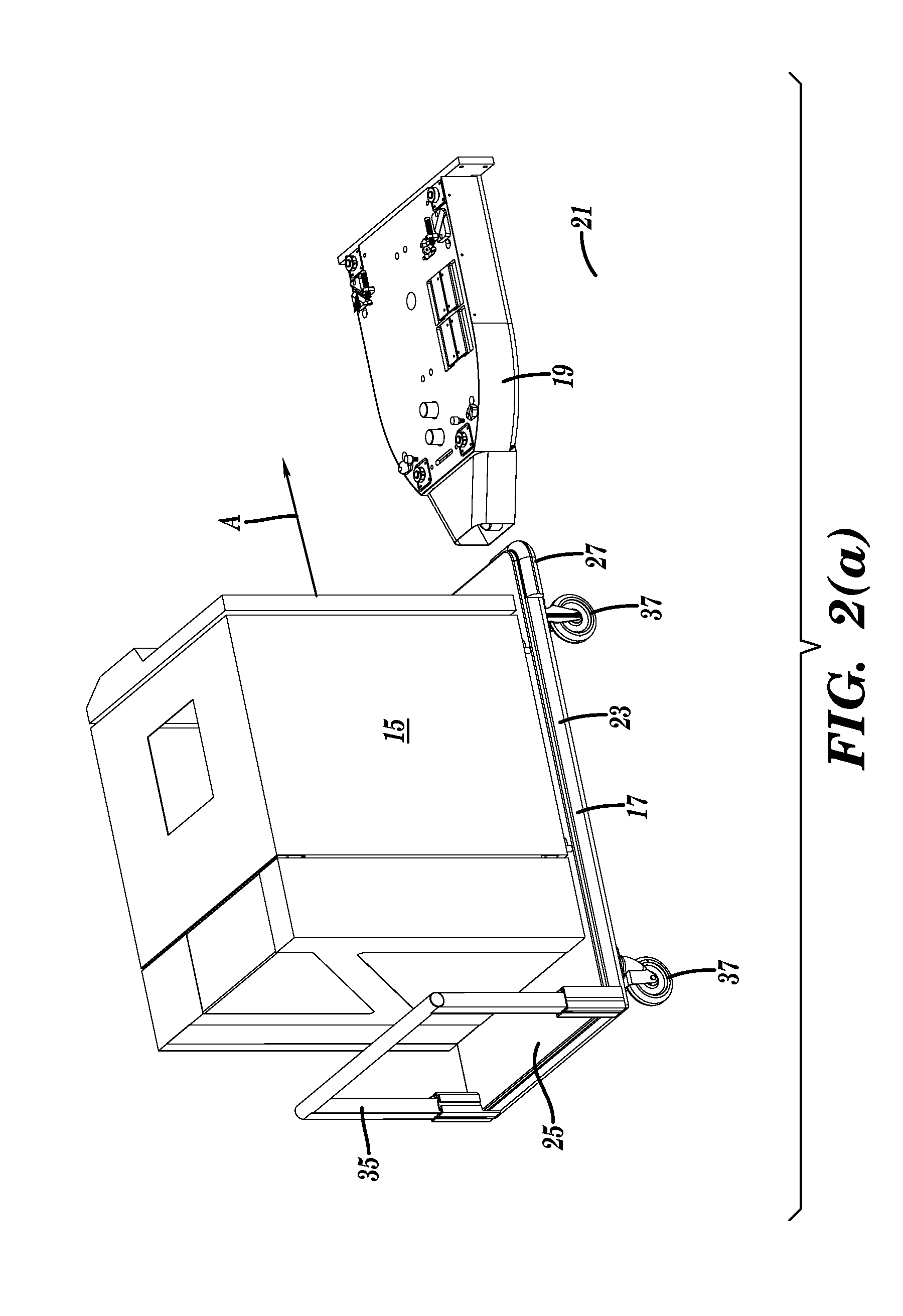

Instrument docking station for an automated testing system

ActiveUS20090246081A1Material analysis by optical meansLaboratory glasswaresDocking stationElectricity

An automated testing system includes one or more laboratory devices that operate together to perform an assay. The testing system is designed such that a laboratory device may be seamlessly integrated with the remaining devices in a quick and effortless manner. Specifically, the laboratory device is securely mounted on a slidable cart with fluid and electrical connections established therebetween. The slidable cart is in turn adapted to releasably engage with a docking station that is fixedly mounted on the workspace floor, the docking station being provided with at least one fluid input connection, an input power connection and at least one communication signal connection that are relatively permanent in nature. In order to couple the cart to the docking station, the cart is rolled generally into position above the docking station using complementary alignment posts and tracks.

Owner:HIGHRES BIOSOLUTIONS INC

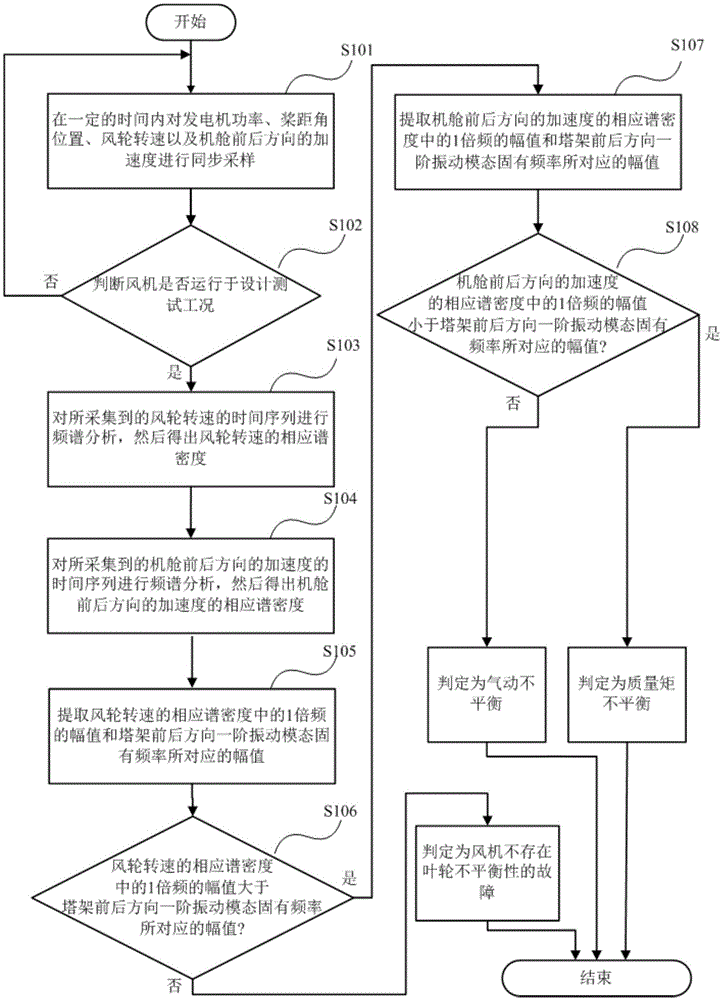

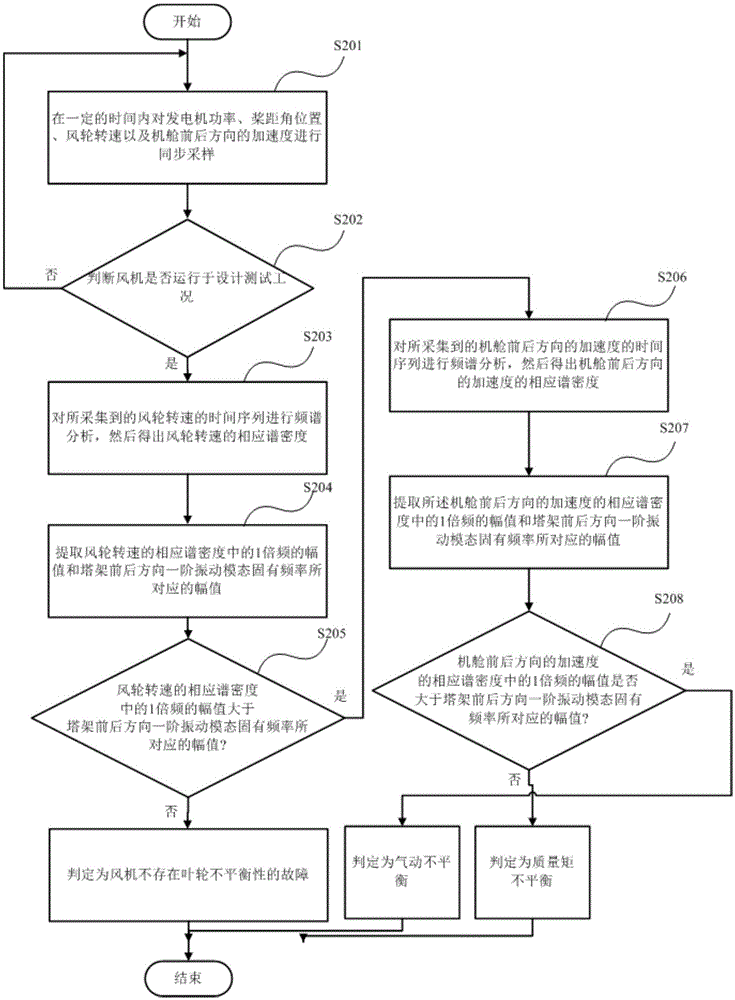

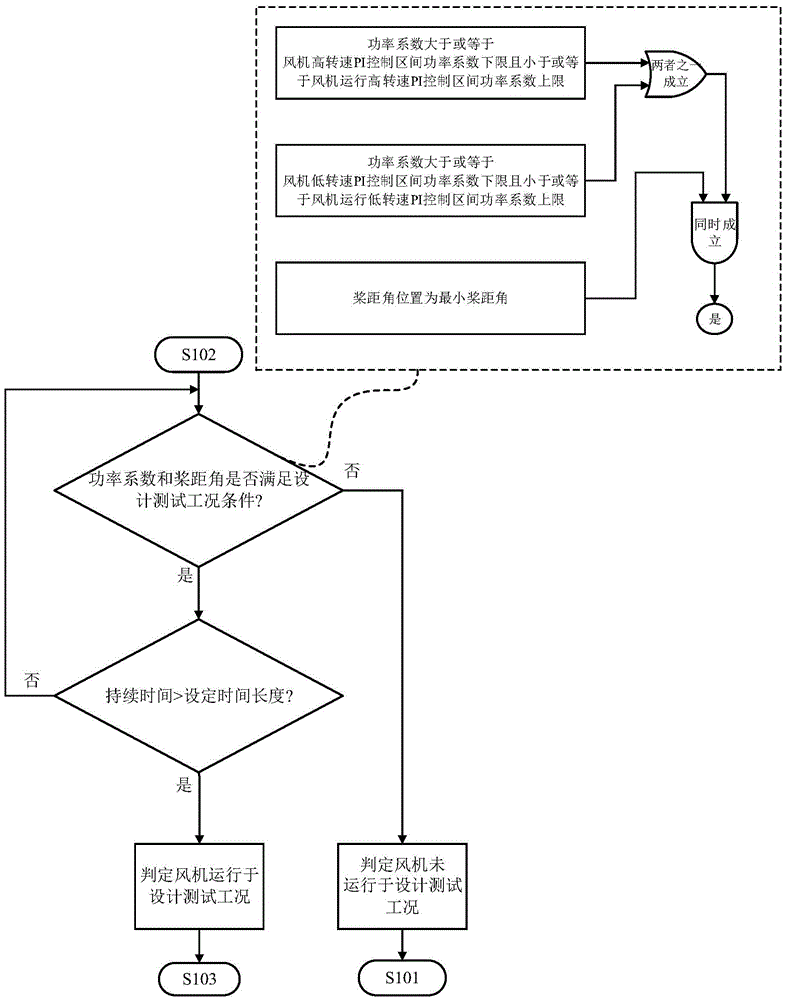

Dynamic unbalance online testing and fault identification method and system for wind turbine generators

ActiveCN105569932AAvoid OverloadingSolve balance problemsEngine fuctionsMachines/enginesElectricityImpeller

The invention discloses a dynamic unbalance online testing and fault identification method and system for wind turbine generators. The method includes the following steps that within a set time duration, synchronous sampling on the generator power, the pitch angle position, the wind wheel rotating speed and the accelerated speed of a cabin in the front and back direction is carried out; according to the generator power and the pitch angle position collected according to synchronous sampling, whether a draught fan runs under the designed testing work condition or not is judged; if it is judged that the draught fan runs under the designed testing work condition, at least spectral analysis is carried out on time series of the collected wind wheel rotating speed; according to results of the spectral analysis on the time series of the collected wind wheel rotating speed, whether the draught fan has impeller unbalance faults or not is judged; if the draught fan has impeller unbalance faults, either pneumatic imbalance or quality moment imbalance is the reason of unbalancedness is judged according to the results of the spectral analysis on the time series of the accelerated speed of the cabin in the front and back direction. The invention further discloses a corresponding system.

Owner:XINJIANG GOLDWIND SCI & TECH

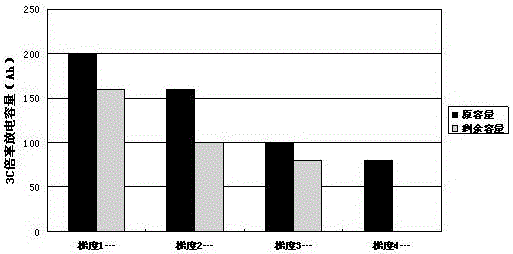

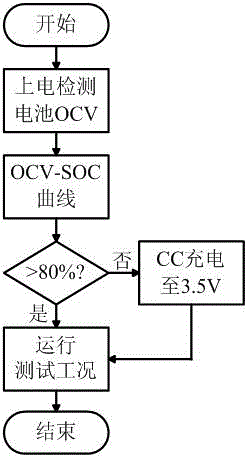

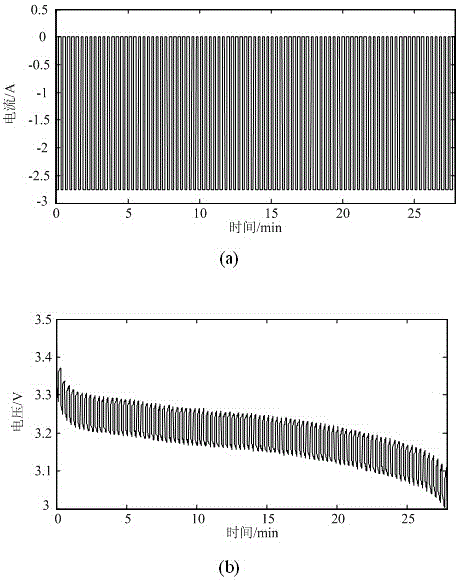

Echelon utilization lithium battery performance evaluation method

The invention discloses an echelon utilization lithium battery performance evaluation method which can be applied to echelon recycling of lithium batteries. The echelon utilization lithium battery performance evaluation method comprises the steps of designing performance test condition of a lithium battery, that is, designing the test time, determining the initial SOC state and designing the discharge intermittent time; extracting health feature data of the lithium battery according to the designed test conditions; then performing SOH estimation based on a health state decision-making method of a multi-health life model data fusion technology; and finally dividing an echelon utilization range of the lithium battery. The echelon utilization lithium battery performance evaluation method can be applied to echelon recycling of the lithium battery, not only can enable the performance of the lithium battery to be given into full play so as to be conducive to energy conservation and emission reduction, but also can relieve pressure brought for the recycling work by a circumstance that a great number of lithium batteries get into a recycling stage.

Owner:ZHENGZHOU UNIVERSITY OF LIGHT INDUSTRY

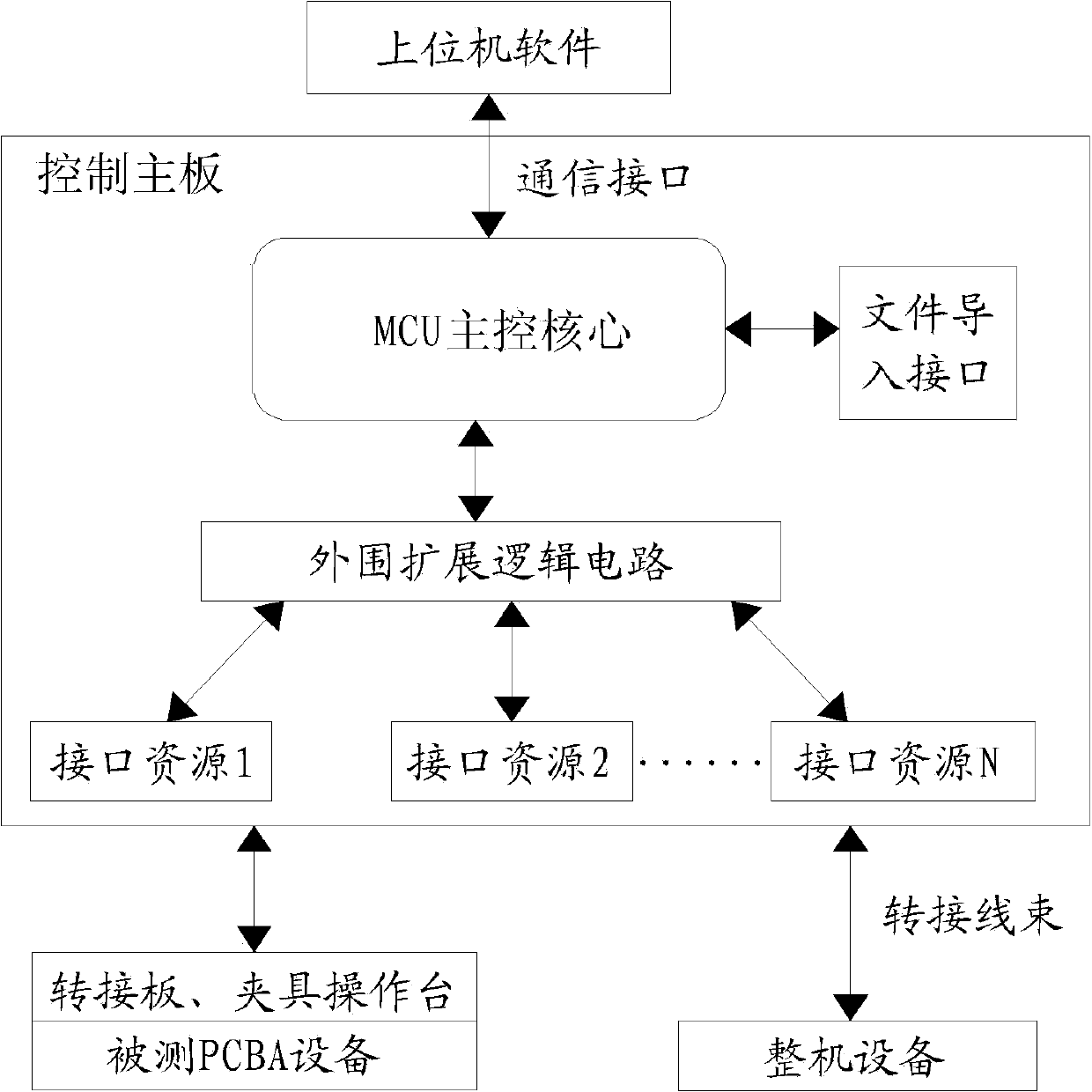

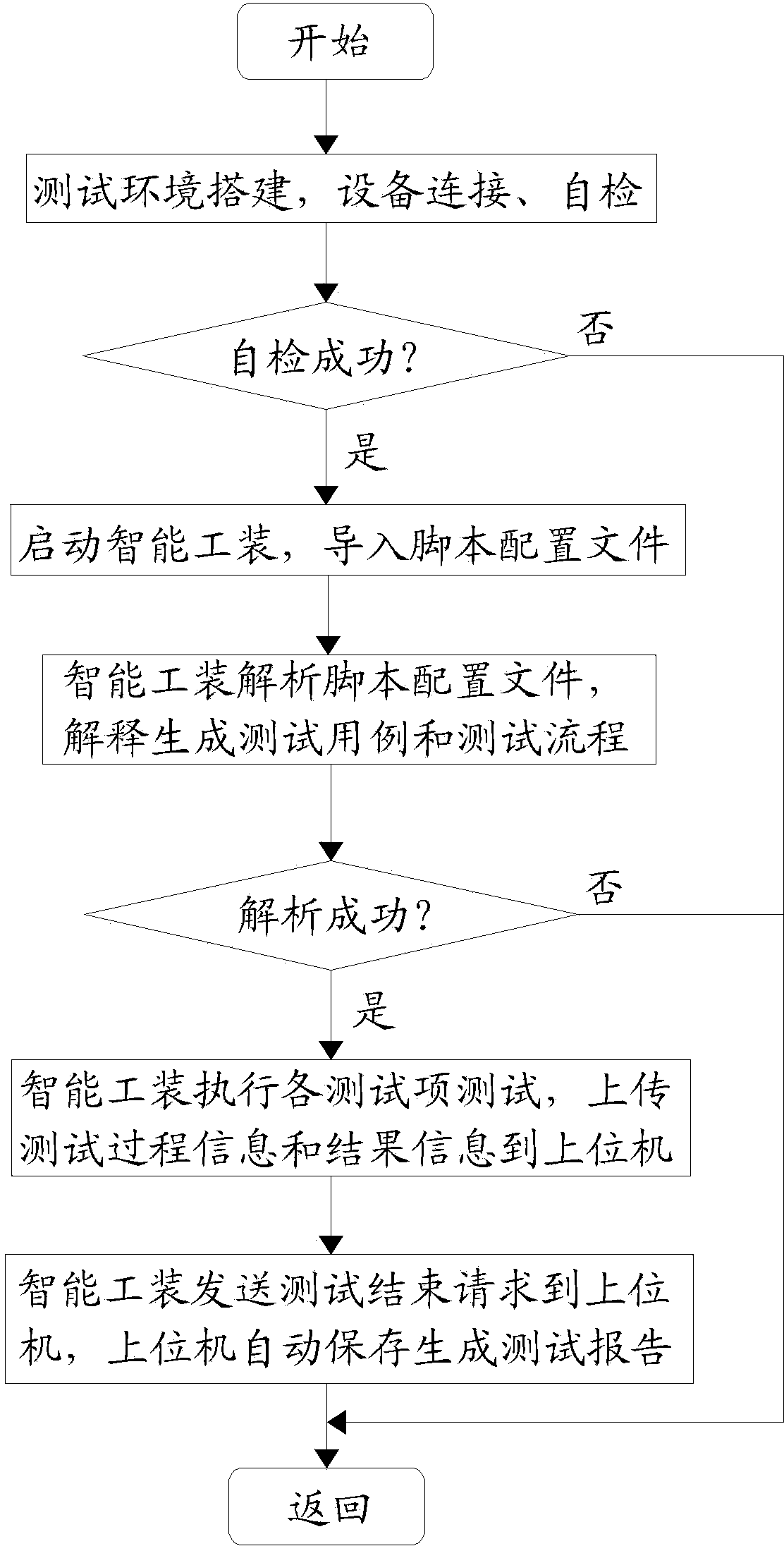

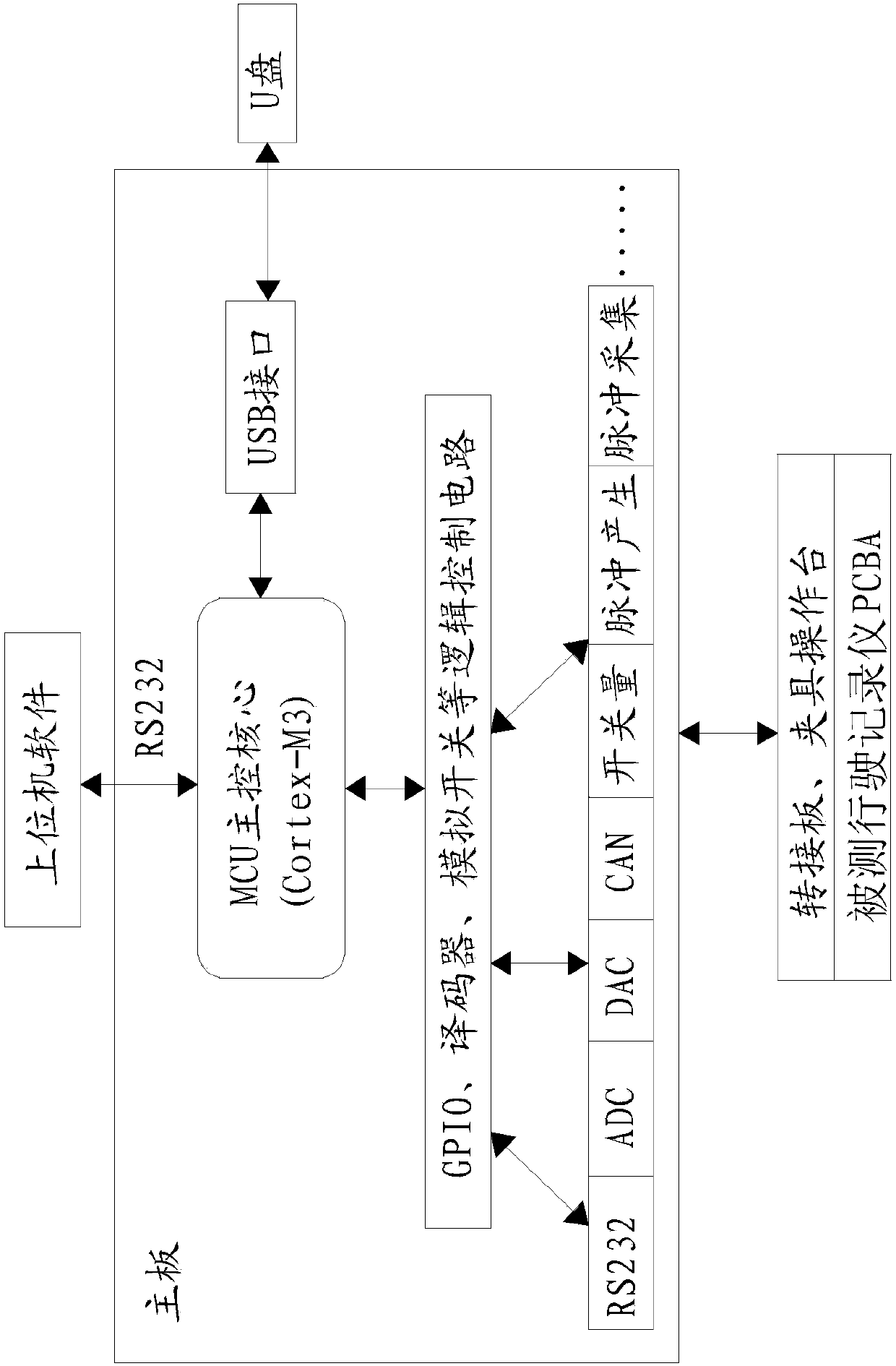

Intelligent tool capable of being flexibly expanded and dynamically configured

InactiveCN104198868ARealize signal acquisitionEasy to detectElectronic circuit testingDesign testingEmbedded software

The invention discloses an intelligent tool capable of being flexibly expanded and dynamically configured. The intelligent tool comprises a hardware module and a software module. The hardware module comprises a control mainboard, to-be-tested equipment, a plurality of testing circuit units, an interface resource set formed by multiple interfaces and a plurality of adapter plates. The software module comprises embedded software and a script configuration file. A testing process includes the steps of firstly, preparing a hardware environment; secondly, preparing the software, to be more specific, forming the script configuration file according to the testing cases and testing flow of the design testing content of the to-be-tested equipment; thirdly, operating the embedded software after the control mainboard is started, importing the script configuration file, allowing the embedded software to analyze the script configuration file, and executing corresponding operations according to the analyzed testing flow so as to test the to-be-tested equipment.

Owner:XIAMEN YAXON NETWORKS CO LTD

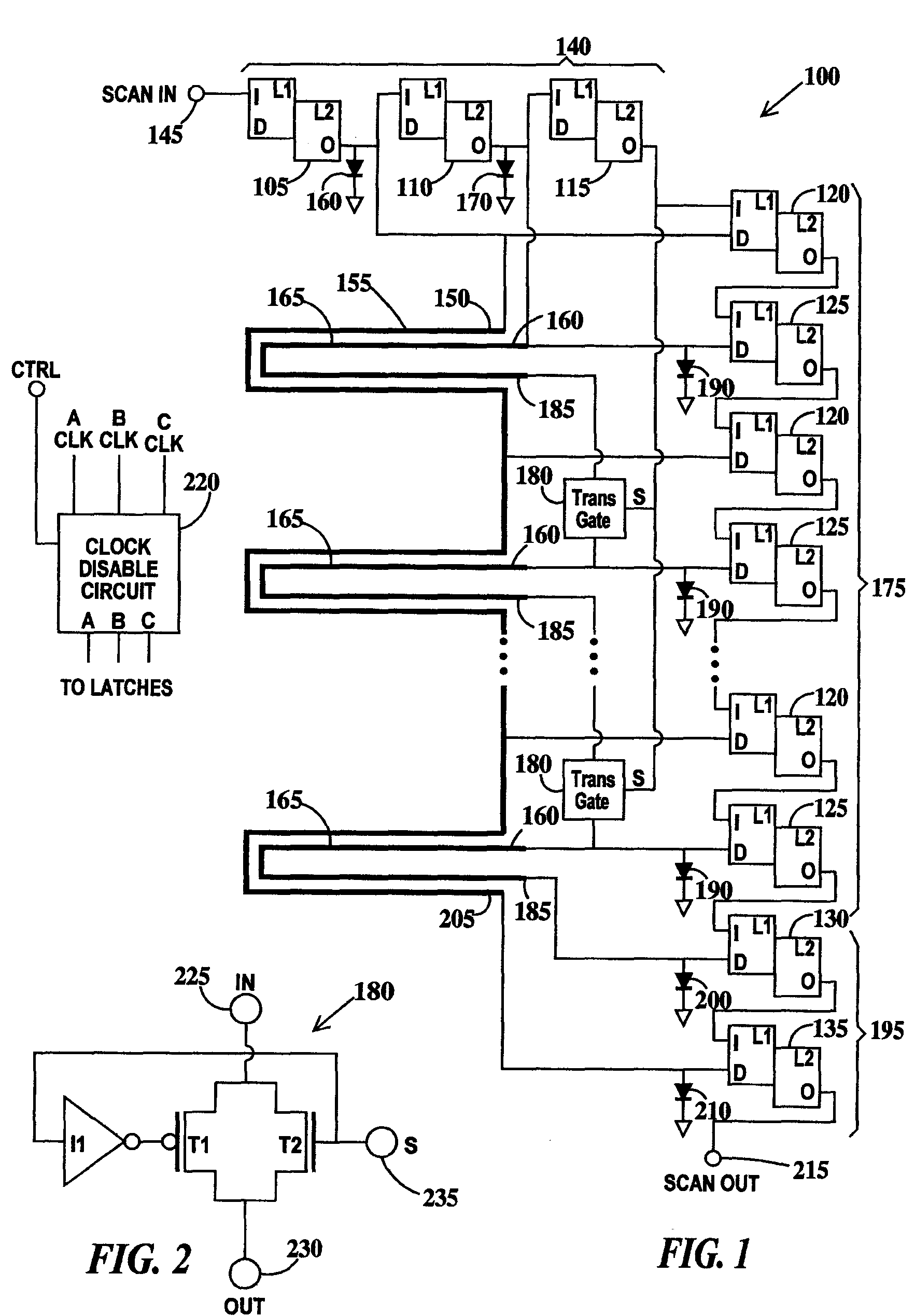

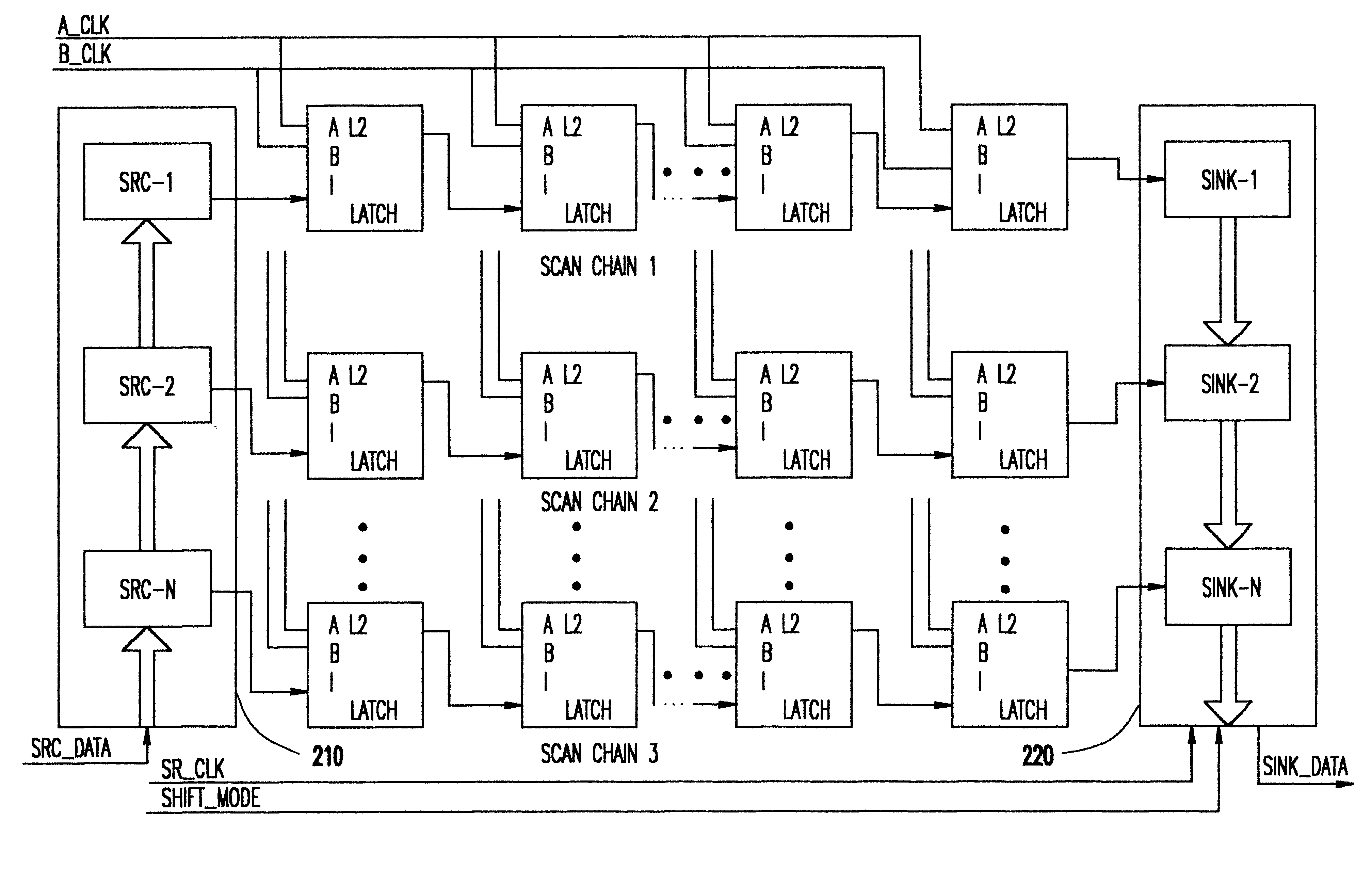

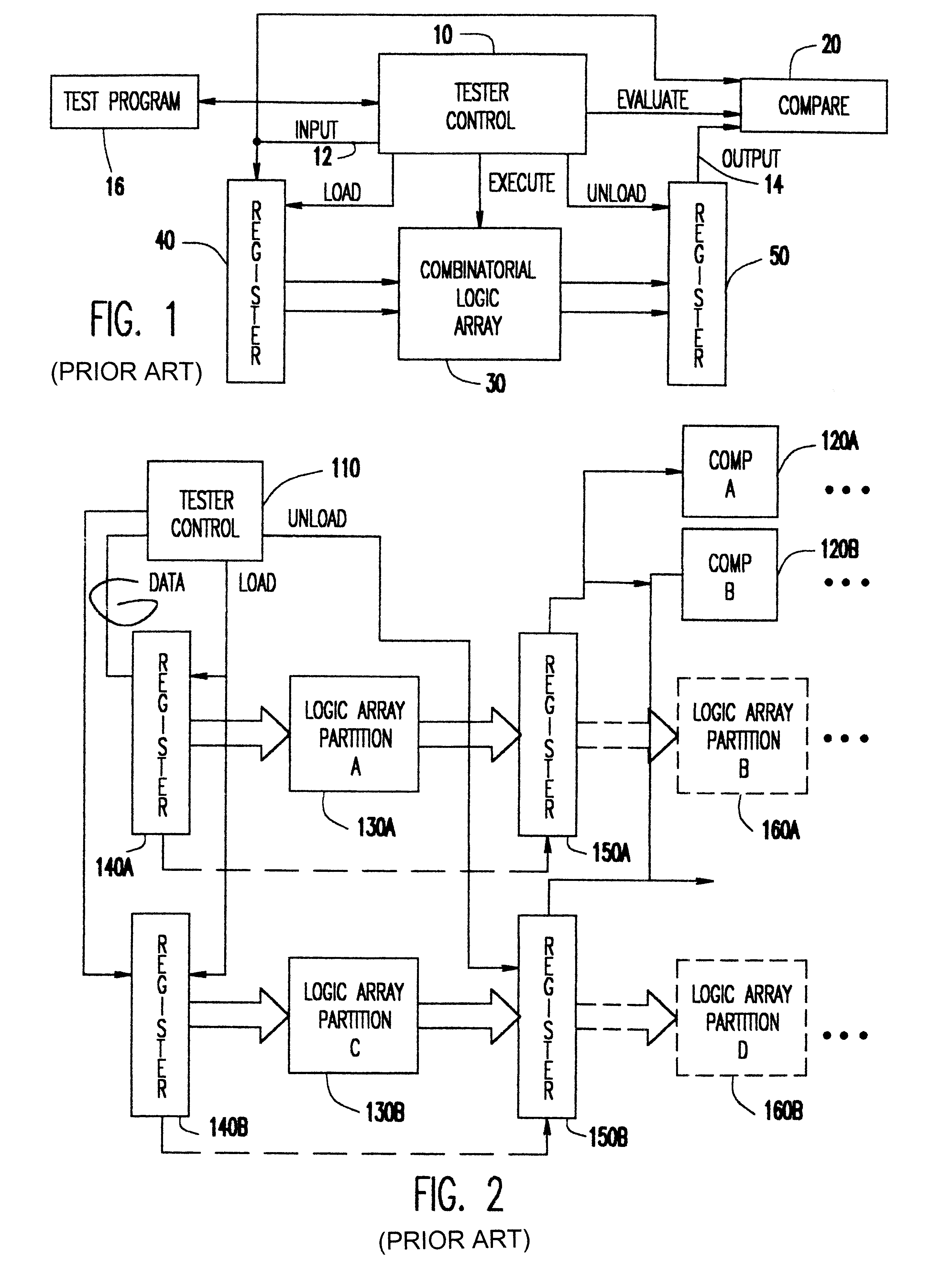

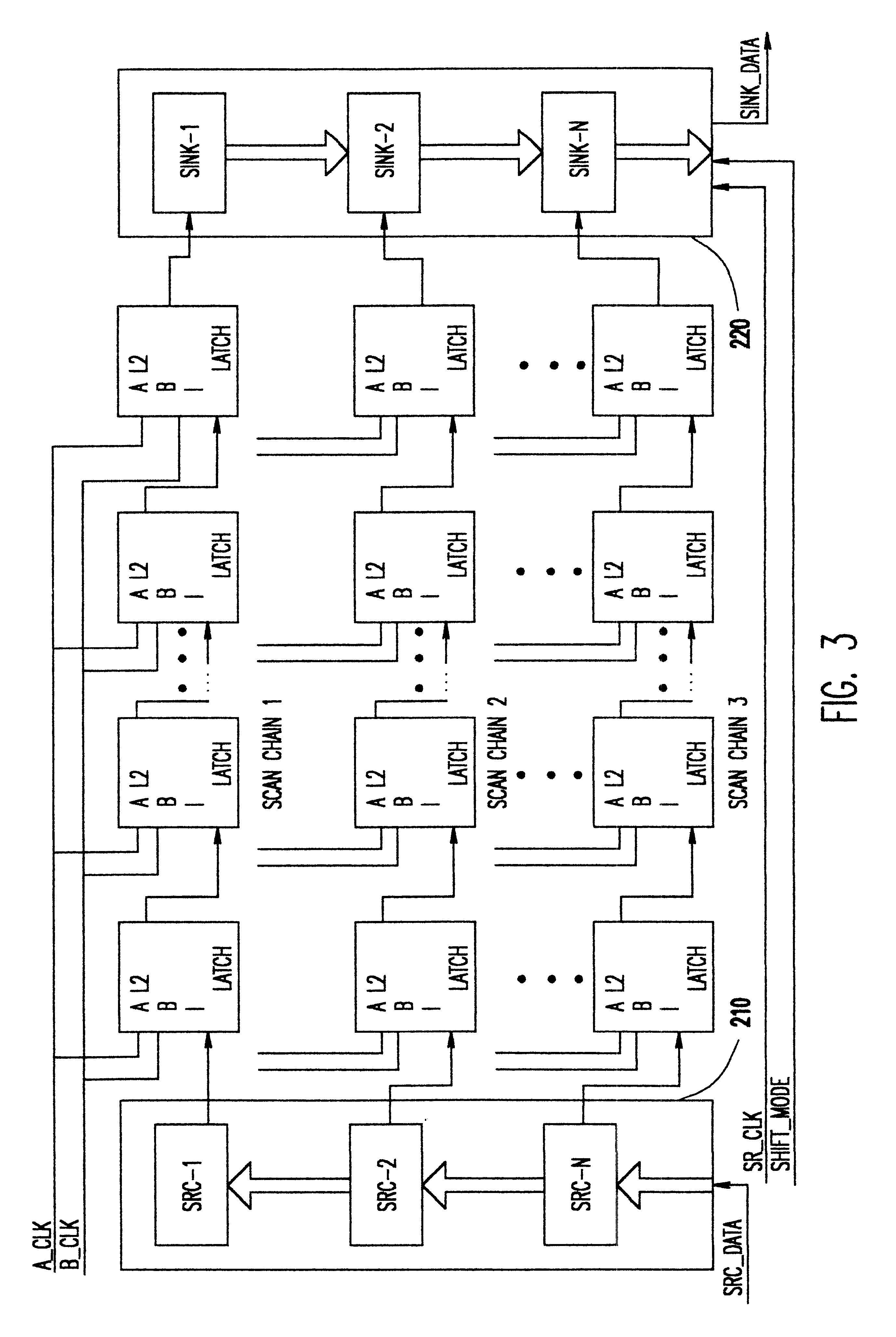

High speed sink/source register to reduce level sensitive scan design test time

InactiveUS6591388B1Reducing time and tester apparatus overheadShorten test timeElectronic circuit testingLogic circuitsRegister allocationShift register

Test data is provided through shift registers, operated at a high clock rate comparable to or exceeding a normal high speed clock rate of a chip being tested, to each of a plurality of scan chains configured from registers present on the chip; respective latches of which are connected to inputs and outputs of logic array partitions to be tested. Reduced test clock rate of input and output circuits of the scan chains is accommodated by high speed source and sink shift registers. The source and sink registers are fully loaded and unloaded between consecutive test clock signals and test signals are preferably applied to and collected from the chip in a single serial string through a single pair of tester input / output pins. Testing time is thus reduced without requiring design time and chip space for a clock tree optimized for high speed operation while use of testers of reduced cost and having an arbitrarily small number of input / output pin pairs and independent of test register configuaration on the chip can be used.

Owner:IBM CORP

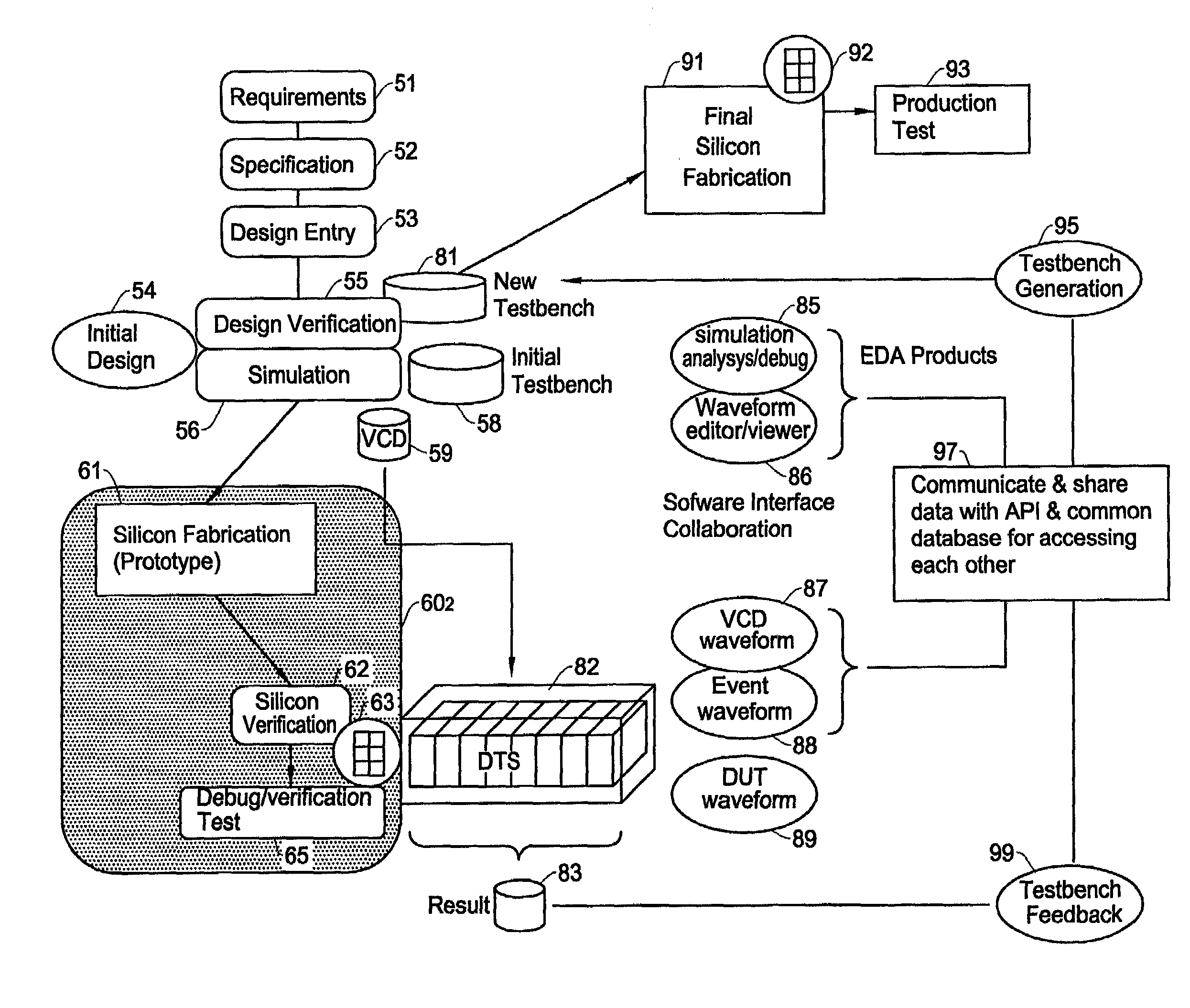

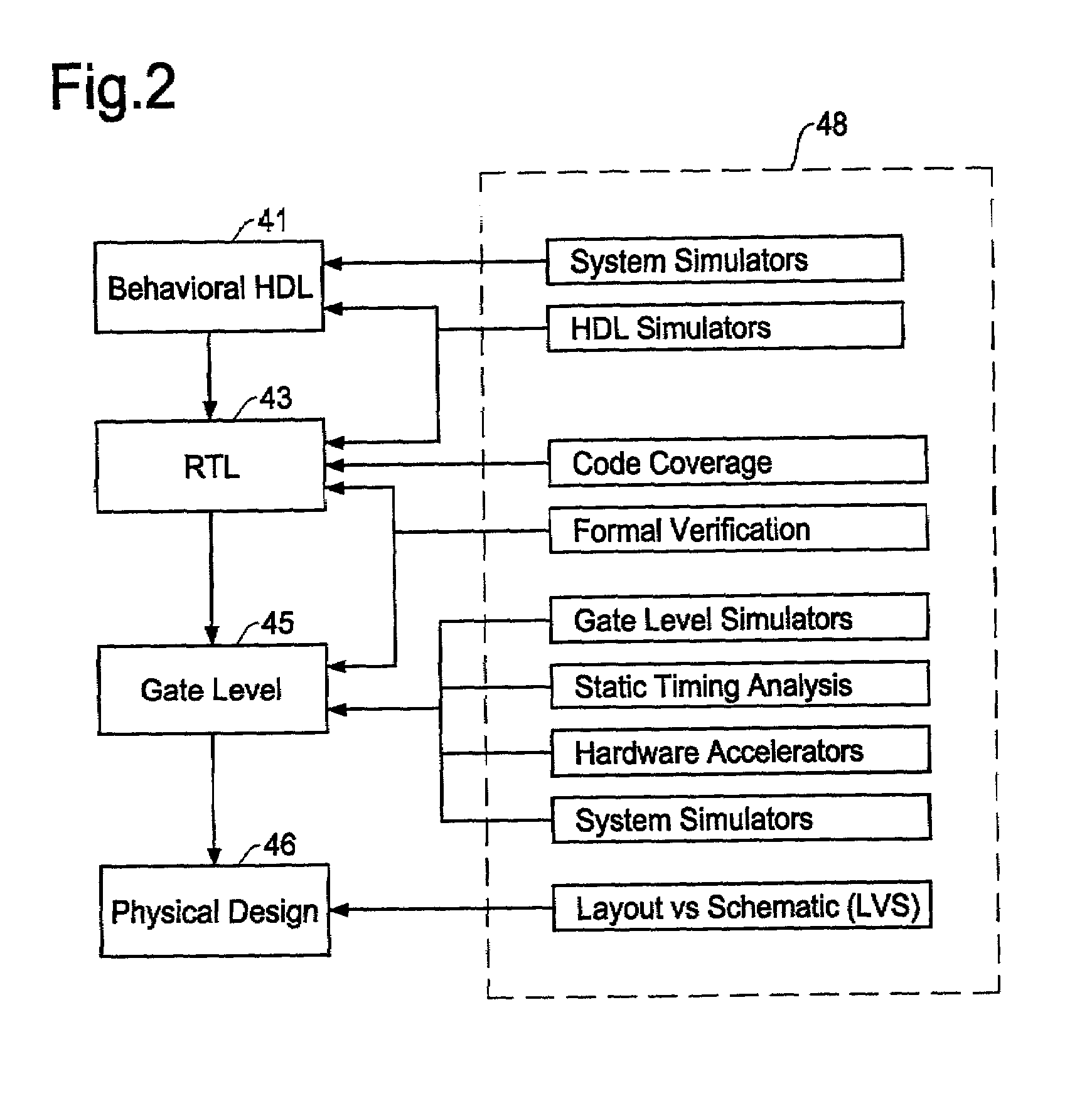

Method for design validation of complex IC

InactiveUS7089517B2Design errorSatisfied with the resultElectronic circuit testingAnalogue computers for electric apparatusComputer architectureDesign testing

A method for design validation of complex IC with use of a combination of electronic design automation (EDA) tools and a design test station at high speed and low cost. The EDA tools and device simulator are linked to the event based test system to execute the original design simulation vectors and testbench and make modifications in the testbench and event based test vectors until satisfactory results are obtained. The event based test vectors are test vectors in an event format in which an event is any change in a signal which is described by its timing and the event based test system is a test system for testing an IC by utilizing the event based test vectors. Because EDA tools are linked with the event based test system, these modifications are captured to generate a final testbench that provides satisfactory results.

Owner:ADVANTEST CORP

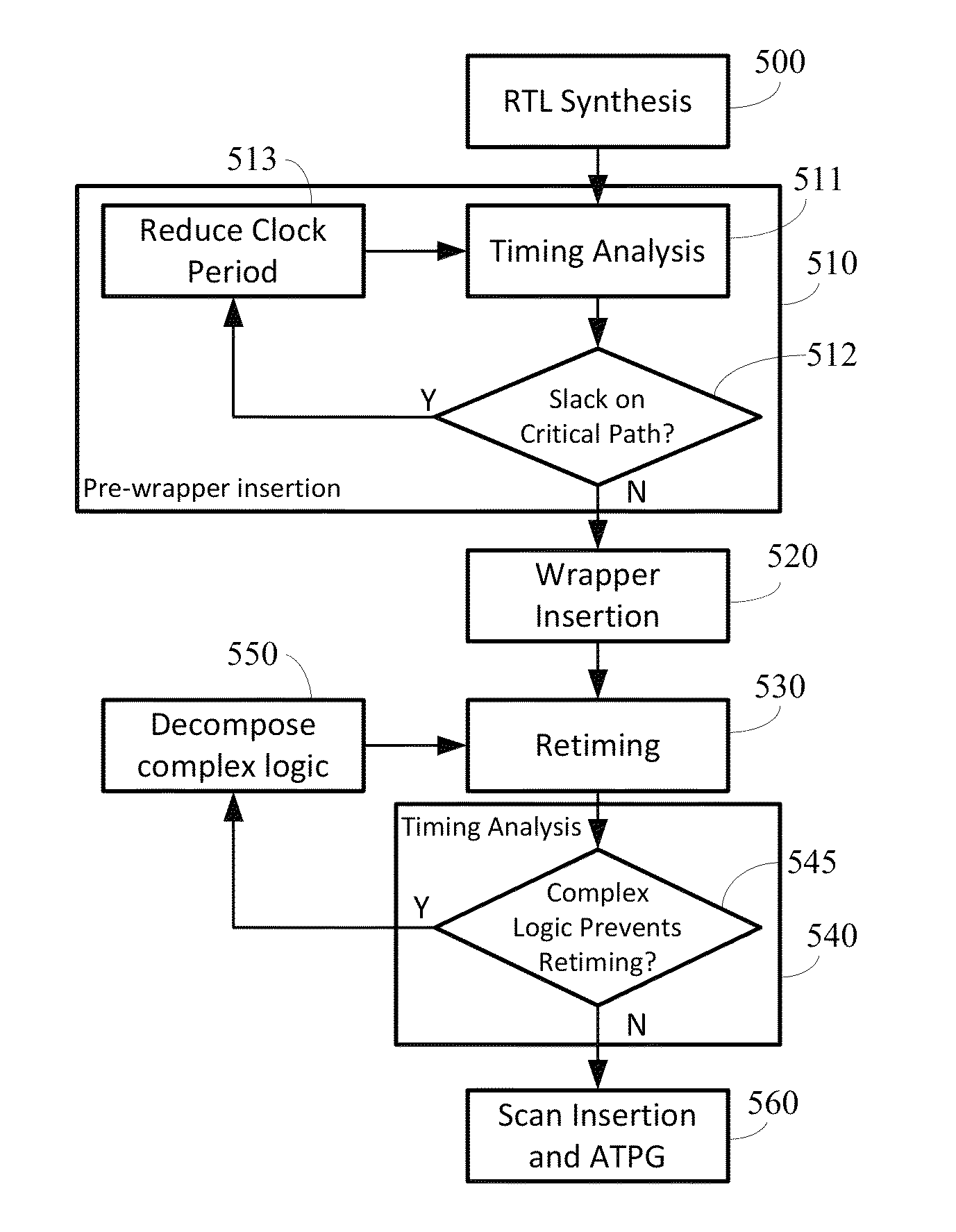

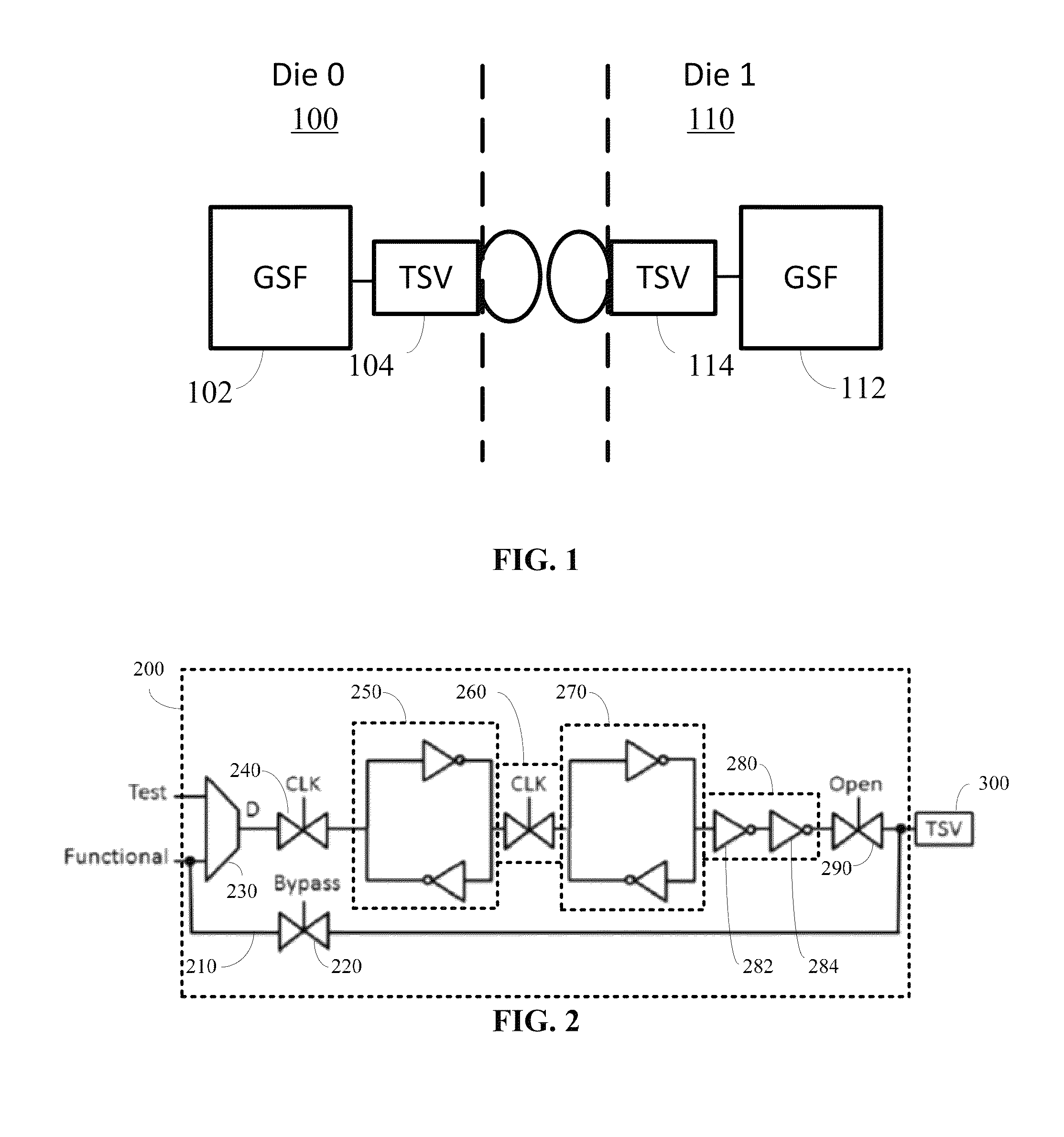

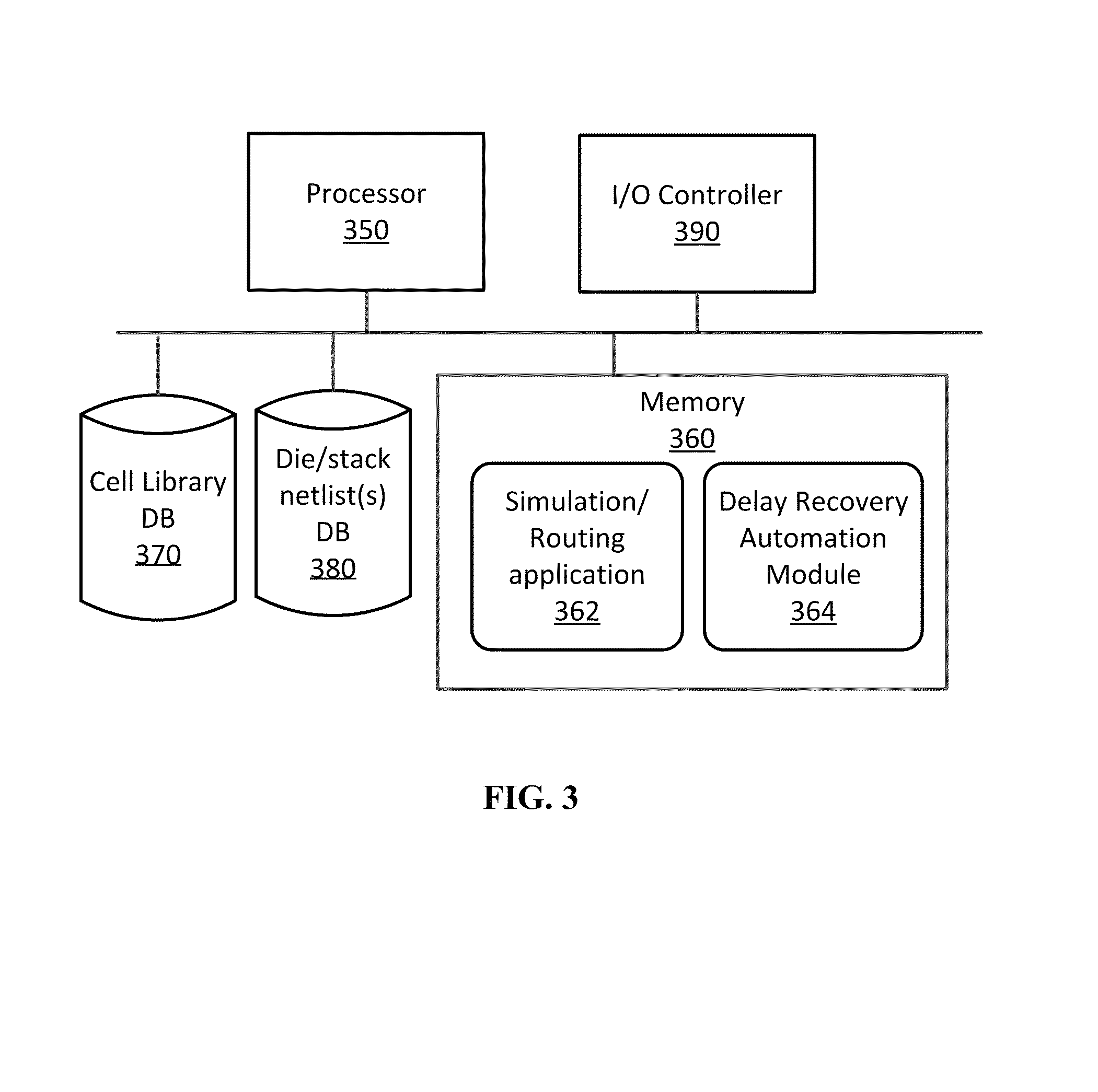

Retiming-based design flow for delay recovery on inter-die paths in 3D ICs

InactiveUS8832608B1Increase delayImprove latencyComputer aided designSpecial data processing applicationsDesign for testingDesign testing

A three dimensional (3D) stacked integrated circuit (IC) design-for-Testing (DfT) die-level wrapper boundary register having a bypass mode and design-level DfT delay recovery techniques are provided. Die wrappers that contain boundary registers at the interface between dies can be inserted into 3D ICs where the boundary registers include a gated scan flop with a bypass line passing the functional input to a through-silicon-via (TSV) in a manner avoiding the clocked stages of the gated scan flop during functional operation. A retiming process can be applied during design layout using a simulation / routing tool or standalone program to recover the additional delay added to the TSV paths by the DfT insertion. Retiming can be performed at both die and stack level, and in further embodiments, logic redistribution across adjacent dies of the stack can be performed for further delay optimization.

Owner:DUKE UNIV

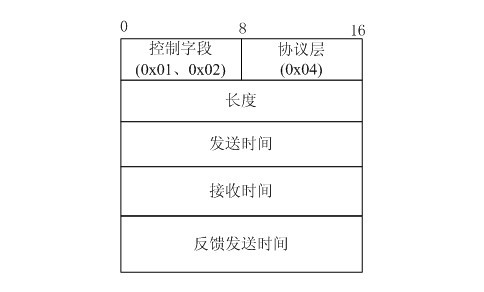

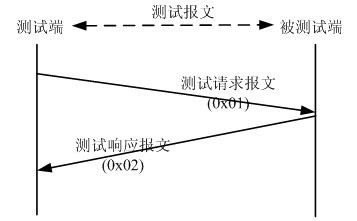

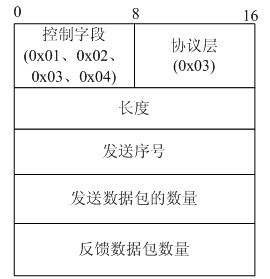

Tree and tabular combined notation (TTCN)-based network protocol performance testing method

InactiveCN102118230AReduce the difficulty of performance testingImprove reuseError prevention/detection by using return channelSoftware testing/debuggingTTCNNetworking protocol

The invention discloses a tree and tabular combined notation (TTCN)-based network protocol performance testing method, which comprises the following steps of: (1) writing test cases, corresponding adapters and corresponding codecs, and selectively designing test control messages in the test cases according to test objects; (2) selecting the test case according to network protocol performance parameters to be tested; (3) performing test configuration according to the test case; (4) compiling the test case by adopting a TTCN platform, and registering the adapter and the codec by using a testingsystem; (5) running the test case and acquiring test records; and (6) performing record counting analysis on the test, and giving a performance test report. The method is applied to ordinary protocolperformance tests; and in the method, a protocol performance testing process is put forward and normalized, and simultaneously a control protocol is selectively applied to the TTCN-based protocol performance test so as to reduce difficulties in the protocol performance test and improve the understandability and reusability of the test.

Owner:HUAZHONG UNIV OF SCI & TECH

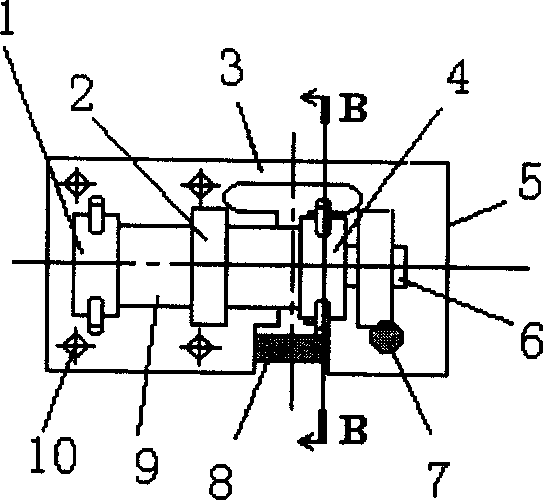

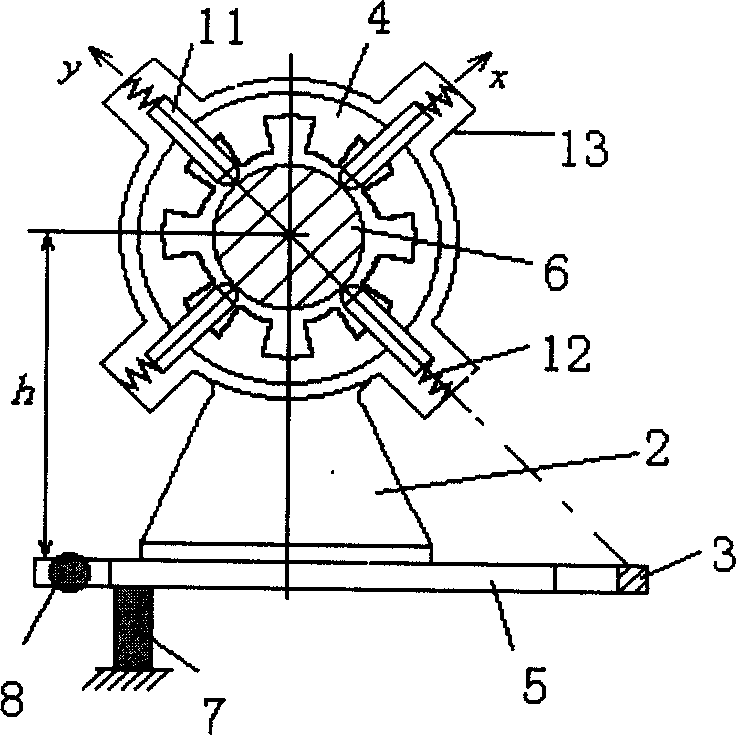

Method for testing coupling property of magnetic suspension rotor system and tesl platform

The invention is a testing method of the coupled property of the magnetic suspension rotor system and the test table. It uses non-superposition of magnetic bearing's magnetic forces and superpositionof the displacement to get coupled parameters such as coupled force, coupled torque, etc, and determine the relationship of the suspension forces of the magnetic pole pair in x or y direction of the magnetic bearing and the currents, namely magnetic pole suspension force-current property curve family. It uses computer to control thermal expansion extension of expansion shaft, to make the deformation beam elastically deform and further simulates micro eccentricity and tilt of rotor to design the test table, namely the whole electric control system.

Owner:WUHAN UNIV OF TECH

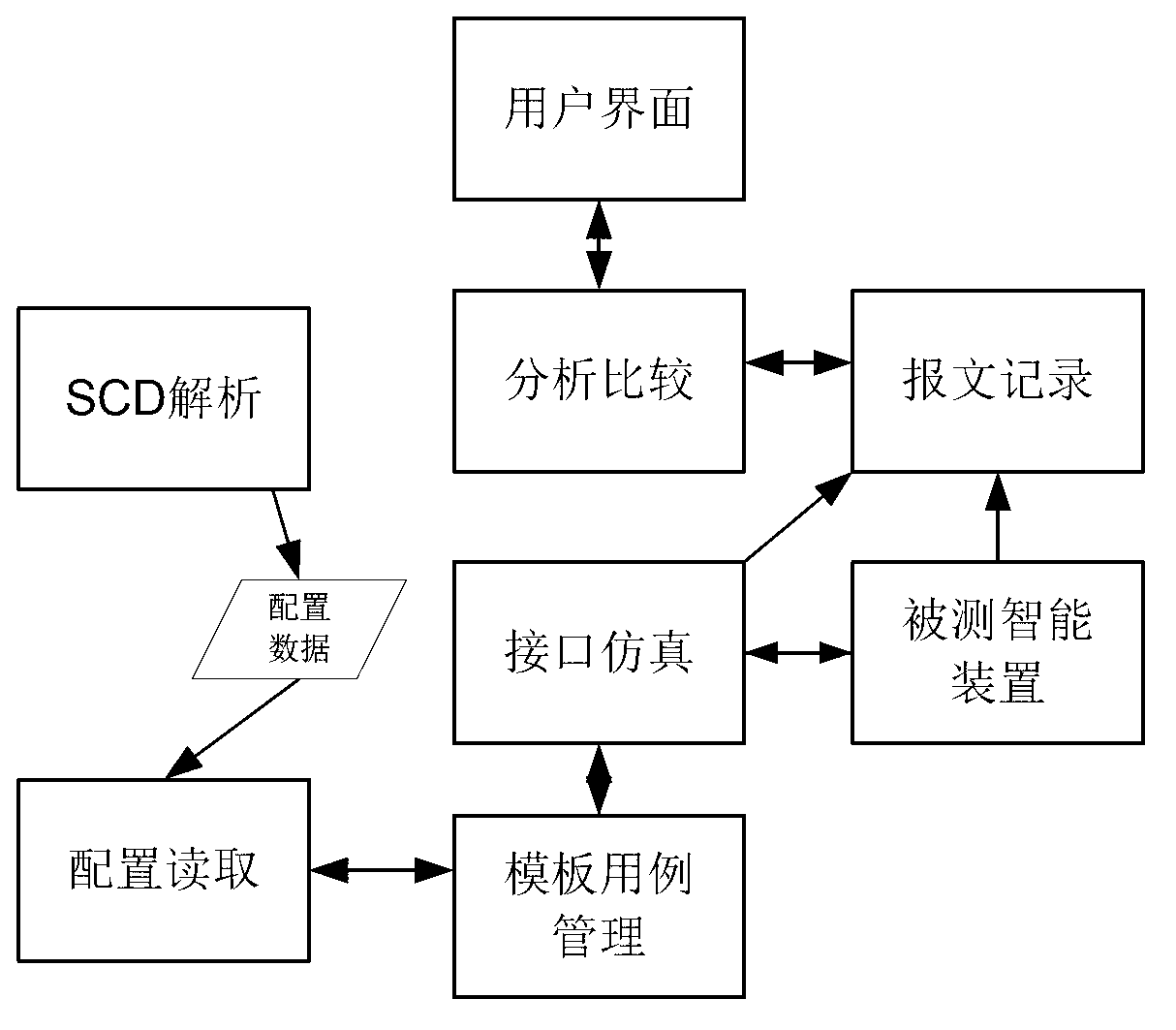

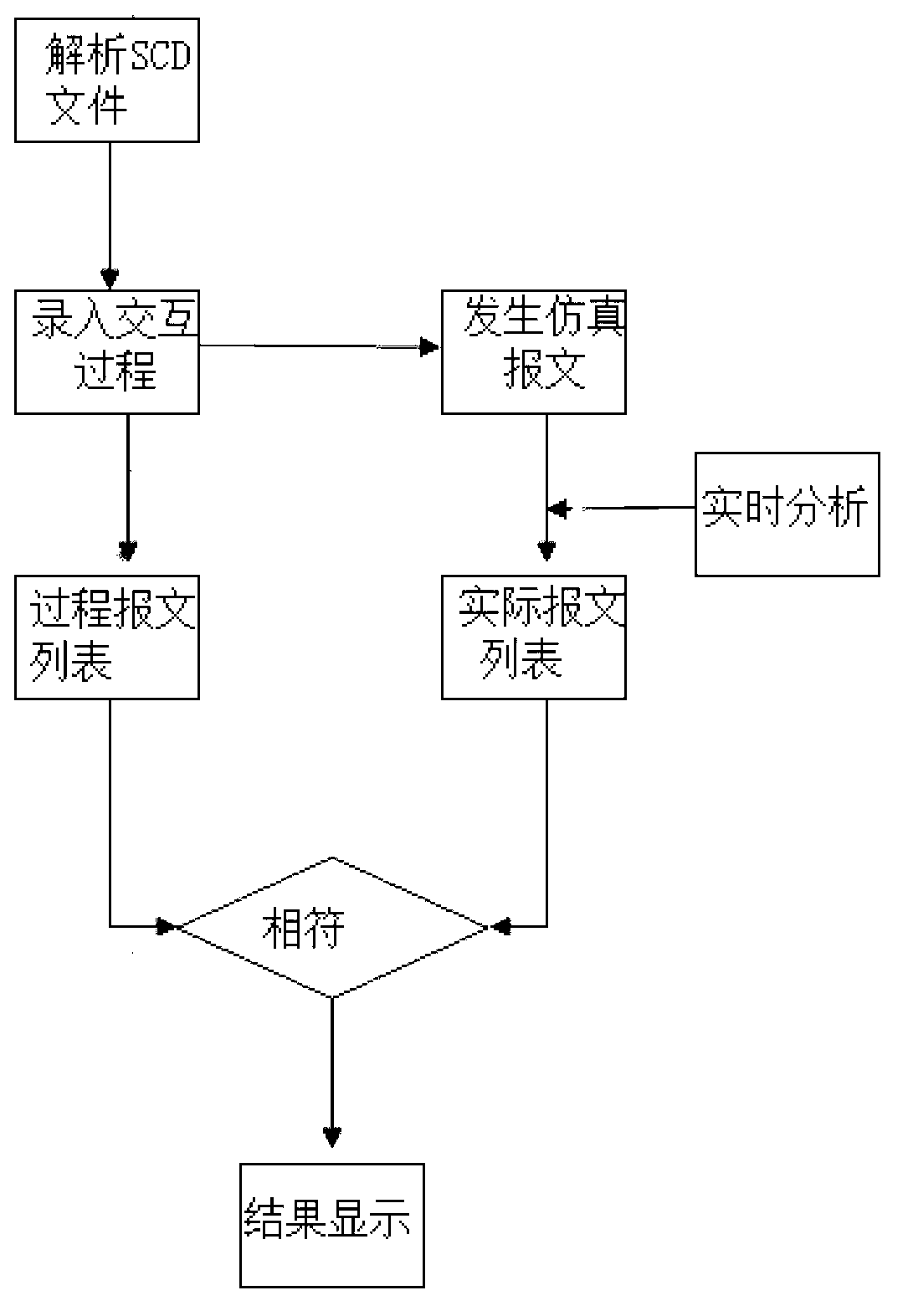

Intelligent substation message simulation testing and association message analysis system and method

ActiveCN103200051AImprove test efficiencyImprove analysis efficiencyData switching networksSmart substationDesign testing

The invention discloses an intelligent substation message simulation testing and association message analysis system and method. The system comprises an SCD (Security Coding Device) file analysis module, a configuration reading module, a template and case management module, an intelligent device interface simulation module, a message recording module and a user interface module, wherein the SCD file analysis module is used for analyzing the configuration descriptive SCD files of a substation; the configuration reading module is used for extracting basic information required by cases of relevant tests; the template and case management module is used for collecting and managing test cases and standard response templates aiming at the test cases; the intelligent device interface simulation module simulates and sends relevant messages accordant with the IEC61850 standard; the message recording module is used for capturing or responding to the sent messages and generated events and alarming; and the user interface module is used for collecting the test cases and the templates and displaying analysis results. According to the invention, artificial intelligence is introduced in rapid analysis on results through a template method, the message simulation capability of the system is used for flexibly designing test cases, intelligently recognizing and realizing test conditions, thus greatly improving the test and analysis efficiency and accuracy.

Owner:STATE GRID CORP OF CHINA +1

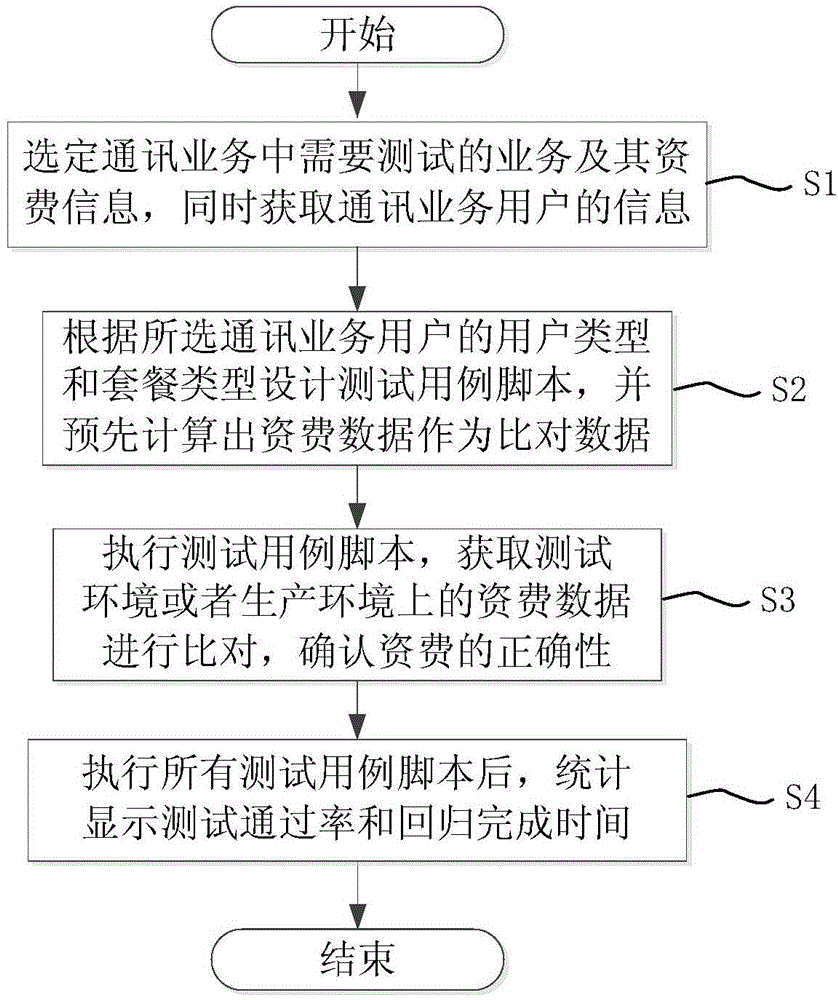

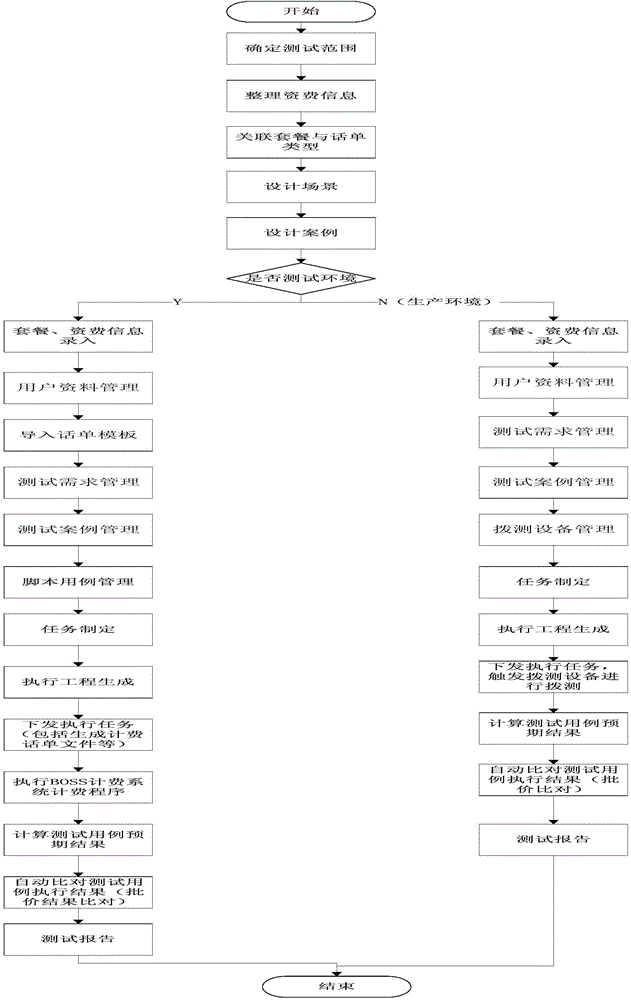

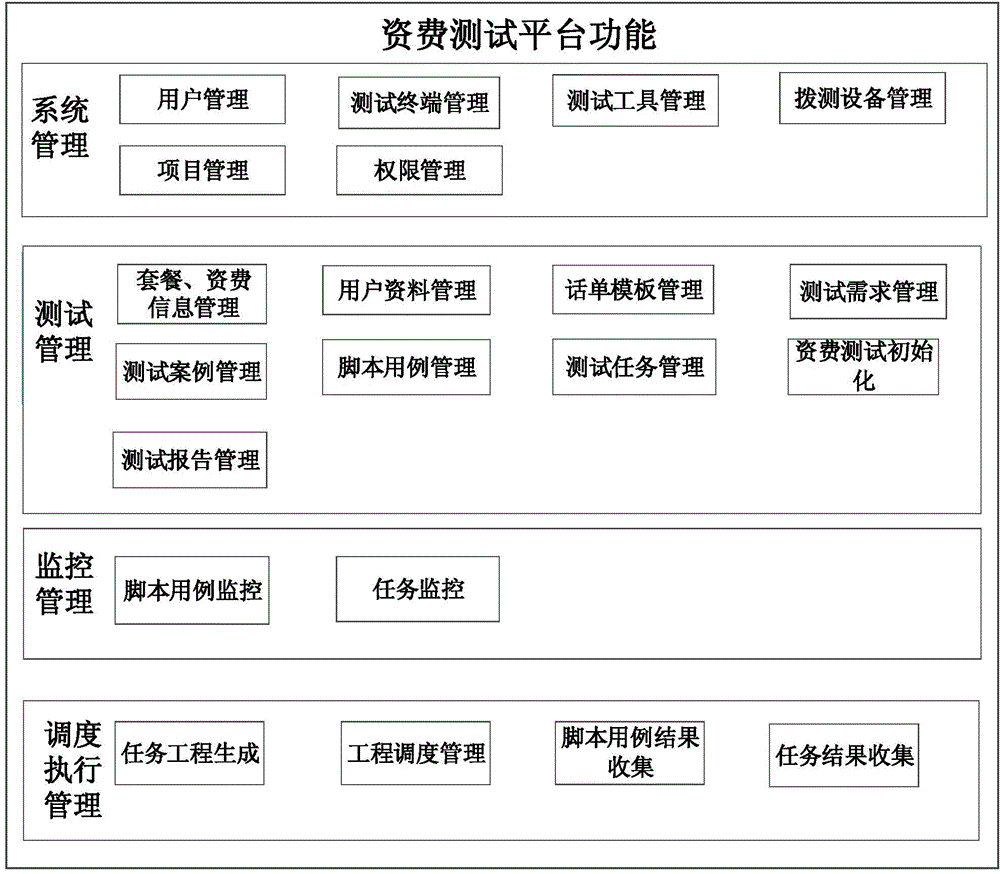

Method for automatically testing communication service expense

ActiveCN104468259ATariff automation test implementationIncrease flexibilityMetering/charging/biilling arrangementsComputer hardwareCompletion time

The invention discloses a method for automatically testing communication service expense. The method includes the following steps: (a) selecting services needing to be tested in communication services and expense information of the services, and meanwhile obtaining information of users of the communication services; (b) designing testing case scripts according to user types and service types of the users of the selected communication services, and pre-calculating expense data which serve as comparison data; (c) executing the testing case scripts, obtaining expense data in the testing environment or the production environment for comparison, and affirming the correctness of the expense; (d) after all the testing case scripts are executed, carrying out statistics and displaying on the testing passing rate and regression completion time. According to the method, the testing case scripts are designed according to the selected user types and the selected service types, the expanse data are pre-calculated to serve as the comparison data, and therefore automatic testing of the expanse is achieved; the method can be suitable for testing the expense of the rapidly-updated services; meanwhile, automatic regression execution can be easily carried out on repeated testing, and the testing labor and the testing cost are greatly reduced.

Owner:SHANGHAI SNC NET INFORMATION TECH CO LTD

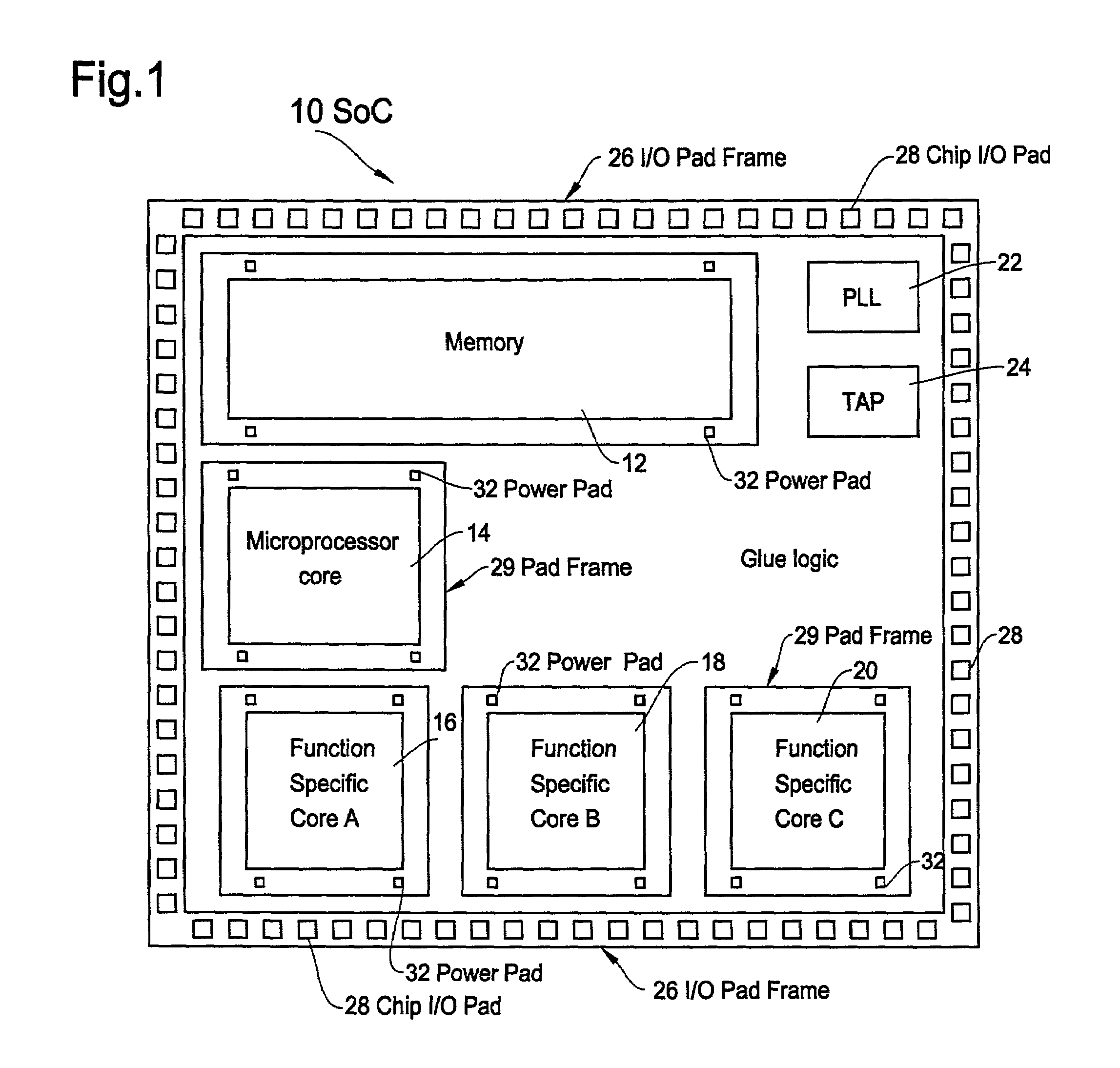

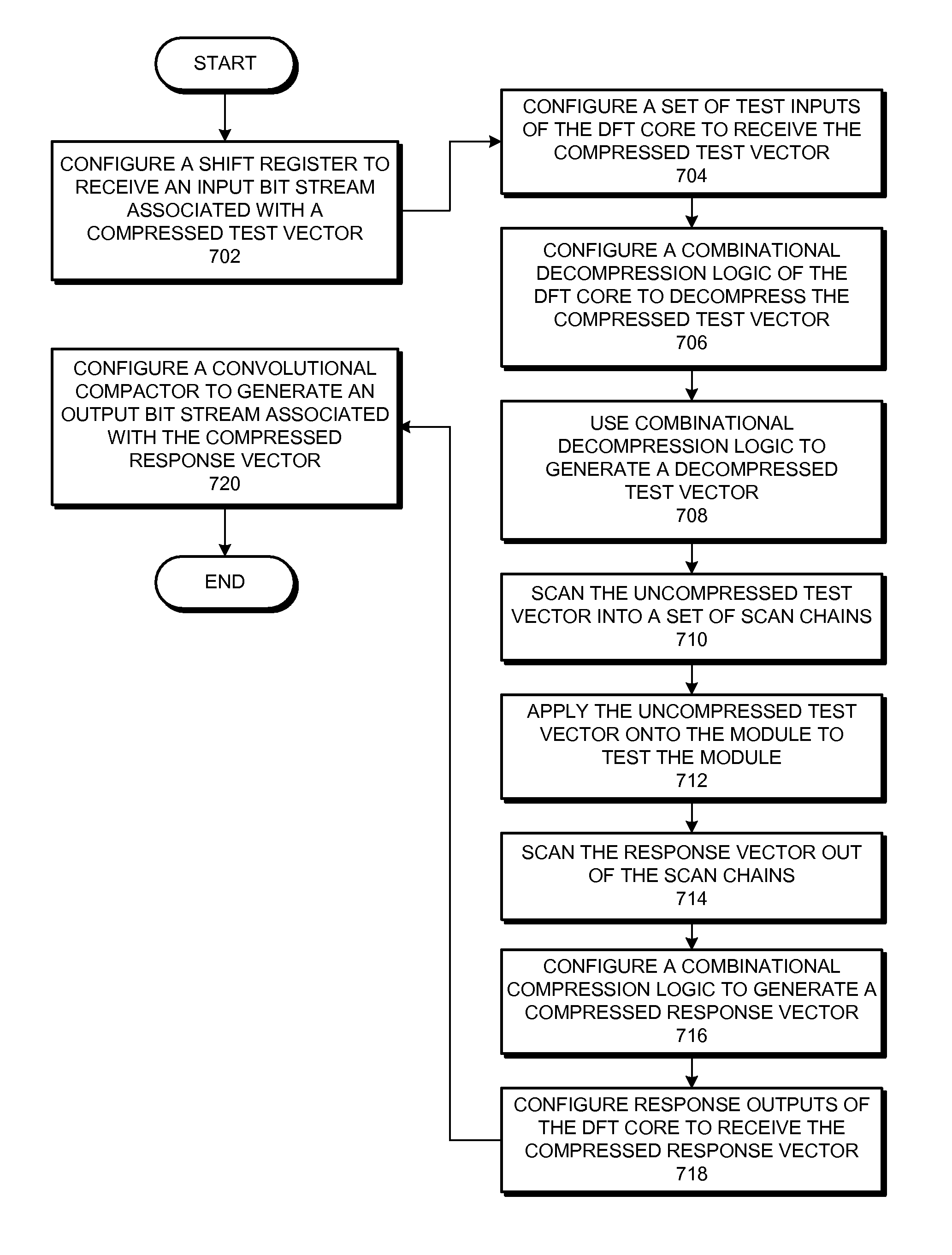

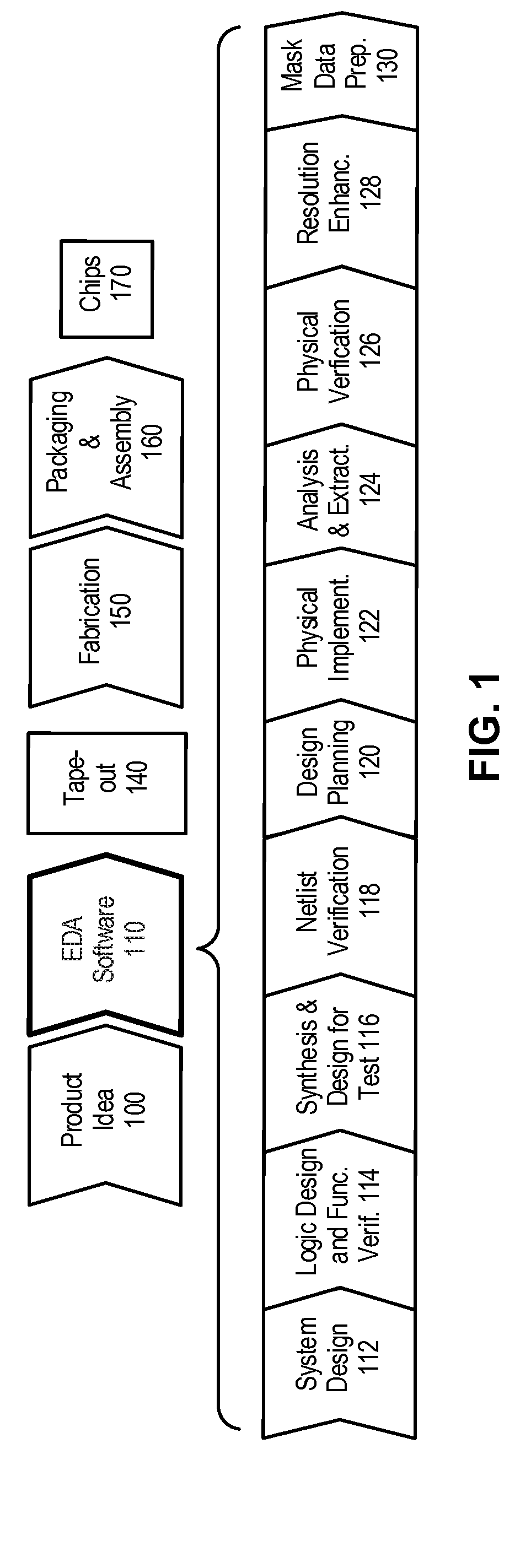

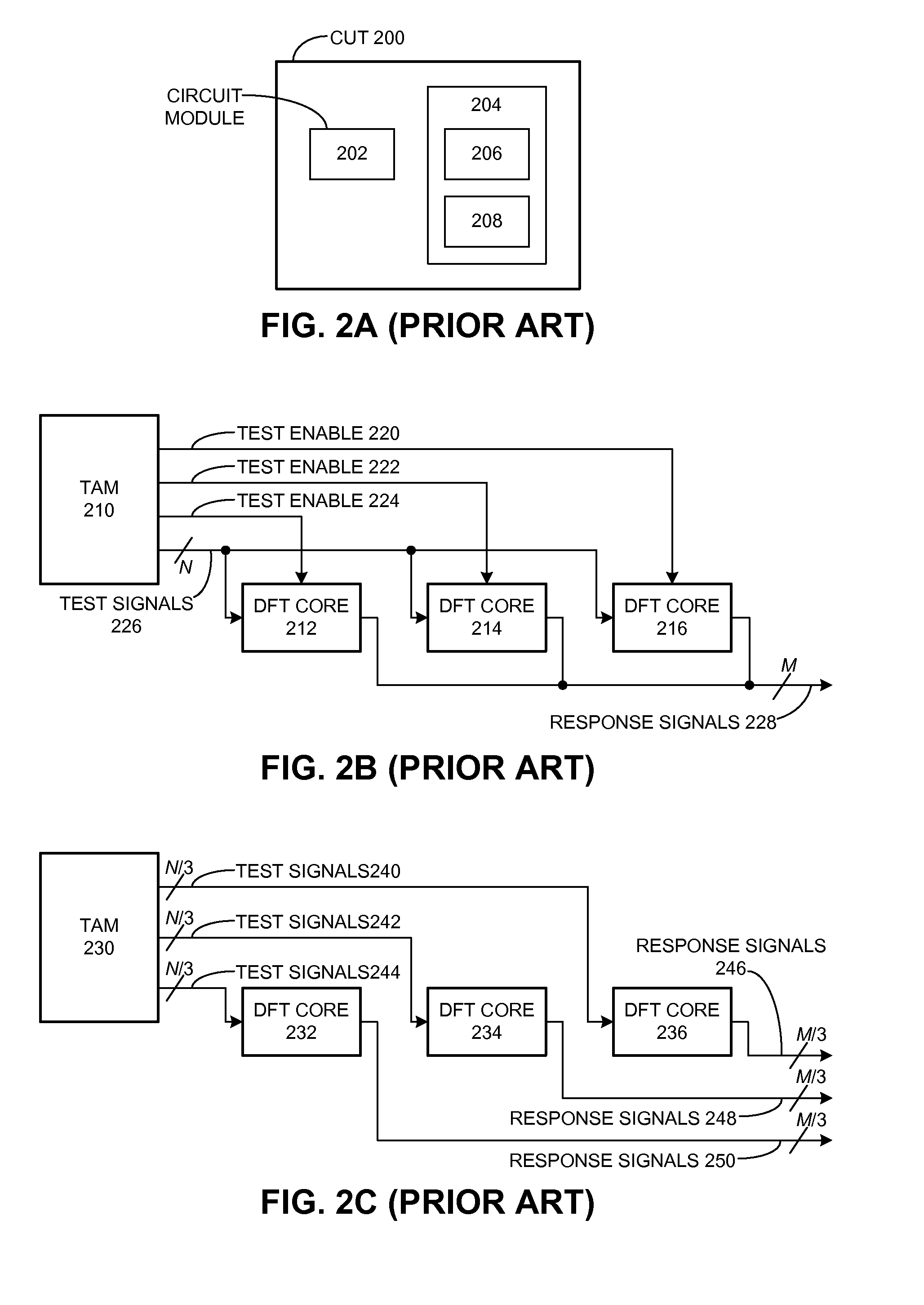

Implementing hierarchical design-for-test logic for modular circuit design

ActiveUS8065651B2Reduce dataReduce testingElectronic circuit testingDetecting faulty computer hardwareDesign testingControl signal

Embodiments of the present invention provide methods and apparatuses for implementing hierarchical design-for-test (DFT) logic on a circuit. The hierarchical DFT logic implements DFT circuitry that can be dedicated to a module, and which can configure DFT circuitry for multiple modules to share a sequential input signal and / or to share a sequential output signal. During operation, the DFT circuitry for a first module can propagate a bit sequence from the sequential input signal to the DFT circuitry of a second module, such that the bit sequence can include a set of control signal values for controlling the DFT circuitry, and can include compressed test vectors for testing the modules. Furthermore, the DFT circuitry for the second module can generate a sequential response signal, which combines the compressed response vectors from the second module and a sequential response signal from the DFT circuitry of the first module.

Owner:SYNOPSYS INC