Patents

Literature

351 results about "Register allocation" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

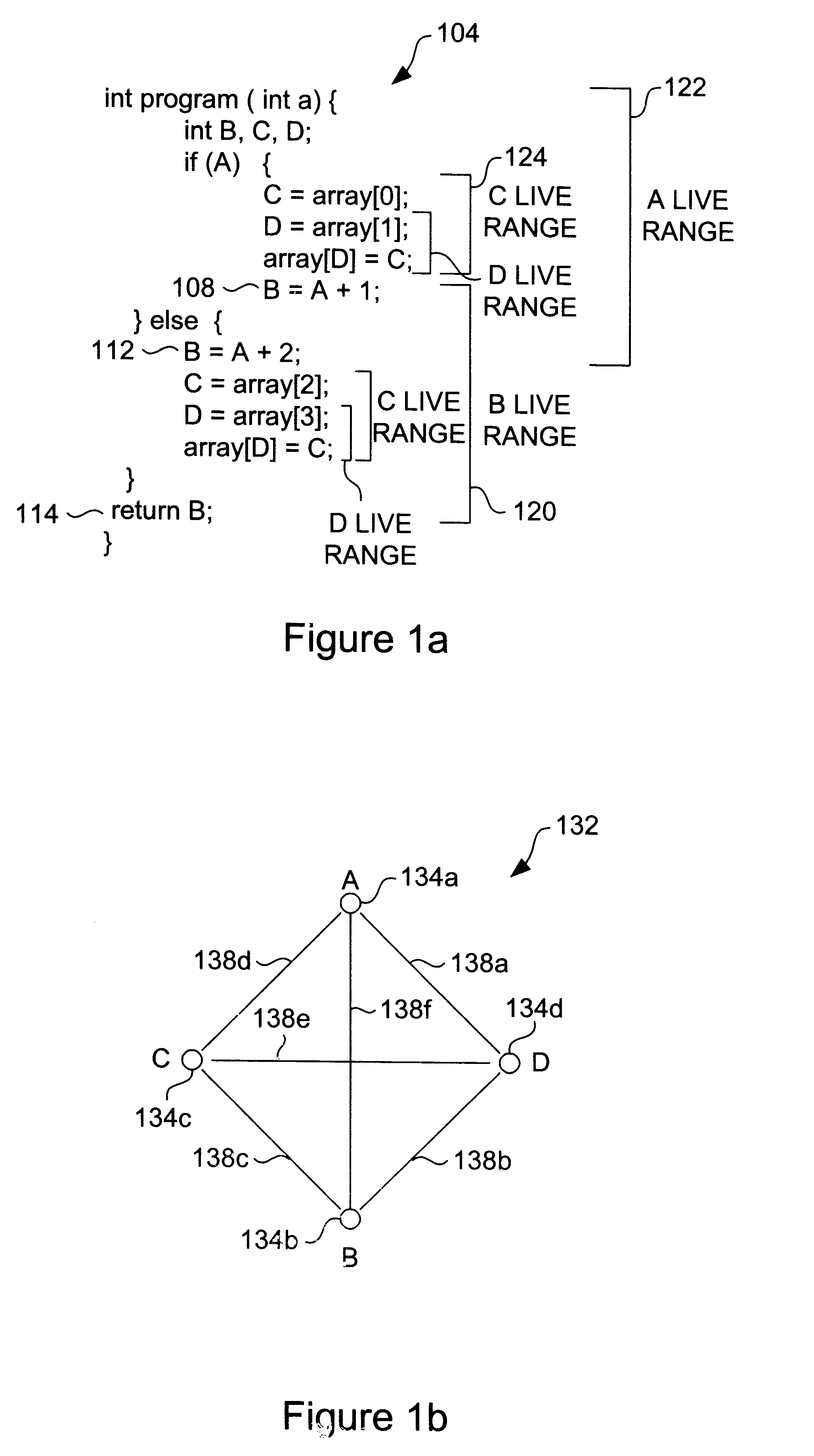

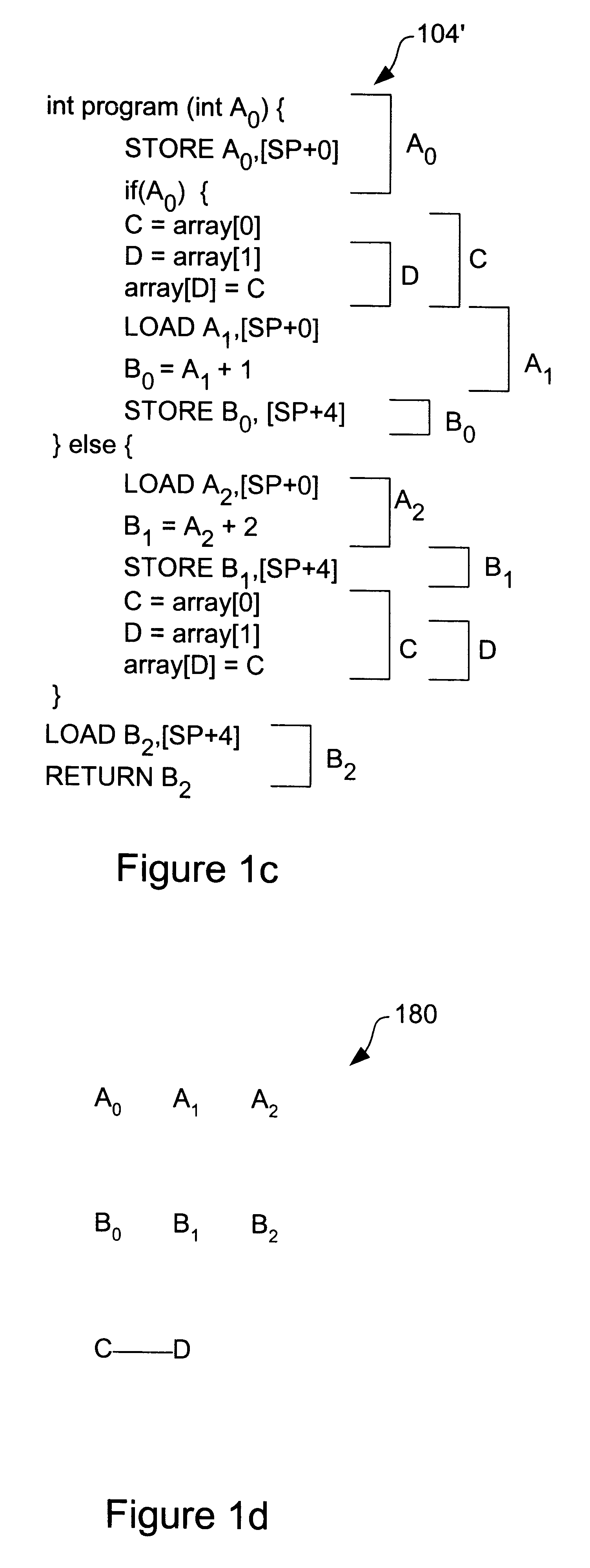

In compiler optimization, register allocation is the process of assigning a large number of target program variables onto a small number of CPU registers. Register allocation can happen over a basic block (local register allocation), over a whole function/procedure (global register allocation), or across function boundaries traversed via call-graph (interprocedural register allocation). When done per function/procedure the calling convention may require insertion of save/restore around each call-site.

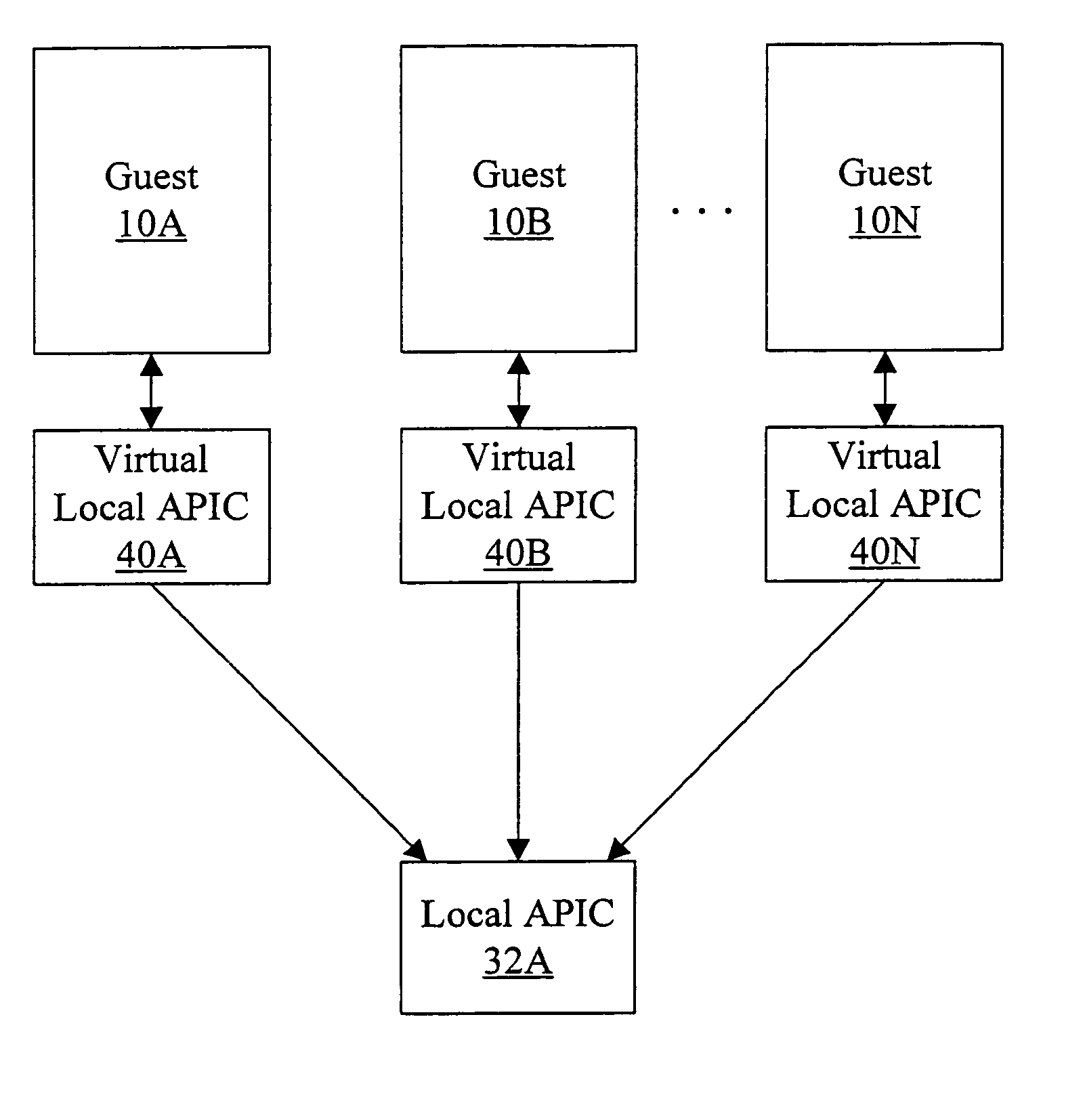

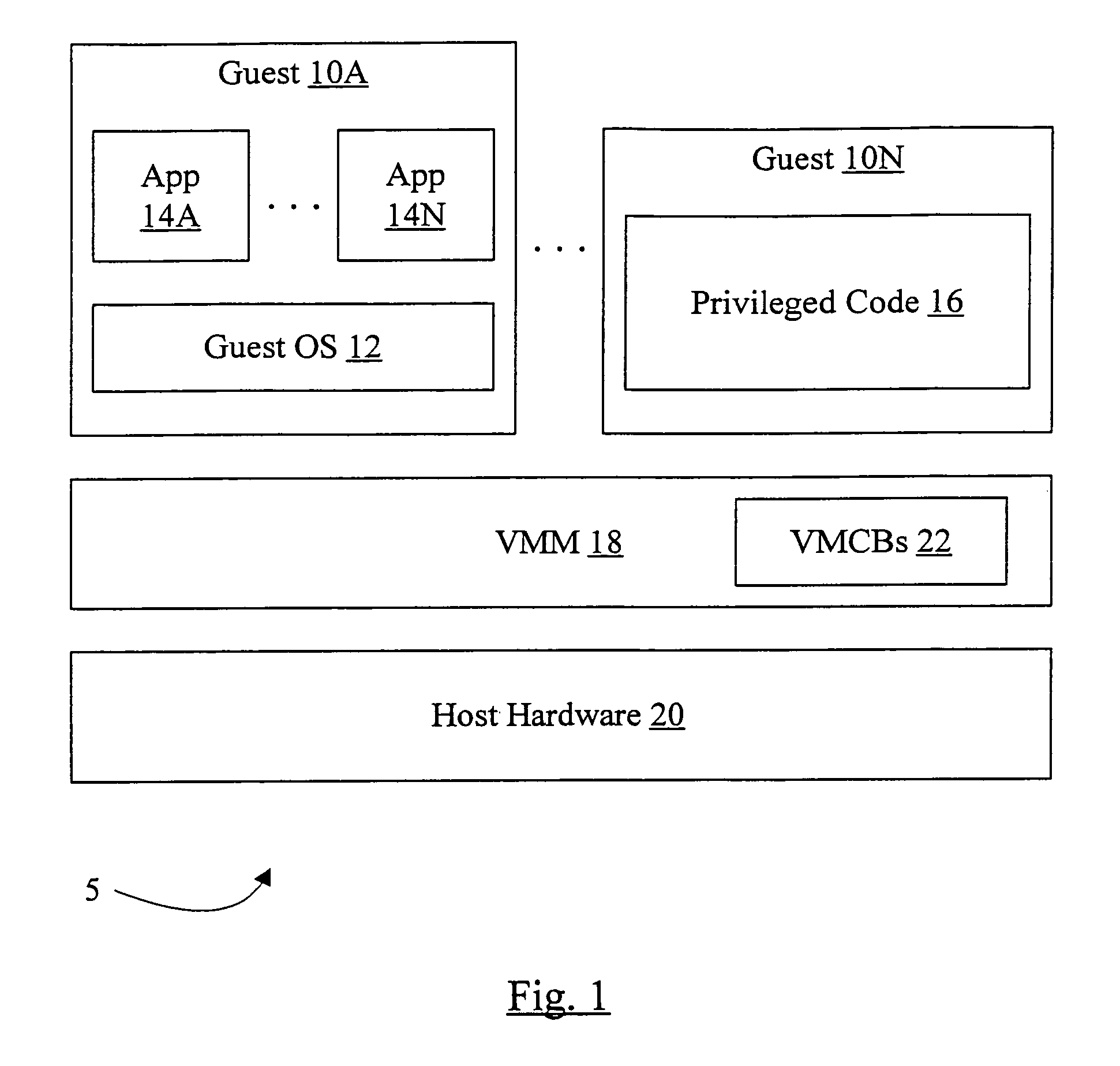

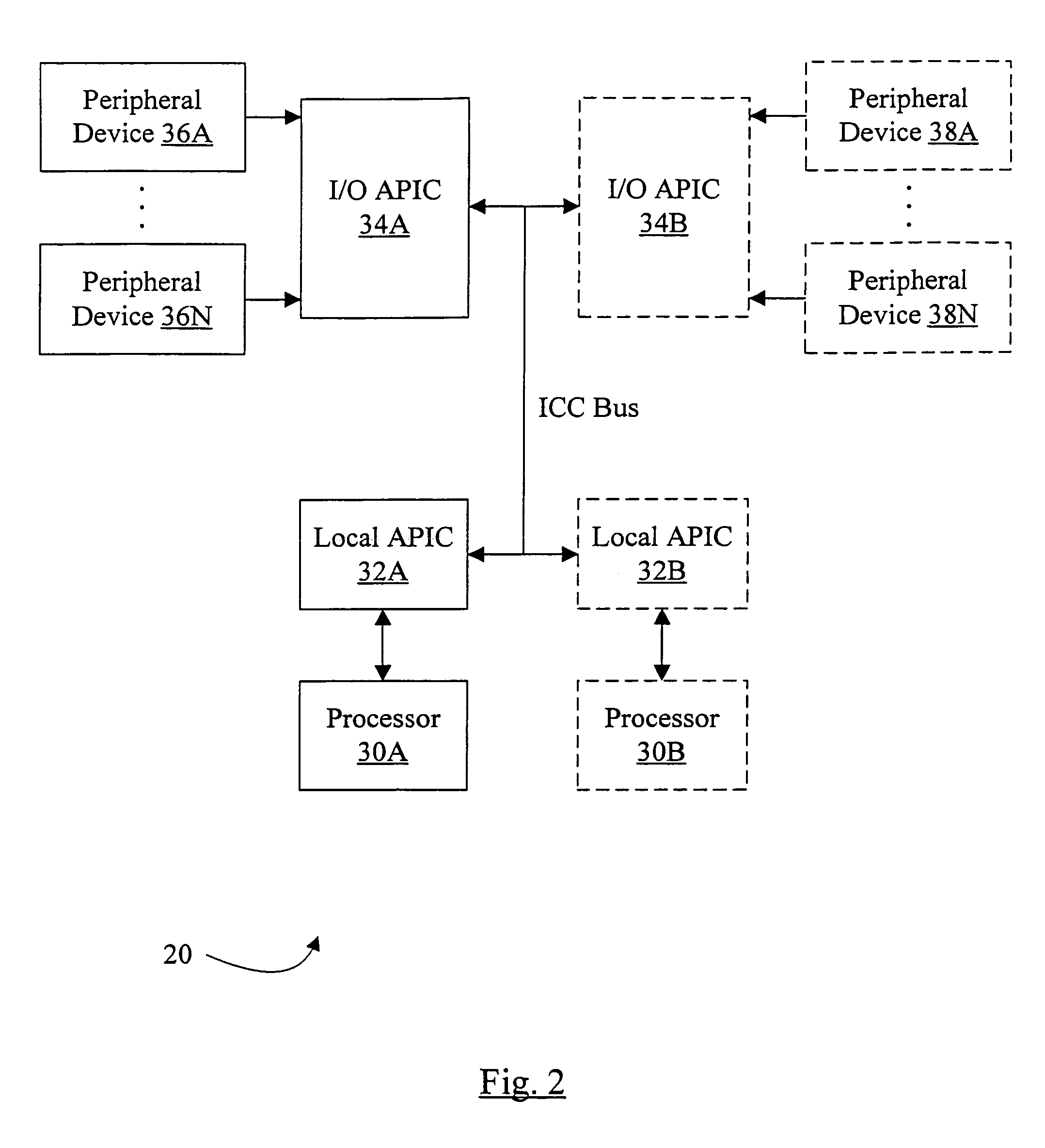

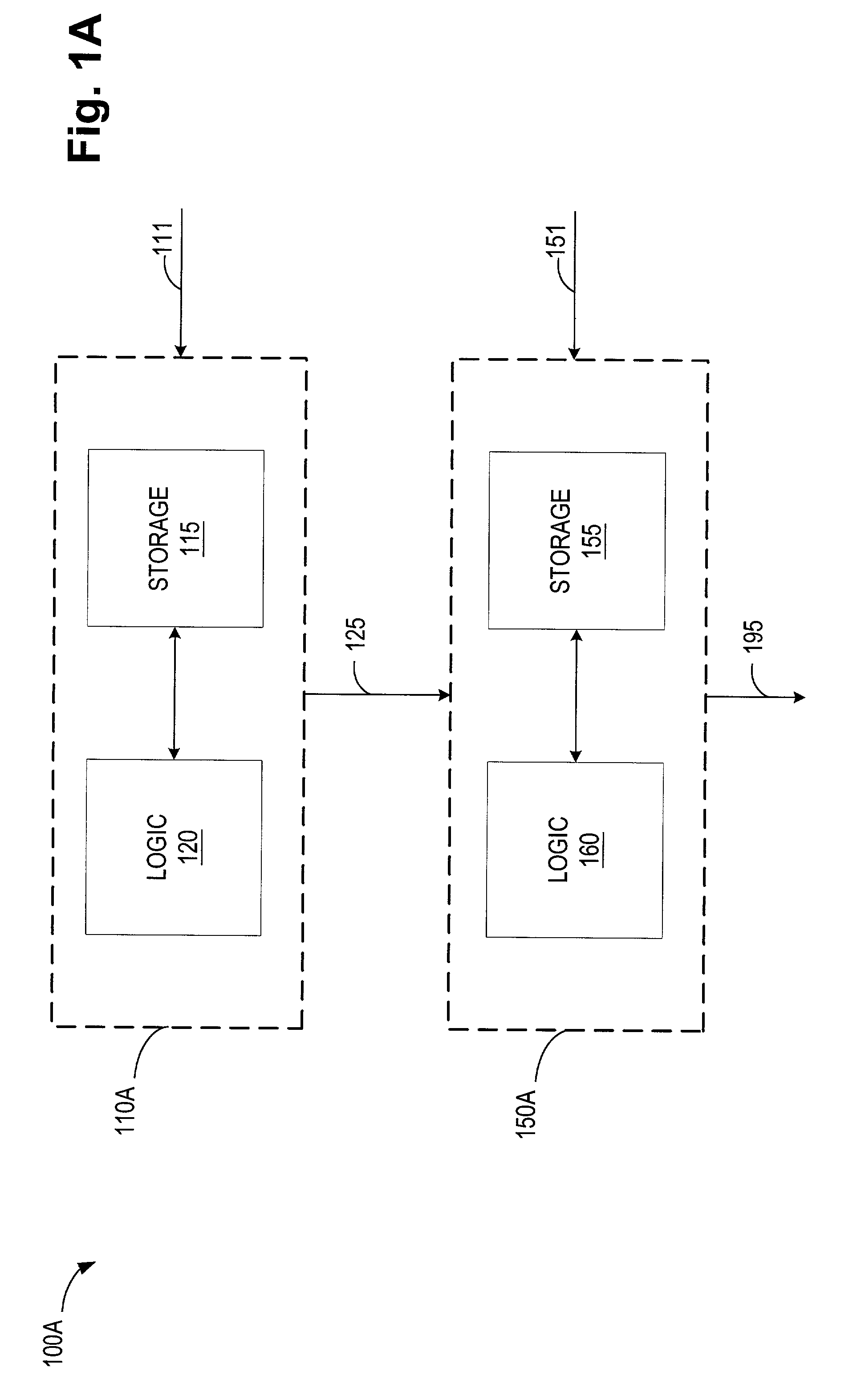

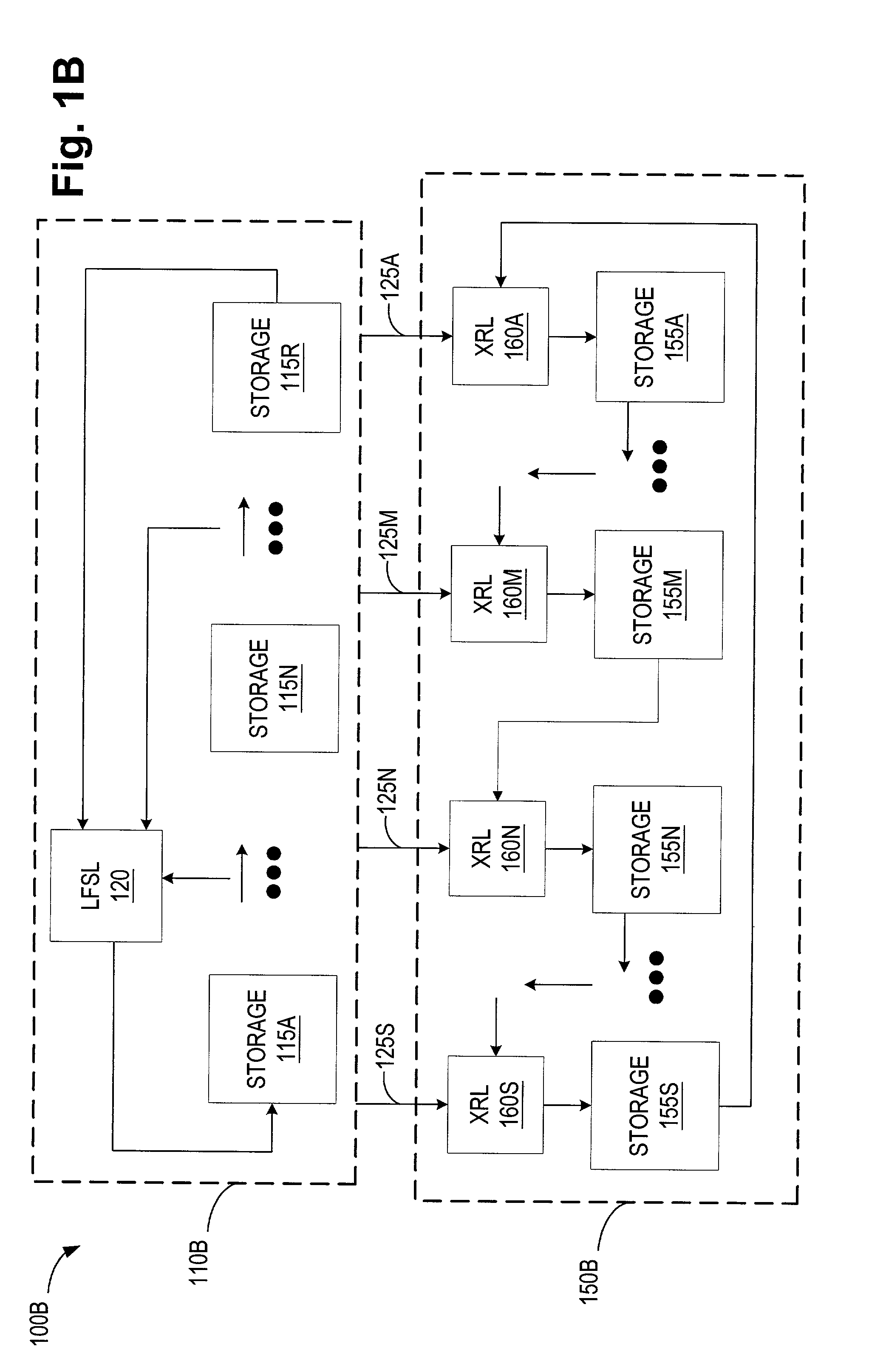

Processor that maintains virtual interrupt state and injects virtual interrupts into virtual machine guests

In one embodiment, a processor comprises one or more registers and a control unit. The registers are configured to store interrupt state describing a virtual interrupt. The control unit is configured to initiate the virtual interrupt responsive to the interrupt state. In another embodiment, a method comprises storing an interrupt state describing a virtual interrupt in a storage area allocated to a guest. A processor initiates the virtual interrupt subsequent to initiating execution of the guest, responsive to the interrupt state. In still another embodiment, a computer accessible medium stores a plurality of instructions comprising instructions which, when executed on a processor in response to a physical interrupt: determine a guest into which a virtual interrupt corresponding to the physical interrupt is to be injected; and store an interrupt state describing the virtual interrupt in a storage area allocated to the guest.

Owner:GLOBALFOUNDRIES US INC

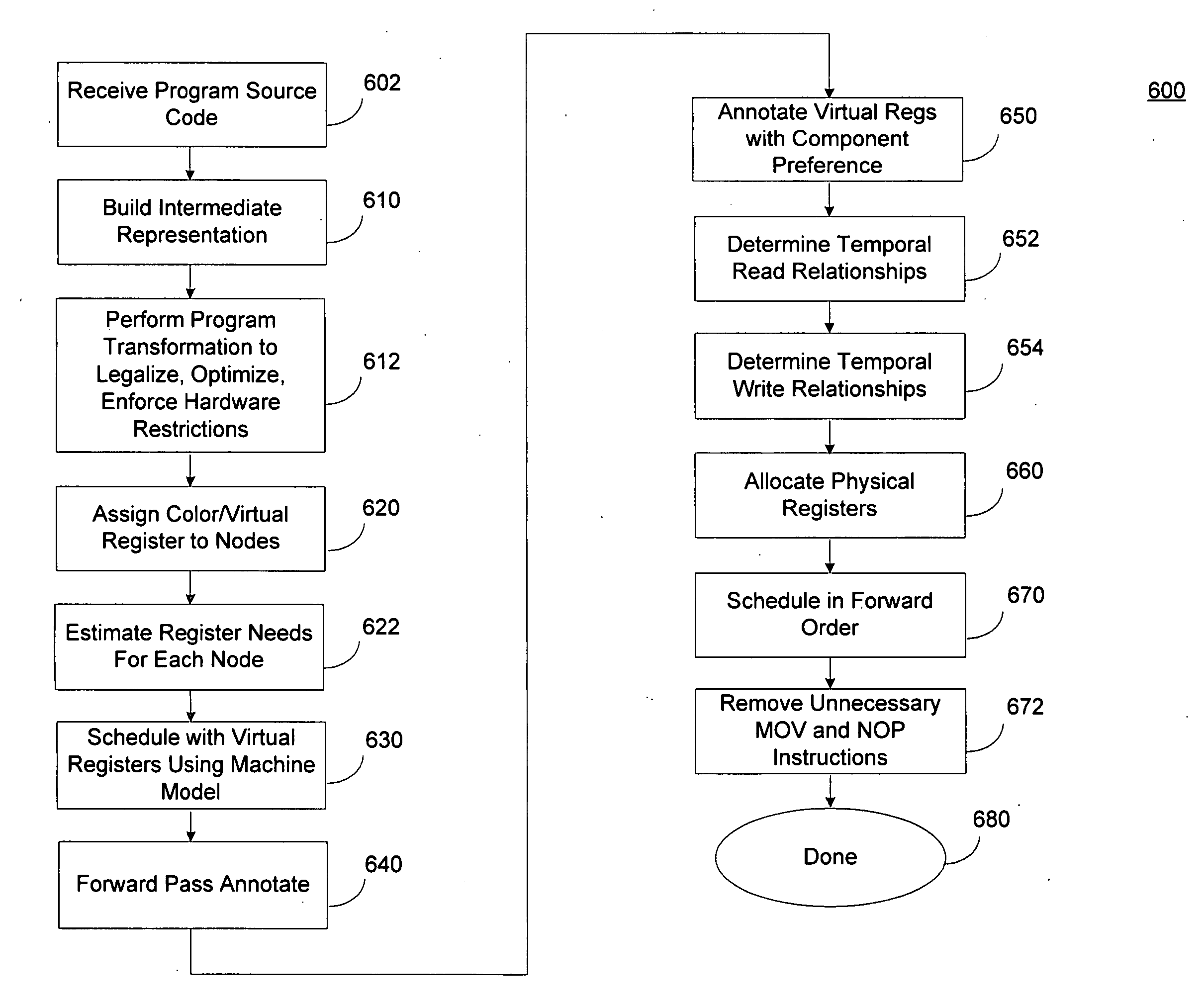

Method and apparatus for register allocation in presence of hardware constraints

ActiveUS20060225061A1Reduce the amount requiredMinimize the numberSoftware engineeringProgram controlRegister allocationParallel computing

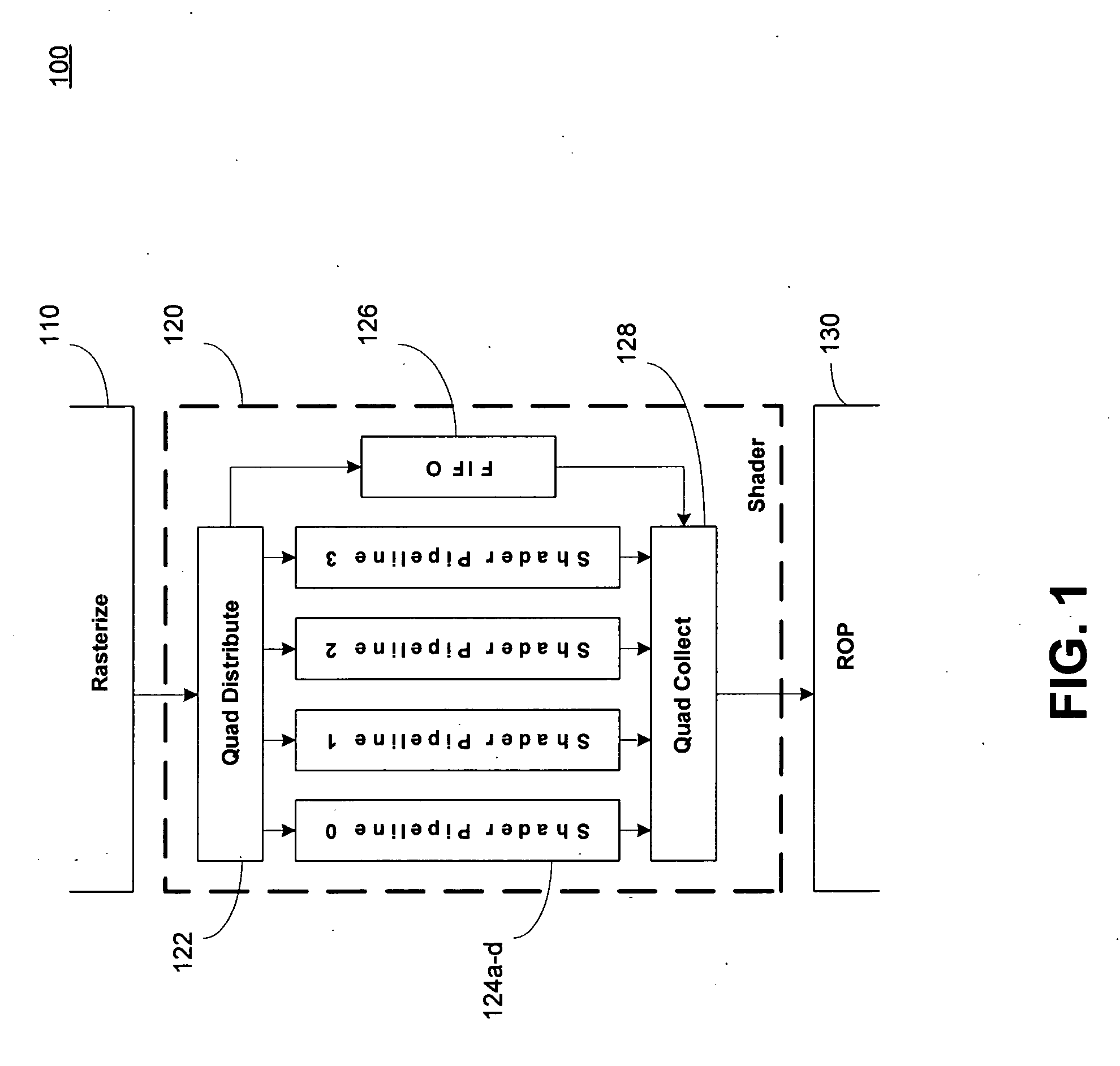

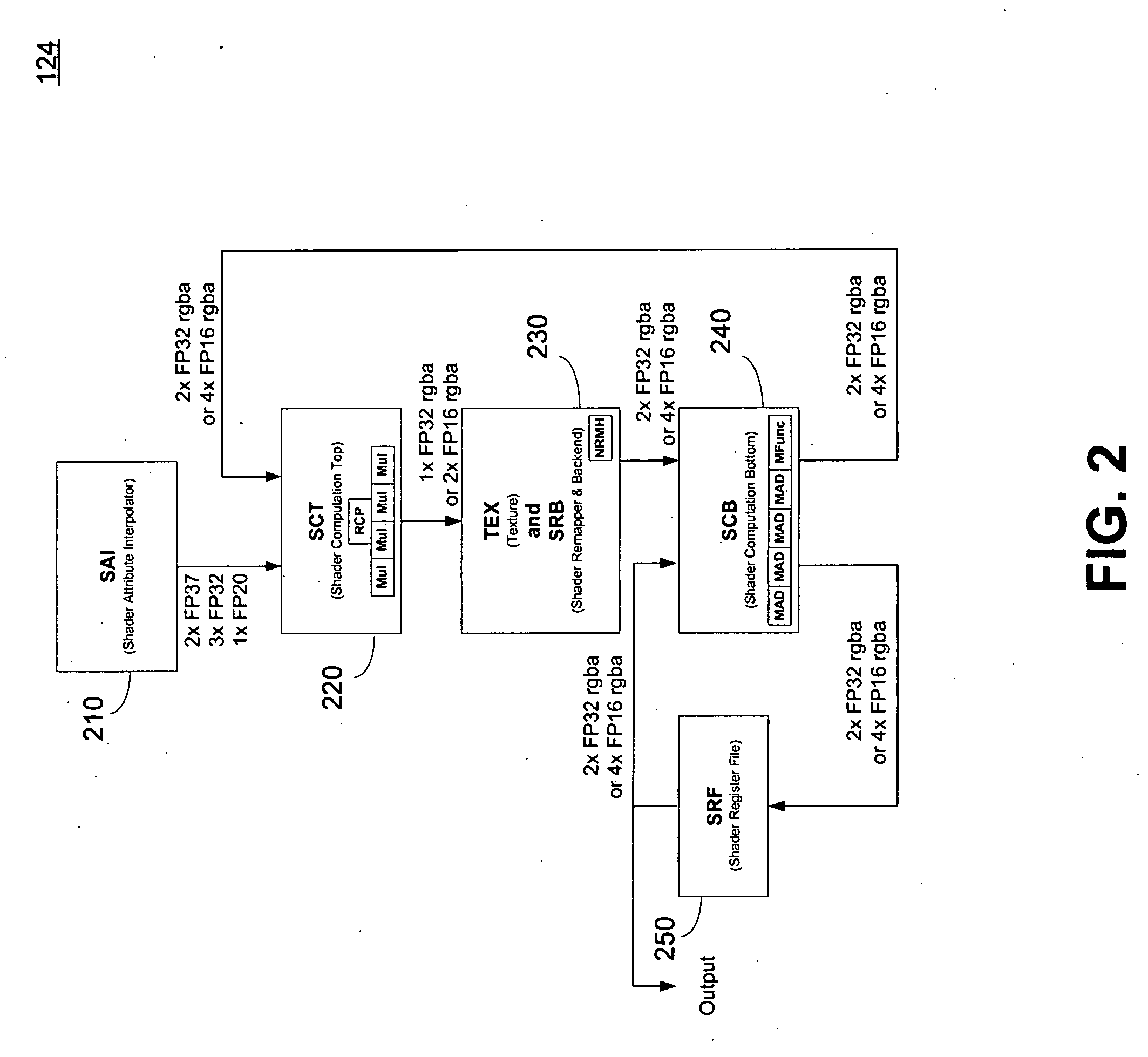

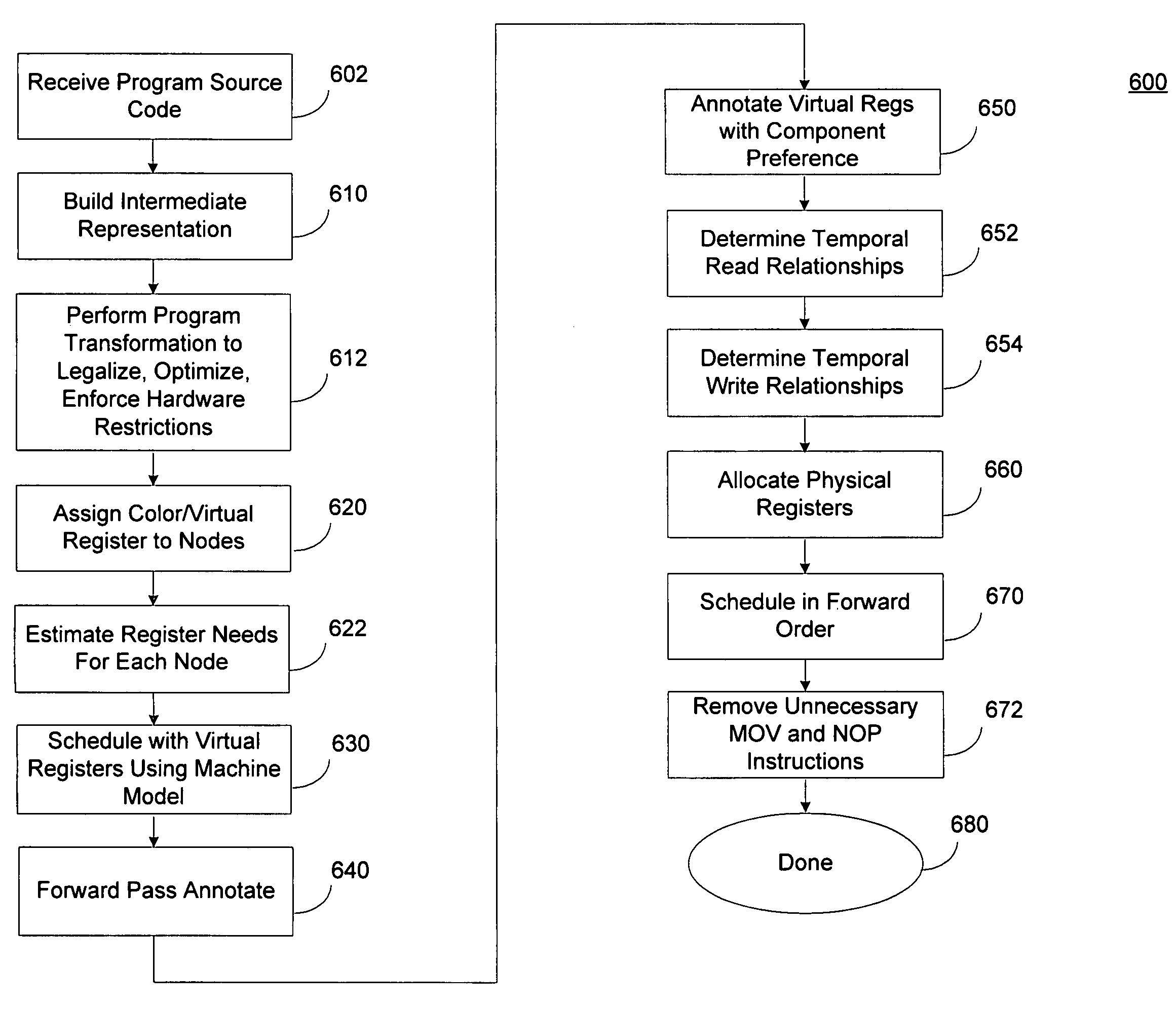

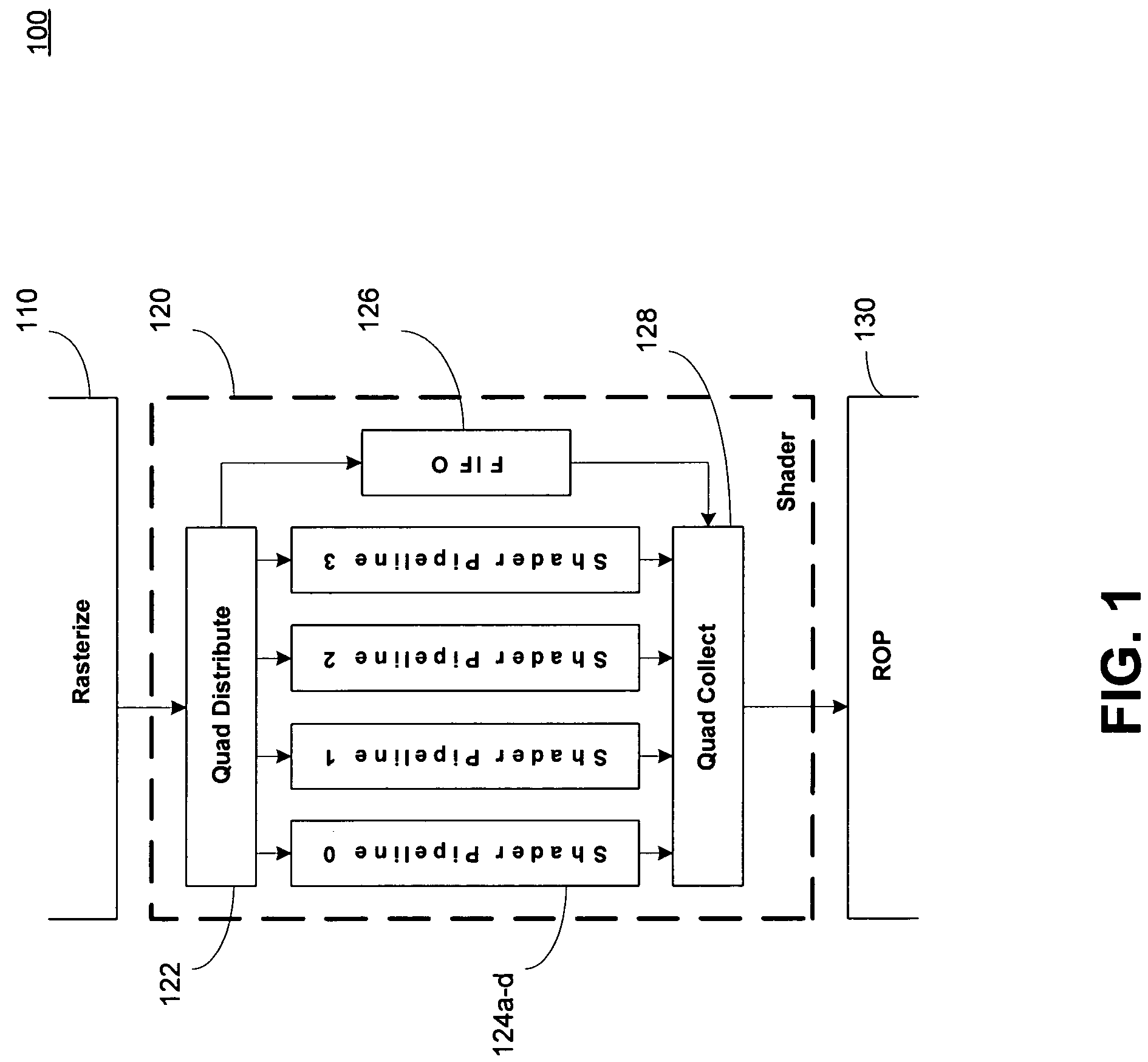

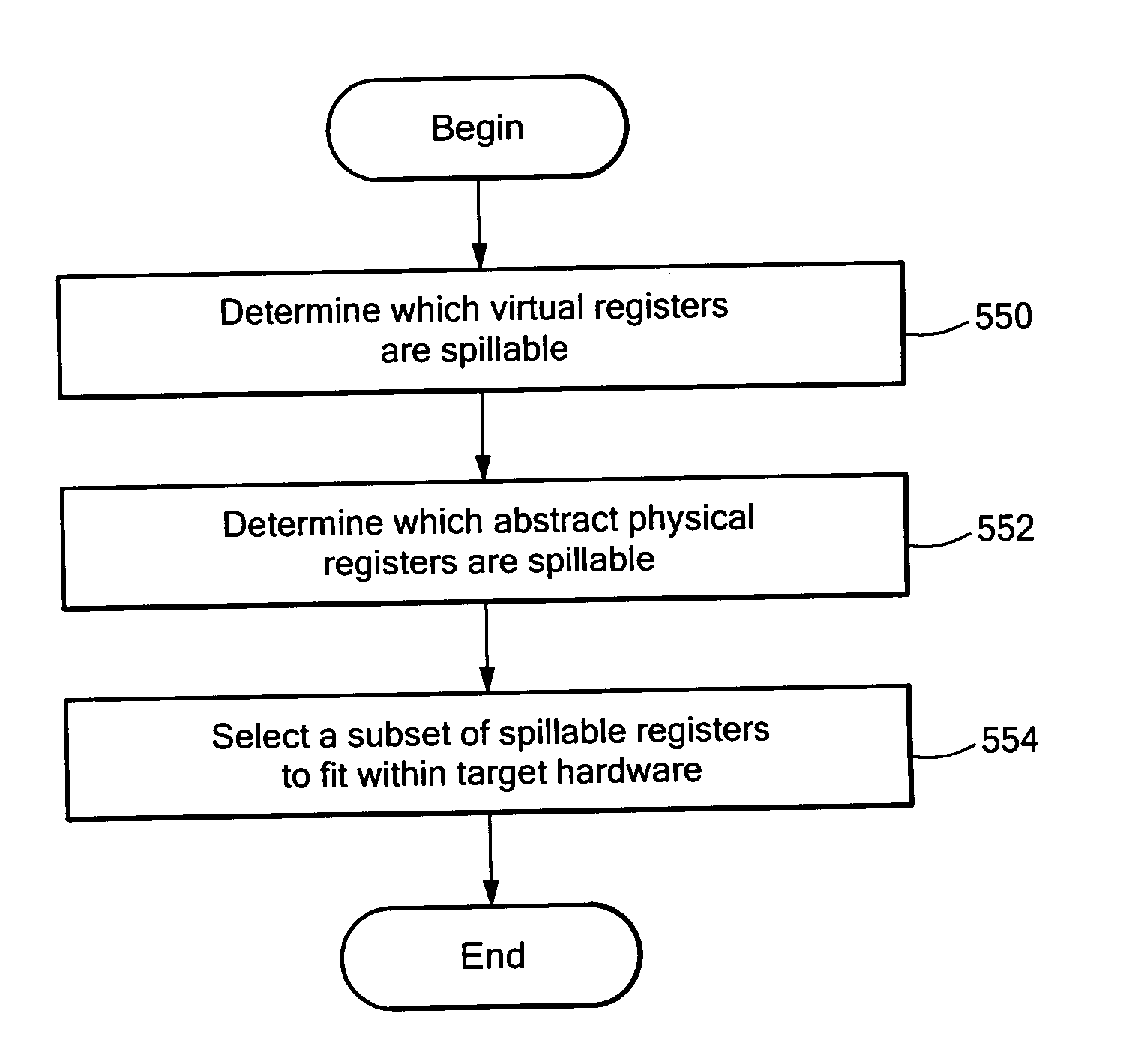

A method and apparatus for optimizing register allocation during scheduling and execution of program code in a hardware environment. The program code can be compiled to optimize execution given predetermined hardware constraints. The hardware constraints can include the number of register read and write operations that can be performed in a given processor pass. The optimizer can initially schedule the program using virtual registers and a goal of minimizing the amount of active registers at any time. The optimizer reschedules the program to assign the virtual registers to actual physical registers in a manner that minimizes the number of processor passes used to execute the program.

Owner:NVIDIA CORP

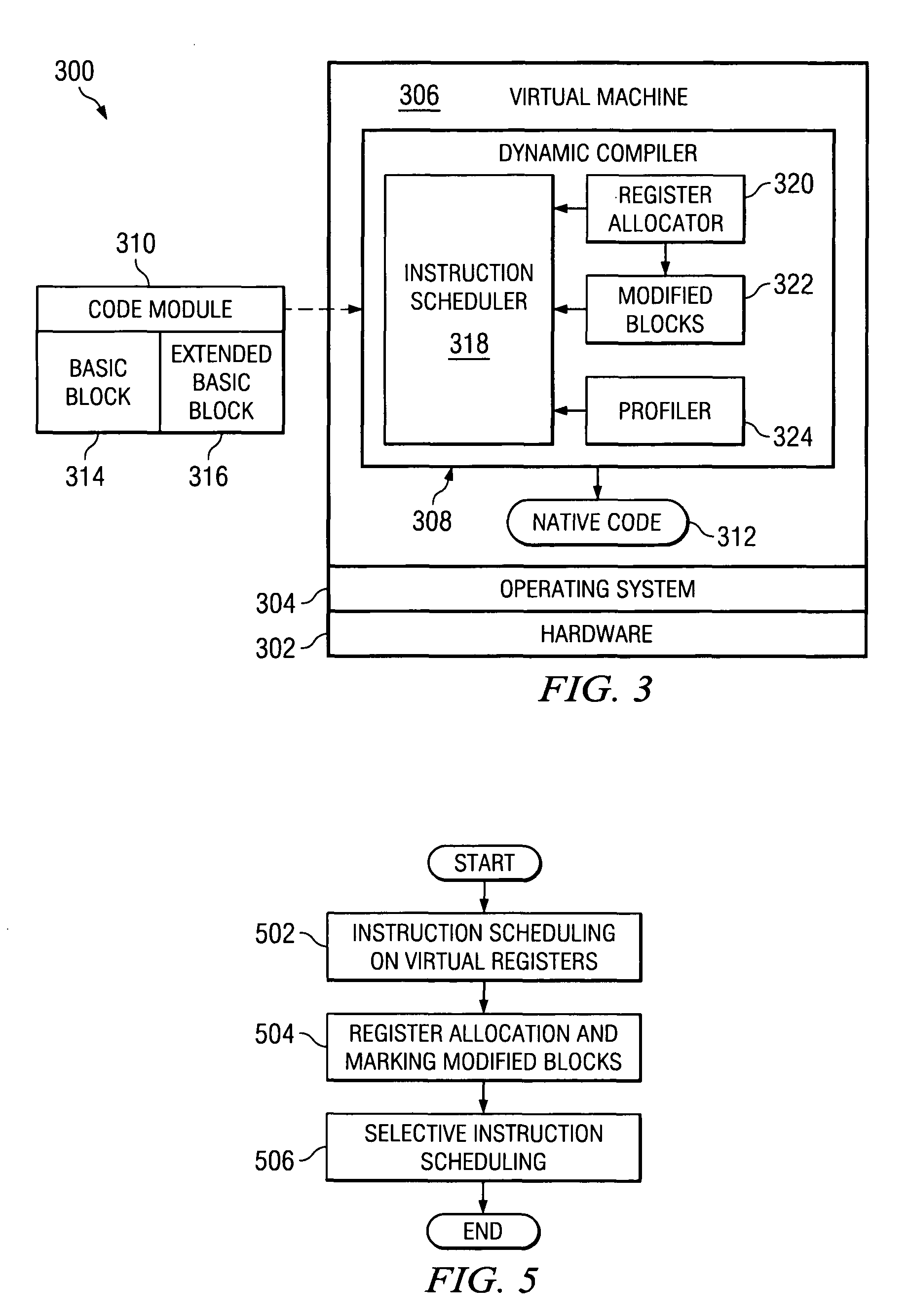

Post-register allocation profile directed instruction scheduling

ActiveUS7770161B2Software engineeringSpecial data processing applicationsRegister allocationProcessor register

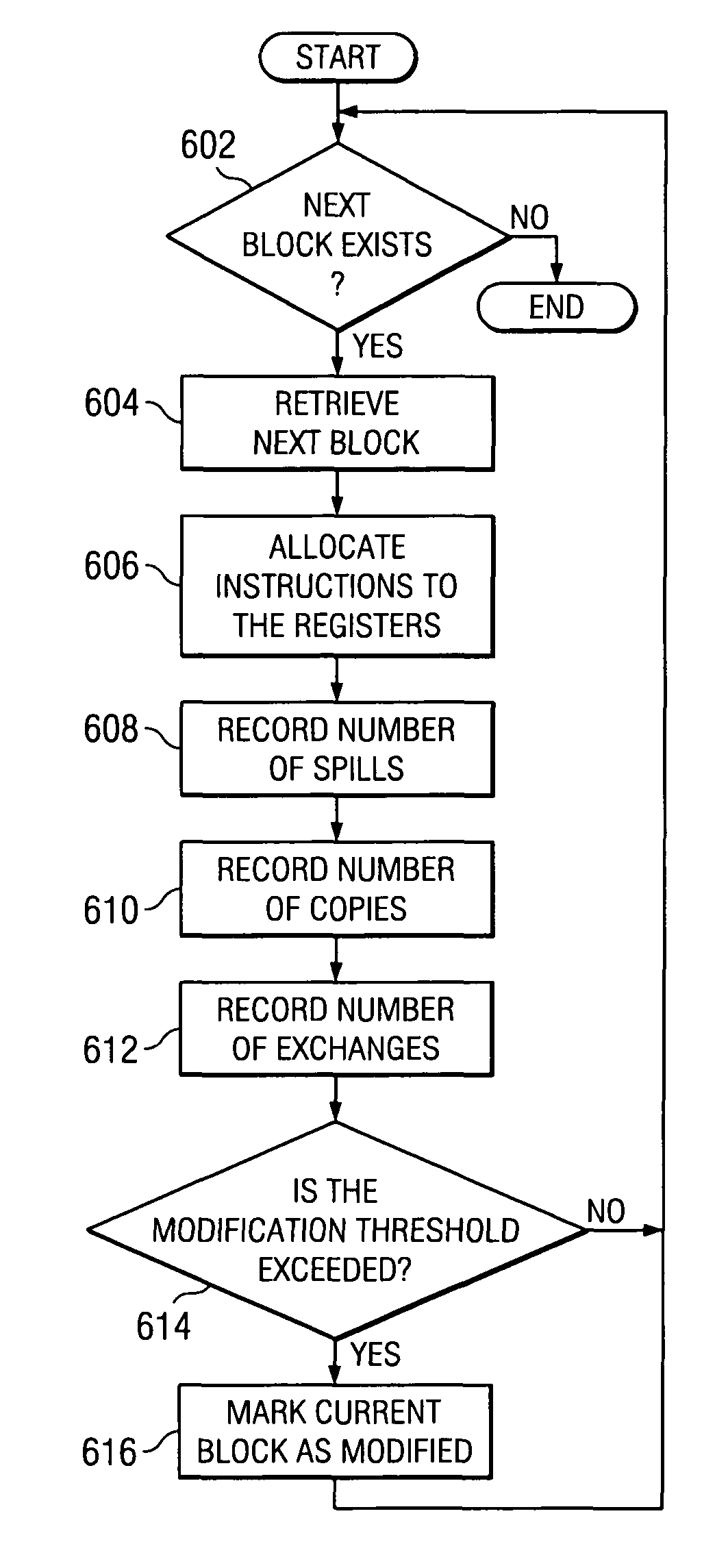

A computer implemented method, system, and computer usable program code for selective instruction scheduling. A determination is made whether a region of code exceeds a modification threshold after performing register allocation on the region of code. The region of code is marked as a modified region of code in response to the determination that the region of code exceeds the modification threshold. A determination is made whether the region of code exceeds an execution threshold in response to the determination that the region of code is marked as a modified region of code. Post-register allocation instruction scheduling is performed on the region of code in response to the determination that the region of code is marked as a modified region of code and the determination that the region of code exceeds the execution threshold.

Owner:TWITTER INC

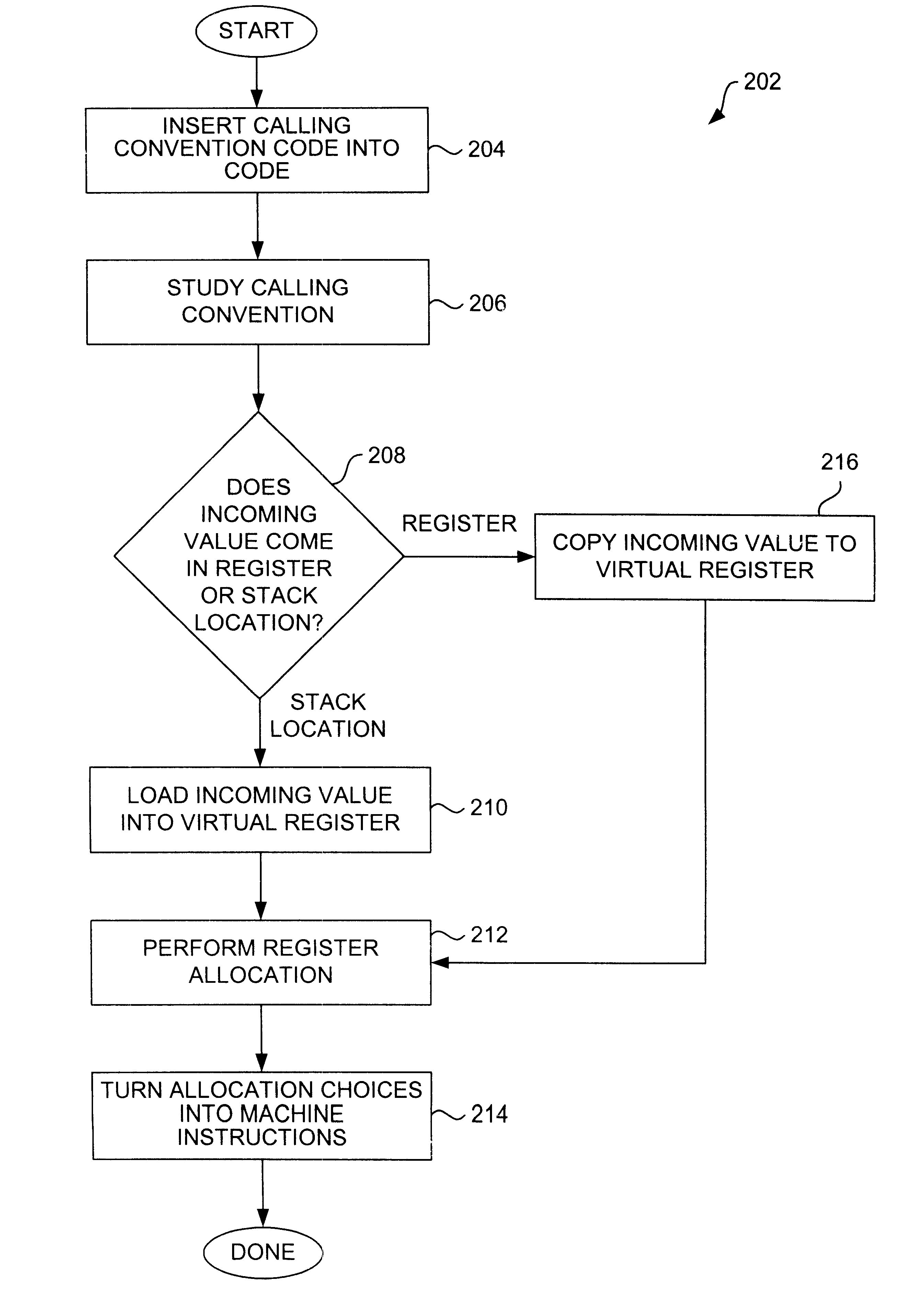

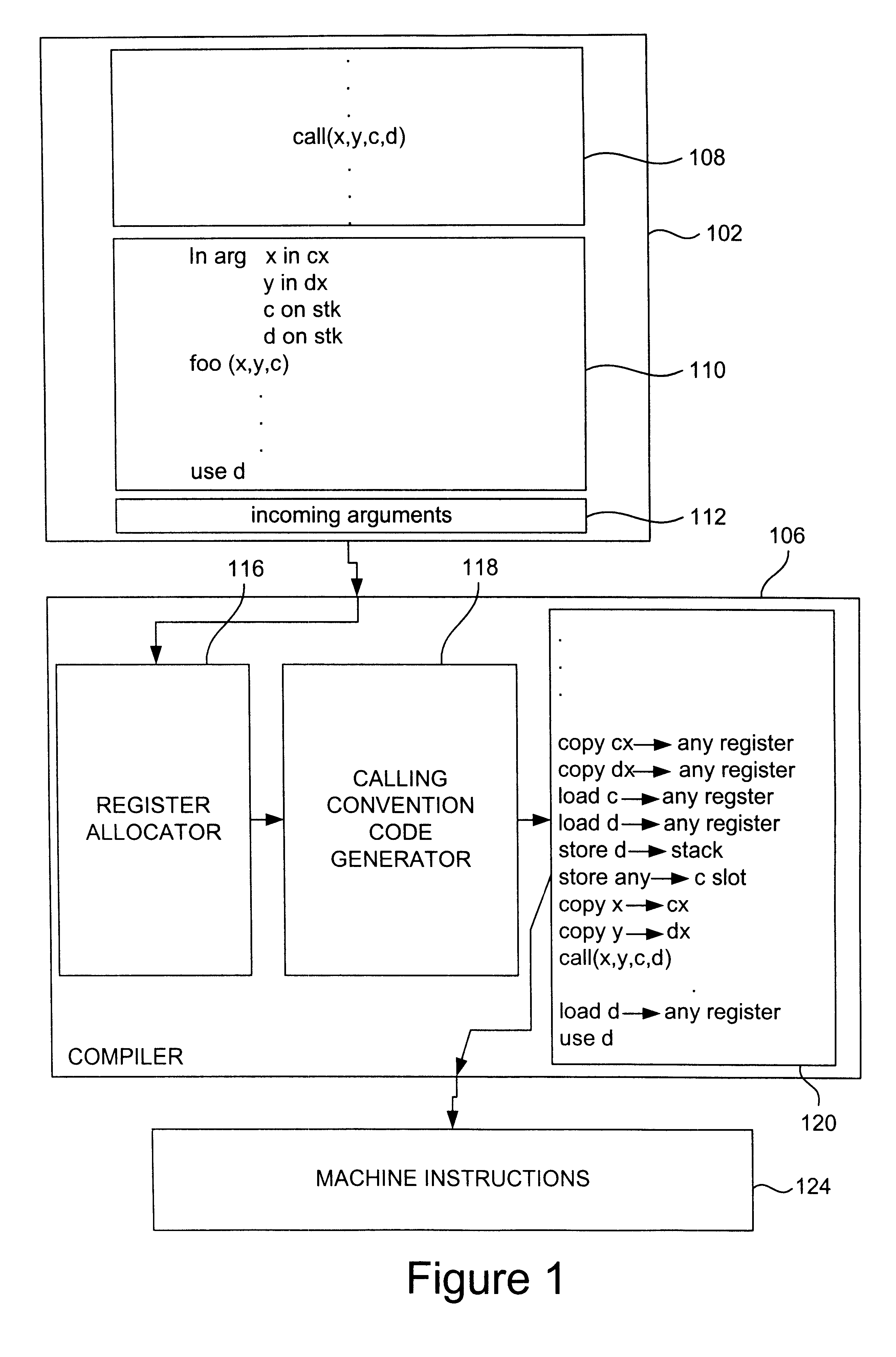

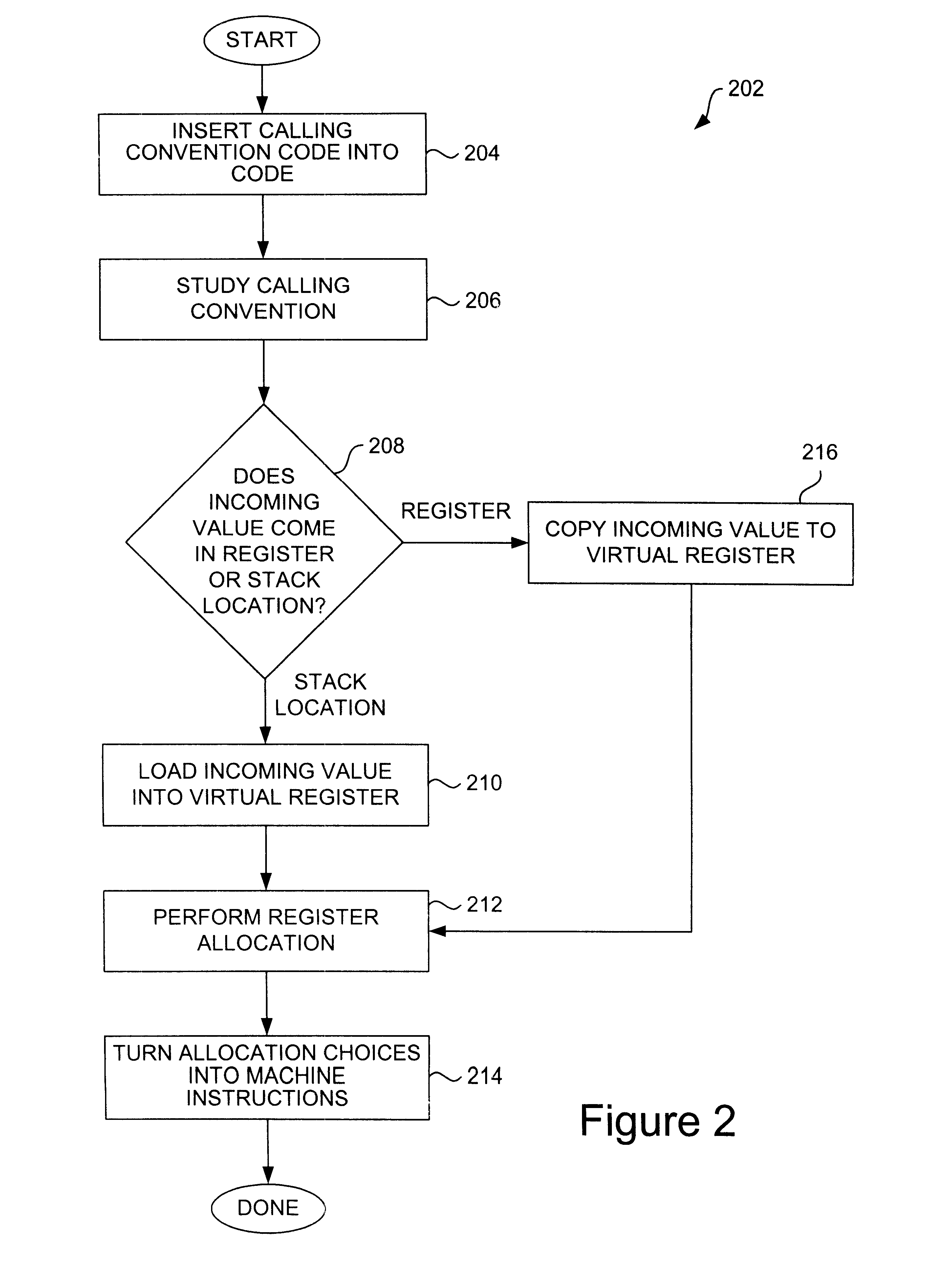

Method and apparatus for building calling convention prolog and epilog code using a register allocator

InactiveUS6408433B1Generate efficientlyEasy to transplantSoftware engineeringProgram controlRegister allocationProcessor register

Methods and apparatus for enabling a register allocator to build a calling convention are disclosed. According to one aspect of the present invention, a computer-implemented method for generating code associated with a calling convention includes obtaining compilable source code, and identifying at least one argument associated with the calling convention. The location of the argument with respect to memory space is described by a register mask. The method also includes performing a register allocation using a register allocator that is arranged to allocate registers. During the register allocation, code associated with the calling convention is produced automatically by the spill-code mechanism in the allocator without requiring the use of a specialized prolog or epilog code generator.

Owner:ORACLE INT CORP

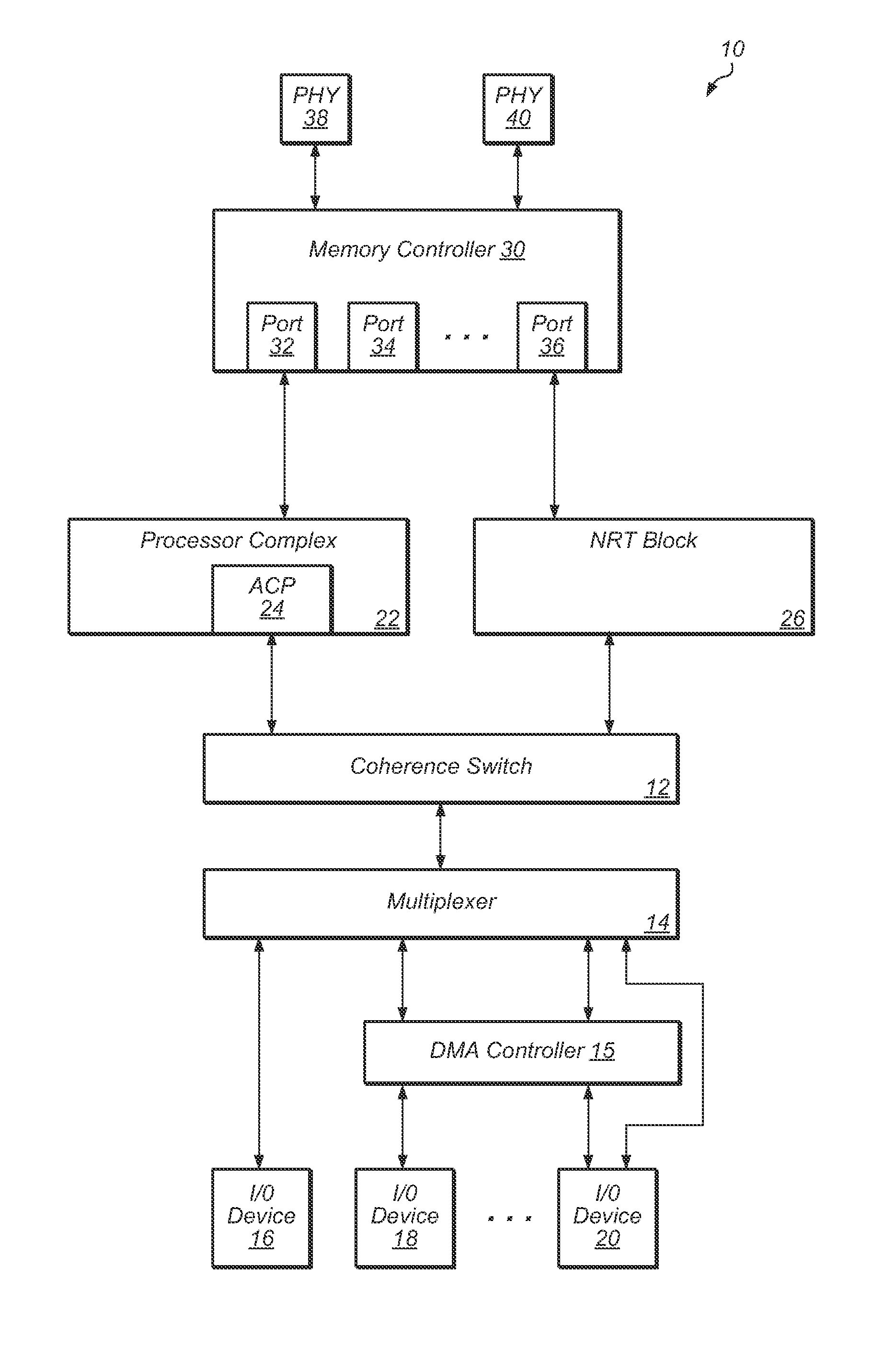

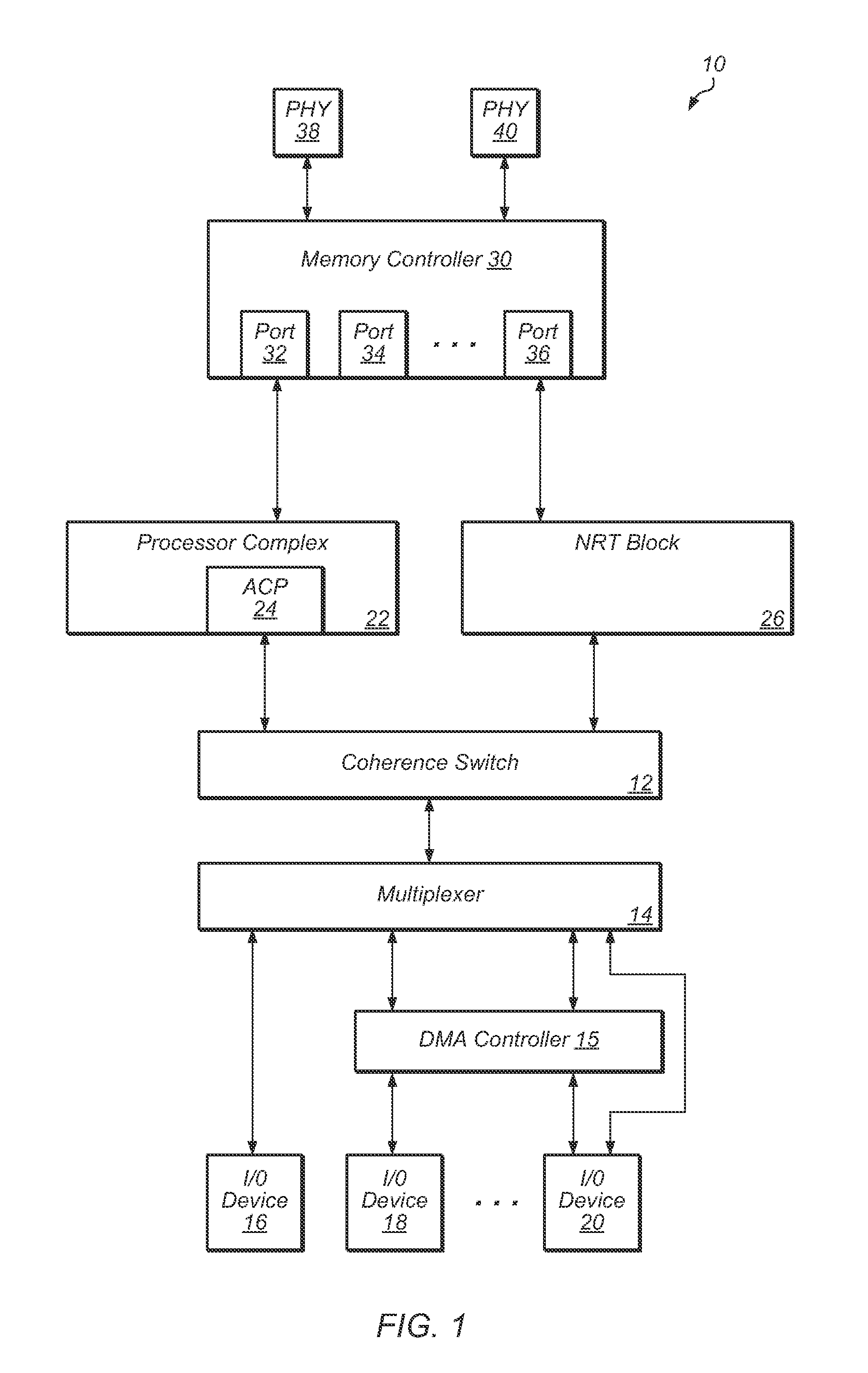

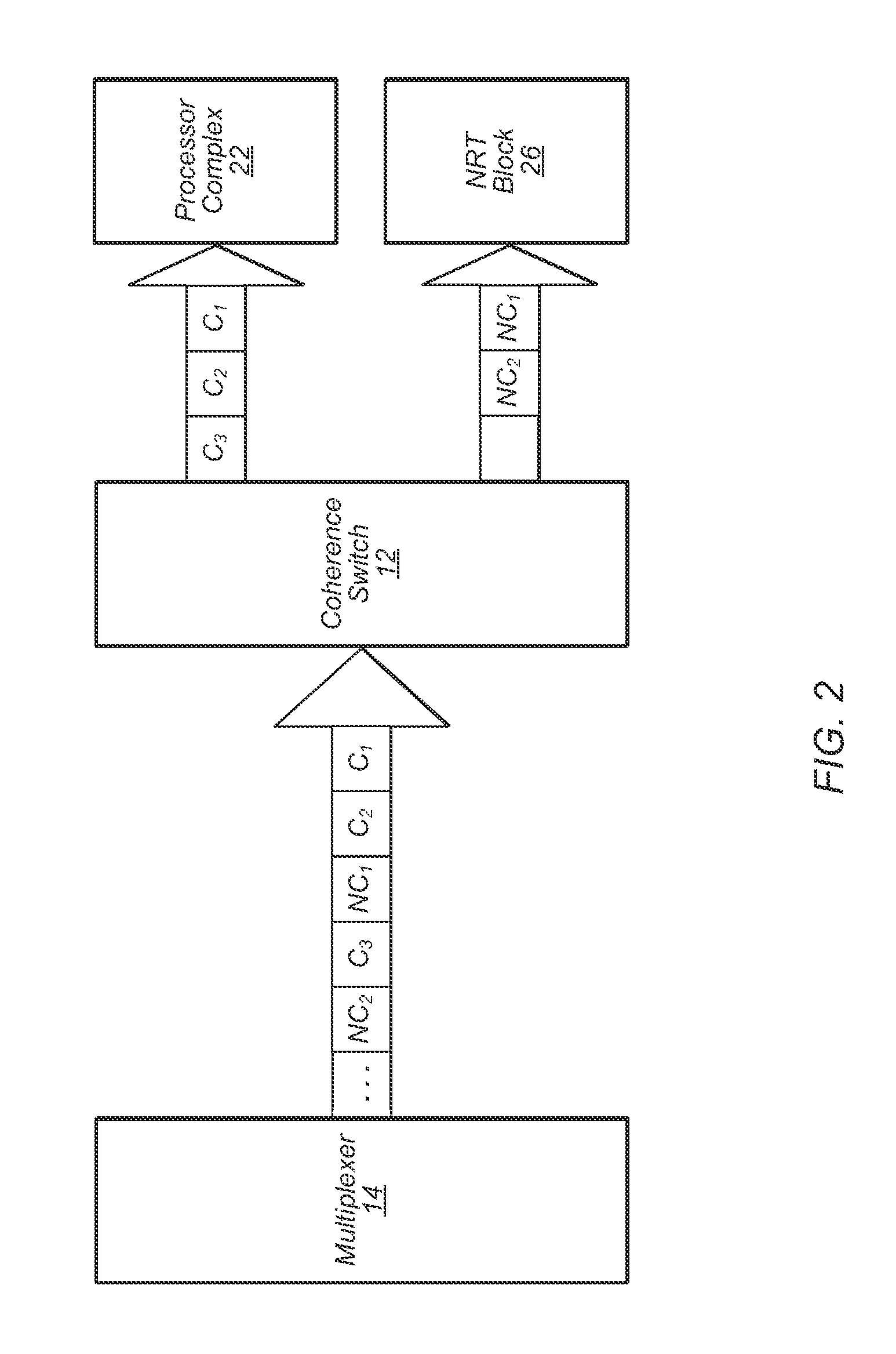

Coherence switch for I/O traffic

ActiveUS9176913B2Easy to switchEnergy efficient ICTComputer security arrangementsTraffic capacityRegister allocation

A system, apparatus, and method for routing traffic in a SoC from I / O devices to memory. A coherence switch routes coherent traffic through a coherency port on a processor complex to a real-time port of a memory controller. The coherence switch routes non-coherent traffic to a non-real time port of the memory controller. The coherence switch can also dynamically switch traffic between the two paths. The routing of traffic can be configured via a configuration register, and while software can initiate an update to the configuration register, the actual coherence switch hardware will implement the update. Software can write to a software-writeable copy of the configuration register to initiate an update to the flow path to memory for a transaction identifier. The coherence switch detects the update to the software-writeable copy, and then the coherence switch updates the working copy of the configuration register and implements the new routing.

Owner:APPLE INC

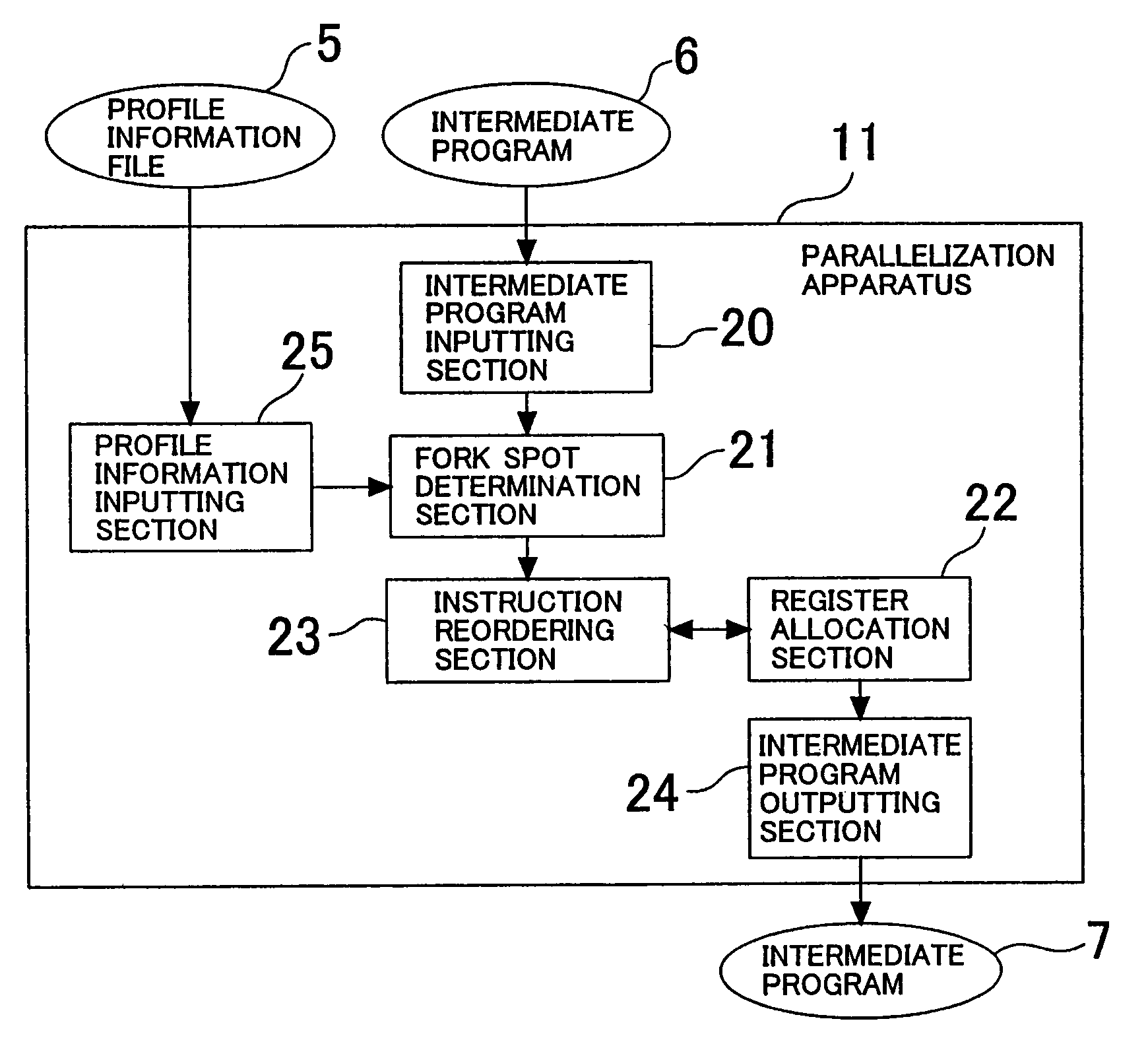

Branch instruction conversion to multi-threaded parallel instructions

InactiveUS7010787B2Process is performedImprove performanceProgram initiation/switchingProgram synchronisationRegister allocationProcessor register

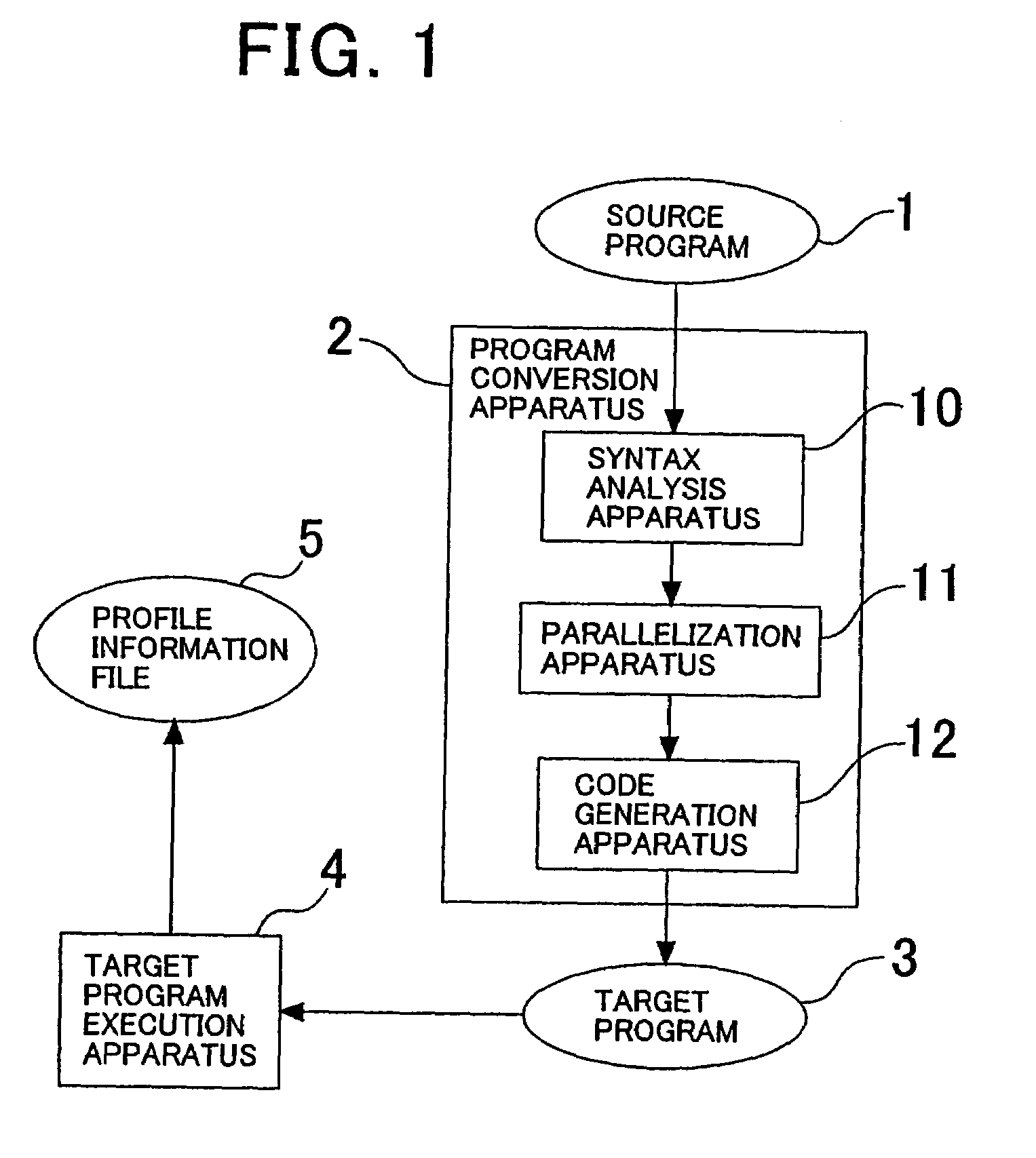

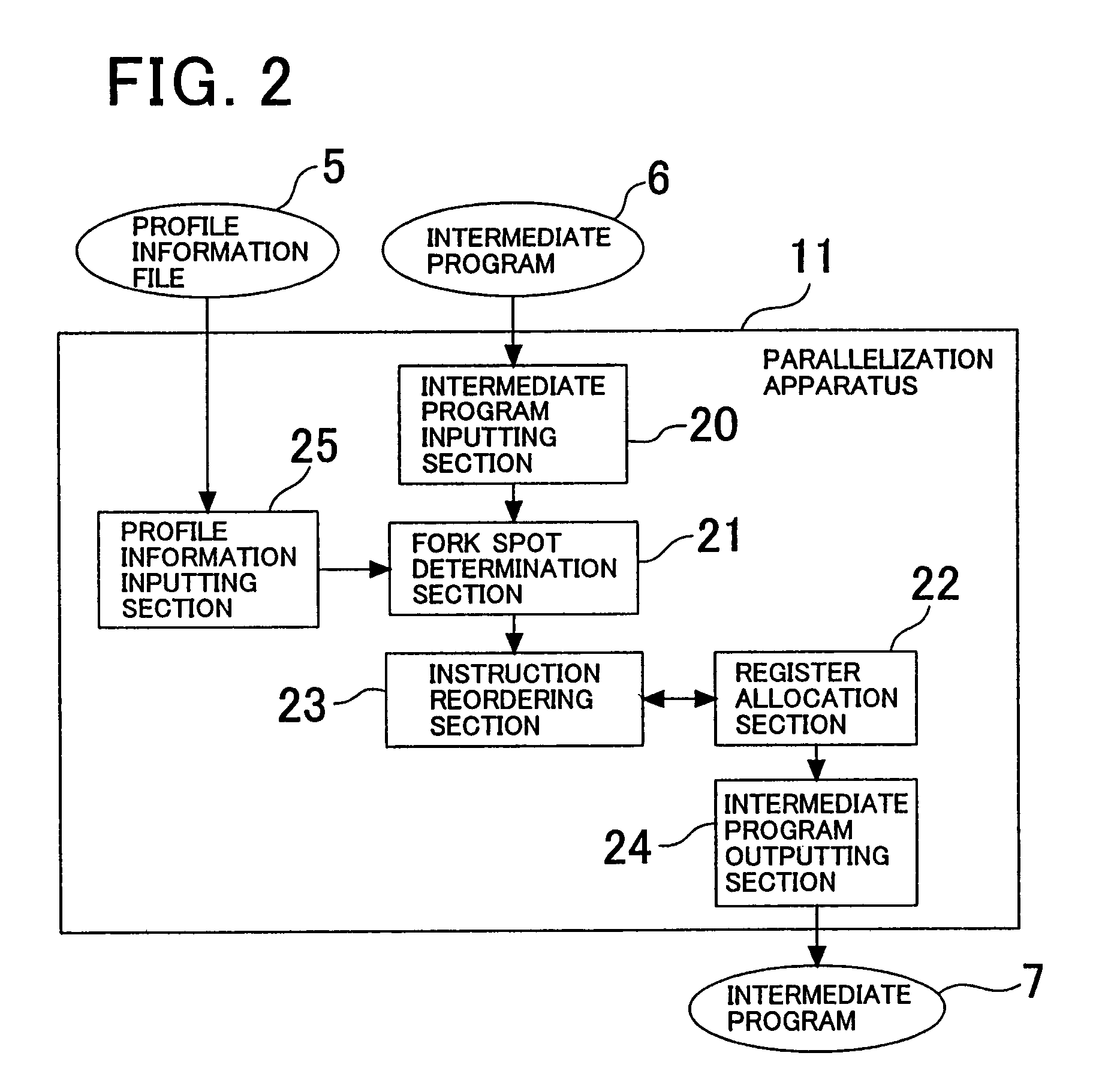

The invention provides a program conversion apparatus which performs parallelization for a multi-thread microprocessor on an intermediate program level. A parallelization apparatus of the program conversion apparatus includes a fork spot determination section, a register allocation section and an instruction reordering section. The fork spot determination section determines a fork spot and a fork system based on a result of a register allocation trial performed by the register allocation section, the number of spots at which memory data dependence is present, and branching probabilities and a data dependence occurrence frequency obtained from a profile information file. The instruction reordering section reorders instructions preceding to and succeeding the FORK instruction in accordance with the determination.

Owner:NEC CORP

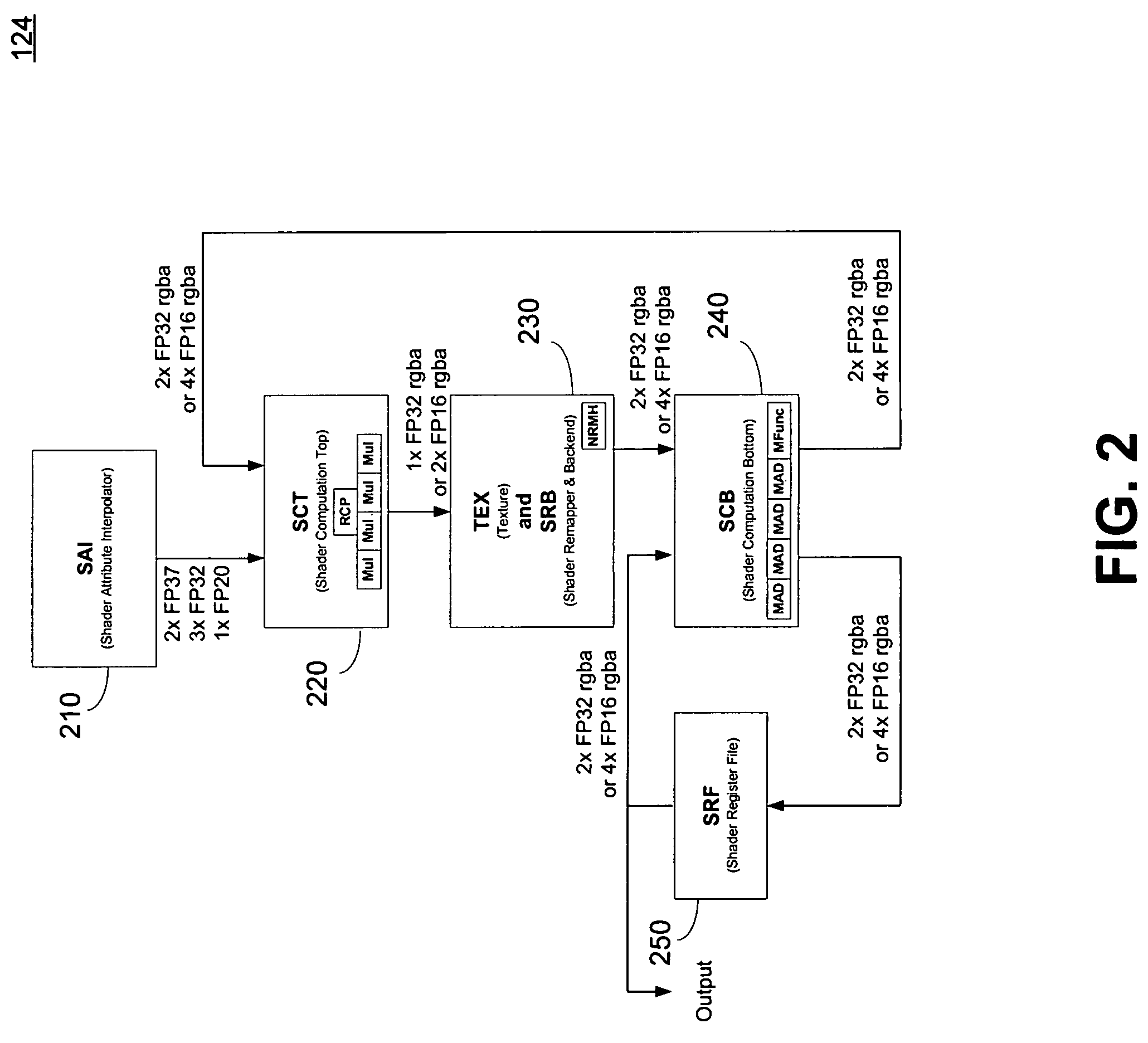

Method and apparatus for register allocation in presence of hardware constraints

ActiveUS7681187B2Reduce the amount requiredMinimize the numberSoftware engineeringProgram controlRegister allocationProcessor register

A method and apparatus for optimizing register allocation during scheduling and execution of program code in a hardware environment. The program code can be compiled to optimize execution given predetermined hardware constraints. The hardware constraints can include the number of register read and write operations that can be performed in a given processor pass. The optimizer can initially schedule the program using virtual registers and a goal of minimizing the amount of active registers at any time. The optimizer reschedules the program to assign the virtual registers to actual physical registers in a manner that minimizes the number of processor passes used to execute the program.

Owner:NVIDIA CORP

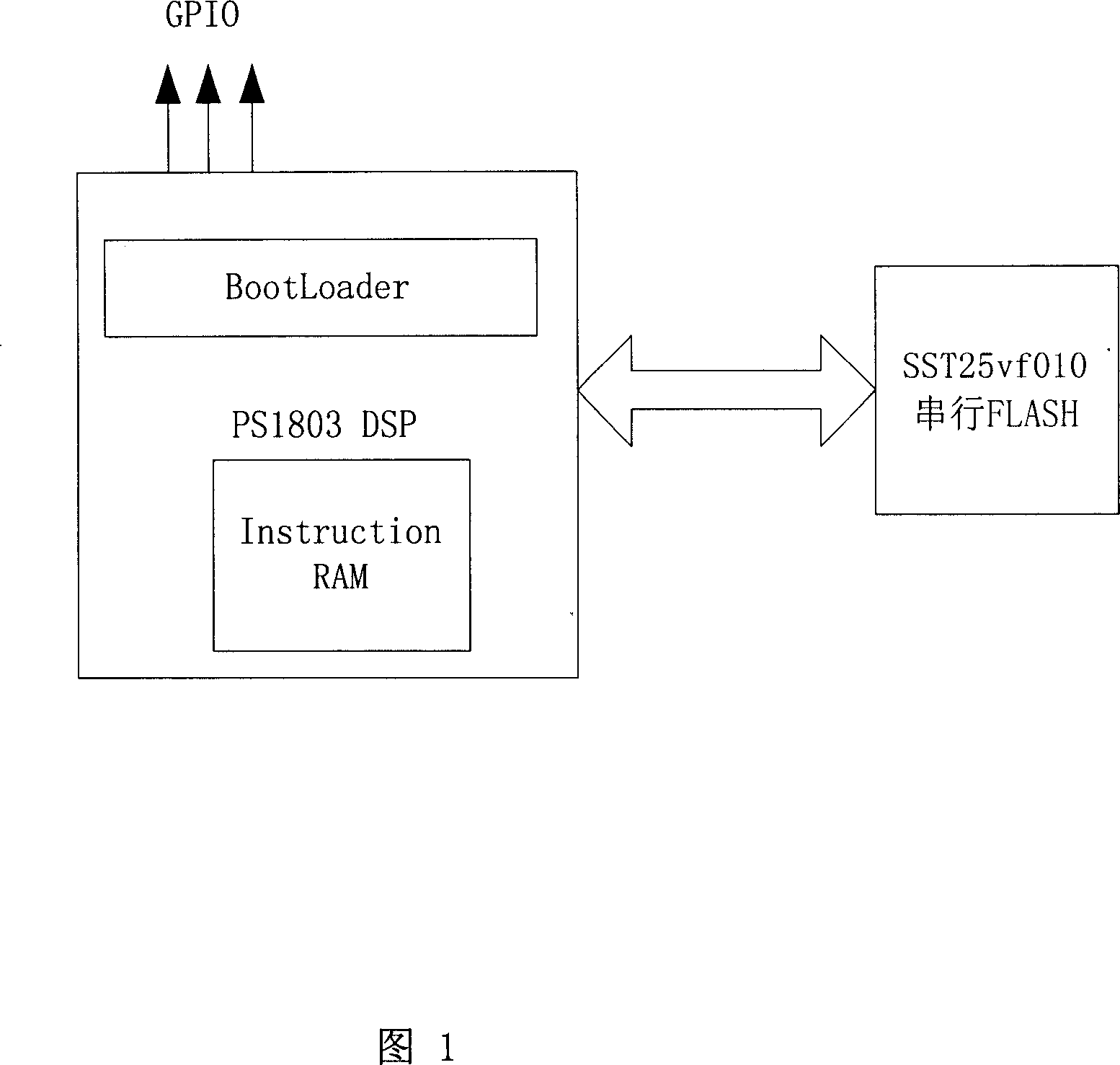

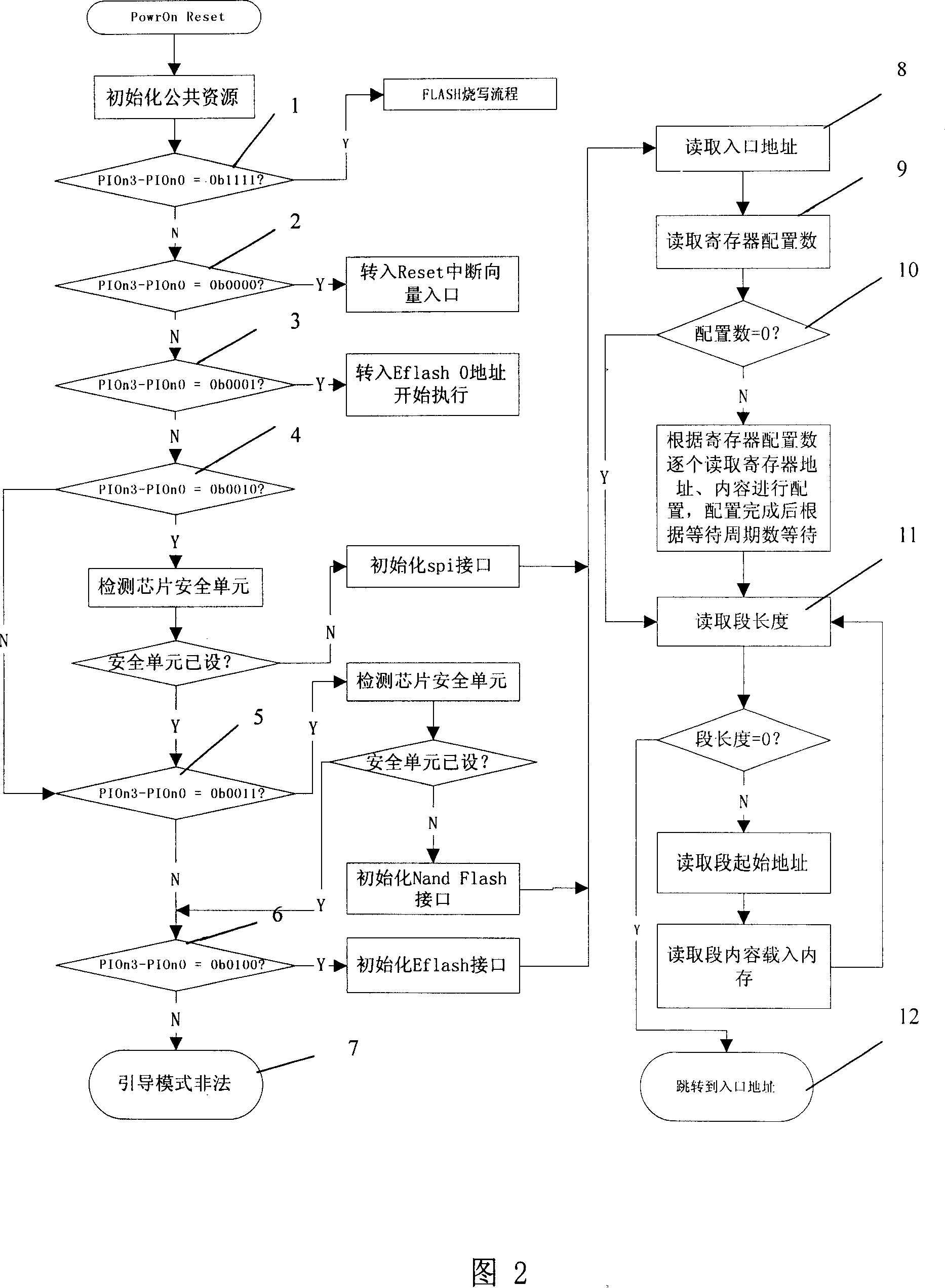

Program bootstrap method after chip power-on

ActiveCN101021794ASimple pull upSimple drop downProgram loading/initiatingRegister allocationProgram segment

The invention relates to a guiding procedure for a chip after loading electricity. Its characteristics are as following: the procedure is stored in a nonvolatile storage, and the procedure is packaged, and the packaged data-application includes: an import-address domain, a configuration register domain and a procedure domain, of which: the import-address domain is used for storing the first address of implementation after loading the procedure, and the configuration register domain is used for storing the number of configured registers and the addresses of registers, configuration content and the clock cycle for configuration in the process, and the procedure domain is used for storing procedures. The guiding procedure includes: it reads data packets according to packaging format, and it checks the addresses of procedures and length of information stored in the non-volatile memory, and it loads the procedures to the operation memory for implementing procedures.

Owner:HANGZHOU SYNOCHIP DATA SECURITY TECH CO LTD

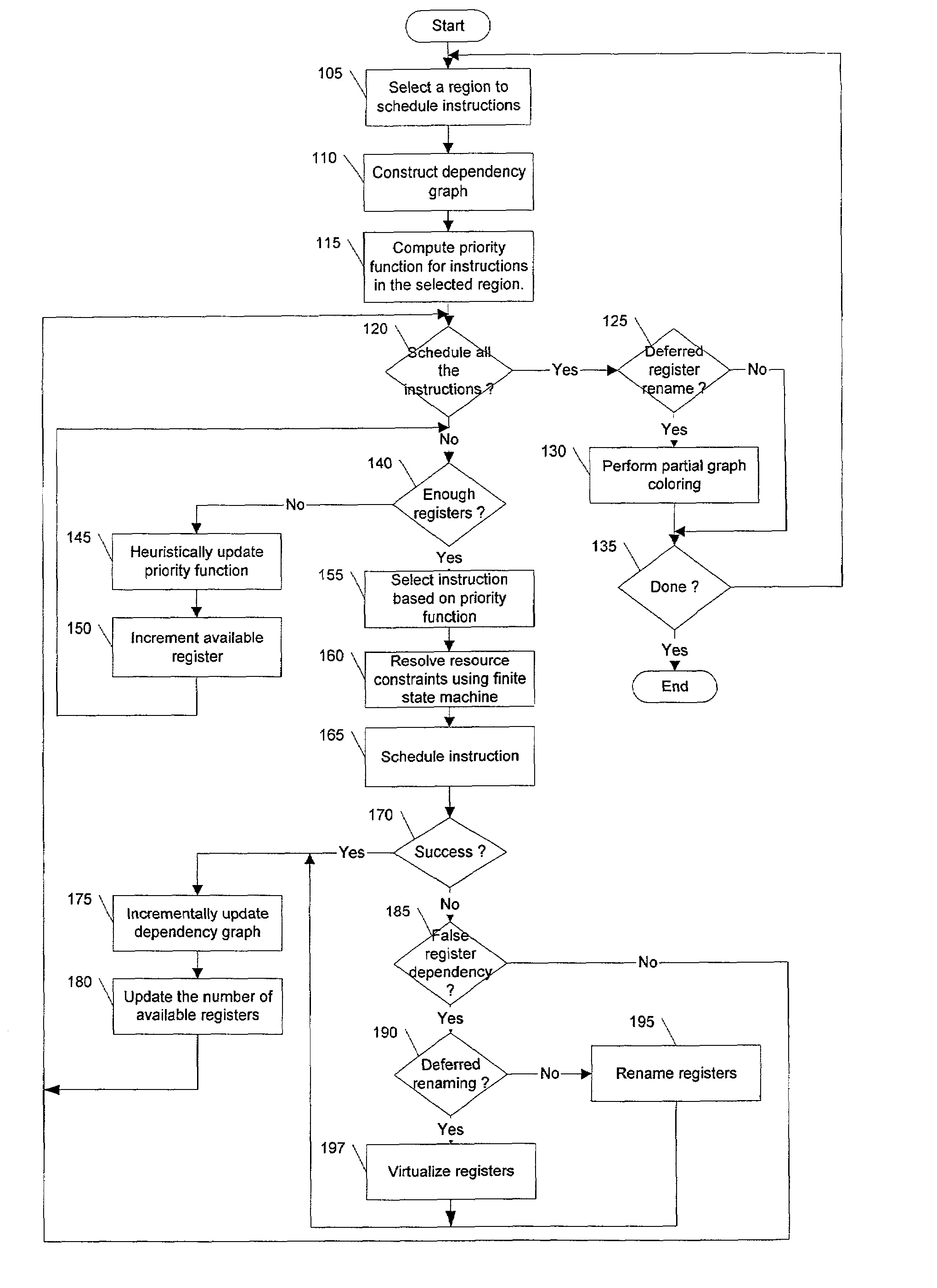

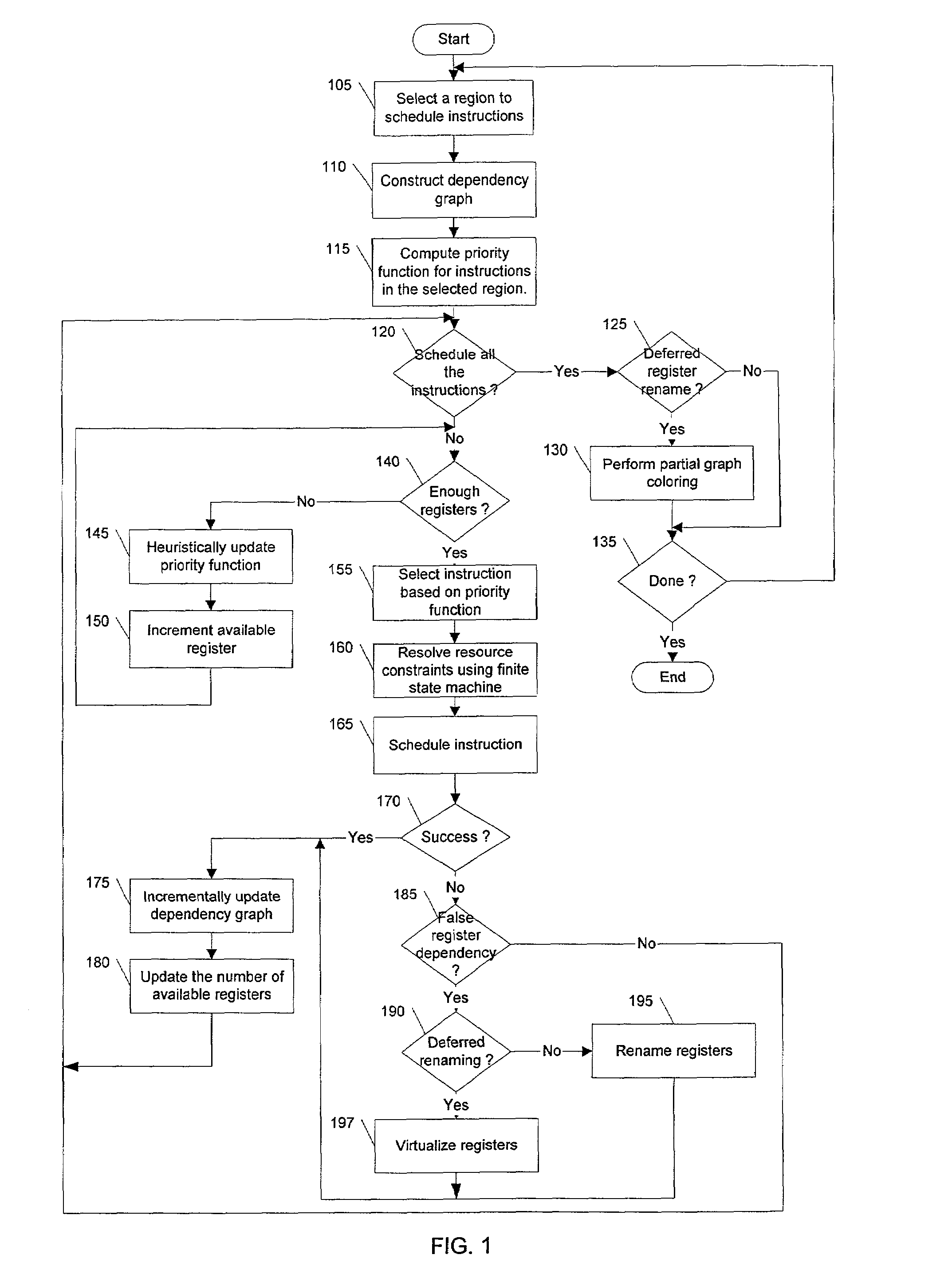

Method and apparatus for integrated instruction scheduling and register allocation in a postoptimizer

The present invention describes a method of efficiently optimizing instruction scheduling and register allocation in a post optimizer. The method removes false register dependencies between pipelined instructions by building an incremental (partial) interference graph of register allocation for scheduled instructions. False dependency graph indicates the amount of parallelism in the data flow graph. The incremental interference graph uses a mix of virtual and physical registers. The interference graph is built incrementally as an instruction schedular schedules each instruction. The optimization is done incrementally on localized code. The physical register mapping is maximized and virtual registers are created on demand basis.

Owner:ORACLE INT CORP

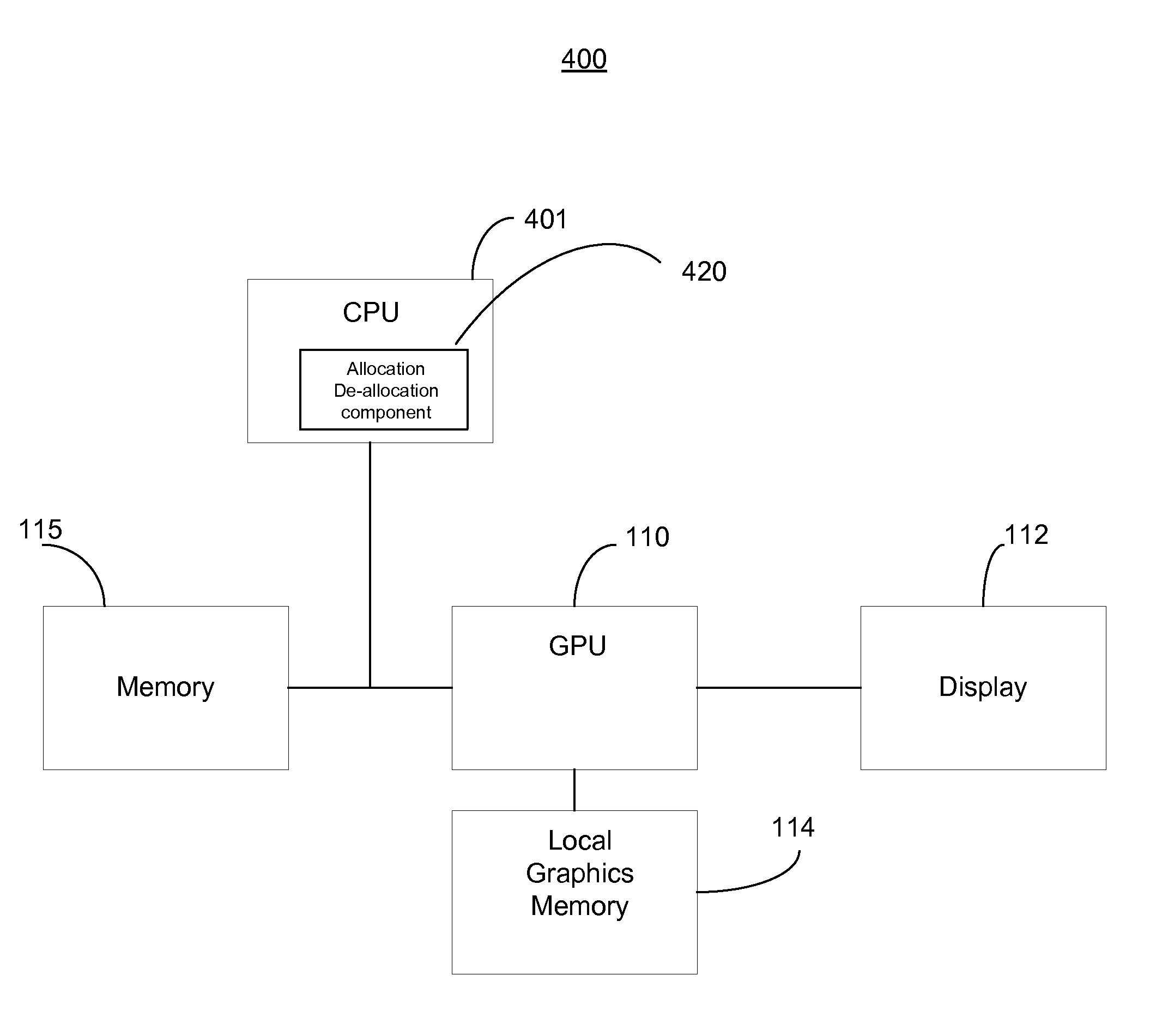

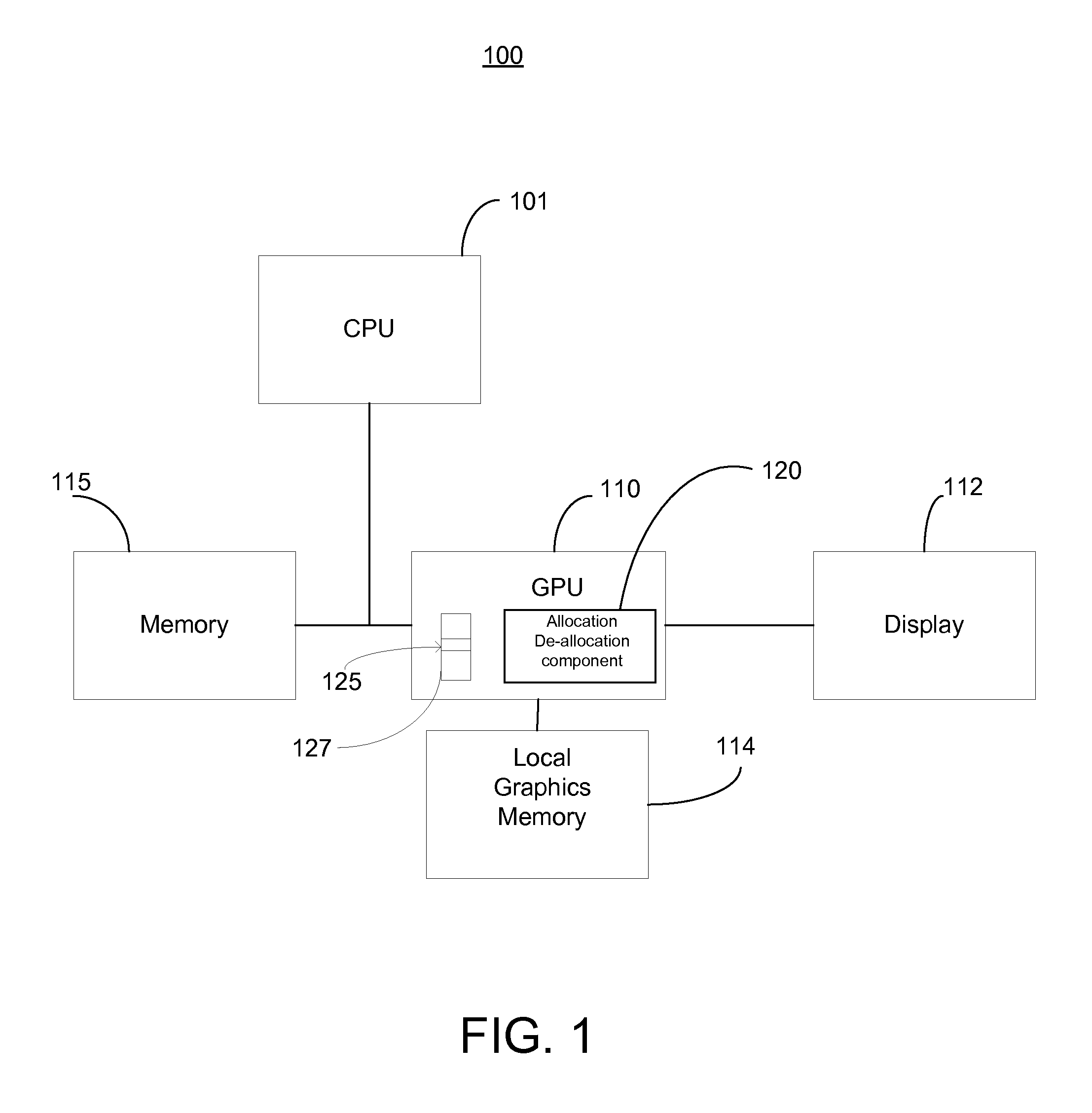

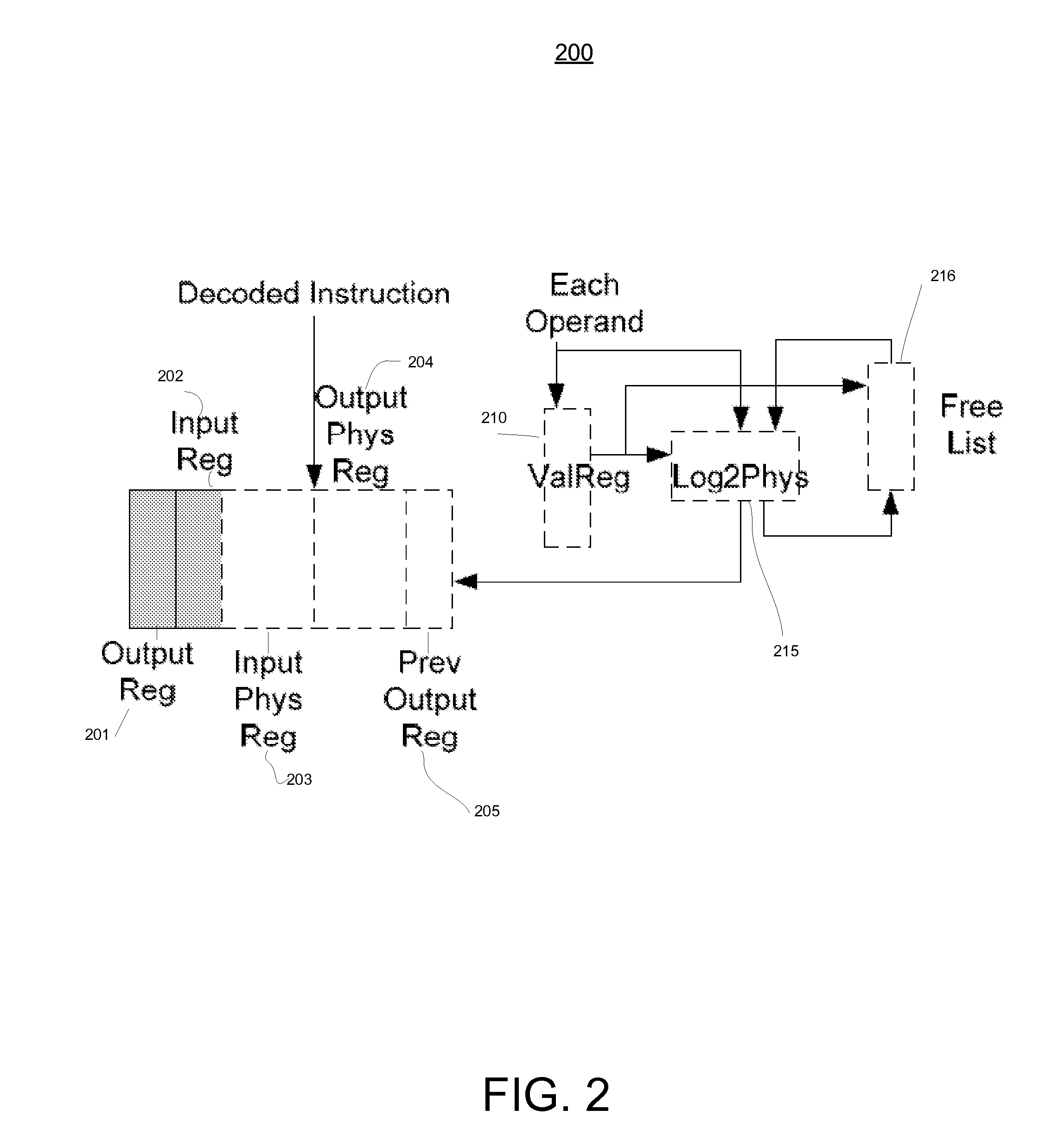

On demand register allocation and deallocation for a multithreaded processor

InactiveUS20110161616A1Increase profitHigh performance lowMemory adressing/allocation/relocationMicro-instruction address formationRegister allocationRegister assignment

A system for allocating and de-allocating registers of a processor. The system includes a register file having plurality of physical registers and a first table coupled to the register file for mapping virtual register IDs to physical register IDs. A second table is coupled to the register file for determining whether a virtual register ID has a physical register mapped to it in a cycle. The first table and the second table enable physical registers of the register file to be allocated and de-allocated on a cycle-by-cycle basis to support execution of instructions by the processor.

Owner:NVIDIA CORP

Signal conversion device and method as well as communication equipment

ActiveCN101989244AReduce complexityReduce usageElectric digital data processingRegister allocationMemory address

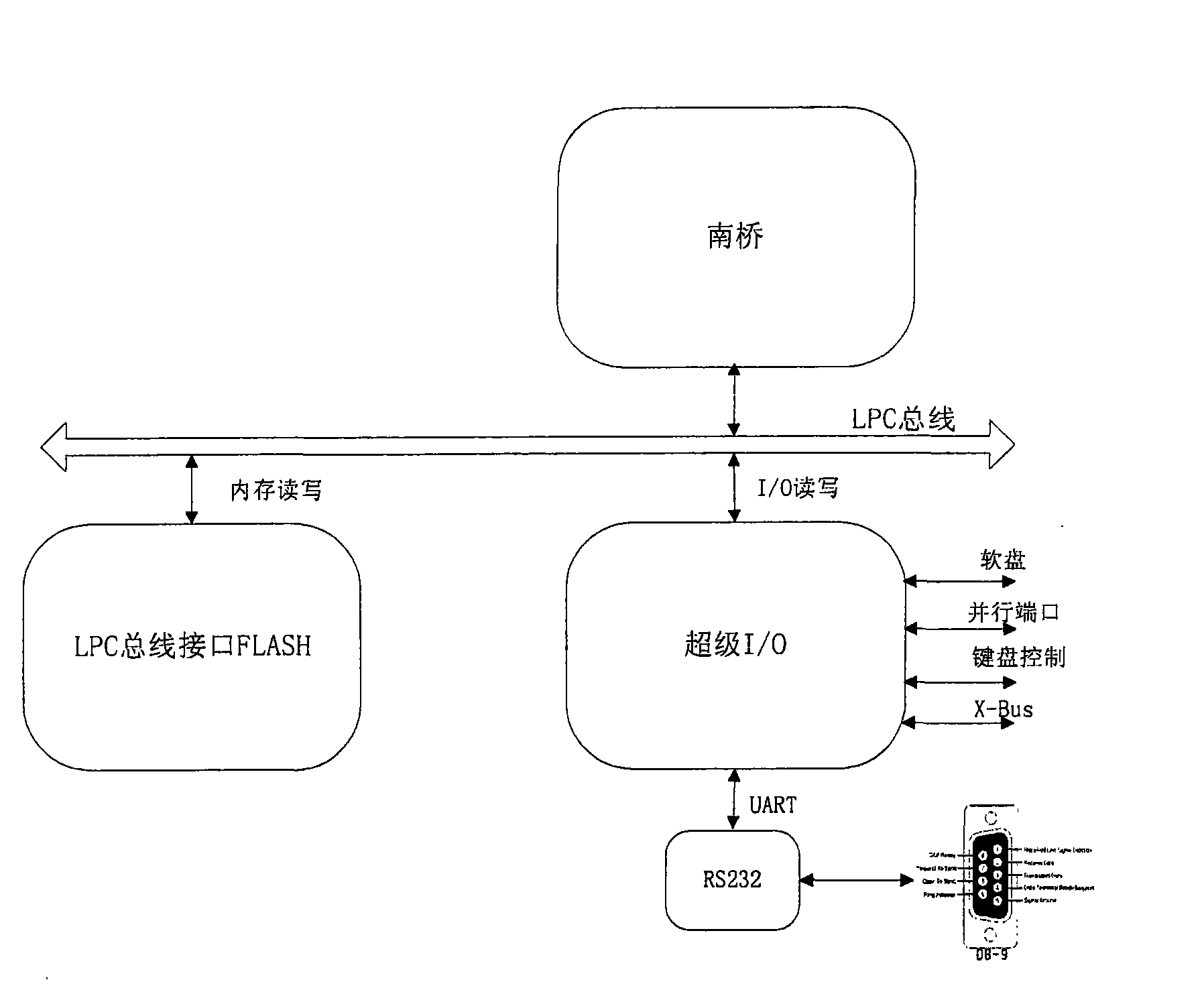

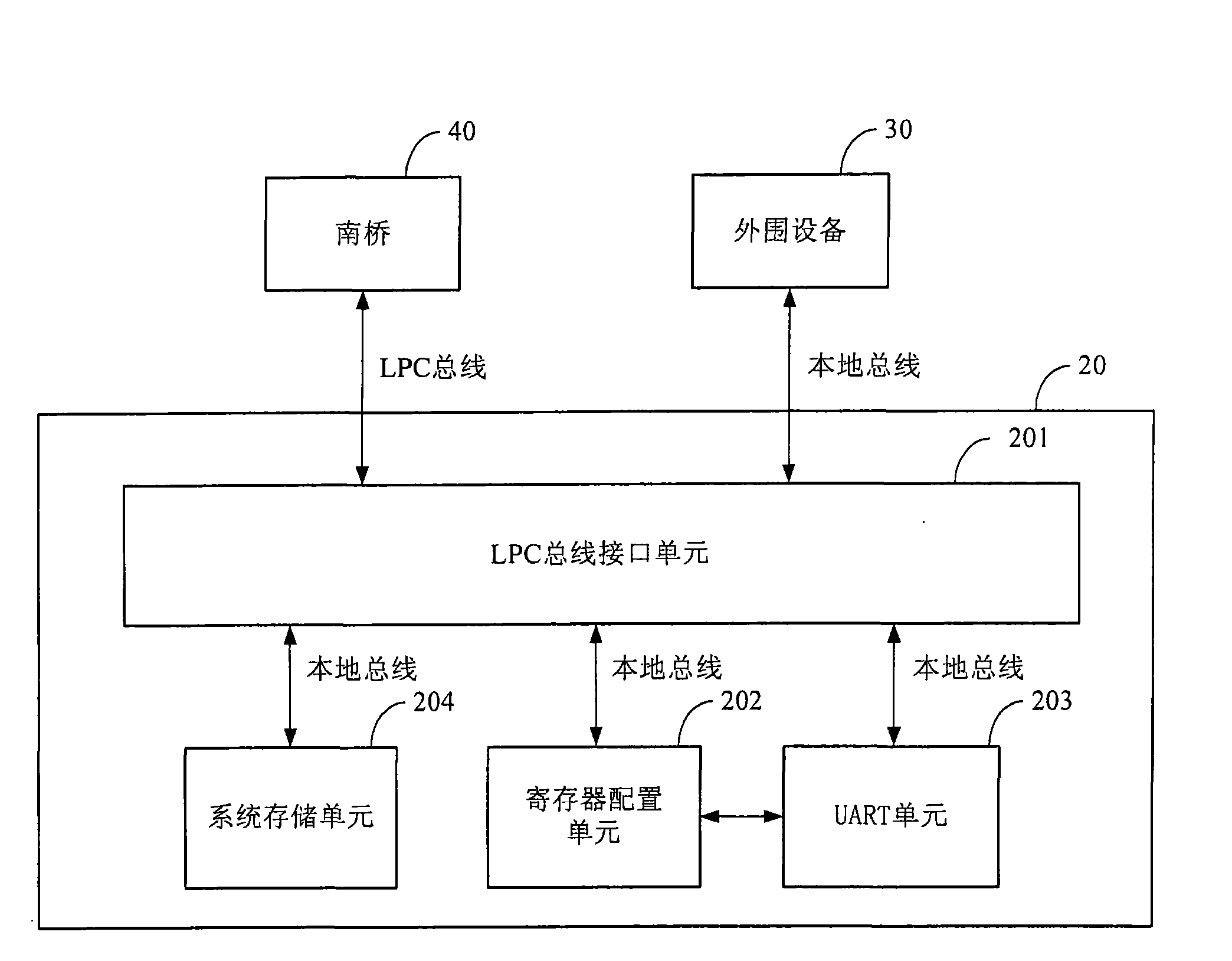

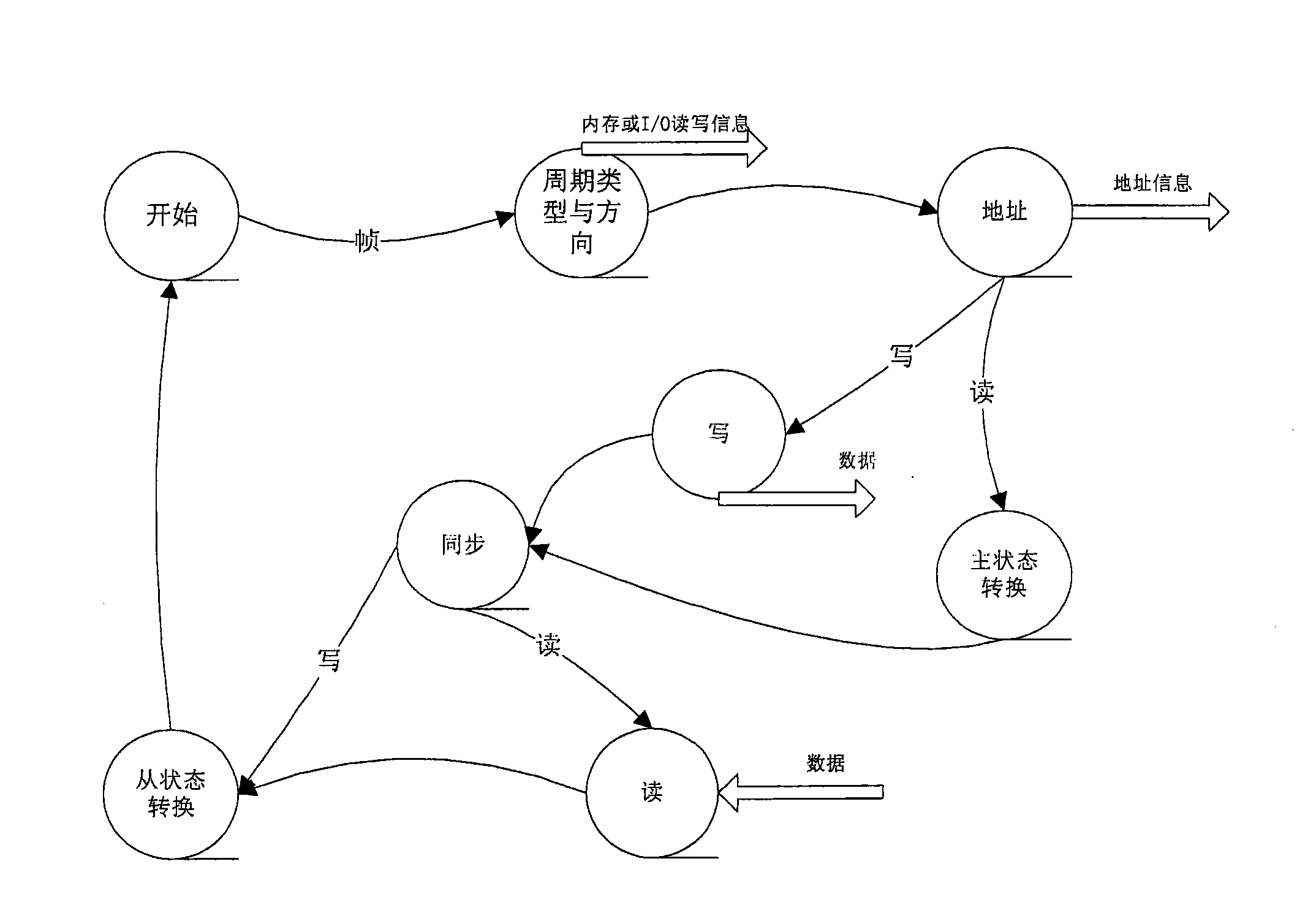

The embodiment of the invention provides a signal conversion device and method as well as communication equipment. The signal conversion device comprises an LPC (Low Pin Count) bus interface unit, a register configuration unit and a UART (Universal Asynchronous Receiver Transmitter) unit, wherein the LPC bus interface unit is used for performing protocol analysis on signals from an LPC bus and outputting local signals through a local bus, and the local signals comprise a control signal, an address signal and a data signal; the register configuration unit is used for configuring registers of the UART unit according to the local signals; the registers of the UART unit are allocated in a memory address space and an I / O address space; and the UART unit is used for converting data from the LPCbus into serial data according to the local signals and the values of configured registers of the UART unit and then outputting the serial data through a UART interface or outputting the serial data received by the UART interface to the LPC bus through the local signals. The embodiment of the invention can simplify the configuration process of the registers of the USRT unit.

Owner:HUAWEI TECH CO LTD

Method for enhancing clock synchronization accuracy in distributed network system

InactiveCN101252429ASolve the problem of crystal oscillator speed deviationSynchronisation signal speed/phase controlRegister allocationTime deviation

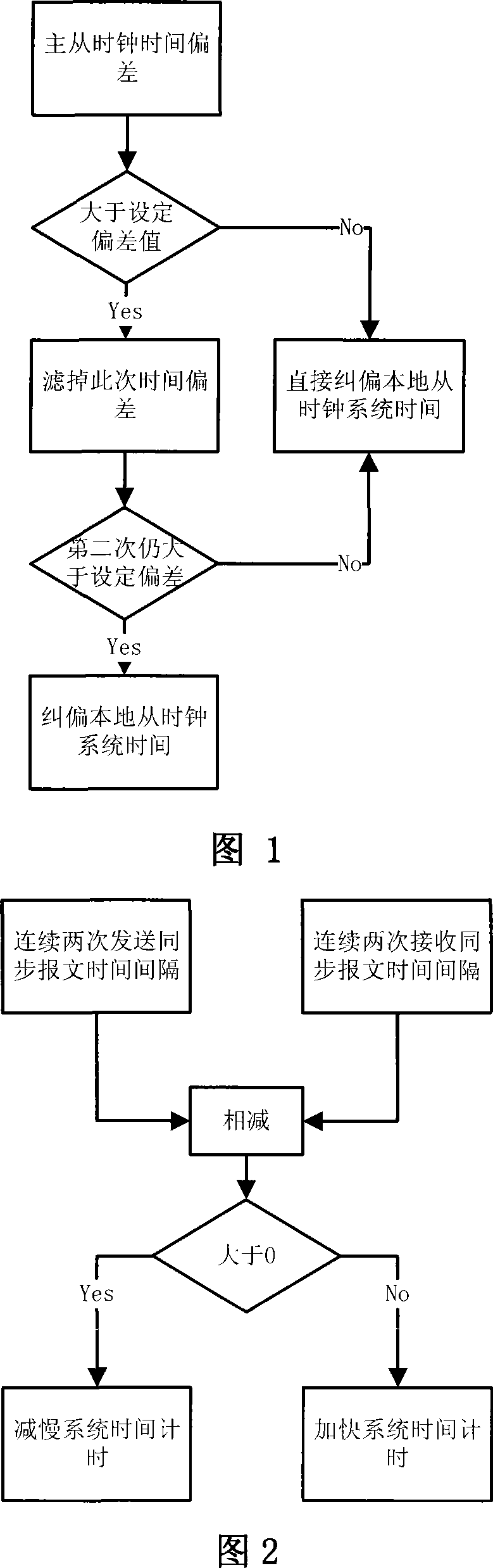

The invention relates to a method for improving the clock synchronization precision in a distributed network system. At present, the synchronized precision is relatively lower. Aiming at uncertainty and large disturbance, the invention only makes adjustment when the time offset between a local slave clock and a master clock is less than or equal to the offset value set through a register by the user; if the adjacent twice time offset is still more than the offset value, the invention adjusts the time of the local slave clock according to the time offset value. As the speed of a clock crystal oscillator is deviated, the time interval at which the local slave clock continuously twice sends sync synchronous messages to the master clock and the time interval at which the local slave clock continuously twice receives the sync synchronous messages from the master clock are compared, and then the difference between the two time intervals is evenly distributed within the synchronization interval. The method of the invention solves the problem of the decreasing of the clock synchronization precision to ensure the clock synchronization precision to reach microsecond level, through a filtering algorithm and the even adjustment of the offset of the crystal oscillator of the slave and the master clocks within the synchronization interval.

Owner:ZHEJIANG UNIV

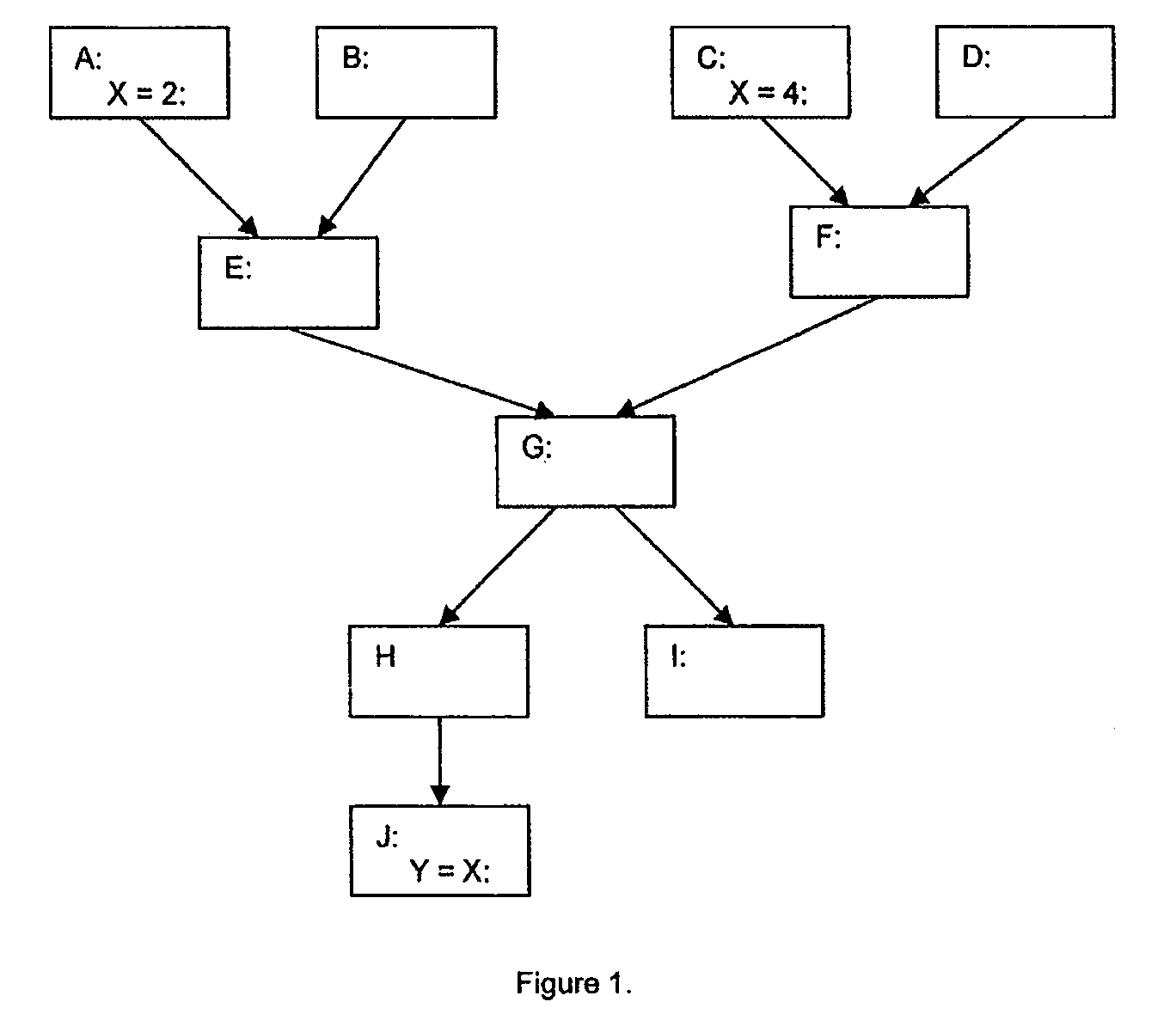

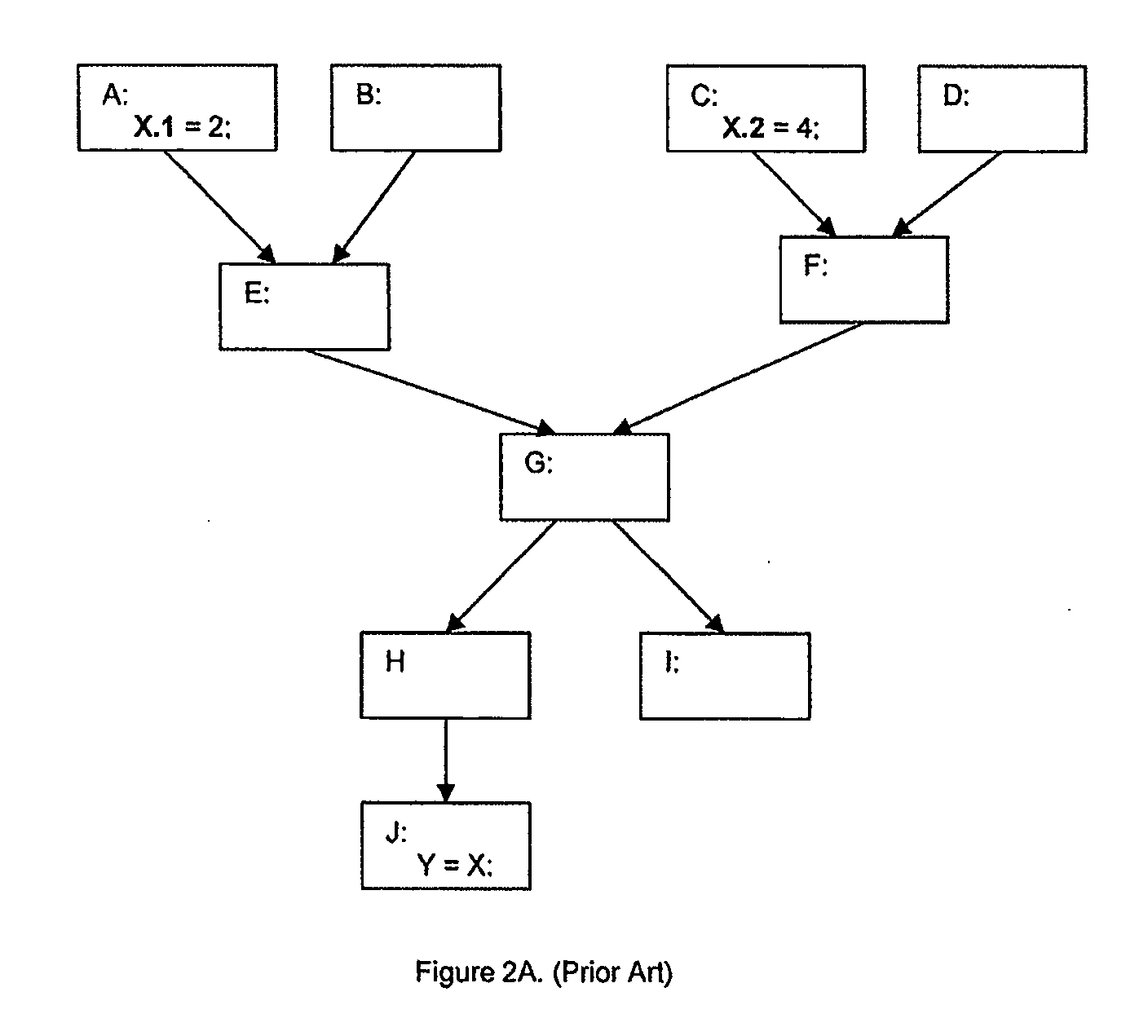

Highly scalable parallel static single assignment for dynamic optimization on many core architectures

A method, system, and computer readable medium for converting a series of computer executable instructions in control flow graph form into an intermediate representation, of a type similar to Static Single Assignment (SSA), used in the compiler arts. The indeterminate representation may facilitate compilation optimizations such as constant propagation, sparse conditional constant propagation, dead code elimination, global value numbering, partial redundancy elimination, strength reduction, and register allocation. The method, system, and computer readable medium are capable of operating on the control flow graph to construct an SSA representation in parallel, thus exploiting recent advances in multi-core processing and massively parallel computing systems. Other embodiments may be employed, and other embodiments are described and claimed.

Owner:INTEL CORP

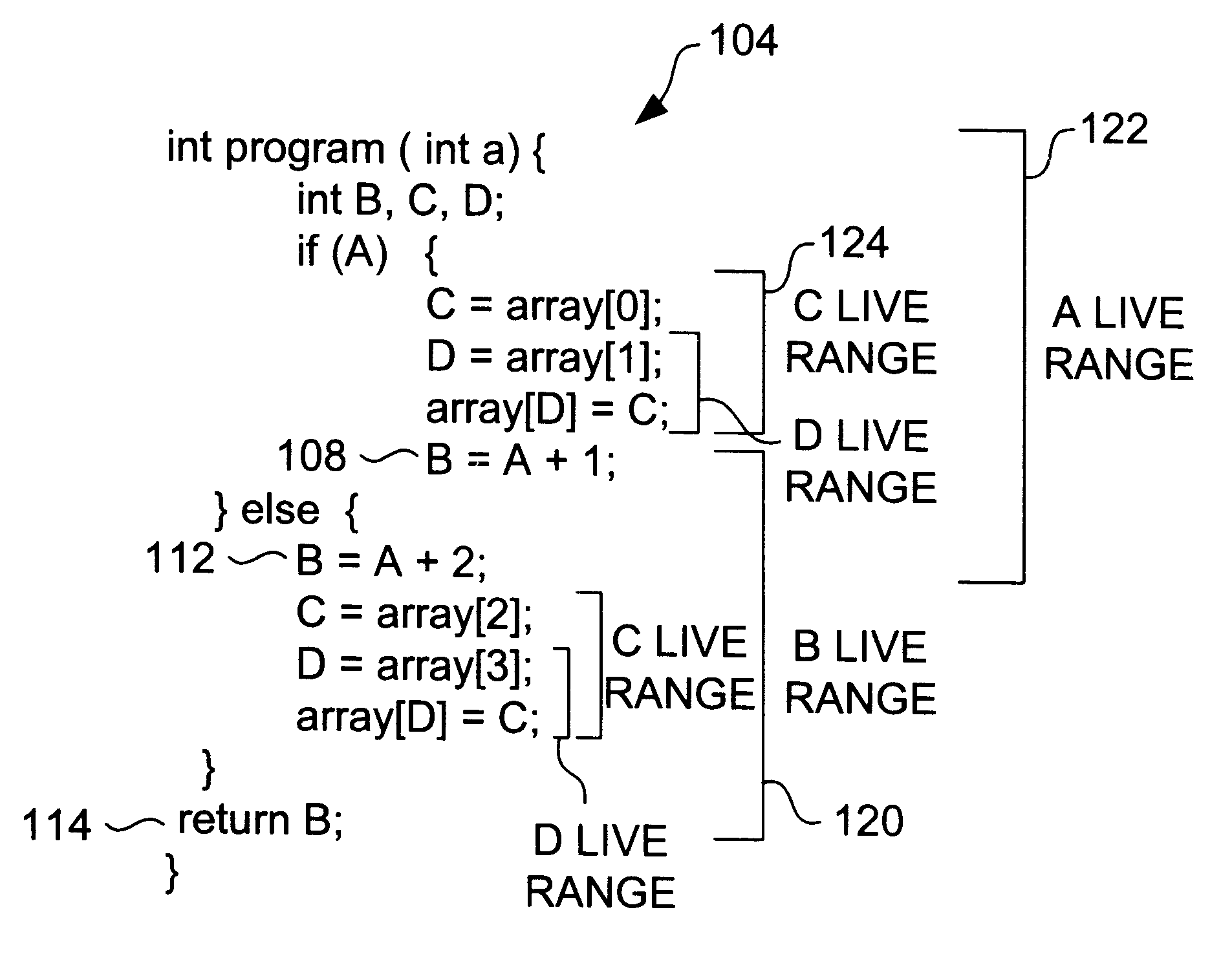

Method and apparatus for allocating stack slots

Methods and apparatus for allocating and using stack space are disclosed. According to one aspect of the present invention, a computer-implemented method for allocating stack space in an object-based system includes obtaining source code that is suitable for compilation and includes a definition associated with a variable. During register allocation, stack slots and machine registers are treated substantially similarly. This includes the steps of building an interference graph, copy coalescing, attempting to color the interference graph, and determining if the attempt to color the interference graph is successful. If the coloring attempt is not successful, then in lieu of normal spill code being inserted, register-to-register copies, e.g., "reg-reg" copies, are inserted in the source code. The "reg-reg" copies include copies associated with both stack slots and machine registers.

Owner:ORACLE INT CORP

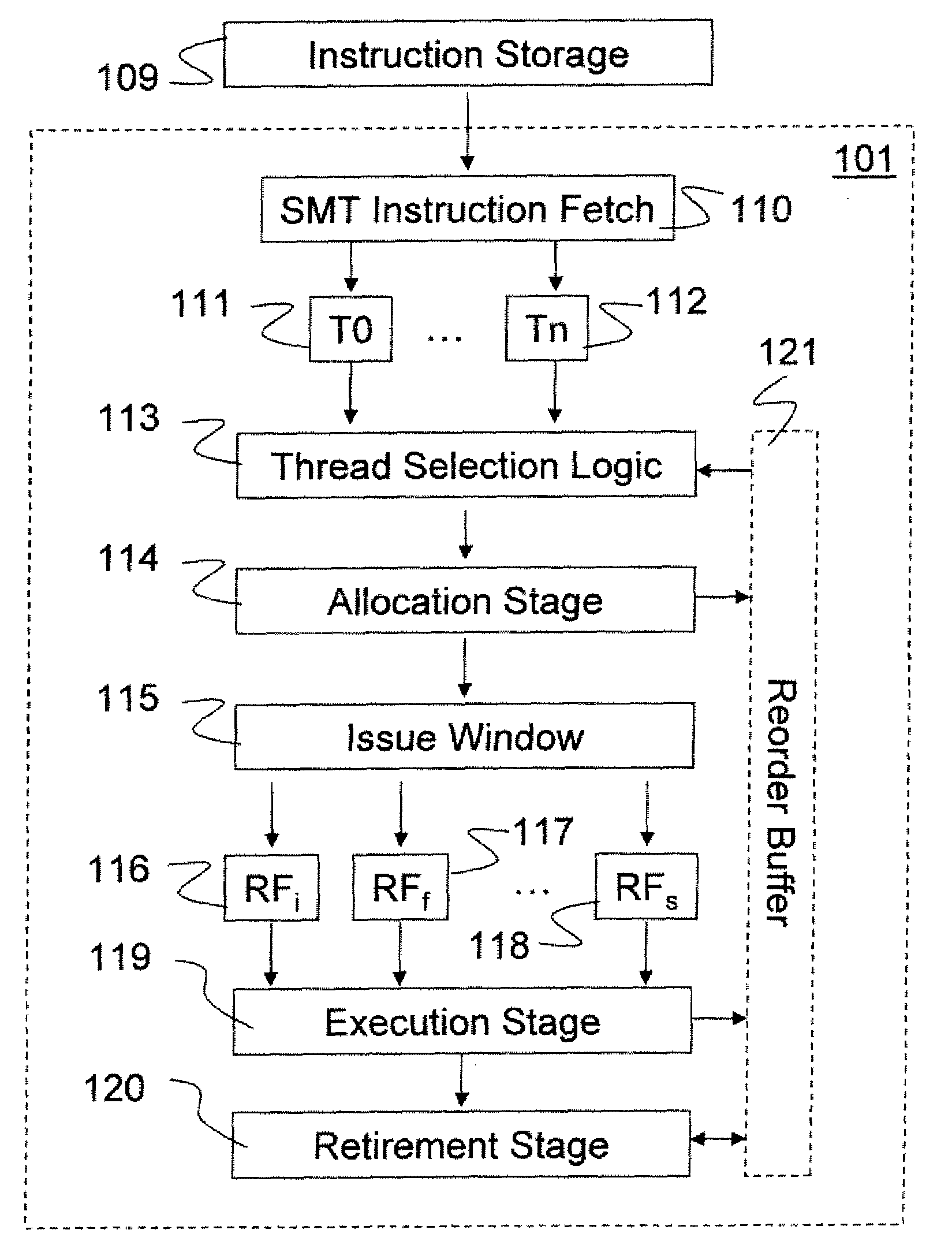

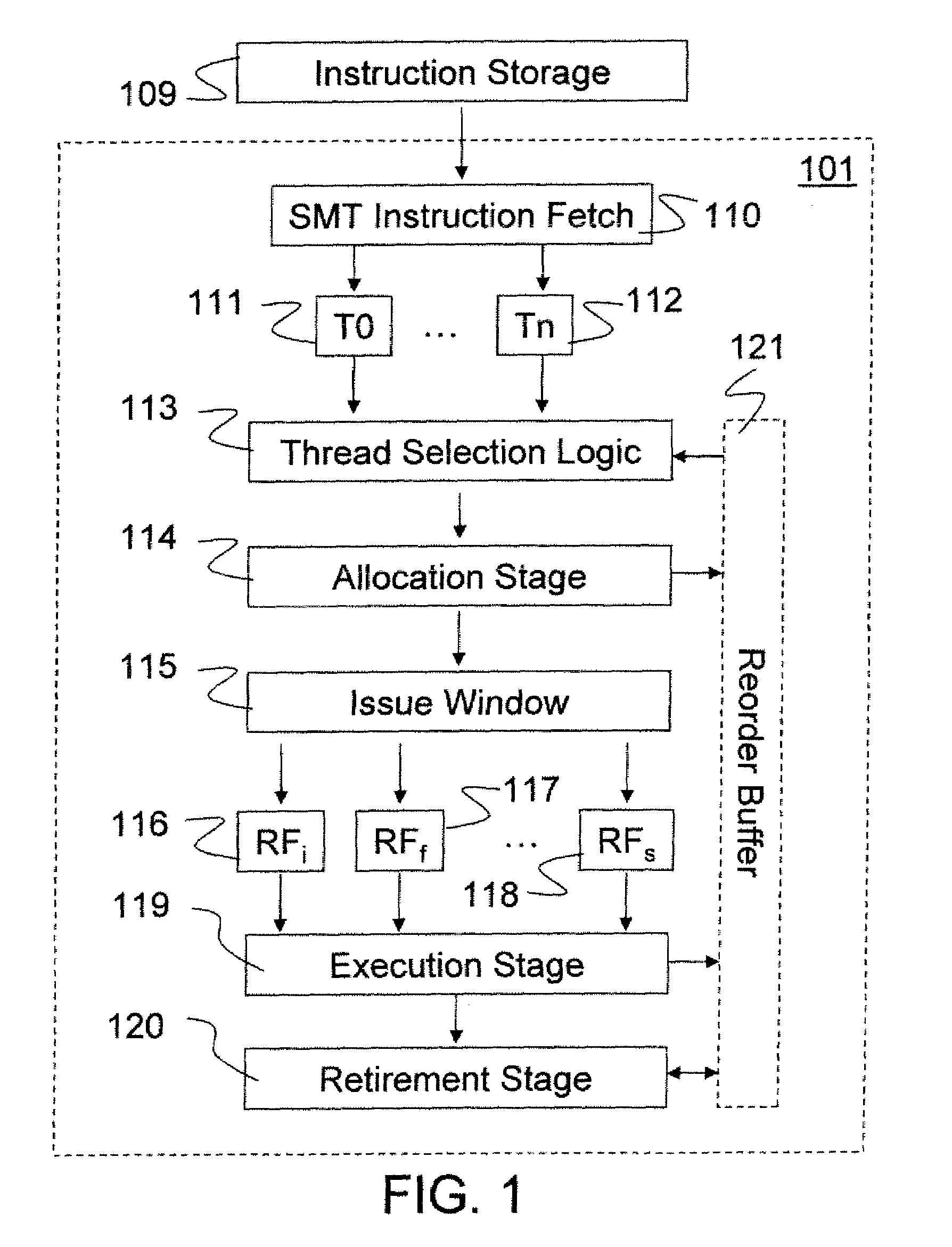

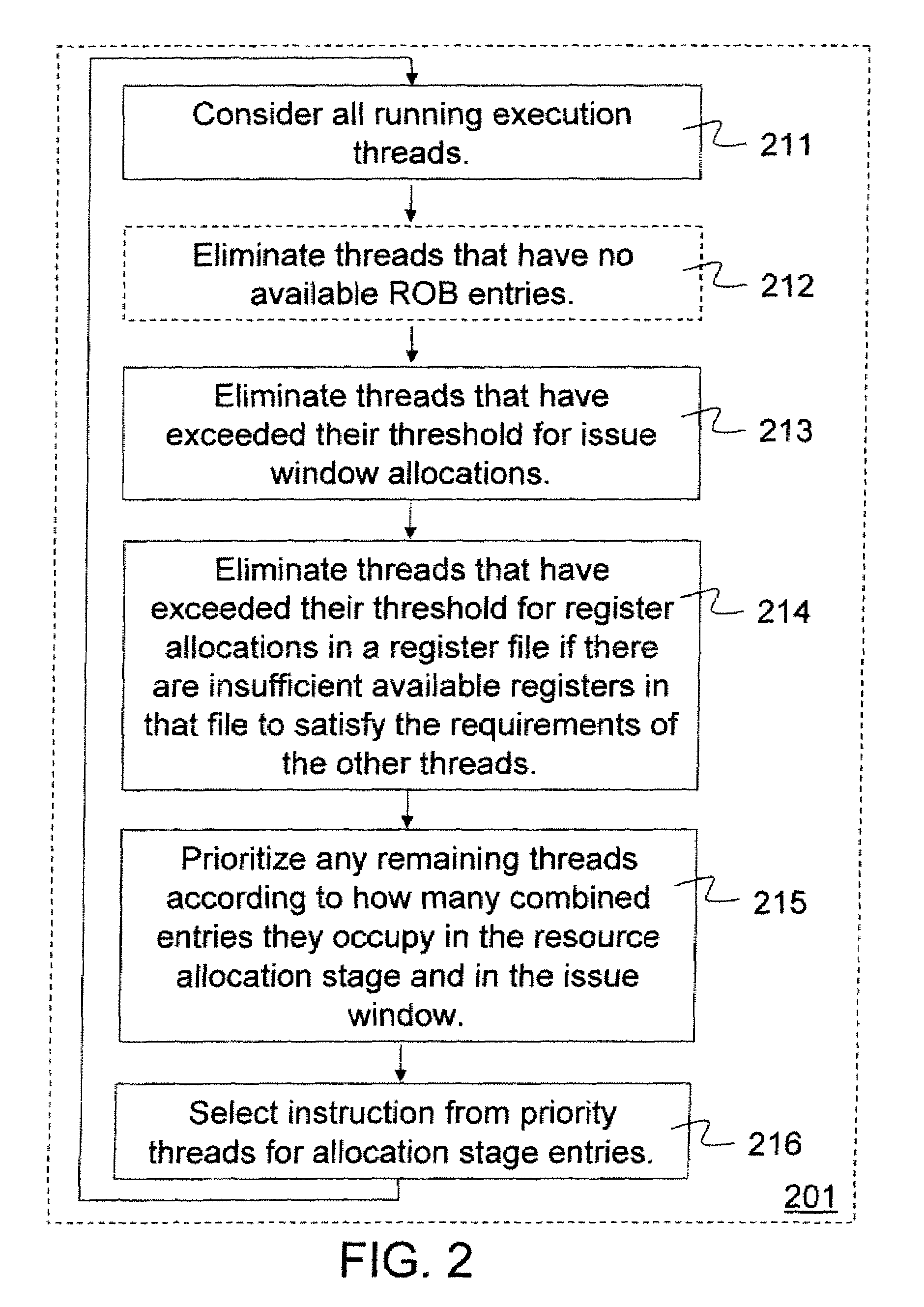

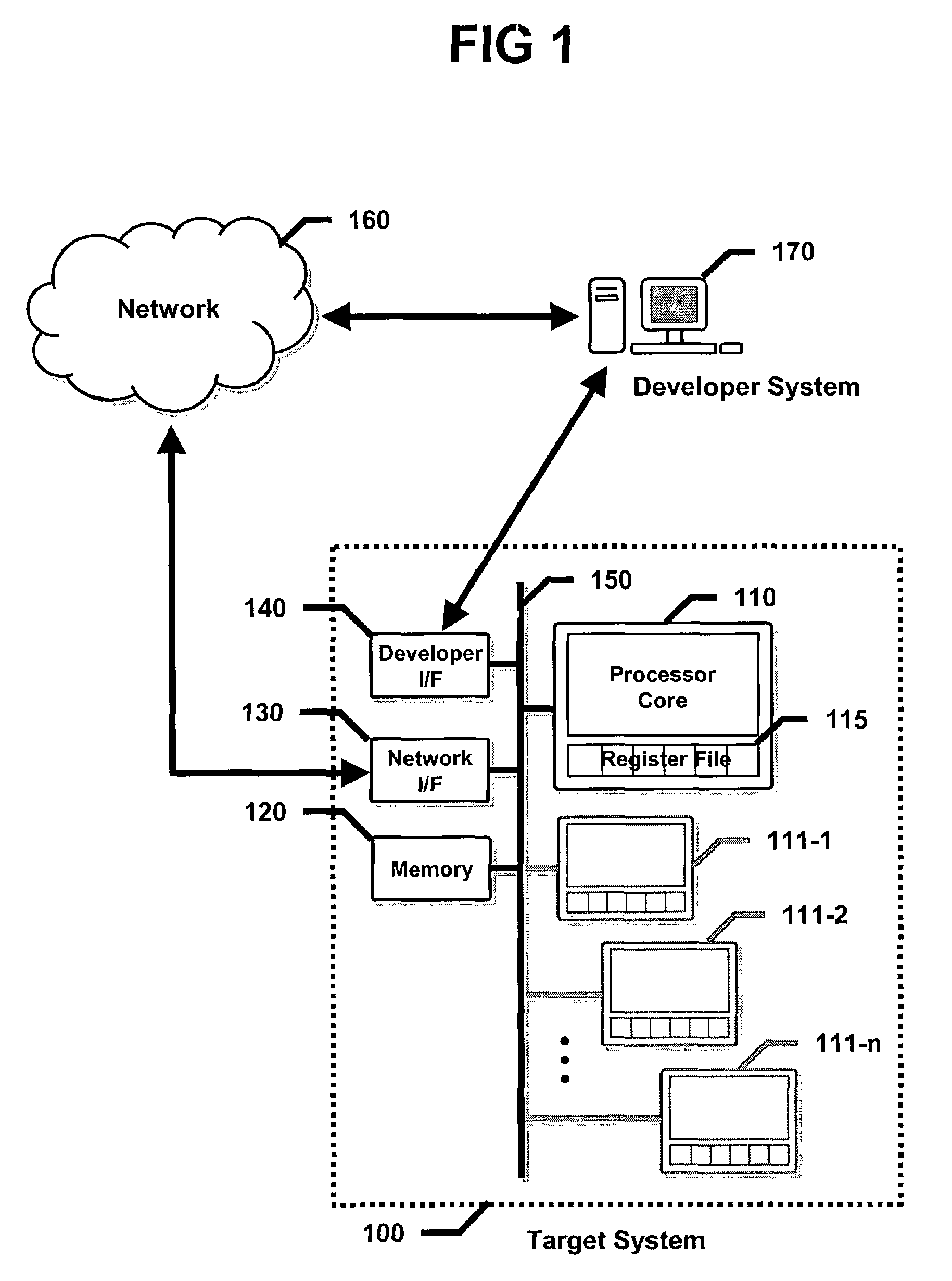

Method and apparatus for selection among multiple execution threads

Methods and apparatus for selecting and prioritizing execution threads for consideration of resource allocation include eliminating threads for consideration from all the running execution threads: if they have no available entries in their associated reorder buffers, or if they have exceeded their threshold for entry allocations in the issue window, or if they have exceeded their threshold for register allocations in some register file and if that register file also has an insufficient number of available registers to satisfy the requirements of the other running execution threads. Issue window thresholds may be dynamically computed by dividing the current number of entries by the number of threads under consideration. Register thresholds may also be dynamically computed and associated with a thread and a register file. Execution threads remaining under consideration can be prioritized according to how many combined entries the thread occupies in the resource allocation stage and the issue window.

Owner:INTEL CORP

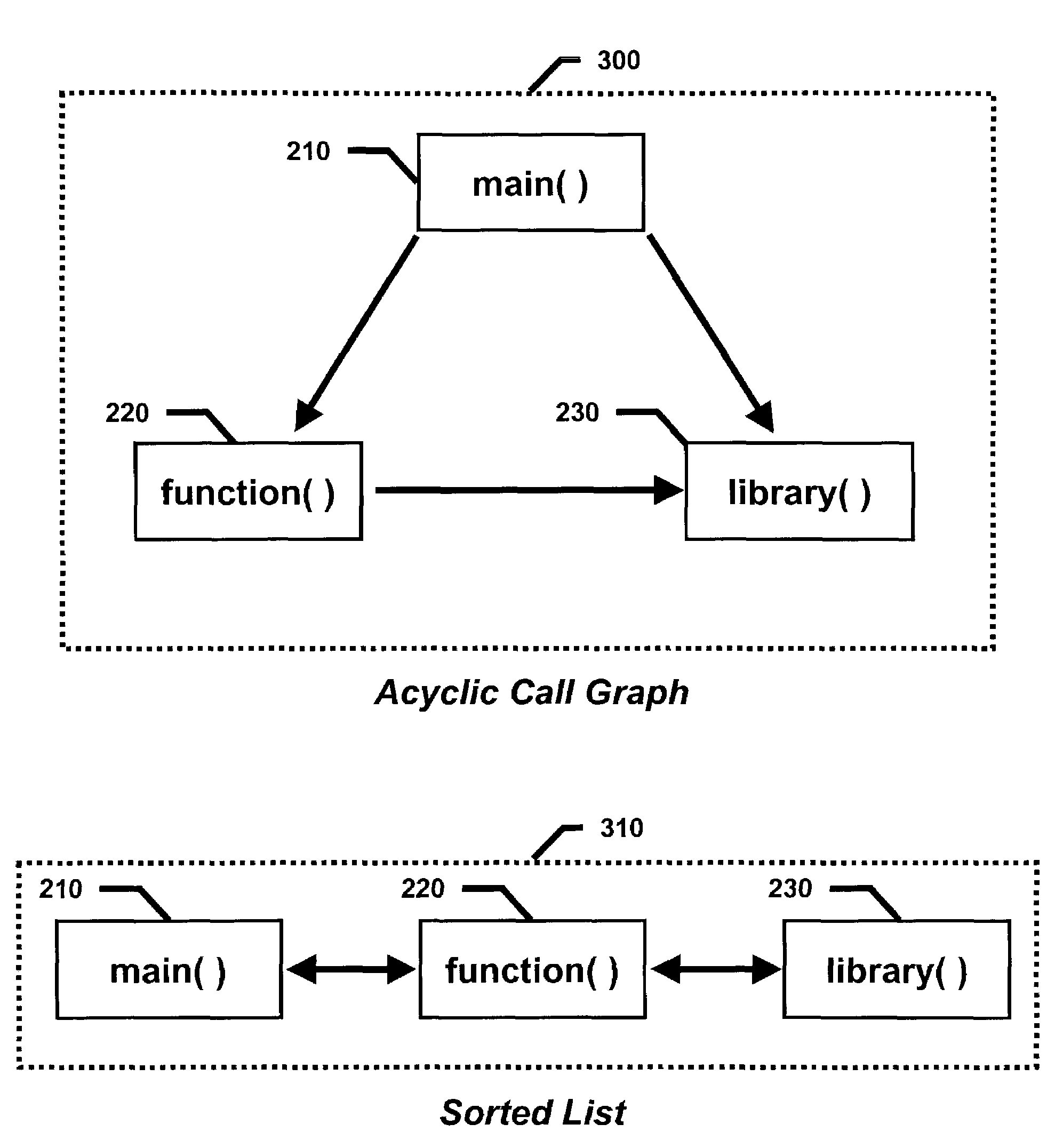

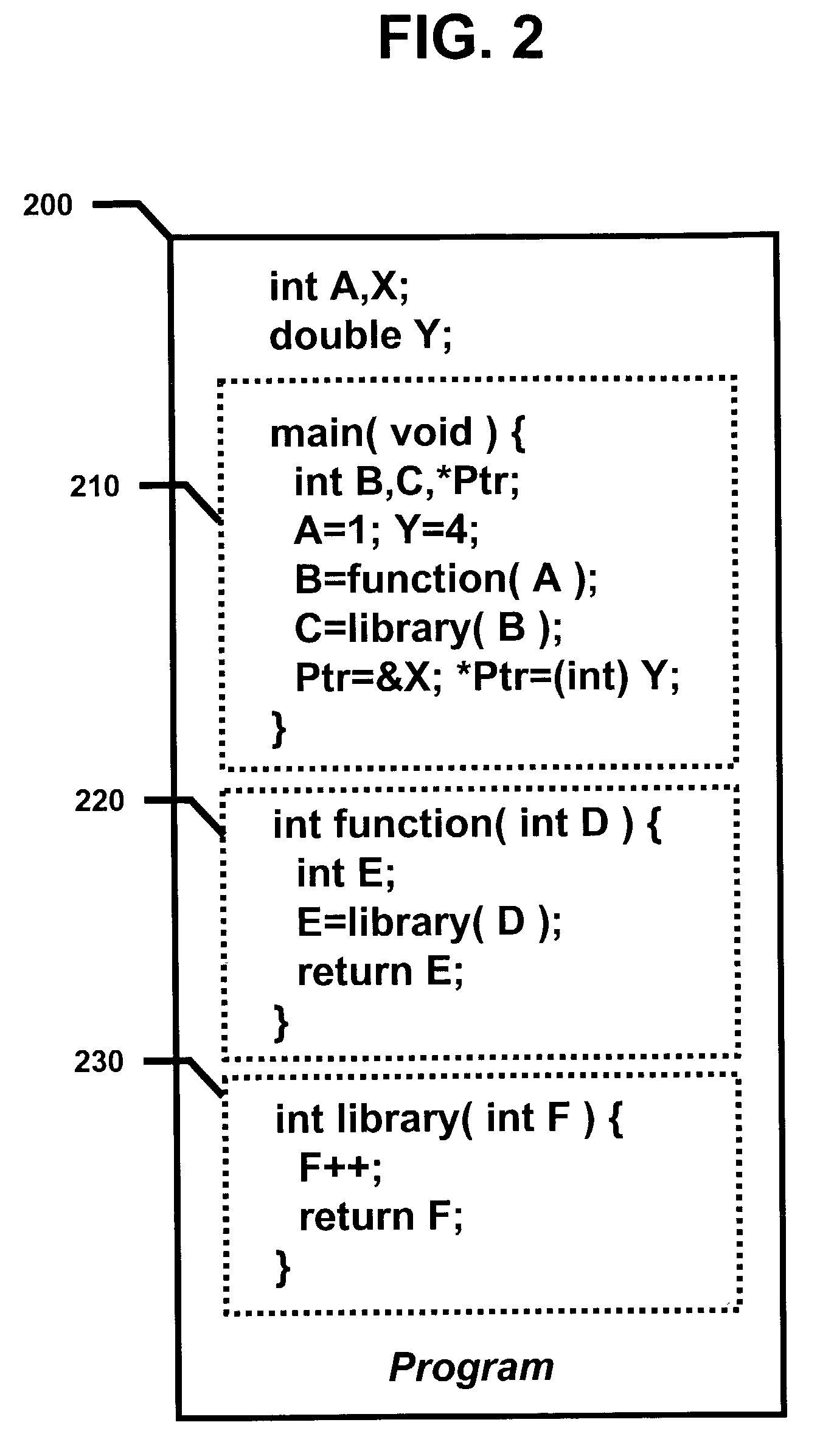

Inter-procedure global register allocation method

Embodiments of the present invention provide a method and system for optimizing processor register allocation. Variables from an acyclic call graph having a plurality of functions may be identified and a plurality of virtual registers may be created by assigning each of the identified variables to at least one virtual register. An interference graph may be constructed based on the plurality of virtual registers and may be colored with a plurality of physical registers. If the interference graph is not colorable, then at least one virtual register may be spilled from the interference graph.

Owner:INTEL CORP

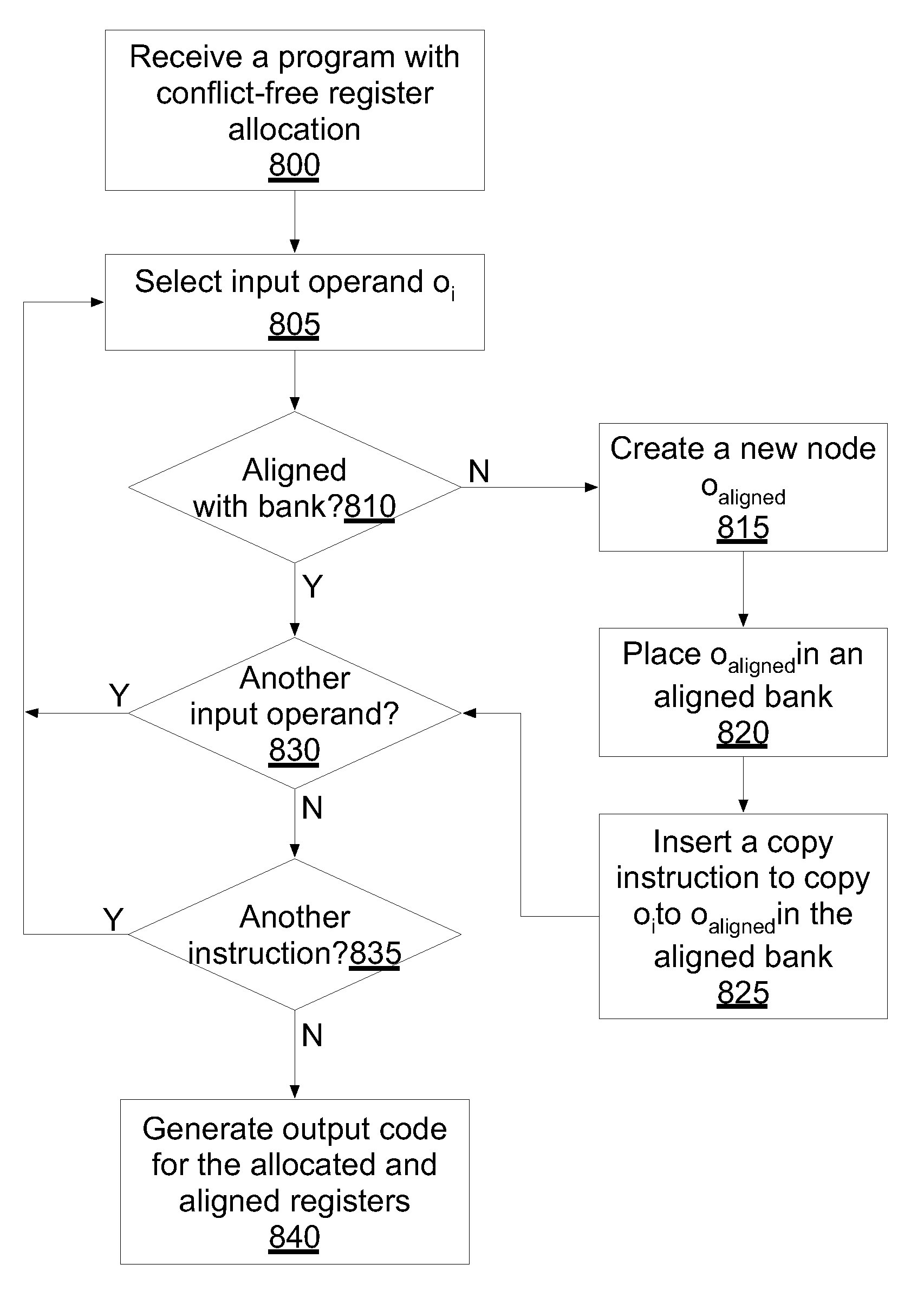

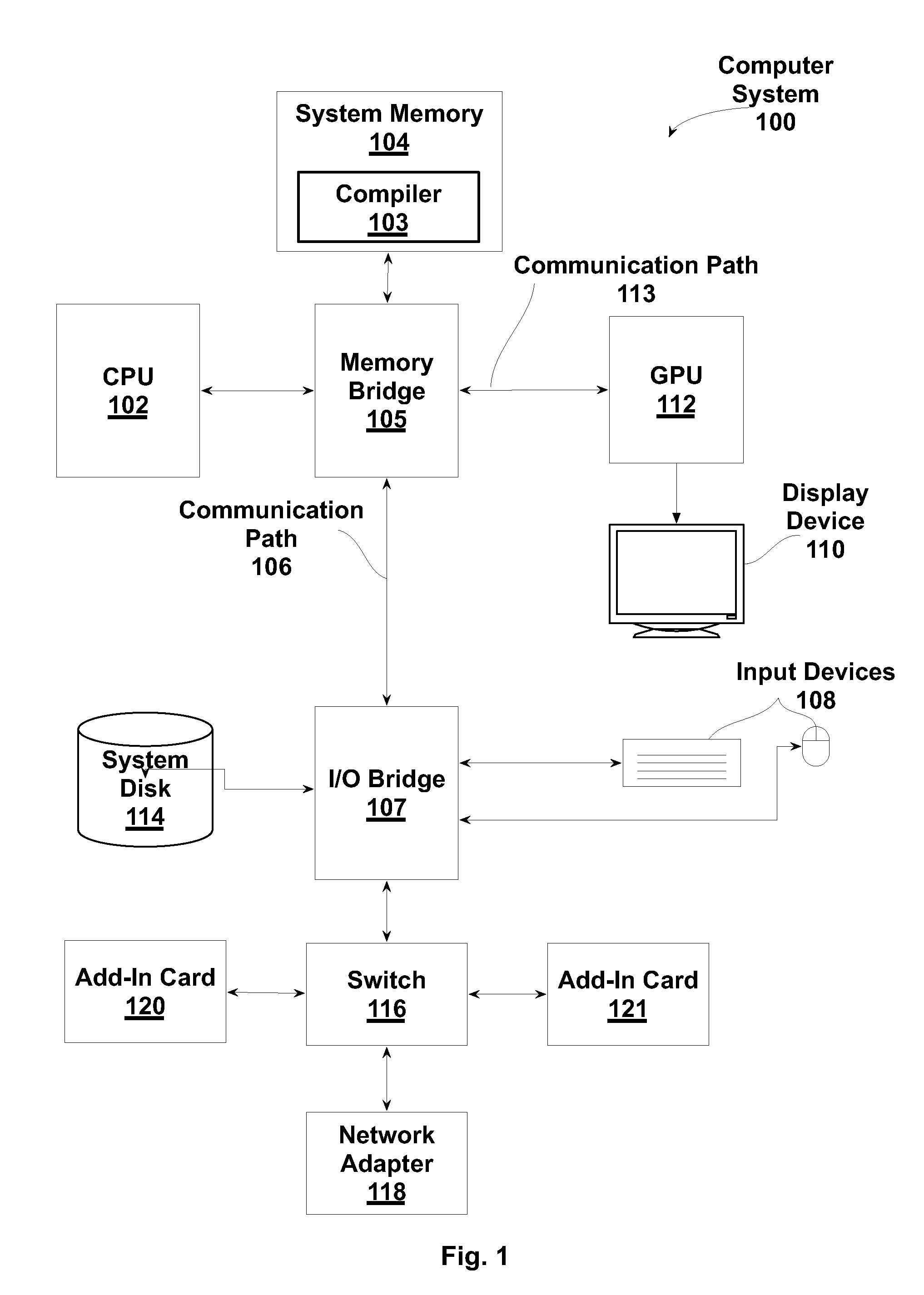

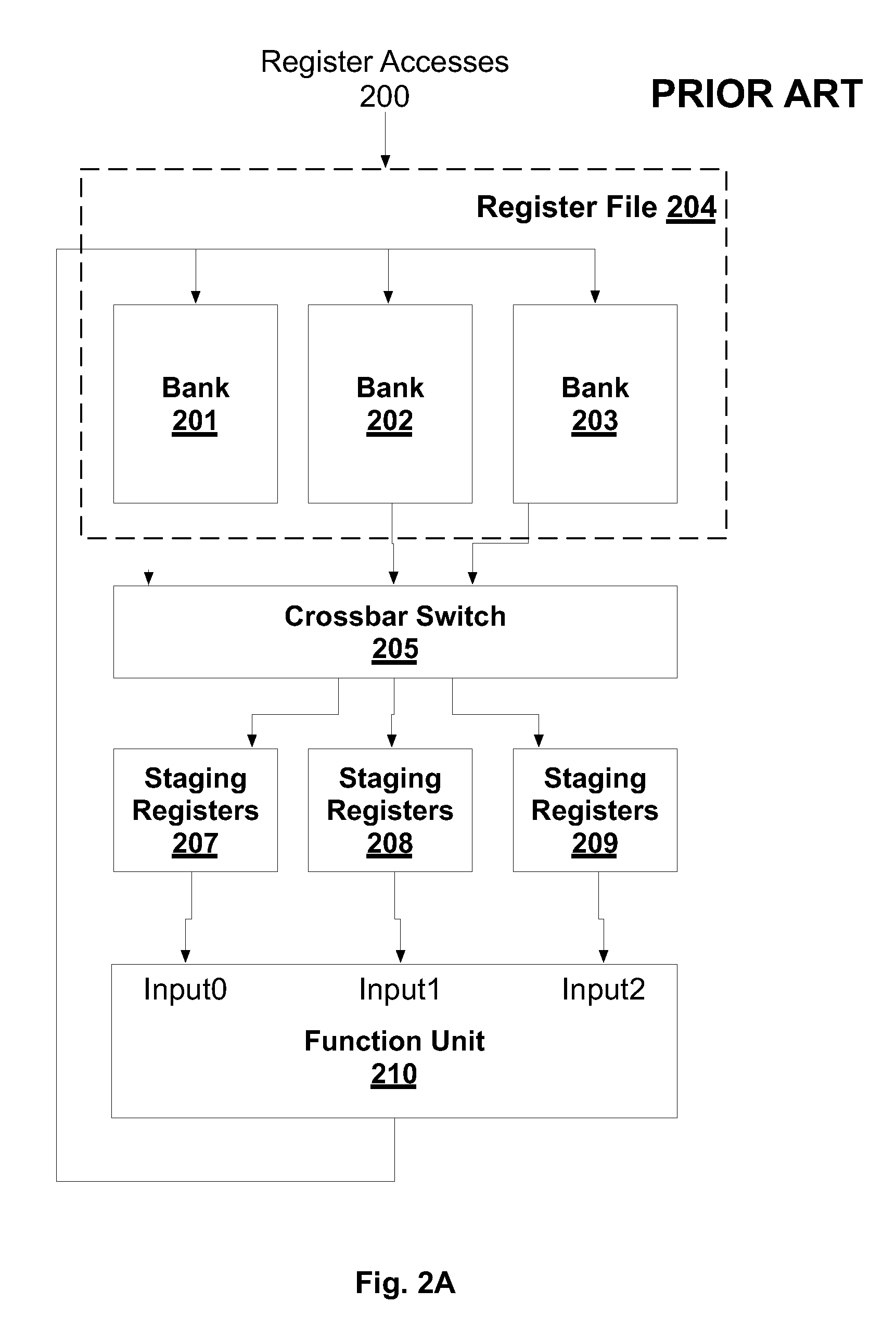

Conflict-free register allocation using a multi-bank register file with input operand alignment

ActiveUS8555035B1Small sizeLower latencySoftware engineeringDigital computer detailsRegister allocationProcessor register

One embodiment of the present invention sets forth a technique for using a multi-bank register file that reduces the size of or eliminates a switch and / or staging registers that are used to gather input operands for instructions. Each function unit input may be directly connected to one bank of the multi-bank register file with neither a switch nor a staging register. A compiler or register allocation unit ensures that the register file accesses for each instruction are conflict-free (no instruction can access the same bank more than once in the same cycle). The compiler or register allocation unit may also ensure that the register file accesses for each instruction are also aligned (each input of a function unit can only come from the bank connected to that input).

Owner:NVIDIA CORP

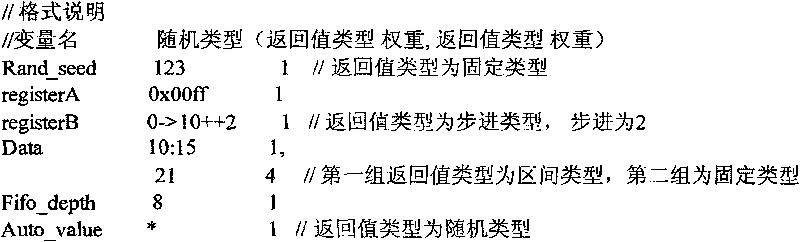

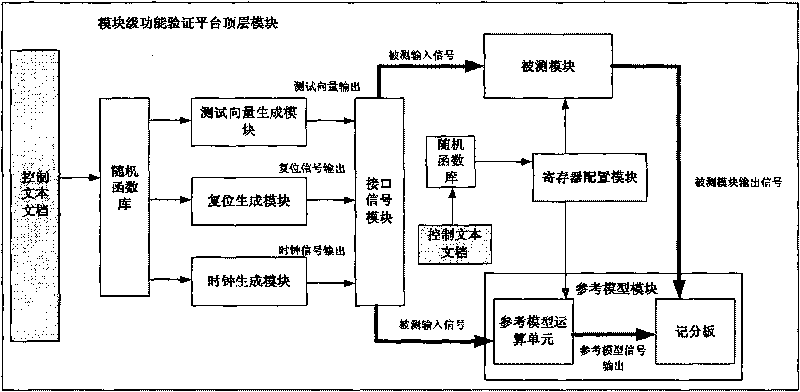

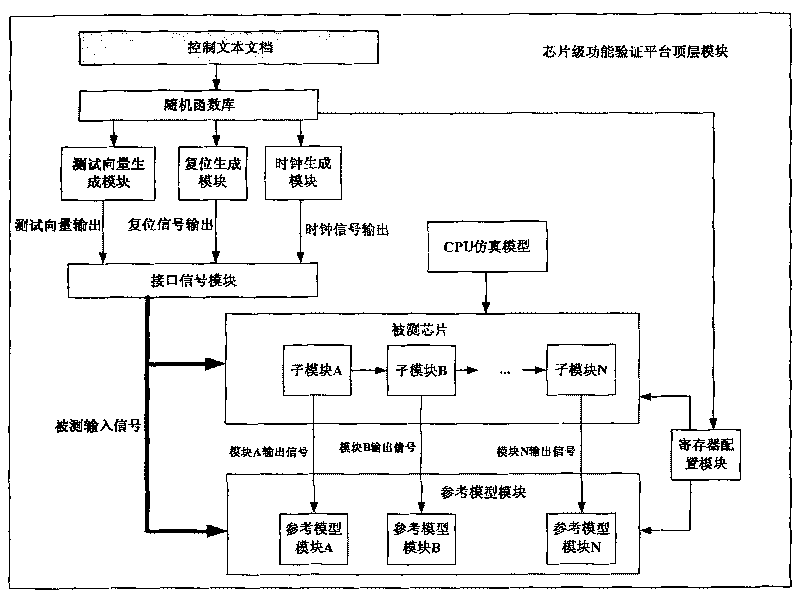

Method for establishing large-scale network chip verification platform

ActiveCN101763451ARealize multiplexingReduce build timeSpecial data processing applicationsRegister allocationReference model

The invention relates to a method for establishing a large-scale network chip verification platform. The method comprises the following steps of: firstly, establishing a control text document, and then writing an initial function of a random function library, and writing a calling function of the random function library; secondly, establishing a module-level function verification platform, comprising the following steps of: generating a top-level module of the module-level function verification platform, establishing a clock generating module and a reset generating module, establishing an interface signal module, establishing a test vector generating module, establishing a register configuring module and establishing a reference model module of a tested module; and thirdly, establishing a chip-level function verification platform, comprising the following steps of: generating a top-level module of the chip-level function verification platform, multiplexing the clock generating module, the rest module, the interface signal module, the test vector generating module, the register configuring module and the reference model module of the module-level function verification platform, and establishing a CPU simulation model. The method has a strong function, high efficiency, stability and simple structure. By means of the invention, the time for setting up the network chip verification platform can be greatly shortened and the stimulation efficiency can be improved.

Owner:丁贤根

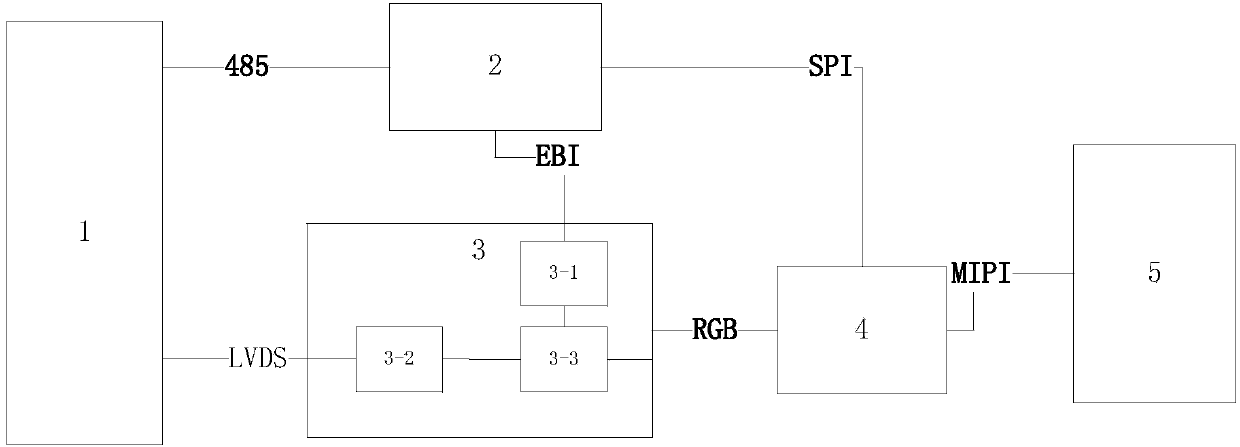

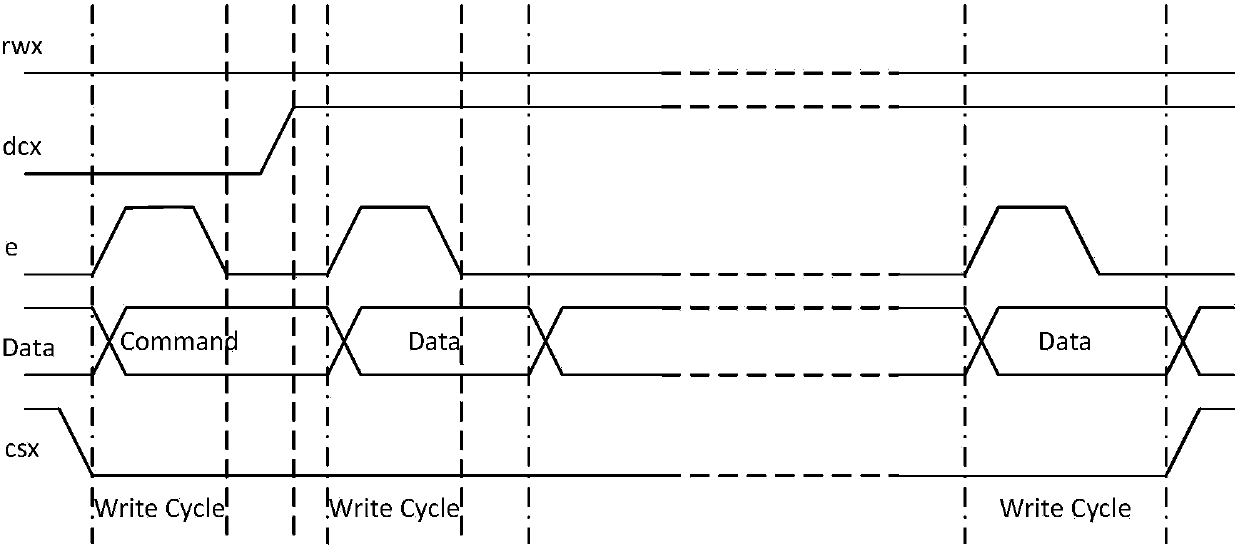

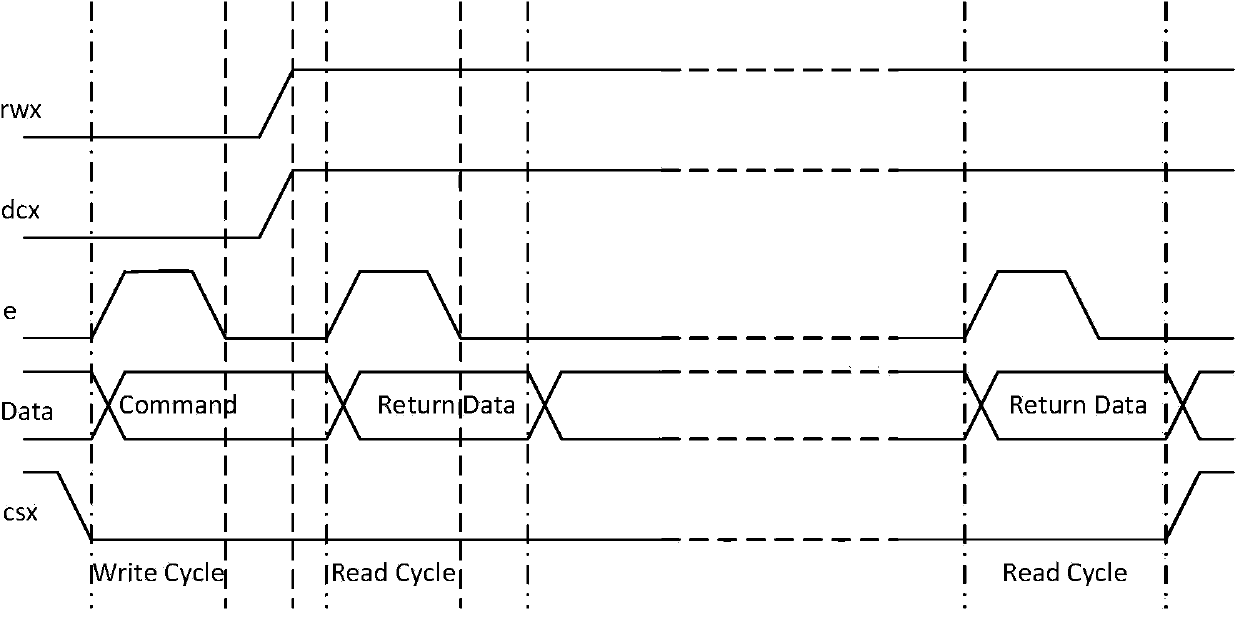

Test method and test system for implementing COMMAND-mode MIPI (mobile industry processor interface) modules

ActiveCN104217667ARealize point screen testImplement configuration parametersStatic indicating devicesRegister allocationCommunications system

The invention discloses a test method and a test system for implementing COMMAND-mode MIPI (mobile industry processor interface) modules and used for configuration testing of the COMMAND-mode MIPI modules before delivery. The test method mainly includes the steps that a PG (program guidance) image generator sets register configuration parameters and image data according to types of the COMMAND-mode MIPI modules, transmits the register configuration parameters to an MCU (microprogrammed control unit), and transmits the image data to an FPGA (field programmable gate array) through an LVDS (low voltage differential signaling) data bus interface; the MCU generates DCS (data communication system) instructions according to the register configuration parameters and transmits the DCS instructions to the FPGA; the FPGA receives image data signals through the LVDS data bus interface and has the DCS instructions and the image data packaged and transmitted to a bridge chip; the bridge chip transmits the DCS instructions for configuration of the MIPI modules and converts the image data to the MIPI signals which are transmitted to the MIPI modules, and the MIPI modules display the image data according to the MIPI signals to complete testing.

Owner:WUHAN JINGCE ELECTRONICS GRP CO LTD

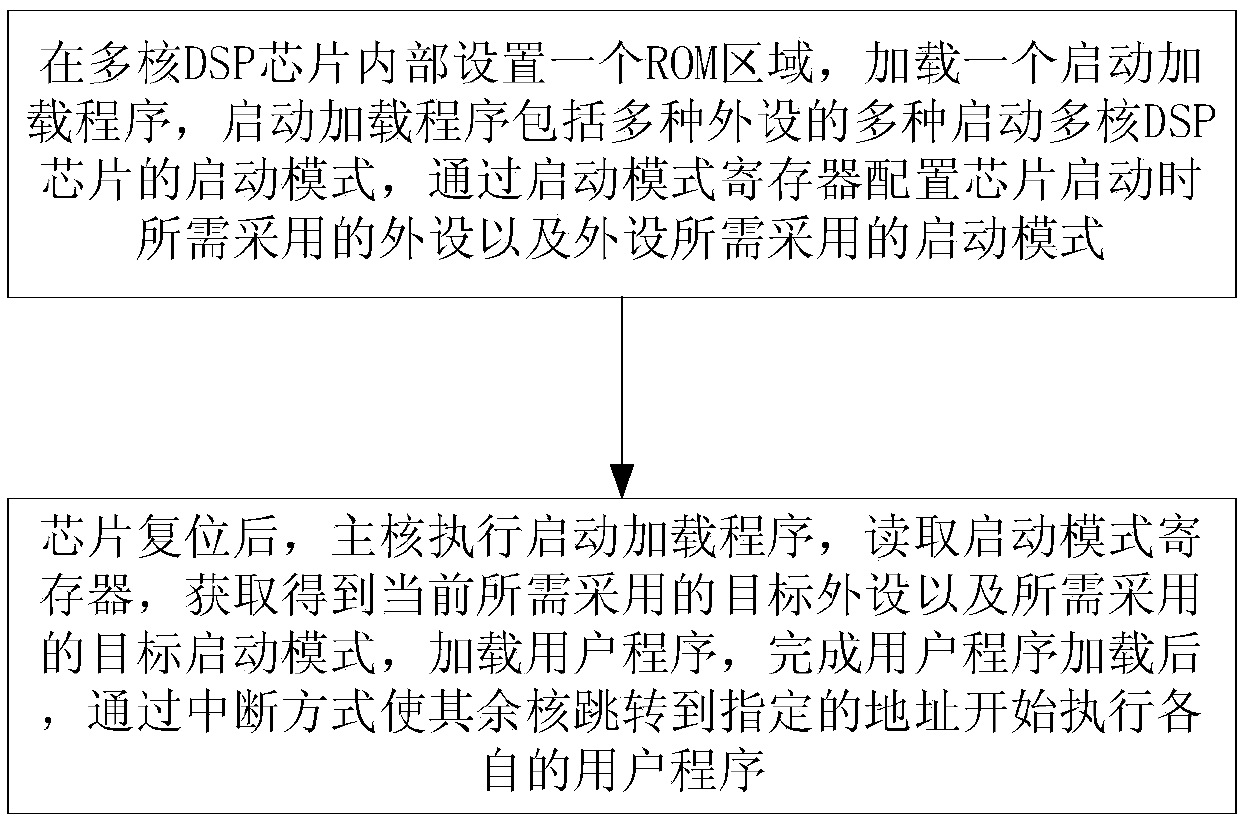

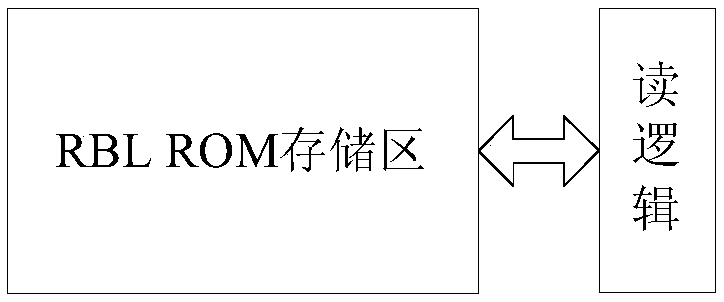

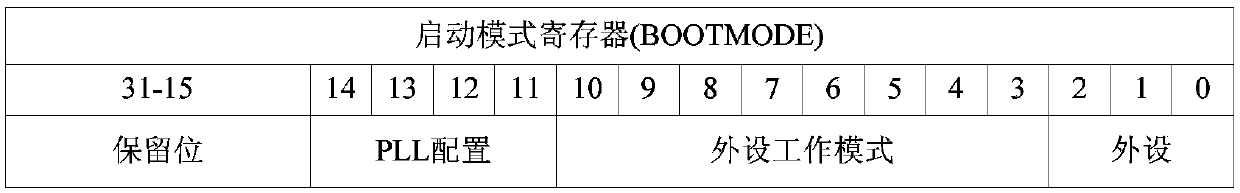

Multi-core DSP starting method

ActiveCN107656773AIncrease flexibilityImprove memory utilizationProgram loading/initiatingRegister allocationProcessor register

The invention discloses a multi-core DSP starting method. The method comprises the steps of S1, arranging an ROM region in a multi-core DSP chip, loading a pre-established start loading program in theROM region, and configuring a peripheral needed to be adopted during chip starting and a starting mode needed to be adopted by the peripheral through a starting mode register, wherein the start loading program comprises multiple starting modes, used for starting the multi-core DSP chip, of multiple peripherals; and S2, after the chip is reset, executing the start loading program by a main core, reading the starting mode register, obtaining the target peripheral needed to be adopted currently and the target starting mode needed to be adopted, loading a user program, and after loading of the user program is finished, enabling other cores to jump to a specified address for starting executing respective user programs in an interrupt mode. The multi-peripheral and multi-mode multi-core DSP starting can be realized; the memory utilization rate and efficiency are high; the application range is wide; and the flexibility is good.

Owner:NAT UNIV OF DEFENSE TECH

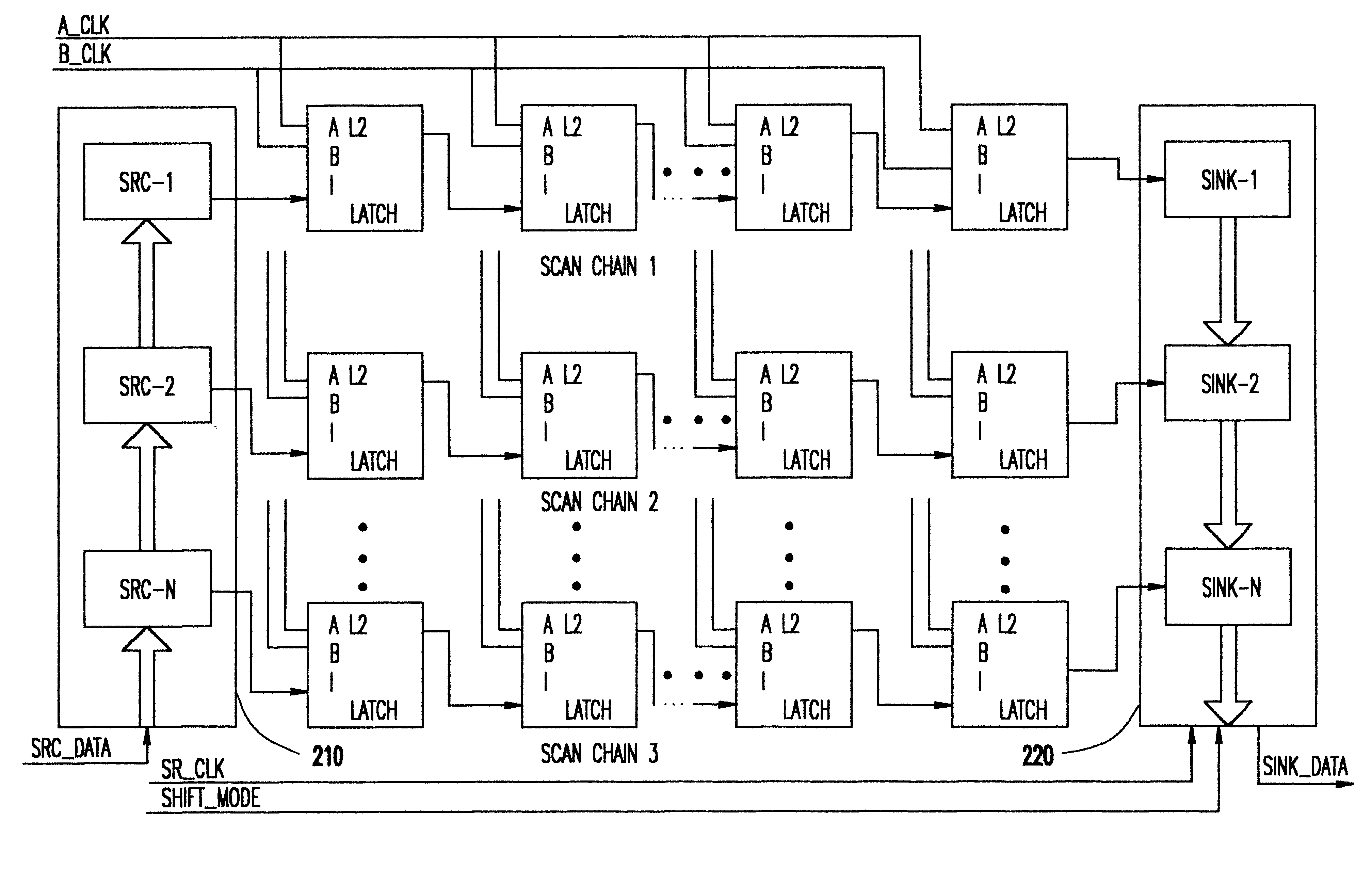

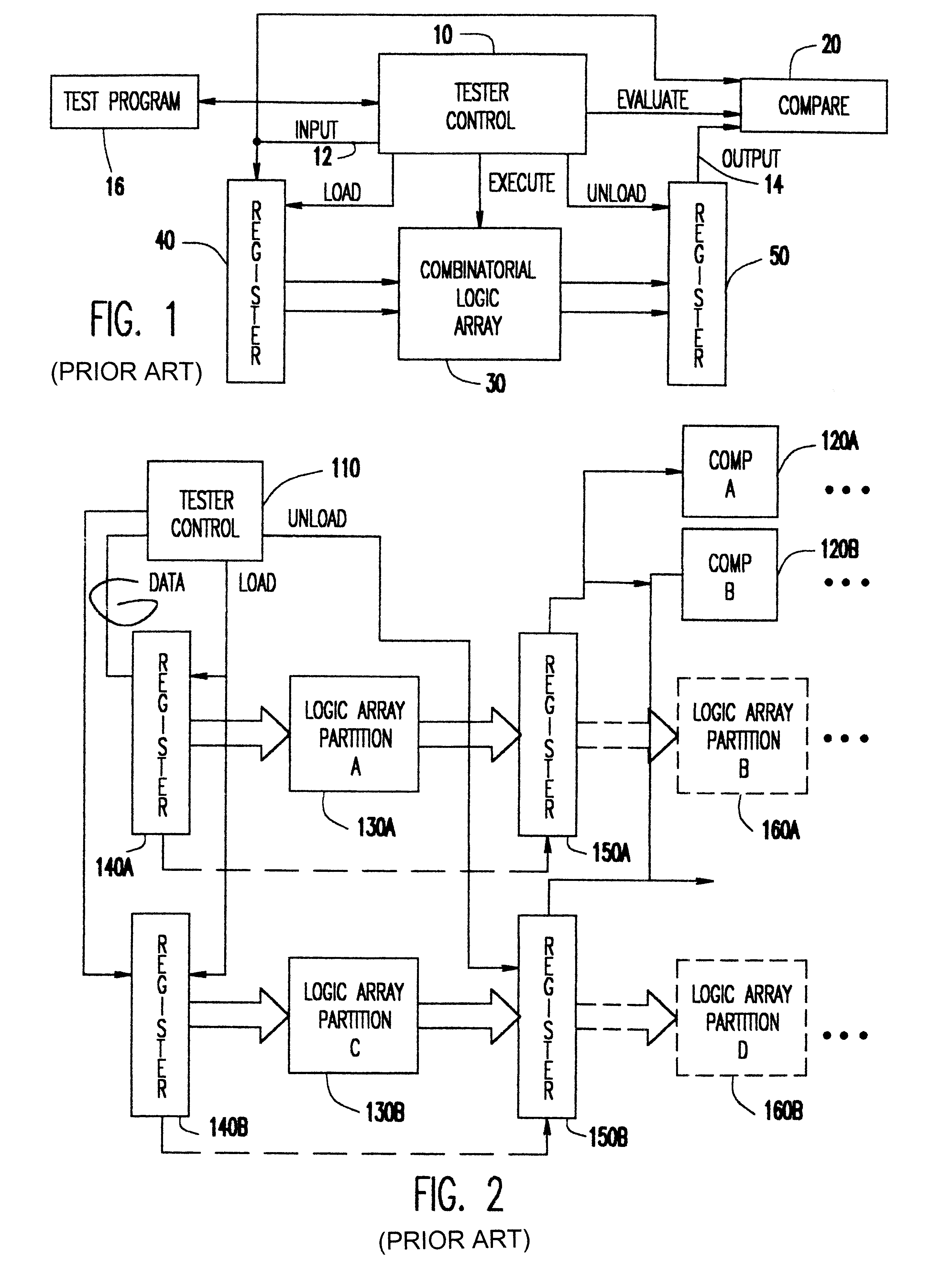

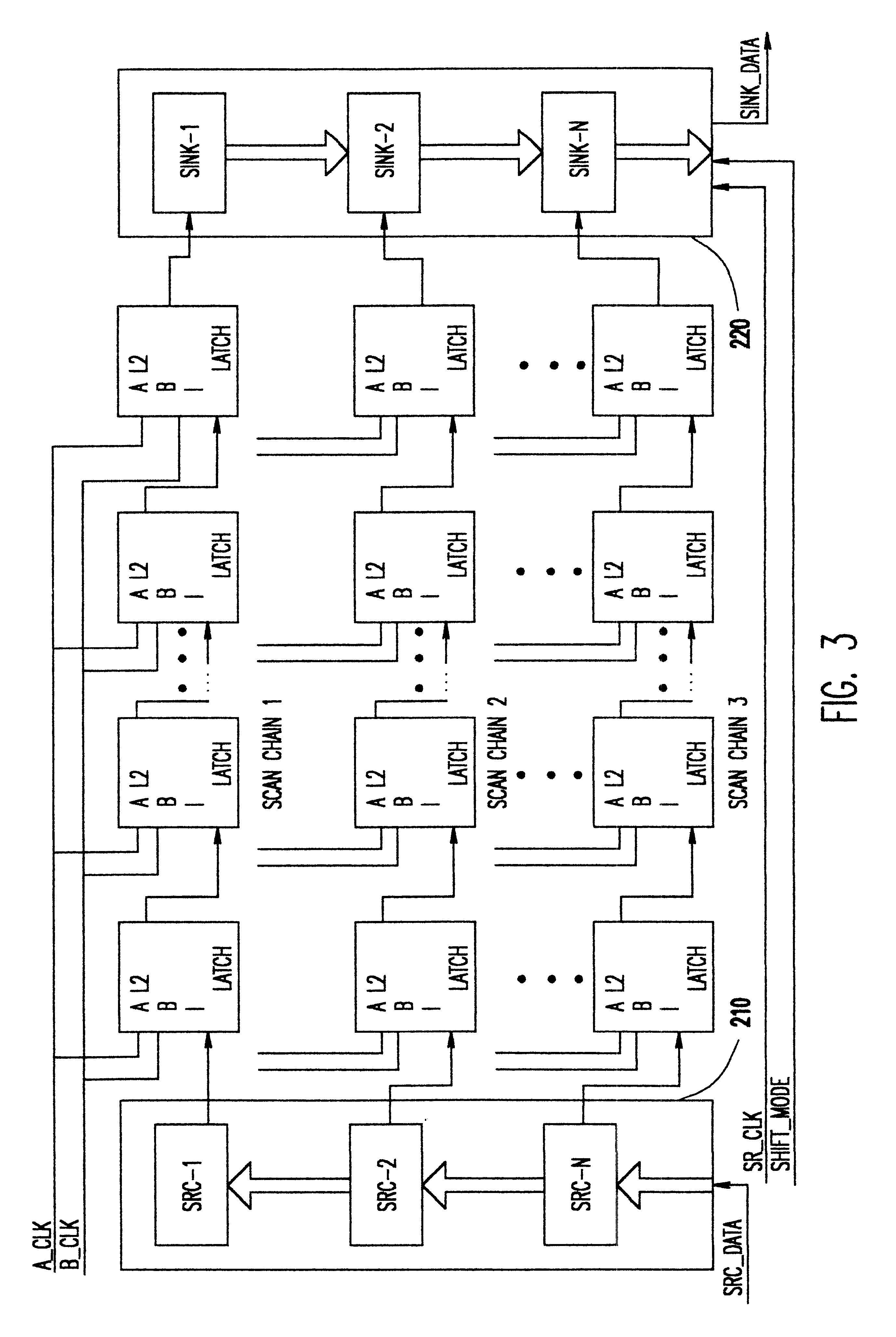

High speed sink/source register to reduce level sensitive scan design test time

InactiveUS6591388B1Reducing time and tester apparatus overheadShorten test timeElectronic circuit testingLogic circuitsRegister allocationShift register

Test data is provided through shift registers, operated at a high clock rate comparable to or exceeding a normal high speed clock rate of a chip being tested, to each of a plurality of scan chains configured from registers present on the chip; respective latches of which are connected to inputs and outputs of logic array partitions to be tested. Reduced test clock rate of input and output circuits of the scan chains is accommodated by high speed source and sink shift registers. The source and sink registers are fully loaded and unloaded between consecutive test clock signals and test signals are preferably applied to and collected from the chip in a single serial string through a single pair of tester input / output pins. Testing time is thus reduced without requiring design time and chip space for a clock tree optimized for high speed operation while use of testers of reduced cost and having an arbitrarily small number of input / output pin pairs and independent of test register configuaration on the chip can be used.

Owner:IBM CORP

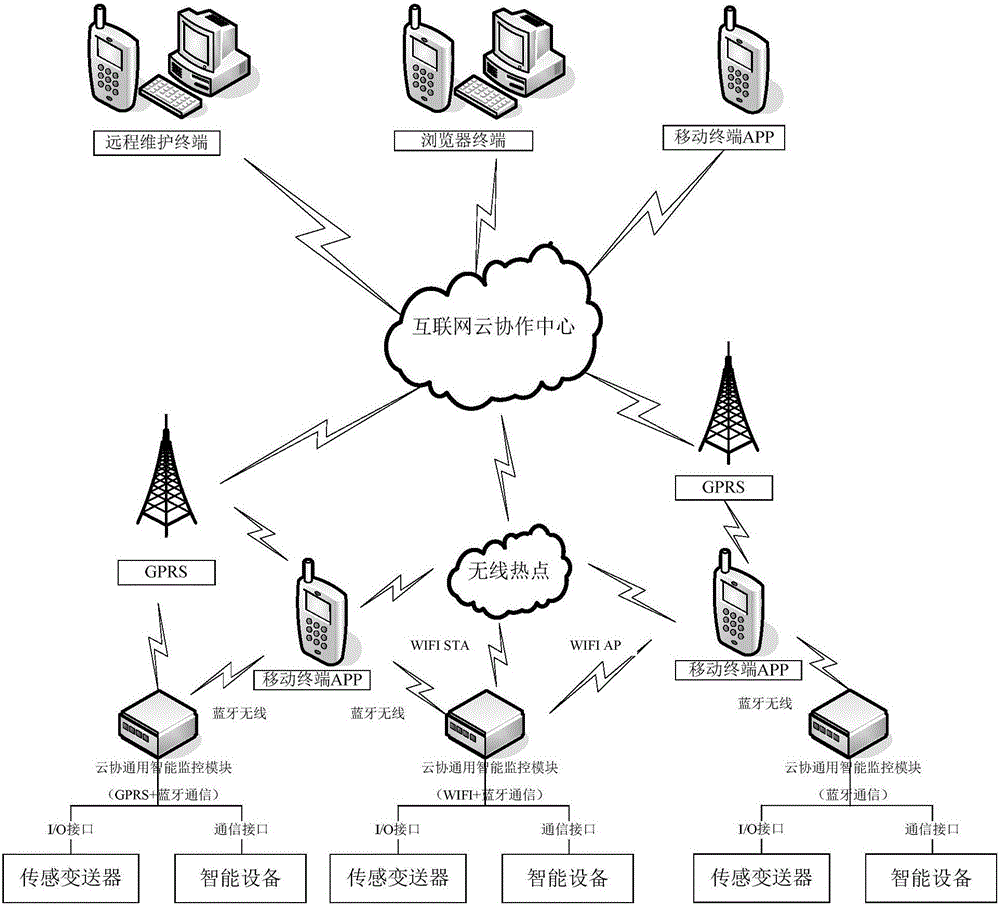

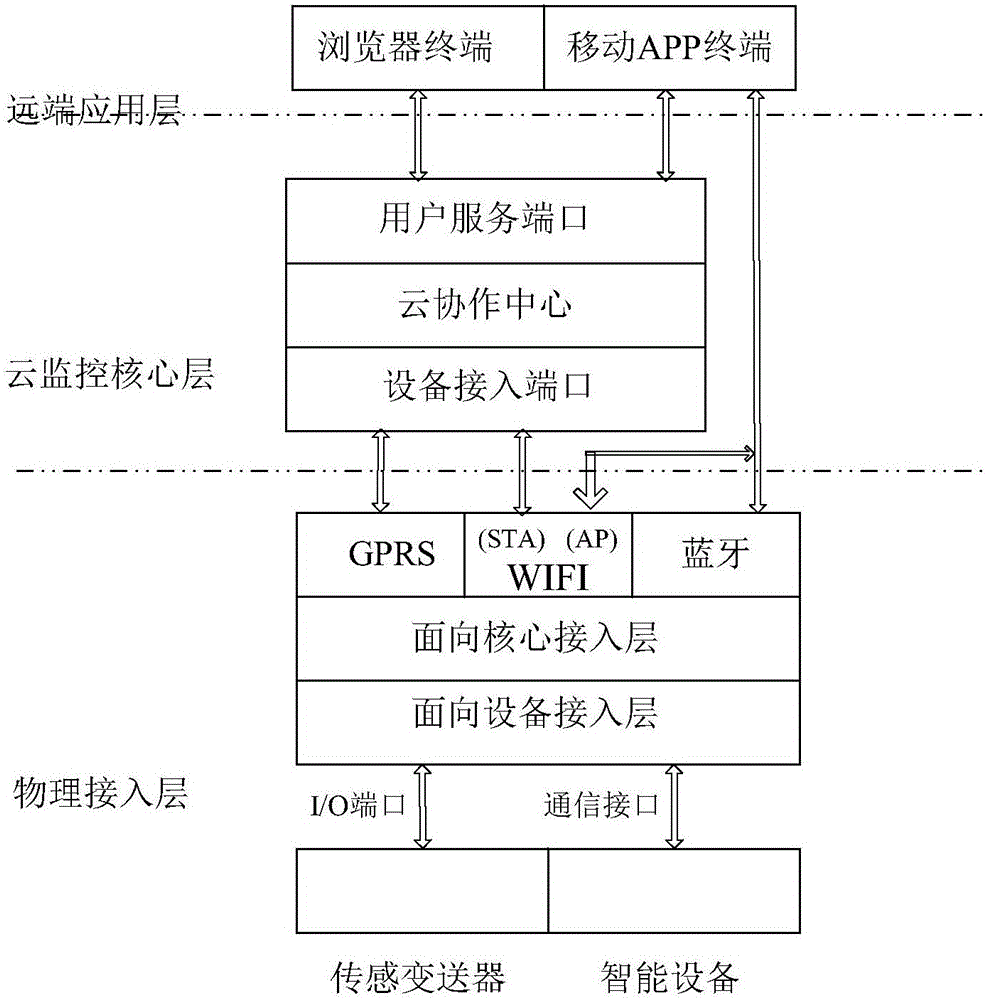

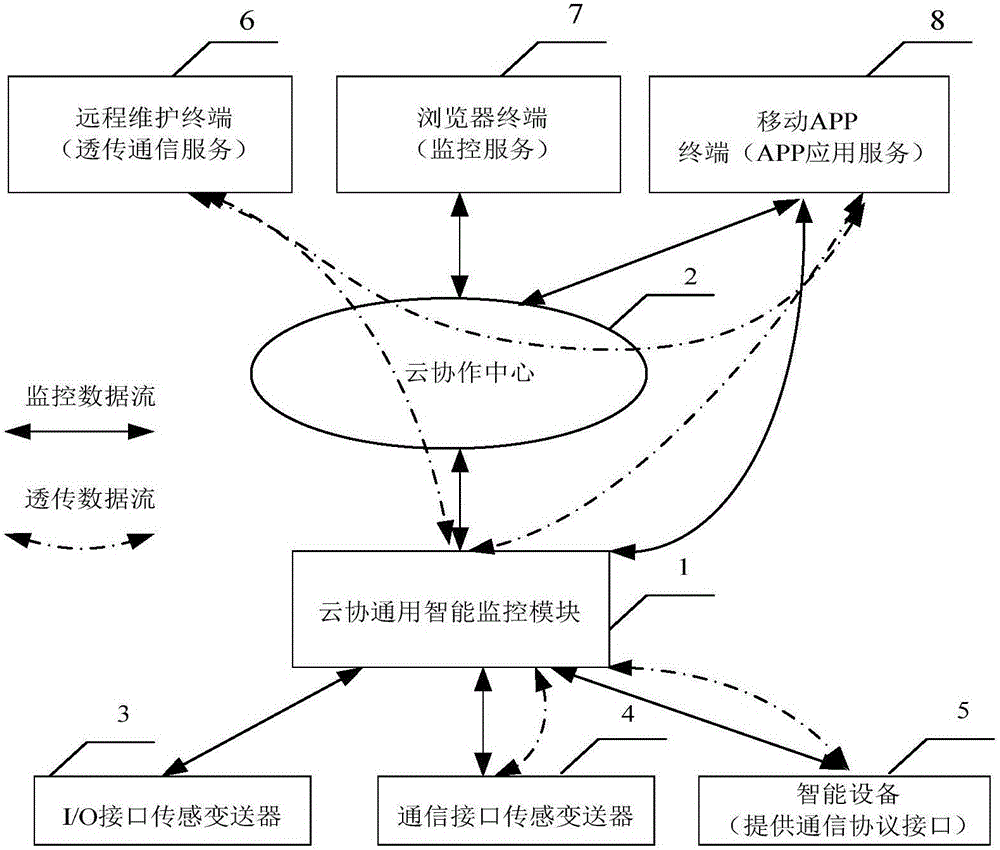

Cloud-cooperation general intelligent remote monitoring system

InactiveCN105717848ASolve local debuggingResolve escalationProgramme controlComputer controlRegister allocationMobile apps

A cloud cooperation general intelligent remote monitoring system, including a cloud collaboration center, a browser terminal, a mobile APP terminal, a remote maintenance terminal, user equipment, and a cloud cooperation general intelligent monitoring module; the cloud collaboration center consists of a cloud server, a cloud database, and a cloud monitoring platform The cloud monitoring platform is deployed on the cloud server, and the cloud collaboration center is connected to the general intelligent monitoring module of the cloud association through the Internet; the user equipment is connected to the general intelligent monitoring module of the cloud association; the general intelligent remote monitoring module of the cloud association is equipped with a device configuration information module , I / O configuration module, smart device configuration module, register configuration information module, I / O channel data detection module, RS485 communication interface detection module, RS232 communication interface detection module, CAN communication interface detection module, Ethernet communication interface detection module, Communication port data transparent transmission module, data packet module.

Owner:湖南云协智造信息科技有限公司 +1

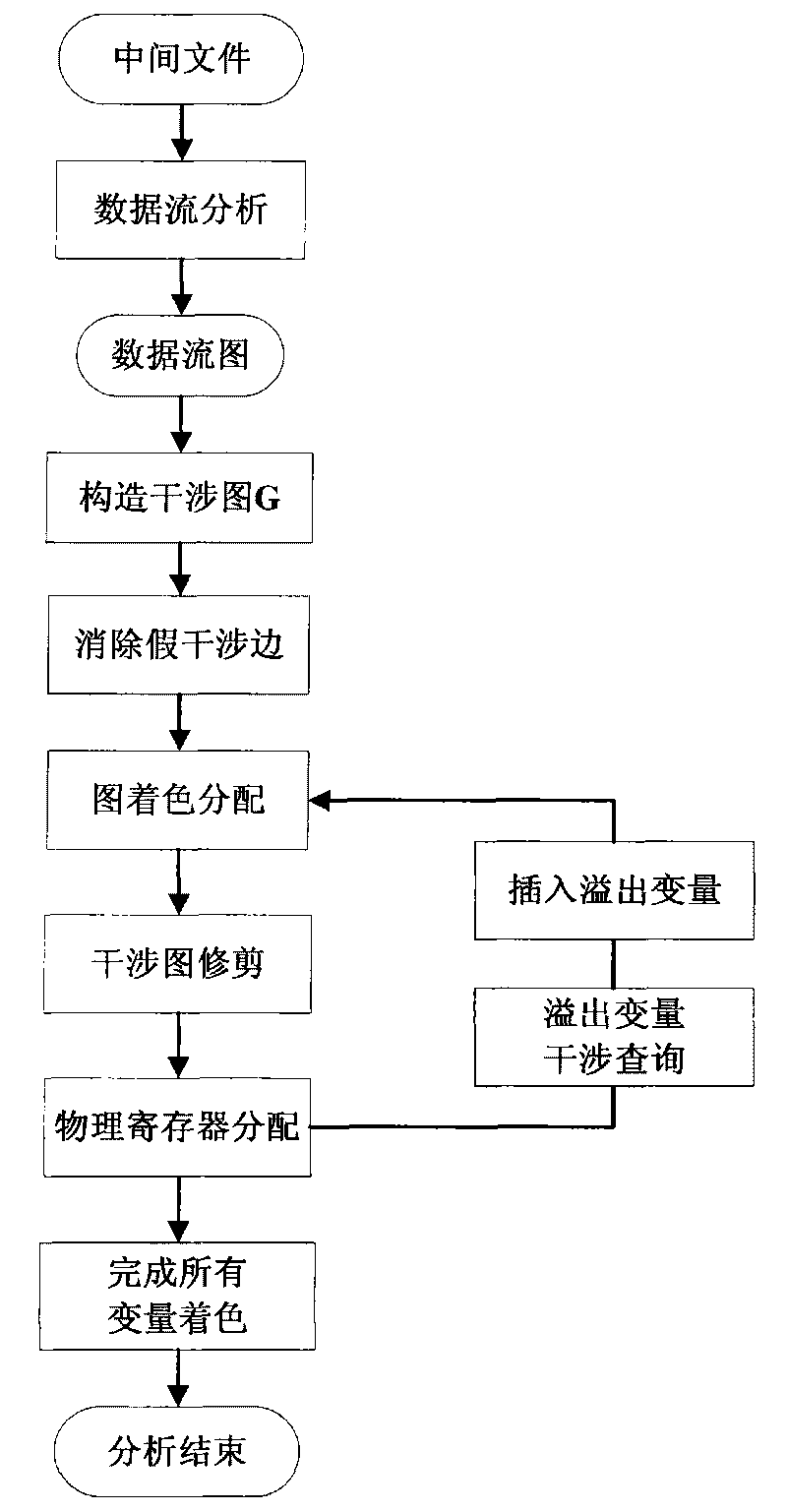

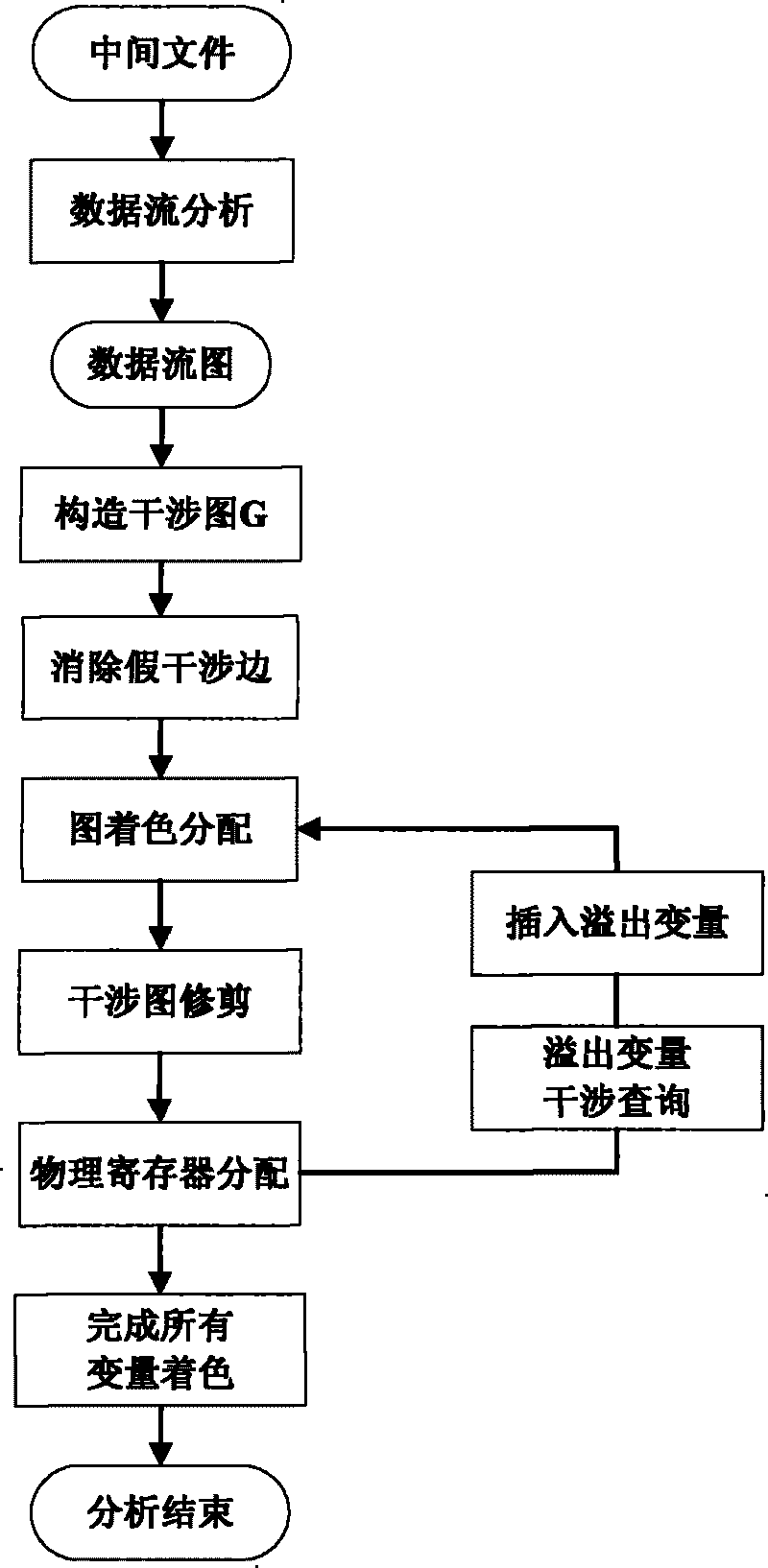

Register allocation method for optimizing stack space

InactiveCN101710291AReduce overflowReduce occupancyProgram controlMemory systemsRegister allocationProcessor register

The invention provides a register allocation method for optimizing stack space, which comprises the following steps: 1, analyzing a program intermediate file by a register allotter to obtain a data flow diagram; 2, constructing interference patterns of program variables according to the data flow diagram; 3, optimizing the interference patterns to eliminate false interference edges; 4, trying to color the interference patterns, if the step is successful, indicating no variable overflow and stopping allocating the registers, and otherwise performing the next step; 5, abridging the interferencepatterns, and overflowing the low-priority variables to a stack; 6, allocating the number of actual physical registers for the highest-priority virtual registers; and 7, aiming at the overflow nodes of the step 5), inserting the corresponding codes, and querying the accurate interference patterns of the step 3) to allocate the same stack offset for noninterference overflow variables. The method for eliminating the false interference edges comprises the steps: for two interference variables, further analyzing interference variables which are not intersected with an inference register to deletea connection line of the two variables and eliminate the false interference edges.

Owner:INST OF ACOUSTICS CHINESE ACAD OF SCI

Debug system having assembler correcting register allocation errors

InactiveUS20050210457A1Error detection/correctionProgram controlRegister allocationParallel computing

An assembler, which can be provided as part of a debugger and / or development system, avoids register allocation errors, such as register bank conflicts and / or insufficient physical registers, automatically.

Owner:INTEL CORP

Method and apparatus for generating pseudo-random numbers

ActiveUS7082449B2Random number generatorsSecuring communicationRegister allocationProcessor register

A method and apparatus for generating pseudo-random numbers. The method includes defining a first set of R bits and defining a second set of S bits different from the first set of R bits. The method also includes updating the second set of S bits using a predetermined process that operates on the first set of R bits and the second set of S bits to form an updated set of S bits. The method also includes updating the first set of R bits using another predetermined process. The apparatus may include a linear feedback shift register and a second register. The linear feedback shift register is configured to store R bits. The second register is configured to store S bits. Each bit of the S bits is updated using a function that operates on one or more of the R bits from the linear feedback shift register and one or more of the S bits.

Owner:ORACLE INT CORP

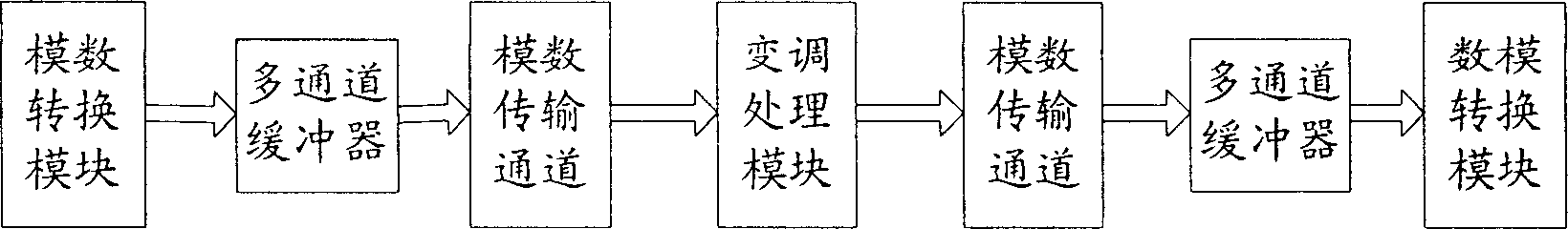

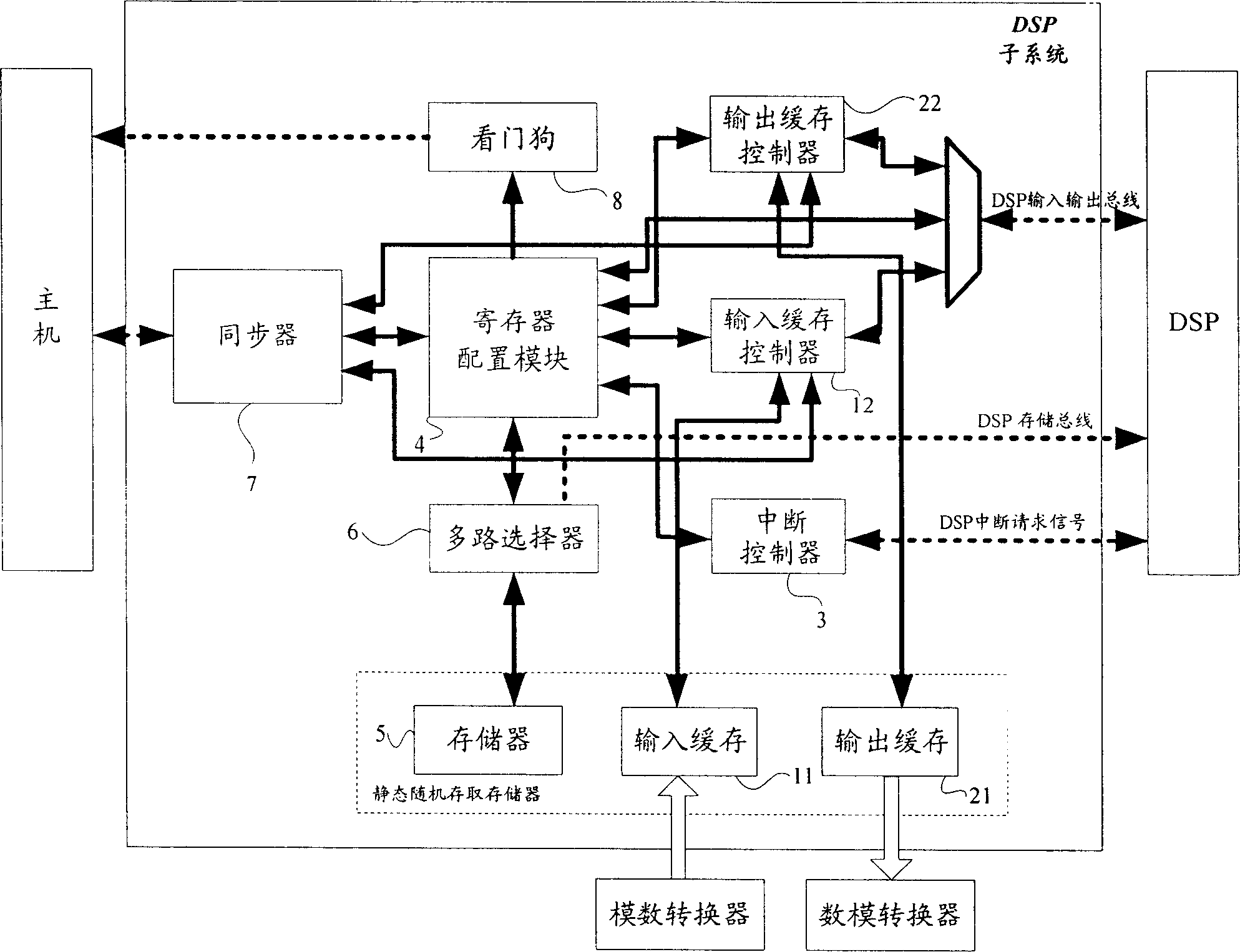

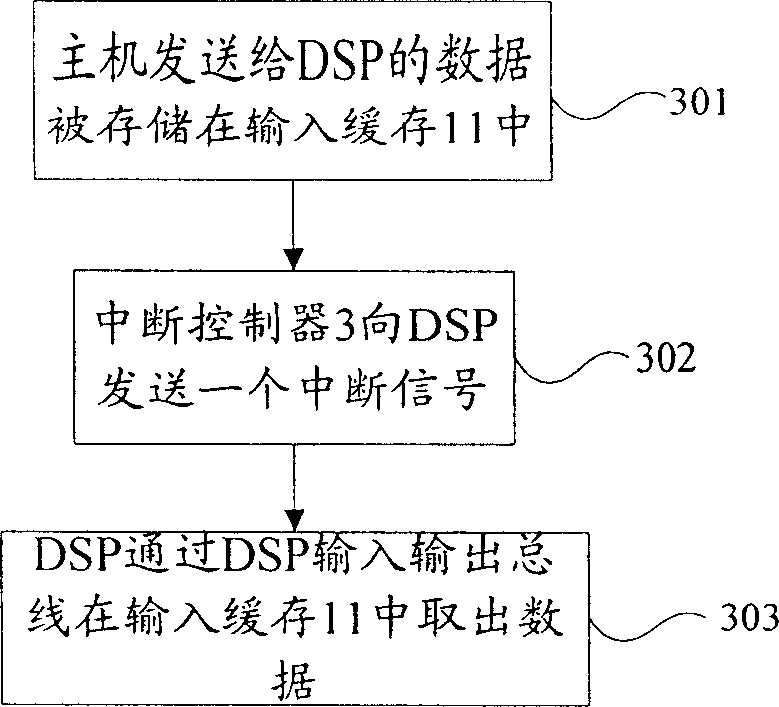

Digital signal processor subsystem and data processing method thereof

InactiveCN1889063AFlexible control of data flow interactionFlexible depth controlElectric digital data processingCollocationRegister allocation

The invention discloses a digital signal processor subsystem connected between the host computer and the digital signal processor. It includes the inputting buffer module to store the inputting data and control the data sending; the outputting buffer module to store the output data and control the data sending; the interrupting controller to send the interrupt request signal; the register collocation module to allocate the parameter. The invention also discloses a data processing method. The data is stored in the inputting buffer memory when the host computer transfers the data to the processor, the processor controlled by the interrupting signal reads the data from the inputting buffer memory; the data is stored in the outputting buffer memory when the processor sends the data to the host computer, when the output buffer memory reaches a setting state, the memory controller will inform the host computer to read the data. The invention can control the depth of the buffer memory module flexibly, so it can use the hard ware resource fully and the other it can control the processing speed of data.

Owner:VIMICRO CORP

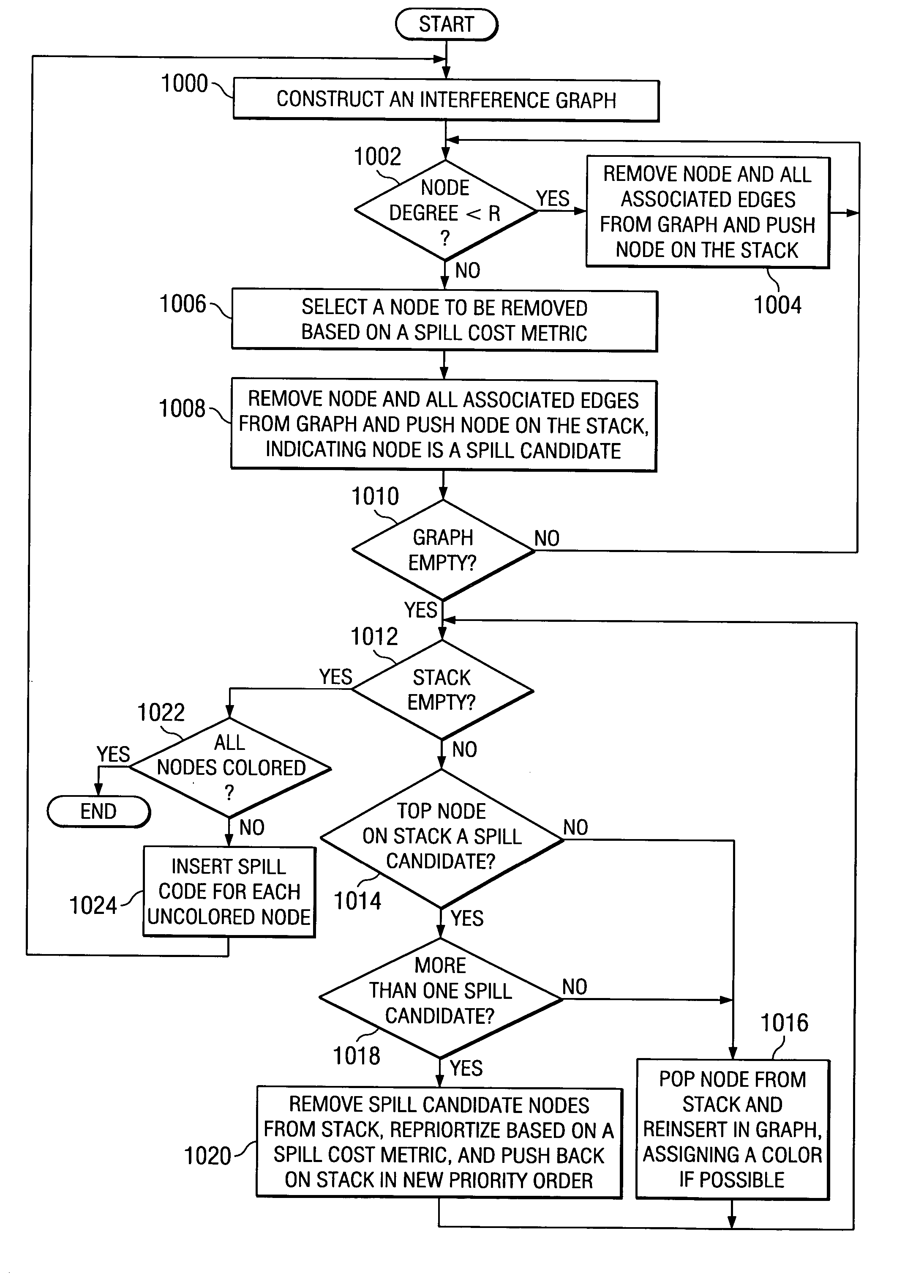

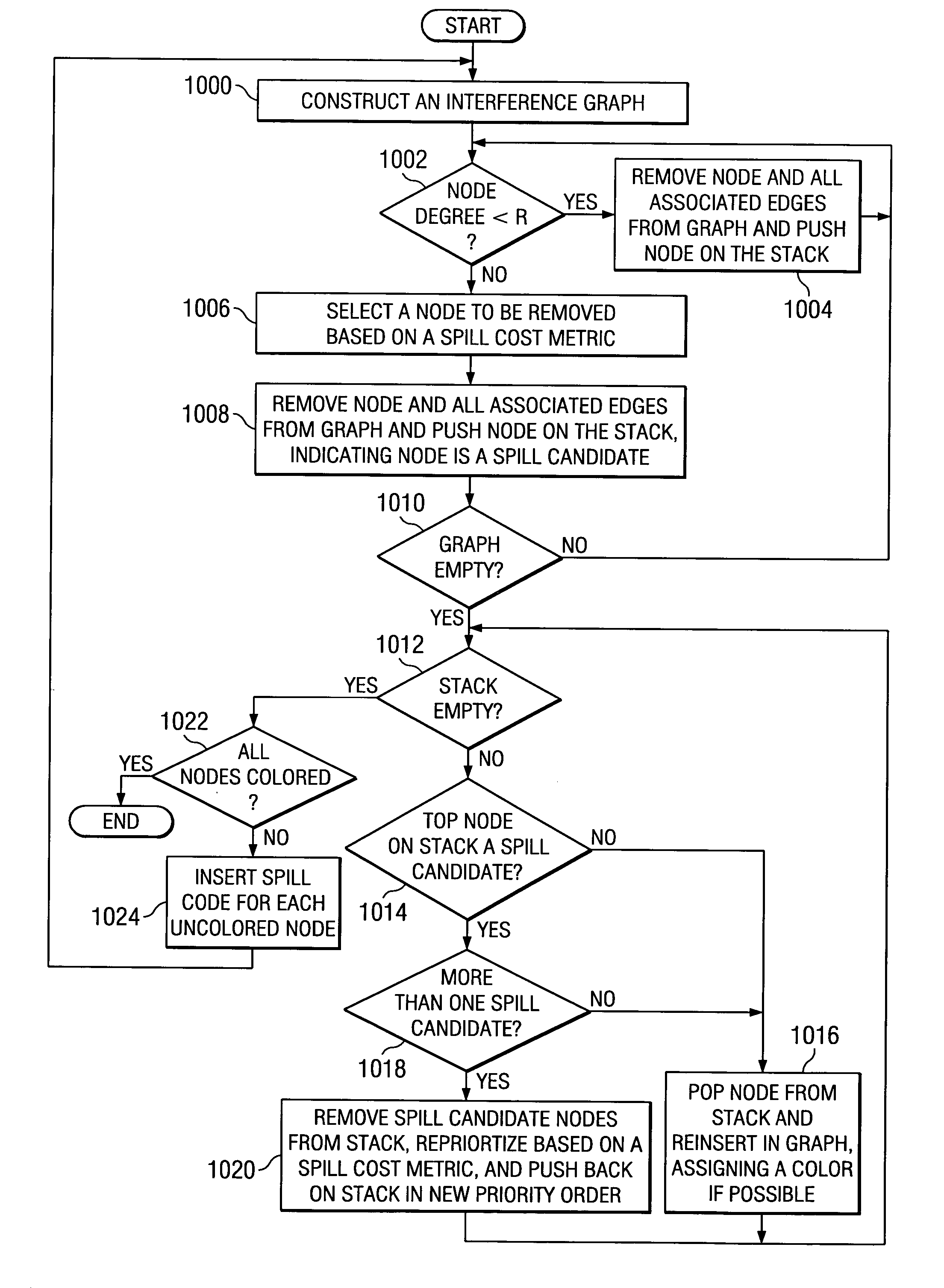

Register allocation and code spilling using interference graph coloring

ActiveUS20050039175A1Achieve colorColor interferenceSoftware engineeringSpecific program execution arrangementsRegister allocationCost metric

An improved method is provided for performing register allocation in a compiler. This method determines the allocation of a plurality R of registers of a processor for use during the execution of a software program. The register allocation process is treated as a graph-coloring problem, such that an interference graph is constructed for the software program, the graph is simplified, and an R-coloring the interference graph to the extent possible is attempted. Then, spill code is inserted in the software program each for each uncolored node of the graph, a new interference graph is constructed, and the process is repeated. During the simplification process, nodes with degree greater than or equal to R are removed from the graph in an order dictated by a spill cost metric. During the coloring process, these same nodes are reinserted in the graph in an order dictated by reapplying the spill cost metric.

Owner:TEXAS INSTR INC

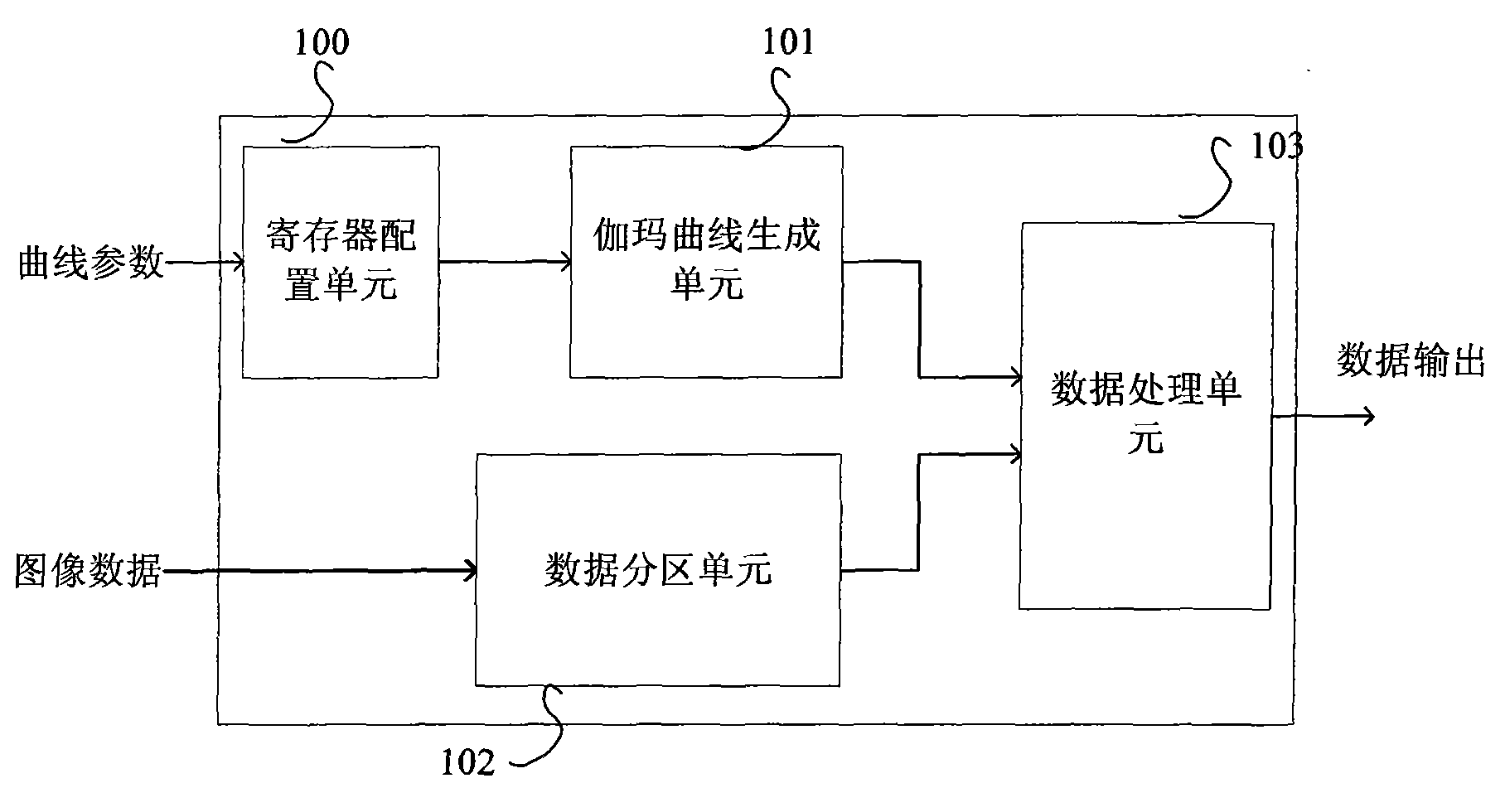

Device and method for regulating image brightness by gamma

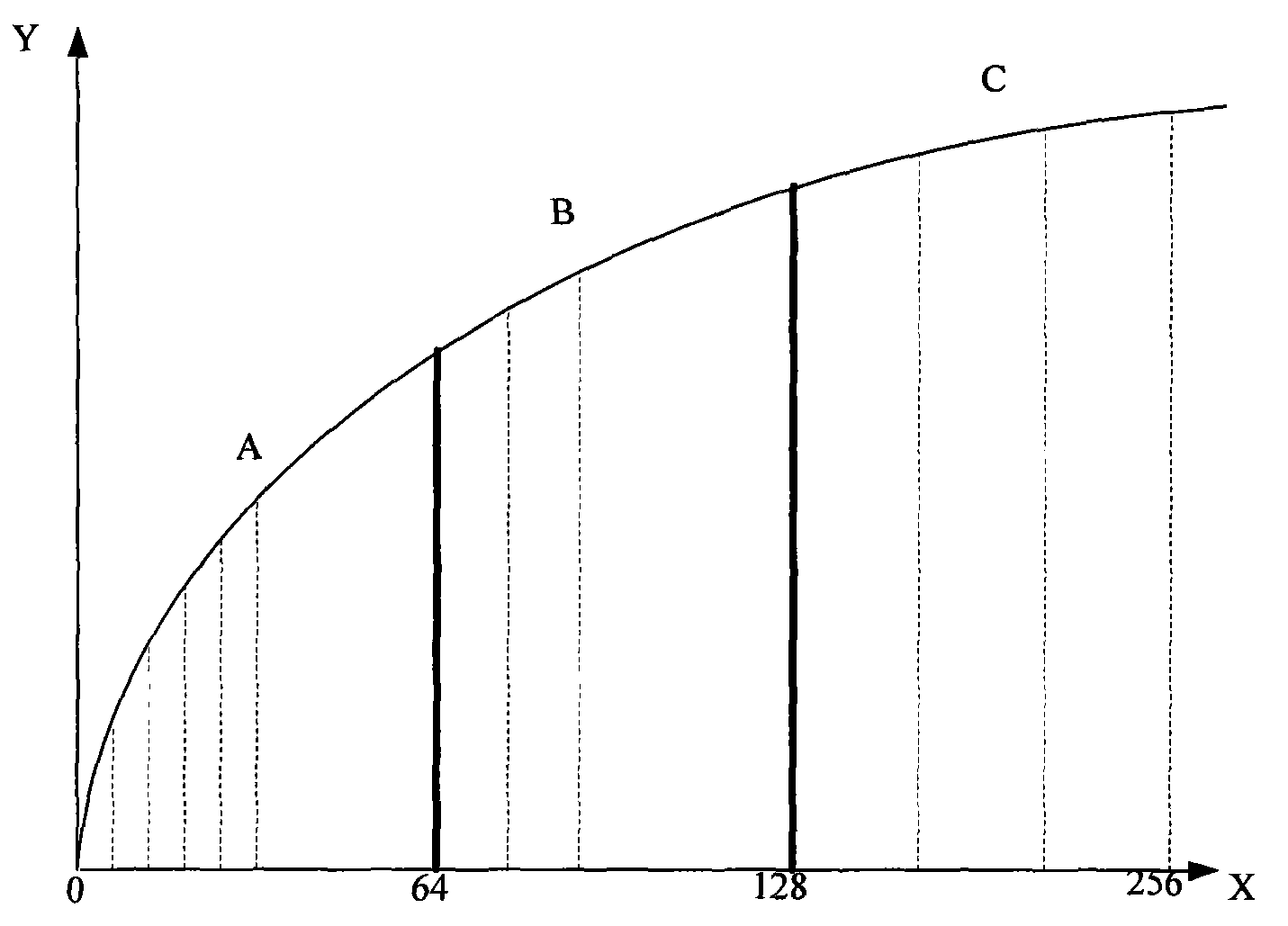

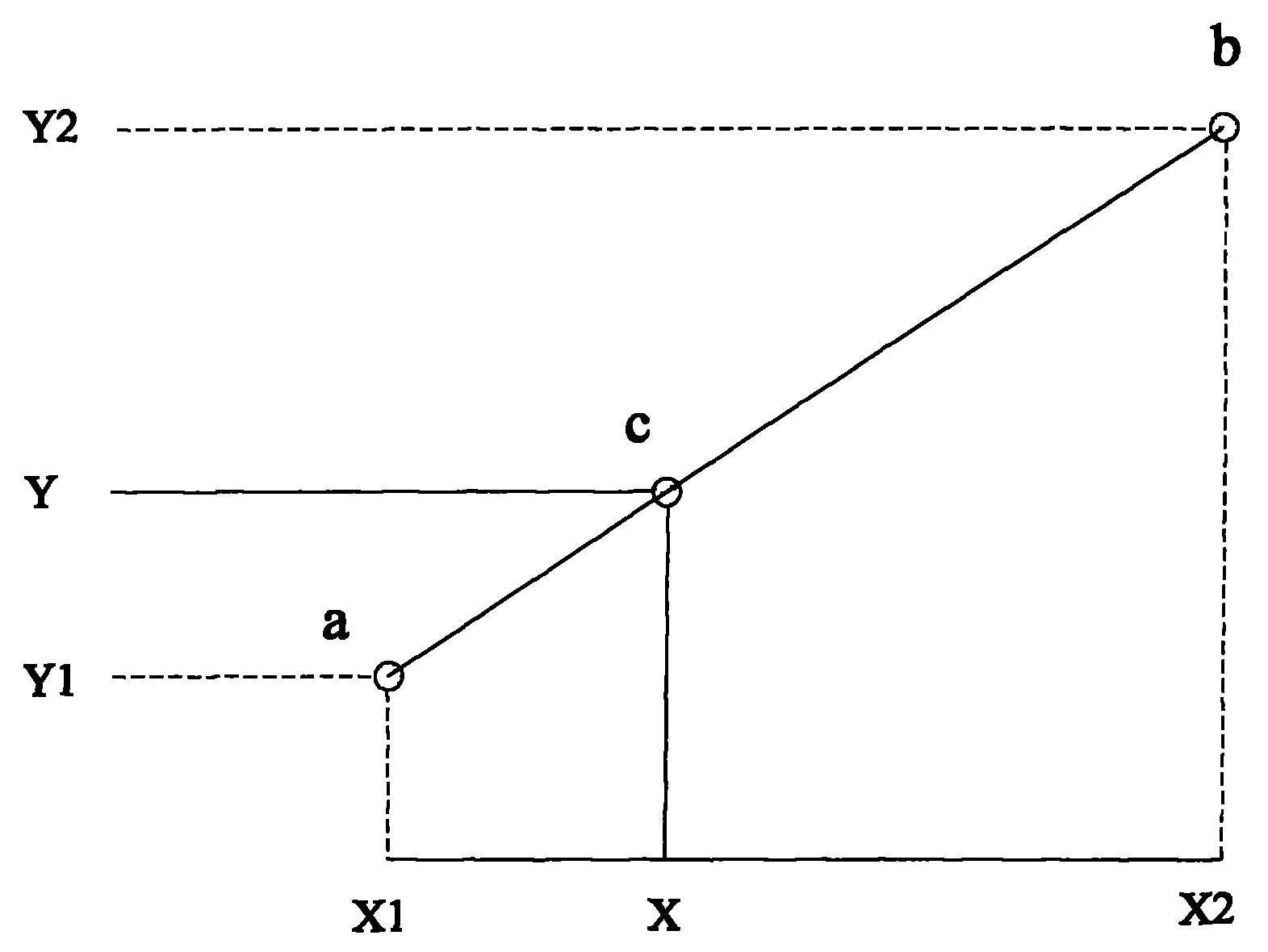

InactiveCN101771827AUniform Brightness TransitionQuality improvementTelevision system detailsColor television detailsRegister allocationPattern recognition

The invention discloses a device for regulating image brightness by gamma, comprising a register configuration unit, a gamma curve generation unit, a data partitioning unit and a data processing unit, wherein, curve parameters are inputted into the register configuration unit to be configured to the corresponding registers and the wanted gamma curves are generated in the gamma curve generation unit according to the configuration values in the registers; meanwhile, image data are inputted into the data partitioning unit for partitioning, the partitioned data and the generated gamma curves are inputted into the data processing unit and the regulated image brightness data are generated. The invention also provides a regulation method according to the device. The device and the method of the invention improve the quality of the outputted image under the situation of saving hardware resource and ensure the outputted image clearer.

Owner:ARKMICRO TECH

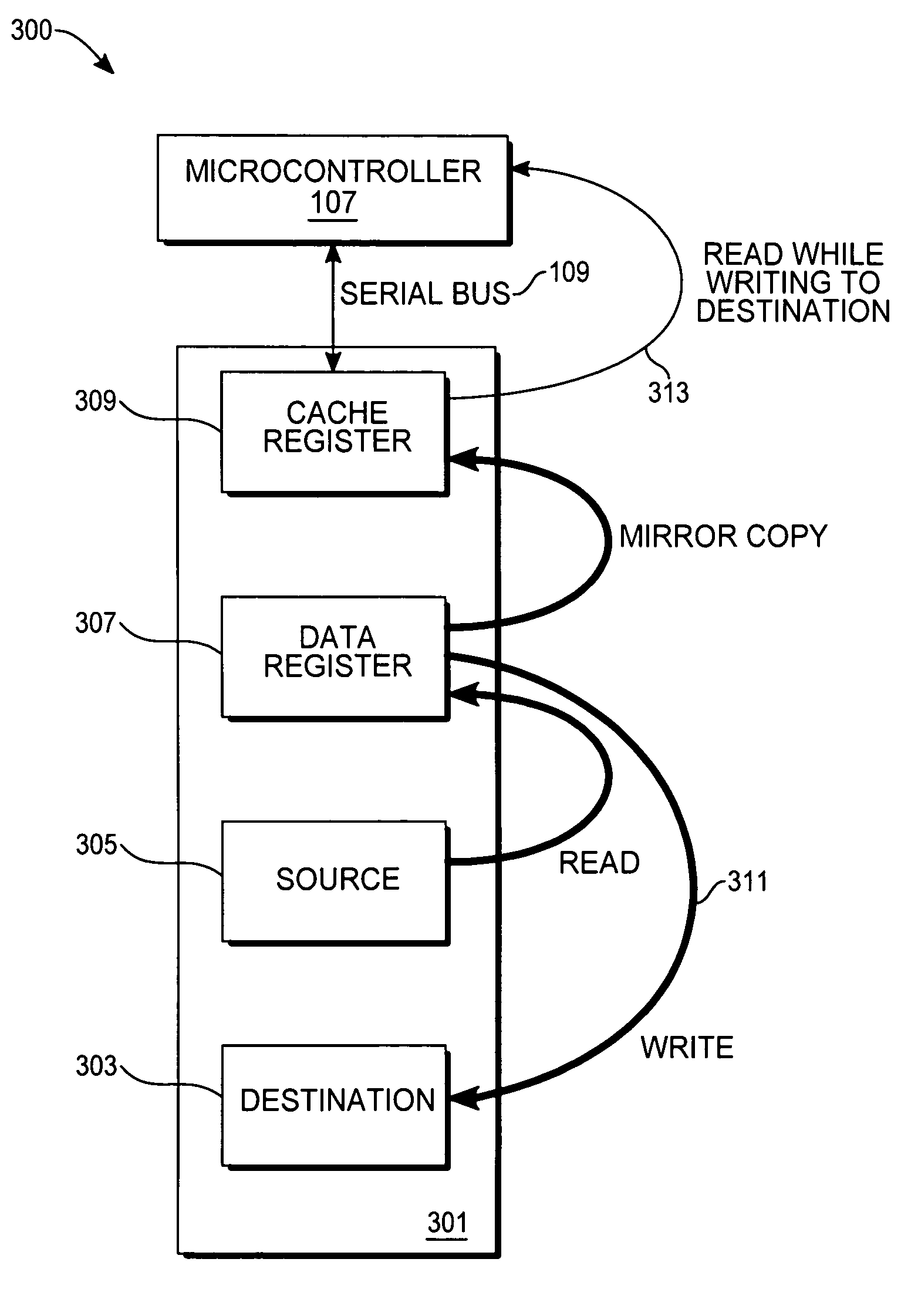

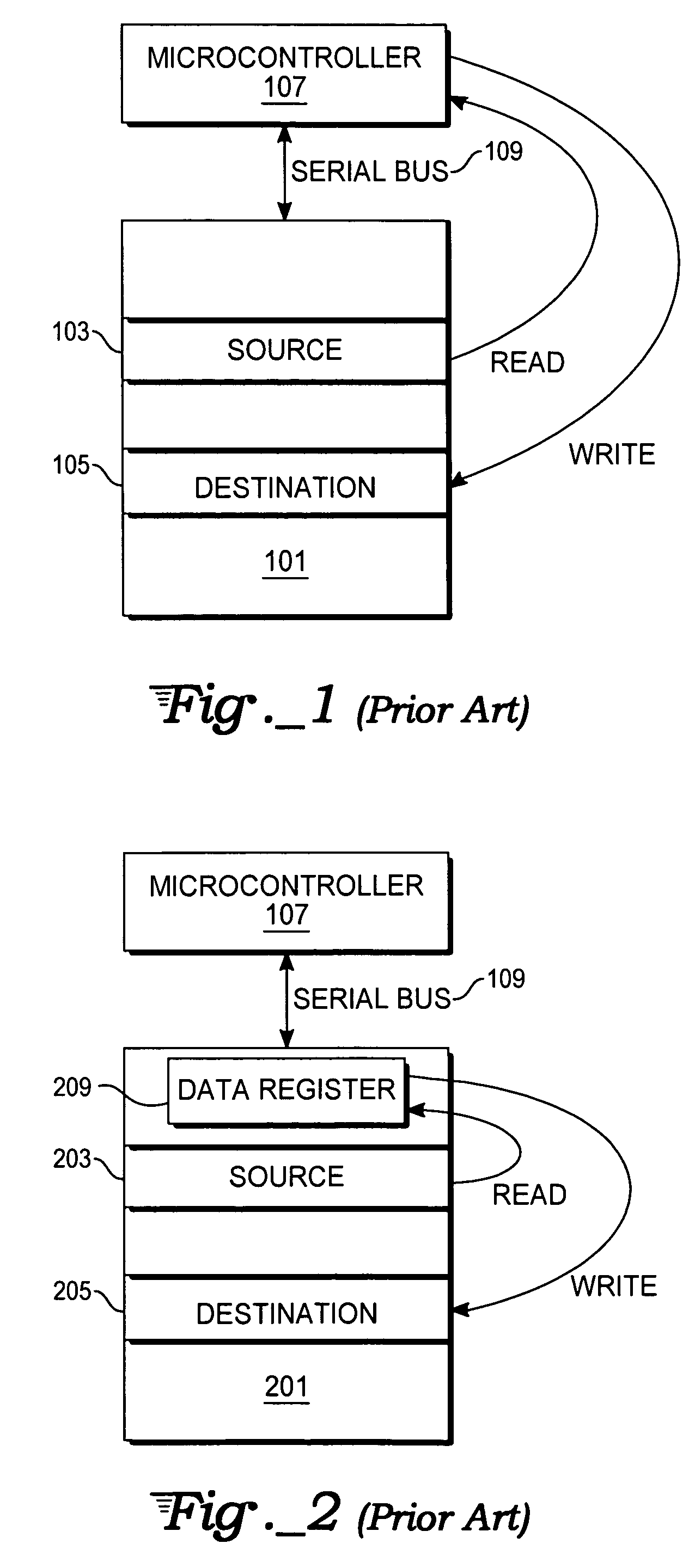

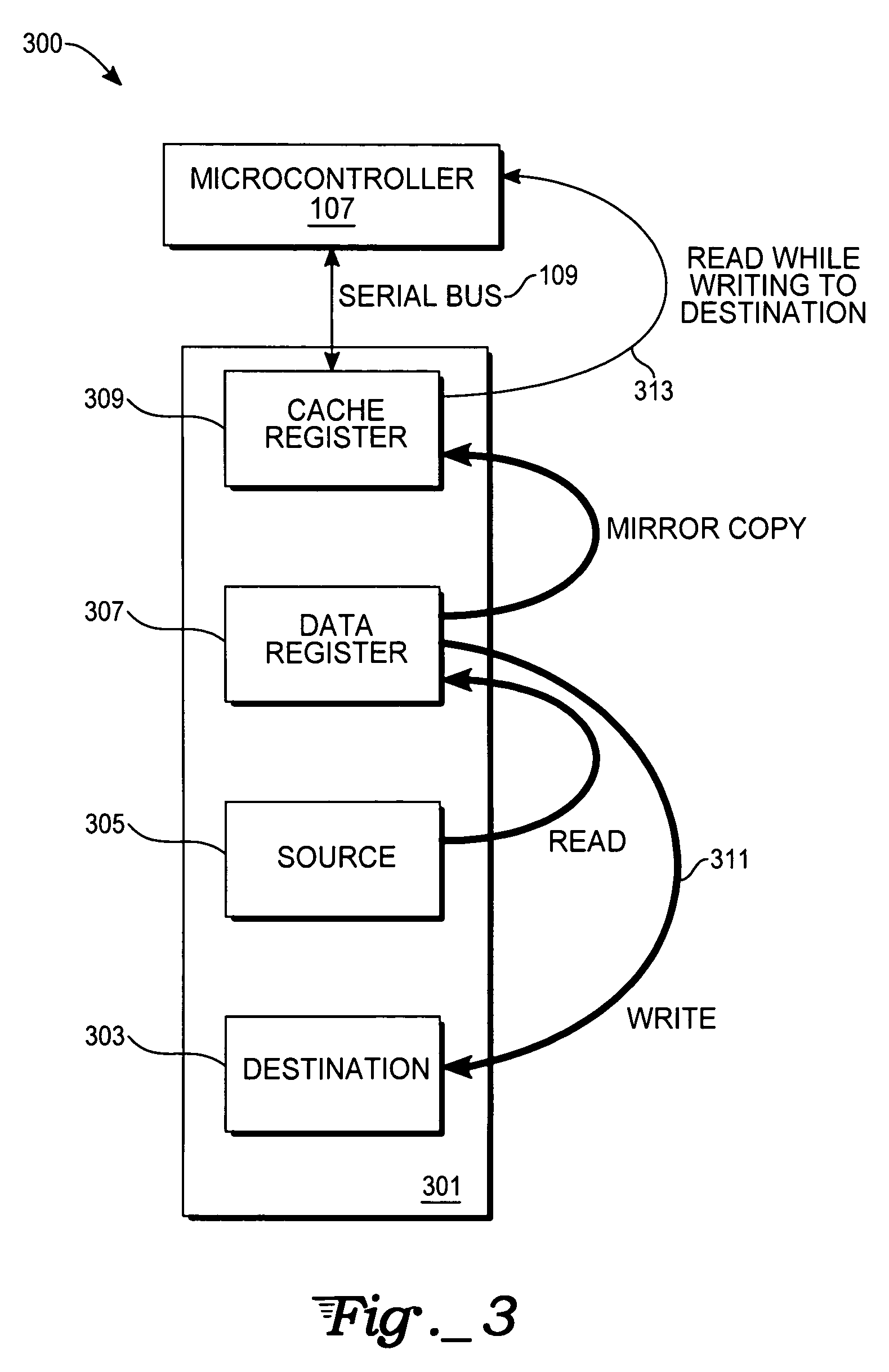

Simultaneous external read operation during internal programming in a flash memory device

InactiveUS7159069B2Memory architecture accessing/allocationMemory loss protectionRegister allocationMicrocontroller

A system and method for performing a simultaneous external read operation during internal programming of a memory device is described. The memory device is configured to store data randomly and includes a source location, a destination location, a data register, and a cache register. The data register is configured to simultaneously write data to the destination and to the cache register. The system further includes a processing device (e.g., a microprocessor or microcontroller) for verifying an accuracy of any data received through electrical communication with the memory device. The processing device is additionally configured to provide for error correction if the received data is inaccurate, add random data to the data, if required, and then transfer the error-corrected and / or random data modified data back to the destination location.

Owner:ATMEL CORP

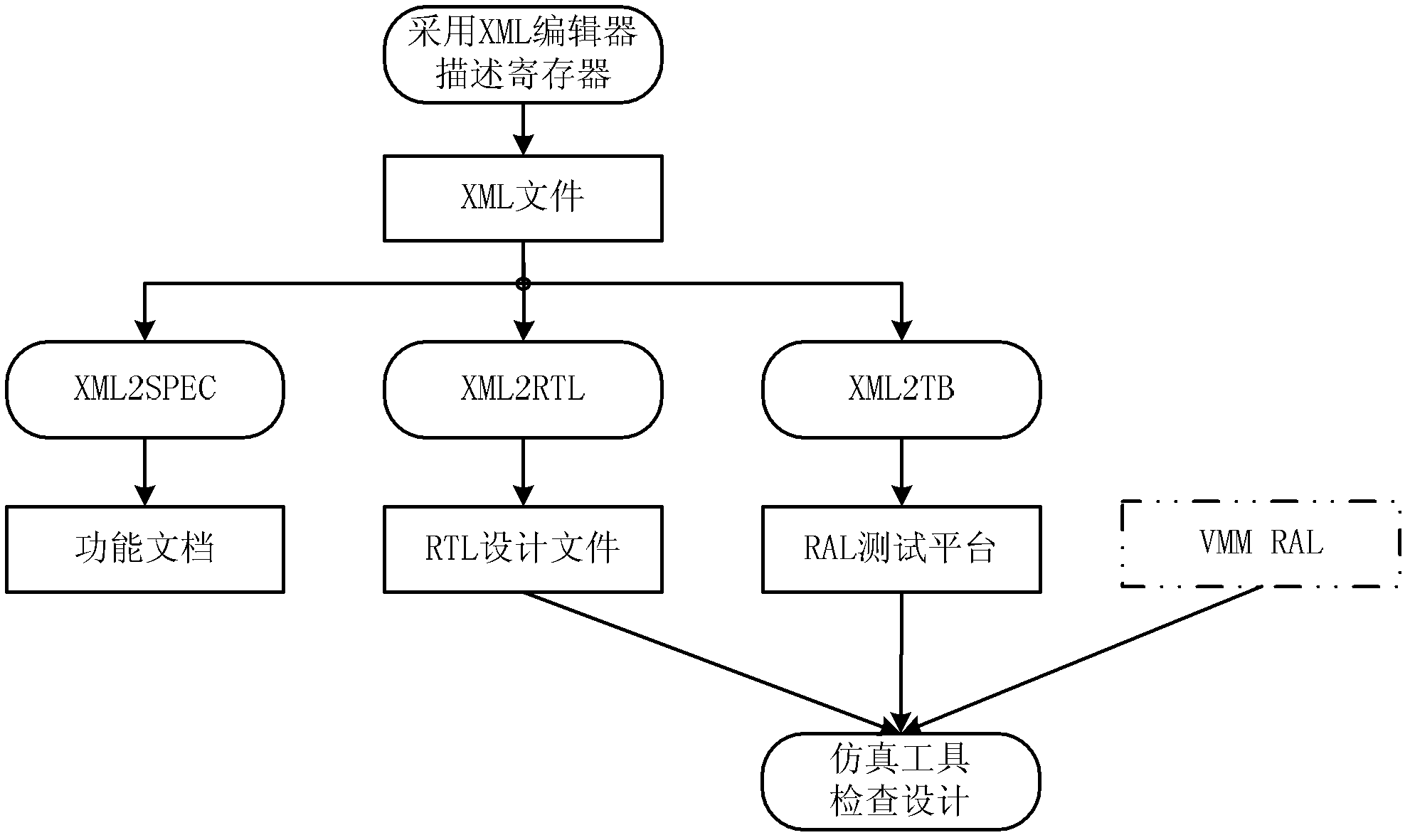

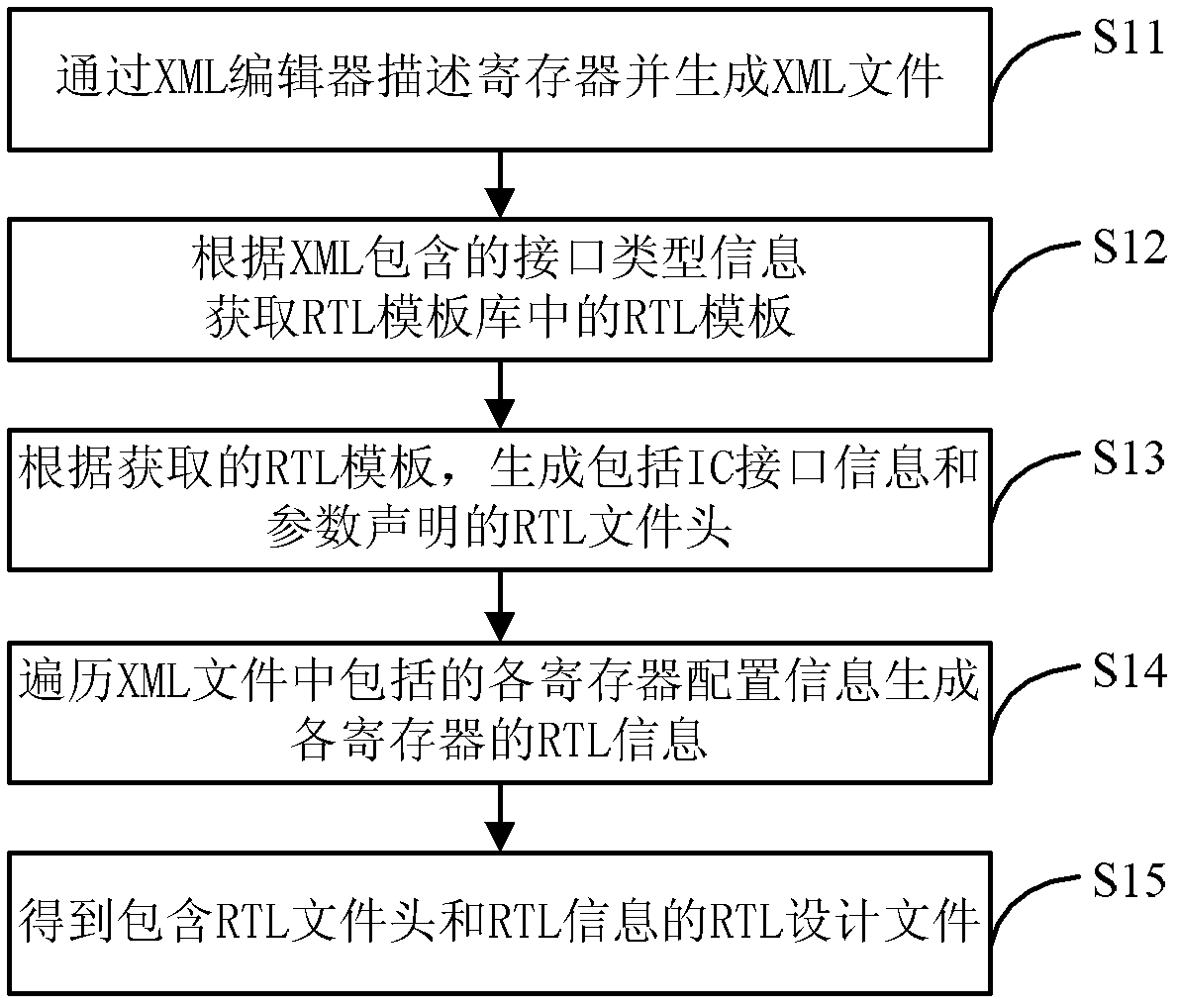

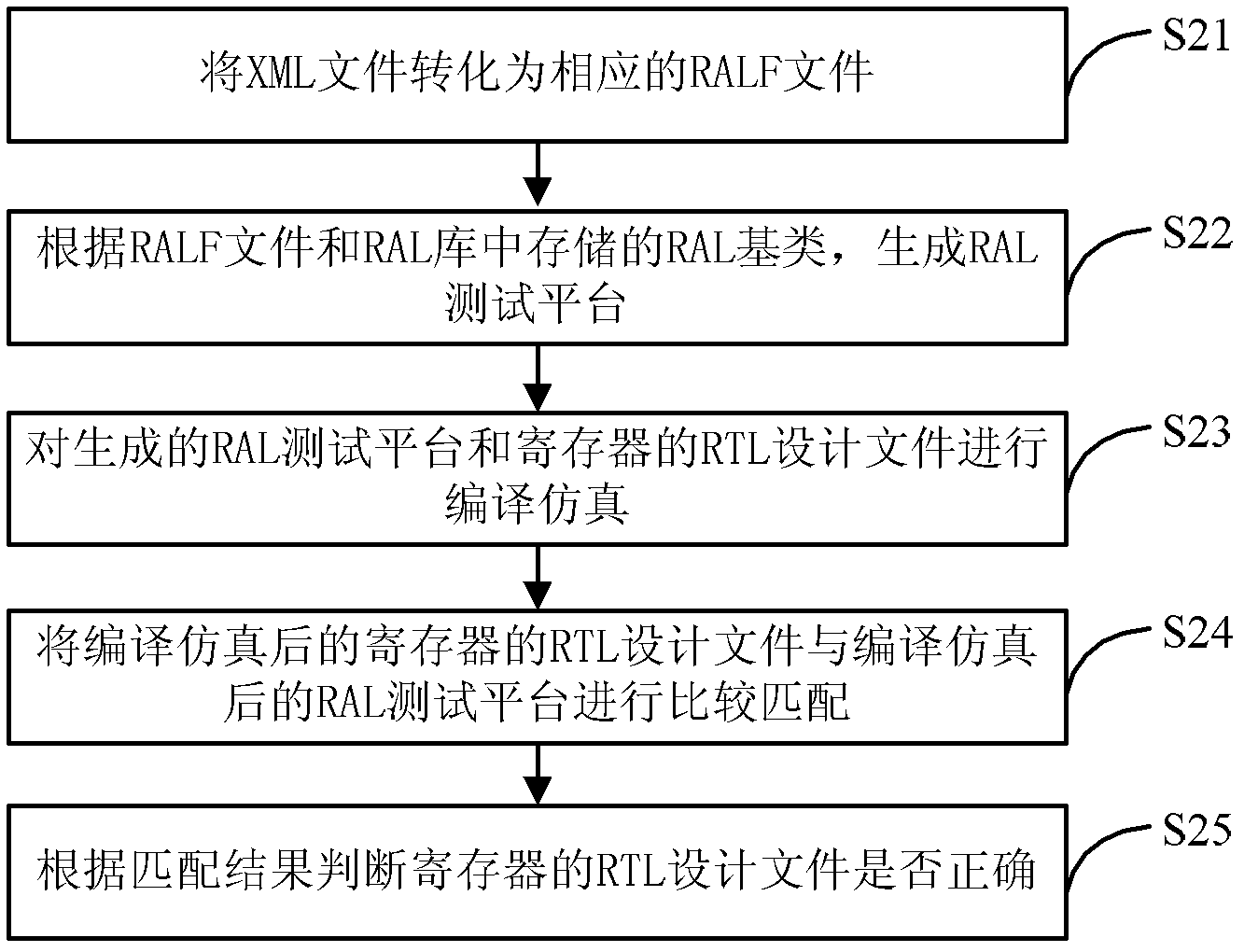

Register designing method and register designing device in integrated circuit designing process

ActiveCN102592023AAvoid the problem of difficult and cumbersome design and maintenanceReduce Design DefectsSpecial data processing applicationsRegister allocationComputer architecture

The invention discloses a register designing method in an integrated circuit designing process. The register designing method comprises the steps of generating an XML (Xtensible Markup Language) file including register configuration information by an XML editor; according to the type of a register interface included in the register configuration information, obtaining an RTL (Register Transfer Level) template in an RTL template base; according to the obtained RTL template and the register configuration information, generating an RTL file header including the register interface information and the parameter declaration; traversing all the register configuration information included in the XML file to generate RTL information of all the registers; and obtaining an RTL designing file including the RTL file header and the RTL information. According to the register designing method of the invention, the IC (Integrated Circuit) designing defects are reduced, and the designing success rate is increased.

Owner:GUANGDONG NUFRONT COMP SYST CHIP