Method for establishing large-scale network chip verification platform

A network chip and verification platform technology, applied in the field of verification method and verification platform construction, can solve the problems of less code, more design gates, time-consuming and other problems, and achieve the effect of powerful function and simple structure

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

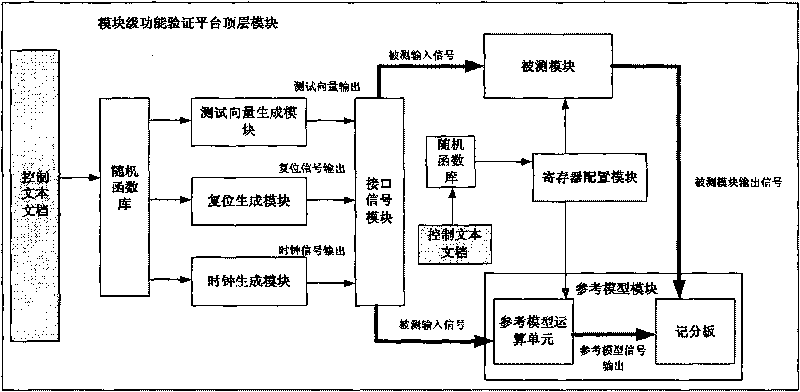

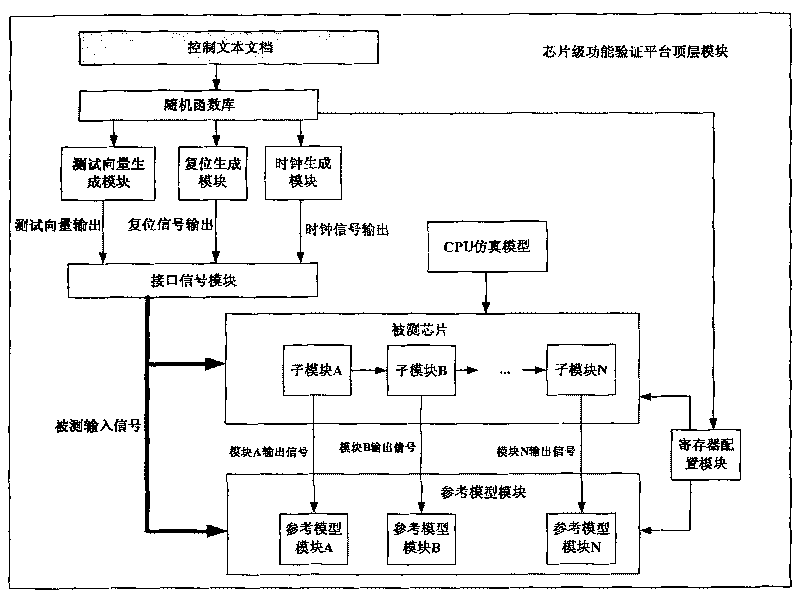

[0046] Specific embodiments of the present invention will be described in detail below in conjunction with the accompanying drawings.

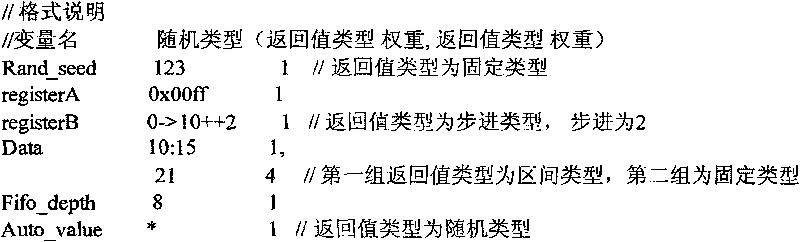

[0047] 1. First create a control text file (control.txt), whose content is variable name and random type. The random type consists of one or more sets of return value types and weights. If there are multiple sets, separate them with ",". Generally, there are fixed value types that are commonly used, and each time a function is called, a fixed value is returned. Interval value type, each call, the return value is within an interval. Step value type, each time the function is called, the return value will be fixedly increased or decreased by a step length. Sequence value type, each time the function is called, the return value is returned in the order of the sequence. There is also a random value type, which generates a corresponding random value based on a different random seed each time, as well as other user-defined types. For random type...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More