Patents

Literature

109 results about "Test vector generation" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

Method for establishing large-scale network chip verification platform

ActiveCN101763451ARealize multiplexingReduce build timeSpecial data processing applicationsRegister allocationReference model

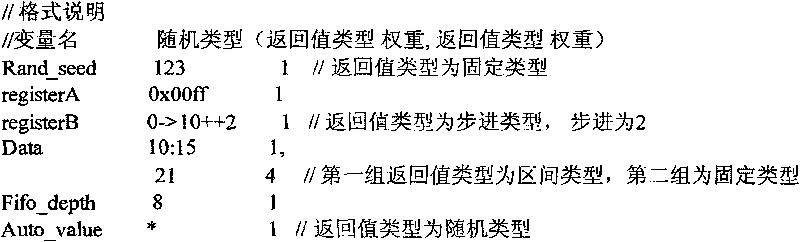

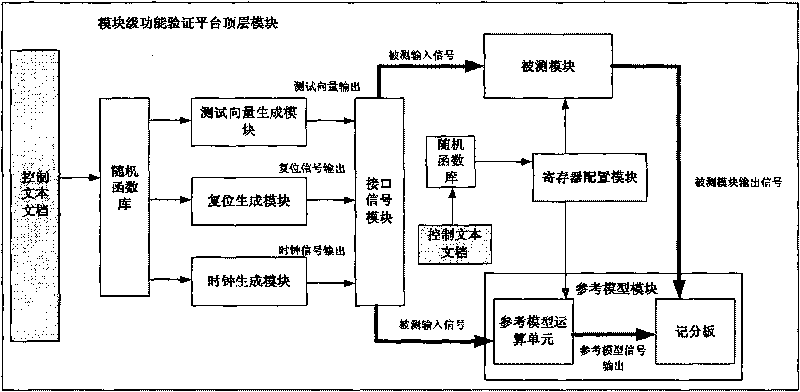

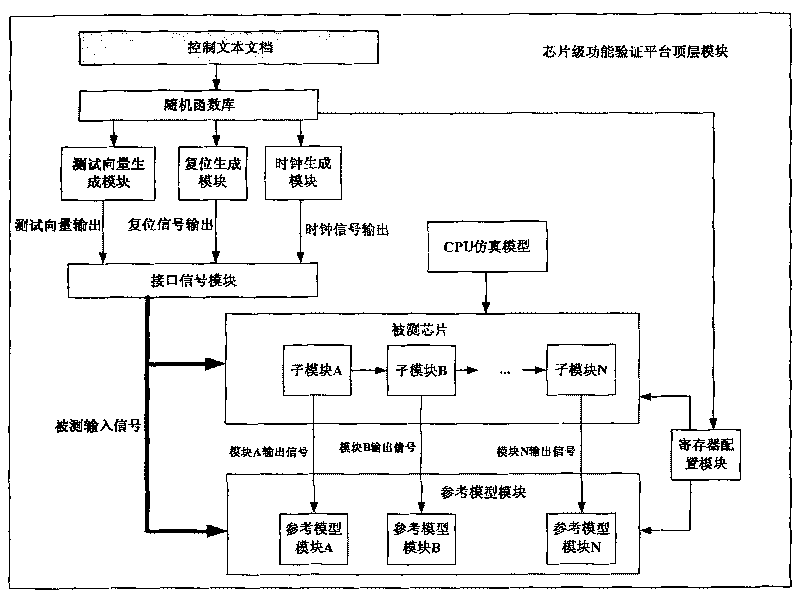

The invention relates to a method for establishing a large-scale network chip verification platform. The method comprises the following steps of: firstly, establishing a control text document, and then writing an initial function of a random function library, and writing a calling function of the random function library; secondly, establishing a module-level function verification platform, comprising the following steps of: generating a top-level module of the module-level function verification platform, establishing a clock generating module and a reset generating module, establishing an interface signal module, establishing a test vector generating module, establishing a register configuring module and establishing a reference model module of a tested module; and thirdly, establishing a chip-level function verification platform, comprising the following steps of: generating a top-level module of the chip-level function verification platform, multiplexing the clock generating module, the rest module, the interface signal module, the test vector generating module, the register configuring module and the reference model module of the module-level function verification platform, and establishing a CPU simulation model. The method has a strong function, high efficiency, stability and simple structure. By means of the invention, the time for setting up the network chip verification platform can be greatly shortened and the stimulation efficiency can be improved.

Owner:丁贤根

Automated test vector generation for complicated video system verification

InactiveUS20060126725A1Color television with pulse code modulationColor television with bandwidth reductionSystem verificationVideo encoding

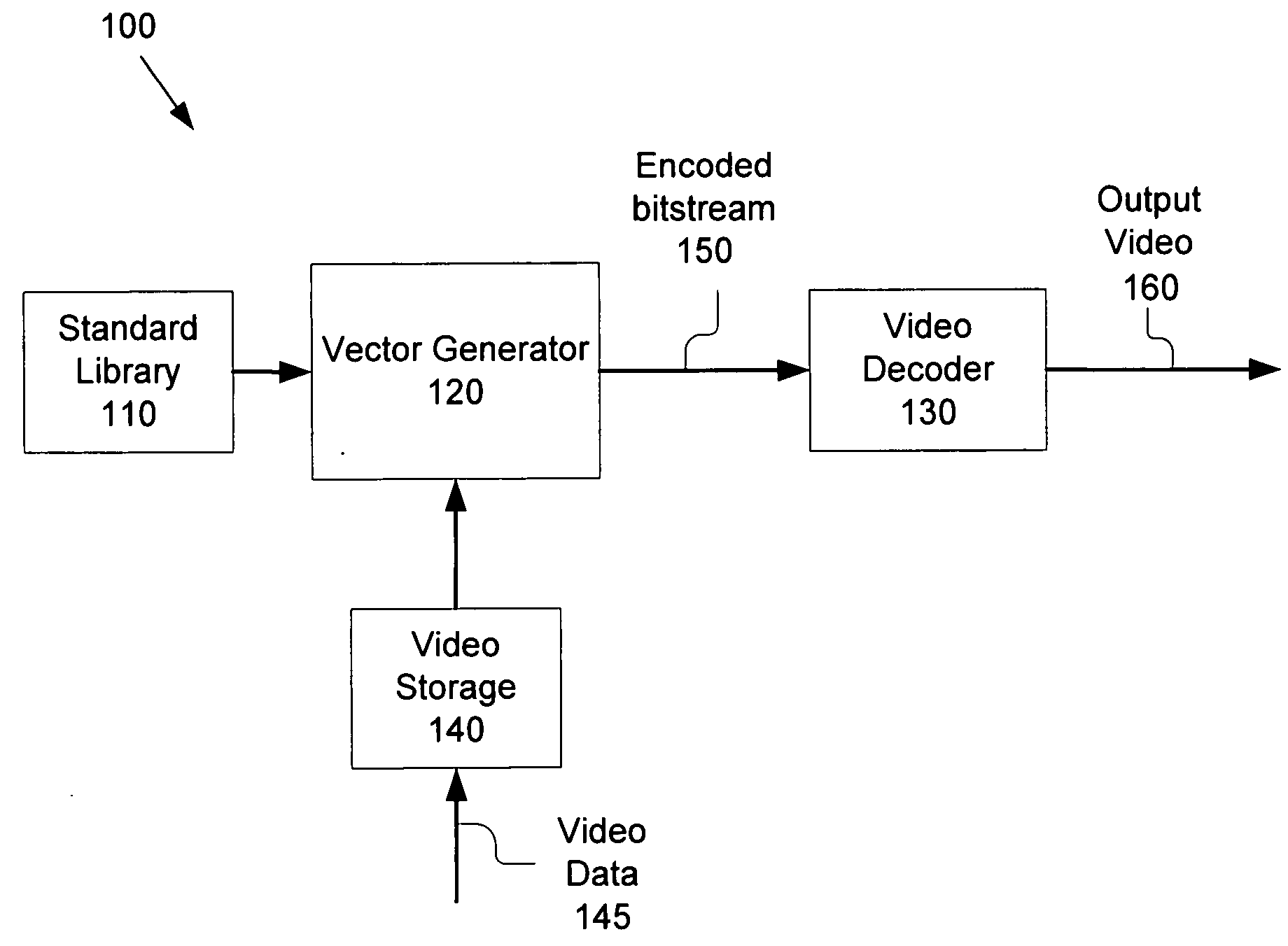

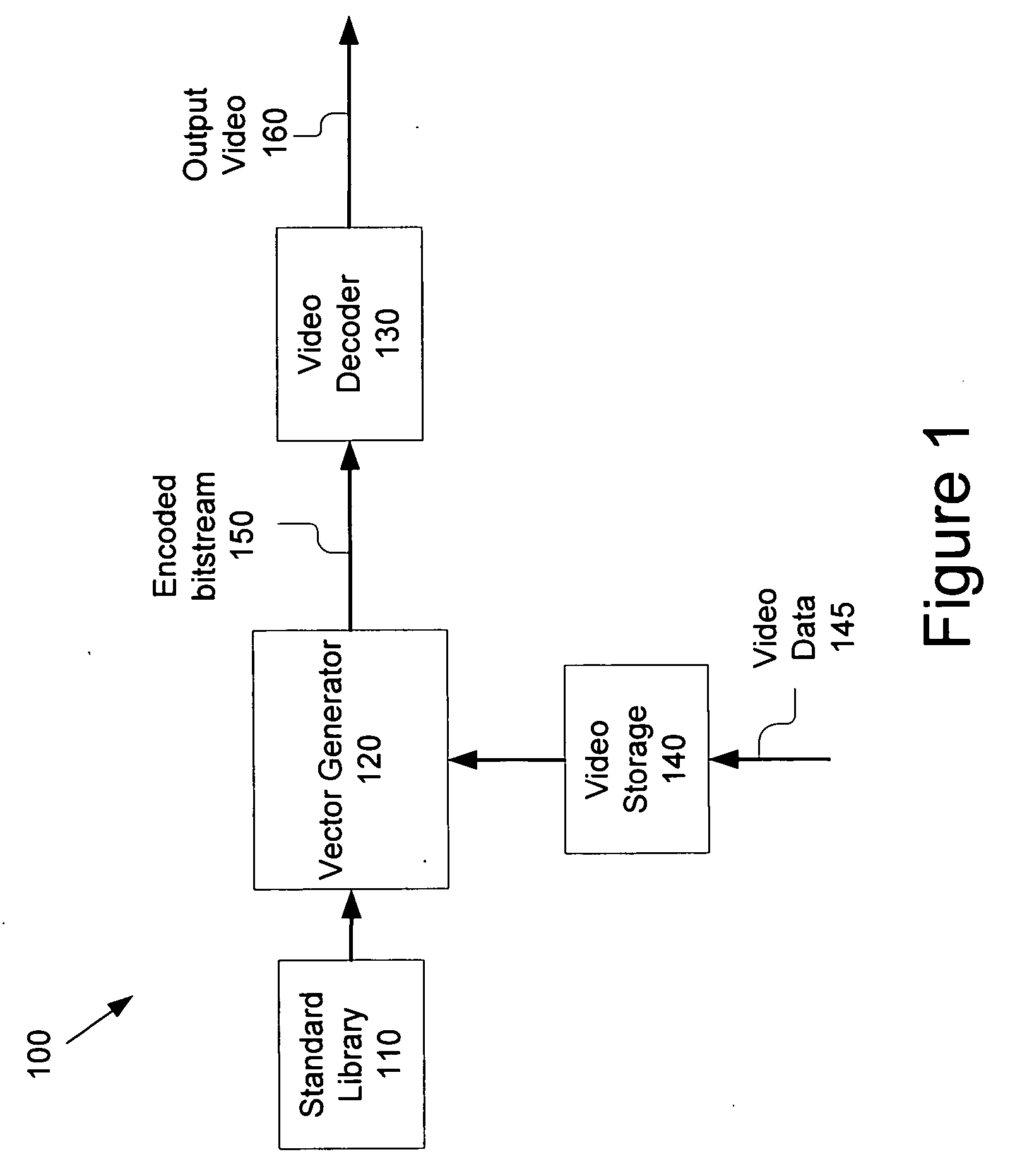

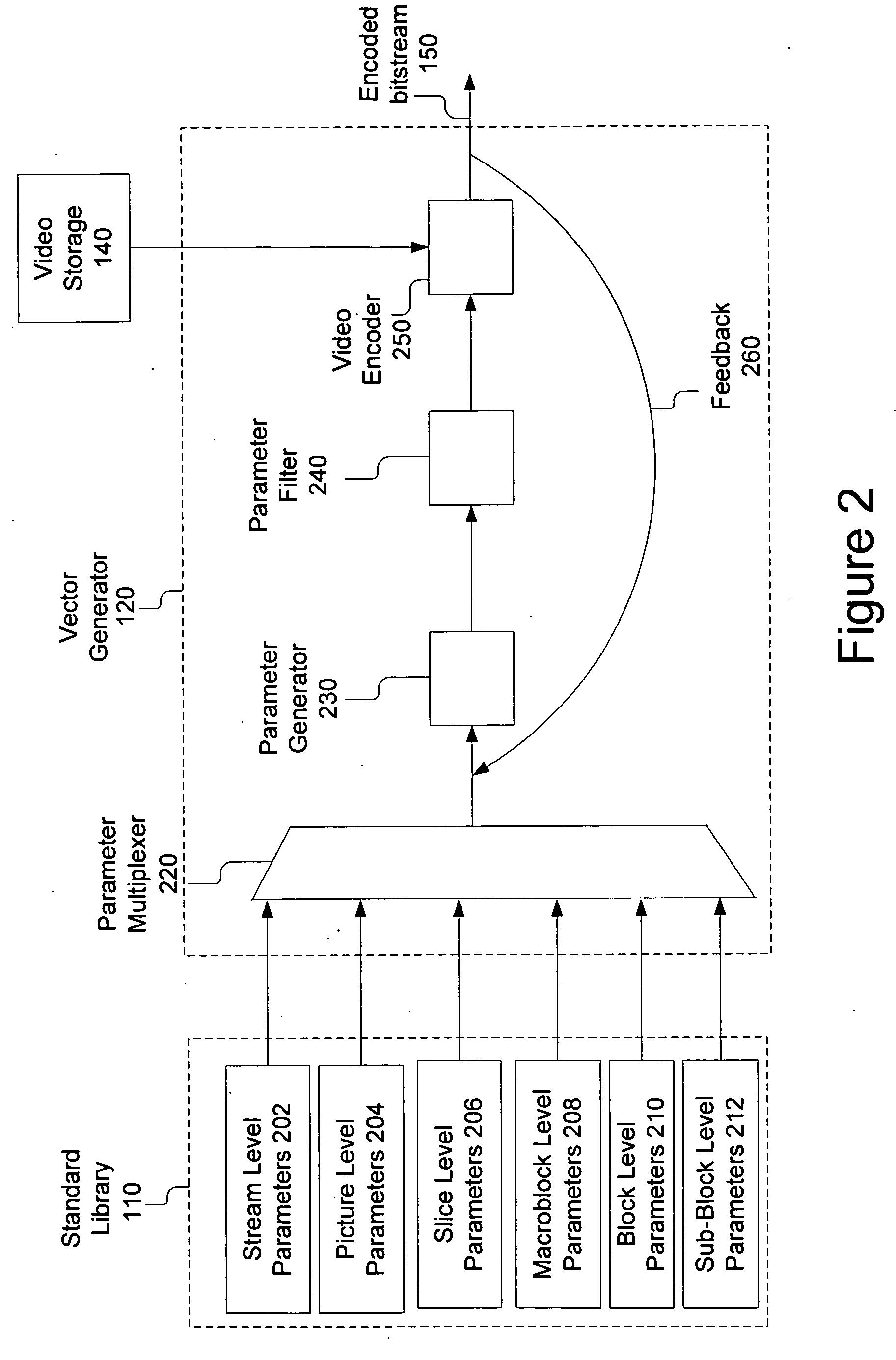

According to one embodiment, the present invention generates a test vector for verification of a video encoder or decoder by encoding video data using a permissible combination of parameters. One embodiment of the present invention provides for verification of a video decoder by performing at least one video decoding operation and comparing a resulting partially or fully decoded test vector to an expected value. Another embodiment of the present invention provides for verification of a video encoder by performing at least one video encoding operation using a selected combination of parameters, and comparing a resulting partially or fully encoded test vector to an expected value.

Owner:MICRONAS

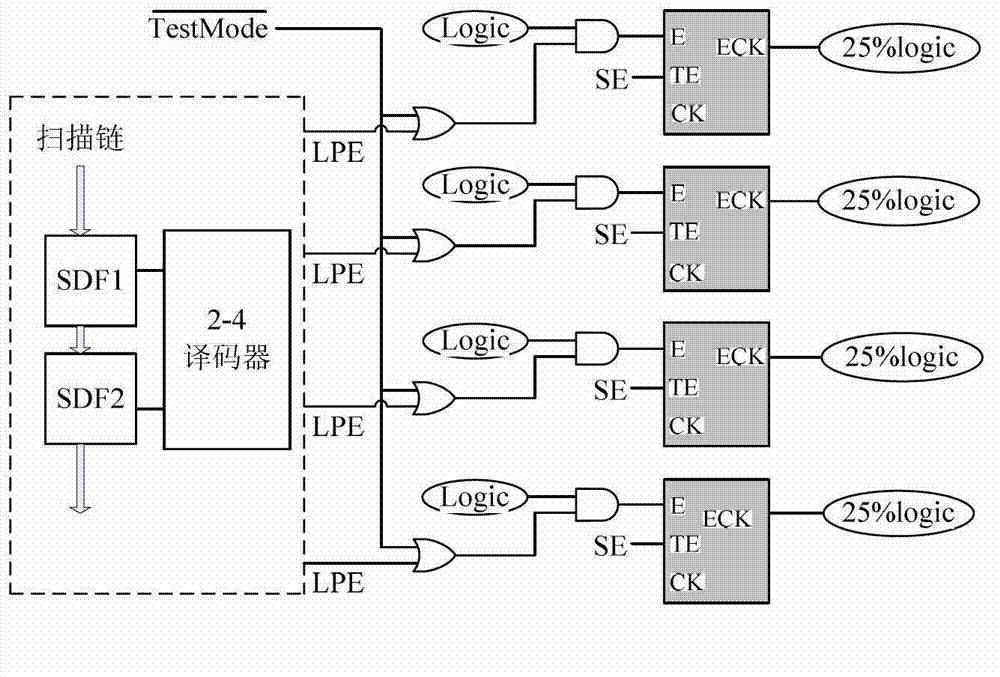

Optimization method of capturing power consumption in scan test

InactiveCN103091620AReduce capture power consumptionElectronic circuit testingSpecial data processing applicationsTest designTest vector

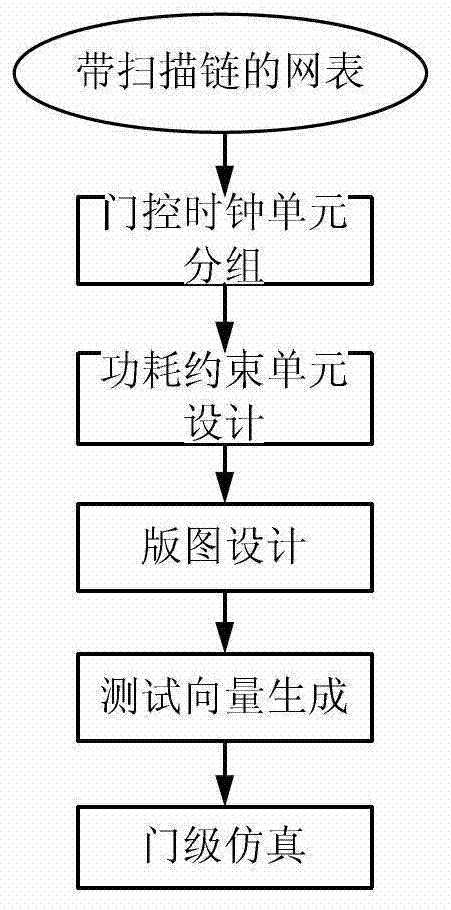

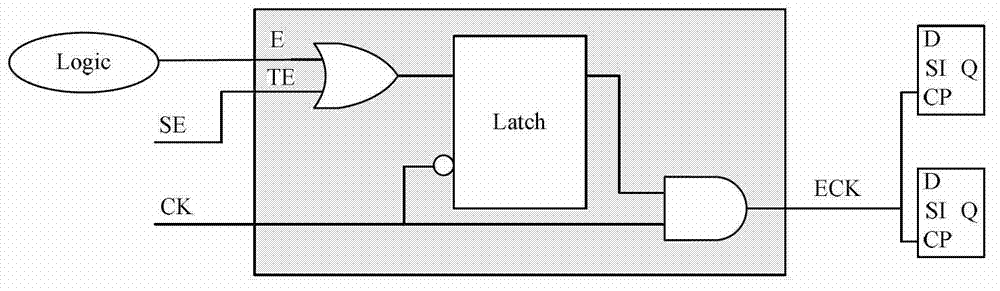

The invention discloses an optimization method of capturing power consumption in a scan test. The optimization method of capturing power consumption in the scan test comprises the following steps: generating a netlist with a scan chain; grouping gating control clock units; designing a power constrain unit; combining with the generated netlist with the scan chain, conducting chip layout design which comprises a floorpan, a layout, a clock tree sythesis and wiring; reading a gate-level netlist with a scan structure, a process library, a timing sequence constrain file and a test protocol into an automatic test vector generating tool after the chip layout design is completed, conducting testability design rule checking, and generating a test vector; and conducting gate-level simulation to the test vector generated. By means of the optimization method of capturing the power consumption in the scan test, the capturing power consumption in a test process can be reduced significantly, the reduction of coverage or the sharp increase of the quantity of test vectors is not generated, changing of a test design process is needless, and realization is easy.

Owner:JIANGSU SEUIC TECH CO LTD

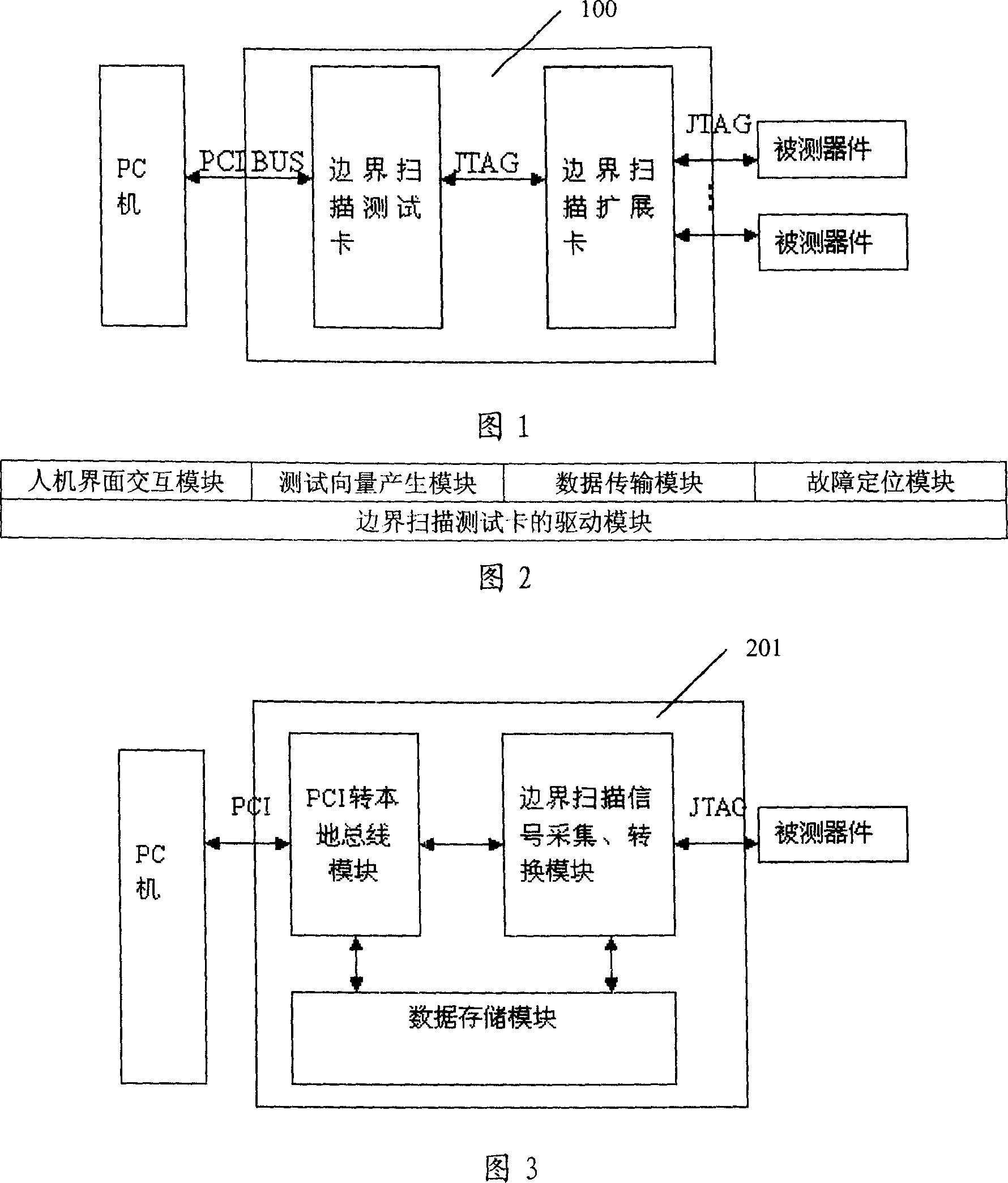

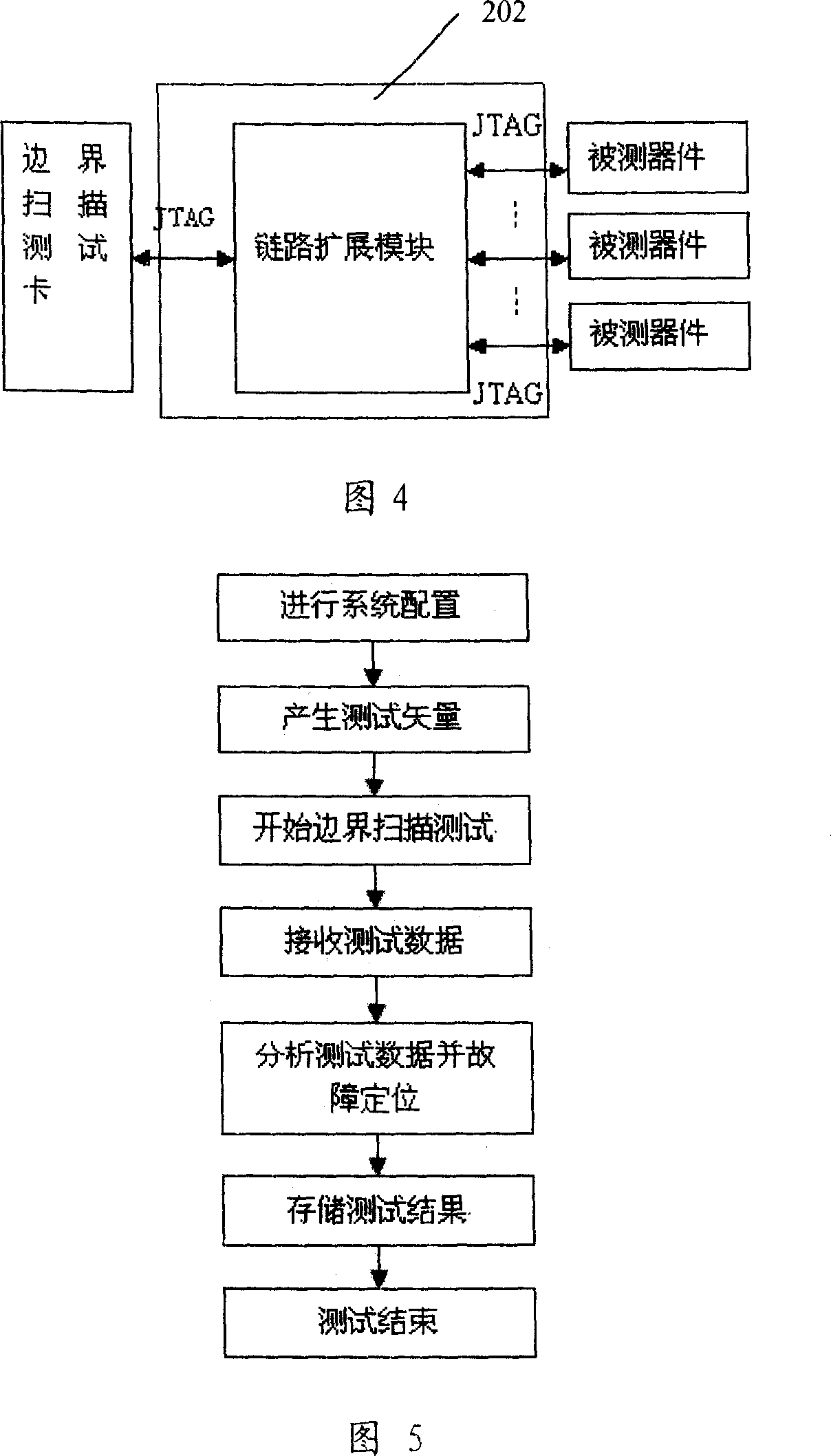

Device and method for realizing border-scanning multi-link test

InactiveCN101071155AExpansion is simple, convenient and flexibleReduce the number of times to replace the scan linkDigital circuit testingExpansion cardTest card

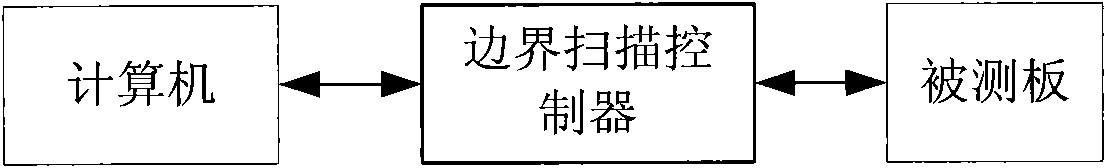

This invention discloses multi-link testing devices and methods which can realize boundary scan. Including: PC module, boundary-scan test card and boundary scan card expansion card; described boundary-scan extended card composed by boundary scan expansion modules , used in a number of boundary-scan test link, through analytical sent from the PC port choice test configuration, boundary scan port expansion card on the number of boundary scan link together into a new boundary scan link , for testing. The invention through the boundary-scan test device provide to PC users easy-to-use interface, test vector generation and the analysis of test data, through PC hardware and procedures rapidly with good boundary-scan test and link extension, chains expansion is easy and convenient flexible scanning, reduced the frequency of chains replacement and increase test coverage and achieve program simple, economical and practical.

Owner:ZTE CORP

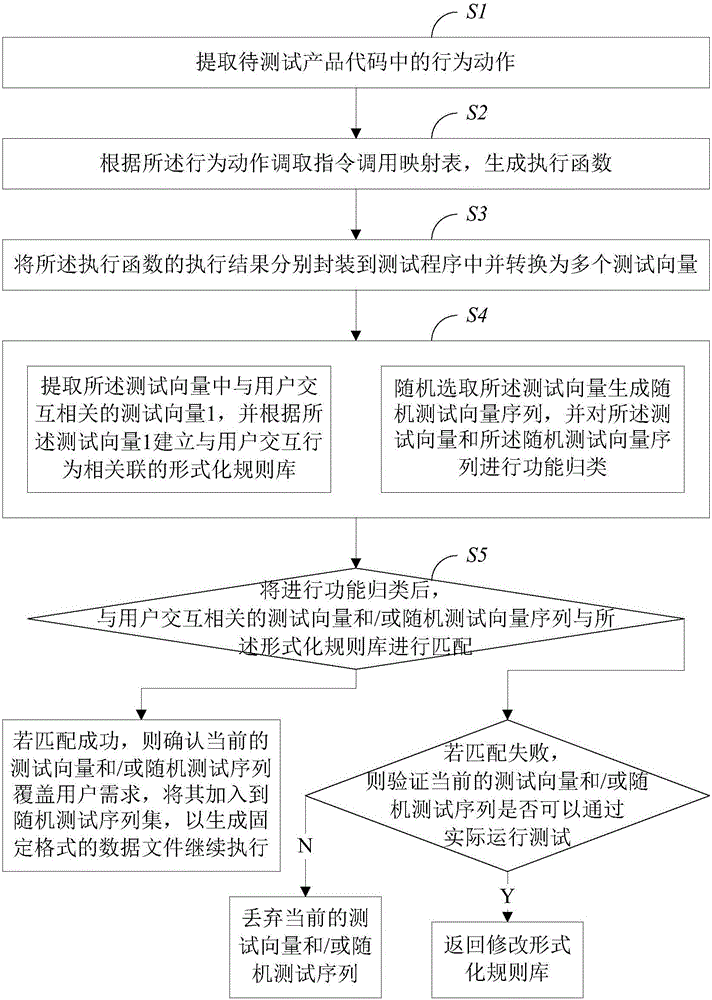

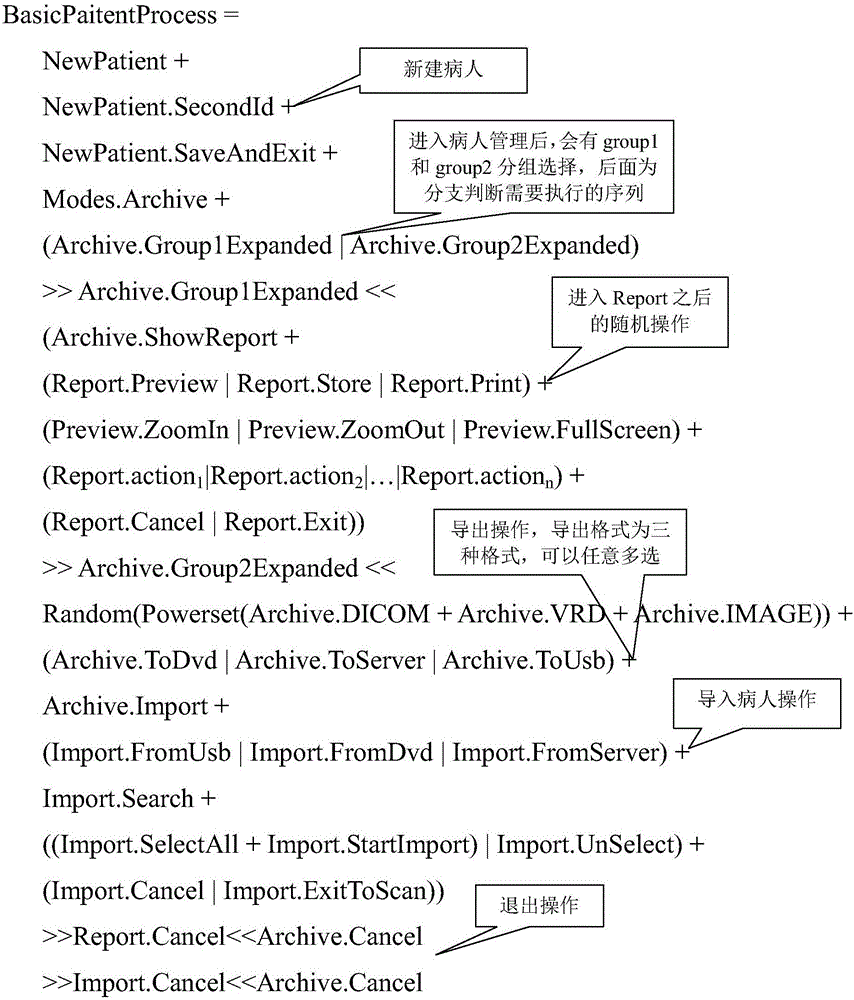

An ultrasonic apparatus reliability testing method and testing system

The invention provides an ultrasonic apparatus reliability testing method and testing system. The method comprises the steps of extracting behavior action in a code of a to-be-tested product; retrieving an instruction invoking mapping table according to the behavior action and generating an execution function; encapsulating the execution results of the execution function into a testing program and converting the same into a plurality of testing vectors; extracting testing vectors associated with user interaction from the testing vectors to establish a formal rule database associated with user interaction behavior; randomly selecting testing vectors to generate random testing vector sequences and performing function classification on the testing vectors and the random testing vector sequences, matching the testing vectors and / or random testing vector sequences subjected to the function classification and associated with user interaction with the formal rule database; after the matching is successful, determining that the current testing vectors and / or random testing sequences cover user requirements and continuing tests. The method and the system optimize testing sequence generate, remove redundant testing sequences and greatly shorten testing time.

Owner:VINNO TECH (SUZHOU) CO LTD

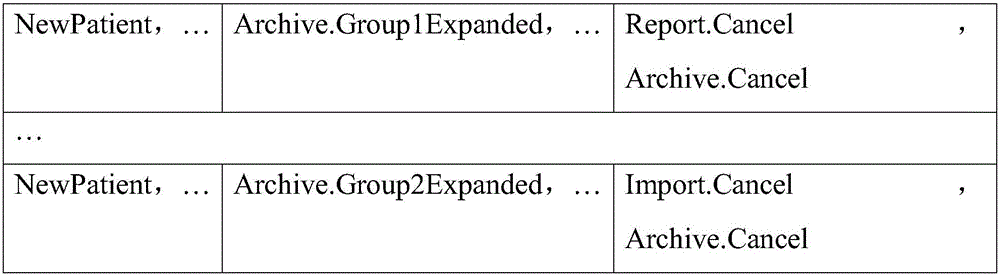

An Automatic Test Vector Generation Method Based on Generalized Folding Sets

An automatic test vector generation method based on a general folding set comprises the following steps of: firstly, classifying faults into faults easy to test and faults difficult to test through random tests, merging the faults difficult to test, dividing the number of the faults difficult to test which can be tested by using the same test vector into groups, selecting two groups of faults having the maximal number of faults capable of being merged together, judging an original input of producing influence during the rollback process to each signal by employing the influence range technology, directing the generation process of the test vectors to generate two corresponding test vectors, determining the corresponding general folding set by the two test vectors, performing fault simulation by using each test vector of the general folding set, and checking all the faults which can be tested by the general folding set; next, generating complete general folding sets for the left faults by the method until all the faults can be completely detected; and finally obtaining a plurality of determined general folding sets. The method provided by the invention has the advantages that test data can be compressed according to a general folding principle, that is to say, the generated data is easier to compress.

Owner:ANQING NORMAL UNIV

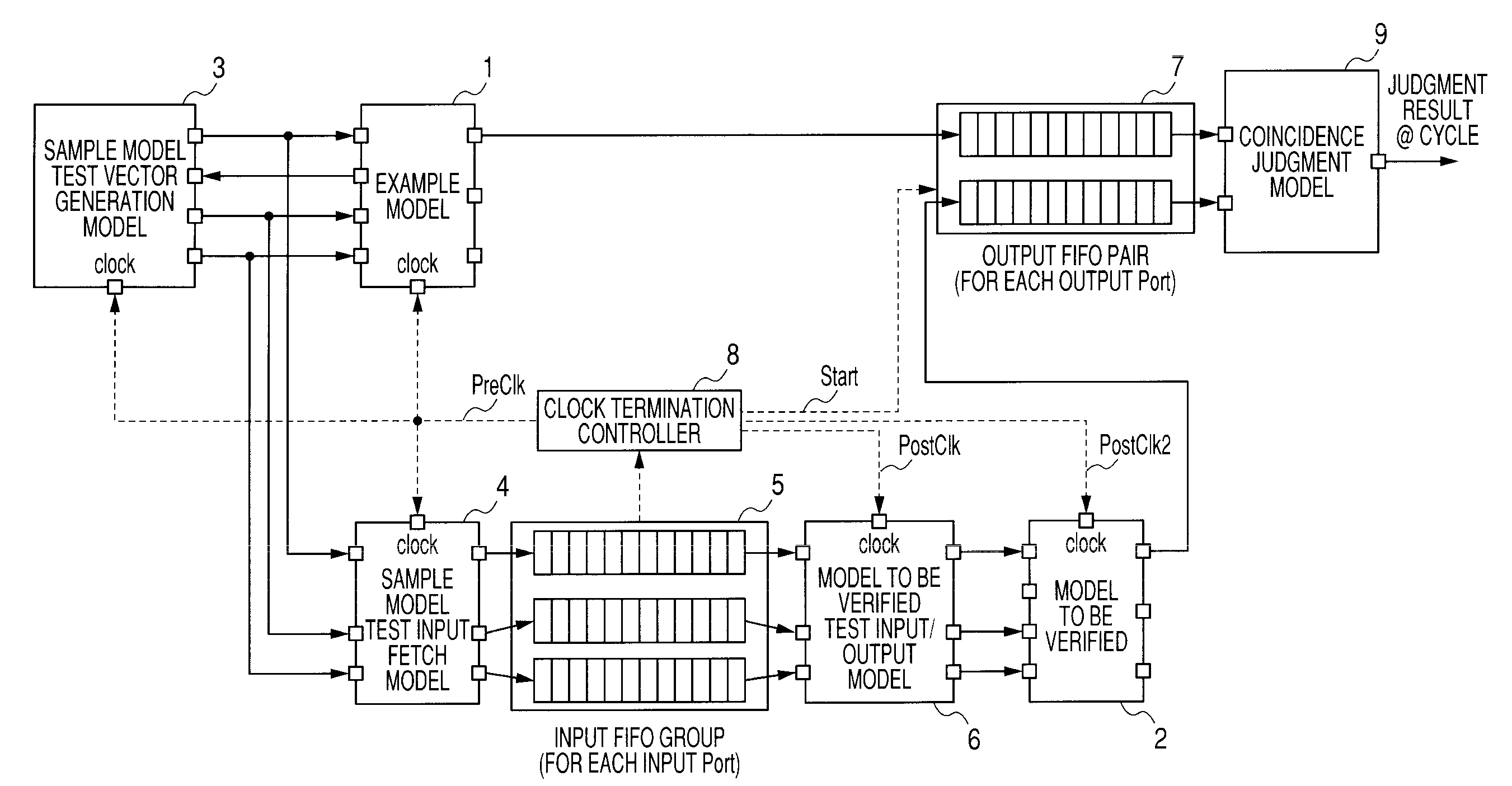

Equivalence checking method, equivalence checking program, and generating method for equivalence checking program

ActiveUS20090241074A1Computer aided designSoftware simulation/interpretation/emulationModel testingCircuit models

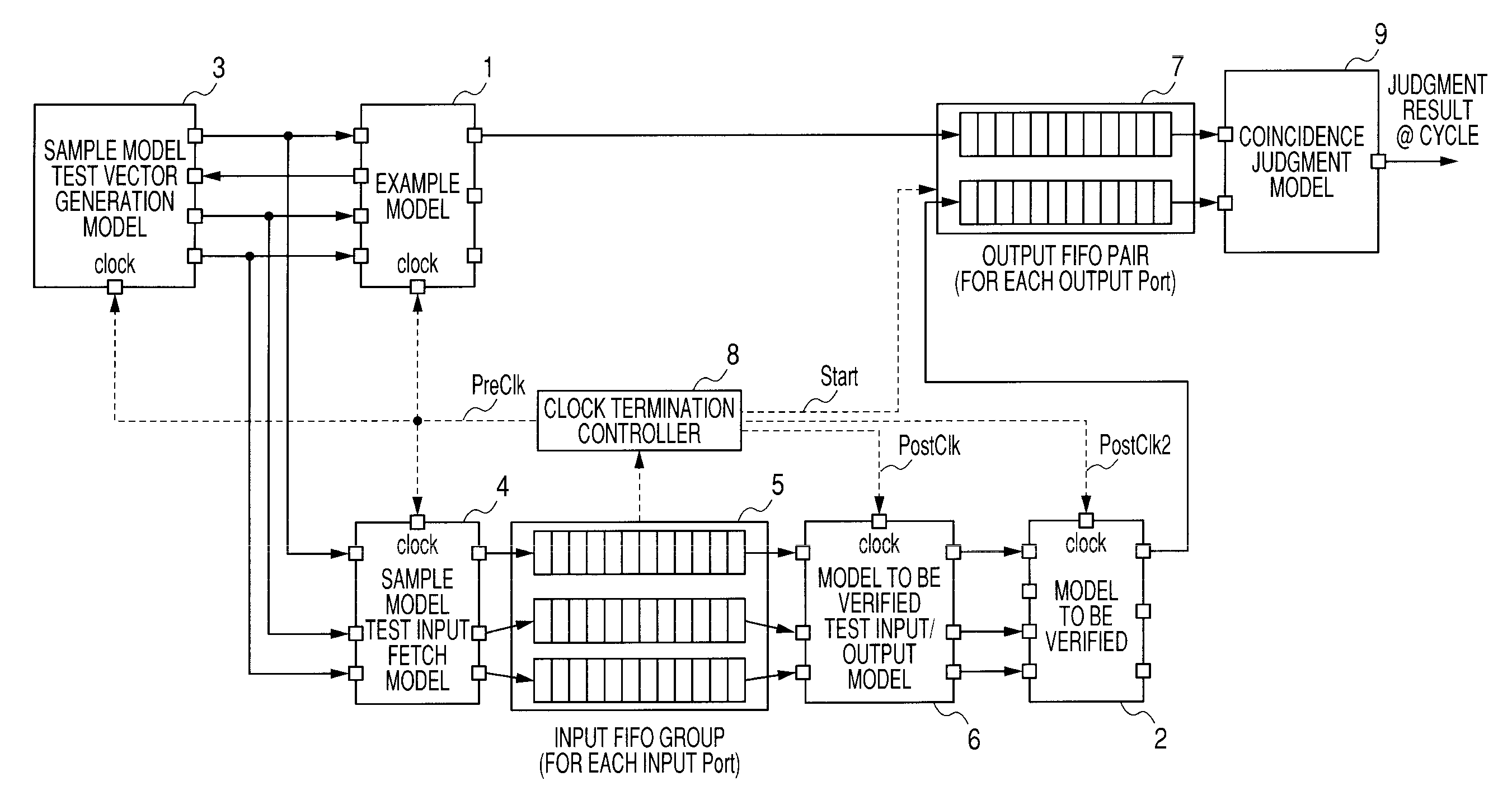

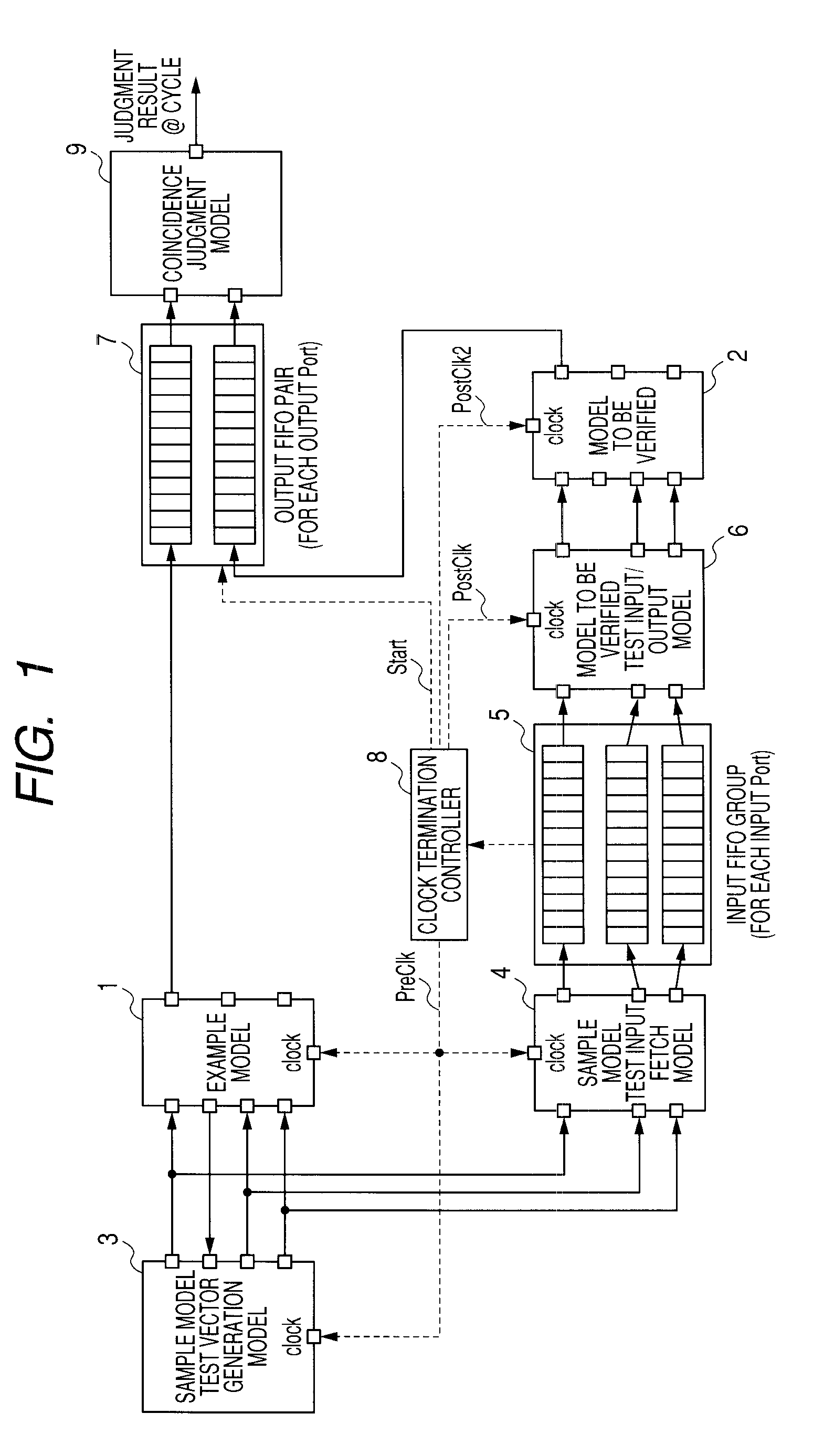

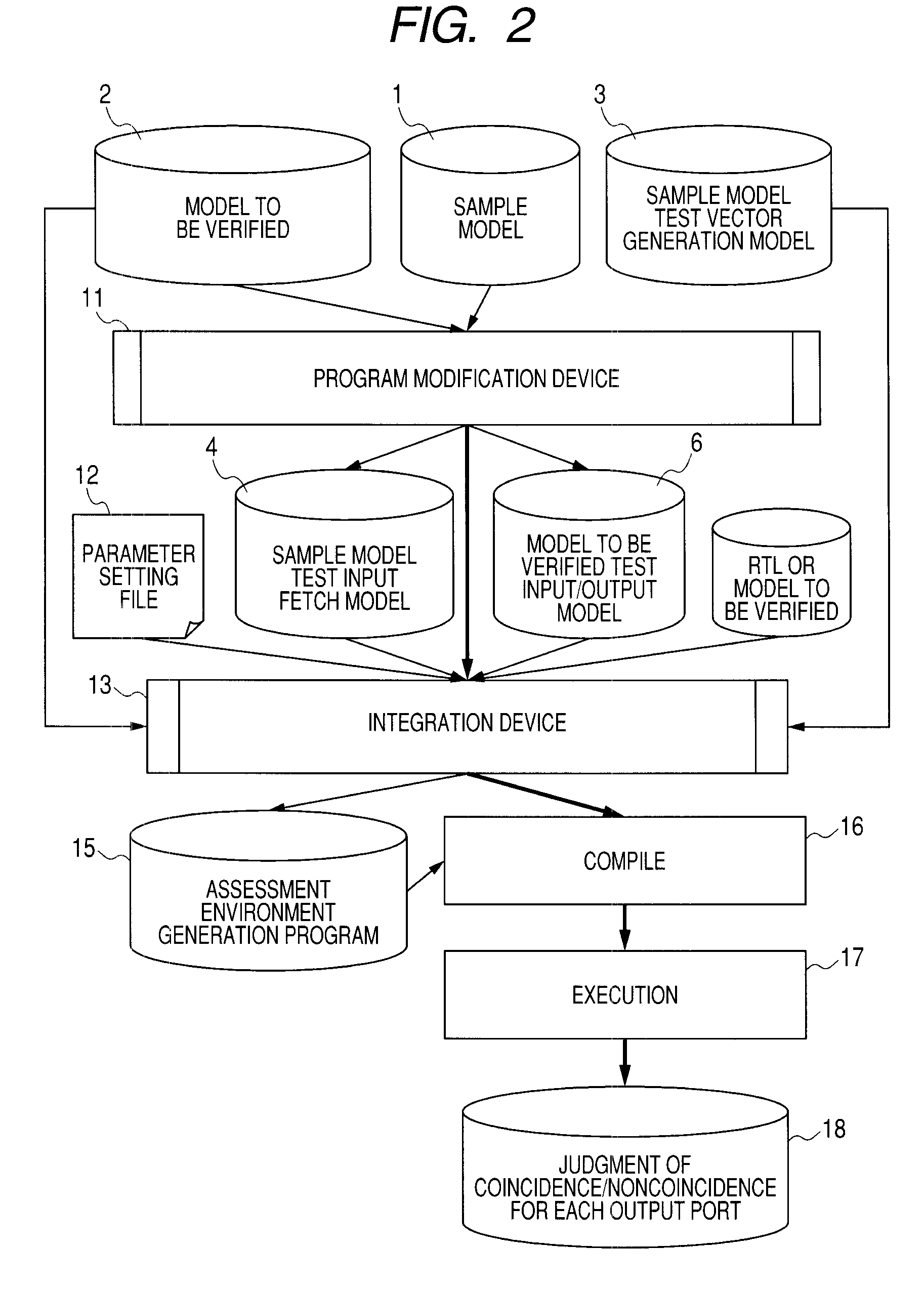

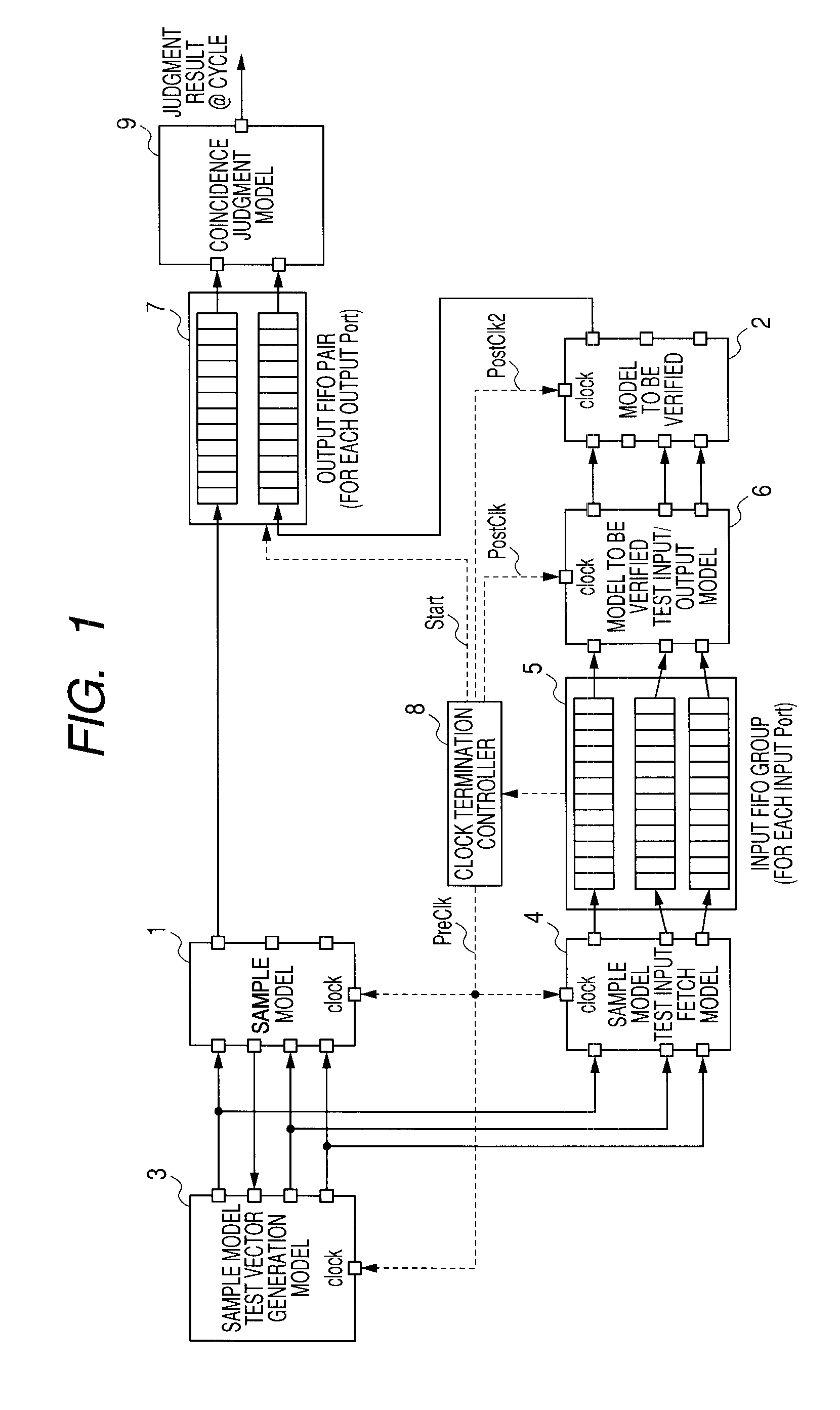

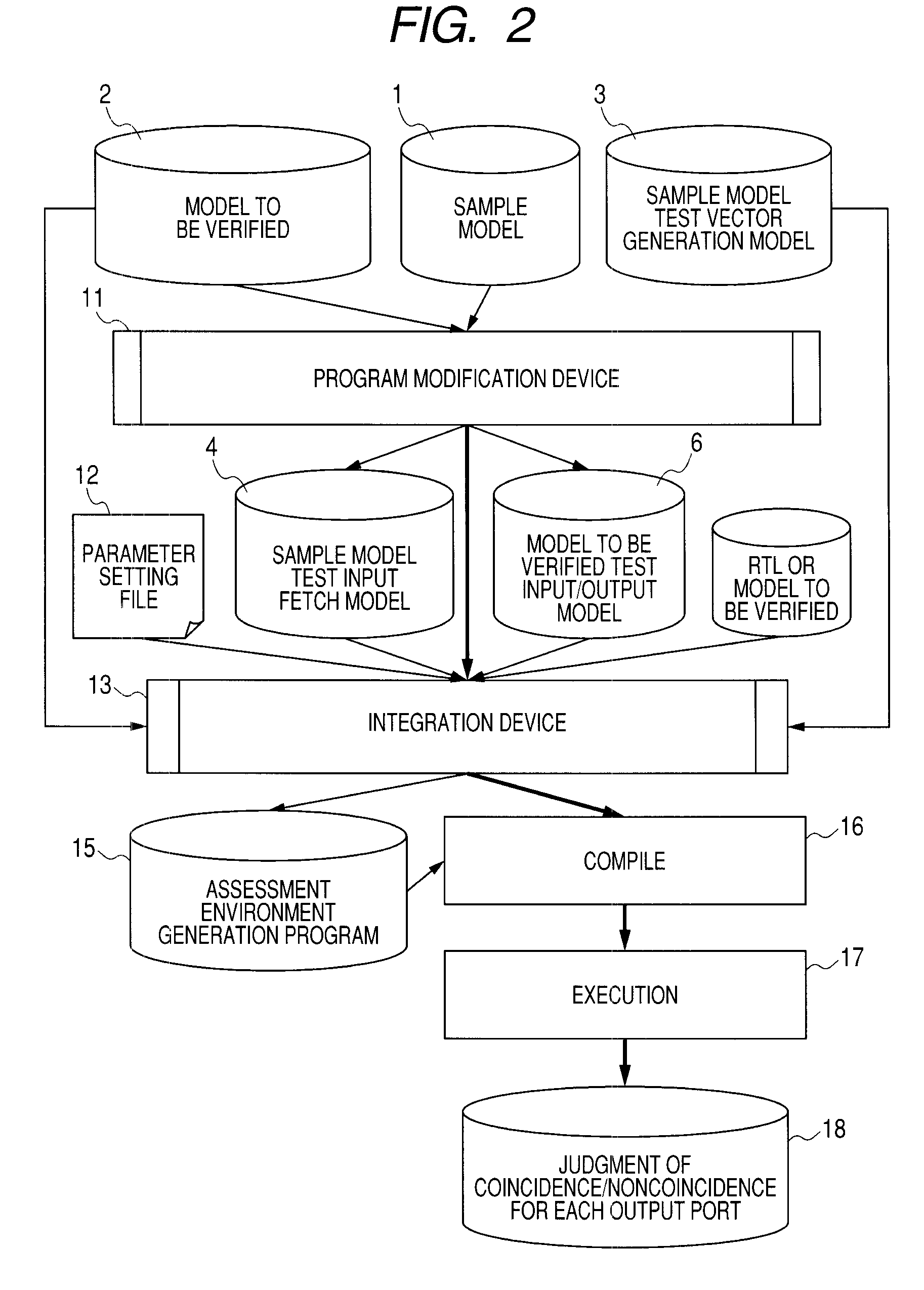

To provide a checking method that utilizes a test bench for a circuit model, which will serve as a fundamental for equivalence checking of a circuit to be newly developed for the fundamental circuit model. In order to check the equivalence of a model to be verified using a sample model a circuit of which has been described in a predetermined language and a test vector generation model for the sample model, a process for writing an output from the sample model test vector generation model into an input FIFO group for each signal of the sample model with the same timing as that of the sample model while the sample model is inputting / outputting a signal from / to the sample model test vector generation model with cycle accuracy and a process for reading data from the input FIFO group with the same operation timing as that of the model to be verified and outputting the data to the model to be verified are carried out. The output of the sample model and the output of the model to be verified are written into an output FIFO pair group for each corresponding signal name and coincidence judgment is carried out for a pair output for each written signal name.

Owner:RENESAS ELECTRONICS CORP

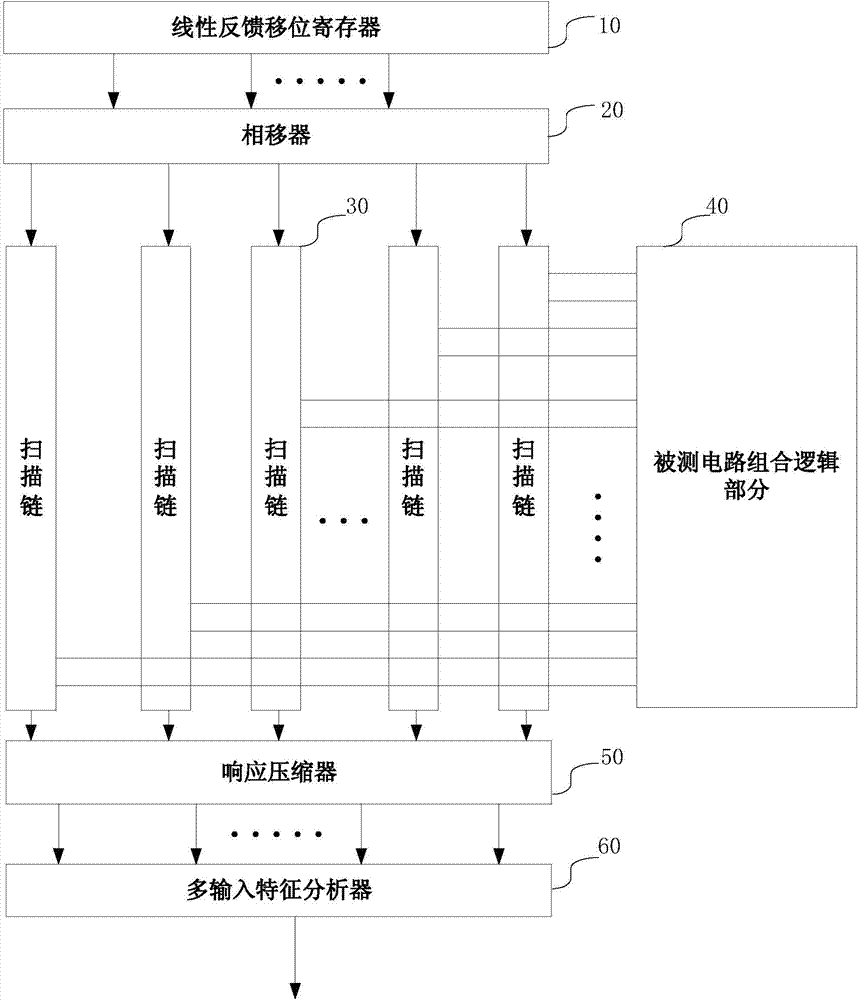

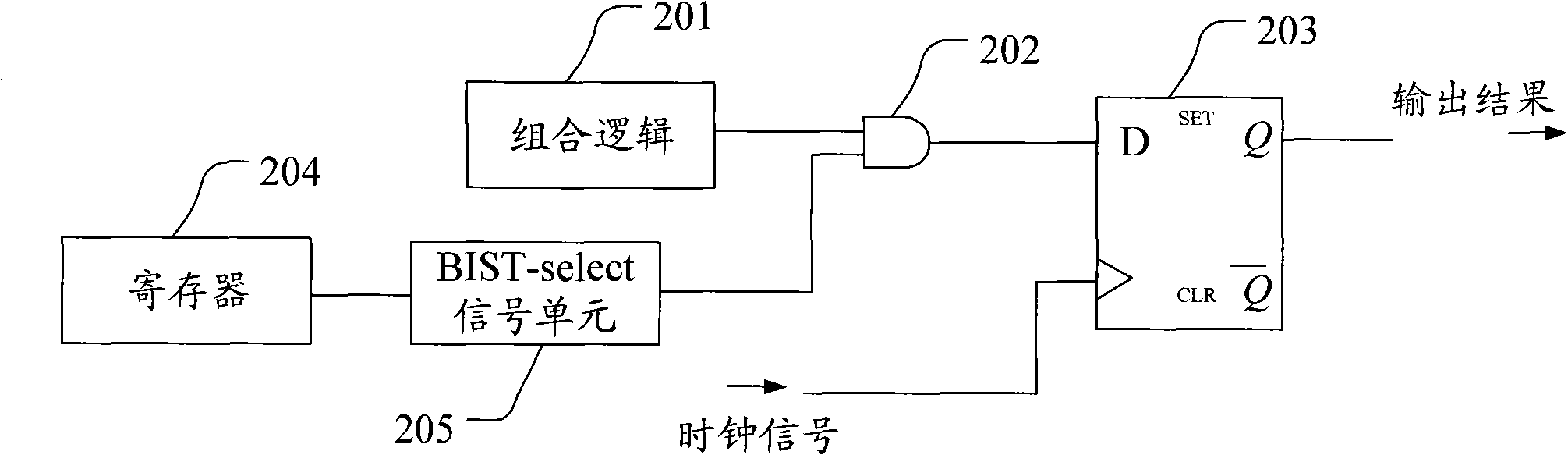

Circuit and method for generating test vectors required by built-in self-test of integrated circuit

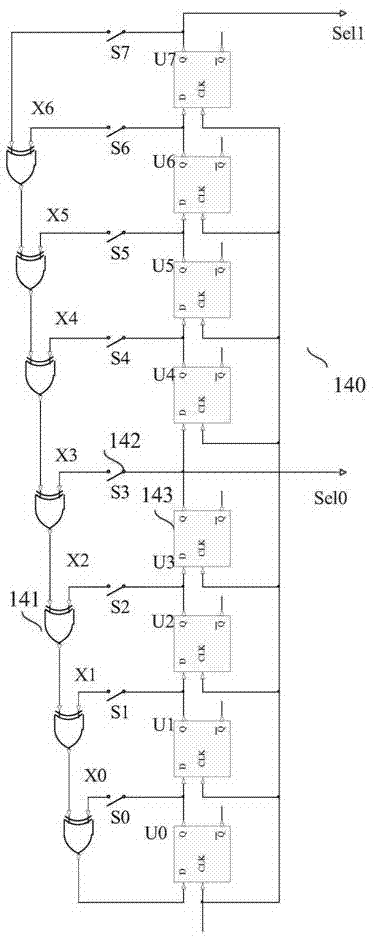

The invention relates to a circuit for generating test vectors required by built-in self-test of an integrated circuit. The circuit comprises an address counter, a sequence counter, a seed and multinomial coefficient storage unit, a sequence generator, a weight generating logical unit, 4-Line to 1-Line data selectors, an input register and scan chains, wherein the address counter is used for sending address data sequences; the sequence counter is used for sending data sequences; the seed and multinomial coefficient storage unit is connected with the address counter and used for sending output values of compressed vectors difficult and easy to test; the sequence generator is connected with the sequence counter and the seed and multinomial coefficient storage unit and used for outputting 2-bit data; the weight generating logical unit is used for outputting four-channel data values; the 4-Line to 1-Line data selectors are connected with the weight generating logical unit and the sequence generator and used for outputting one-channel data; the input register is connected with the 4-Line to 1-Line data selectors and used for registering data and loading updated data; the scan chains are connected with the input register and a tested circuit combinatorial logic unit and used for outputting the updated data. A tested circuit is connected with the scan chains and used for detecting faults of the tested circuit. The invention further provides a method for generating the test vectors required by built-in self-test of the integrated circuit.

Owner:INST OF AUTOMATION CHINESE ACAD OF SCI

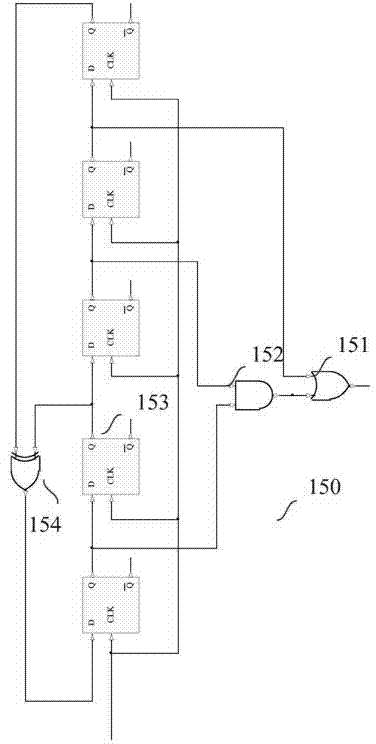

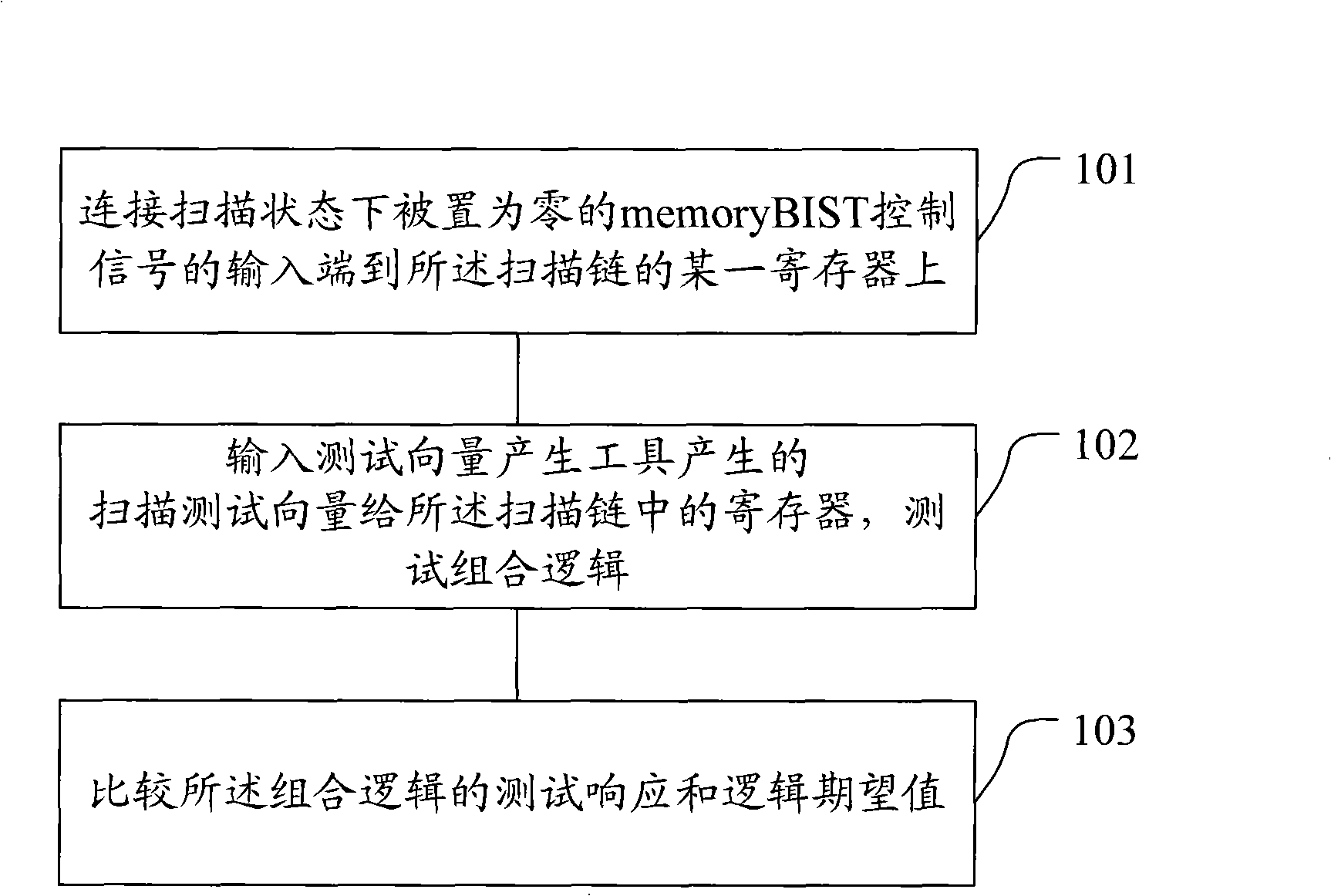

Method for increasing test coverage of scan chain and device thereof

ActiveCN101515479AImprove test coverageImprove testabilityStatic storageControl signalProcessor register

The invention provides a method for increasing the test coverage of a scan chain and a device thereof; wherein, the method for increasing the test coverage of the scan chain comprises: an input end of built-in self testing control signals of a memory being set to be zero in a scanning mode is connected into one register in the scan chain; scan test vector generated by a test vector generation tool is input into the scan chain comprising the register to test combinational logic; the test response and logic expected value of the combinational logic are compared. The method for increasing the test coverage of the scan chain provided by the invention causes that the built-in self testing control signals of the memory can be controlled when the scan chain tests, and realizes the testability of the built-in self testing logic of the memory in the scan mode, thus increasing the logic test coverage of the scan chain test and further increasing the whole test coverage of a chip.

Owner:BEIJING VIMICRO ARTIFICIAL INTELLIGENCE CHIP TECH CO LTD

Test vector generation method

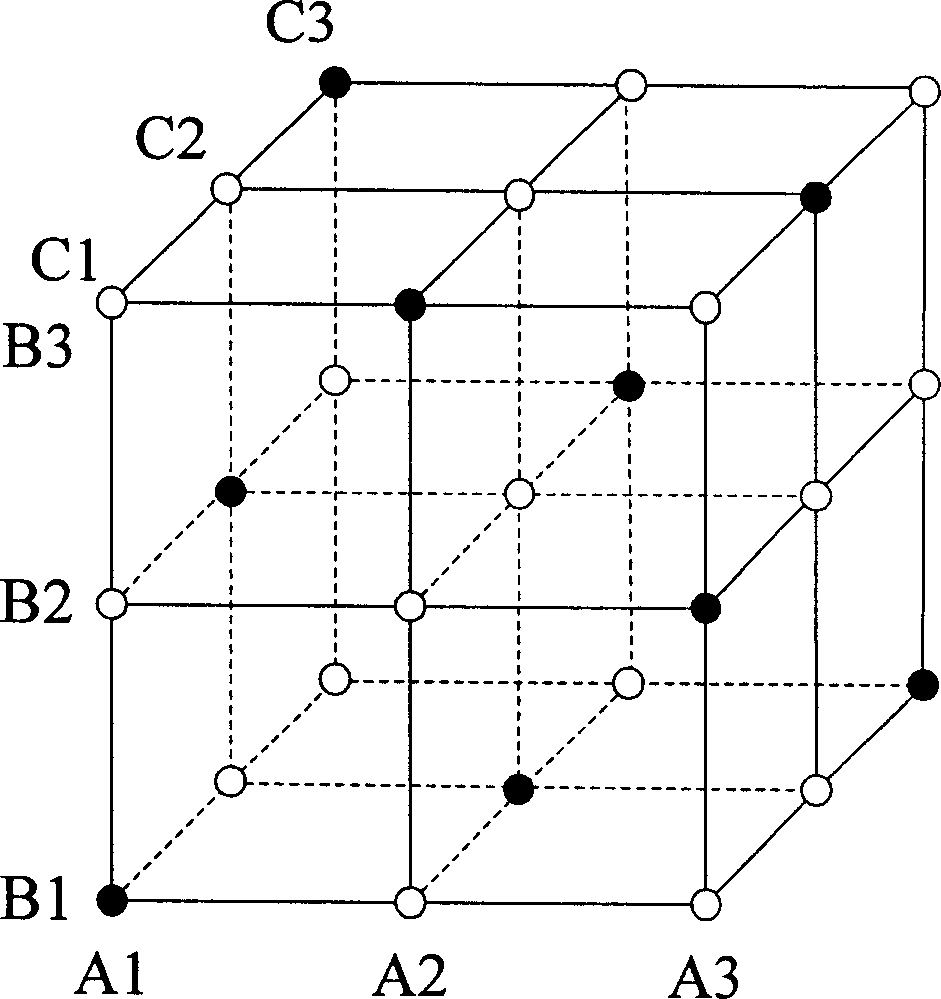

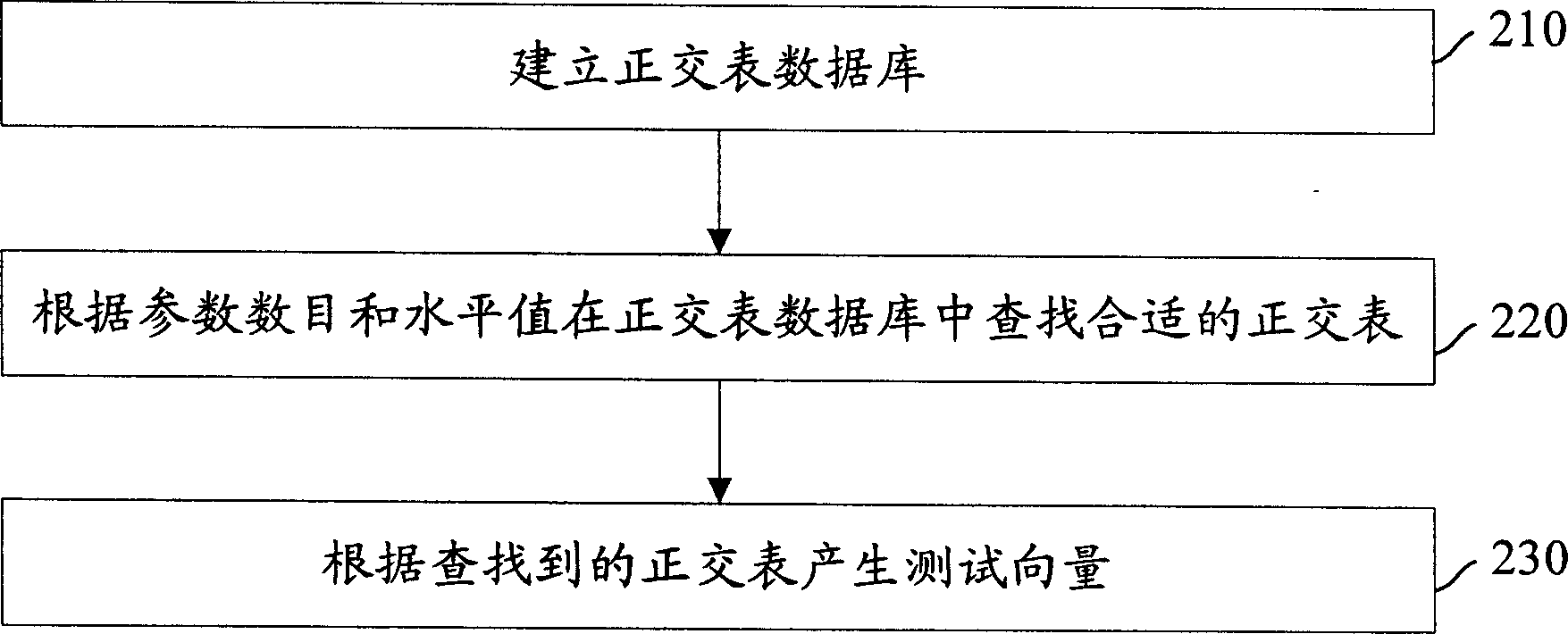

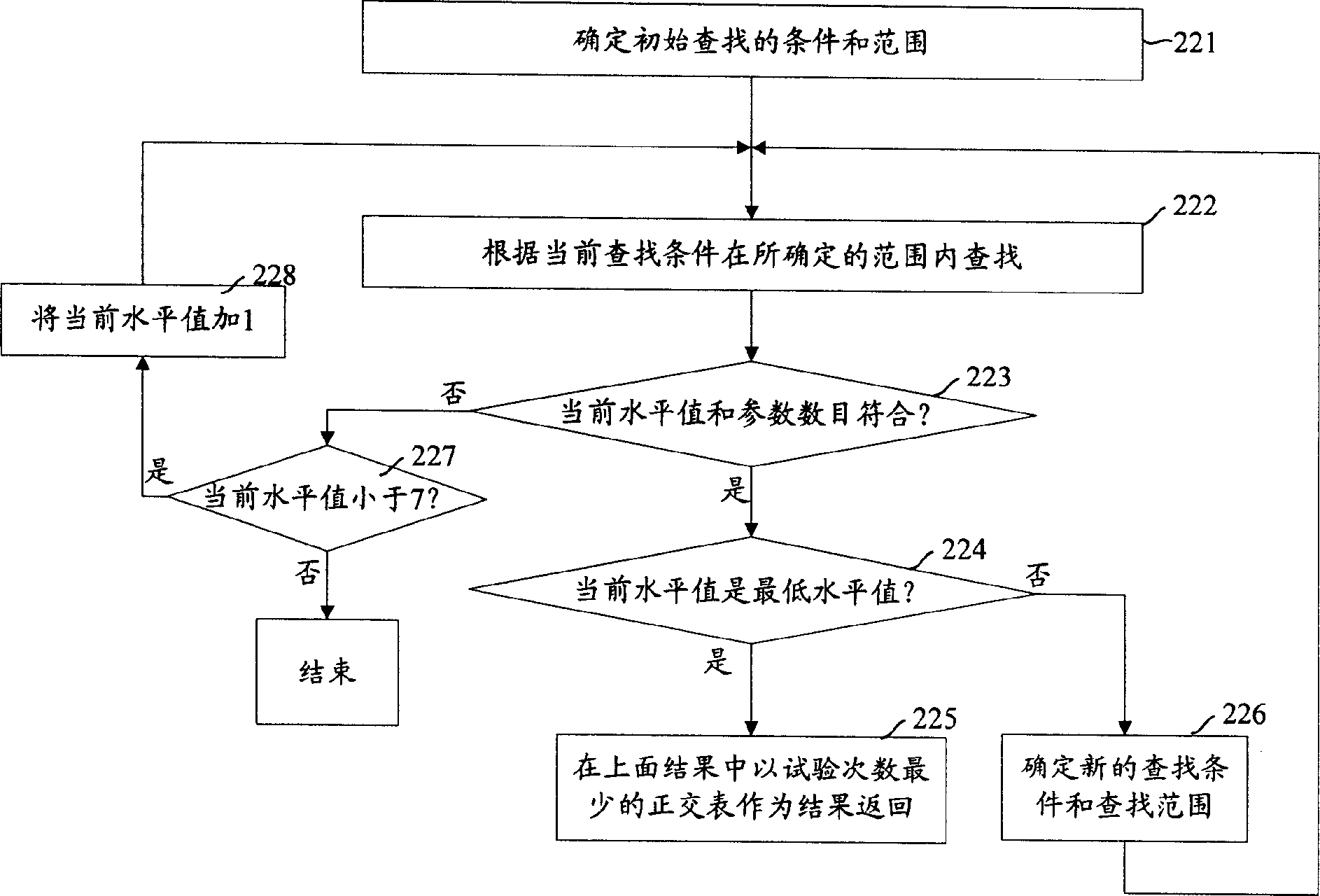

InactiveCN1845079AReduce the numberEasy to useSoftware testing/debuggingTheoretical computer scienceLow input

The invention relates to a method for generating test vector, which comprises: building an orthogonal table database; according to the test conditions, finding input level values and relative input parameters; selecting the orthogonal tables with same level values, and using highest input level value as the initial present input level value; finding the correct orthogonal table in the orthogonal table group according to present input level value; judging if the met orthogonal table subgroup is found in the orthogonal table group, if it is, judging if present input level value is the lowest level value, if it is, using the orthogonal table with minimum test times as the result to be feedback, or else, continuously searching in the results according to the second lower input level value, or completing the process; then generating test vector according to the result orthogonal table to process test. The invention can reduce the number of vector, the test time and cost, with confirmed effect.

Owner:HUAWEI TECH CO LTD

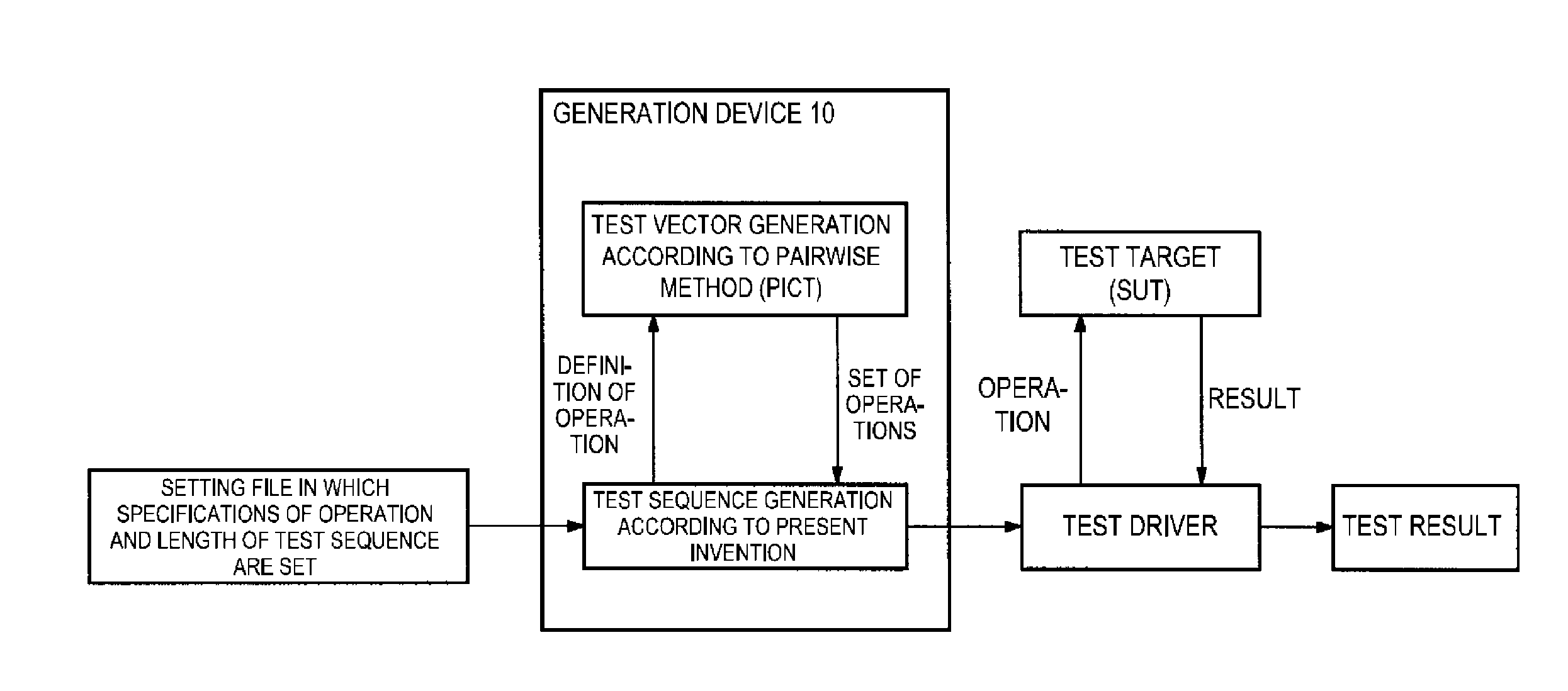

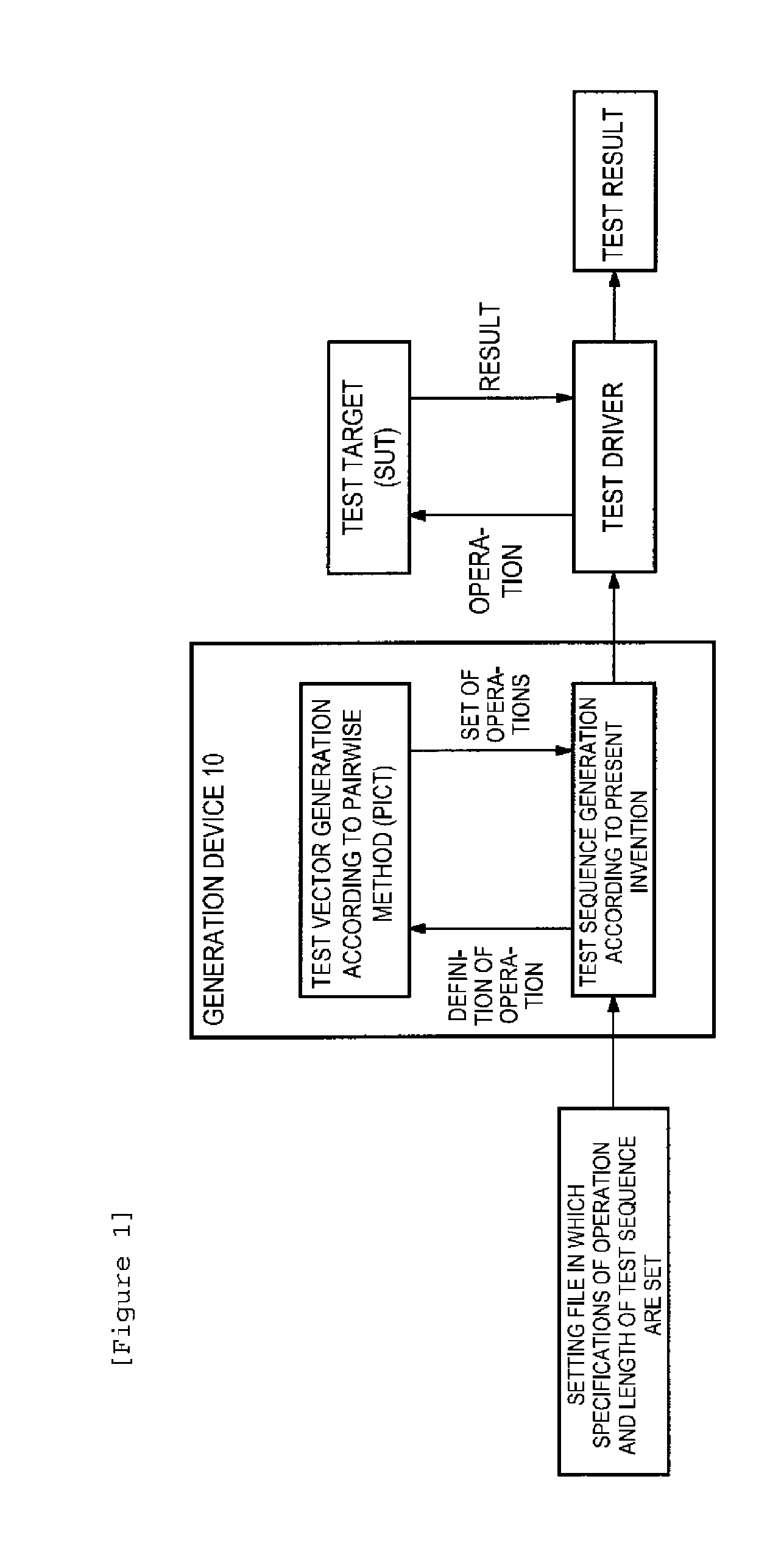

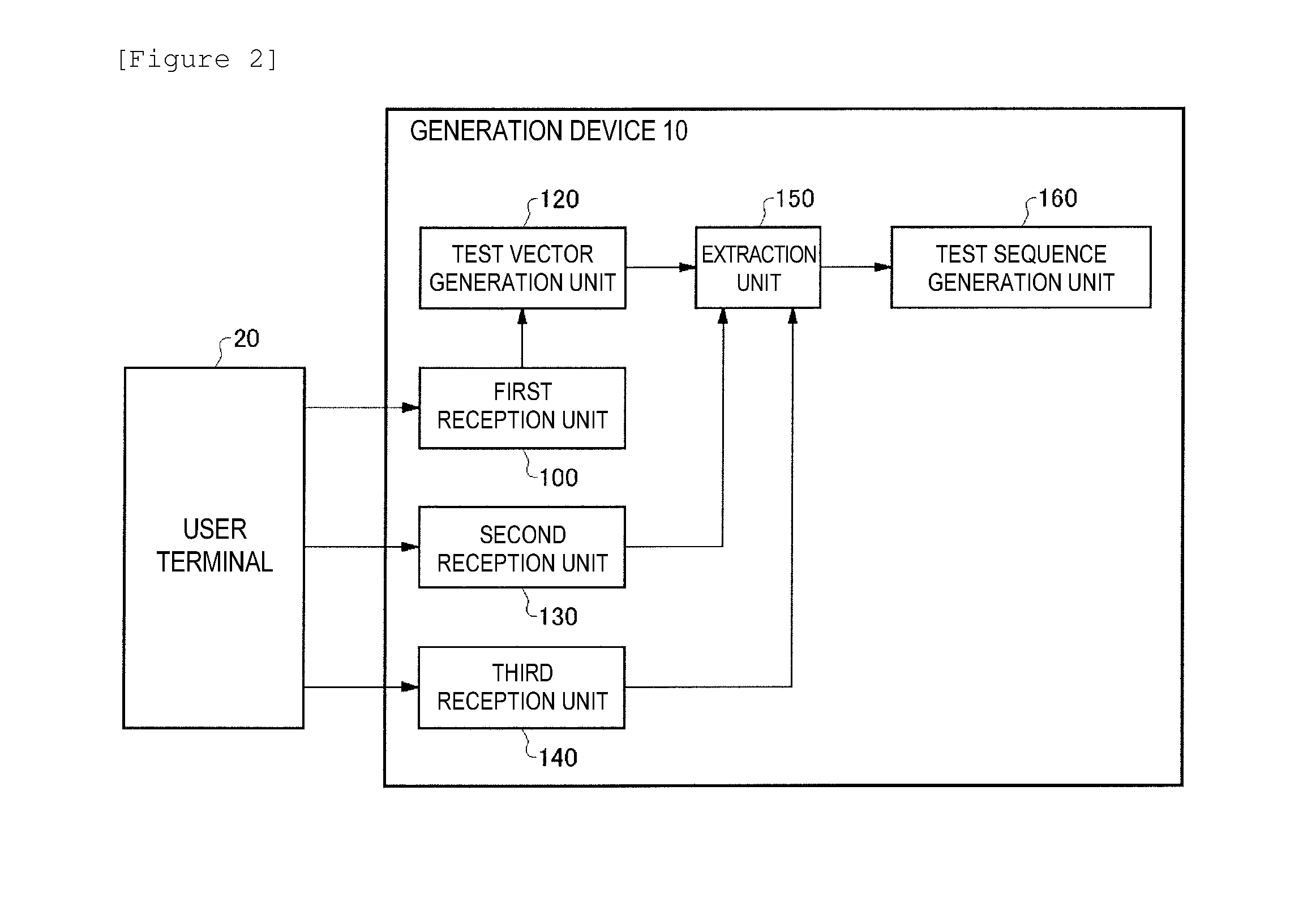

Generation device, generation method, and program

InactiveUS20150234007A1Large coverageError detection/correctionElectrical testingTest sequenceTest vector

Provided is a generation device including: a test vector generation unit for selecting, for each of parameters to be included in a test vector, one value from among possible values for the parameter to generate test vectors whose combinations of values are different from each other; an extraction unit for extracting, as partial sequences each including one or more test vectors, portions of a series including the test vectors output by the test vector generation unit; and a test sequence generation unit for generating a test sequence based on the extracted partial sequences.

Owner:IBM CORP

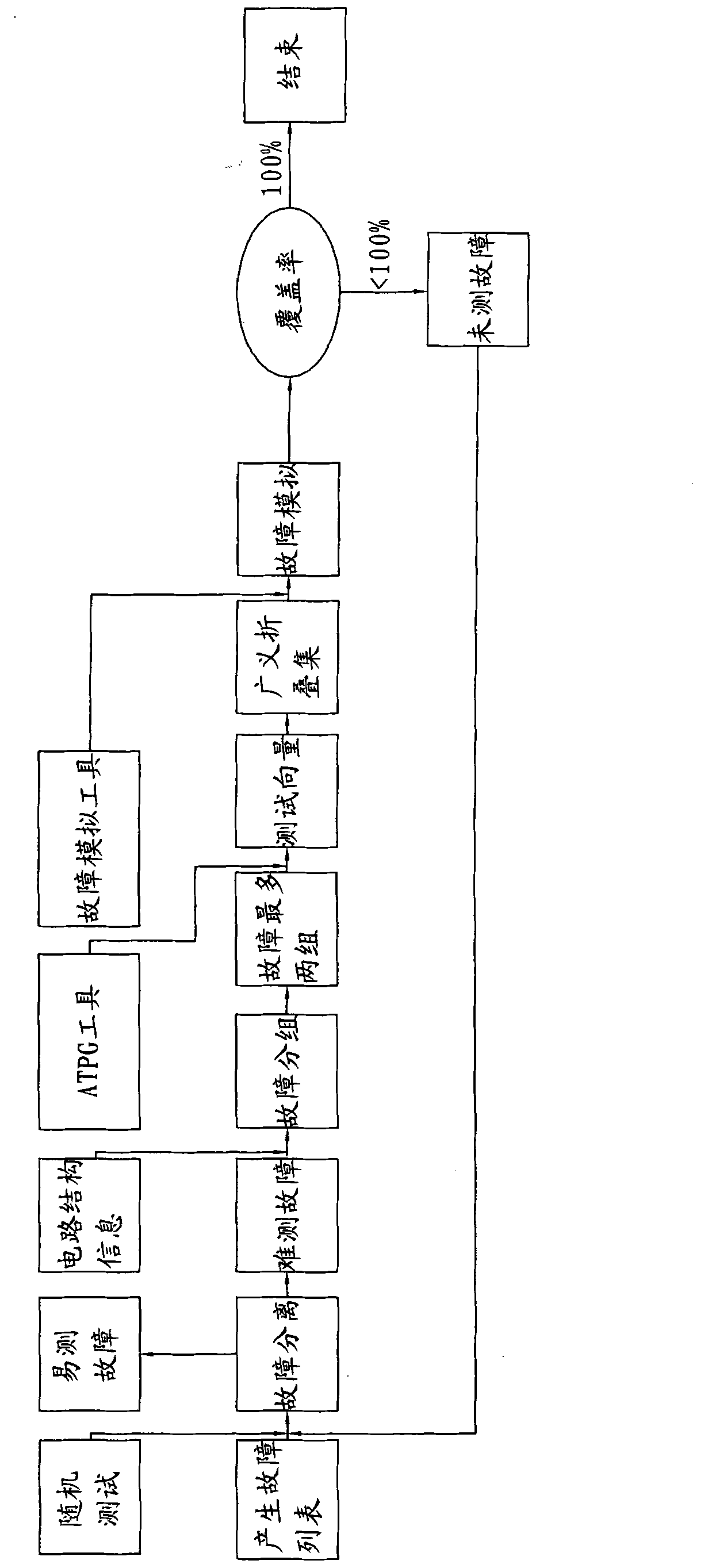

Compression method for test data of irrational number storage test vector

ActiveCN104753541AReduce the number of codesReduce the number of test vectorsElectronic circuit testingCode conversionFault coverageCompression method

The invention discloses a compression method for test data of an irrational number storage test vector and relates to a fault coverage guided compression method for the test data of the irrational number storage test vector. The compression method comprises the following steps of firstly, generating a fault list according to a circuit structure of an integrated circuit to be tested; secondly, running an automatic test vector generation tool for faults to generate test vectors of corresponding faults; thirdly, counting the lengths of runs; fourthly, performing preliminary estimation on corresponding ranges of irrational numbers; fifthly, dichotomising the ranges of the irrational numbers, and successively approximating; sixthly, filling independent bits; seventhly, performing random test; eighthly, judging whether the fault list in the seventh step is empty or not, if the fault list is empty, turning to the ninth step, and otherwise, turning to the second step; ninthly, ending, and returning all records such as integers m and l corresponding to all the irrational numbers. According to the compression method disclosed by the invention, the coding of the irrational numbers and the generation of the automatic test vectors are combined, so that on one hand, coding numbers, corresponding to the test vectors, of easily-detected fault points are reduced, and on the other hand, the fault coverage is improved.

Owner:池州华宇电子科技股份有限公司

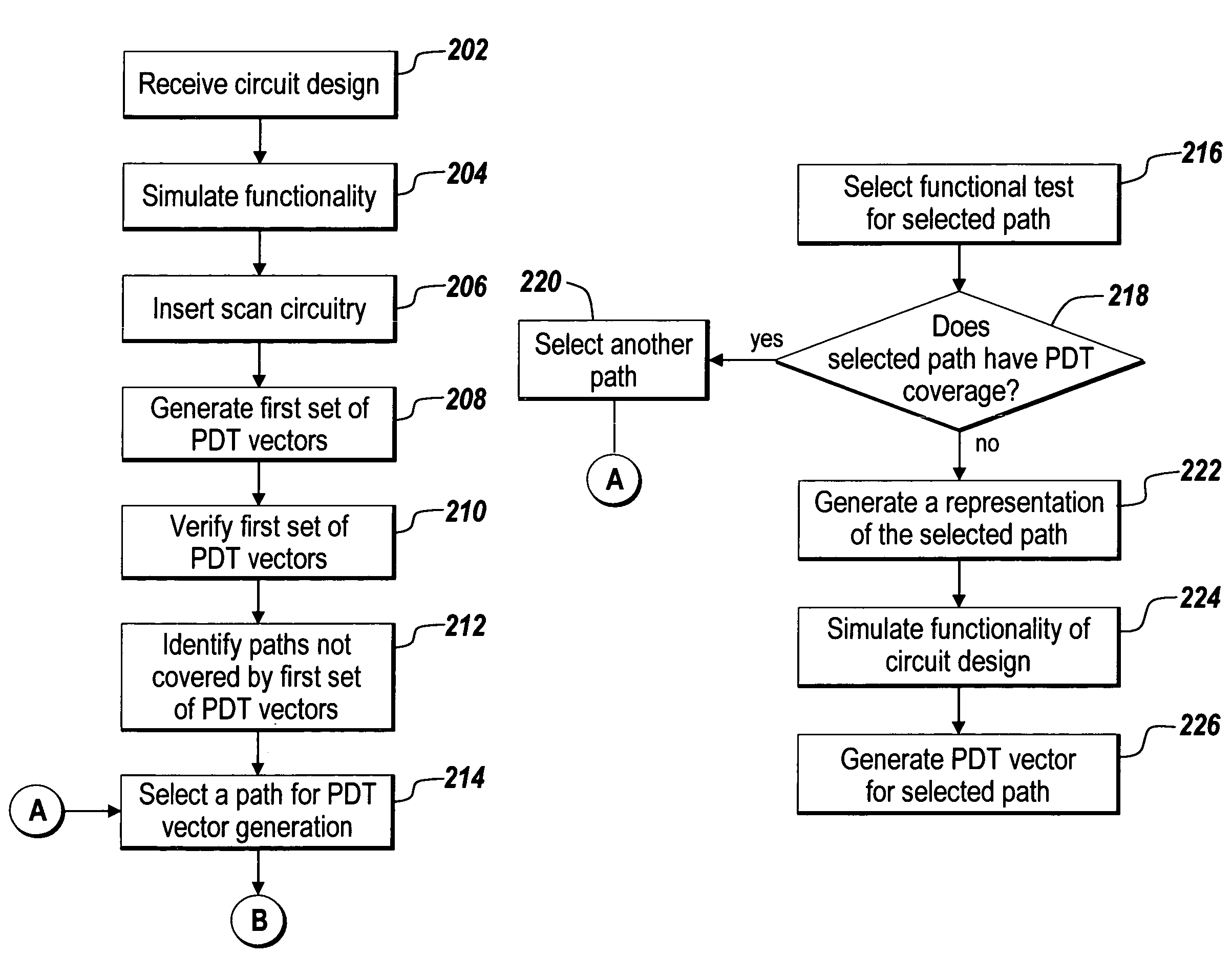

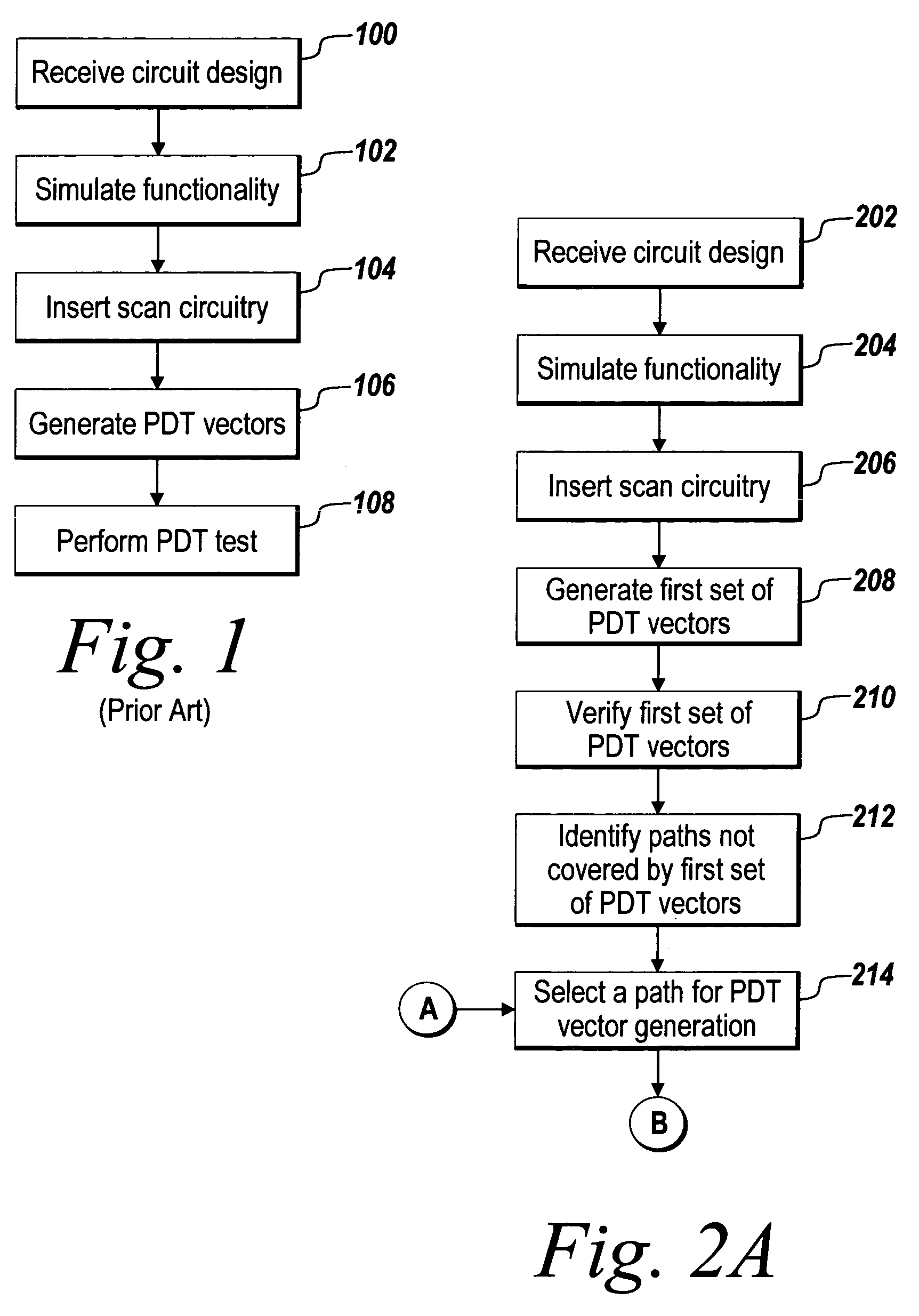

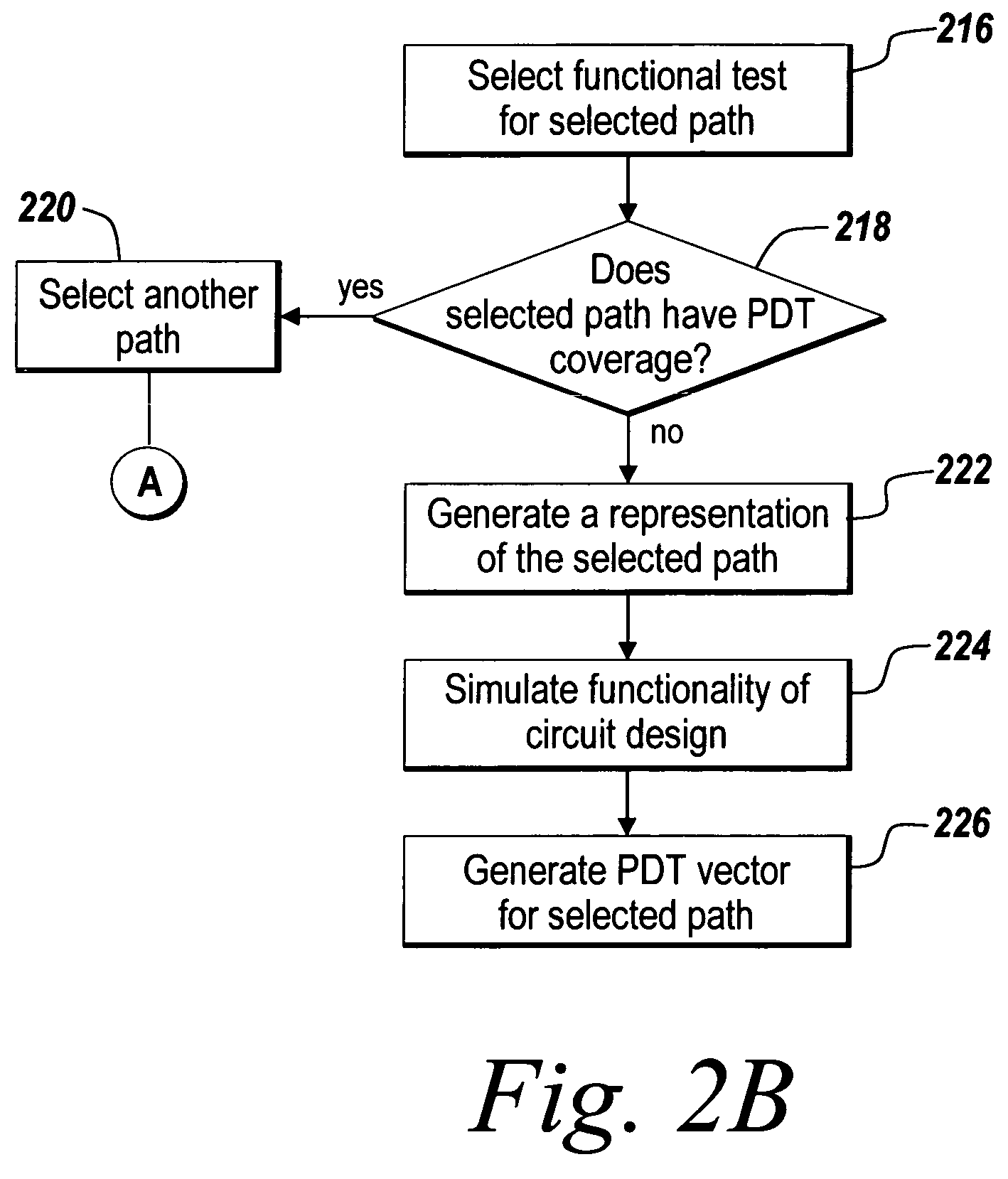

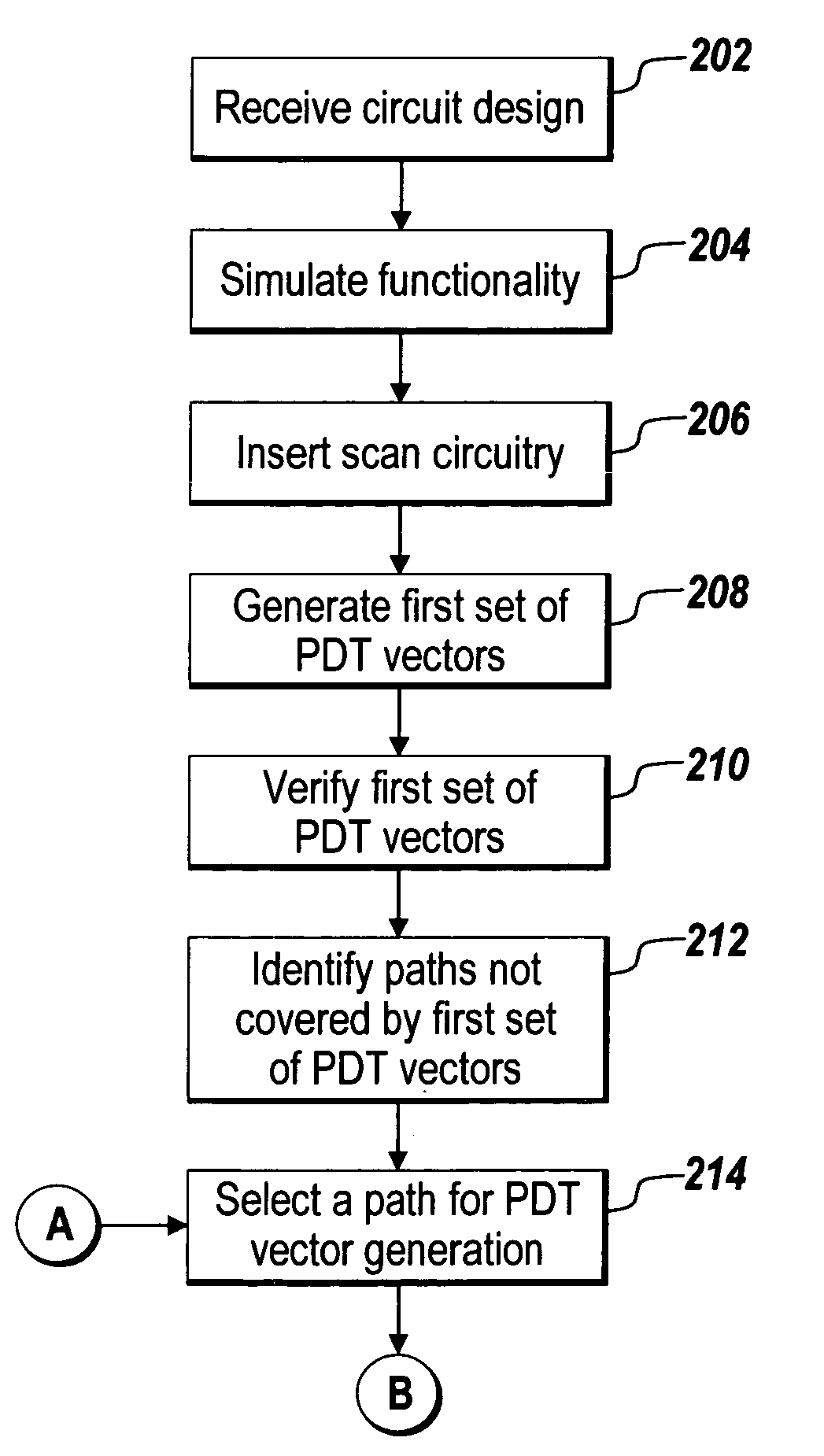

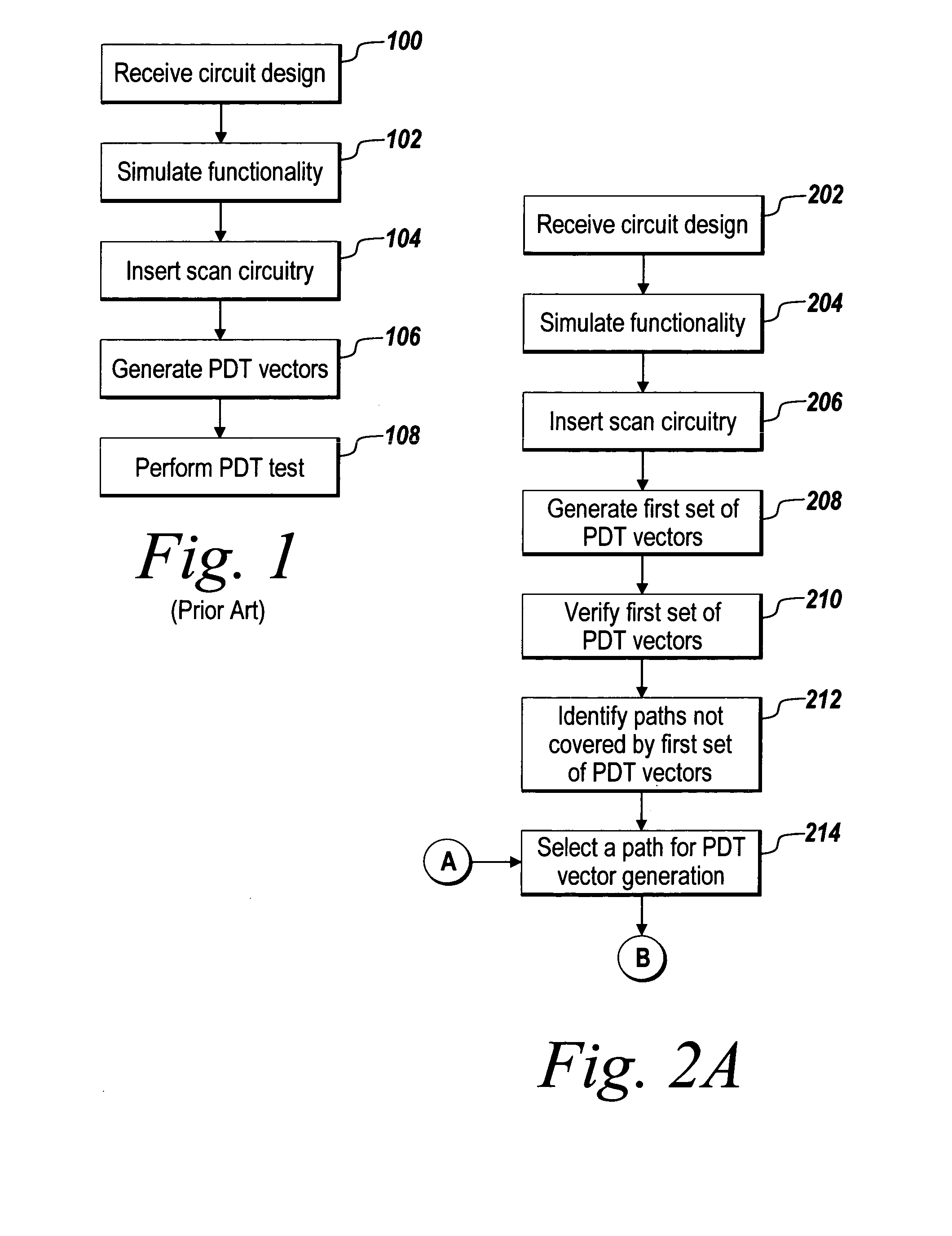

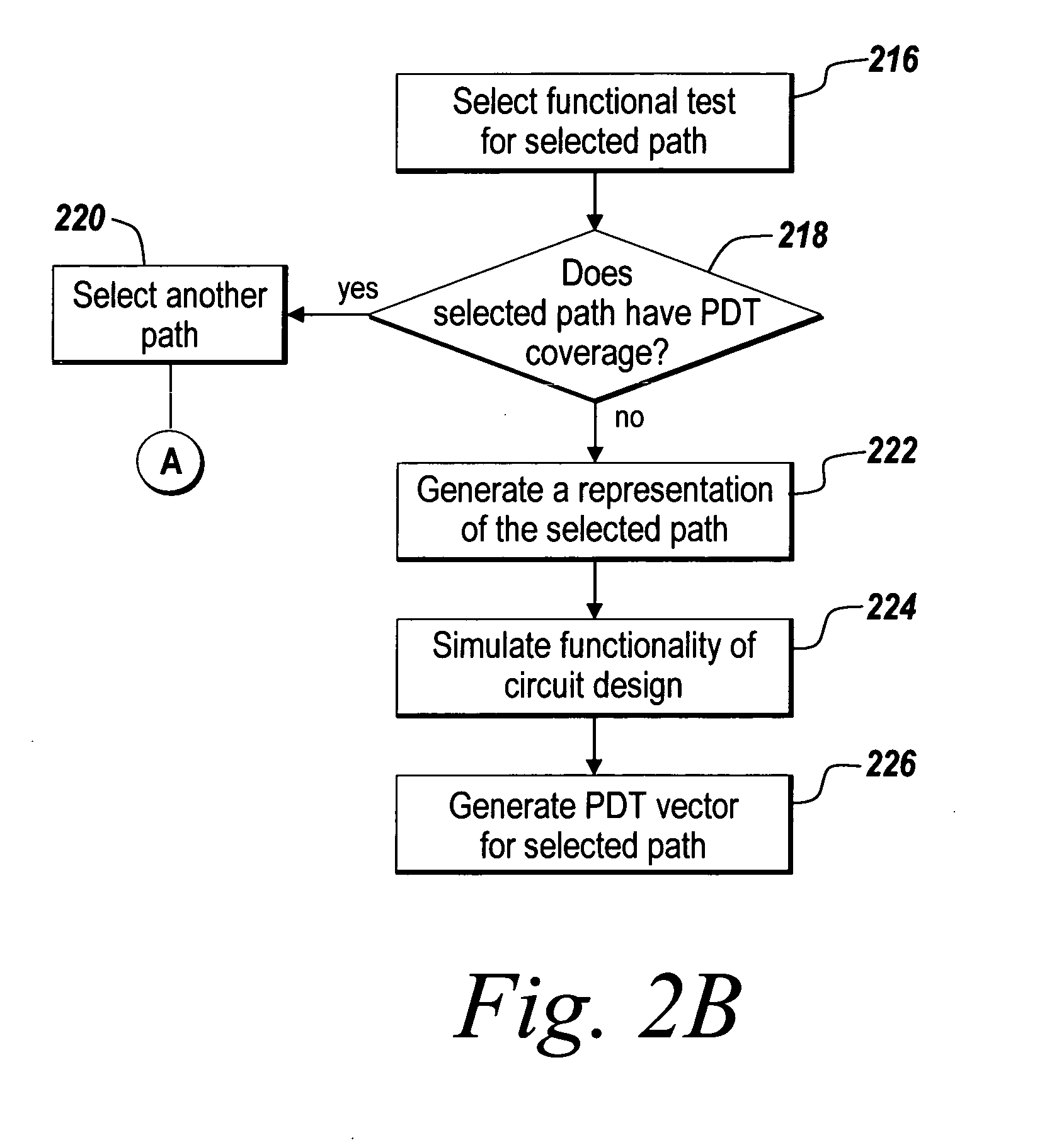

Method and system for automated path delay test vector generation from functional tests

ActiveUS7640476B2Increase PDT test coverageElectronic circuit testingError detection/correctionFunctional testingEngineering

Disclosed herein are methods and systems for generating test vectors for use in verification of a circuit design and for hardware testing on a fabricated circuit representative of the circuit design. The system and methods can systematically and automatically perform functional and structural testing on selected paths of the circuit design and, in turn, generate one or more test vectors to increase PDT test coverage using the results of the structural test on the selected path.

Owner:ORACLE INT CORP

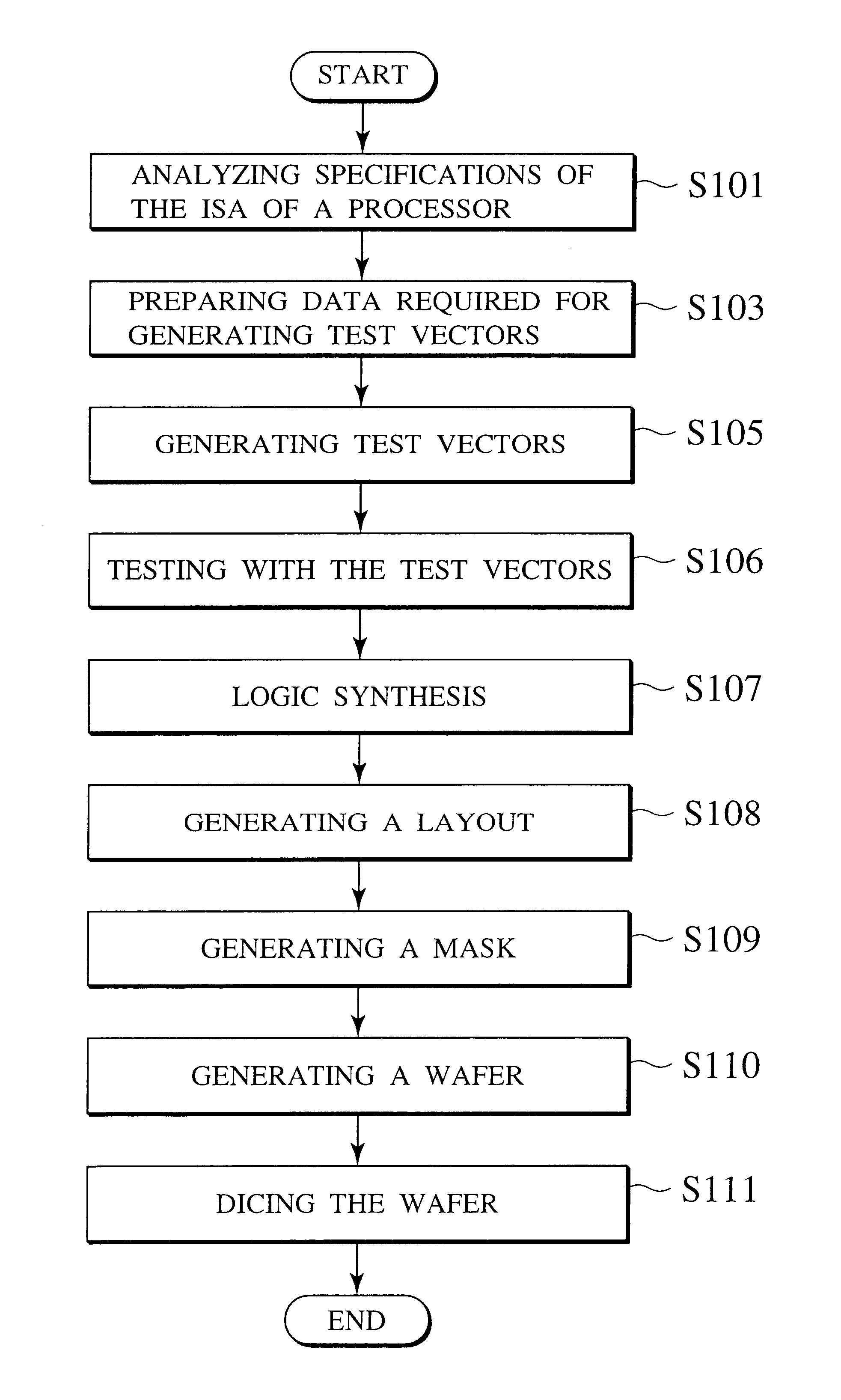

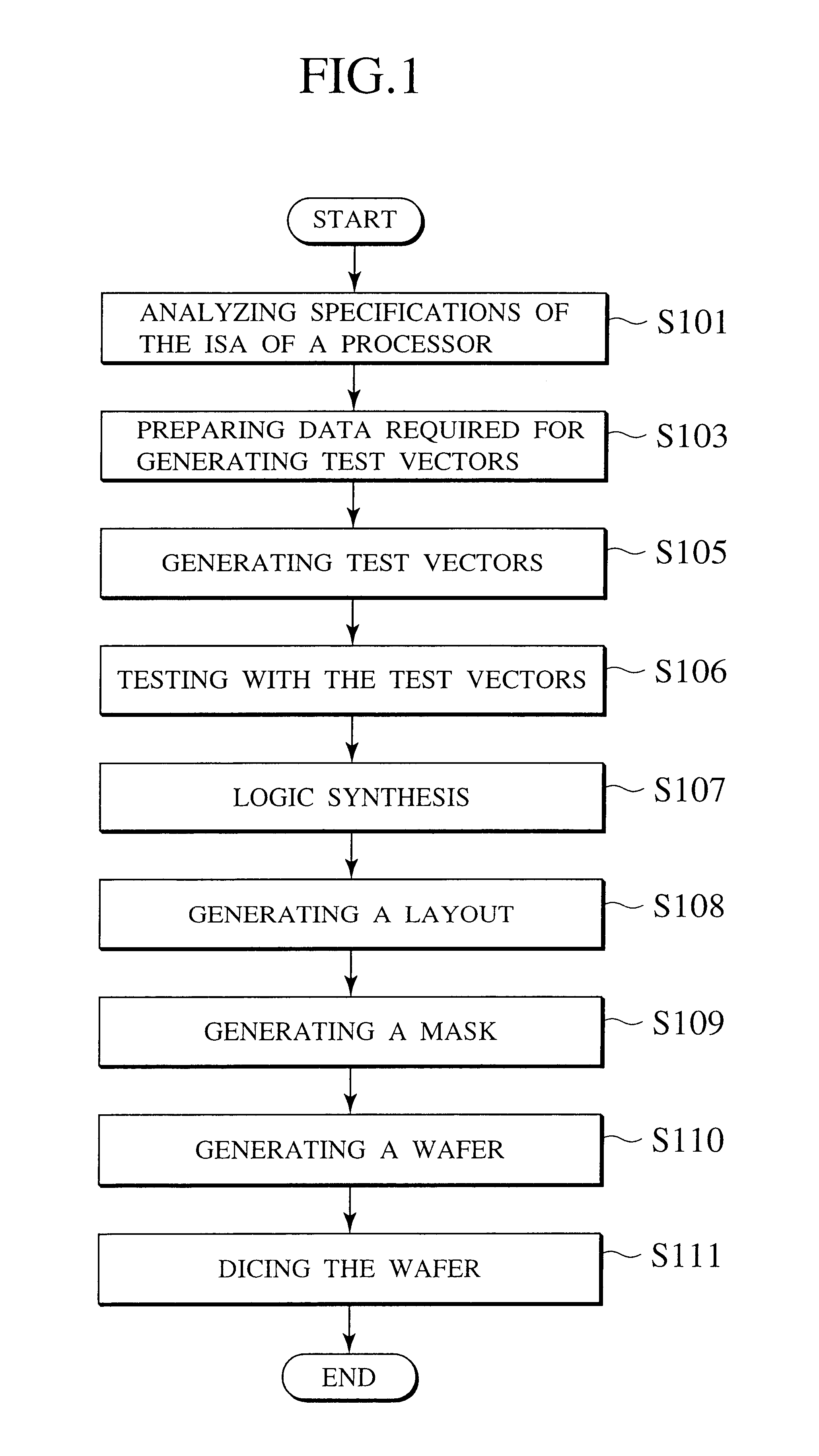

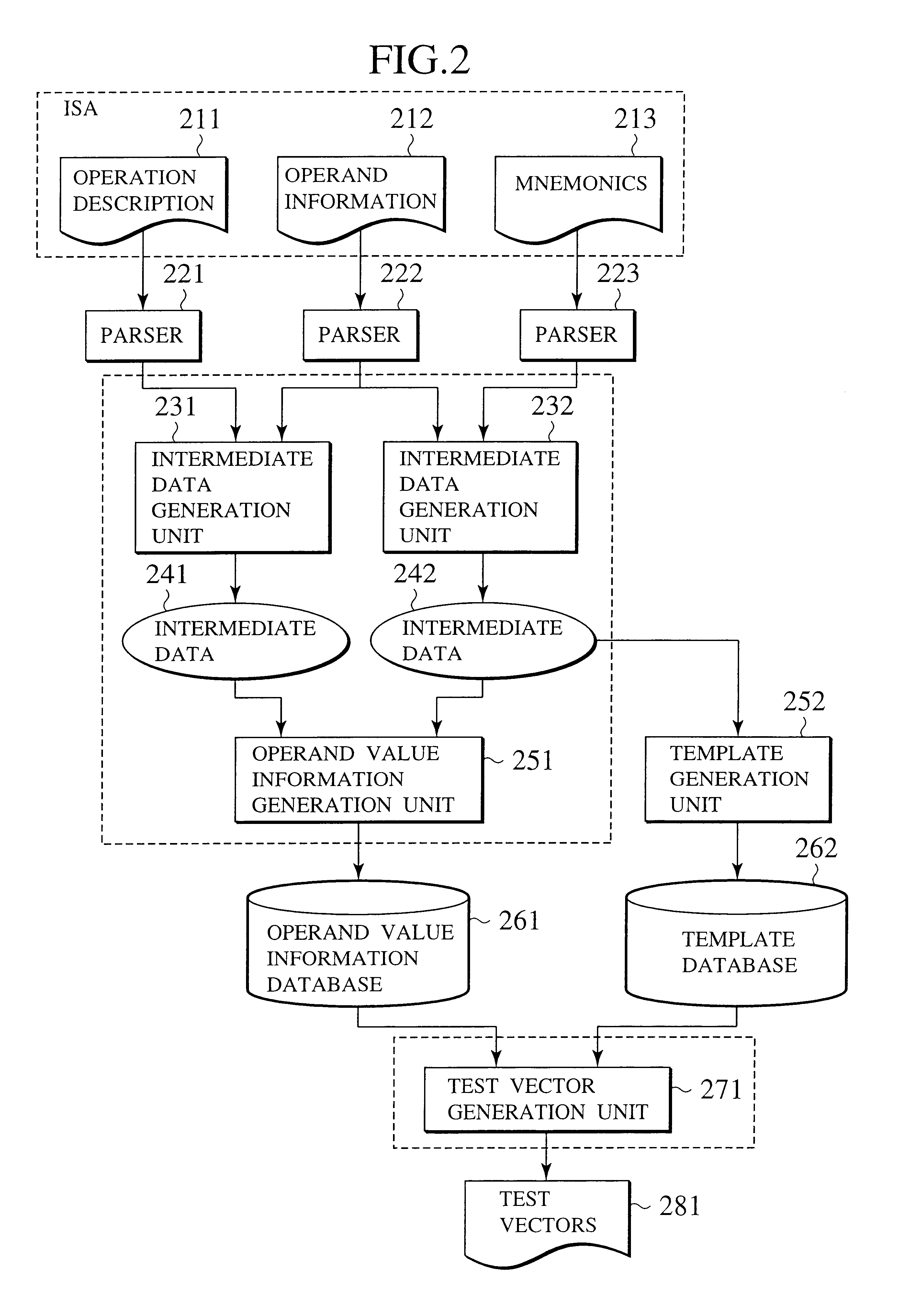

Automatic test vector generation method, test method making use of the test vectors as automatically generated, chip manufacturing method and automatic test vector generation program

InactiveUS6611779B2Resistance/reactance/impedenceDetecting faulty computer hardwareData preparationTest vector

A technique for automatically generating test vectors comprises an ISA specification analysis step of analyzing specifications of an instruction set architecture (ISA) of a processor (S101); a test vector generation data preparation step of preparing data required for generating test vectors (S103); and a test vector generation step of generating test vectors by the use of said data (S105).

Owner:KK TOSHIBA

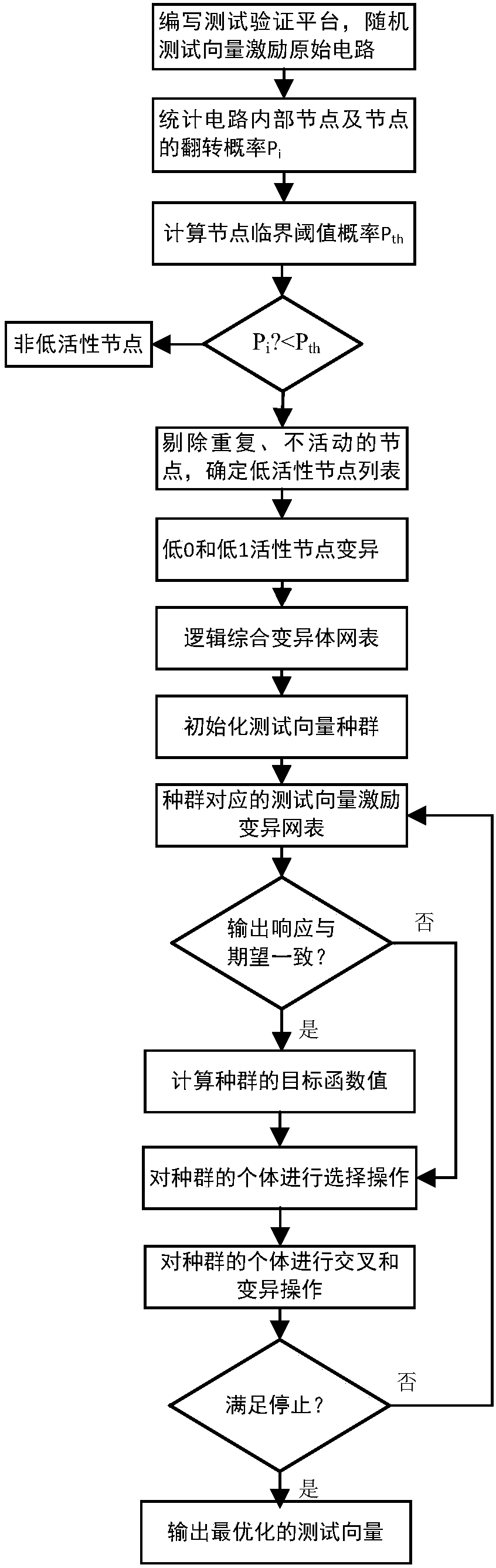

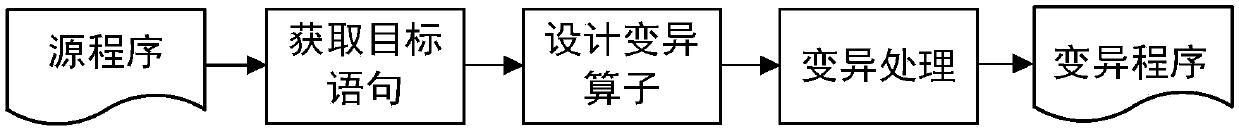

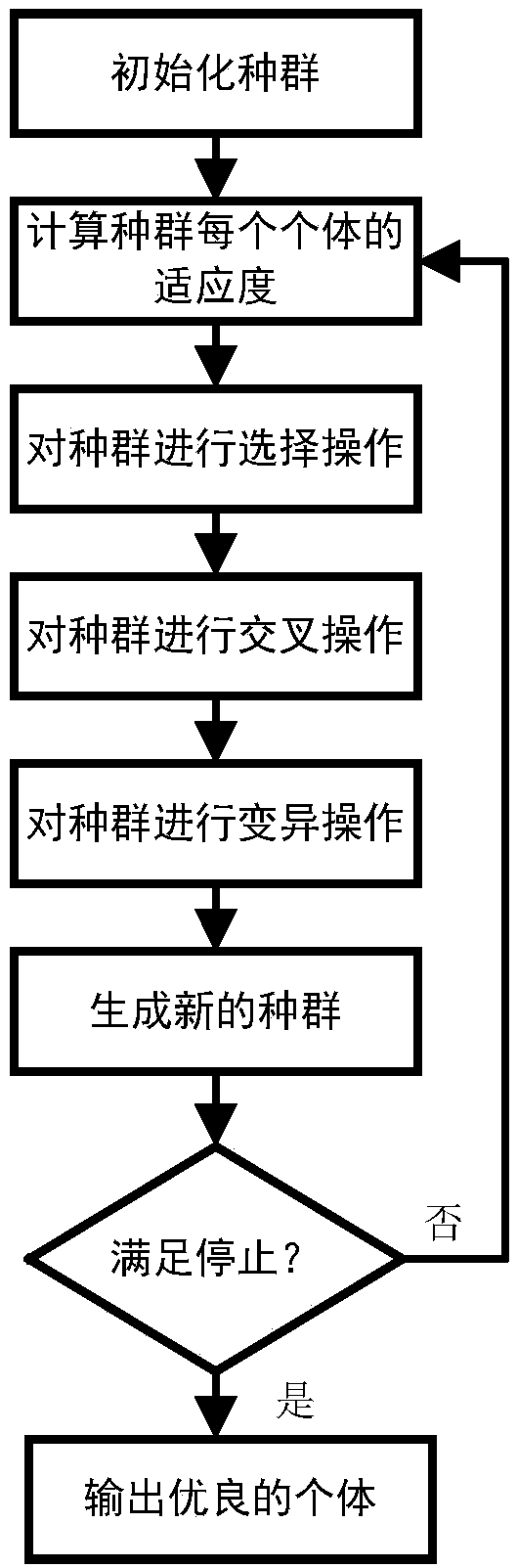

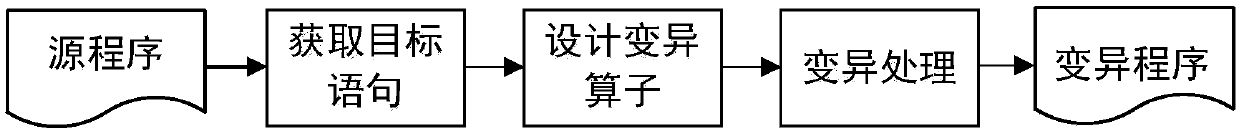

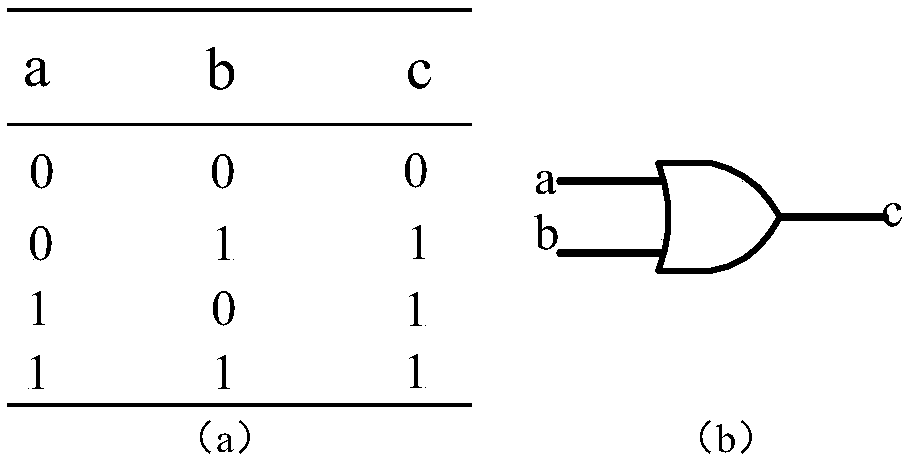

Optimized test vector generation method based on genetic algorithm and variation analysis

InactiveCN107590313AEasy to identifyPurposefulGenetic modelsSpecial data processing applicationsHardware TrojanMutant

The invention relates to the technical field of trustworthiness of integrated circuits, and provides a hardware Trojan optimized test vector generation method. The method searches test vector spaces in parallel, is strong in purposiveness and more compactor in directionally-screened test vector, can activate hardware Trojan more effectively, and has higher test efficiency; the method can assist manifesting of the hardware Trojan and analysis of bypass signals to improve a hardware Trojan recognition level, and has certain actual meaning and reference value. The invention adopts a technical scheme as follows: the hardware Trojan optimized test vector generation method based on a genetic algorithm and variation analysis screens out low-activity nodes of a circuit through analyzing characteristics of a parent circuit meshwork list, performs mutation operation on the circuit structure of the low-activity node by using a mutation thought of a software test to generate a mutant, and at lastscreens out a test vector capable of killing mutant by combing with a method of a search thought of the genetic algorithm. The method provided by the invention is mainly applied to design and manufacture occasions of the integrated circuits.

Owner:TIANJIN UNIV

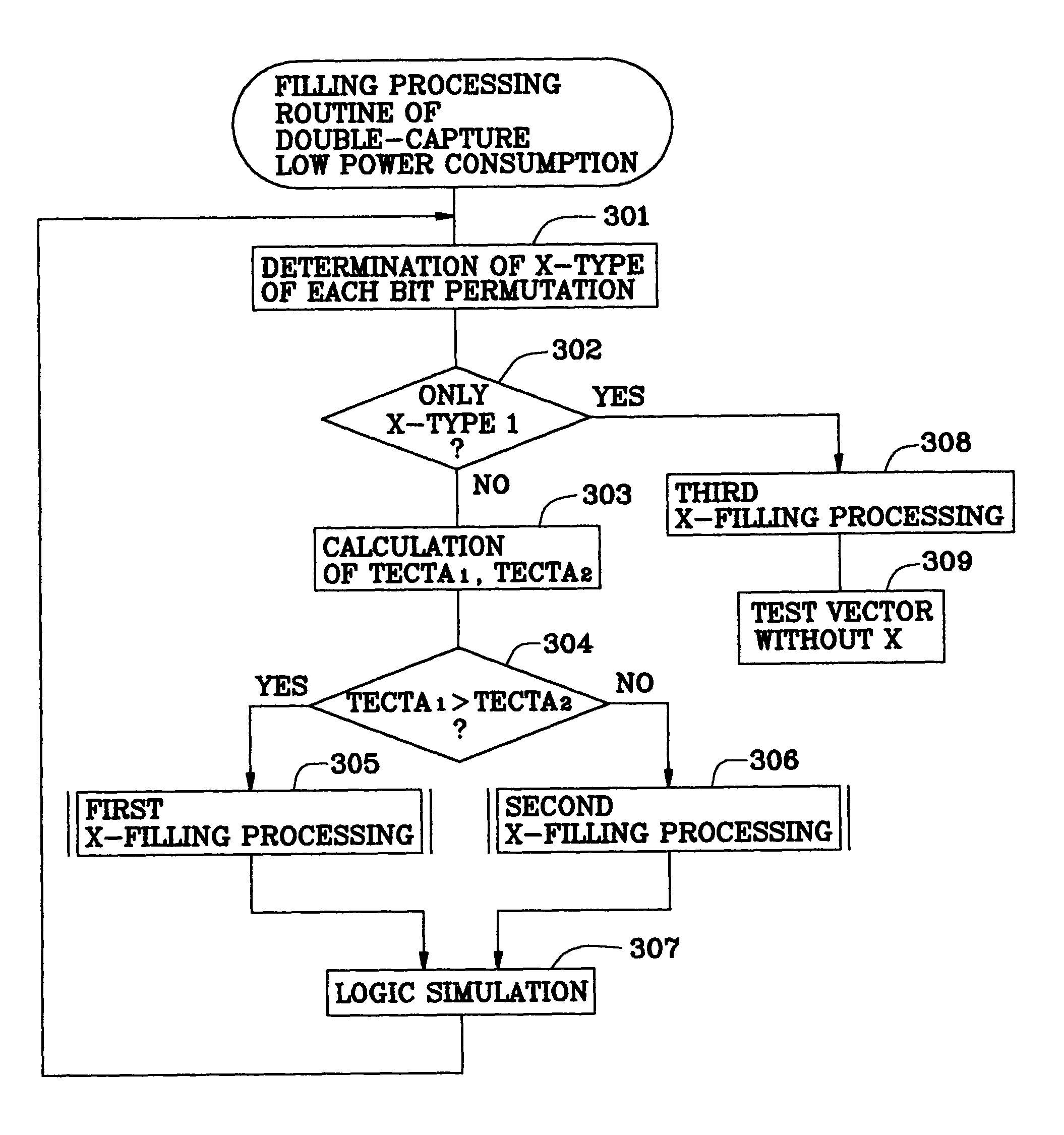

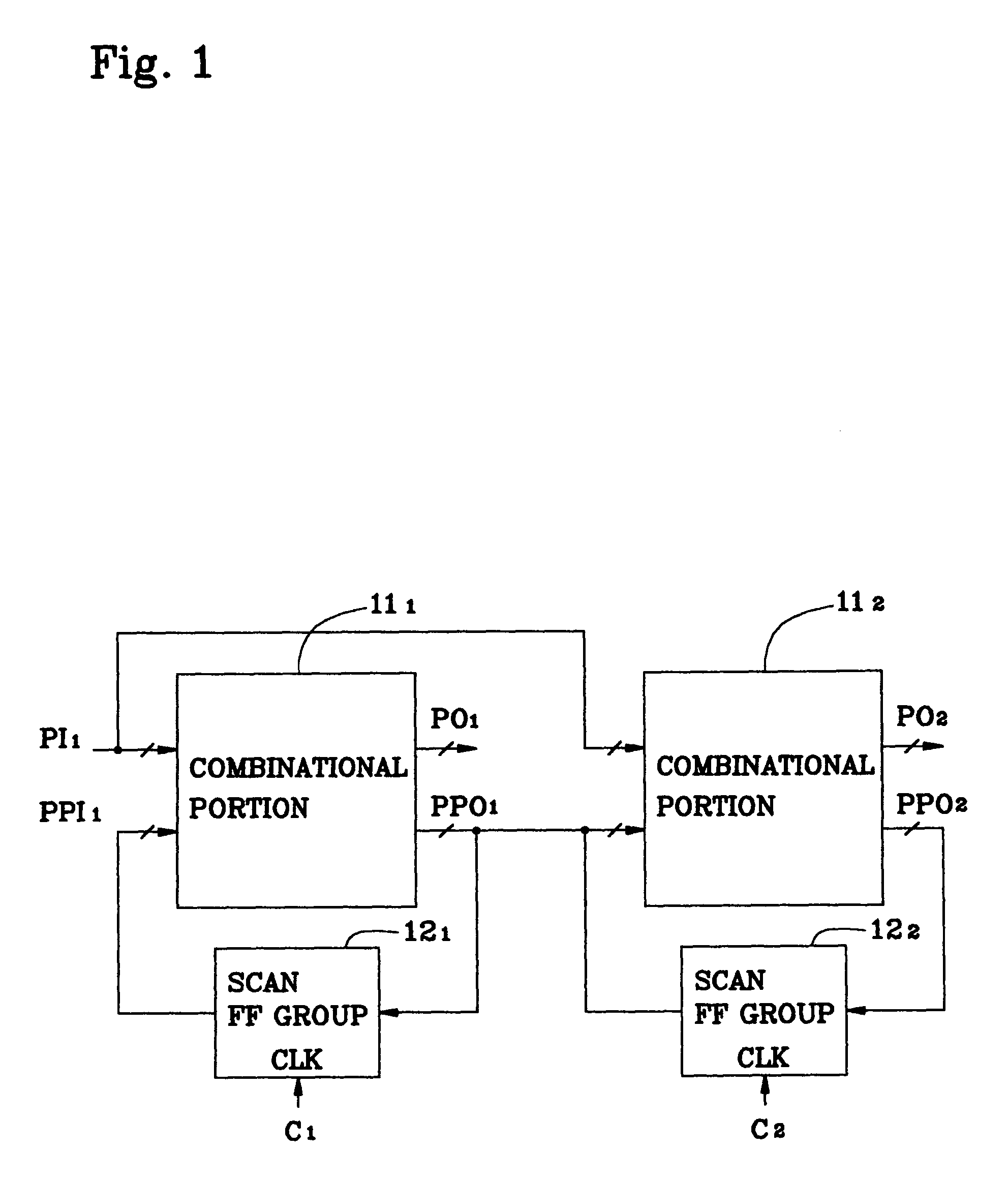

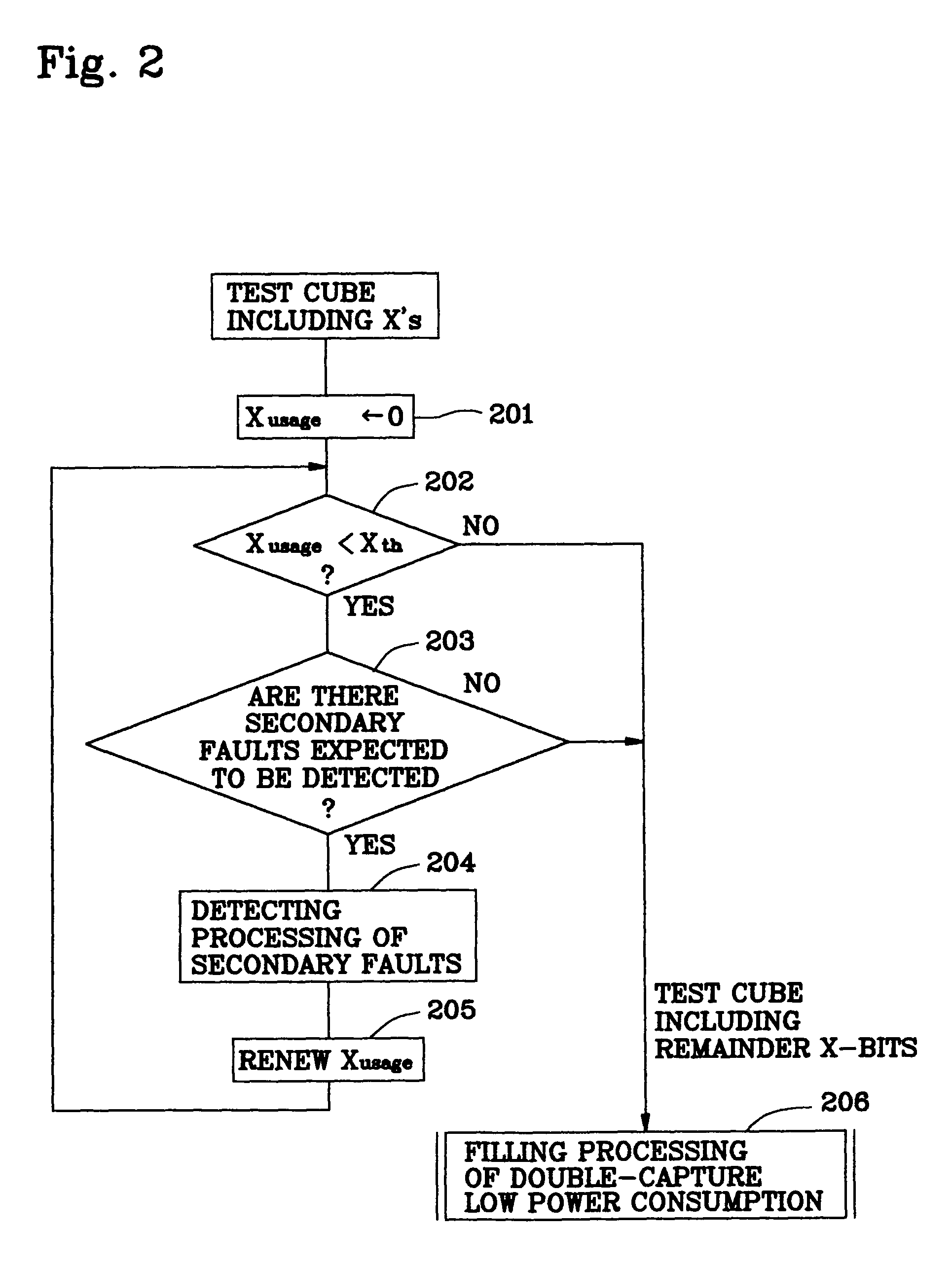

Test vector generating method and test vector generating program of semiconductor logic circuit device

InactiveUS7743306B2Reduce power consumptionAvoid testingElectronic circuit testingError detection/correctionComputer scienceSemiconductor

The X-type of each bit permutation is determined (step 301). When there are X-types except for X-type 1, i.e., X-type with no don't-care bits, total capture state transition numbers TECTA1 and TECTA2 for capture clock pulses C1 and C2 are calculated (step 303). As a result, when TECTA1>TECTA2, an X-type is selected for the capture clock pulse C1 and a first X-filling processing is performed (see step 305). On the other hand, when TECTA1≦TECTA2, an X-type is selected for the capture clock pulse C2 and a second X-filling processing is performed (step 306).

Owner:LPTEX

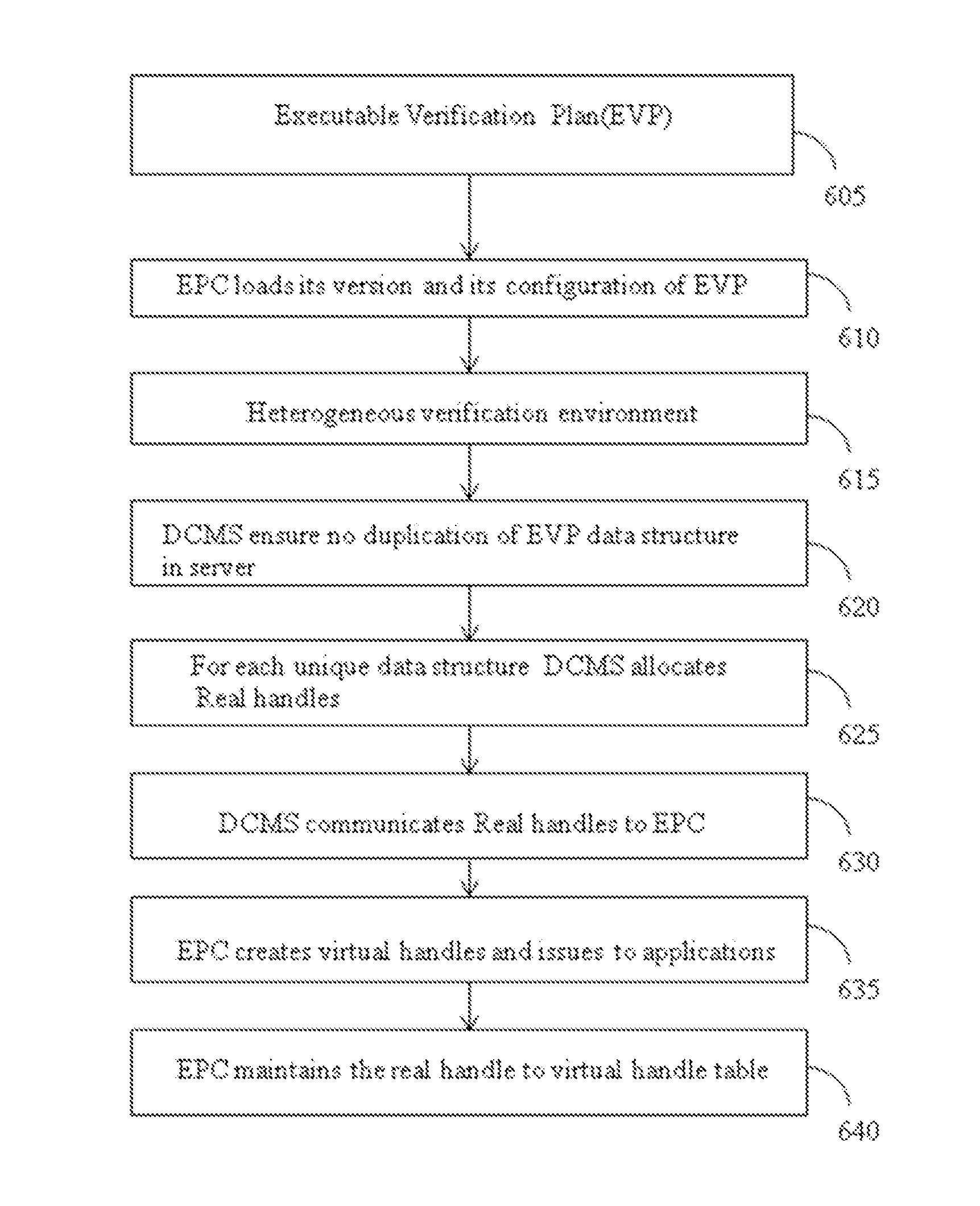

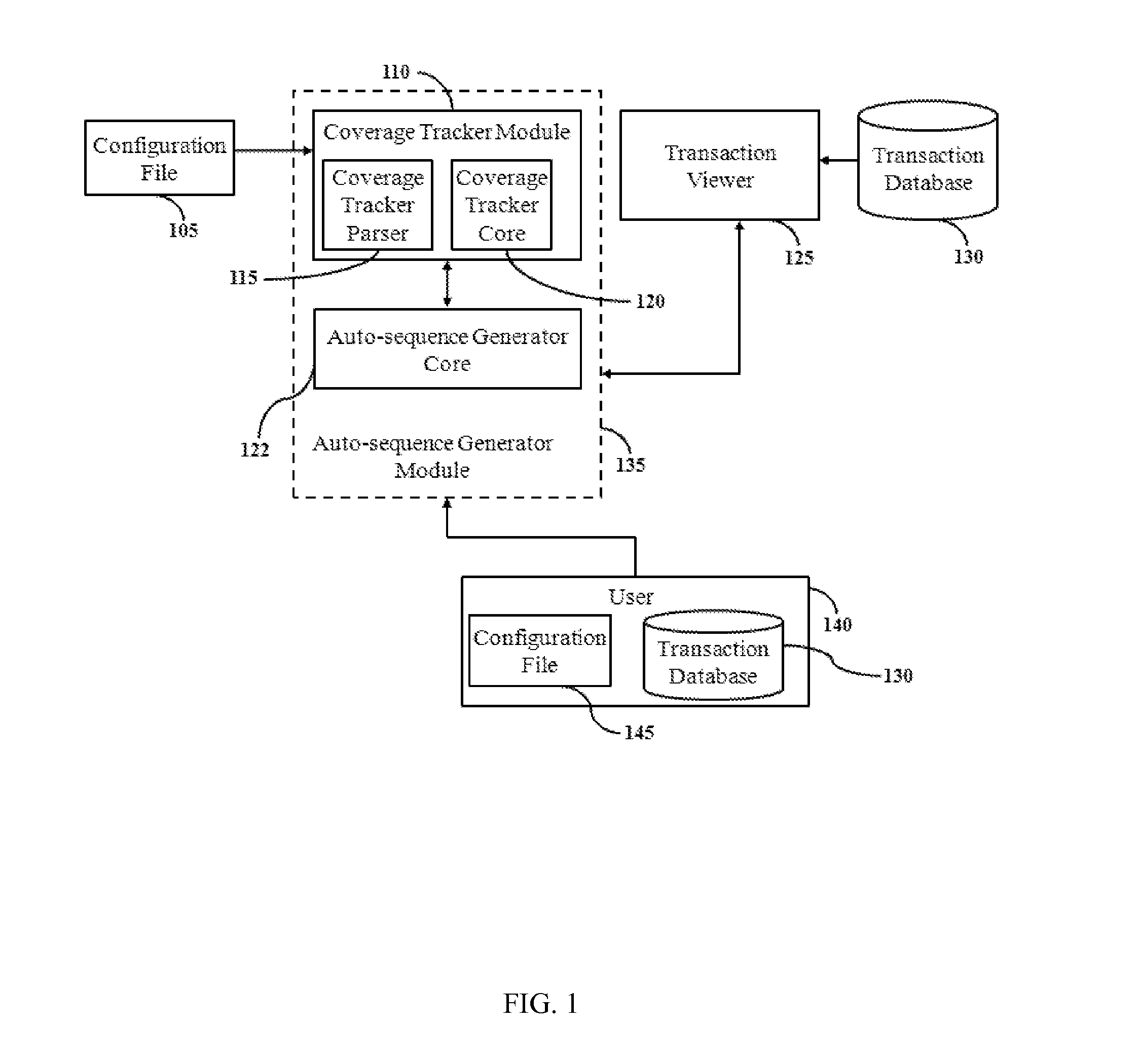

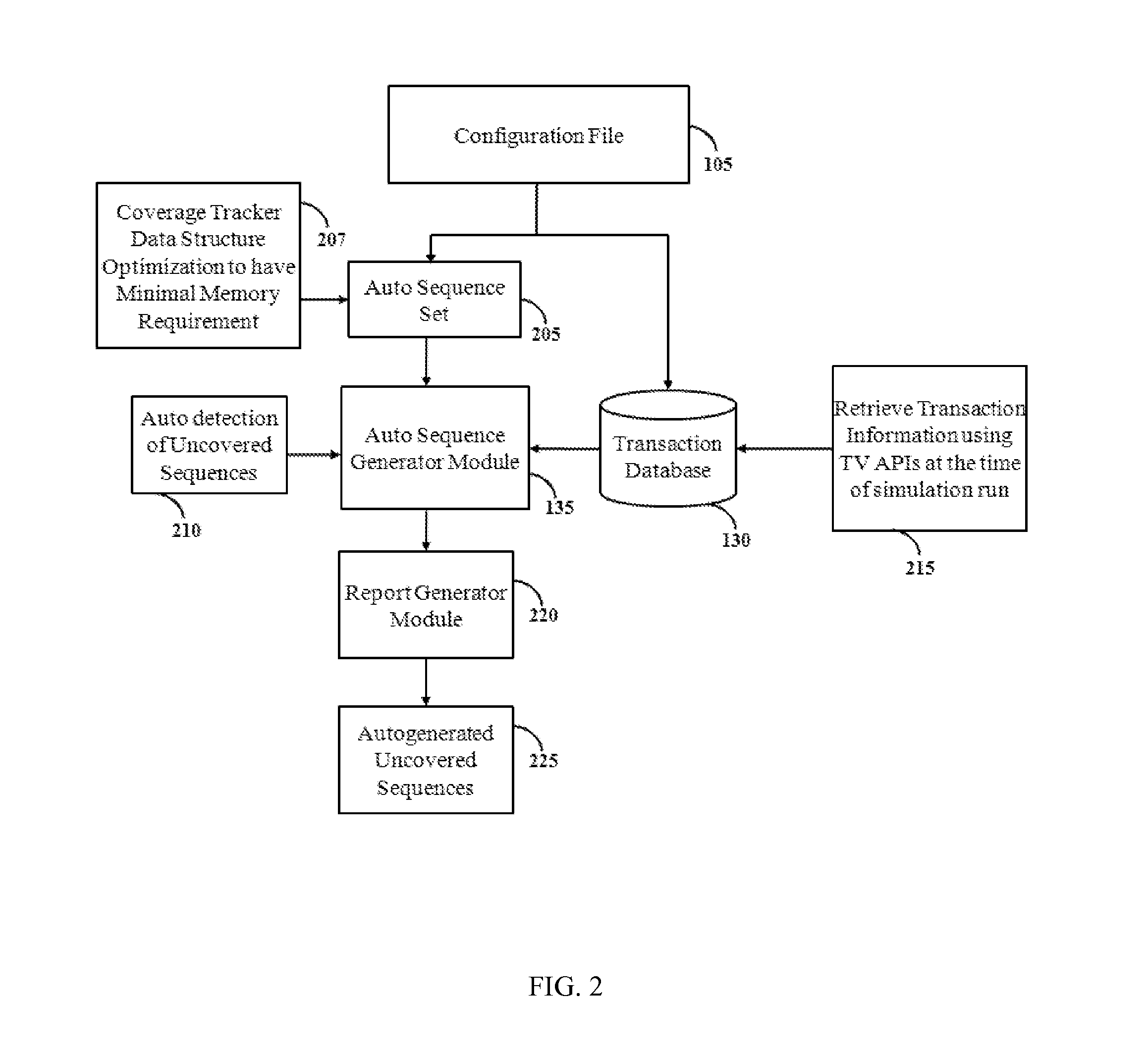

Method and system for test vector generation

ActiveUS20130014066A1Narrow downEliminates test vector duplicationElectrical testingSoftware simulation/interpretation/emulationComputer architectureDesign intent

The various embodiments of the present invention provide a method for automatically generating a unique set of test vectors for verifying design intent of integrated circuit chips. The method includes obtaining configuration parameters associated with a plurality of integrated circuit chips, generating an Executable Verification Plan pertaining to the configuration parameters of a plurality of integrated circuit chips in one or more execution PCs (EPs), creating a plurality of data structures corresponding to the configuration parameters, communicating the data structures created to a DCMS server, mapping the data structures of the Execution PCs with one or more data structures present in a database of the DCMS server, customizing the executable verification plan based on changes in the configurations of the integrated circuit chips, generating a unique set of test vectors based on mapping of the data structures and performing automatic design verification of the plurality of integrated circuit chips.

Owner:RAJARAO RAVISHANKAR +1

Method and system for automated path delay test vector generation from functional tests

ActiveUS20080092004A1Increase PDT test coverageElectronic circuit testingError detection/correctionFunctional testingEngineering

Disclosed herein are methods and systems for generating test vectors for use in verification of a circuit design and for hardware testing on a fabricated circuit representative of the circuit design. The system and methods can systematically and automatically perform functional and structural testing on selected paths of the circuit design and, in turn, generate one or more test vectors to increase PDT test coverage using the results of the structural test on the selected path.

Owner:ORACLE INT CORP

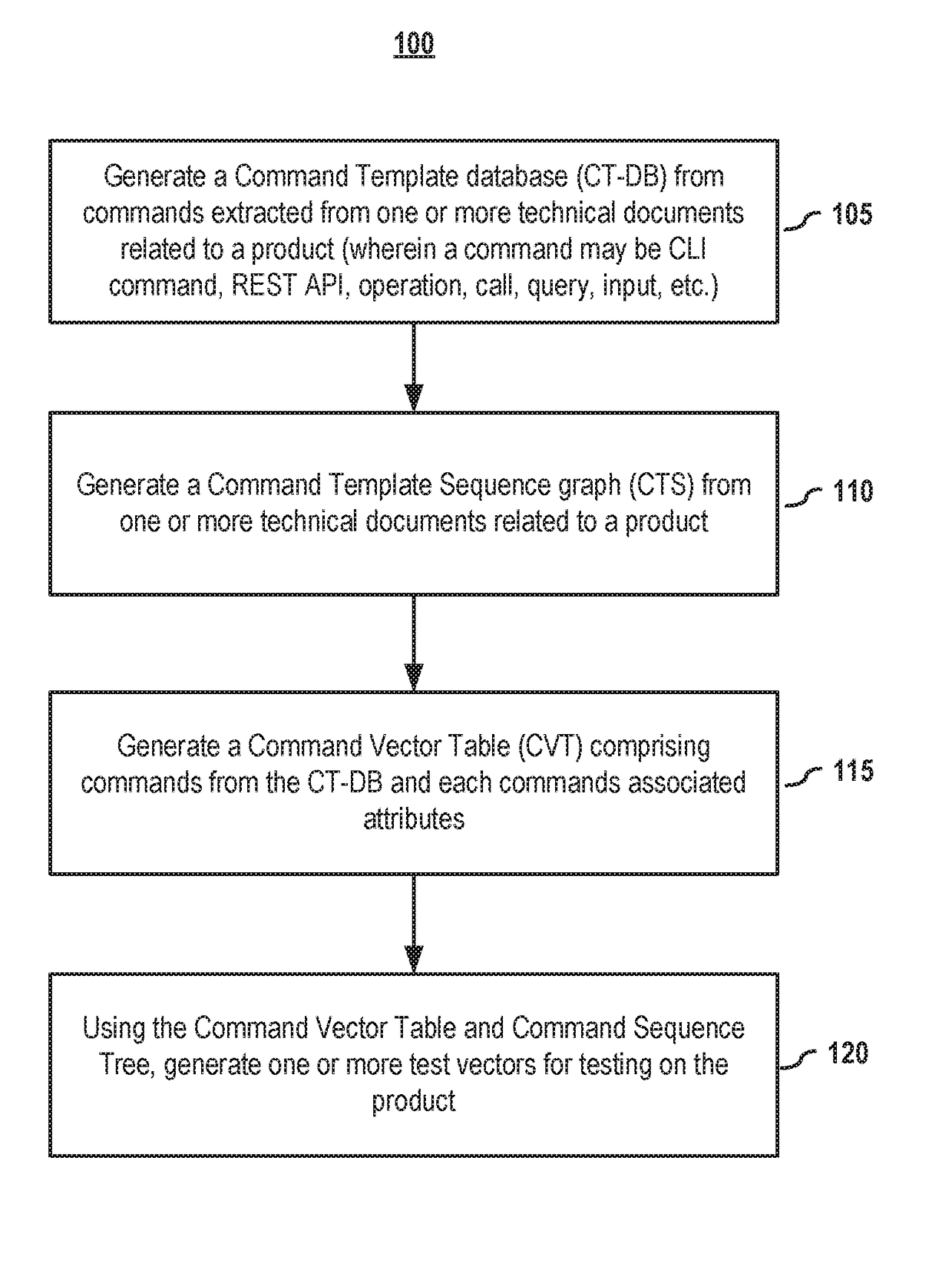

Test vector generation from documentation

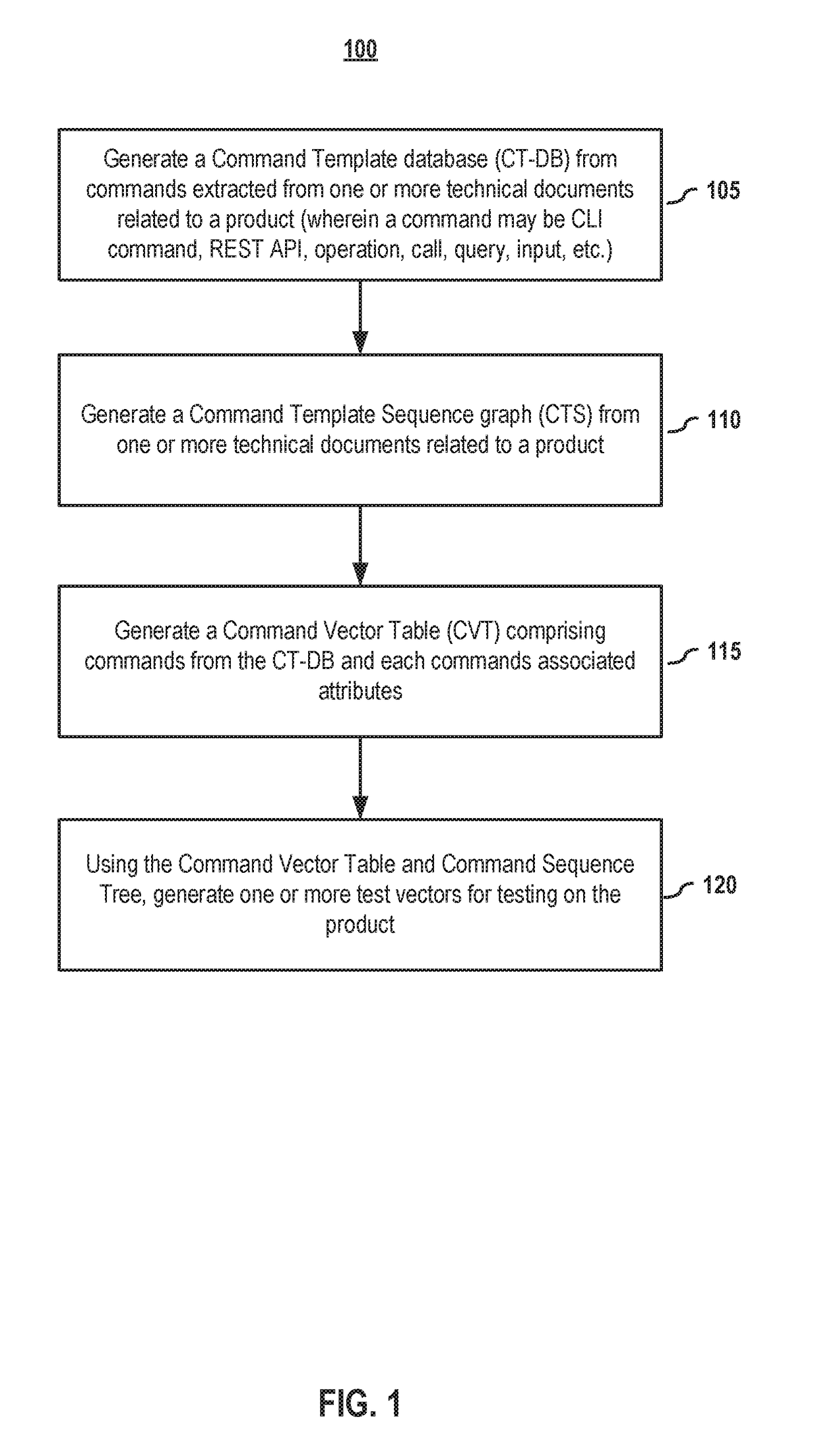

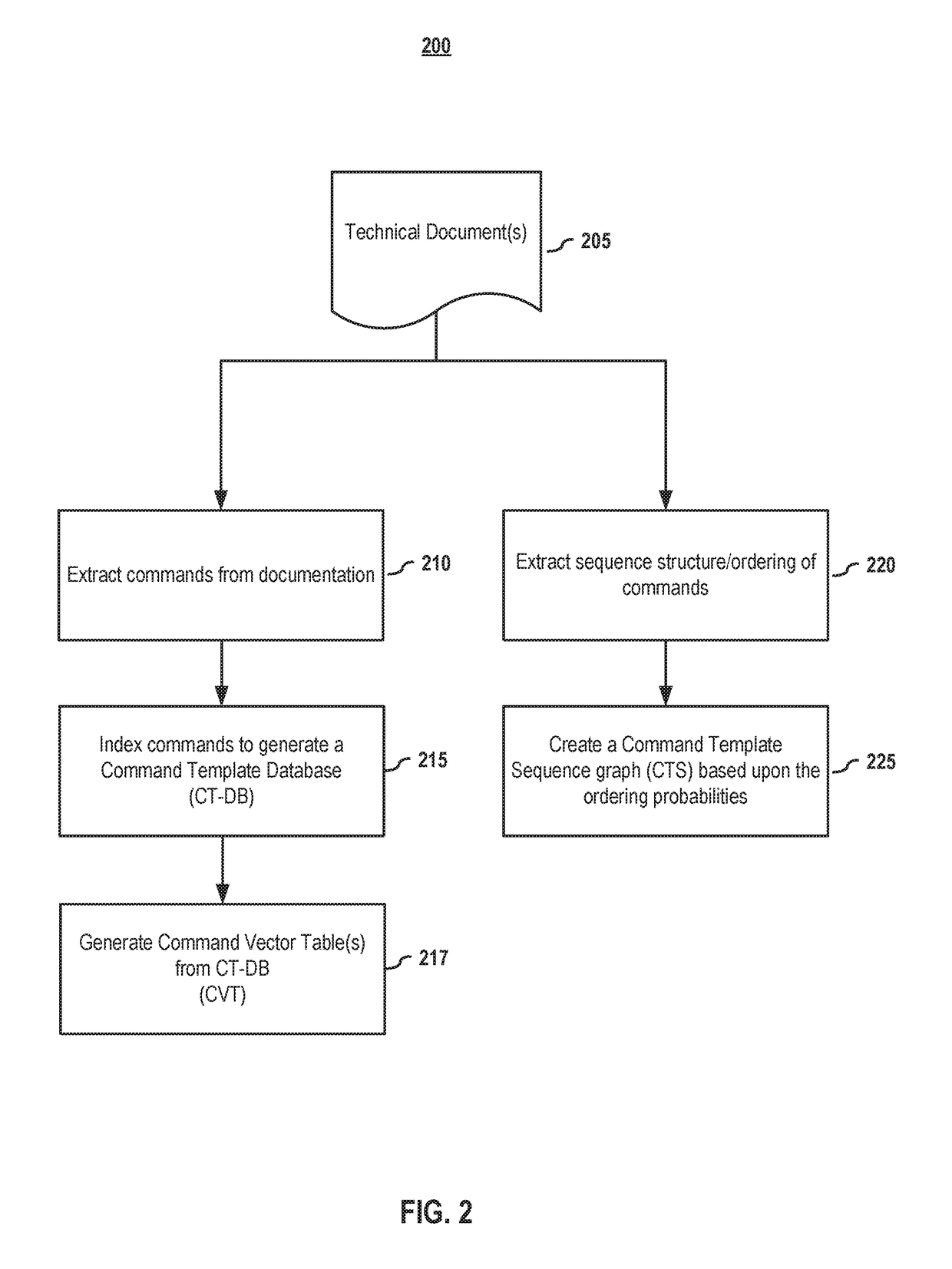

ActiveUS20170109698A1Office automationSpecial data processing applicationsRelease notesCommand-line interface

Aspects of the present disclosure relate to systems and methods that help automate the generation of a test vector. Every functional product, be it a service, device, or combination thereof, has one or more documents associated with it. These documents may include such documentation as: (1) Release Notes; (2) Configuration Guides; (3) command line interfaces (CLIs) / application program interfaces (APIs); (4) Data Sheets; (5) Installation Guides; (6) User Manuals; (7) Errata notices; and (8) other documentation. In embodiments, command data-models and ranges and sequence of valid inputs to the data-model are extracted from natural language expressions in documentation related to a specific product. In embodiments, this extracted information is used to generate one or more table of attributes and properties or constraints about which a test vector may be generator for testing a command.

Owner:DELL PROD LP

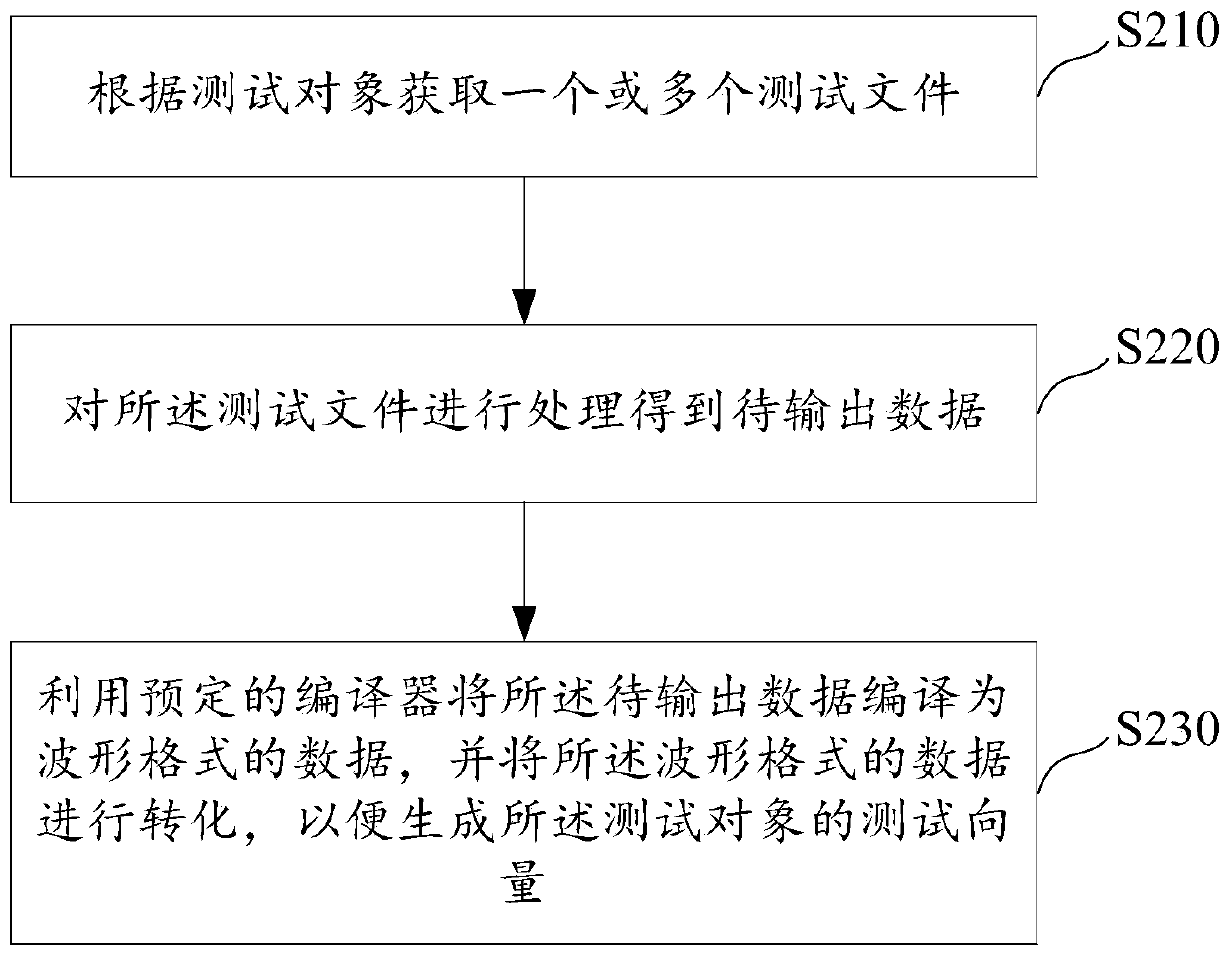

Test vector generation method based on test object and storage medium

ActiveCN110632499AImprove production efficiencyImprove readabilityElectronic circuit testingParallel computingTest vector generator

The invention provides a test vector generation method based on a test object and a storage medium. The test vector generation method based on the test object comprises the steps of obtaining one or more test files according to the test object; processing the test file to obtain to-be-output data; and compiling the to-be-output data into data in a waveform format by using a predetermined compiler,and converting the data in the waveform format so as to generate a test vector of the test object. Based on the technical scheme of the invention, the generation efficiency of the test vector is improved, the readability of the generated test vector is high, and the online debugging of the test vector is facilitated.

Owner:GREE ELECTRIC APPLIANCES INC

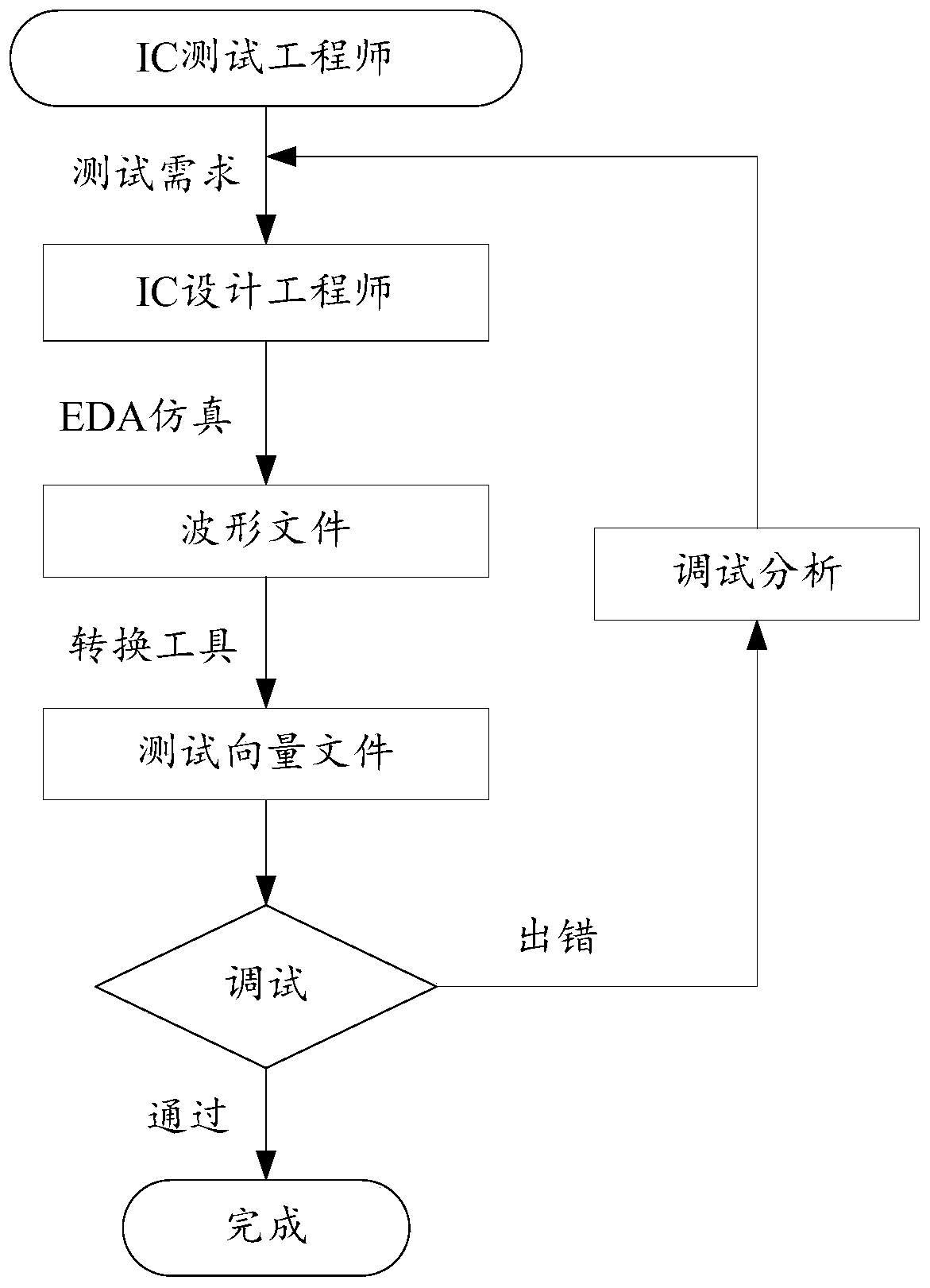

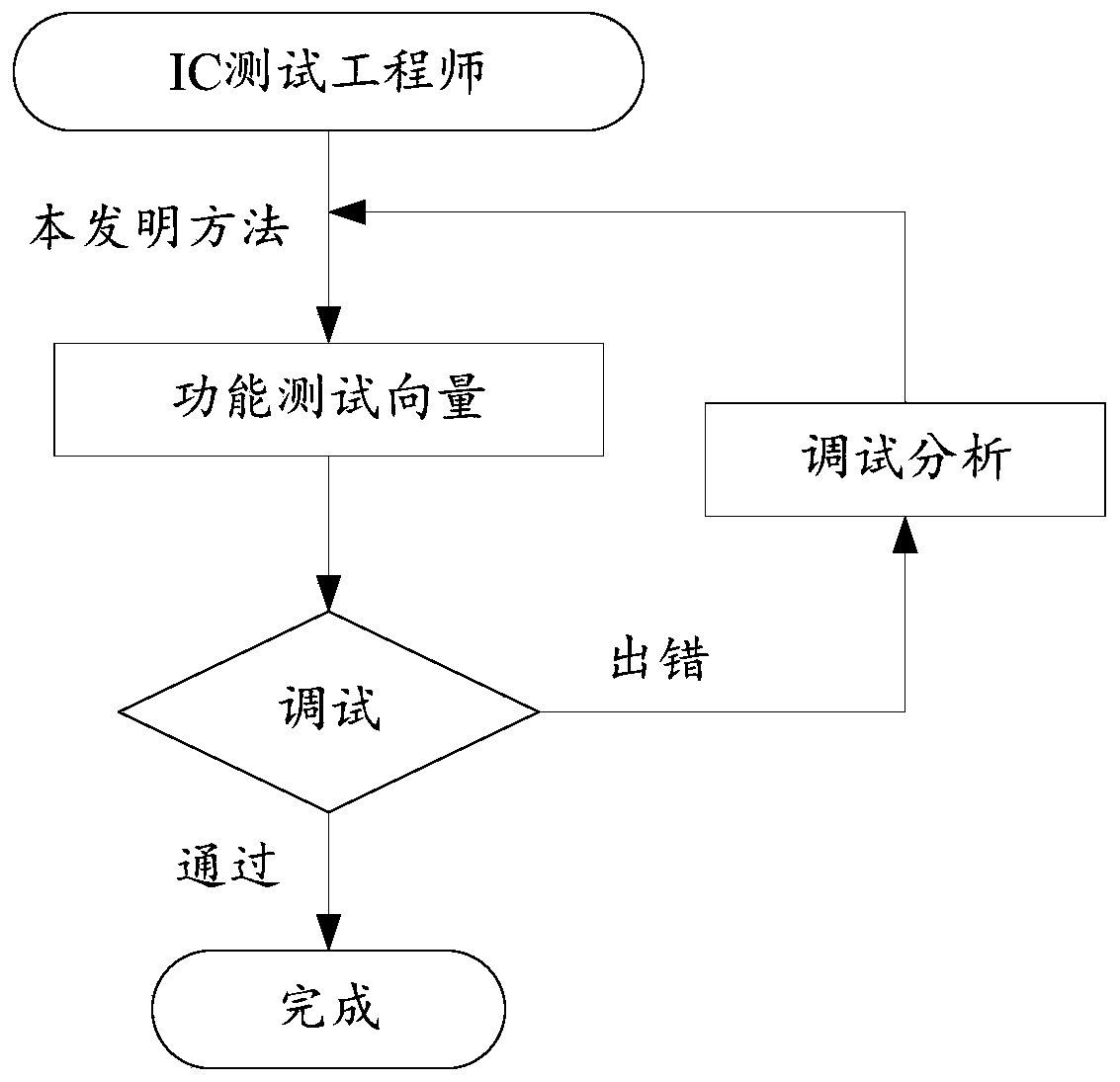

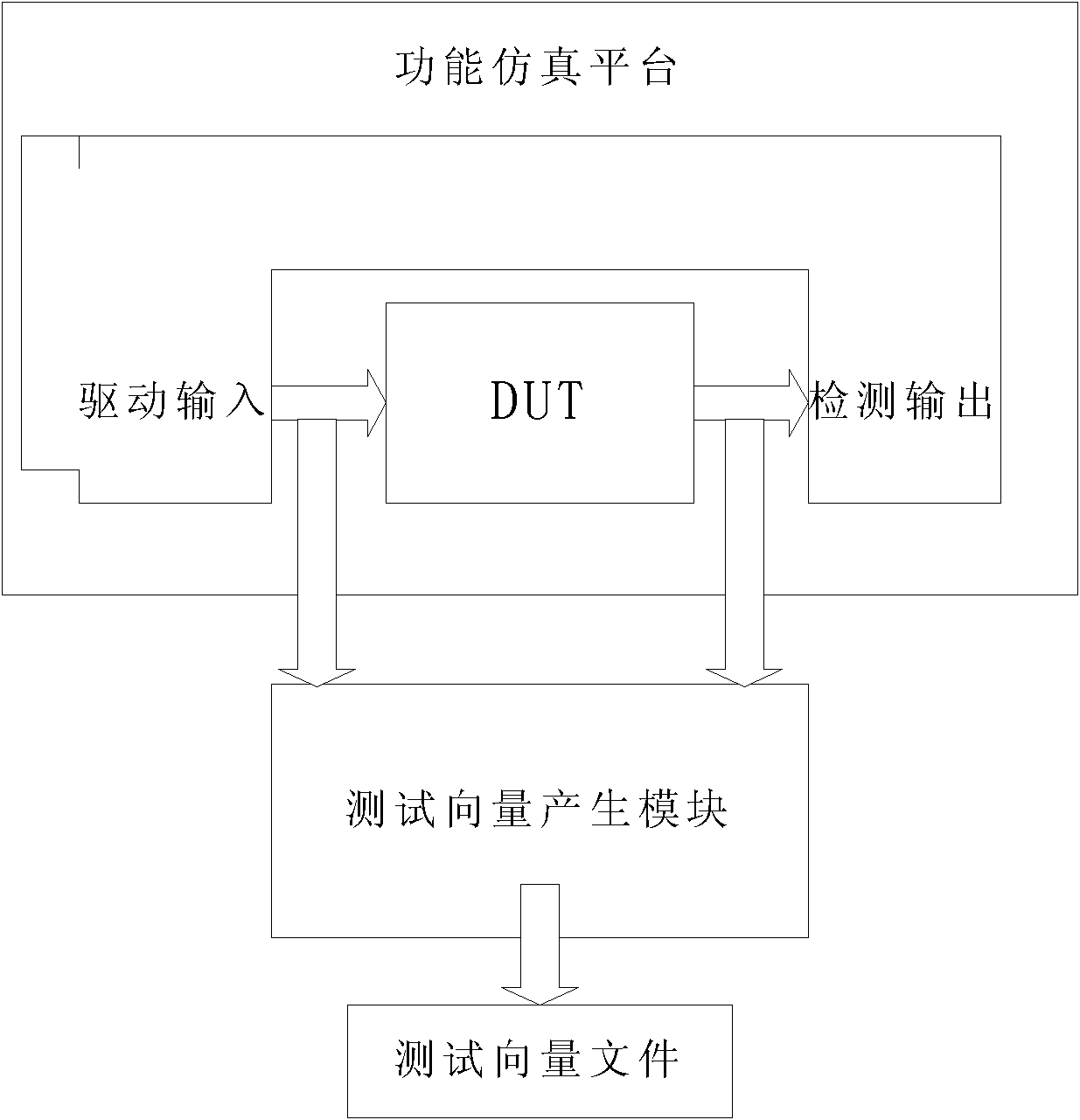

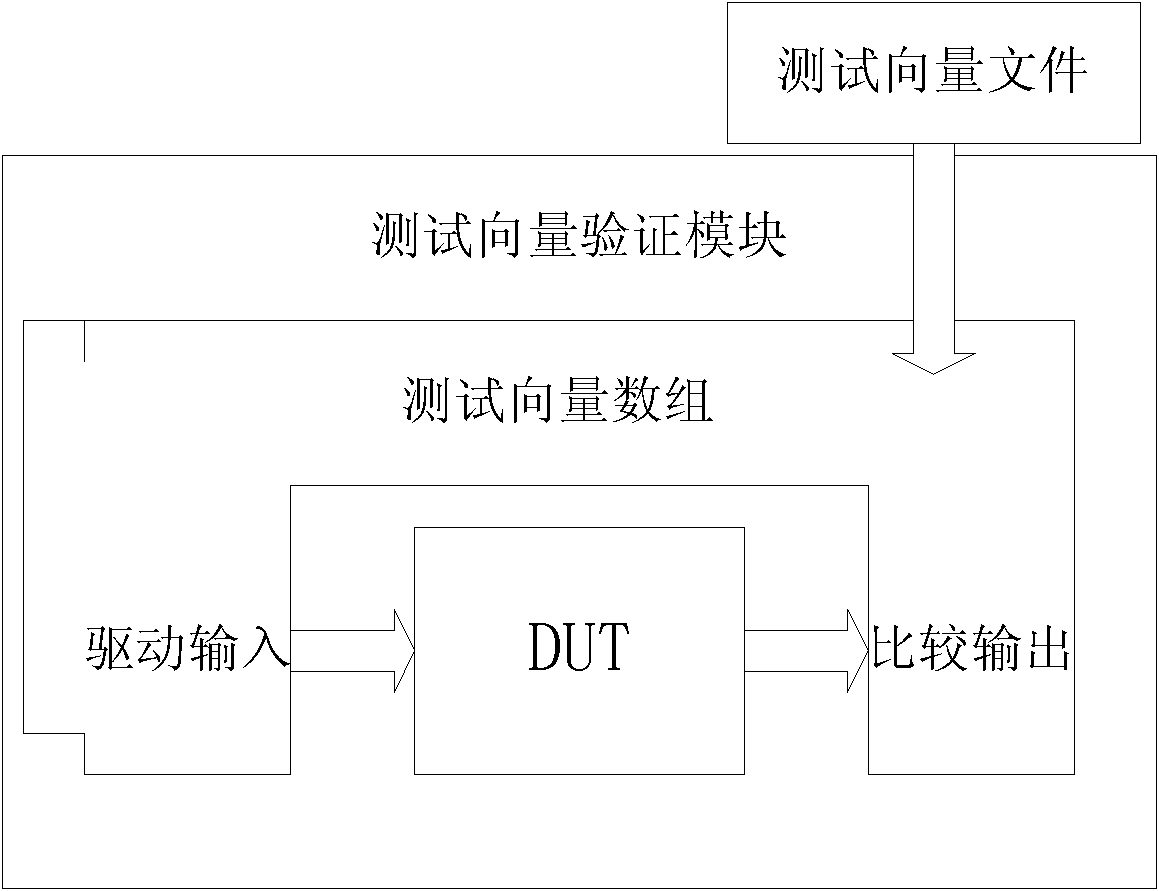

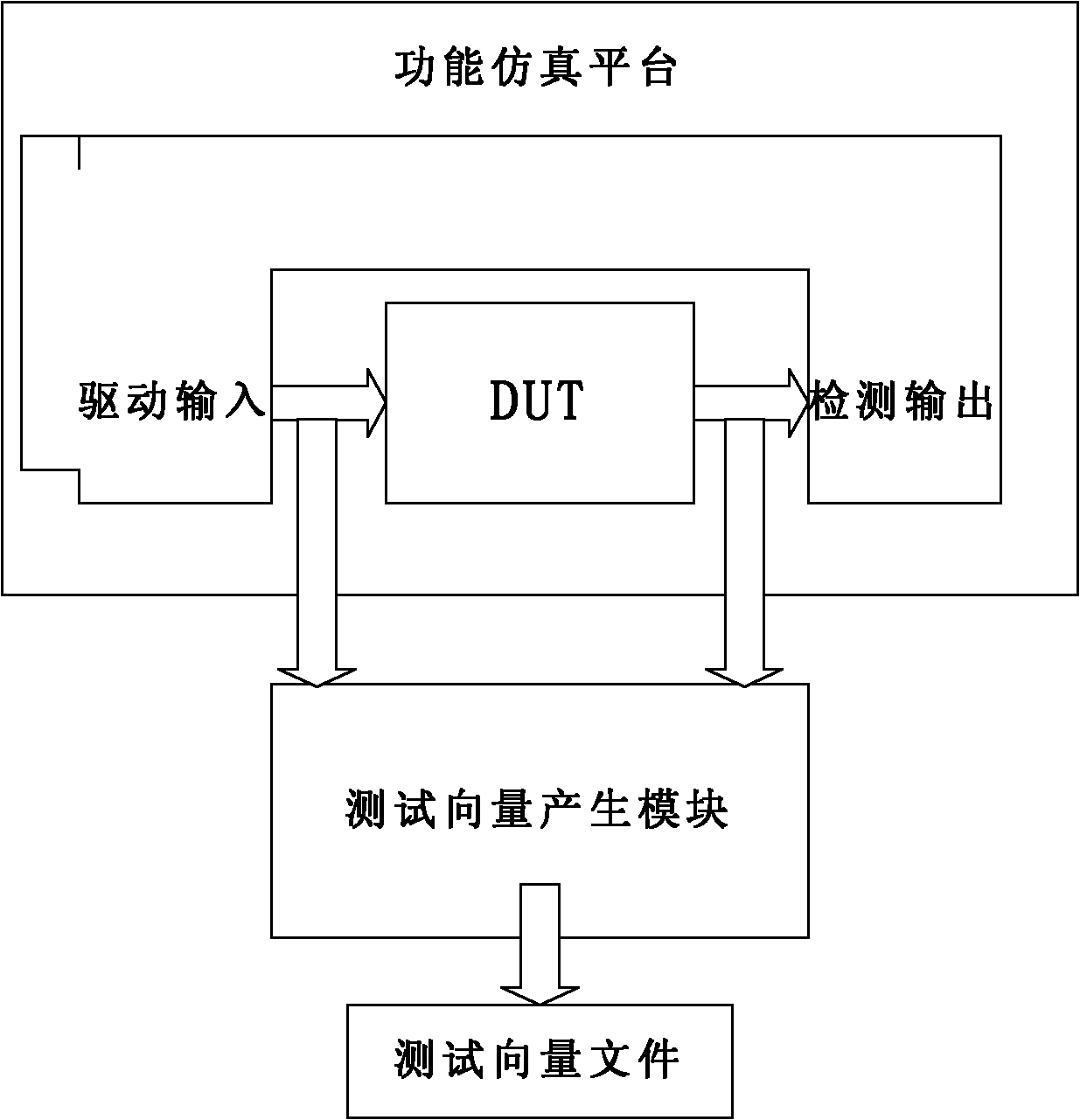

Generation and verification method of test vector

ActiveCN102565683ASimple processIncrease productivityElectrical testingAutomatic test equipmentValidation methods

The invention relates to a generation and verification method of a test vector. A simulation environment is established by utilizing hardware description language, the changes of signals to be recorded can directly recorded into a designated file according to the requirements of vector format of an automatic test device during the simulation, corresponding input excitation can be added to a hardware model by reading back the contents of the file, output is compared to realize verification on a recorded test vector, the test vector required by ATE (automatic test equipment) is directly generated during the simulation and verified by simulation, and manual processing is not required, therefore, the whole process is simplified, the production efficiency is improved and the generation and verification method can be used for testing a digital integrated circuit.

Owner:西安翔腾微电子科技有限公司

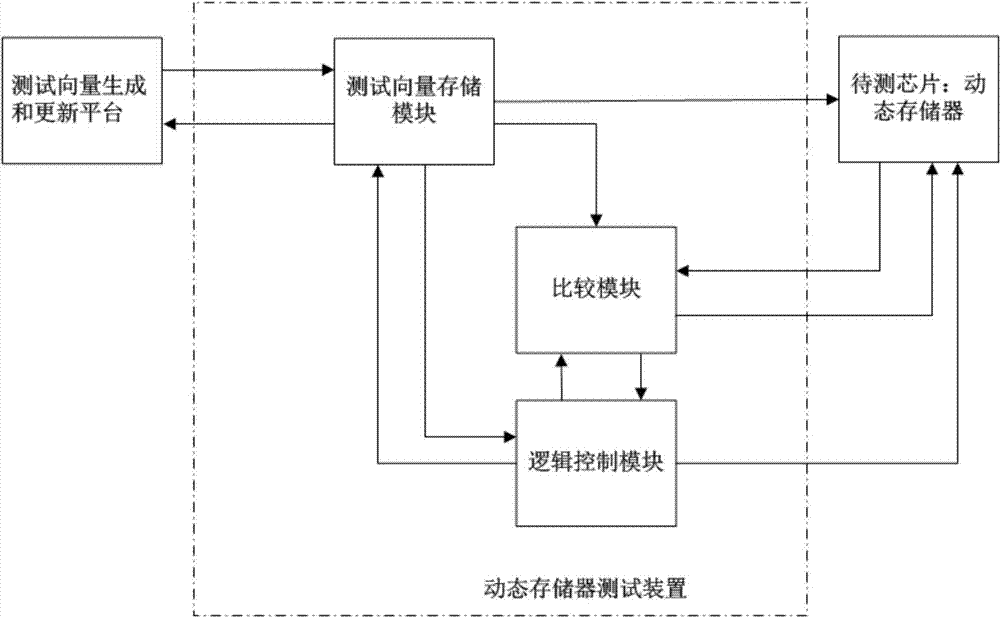

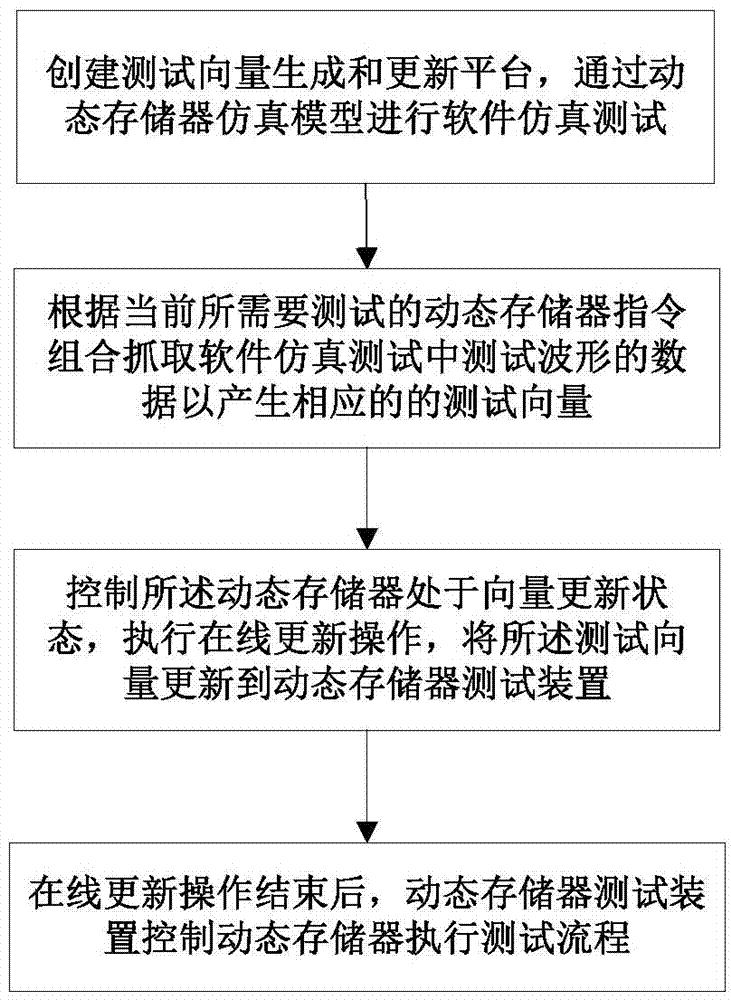

Dynamic memory testing system and dynamic memory testing method

The invention discloses a dynamic memory testing system and a dynamic memory testing method. The dynamic memory testing system comprises a test vector generation and update platform and a dynamic memory testing device, wherein the test vector generation and update platform is used for software simulation test by virtue of a dynamic memory simulation model, is used for grasping data in a test waveform to generate special test vectors according to current test, controlling the dynamic memory to be in a vector updating state, executing an operation of updating the vectors and updating the test vectors to the dynamic memory testing device; the dynamic memory testing device is used for storing the test vector used for current test and controlling the dynamic memory to execute the test flow. According to the system and the method disclosed by the invention, due to the test vector generation and update platform, various test vectors required by complete testing dynamic memory command combination can be generated, and are transmitted to the dynamic memory testing device on line to dynamically update the testing vectors so as to quickly and completely test the dynamic memory. The dynamic memory testing system and the dynamic memory testing method disclosed by the invention can be widely applied to the field of digital test.

Owner:SHENZHEN STATE MICROELECTRONICS CO LTD

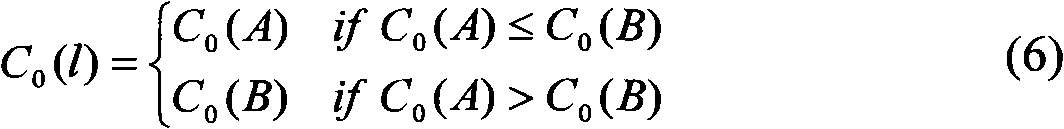

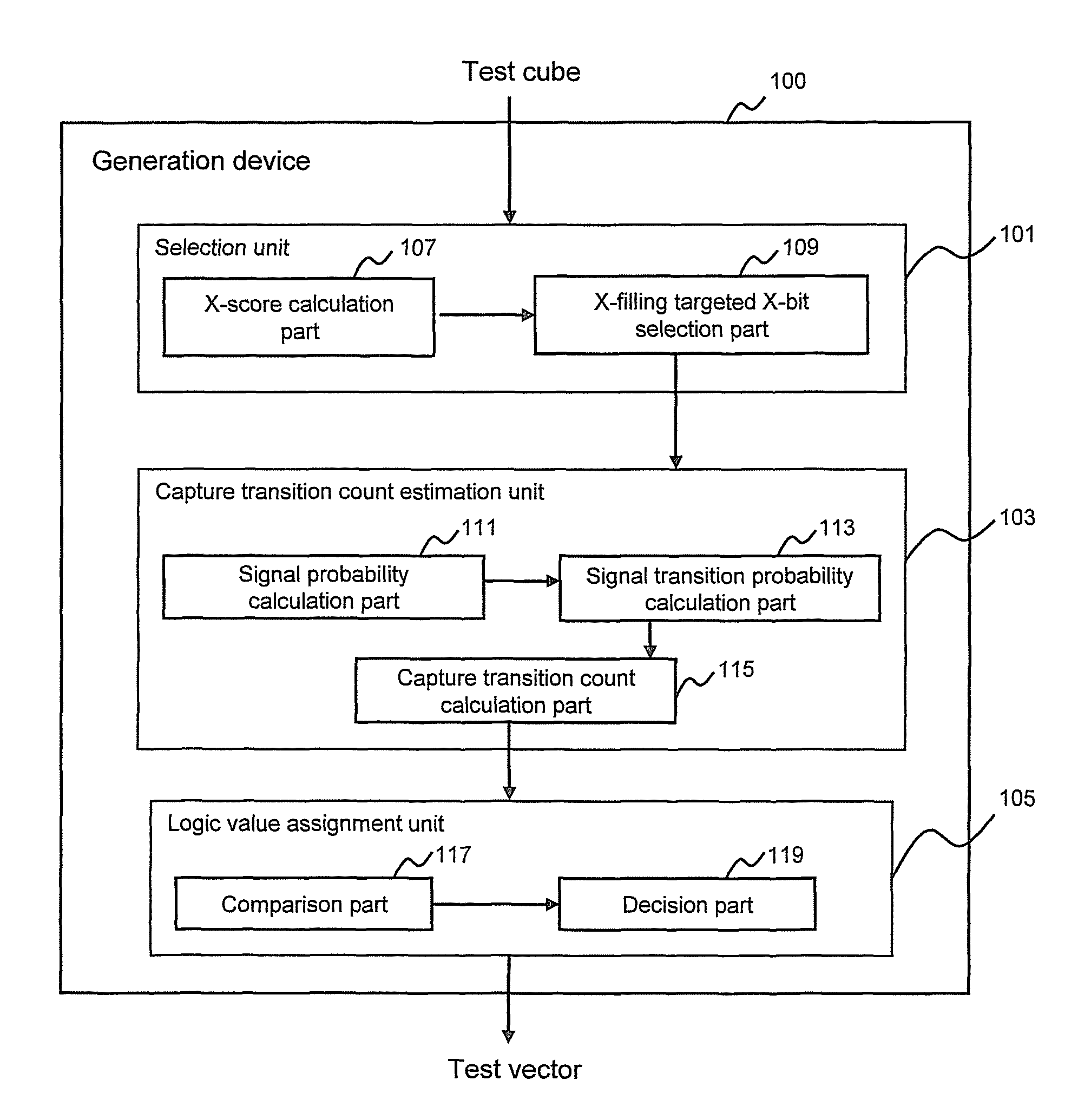

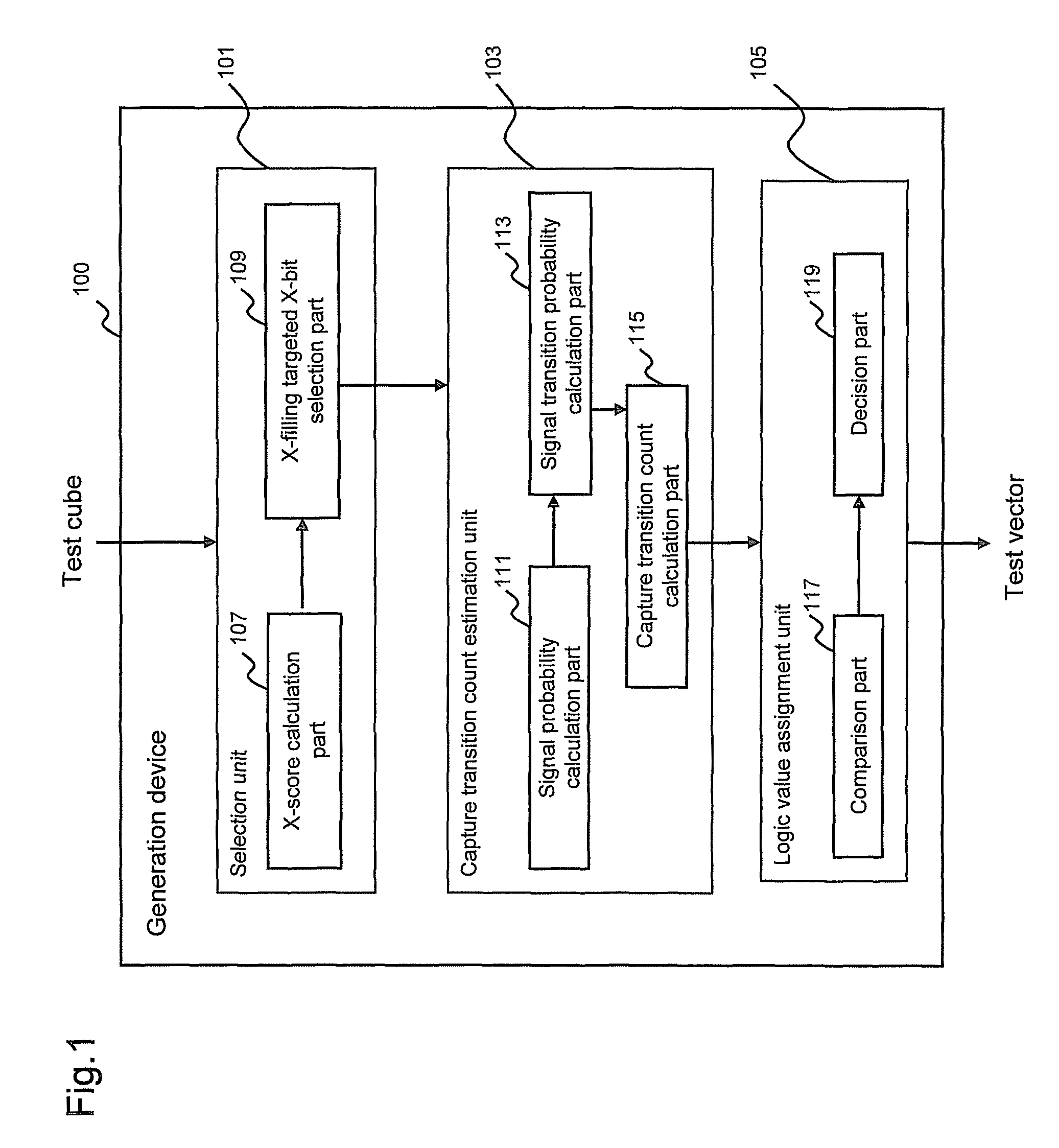

Generating device, generating method, program and recording medium

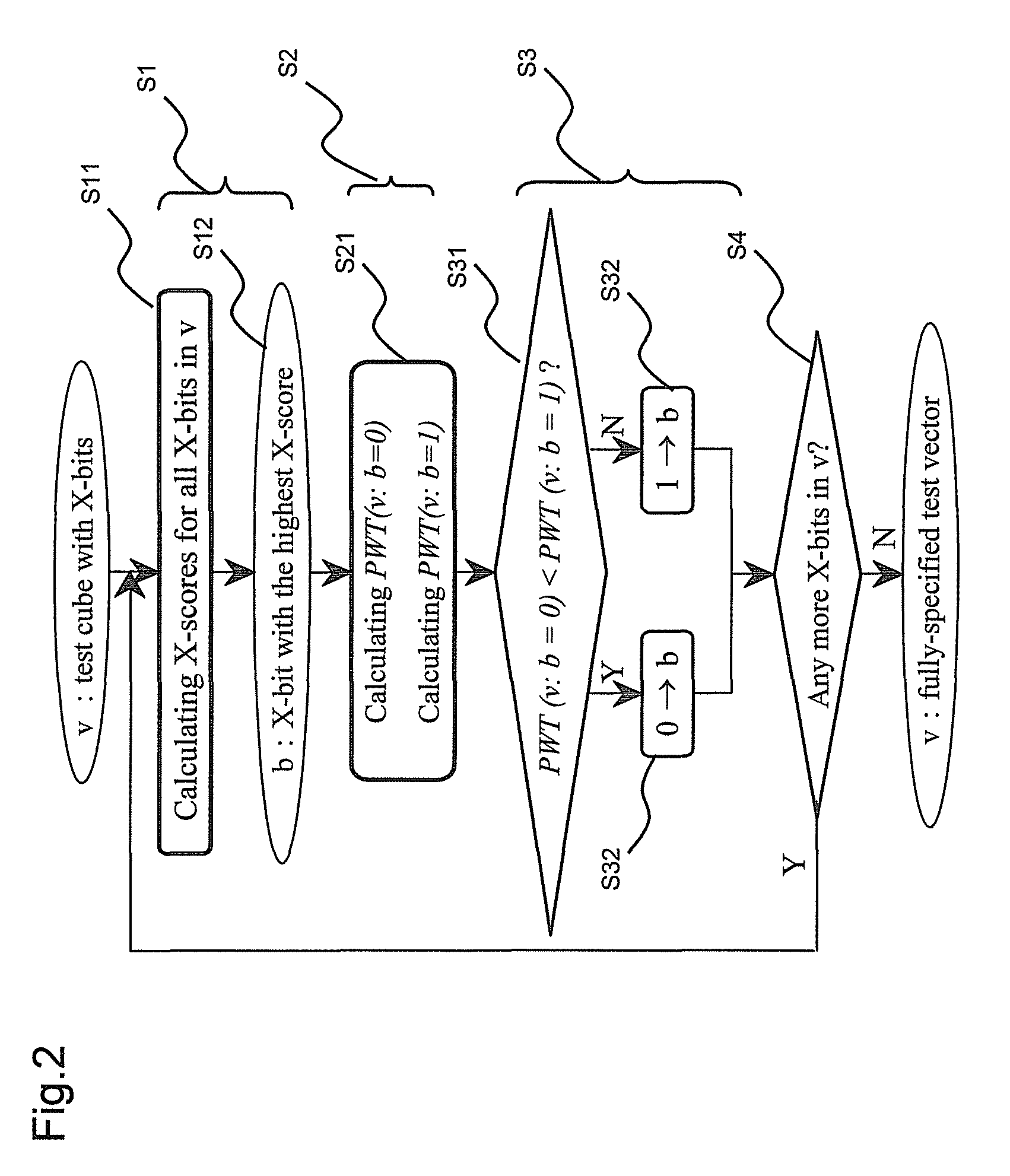

InactiveUS7979765B2Delay transitionCaptured powerElectronic circuit testingError detection/correctionData setValue assignment

Provided are a generation device and the like for generating a test vector which can reduce capture power efficiently. The generation device 100 generates a test vector for a logic circuit by assigning logic values to each of a plurality of unspecified bits (X-bits) included in a test cube. The generation device 100 includes a selection unit 101 for selecting, among the plurality of X-bits, a target X-bit, which is a target of assigning a logic value, a capture transition metric calculation unit 103 for calculating capture transition metric caused by a test cube including an X-bit, and a logic value assignment unit 105 for assigning, to the selected target X-bit, a logic value which causes the smaller capture transition metric, by applying the capture transition metric calculation means to a first test cube obtained by assigning a logic value 0 to the selected target X-bit and to a second test cube obtained by assigning a logic value 1 to the selected target X-bit, and by comparing a capture transition metric caused by a first test cube and a capture transition metric caused by a second test cube.

Owner:JAPAN SCI & TECH CORP +2

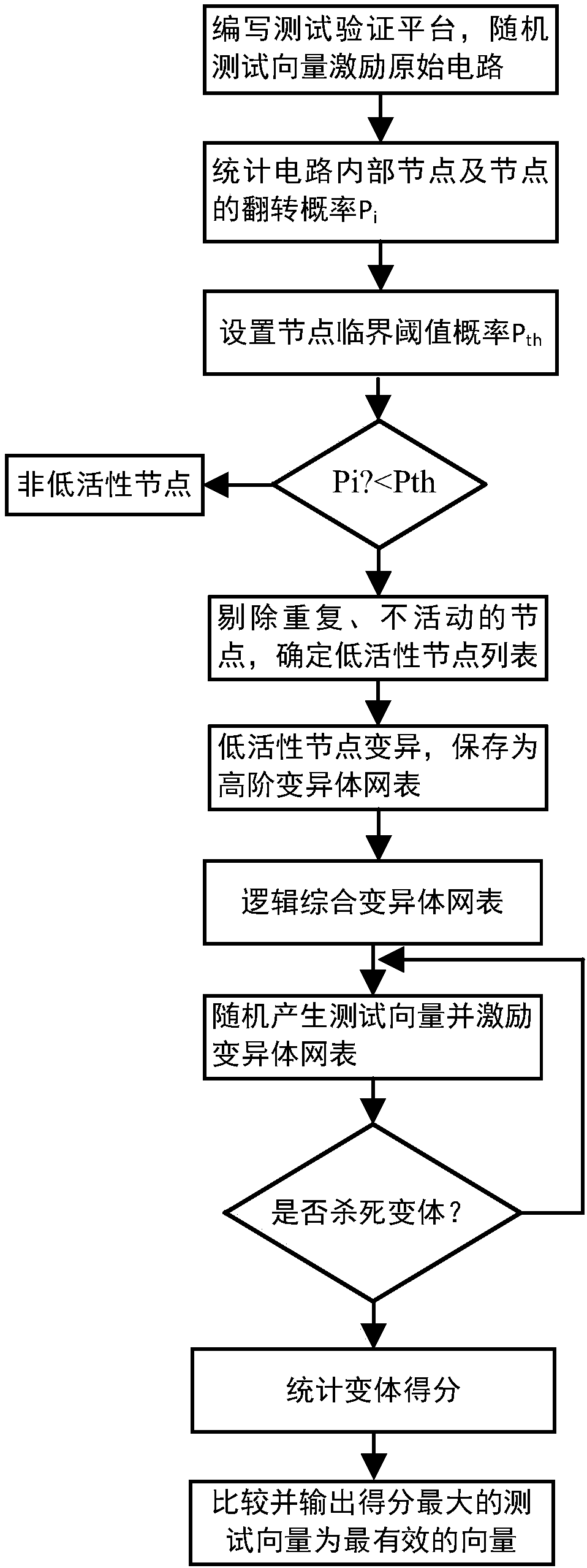

Testing vector generating method based on variation analysis for effectively activating hardware trojan horses

PendingCN107783877AVulnerability testing methods are maturePurposefulError detection/correctionTest efficiencyLow activity

The invention relates to the technical field of credibility of integrated circuits, and discloses a testing vector generating method for effectively activating hardware trojan horses. The method is high in purposiveness, low in testing cost, high in testing efficiency and capable of more effectively activating the hardware trojan horses and has certain actual meaning and reference value for manifesting the hardware trojan horses and analyzing bypass signals, and generated testing sequences are more simplified. In order to achieve the advantages above, according to the adopted technical scheme,the testing vector generating method based on the variation analysis for effectively activating the hardware trojan horses comprises the steps of analyzing the structural characters of a mother circuit, screening out nodes with low activity, utilizing a variation method to execute a variation operation on the circuit structure of the nodes with the low activity to generate high-level variants, and utilizing a functional testing method to screen out testing vectors capable of killing the variants. The method is mainly applied to the safety detection occasion of an integrated circuit.

Owner:TIANJIN UNIV

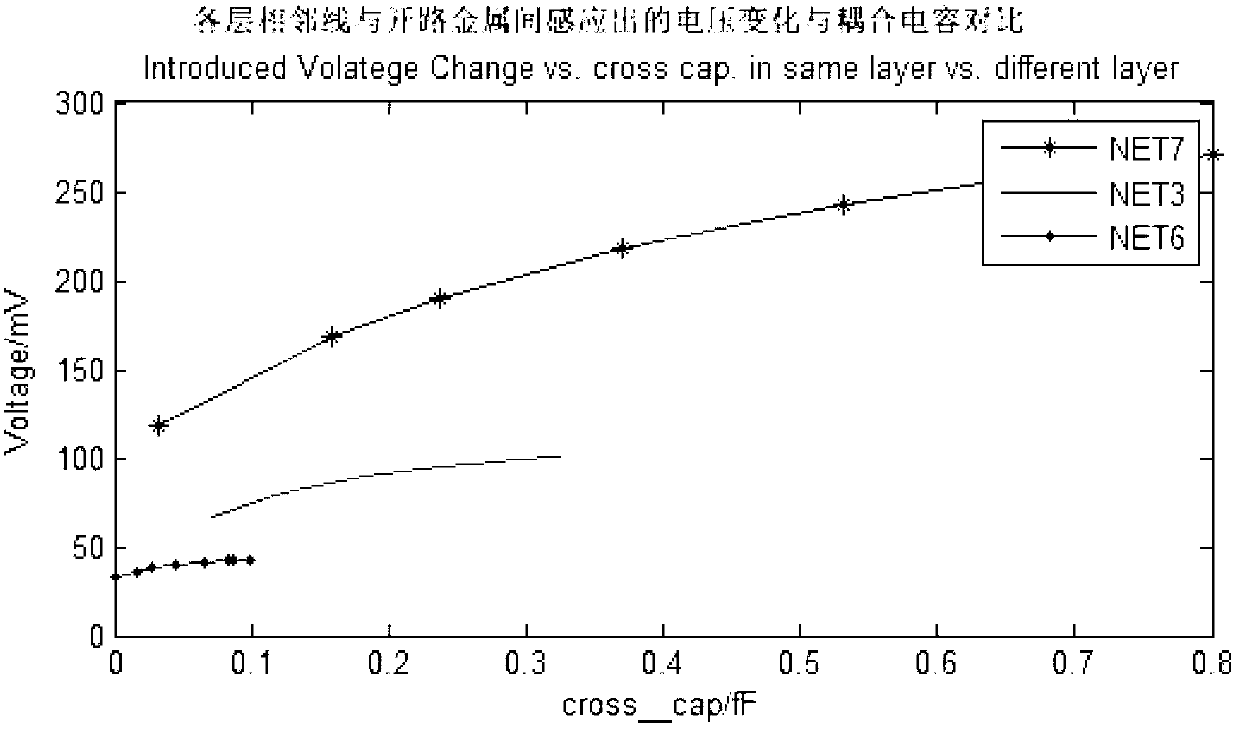

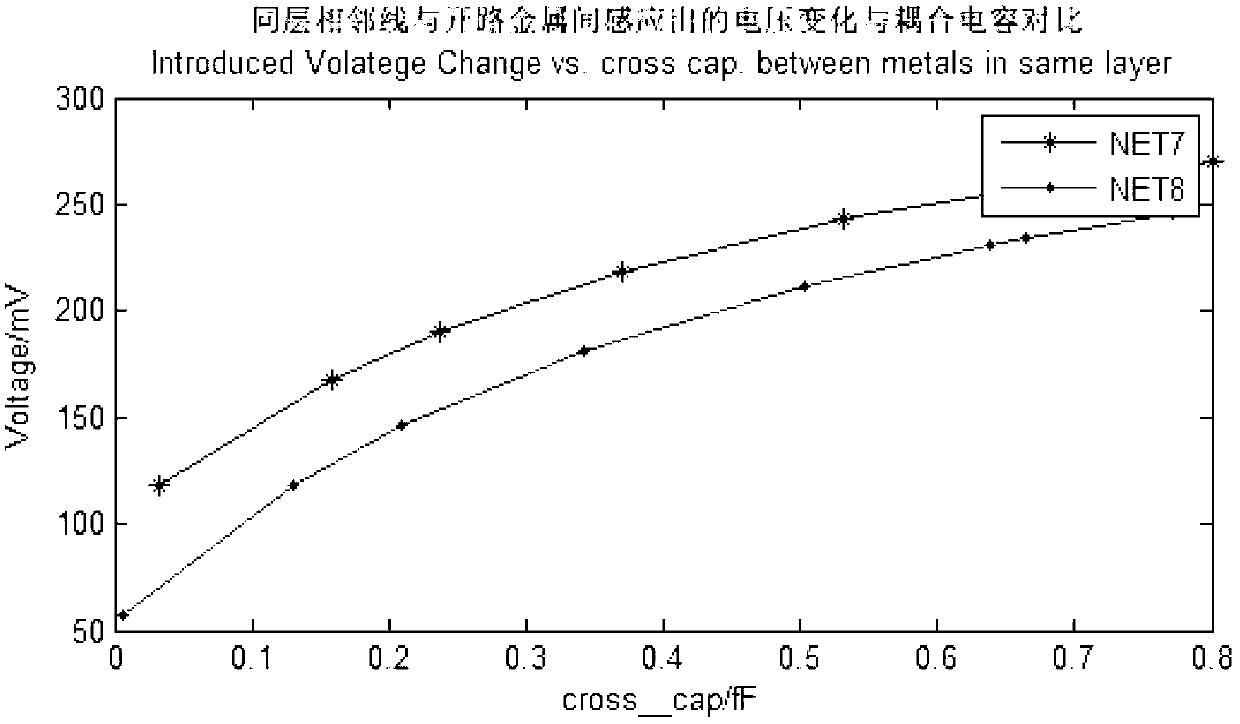

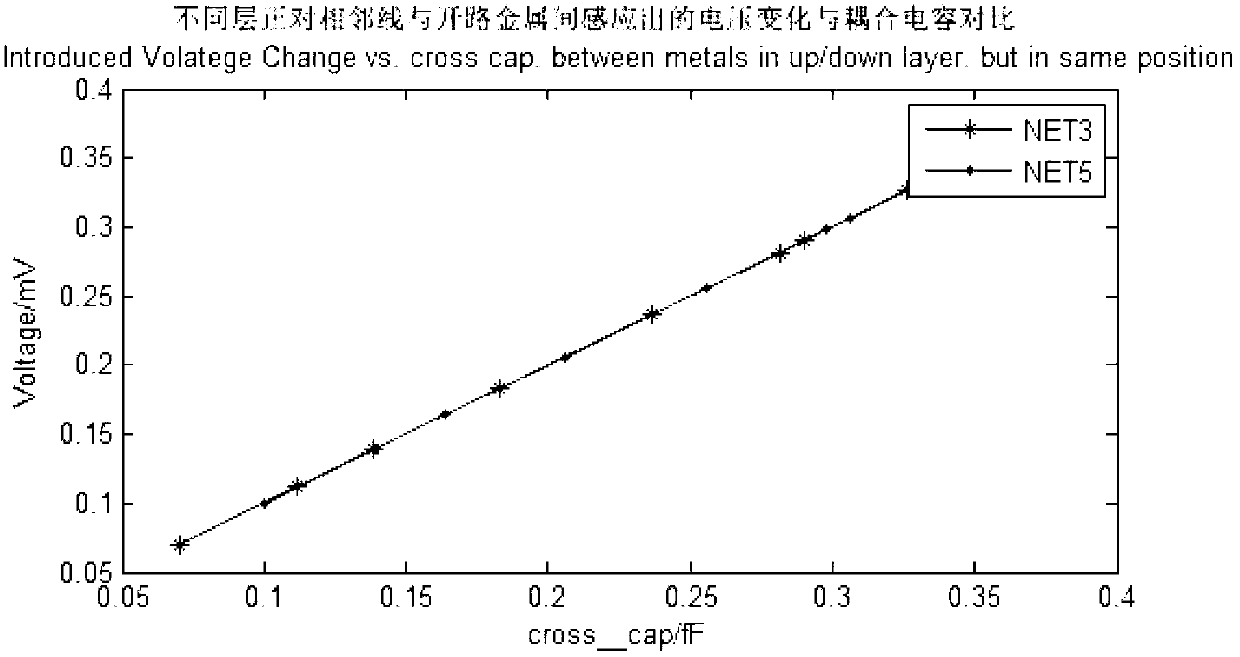

Method for predicting voltage value of full-open defect of interconnecting wire of deep sub-micron integrated circuit

InactiveCN102708219APredict the voltage value of the fully open defect pointSpecial data processing applicationsCapacitanceCoupling

The invention discloses a method for predicting a voltage value of a full-open defect of an interconnecting wire of a deep sub-micron integrated circuit. By the method, the voltage at a full-open defect spot of an interconnecting wire can be accurately and efficiently determined in the designing stage of a chip. The method comprises the following steps of: establishing a first voltage prediction model, and establishing a second voltage prediction model based on the first voltage prediction model; extracting coupling capacitance values of peripheral signal wires of a metal wire which is suspected to have an open defect, and calculating a voltage logic by using the second voltage prediction model; and in the automatic test vector generating step of testability design, loading a test vector which is opposite to the calculated voltage logic, and finding the full-open defect on the metal wire if the situation that an open voltage logic is equal to the calculated value obtained by the second voltage prediction model is observed. The method has the advantages that two voltage models which are accurate and feasible in engineering are established, and a complete method for combining the two models is provided.

Owner:XI AN JIAOTONG UNIV

Equivalence checking method, equivalence checking program, and generating method for equivalence checking program

ActiveUS8122402B2Computer aided designSoftware simulation/interpretation/emulationAlgorithmModel testing

Owner:RENESAS ELECTRONICS CORP

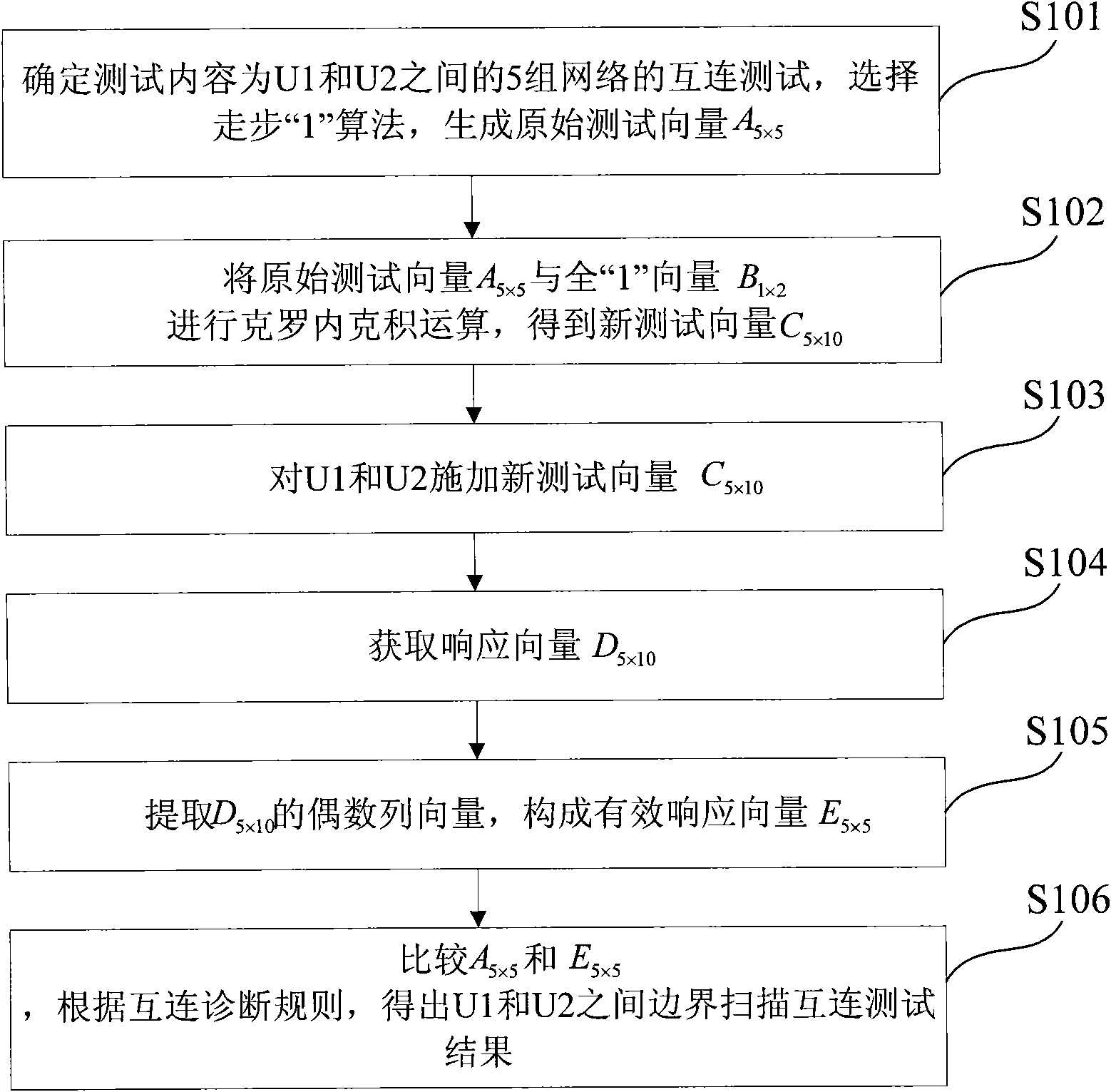

Boundary scan test method and device for reducing noise

The invention discloses a boundary scan test method and a boundary scan test device for reducing noise. The method comprises the following steps of: generating the original test vector according to test contents; processing the original test vector to acquire a new test vector; applying the new test vector to a tested object to acquire a response vector at the same time; extracting the response vector corresponding to the newly-added test vector; and performing diagnosis on the boundary scan test by using the extracted response vector as a final effective analysis vector. The device comprises an original test vector generation module, a new test vector generation module, a test implementation module, an effective response vector acquisition module and a diagnosis analysis module. The method and the device can effectively reduce the noise caused by the boundary scan test, improve the accuracy of the test, are simple to implement, do not need to add any test hardware and have high fault coverage rate.

Owner:BEIJING AEROSPACE MEASUREMENT & CONTROL TECH

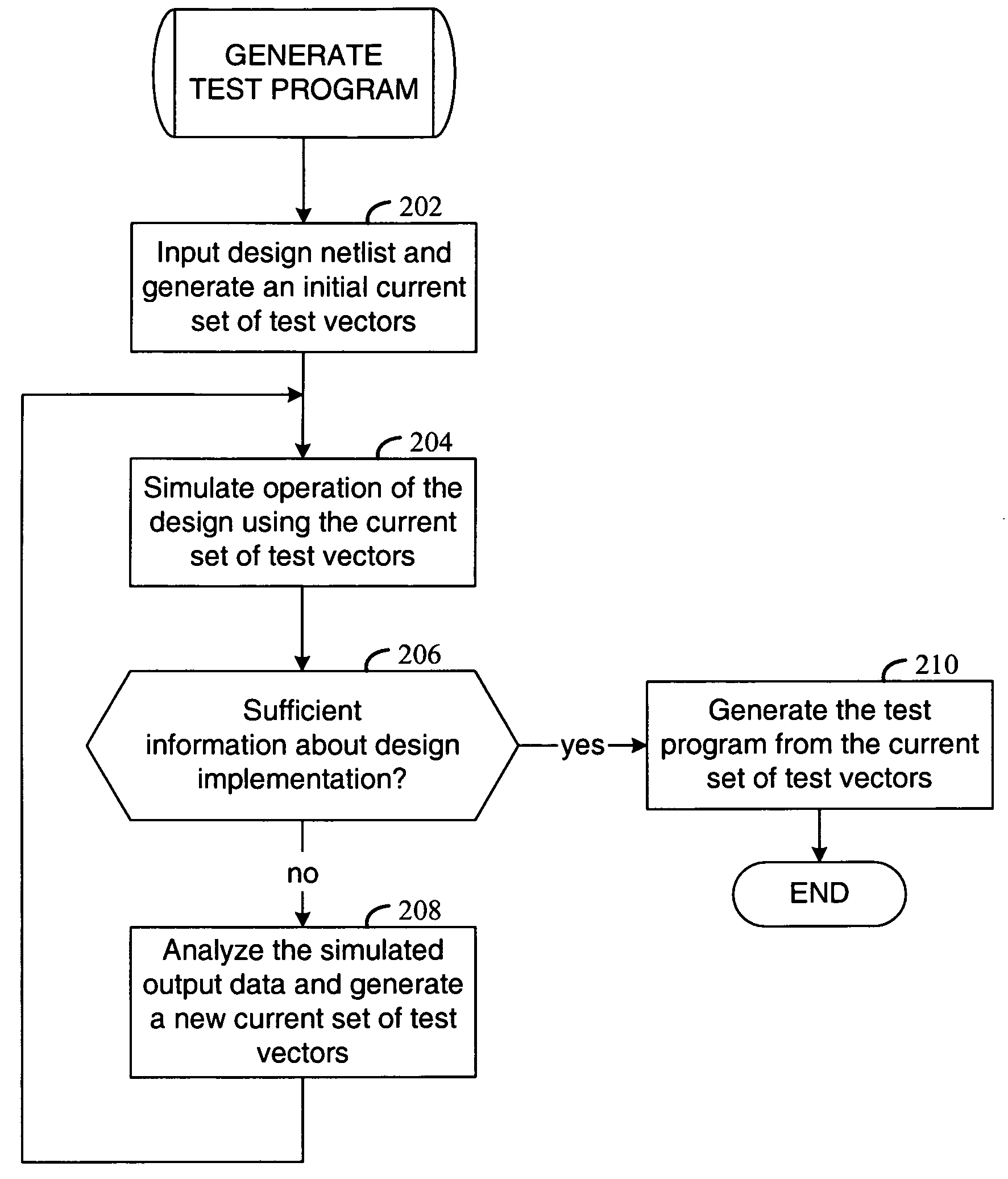

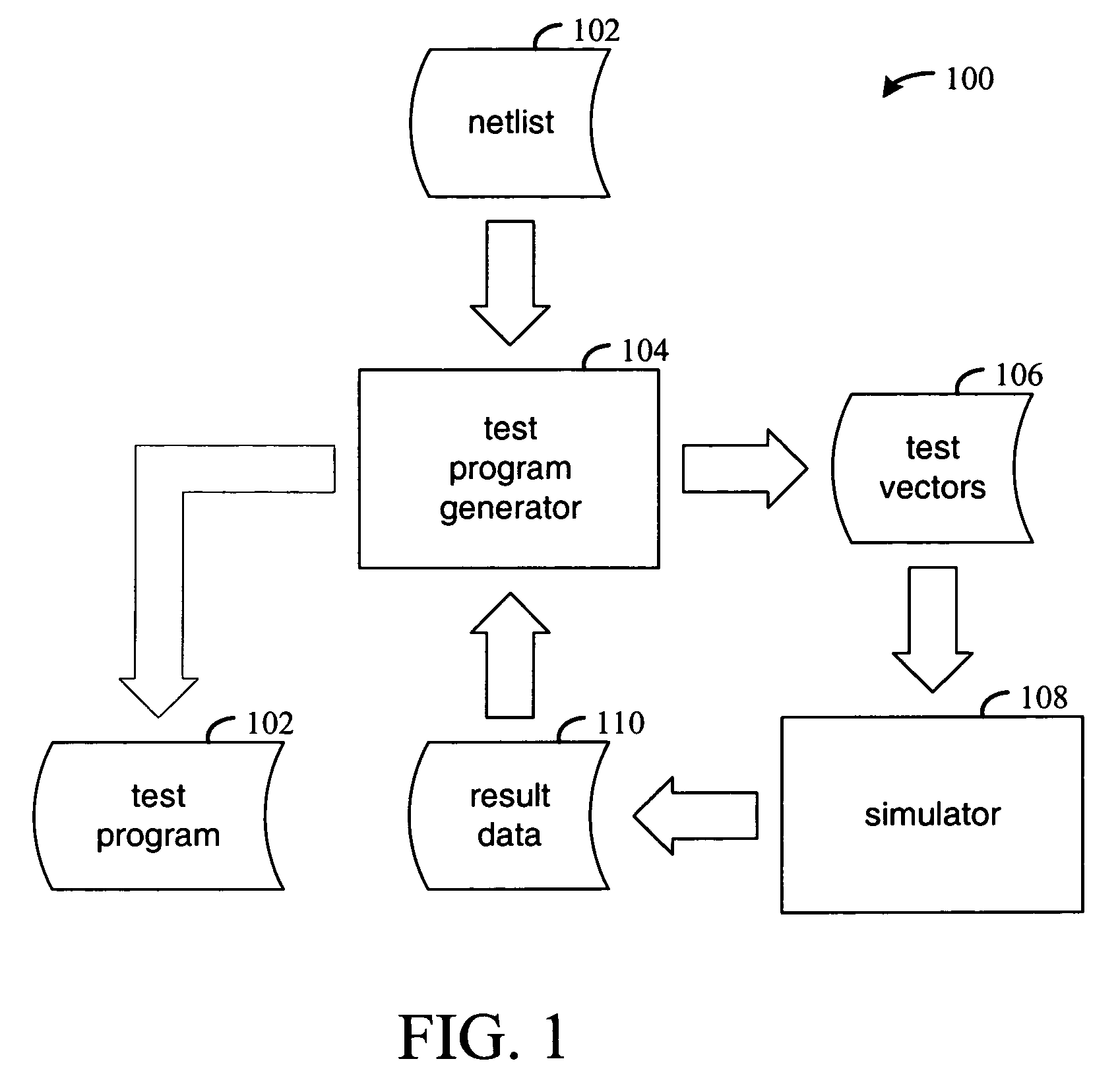

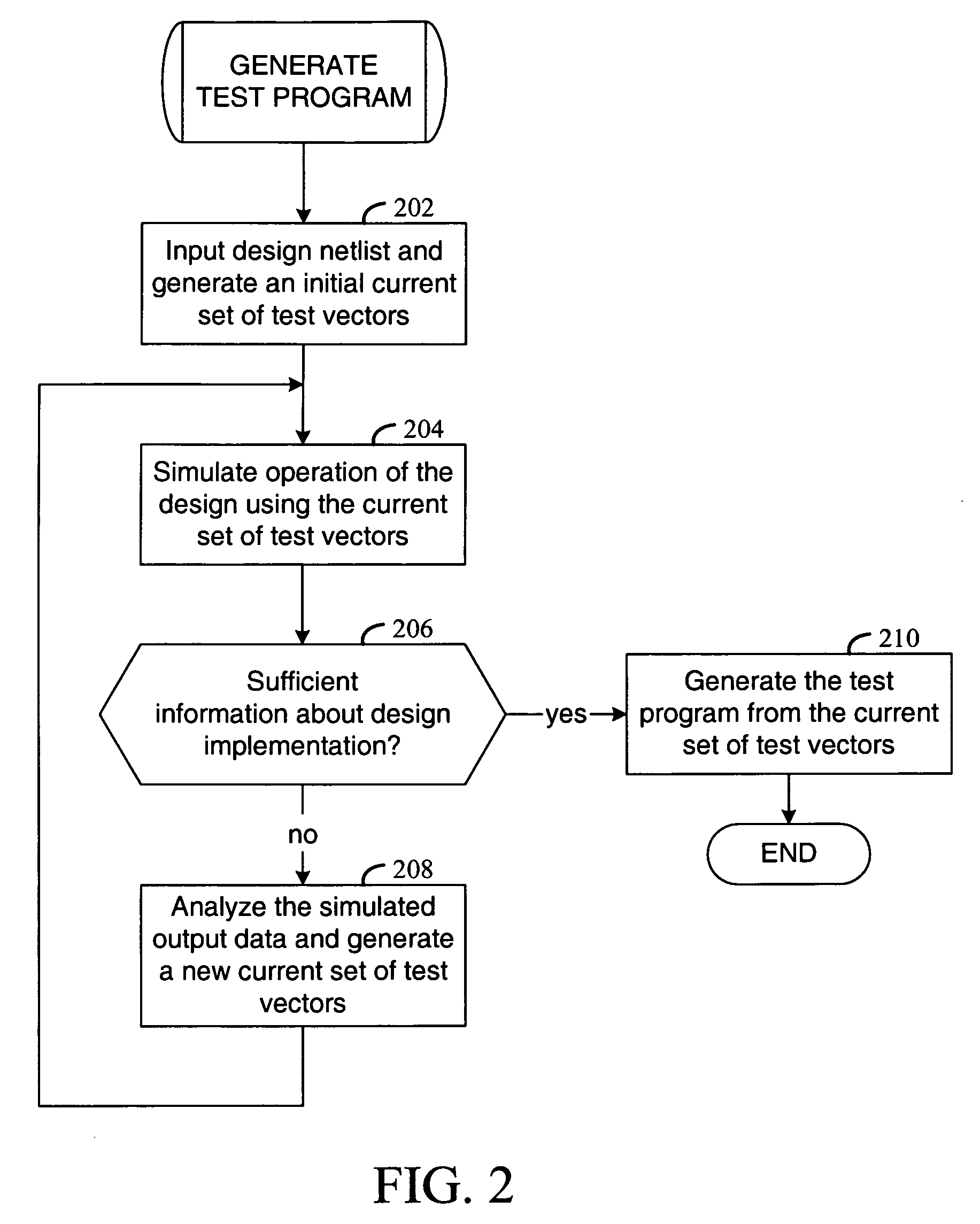

Boundary scan analysis

ActiveUS7188043B1Resistance/reactance/impedenceSpecial data processing applicationsComputer scienceNetlist

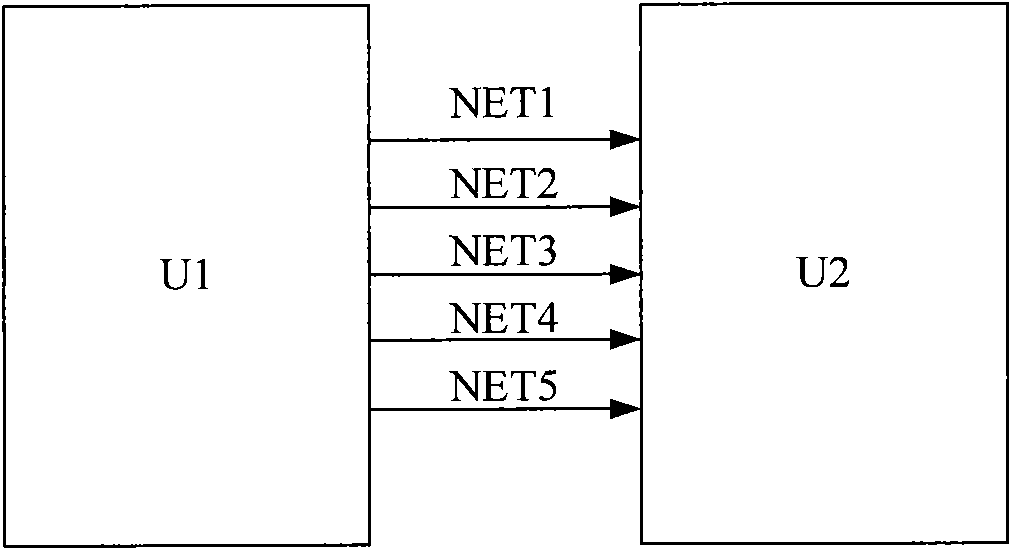

A circuit testing approach involves the generation of boundary scan information using test vectors to identify characteristics of a circuit design and a boundary scan implementation therefor. According to an example embodiment of the present invention, test vectors are used in simulation to identify circuit design characteristics for establishing a boundary scan test program. The test vectors are generated using a netlist of the circuit design. The test vectors are used to simulate operation of the circuit, and responses to the simulation are detected and used to identify design-specific circuit characteristics and a boundary scan test program is generated using the design-specific circuit characteristics.

Owner:XILINX INC

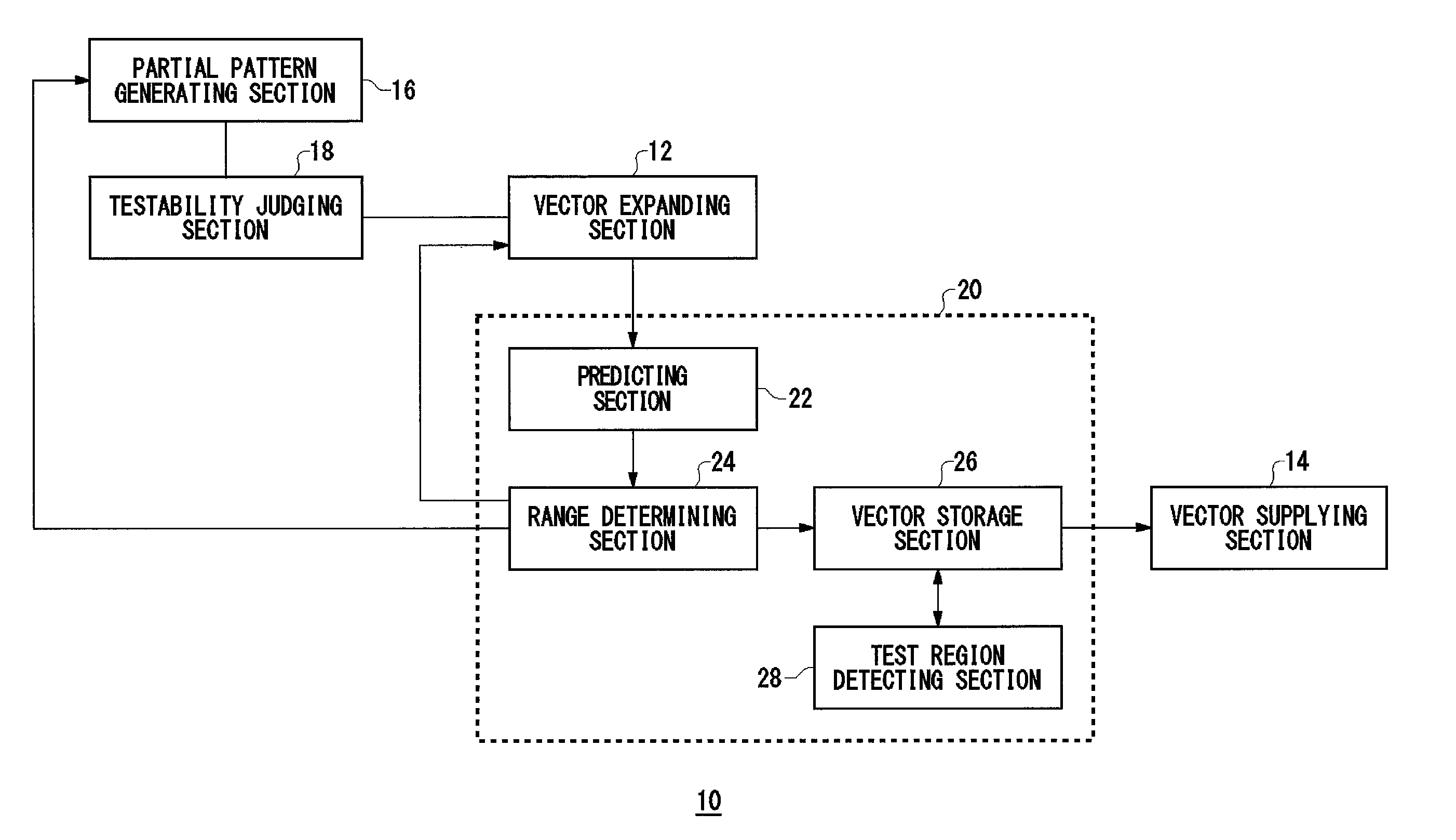

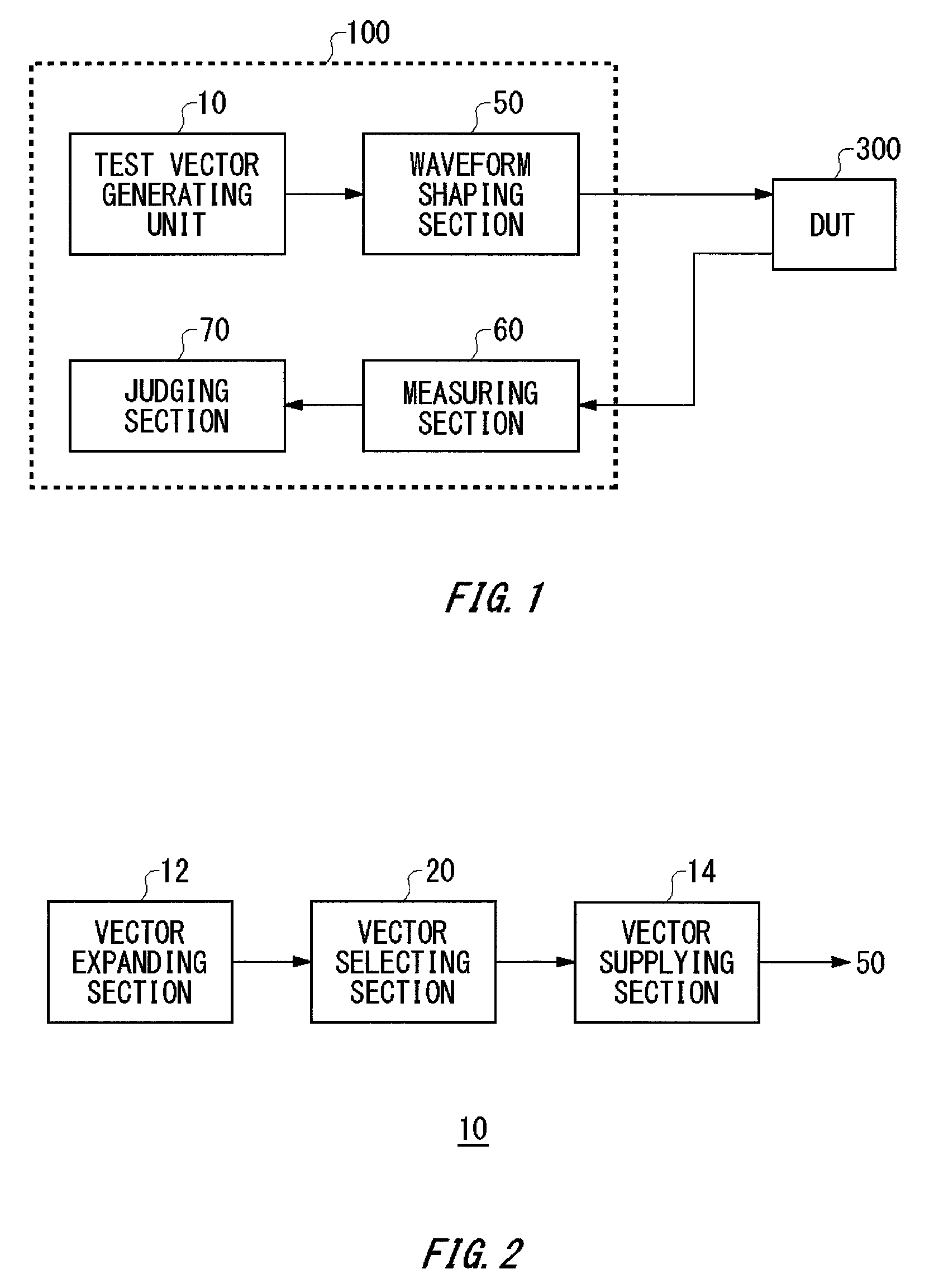

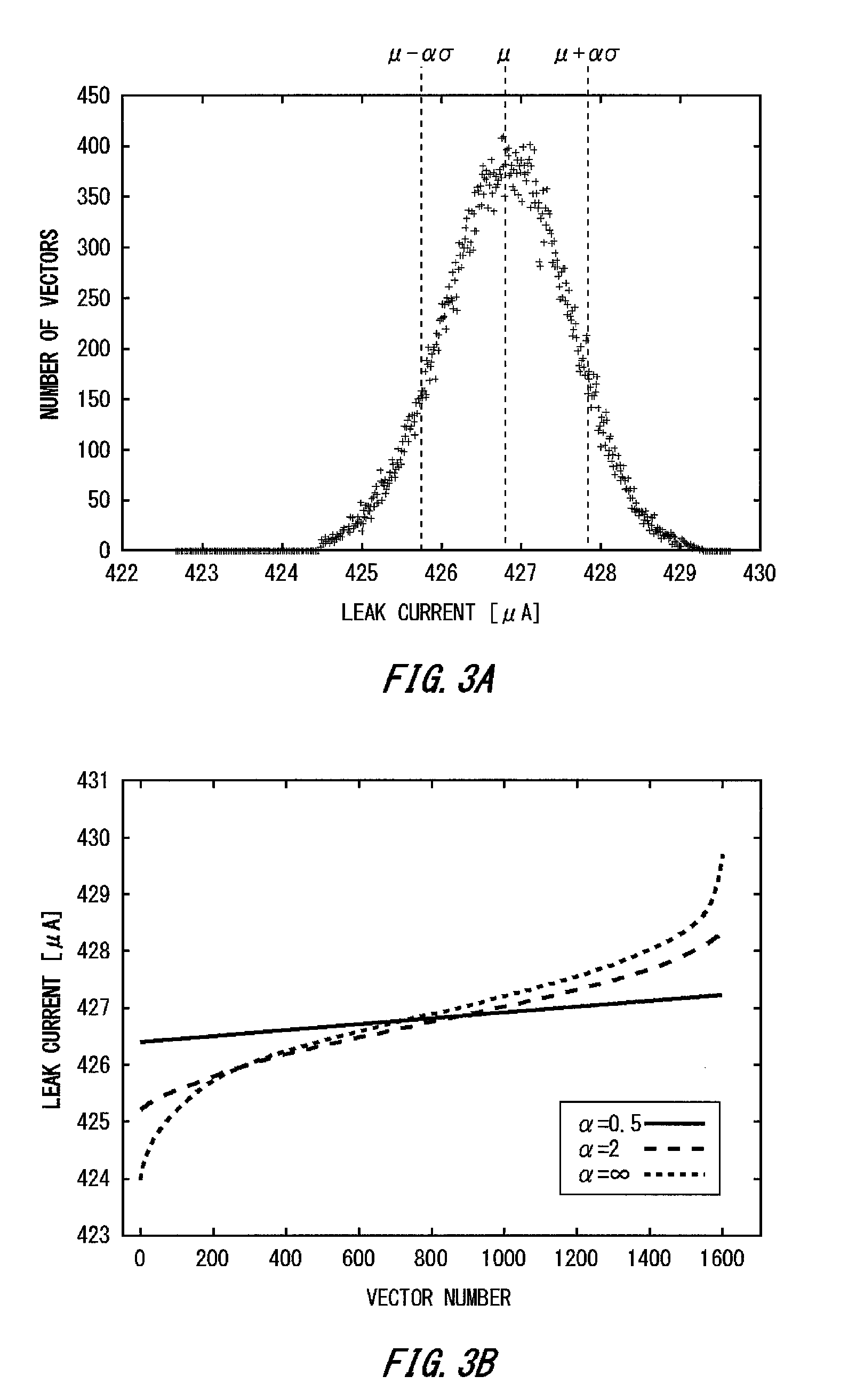

Test apparatus, test vector generate unit, test method, program, and recording medium

Provided is a test apparatus that tests a device under test, including a vector expanding section that sequentially generates a plurality of test vectors; a vector selecting section that selects test vectors that cause a prescribed characteristic of the device under test, which is to be measured when test signals that are each based on one of the test vectors are supplied to the device under test, to fulfill a preset condition; and a judging section that judges pass / fail of the device under test based on measured values of the prescribed characteristic of the device under test supplied with the test signal based on the test vectors selected by the vector selecting section.

Owner:ADVANTEST CORP +1

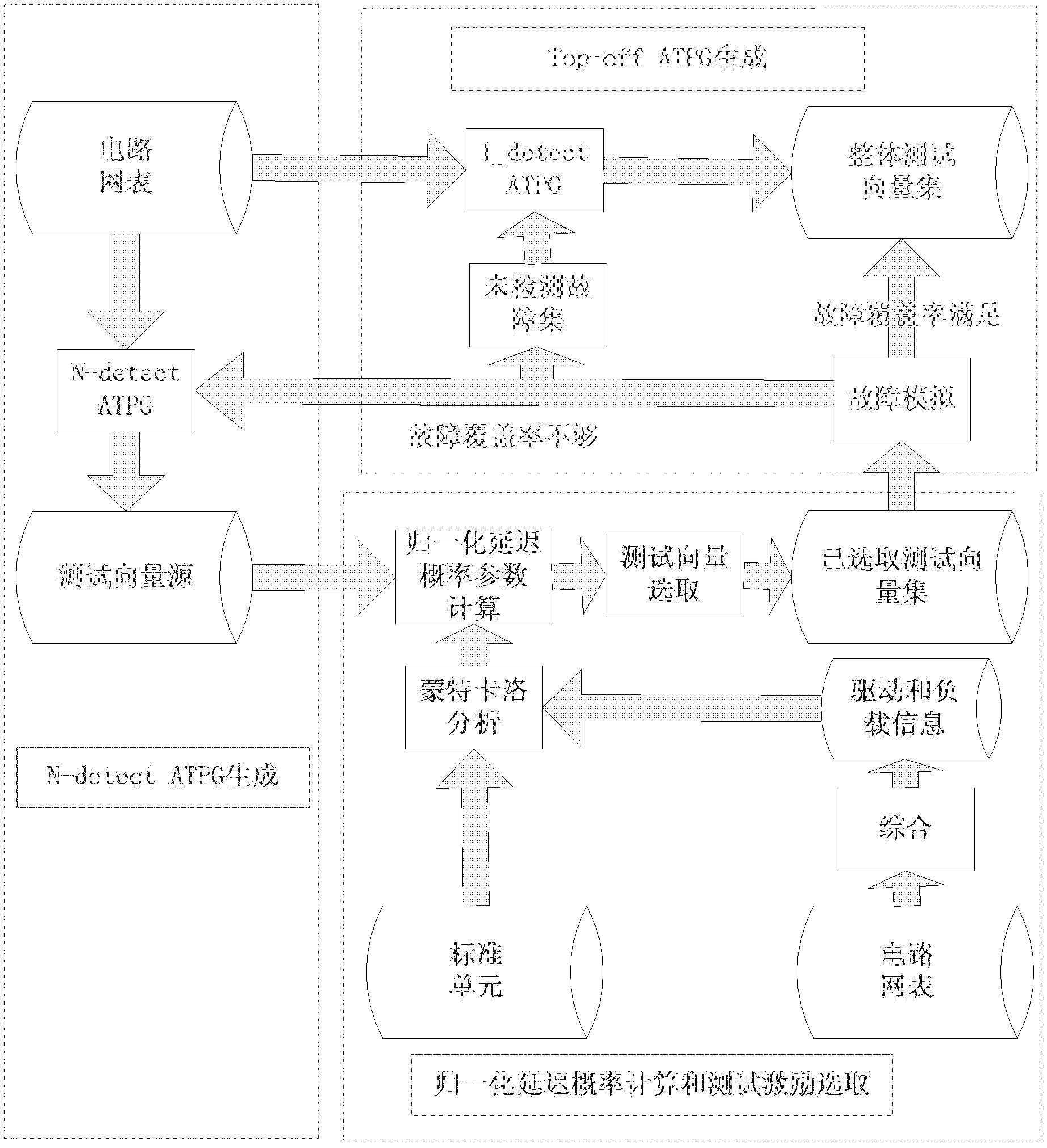

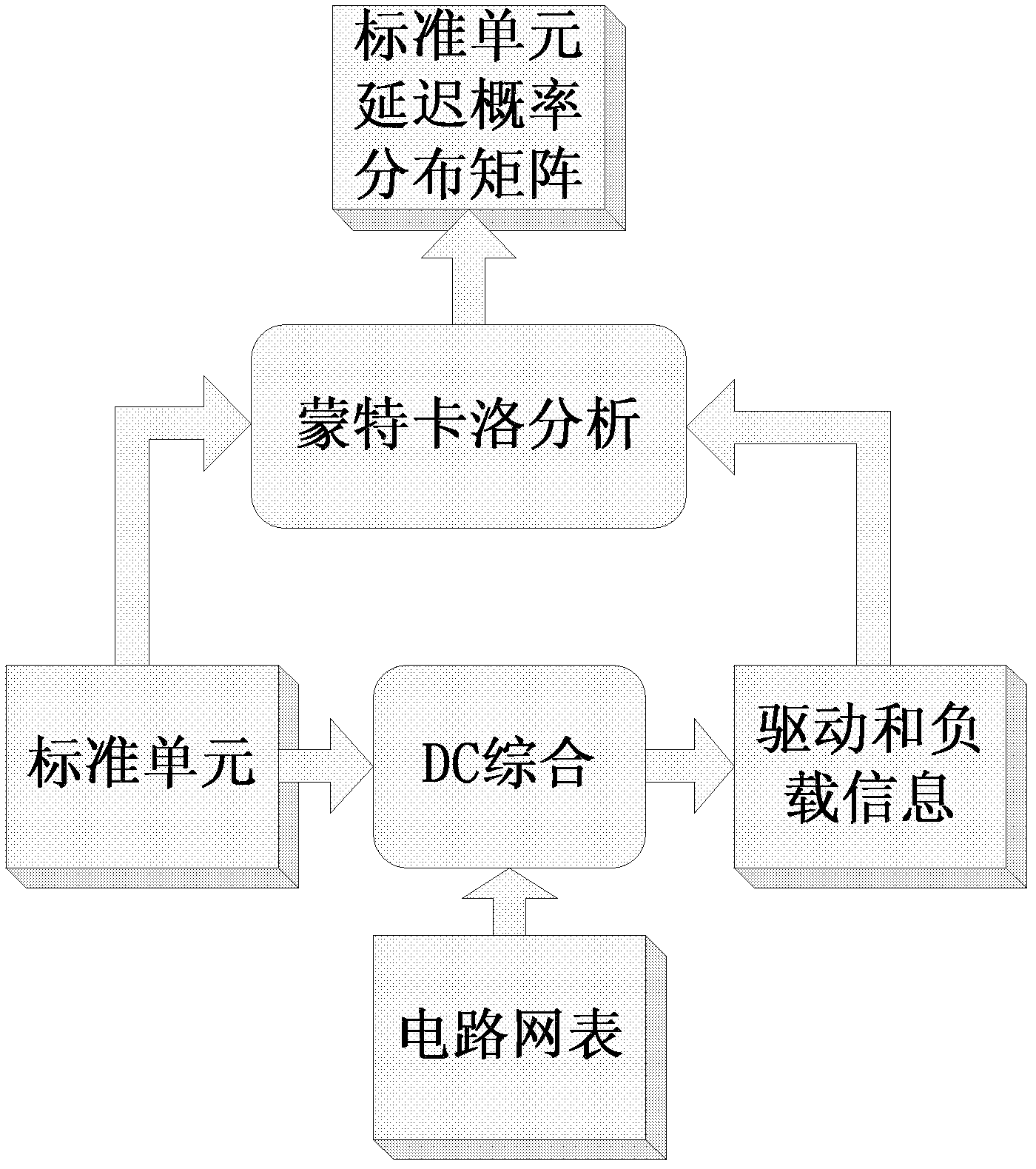

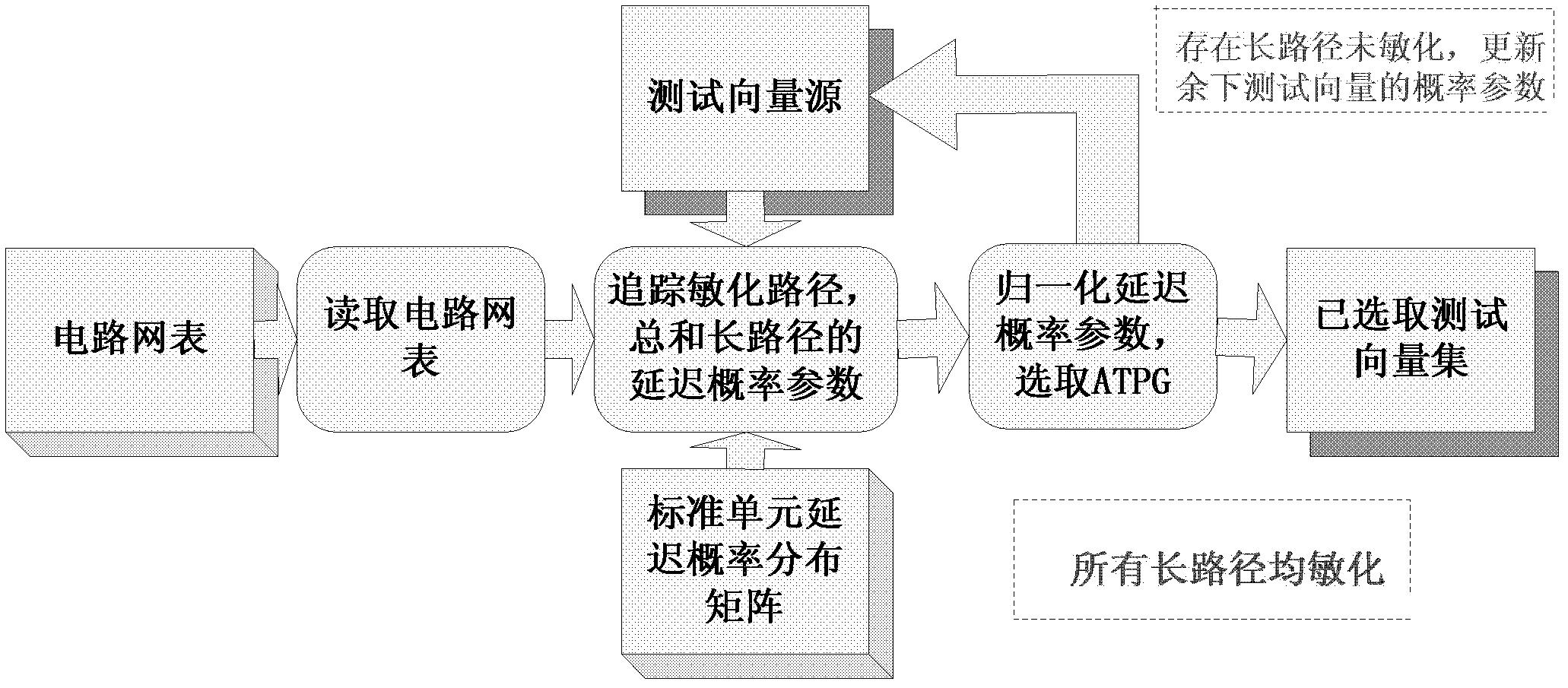

Method for testing small delay defects based on normalization delay probability distribution

InactiveCN102621477AReduce build timeGuaranteed validityElectronic circuit testingSoftware engineeringPattern selection

The invention discloses a method for testing small delay defects based on normalization delay probability distribution. The method comprises the following three steps of: N-detect automatic test pattern generation (ATPG), normalization delay probability calculation and test pattern selection, and Top-off ATPG. The N-detect test pattern source of the conventional ATPG tool is used, the problems of process fluctuation, process mismatching and the like are solved, test patterns with the maximum normalization probability value are selected to form a new test pattern set for detecting the small delay defects, and the test effectiveness of the small delay defects caused by process fluctuation, process mismatching and the like is improved. Compared with the prior art, the method has the advantages that the scale of the test patterns can be reduced, and the test effectiveness of the small delay defects can be improved.

Owner:PEKING UNIV