Method for increasing test coverage of scan chain and device thereof

A test coverage and scan chain technology, applied in static memory, instruments, etc., can solve the problems of reducing logic coverage and low chip test coverage, to improve overall test coverage, achieve testability, and improve logic testing. The effect of coverage

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0029] In order to make the above objects, features and advantages of the present invention more comprehensible, the present invention will be further described in detail below in conjunction with the accompanying drawings and specific embodiments.

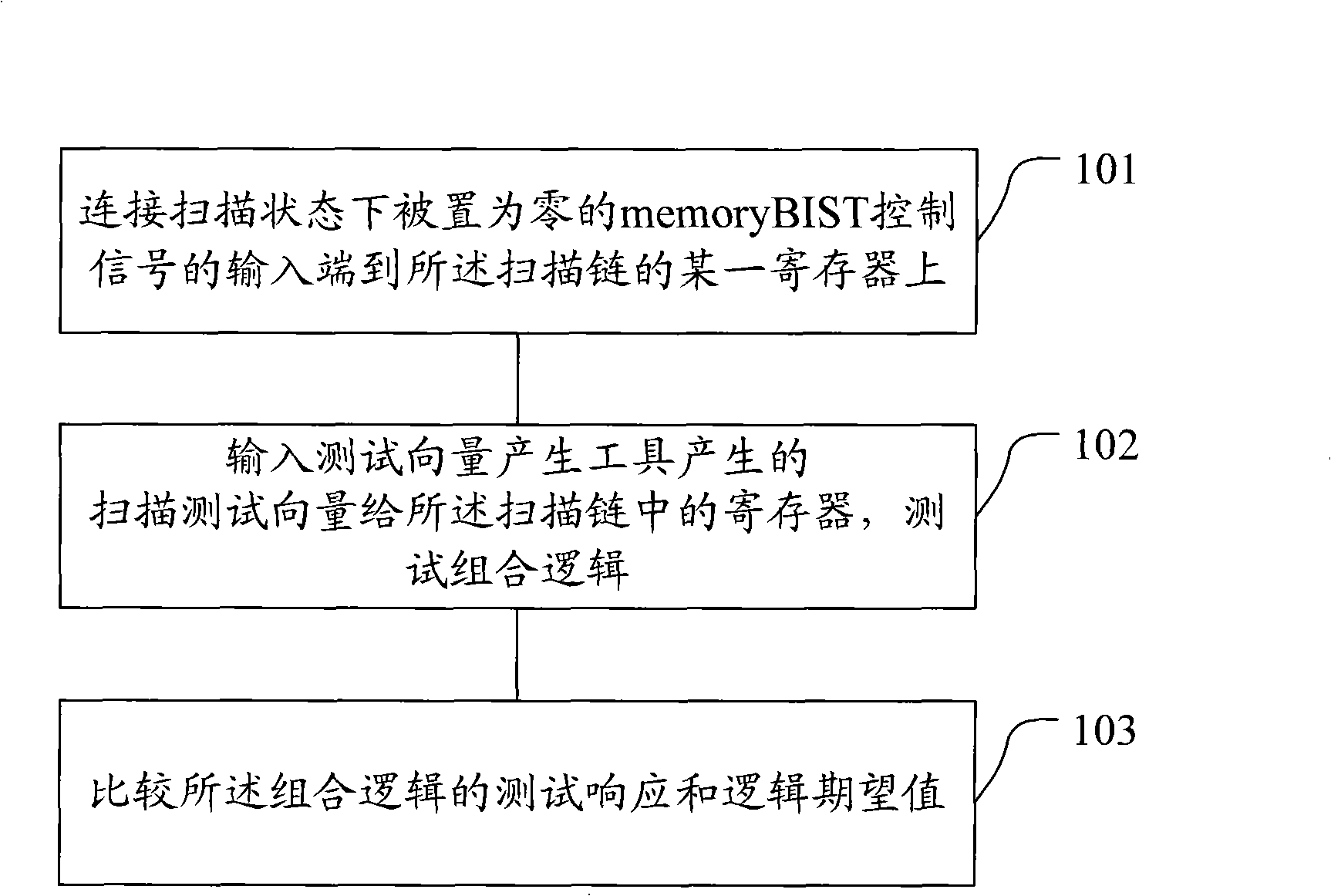

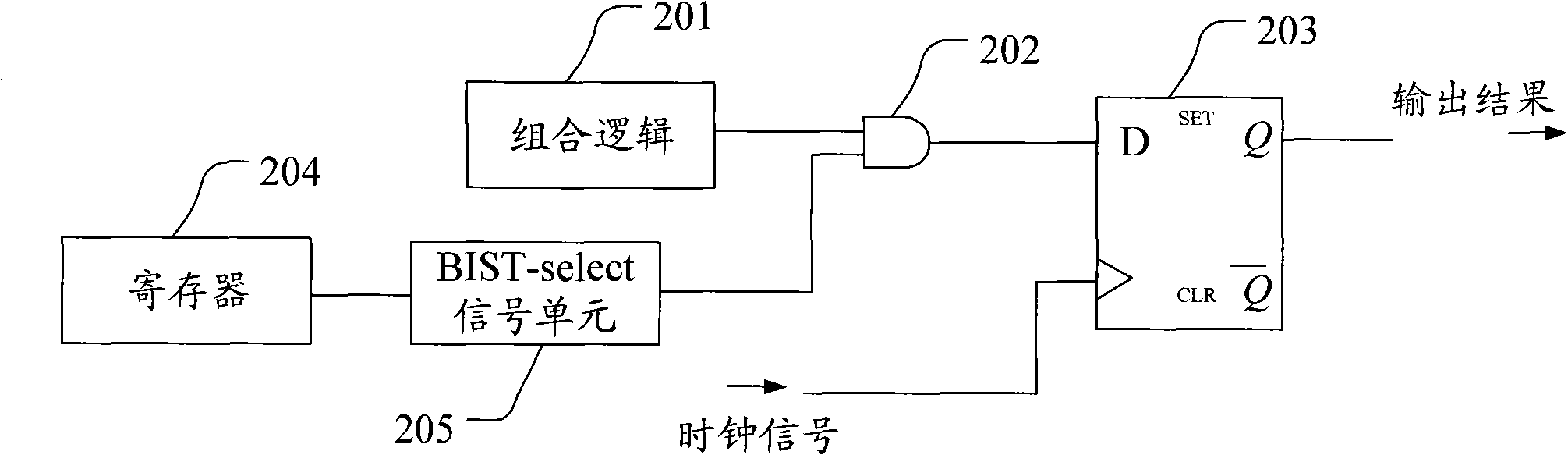

[0030] The solution provided by the present invention improves the logic test coverage of the chip by improving the control logic of the built-in self-test (BIST) of the memory (memory) during the scan chain test, thereby improving the overall test coverage of the chip.

[0031] The embodiment of the present invention relates to a chip designed to improve scan chain test coverage. In the chip design, many memories are used, including registfile, 6T-sram, and oneT-sram.

[0032] When performing the scan chain test, it was found that the test coverage rate of the memory BIST logic was very low, only about 40%. After testing, it is found that it is because a lot of memory is used in the above-mentioned chip design, and these memories...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More