Patents

Literature

106 results about "Built in self testing" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

System and method of controlling power consumption in an electronic system

ActiveUS20050188230A1Readily apparentEnergy efficient ICTElectric devicesSystems designElectronic systems

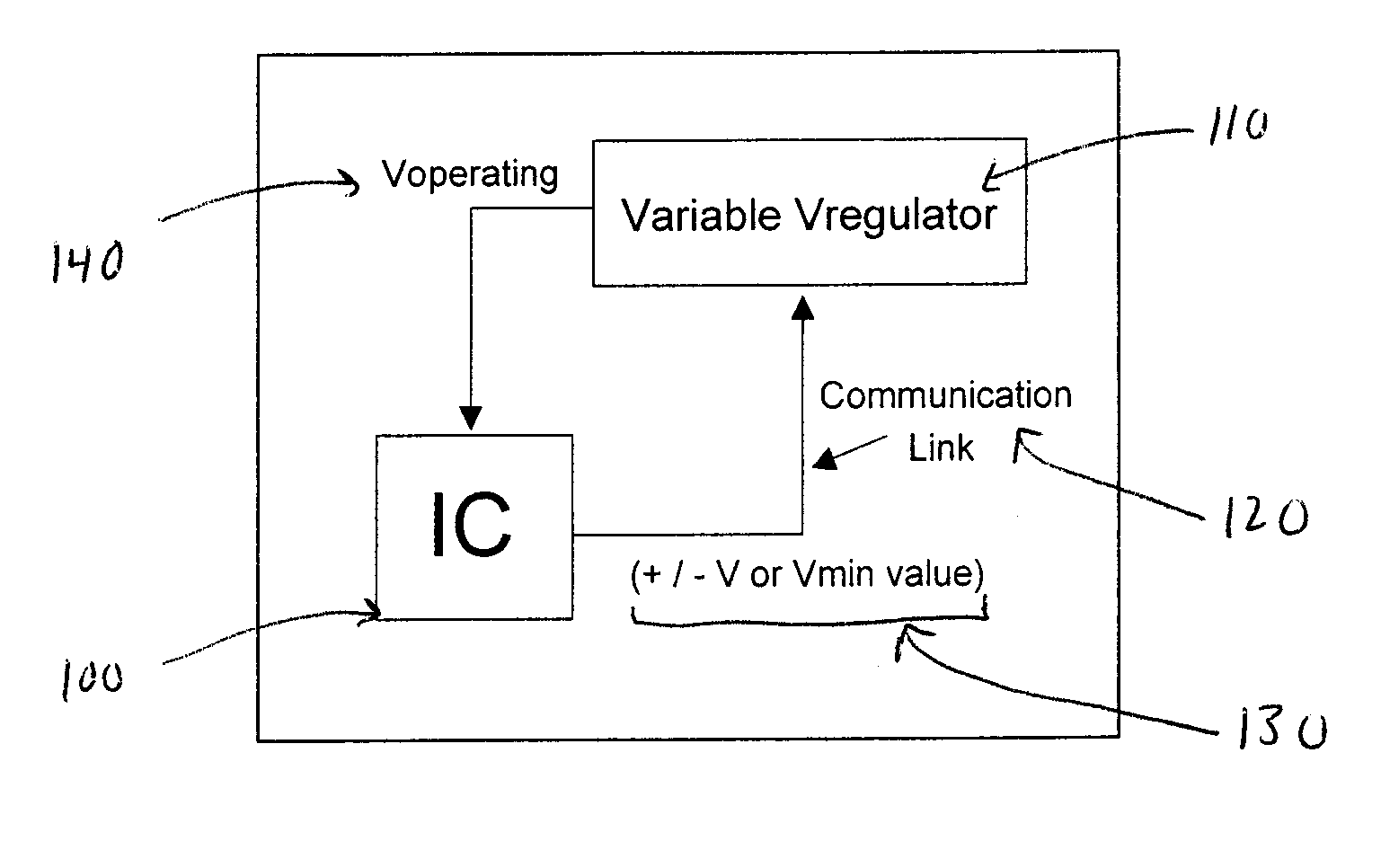

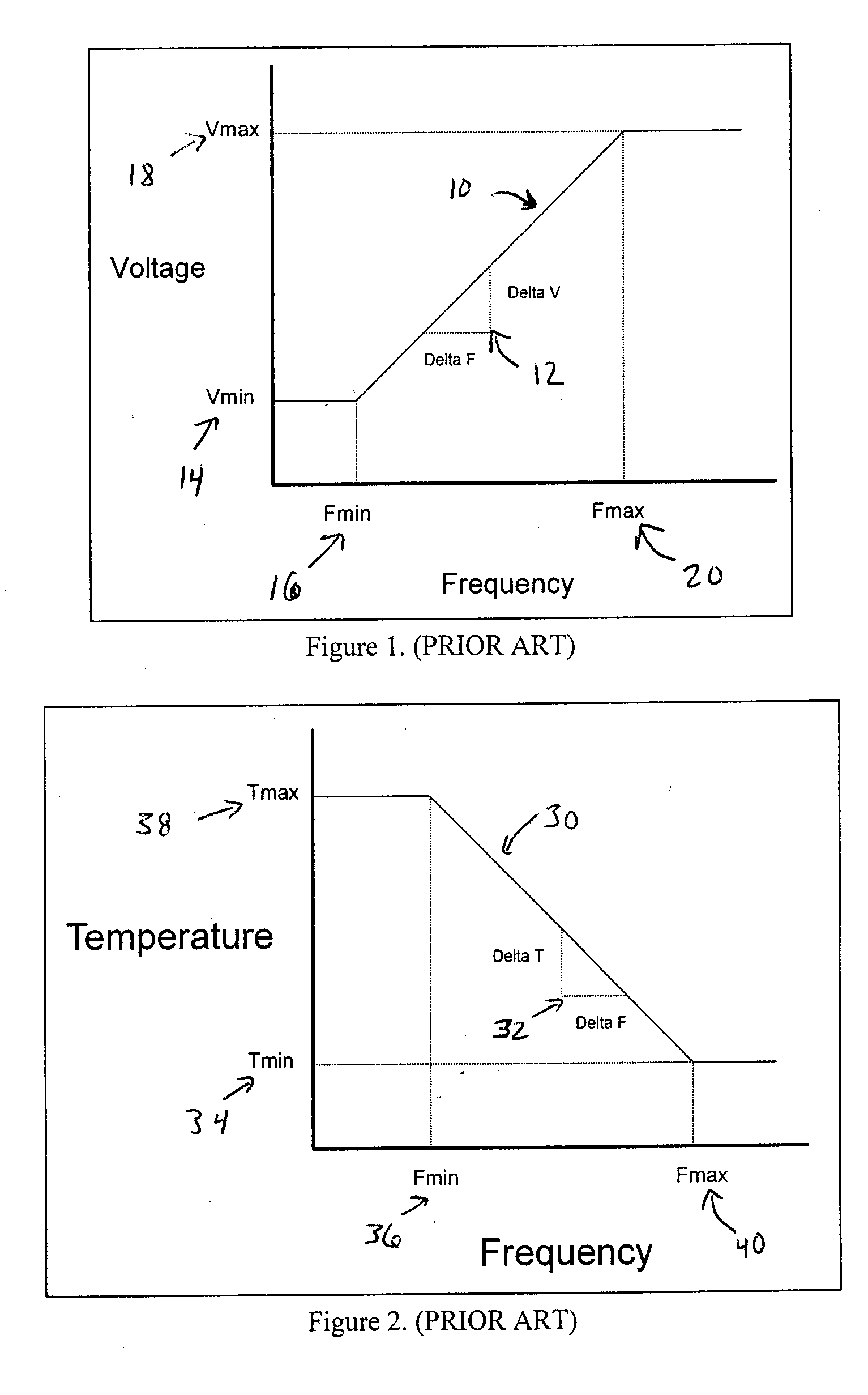

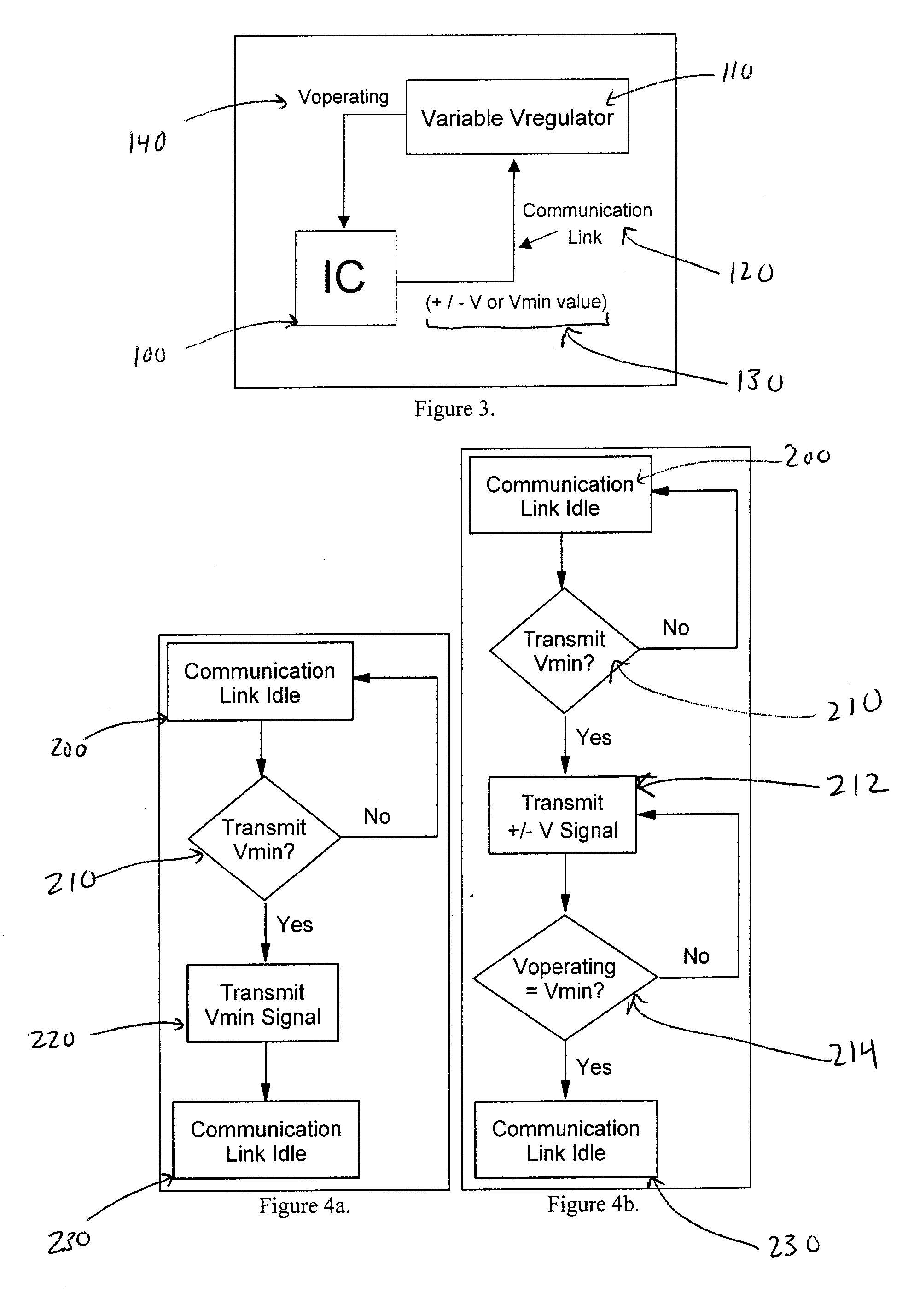

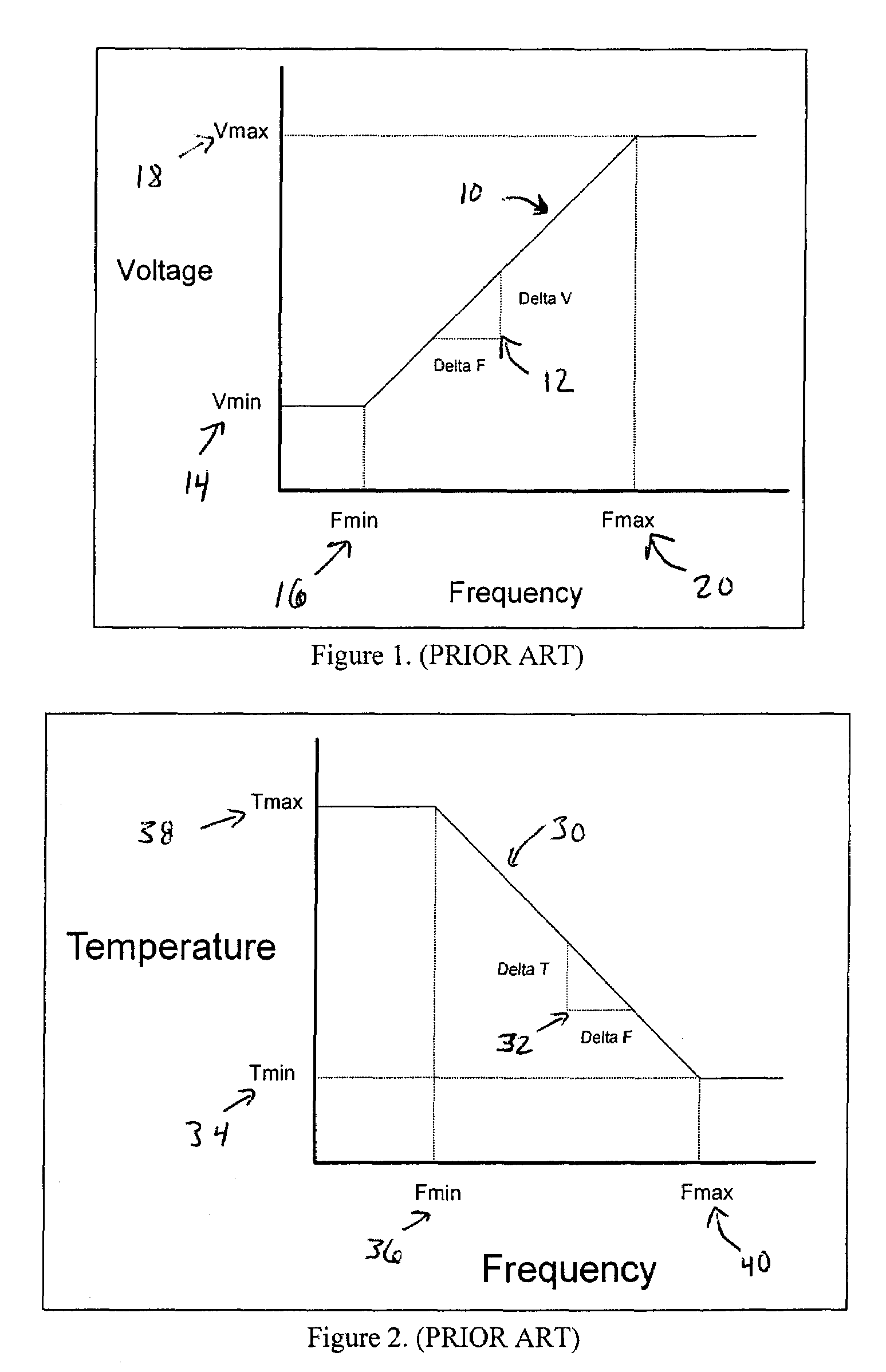

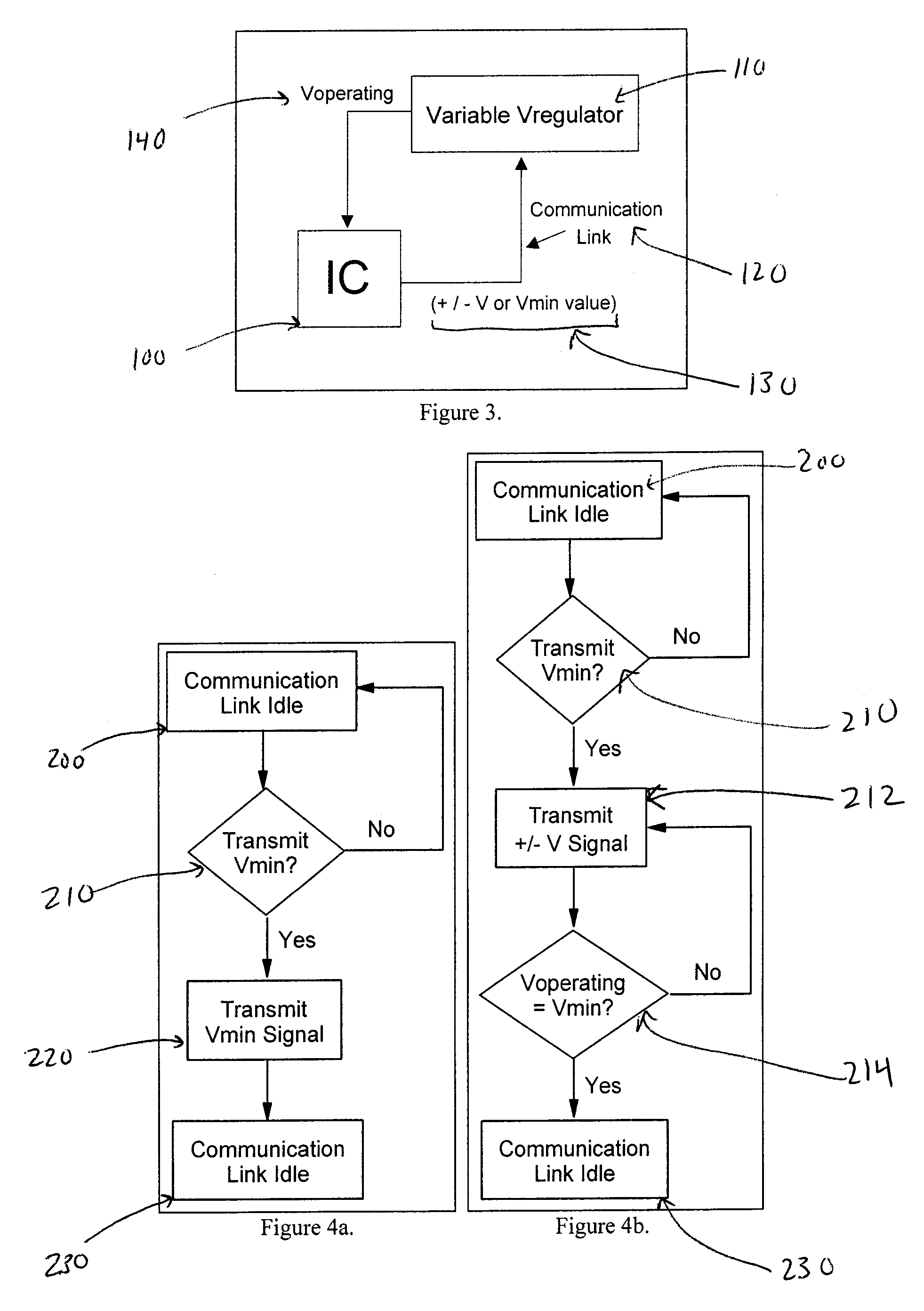

A method and apparatus for adaptively adjusting the operating voltage of an integrated circuit in response to tester-to-system variations, worst-case testing techniques, process variations, temperature variations, or reliability wearout mechanisms. The minimum operating voltage of an integrated circuit is determined either during external testing of the integrated circuit or during built-in-self-testing. The minimum operating voltage is transmitted to a variable voltage regulator where it is used to set the output of the regulator. The output of the regulator supplies the integrated circuit with its operating voltage. This technique enables tailoring of the operating voltage of integrated circuits on a part-by-part basis which results in power consumption optimization by adapting operating voltage in response to tester-to-system variations, worst-case testing techniques, process variations, temperature variations or reliability wearout mechanisms. Alternatively, the invention enables adaptive adjustment of the operating frequency of an integrated circuit. The invention enables system designers to adaptively optimize either system performance or power consumption on a part-by-part basis in response to tester-to-system variations, worst-case testing techniques, process variations, temperature variations or reliability wearout mechanisms.

Owner:IBM CORP

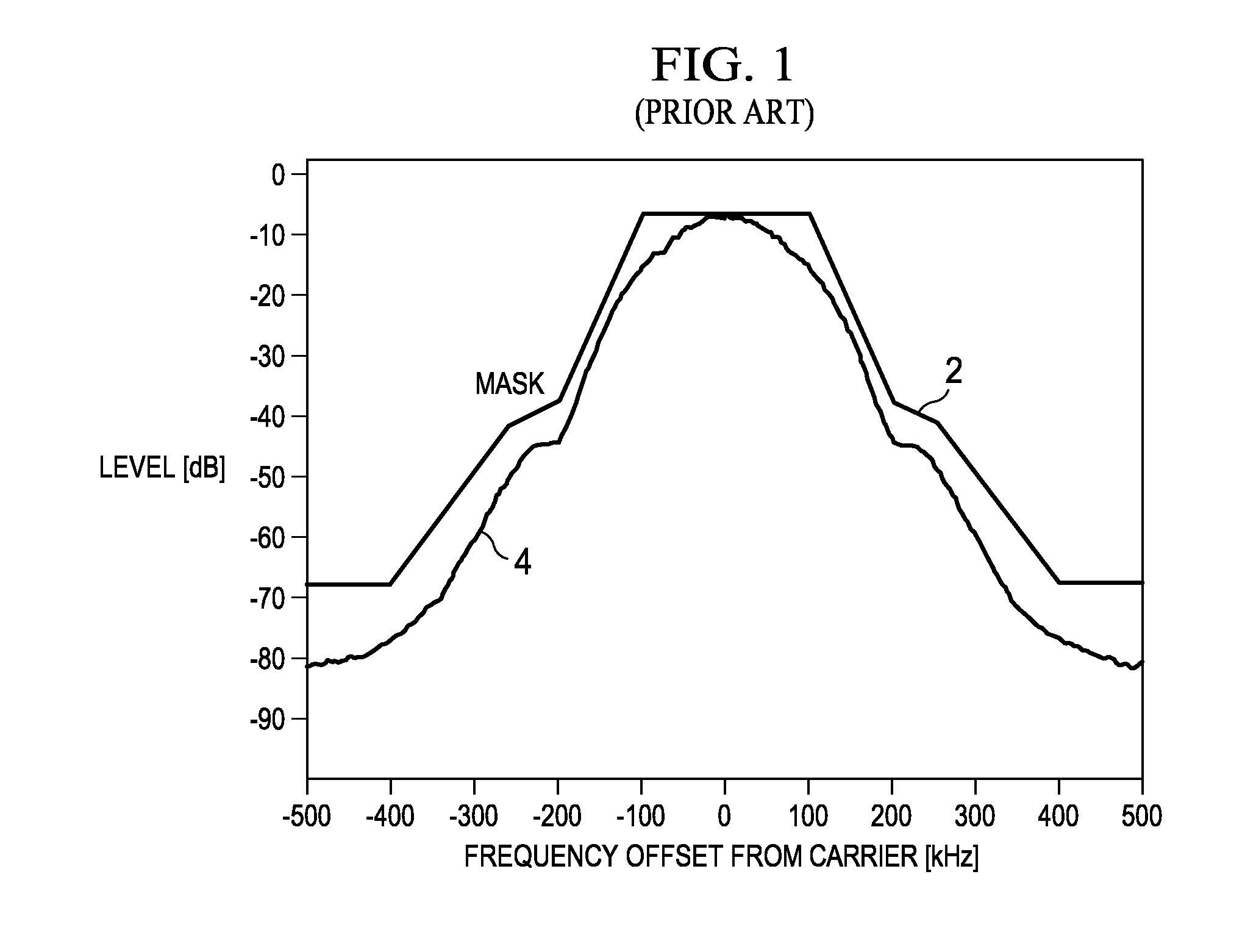

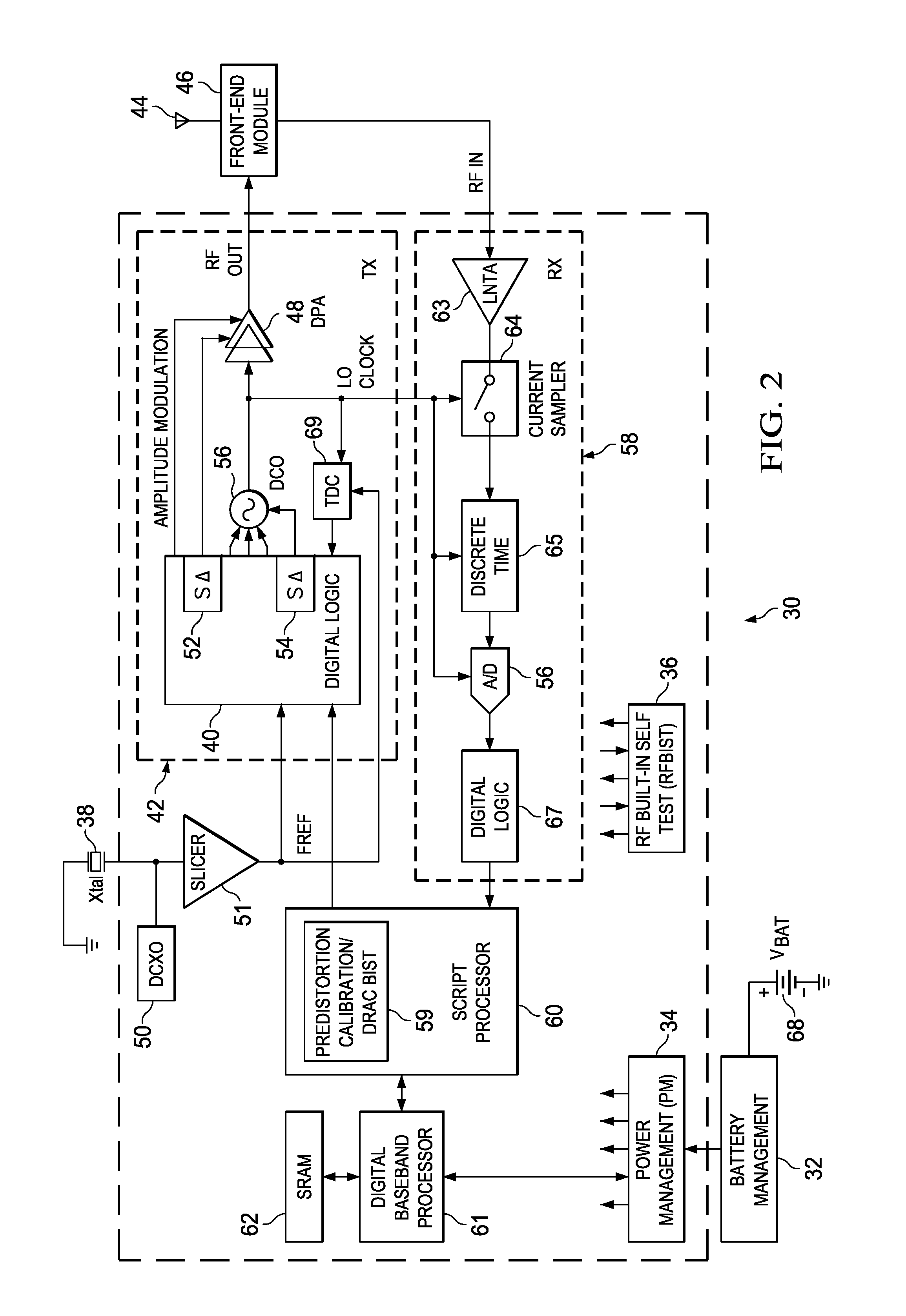

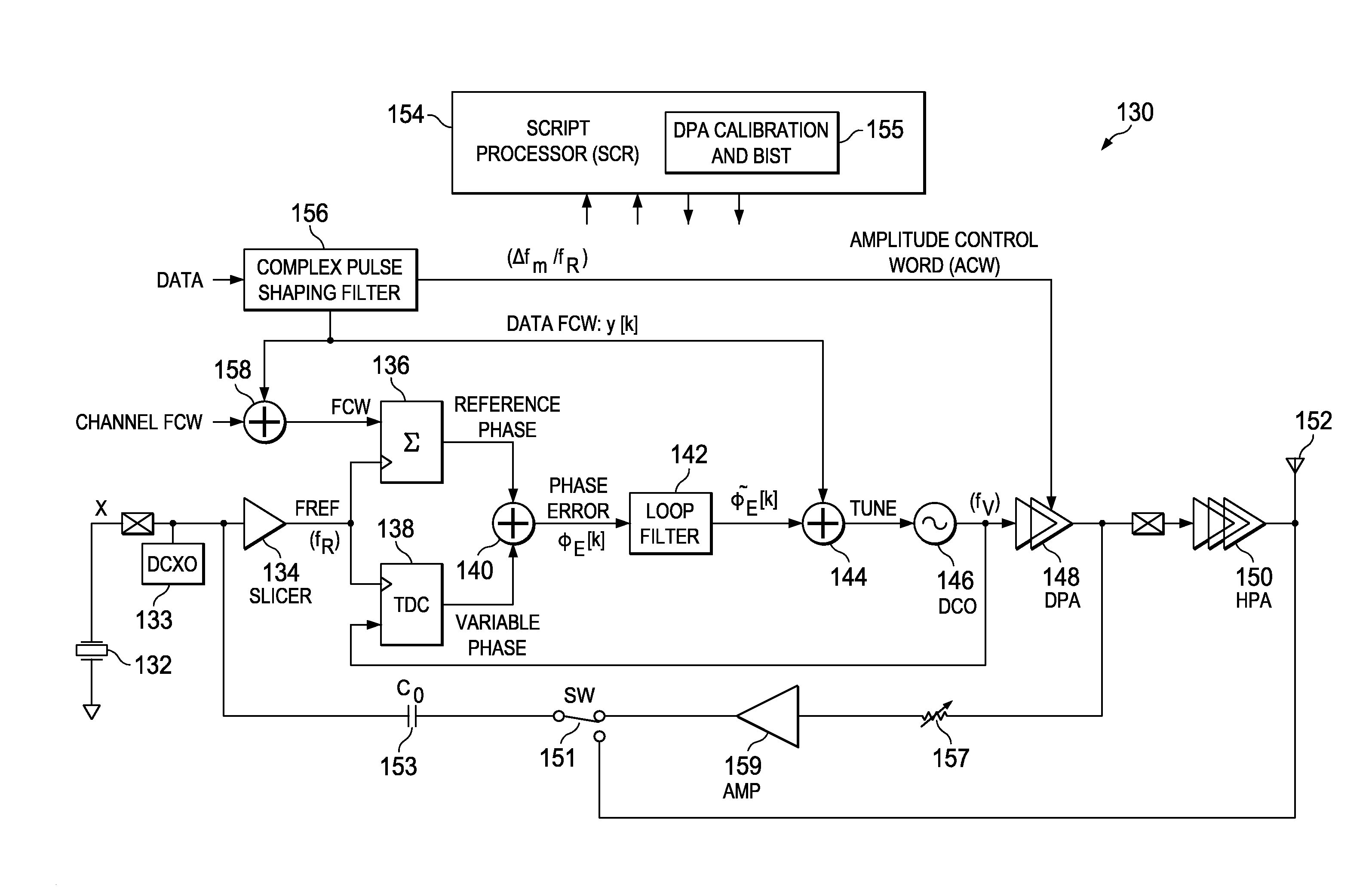

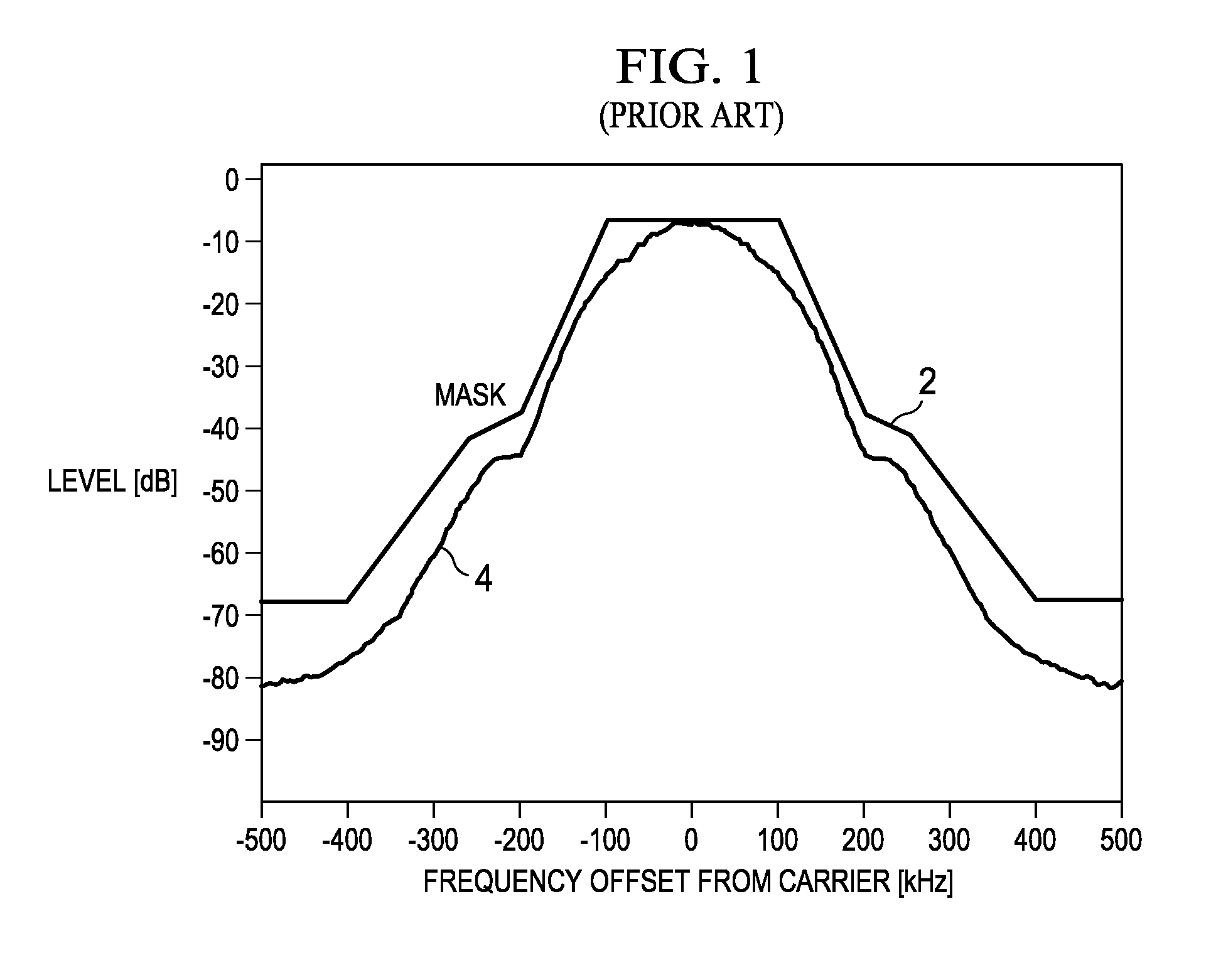

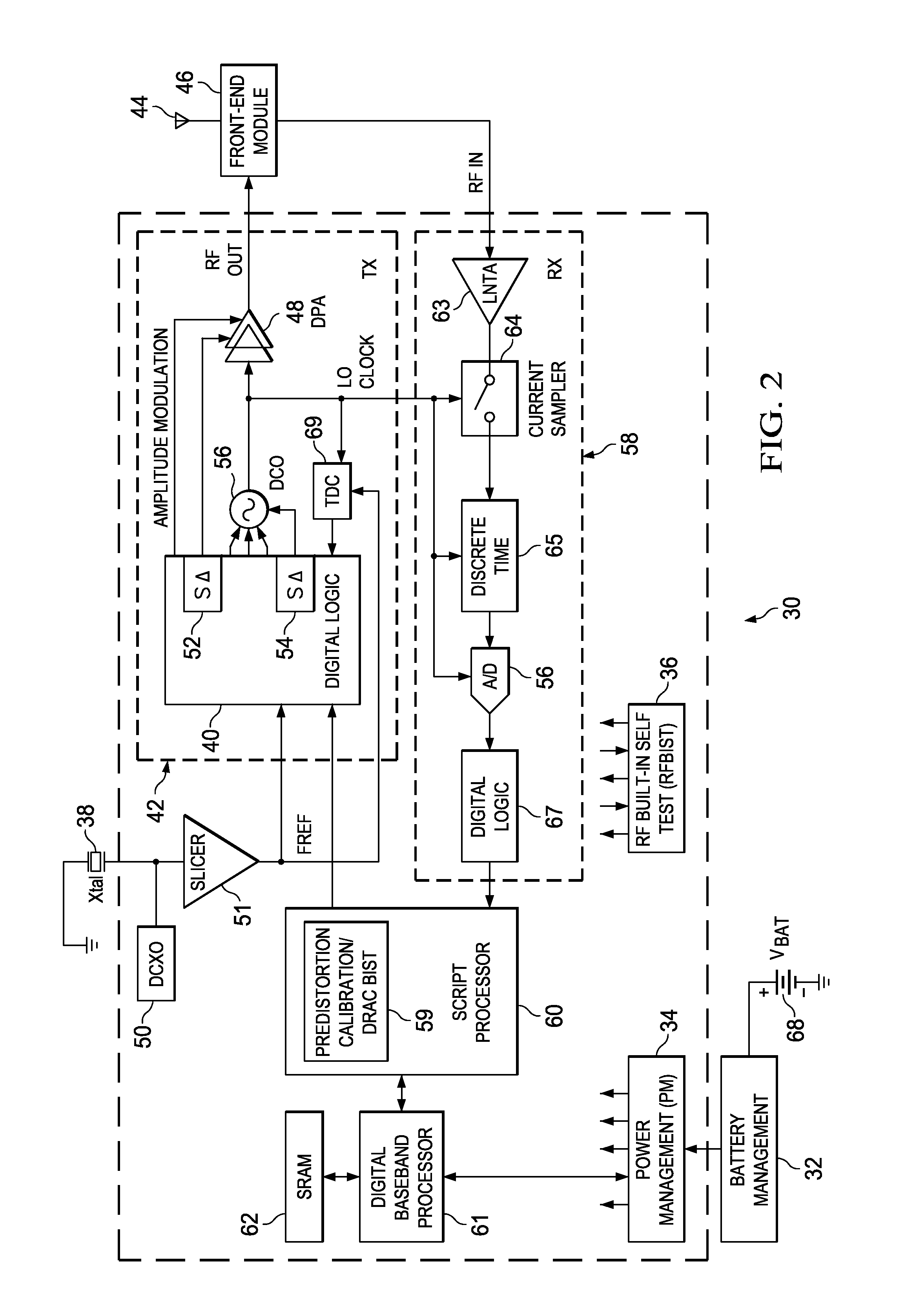

Predistortion calibration and built in self testing of a radio frequency power amplifier using subharmonic mixing

ActiveUS20120252382A1No significant hardware overheadStrain is placedTransmitters monitoringPower amplifiersHarmonicTested time

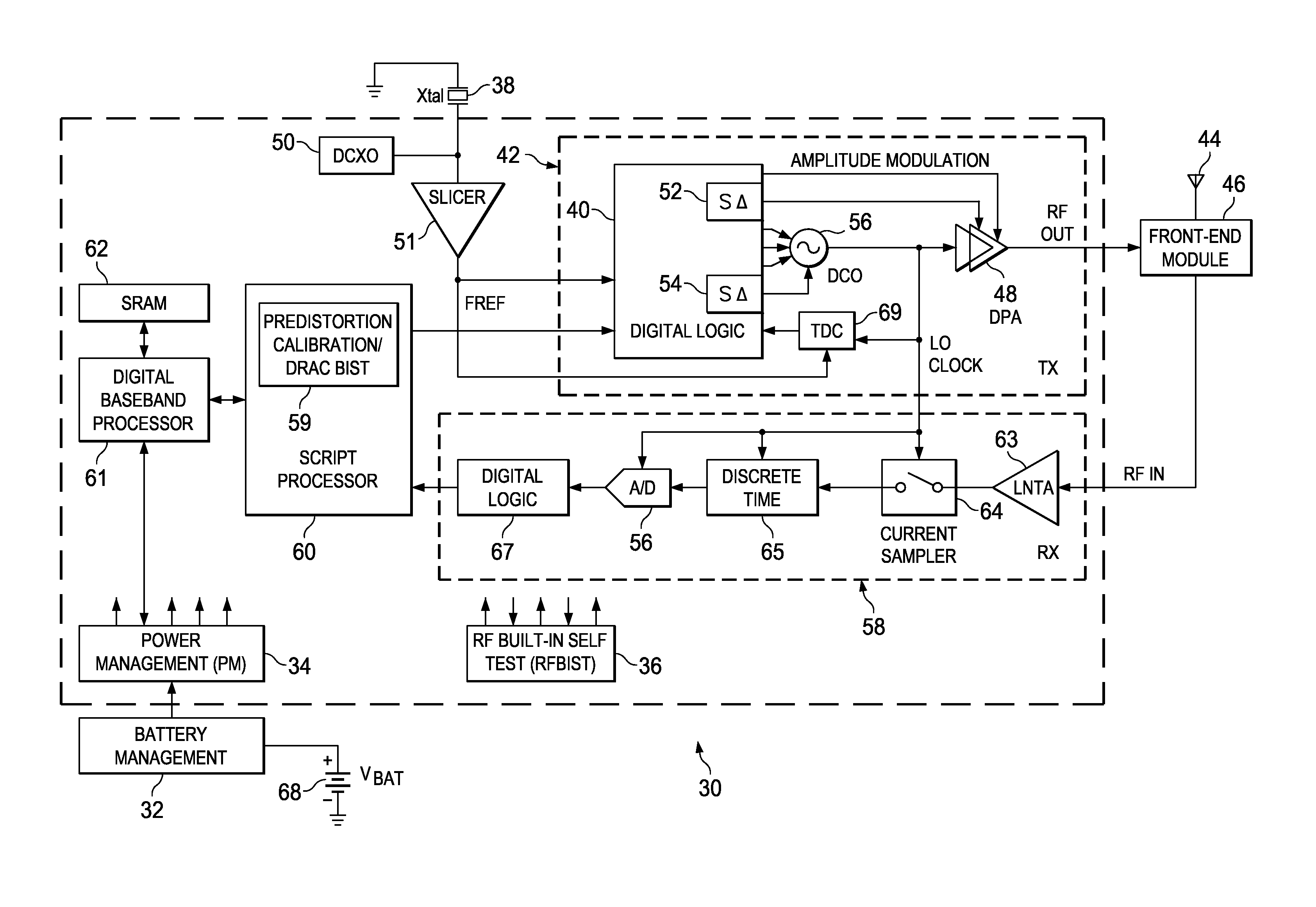

A novel and useful apparatus for and method of predistortion calibration and built-in self testing (BIST) of a nonlinear digitally-controlled radio frequency (RF) power amplifier (DPA) using subharmonic mixing. The RF power amplifier output is temporarily coupled into the frequency reference (FREF) input and the phase error samples generated in the phase locked loop (PLL) are then observed and analyzed. The digital predistortion and BIST mechanisms process the phase error samples to calibrate and test the DPA in the transmitter of the Digital RF Processor (DRP). The invention enables the characterization of nonlinearities, the configuration of internal predistortion, as well as the testing of the transmitter's analog / RF circuitry, thereby eliminating commonly employed RF performance testing using high-cost test equipment and associated extended test times.

Owner:TEXAS INSTR INC

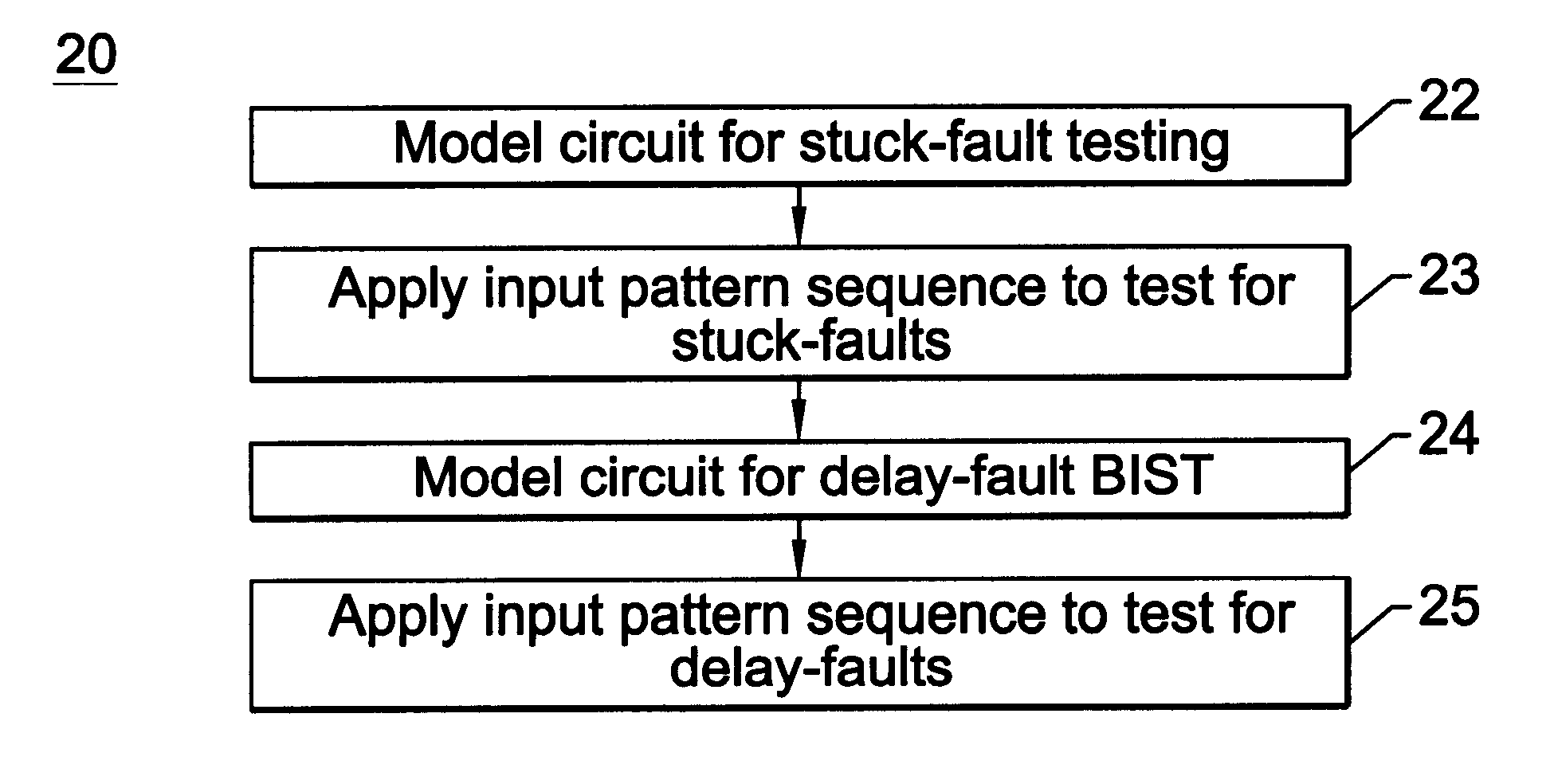

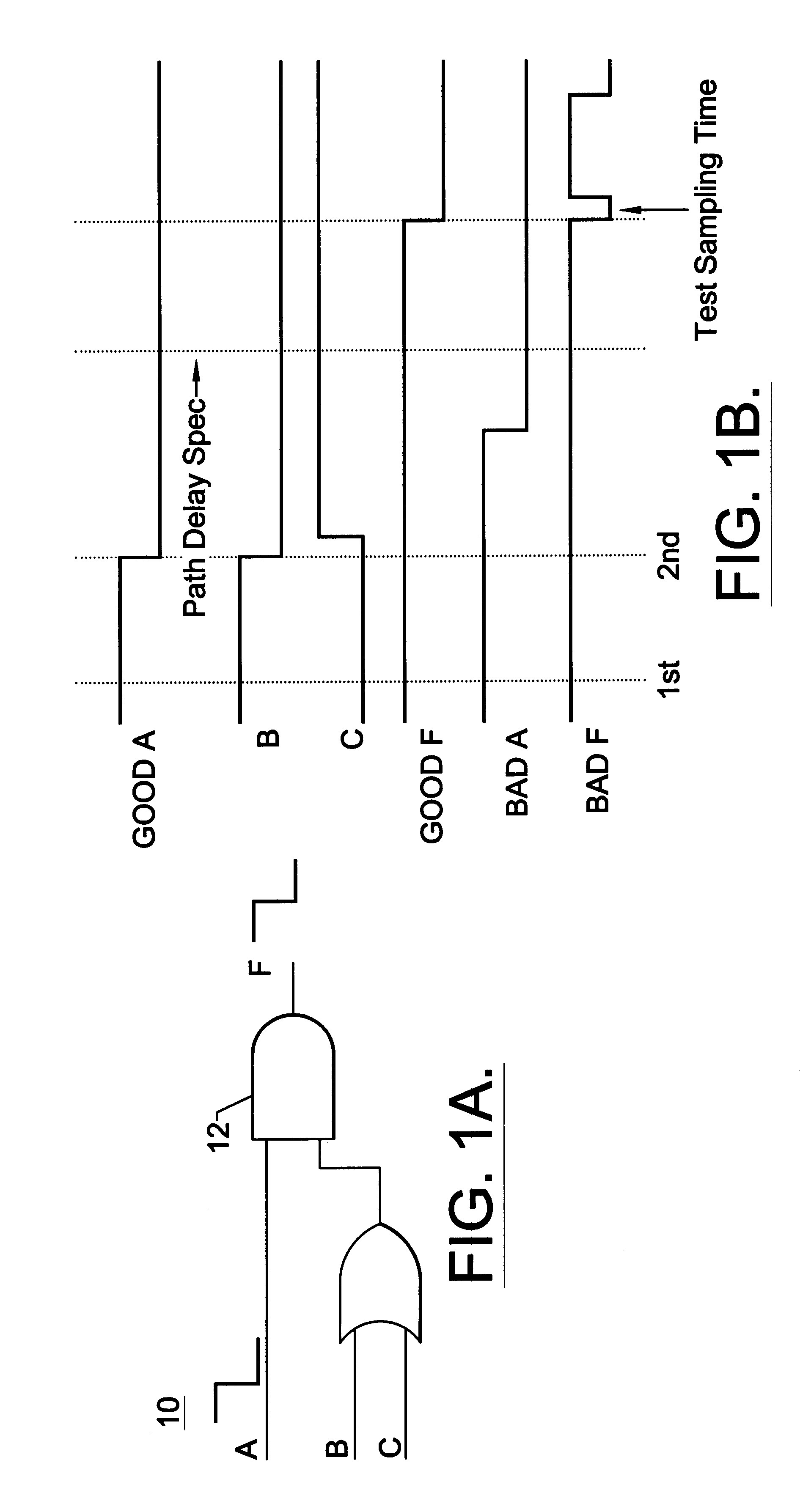

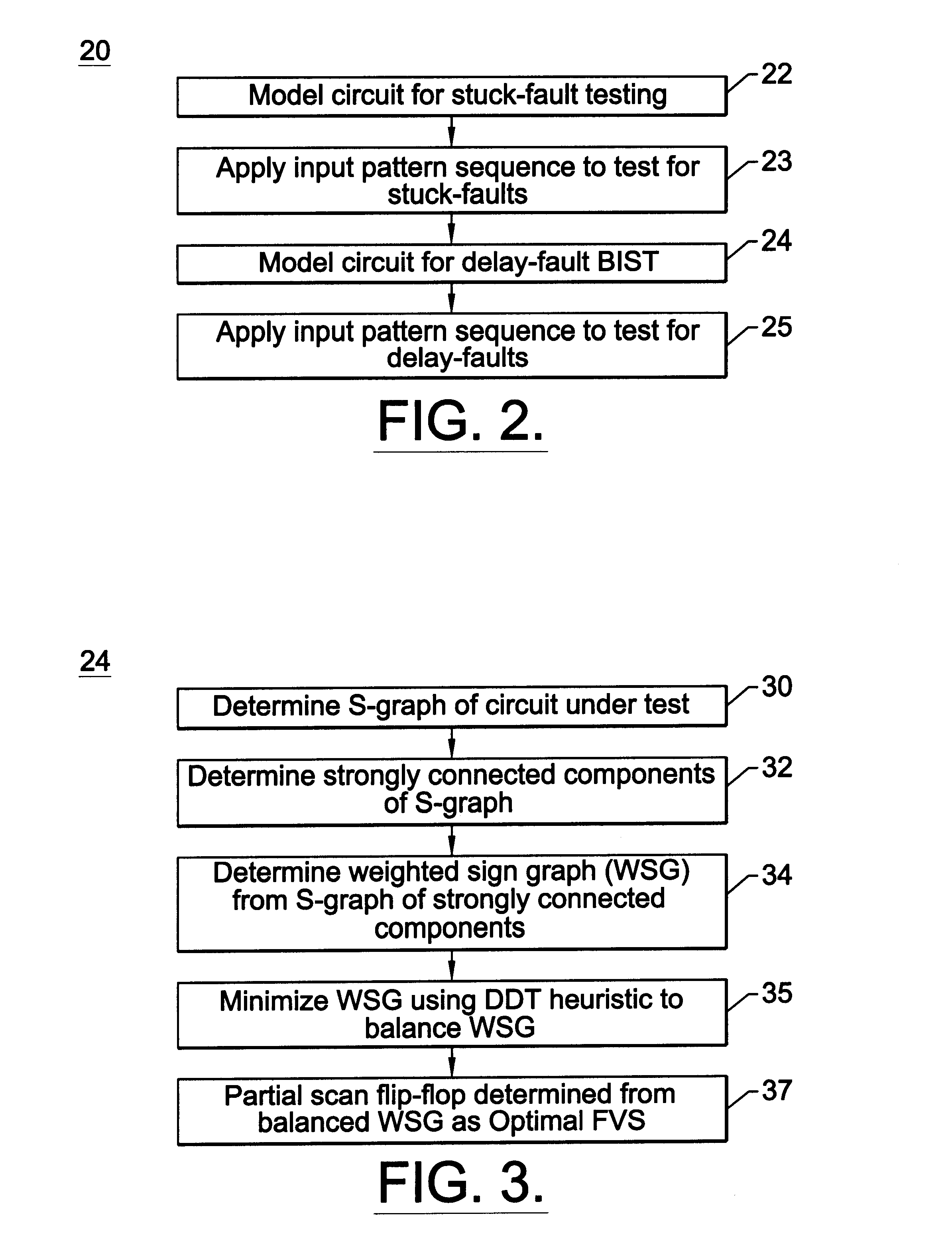

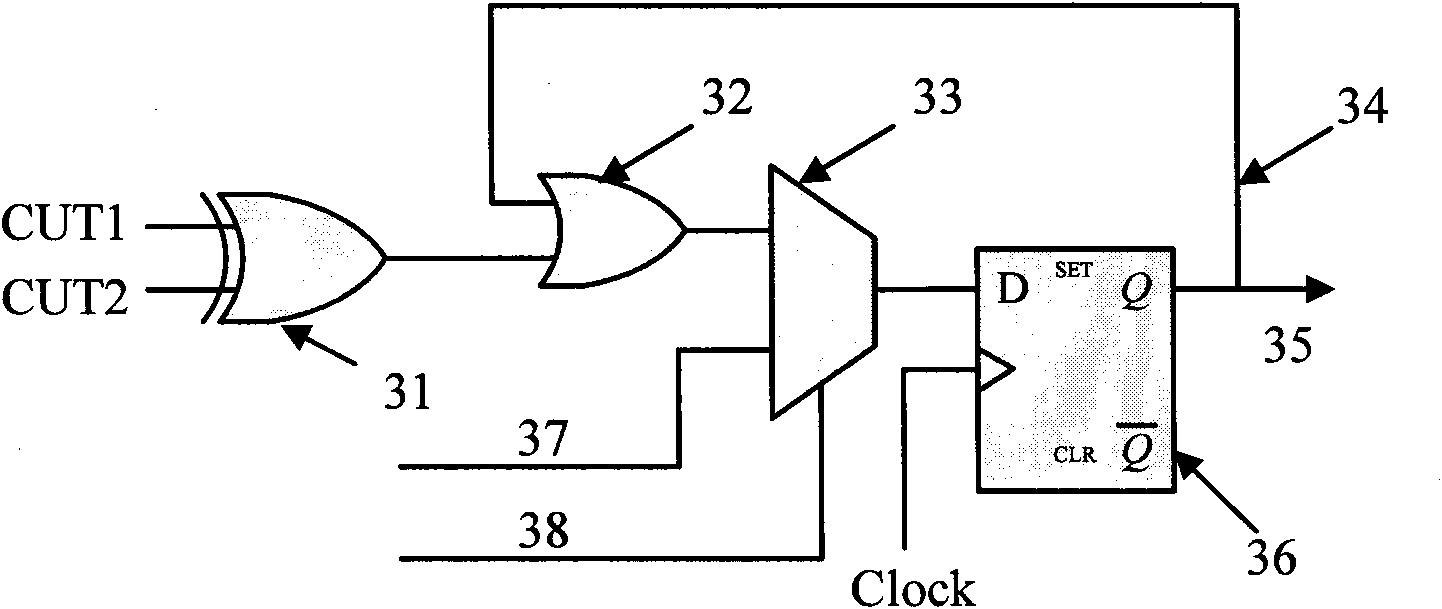

Method and apparatus for combined stuck-at fault and partial-scanned delay-fault built-in self test

InactiveUS6247154B1Electronic circuit testingError detection/correctionStuck-at faultBuilt in self testing

This invention relates to a method and apparatus for combined stuck-fault testing and partial scan delay-fault built-in self testing (BIST). For partial scan delay-fault BIST, the circuit is modeled for breaking all flip-flop feedback cycles in the circuit. A selection of flip-flops to be scanned to break all sequential cycles is determined from an optimal feedback vertex set. A digest, devour and tidy-up (DDT) heuristic can be used on a weighted signed graph formed from an S-graph of the circuit to determine an optimal feedback vertex set. Determined partial scan delay fault BIST hazards can be removed from the circuit by inserting parity flippers to invert selected paths during testing. The same DDT heuristic can be used to determine optimal placement of the parity flippers in the circuit.

Owner:RUTGERS THE STATE UNIV

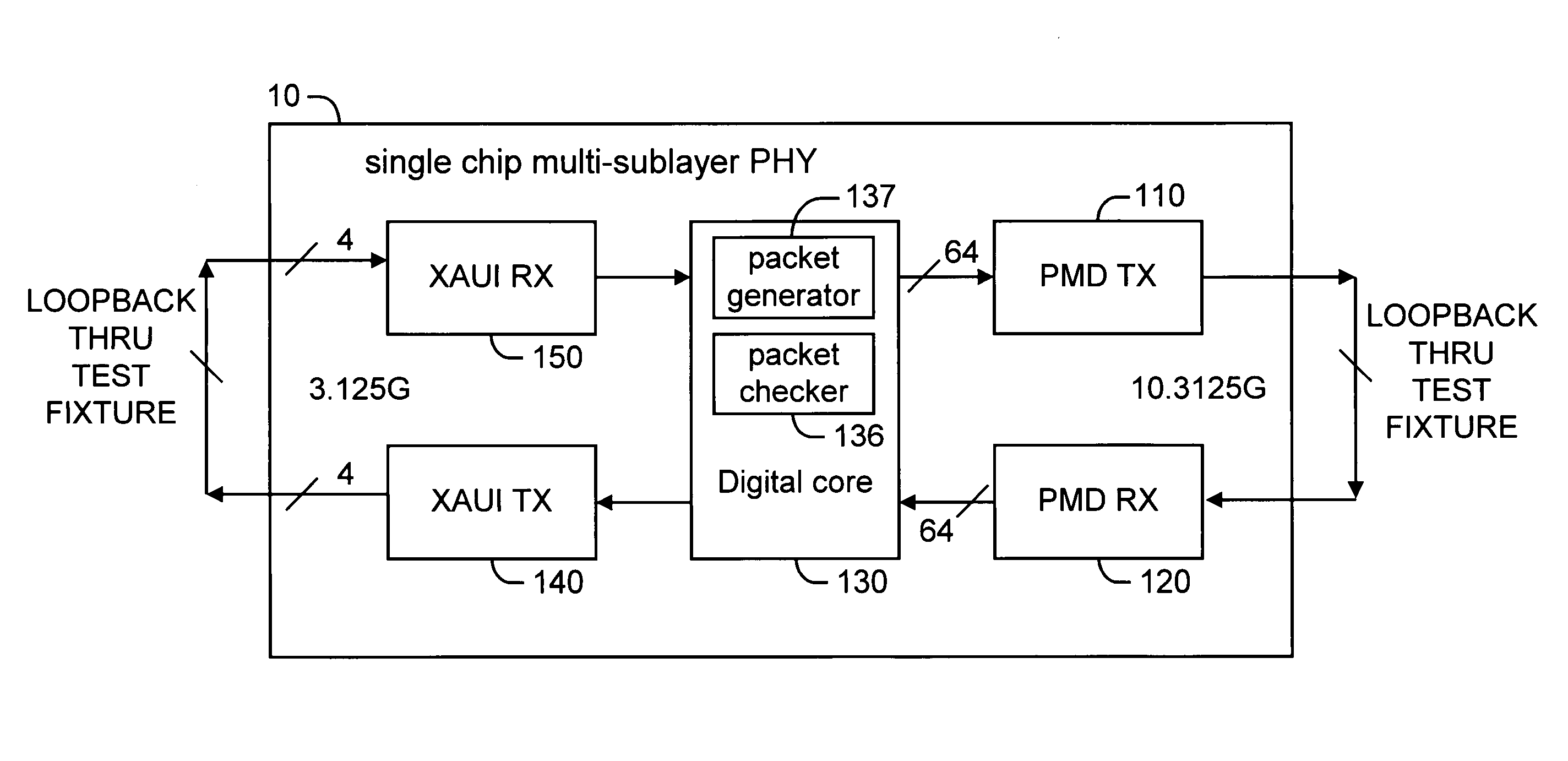

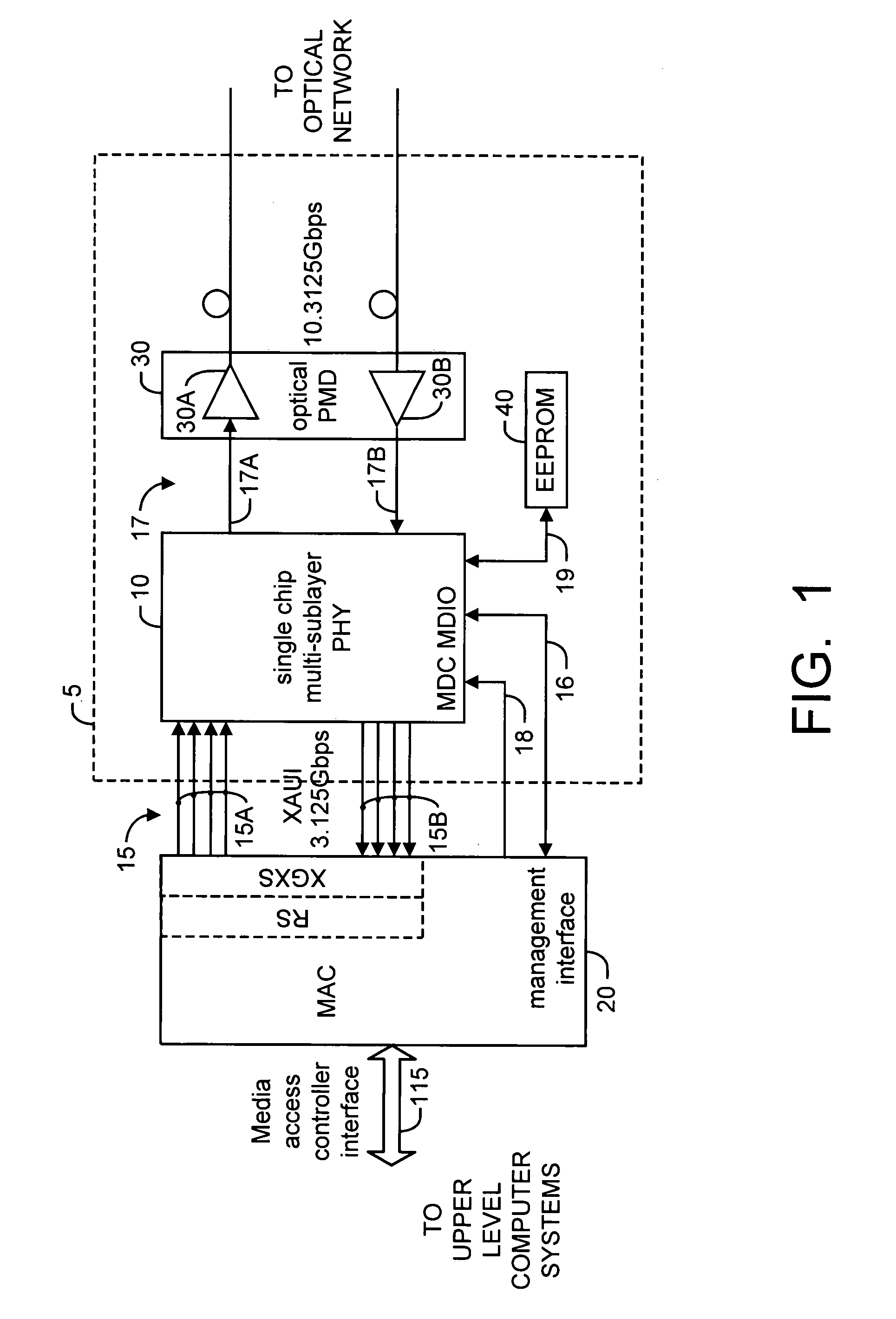

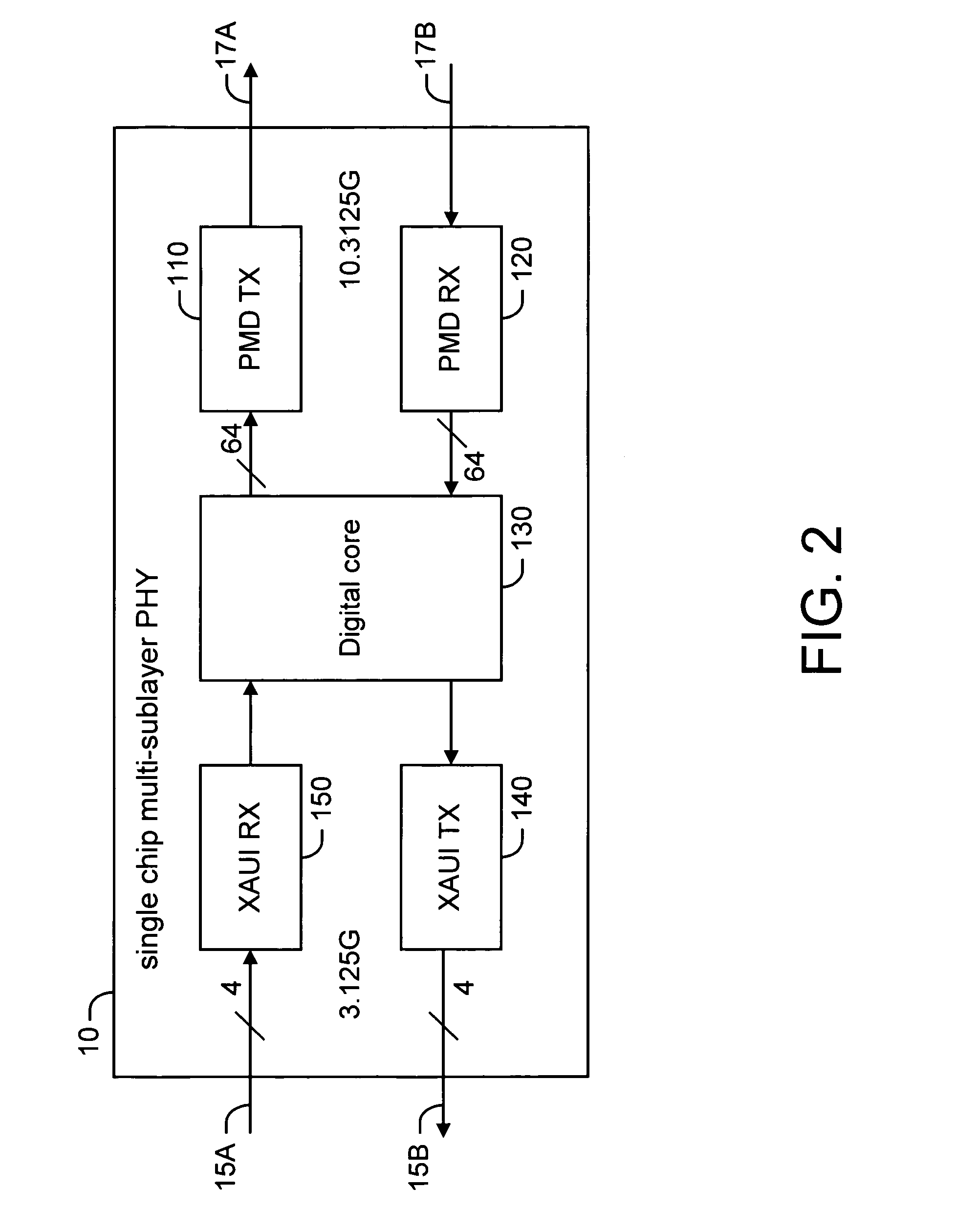

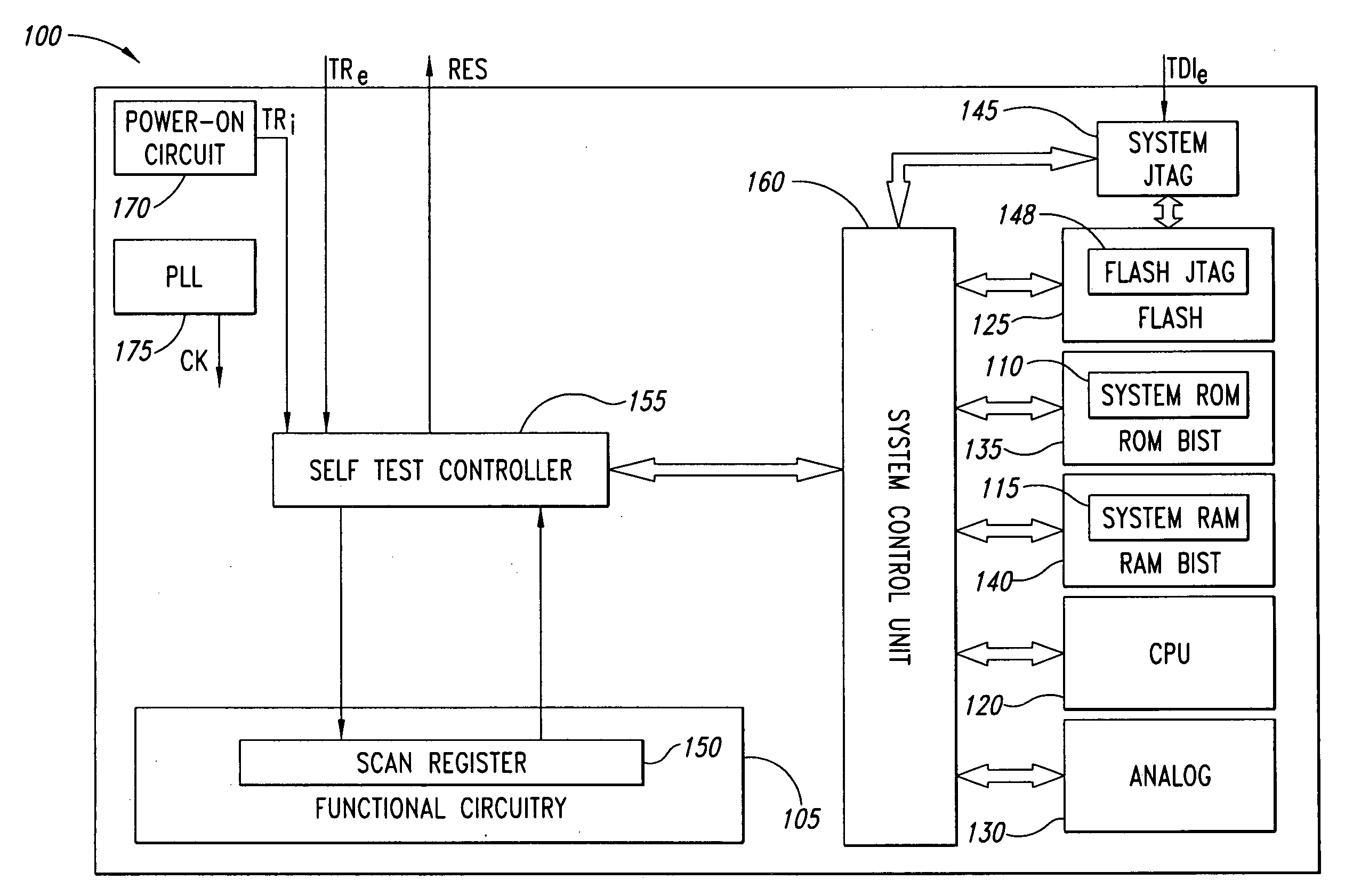

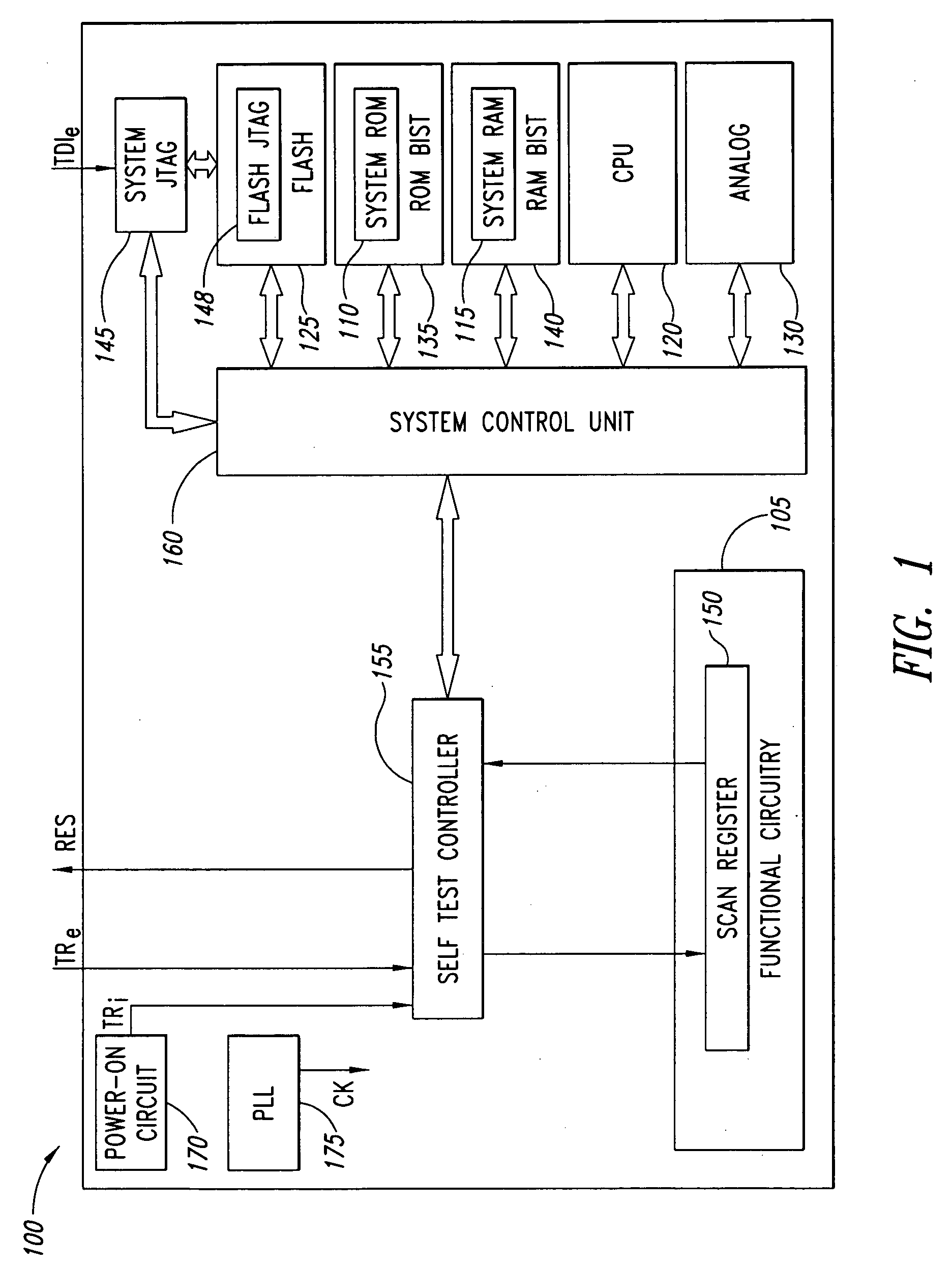

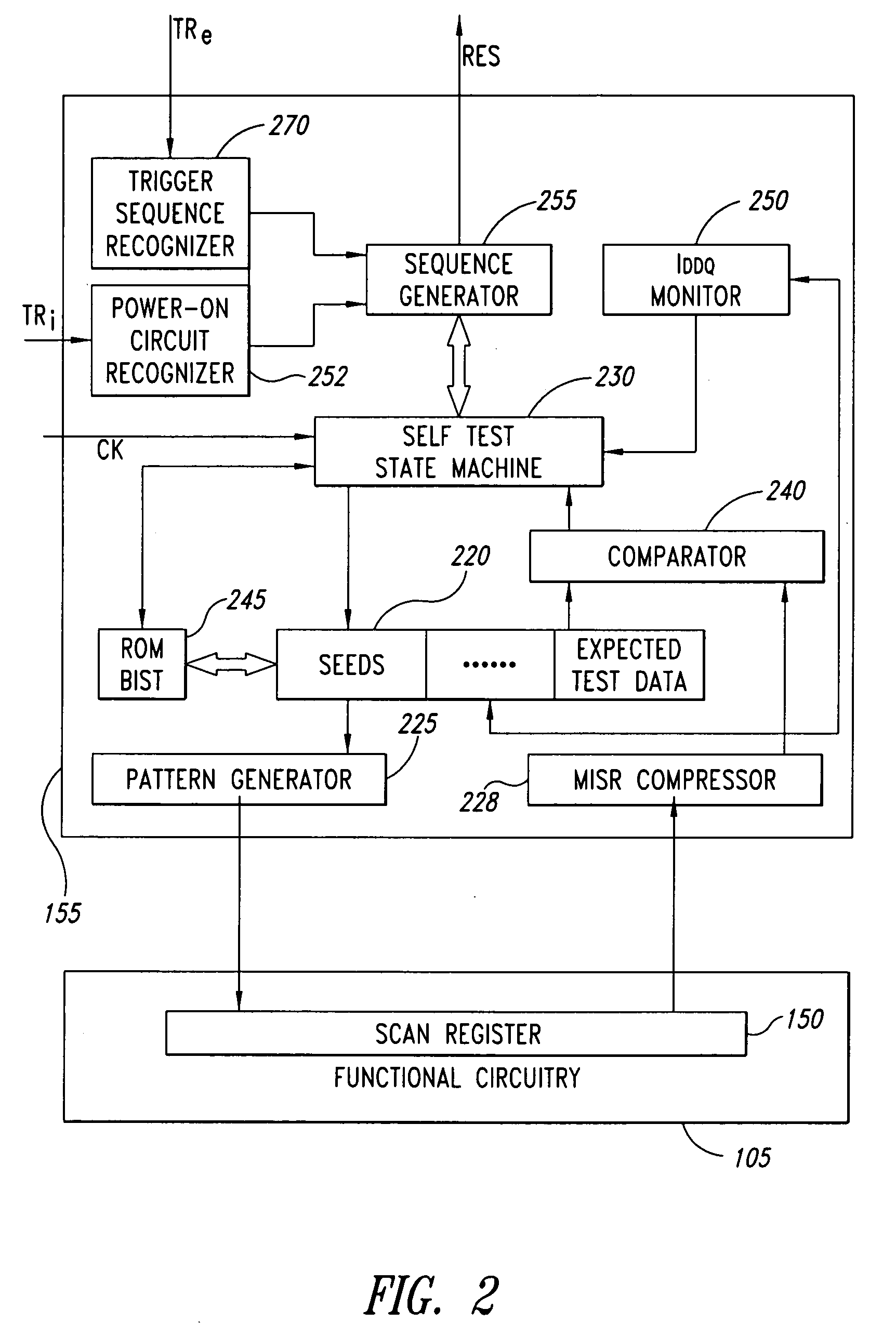

On-chip standalone self-test system and method

A method and system are disclosed for providing standalone built-in self-testing of a transceiver chip. The transceiver chip includes packet generators for generating test packets and packet checkers for comparing received packets with expected packets. The transceiver chip may be configured for testing through at least two wraparound test paths—a first test path that includes an elastic FIFO of a transmit path of the transceiver chip, and a second test path that includes an elastic FIFO of a receive path of the transceiver chip. During testing, the test packets are generated by packet generators within the transceiver chip and routed through the at least two wraparound test paths to packet checkers within the same transceiver chip. The packet checkers compare the returned packets to the expected packets. If the returned packets are inconsistent with the expected packets, the transceiver chip is defective.

Owner:AVAGO TECH WIRELESS IP SINGAPORE PTE

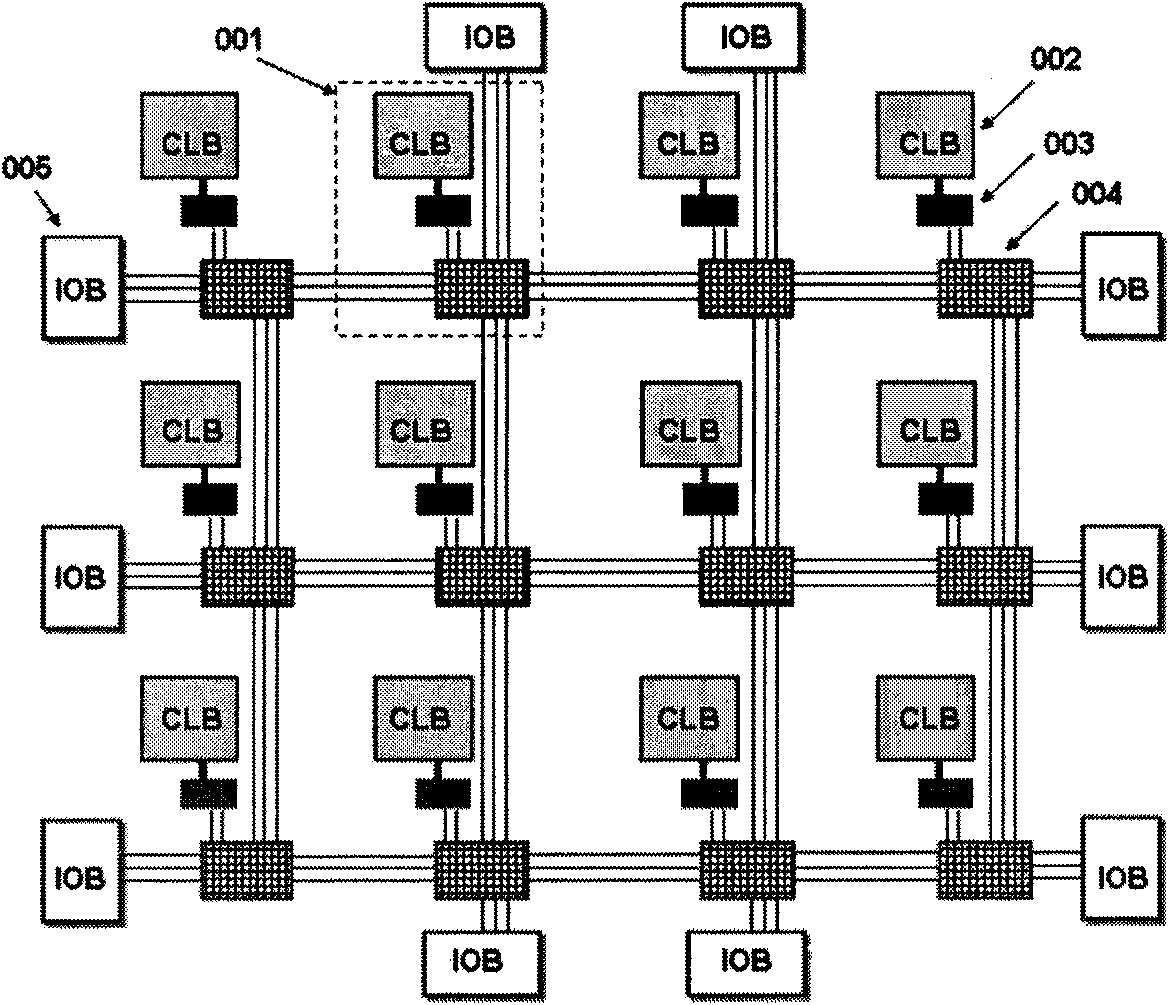

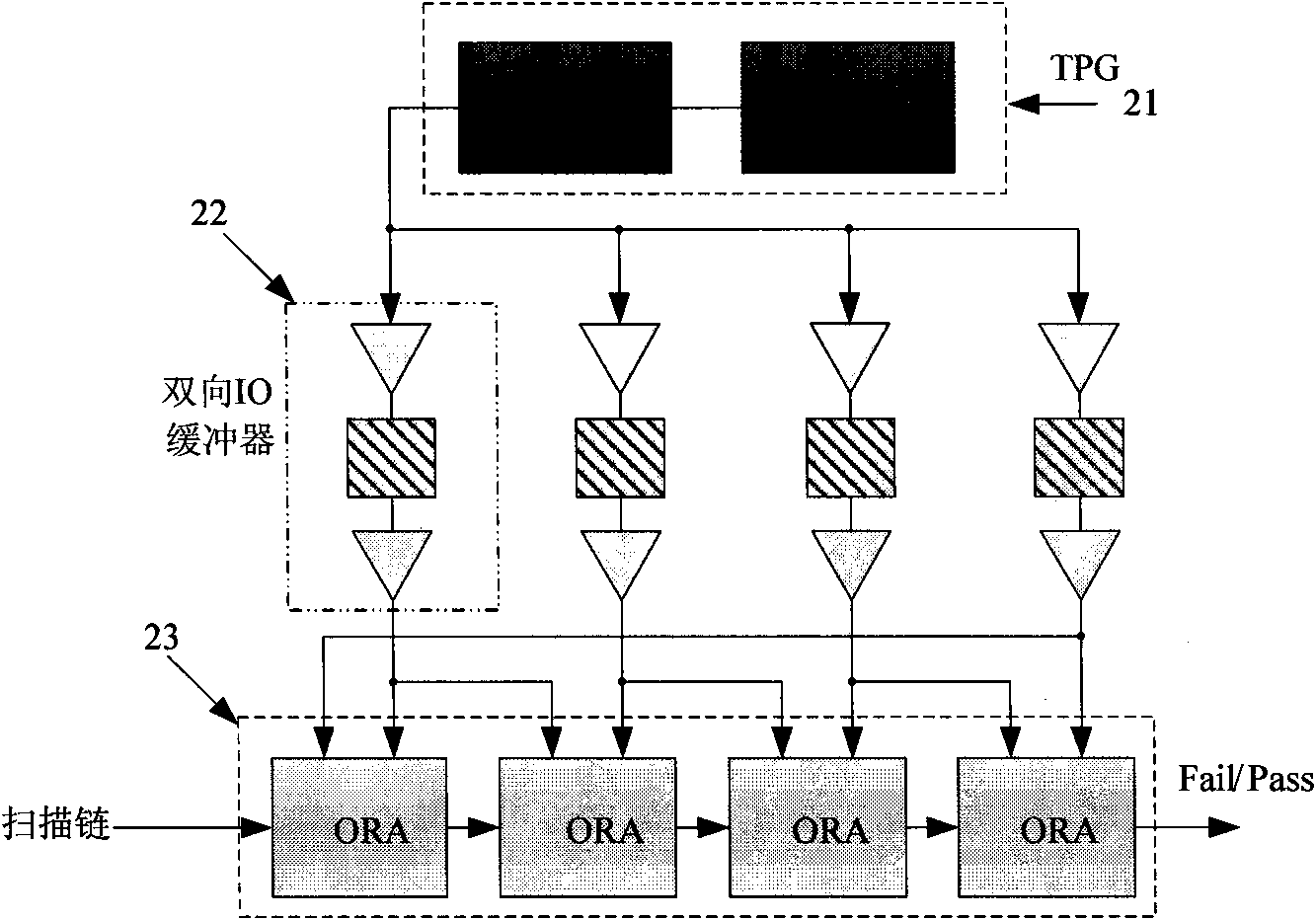

Built-in self-testing method of FPGA input/output module

The present invention provides a built-in self-testing method of FPGA input / output module. Firstly all input / output modules in FPGA are configured to that a bidirectional IO buffer is used as a circuit to be tested. The logical resource of middle part of FPGA device is configured to a test vector generating circuit. The logical resource surrounding the IO buffer is configured to an output response analysis circuit of scanning chain structure. In testing, the test vector generating circuit generates a pseudo-random exhaustive vector for exerting a test pattern for each circuit to be tested; after executing the test vector, actuating the operation of scanning chain of output response analysis circuit, outputting the built-in self-testing result which is configured this time by the input / output module in the control of test clock by the output response analysis circuit until when the test covers all resources in the input / output module. The method of the invention has the following advantages: simplified built-in self-testing result retrieval mode, reduced test configuration number of times, reduced test cost and increased test efficiency under the precondition of guaranteeing 100% test coverage rate.

Owner:BEIJING MXTRONICS CORP +1

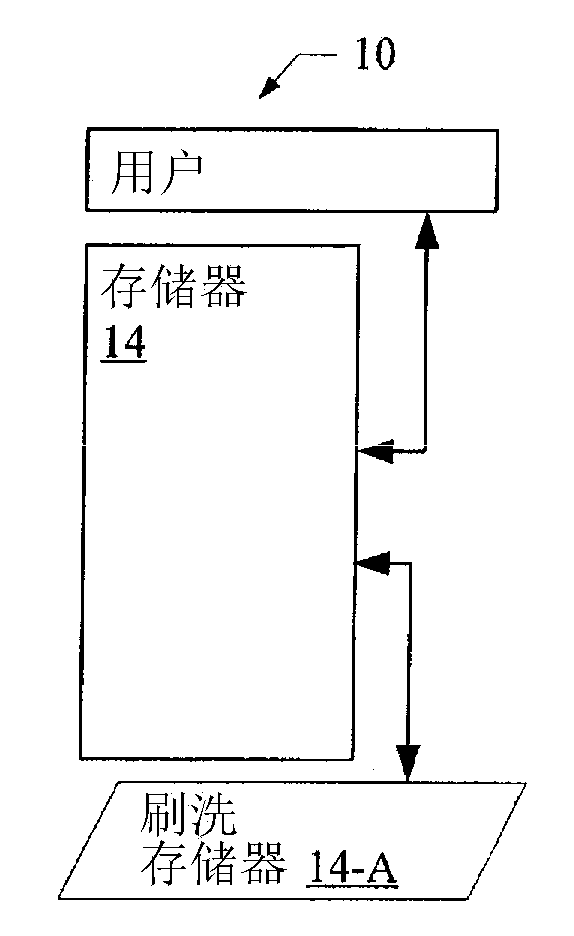

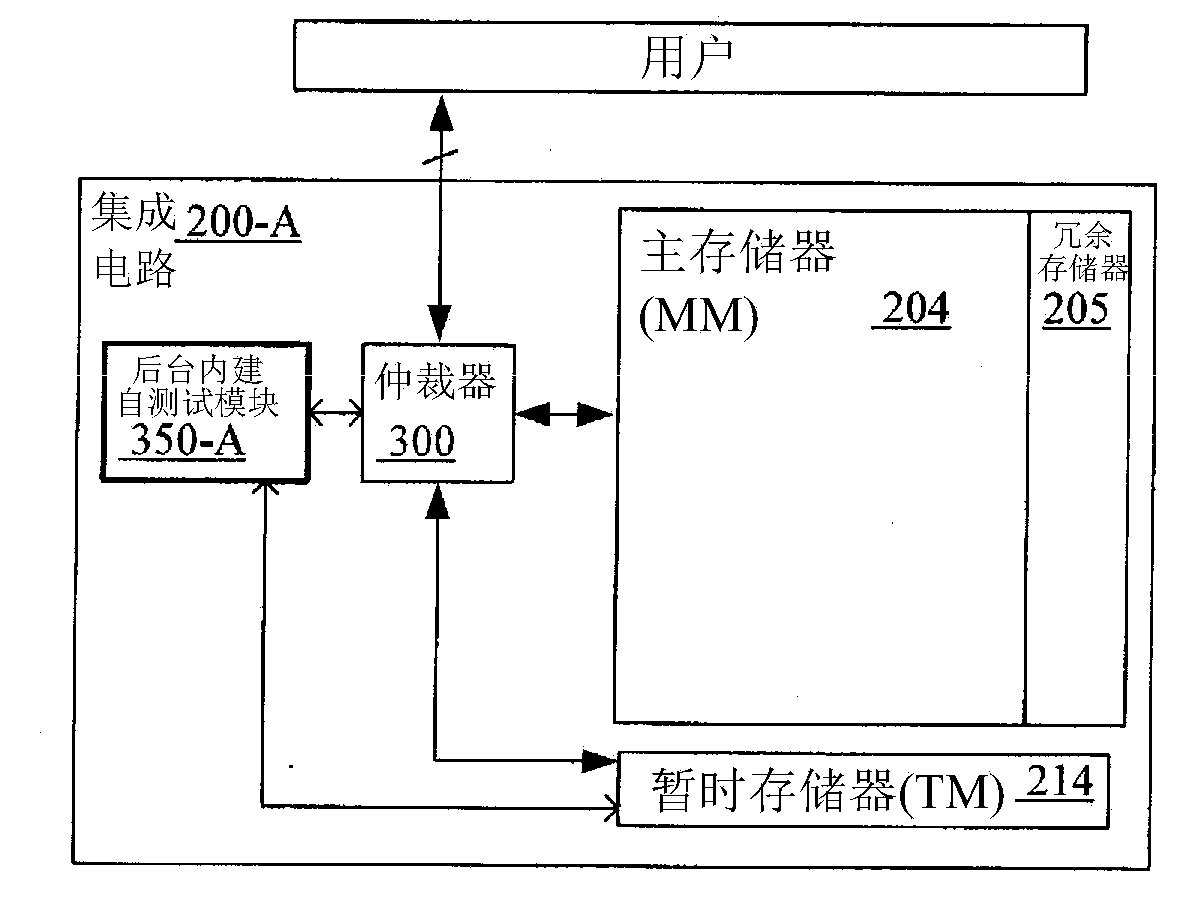

Built in self-testing and repair device and method

A memory device with background built-in self-testing (BBIST) includes a plurality of memory blocks; a memory buffer to offload data from one of the plurality of memory blocks temporarily; and a memory block stress controller to control a stress test applied to the one of the memory blocks when the data is temporarily offloaded on the memory buffer. The stress test tests for errors in the one of the plurality of the memory blocks.

Owner:MOSYS INC

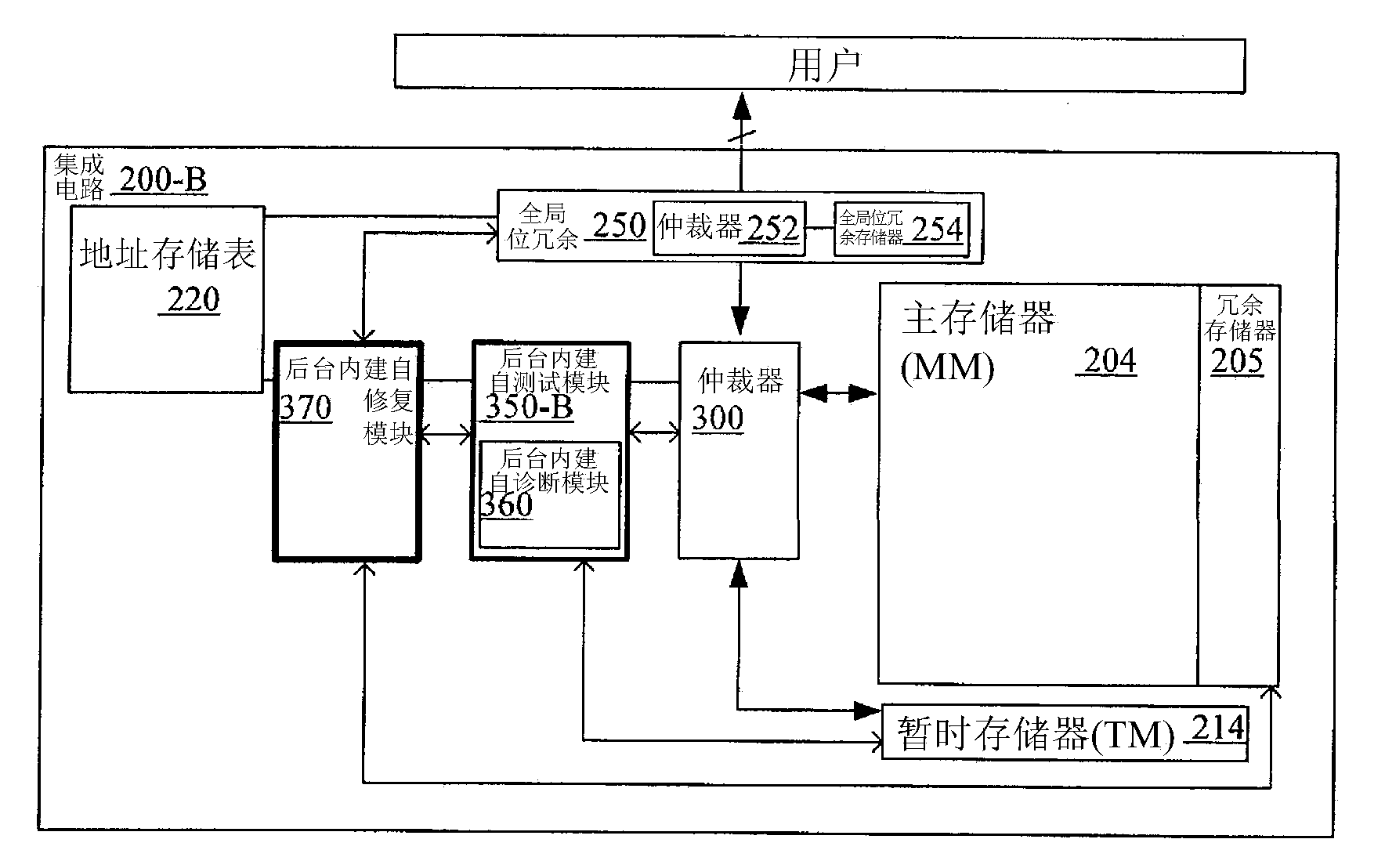

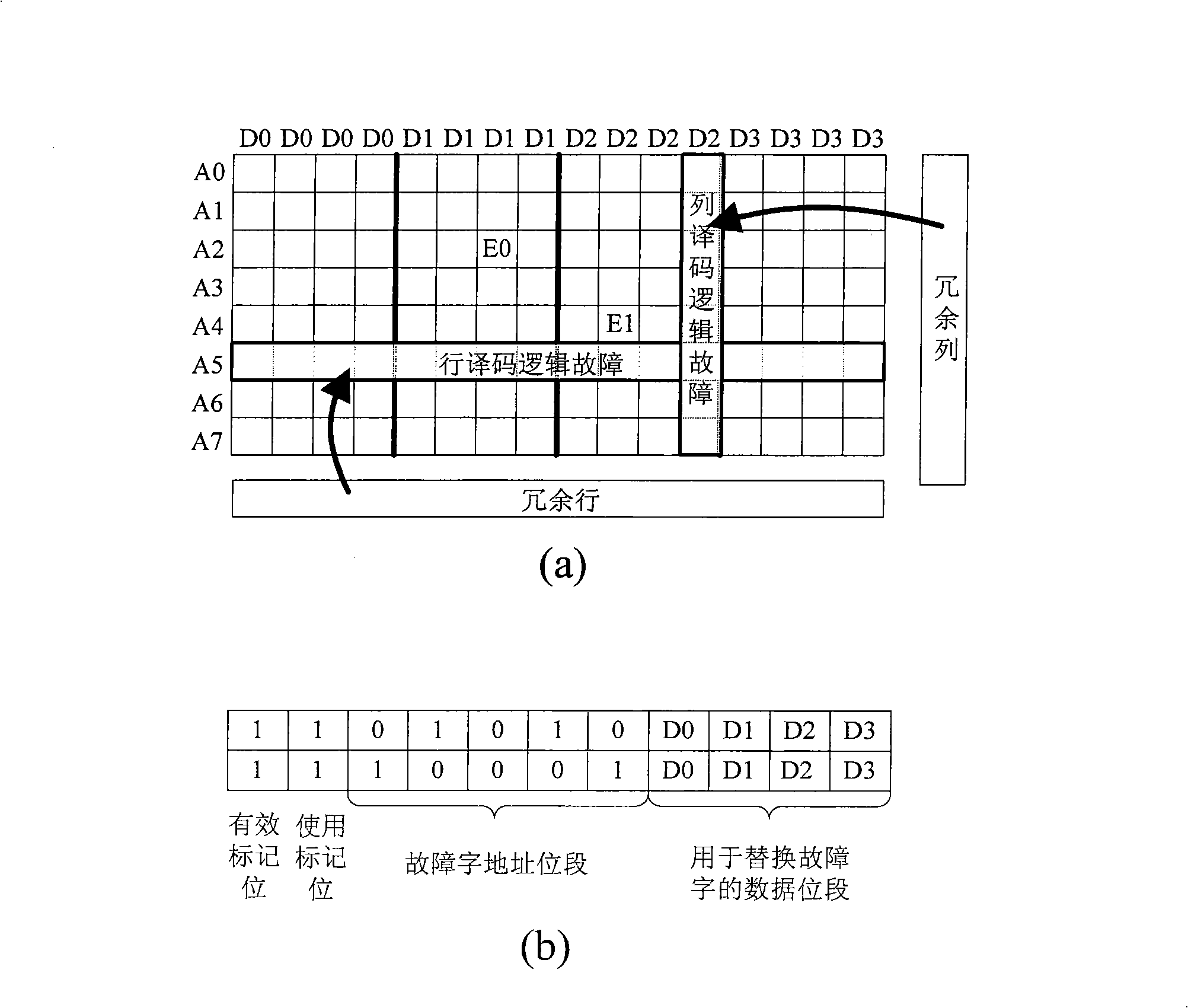

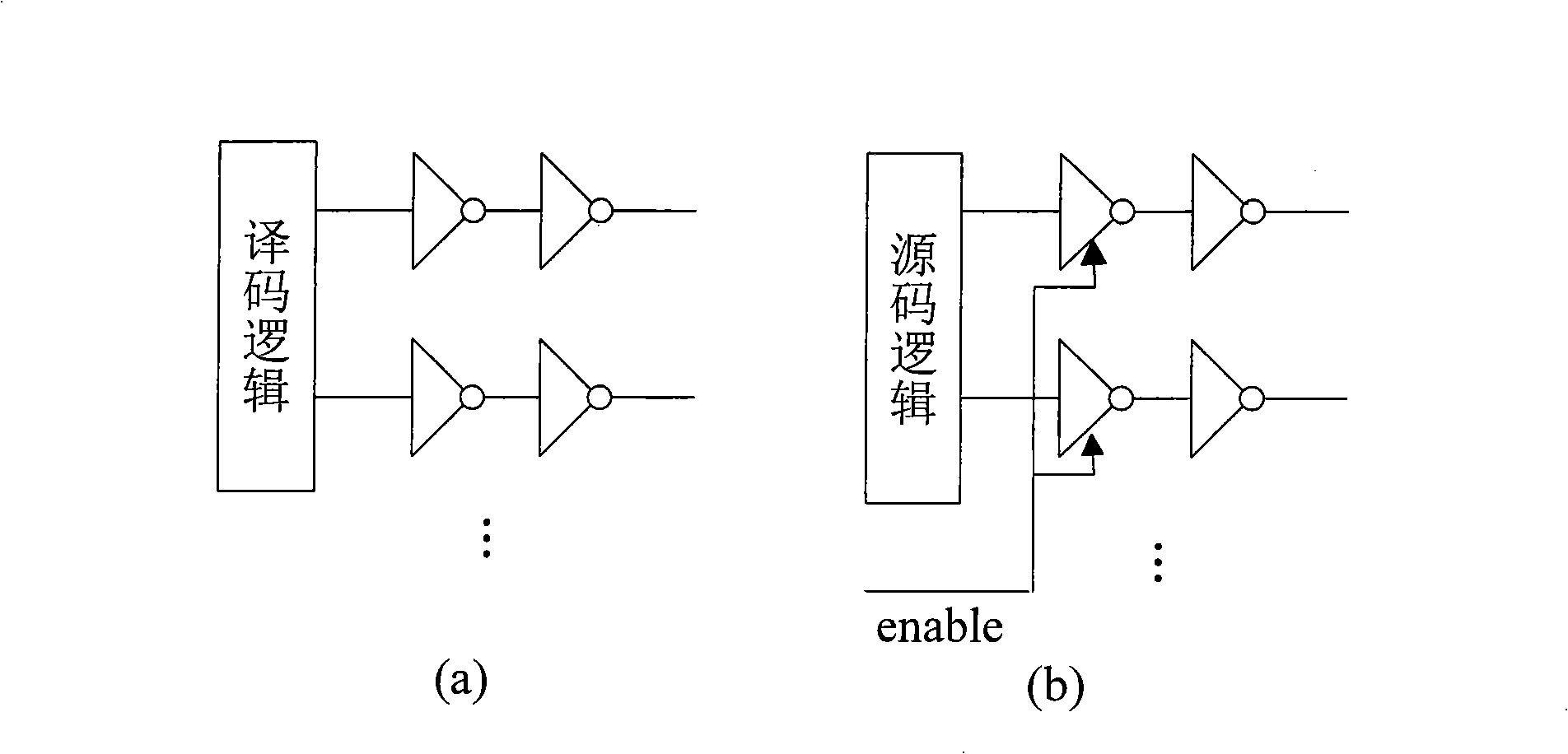

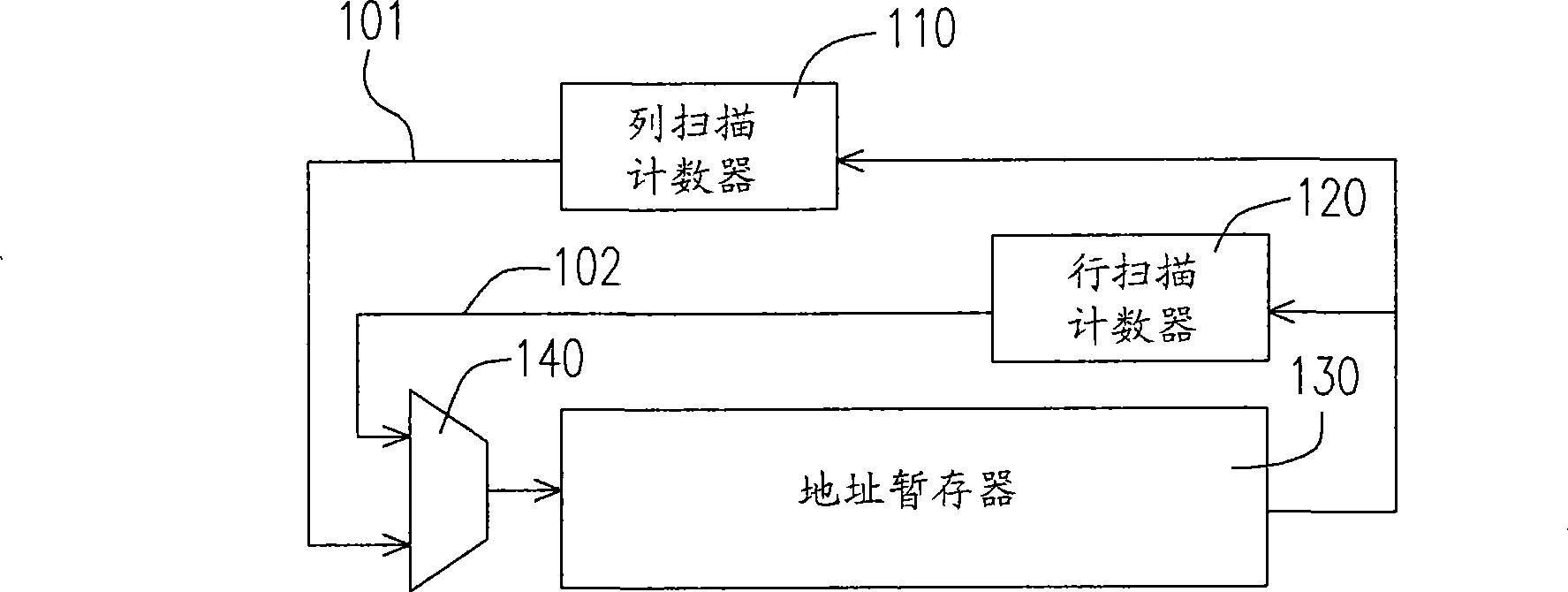

Built-in self-repairing system and method for memory

The invention provides a memory built-in self-repairing system which comprises a built-in self-testing circuit, a built-in self-diagnostic circuit, a built-in self-repairing circuit and a redundant row / column and is characterized in that: the built-in self-repairing circuit comprises a word repairing circuit provided with a redundant content addressable memory which is specially used for repairing the unit failures of a main memory; the redundant row / column is specially used for repairing the coding failures of the main memory. The invention also provides a corresponding built-in self-repairing method. The built-in self-repairing system and the built-in self-repairing method have the advantages of fining the granularity of redundant resources, increasing the utilization rate of the memory redundant resources, promoting the reliability of the memory after repairing by avoiding failed units with accessing defects, having simple default diagnosis and redundancy allocation algorithm that are easy to realize, making full use of the redundant resources and having better repairing effect.

Owner:INST OF COMPUTING TECH CHINESE ACAD OF SCI

Predistortion calibration and built in self testing of a radio frequency power amplifier using subharmonic mixing

ActiveUS8463189B2Efficient couplingHigh sensitivityTransmitters monitoringPower amplifiersHarmonicEngineering

A novel and useful apparatus for and method of predistortion calibration and built-in self testing (BIST) of a nonlinear digitally-controlled radio frequency (RF) power amplifier (DPA) using subharmonic mixing. The RF power amplifier output is temporarily coupled into the frequency reference (FREF) input and the phase error samples generated in the phase locked loop (PLL) are then observed and analyzed. The digital predistortion and BIST mechanisms process the phase error samples to calibrate and test the DPA in the transmitter of the Digital RF Processor (DRP). The invention enables the characterization of nonlinearities, the configuration of internal predistortion, as well as the testing of the transmitter's analogRF circuitry, thereby eliminating commonly employed RF performance testing using high-cost test equipment and associated extended test times.

Owner:TEXAS INSTR INC

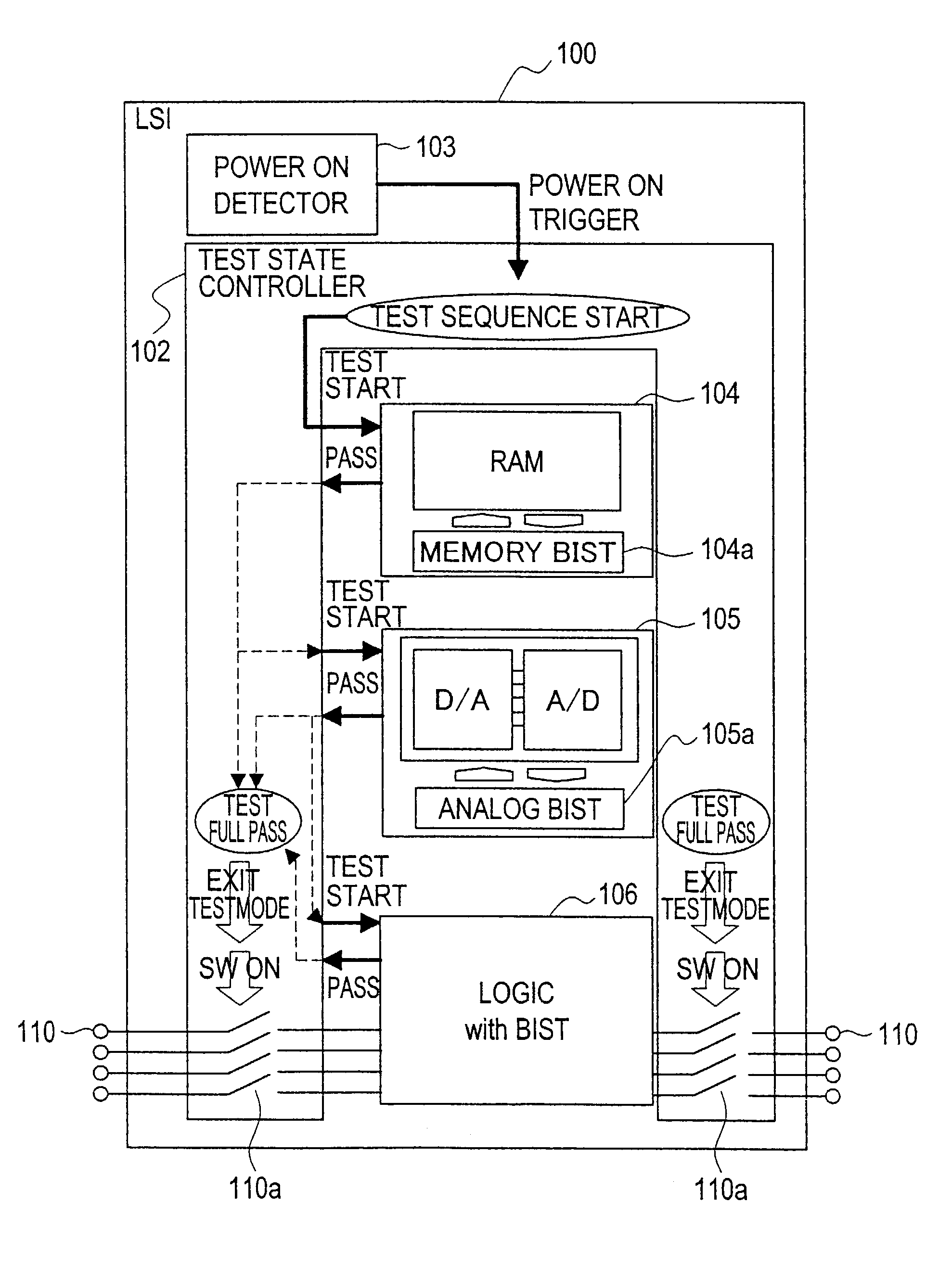

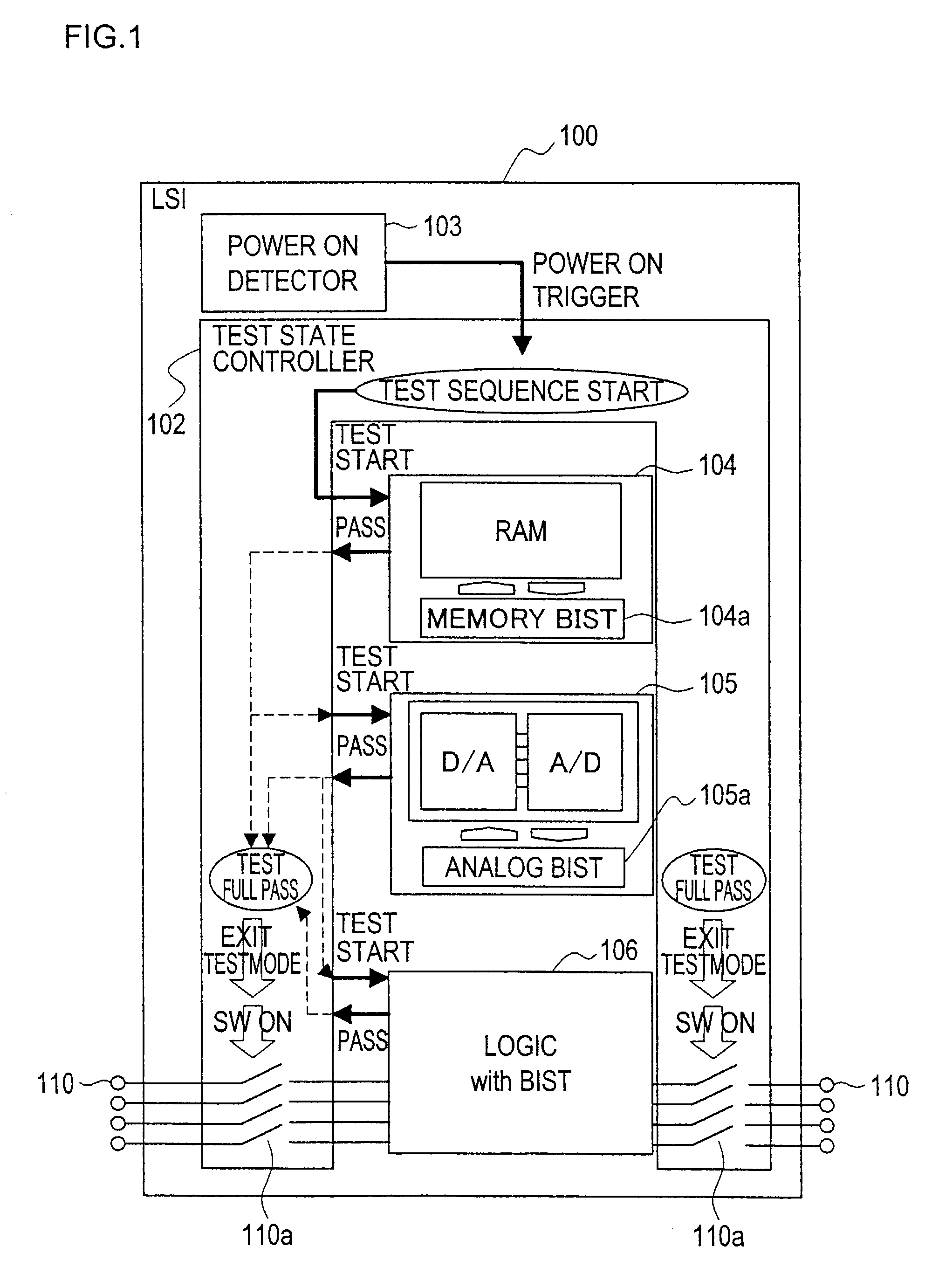

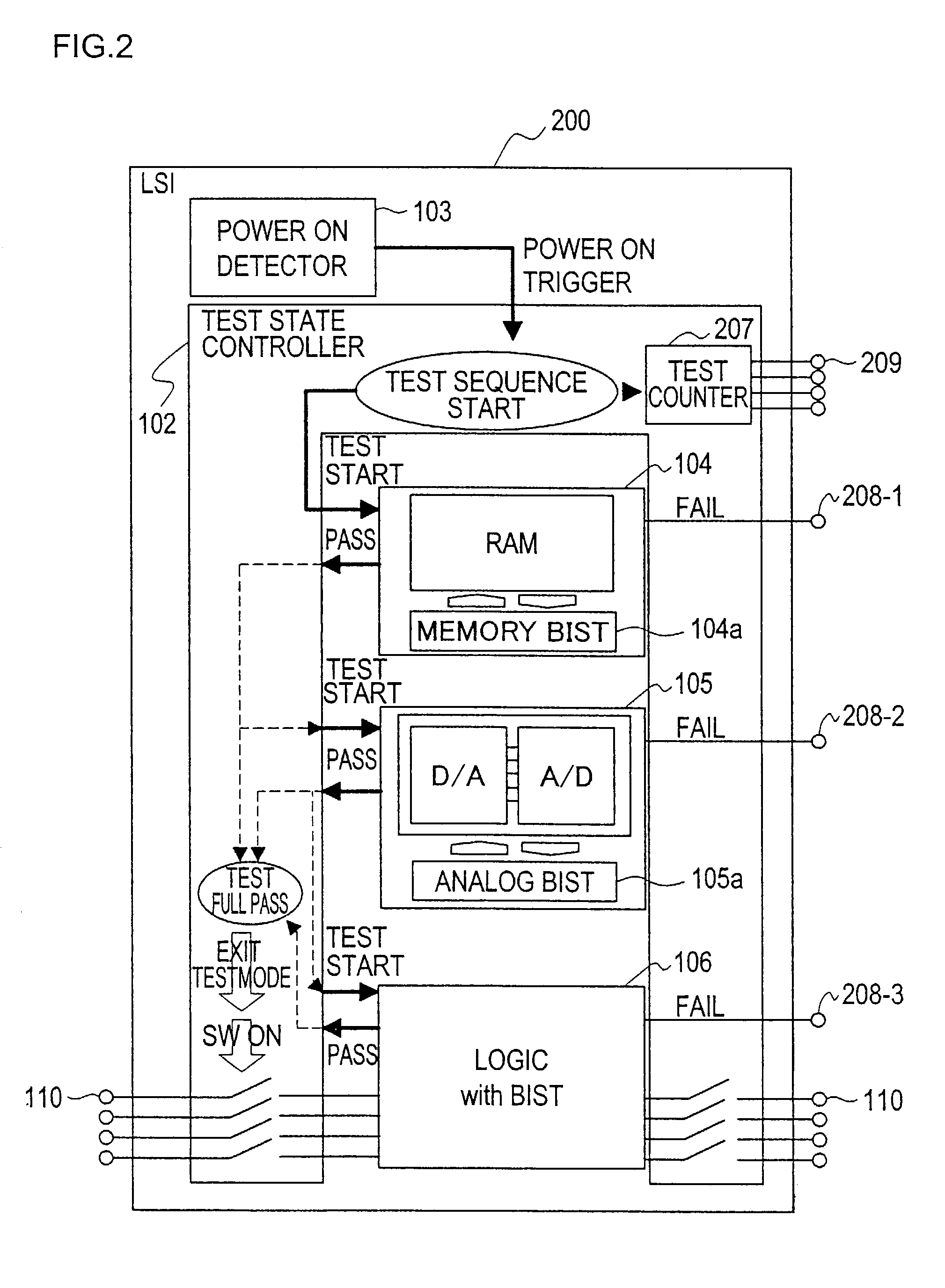

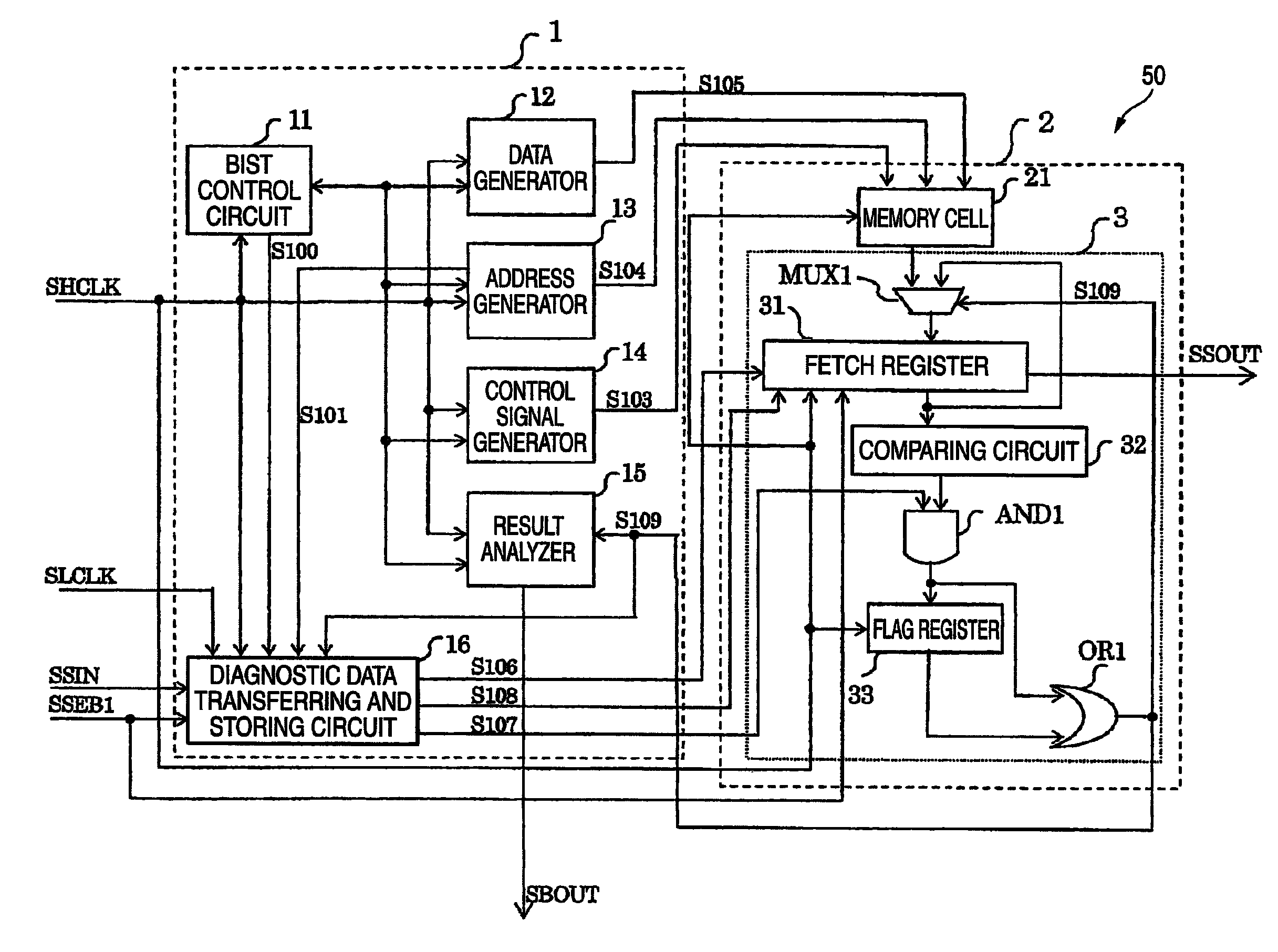

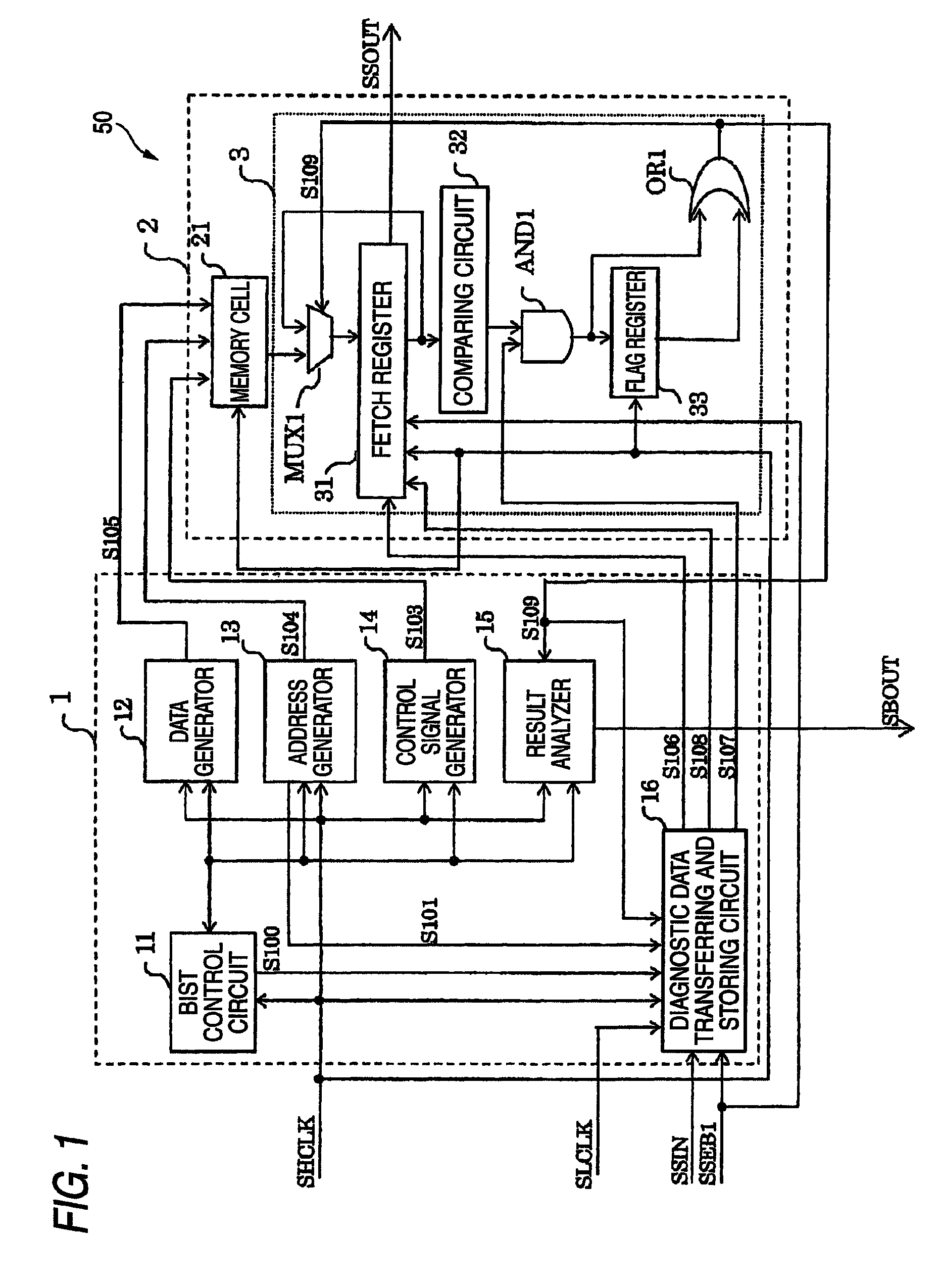

Semiconductor integrated circuit having functional modules each including a built-in self testing circuit

ActiveUS7096386B2Improve accuracyReduce problem sizeDigital circuit testingError detection/correctionComputer moduleEngineering

A semiconductor integrated circuit that allows a self test of an integrated circuit built into a system to be conducted through a circuit structure on a smaller scale and achieves an improvement in the accuracy of the self test is provided. An integrated circuit includes functional modules respectively provided with built-in self testing circuits and a self test control circuit that individually controls the built-in self testing circuits. This structure allows self tests to be automatically performed within the integrated circuit without requiring external components. The scale of the system having the built-in integrated circuit may thus be reduced. Also, by building up the built-in self testing circuits in the individual functional modules to a sufficient degree, a high-quality self test comparable to that conducted prior to shipment can be performed even after the integrated circuit is built into the system.

Owner:LAPIS SEMICON CO LTD

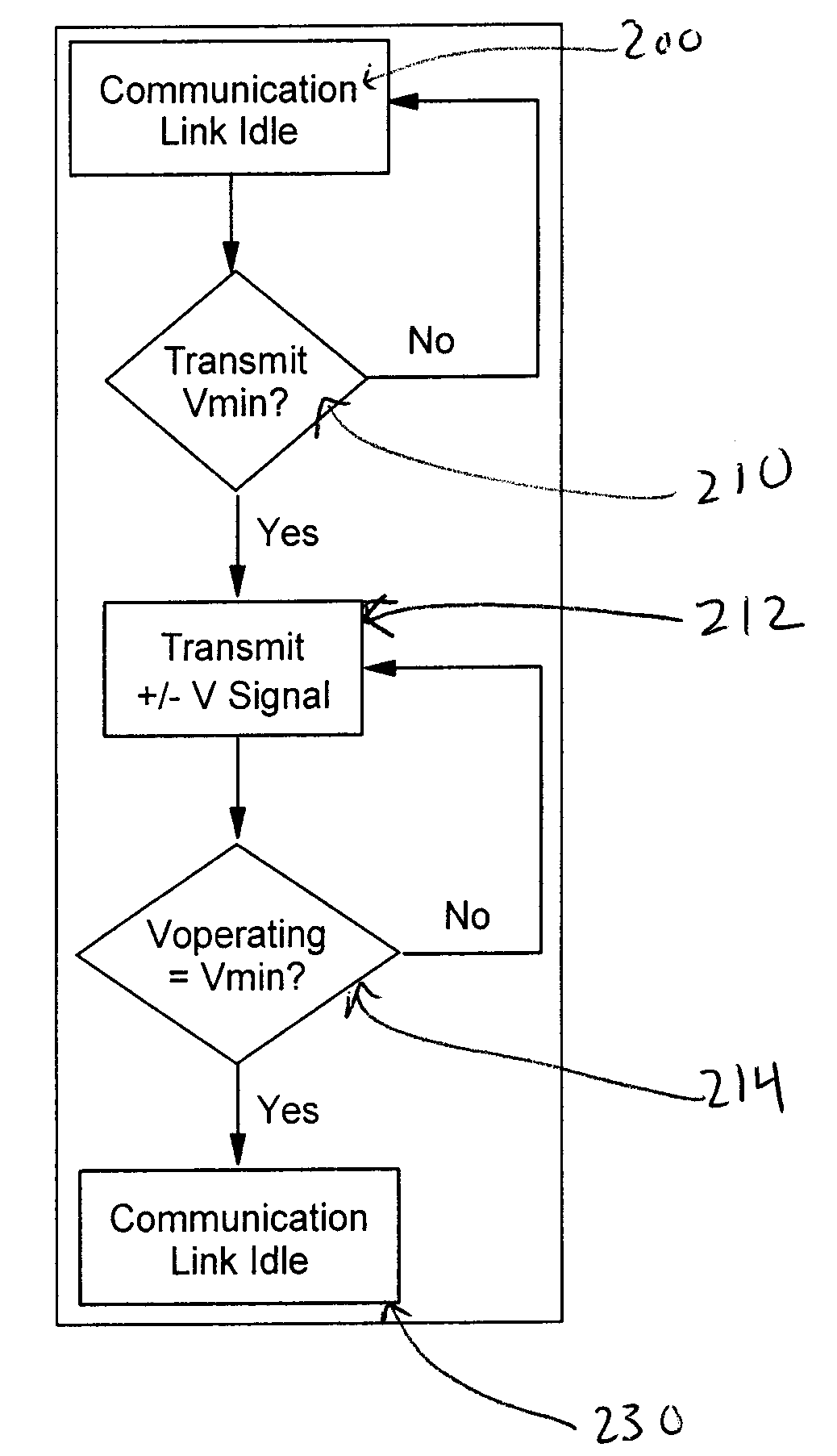

System and method of controlling power consumption in an electronic system by applying a uniquely determined minimum operating voltage to an integrated circuit rather than a predetermined nominal voltage selected for a family of integrated circuits

A method and apparatus for adaptively adjusting the operating voltage of an integrated circuit in response to tester-to-system variations, worst-case testing techniques, process variations, temperature variations, or reliability wearout mechanisms. The minimum operating voltage of an integrated circuit is determined either during external testing of the integrated circuit or during built-in-self-testing. The minimum operating voltage is transmitted to a variable voltage regulator where it is used to set the output of the regulator. The output of the regulator supplies the integrated circuit with its operating voltage. This technique enables tailoring of the operating voltage of integrated circuits on a part-by-part basis which results in power consumption optimization by adapting operating voltage in response to tester-to-system variations, worst-case testing techniques, process variations, temperature variations or reliability wearout mechanisms. Alternatively, the invention enables adaptive adjustment of the operating frequency of an integrated circuit. The invention enables system designers to adaptively optimize either system performance or power consumption on a part-by-part basis in response to tester-to system variations, worst-case testing techniques, process variations, temperature variations or reliability wearout mechanisms.

Owner:INT BUSINESS MASCH CORP

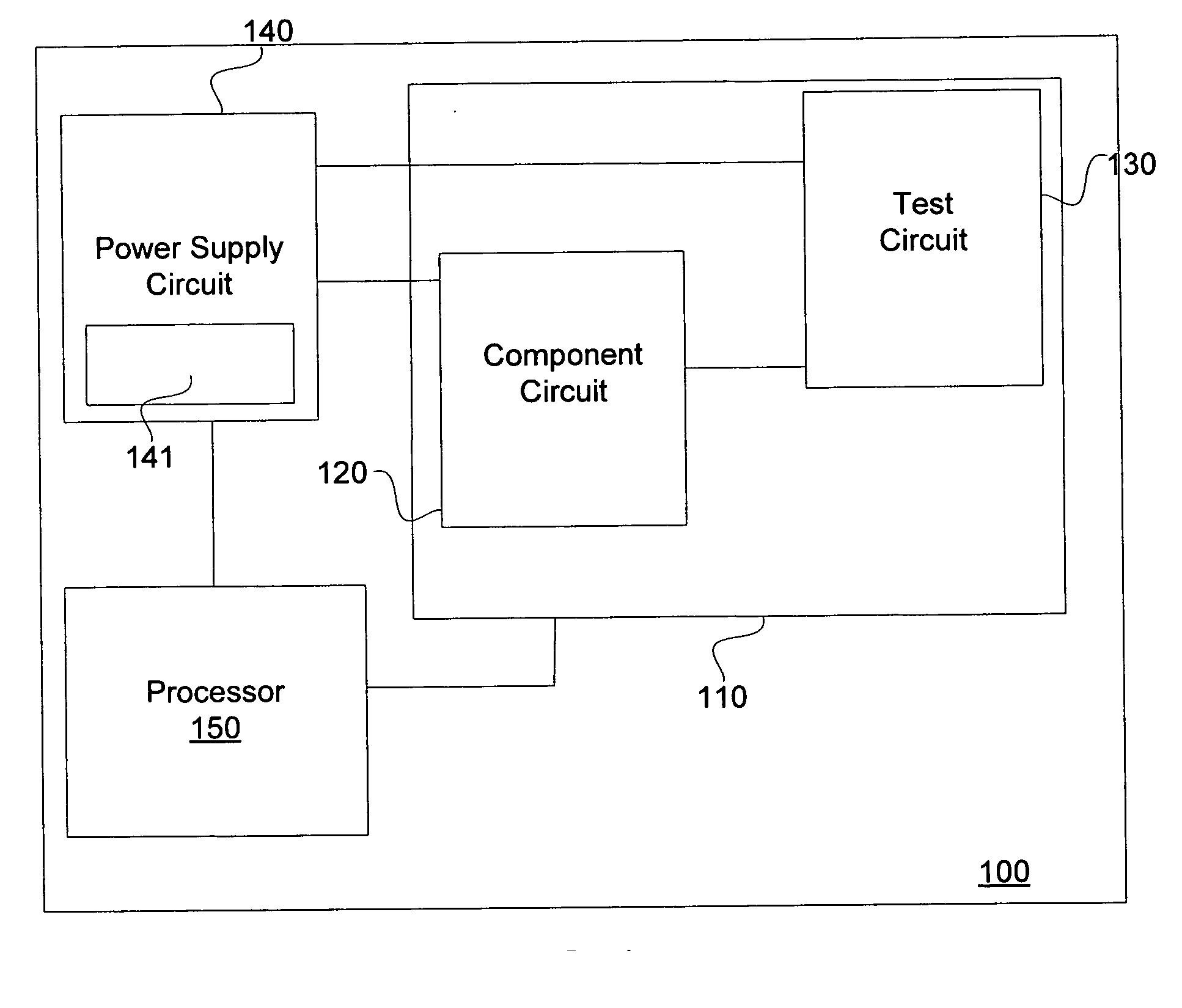

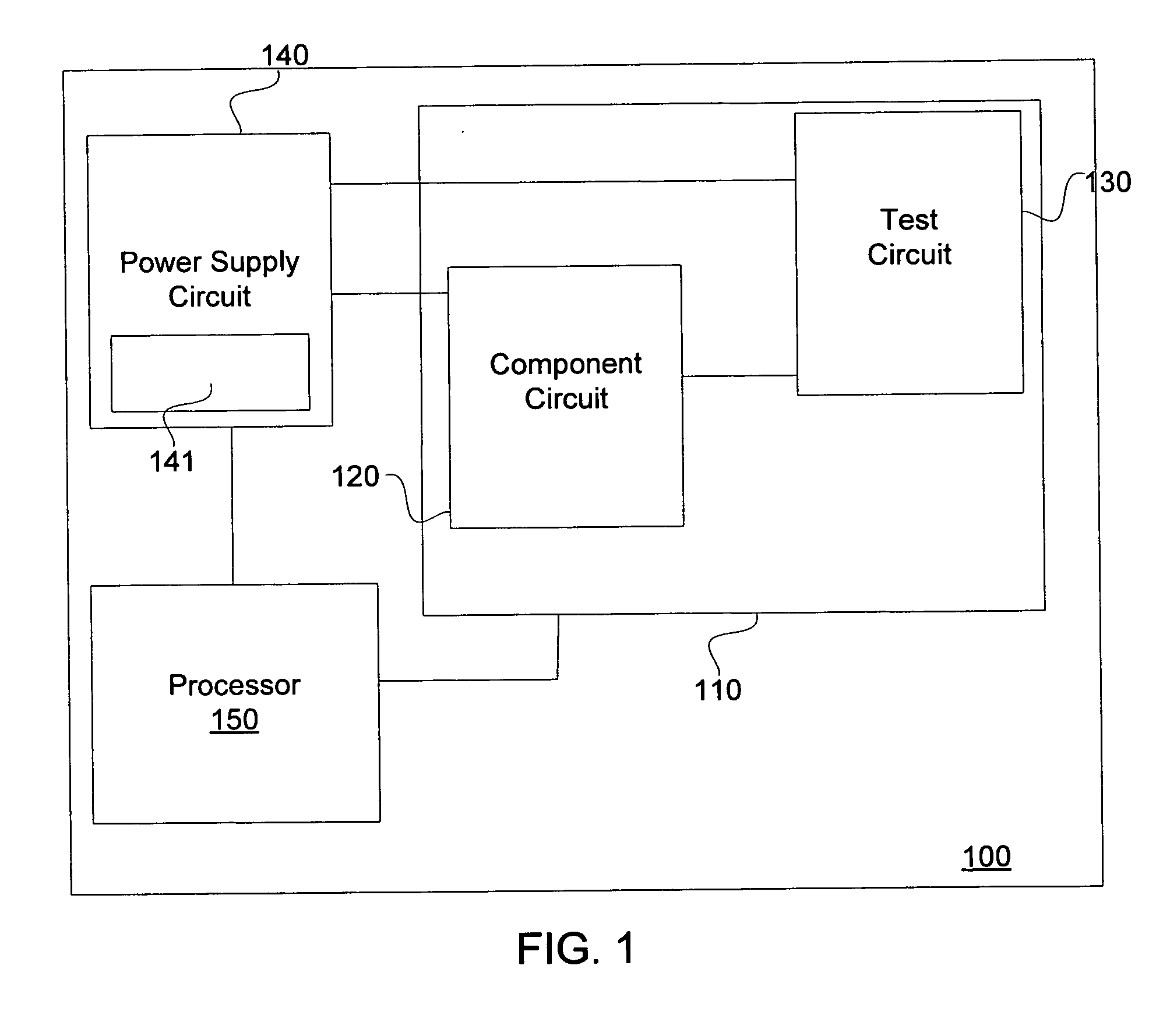

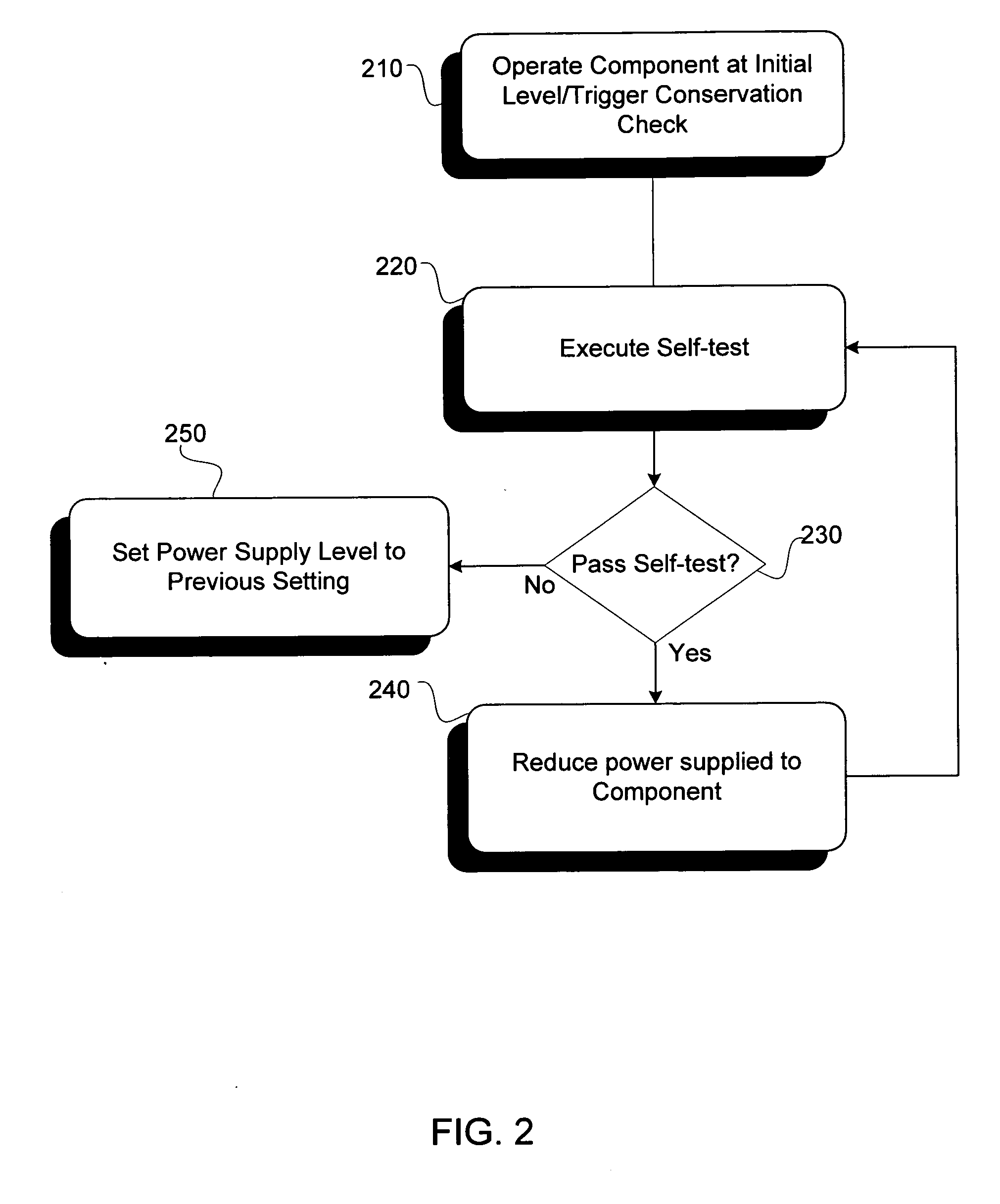

System and method for managing power consumption

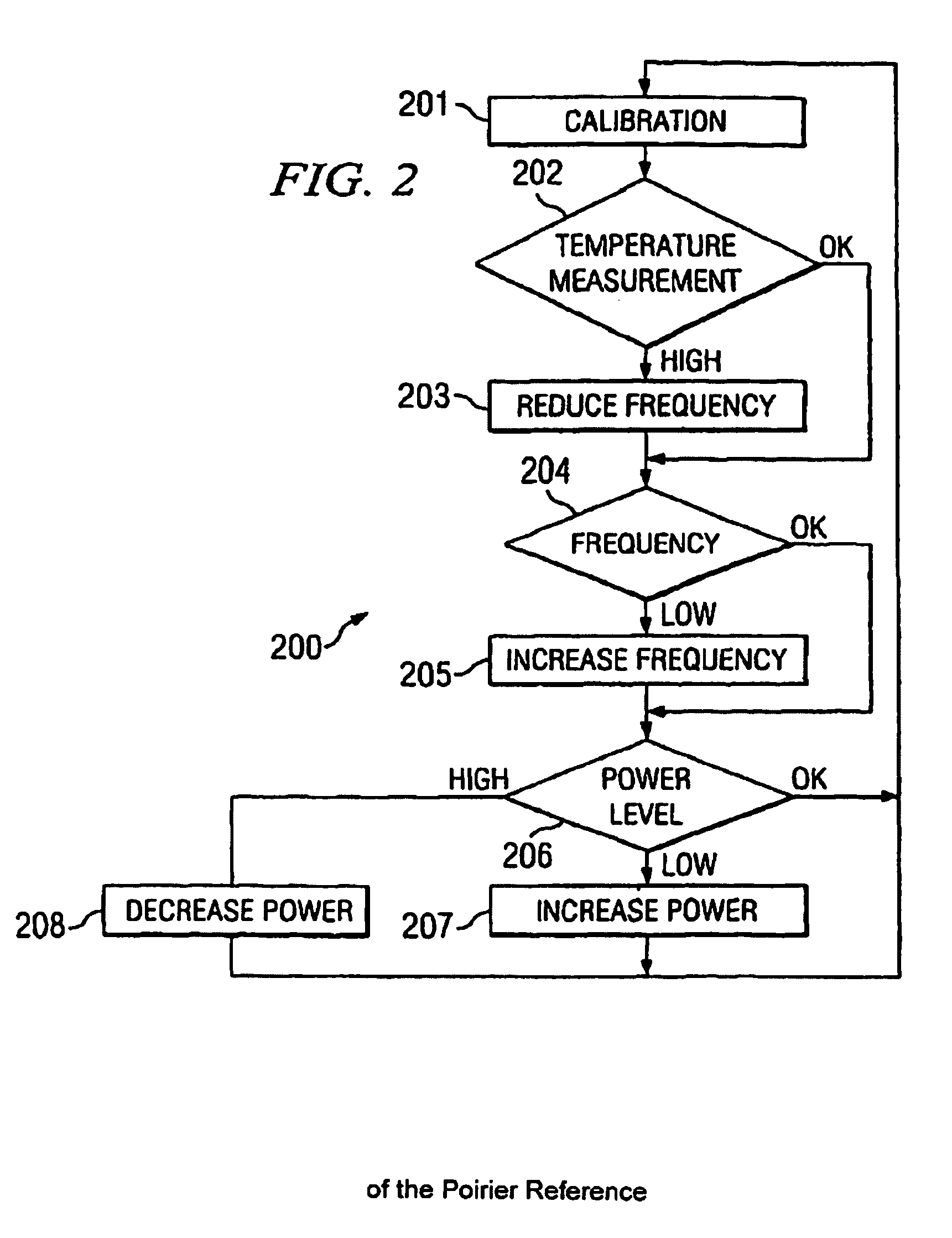

InactiveUS7539880B2Energy efficient ICTVolume/mass flow measurementBuilt in self testingElectric power

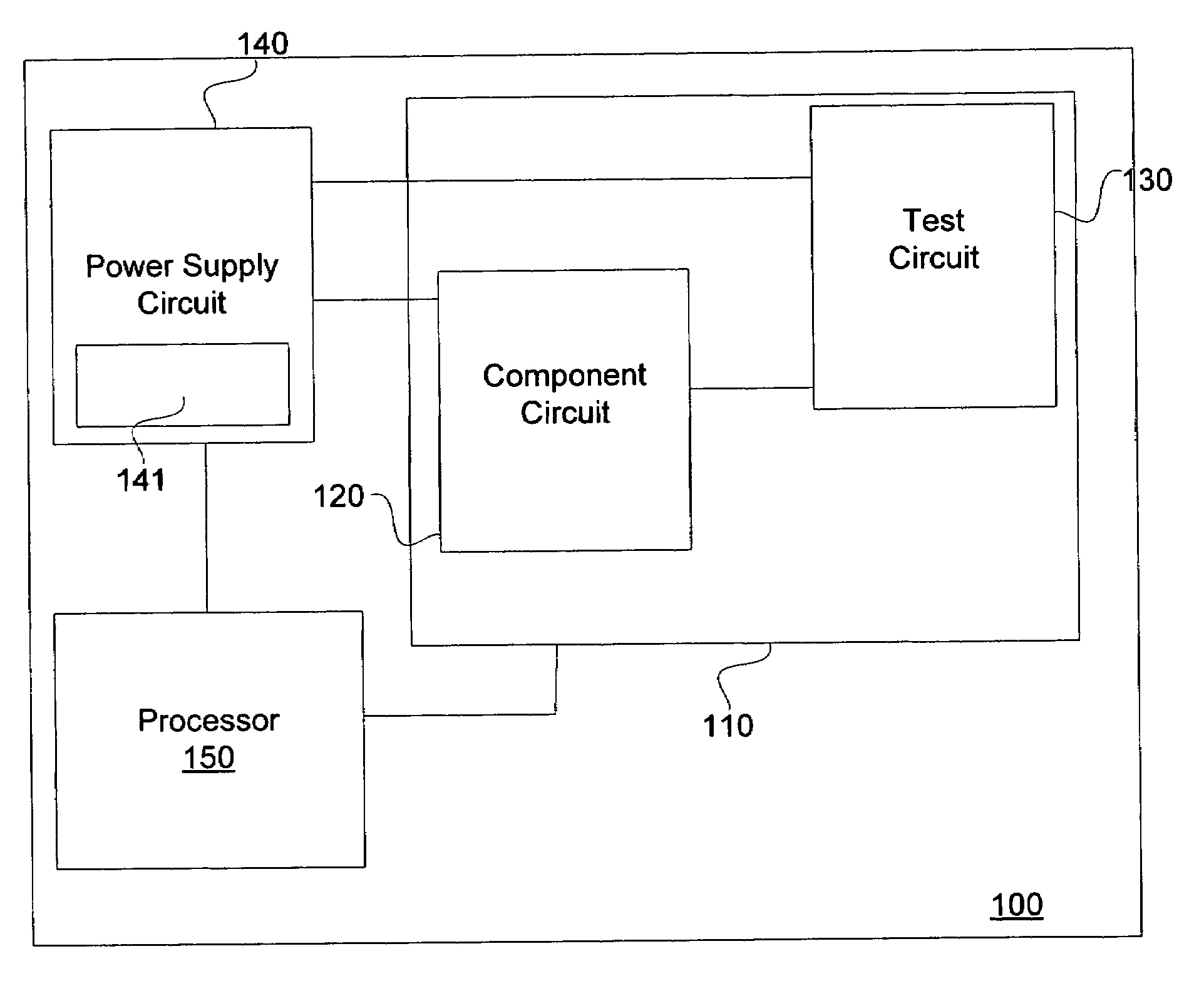

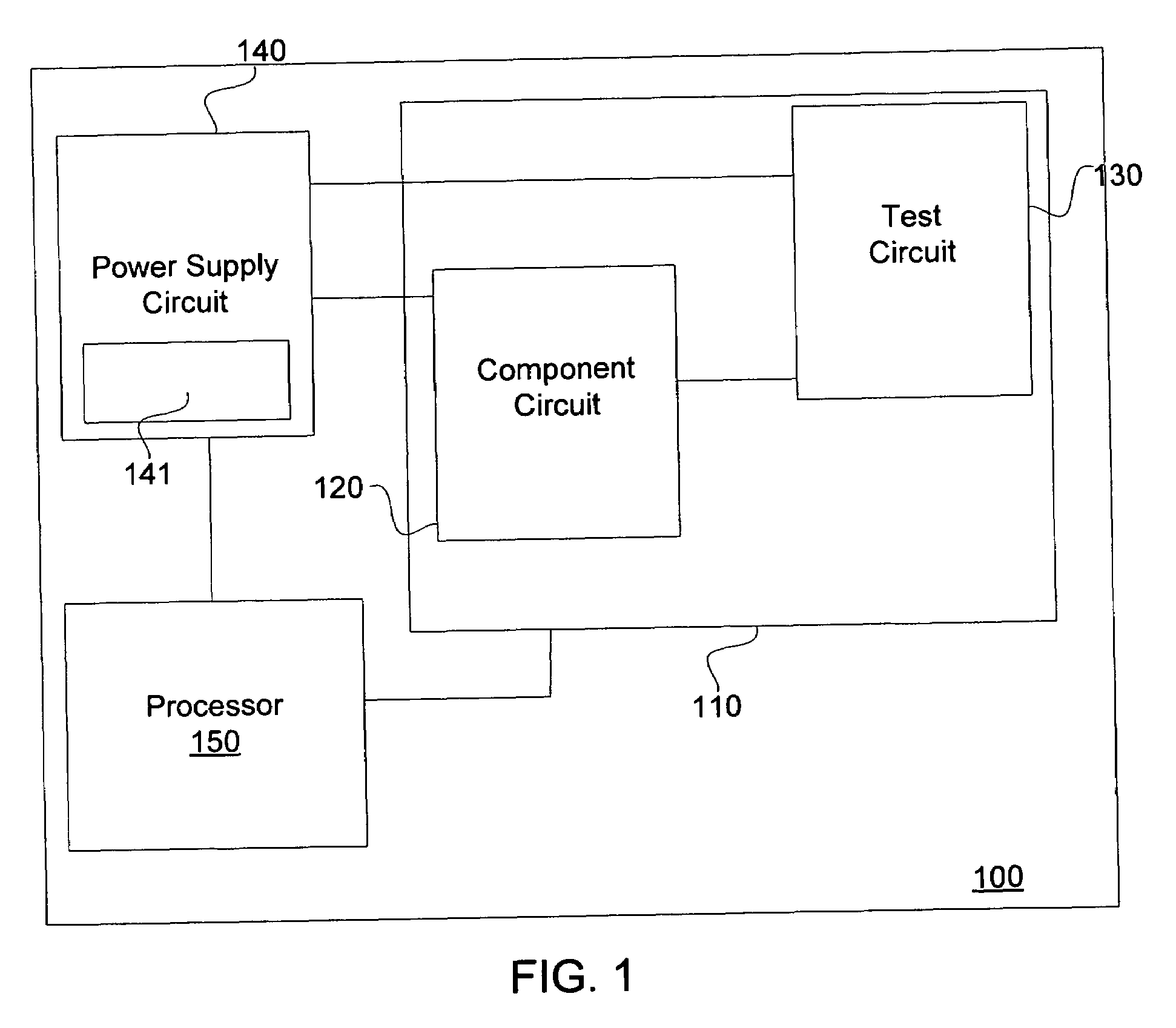

An electronic circuit having built-in self testing capabilities for optimizing power consumption. Typically, the electronic circuit includes a component circuit that operates at some known or unknown optimal operating power level. Further, the electronic circuit includes a power supply coupled to the component circuit such that the power supply provides power to the component circuit. Further yet, the electronic circuit includes a test circuit coupled to the component circuit and coupled to the power supply. The test circuit is operable to monitor the power supplied to the component circuit and operable to control the power supply. In an iterative manner, the test circuit reduces the power supplied to the component circuit until the power supplied to the component circuit is operating at the optimal operating power level.

Owner:BROADCOM INT PTE LTD

Integrated device with an improved BIST circuit for executing a structured test

ActiveUS20050034041A1Digital circuit testingError detection/correctionComputer hardwareBuilt in self testing

Owner:STMICROELECTRONICS SRL

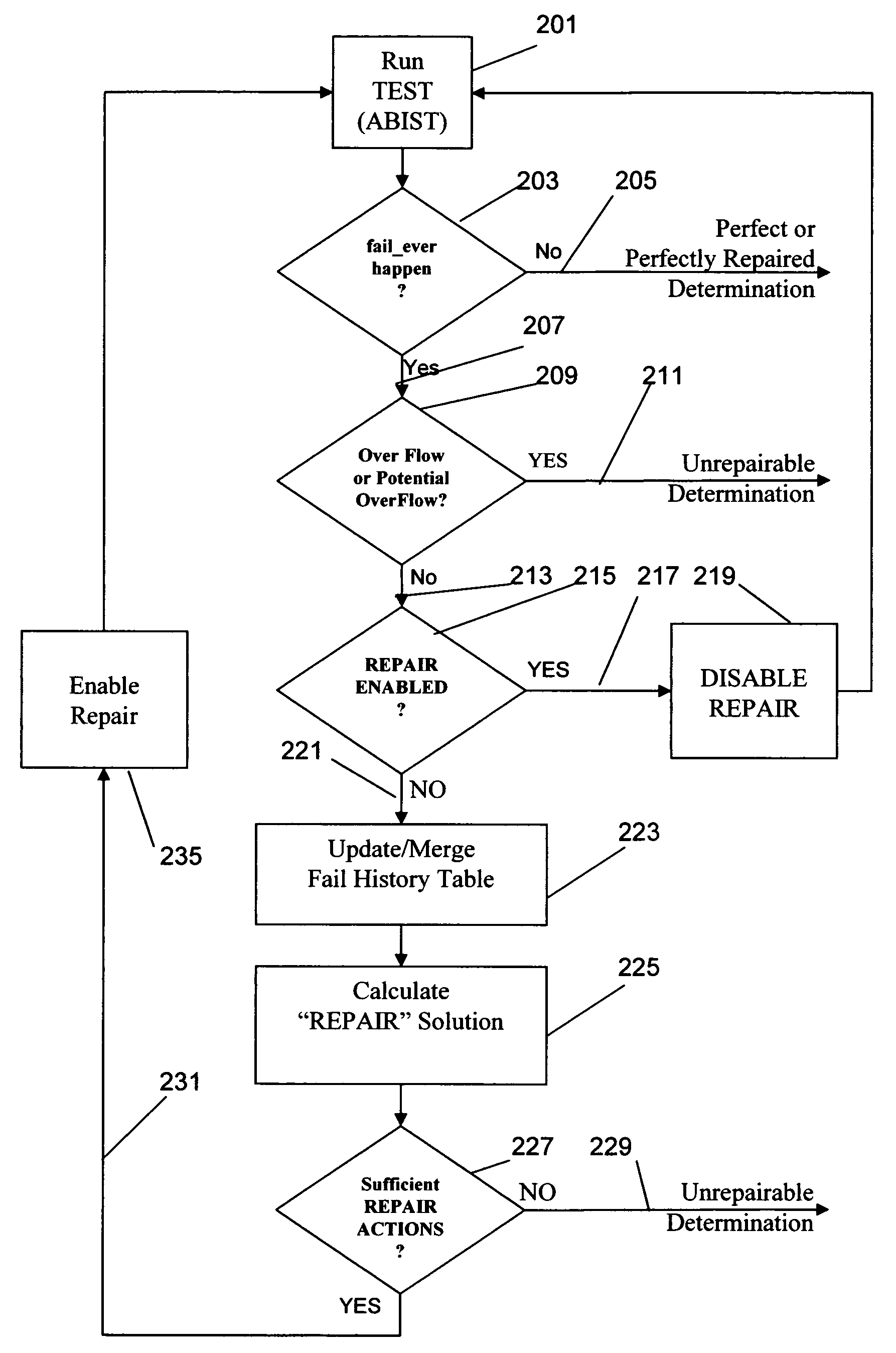

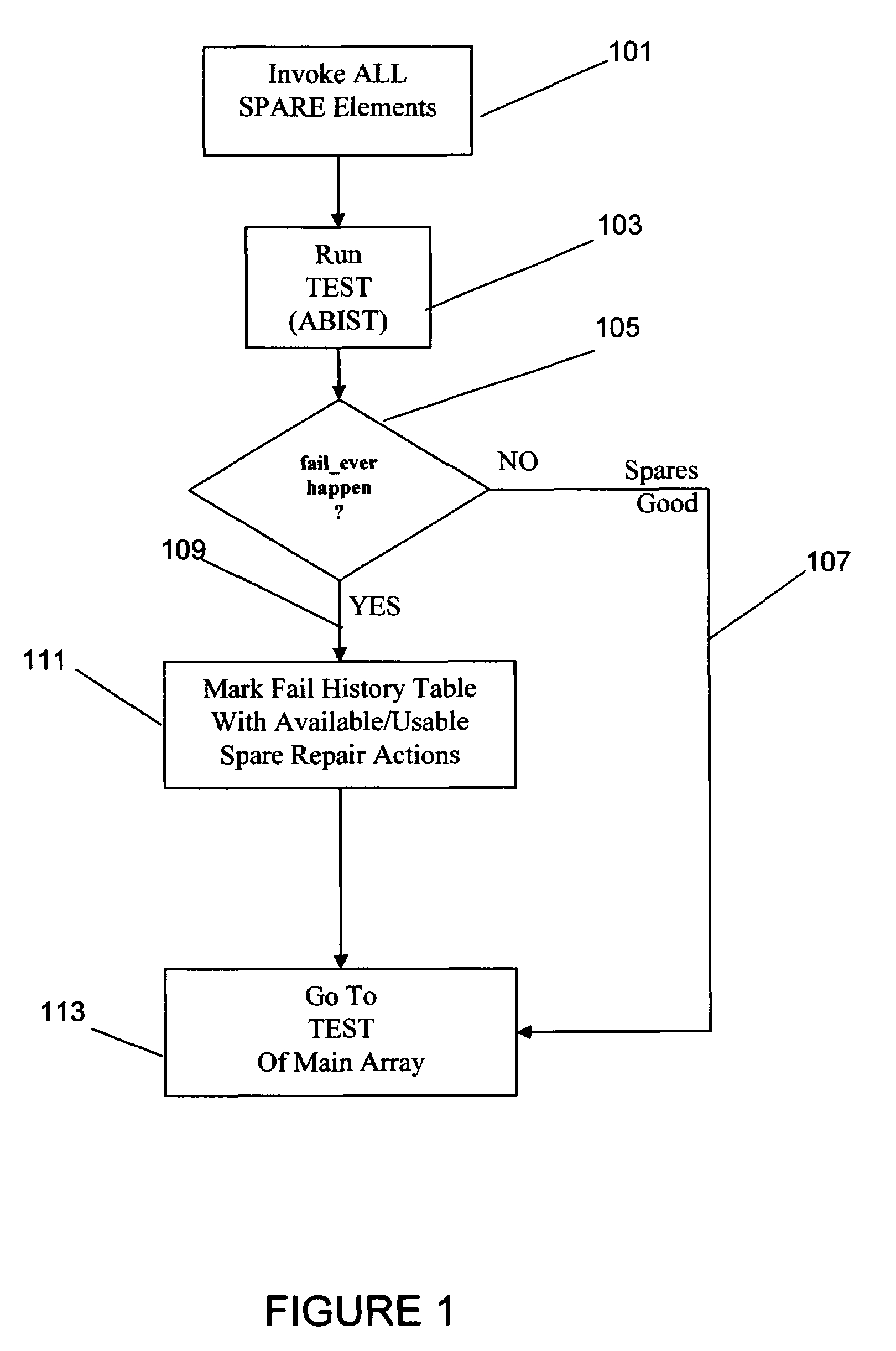

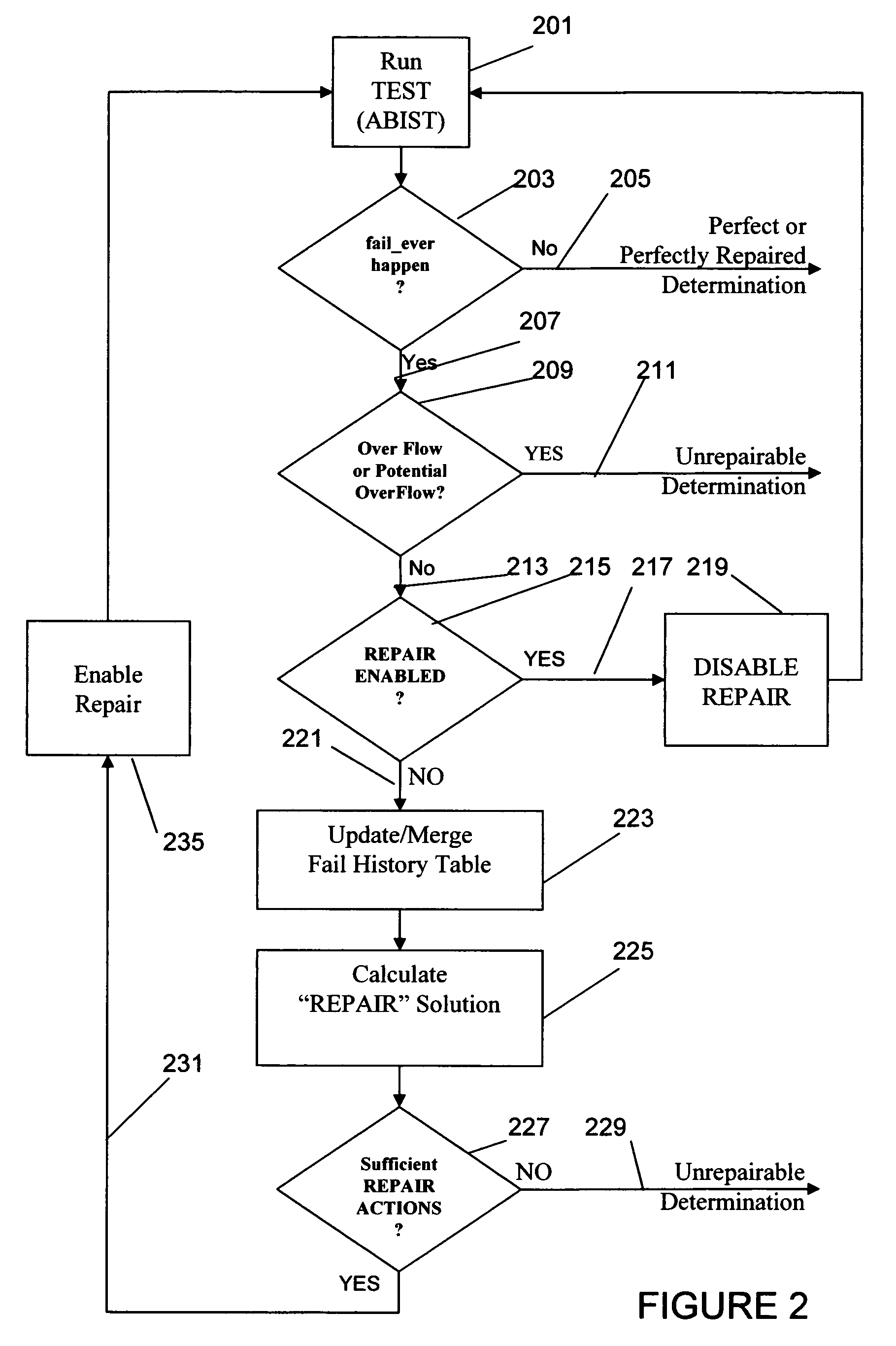

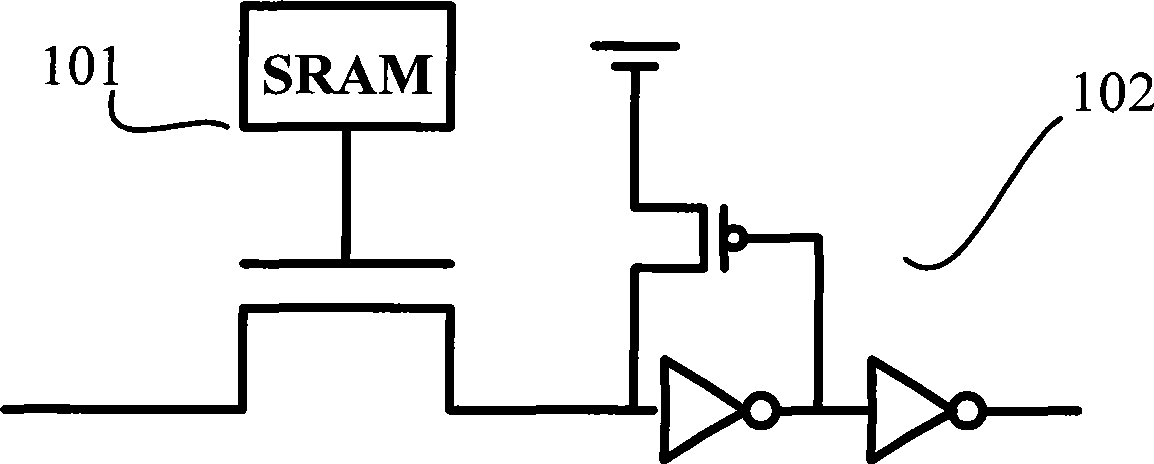

Efficient method of test and soft repair of SRAM with redundancy

Memory array built in self testing utilizing including a simple data history table. The table is used to track failing locations observed during any level of assembly test of processor or logic semiconductor chips where the chips contain SRAM macros with redundant elements for failure relief.

Owner:GLOBALFOUNDRIES INC

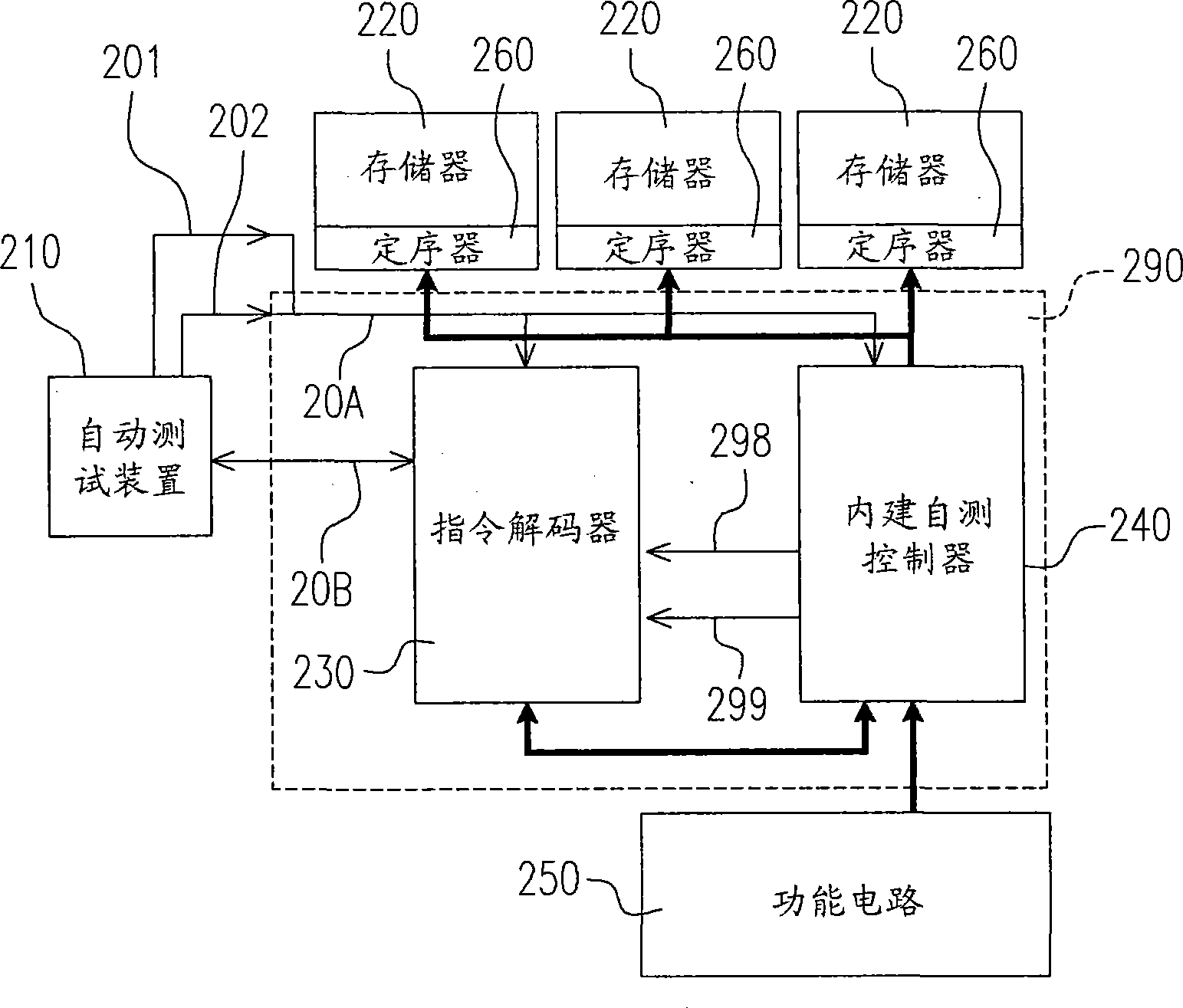

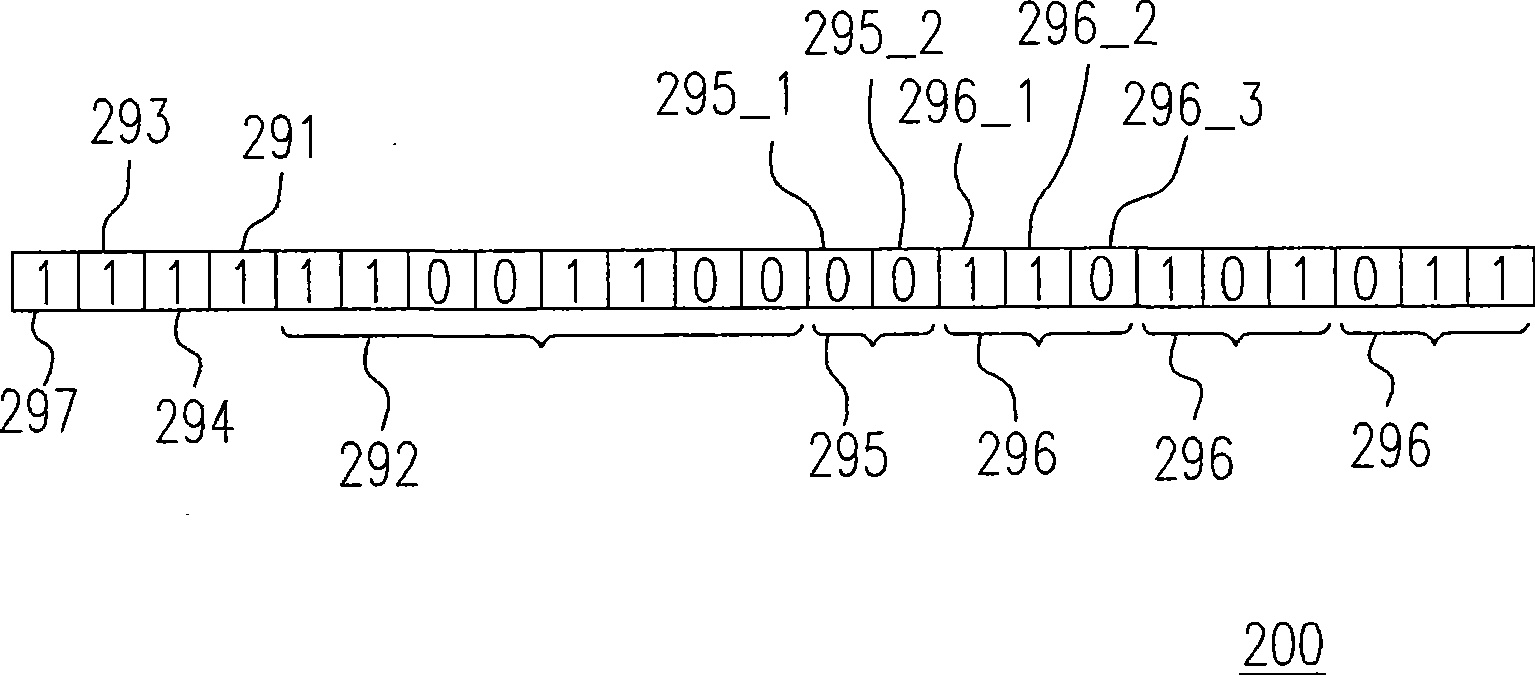

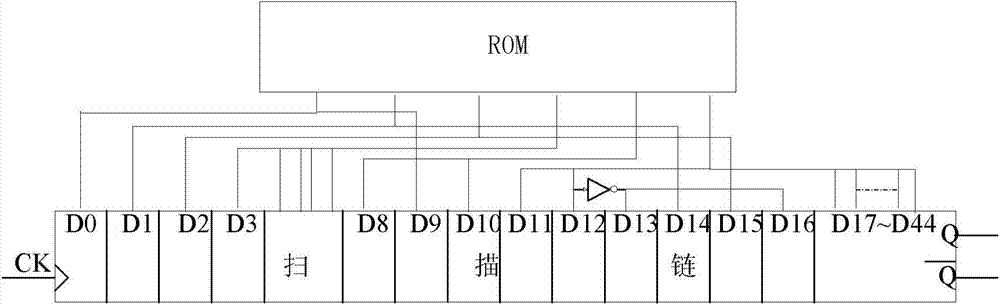

Built-in self-testing circuit and clock switching circuit of programmable memory

InactiveCN101399087AMeet the testing needs of different applicationsQuality improvementStatic storageFault coverageHemt circuits

The invention provides a programmable memory build-in self-test circuit and a clock switching circuit. Through an instruction decoder and a built-in test controller, more self-test functions can be set by users, abundant circuits in the traditional technology are simplified, and the area of a chip is lowered to reduce the cost. Control circuits around the memory are also provided. Less area is occupied. The position of the memory can be tested more flexibly. The clock switching circuit is also provided. The chip can be correctly tested at clocks of different speeds. The testability and the analyzability of the memory in the chip can be improved. And the error covering rate is improved.

Owner:FARADAY TECH CORP

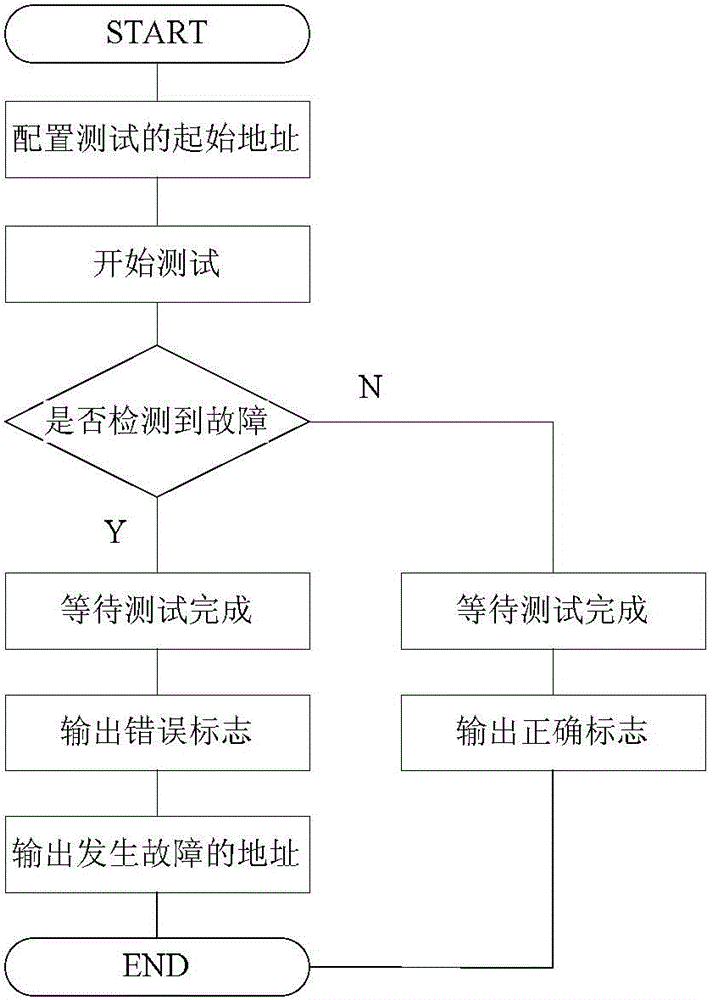

On-chip RAM built-in self-testing method and circuit

ActiveCN104361909AImprove static fault coverageAdd configurable functionsStatic storageBuilt in self testingComputer science

The invention discloses an on-chip RAM built-in self-testing method and circuit. The method comprises the following steps: configuring an initial address of a test; operating each address in a preset range from the initial address; writing zero according to the ascending sequence of the addresses; and carrying out twice zero-read and twice one-write operations according to the descending sequence of addresses; carrying out one-read operation, zero-write operation, zero-read operation and one-write operation according to the ascending sequence of addresses; carrying out twice one-write operations and twice zero-read operations; carrying out zero-read operation, one-write operation, one-read operation and zero-write operation; and carrying out zero-read operation. In the operation processes, when the read-out data of a certain tested address is not accordant to expected data, the tested address is determined to be failed, and an error mark and the tested address with failure are output after testing is completed. The on-chip RAM built-in self-testing method and circuit can be used for solving the problem that the static failure of a single unit cannot completely detected in the prior art.

Owner:DATANG MICROELECTRONICS TECH CO LTD

System and method for managing power consumption

InactiveUS20070061599A1Increase power consumptionReduce supplyEnergy efficient ICTVolume/mass flow measurementBuilt in self testingPower consumption

An electronic circuit having built-in self testing capabilities for optimizing power consumption. Typically, the electronic circuit includes a component circuit that operates at some known or unknown optimal operating power level. Further, the electronic circuit includes a power supply coupled to the component circuit such that the power supply provides power to the component circuit. Further yet, the electronic circuit includes a test circuit coupled to the component circuit and coupled to the power supply. The test circuit is operable to monitor the power supplied to the component circuit and operable to control the power supply. In an iterative manner, the test circuit reduces the power supplied to the component circuit until the power supplied to the component circuit is operating at the optimal operating power level.

Owner:BROADCOM INT PTE LTD

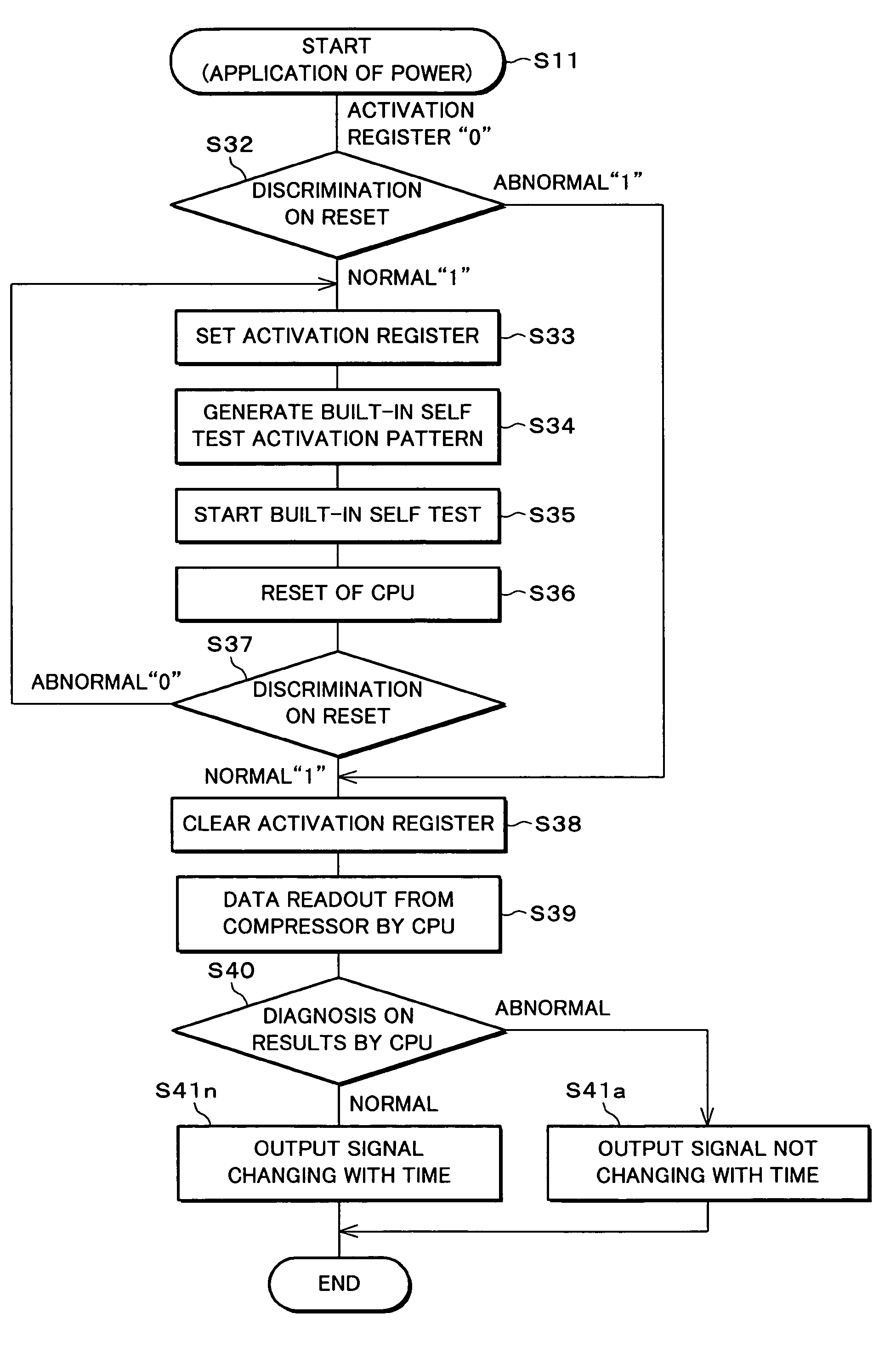

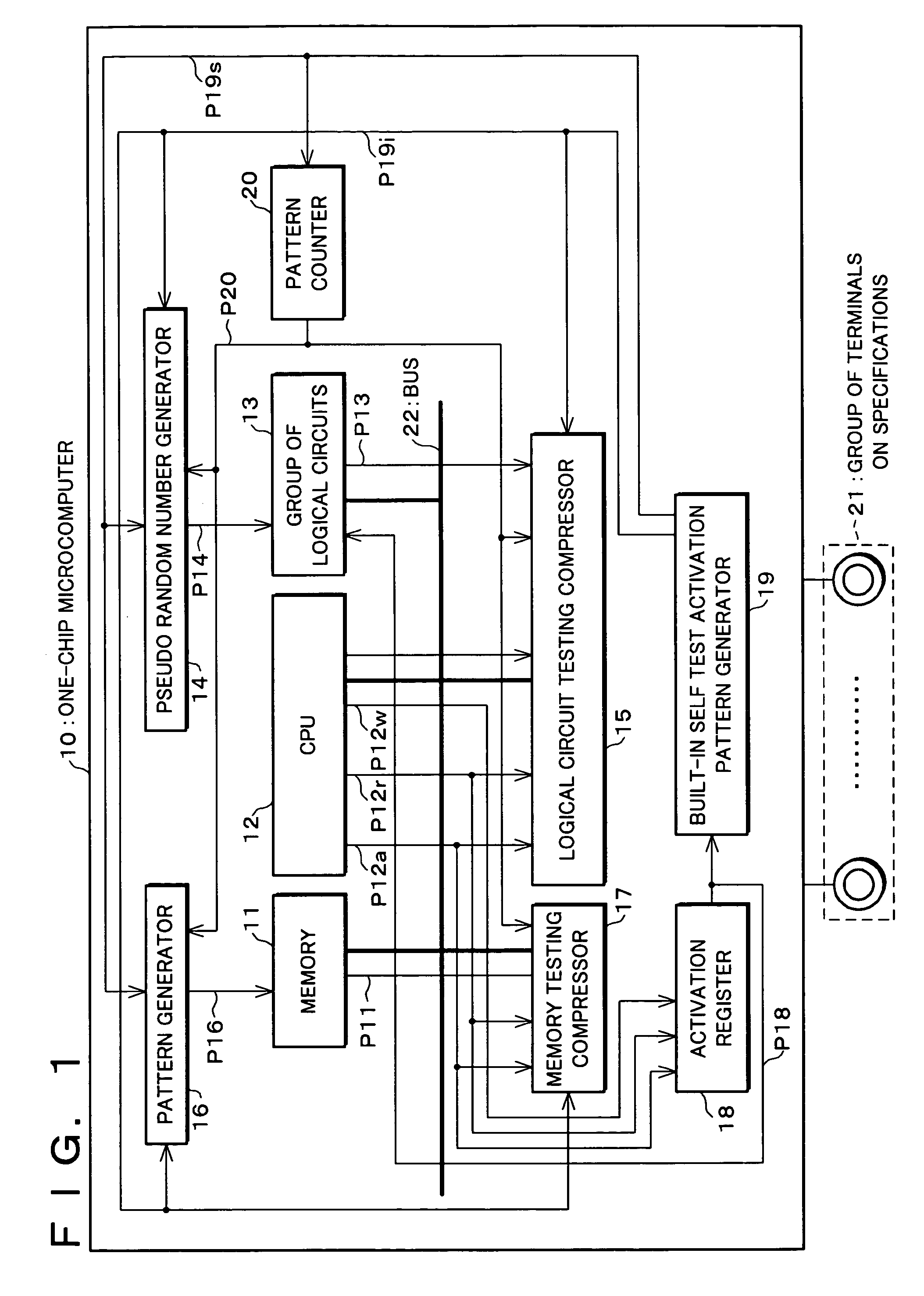

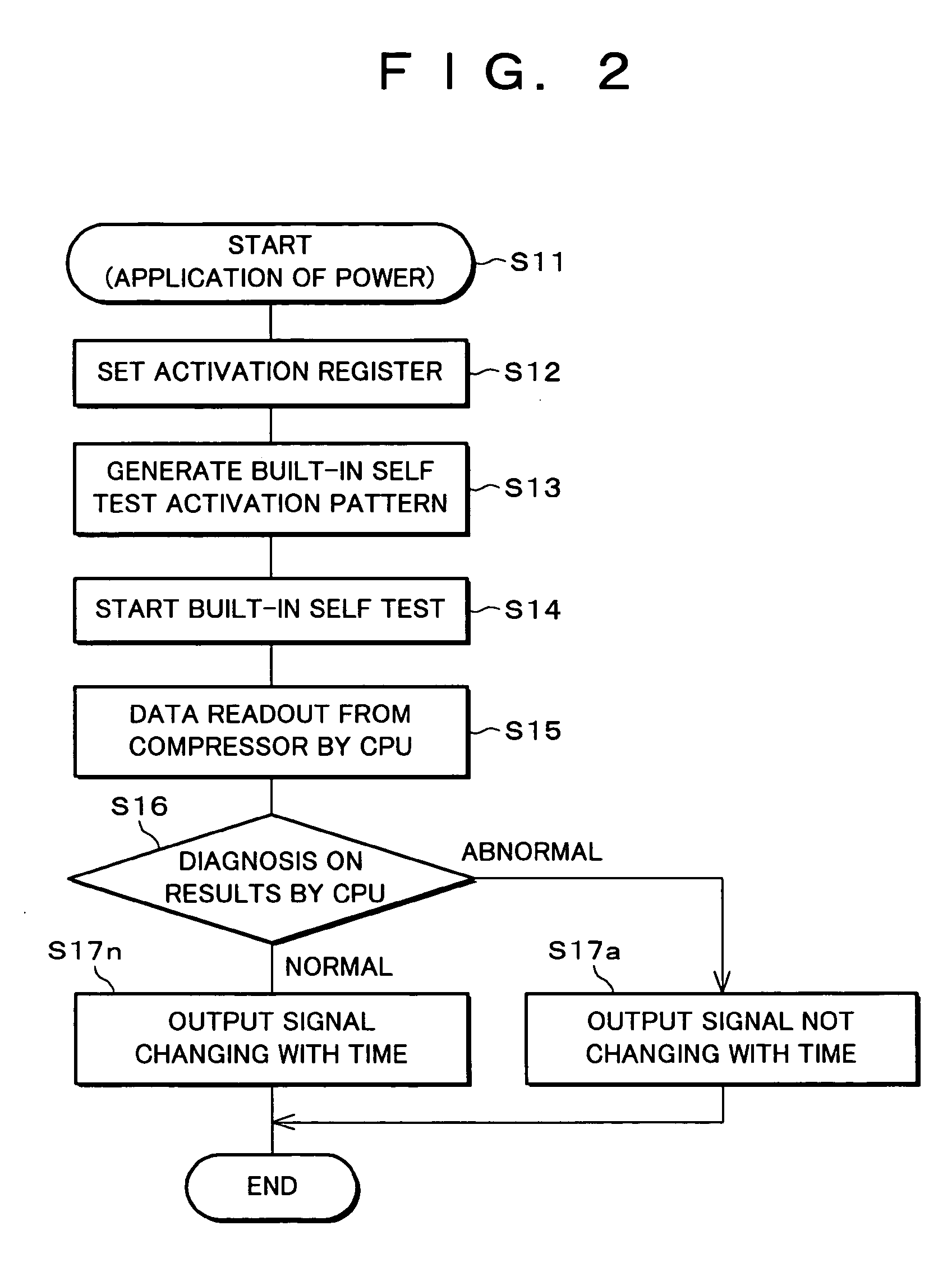

One-chip microcomputer and control method thereof as well as an IC card having such a one-chip microcomputer

InactiveUS6934884B1Increase the number ofDevelopment periodElectronic circuit testingFunctional testingMicrocontrollerBiological activation

In order to provide a built-in self testing function, a one-chip microcomputer is equipped with an activation register for activating the test operation and a built-in self test activation pattern generator for setting initial values at test control circuits (pseudo random number generator, logical circuit testing compressor, pattern generator, and memory testing compressor). In accordance with an instruction from the CPU, a built-in self test is activated so that the results of tests of the memory and the group of logical circuits are read from the memory testing compressor and the logical circuit testing compressor, and respectively compared with expected values preliminarily stored in the memory in the one-chip microcomputer; thus, the results are diagnosed. Thus, it is possible to carry out a built-in self test without using a plurality of exclusively-used test terminals.

Owner:SHARP KK +1

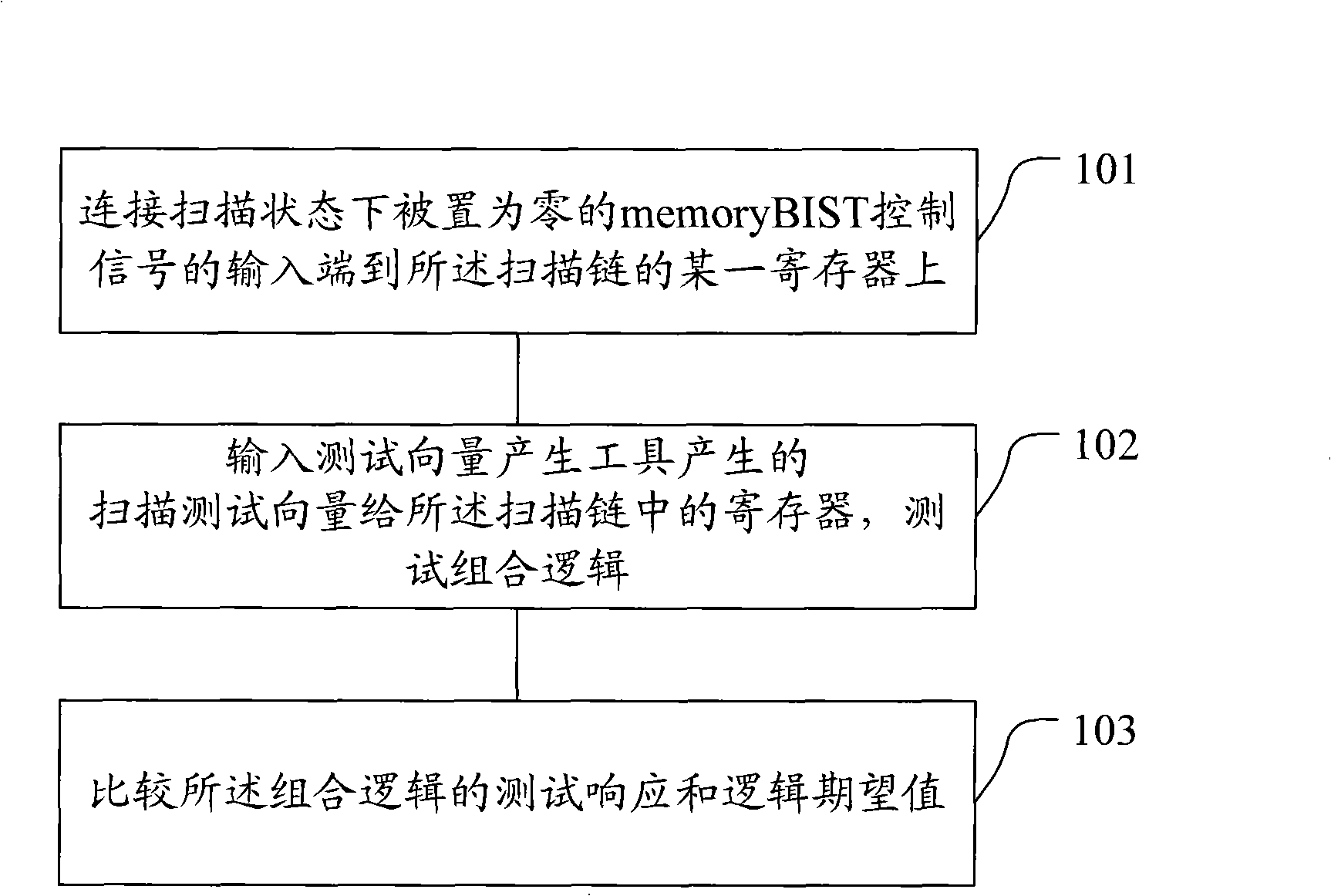

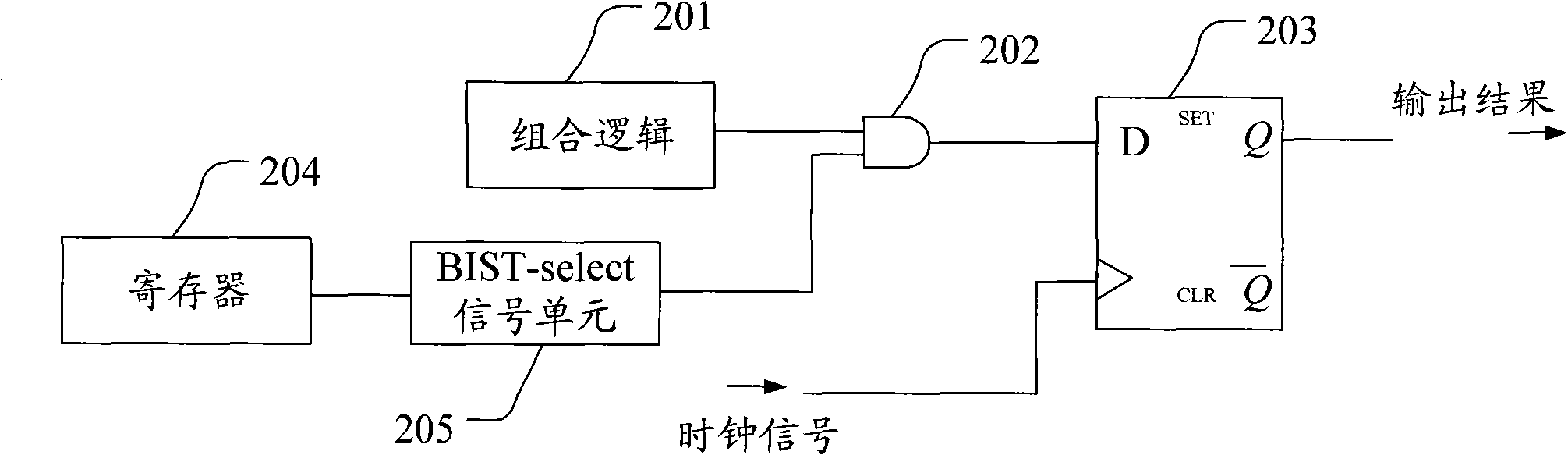

Method for increasing test coverage of scan chain and device thereof

ActiveCN101515479AImprove test coverageImprove testabilityStatic storageControl signalProcessor register

The invention provides a method for increasing the test coverage of a scan chain and a device thereof; wherein, the method for increasing the test coverage of the scan chain comprises: an input end of built-in self testing control signals of a memory being set to be zero in a scanning mode is connected into one register in the scan chain; scan test vector generated by a test vector generation tool is input into the scan chain comprising the register to test combinational logic; the test response and logic expected value of the combinational logic are compared. The method for increasing the test coverage of the scan chain provided by the invention causes that the built-in self testing control signals of the memory can be controlled when the scan chain tests, and realizes the testability of the built-in self testing logic of the memory in the scan mode, thus increasing the logic test coverage of the scan chain test and further increasing the whole test coverage of a chip.

Owner:BEIJING VIMICRO ARTIFICIAL INTELLIGENCE CHIP TECH CO LTD

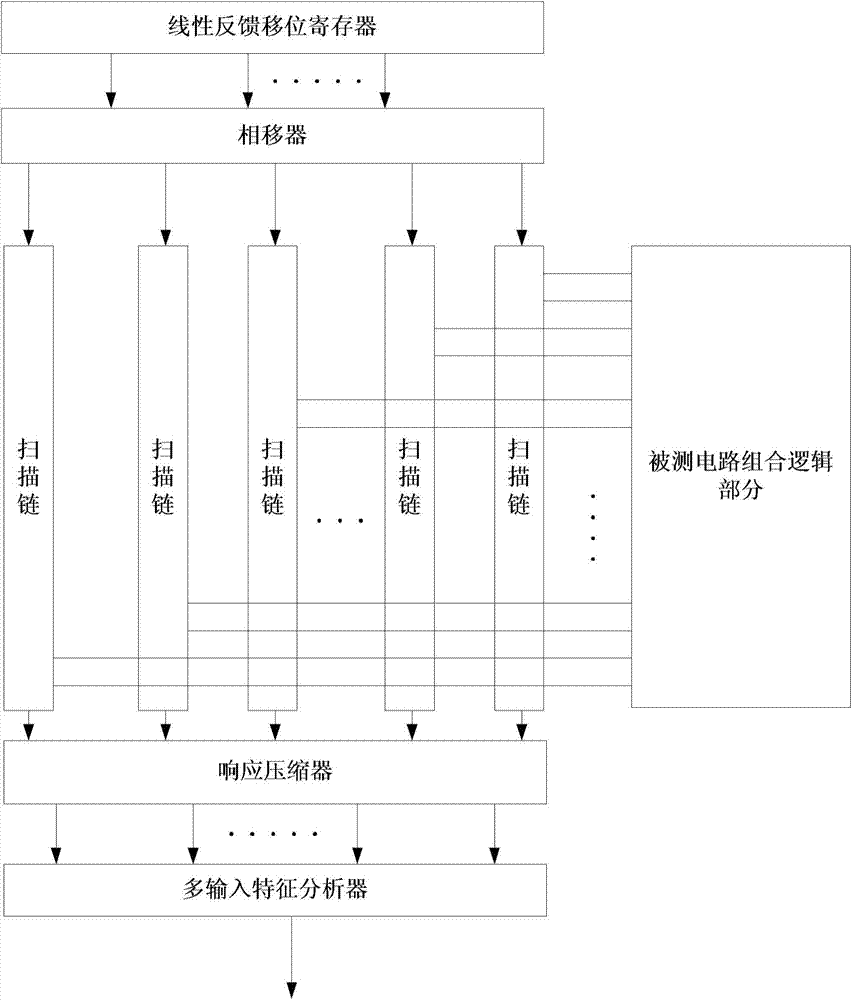

Test data compression method, data uncompress device and data uncompress method

ActiveCN103499787AReduce the number of bitsSave storage spaceElectrical testingShift registerExclusive or

The invention discloses a deterministic self-testing test data compression method, a data uncompress device and a data uncompress method. The compression method comprises cluster compression, and the combination of the cluster compression, input simplification compression and shifting compression. The data uncompress device comprises a bit counter, a vector quantity counter, a shift counter, a cluster shifting register, an address counter, a comparator, a exclusive-OR gate, an input compression register and a phase inverter. According to the scheme, due to the fact the cluster shifting input simplification compression method is adopted, input compression is firstly conducted on test data with faults difficult to test, cluster compression is conducted on the test data processed by input compression, and shifting compression is conducted on the test data processed by cluster compression, so that the number of memory cells which need to be stored in a built-in self-testing circuit ROM is reduced, and hardware overhead of the built-in self-testing circuit is saved.

Owner:INST OF AUTOMATION CHINESE ACAD OF SCI

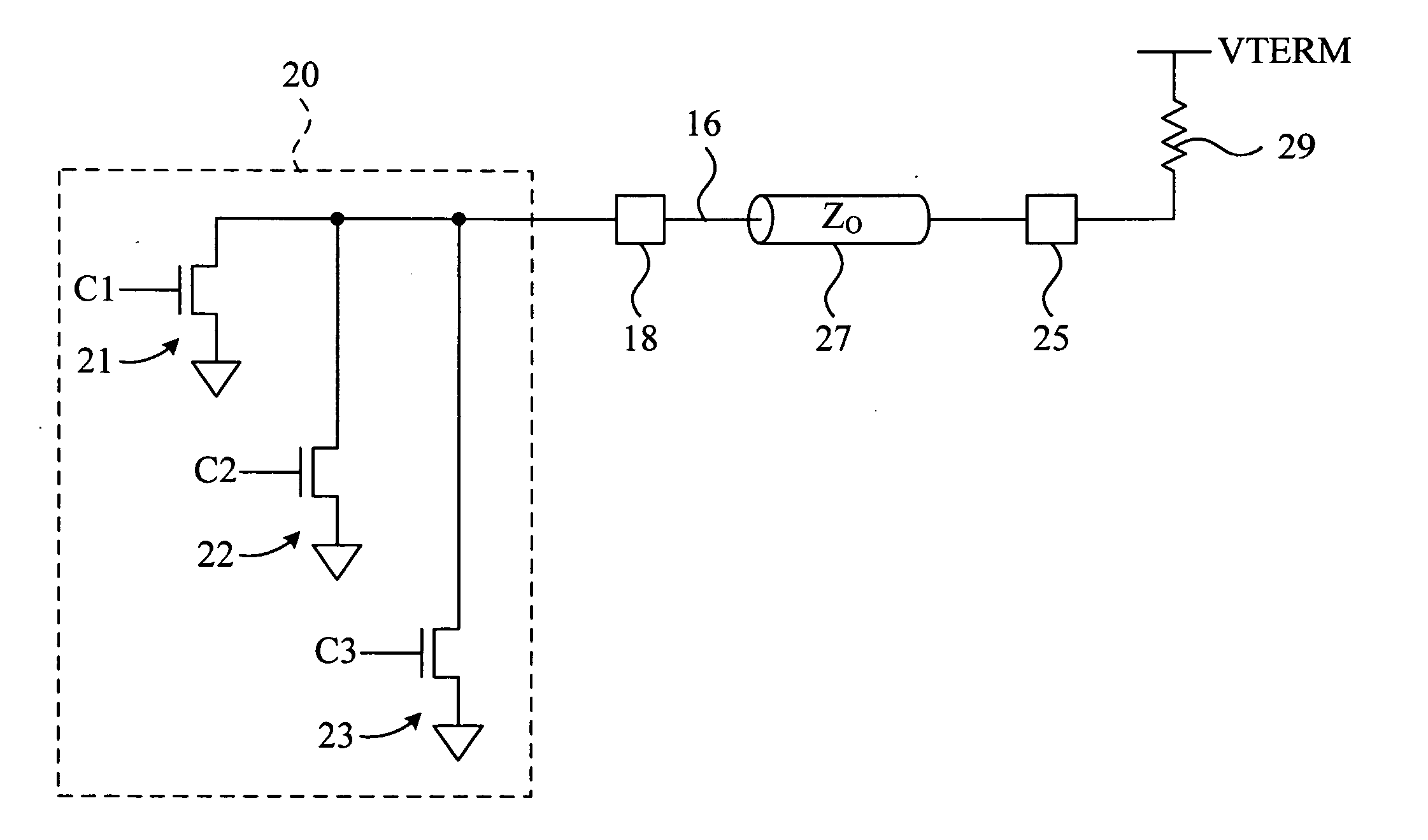

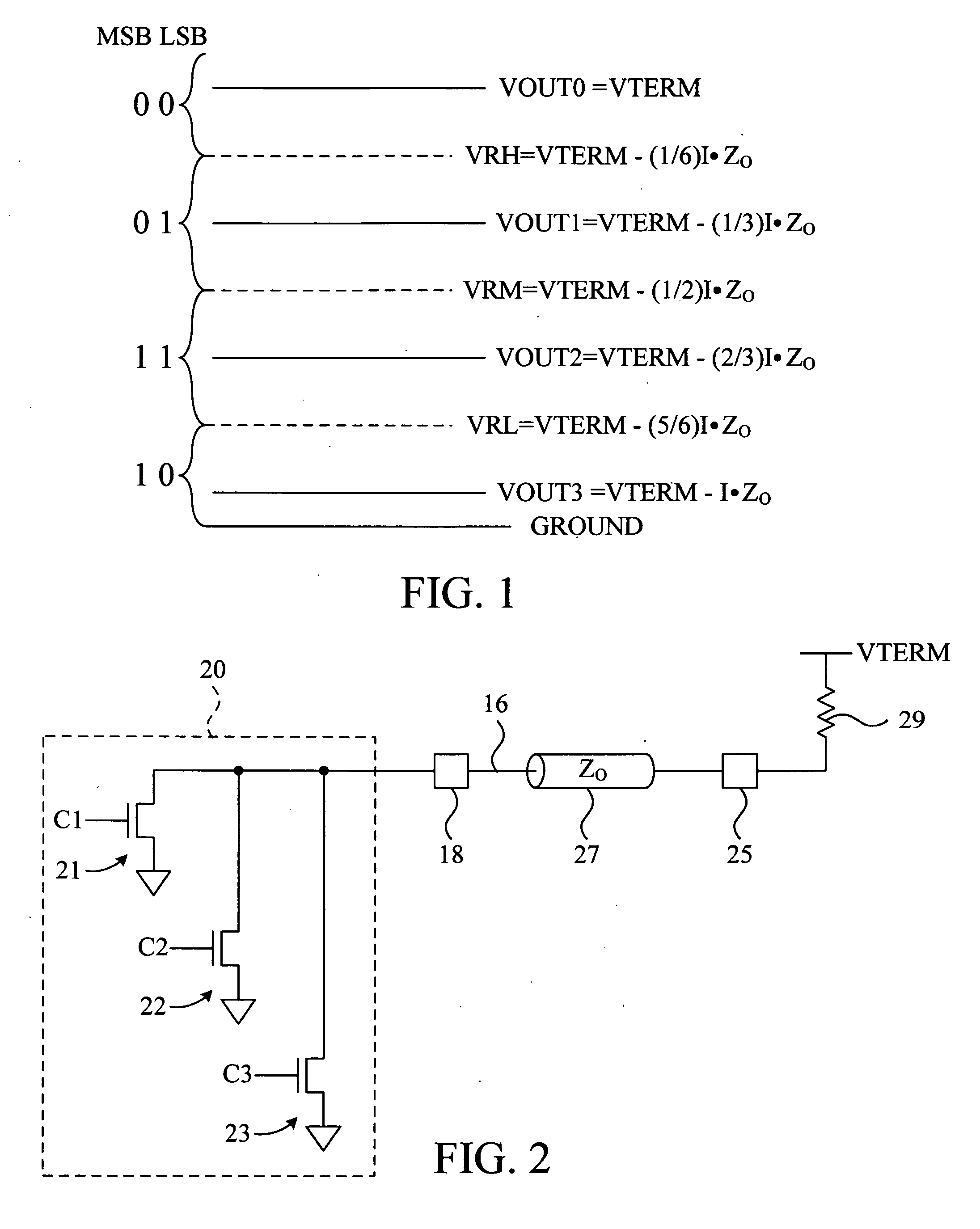

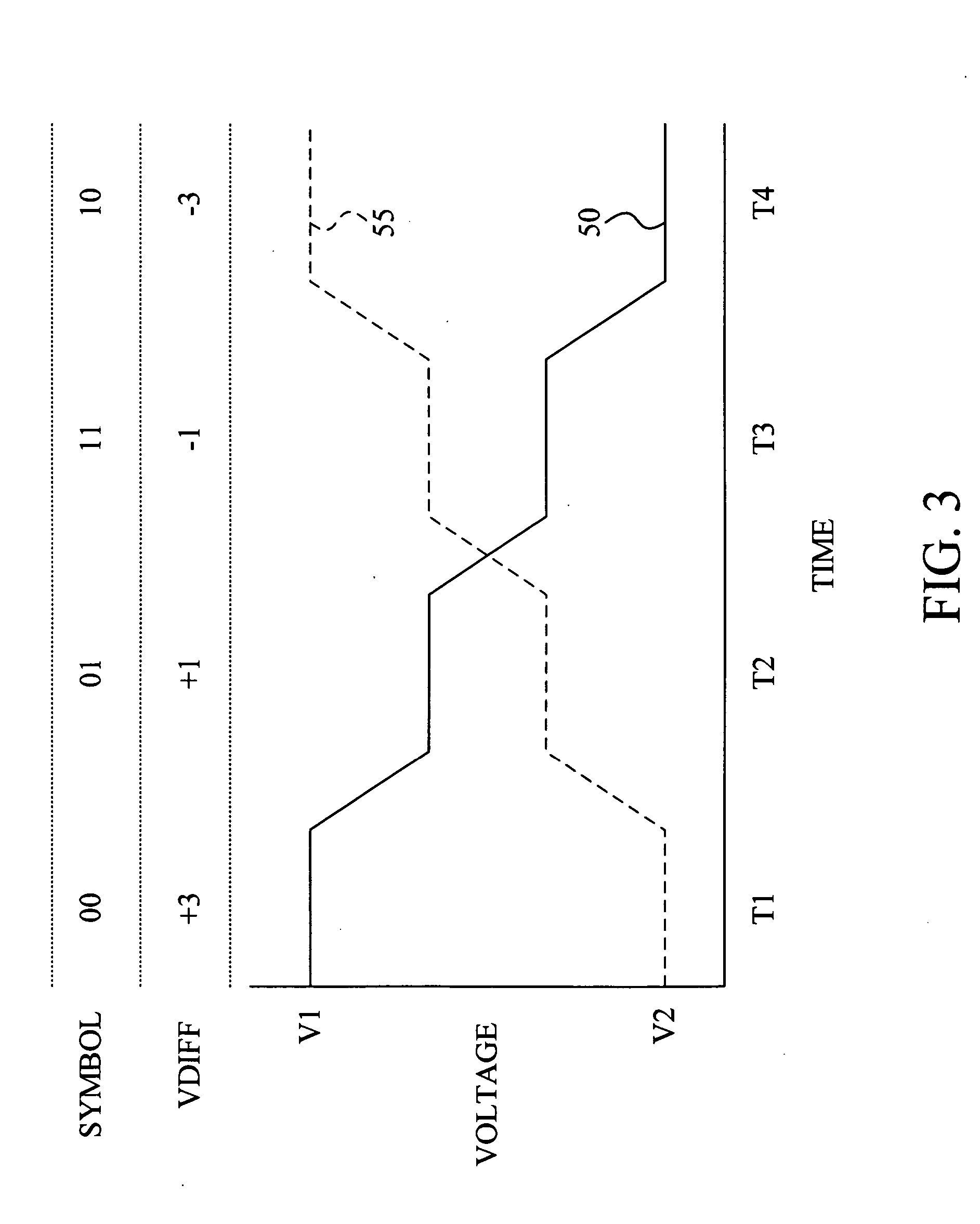

Built-in self-testing of multilevel signal interfaces

InactiveUS20060242483A1Easy to testDigital circuit testingRead-only memoriesEngineeringMemory circuits

Error detection mechanisms for signal interfaces, including built-in self-test (BIST) mechanisms for testing multilevel signal interfaces. The error detection mechanisms are provided in an integrated circuit (IC) chip that contains at least one of the signal interfaces or are coupled to the interfaces on a printed circuit board (PCB). BIST mechanisms may include, for example, test signal generators and mechanisms for determining whether the test signals generated are accurately transmitted and received by the interface. The BIST mechanisms may check a single input / output interface, a group of interfaces or may operate with a master device that tests a plurality of interfaces by sending test signals for storage by and retrieval from one or more slave memory devices. The error detection mechanisms test memory circuits designed to communicate according to multi-PAM signals over printed circuit boards.

Owner:RAMBUS INC

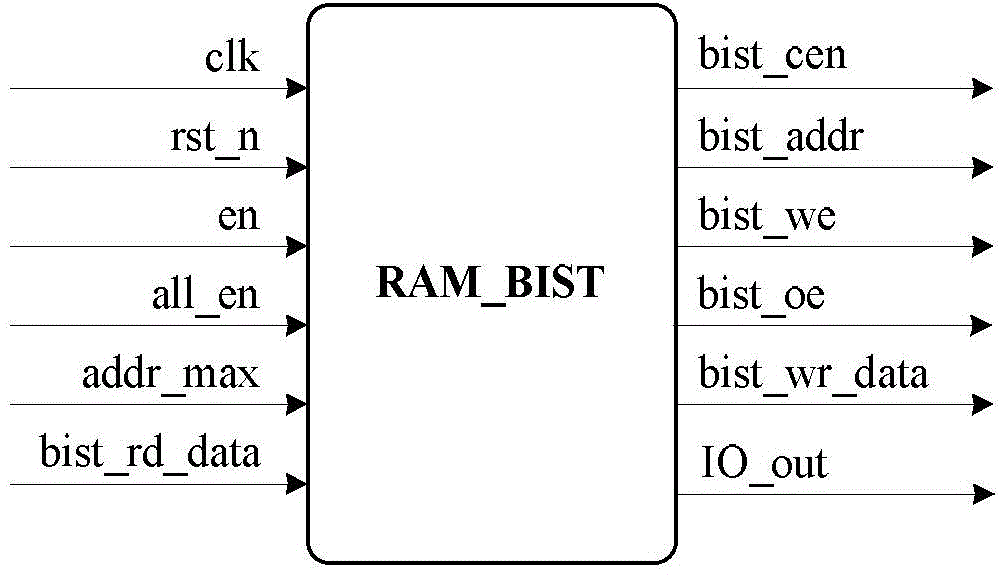

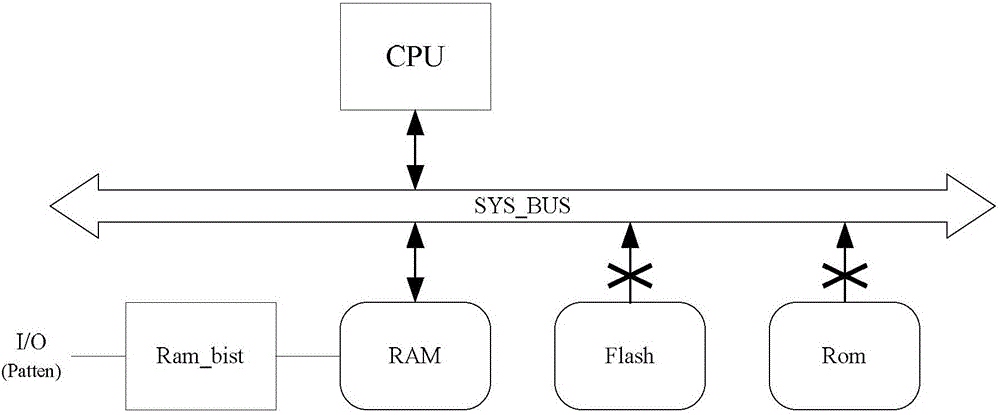

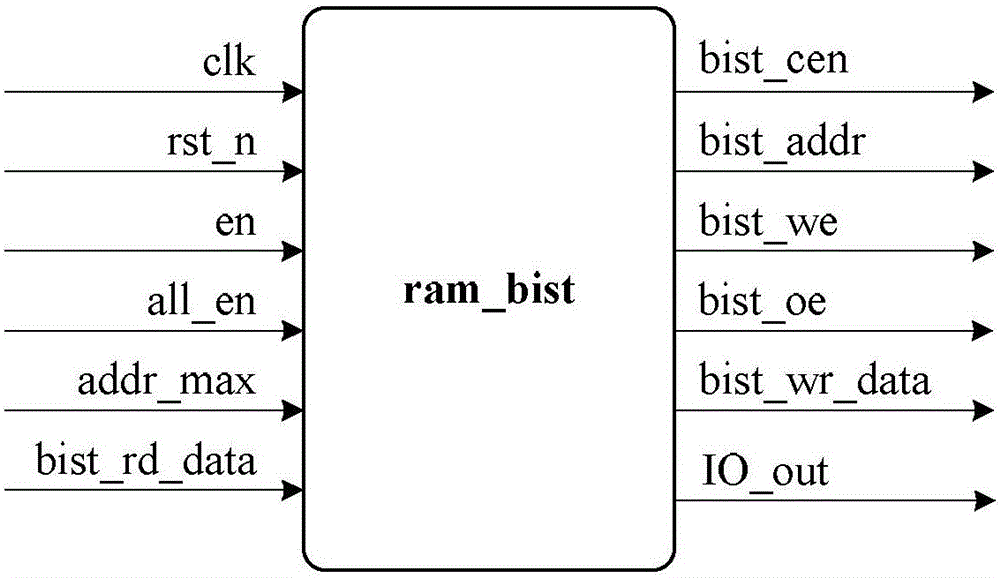

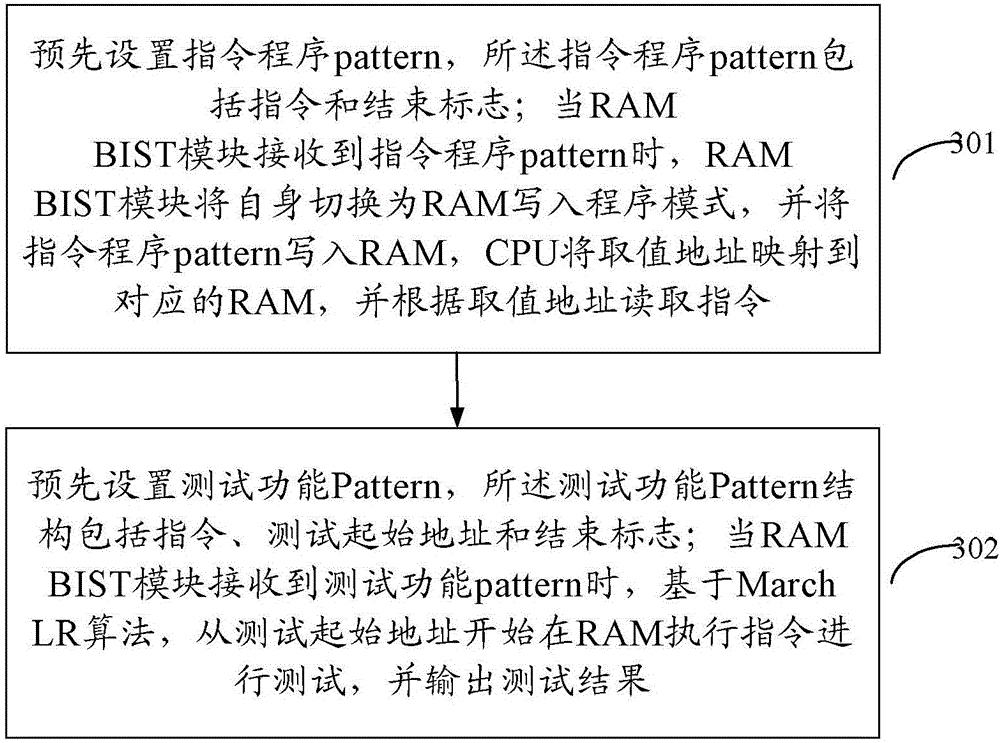

On-chip random access memory built-in self-testing method and device

ActiveCN105760268AIncrease the number ofReduce testing costsFaulty hardware testing methodsTest efficiencyStatic random-access memory

The embodiment of the invention provides an on-chip random access memory built-in self-testing (RAM BIST) method and device.The method includes the steps that a writing-in functional mode Pattern and a testing function Pattern are preset; when an RAM BIST module receives the writing-in function Pattern, the RAM BIST module is switched into an RAM writing-in program state, an instruction in the writing-in function Pattern is written in an RAM, a CPU maps a valuing address into a corresponding RAM, and the instruction is read according to the valuing address; when the RAM BIST module receives the testing function Pattern, based on a March LR algorithm, the instruction starts to be executed on the RAM for testing from a testing starting address, and a testing result is output.By means of the embodiment of the invention, the number of testing chips can be increased, detection time can be saved, detection steps can be reduced, and therefore chip testing cost is reduced, and testing efficiency is improved.

Owner:DATANG MICROELECTRONICS TECH CO LTD +1

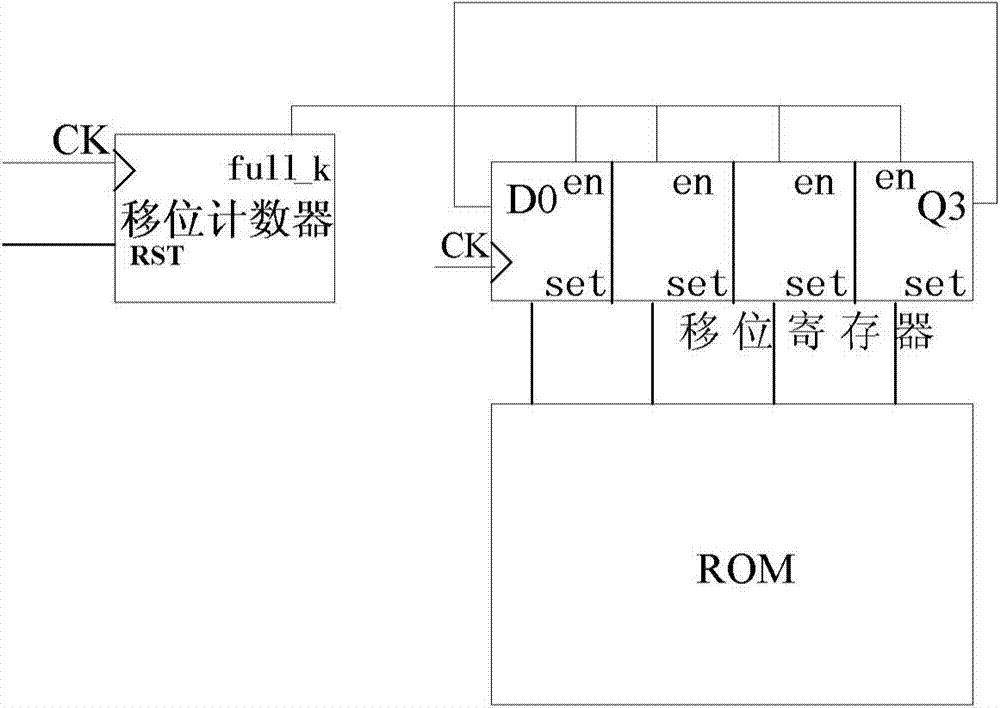

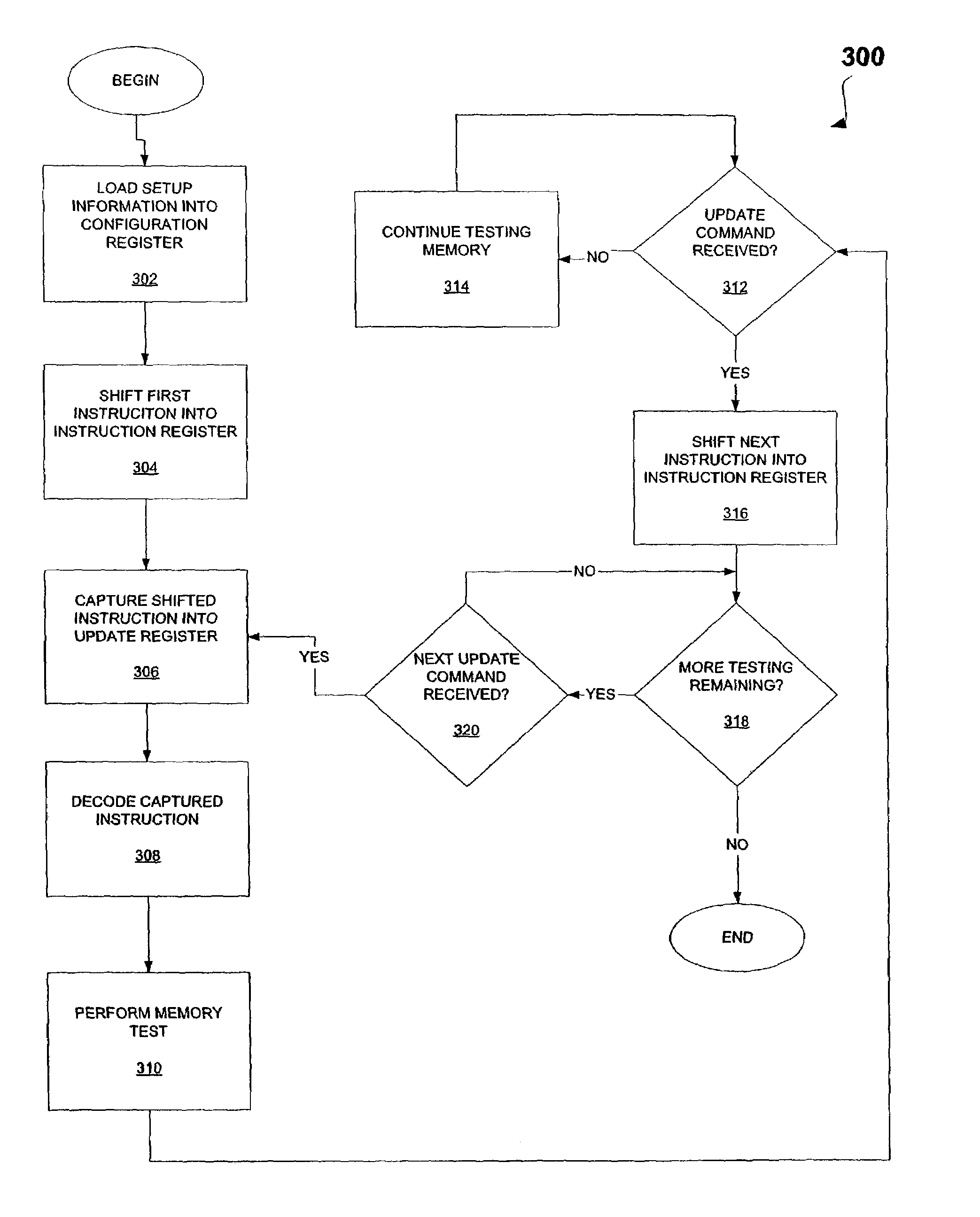

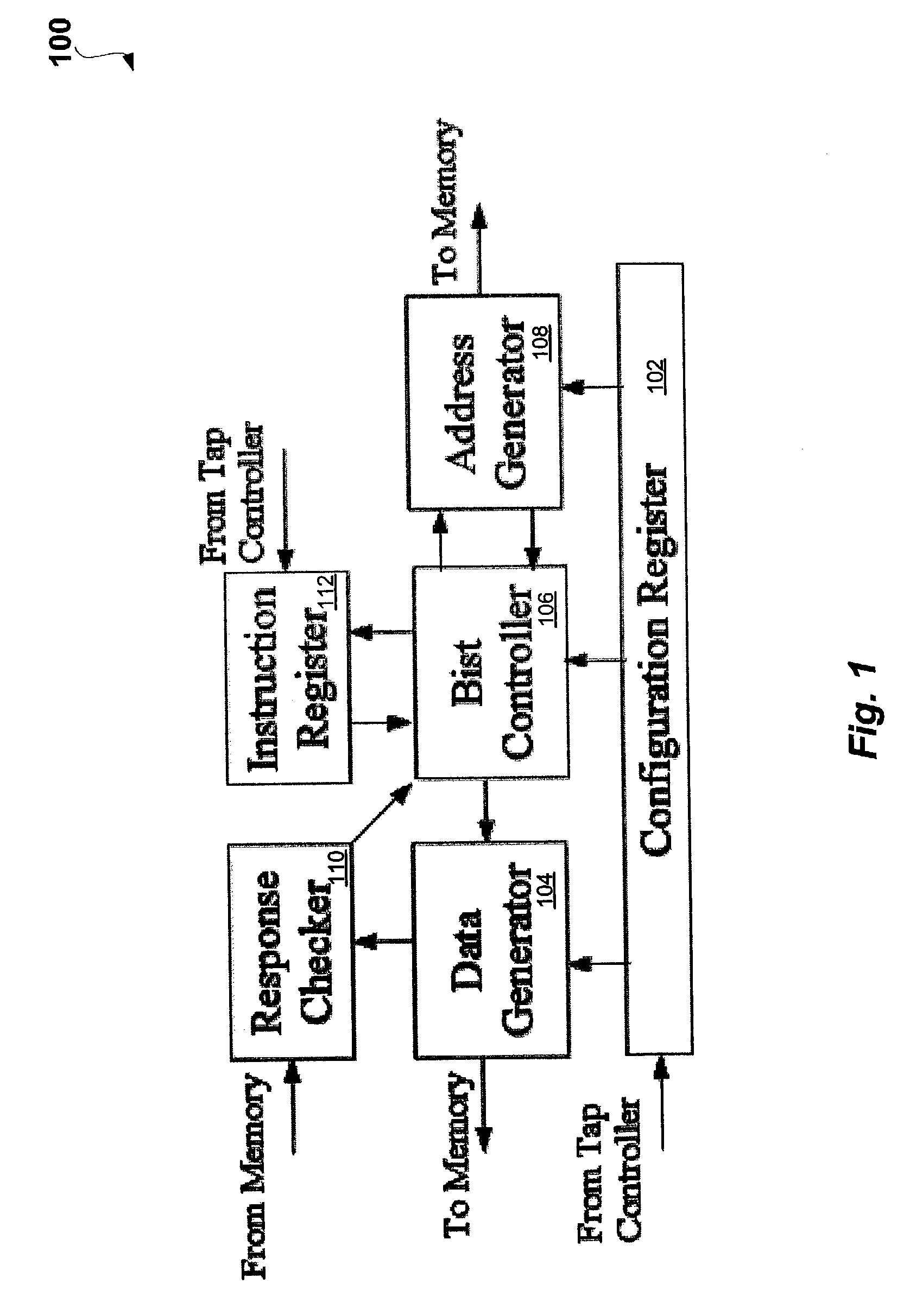

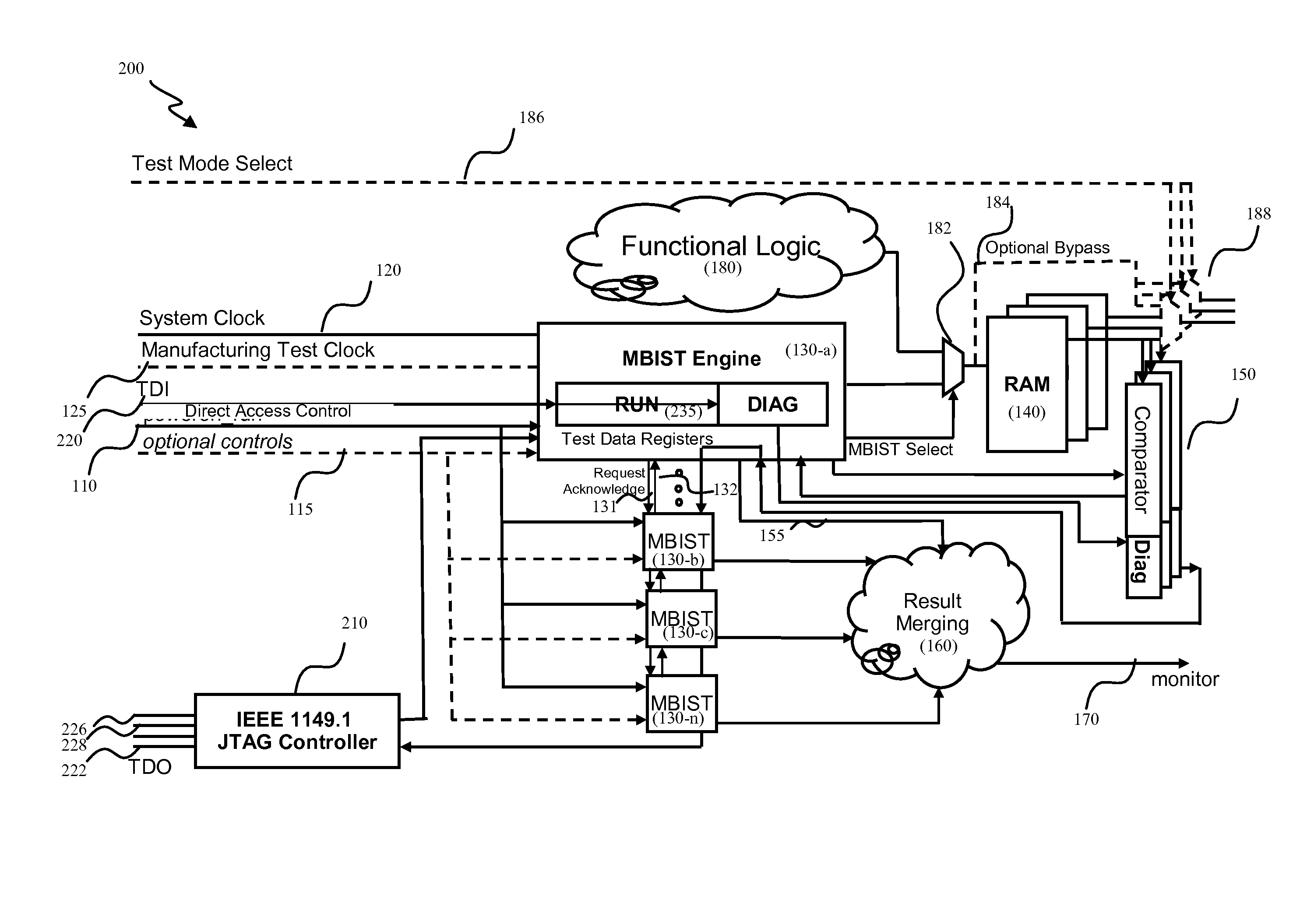

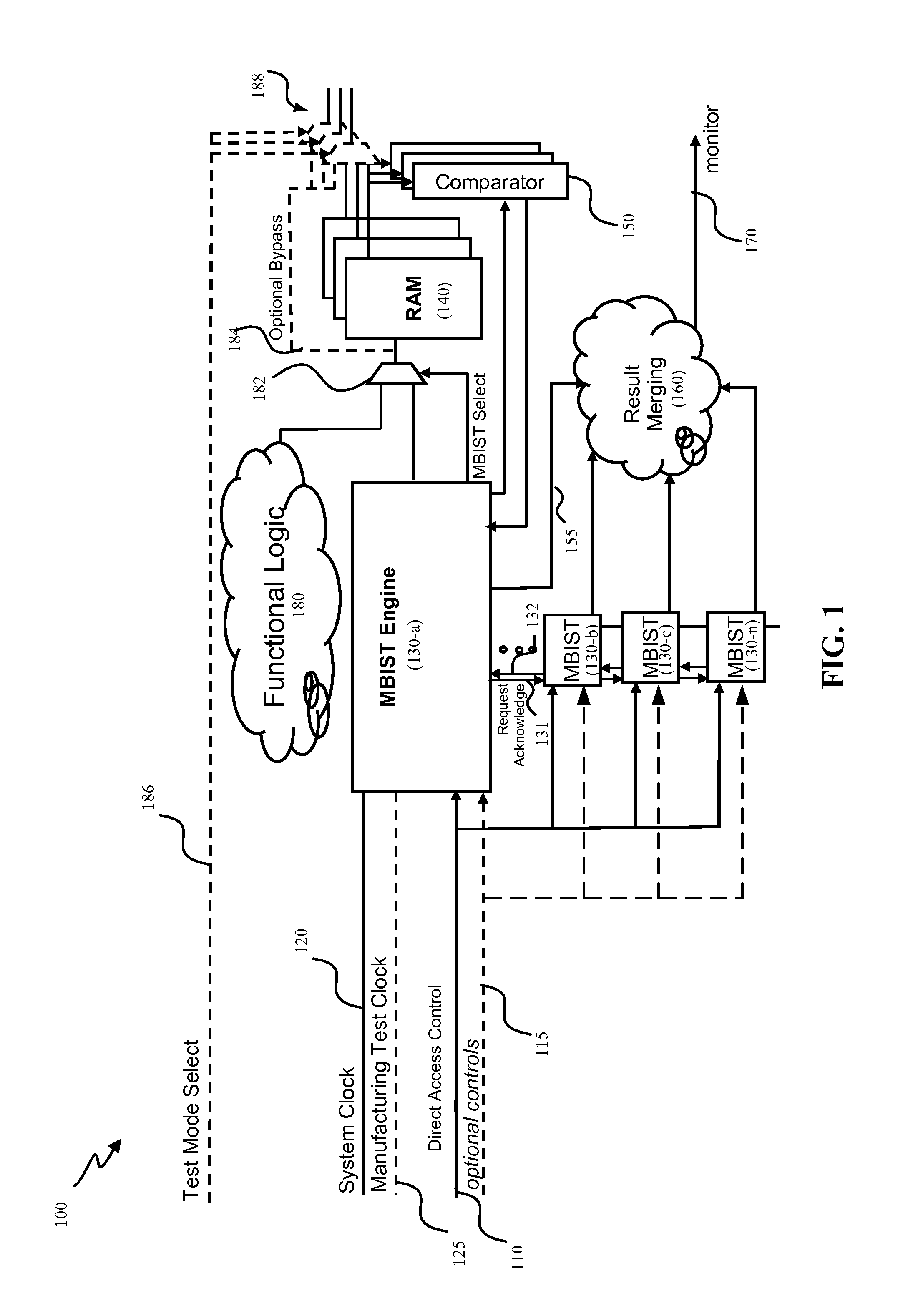

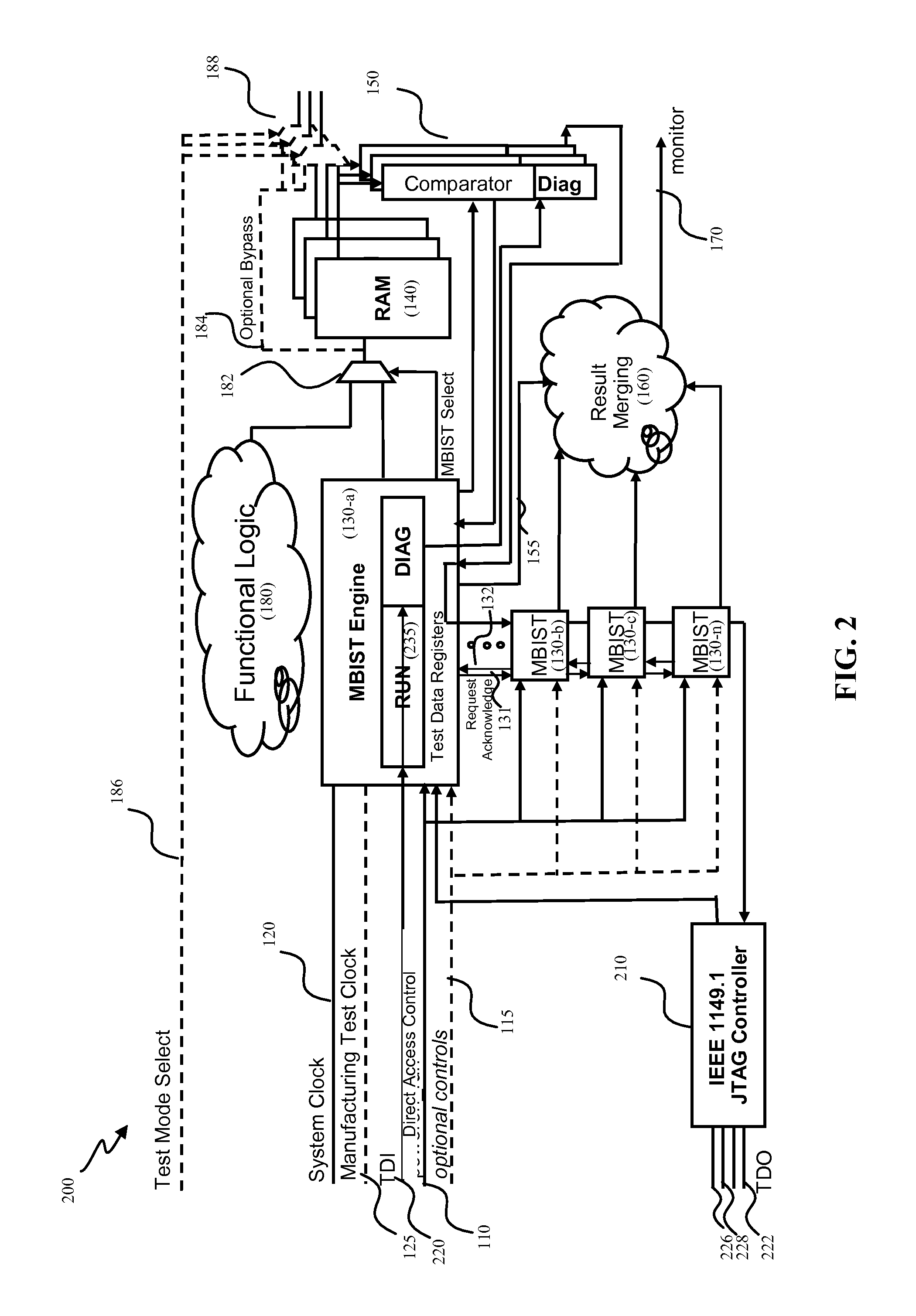

Concurrently programmable dynamic memory built-in self-test (BIST)

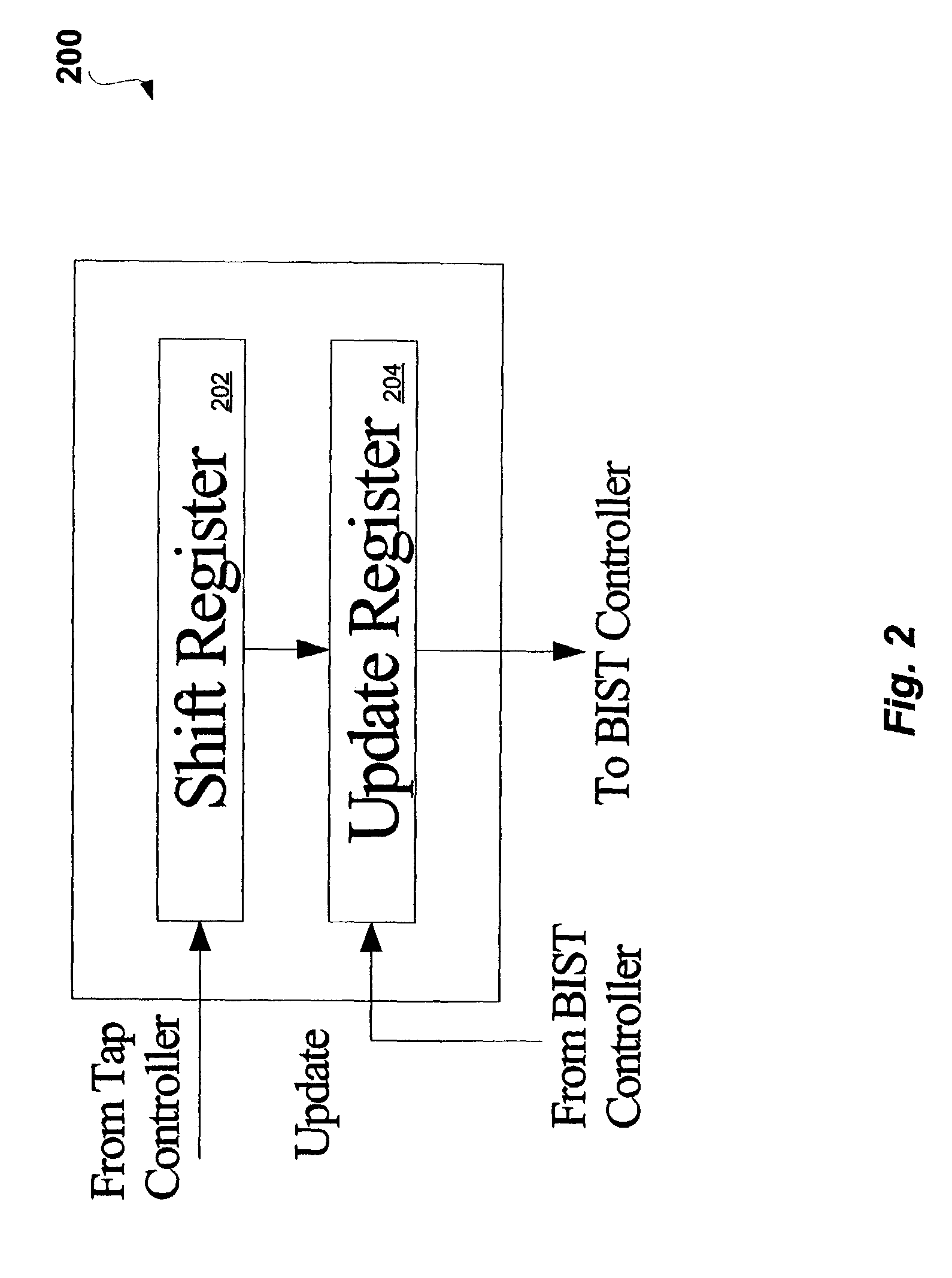

ActiveUS7062694B2Efficiently provideElectronic circuit testingError detection/correctionShift registerComputer architecture

Disclosed are novel methods and apparatus for efficiently providing concurrently programmable dynamic memory built-in self-testing (BIST). In an embodiment of the present invention, a method of utilizing a BIST system is disclosed. The method includes: loading setup data into a configuration register; loading a first instruction into a shift register; loading the first instruction into an update register; executing the loaded first instruction to perform a memory test; upon receiving a first update command, loading a second instruction into the shift register; and upon receiving a second update command, loading the second instruction into the update register.

Owner:AGILENT TECH INC

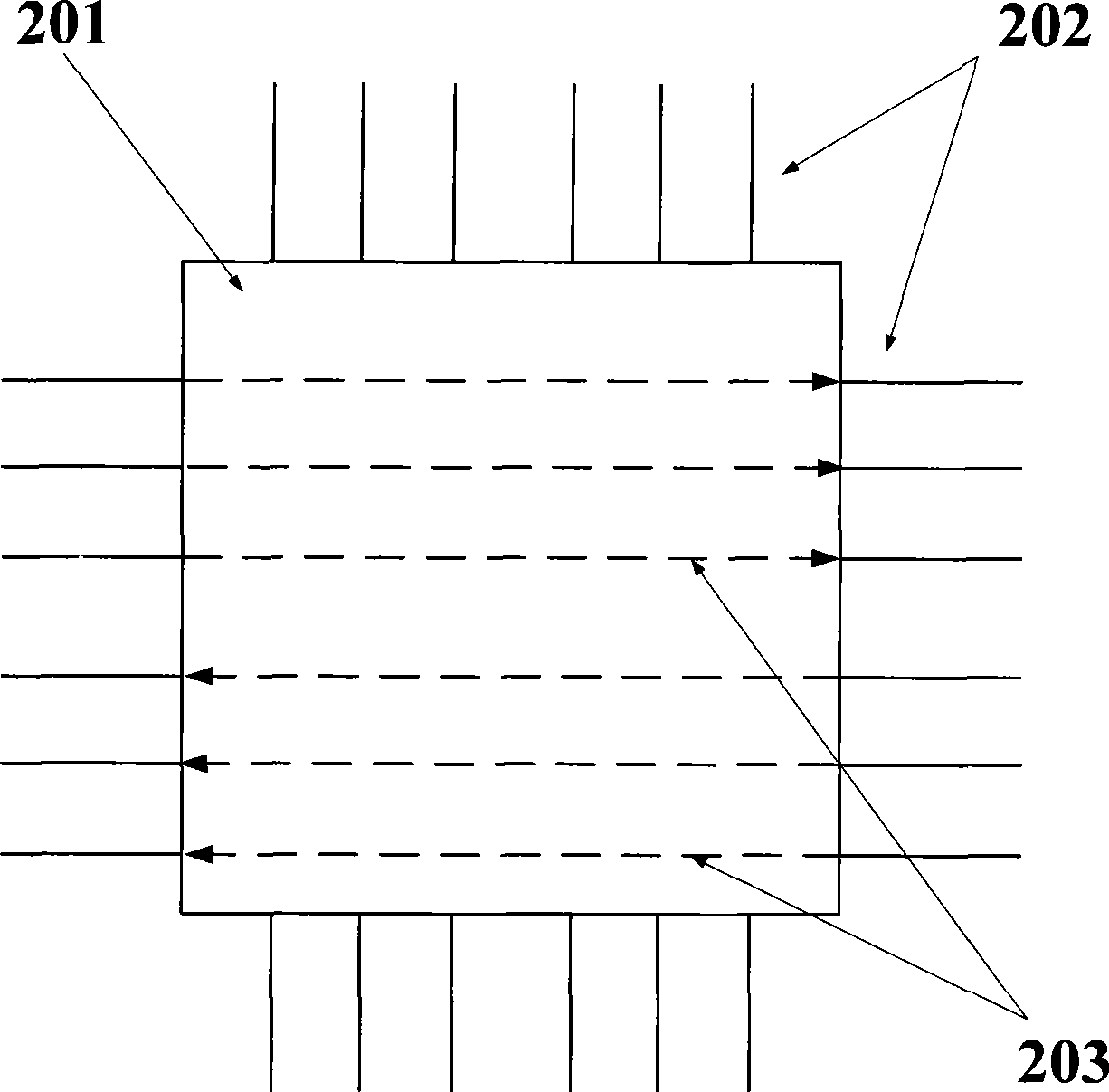

Interconnection line test circuit used in field programmable gate array device

InactiveCN101464494ASolve the disadvantage of limited resourcesReduce configurationDigital circuit testingTwo-vectorProcessor register

The invention relates to an interconnection line testing circuit used in a field programmable gate array device, which comprises even number of vector generation and respond analyzers. Each vector generation and respond analyzer in the even number of vector generation and respond analyzers comprises an n-input and n-output logic combined circuit and a group of n-bit registers, wherein, n is a natural number; and every two vector generation and respond analyzers are connected by interconnection lines with opposite direction and the bit width of n and are combined into a built-in self-testing circuit. The built-in self-testing circuit can achieve the simultaneous test of the two groups of interconnection lines with opposite direction and larger bit width on the condition that the number of the registers is not changed, shorten the testing time of a FPGA device, and reduce the testing cost of the FPGA device.

Owner:无锡引速得科技有限公司

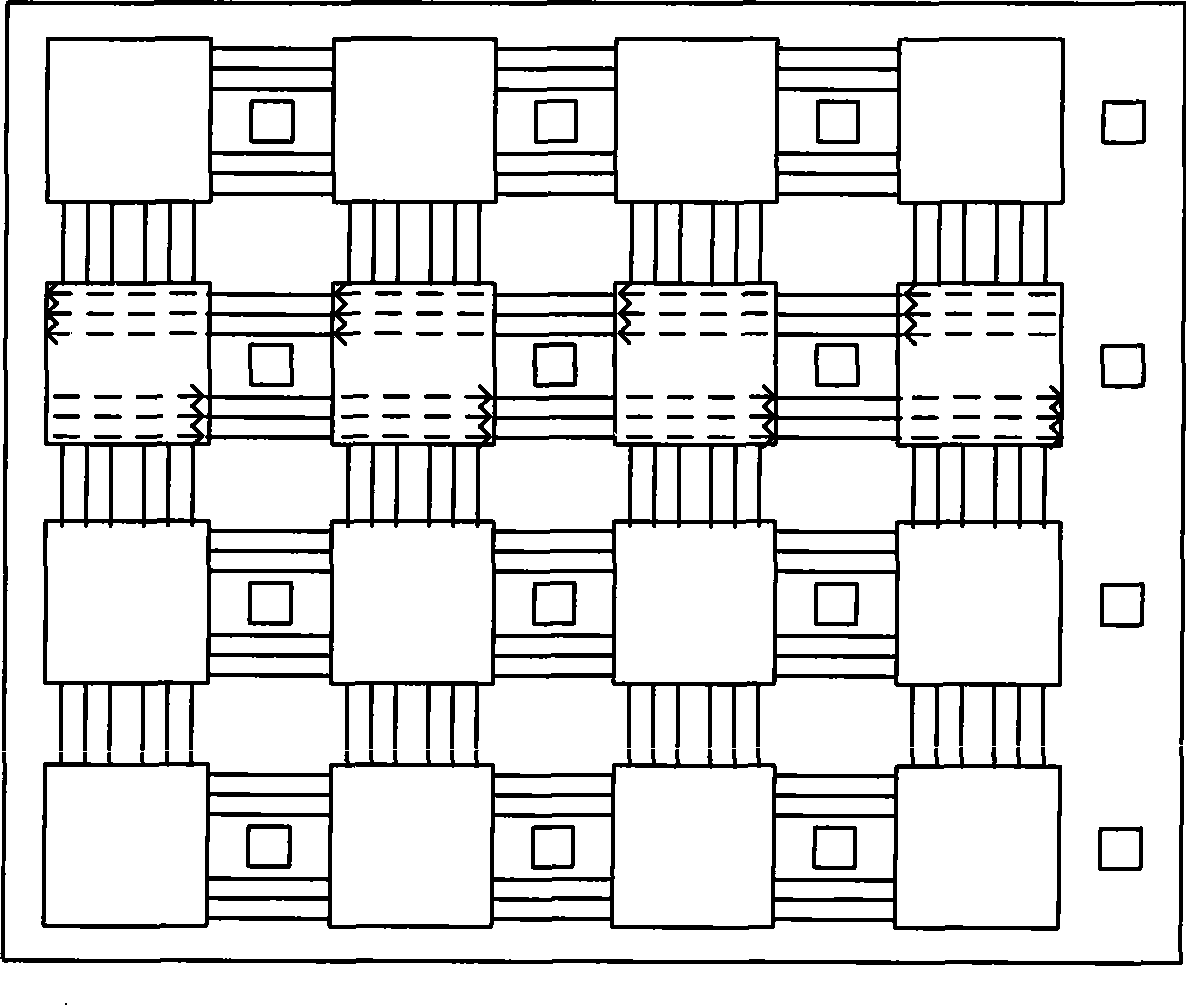

Built-in self-testing circuit of memory suitable for various periodic testing algorithms

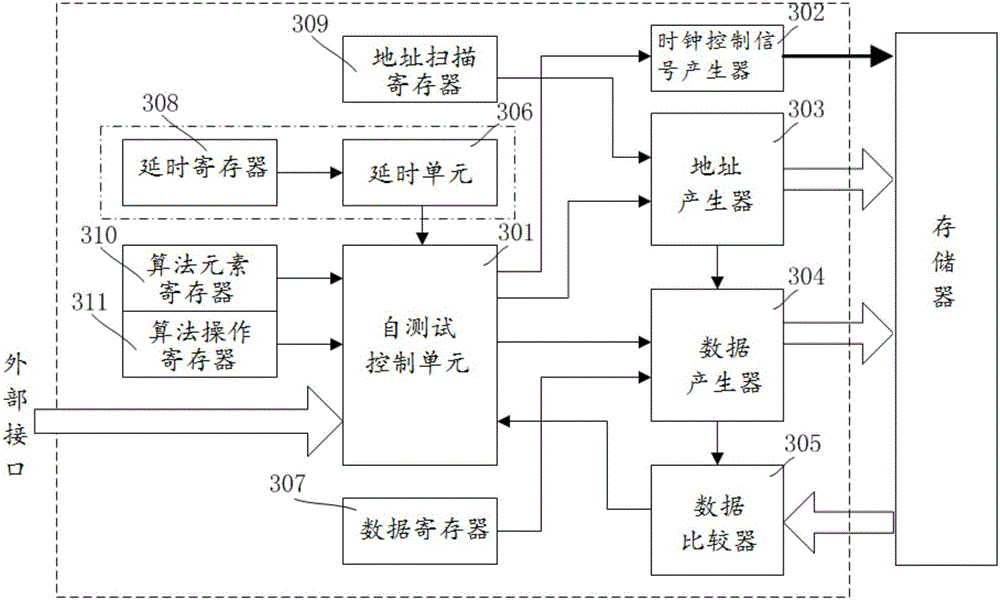

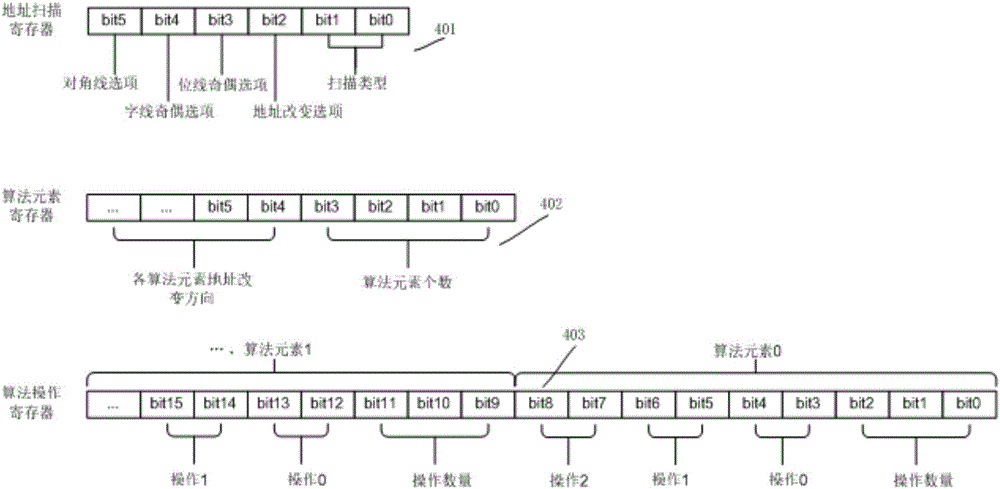

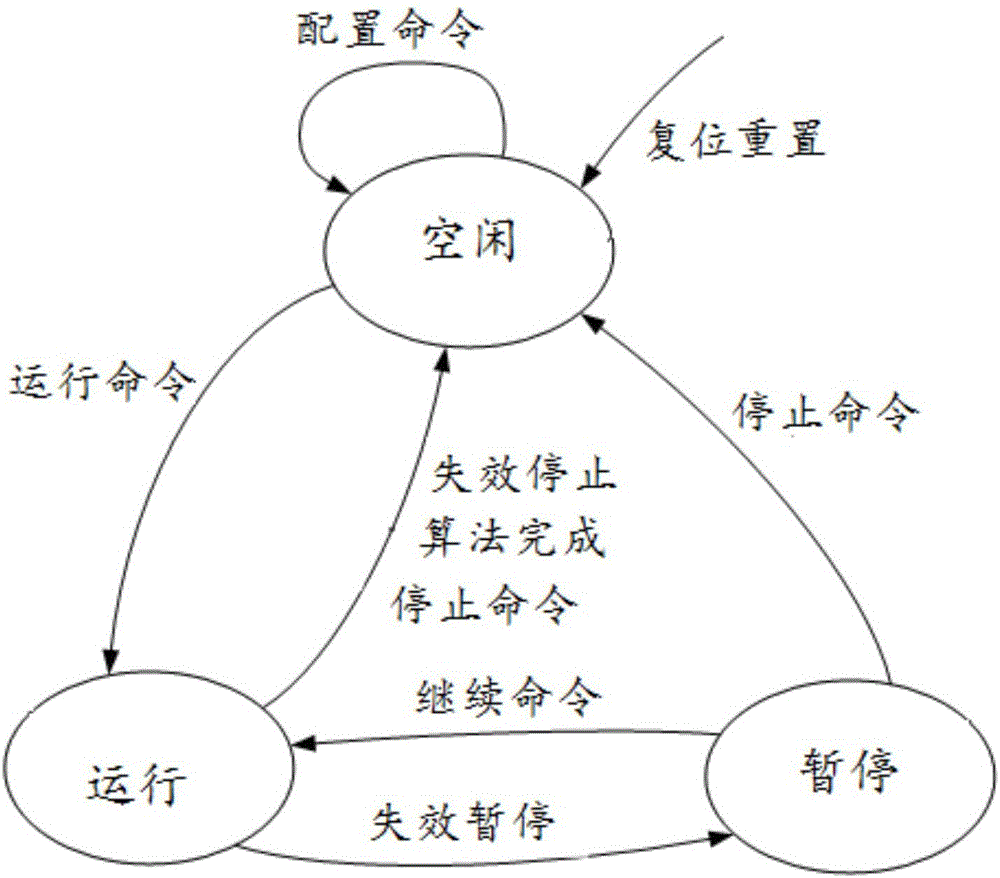

ActiveCN106409343AReduce design difficultyImprove testing flexibilityStatic storageAddress generatorTest algorithm

The invention provides a built-in self-testing circuit of a memory suitable for various periodic testing algorithms. A composition module comprises a built-in self-testing control unit, a clock control signal generator, an address generator, a data generator, a data comparator, an optional delay unit and a plurality of control registers, wherein each control register comprises an address scanning register, an algorithm element register, an algorithm operation register, a data register and a delay register; the built-in self-testing control unit controls other modules to cooperatively work; the clock control signal generator, the address generator and the data generator generate a clock control signal, an address signal and a data signal required by the memory for operation respectively; and the data comparator judges the data reading correctness of the memory and feeds the result back to the built-in self-testing control unit. Various common periodic memory testing algorithms can be achieved by arranging the control registers; and testing and problem analysis work of the memory can be conveniently completed by a corresponding command and an operating state machine design.

Owner:SHANGHAI HUALI MICROELECTRONICS CORP

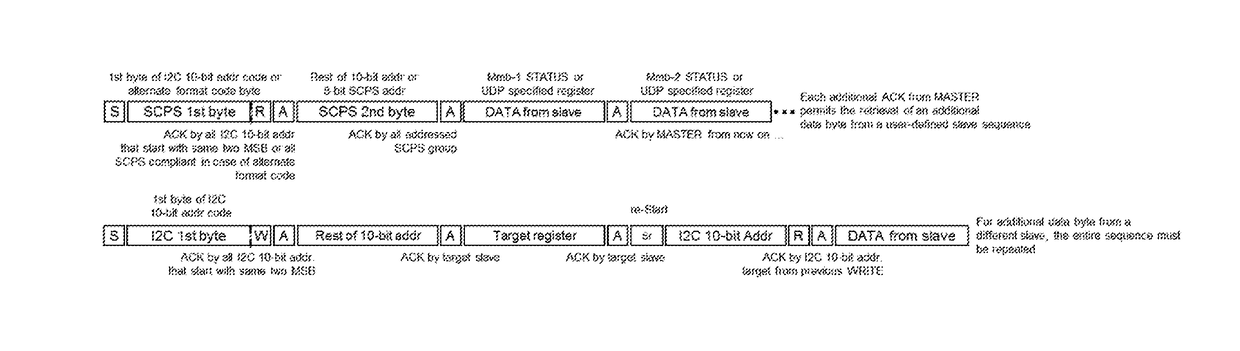

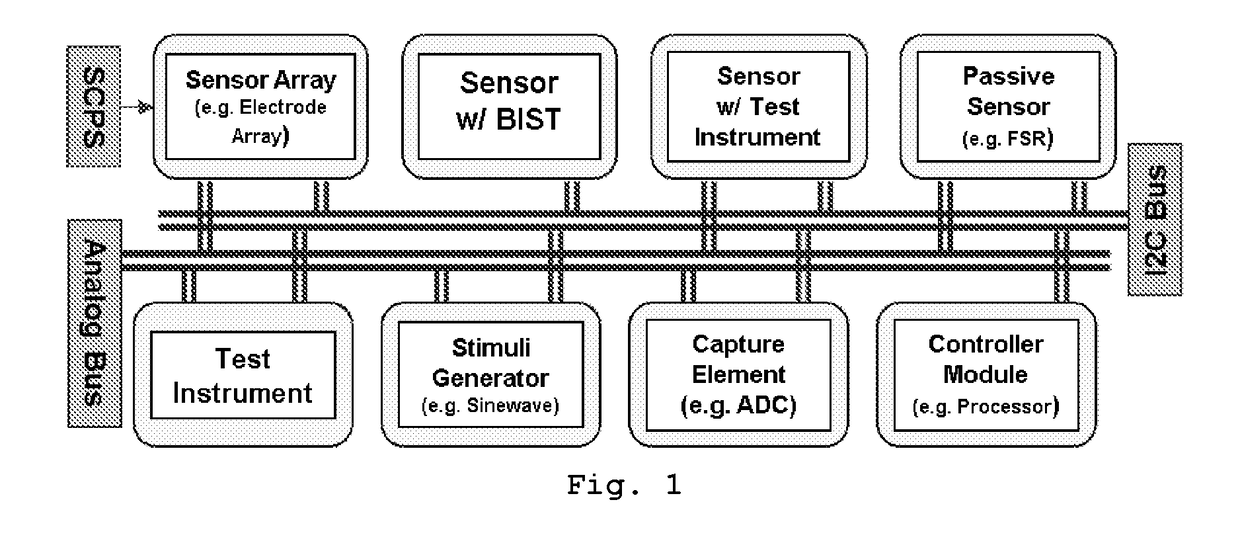

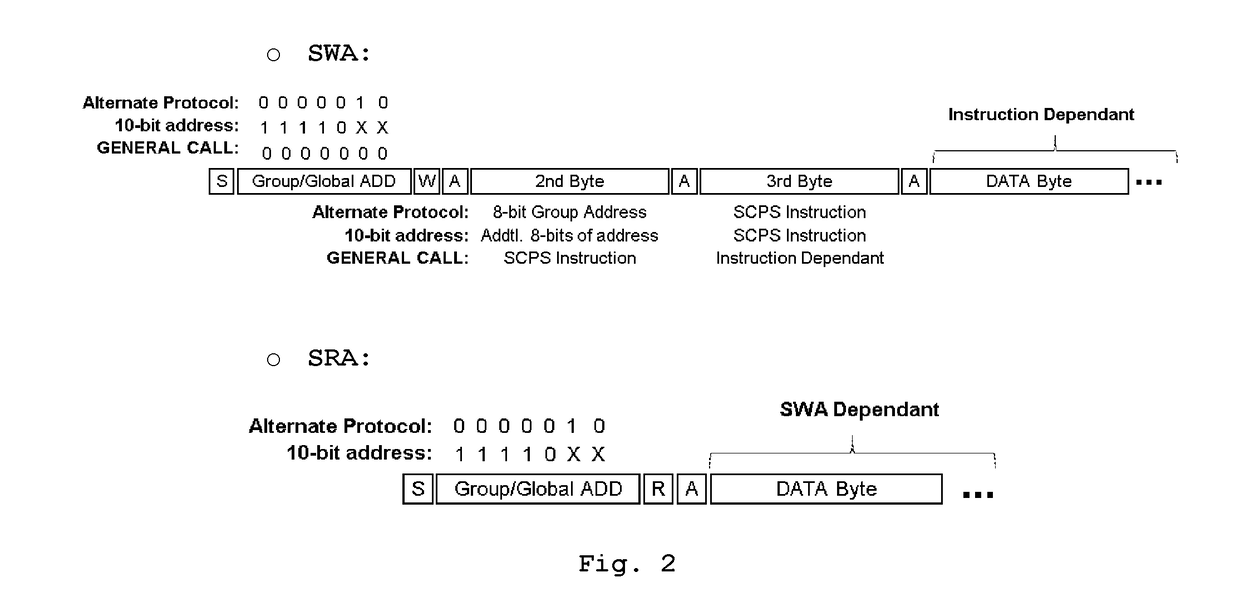

Control module for multiple mixed-signal resources management

ActiveUS20170115987A1Easy to optimizeReducing communication sequenceStatic storageMachine execution arrangementsInitResource management

The present solution targets independent or inter-dependent resource management scenarios such as multi-sensor and other scenarios of possible process / component sharing, intended for individual or group synchronized core task management as part of a flexible long-term solution for monitoring, self-calibration, built-in self-testing, measurements and / or group synchronization dependant strategies. An extension to I2C compatible instruments is described. Disclosed is a module comprising an interpreter sub-module, for receiving and responding to I2C sequences and a register bank module comprising a plurality of registers for storing values. The disclosed module and method of operation can be used for initialization, measurement, and resource management through mixed-signal analog bus scheduling, synchronization and group addressing for built-in calibration strategies for example.

Owner:IP3 2021 SERIES 600 OF ALLIED SECURITY TRUST I

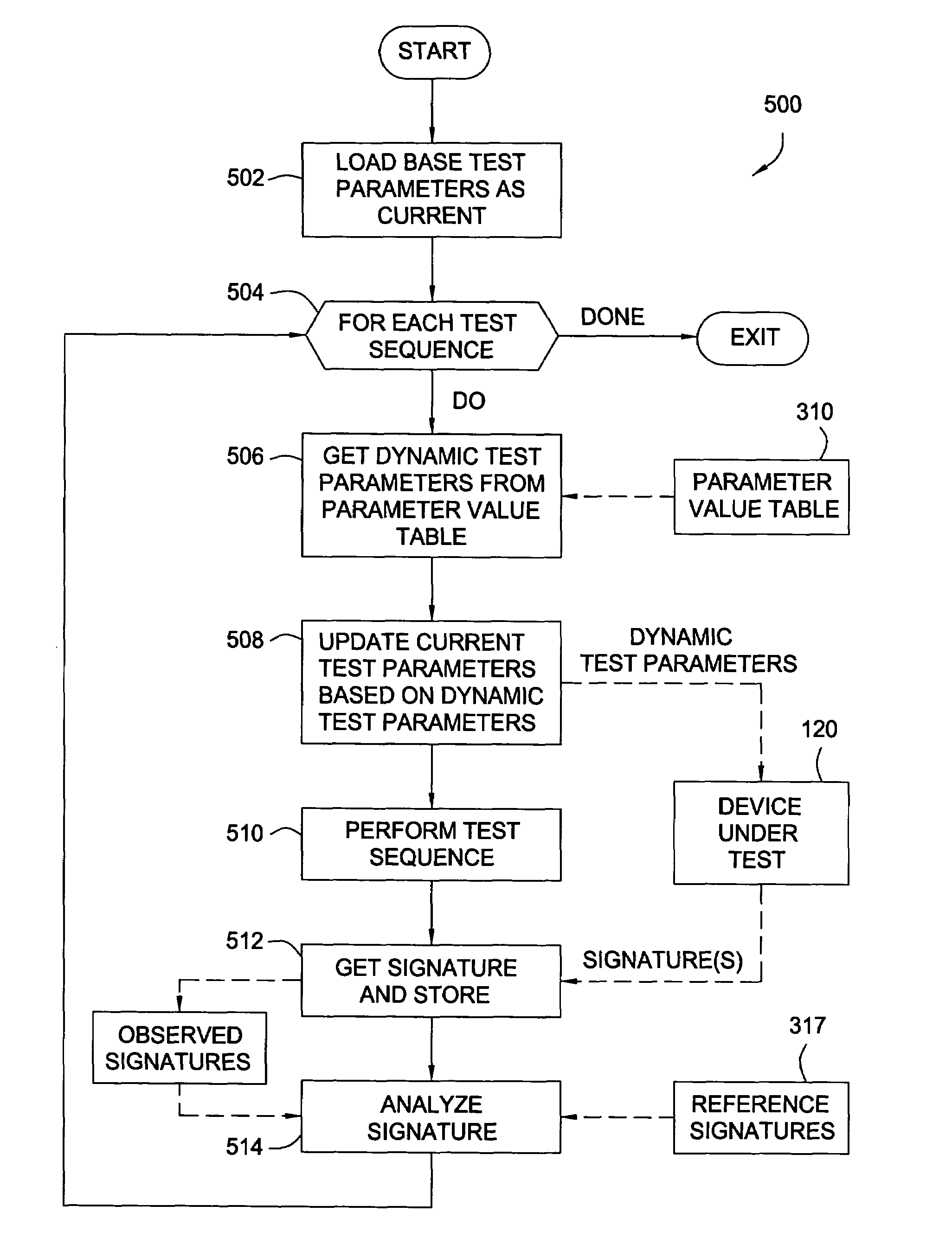

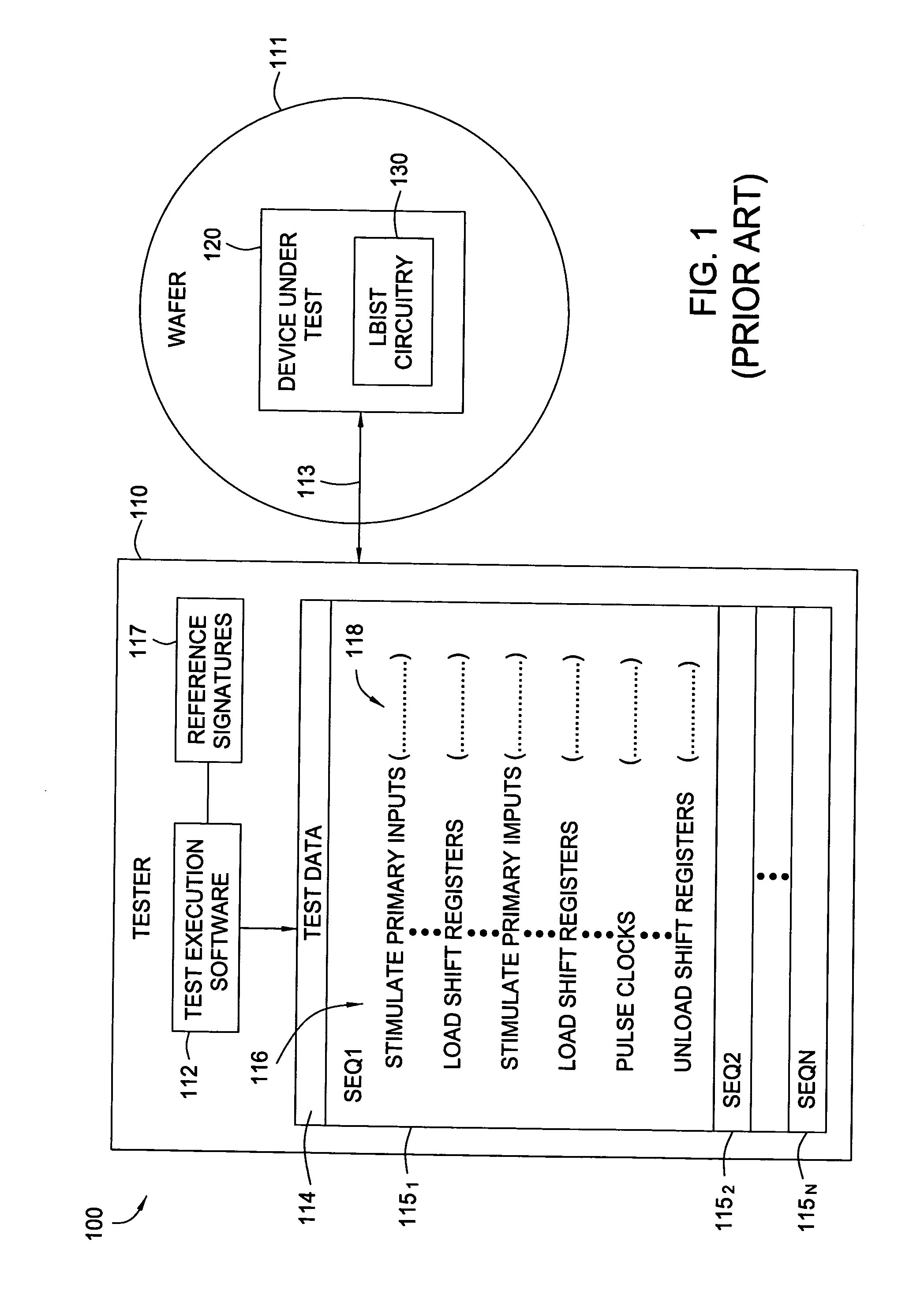

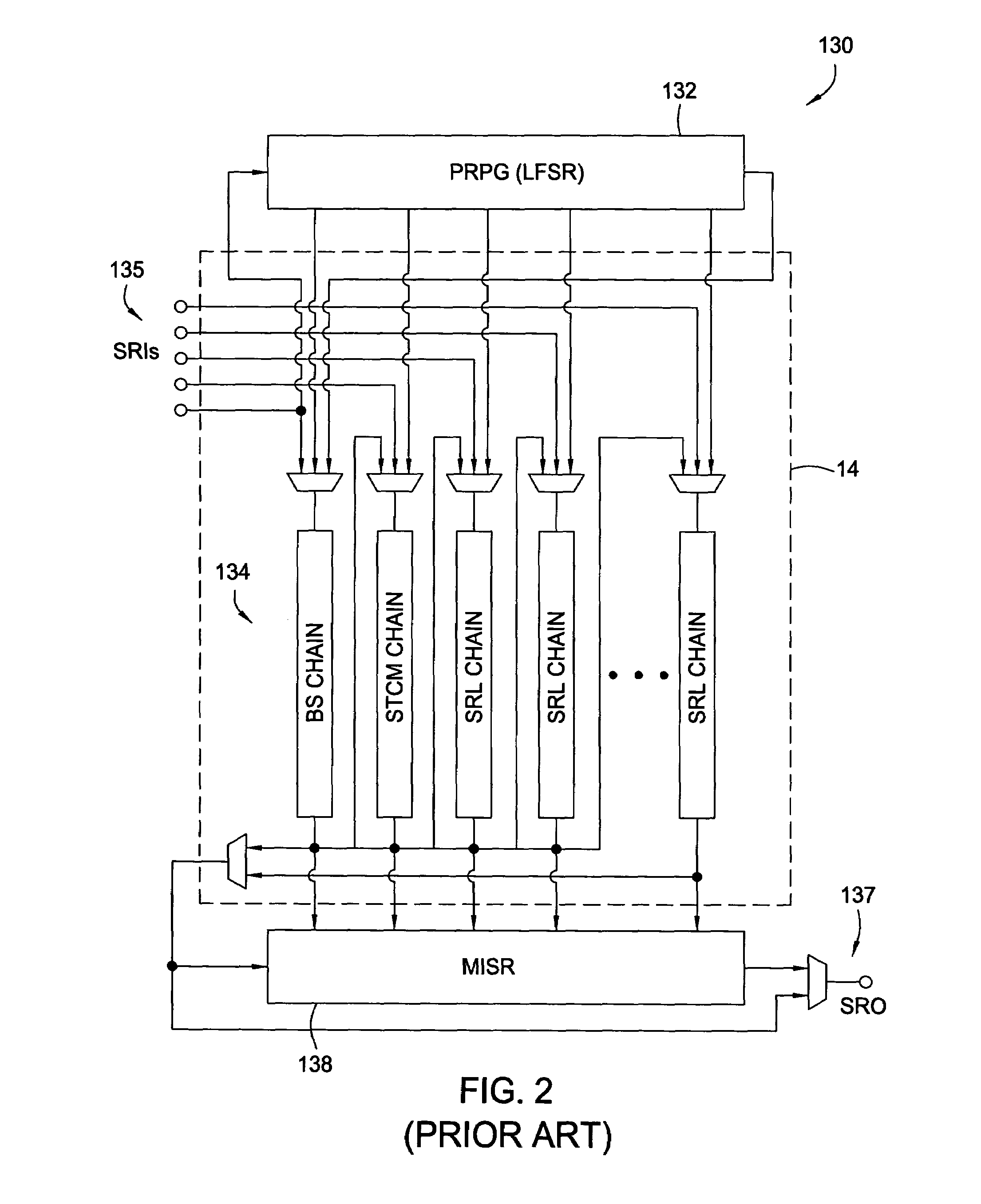

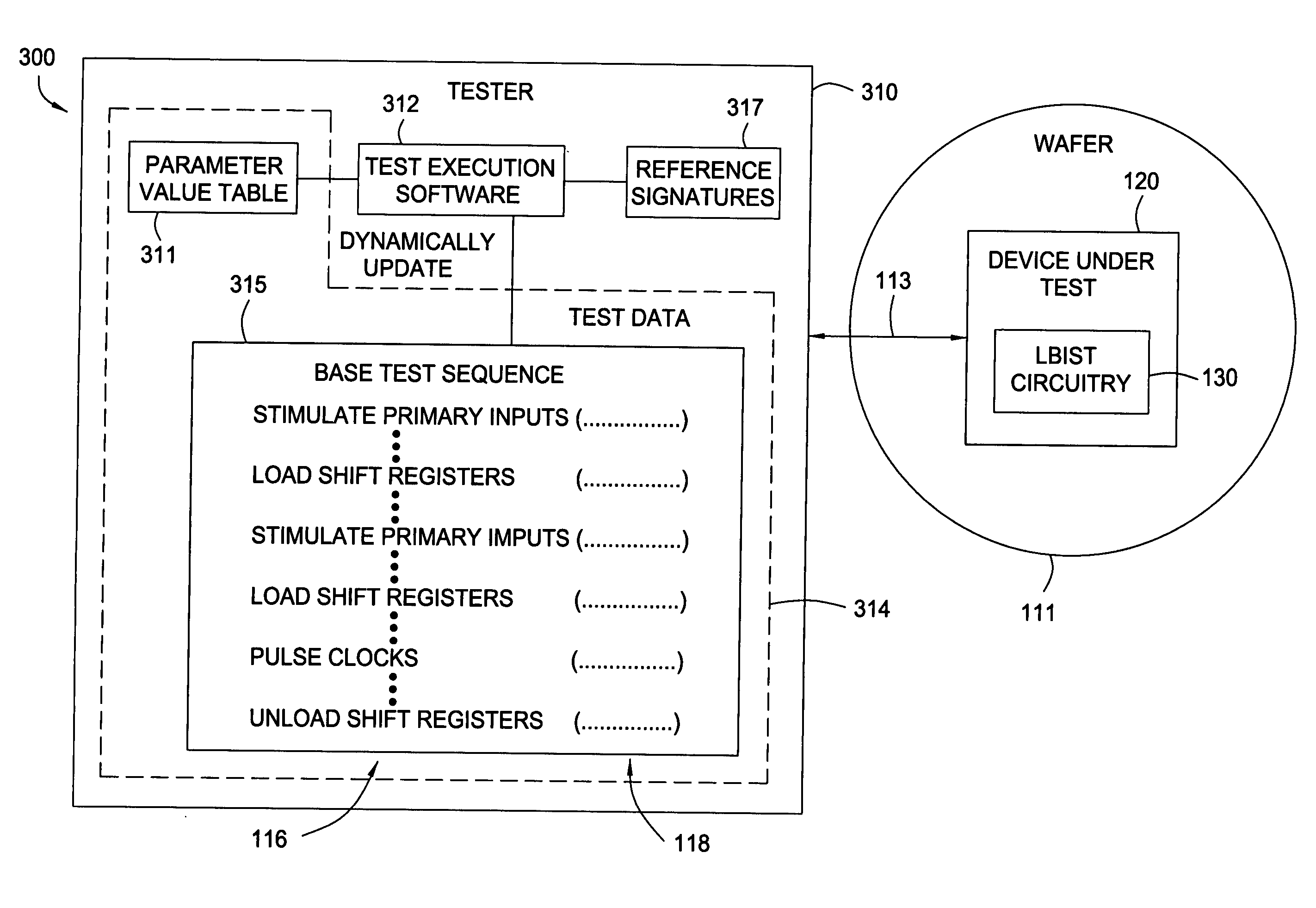

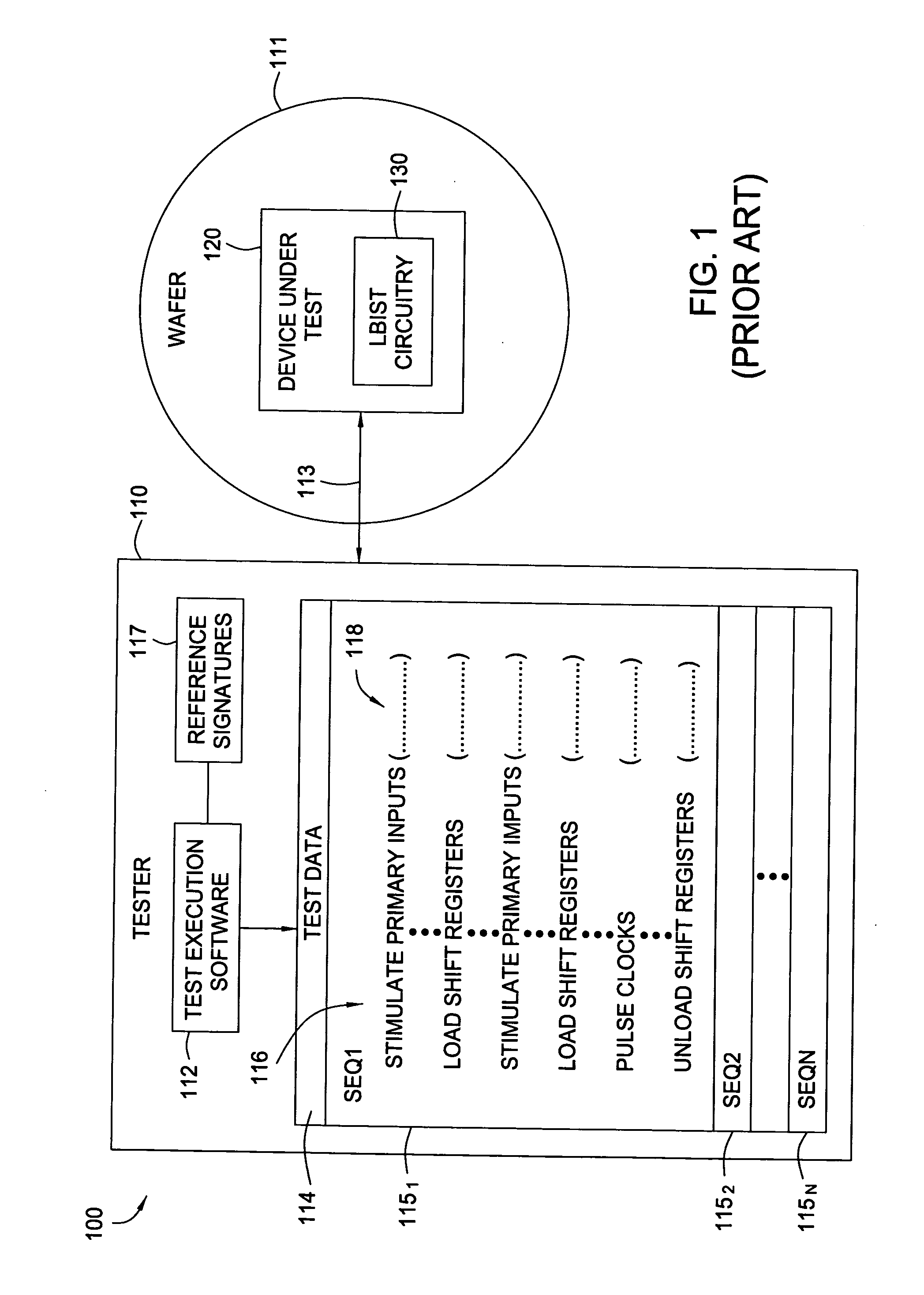

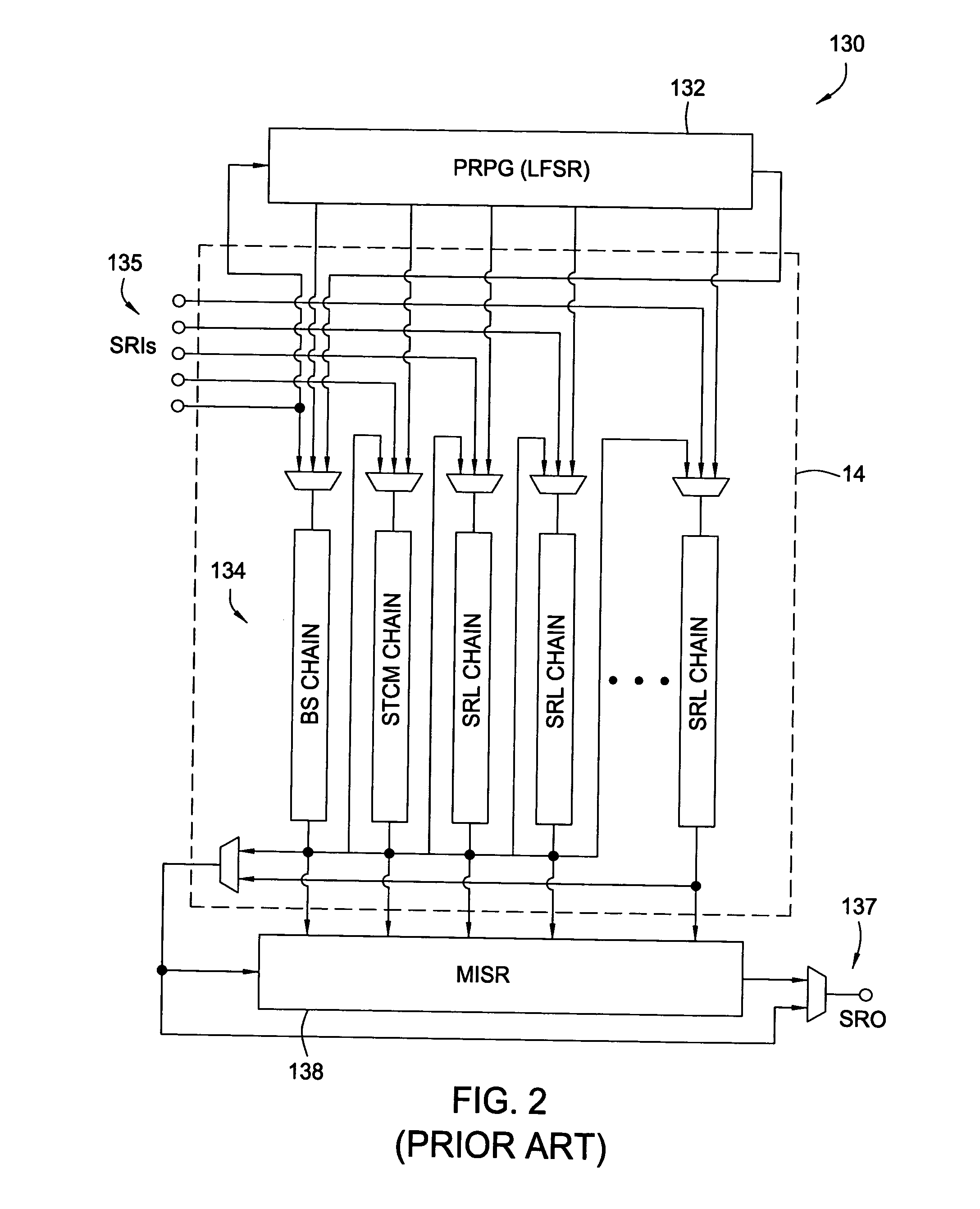

Automated BIST test pattern sequence generator software system and method

InactiveUS7117415B2Lower the volumeElectronic circuit testingError detection/correctionPattern sequenceSoftware system

Methods and systems for reducing the volume of test data associated with built in self testing (BIST) test methodologies (e.g., logical BIST, array BIST, etc.) and pattern structures are provided. Embodiments of the present invention store a limited number of “dynamic” test parameters for each test sequence that have changed relative to a previous test sequence.

Owner:IBM CORP

Automated bist test pattern sequence generator software system and method

InactiveUS20050160339A1Lower the volumeElectronic circuit testingError detection/correctionPattern sequenceSoftware system

Methods and systems for reducing the volume of test data associated with built in self testing (BIST) test methodologies (e.g., logical BIST, array BIST, etc.) and pattern structures are provided. Rather than store the entire set of test parameters for each of a plurality of test sequences to be performed, as with conventional test systems, embodiments of the present invention only store a limited number of “dynamic” test parameters for each test sequence that have changed relative to a previous test sequence.

Owner:IBM CORP

Low cost production testing for memory

Embodiments provide methods, systems, devices, and / or machine readable storage medium for memory built-in self testing (memory BIST) that may not require JTAG. Embodiments may provide less chip overhead through the use of one or more direct access pins. Embodiments may provide simple checks to determine if the memories on a chip are good or bad with minimal cost, for example. In some cases, the memory BIST may determine whether or not memories are good when the chip powers on. Some embodiments may also perform stress testing on the memories to force early life failures of the memories. Embodiments do not necessarily have to diagnose failures.

Owner:CADENCE DESIGN SYST INC

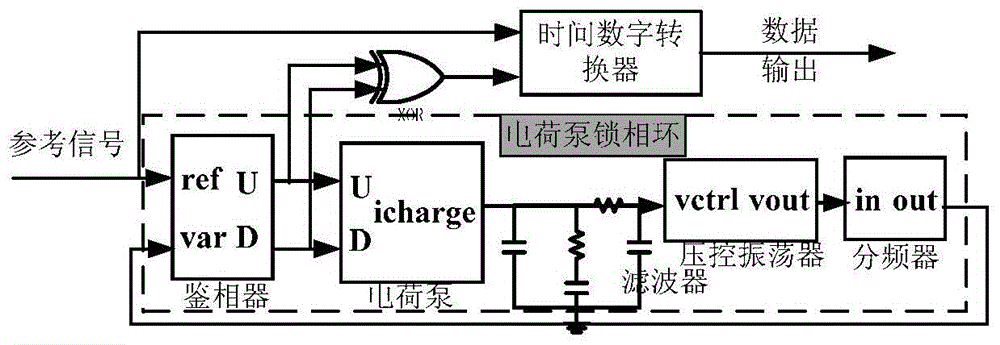

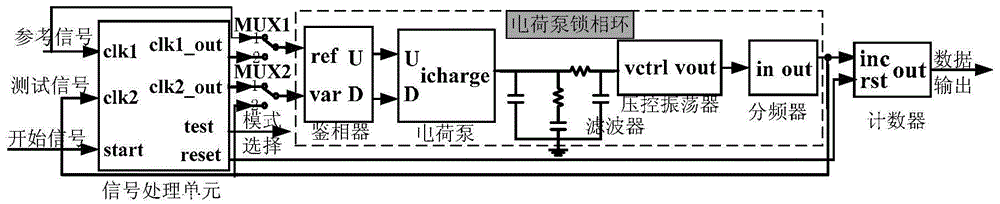

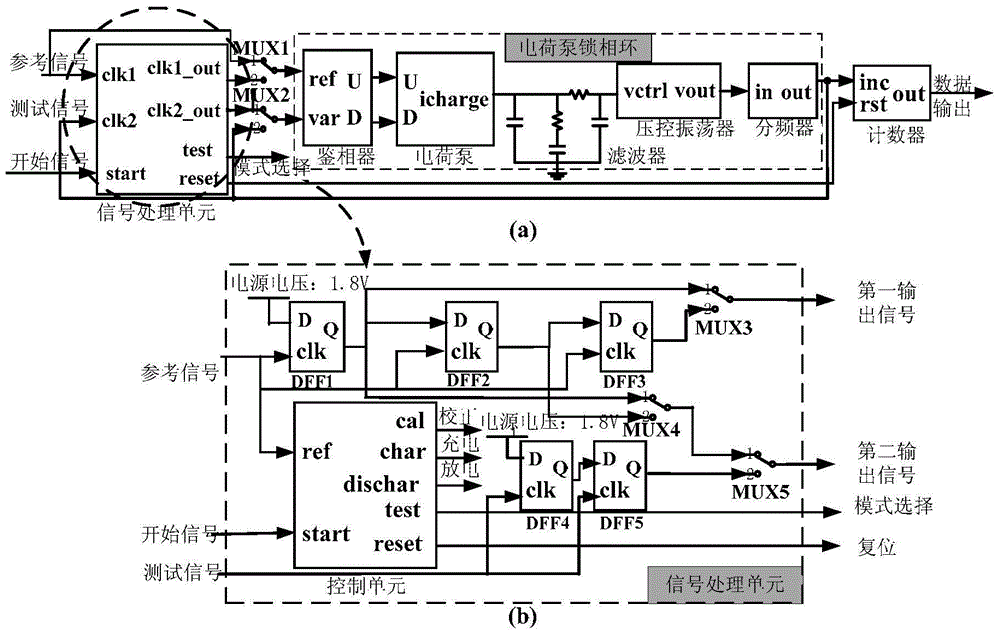

All-digital phase-locked loop built-in self-testing structure

The invention discloses an all-digital phase-locked loop built-in self-testing structure. The time difference between a reference signal and a test signal is converted into a digital signal to be output. The all-digital phase-locked loop built-in self-testing structure comprises a signal processing unit, a first dual-path switch MUX1, a second dual-path switch MUX2, a phase-locked loop to be tested and a counter. The phase-locked loop to be tested is a charge pump phase-locked loop. The reference signal and the test signal are connected to the input end of the phase-locked loop to be tested through the first dual-path switch MUX1 and the second dual-path switch MUX2 respectively, the time difference delta T of two input signals is converted into frequency variation delta f through the phase-locked loop to be tested, then the number of pulses is counted through the counter, and the frequency variation delta f is converted into count value variation delta N. The all-digital phase-locked loop built-in self-testing structure has the advantages of being fully digital, high in precision and low in cost.

Owner:SOUTHEAST UNIV

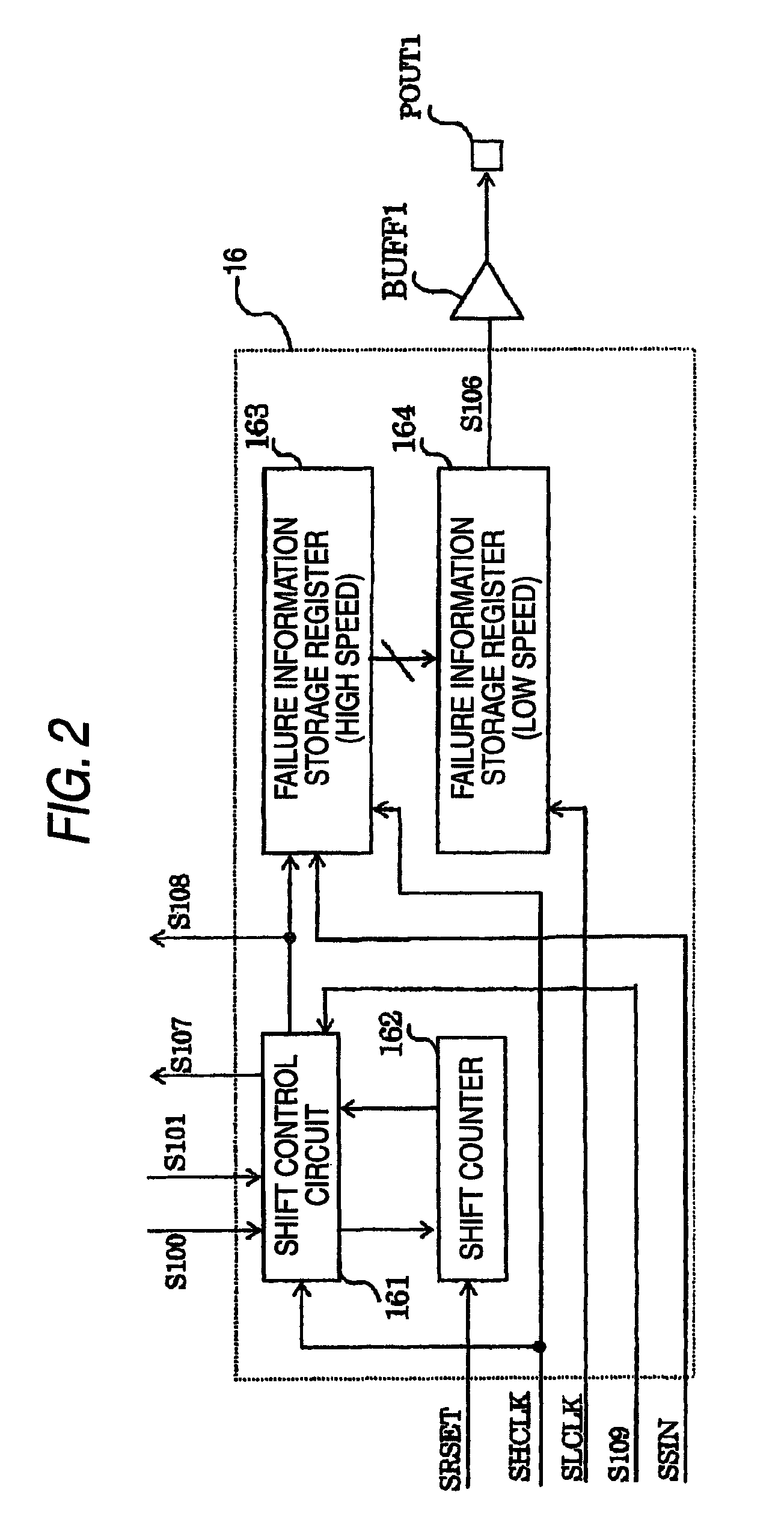

Built-in self testing circuit with fault diagnostic capability

A semiconductor integrated circuit includes: a memory collars including: a memory cell; a fetch register that is configured to fetch data as a first fetch data; a comparing unit that is configured to compare the first fetch data with an expected value; a failure detecting signal output unit that is configured to receive the compared result and output a failure detecting signal; and a BIST circuit including: a BIST control unit that is configured to output an instruction and output a BIST status; a shift controller that is configured to receive a first clock signal, the BIST status signal, and the failure detecting signal and output sift enable signal; a shift counter that counts the number of clock pulses on the first clock signal; a first storage register that is configured to receive the first clock signal and the shift enable signal, and a second storage register that is configured to receive a second clock signal.

Owner:KK TOSHIBA