Built-in self-testing circuit and clock switching circuit of programmable memory

A built-in self-test circuit and built-in self-test technology, applied in static memory, instruments, etc., can solve the problems of increased production cost, difficult test work, large chip area, etc., to reduce the area, increase the area, and reduce the chip size. area effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

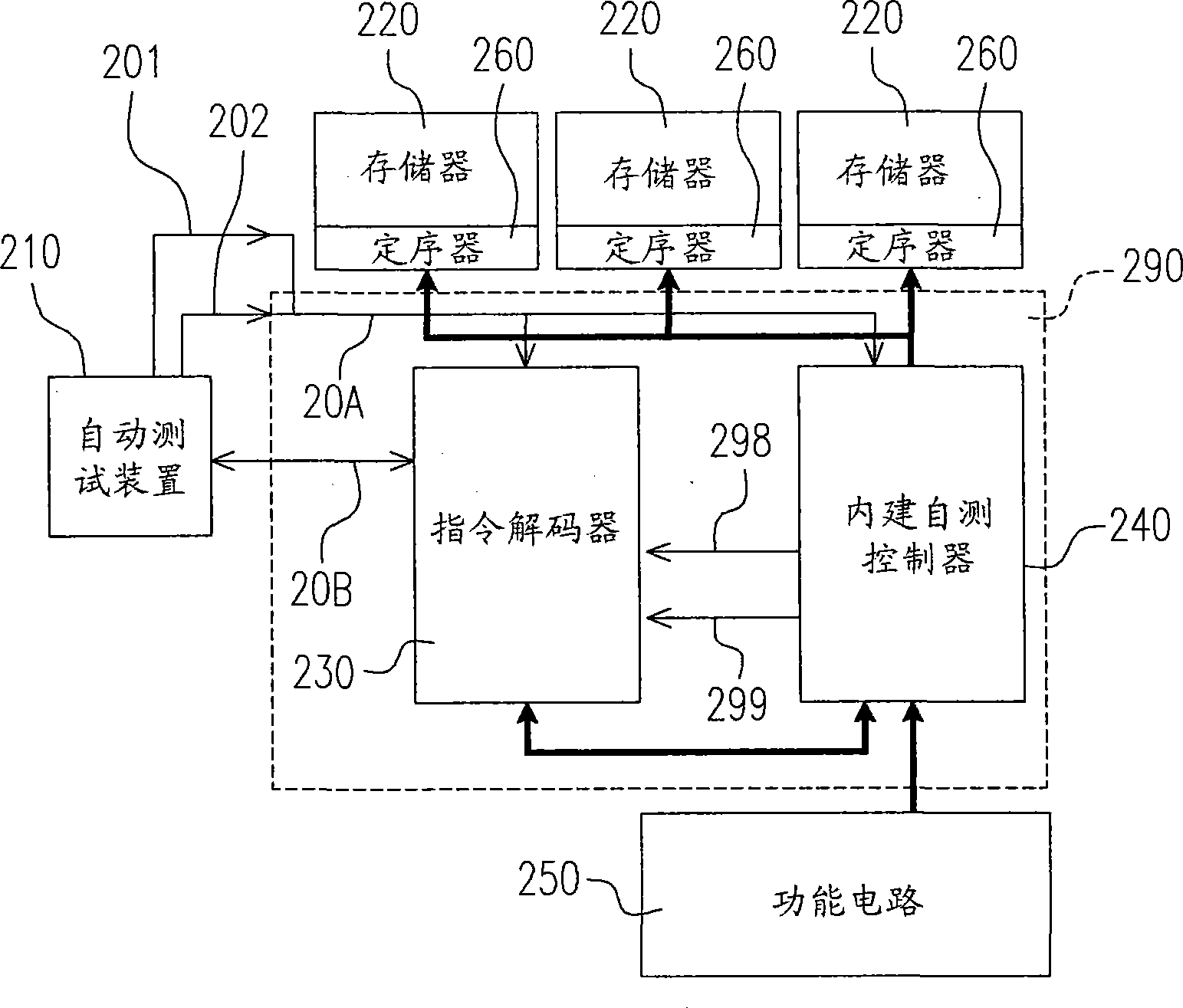

[0076] Figure 2A It is an embodiment of the memory built-in self-test circuit of the present invention, which includes a memory built-in self-test circuit 290, a memory under test 220, a sequencer (sequencer) 260 to which the memory under test 220 belongs, and an external automatic test device 210 and a functional circuit 250 . Each tested memory 220 and its corresponding sequence generator 260 are respectively coupled with the memory built-in self-test circuit 290, the memory built-in self-test circuit 290 is coupled with the automatic test device 210, and the function circuit 250 is also connected with the memory built-in self-test circuit 290. Built-in self-test circuit 290 is coupled.

[0077] Please refer to Figure 2A As shown, the memory built-in self-test circuit 290 includes a command decoder 230 and a built-in self-test controller 240 coupled to each other. The built-in self-test controller 240 and the instruction decoder 230 receive the control signal 20A, where...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More