Interconnection line test circuit used in field programmable gate array device

A technology for testing circuits and interconnecting wires, applied in the direction of measuring electricity, measuring electrical variables, and electronic circuit testing, etc., can solve problems such as inapplicability, and achieve the effects of improving reliability, reducing configuration, and shortening test time

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0037] In order to make the above objects, features and advantages of the present invention more comprehensible, the present invention will be further described in detail below in conjunction with the accompanying drawings and specific embodiments.

[0038] FPGA devices have the advantages of high integration, small size, special application functions can be realized through user programming, short design and development cycle, reconfigurability, etc., and then become a hot spot in the development of electronic systems.

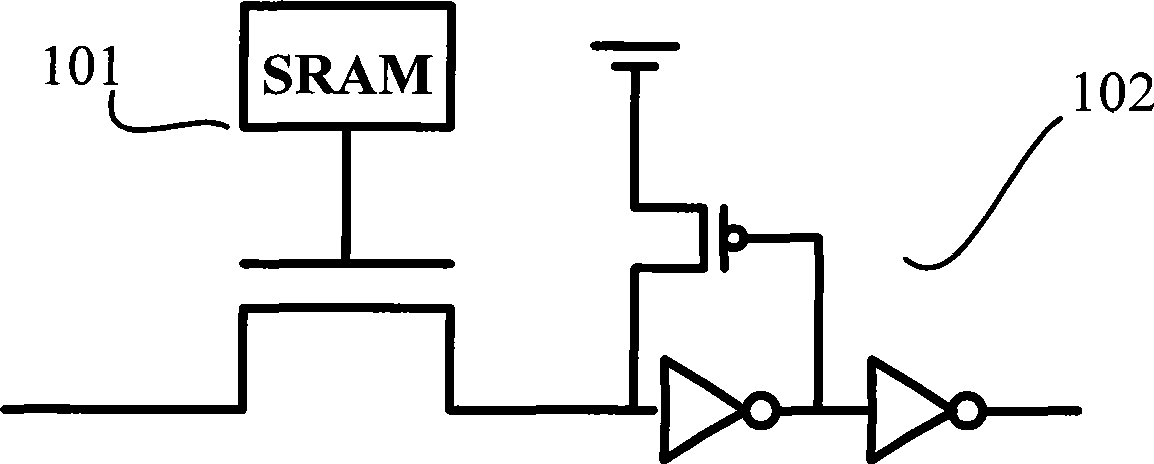

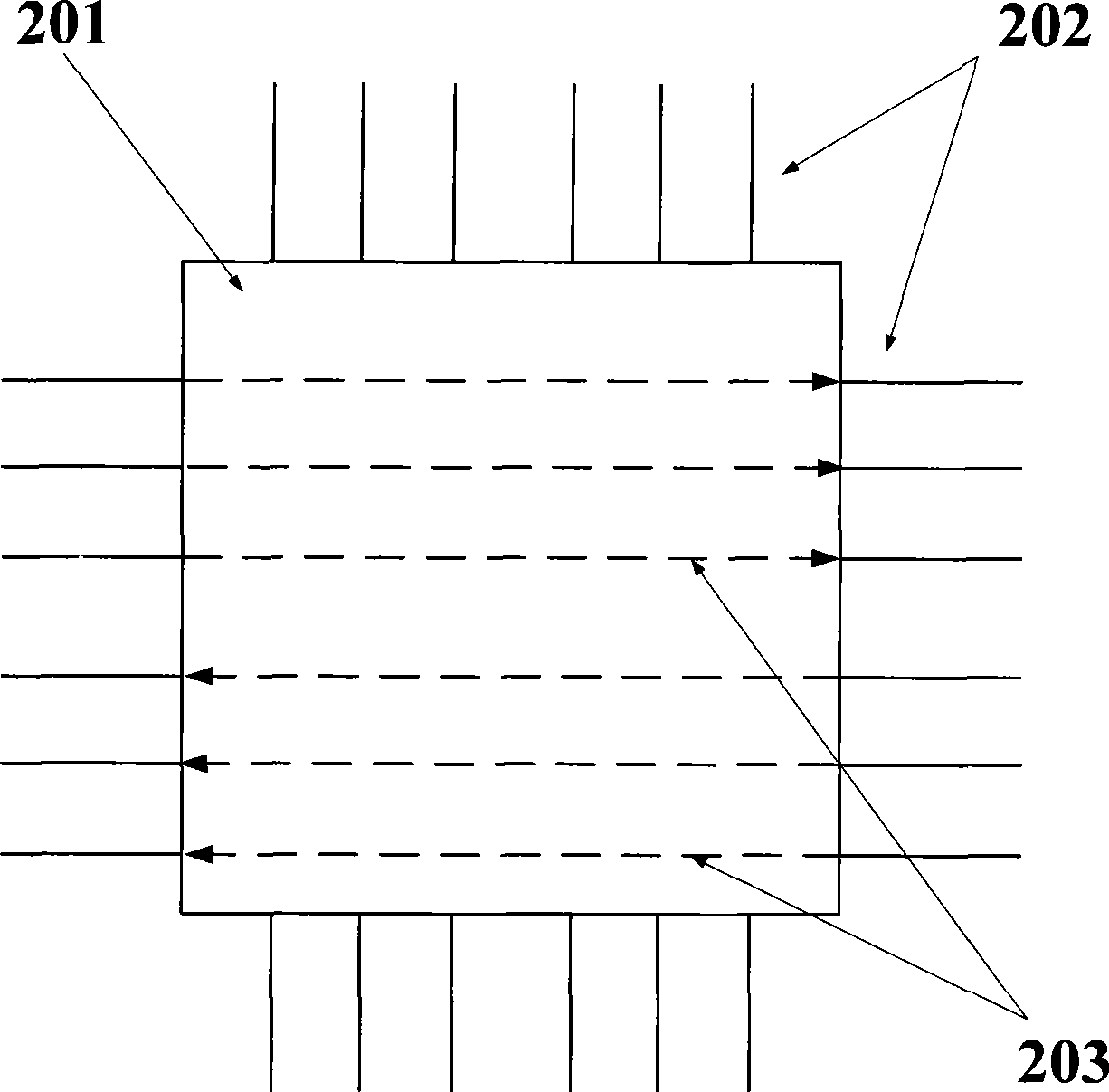

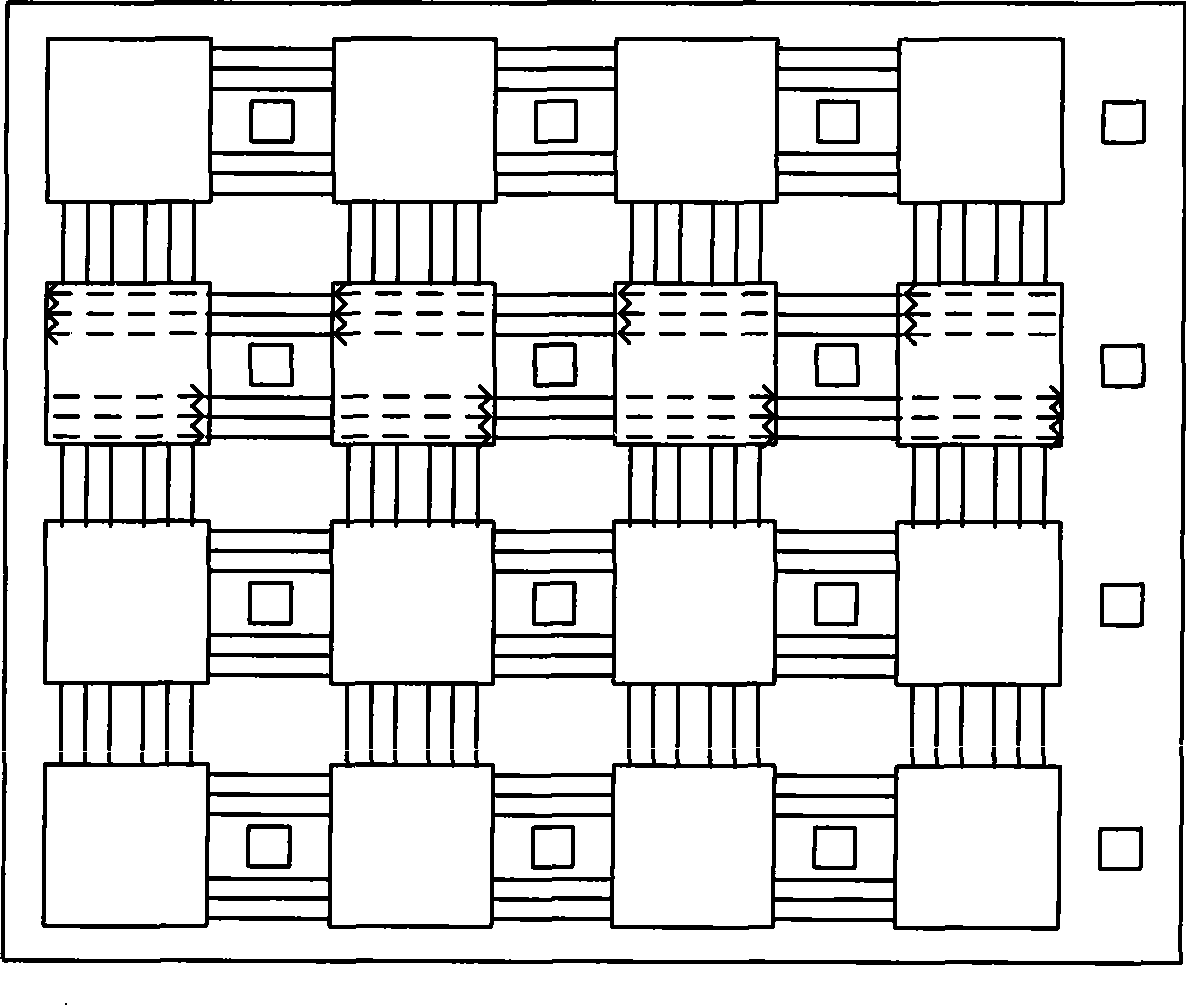

[0039] In the basic structure of FPGA, CLB is the basic unit for realizing user functions. Multiple logic function blocks are usually arranged in an array structure regularly and distributed throughout the FPGA chip; IOB completes the interface between the internal logic of FPGA chip and external pins, and surrounds Around the logic cell array; IR includes wiring segments of various lengths and some programmable connection switches, which connect each CLB or I...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More