Built-in self-testing method of FPGA input/output module

An input and output module, built-in self-test technology, applied in the direction of measuring electricity, measuring devices, measuring electrical variables, etc., can solve the problems of difficult test implementation, complicated theoretical design, and time-consuming testing, so as to reduce the number of test configurations, The effect of simplifying retrieval methods and reducing testing costs

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

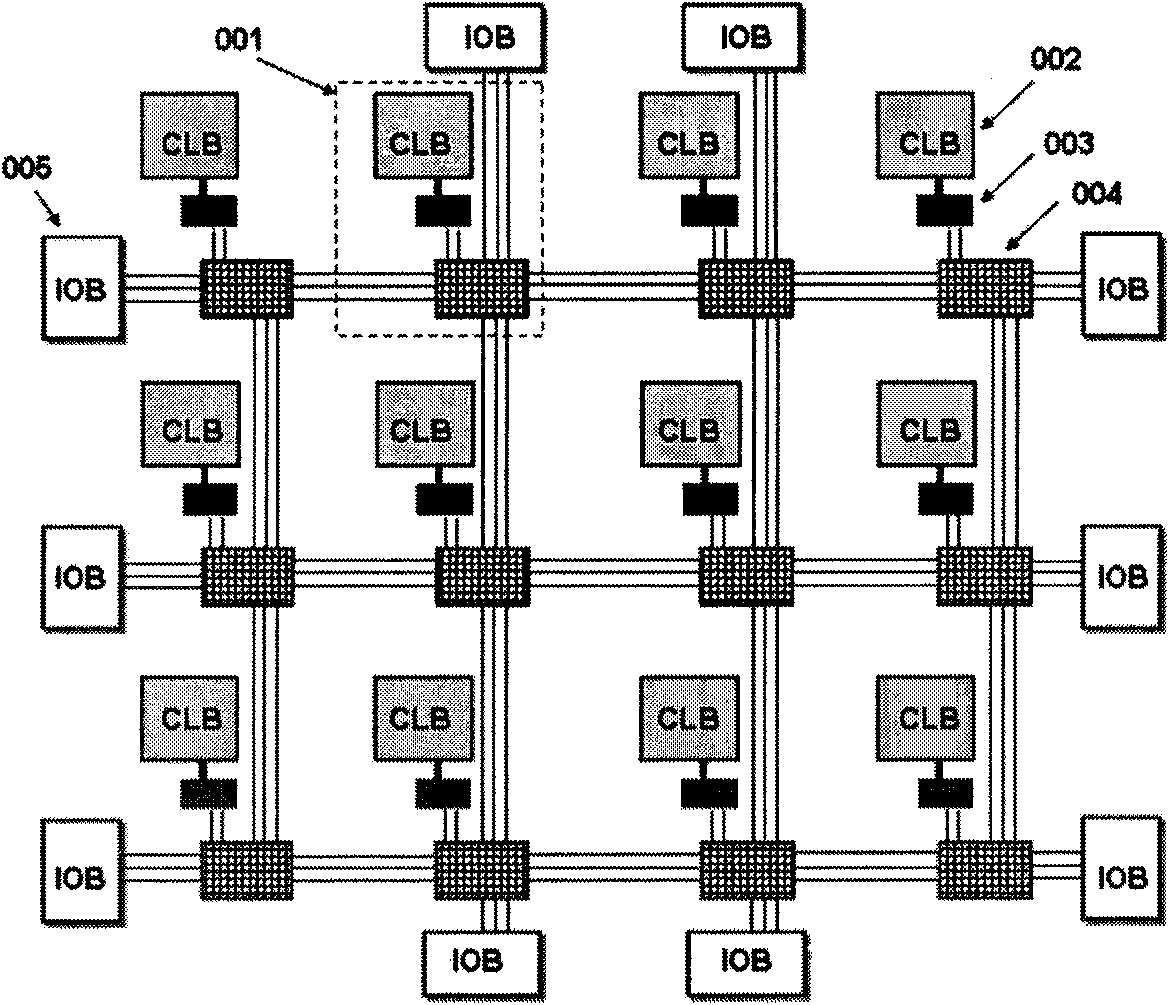

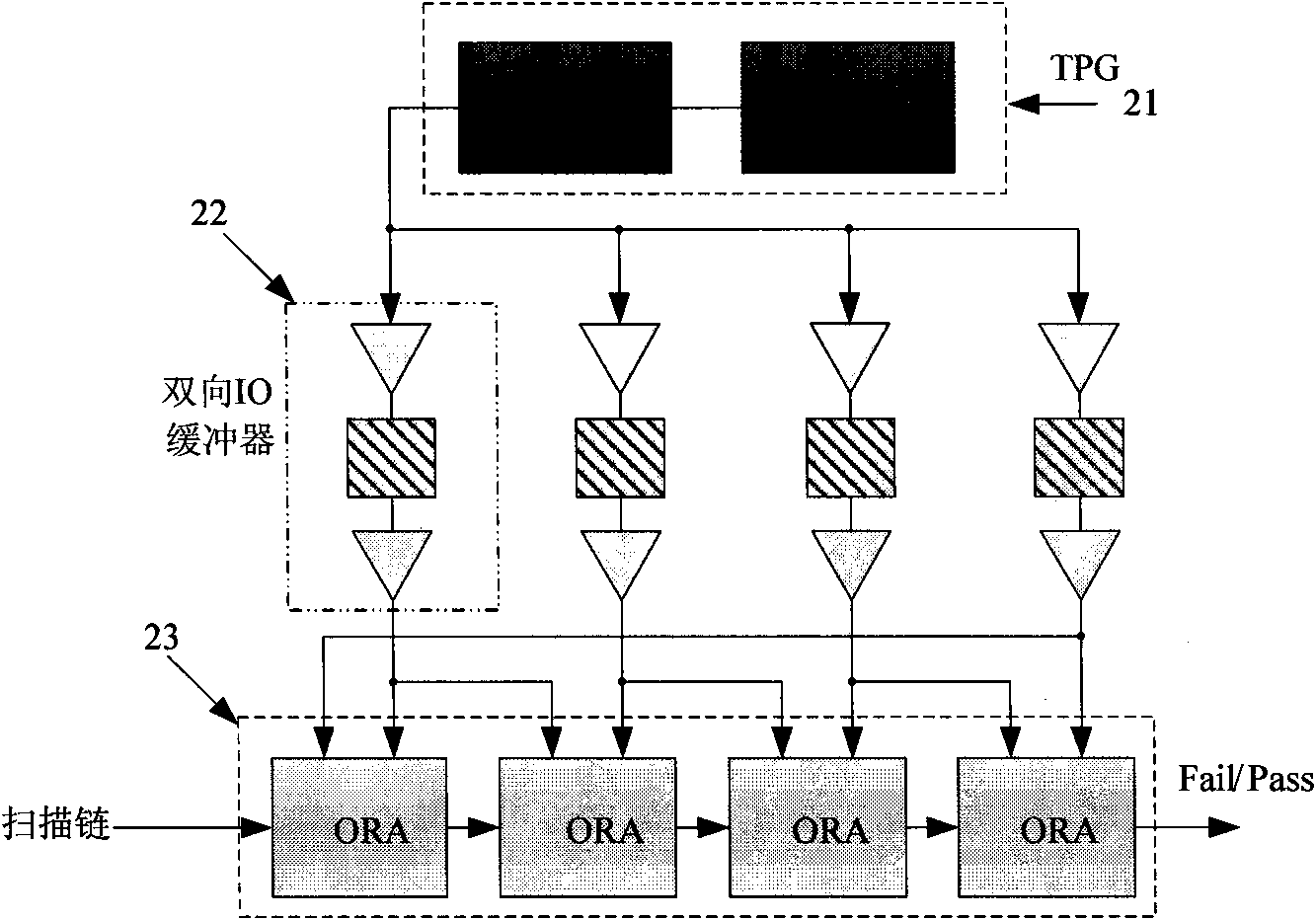

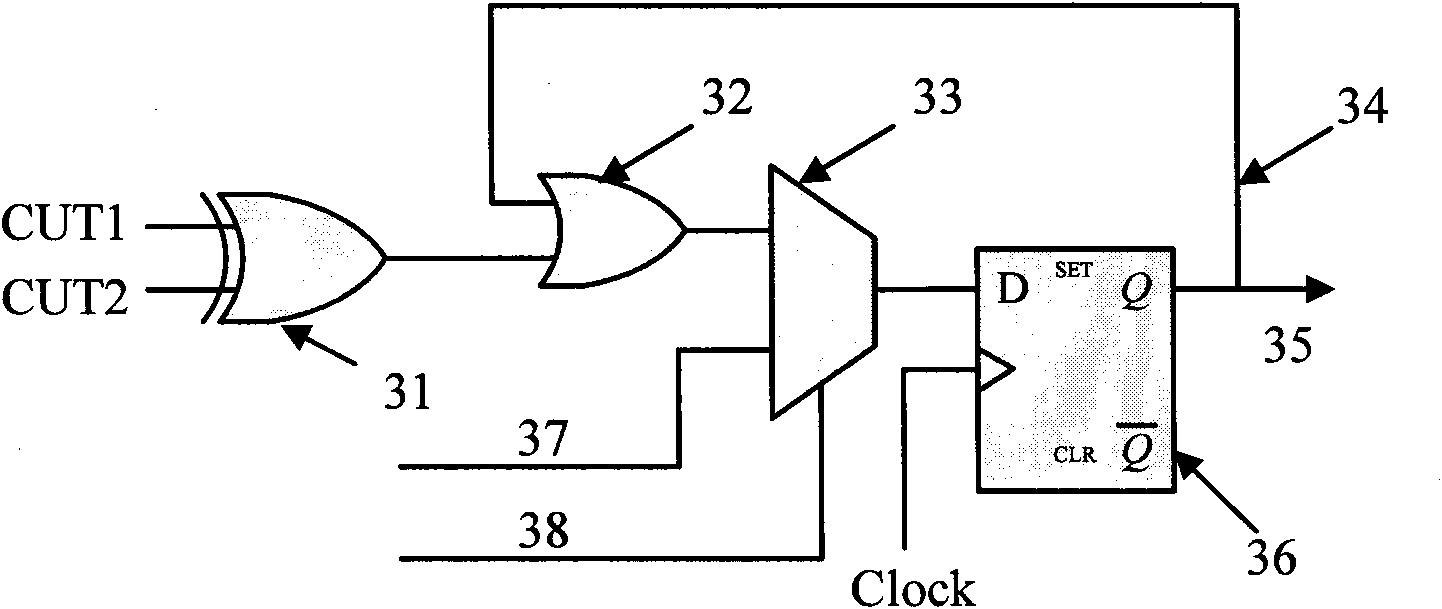

[0025] FPGA basic circuit structure such as figure 1 As shown, it is mainly composed of TITLE array 001 and input and output module 005. Programmable logic module 002 is a logic unit in one of TITLE array 001, and it realizes interconnection with surrounding programmable logic modules through IMUX003 and switch matrix 004 , users can flexibly implement various functions by configuring the programmable logic module 002. In traditional FPGA testing methods, it is often necessary to first ensure the correct function of the input and output modules before testing other modules. In the present invention, all input and output modules are configured as bidirectional IO buffers, such as figure 2 As shown, the internal resources of the IO buffer are tested through the optimized configuration, and the test results are output through the scan register chain. First part logic resources are configured into test vector generation circuit 21 and output response analysis circuit 23, all IO...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More