Patents

Literature

49 results about "Stuck-at fault" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

A stuck-at fault is a particular fault model used by fault simulators and automatic test pattern generation (ATPG) tools to mimic a manufacturing defect within an integrated circuit. Individual signals and pins are assumed to be stuck at Logical '1', '0' and 'X'. For example, an input is tied to a logical 1 state during test generation to assure that a manufacturing defect with that type of behavior can be found with a specific test pattern. Likewise the input could be tied to a logical 0 to model the behavior of a defective circuit that cannot switch its output pin. Not all faults can be analyzed using the stuck-at fault model. Compensation for static hazards, namely branching signals, can render a circuit untestable using this model. Also, redundant circuits cannot be tested using this model, since by design there is no change in any output as a result of a single fault.

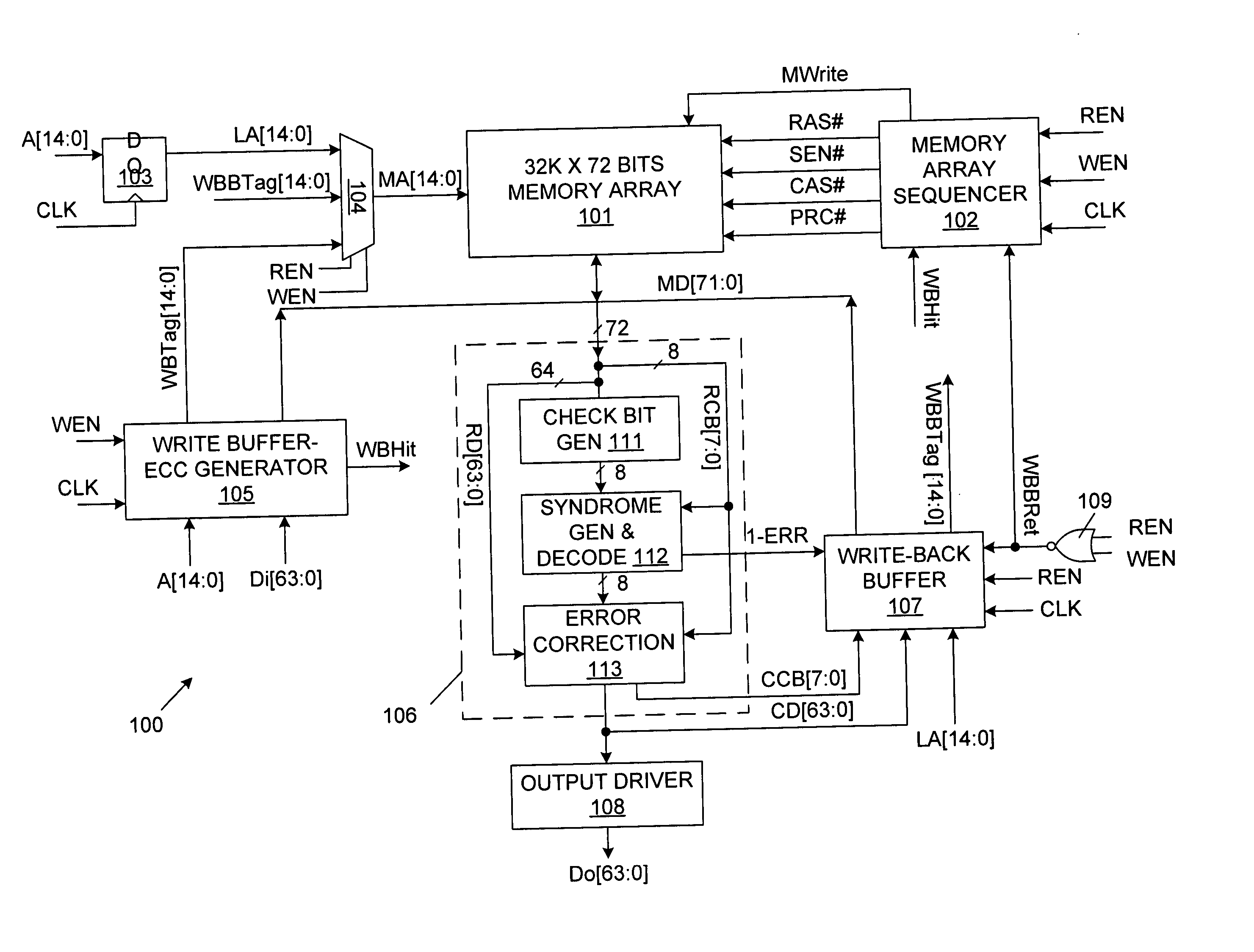

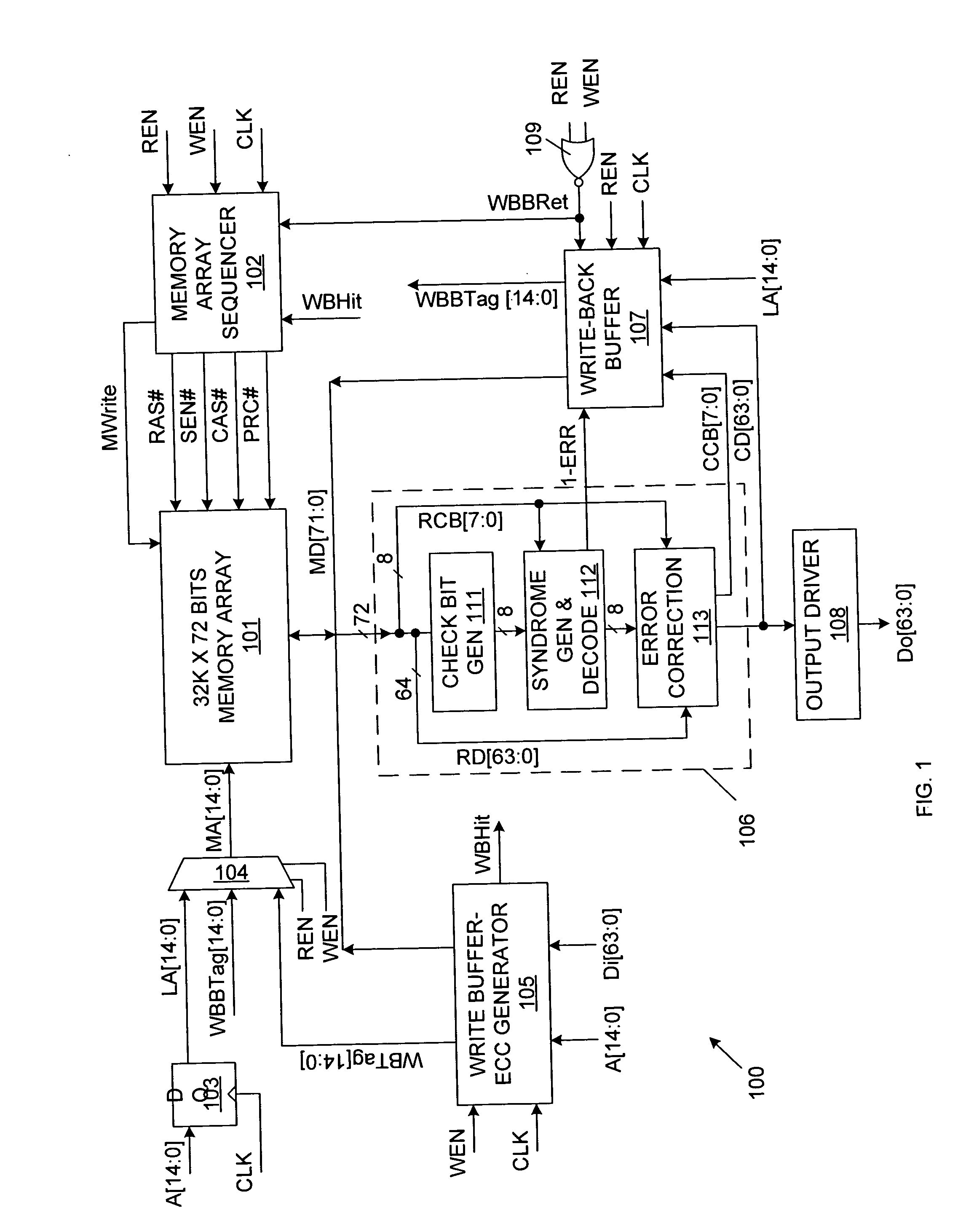

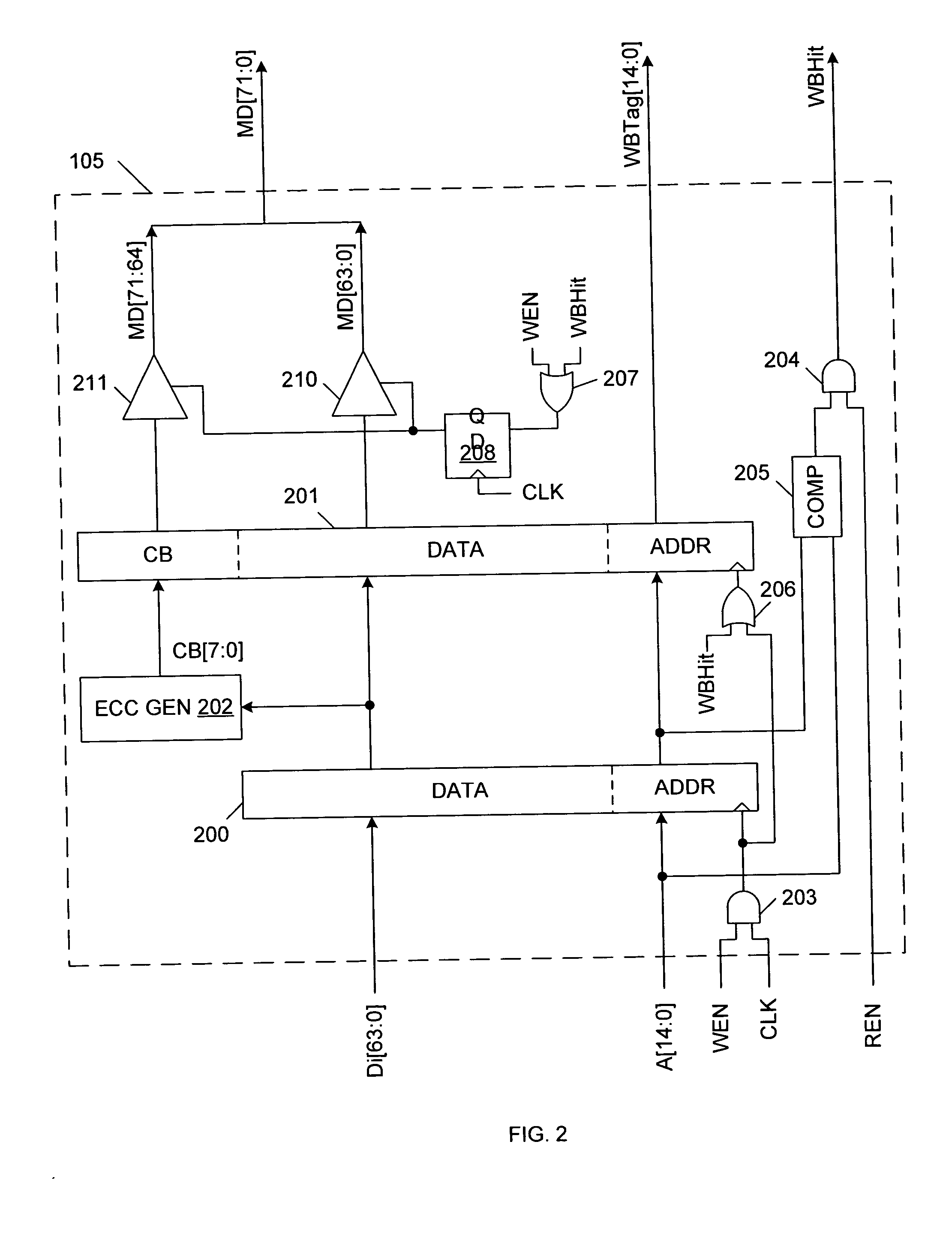

Transparent error correcting memory

InactiveUS20050044467A1Not increase write access timeShorten the timeCode conversionCoding detailsMemory interfaceTerm memory

A memory system with transparent error correction circuitry provides full stuck-at fault coverage for both test data patterns and the corresponding error correction code (ECC) values. The memory system includes a semiconductor memory having a memory array, a memory interface and an error detection / correction unit. The memory array is configured to store test data patterns and corresponding error correction code (ECC) values. The memory interface is configured such that the ECC values are not directly accessible. The error detection / correction unit is configured to correct single-bit errors in the test data patterns and corresponding ECC values. A set of test data patterns associated with the semiconductor memory is selected such that any multiple-bit error in a test data pattern and the corresponding ECC value causes the error detection / correction unit to provide an output data pattern having an error, thereby rendering multiple-bit faults 100% detectable.

Owner:MOSYS INC

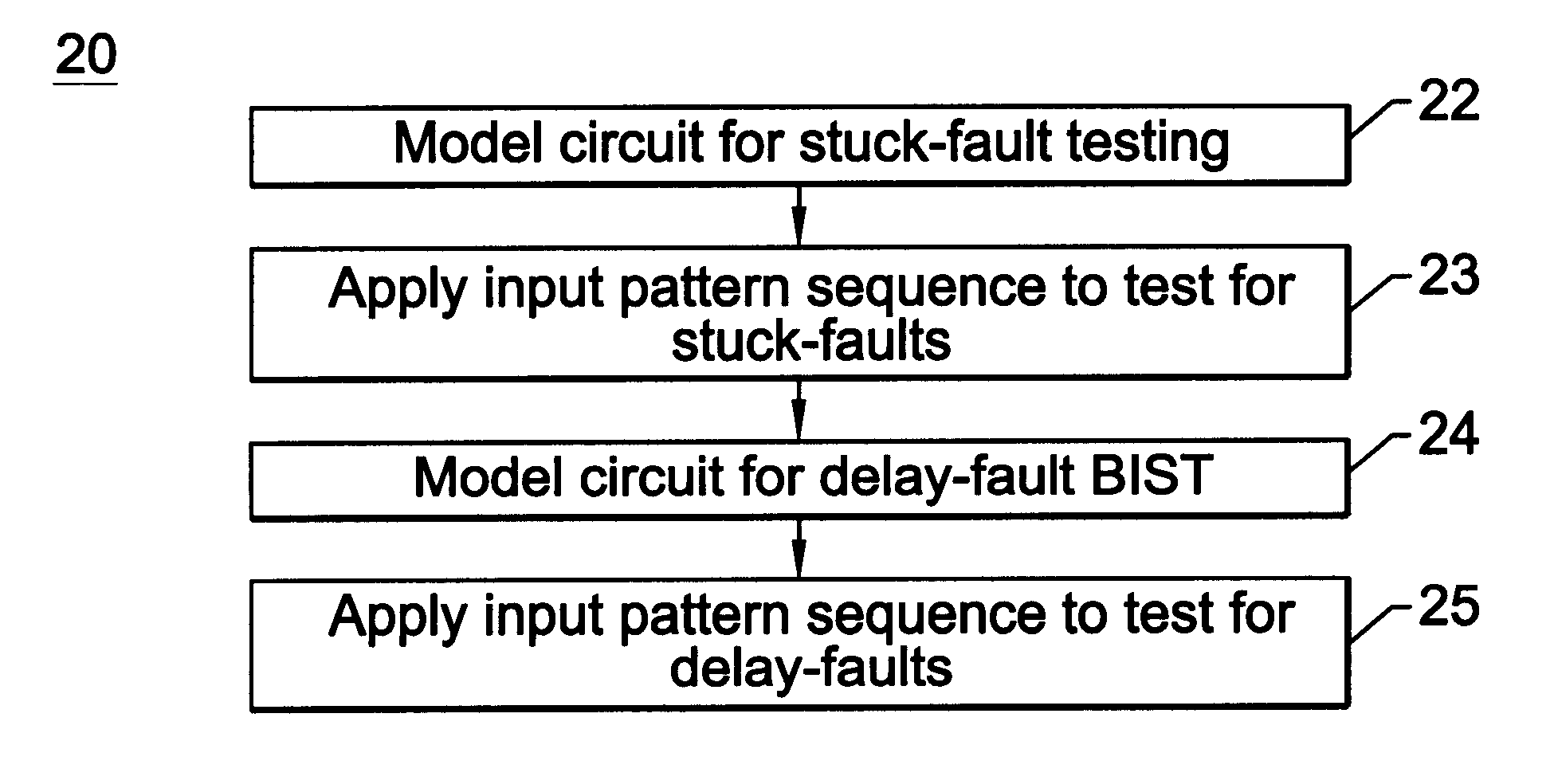

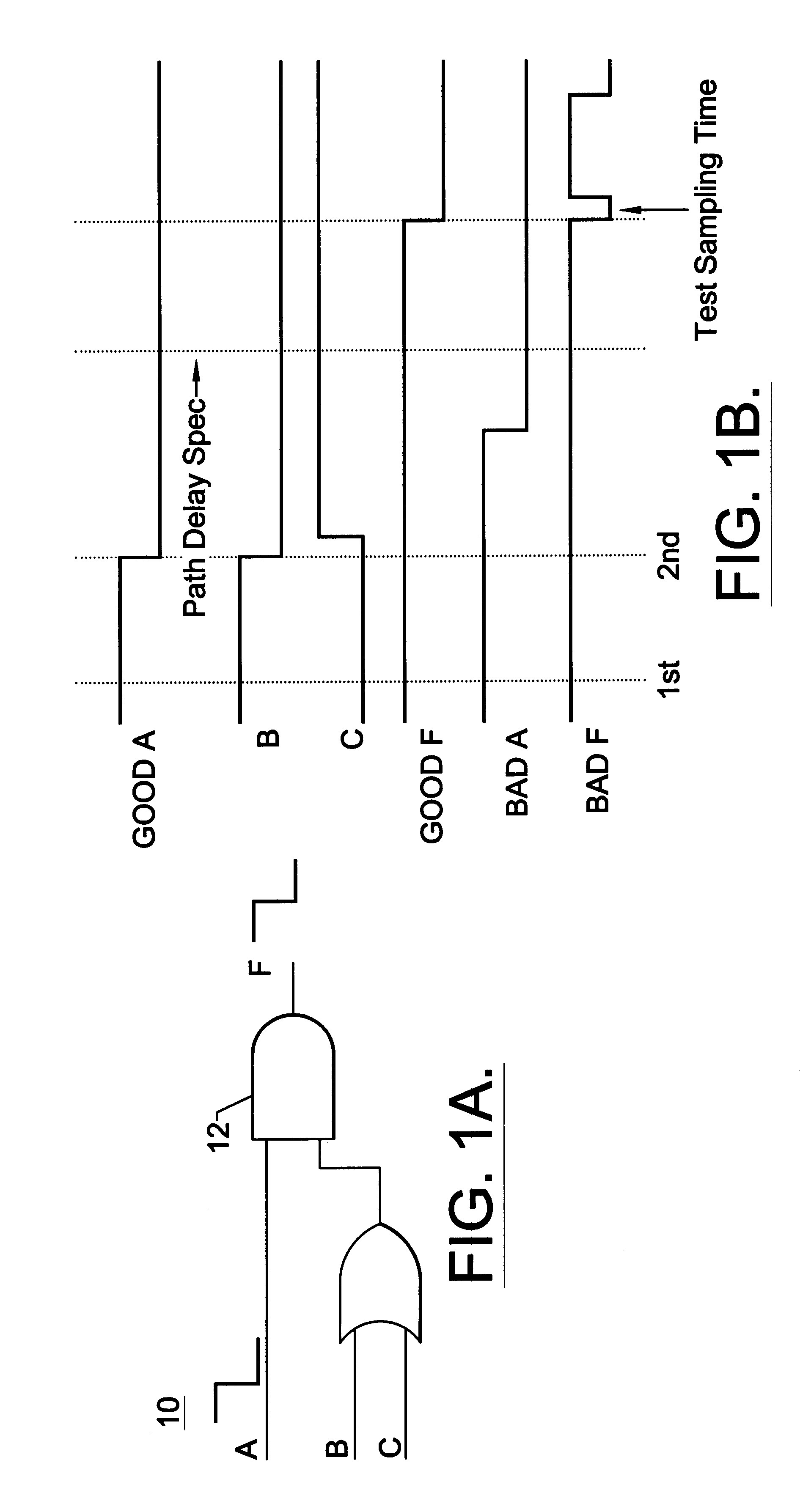

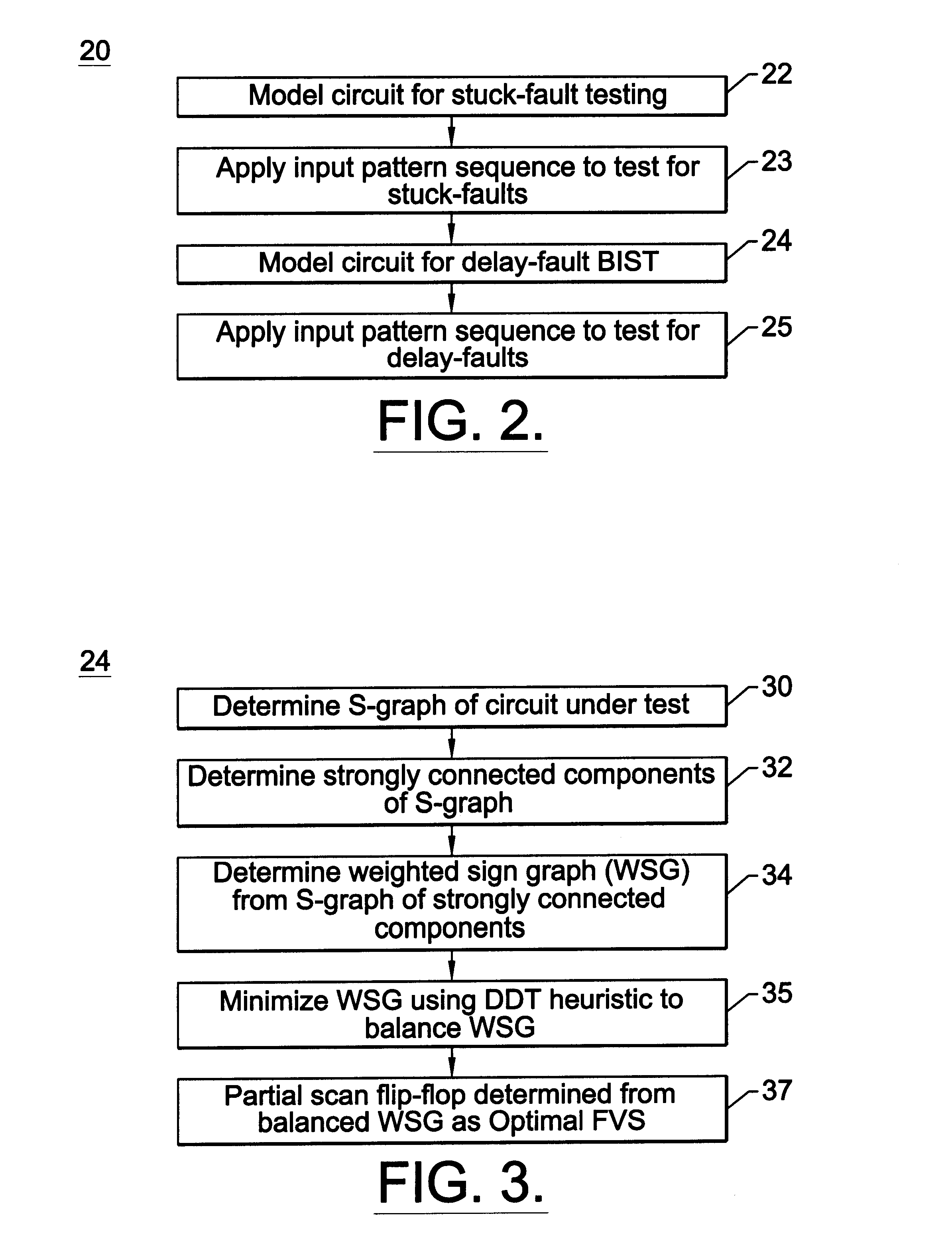

Method and apparatus for combined stuck-at fault and partial-scanned delay-fault built-in self test

InactiveUS6247154B1Electronic circuit testingError detection/correctionStuck-at faultBuilt in self testing

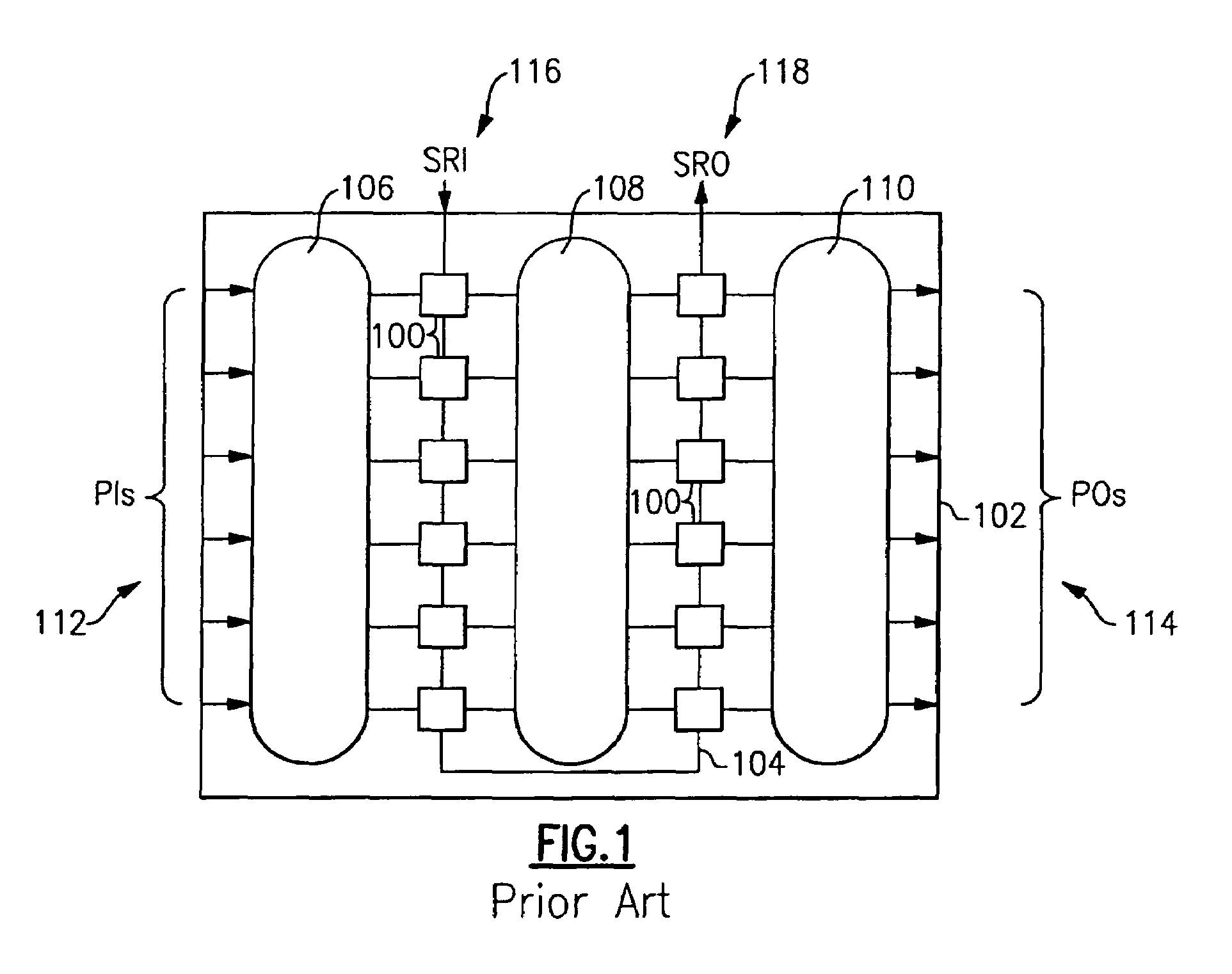

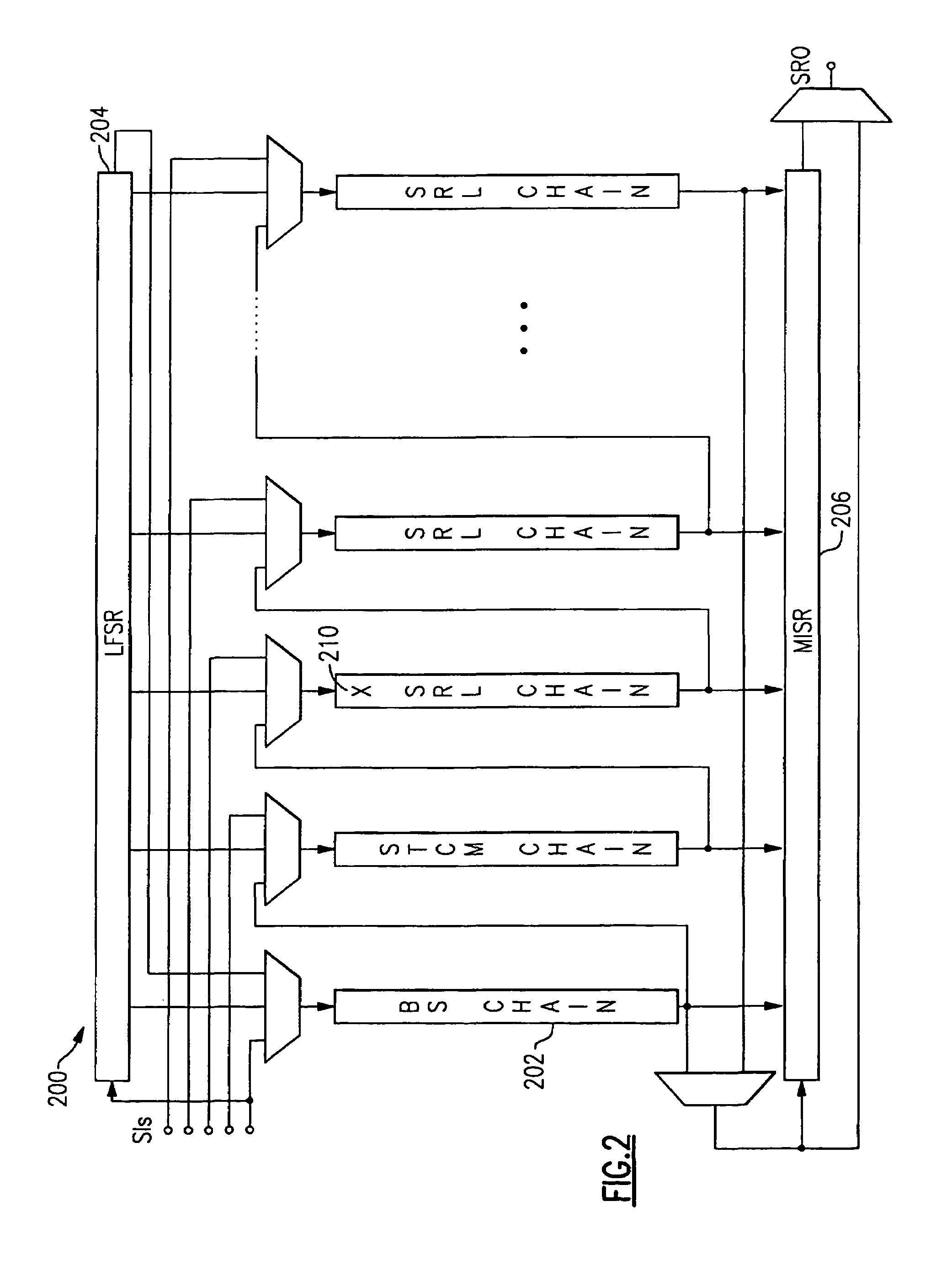

This invention relates to a method and apparatus for combined stuck-fault testing and partial scan delay-fault built-in self testing (BIST). For partial scan delay-fault BIST, the circuit is modeled for breaking all flip-flop feedback cycles in the circuit. A selection of flip-flops to be scanned to break all sequential cycles is determined from an optimal feedback vertex set. A digest, devour and tidy-up (DDT) heuristic can be used on a weighted signed graph formed from an S-graph of the circuit to determine an optimal feedback vertex set. Determined partial scan delay fault BIST hazards can be removed from the circuit by inserting parity flippers to invert selected paths during testing. The same DDT heuristic can be used to determine optimal placement of the parity flippers in the circuit.

Owner:RUTGERS THE STATE UNIV

Application of special ECC matrix for solving stuck bit faults in an ECC protected mechanism

ActiveUS7069494B2Simple structureEasy to useSpringsMemory loss protectionStuck-at faultData application

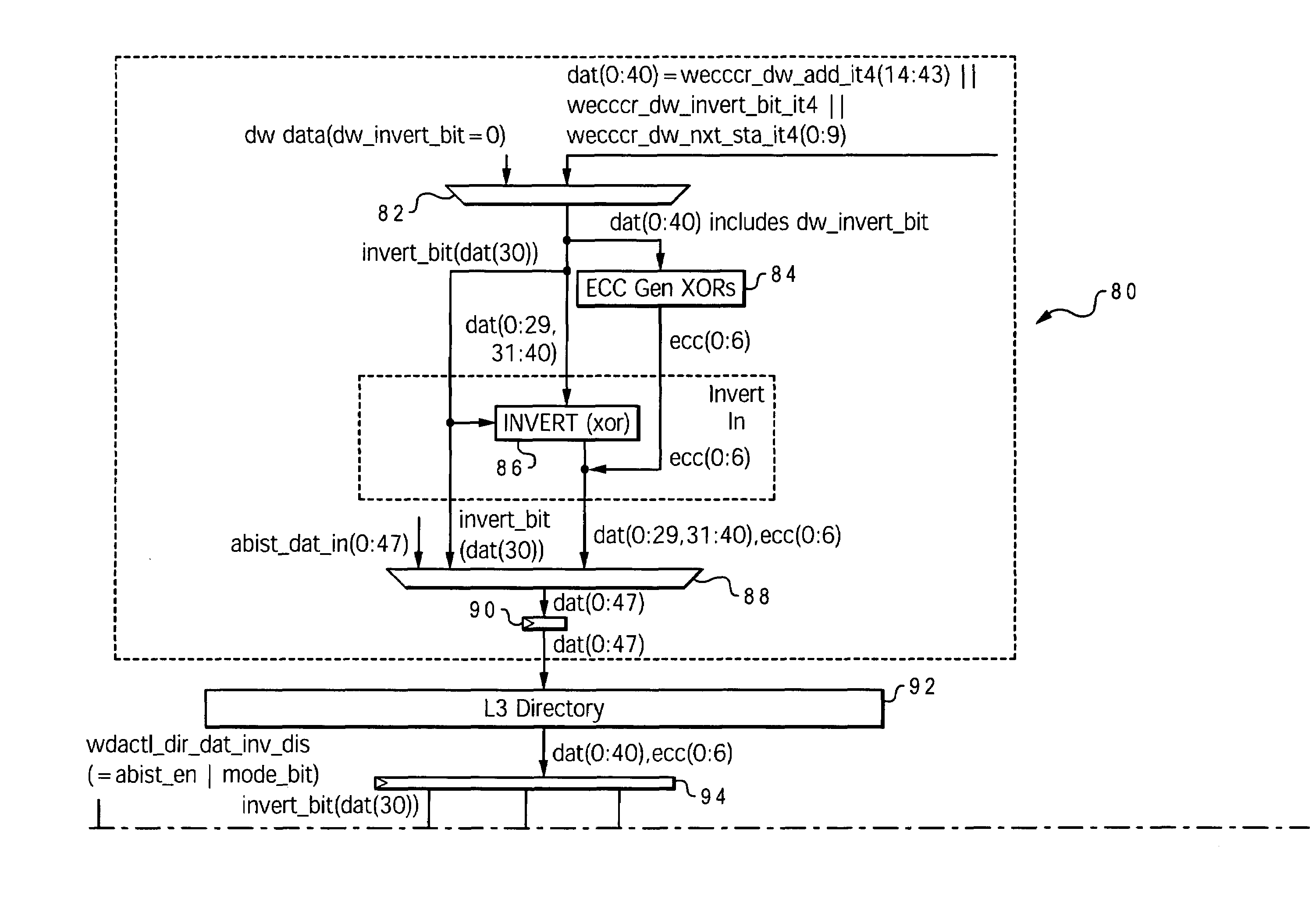

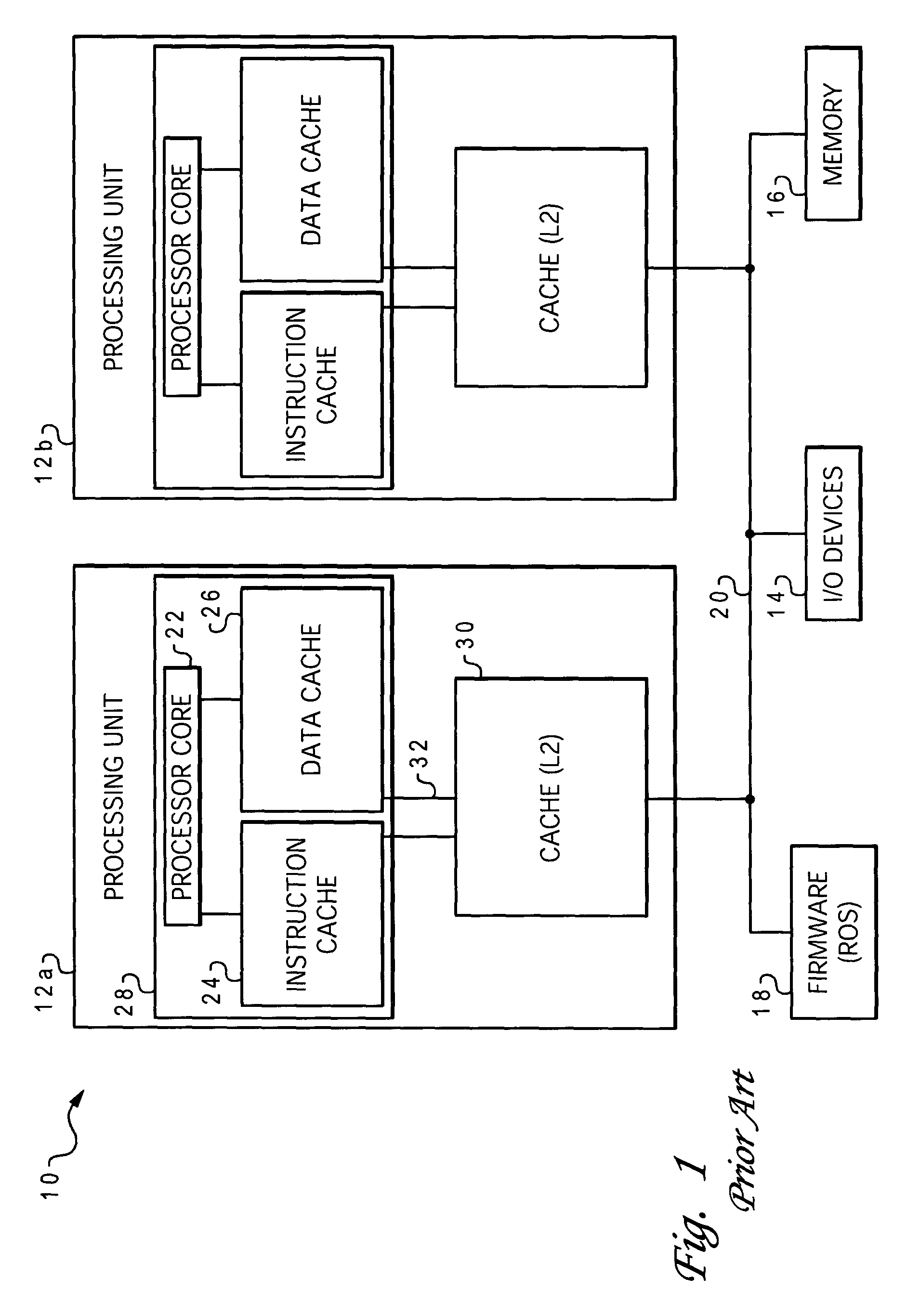

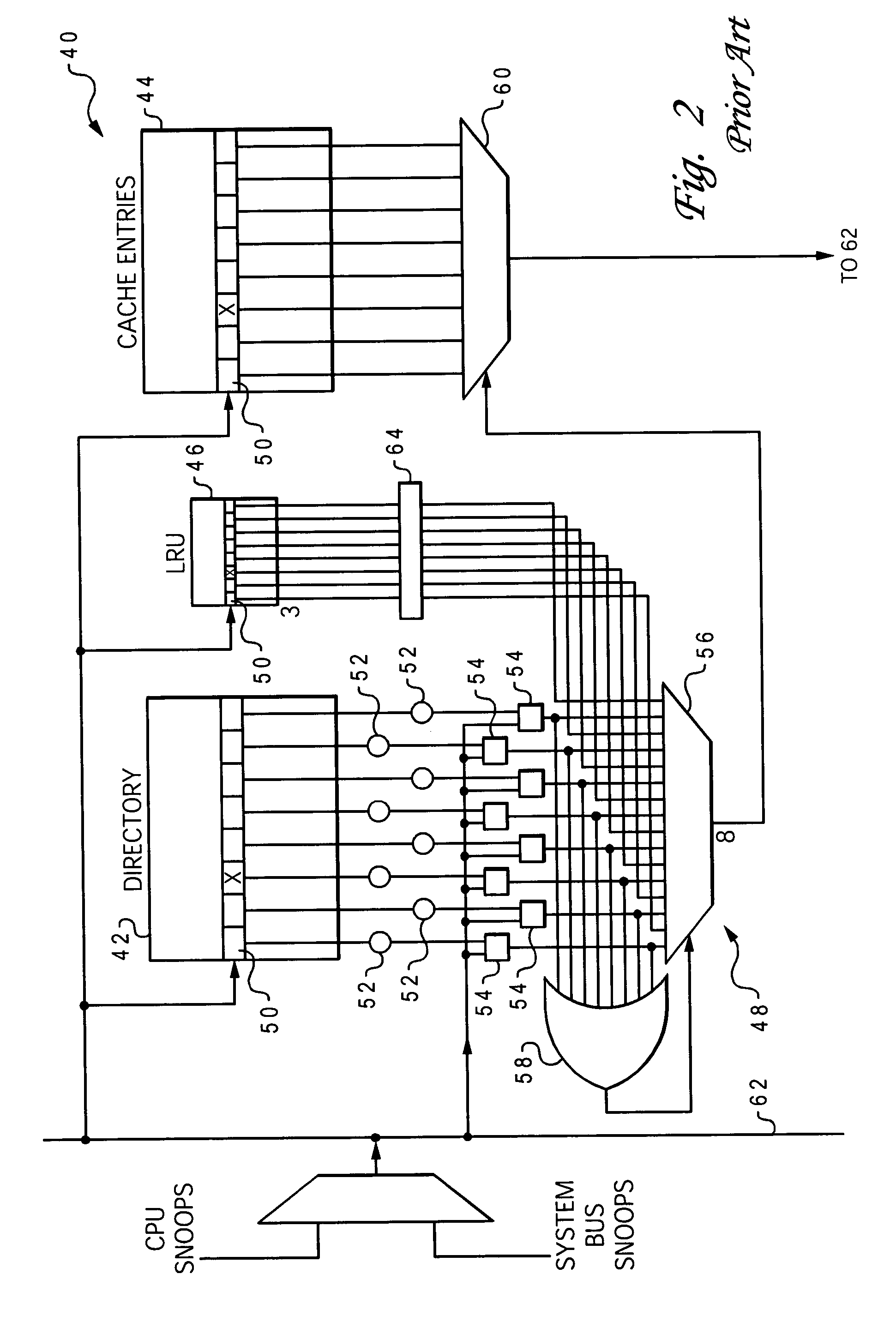

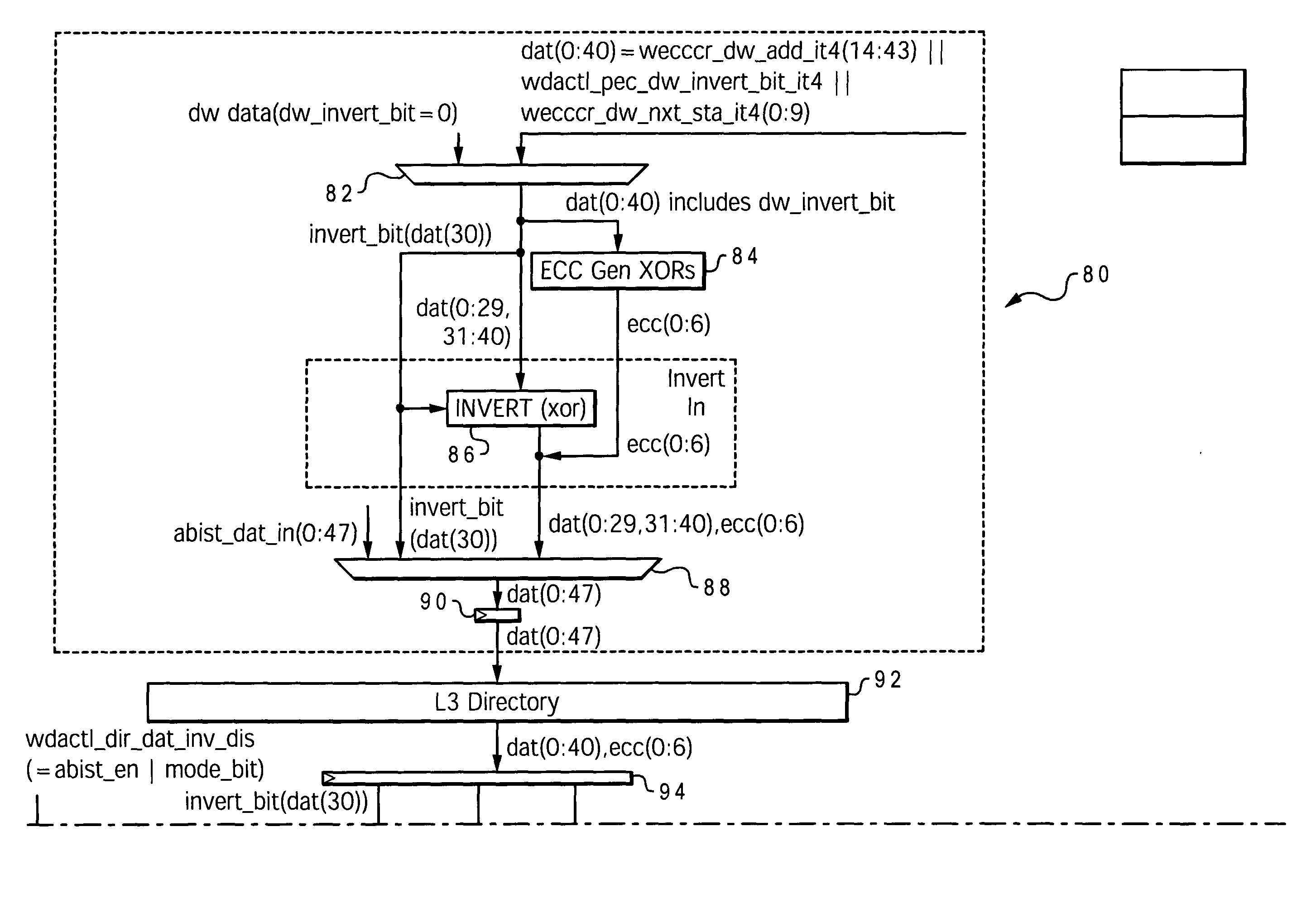

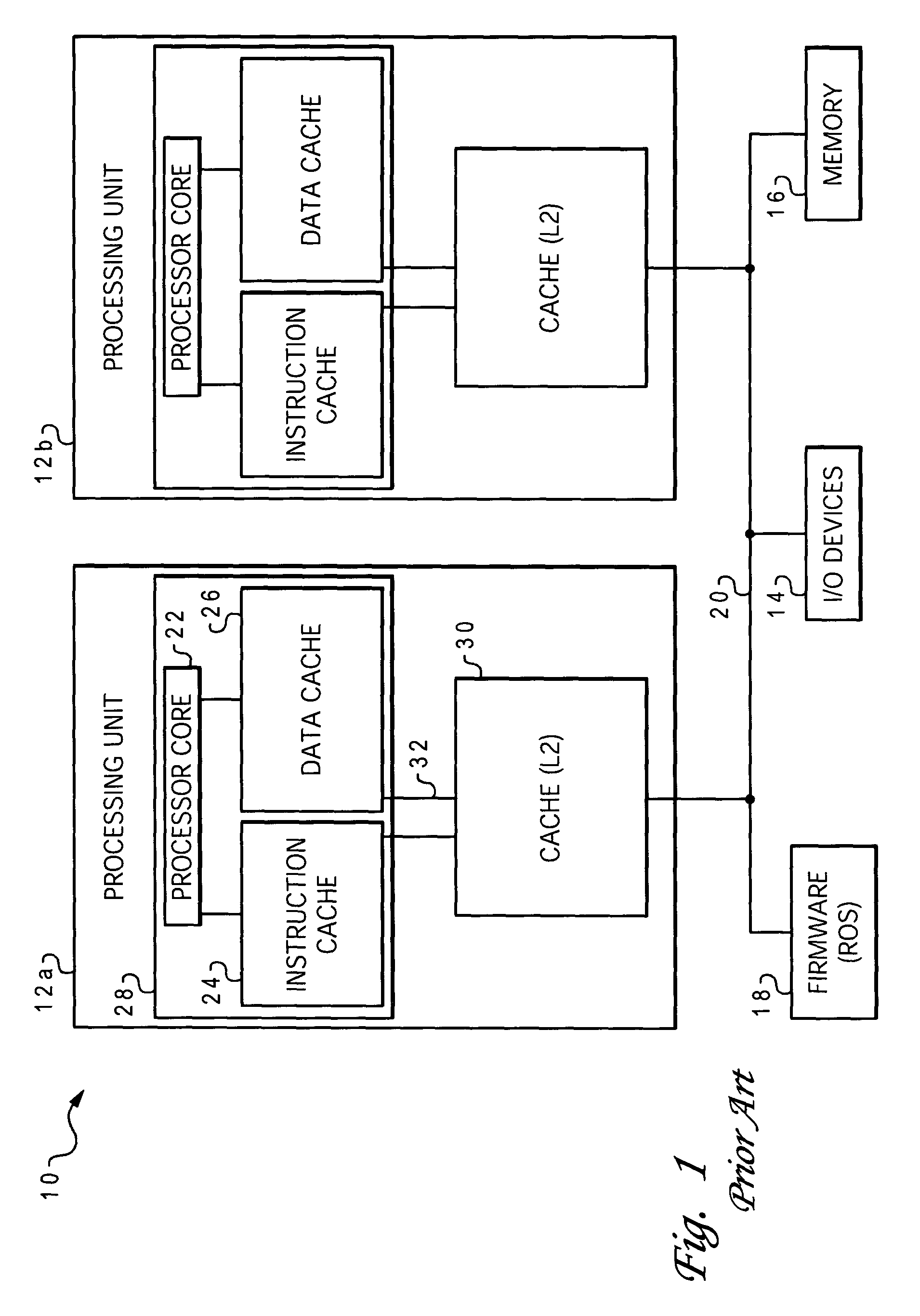

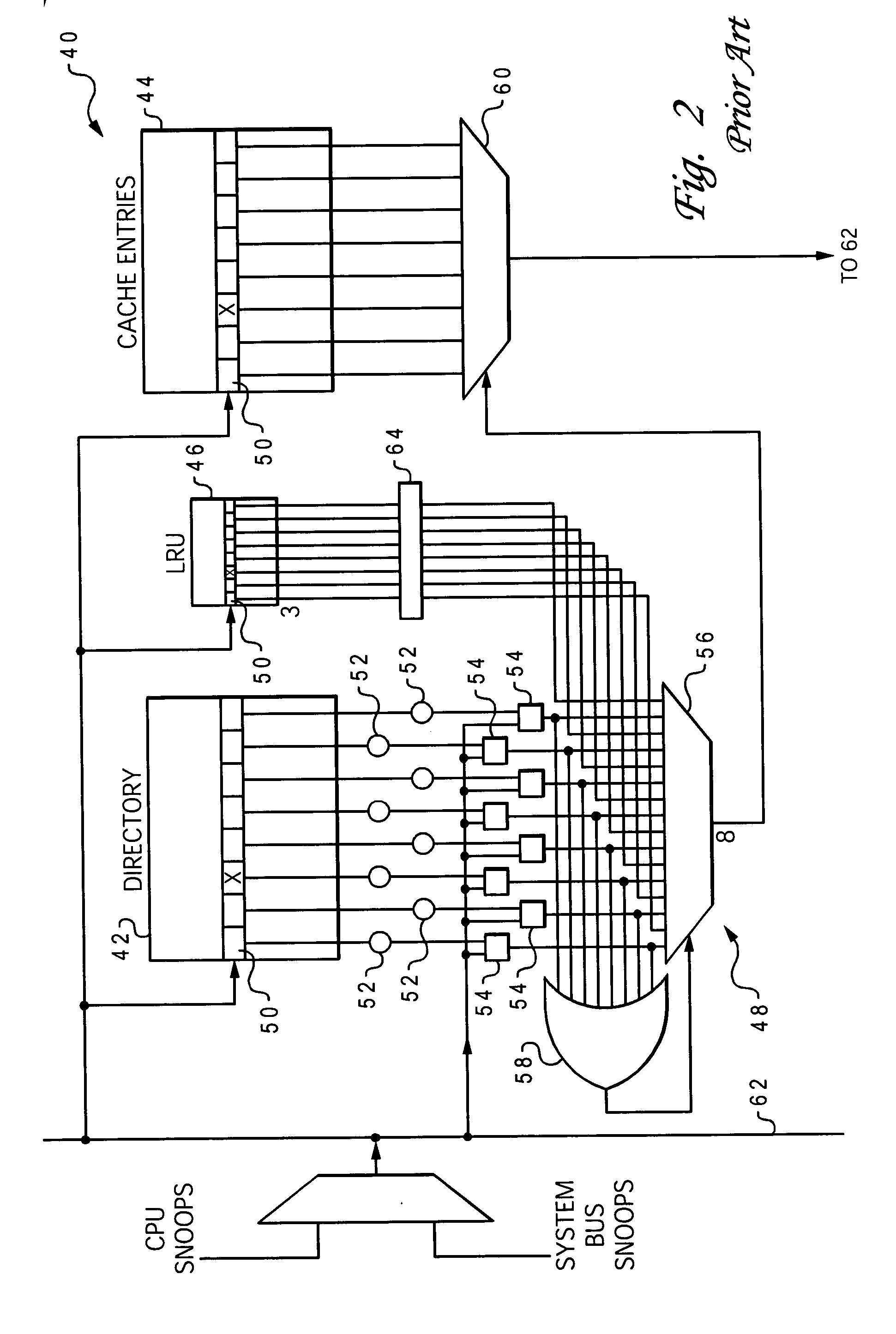

A method of correcting an error in an ECC protected mechanism of a computer system, such as a cache or system bus, by applying data with a number of bits N to an error correction code (ECC) matrix to yield an error detection syndrome, wherein the ECC matrix has a plurality of rows and columns with a given column corresponding to a respective one of the data bits, and selected bits are set in the ECC matrix along each column and each row such that encoding for the ECC matrix allows N-bit error correction and (N−1)-bit error detection. In the illustrative embodiment, the ECC matrix has an odd number of bits set in each row thereof. In the case of an ECC protected mechanism such as a memory device, these properties facilitate the use of an inversion bit for correcting hard faults in the stored data. When an error is detected and after it is corrected, the corrected data is inverted and then rewritten to the cache array. The corresponding inversion bit for this entry is accordingly set to indicate that the data as currently stored is inverted. Thereafter, the data is re-read from the array, and if the error was due to a hard fault (stuck bit), it will appear correct (after applying the polarity indicated by the inversion bit), since the inversion will have changed the value of the defective bit to the stuck value. The inversion bit may be part of the data itself. In this case, one of the columns in the ECC matrix corresponds to the inversion bit, and each bit in that column of the matrix is set. In the case of an ECC protected mechanism such as a system bus, once a stuck bit condition is detected, the sending device can elect to send data such that the polarity of the data for that bit is always flipped to match the logic level of the stuck value on the wire. This approach allows for full single-bit correct, double-bit detect even in the presence of a stuck bit.

Owner:IBM CORP

Application of special ECC matrix for solving stuck bit faults in an ECC protected mechanism

A method of correcting an error in an ECC protected mechanism of a computer system, such as a cache or system bus, by applying data with a number of bits N to an error correction code (ECC) matrix to yield an error detection syndrome, wherein the ECC matrix has a plurality of rows and columns with a given column corresponding to a respective one of the data bits, and selected bits are set in the ECC matrix along each column and each row such that encoding for the ECC matrix allows N-bit error correction and (N-1)-bit error detection. In the illustrative embodiment, the ECC matrix has an odd number of bits set in each row thereof. In the case of an ECC protected mechanism such as a memory device, these properties facilitate the use of an inversion bit for correcting hard faults in the stored data. When an error is detected and after it is corrected, the corrected data is inverted and then rewritten to the cache array. The corresponding inversion bit for this entry is accordingly set to indicate that the data as currently stored is inverted. Thereafter, the data is re-read from the array, and if the error was due to a hard fault (stuck bit), it will appear correct (after applying the polarity indicated by the inversion bit), since the inversion will have changed the value of the defective bit to the stuck value. The inversion bit may be part of the data itself. In this case, one of the columns in the ECC matrix corresponds to the inversion bit, and each bit in that column of the matrix is set. In the case of an ECC protected mechanism such as a system bus, once a stuck bit condition is detected, the sending device can elect to send data such that the polarity of the data for that bit is always flipped to match the logic level of the stuck value on the wire. This approach allows for full single-bit correct, double-bit detect even in the presence of a stuck bit.

Owner:IBM CORP

Stuck-at fault scan chain diagnostic method

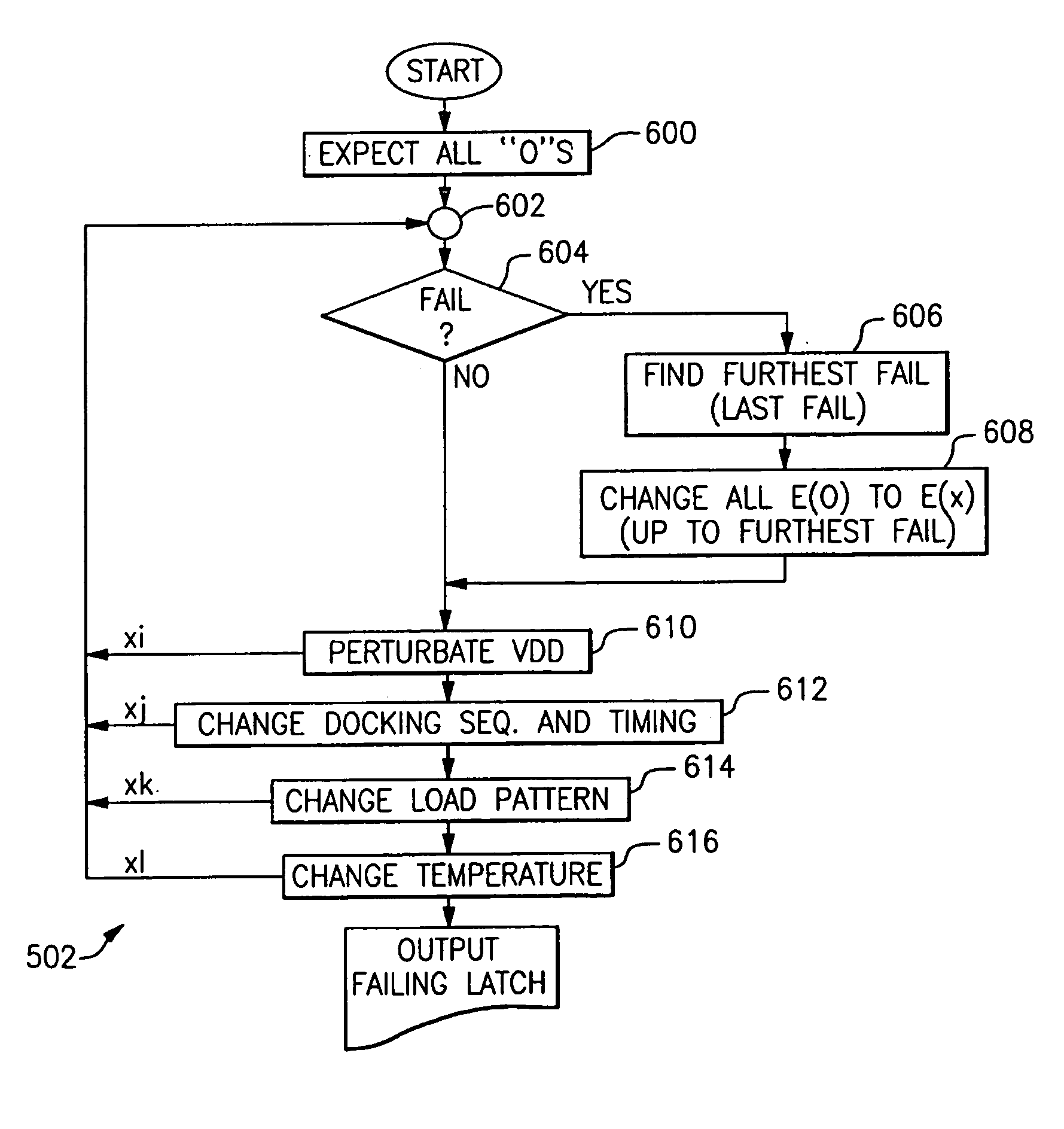

While data cannot be transmitted down a scan chain through a stuck-at fault location, data in properly operating latches downstream of the stuck-at fault location can be shifted down the chain. By varying operating parameters, such as power supply and reference voltages, clock timing patterns, temperature and timing sequences, one or more latches down the SRL chain from the stuck-at fault location may be triggered to change state from the stuck-at fault value. The SRL chain is then operated to shift data out the output of the SRL chain. The output is monitored and any change in value from the stuck-at state is noted as identifying all good latch positions to end of the chain. The process is repeated: varying each of the selected operating parameters until the latch position following the stuck-at fault latch is identified.

Owner:IBM CORP

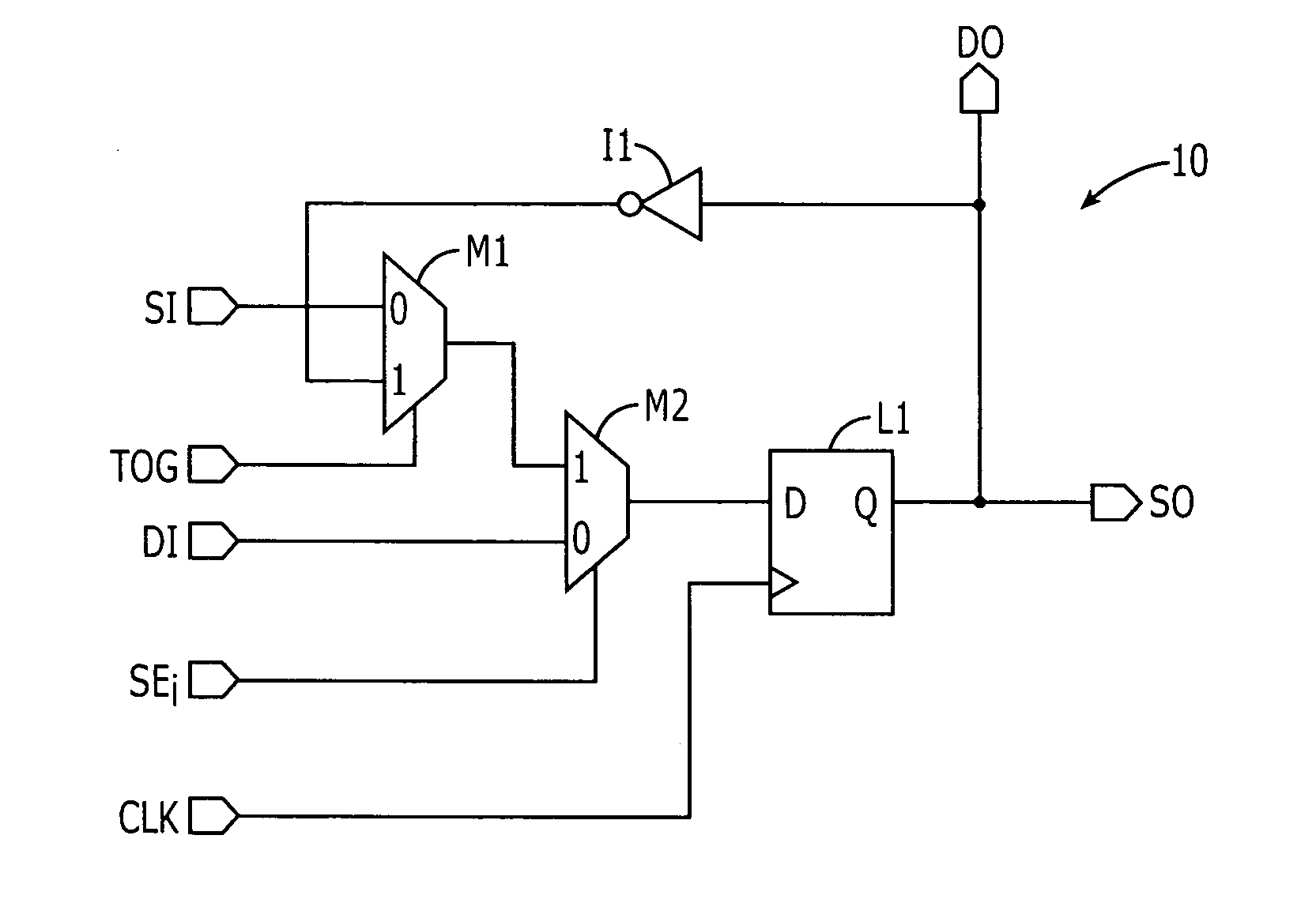

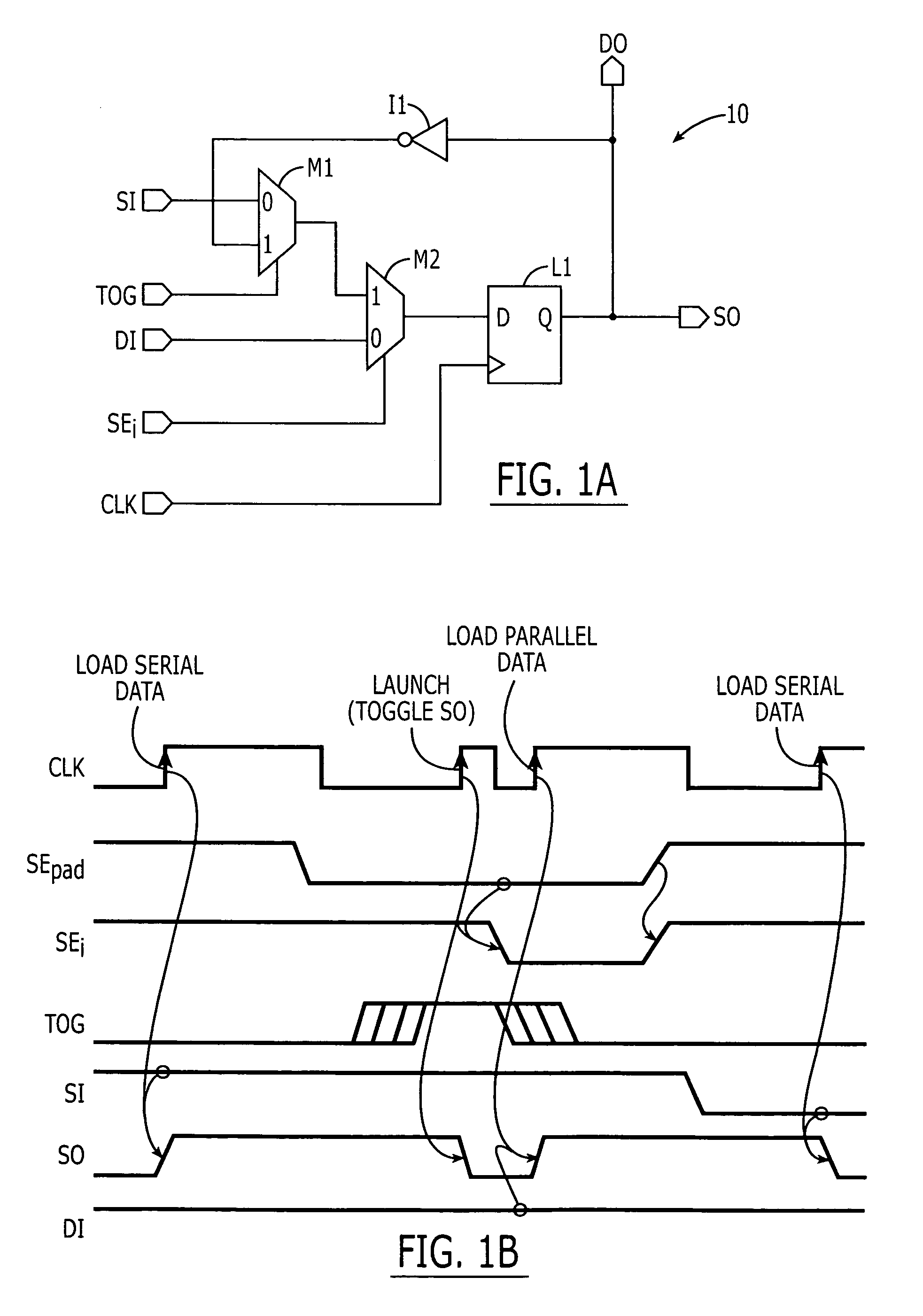

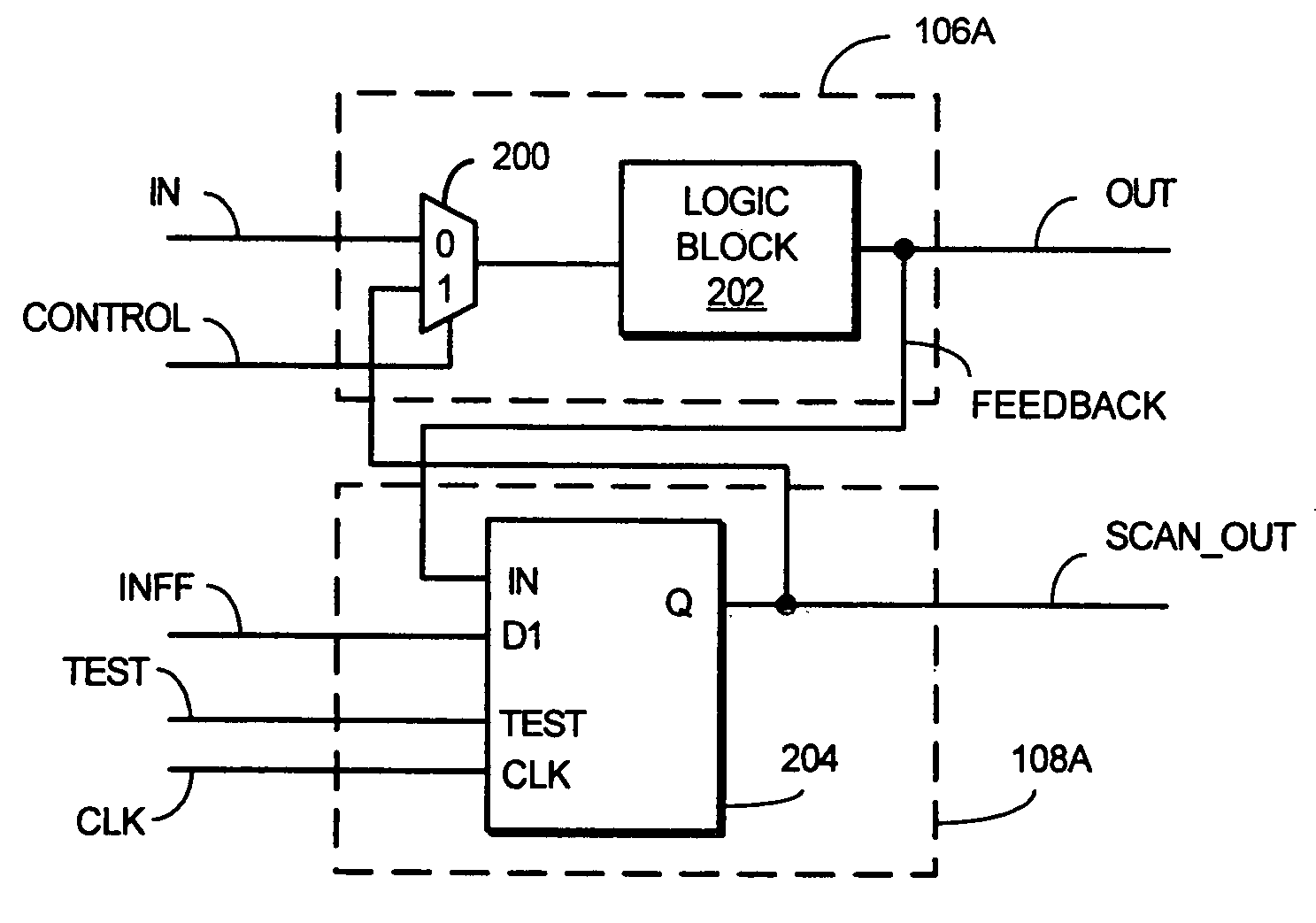

Scan chain registers that utilize feedback paths within latch units to support toggling of latch unit outputs during enhanced delay fault testing

An integrated circuit device utilizes a serial scan chain register to support efficient reliability testing of internal circuitry that is not readily accessible from the I / O pins of the device. This reliability testing includes the performance of, among other things, delay fault and stuck-at fault testing of elements within the internal circuitry. The scan chain register has scan chain latch units that support a toggle mode of operation. The scan chain register is provided with serial and parallel input ports and serial and parallel output ports. Each of the plurality of scan chain latch units includes a latch element and additional circuit elements that are configured to selectively establish a feedback path in the respective latch unit. This feedback path operates to pass an inversion of a signal at an output of the latch to an input of the latch when the corresponding scan chain latch unit is enabled to support a toggle mode of operation. Thus, if the output of the latch is set to a logic 1 level, then a toggle operation will cause the output of the latch to switch to a logic 0 level and vice versa. Because of the presence of a respective feedback path within each scan chain latch unit, the toggle operation at the output of a scan chain latch unit will be independent of the value of any other output of other scan chain latch units within the scan chain.

Owner:INTEGRATED DEVICE TECH INC

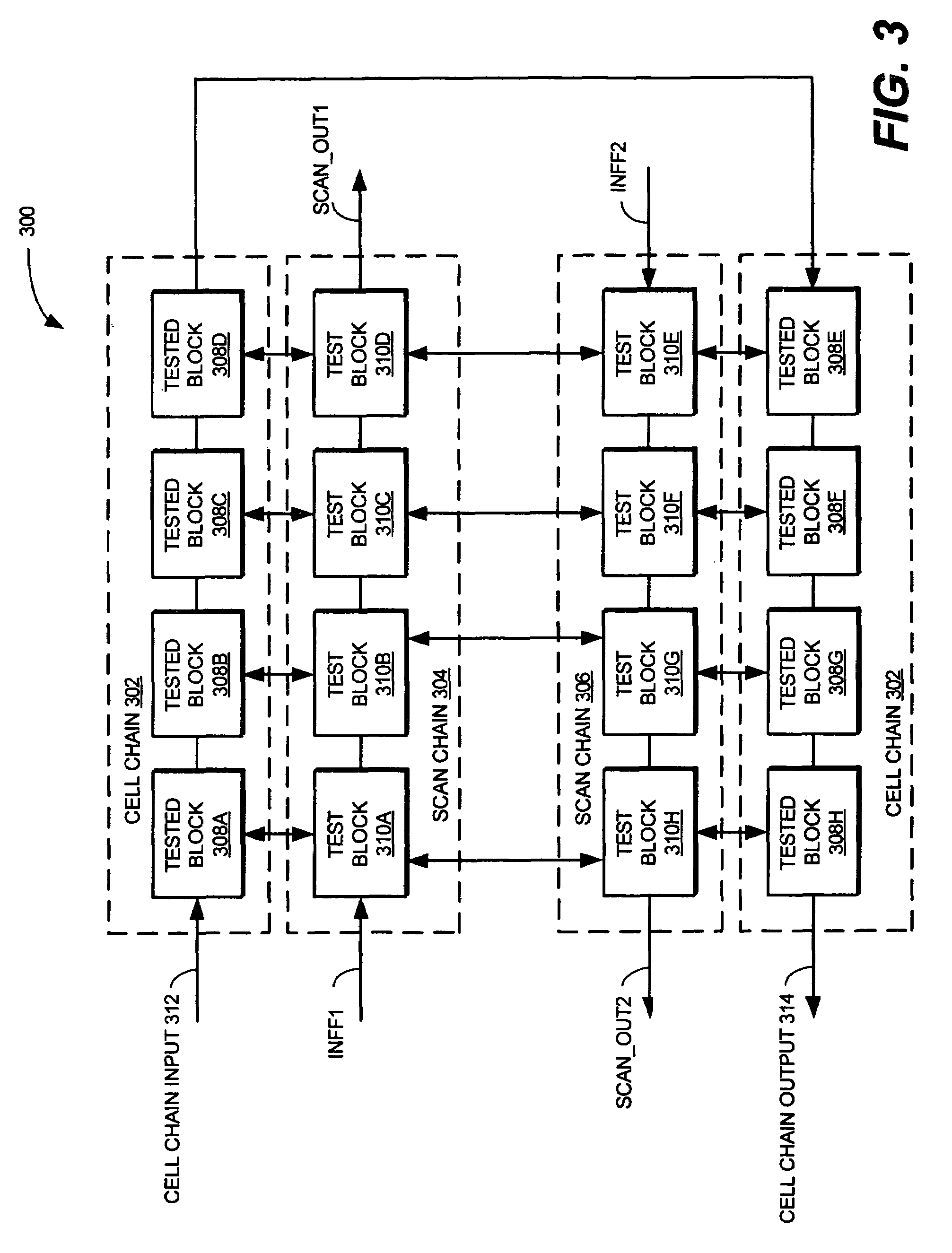

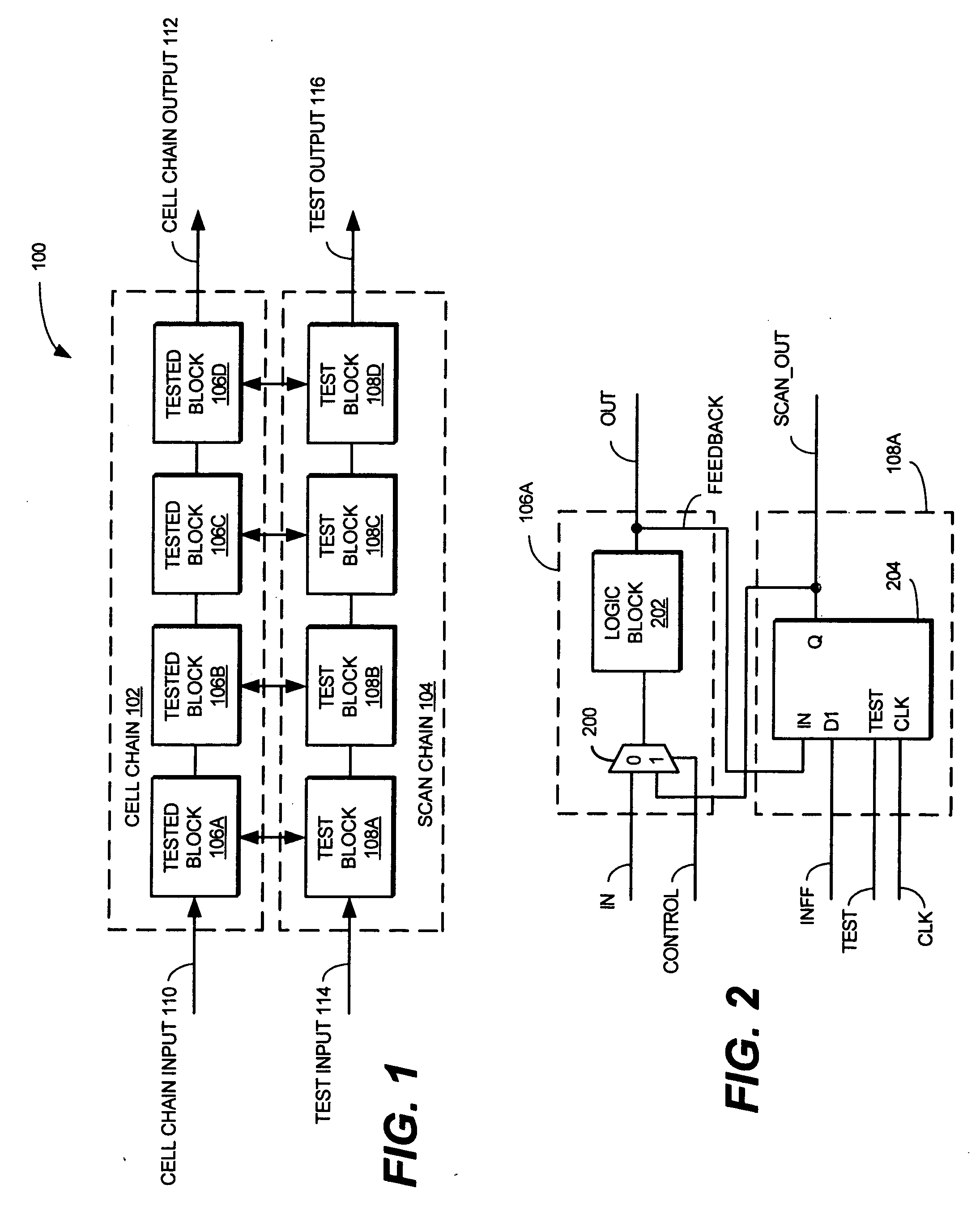

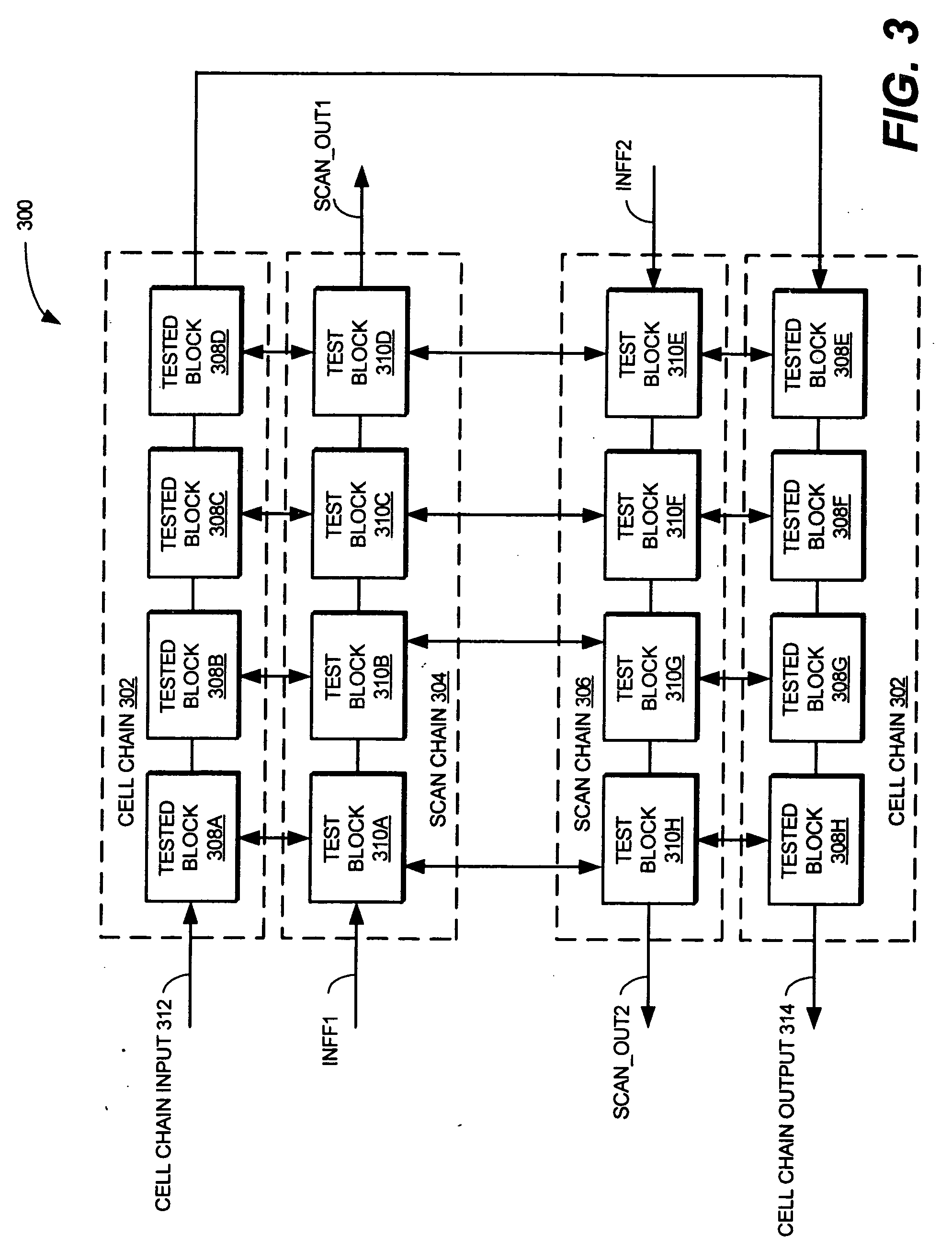

Method and apparatus for determining stuck-at fault locations in cell chains using scan chains

InactiveUS7392448B2Rapid positioningElectronic circuit testingError detection/correctionStuck-at faultDigital electronics

Owner:ATMEL CORP

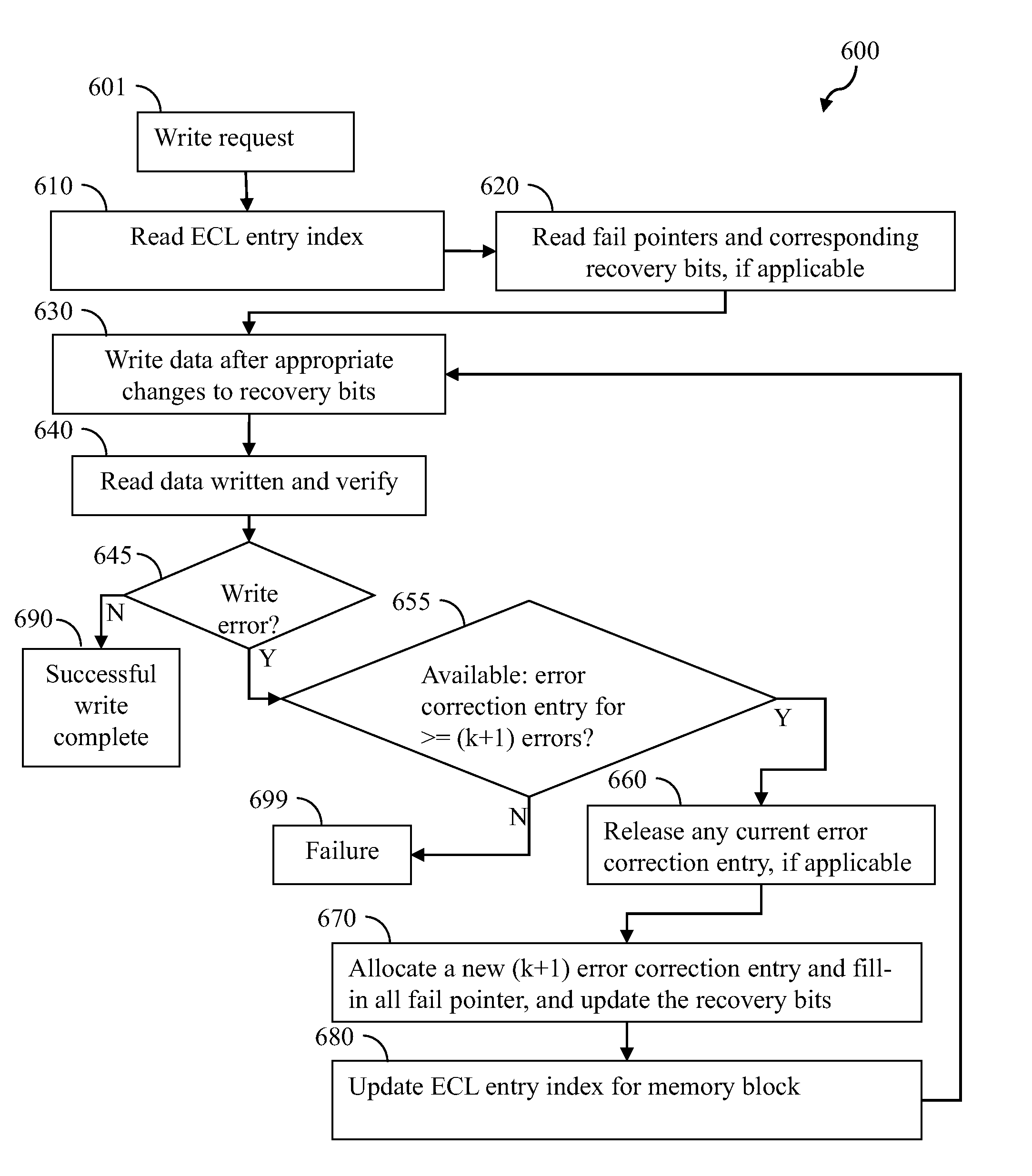

Adaptive multi-bit error correction in endurance limited memories

InactiveUS20130013977A1Sufficient error correctionExtended service lifeRead-only memoriesError correction/detection using block codesStuck-at faultSelf adaptive

Multi-bit stuck-at fault error recovery can be enabled by adaptive multi-bit error correction method, in which the overhead of error correction hardware is reduced without affecting the lifetime of the memory device. Error correction logic hardware is decoupled from memory blocks. An error correction logic block is partitioned such that error correction logic entries support different number of error correction capabilities based on the probability of occurrence of the different number of errors in different memory blocks. Faulty memory blocks are mapped to appropriate error correction logic entries. The mapping can be one-to-one or many-to-one depending on embodiments. The adaptive partitioning of the error correction logic entries can be configured to match projected statistical distribution of errors in logic blocks, and can reduce the total error correction logic overhead, provide sufficient error correction, and / or extend the lifetime of the memory device.

Owner:IBM CORP

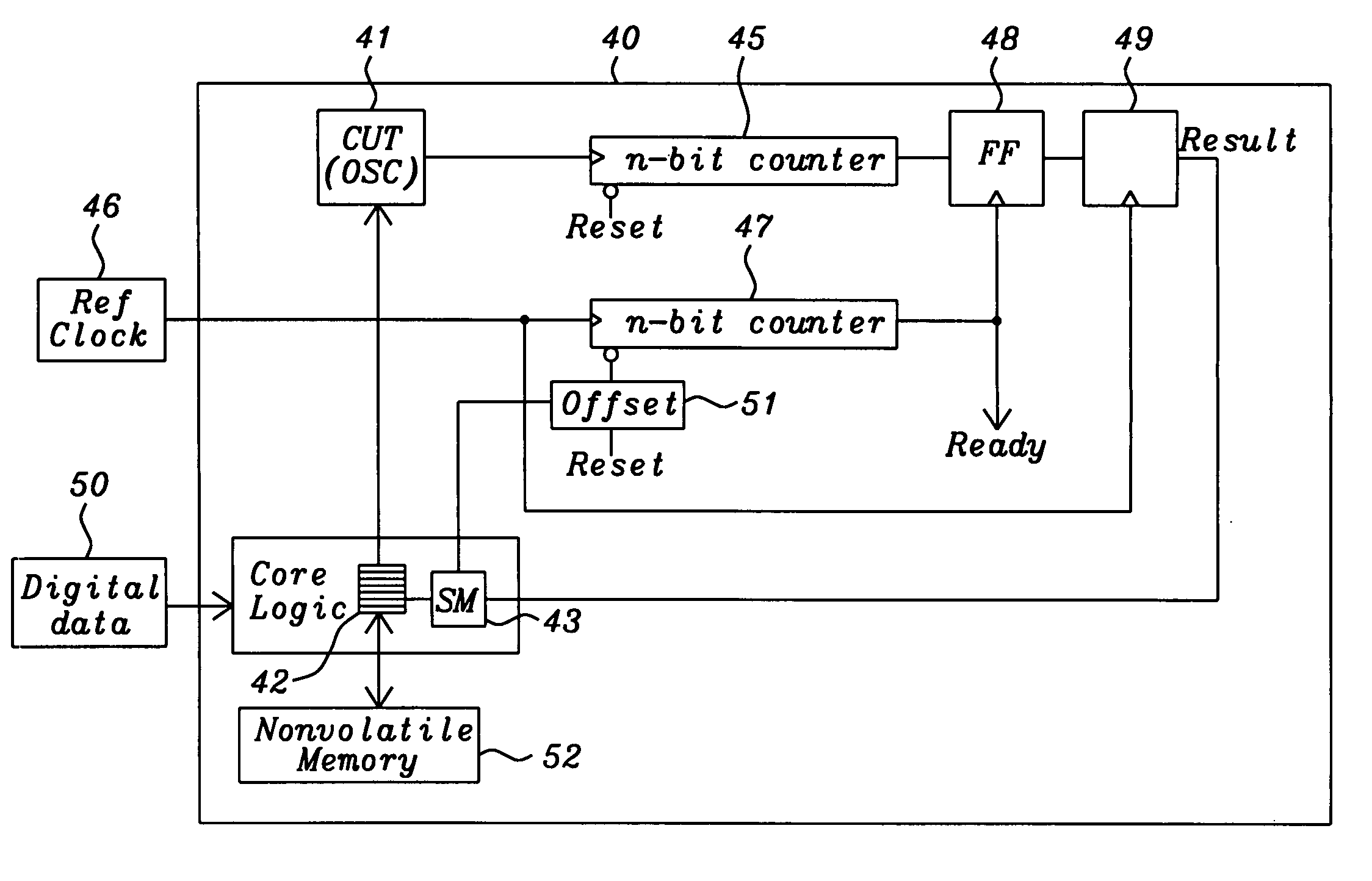

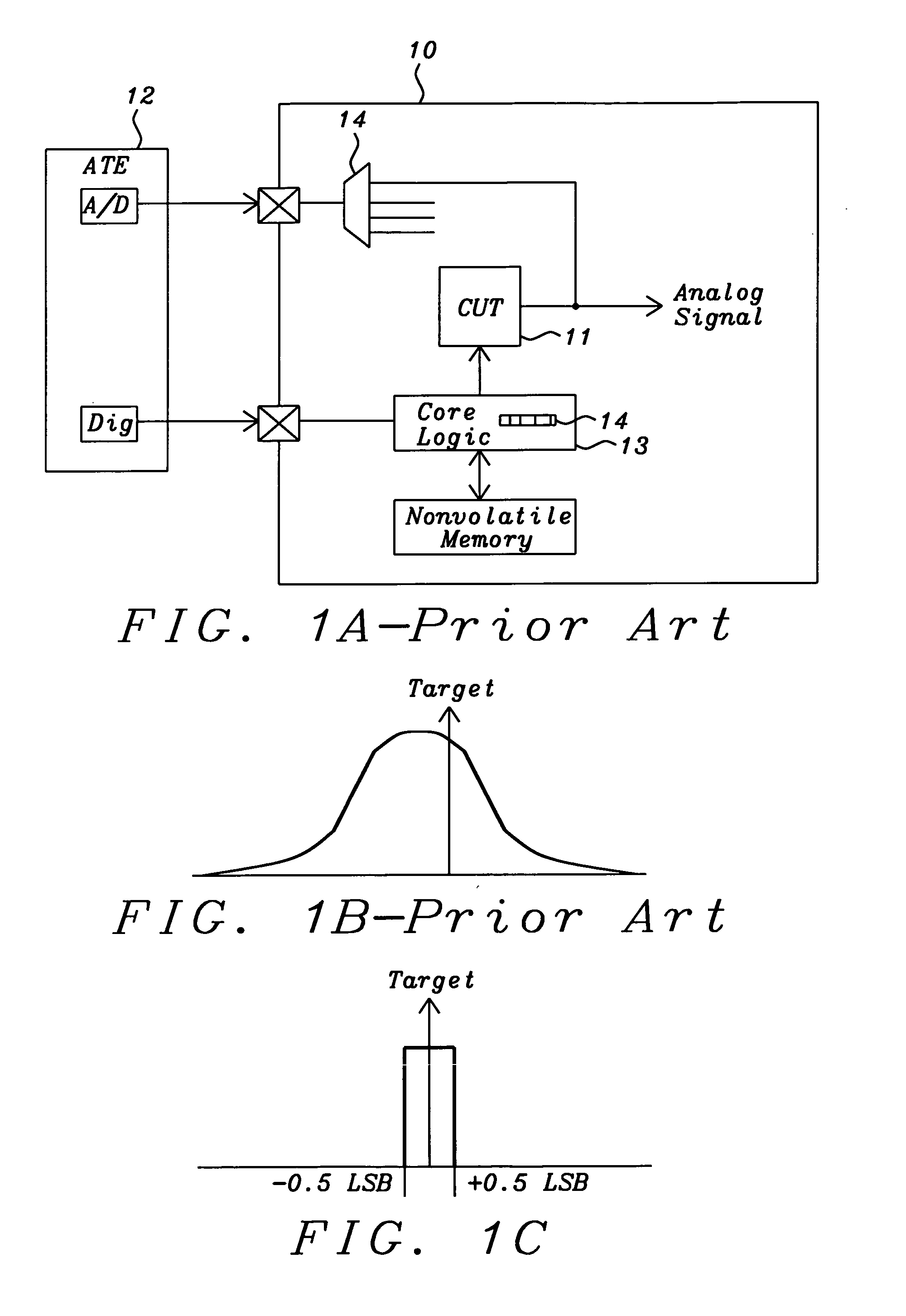

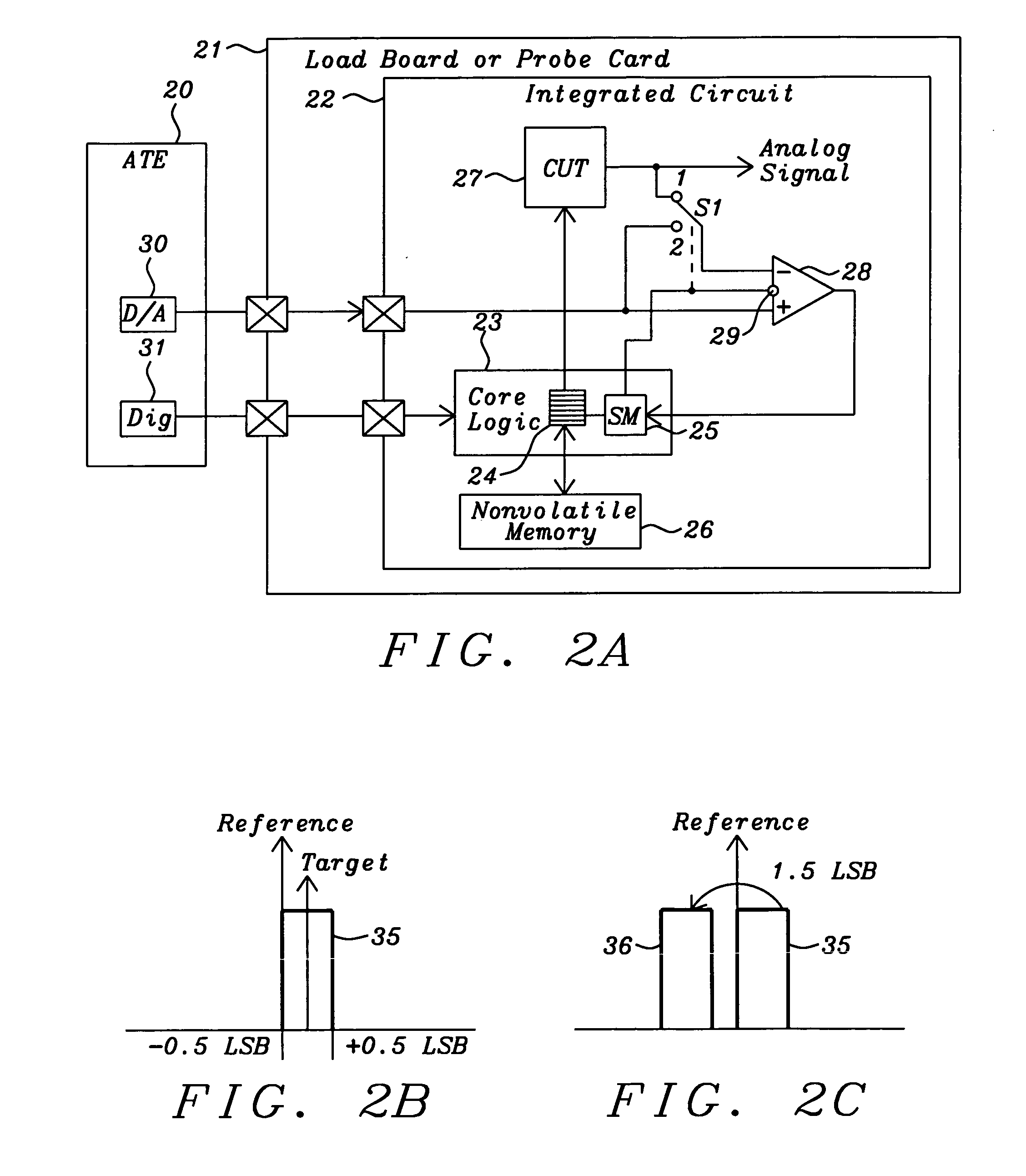

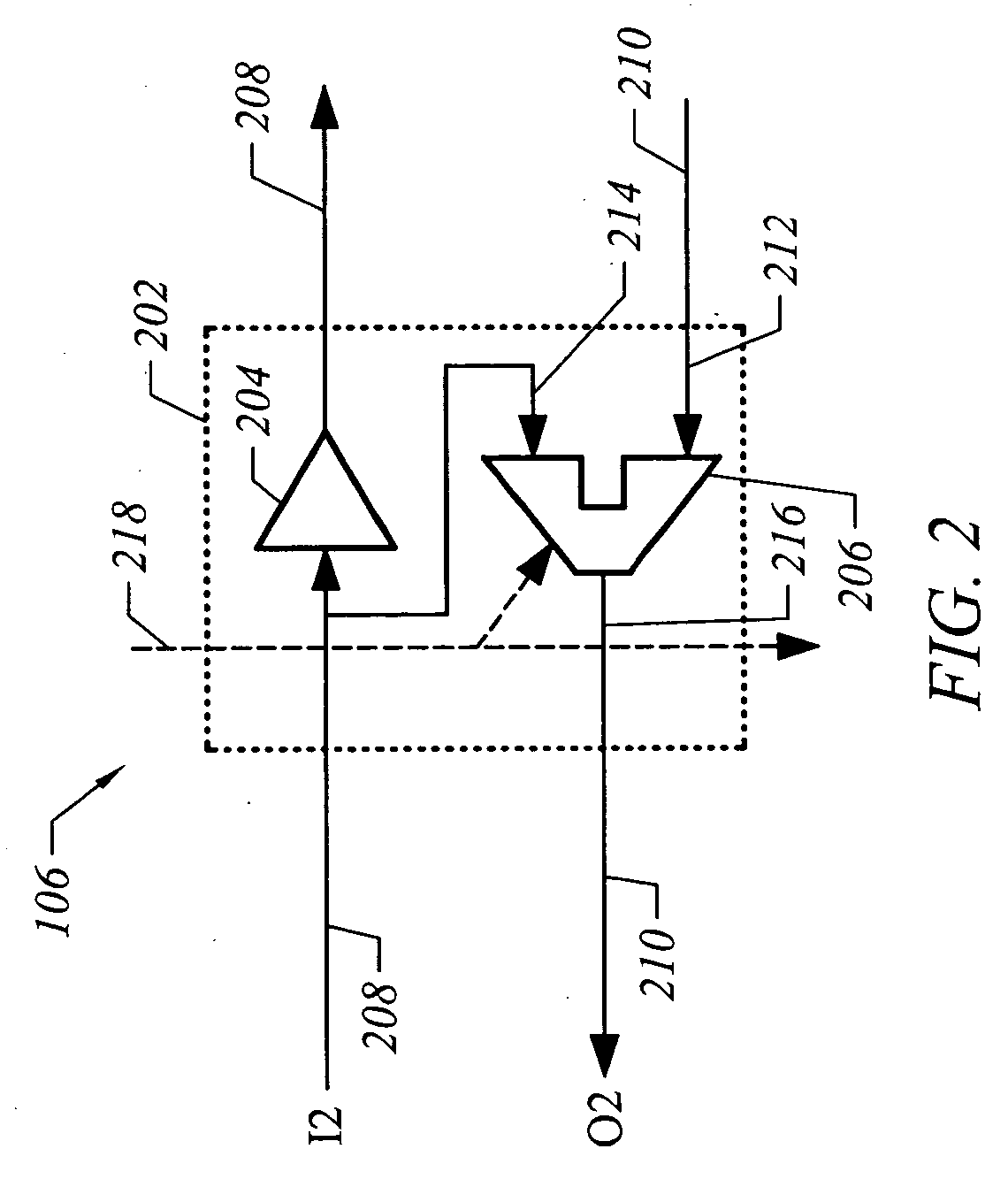

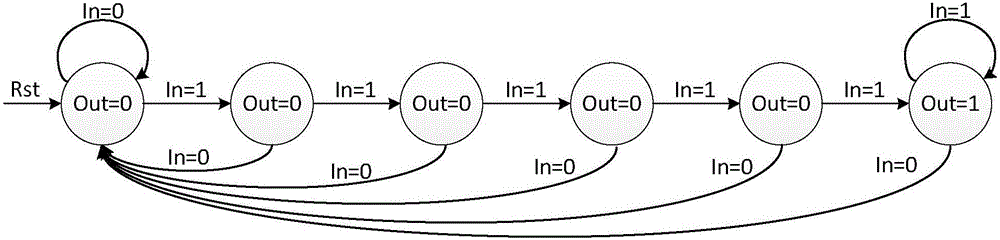

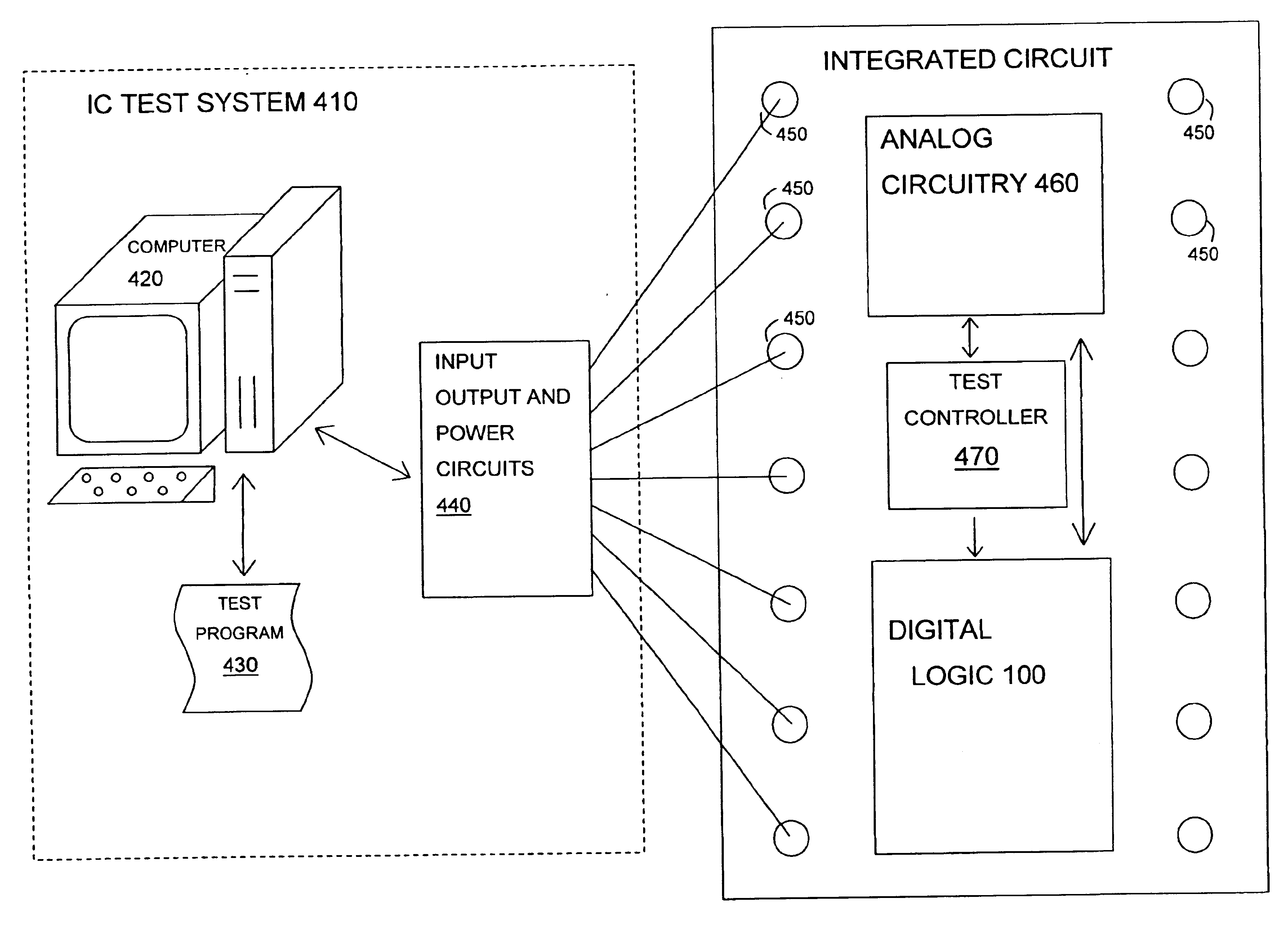

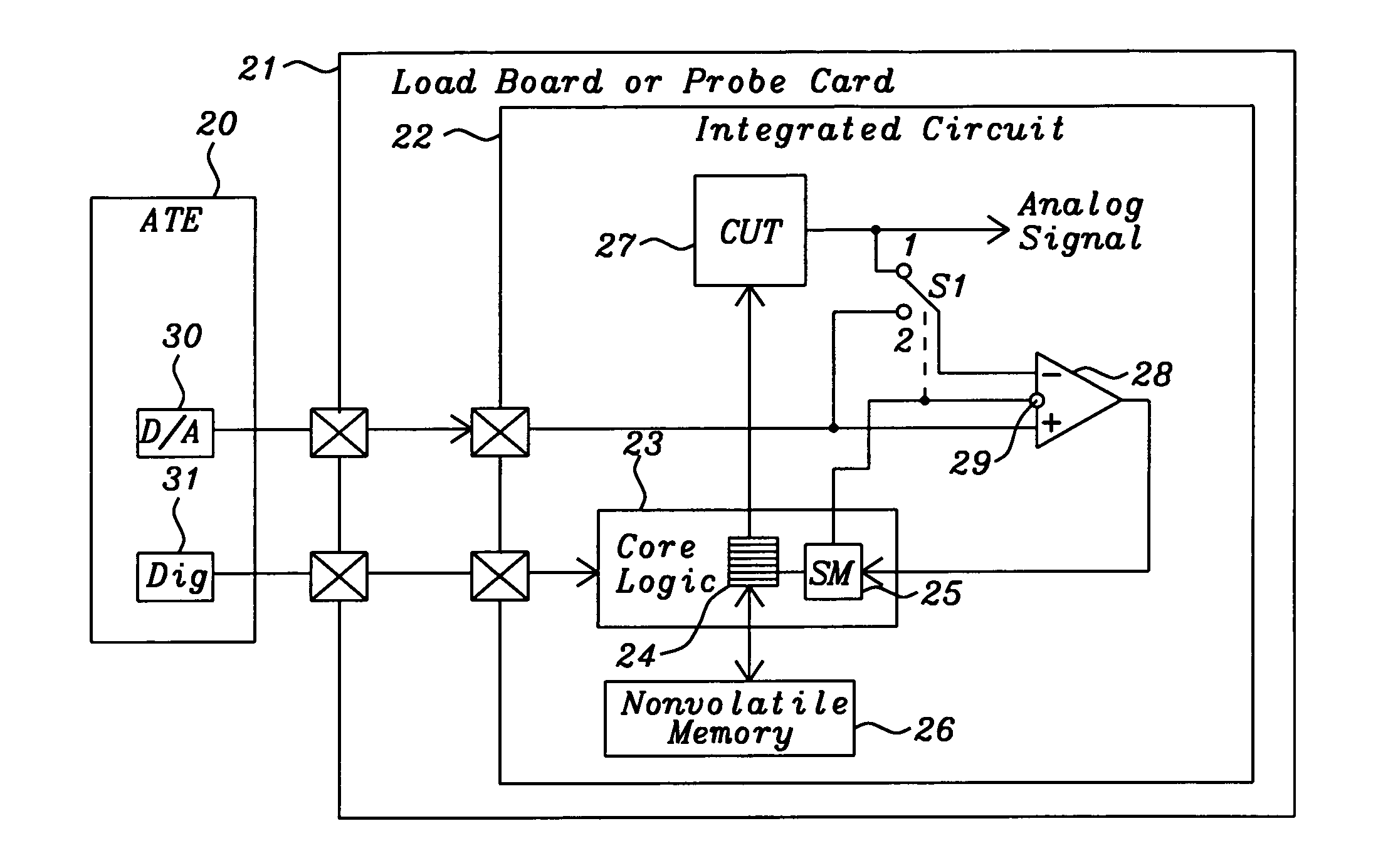

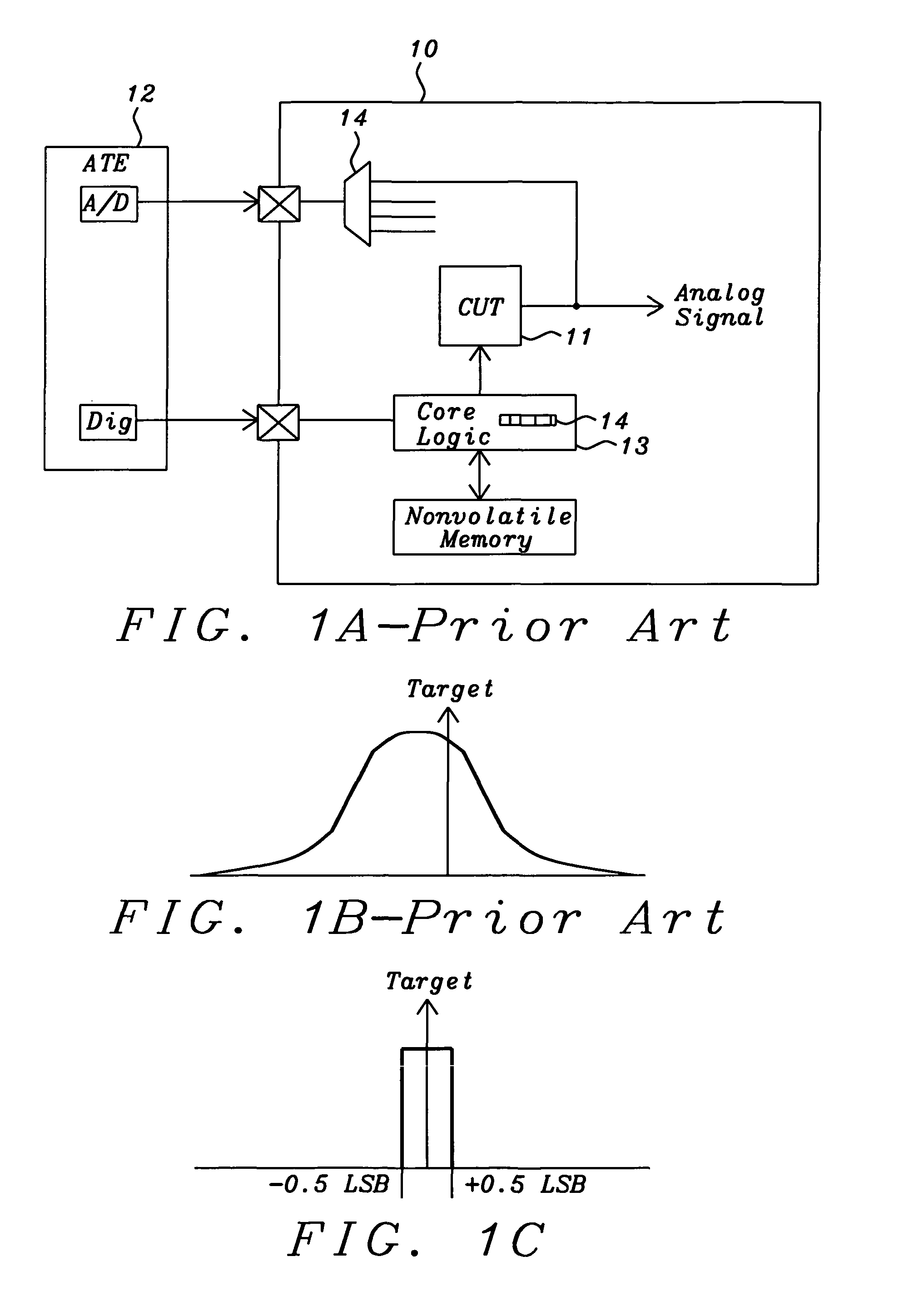

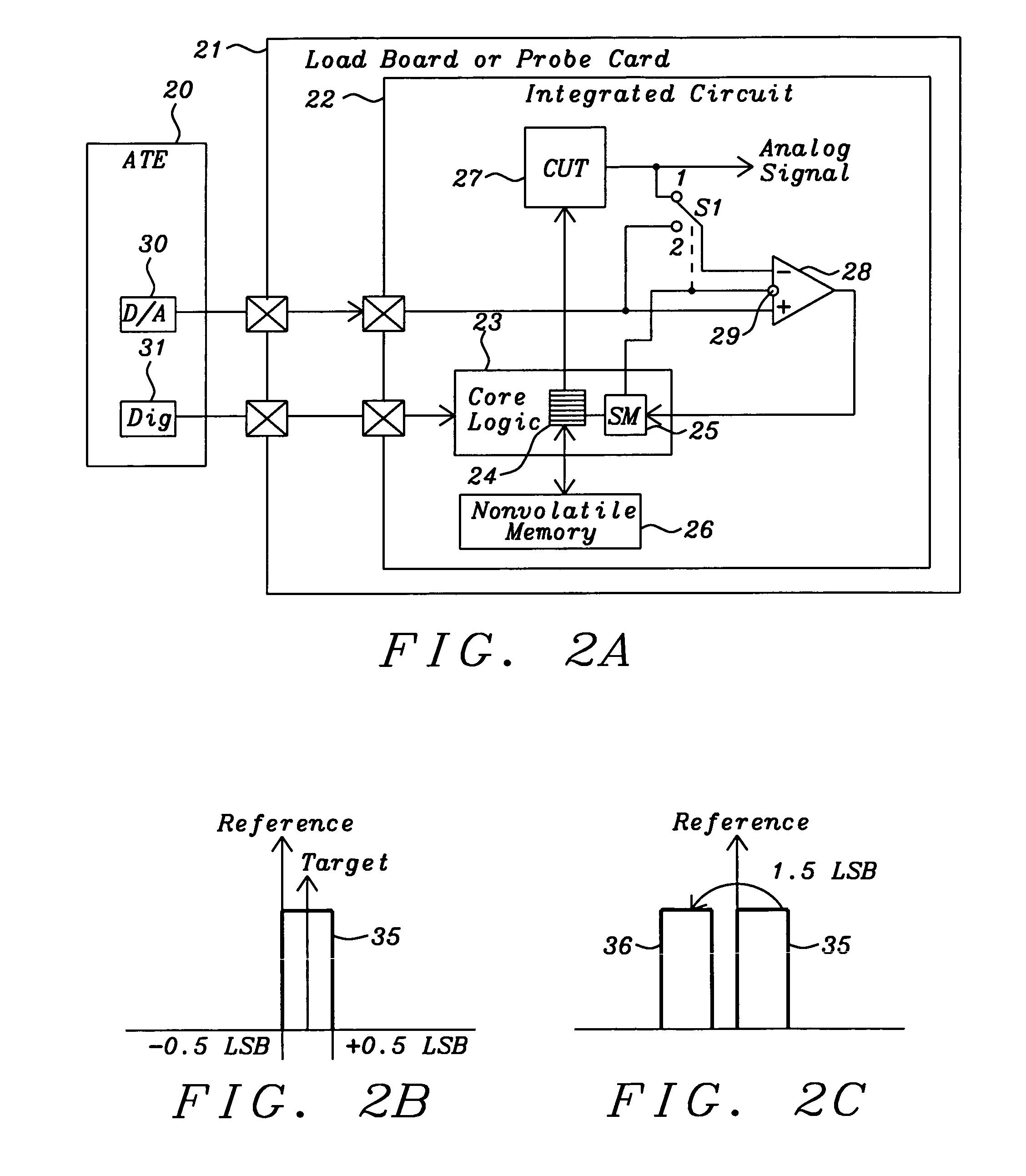

Self-trim and self-test of on-chip values

A self-trim circuit provides a technique to trim a CUT (circuit under trim) using a LSB offset to determine the best digital value to trim the CUT. The self-trim circuit is also used to self-test the digital and analog portions of the self-trim circuitry, whereby the existence of a digital stuck at fault condition is detected. A state machine controls a digital stack to couple digital trim data to the CUT and read the output of a comparator circuit that signifies when a proper digital trim value has been used. Thereafter the proper digital trim value is stored into a nonvolatile memory.

Owner:DIALOG SEMICONDUCTOR GMBH

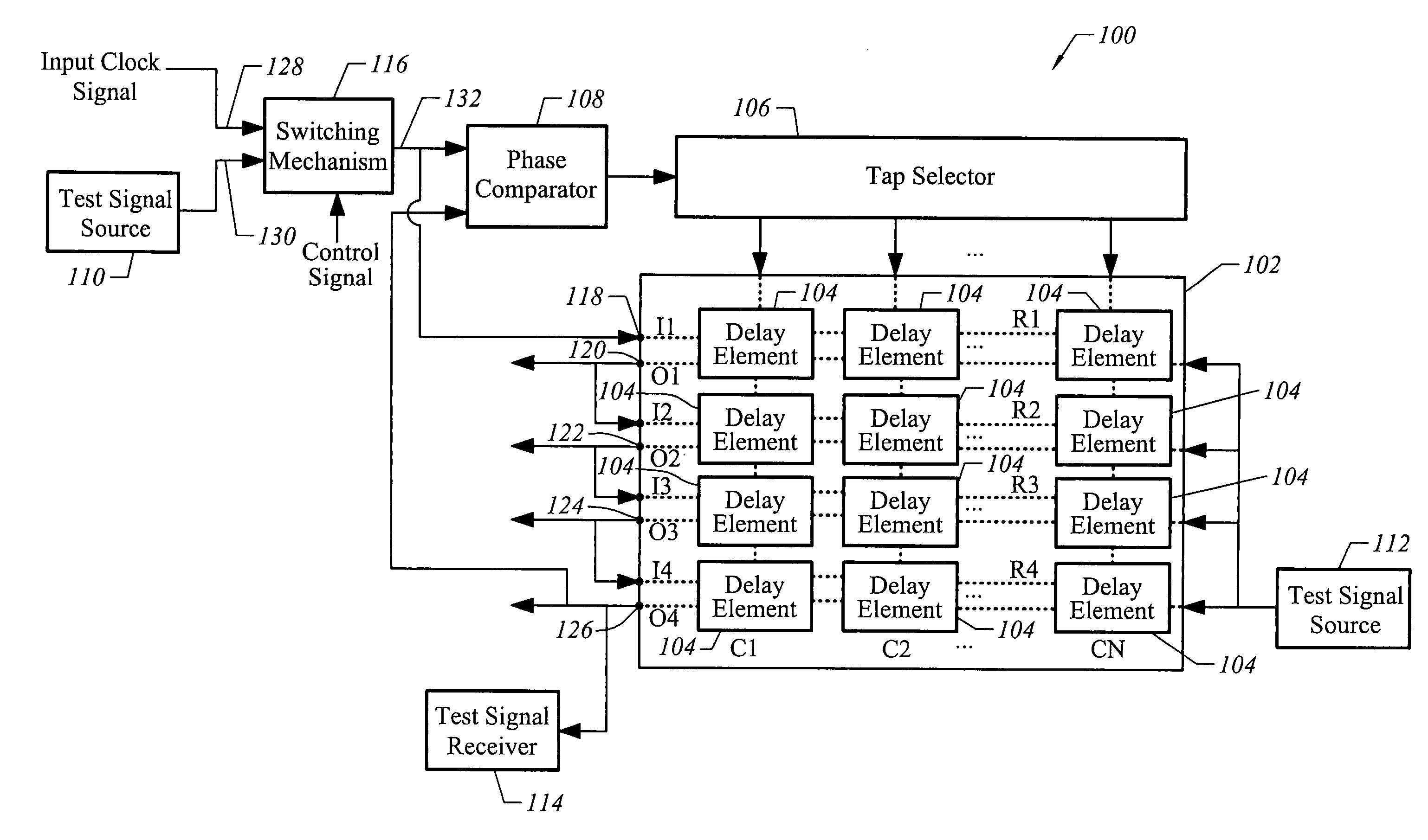

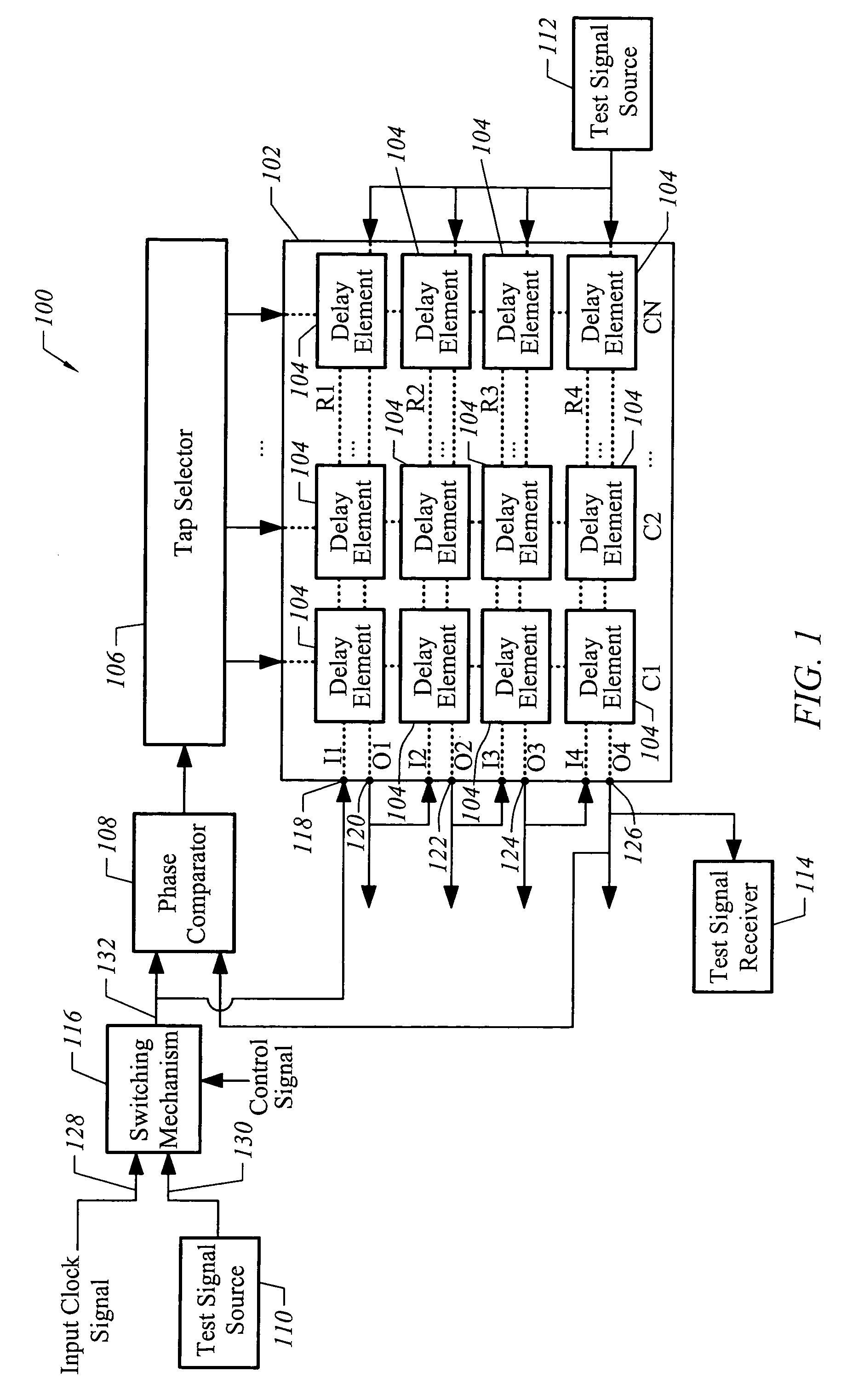

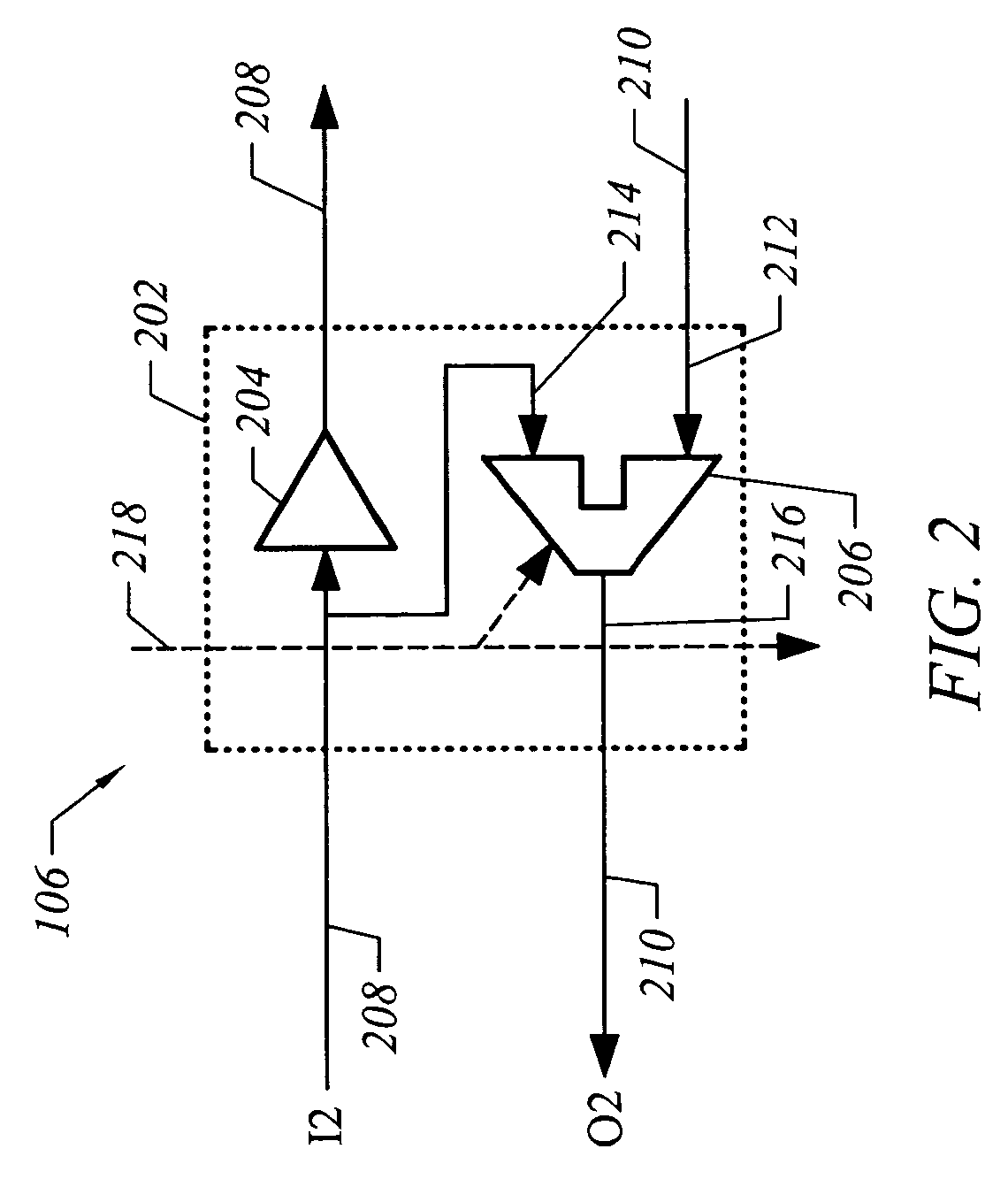

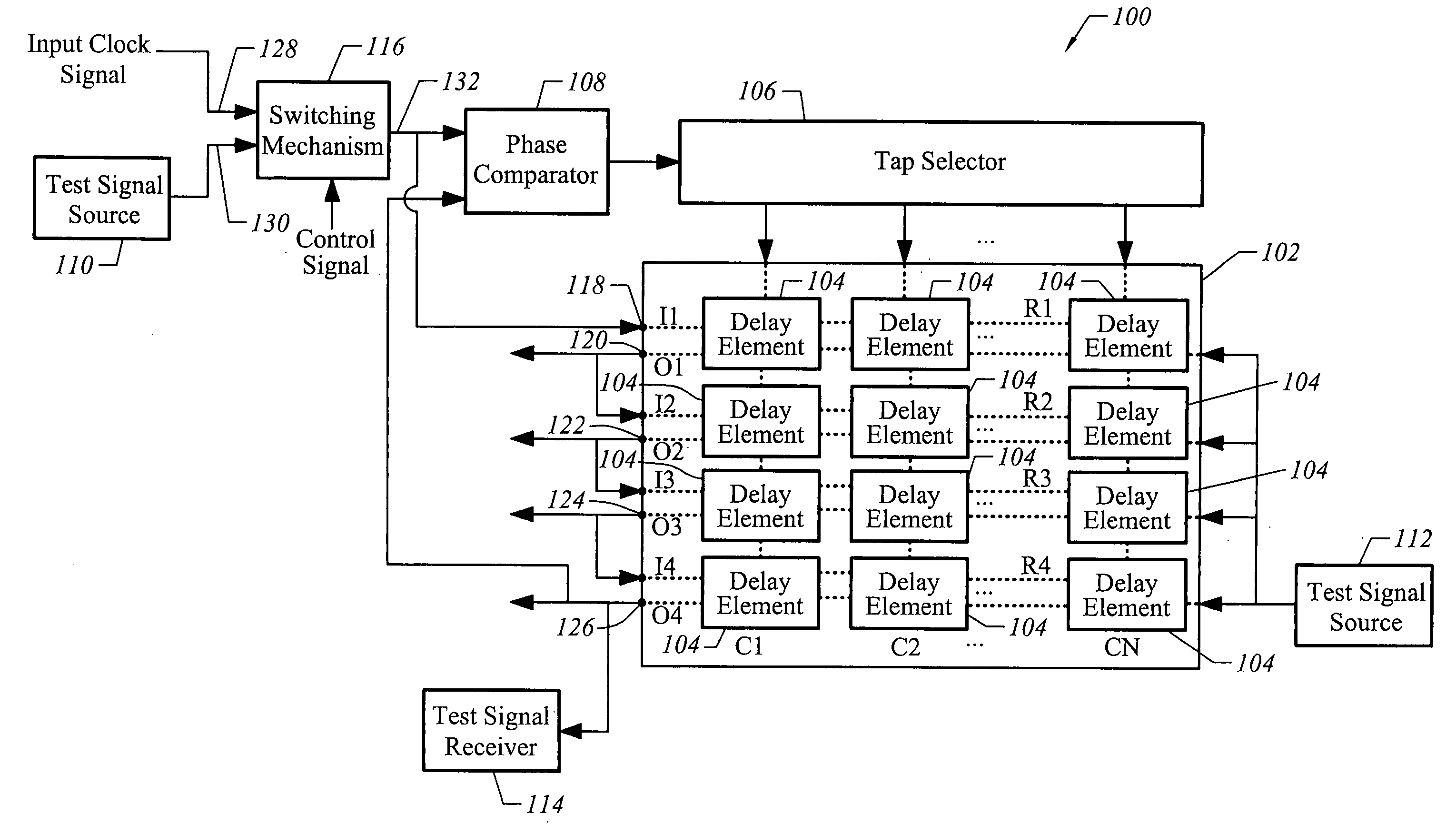

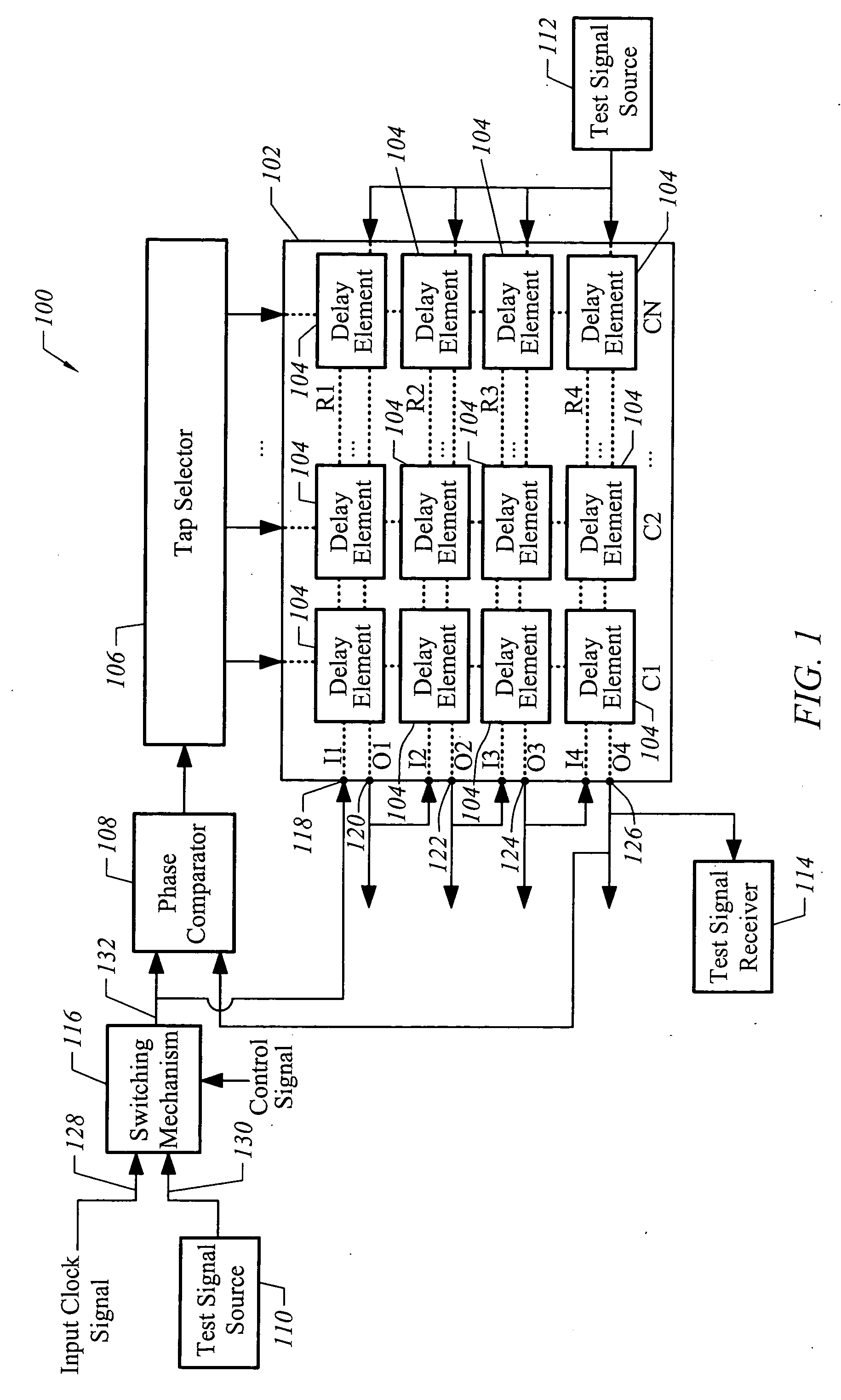

Delay locked loop circuit and method for testing the operability of the circuit

A delay locked loop (DLL) circuit and method for testing the operability of the circuit utilizes one or more test signal sources and a test signal receiver to selectively transmit test signals, for example, static test signals, through an array of delay elements of the DLL circuit. The resulting output signals of the array are used to determine whether any delay element or a tap selector of the DLL circuit has malfunctioned, e.g., stuck-at fault.

Owner:AVAGO TECH INT SALES PTE LTD

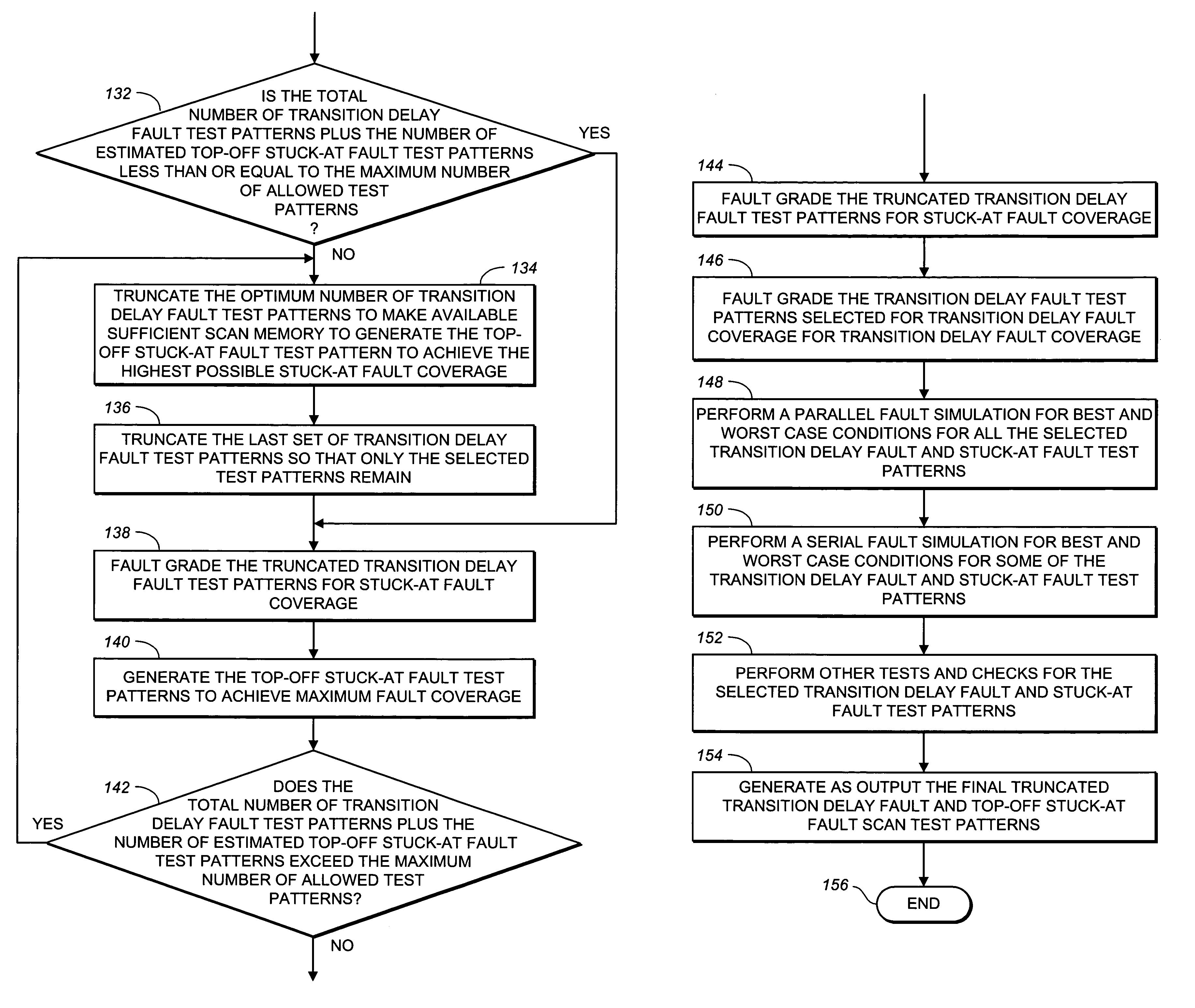

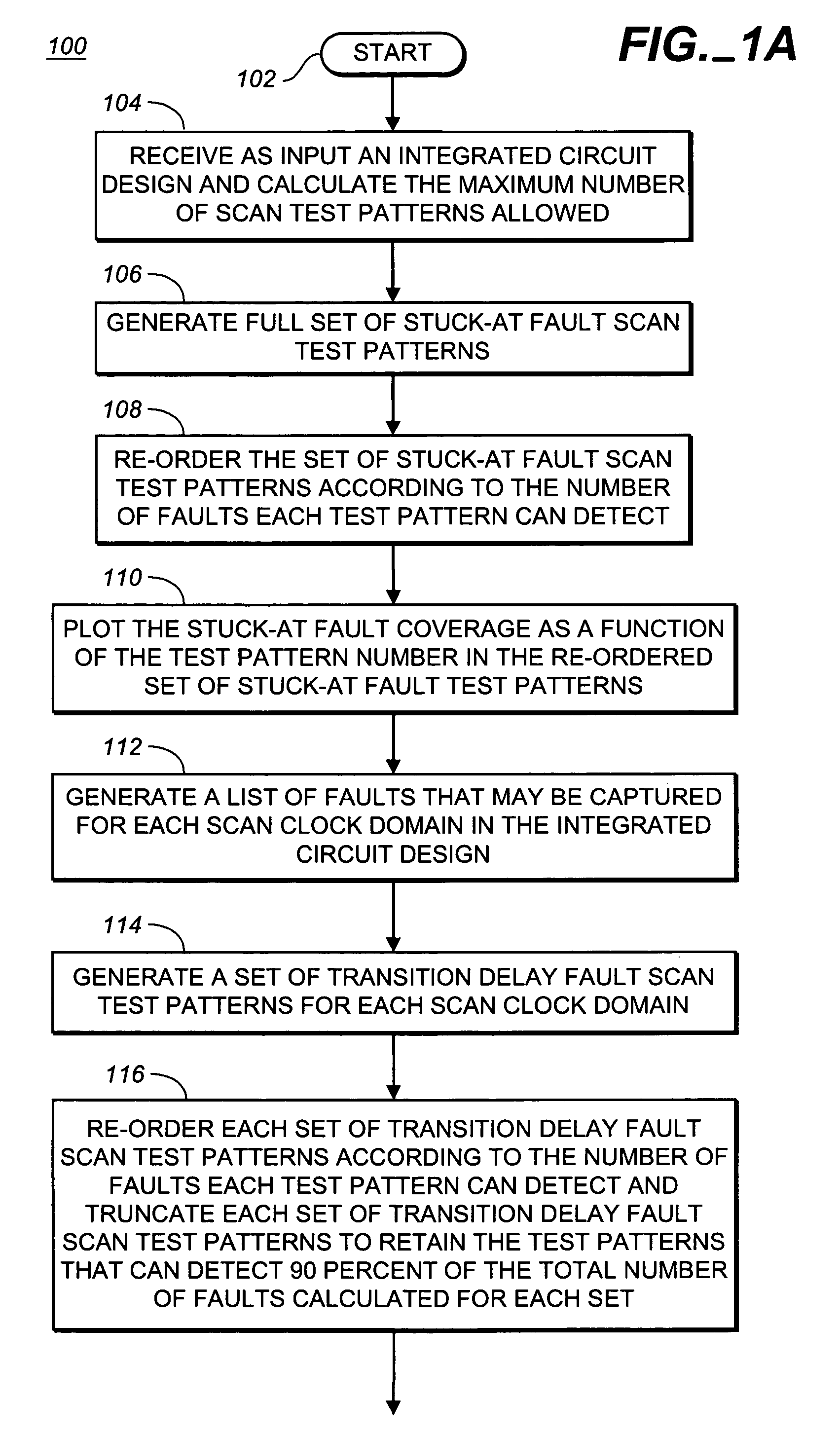

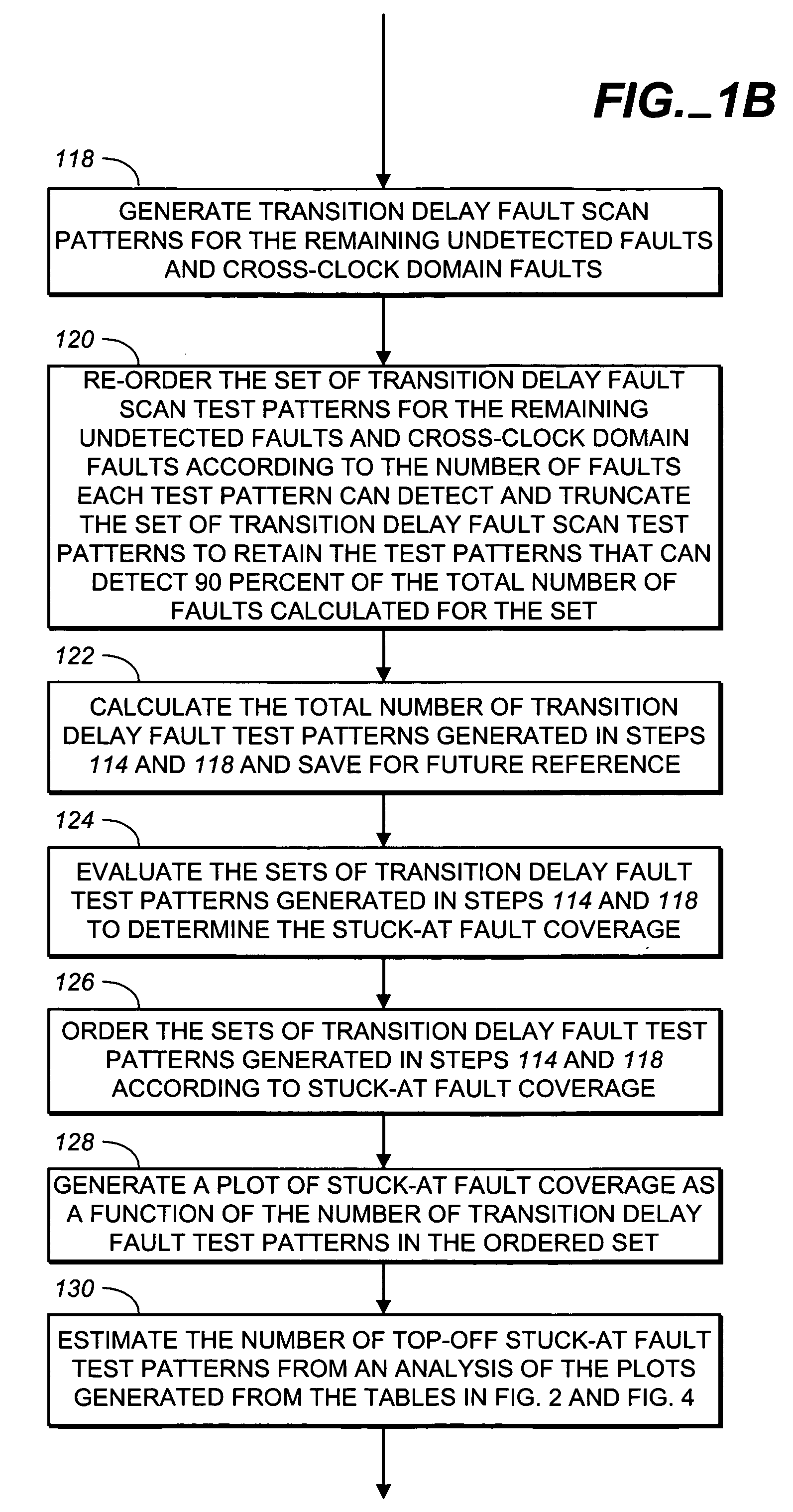

Method of generating an efficient stuck-at fault and transition delay fault truncated scan test pattern for an integrated circuit design

A method of generating a truncated scan test pattern for an integrated circuit design includes steps of: (a) receiving as input an integrated circuit design; (b) estimating a number of transition delay fault test patterns and a corresponding number of top-off stuck-at fault patterns to achieve maximum stuck-at fault and transition delay fault coverage; (c) truncating the estimated number of transition delay fault patterns to generate a truncated set of transition delay fault patterns so that the truncated set of transition delay fault patterns and the corresponding number of top-off stuck-at fault patterns achieve maximum stuck-at fault and transition delay fault coverage within a selected scan memory limit; and (d) generating as output the truncated set of transition delay fault patterns and the corresponding number of top-off stuck-at fault patterns.

Owner:BELL SEMICON LLC

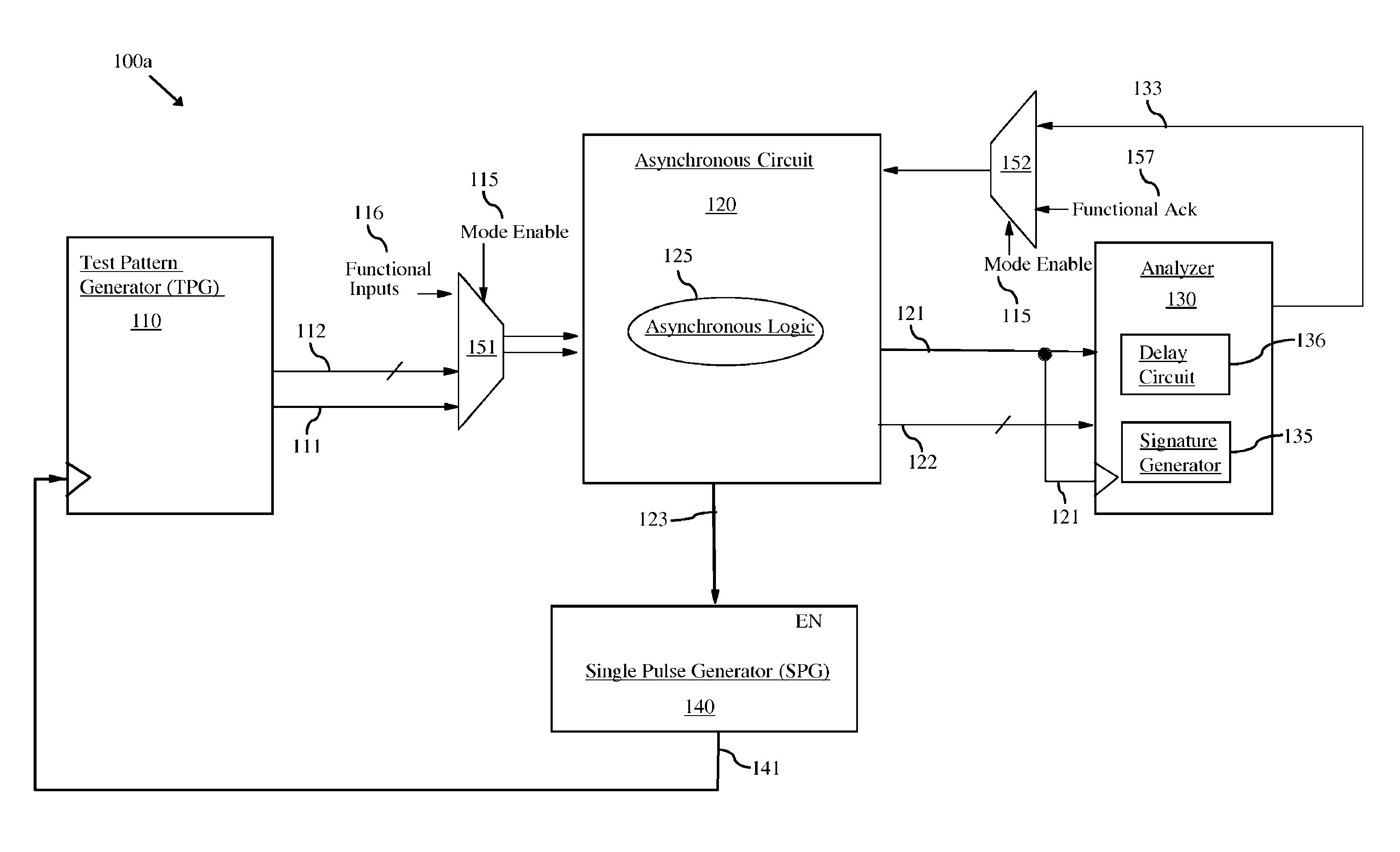

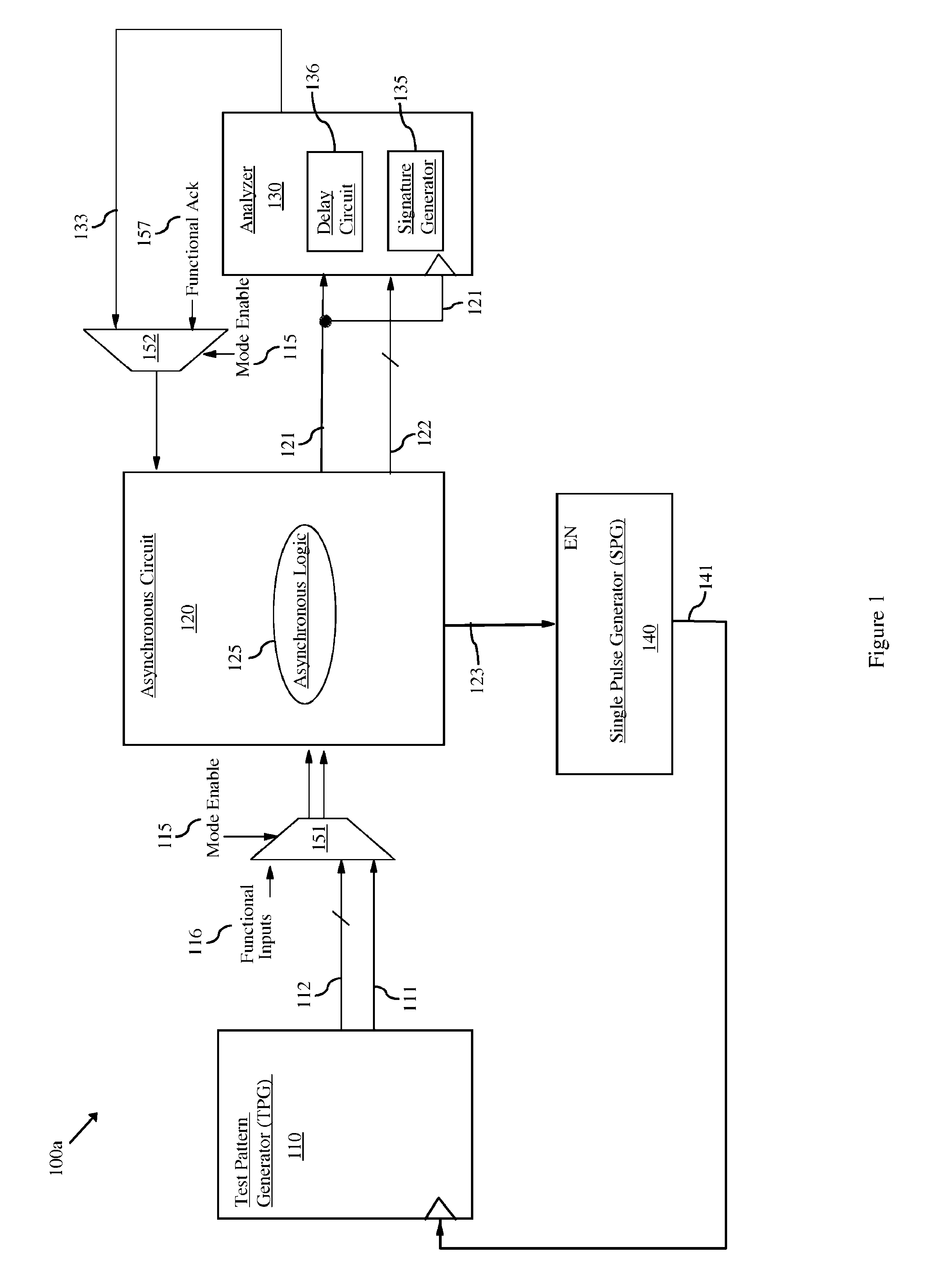

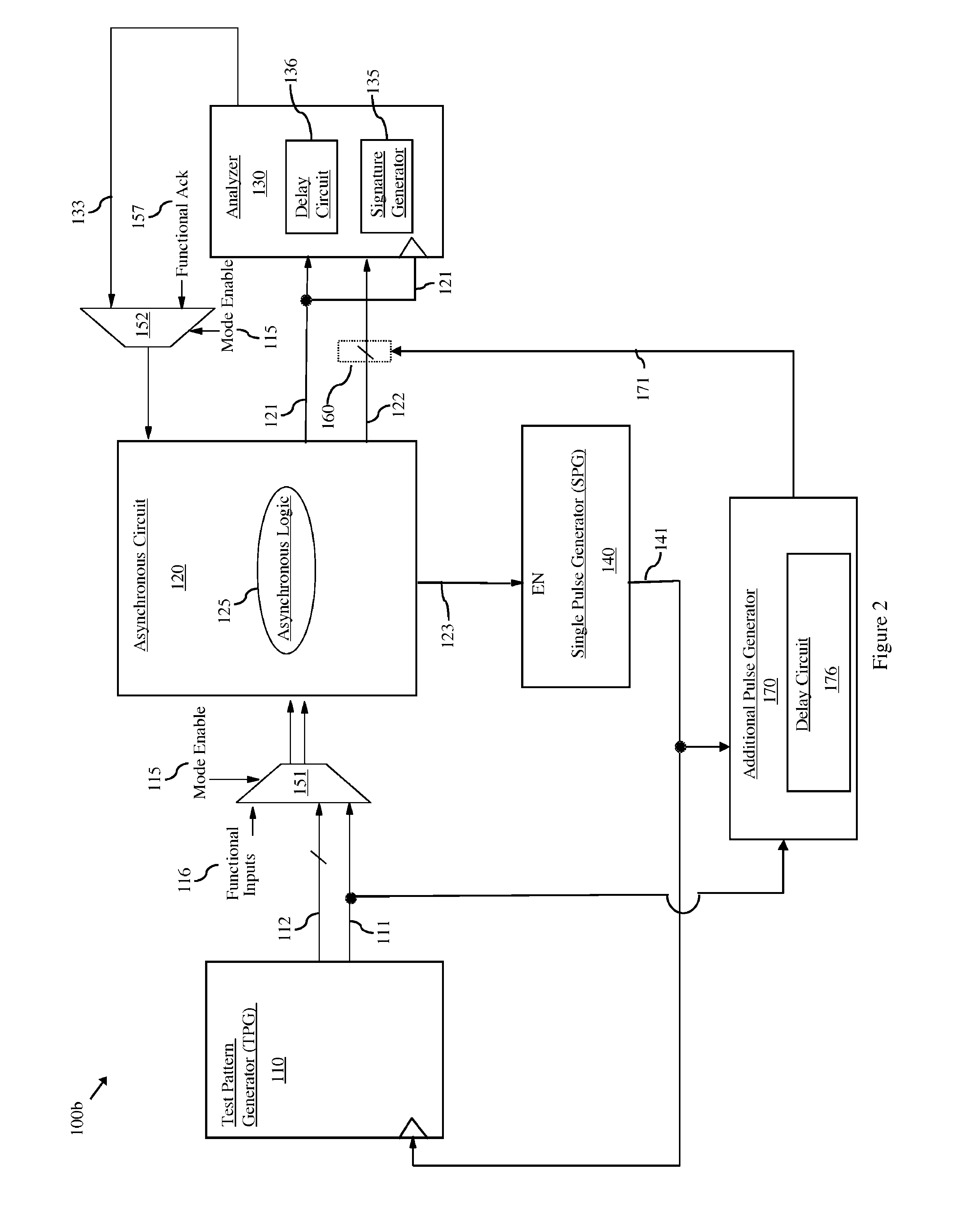

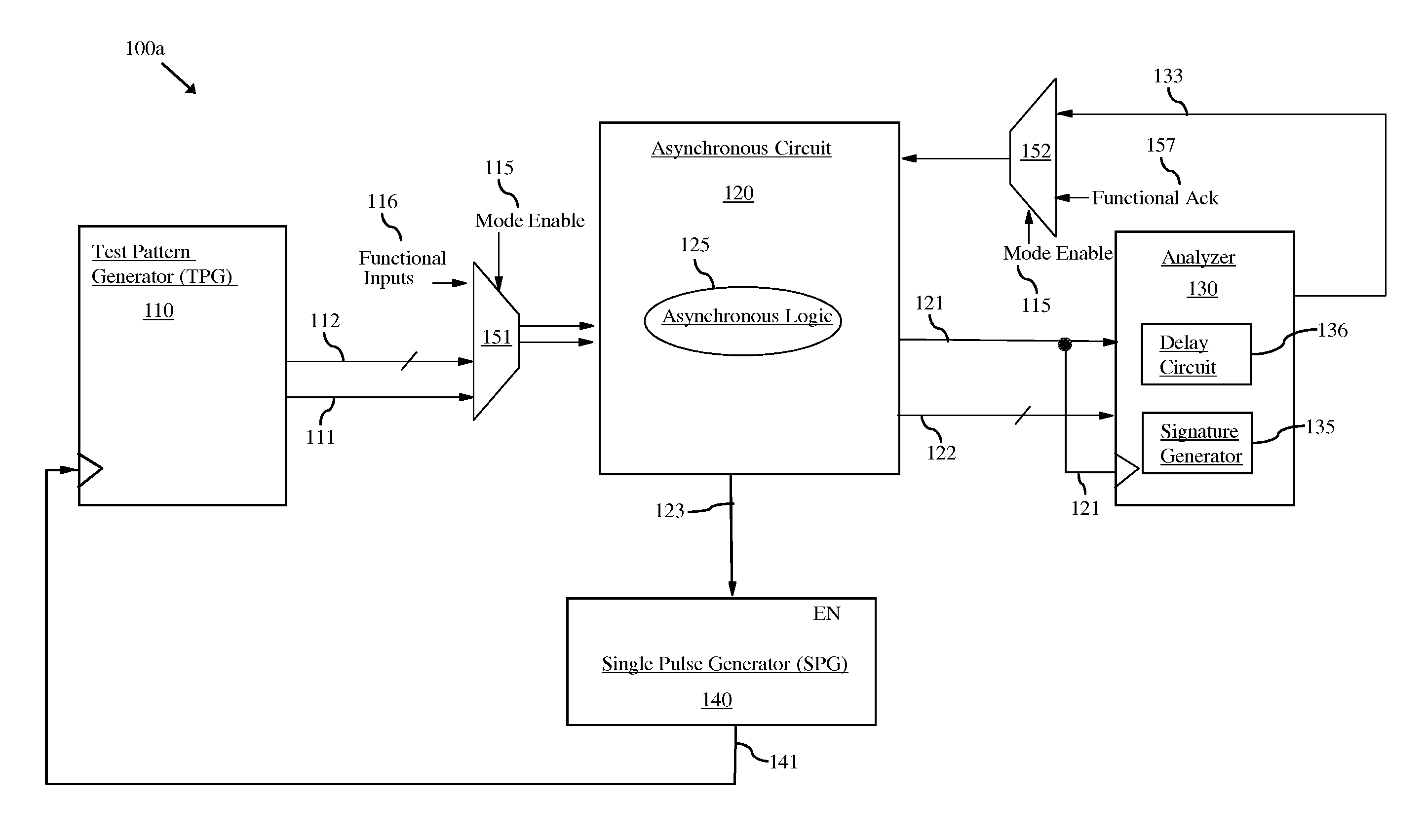

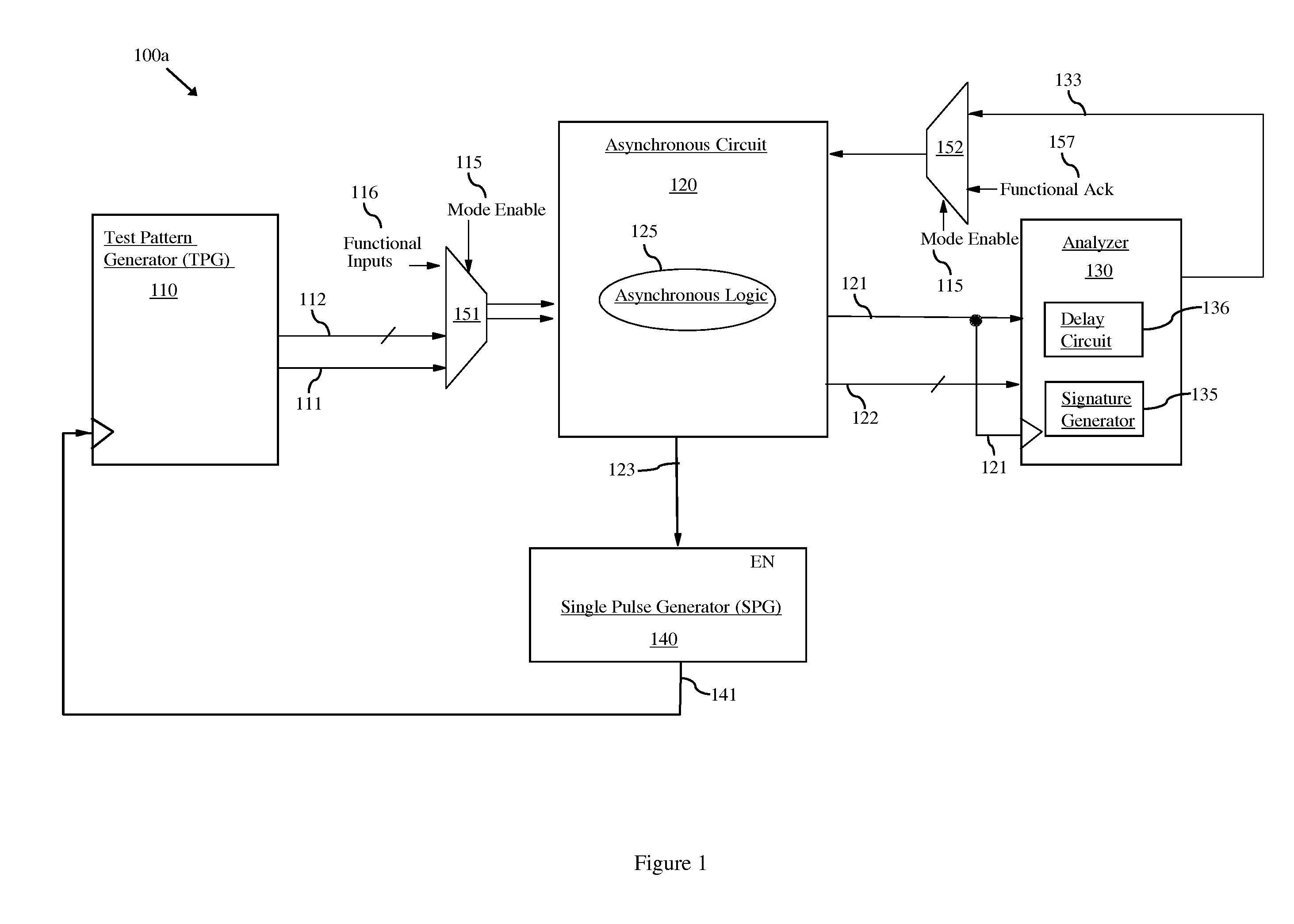

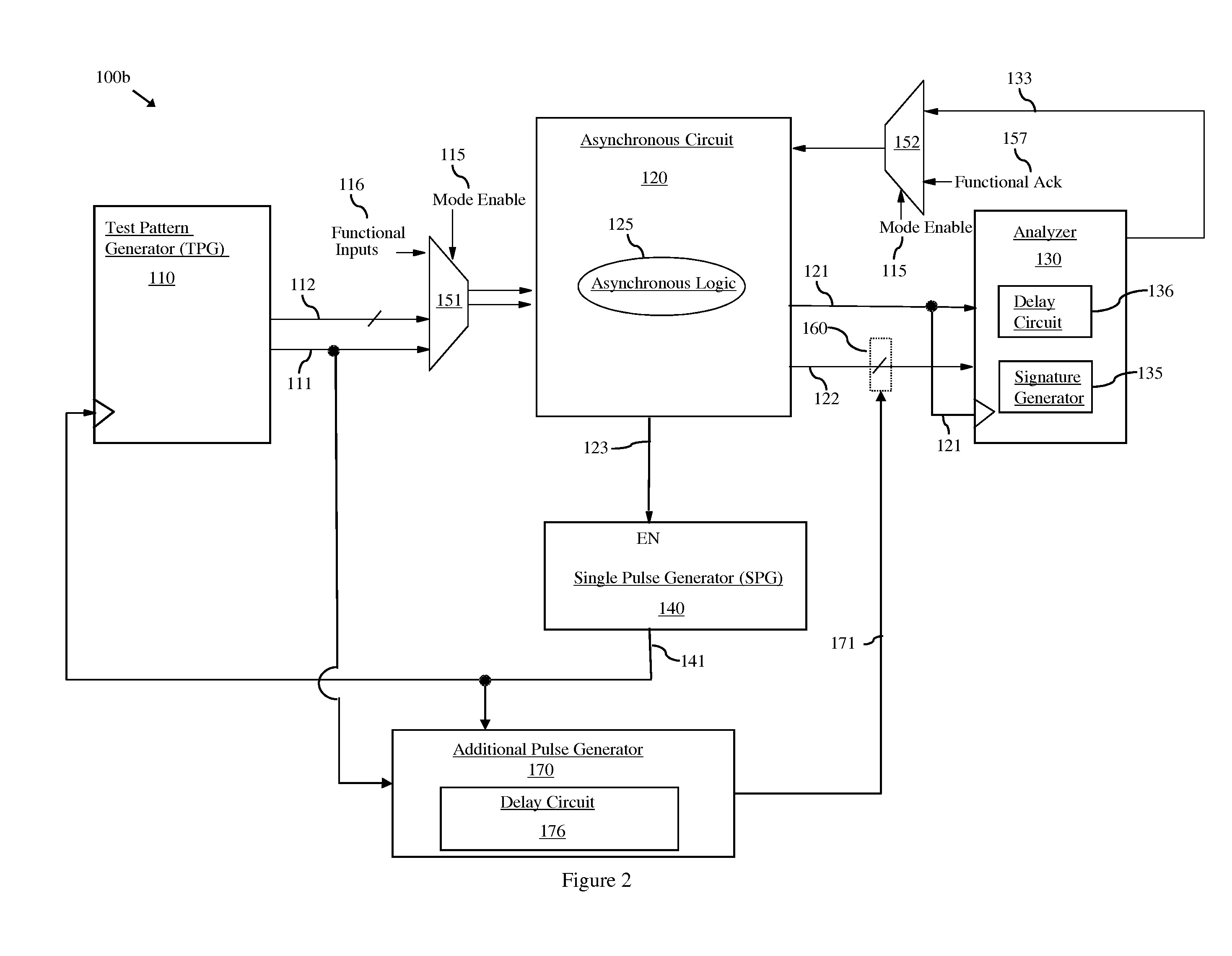

Asynchronous circuit with an at-speed built-in self-test (BIST) architecture

ActiveUS8612815B2Electronic circuit testingError detection/correctionAsynchronous circuitStuck-at fault

Disclosed are integrated circuits that incorporate an asynchronous circuit with a built-in self-test (BIST) architecture using a handshaking protocol for at-speed testing to detect stuck-at faults. Specifically, a test pattern generator applies test patterns to an asynchronous circuit and an analyzer analyzes the output test data. The handshaking protocol is achieved through the use of a single pulse generator, which applies a single pulse to the test pattern generator to force switching of the test pattern request signal and, thereby to control application of the test patterns to the asynchronous circuit and subsequent switching of the test pattern acknowledge signal. Generation of this single pulse can in turn be forced by the switching of the test pattern acknowledge signal.

Owner:MARVELL ASIA PTE LTD

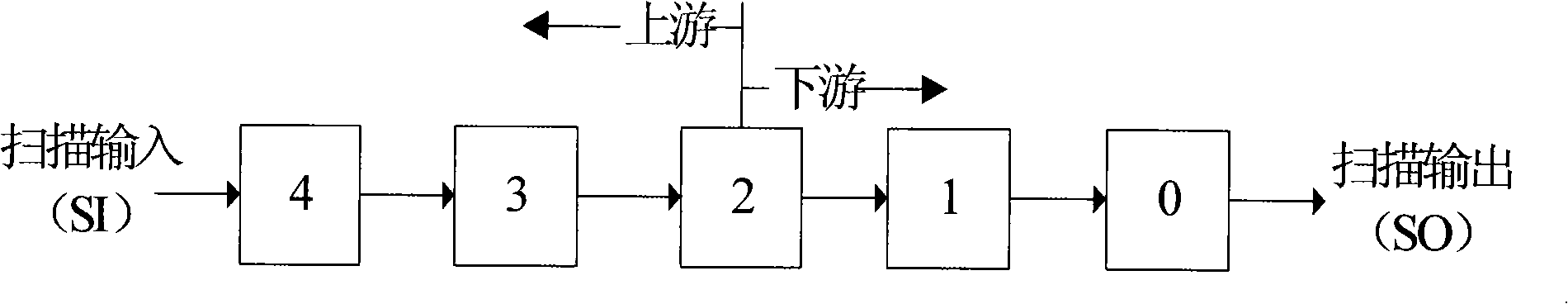

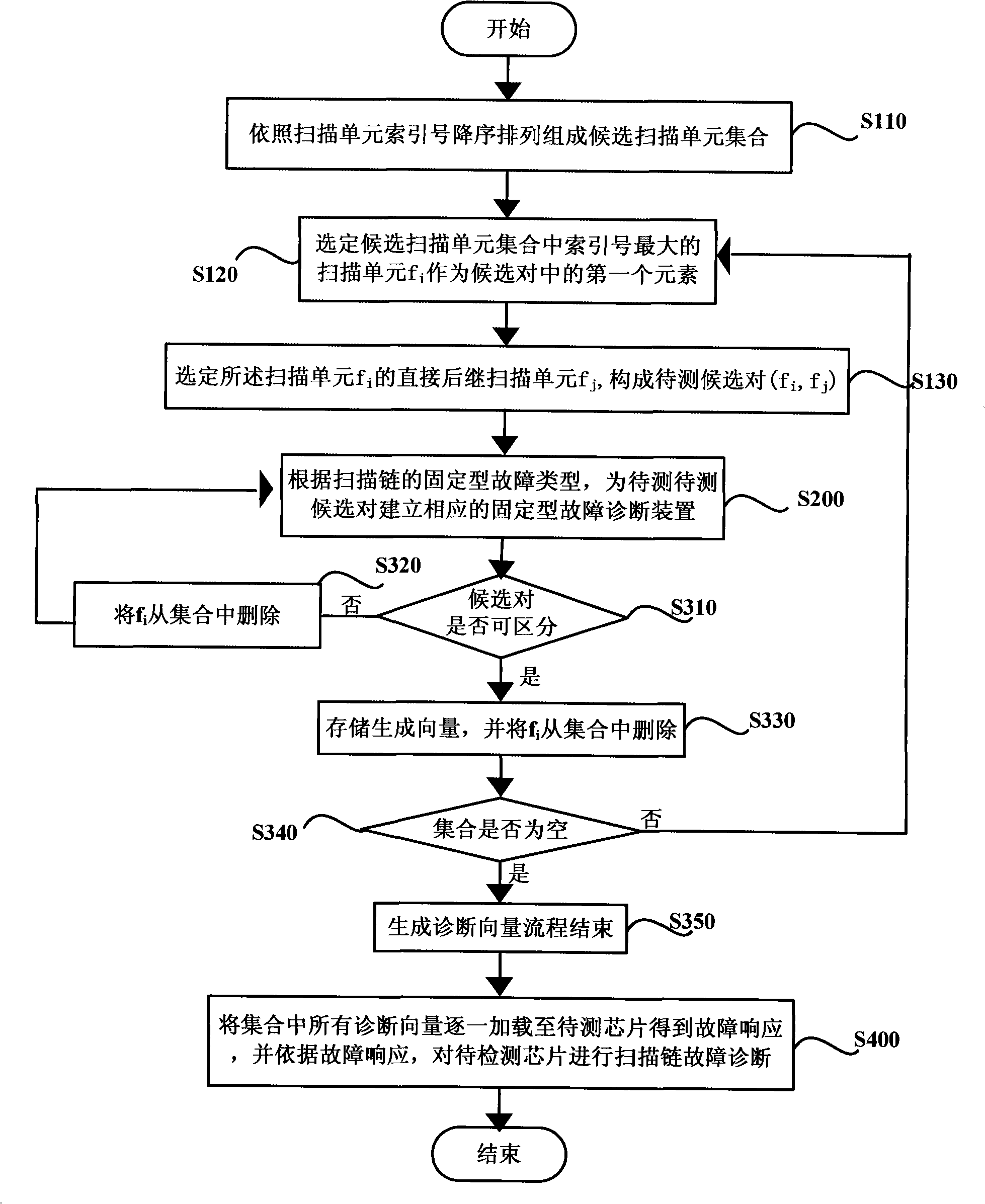

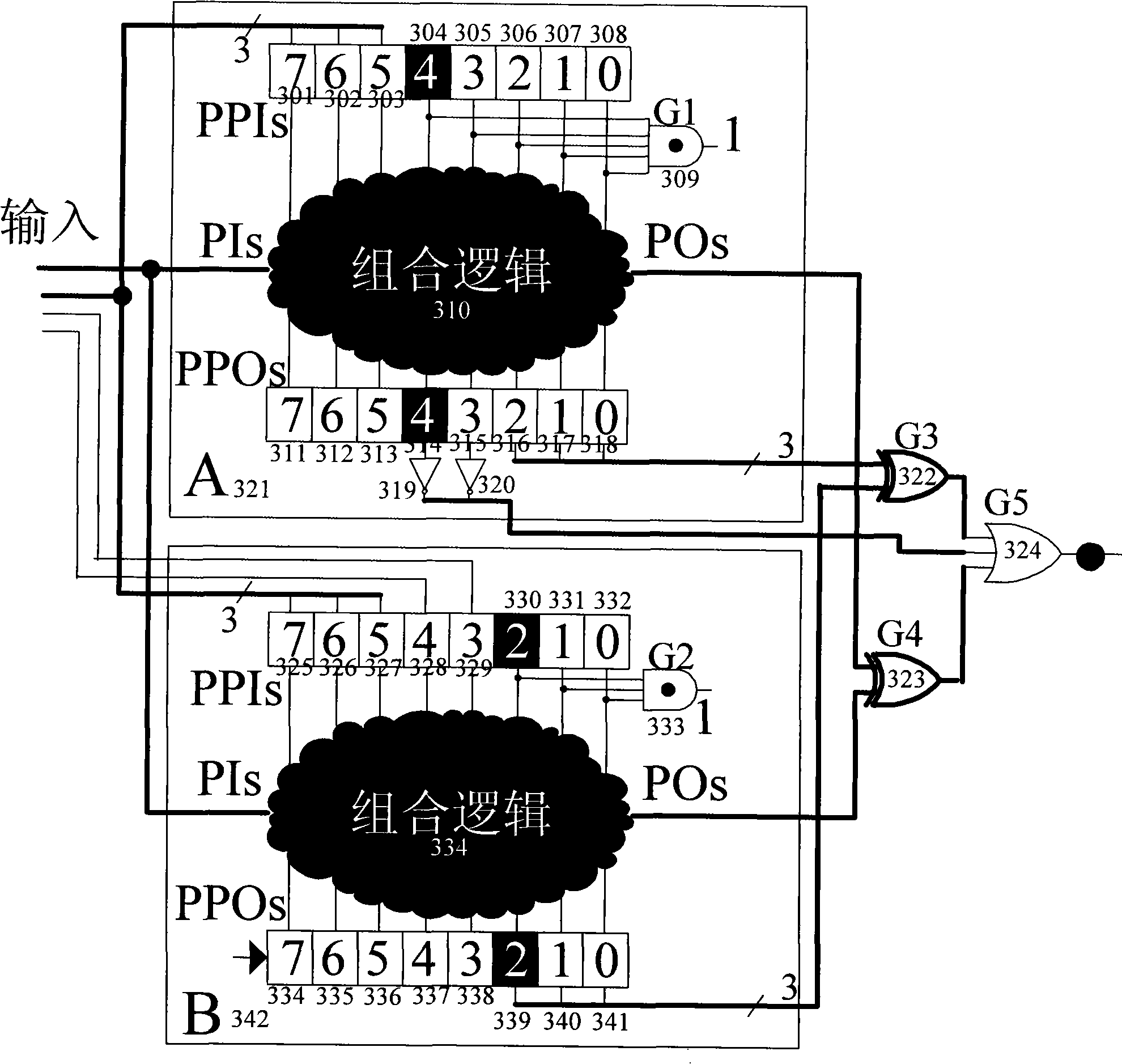

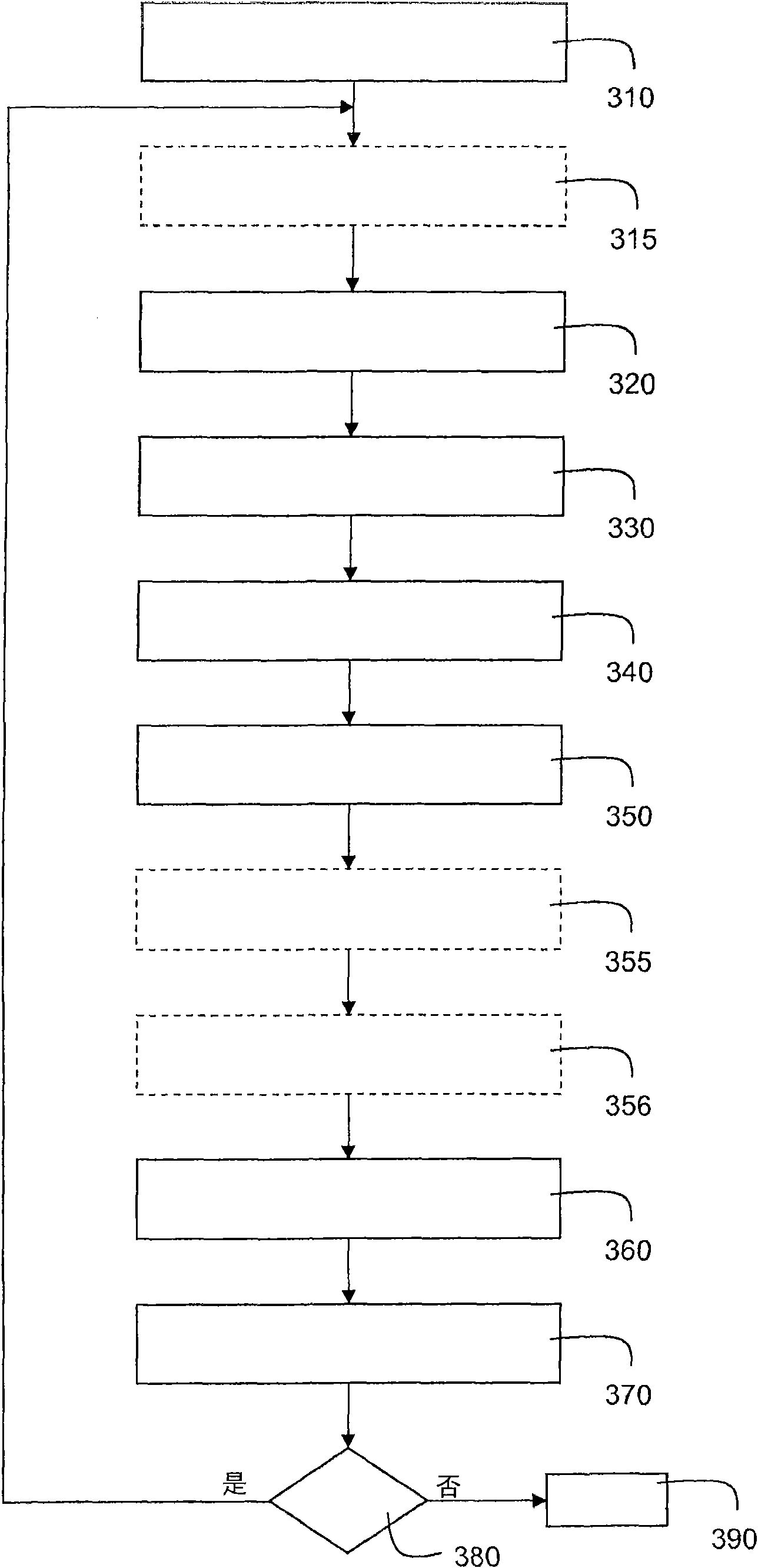

Scanning chain fault diagnosis method and system

InactiveCN101315412ADiagnosing Stuck FaultsDoes not change the design test processElectrical testingStuck-at faultReliability engineering

The invention discloses a scan chain failure diagnosis method and a system thereof. The method comprises the following steps: a candidate scan unit assembling is made up of scan units in the scan chain of a chip to be tested, and a candidate pair to be tested is selected in the assembling; according to the failure types, a corresponding fixation type failure diagnosis device is established for the candidate pair to be tested; diagnosis vectors are generated for the candidate pair to be tested by utilizing the device, and are stored in the diagnosis vector assembling for processing scan chain failure diagnosis to the chip to be tested. The method also comprises the following steps: all the diagnosis vectors in the diagnosis vector assembling are loaded to the chip to be tested one by one to get failure responses; and according to the failure responses, the scan chain failure diagnosis for the chip to be tested is processed. The failure scan chain is diagnosed in the circumstances without any spending of area and routing by adopting the method, and the traditional scan chain diagnosis flow is not changed, thereby the logic diagnosis cost is reduced.

Owner:INST OF COMPUTING TECH CHINESE ACAD OF SCI

Asynchronous circuit with an at-speed built-in self-test (BIST) architecture

ActiveUS20130159803A1Electronic circuit testingError detection/correctionAsynchronous circuitStuck-at fault

Disclosed are embodiments of an integrated circuit that incorporates an asynchronous circuit with a built-in self-test (BIST) architecture using a handshaking protocol for at-speed testing to detect stuck-at faults. In the embodiments, a test pattern generator applies test patterns to an asynchronous circuit and an analyzer analyzes the output test data. The handshaking protocol is achieved through the use of a single pulse generator, which applies a single pulse to the test pattern generator to force switching of the test pattern request signal and, thereby to control application of the test patterns to the asynchronous circuit and subsequent switching of the test pattern acknowledge signal. Generation of this single pulse can in turn be forced by the switching of the test pattern acknowledge signal. Optionally, a time constraint can be added to the capture of the output test data to allow for detection of delay faults.

Owner:MARVELL ASIA PTE LTD

Delay locked loop circuit and method for testing the operability of the circuit

A delay locked loop (DLL) circuit and method for testing the operability of the circuit utilizes one or more test signal sources and a test signal receiver to selectively transmit test signals, for example, static test signals, through an array of delay elements of the DLL circuit. The resulting output signals of the array are used to determine whether any delay element or a tap selector of the DLL circuit has malfunctioned, e.g., stuck-at fault.

Owner:AVAGO TECH INT SALES PTE LTD

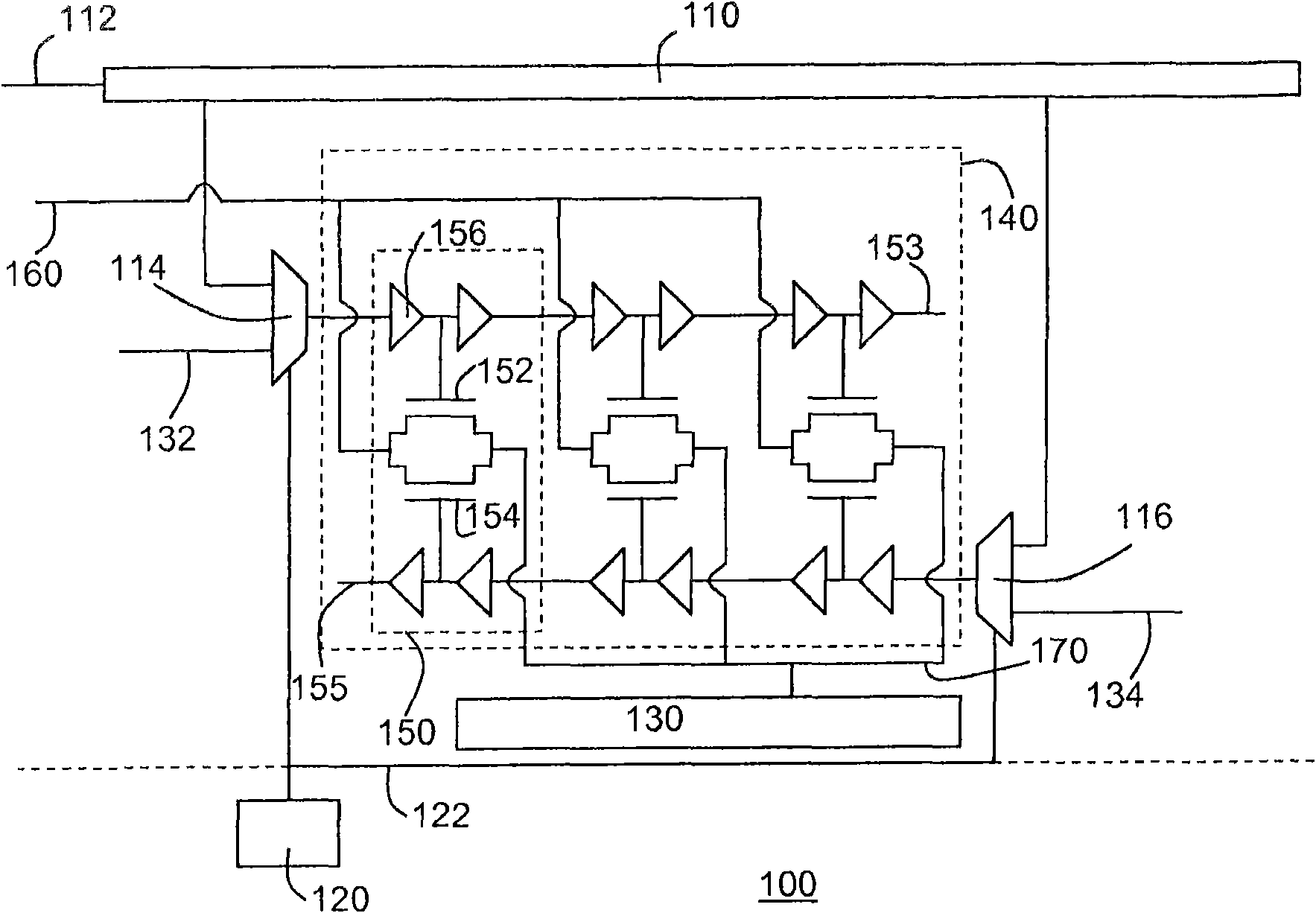

Testable integrated circuit and test method

InactiveCN101688896ADigital circuit testingSemiconductor/solid-state device detailsHigh resistanceEngineering

An integrated circuit (100) is disclosed comprising a plurality of circuit portions (130), each of the circuit portions having an internal supply rail (170) coupled to a global supply rail (160) via acluster (140) of switches (152; 154) coupled in parallel between the internal supply rail (170) and the global supply rail (160). Each cluster (140) of switches (152; 154) has a first switch (152) having a first size and a second switch (154) having a second size, a fault-free first switch (152) having a higher resistance than a fault-free second switch (154). The IC (100) further comprises a test arrangement for testing the respective clusters (140) of switches (152; 154) in a test mode. The test arrangement comprises a test control input; a test output coupled to the respective internal supply rails (170) and control means (110, 114, 116) coupled to the test control input for enabling a selected cluster (140) of switches (152; 154) in the test mode. The control means comprise first selection means (114) for selectively enabling the first switch (152) and second selection means (116) for selectively enabling the second switch (154) of the selected cluster (140) in the test mode. Thisarrangement allows for the accurate measurement of the resistance of power switches (152; 154) between a global power rail (160) and an internal power rail (170) of a circuit portion (130), thus facilitating the detection of both resistive and stuck-at faults in these switches (152; 154).

Owner:NXP BV

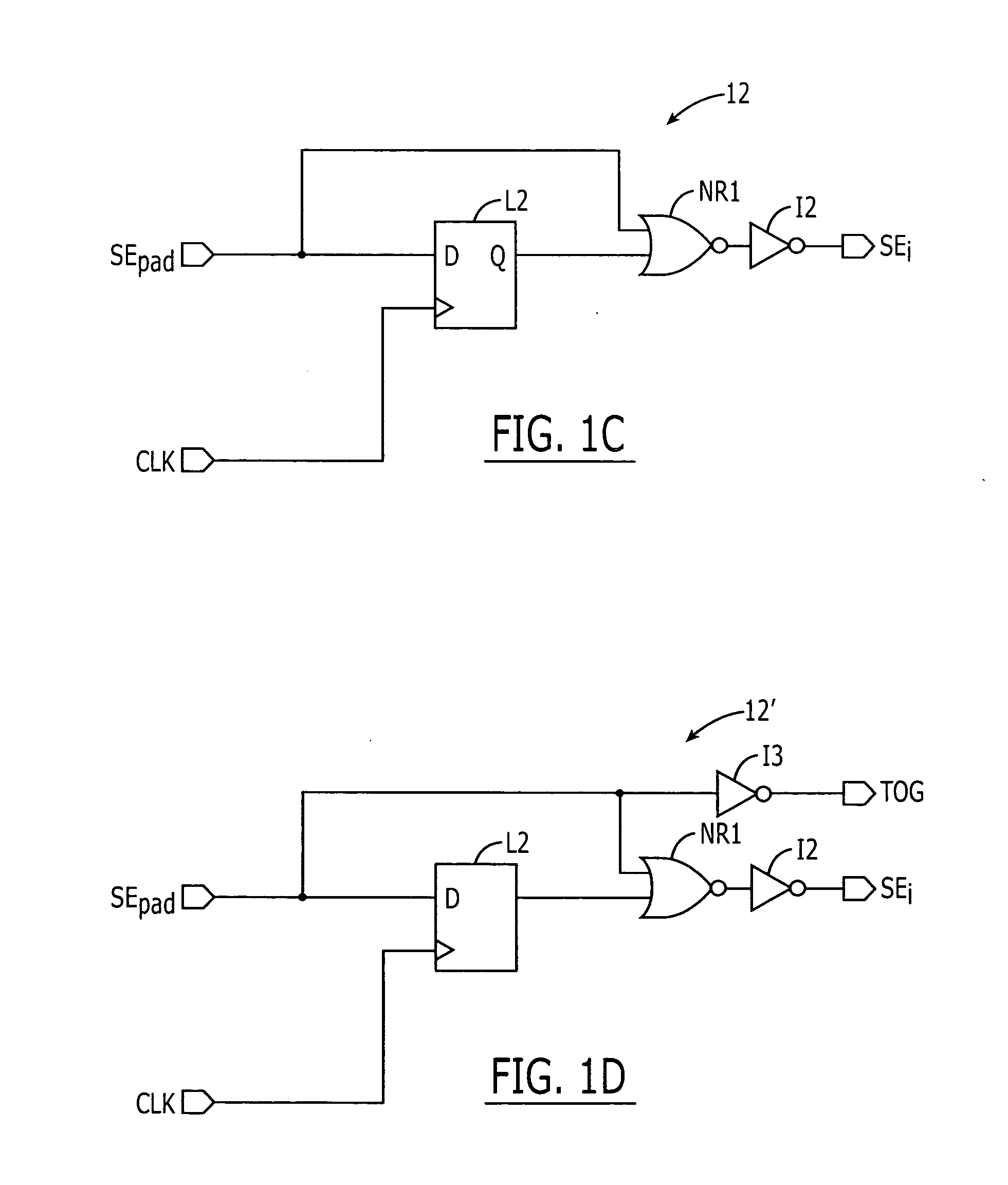

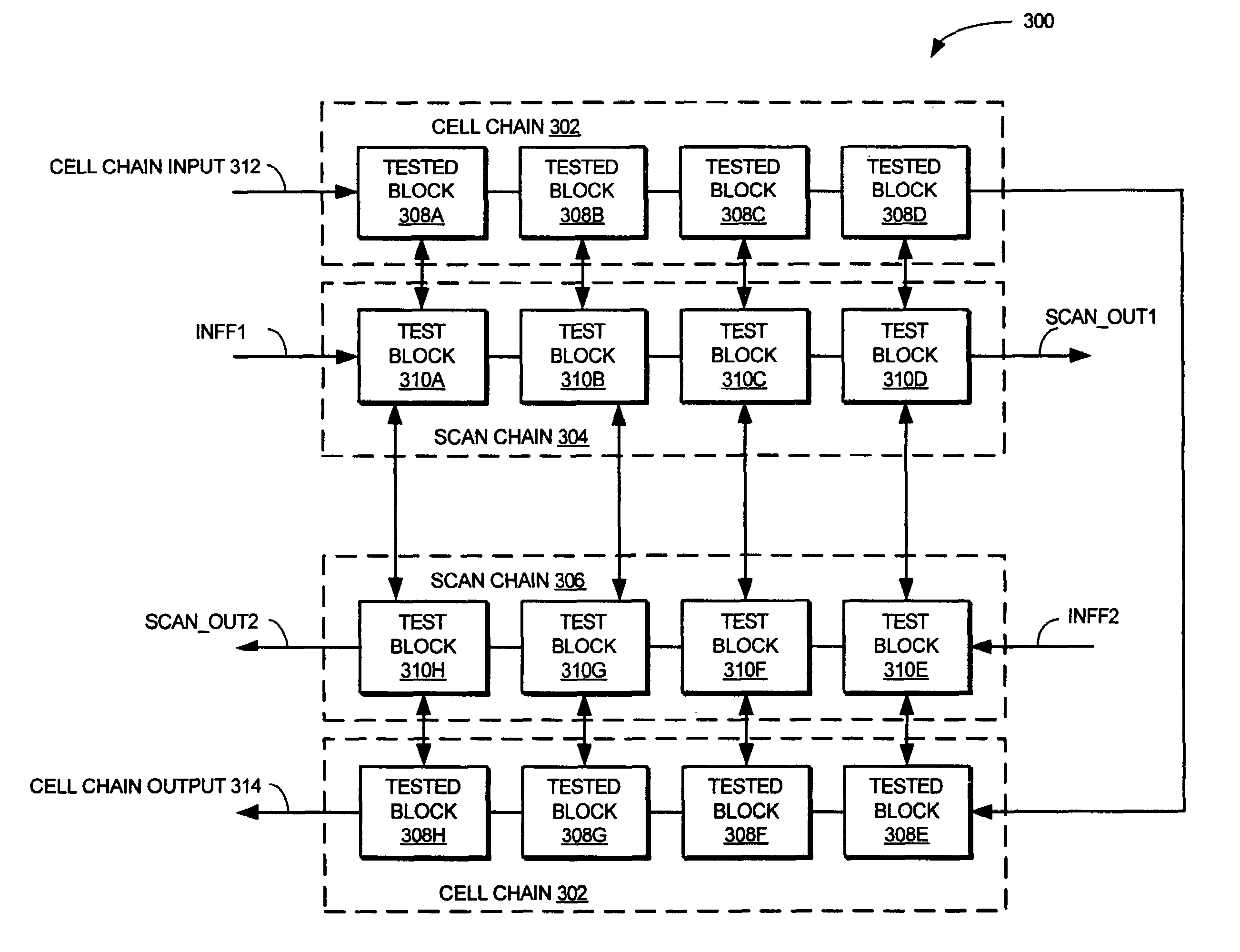

Method and apparatus for determining stuck-at fault locations in cell chains using scan chains

InactiveUS20070022340A1Rapid positioningElectronic circuit testingError detection/correctionEngineeringStuck-at fault

Methods and apparatus are provided for testing digital circuits. In one implementation, a scan chain test structure is provided that includes a cell chain, a first scan chain, and a second scan chain. The first scan chain is operable to test digital circuitry within a first portion of the cell chain, and the second scan chain is operable to test digital circuitry within a second portion of the cell chain. The first scan chain is further operable to test digital circuitry within the second scan chain, and the second scan chain is further operable to test digital circuitry within the first scan chain.

Owner:ATMEL CORP

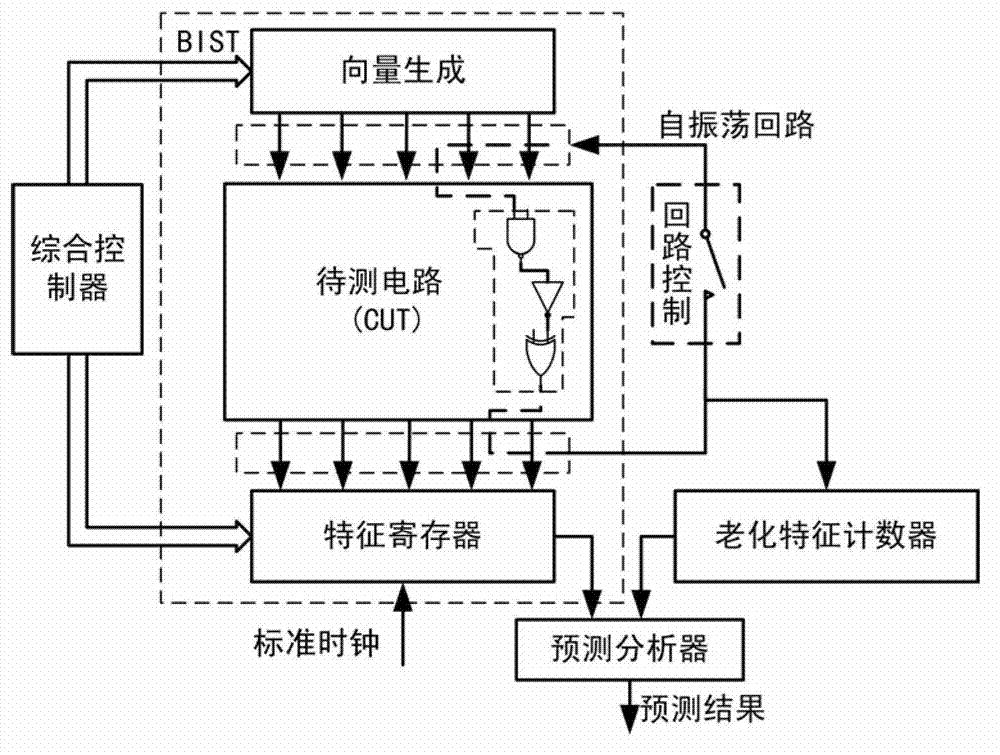

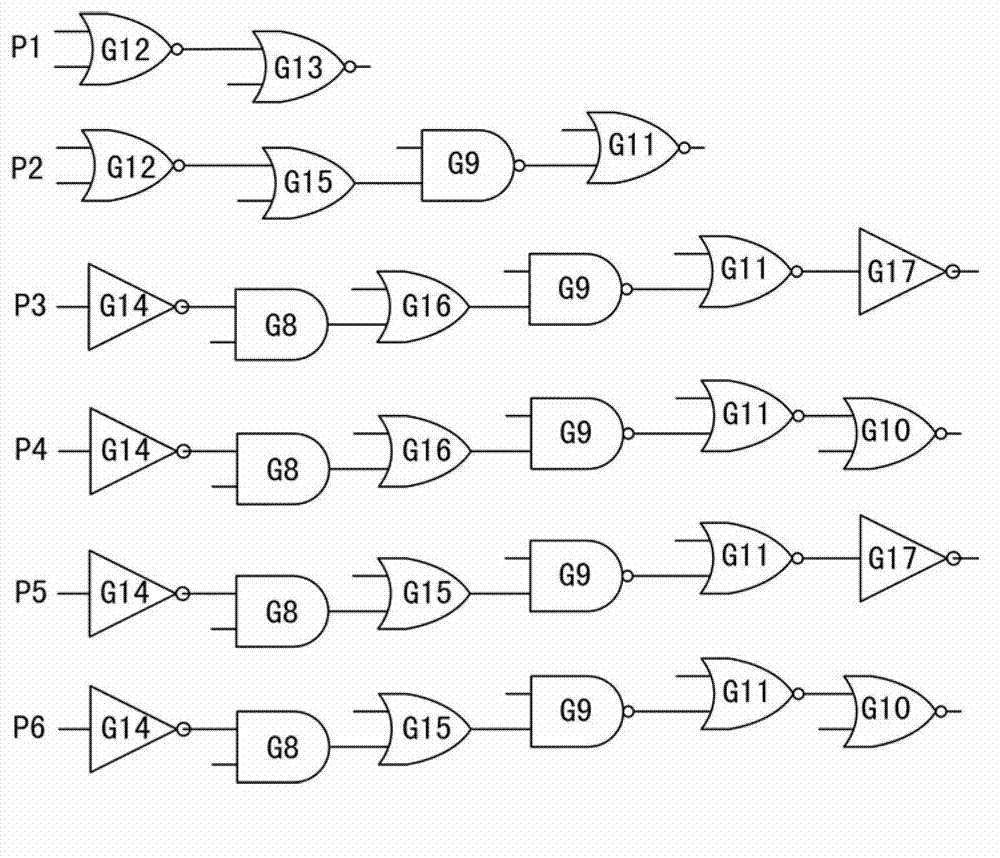

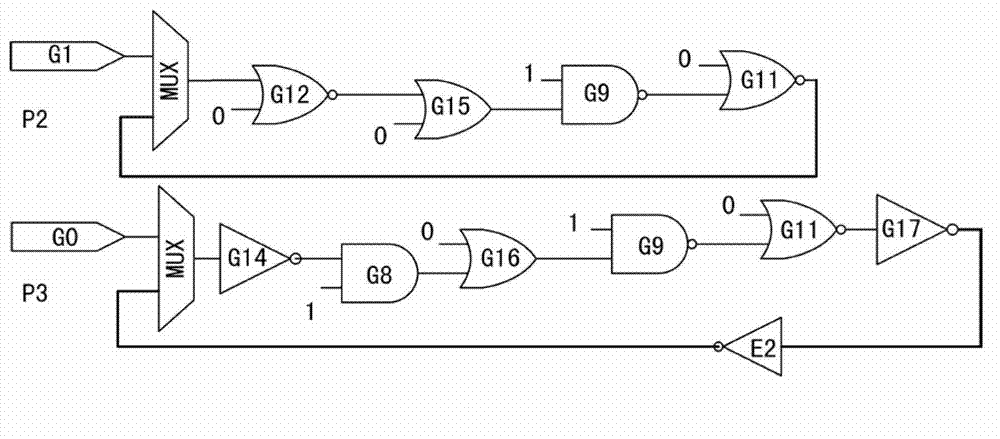

Circuit ageing detection method based on self-oscillation circuit

InactiveCN103116121AAvoid interferenceReflect the actual aging degreeElectronic circuit testingStatic timing analysisNegation

The invention discloses a circuit ageing detection method based on a self-oscillation circuit. The method includes choosing an ageing characteristic access collection T in a to-be-detected circuit according to static timing analysis and correlation among ways, remaining logical negation with odd power on each to-be-detected way in the ageing characteristic access collection T to form the self-oscillation circuit, producing a detection vector quantity to excite the self-oscillation circuit to produce a detection level signal by means of a detection production method of a fixed-type fault, and obtaining a circuit ageing characteristic value through the fact that a counter samples the self-oscillation circuit and measuring the ageing degree of the to-be-detected circuit. The method can precisely measure the ageing degree of the circuit at low power consumption, and provides precise bases for circuit ageing failure protection.

Owner:HEFEI UNIV OF TECH

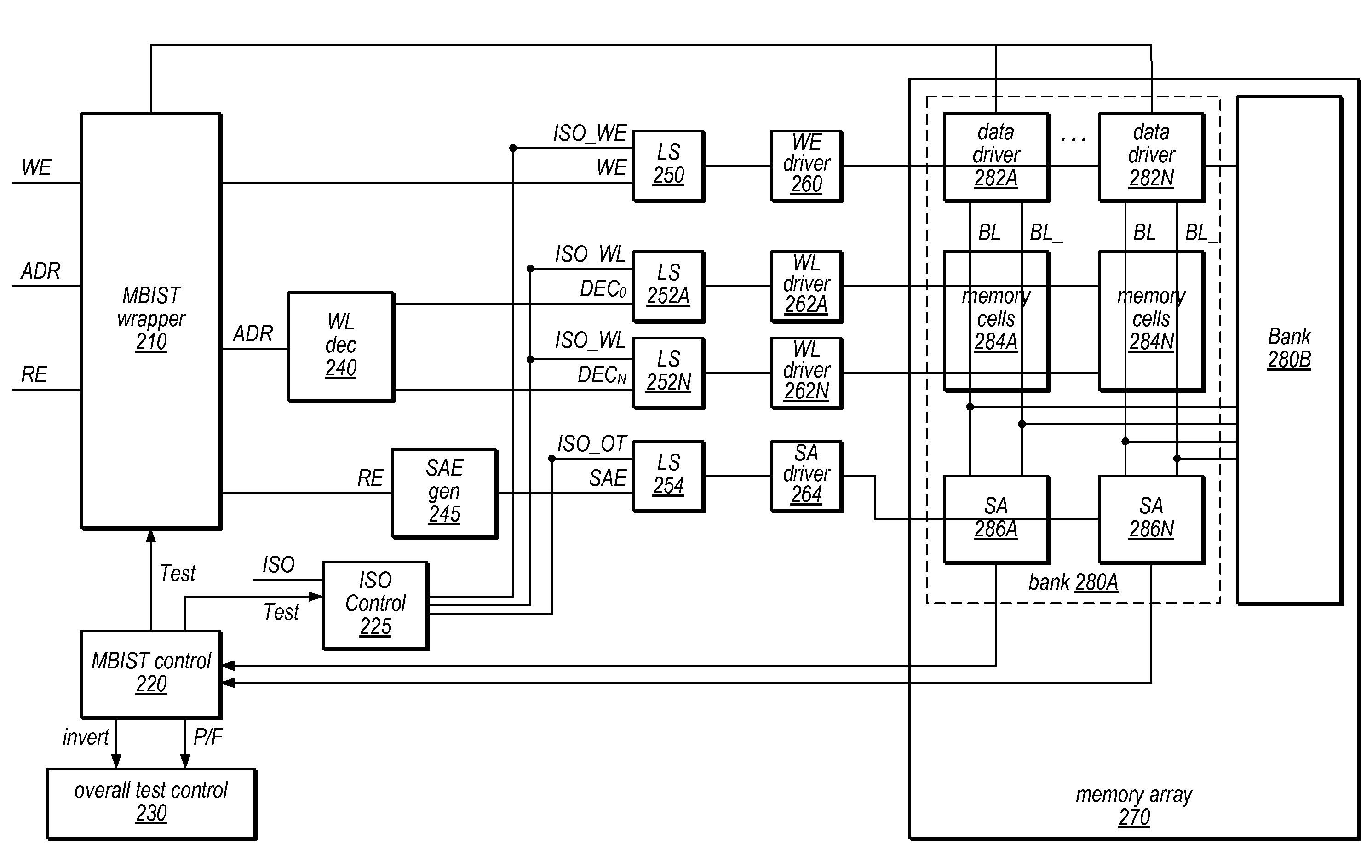

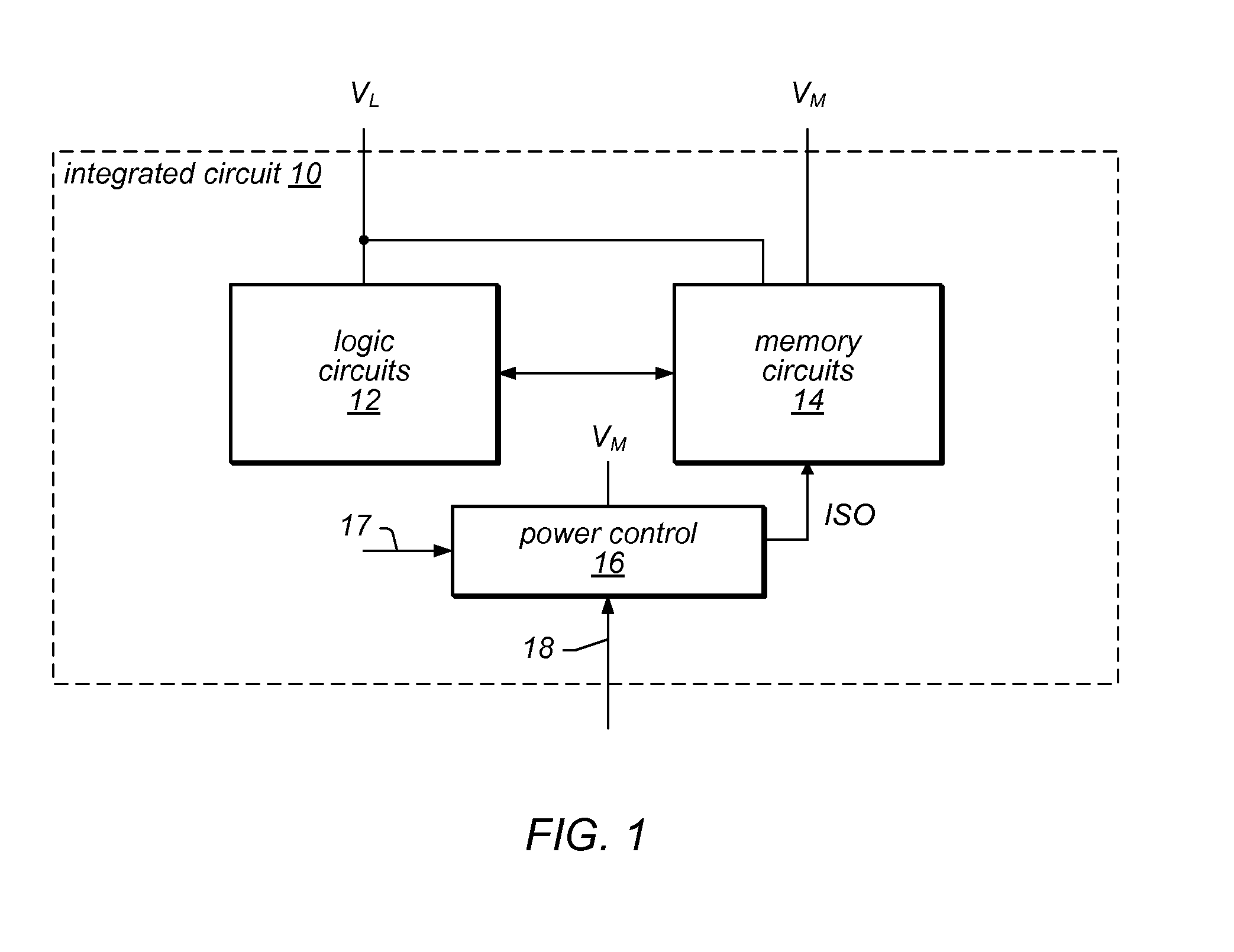

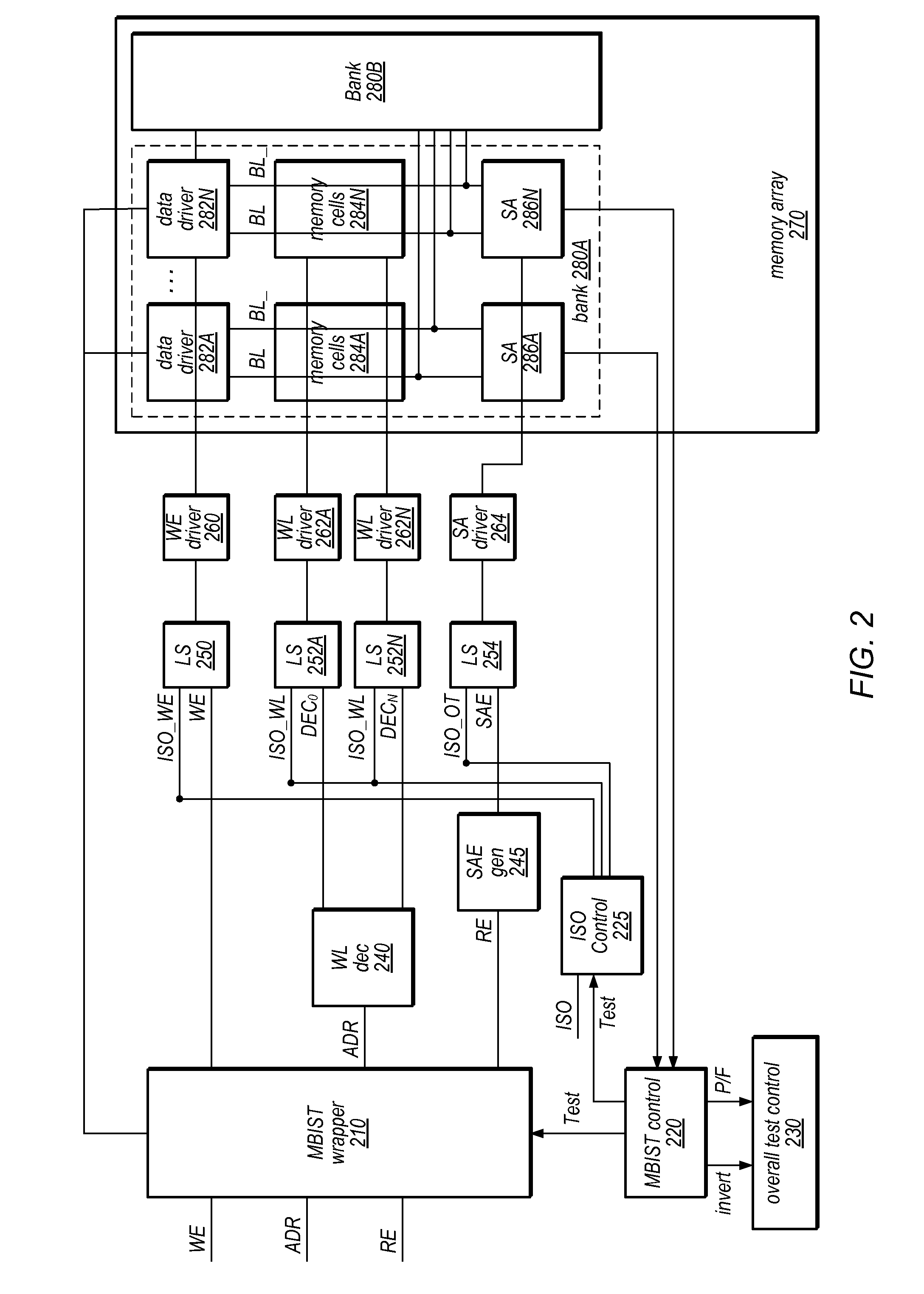

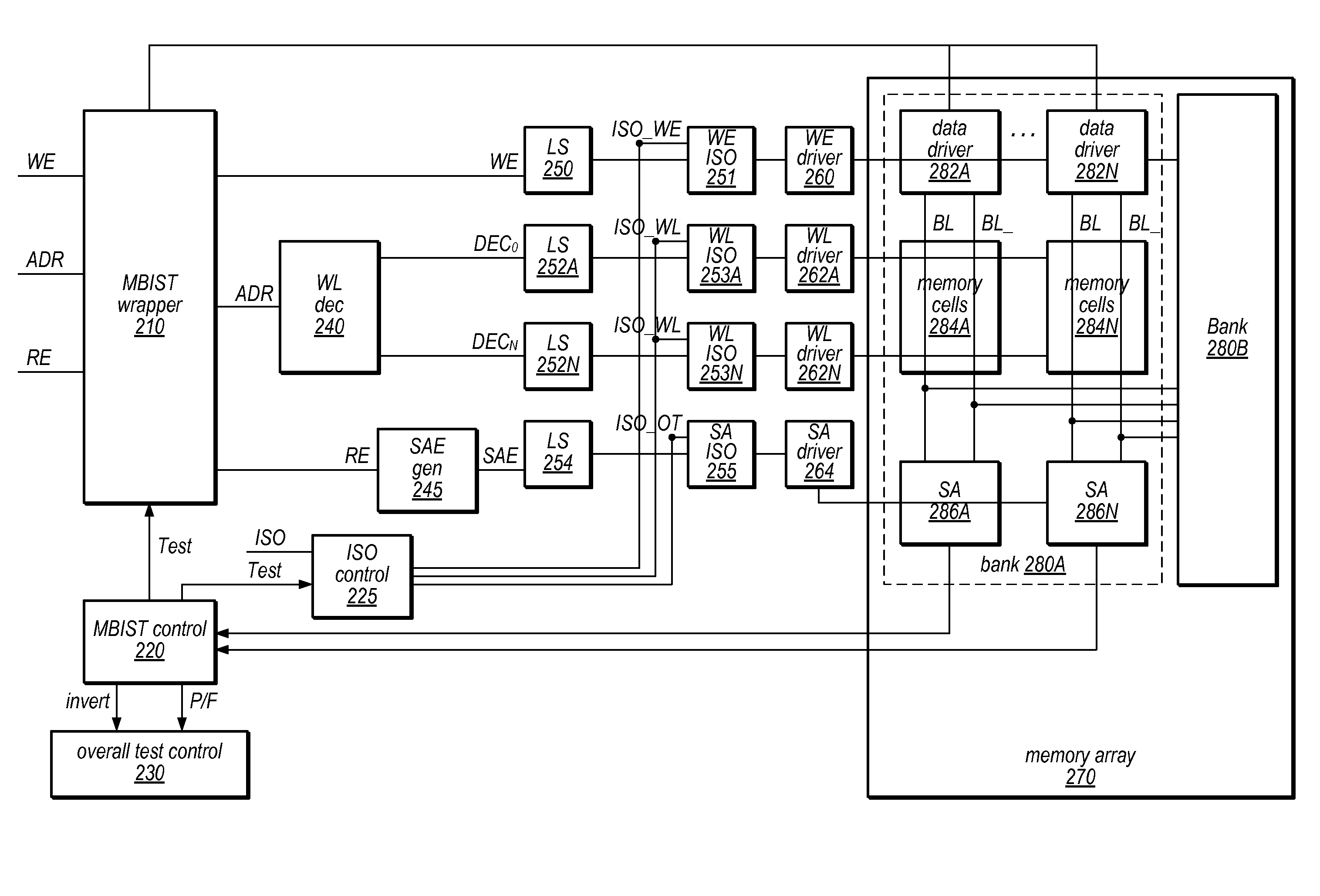

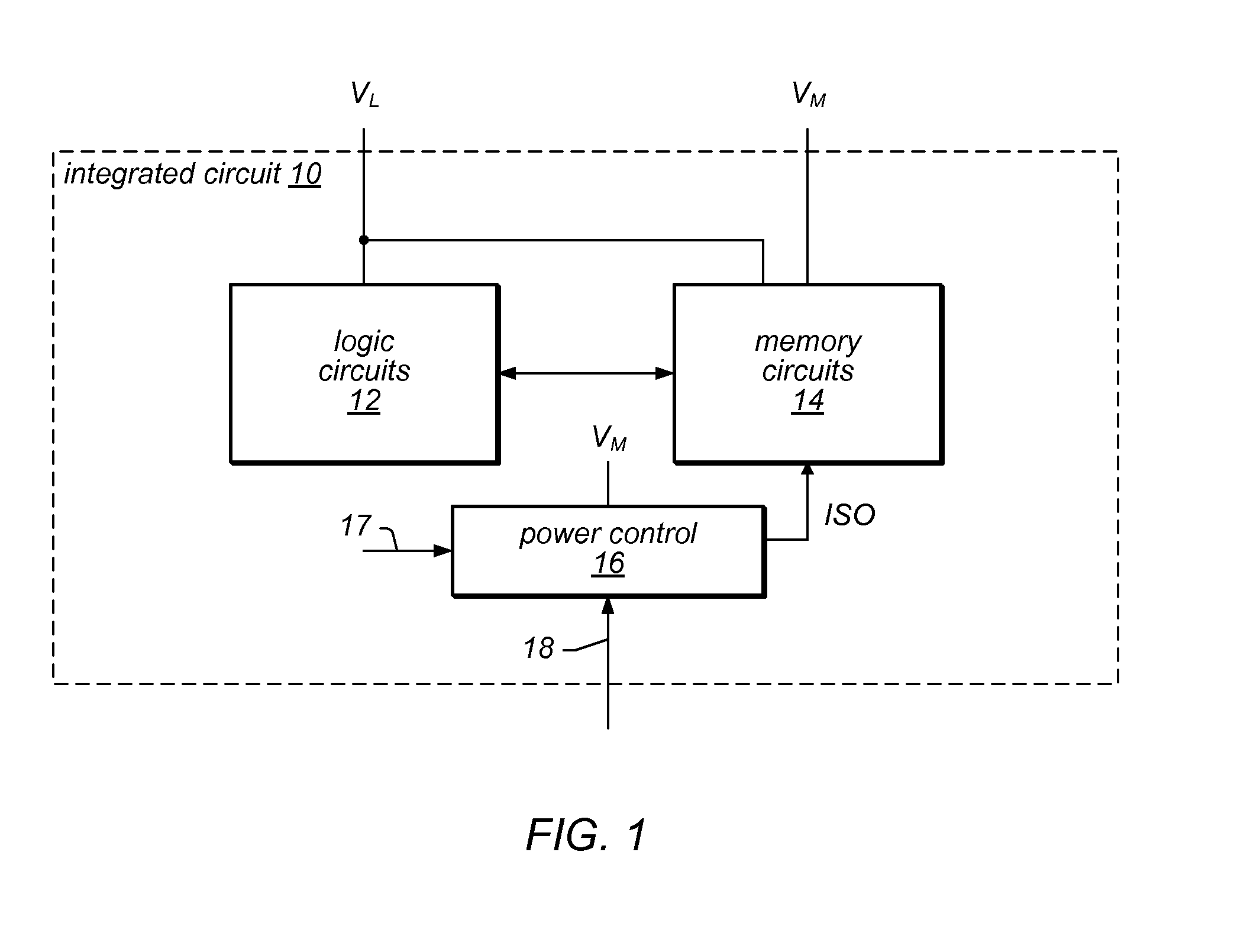

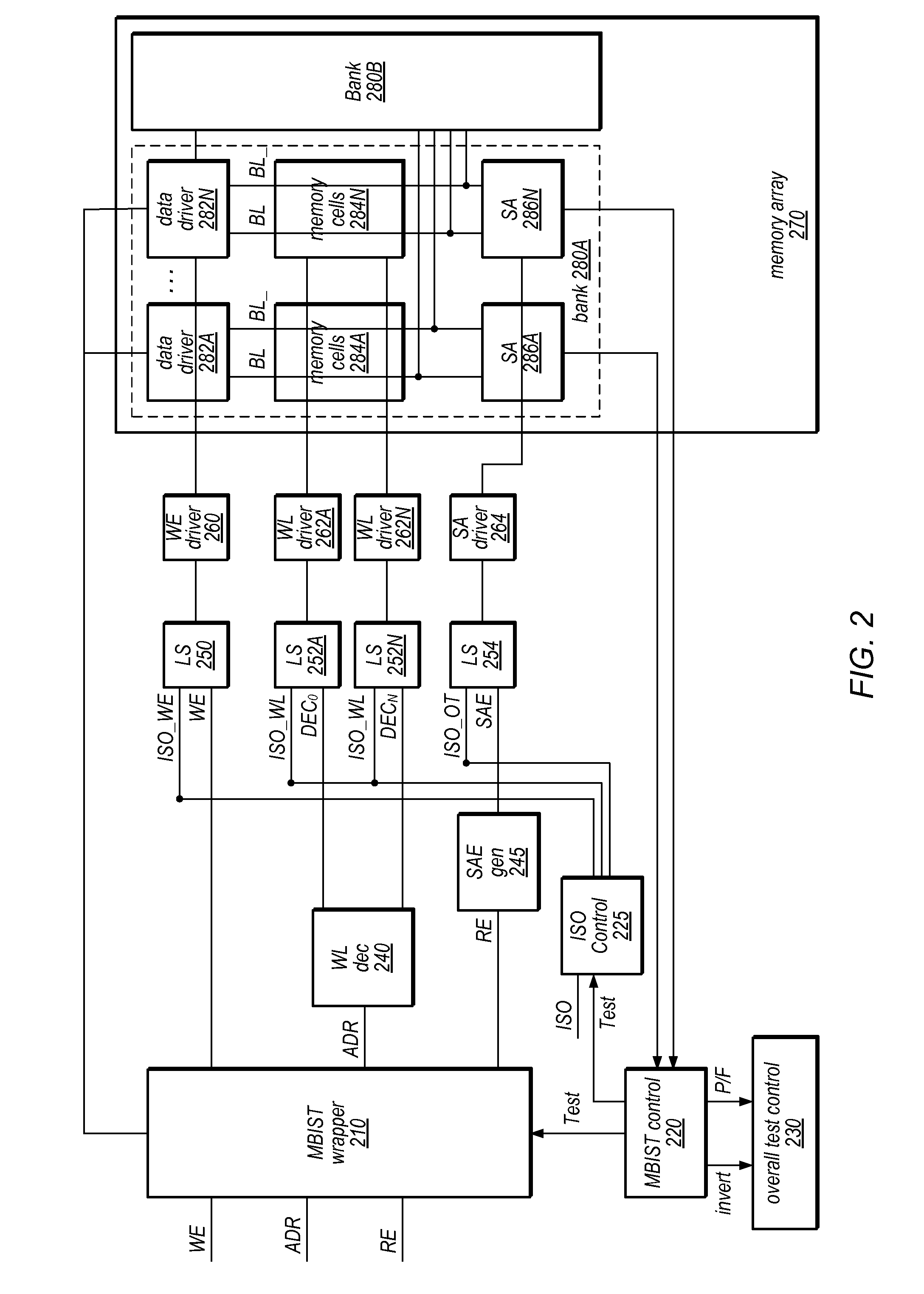

Performing Stuck-At Testing Using Multiple Isolation Circuits

A memory may include a memory array, a plurality of control circuits, and a plurality of isolation circuits. The plurality of control circuits may be configured to generate control signals for the memory array. For example, the plurality of control circuits may include a plurality of word line driver circuits. The plurality of isolation circuits may be configured to receive the control signals from the plurality of control circuits and a plurality of isolation signals. A first isolation signal may correspond to the plurality of word line driver circuits and at least one second isolation signal may correspond to other ones of the plurality of control circuits. The first isolation signal and the second isolation signal may be independently controlled during memory tests to detect stuck-at faults associated with the plurality of isolation signals.

Owner:APPLE INC

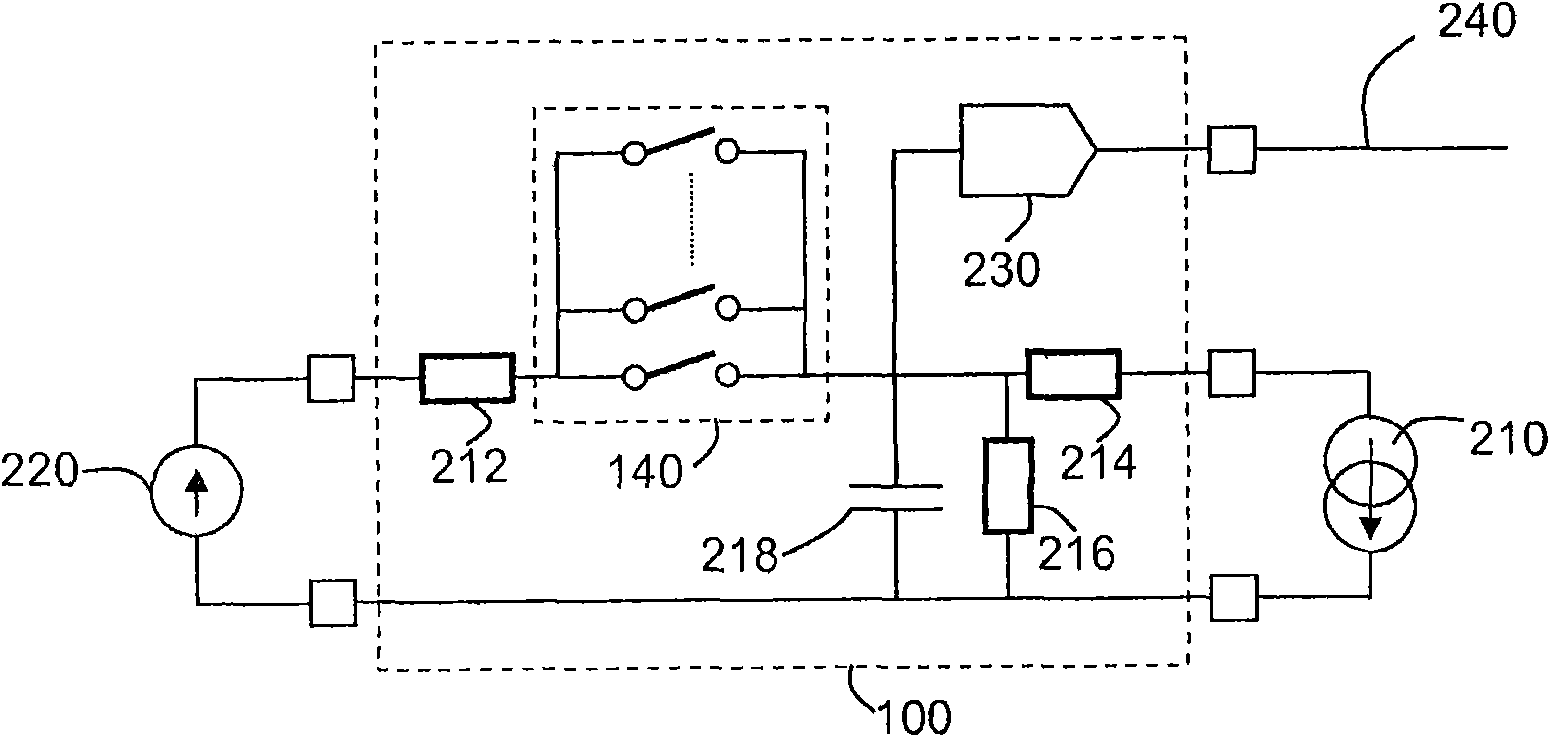

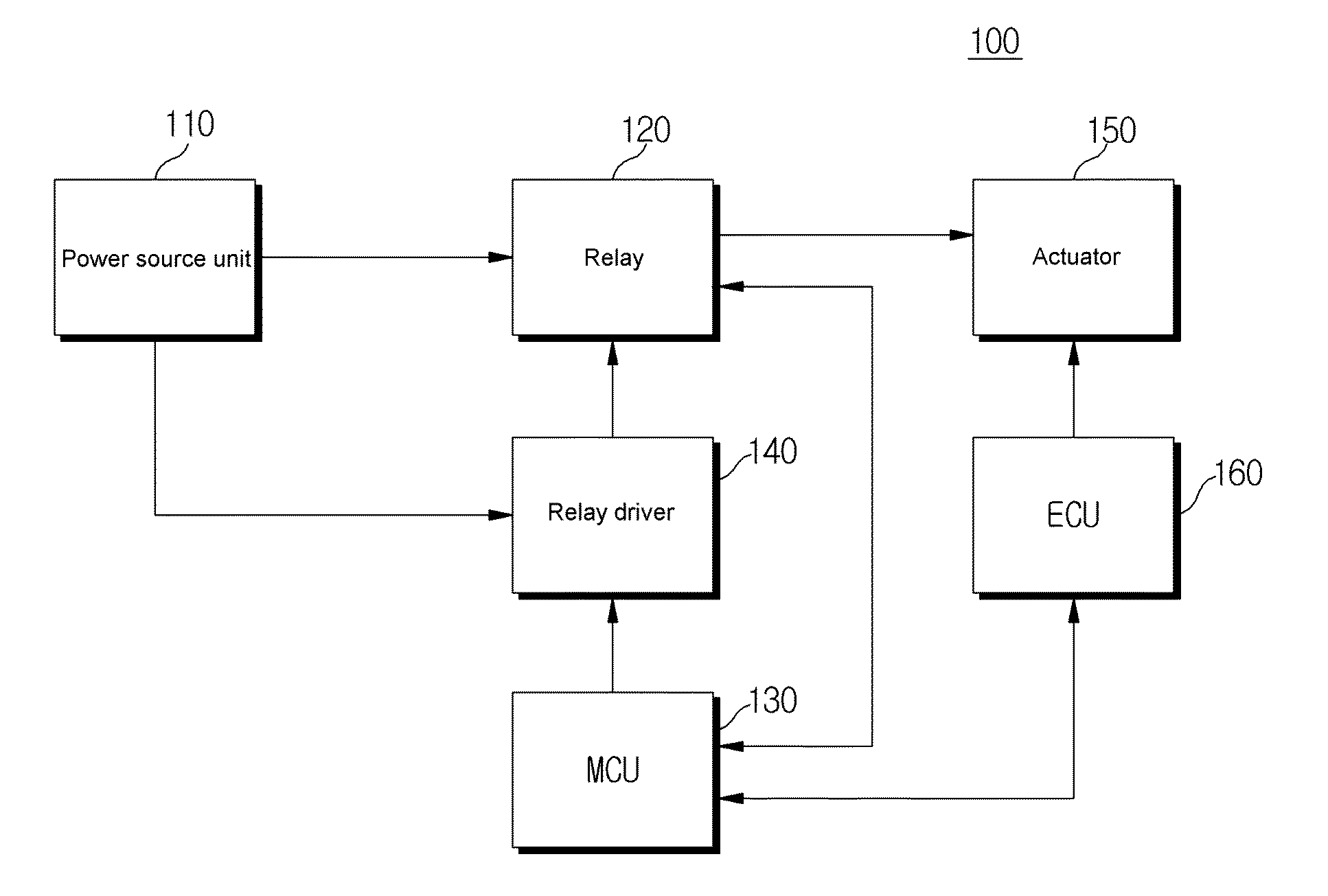

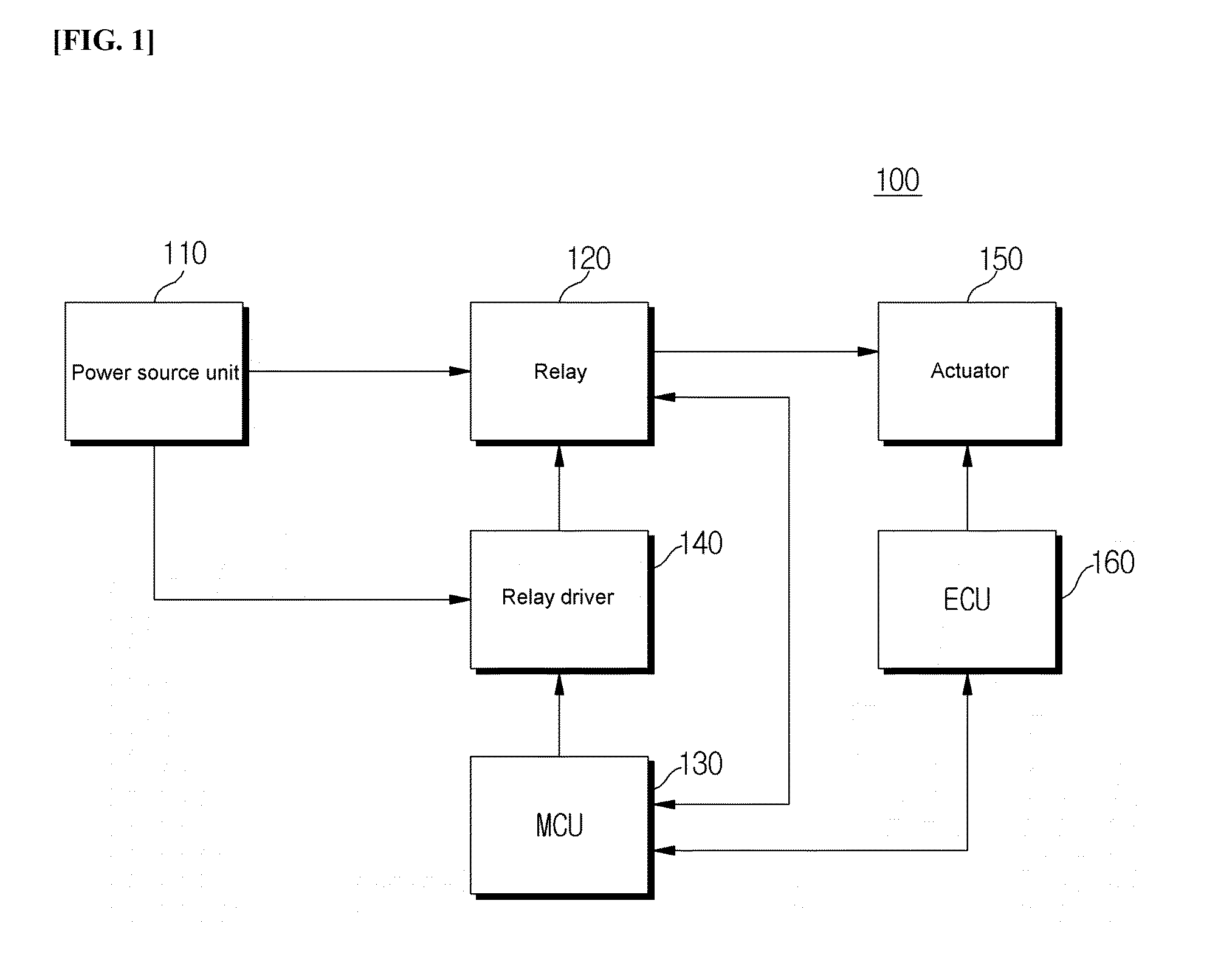

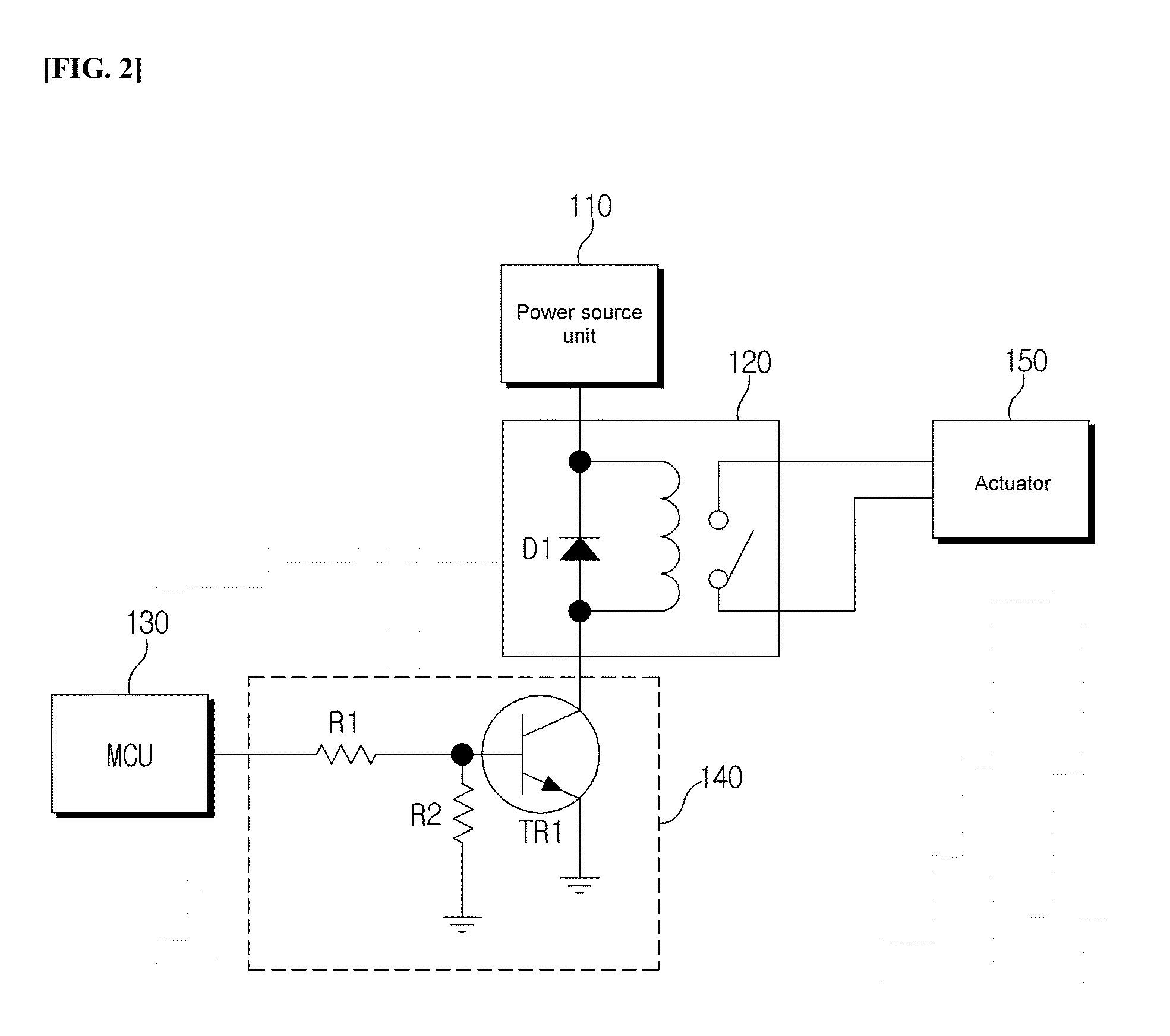

Method and apparatus for restoring mechanical relay from stuck fault to normal condition

ActiveUS20150055269A1Failure can be detectedContact testing/inspectionElectric/fluid circuitEngineeringStuck-at fault

Disclosed herein are a method and apparatus for restoring a mechanical relay from a stuck fault to a normal condition. The method may include detecting, by an MCU, a short state or open state of a relay, repeatedly transferring, by the MCU, a current application signal and a current non-application signal to a relay driver when the relay is in the short state, repeating, by the relay driver, an operation of periodically applying an electric current from a power source unit to the relay in response to the current application signal and the current non-application signal so that the release of the contact point of the relay is induced, detecting, by the MCU, the release state of the contact point of the relay, and maintaining, by the MCU, an ECU in an operating state when the contact point of the relay is released.

Owner:HL MANDO CORP

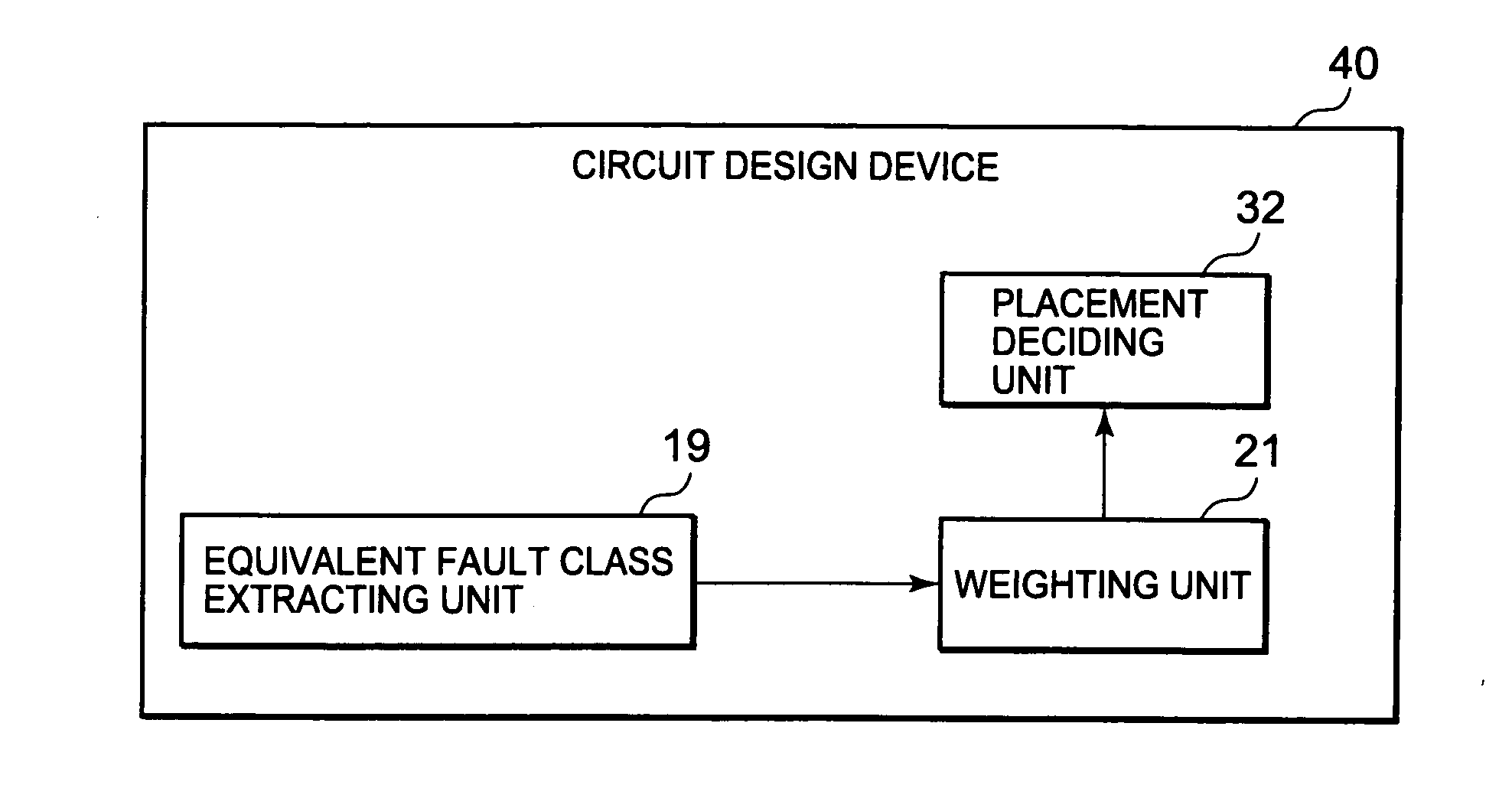

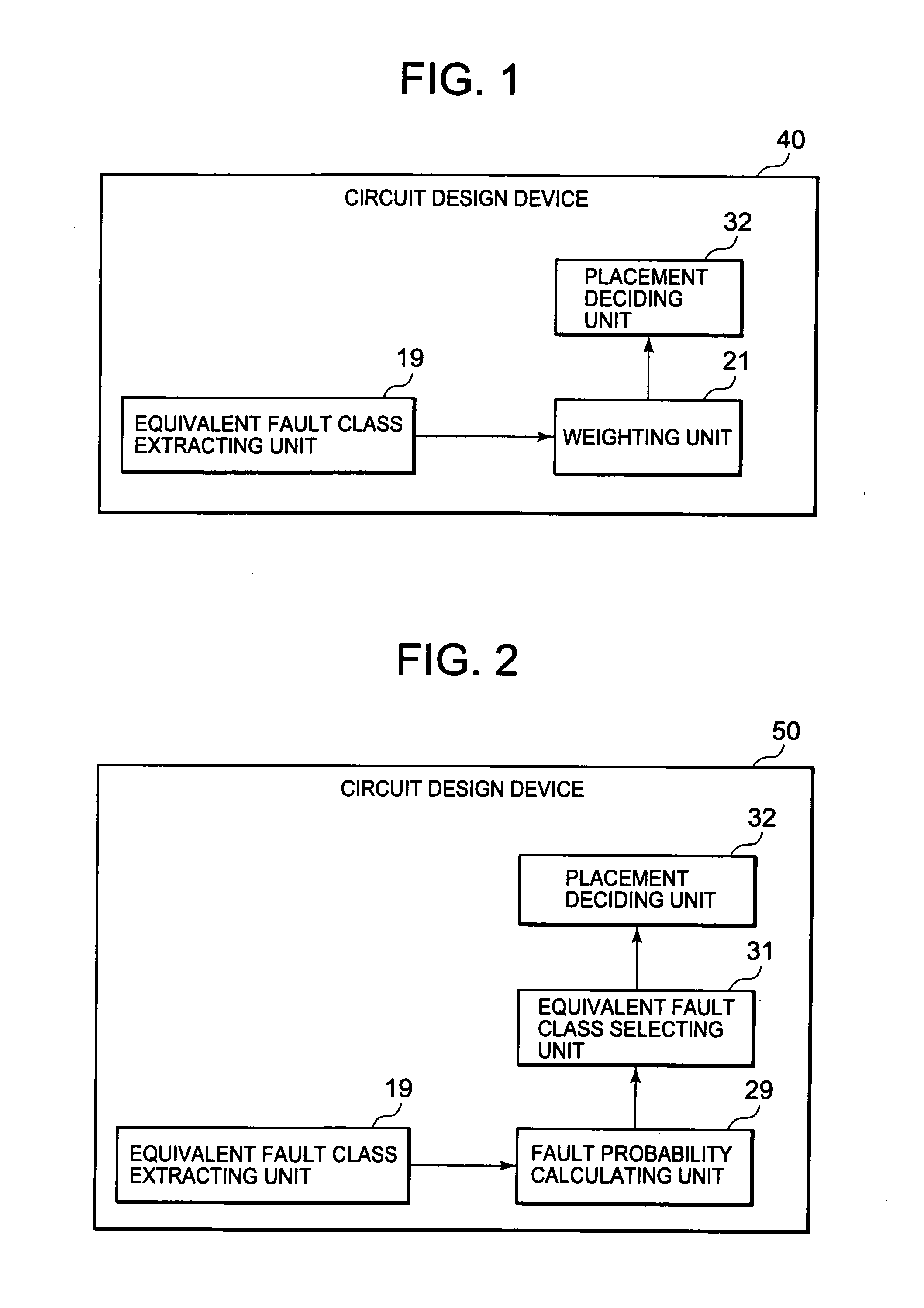

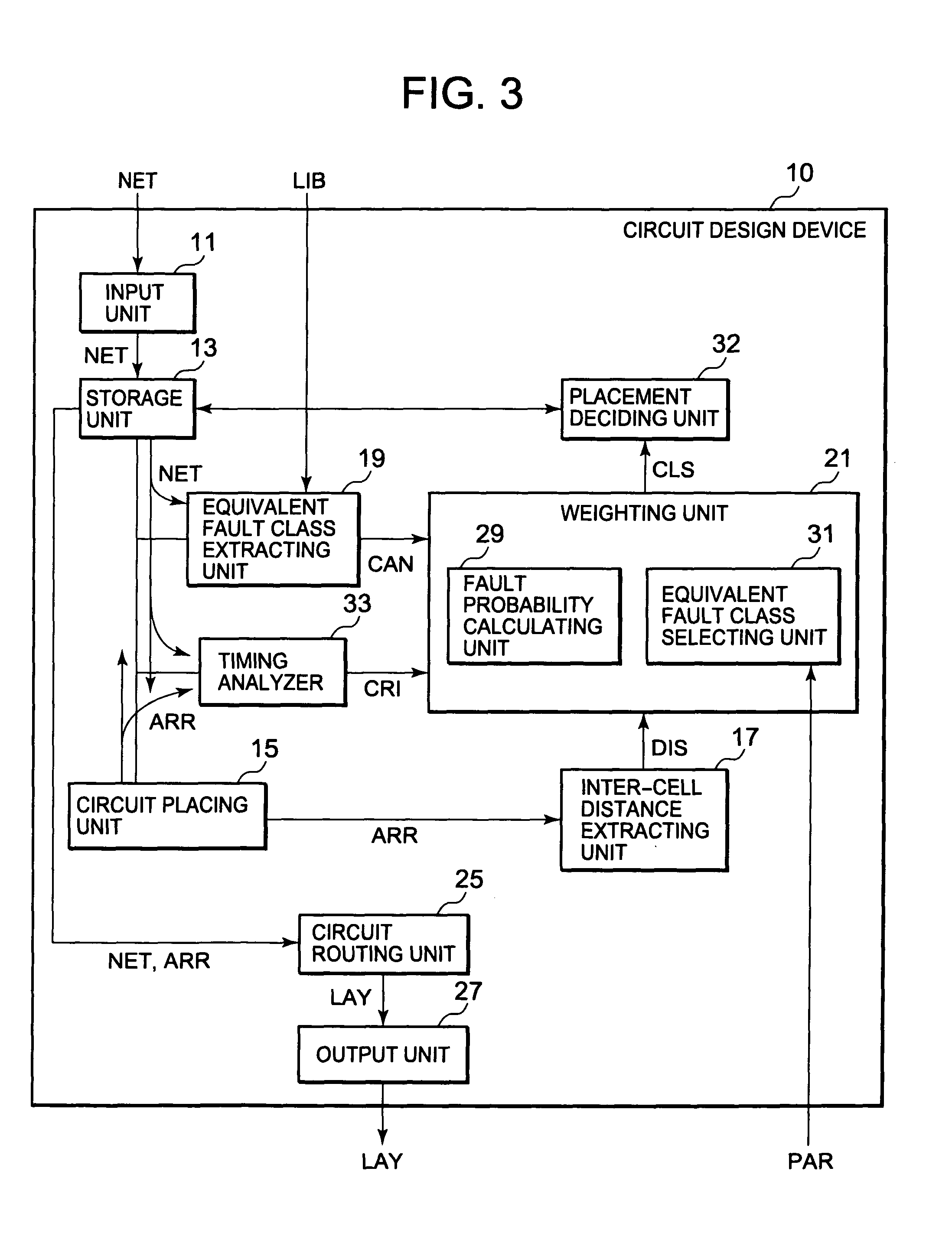

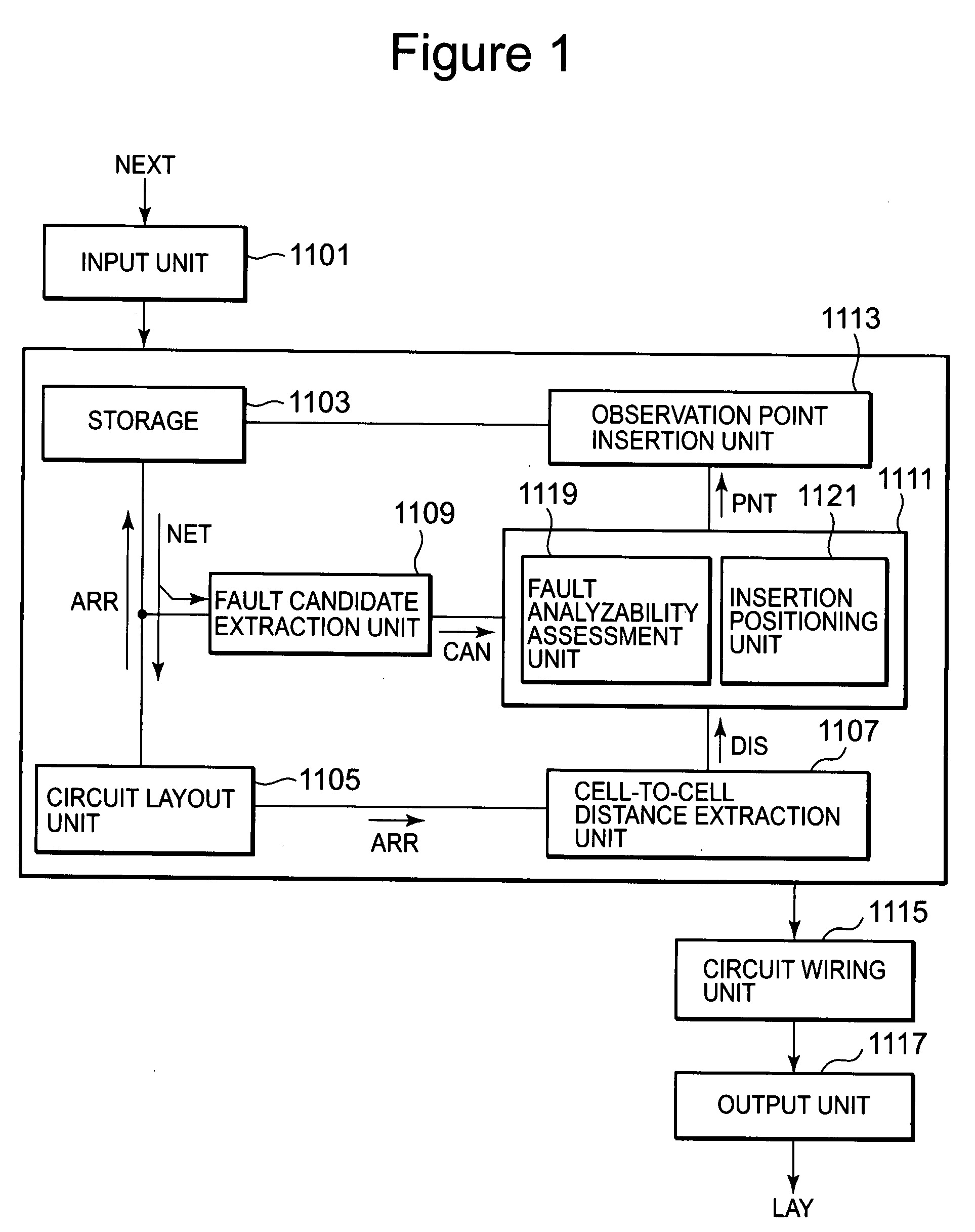

Circuit design device for conducting failure analysis facilitating design

InactiveUS20100115485A1Low failure rateFailed analysisDetecting faulty computer hardwareCAD circuit designInterconnectionFault class

A circuit design device decides placement of elements and interconnections included in a circuit, on the basis of connection information of the circuit. The circuit design device includes an equivalent fault class extracting unit, a weighting unit, and a placement deciding unit. The equivalent fault class extracting unit extracts one or more classes (hereinbelow referred to as “equivalent fault classes”) having, as members, interconnections (hereinbelow referred to as “equivalent fault interconnections”) which mutually cause an equivalent fault in the circuit. The weighting unit gives a greater weight to the equivalent fault class or the equivalent fault interconnections included in the equivalent fault class, as the number of the members in the equivalent fault class (hereinbelow referred to as the “number of equivalent fault interconnections”) increases. The placement deciding unit decides placement of the elements and the interconnections so that, among the equivalent classes, an equivalent fault class having a larger number of equivalent fault interconnections would have a lower probability of including a single stuck-at fault.

Owner:RENESAS ELECTRONICS CORP

Performing stuck-at testing using multiple isolation circuits

A memory may include a memory array, a plurality of control circuits, and a plurality of isolation circuits. The plurality of control circuits may be configured to generate control signals for the memory array. For example, the plurality of control circuits may include a plurality of word line driver circuits. The plurality of isolation circuits may be configured to receive the control signals from the plurality of control circuits and a plurality of isolation signals. A first isolation signal may correspond to the plurality of word line driver circuits and at least one second isolation signal may correspond to other ones of the plurality of control circuits. The first isolation signal and the second isolation signal may be independently controlled during memory tests to detect stuck-at faults associated with the plurality of isolation signals.

Owner:APPLE INC

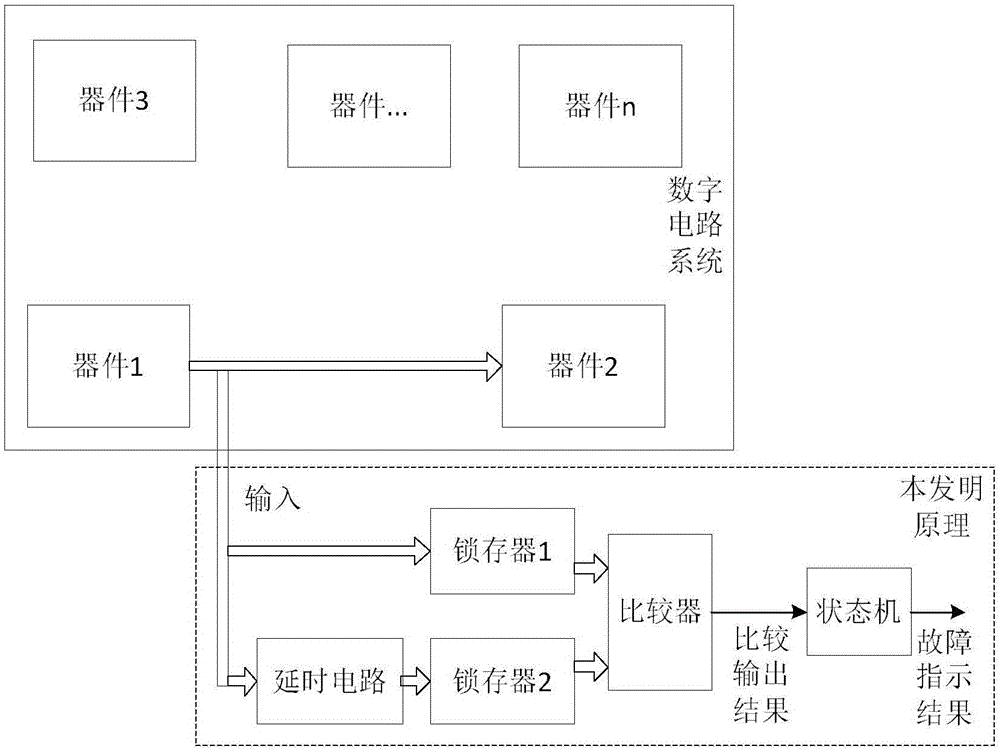

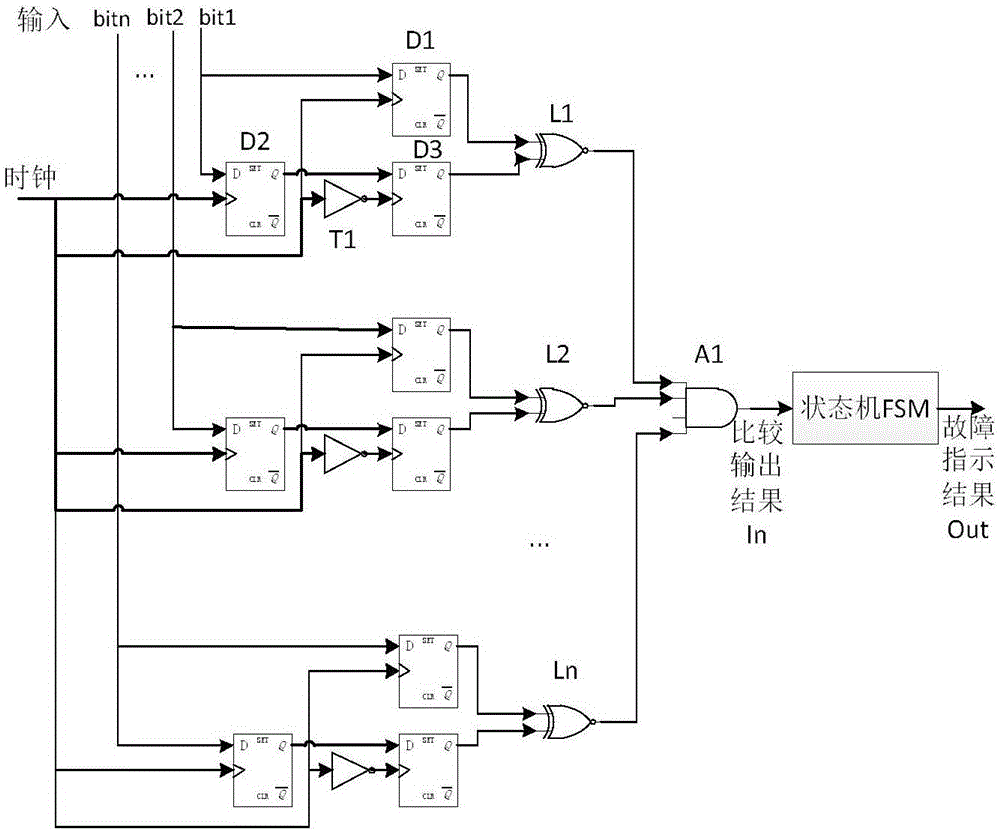

Method for testing output locking or no-output fault of digital circuit

ActiveCN106383306AImprove fault diagnosis efficiencyEasy to testDigital circuit testingElectricityTime delays

The invention provides a method for testing a stuck-at fault or an open-circuit fault of a digital circuit. Output faults of the digital circuit can be diagnosed online according to the method, and the false alarm rate of a system is reduced. The method is implemented according to the following technical scheme: a latch 1 and a latch serially connected through a time delay device are electrically connected to two input ends of an XNOR comparator respectively; as for data signals outputted by a device of a digital circuit system at the current moment, the XNOR comparator firstly delays the inputted current data for a moment through a time delay and latch circuit formed by the latch 2 serially connected through a time delay circuit and then sends the delayed data to the latch 2 so as to be latched; and the XNOR comparator performs XNOR operation and comparison on latch data of the latch 2 at the previous moment and latch data of the latch 1 at the current output moment, and judging whether results of continuous and repeated comparisons are consistent or not, wherein if the results are not consistent, it is shown that circuit output is normal, if the results are consistent, it is shown that a stuck-at fault or an open-circuit fault occurs in output of the digital circuit. The method provided by the invention realizes online test and diagnosis for system faults of the digital circuit.

Owner:10TH RES INST OF CETC

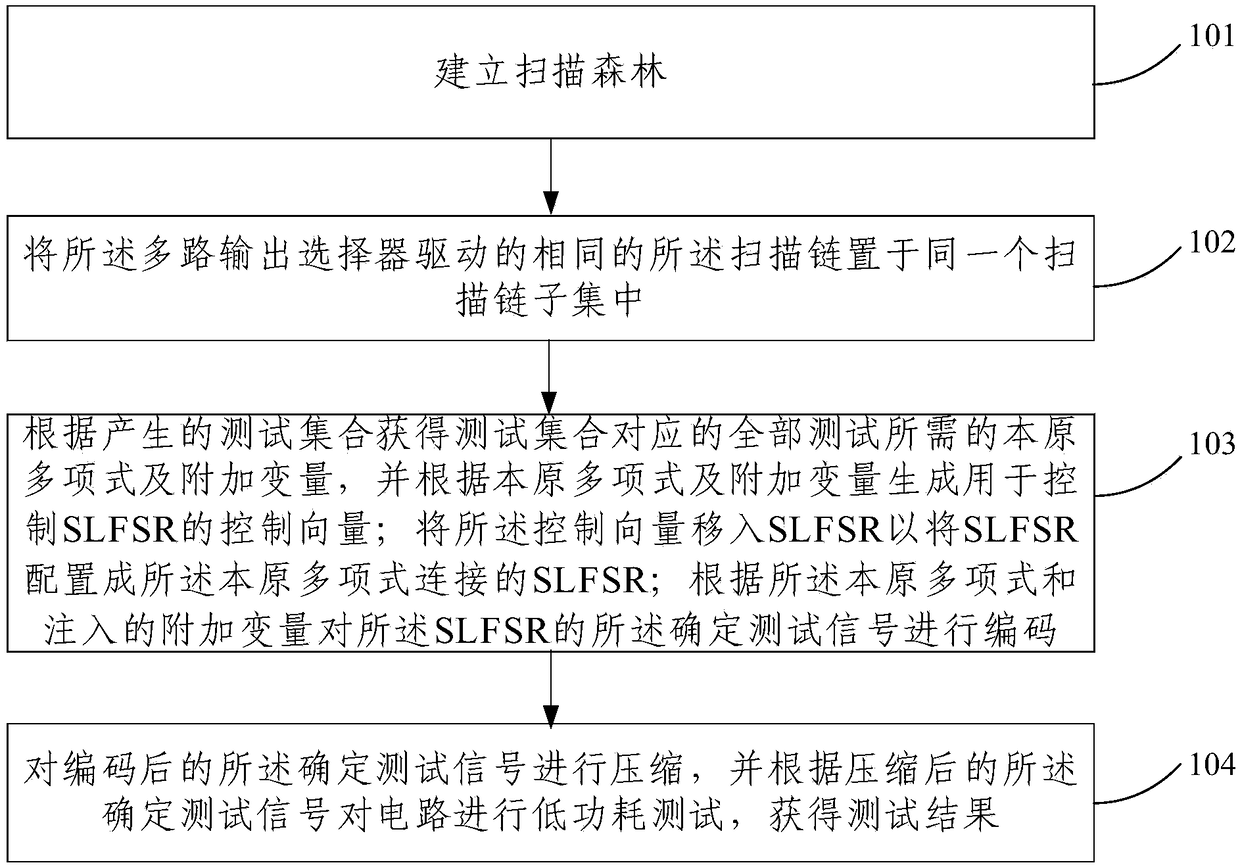

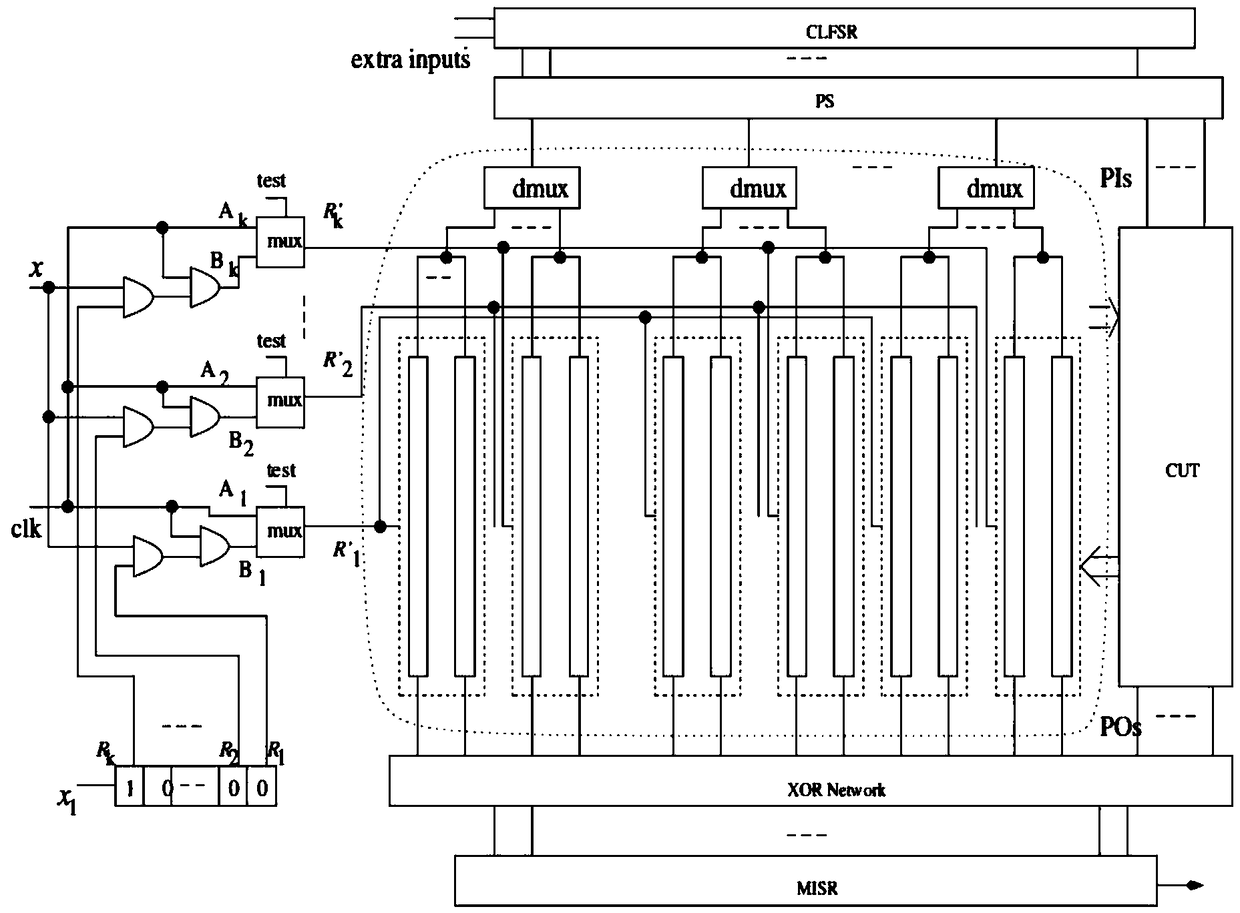

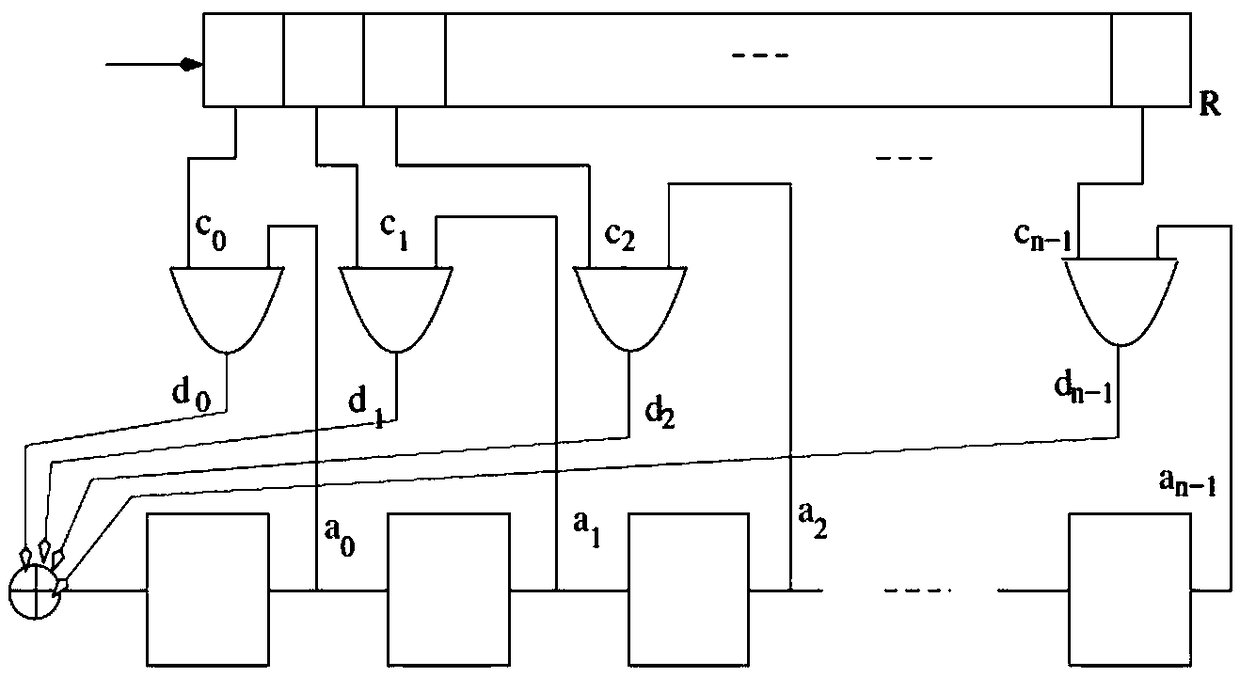

Low power consumption testing method for single stuck-at fault

The embodiment of the invention provides a low power consumption testing method for a single stuck-at fault. The method comprises the steps of establishing a scan forest; placing the same scan chainsdriven by a demultiplexer in the same scan chain subset; placing the activated scan chain subset in a determination test signal; obtaining a primitive polynomial and additional variables required by all tests corresponding to a generated test set according to the test set, and generating a control vector used for controlling an SLFSR (Software-defined Linear Feedback Shift Register) according to the primitive polynomial and additional variables; moving the control vector into the SLFSR so as to configure the SLFSR into an SLFSR connected by the primitive polynomial; coding the determination test signal of the SLFSR; and compressing the coded determination test signal, and conducting a low power consumption test on the circuit according to the compressed determination test signal so as to obtain a test result. The embodiment of the invention is low in hardware overhead, reduces the energy consumption, does not bring additional delay overhead and is convenient for being widely applied inindustry.

Owner:TSINGHUA UNIV

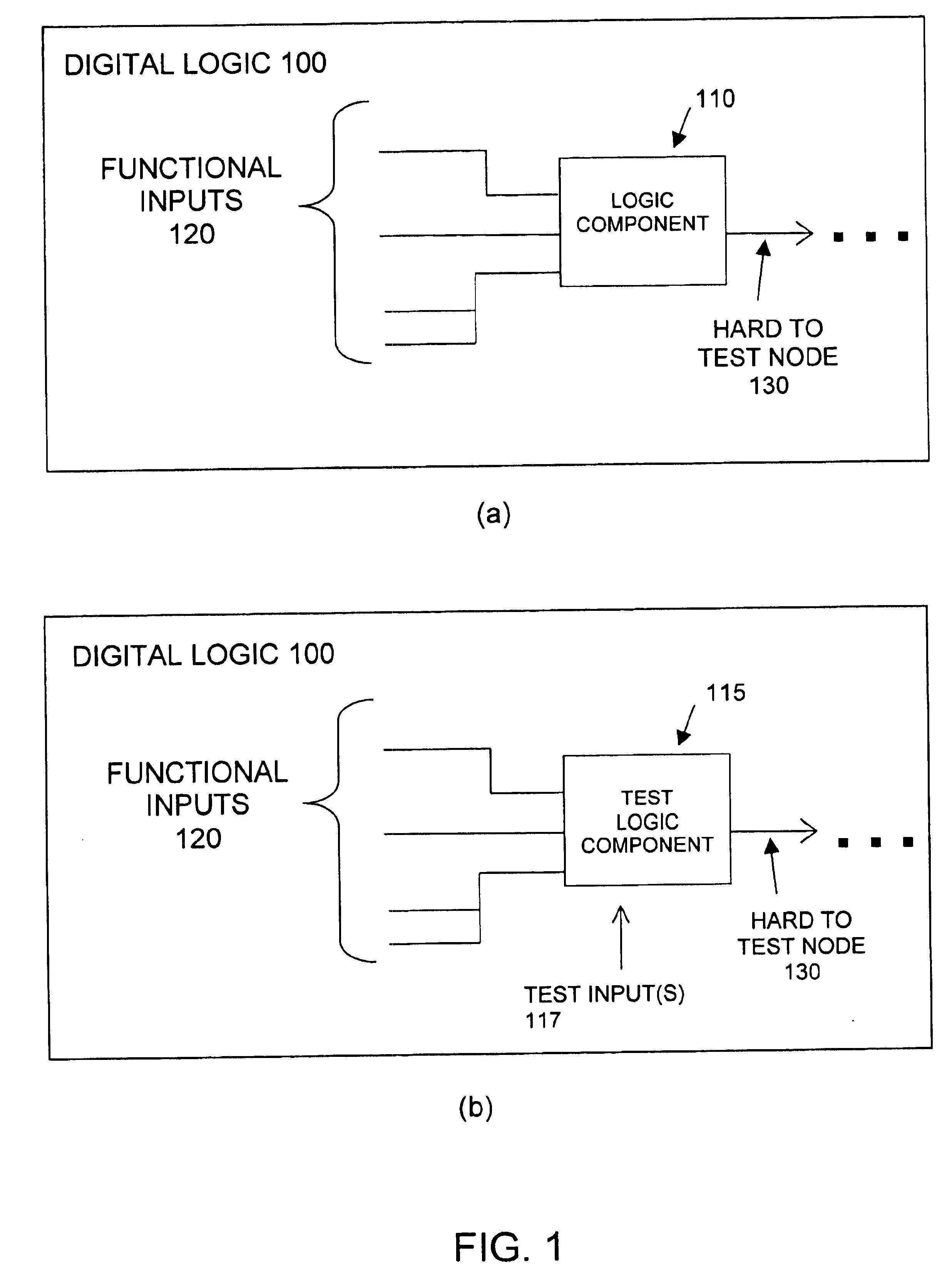

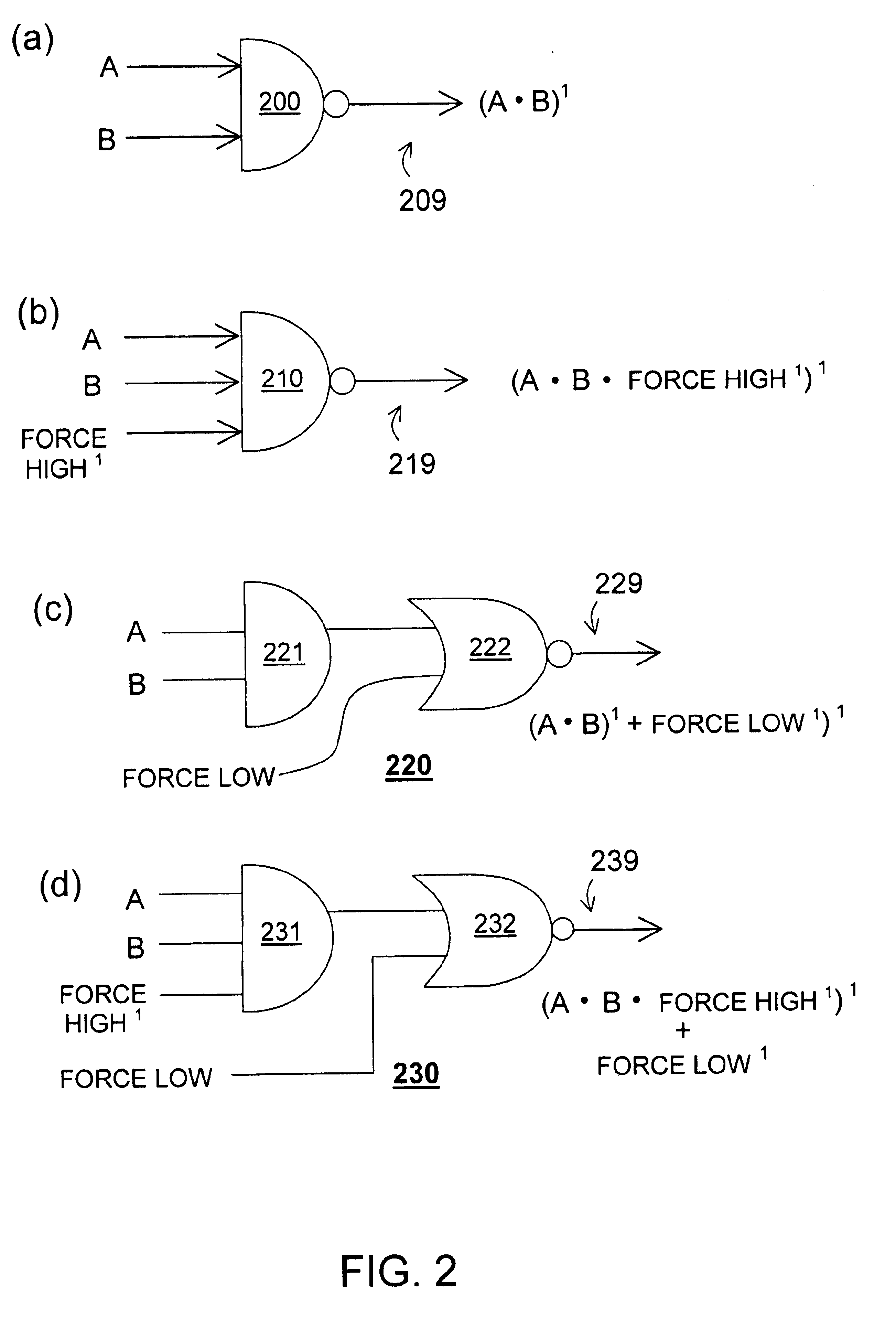

Fault coverage and simplified test pattern generation for integrated circuits

InactiveUS6874112B1Improve fault coverageSimplified test pattern generationElectronic circuit testingError detection/correctionFault coverageTest input

An integrated circuit with improved testability includes a test logic component that replaces a corresponding regular logic component and that generates a logic high or low whenever a test input is activated. Alternatively, it may generate either high or low depending on which of two test inputs is activated. A test program may be augmented with instructions to activate such test inputs. An integrated circuit design may be analyzed to select a node that is not covered by a test program and to identify which logic component generates an output on the node. Then the design may be altered to replace the identified logic component with a corresponding test logic component. Test coverage analysis may be based on determining whether the test program toggles the node, or determining whether a stuck at fault on the node propagates so as to be observed.

Owner:QUALCOMM INC

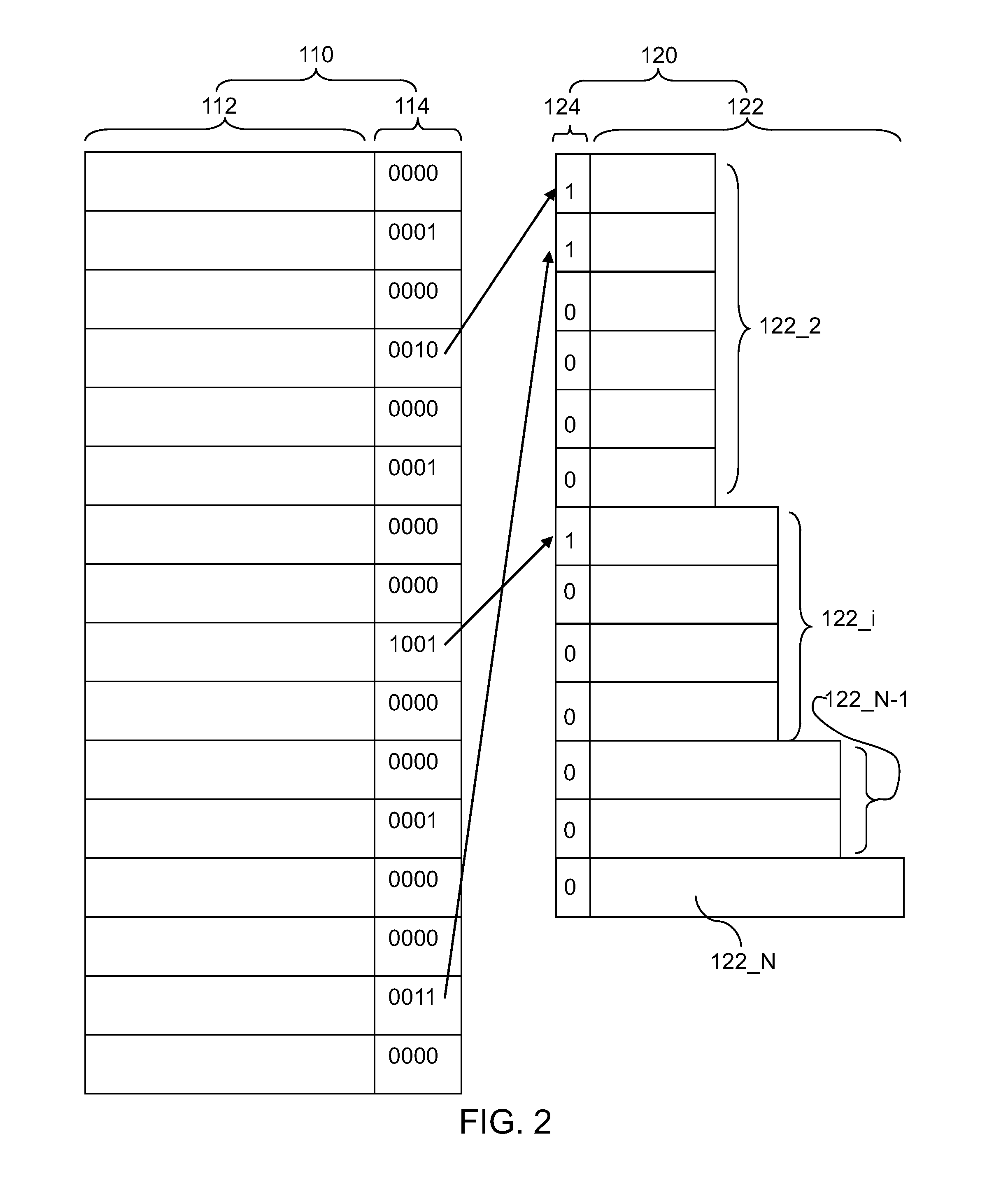

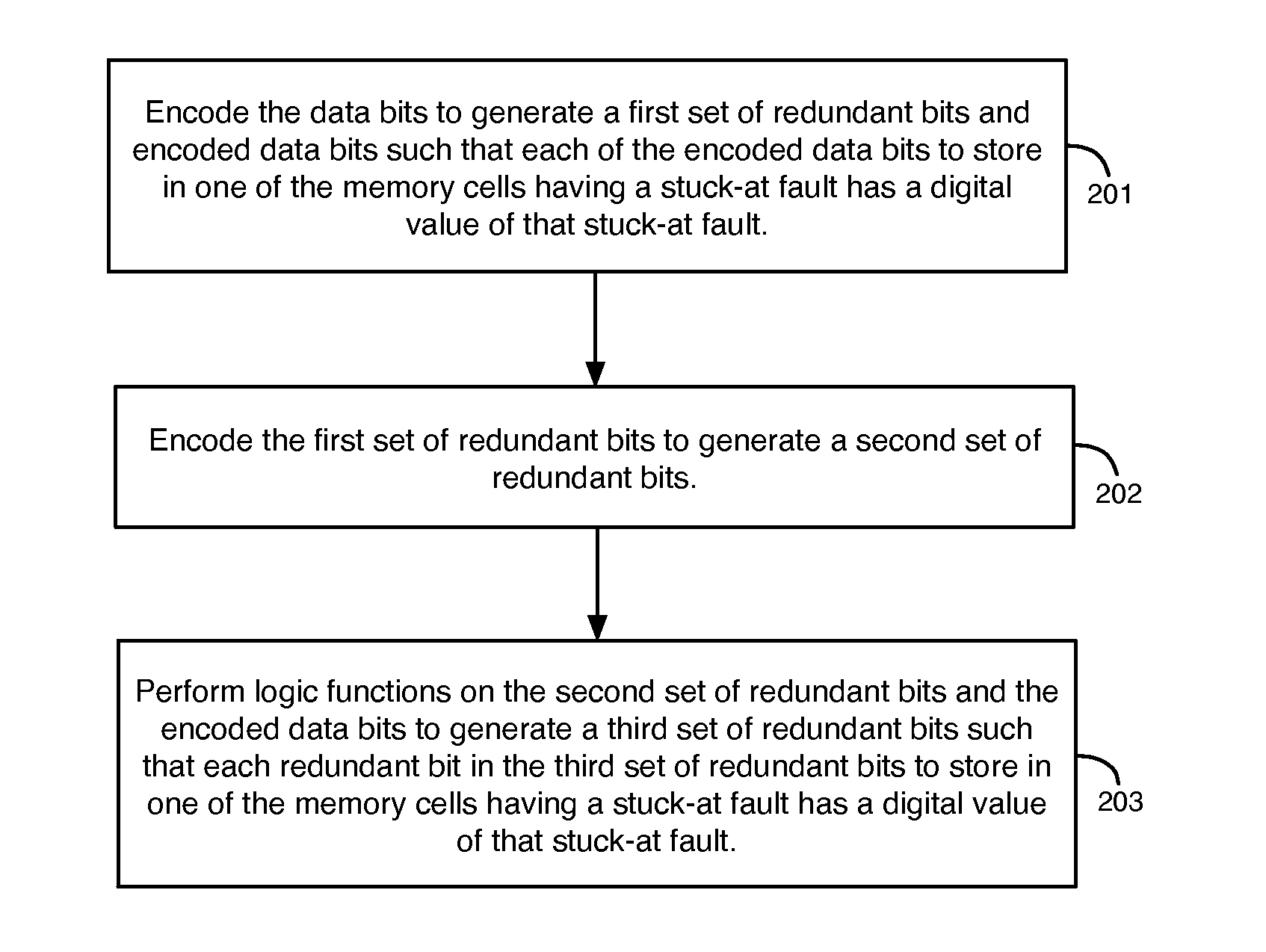

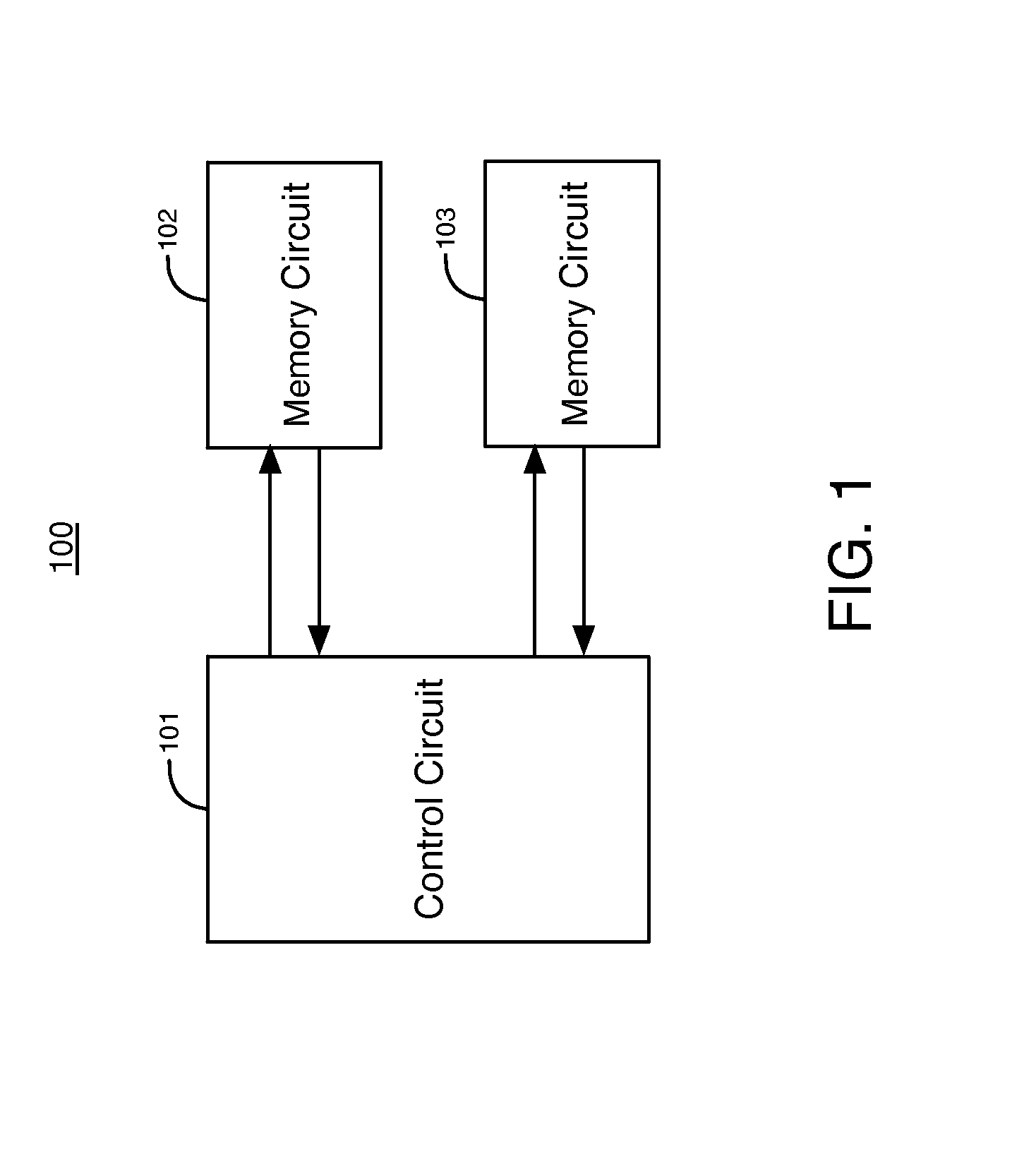

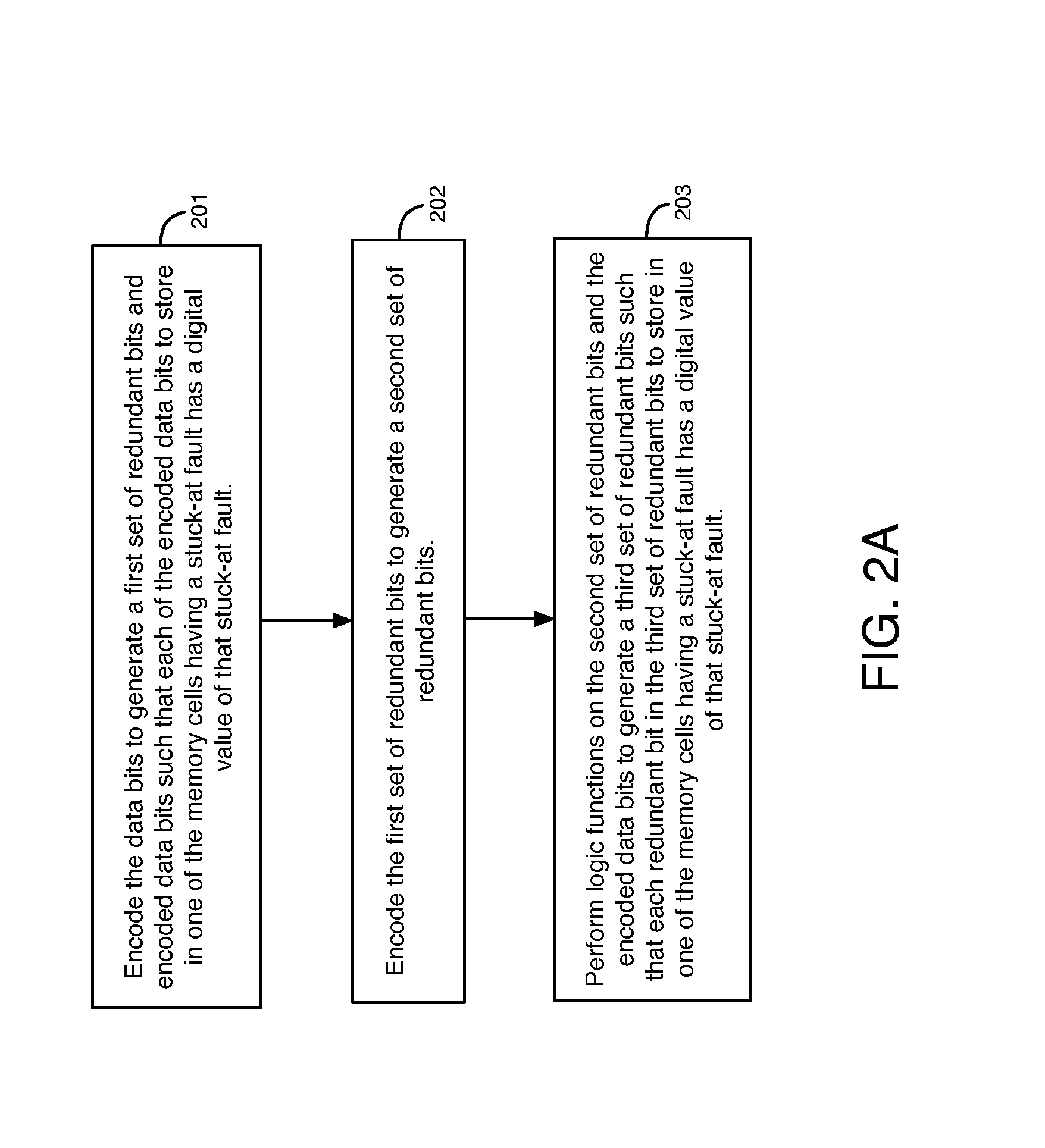

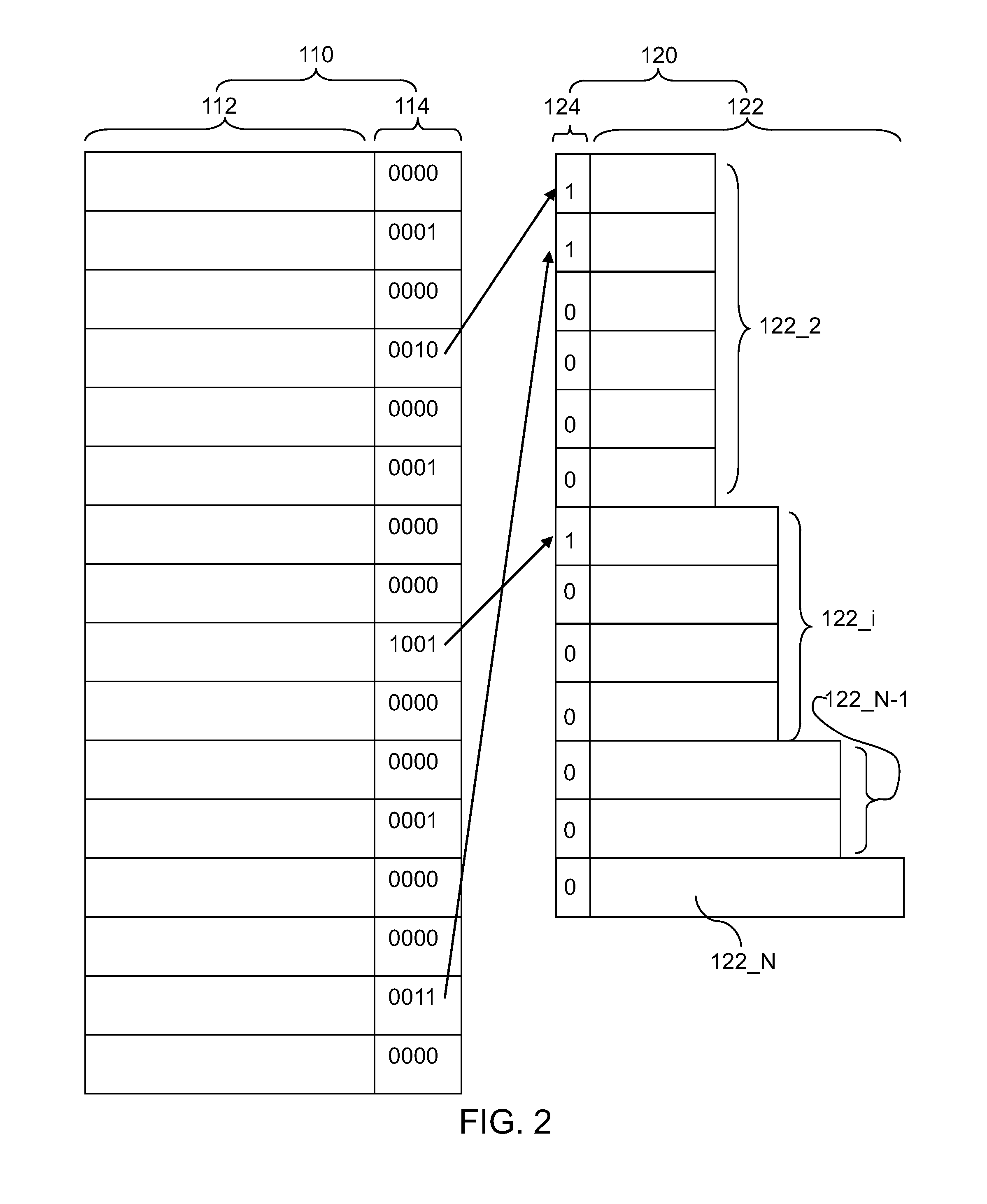

Encoding and Decoding Redundant Bits to Accommodate Memory Cells Having Stuck-At Faults

A data storage system has a memory circuit that comprises memory cells and a control circuit that receives data bits provided for storage in the memory cells. The control circuit encodes the data bits to generate a first set of redundant bits and encoded data bits, such that the encoded data bits selected for storage in a first subset of the memory cells with first stuck-at faults have digital values of corresponding ones of the first stuck-at faults. The control circuit encodes the first set of redundant bits to generate a second set of redundant bits. The control circuit performs logic functions on the second set of redundant bits and the encoded data bits to generate a third set of redundant bits, such that redundant bits in the third set of redundant bits selected for storage in a second subset of the memory cells with second stuck-at faults have digital values of corresponding ones of the second stuck-at faults.

Owner:WESTERN DIGITAL TECH INC

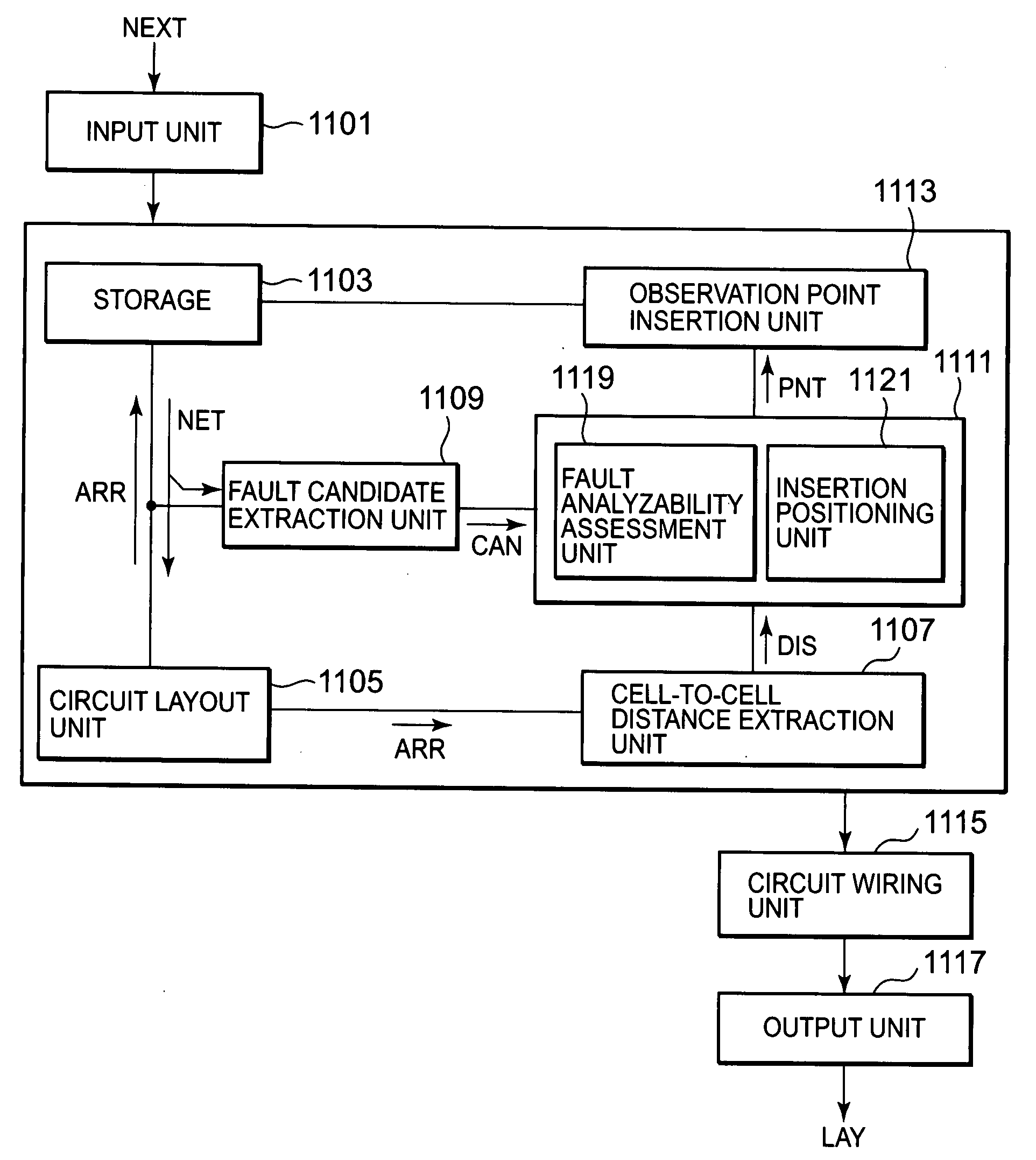

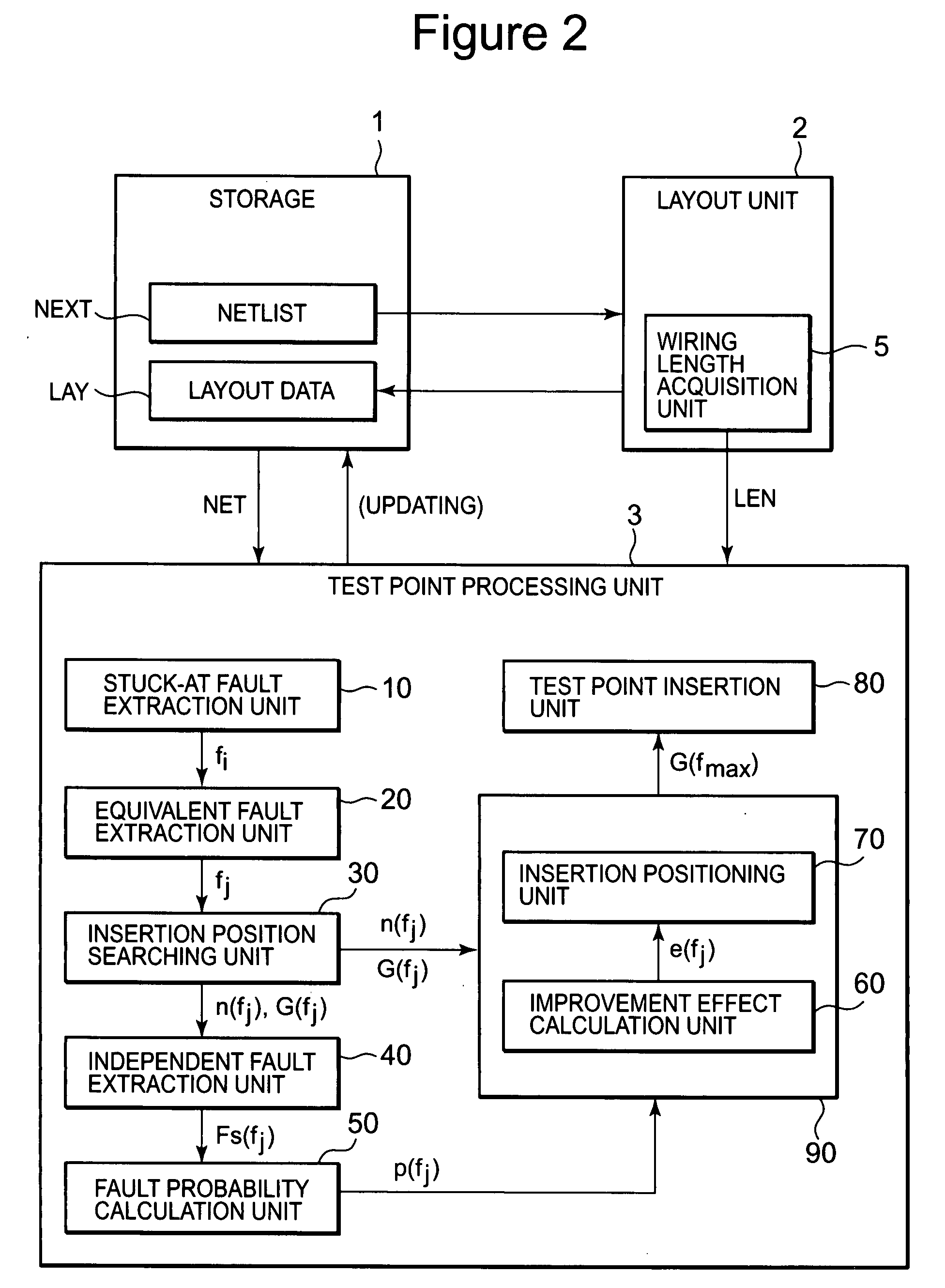

Circuit designing program and circuit designing system having function of test point insetion

InactiveUS20080091987A1Increase probabilityFault analyzability is improvedElectronic circuit testingDetecting faulty computer hardwareStuck-at faultComputer science

A circuit design program product to cause a computer to execute a circuit design process based on a test point insertion, includes: a step for making reference to a netlist to extract a plurality of equivalent faults fj; a step for searching a number n(fj) of test point required for a number of the equivalent fault keeping equivalent relation with a search object equivalent fault fj with each of a plurality of equivalent faults as the search object equivalent fault to become a predetermined number and a insertion position G(fj); a step for calculating probability p(fj) of a single stuck-at fault being included in a set of equivalent faults including at least a search object equivalent fault fj at an occasion when the relevant stuck-at fault takes place in the circuit; a step for calculating a parameter e(fj) derived by an equation: e(fj)=p(fj) / n(fj) on each pattern of an insertion position G(fj); and a step for determining the insertion position G(fmax) giving the maximum value among the calculated parameters e(fj) as a position where the test point is inserted.

Owner:RENESAS ELECTRONICS CORP

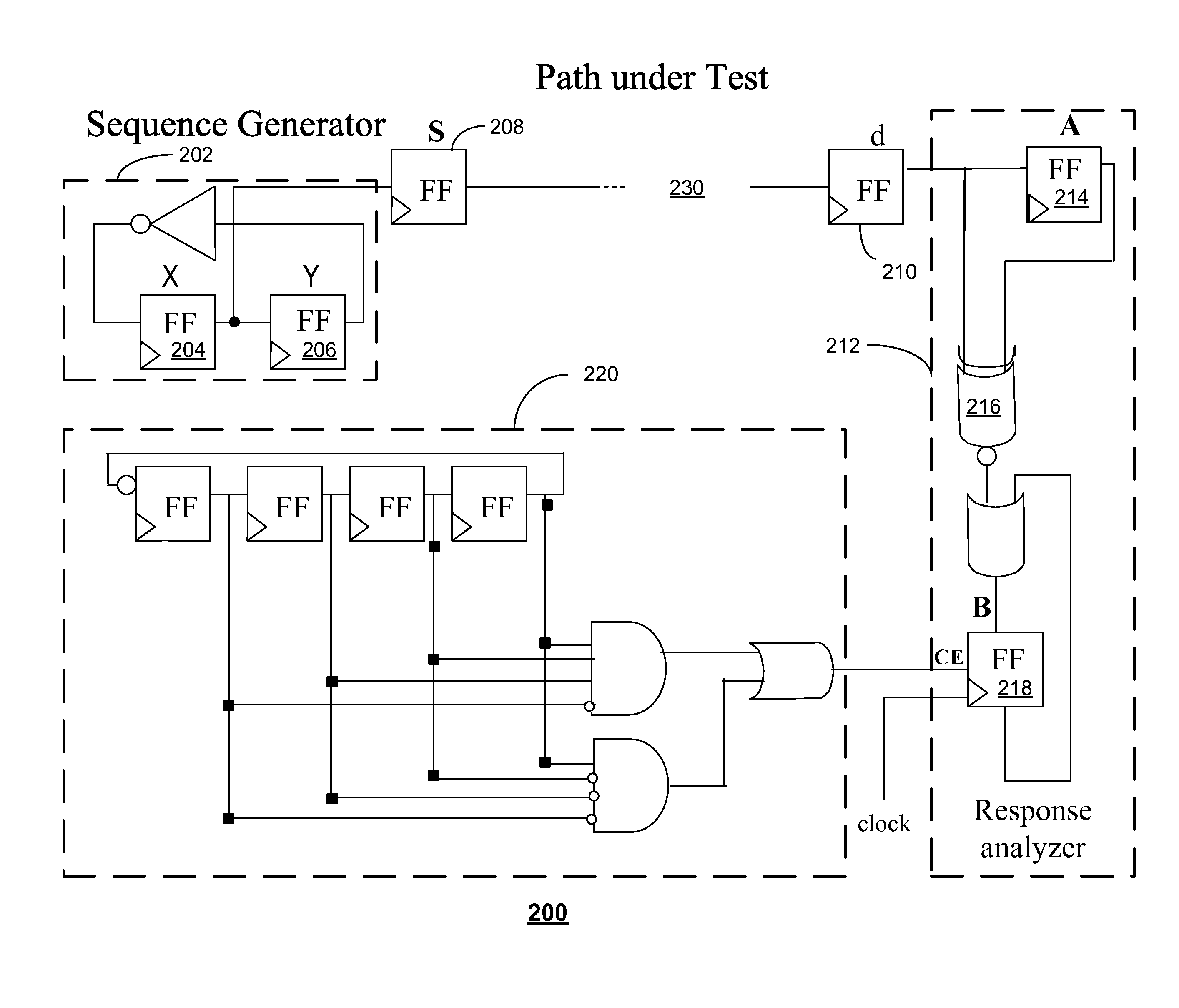

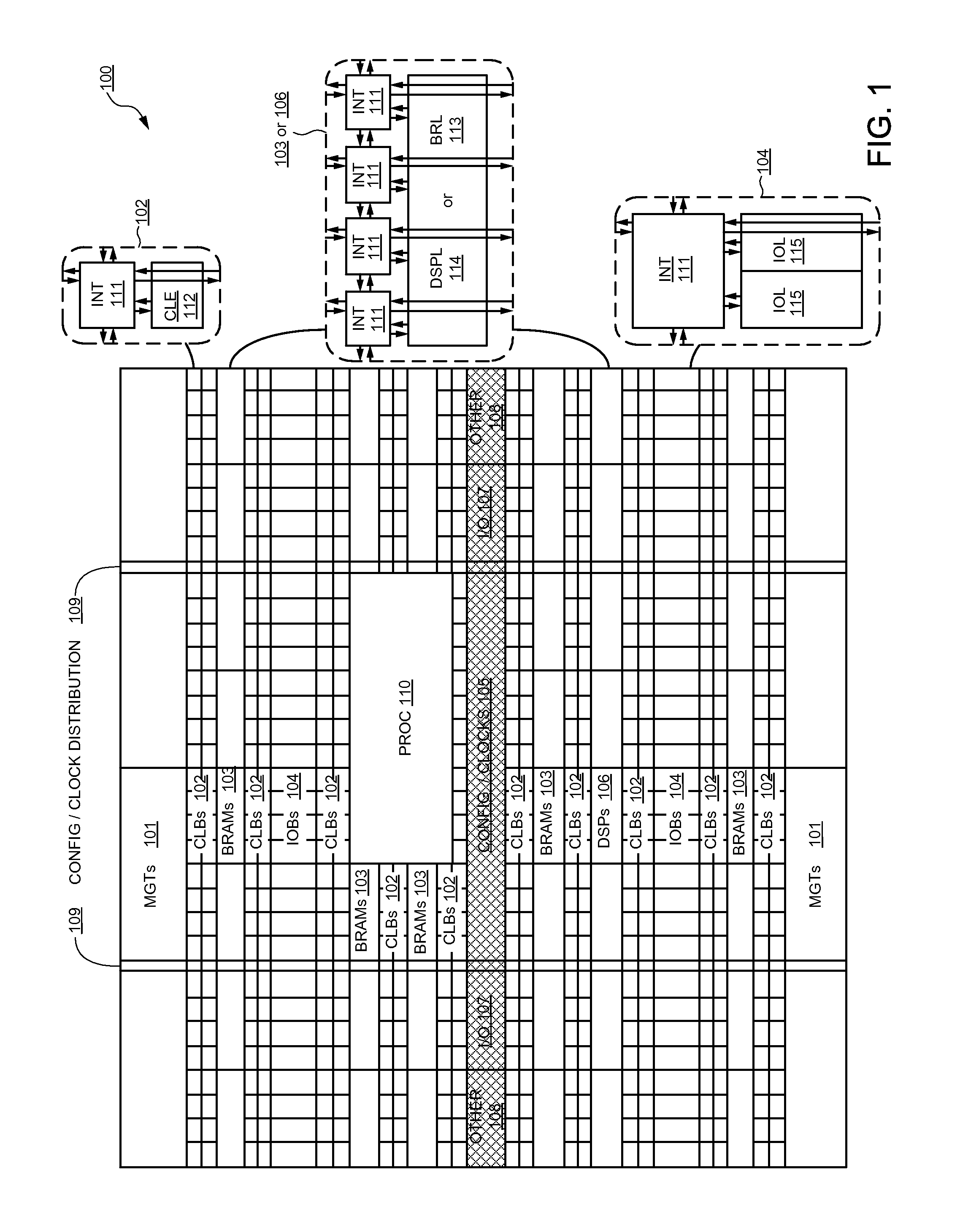

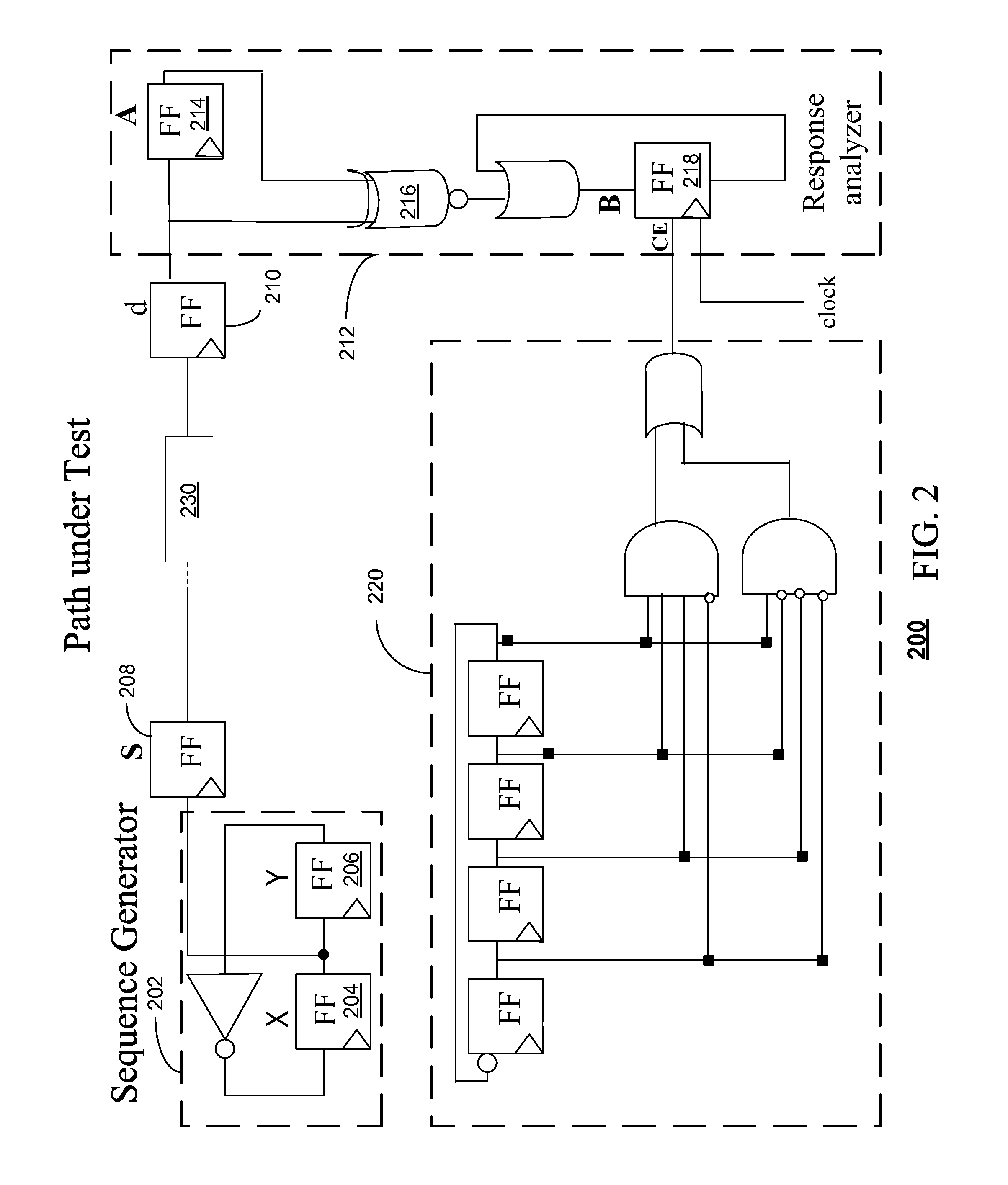

On-chip stuck-at fault detector and detection method

An on-chip stuck-at fault detector in an integrated circuit using a test circuit for critical path testing can include a sequence circuit having a first sequential circuit and a second sequential circuit to sensitize the critical path between a source sequential circuit and a destination sequential circuit, an analyzer circuit for capturing an output from the destination sequential circuit and comparing a signal between the destination sequential circuit and the analyzer circuit at predetermined clock cycles, and a controller for strobing the analyzer circuit at the predetermined clock cycles. The first sequence and second circuits can both be initialized to a zero mode (e.g., x=0 and y=0). Thus, no stuck-at faults are determined if the destination sequential circuit and an analyzer sequential circuit in the analyzer circuit have different values and a zero result is captured at a sticky-bit flip flop.

Owner:XILINX INC

Adaptive multi-bit error correction in endurance limited memories

InactiveUS8589762B2Extended service lifeOverhead of error correction hardware is reducedError detection/correctionRead-only memoriesStuck-at faultSelf adaptive

Multi-bit stuck-at fault error recovery can be enabled by adaptive multi-bit error correction method, in which the overhead of error correction hardware is reduced without affecting the lifetime of the memory device. Error correction logic hardware is decoupled from memory blocks. An error correction logic block is partitioned such that error correction logic entries support different number of error correction capabilities based on the probability of occurrence of the different number of errors in different memory blocks. Faulty memory blocks are mapped to appropriate error correction logic entries. The mapping can be one-to-one or many-to-one depending on embodiments. The adaptive partitioning of the error correction logic entries can be configured to match projected statistical distribution of errors in logic blocks, and can reduce the total error correction logic overhead, provide sufficient error correction, and / or extend the lifetime of the memory device.

Owner:IBM CORP

Self-trim and self-test of on-chip values

A self-trim circuit provides a technique to trim a CUT (circuit under trim) using a LSB offset to determine the best digital value to trim the CUT. The self-trim circuit is also used to self-test the digital and analog portions of the self-trim circuitry, whereby the existence of a digital stuck at fault condition is detected. A state machine controls a digital stack to couple digital trim data to the CUT and read the output of a comparator circuit that signifies when a proper digital trim value has been used. Thereafter the proper digital trim value is stored into a nonvolatile memory.

Owner:DIALOG SEMICONDUCTOR GMBH