Scanning chain fault diagnosis method and system

A fault diagnosis system and fault diagnosis technology, applied in the direction of measuring devices, instruments, measuring electronics, etc., can solve problems such as inability to perform, and achieve the effect of reducing the number of comparisons, reducing vector generation and testing time, and reducing the number

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

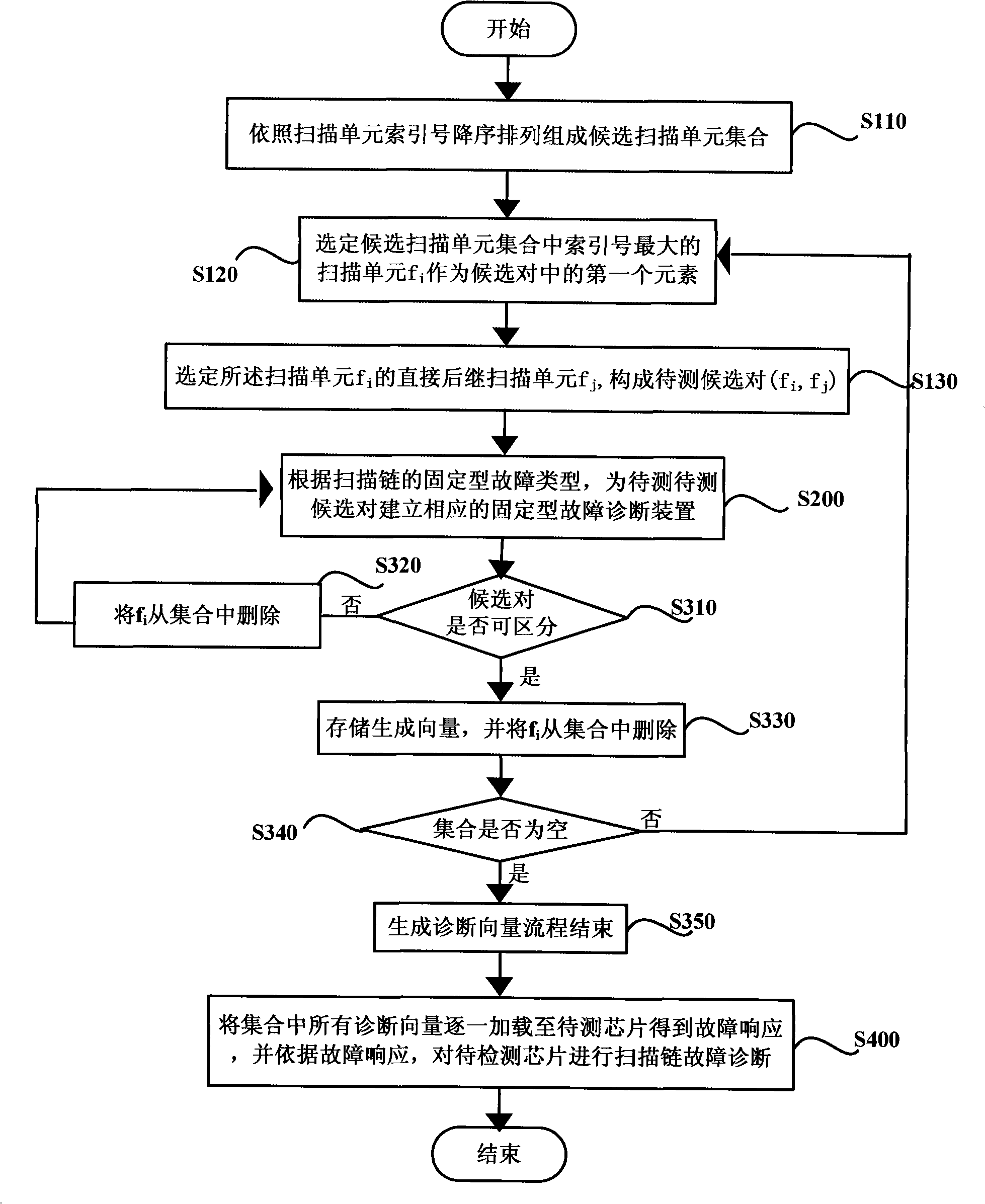

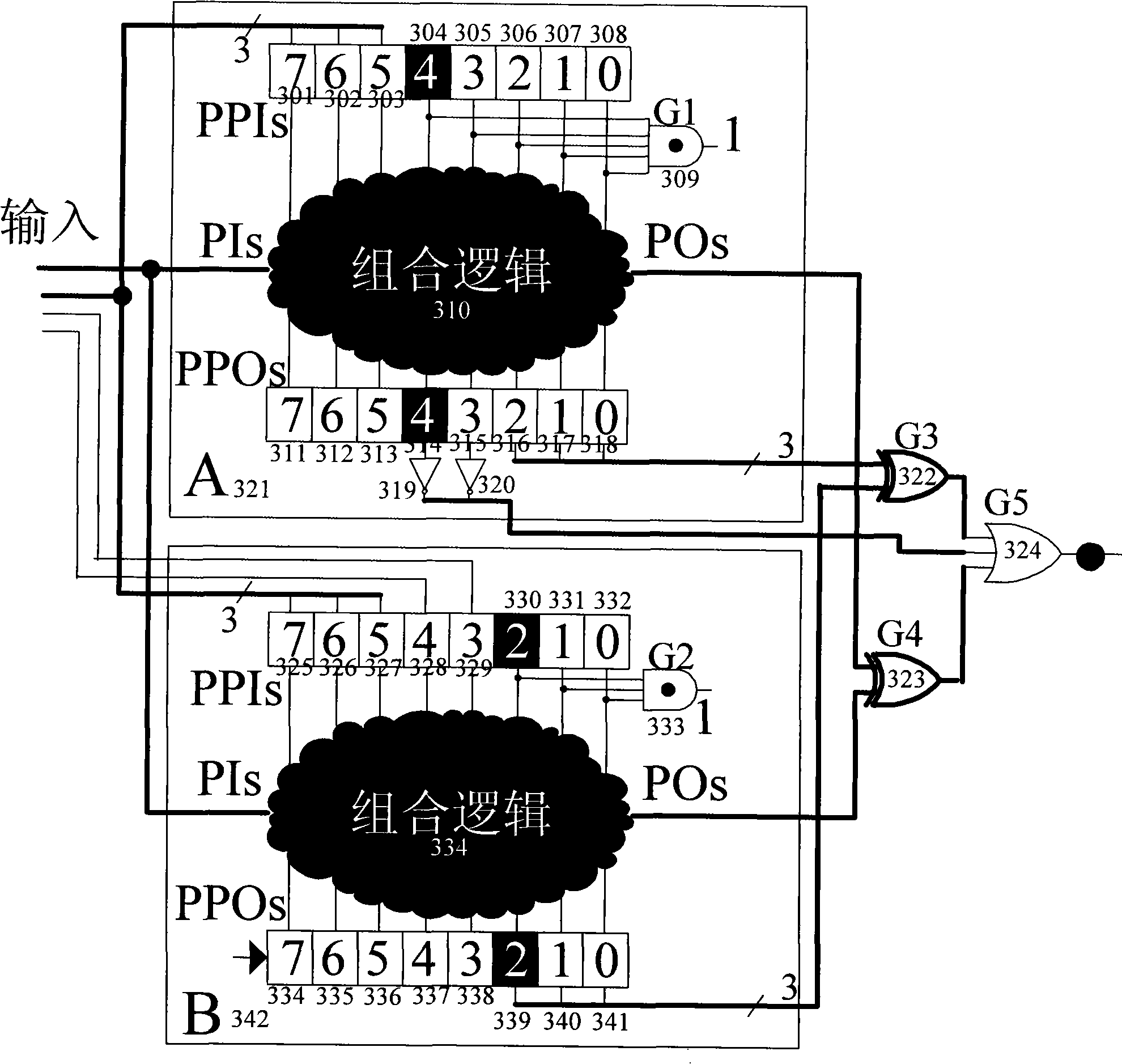

[0081] In order to make the purpose, technical solution and advantages of the present invention clearer, a scan chain fault diagnosis method and system of the present invention will be further described in detail below in conjunction with the accompanying drawings and embodiments. It should be understood that the specific embodiments described here are only used to explain the present invention, not to limit the present invention.

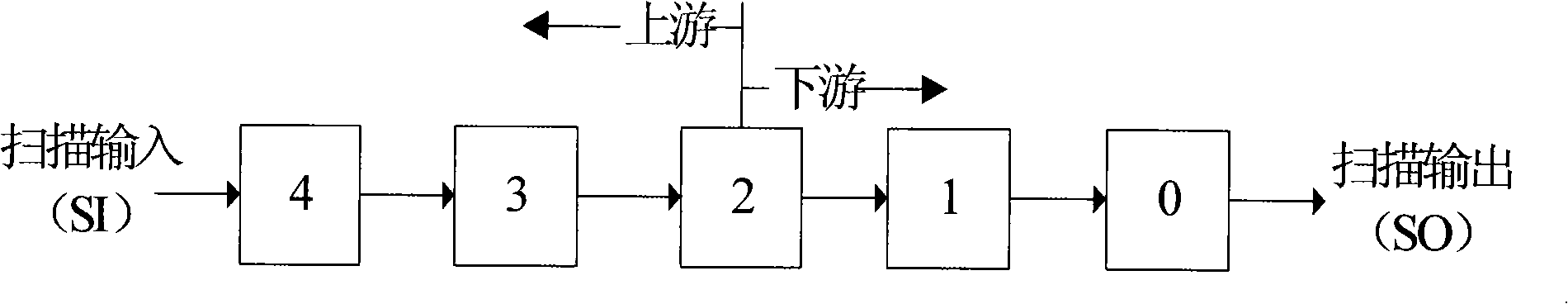

[0082] A scan chain fault diagnosis method provided by the present invention is to establish a fault diagnosis device according to the fixed fault type of the scan chain and the selected candidate pairs to be tested, and use the fixed fault test generation tool to obtain the scan chain diagnosis vector, for Locate stuck-at faults in the scan chain. The method diagnoses the faulty scan chain without any area and wiring overhead, and does not change the traditional scan chain diagnosis process, thereby reducing the cost of logic diagnosis.

[0083] ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More