Patents

Literature

92 results about "Path testing" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

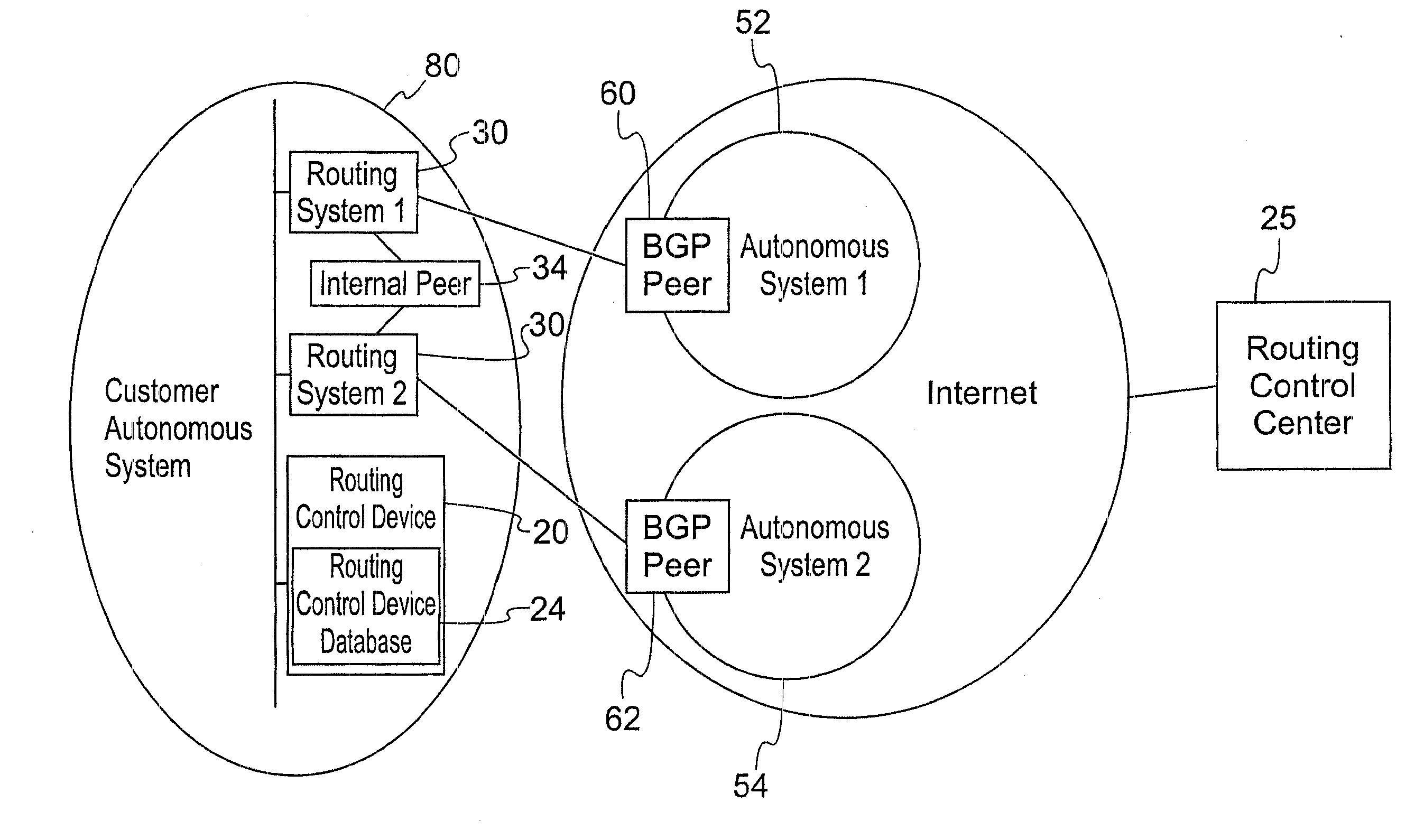

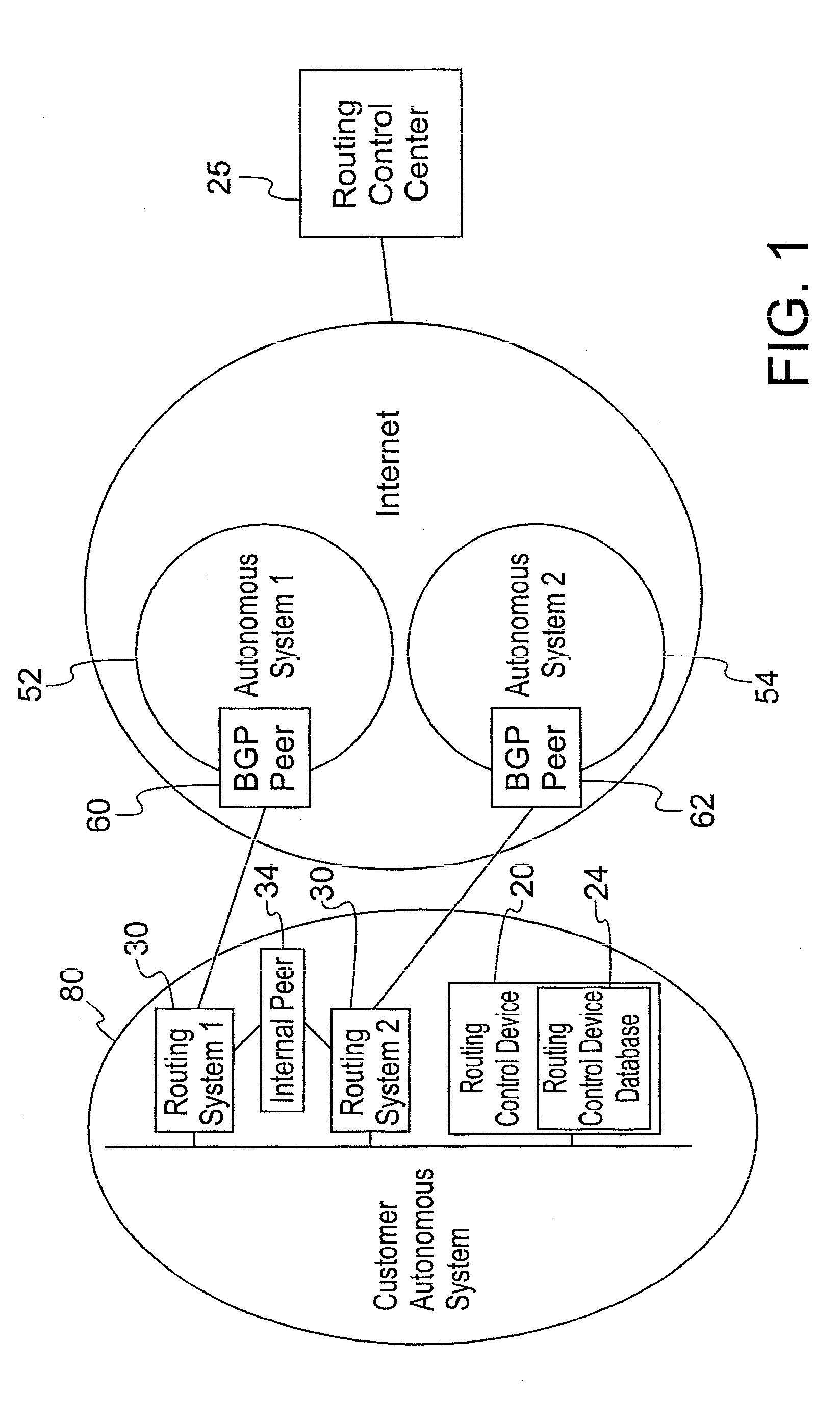

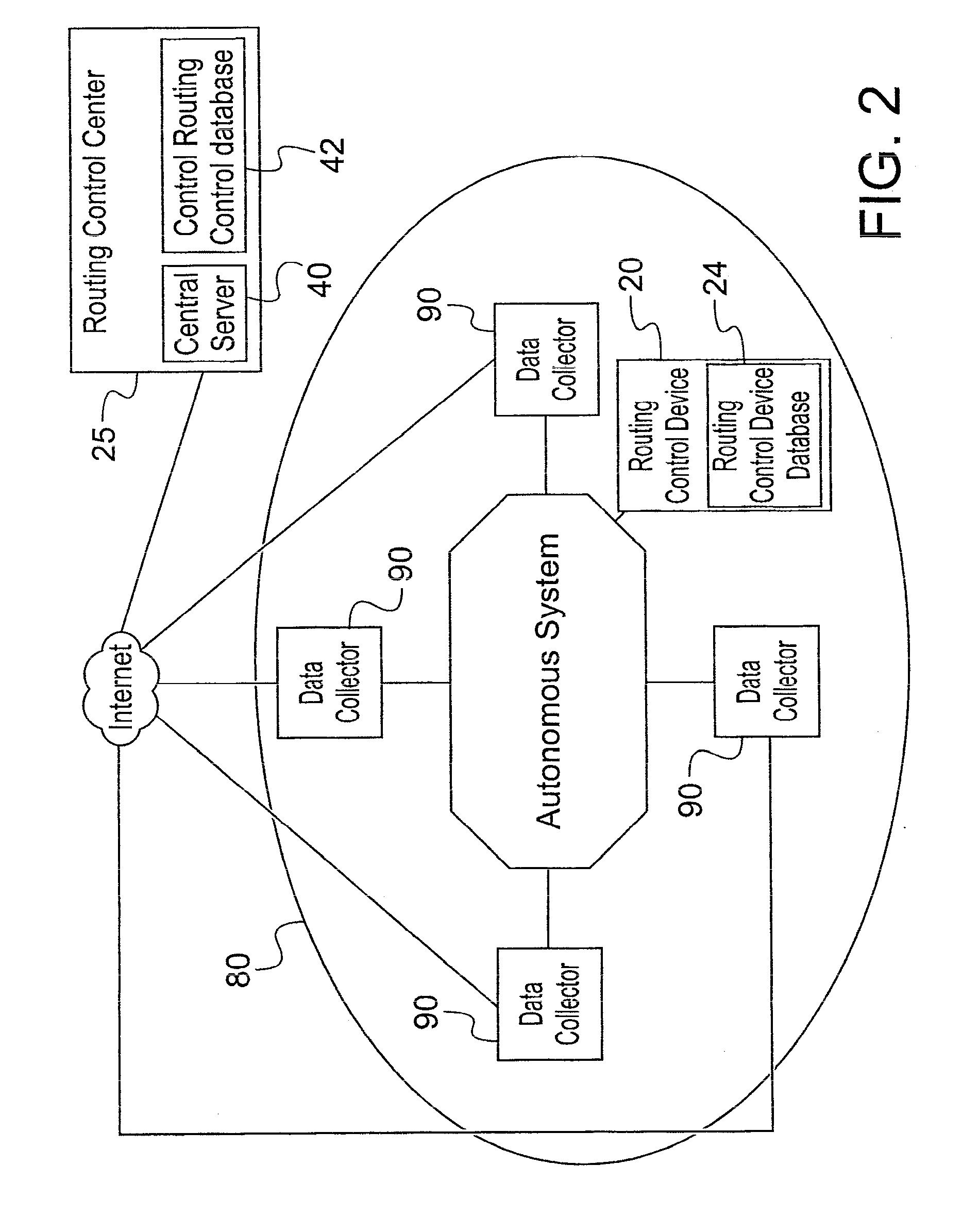

Methods, apparatuses and systems facilitating determination of network path metrics

InactiveUS7260645B2Easy to configureEasy to deployMultiple digital computer combinationsData switching networksThe InternetTime of day

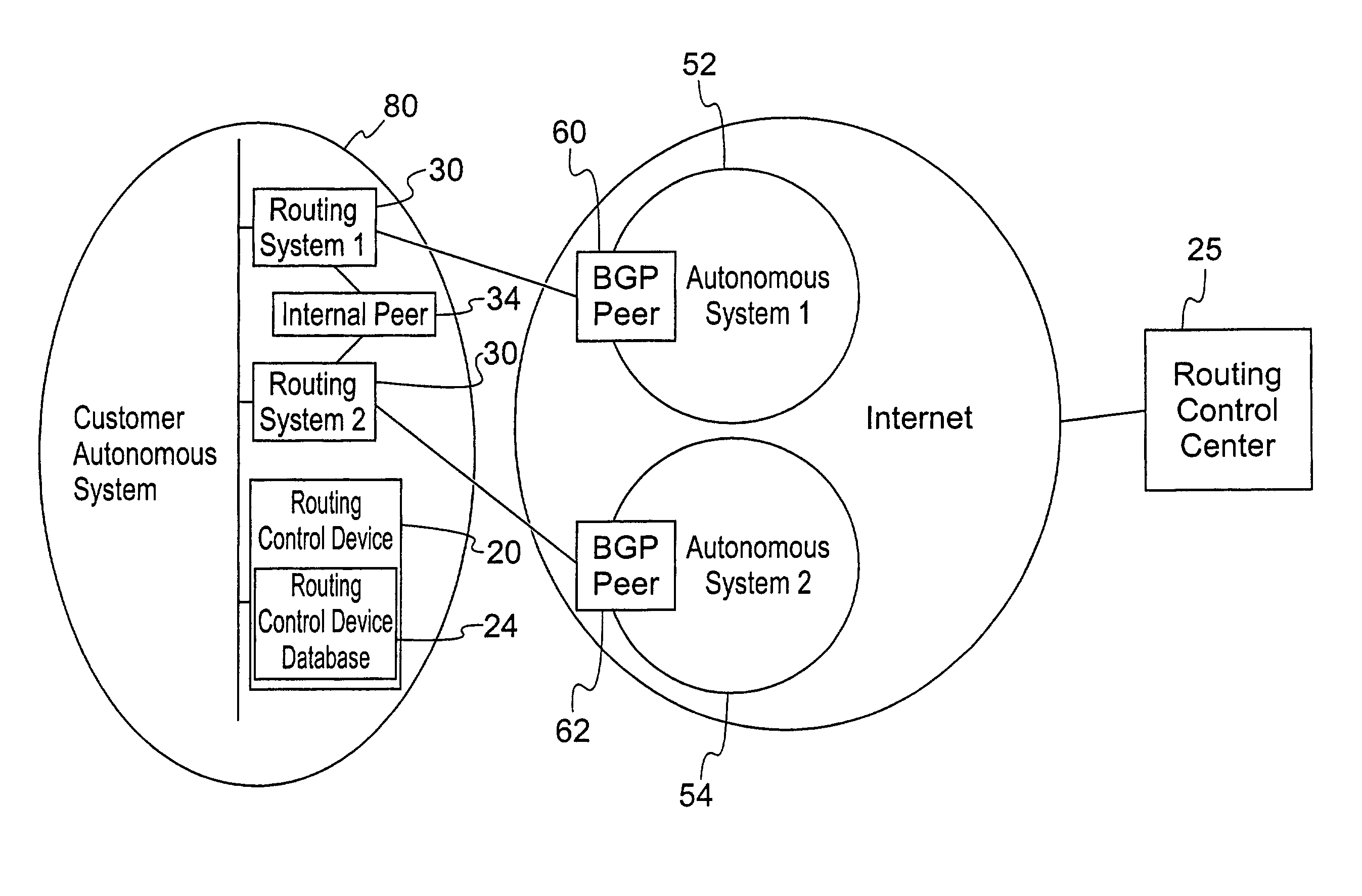

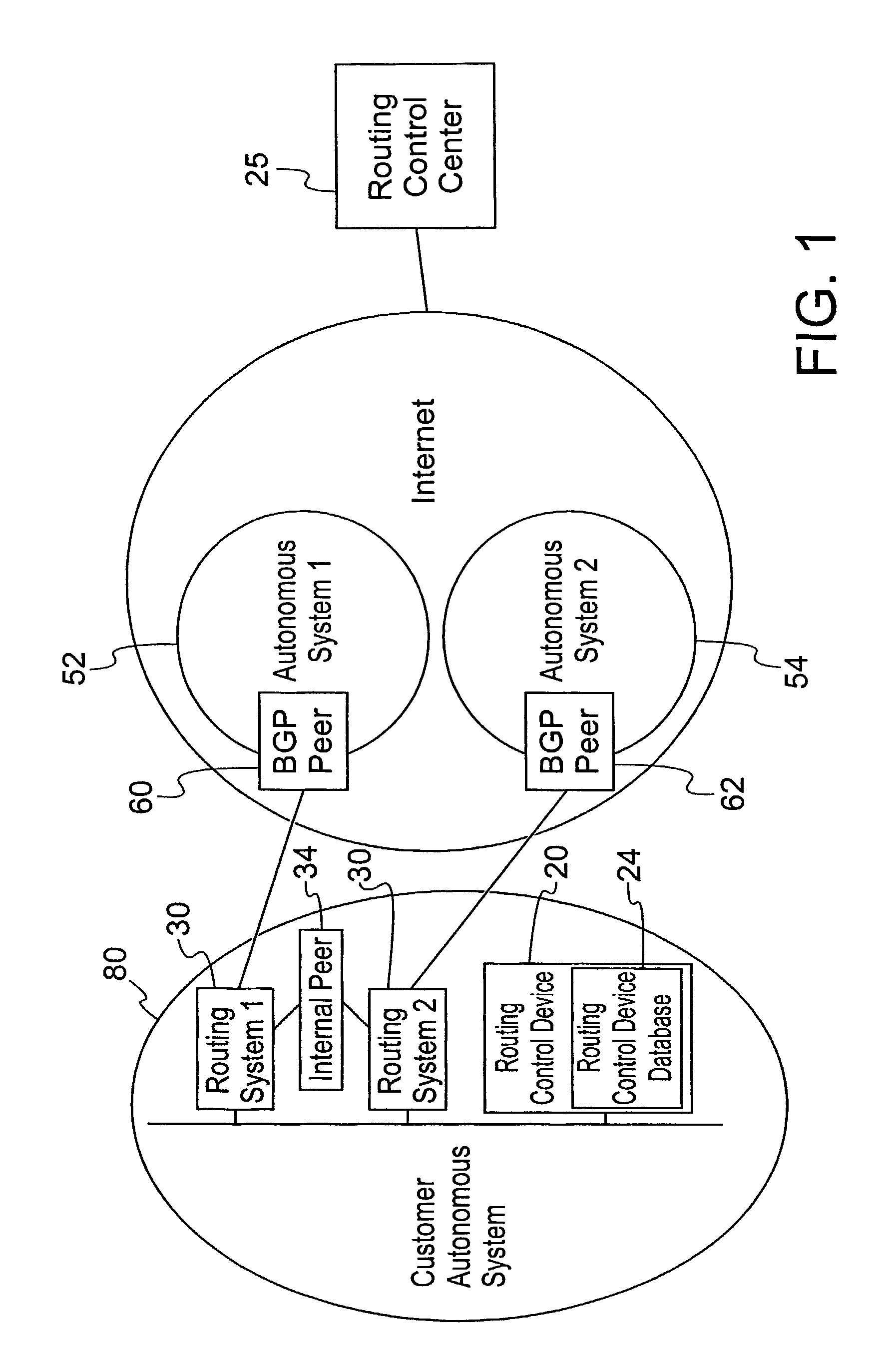

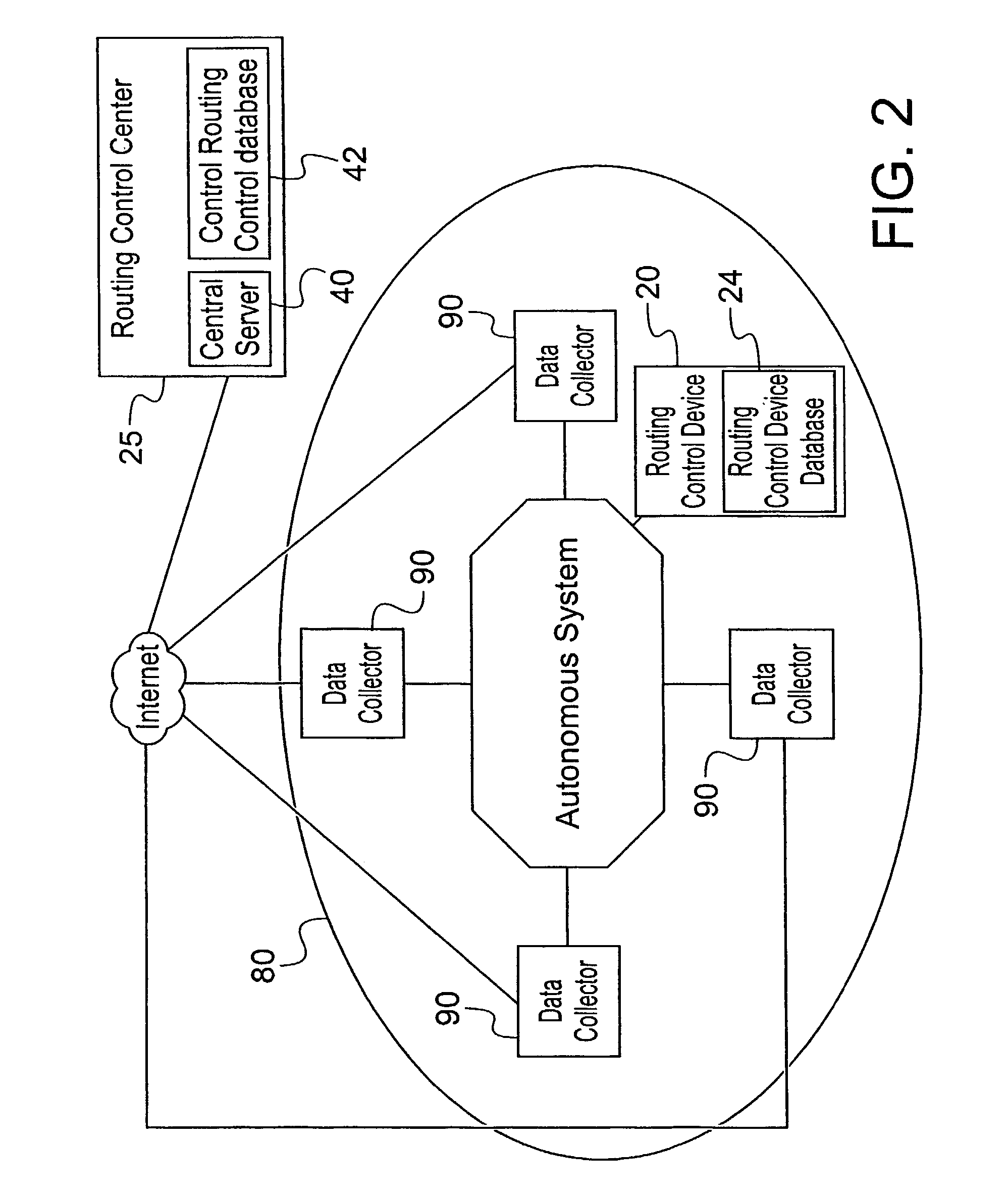

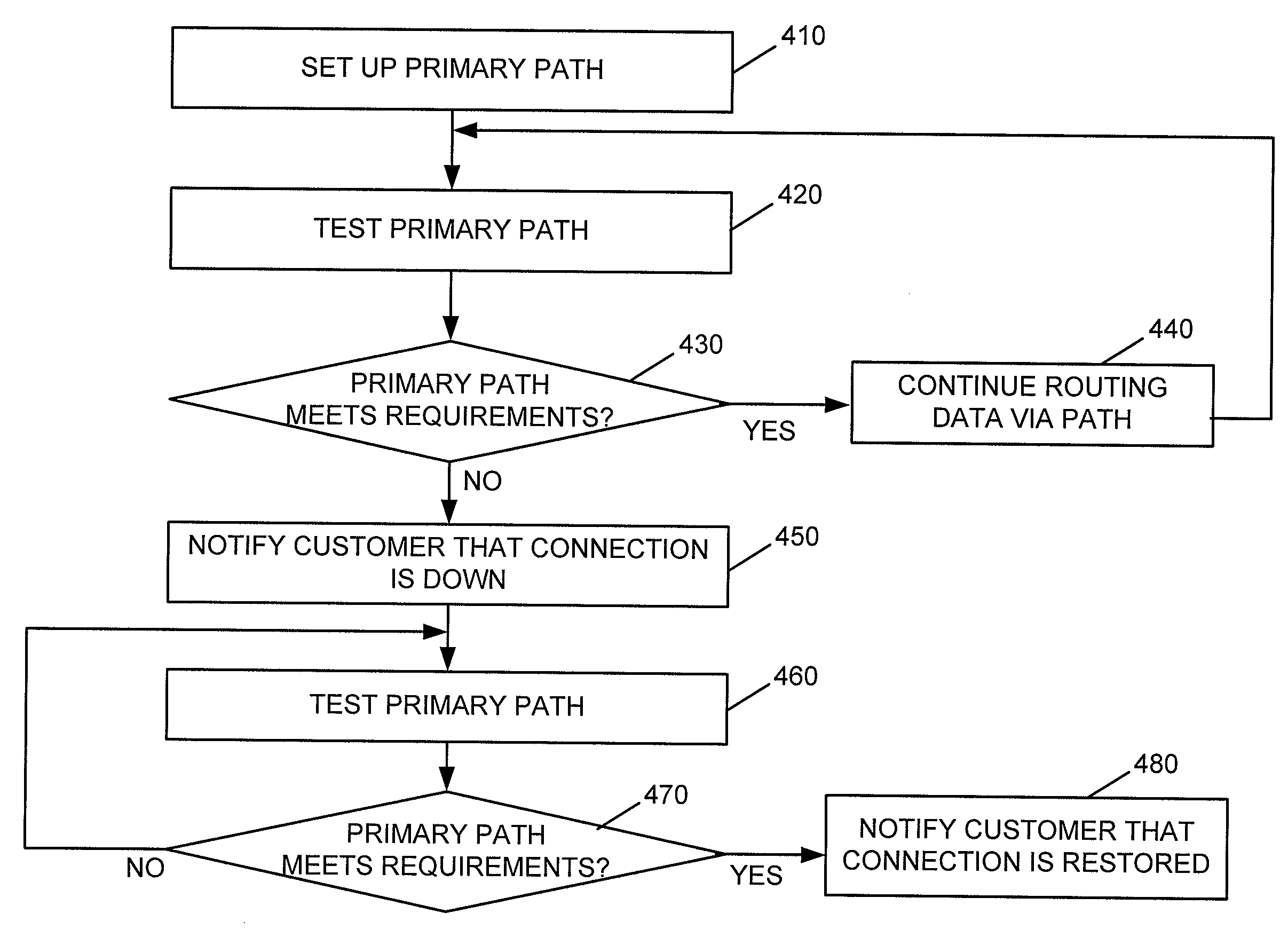

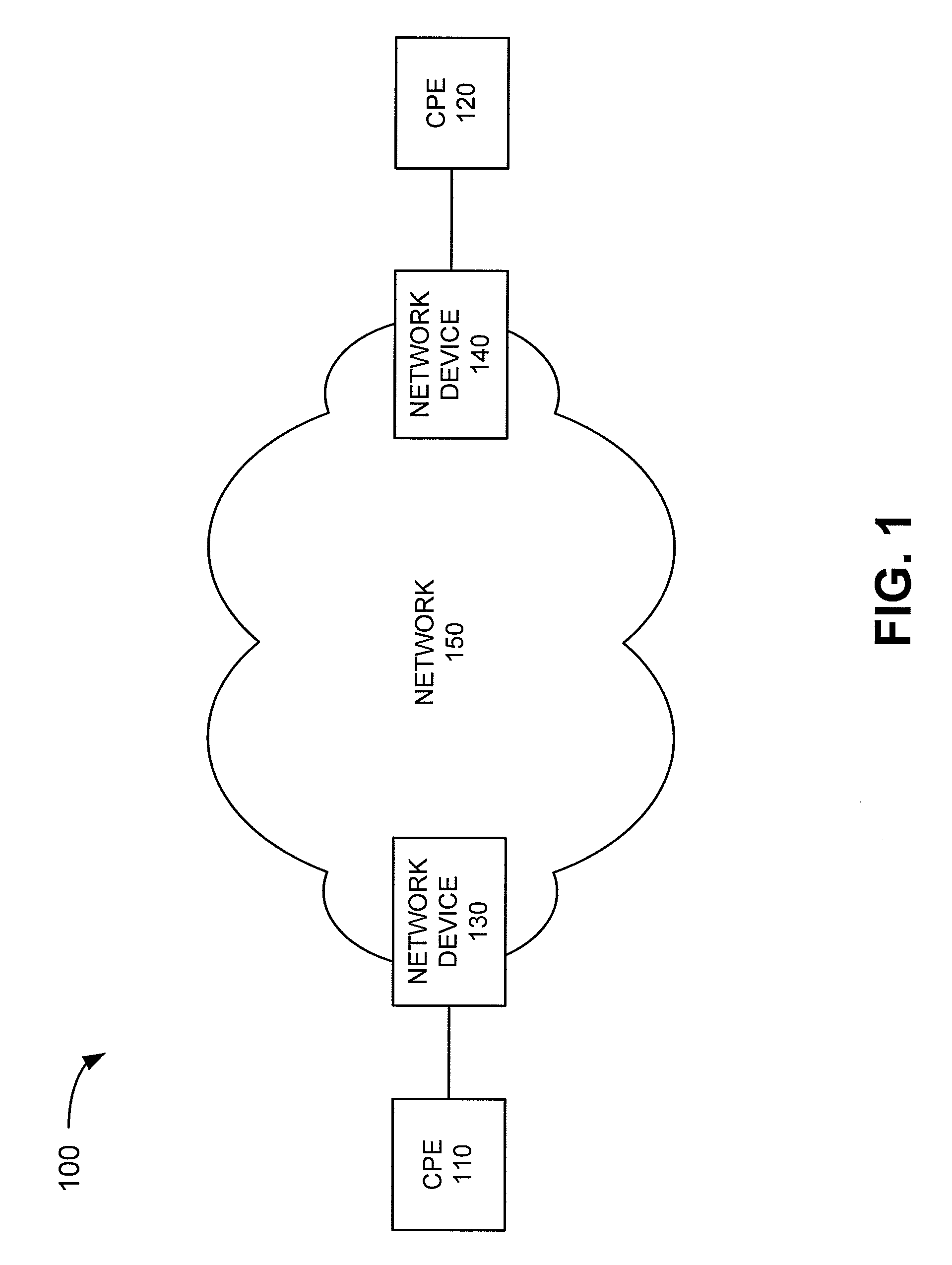

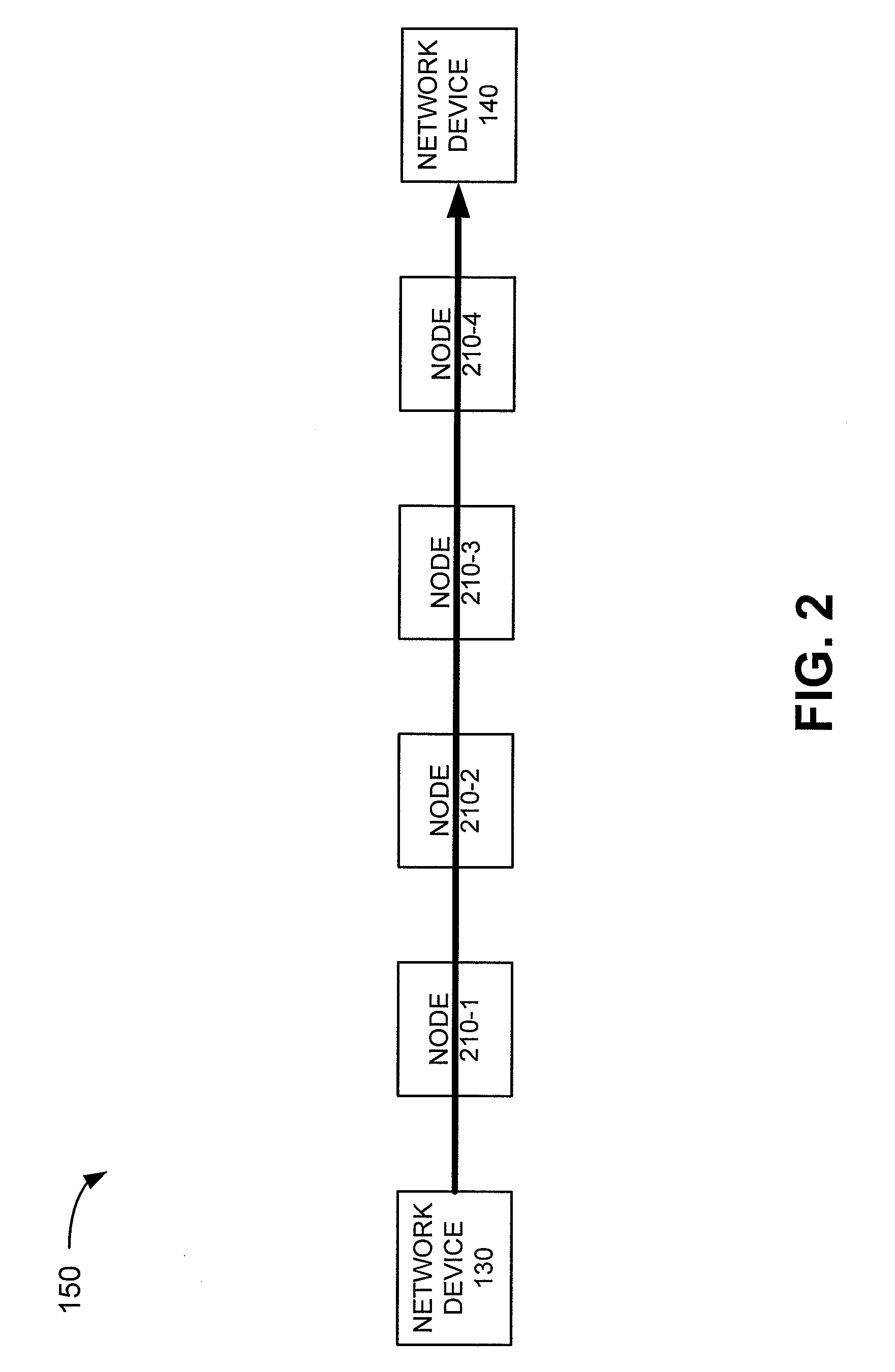

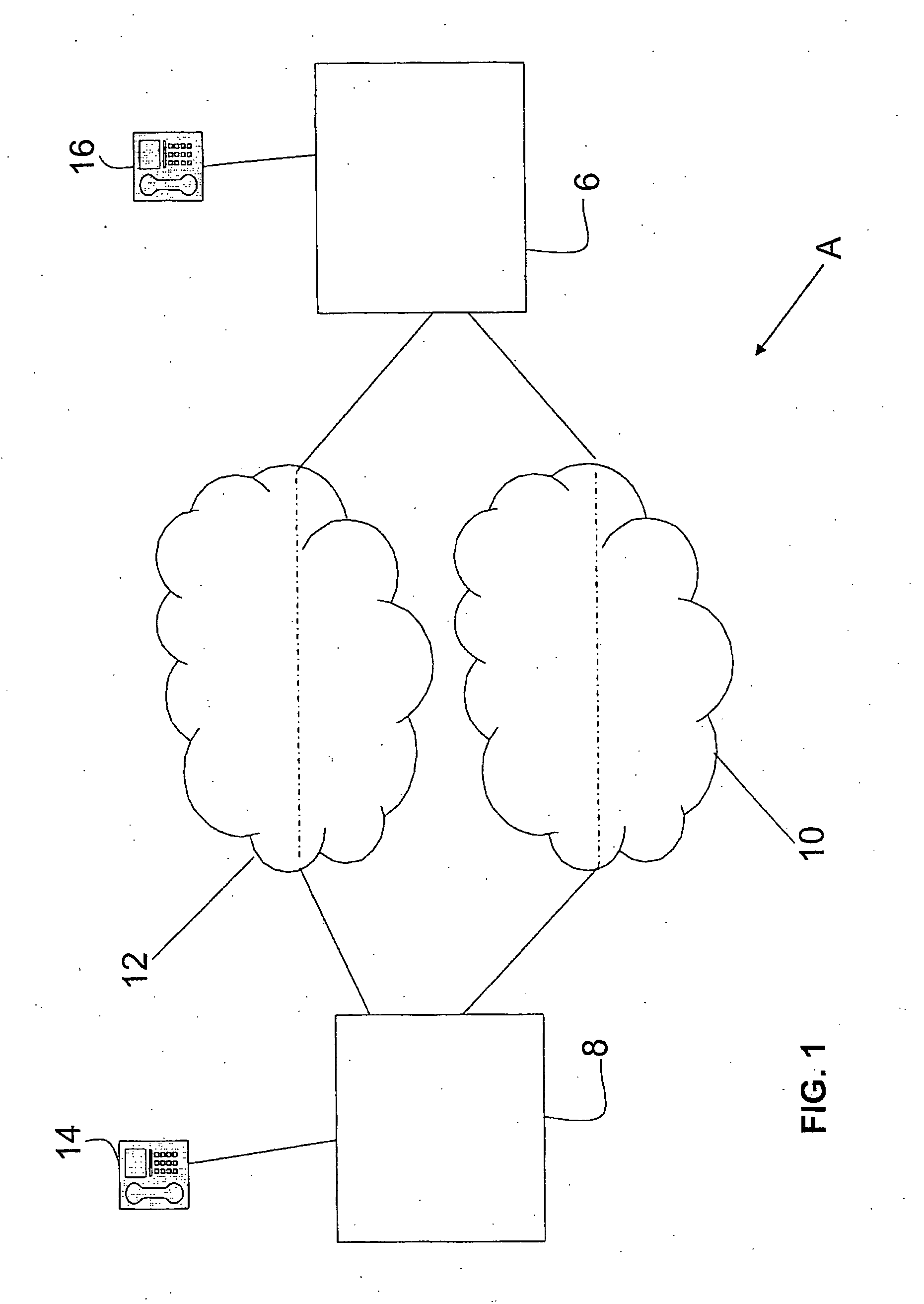

Methods, apparatuses and systems relating to the control and application of policies for routing data over a computer network, such as the Internet. Some implementations of the invention facilitate the configuration, deployment and / or maintenance of network routing policies. Some implementations of the invention are particularly useful for controlling the routing of data among autonomous systems or organizations. Certain implementations allow for dynamic modification of routing policy based on such factors as current Internet performance, load sharing, user-defined parameters, and time of day. In one embodiment, the present invention provides methods, apparatuses and systems implementing enhanced network path testing methodologies that enhance the efficiency of processes associated with testing of a network path, while reducing the perceived intrusiveness of test packets associated with such metrics tests.

Owner:SUNTRUST BANK AS SUCCESSOR AGENT +1

Path testing and switching

Owner:VERIZON PATENT & LICENSING INC

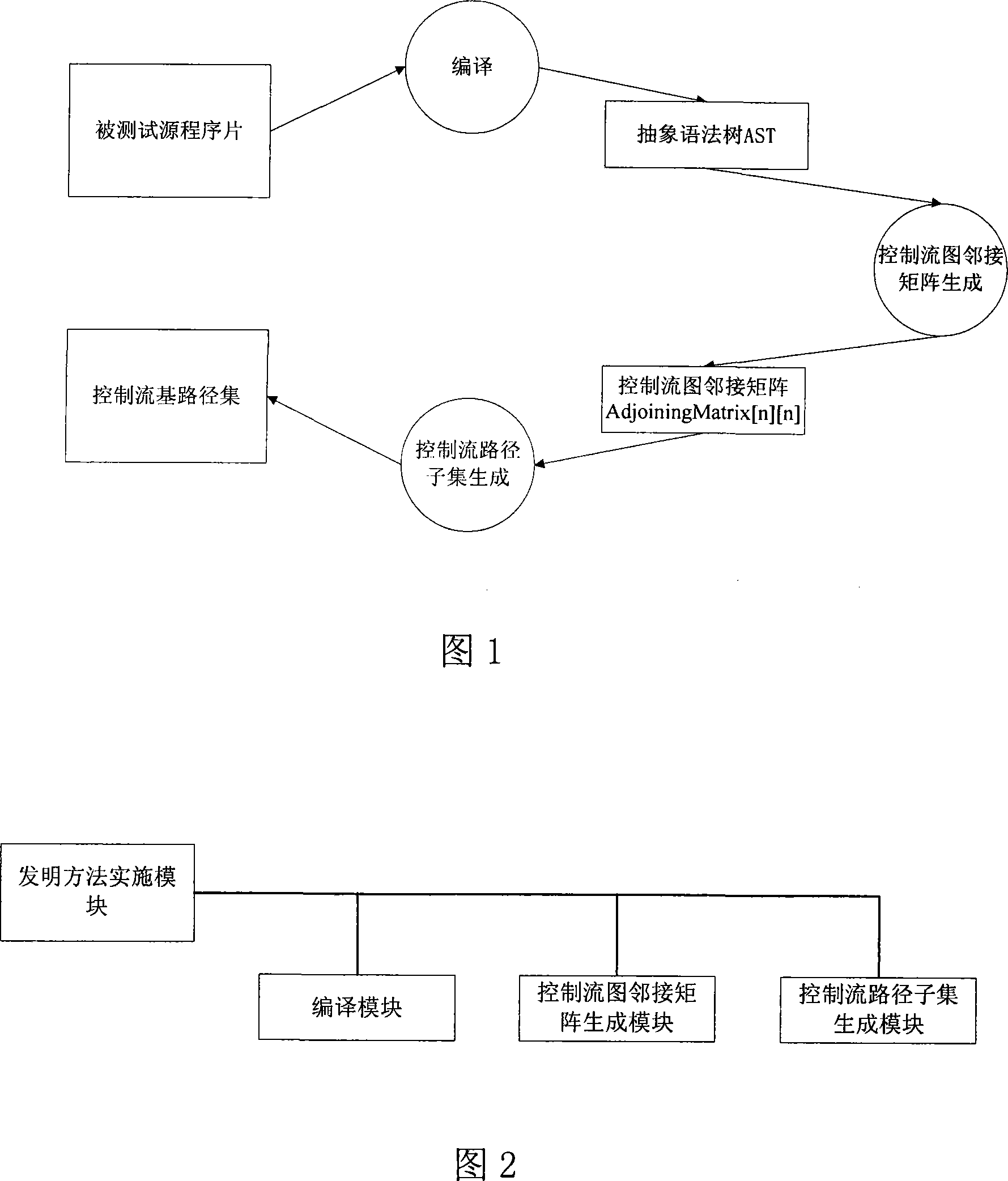

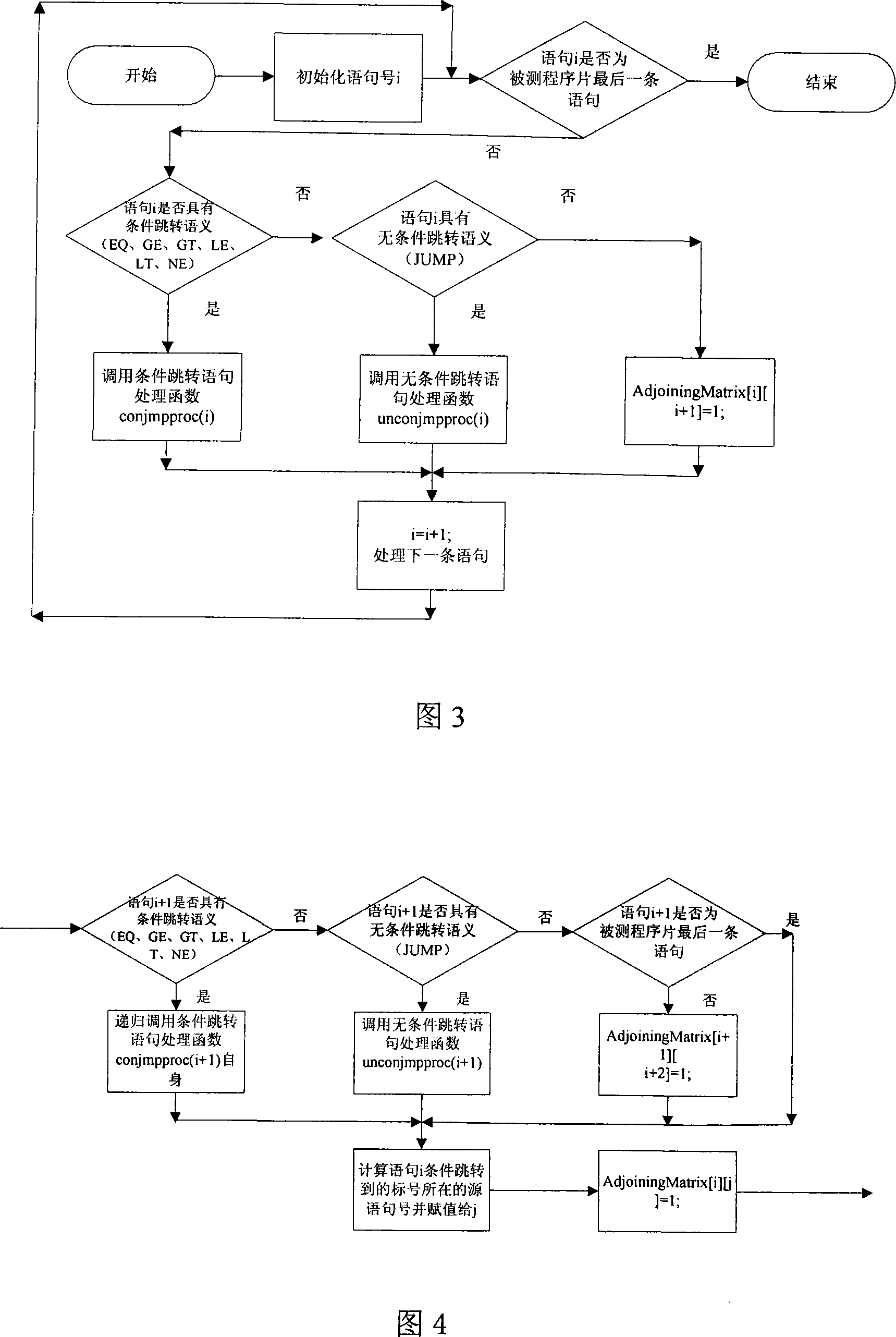

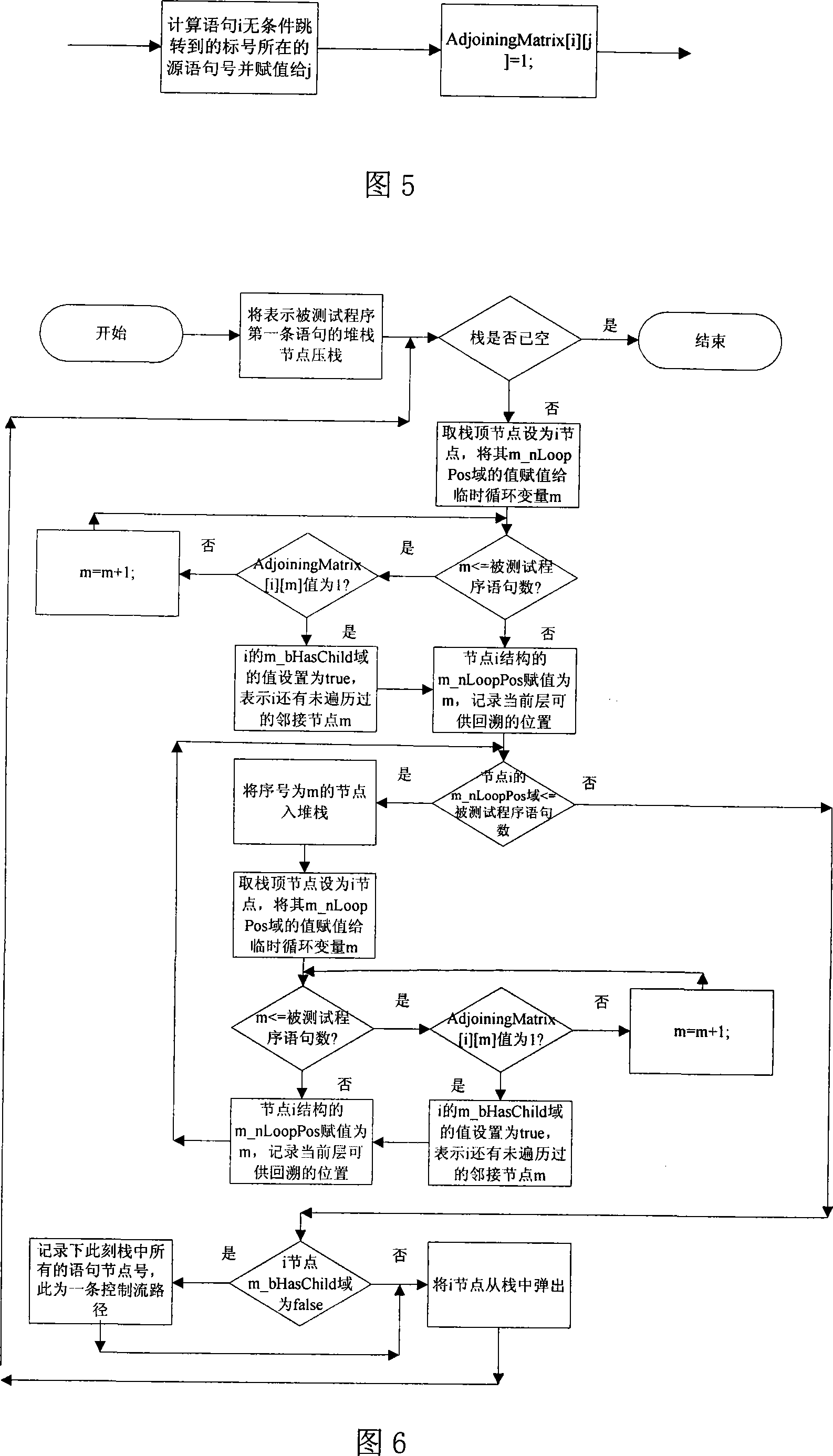

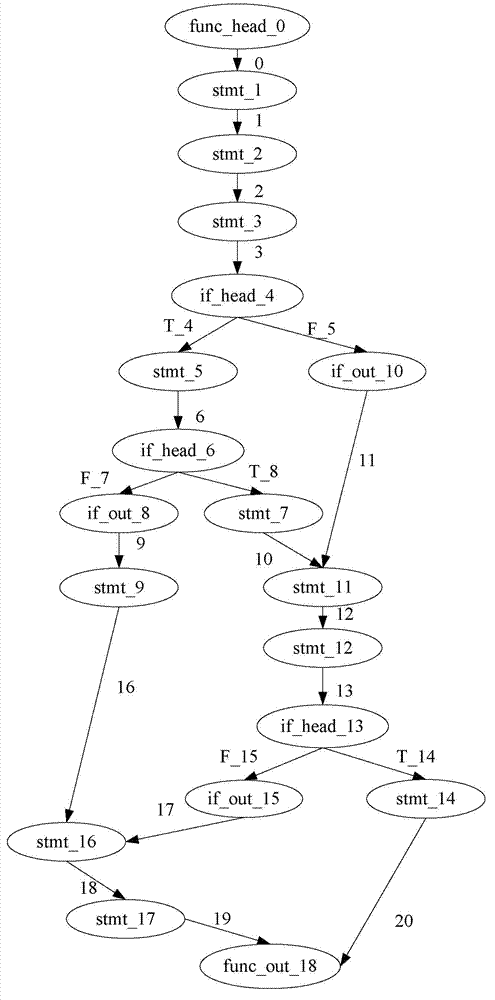

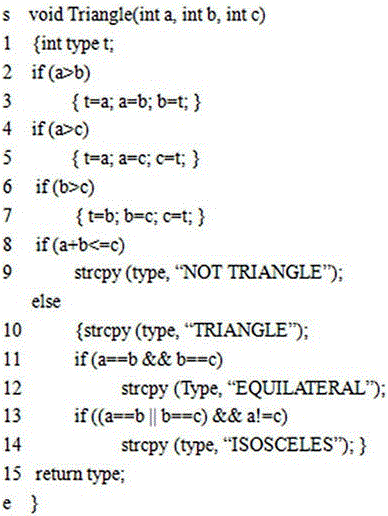

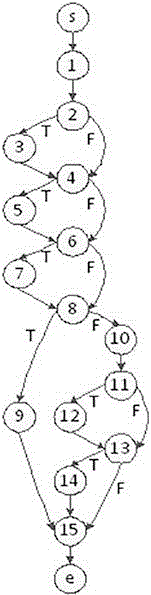

Test program control stream path set creation method based on base path

InactiveCN101216803ASolve the completeness problemSolving automation problemsSoftware testing/debuggingPath generationProgram testing

The invention pertains to a path testing in a program testing. The concept of a program control flow base path is defined through bringing in the concept of base in mathematics, a data structure showing a program structure of a source program slice is obtained by using a compiler module first; then through traversing the data structure, a control flow path generating algorithm is utilized to generate a subset compiler module of a program control flow path which is based on a base path to interpret the semanteme on a tested source program, an abstract syntax tree structure showing the structural information of the tested program control flow is output. An adjacency matrix of a control flow graph generates a module ergodicity abstract syntax tree structure, and generates the adjacency matrix representation of a program flow chart. A control flow path subset generating module acquires the control flow information of the tested program through traversing the adjacency matrix, traverses the adjacency matrix by adopting a depth-first multiple backtracking method, and processes sentence nodes, thus a program control flow path subset based on the base path is generated. The method has the outstanding advantages in generating results and flows, and can be widely used in the engineering practice of a path cover testing in a software structure testing.

Owner:SICHUAN UNIV

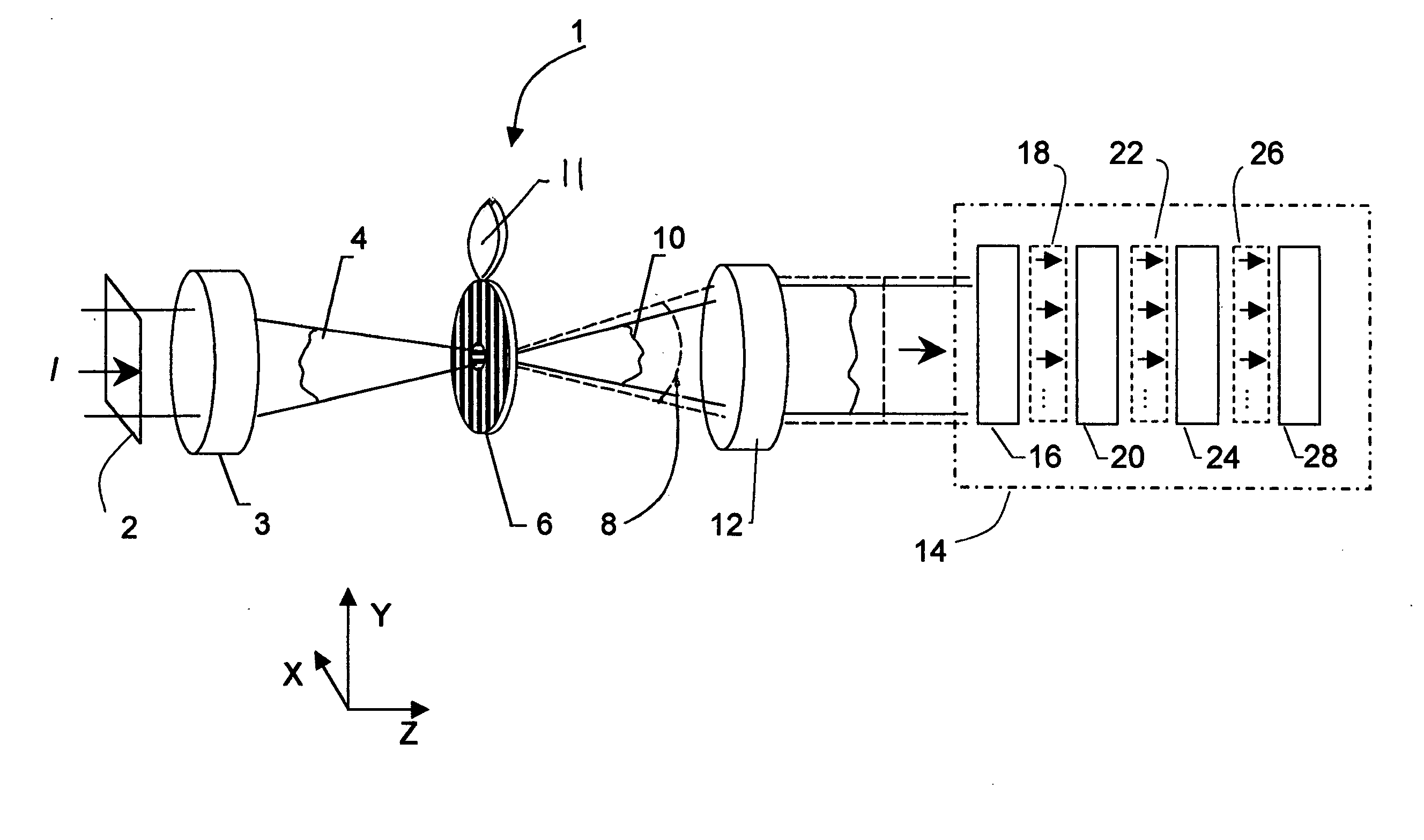

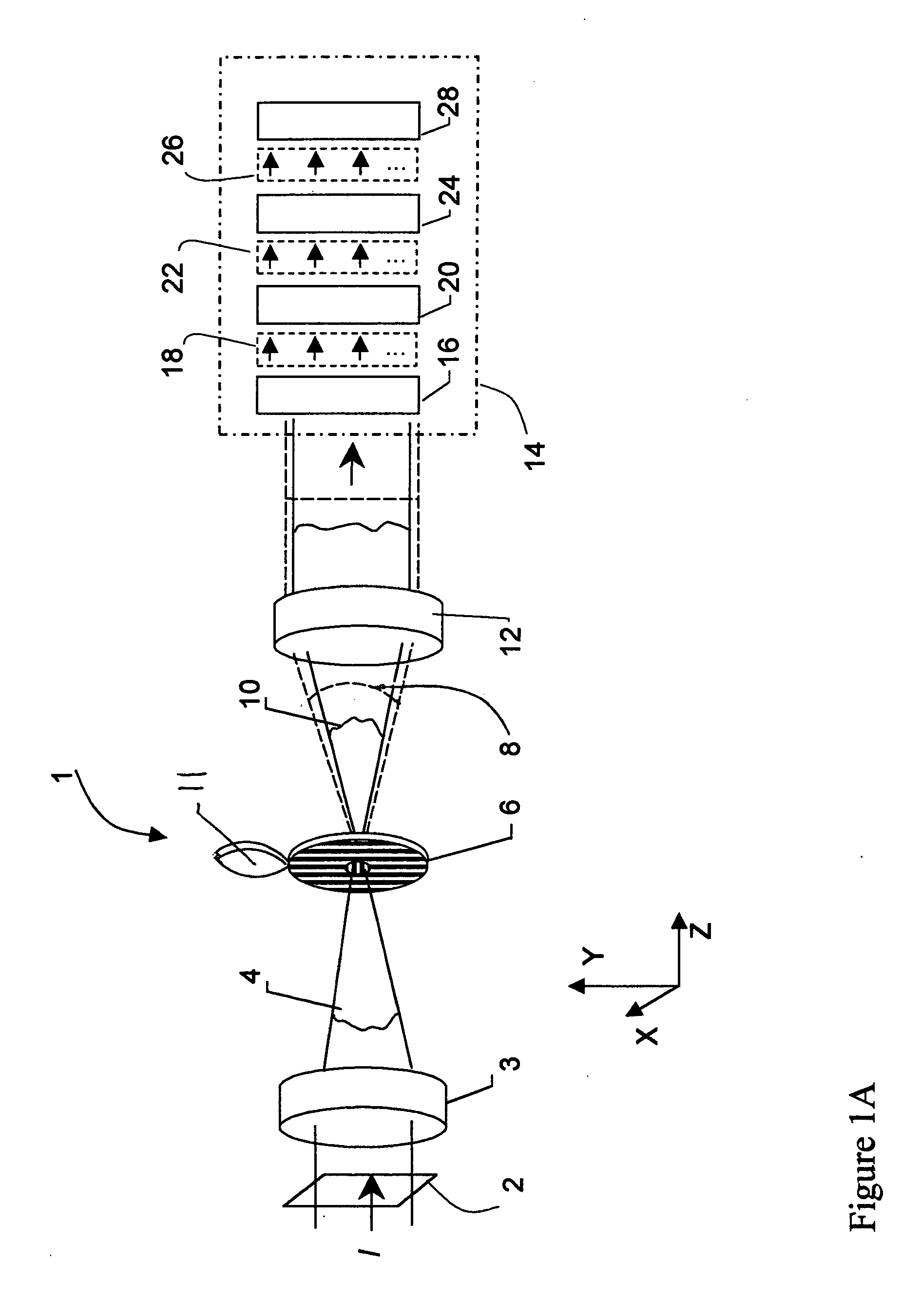

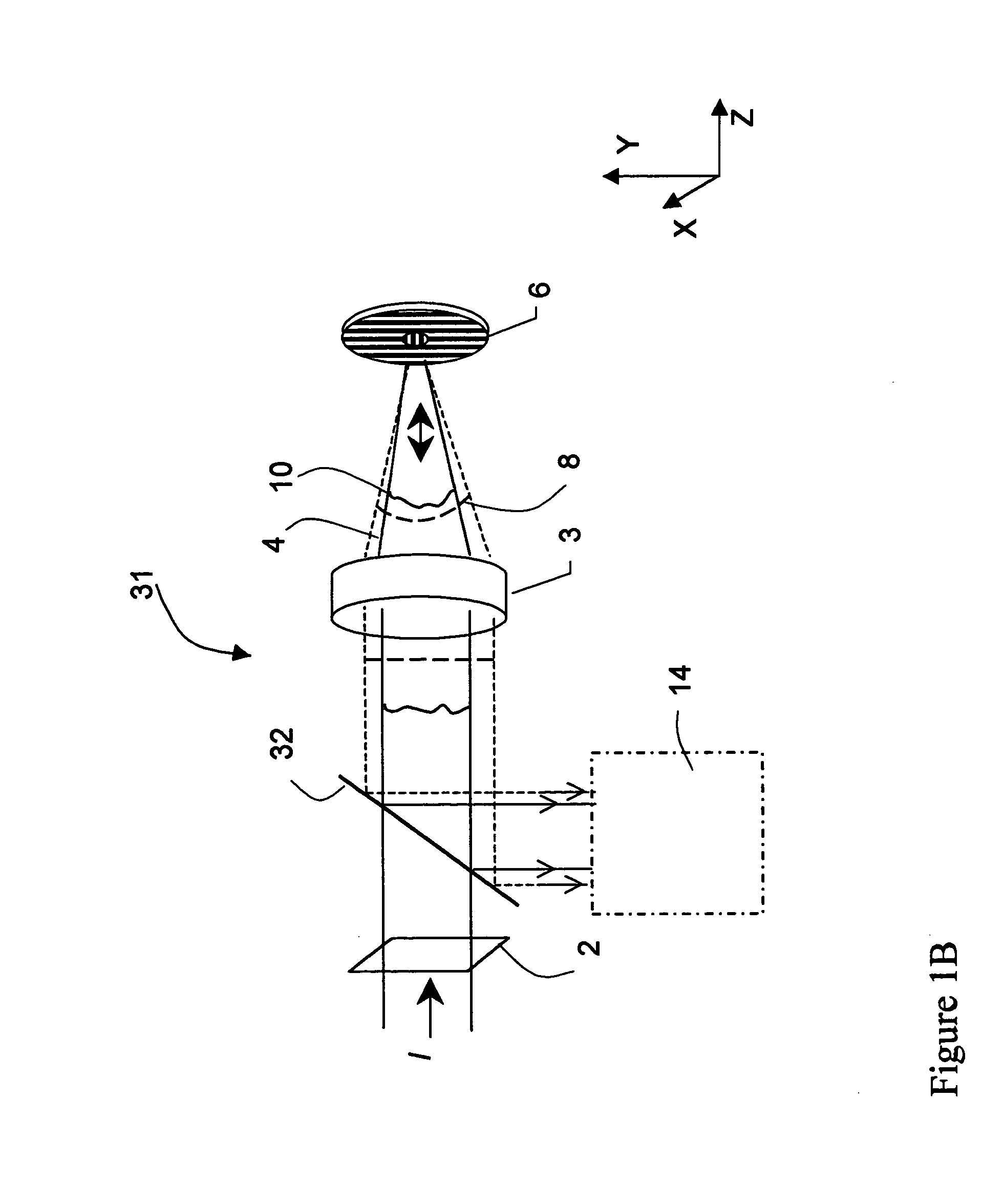

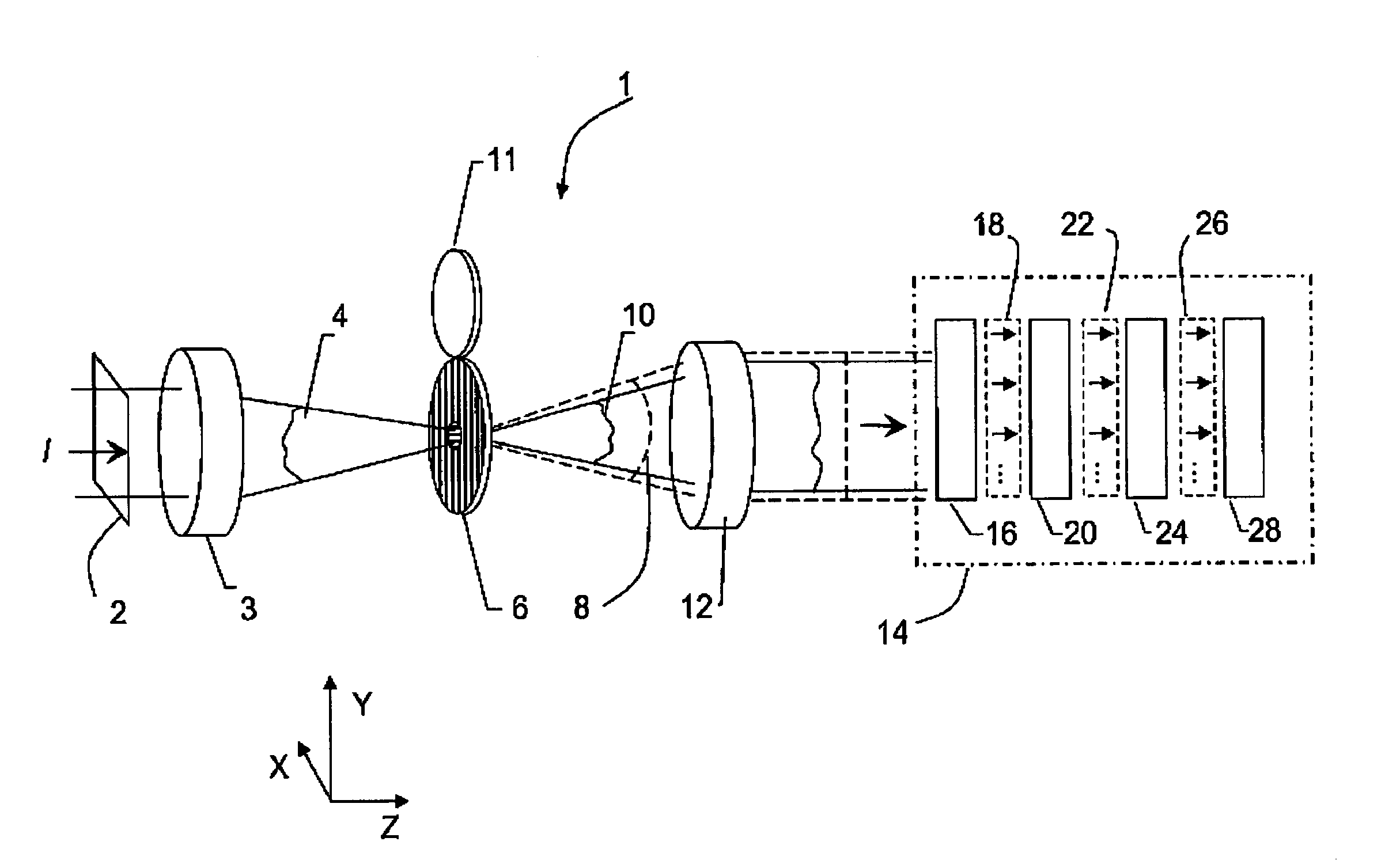

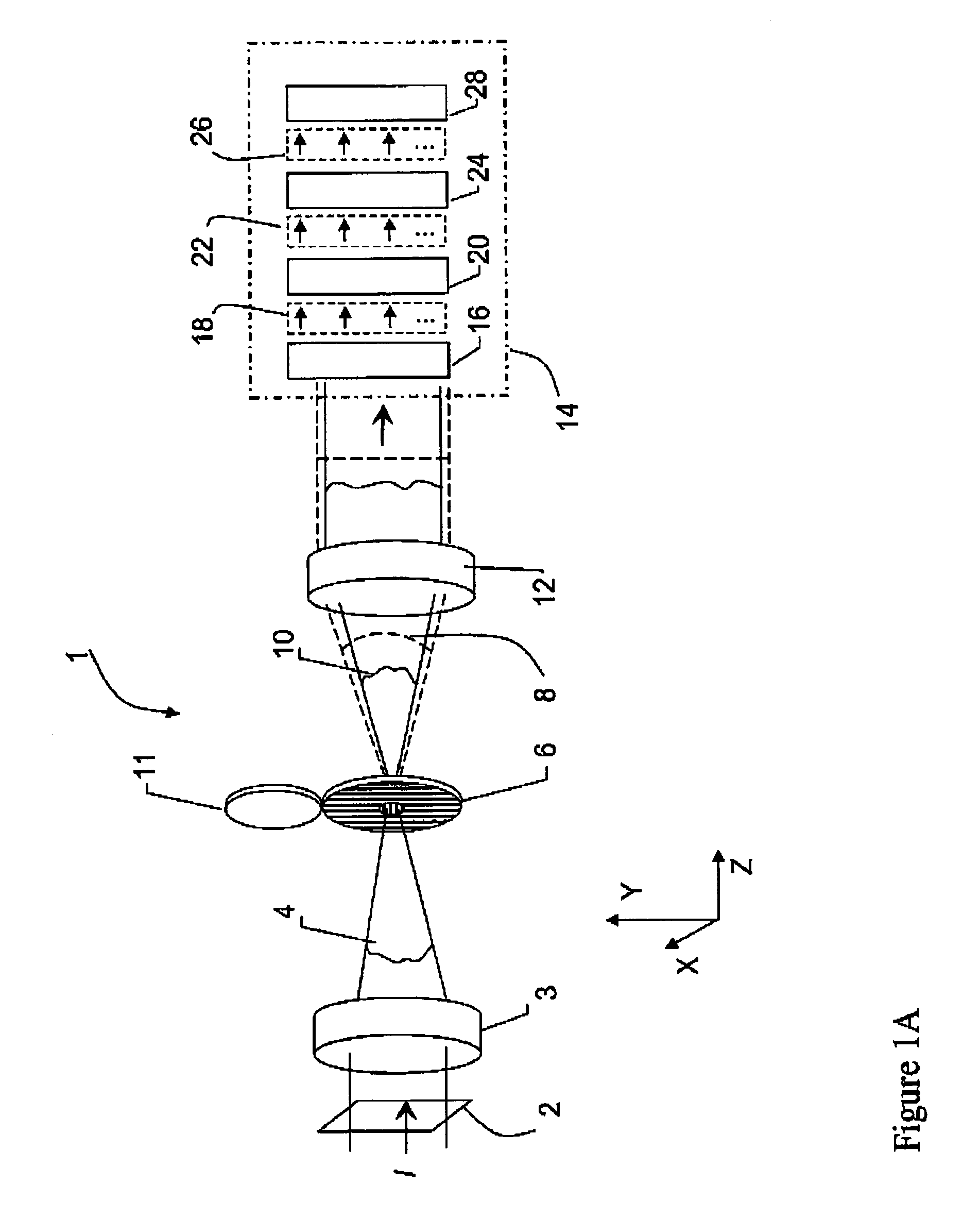

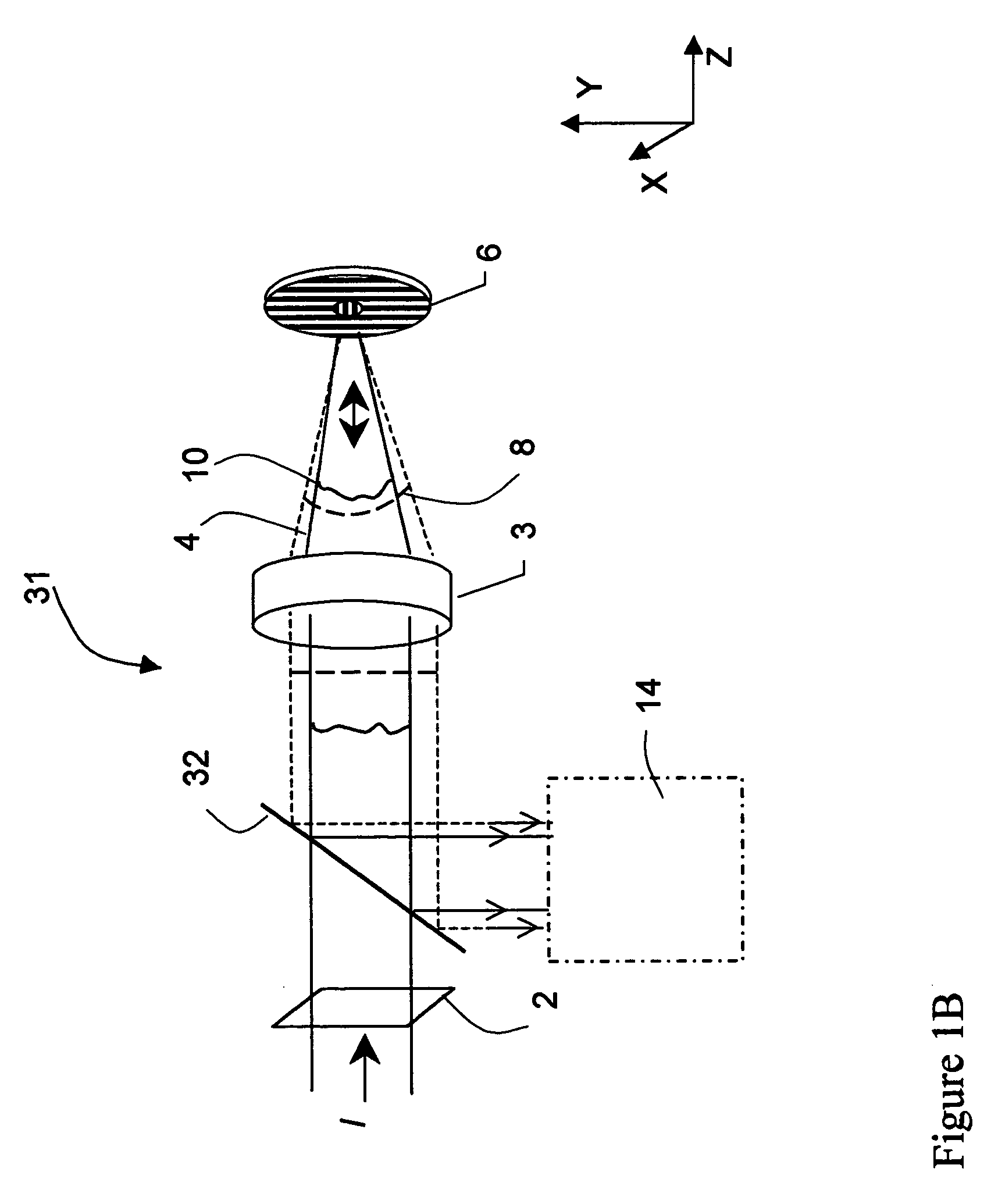

Common optical-path testing of high-numerical-aperture wavefronts

ActiveUS20050046863A1Improve polarizationIncreased Polarization PurityOptical measurementsInterferometersWavefrontPhase shifted

A polarizing point-diffraction plate is used to produce common-path test and reference wavefronts with mutually orthogonal polarizations from an input wavefront. The common-path test and reference wavefronts are collimated, phase shifted and interfered, and the resulting interferograms are imaged on a detector. The interference patterns are then processed using conventional algorithms to characterize the input light wavefront.

Owner:ONTO INNOVATION INC

Method and apparatus for testing, characterizing and monitoring a chip interface using a second data path

InactiveUS20060190642A1Accurate measurementAccurately determineInput/output to record carriersResistance/reactance/impedenceComputer scienceData path

A data receiver circuit in a receiving chip provides the capability to characterize an interface, which includes one or more inter-chip communication lines, between a transmitting chip and the receiving chip by transmitting the data across a primary data path and a secondary data path, latching the data in the secondary data path using a clock signal that is skewed relative to a clock signal used to latch the primary data path, comparing the data latched from the primary and secondary data paths, and recording errors. Because the primary data path is not impacted by the test cycle, the test cycle may be run while data associated with applications running on the system are transmitted across the inter-chip communication lines.

Owner:LENOVO GLOBAL TECH INT LTD

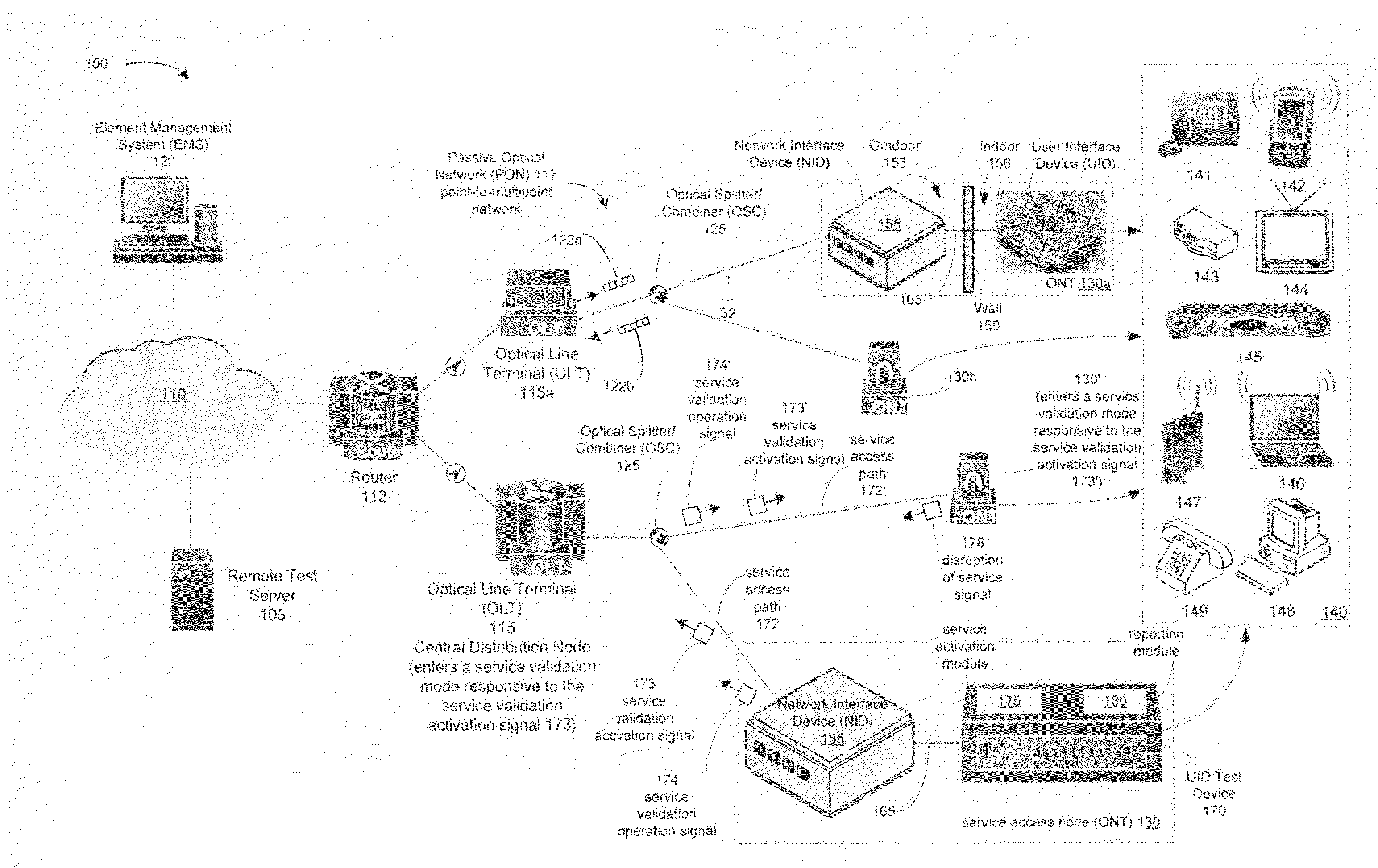

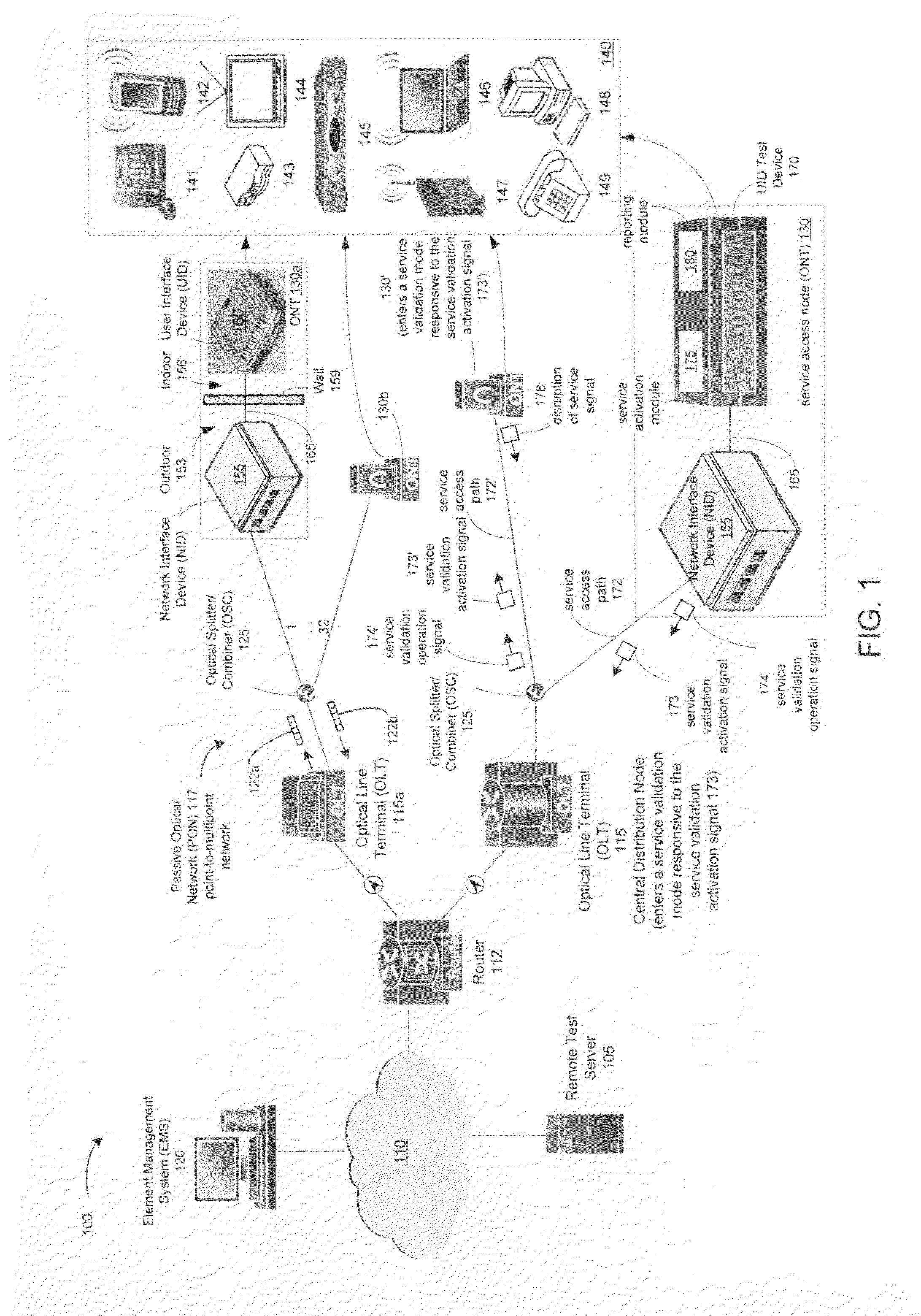

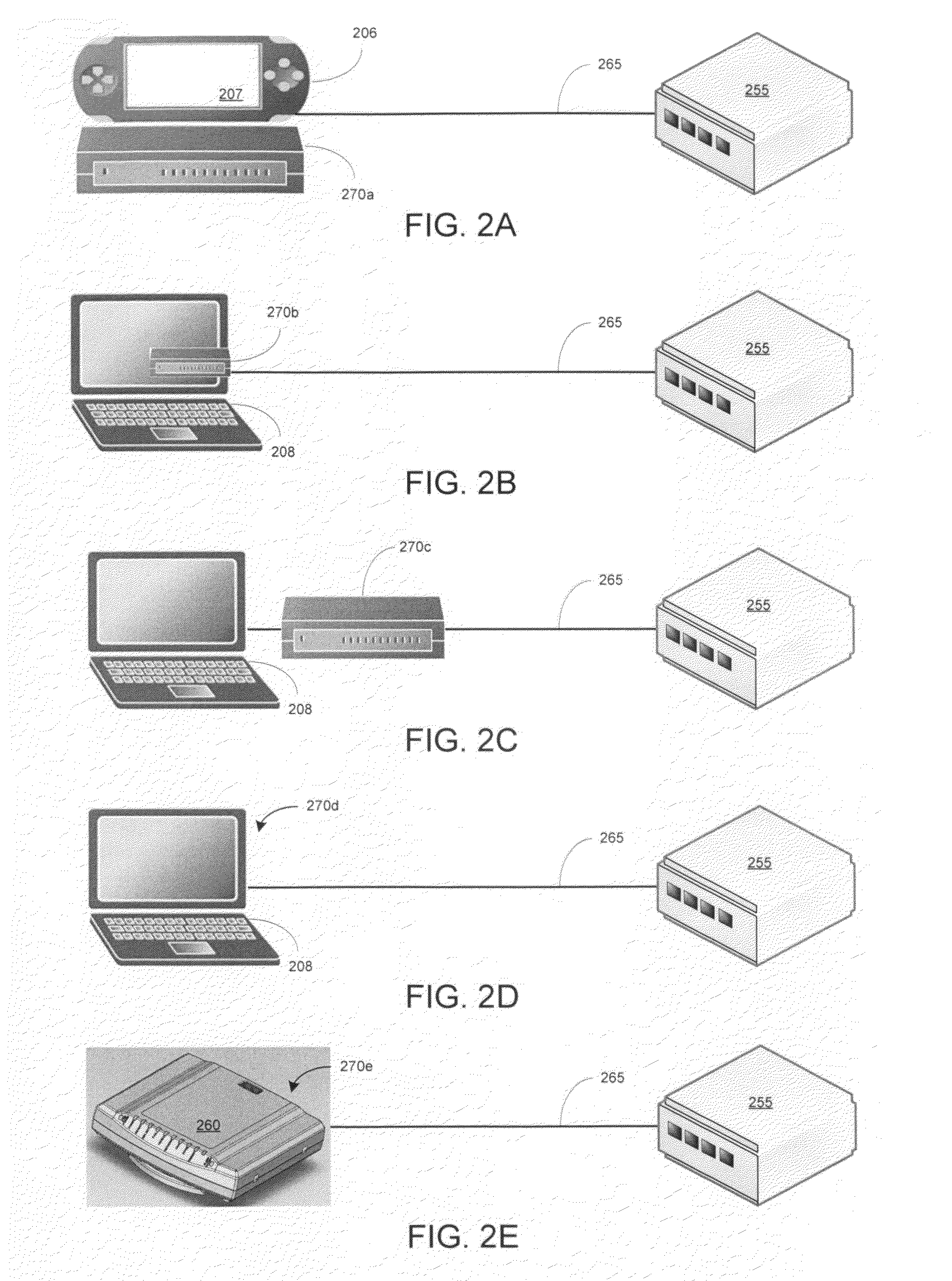

Method and apparatus to support customer premises diagnostics and service simulation via test user interface devices

Because networks, such as Optical Distributed Networks (ODNs), dynamically change over time as more users and services are added, service providers are challenged to test operational robustness following installation of equipment or provisioning of services or upgrades. Example embodiments of the present invention allow testing of various services along a communications path, including software upgrades, throughput tests and simulations, and combinations of simulated scenarios with live customer traffic. The example embodiments allow generation of reports based on the testing of various services so that a technician may correct errors and ensure proper provisioning during equipment installation. Such testing may be useful to detect installation or activation problems encountered when a subscriber activates a service at a later date or adds additional devices. The example embodiments simplify installation and provisioning, saving service providers cost on a per installation or provisioning basis.

Owner:TELLABS VIENNA

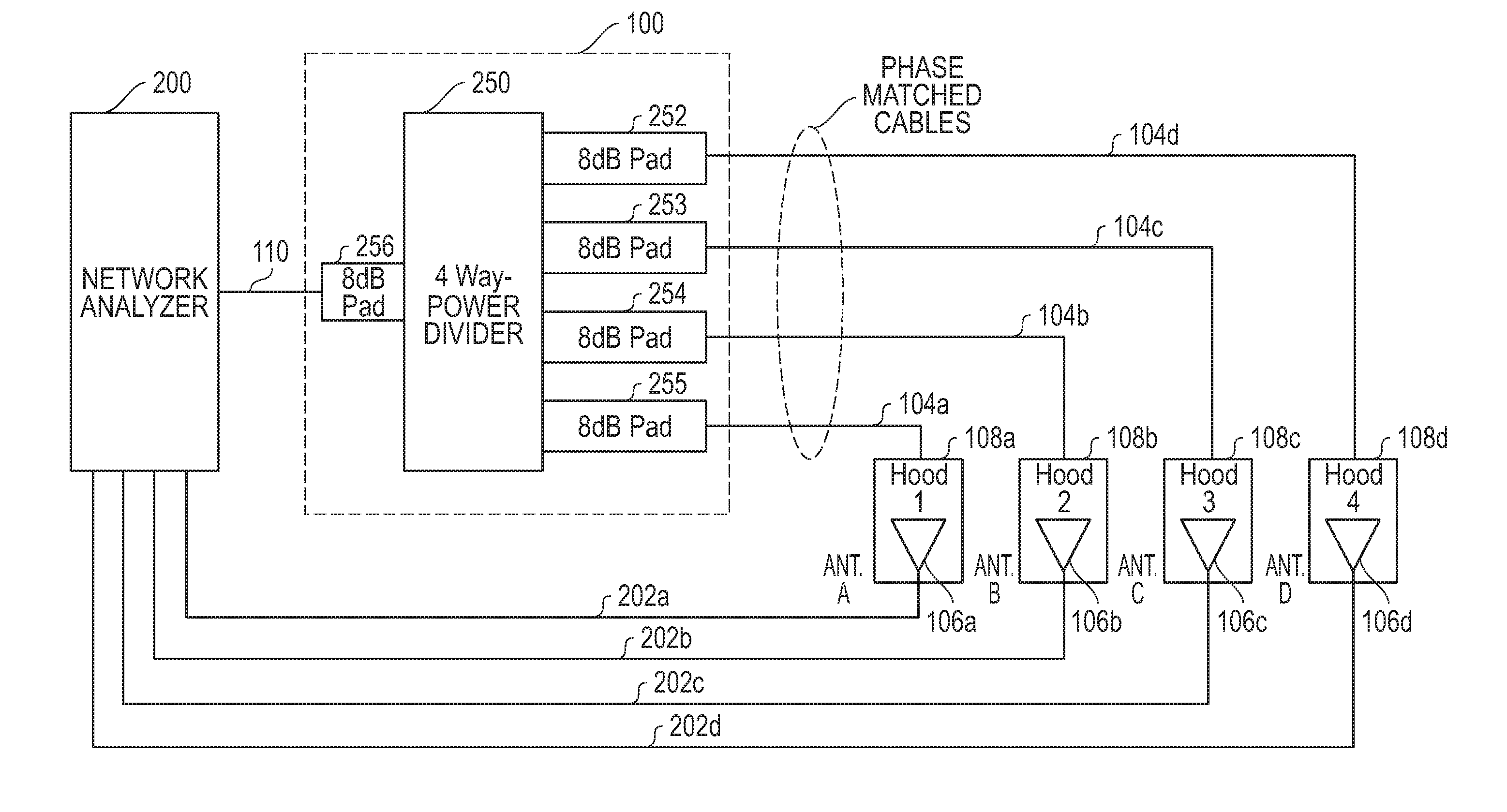

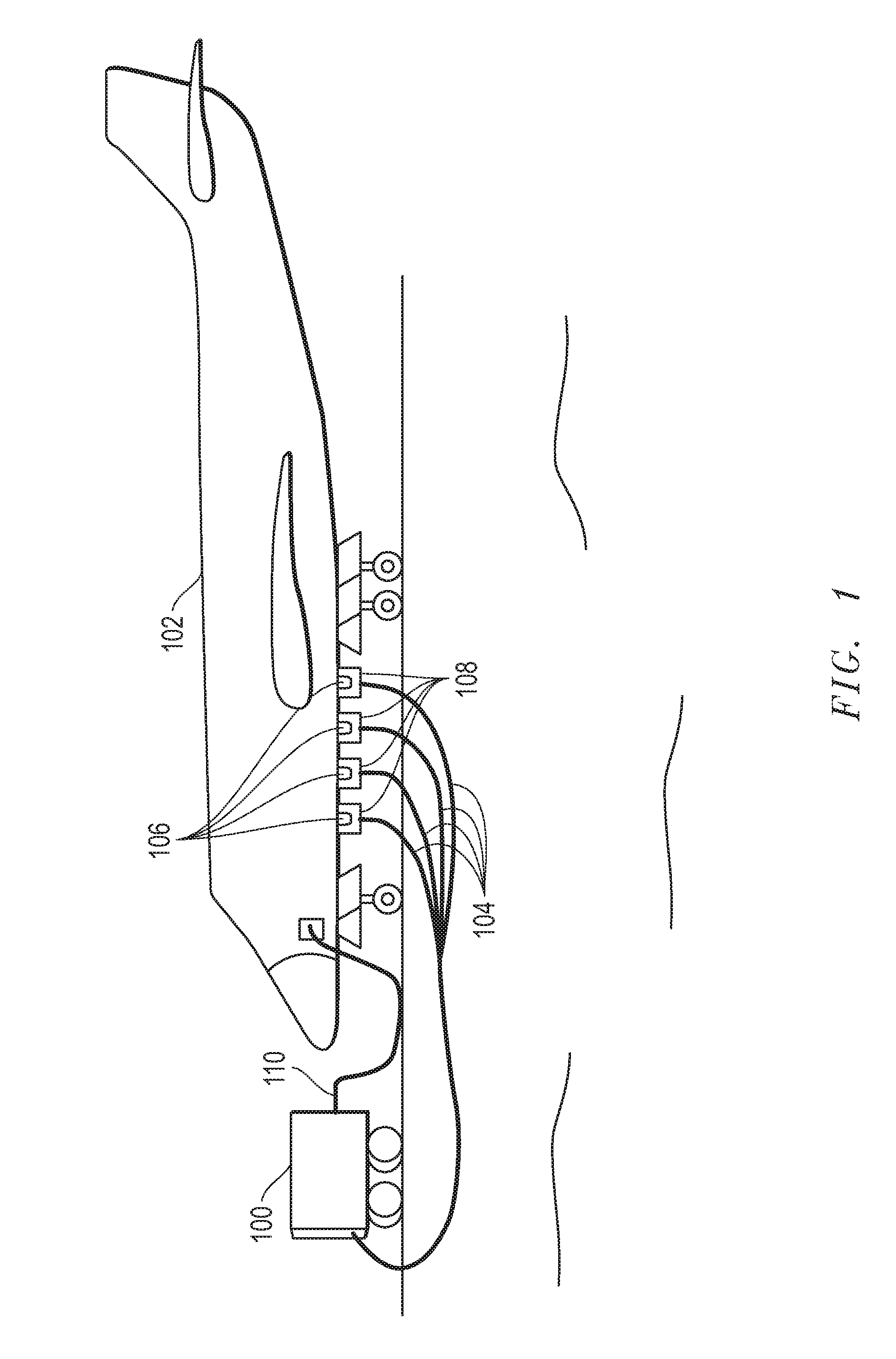

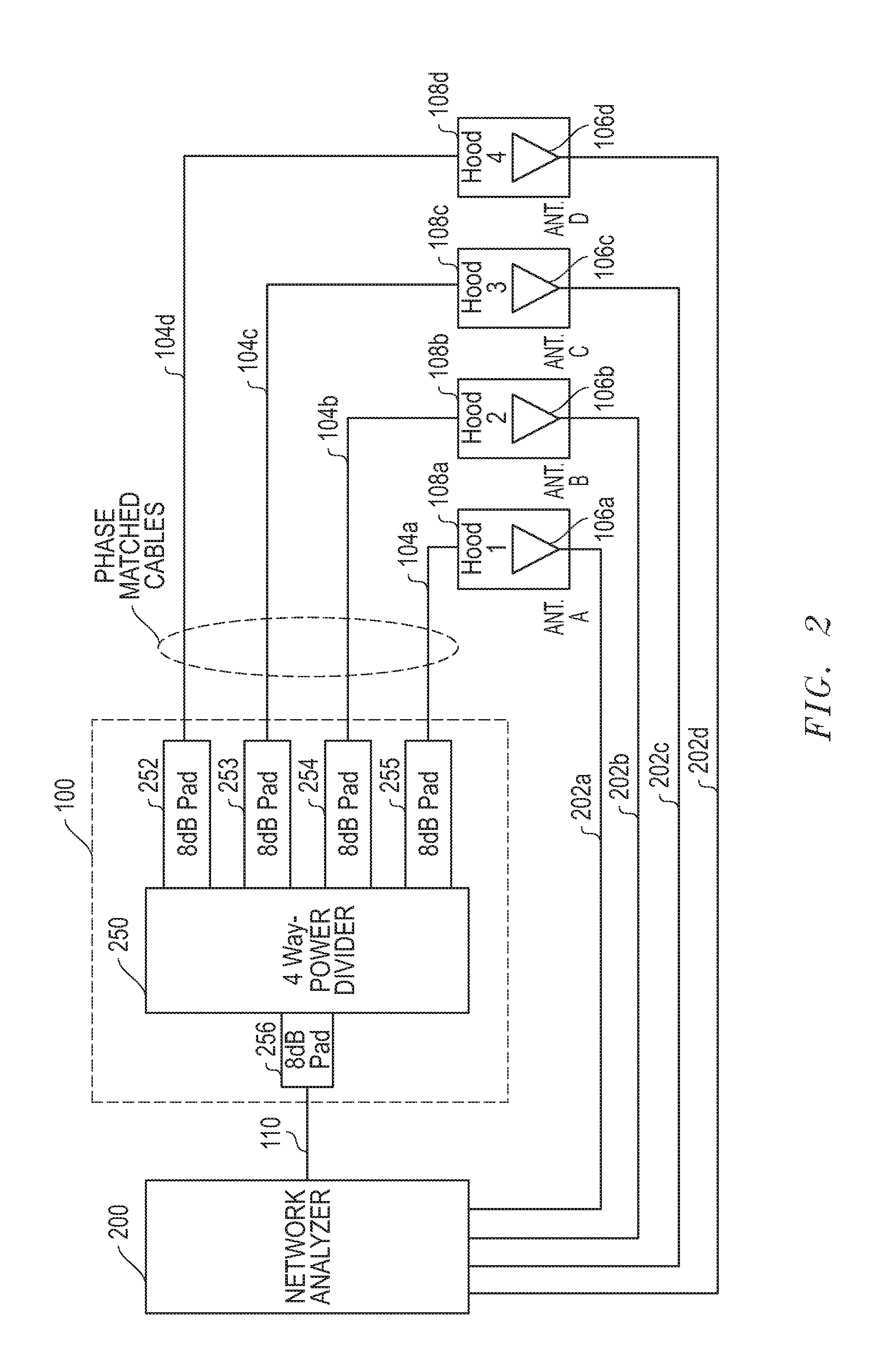

Antenna testing enclosures and methods for testing antenna systems therewith

InactiveUS20130154887A1Improve noiseImprove test accuracyElectromagentic field characteristicsAntenna radiation diagramsEngineeringElectron

Antenna enclosure apparatus are provided that may be used to verify the signal path integrity, amplitude and / or phase of a single antenna or multiple antennas of direction finding (DF) antenna array and associated electronics without interference of external signals such as ground interference signals present when an aircraft-based antenna is tested on the ground. An individual antenna test enclosure may in one embodiment be provided as an antenna hood having a cavity dimensioned for internally receiving an antenna, such as an aircraft external blade antenna. The cavity of the antenna enclosure may be lined with a RF absorbing material inside the enclosure to allow for RF path testing with substantially no “ringing”, so that accurate phase and gain testing of a received antenna and its RF signal path may be accomplished.

Owner:L 3 COMM INTEGRATED SYST

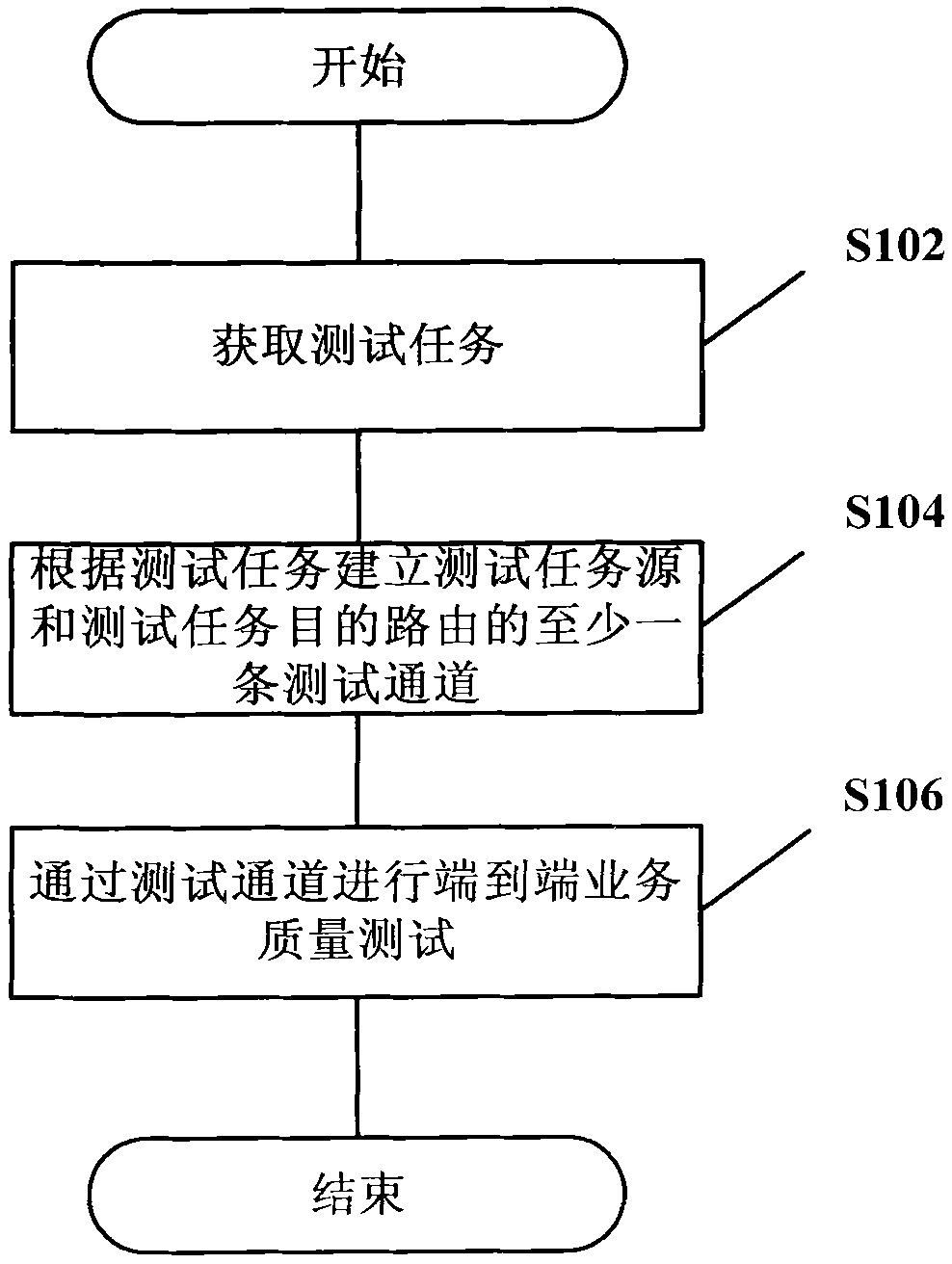

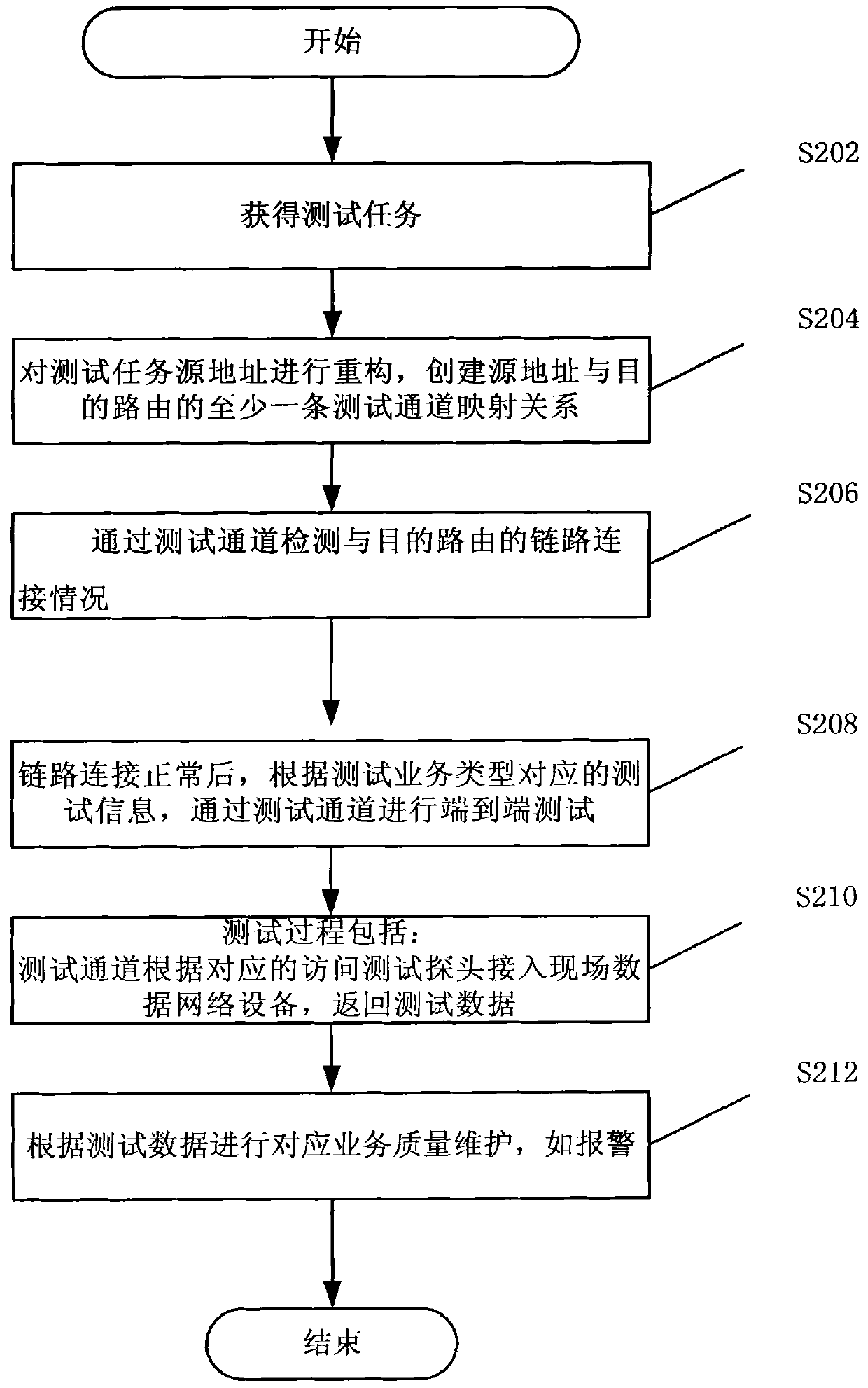

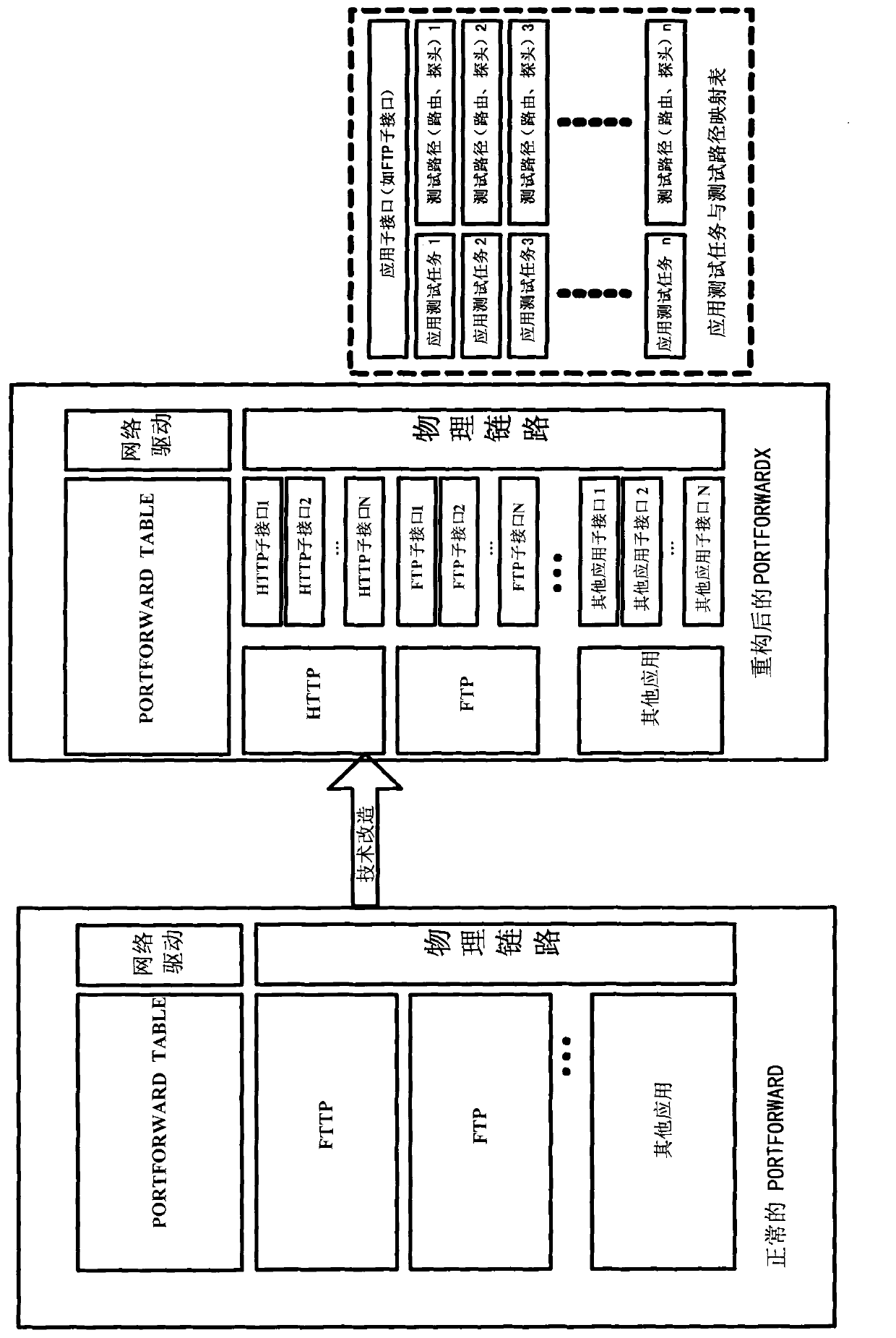

Method, device and system for testing service

InactiveCN102571466ARealize end-to-end business testingSatisfy business qualityData switching networksTest channelInternet business

The invention discloses a method, device and system for testing a service, wherein the method for testing the service comprises the steps of establishing a test task source and at least one application path test channel of a test task target route according to a test task, and performing end-to-end service quality test by simulating a test channel accessed to a customer network environment. By simulating the customer network environment to access to a conventional network data device, the method, device and system for testing the service, disclosed by the invention, have the advantages of realizing customer perception oriented end-to-end service test, satisfying end-to-end Internet service quality required by a test customer and solving end-to-end automatic test tasks of the Internet, which cannot be realized in the prior art at a relatively low cost.

Owner:CHINA MOBILE GROUP ANHUI

Common optical-path testing of high-numerical-aperture wavefronts

ActiveUS7057737B2Improve polarizationIncreased Polarization PurityOptical measurementsInterferometersWavefrontPhase shifted

Owner:ONTO INNOVATION INC

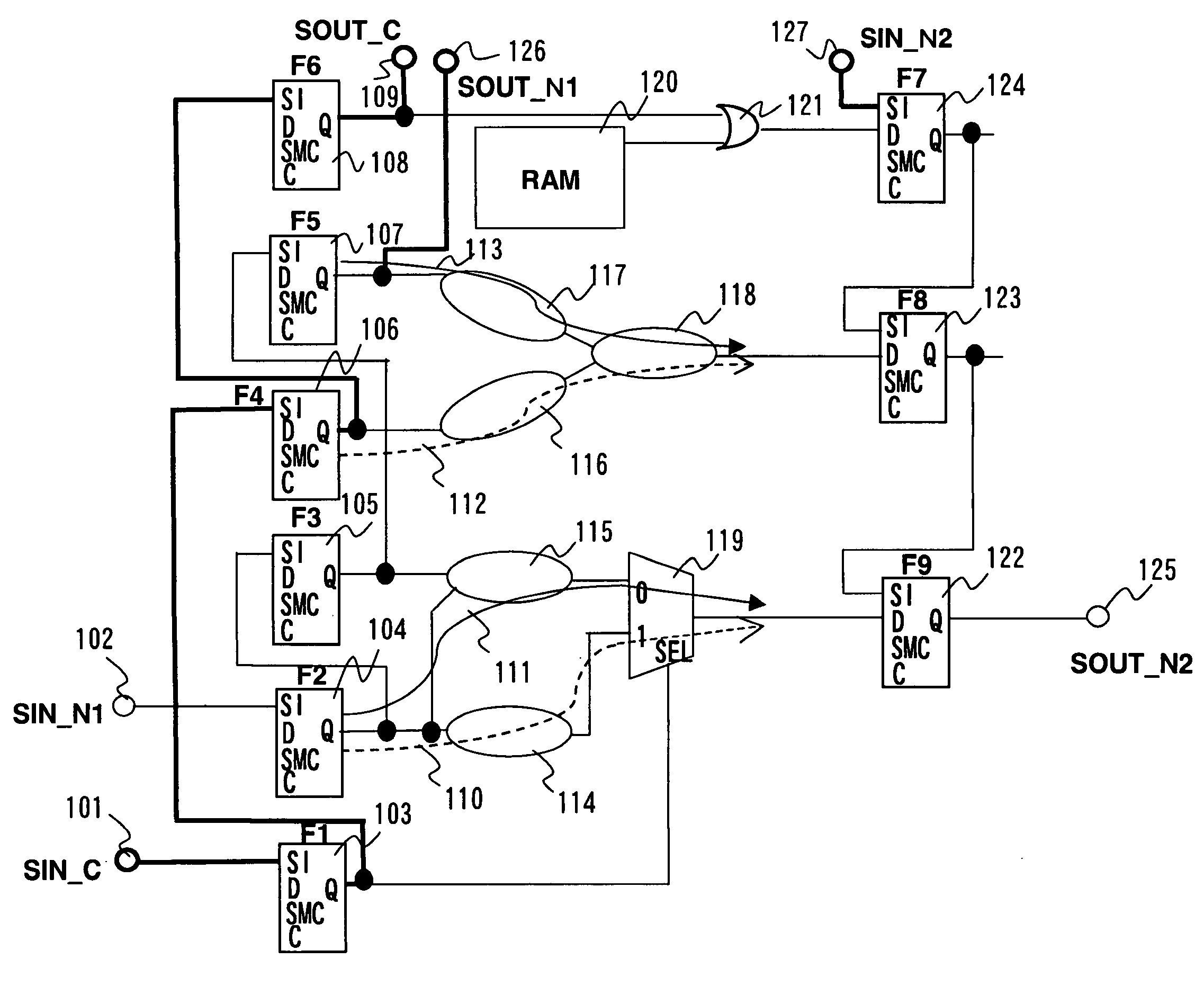

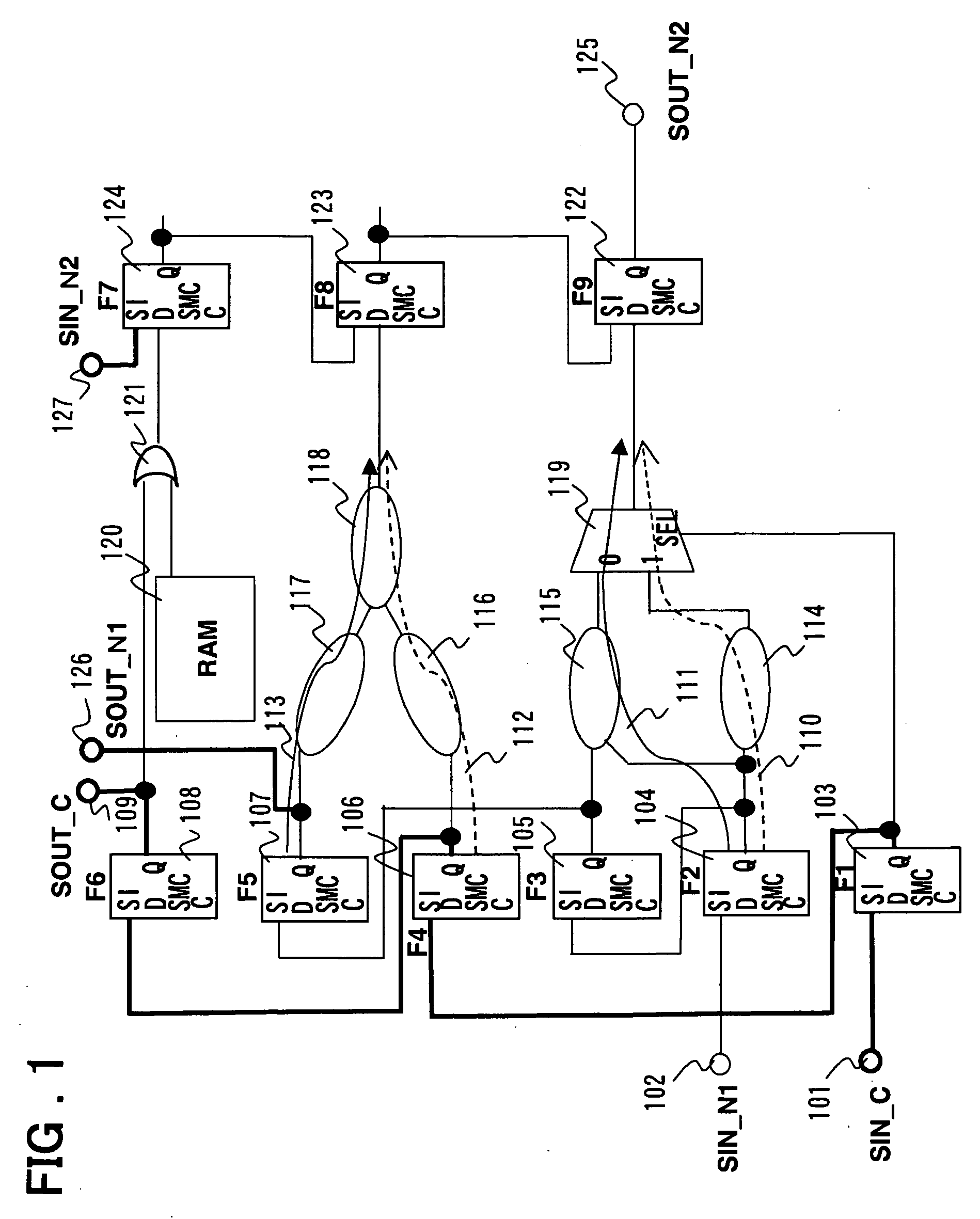

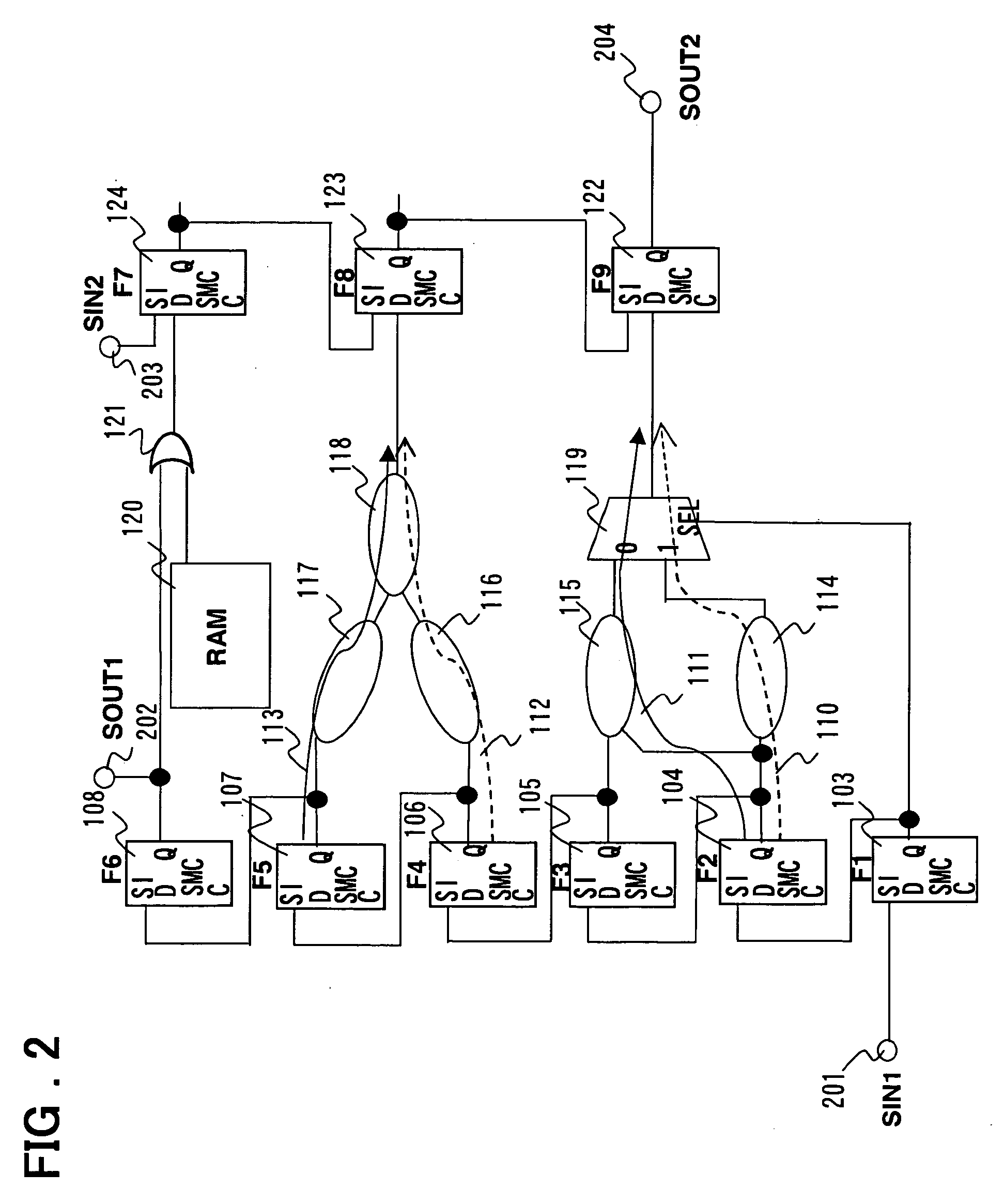

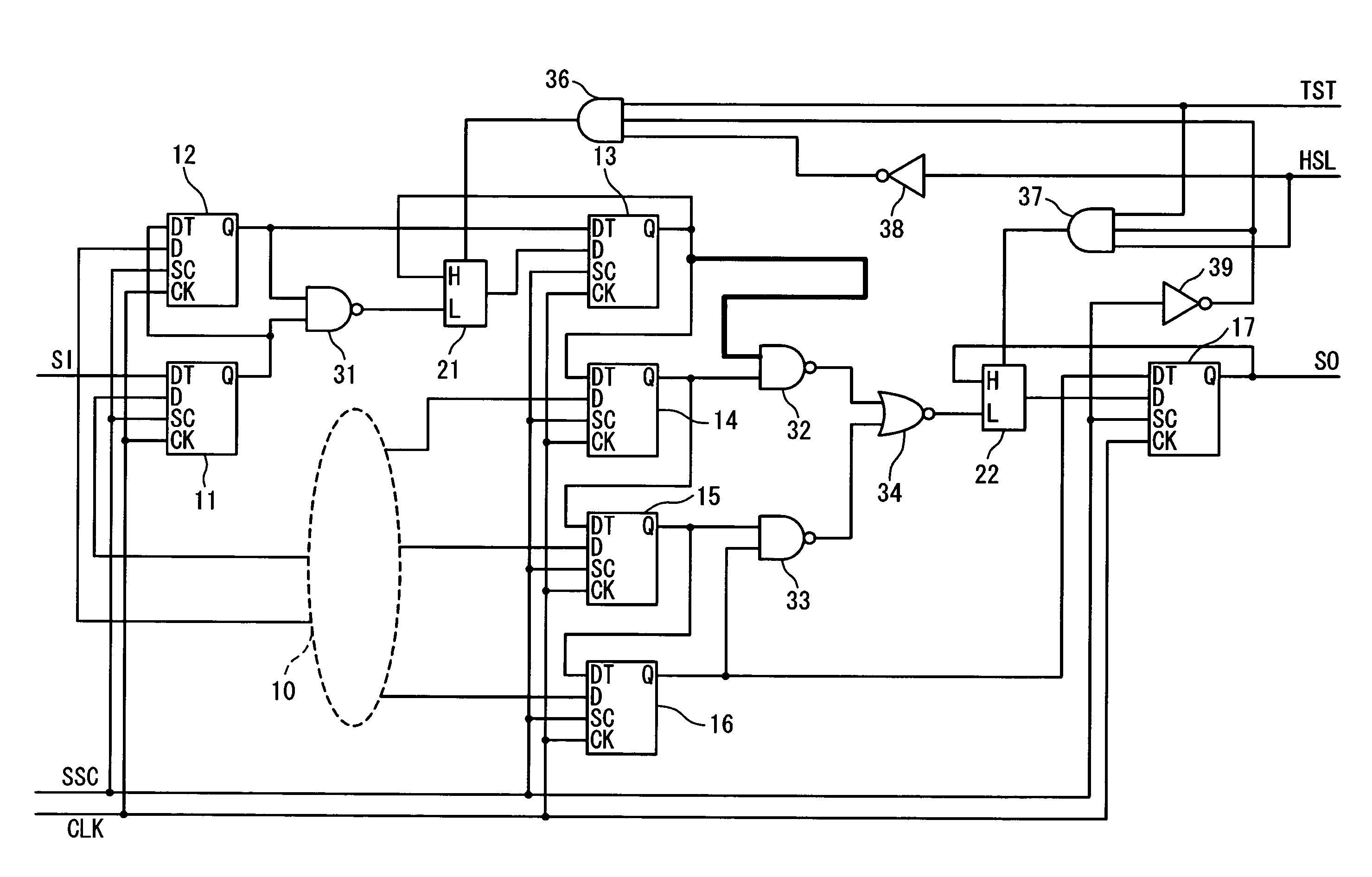

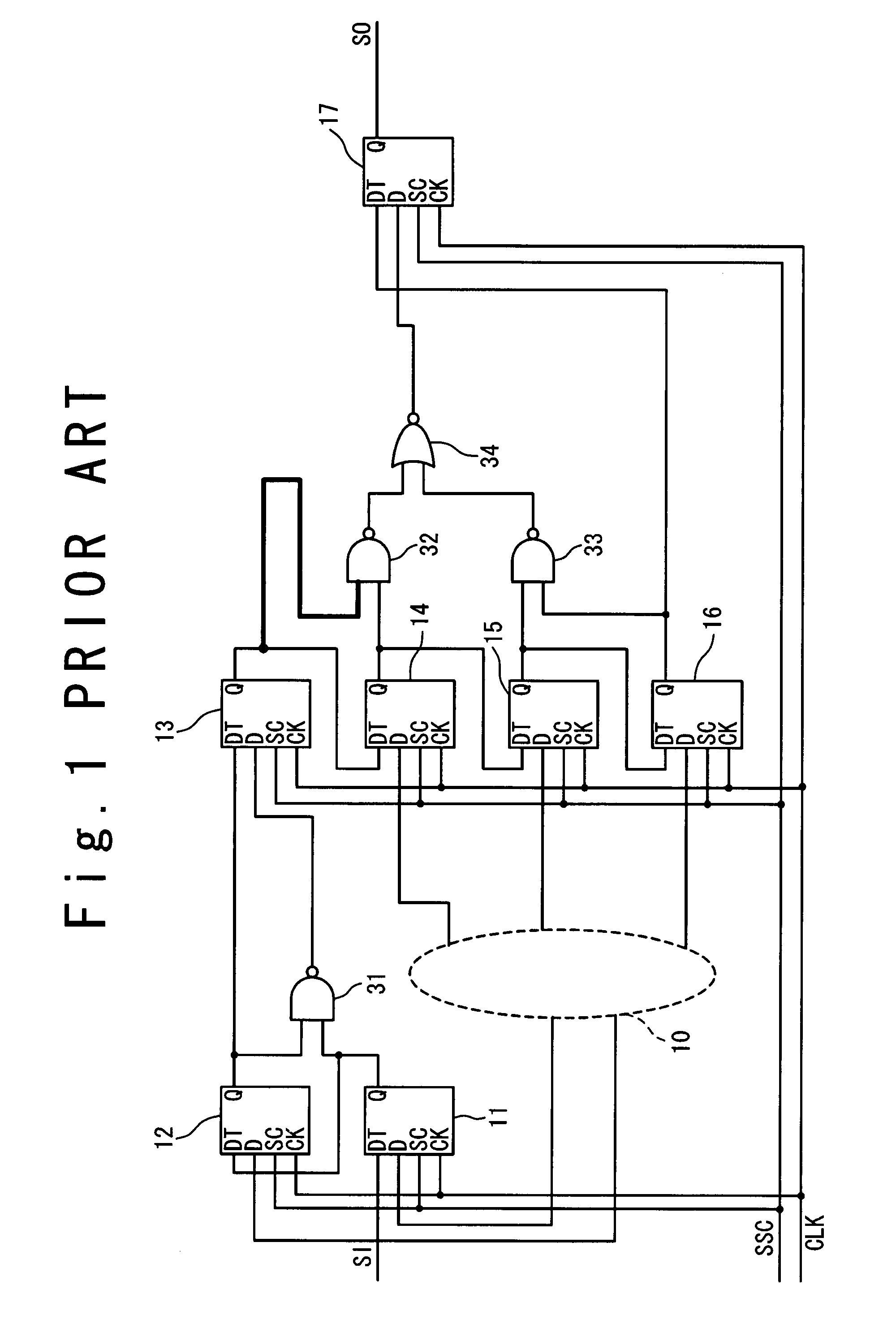

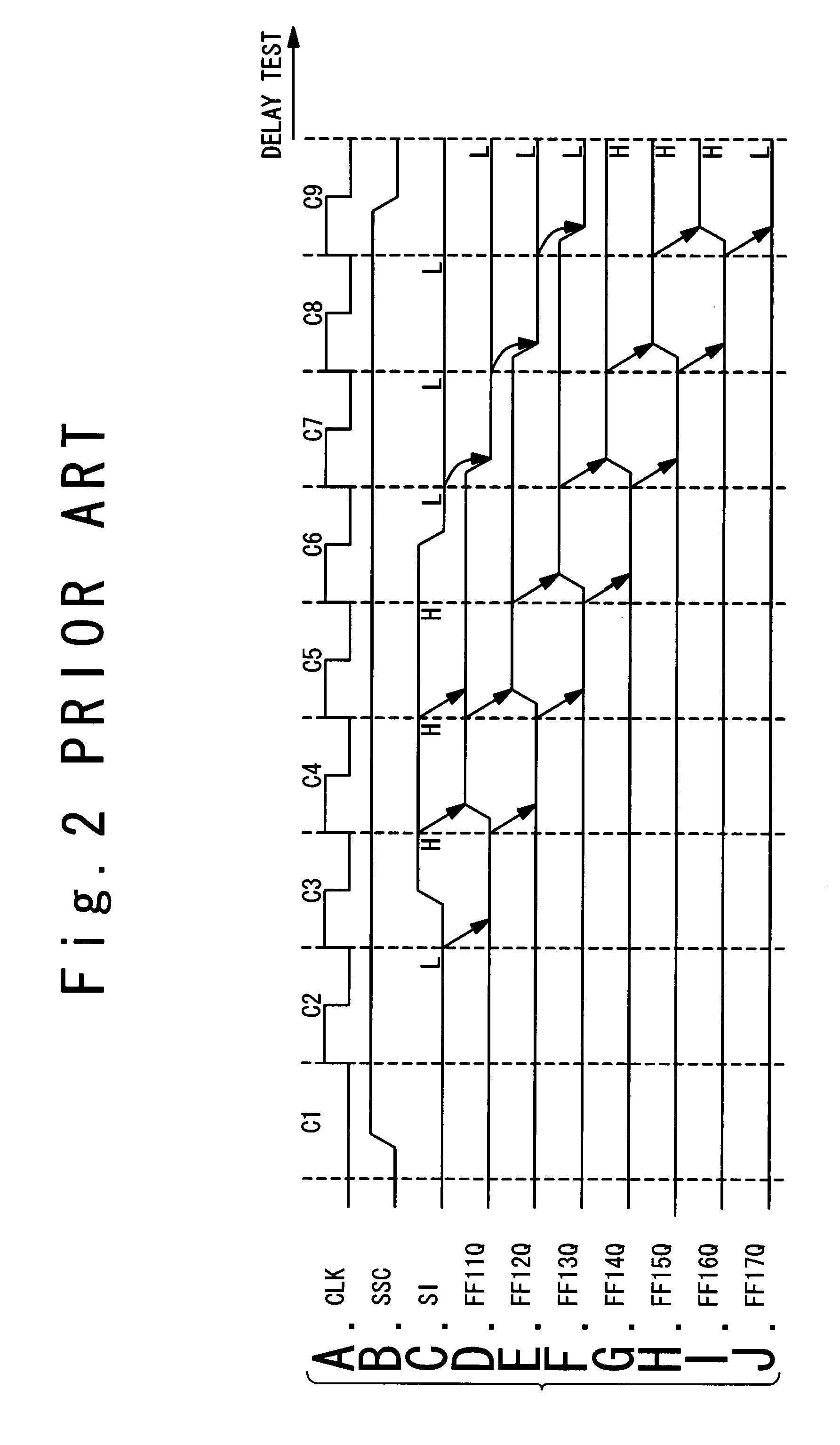

Semiconductor integrated circuit device and test method thereof

InactiveUS20050235184A1Test accurateHinders its propagationDigital circuit testingDetecting faulty computer hardwareControl signalSemiconductor

Disclosed is a semiconductor integrated circuit device using a scan path test in which propagation of an indefinite value to a test target path is inhibited while suppressing an increase in a circuit area, and a test method thereof. When a plurality of flip-flops within a logic circuit is serially connected to form scan chains and a scan path test is conducted, one or a plurality of flip-flops within the logic circuit are provided as indefinite state control flip-flops for holding values for preventing an indefinite value from propagating through a test target path and being captured by the scan chain on an output side during the test. The indefinite state control flip-flops are serially connected based on a control signal, and constitute a chain of flip-flops, different from the scan chain of other flip-flops. A value serially input from an input terminal is set in the plurality of indefinite state control flip-flops, respectively.

Owner:NEC ELECTRONICS CORP

Methods, Apparatuses and Systems Facilitating Determination of Network Path Metrics

InactiveUS20090016335A1Easy to testReducing perceived intrusivenessError detection/correctionData switching by path configurationThe InternetComputer science

Methods, apparatuses and systems relating to the control and application of policies for routing data over a computer network, such as the Internet. Some implementations of the invention facilitate the configuration, deployment and / or maintenance of network routing policies. Some implementations of the invention are particularly useful for controlling the routing of data among autonomous systems or organizations. Certain implementations allow for dynamic modification of routing policy based on such factors as current Internet performance load sharing, user-defined parameters, and time of day. In one embodiment, the present invention provides methods, apparatuses and systems implementing enhanced network path testing methodologies that enhance the efficiency of processes associated with testing of a network path, while reducing the perceived intrusiveness of test packets associated with such metrics tests.

Owner:TRANSACTION NETWORK SERVICES

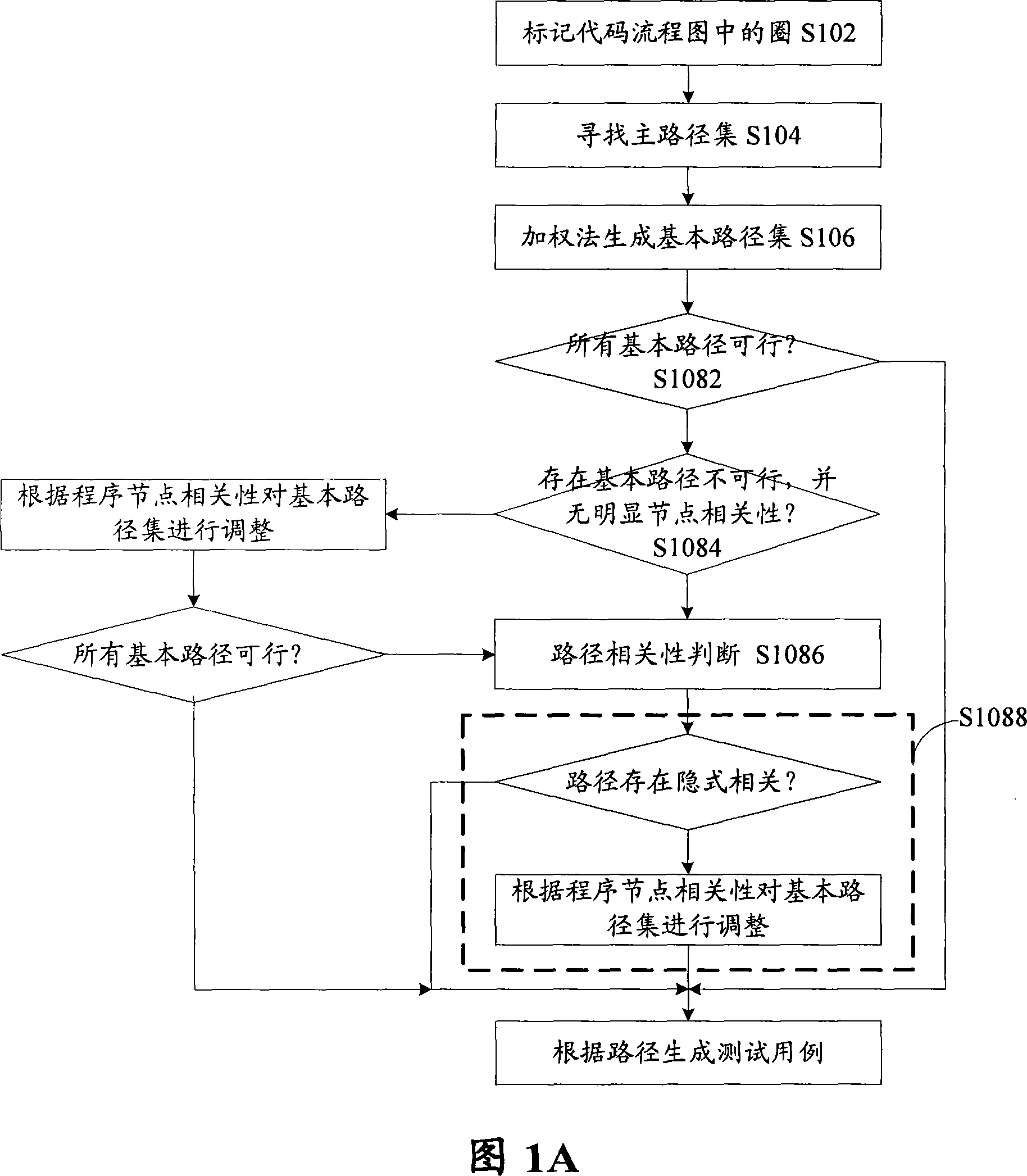

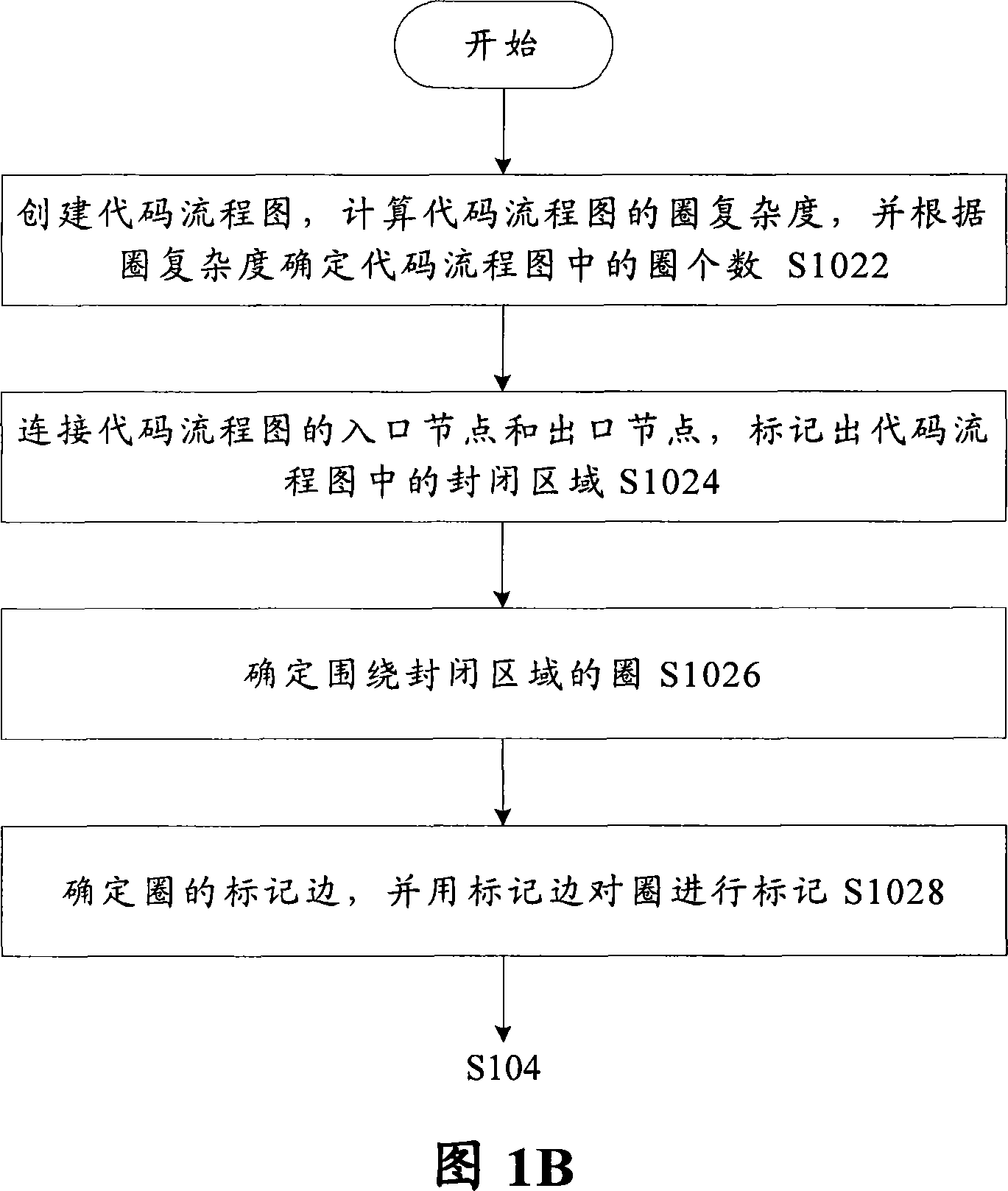

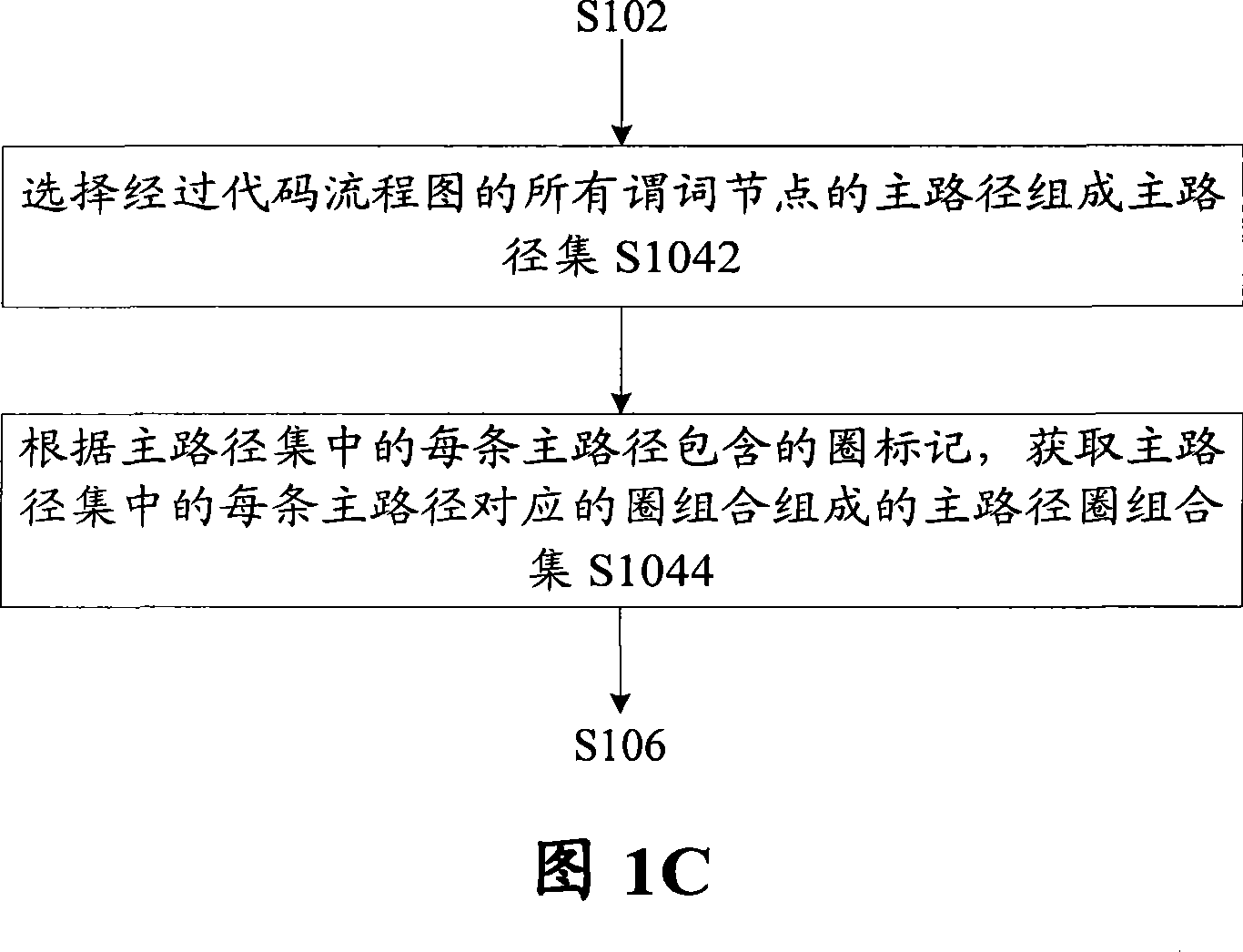

Method for generating examples of white-box path test

InactiveCN101075208AGuaranteed test qualityReduce complexitySoftware testing/debuggingSpecific program execution arrangementsTest sampleParallel computing

A method for generating test sample used on path test of blank case includes labeling all circles in code flow drawing, generating master path set formed by at least one branch path passing all circles in code flow drawing, generating basic path set by utilizing master path set through circle-adding means and generating test sample according to feasible conditions of each basic path in basic path set.

Owner:ZTE CORP

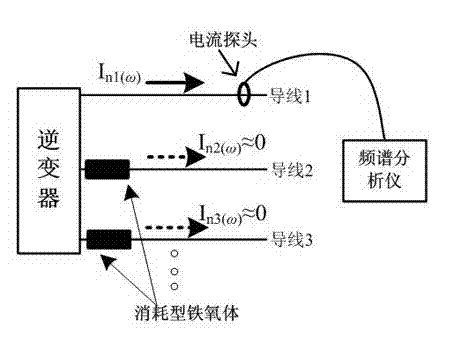

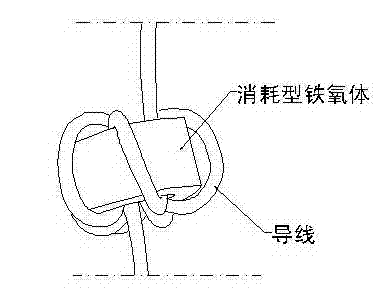

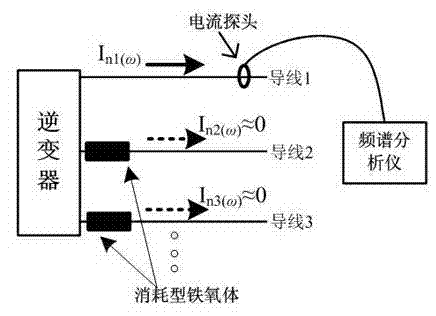

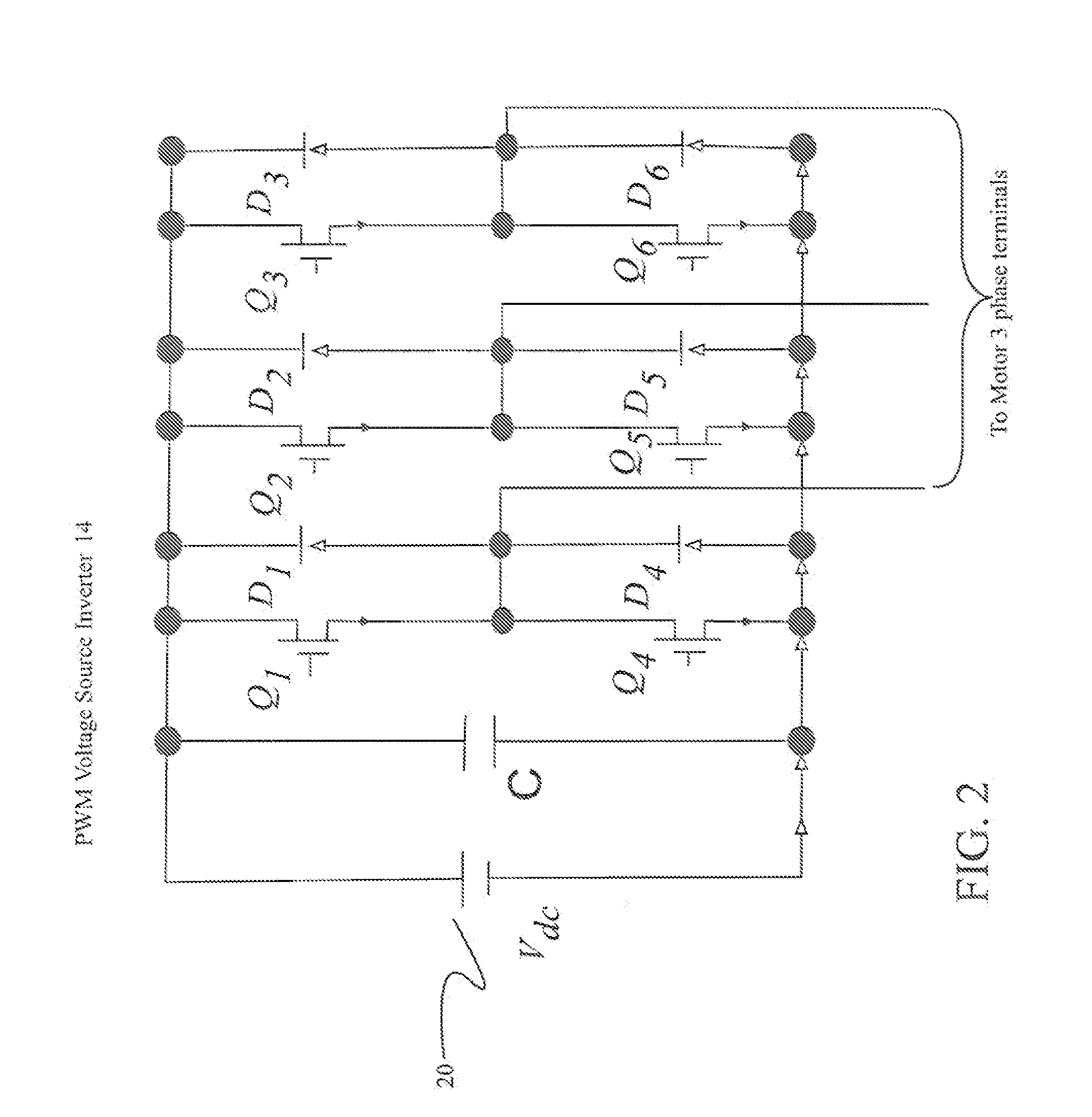

Method for testing electromagnetic interference propagation path of motor drive system of pure electric vehicle

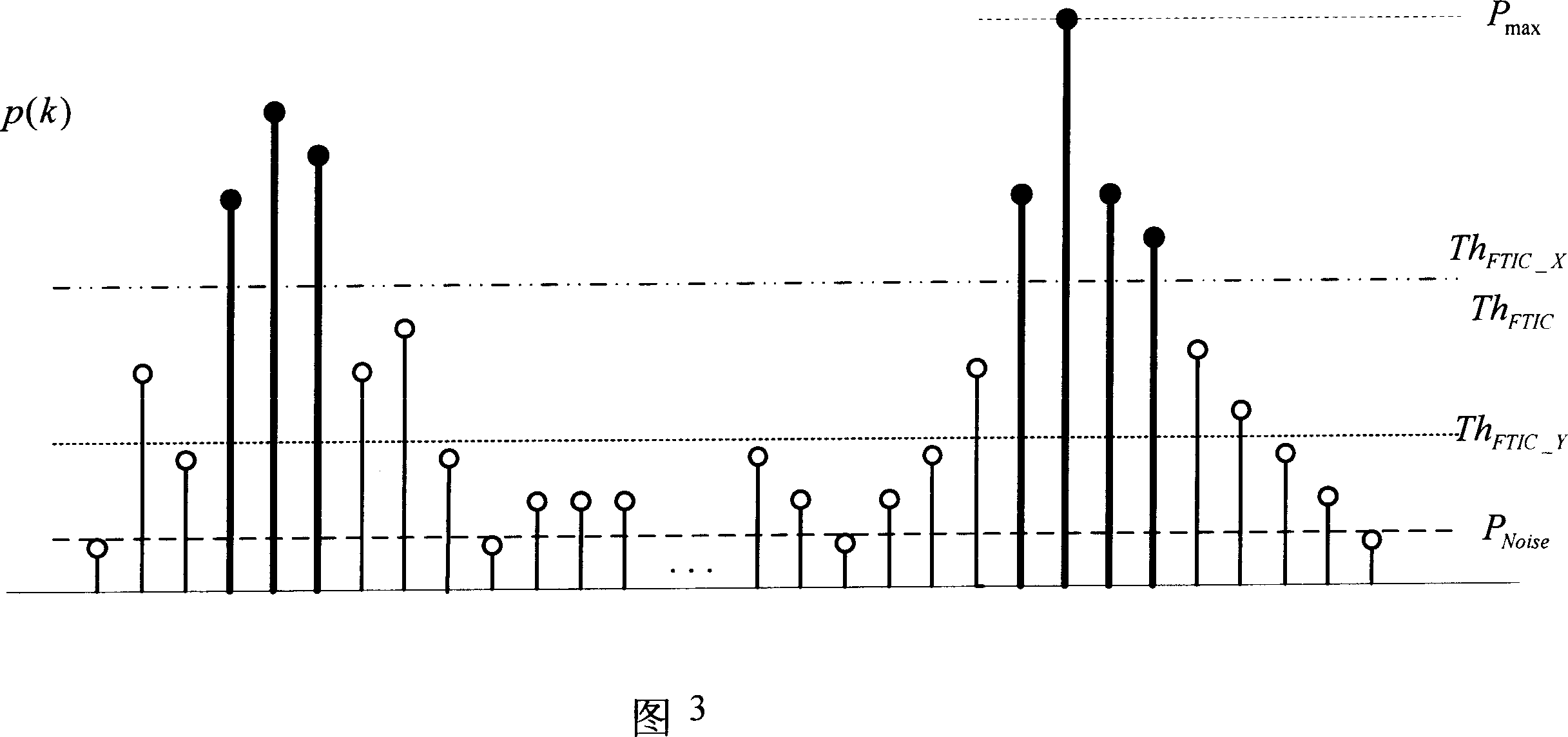

InactiveCN102313851AImprove compatibilityEasy to rectifyElectrical testingElectromagentic field characteristicsFrequency spectrumMotor drive

The invention discloses a method for testing an electromagnetic interference propagation path of a motor drive system of a pure electric vehicle. The method comprises the steps of platform building, lead wire numbering, frequency spectrum testing, comparing and analyzing and the like. By the method, the main propagation path of the electromagnetic interface in the system can be detected, and the intensity and the frequency band range of the electromagnetic interference on each propagation path can also be detected so as to help the engineering technicians to analyze the electromagnetic interference on the system harness, and direct the technicians to perform good electromagnetic compatibility design and rectification on the motor drive system, thereby improving the electromagnetic compatibility of the overall vehicle. The method disclosed by the invention is simple and easy to operate and has strong universality.

Owner:CHONGQING UNIV

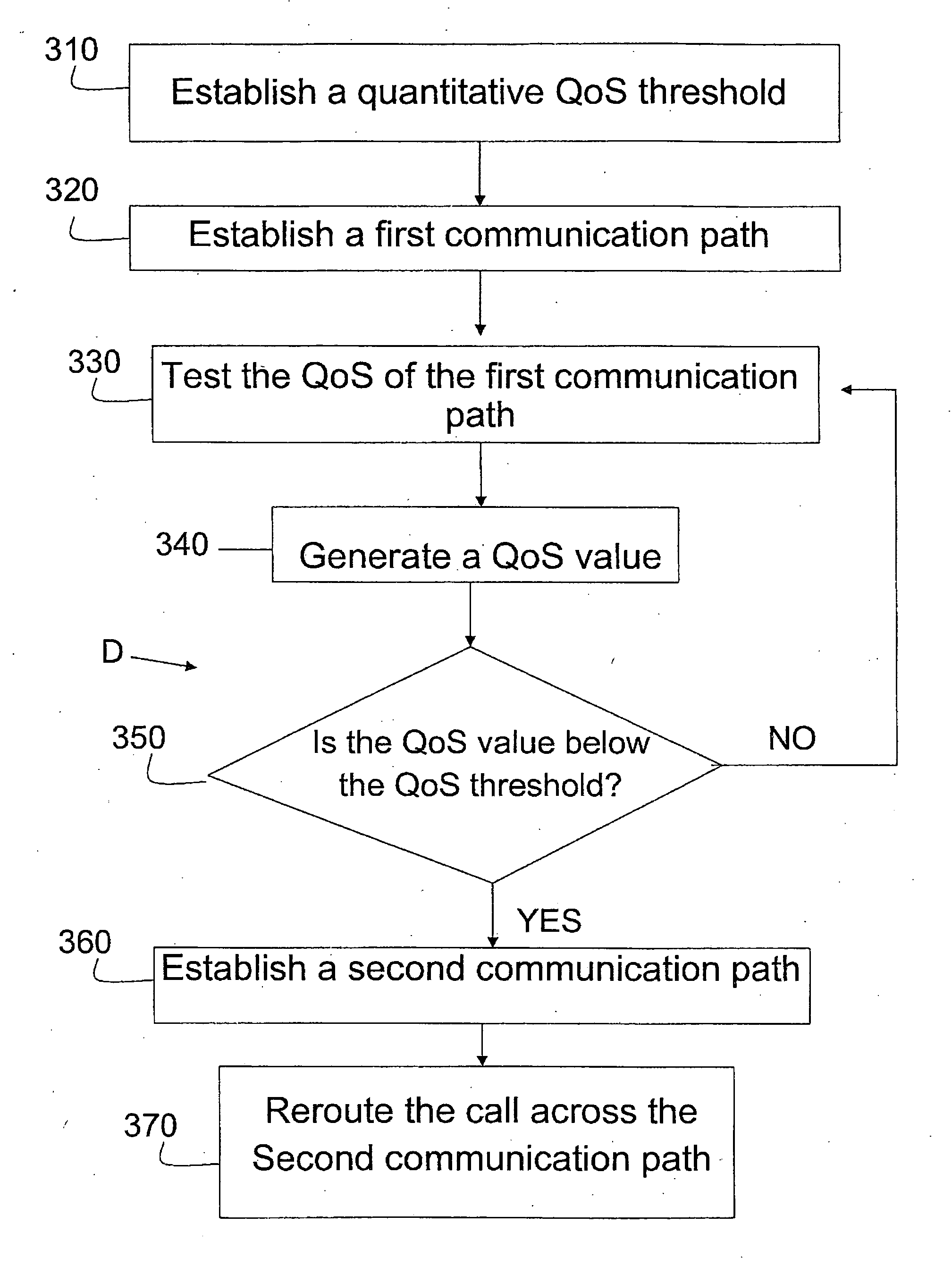

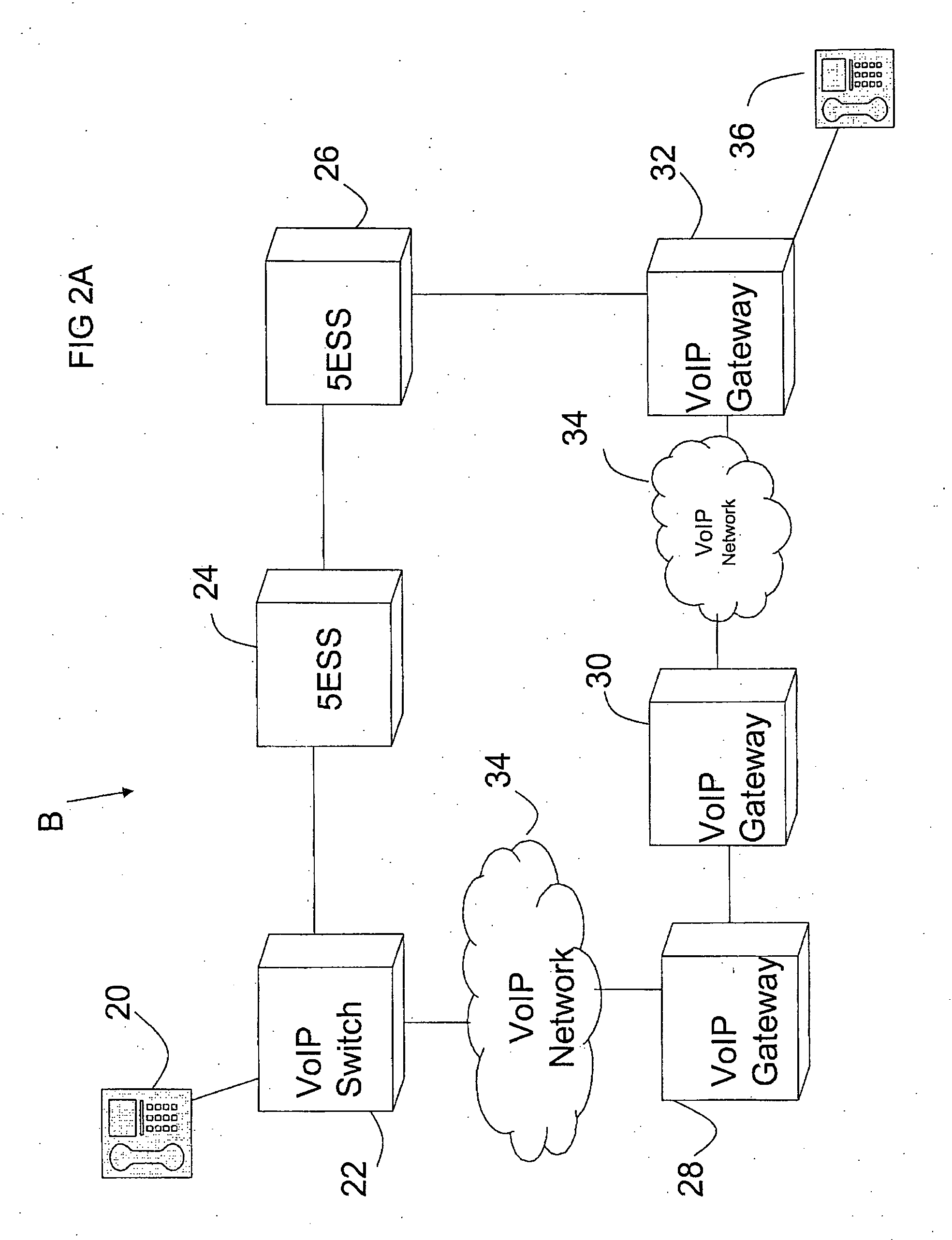

VoIP voice quality remote for switch-to-switch connections

A method to reroute a call with a first and second termination point based upon Quality of Service (QoS) is disclosed. The method comprises establishing a quality of service threshold, connecting a first communication path between the two termination points through the network elements, testing said quality of service along said first communication path and generating a quantitative value based at least in part on said quality of service. The method continues with establishing a second communication path between the network elements if the quantitative value is not up to the level of said quantitative quality of service threshold; and rerouting said data transmission through the newly established second communication path between the network elements while maintaining said termination points.

Owner:LUCENT TECH INC

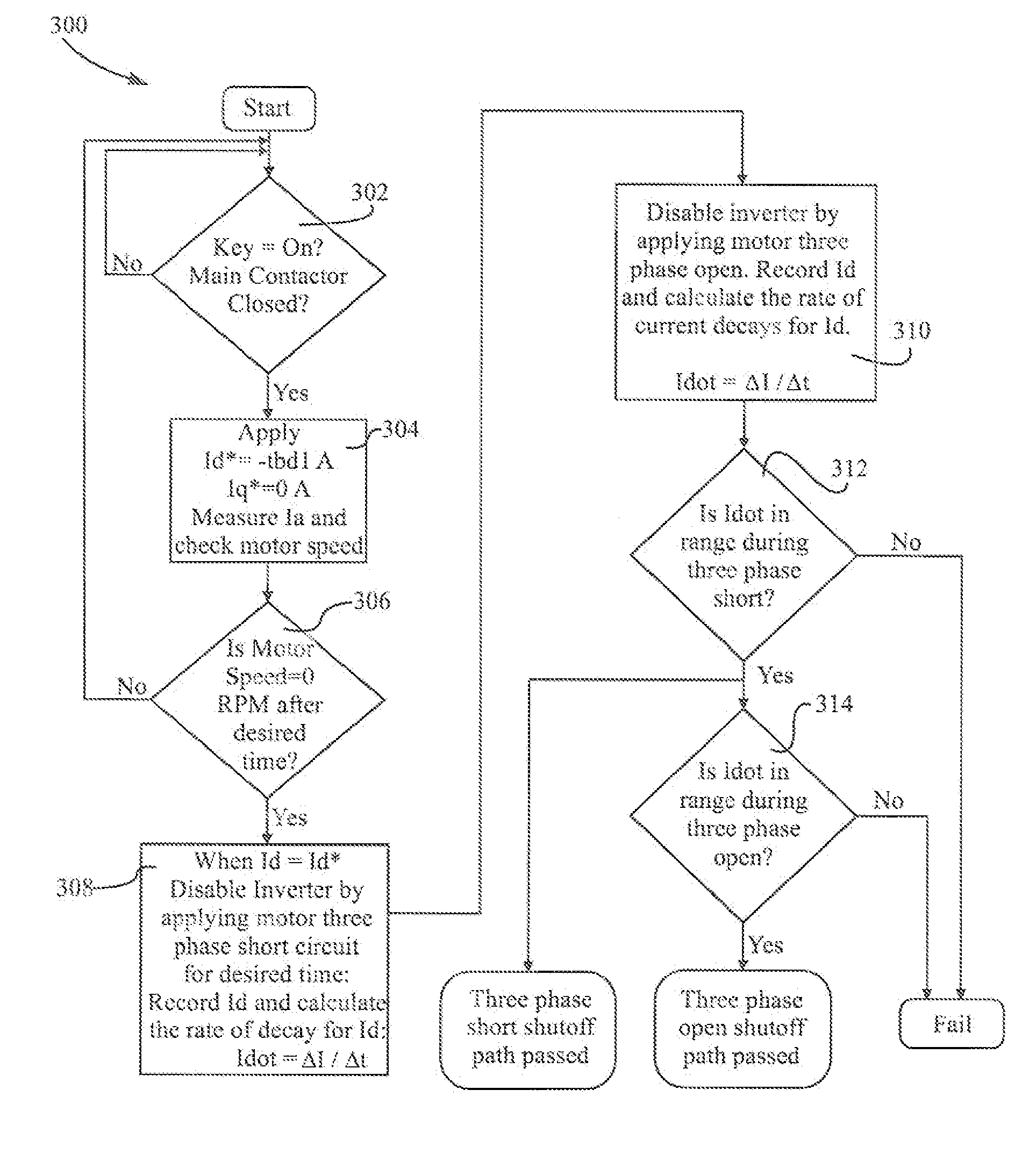

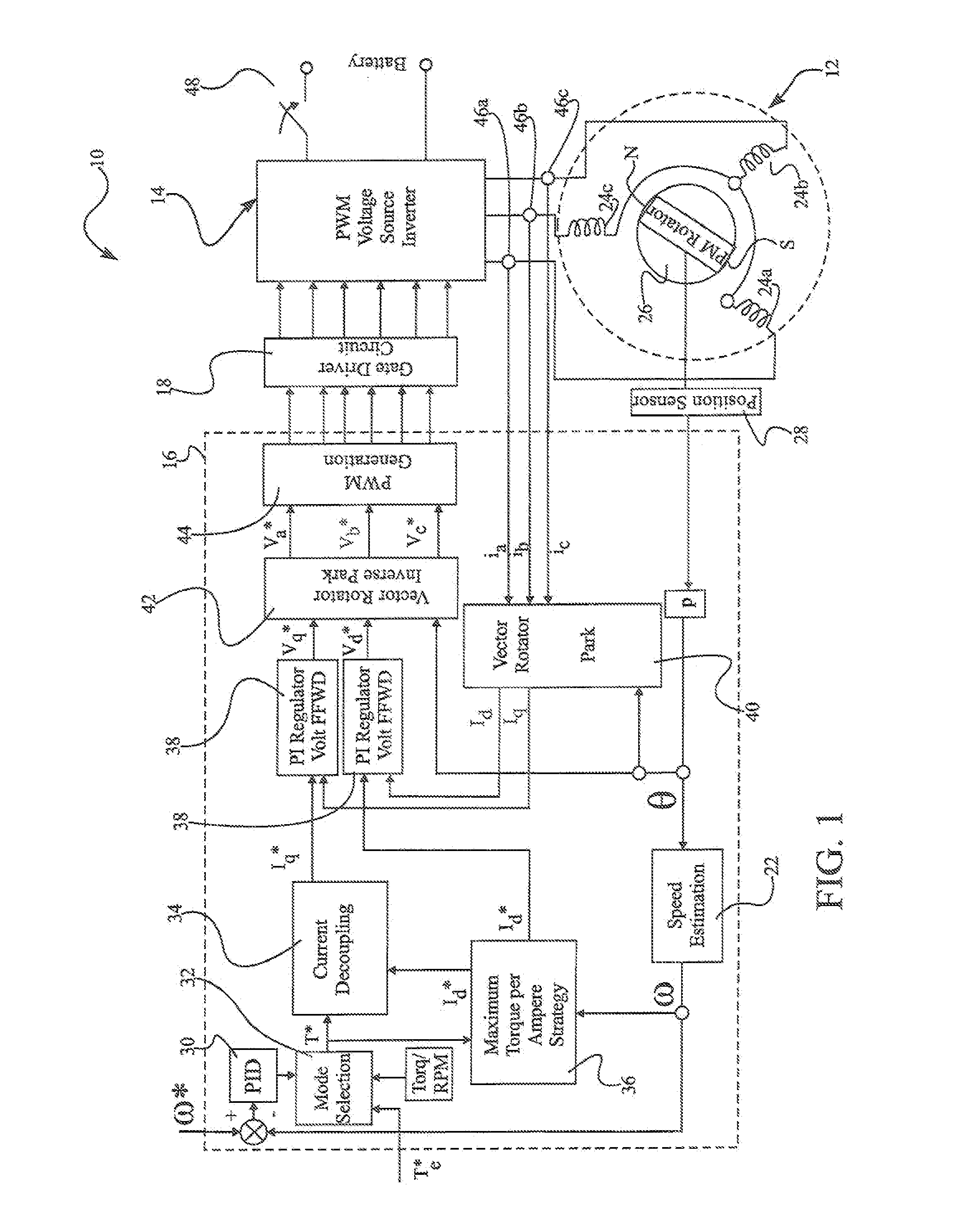

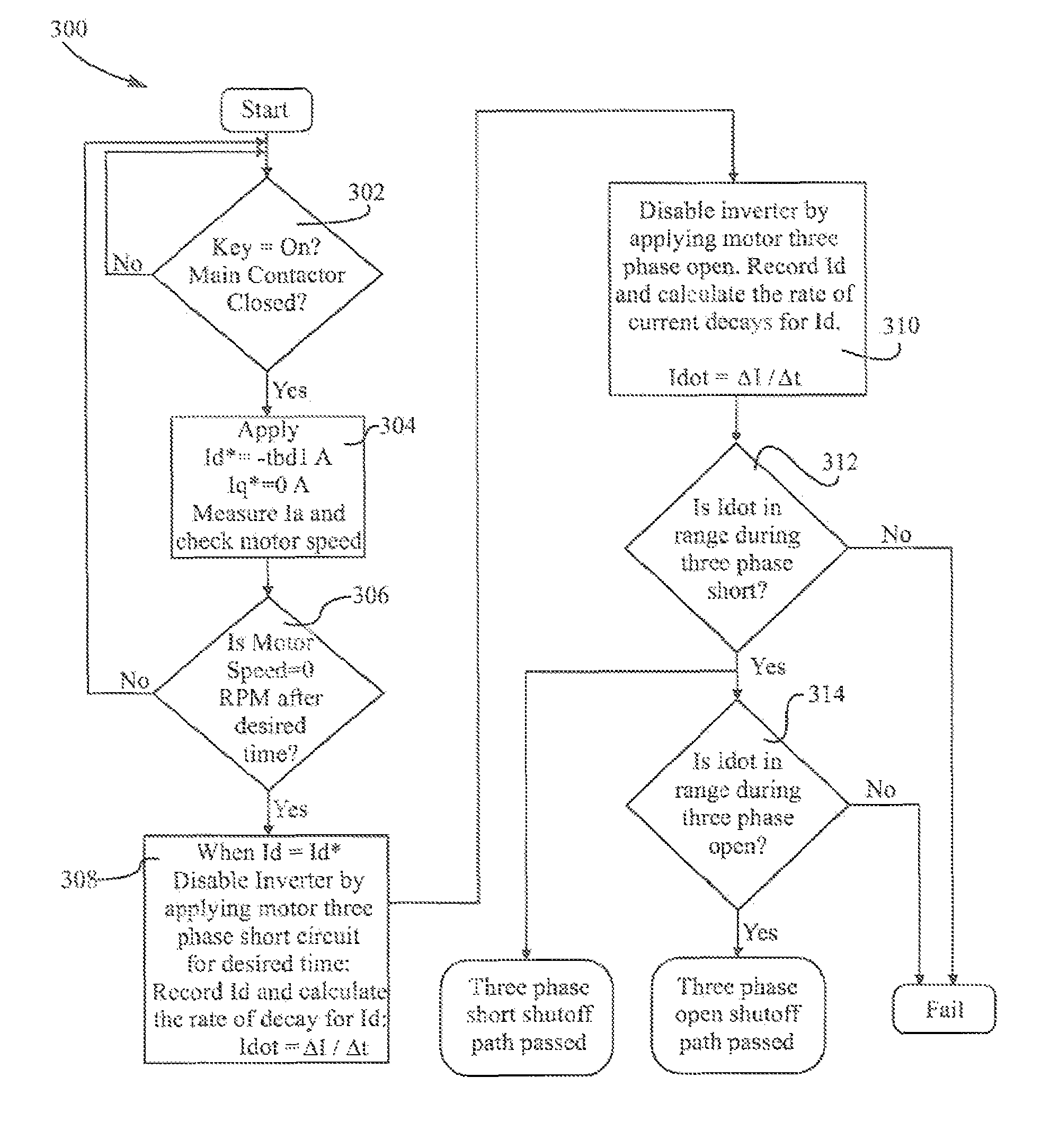

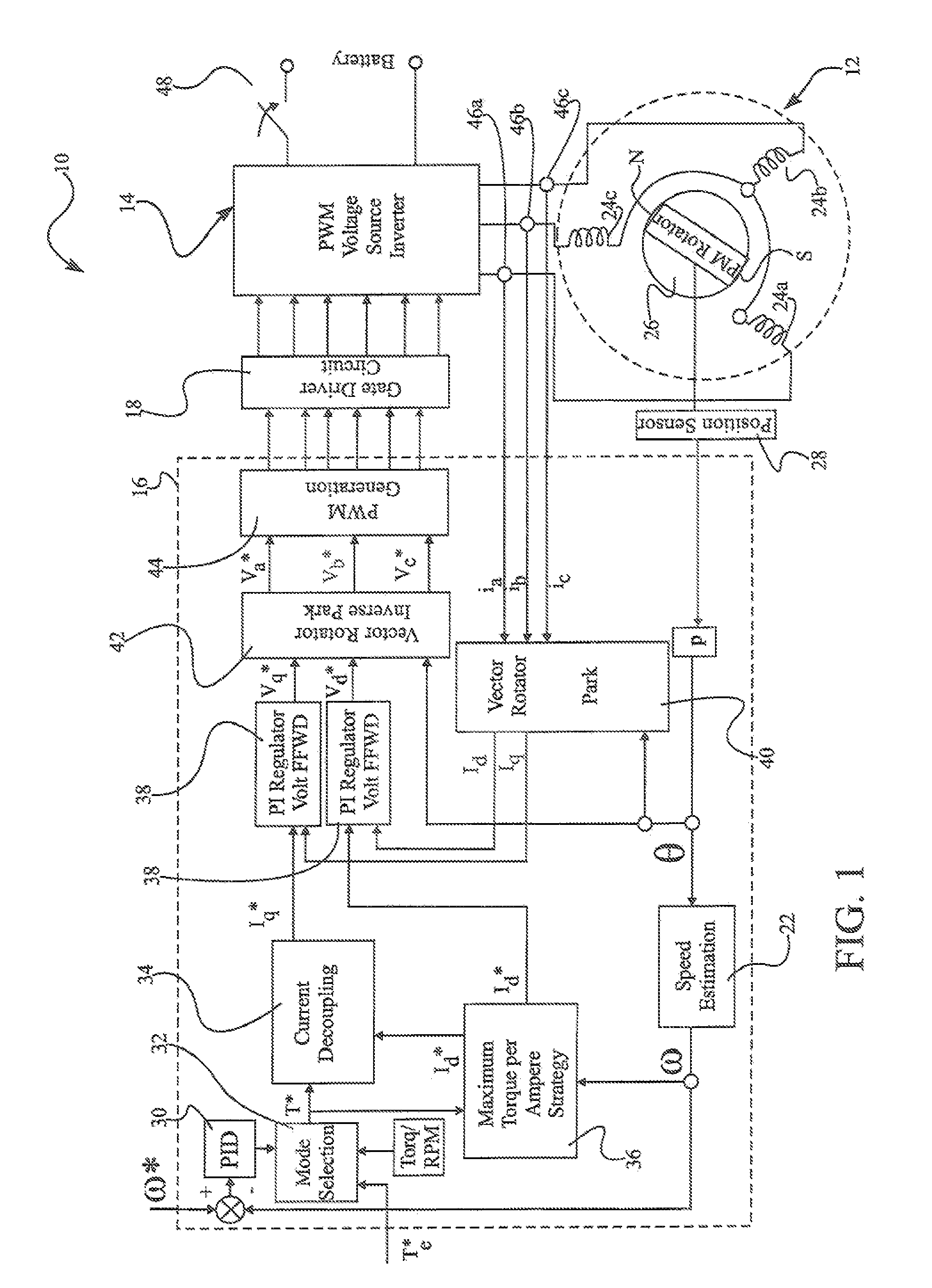

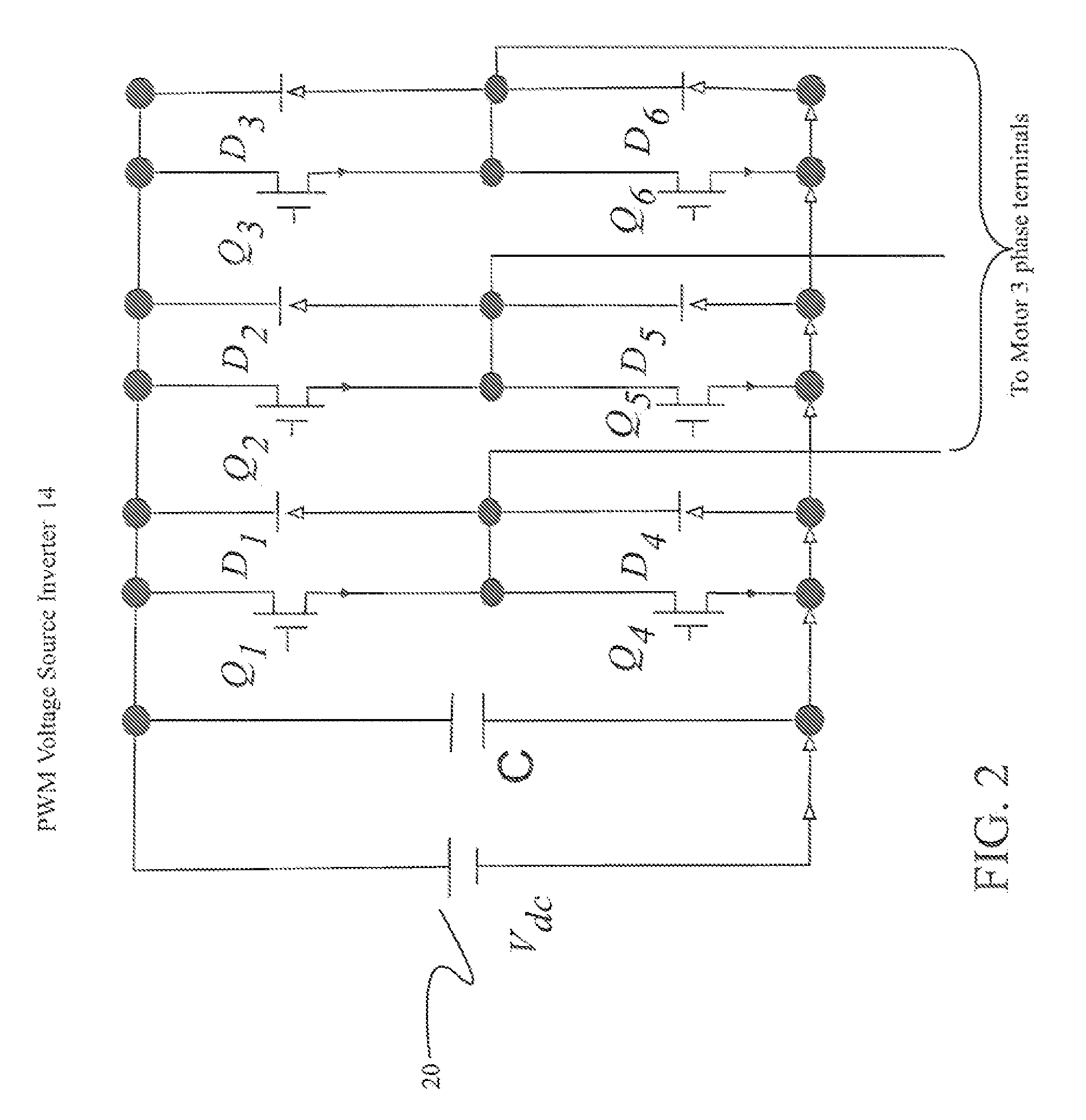

Testing Inverter Driven Electric Motor Shut-Off Path

A method for testing electric motor shut-off including injecting current into an electric motor, applying at least one of a short or an open to the electric motor for a predetermined length of time, calculating the rate of decay of the current and comparing rate of the decay with a predetermined decay criteria. In one implementation, a predefined sequence of opening and short circuiting the electric motor is used, and the shut-off path tests for the motor three phases can be verified with one test.

Owner:GM GLOBAL TECH OPERATIONS LLC +3

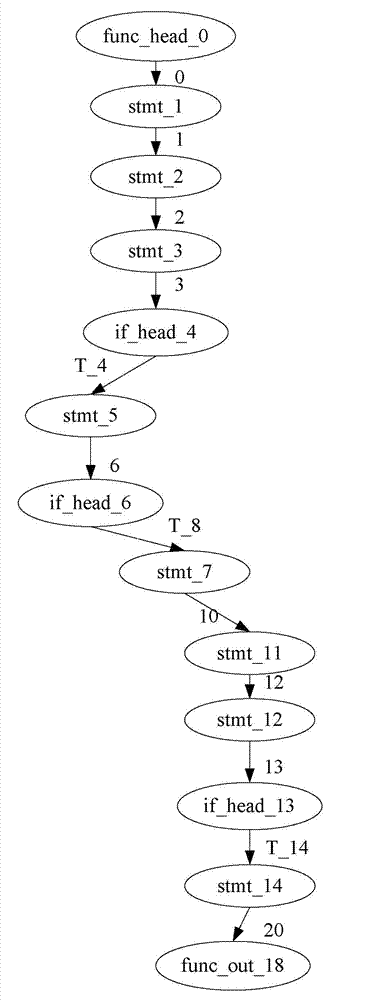

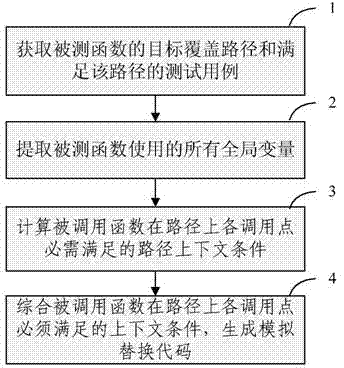

Method for determining context environmental effect of function call in program path

ActiveCN102708053AImprove efficiencyIncrease coverageSoftware testing/debuggingInterval arithmeticTest efficiency

The invention discloses a method for determining a context environmental effect of a function call in a program path. The method comprises the steps: using a return value, a global variable redefined by a called function, a pointer or a referenced parameter as an output variable of the called function; calculating the context condition which must be met by call point output variables in the path of the called function by a path-sensitive and context-sensitive symbolic interval arithmetic technology; and finally generating a simulative replacement function according to the condition, wherein the value of the output variables can be dynamically adjusted by the simulative replacement function according to the condition of the call points and the condition that the program is executed according to a target path is ensured. The method can be used for path-oriented test in an automated unit test and comprises a full path-oriented test, a sub path-oriented test and a target-oriented test and the like. The experiment shows that the method provided by the invention is adopted to ensure that the tested program is executed according to the target path and the unit test efficiency is improved.

Owner:BEIJING UNIV OF POSTS & TELECOMM

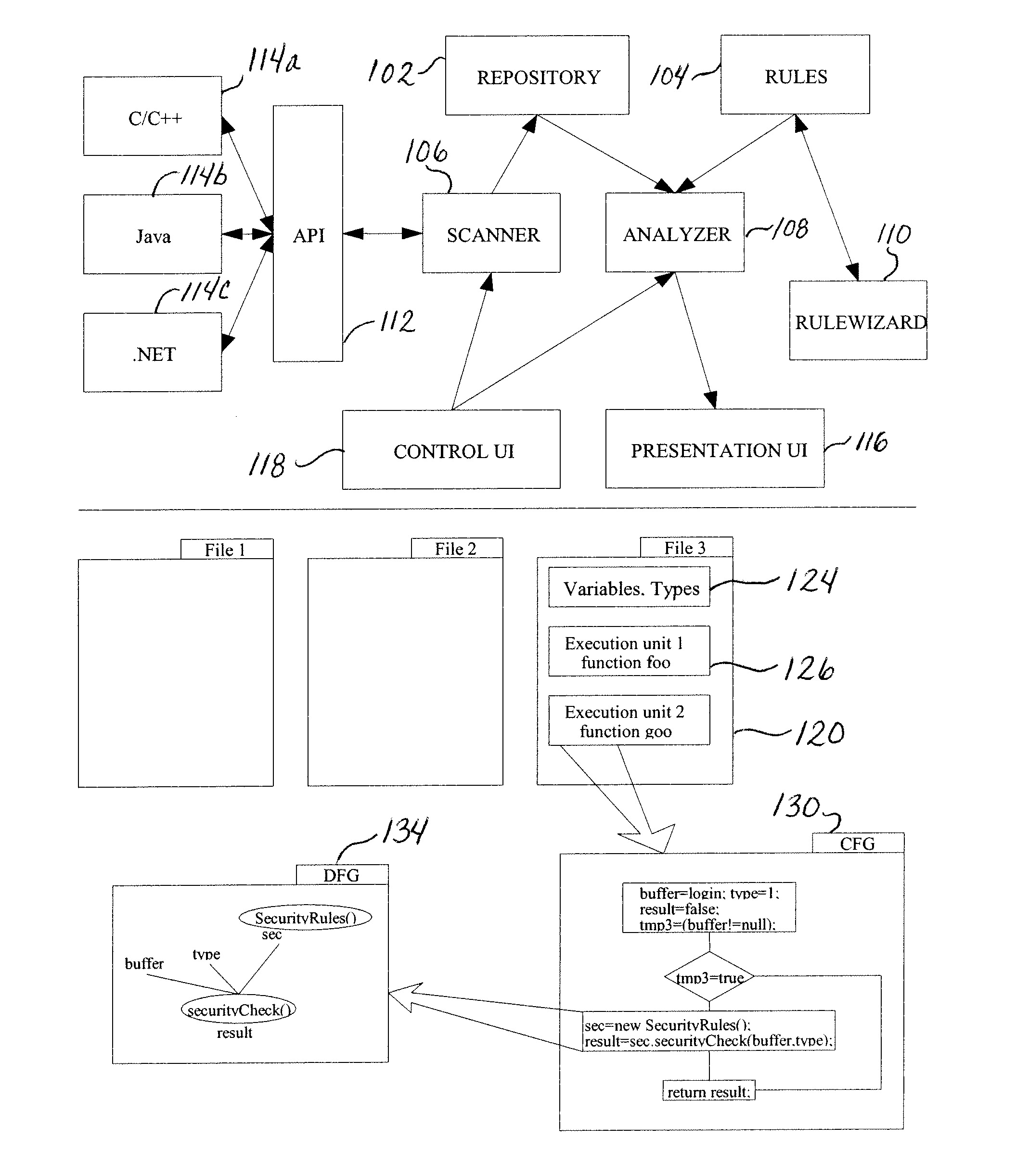

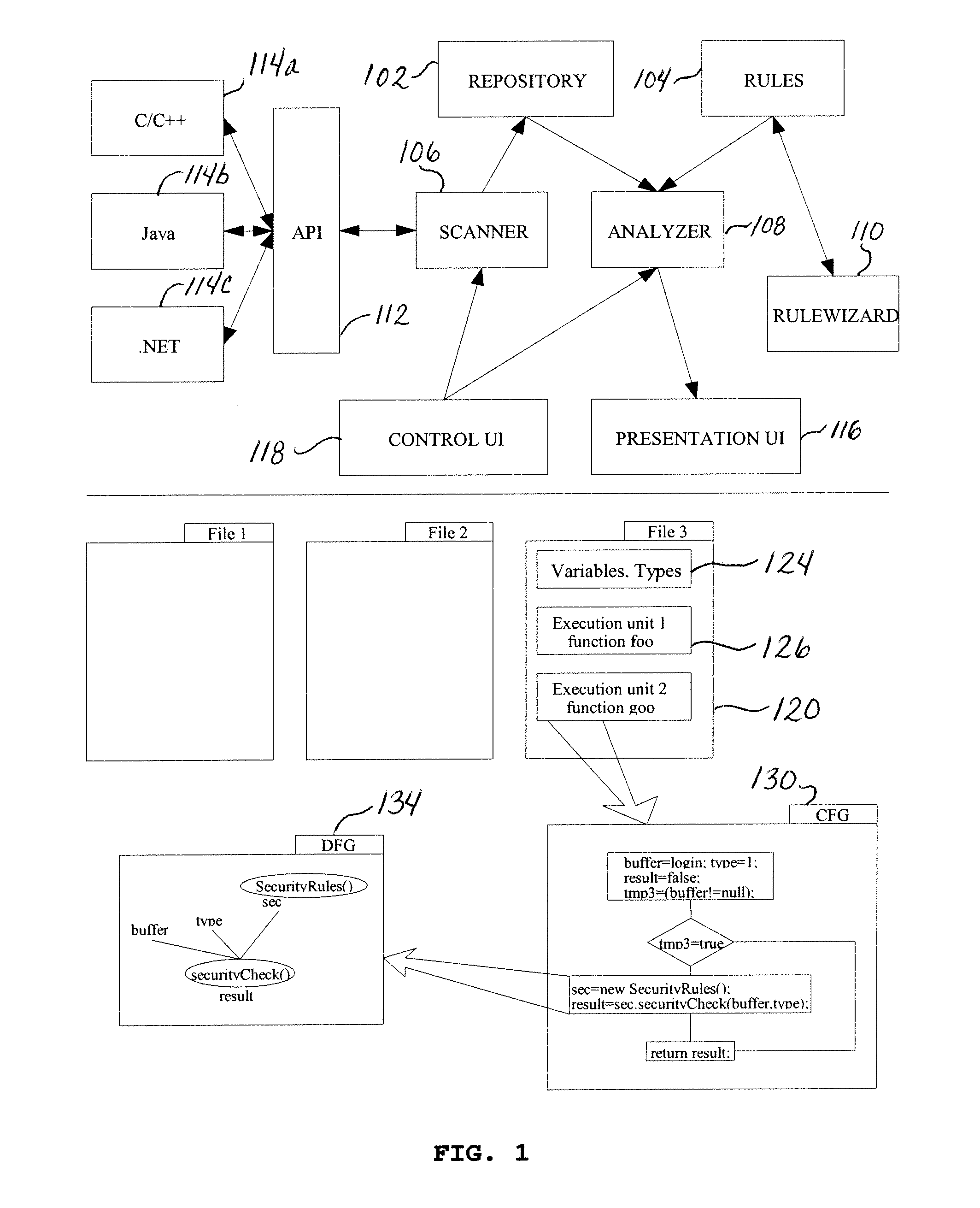

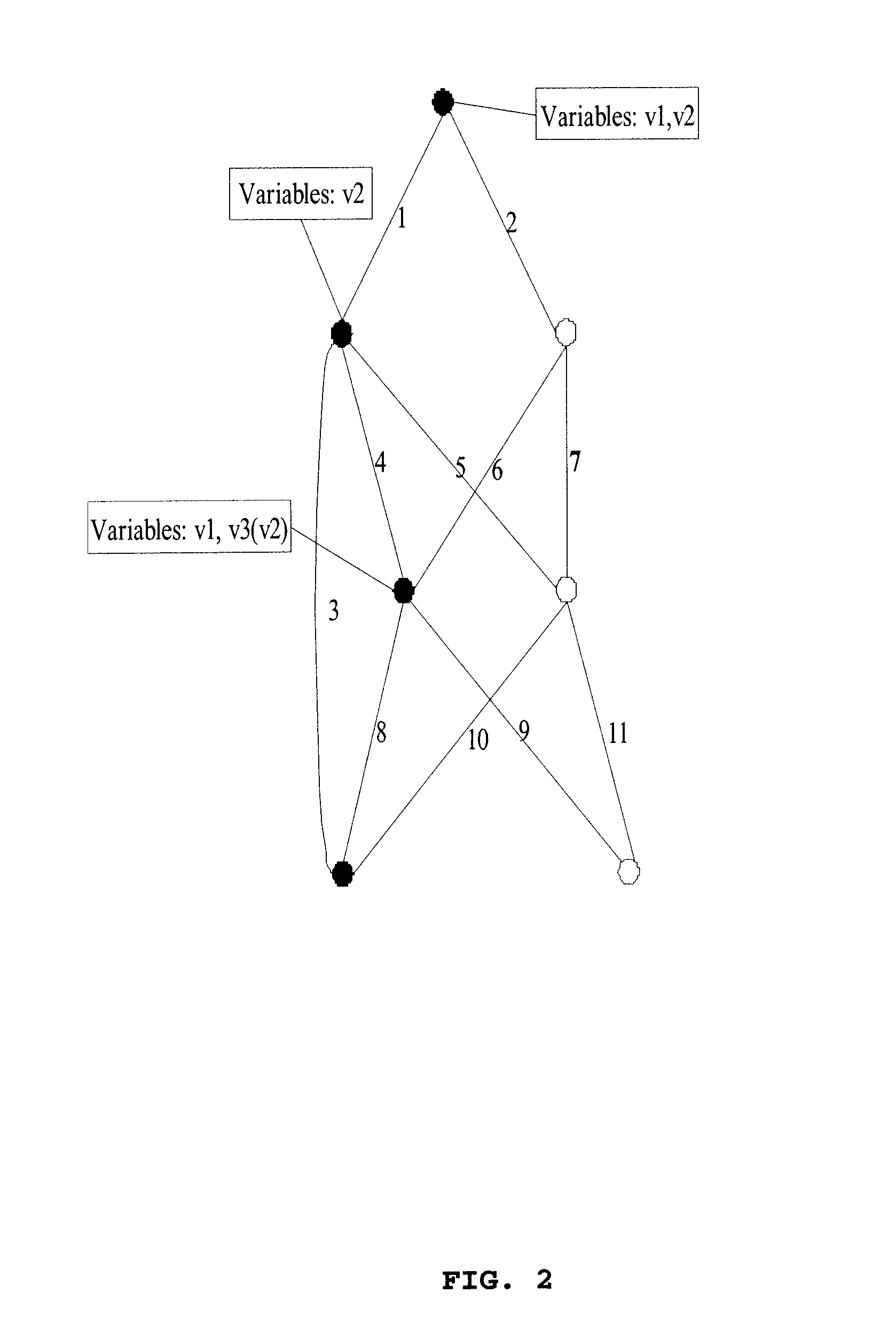

System and method for generating unit test based on recorded execution paths

ActiveUS8732676B1Software testing/debuggingSpecific program execution arrangementsSoftware systemParallel computing

A method and system for testing a computer software system based on execution paths including: executing the computer program to obtain an execution path in the computer software; recording the execution path; modifying variables in the recorded execution path to create one or more perturbed paths; analyzing the one or more perturbed paths to detect potential errors; and generating unit tests for the one or more perturbed paths having the detected potential errors. The created test units may then be executed to test the computer software.

Owner:PARASOFT

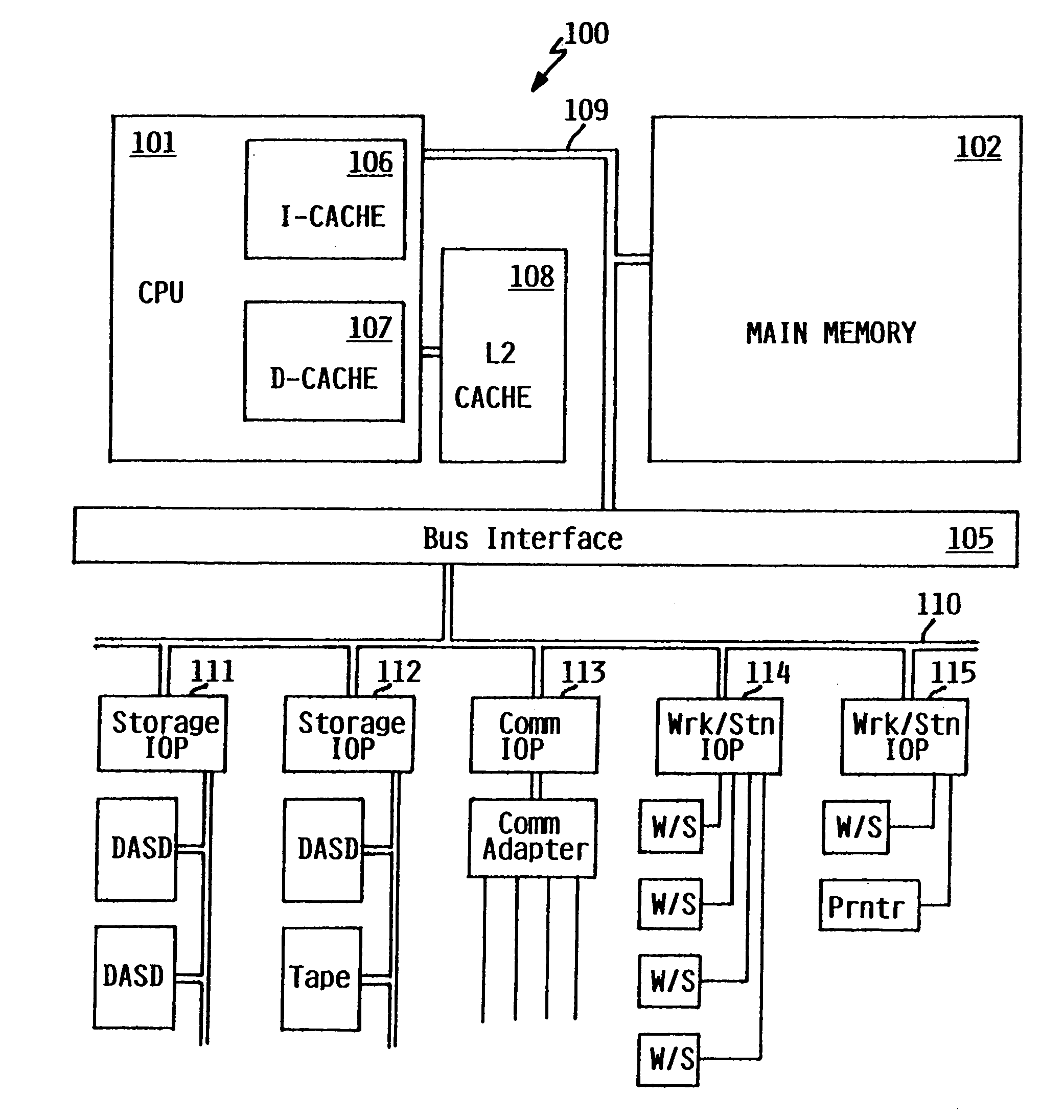

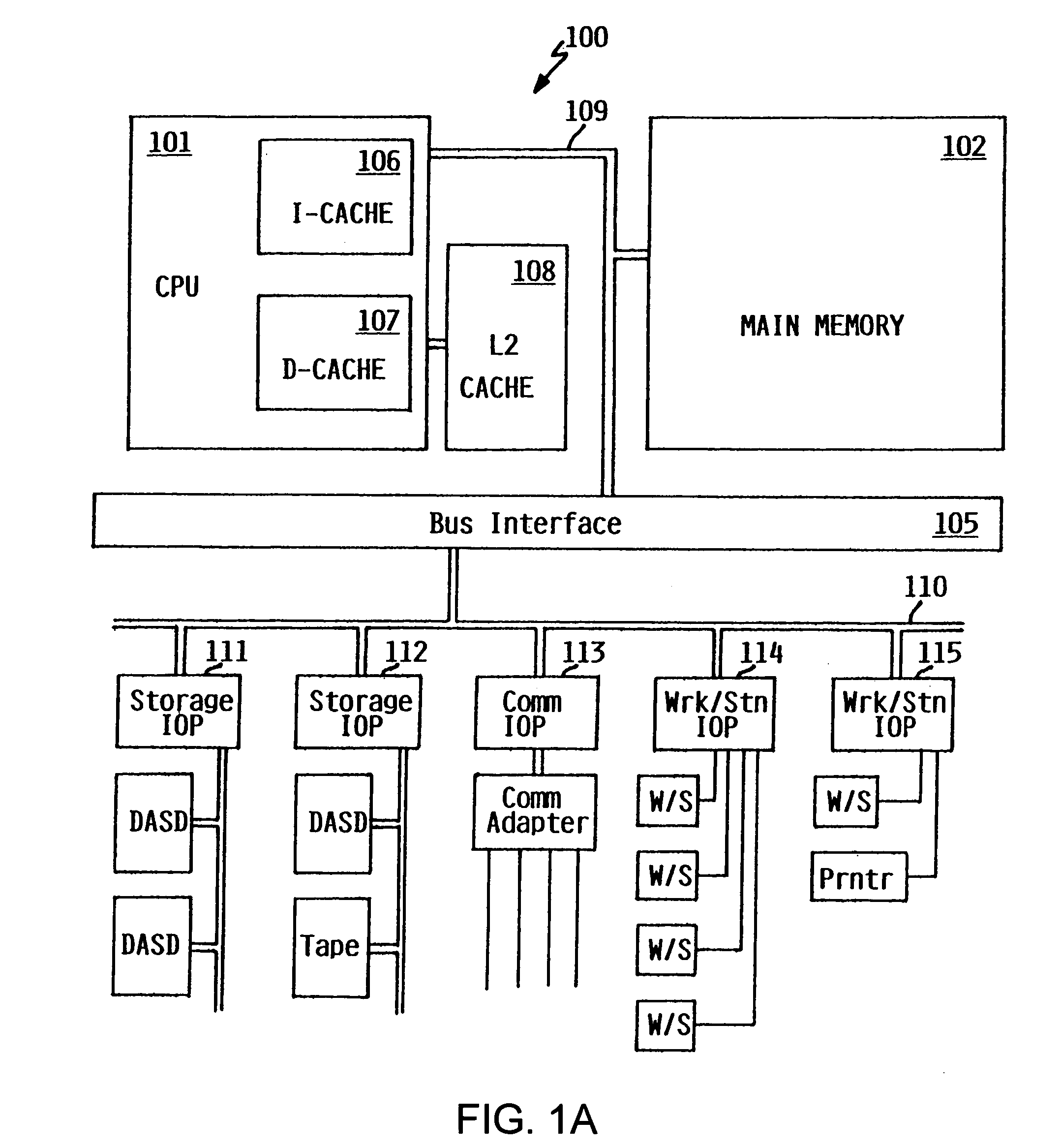

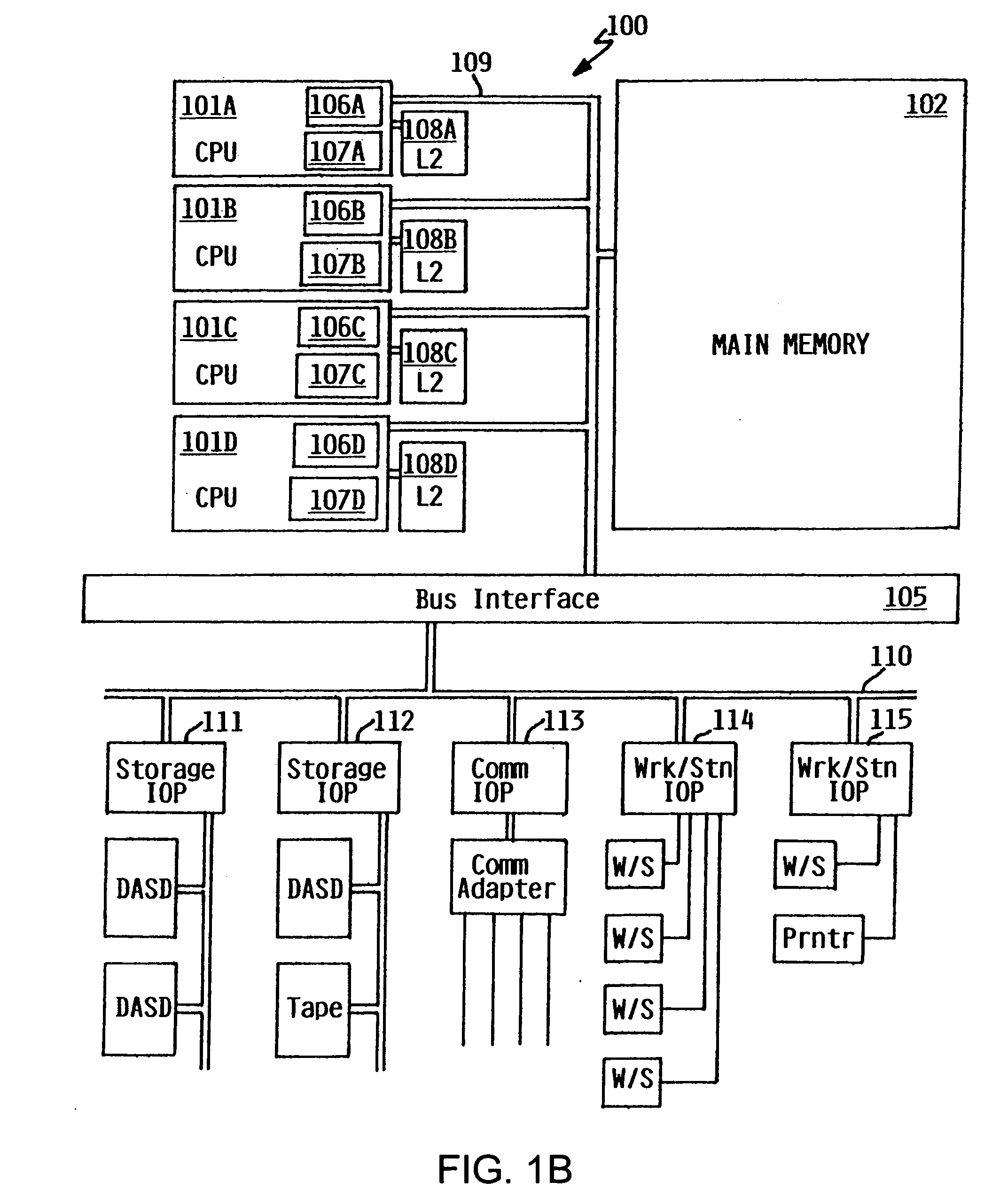

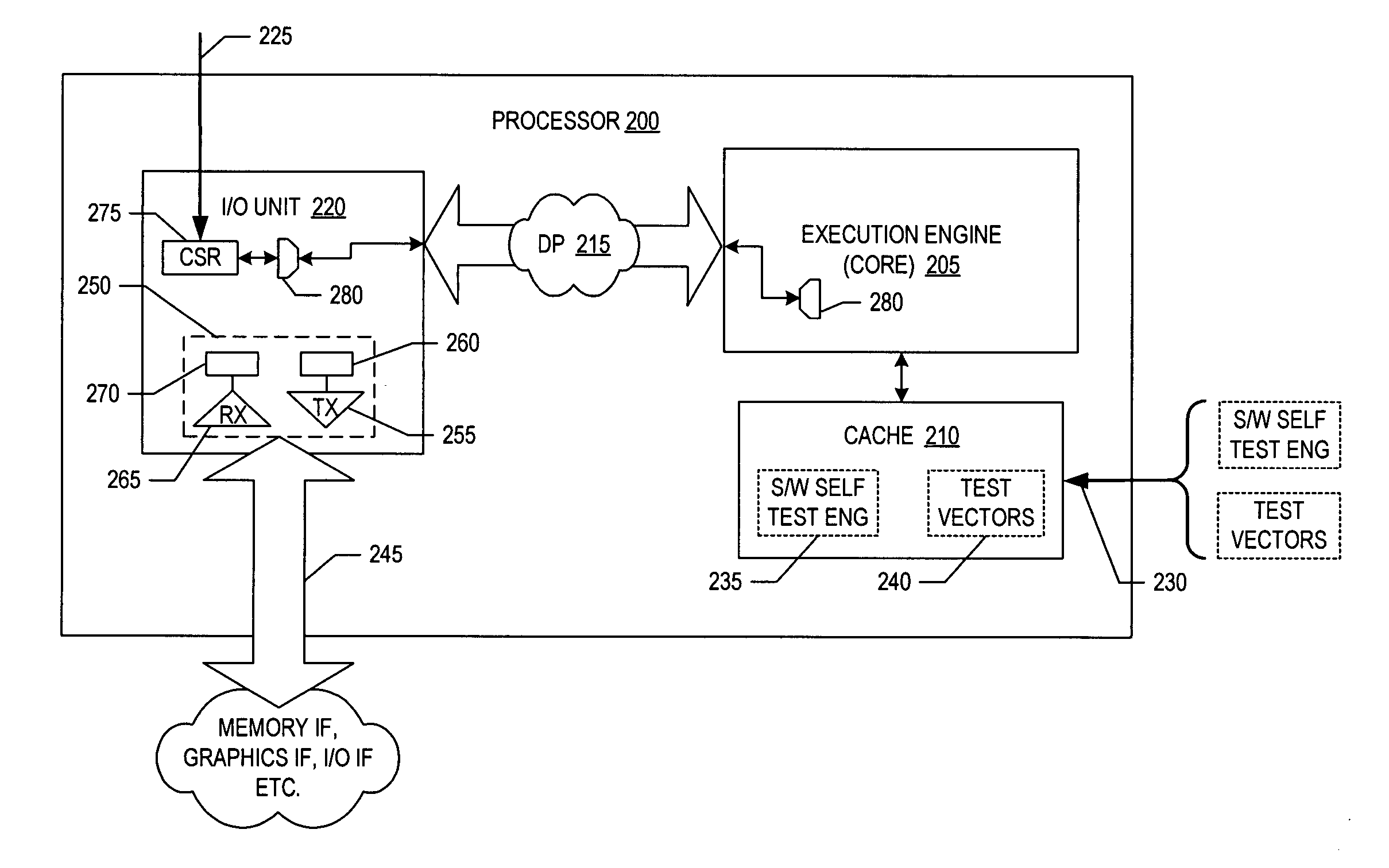

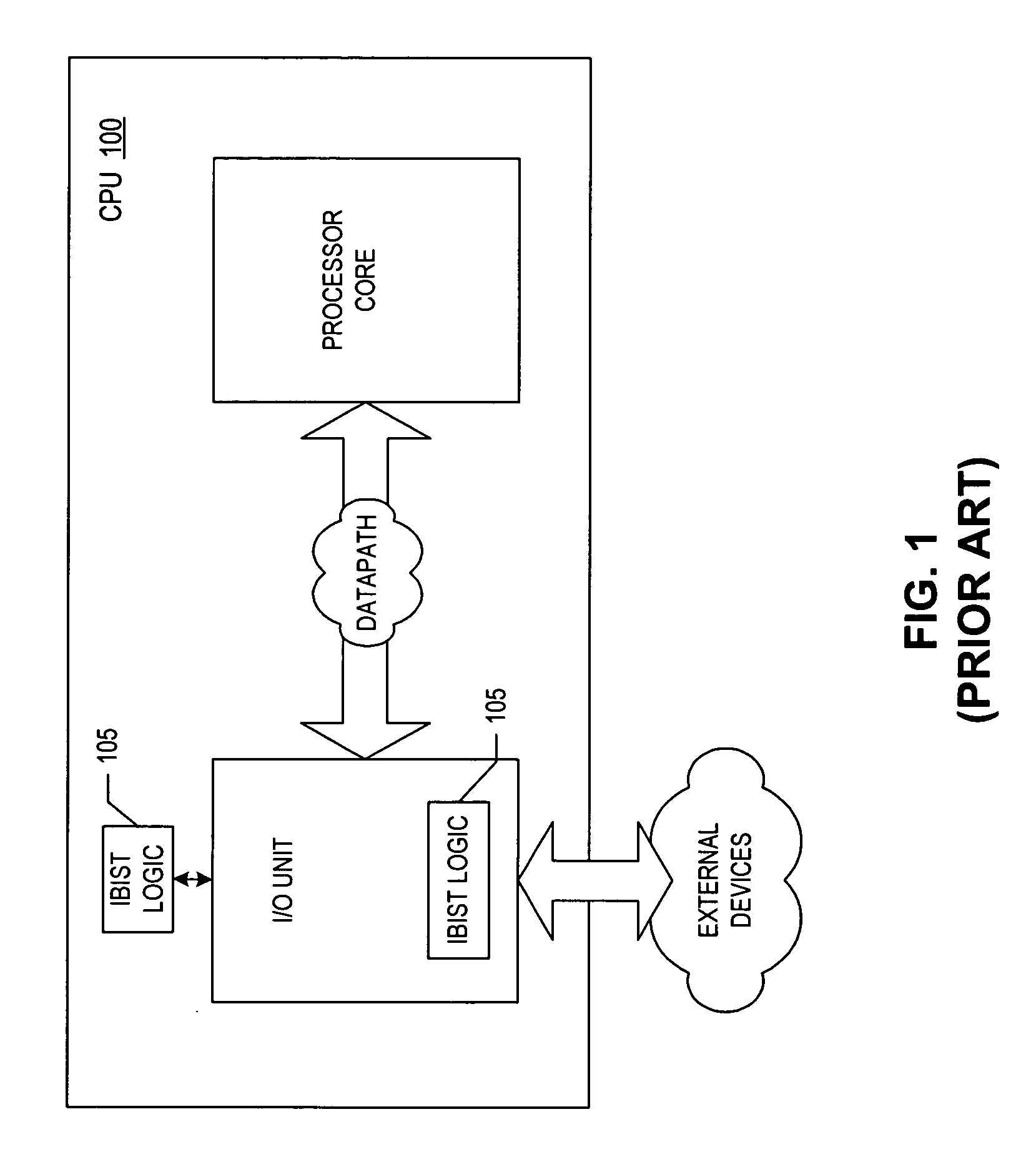

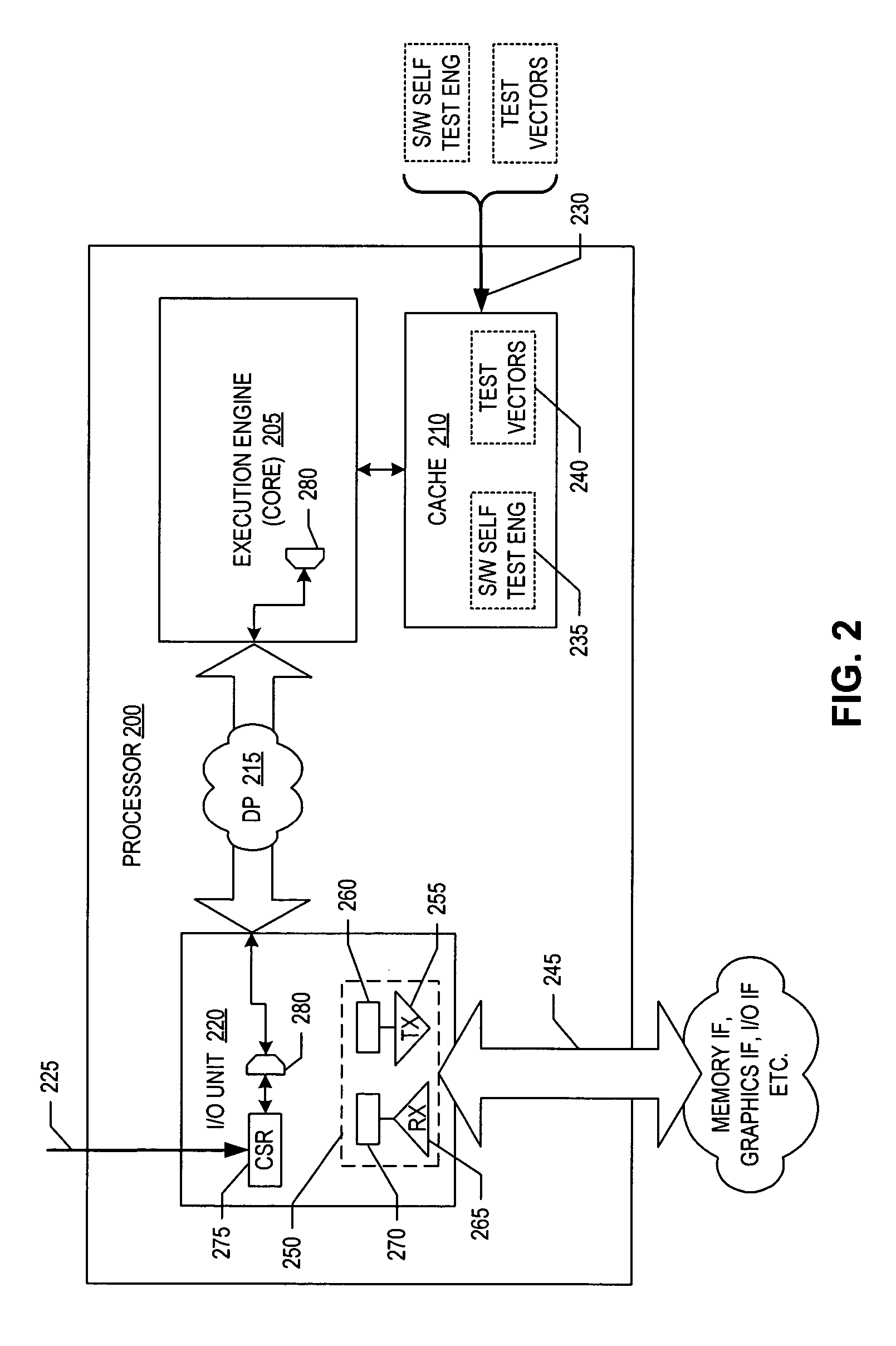

Cache based physical layer self test

A software self test engine is executed from a cache of a processor. The software self test engine is executed using an execution engine of the processor to perform a physical layer self test. The physical layer self test is performed by transmitting a test vector from the execution engine under control of the self test engine to an input / output (“I / O”) unit of the processor along a datapath coupling the execution engine to the I / O unit. The test vector is transmitted along a loop back path including the I / O unit and the datapath to test a hardware device along the loop back path.

Owner:INTEL CORP

Testing inverter driven electric motor shut-off path

Owner:GM GLOBAL TECH OPERATIONS LLC +3

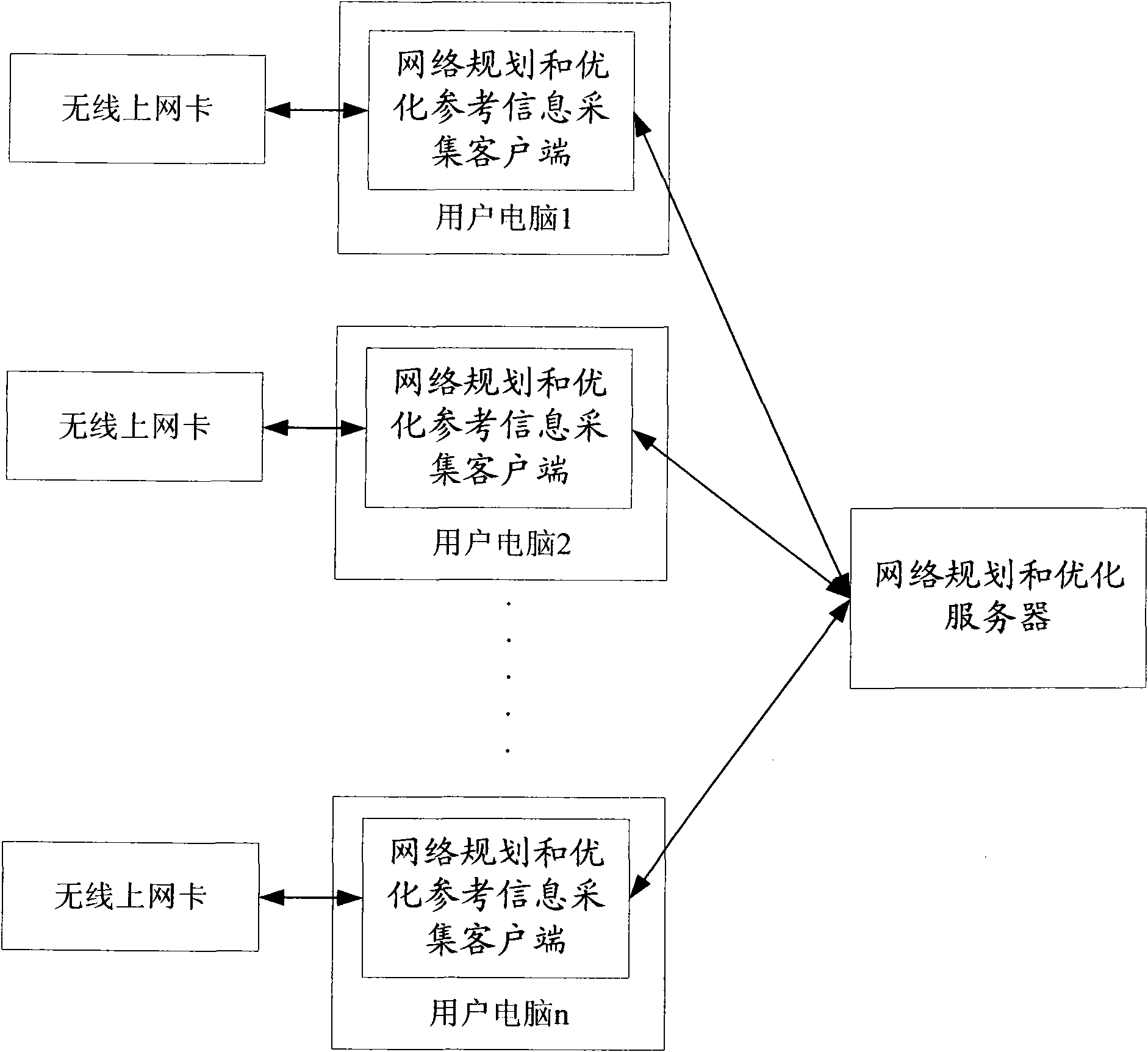

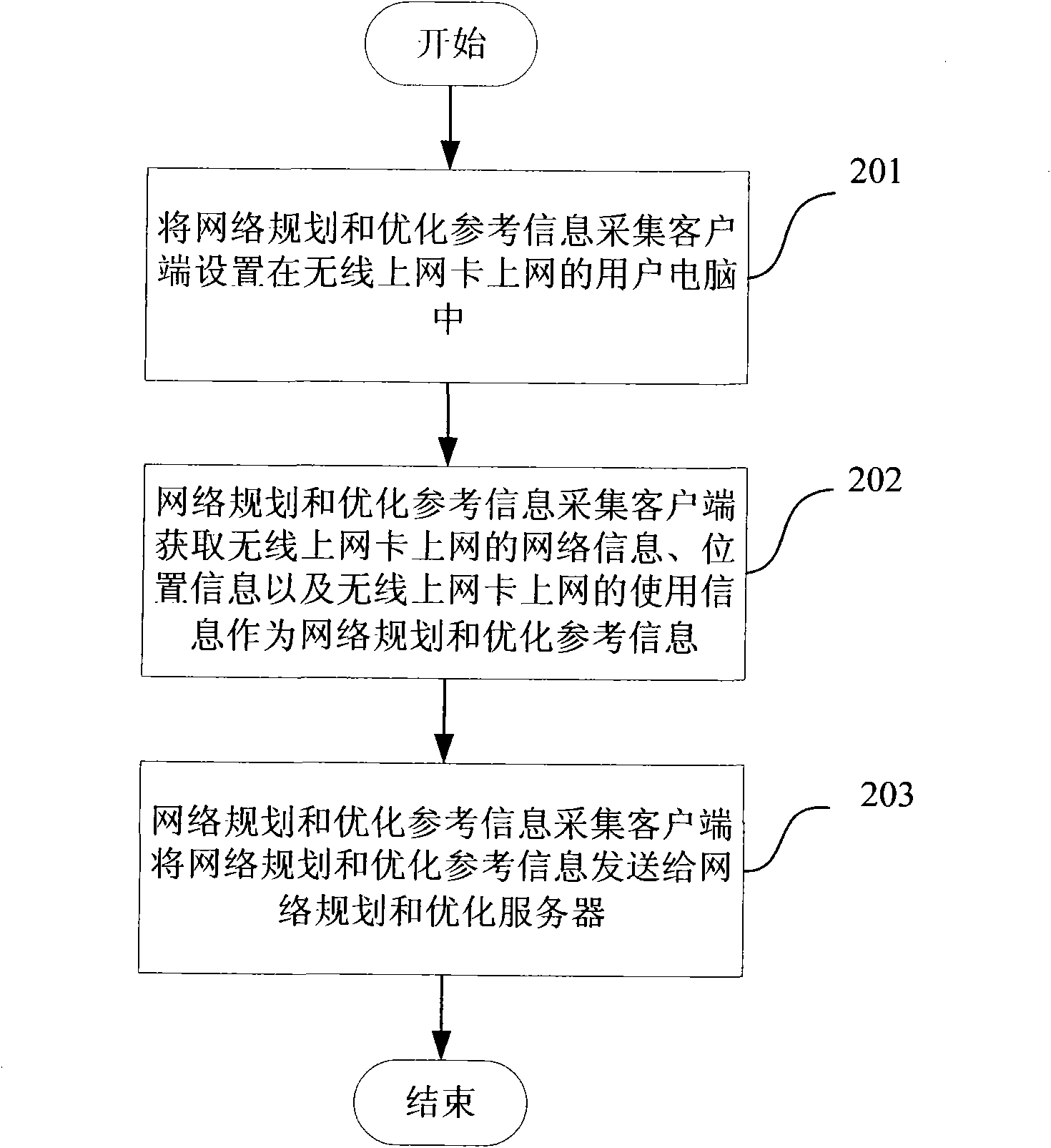

Method and system for collecting network programming and optimizing reference information

InactiveCN101621809AMaster the actual experienceQuick response to demandNetwork planningWireless internet accessClient-side

The invention discloses a method and a system for collecting network programming and optimizing reference information. The collection method comprises the following steps: setting a network programming and optimizing reference information collecting client in a user computer getting on-line by a wireless card; acquiring the network information of the wireless card by the network programming and optimizing reference information collecting client and using the network information as the network programming and optimizing reference information; and sending the network programming and optimizing reference information to a network programming and optimizing server by the network programming and optimizing reference information collecting client. The invention can greatly improve the network programming and optimizing efficiency, know well actual use feels of users and save the path testing cost.

Owner:ZTE CORP

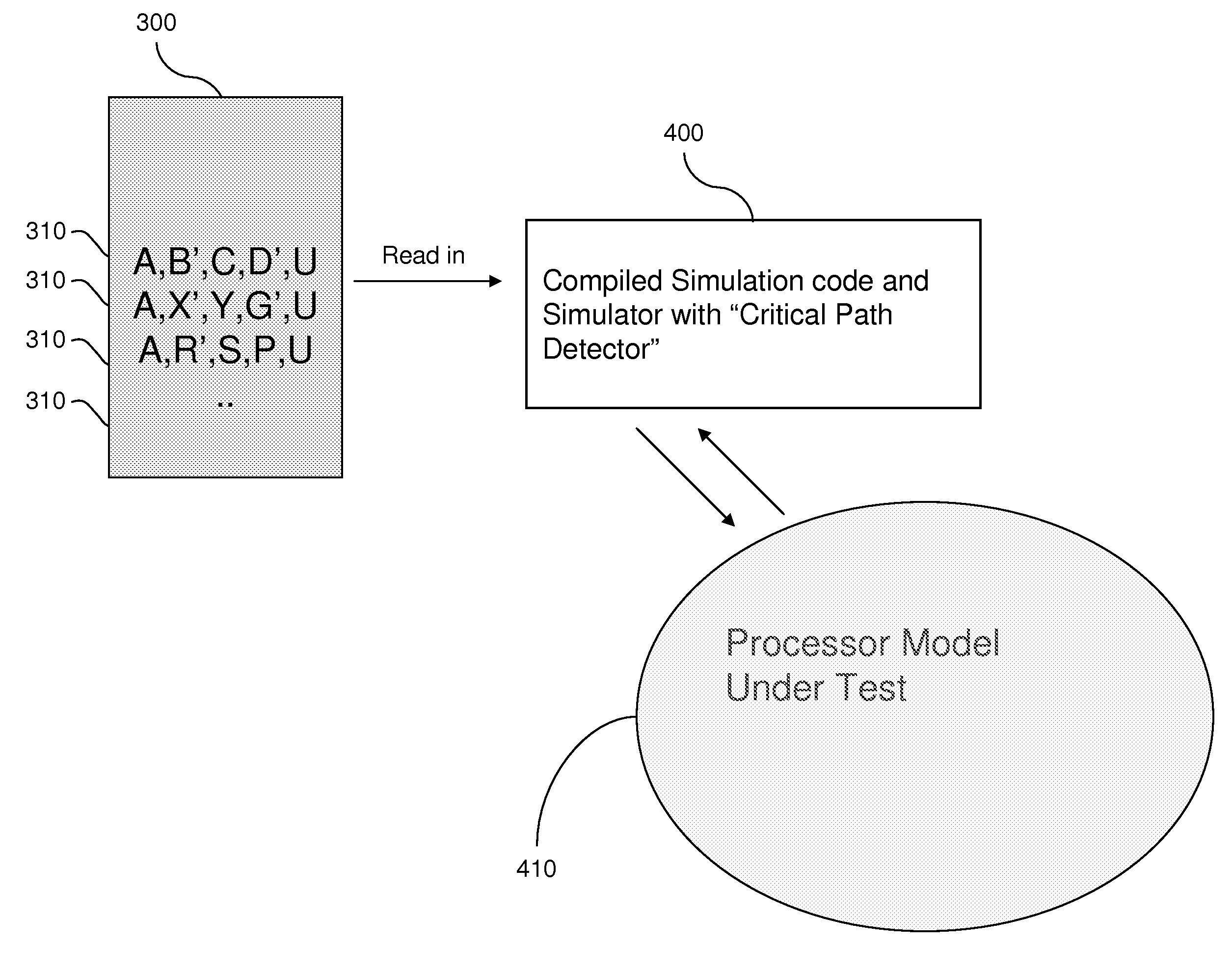

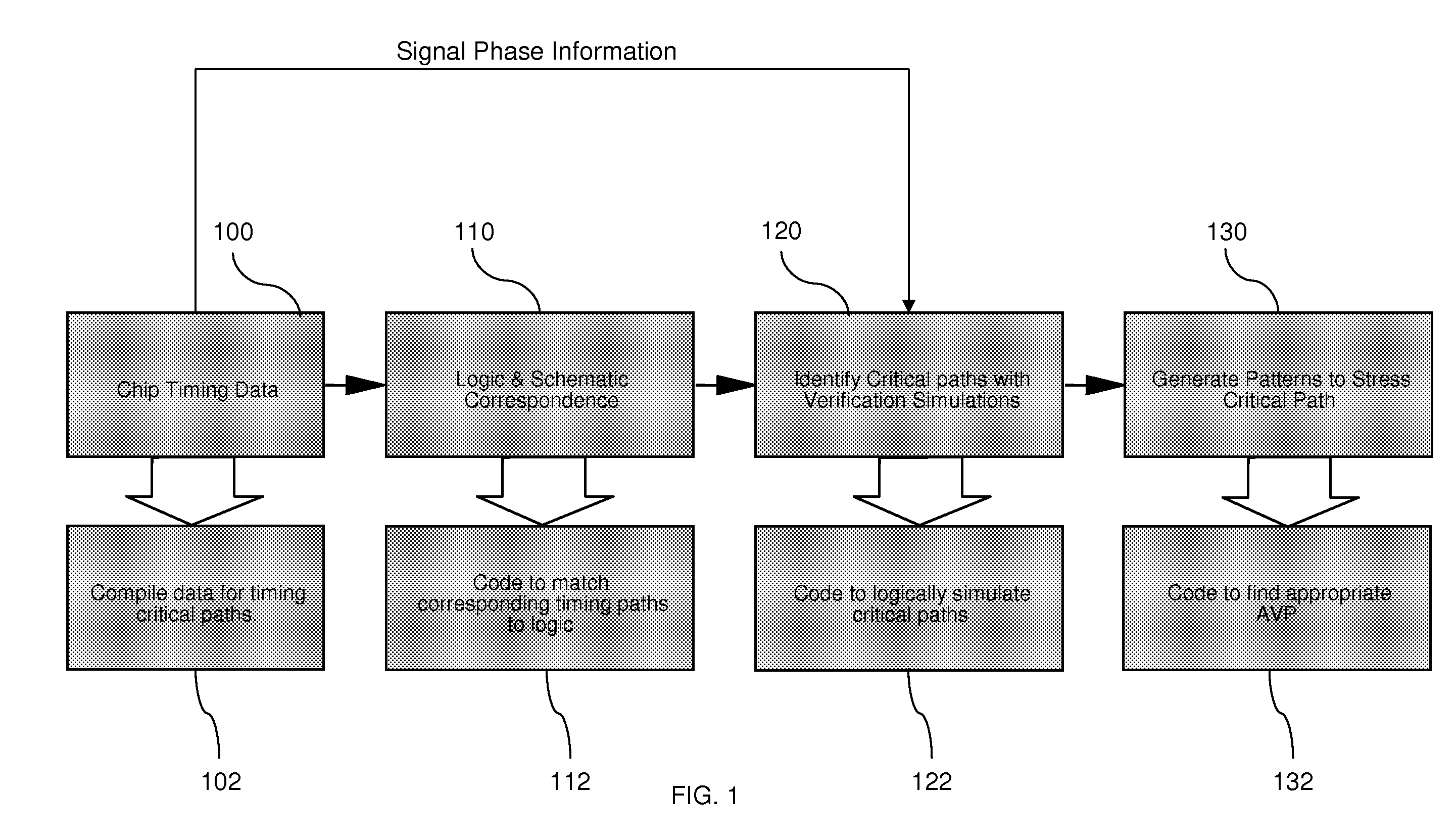

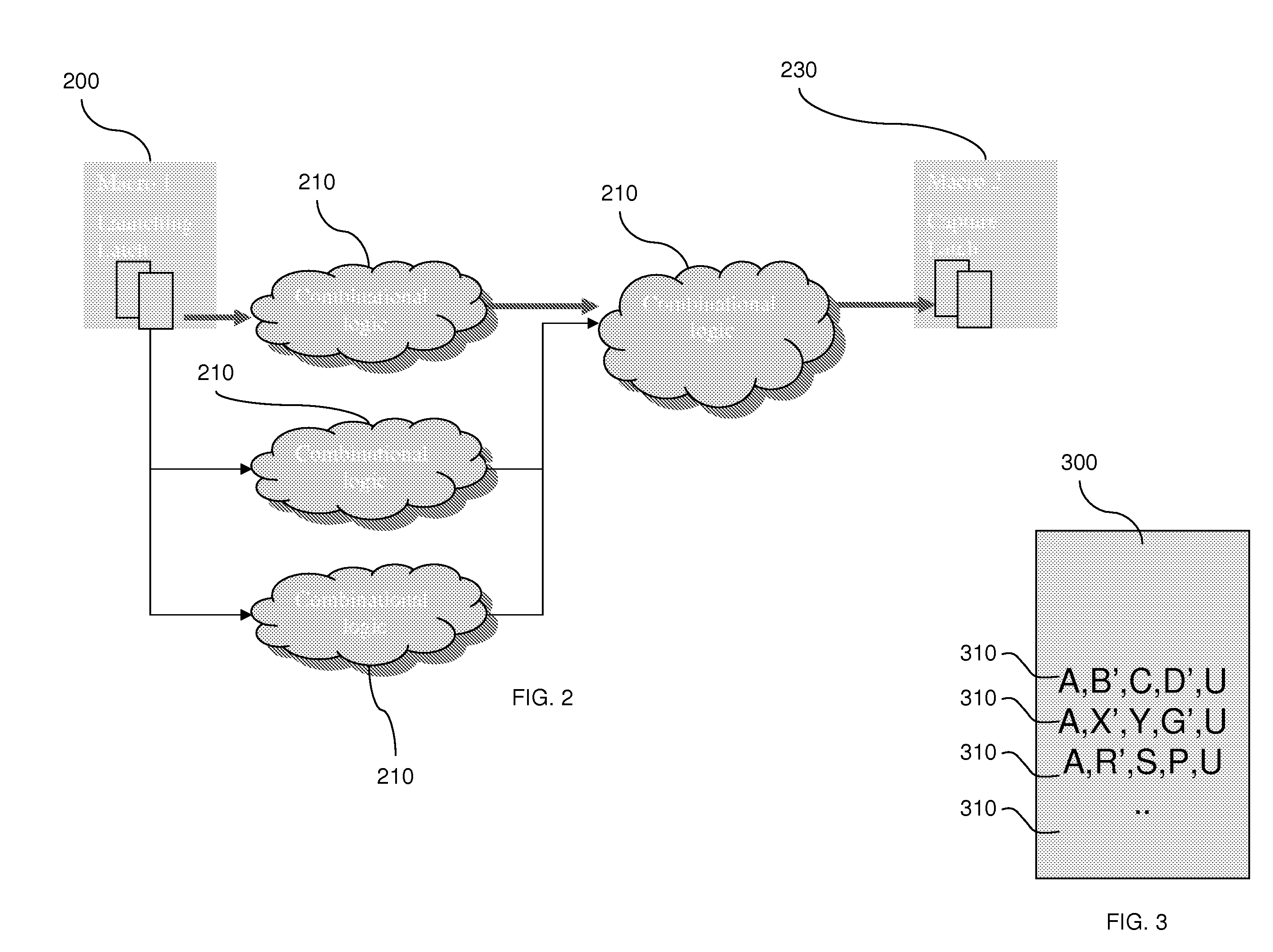

Method to identify and generate critical timing path test vectors

InactiveUS20080263489A1Shorten test timeEasy to integrateElectrical testingComputer aided designFunctional testingCritical path method

A method of testing critical paths in integrated circuits begins by simulating at least one operation of an integrated circuit chip design to produce chip timing data. Next, critical paths of the integrated circuit chip design are identified based on the chip timing data. The method applies functional test signals to simulations of the critical paths and monitors the number of times each of the functional test signals propagate from the beginning to the end of each of the critical paths. This allows the method to identify stress producing test signals as those that propagate along the critical paths more than other test signals. These stress producing test signals are applied to integrated circuit chip hardware manufactured according to the integrated circuit chip design to stress test the hardware.

Owner:IBM CORP

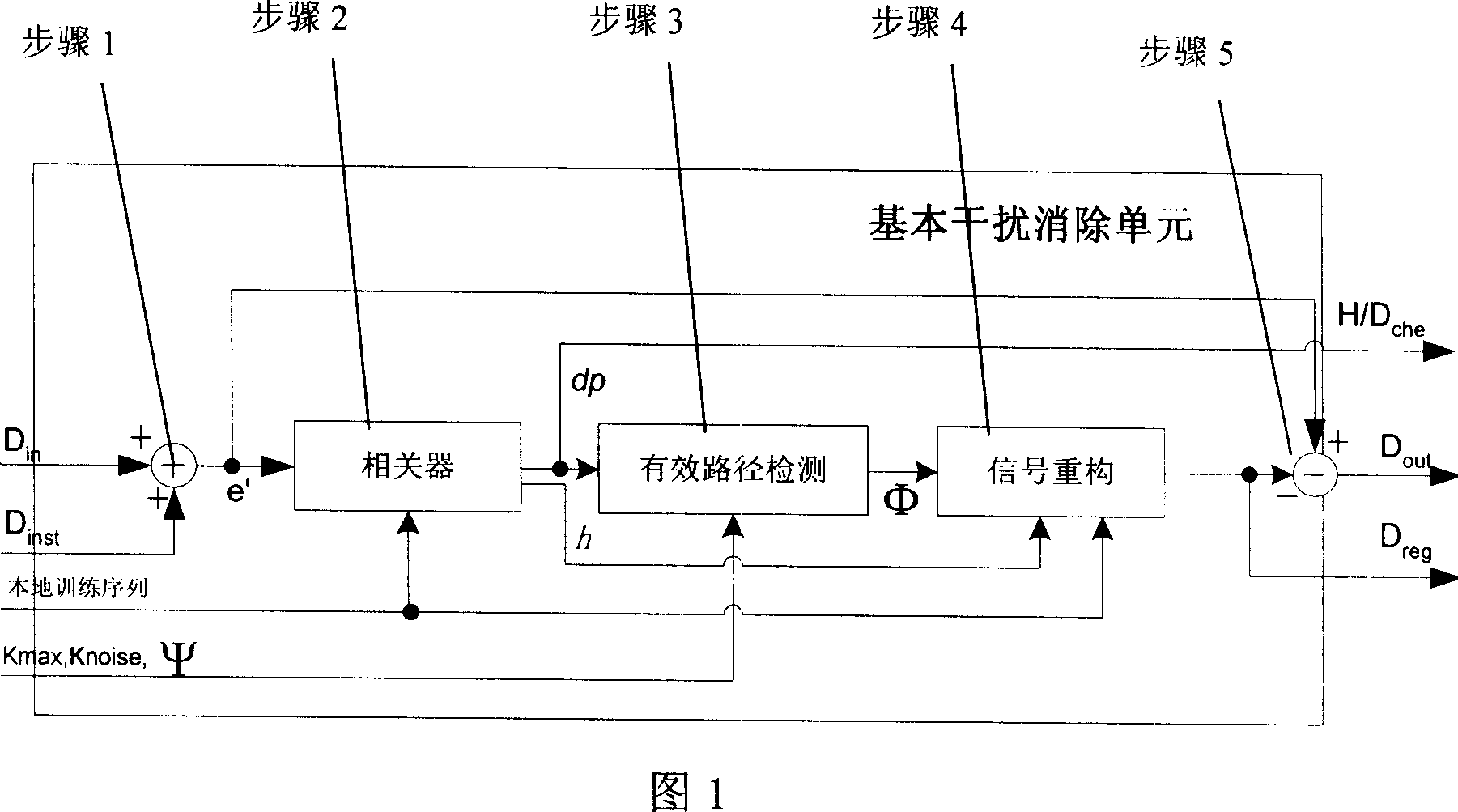

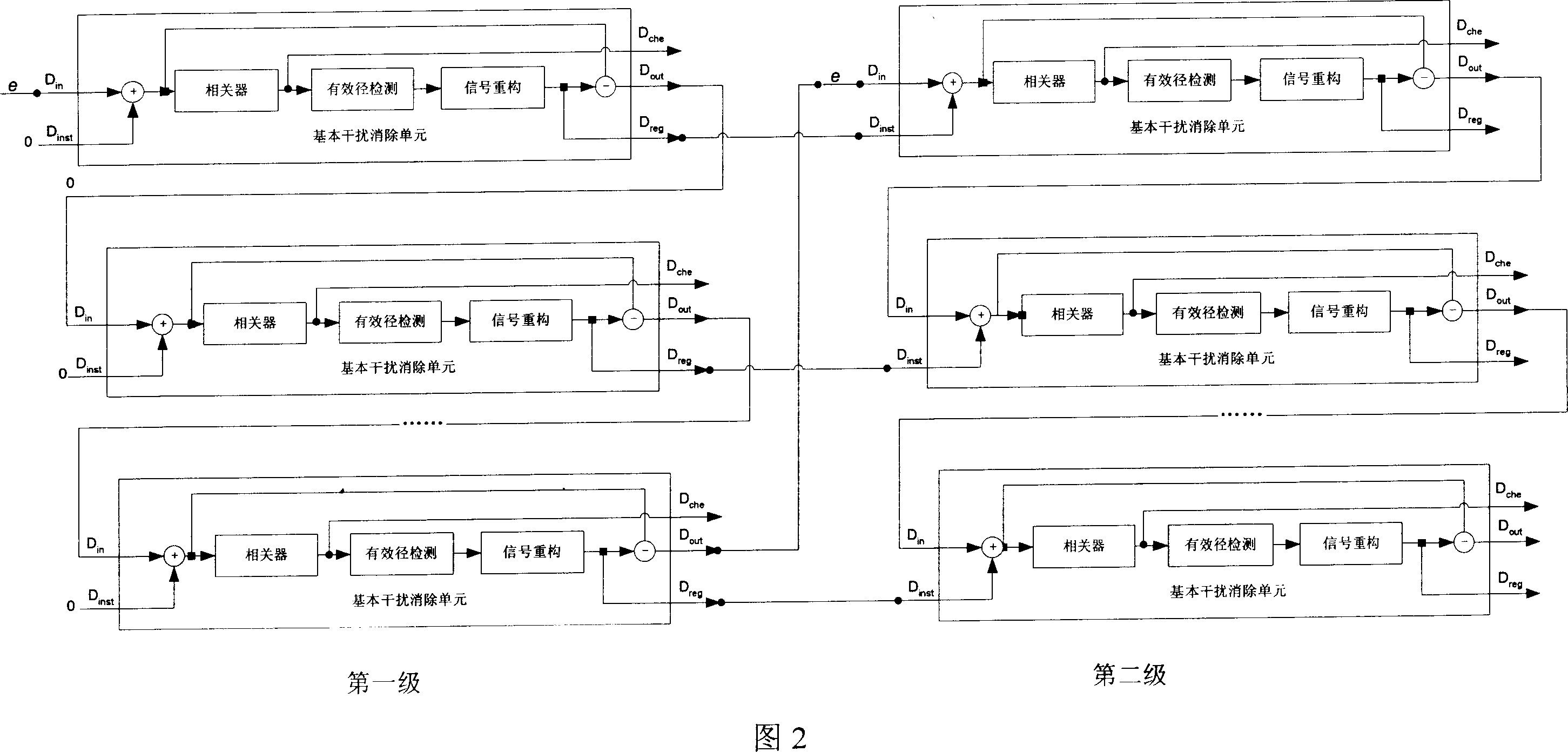

Multi-cell channel estimation method based on elimination of serial interference

InactiveCN1972509AImprove reasonable timingAccurate and reasonable timingCode division multiplexRadio/inductive link selection arrangementsInterference eliminationEstimation methods

This invention relates to one multiple area signal estimation method based on series interference elimination, which adopts series interference method to remove interference, which comprises steps of interference reconstruction, signal correlating, effect path testing, signal reconstruction and interference removing. This invention method can effectively overcome receive environment interference to improve signal channel decline of accuracy to improve system property.

Owner:XUANPU INDUSTRY CO LTD

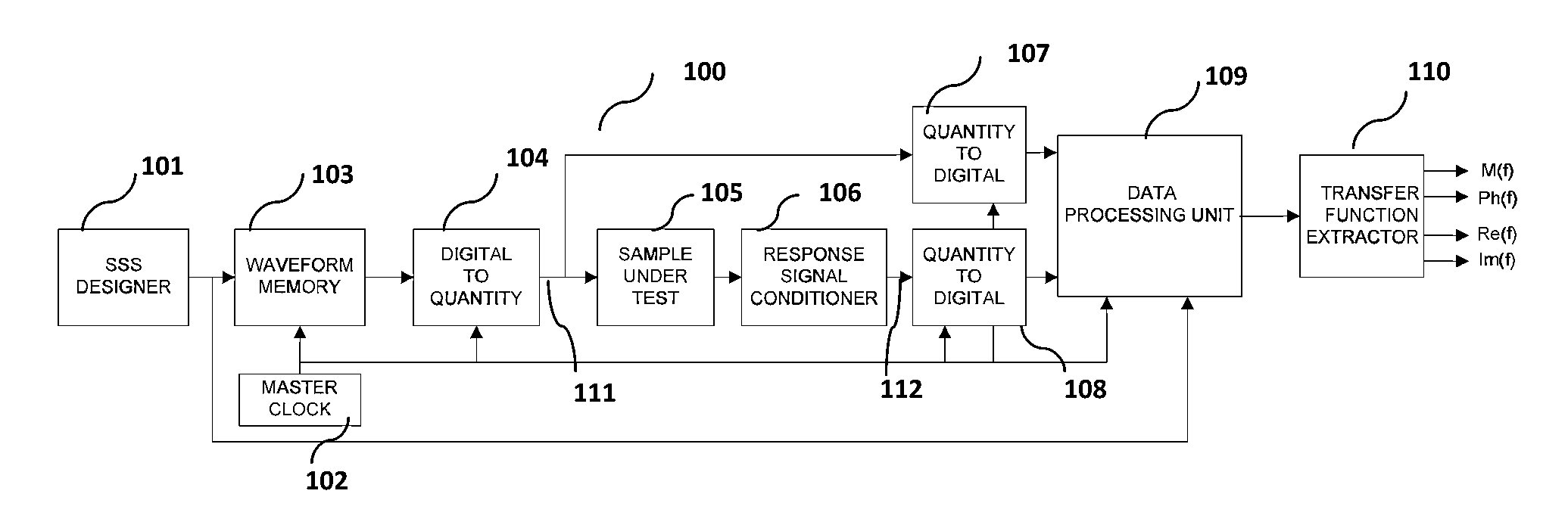

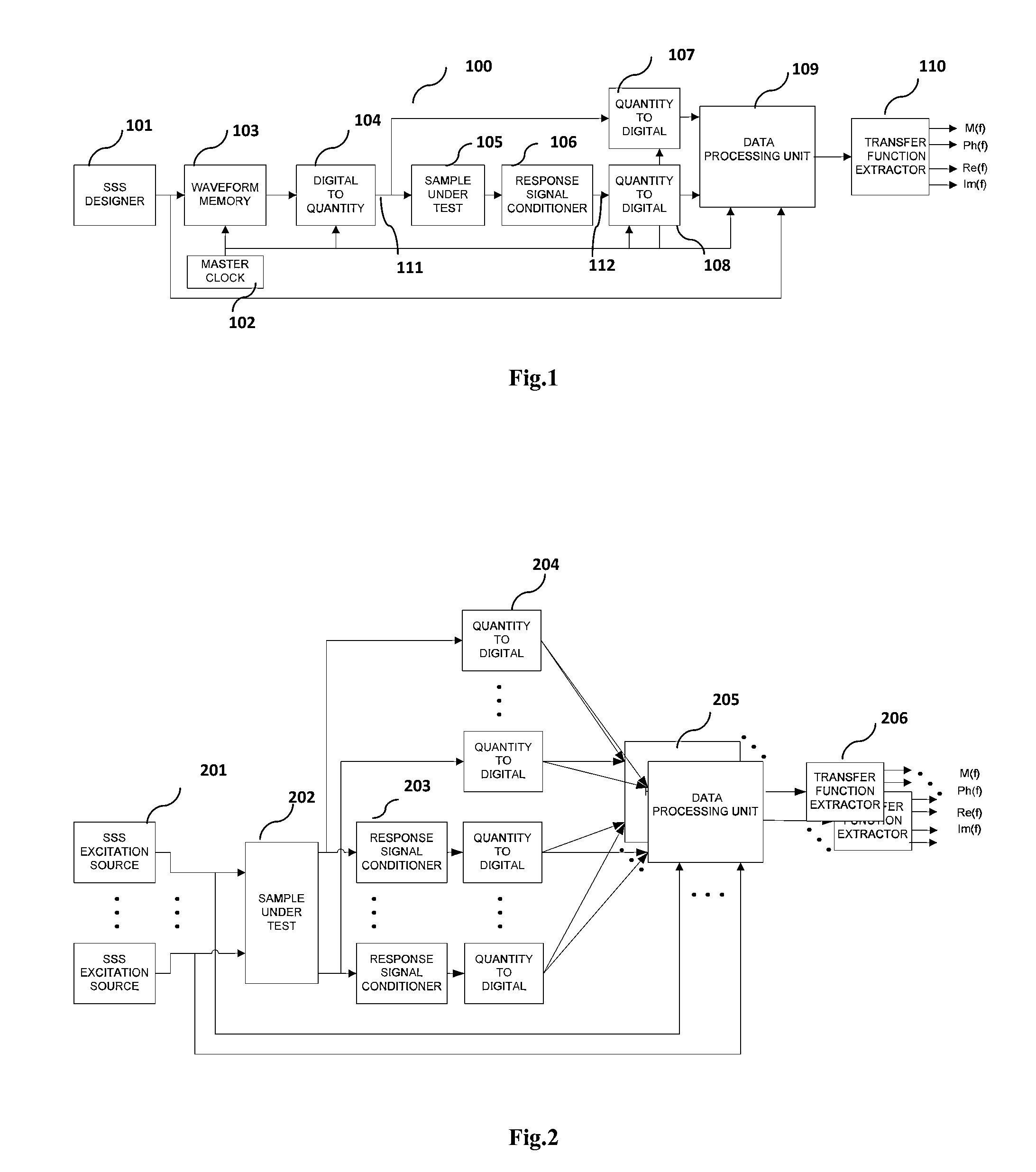

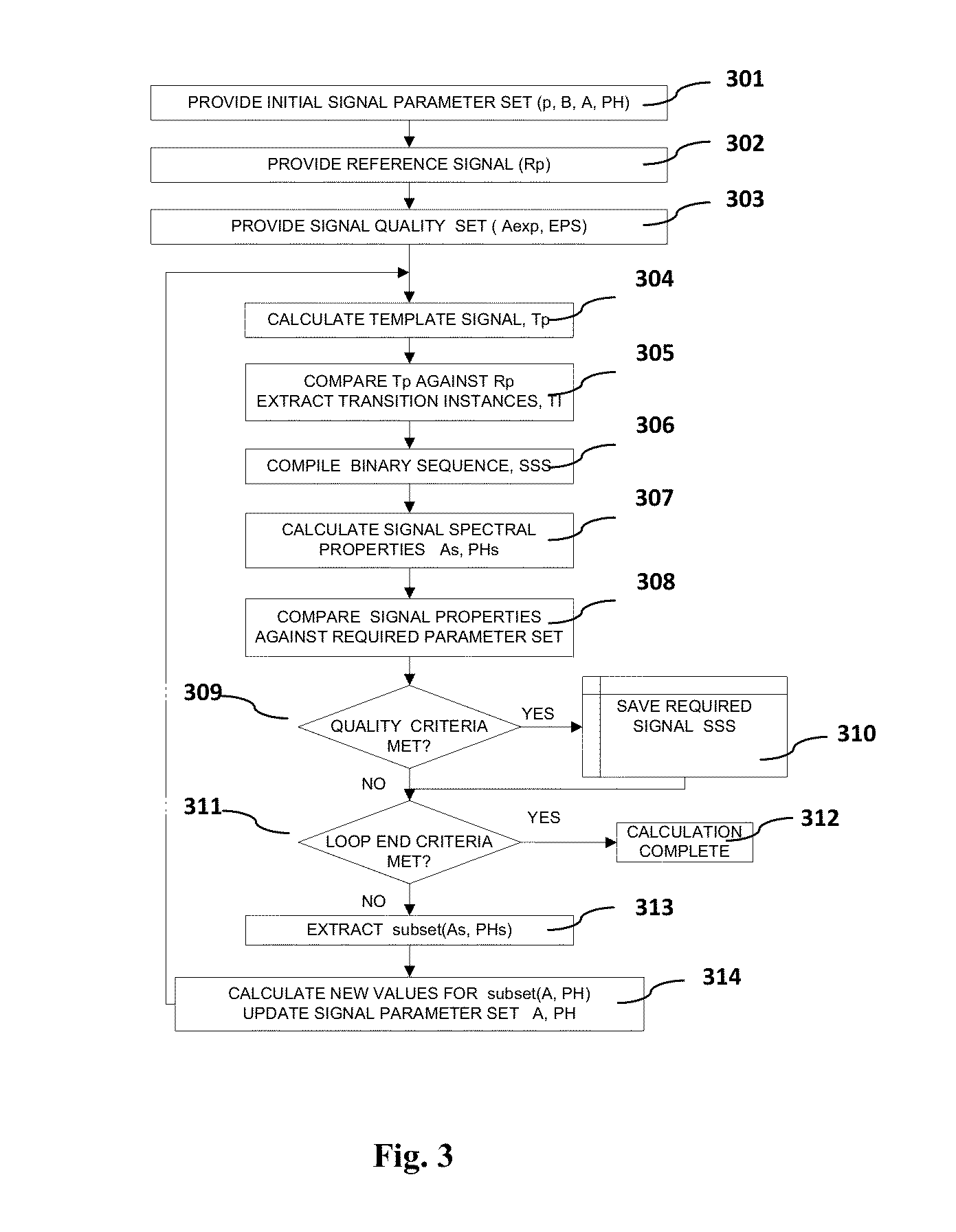

Method and device for broadband analysis of systems and substances

ActiveUS20130054178A1Reduce necessityEasy to implementElectric signal transmission systemsResistance/reactance/impedencePeriodic excitationFrequency spectrum

A method and device for high speed broadband testing of systems and substances using a binary, spectrally sparse sequence (SSS) as a periodic excitation waveform. The sequences with controllable frequency and magnitude spectra content are designed by component manipulation method or by edge manipulation method. The excitation waveform is typically pre-calculated, and kept in waveform memory, from where it is shifted out into digital to physical quantity converter (DQC).The sparse spectrum of the SSS makes it easy to create plenty of uncorrelated frequency sets with adjacent, but sufficiently different frequencies to form multi-path test systems, where all the paths can be measured simultaneously.The response of the sample under test (SUT) is sampled and the complex transfer function is calculated directly or indirectly via Impulse Response by Discrete Fourier Transform technique and its derivatives. The sequence bit interval and sampling interval have a predetermined ratio.

Owner:TALLINN UNIVERSITY OF TECHNOLOGY +1

Execution base path evolution generation method based on statistical analysis

InactiveCN106502908AImprove test efficiencyDiversity guaranteedSoftware testing/debuggingGenetic algorithmsStatistical analysisPath generation

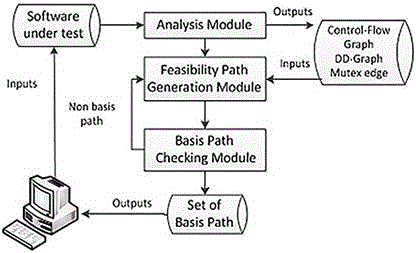

The invention discloses an executable base path evolution generation method based on statistical analysis, in order to make the generated test path can be applied to any path test technology, so as to improve the efficiency of software testing. First, the statistical analysis method is used to design and analyze the model to determine the control flow graph, DD-graph and mutex sides of the tested program. Then, a variable length genetic algorithm based on statistical analysis is proposed. The method is used for designing the executable path generation model and a basic path detection model that evolves to generate an executable base path. The prior method is to generate the test path and detect the executable path separately. The invention designs a two-part content in one way. The basic path of the evolution is itself an executable path and overcomes the loop problem in the control flow graph , and can greatly improve the efficiency of the test path generation.

Owner:MUDANJIANG NORMAL UNIV

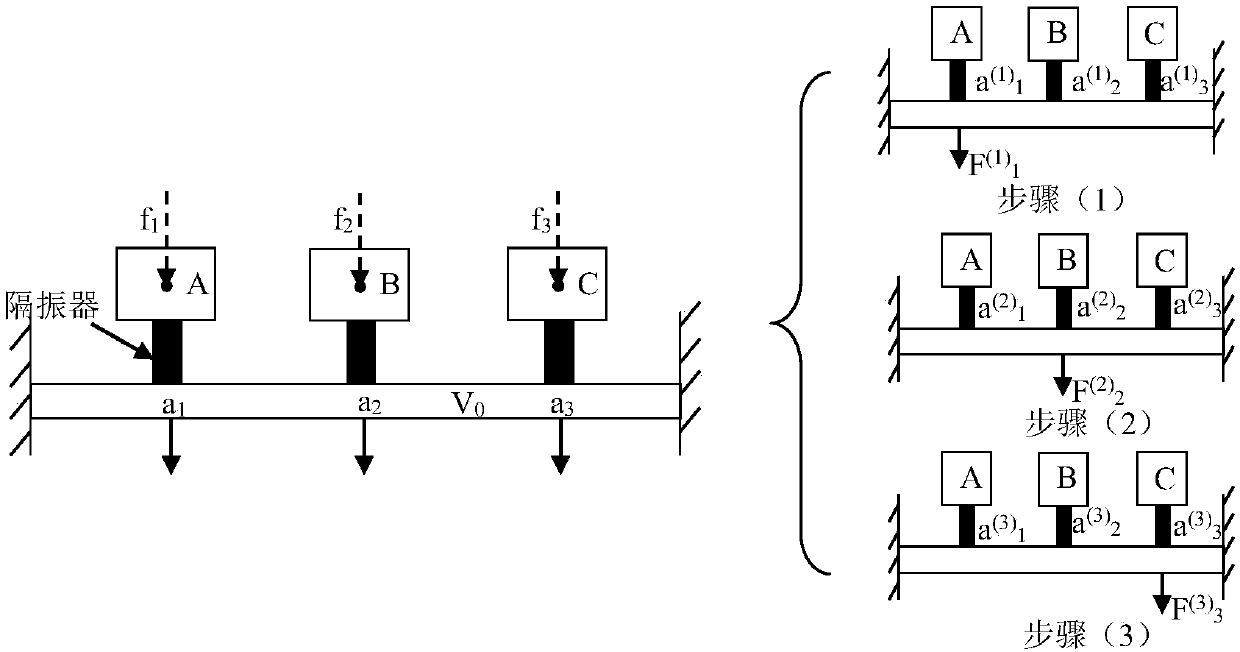

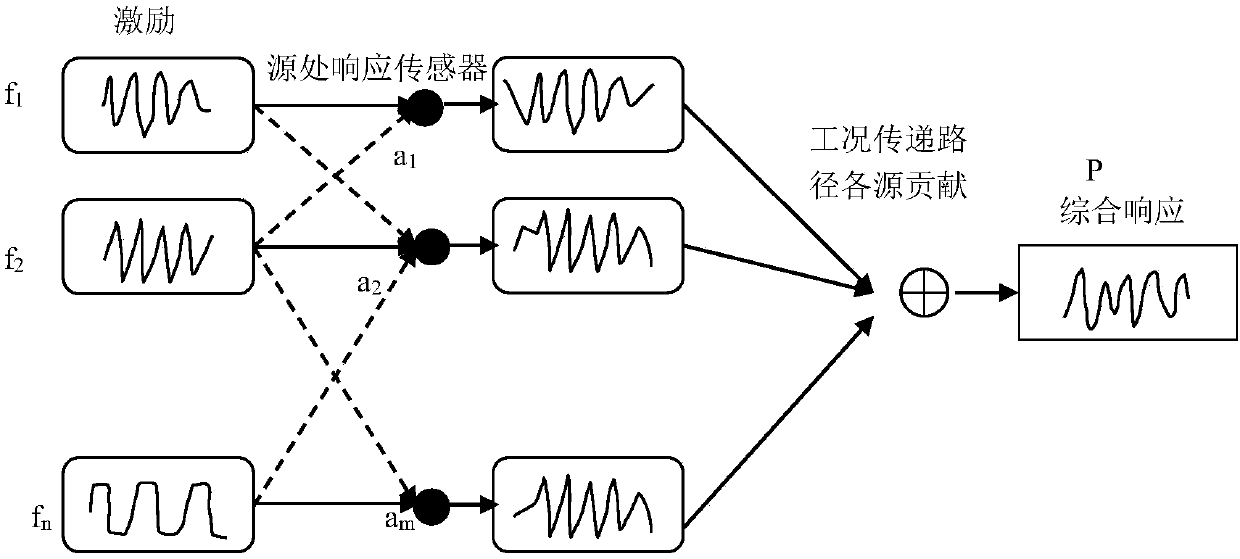

Crosstalk eliminating vibration transfer path testing method

ActiveCN108267221AHigh precisionEasy to implementSubsonic/sonic/ultrasonic wave measurementTransfer matrixEngineering

The invention relates to a crosstalk eliminating vibration transfer path testing method, which comprises the steps of obtaining a crosstalk removing transfer matrix by adopting the mode of a measurement transfer function or a non-orthogonal vector, and calculating a crosstalk removing generalized reference signal or a blocking force; analyzing an operating condition transfer path based on the generalized reference signal or the blocking force to obtain a transfer coefficient; and calculating the contribution of each vibration source at a response position according to the generalized referencesignal or the blocking force and the transfer coefficient.

Owner:INST OF ACOUSTICS CHINESE ACAD OF SCI

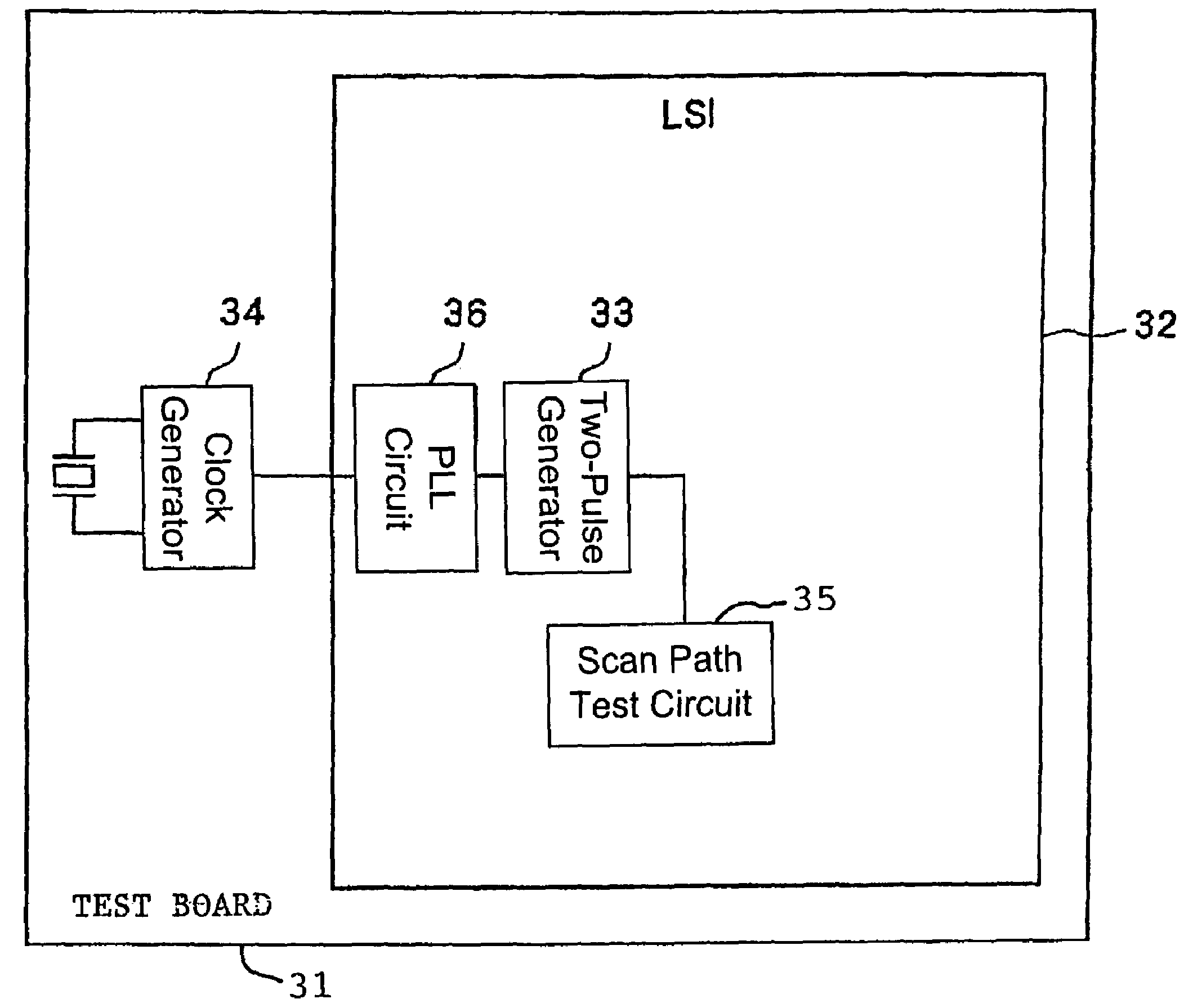

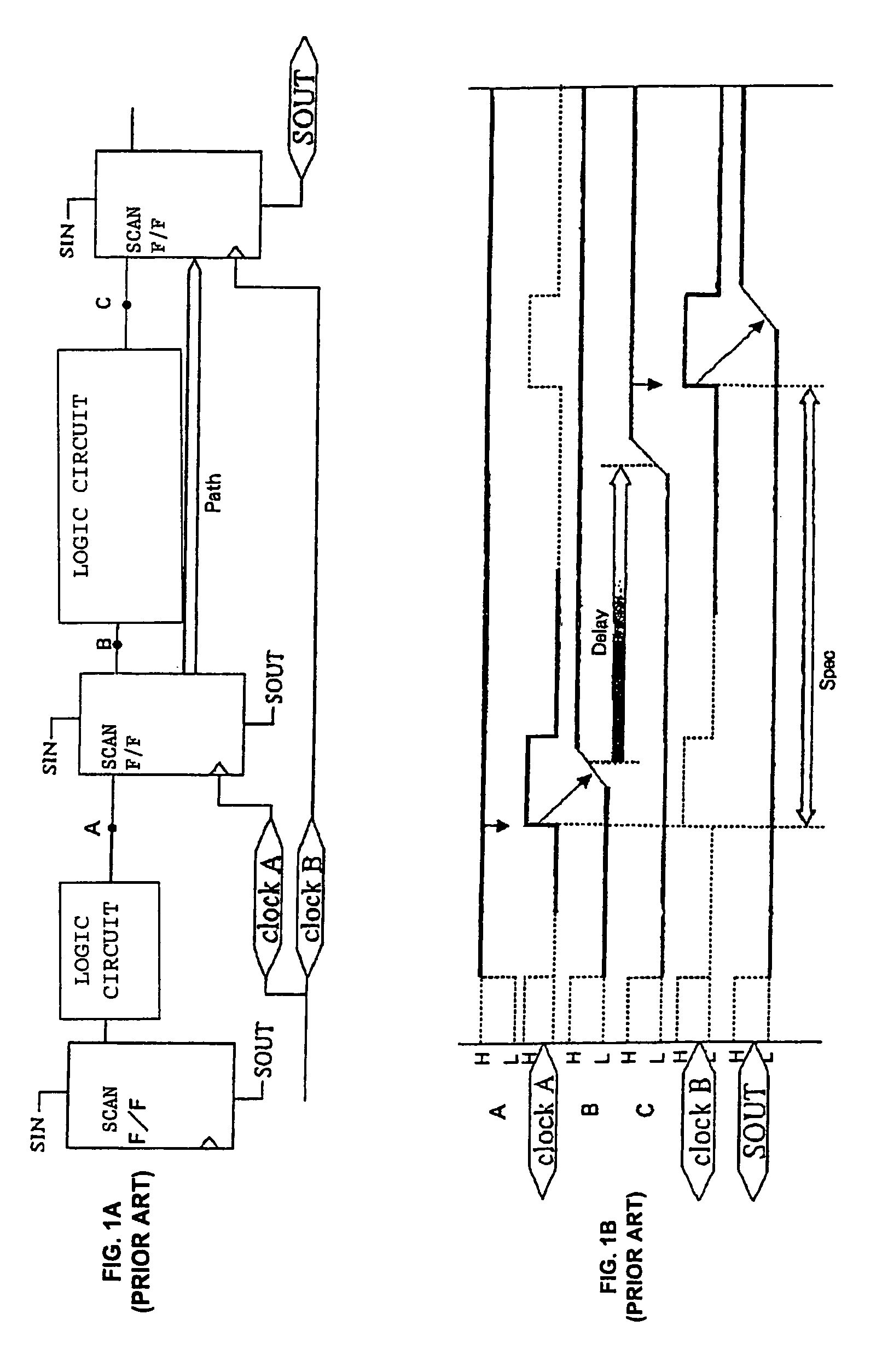

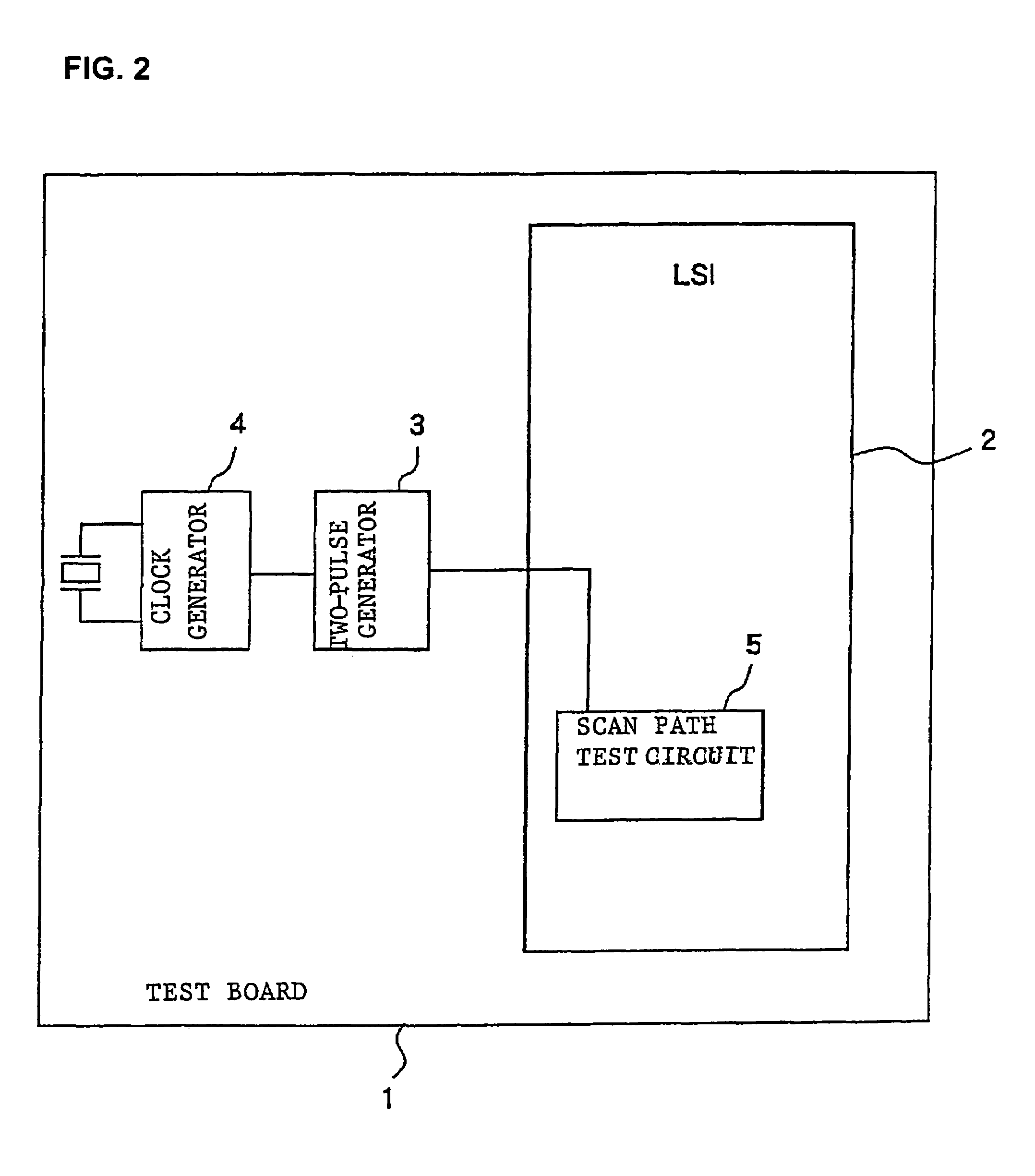

Semiconductor integrated circuit device and device for testing same

InactiveUS7131041B2Tested rather inexpensivelyInexpensively be putDigital circuit testingSolid-state devicesEngineeringSemiconductor

A device for testing a semiconductor integrated circuit device has a test board on which the semiconductor integrated circuit device to be tested is removably mounted, and a two-pulse generator mounted on the test board, for generating two pulses spaced from each other by a pulse interval equal to the period of a test clock for the delay test, from the test clock, and supplying the generated two pulses to the scan path test circuit. The device also has a PLL circuit for multiplying the frequency of the test clock and supplying a signal having the multiplied-frequency to the two-pulse generator.

Owner:RENESAS ELECTRONICS CORP

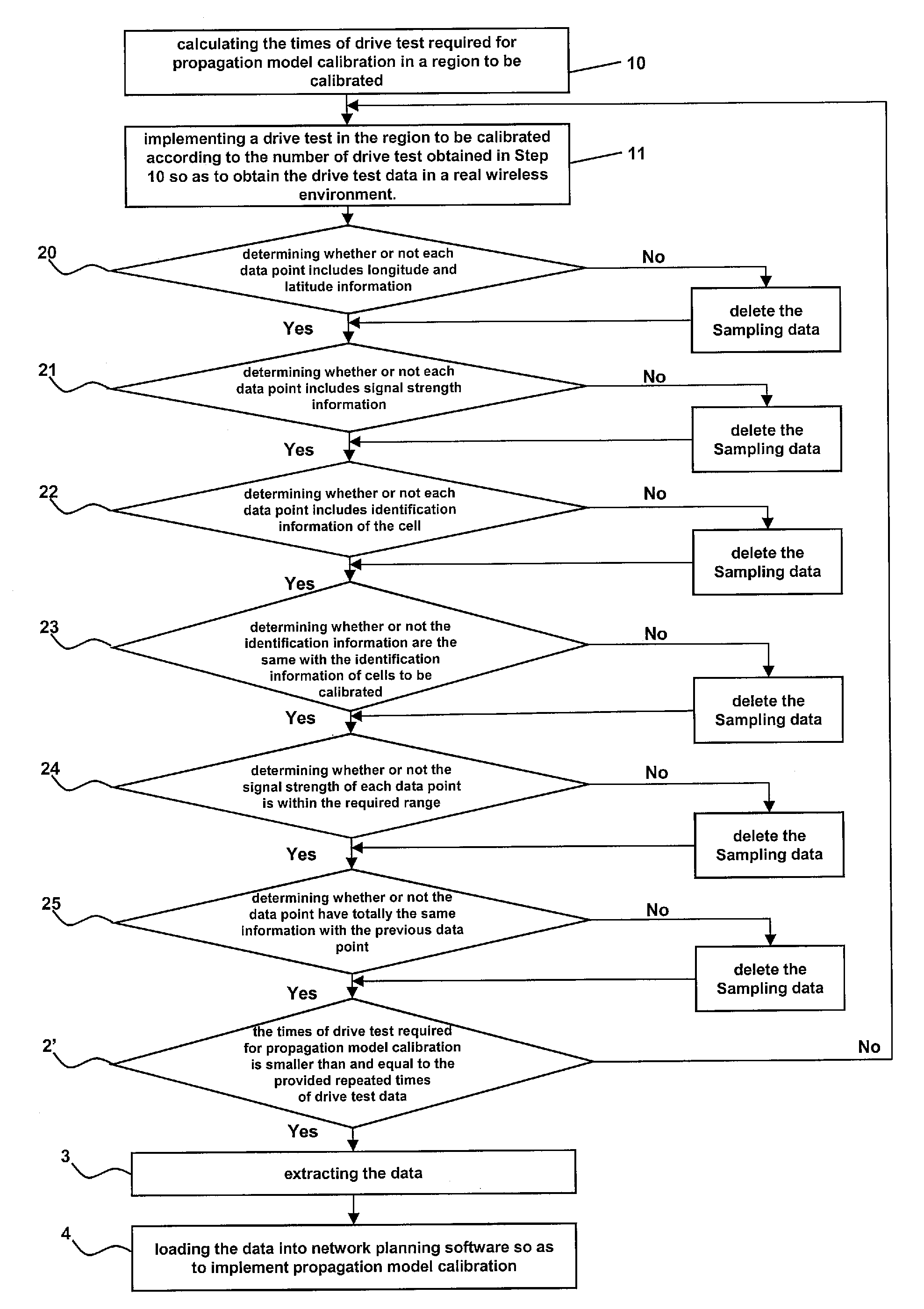

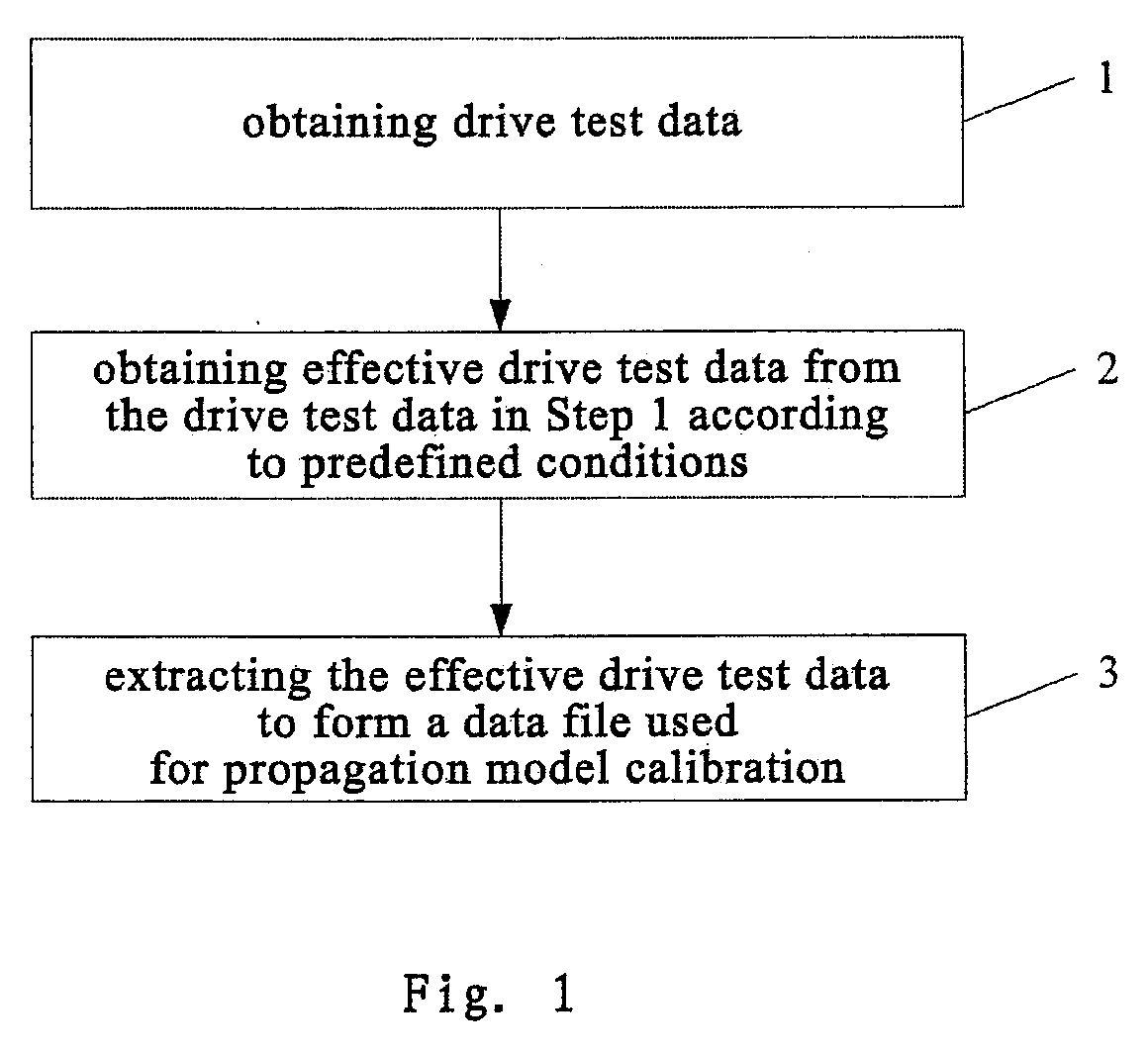

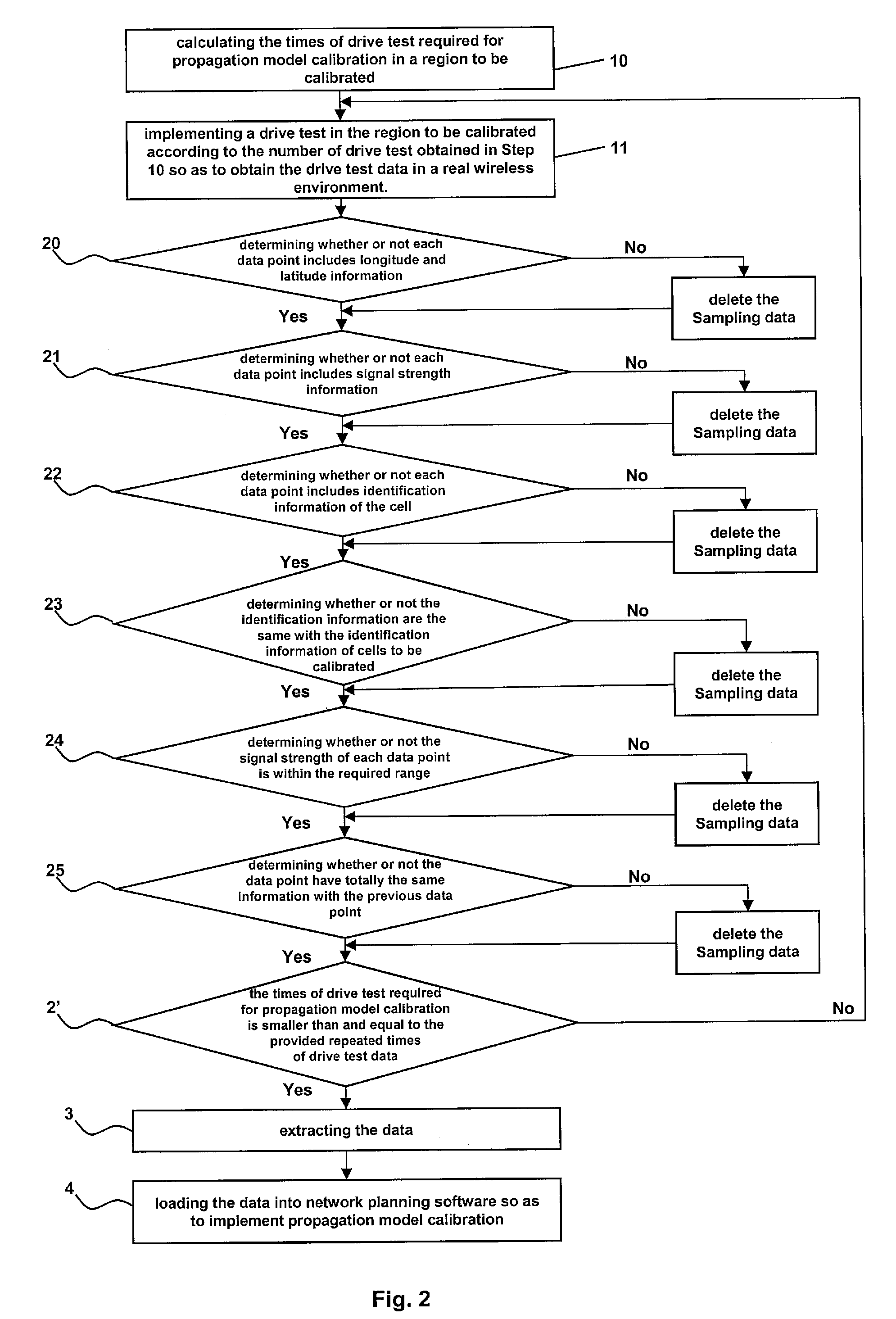

Method and apparatus of using drive test data for propagation model calibration

InactiveUS20090157342A1Reduce network construction costsAccurately reflect propagation characteristicDesign optimisation/simulationTesting/calibration of speed/acceleration/shock measurement devicesData fileComputer science

A method using drive test data for propagation model calibration includes: step 1, obtaining original drive test data; step 2, selecting the data from the drive test data according to predefined conditions as effective drive test data; and step 3, extracting the effective drive test data to form a data file used for propagation model calibration. An apparatus using drive test data for propagation model calibration includes: a drive test data obtaining module, configured to obtain the drive test data in the regions to be calibrated; an effective drive test data generation module, configured to generate effective drive test data from the drive test data according to predefined conditions; and a data file generation module, configured to extract the effective drive test data to form a data file used for propagation model calibration. The present invention utilizes drive test data of existing networks to largely decrease the CW test work and reduce the network building cost. It is believed that the calibrated model can relatively accurately reflect the propagation characteristics in the field. Furthermore, base stations can be optimally allocated.

Owner:CHINA MOBILE GROUP DESIGN INST +2

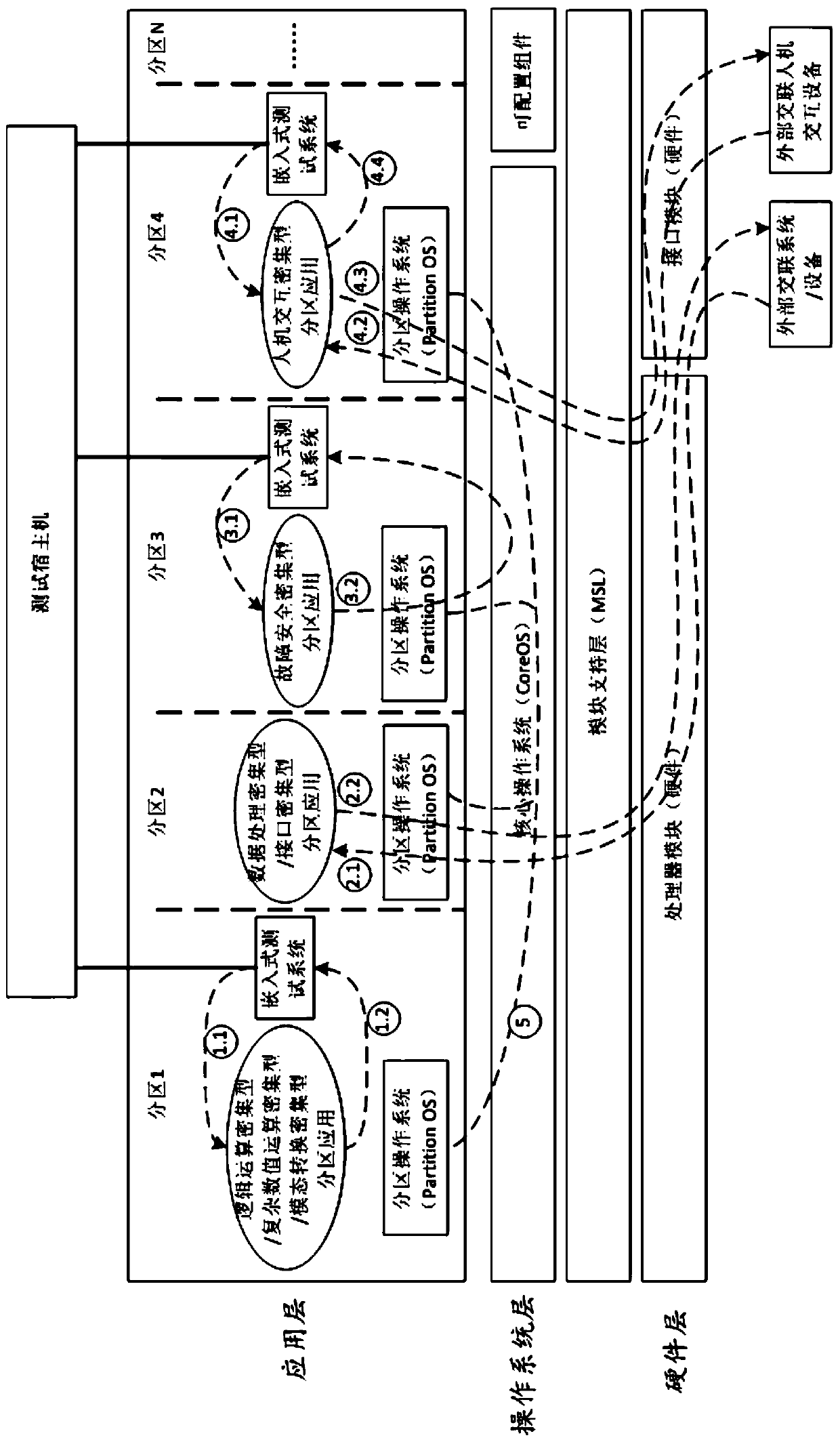

Method for testing multi-partition airborne software

ActiveCN111124927AImprove test efficiencyImprove integritySoftware testing/debuggingEnergy efficient computingOperational systemAlgorithm

The embodiment of the invention discloses a method for testing multi-partition airborne software, which comprises the following steps of: performing type division on partition application software according to the application field and task characteristics of the partition application software; according to the types of the partition application software, testing the partition application softwareby adopting a test mode corresponding to the types, and testing the partition operating system of each partition, wherein a test excitation path and a test output path are formulated for test modes adopted by different types of partition application software, and the test object comprises each layer and partition application software through which the path passes. According to the embodiment of the invention, the test problem of multi-application type software of multi-partition large-scale complex integrated system airborne software is solved, the test requirements of different application type software on IMA and high-security partition airborne operation can be met, and the method is suitable for unit component configuration items and system tests and has good generalization performance.

Owner:XIAN AIRCRAFT DESIGN INST OF AVIATION IND OF CHINA

Semiconductor integrated circuit device and delay fault testing method

InactiveUS7778790B2Electronic circuit testingResistance/reactance/impedenceShift registerControl signal

A semiconductor integrated circuit device includes a plurality of flip-flops configured to form a scan chain in a scan path test to operate as a shift register. The first flip-flop of the plurality of flip-flops latches a first input signal in synchronization with a clock signal, outputs a first output signal and fixes the first output signal based on the first selection control signal. A second flip-flop of the plurality of flip-flops latches a second input signal in synchronization with the clock signal, outputs a second output signal, and fixes the second output signal based on a second selection control signal. The semiconductor integrated circuit device further includes a control circuit configured to generate the first and second selection control signals such that a period during which the first flip-flop fixes the first output signal is different from a period during which the second flip-flop fixes the second output signal.

Owner:RENESAS ELECTRONICS CORP

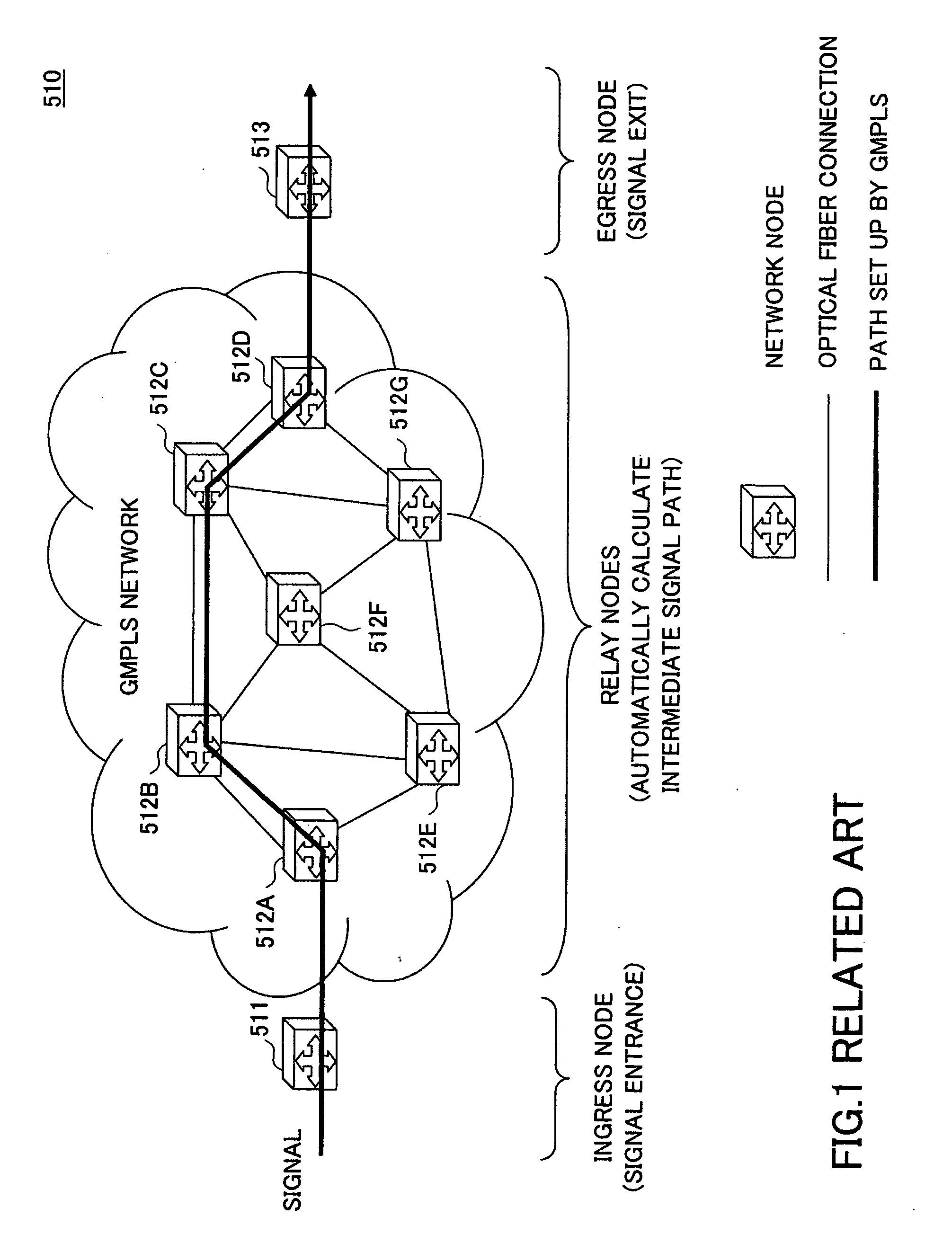

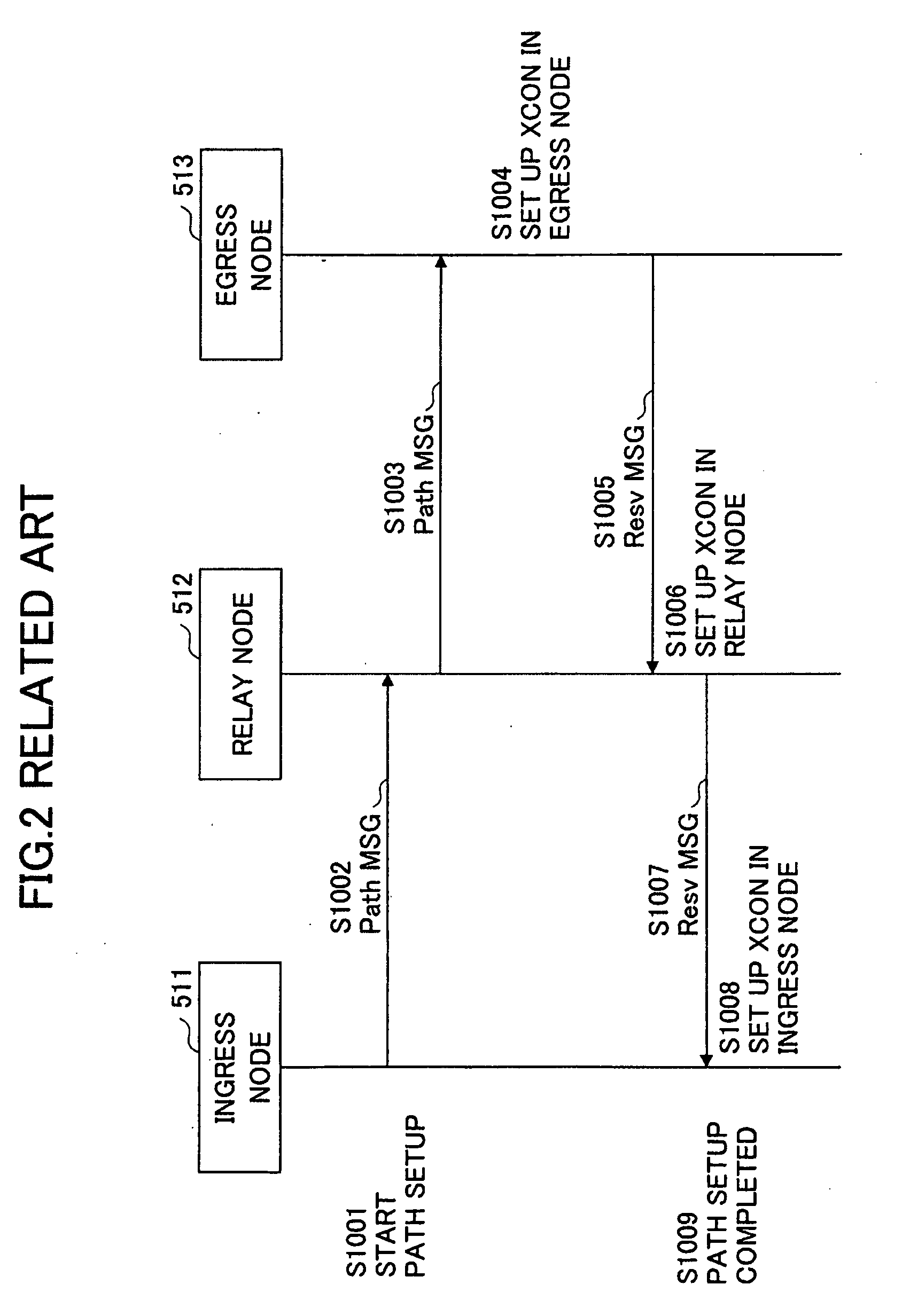

Transmission apparatus, path testing method, and storage medium

InactiveUS20090297141A1Delay in testingEasy to set upError preventionFrequency-division multiplex detailsComputer scienceReal-time computing

A transmission apparatus in a network where a path is set up is disclosed that includes a processing part configured to transmit a frame of the network to an egress node of the path when being set as an ingress node of the path, the frame having setup information of the path written therein, and to loop back the frame when being set as the egress node, the frame having response information written therein based on the setup information read from the frame, the response information indicating that the path is set up correctly.

Owner:FUJITSU LTD