Patents

Literature

613 results about "Test input" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

Test_input is a user defined function and not a function built into PHP. Looking at the code it does indeed mean that if no comment has been inserted then it will be empty, however if it is not empty run the comment through the test_input function.

Automated test input generation for web applications

ActiveUS20090125976A1Error detection/correctionSoftware engineeringSource transformationString operations

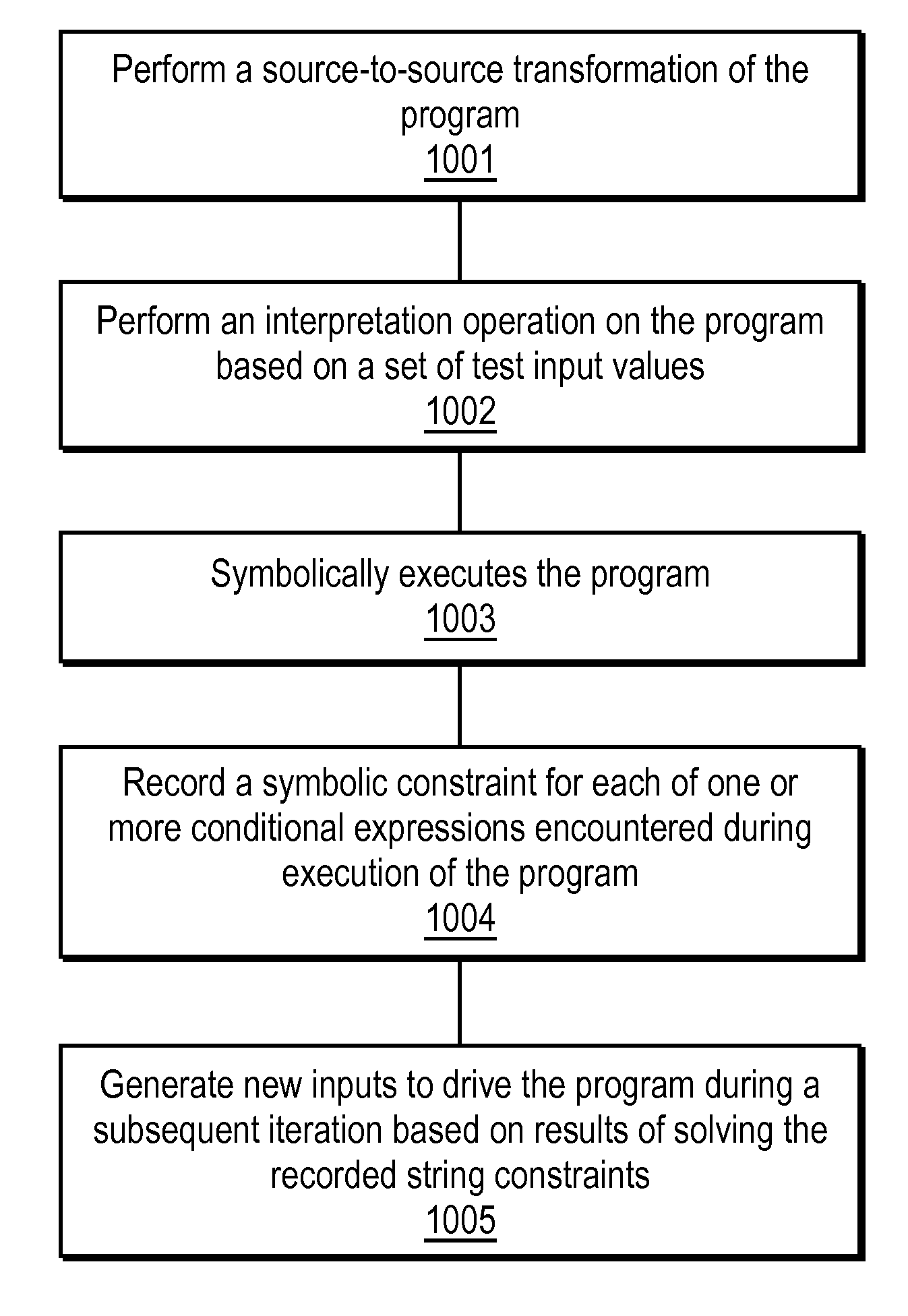

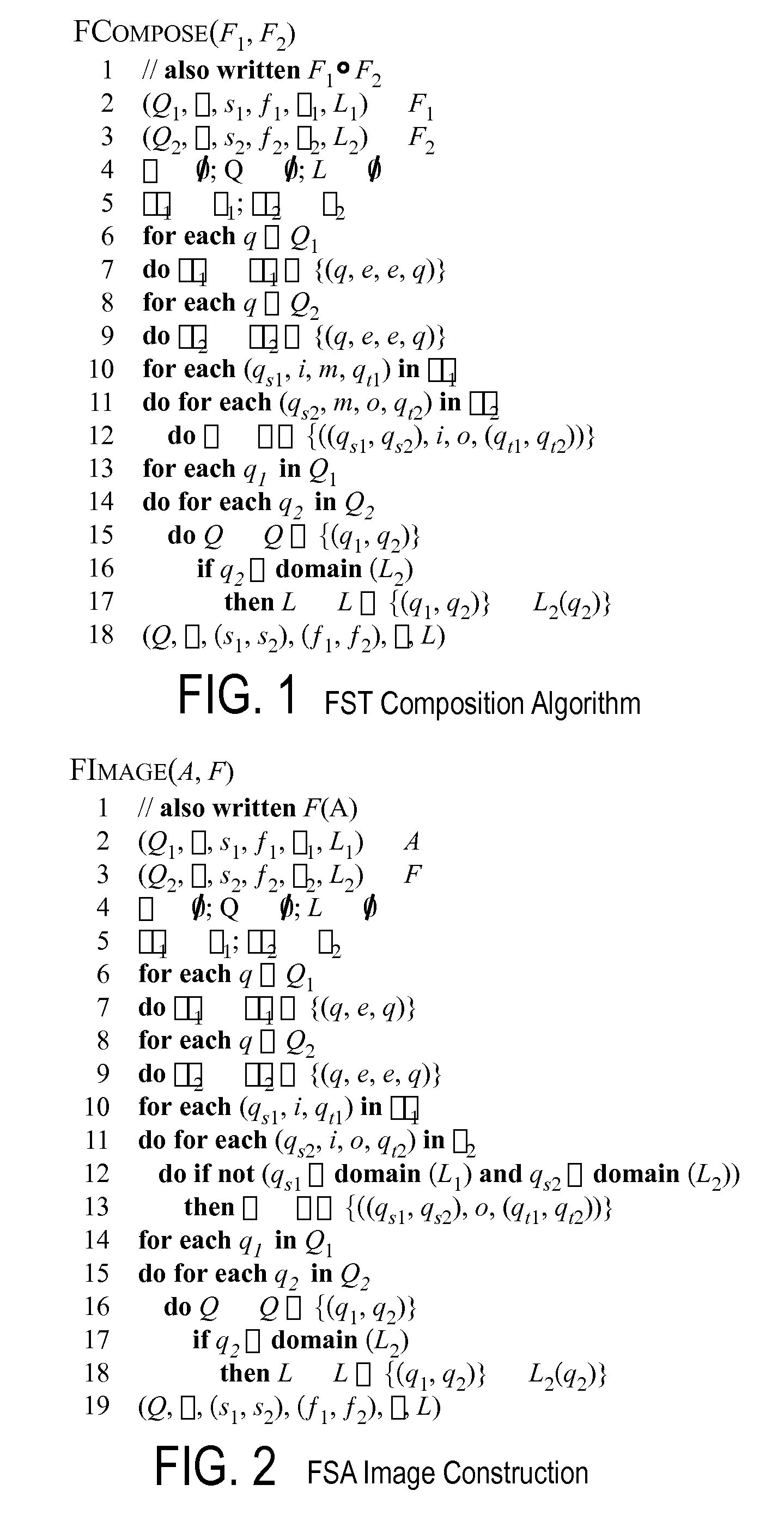

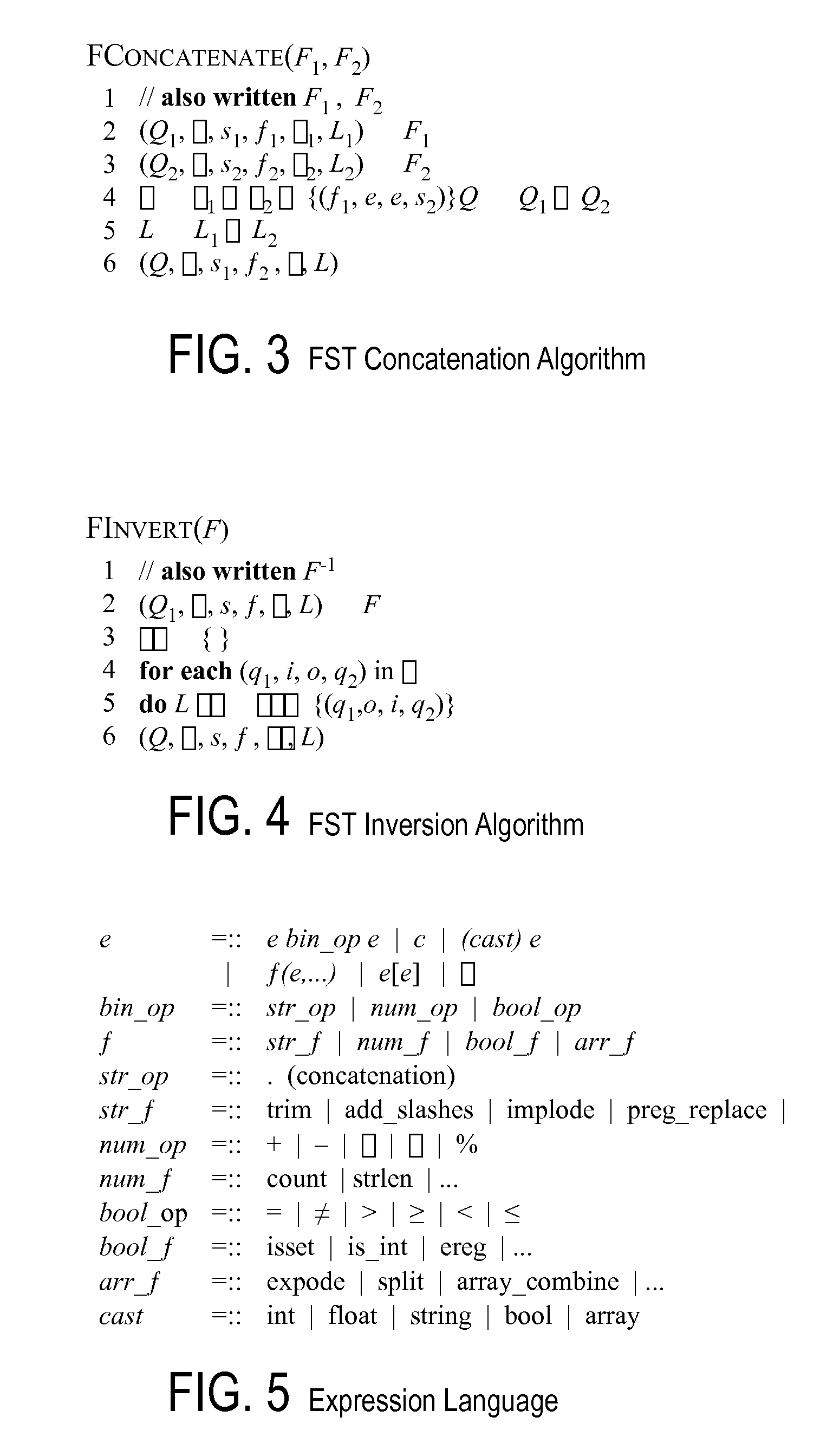

A method and apparatus is disclosed herein for automated test input generation for web applications. In one embodiment, the method comprises performing a source-to-source transformation of the program; performing interpretation on the program based on a set of test input values; symbolically executing the program; recording a symbolic constraint for each of one or more conditional expressions encountered during execution of the program, including analyzing a string operation in the program to identify one or more possible execution paths, and generating symbolic inputs representing values of variables in each of the conditional expressions as a numeric expression and a string constraint including generating constraints on string values by modeling string operations using finite state transducers (FSTs) and supplying values from the program's execution in place of intractable sub-expressions; and generating new inputs to drive the program during a subsequent iteration based on results of solving the recorded string constraints.

Owner:NTT DOCOMO INC

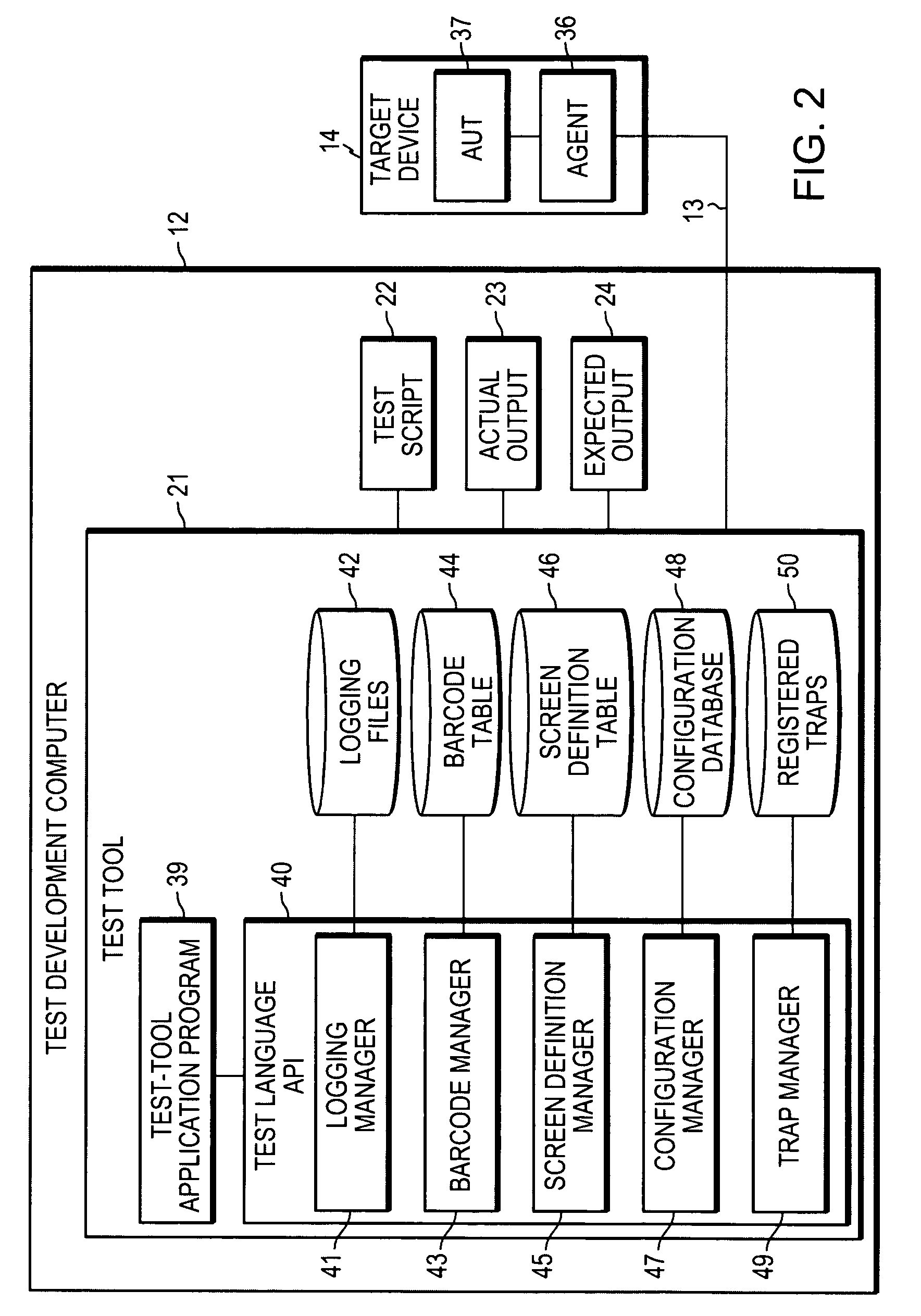

Automated test system for testing an application running in a windows-based environment and related methods

ActiveUS20050204343A1Software testing/debuggingNon-redundant fault processingComputer hardwareGraphics

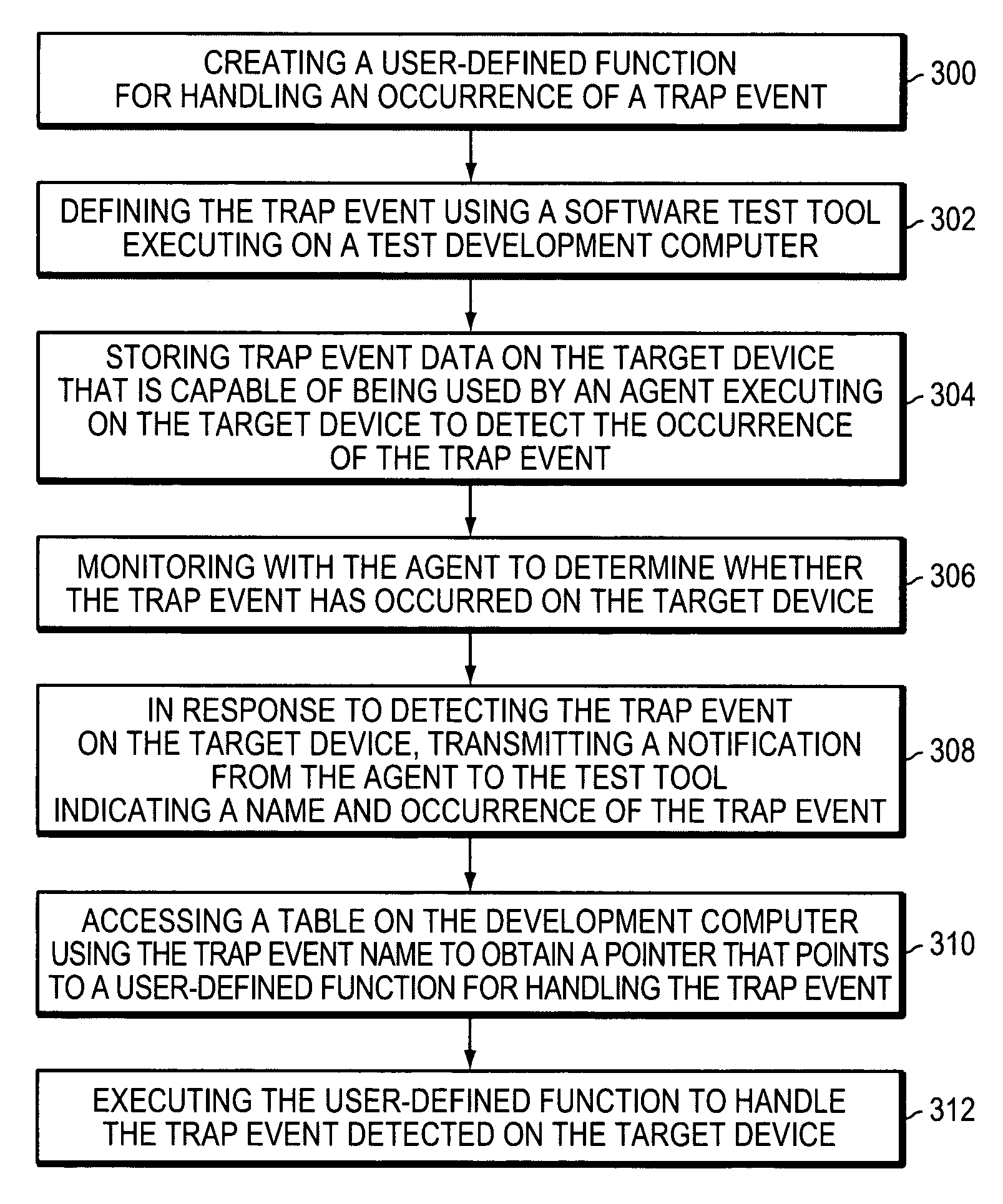

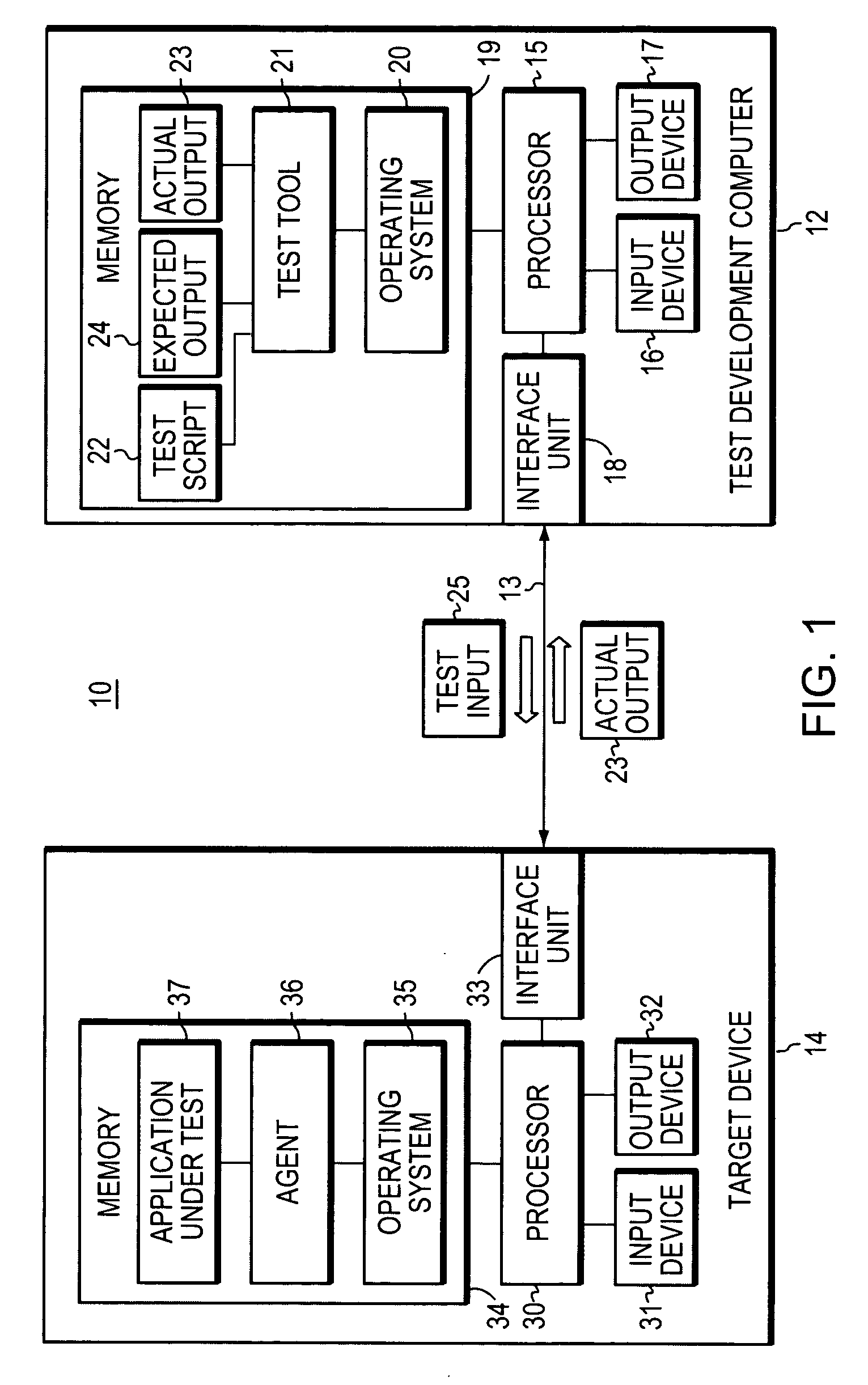

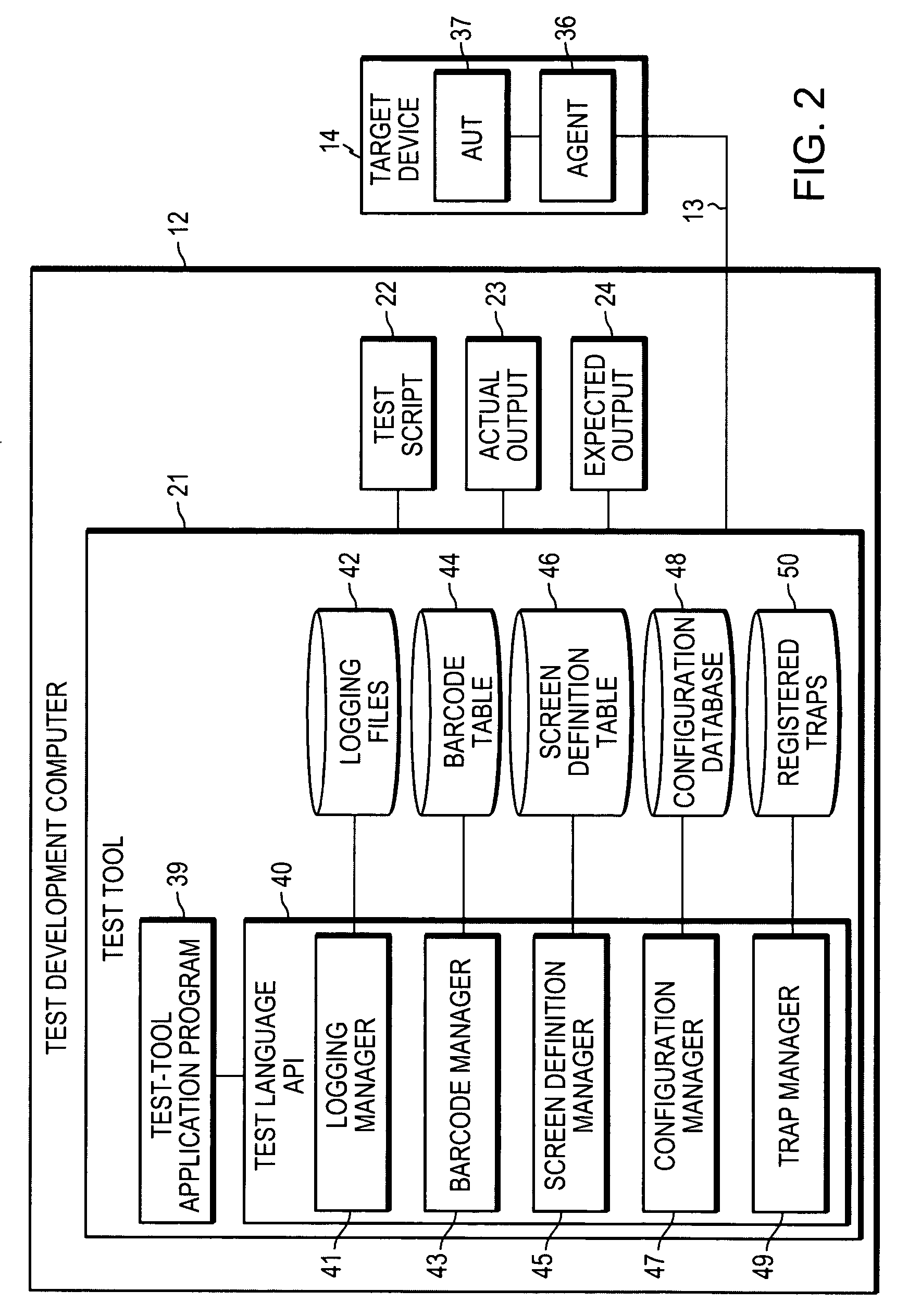

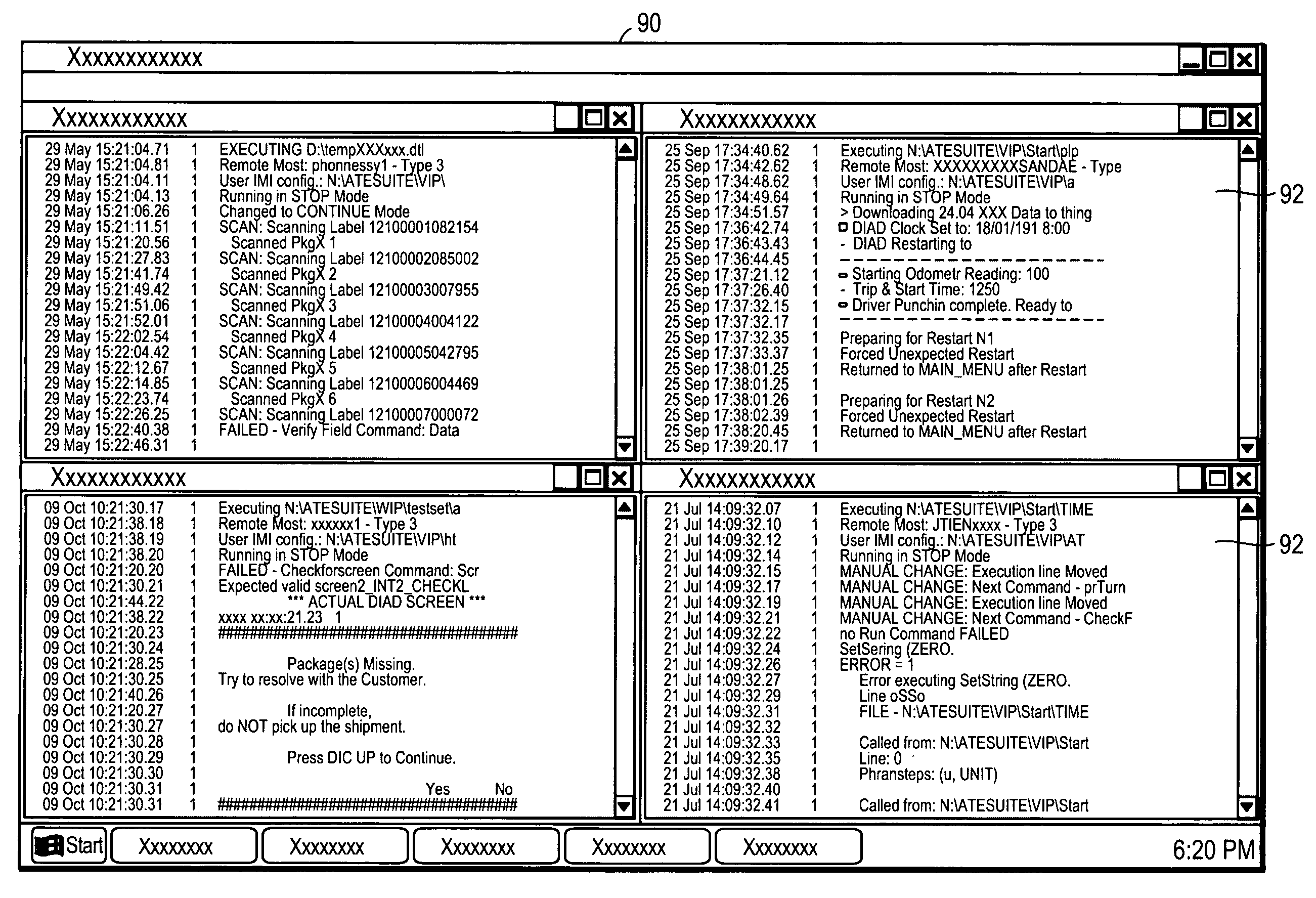

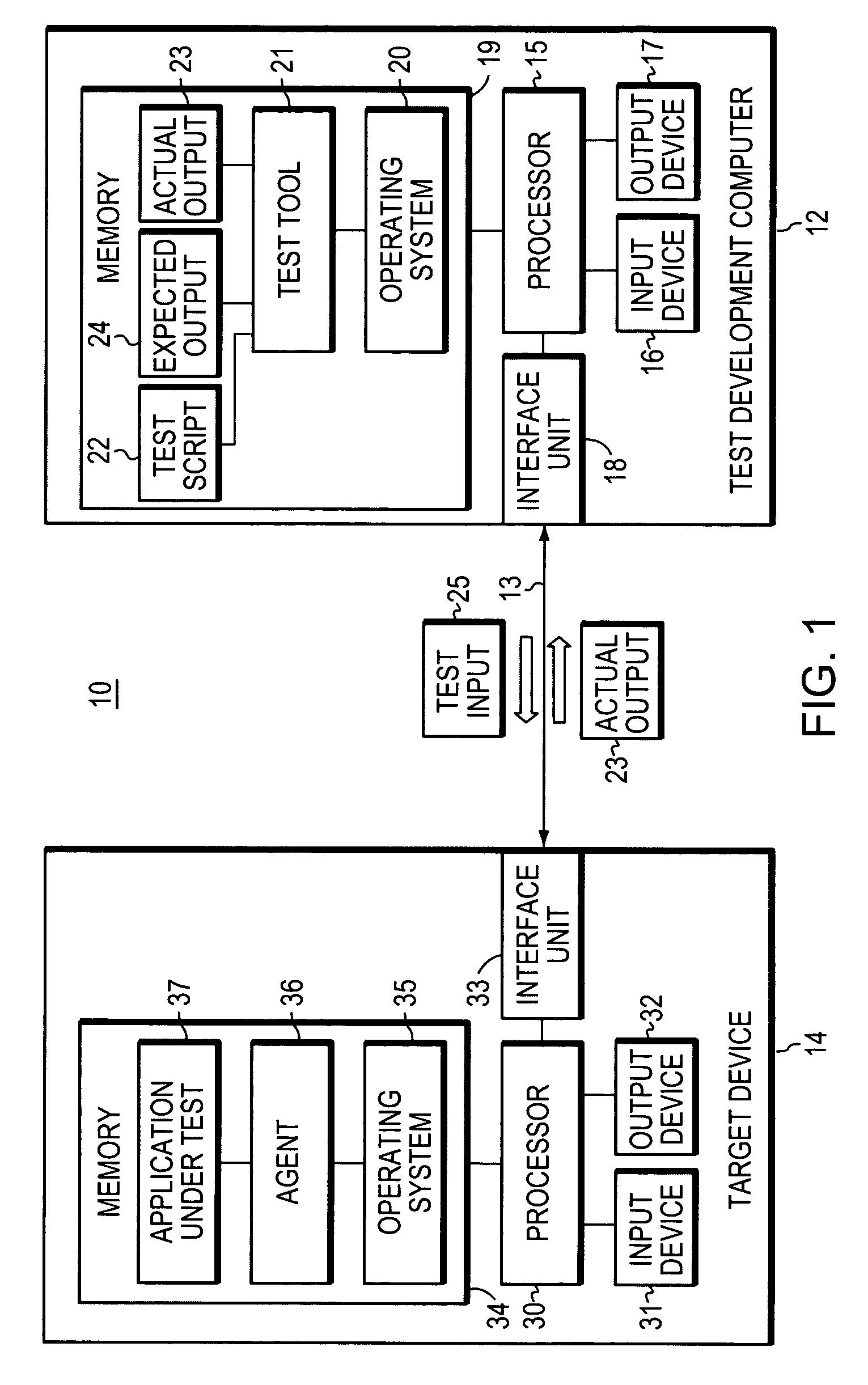

Methods and systems disclosed herein can be used for testing an application's rendering of output to individual controls of a Graphical User Interface (GUI), displayed on a target device executing the application. A system according to the present invention includes a test tool running on a development computer that communicates with an agent executing on the target device. Testing is performed by using the test tool to execute test scripts, which cause test input to be injected via the agent into the application on the target device. The test tool can validate whether actual output on the target device matches expected output known to the test tool. The present invention includes a variety of key components, such as a flexible trap manager for handling unexpected screens that appear during an automated test, and a configuration manger for testing against multiple languages and platform configurations.

Owner:UNITED PARCEL SERVICE OF AMERICAN INC

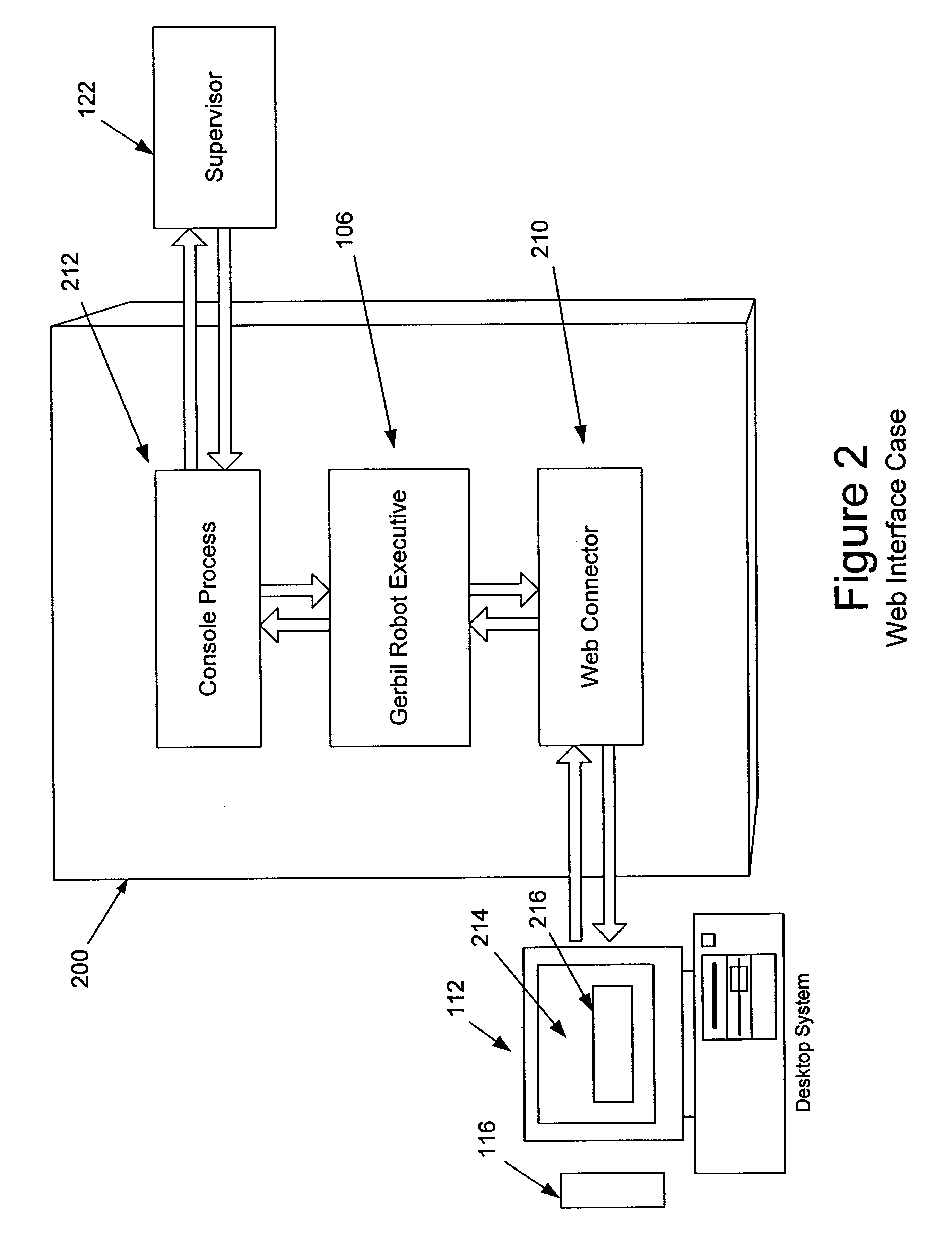

System and method for automatically verifying the performance of a virtual robot

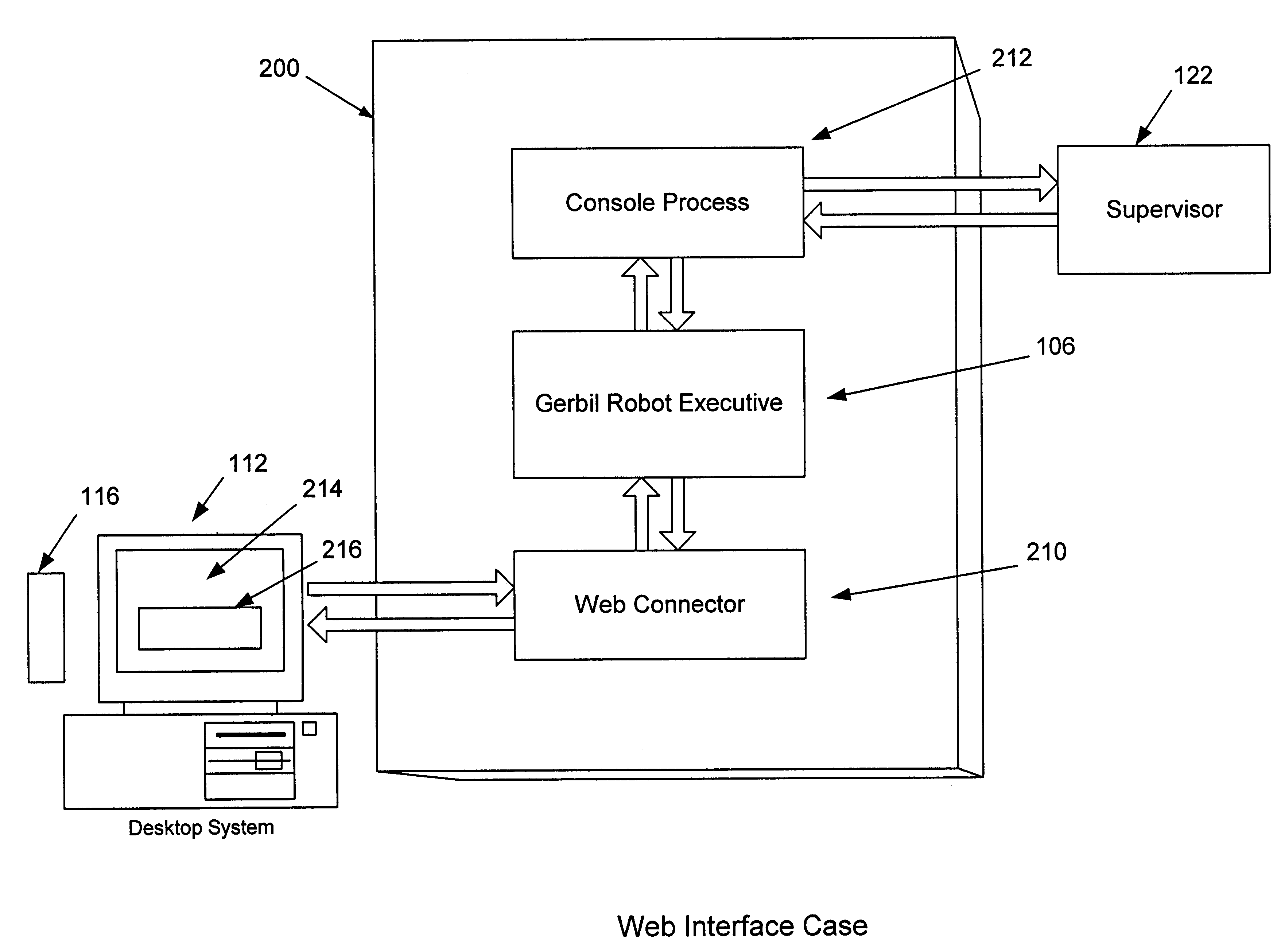

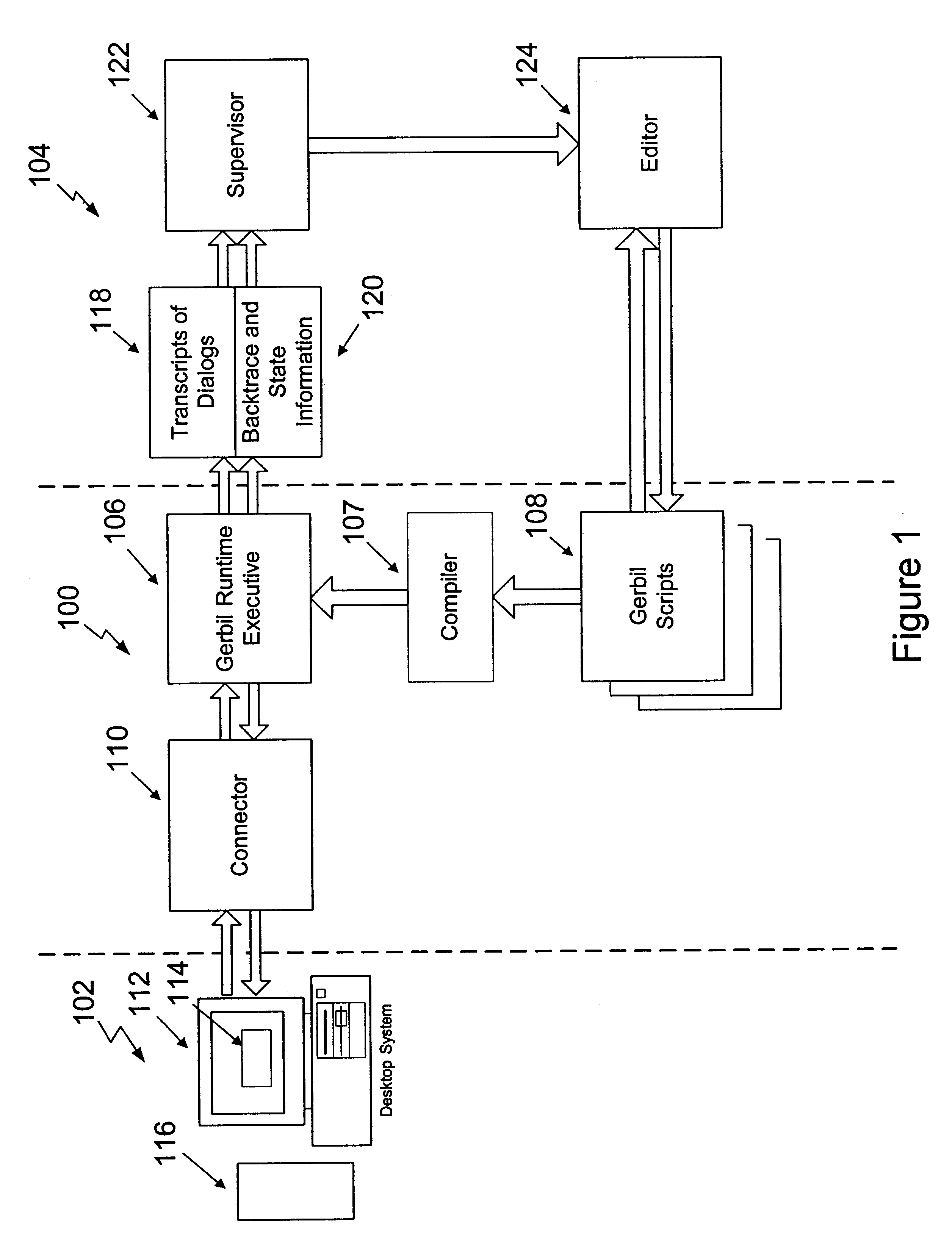

In an automated interface program designed to interact and communicate with users, said program executing actions when a category among a predefined set of categories is activated, a method is disclosed for automatically verifying the performance of said program, the steps of said method comprising: specifying inputs under which the program should be tested; associating said inputs with conditions within categories in the program, each said condition comprising at least one response which could be given if said condition is satisfied; executing said program under at least one said input; determining whether the associated condition is satisfied upon said input; and determining whether the response associated with said condition is given upon said input. In another aspect of the present invention, the test inputs are embedded within the script itself, and specifically, within categories that can be automatically listed upon compilation of the script. Such list of test inputs can then be automatically executed to test the program. The execution of a test input can be used to check whether the test input activated the category in which the test input is embedded. The response given upon execution of a test input can then determine whether other categories are erroneously activated; or whether inputs, other than the test input, erroneously activate the category associated with the test input.

Owner:MICRO FOCUS LLC

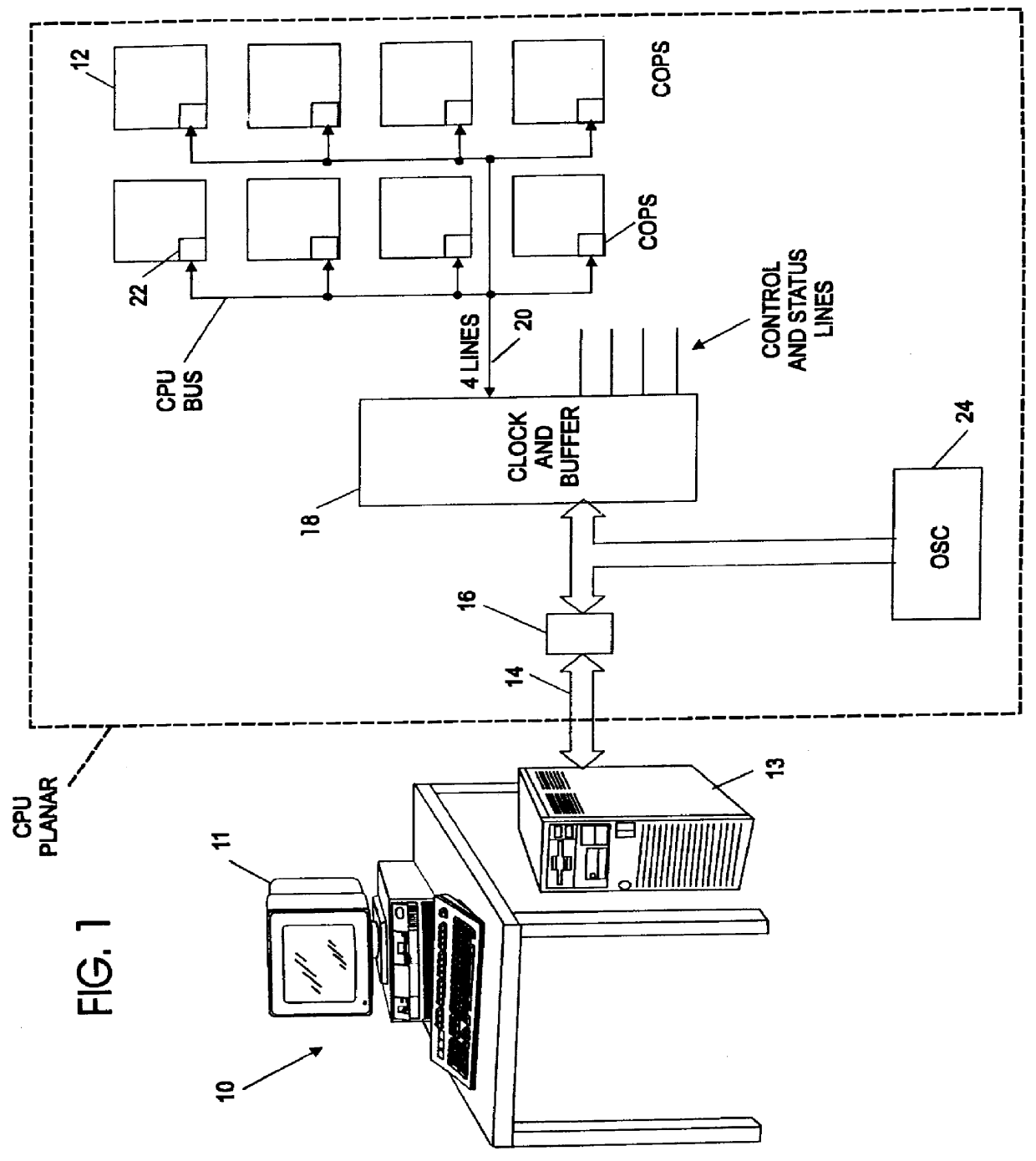

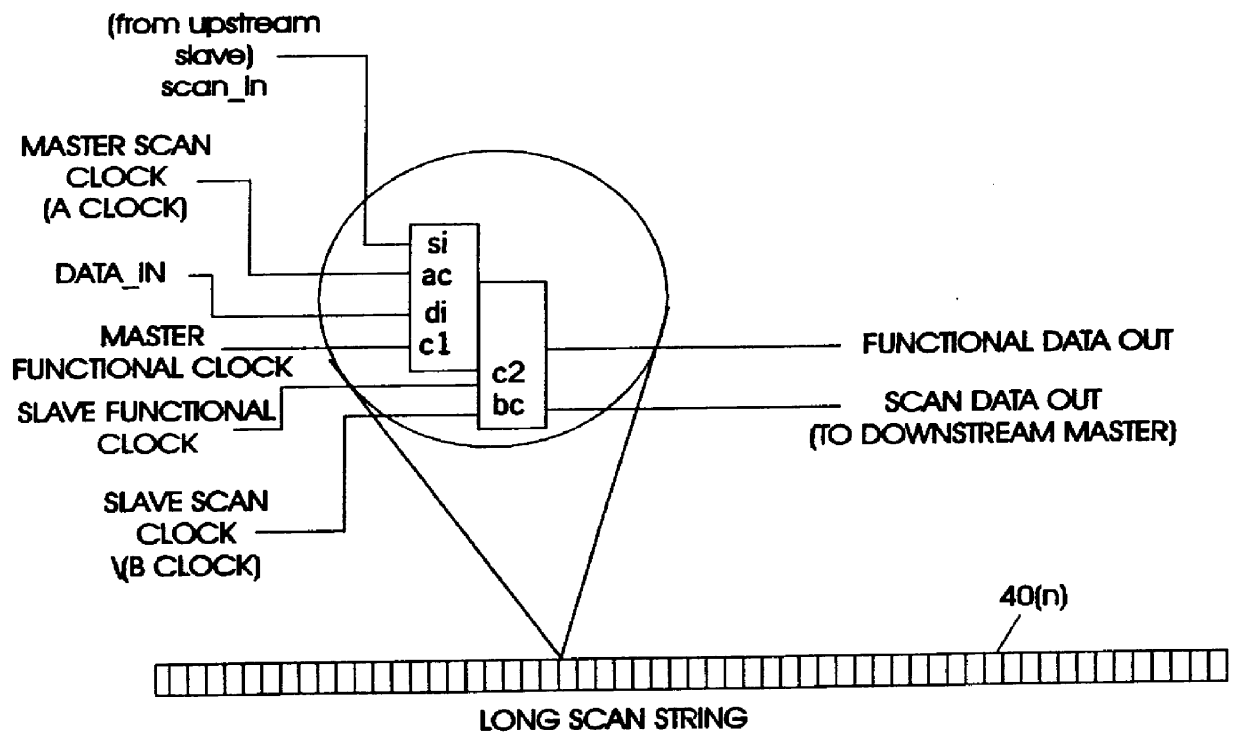

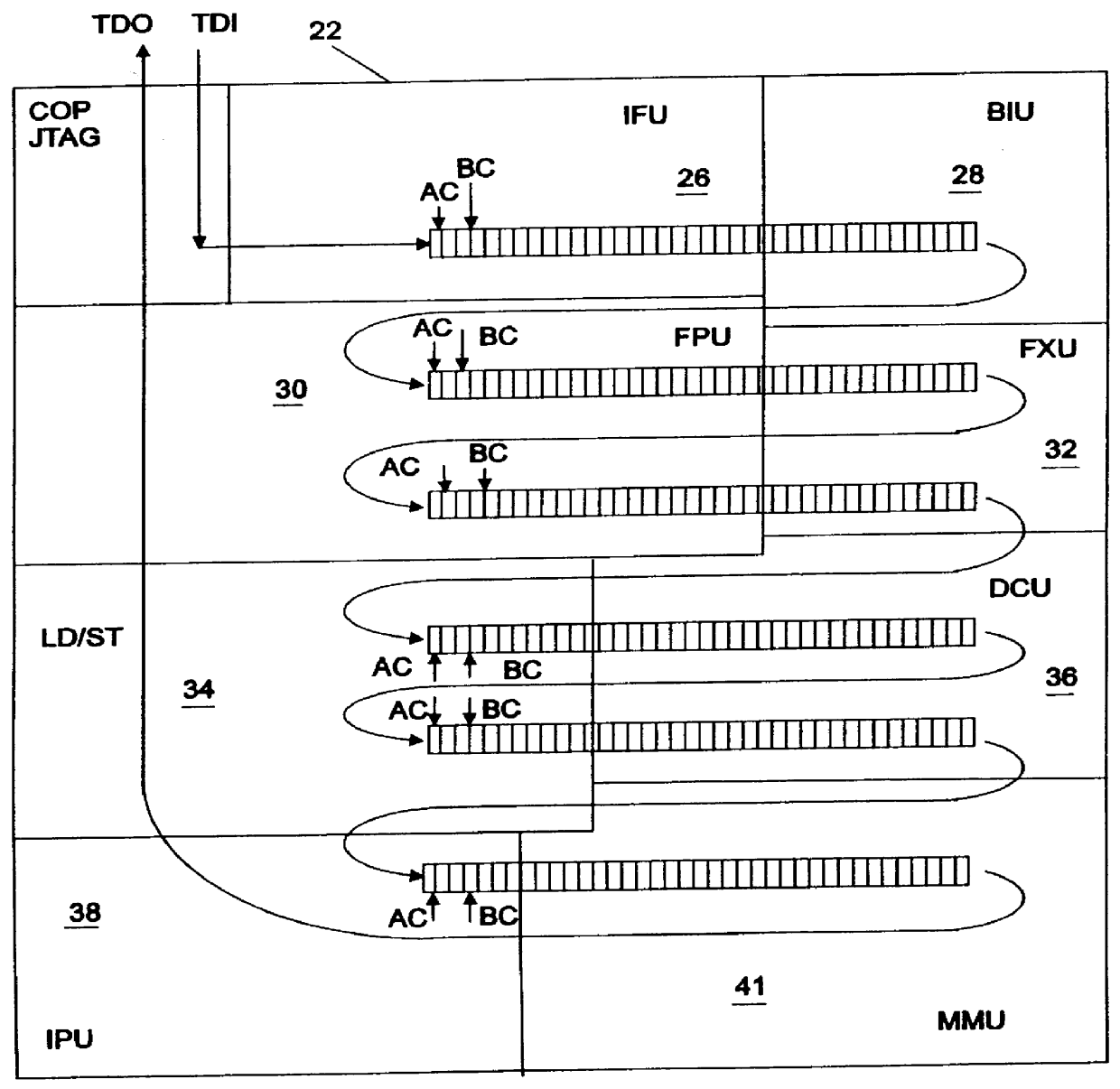

Apparatus and methods for testing a microprocessor chip using dedicated scan strings

InactiveUS6028983AReduce memory requirementsReduce scan timeElectronic circuit testingError detection/correctionTest inputJoint Test Action Group

A test apparatus and method for design verification of at least one microprocessor chip includes a compatible Joint Task Action Group (JTAG) terminal for access to a plurality of computer functional units contained in the chip. A test input terminal included in the JTAG terminal receives a scan string, the string being coupled to each computer functional unit through a first multiplexer. The scan input string is separated by the JTAG terminal under program control into a series of dedicated scan strings, each dedicated scan string being supplied to a selected functional unit through the first multiplexer. Each functional unit includes start and stop scan clocks for testing the functional under program control using the dedicated scan train for the functional unit. A test output terminal included in the JTAG terminal is coupled to each functional unit through a second multiplexer. The test results of the dedicated scan string under control of the scan clock are supplied to the output terminal through the second multiplexer. The compatible JTAG terminal includes further elements for controlling the scan clocks to select a targeted functional unit for testing purposes while the scan strings for non-targeted functional units remain in an inactive state.

Owner:GOOGLE LLC

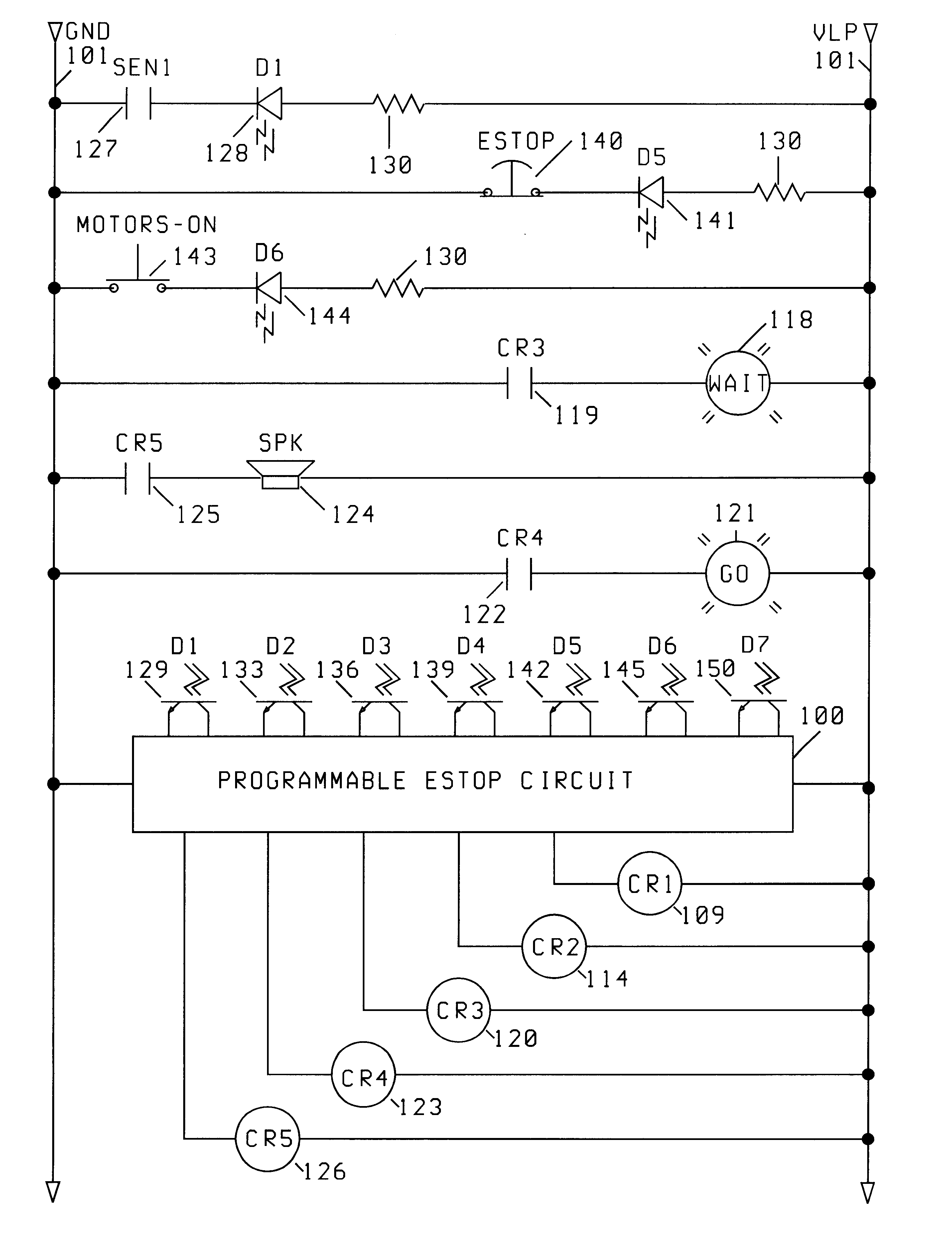

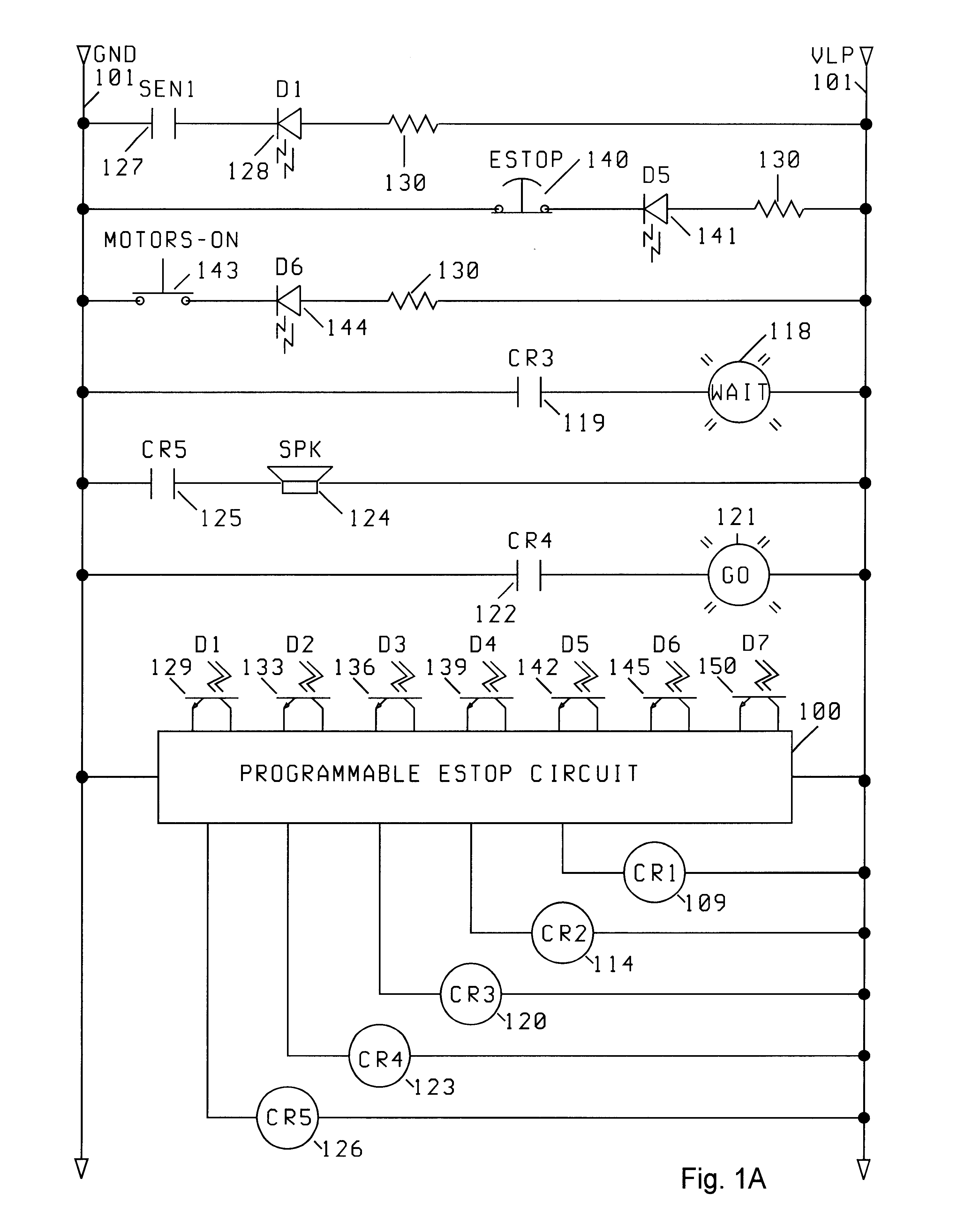

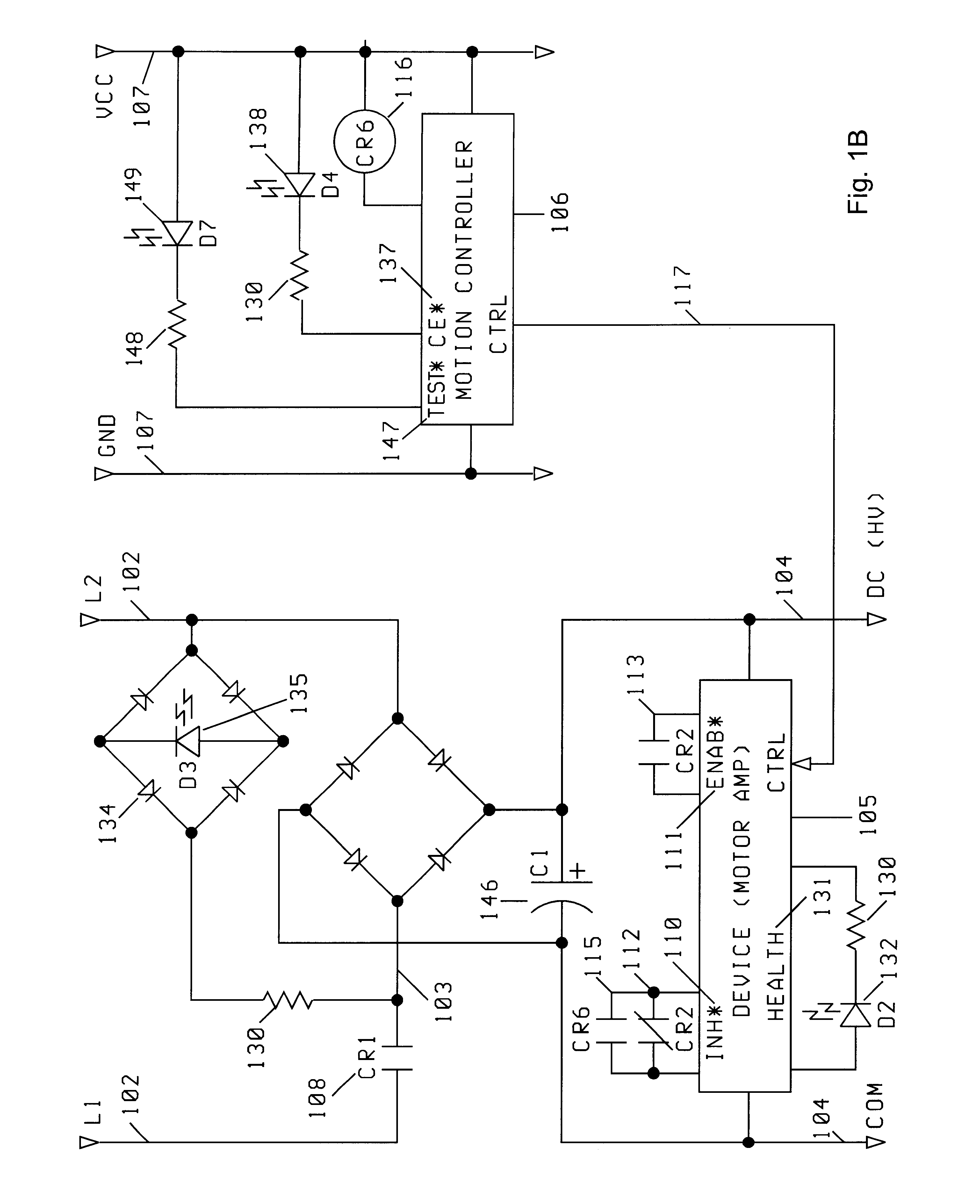

Programmable emergency-stop circuit with testing

InactiveUS6734581B1Safely incorporatedReduce sensitivityBatteries circuit arrangementsEmergency protective circuit arrangementsTest inputKill switch

The invention includes a programmable emergency-stop circuit apparatus and method that provides advanced function not found in other systems. The circuit centralizes the control of high voltage motor power into one place, by providing connections for, in its minimum configuration, several different kill switches, a motors-on button, and an AC motor power relay coil. In the present invention, kill switches, test inputs, emergency-stop and motors-on buttons, computer ready and watchdog signals are all conveniently connected in one location, alongside the AC motor power relay coil driver. Programmable options exist for testing kill inputs online, while the emergency stop is energized.

Owner:EIGENPOINT

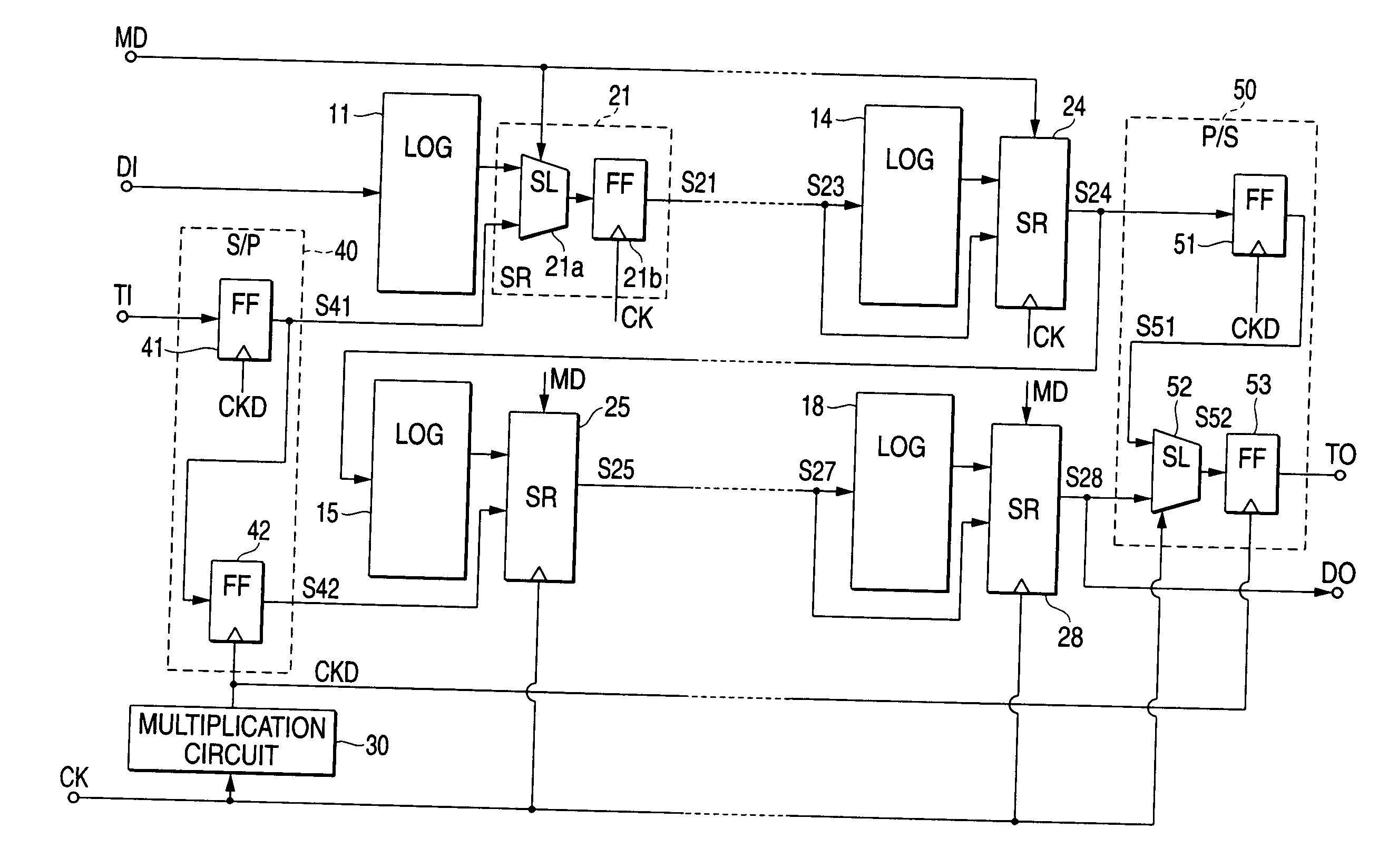

Semiconductor integrated circuit with a test circuit

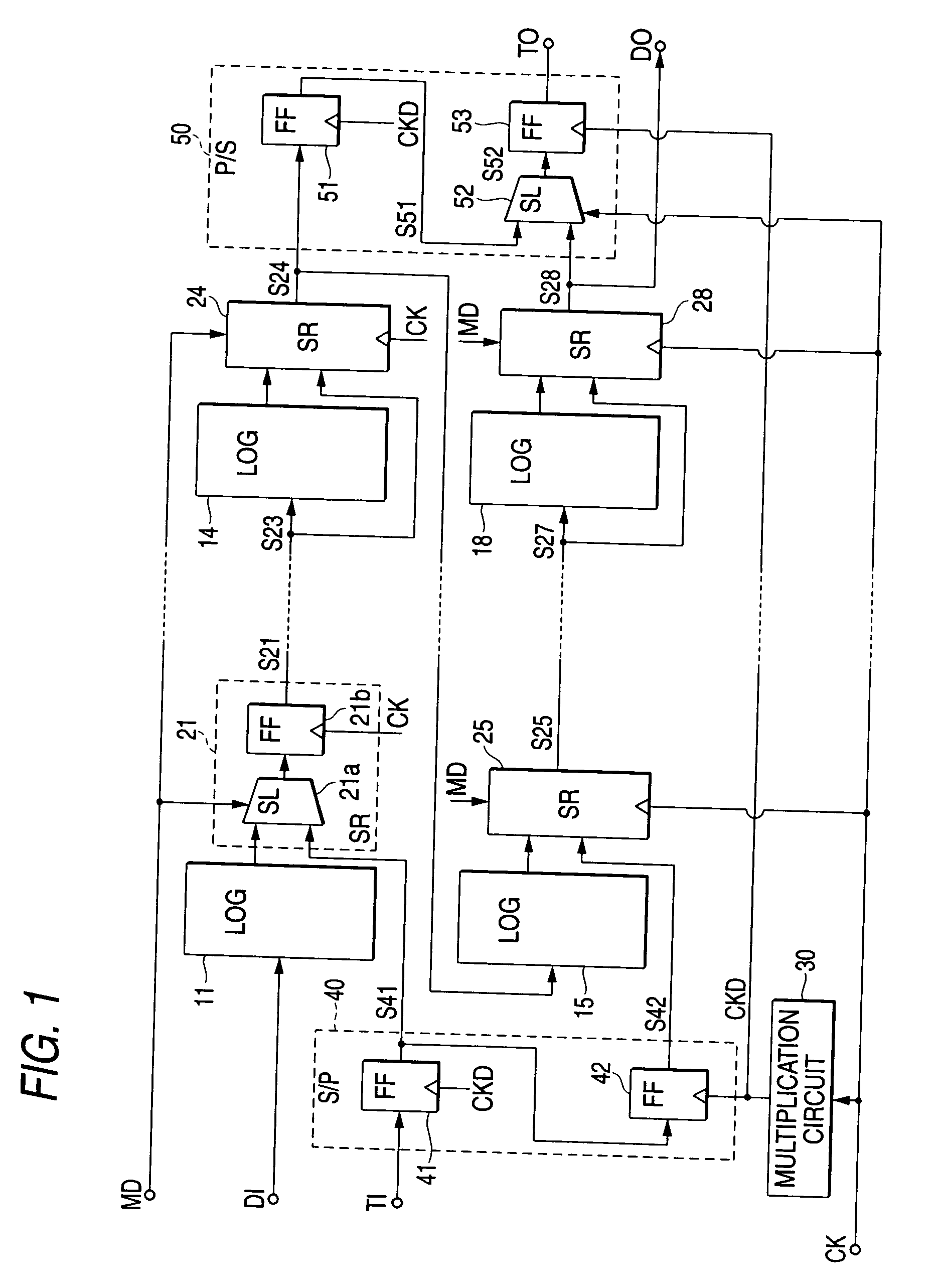

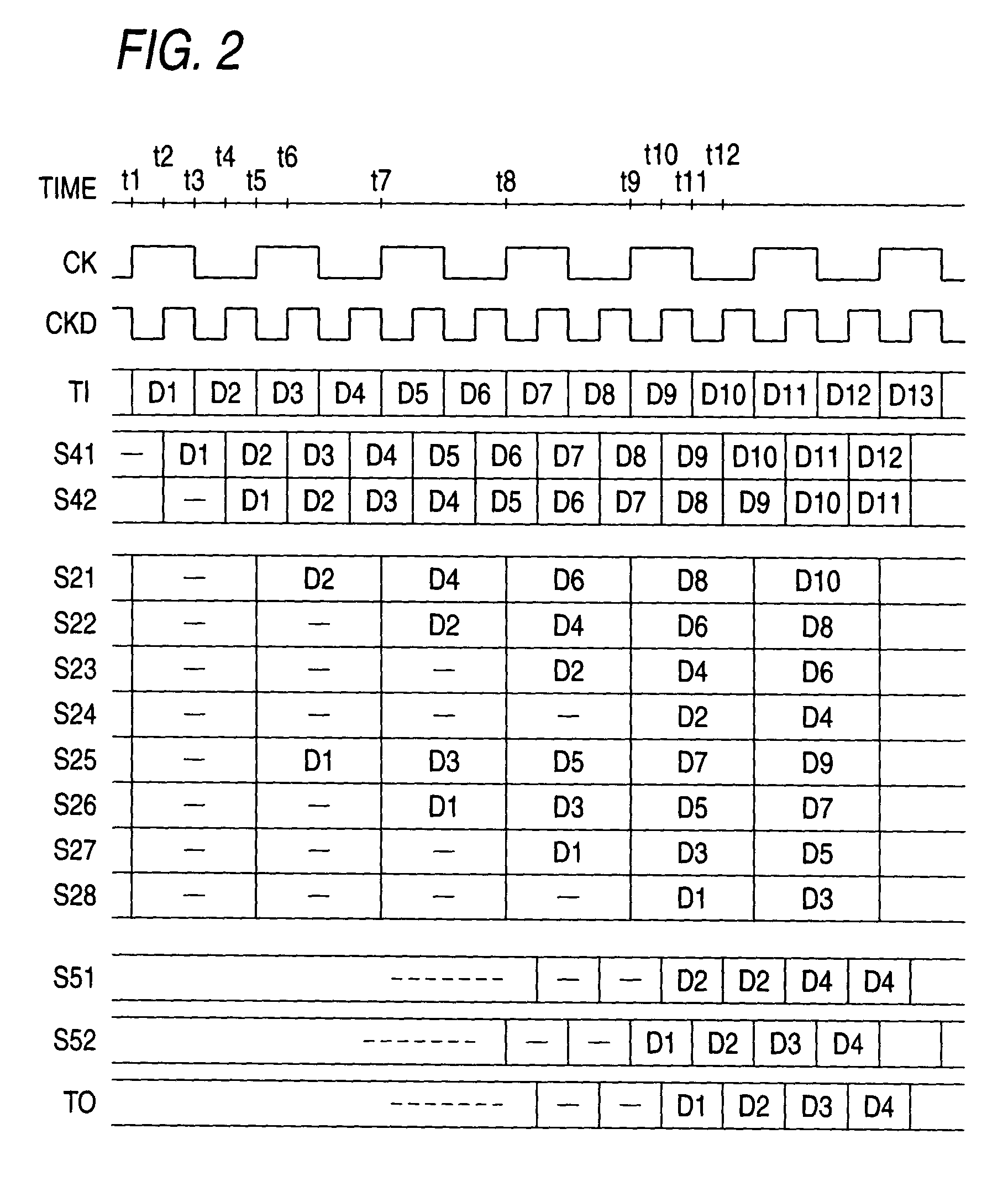

A shift scan chain includes logic circuit blocks 11-18 and scan registers 21-28 connected at stages succeeding them. The shift chain is divided into divisional chains including the scan registers 21-24 and the scan registers 25-28. In the test operation mode of a semiconductor integrated circuit, test input data TI are supplied in synchronism with a multiplied clock signal CKD at a frequency twice of that of a clock signal CK. The test input data TI are converted by a serial / parallel conversion circuit 40 into parallel data S41 and S42, which are respectively supplied to the head scan registers 21 and 25 of the corresponding divisional chains. The length of each divisional chains becomes ½, and a test time period can be shortened.

Owner:LAPIS SEMICON CO LTD

Automated test system for testing an application running in a windows-based environment and related methods

Methods and systems disclosed herein can be used for testing an application's rendering of output to individual controls of a Graphical User Interface (GUI), displayed on a target device executing the application. A system according to the present invention includes a test tool running on a development computer that communicates with an agent executing on the target device. Testing is performed by using the test tool to execute test scripts, which cause test input to be injected via the agent into the application on the target device. The test tool can validate whether actual output on the target device matches expected output known to the test tool. The present invention includes a variety of key components, such as a flexible trap manager for handling unexpected screens that appear during an automated test, and a configuration manger for testing against multiple languages and platform configurations.

Owner:UNITED PARCEL SERVICE OF AMERICAN INC

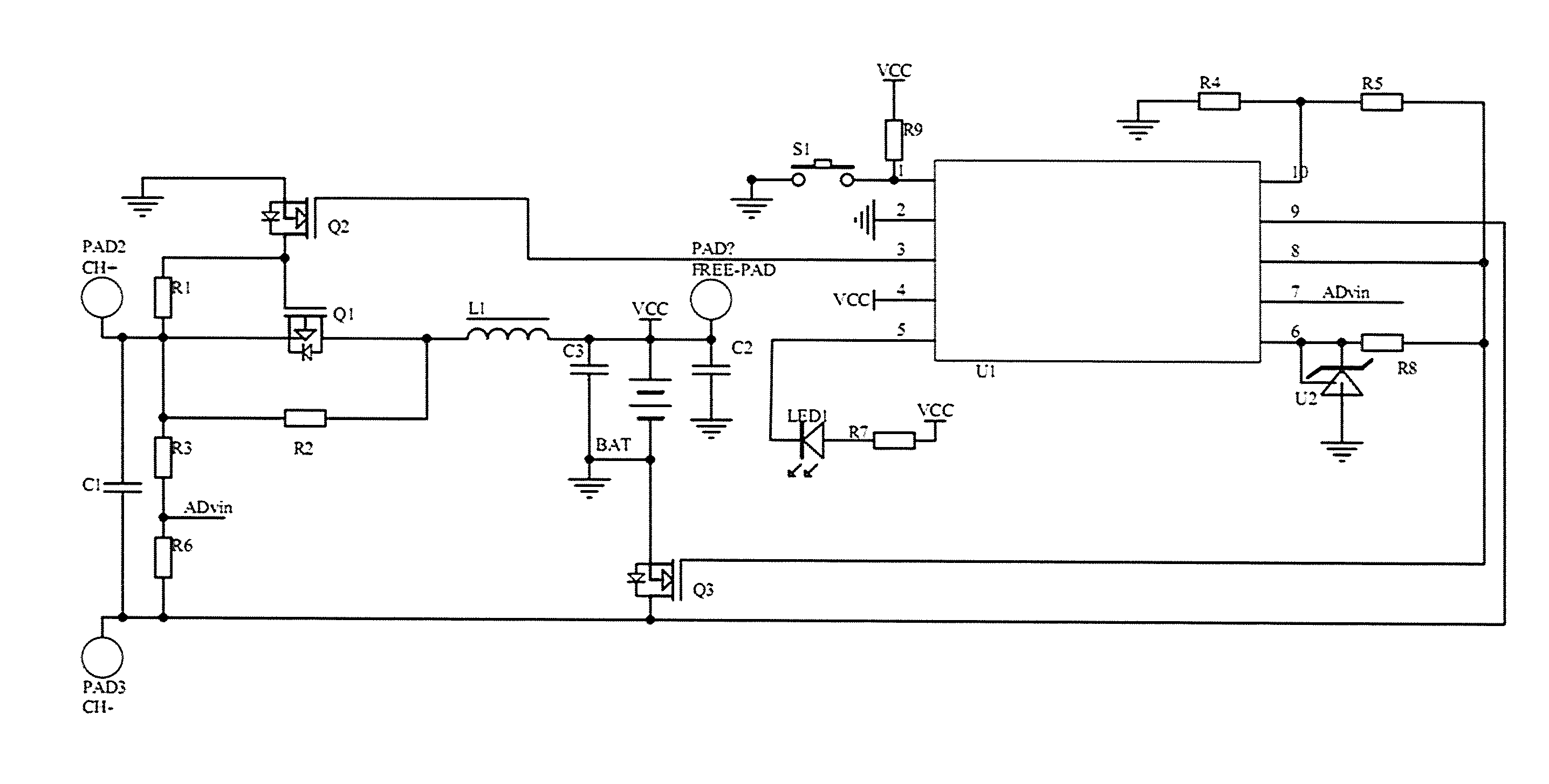

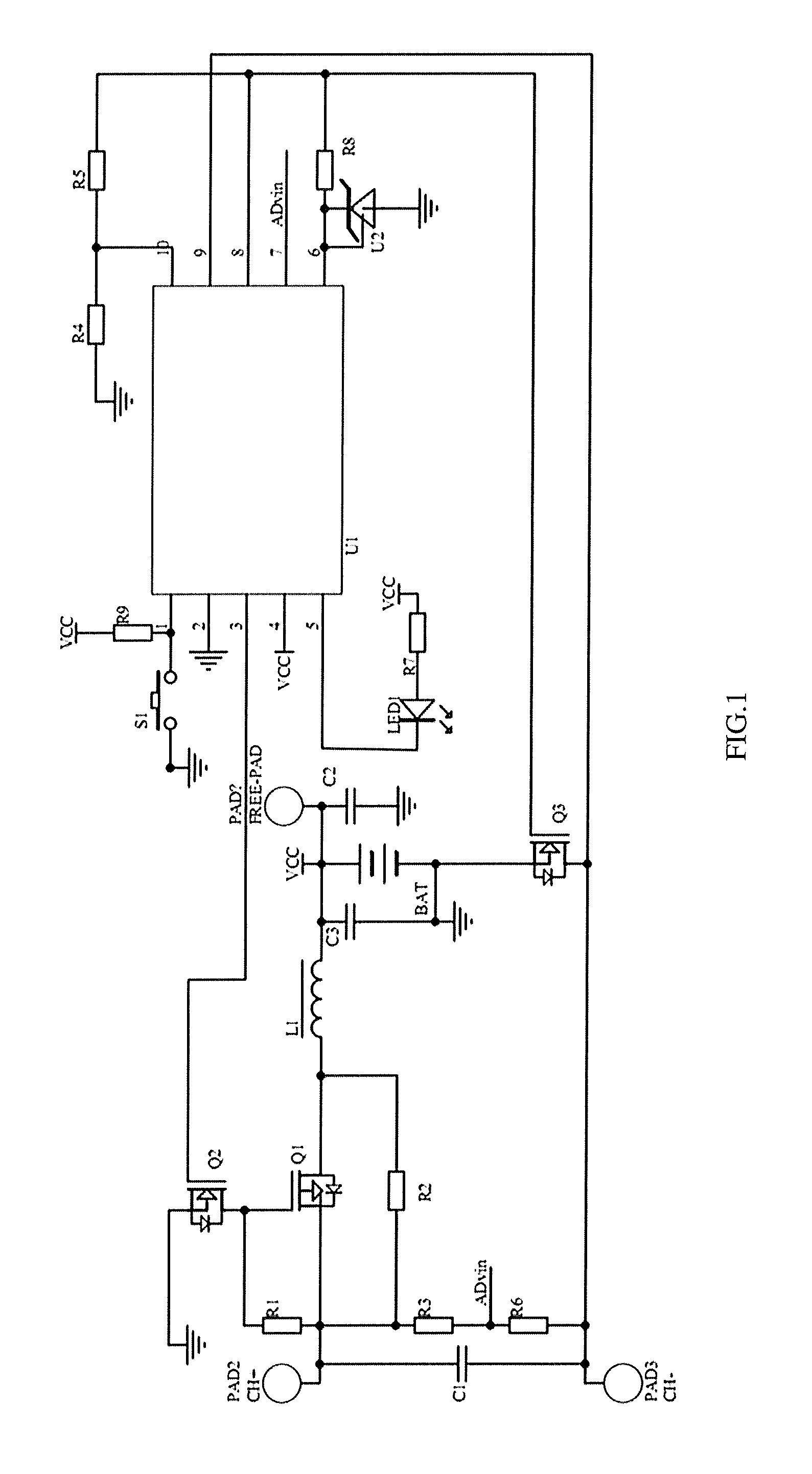

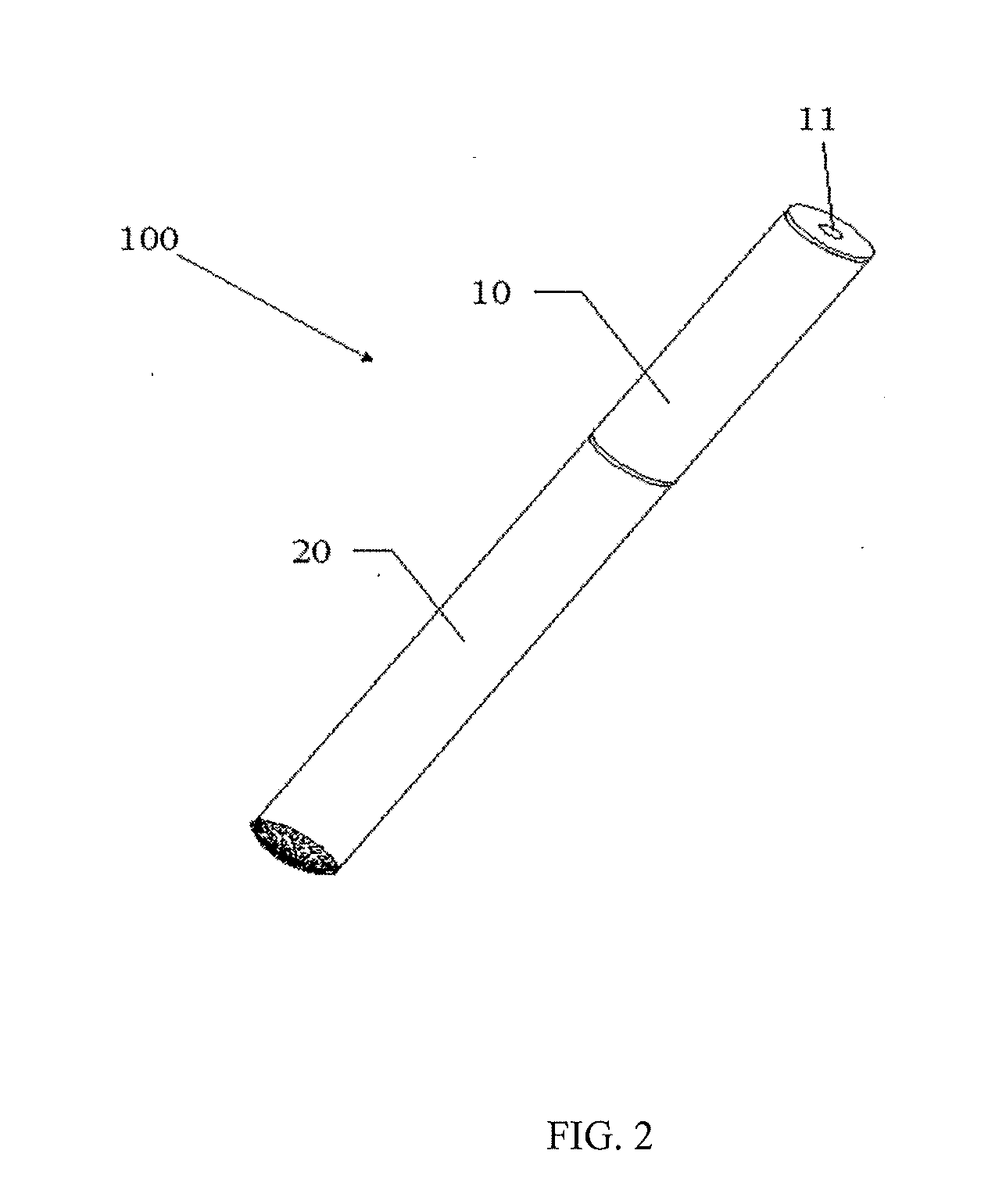

Intelligent charge-discharge controller for battery and electronic device having same

An intelligent charge-discharge controller for a battery includes a charging voltage test circuit configured for testing an input voltage of the battery when in charge; a charging current control circuit configured for controlling an input current of the battery based on the tested input voltage; a battery voltage test circuit configured for testing a current voltage of the battery; and a discharging current control circuit configured for controlling a discharging current of the battery. The charging voltage test circuit and the battery voltage test circuit each are electrically connected to the charging current control circuit, and the charging voltage test circuit and the discharging current control circuit have a common circuit section. An electronic device having the intelligent charge-discharge controller is also provided.

Owner:SHENZHEN FIRST UNION TECH CO LTD

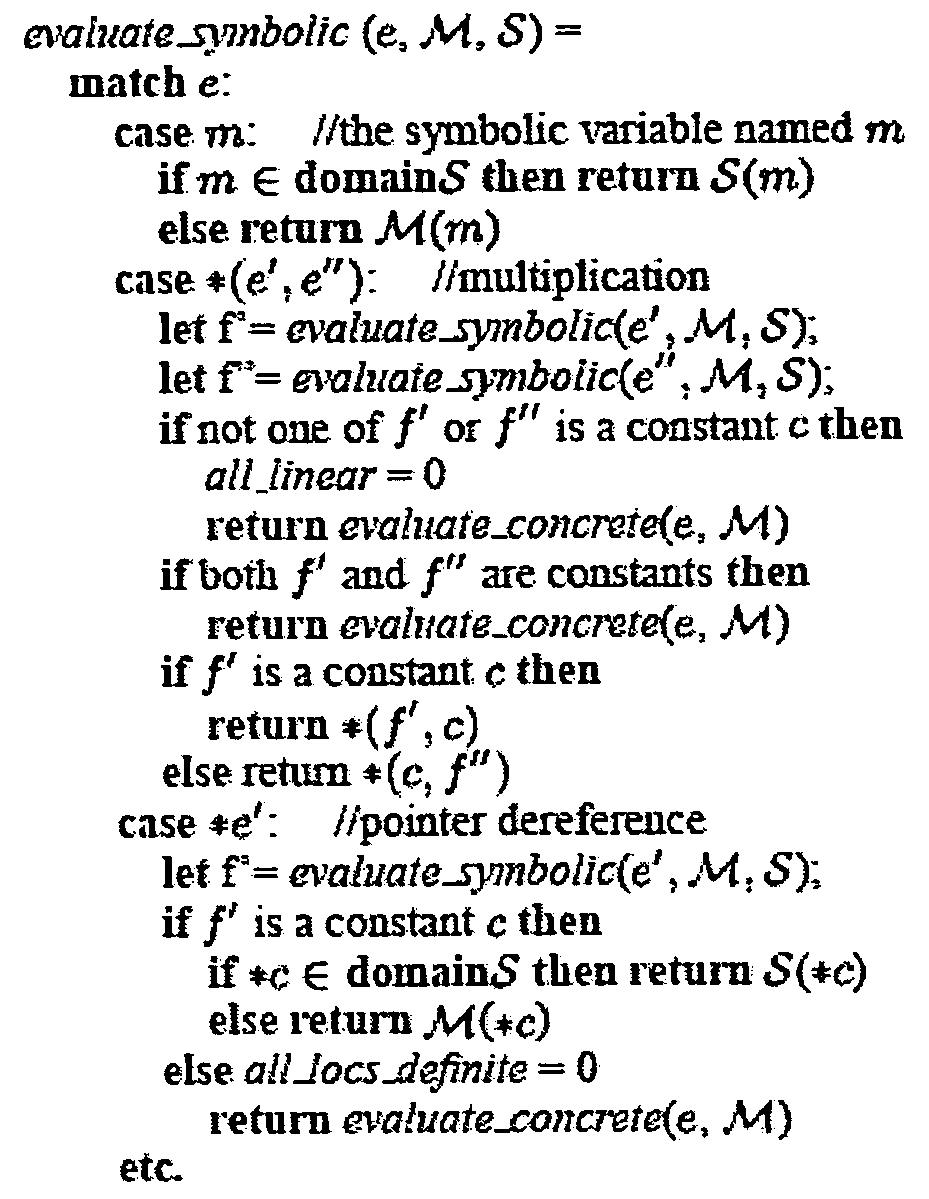

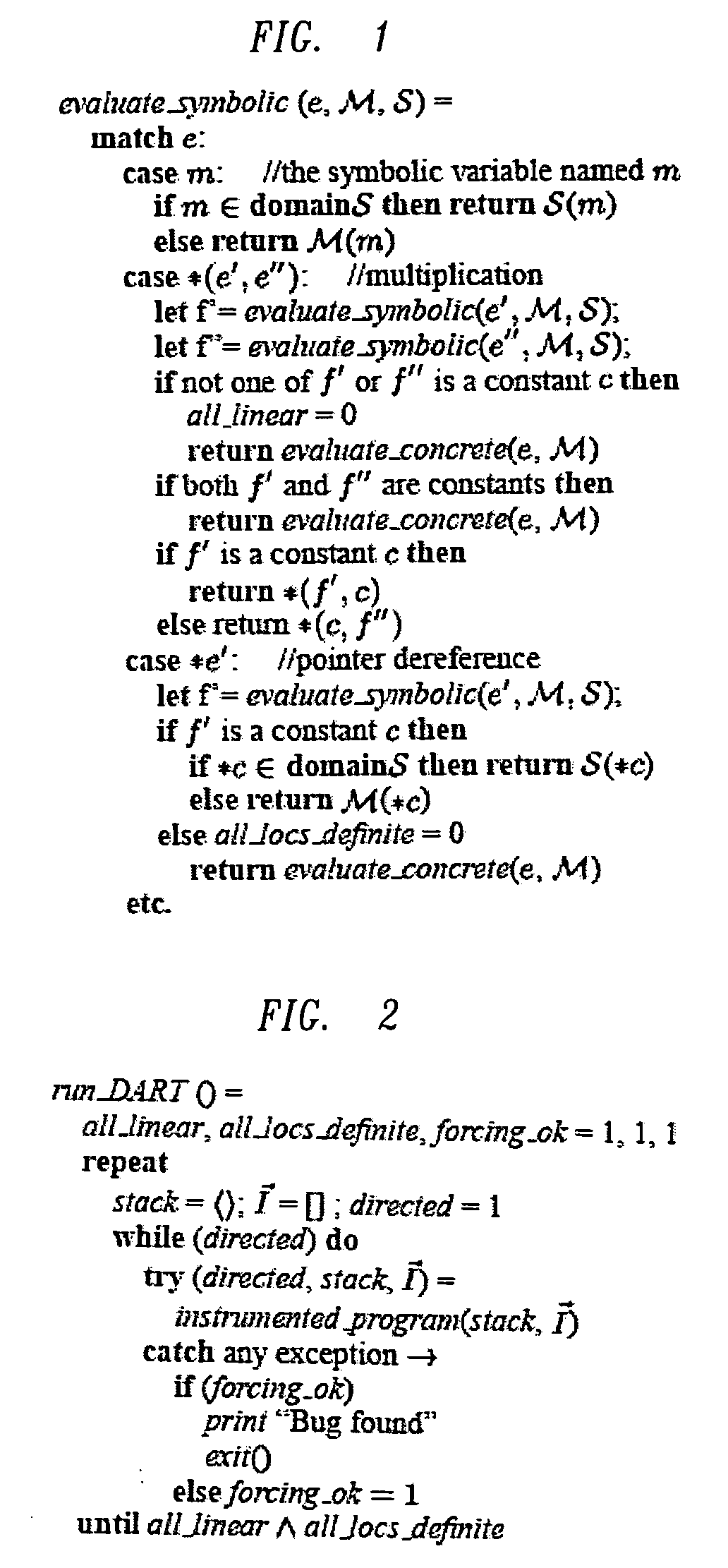

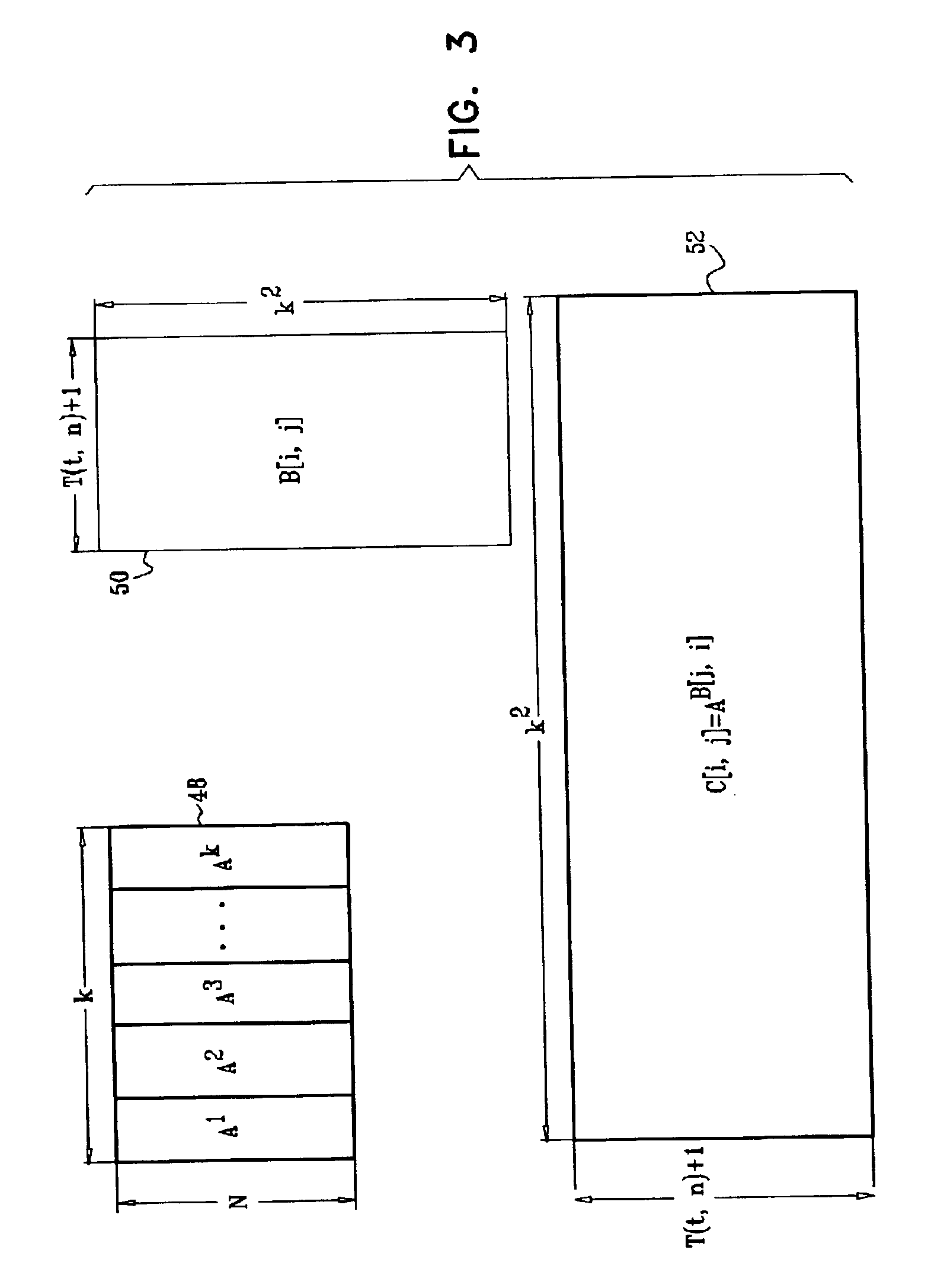

Method and apparatus for performing unit testing of software modules with use of directed automated random testing

A method and apparatus for performing unit testing of software modules uses a novel directed automated random testing approach that advantageously combines automated extraction of the interface of a program with its external environment using static source code parsing; automatic generation of a test driver for this interface that advantageously performs random testing to simulate the most general environment the program can operate in; and dynamic analysis of how the program behaves under random testing and automatic generation of new test inputs to direct systematically the execution along alternative program paths. Together, these techniques constitute a directed automated random testing approach (DART). With DART, testing can be performed completely automatically on any program that compiles without the need to write any test driver or harness code. During testing, DART detects standard errors such as program crashes, assertion violations, and non-termination conditions.

Owner:LUCENT TECH INC

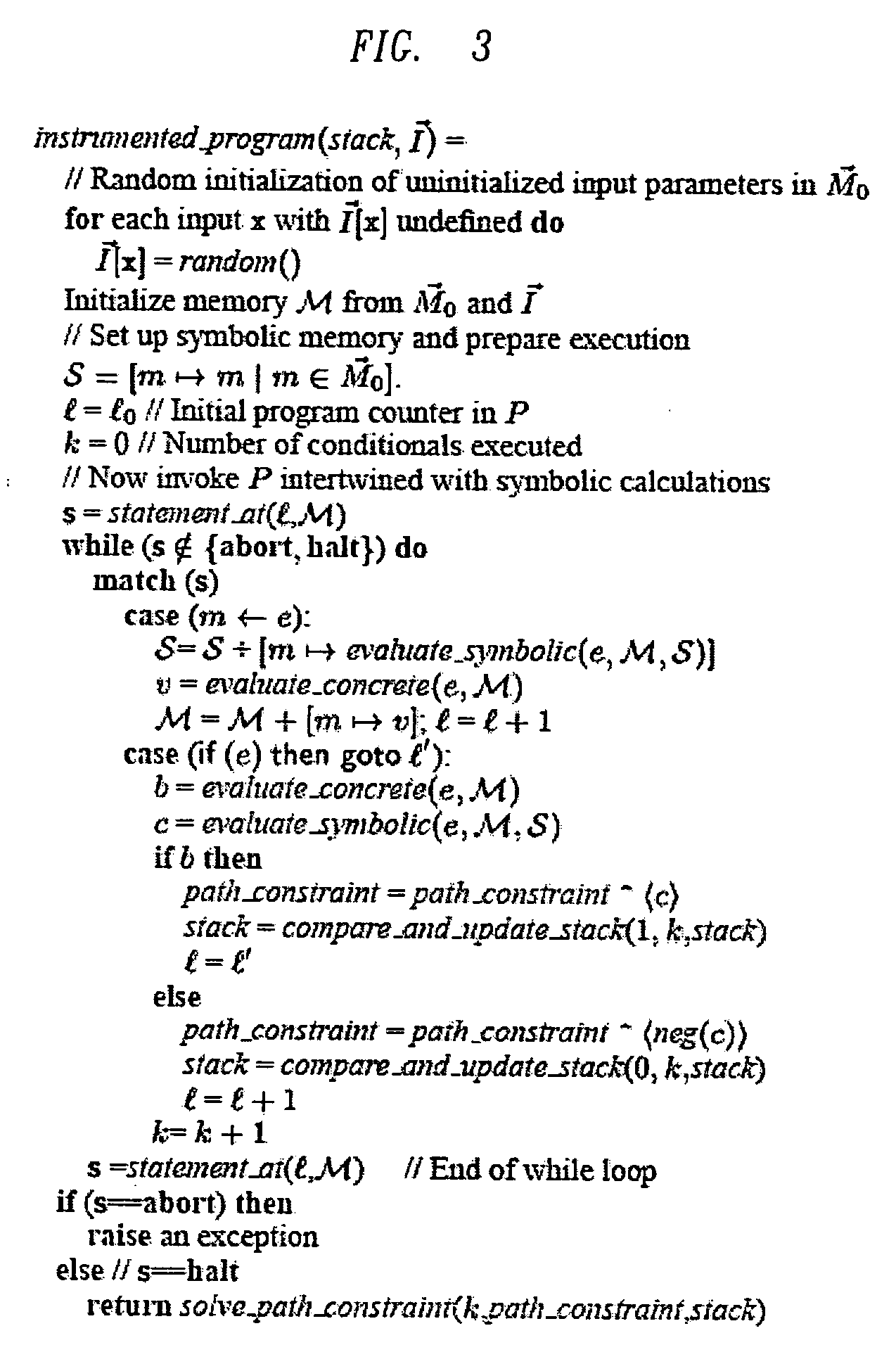

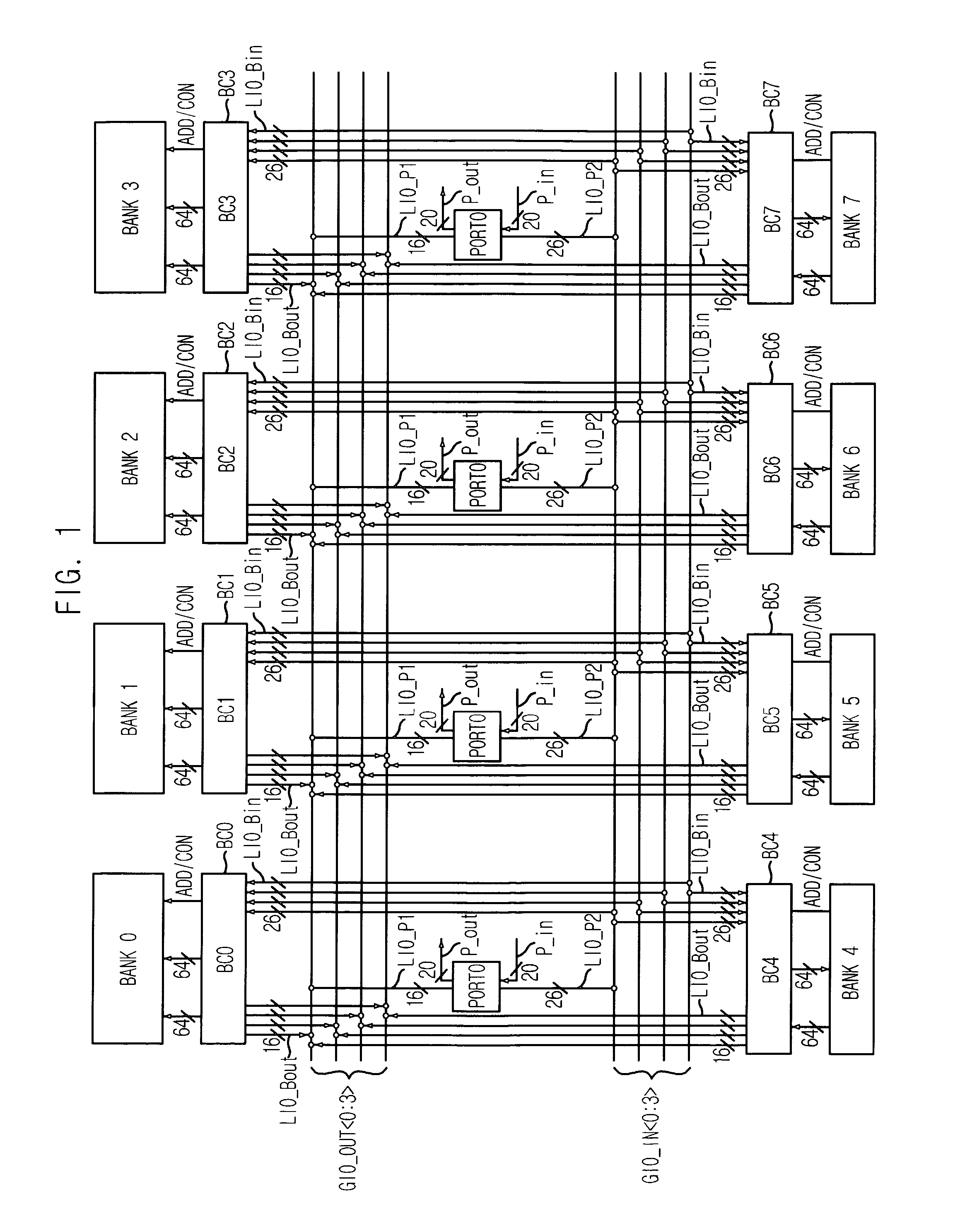

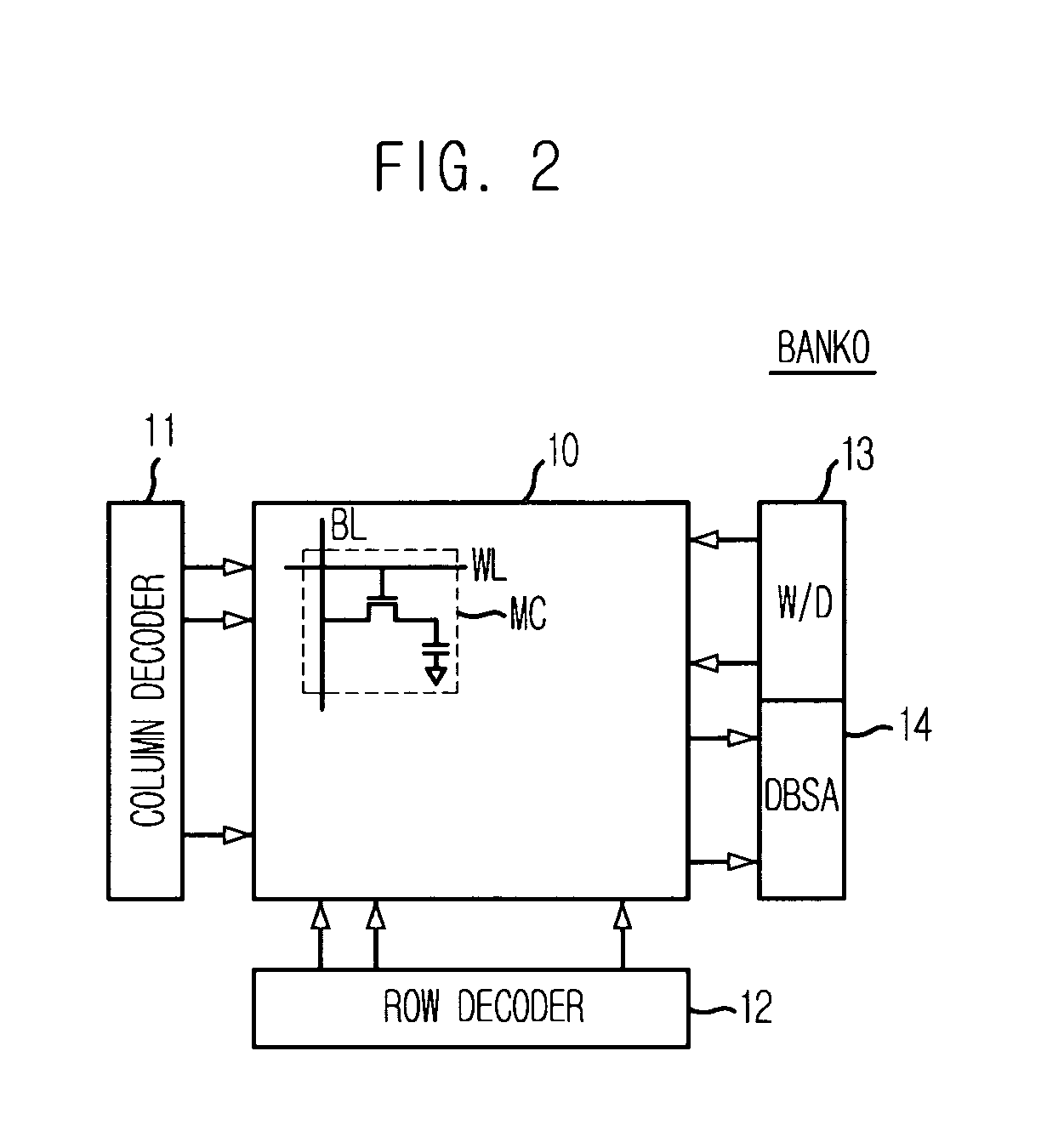

Test operation of multi-port memory device

Owner:SK HYNIX INC

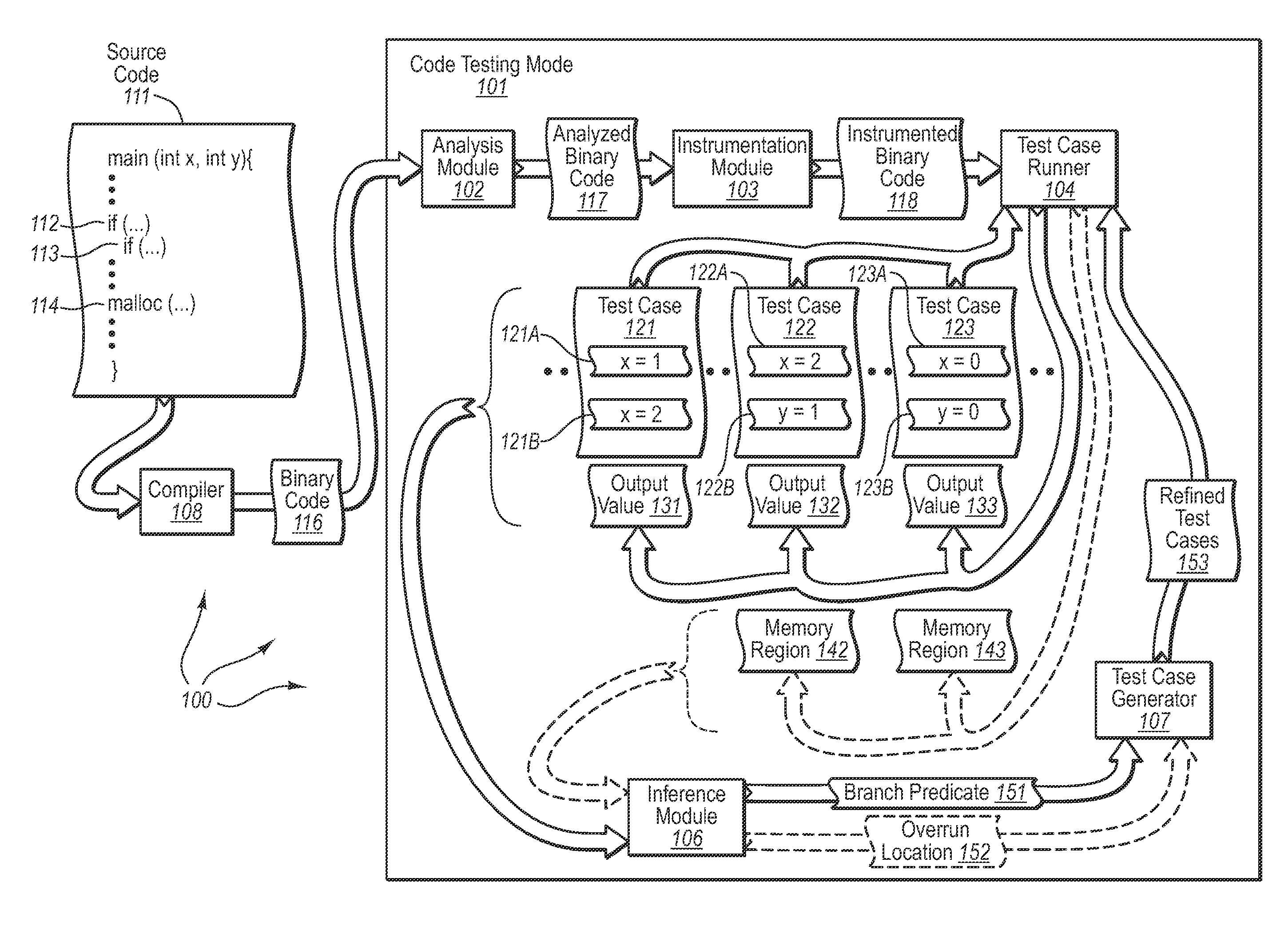

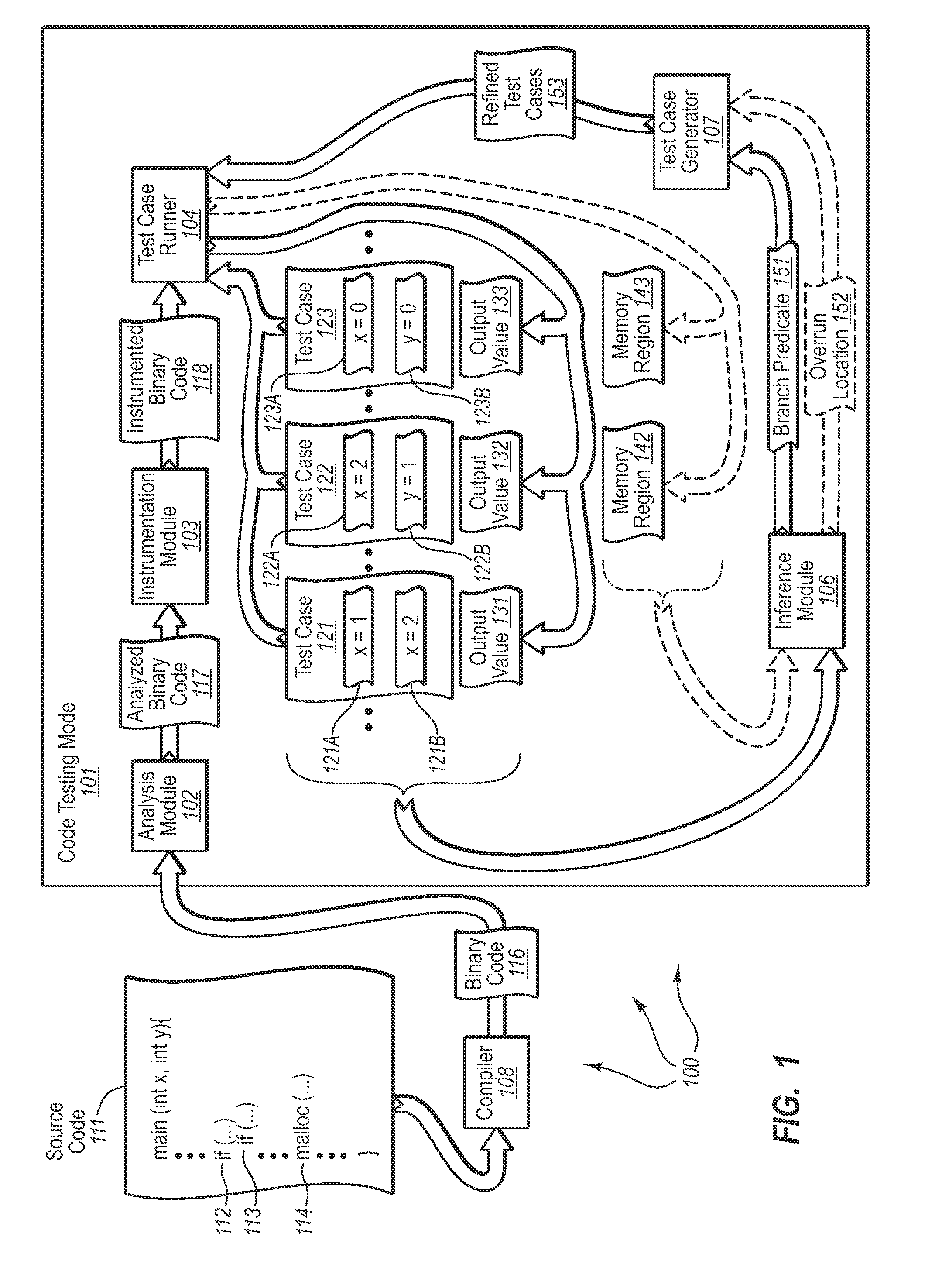

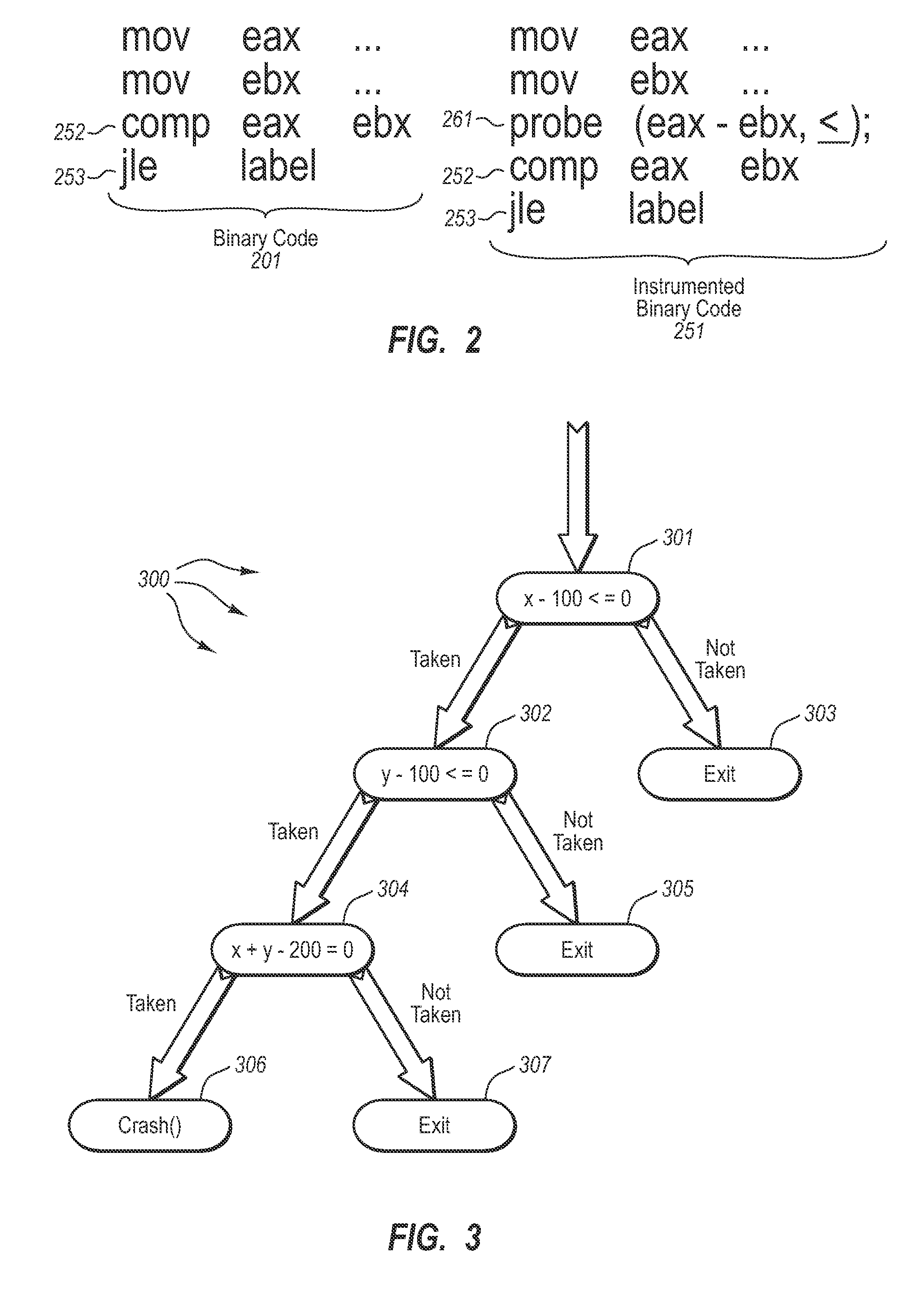

Automatically generating test cases for binary code

InactiveUS20090007077A1Efficient testingError detection/correctionSpecific program execution arrangementsTest inputParallel computing

The present invention extends to methods, systems, and computer program products for automatically generating test cases for binary code. Embodiments of the present invention can automatically generate test inputs for systematically covering program execution paths within binary code. By monitoring program execution of the binary code on existing or random test cases, branch predicates on execution paths can be dynamically inferred. These inferred branch predicates can then be used to drive the program along previously unexplored execution paths, enabling the learning of further execution paths. Embodiments of the invention can be used in combination with other analysis and testing techniques to provide better test coverage and expose program errors.

Owner:MICROSOFT TECH LICENSING LLC

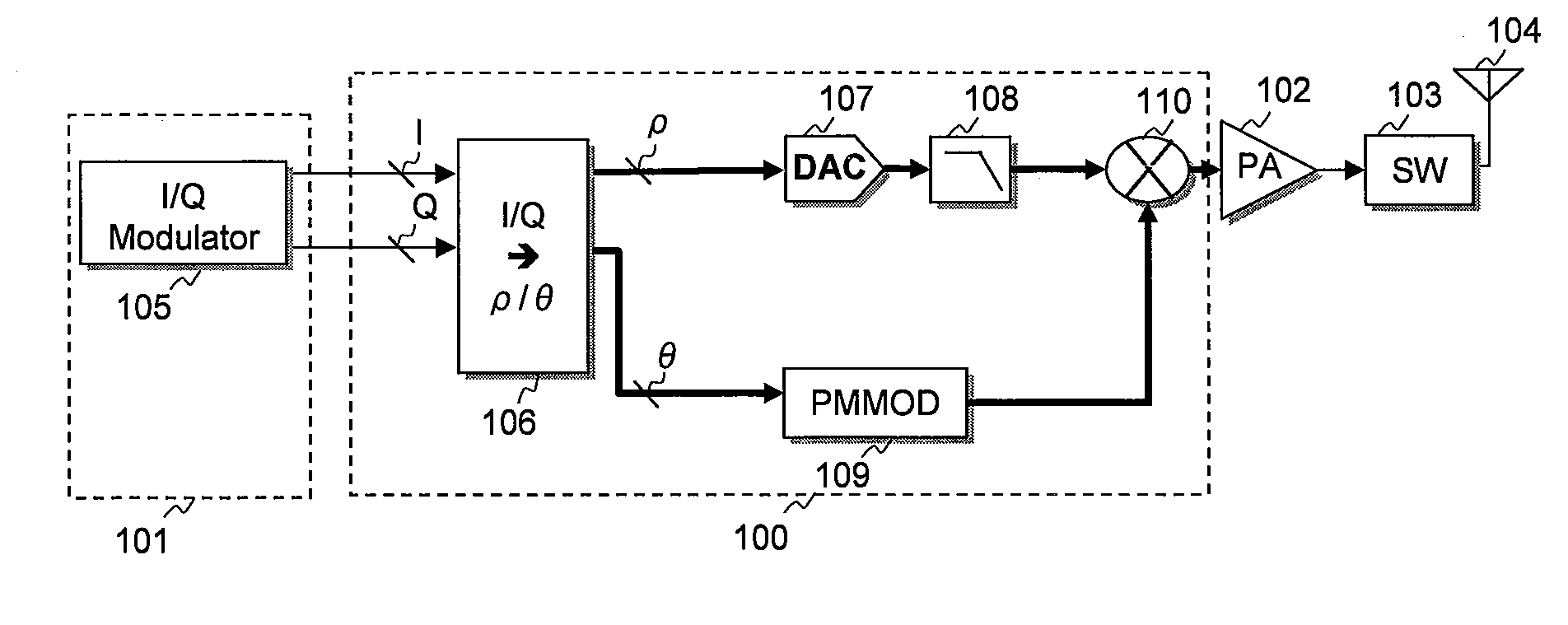

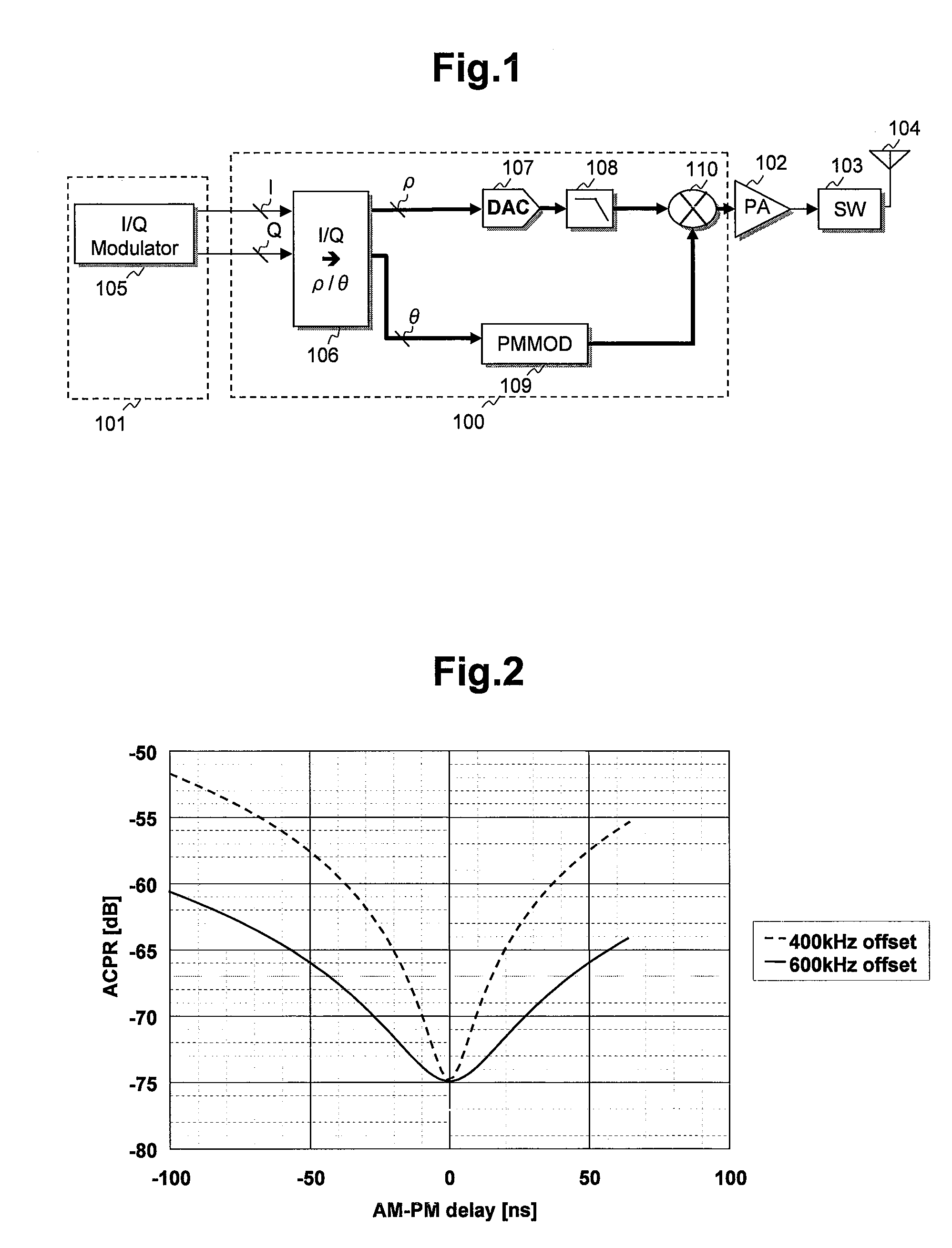

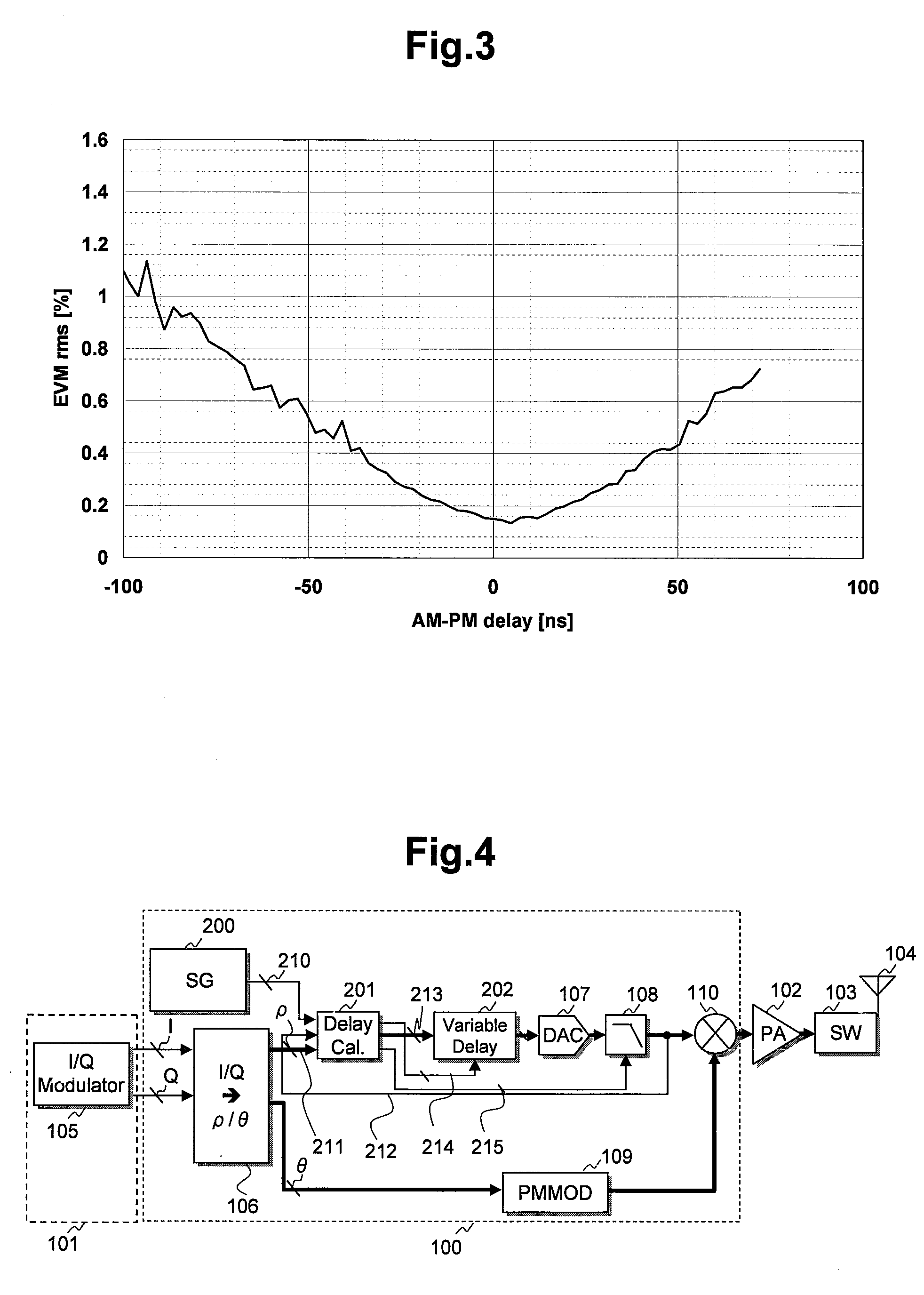

Transmitter and semiconductor integrated circuit available for it

InactiveUS20110059704A1Improve accuracyIncrease speedSimultaneous amplitude and angle modulationAngle modulationTest inputLow-pass filter

The transmitter synthesizes amplitude and phase components and calibrates a delay mismatch between amplitude and phase components with high accuracy at high speed. The transmitter has: a digital-to-analog converter (DAC) and a low-pass filter (LPF) in its amplitude-signal path; and a phase modulator operable to convert up a phase component into an RF component in its phase-signal path. In an operation of delay calibration, a test input signal is supplied to a delay-calibrating unit in the amplitude-signal path, and the delay-calibrating unit provides a test input signal to DAC. Then, LPF generates a test output signal. The delay-calibrating unit detects a delay of the test output signal relative to the test input signal, calibrates an amplitude signal delay in a range from the input of the delay-calibrating unit to the output of LPF, reduces the difference between amplitude and phase signal delays of the phase modulator in the phase-signal path.

Owner:RENESAS ELECTRONICS CORP

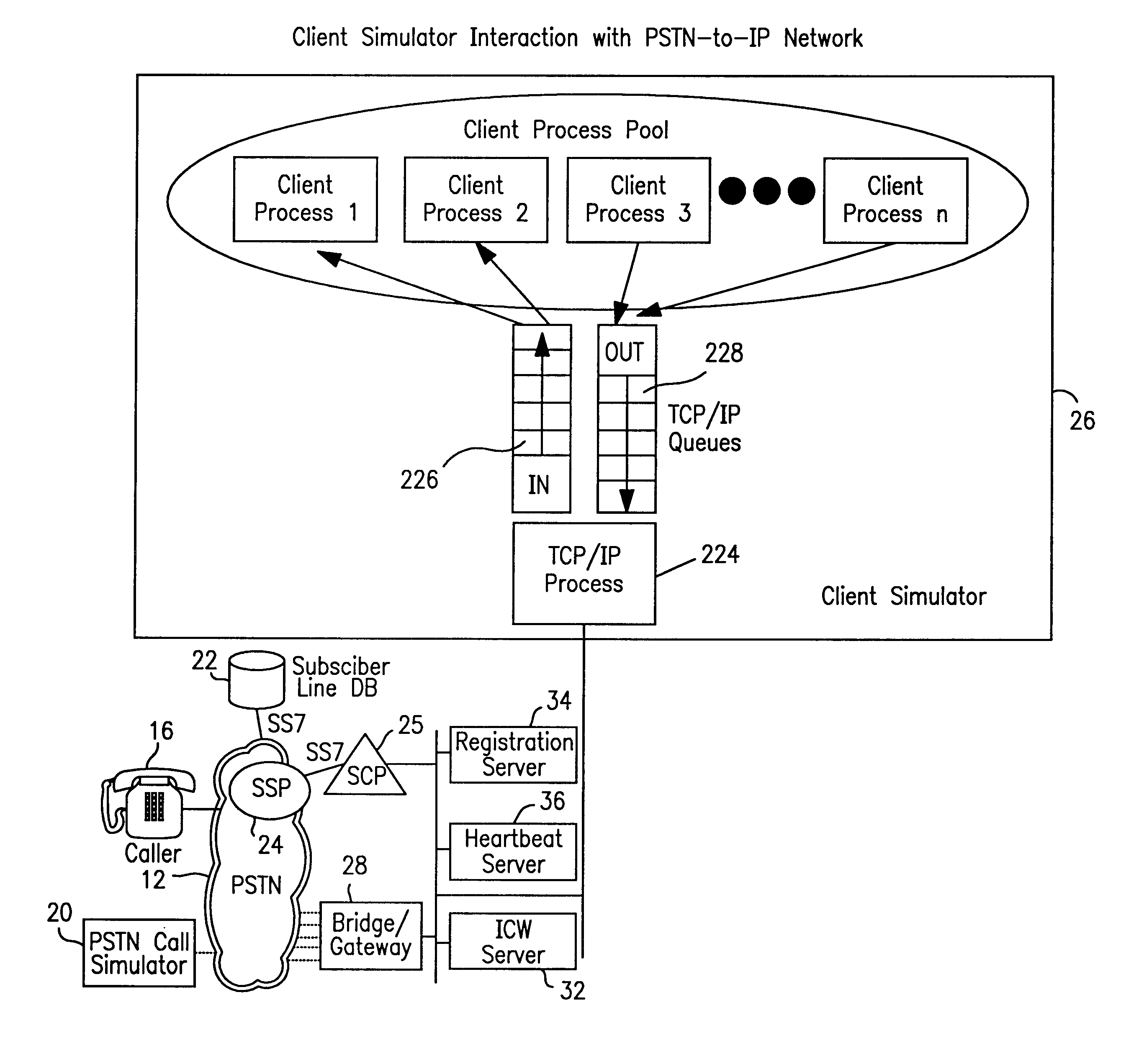

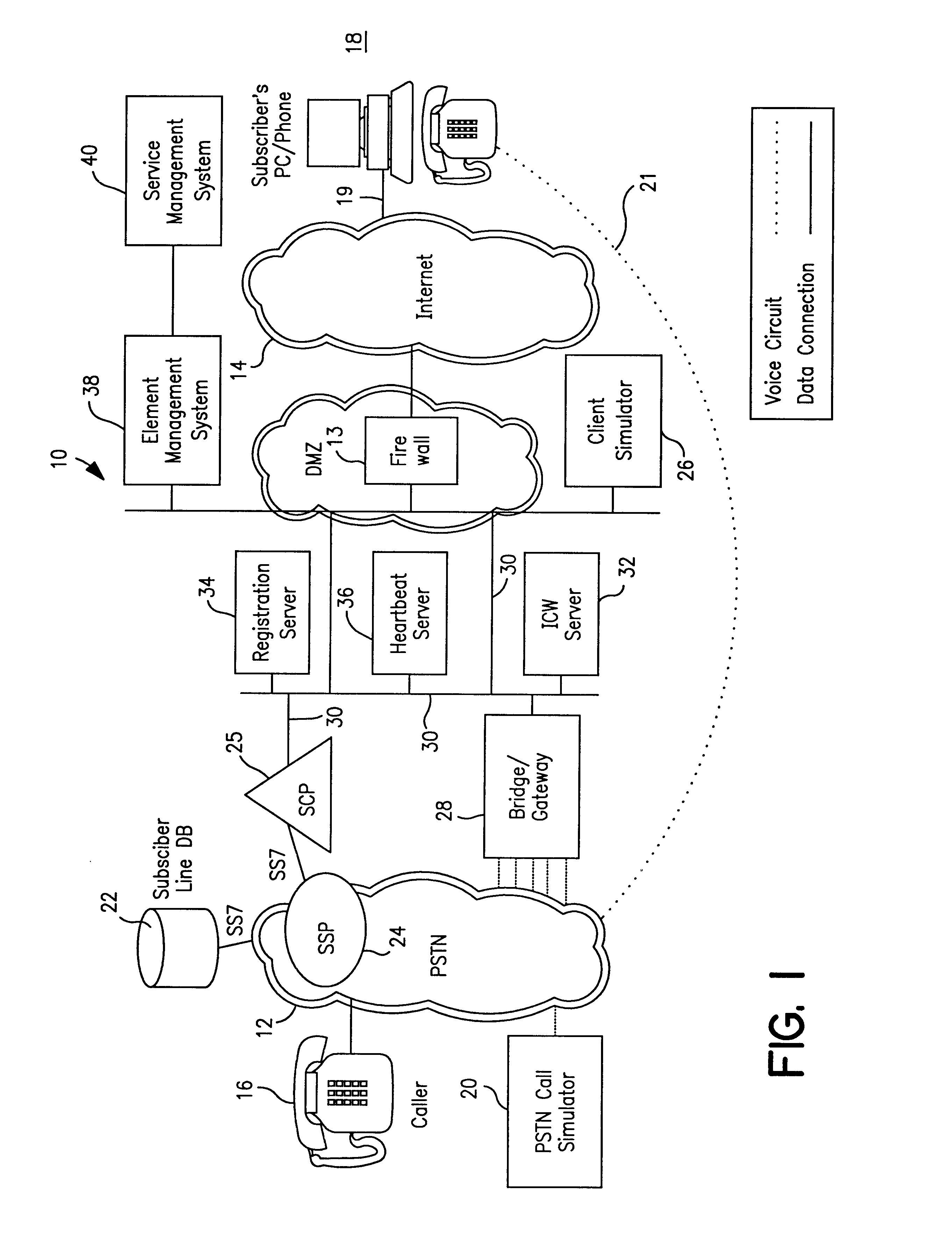

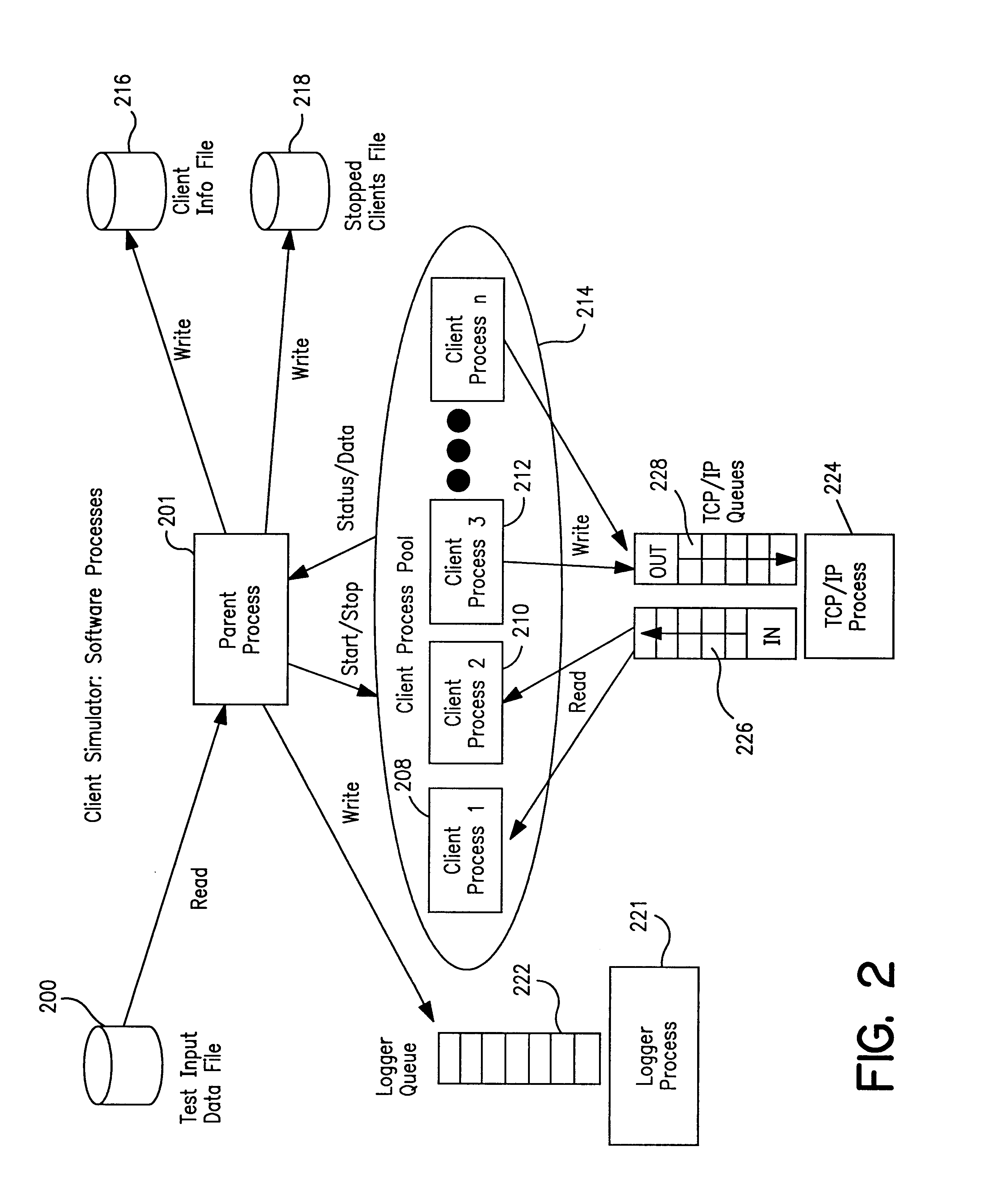

Client simulator and method of operation for testing PSTN-to-IP network telephone services for individual & group internet clients prior to availability of the services

InactiveUS6421424B1Telephone data network interconnectionsSupervisory/monitoring/testing arrangementsTest inputNetwork link

A client simulator for simulating client behavior in groups or individuals to telephone services in a test system for testing telephone services between subscribers in a PSTN and clients in a distributed information network, for example, the Internet (IP Network), prior to availability of the telephone services to the subscribers and clients. A processor is coupled to a TCP / IP data network linked to the PSTN via a System Control Point (SCP) and the IP Network via an application server. A storage means is coupled to the processor through input / output registers and includes stored instruction for a parent process and a pool of client processes. e storage means further includes: a) a test input data file which contains client behavior profiles of either groups or individual client processes to call data messages; b) a logger queue file which allows the parent process to write event messages indicating start or stopped client processes with time stamp; c) a client information file which contains information and data for the total number of processes identified as being part of the test; d) a stopped client file used to track client processes that have stopped. The parent process is responsible for reading the test input data file and passing the client process behavior profile to the client processes. Each client process is responsible for returning state information to the PSTN; call handling actions and providing call handling statistics. The client process includes a client behavior control functions which processes and maintains the behavior parameters passed by the parent process. The behavior function, inter alia, accepts the call message, forward the call message according to the client behavior profile. The client process further includes a send / receive function to read and write to the registers coupled to the TCP / IP data network and support voice over IP protocols. A test originated by the PSTN is passed to the test input data file by the SCP and application file. The parent processes passes the call message to the client process. The client process provides a variety of call handling options including (a) accepting the call on the client's PC; sending a voice message to the caller. The call data messages responses are sent back to the SCP through the application server. The SCP directs the PSTN on how to handle the message call response.

Owner:LINKEDIN

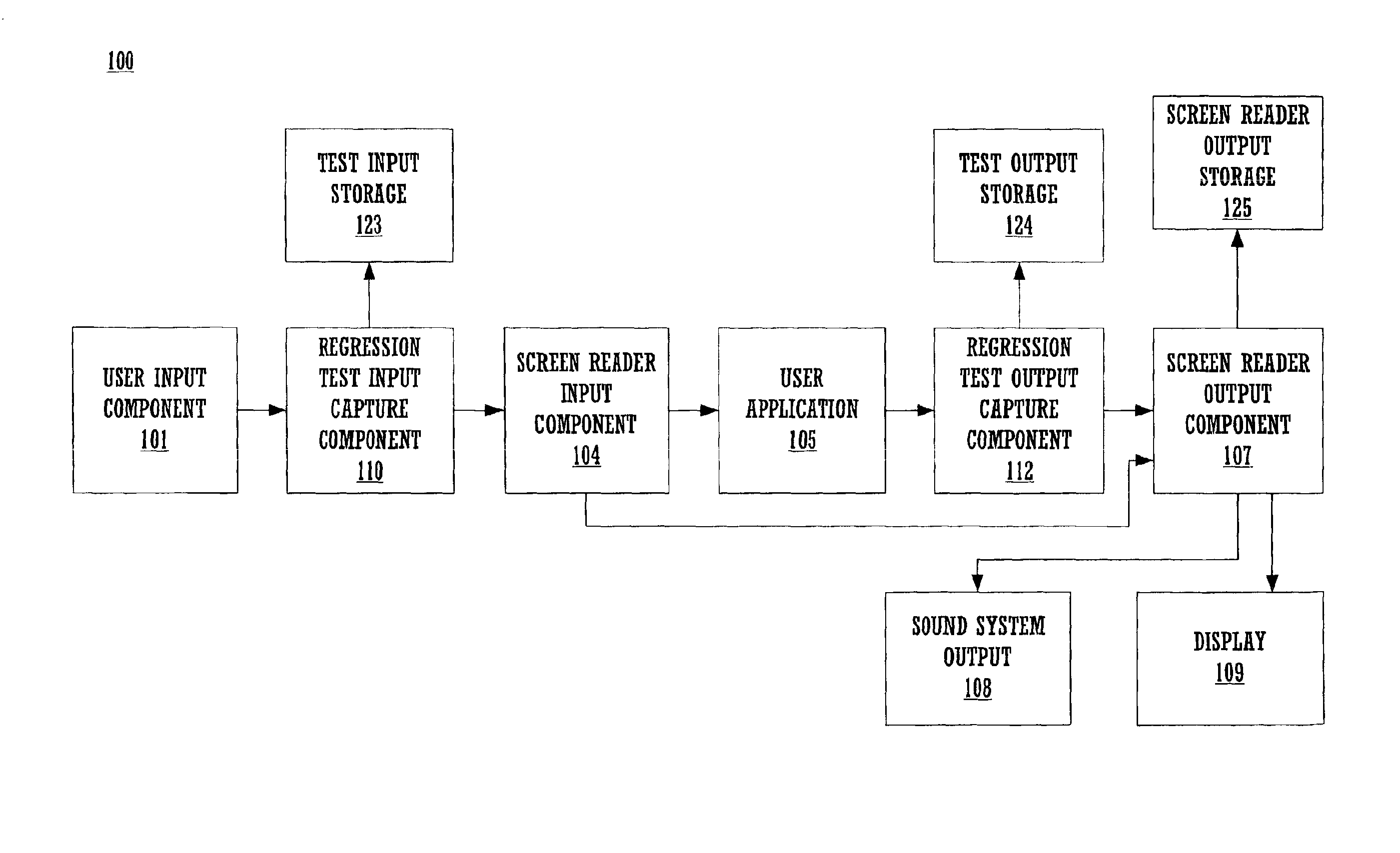

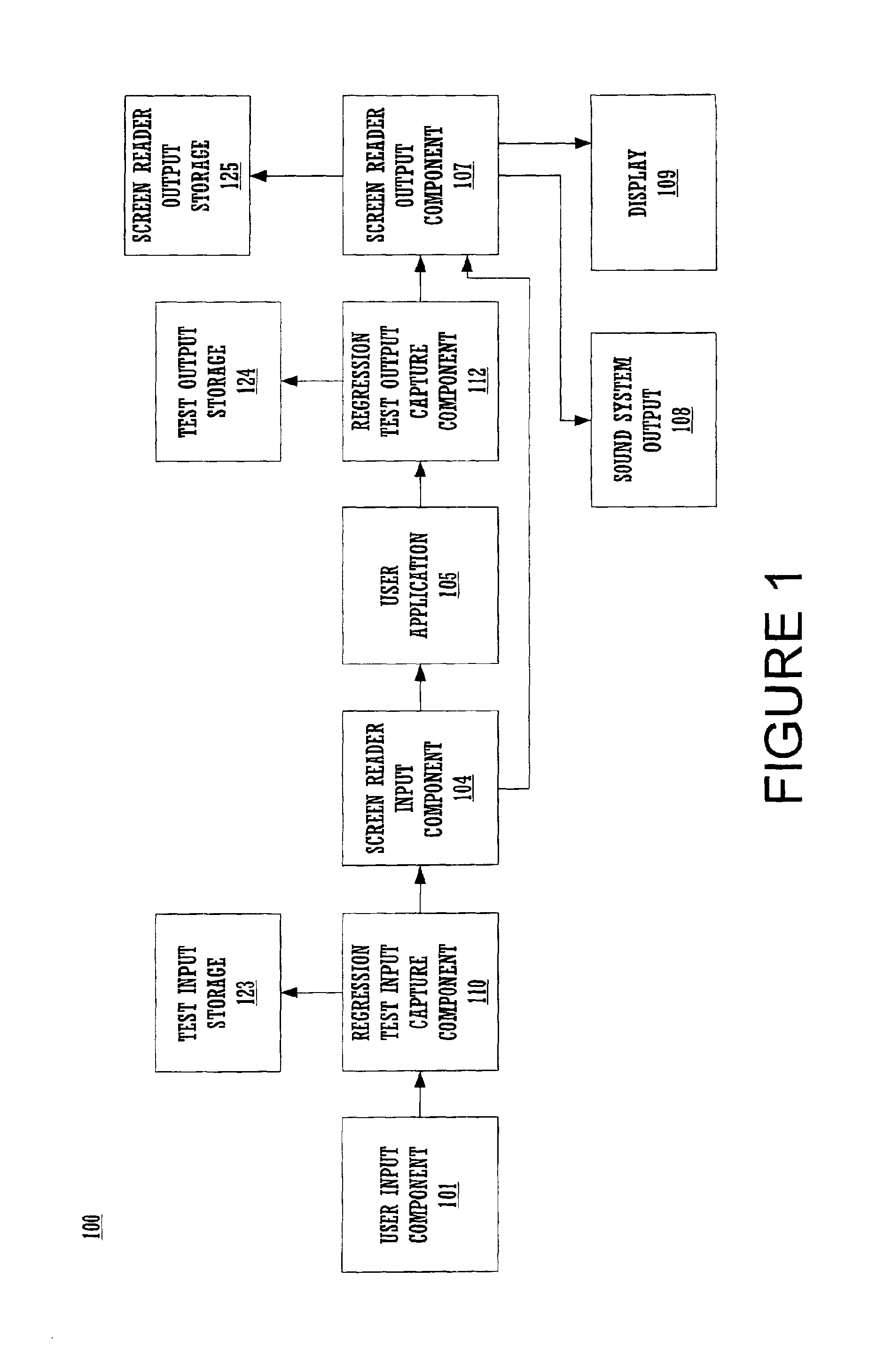

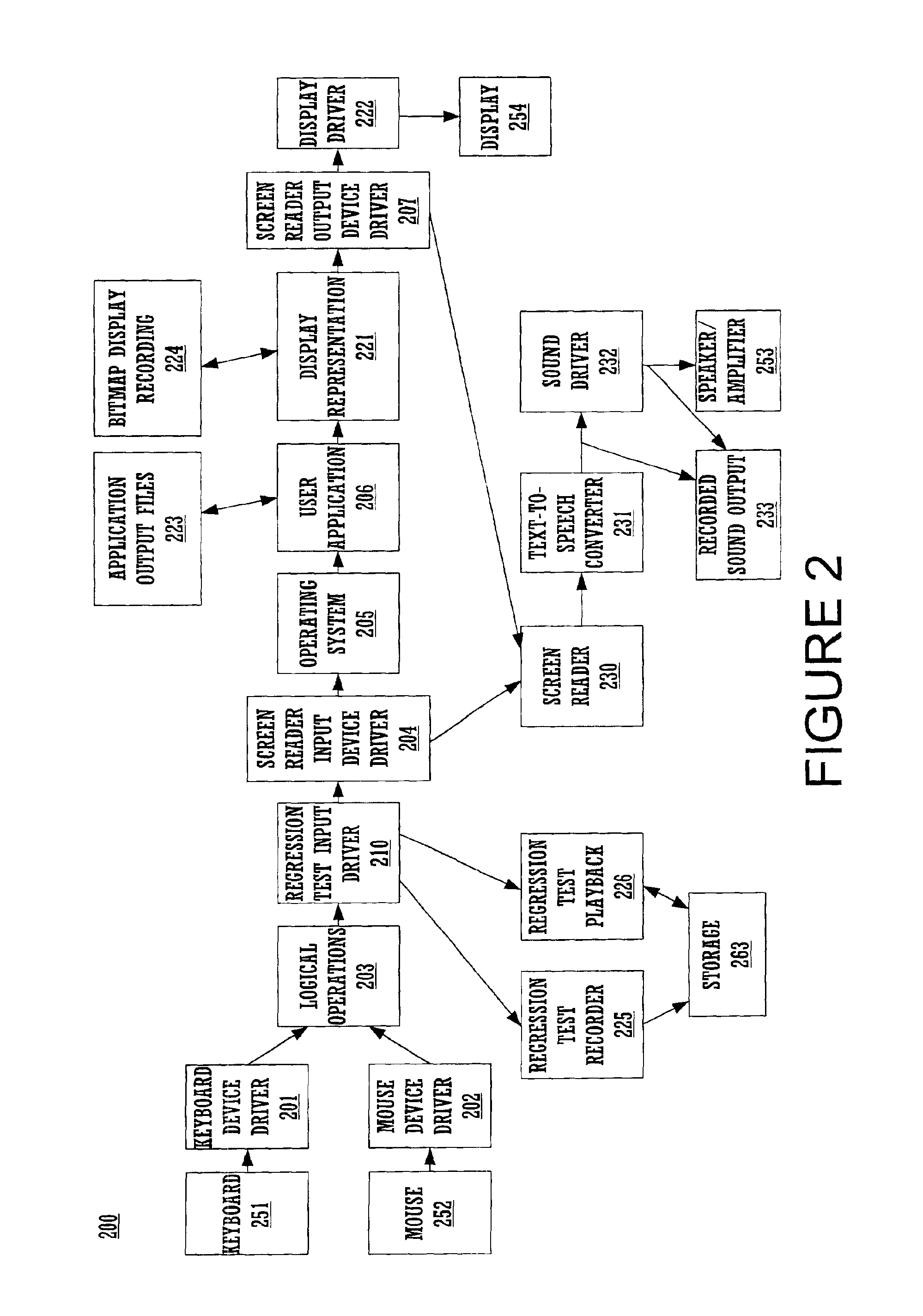

Method and system for screen reader regression testing

A method for repeatable application testing on a computer system for audible output generated by the application in conjunction with a screen reader or similar assistive technology. The method includes recording user inputs to a user application using a test input component. The user inputs are also accessed by a screen reader input component. Outputs of the user application are recorded using a test output component. The outputs of the user application are also accessed by a screen reader output component. The resulting screen reader outputs are recorded and are analyzed with respect to the recorded user inputs and the recorded outputs of the user application. The user inputs to the user application can be keyboard inputs or mouse inputs, and inputs of other input devices. The outputs of the user application can be graphical outputs or alphanumeric outputs for a display of the computer system. The resulting screen reader outputs can be sound output signals (or representations thereof) for a sound system of the computer system.

Owner:ORACLE INT CORP

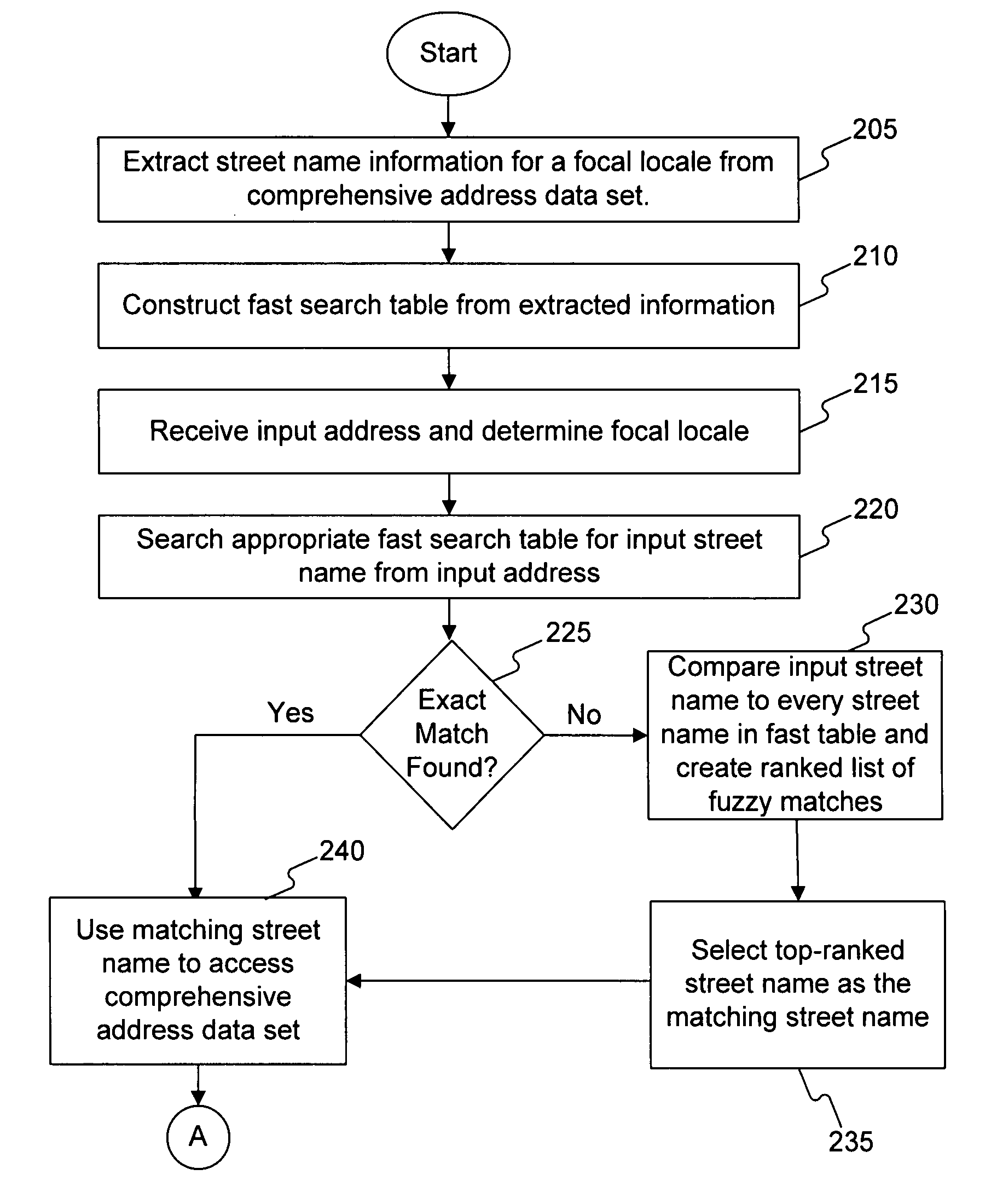

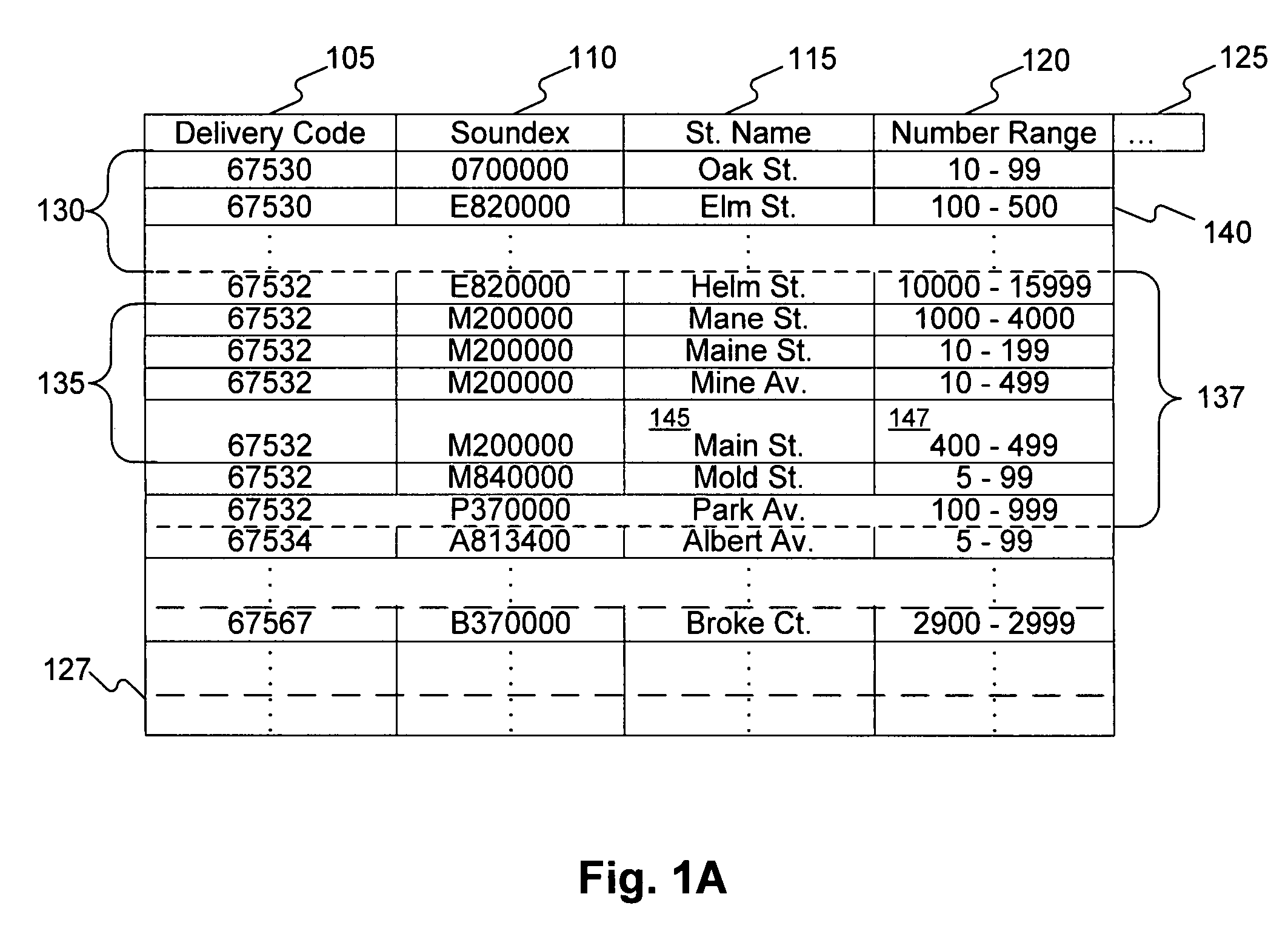

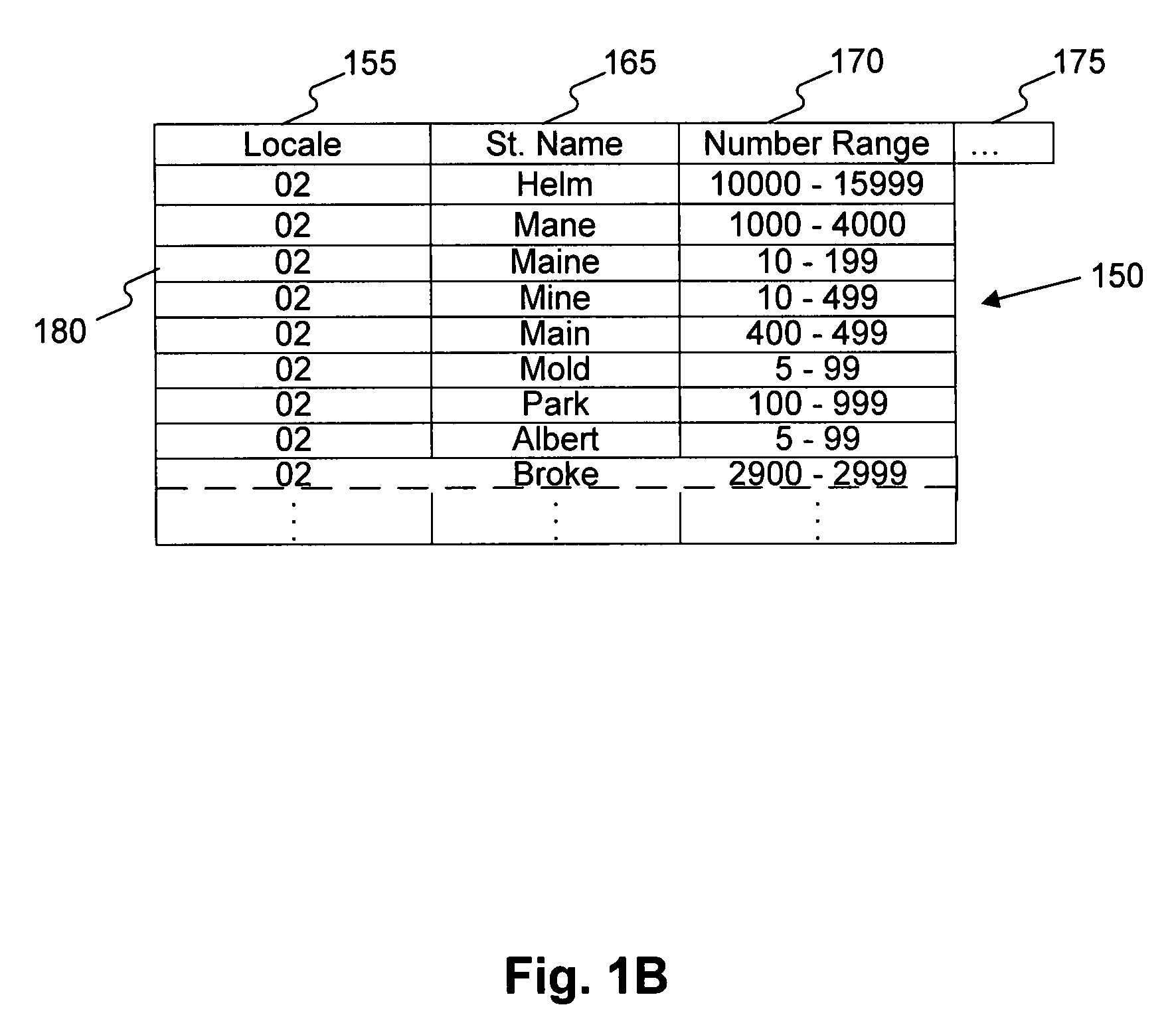

Systems and methods for validating an address

Systems, methods, and software determine whether a field of an input digital representation of information, such as the street name field in an address, is correct by quickly comparing the field to a list of valid choices for that field. The list of valid choices is generated based on information from the input digital representation, such as a character string. If an exact match is not found, a fuzzy match comparison determines the most closely matching valid choice. If a suitable fuzzy match is not found, then the input information is invalid. Otherwise, another field of the input information, such as the building number field of an address, is tested for validity. If the second field passes the validity check, then the fuzzy match (or exact match) for the field is valid. A fuzzy matching field may replace the input field, thereby correcting the input information.

Owner:US POSTAL SERVICE

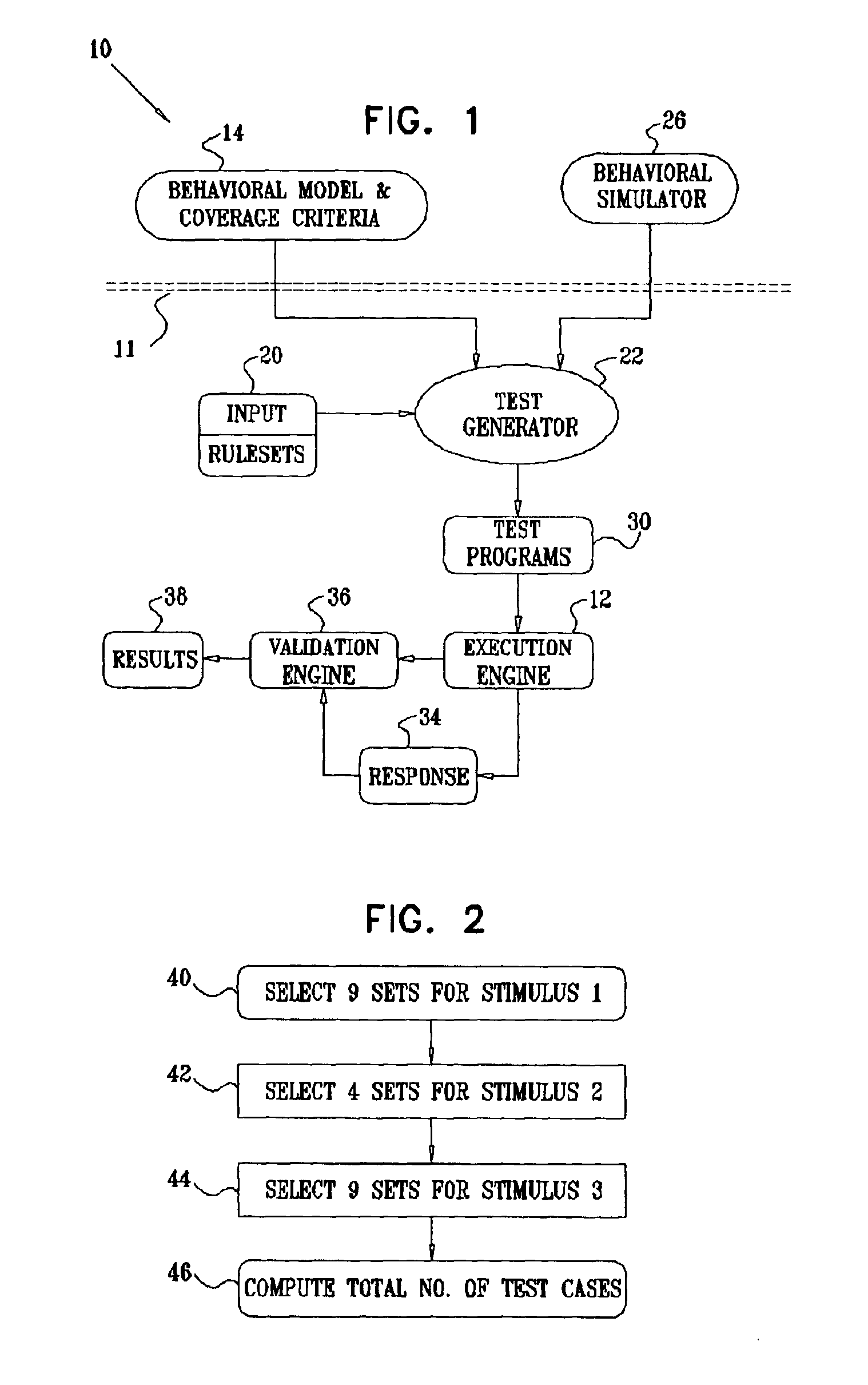

Reducing the complexity of finite state machine test generation using combinatorial designs

InactiveUS7024589B2Generate efficientlyGuaranteed test coverageElectronic circuit testingError detection/correctionTest inputTheoretical computer science

A design verification system generates a small set of test cases, from a finite state machine model of the application under test. The finite state machine is reduced by creating efficient samples of the inputs to the application under test which are prepared by combinatorial input parameter selection. The test cases are generated by finite state machine traversal of the reduced state machine, and tests interacting combinations of input parameters in an efficient way. The technique is integrated into a test generator based on a finite state machine. Using an extended language, partial rulesets are employed to instruct the test generator to automatically employ combinatorial input parameter selection during test generation. Another technique for test case generation is disclosed, which uses combinatorial selection algorithms to guarantee coverage of the system under test from the aspect of interaction between stimuli at different stages or transitions in the test case.

Owner:IBM CORP

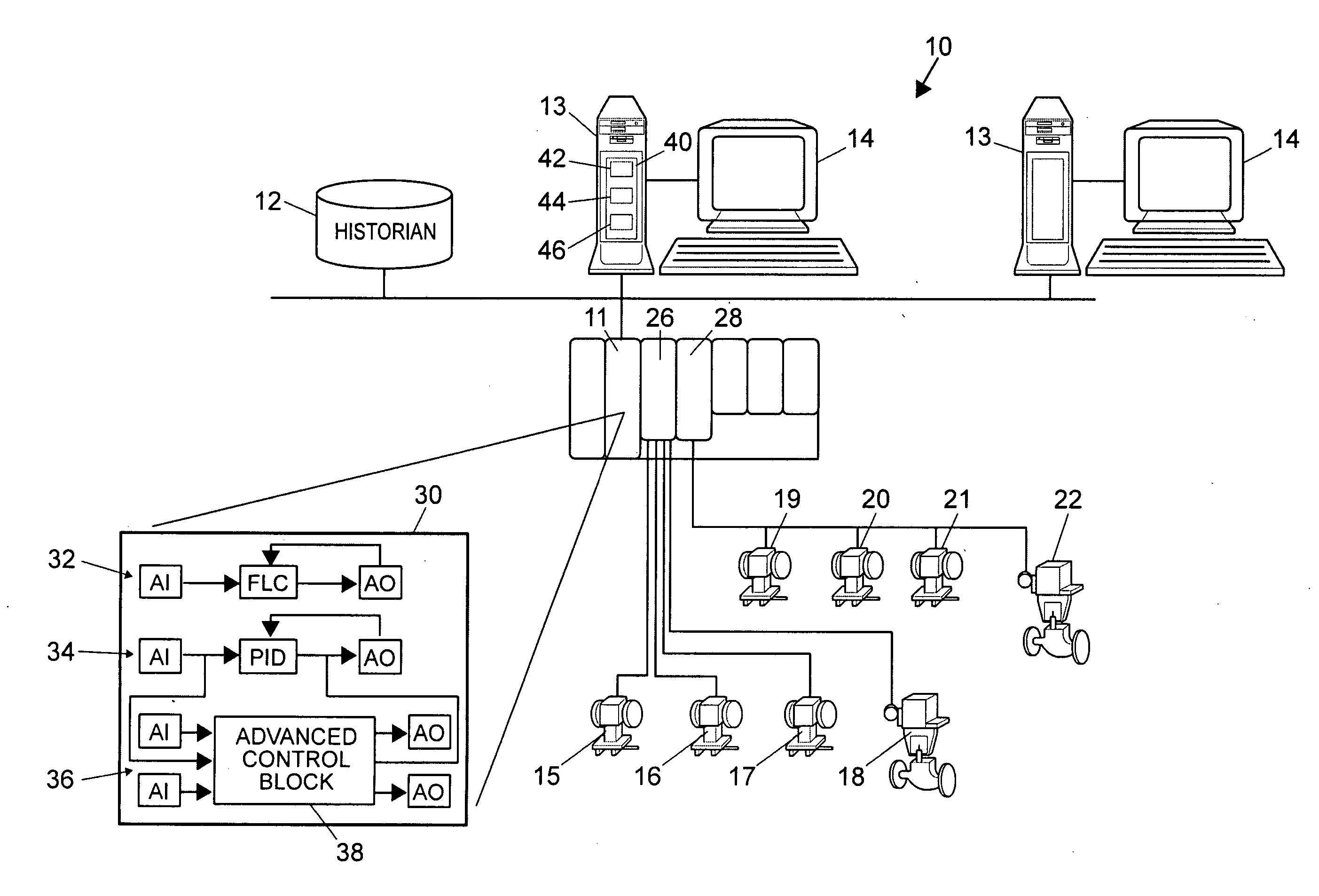

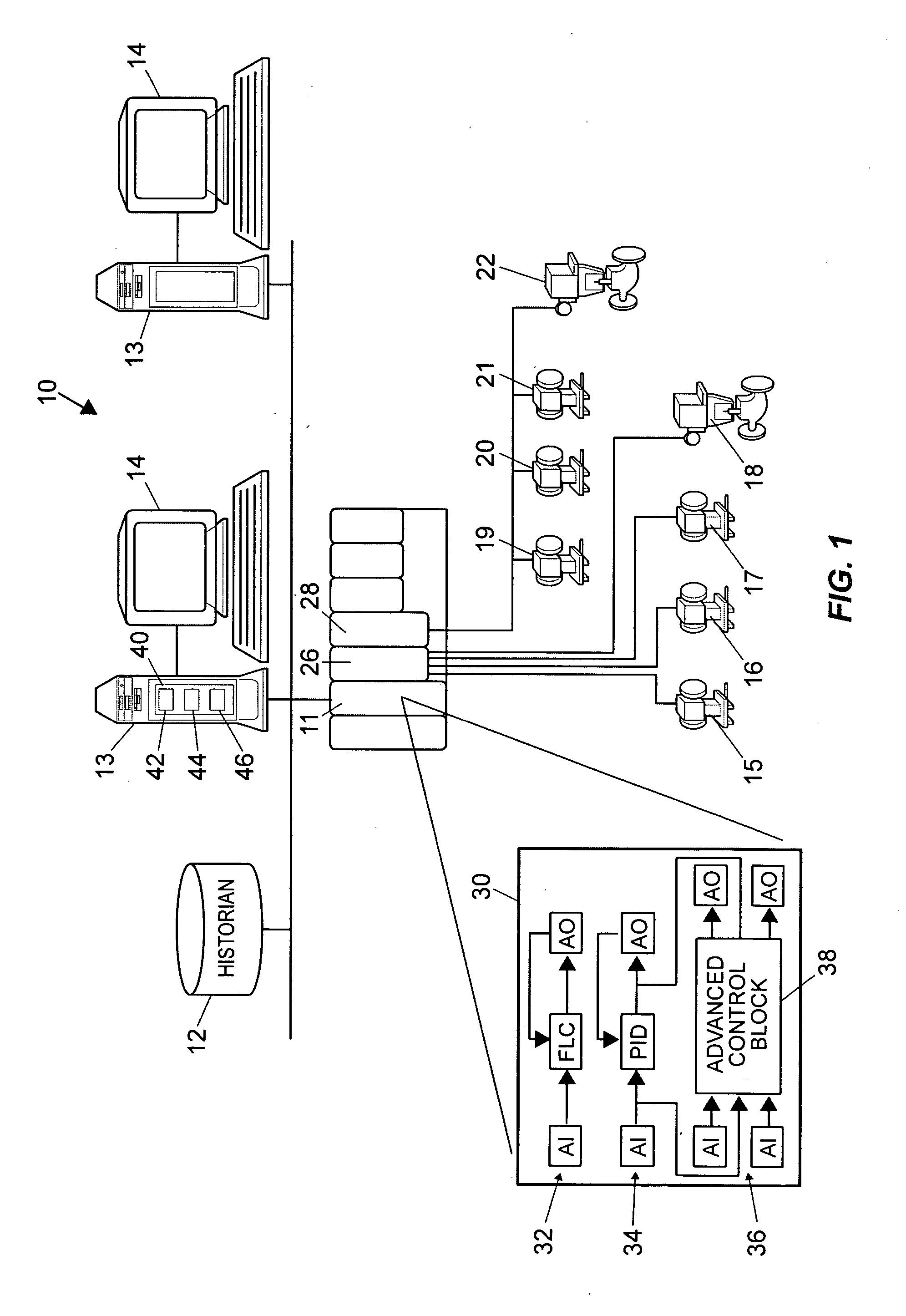

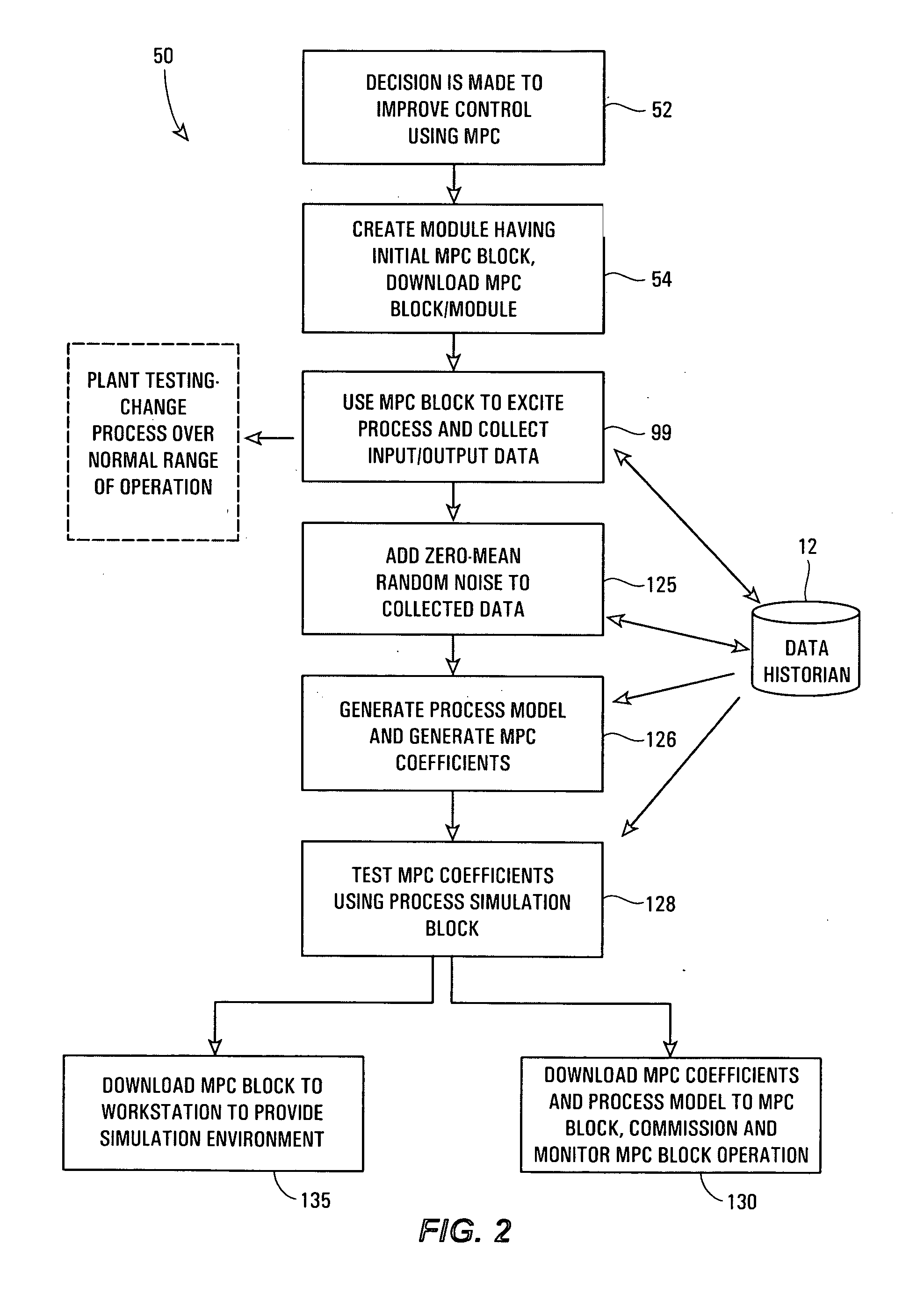

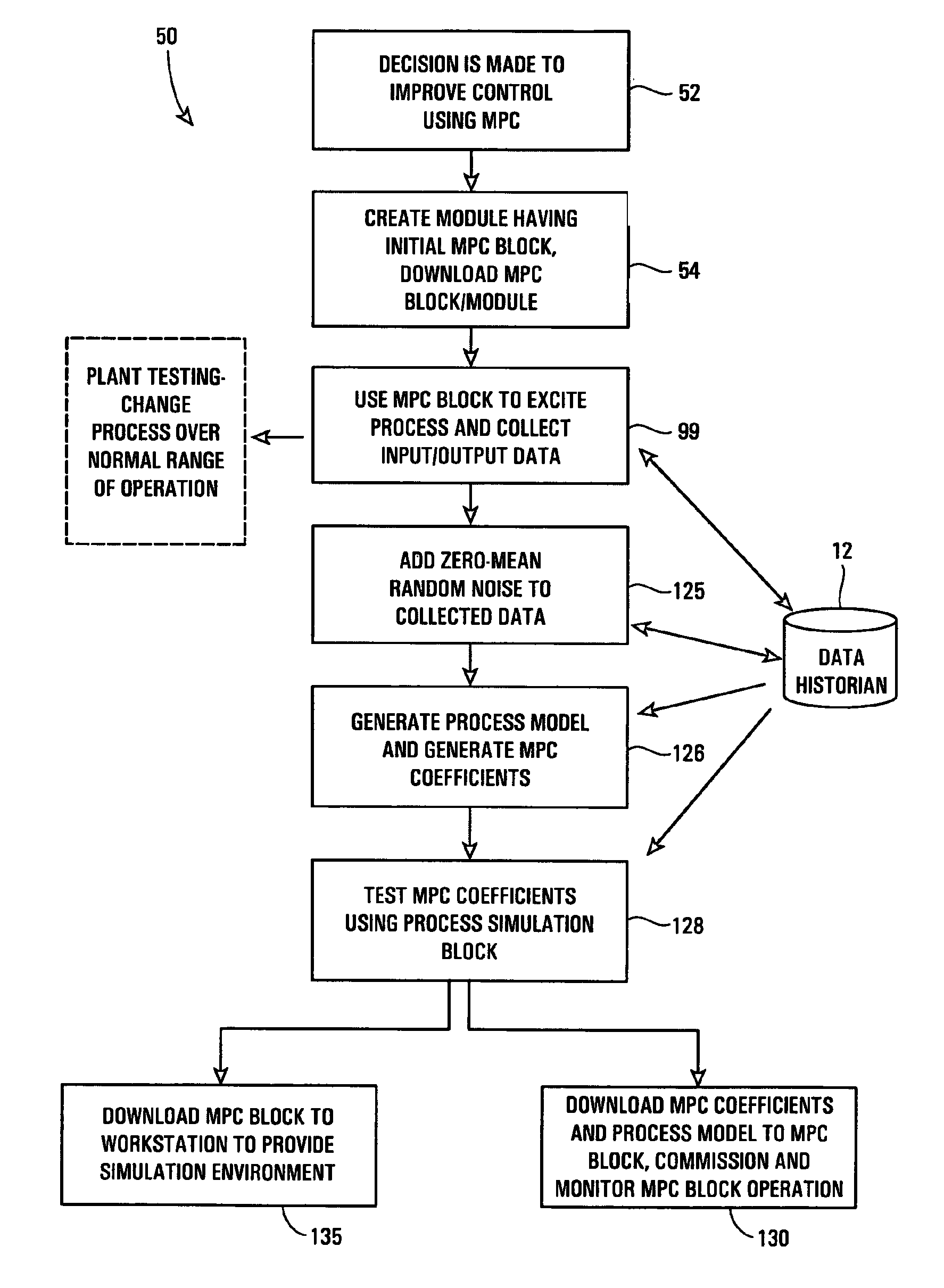

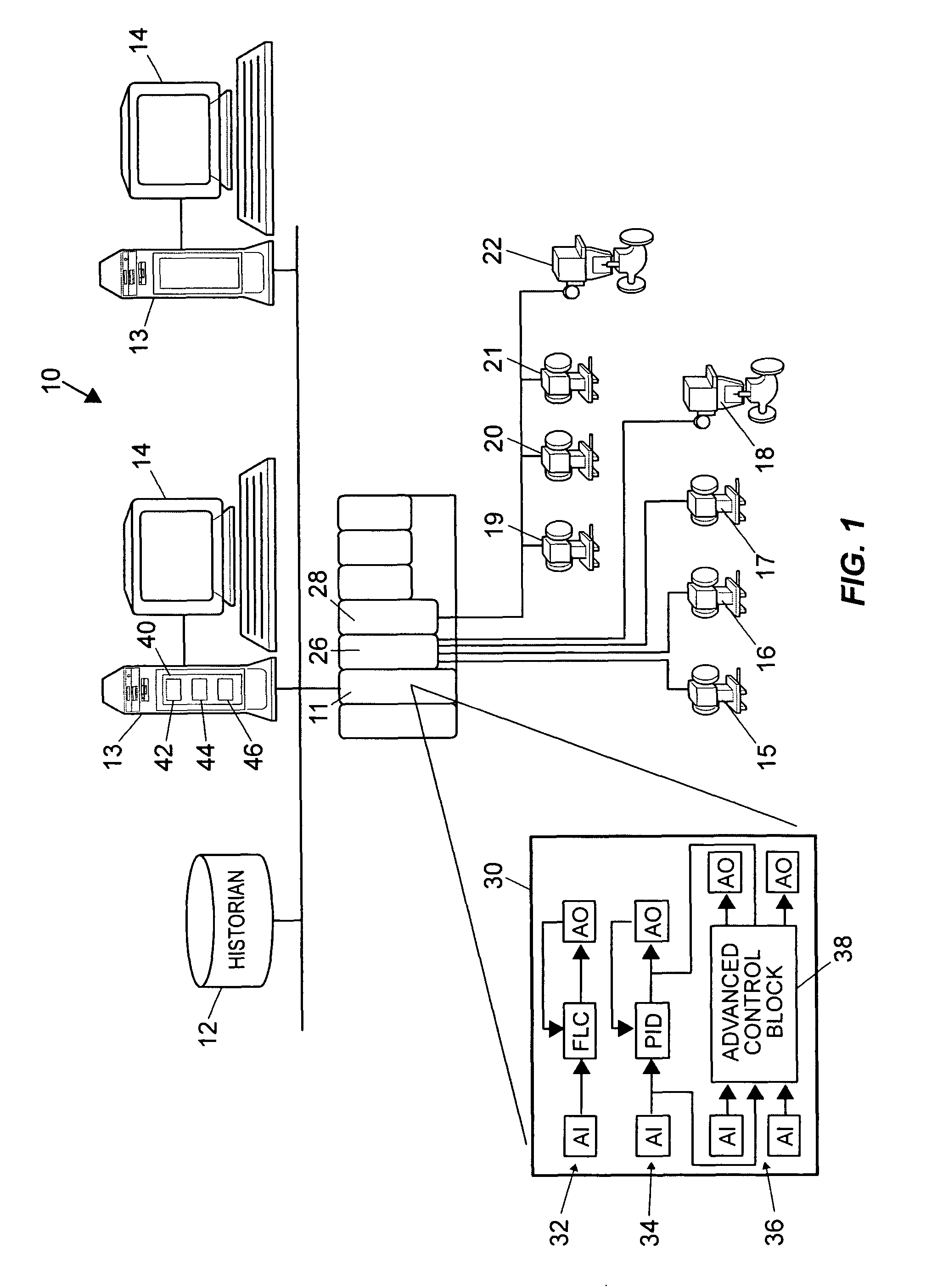

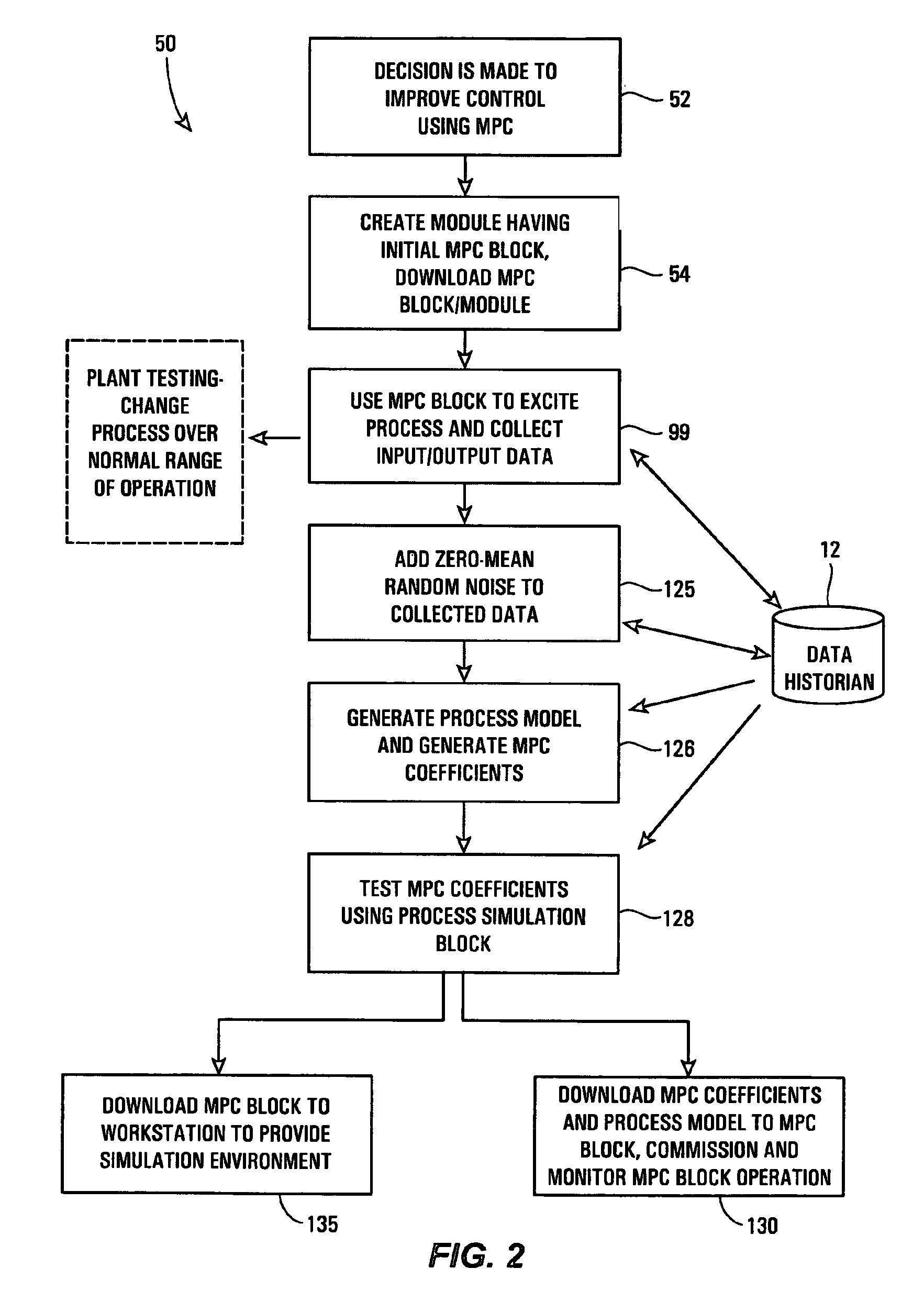

Robust process model identification in model based control techniques

ActiveUS20070244575A1Robust methodAmplifier modifications to reduce noise influenceSimulator controlGeneration processTest input

A robust method of creating process models for use in controller generation, such as in MPC controller generation, adds noise to the process data collected and used in the model generation process. In particular, a robust method of creating a parametric process model first collects process outputs based on known test input signals or sequences, adds random noise to the collected process data and then uses a standard or known technique to determine a process model from the collected process data. Unlike existing techniques for noise removal that focus on clean up of non-random noise prior to generating a process model, the addition of random, zero-mean noise to the process data enables, in many cases, the generation of an acceptable parametric process model in situations where no process model parameter convergence was otherwise obtained. Additionally, process models created using this technique generally have wider confidence intervals, therefore providing a model that works adequately in many process situations without needing to manually or graphically change the model.

Owner:FISHER-ROSEMOUNT SYST INC

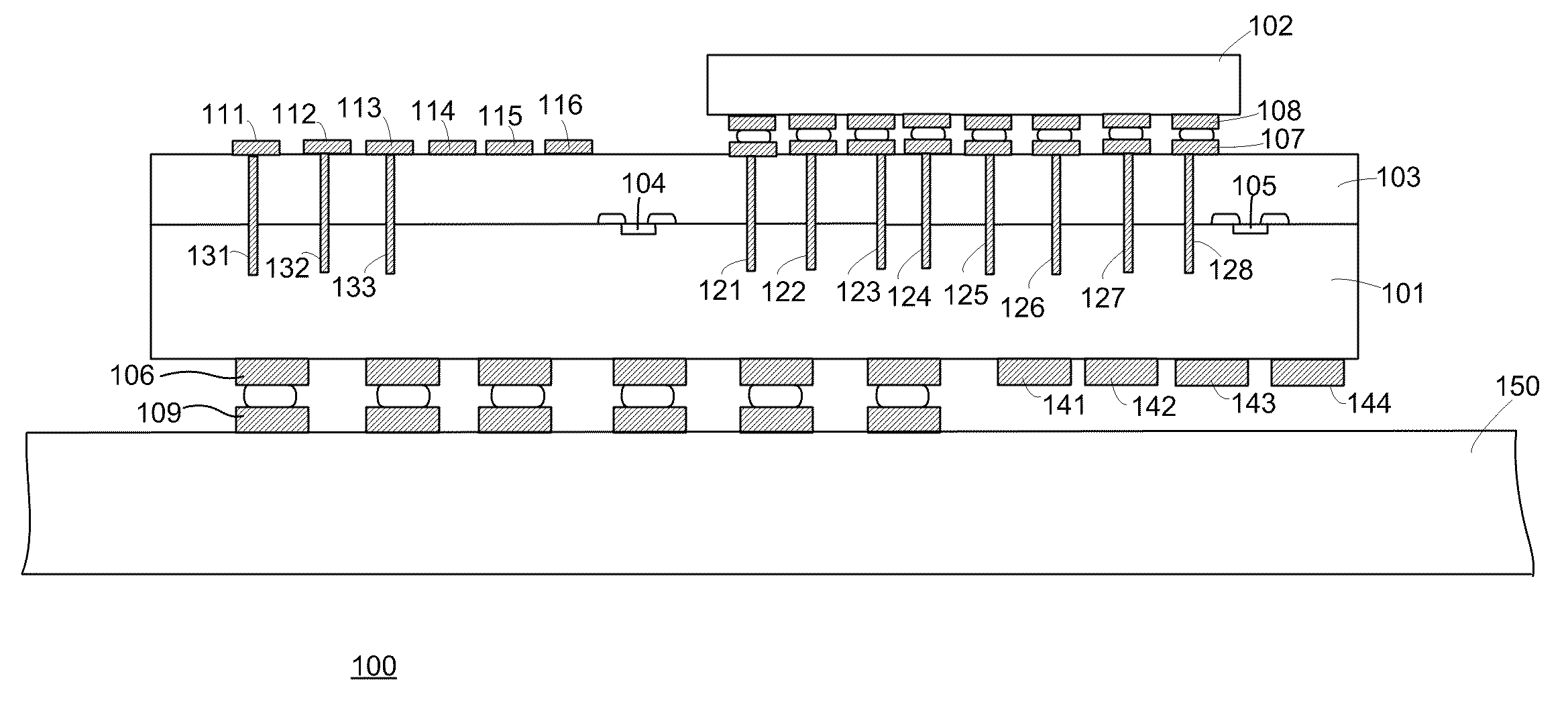

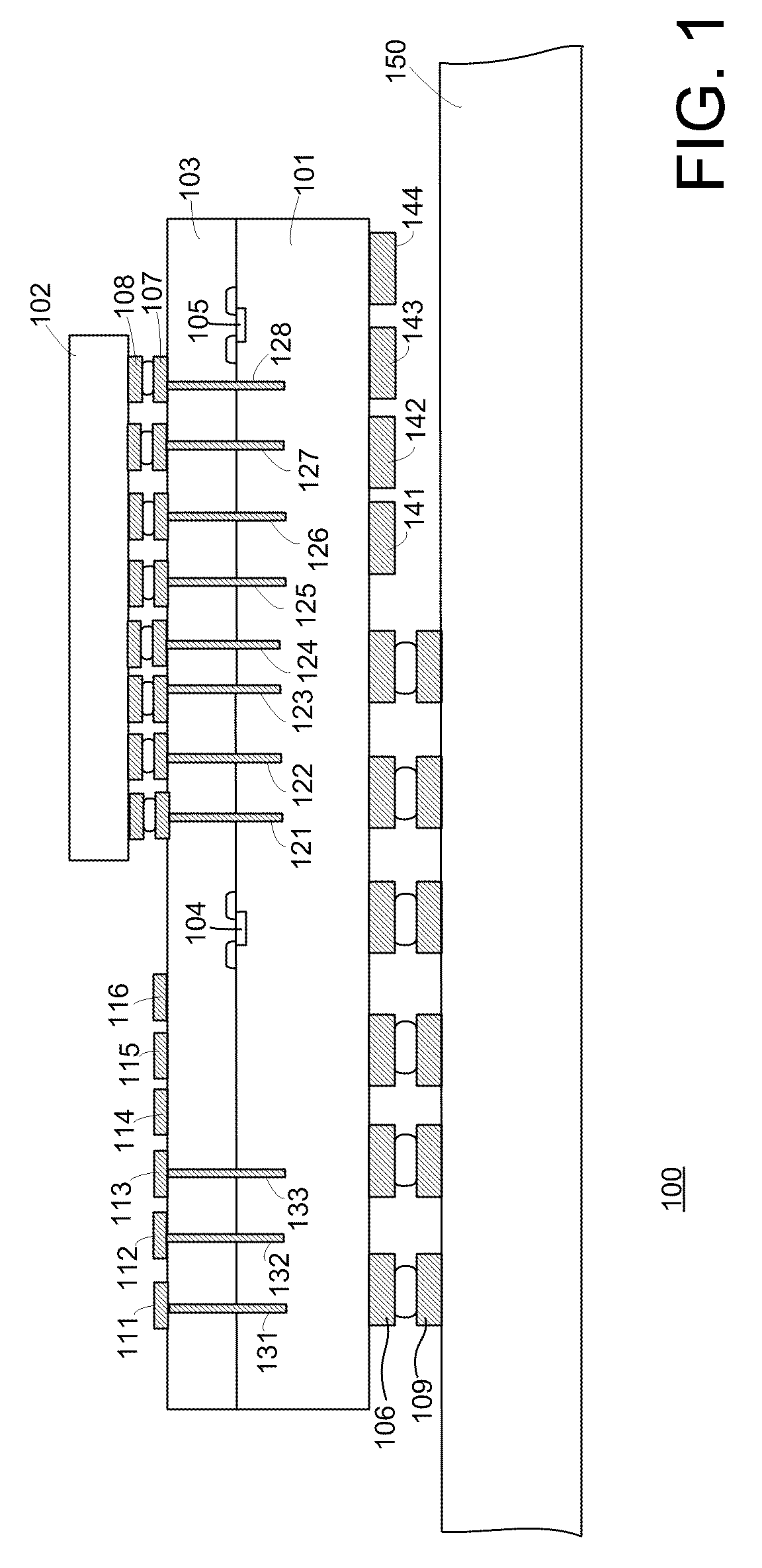

Apparatus and method for testing of stacked die structure

ActiveUS8063654B2Less timeShorten the timeSolid-state devicesSemiconductor devicesTest inputControl signal

An integrated circuit device includes a stacked die and a base die having probe pads that directly couple to test logic of the base die to implement a scan chain for testing of the integrated circuit device. The base die further includes contacts disposed on a back side of the base die and through-die vias coupled to the contacts and coupled to programmable logic of the base die. The base die also includes a first probe pad configured to couple test input, a second probe pad configured to couple test output, and a third probe pad configured to couple control signals. Test logic of the base die is configured to couple to additional test logic of the stacked die to implement the scan chain. The probe pads are coupled directly to the test logic such that configuration of the programmable logic is not required to implement the scan chain.

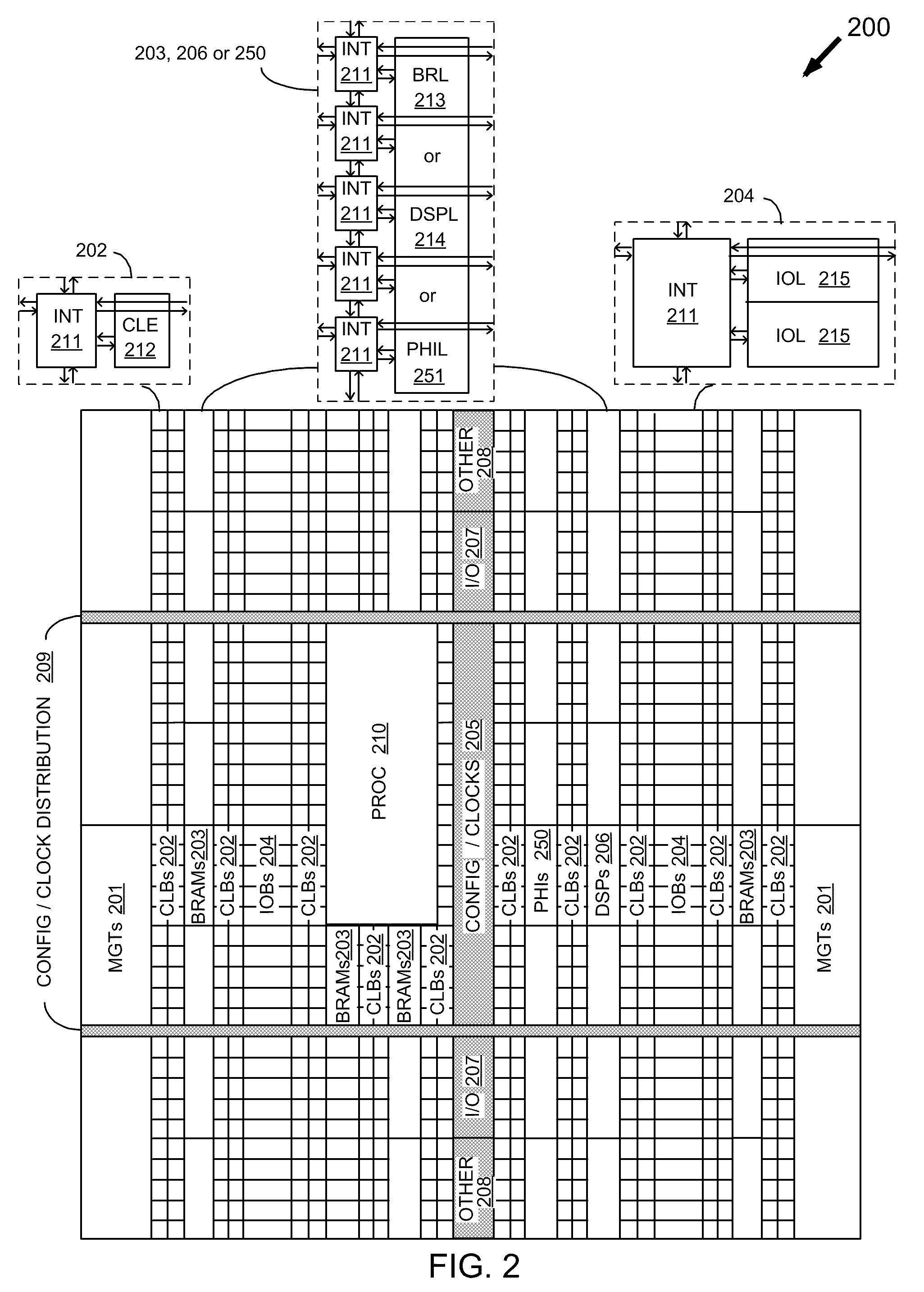

Owner:XILINX INC

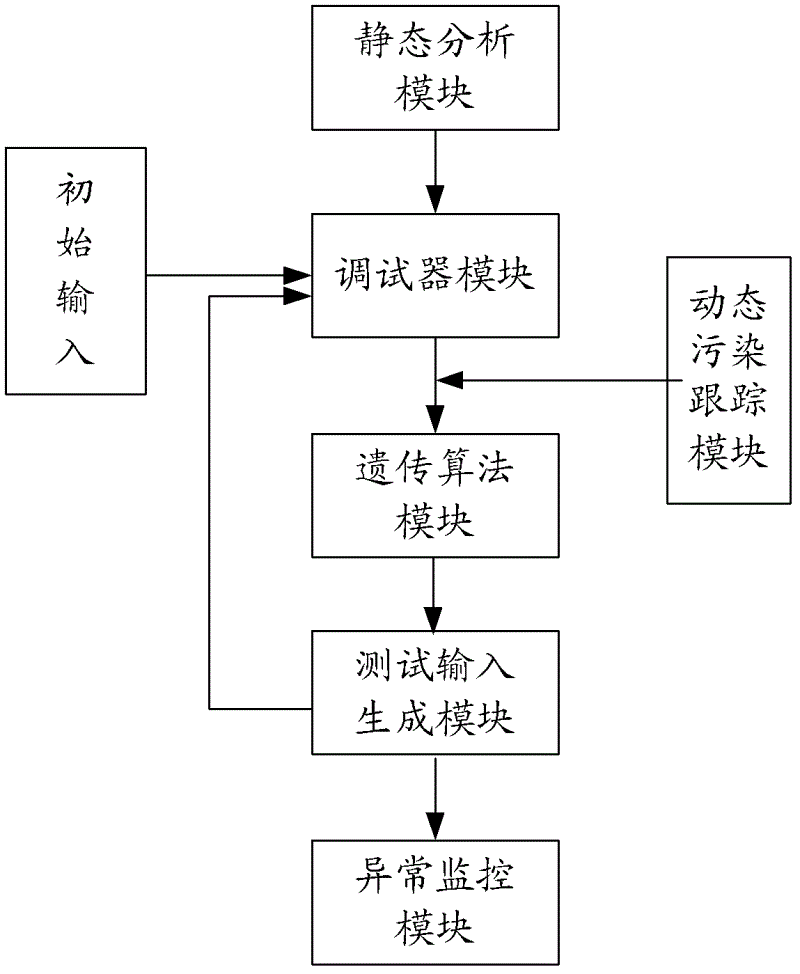

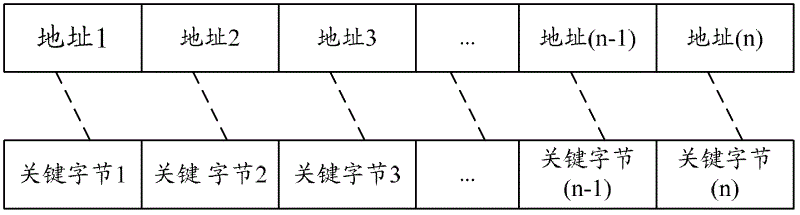

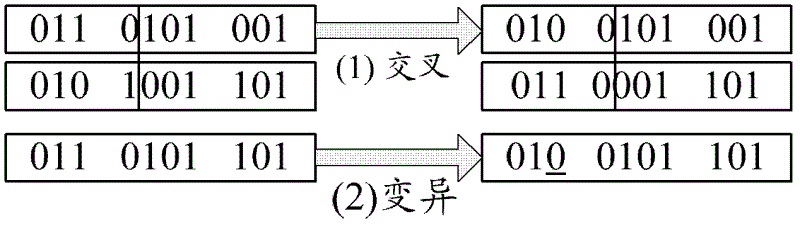

Excavating device and excavating method of binary system program loopholes

InactiveCN102622558AAvoid blindnessPath maximizationPlatform integrity maintainanceTest inputTheoretical computer science

Provided are an excavating device and an excavating method of binary system program loopholes. The excavating device is provided with a static analysis module, a debugger module, a genetic algorithm module, a test input generation module and an abnormal monitoring module which are sequentially connected and a dynamic pollution tracking module located between the debugger module and the genetic algorithm module. The excavating device is guided to generate a test case by aid of a fitness function of the genetic algorithm, the multi-objective fitness function is designed, and the test case is evaluated in view of quantification. Dynamic pollution tracking is used for identifying key bytes in input files to narrow search space of the genetic algorithm. The excavating device combines advantages of the genetic algorithm and the dynamic pollution tracking and is guided to generate the test case, so that the generated test case is strong in pertinence, generated test data are high in accuracy and efficiency, further qualitative analysis and quantitative calculation are combined, and therefore path explosion in binary system program testing based on the symbolic execution and constraint solving technology is avoided.

Owner:BEIJING UNIV OF POSTS & TELECOMM

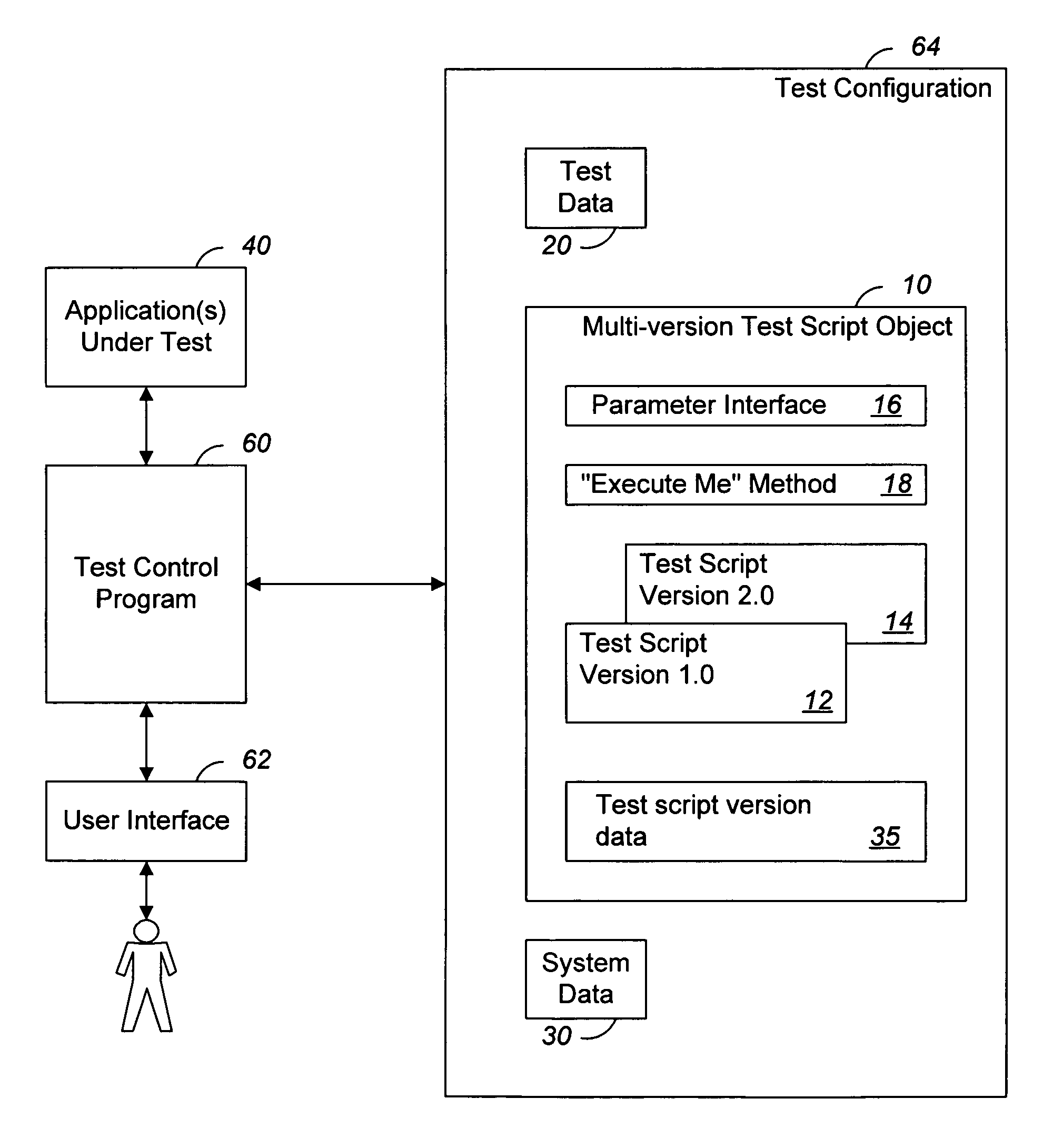

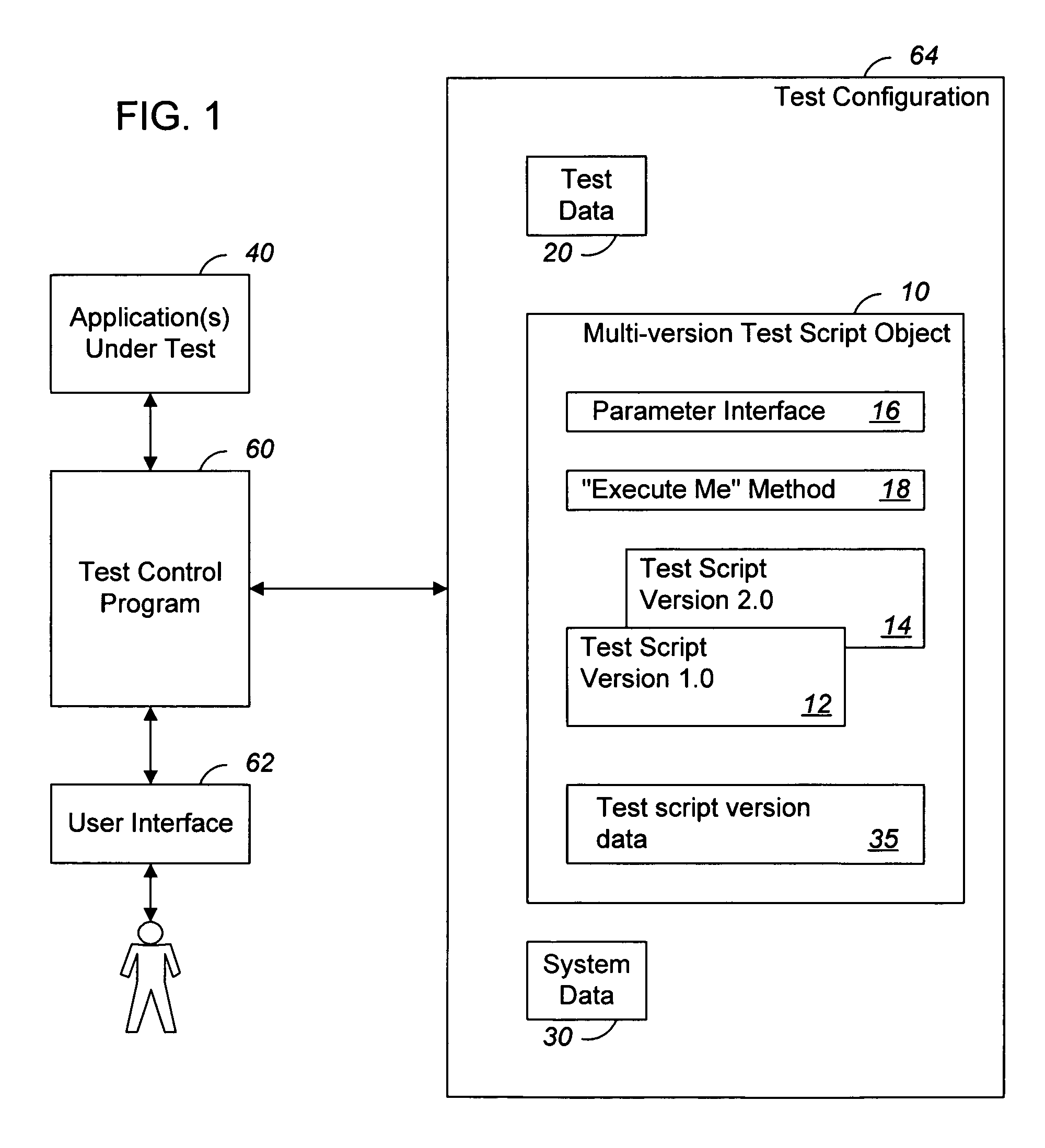

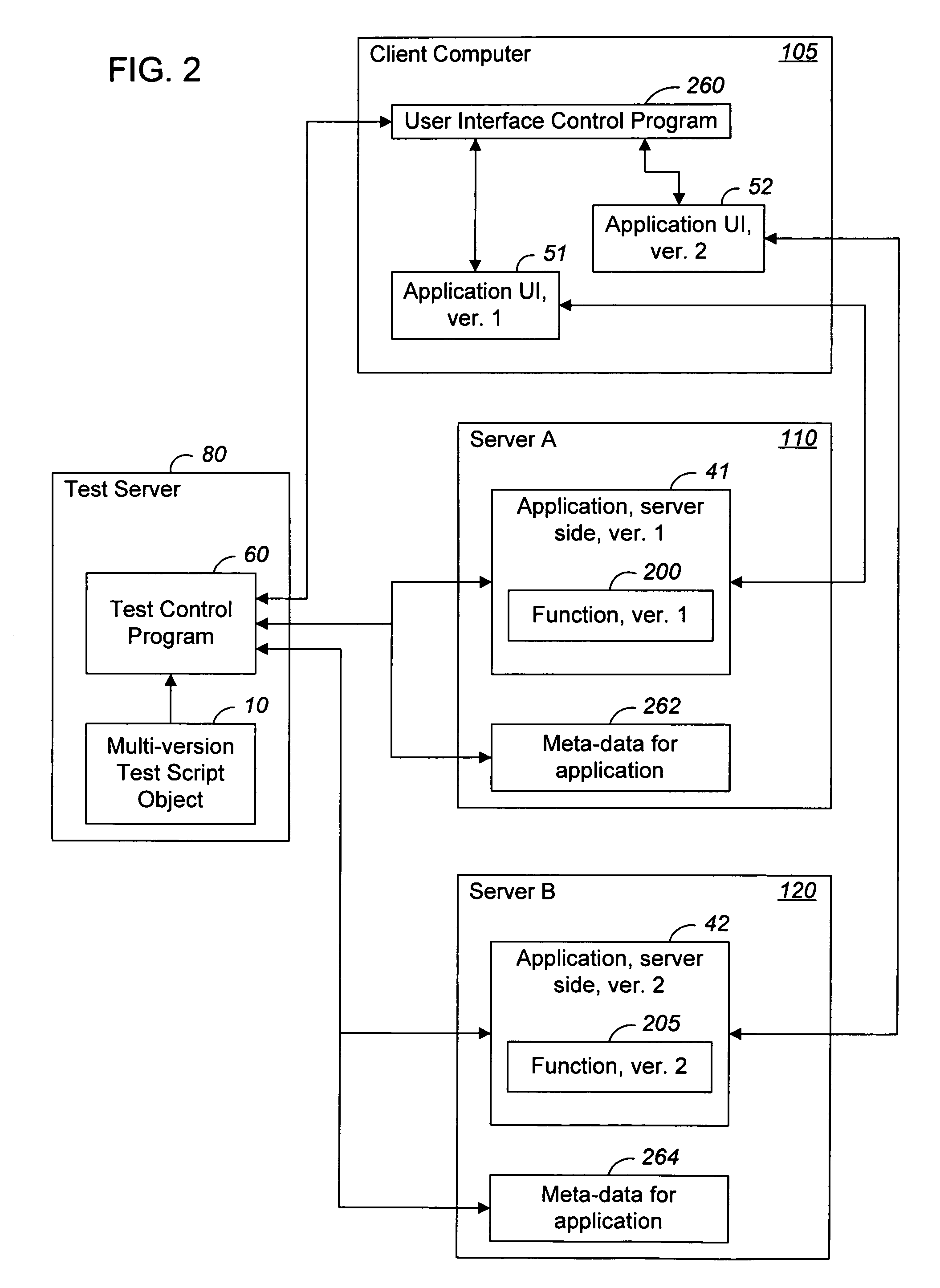

Handling parameters in test scripts for computer program applications

InactiveUS7305659B2Improve efficiencyManageable sizeError preventionDigital computer detailsComputer hardwareTest script

Methods and apparatus, including computer program products, for handling parameters in a test script for testing a computer program application. A method includes executing a test script for testing a function of a computer program, the test script including a command invoking the function, the command having arguments, the command arguments in the test script including a set of test input parameters for the function; determining the required input parameters for the function; and detecting an error if there is a mismatch between the required input parameters and the test input parameters.

Owner:SAP AG

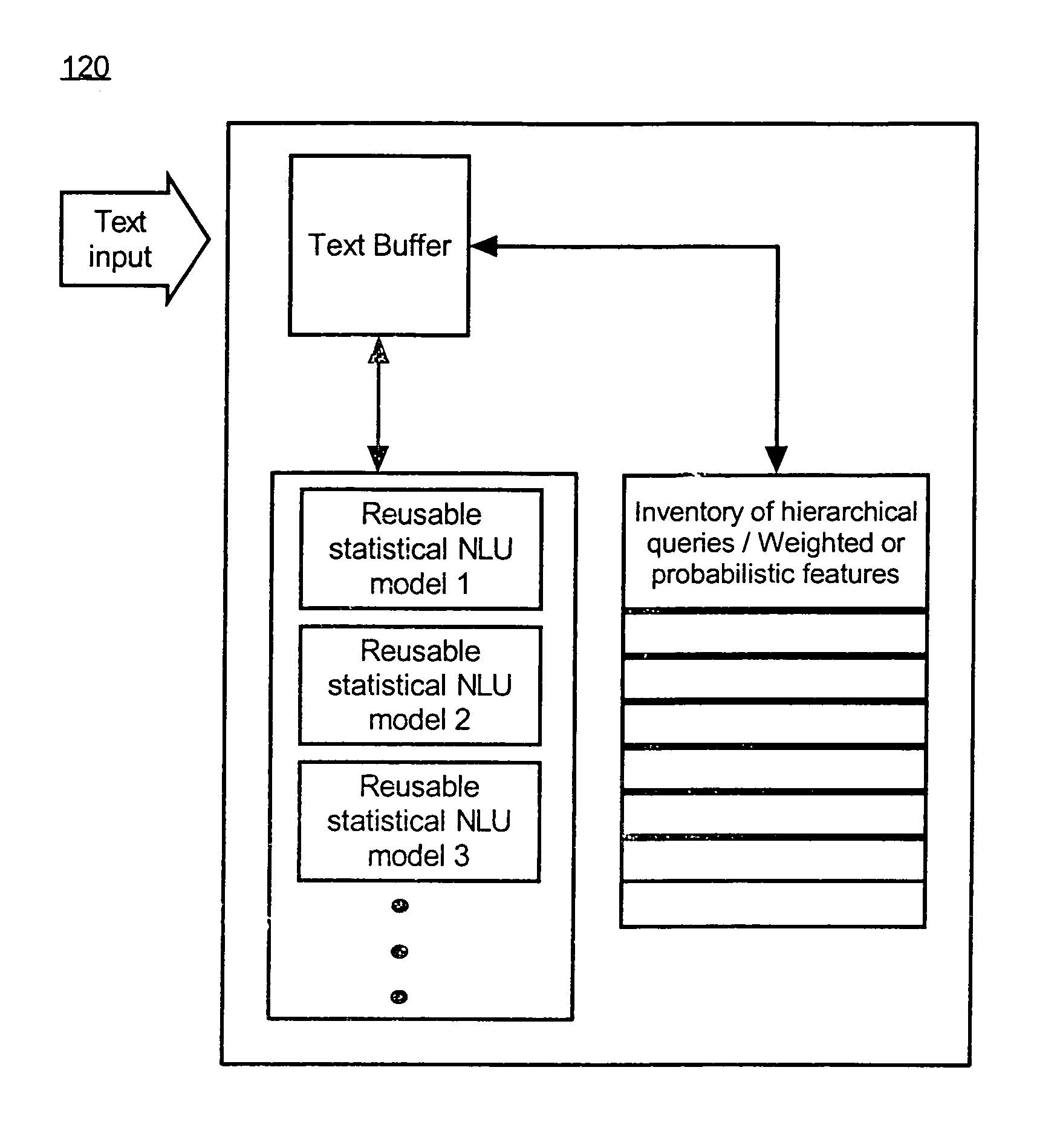

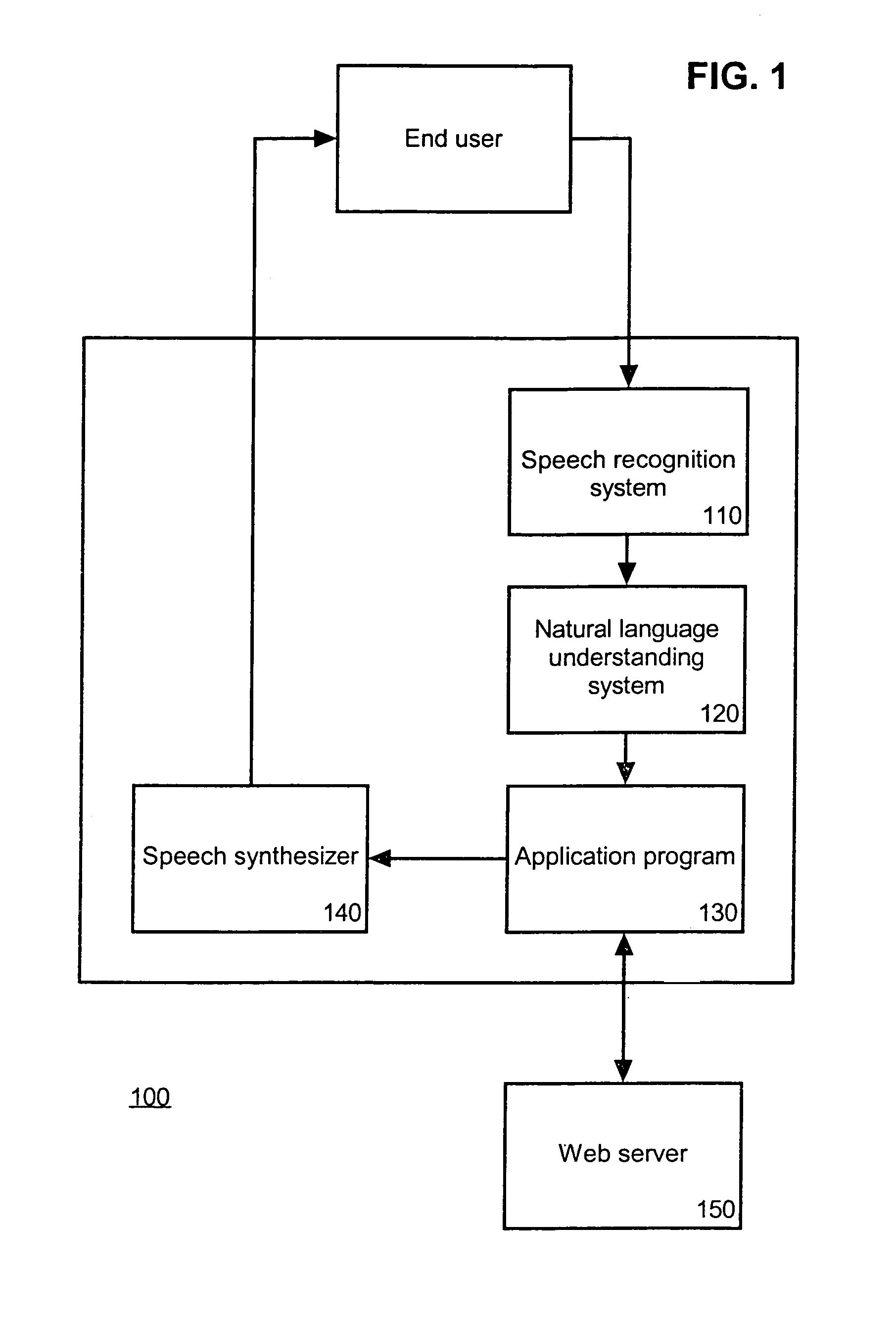

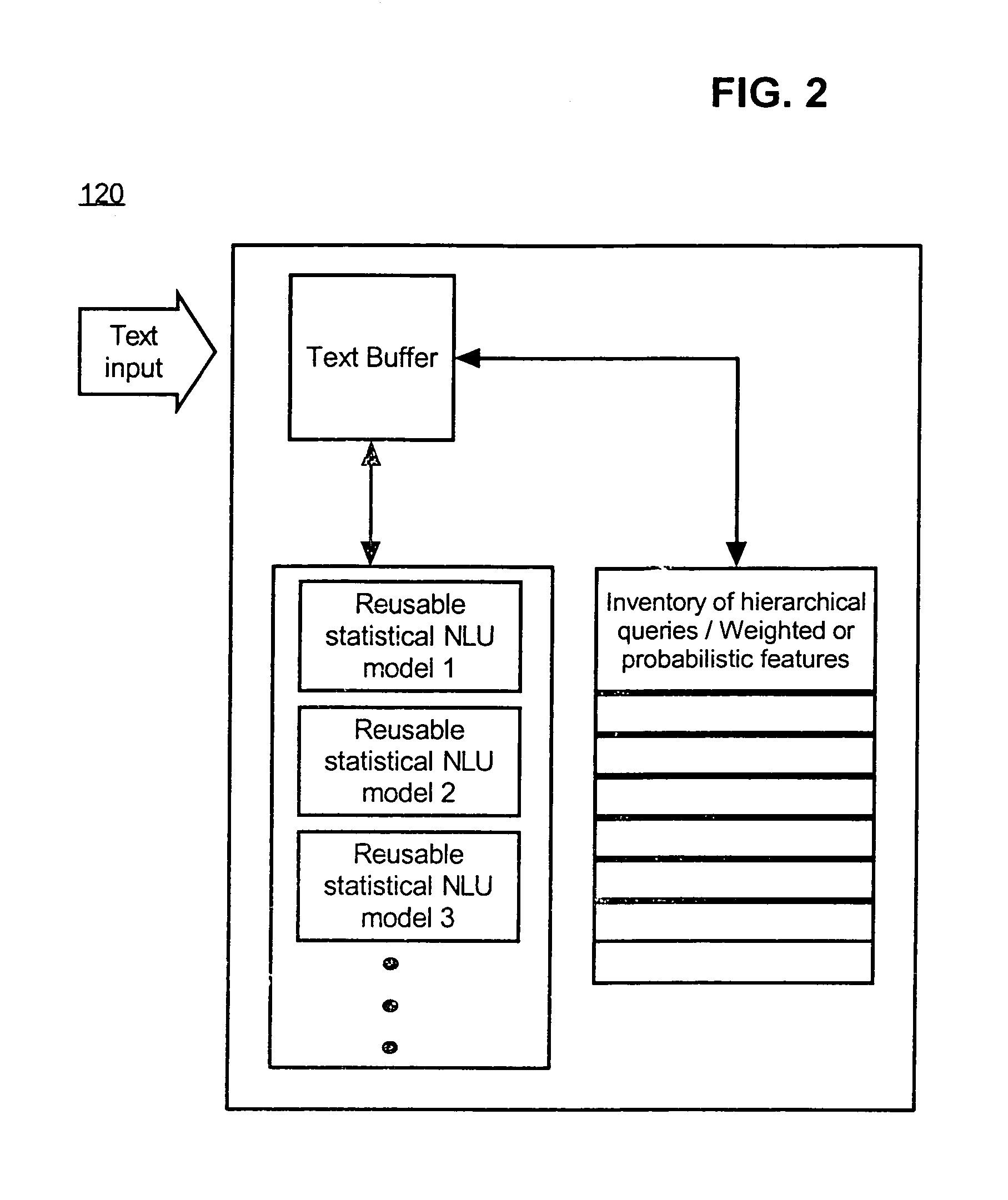

Including statistical NLU models within a statistical parser

ActiveUS6963831B1Speech analysisNatural language data processingNatural language understandingTest input

A method and system for statistical parsing. The method involves a series of steps. The system can apply a statistical natural language understanding (NLU) model to test input for identifying substrings within the text input. The statistical NLU model can be selected for identifying a particular class of substring. The system can examine each identified substring using an inventory of queries corresponding to the reusable statistical NLU model.

Owner:NUANCE COMM INC

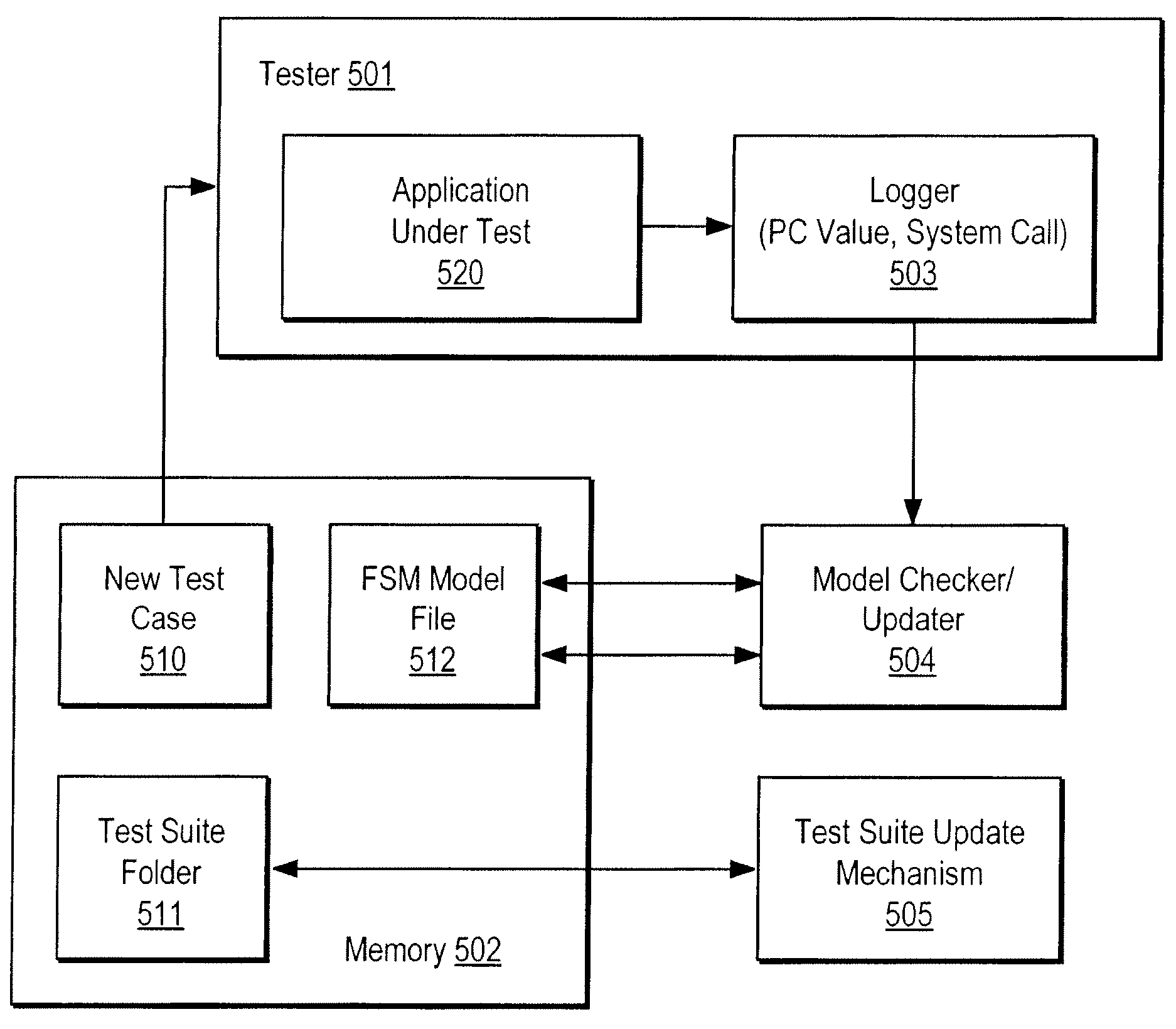

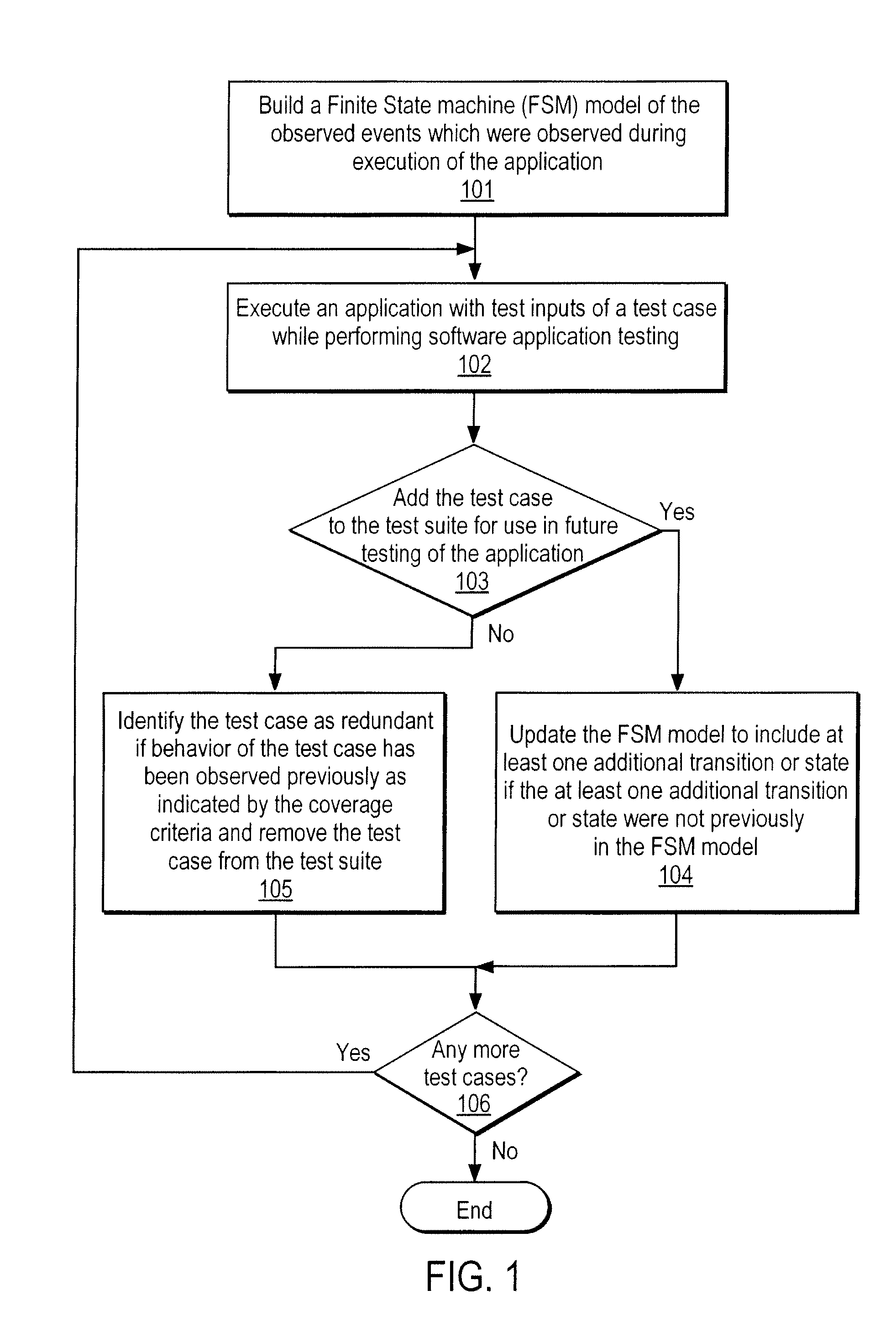

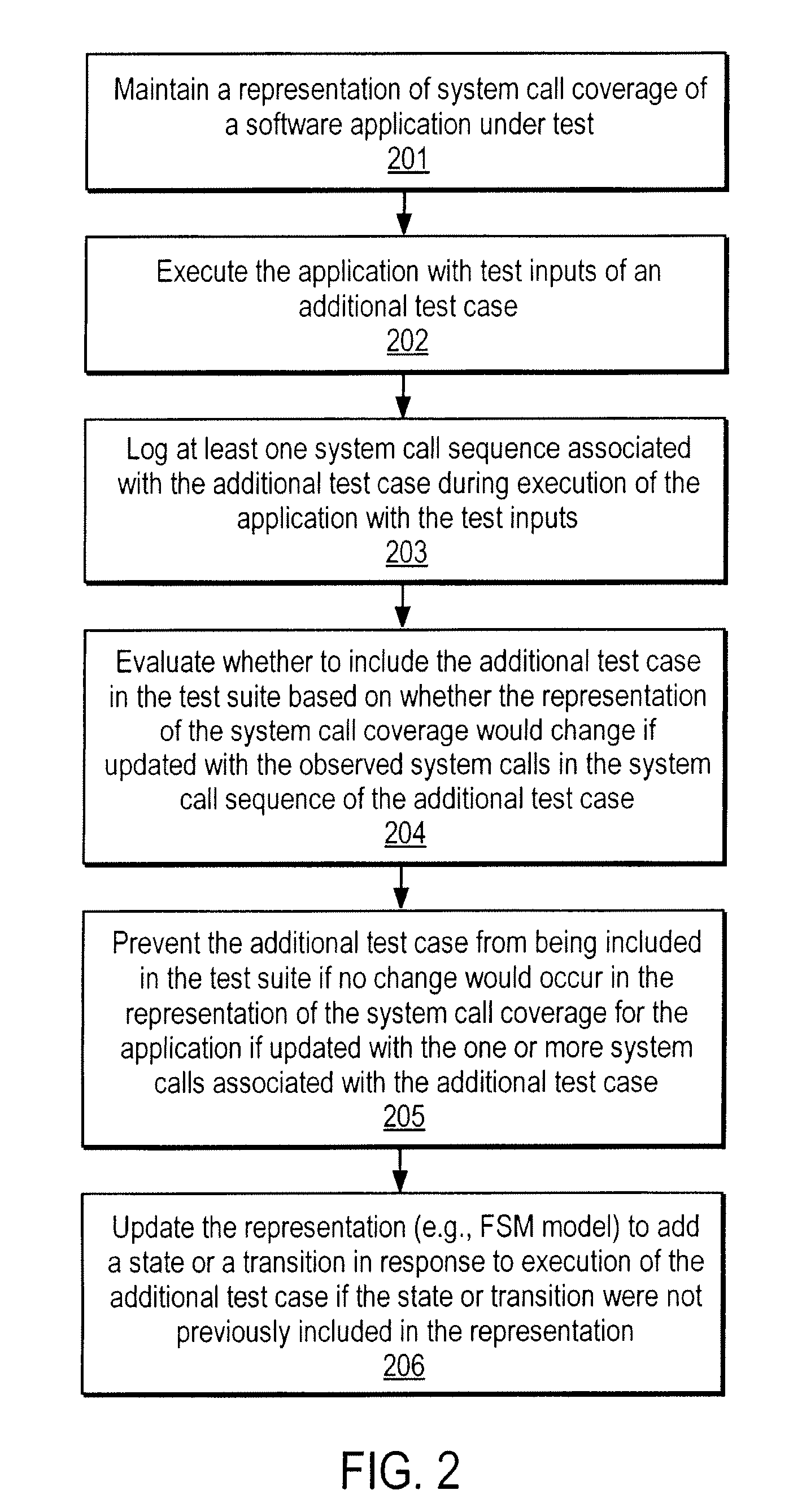

Method for test suite reduction through system call coverage criterion

InactiveUS20090070746A1Software testing/debuggingSpecific program execution arrangementsTest inputTest suite

A method and apparatus is disclosed herein for determining whether a test case is to be included in a test suite. In one embodiment, the method comprises executing an application with test inputs of a test case during performance of software application testing and using a Finite State Machine (FSM) model of observable events generated from execution of other test cases in the test suite to determine whether to include the test case in the test suite for use in future testing of the application.

Owner:NTT DOCOMO INC

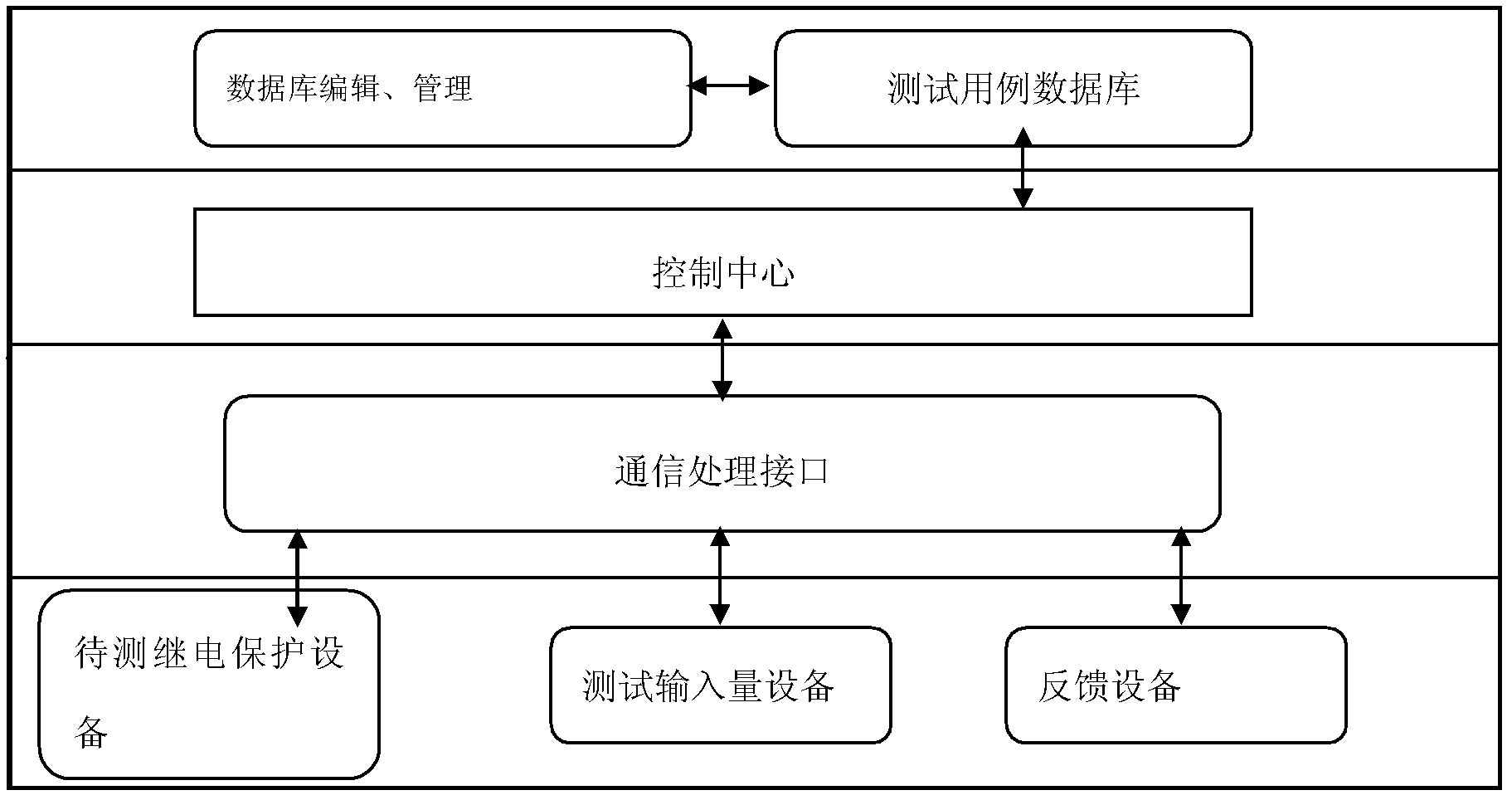

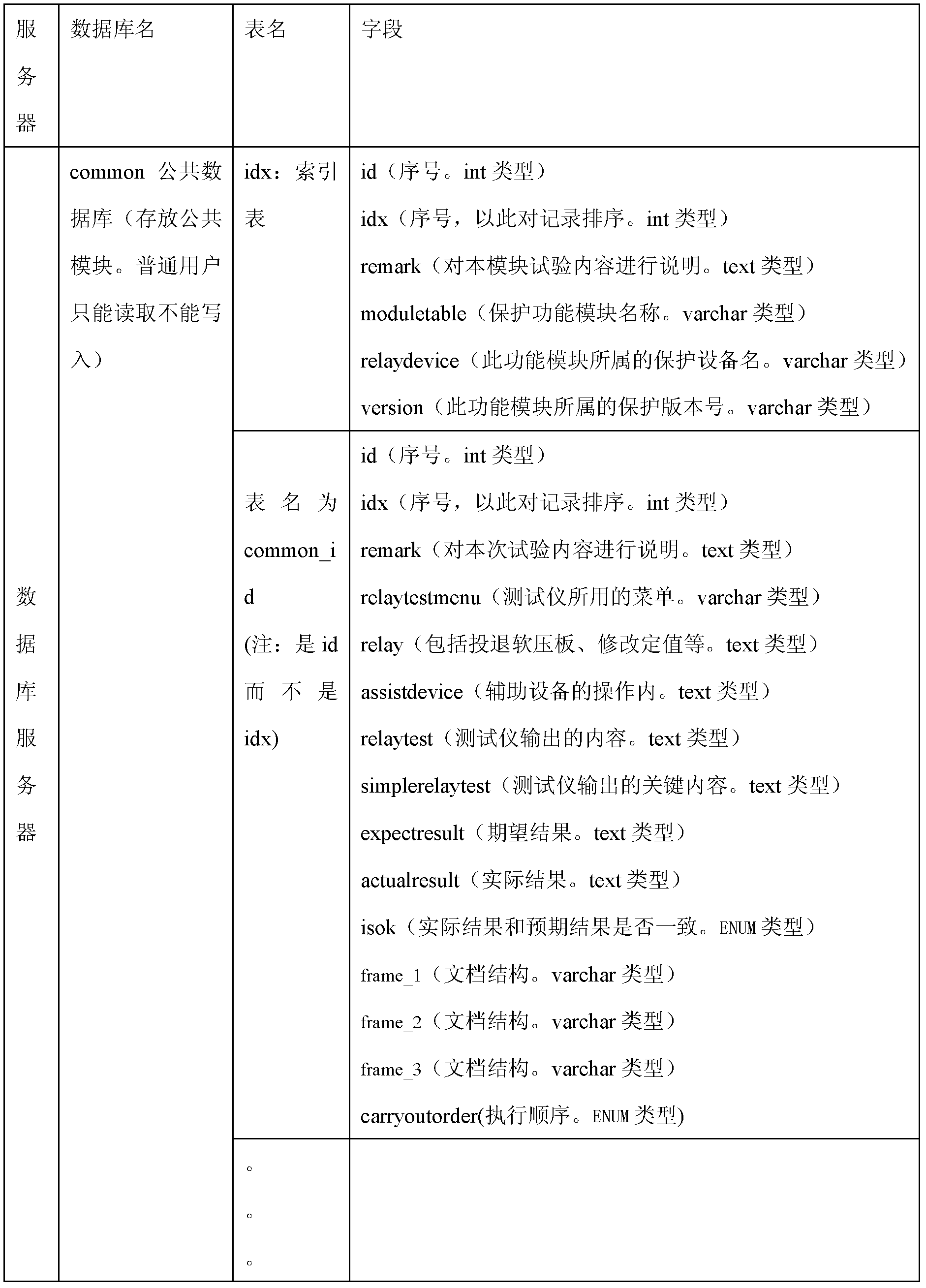

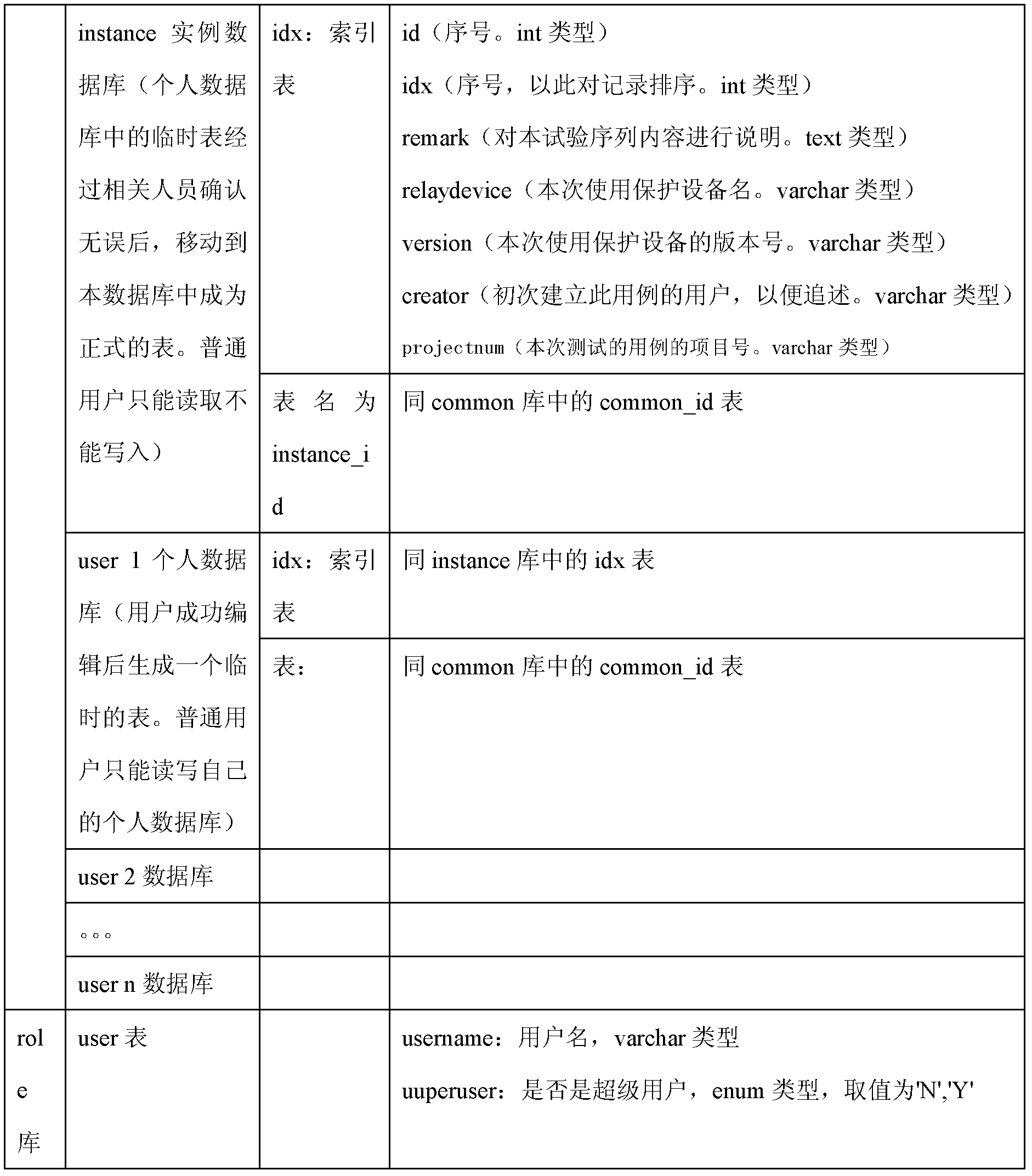

Method for automatically testing relay protection equipment

The invention provides a method for automatically testing relay protection equipment. The method comprises the steps of: generating a test input quantity, detecting an output quantity of an object to be tested, and monitoring an intermediate quantity of the object to be tested through a distributed simulation environment, and forming a complete process of a closed-loop test; storing a fixed value, a pressure plate, a message and other information of relay protection equipment to be tested through a manner of a database, and storing the test input quantity and the output quantity of the object to be tested during the testing process; testing input equipment and the object to be tested through network connection; and controlling test input through a manner of command, then receiving the feedback of the object to be tested, finally intelligently comparing with an expected result stored in the database, and storing a feedback result in the database. By adopting the method for automatically testing the relay protection equipment provided by the invention, external properties of the relay protection equipment can be automatically monitored, the reliability of testing of the relay protection equipment and the testing efficiency are improved, and the probability of finding of hidden defects is increased.

Owner:BEIJING SIFANG JIBAO AUTOMATION

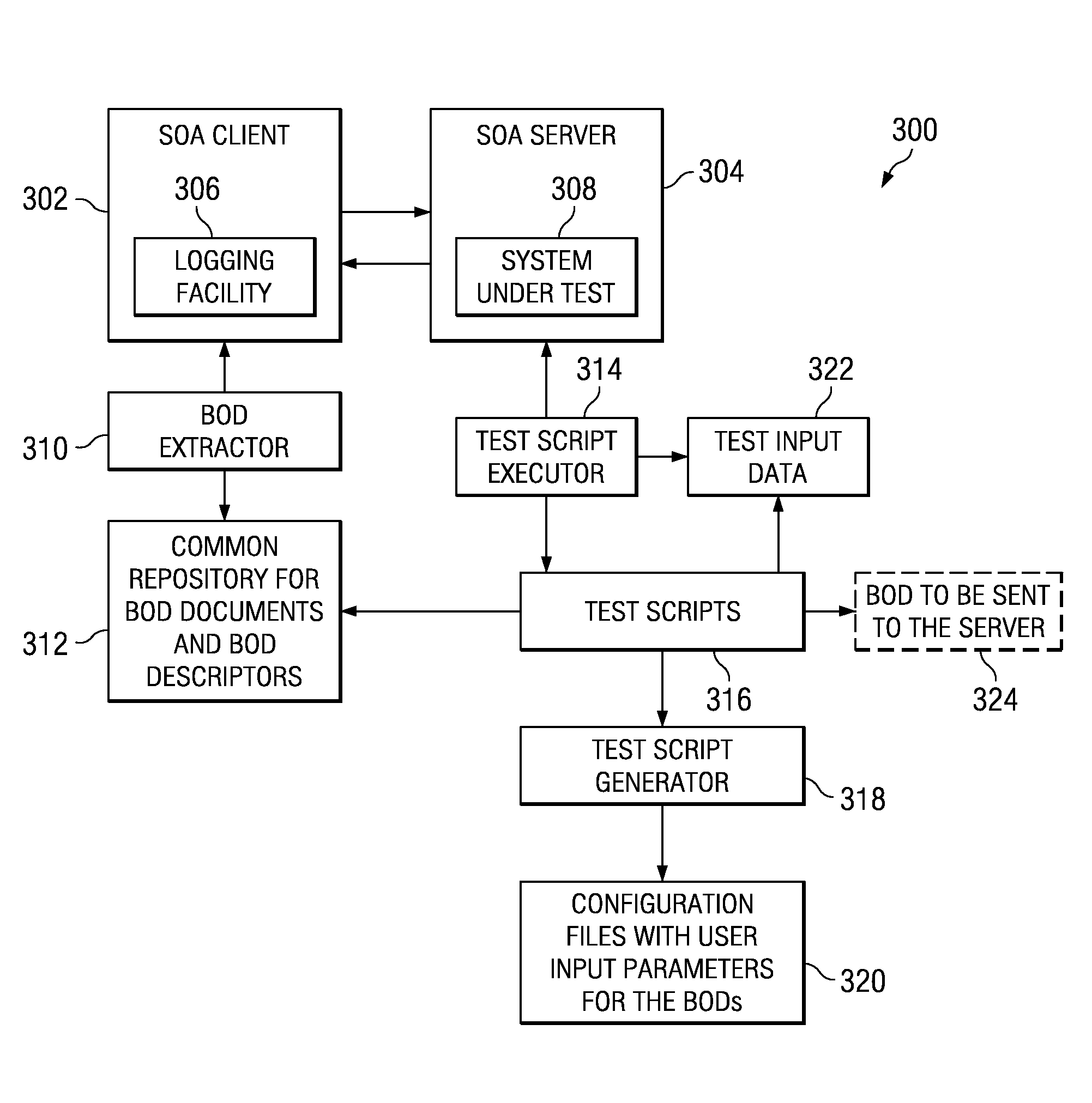

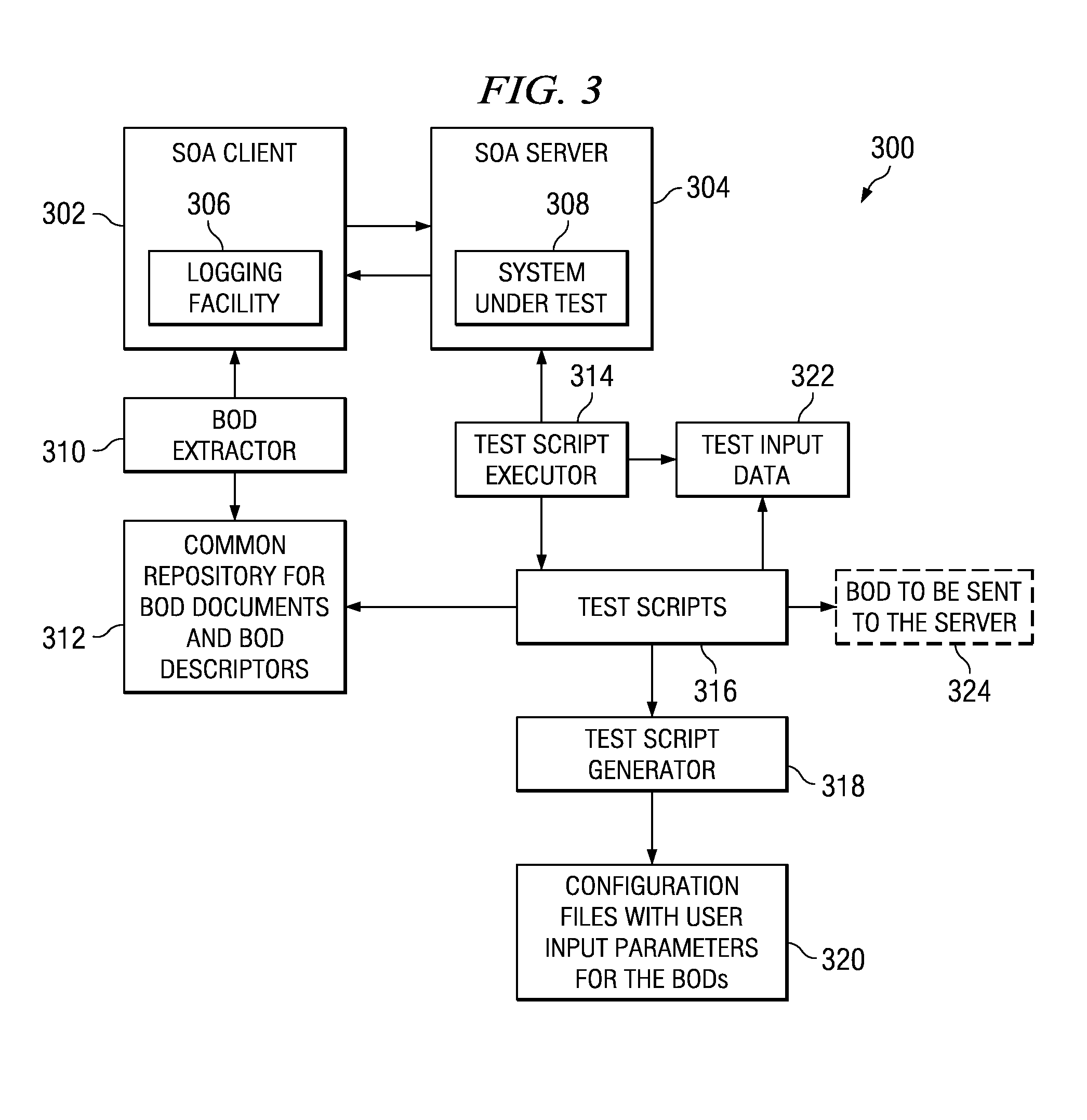

Efficient stress testing of a service oriented architecture based application

InactiveUS20080126390A1Error detection/correctionSpecial data processing applicationsTest inputTest script

A method for efficiently stress testing a service oriented architecture based application. A business process flow is recorded between a client and a server. When an XML document is extracted from the recorded business process flow, an XML document file is created for the extracted XML document, an XML document descriptor file is created comprising XPath queries for data elements in the XML document file, a configuration file is created comprising user input parameters obtained from the recorded business process flow, and test input data file is created. The user input parameters in the configuration file are used to generate a test script to test the service oriented architecture based application, wherein data values from the test input data file are inserted into a template of the XML document file at locations specified by the XPath queries in the XML document descriptor file. The test script is then executed.

Owner:IBM CORP

Robust process model identification in model based control techniques

ActiveUS7840287B2Robust methodAmplifier modifications to reduce noise influenceSimulator controlGeneration processTest input

A robust method of creating process models for use in controller generation, such as in MPC controller generation, adds noise to the process data collected and used in the model generation process. In particular, a robust method of creating a parametric process model first collects process outputs based on known test input signals or sequences, adds random noise to the collected process data and then uses a standard or known technique to determine a process model from the collected process data. Unlike existing techniques for noise removal that focus on clean up of non-random noise prior to generating a process model, the addition of random, zero-mean noise to the process data enables, in many cases, the generation of an acceptable parametric process model in situations where no process model parameter convergence was otherwise obtained. Additionally, process models created using this technique generally have wider confidence intervals, therefore providing a model that works adequately in many process situations without needing to manually or graphically change the model.

Owner:FISHER-ROSEMOUNT SYST INC

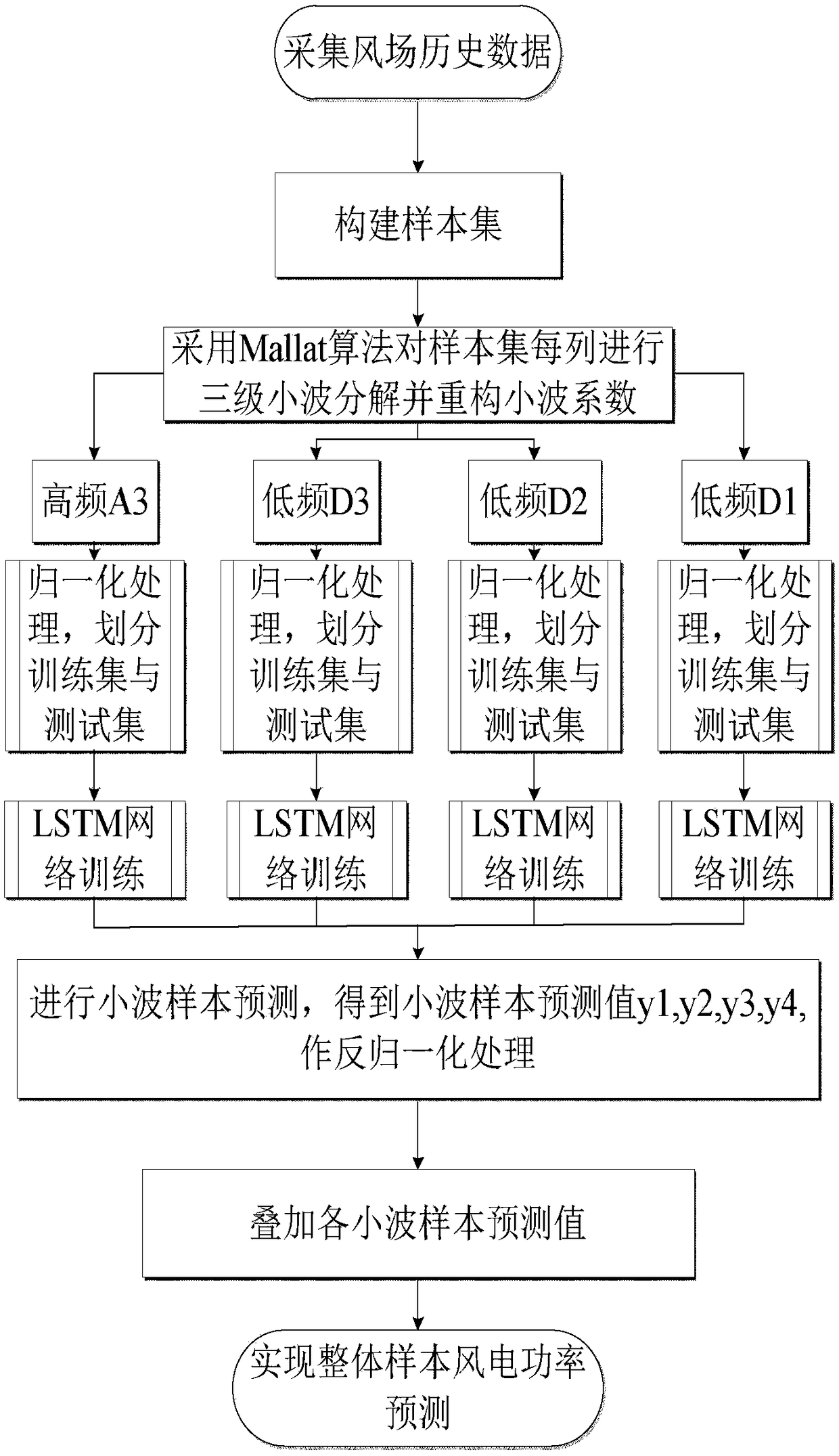

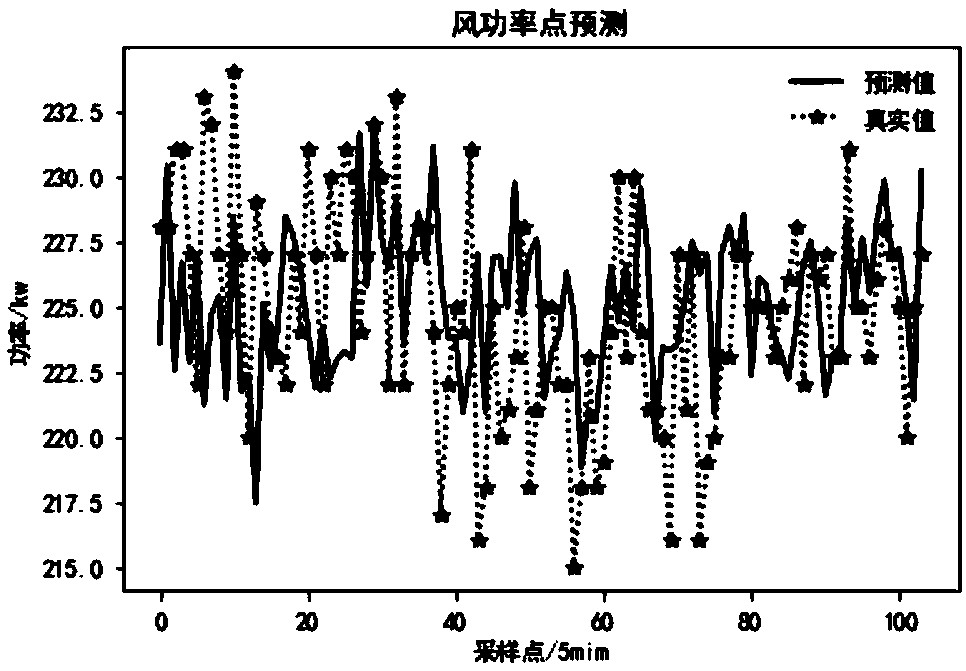

An ultra-short-term wind power forecasting method based on small wavelength short-term memory network

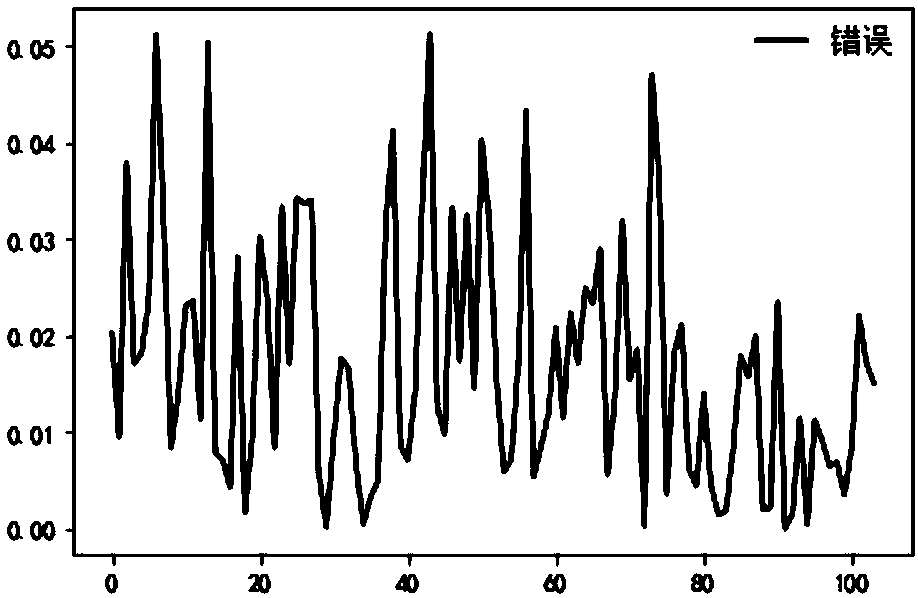

ActiveCN109214575AEasy to handleRealize Observational AnalysisForecastingCharacter and pattern recognitionTest inputShort-term memory

The invention discloses an ultra-short-term wind power prediction method based on a small wavelength short-term memory network, which generates input variables according to historical data and takes the corresponding wind power historical data as output to obtain a training sample. Using wavelet analysis method to decompose the training samples into four wavelet samples, and using short-term and long-term memory network model to train the four wavelet samples respectively, the small-wavelength short-term memory network prediction model after training is obtained. According to the actual data of the four wavelet samples at the time to be predicted, the test input data are generated and input to the prediction model, and the output is the ultra-short-term wind power prediction value at the time to be predicted. The invention combines wavelet analysis method with long-term and short-term memory depth network, can realize data stabilization processing and depth learning at the same time, improves prediction accuracy and enhances model generalization ability.

Owner:HOHAI UNIV

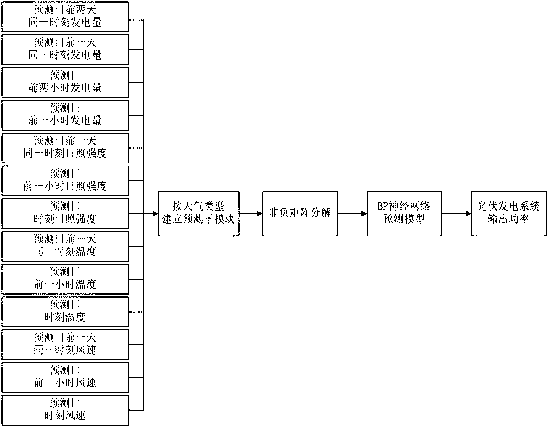

Method for predicating output power of photovoltaic power generation system based on BP (Back Propagation) neural network model

InactiveCN103218674AGood precisionImprove generalization abilityForecastingInformation technology support systemTest inputPredictive methods

The invention discloses a method for predicating the output power of a photovoltaic power generation system based on a BP (Back Propagation) neural network model. The method comprises the following steps of selecting influencing factors of the output power of the photovoltaic power generation system; generating input vectors according to the historical data of the selected influencing factors, and utilizing the historical data of the output power of the corresponding photovoltaic power generation system as output, thereby obtaining training samples; training a BP neural network by utilizing the training samples, thereby obtaining the trained BP neural network; generating test input vectors according to real data at the to-be-predicated moment of the selected influencing factors, inputting the test input vectors into the trained BP neural network, so that the output is the predicted value of the output power of the photovoltaic power generation system at the to-be predicated moment. According to the method for predicating the output power of the photovoltaic power generation system, modeling prediction is performed; the invention provides a predication method based on the BP neural network; the favorable nonlinear function approximation capability of the BP neural network is utilized, so that the precision and generalization capability of a prediction model are improved.

Owner:STATE GRID CORP OF CHINA +2

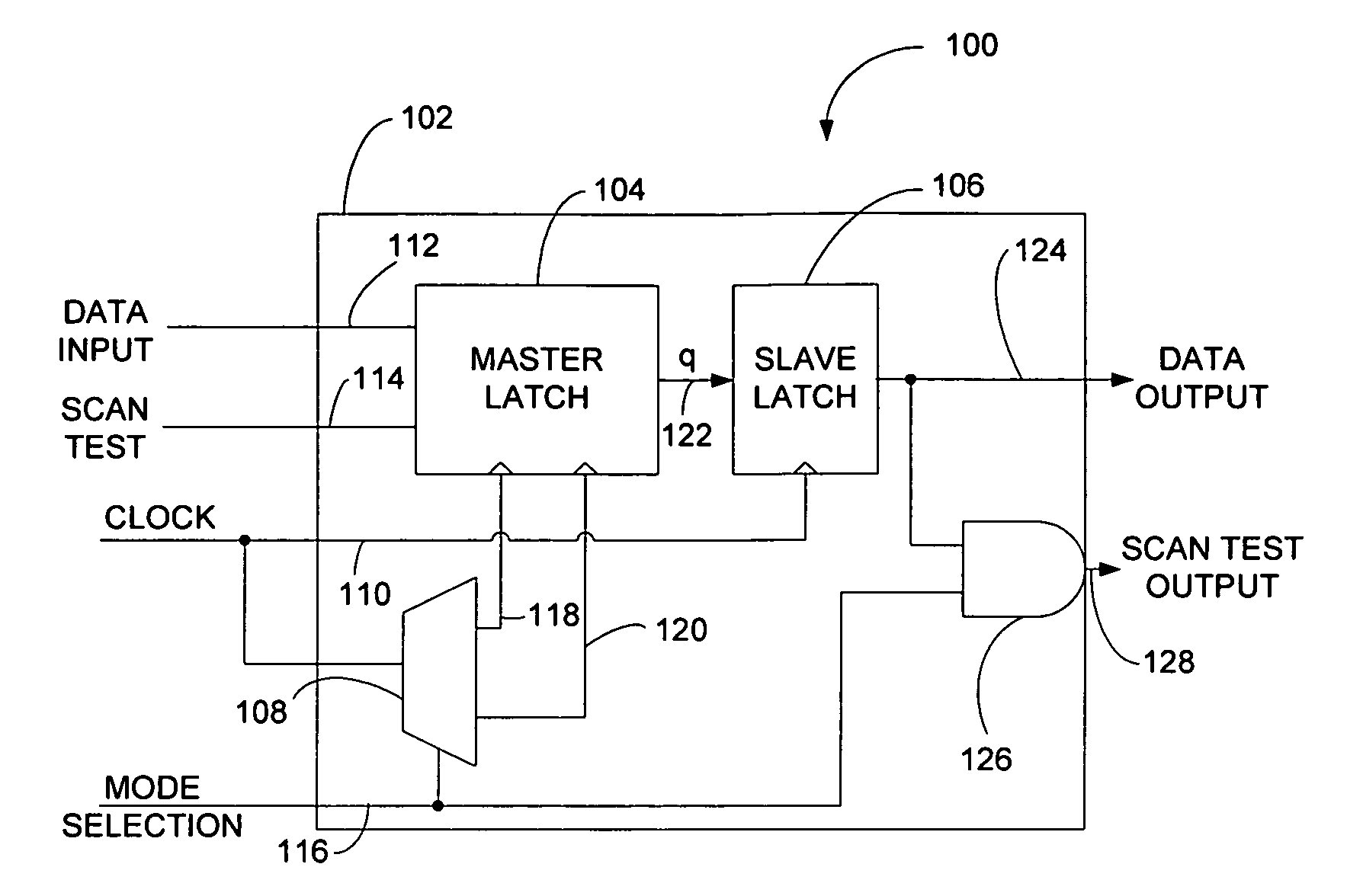

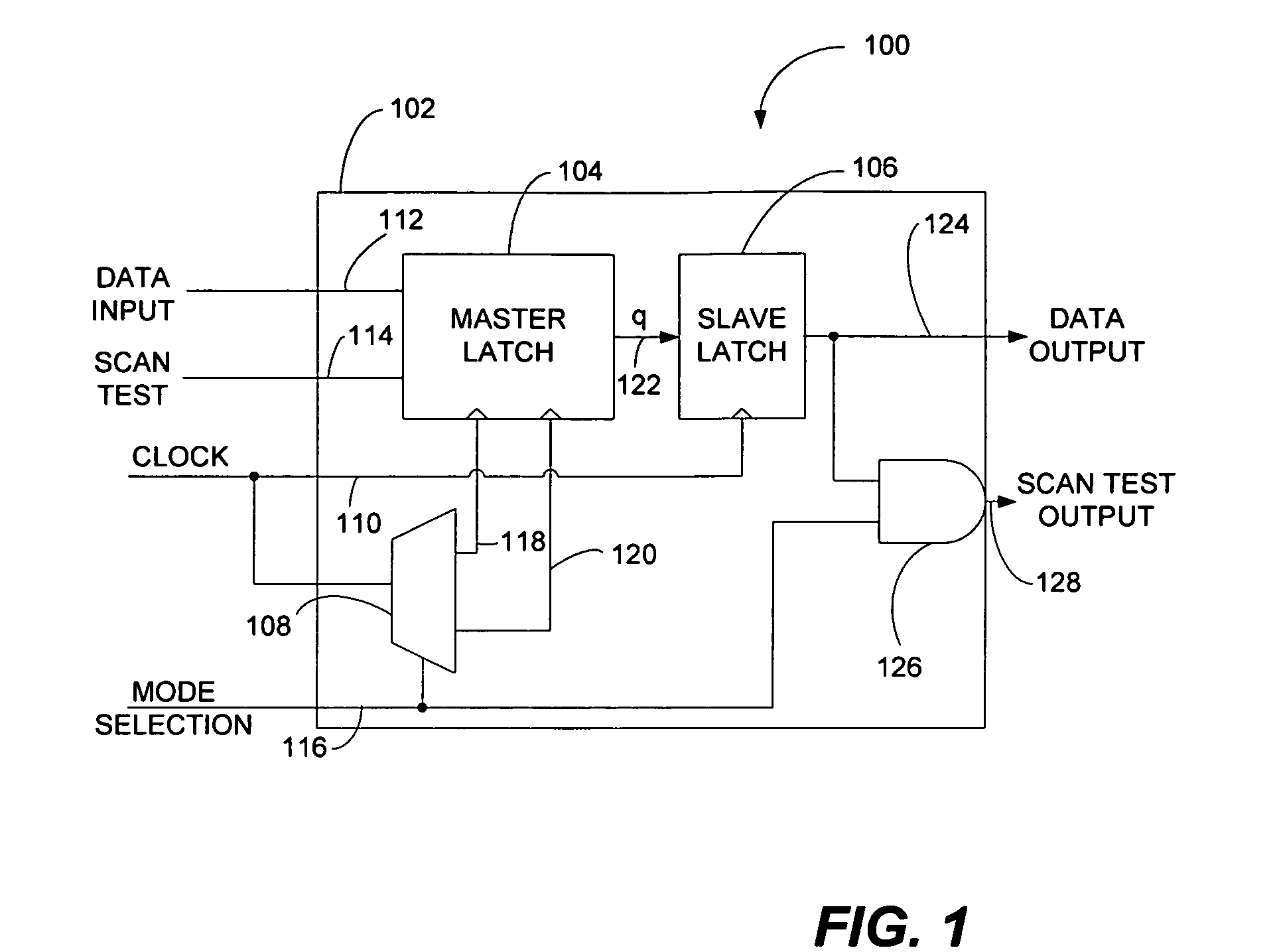

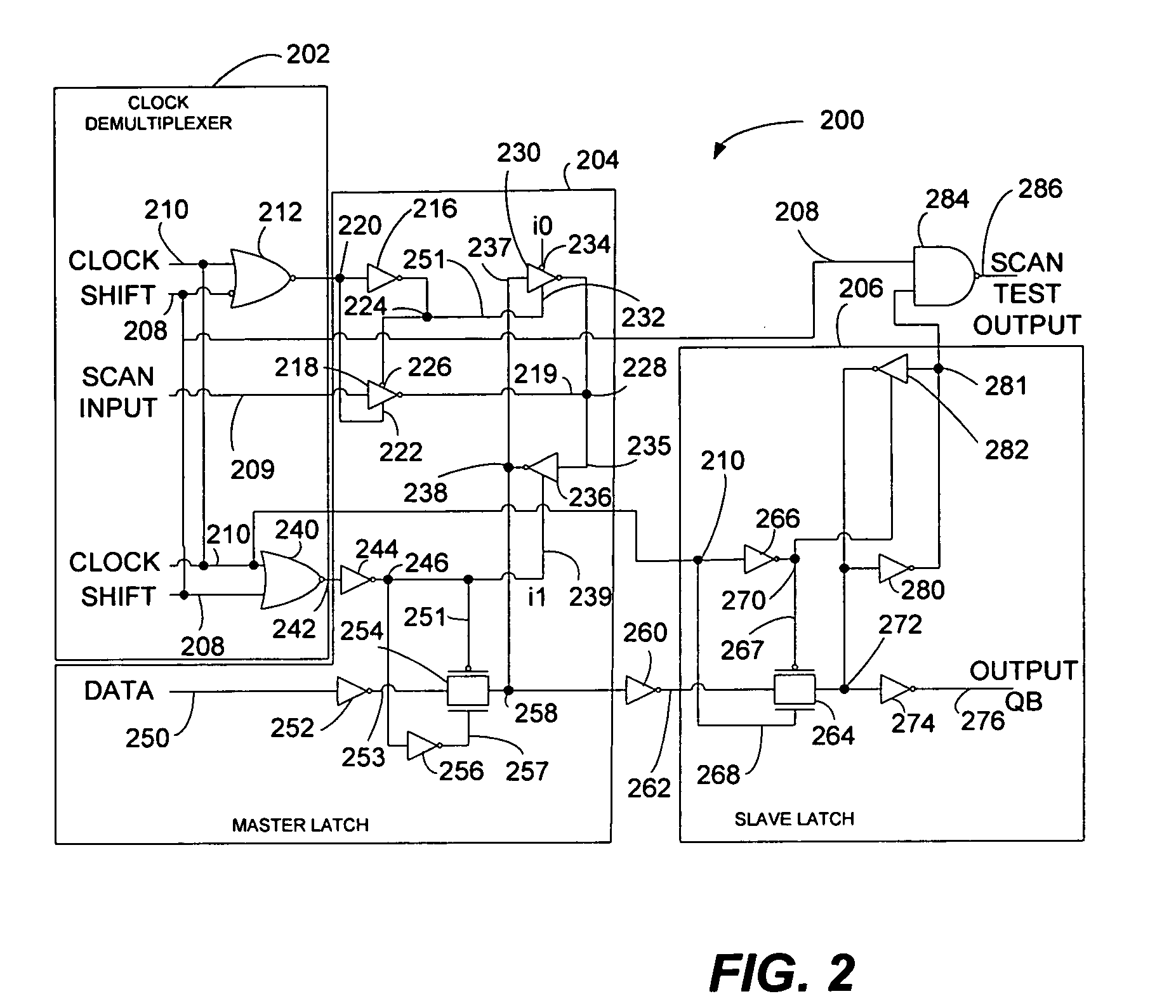

Logic device and method supporting scan test

A logic device includes a data input, a scan test input, a clock demultiplexer, and a master latch. The clock demultiplexer is responsive to a clock input to selectively provide a first clock output and a second clock output. The master latch is coupled to the data input and to the scan test input and includes an output. The master latch is responsive to the first clock output of the clock demultiplexer and the second clock output of the clock demultiplexer to selectively couple the data input or the scan test input to the output.

Owner:QUALCOMM INC

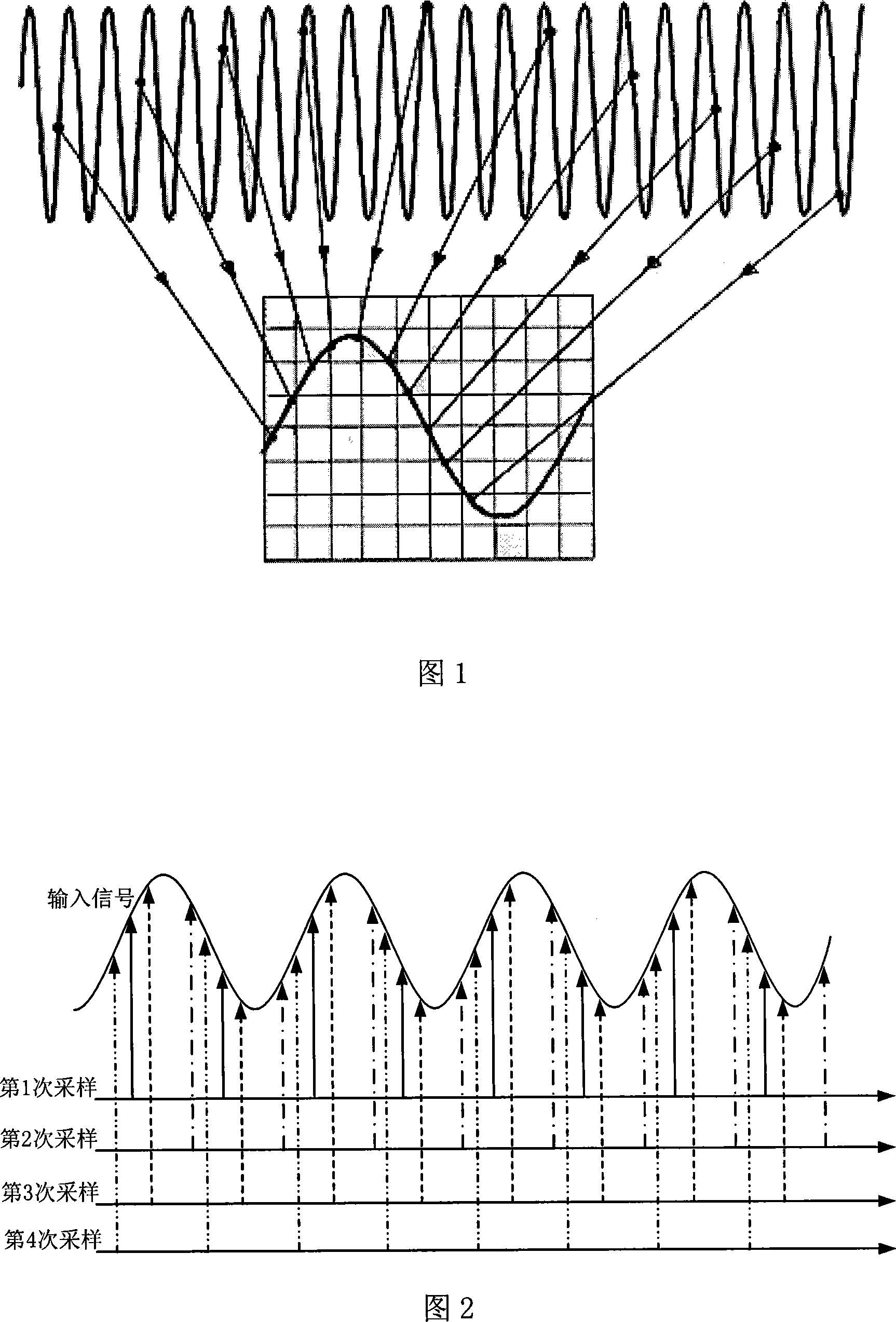

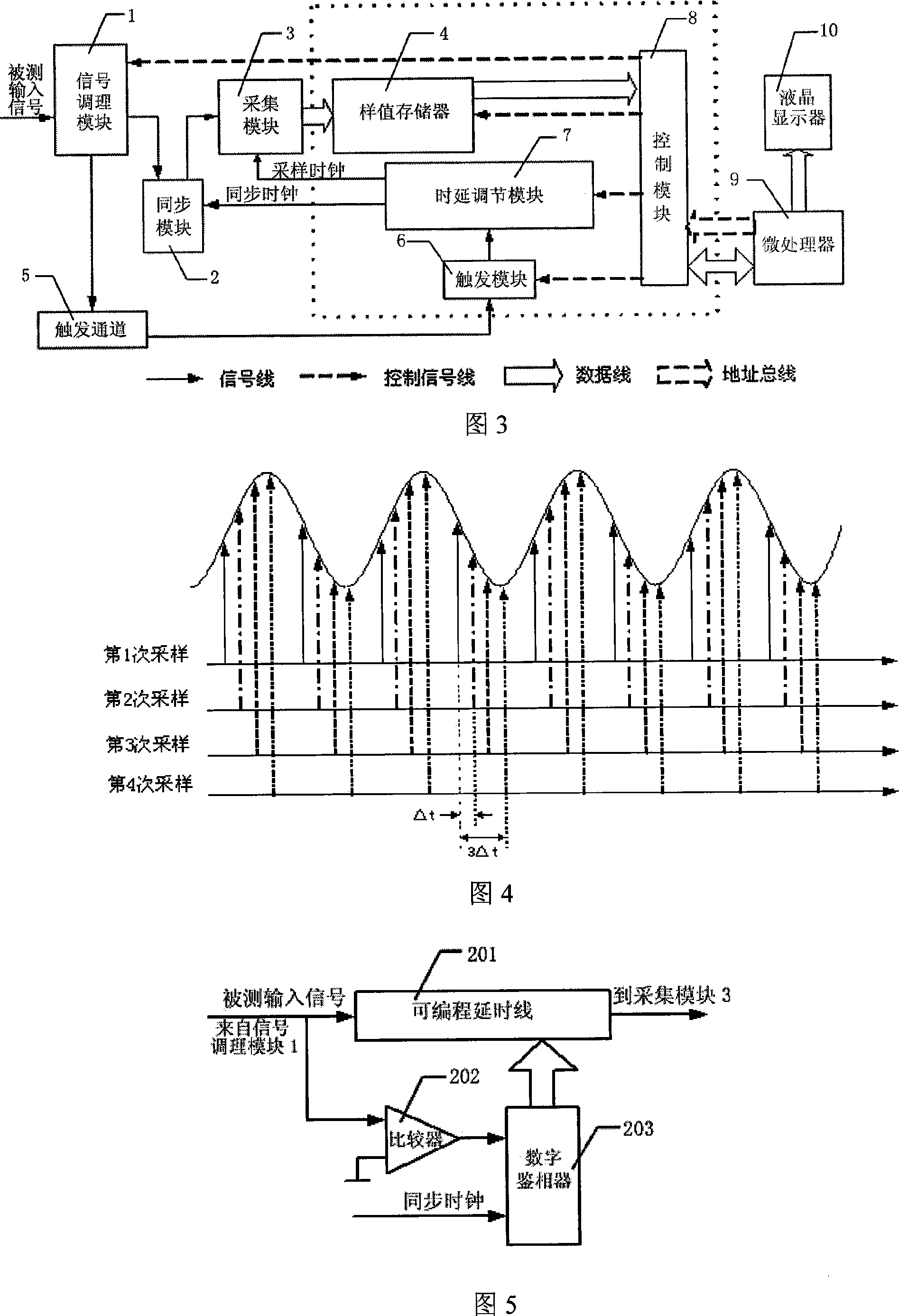

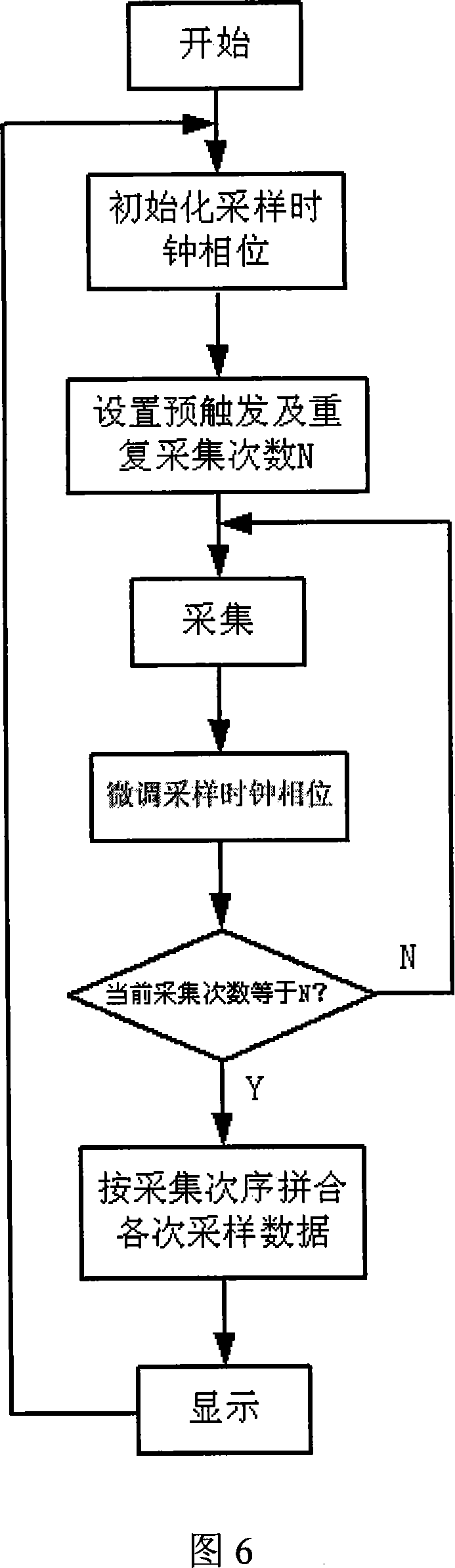

Equivalent sampling device

InactiveCN101144835AChange the sampling intervalHigh indexDigital variable/waveform displayTest inputData collecting

The present invention discloses an equivalent sampling device. A delay adjusting module outputs a sampling clock and a synchronous clock. The phase of the sampling clock can change accurately within a certain range, and a single change can collect a group of data. A certain phase relationship exists between the synchronous clock and the sampling clock. The synchronous module synchronizes and outputs the tested input signal and the synchronous clock to a collecting module, and collects data under the control of the sampling clock. A route of triggering signal is outputted to a triggering module through a triggering passage, the triggering module outputs the triggering signal to ensure the delay adjusting module to trigger for one time for a time of data collecting. Since the sampling can be independent of the triggering, the interval between the sample times is a known period, when the triggering comes, the interior of the triggering module can sample continuously, and the triggering depth can be preset for observing the signal before being triggered. At the same time, using the delay method to change the phase can change the sampling interval of the sampling clock, and the circuit is easy and simple.

Owner:UNIV OF ELECTRONICS SCI & TECH OF CHINA

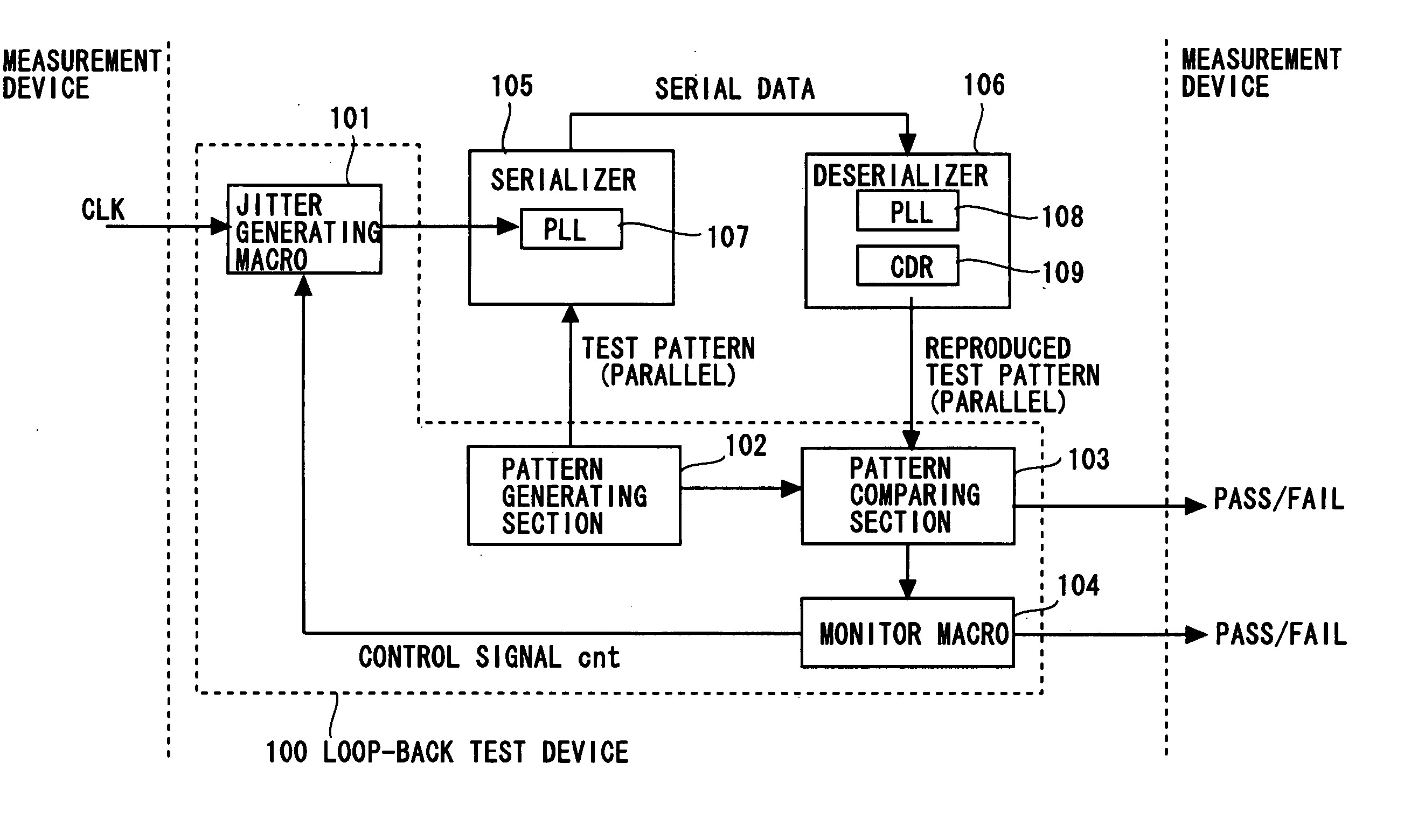

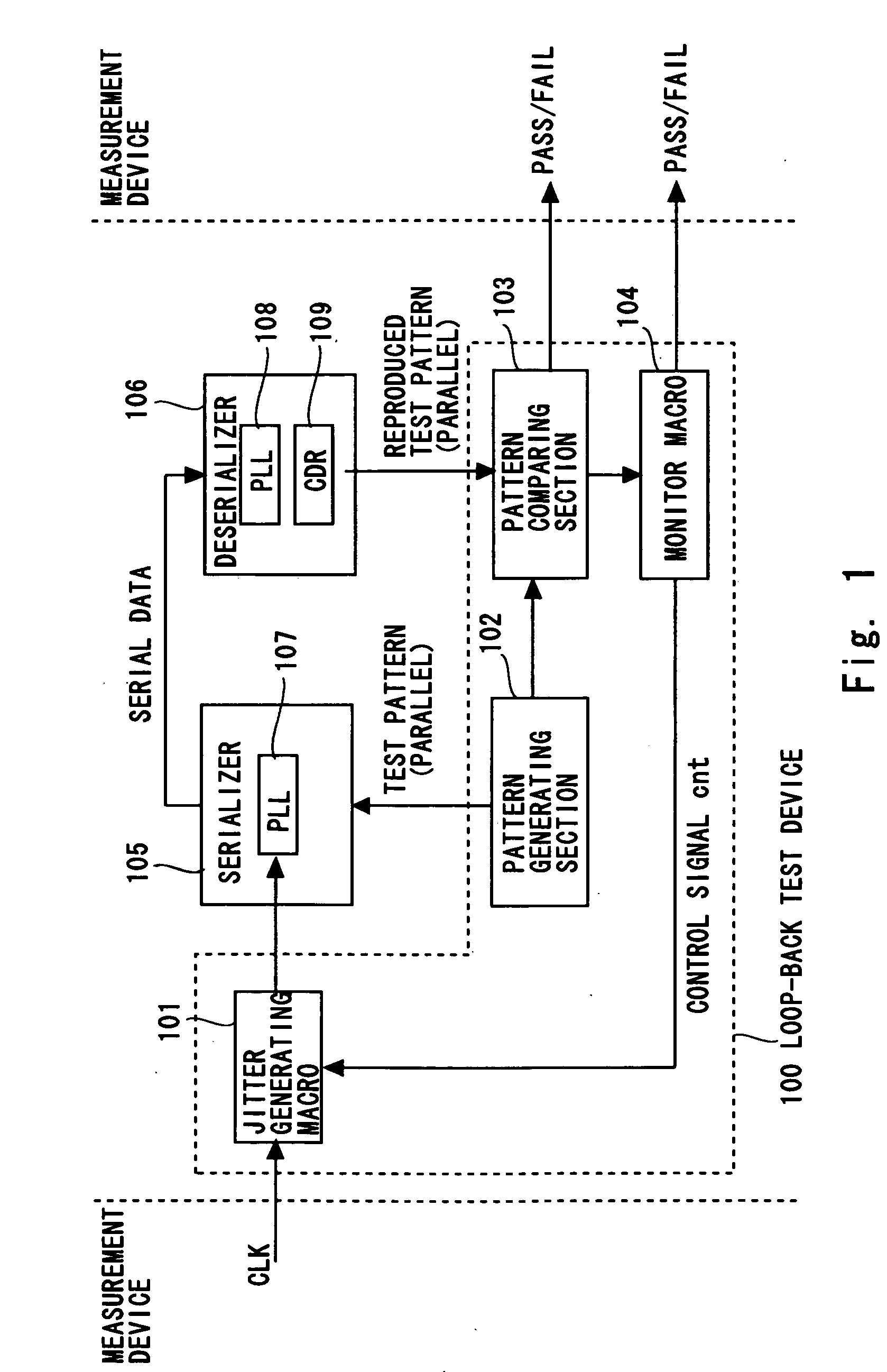

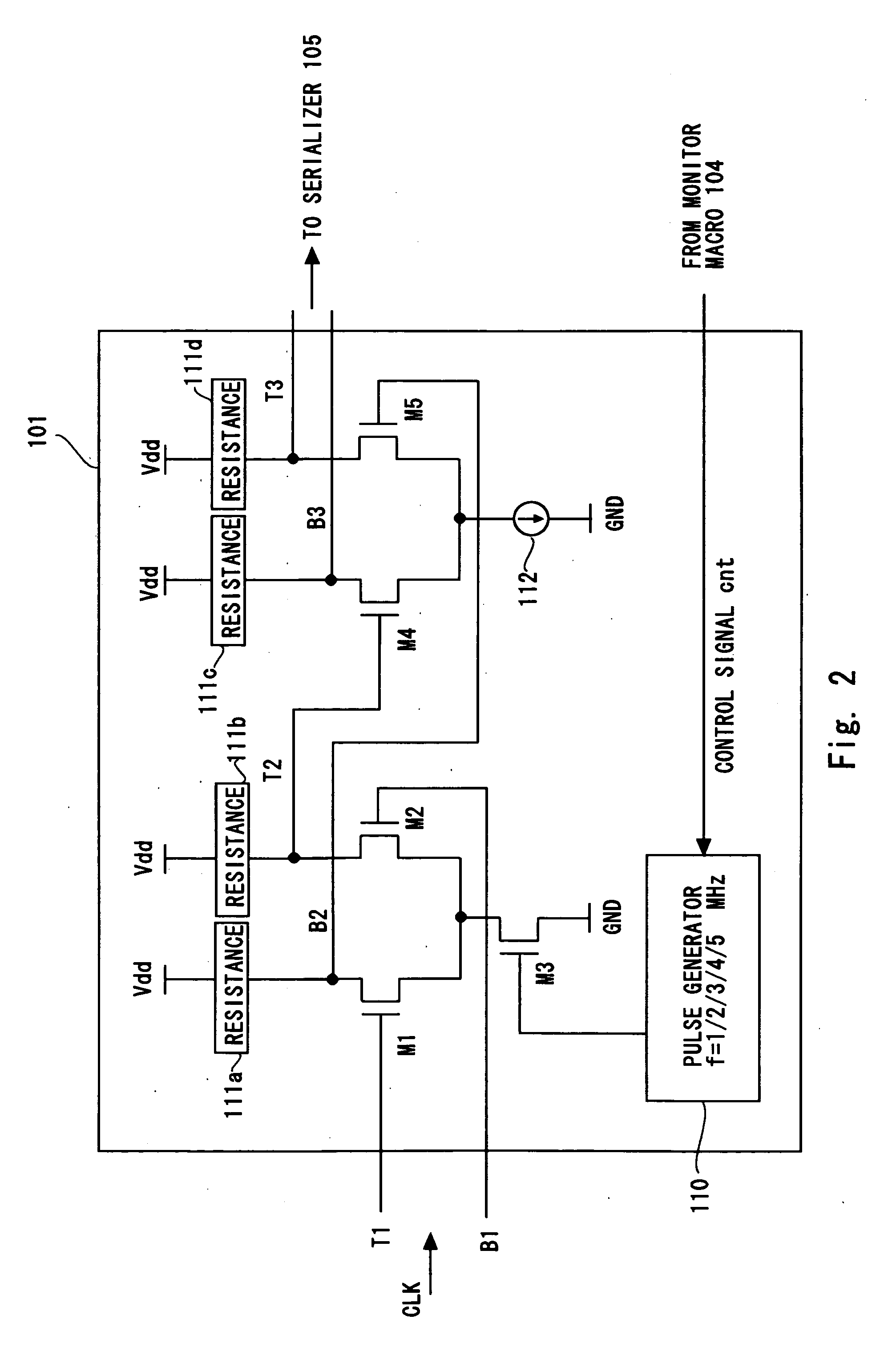

Combination test method and test device

InactiveUS20050156586A1Easy to testAccurate dataDigital circuit testingGenerating/distributing signalsTest inputLow speed

In the combination test method according to the present invention, by applying jitter to a first clock signal having a lower frequency than a second clock signal having a second frequency, jitter is superimposed onto data of a second format output by a transmission device at a data rate corresponding to the second frequency. Conventionally, in order to apply jitter to data having a high data rate, it has been necessary to use a highly expensive jitter generating device that is compatible with a high-speed signal, but in the present invention, since the signal to which the jitter is applied is a first clock signal of low speed, then a highly expensive jitter generating device is not required. Therefore, it is possible to easily test whether or not a receiving device inputting data of a second format can accurately reproduce data of a first format.

Owner:NEC ELECTRONICS CORP