Method for testing output locking or no-output fault of digital circuit

A digital circuit and testing method technology, applied in the direction of digital circuit testing, electronic circuit testing, measuring electricity, etc., can solve the problems of signal line damage, increased difficulty, unsound working environment, etc., and achieve accuracy and reliability improvement, connection Easy to enter the form, easy to test the effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

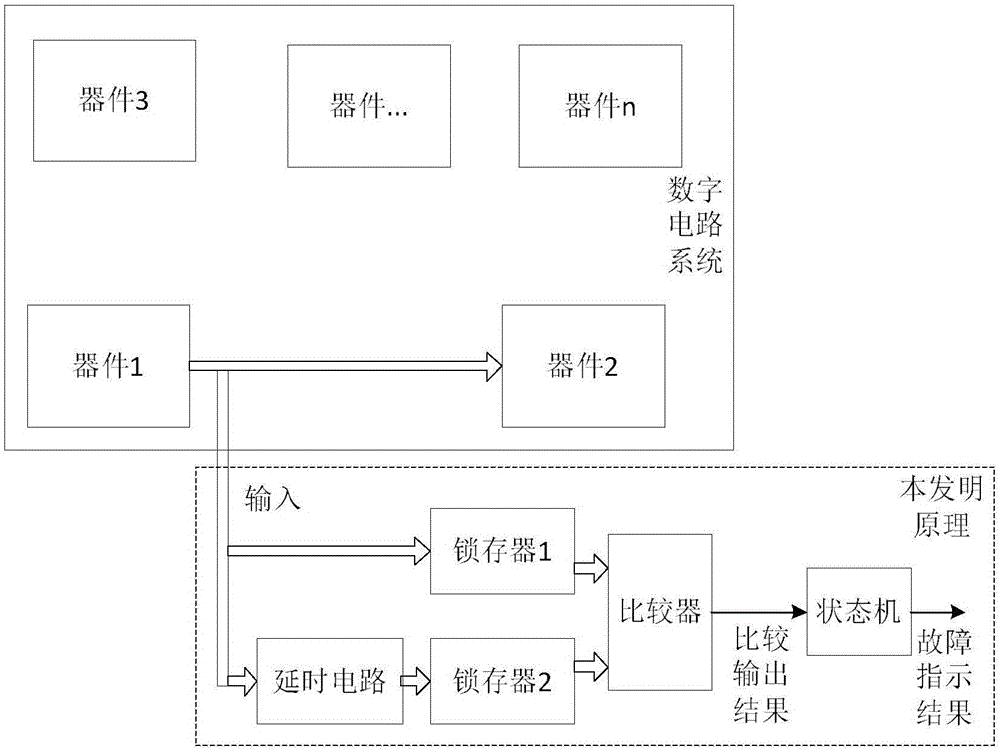

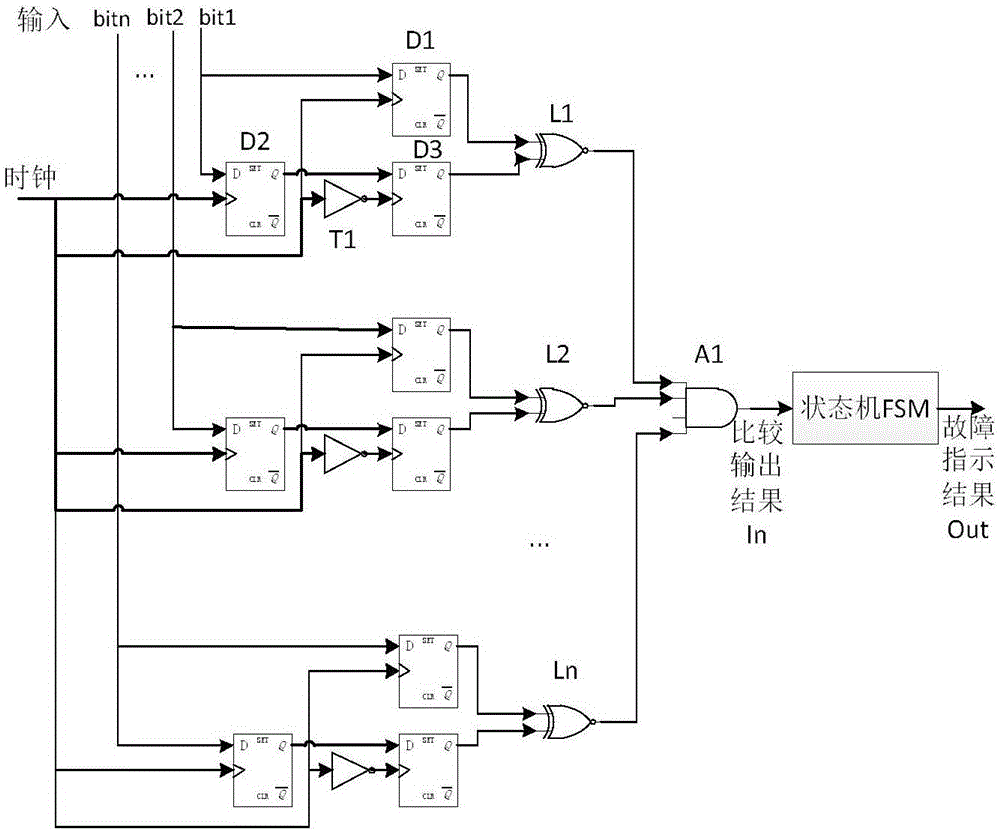

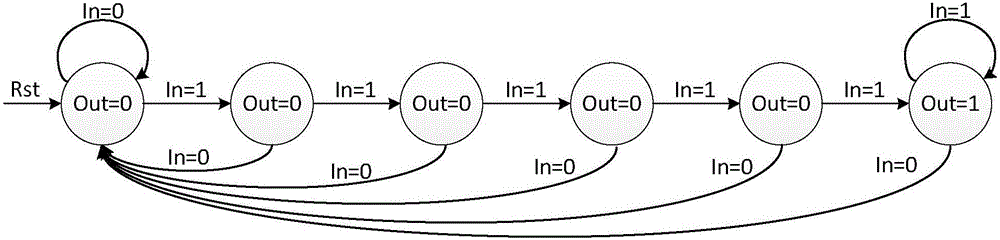

[0027] refer to figure 1 . According to the present invention, a delayer, two latches, a NOR comparator and a state machine are used to form a digital circuit fault diagnosis system, and the two input terminals of the NOR comparator are electrically connected to the latches respectively 1 output terminal and the latch 2 output terminal connected in series through the delayer; during the test, the NOR comparator is first formed by connecting the latch 2 in series with the delay circuit to the data signal output from the device on the digital circuit system at the current moment Delay and latch circuit, the current input data is delayed for a moment and then sent to latch 2 for latching; the same OR comparator will latch the data at the previous moment of latch 2 and the current output of latch 1 The data is latched at all times for NOR operation comparison. The comparison output results are counted by the state machine judgment circuit to judge whether the comparison results a...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More