Patents

Literature

503 results about "Test response" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

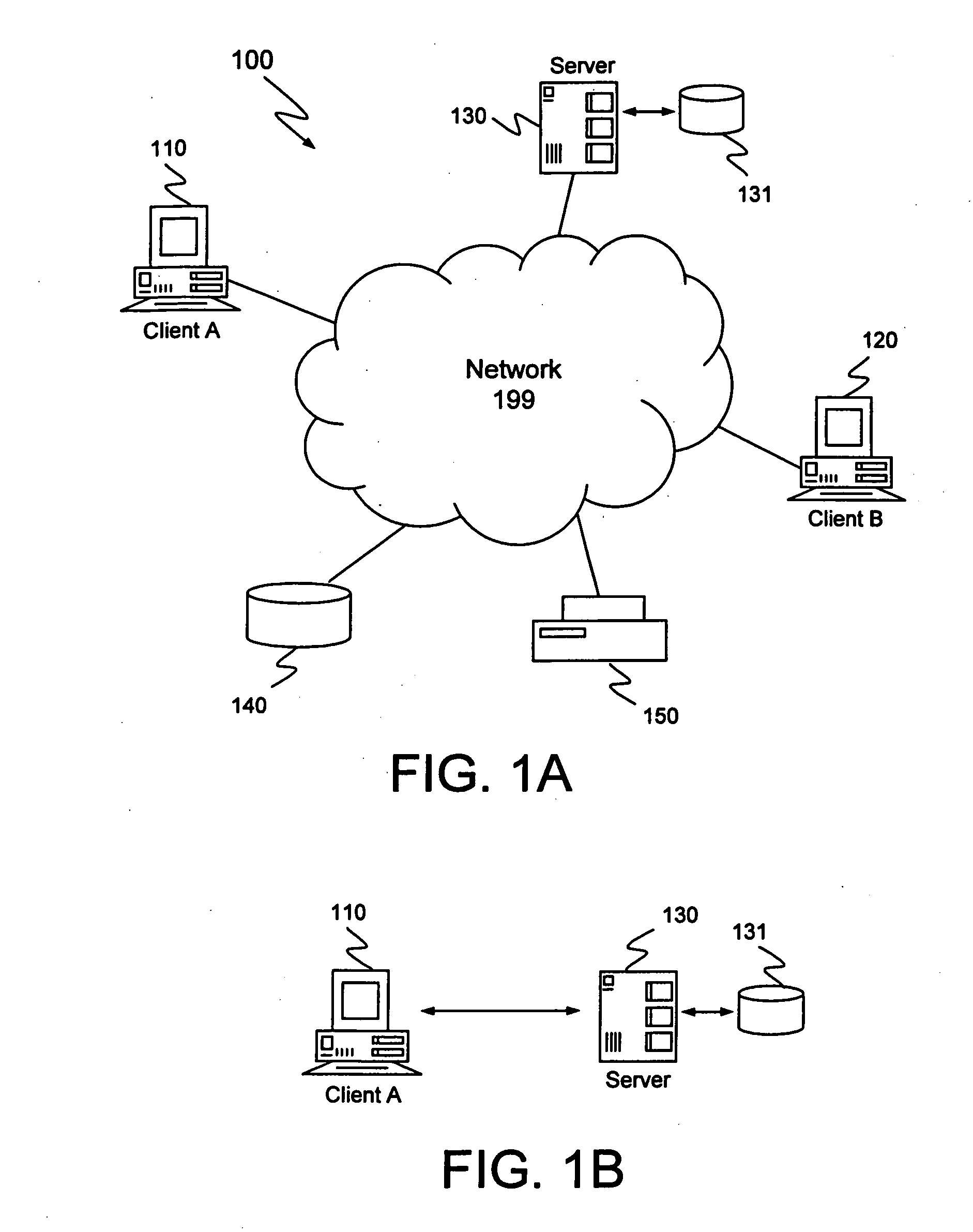

Method and apparatus for diagnosing a fault in a network path

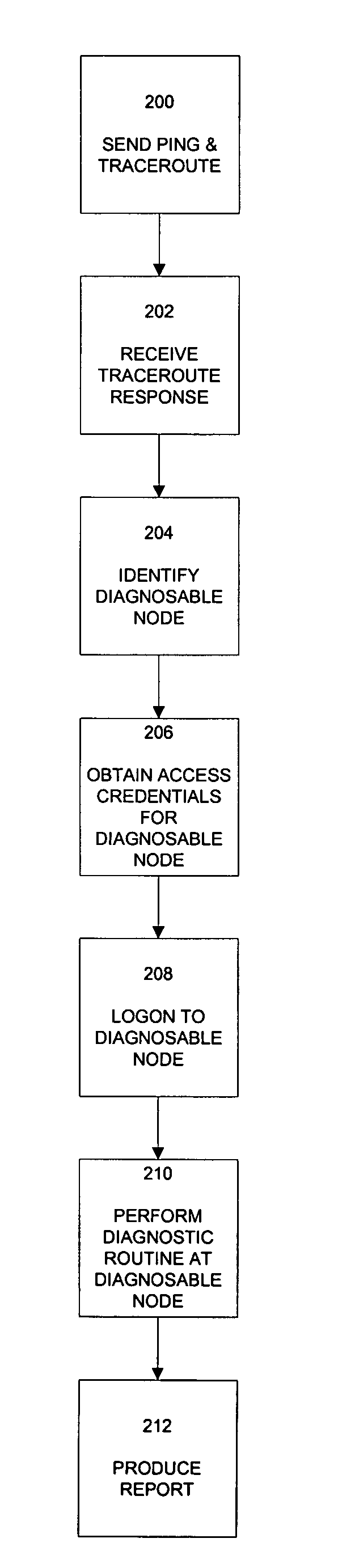

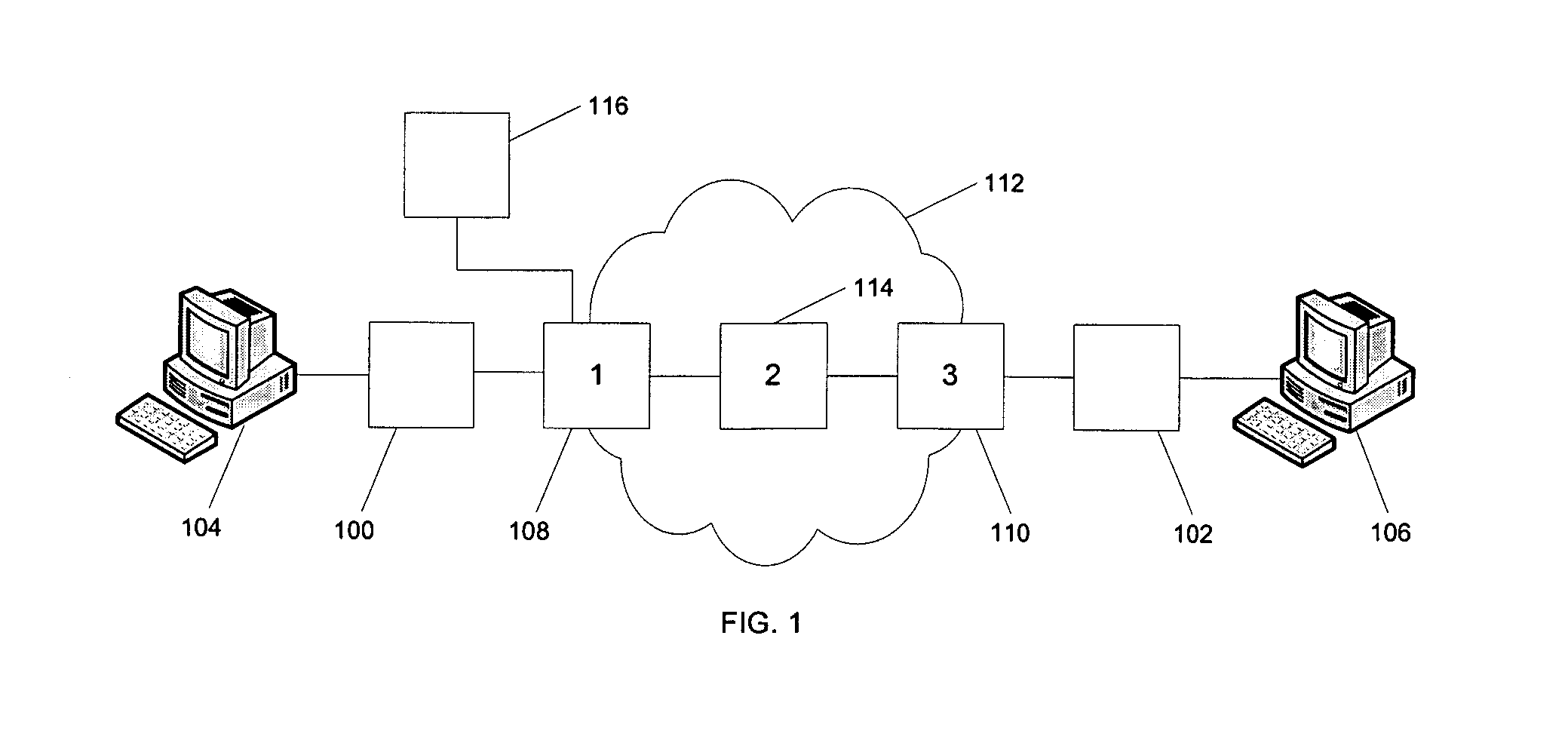

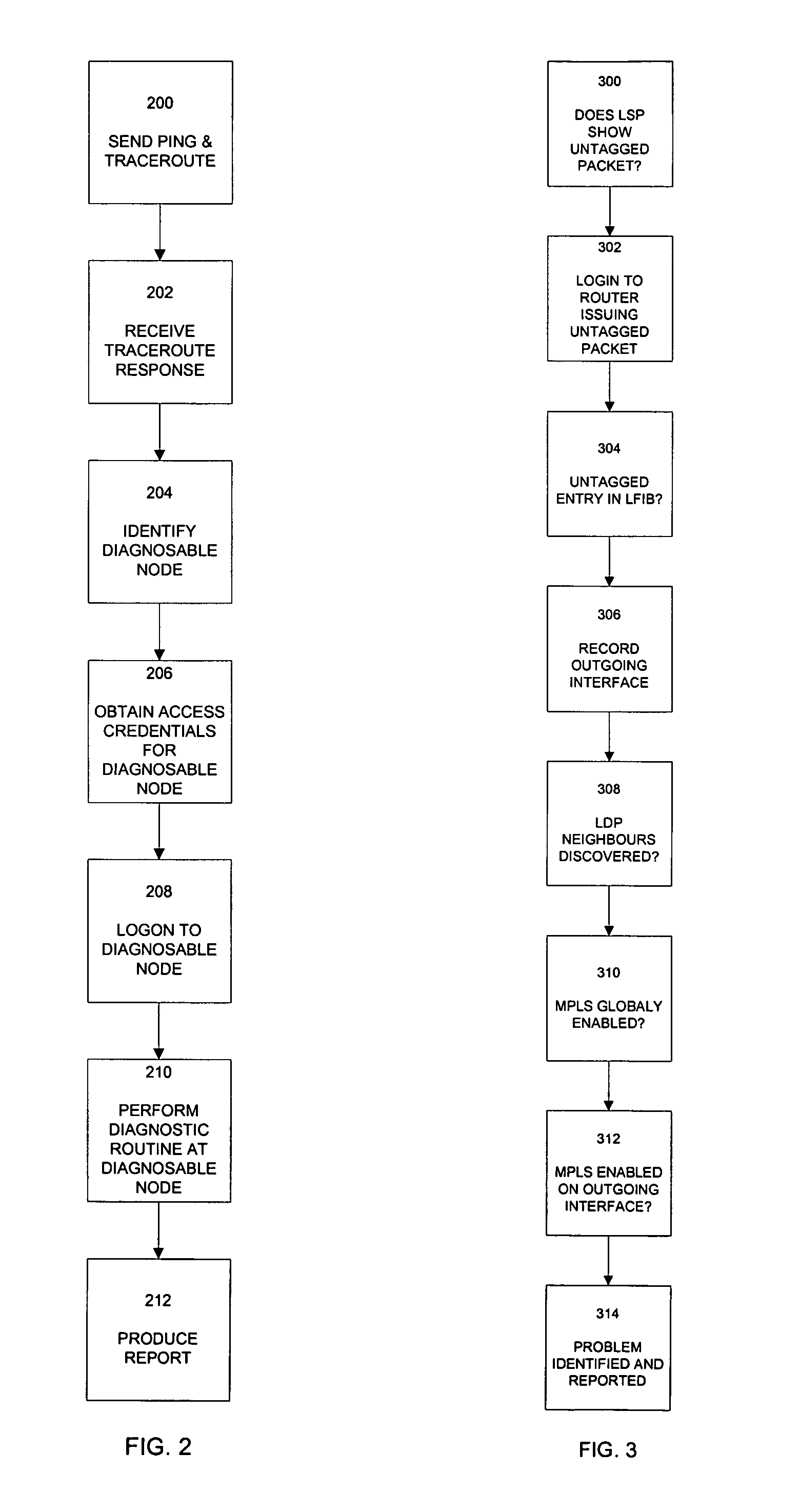

A method of diagnosing a fault in a network path comprises the steps, performed at a diagnosing node, of initiating a path discovery test. The diagnosing node receives at least one path discovery test response and identifies the diagnosable node on the network path from a path discovery test response. The diagnosing node remotely accesses said diagnosable node and performs a diagnostic routine at said diagnosable node.

Owner:CISCO TECH INC

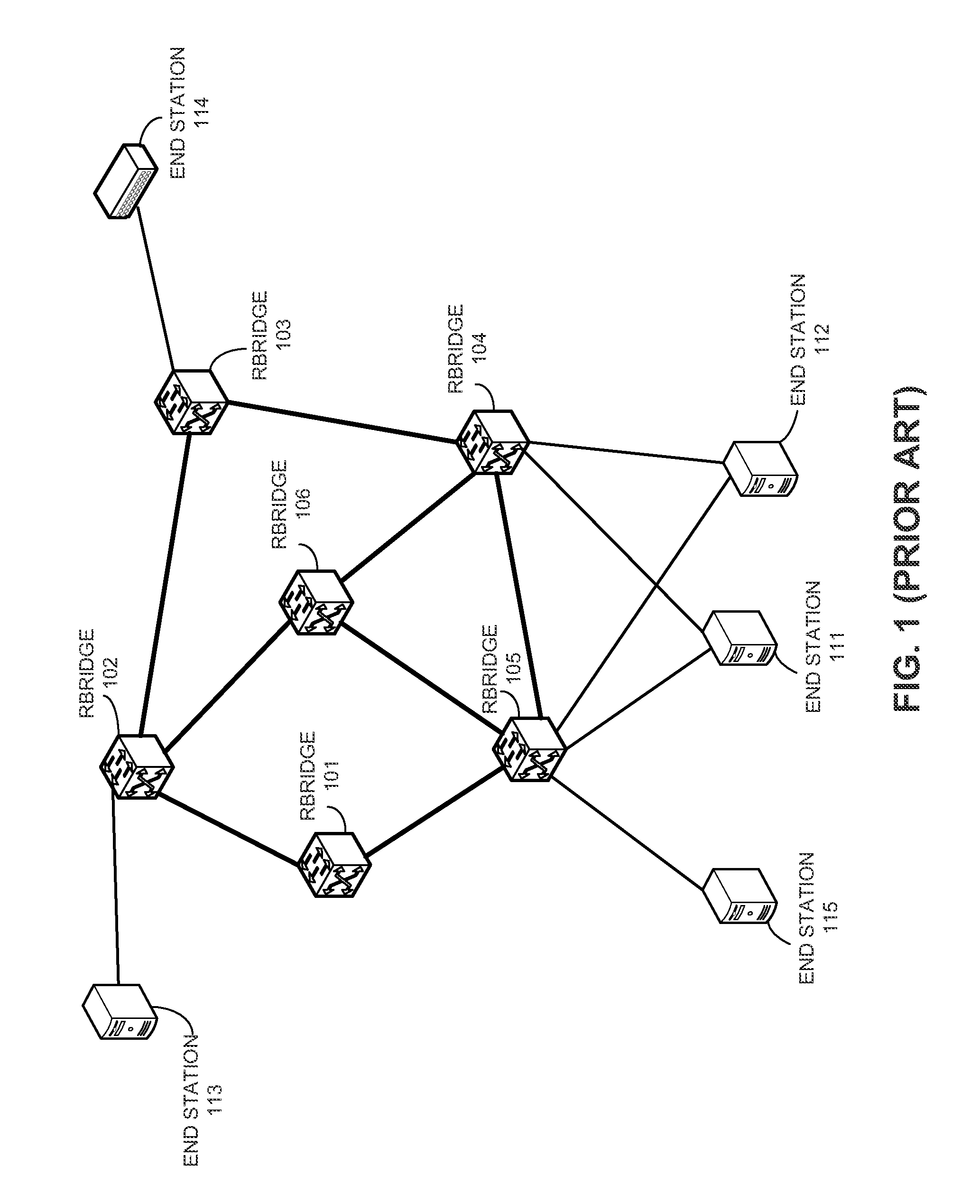

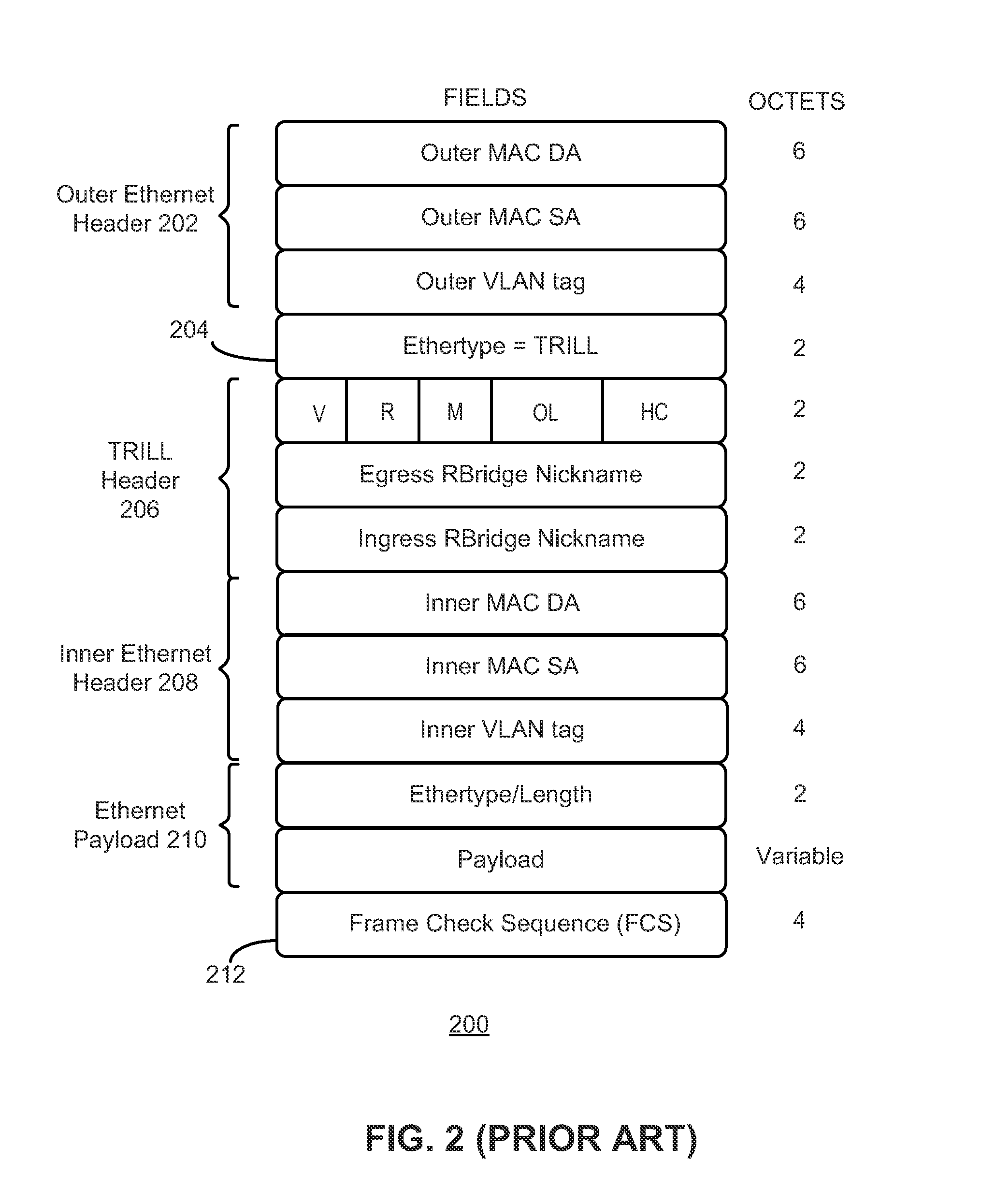

Path detection in trill networks

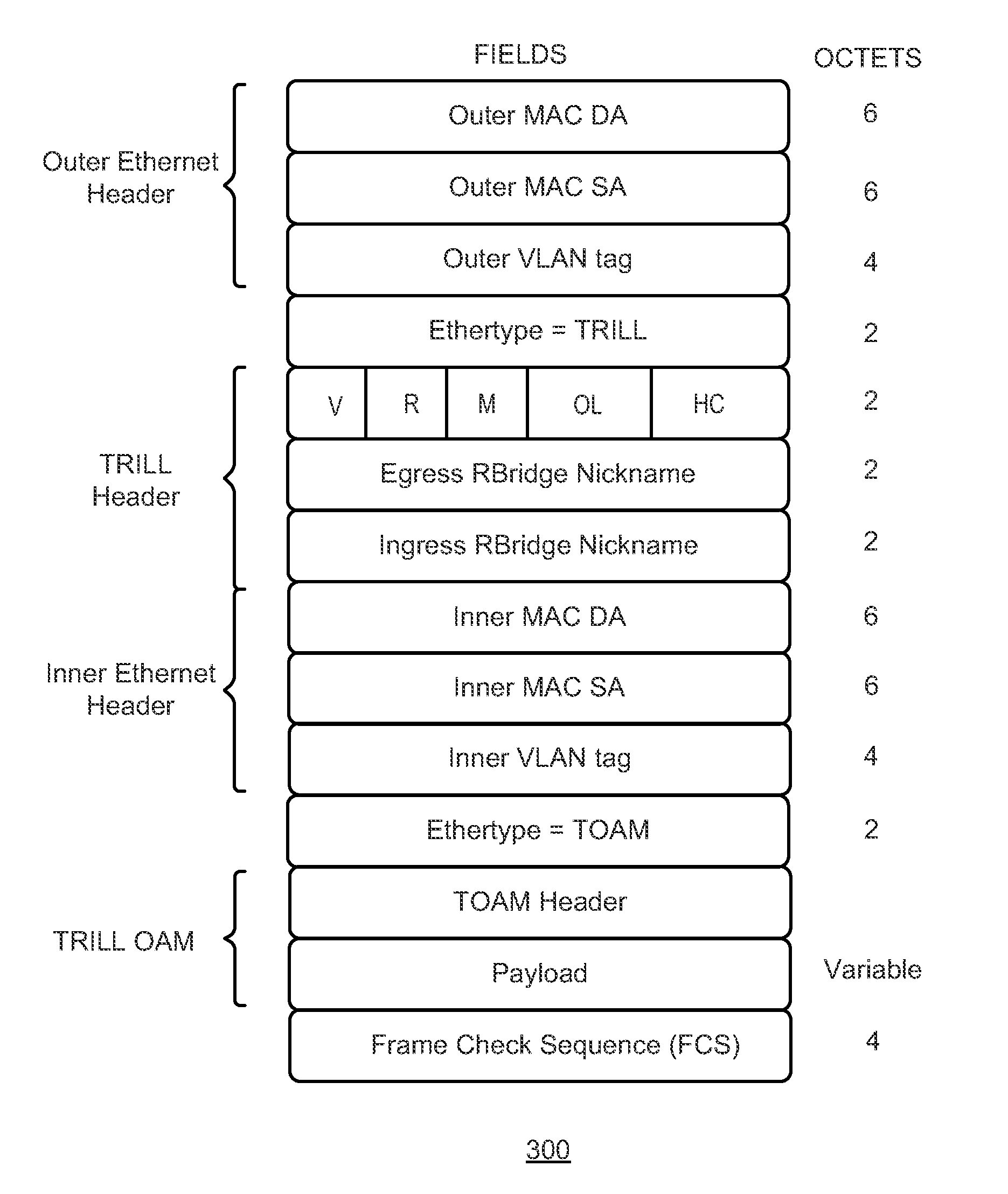

One embodiment of the present invention provides a system for detecting a path between two nodes. During operation, the system transmits a network-testing request frame, which includes a time-to-live (TTL) field within a Transparent Interconnection of Lots of Links (TRILL) header, from a source node to a destination node. In response to receiving a network-testing response frame sent from an intermediate node, the system increments the TTL value by 1 and re-transmits the network-testing frame to the destination node. In response to receiving a network-testing response frame sent from the destination node, the system determines a path between the source node and the destination node. The network-testing request or response frames is not processed on an Internet Protocol (IP) layer.

Owner:AVAGO TECH INT SALES PTE LTD

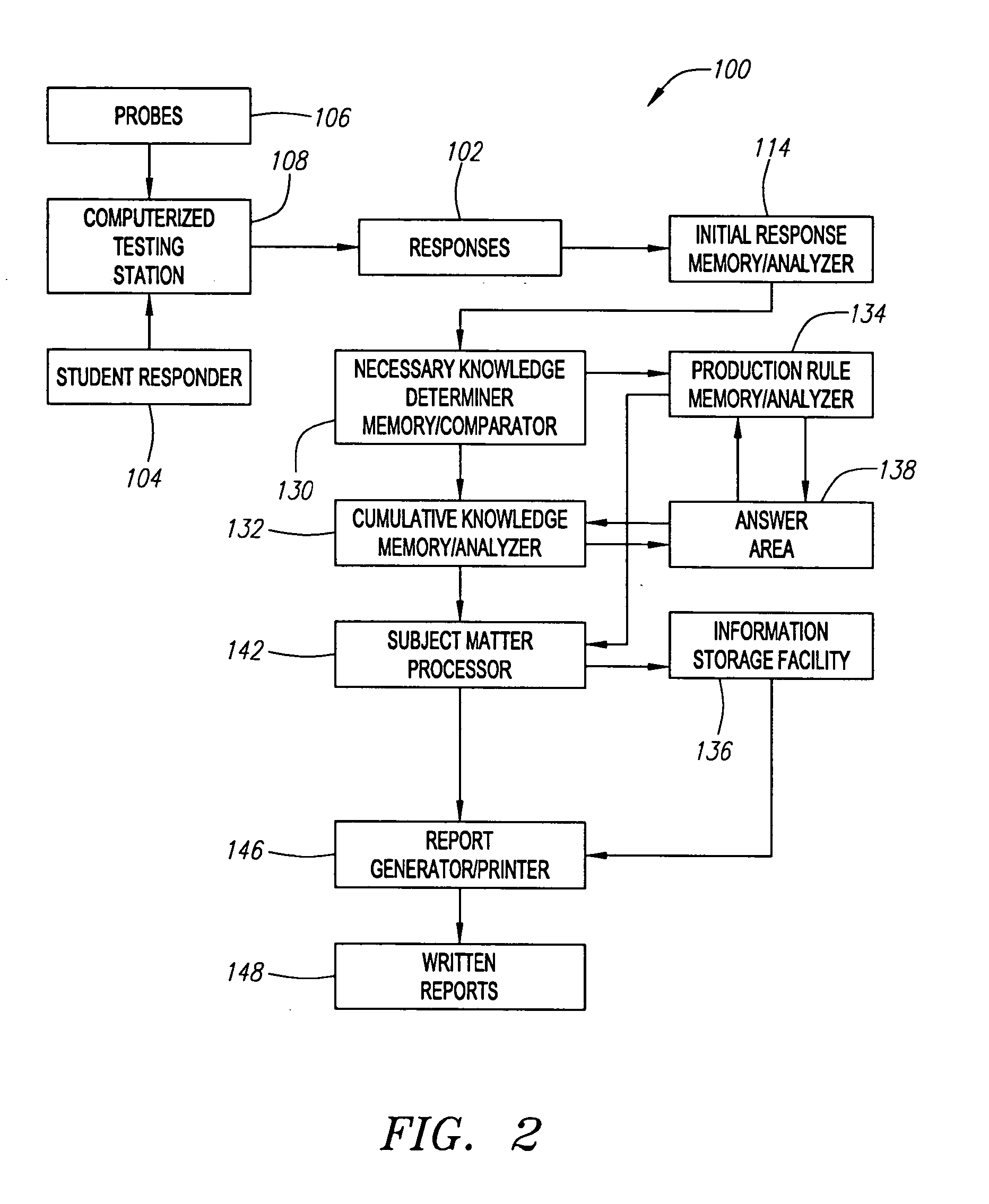

System and method for diagnosing deficiencies and assessing knowledge in test responses

A system and method for diagnosing deficiencies and assessing knowledge in test responses comprises a computerized testing station for presenting a question to a responder. An initial response analyzer communicates with the testing station for determining the correctness of an initial response by the responder to the question. A necessary knowledge determiner is disposed to analyze an incorrect initial response from the initial response analyzer for detecting responder's deficiencies in past cumulative knowledge and in new subject matter knowledge. A cumulative knowledge analyzer is provided for analyzing the incorrect initial response for identifying specific deficiencies in past cumulative knowledge. A production rule analyzer is provided for analyzing the incorrect initial response for identifying specific deficiencies in new subject matter knowledge. Finally, a report generator communicates with the cumulative knowledge analyzer and the production rule analyzer for generating a written deficiency report.

Owner:WEINSTEIN PINI A

Method and device for testing chip

InactiveCN101038325AEasy to debugReduce testing costsDigital circuit testingTester deviceTest response

The invention discloses a device for testing the chip, including the mutually stand-alone server, simulator, control circuit board and running circuit board, in which: the server is used for creating the test program according to the test tasks, and output to the simulator; the simulator is connected with the server for simulation processing of the test program, and creating the simulation document with test data and sending to the control circuit board; the control circuit board is connected with the simulator for reading the relevant test vectors from the simulation document, and sending this test vector to the running circuit board, and decide whether the relevant chip is in good conditions or not according to the test response feedback from the running circuit board; the running circuit board is connected with the control circuit board for testing the relevant chip according to the test vector from the control circuit board, and sending the test response to the control circuit board. Thus, during the batch production testing of chip, the automatic tester with expensive rent may be not rented, thereby greatly reduce the test cost. The invention still discloses a test method for chip.

Owner:VIMICRO CORP

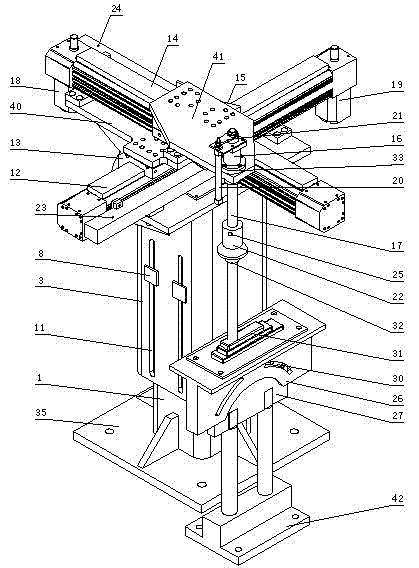

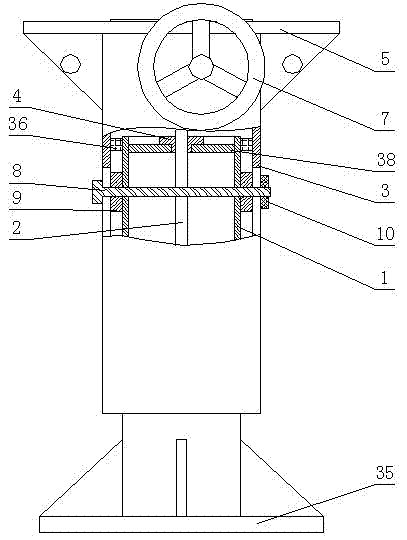

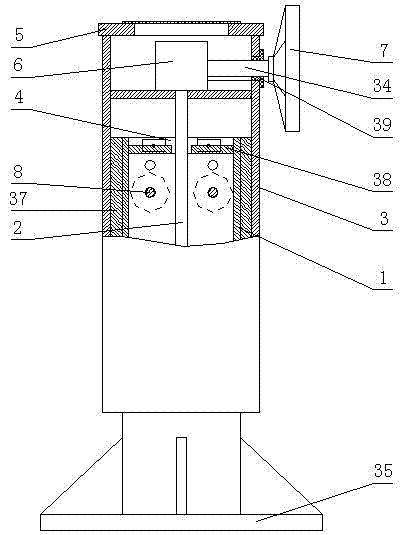

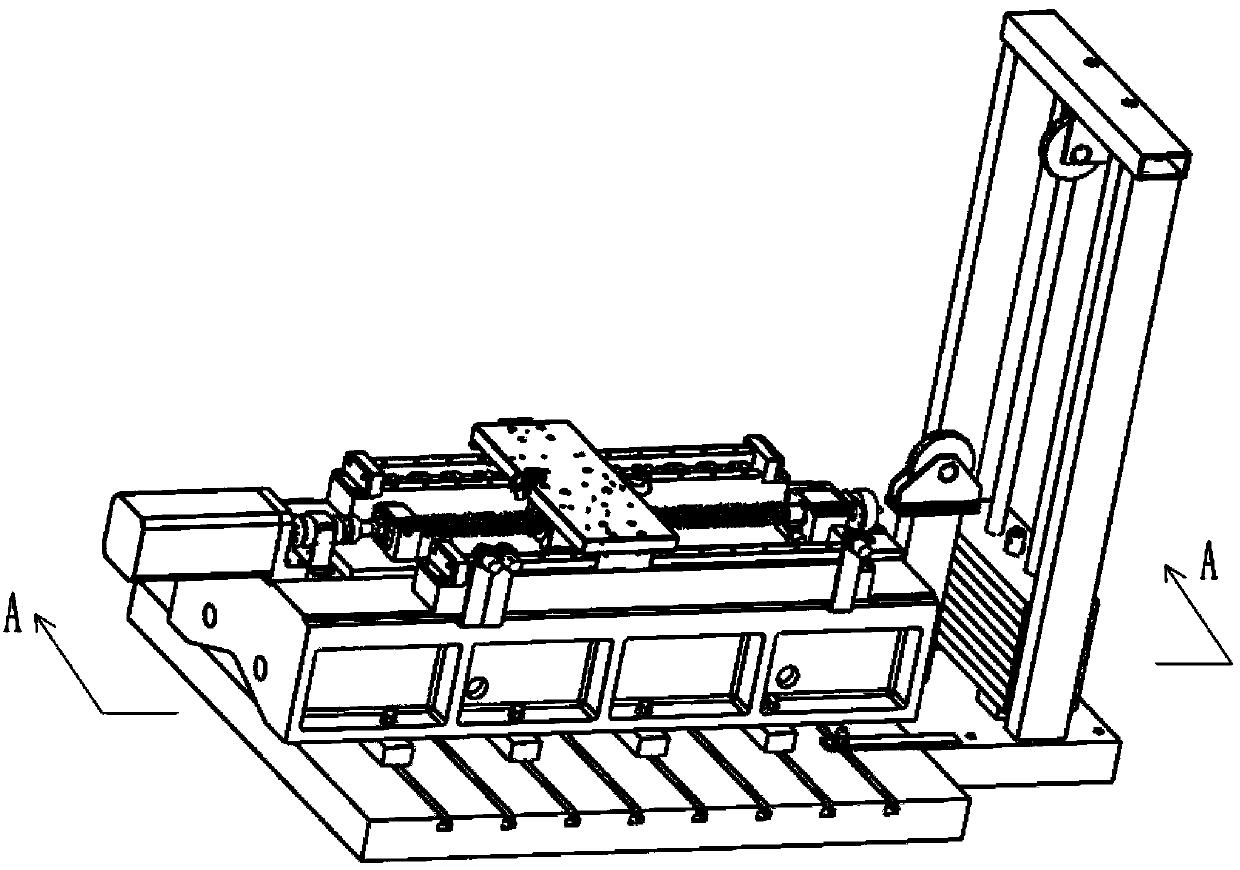

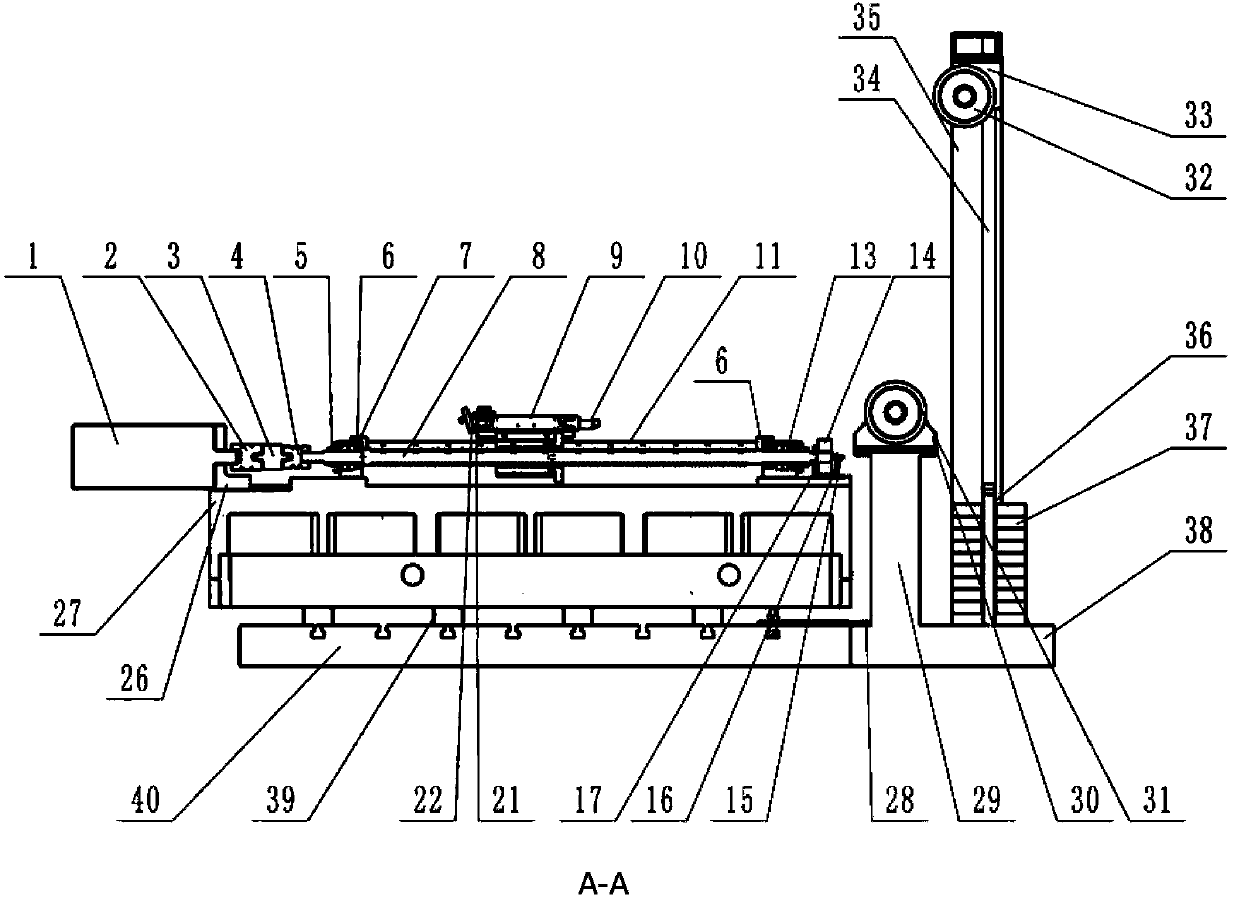

Gear-selecting and shifting performance automatic testing device and method

ActiveCN102967460APrecise repositioningEliminate abnormal impactVehicle testingMachine gearing/transmission testingLocking mechanismSlide plate

The invention discloses a gear-selecting and shifting performance automatic testing device, comprising a lifting mechanism, a locking mechanism, a gear-selecting and shifting mechanism and a gear rod support, wherein the lifting mechanism comprises an annular inner wall, a lead screw, an annular outer wall, a nut, a top cover plate, a worm wheel and worm mechanism and a handle which is used for driving a worm of the worm wheel and worm mechanism; the locking mechanism comprises a locking screw rod, a locking pad block and a locking unit; the gear-selecting and shifting mechanism comprises a longitudinal slide rail, a longitudinal sliding plate, a transverse slide rail, a transverse sliding plate, a spring, a connection rod, a longitudinal sliding plate driving mechanism and a transverse sliding plate driving mechanism; and the gear rod support comprises a supporting plate I and a supporting plate II. Simultaneously, the invention also discloses a gear-selecting and shifting performance automatic testing method. The gear-selecting and shifting performance automatic testing device and method disclosed by the invention has the advantage of being capable of precisely and quickly carrying out a gear-selecting and shifting operation and dynamically measuring performance parameters in a gear-selecting and shifting process, and having quick test response, reliable test data and high precision.

Owner:重庆理工清研凌创测控科技有限公司

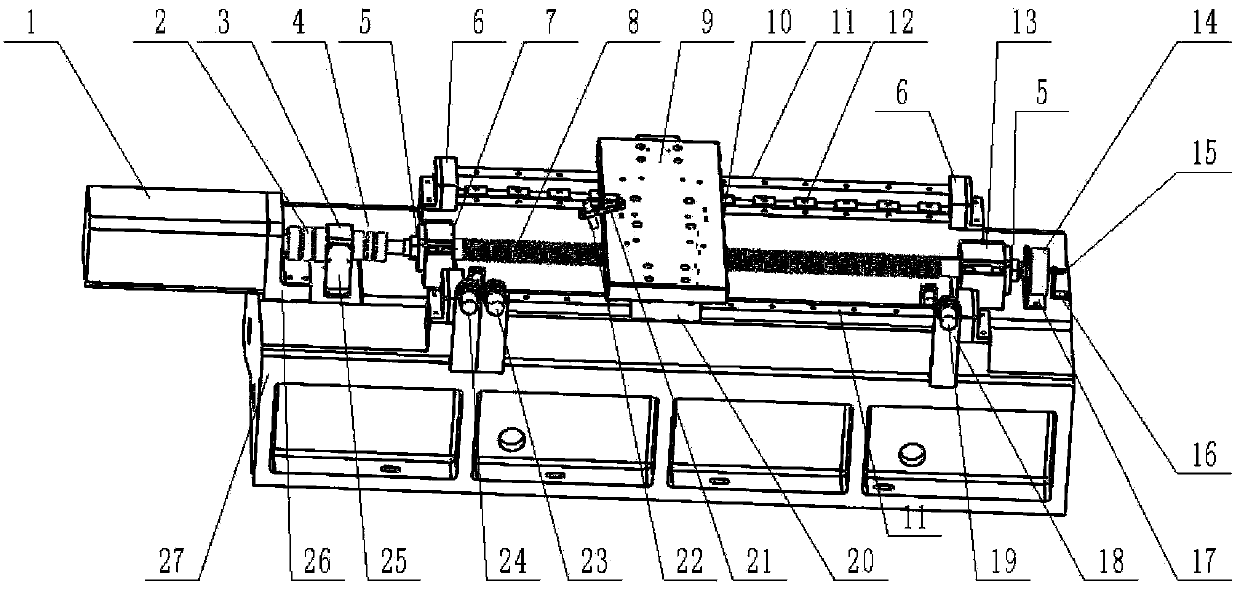

Device for detecting comprehensive performance of ball screw assembly in loaded state

InactiveCN103389205ARealize detectionReal-time detection of the number of rotationsMachine gearing/transmission testingCouplingBall screw

A device for detecting comprehensive performance of a ball screw assembly in a loaded state comprises a testboard machine body fixed on a cast iron platform, wherein a servomotor is arranged at one end of the testboard machine body; the output shaft of the servomotor is connected to one end of the ball screw assembly through a first coupler, a dynamic torque sensor and a second coupler; an eddy current sensor and a rotary encoder are arranged at the other end of the testboard machine body; a grating scale and an infrared temperature sensor are arranged on the testboard machine body; a rolling guide rail is arranged on the testboard machine body, and is provided with an analog working table; the analog working table is connected to the rolling guide rail through a rolling guide rail slide block, and is connected to a loading device; a ball screw assembly nut is arranged on the analog working table through a nut support base. The device is stable in properties, quick in movement and testing response speed, comprehensive and accurate in testing performance parameters, and simple in structure, and can realize the comprehensive performance detection of ball screw assemblies with different models in no-loaded states or loaded states.

Owner:XI AN JIAOTONG UNIV

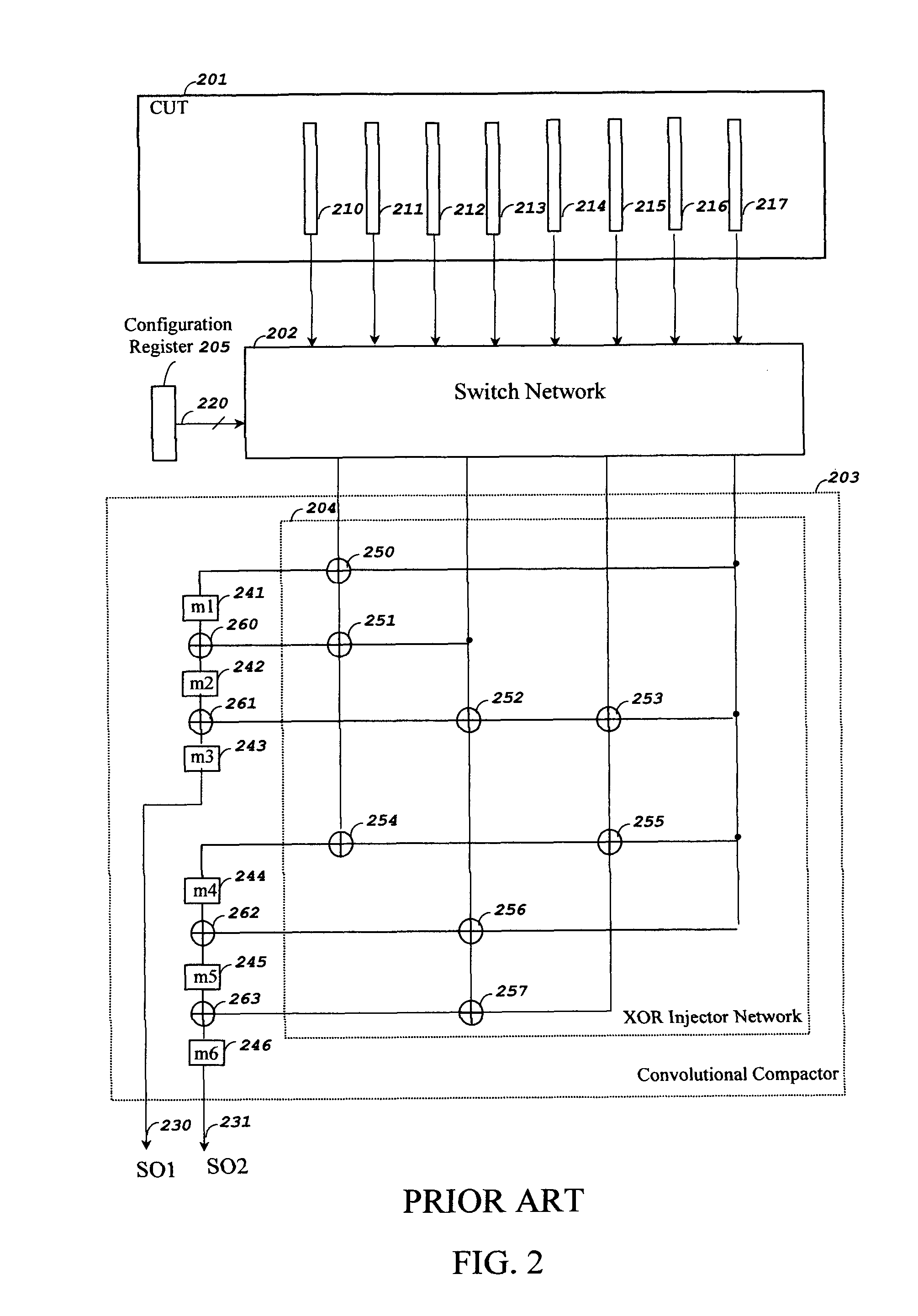

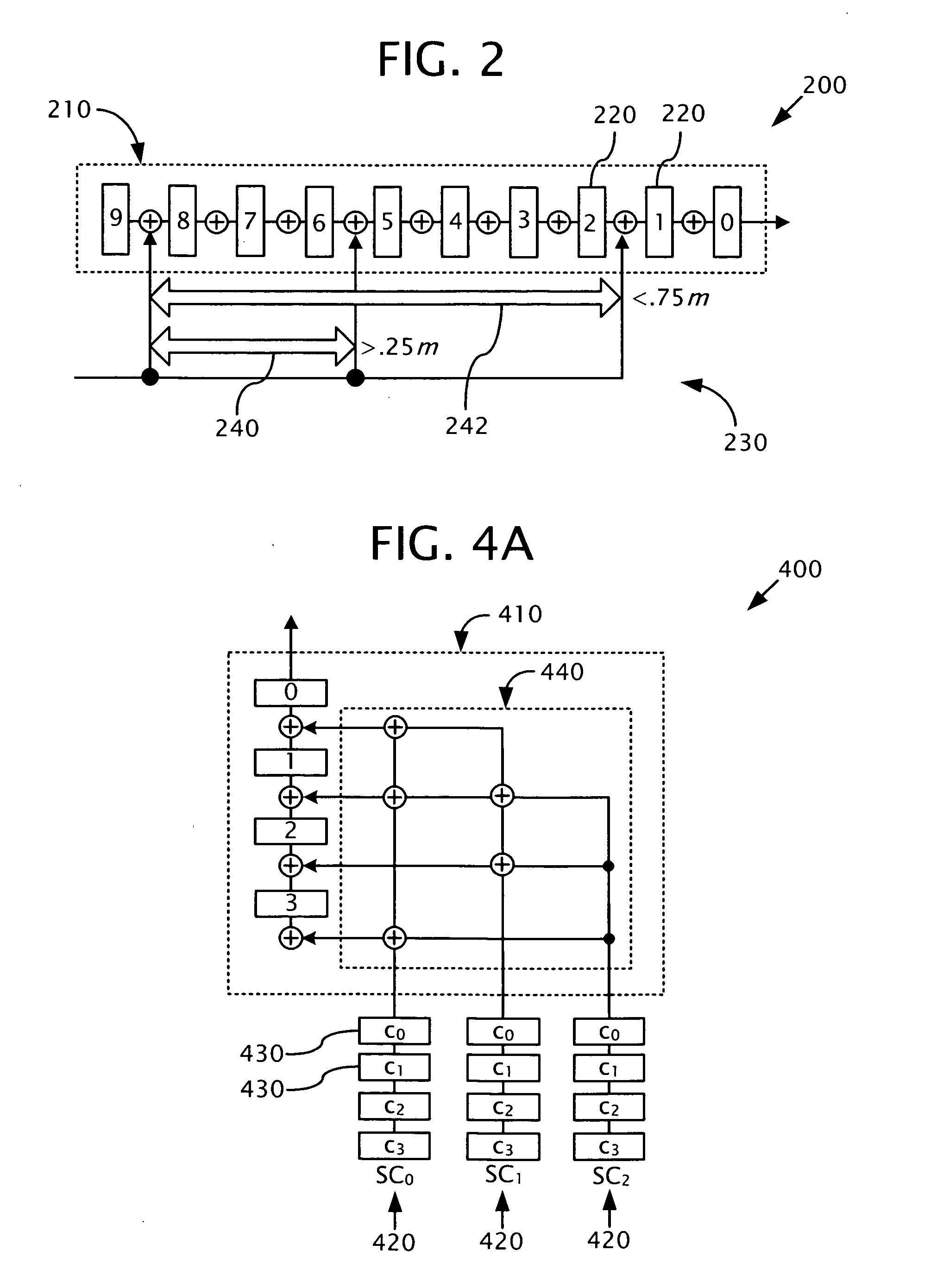

Adaptive fault diagnosis of compressed test responses

ActiveUS7302624B2Electronic circuit testingError detection/correctionCircuit under testSelf adaptive

Methods, apparatus, and systems for diagnosing failing scan cells from compressed test responses are disclosed herein. For example, in one nonlimiting exemplary embodiment, one or more signatures are received that indicate the presence of one or more errors in one or more corresponding compressed test responses. Scan cells in the circuit-under-test that caused the errors are identified by analyzing the signatures. In this exemplary embodiment, the analysis includes selecting a scan cell candidate that potentially caused an error in a compressed test response based at least partially on a weight value associated with the scan cell candidate, the weight value being indicative of the likelihood that the scan cell candidate caused the error. Tangible computer-readable media comprising computer-executable instructions for causing a computer to perform any of the disclosed methods are also provided. Tangible computer-readable media comprising lists of failing scan cells identified by any of the disclosed methods are also provided.

Owner:SIEMENS PROD LIFECYCLE MANAGEMENT SOFTWARE INC

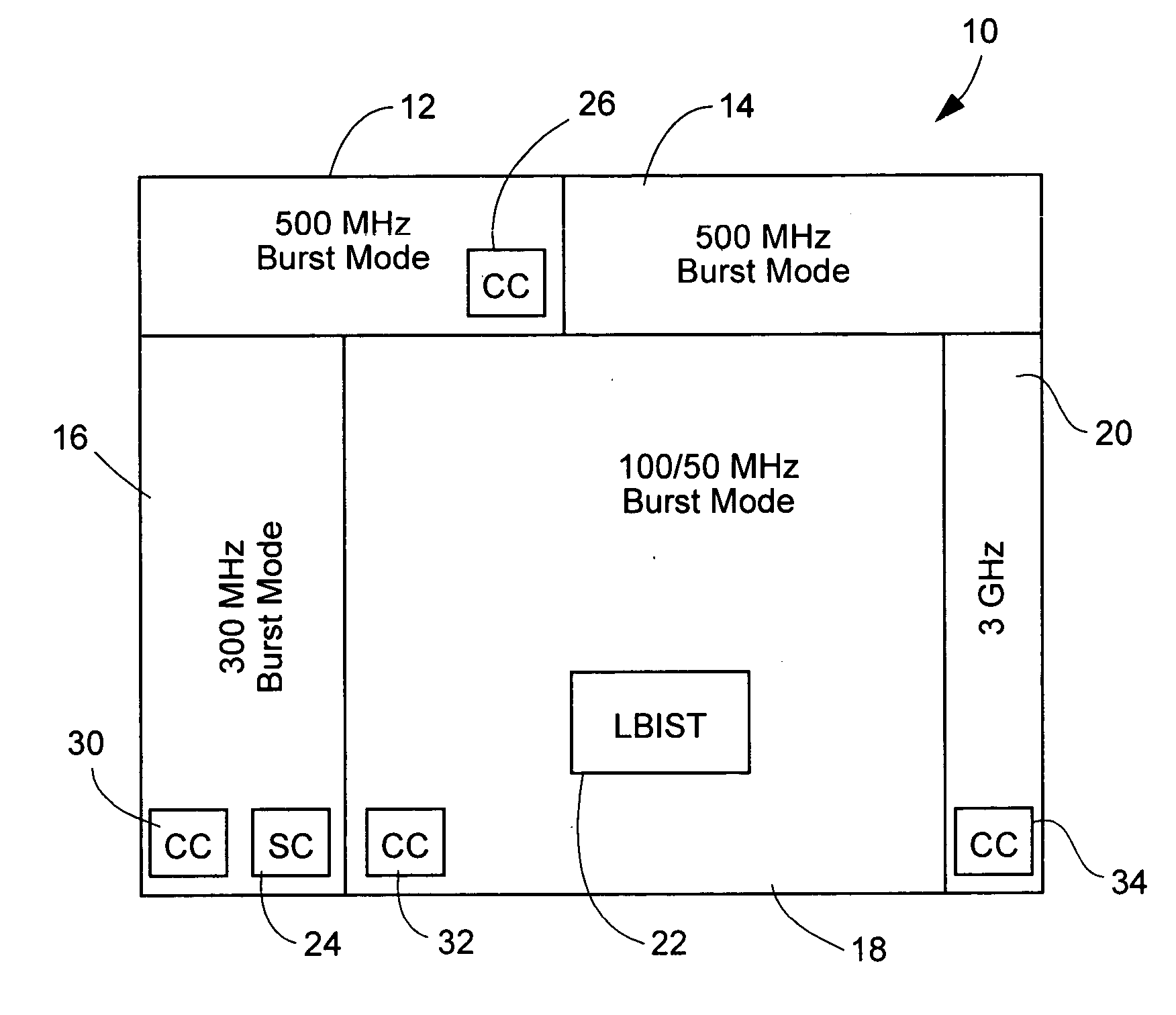

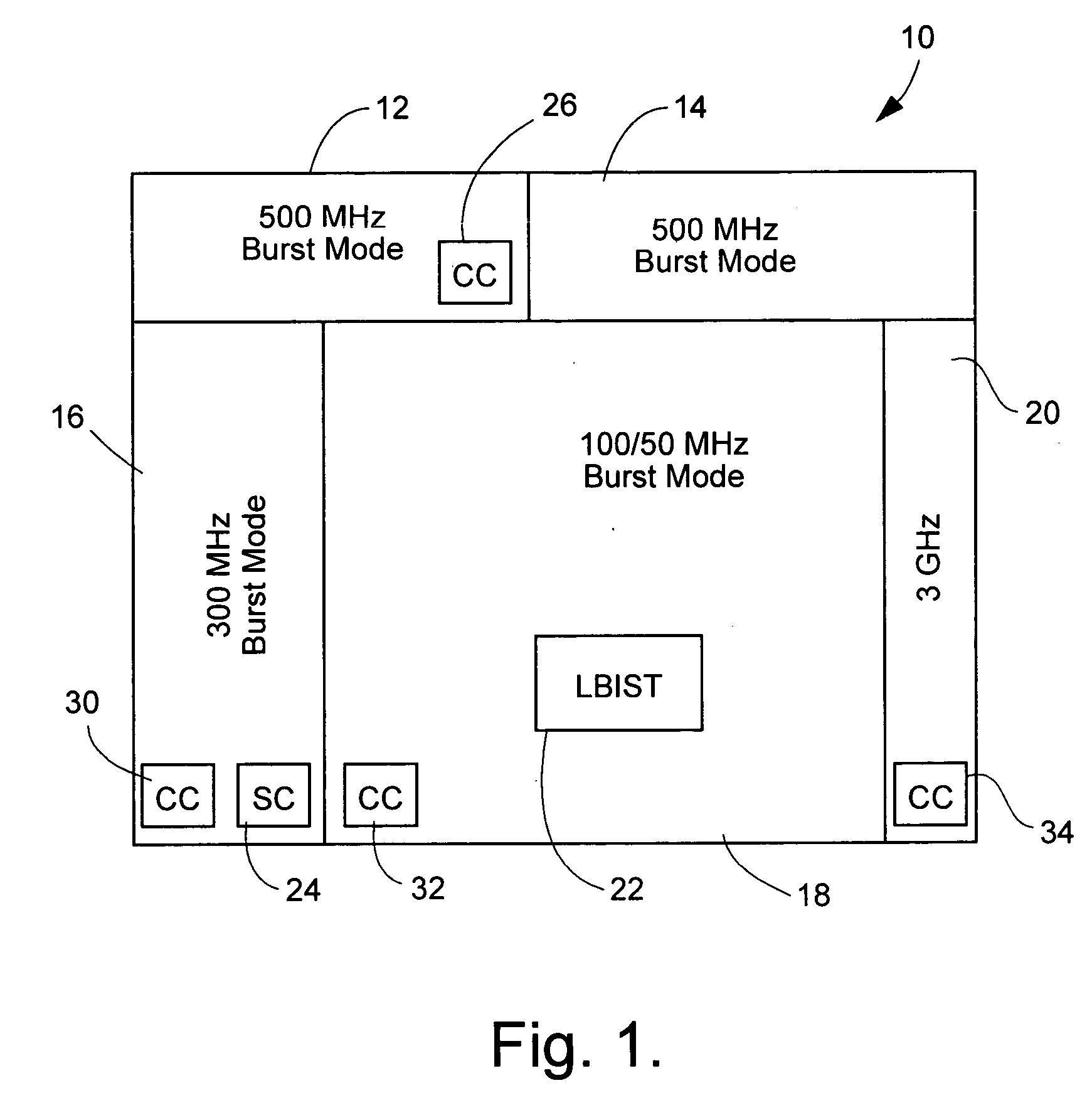

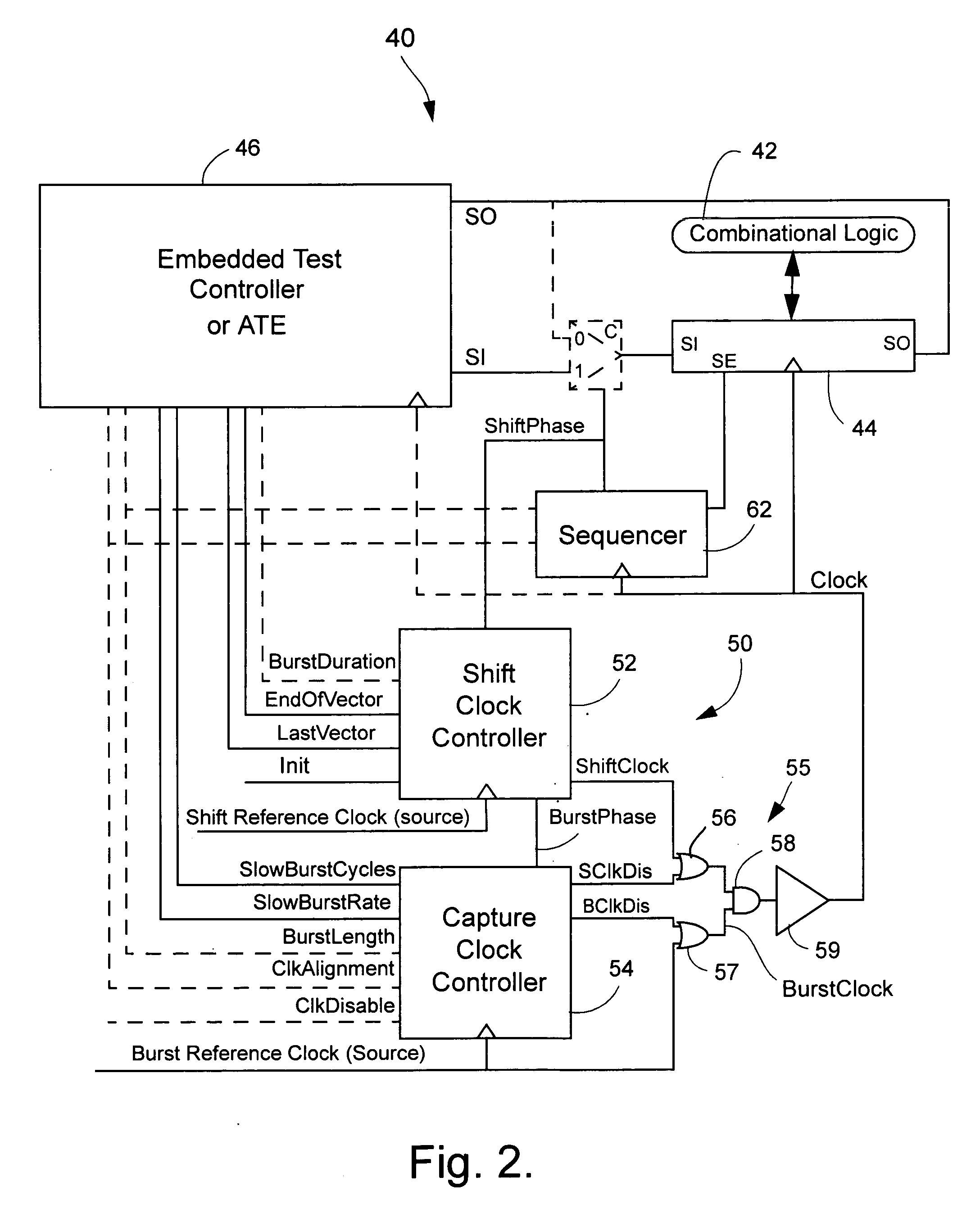

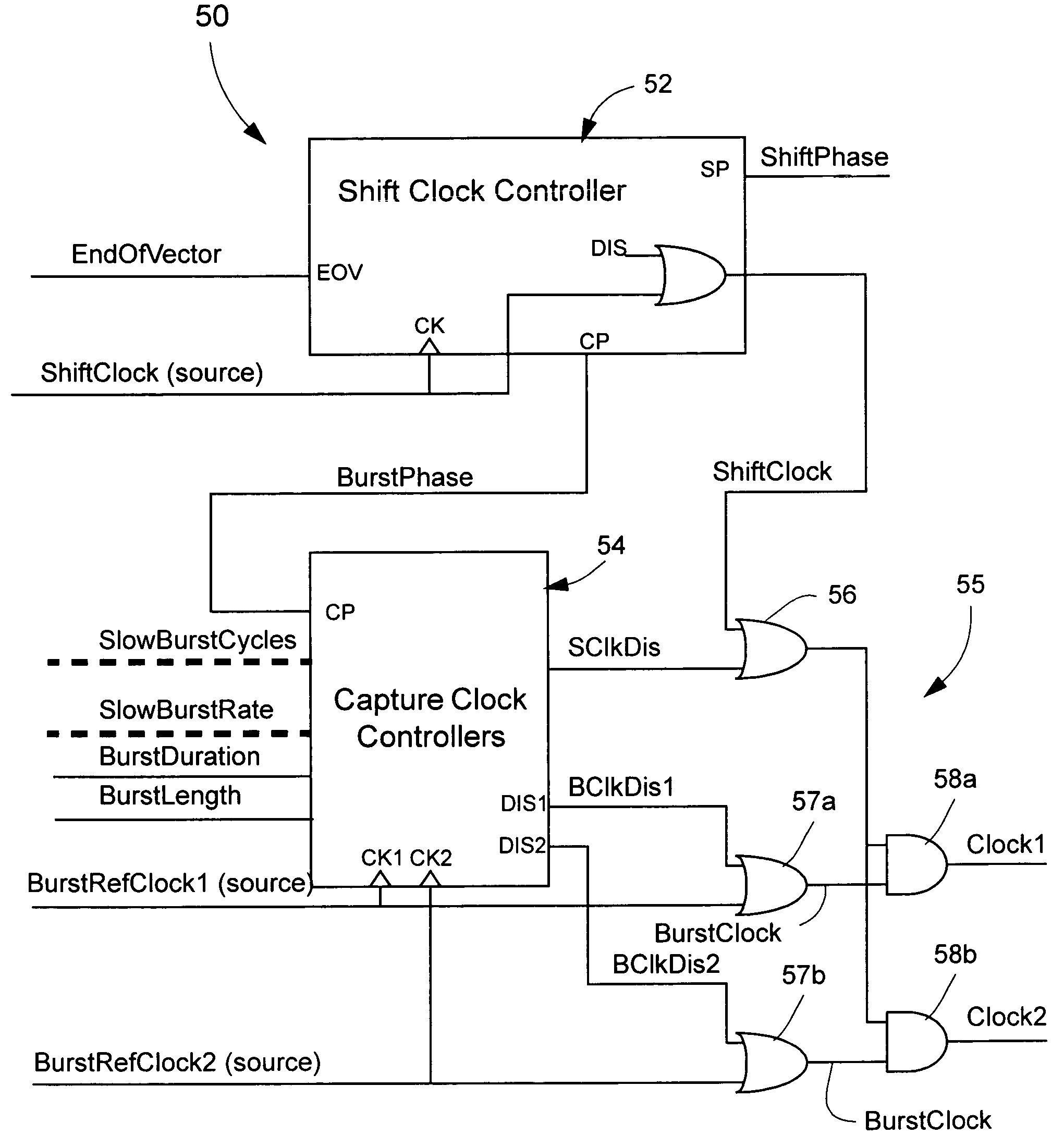

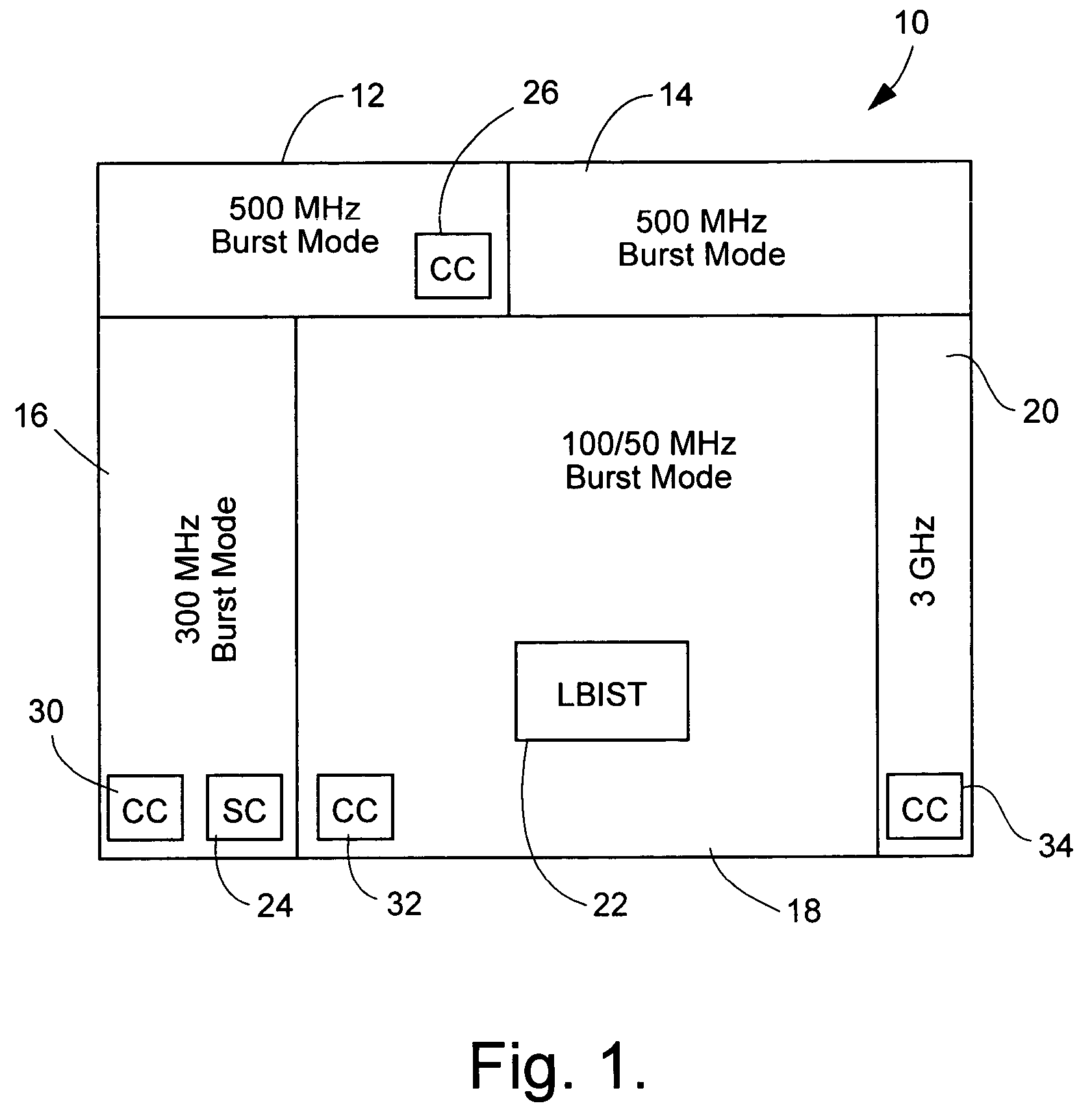

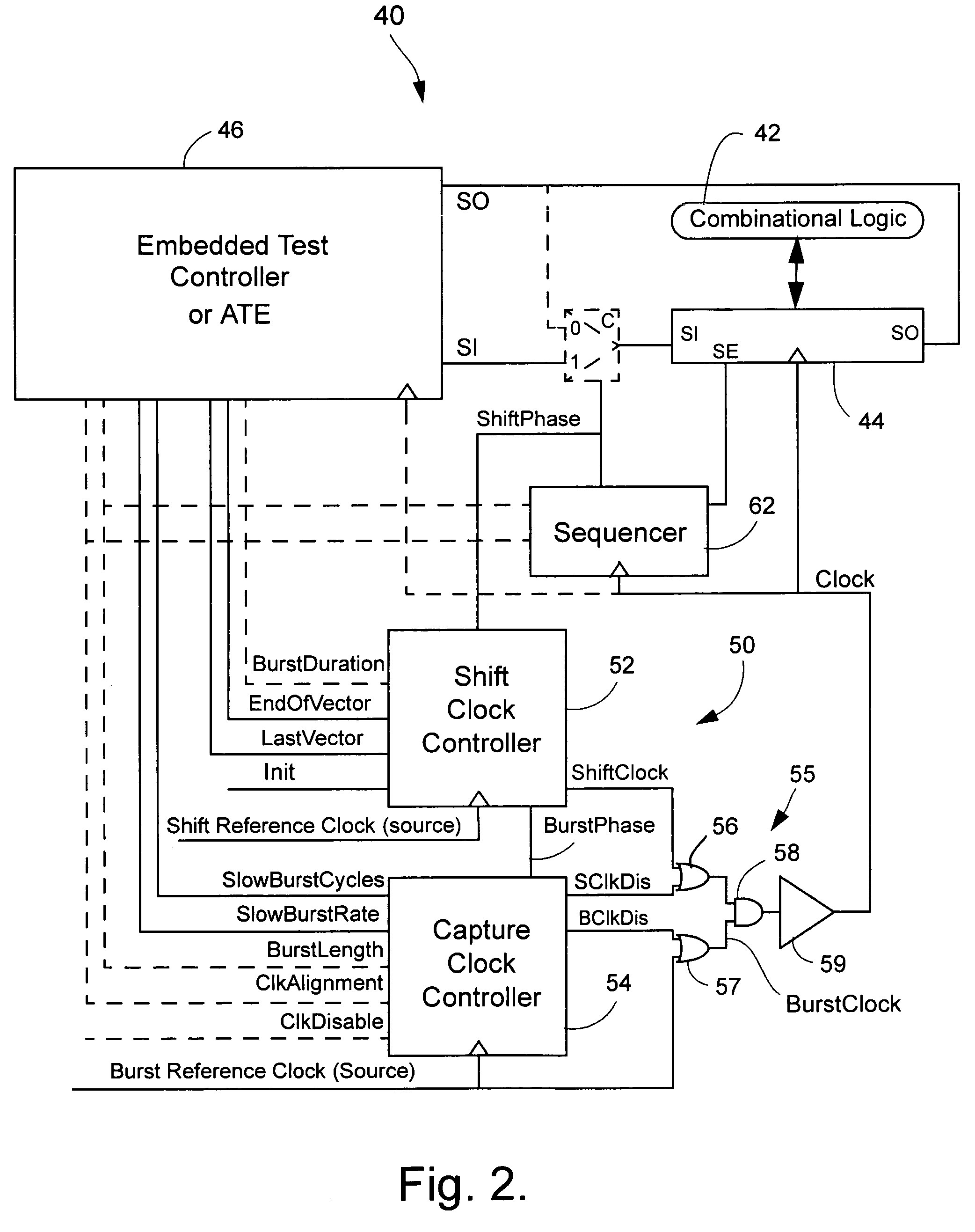

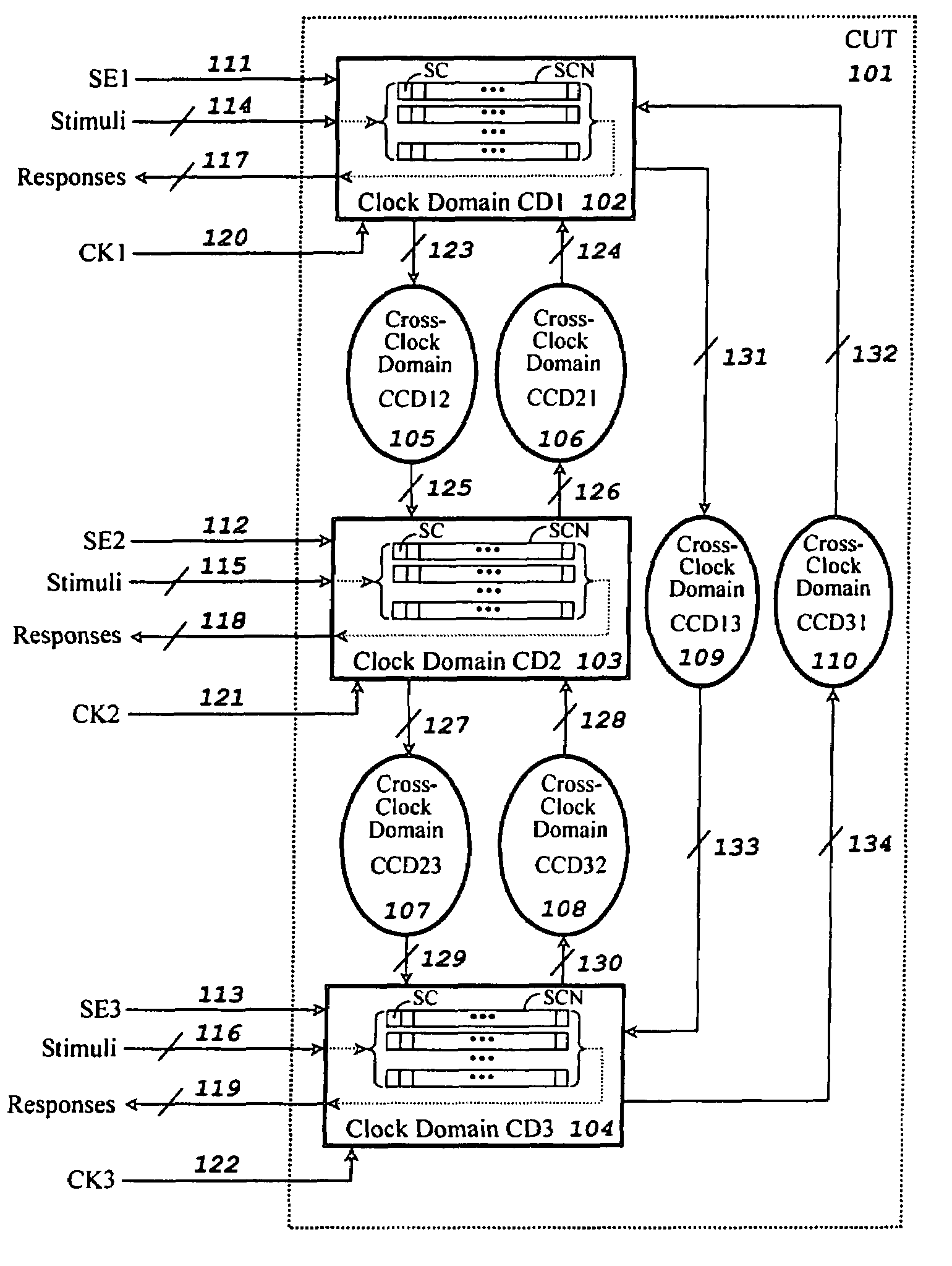

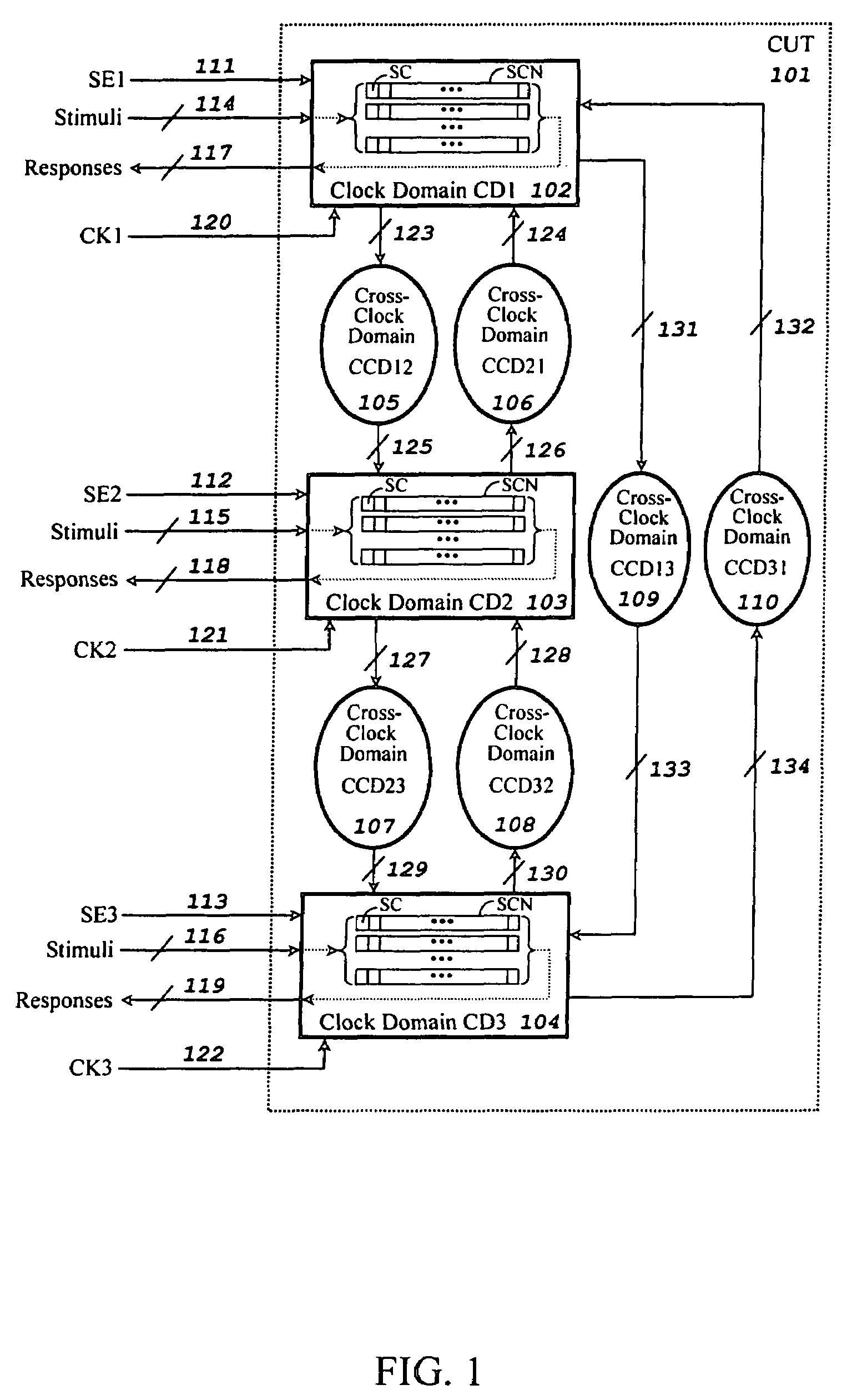

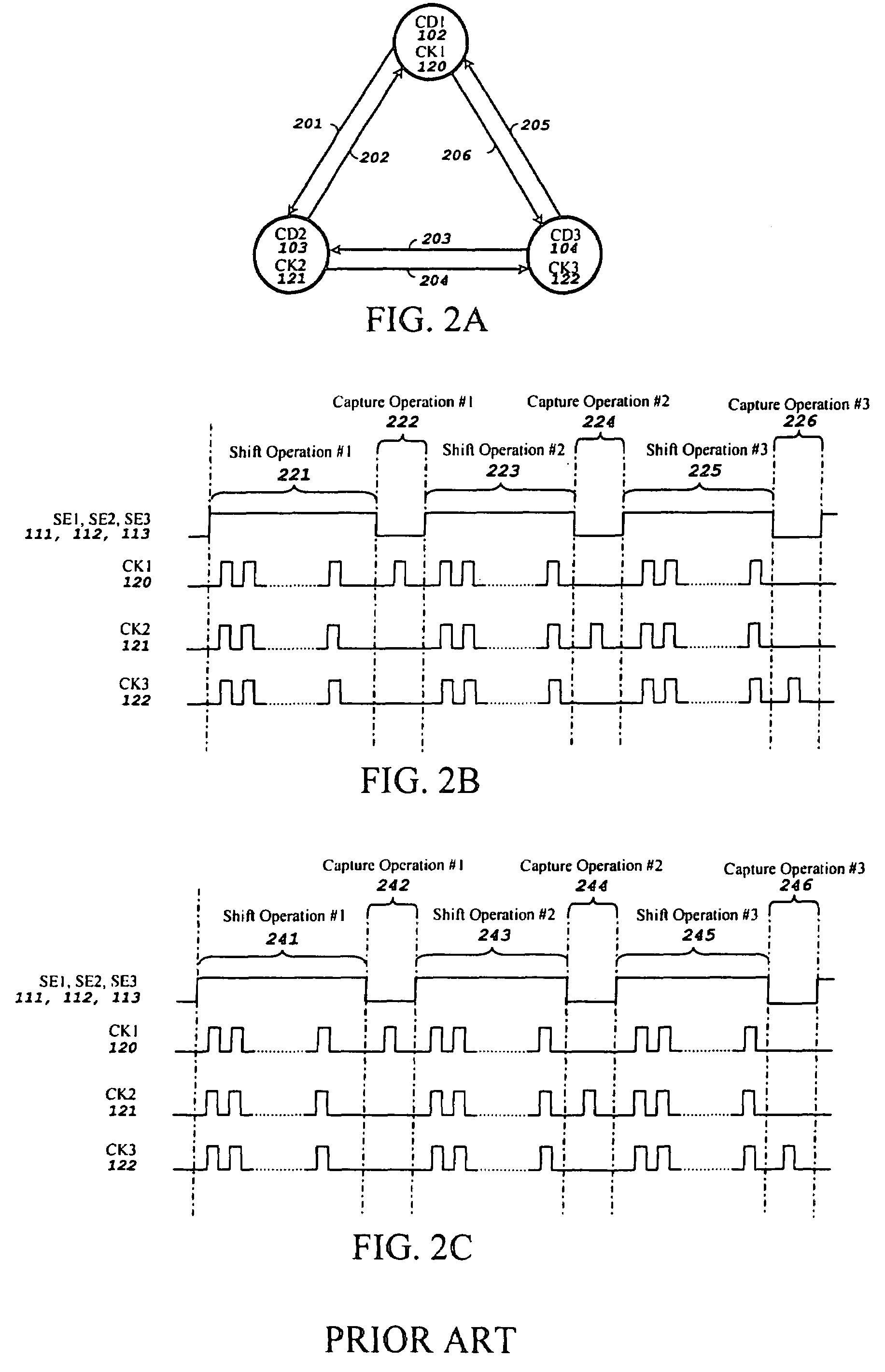

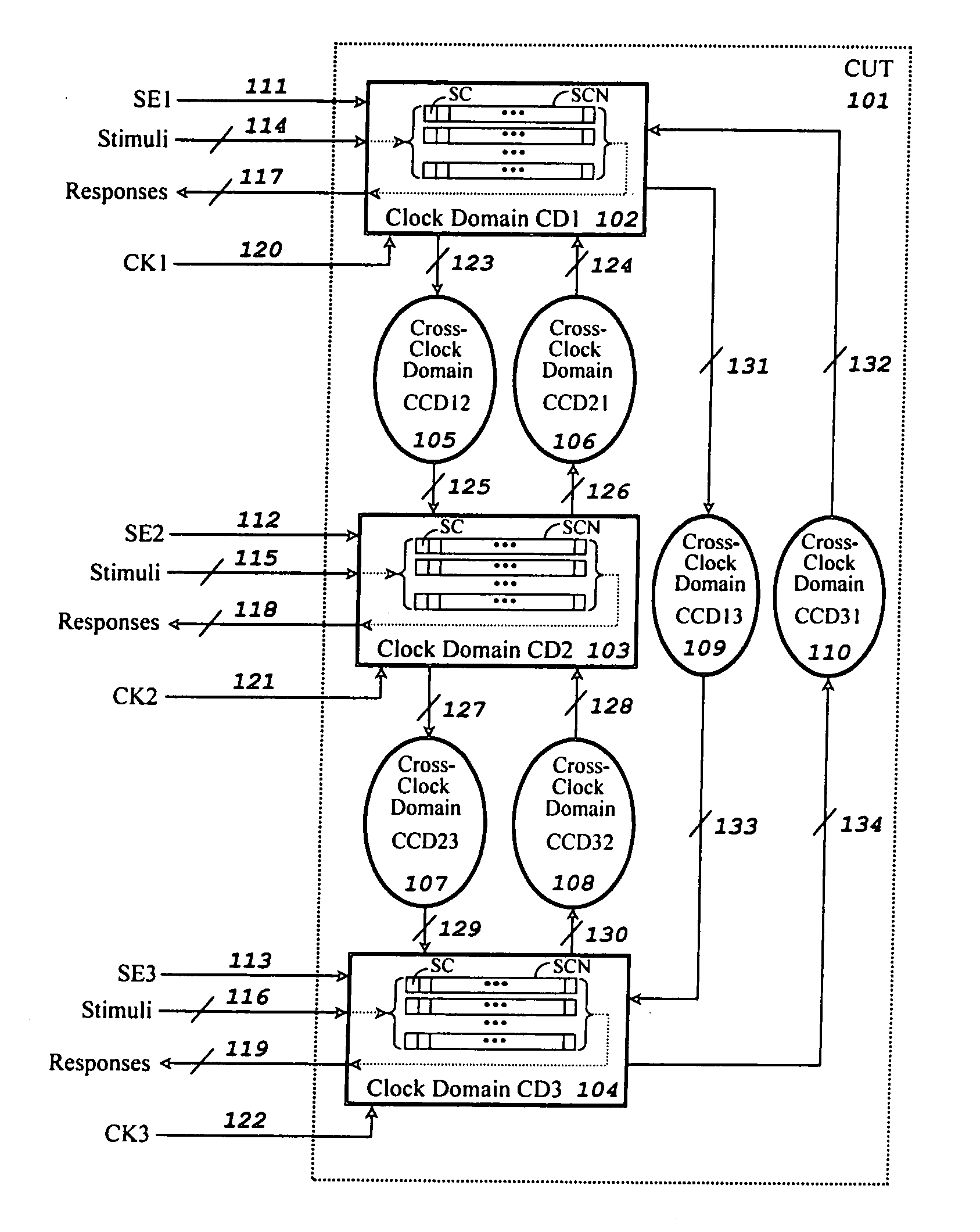

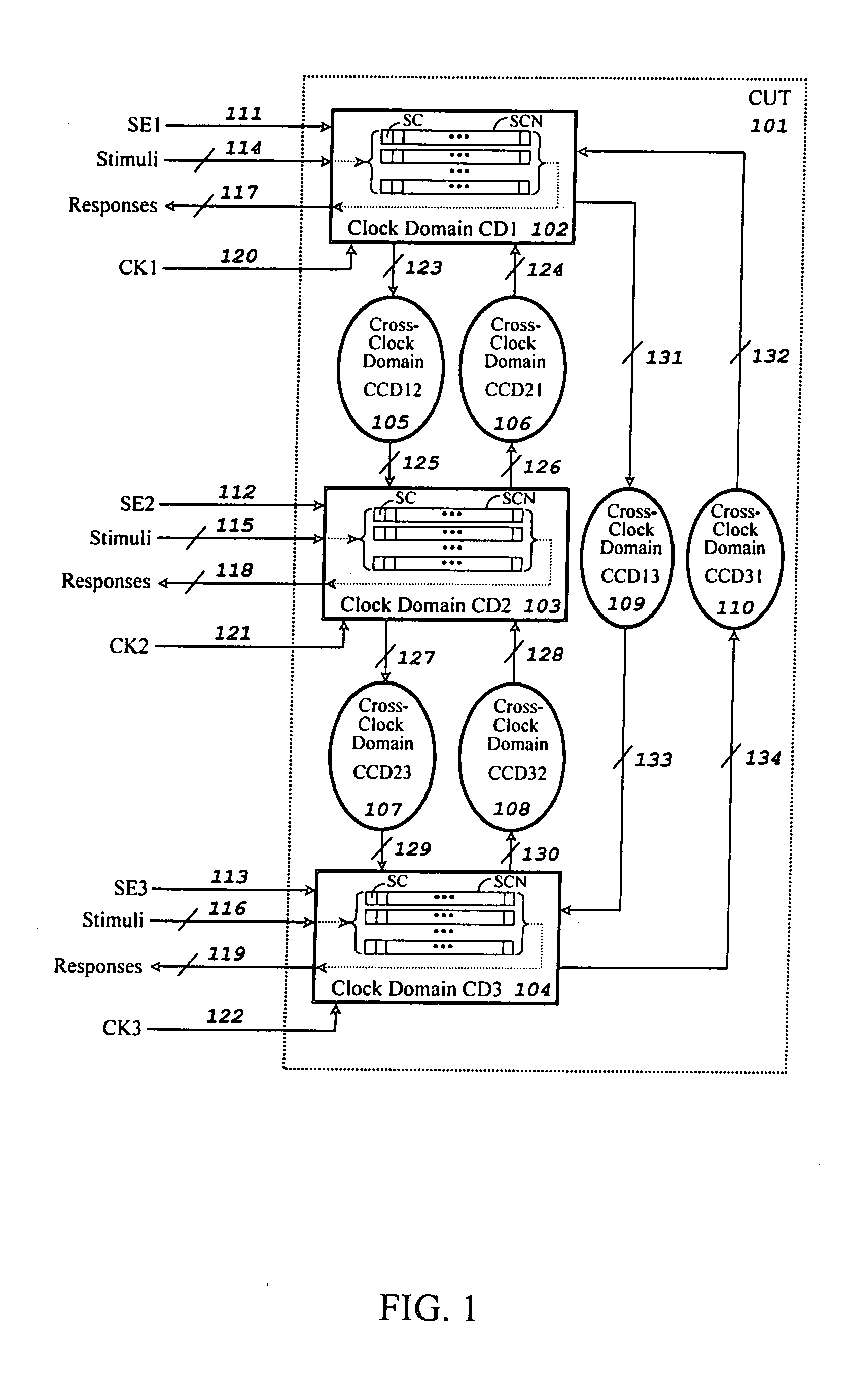

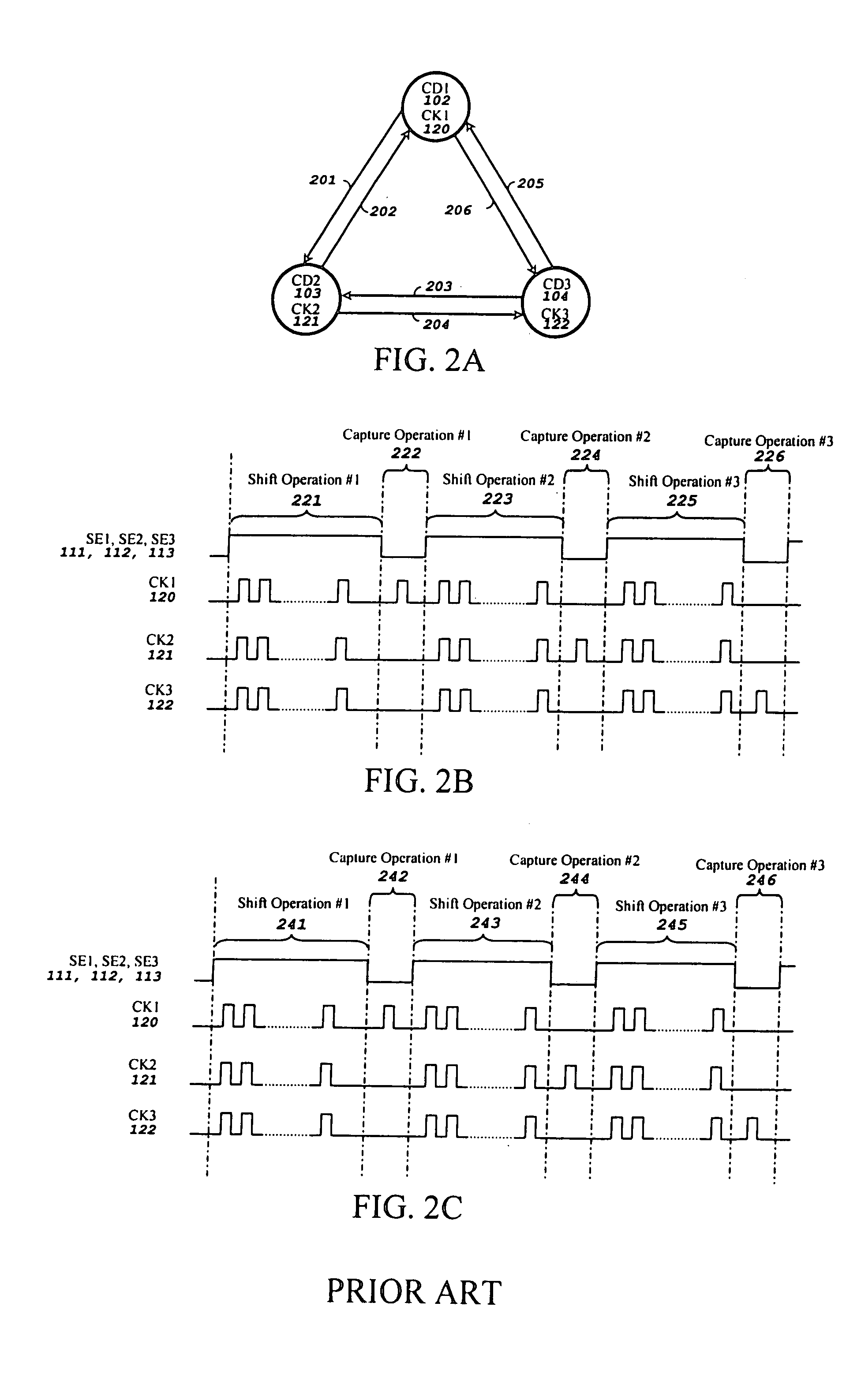

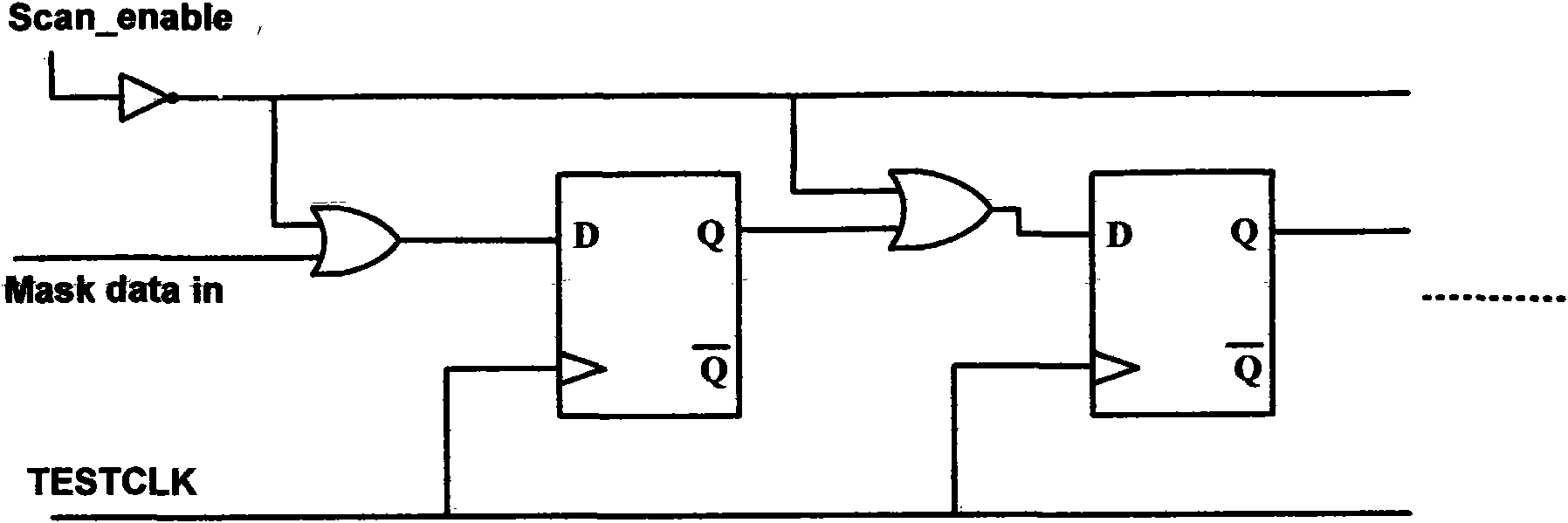

Clock controller for at-speed testing of scan circuits

A test clock controller for generating a test clock signal for scan chains in integrated circuits having one or more clock domains, comprises a shift clock controller for generating a shift clock signal for use in loading test patterns into scan chains in the clock domains and for unloading a test response patterns from the scan chains and for generating a burst phase signal after loading a test pattern; and a burst clock controller associated with each of one or more clock domains and responsive to a burst phase signal for generating a burst of clock pulses derived from a respective reference clocks and including a first group of burst clock pulses having a selected reduced frequency relative to the reference clock and a second group of burst clock pulses having a frequency corresponding to that of the reference clock.

Owner:SIEMENS PROD LIFECYCLE MANAGEMENT SOFTWARE INC

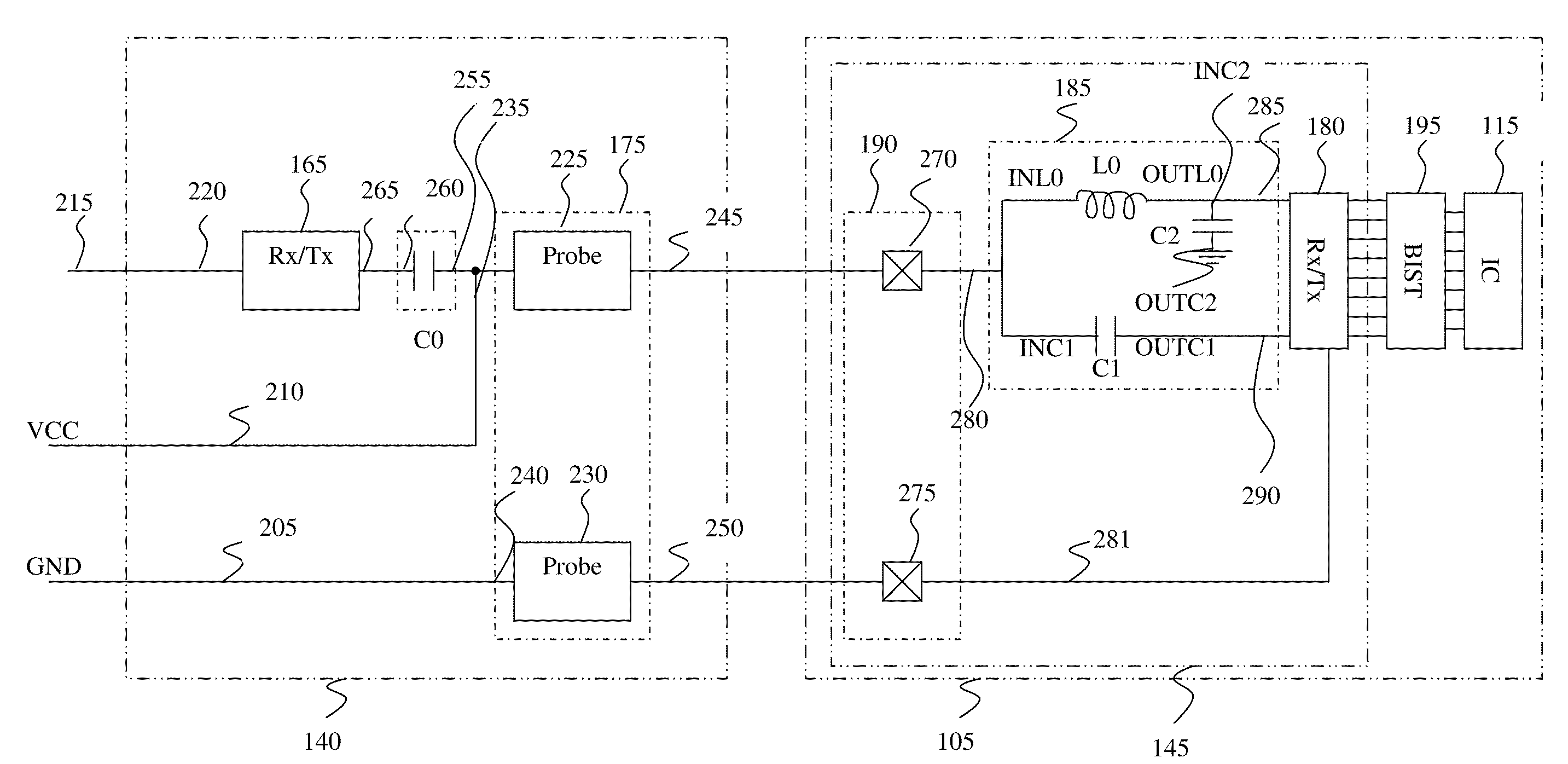

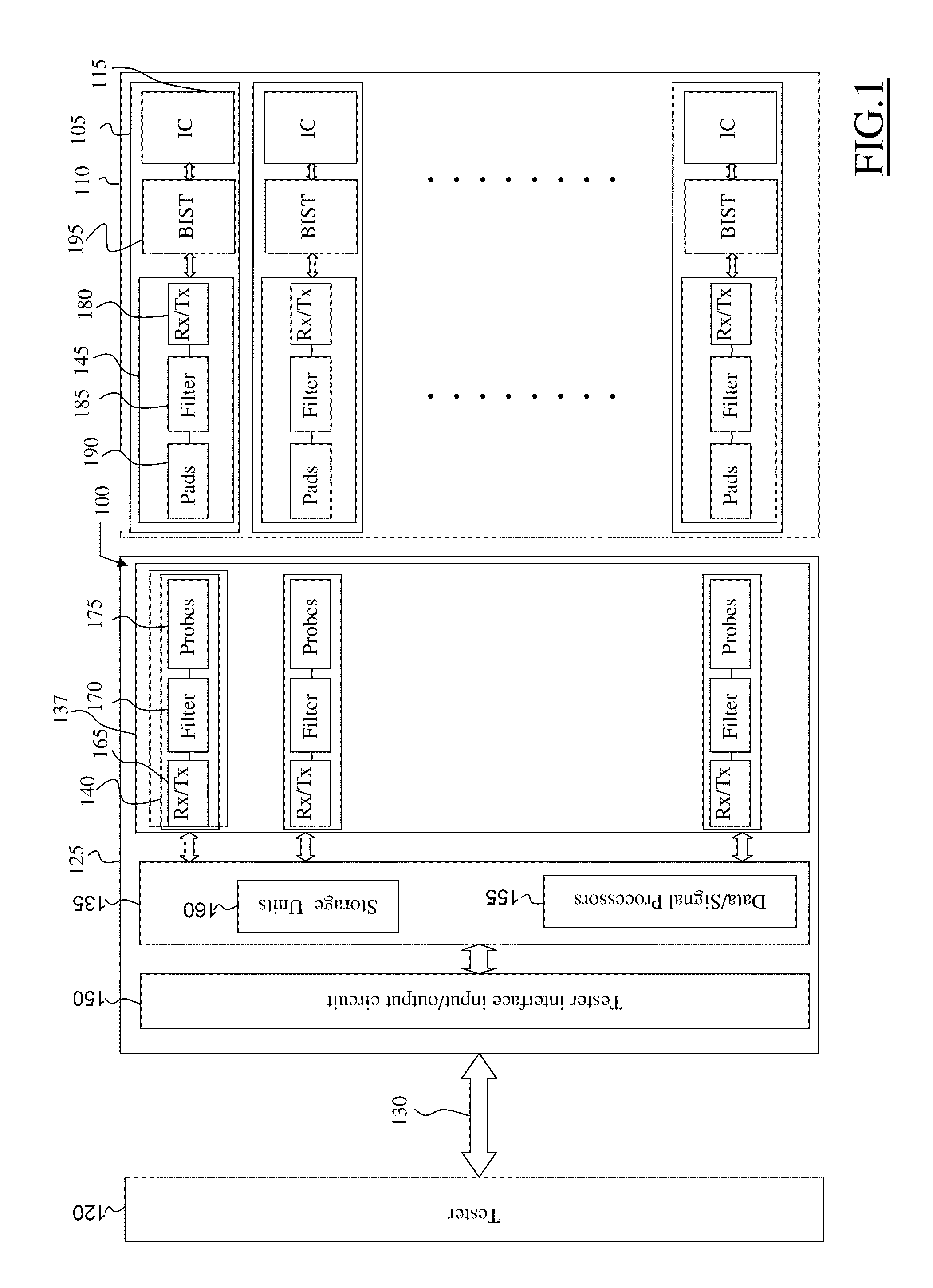

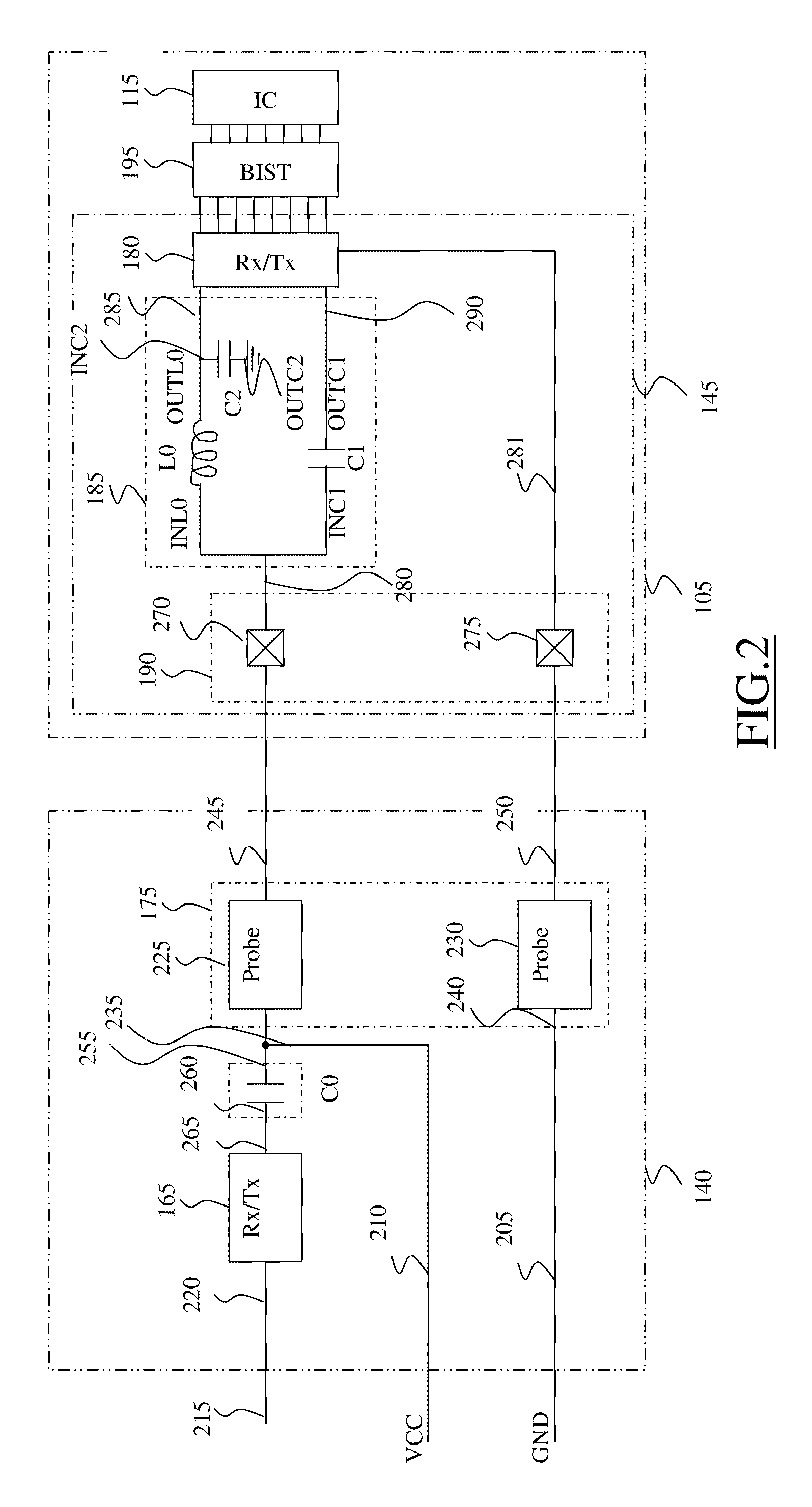

Testing integrated circuits using few test probes

ActiveUS20090224784A1Reduce in quantitySemiconductor/solid-state device testing/measurementSolid-state devicesCarrier signalEngineering

A method of testing integrated circuits, including: establishing at least a first physical communication channel between a test equipment and an integrated circuit under test by having at least a first probe of the test equipment contacting a corresponding physical contact terminal of the integrated circuit under test; having the test equipment and the integrated circuit under test exchange, over said first physical communication channel, at least two signals selected from the group including at least two test stimuli and at least two test response signals, wherein said at least two signals are exchanged by means of at least one modulated carrier wave modulated by the at least two signals.

Owner:STMICROELECTRONICS SRL

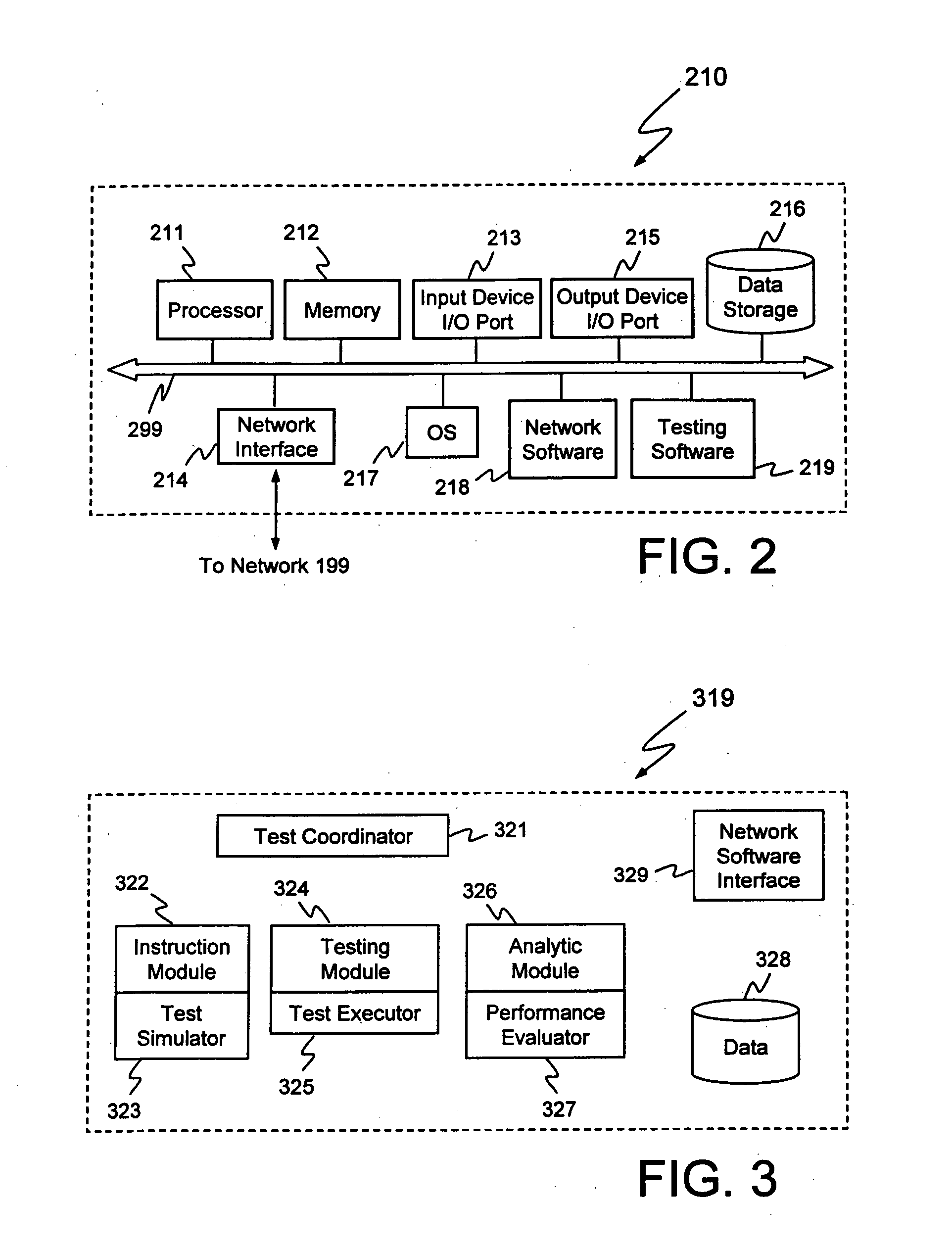

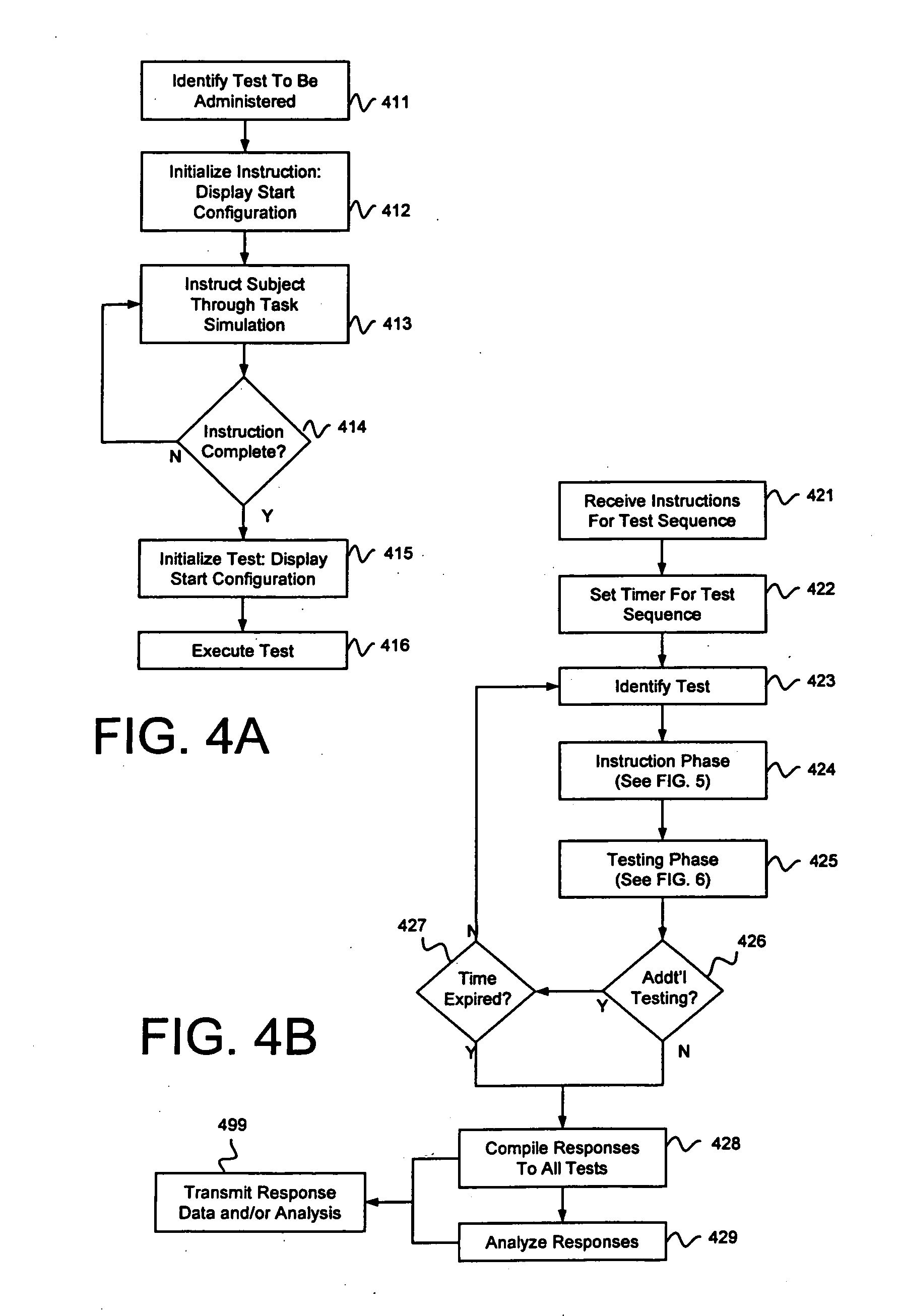

System and method of testing cognitive function

A system and method of diagnosing the onset and monitoring the progression of cognitive impairment may incorporate administering one or more psychological tests and instructing a subject regarding rules for responding to the one or more tests without providing cultural cues such as may be introduced in language-based instruction techniques. Proper test responses may be simulated during an instruction phase preceding the testing phase. An apparatus, system, and method of testing cognitive function may be implemented in a computerized system.

Owner:COGSTATE

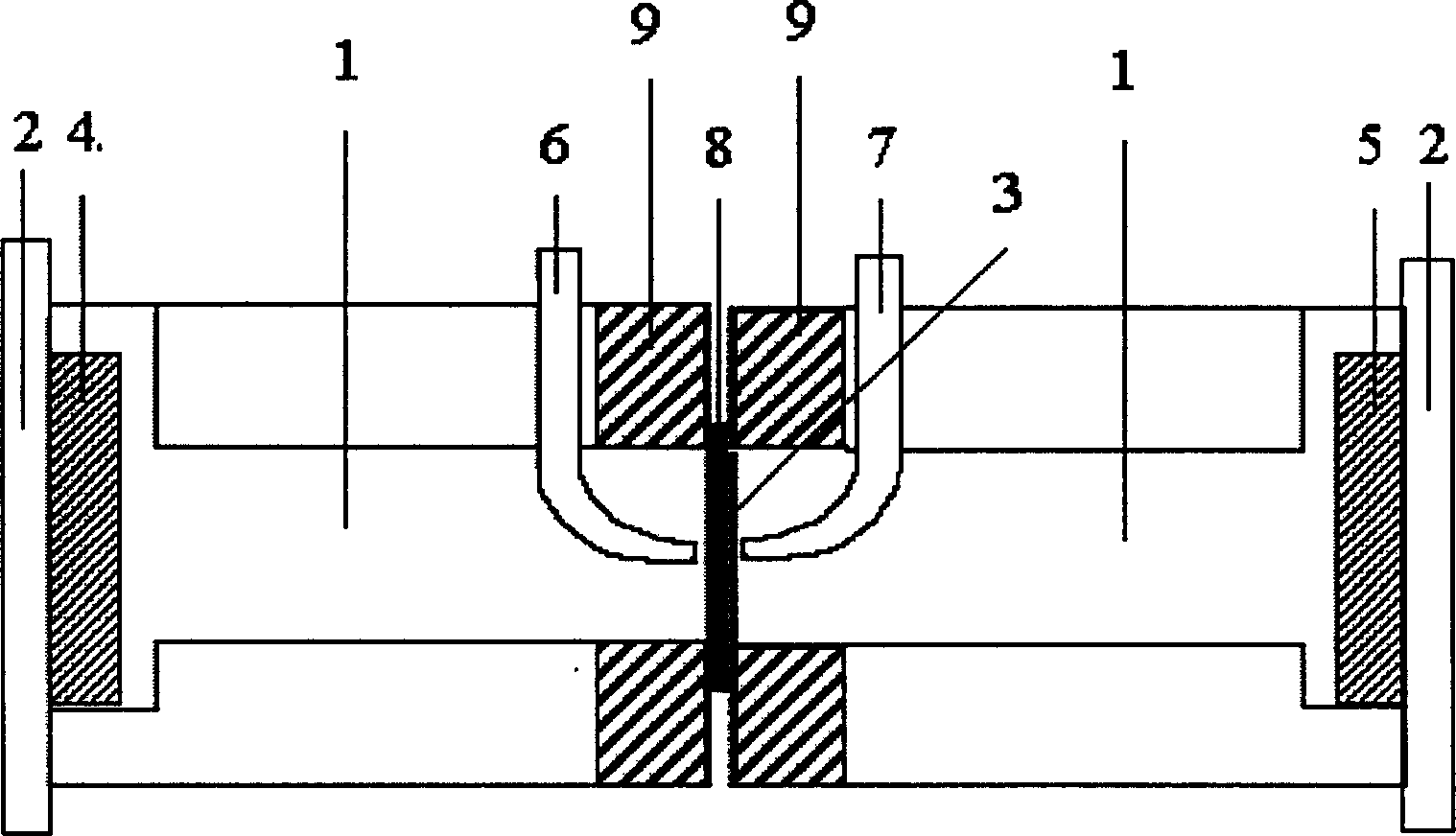

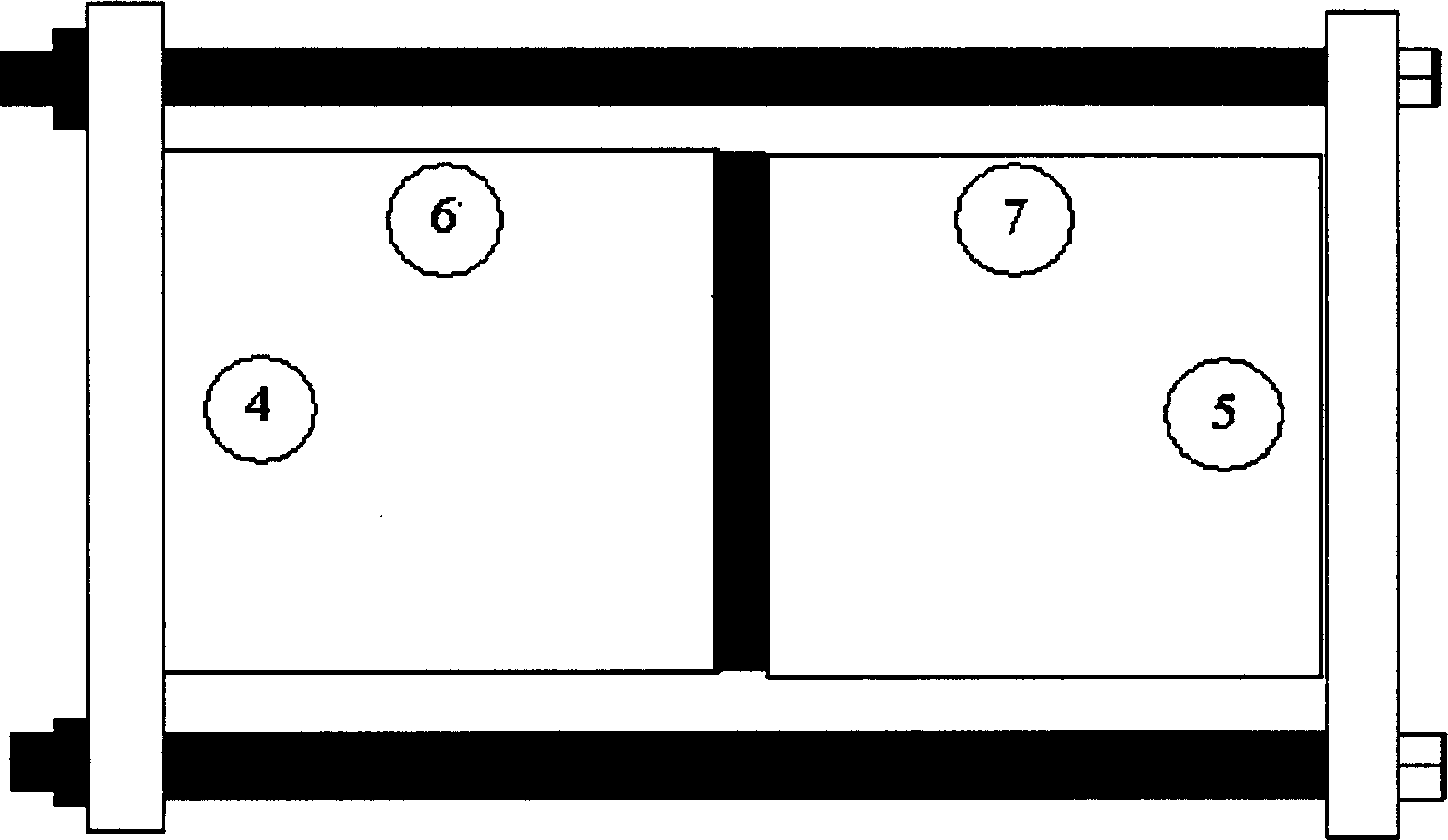

Testing method and appliance for horizontal conductivity of fuel cell proton exchange membrane

InactiveCN1564014AAvoid polarizationSolve measurement problemsElectrical testingAuxiliary electrodeEngineering

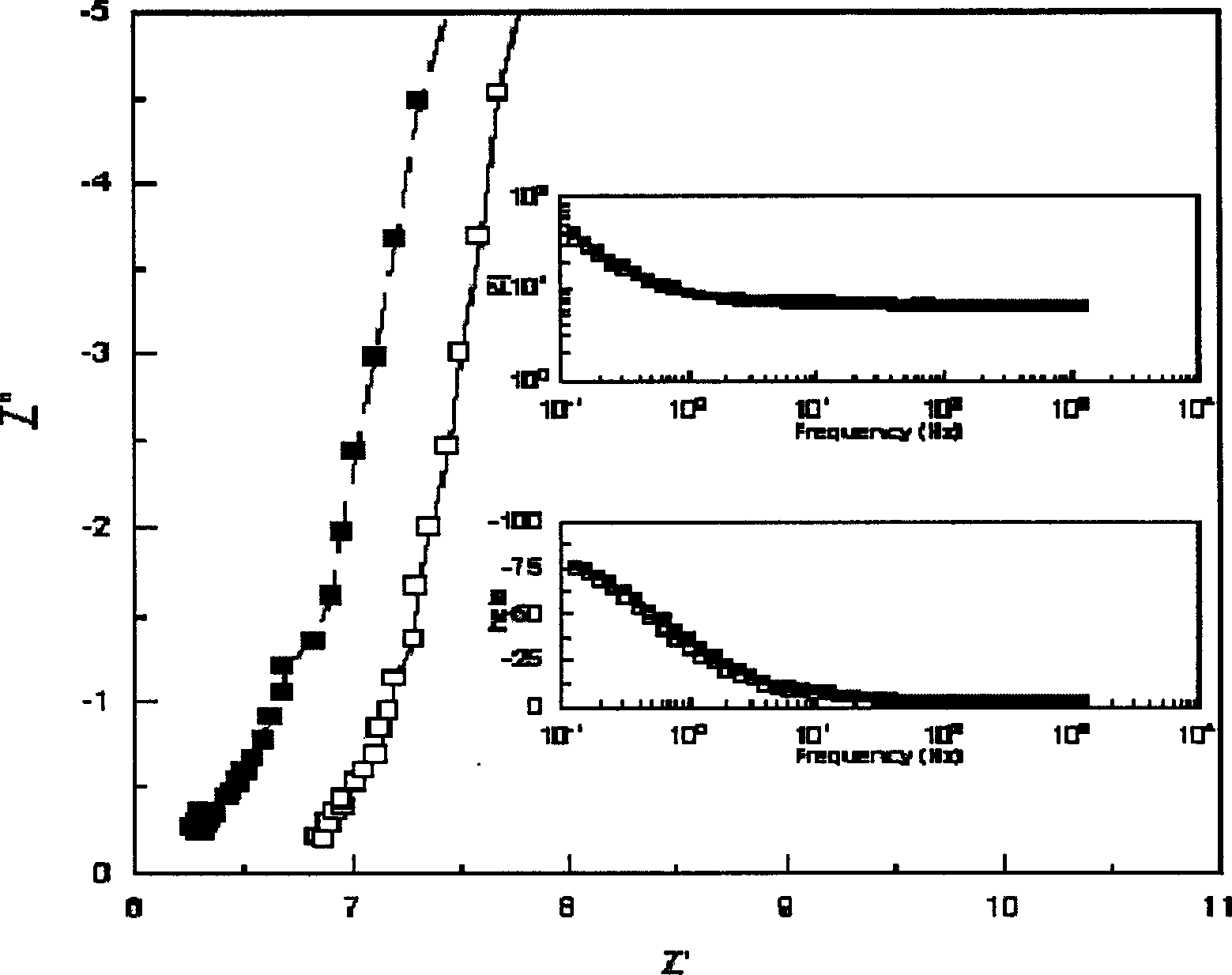

Four electrodes or three electrodes system are adopted in the invention. Carbon electrode is in sue for working electrode and auxiliary electrode for loading test current, and saturated calomel electrode is in use for reference electrode for testing response voltage. In testing, exchange membrane is placed in middle of connection hole corresponding to two electrolytic cells. Transverse resistance is measured by using AC impedence method. Conductivity of membrane is calculated out from thickness of membrane and area of the connection hole. The invented method prevents polarization issue occurred in DC test method is applicable to testing transverse conductivity of diaphragms used in other fuel cells and lithium ion cells.

Owner:UNIV OF SCI & TECH BEIJING

Clock controller for at-speed testing of scan circuits

A test clock controller for generating a test clock signal for scan chains in integrated circuits having one or more clock domains, comprises a shift clock controller for generating a shift clock signal for use in loading test patterns into scan chains in the clock domains and for unloading a test response patterns from the scan chains and for generating a burst phase signal after loading a test pattern; and a burst clock controller associated with each of one or more clock domains and responsive to a burst phase signal for generating a burst of clock pulses derived from a respective reference clocks and including a first group of burst clock pulses having a selected reduced frequency relative to the reference clock and a second group of burst clock pulses having a frequency corresponding to that of the reference clock.

Owner:SIEMENS PROD LIFECYCLE MANAGEMENT SOFTWARE INC

Smart capture for ATPG (automatic test pattern generation) and fault simulation of scan-based integrated circuits

InactiveUS7124342B2Improve performanceHigh simulationError detection/correctionMarginal circuit testingHemt circuitsAutomatic test pattern generation

A method for generating stimuli and test responses for testing faults in a scan-based integrated circuit in a selected scan-test mode or a selected self-test mode, the scan-based integrated circuit containing a plurality of scan chains, N clock domains, and C cross-clock domain blocks, each scan chain comprising multiple scan cells coupled in series, each clock domain having one capture clock, each cross-clock domain block comprising a combinational logic network. The method comprises compiling the scan-based integrated circuit into a sequential circuit model; specifying input constraints on the scan-based integrated circuit during a shift and capture operation; specifying a clock grouping to map the N clock domains into G clock domain groups, where N>G>1; transforming the sequential circuit model into an equivalent combinational circuit model according to the input constraints and the clock grouping; and generating the stimuli and test responses on the equivalent combinational circuit model according to the input constraints.

Owner:SYNTEST TECH

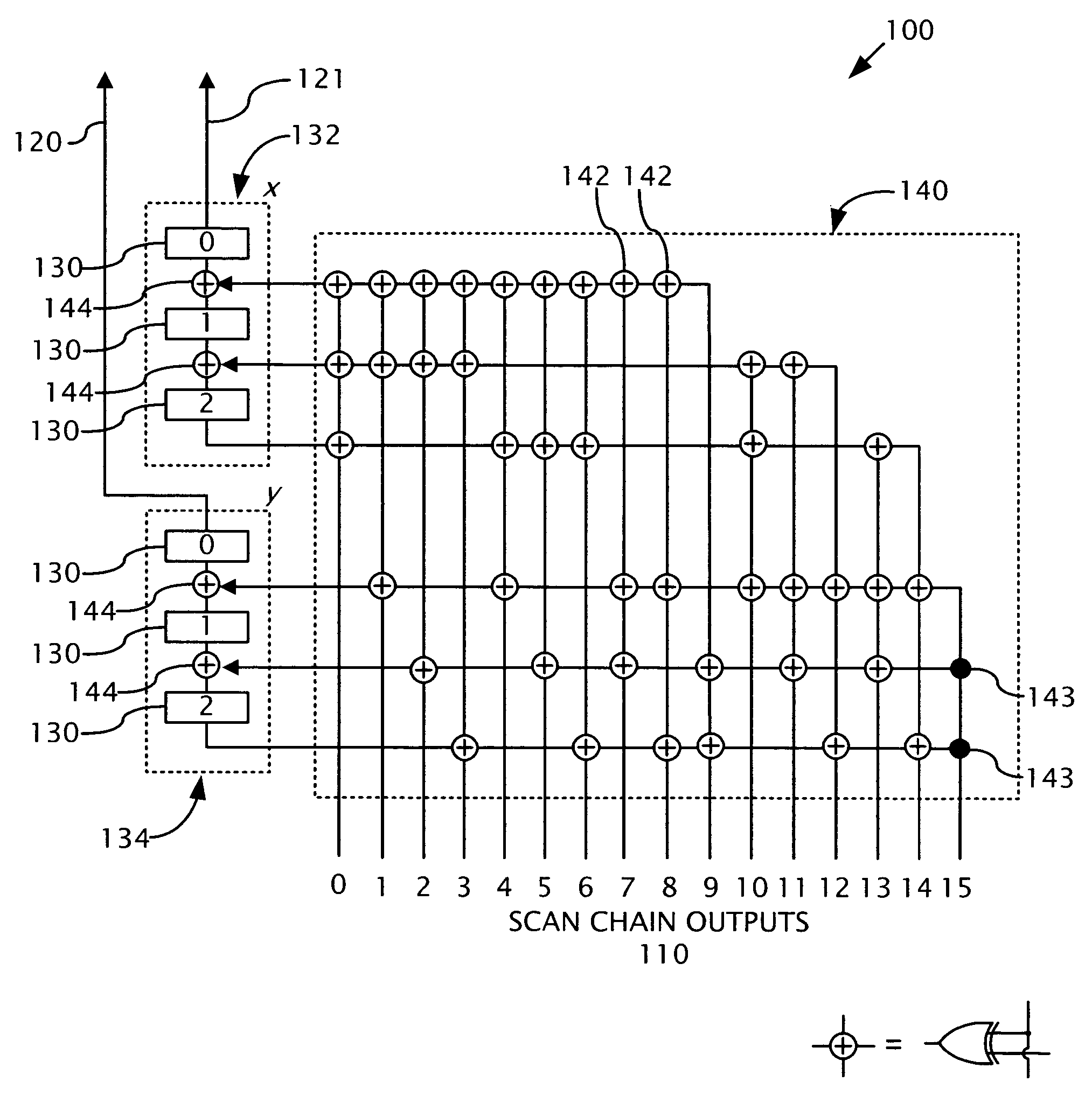

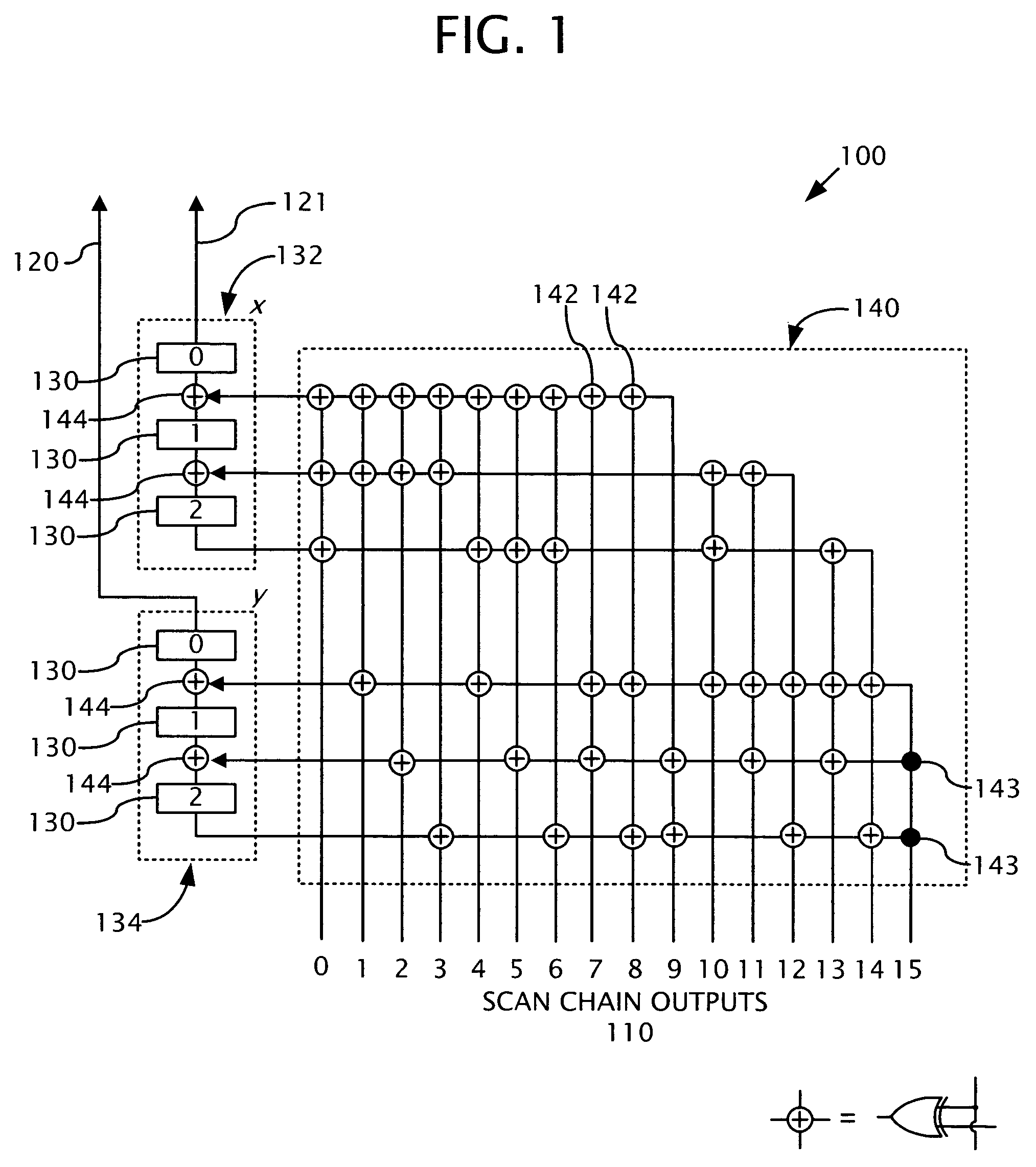

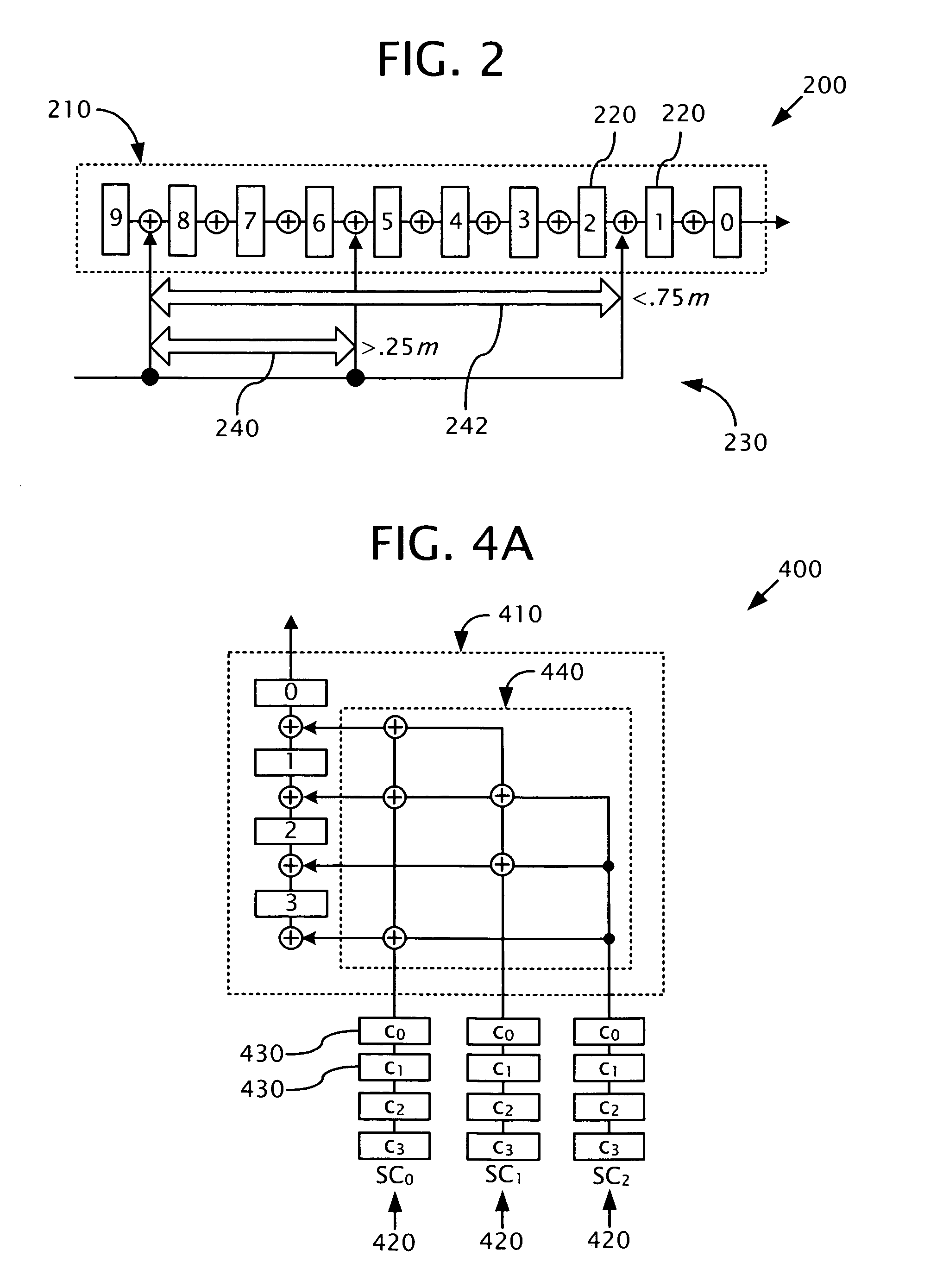

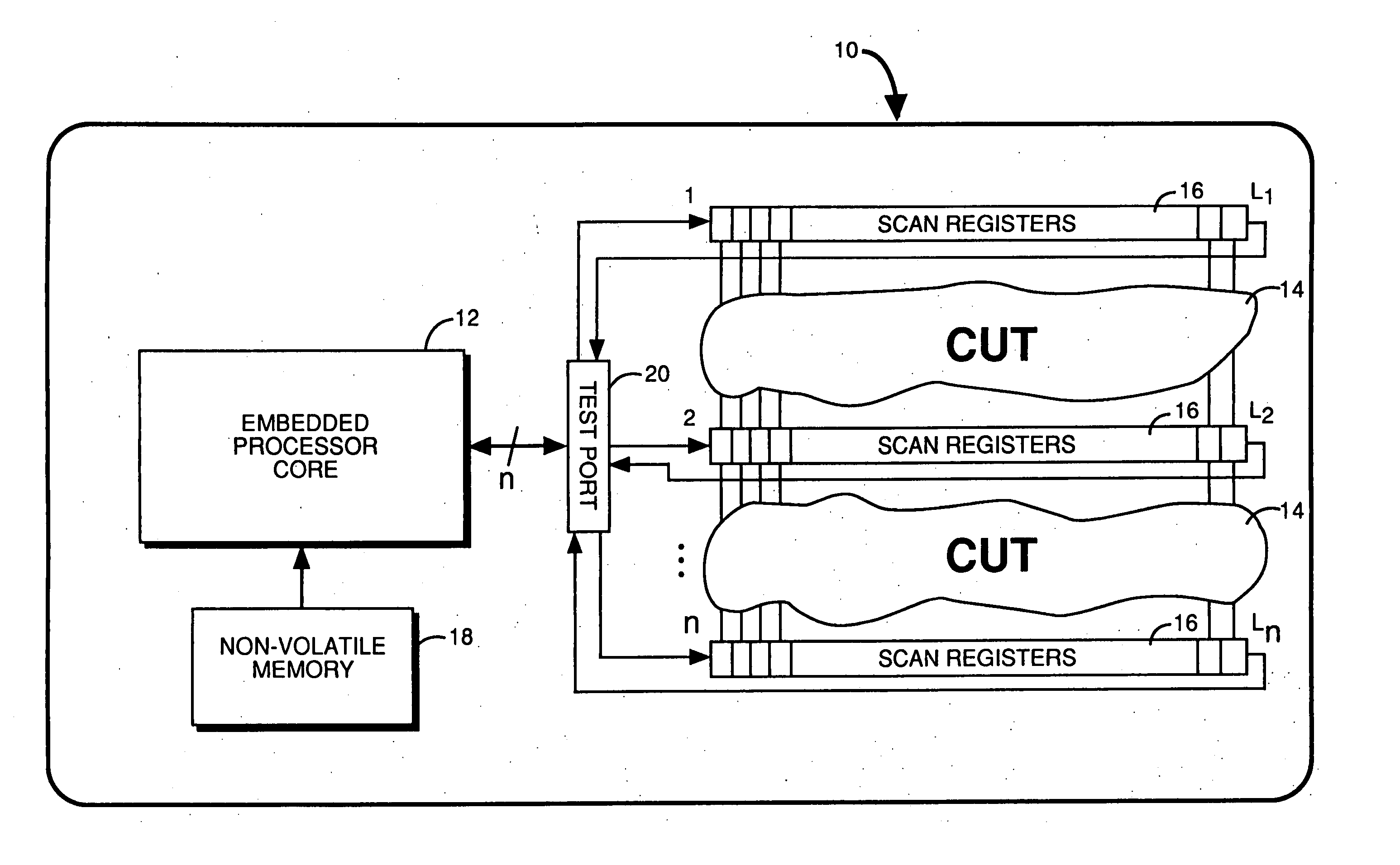

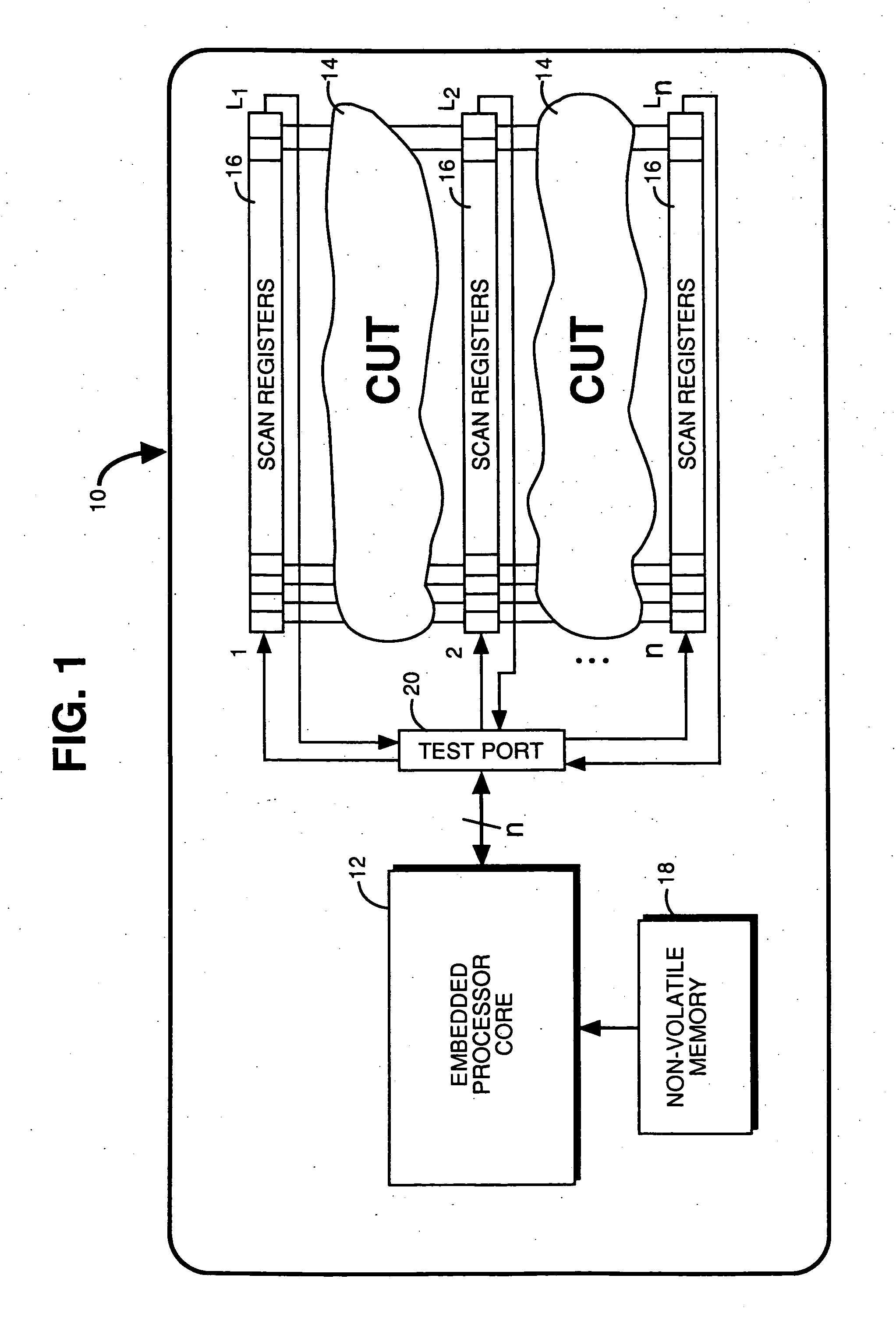

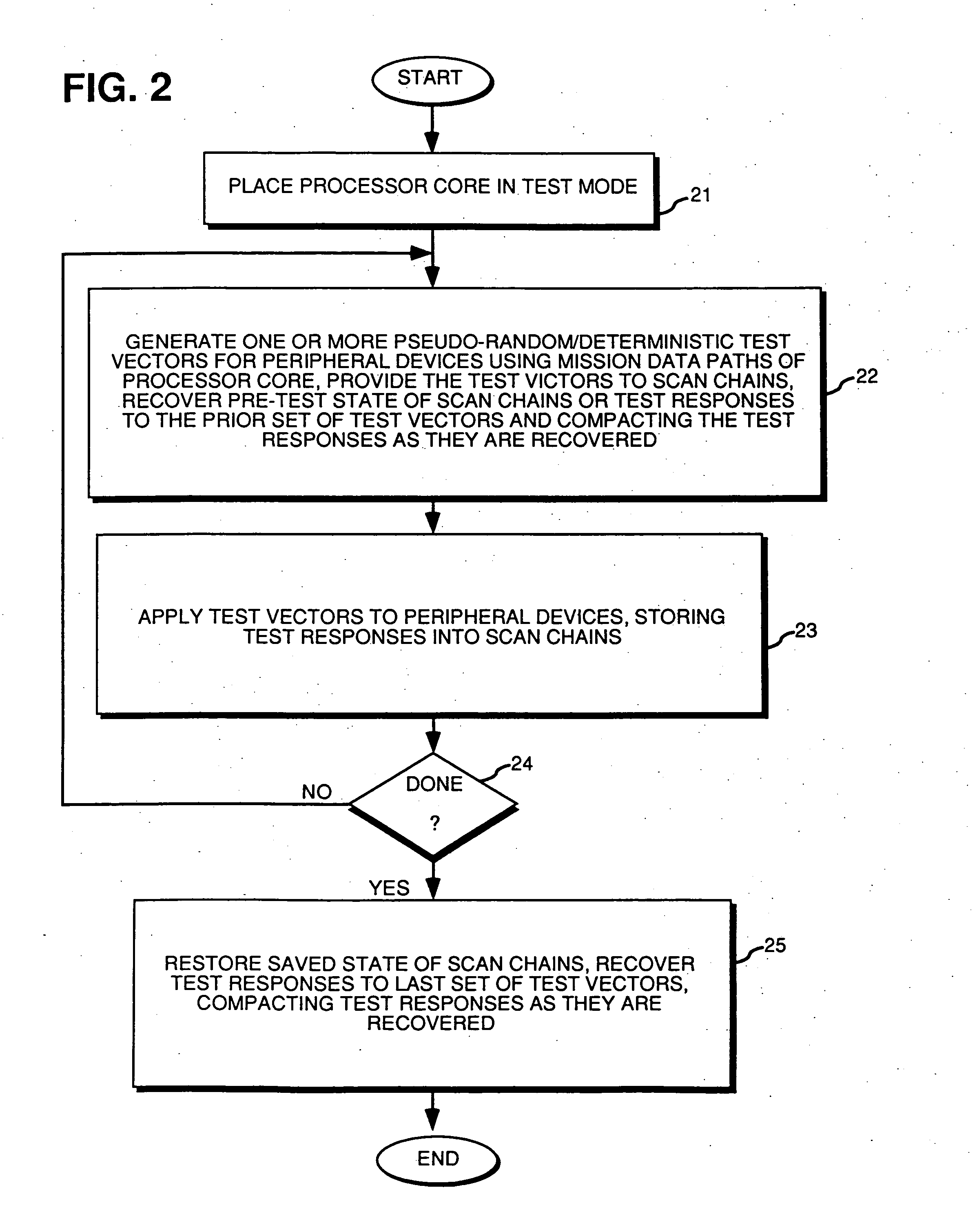

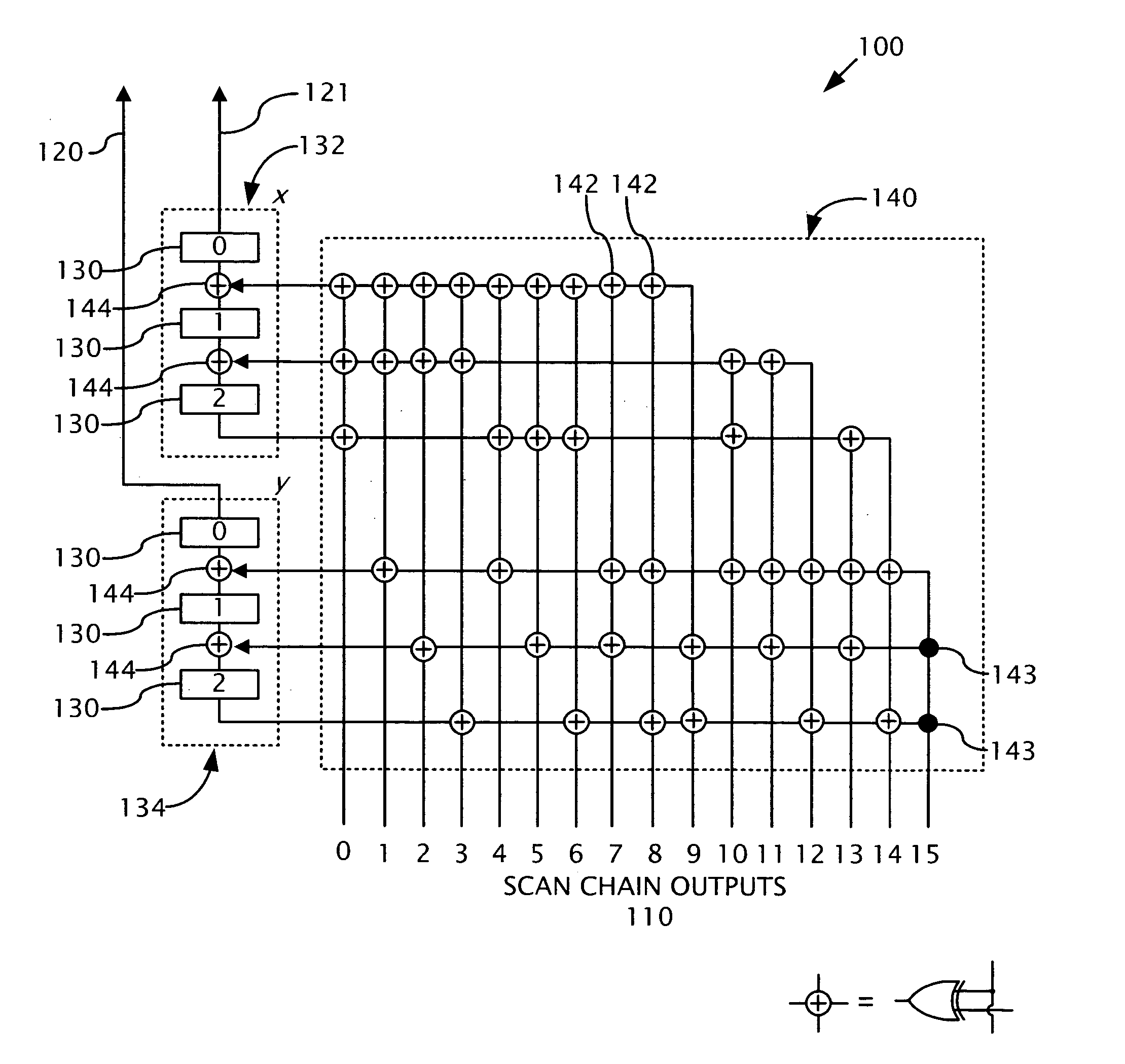

Arithmetic built-in self-test of multiple scan-based integrated circuits

InactiveUS20050060626A1Reduce error impactElectronic circuit testingError detection/correctionTest vector generatorNumber generator

In one embodiment, an IC with an embedded processor core, peripheral devices, and associated multiple scan chains, is provided with microcode that implements an arithmetic pseudo-random number generator and an arithmetic deterministic test vector generator, when executed by the embedded processor core, generates 2-D pseudo-random and deterministic test vectors for testing the peripheral devices respectively. The IC is further provided with microcode that implements an arithmetic test response compactor, which when executed by the embedded processor core, compacts test responses of the peripheral devices into a signature. The IC further includes a test port register and microcode that implements a number of ABIST instructions.

Owner:MENTOR GRAPHICS CORP

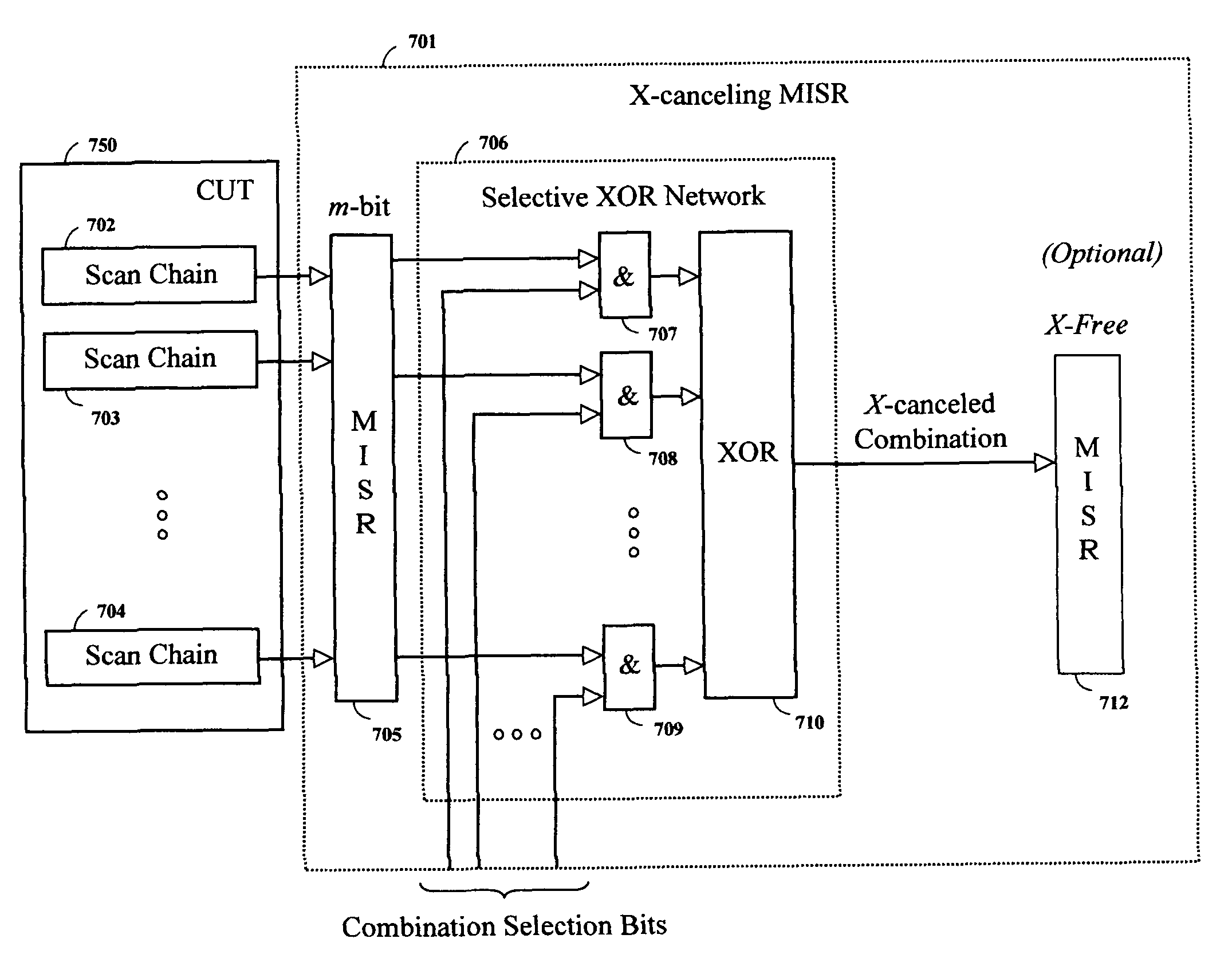

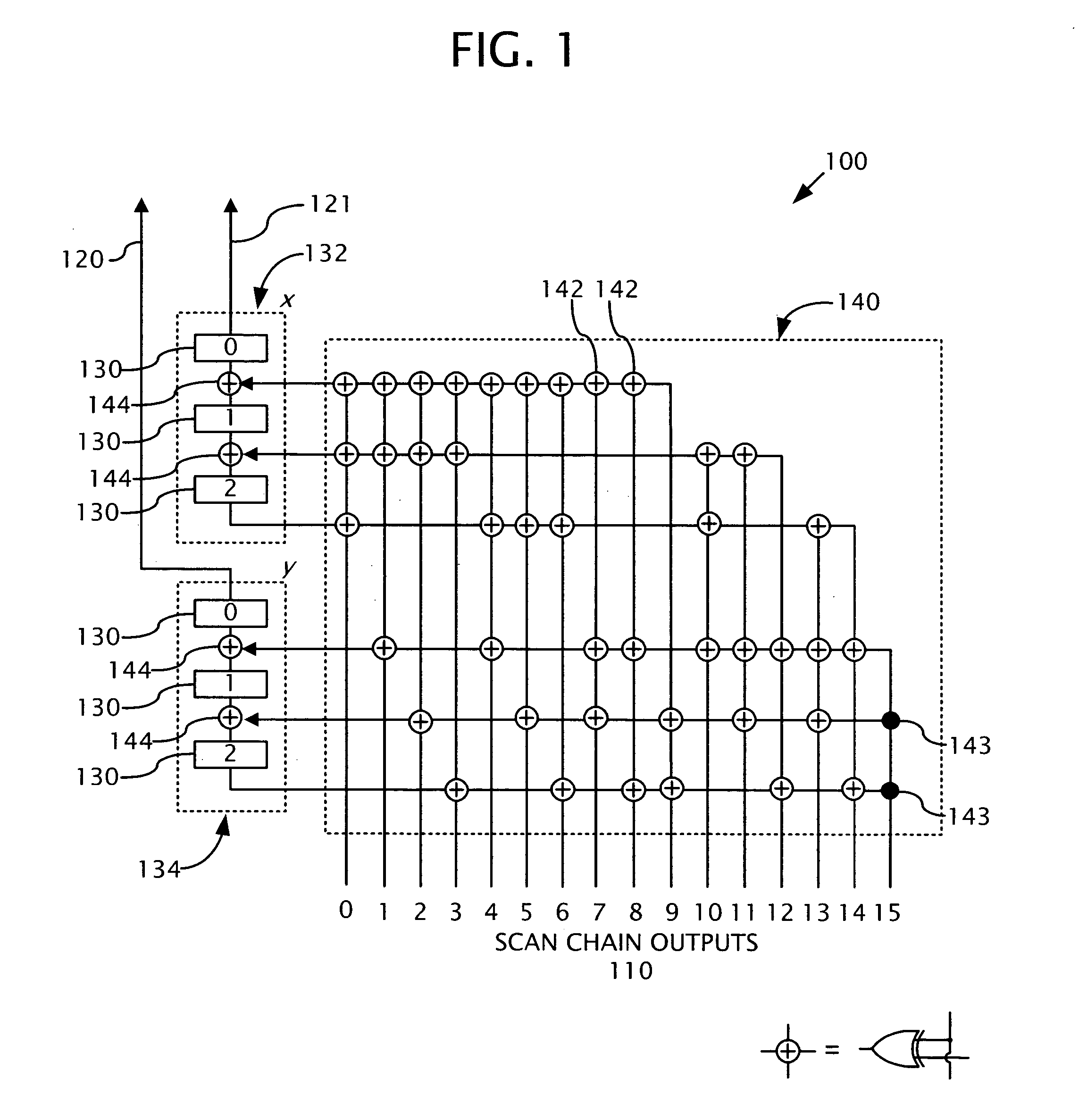

X-canceling multiple-input signature register (MISR) for compacting output responses with unknowns

InactiveUS7925947B1Small area overheadElectronic circuit testingLinear correlationProcessor register

A method and apparatus for compacting test responses containing unknown (X) values in a scan-based integrated circuit using an X-canceling multiple-input signature register (MISR) to produce a known (non-X) signature. The known (non-X) signature is obtained by selectively exclusive-ORing (XORing) together combinations of MISR bits which are linearly dependent in terms of the unknown (X) values using a selective XOR network.

Owner:SYNTEST TECH

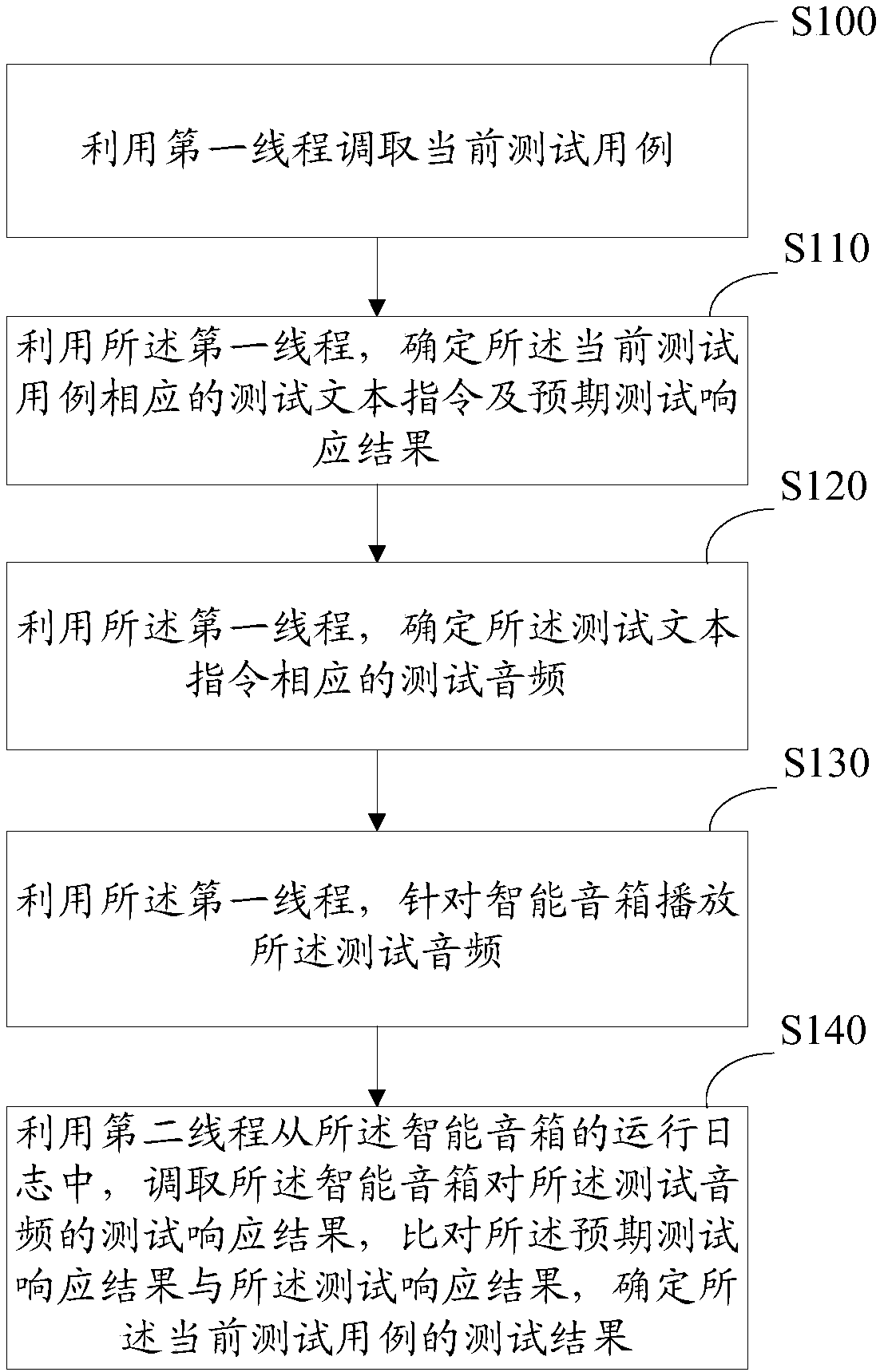

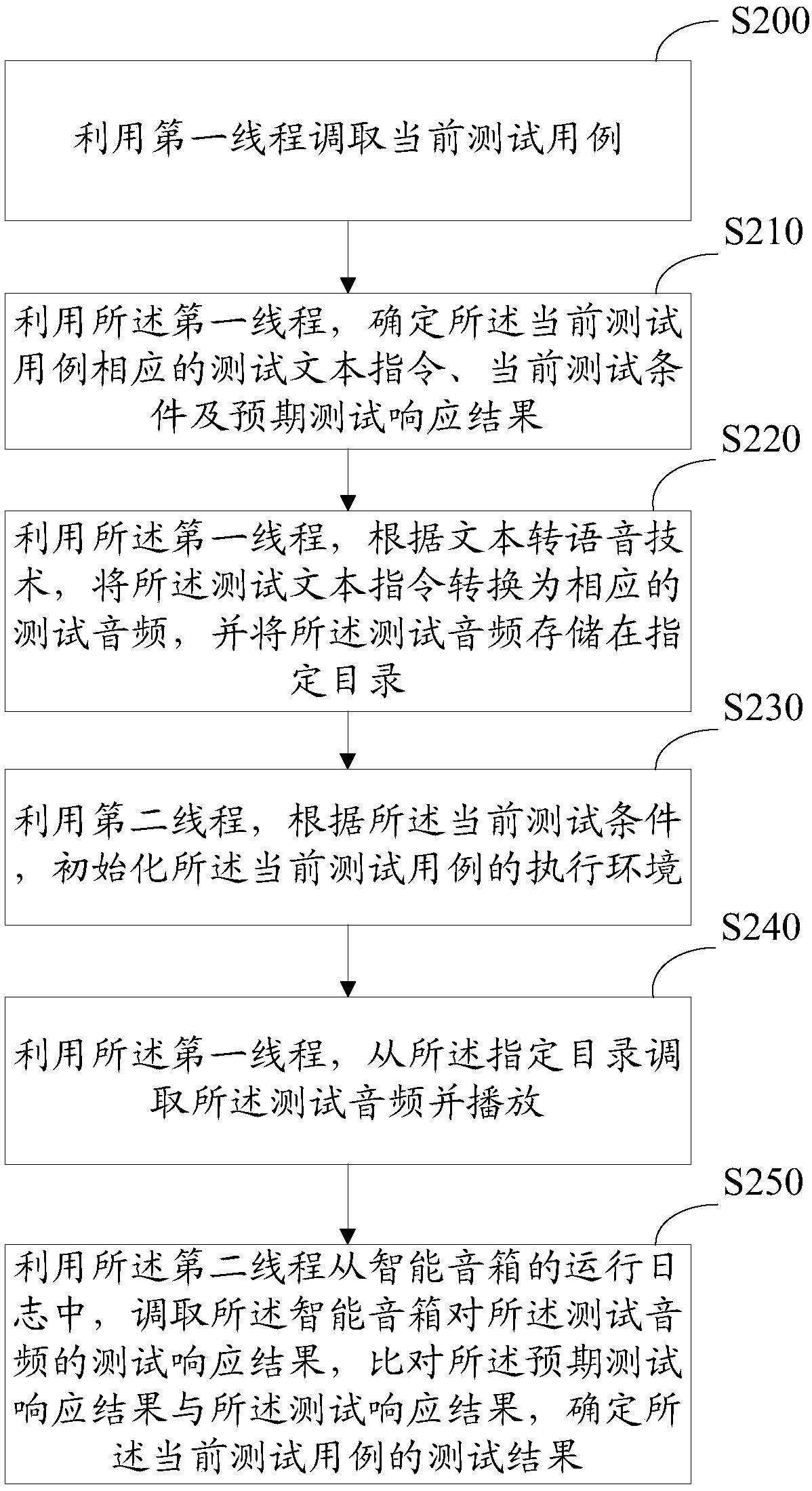

Testing method and device, testing equipment and storage medium

PendingCN108228468AImplement test inputSolve the problem of automated testingSoftware testing/debuggingComputer hardwareTest response

An embodiment of the invention provides a testing method and device, testing equipment and a storage medium. The method includes: using a first thread to call a current testing case; using the first thread to determine a testing text instruction and an expected testing response result corresponding to the current testing case; using the first thread to determine a testing audio corresponding to the testing text instruction; using the first thread to play the testing audio for voice interaction equipment; using a second thread to call the testing response result of the voice interaction equipment to the testing audio from the operation log of the voice interaction equipment, and comparing the expected testing response result with the testing response result to determine the testing result of the current testing case. The method has the advantages that testing case execution and testing response result verification can be achieved without a user interface, and the method is applicable tothe end-to-end automatic testing of UI-free equipment.

Owner:TENCENT TECH (SHENZHEN) CO LTD

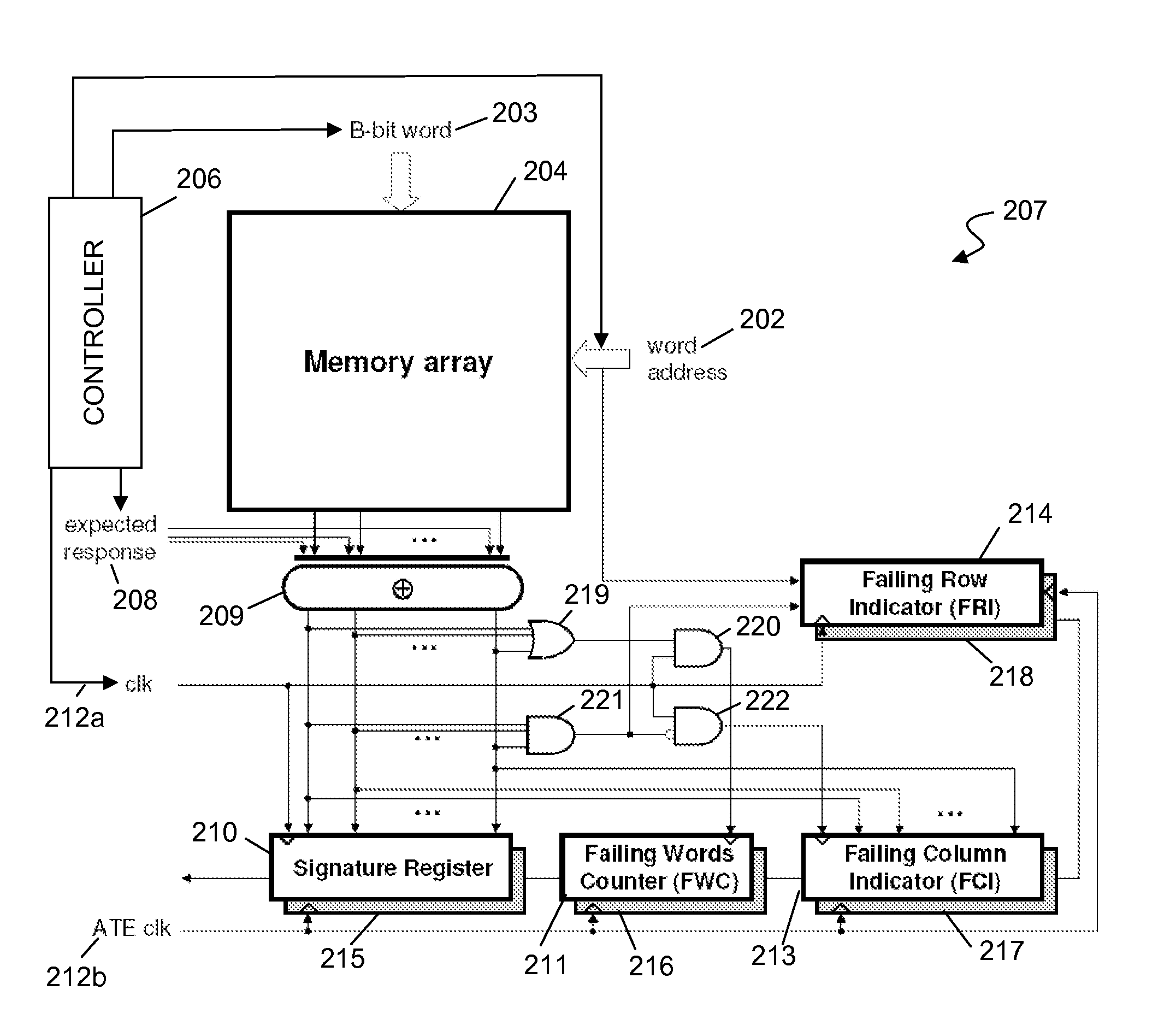

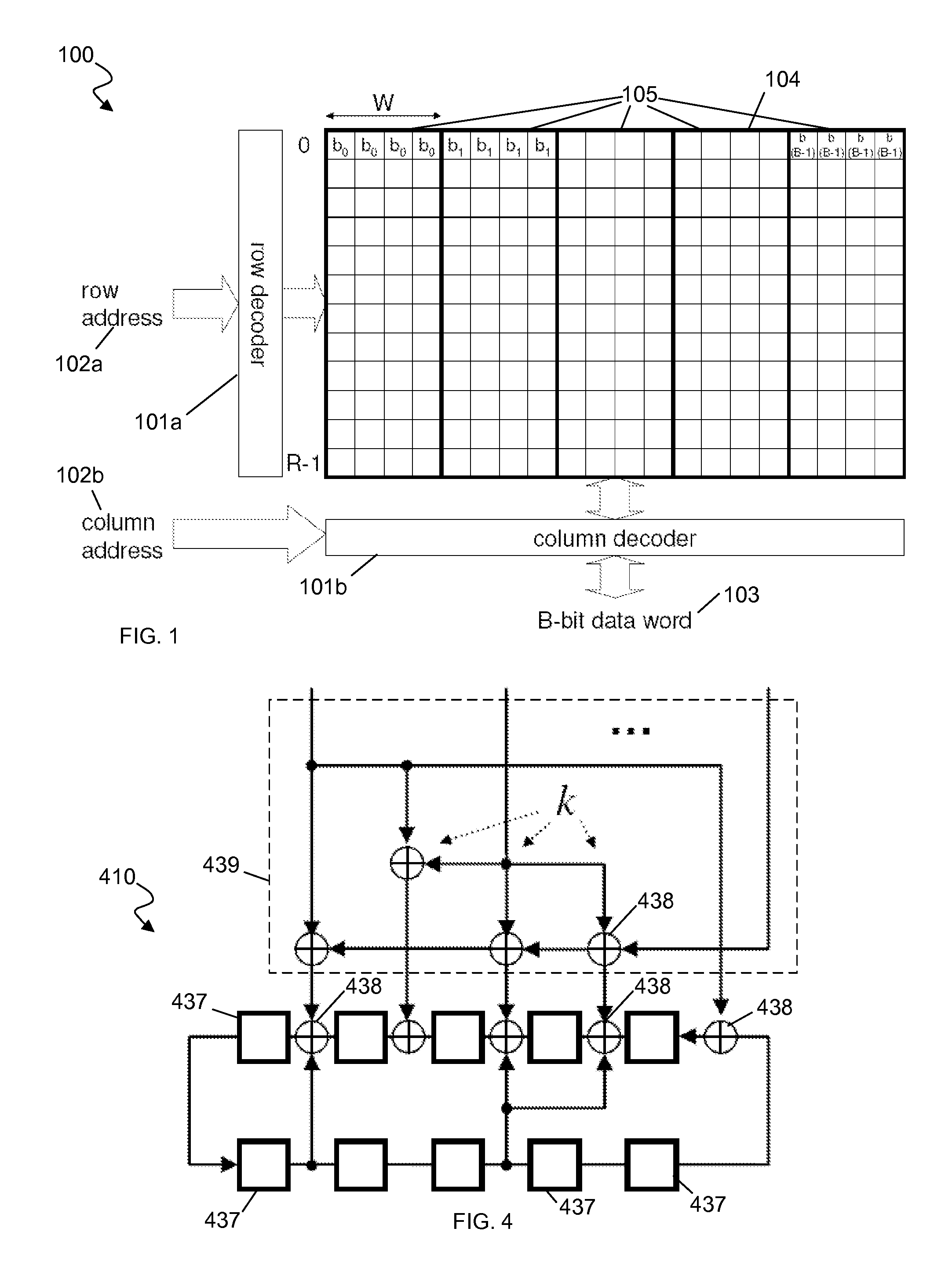

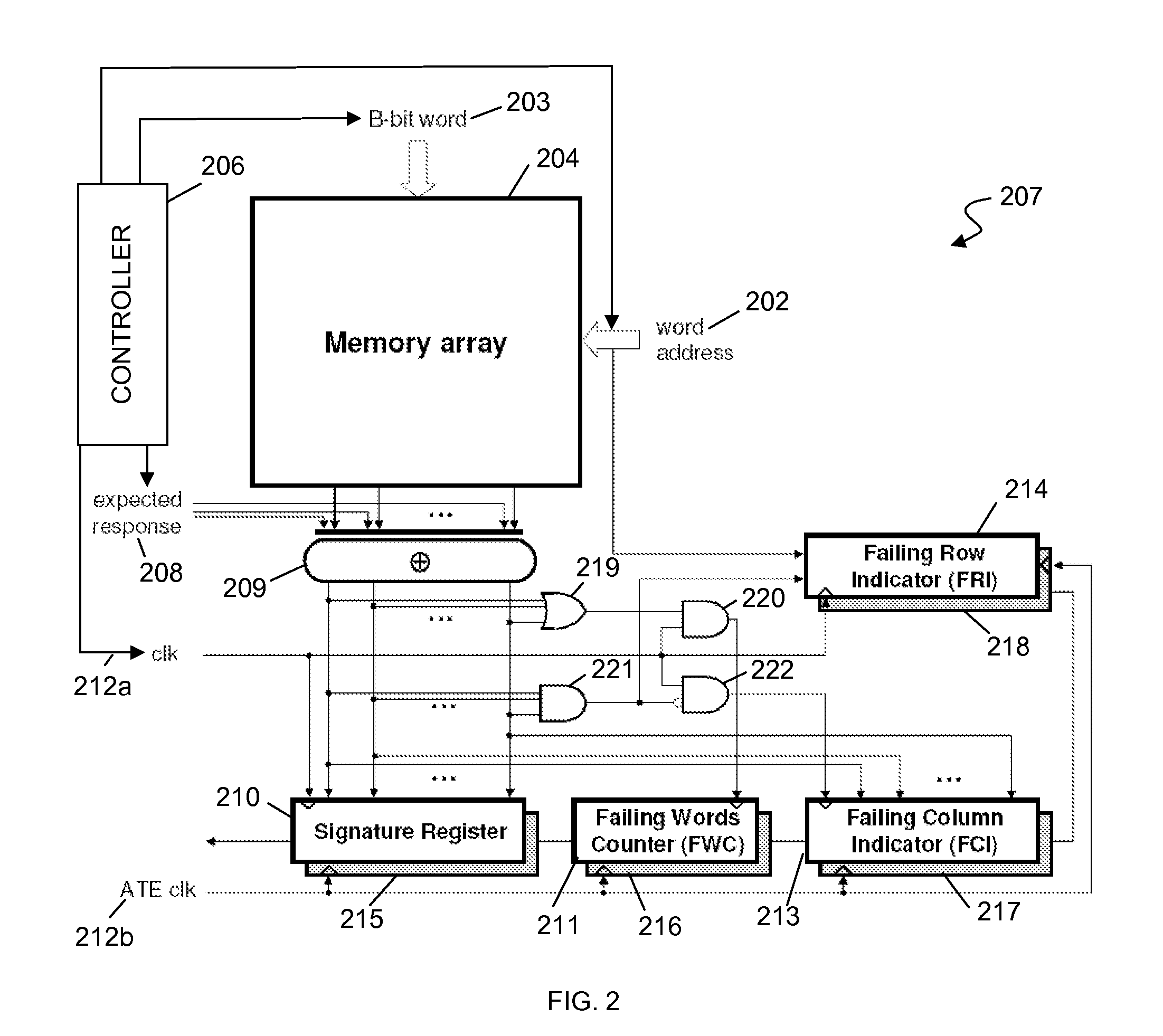

Fault diagnosis in a memory bist environment

InactiveUS20110055646A1Data failureProvide time efficiencyFunctional testingStatic storageBack structureAutomatic test equipment

Disclosed are methods and devices for temporally compacting test response signatures of failed memory tests in a memory built-in self-test environment, to provide the ability to carry on memory built-in self-test operations even with the detection of multiple time related memory test failures. In some implementations of the invention, the compacted test response signatures are provided to an automated test equipment device along with memory location information. According to various implementations of the invention, an integrated circuit with embedded memory (204) and a memory BIST controller (206) also includes a linear feed-back structure (410) for use as a signature register that can temporally compact test response signatures from the embedded memory array during a test step of a memory test. In various implementations the integrated circuit may also include a failing words counter (211), a failing column indicator (213), and / or a failing row indicator (214) to collect memory location information for a failing test response.

Owner:MENTOR GRAPHICS CORP

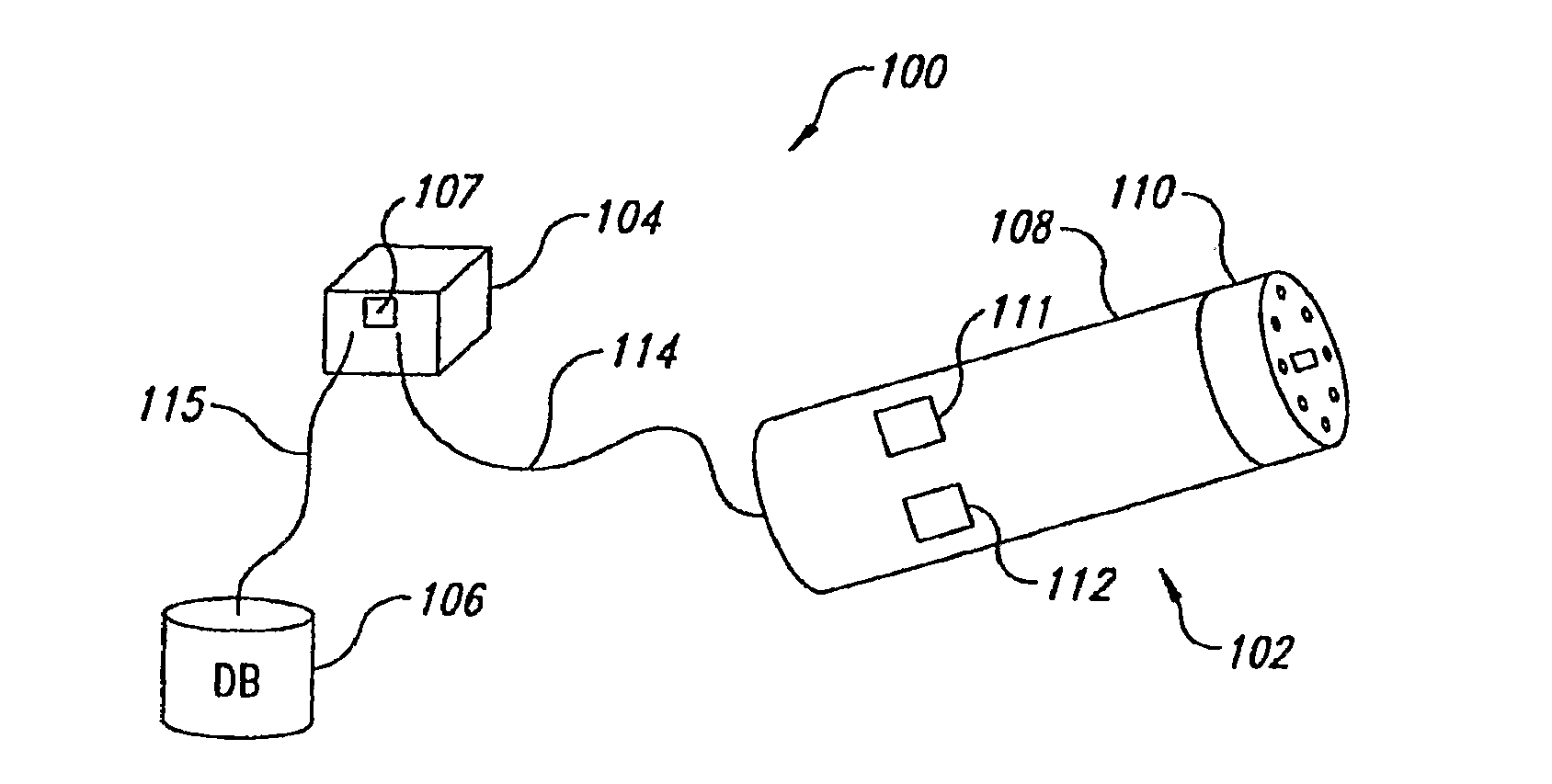

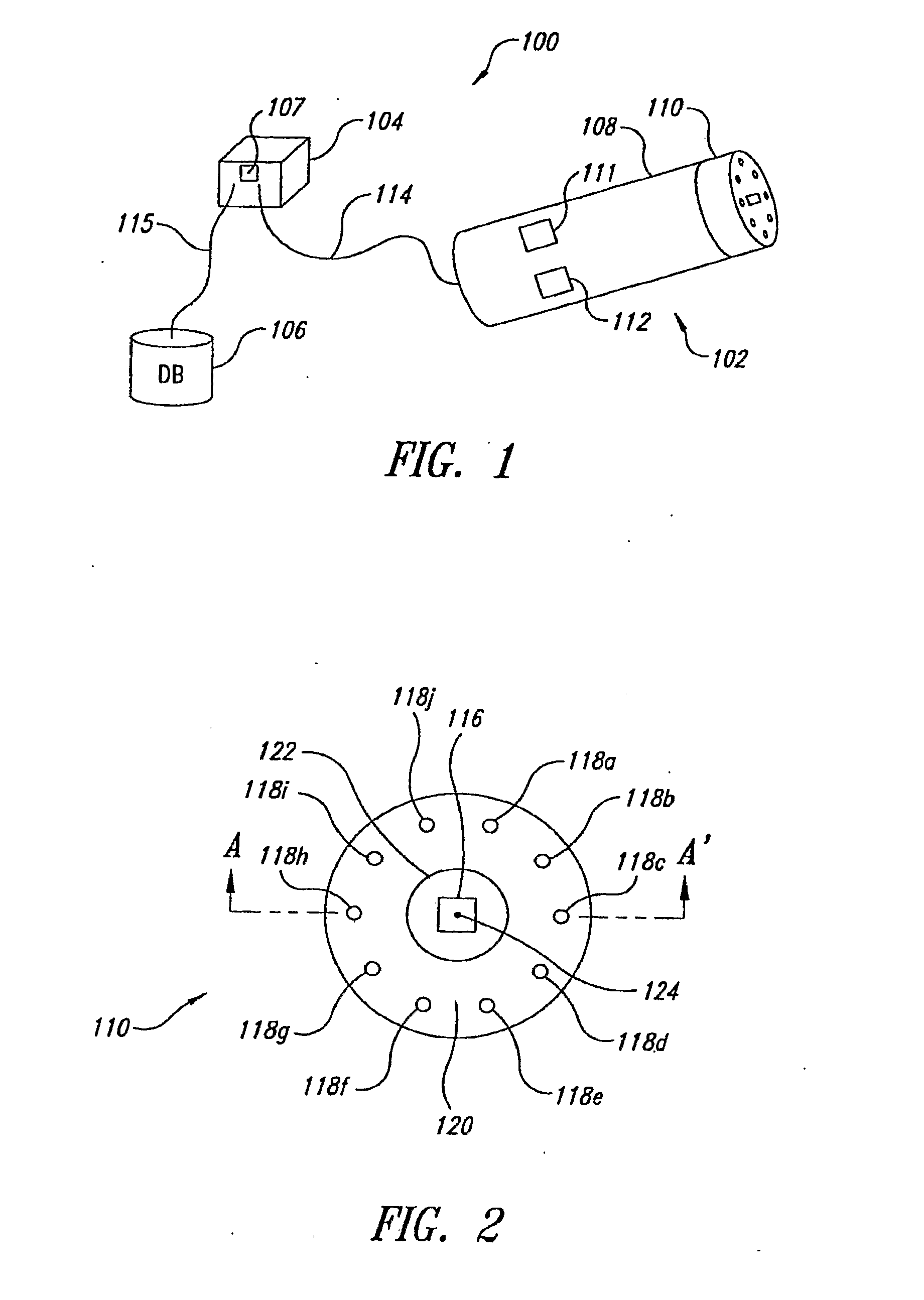

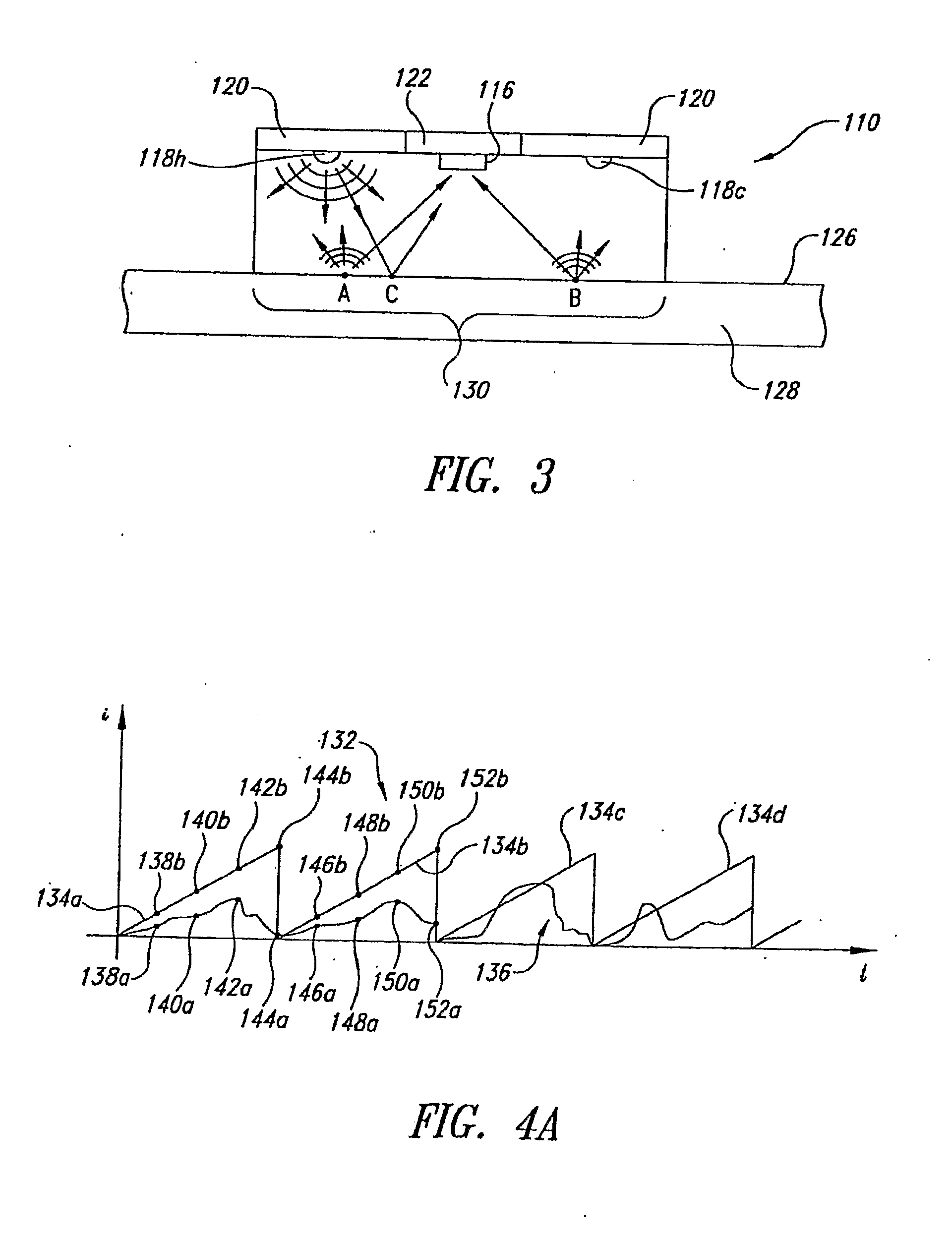

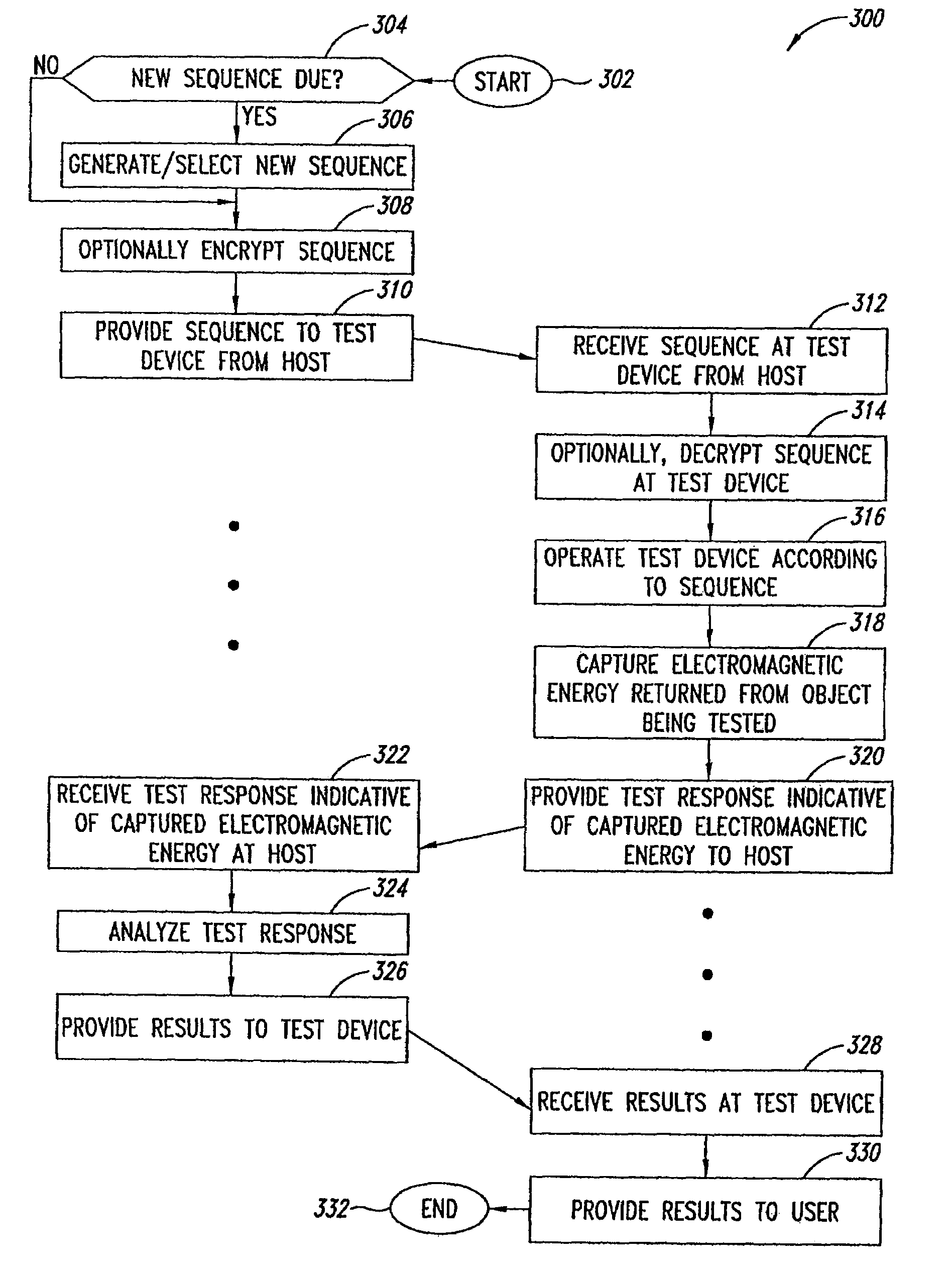

System and method of evaluating an object using electromagnetic energy

ActiveUS20100208240A1Low costPermit useRadiation pyrometryColor measuring devicesElectromagnetic responseEngineering

A system for evaluating subject objects includes at least one physical source (118) operable to emit electromagnetic energy and driver electronics (111) drivingly coupled to at least one physical source. The driver electronics is configured to drive at least one physical source as a number of logical sources, using an electromagnetic forcing function. The number of logical sources is greater than the number of physical sources In addition, the system includes a sensor (116) configured to receive an electromagnetic response from at least a portion of an evaluation object illuminated by one or more physical sources operated as logical sources, and convert the electromagnetic response to a test response signal indicative of the electromagnetic response of the evaluation object

Owner:VISUALANT

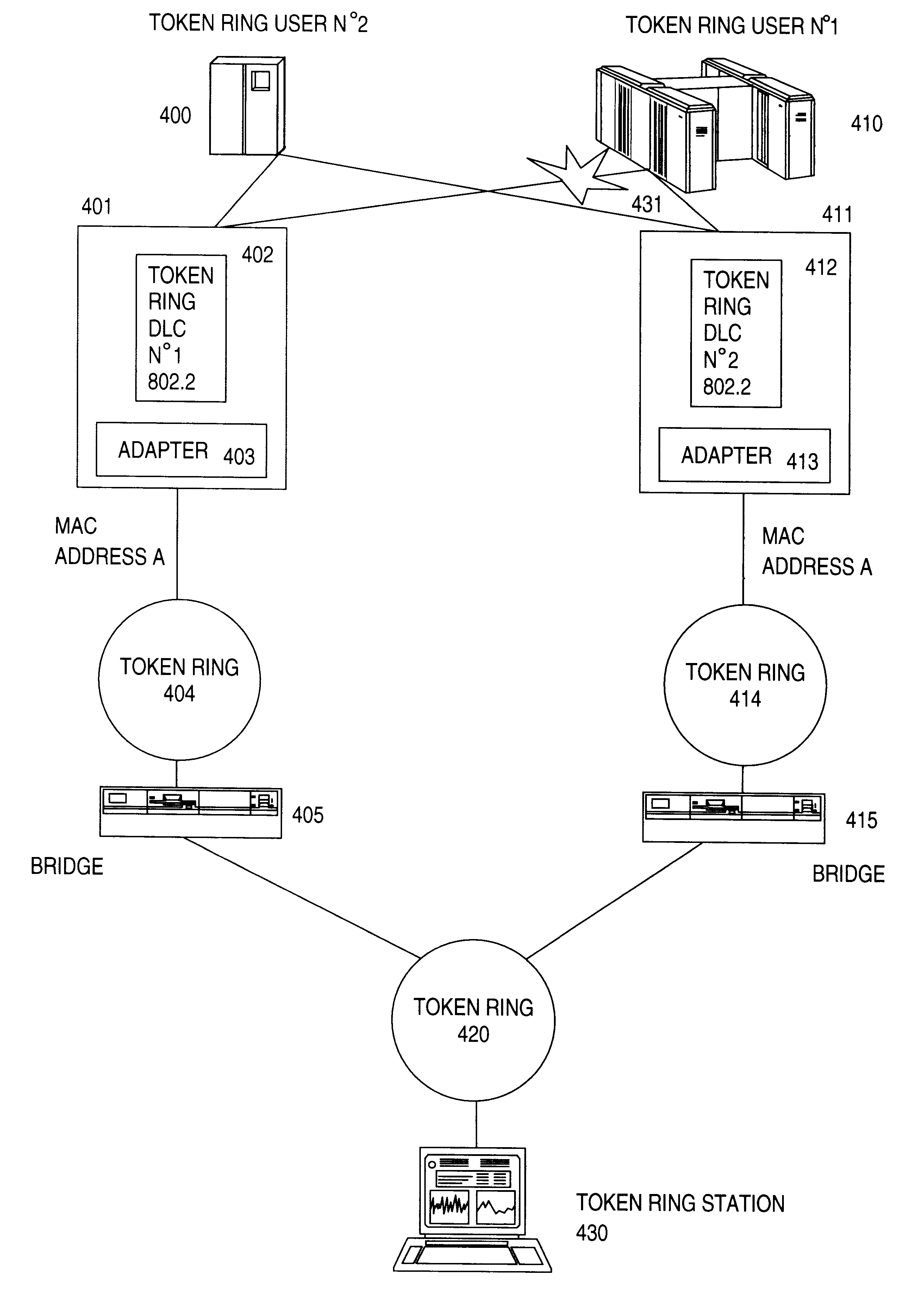

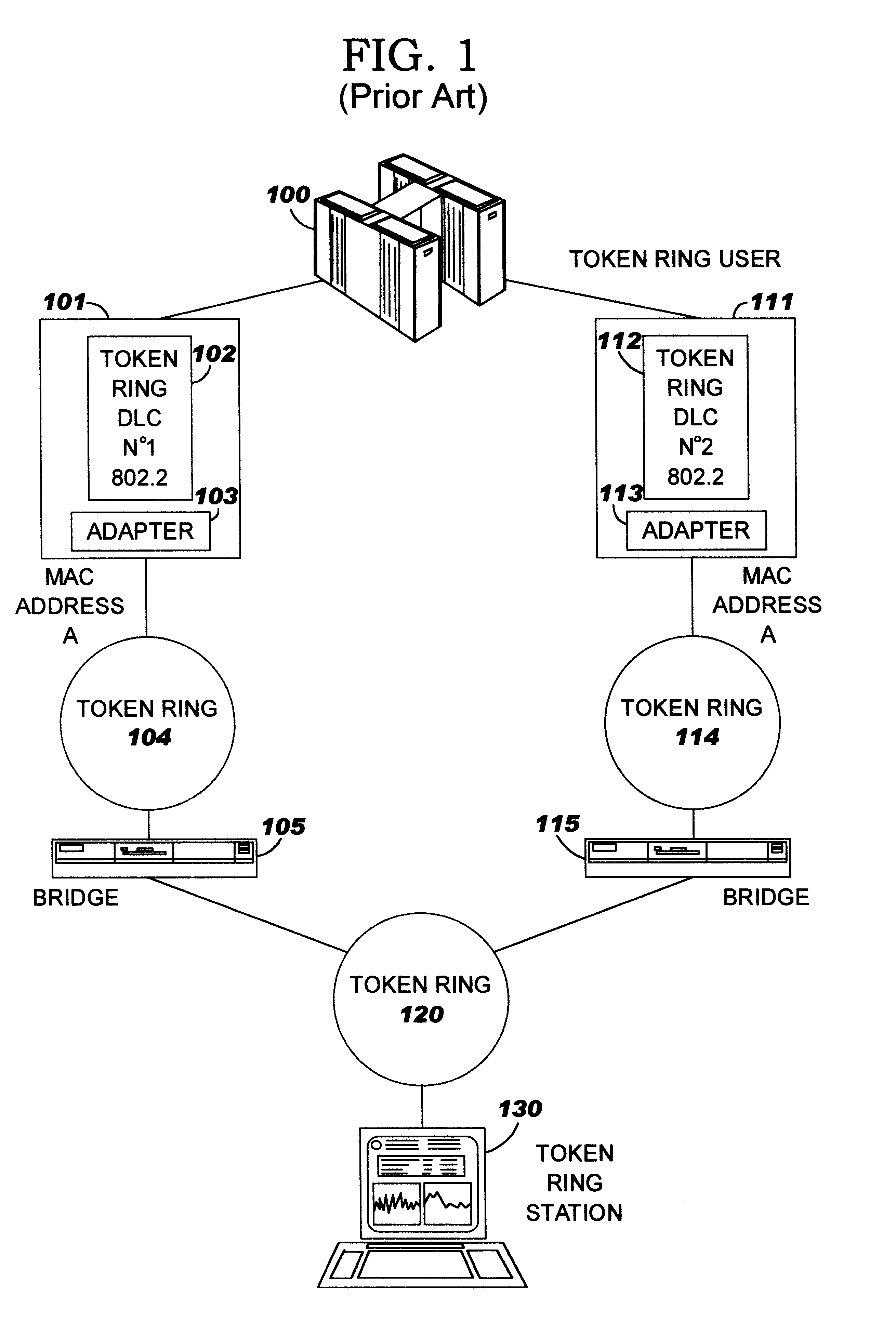

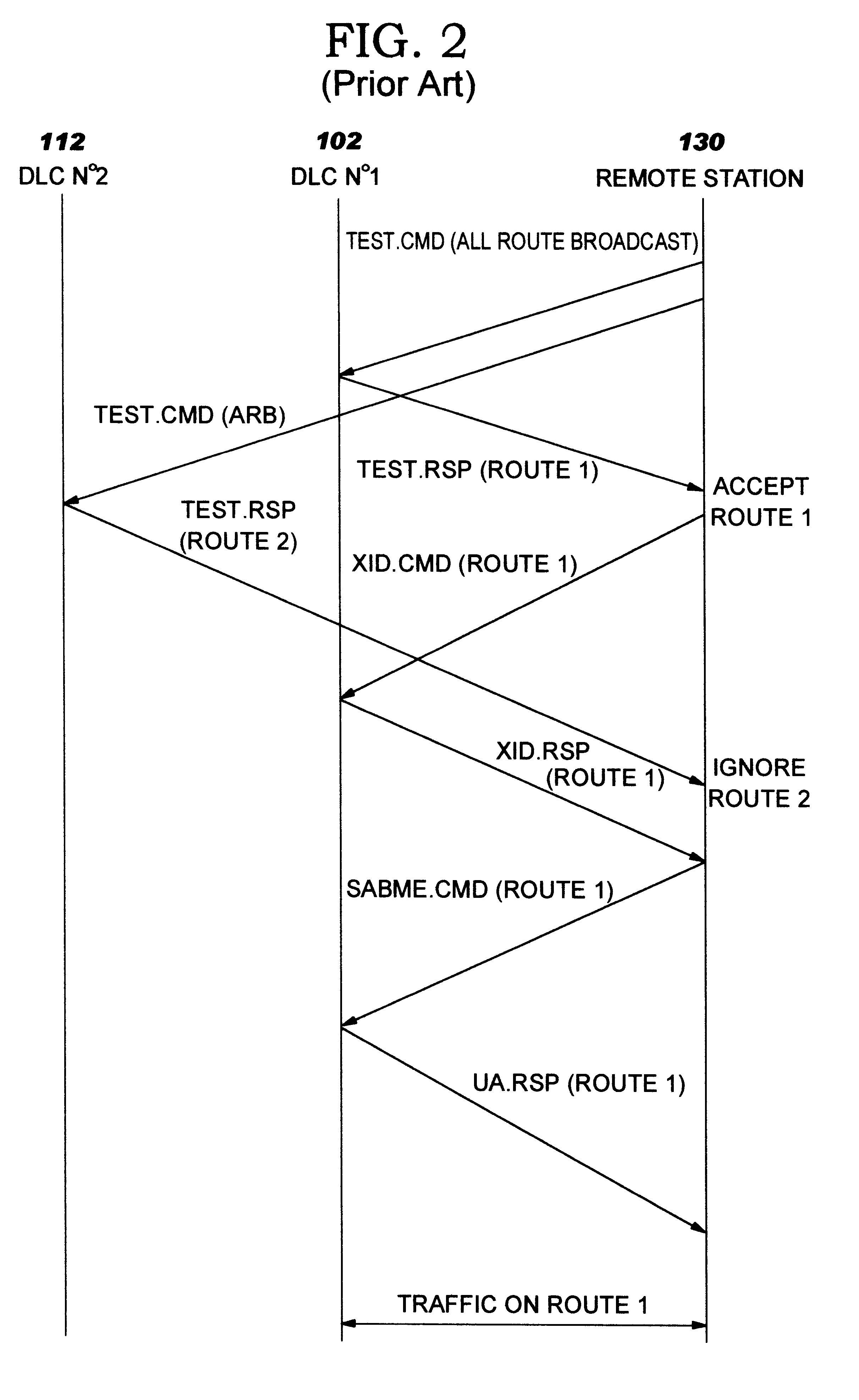

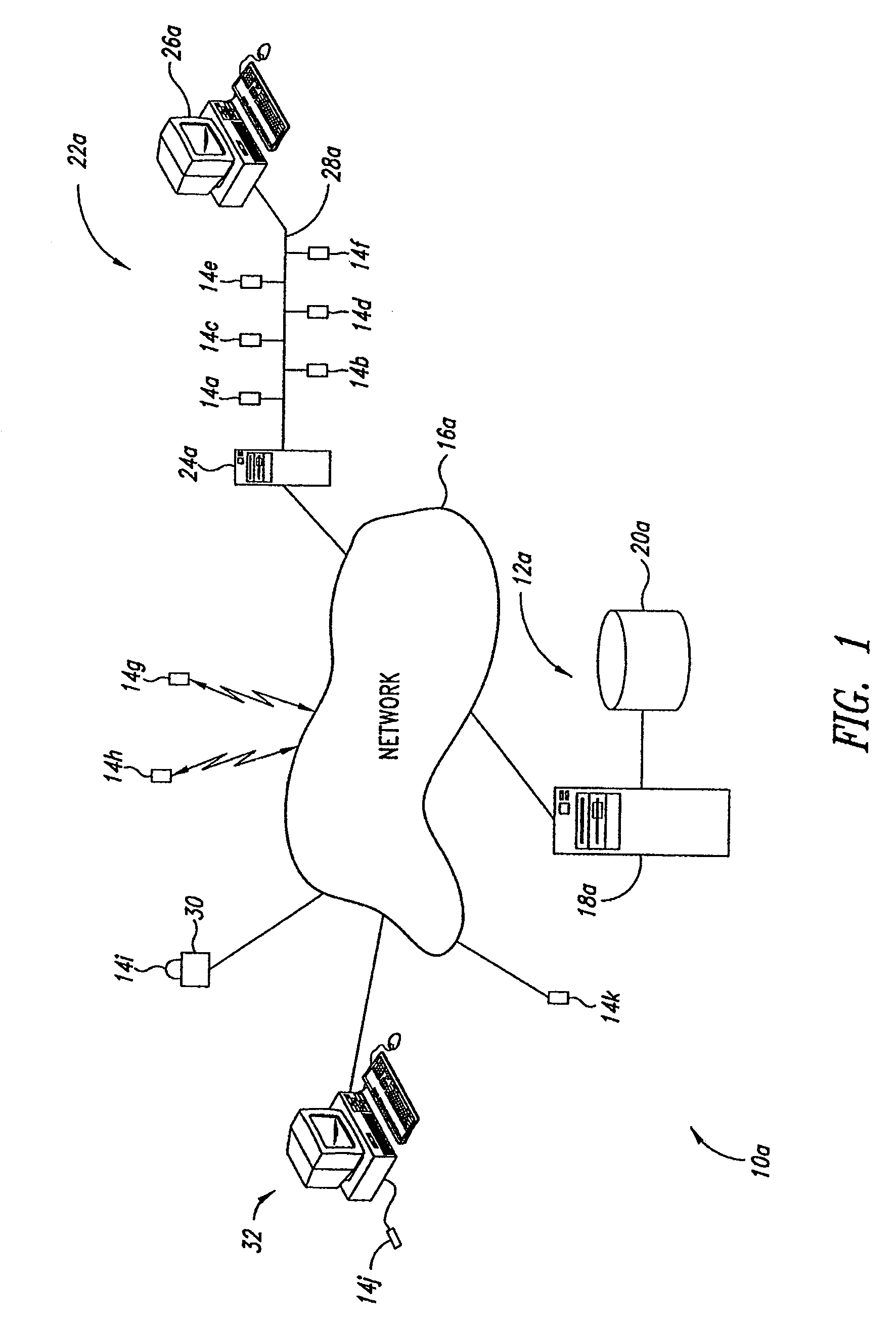

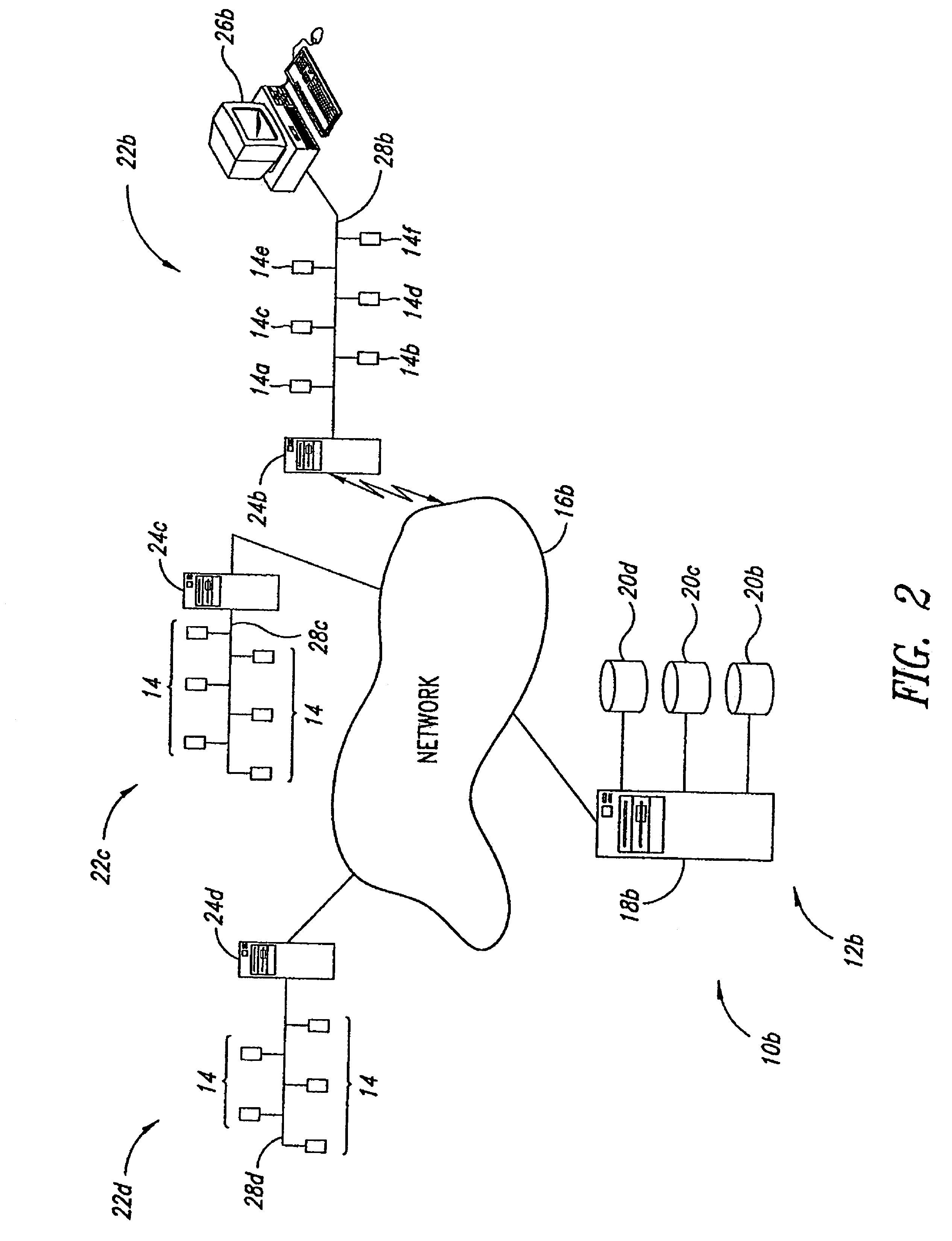

Method and apparatus for an automatic load balancing and back-up of a multi-users network

The invention aims to implement the Load Balancing / Backup function in a Multi-Users environment and to allow a remote station to have an alternate route through another Token Ring DLC to backup. By directing the connection to another route, it postpones the connection from a remote station to a Token Ring user through a first selected Token Ring DLC for a predetermined delay. For that purpose, each Token Ring DLC stores parameters of the remote station that has an unsuccessful connection in its own Connection Cache Table. In this way, when a Test frame is received in each DLC, this latter checks in the Connection Cache Table before responding to the Test frame. The Test frame is ignored and no Test response is sent back to the remote station when the remote station is identified in the table so as to allow the remote station to detect an alternate route with a backup DLC if it exists. Each Token Ring DLC manages its own Connection Cache table which contains an entry, a source MAC address and a Source SAP and a counter indicating the number of unsuccessful attempted Test frames received from that remote station. If the counter reaches a value N, then the entry corresponding to the remote station is removed from the table. Thus, the next time a Test frame is received from this remote station, it is accepted and a response is sent from the DLC. It gives a new opportunity to the remote station to establish a connection to the user in case this latter would become available again.

Owner:IBM CORP

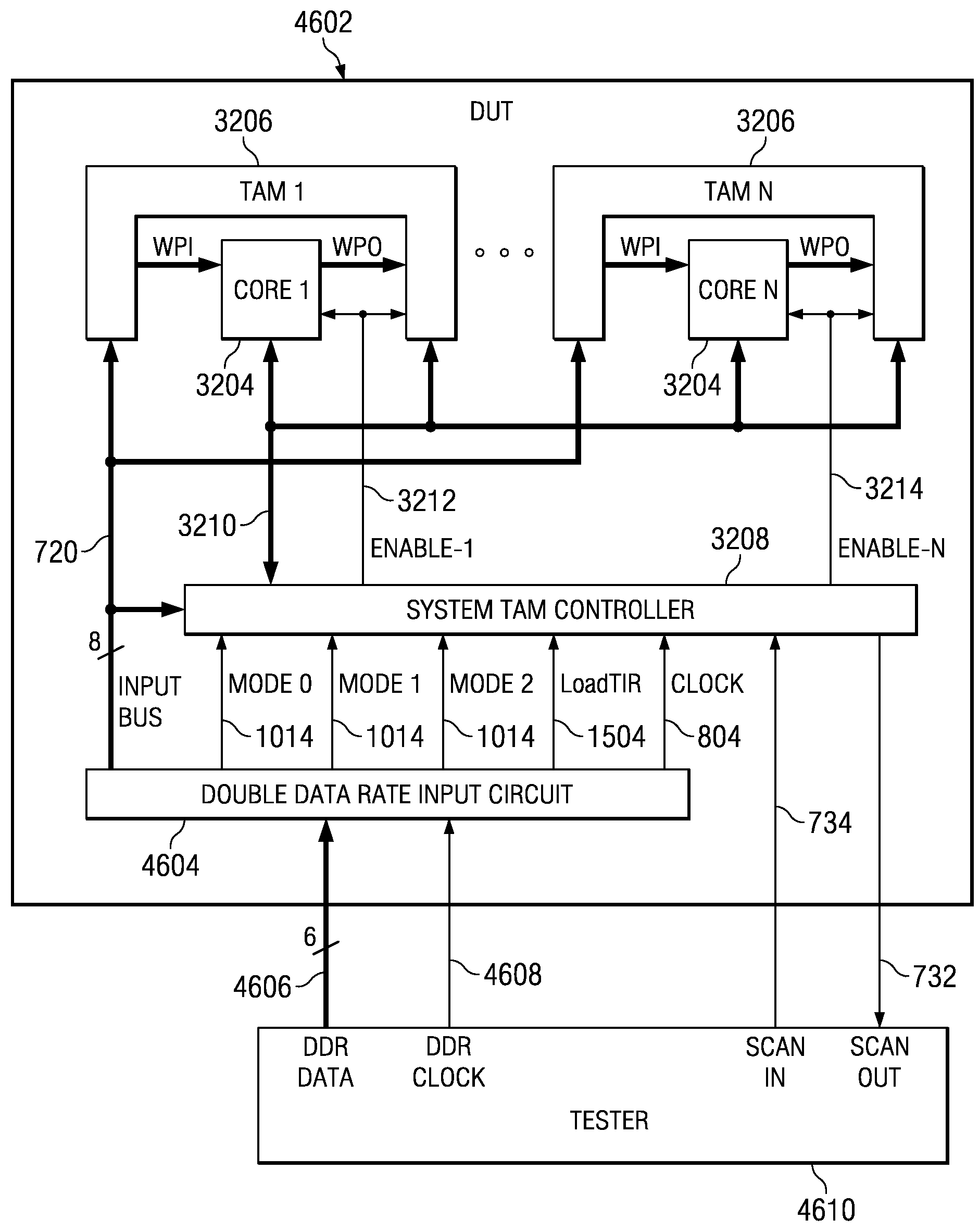

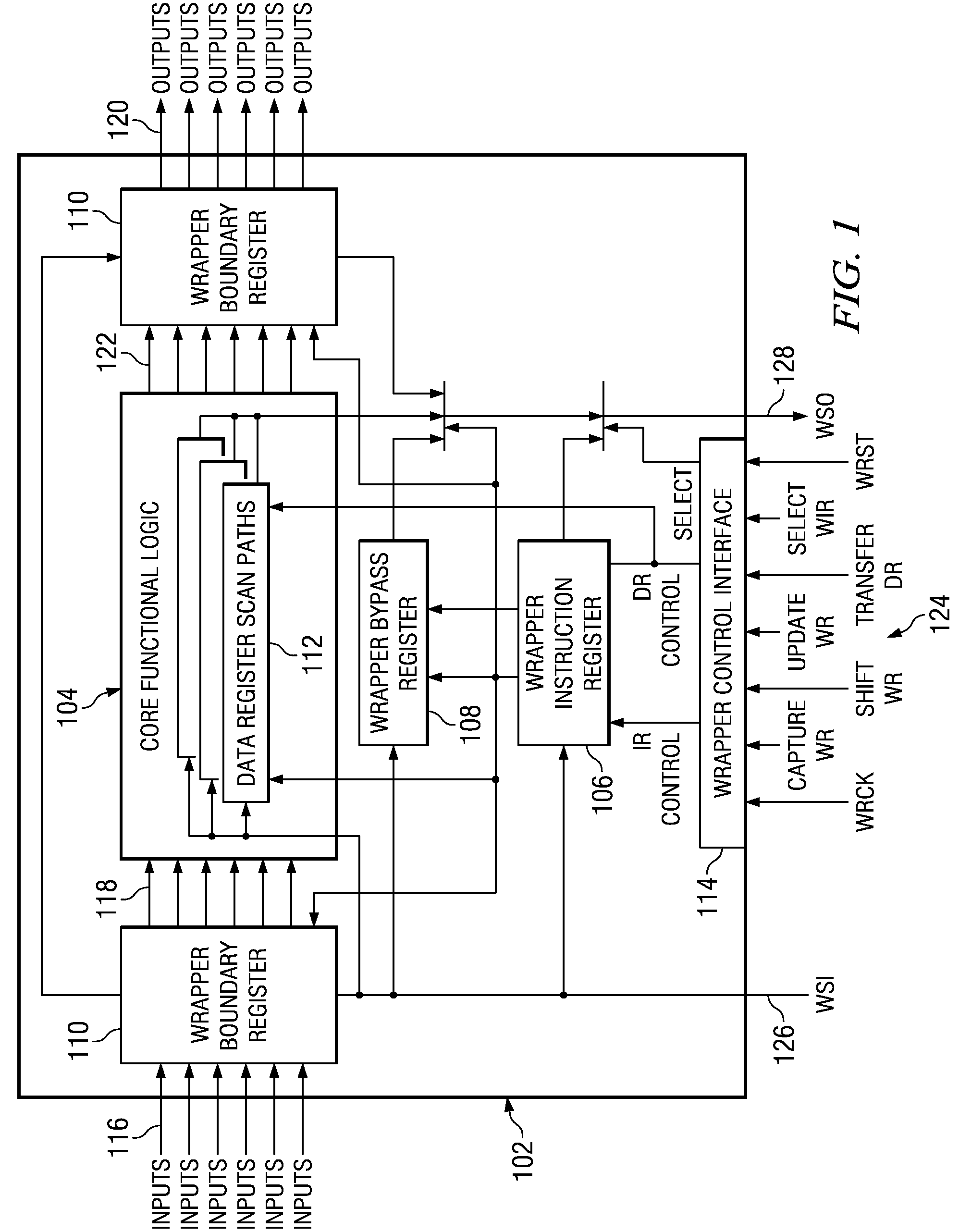

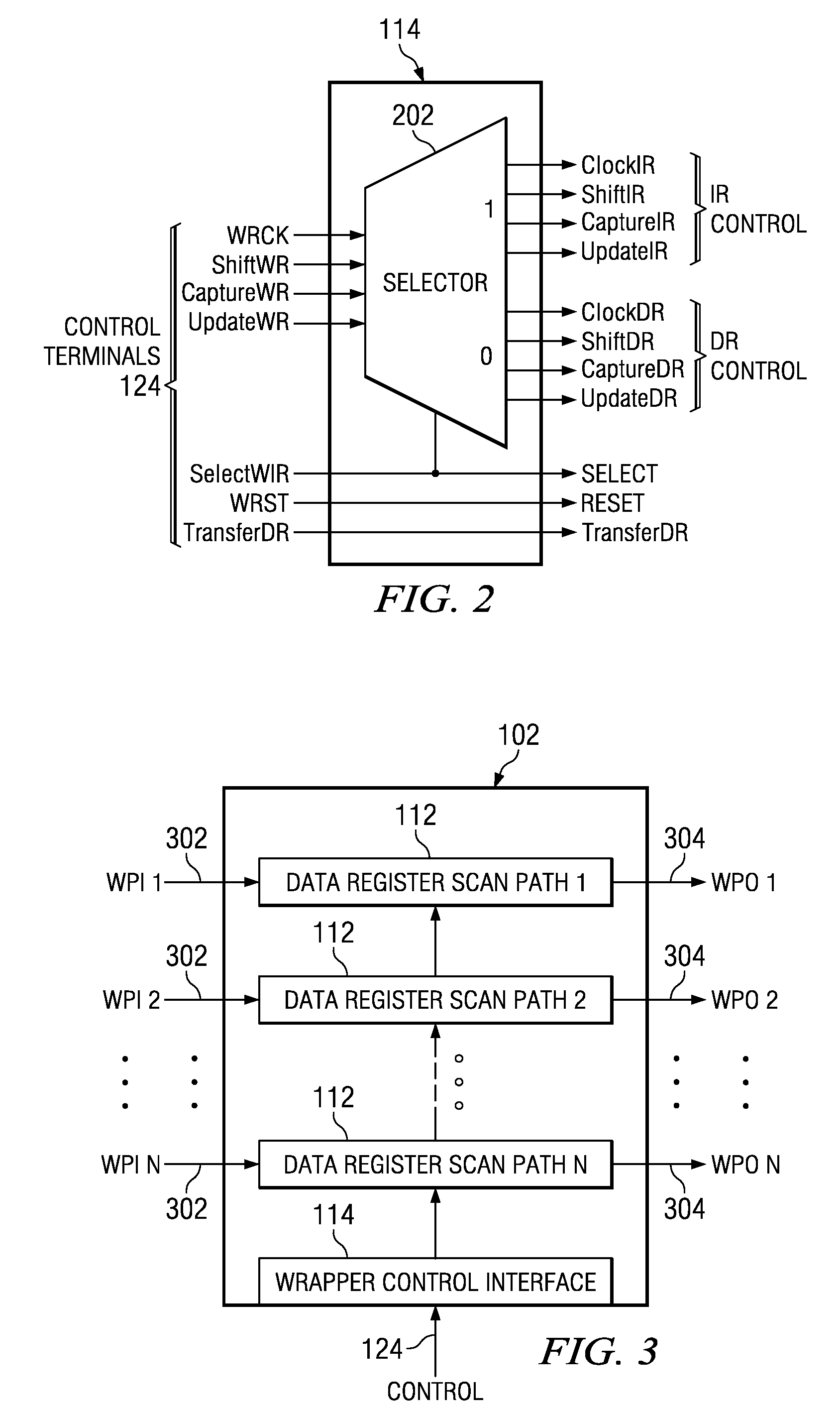

DDR input interface to IC test controller circuitry

ActiveUS7529996B2Efficient testingSimplifies testerElectronic circuit testingDouble data rateProgrammable logic controller

Owner:TEXAS INSTR INC

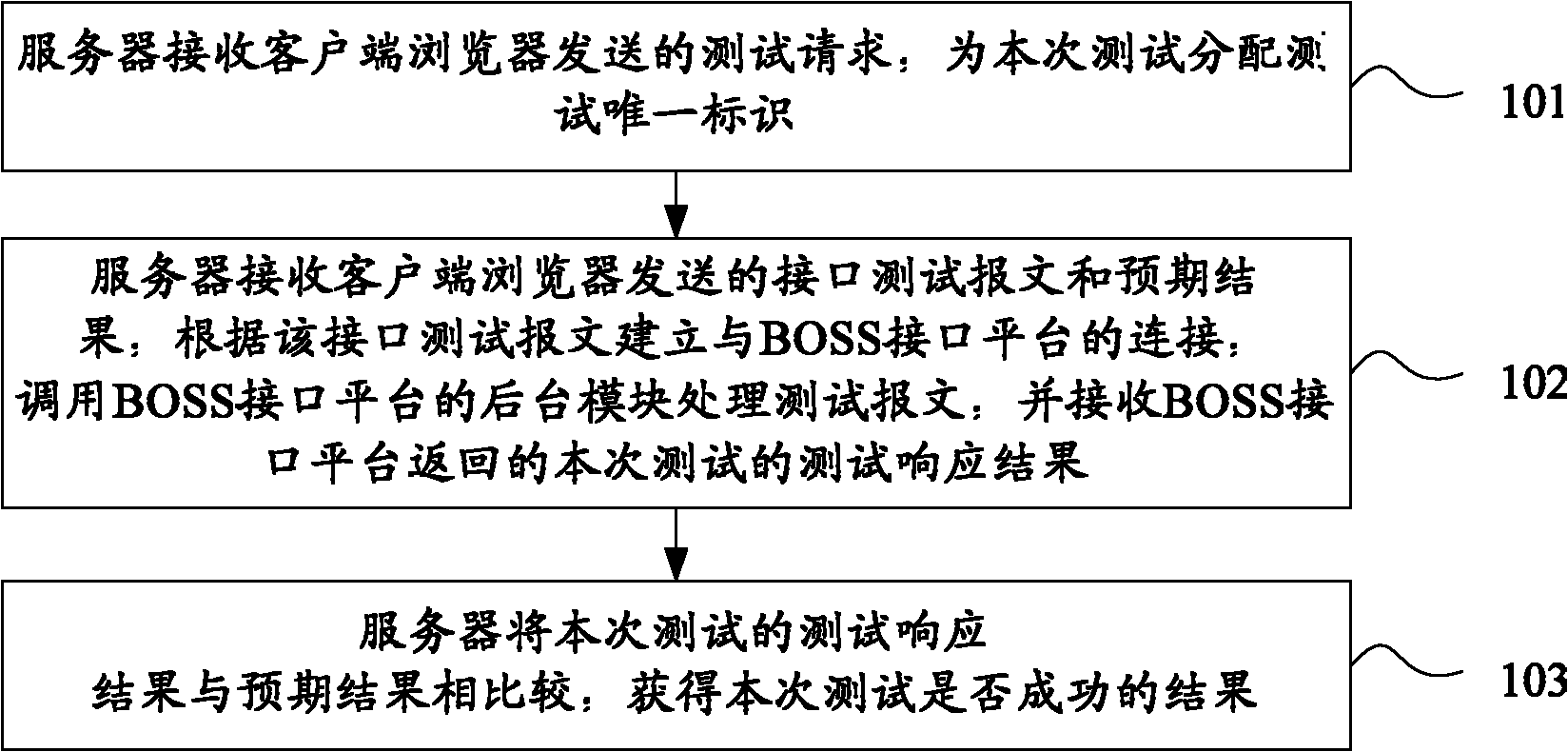

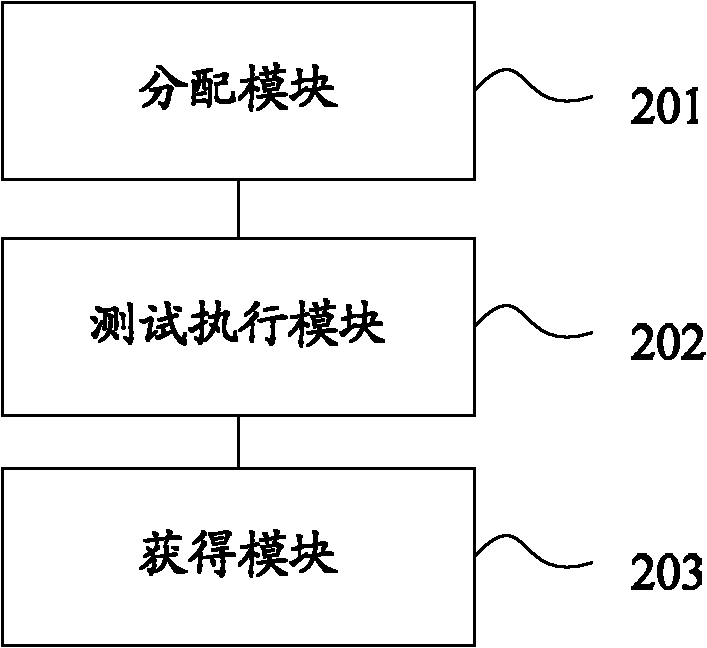

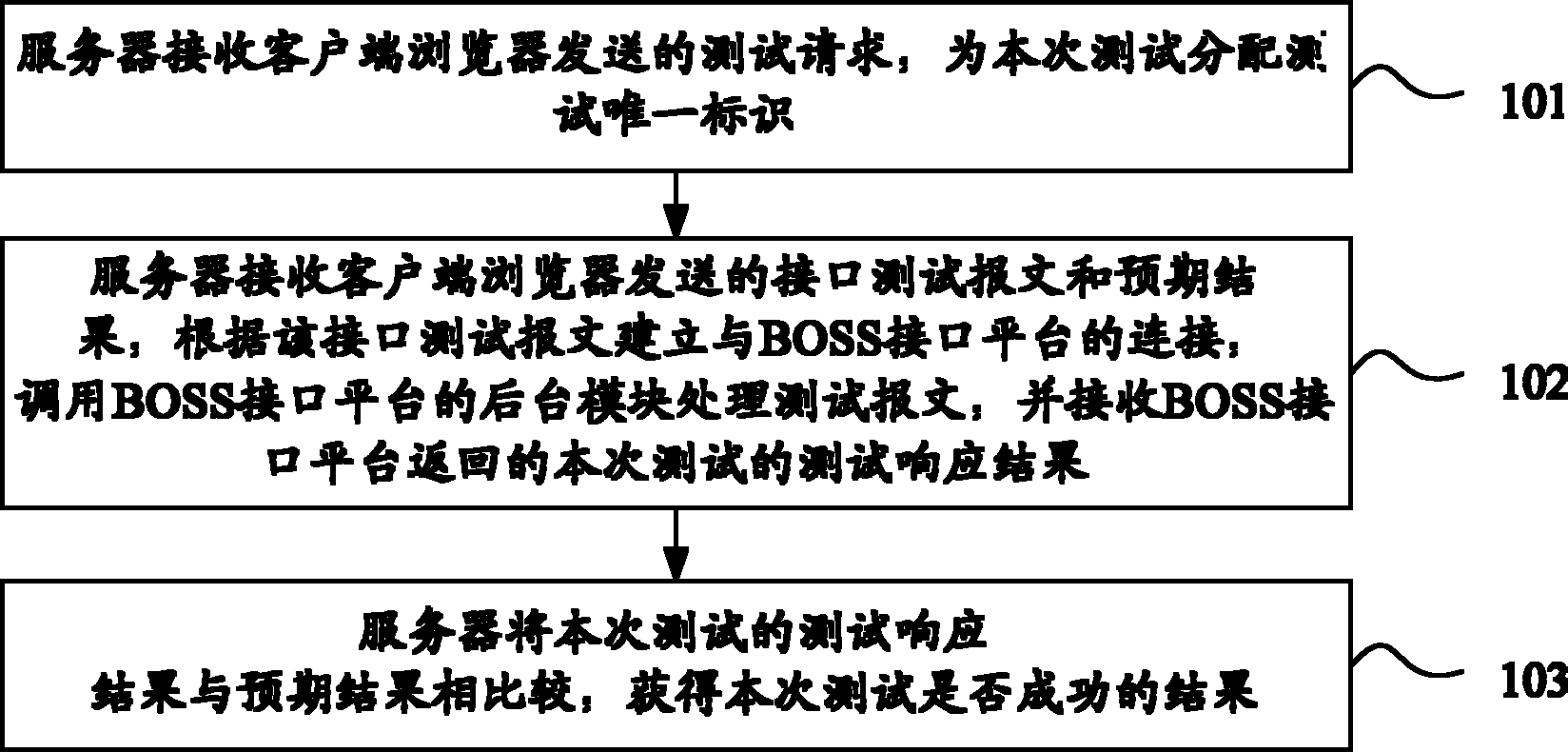

Automatic interface testing method and server

InactiveCN102185734AImprove test efficiencySimplify and standardize automated testing stepsData switching networksComputer moduleTest Standardization

The invention provides an automatic interface testing method and a server. The method comprises that: a server receives a testing request from a client browser, and allocates a unique testing identifier to a test; the server receives an interface testing message and expected results of the test from the client browser; the server establishes connection with a business operation support system (BOSS) interface platform according to the interface testing message to make the BOSS interface platform obtains test response results of the test according to the interface testing message and return the obtained test response results to the server; and the server compares the test response results with the expected results to acquire a result indicating whether the test is successful or not. The server comprises an allocation module, a test execution module and an acquisition module. By the scheme provided by the invention, the automatic interface test and instance test standardization can be effectively realized.

Owner:HUAWEI SOFTWARE TECH

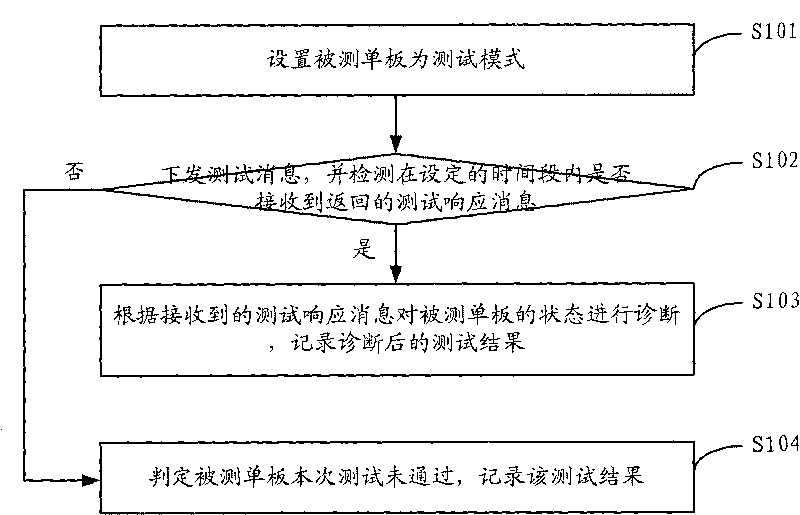

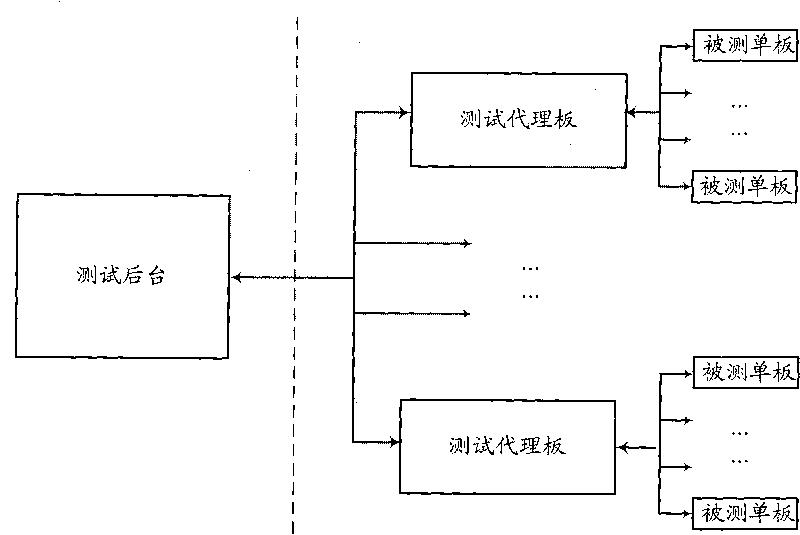

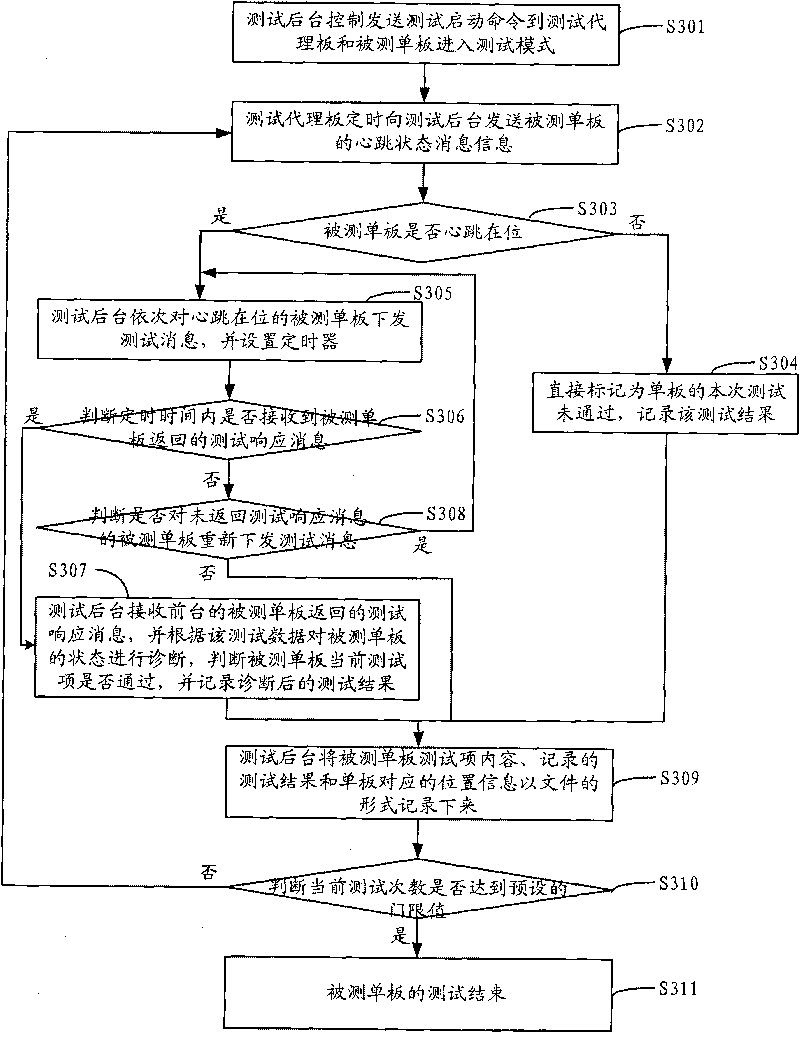

Single plate hardware fault detection method and device

InactiveCN101699410ADescribe objectively and in detailPrecise deliveryDetecting faulty computer hardwareData switching networksComputer hardwareSingle plate

The invention discloses a single plate hardware fault detection method and a device; the method comprises the flowing steps: a single plate to be detected is set into a test mode, a test message is sent to the single plate to be detected, and weather a test response message returned by the single plate to be detected is received within setting time bucket is detected, if yes, the state of the single plate to be detected is diagnosed according to the received test response message, and the test result after being diagnosed is recorded, if not, the single plate to be detected is judged not to pass the test, and the test result is recorded. The single plate hardware fault detection device comprises a mode setting unit and a detection processing unit; the method provided by the invention can realize reliable detection to the faults of the single plate.

Owner:ZTE CORP

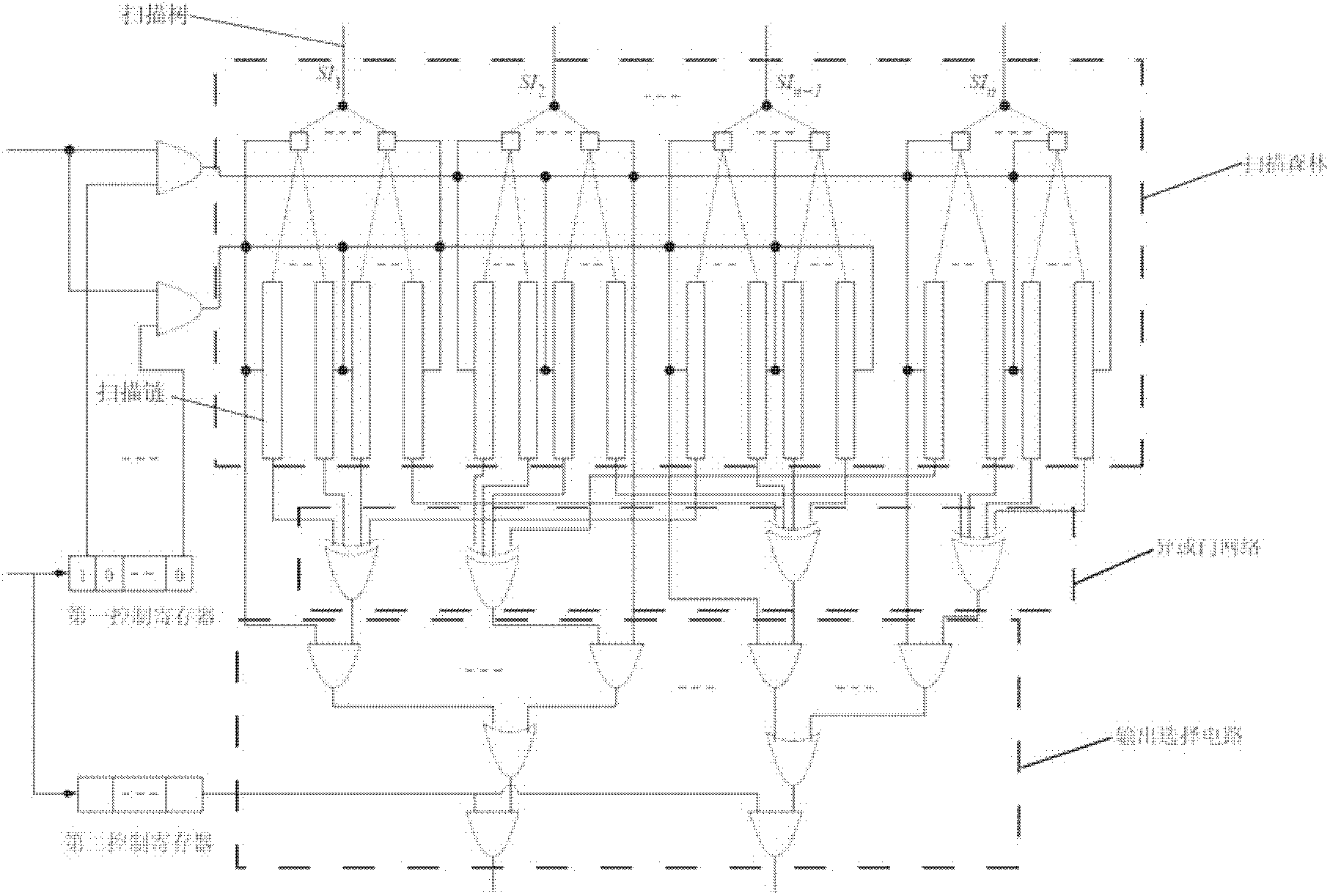

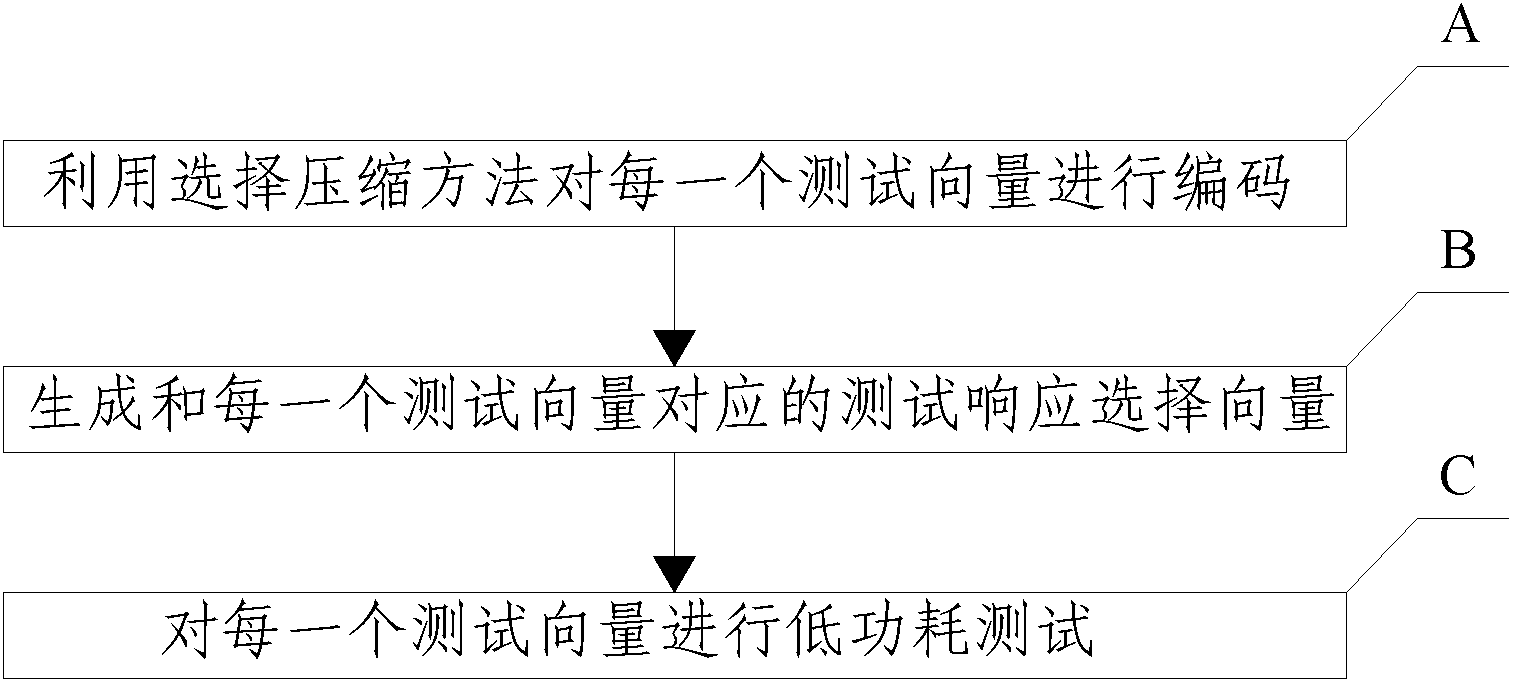

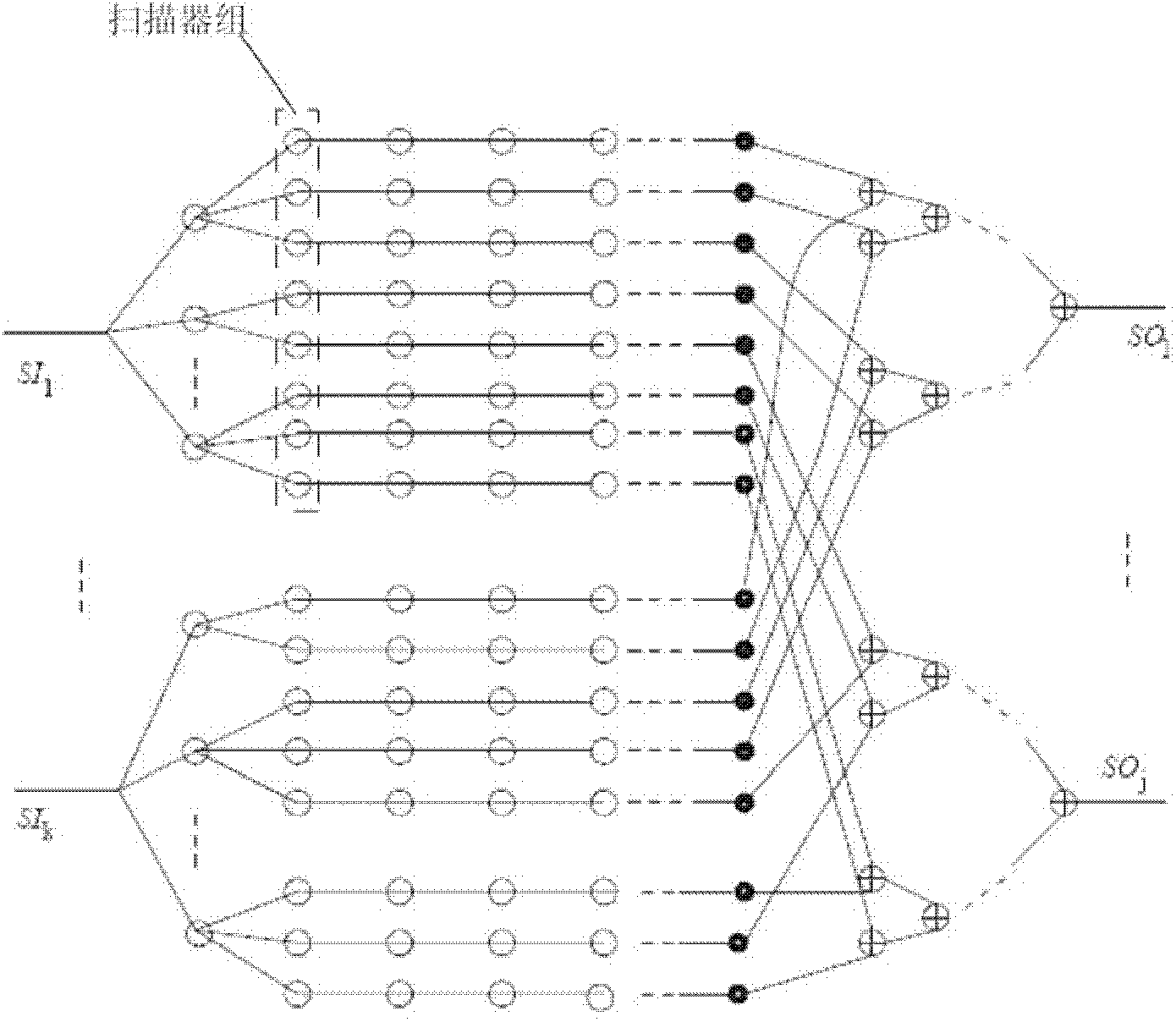

Low power consumption integrated circuit testing device with compressible data and method using same

ActiveCN102305912AAchieve compressionReduce jumpingDigital circuit testingProcessor registerControl register

The invention discloses a low power consumption integrated circuit testing device with compressible data and a method using the same. The device comprises a scanning forest, an XOR gate network, an output selection circuit, a first control register and a second control register, wherein the scanning forest comprises a plurality of scanning input ends and a plurality of mutually connected scanning trigger groups; the scanning input ends are connected to all scanning triggers in the first scanning trigger group; all scanning triggers in each scanning trigger group are connected with the output ends of the scanning triggers in the previous scanning trigger group; the input end of each XOR gate in the XOR gate network is connected with the output ends of the scanning triggers in the last group of scanning trigger group; and the output selection circuit is connected with the XOR gate network. According to the low power consumption integrated circuit testing device, node hop in the circuit can be reduced, energy consumption is lowered, and meanwhile compression of test response data can be achieved.

Owner:TSINGHUA UNIV

Method, apparatus, and article to facilitate distributed evaluation of objects using electromagnetic energy

ActiveUS7996173B2Low costPermit useAbsorption/flicker/reflection spectroscopyPayment architectureUltravioletElectromagnetic spectrum

Owner:VISUALANT

Smart capture for ATPG (automatic test pattern generation) and fault simulation of scan-based integrated circuits

InactiveUS20050262409A1Improve accuracyGreat measured fault coverageError detection/correctionMarginal circuit testingTest responseCircuit models

A method for generating stimuli and test responses for testing faults in a scan-based integrated circuit in a selected scan-test mode or a selected self-test mode, the scan-based integrated circuit containing a plurality of scan chains, N clock domains, and C cross-clock domain blocks, each scan chain comprising multiple scan cells coupled in series, each clock domain having one capture clock, each cross-clock domain block comprising a combinational logic network. The method comprises compiling the scan-based integrated circuit into a sequential circuit model; specifying input constraints on the scan-based integrated circuit during a shift and capture operation; specifying a clock grouping to map the N clock domains into G clock domain groups, where N>G>1; transforming the sequential circuit model into an equivalent combinational circuit model according to the input constraints and the clock grouping; and generating the stimuli and test responses on the equivalent combinational circuit model according to the input constraints.

Owner:SYNTEST TECH

Adaptive fault diagnosis of compressed test responses

ActiveUS20060041813A1Increasing hardware overheadEffective diagnosisElectronic circuit testingError detection/correctionCircuit under testTest response

Methods, apparatus, and systems for diagnosing failing scan cells from compressed test responses are disclosed herein. For example, in one nonlimiting exemplary embodiment, one or more signatures are received that indicate the presence of one or more errors in one or more corresponding compressed test responses. Scan cells in the circuit-under-test that caused the errors are identified by analyzing the signatures. In this exemplary embodiment, the analysis includes selecting a scan cell candidate that potentially caused an error in a compressed test response based at least partially on a weight value associated with the scan cell candidate, the weight value being indicative of the likelihood that the scan cell candidate caused the error. Tangible computer-readable media comprising computer-executable instructions for causing a computer to perform any of the disclosed methods are also provided. Tangible computer-readable media comprising lists of failing scan cells identified by any of the disclosed methods are also provided.

Owner:SIEMENS PROD LIFECYCLE MANAGEMENT SOFTWARE INC

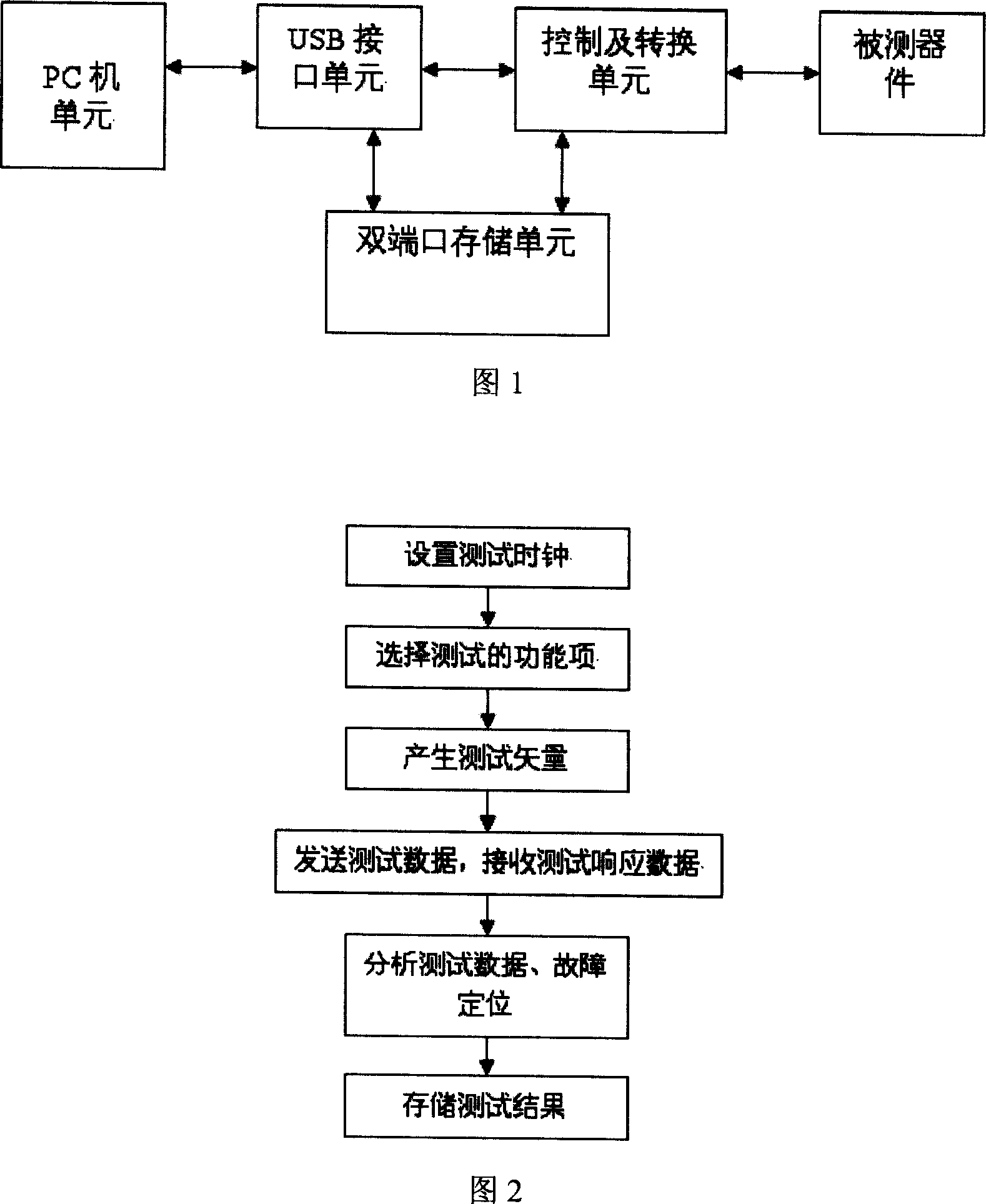

Boundary scan testing controller and testing method thereof

ActiveCN101097242AImplement storageBoundary Scan Test ImplementationElectronic circuit testingElectric digital data processingTransducing UnitTest response

The invention discloses a controller and testing method of boundary scanning, said controller includes PC unit, USB interface unit, two-end memory unit, control and transforming unit; said PC unit can set test, generate test vector, send and receive test data, analyze test data, store test result and USB drive of controller; said USB interface unit realizes communication between boundary scanning test controller and computer; said two-end memory unit realizes memory of test vector and stores test response; said control and transforming unit generates boundary scanning test clock to realize transforming test data to JTAC signal, and realizes reading and writing of data from two-end memory unit. The invention adopts USB interface, memory of two-end memory unit and FPGA design, plug and play, data transmission and boundary scanning test can be preceded at the same time, test speed is increased.

Owner:ZTE CORP

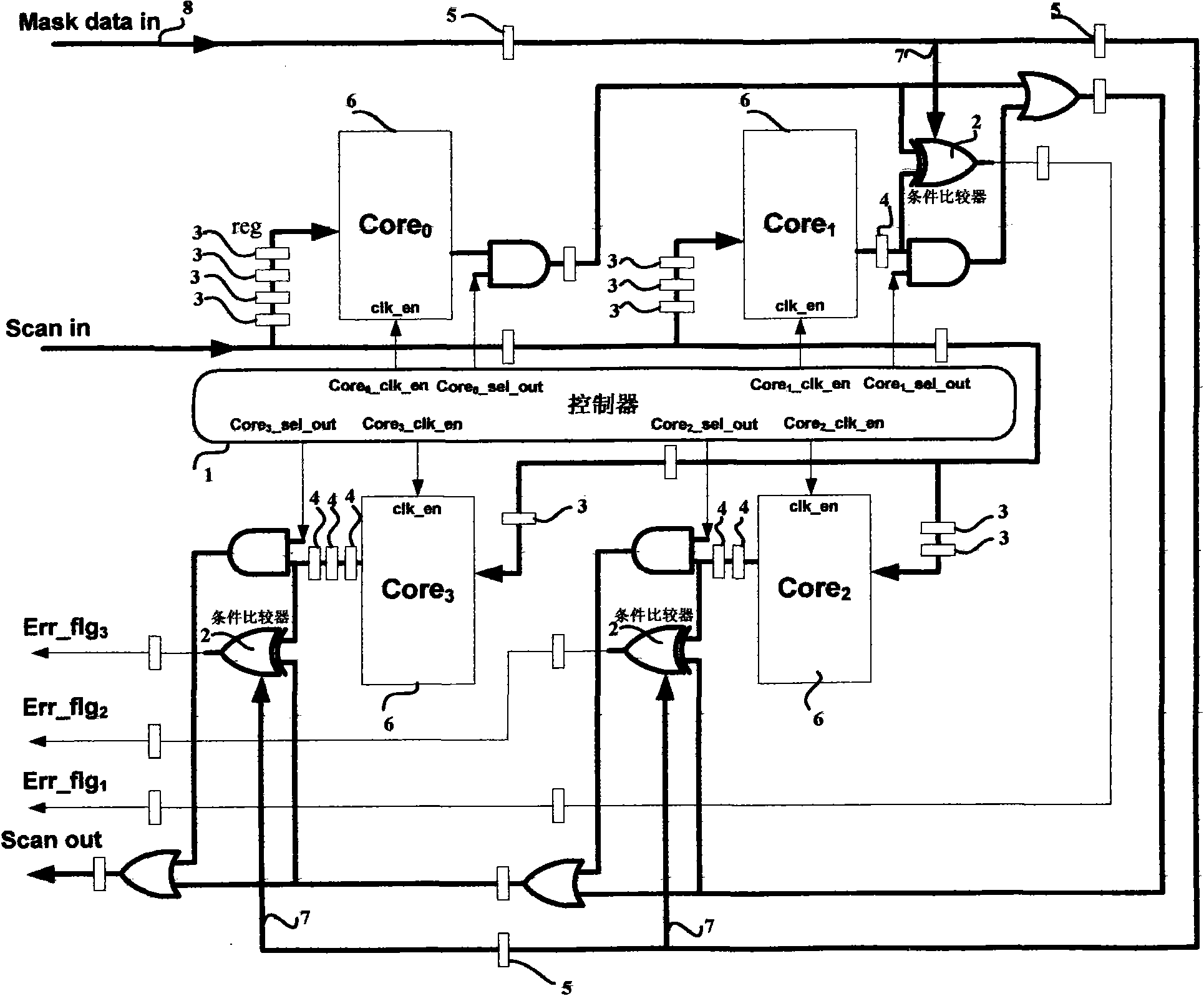

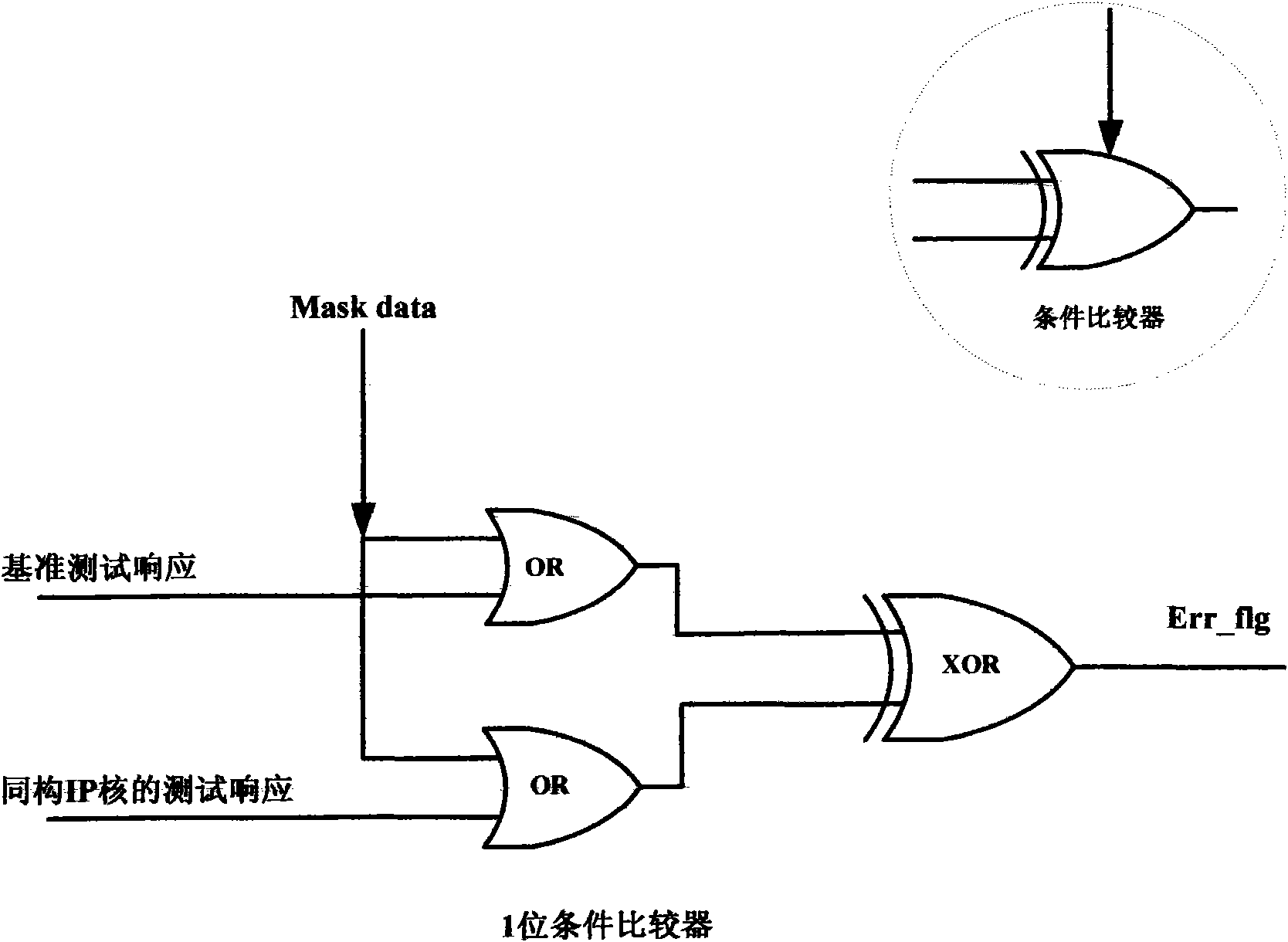

Device and method for testing system-on-chip chip with multiple isomorphic IP cores

ActiveCN101788644AReduced amount of test dataAvoid time costDigital circuit testingComputer hardwareReference test

The invention discloses a device and a method for testing a system-on-chip chip with a plurality of isomorphic IP cores. The device comprises a controller and a condition comparator, wherein the controller is provided with a plurality of control signal interfaces connected to each corresponding isomorphic IP core and is used for inputting a test control signal to each isomorphic IP core, controlling the test on one or more isomorphic IP cores, broadcasting the same test excitation data to the IP cores and simultaneously controlling the output of a test response of a certain IP core; the test response serves as a reference test response and is compared with the test responses of other IP cores; and the condition comparator is used for comparing the test response of a corresponding IP core with the reference test response and processing the comparison result to produce a one-bit error identification signal for identifying whether the comparison is accordant.

Owner:LOONGSON TECH CORP

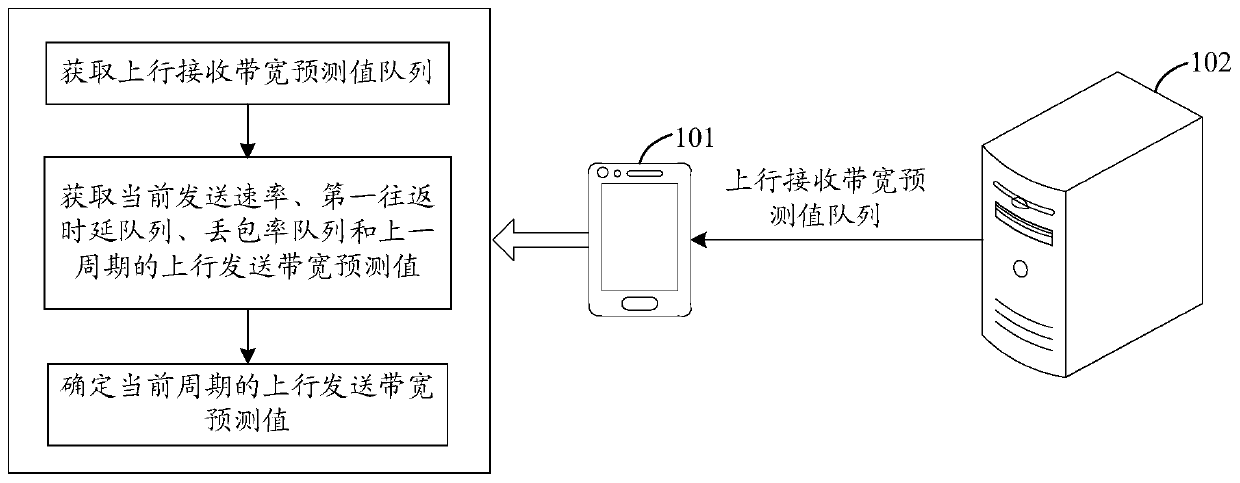

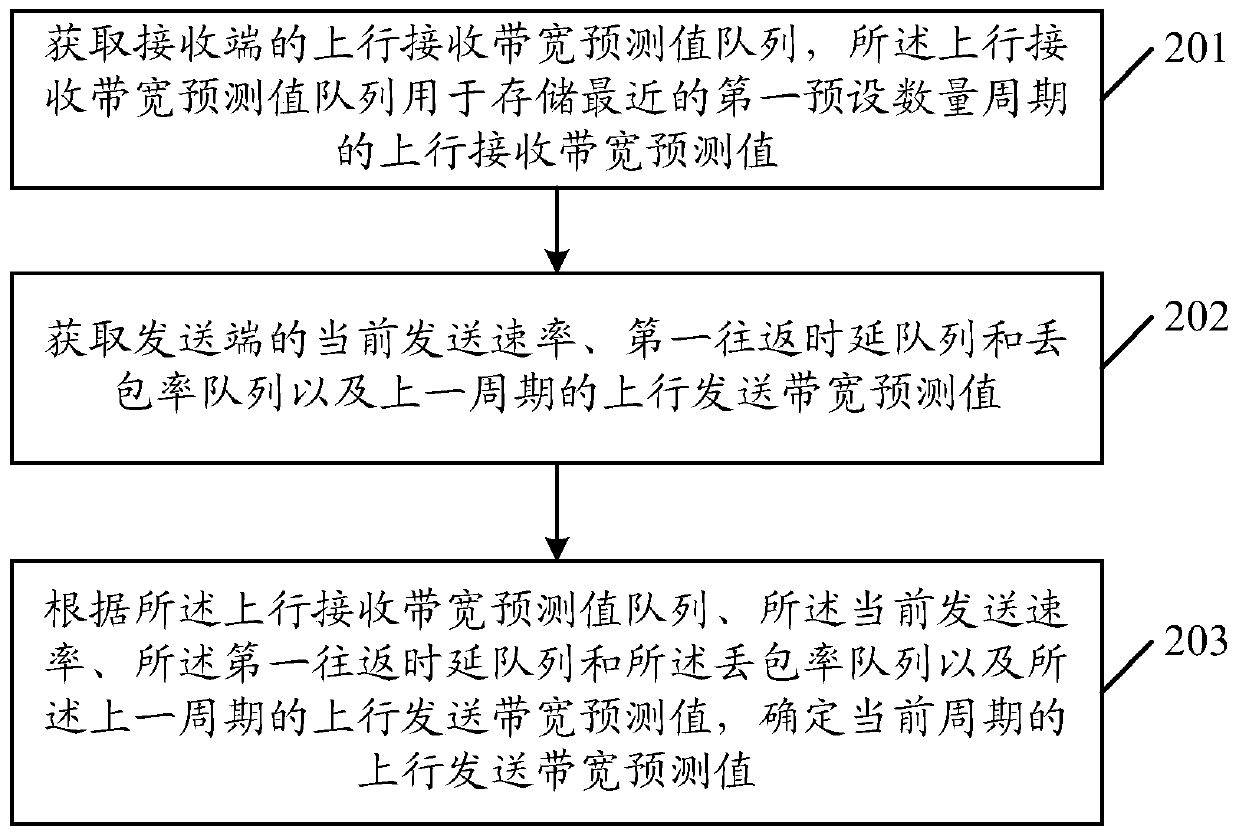

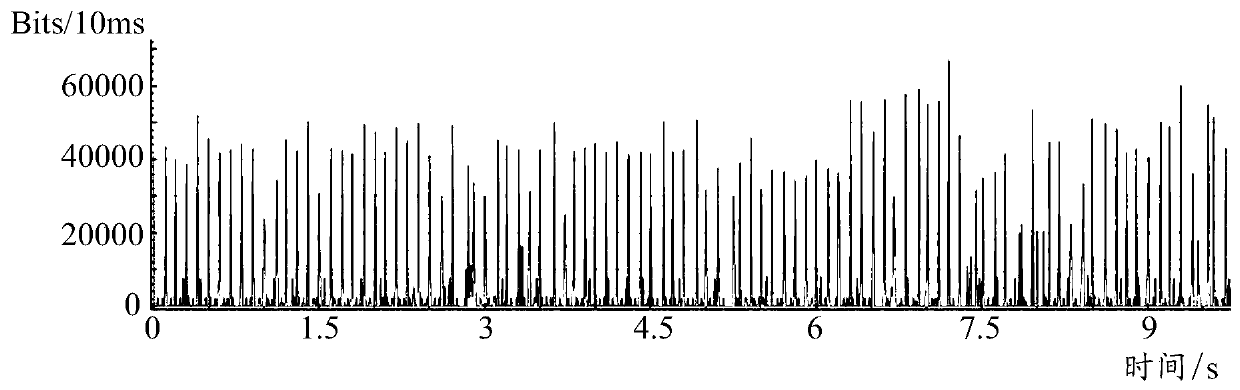

Bandwidth prediction method, device and equipment and storage medium

ActiveCN110266551AReduce overheadSave resourcesData switching networksUplink transmissionPacket loss rate

The embodiment of the invention discloses a bandwidth prediction method and device, equipment and a storage medium, and the method comprises the steps: obtaining an uplink receiving bandwidth prediction value queue of a receiving end; obtaining a current sending rate, a first round trip delay queue and a packet loss rate queue of the sending end and an uplink sending bandwidth prediction value of a previous period; wherein the round-trip delay in the first round-trip delay queue is determined according to the sending time that the sending end sends the test data packet in each period and the time that the sending end receives the test response data packet from the receiving end; and determining the uplink transmission bandwidth predicted value of the current period according to the uplink receiving bandwidth predicted value queue, the current transmission rate, the first round-trip delay queue, the packet loss rate queue and the uplink transmission bandwidth predicted value of the previous period. According to the method, the network bandwidth can be accurately predicted, and network resources can be saved.

Owner:TENCENT TECH (SHENZHEN) CO LTD

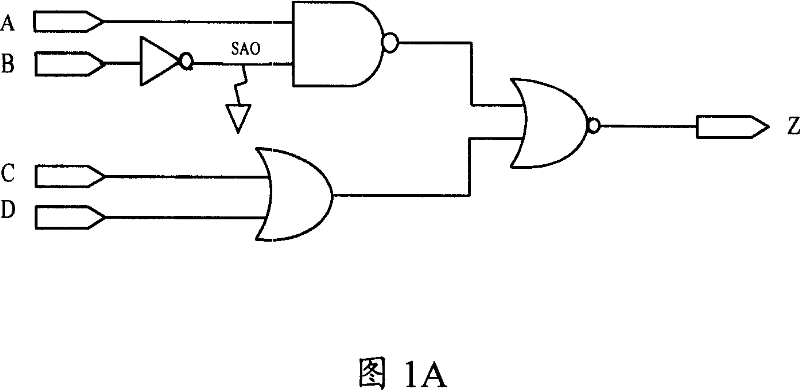

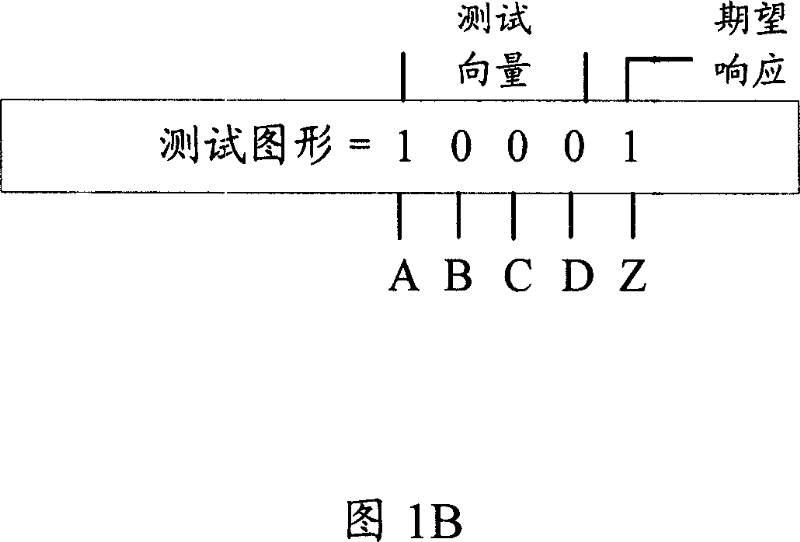

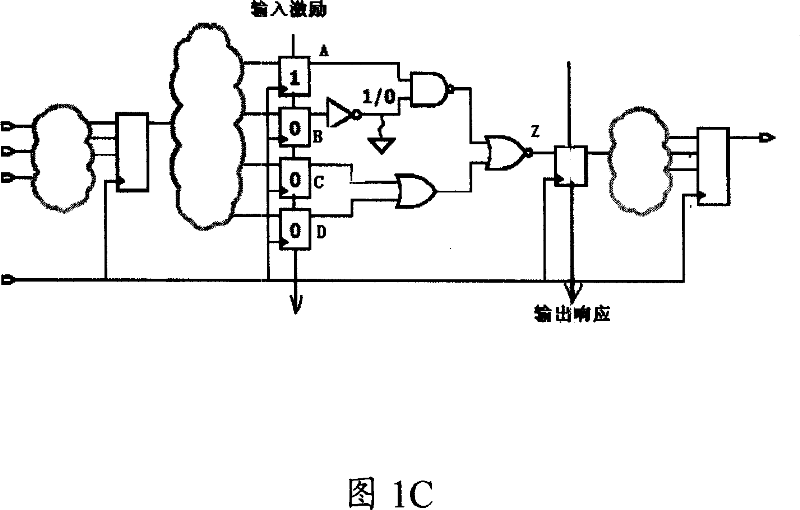

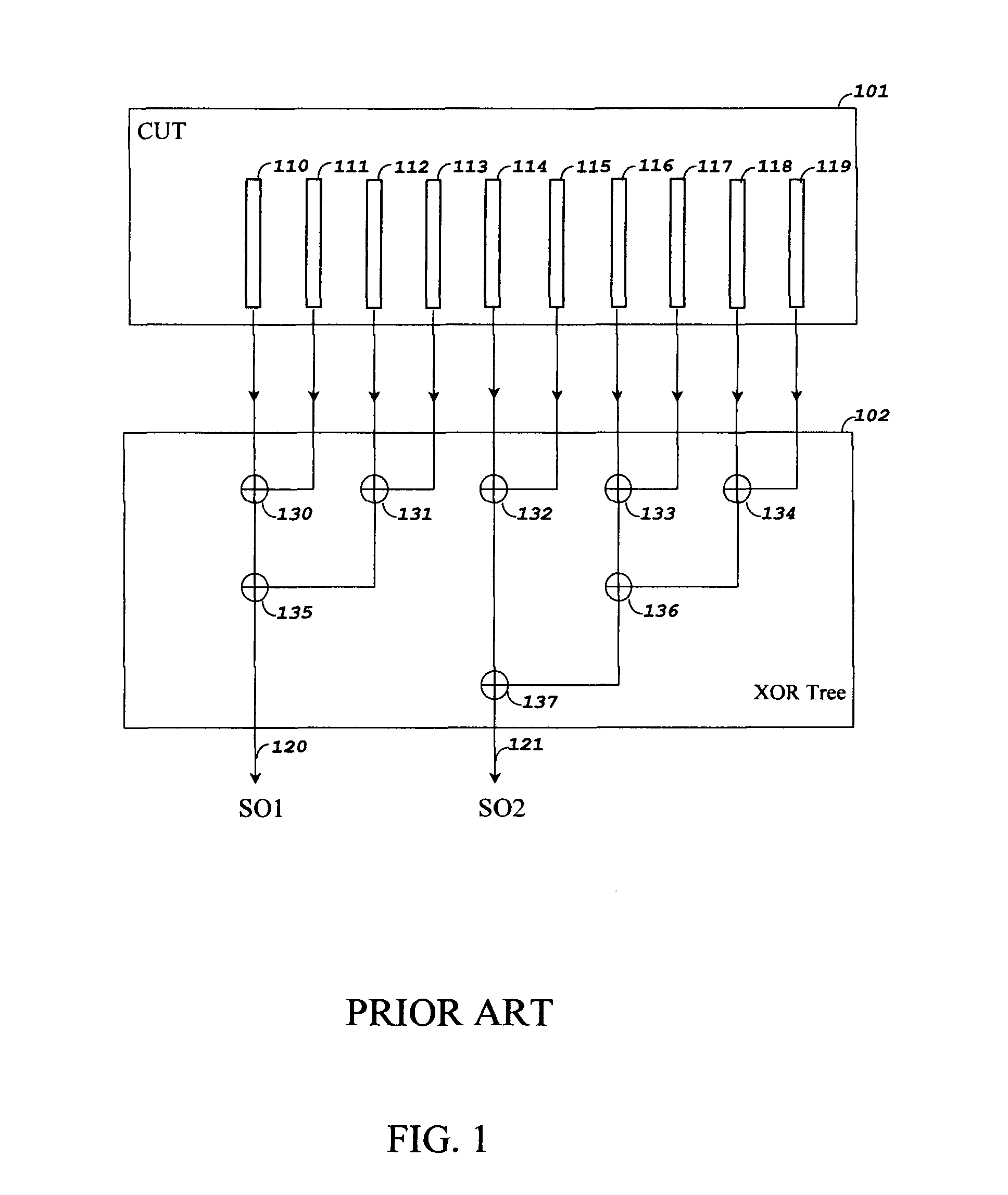

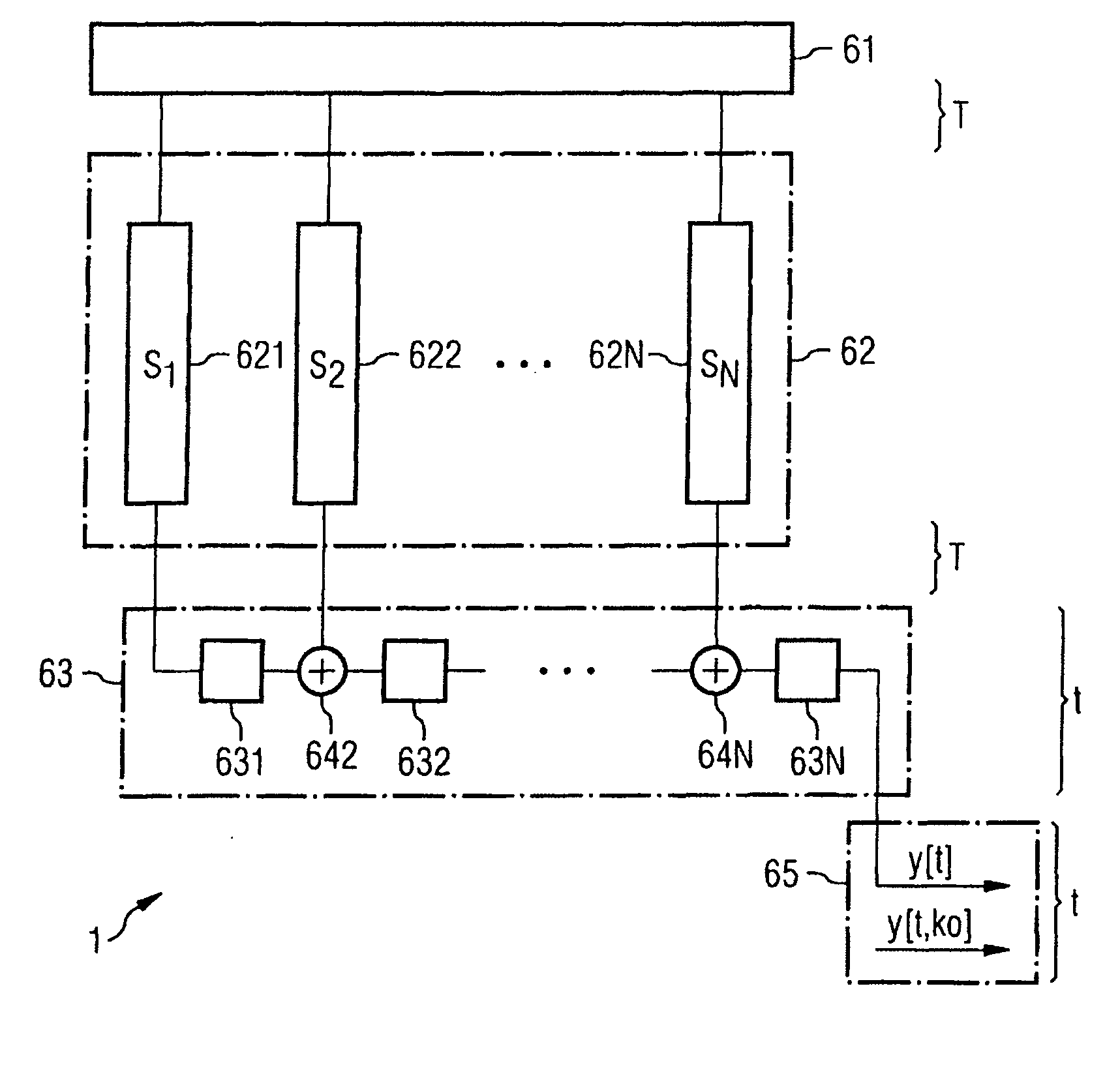

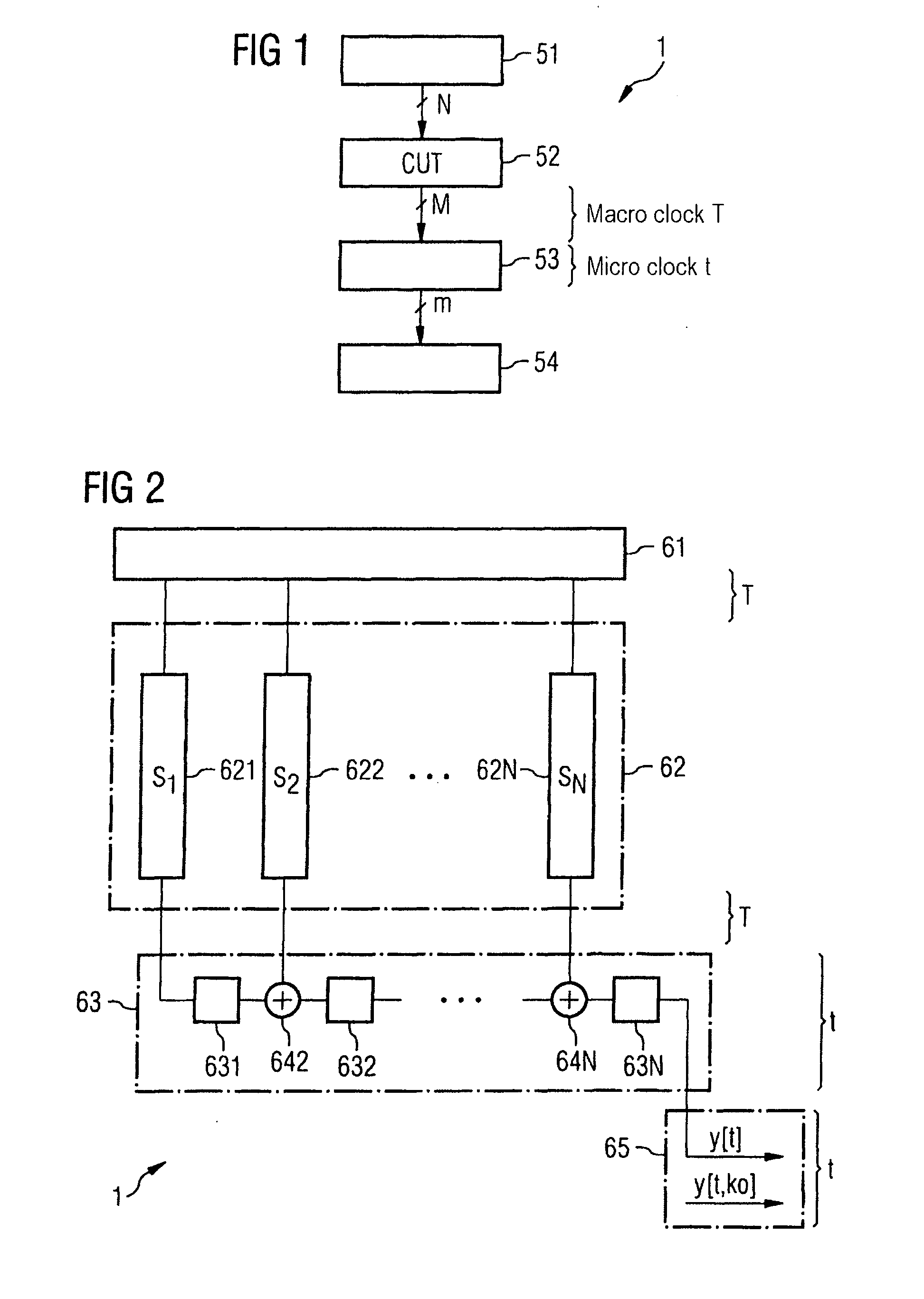

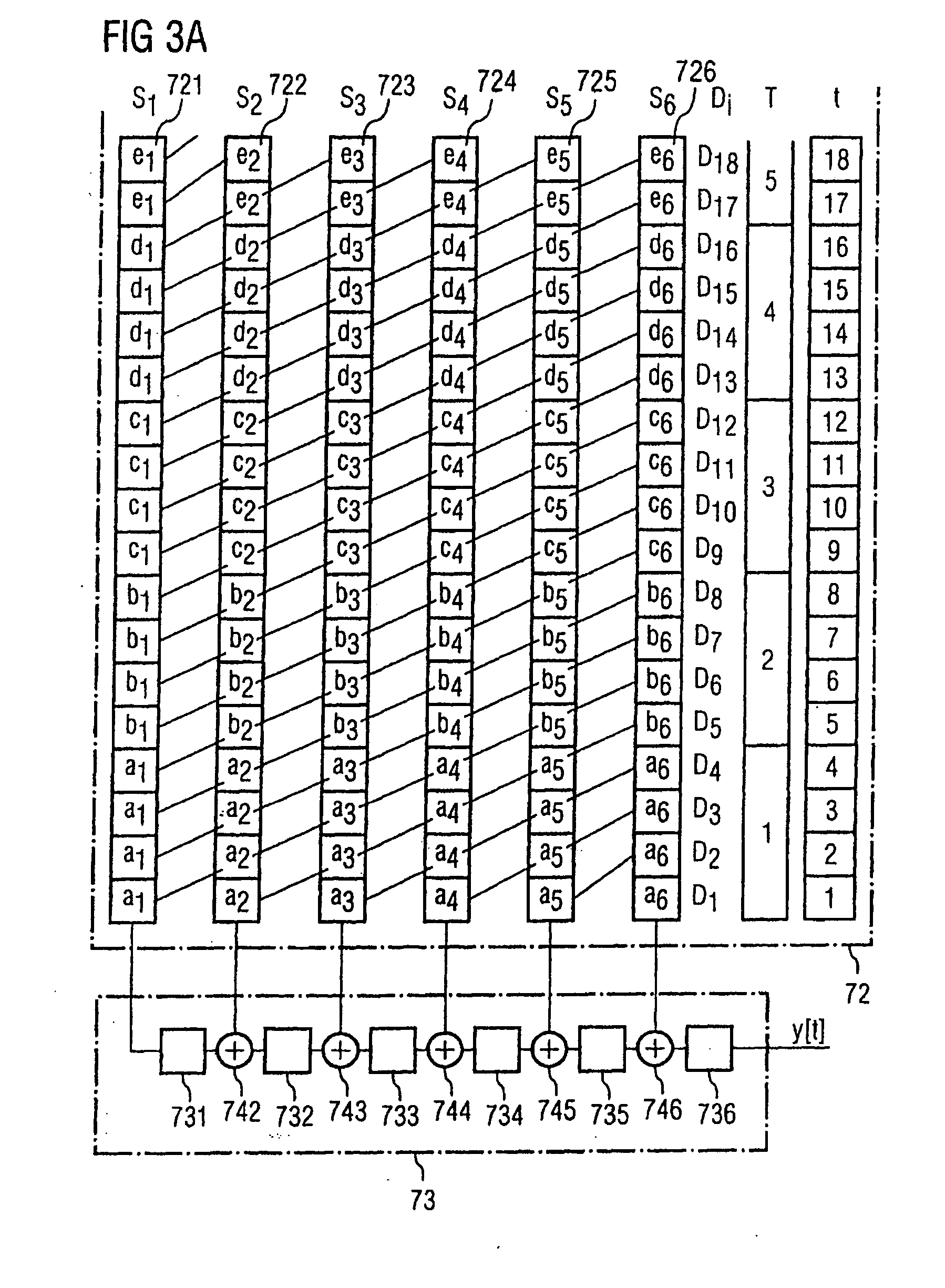

Device and method for testing and for diagnosing digital circuits

InactiveUS20070168814A1Effort controlElectronic circuit testingError detection/correctionTest inputEngineering

A test apparatus includes a test input signal generator that generates a test input signal of word width N, and terminals that connect to inputs and outputs of an electrical circuit to be tested. The electrical circuit includes N digital test inputs and M digital test outputs. The terminals for the test inputs are connected to the test input signal and an electrical circuit is driven such that it outputs at its test outputs data with a macro clock cycle T of length L as test response. A compactor includes M inputs that are connected to the terminals for the test outputs of the circuit to be tested. The compactor compacts the test response with a micro clock cycle t of length l and outputs a data word of width m, where the length L is at least twice as large as the length l.

Owner:INFINEON TECH AG