Low power consumption integrated circuit testing device with compressible data and method using same

A technology for integrated circuits and testing devices, applied in the field of low-power integrated circuit testing devices, can solve problems such as weakening the compression effect of test data, and achieve the effect of reducing jumps and realizing compression.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0050] The specific implementation manners of the present invention will be further described in detail below in conjunction with the accompanying drawings and embodiments. The following examples are used to illustrate the present invention, but are not intended to limit the scope of the present invention.

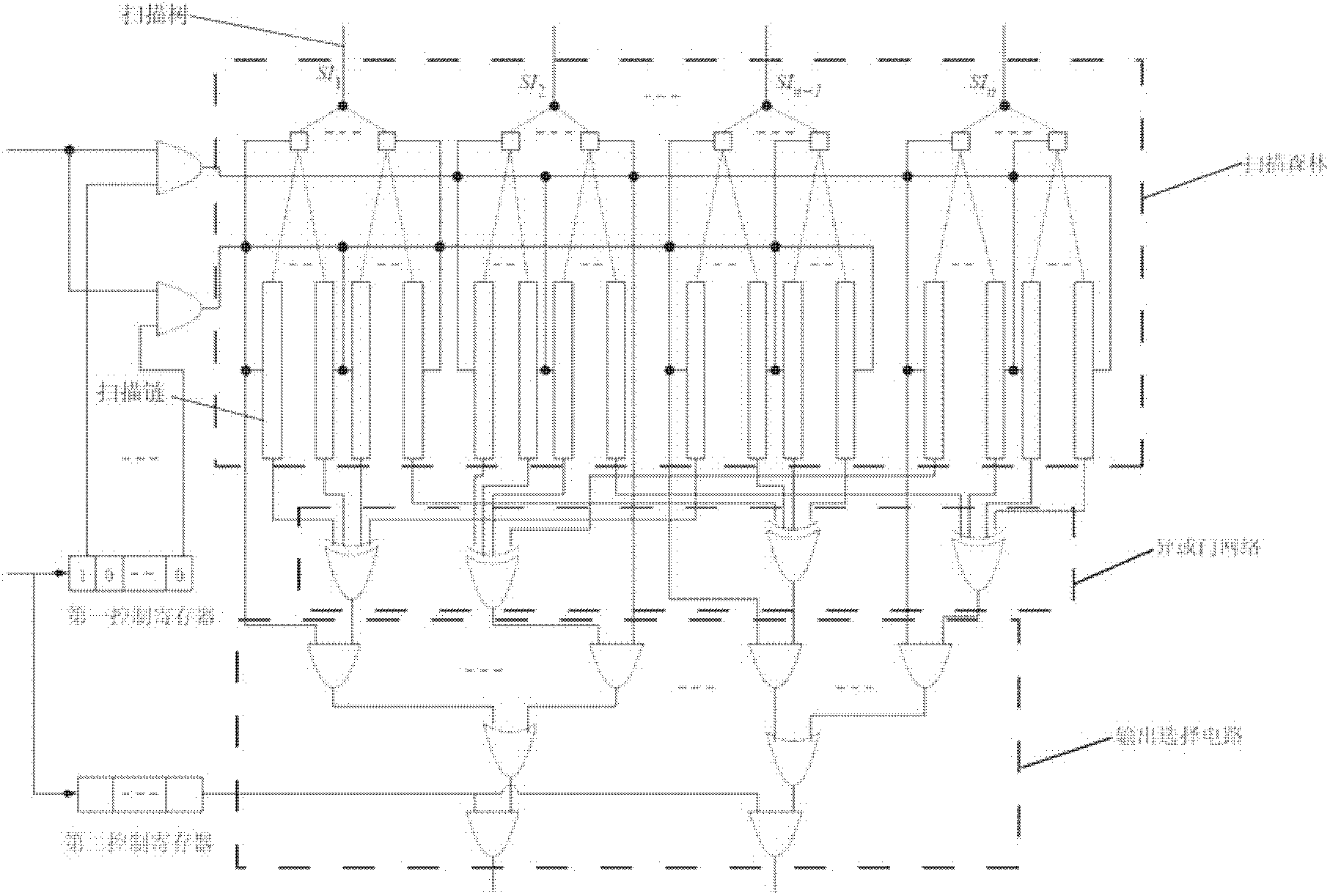

[0051] Such as figure 1 As shown, the data-compressible low-power integrated circuit testing device of the present invention includes: scan forest, XOR gate network, output selection circuit, first control register and second control register; wherein,

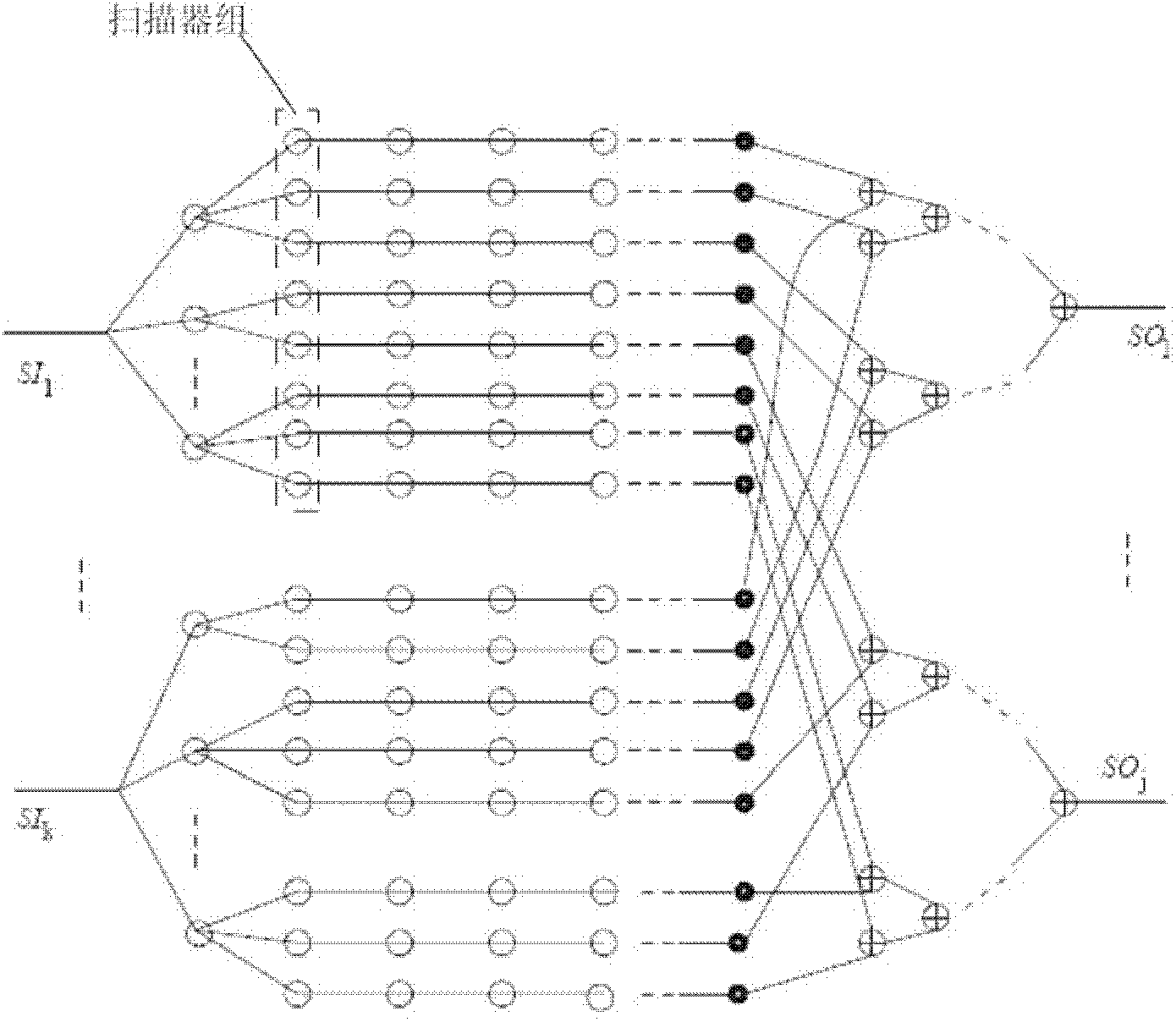

[0052] The scan forest includes multiple scan input terminals and multiple scan flip-flop groups connected to each other, the scan input terminals are connected to all scan flip-flops in the first scan flip-flop group, and all scan flip-flops in each scan flip-flop group The scan flip-flops are connected to the output terminals of the scan flip-flops in the previous scan flip-flop group, the multiple scan input terminals ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More