Patents

Literature

41 results about "Test vector generator" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

Test vector generator is a program used to automatically generate test data for use in automated testing of software. This can generate many individual test vectors. Automatic test pattern generation is a term of art in electronic design automation for the automatic generation of test vectors for electronic circuits.

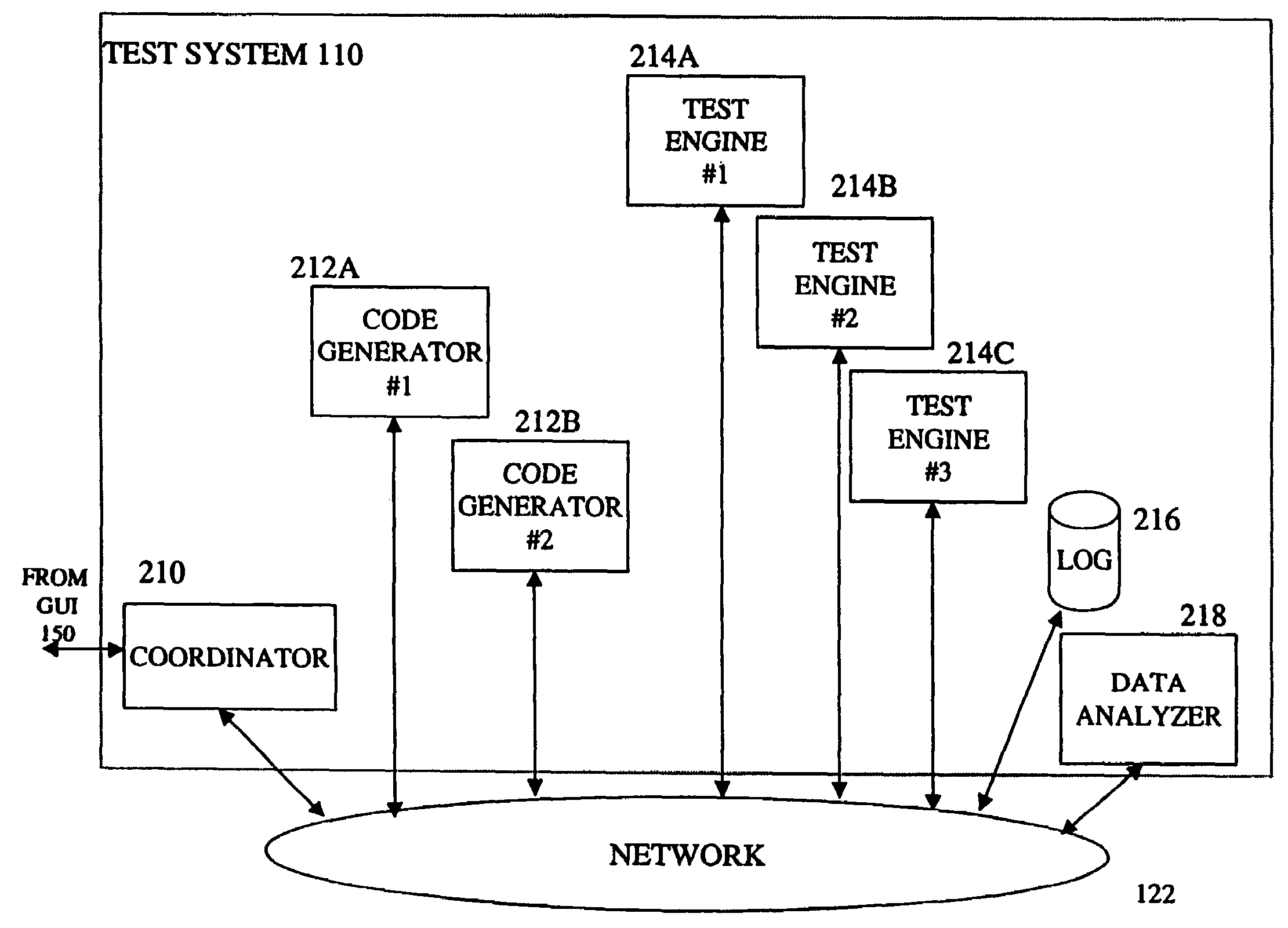

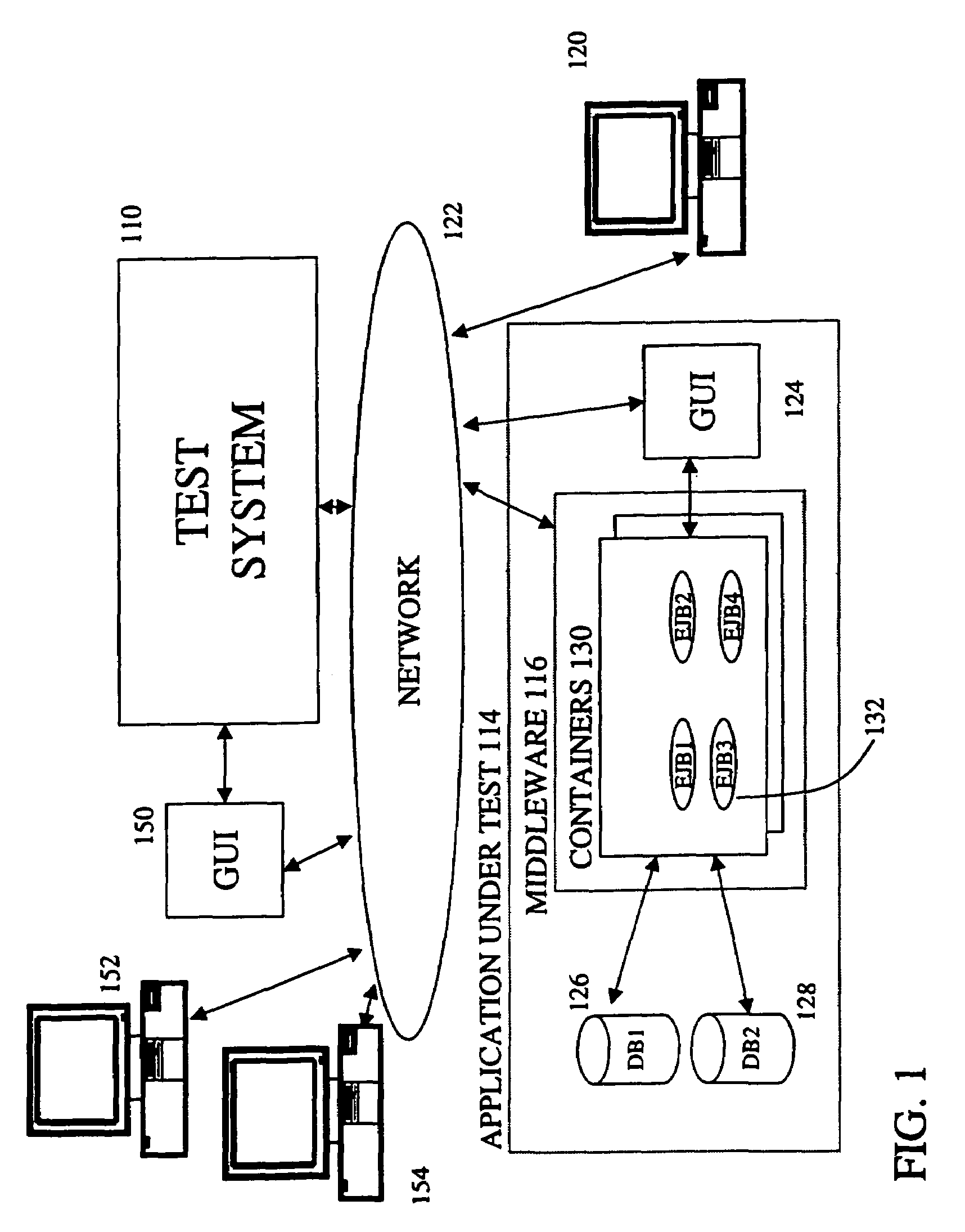

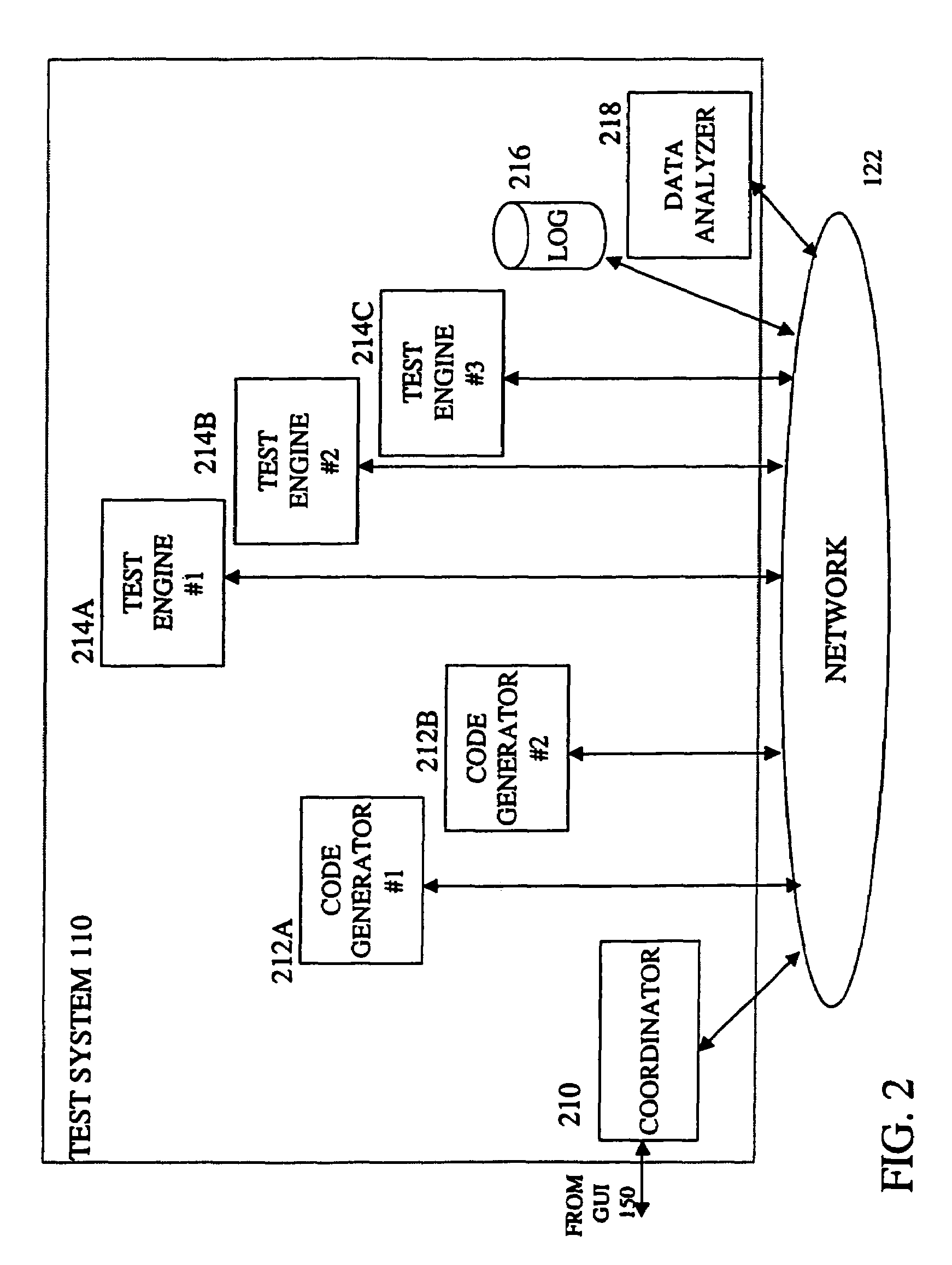

Test code generator, engine and analyzer for testing middleware applications

InactiveUS7000224B1Facilitate load based testing of N-tieredReduce physical laborElectronic circuit testingError detection/correctionProgramming languageData profiling

A system for testing middleware of applications in the N-tiered model. The test system contains test code generators, test engines to execute multiple copies of the test code and a data analyzer to analyze and present the results to a human user. The system is able to automatically generate test code to exercise components of the middleware using information about these components that would otherwise be available to the application under test. Multiple copies of the test code are executed in a synchronized fashion. Execution times of multiple events are recorded and then presented in one of several formats. With the system, an application developer can identify components that represent performance bottlenecks or can gather information on deployment properties of individual components that can be used to enhance the performance of the application under test.

Owner:ORACLE INT CORP

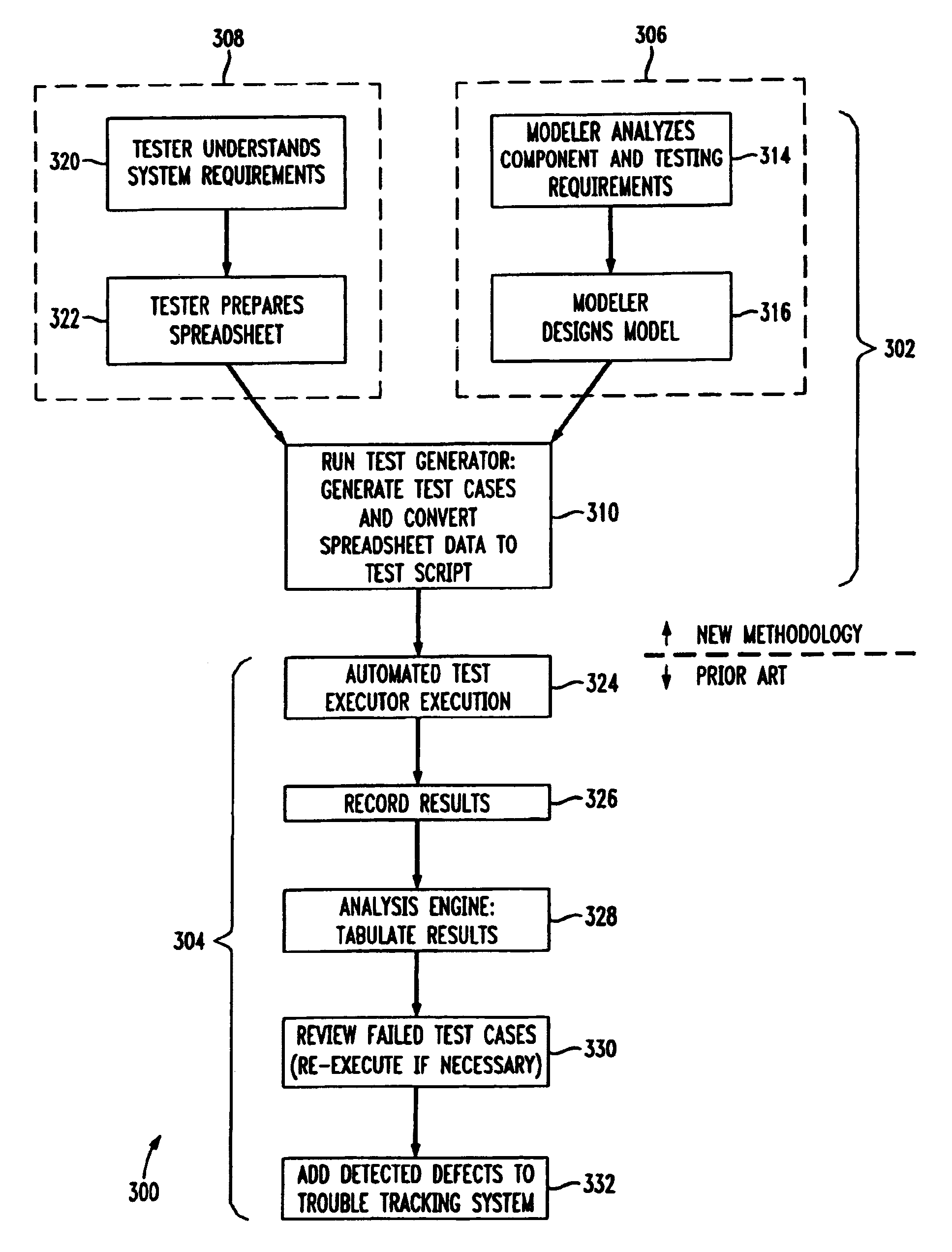

Test generator for converting a model of computer component object behavior and stimulus values to test script

InactiveUS7076713B1Electronic circuit testingError detection/correctionTest scriptTest vector generator

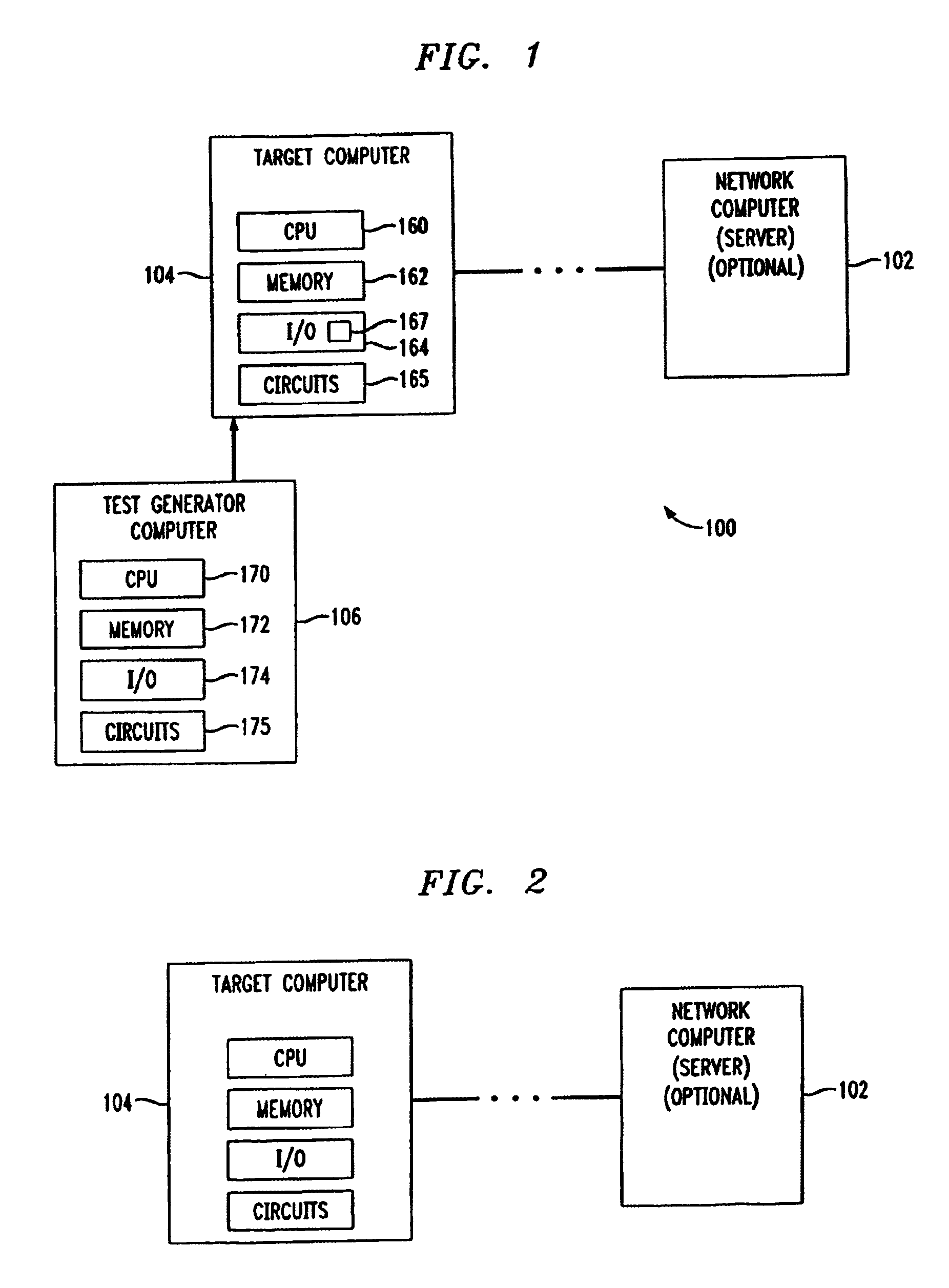

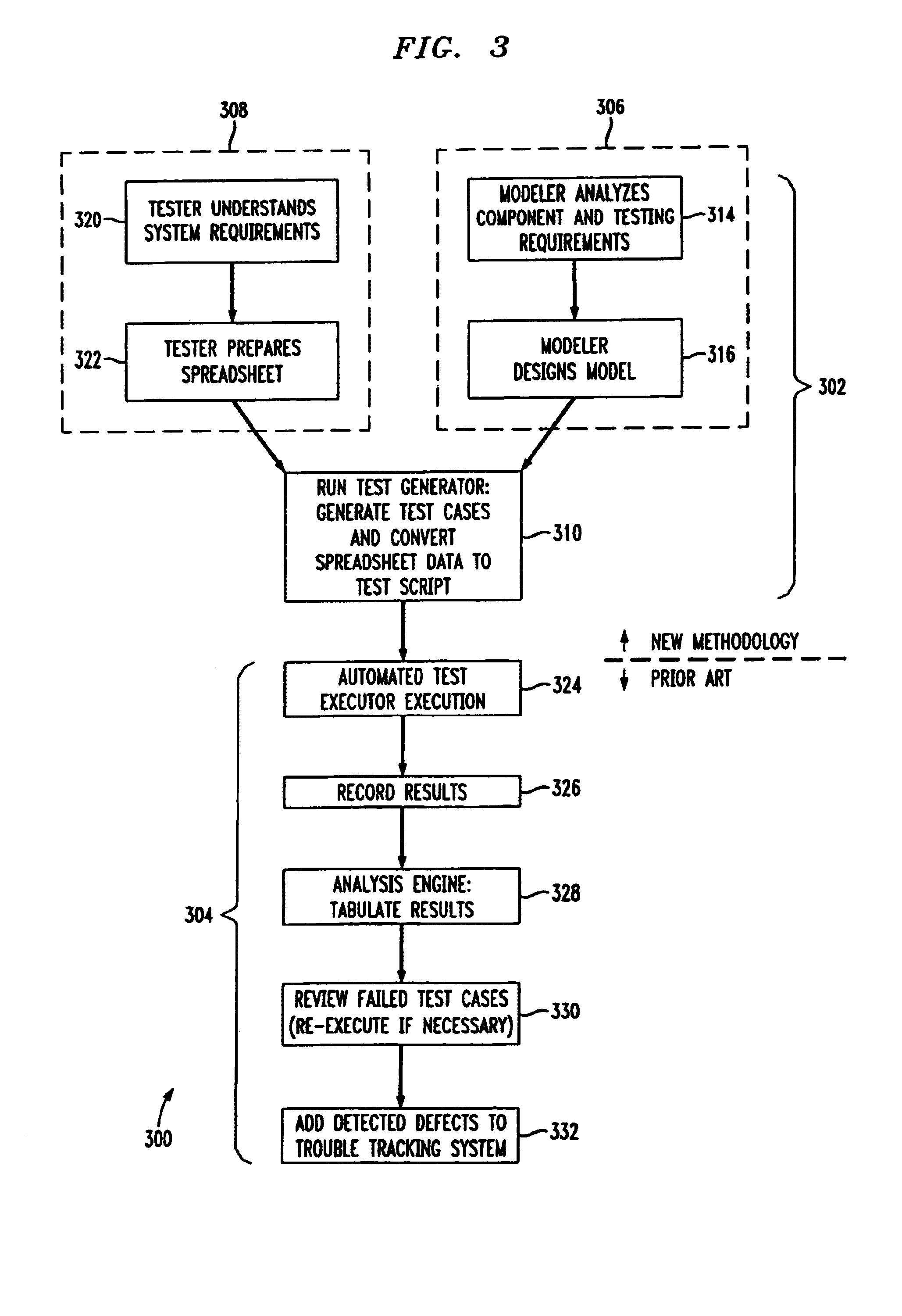

This invention relates to an apparatus and an associated method that tests the response of a computer component. The apparatus includes a modeler, a tester, and a test generator. The modeler provides a model of the computer component object behavior. The tester provides stimulus values to be applied to the computer component object. The test generator converts the model of the computer component object behavior and the stimulus values into test script. The test script can be executed by an automated test executor.

Owner:WSOU INVESTMENTS LLC +1

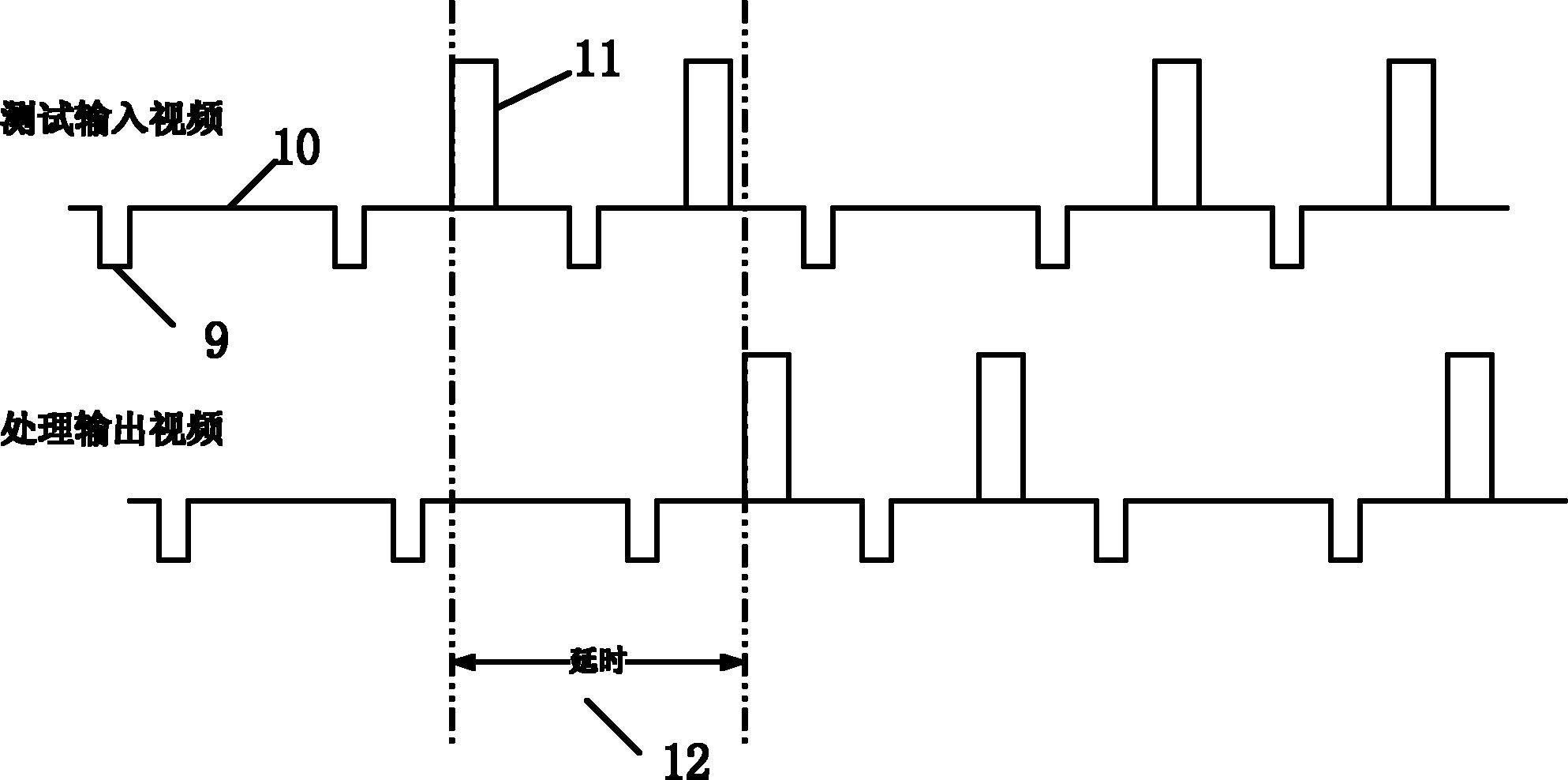

Delay test method for video image processing system

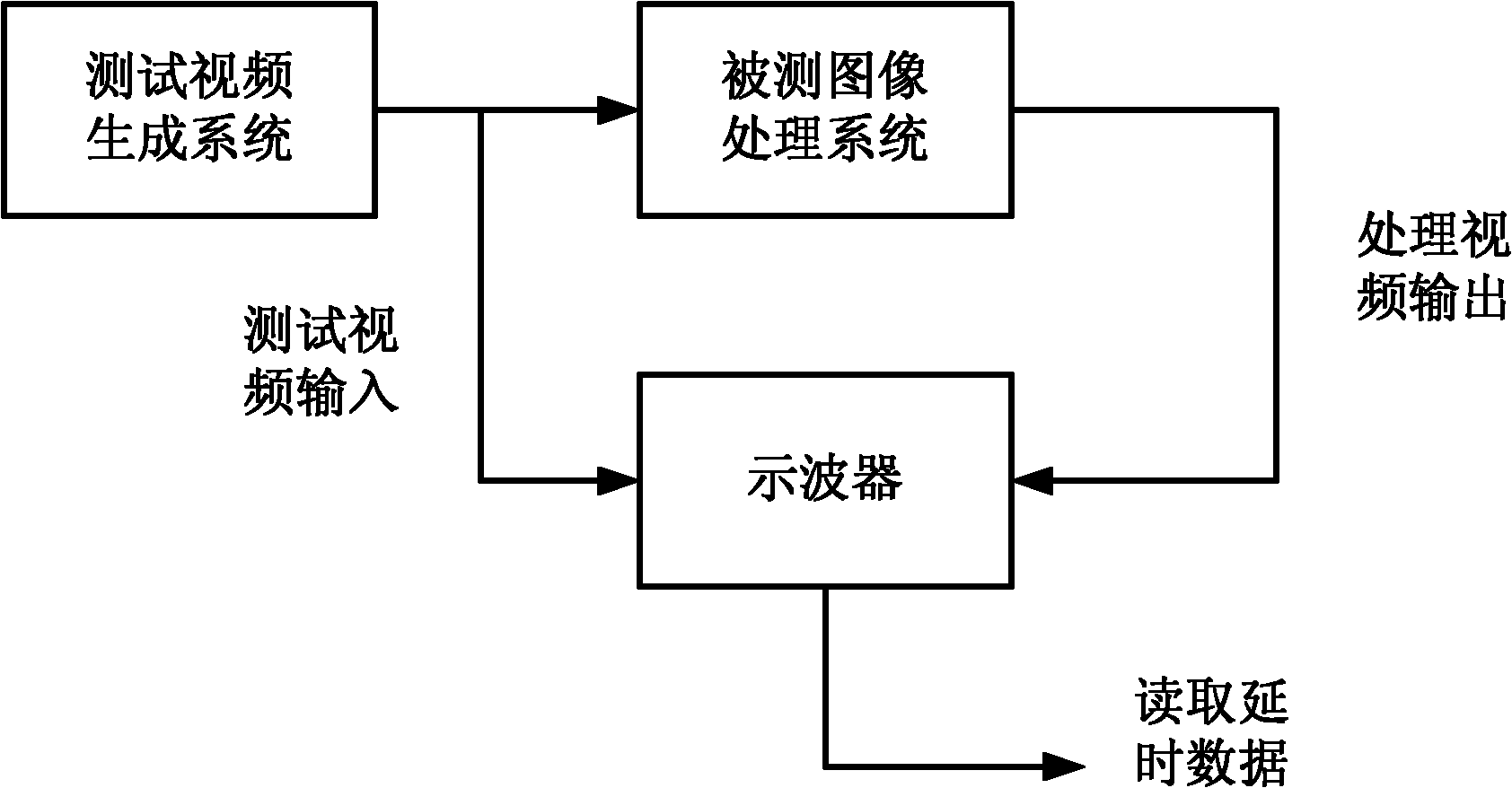

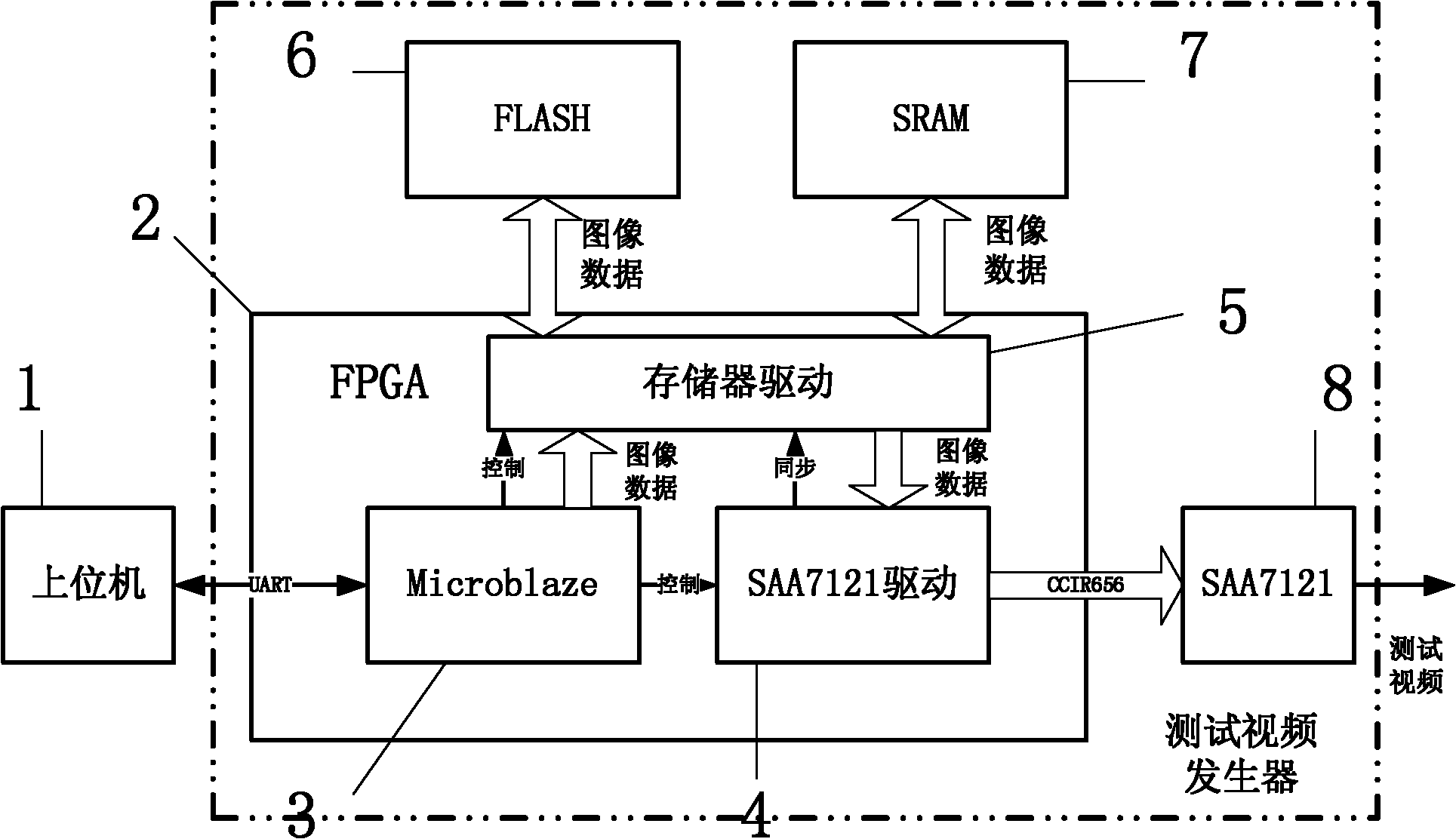

The invention relates to a delay test method for a video image processing system, which comprises the following steps: 1) editing a to-be-tested image by the using of a PC (personal computer), sending the to-be-tested image to a tested video generator, storing the to-be-tested image in a flash by the tested video generator, and standing by; 2) at the moment of testing, selecting the to-be-tested image by an upper computer according to a video standard of tested system and testing the specific sequence form and video format; 3) sending a to-be-tested video into the tested system; and 4) sending the to-be-tested video generated from the step 2) and the video outputted by the tested system to an oscilloscope or logic analysis meter, and reading the time difference of input and output, namely acquiring the system delayed volume. The tested images in the tested video are continuously outputted at intervals. The invention provides a simple, direct and practical method, which can be used for accurately testing the delay of the video image processing system.

Owner:BEIJING INSTITUTE OF TECHNOLOGYGY

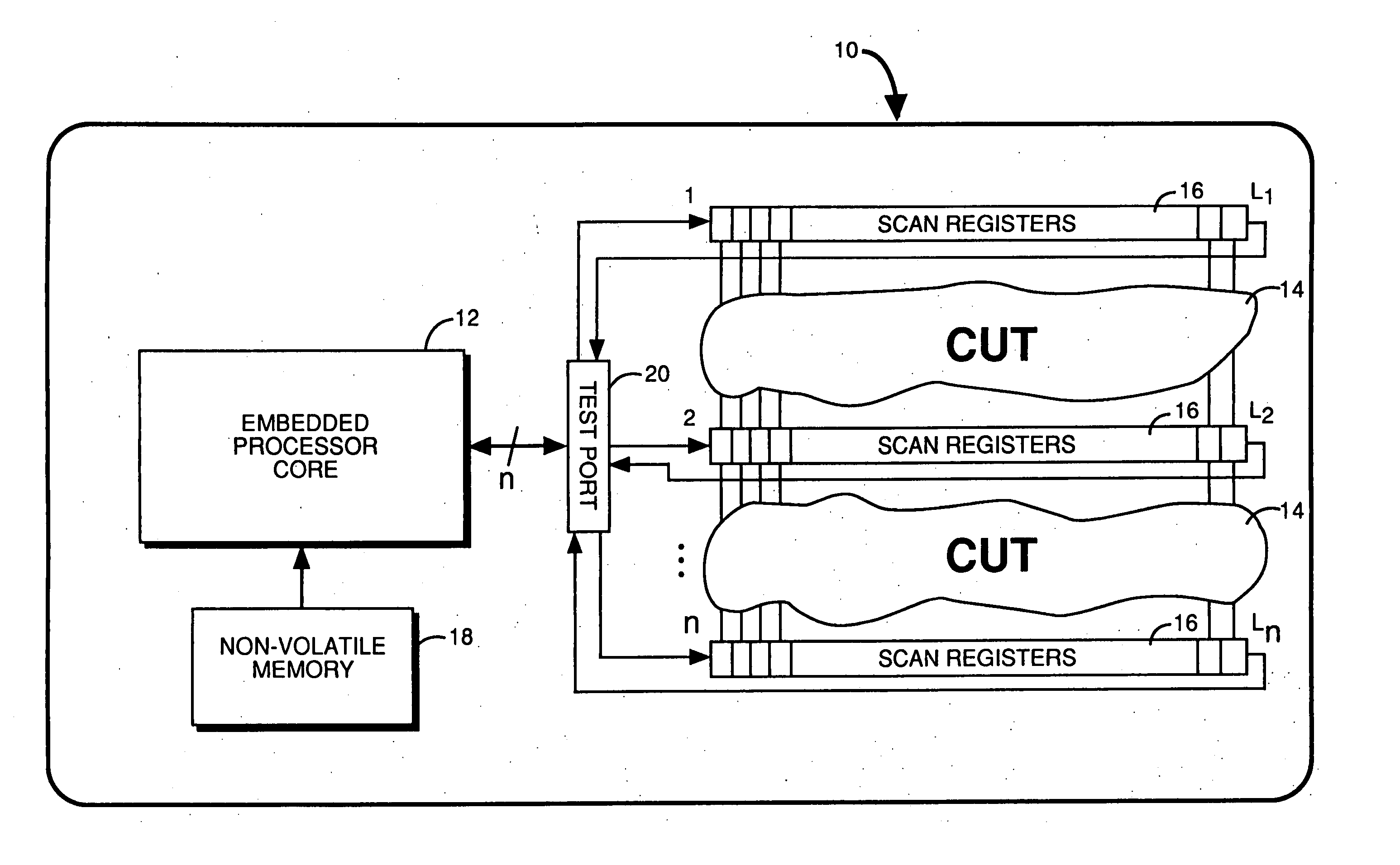

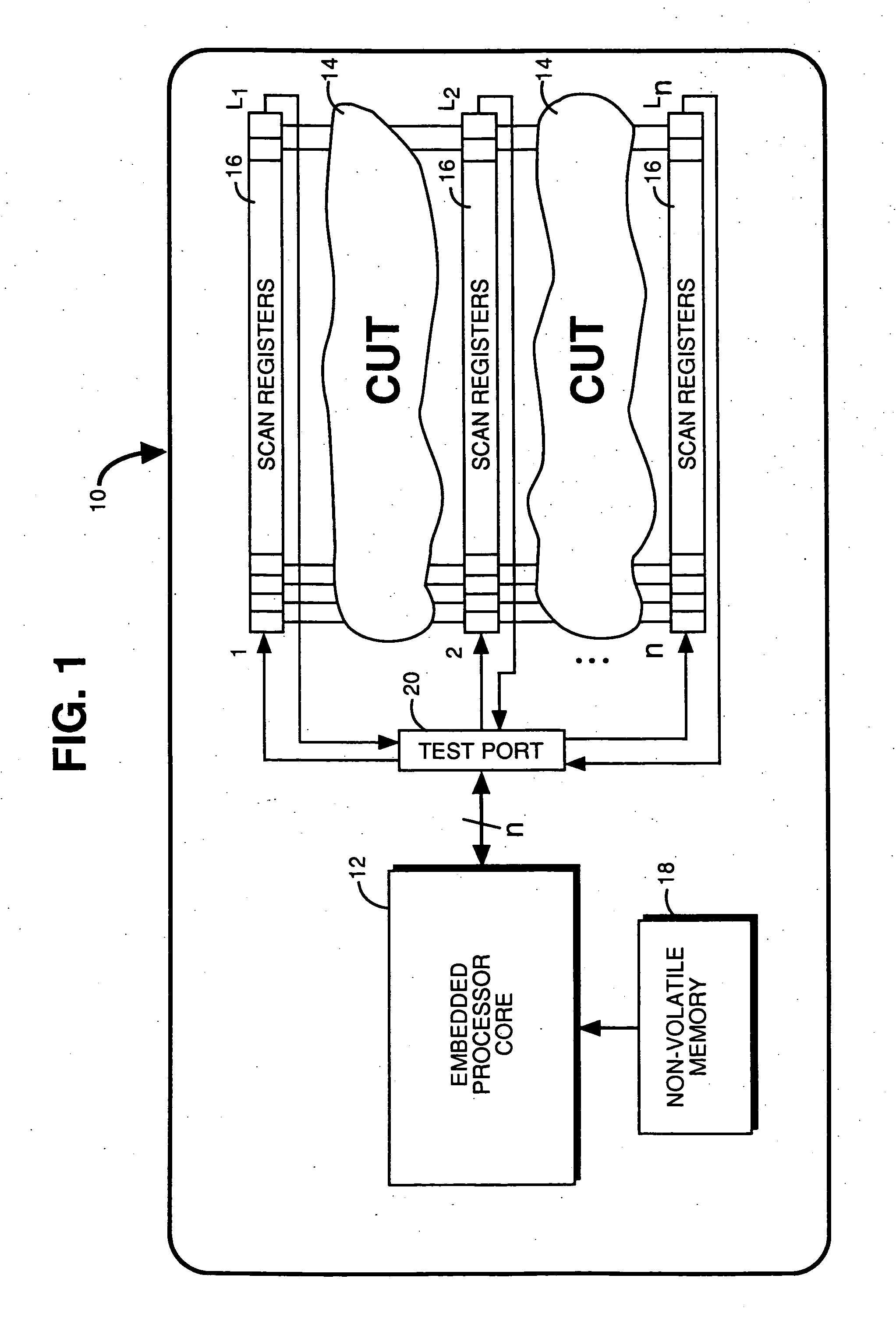

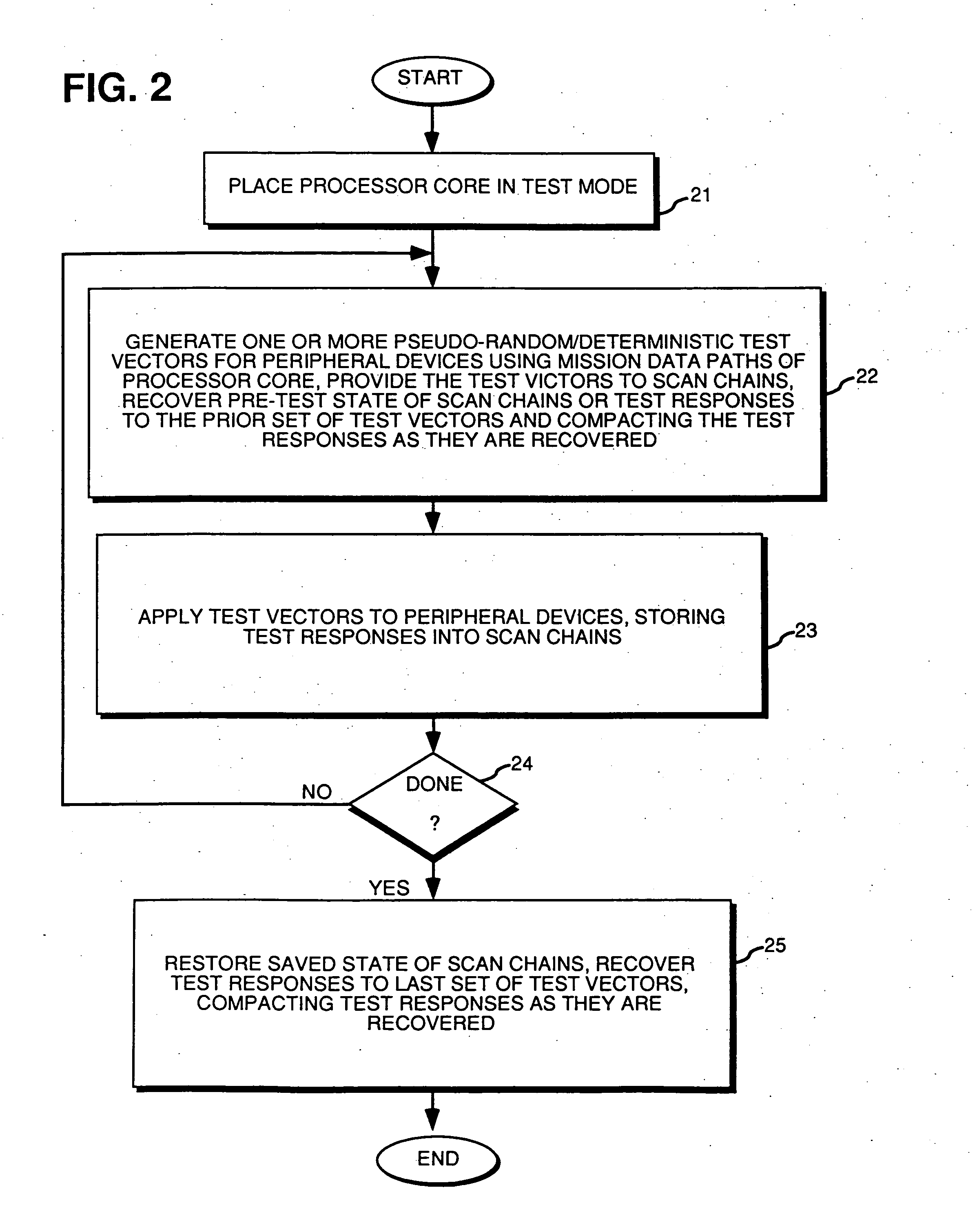

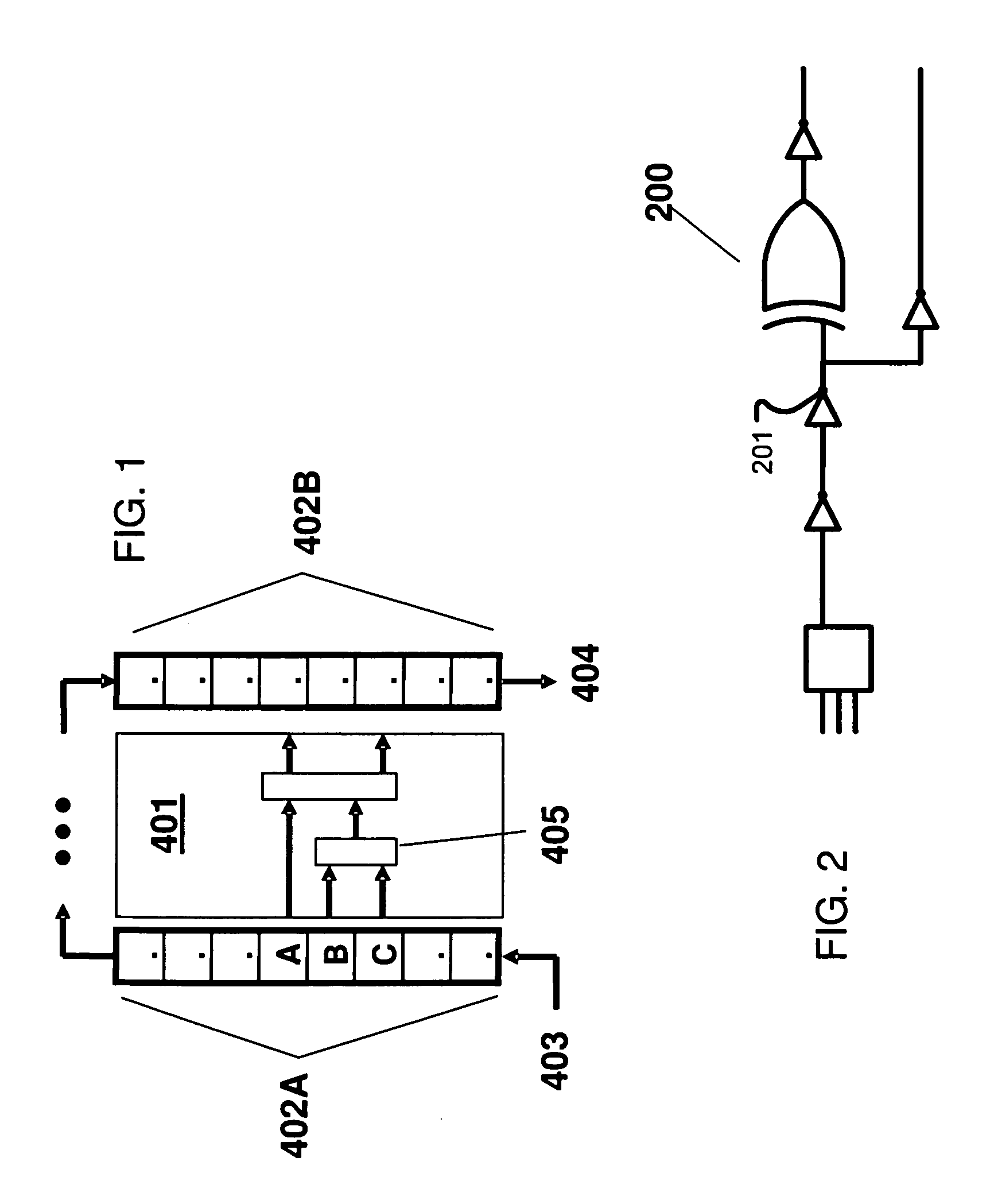

Arithmetic built-in self-test of multiple scan-based integrated circuits

InactiveUS20050060626A1Reduce error impactElectronic circuit testingError detection/correctionTest vector generatorNumber generator

In one embodiment, an IC with an embedded processor core, peripheral devices, and associated multiple scan chains, is provided with microcode that implements an arithmetic pseudo-random number generator and an arithmetic deterministic test vector generator, when executed by the embedded processor core, generates 2-D pseudo-random and deterministic test vectors for testing the peripheral devices respectively. The IC is further provided with microcode that implements an arithmetic test response compactor, which when executed by the embedded processor core, compacts test responses of the peripheral devices into a signature. The IC further includes a test port register and microcode that implements a number of ABIST instructions.

Owner:MENTOR GRAPHICS CORP

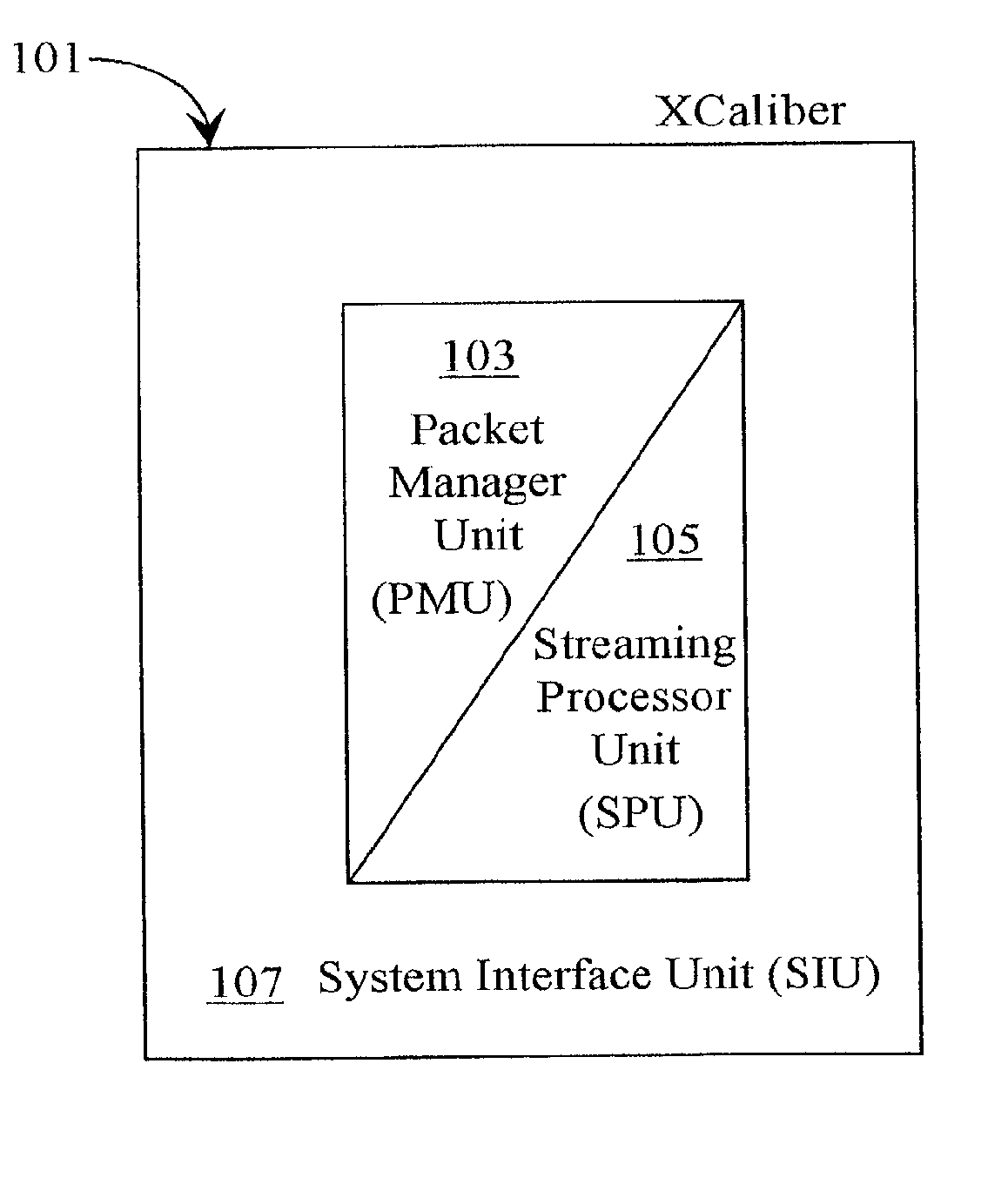

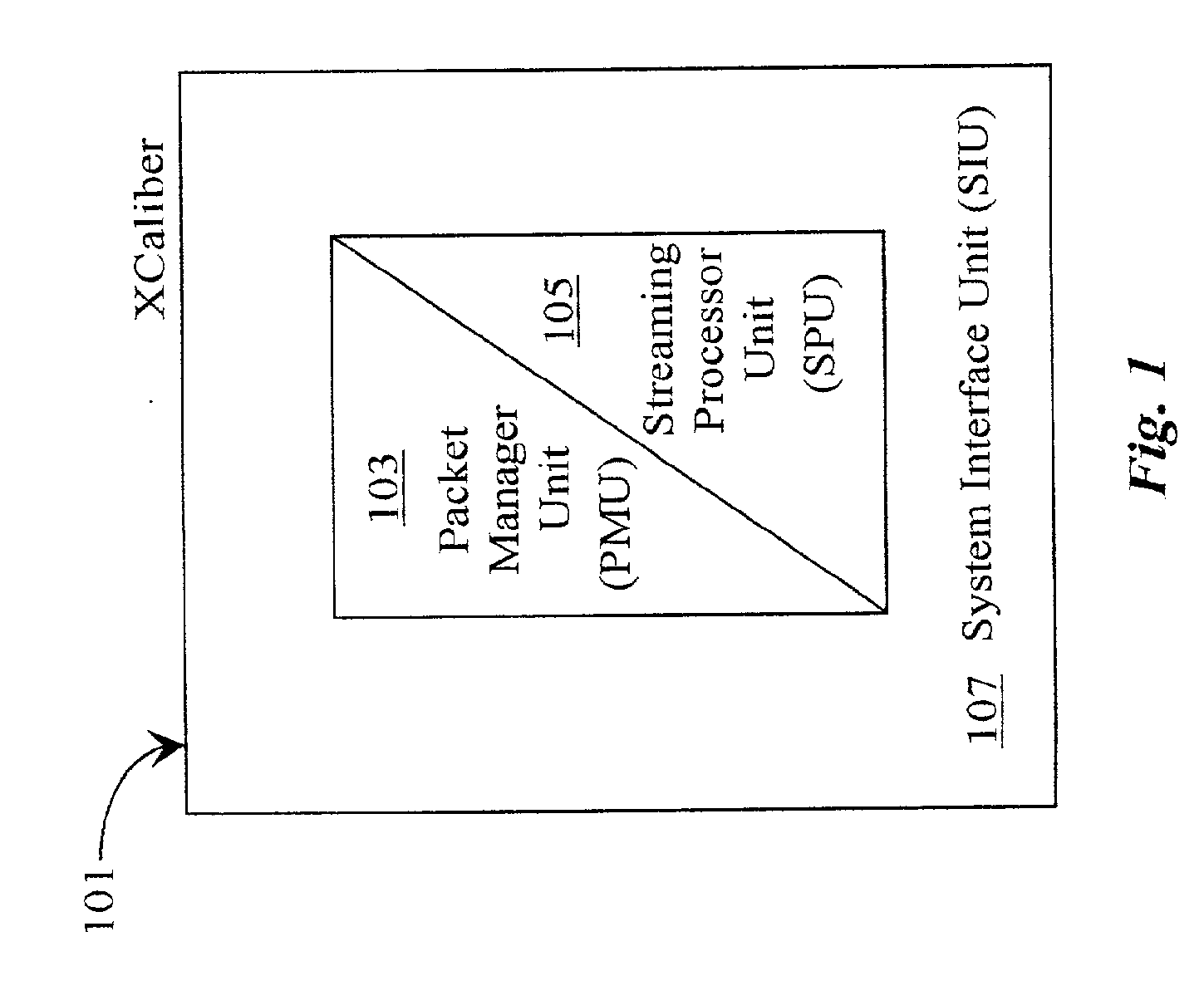

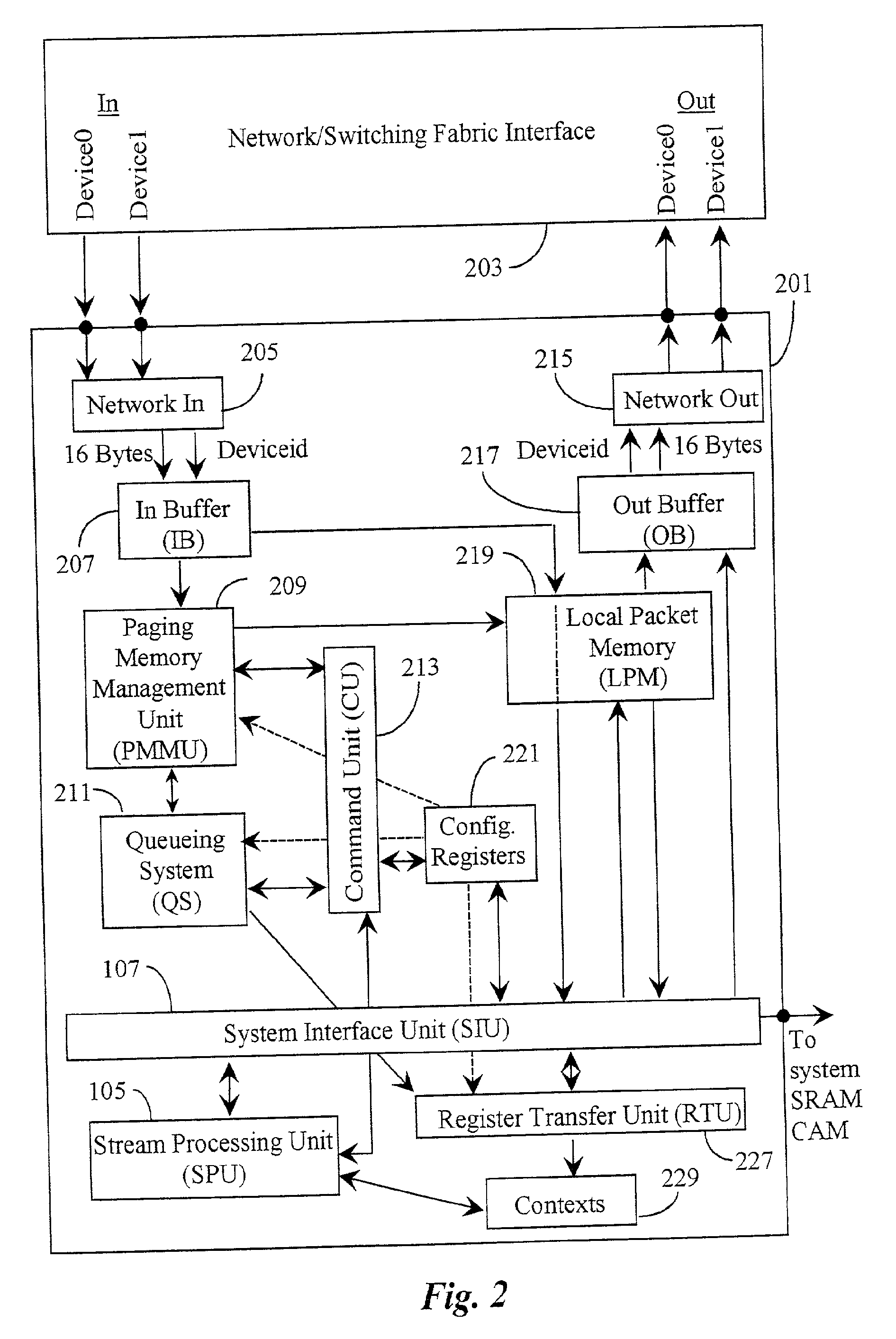

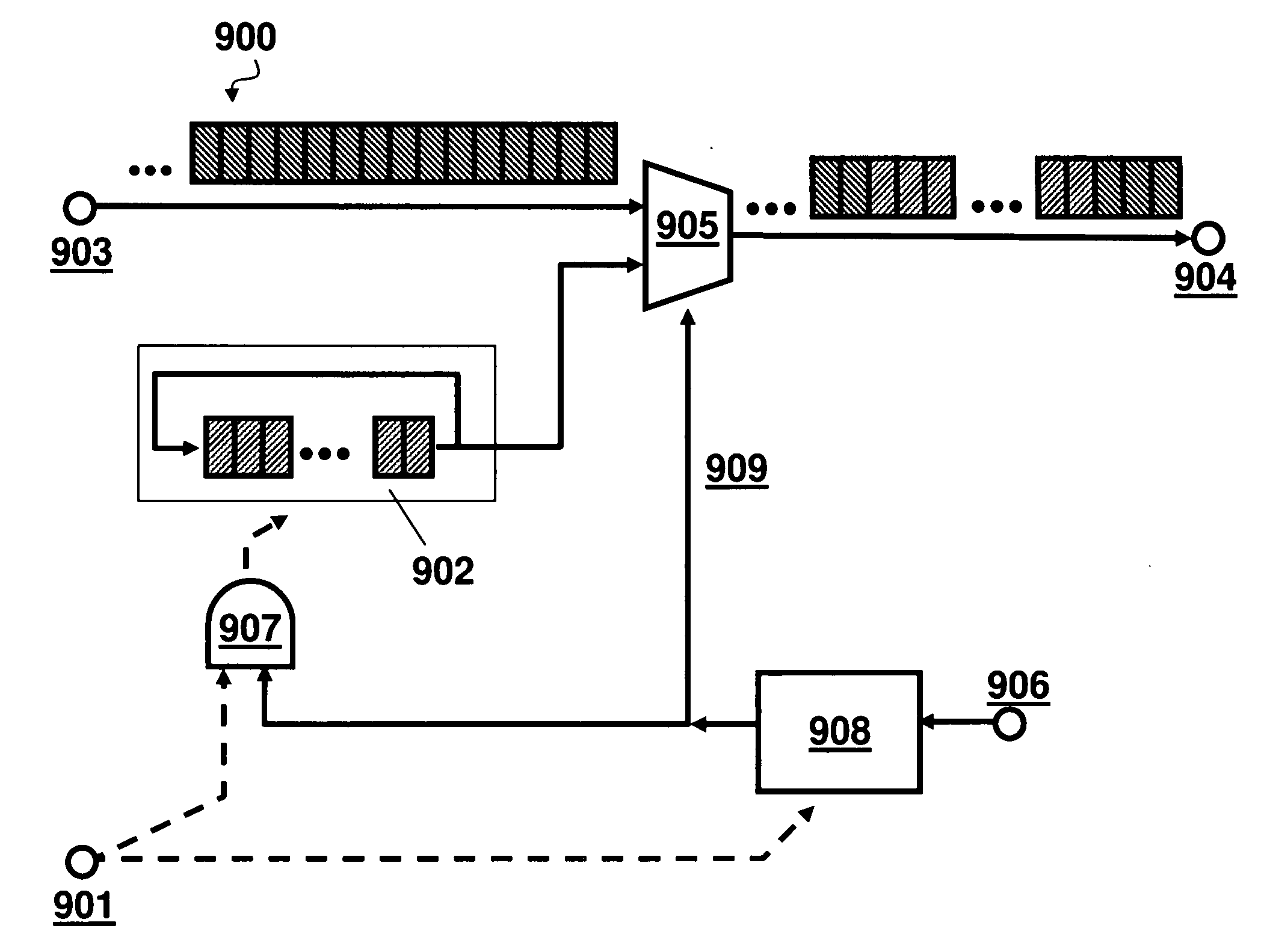

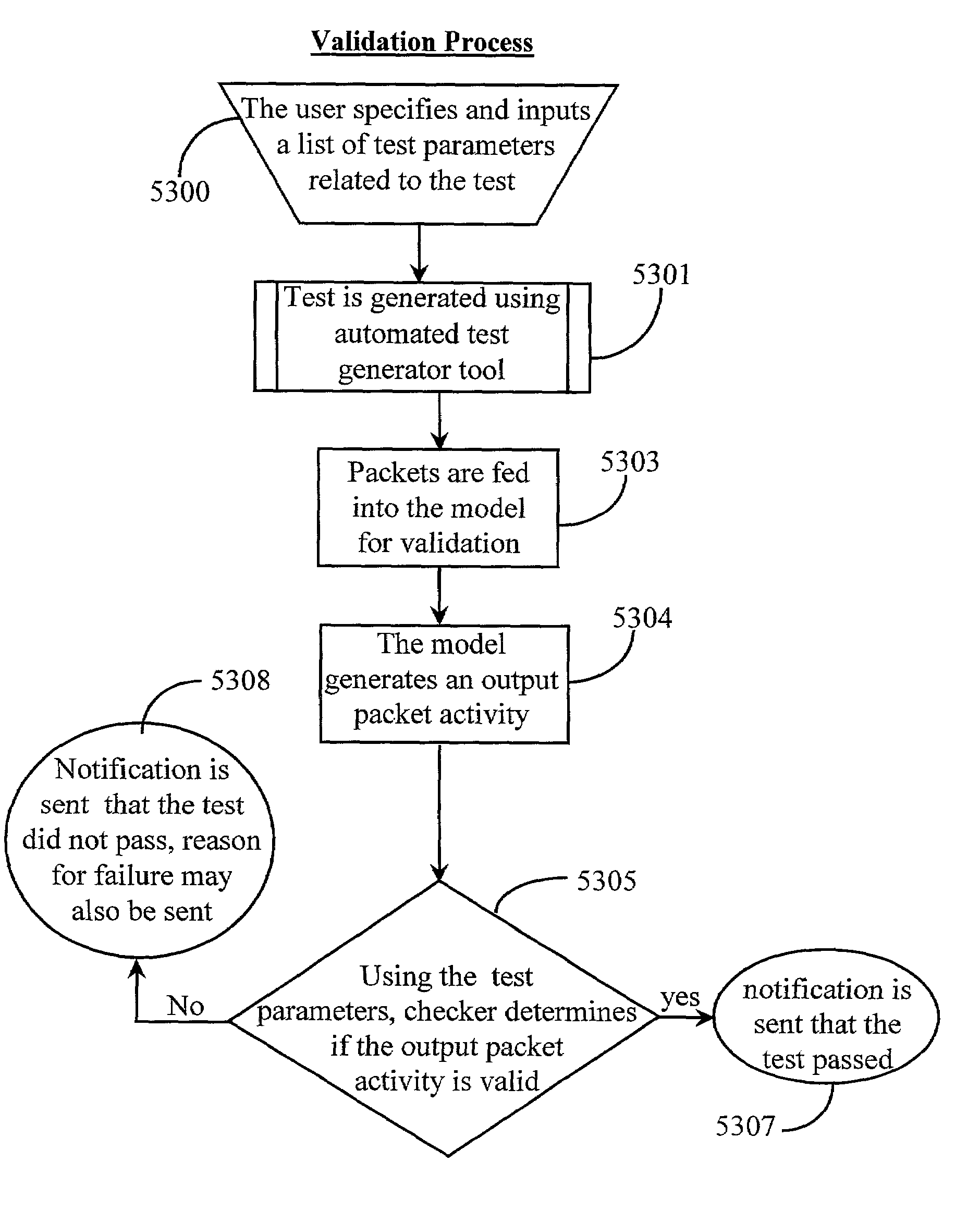

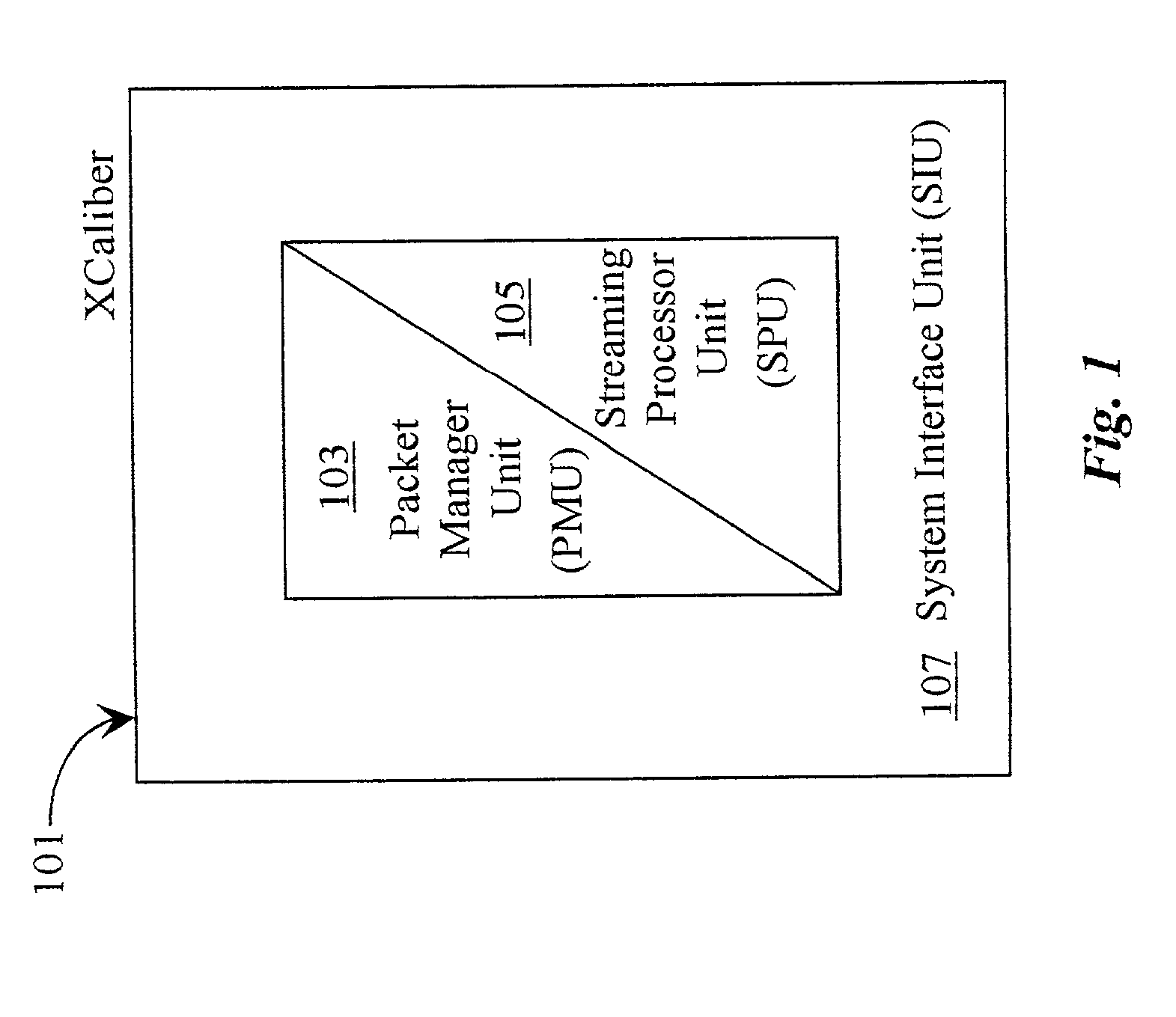

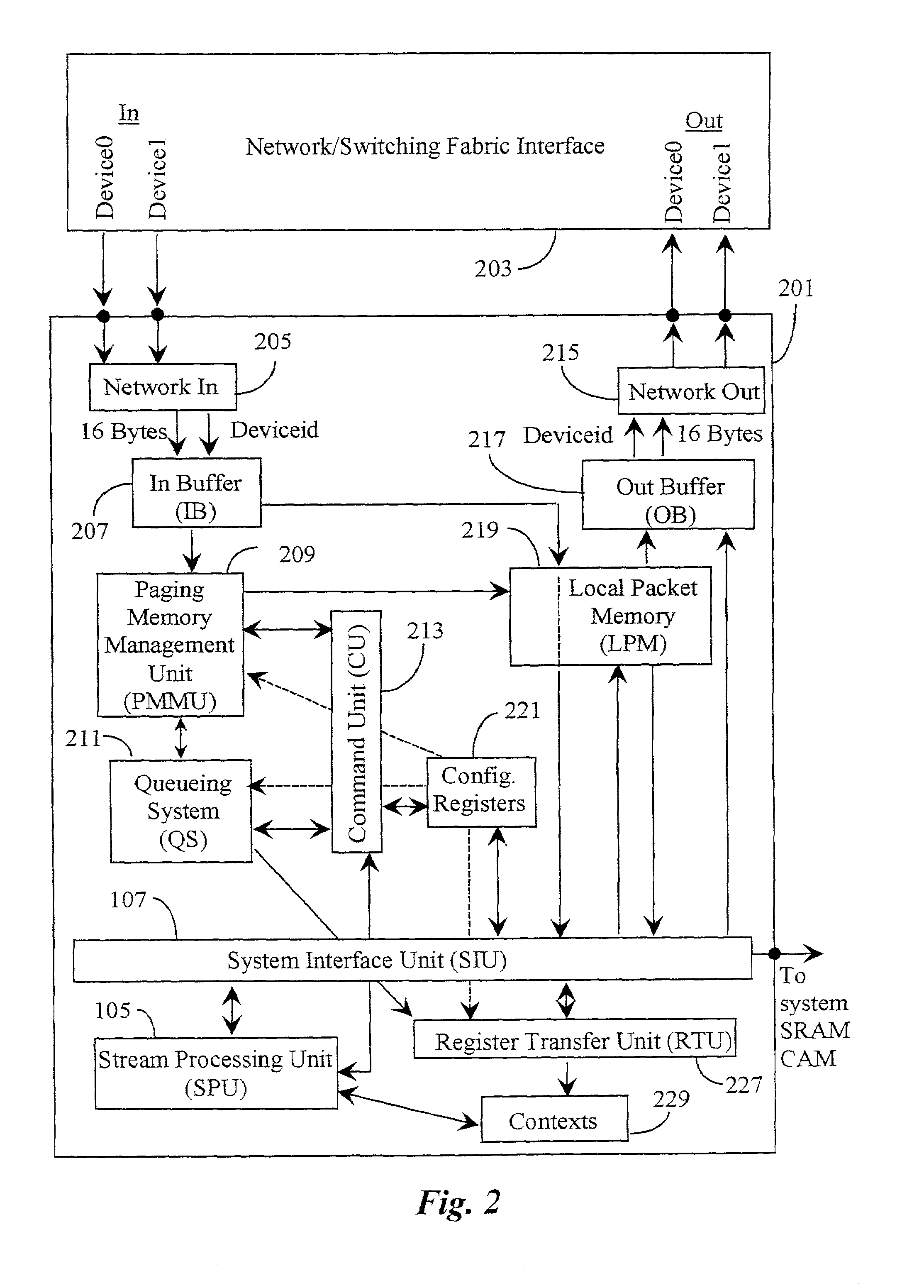

Functional validation of a packet management unit

InactiveUS20070168748A1Cost-effective and reliablePrecise designError detection/correctionProgram controlRandom test generatorUser interface

A validation system is disclosed for validating function of a packet-management unit operationally coupled through a system interface to a processing unit of a processor system. The validation system comprises a user interface for creating an inputting test parameters and test code into the system, a test generator coupled to the user interface, the test generator for generating input packet activity in the form of a packet stream, a model coupled to the test generator for emulating separate and integrated function of the packet management unit, the system interface, and a stream-processing unit and an evaluation software for checking and validating or not validating results. The system validation function relies, in a preferred embodiment, on comparing output results with criteria of the selected test code resulting in an indication of pass or failure of the test. In a preferred embodiment, the system also notifies to cause of failure.

Owner:ARM FINANCE OVERSEAS LTD

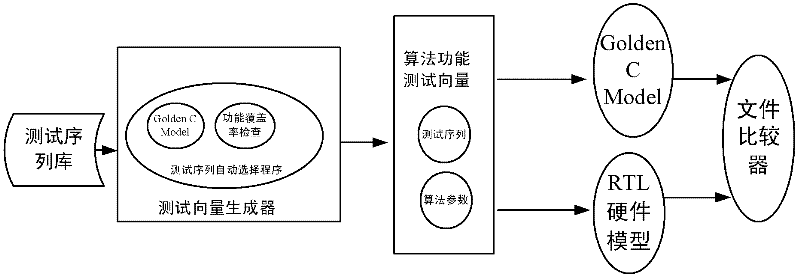

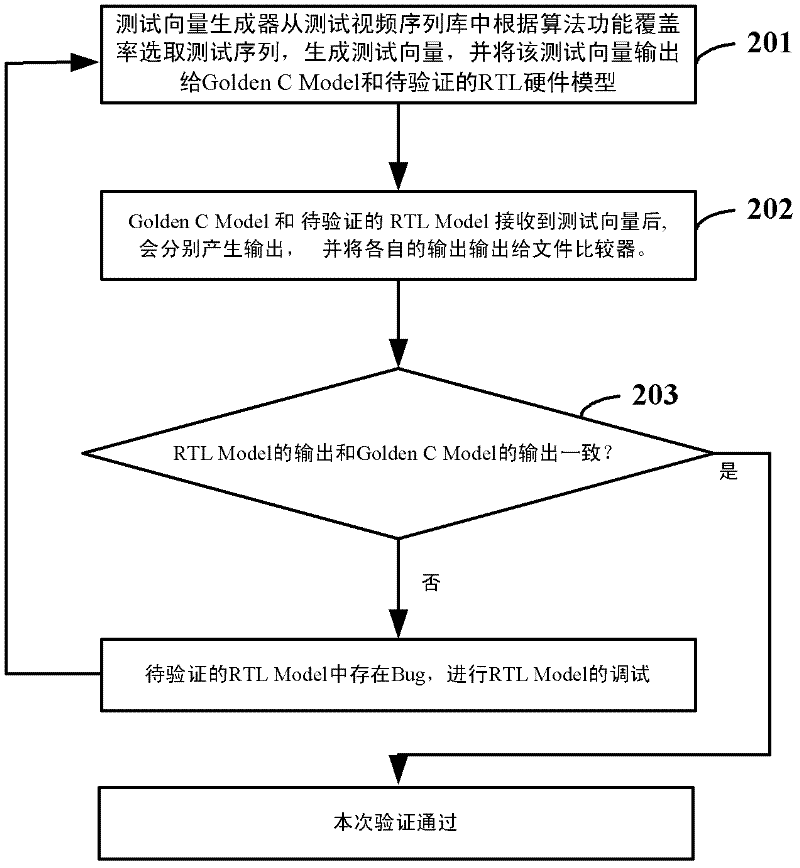

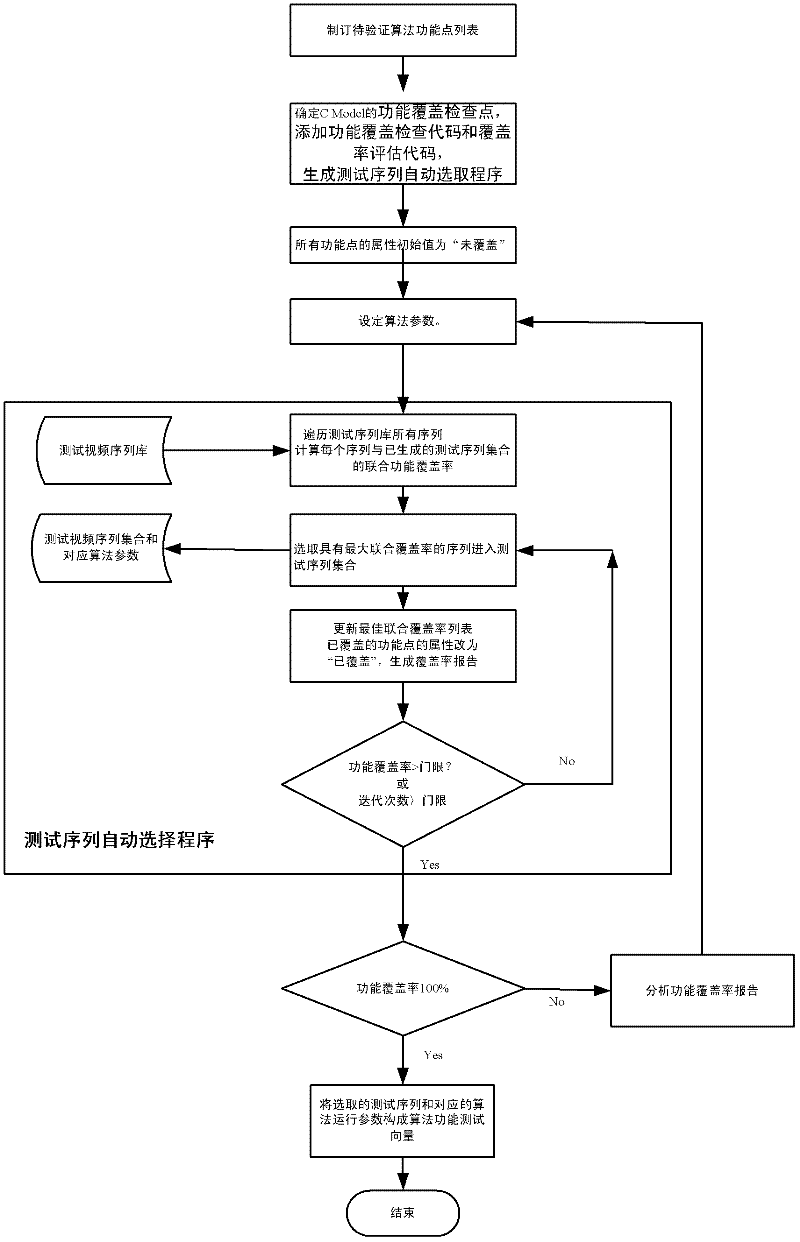

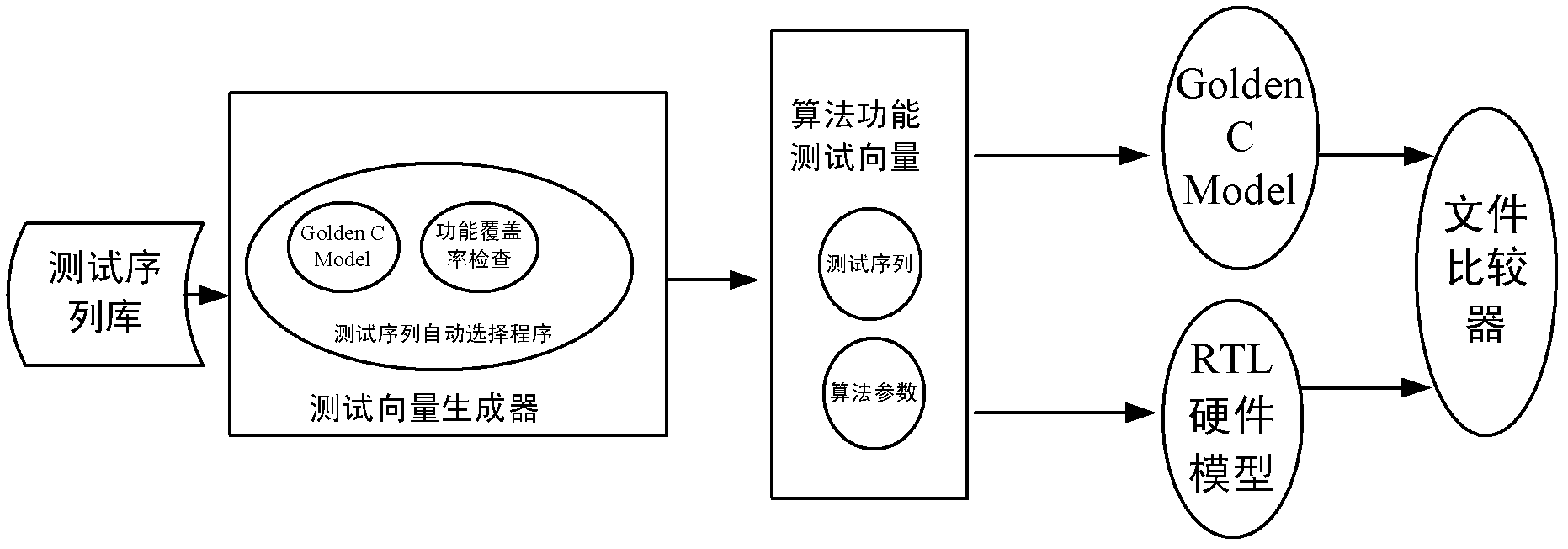

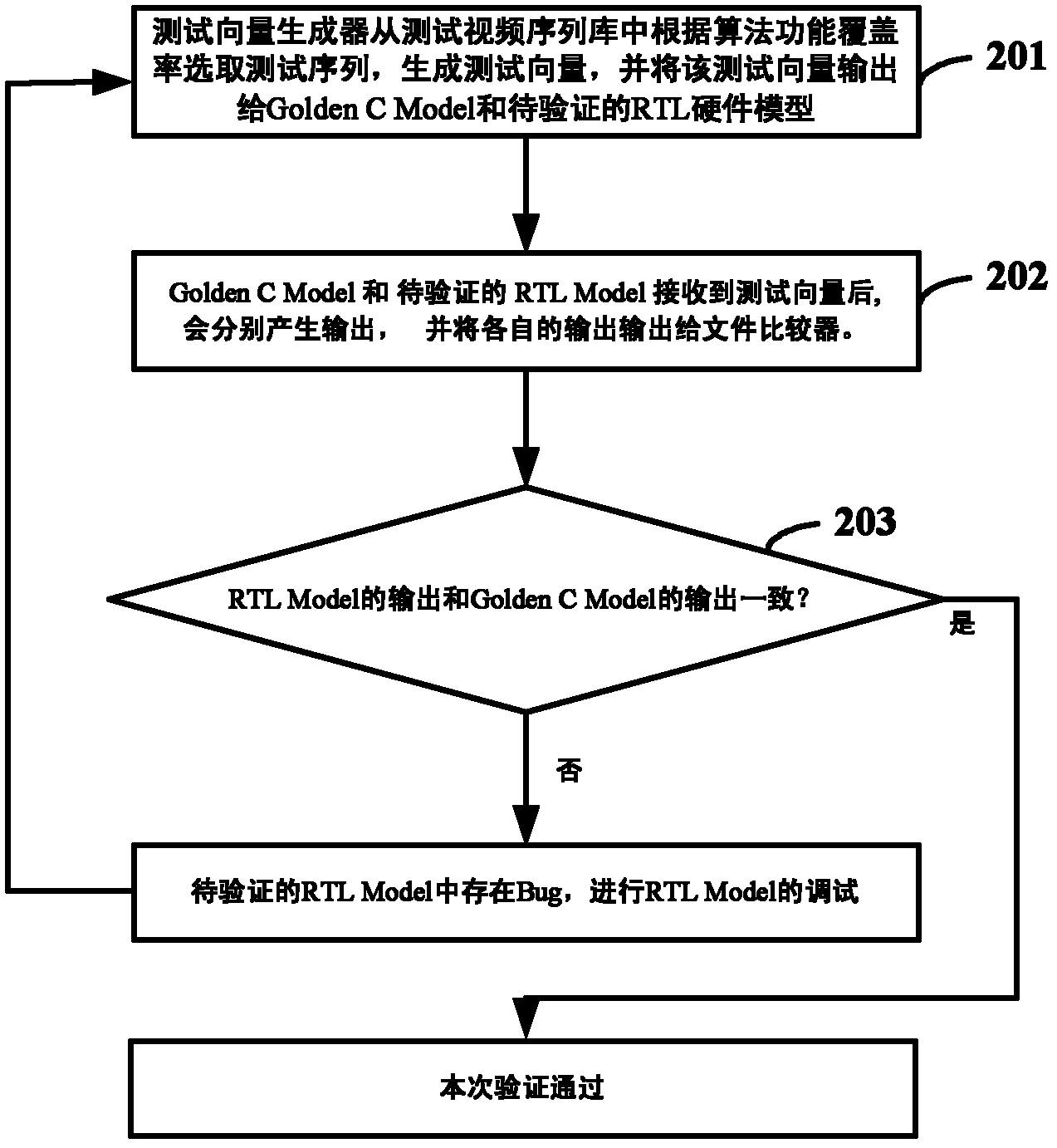

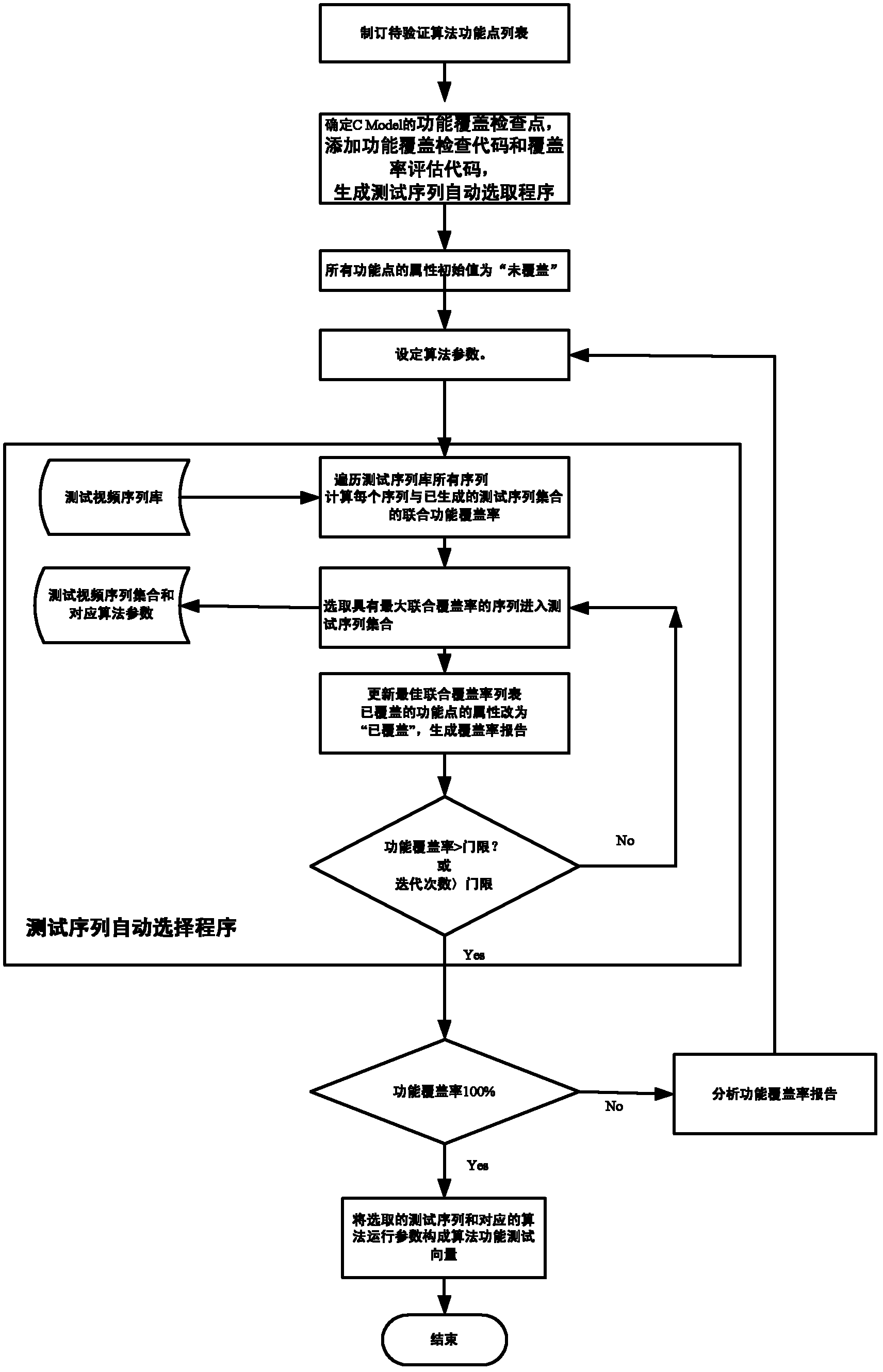

System and method for verifying register transfer level (RTL) hardware

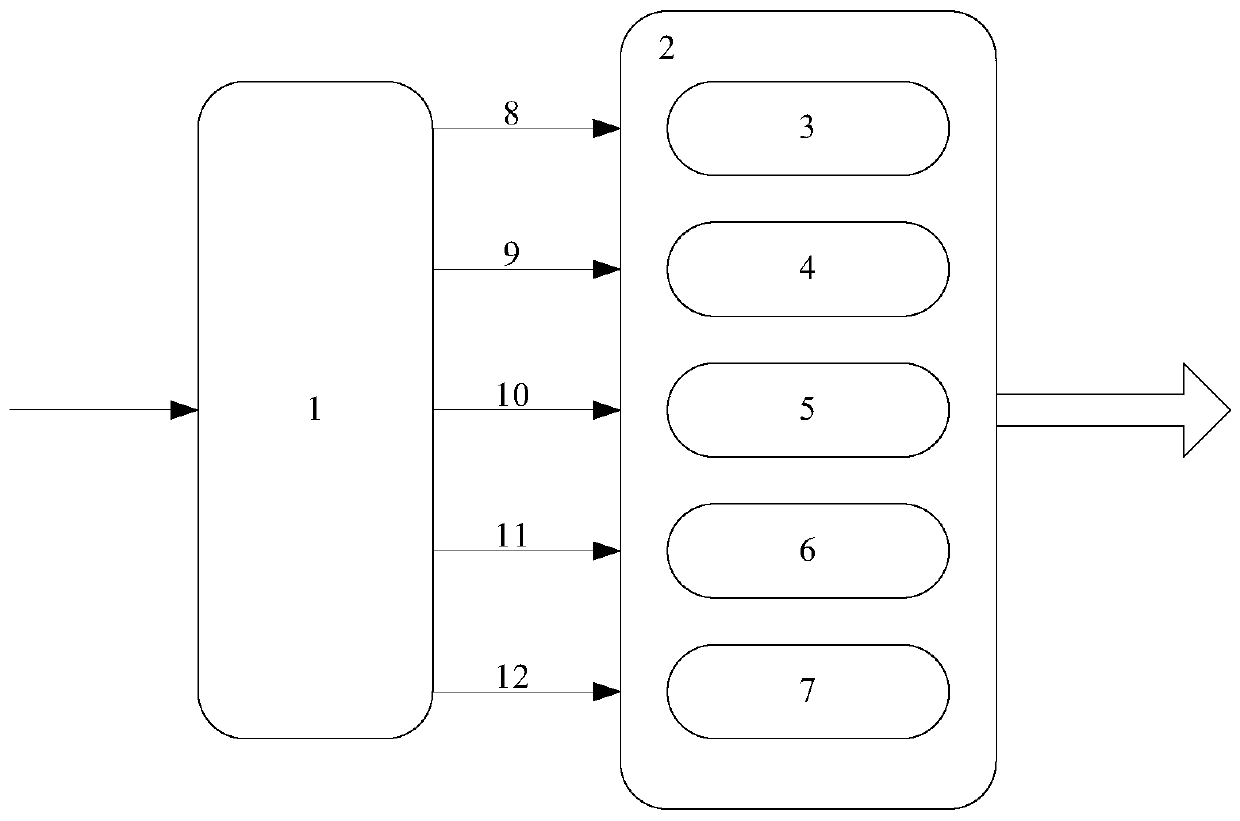

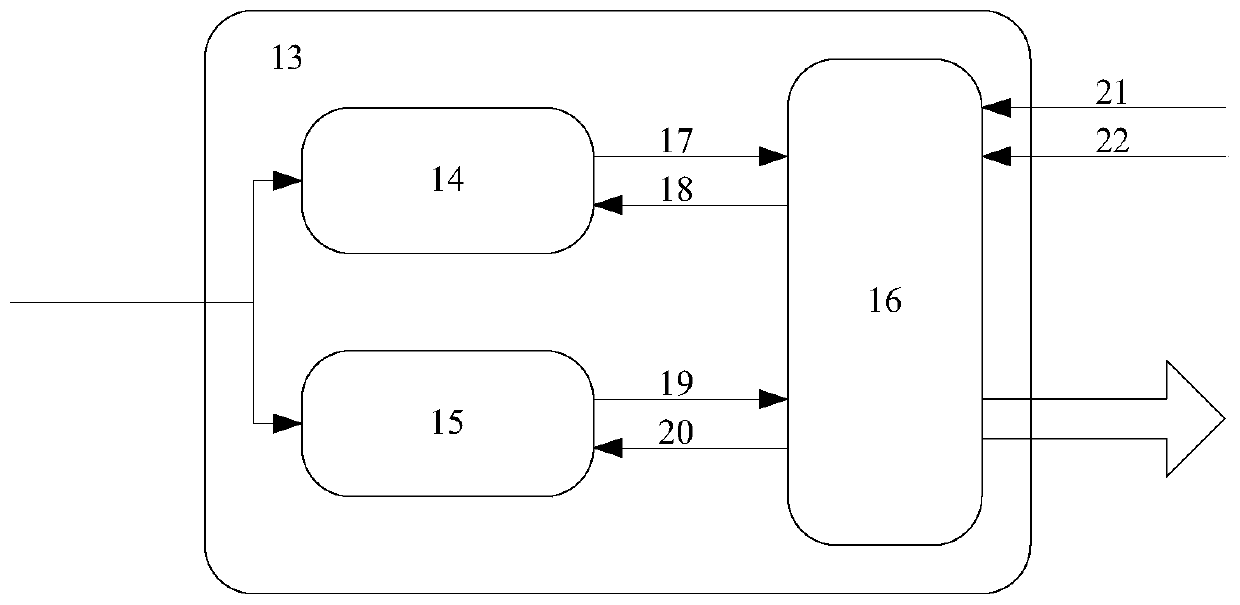

ActiveCN102567165AImprove verification efficiencyImprove accuracyFunctional testingProcessor registerVideo sequence

The invention discloses a system and a method for verifying register transfer level (RTL) hardware of a video algorithm. The system comprises a test video sequence library, a test vector generator, a golden C language model, an RTL hardware model to be verified and a file comparator, wherein the test video sequence library is used for storing a test sequence required by verifying the design of the RTL hardware of the video algorithm; the test vector generator is used for selecting the test sequence from the test video sequence library according to the functional coverage of the algorithm, generating a test vector and outputting the test vector to the golden C language model and the RTL hardware model to be verified; the golden C language model and the RTL hardware model to be verified are used for respectively generating output after receiving the test vector and outputting the respective output to the file comparator; and the file comparator is used for comparing whether the output of the golden C language model is consistent with the output of the RTL hardware model to be verified or not, indicating that the RTL hardware passes verification if the outputs are consistent, and indicating that the RTL hardware does not pass verification if the outputs are inconsistent. By the system and the method, the efficiency and correctness of verifying the design of the RTL hardware of the video algorithm are improved.

Owner:北京集朗半导体科技有限公司

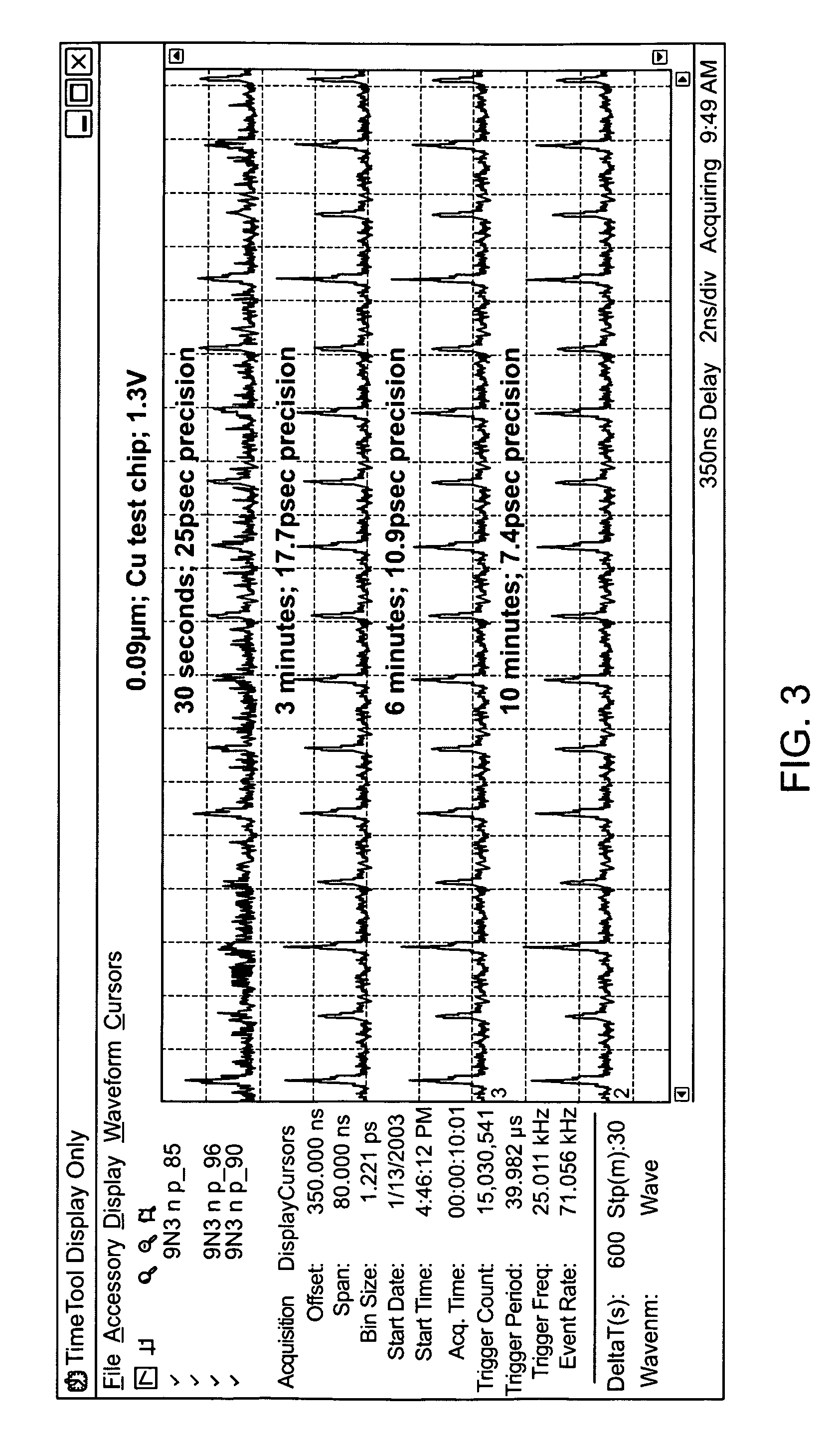

IC test vector generator for synchronized physical probing

InactiveUS20080284453A1Efficiently introducedContactless circuit testingTest vector generatorBiological activation

Systems, methods, and computer readable media storing instructions for such methods relate to generating test vectors that can be used for exercising a particular area of interest in an integrated circuit. The test vectors generally include a non-overlapping repeating and / or predictable sequence of care bits (a care bit pattern) that can be used by a tester to cause the exercise of the area and collect emissions caused by exercising the area. Such emissions can be used for analysis and debugging of the circuit and / or a portion of it. Aspects can include providing a synchronization signal that can be used by a tester to allow sensor activation at appropriate times.

Owner:CADENCE DESIGN SYST INC

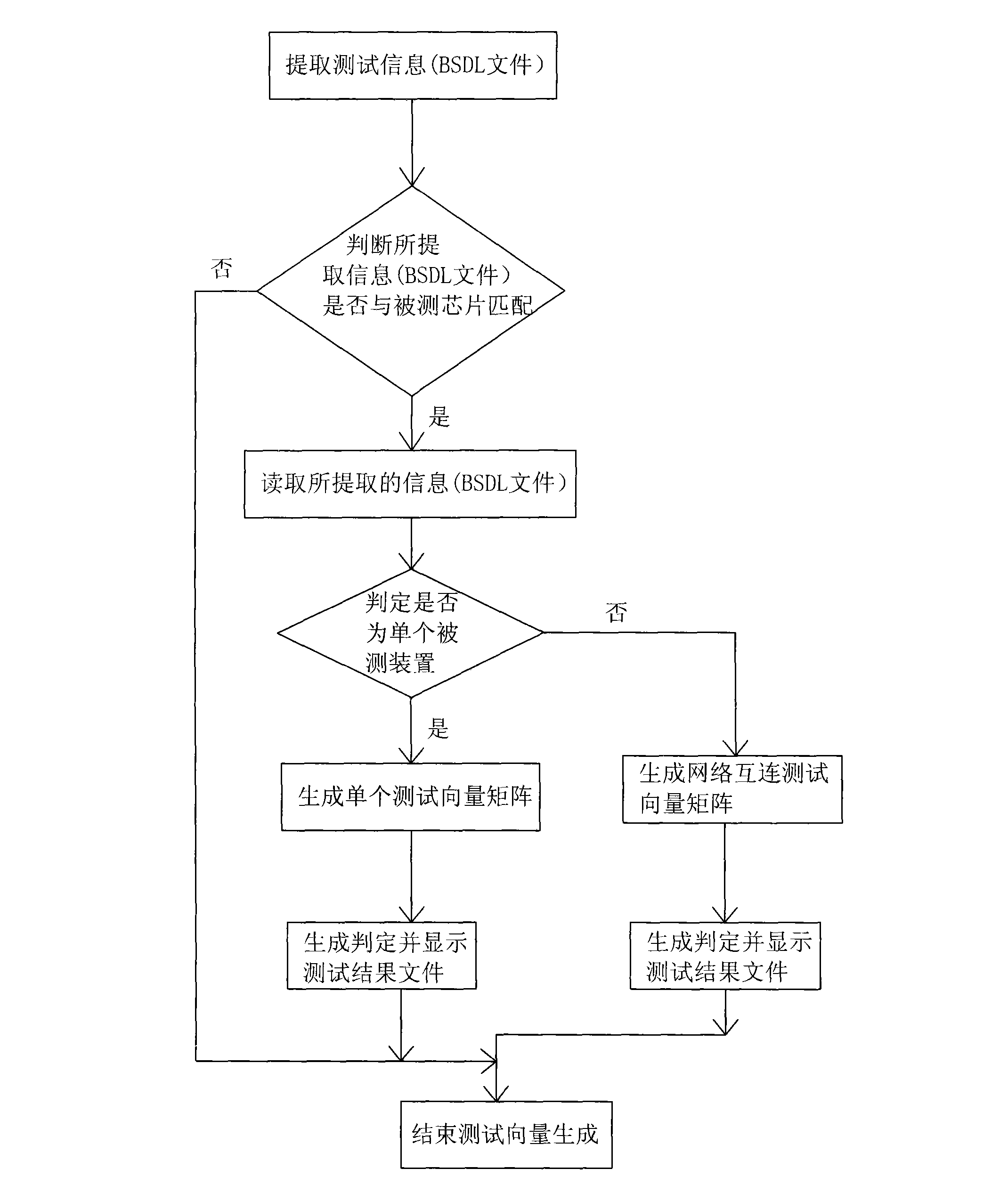

Test vector generating method for boundary scanning

InactiveCN101526582APromote generationComplete detectionElectronic circuit testingThe InternetTest vector generator

The invention discloses a test vector generating method for boundary scanning, which generates a test vector by integrating test information of a tested device. The method comprises the following specific steps: a, extracting the test information; and b, analyzing the test information, and generating a test vector matrix, wherein the vector matrix can be a single test vector matrix and a network interconnecting test vector matrix, and can perform self test and internet test of a single device respectively. The method generates the test vector by integrating the test information of the tested device; the method can conveniently generate the test vector and extract the information required by diagnosis; and simultaneously, the generated test vector is favorable for complete detection and more convenient operation.

Owner:MITAC COMP (SHUN DE) LTD

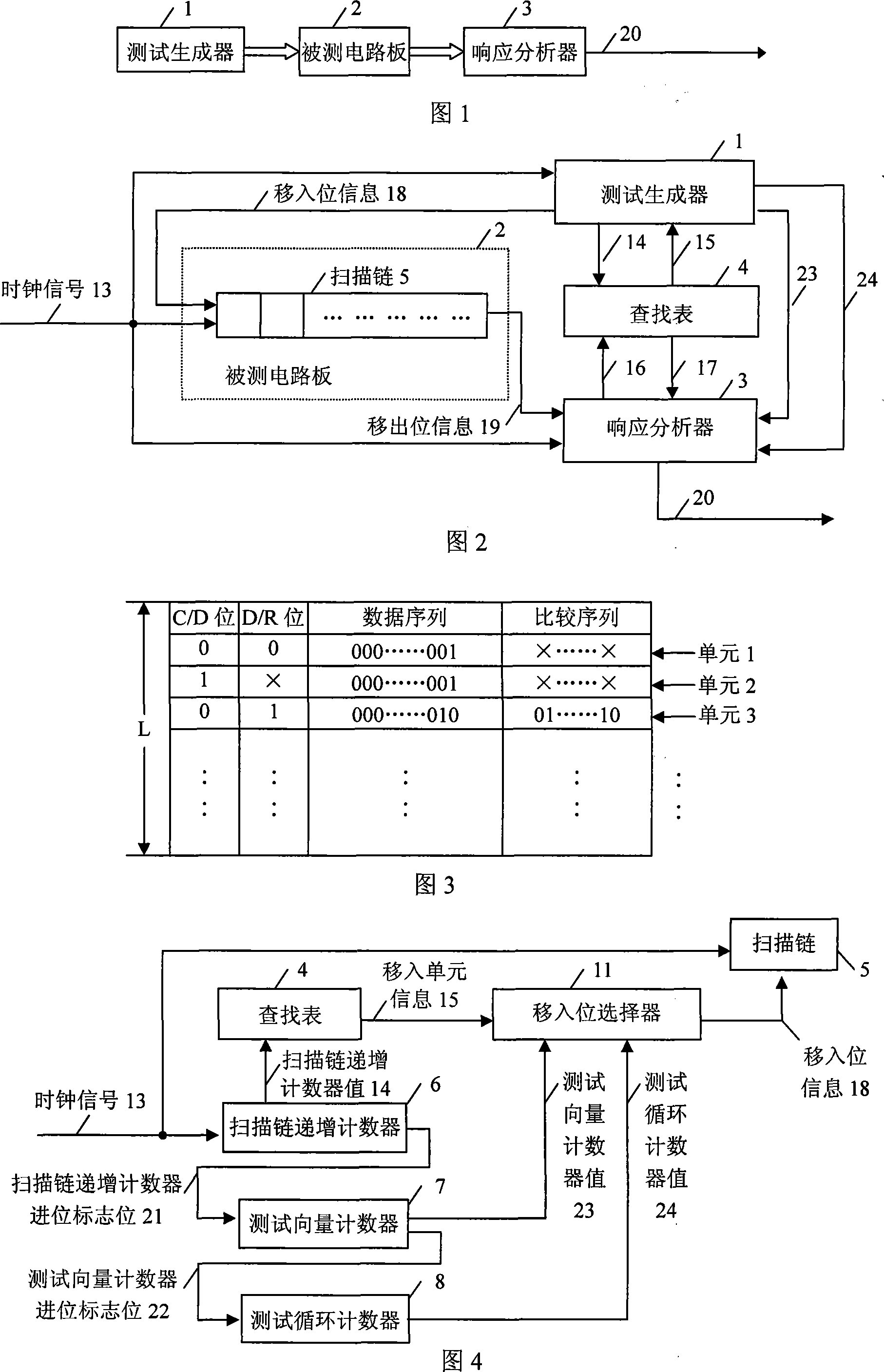

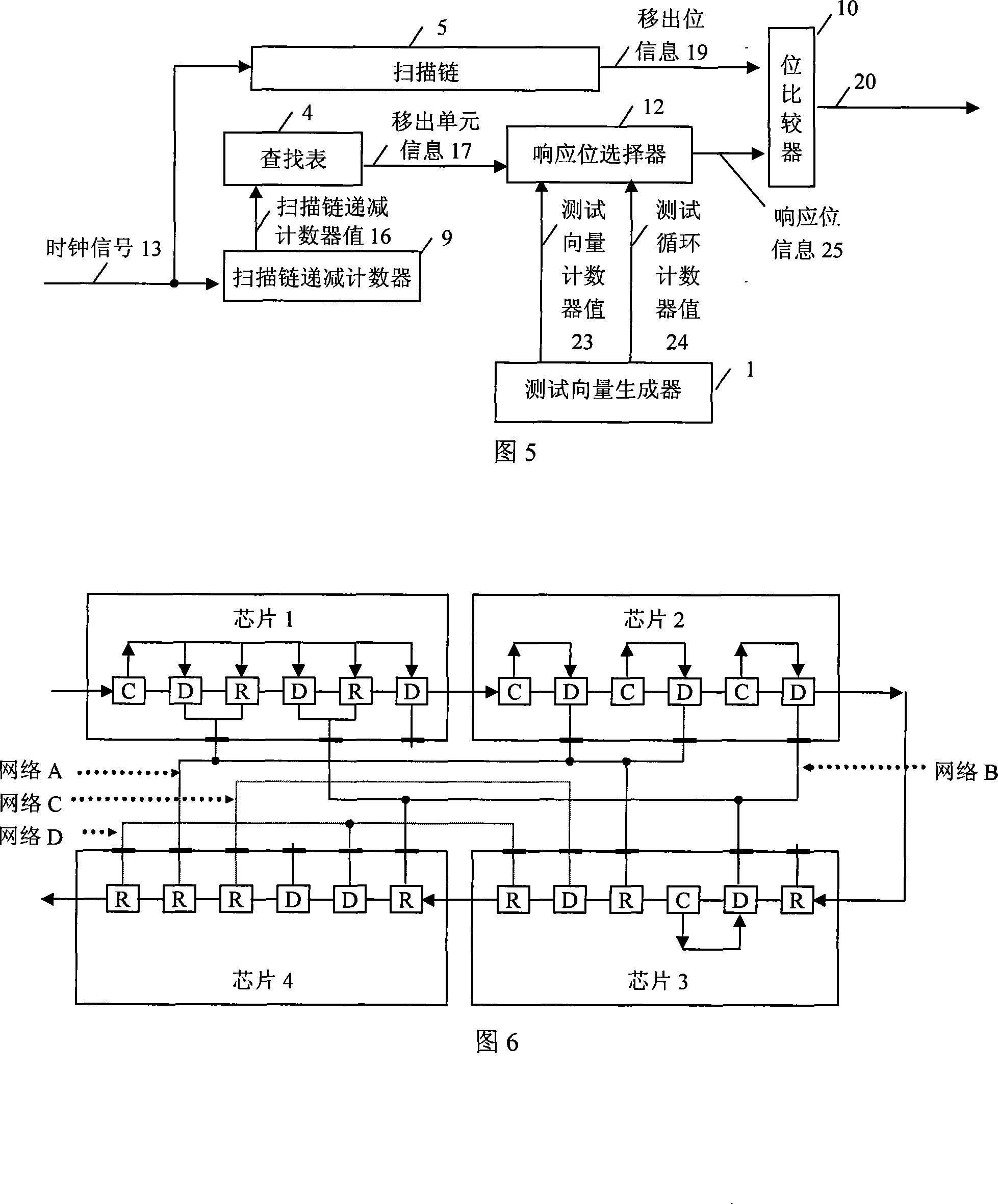

Built-in testing realization method of circuit board interconnect fault under boundary scanning environment

InactiveCN101183131ASolve conflictsTest securityDigital circuit testingFault detection rateTest vector generator

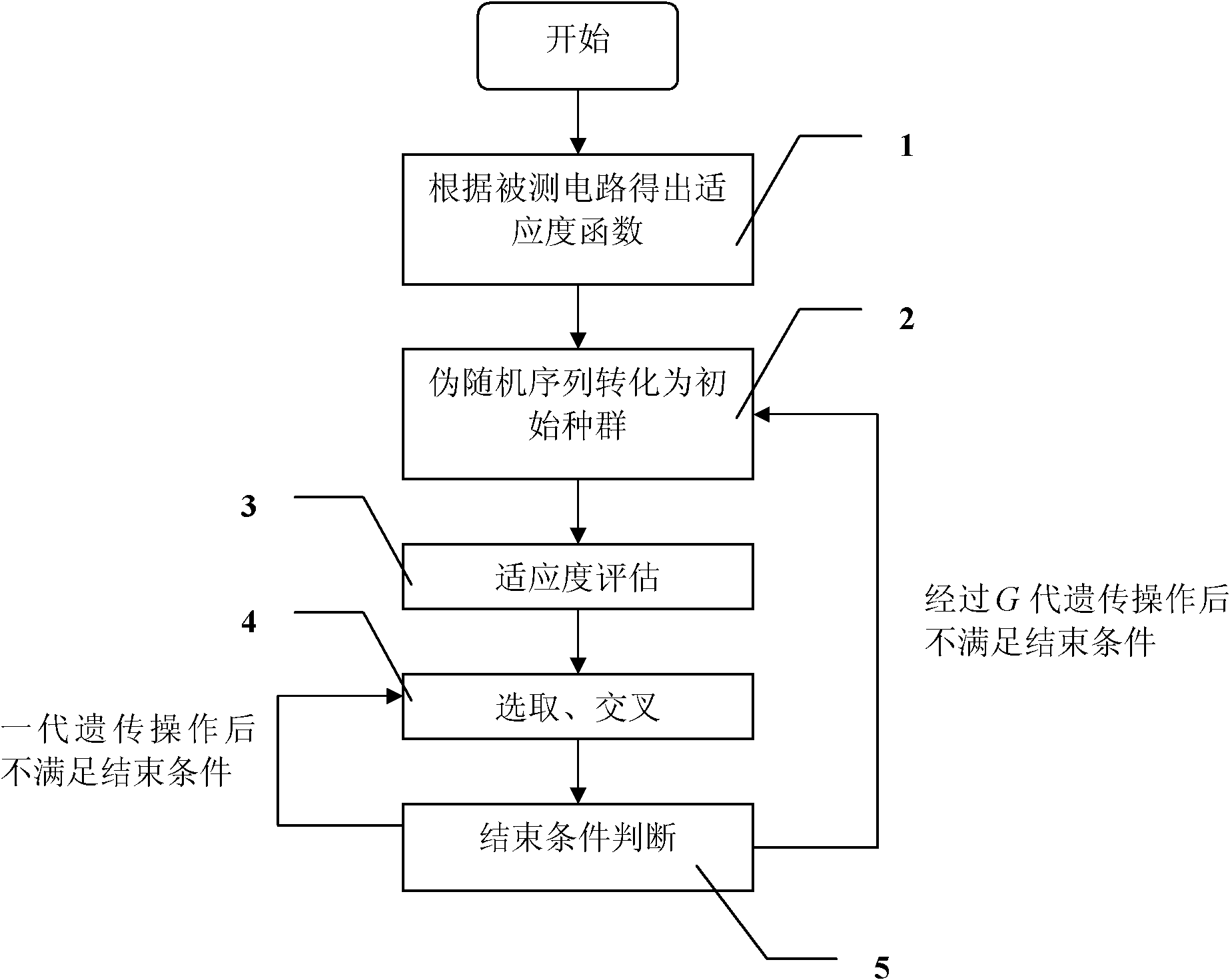

The invention relates to a built-in test implementation method for circuit board interconnection faults in a boundary scan environment. The improved counting sequence algorithm and the single enable method are used as the test generation algorithms for the drive unit and the control unit respectively. The overall design of the invention is mainly composed of search Table, Test Generator and Response Analyzer are composed of three parts. This method can achieve 100% fault detection rate for all interconnection faults, including short circuit, open circuit and sluggish fault; it can avoid the problem of multi-driver conflict, so that the test can be carried out safely; and the design process is simple and easy for engineering implementation; in addition, it It also has the advantages of high reliability, fast test speed, and small hardware overhead.

Owner:BEIHANG UNIV

Integrated test waveform generator (TWG) and customer waveform generator (CWG), design structure and method

InactiveUS7996807B2Detecting faulty computer hardwareContinuous to patterned pulse manipulationIntegration testingEngineering

Disclosed are embodiments of a clock generation circuit, a design structure for the circuit and an associated method that provide deskewing functions and that further provide precise timing for both testing and functional operations. Specifically, the embodiments incorporate a deskewer circuit that is capable of receiving waveform signals from both an external waveform generator and an internal waveform generator. The external waveform generator can generate and supply to the deskewer circuit a pair of waveform signals for functional operations. The internal waveform generator can be uniquely configured with control logic and counter logic for generating and supplying a pair of waveform signals to the deskewer circuit for any one of built-in self-test (BIST) operations, macro-test operations, other test operations or functional operations. The deskewer circuit can selectively gate an input clock signal with the waveform signals from either the external or internal waveform generator in order to generate the required output clock signal.

Owner:GLOBALFOUNDRIES INC

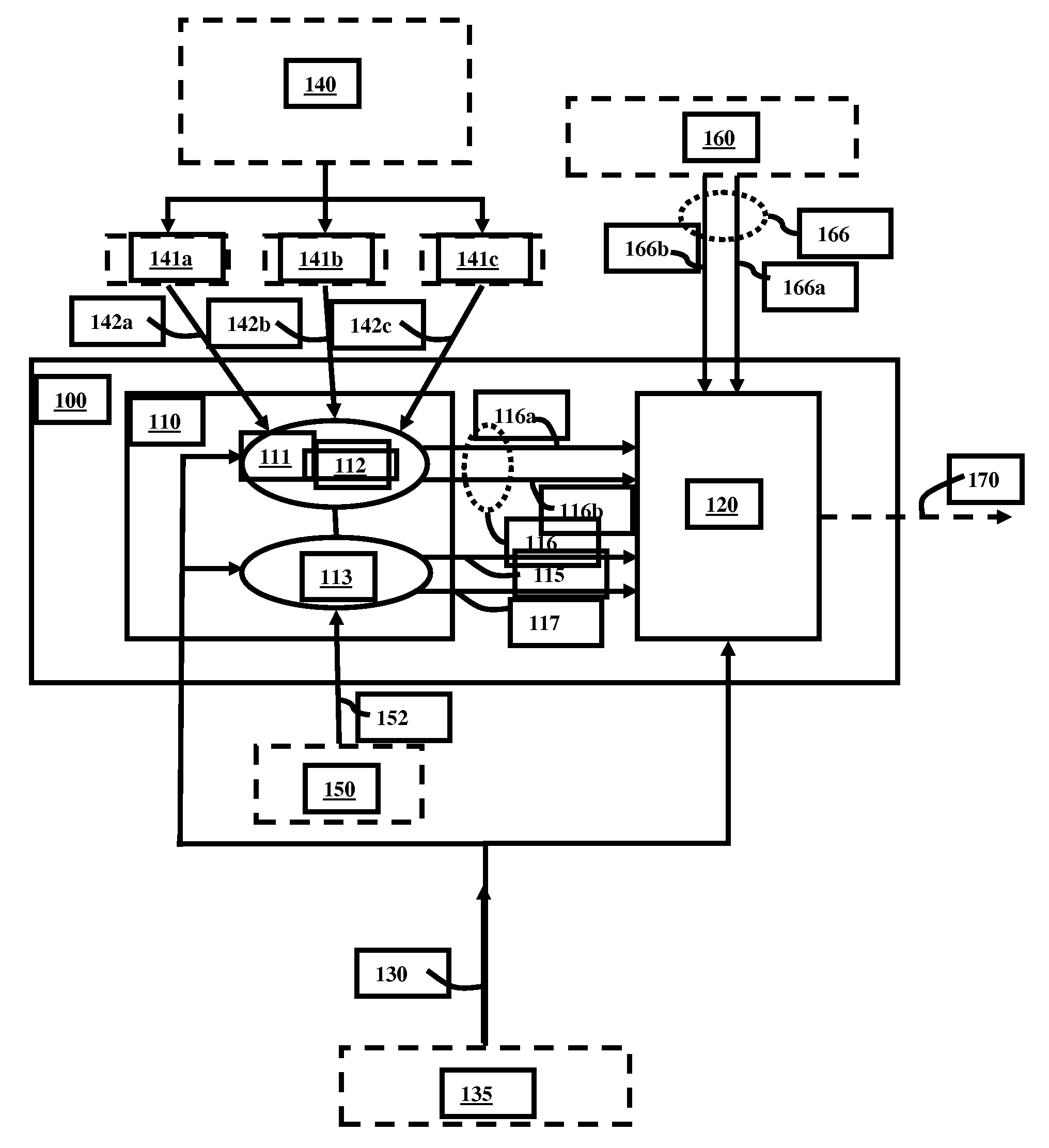

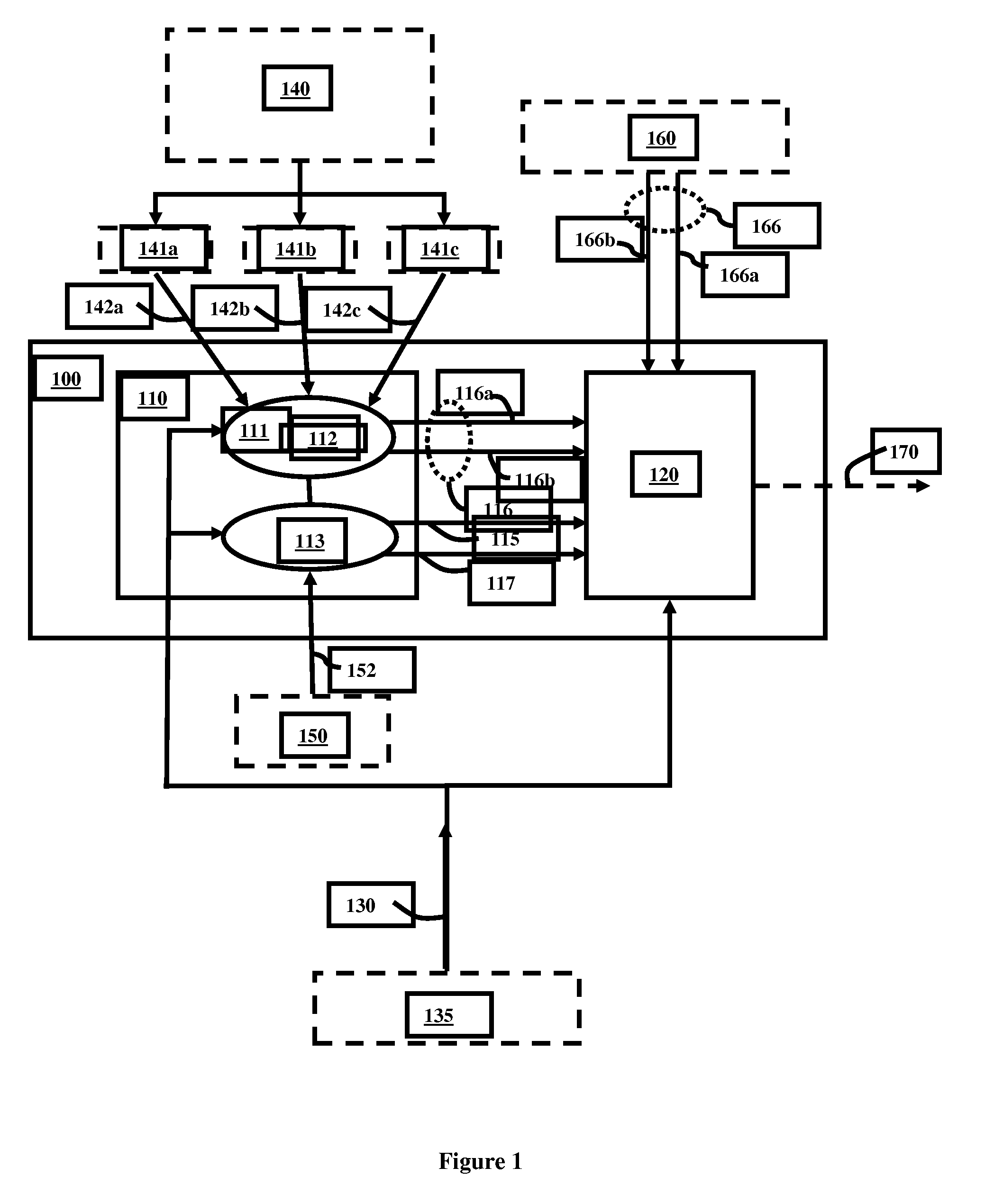

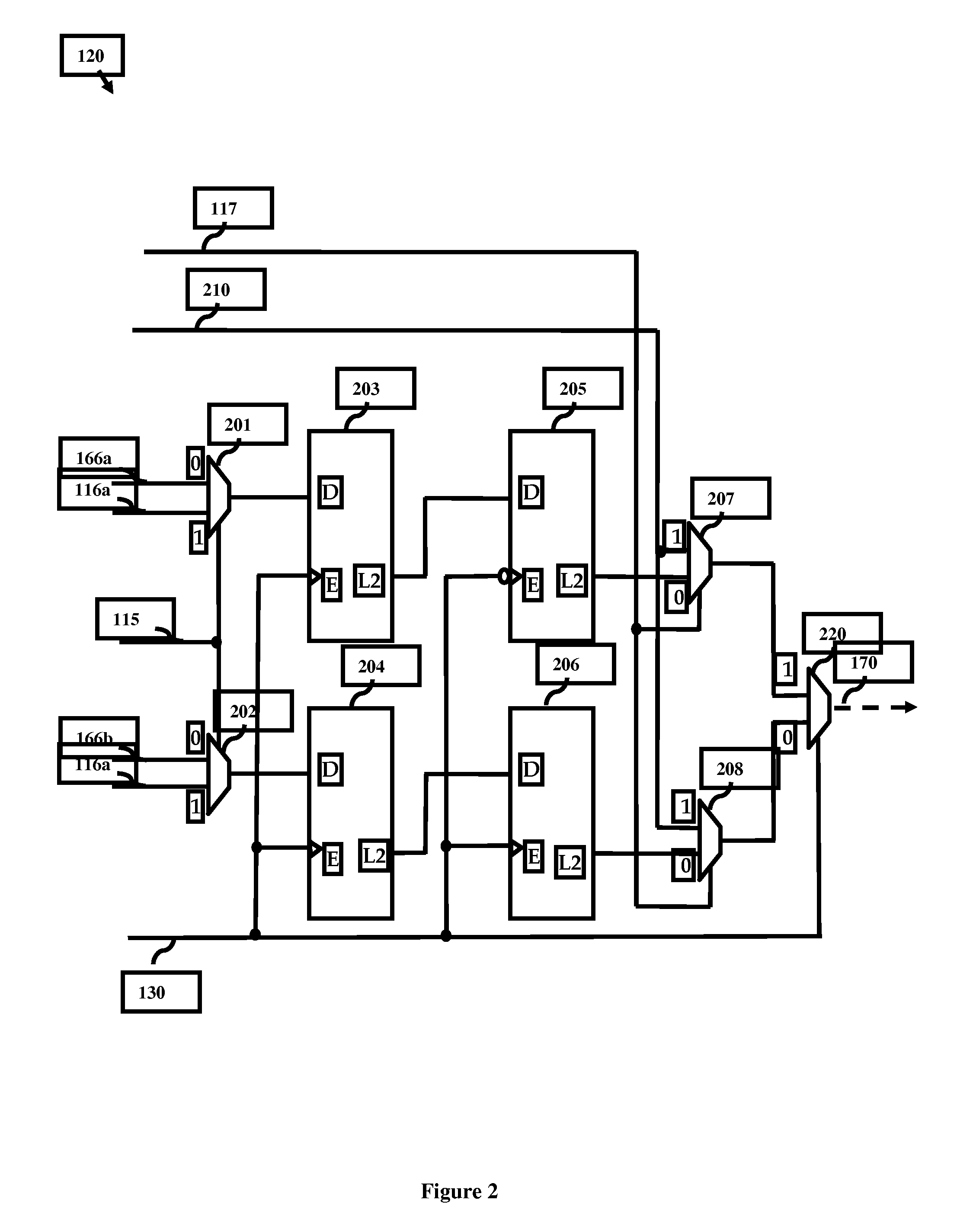

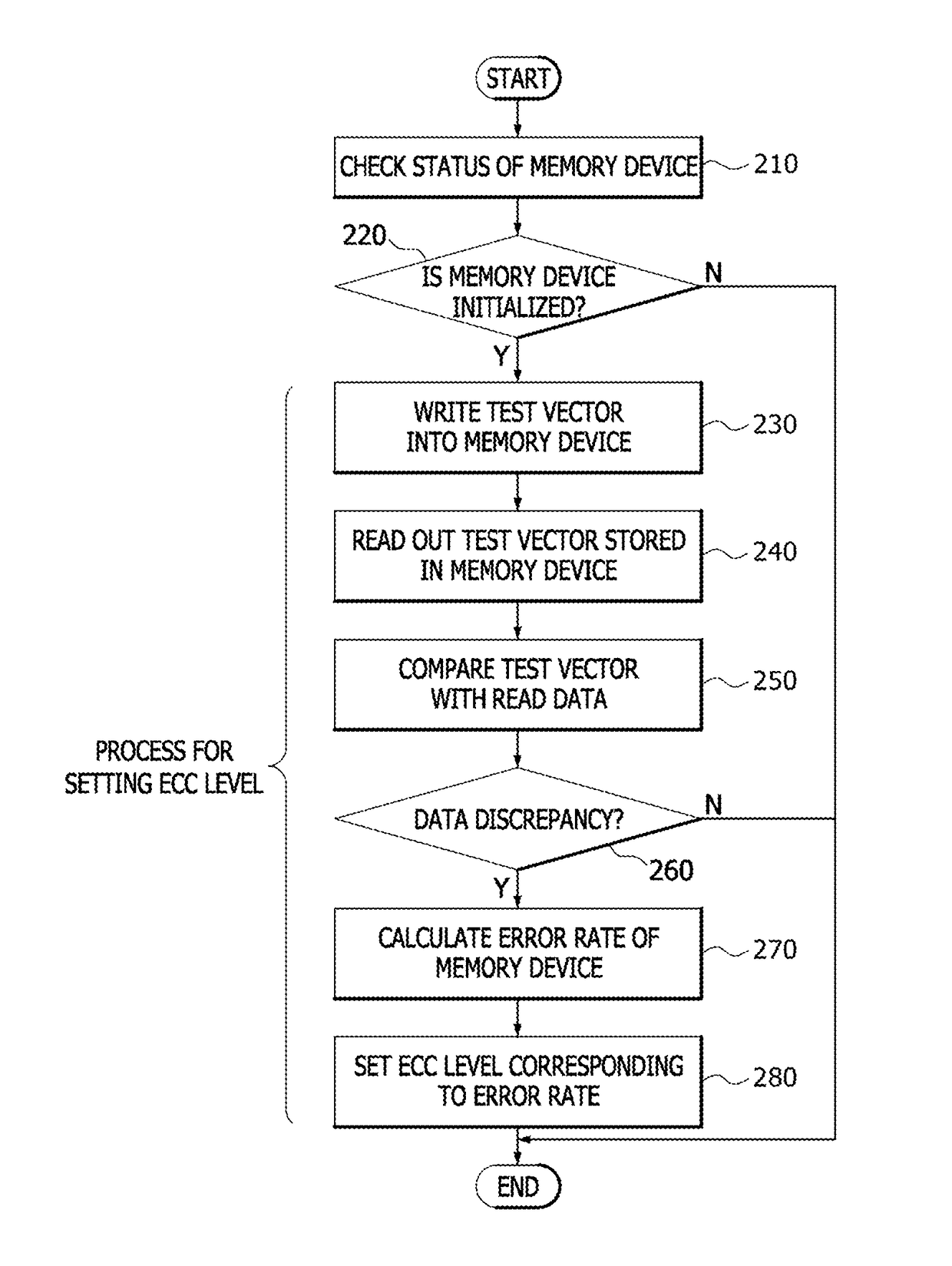

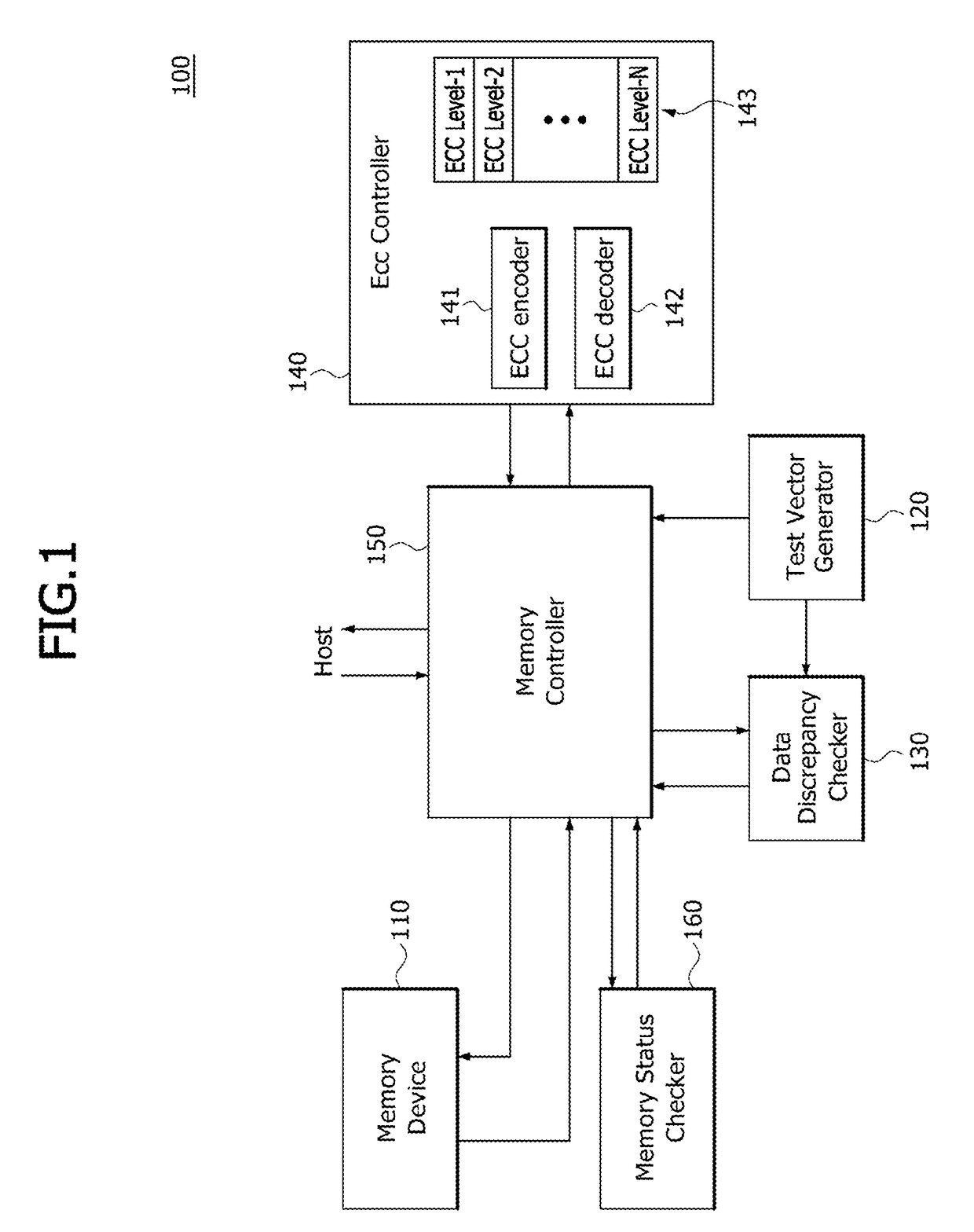

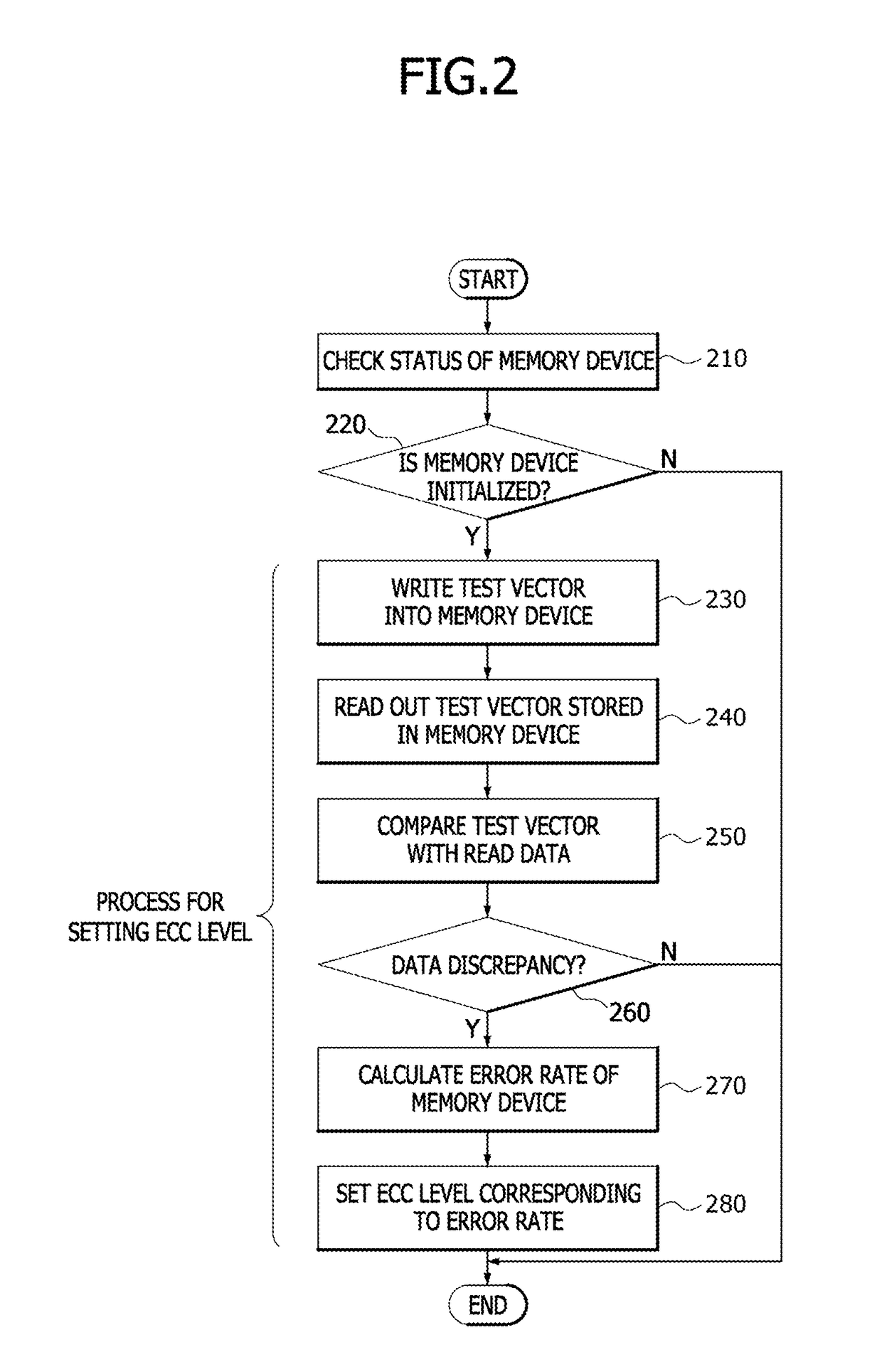

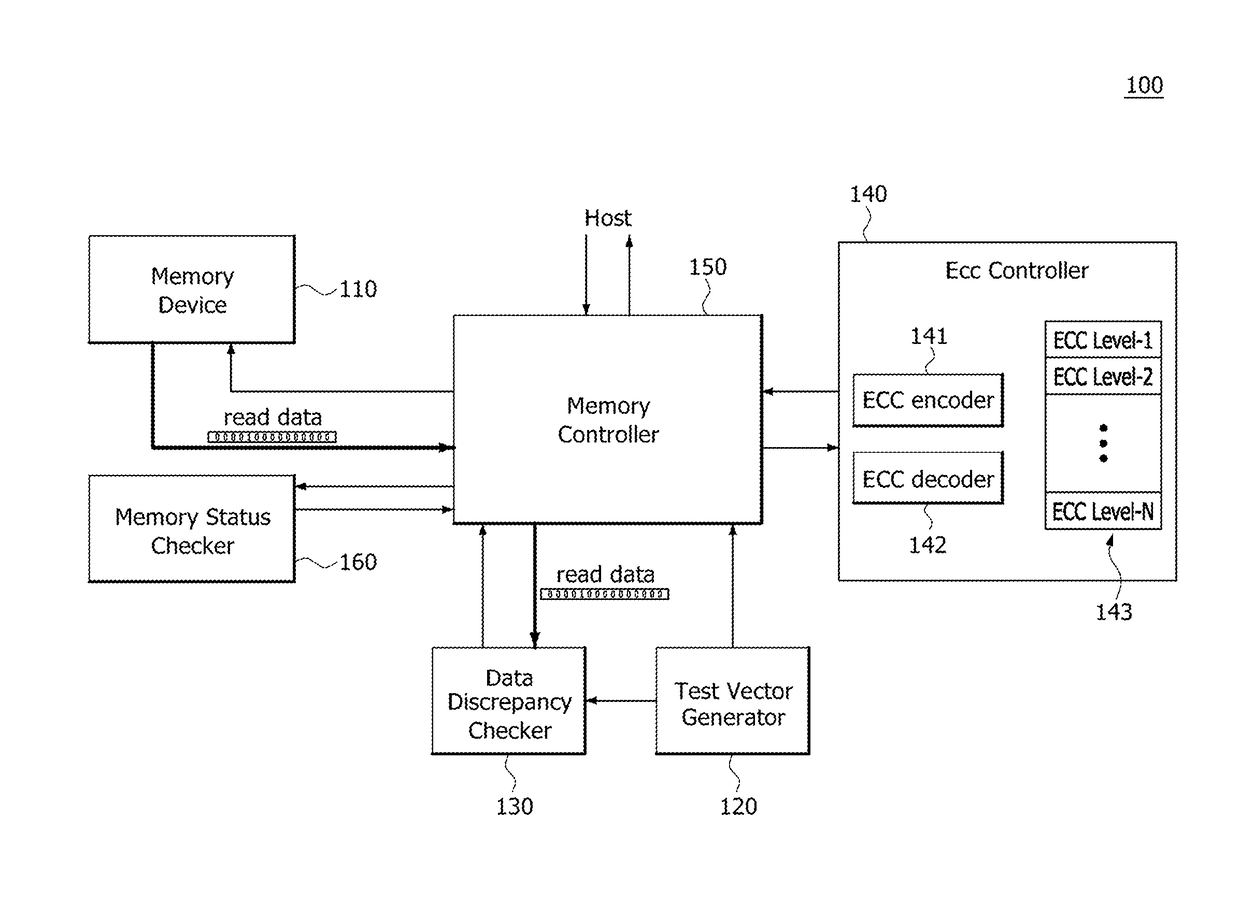

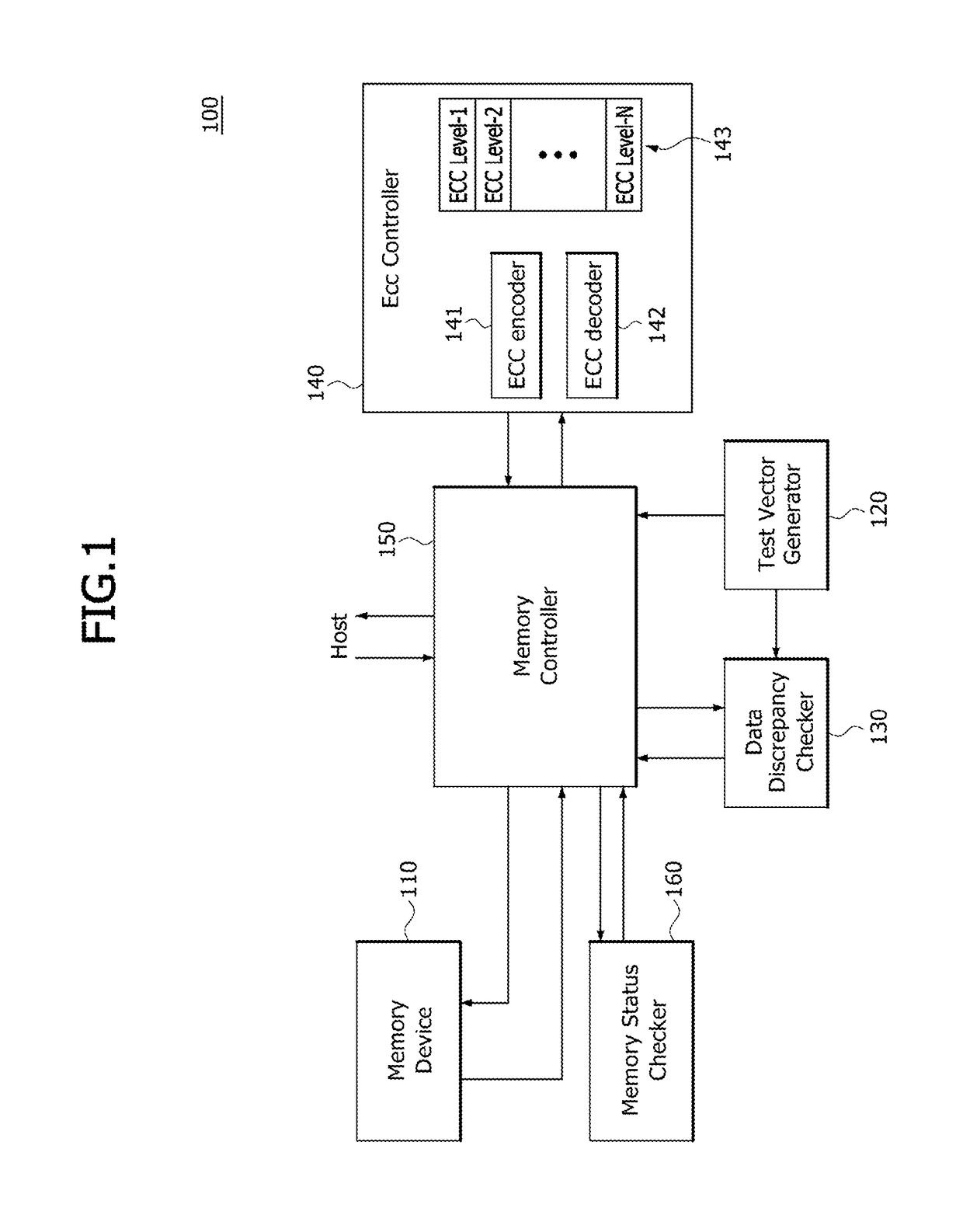

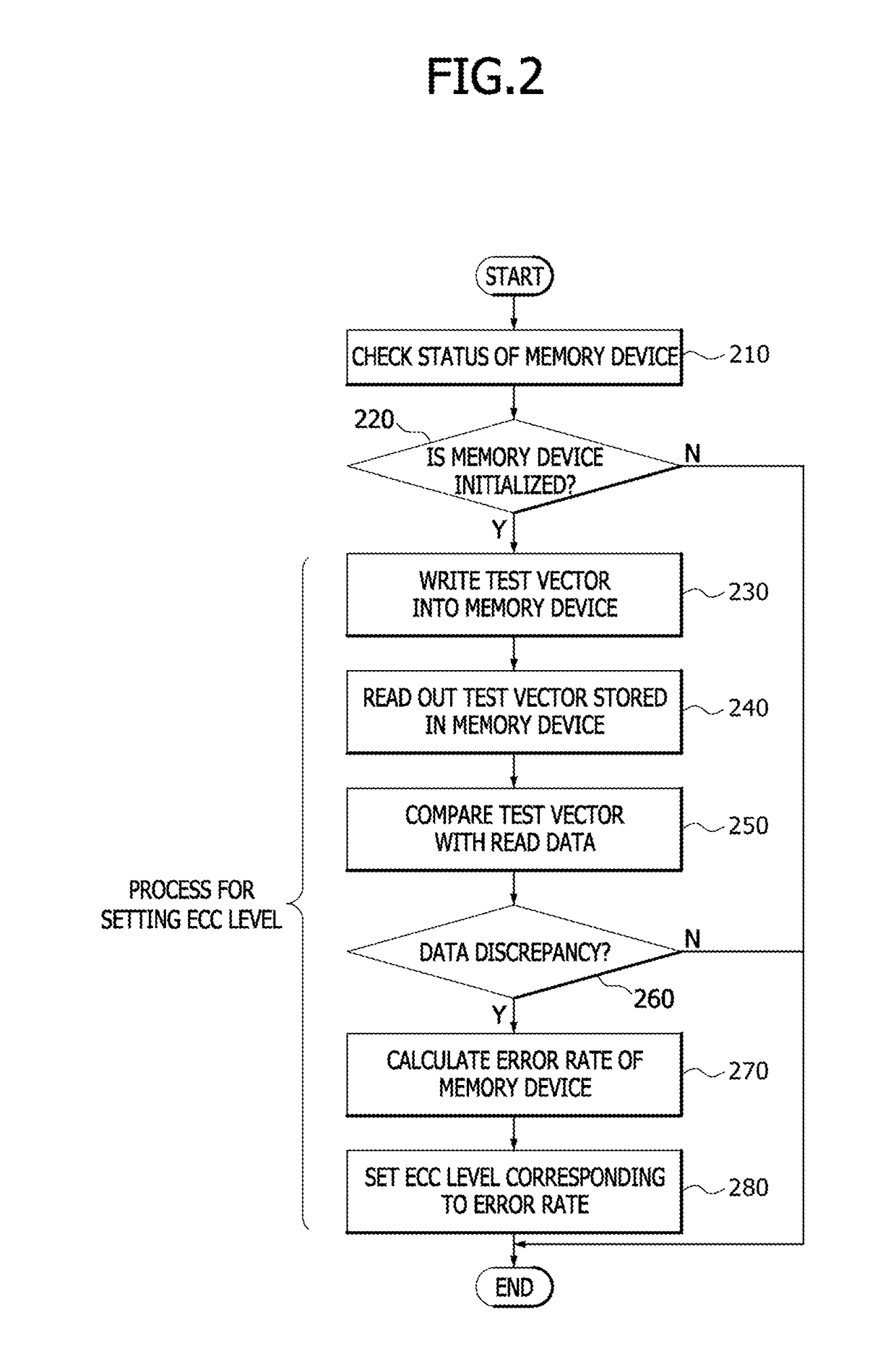

Memory systems and electronic systems performing an adaptive error correction operation with pre-checked error rate, and methods of operating the memory systems

ActiveUS20180210786A1Memory architecture accessing/allocationMemory adressing/allocation/relocationElectronic systemsControl signal

A memory system may include a test vector generator configured for generating a test vector to be written into a memory device, a data discrepancy checker configured for comparing read data outputted from the memory device with the test vector to generate an information signal corresponding to a comparison between the read data and the test vector, an error correction code (ECC) controller configured for performing an ECC encoding operation and an ECC decoding operation according to any one among a plurality of ECC levels based on a control signal, and a memory controller controlling the test vector generator, the data discrepancy checker and the ECC controller. The memory controller configured to transmit the control signal corresponding to an error rate of the memory device to the ECC controller, based on the information signal generated by the data discrepancy checker.

Owner:SK HYNIX INC

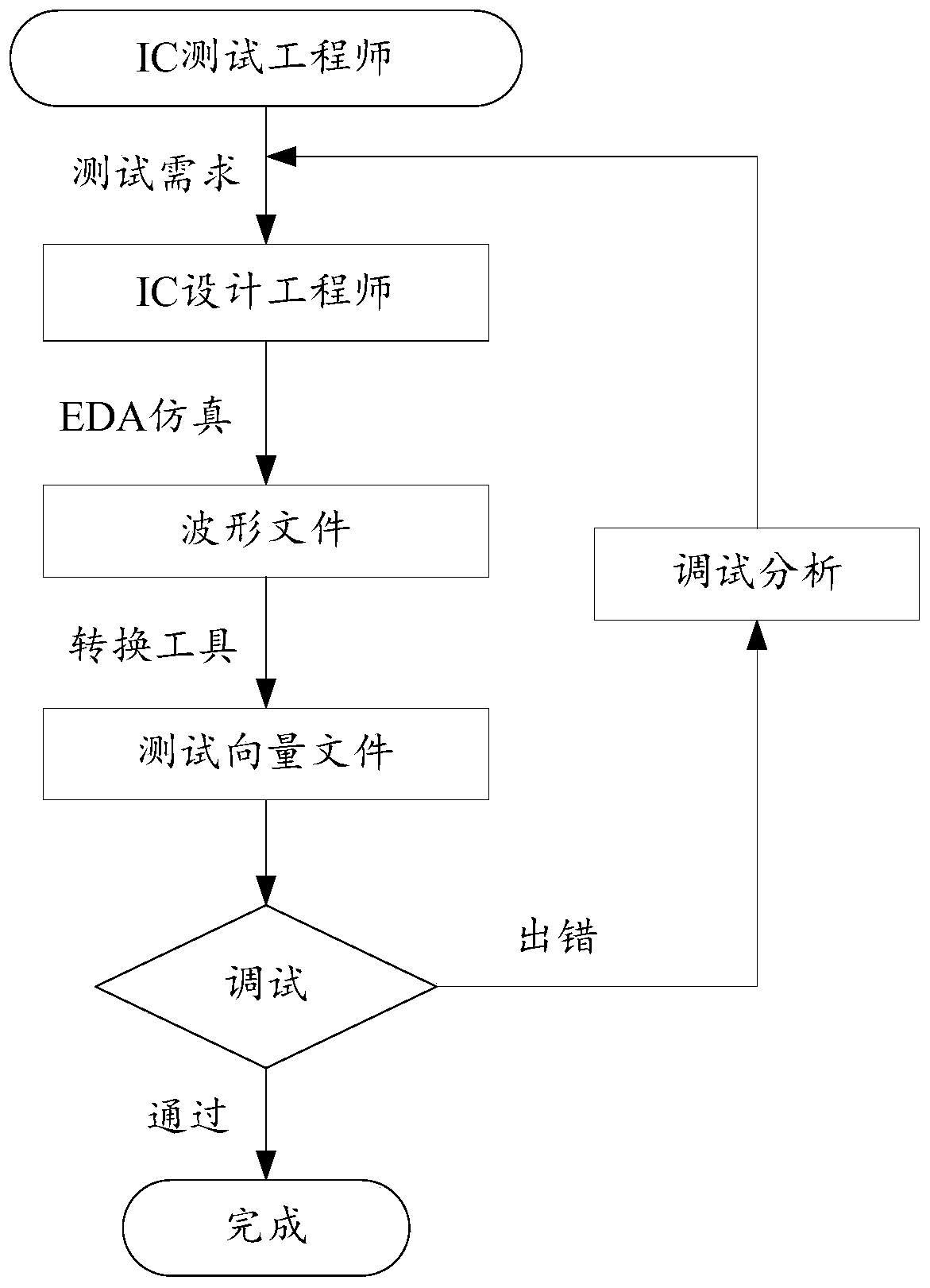

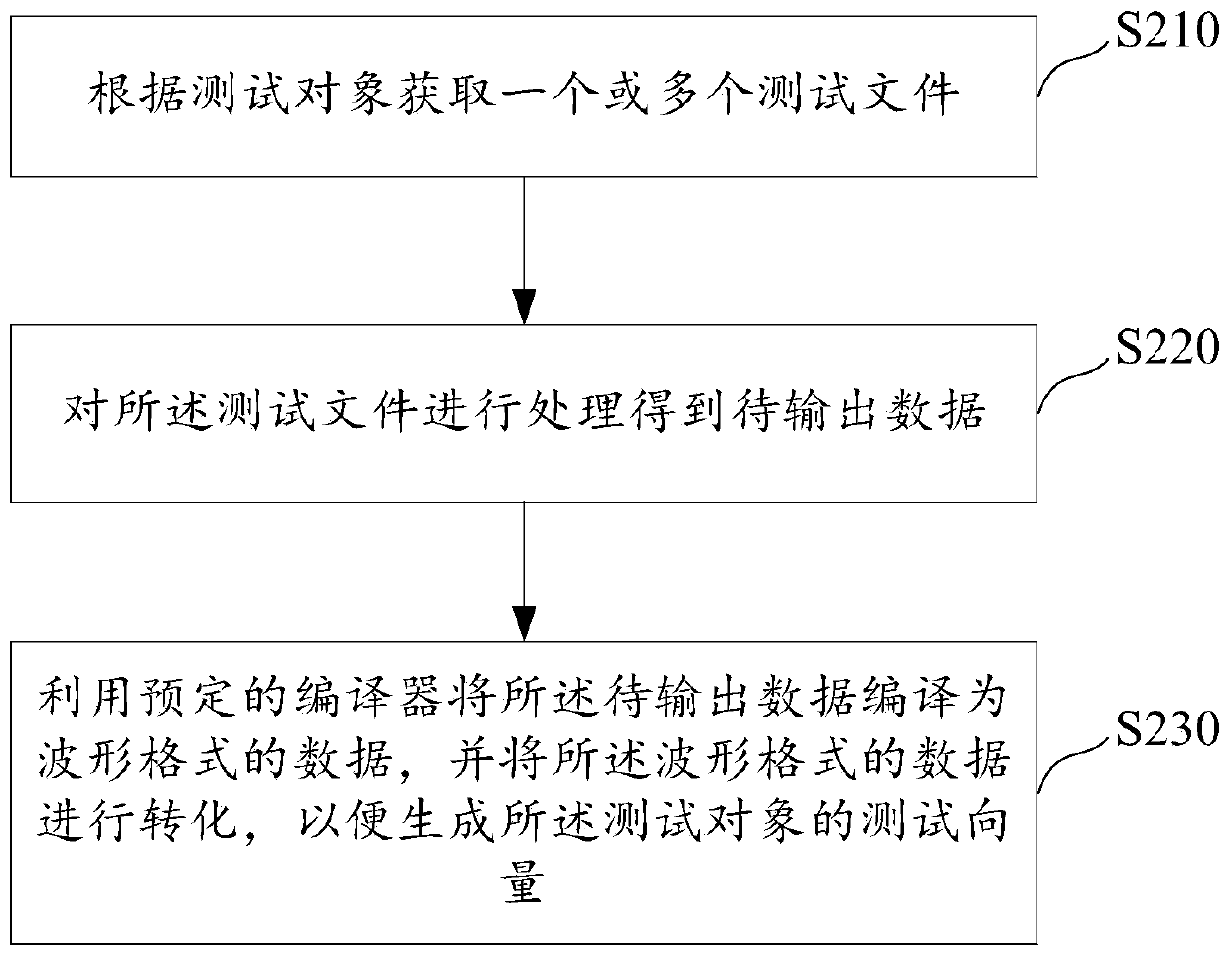

Test vector generation method based on test object and storage medium

ActiveCN110632499AImprove production efficiencyImprove readabilityElectronic circuit testingParallel computingTest vector generator

The invention provides a test vector generation method based on a test object and a storage medium. The test vector generation method based on the test object comprises the steps of obtaining one or more test files according to the test object; processing the test file to obtain to-be-output data; and compiling the to-be-output data into data in a waveform format by using a predetermined compiler,and converting the data in the waveform format so as to generate a test vector of the test object. Based on the technical scheme of the invention, the generation efficiency of the test vector is improved, the readability of the generated test vector is high, and the online debugging of the test vector is facilitated.

Owner:GREE ELECTRIC APPLIANCES INC

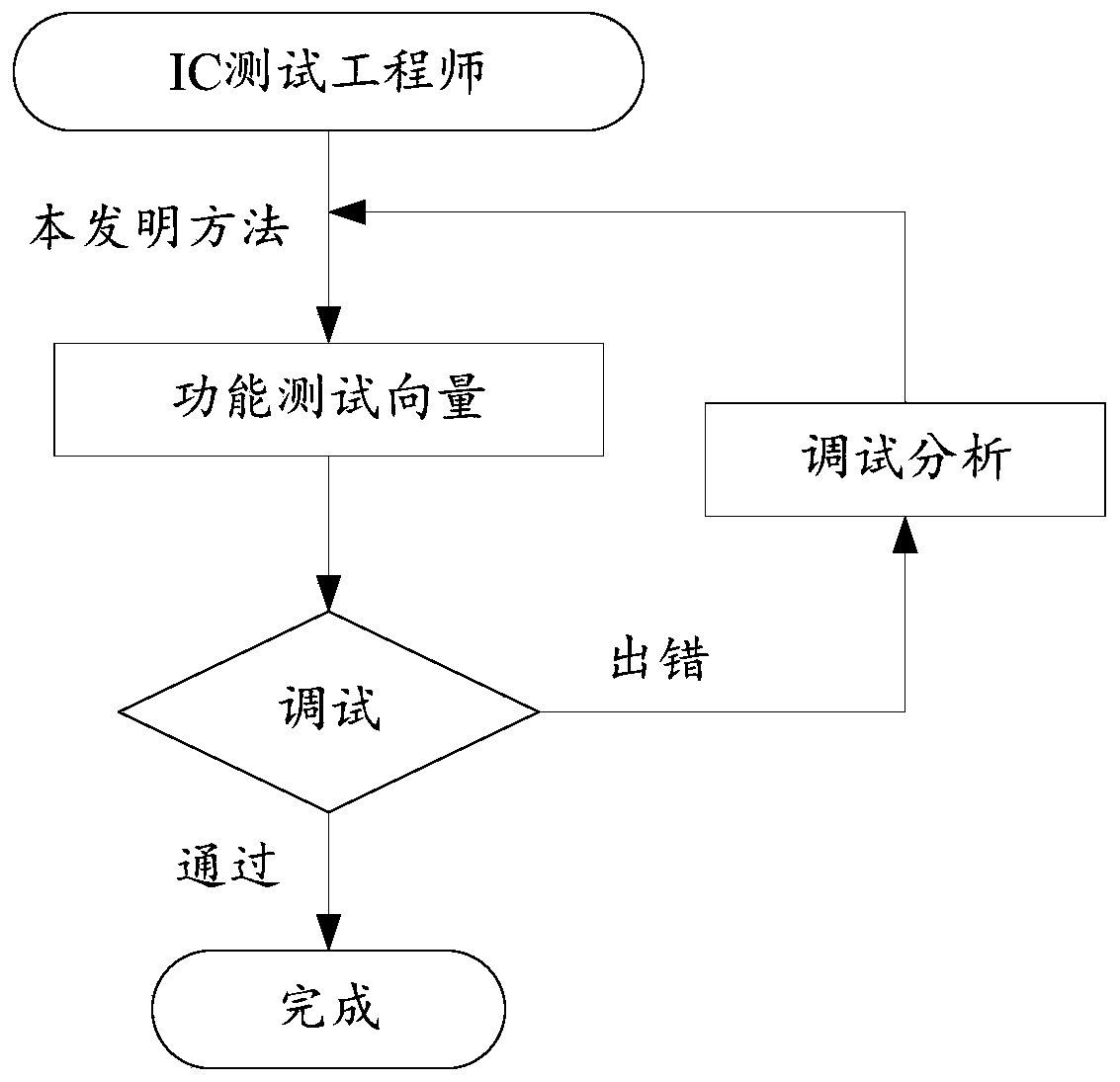

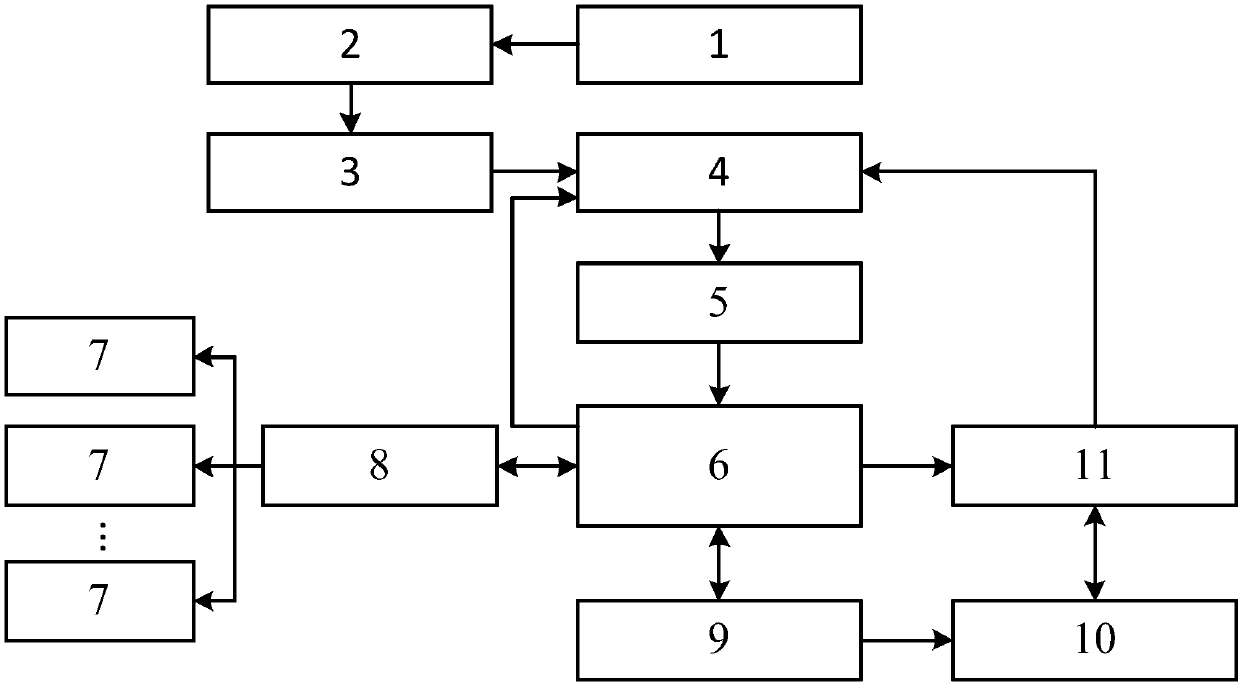

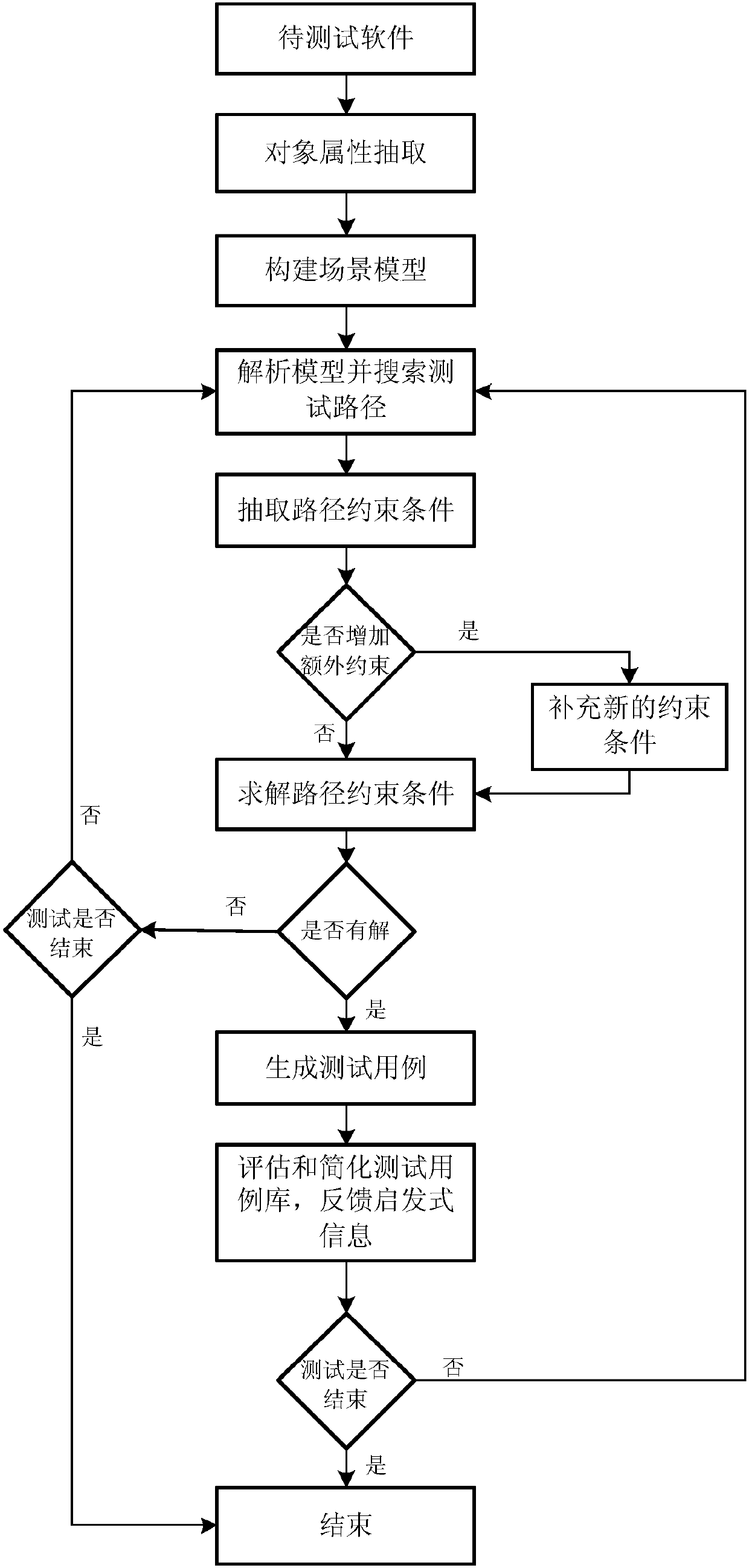

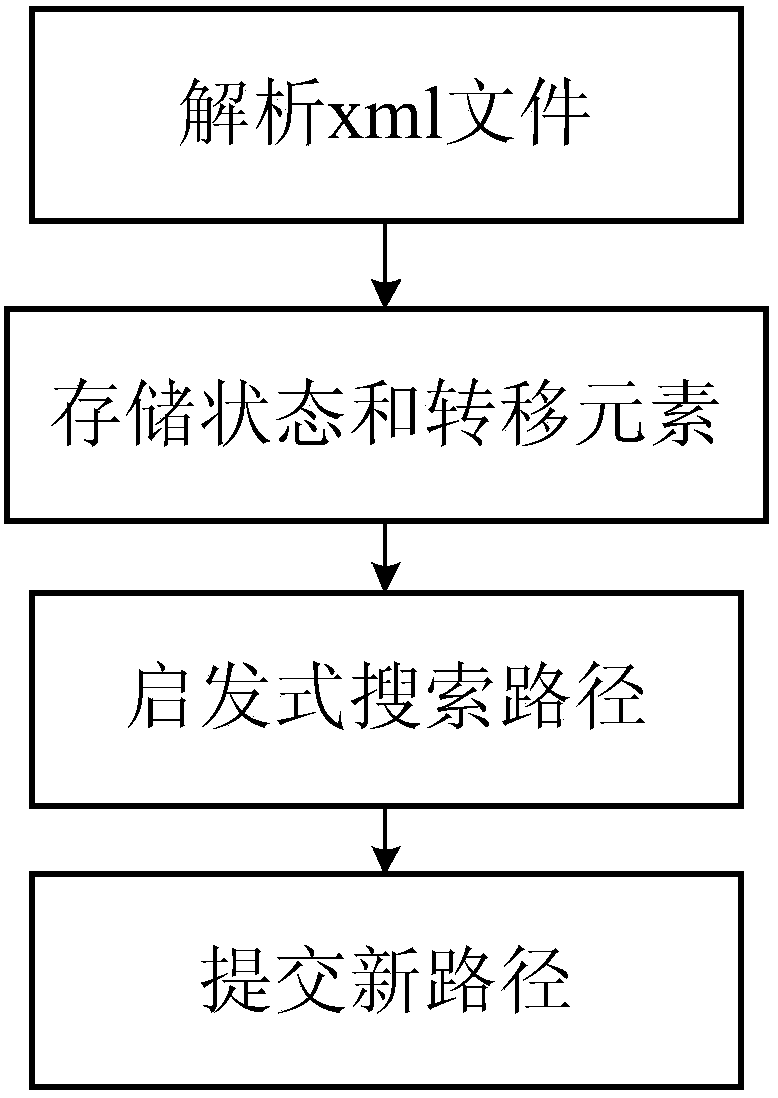

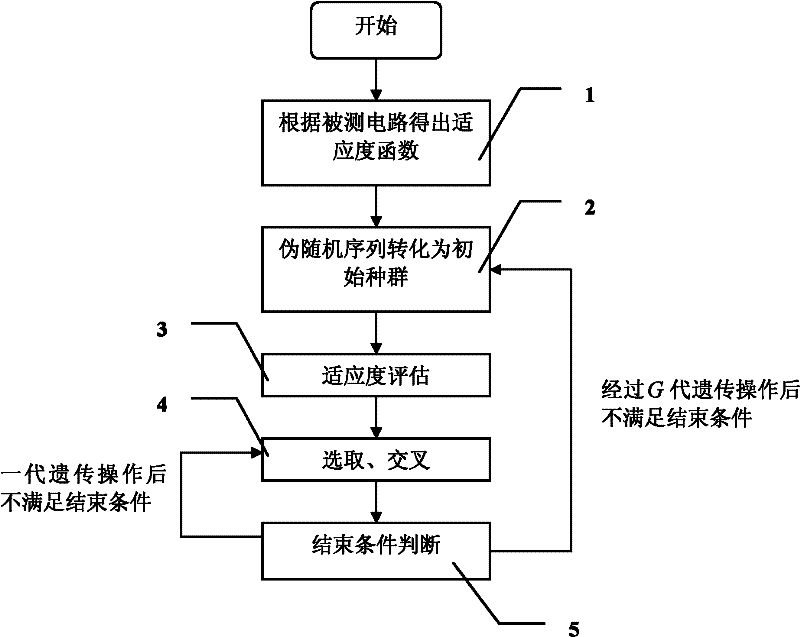

Automatic test system based on scene description and implementation method thereof

ActiveCN107783893AReduce testing costsEnsure test adequacySoftware testing/debuggingTest efficiencyInformation analysis

The invention discloses an automatic test system based on scene description. The automatic test system includes a rule base, an object attribute extractor, a scene model builder, a parsing engine, a path constraint extractor, a core controller, a constraint solver, a solver adapter, a test case generator, a test case library and an optimization engine. According to the automatic test system, attributes of a test object are extracted according to the specific rule base and added to a scene model, the information of the model itself and a heuristic information analysis model extracted from the test case library are combined to automatically generate a test path, a corresponding test input is generated by using the constraint solver, the test path and the test input are integrated to generatea test case and the test case is optimized. While ensuring test adequacy, the test cost of a manual test is reduced, and the test efficiency is improved. The invention also discloses an implementation method of the automatic test system based on scene description.

Owner:SHANGHAI DEV CENT OF COMP SOFTWARE TECH

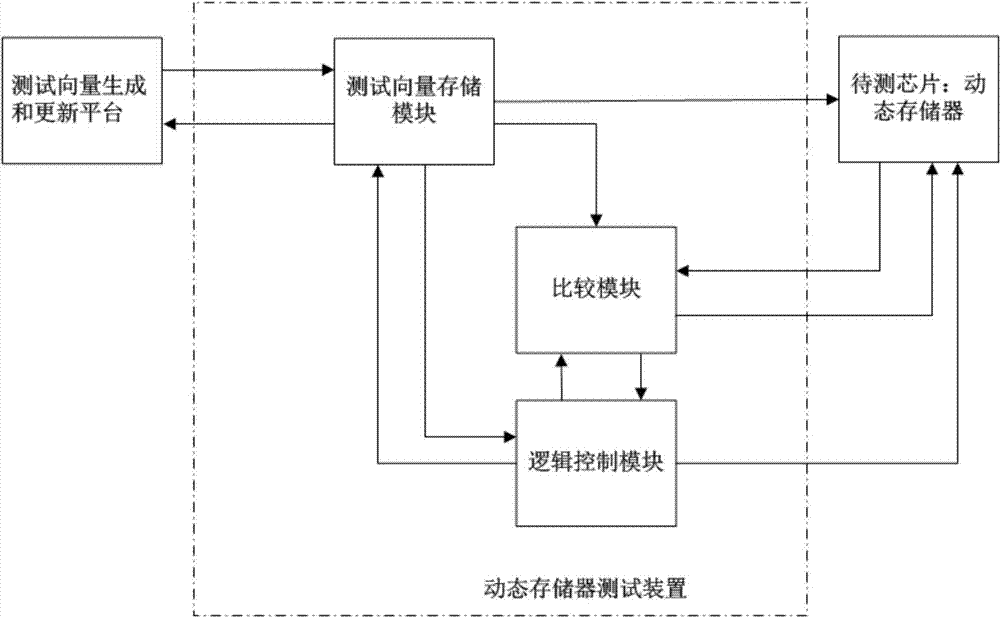

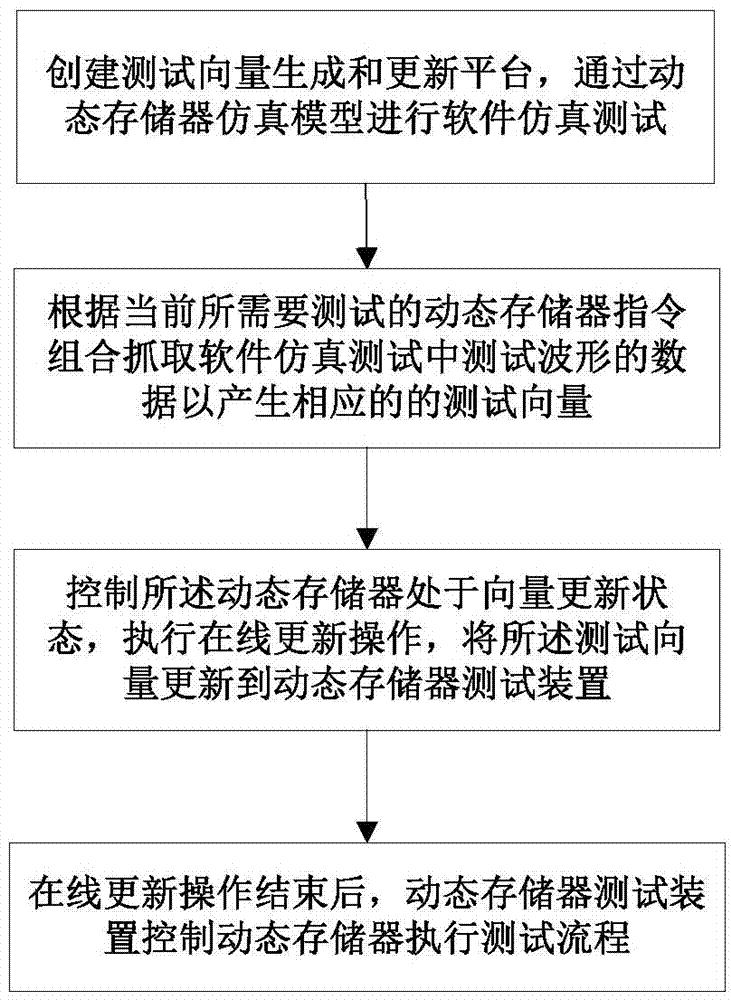

Dynamic memory testing system and dynamic memory testing method

The invention discloses a dynamic memory testing system and a dynamic memory testing method. The dynamic memory testing system comprises a test vector generation and update platform and a dynamic memory testing device, wherein the test vector generation and update platform is used for software simulation test by virtue of a dynamic memory simulation model, is used for grasping data in a test waveform to generate special test vectors according to current test, controlling the dynamic memory to be in a vector updating state, executing an operation of updating the vectors and updating the test vectors to the dynamic memory testing device; the dynamic memory testing device is used for storing the test vector used for current test and controlling the dynamic memory to execute the test flow. According to the system and the method disclosed by the invention, due to the test vector generation and update platform, various test vectors required by complete testing dynamic memory command combination can be generated, and are transmitted to the dynamic memory testing device on line to dynamically update the testing vectors so as to quickly and completely test the dynamic memory. The dynamic memory testing system and the dynamic memory testing method disclosed by the invention can be widely applied to the field of digital test.

Owner:SHENZHEN STATE MICROELECTRONICS CO LTD

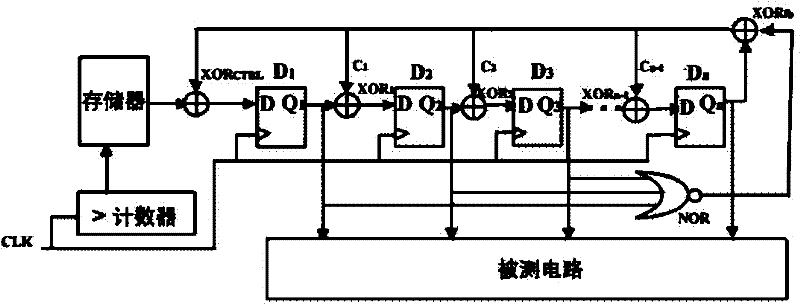

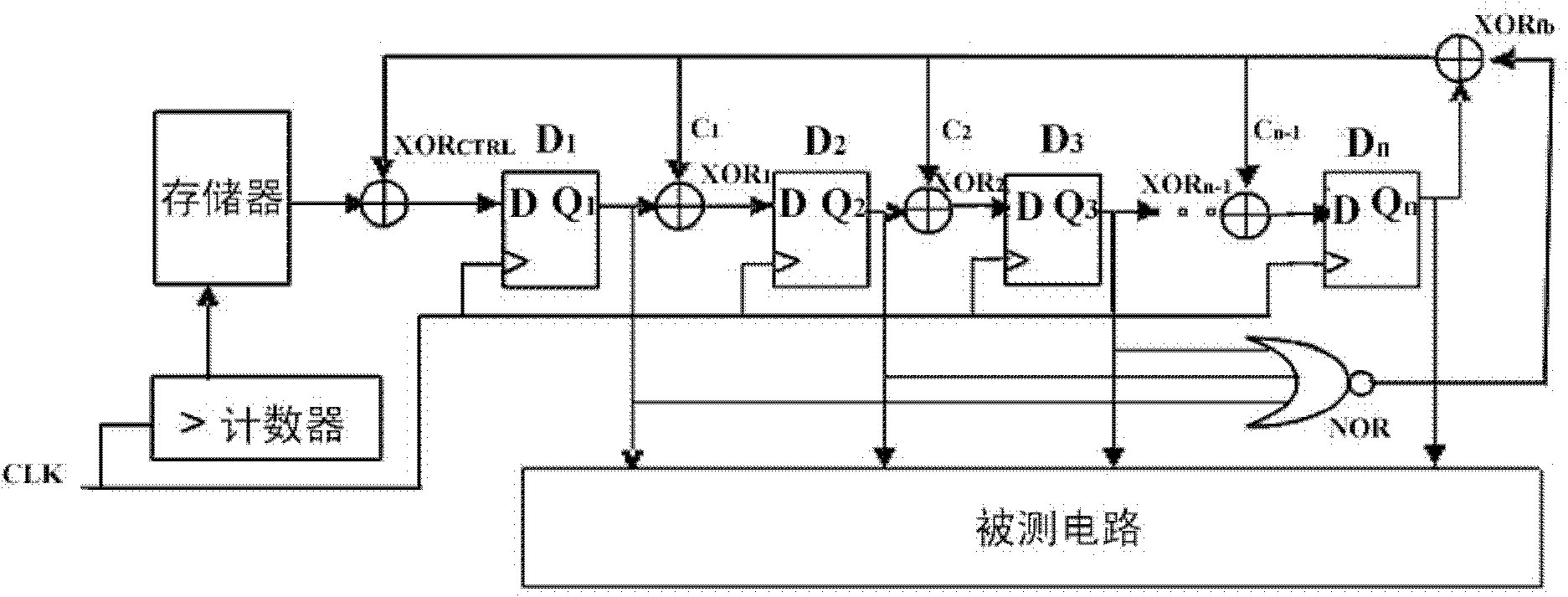

Controllable test vector generator based on linear feedback shift register

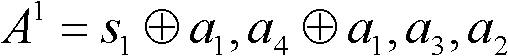

InactiveCN102226947AReduce overheadReduce testing costsStatic storageExclusive orTest vector generator

The invention discloses a controllable test vector generator based on a linear feedback shift register (LFSR). The controllable test vector generator comprises three sections: 1, a control code sequence generation section comprising a counter and a memory; 2, a sequence pseudo random test vector sequence generation section comprising a inscribe LFSR; 3, a feedback network section formed by n-1 bit input or a non-gate NOR and an exclusive-OR gate XORfb. Depending on the test vectors required to be generated, the control code sequence is acquired, wherein the control code sequence is stored in the memory and is provided for controlling a run of the inscribe LFSR, such that the sequence or jump output pseudo random sequence of the inscribe LFSR is adopted as the test vector. With the present invention, only the control code memory, the counter, the feedback network section formed by the n-1 bit input or the non-gate NOR and the exclusive-OR gate XORfb, and a control exclusive-OR gate XORCTRL are added on the base of the inscribe LFSR, such that hardware expense is few, and test cost is low.

Owner:UNIV OF ELECTRONICS SCI & TECH OF CHINA

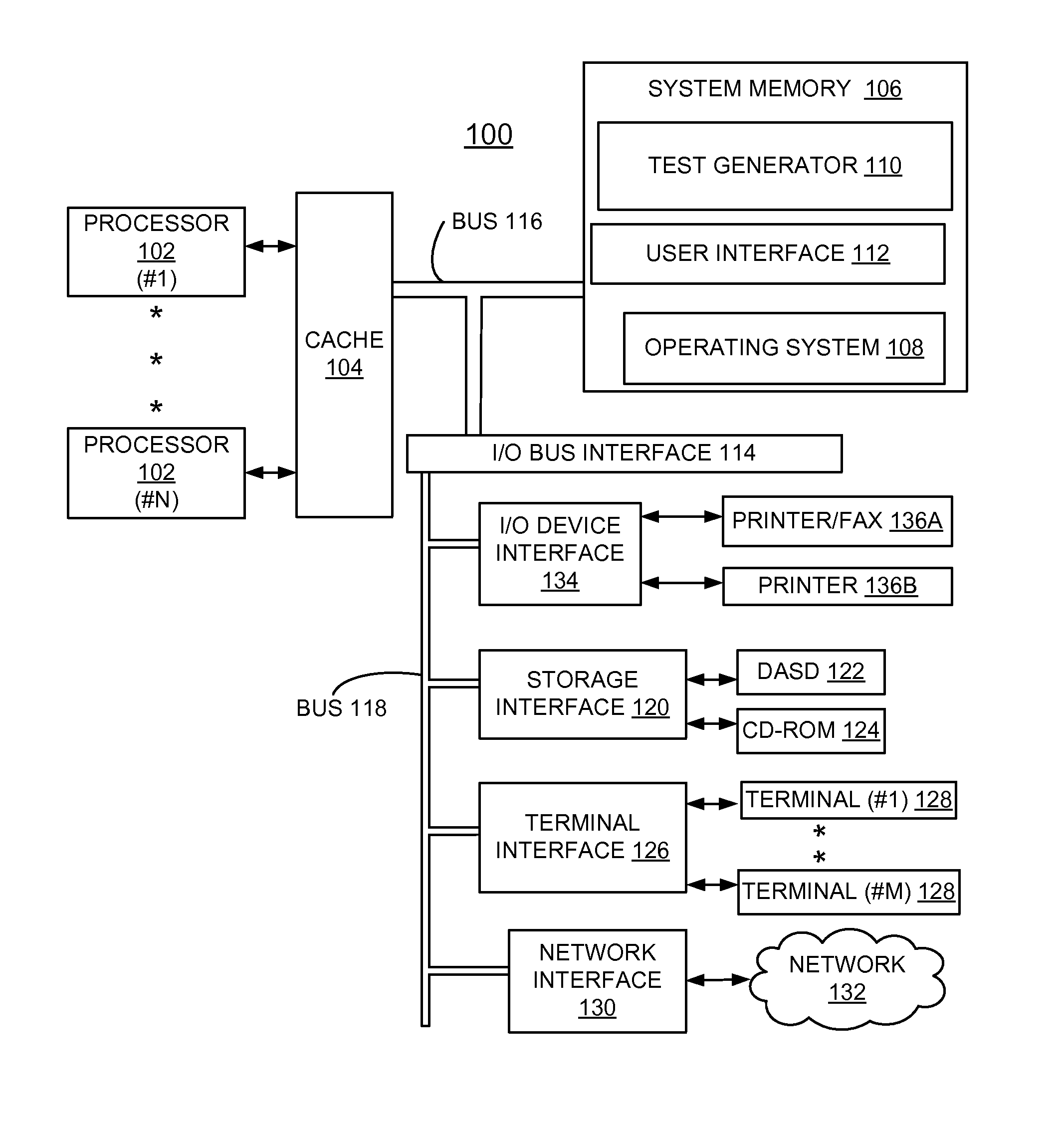

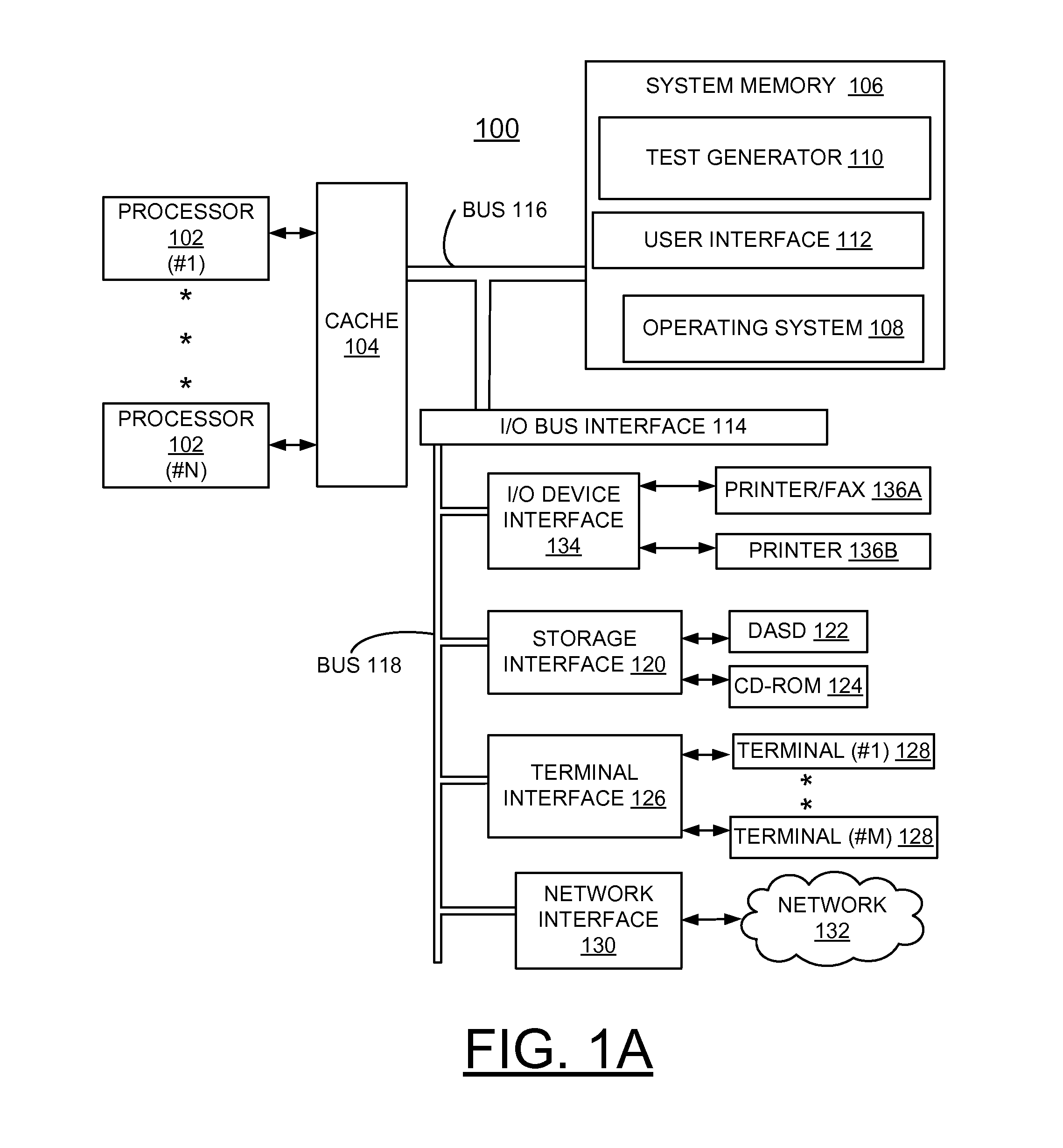

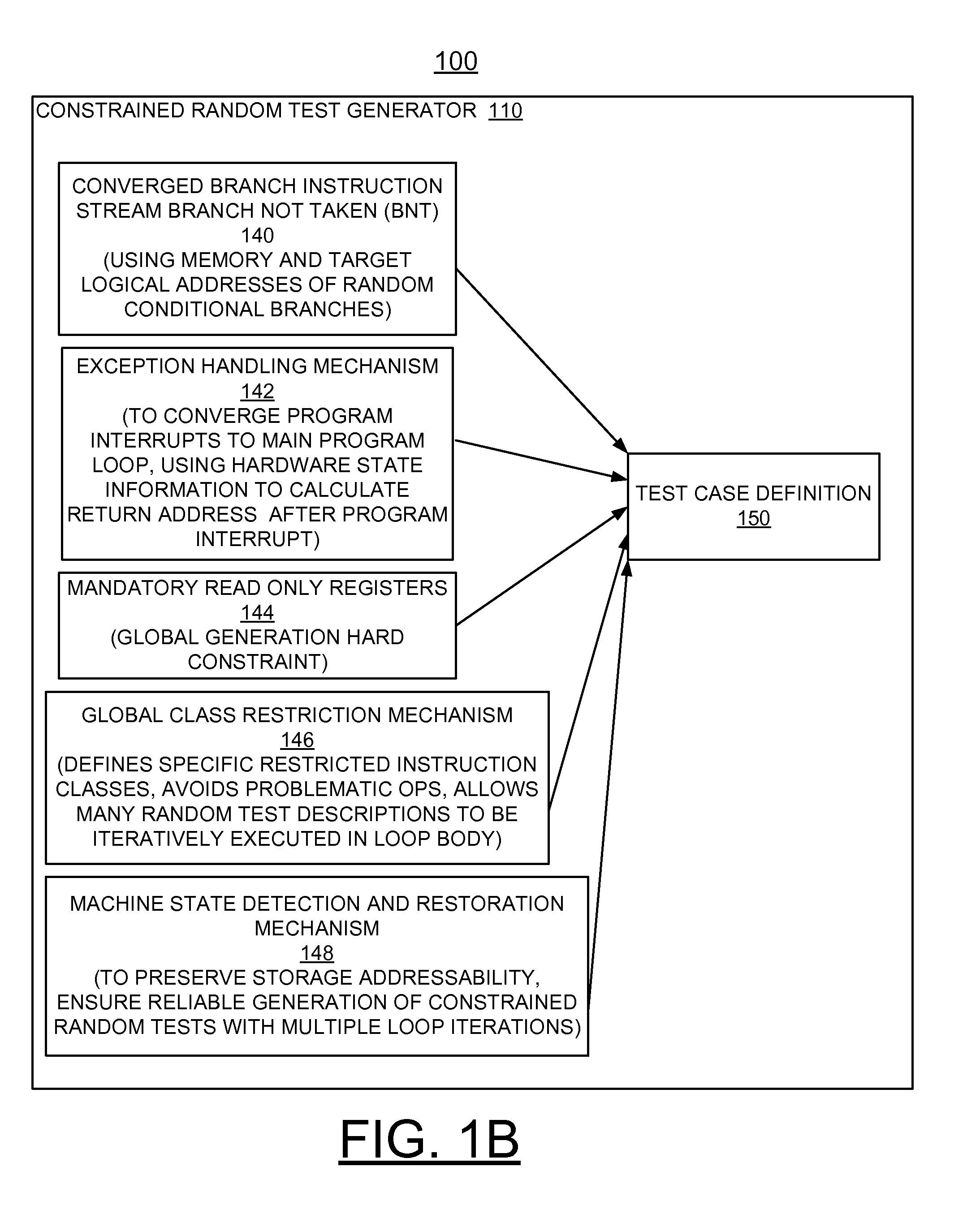

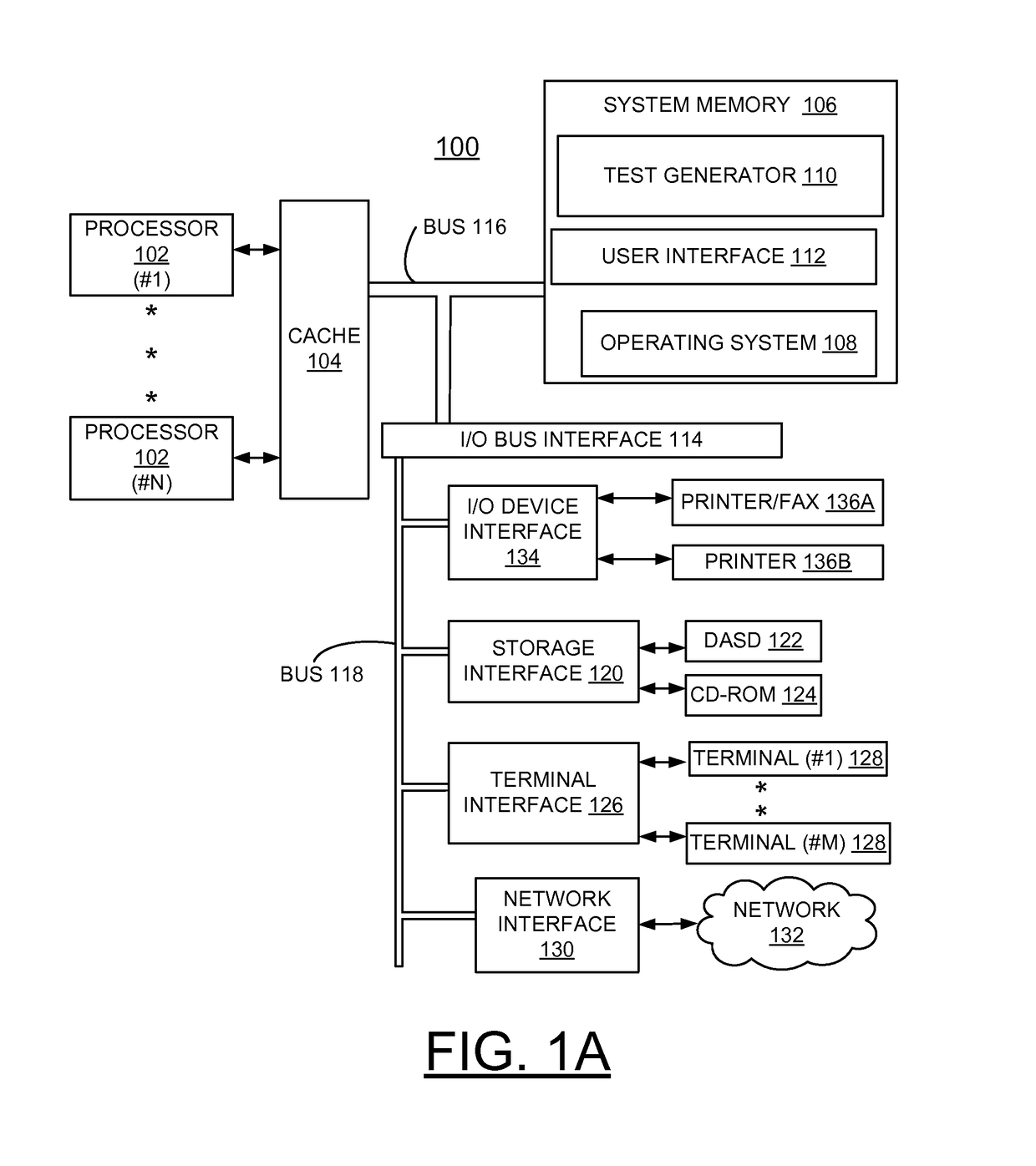

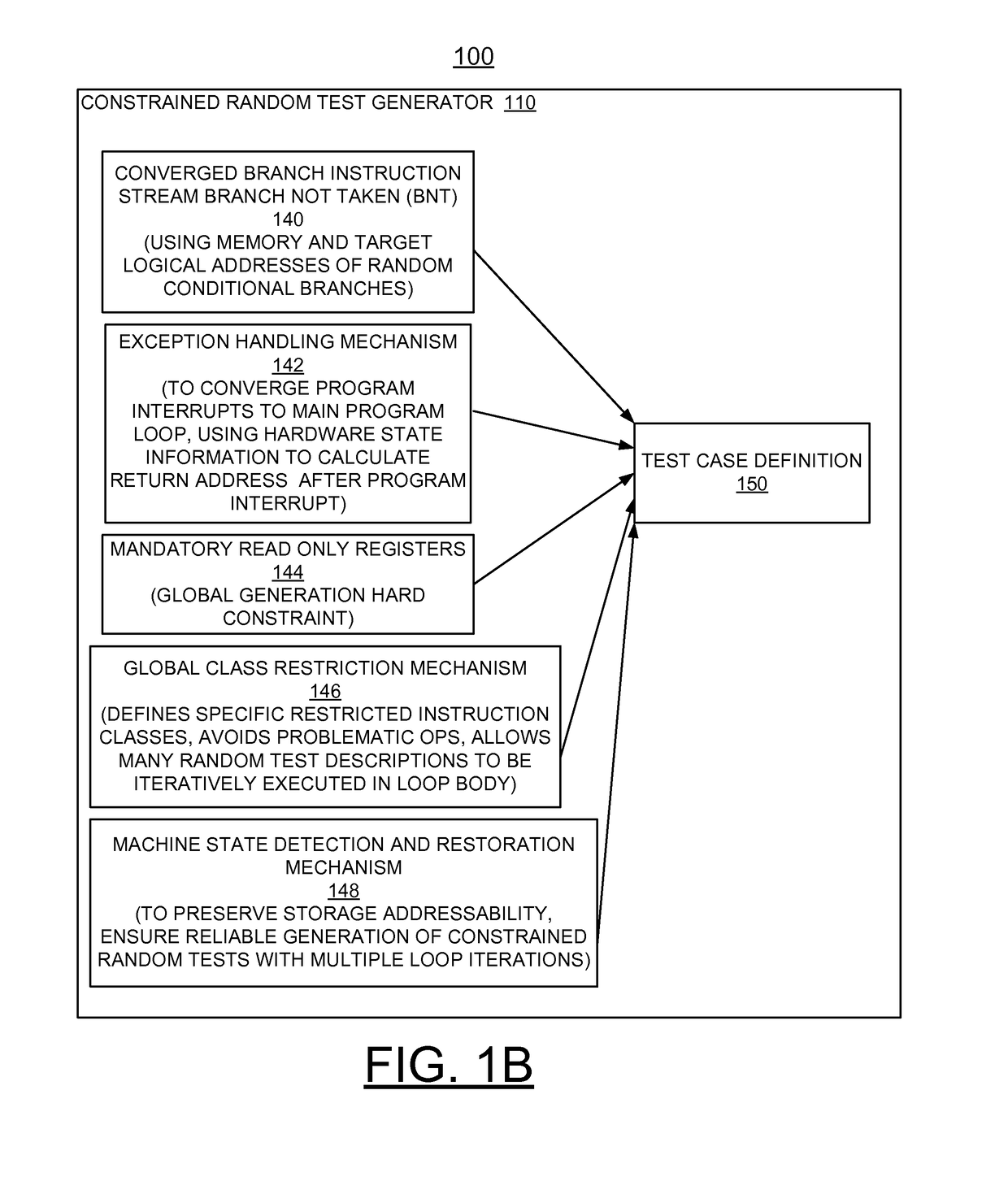

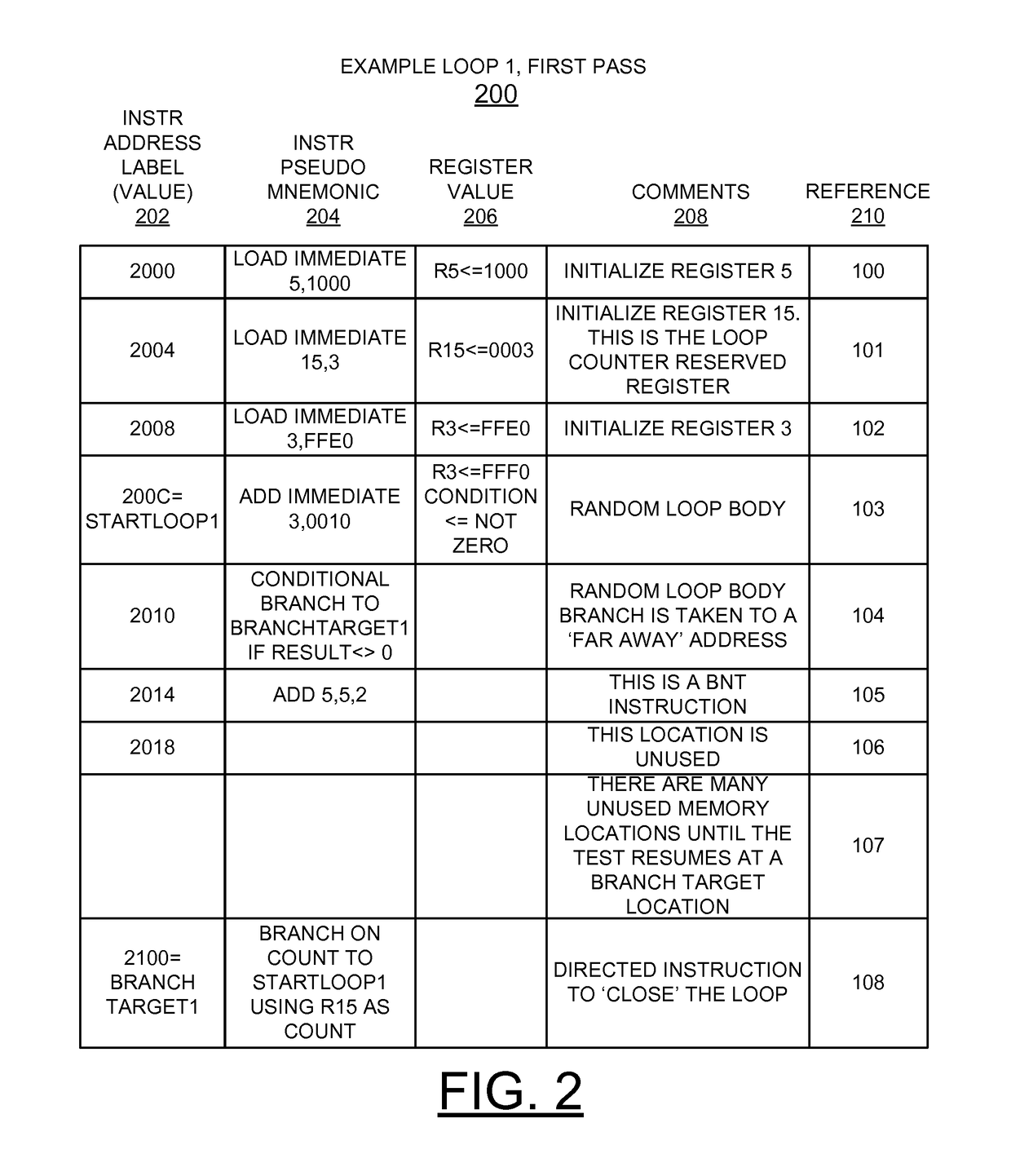

Implementing random content of program loops in random test generation for processor verification

ActiveUS20140257739A1Negative effectAvoids inherently problematic operationError detection/correctionSpecial data processing applicationsNetwork address translationRandom test generator

A method and apparatus are provided for implementing random content of program loops in random test generation for processor verification. A converged branch instruction stream is used by a test generator to ensure that all random conditional branches converge to a main program loop. A built in exception handling mechanism of the test generator enables program interrupts to converge to the main program loop. Mandatory read only registers applied to the test generator allow all register based storage addresses to use registers that maintain a value and thus stabilize the storage address translations through subsequent iterations of the loop. A global class restriction mechanism defines specific restricted instruction classes applied to the test generator avoids inherently problematic operations for the program loops. Machine state detection and restoration mechanisms in the test generator are provided to preserve storage addressability.

Owner:IBM CORP

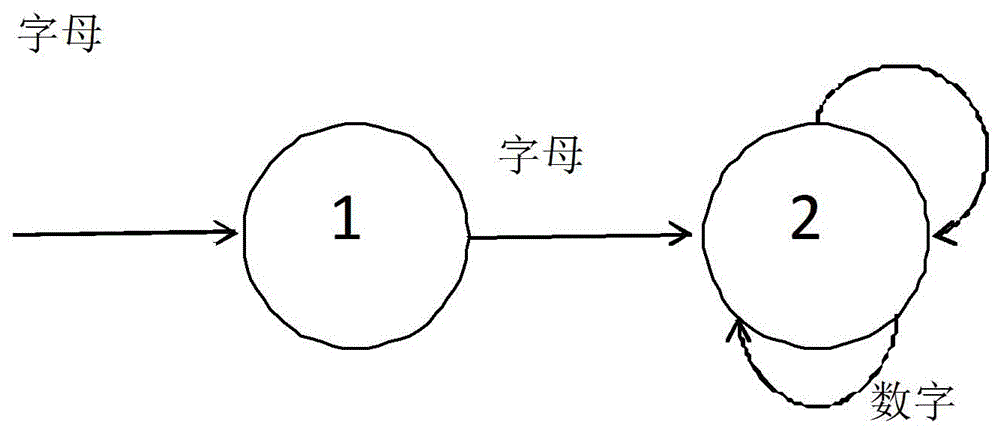

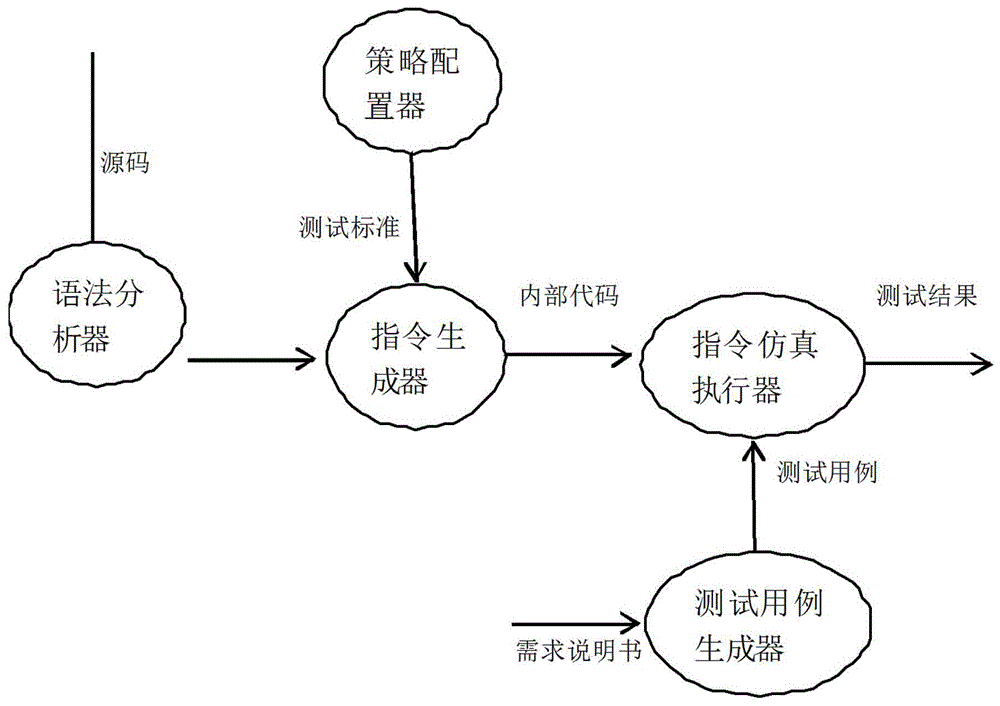

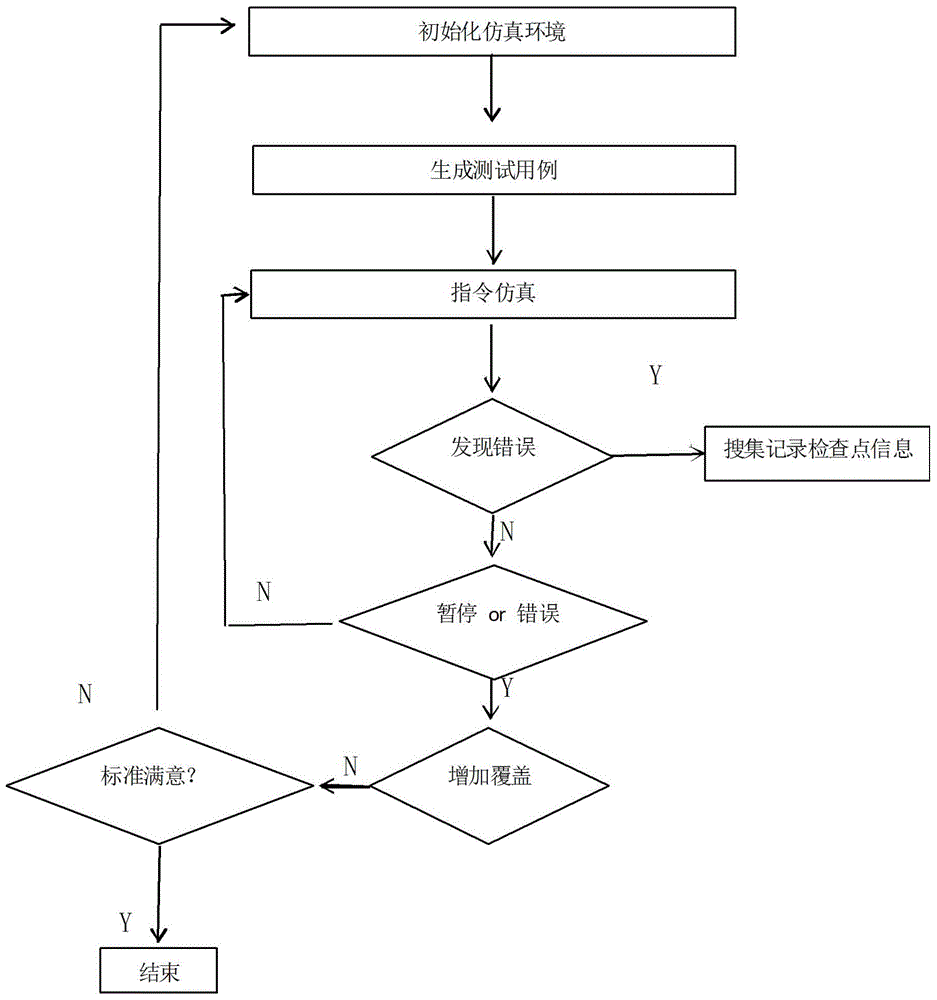

Automatic frame model for program structure analysis

InactiveCN106021109AHigh degree of automationGuaranteed validitySoftware testing/debuggingSpecific testActuator

The invention discloses an automatic framework model for program structure analysis, which includes the following five basic modules: a syntax analyzer, which is a complete compiling module, and the objects processed are a subset of standard languages; a strategy configurator, which is based on The test method to be adopted is used to design the support of the test model for specific test activities; the instruction generator calculates the test work to be processed when the program is dynamically executed, generates a test processing module and inserts it into the source program, and constitutes a test program with self-contained test information , submitted to the simulation execution module to run; the test case generator, the test activity is repeated according to the completeness of the test; the instruction simulation executor provides a simulation execution environment inside the test framework. Compared with the prior art, the automatic framework model oriented to program structure analysis can complete the automatic testing process of the program, can reduce manual labor, improve the automation degree of testing, has strong practicability, and is easy to popularize.

Owner:LANGCHAO ELECTRONIC INFORMATION IND CO LTD

Functional validation of a packet management unit

InactiveUS7082552B2Cost-effective and reliablePrecise designError detection/correctionTime-division multiplexRandom test generatorUser interface

A validation system is disclosed for validating function of a packet-management unit operationally coupled through a system interface to a processing unit of a processor system. The validation system comprises a user interface for creating an inputting test parameters and test code into the system, a test generator coupled to the user interface, the test generator for generating input packet activity in the form of a packet stream, a model coupled to the test generator for emulating separate and integrated function of the packet management unit, the system interface, and a stream-processing unit and an evaluation software for checking and validating or not validating results. The system validation function relies, in a preferred embodiment, on comparing output results with criteria of the selected test code resulting in an indication of pass or failure of the test. In a preferred embodiment, the system also notifies to cause of failure.

Owner:ARM FINANCE OVERSEAS LTD

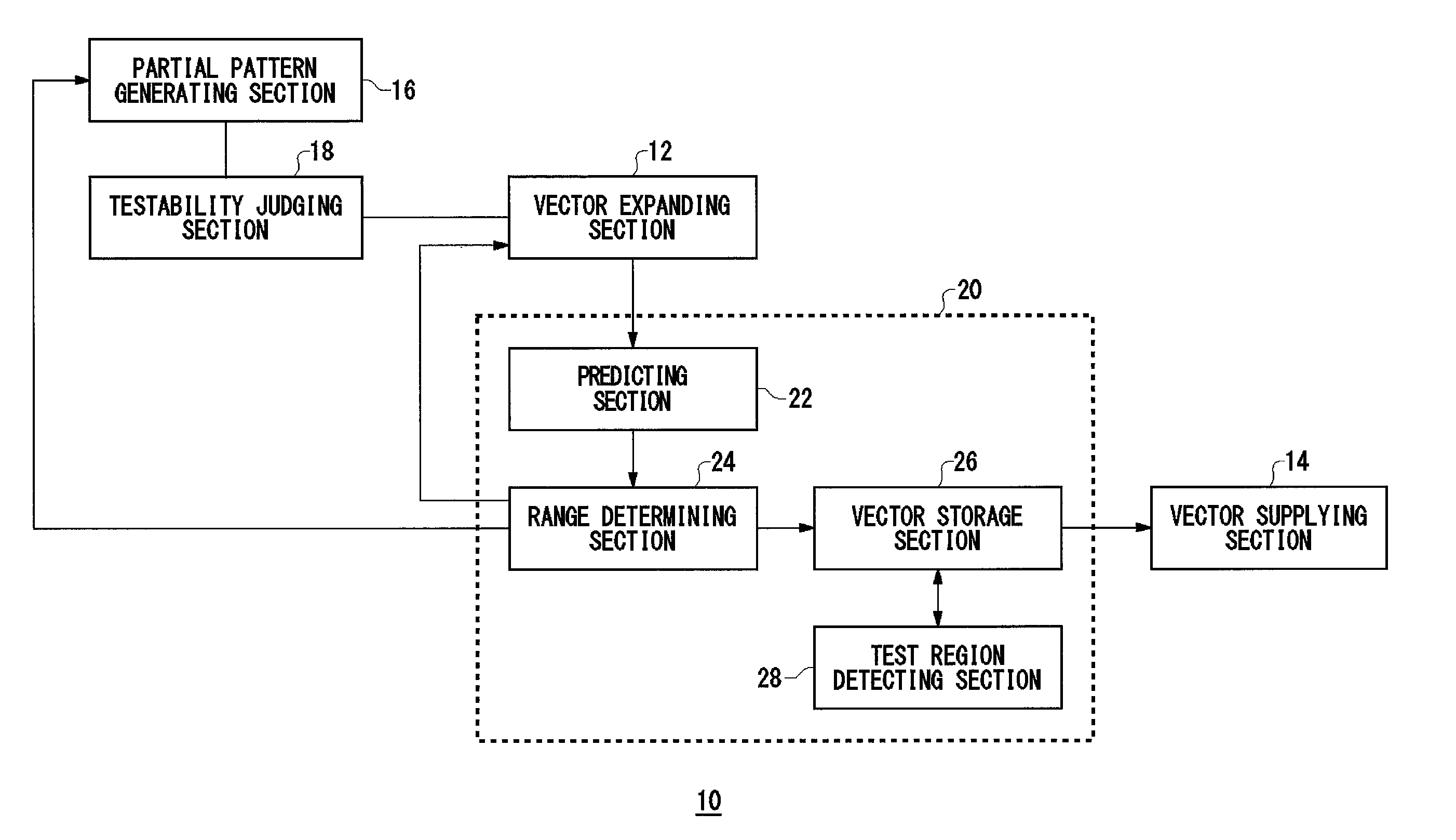

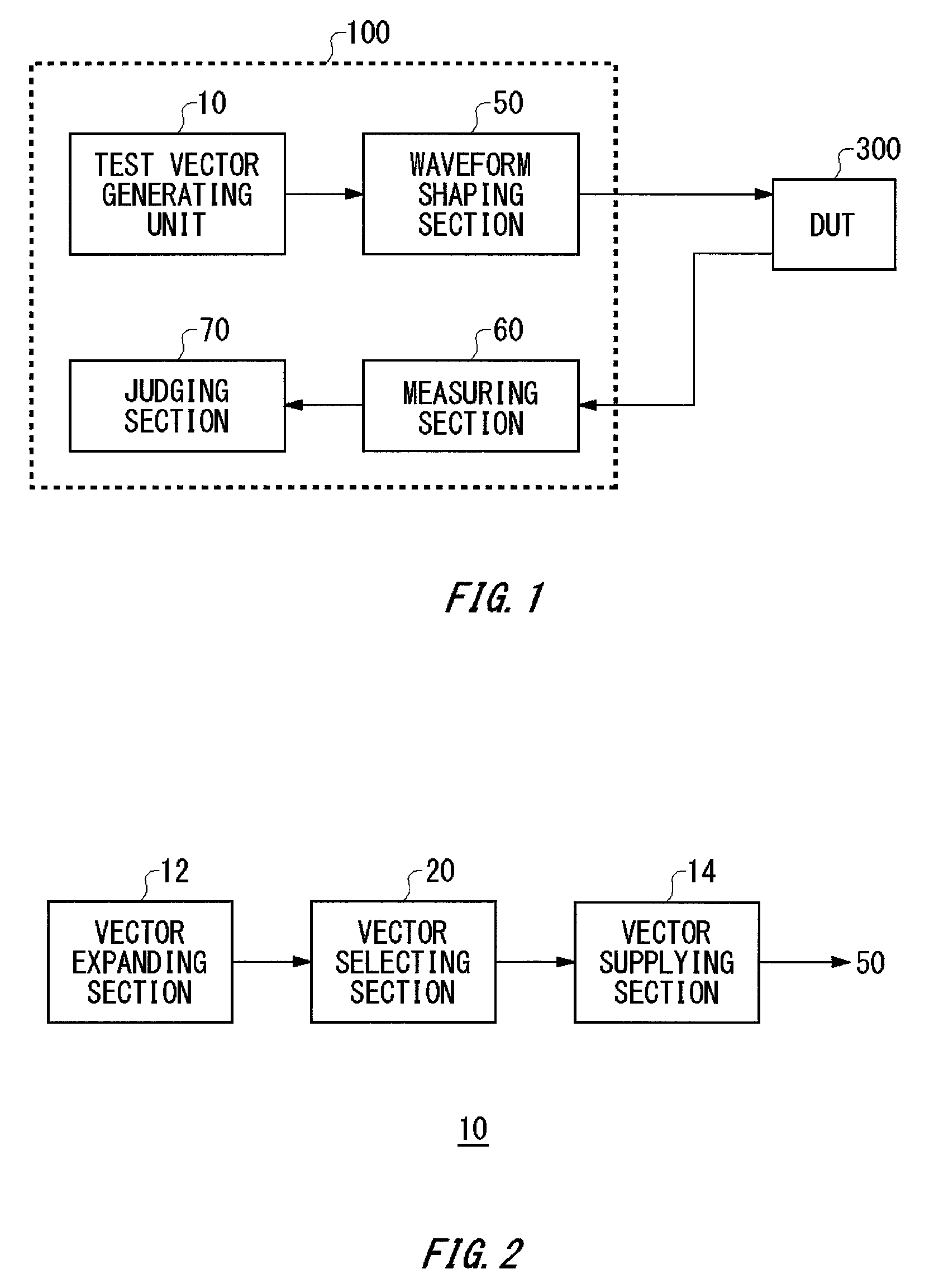

Test apparatus, test vector generate unit, test method, program, and recording medium

Provided is a test apparatus that tests a device under test, including a vector expanding section that sequentially generates a plurality of test vectors; a vector selecting section that selects test vectors that cause a prescribed characteristic of the device under test, which is to be measured when test signals that are each based on one of the test vectors are supplied to the device under test, to fulfill a preset condition; and a judging section that judges pass / fail of the device under test based on measured values of the prescribed characteristic of the device under test supplied with the test signal based on the test vectors selected by the vector selecting section.

Owner:ADVANTEST CORP +1

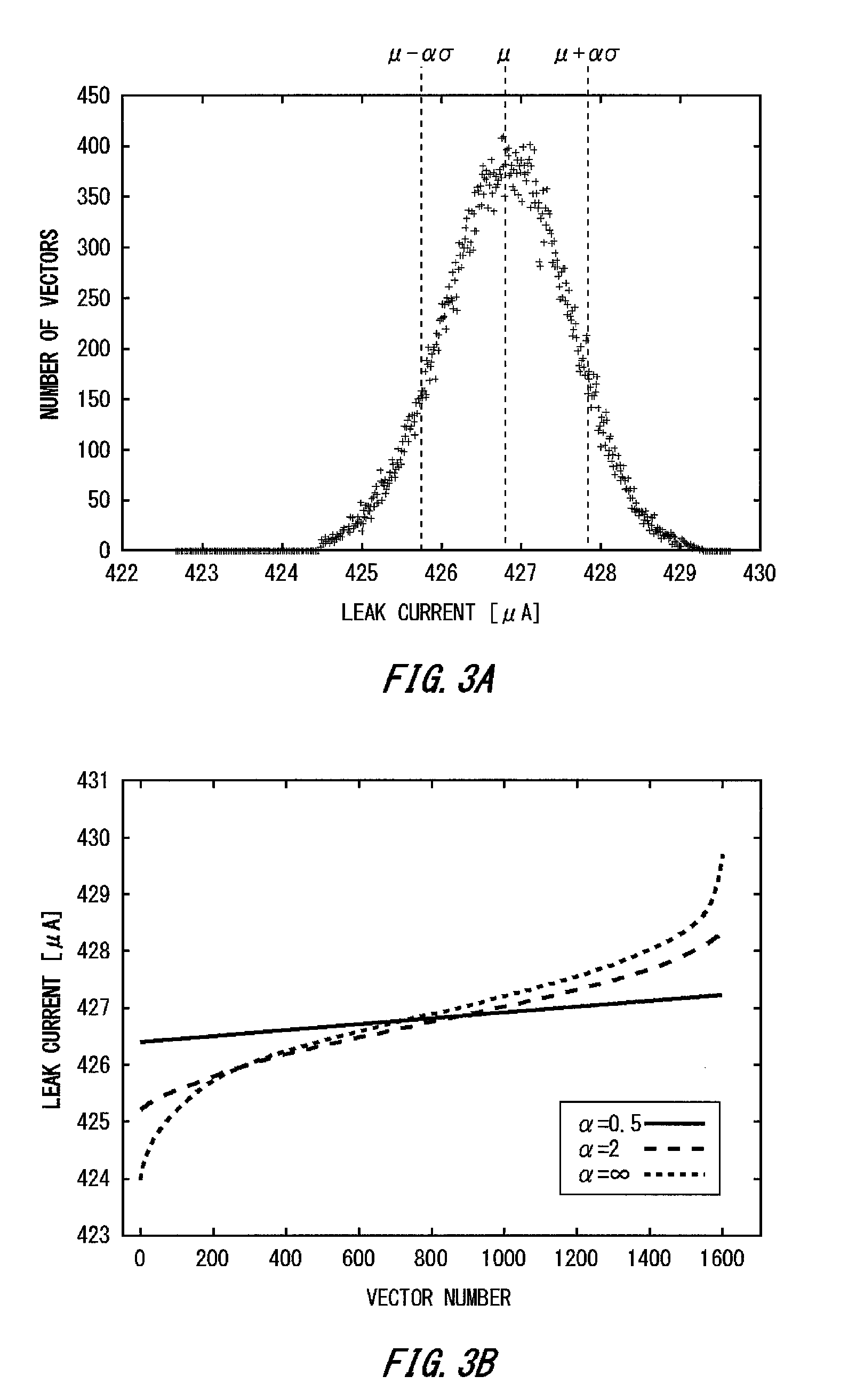

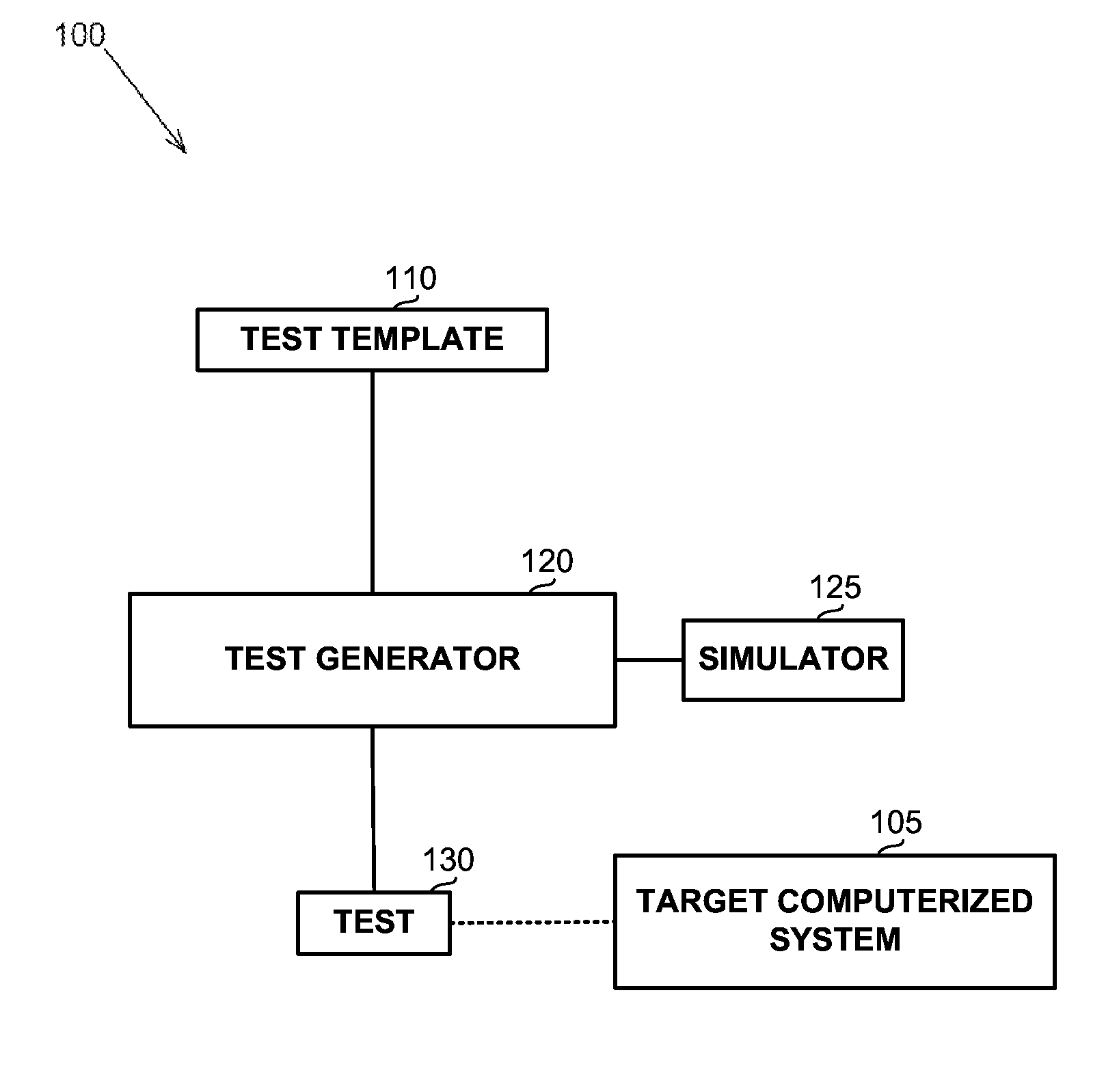

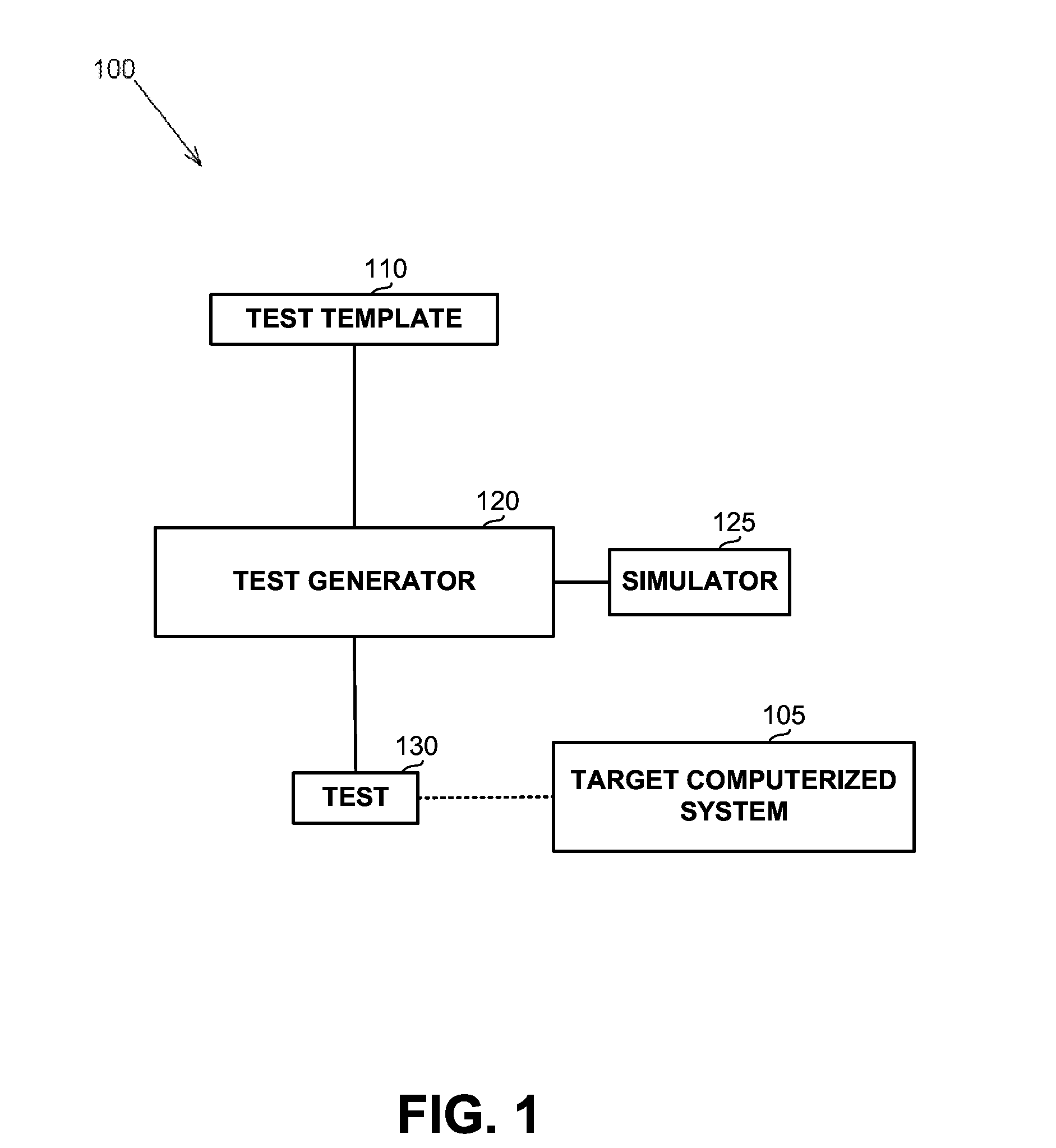

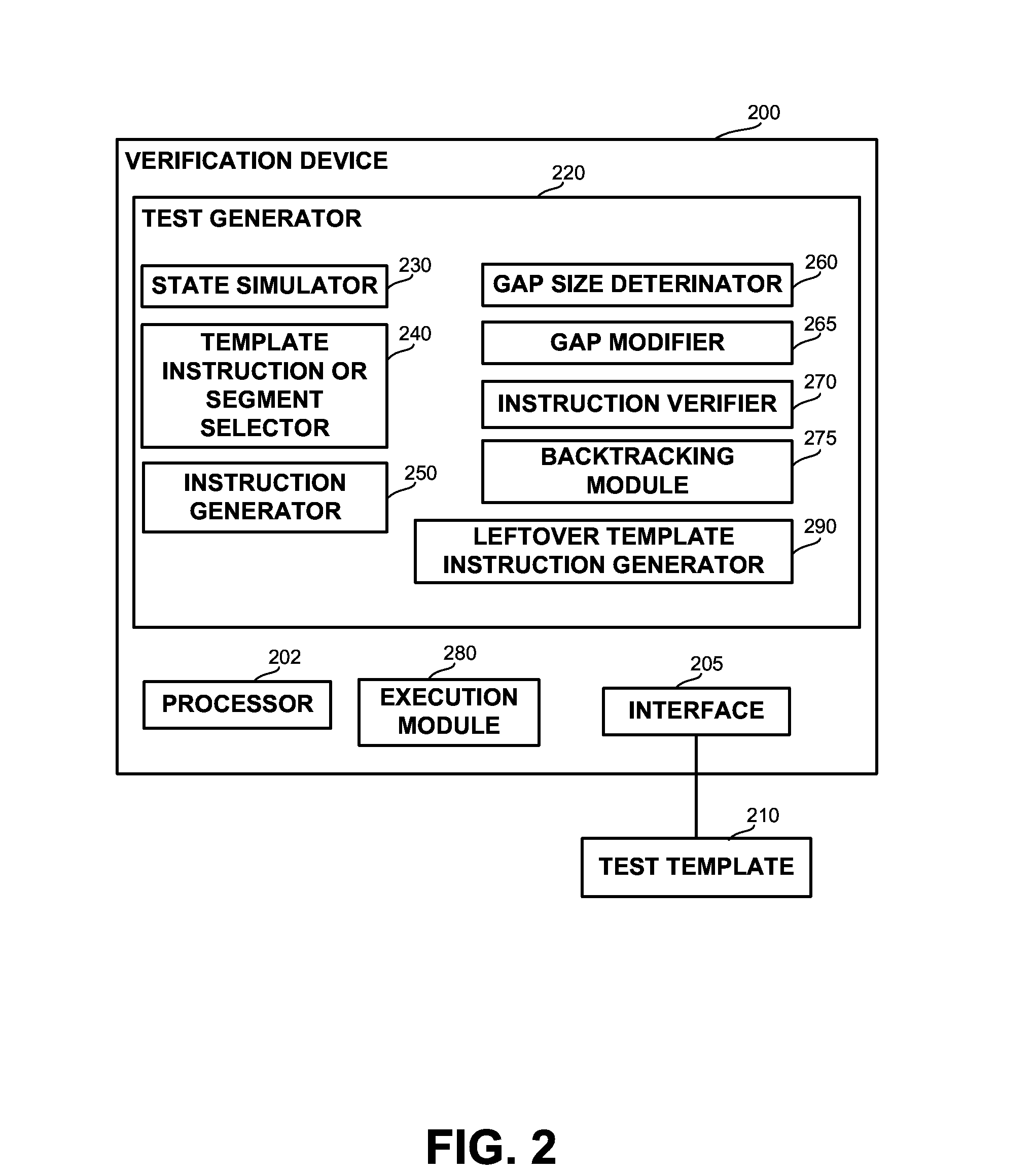

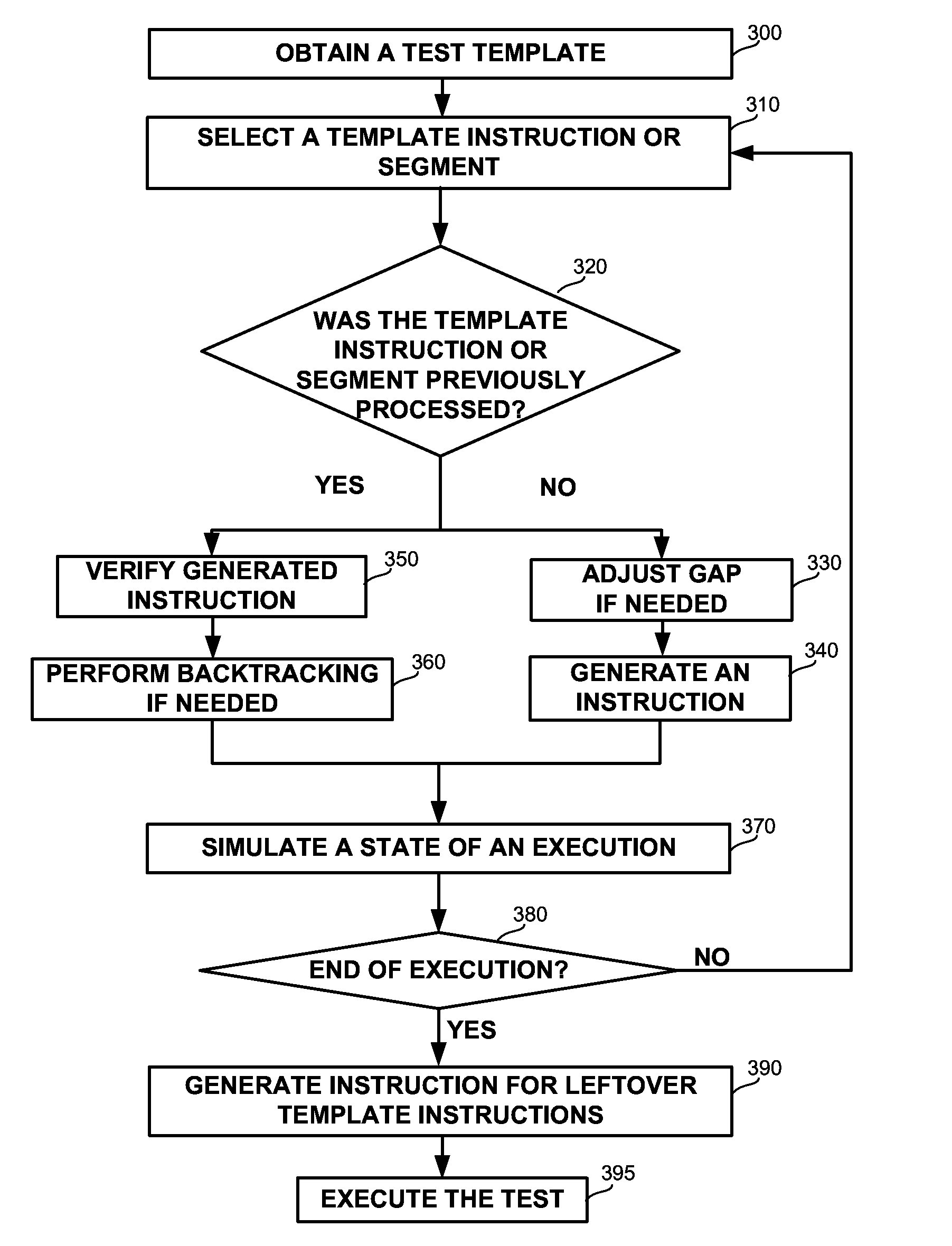

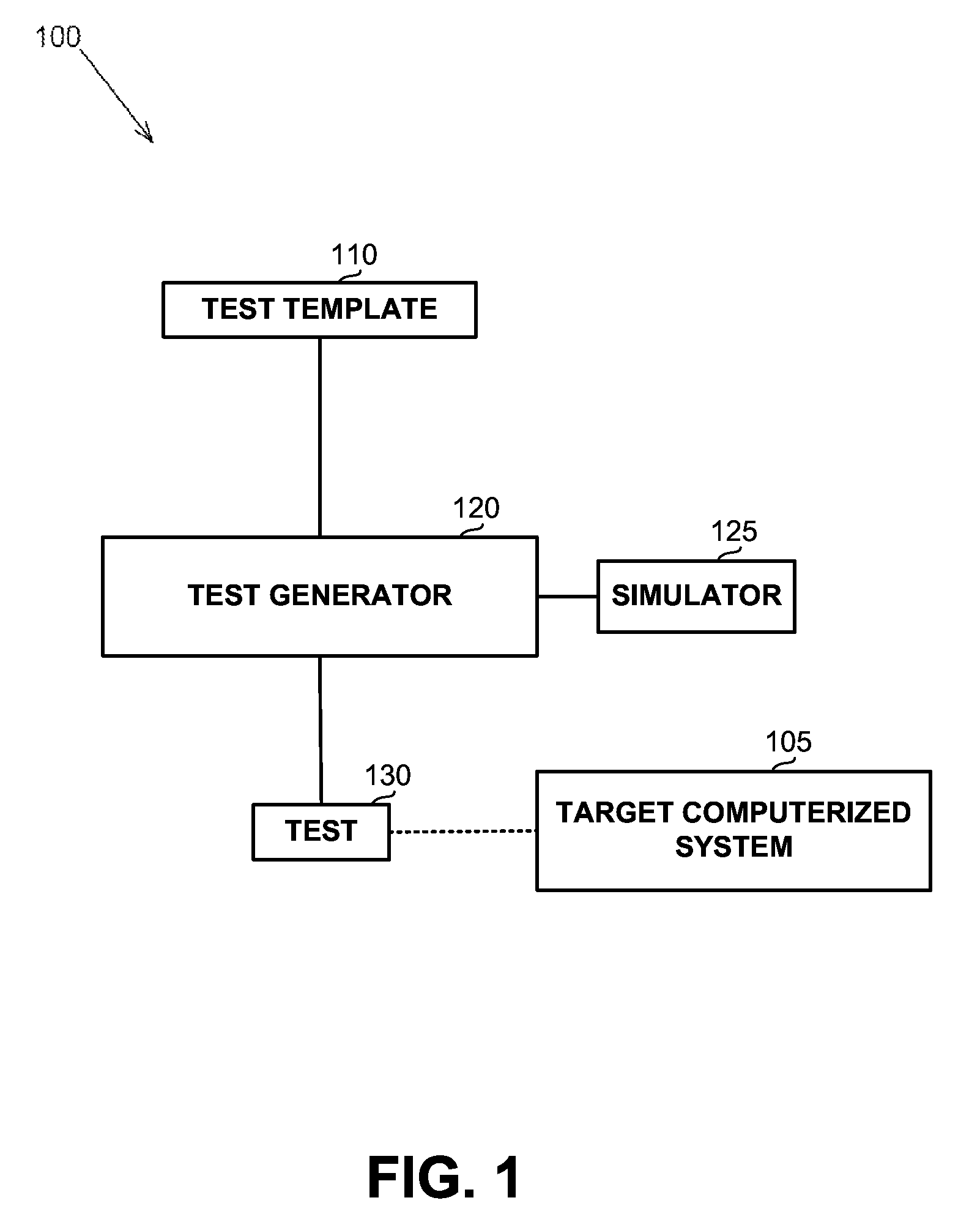

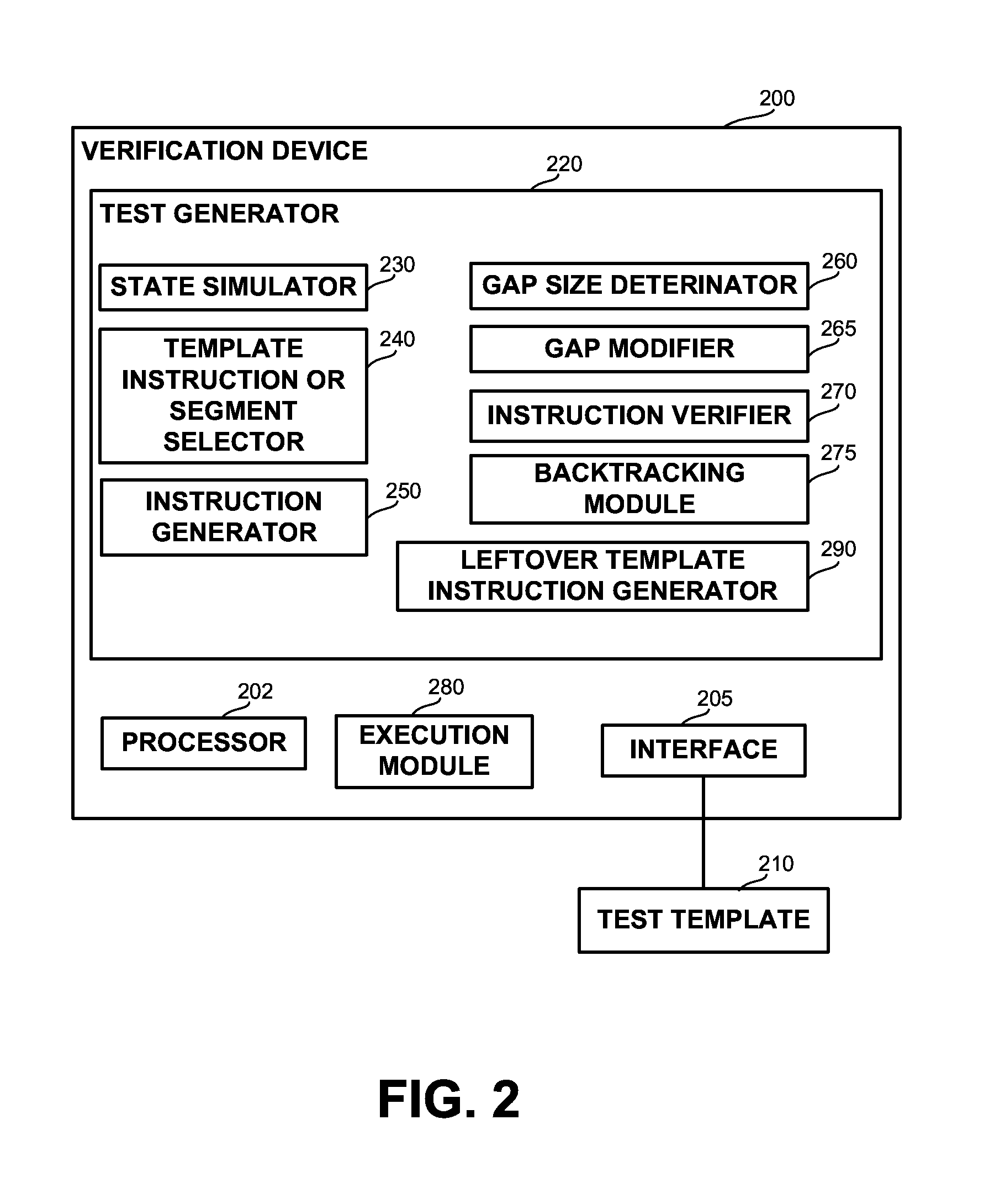

Dynamic generation of test segments

InactiveUS20130311164A1Software testing/debuggingSoftware simulation/interpretation/emulationProgramming languageComputerized system

A computerized apparatus, method and computer product for generating tests. The apparatus comprises: a processor; an interface for obtaining a test template associated with a target computerized system, the test template comprises a template segment, the template segment comprising one or more instruction and one or more directives or control constructs related to the instructions; a test generator for generating a test associated with the template segment, said test generator comprises: a state simulator for determining a state of the target computerized system associated with an execution of the test; a template instruction or segment selector for selecting a template instruction or segment from the test template based on the state of the target system determined by said state simulator; and an instruction template segment generator configured to generate a multiplicity of instructions based on the state of the target computerized system and the template segment selected by said template instruction selector, wherein the test generator further comprises an instruction verifier configured to verify that a previously generated instruction is in line with the current state of the target computerized system and with the template instruction or segment selected by said template instruction or segment selector.

Owner:GLOBALFOUNDRIES INC

Implementing random content of program loops in random test generation for processor verification

ActiveUS10061672B2Negative effectAvoids inherently problematic operationDetecting faulty computer hardwareNetwork address translationRandom test generator

Owner:INT BUSINESS MASCH CORP

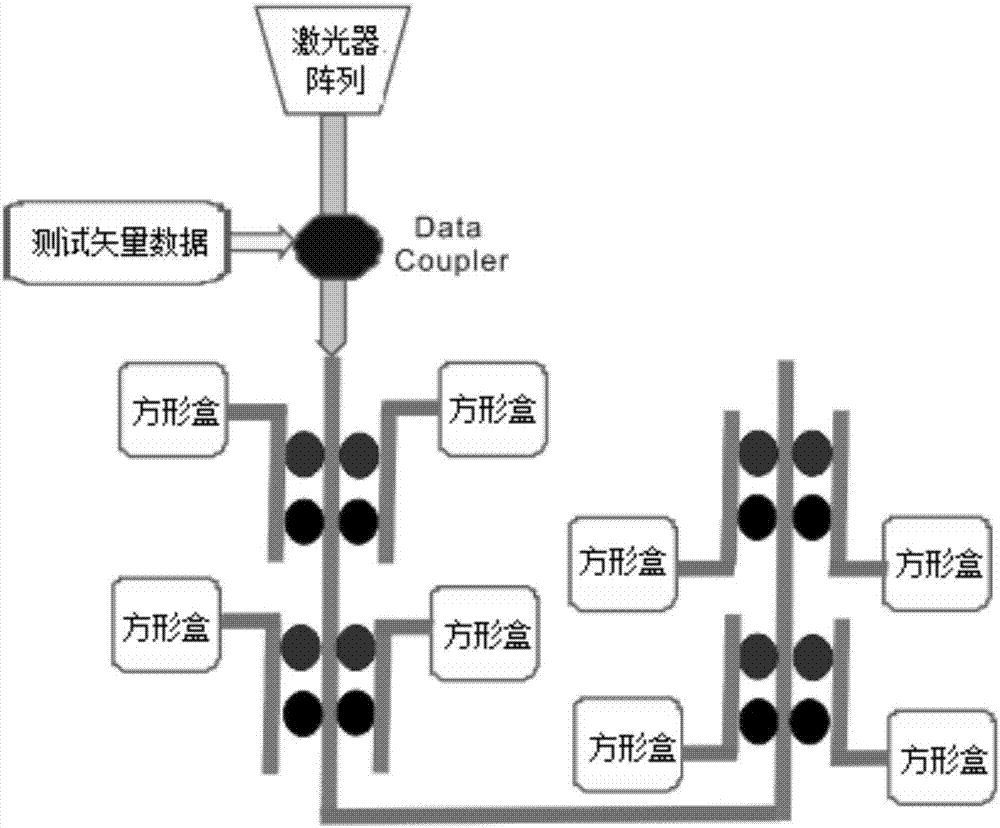

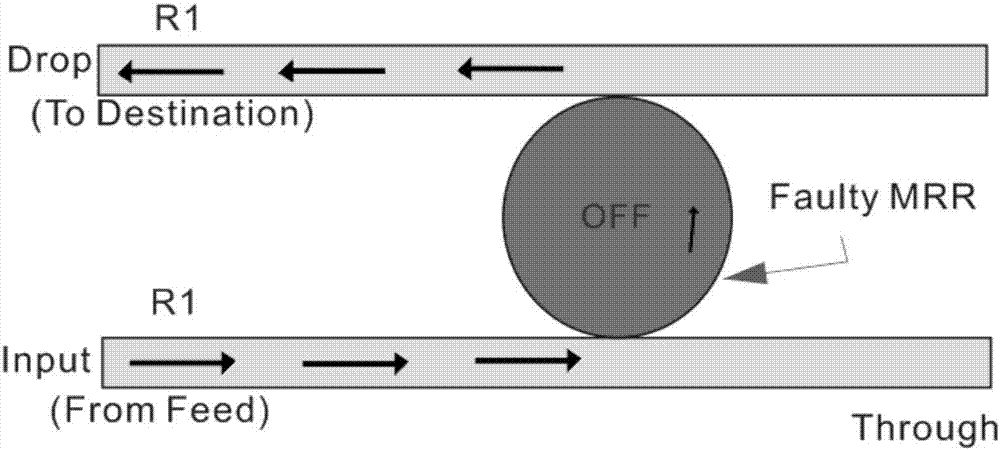

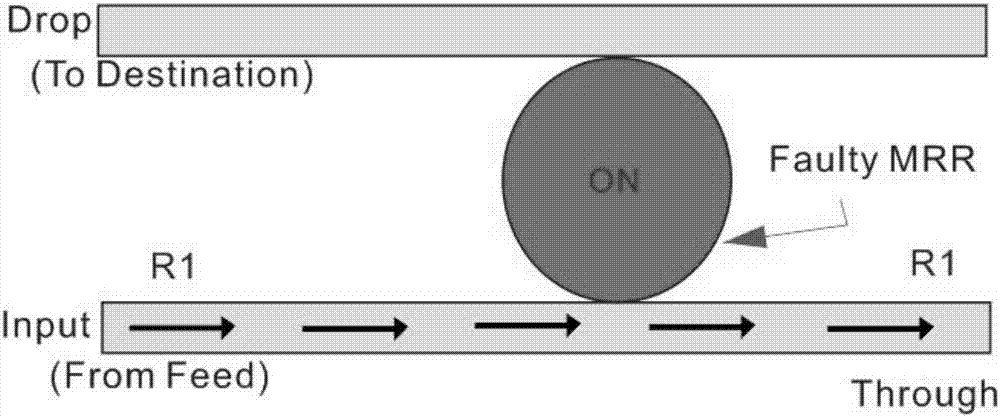

Fault detection device and fault detection method for MRR fault in PNoC

The invention discloses a fault detection device and a fault detection method for an MRR (Micro Ring Resonator) fault in a PNoC (Photonic Network-on-Chip). In view of a fault caused by manufacturing defects and the sensitiveness of an MRR to great temperature fluctuation, a fault model is built, and a PNOC architecture composed of a laser array, a test vector generator, a control vector generator, a data coupler, an MRR under test and a square box is designed. The data coupler couples test data into an optical path. The on-off state of the MRR is controlled. Fault analysis and diagnosis are carried out based on collected test response.

Owner:GUILIN UNIV OF ELECTRONIC TECH

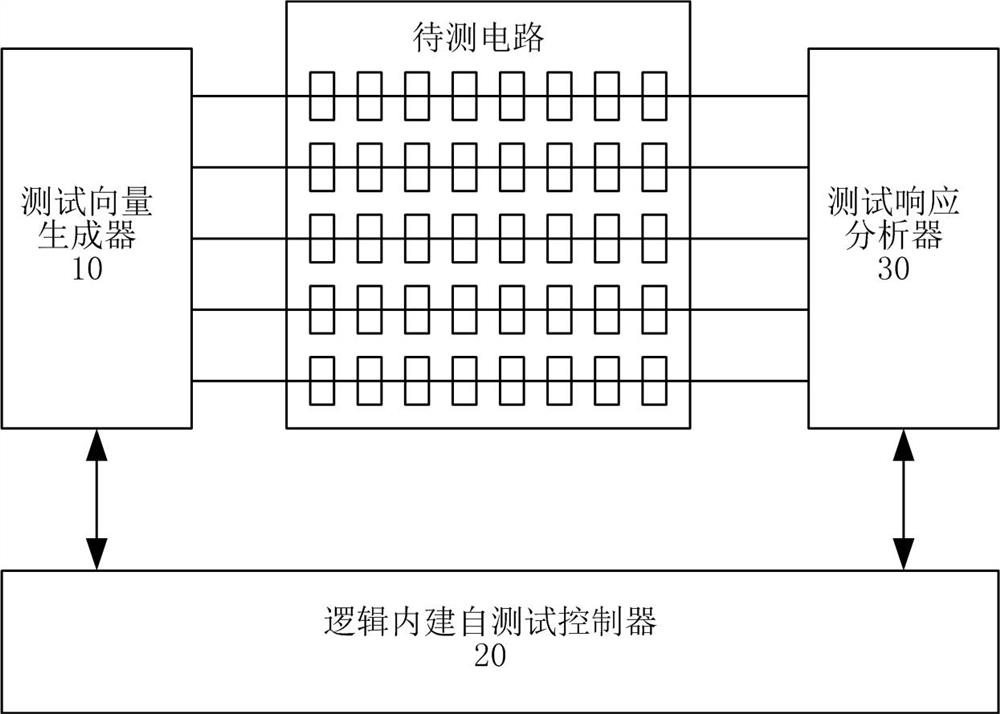

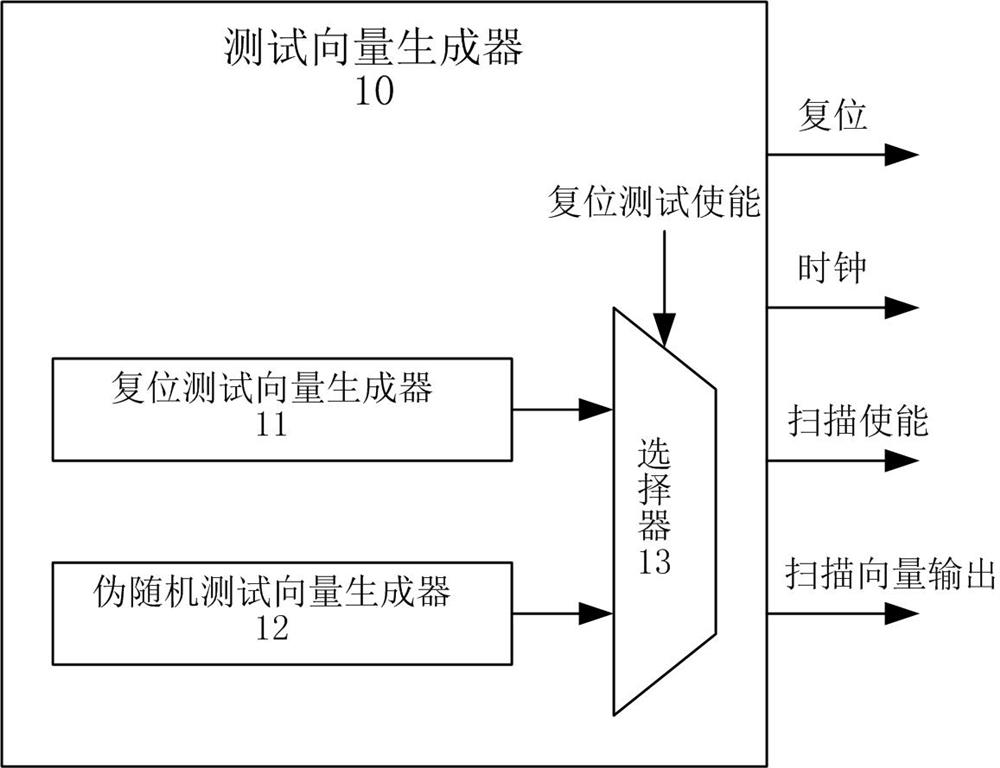

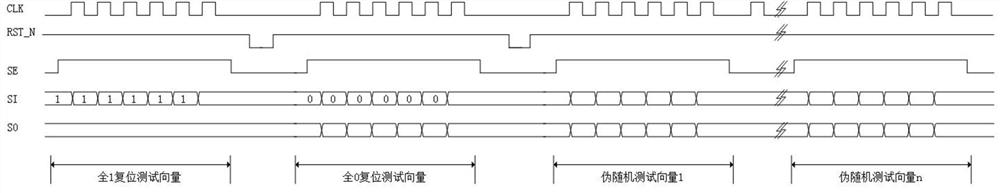

Reset circuit test system and method for logic built-in self-test

ActiveCN114360622ASolve problems that cannot be coveredMany test vectorsStatic storageFault coverageControl engineering

A logic built-in self-test reset circuit test system comprises a test vector generator, a logic built-in self-test controller and a test response analyzer, the test vector generator generates a reset test vector and a pseudo-random test vector, receives an instruction of the logic built-in self-test controller, and analyzes the reset test vector and the pseudo-random test vector according to the instruction of the logic built-in self-test controller. The reset signal, the clock signal, the scanning enable signal and the scanning vector output signal are output to a circuit to be tested; the logic built-in self-test controller is used for respectively controlling the signal output of the test vector generator and controlling the test response analyzer to test the circuit to be tested; and the test response analyzer receives an instruction of the logic built-in self-test controller and tests the circuit to be tested. The invention also provides a reset circuit test method for logic built-in self-test, which solves the problem that the reset signal cannot be highly covered in the traditional logic built-in self-test by using less logic, and improves the fault coverage rate.

Owner:NANJING SEMIDRIVE TECH CO LTD

Dynamic generation of test segments

InactiveUS9117023B2Software testing/debuggingSoftware simulation/interpretation/emulationProgramming languageTemplate based

A computerized apparatus, method and computer product for generating tests. The apparatus comprises: a processor; an interface for obtaining a test template associated with a computerized system that comprises a template segment comprising instructions and directives or related control constructs; a test generator for generating a test associated with the template segment, comprising: a simulator for determining a state of the system associated with an execution of the test; a selector for selecting a template instruction or segment from the test template based on the state of the system; and a generator configured to generate a multiplicity of instructions based on system's state and on the selected template segment, wherein the test generator further comprises a verifier configured to verify that a previously generated instruction is in line with the current state of the system and with the selected template instruction or segment.

Owner:GLOBALFOUNDRIES INC

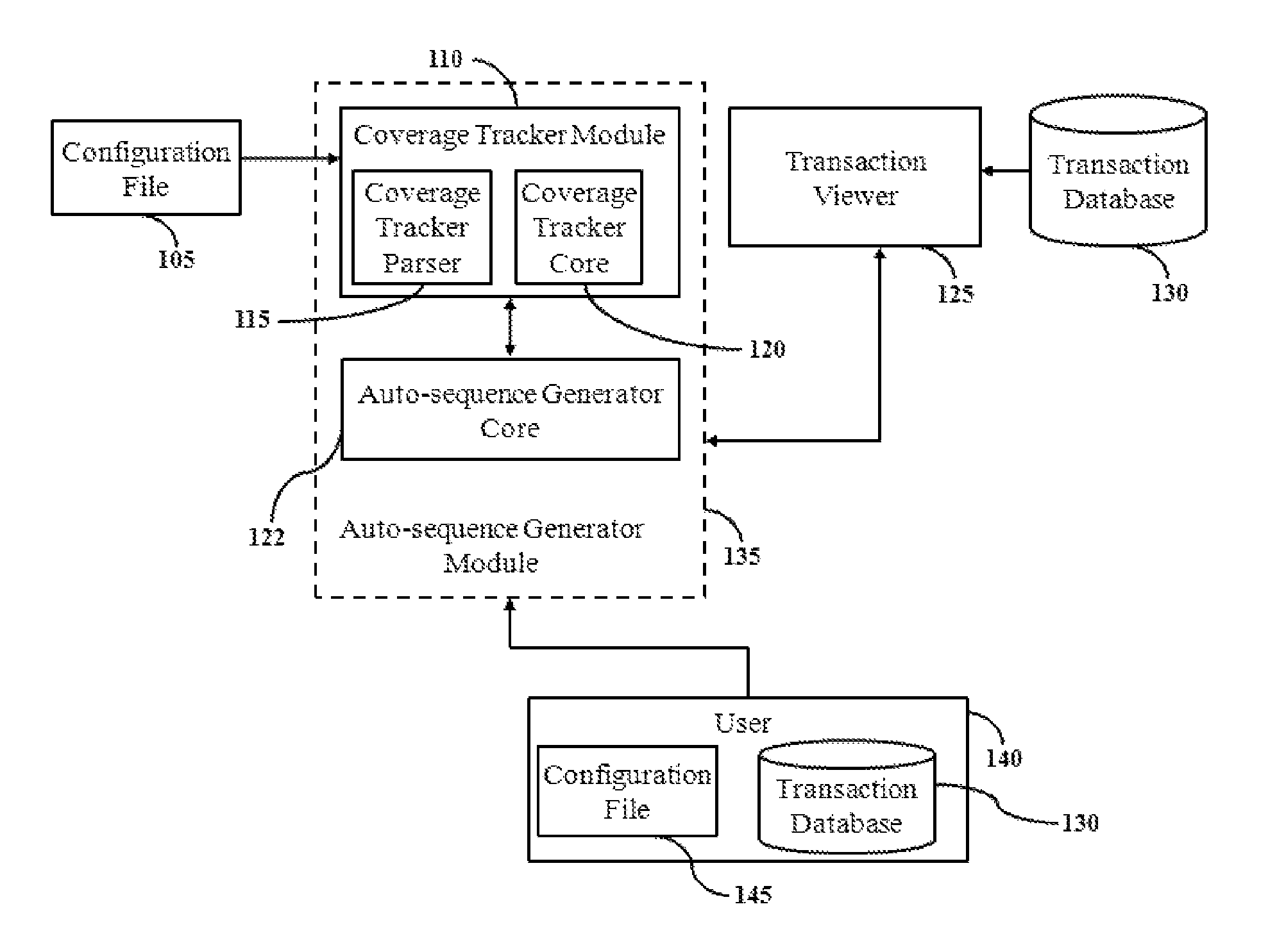

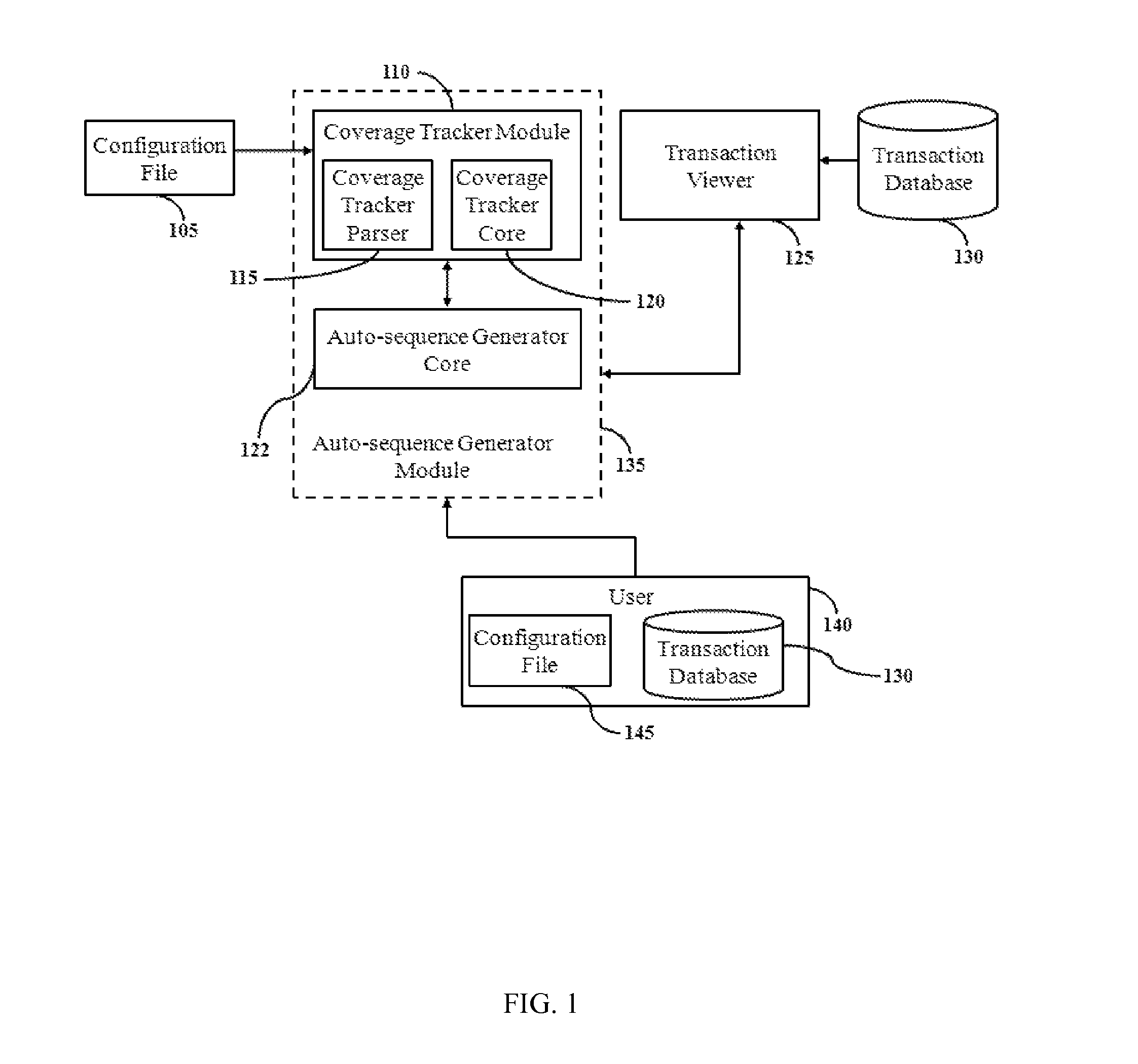

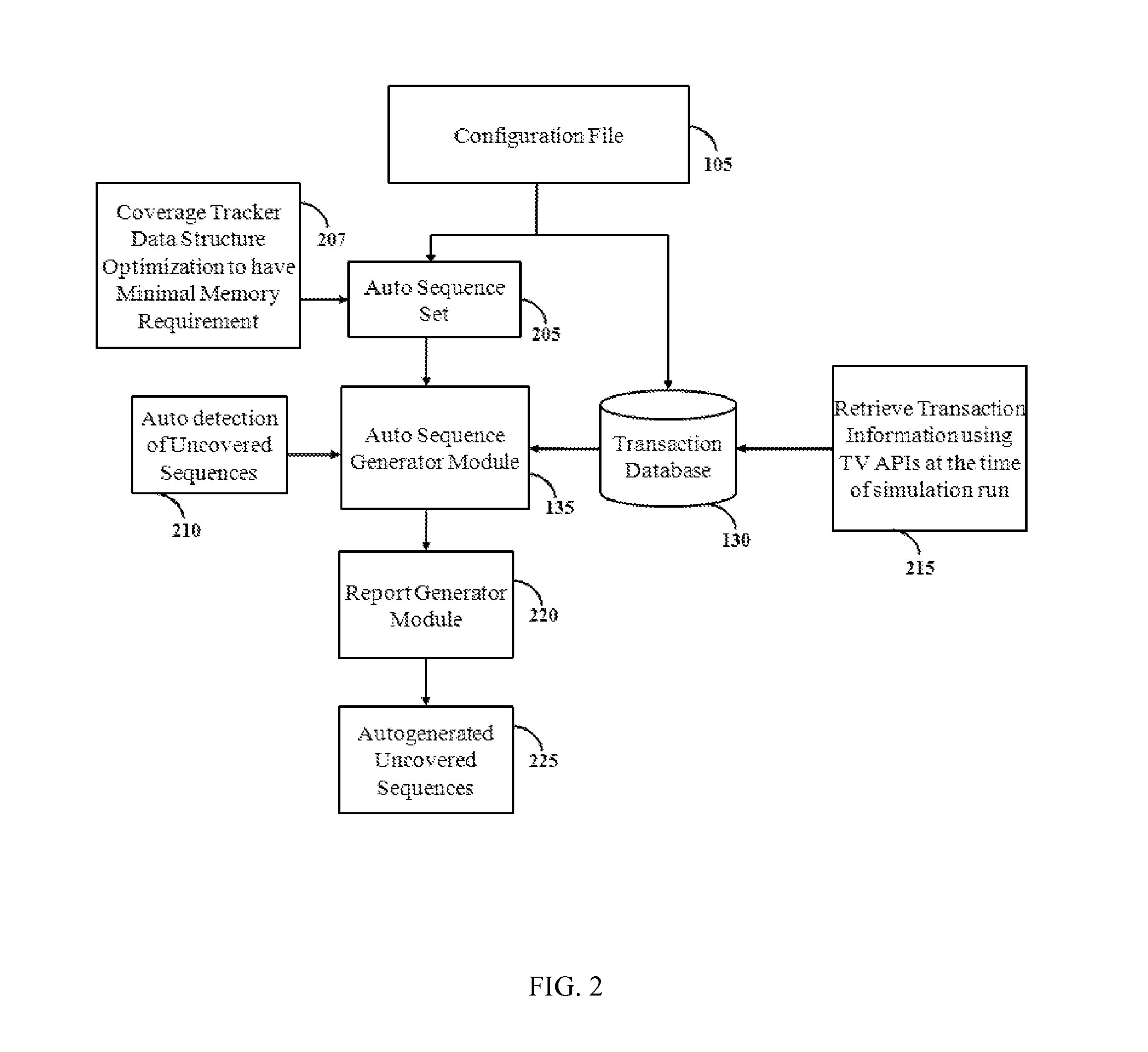

Method and system for test vector generation

ActiveUS8661305B2Easy accessElectronic circuit testingError detection/correctionComputer architectureProgram planning

Owner:RAJARAO RAVISHANKAR +1

Memory systems and electronic systems performing an adaptive error correction operation with pre-checked error rate, and methods of operating the memory systems

ActiveUS10114693B2Memory architecture accessing/allocationMemory adressing/allocation/relocationElectronic systemsControl signal

A memory system may include a test vector generator configured for generating a test vector to be written into a memory device, a data discrepancy checker configured for comparing read data outputted from the memory device with the test vector to generate an information signal corresponding to a comparison between the read data and the test vector, an error correction code (ECC) controller configured for performing an ECC encoding operation and an ECC decoding operation according to any one among a plurality of ECC levels based on a control signal, and a memory controller controlling the test vector generator, the data discrepancy checker and the ECC controller. The memory controller configured to transmit the control signal corresponding to an error rate of the memory device to the ECC controller, based on the information signal generated by the data discrepancy checker.

Owner:SK HYNIX INC

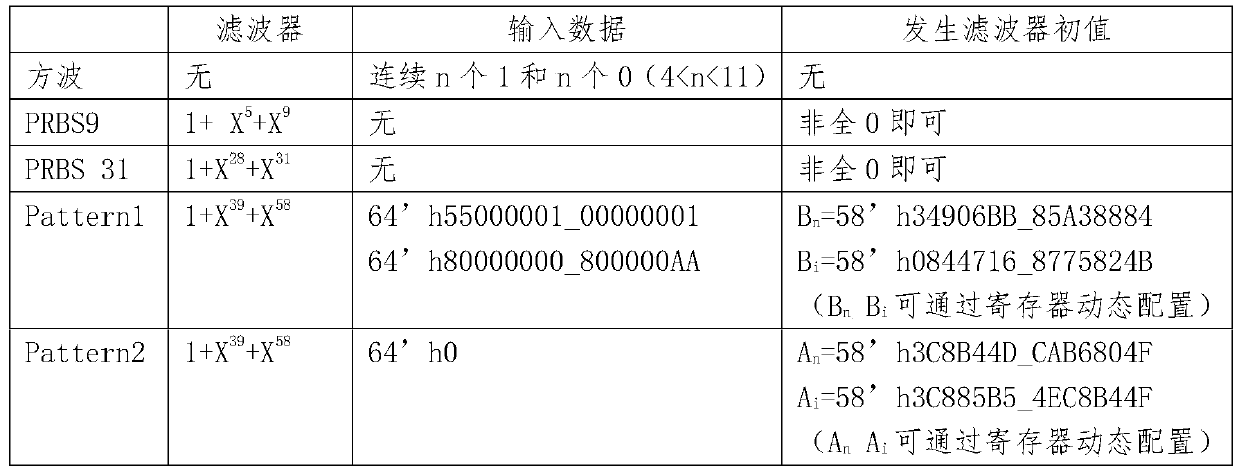

Test vector generation and detection system and method for multi-type test sequence

ActiveCN110120856AEasy to operateError detection/prevention using signal quality detectorCorrect operation testingSquare waveformTest vector generator

The invention discloses a test vector generation and detection system and method for a multi-type test sequence. The system comprises a test vector generation unit and a test vector detection unit. The test vector generation unit comprises a test vector control unit and a test sequence generation unit; the test vector control unit is used for selecting and switching a test mode and configuring aninitial value of the filter; and the test vector detection unit is used for receiving the PRBS31 test sequence, the Patter1 test sequence and the Patter2 test sequence, descrambling the data obtainedby the receiving end, comparing whether the received test vector is a correct pseudorandom sequence or not, recording the number of errors and feeding back the number of errors. The PCS sub-layer testvector management method provided by the invention is stable and is suitable for a common high-speed Ethernet communication controller; the system can work in five test sequence modes of square waves, PRBS9, PRBS31, Pattern1 and Pattern2, the application range is wide, and the requirements of different Ethernet link test platforms can be met.

Owner:XIAN MICROELECTRONICS TECH INST

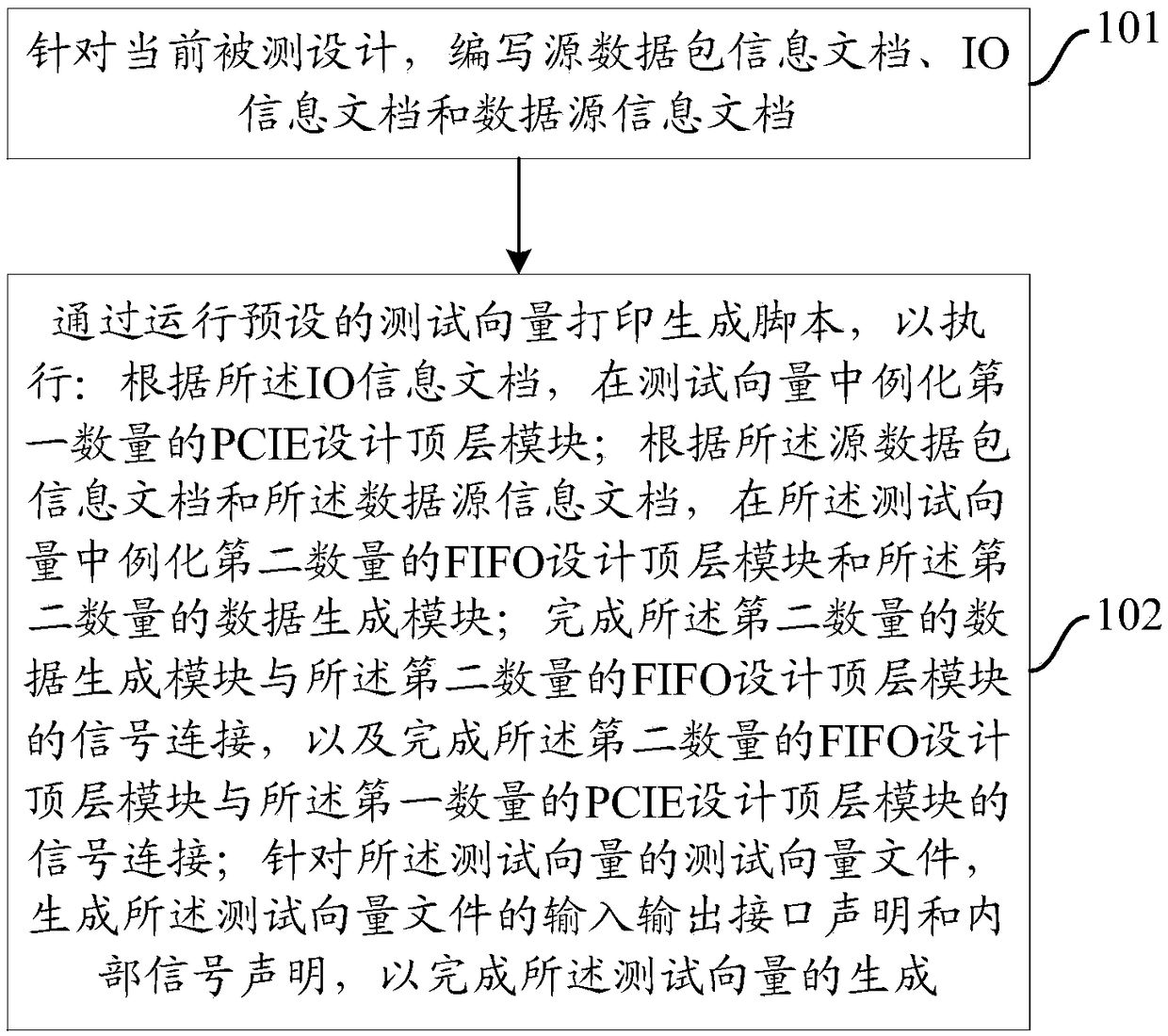

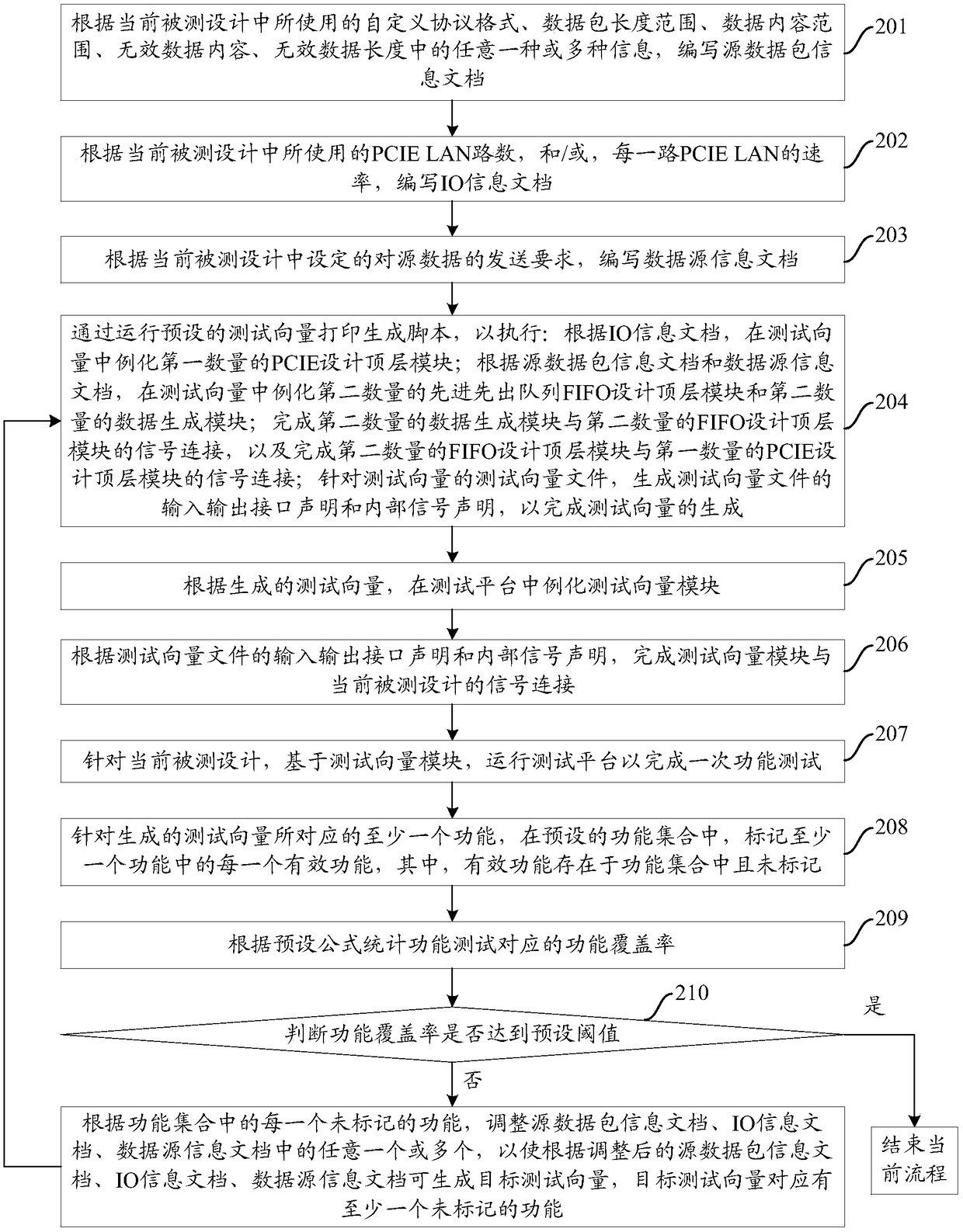

A test vector generation method and apparatus for a PCIE interface

The invention provides a test vector generation method and a device for a PCIE interface. The method comprises the following steps: compiling a source data packet information document, an IO information document and a data source information document according to a current design under test; The scripts are generated by running the preset test vectors. According to the IO information document, thefirst number of PCIE design top-level modules are instantiated in the test vectors. A second number of FIFO design top-level modules and a second number of data generation modules are instantiated inthe test vector according to the source packet information document and the data source information document; the data generation module and an FIFO design top-level module, an FIFO design top-levelmodule and a PCIE design top-level module are in signal connection; for the test vector file of the test vector, the input and output interface declarations and internal signal declarations are generated to complete the test vector generation. The scheme can automatically generate test vectors, and can reduce the workload of generating test vectors.

Owner:JINAN INSPUR HIGH TECH TECH DEV CO LTD

System and method for verifying register transfer level (RTL) hardware

ActiveCN102567165BImprove verification efficiencyImprove accuracyFunctional testingProcessor registerVideo sequence

Owner:北京集朗半导体科技有限公司

Controllable test vector generator based on linear feedback shift register

InactiveCN102226947BGood cross-correlationTypes of added fault detectionStatic storageExclusive orTest vector generator

The invention discloses a controllable test vector generator based on a linear feedback shift register (LFSR). The controllable test vector generator comprises three sections: 1, a control code sequence generation section comprising a counter and a memory; 2, a sequence pseudo random test vector sequence generation section comprising a inscribe LFSR; 3, a feedback network section formed by n-1 bit input or a non-gate NOR and an exclusive-OR gate XORfb. Depending on the test vectors required to be generated, the control code sequence is acquired, wherein the control code sequence is stored in the memory and is provided for controlling a run of the inscribe LFSR, such that the sequence or jump output pseudo random sequence of the inscribe LFSR is adopted as the test vector. With the present invention, only the control code memory, the counter, the feedback network section formed by the n-1 bit input or the non-gate NOR and the exclusive-OR gate XORfb, and a control exclusive-OR gate XORCTRL are added on the base of the inscribe LFSR, such that hardware expense is few, and test cost is low.

Owner:UNIV OF ELECTRONICS SCI & TECH OF CHINA