Test vector generating method for boundary scanning

A technology of boundary scan testing and test vectors, applied in the direction of measuring electricity, measuring devices, measuring electrical variables, etc.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0015] Embodiments of the present invention will be described in detail below in conjunction with the accompanying drawings.

[0016] Method of the present invention is to utilize the BSDL (Boundary-Scan Description Language) file of the chip that supports JTAG (Joint Text Action Group) standard and the .NET file (for example: Board Netlist file) of circuit board to generate the .NET file that can be used for JTAG boundary scan failure detection Test vector files and diagnostic information files.

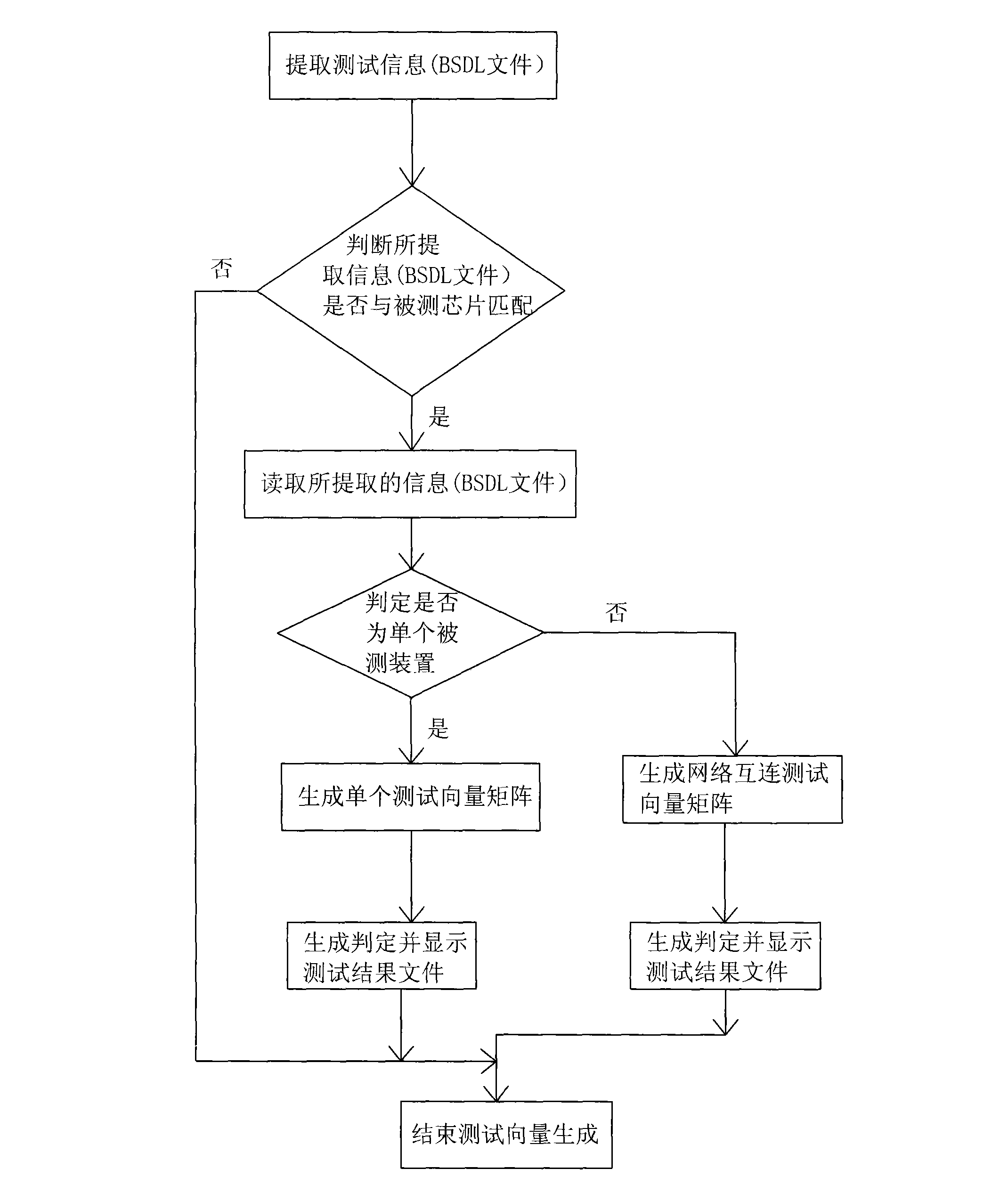

[0017] figure 1 It is a schematic flow chart of the method of the present invention, as shown in the figure, a method for generating a boundary scan test vector, which generates a test vector by integrating test information of a device under test (chip);

[0018] Specific steps are as follows:

[0019] a. Extract test information; extract the relevant information in the BSDL file of each chip provided by the user and the .NET file of the circuit board;

[0020] a1. following step...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More