Built-in testing realization method of circuit board interconnect fault under boundary scanning environment

A technology of boundary scan and built-in testing, applied in digital circuit testing, electronic circuit testing, electrical measurement, etc., can solve the problem of test response diversity and disordered response analyzer 3', which is inconvenient to design, test incentives are not uniform, and increase Response analyzer 3'hardware overhead and other issues

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0104] The specific embodiments of the present invention will be further described in detail below in conjunction with the accompanying drawings.

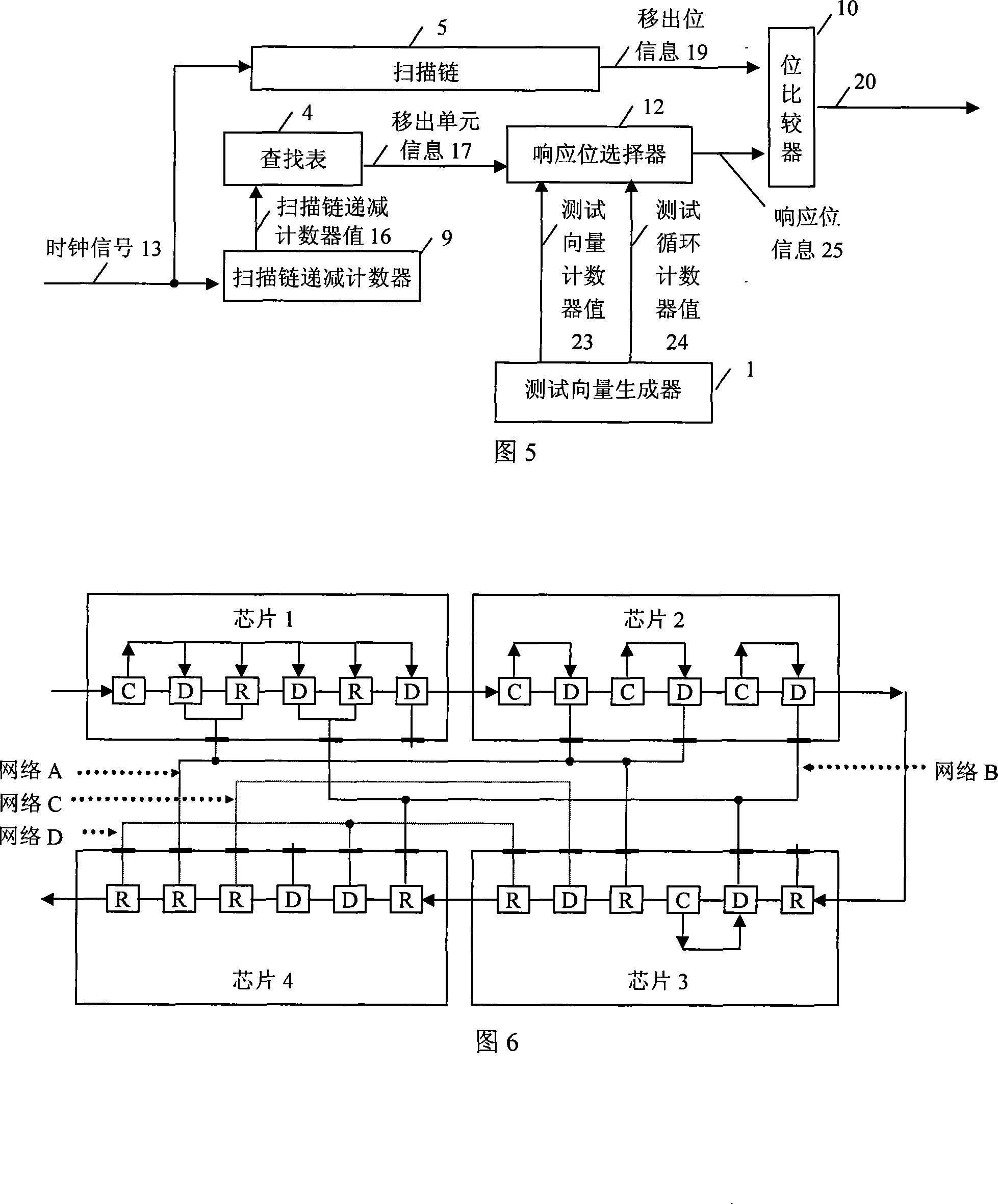

[0105] FIG. 6 is a simplified schematic diagram of the interconnection network of a circuit board 2 under test. The scan chain 5 of this circuit board includes 24 boundary scan units (these 24 scan units are respectively named "unit 1", "unit 2", ..., "unit 24" according to the flow direction of the arrow). "C" in the figure indicates the control unit, "D" indicates the drive unit, and "R" indicates the receiver unit; if the drive unit and the receiver unit share the same pin, it indicates a bidirectional unit, for example, "unit 2" and "unit 3" indicate A bi-directional unit; the arrow on the control unit indicates which drive unit or bi-directional unit it controls, e.g. "Unit 1" controls "Unit 2", "Unit 3", "Unit 4", "Unit 5" and "Unit 6 ".

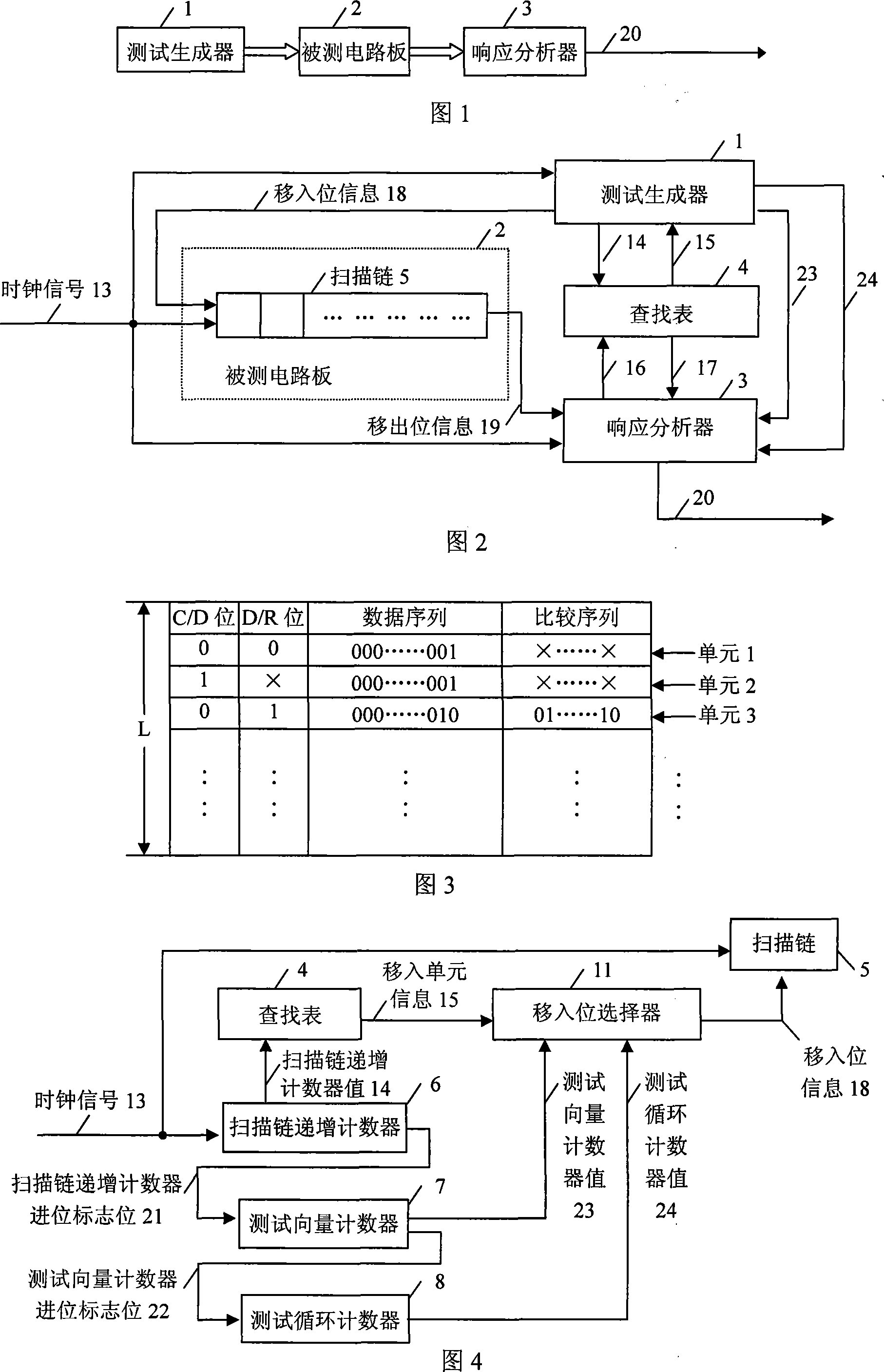

[0106] The overall design of the hardware part of the present invention is shown in F...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More