Patents

Literature

112 results about "Test stimulus" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

The “test stimulus” (that is, the visual representation of the design) you use can be easily adapted to work with several different types of research studies. When conducting in-person visual-design evaluations, you can simply show people a static image, either printed on paper or displayed on a screen.

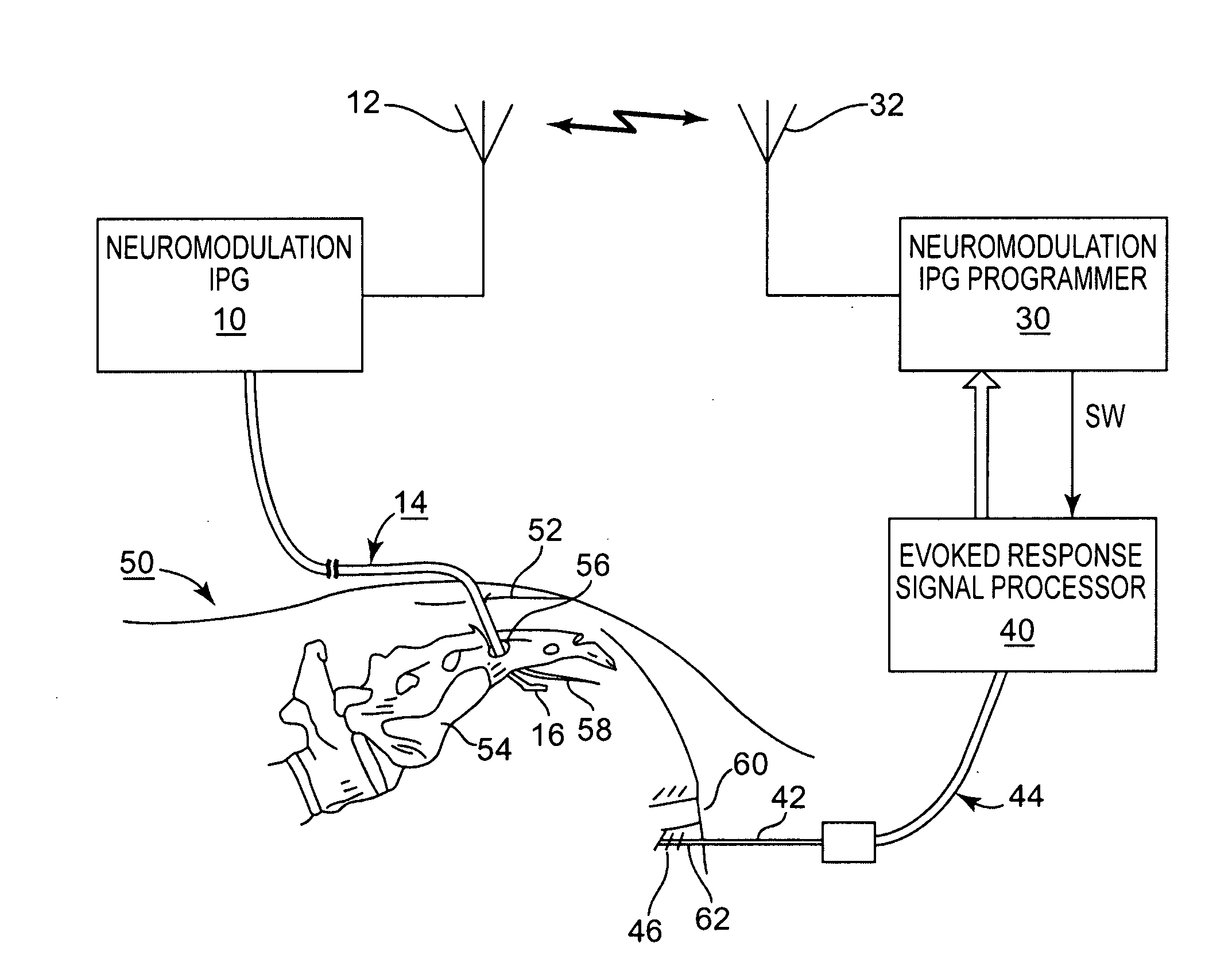

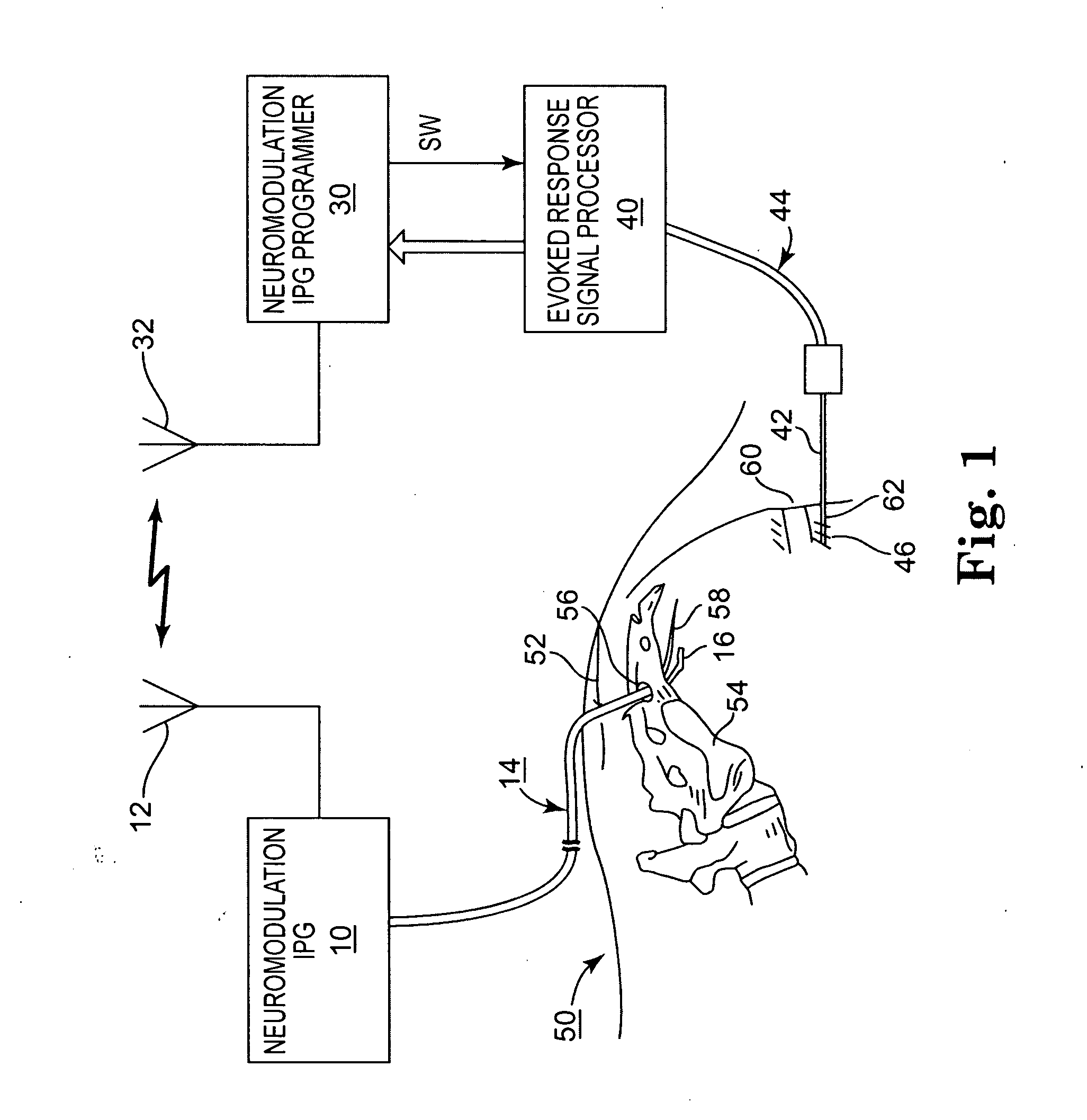

Testing Efficacy of Therapeutic Mechanical or Electrical Nerve or Muscle Stimulation

InactiveUS20070265675A1Rule out the possibilityReduce complicationsElectrotherapyMuscle tissuePelvic nerve

Methods and apparatus for testing of the efficacy of therapeutic stimulation of pelvic nerves or musculature to alleviate one of incontinence or sexual dysfunction are disclosed. A therapy delivery device is operable in a therapy delivery mode and a test mode and an evoked response detector is employed in the test mode to detect the evoked response to applied test stimuli. The test stimuli parameters of the test stimulation regimen are adjusted prior to delivery of each test stimulation regimen, and the evoked responses to the applied test stimulation regimens are compared to ascertain an optimal test stimulation regimen. The therapy stimulation regimen parameters are selected as a function of the test electrical stimulation parameters causing the optimal evoked response.

Owner:AMS RES CORP

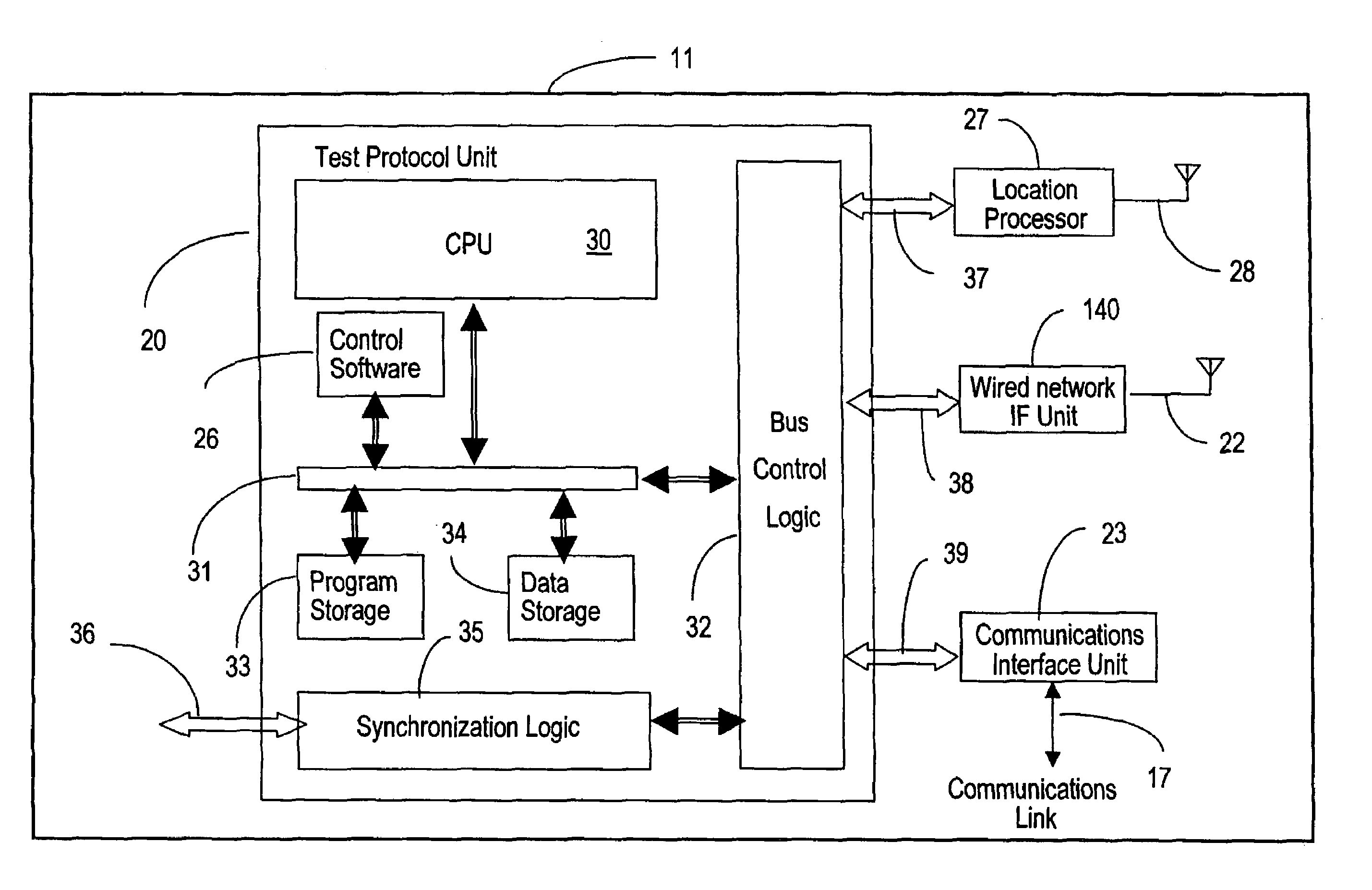

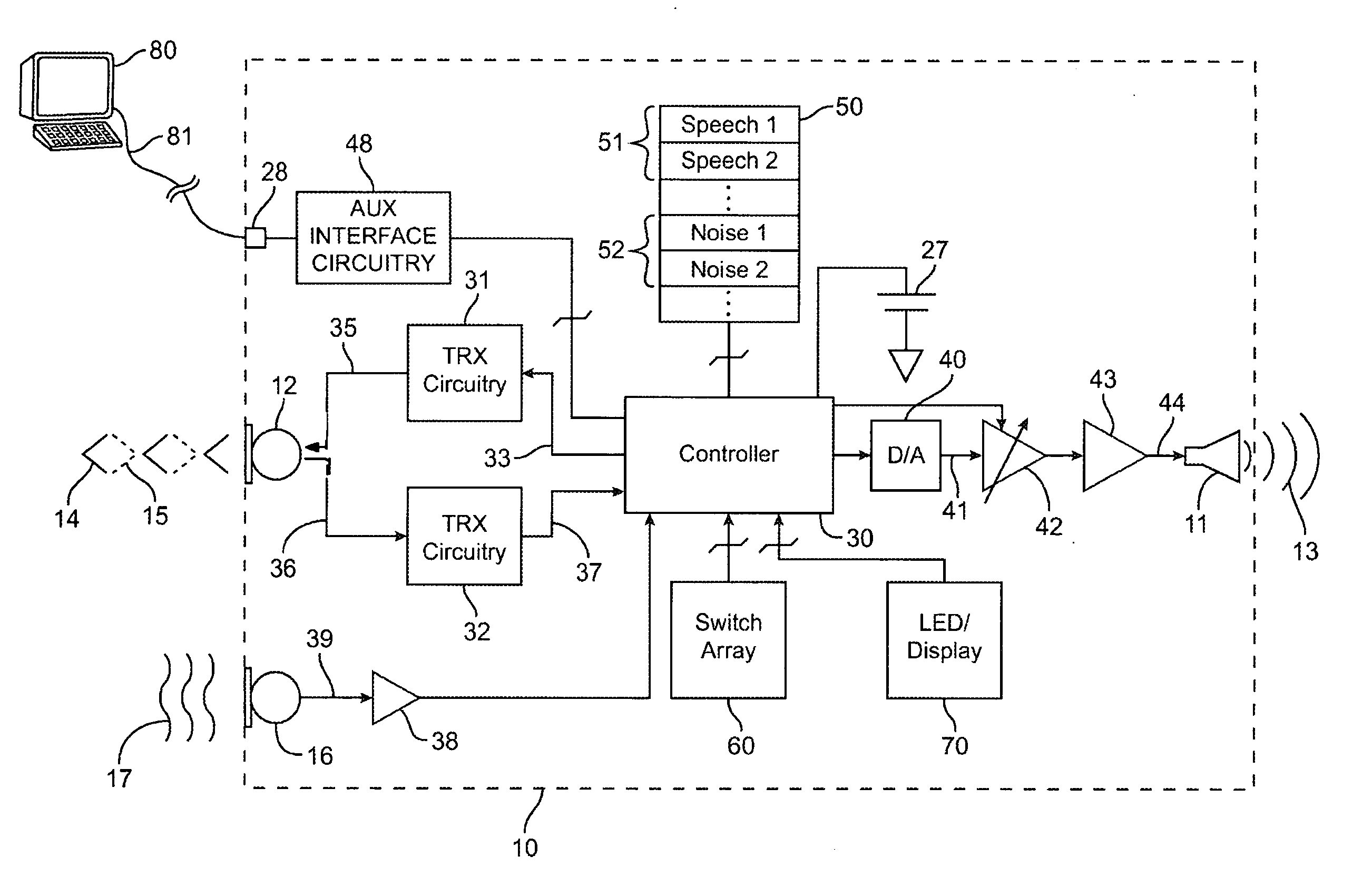

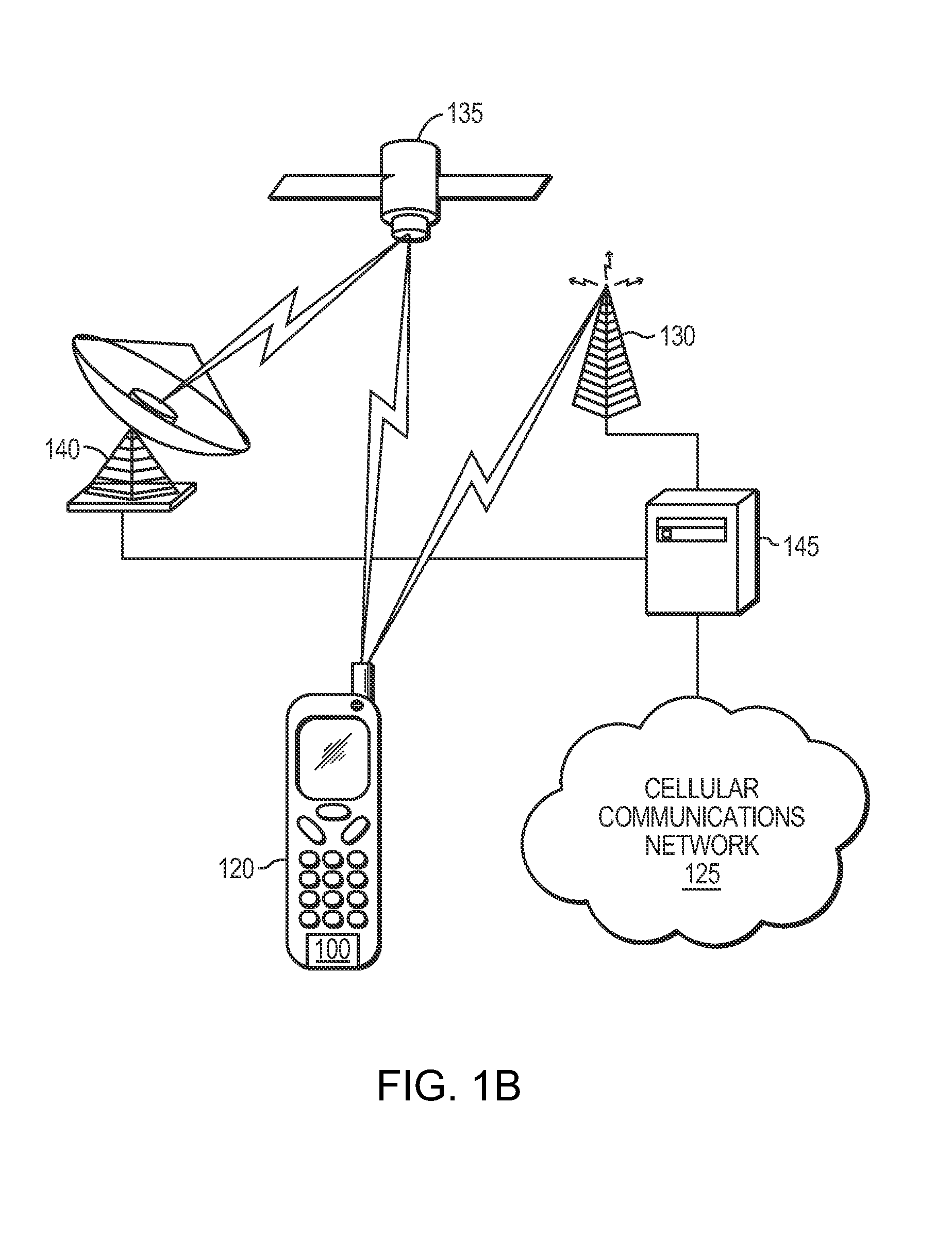

Location-based testing for wireless data communication networks

ActiveUS7539489B1Easy to optimizeFacilitate data communicationError preventionFrequency-division multiplex detailsTest stimulusSystem under test

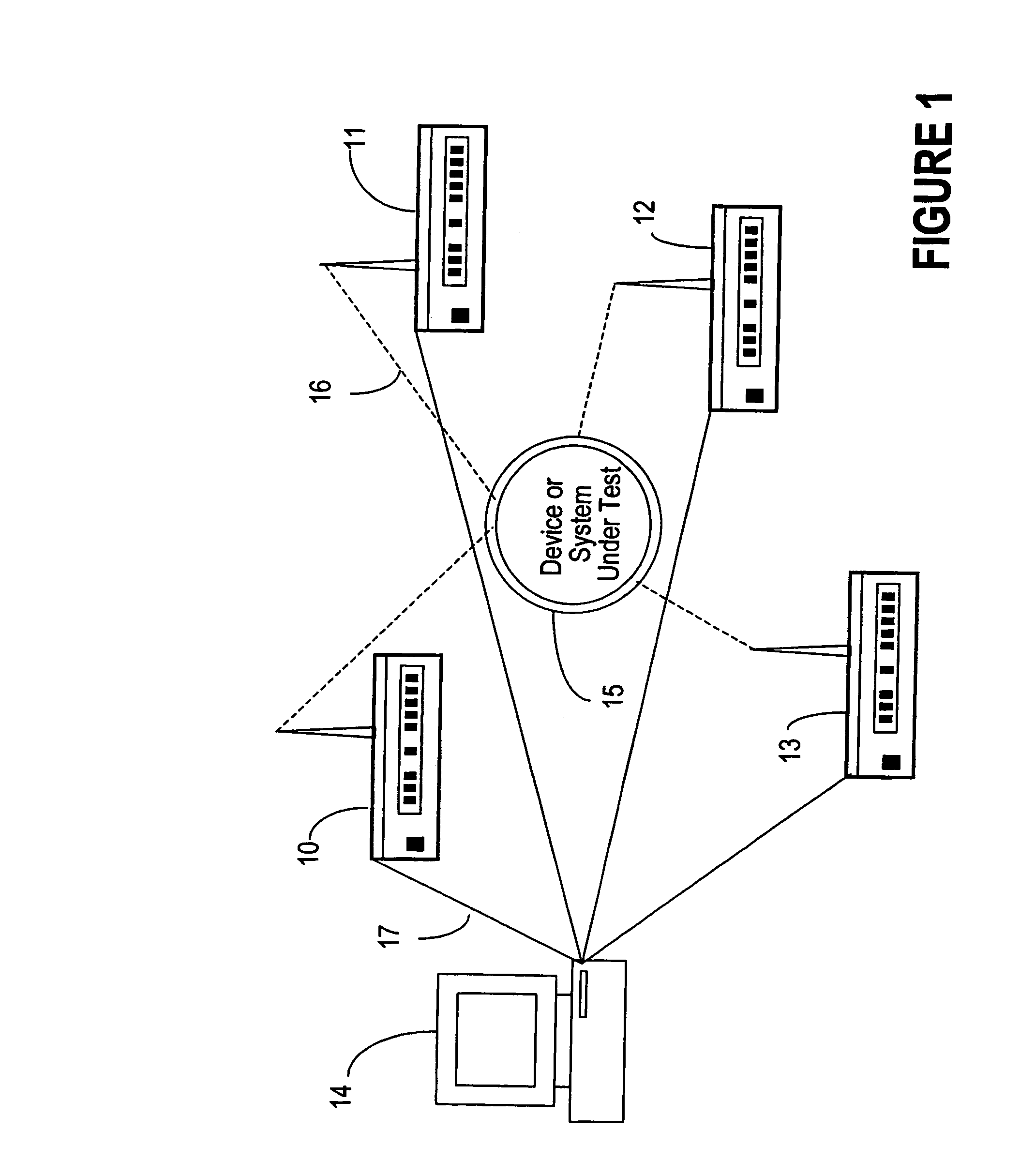

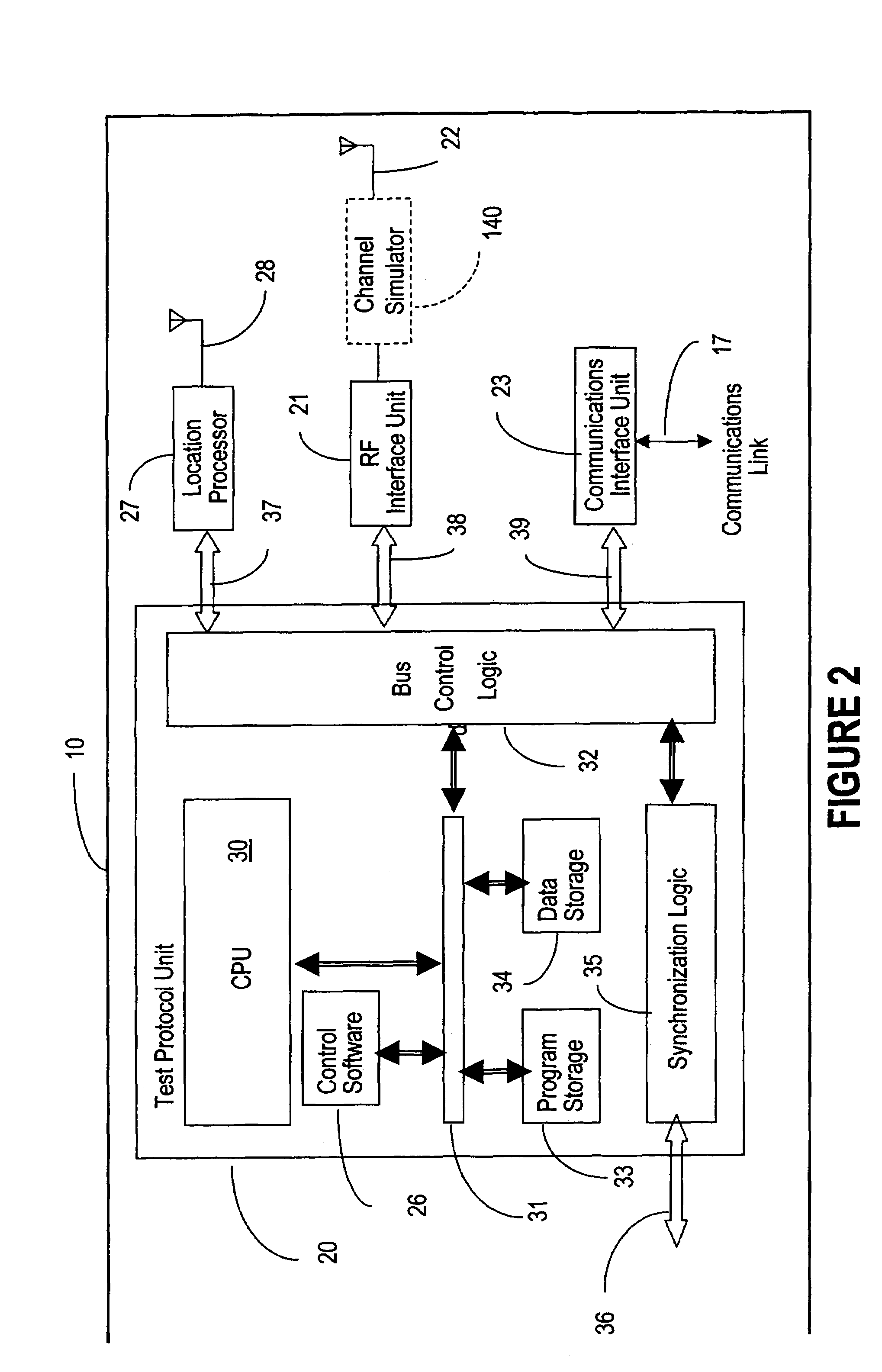

Apparatus and methods facilitating a distributed approach to performance and functionality testing of location-sensitive wireless data communication systems and equipment are described. A plurality of test units, geographically distributed at arbitrary points in a three-dimensional volume surround the system or equipment under test. Each test unit generates test stimuli and records responses from the device under test, and emulates the effects of changes in spatial location within an actual wireless network environment. A central controller co-ordinates the set of test units to ensure that they act as a logical whole, and enables testing to be performed in a repeatable manner in spite of the variations introduced by the location sensitive characteristics of wireless data communication networks. The central controller also maintains a user interface that provides a unified view of the complete test system, and a unified view of the behavior of the system or equipment under test. For diagnostic purposes, the recorded responses may be regenerated to view any defects as many times as necessary to correct them. Alternatively, each test unit may have either wired network interface units, instead of a wireless interface unit to test systems or equipment forming part of a wired network portion in the wireless data communication system.

Owner:KEYSIGHT TECH SINGAPORE (SALES) PTE LTD

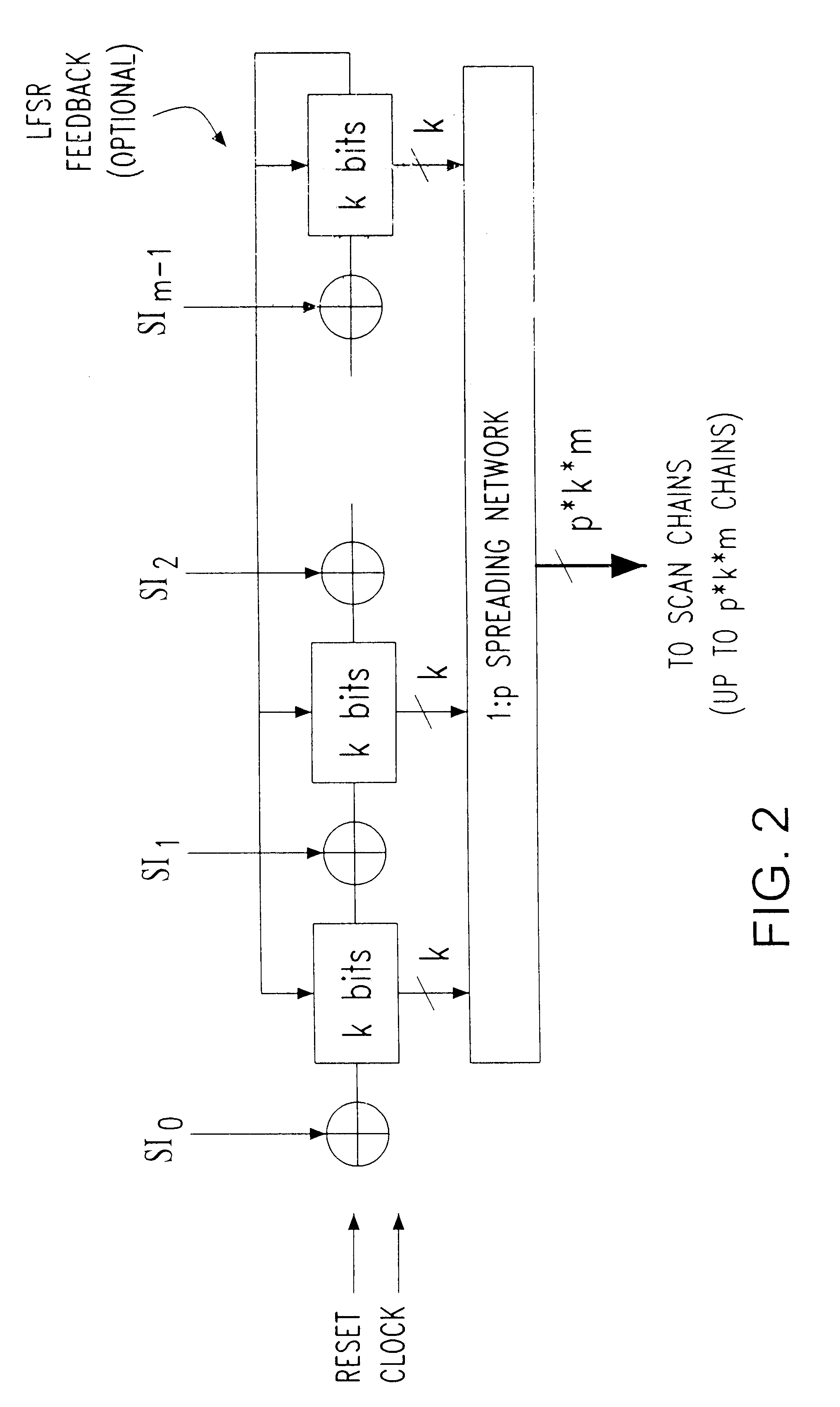

Real-time decoder for scan test patterns

InactiveUS6611933B1Cost-efficiently integratedForming accuratelyElectronic circuit testingError detection/correctionComputer hardwareTest efficiency

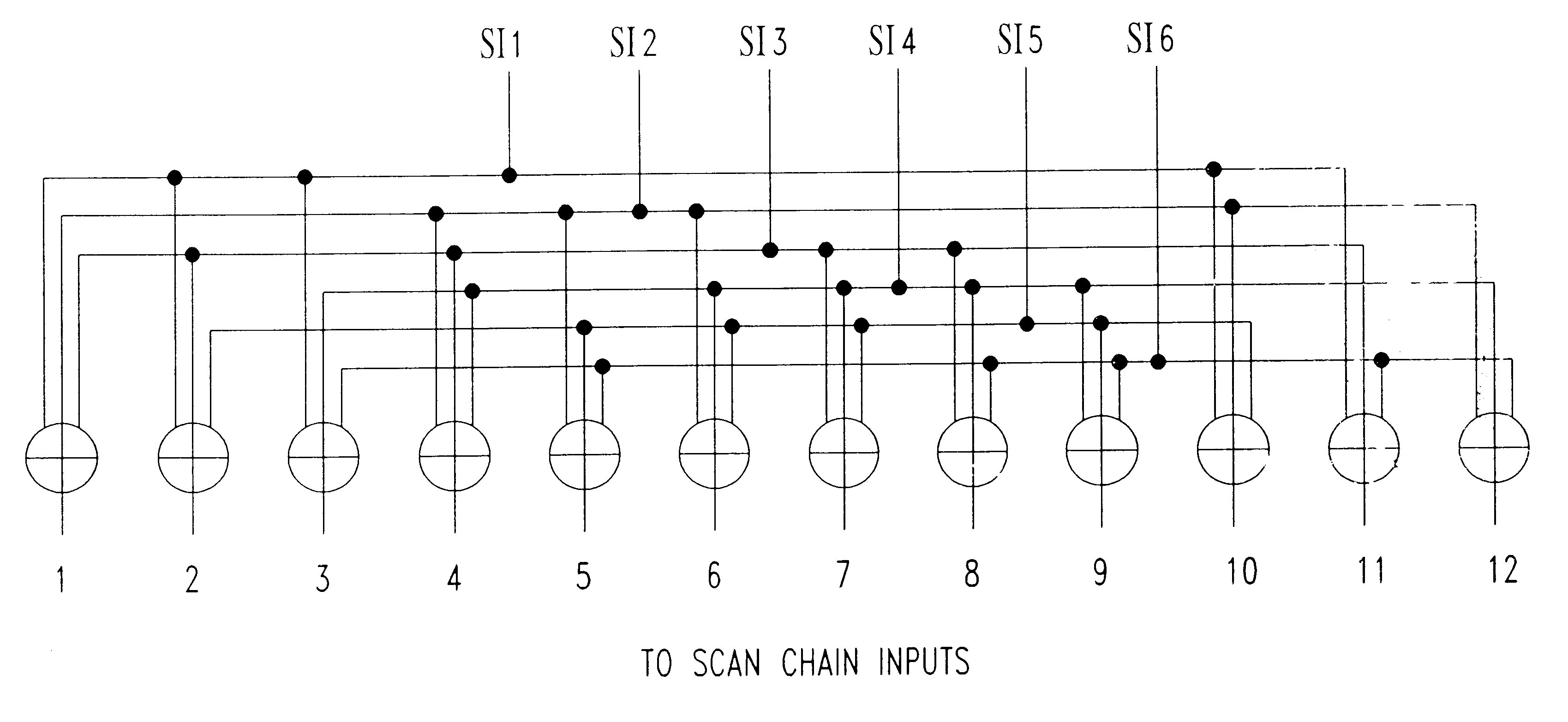

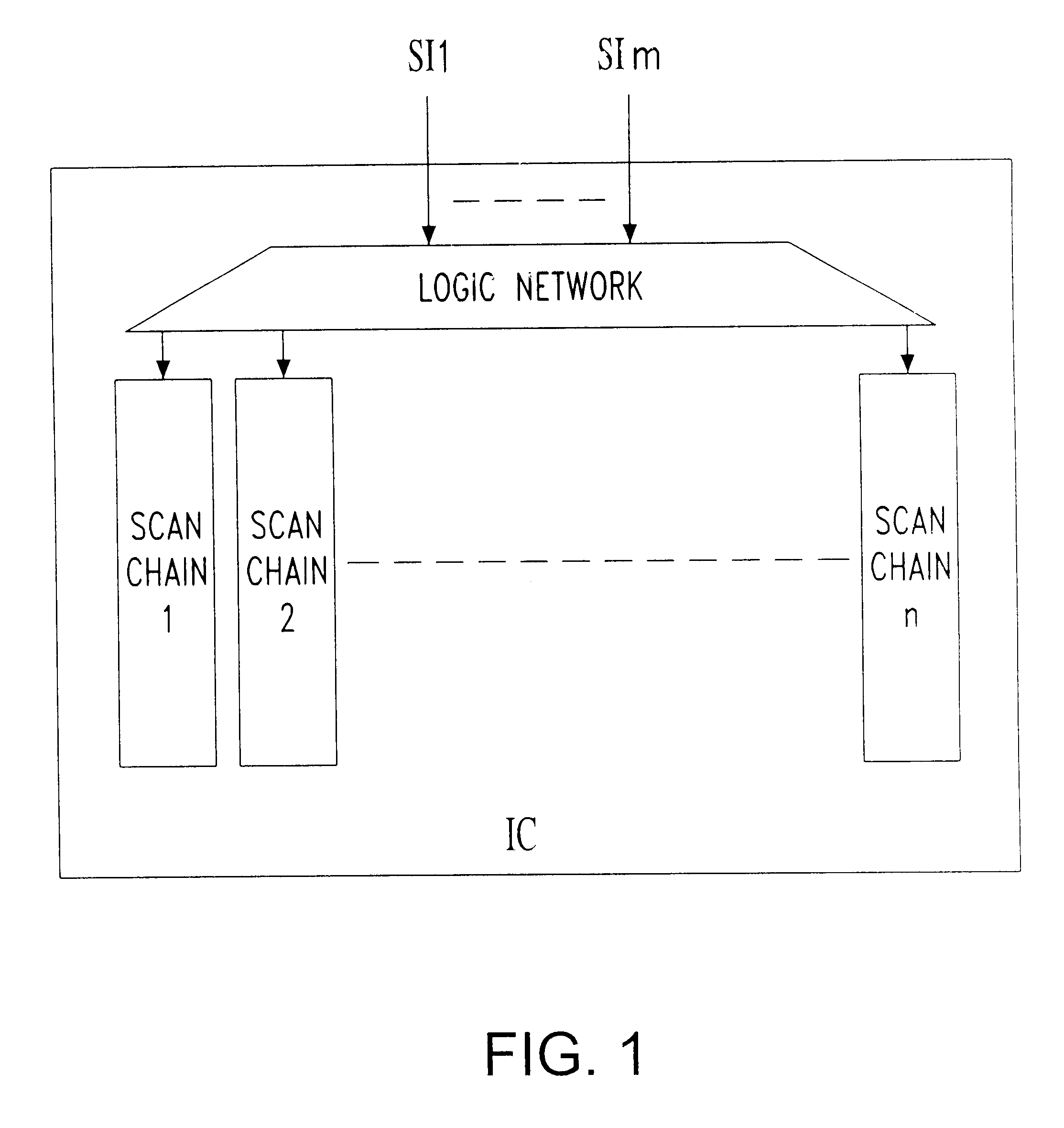

A method and apparatus for improving the efficiency of scan testing of integrated circuits is described. This efficiency is achieved by reducing the amount of required test stimulus source data and by increasing the effective bandwidth of the scan-load operation. The reduced test data volume and corresponding test time are achieved by integrating a real-time test data decoder or logic network into each integrated circuit chip. The apparatus, servicing a plurality of internal scan chains wherein the number of said internal scan chains exceeds the number of primary inputs available for loading data into the scan chains, includes: a) logic network positioned between the primary inputs and the inputs of the scan chains, the logic network expanding input data words having a width corresponding to the number of the primary inputs, and converting the input data words into expanded output data words having a width that corresponds to the number of the internal scan chains; and b) coupled to the internal scan chains, registers loaded with bit values provided by the expanded output data words while data previously loaded into the scan chains shifts forward within the scan chains by one bit position at a time; wherein a first plurality of the input data words supplied to the primary inputs produce a second plurality of expanded data words that are loaded into the internal scan chains to achieve an improved test coverage.

Owner:GOOGLE LLC

Personal hearing evaluator

InactiveUS20060210090A1Eliminate errorsRemoved positioningStethoscopeAudiometeringTest stimulusHand held

Owner:INSOUND MEDICAL INC

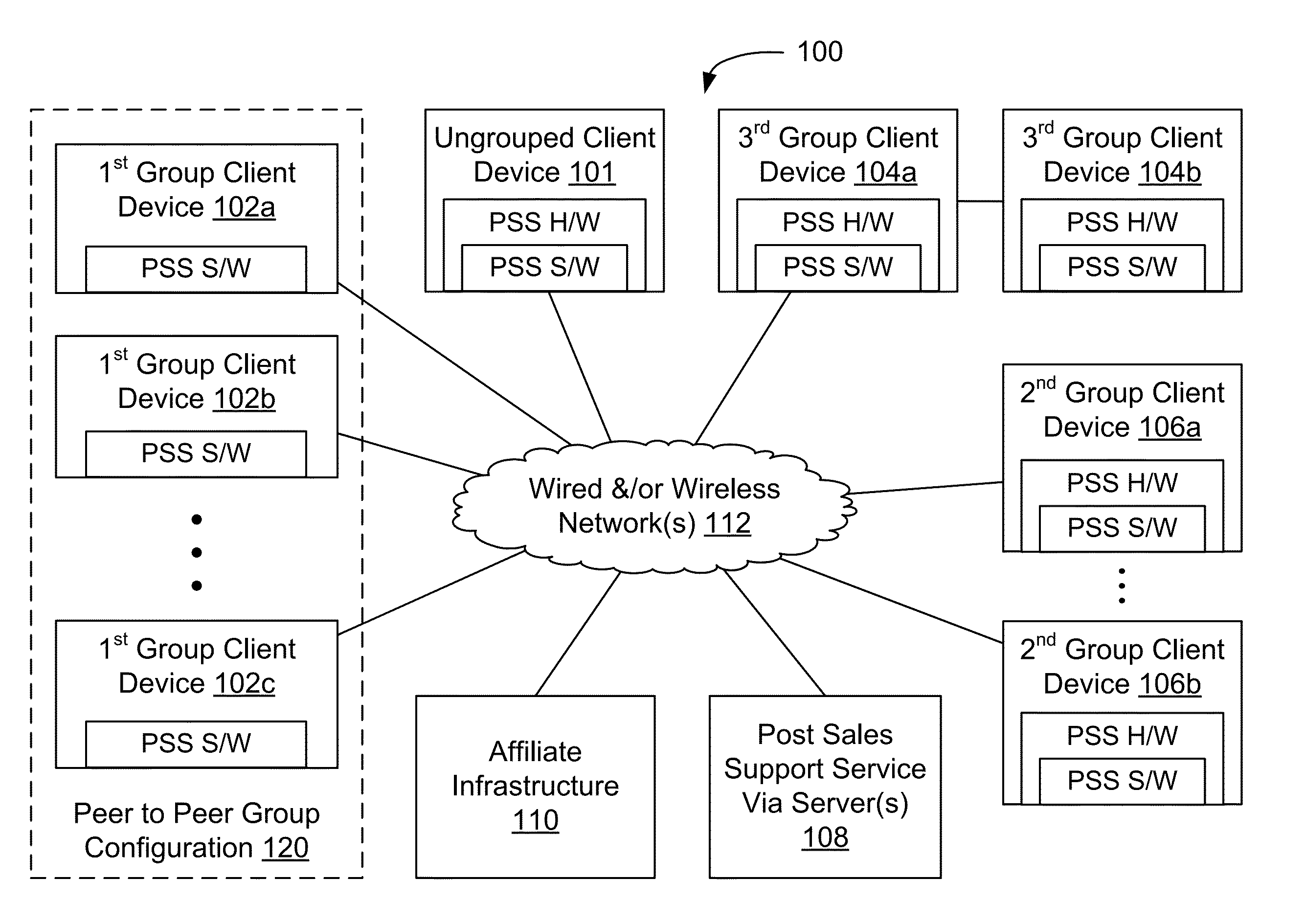

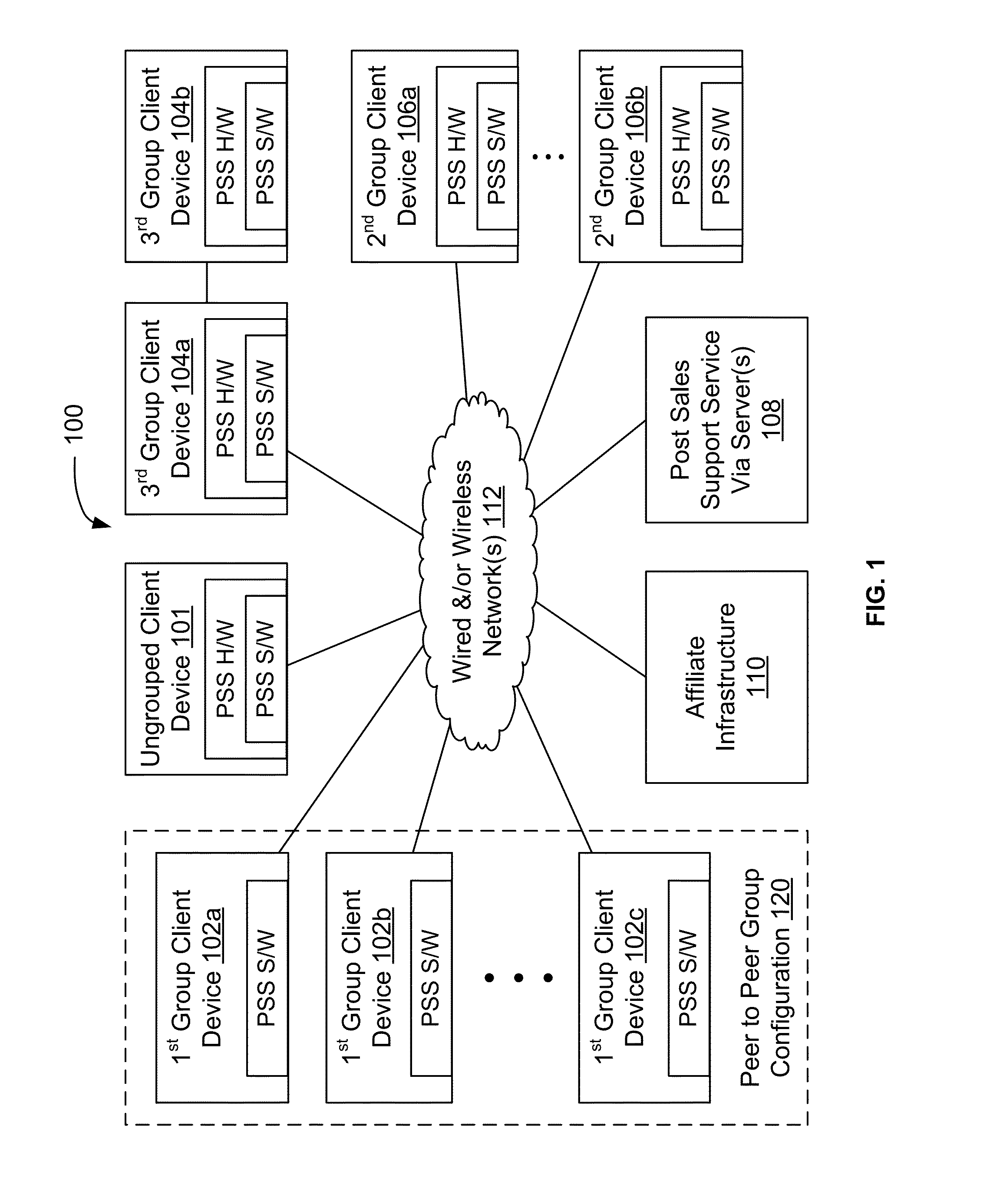

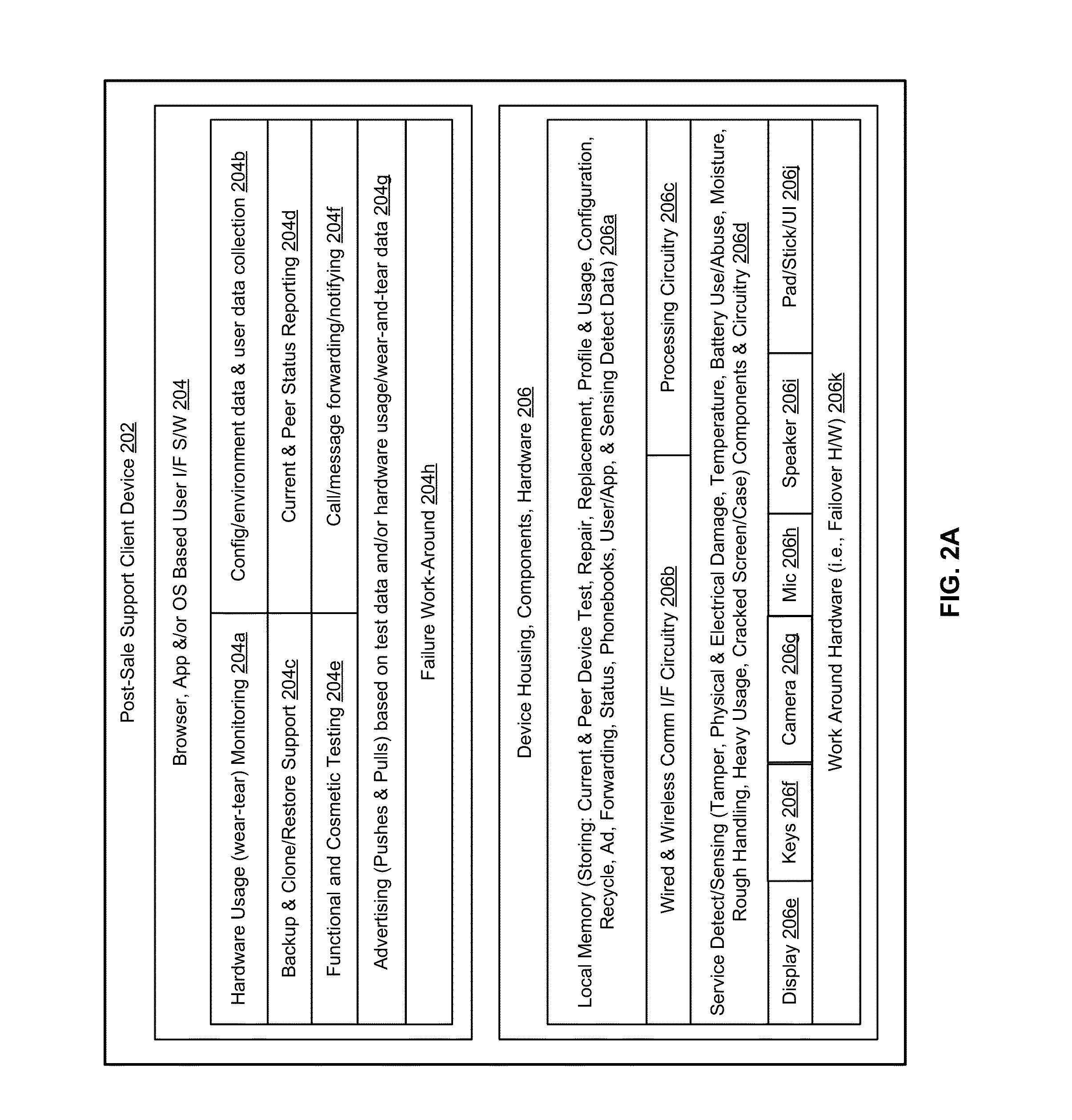

Electronic device post-sale support system

A system comprises a device under test, a testing device coupled to said device under test via a direct connection, and a post-sales support server communicatively coupled to said testing device via a wide area network connection. The testing device is operable to collect, from said device under test via said direct connection, responses to test stimuli generated in accordance with test code. The testing device is operable to provide said responses to said post-sale support server. The post-sale support server is operable to generate a valuation of said device under test based on said responses, and make said valuation available to a user of said device under test. The valuation may comprise a monetary value based offer associated with third party repair, resale and recycling.

Owner:BENNETT JAMES DUANE

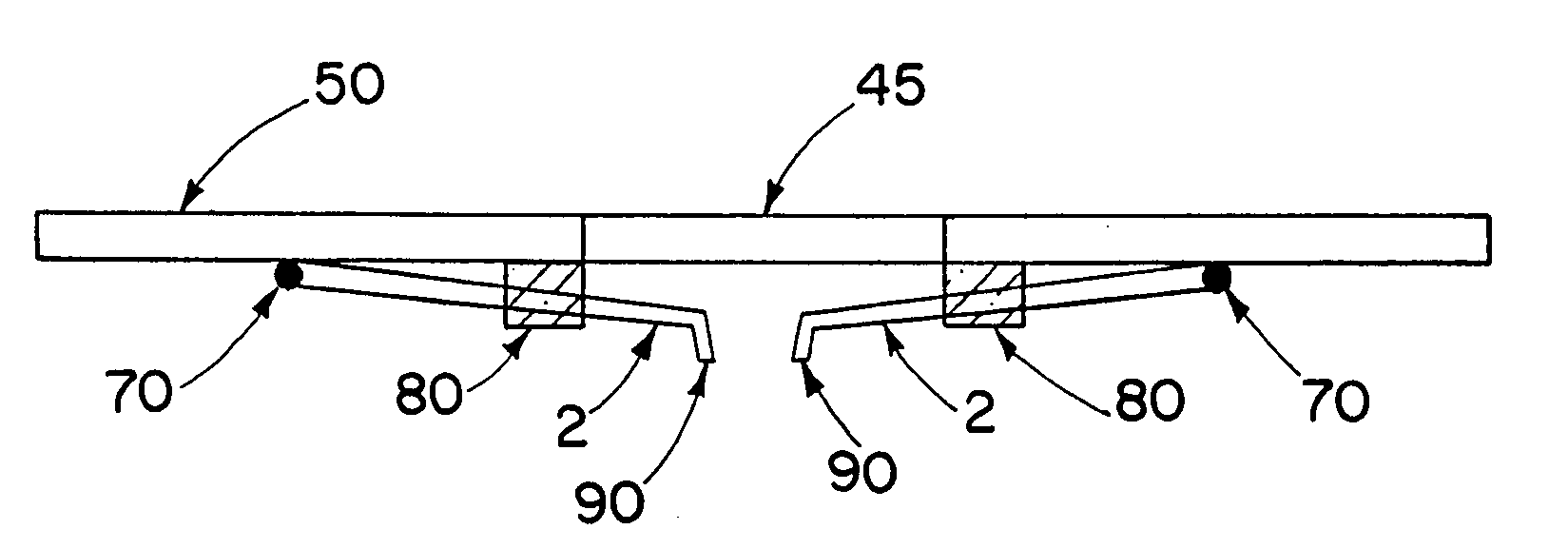

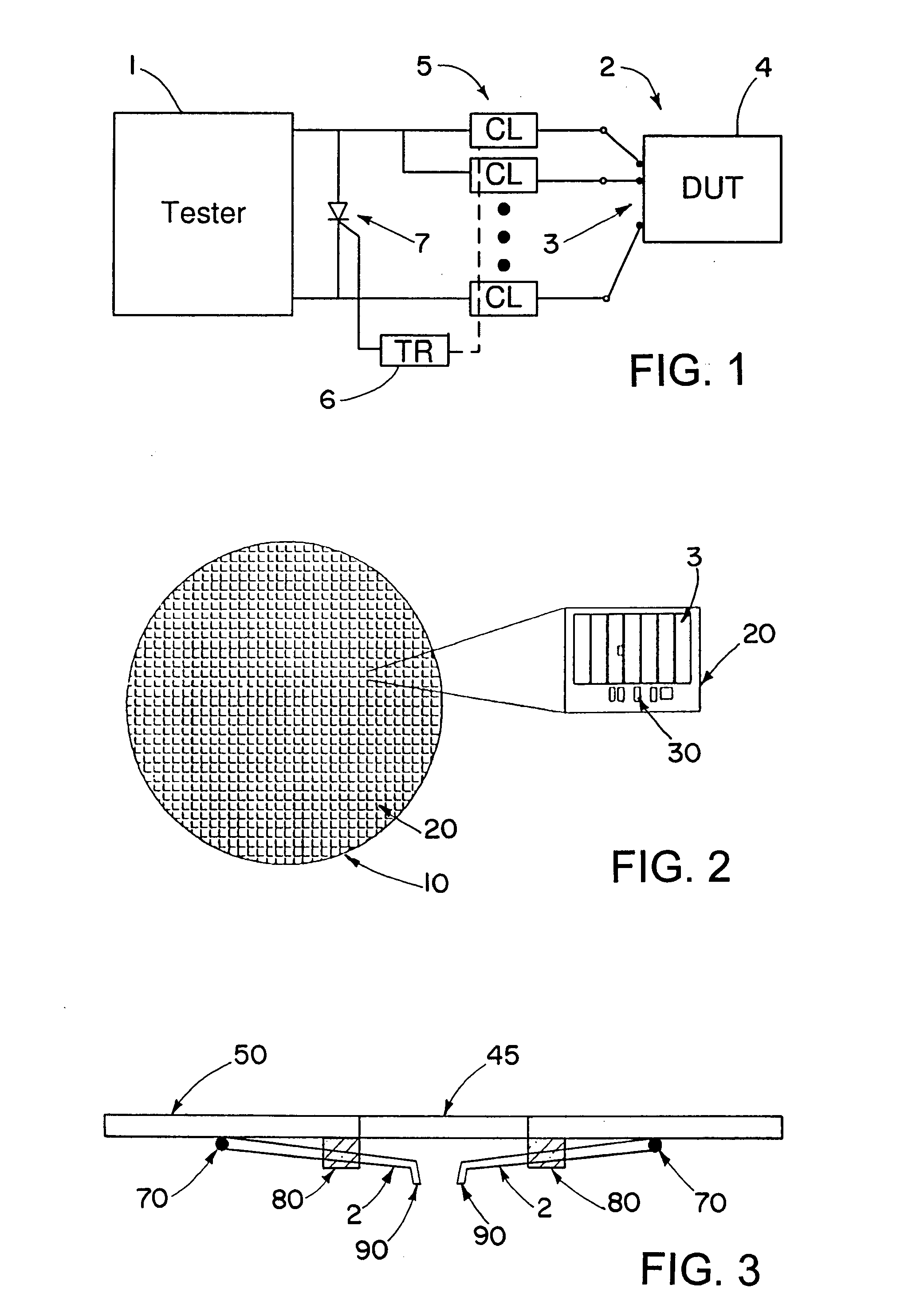

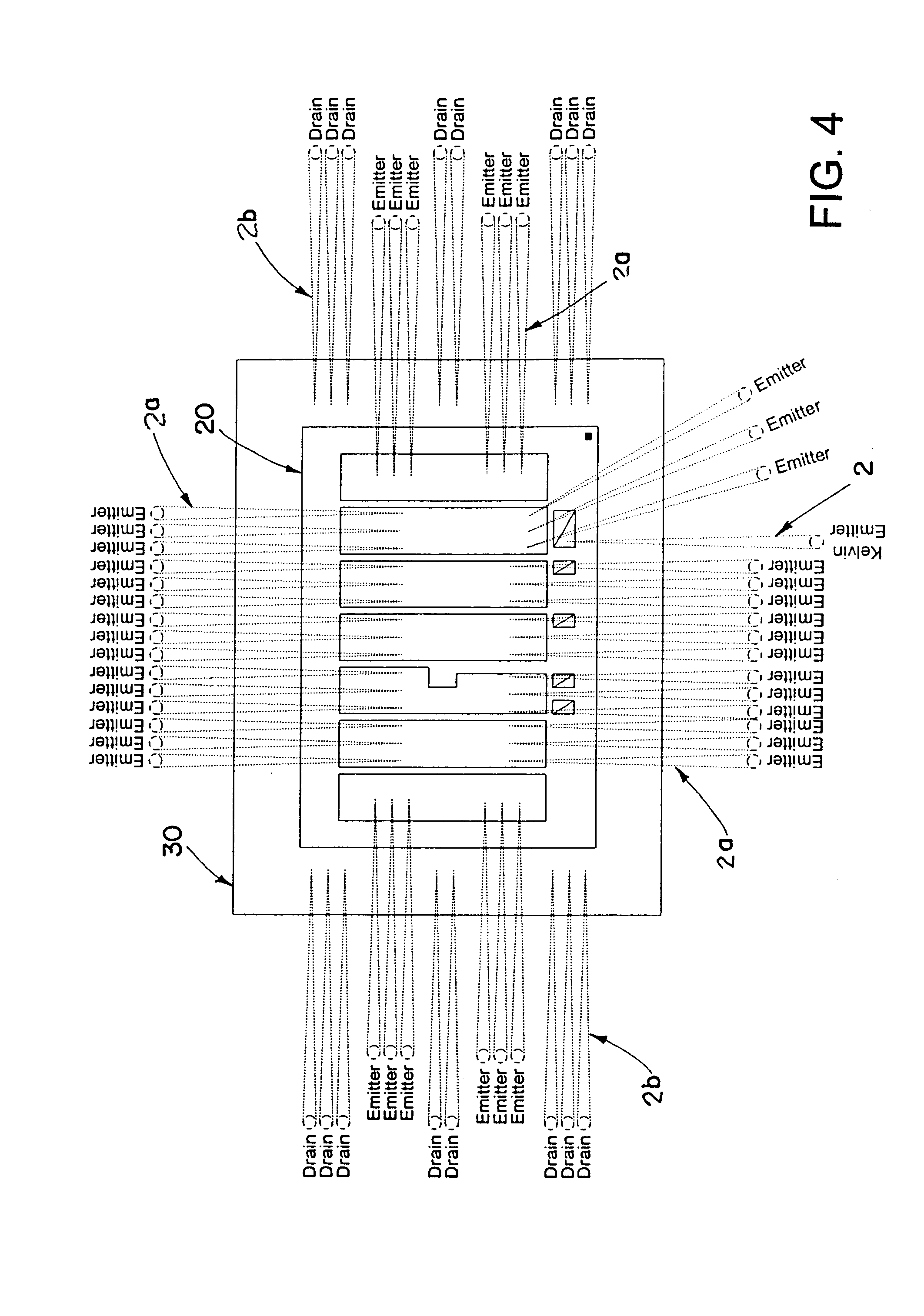

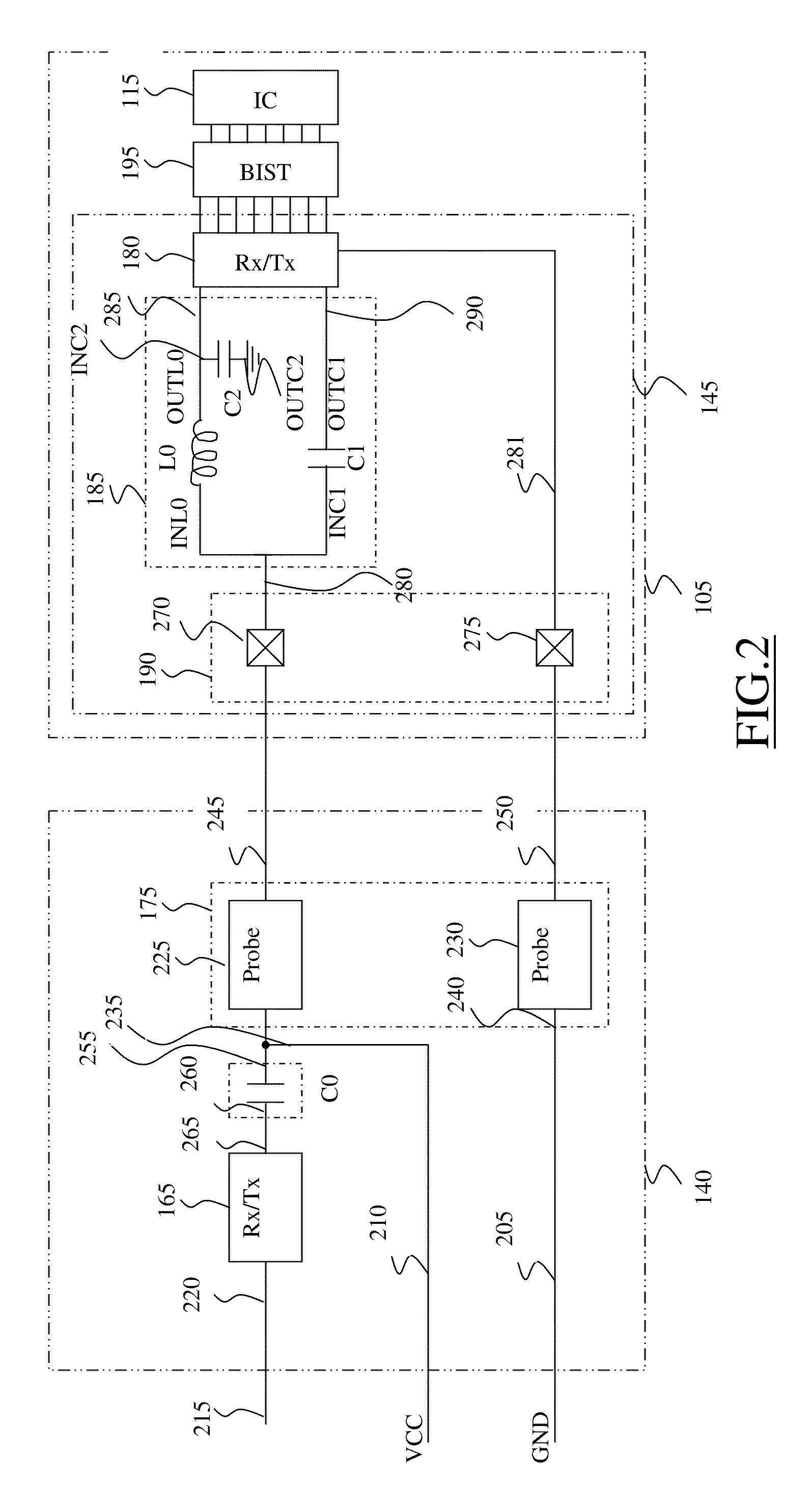

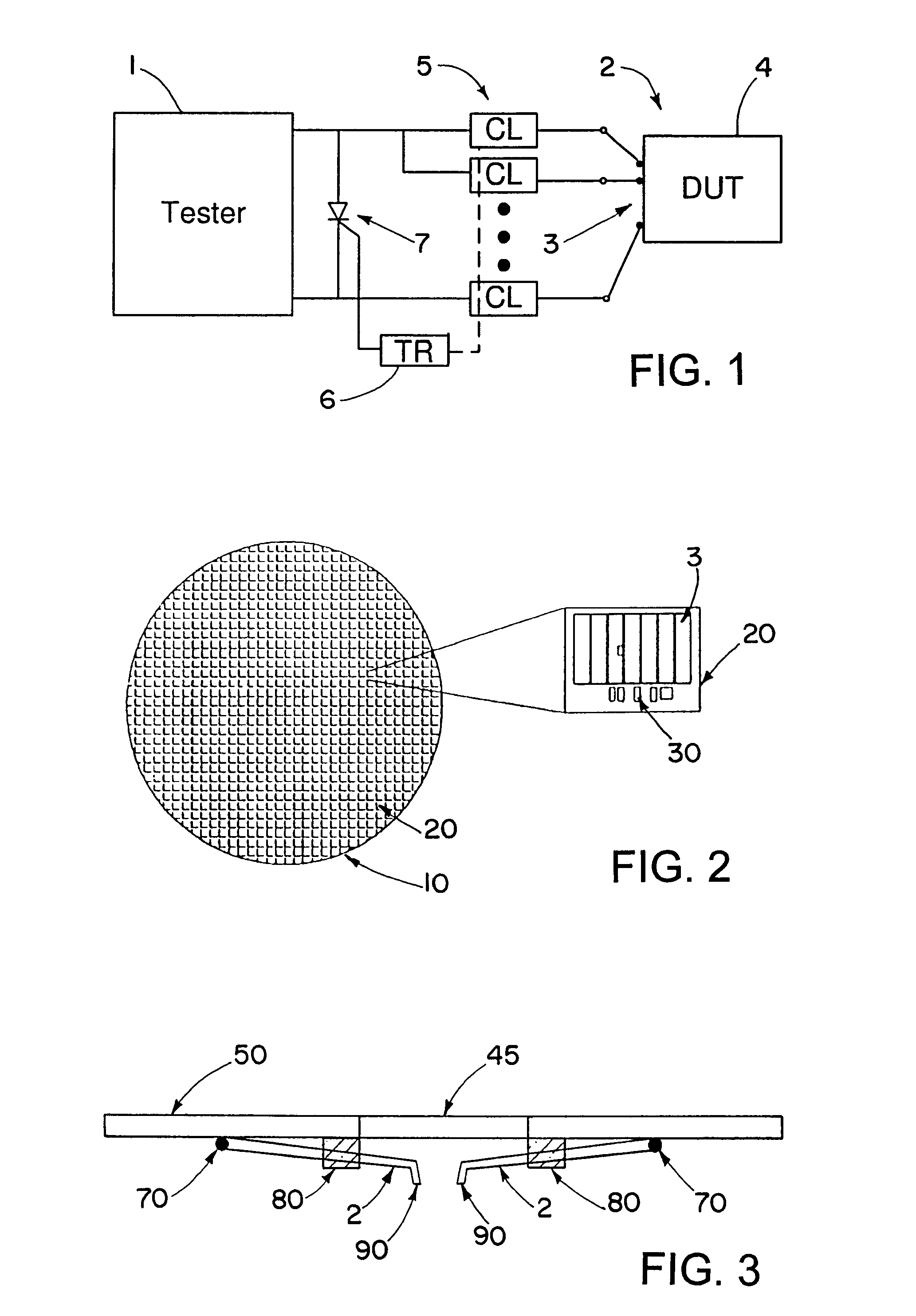

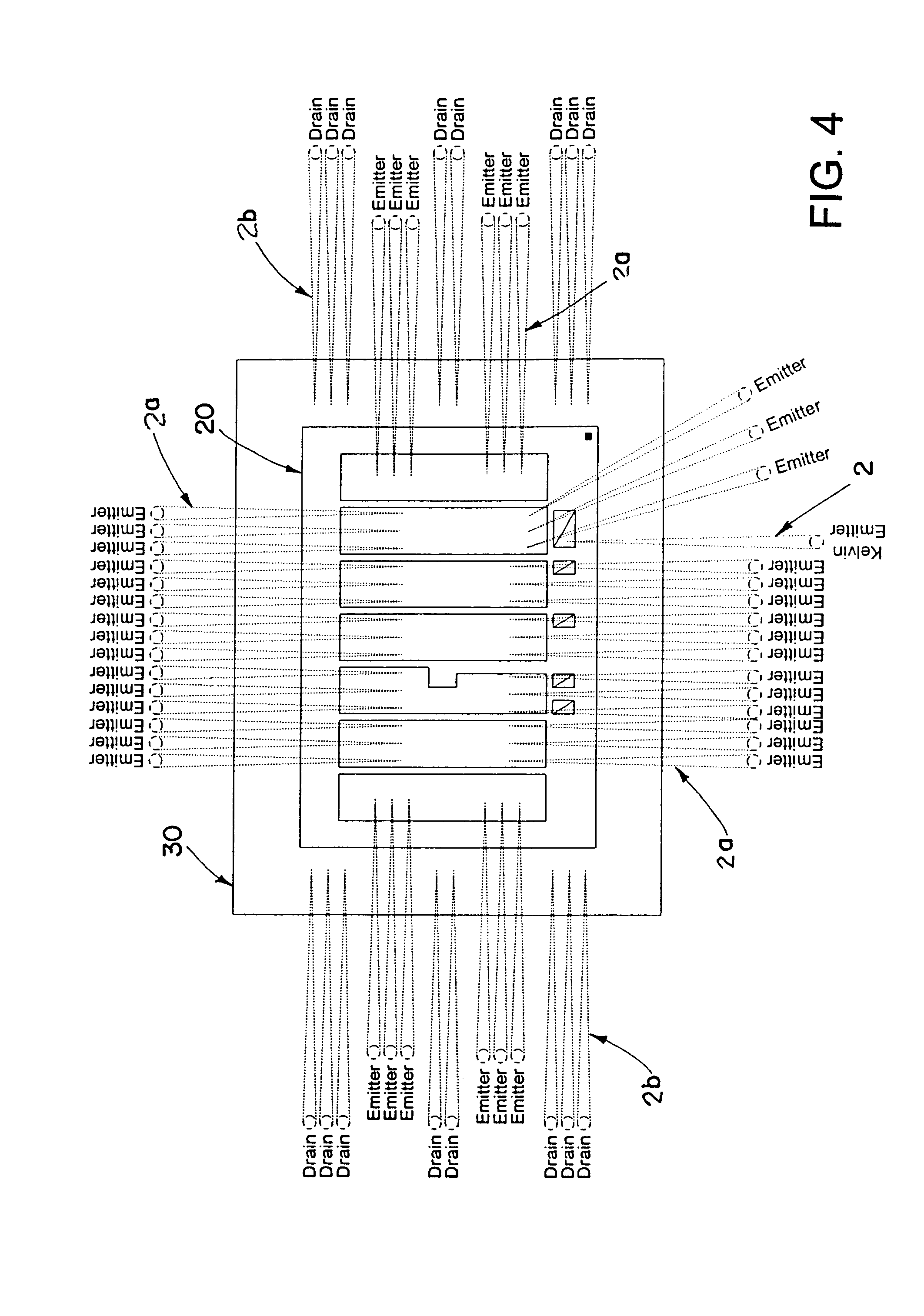

Probe needle protection method for high current probe testing of power devices

ActiveUS20080290882A1High currentRemoval of powerOverload protection arrangementsElectrical testingElectricityCurrent limiting

A test system, apparatus and method for applying high current test stimuli to a semiconductor device in wafer or chip form includes a plurality of probes for electrically coupling to respective contact points on the semiconductor device, a plurality of current limiters electrically coupled to respective ones of the plurality of probes, and a current sensor electrically coupled to the plurality of probes. The current limiters are operative to limit current flow passing through a respective probe, and the current sensor is operative to provide a signal when detected current in any contact of the plurality of probes exceeds a threshold level.

Owner:INTEGRATED TECH

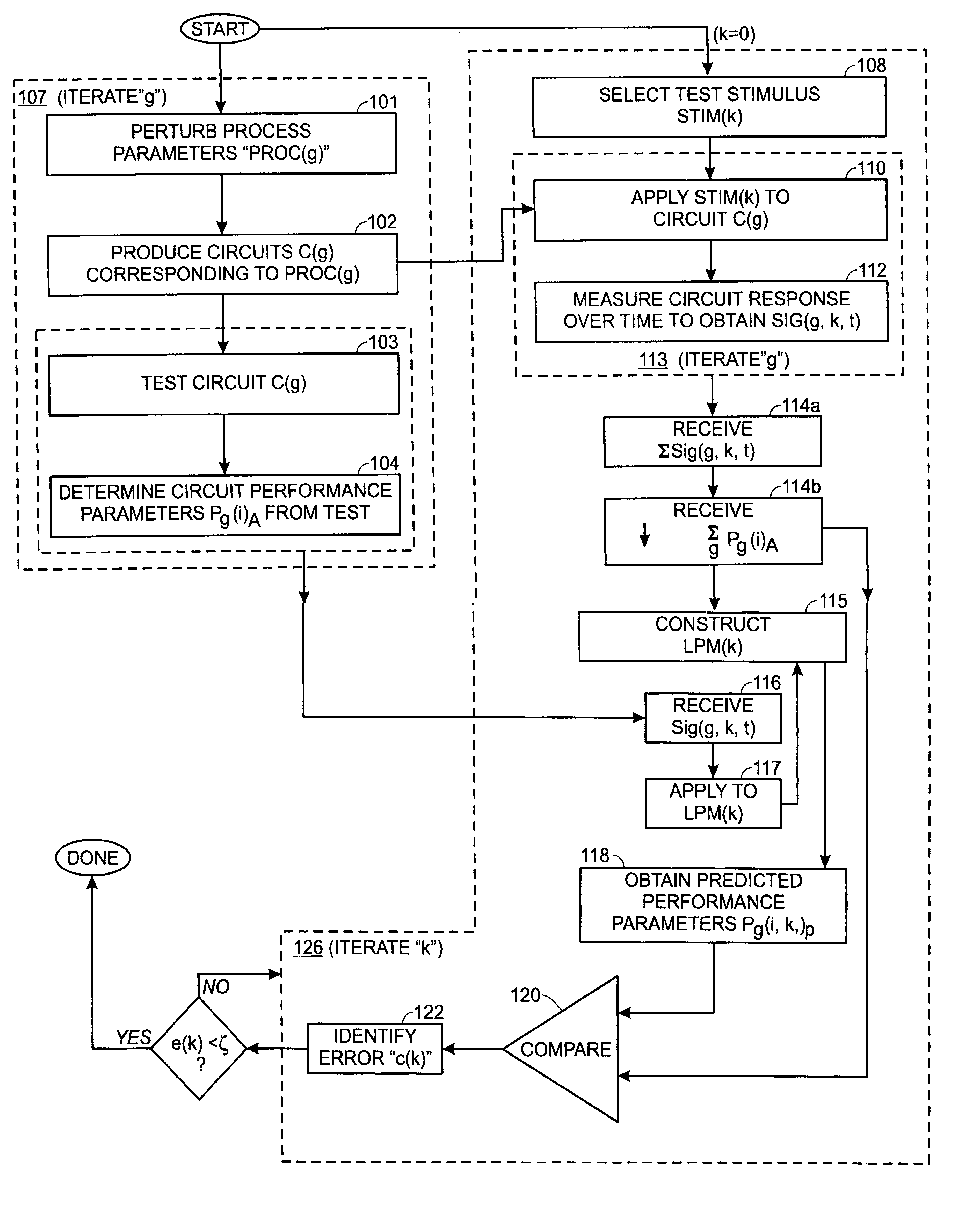

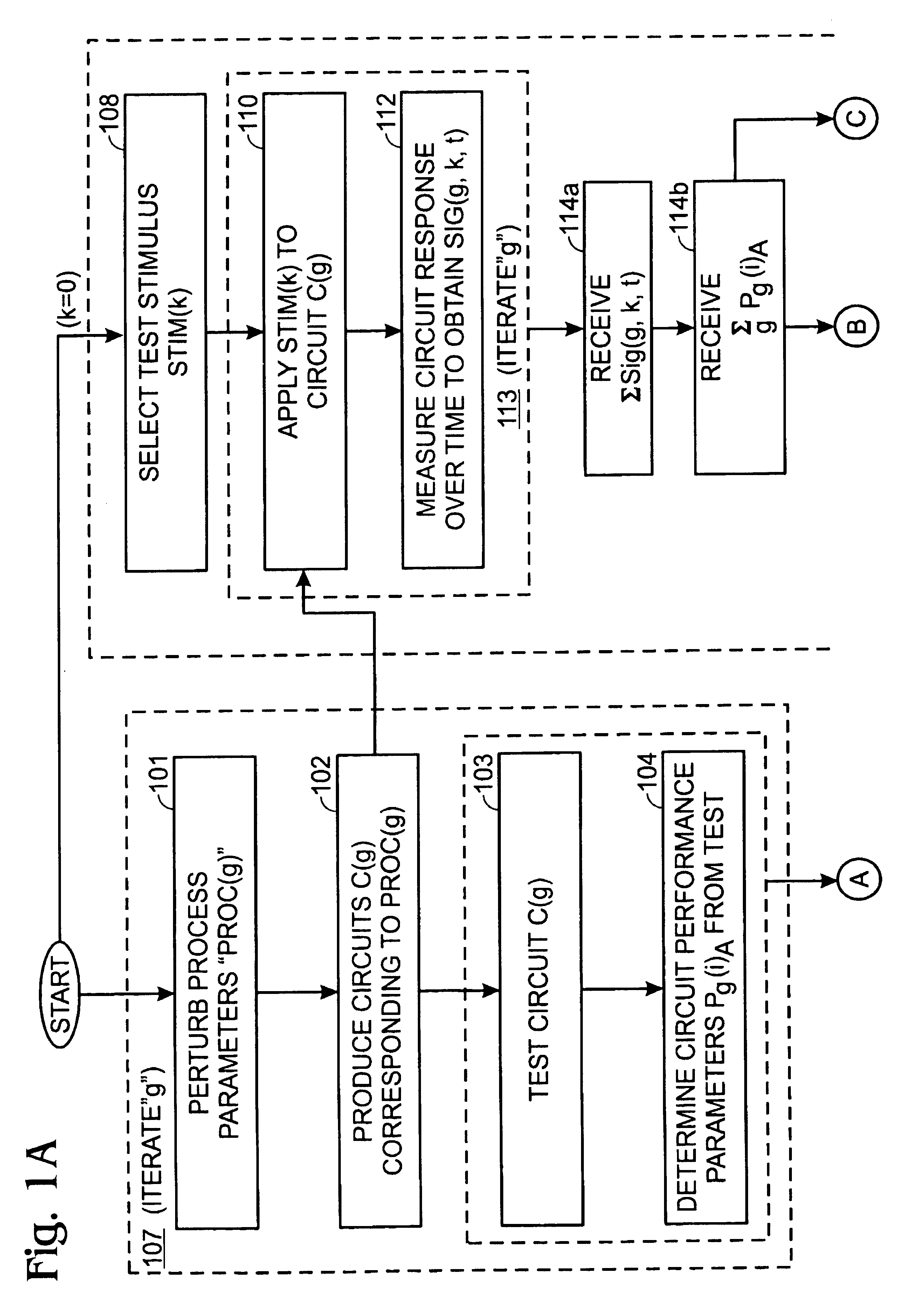

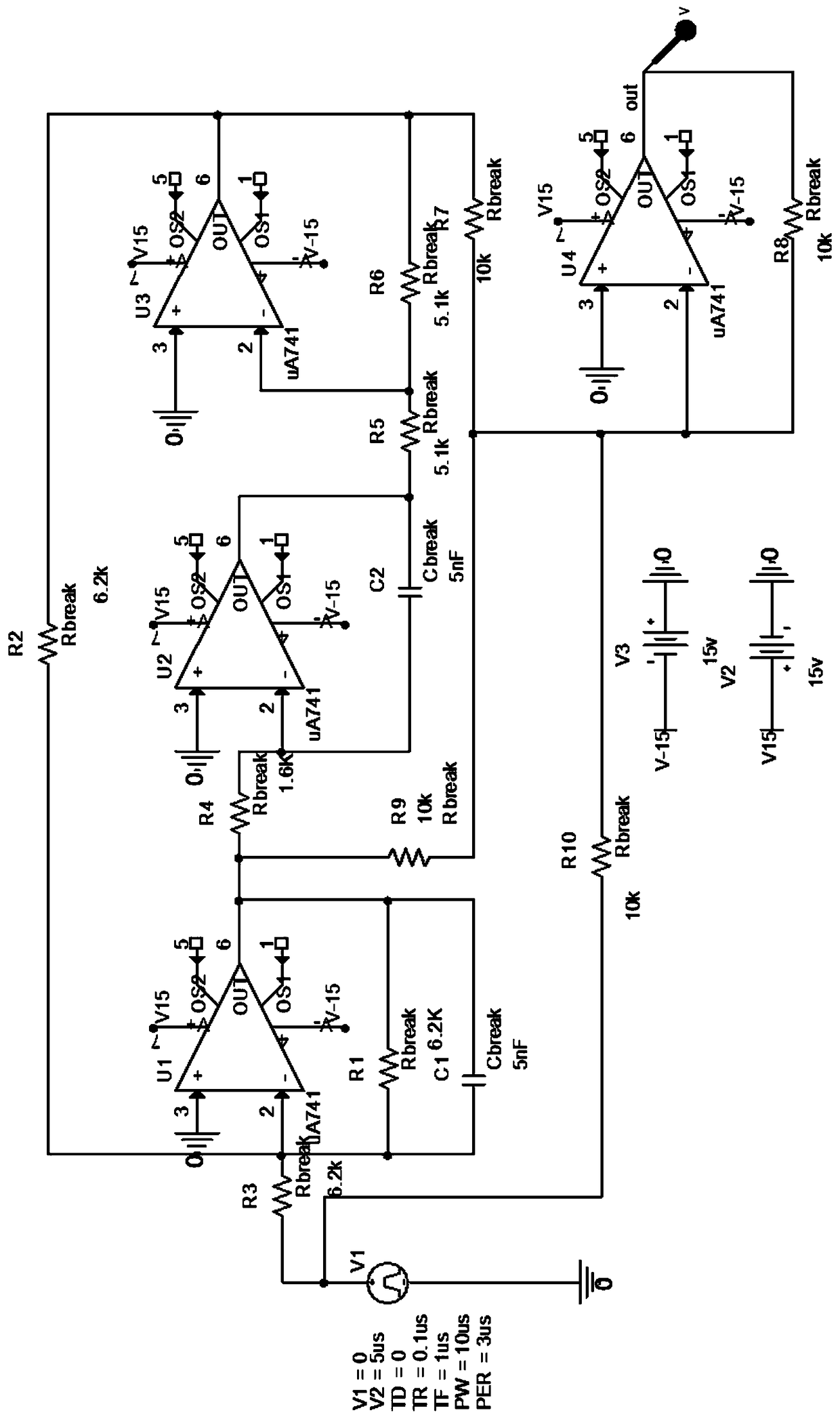

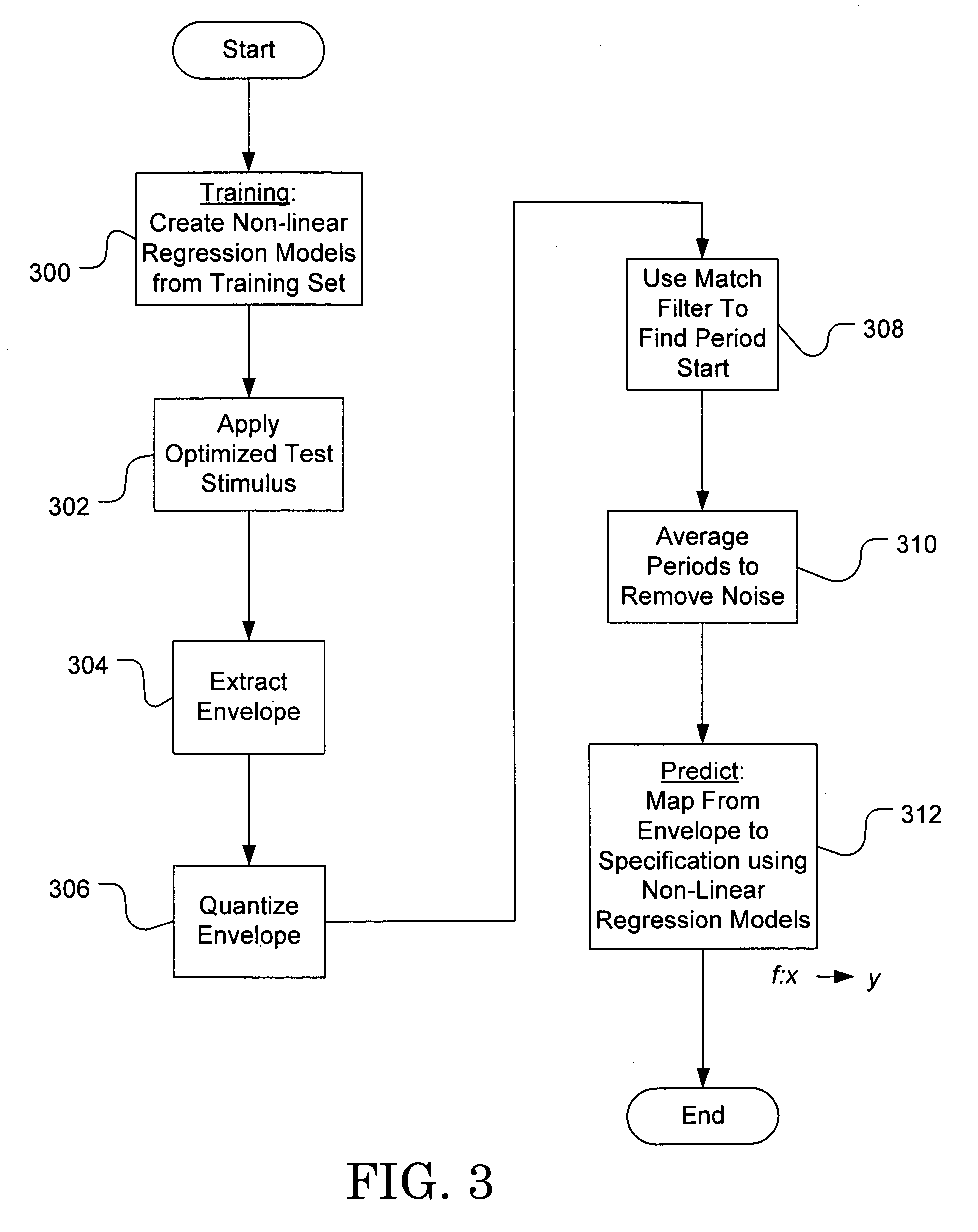

Method and apparatus for low cost signature testing for analog and RF circuits

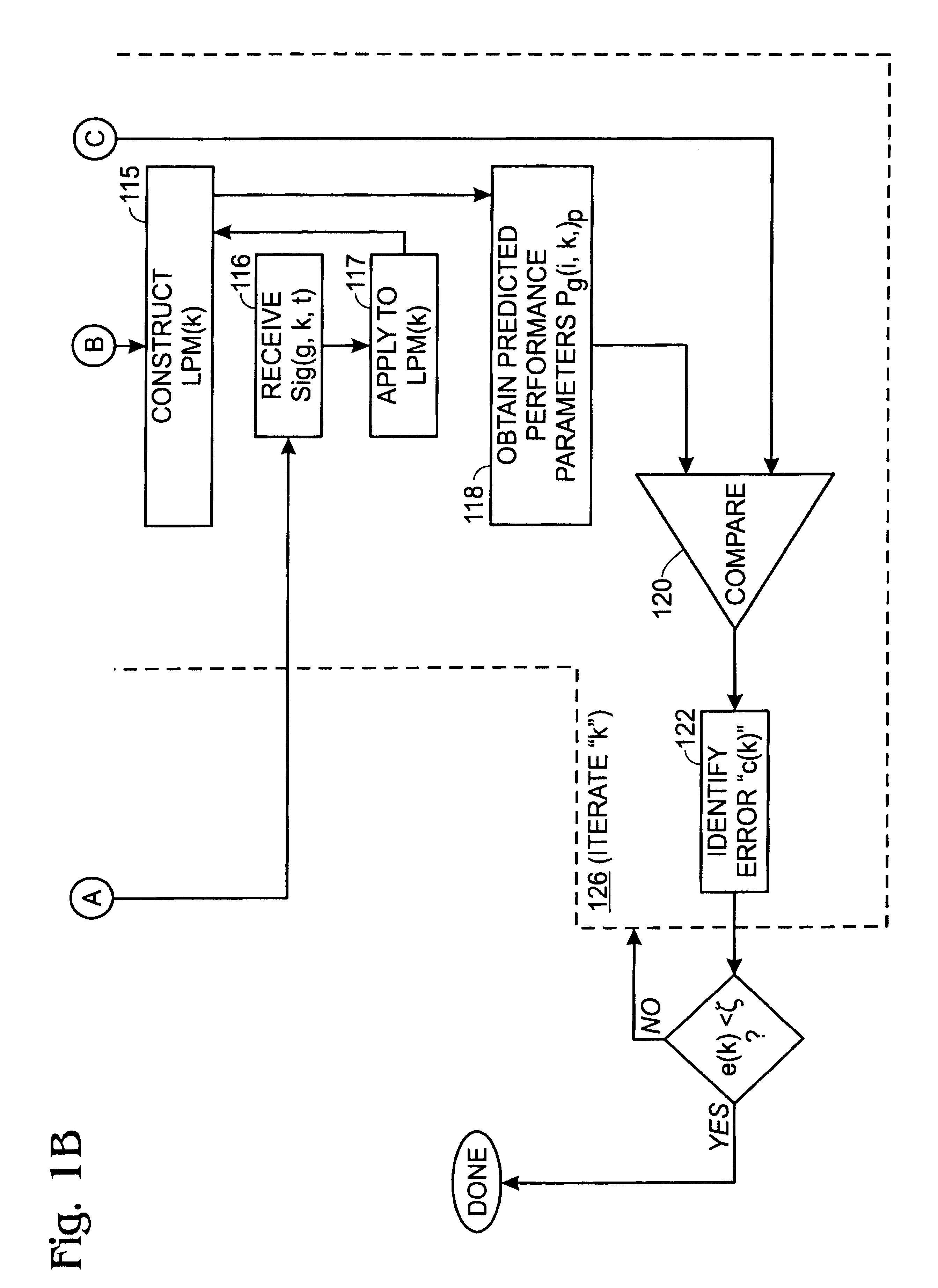

InactiveUS7006939B2Error minimizationLow costResistance/reactance/impedenceElectronic circuit testingTest stimulusPredicting performance

A low cost signature test for RF and analog circuits. A model is provided to predict one or more performance parameters characterizing a first electronic circuit produced by a manufacturing process subject to process variation from the output of one or more second electronic circuits produced by the same process in response to a selected test stimulus, and iteratively varying the test stimulus to minimize the error between the predicted performance parameters and corresponding measured values for the performance parameters, for determining an optimized test stimulus. A non-linear model is preferably constructed for relating signature test results employing the optimized test stimulus in manufacturing testing to circuit performance parameters.

Owner:GEORGIA TECH RES CORP

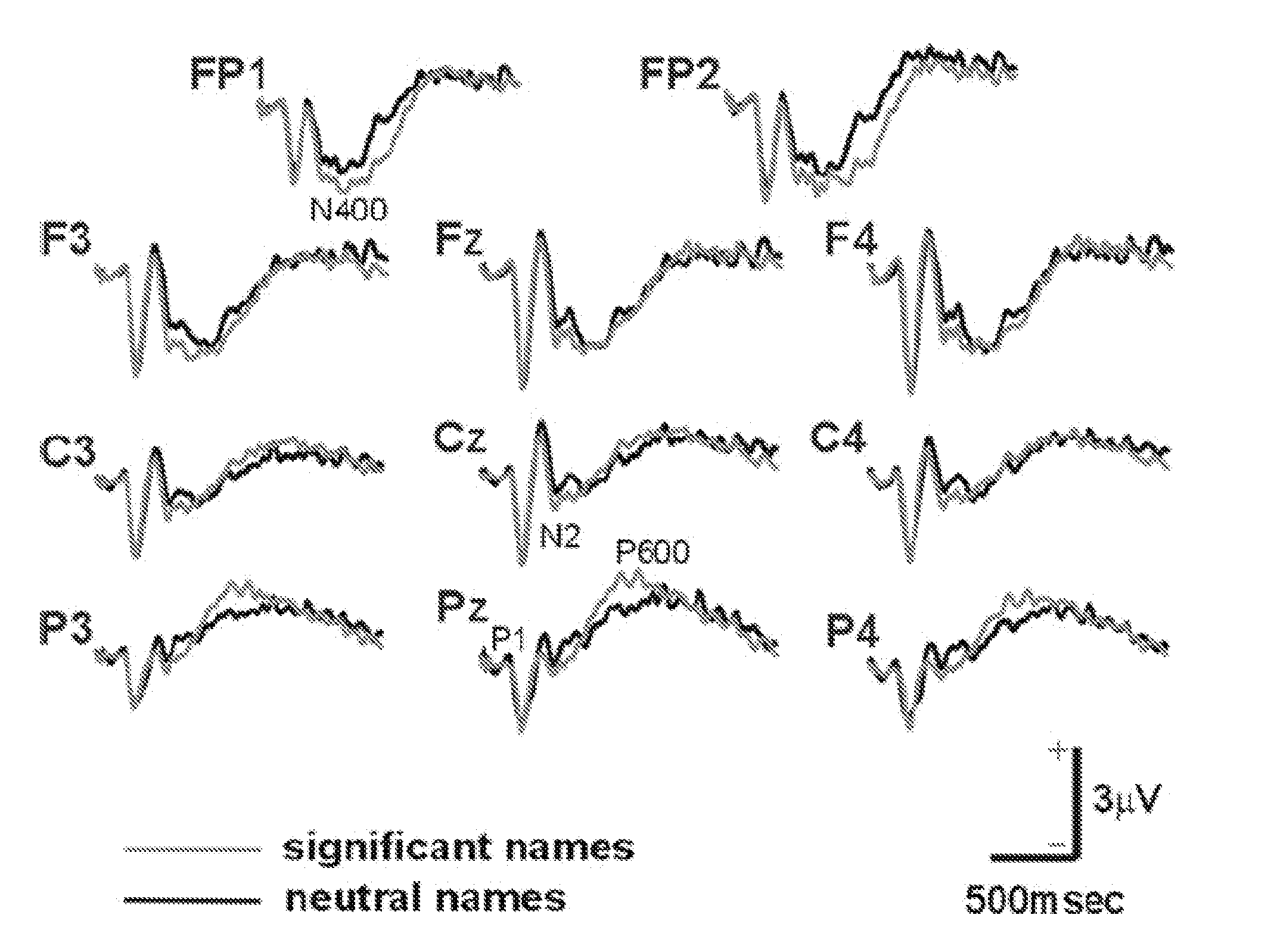

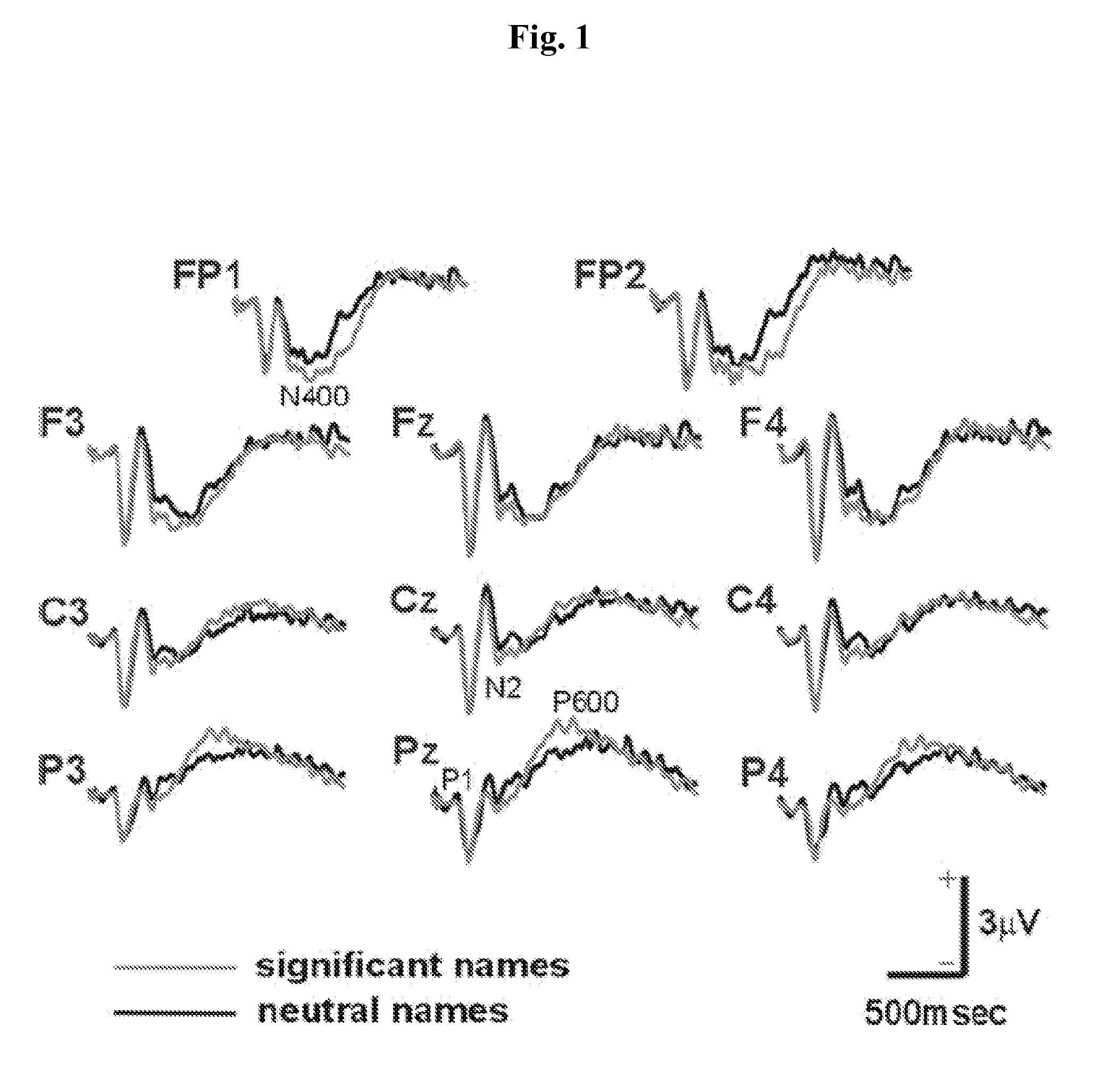

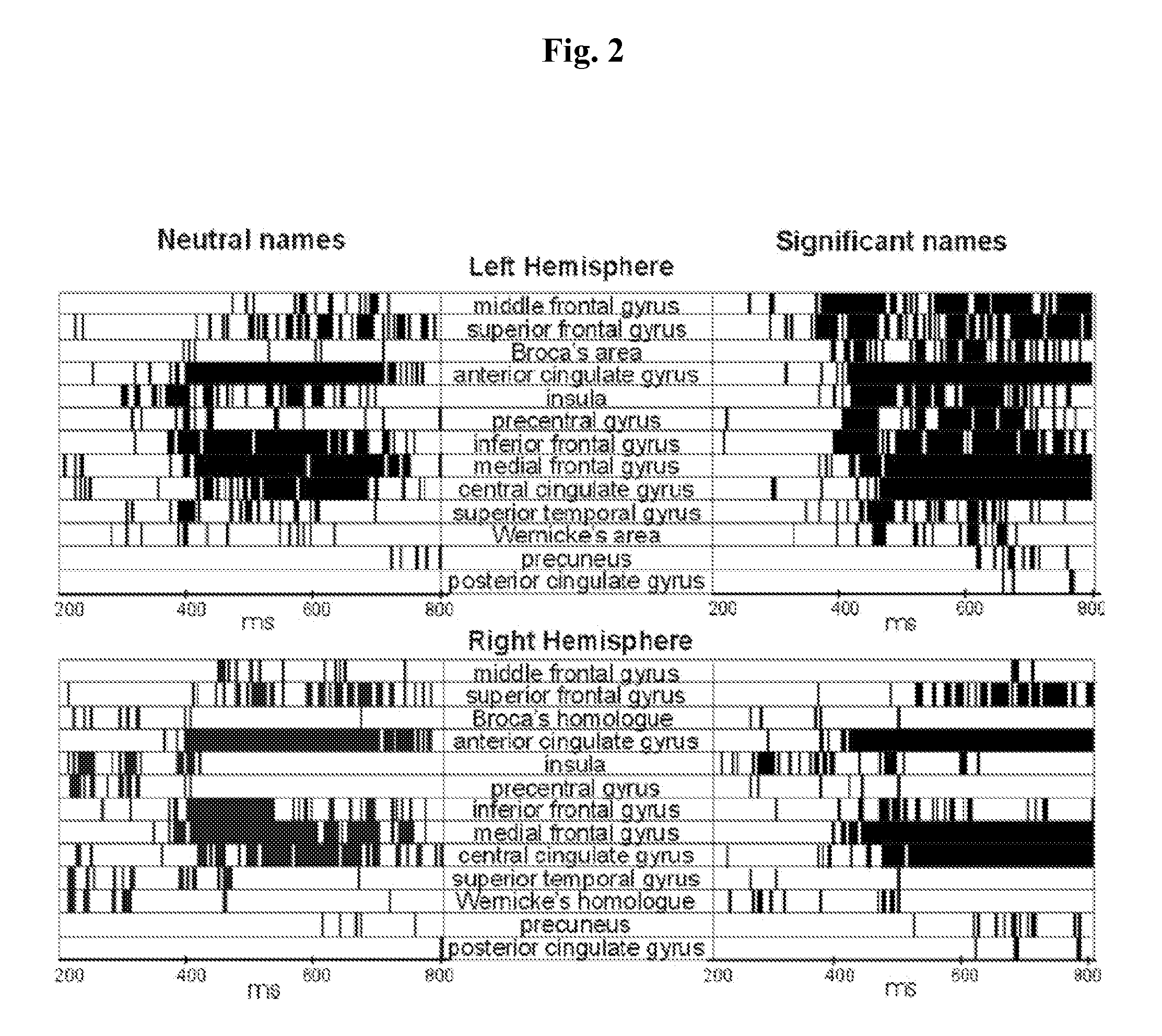

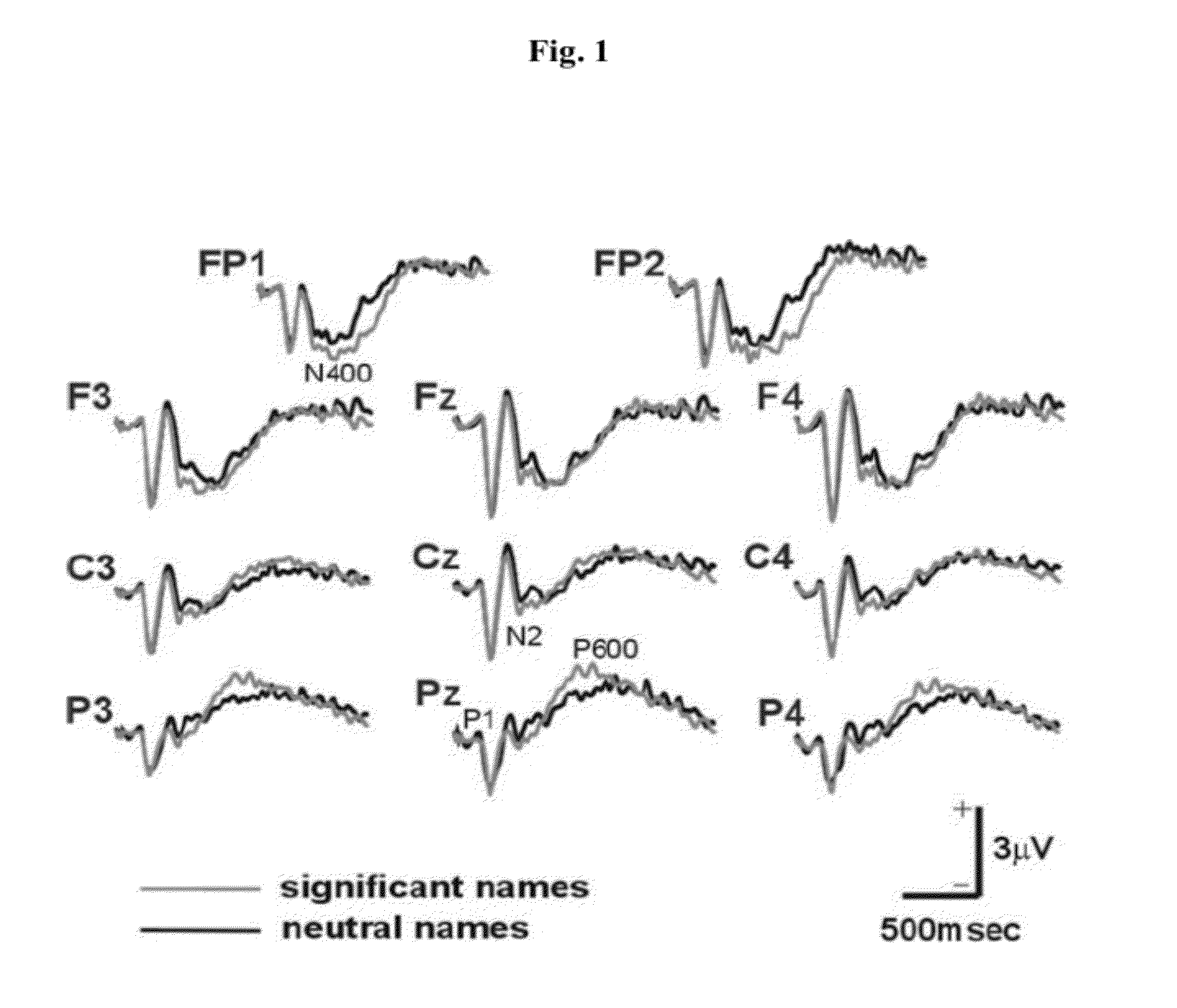

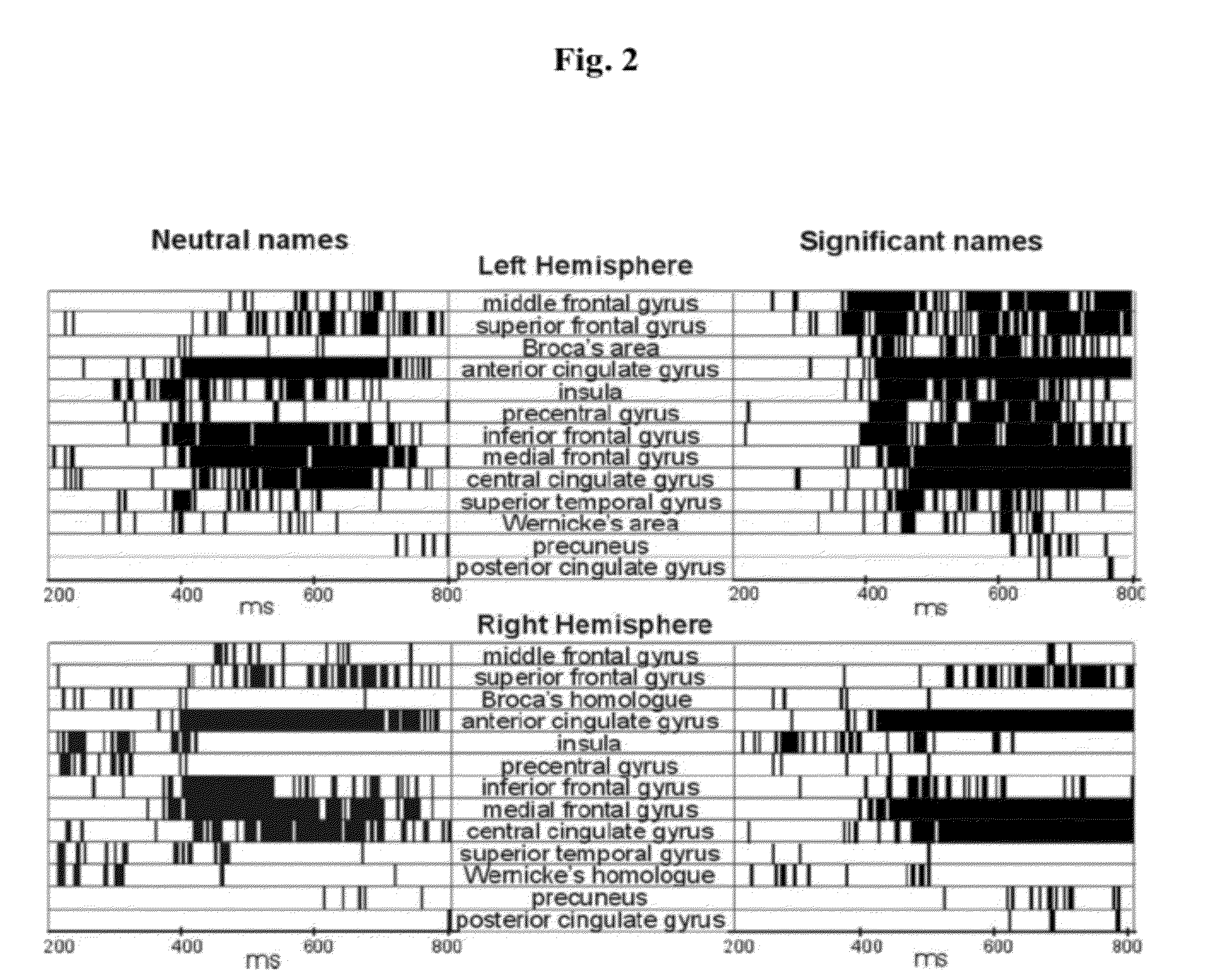

Subjective significance evaluation tool, brain activity based

InactiveUS20080097235A1Good precisionResult is less-preciseElectroencephalographySensorsMedicineElectroencephalography

A method and system for determining the subjective state of mind of a human subject presented with a test audible or visual stimulus. An electroencephalogram (EEG) recording unit is connected to the human subject, recording the subject's EEG when presented with one or more test stimuli. The recorded EEG signal is then transformed to a 3-D map in order to visualize the brain areas that were active when presenting the test stimuli. The given 3-D map of the test stimuli is then compared with reference 3-D maps of neutral and subjectively significant stimuli.

Owner:TECHNION RES & DEV FOUND LTD

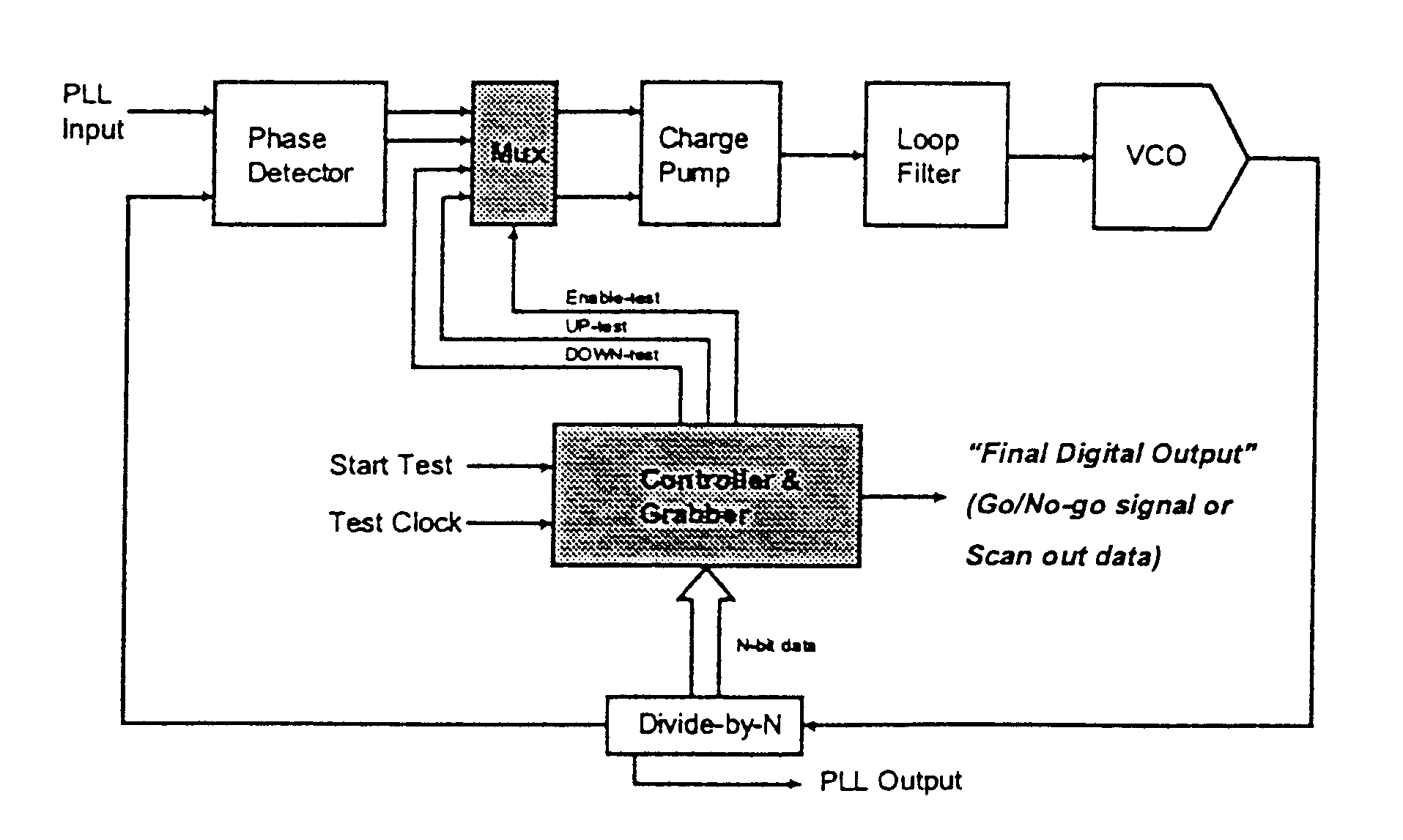

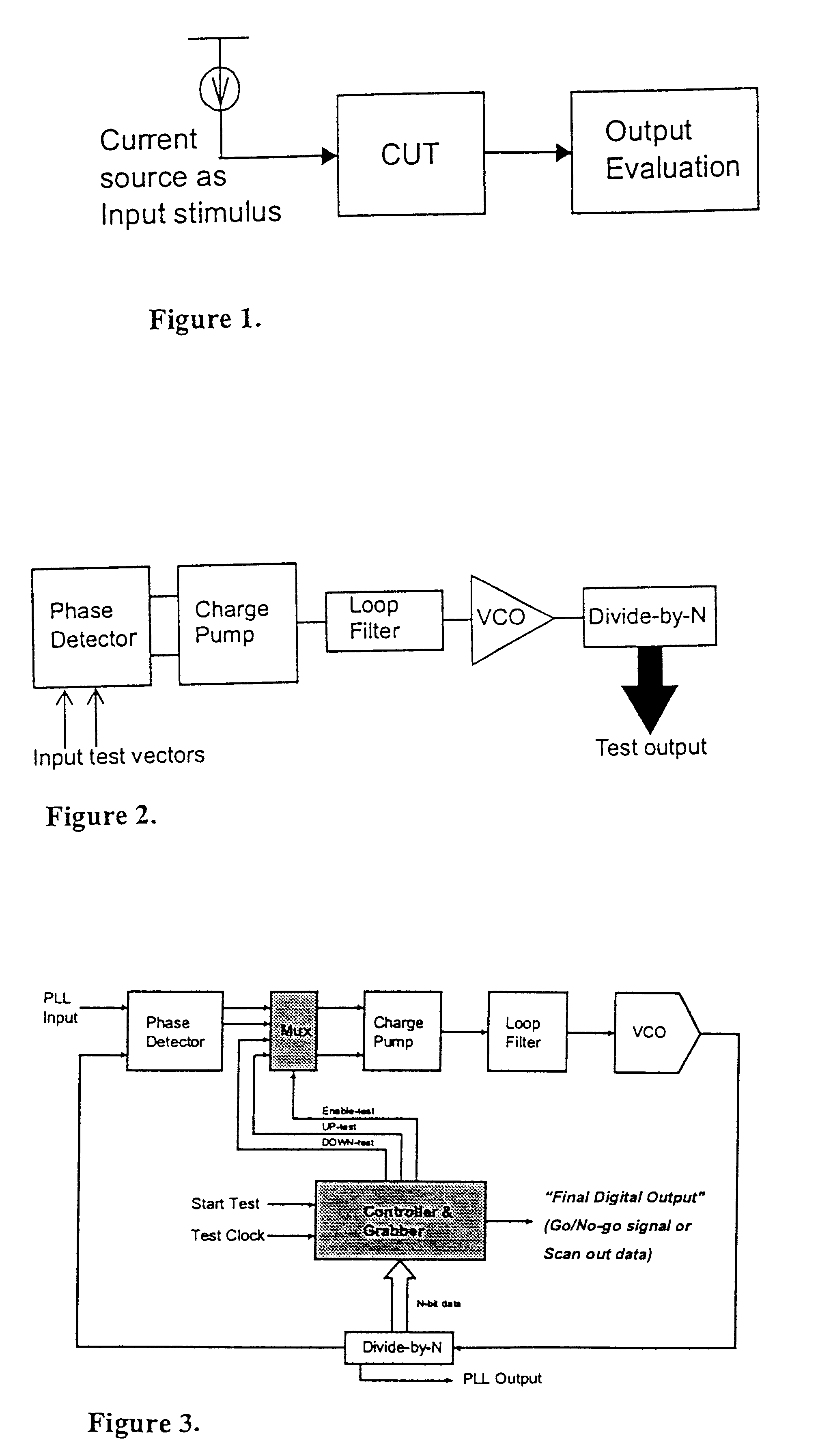

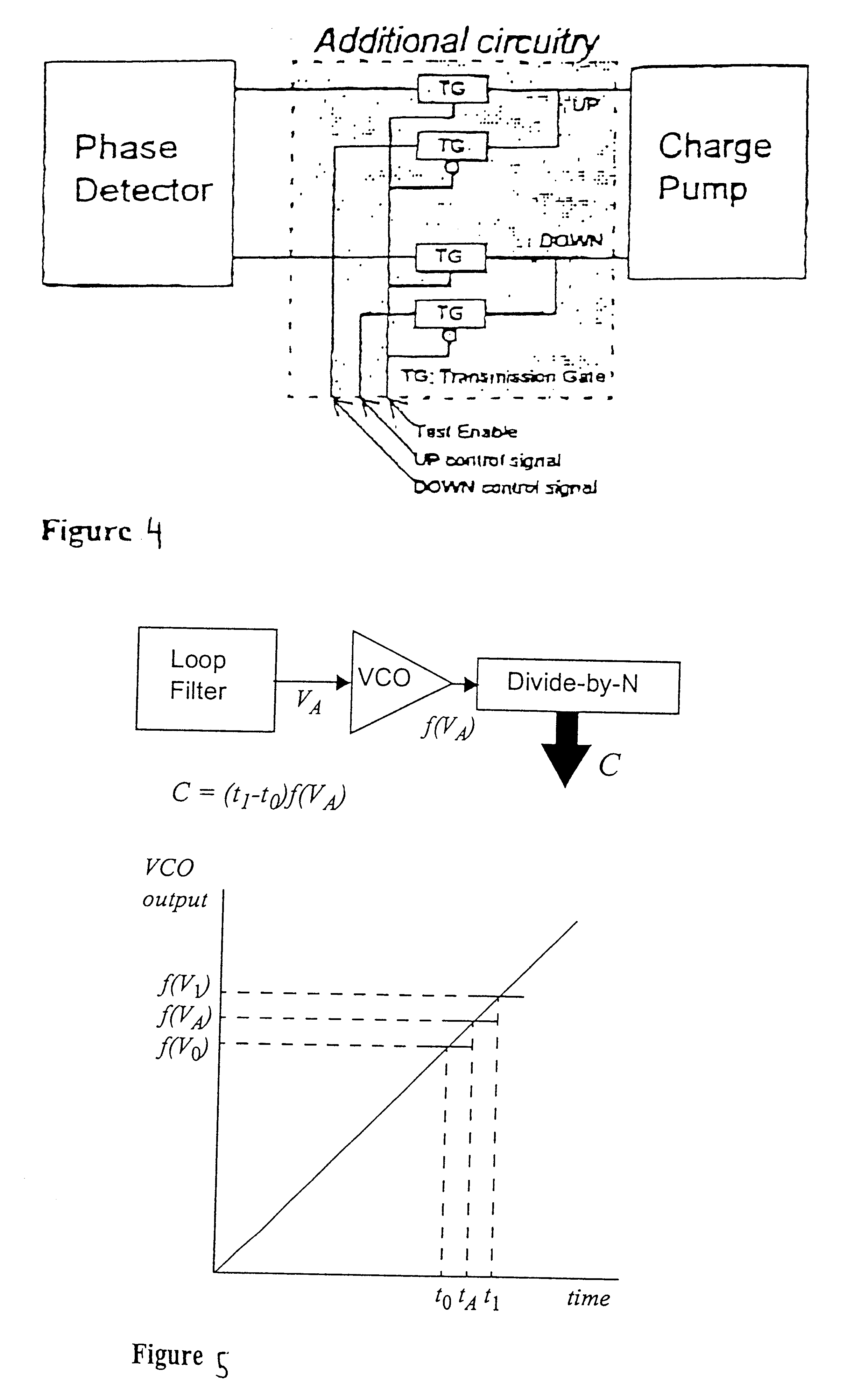

Charge-based frequency measurement bist

A charge-based frequency measurement BIST (CF-BIST) for clock circuits and oscillator circuits is described that requires no outside test stimulus and produces a digital test output. The CF-BIST technique performs structural and defect-oriented testing and uses existing blocks to save die area. The technique adds a multiplexer to the non-sensitive digital path. The system uses the existing VCO as the measuring device and divide-by-N as a frequency counter to reduce the area overhead. The described technique produces an efficient pass / fail evaluation, low-cost and practical implementation of on-chip BIST structure.

Owner:UNIV OF WASHINGTON

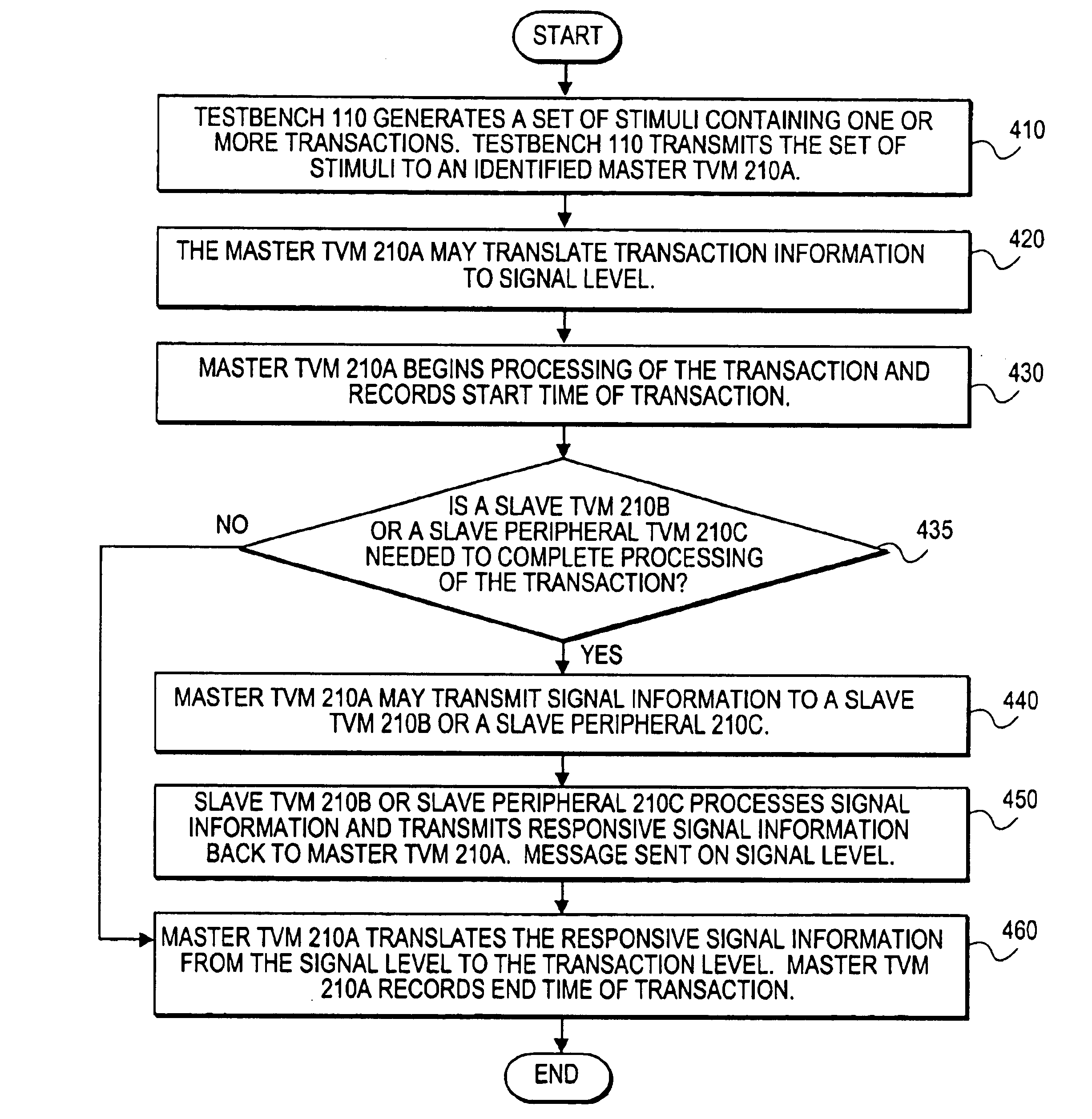

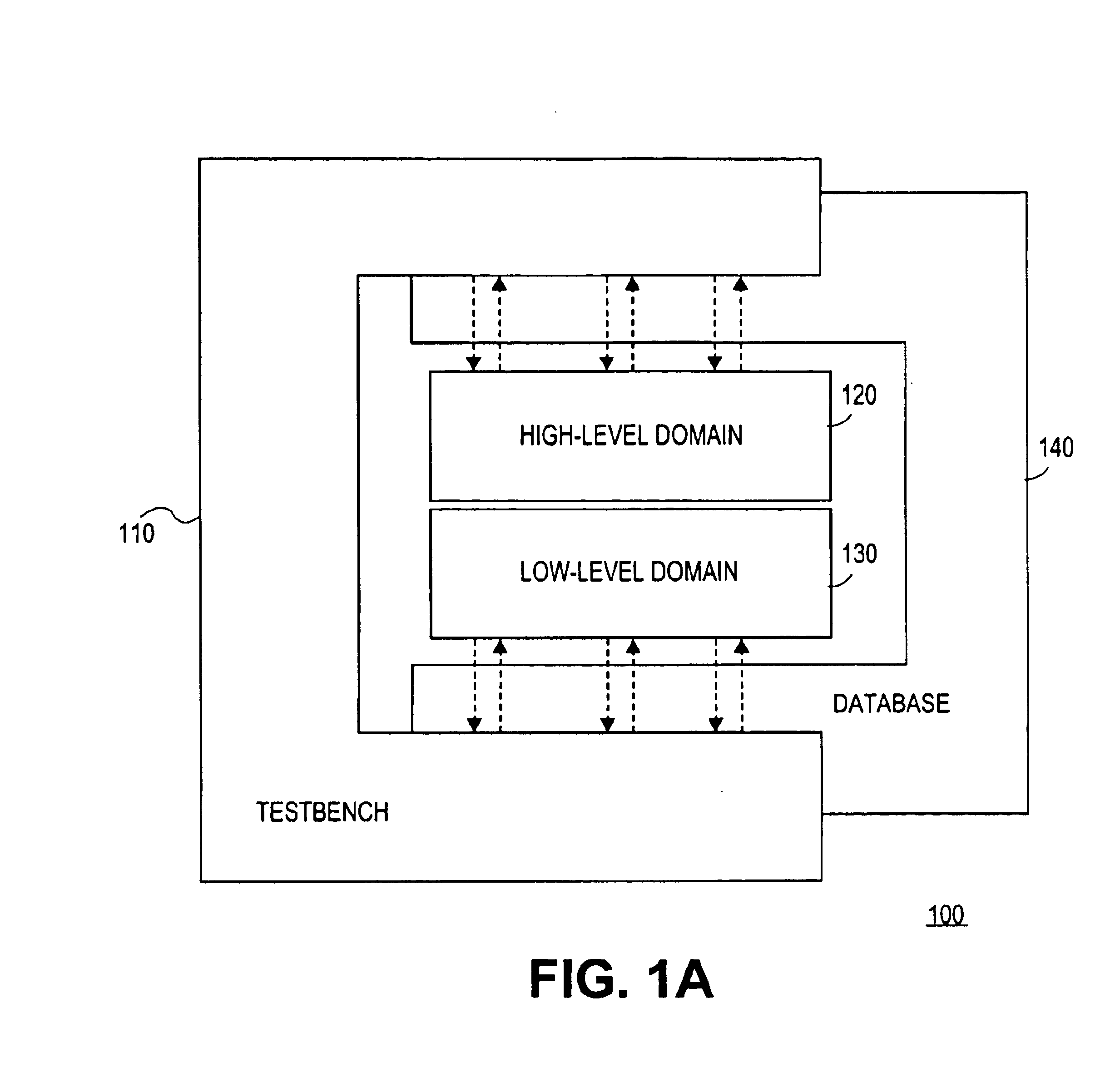

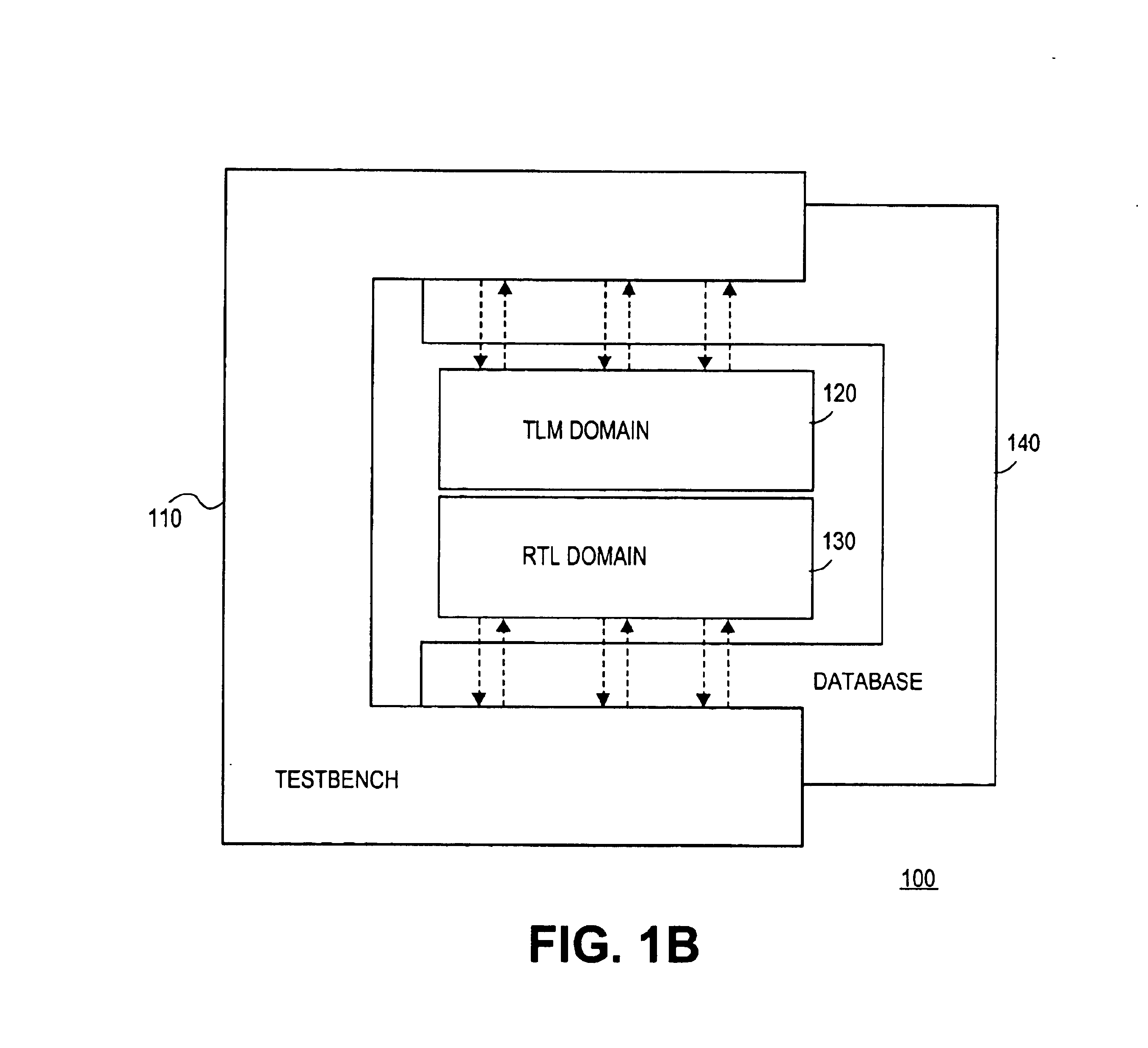

Method and mechanism for improved performance analysis in transaction level models

InactiveUS6845341B2Large and more complexImprove performanceAmplifier modifications to reduce noise influenceNuclear monitoringTest stimulusTransaction model

A method and mechanism for performing improved performance analysis upon transaction level models. A system block may be modeled using transaction model at different levels of abstraction. A testbench may be used to apply a set of stimuli to a transaction model (e.g. a TLM model) and a RTL equivalent model, and store the resulting timing information into a database. The timing information stored in the database may be used to validate the performance of the transaction models and system block. The testbench may analyze transaction models in the TLM domain and the RTL domain through the employment of TVM (transaction verification models) which are components that maps the transaction-level requests made by a test stimulus generator to a detailed signal-level protocol on the RTL design.

Owner:CADENCE DESIGN SYST INC

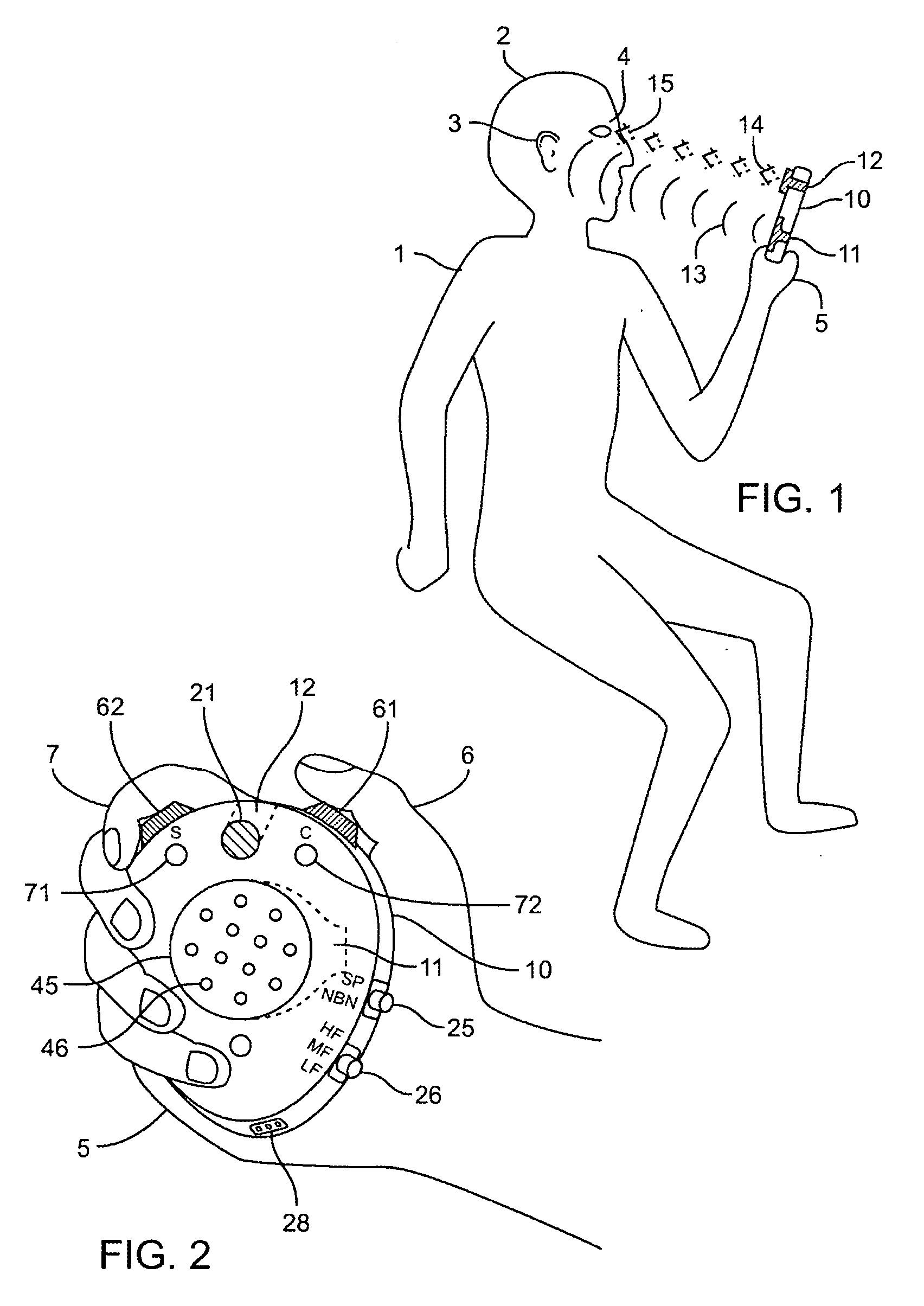

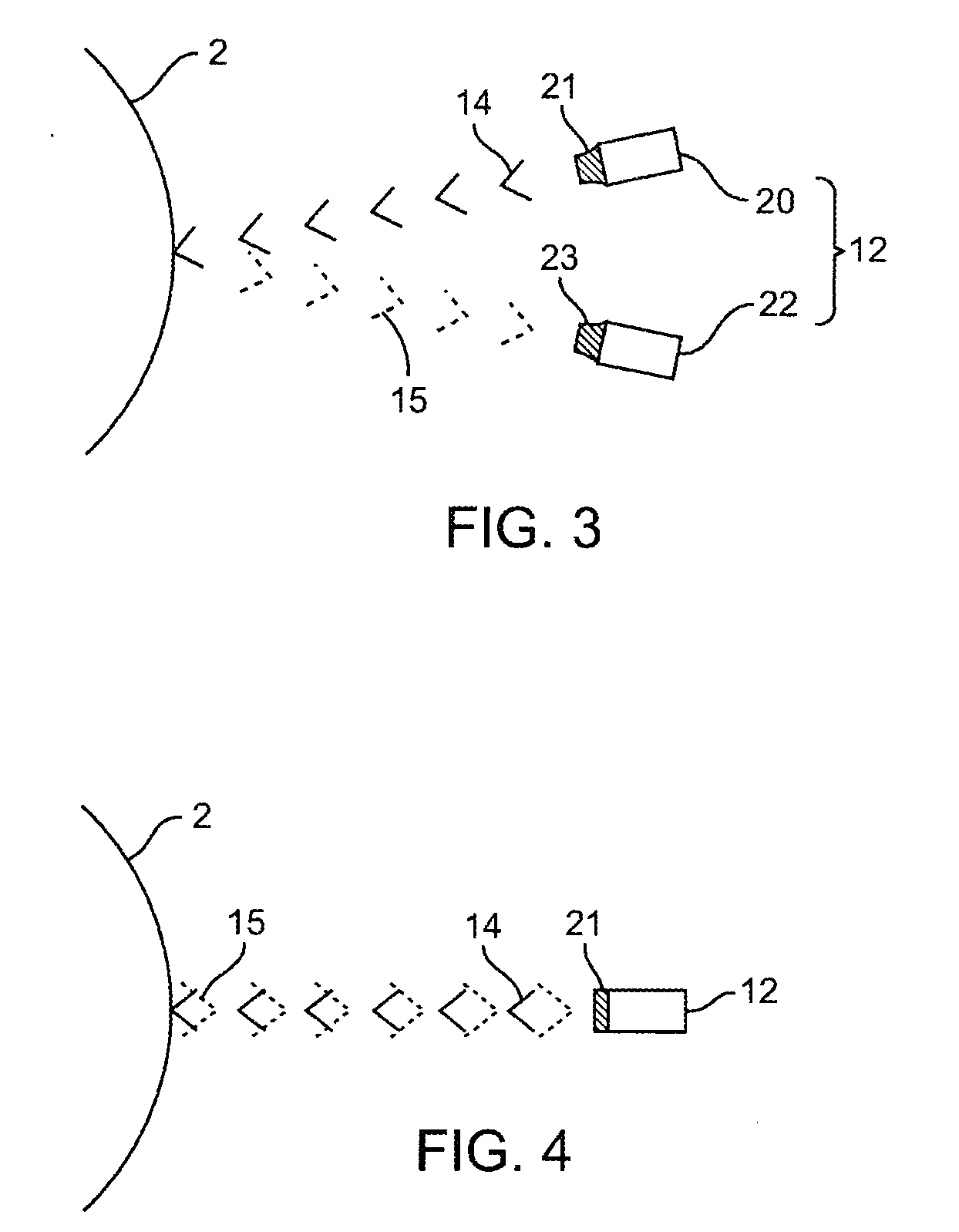

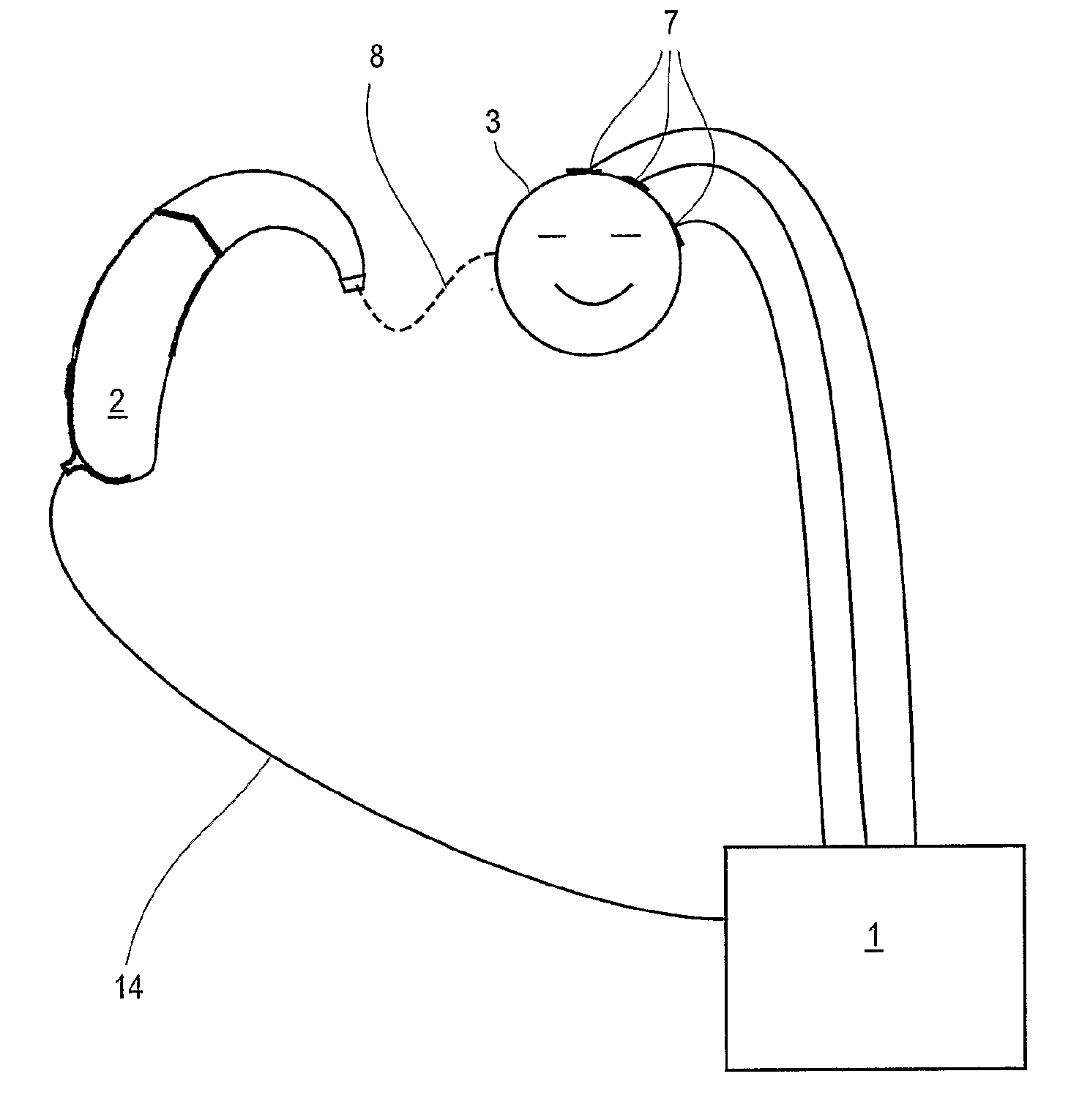

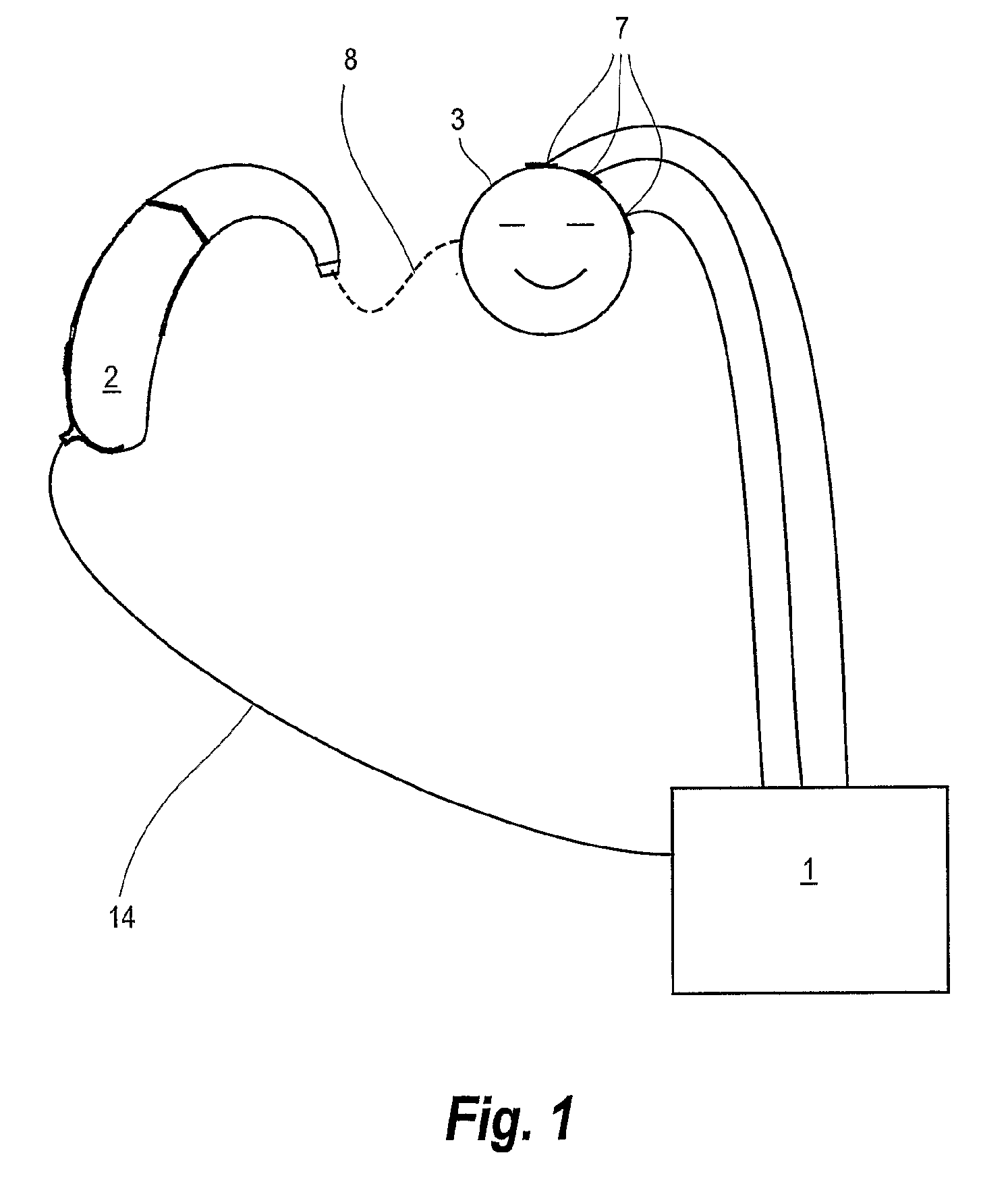

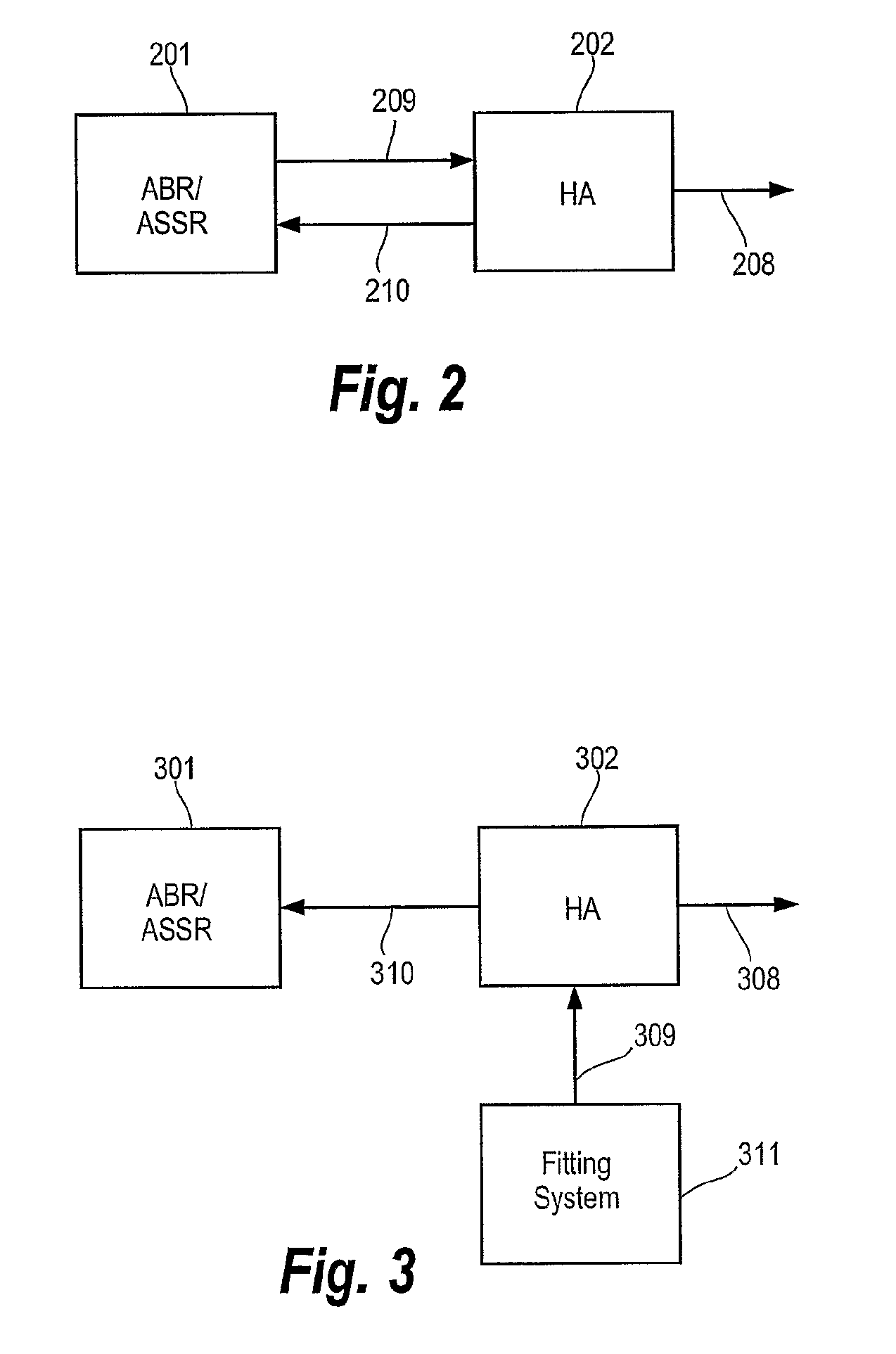

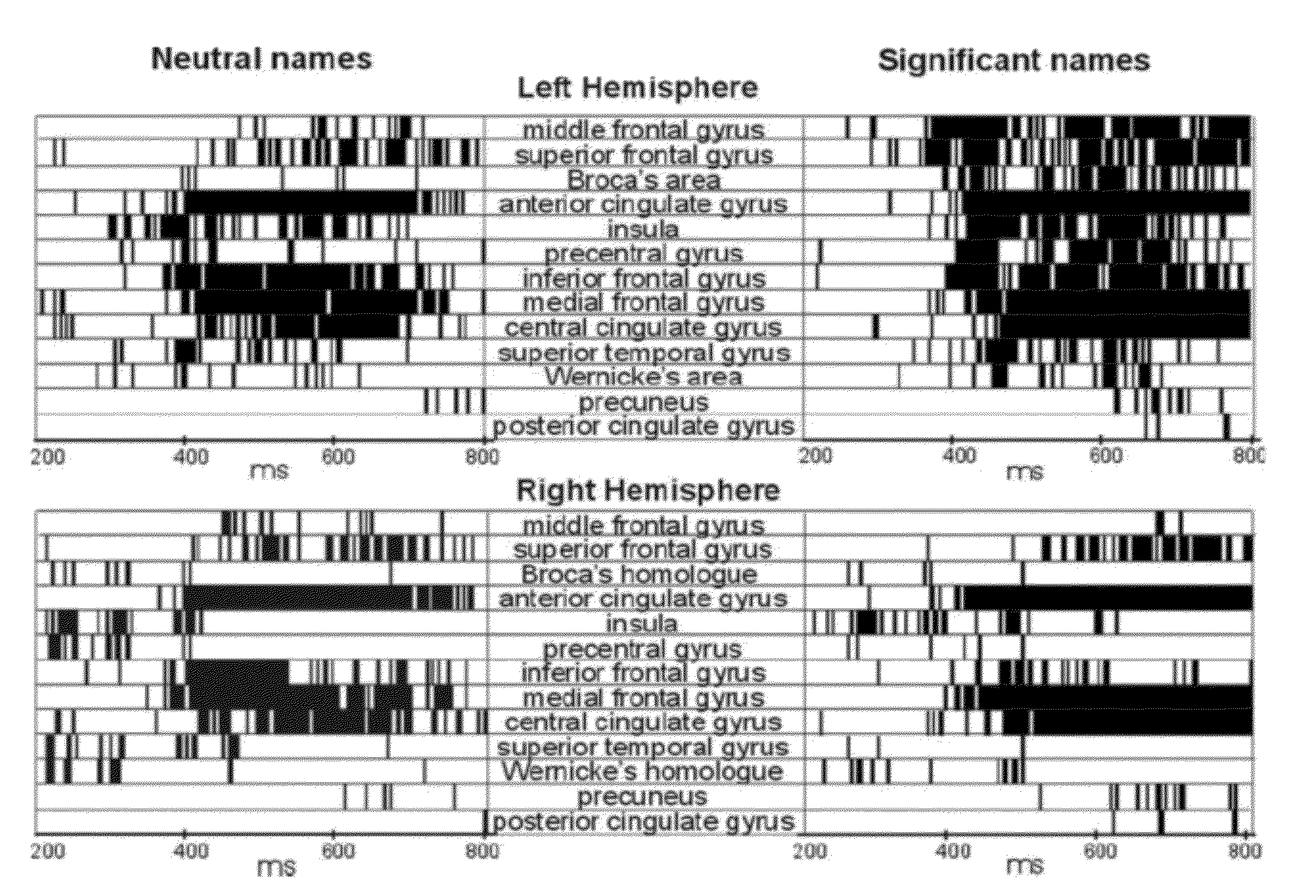

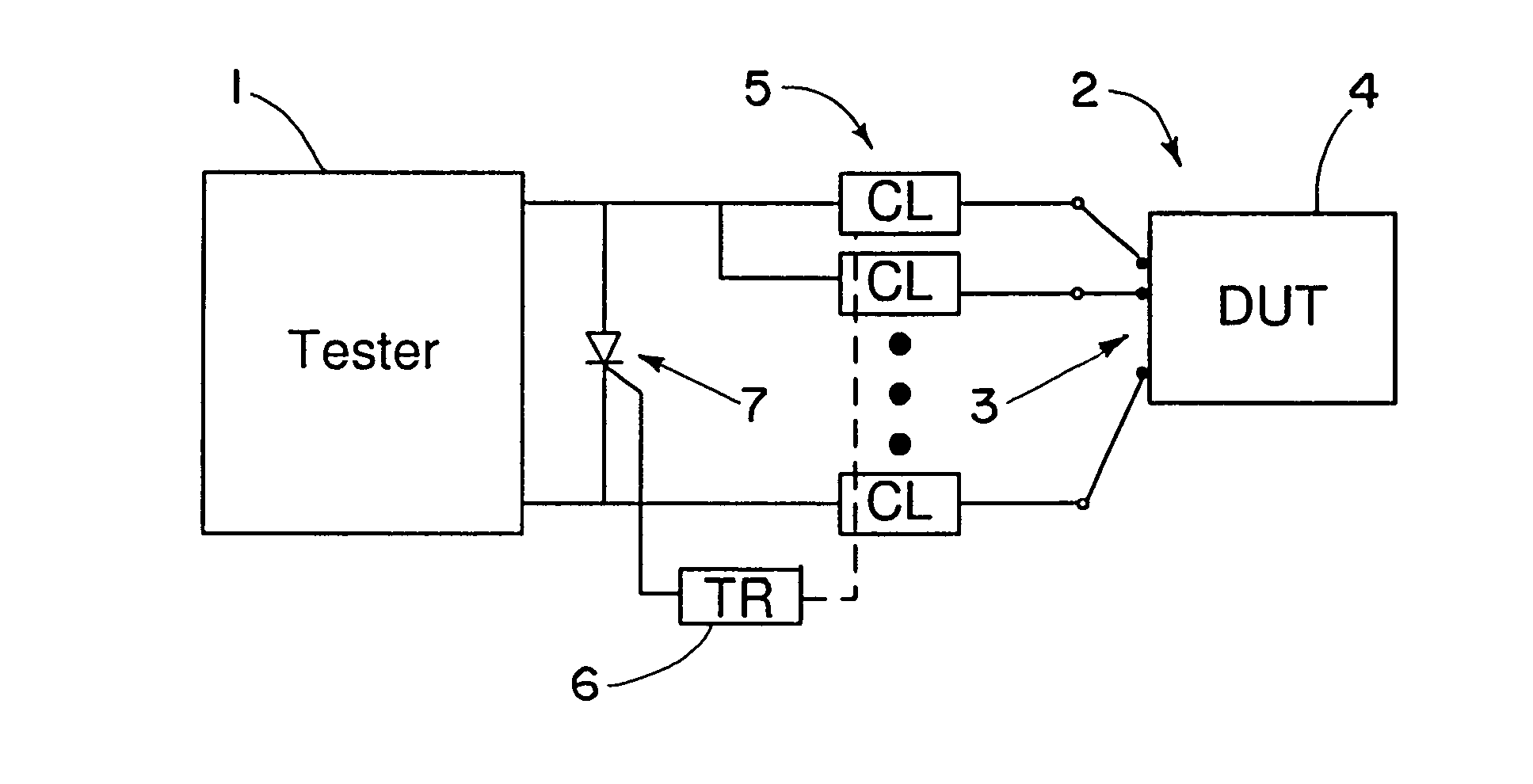

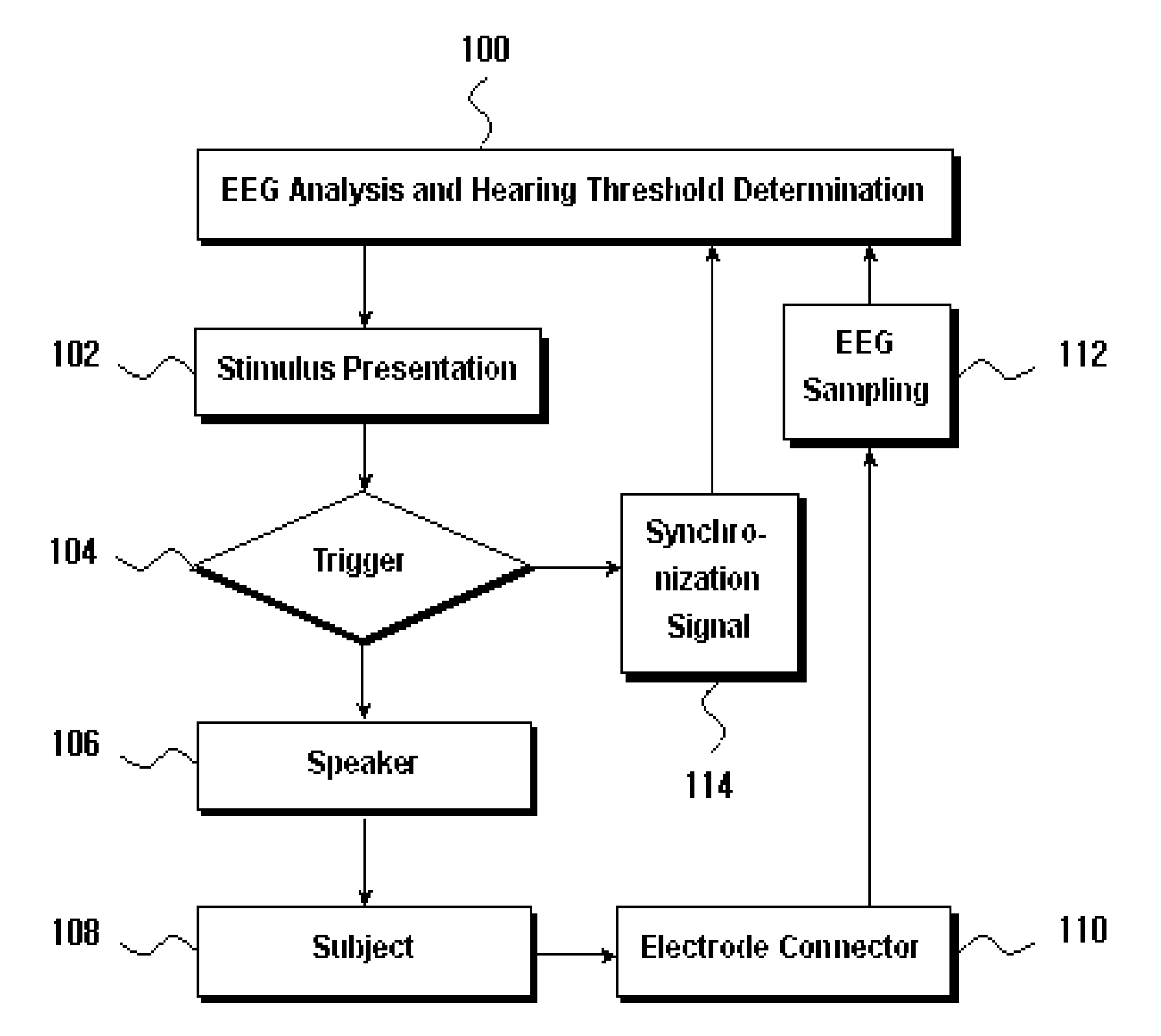

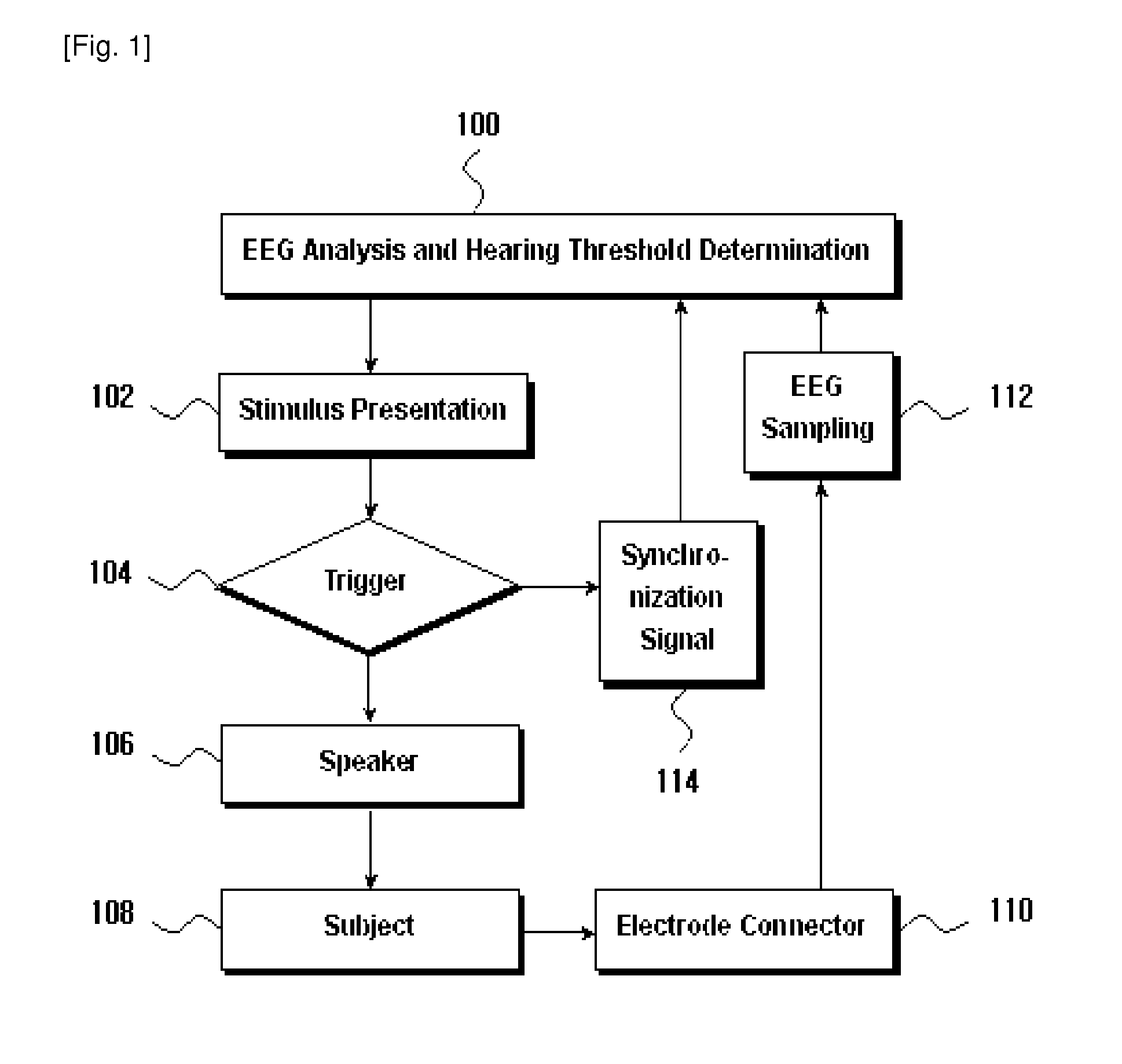

System and method for the objective measurement of hearing ability of an individual

A system for determining the hearing ability of an individual comprises a generator for generating a test stimulus signal, a hearing aid (2) having a digital signal processor for processing said test stimulus signal and converting it in order to output an acoustic stimulus signal, and a first synchronizing means. The system further comprises an electrophysiological instrument (1) having a second synchronizing means, and means (7) for establishing from said individual an evoked response to said acoustic signal. The first synchronizing means and said second synchronizing means exchange a synchronization signal in order to synchronize said evoked response to said acoustic stimulus signal. The invention also provides a hearing aid and a method for carrying out electrophysiological measurement of the hearing ability of an individual.

Owner:WIDEX AS

Subjective significance evaluation tool, brain activity based

A method and system for determining the subjective state of mind of a human subject presented with a test audible or visual stimulus. An an electroencephalogram (EEG) recording unit is connected to the human subject, recording the subject's EEG when presented with one or more test stimuli. The recorded EEG signal is then transformed to a 3-D map in order to visualize the brain areas that were active when presenting the test stimuli. The given 3-D map of the test stimuli is then compared with reference 3-D maps of neutral and subjectively significant stimuli.

Owner:OFEK EINAT

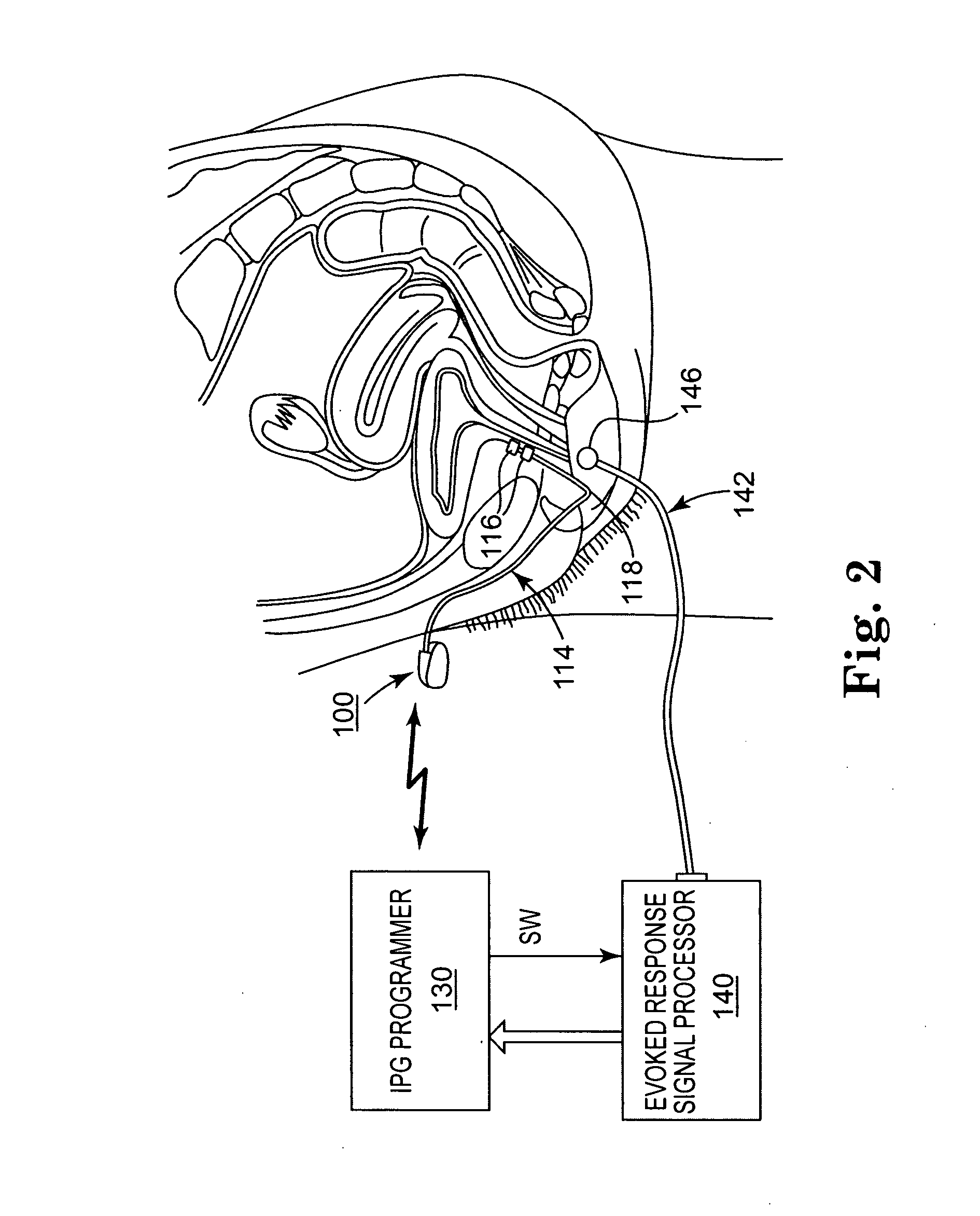

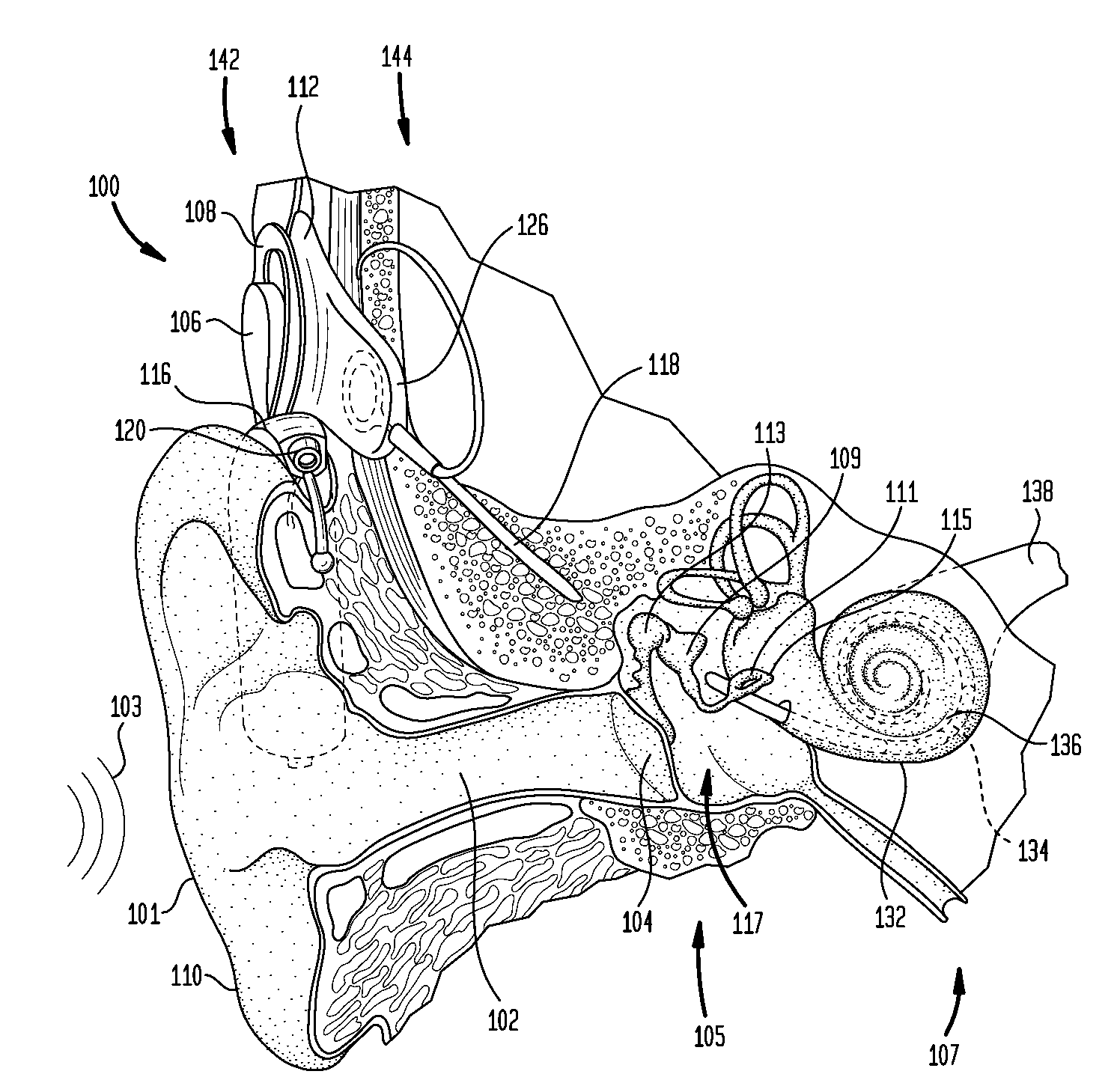

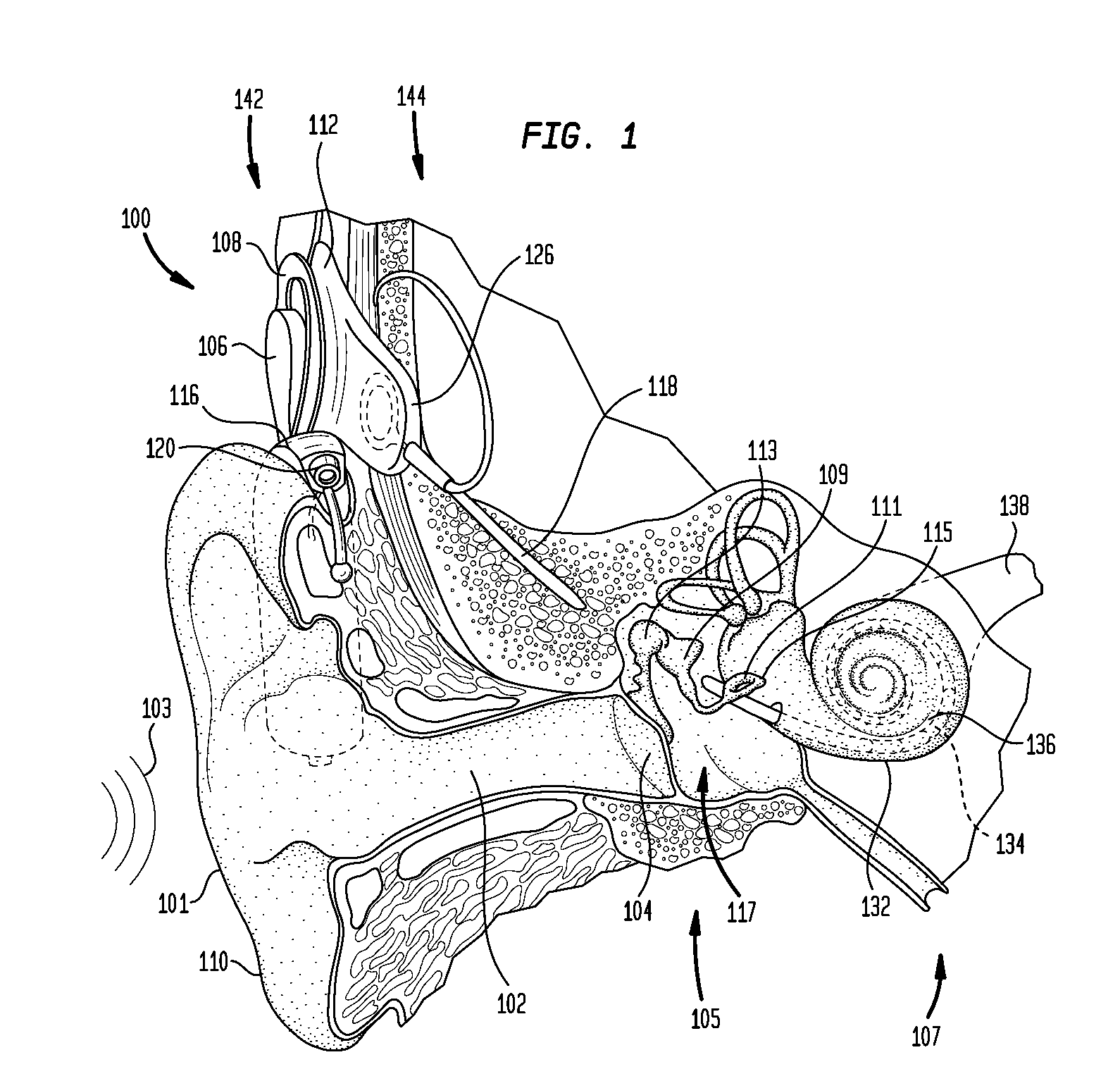

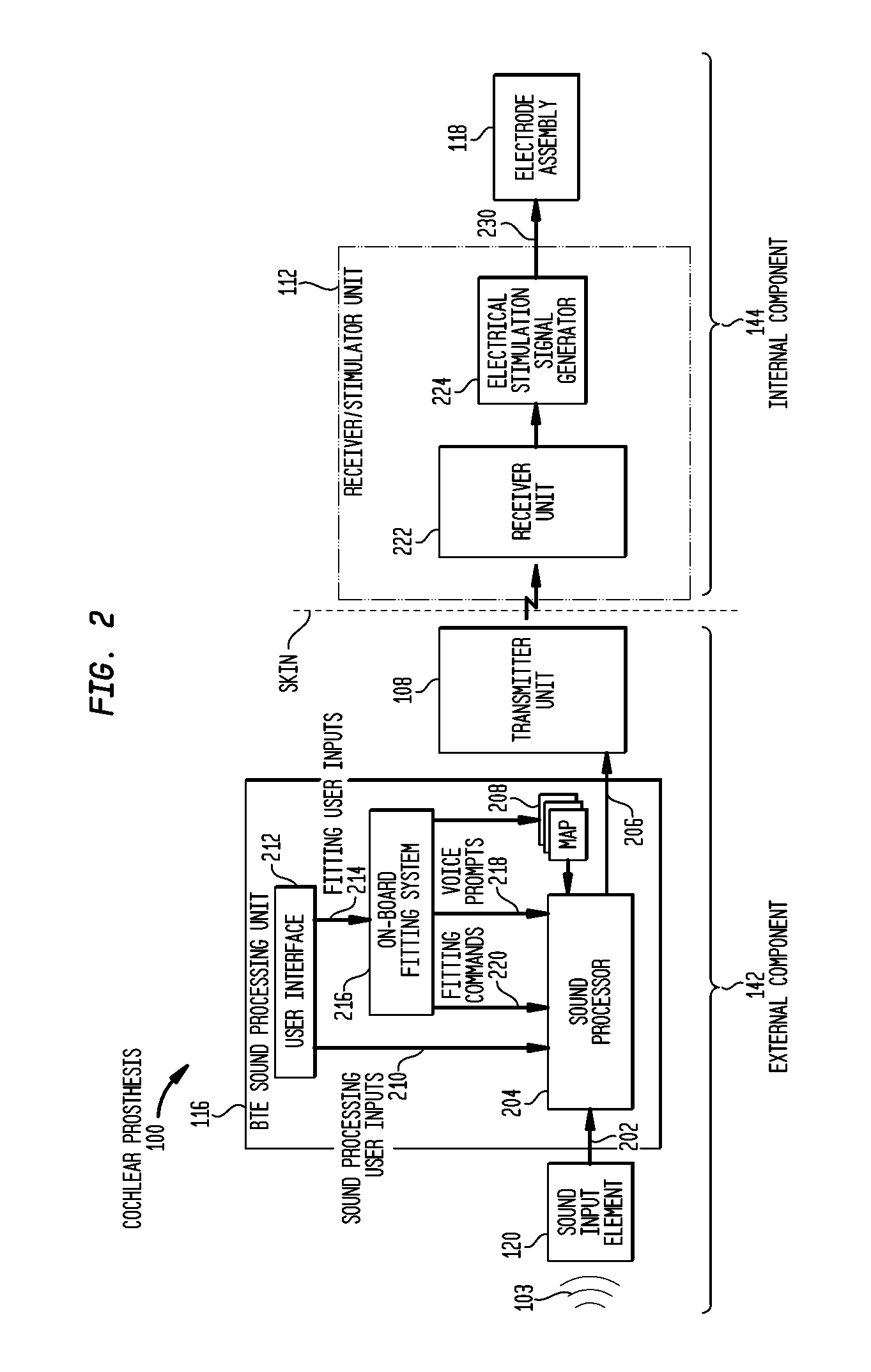

Recipient-controlled fitting of a hearing prosthesis

A method for fitting to a recipient a cochlear prosthesis having a sound processor that processes received sound in accordance with a MAP, the method comprises providing, by the hearing prosthesis, combinations of voice prompts and test stimuli for testing values of an element of the MAP; receiving from the recipient an indication of which of said values are desirable; and revising the MAP with the desired value for the tested element. A neural-stimulating device for stimulating nerve cells of a recipient is provided.

Owner:COCHLEAR LIMITED

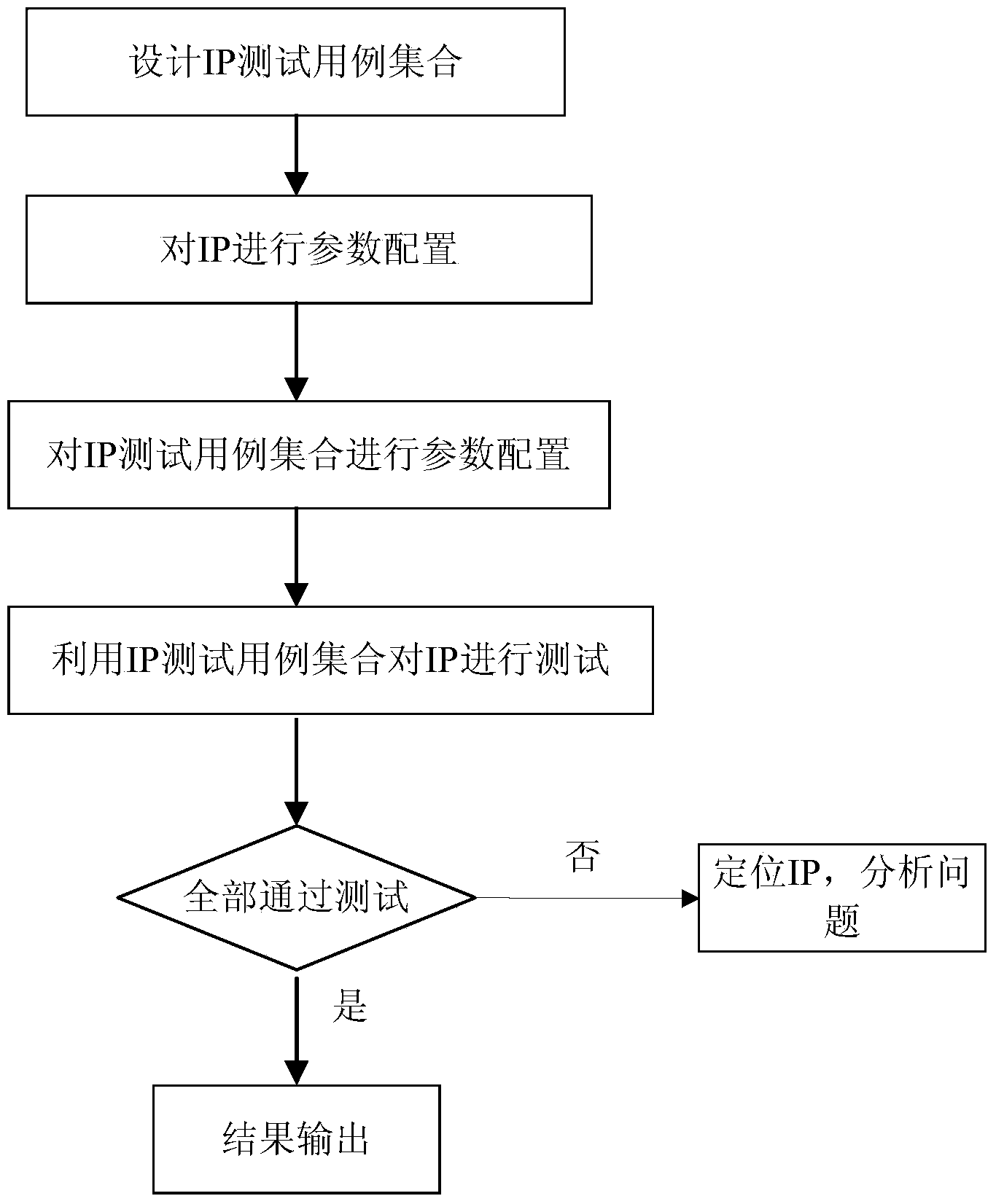

Automatic chip validation method based on parameterized IP test case set

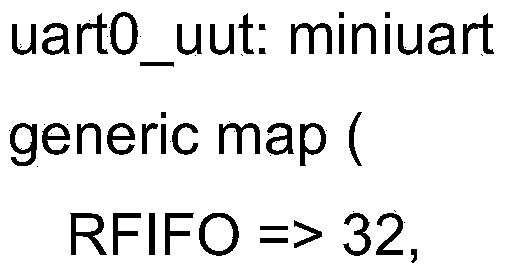

ActiveCN104268078AFully automatedImprove verification efficiencySoftware testing/debuggingProgramming languageTest stimulus

The invention discloses an automatic chip validation method based on a parameterized IP test case set. The automatic chip validation method is achieved by adding test stimulus of IP test cases to the traditional validation method. The automatic chip validation method includes the following steps: designing the test case set of each IP constituting a chip; setting the parameter of each IP constituting the chip; setting the corresponding test case set according to the parameter definition of each IP during design; testing each IP in the chip on the basis of the set test case set to verify the correctness of the design. The automatic chip validation method can be achieved simply, greatly reduces expenses for re-writing of the test cases for the same IP, and improves the IP-based chip validation efficiency.

Owner:BEIJING INST OF CONTROL ENG

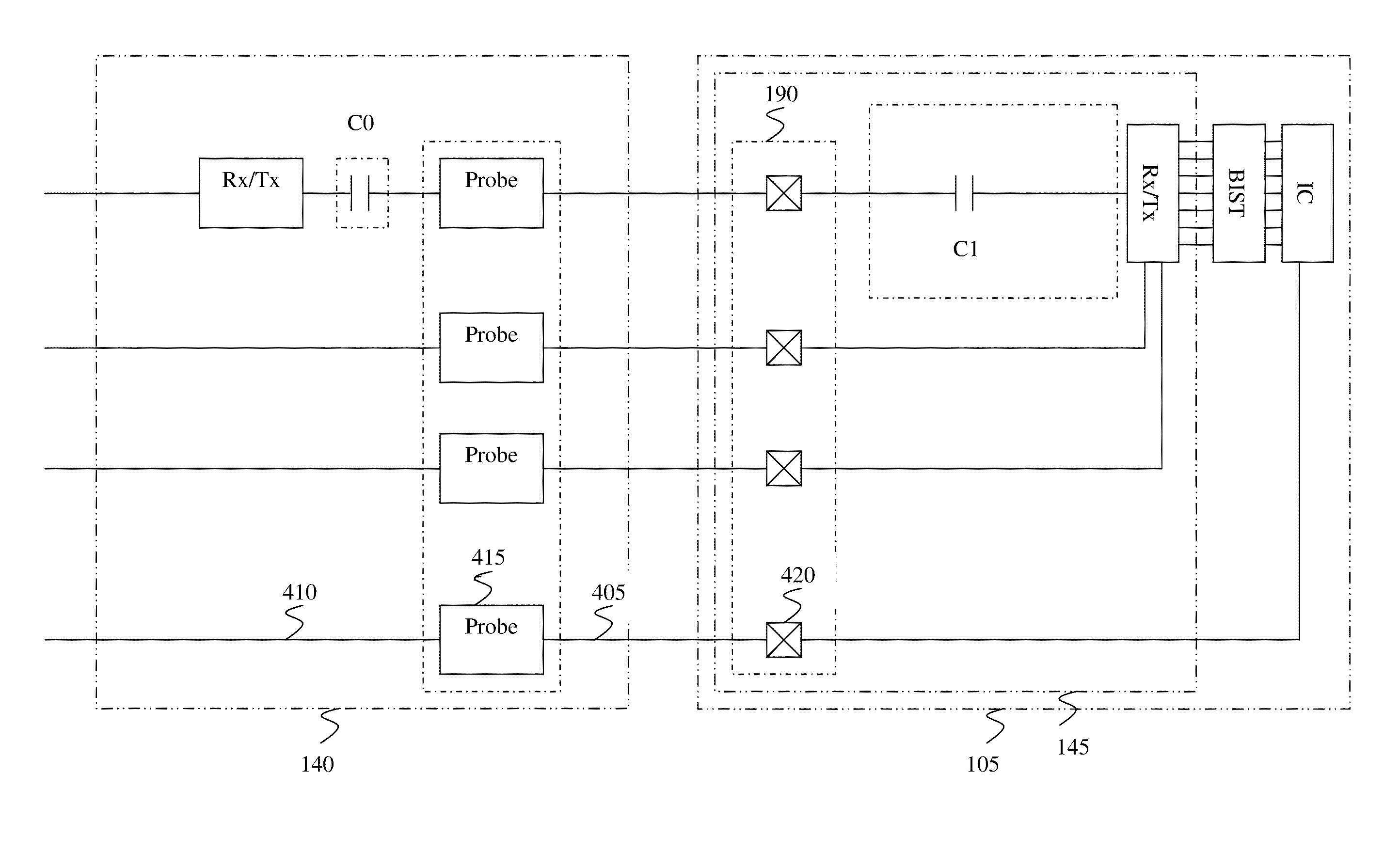

Testing integrated circuits

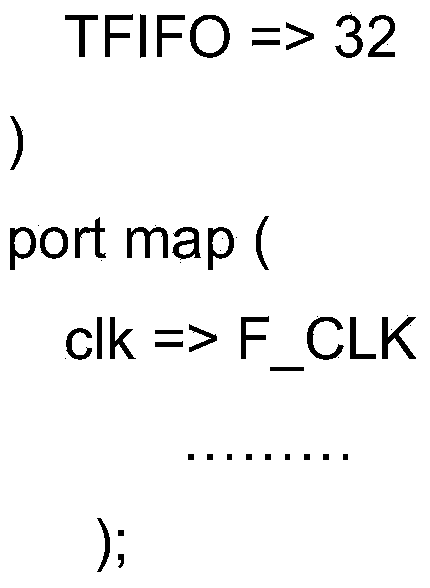

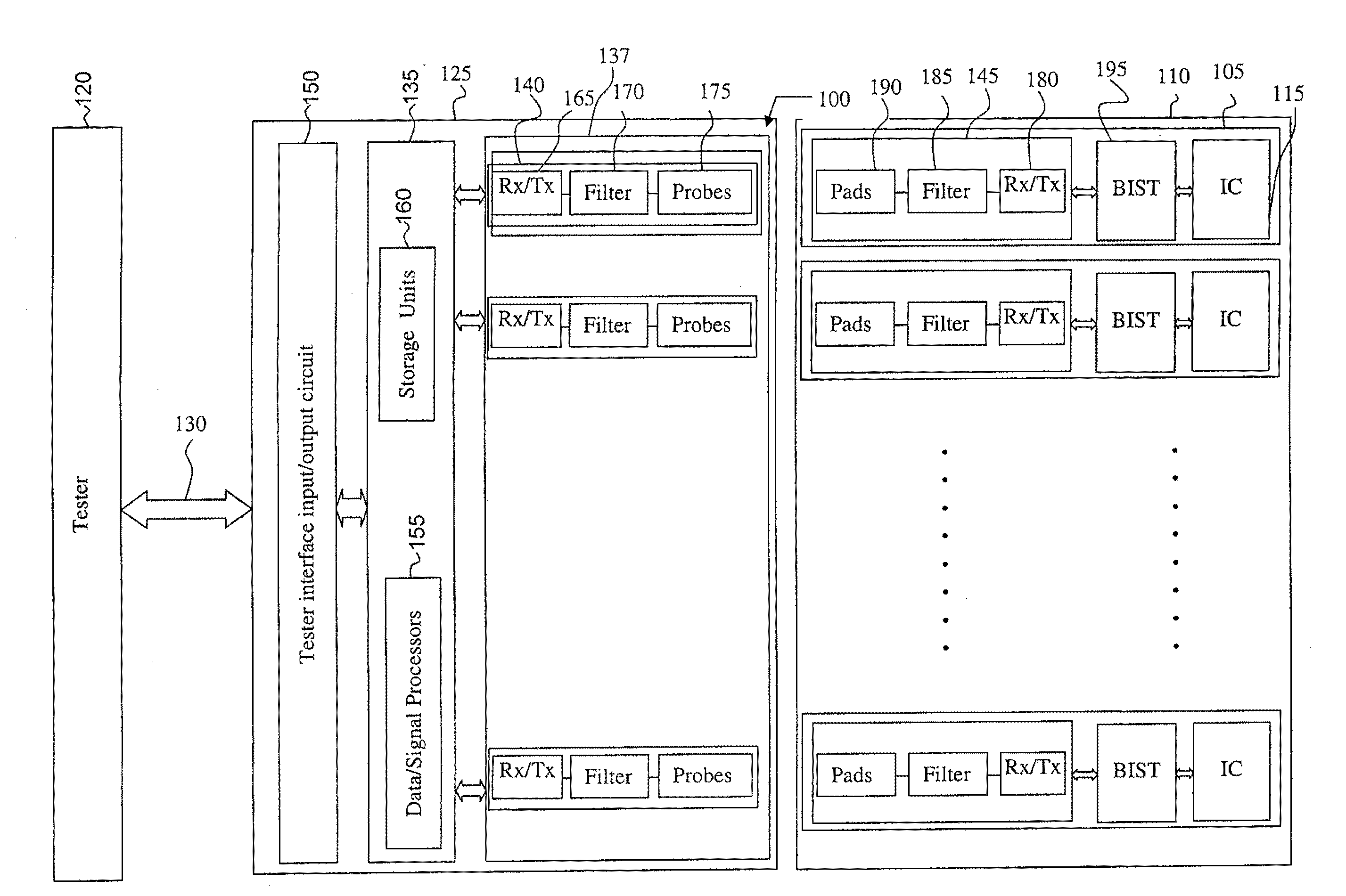

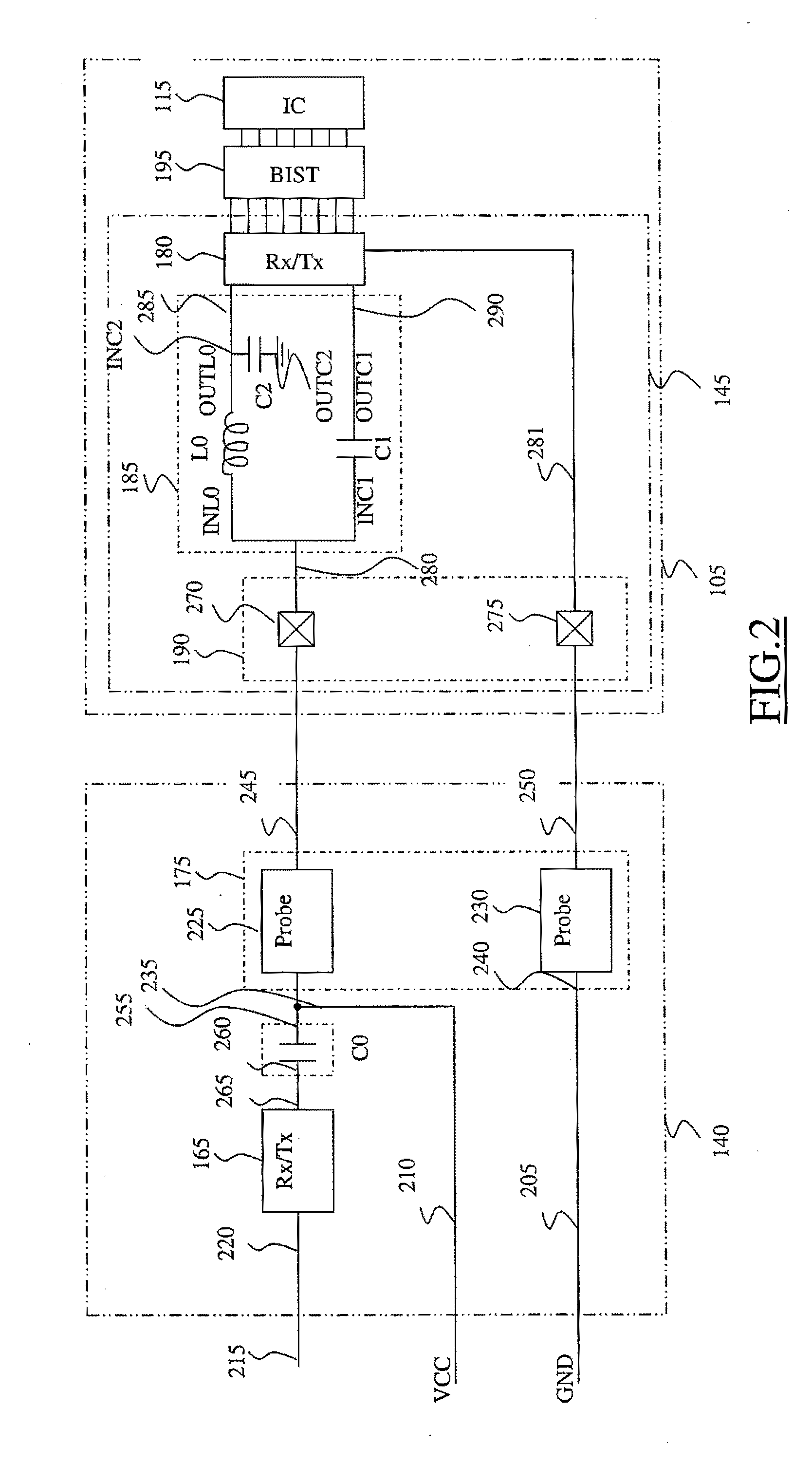

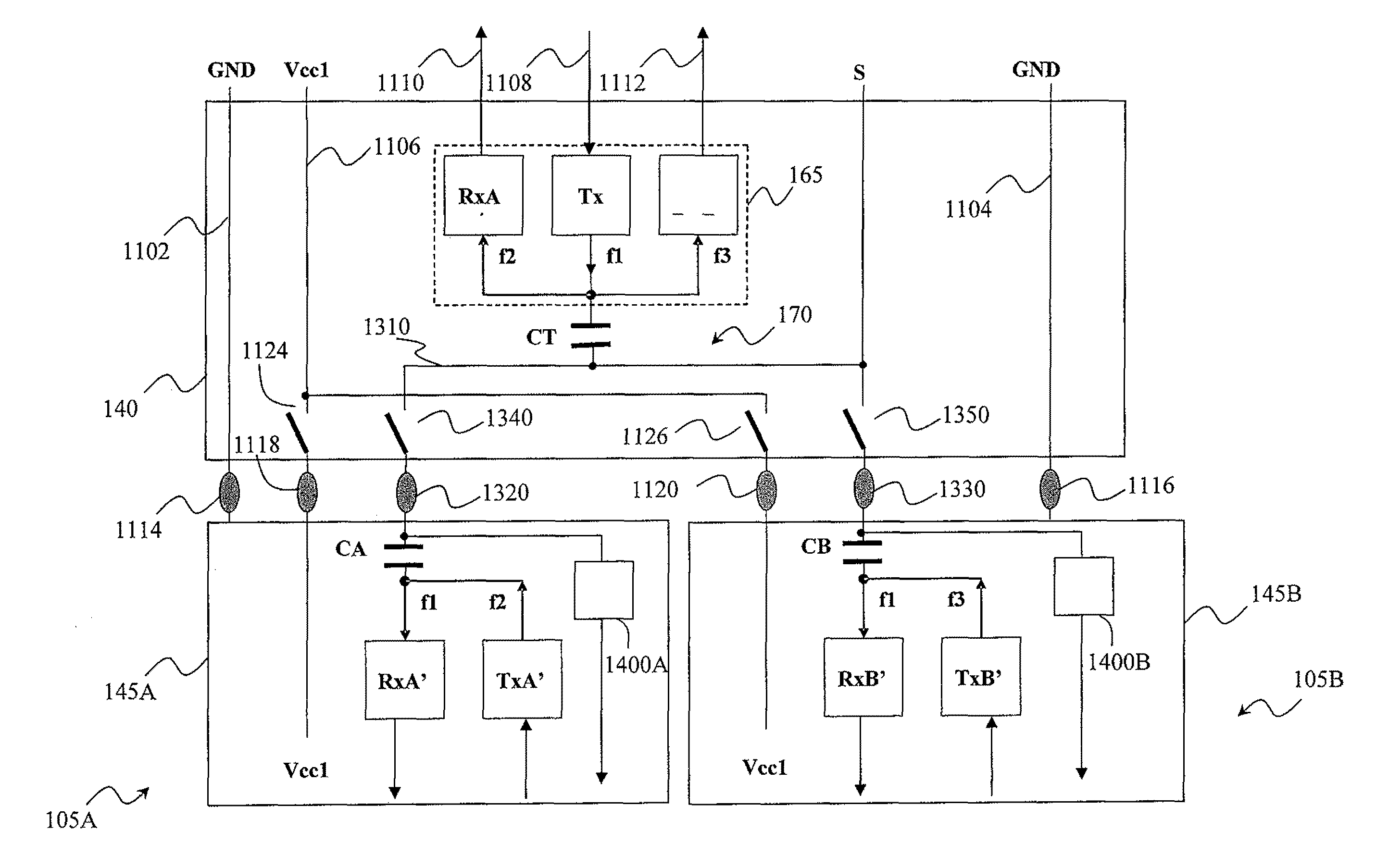

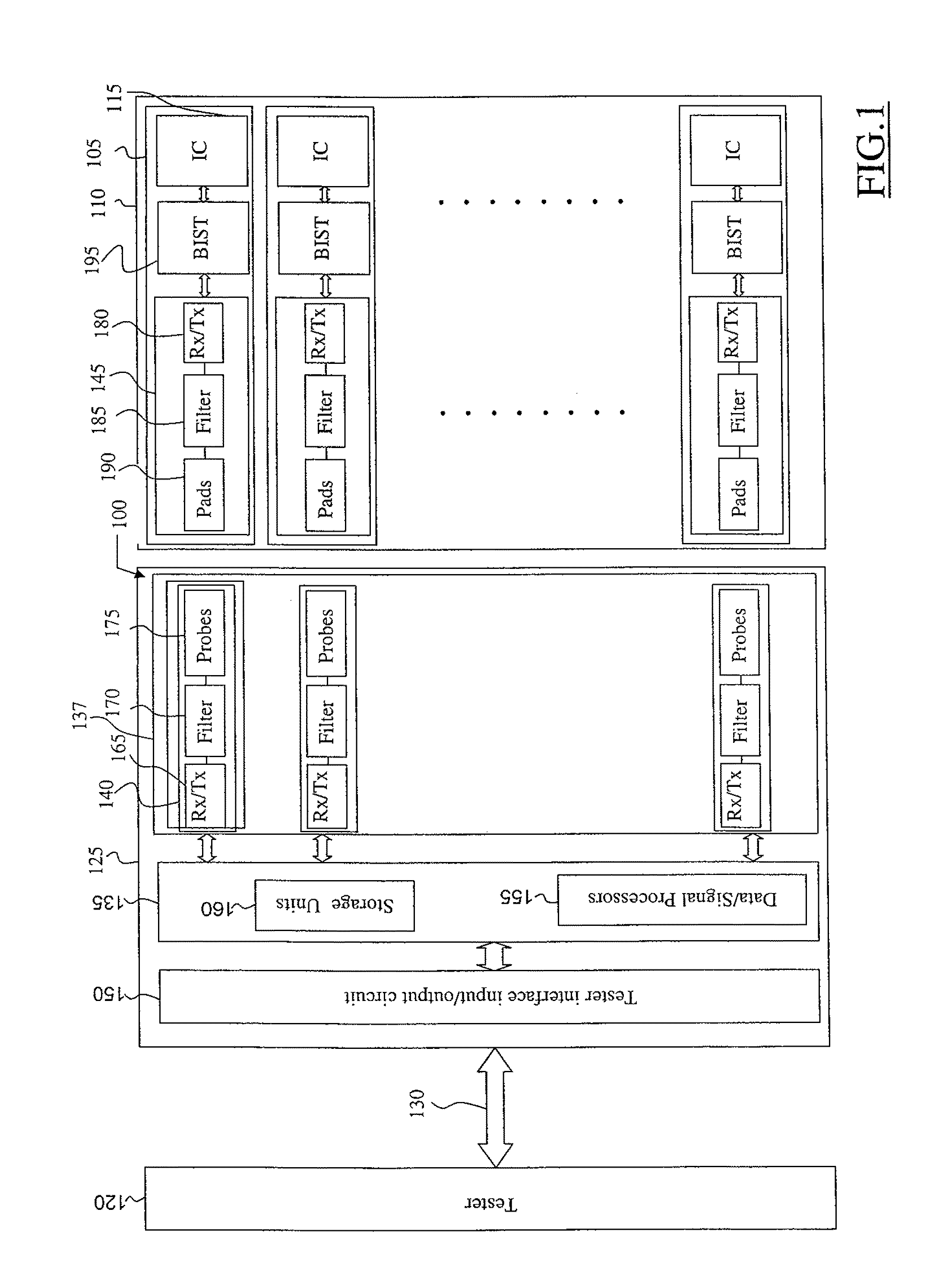

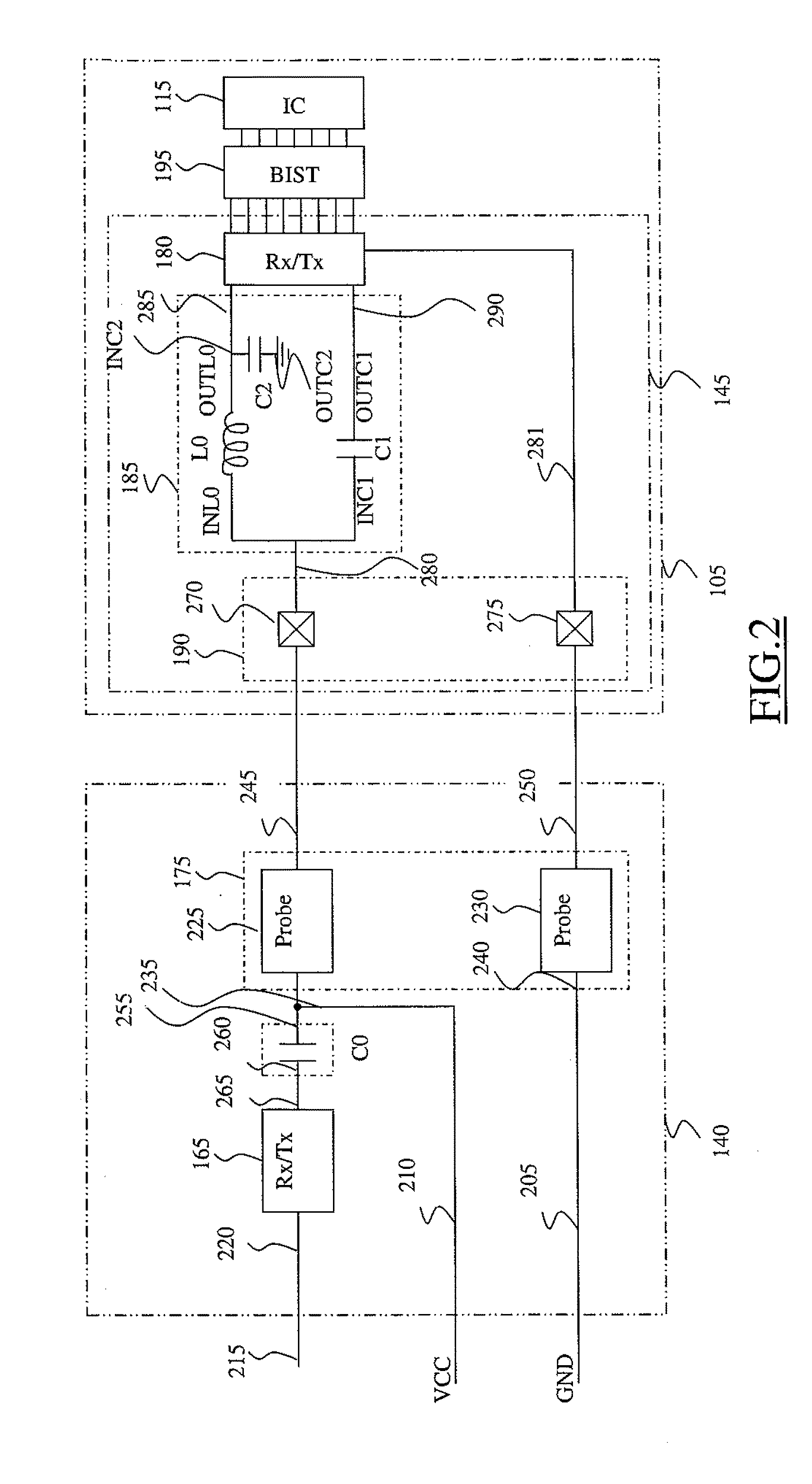

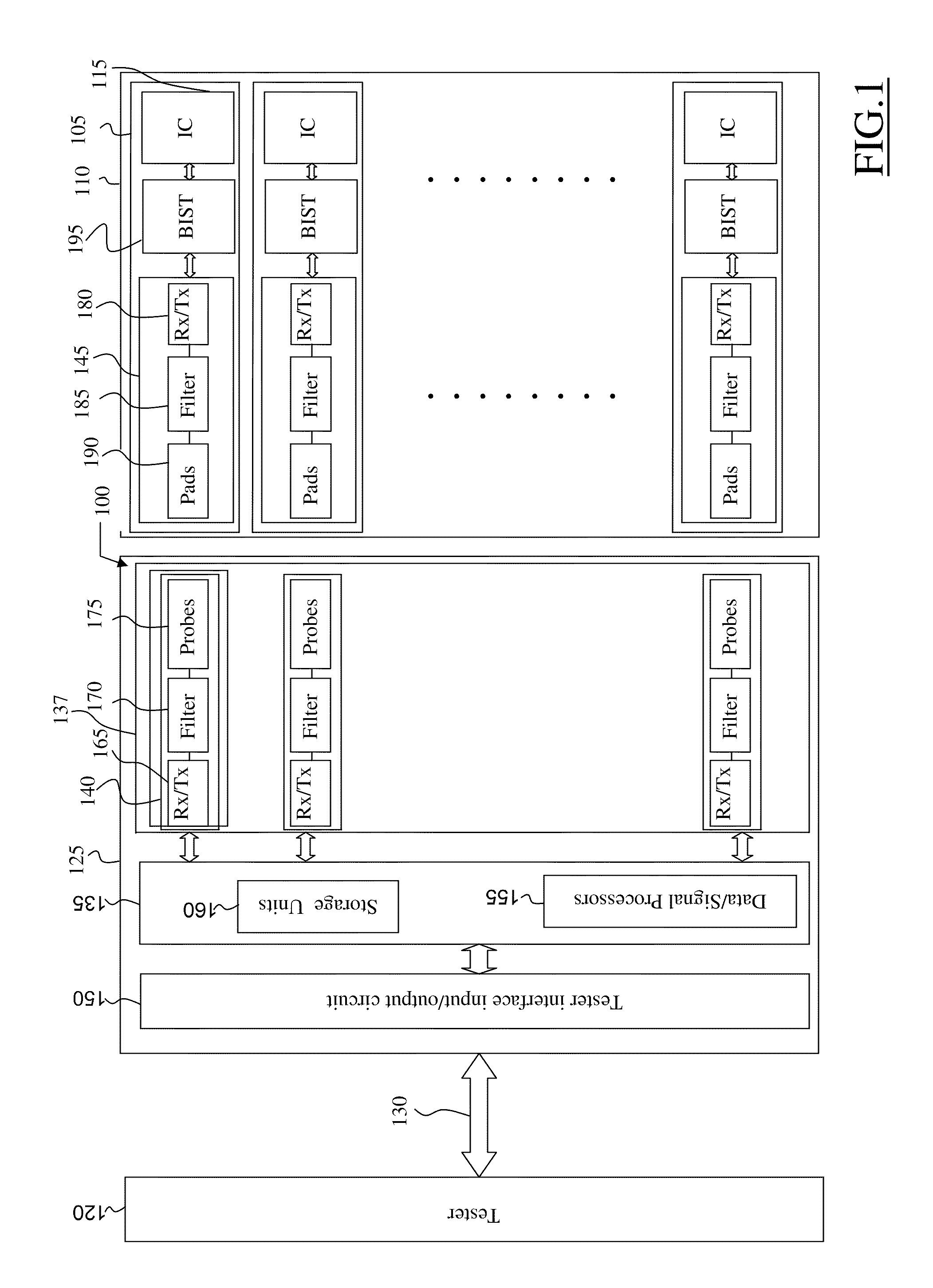

ActiveUS20110291679A1Reduce in quantityFault location by increasing destruction at faultElectrical testingCarrier signalTest stimulus

A method of testing integrated circuits is provided. The method includes establishing at least one first physical communication channel between a test equipment and a respective group of integrated circuits under test by having probes of the test equipment contacting at least one corresponding physical contact terminal of each integrated circuit of the respective group. The method further includes having the test equipment exchanging, over the at least one first physical communication channel, the same test stimuli with each integrated circuit of the group. The method still further includes having each integrated circuit of the group establishing a corresponding second physical communication channel with the test equipment by having at least one physical contact terminal of the integrated circuit contacted by a corresponding probe of the test equipment. The method further includes having each integrated circuit of the group exchanging, over the second physical communication channel, a corresponding test response signal based on the received test stimuli with the test equipment. The test stimuli are exchanged by modulating at least one first carrier wave based on the test stimuli; the at least one first carrier wave has at least one first frequency. The test response signals of each integrated circuit of the group are exchanged by modulating at least one respective second carrier wave based on the test response signals; each second carrier wave have at least one respective second frequency.

Owner:STMICROELECTRONICS SRL

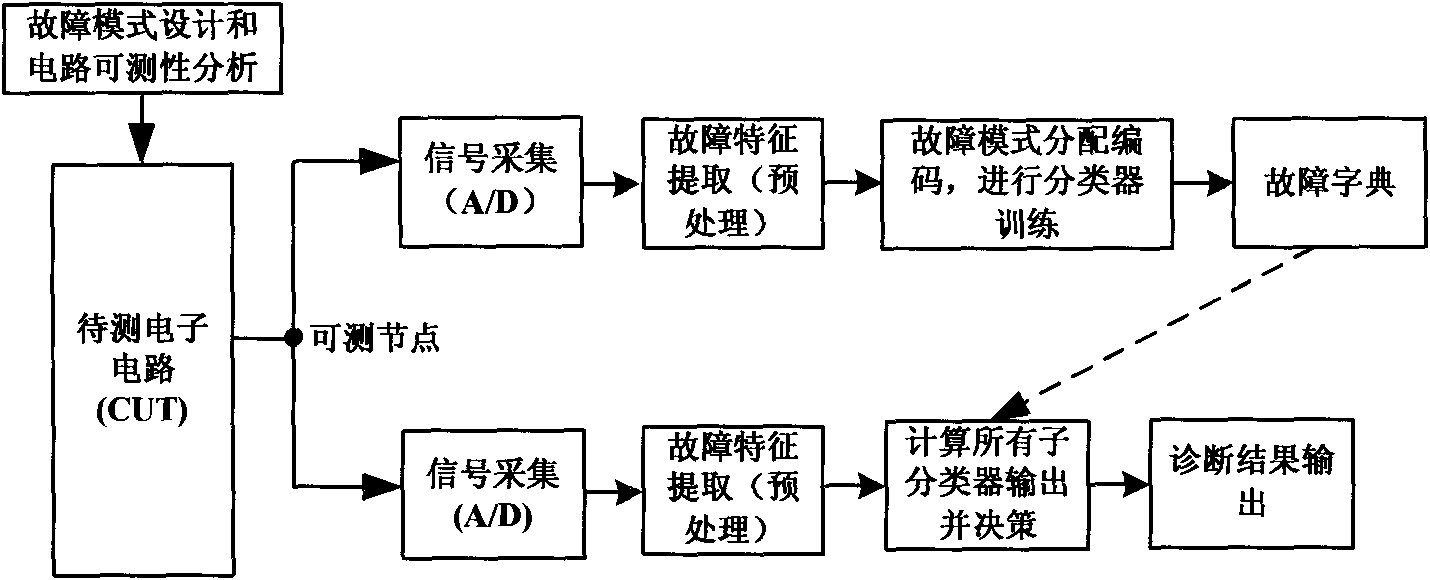

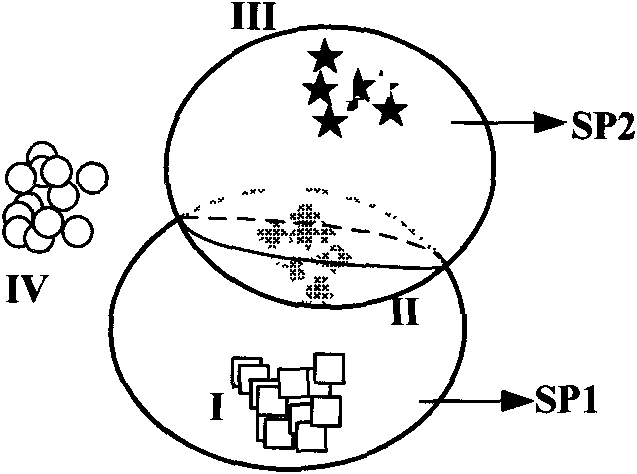

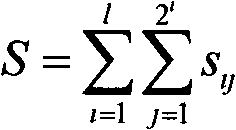

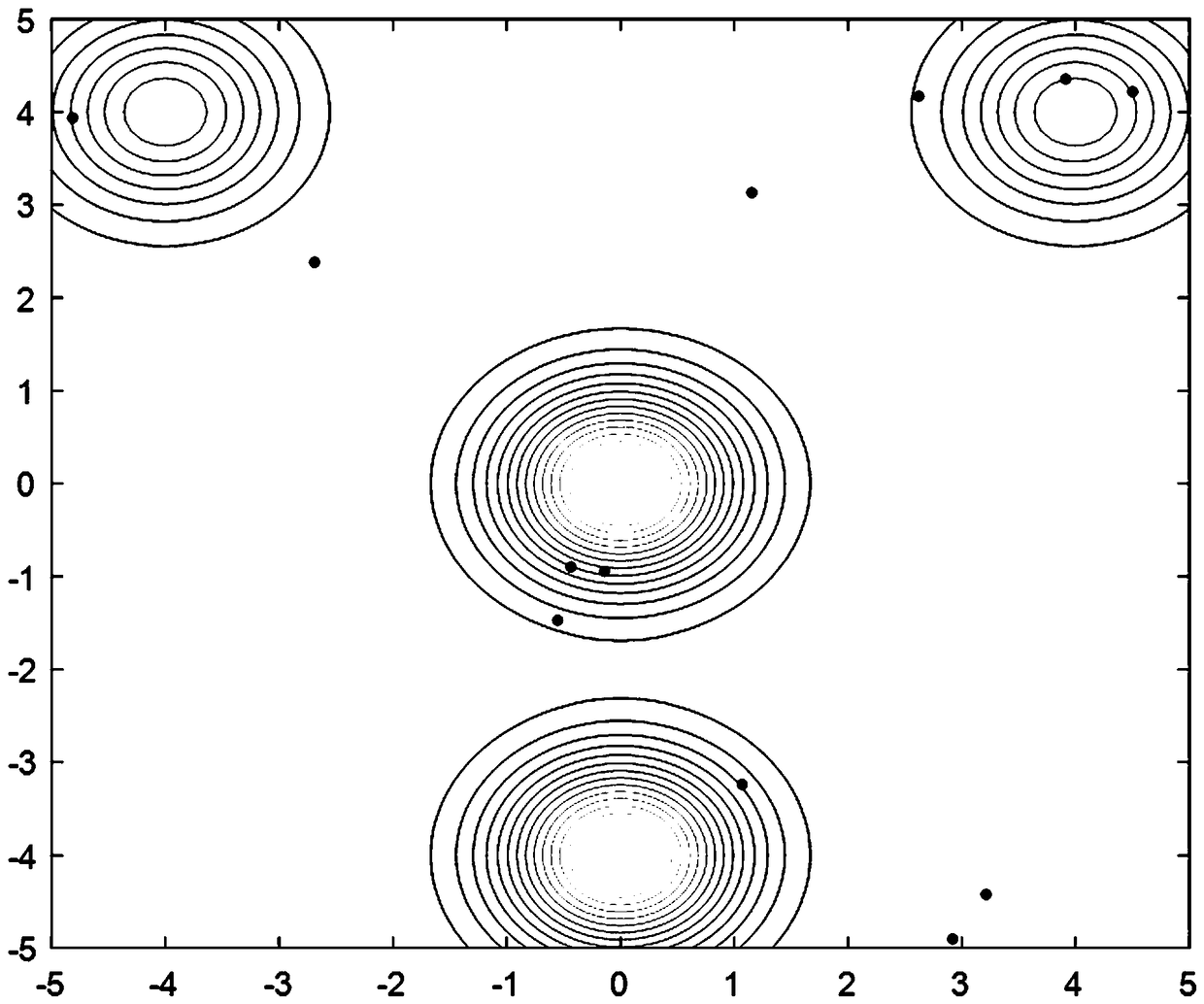

Analogical electronic circuit fault diagnostic method based on M-ary-structure classifier

InactiveCN101614787AReduce the numberImprove diagnostic accuracyAnalog circuit testingTest stimulusTestability analysis

The invention discloses an analogical electronic circuit fault diagnostic method based on an M-ary-structure classifier, which belongs to the field of analogical circuit network test. The invention comprises the following steps: firstly, analyzing the testability of an analogical circuit to determine proper test stimulus and a test point; secondly, acquiring to-be-tested outputting signals at a testable node of an electronic circuit; thirdly, compressing acquired circuit fault information to extract fault characteristic samples; finally, designing the tags of the samples in an M-ary encoding way, establishing a hyperspherical sub-classifier in the way of a SVDD classifier, training the samples, and storing information to form a fault dictionary after training. The invention has the advantages of less classifiers, simple method, high reliability, and the like, thereby improving the automation degree and the efficiency of the online fault diagnosis of a power electronic circuit.

Owner:NANJING UNIV OF AERONAUTICS & ASTRONAUTICS

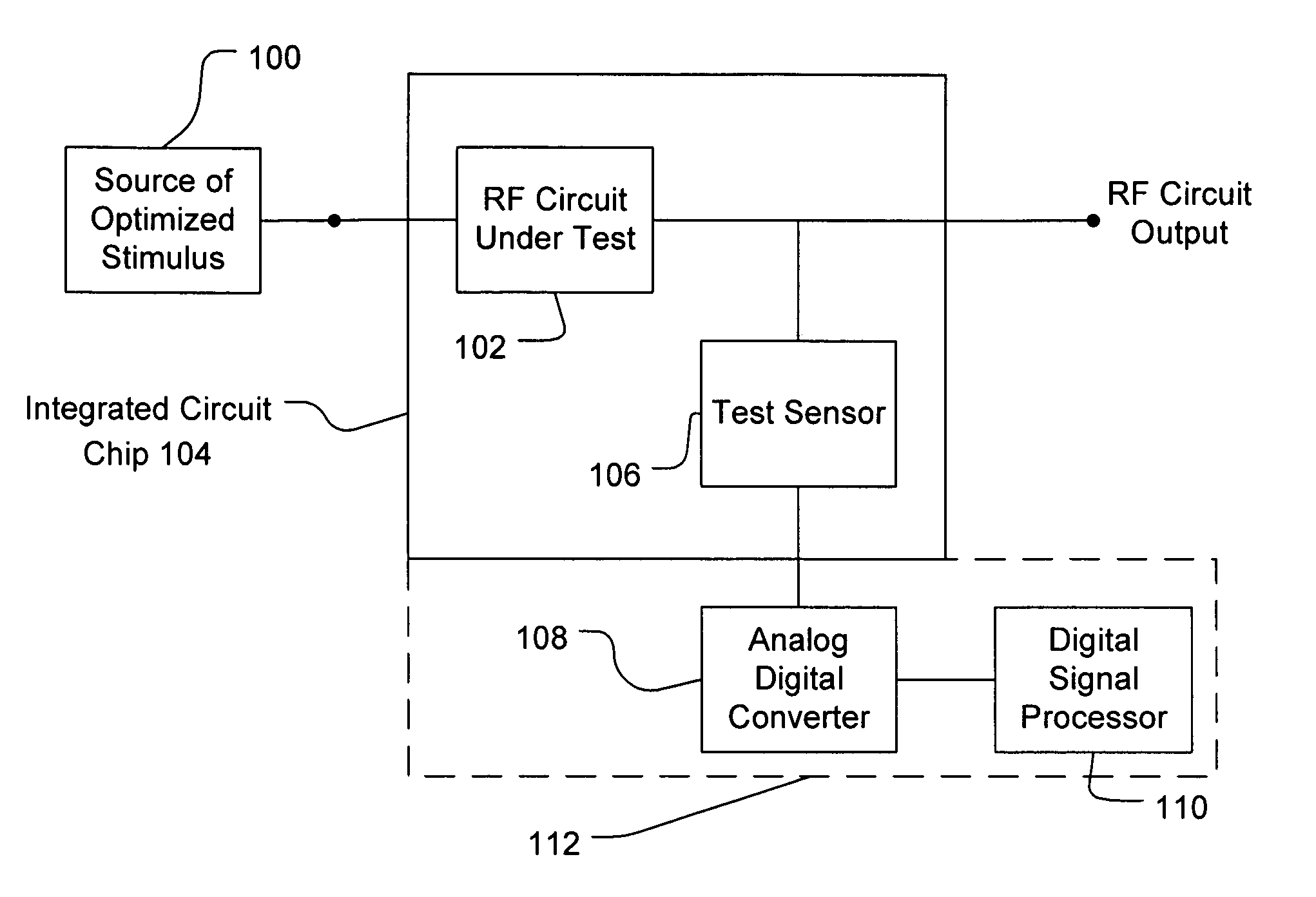

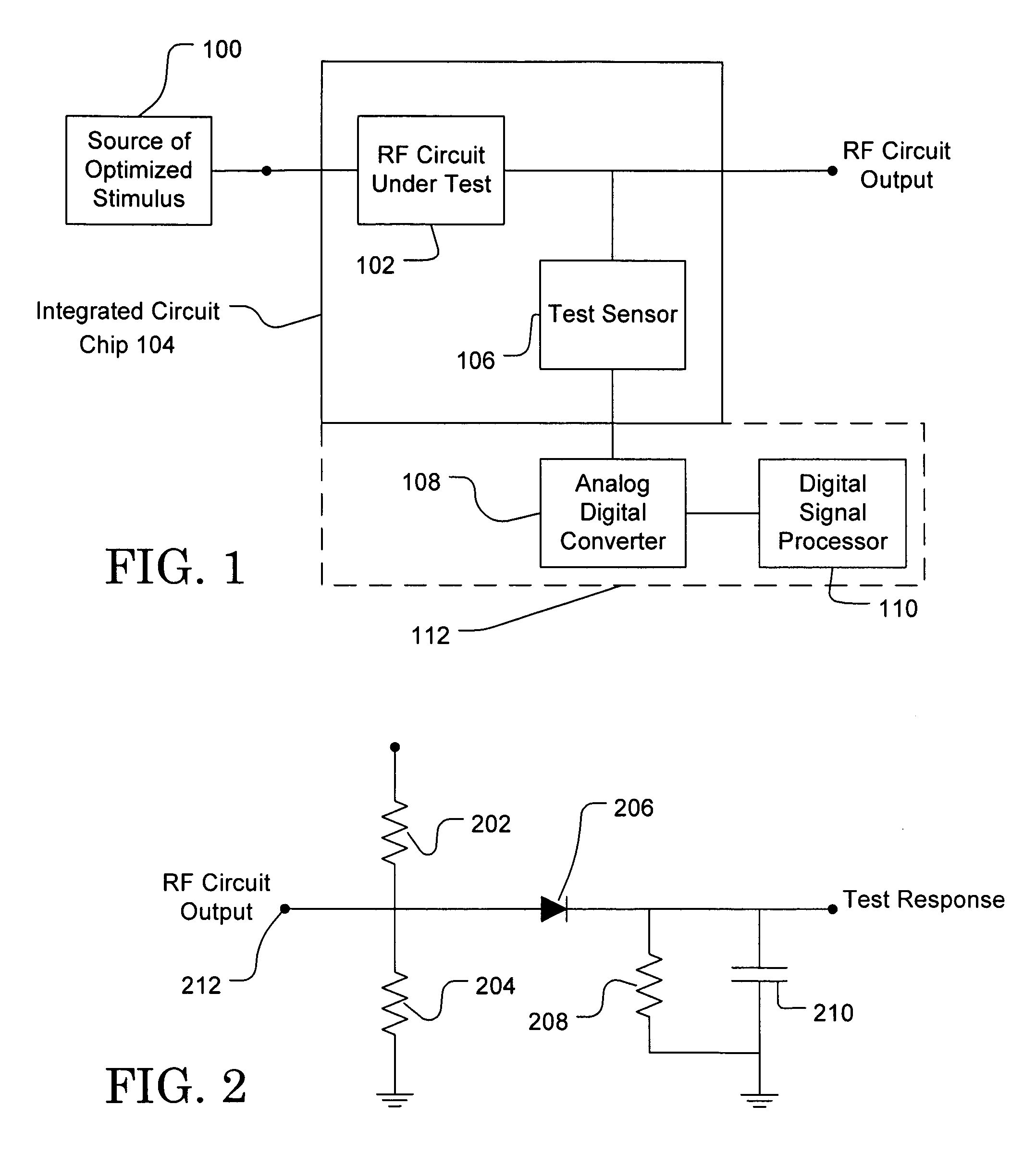

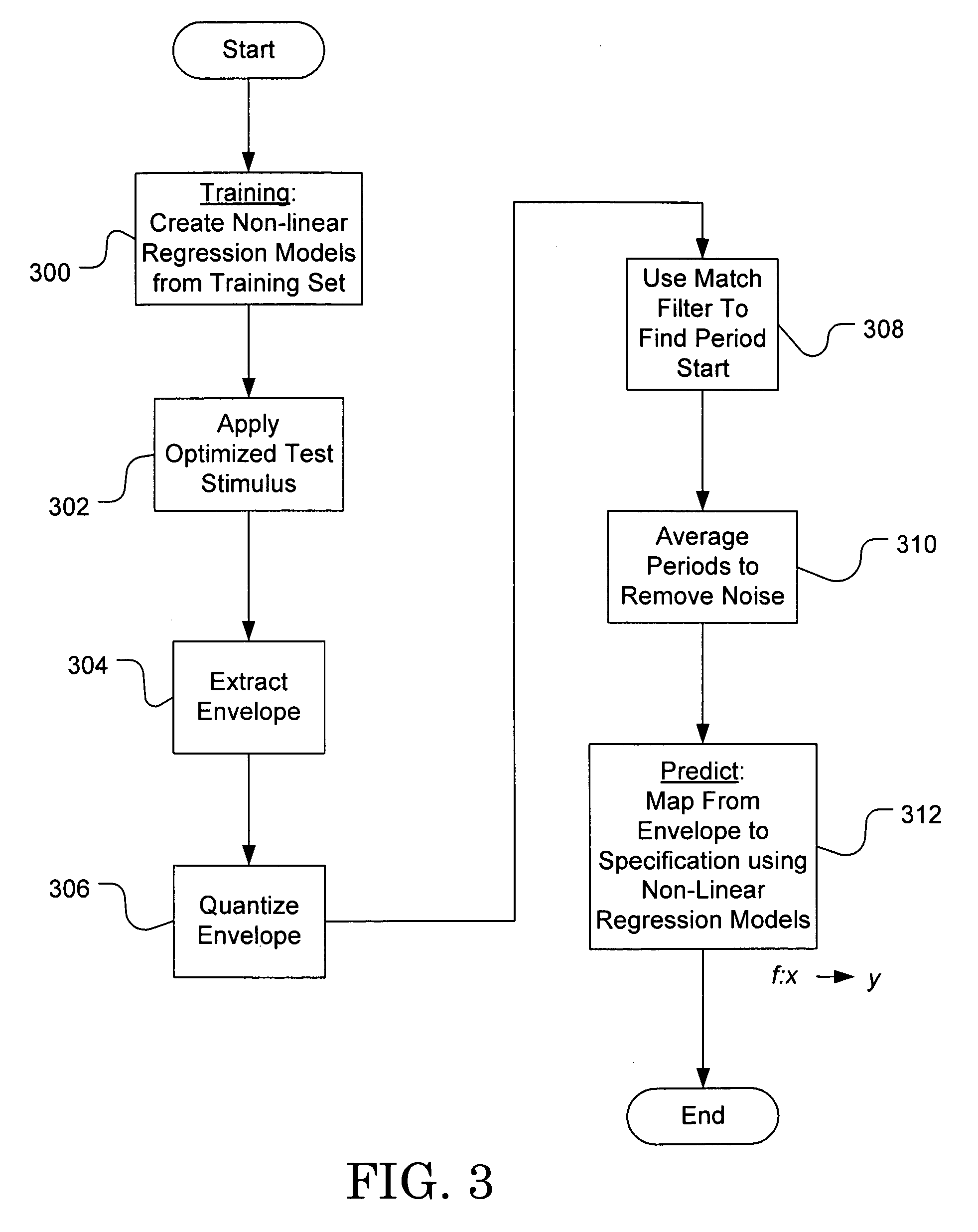

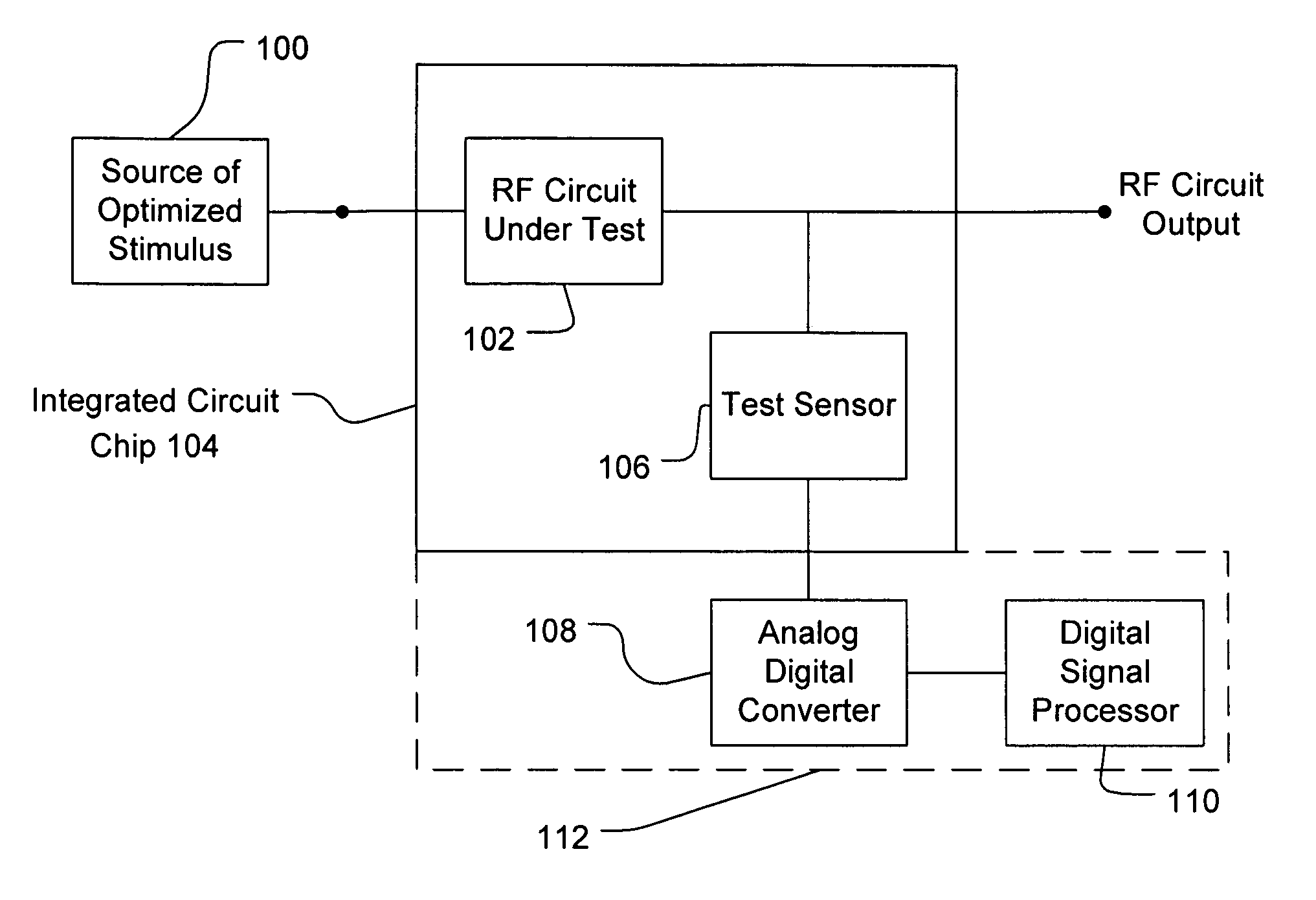

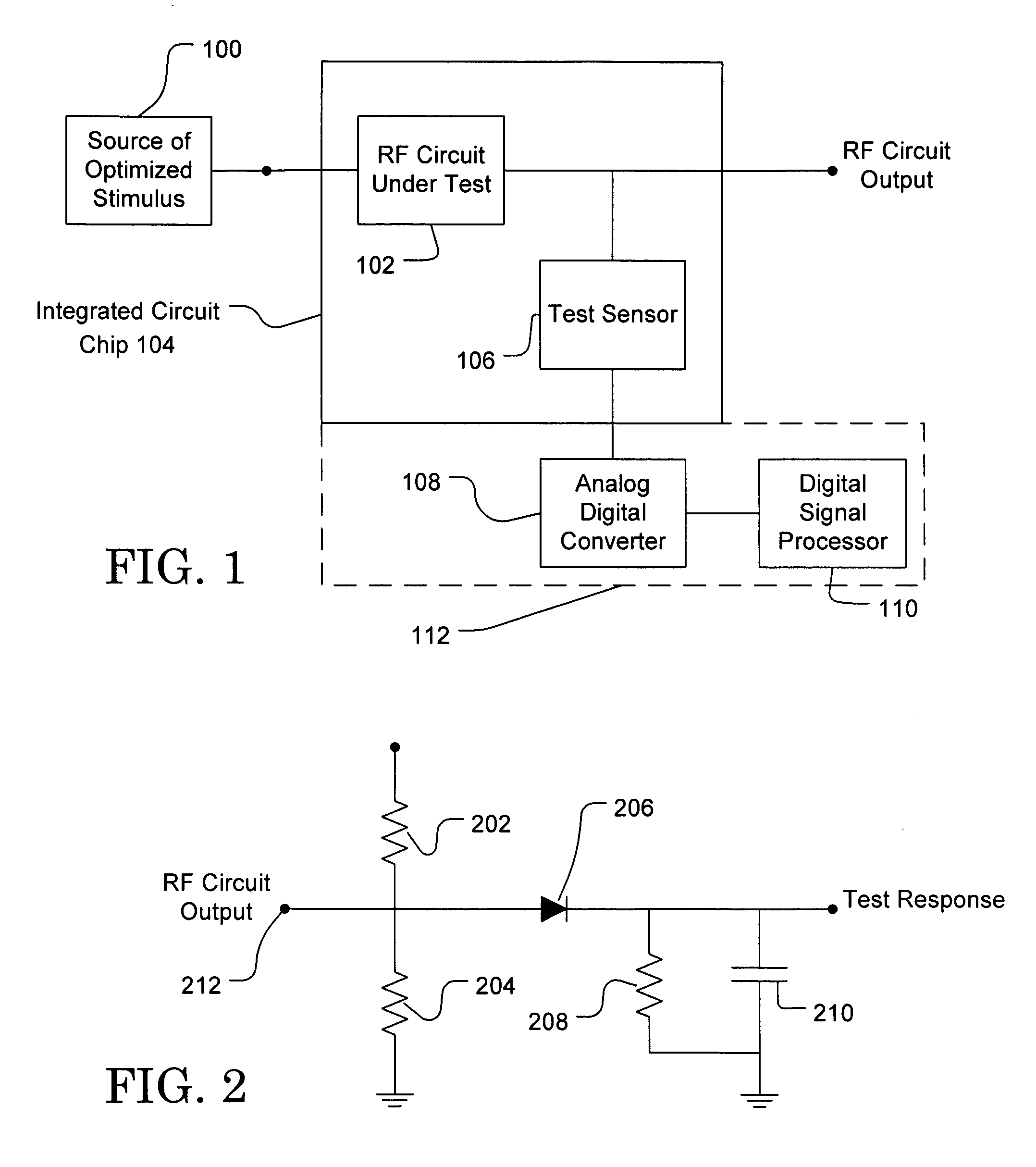

Production test technique for RF circuits using embedded test sensors

InactiveUS7554335B2Accurate diagnosisLittle to test timeResistance/reactance/impedenceError detection/correctionTest stimulusCircuit under test

A single test stimulus and a simple test configuration with embedded envelope detectors are used to estimate all the specification values of interest for an RF circuit under test in an integrated circuit chip. Envelope detectors are deployed as sensors inside the circuit under test. Where more than one circuit is in an RF device in the integrated circuit, each RF circuit in the device may have its own envelope detector. A signal having, for example, time-varying envelopes is used as an optimized test stimulus. The test uses the time-varying and low frequency envelope of the test response. The circuit's response under test to the optimized test stimulus has features highly correlated with the specifications of interest. The test stimulus is optimized for a set of training circuits, and each training circuit in the set is selected to provide one of a spectrum of test responses to the stimulus.

Owner:GEORGIA TECH RES CORP

Assessment of cognitive impairment

A method of assessing cognitive impairment of a user includes presenting a visual test stimulus to the user for a pre-determined test stimulus exposure duration. The test stimulus is then masked and a response from the user is measured. The response provides information about the user's perception of a characteristic of the test stimulus together with the time taken for the user to respond. These steps are repeated to develop a user profile and cognitive impairment in the user is assessed by comparing the user profile with a reference profile. A method of assessing cognitive impairment of a user includes presenting a visual test stimulus to the user for a pre-determined test stimulus exposure duration. The test stimulus is then masked and a response from the user is measured. The response provides information about the user's perception of a characteristic of the test stimulus together with the time taken for the user to respond. These steps are repeated to develop a user profile and cognitive impairment in the user is assessed by comparing the user profile with a reference profile.

Owner:MONASH UNIV

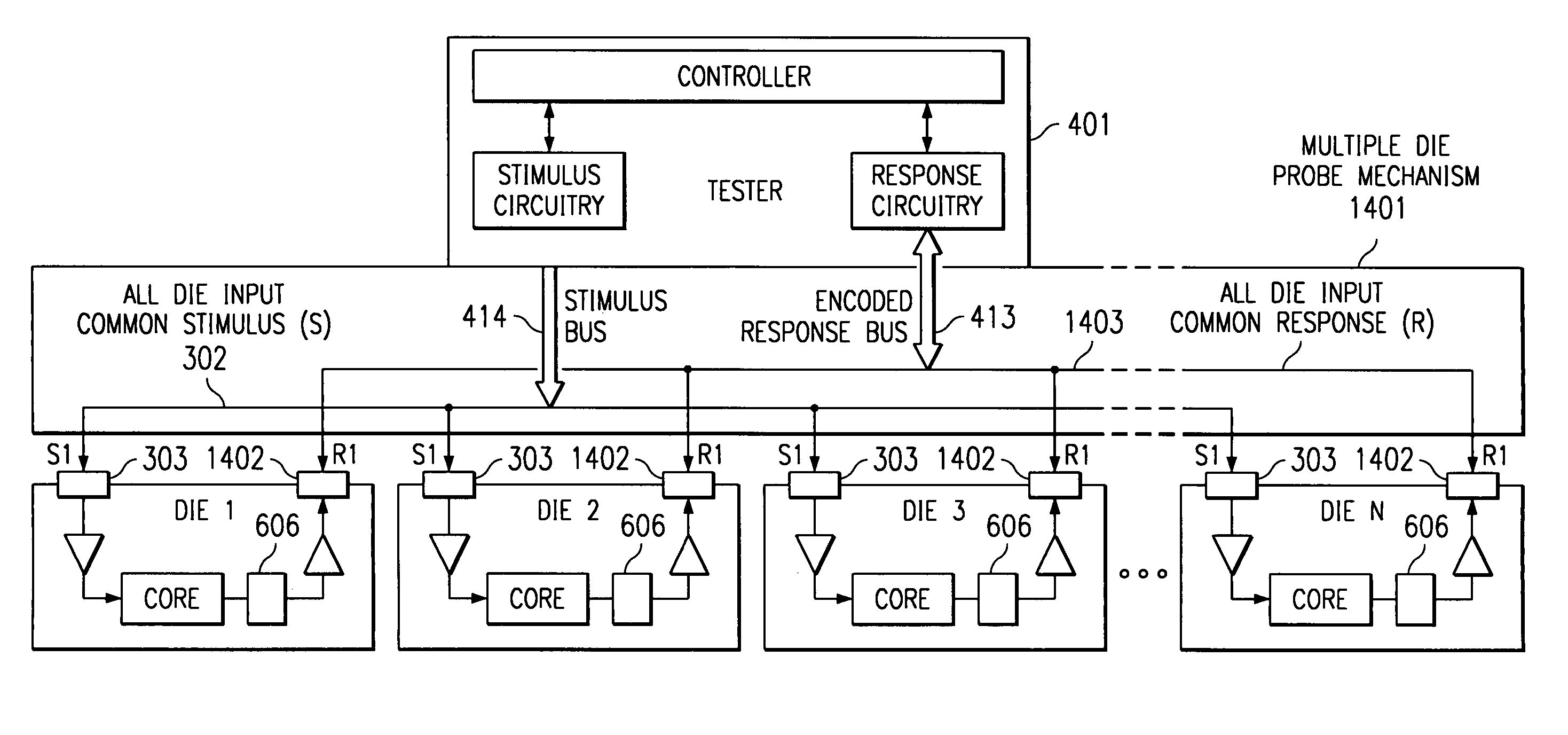

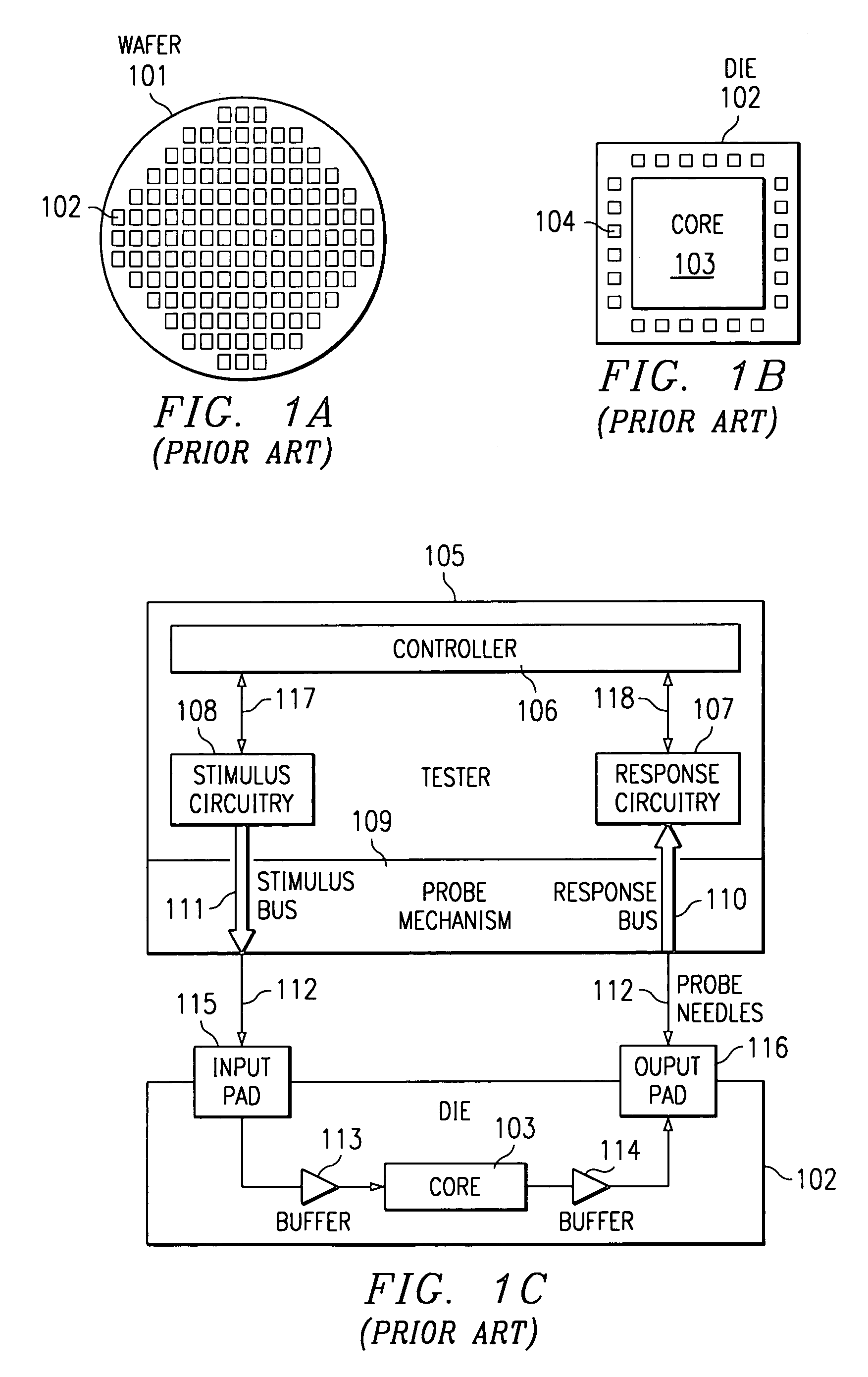

Comparing on die response and expected response applied to outputs

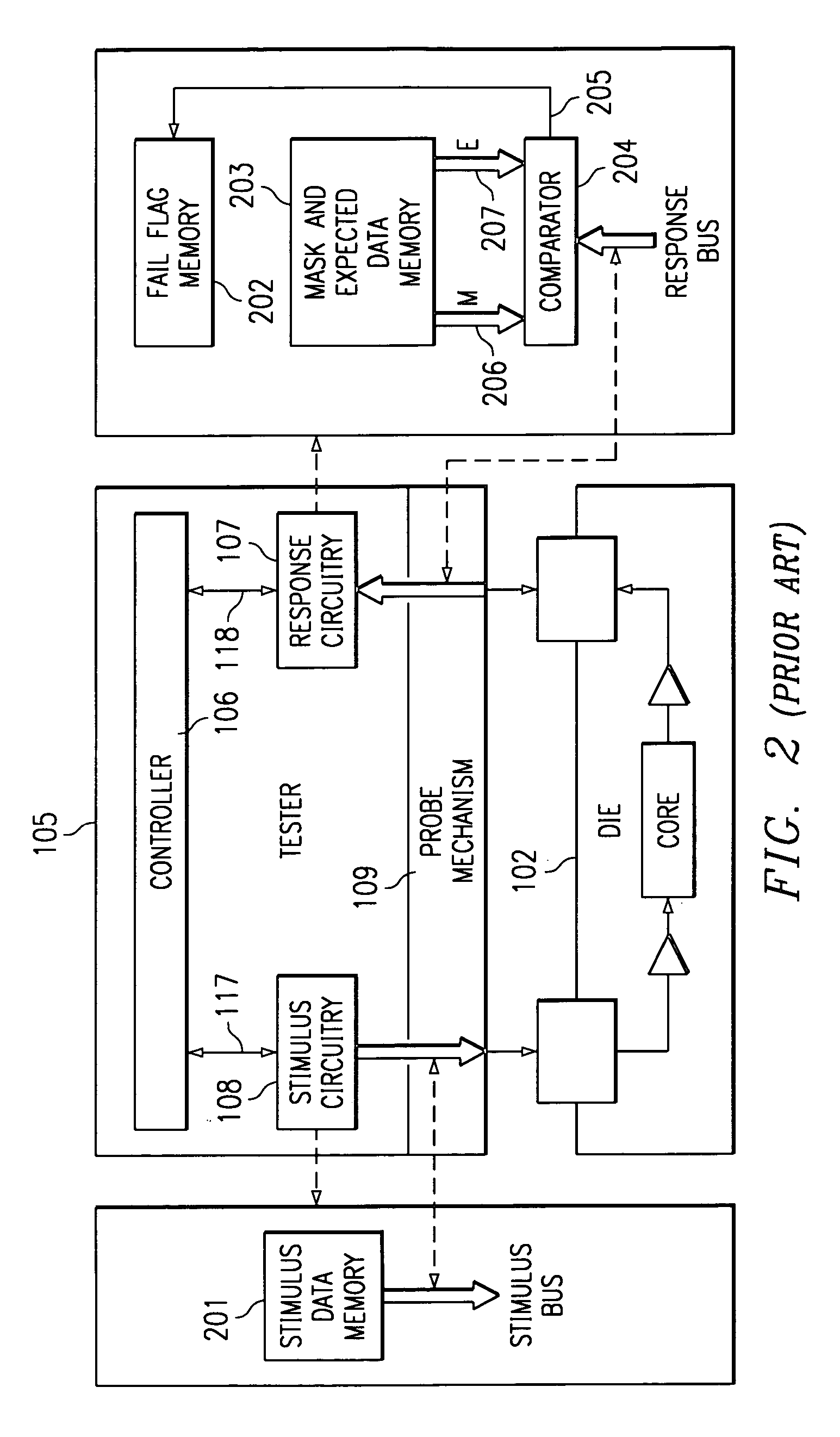

A test controller applies test stimulus signals to the input pads of plural die on a wafer in parallel. The test controller also applies encoded test response signals to the output pads of the plural die in parallel. The encoded test response signals are decoded on the die and compared to core test response signals produced from applying the test stimulus signals to core circuits on the die. The comparison produces pass / fail signals that are loaded in to scan cells of an IEEE 1149.1 scan path. The pass / fail signals then may be scanned out of the die to determine the results of the test.

Owner:TEXAS INSTR INC

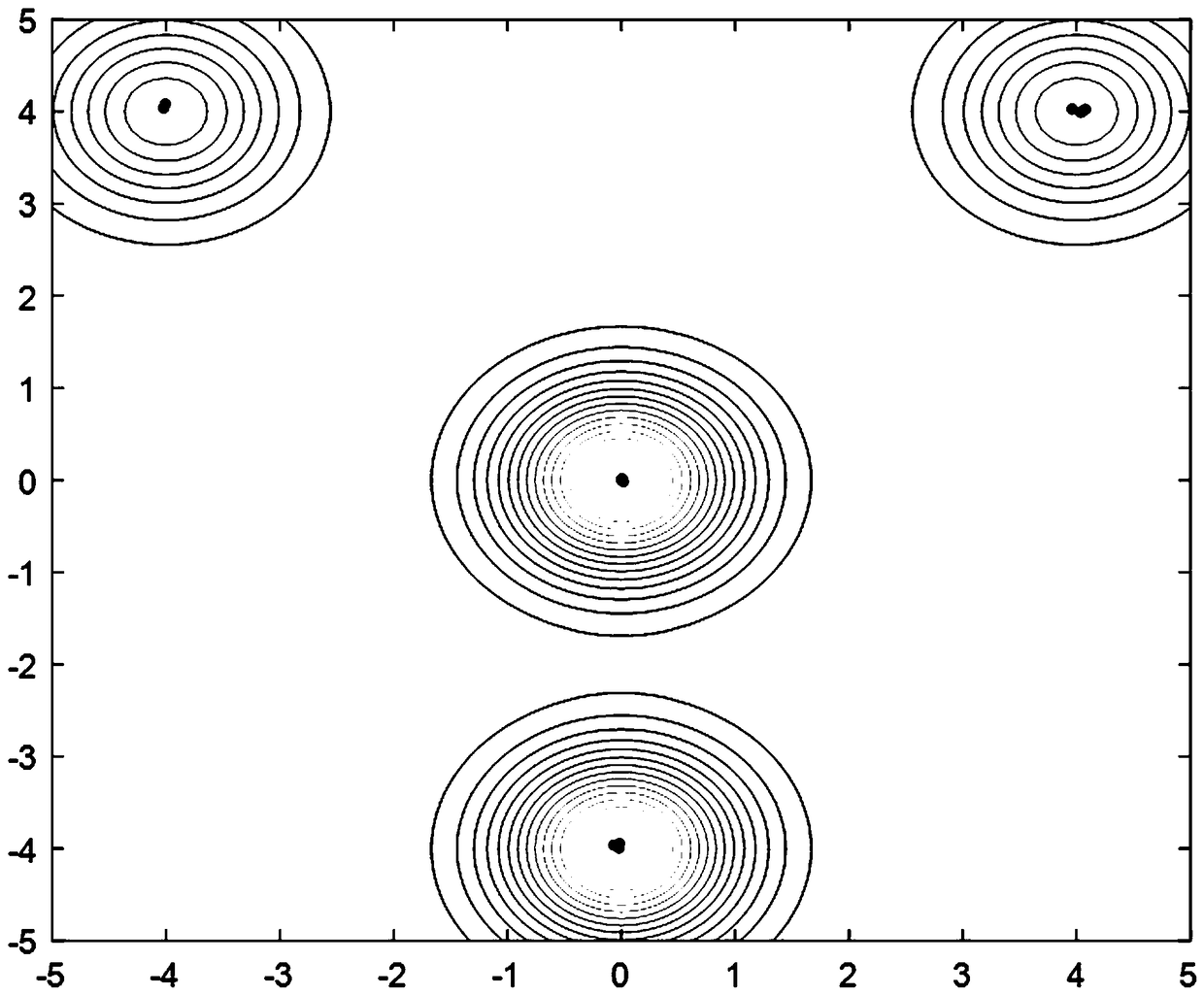

Analog circuit fault diagnosis method based on chaos cloud model adaptive firefly algorithm

ActiveCN108828436AAddress deficienciesFast convergenceAnalog circuit testingArtificial lifeNODALFeature set

The present invention discloses an analog circuit fault diagnosis method based on a chaos cloud model adaptive firefly algorithm. The method comprises the steps of: applying a certain test stimulus toa tested circuit, and collecting output response signals of the tested circuit at a measurable node of the circuit; employing the wavelet fusion method to perform extraction of a circuit fault feature set from the output response signals; employing the CCAFA-LSSVM (Chaos Cloud Model Adaptive Firefly Algorithm-Least Squares Support Veotor Maohine) to perform fault diagnosis of the fault feature set to achieve classification and location operation of the circuit faults. The analog circuit fault diagnosis method employs a cloud model with a capacity of processing object fuzziness and randomnessto perform corresponding improvement of the firefly algorithm and allow the firefly algorithm to have a good generalization ability and a high robustness. Therefore, when the fault diagnosis is performed, the resolution ratio of the fault mode is high, the diagnosis performance is good, and the fault elements can be accurately located, and the diagnosis performance and the efficiency of the testedanalog circuit can be improved.

Owner:GUILIN UNIV OF ELECTRONIC TECH

Testing integrated circuits

ActiveUS8358147B2Reduce in quantityIndividual semiconductor device testingTest stimulusCarrier signal

A method of testing integrated circuits is provided. The method includes establishing at least one first physical communication channel between a test equipment and a respective group of integrated circuits under test by having probes of the test equipment contacting at least one corresponding physical contact terminal of each integrated circuit of the respective group. The method further includes having the test equipment exchanging, over the at least one first physical communication channel, the same test stimuli with each integrated circuit of the group. The method still further includes having each integrated circuit of the group establishing a corresponding second physical communication channel with the test equipment by having at least one physical contact terminal of the integrated circuit contacted by a corresponding probe of the test equipment. The method further includes having each integrated circuit of the group exchanging, over the second physical communication channel, a corresponding test response signal based on the received test stimuli with the test equipment. The test stimuli are exchanged by modulating at least one first carrier wave based on the test stimuli; the at least one first carrier wave has at least one first frequency. The test response signals of each integrated circuit of the group are exchanged by modulating at least one respective second carrier wave based on the test response signals; each second carrier wave have at least one respective second frequency.

Owner:STMICROELECTRONICS SRL

Production test technique for RF circuits using embedded test sensors

InactiveUS20070033474A1Accurate diagnosisLittle to test timeResistance/reactance/impedenceError detection/correctionTest stimulusCircuit under test

A single test stimulus and a simple test configuration with embedded envelope detectors are used to estimate all the specification values of interest for an RF circuit under test in an integrated circuit chip. Envelope detectors are deployed as sensors inside the circuit under test. Where more than one circuit is in an RF device in the integrated circuit, each RF circuit in the device may have its own envelope detector. A signal having, for example, time-varying envelopes is used as an optimized test stimulus. The test makes use of the time-varying and low frequency envelope of the test response. The response of the circuit under test to the optimized test stimulus has features highly correlated with the specifications of interest. The test stimulus is optimized for a set of training circuits, and each training circuit in the set is selected to provide one of a spectrum of test responses to the stimulus. Non-linear regression-based models are built from the set of specification values and set of envelopes derived from testing the training set of circuits. Thereafter when a circuit under test is tested by applying an optimized stimulus, the non-linear regression models are used to map an envelope from the test response of the circuit under test to specification values for the circuit.

Owner:GEORGIA TECH RES CORP

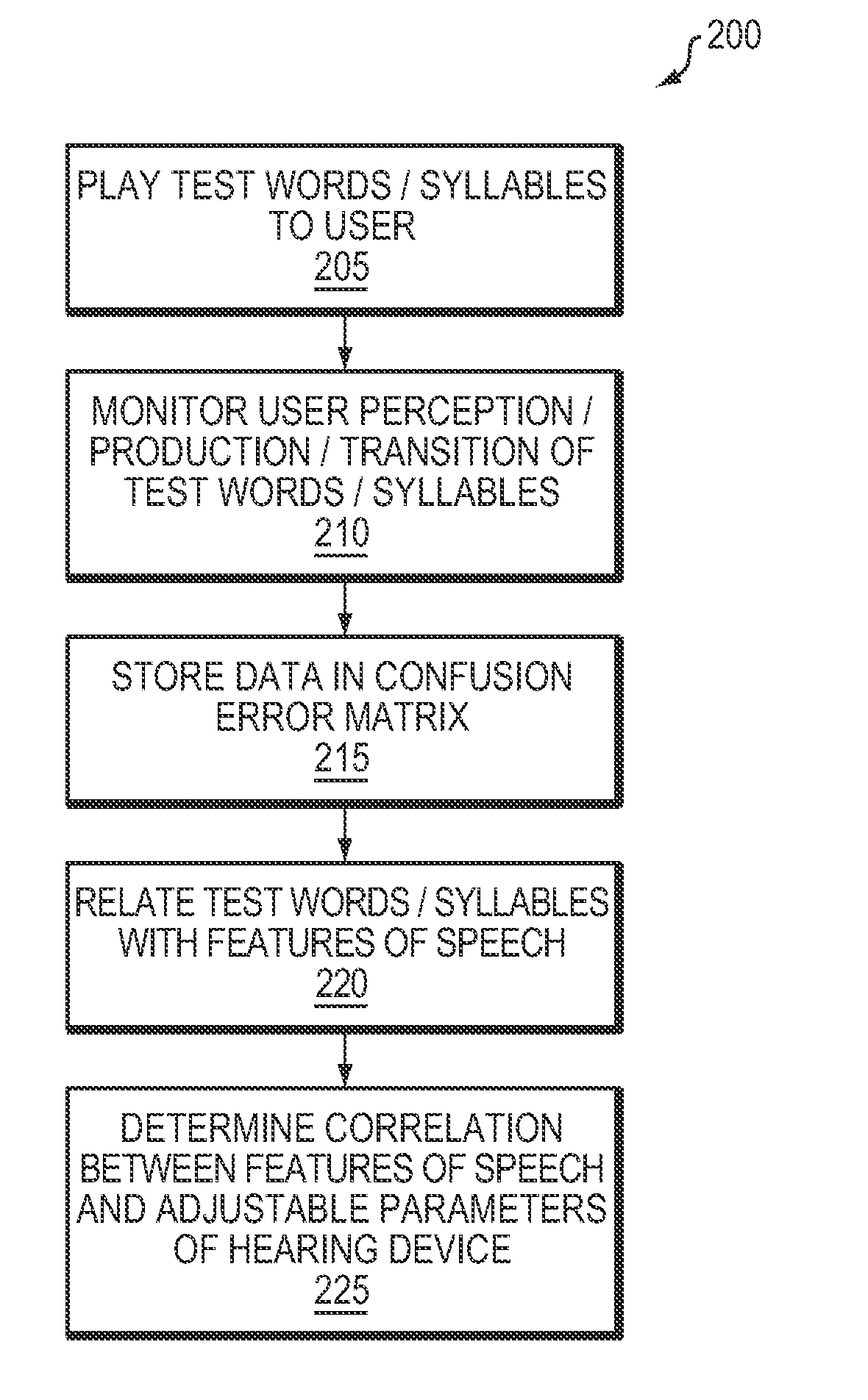

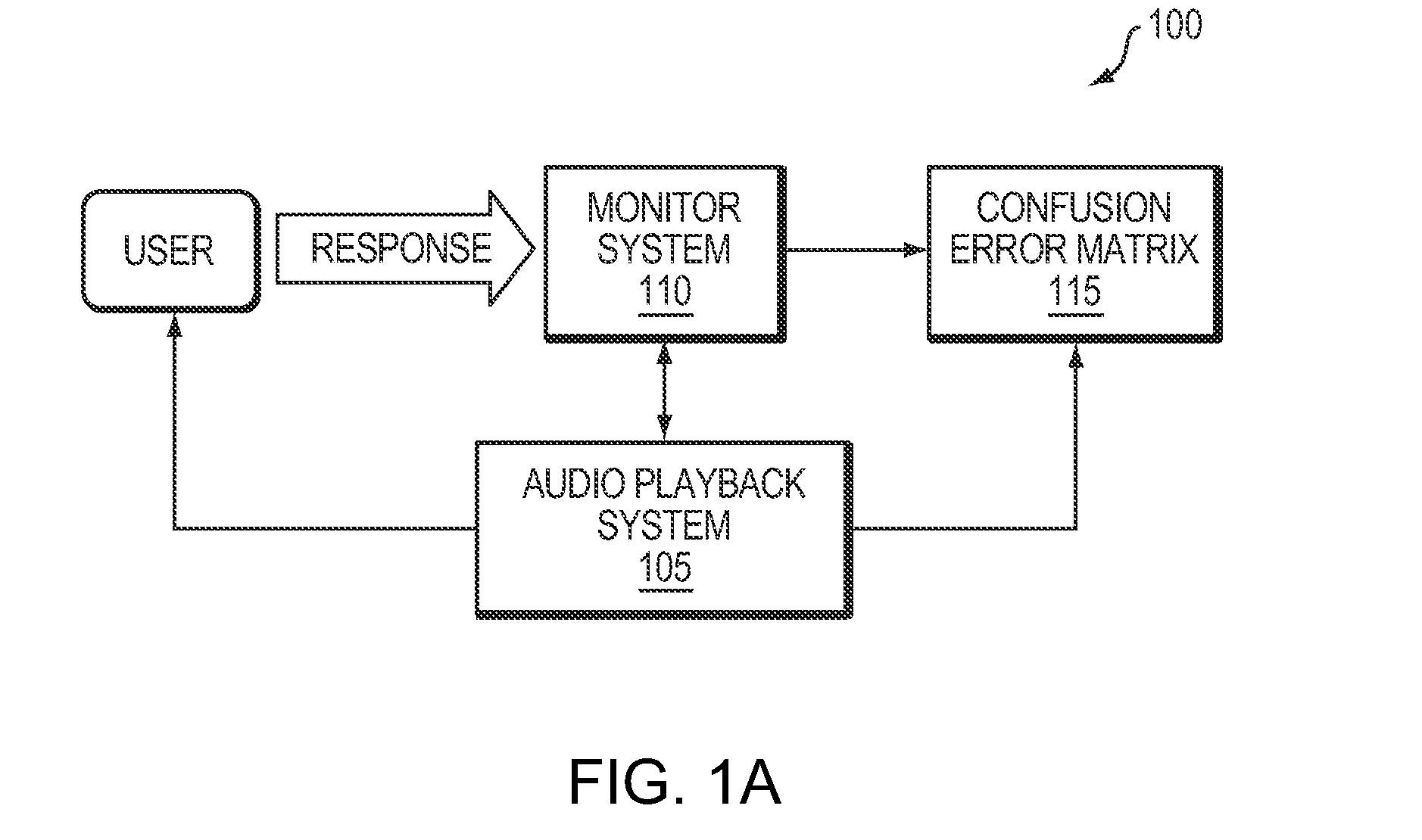

Systems and Methods for Tuning Automatic Speech Recognition Systems

InactiveUS20100246837A1Improve performanceElectrotherapyHearing aids signal processingControl systemTest stimulus

A tuning system for tuning a speech recognition system includes a transmitter for sending a user response to a speech recognition system. The user response is based at least in part on a test stimulus that may be generated by the control system. A receiver receives a recognized response from the speech recognition system; this recognized response is based at least in part on the associated user response. An adjustment module adjusts at least one parameter of the speech recognition system based at least in part on at least one of the test stimulus, the associated user response, and the recognized response.

Owner:COCHLEAR LIMITED +1

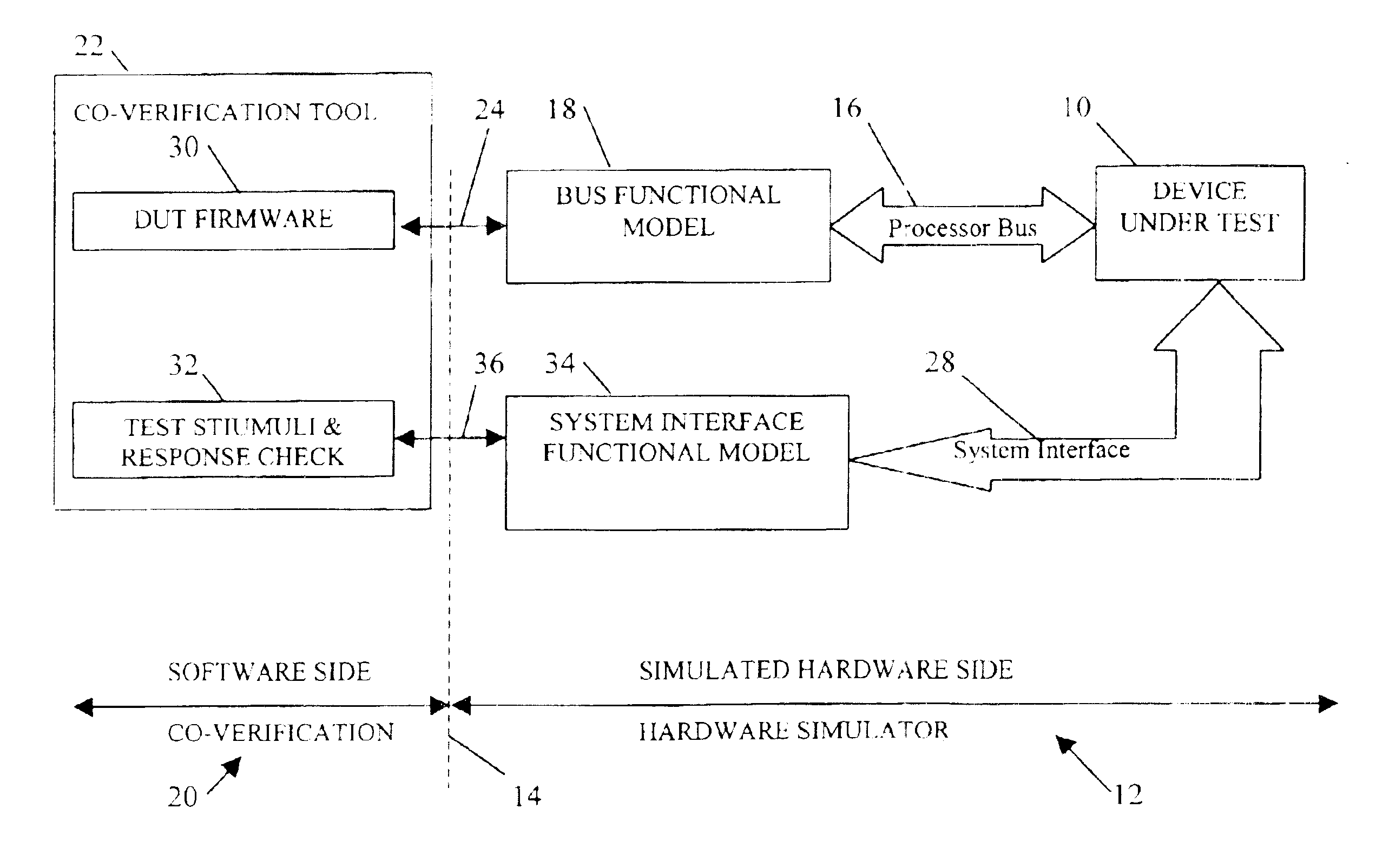

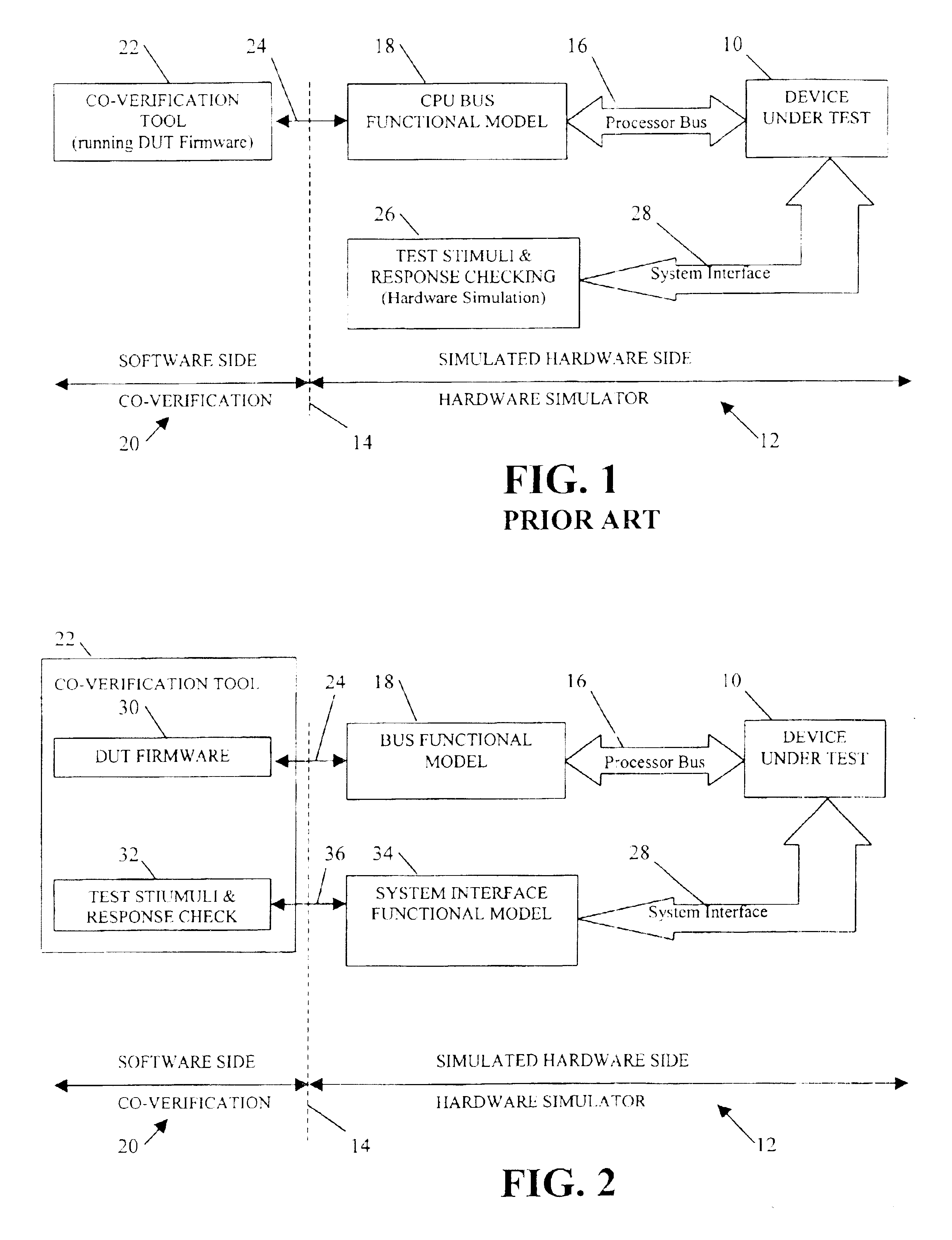

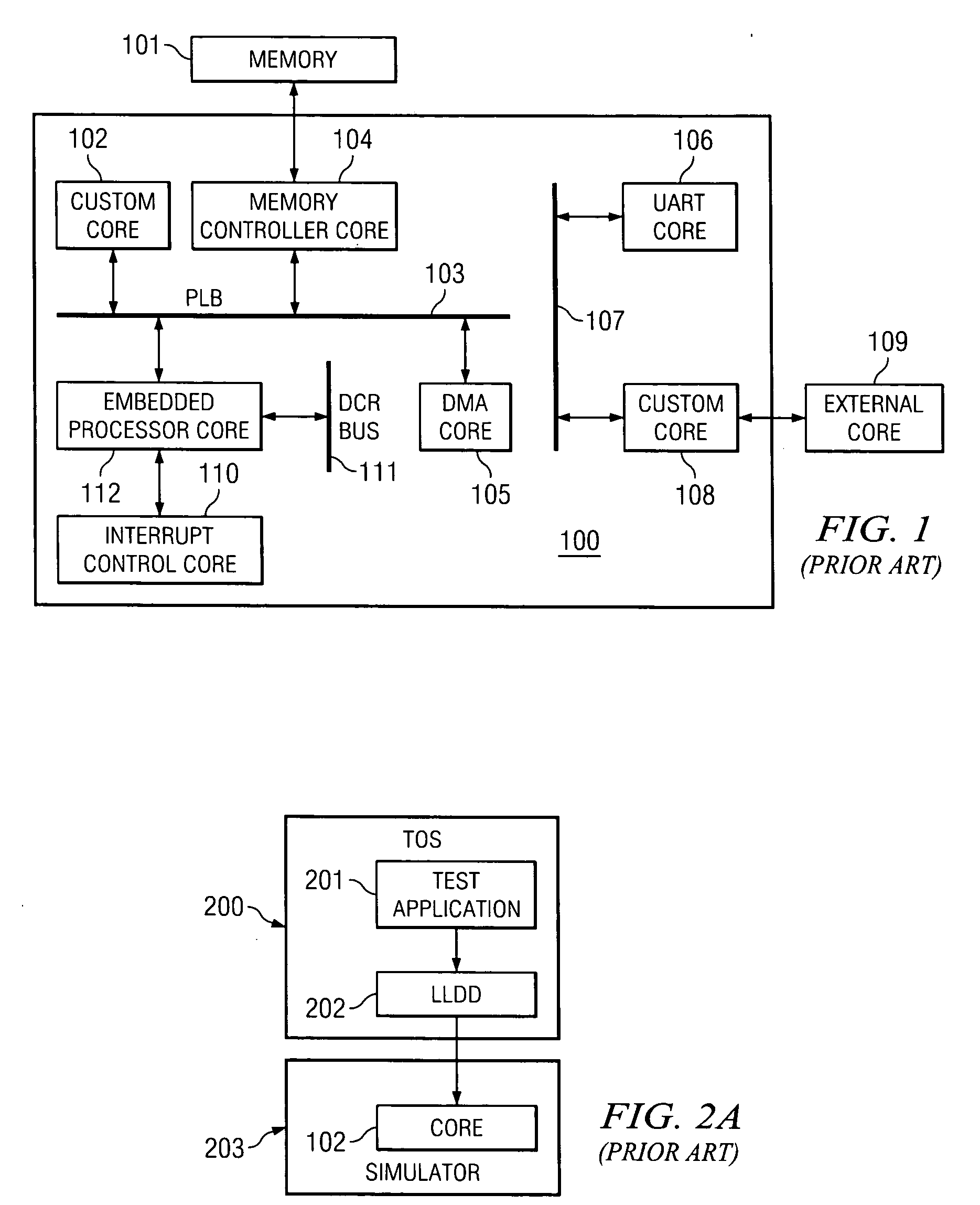

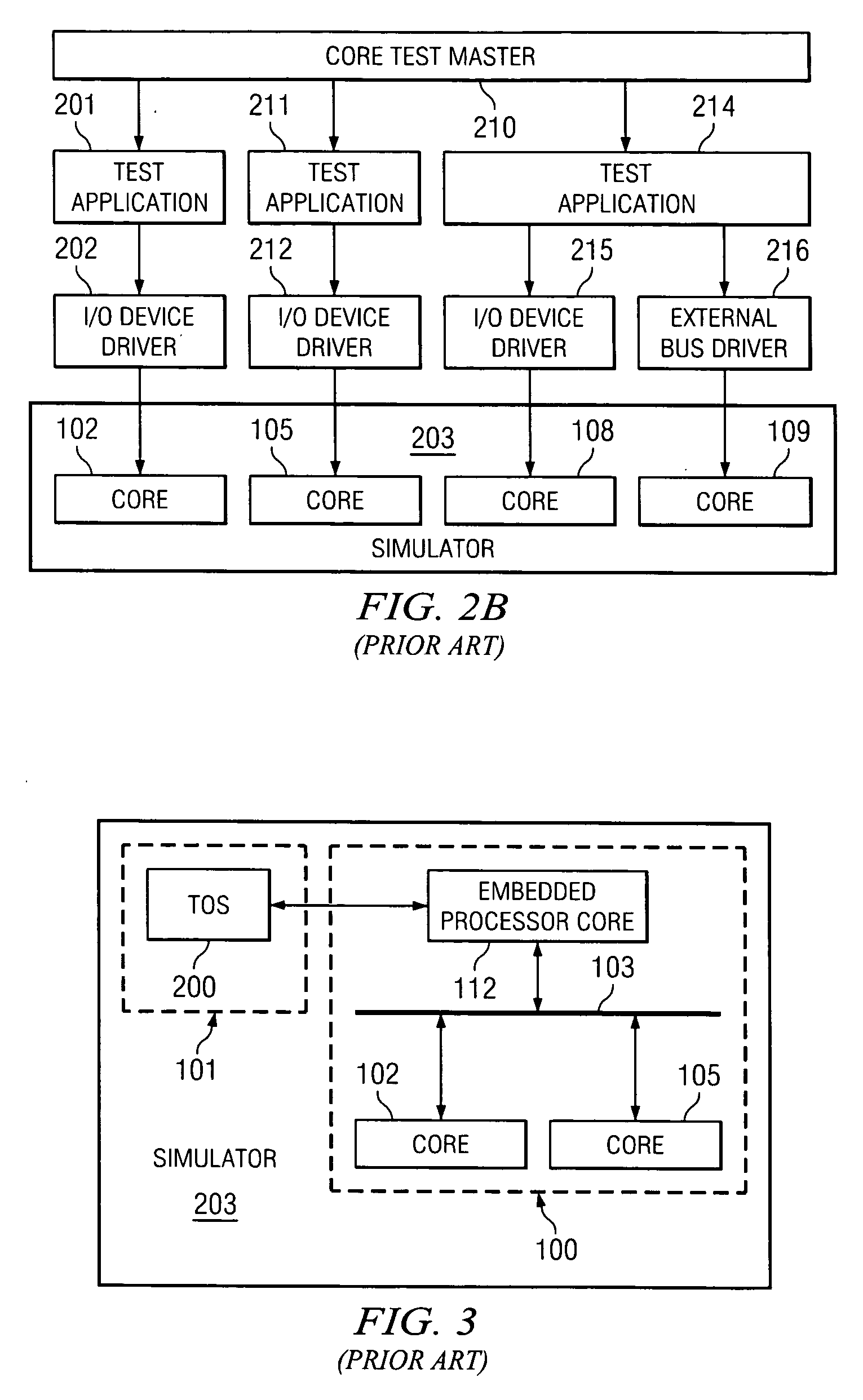

Application of co-verification tools to the testing of IC designs

An IC design is tested on a workstation through a hardware simulator. The workstation includes a co-verification software tool that executes IC firmware to operate the IC design and test the IC design and IC firmware. The co-verification software tool further operates to supply test stimuli to the IC design and to receive responses for analysis. The test stimuli are written in a programming language, which permits ease of testing and analysis of the IC design.

Owner:BELL SEMICON LLC

Testing integrated circuits using few test probes

ActiveUS8362796B2Reduce in quantitySemiconductor/solid-state device testing/measurementSolid-state devicesTest stimulusCarrier signal

A method of testing integrated circuits, including: establishing at least a first physical communication channel between a test equipment and an integrated circuit under test by having at least a first probe of the test equipment contacting a corresponding physical contact terminal of the integrated circuit under test; having the test equipment and the integrated circuit under test exchange, over said first physical communication channel, at least two signals selected from the group including at least two test stimuli and at least two test response signals, wherein said at least two signals are exchanged by means of at least one modulated carrier wave modulated by the at least two signals.

Owner:STMICROELECTRONICS SRL

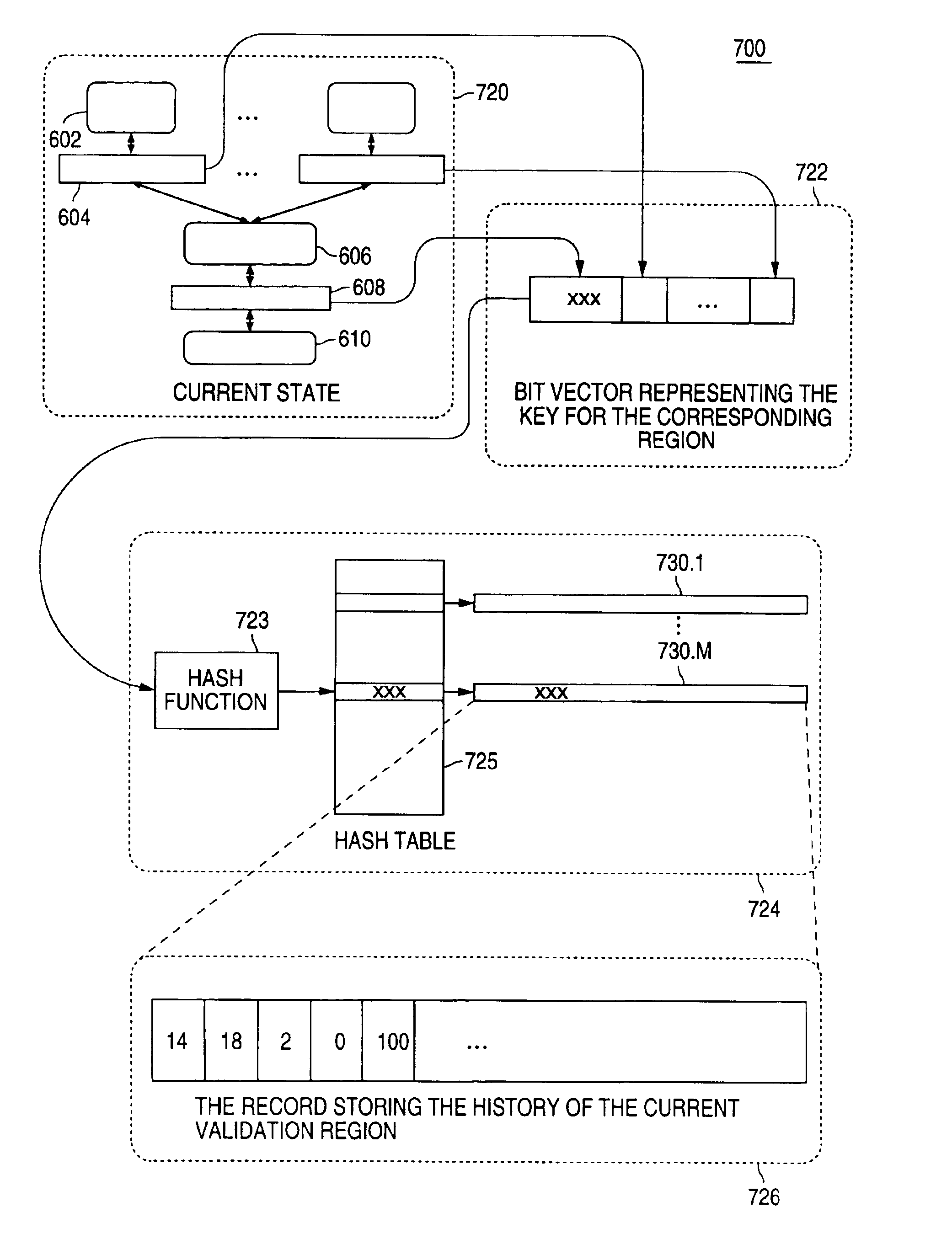

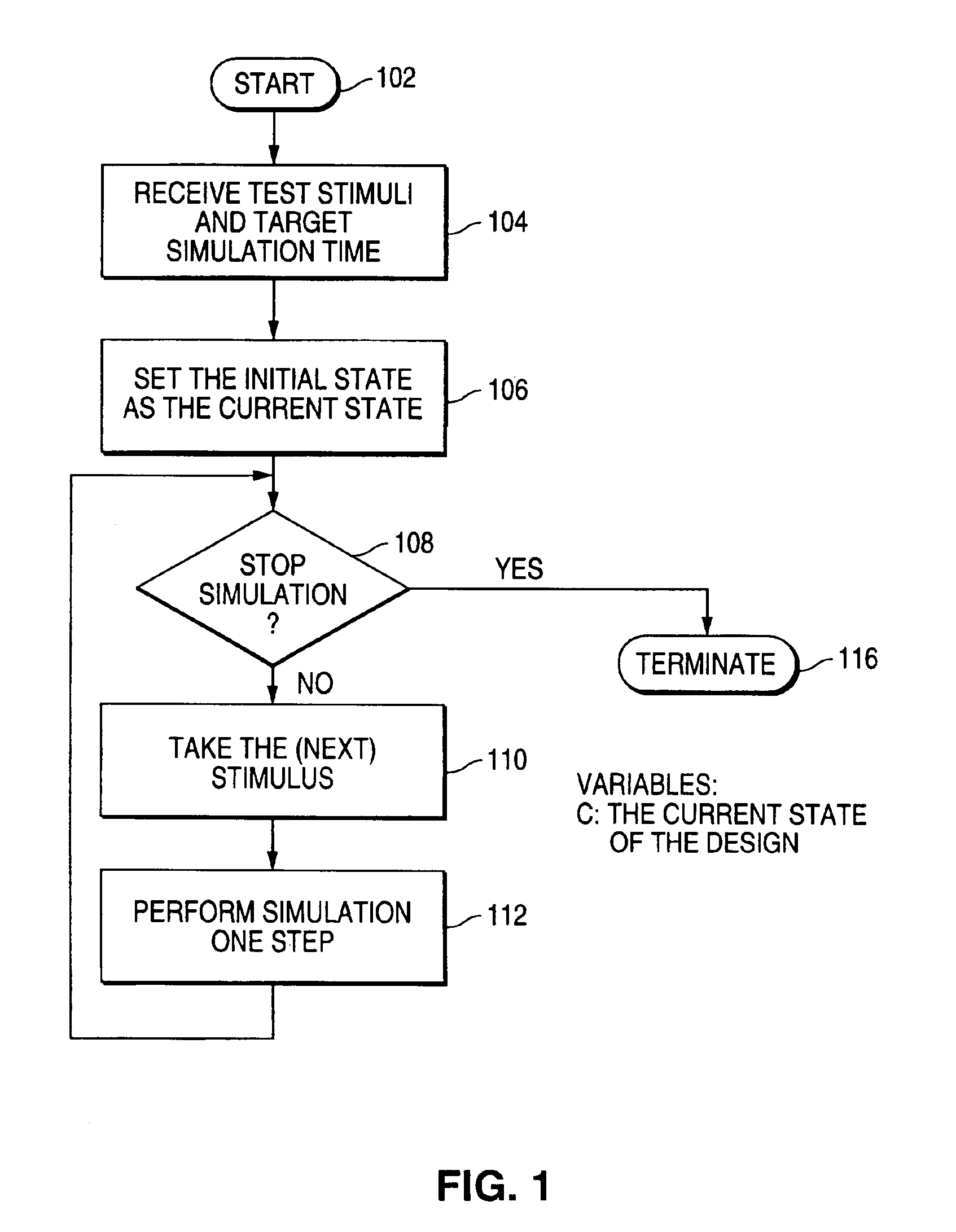

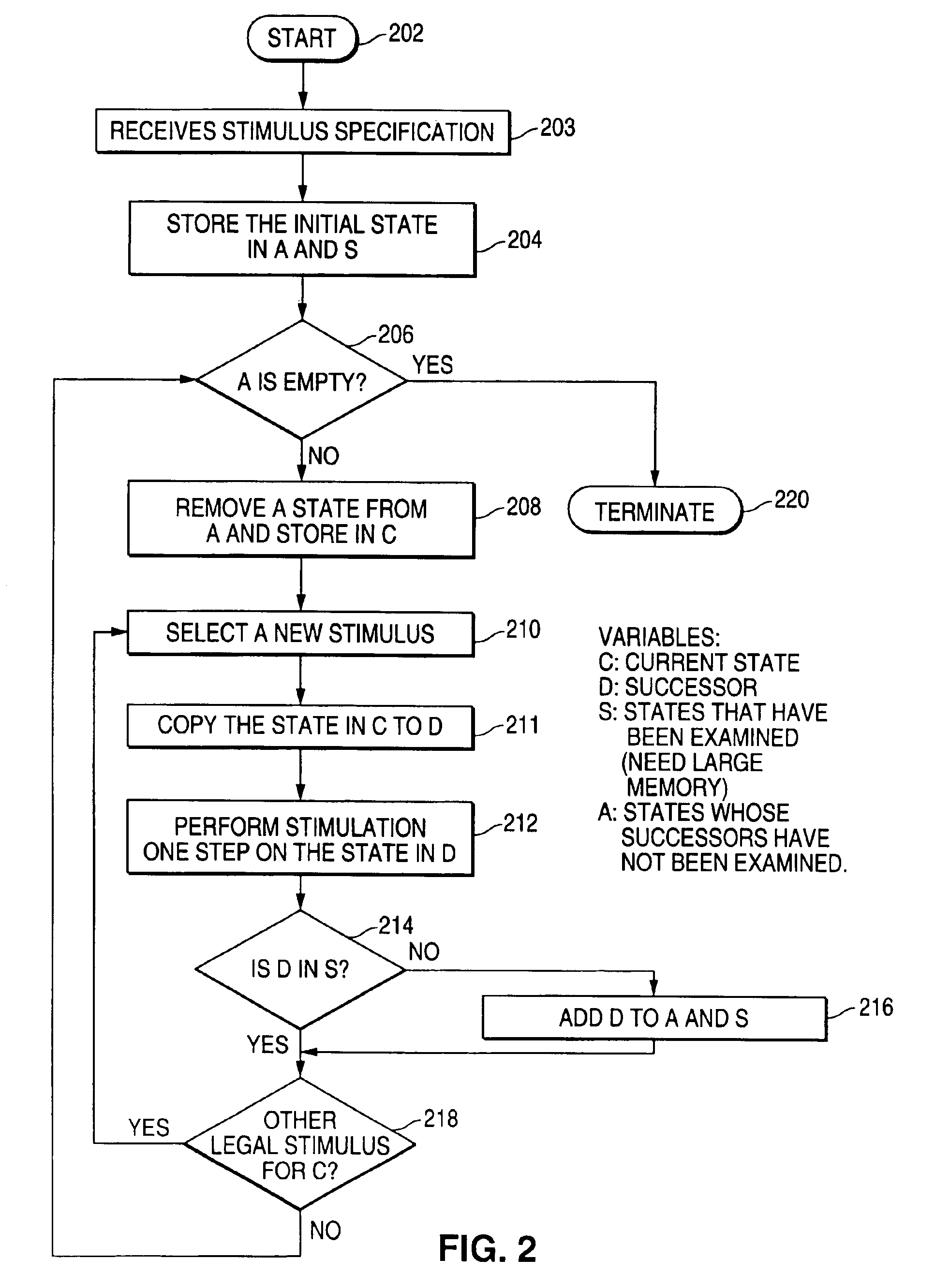

Method and apparatus for transforming test stimulus

InactiveUS6915248B1Analogue computers for electric apparatusCAD circuit designTest stimulusTheoretical computer science

Described is a method for validating a digital design using a simulation process. All possible design states of the design are divided into a plurality of validation regions. In the simulation-process, the method records and updates the simulation history for each of t he validation region. When a particular stimulus is specified by the designer to perform a step of simulation for a current state within one of the validation regions, the process determines simulation efficiency by examining the specified stimulus and the simulation history of the validation region. The method may transform the specified stimulus into a more interesting stimulus to improve the efficiency and coverage of the simulation process.

Owner:CADENCE DESIGN SYST INC

Probe needle protection method for high current probe testing of power devices

ActiveUS7521947B2Improve testHigh currentOverload protection arrangementsIndividual semiconductor device testingElectricityCurrent limiting

Owner:INTEGRATED TECH

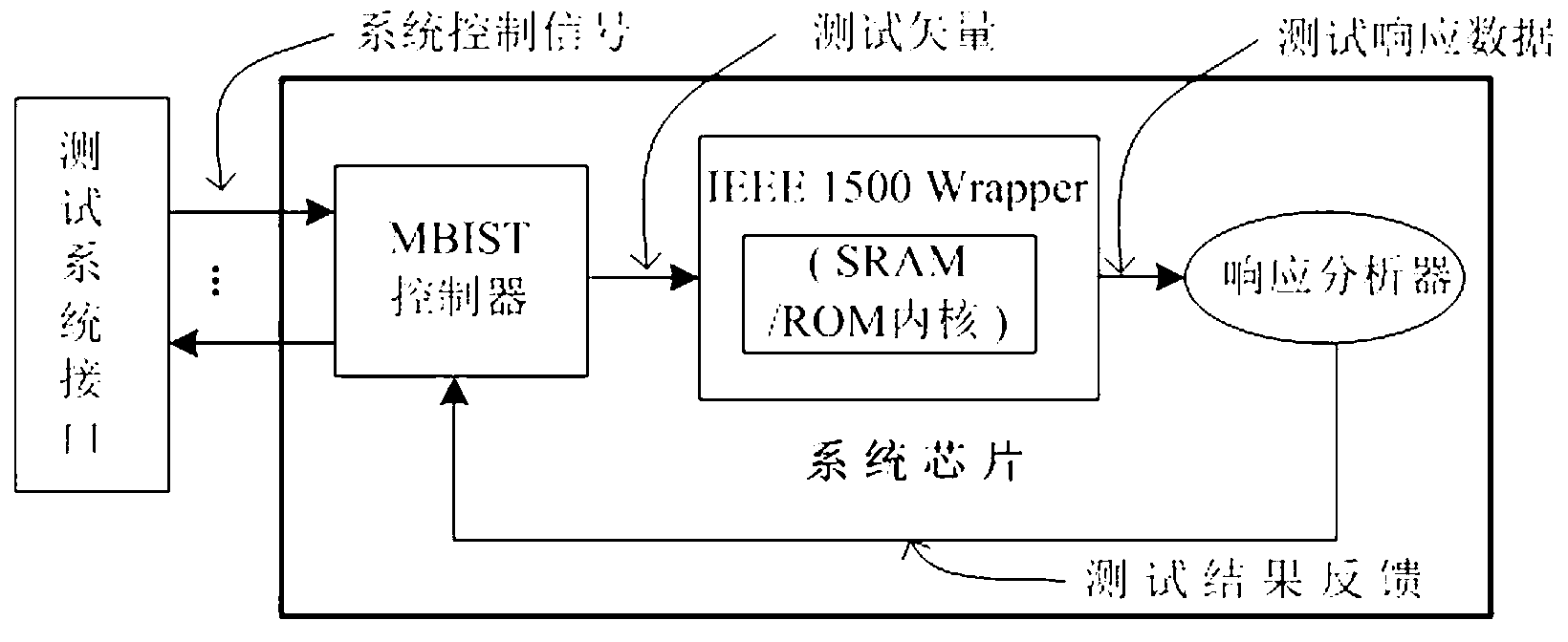

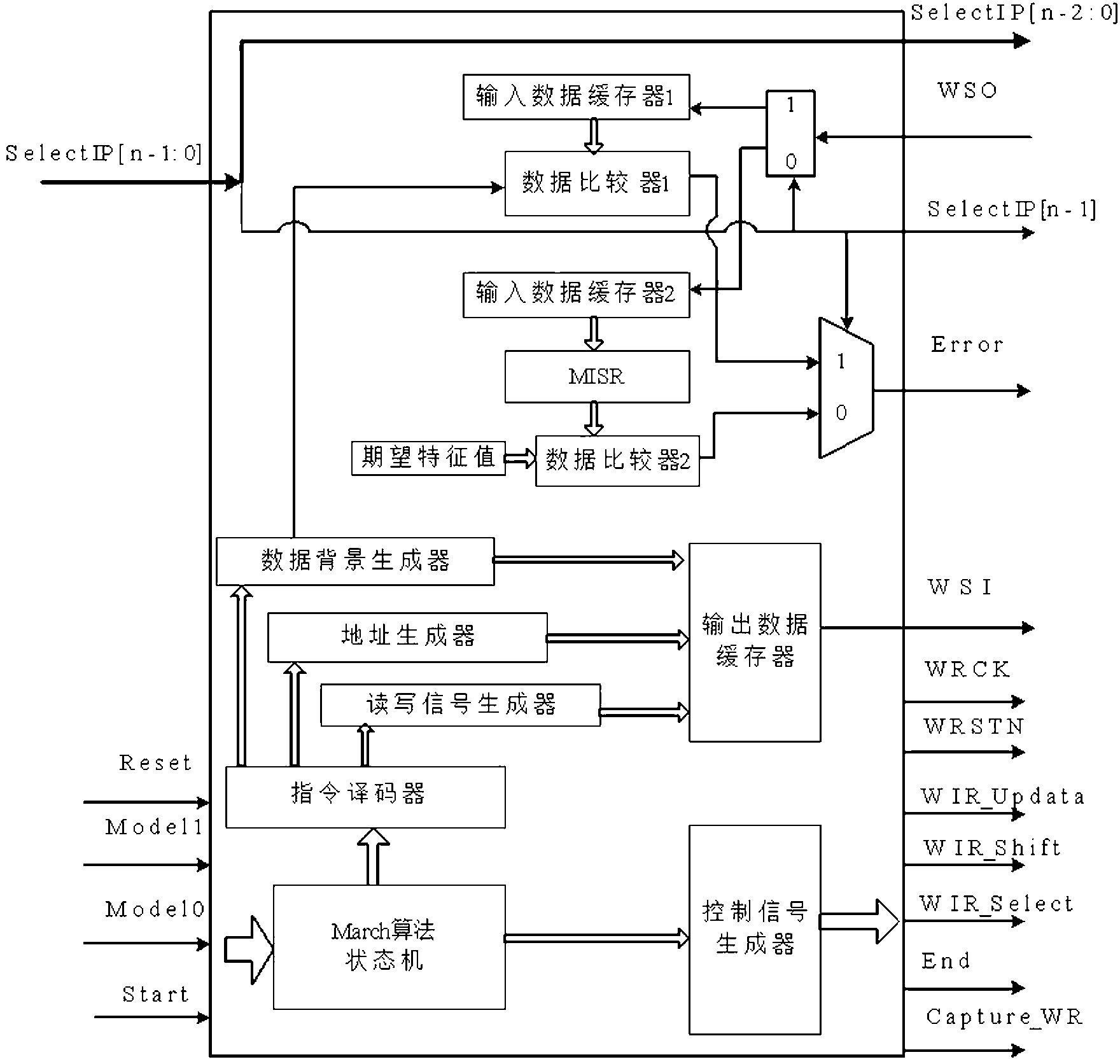

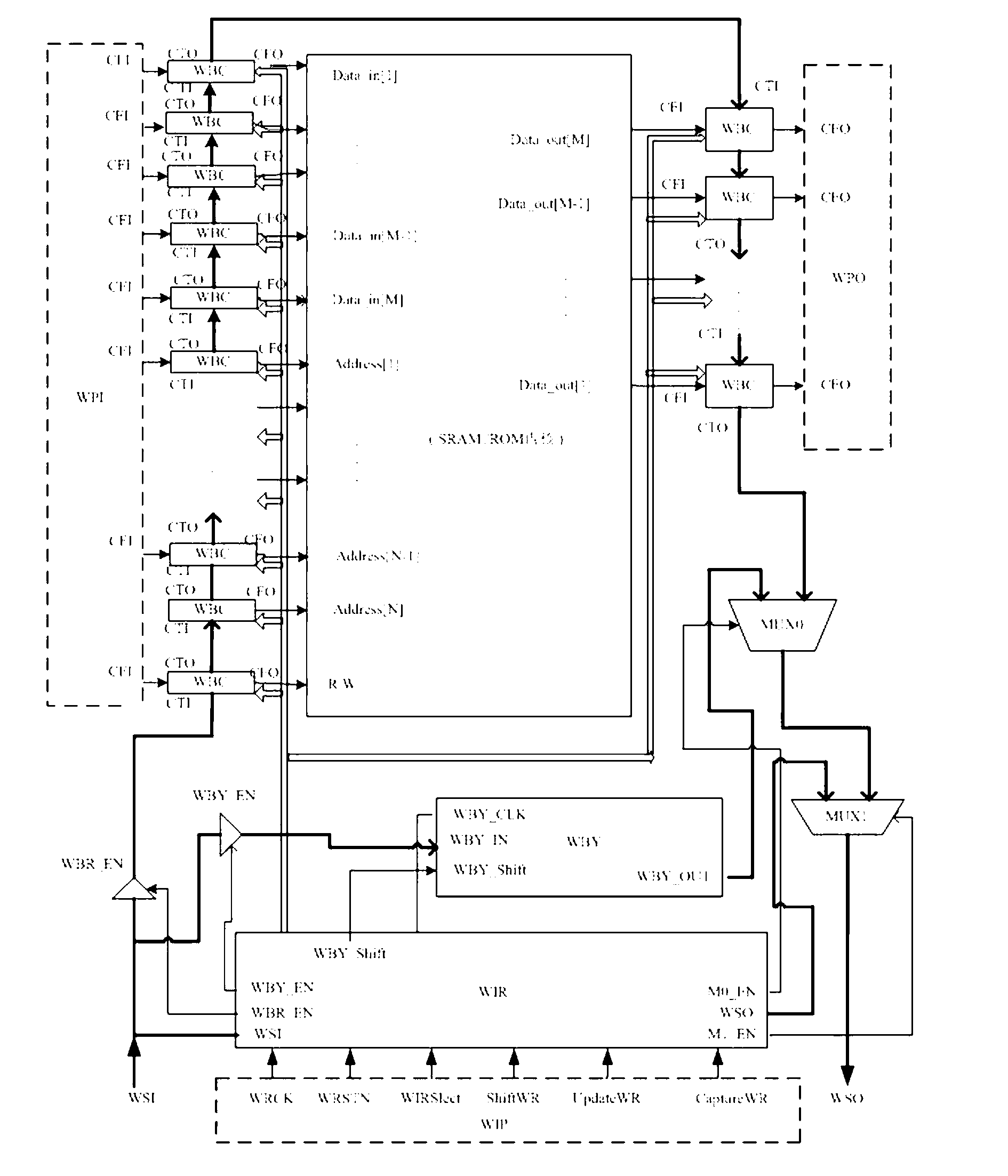

MBIST (Memory Built In Self Test) controller structure system based on IEEE (Institute of Electrical and Electronics Engineers) 1500 standard and compatible with SRAM/ROM (Static Random Access Memory/Read Only Memory)

The invention discloses a testing structure and a testing method based on an IEEE (Institute of Electrical and Electronics Engineers) 1500 standard and compatible with an SRAM / ROM (Static Random Access Memory / Read Only Memory) test. A testing structure is combined with a method of embedded type core testing standard IEEE1500 and a BIST; the testing structure supports to carry out the BIST on a plurality of embedded type SRAMs and ROMs with different types. The structure is formed by two parts, including a testing shell package of the embedded type SRAM and the ROM and an MBIST controller. The testing shell package solves the control problems of testing access, testing isolation and testing of the embedded type SRAM and the ROM. The MBIST controller generates testing stimulation data needed by an SRAM test according to a testing algorithm, controls a package shell Wrapper, carries out response analysis and outputs a testing result; an MISR (Multiple Input Shift Register) is used for finishing data compression operation on data in the ROM. With the adoption of the testing structure and the testing method, the faults of the embedded type SRAM and the ROM can be detected, so as to be good for test reuse of the embedded type SRAM and the ROM; the integration efficiency of an SoC (System on Chip) is effectively improved and the consumption of hardware of an MBIST system is also reduced.

Owner:GUILIN UNIV OF ELECTRONIC TECH

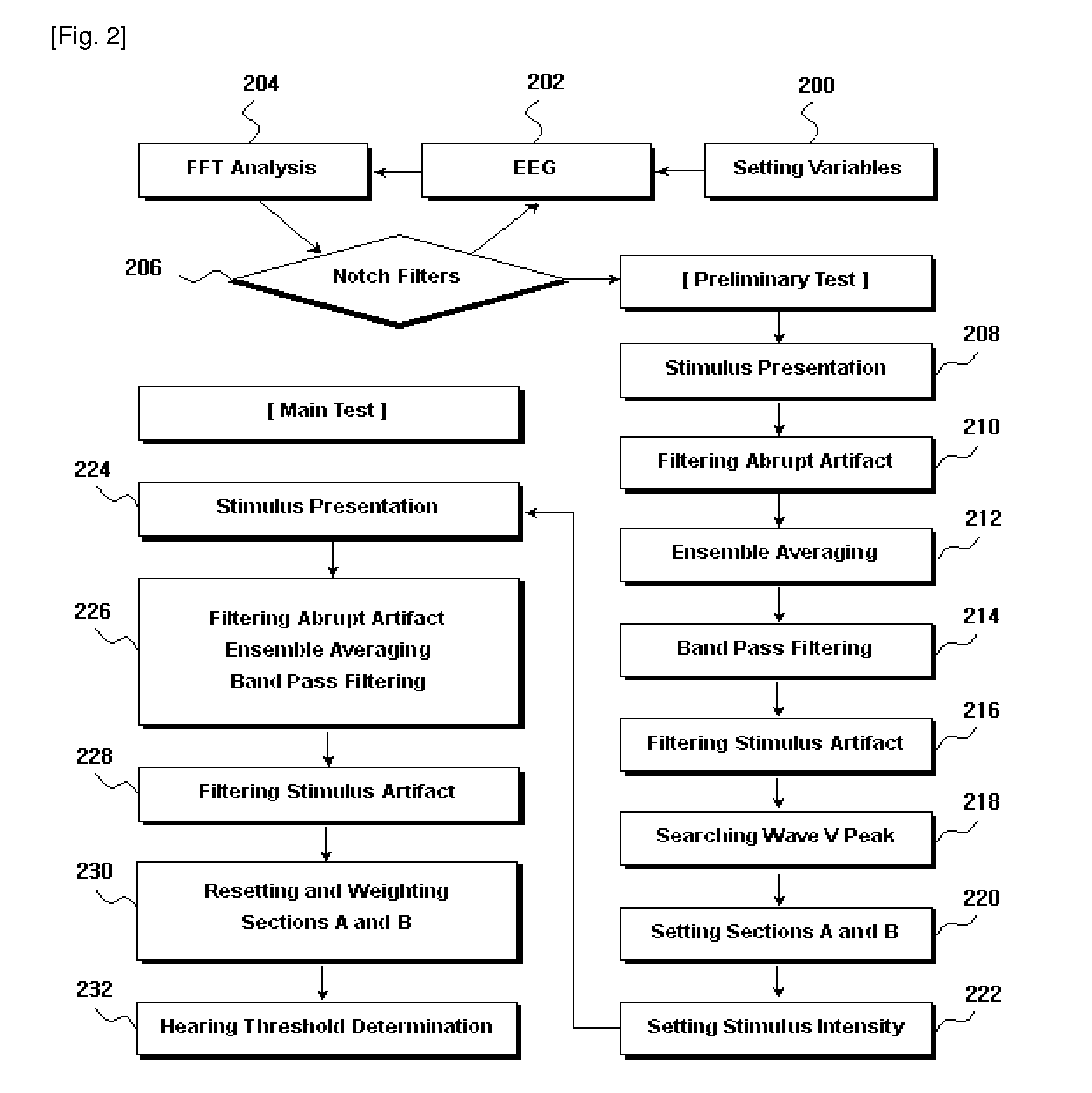

Method and device for objective automated audiometry

ActiveUS20100076338A1Large signal to noise ratioReduce the amplitudeElectroencephalographyAudiometeringTest stimulusHearing test

The present invention relates to a method for automation of objective hearing test based on the assessment of auditory evoked potential (AEP), for shortening of testing time, and for the minimization of inaccuracy and errors which may be resulted from the automation and time shortening. The method includes the steps for: as a preliminary test, presenting standard test stimulus to a subject; searching the wave V peak and SN1 0 peak; and as a main test, presenting test stimulus of each frequency, searching the minimal intensity and determining objective hearing threshold of each frequency.

Owner:EARLOGIC KOREA +1

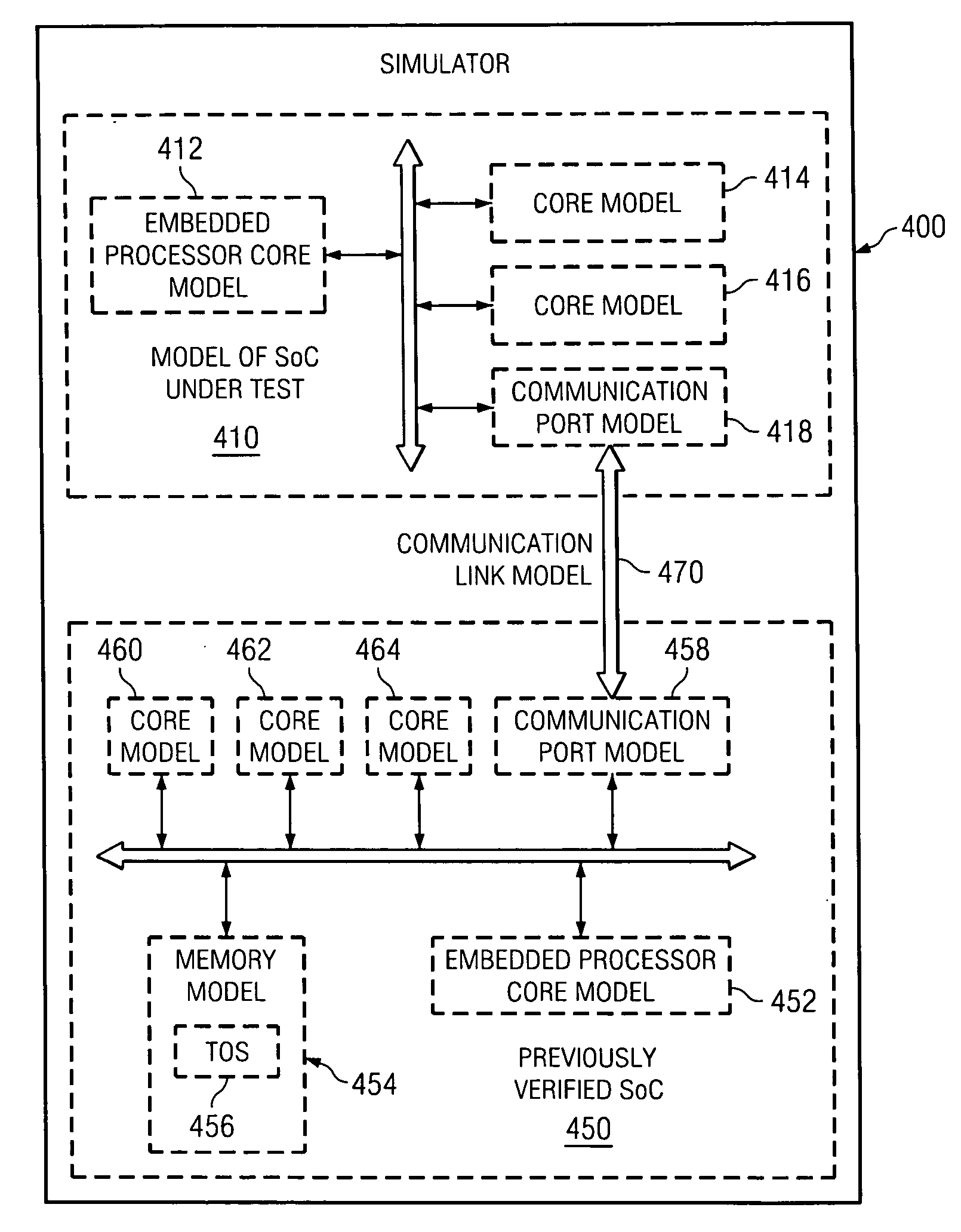

Apparatus and method for testing sub-systems of a system-on-a-chip using a configurable external system-on-a-chip

InactiveUS20070016880A1Shorten the timeAnalogue computers for electric apparatusDetecting faulty computer hardwareCommunication interfaceSystem testing

An apparatus and method are provided in which a previously verified SoC is coupled to a SoC under test via a communication bus or other type of communication interface. The previously verified SoC is provided with the same test stimuli as the SoC under test and thus, generates expected test results data. The test stimuli are sent to the SoC under test via a peripheral communication interface between the previously verified SoC and the SOC under test. The SoC under test generates actual test result data that is output to the previously verified SoC. The previously verified SoC may then compare the expected test results data with the actual test result data generated by the SoC under test to determine if they match. If the two sets of data do not match, then a mismatch notification may be generated and output.

Owner:GLOBALFOUNDRIES INC