Automatic chip validation method based on parameterized IP test case set

An automated verification and test case technology, applied in the field of automated verification, can solve the problems of difficulty in meeting the verification requirements of a large number of IP usage and the increase of verification time, so as to shorten the time for analysis and design improvement, reduce time overhead, and improve verification efficiency Effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0017] The present invention will be further described in detail below in conjunction with the accompanying drawings and specific chip verification implementation cases:

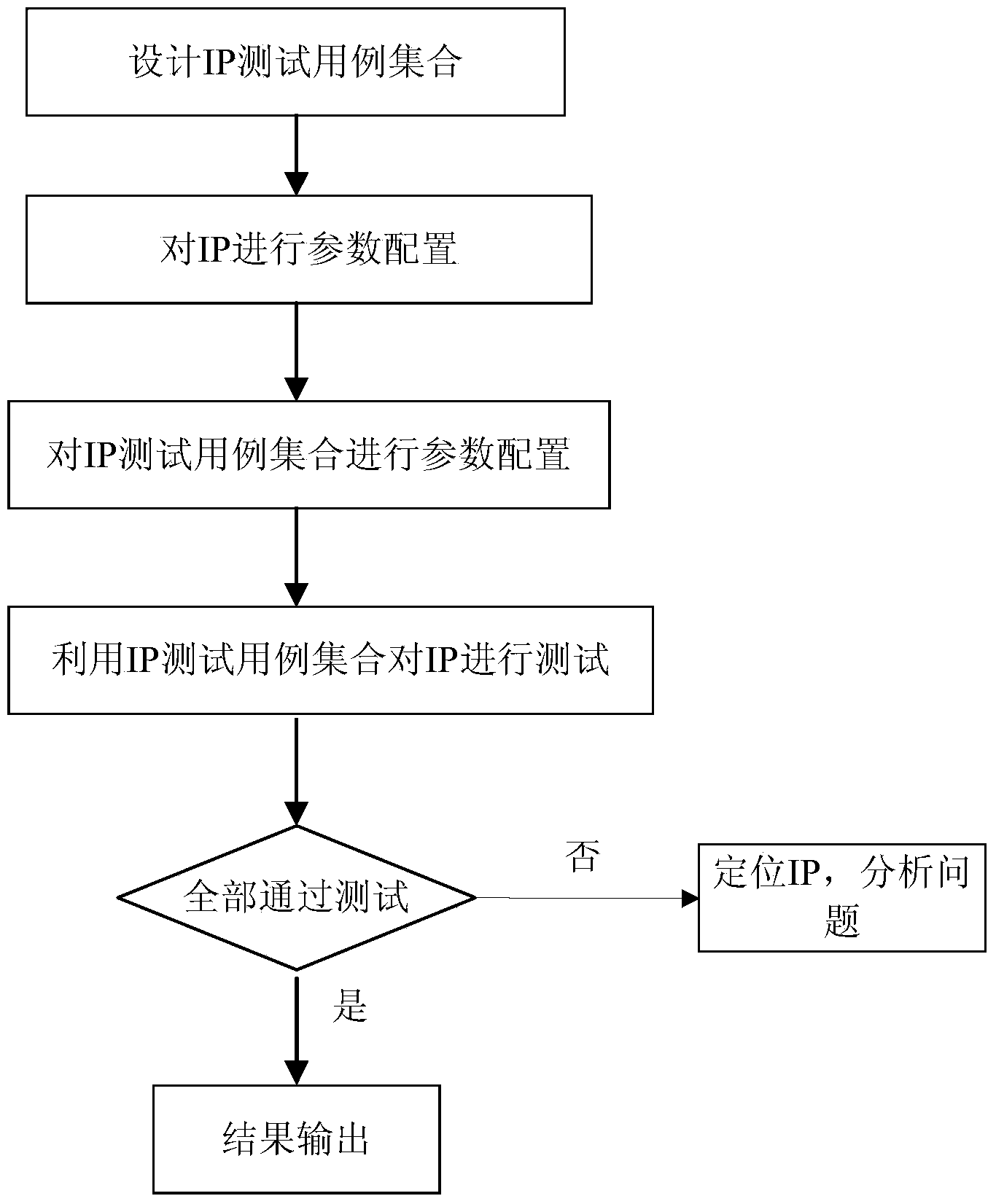

[0018] Such as figure 1 Shown is the schematic flow chart of the chip automatic verification method based on the set of parameterized IP test cases of the present invention, and the specific steps are as follows:

[0019] (1) Design test cases for each IP, the input and output of the test cases are represented by the parameters of the IP, and the test cases covering all functions of the IP constitute the configurable test case set TIP of the IP;

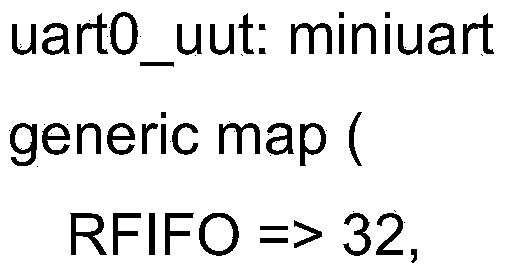

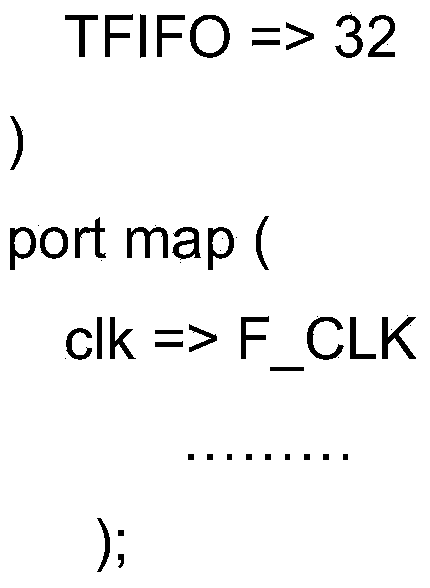

[0020] (2) According to the actual design requirements, configure the configurable parameters of all the IPs that make up the chip, such as the FIFO size used in the IP, etc. After the configuration is completed, instantiate it in the design and assign its parameters, such as VHDL The language uses the generic map statement for instantiation.

[0021] Carry out t...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More