MBIST (Memory Built In Self Test) controller structure system based on IEEE (Institute of Electrical and Electronics Engineers) 1500 standard and compatible with SRAM/ROM (Static Random Access Memory/Read Only Memory)

A controller and standard technology, applied in the direction of instruments, static memory, etc., can solve problems such as unfavorable promotion and development of MBIST technology, reducing test costs, disadvantages, etc.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0064] The specific embodiments of the present invention will be described in detail below with reference to the drawings and embodiments.

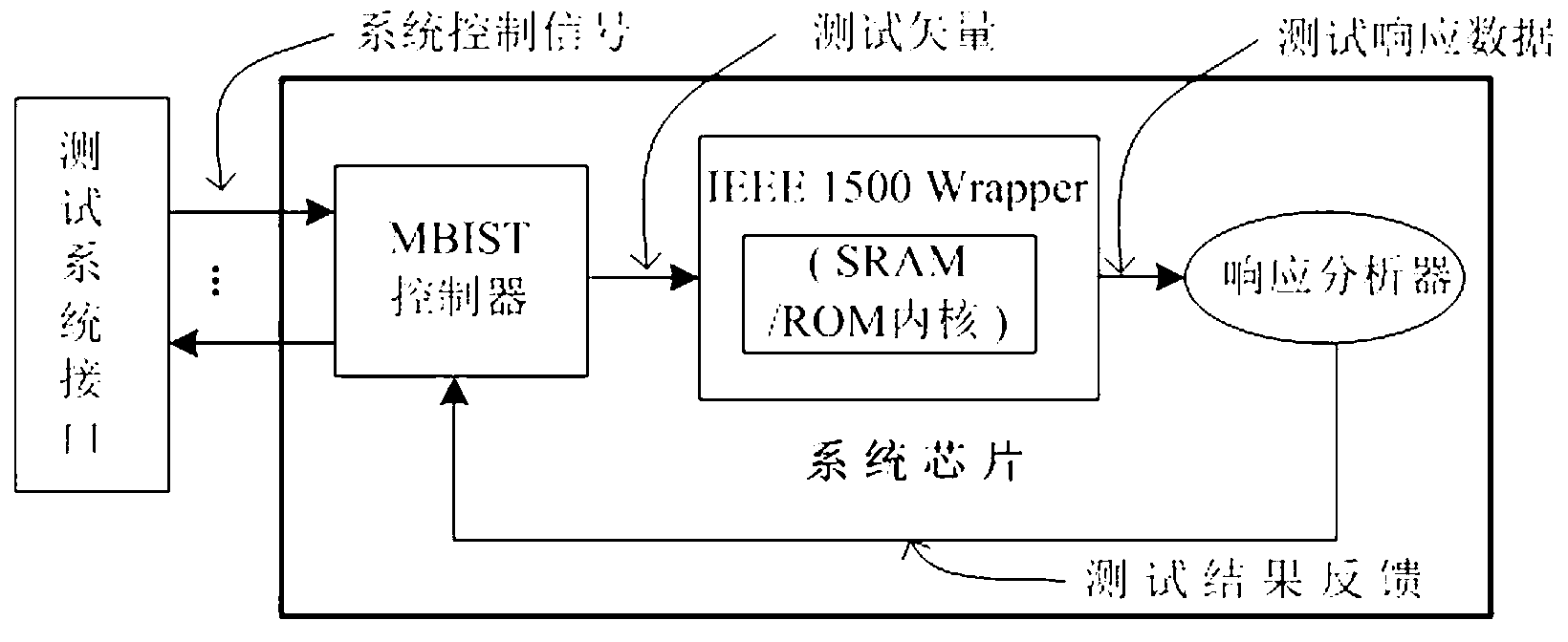

[0065] see figure 1 . The MBIST controller with the March algorithm state machine and the multi-input linear feedback shift register MISR are respectively connected to the peripheral test system interface, the test shell wrapper and response analysis based on the IEEE 1500 standard surrounding the tested embedded SRAM and ROM core The test shell Wrapper based on the IEEE 1500 standard is connected with the response analyzer. The test shell Wrapper and the response analyzer based on the IEEE 1500 standard are both embedded in the system chip.

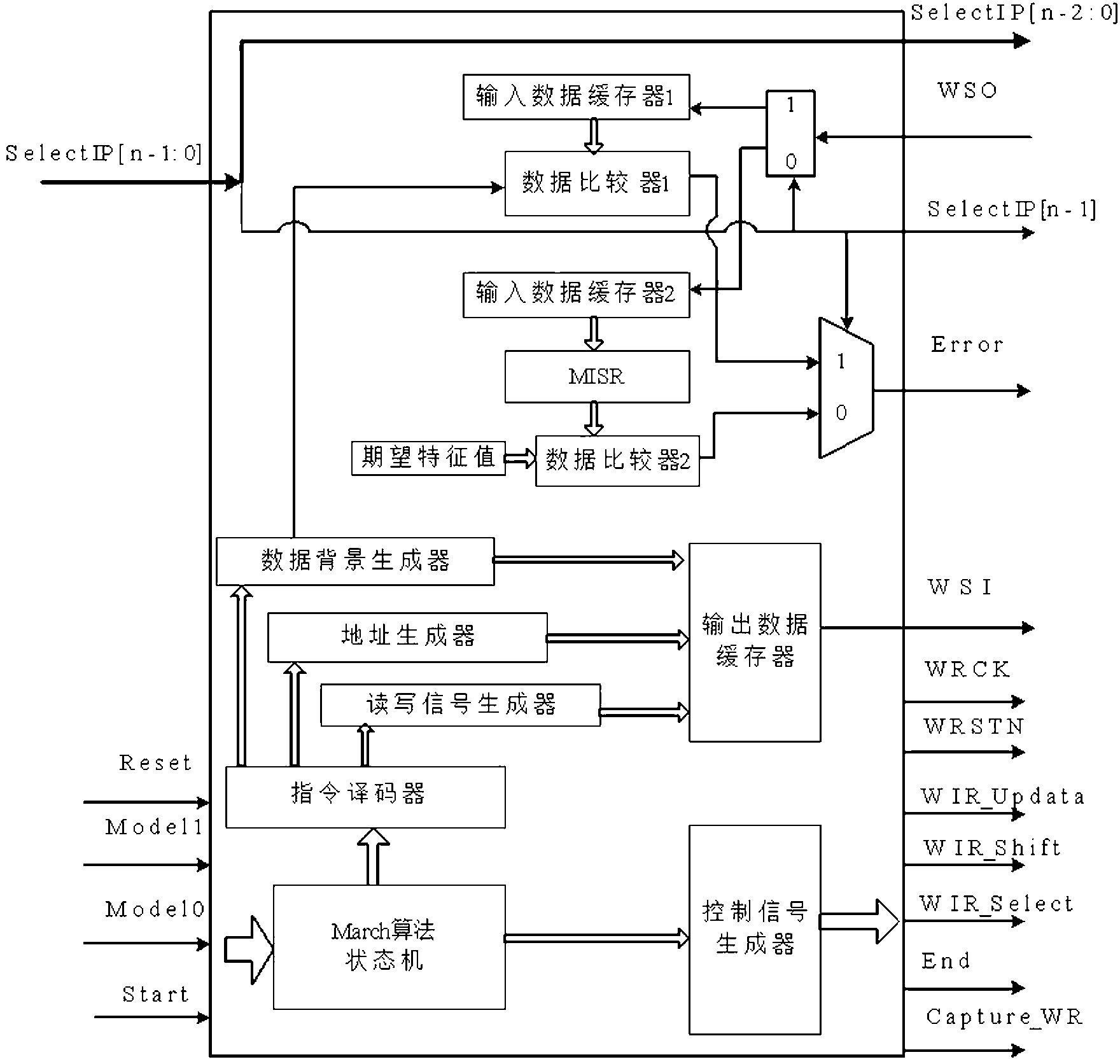

[0066] see figure 2 . In the MBIST controller, the March algorithm state machine is followed by the instruction decoder and the control signal generator. After the instruction decoder, the data background generator, address generator and read-write signal generator, data background generator, address ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More