Patents

Literature

77results about How to "Address competition" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

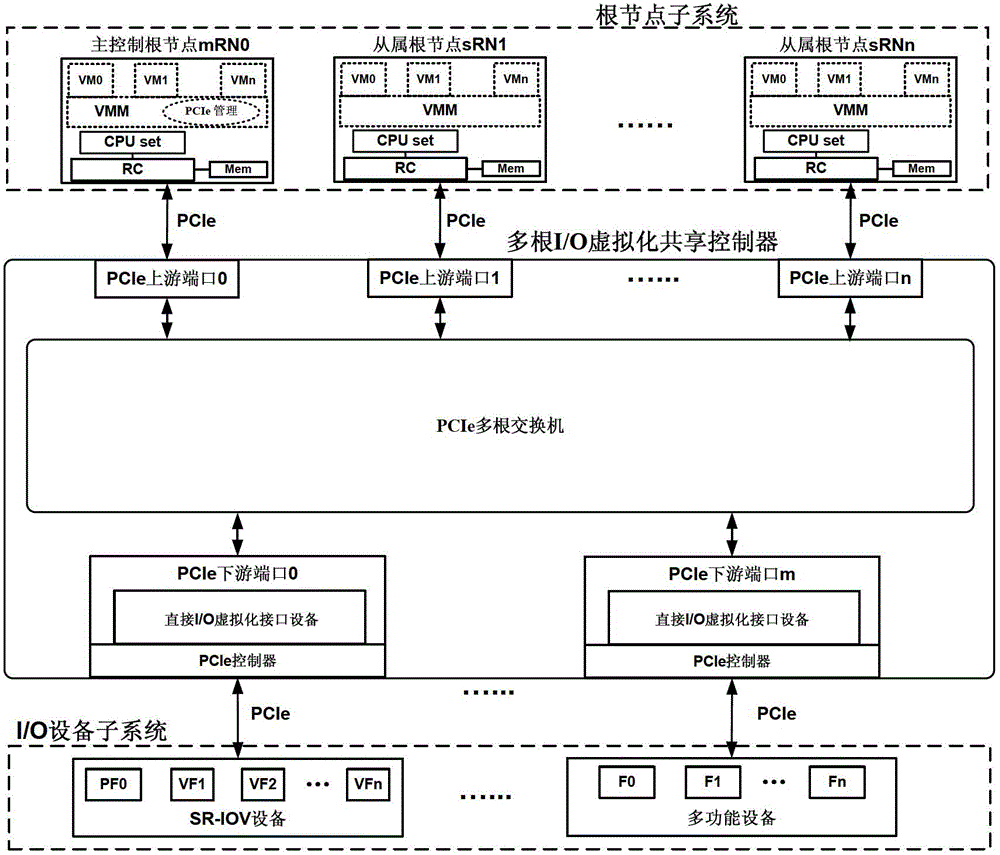

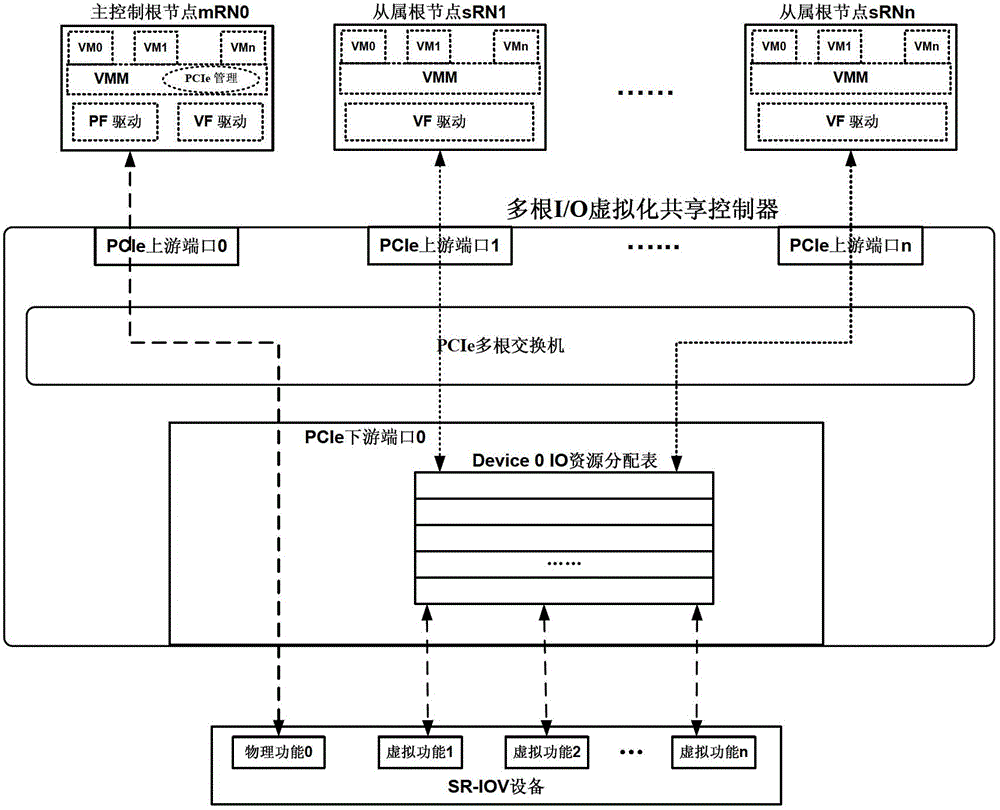

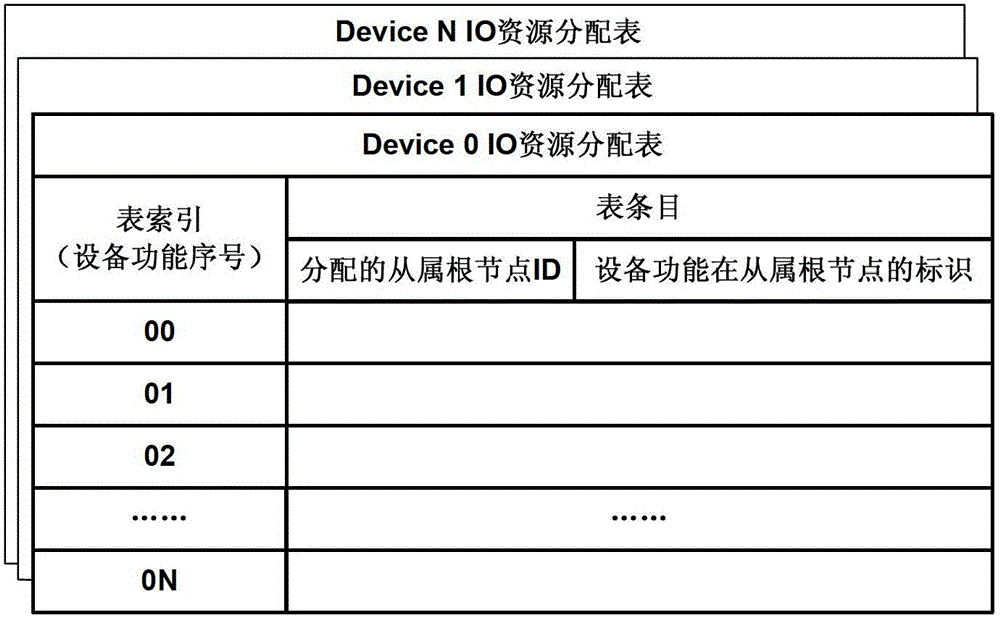

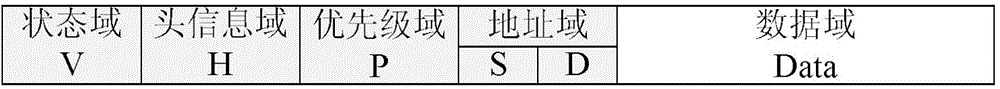

Input/output (I/O) resource management method for multi-root I/O virtualization sharing system

ActiveCN102722414AAddress competitionSolve conflictsResource allocationSoftware simulation/interpretation/emulationVirtualizationControl system

The invention discloses an input / output (I / O) resource management method for a multi-root I / O virtualization sharing system. The method for implementing centralized initialization configuration and allocation management on all I / O equipment in the multi-root I / O virtualization sharing system by using a master control root node comprises the following steps of: 1, performing enumeration discovery and initialization configuration on I / O resources in the system by the master control root node; 2, assisting a management user in managing and controlling I / O equipment resources in the system through a peripheral component interconnect express (PCIe) management module by the master control root node, and executing an I / O resource allocation strategy formulated by the management user; and 3, establishing a mapping relation between equipment functions and root nodes thereof according to the PCIe management module and an I / O resource allocation table by the master control root node to realize dynamic allocation of t he I / O resources.

Owner:INST OF COMPUTING TECH CHINESE ACAD OF SCI

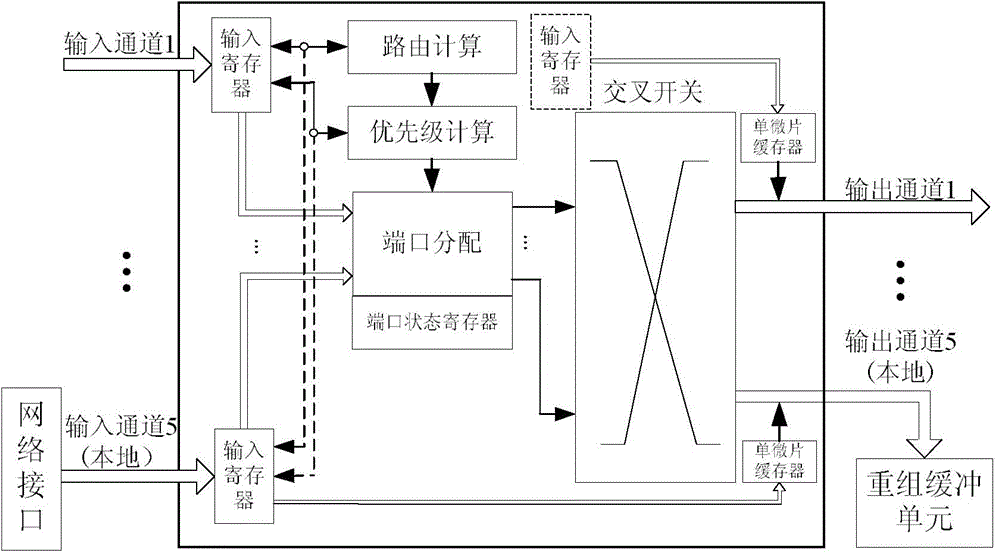

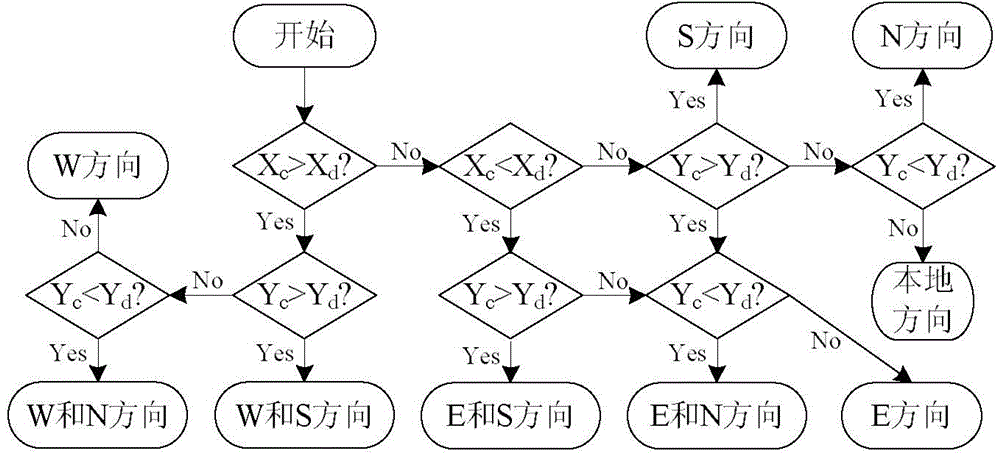

Network-on-chip router with low buffer area and routing method

The invention discloses a network-on-chip router with a low buffer area. The network-on-chip router comprises n input ports, n input registers, a routing computation module, a priority computation module, a port distribution module, a crossbar switch, p single microchip buffers and p output ports, wherein when microchips with high priority and secondary high priority compete for an effective output port, the port distribution module transmits the microchip with secondary high priority to the corresponding single micro-chip buffer according to a priority arbitration strategy, when other micro-chips with low priority compete for the port, a deflected output port is distributed; when the output port is idle, the microchip with secondary high priority is directly output to a lower routing node. According to the network-on-chip router, the area and the power consumption of a network-on-chip can be effectively reduced, meanwhile, the delay performance and the throughput performance are guaranteed, and the network-on-chip router with the low buffer area and the routing method are suitable for constructing a high-performance system on a chip.

Owner:CHINESE AERONAUTICAL RADIO ELECTRONICS RES INST

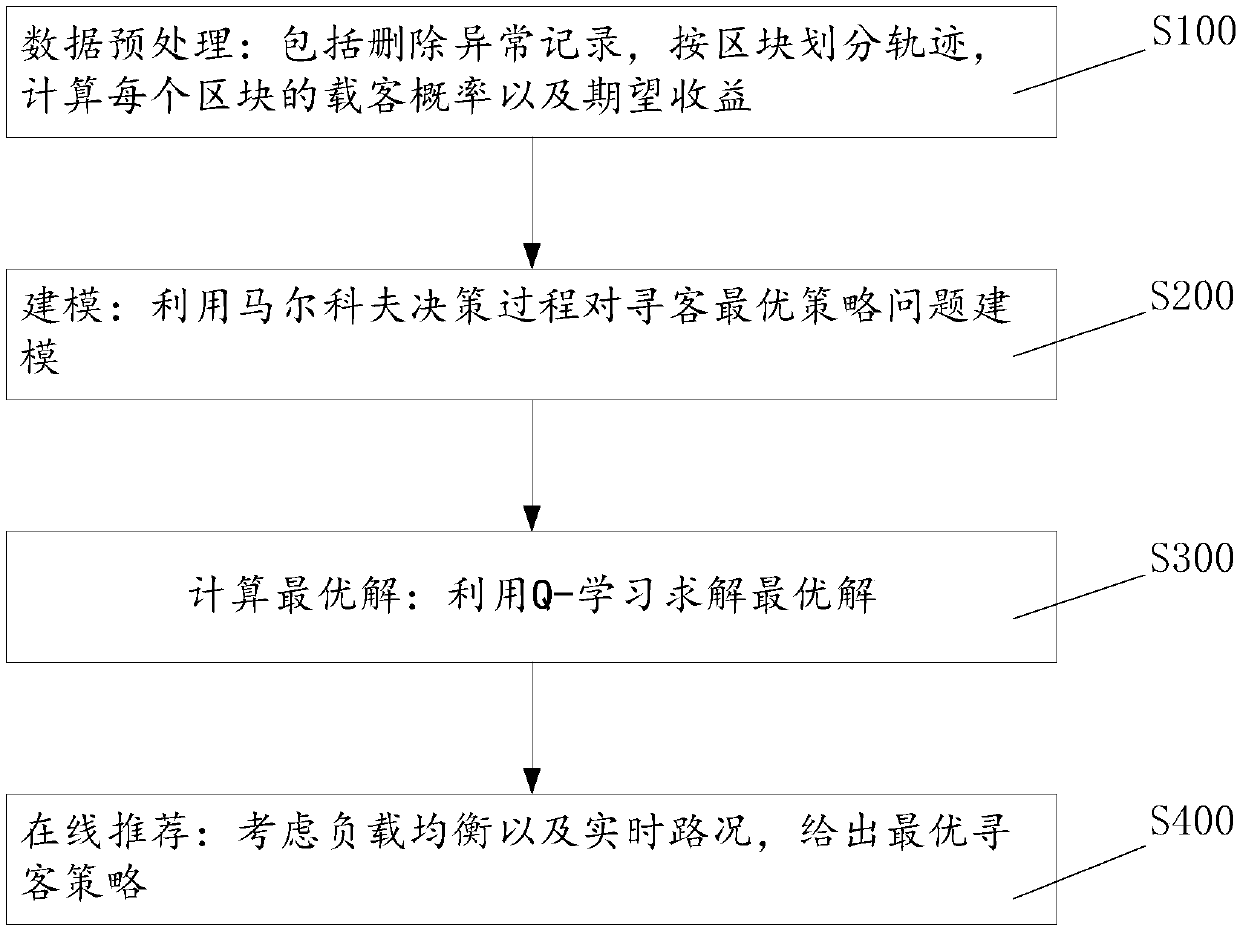

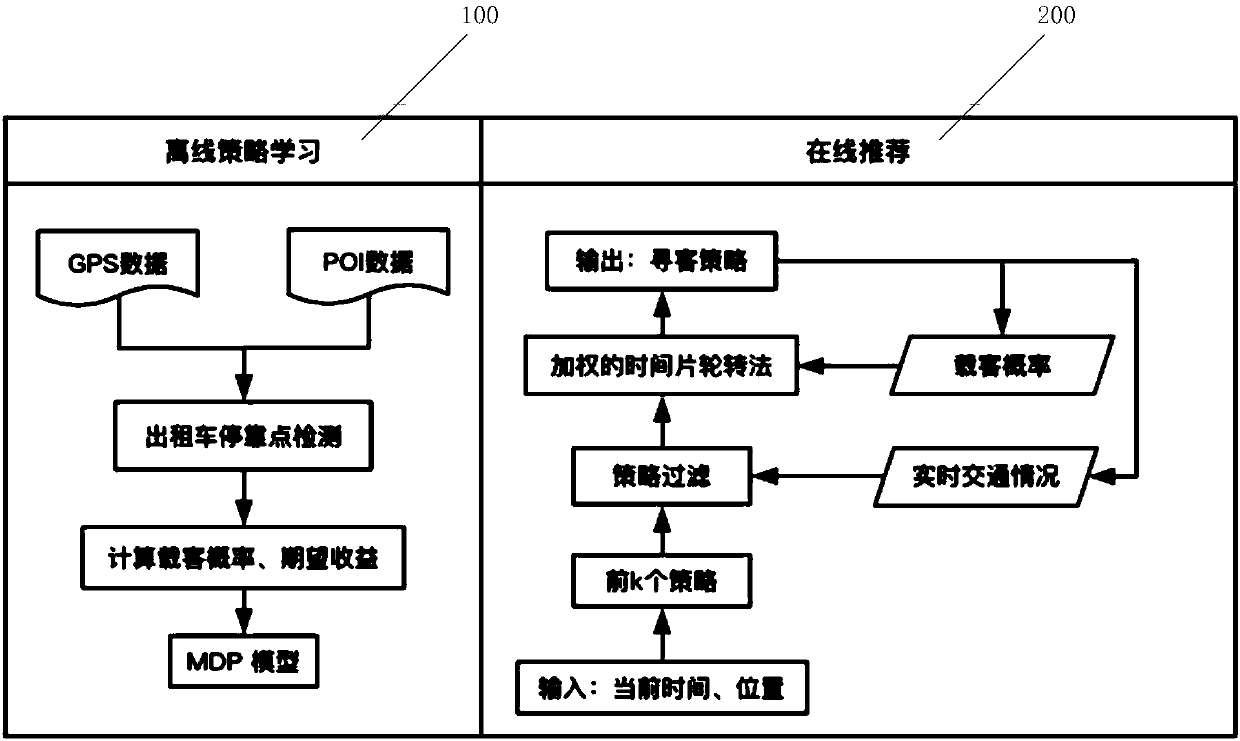

Method for recommending taxi passenger-searching strategy based on Markov decision process

InactiveCN107832882AAddress competitionAvoid driving intoForecastingBuying/selling/leasing transactionsQ-learningTraffic conditions

The invention provides a method for recommending a taxi passenger-searching strategy based on a Markov decision process. The method comprise the following steps of data preprocessing: including deleting abnormal records, determining trajectories according to blocks, and calculating the passenger carrying probability and the expected revenue of each block; modeling: using a Markov decision processto model a passenger-searching optimal strategy problem; calculating the optimal solution: Using Q-learning to solve the optimal solution; online recommendation: giving the optimal passenger-searchingstrategy in consideration of load balancing and real-time traffic conditions. The method for recommending a taxi passenger-searching strategy based on a Markov decision process provides two differentstrategies for the waiting area and the searching areas, can calculate the expected revenue of each strategy according to the historical trajectories, receives the real-time traffic conditions and processes the taxi recommendation requests by a dispatching system so that the optimal strategy recommendation can be given after a taxi passenger gets off.

Owner:SHANGHAI JIAO TONG UNIV

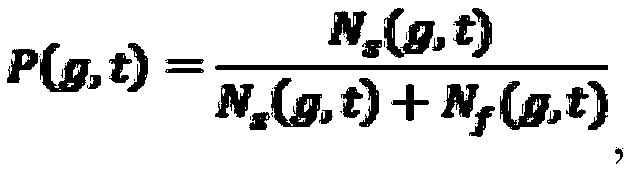

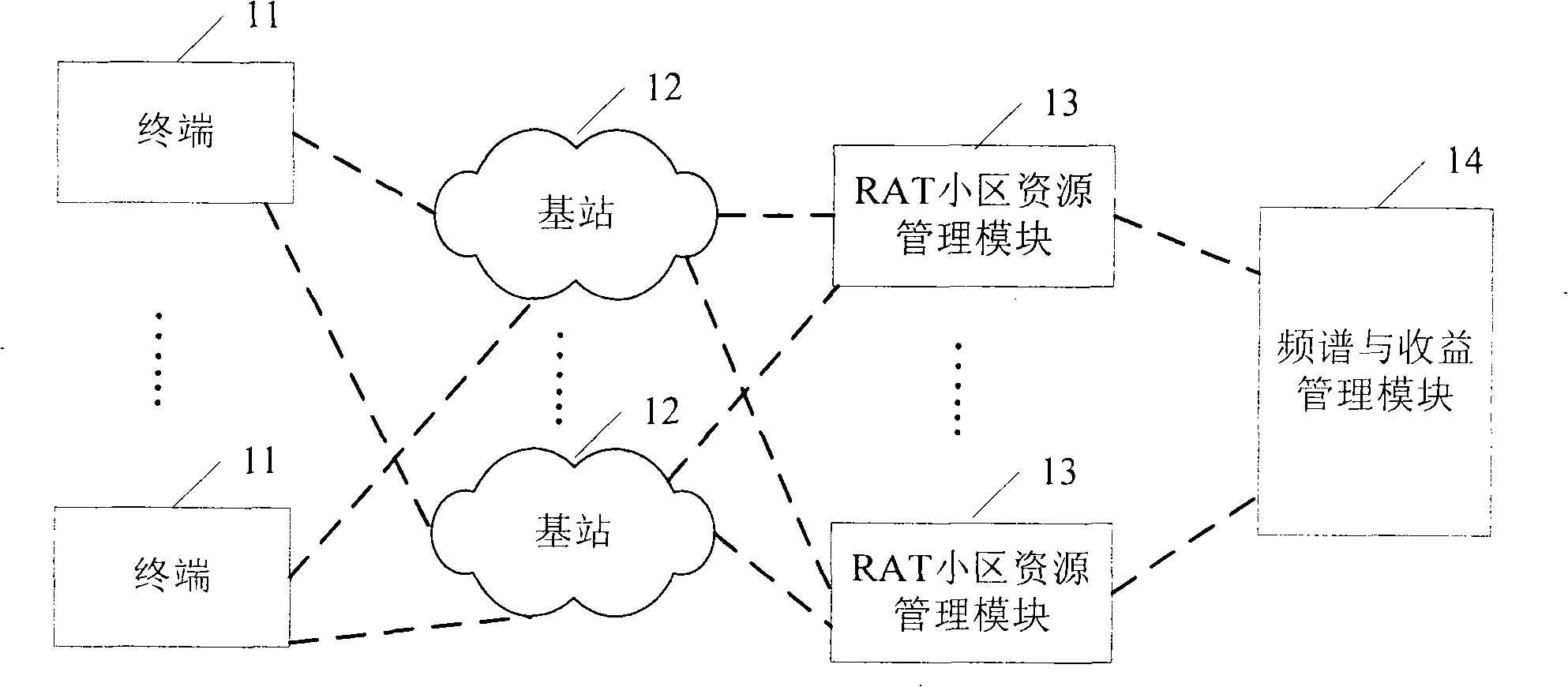

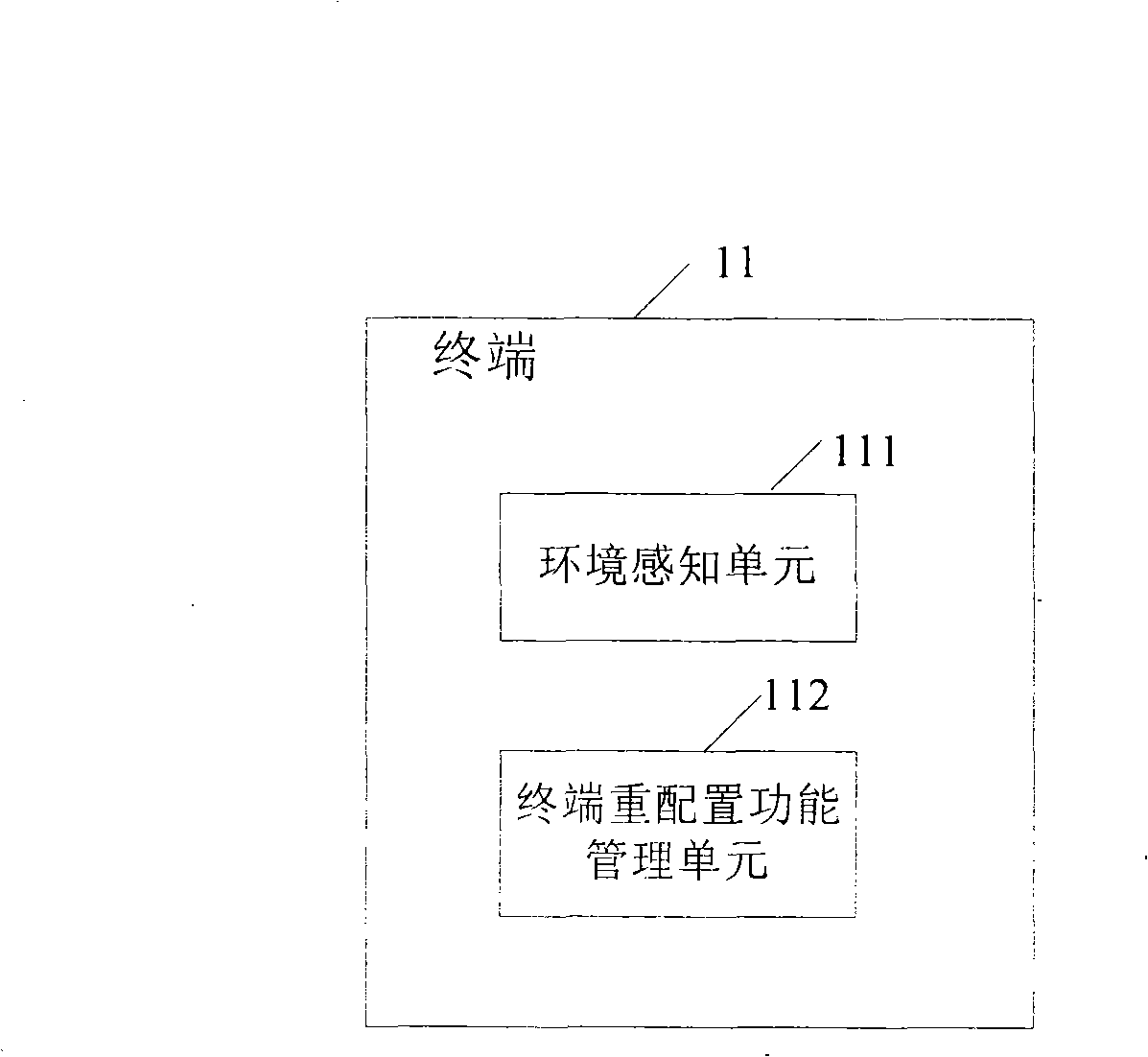

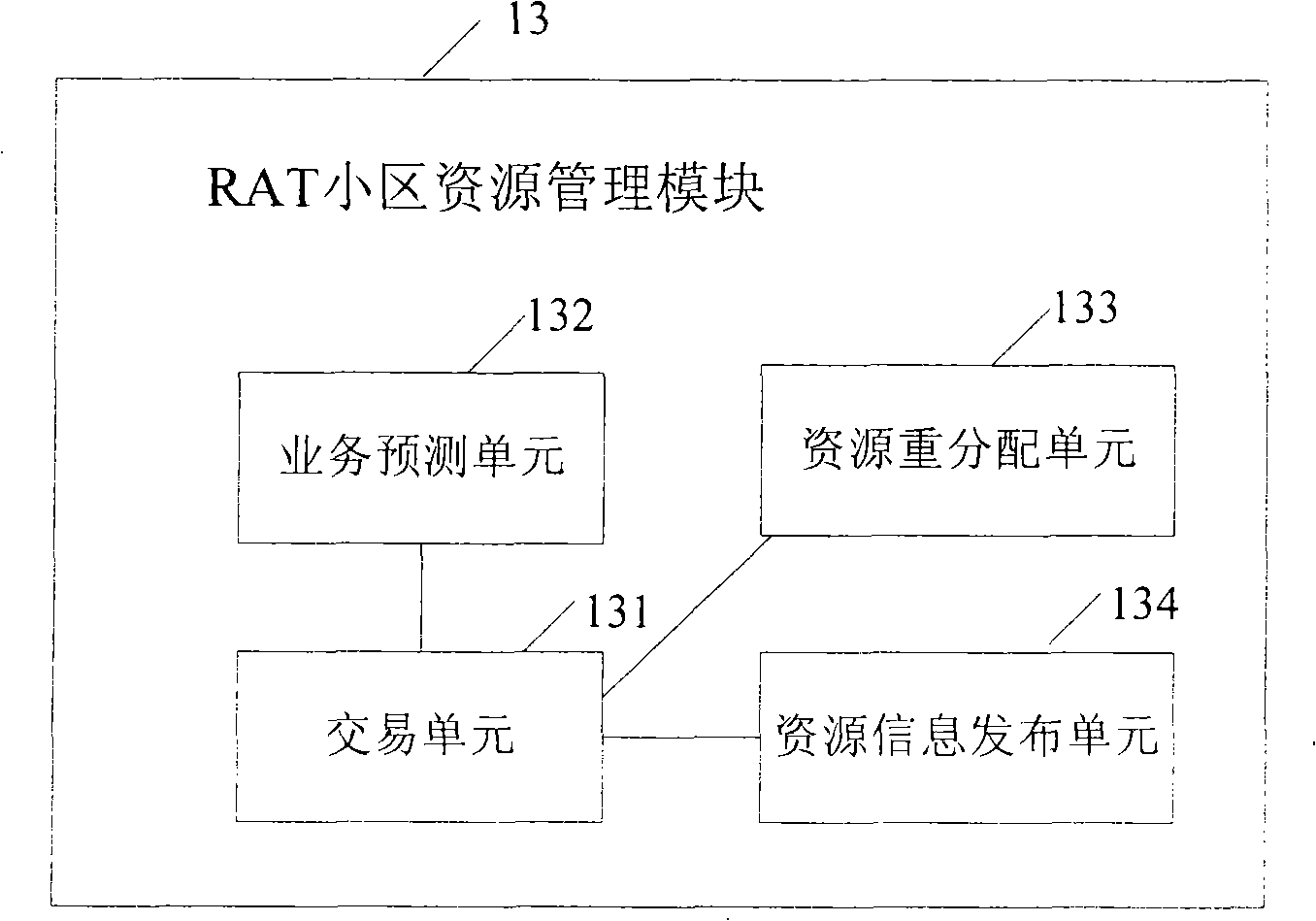

Method and system for managing centralized dynamic spectrum among wireless networks

InactiveCN101277542AImprove spectral efficiencyAddress competitionTransmission control/equalisingRadio/inductive link selection arrangementsWireless mesh networkFrequency spectrum

The present invention provides a centralized dynamic spectrum management method and system between wireless networks. The spectrum resource is dynamically distributed to a RAT cell according to the spectrum requirement, network gain of the RAT cell, the position information of the base station, the expected maximum emitting power of the base station and relative parameters, and the gain acquired in the dynamic spectrum management is distributed to each RAT in a fairly and reasonable mode. The invention sufficiently utilizes the difference of different wireless system to the spectrum requirement on time and spatial dimension, thereby enhancing the spectrum efficiency and the gain of operator, the dynamic spectrum management is realized in the real communication network by introducing an interference inhibition technology to ensure interference between systems and introducing a cooperation based on market and competition rules to resolve the benefits competing relation between different networks.

Owner:天津市观云科技有限公司

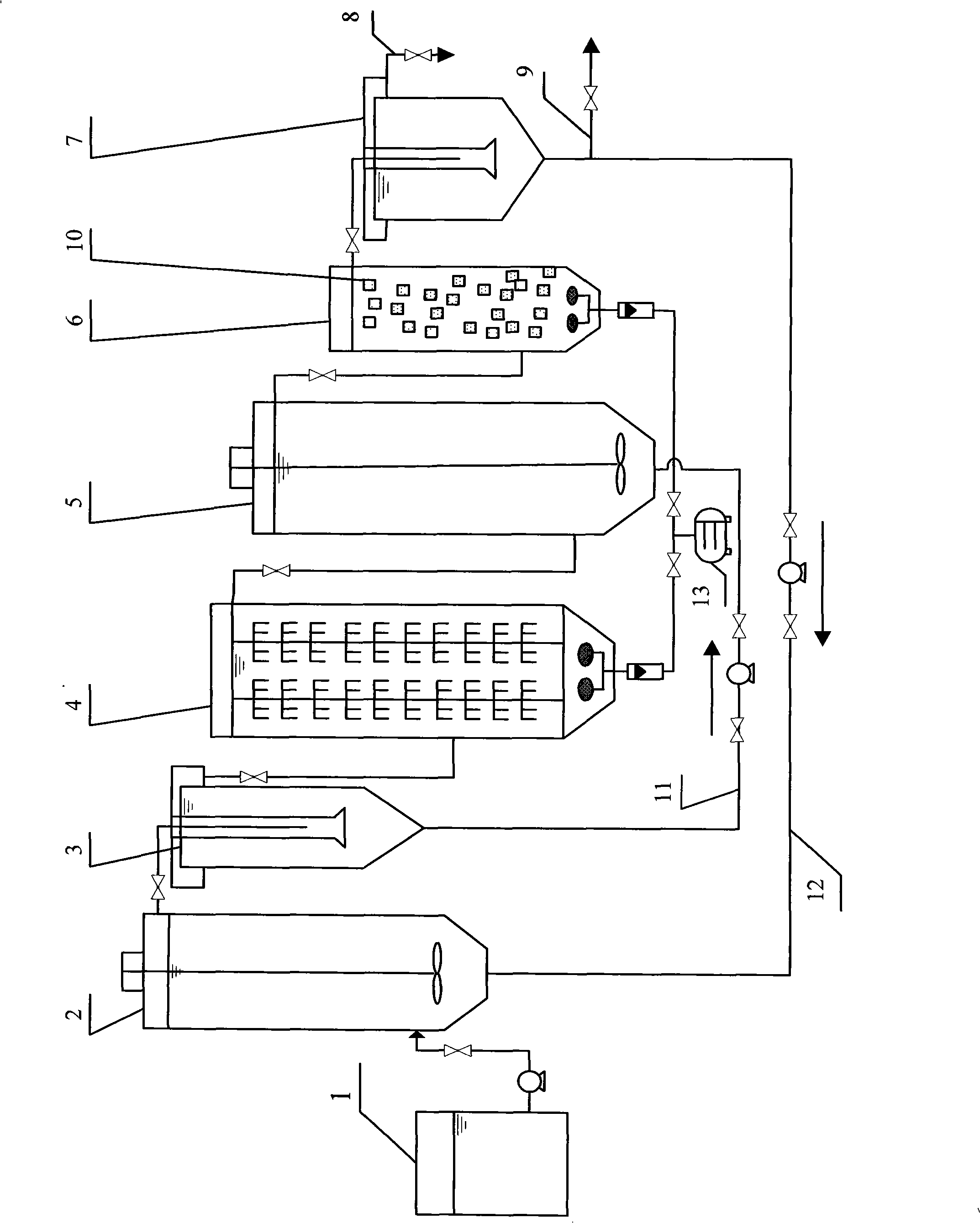

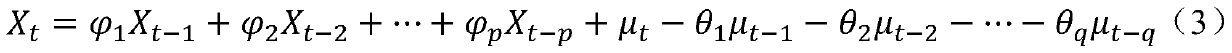

Improved A*N denitrifying dephosphatation and deep denitrification device and method

ActiveCN101538104ASolve the problem of excessive ammonia nitrogenFully release phosphorusTreatment with aerobic and anaerobic processesMultistage water/sewage treatmentBiofilmAmmoniacal nitrogen

The invention relates to an improved A2N denitrifying dephosphatation and deep denitrification device and a method, belonging to the field of sewage treatment. The device is characterized in that a combined aeration tank is arranged between an anoxic tank and a final depositing tank; the combined aeration tank realizes synchronous aerobic phosphorus absorption and biofilm nitrification; a cube sponge filling is filled; the batching ratio of filling is 20 to 30 percent of effective volume of a reactor; and the combined aeration tank is provided with an air pump, an air flow meter and an aerator pipe. Under the condition of adding no reaction area in the original A2N technique, the invention replaces a post aeration reaction tank with the combined aeration tank adopting suspending sponge filling as carrier of nitrobacteria, and controls the parameters of aeration amount and temperature and the like to realize the nitrification and synchronous of nitrification-denitrification of ammonia nitrogen. The invention does not add the process flow and energy consumption of operation, solves the fatal problem of the traditional technique, and guarantees the stable and high-efficiency removal of nitrogen and phosphorus in effluent quality.

Owner:SDIC XINKAI WATER ENVIRONMENT INVESTMENT CO LTD

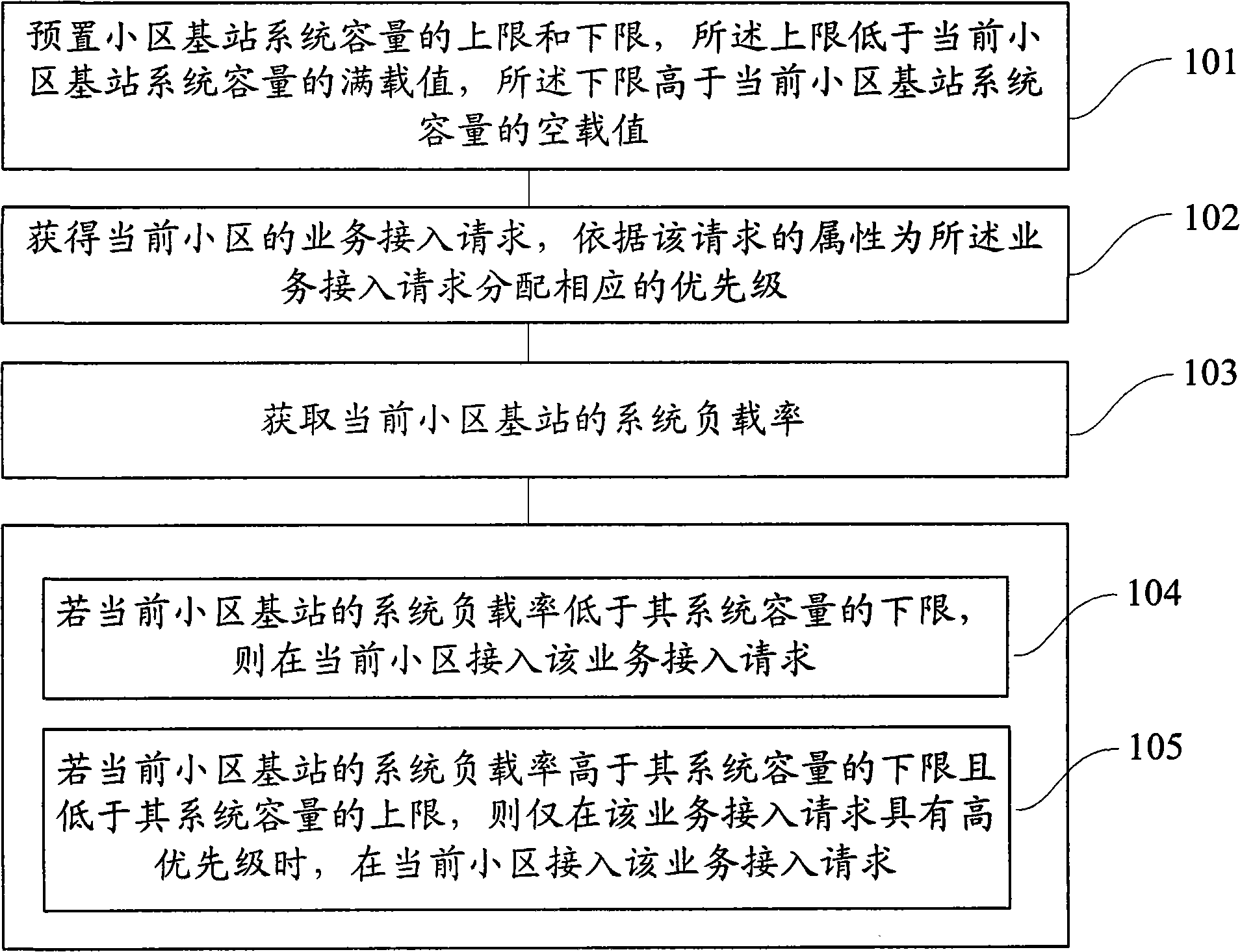

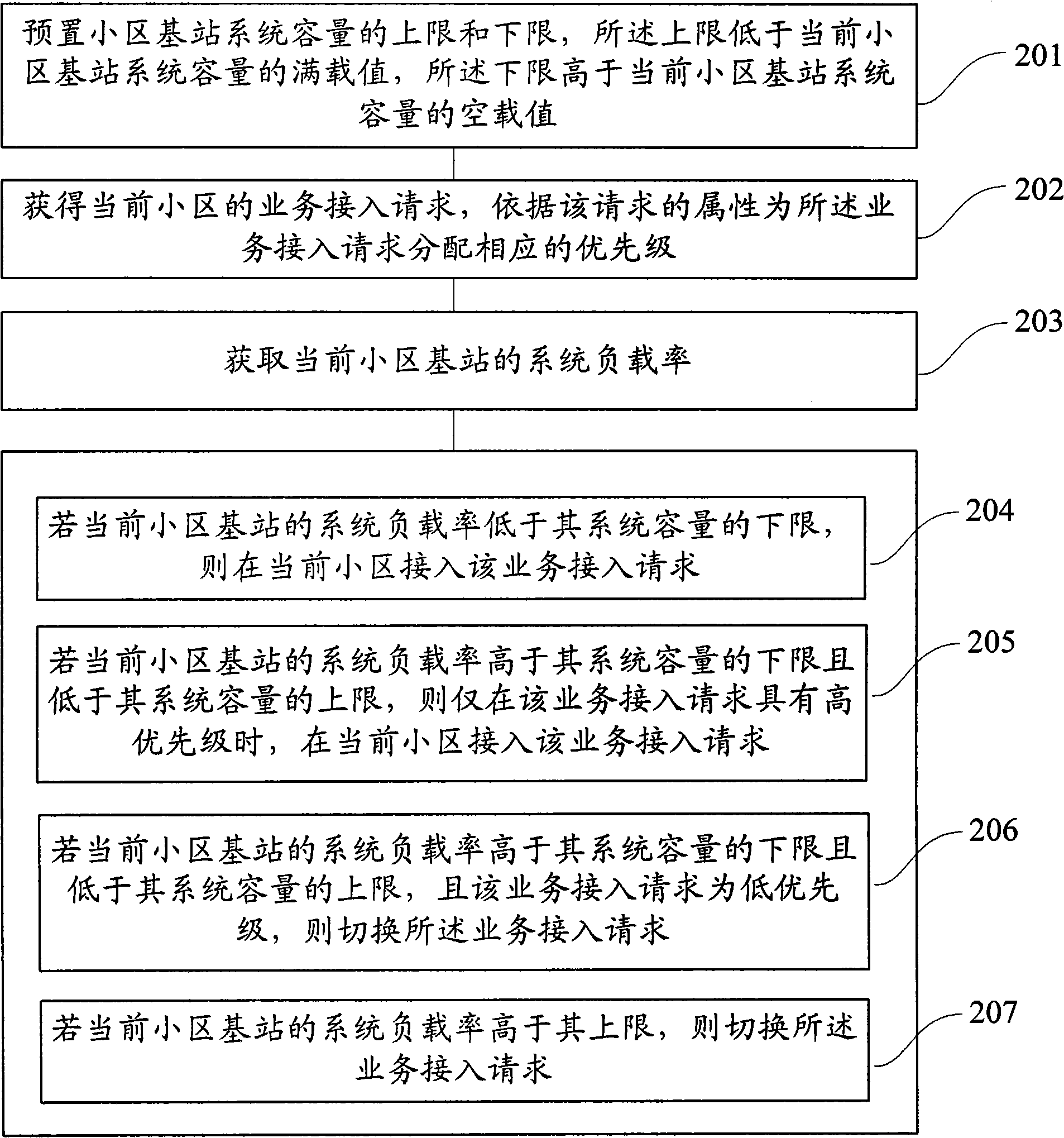

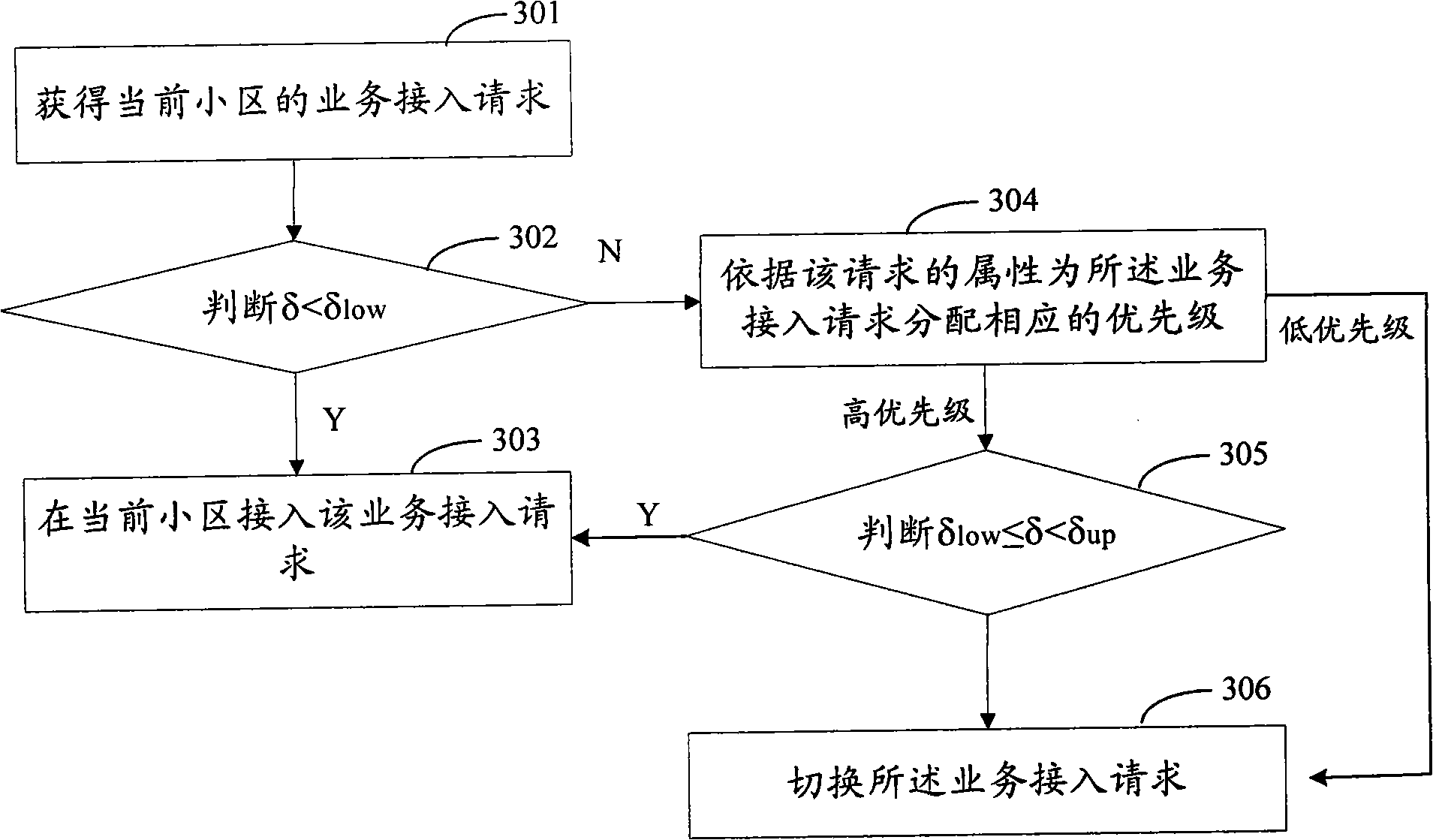

Access control method, device and cell base station of wireless communication network

InactiveCN101990262AAvoid no loadImprove resource utilization efficiencyAssess restrictionLower limitCurrent cell

The invention discloses an access control method of a wireless communication network. The method comprises the following steps: presetting the upper limit and lower limit of the system capacity of a cell base station, wherein the upper limit is lower than the full load value of the system capacity of the cell base station, and the lower limit is higher than the no-load value of the system capacity of the cell base station; acquiring the service access request of the current cell, distributing a corresponding priority for the service access request according to the attribute of the request; acquiring the system load rate of the current cell base station; accessing the service access request in the current cell if the system load rate of the current cell base station is lower than the lower limit of the system capacity; and accessing the service access request in the current cell when the service access request has a high priority and the system load rate of the current cell base station is higher than the lower limit of the system capacity and lower than the upper limit of the system capacity. The method can be used to improve the effective utilization efficiency of the wireless system capacity, improve the communication service quality, and optimize the overall performance of the wireless communication network.

Owner:PEKING UNIV

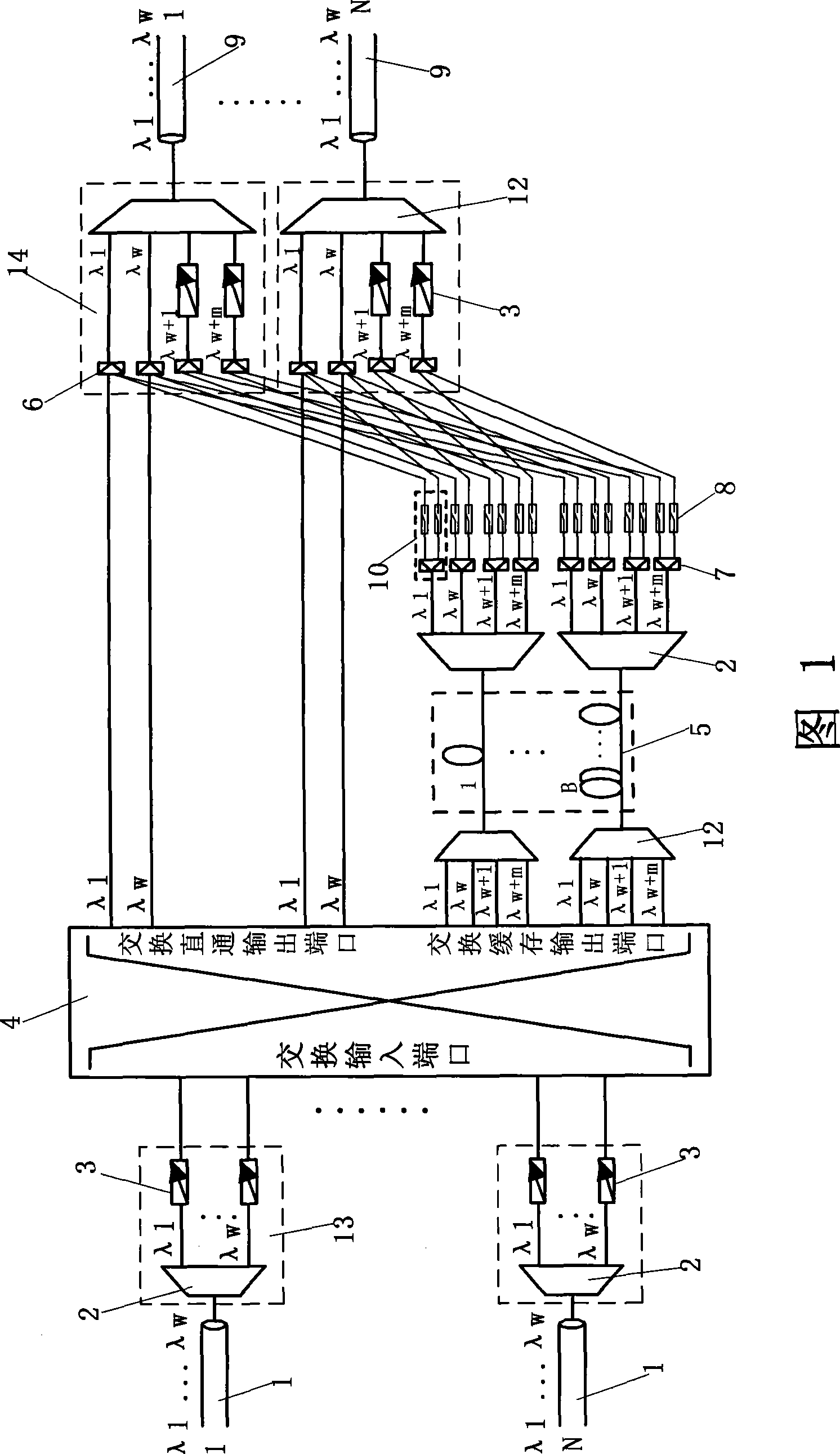

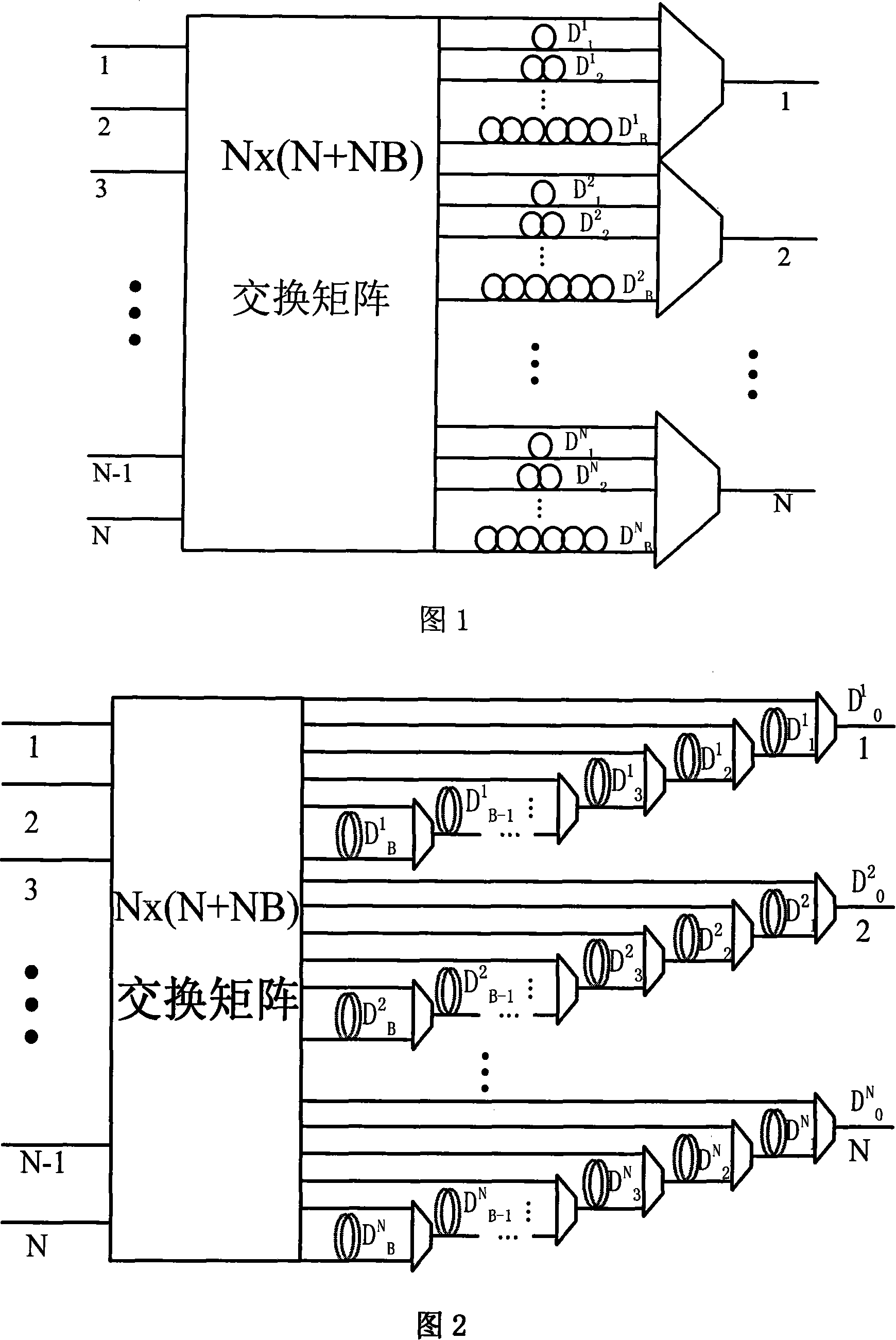

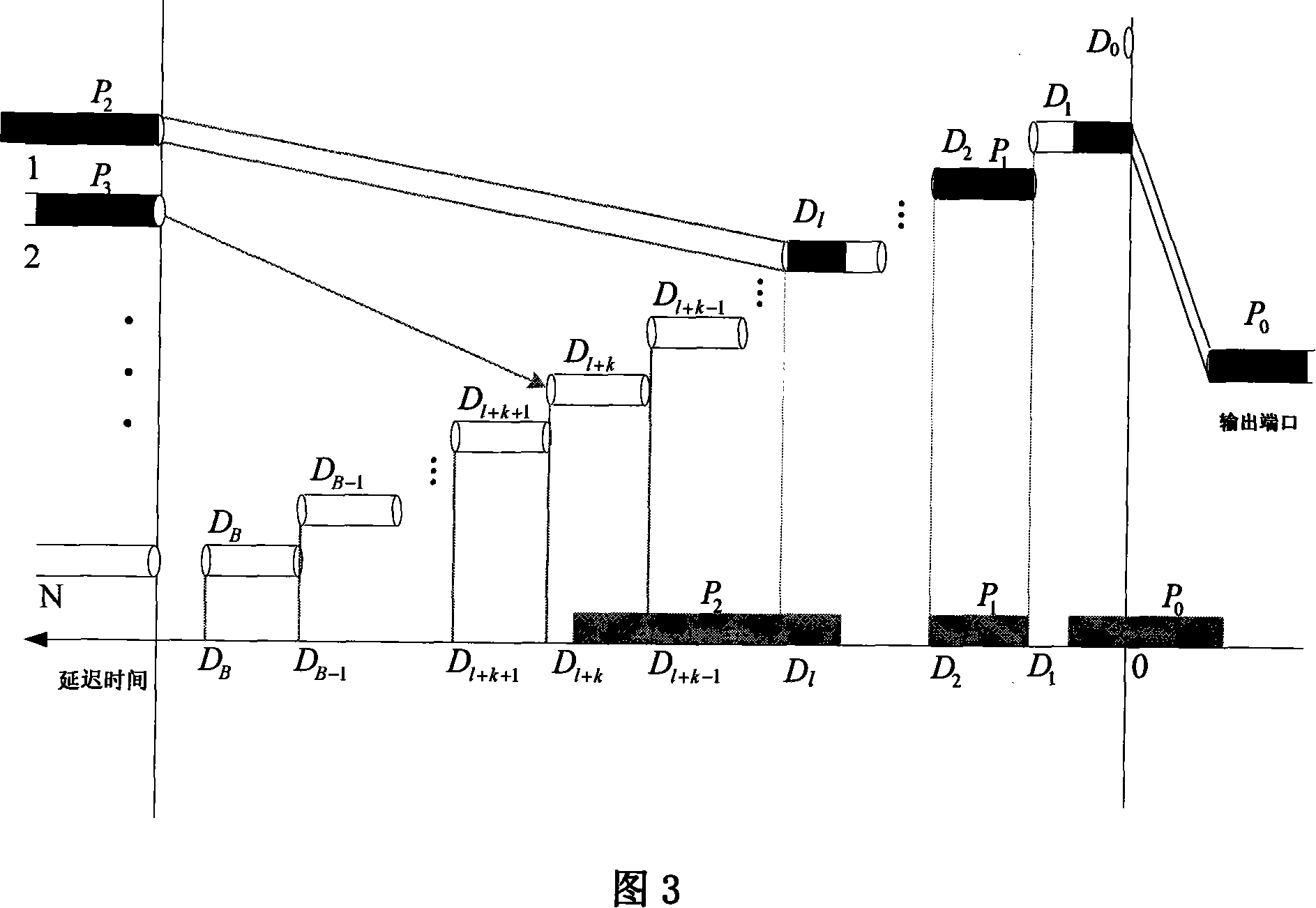

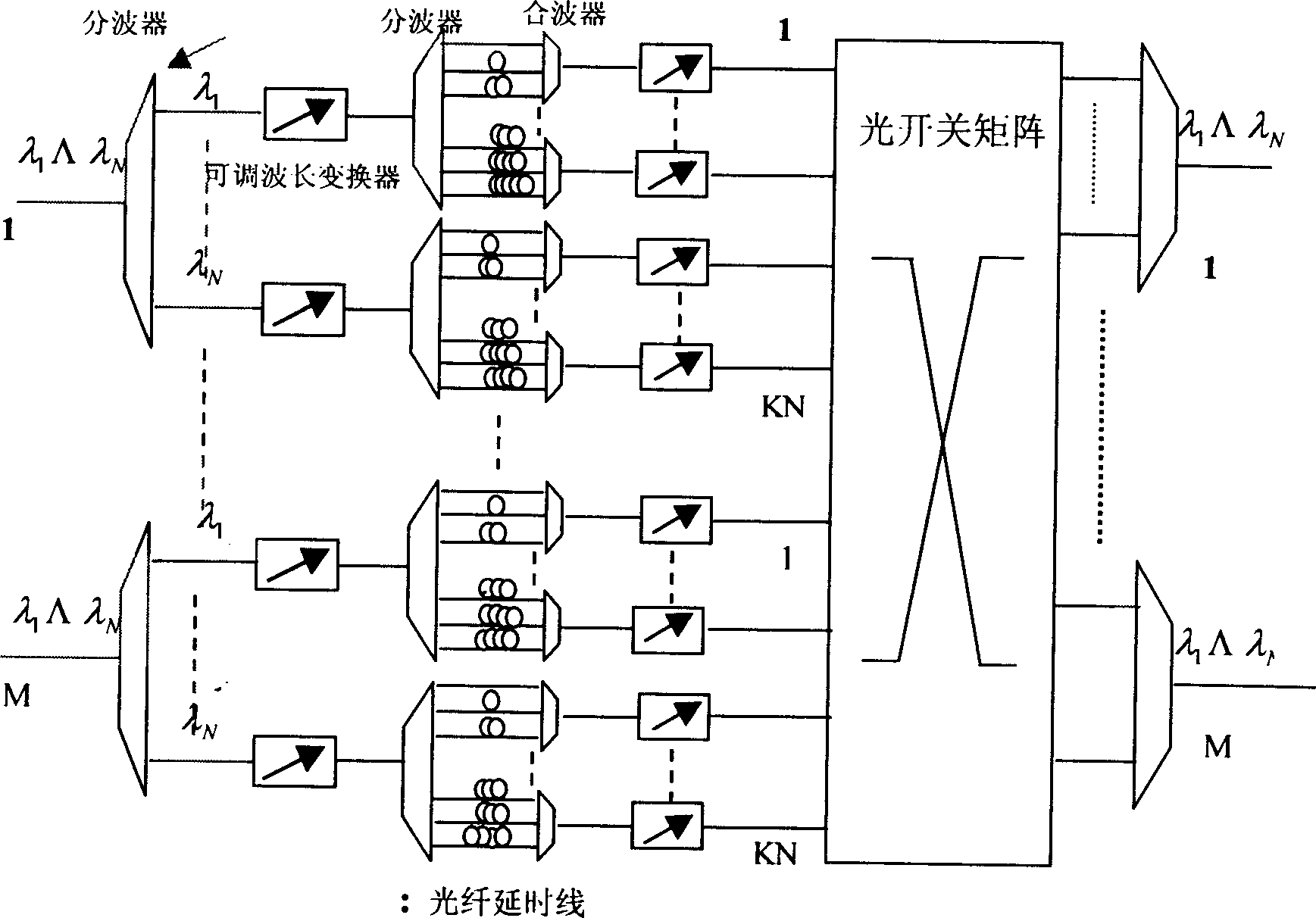

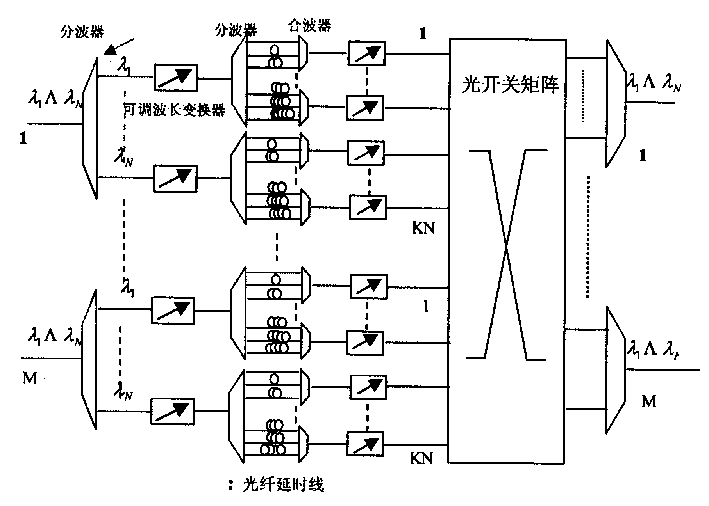

Sharing type optical packet switching node structure based on inside wavelength

InactiveCN101370315ALarge capacityAddress competitionMultiplex system selection arrangementsWavelength-division multiplex systemsTime delaysOptical packet

The invention relates to a shared optical packet exchange node structure based on internal wavelength comprising wavelength-division demultiplexer, adjustable wavelength shifter, optic switch matrix, wavelength-division multiplex, optical fiber delay line, splitter, SOA light gate, passive coupler. Using a group of shared optical fibre delay line for solving competition of light grouping, and increasing optical buffer capacity by internal wavelength method, Solving FDL competition of shared optical cache; Each optical fibre delay line being degeneratively arranged, Each optical fibre delay line cache wavelength comprising transmission wavelength in input / output optical fiber, and also increasing proper internal wavelength to enlarge capacity of optical cache according to need, introducing extra internal wavelength to optical fibre delay line to enhance capacity of FDL optical cache; Node structure with compact appearance being simply controlled. Packet loss rate can be largely reduced for exchange node without increasing optical packet cache time delay, which effectively solves FDL competition problem of shared optical cache.

Owner:SHANGHAI UNIVERSITY OF ELECTRIC POWER

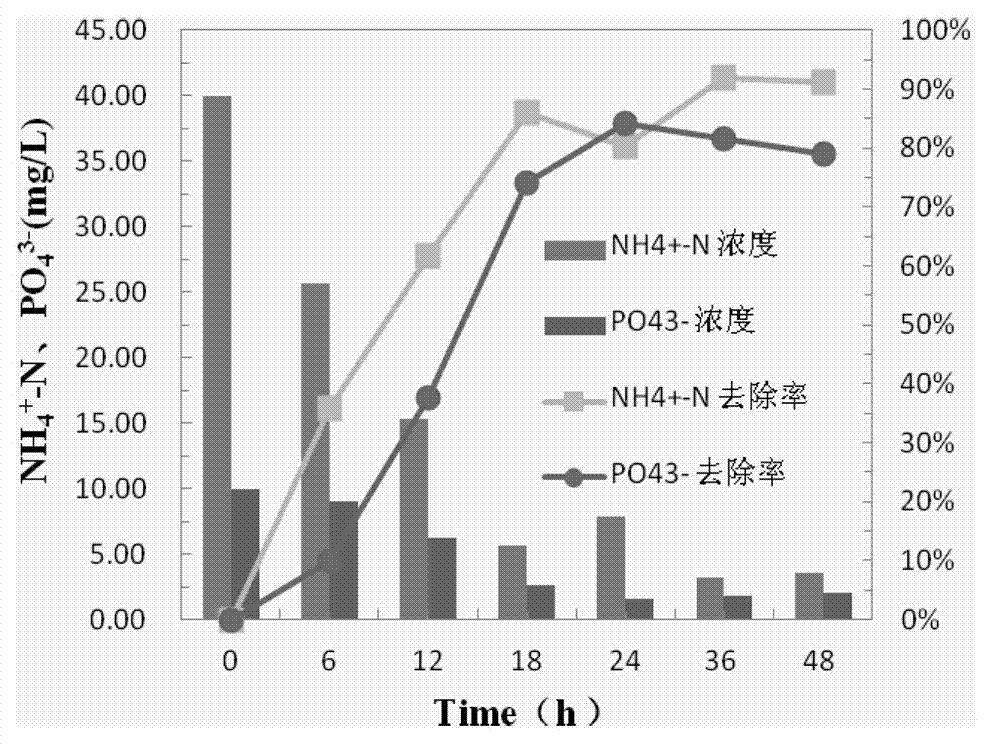

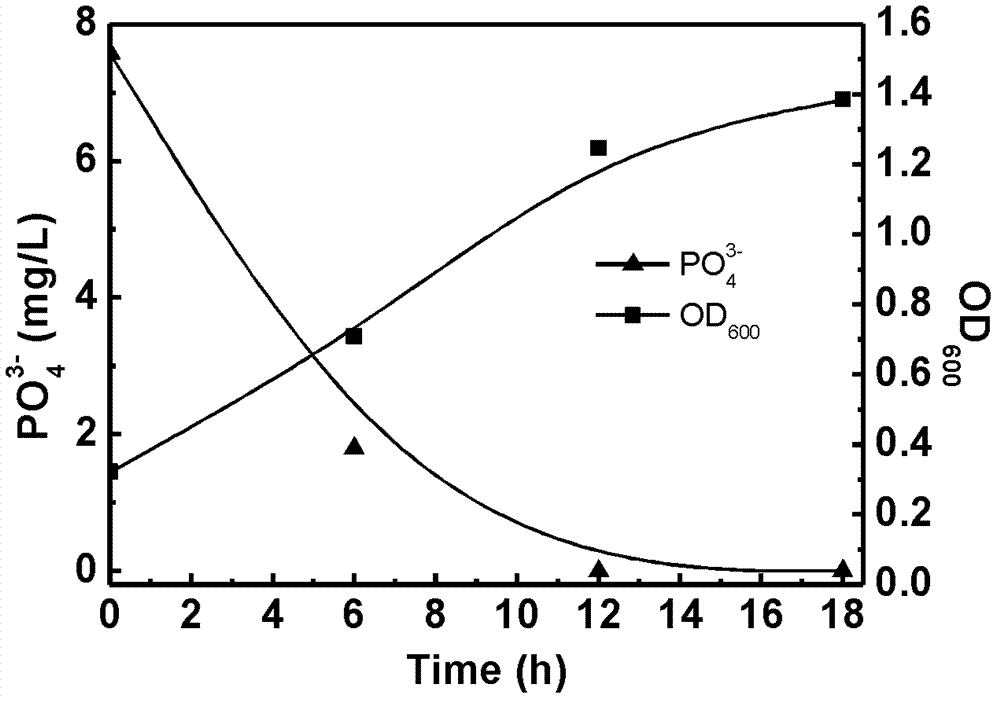

Application of salt-tolerant nitrogen and phosphorus removing bacillus altitudinis to wastewater treatment

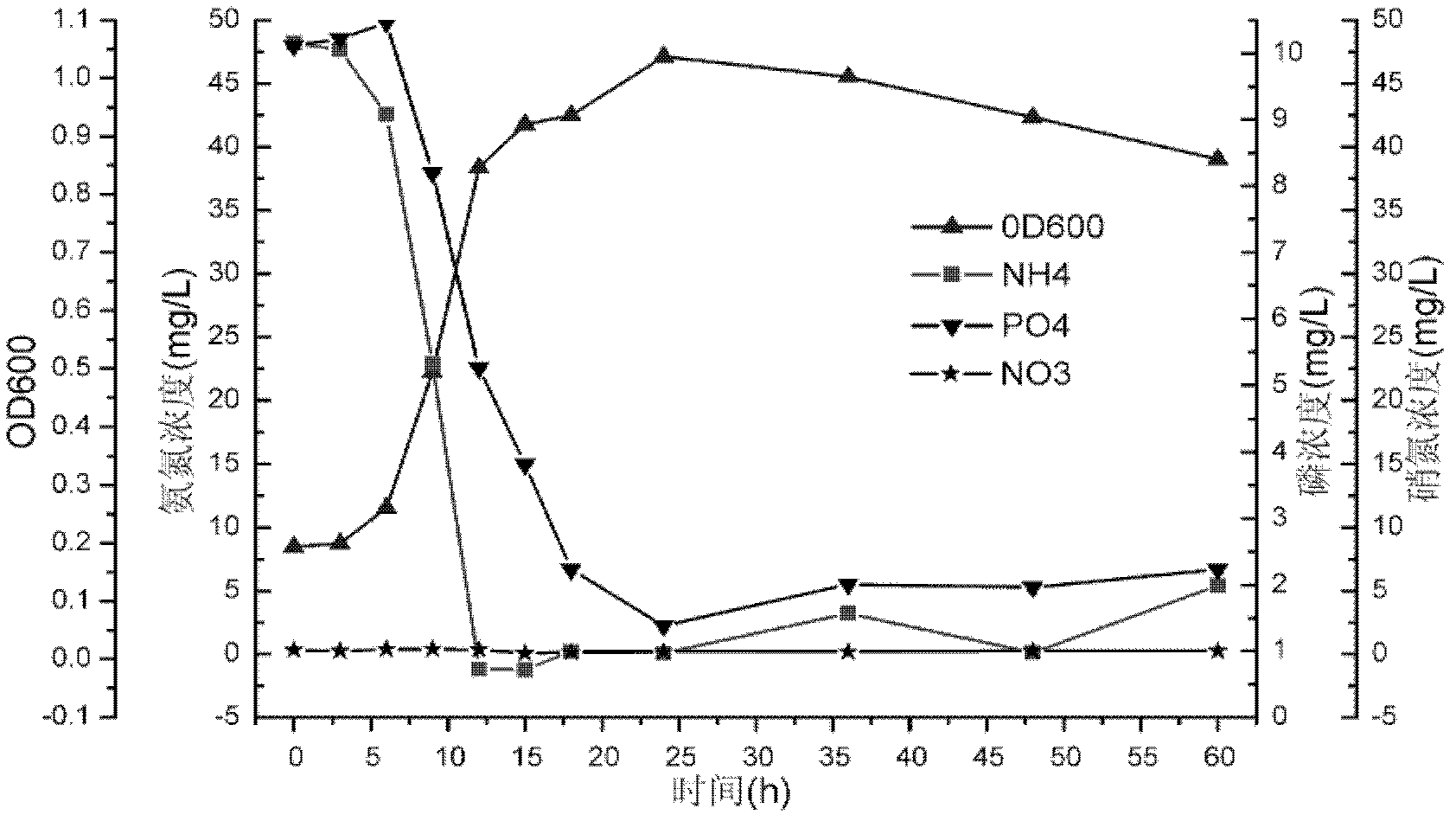

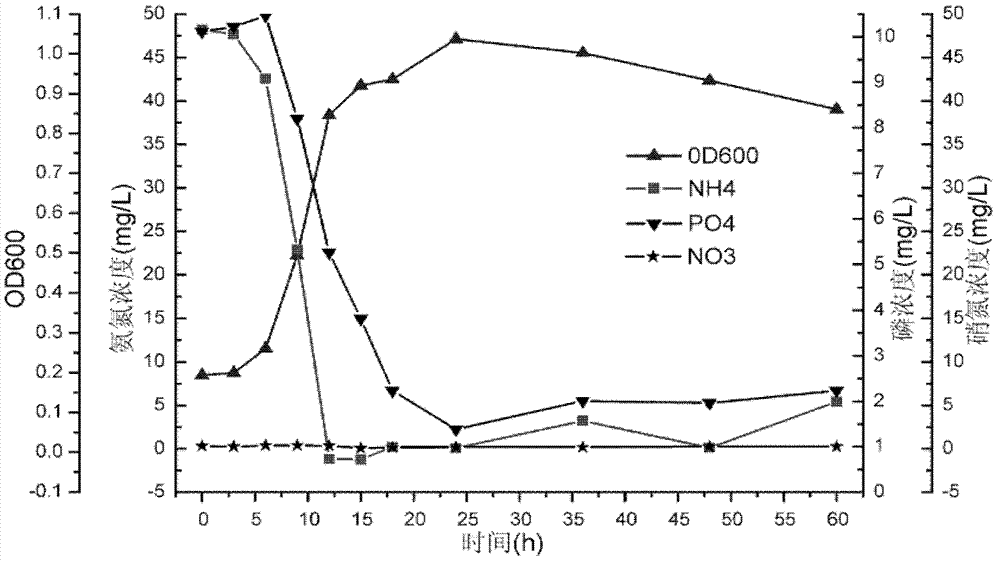

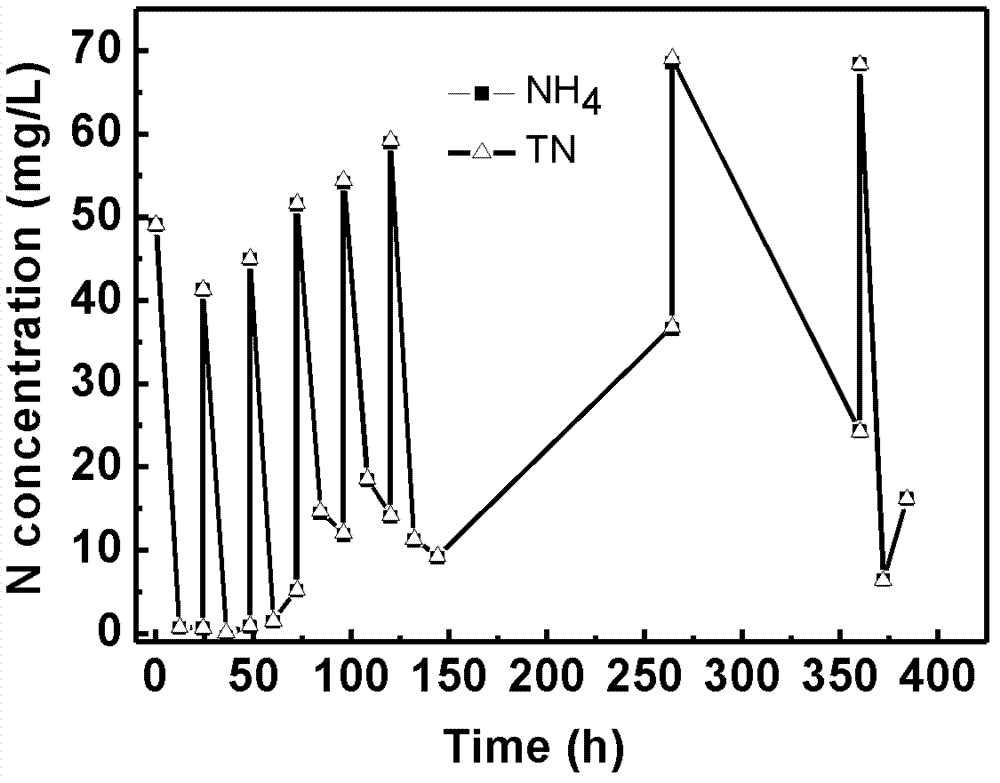

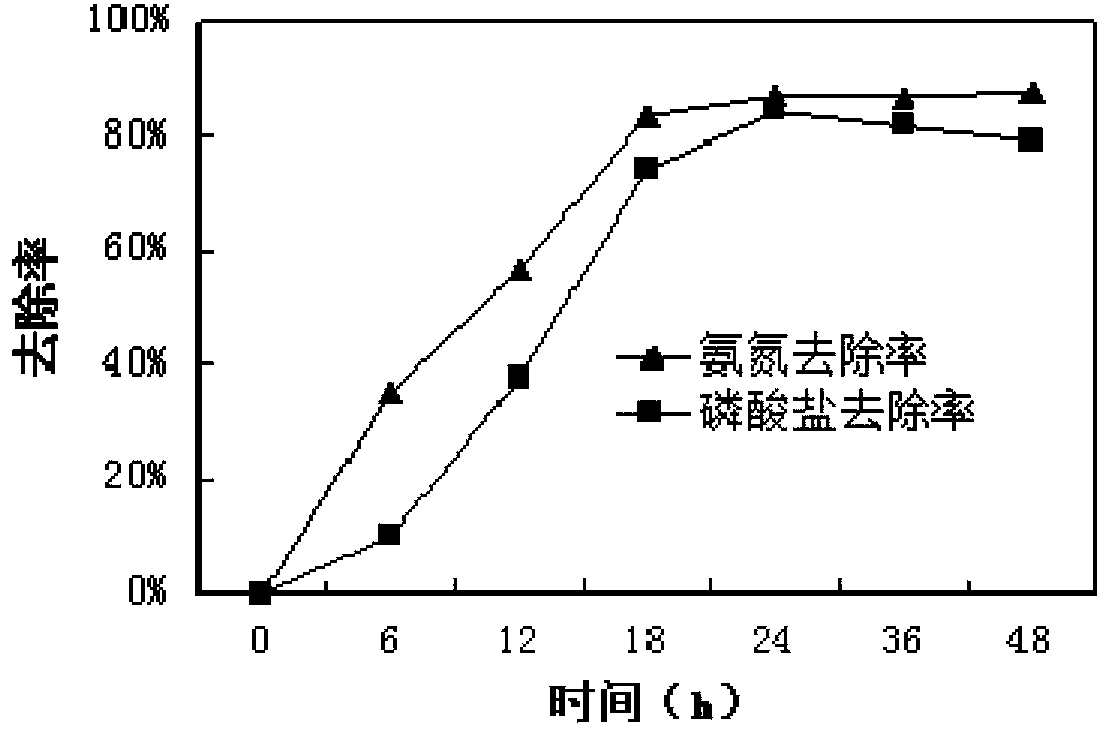

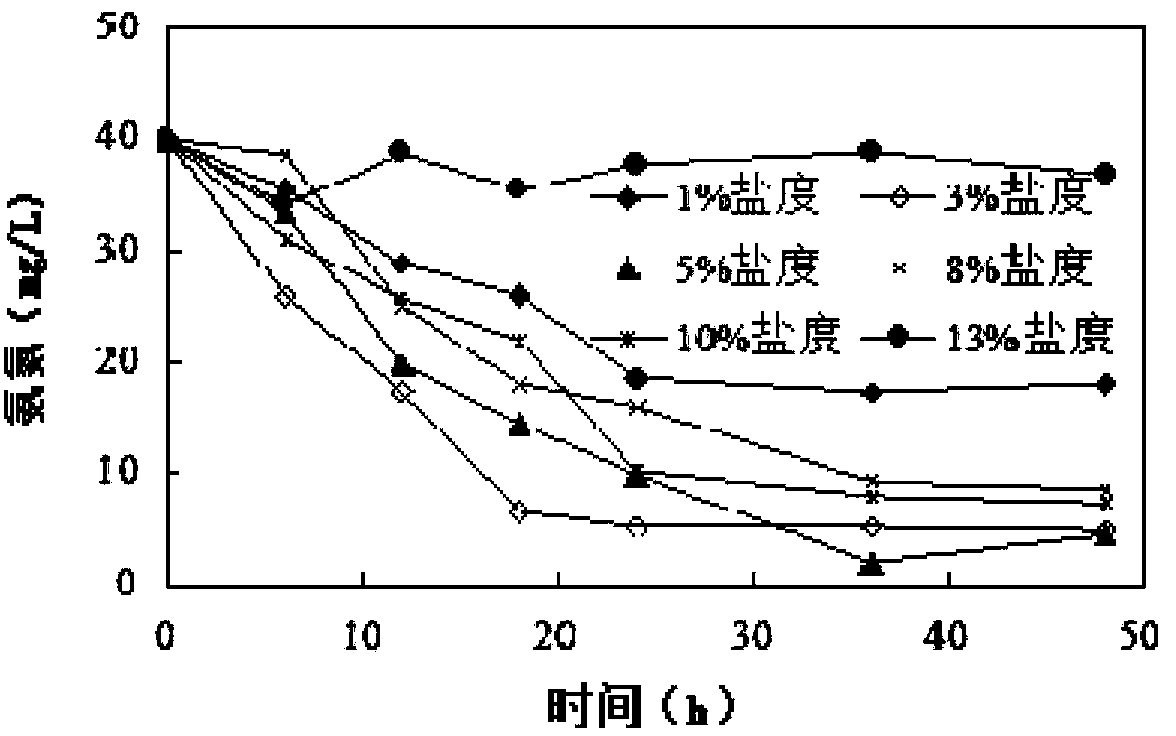

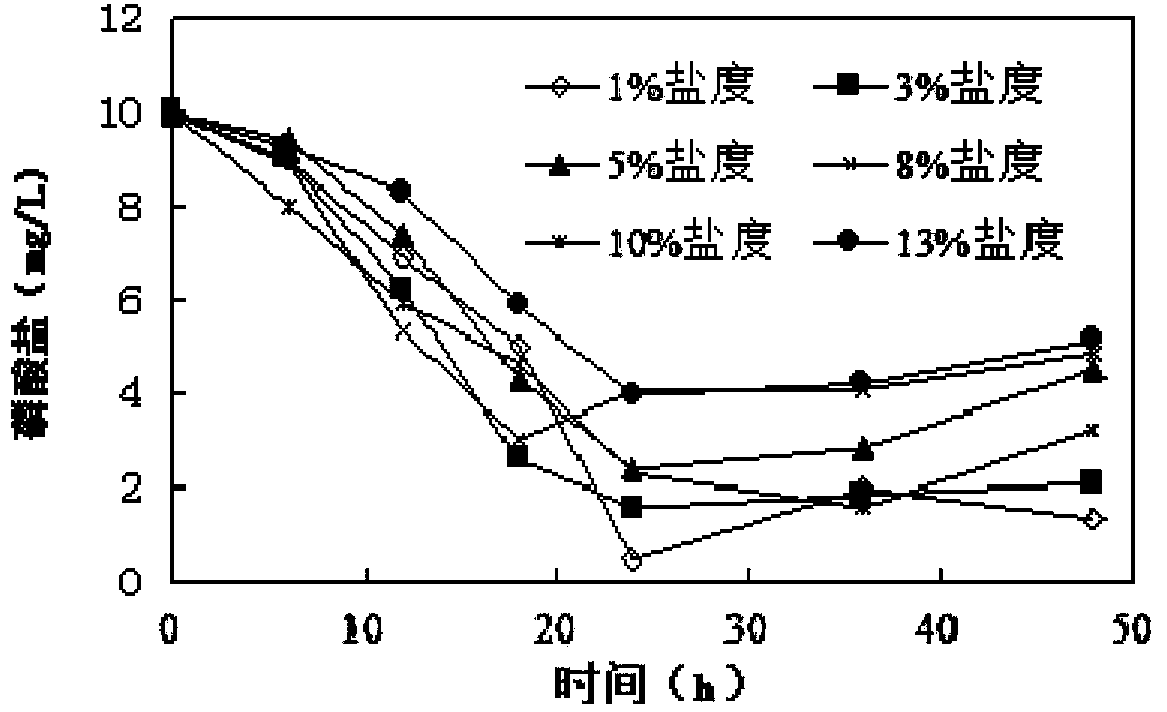

ActiveCN102703350BStrong toleranceRealize synchronous removalBacteriaWater contaminantsNitrate nitrogenSewage

The invention relates to a high salt-tolerant bacillus alitudinis with functions of heterotrophic nitrification-aerobic denitrification and phosphorous removal and application thereof to wastewater treatment. The bacillus alitudinis has strong high salt environment tolerance, grows well under a high-salt condition, and can metabolize by taking organic carbon as one and only carbon source and ammonia nitrogen as one and only nitrogen source; through the heterotrophic nitrification-aerobic denitrification, the ammonia nitrogen is directly converted into a gaseous product so as to achieve a denitrifying purpose; the bacillus alitudinis can also take nitrate nitrogen as one and only nitrogen source, the nitrate nitrogen is converted into a gaseous product through the aerobic denitrification; and under aerobic conditions inorganic phosphorus can be taken into a body and converted into a component of the body so as to realize a purpose of removing phosphorus in sewage. The bacillus alitudinis is applied to high-salt wastewater treatment, can achieve synchronization removal of nitrogen and phosphorus under a single aerobic condition, and provides a new way for solving a problem of biological removal of the nitrogen and phosphorus under the high-salt condition.

Owner:北京大学科技开发有限公司

Achromobacter xylosoxidans with denitrification and dephosphorization function and application of Achromobacter xylosoxidans

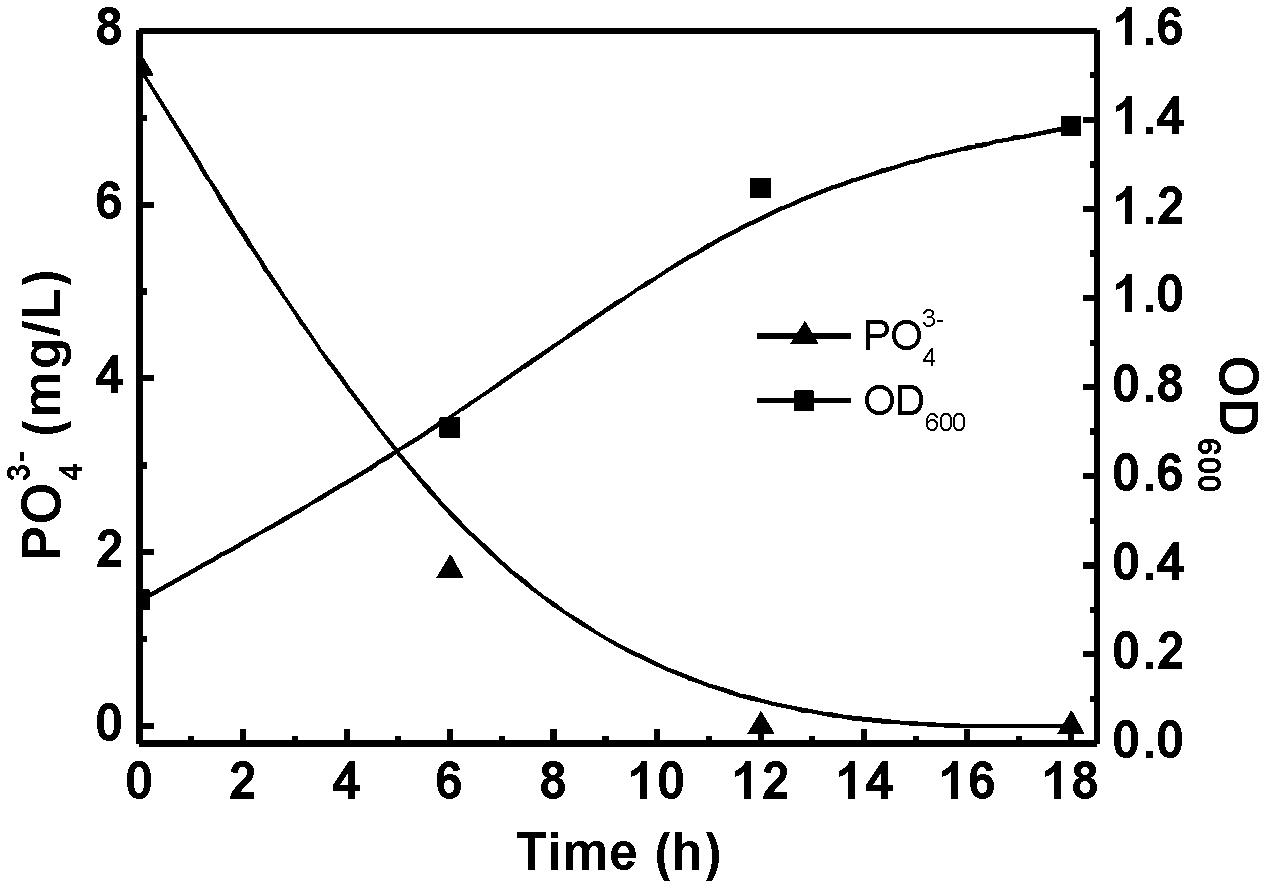

ActiveCN102533623ARealize synchronous removalSolve bottlenecksBacteriaTreatment using aerobic processesPhosphateInorganic phosphorus

The invention relates to application of Achromobacter xylosoxidans with a heterotrophic nitrification-aerobic denitrification and dephosphorization function in wastewater treatment. The Achromobacter xylosoxidans can metabolize by using organic carbon as a unique carbon source and using ammonia nitrogen as a unique nitrogen source and can directly convert the ammonia nitrogen into gas products through the action of heterotrophic nitrification-aerobic denitrification so as to achieve the aim of denitrification, can also take nitrate nitrogen as a unique nitrogen source and convert the nitrate nitrogen into gas products through the action of aerobic denitrification, and can further ingest inorganic phosphorus and convert the inorganic phosphorus into a tissue of the Achromobacter xylosoxidans under an aerobic condition so as to achieve the aim of removing phosphorus from wastewater. The Achromobacter xylosoxidans are applied to the wastewater treatment, the simultaneous removal of nitrogen and phosphorus can be achieved under the single aerobic condition, and the difficult problem that the biological denitrification and dephosphorization in the traditional wastewater treatment need to adopt the segmented treatments of anaerobic phosphate release, anoxic denitrification and aerobic nitrification and phosphorus absorption, is better solved, so that the Achromobacter xylosoxidans have broad application prospects.

Owner:PEKING UNIV

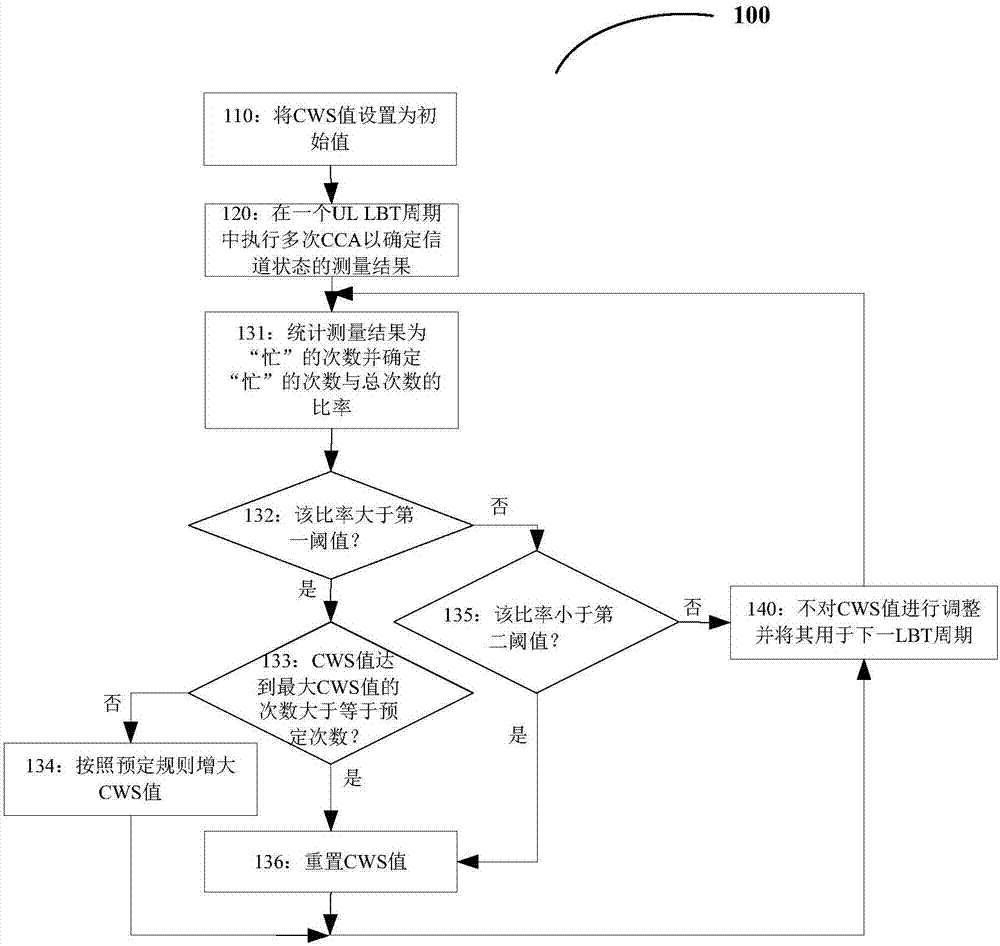

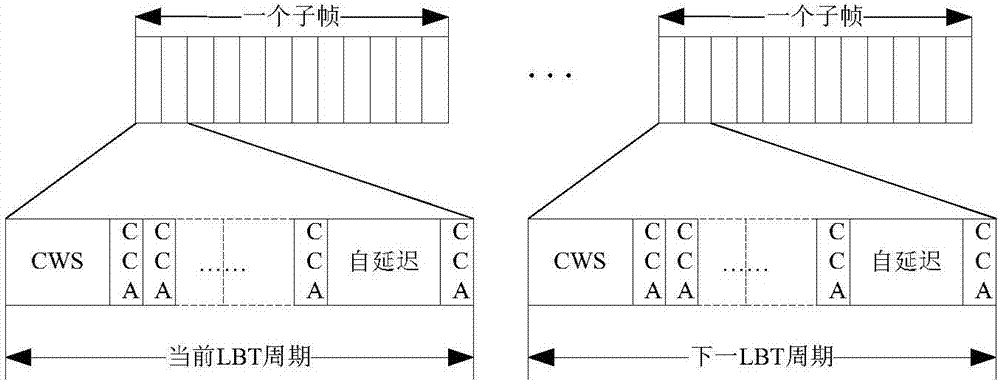

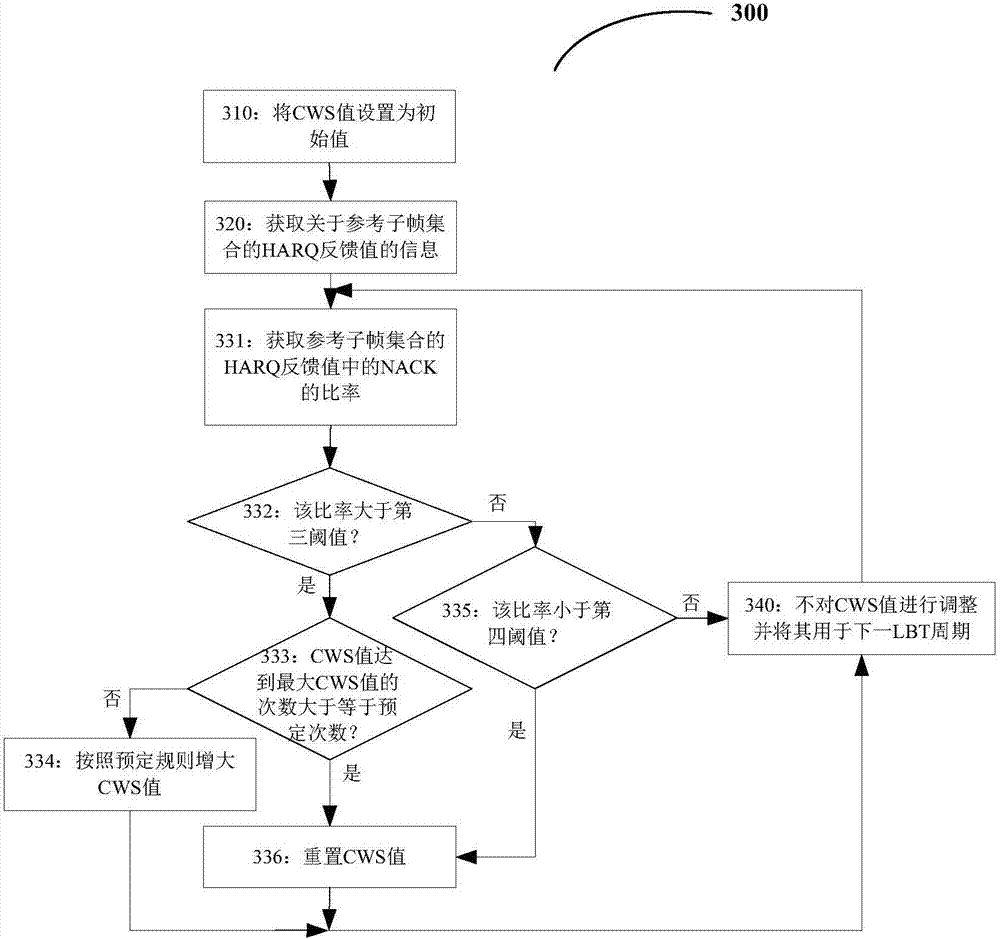

Method and device for adjusting CWS (Contention Window Size) value at UE (User Equipment) side for UL (uplink) transmission

ActiveCN107294662AImprove regulation efficiencyResolve interlockError prevention/detection by using return channelWireless communicationChannel assessmentUser equipment

The invention provides a method and a device for adjusting a CWS (Contention Window Size) value at a UE (User Equipment) side for UL (uplink) transmission. The CWS value is between a preset maximum CWS value and a minimum CWS value. The method comprises steps: in one UL LBT (Listen-before-Talk) cycle, multiple times of CCA (Clear Channel Assessment) are executed to determine the channel state measurement result in each time of CCA; and according to the channel state measurement results in the multiple times of CCA, the CWS value is adjusted to be used in a next UL LBT cycle.

Owner:ALCATEL LUCENT SHANGHAI BELL CO LTD

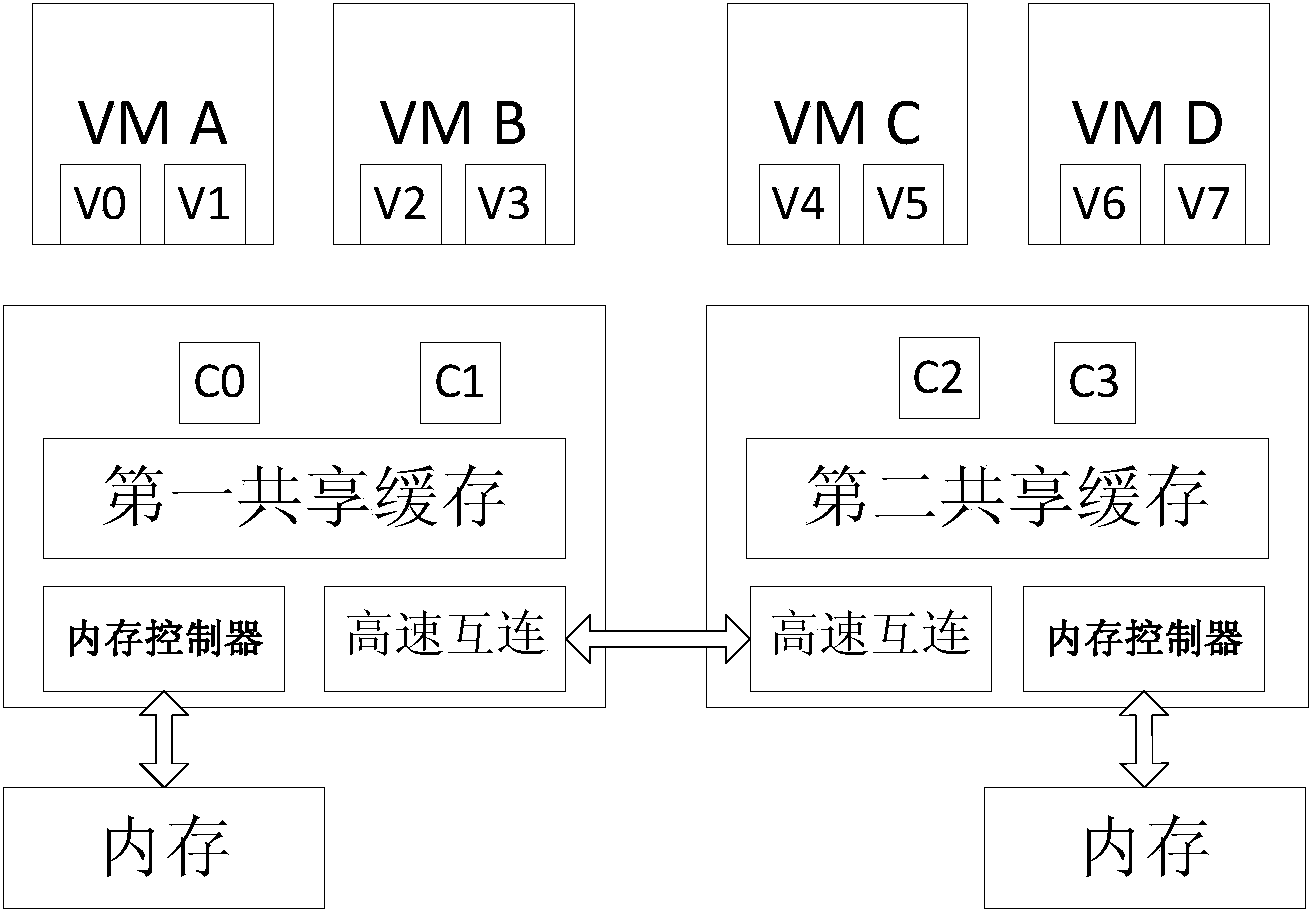

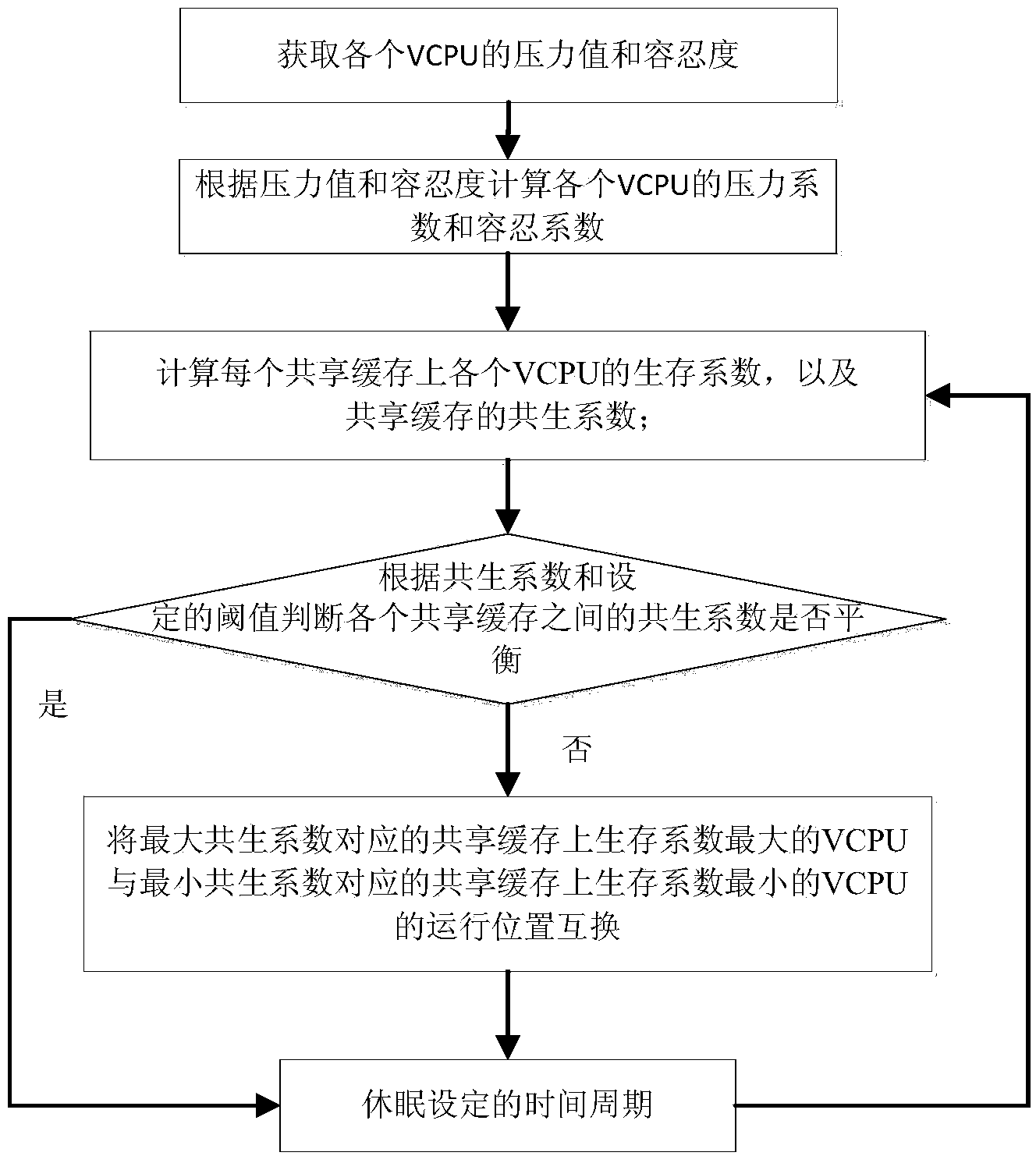

Virtual machine scheduling method based on coexisting coefficient balance

InactiveCN103955396AImprove operational efficiencyImprove the operating environmentResource allocationSoftware simulation/interpretation/emulationMemory controllerVirtual machine scheduling

The invention discloses a virtual machine scheduling method based on coexisting coefficient balance. The virtual machine scheduling method comprises the following steps: based on pressure values and tolerance degrees of VCPUs (Virtual Central Processing Units) running on a multi-core physical server, calculating to obtain the pressure coefficients and tolerance coefficients of the VCPUs, calculating the existing coefficients of the VPCUs on shared caches and the coexisting coefficients of the shared caches according to the pressure coefficients and the tolerance coefficients, judging whether the coexisting coefficients of the shared cache in a virtual machine system are in balance or not according to the coexisting coefficients and set thresholds; when the coexisting coefficients are not in balance, performing VCPU scheduling according to the coexisting coefficients of the VCPUs, so as to keep the coexisting coefficients of the shared caches in balance. By adopting the virtual machine scheduling method, the problem that virtual machines compete with one another to obtain shared cache resource, a memory controller and memory bandwidth resource in a multi-core processor is effectively solved, the situation that the virtual machines compete for and use the shared resource is identified, the operation environment of the virtual machines is optimized, and the service quality of the virtual machines is improved.

Owner:ZHEJIANG UNIV

A buffering structure for sectioned share optical loop switching network

InactiveCN101106523AReduce the numberSolve the problem of port contentionMultiplex system selection arrangementsWavelength-division multiplex systemsTime delaysTime difference

The invention protects a sectional type shared packet switching network buffering structure and relates to optical communication technology field. The invention provides a novel optical packet switching network buffering structure, aiming at the property of the current optical packet switching network buffering structure about low optical fiber operating factor and high cost. The buffering structure adopts optical fiber sectional type share mechanism and consists of a plurality of optical fiber delay units with the same time delay. Except for the next level of delay optical fiber is directly connected with the optical packet switching matrix, two inlets of other optical delay unit on each level are connected with the outlet of the next level of delay optical fiber and are directly connected with the outlet of the optical packet switching matrix. The optical packet data packet in need of time delay chooses different delay optical fiber inlet, according to the time difference of the optical packet switching matrix outlet. The structure can fully improve the operating factor of the optical fiber delay line, reduce the core node cost and solve the interface competition problem of optical packet switching network.

Owner:CHONGQING UNIV OF POSTS & TELECOMM

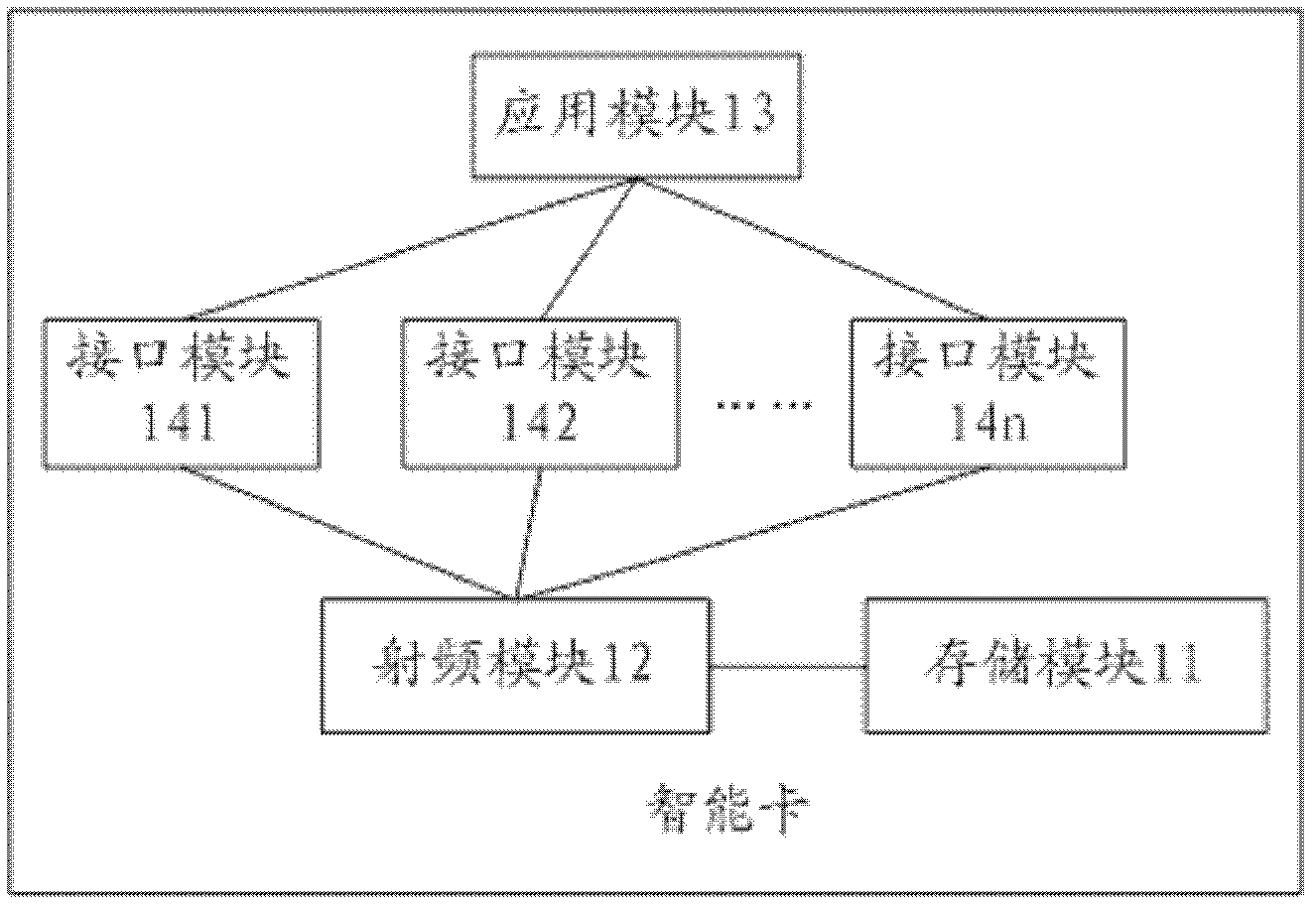

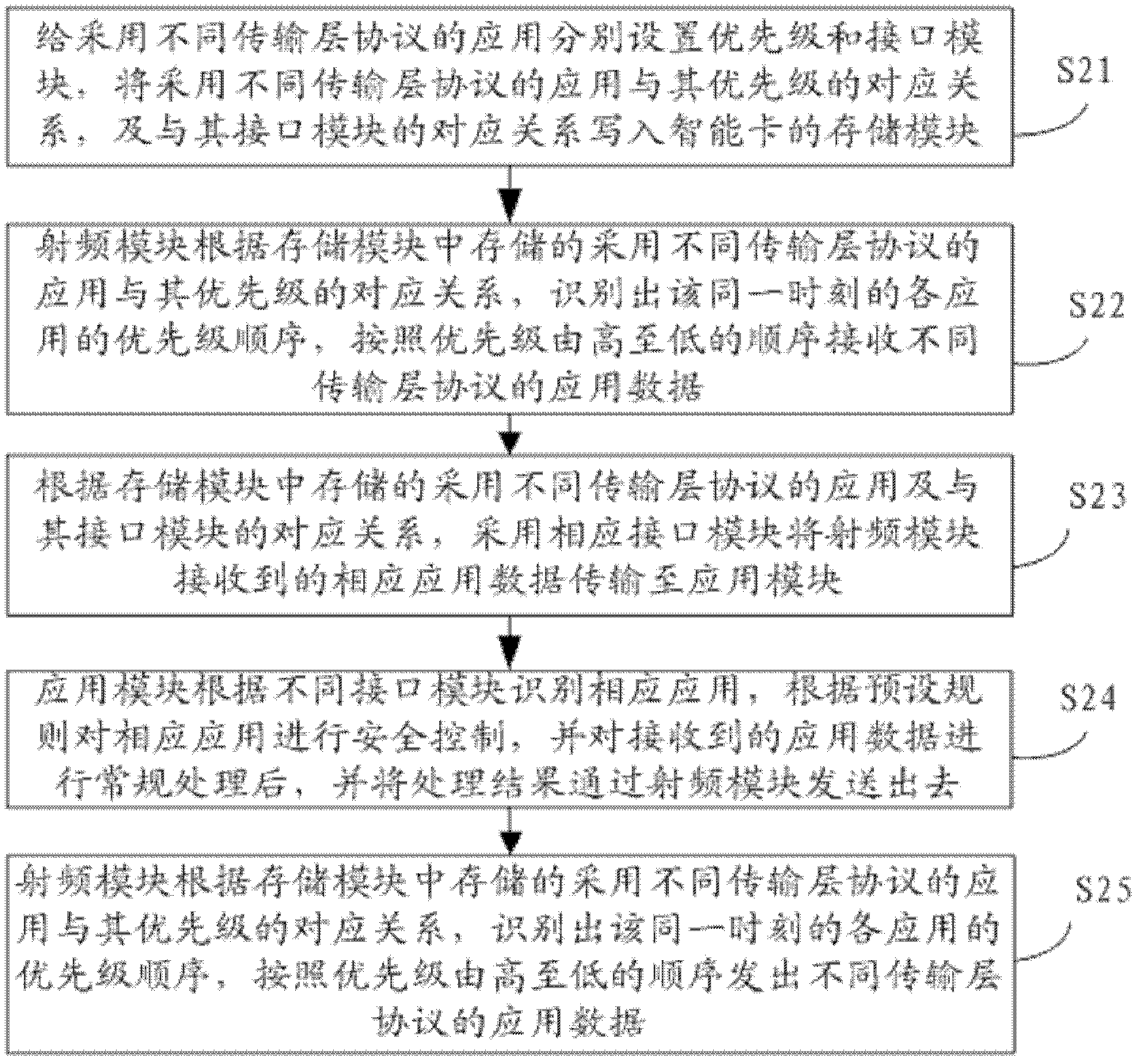

Intelligent-card working method and intelligent card

ActiveCN103186810AAddress competitionEasy to useRecord carriers used with machinesTransport layerComputer module

The invention discloses an intelligent-card working method and an intelligent card. The intelligent-card working method comprises the steps of setting different priority levels for applications using different transport layer protocols, and writing the corresponding relations between all the applications and the priority levels of the applications into the intelligent card; and receiving and sending data of all the applications through the same radio frequency module according to the sequence from the highest priority level to the lowest priority level. By means of the technical scheme of the intelligent-card working method and the intelligent card, the problem that the applications utilizing the different transport layer protocols share the same radio frequency module is resolved.

Owner:NATIONZ TECH INC

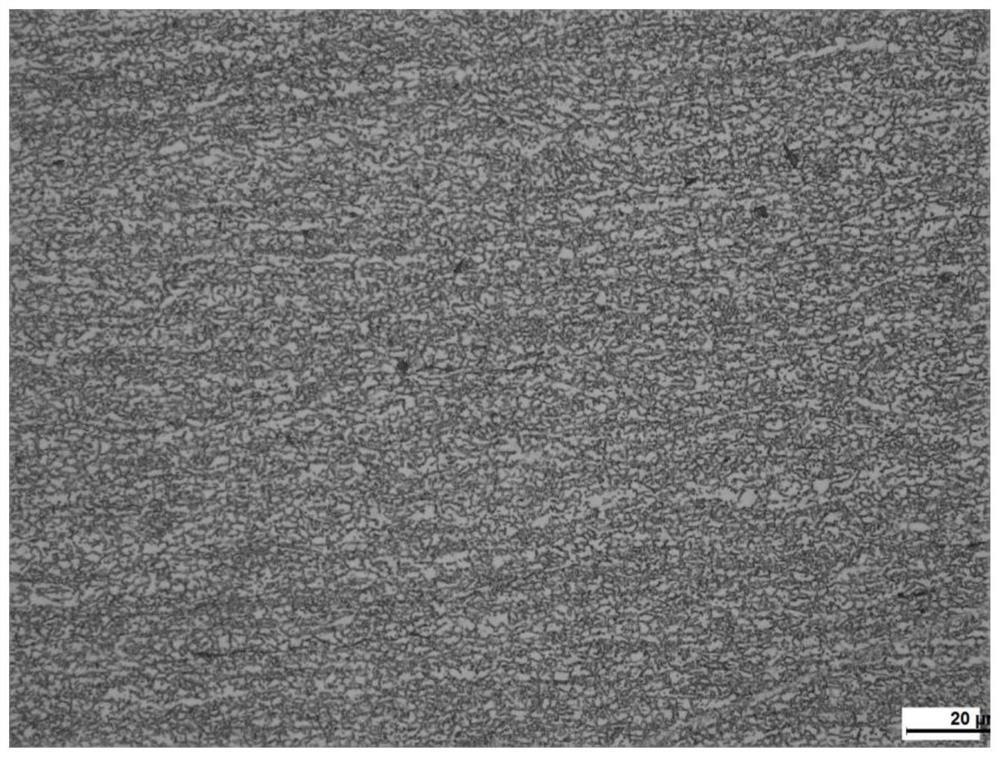

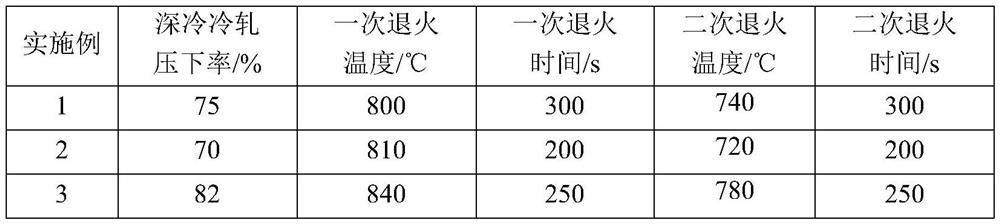

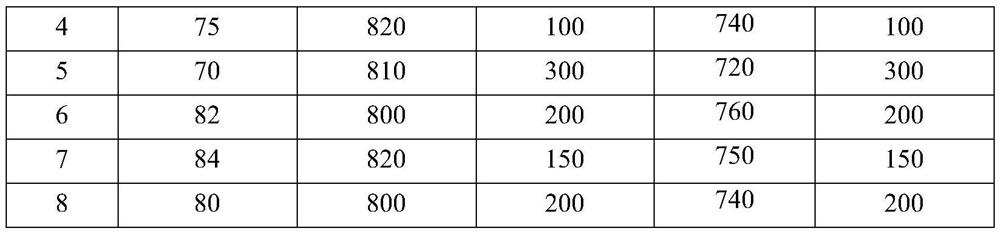

Mn-TRIP steel plate with product of strength and elongation of 50 GPa% for automobile and preparation method of Mn-TRIP steel plate

ActiveCN113073261AAdd lessImprove processing stabilityProcess efficiency improvementTRIP steelChemical composition

The invention relates to a Mn-TRIP steel plate with a product of strength and elongation of 50 GPa% for an automobile and a preparation method of the Mn-TRIP steel plate. The steel plate comprises the following chemical components of, in percentage by mass, 0.18%-0.28% of C, 0.3%-1.2% of Si, 2.8%-3.8% of Mn, 0.9%-1.9% of Al, less than or equal to 0.05% of P, less than or equal to 0.05% of S, 0.10%-0.20% of V and the balance of Fe and inevitable impurities. According to the steel plate, the addition amount of alloy elements in the steel plate is greatly reduced compared with that of traditional medium manganese steel, no precious alloy elements such as Cr and Mo needs to be added, and the deep cooling rolling process and the double annealing process are combined to achieve the effect of strengthening and plastification; and the process stability is good, the structure homogenization degree is high, and the production safety is high.

Owner:ANGANG STEEL CO LTD

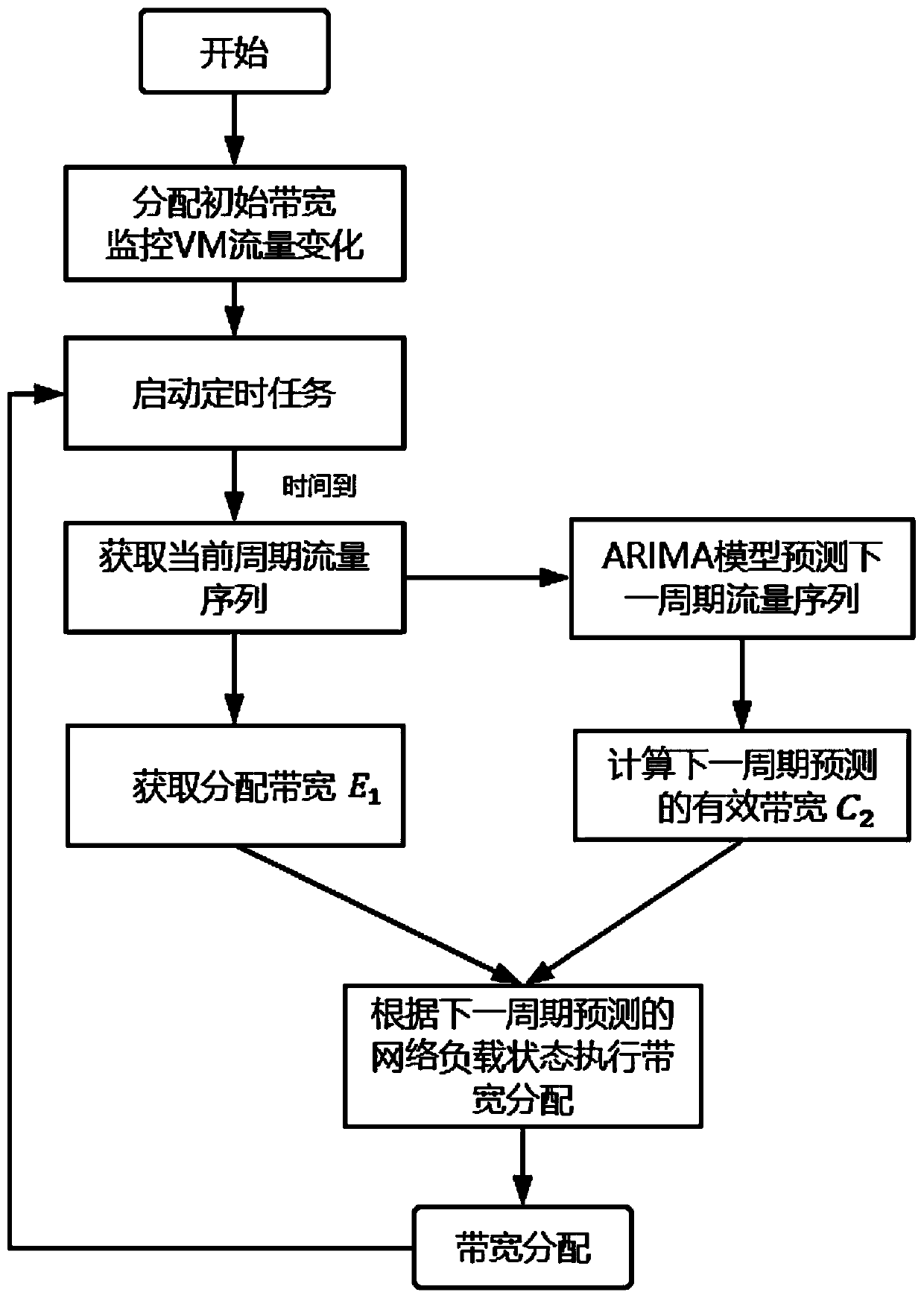

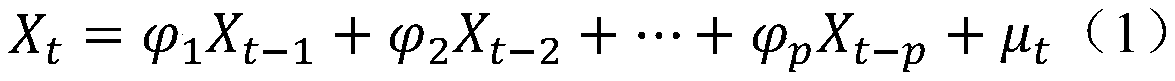

Virtual machine bandwidth allocation method of OpenStack based on application service

InactiveCN110365518AImplement dynamic allocationAddress competitionData switching networksSoftware simulation/interpretation/emulationDynamic bandwidth allocationResource utilization

The invention discloses a virtual machine bandwidth allocation method of OpenStack based on application service. The virtual machine bandwidth allocation method comprises the following steps: 1, specifying a network QoS index of an OpenStack cloud platform application; step 2, determining an ARIMA prediction model; 3, calculating an effective bandwidth based on the QoS of the application accordingto the statistical characteristics of the application flow; 4, predicting the network load state of the virtual machine in the next period according to the effective bandwidth; and 5, allocating thebandwidth by the network load state of the virtual machine according to different allocation strategies. The virtual machine dynamic bandwidth allocation method overcomes the defect that a static bandwidth allocation method is low in resource utilization rate, overcomes the defect that a traditional bandwidth allocation method cannot guarantee QoS of an application network, reasonably and effectively utilizes OpenStack cloud platform bandwidth resources, increases the bandwidth resource utilization rate, and meanwhile guarantees QoS of virtual machine application.

Owner:SOUTH CHINA UNIV OF TECH

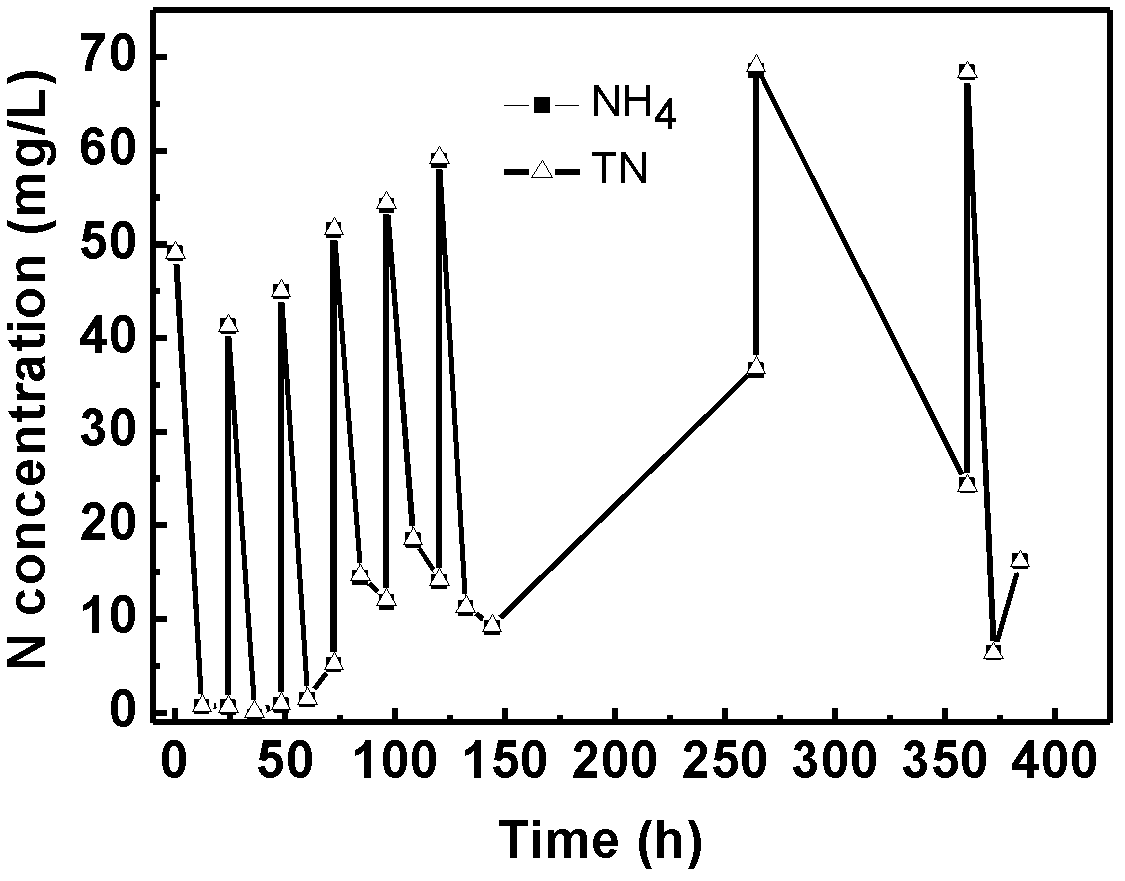

Process for treating high-concentration nitrate and ammonia-nitrogen wastewater by using sludge fermentation liquor as carbon source through series connection of short-cut denitrification and anaerobic ammonia oxidation

InactiveCN113023870AAchieve reductionLow additional costWater treatment parameter controlBiological treatment regulationVolatile fatty acidsNitration

The invention discloses a process for treating high-concentration nitrate and ammonia-nitrogen wastewater by using sludge fermentation liquor as a carbon source through series connection of short-cut denitrification and anaerobic ammonia oxidation, and belongs to the field of sewage treatment. The device comprises a sludge fermentation tank, a PD-SBR reactor, an AMX-SBR reactor and the like. The method comprises the following steps: the residual sludge is fermented under a medium-temperature alkaline anaerobic condition, and converting refractory organic matters into easily degradable organic matters; denitrifying bacteria perform short-cut denitrification by utilizing volatile fatty acid in the fermentation liquor, and nitrate is converted into nitrite; and effluent and high-ammonia-nitrogen wastewater enter an anaerobic ammonium oxidation film reactor together for autotrophic nitrogen removal, and the polyurethane sponge filler is used for holding anaerobic ammonium oxidation bacteria. According to the method, the aeration energy consumption is reduced, the sludge fermentation liquid is used as the external carbon source, a high-quality carbon source is provided for denitrification, sludge reduction is realized, the sludge treatment cost and the external carbon source addition cost are reduced, stable nitrite accumulation is realized by short-cut denitrification, and synchronous treatment of high-nitrate wastewater and high-ammonia-nitrogen wastewater is realized by combining anaerobic ammonia oxidation.

Owner:BEIJING UNIV OF TECH

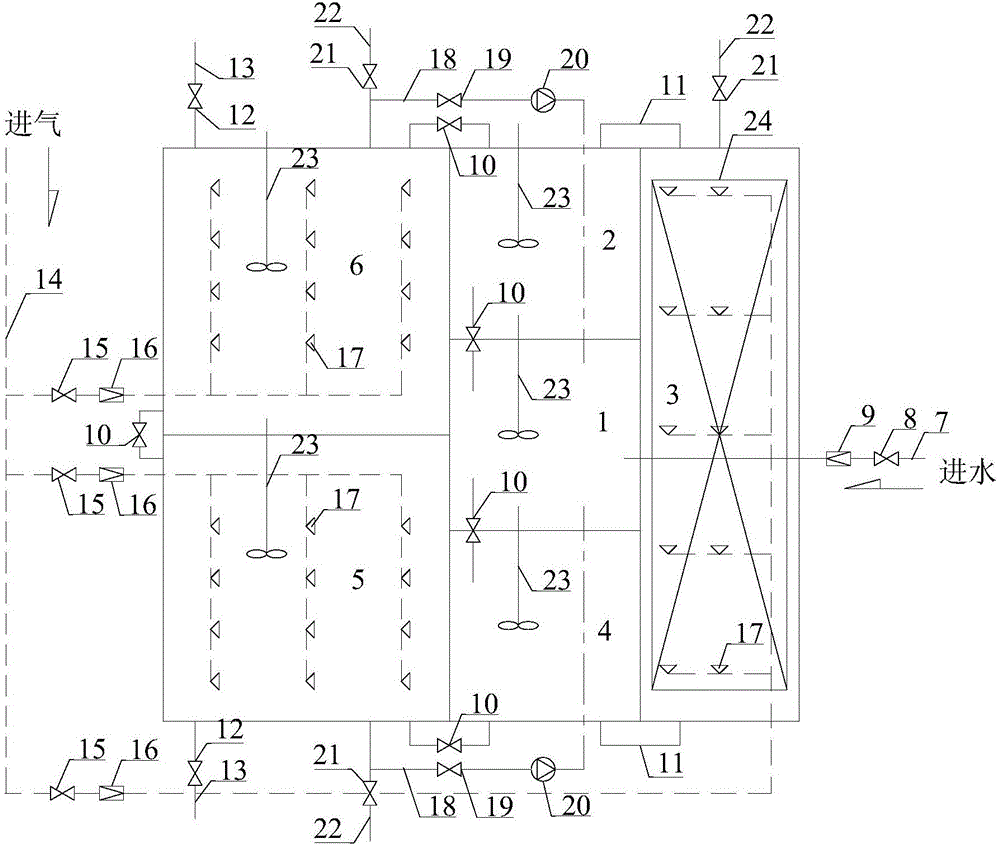

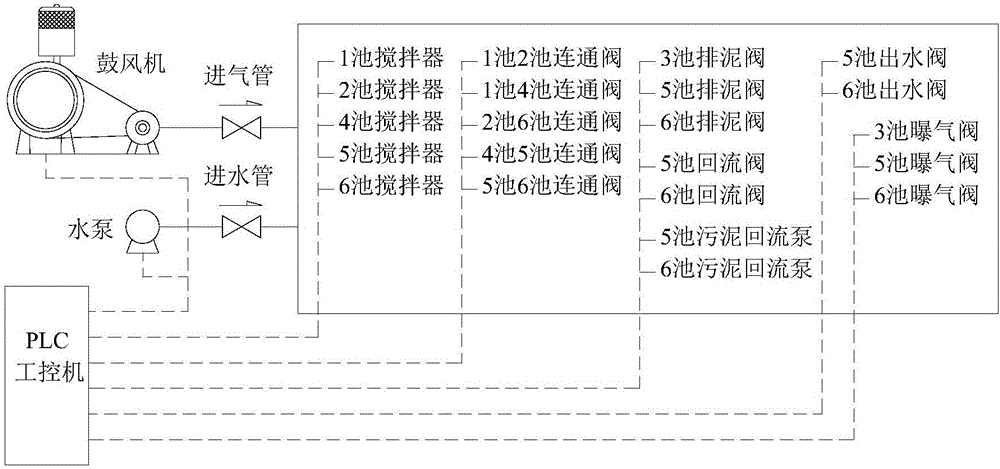

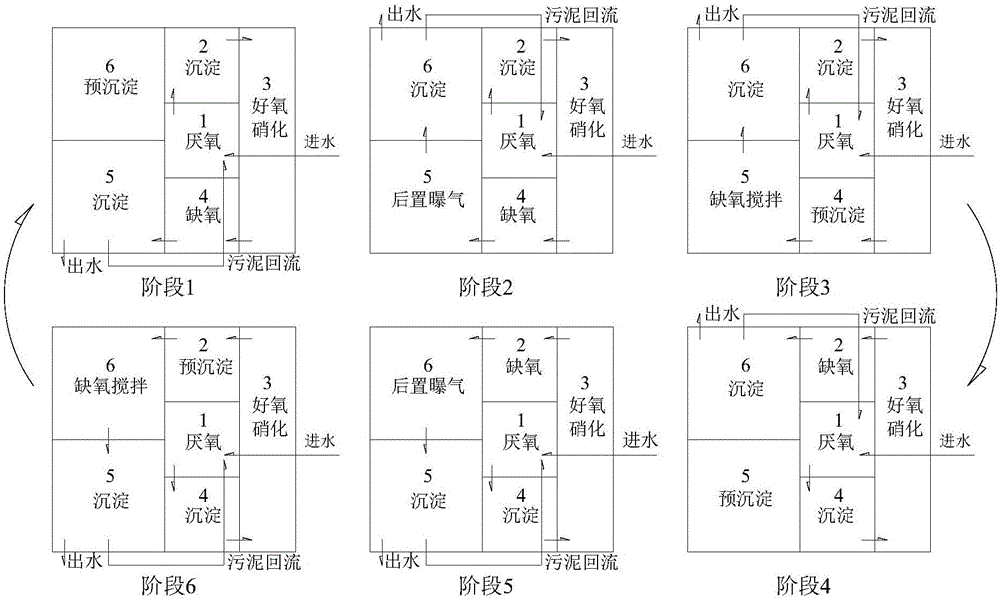

Six-box integrated two-sludge denitrifying phosphorus removal system and technology

ActiveCN106007258ASolve conflictsAddress competitionWater contaminantsSludge processingSludgeClosed loop

The invention discloses a six-box integrated sewage treatment technology with an enhanced denitrifying phosphorus removal function. Rectangular reaction tanks spaced into six units are connected in series through a communication valve or communication pipe to form a closed loop, the functions of organic matter degradation, nitrogen and phosphorus removal and precipitation are integrated, and the land occupation of a project is effectively saved. Through alternate water output of the tanks and the switch among the states of anoxic stirring, aeration and precipitation, the functions of each stage of the A2N two-sludge technology are realized, the contradiction and competition of nitrifying bacteria, denitrifying bacteria and phosphorus-accumulating bacteria on the needs for organic load, sludge age and carbon source are solved, the energy consumption is low, the needs for carbon source are few, and the residual sludge quantity is small; and in the system operation process, the sludge-crossing backflow can be automatically realized through the reversing flow of water and without adding sludge-crossing backflow equipment, thereby saving the investment and operation cost. A PLC (programmable logic controller) controls the start / stop of the stirring equipment, aeration equipment and valve according to the regulated control technology, and full-flow automatic operation is realized.

Owner:SOUTHEAST UNIV

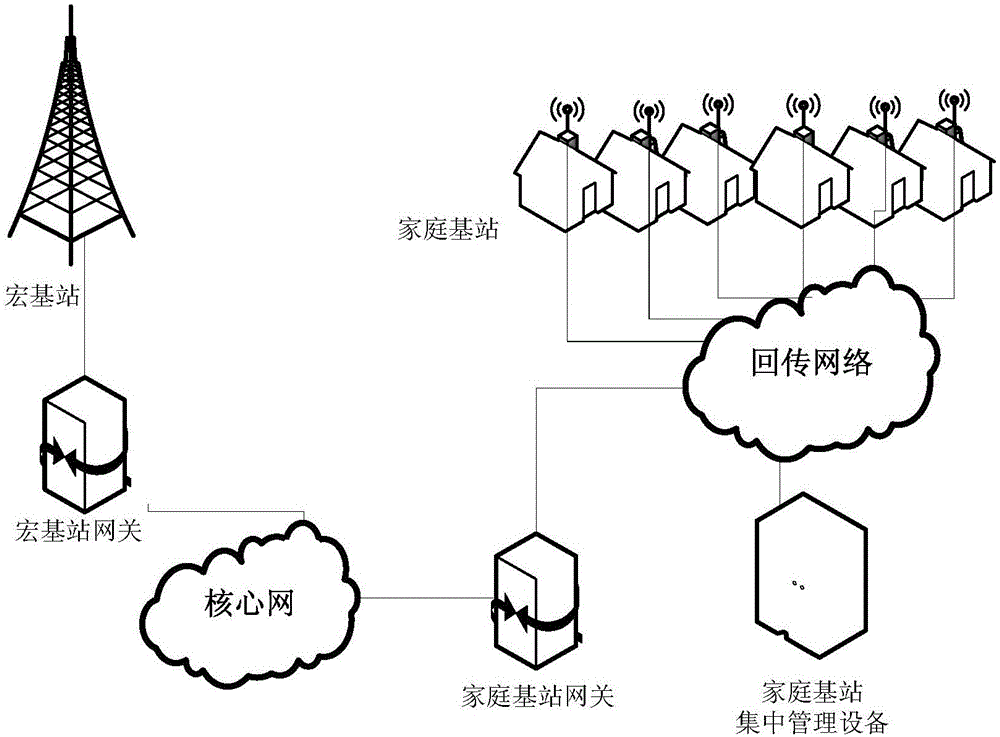

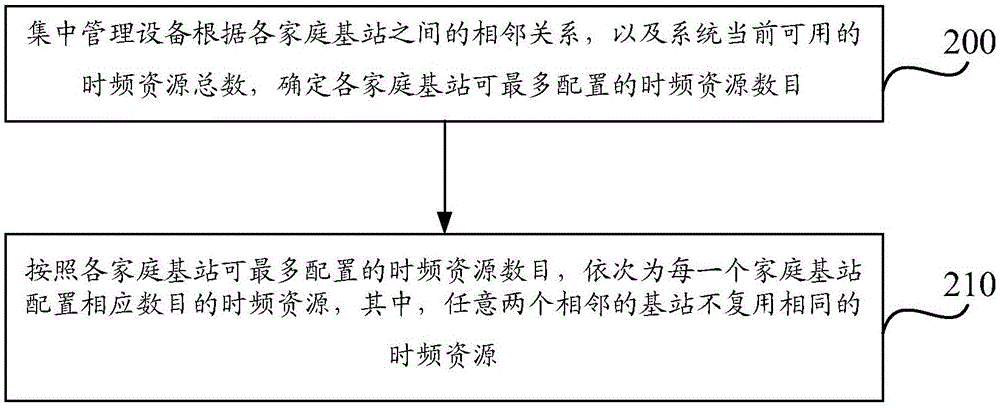

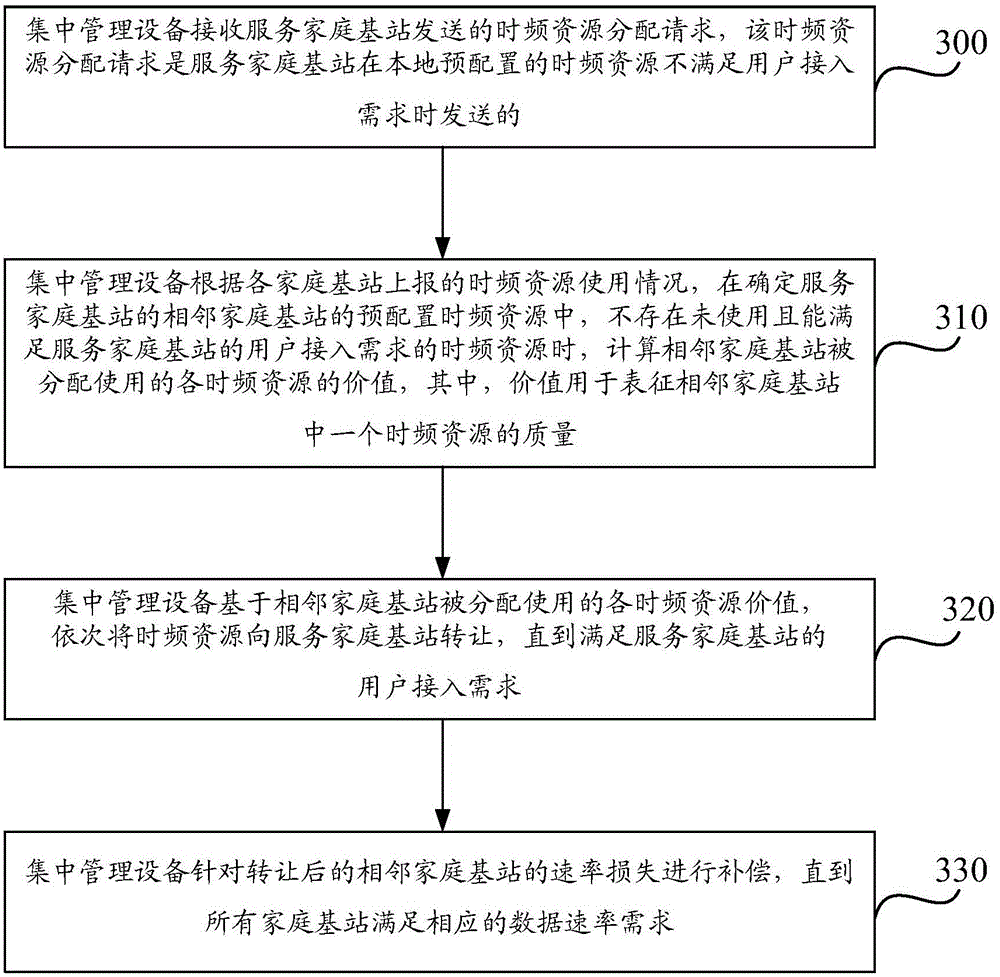

Method of configuring time frequency resource between household base stations cooperatively and device of configuring time frequency resource between household base stations cooperatively

ActiveCN105050187AImprove throughputImprove stabilityWireless communicationQuality of serviceData rate

The present invention discloses a method of configuring time frequency resource between household base stations cooperatively and a device of configuring the time frequency resource between the household base stations cooperatively, which are used for improve the reliability and the service quality of a network. The method comprises the steps of using a centralized management device to receive the time frequency resource distribution requests sent by the service household base stations, wherein the time frequency resource distribution requests are sent when the local pre-configured time frequency resources do not satisfy the user access demands, when the time frequency resources which are not used and can satisfy the user access demands are determined not to exist in the pre-configured time frequency resources of the adjacent household base stations, transferring the time frequency resources to the service household base stations orderly according to an order from small to large of the values of the time frequency resources distributed to and used by the users of the adjacent household base stations until the time frequency resources satisfy the user access demands, and compensating aiming at the rate loss of the transferred household base stations until all household base stations satisfy the data rate demands of the users. Therefore, a household base station wireless resource distribution conflict is solved in a local range cooperatively, the channel condition of the network is optimized, and the throughput, stability, reliability and service quality of the network are improved.

Owner:XIAMEN UNIV +1

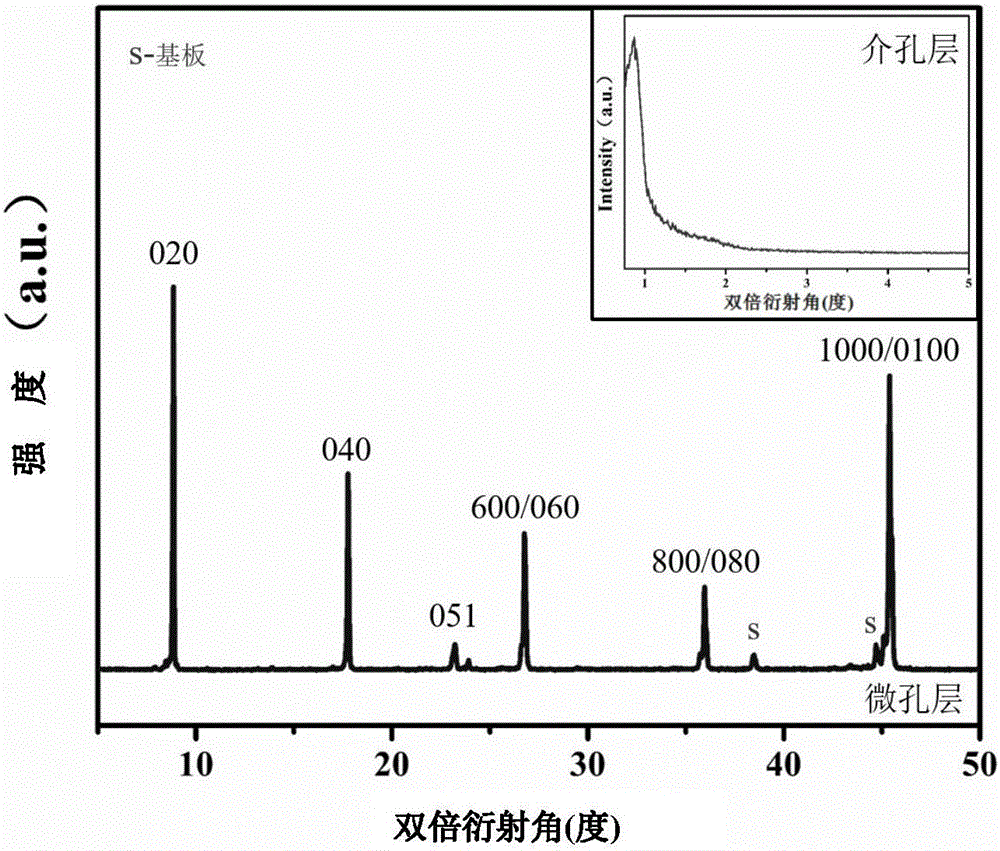

Gradient composite structure hierarchical pore thin film and preparation method thereof

ActiveCN106179195AAvoid competition problemsHigh crystallinityCatalytic crackingMolecular sieve catalystsMacroporeComposite structure

The invention provides a gradient composite structure hierarchical pore thin film and a preparation method thereof. The thin film is a hierarchical pore thin film in a micropore / mesopore system and has the micropore / mesopore system or a micropore / macropore system or a micropore / mesopore / macropore system. The preparation method of the thin film includes the steps that a mesopore layer with a three-dimensional pore canal is deposited on the surface of a micropore layer, a sample of a micropore / macropore structure is obtained, or a macropore layer with an open pore canal is deposited on the surface of the micropore layer, and a sample of a micropore / macropore structure is obtained, or multiple mesopore layers and macropore layers are deposited on the surface of the micropore layer sequentially, and a sample of a micropore / mesopore / macropore gradient pore structure is obtained. The thin film sample of the gradient pore structure is put in an atmosphere oven, all templates are removed through one-step calcination, a metal base plate is removed through soaking of low-concentration inorganic acid, and the gradient composite structure hierarchical pore thin film is obtained. Operation is easy and convenient, the production period is short, the application range of products is wide, and the thin film is used for the field of catalytic cracking of heavy oil and residual oil and the separation field such as sea water desalination.

Owner:WUHAN UNIV OF TECH

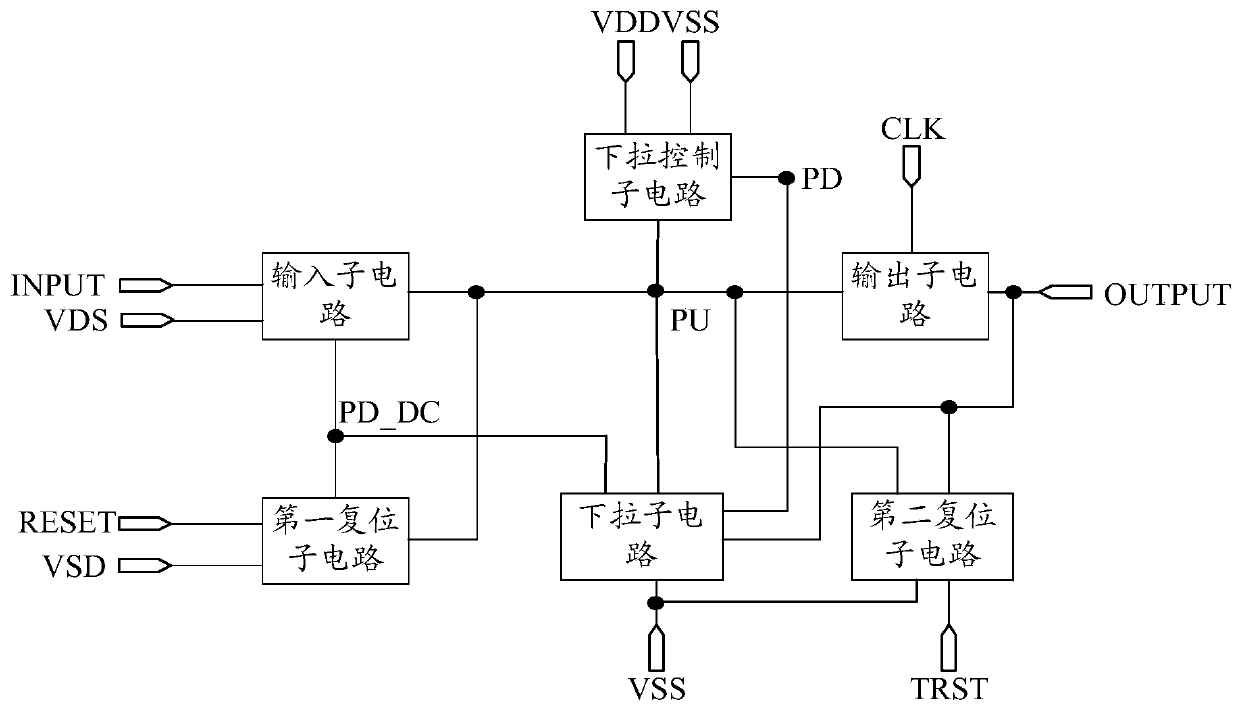

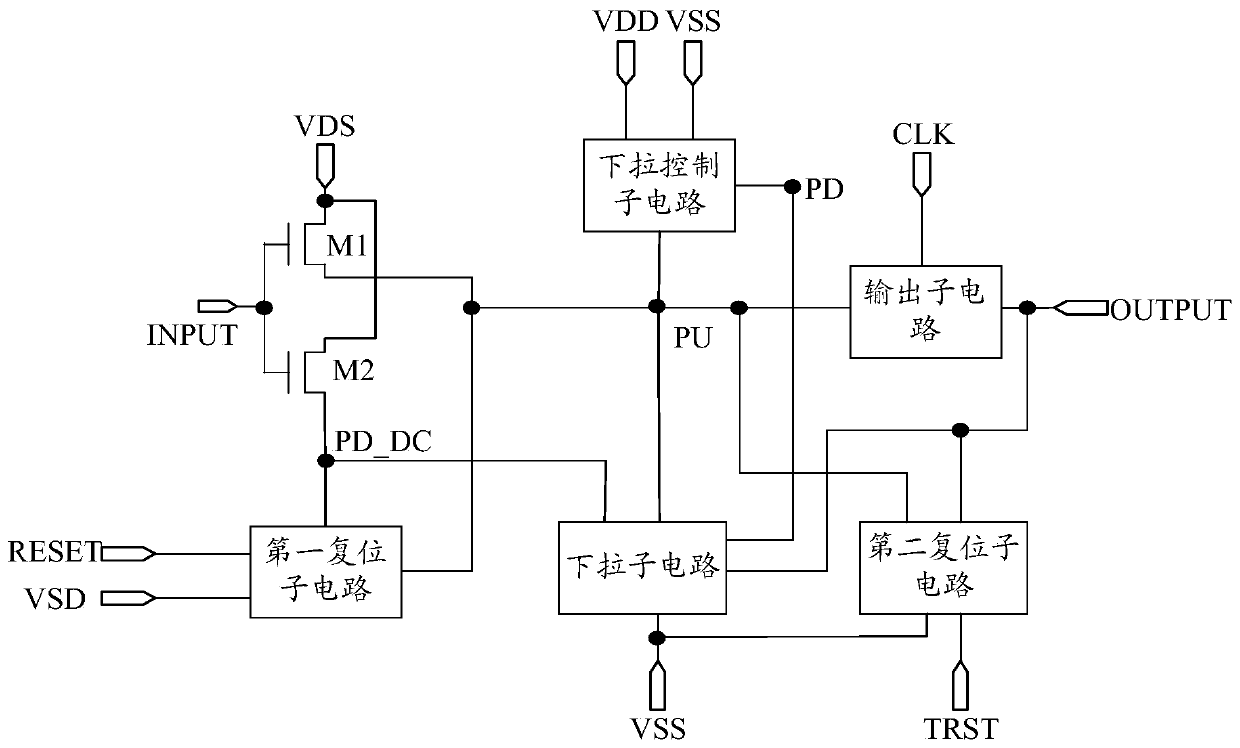

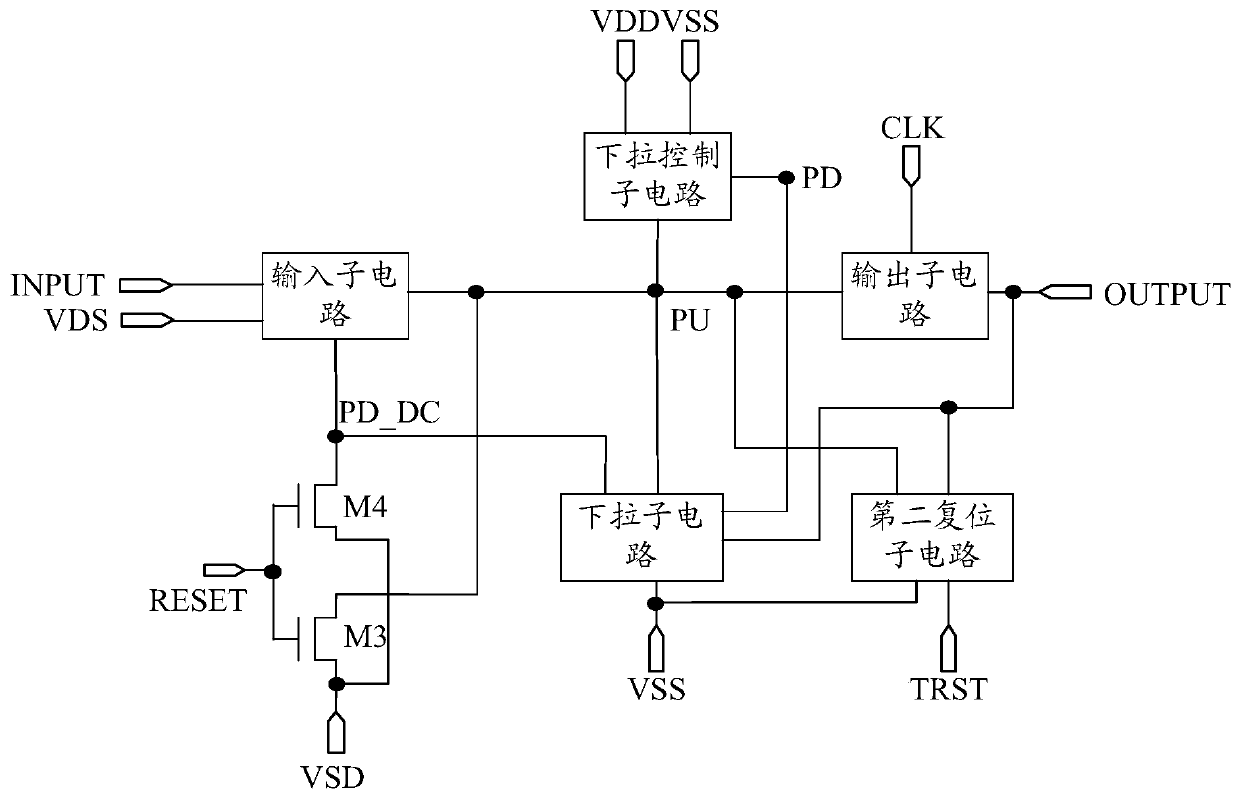

Shifting register, driving method thereof and gate driving circuit

ActiveCN111243489AAddress competitionImprove display qualityStatic indicating devicesDigital storageShift registerDriver circuit

The invention relates to a shift register, a driving method thereof and a gate driving circuit. The shift register comprises an input sub-circuit, a first reset sub-circuit, an output sub-circuit, a pull-down sub-circuit, a pull-down control sub-circuit and a second reset sub-circuit. The input sub-circuit provides a signal of a first voltage source for a pull-up node and a first node under the control of a signal input end; the first reset sub-circuit provides a signal of a second voltage source for the pull-up node and the first node under the control of a reset end; the output sub-circuit outputs a signal of a clock signal end to a signal output end according to the level of the pull-up node; the pull-down control sub-circuit controls the level of a pull-down node according to the levelof the pull-up node and a signal of a third voltage source; and the pull-down sub-circuit outputs the level of a fourth voltage source to the pull-down node according to the level of the first node,and outputs the level of the fourth voltage source to the pull-up node and the signal output end according to the level of the pull-down node. According to the invention, the problem that the pull-upnode and the pull-down node compete with each other during bidirectional scanning is solved.

Owner:HEFEI XINSHENG OPTOELECTRONICS TECH CO LTD +1

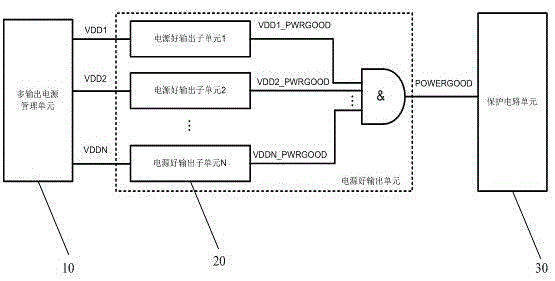

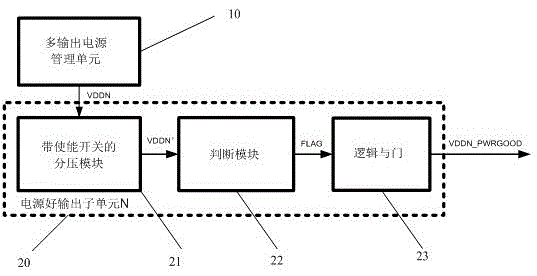

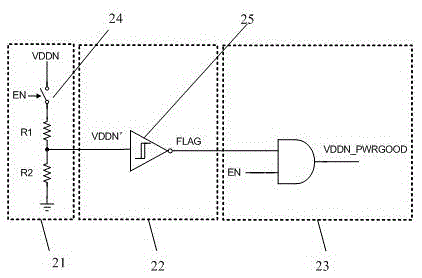

Power good signal output method and power good signal output device

ActiveCN105654885AImprove the accuracy of judgmentAddress competitionStatic indicating devicesFlag signalsFlip-flop

The invention provides a power good signal output method and a power good signal output device. The power good signal output device comprises the components of a voltage bleeding module which is provided with an enabling switch and is used for converting an input power voltage to a detecting sub-voltage for determination, wherein the enabling switch responds to the enabling signal, and the power voltage is positive or negative; a forward determination module or a backward determination module which is used for determining the detecting sub-voltage and outputting a mark signal; and a trigger which is used for processing the enabling signal and the mark signal and outputting the power good signal. According to the power good signal output method and the power good signal output device, the enabling signal and the mark signal are processed by means of the trigger for outputting the power good signal. Not only can zero-power-consumption static current realized in a deep-sleep or shutdown manner, but also a competition problem and a risk problem caused by different time delays of the enabling switch and a determining module can be settled. The power good signal output method and the power good signal output device have advantages of eliminating a burr phenomenon in actual response output, improving determination accuracy for the power good state, and improving integral performance of a display driving chip.

Owner:GALAXYCORE SHANGHAI

Optical packet-switched networks node structure based on adjustable laser

InactiveCN1434310ASmall scaleReduce and avoid adverse effectsMultiplex system selection arrangementsWavelength-division multiplex systemsNetwork structureOptical packet

The invention is a node structure of optical packet-switched network, based on adjustable laser. The node input fibre-optical is divided into multiple paths by the wave-division device and then respectively links with an adjustable wavelength converter, the output end of each converter linked with the different-length fibre-optical delayed line by one wave-division device, that of each group of delayed lines linked with the optical switch array by a wave-combing apparatus and an adjustable wavelength converter and that of the array linked with the waving-combing device whose number is same tothe node input end, so as to output the optical signal to the aim node. It adopts the converter to realize the path selection and transmission of the optical package and multiple wave-combing and wave-division devices to select the delayed line.

Owner:SHANGHAI JIAO TONG UNIV

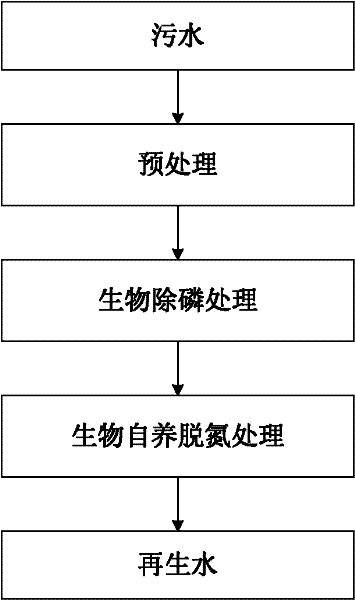

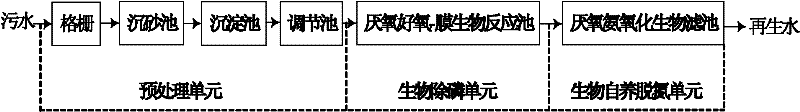

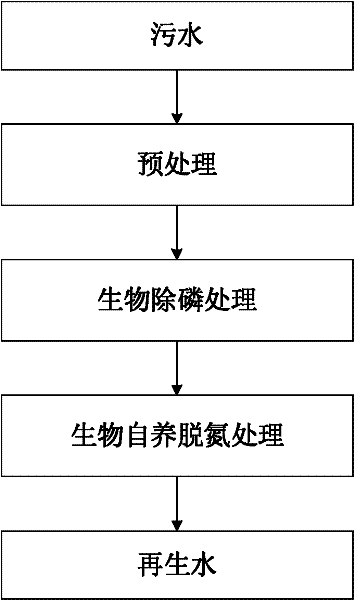

Method and System for Phosphorus and Nitrogen Removal in Sewage

InactiveCN102267783AShort hydraulic retention timeLow costMultistage water/sewage treatmentOxygenLarge particle

The invention discloses a method and system for removing phosphorus and nitrogen from sewage, belonging to the field of sewage treatment. The method includes: pretreatment: making the sewage enter the pretreatment unit for pretreatment, removing large suspended solids in the sewage, and adjusting the sewage from which the suspended solids have been removed; biological phosphorus removal treatment: making the effluent after the above pretreatment enter the Biological phosphorus removal and organic matter removal are carried out in the biological phosphorus removal unit; biological autotrophic denitrification treatment: the effluent after the above biological phosphorus removal treatment enters the biological autotrophic denitrification unit, and passes through the The autotrophic metabolism of anammox bacteria in the bioautotrophic denitrification unit removes nitrogen in sewage, and the effluent from the bioautotrophic denitrification unit is used as regenerated water for phosphorus and nitrogen removal. The method has short technological process, good phosphorus and nitrogen removal effects, and low cost.

Owner:BEIJING YIPU INT WATER AFFAIRS

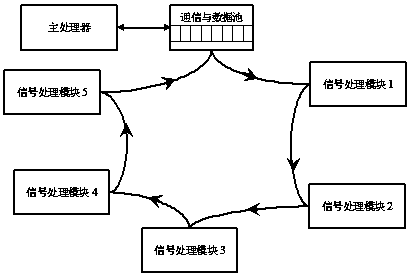

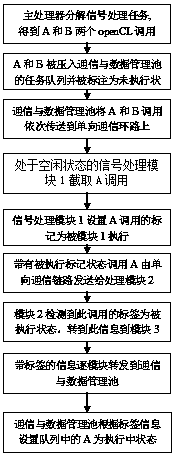

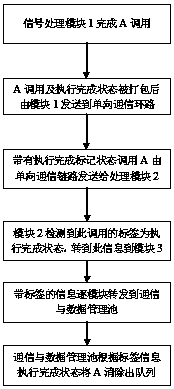

On-chip communication method of complex SOC

InactiveCN108304343ASimplify complexityAvoid difficultyDigital computer detailsLoop networksParallel computingData management

The invention relates to an on-chip communication method of a complex SOC. The method comprises the steps that a main processor receives a to-be-solved signal, disintegrates a processing algorithm ofthe to-be-solved signal into multiple openCL invocations, and sends the openCL invocations to a communication and data management pool; the communication and data management pool sends the received openCL invocations to a communication loop in sequence; the openCL invocations are processed by all signal processing modules on the communication loop, then return to the communication and data management pool, and are collected by the communication and data management pool to be sent to the main processor. According to the on-chip communication method of a complex SOC, on the basis of unidirectional annular structure scheduling of the communication and data management pool, communication management when a large quantity of signal processing modules exist can be achieved, the processing modulesin the complex SOC can ensure the transmission efficiency during communication, the difficulty of star topology and bus topology structures during chip design is avoided, and the competition and conflict problems when multiple processing modules can complete the same openCL invocation are solved.

Owner:深圳市德赛微电子技术有限公司

Achromobacter xylosoxidans with denitrification and dephosphorization function and application of Achromobacter xylosoxidans

ActiveCN102533623BRealize synchronous removalSolve bottlenecksTreatment using aerobic processesBacteriaPhosphateInorganic phosphorus

The invention relates to application of Achromobacter xylosoxidans with a heterotrophic nitrification-aerobic denitrification and dephosphorization function in wastewater treatment. The Achromobacter xylosoxidans can metabolize by using organic carbon as a unique carbon source and using ammonia nitrogen as a unique nitrogen source and can directly convert the ammonia nitrogen into gas products through the action of heterotrophic nitrification-aerobic denitrification so as to achieve the aim of denitrification, can also take nitrate nitrogen as a unique nitrogen source and convert the nitrate nitrogen into gas products through the action of aerobic denitrification, and can further ingest inorganic phosphorus and convert the inorganic phosphorus into a tissue of the Achromobacter xylosoxidans under an aerobic condition so as to achieve the aim of removing phosphorus from wastewater. The Achromobacter xylosoxidans are applied to the wastewater treatment, the simultaneous removal of nitrogen and phosphorus can be achieved under the single aerobic condition, and the difficult problem that the biological denitrification and dephosphorization in the traditional wastewater treatment need to adopt the segmented treatments of anaerobic phosphate release, anoxic denitrification and aerobic nitrification and phosphorus absorption, is better solved, so that the Achromobacter xylosoxidans have broad application prospects.

Owner:PEKING UNIV

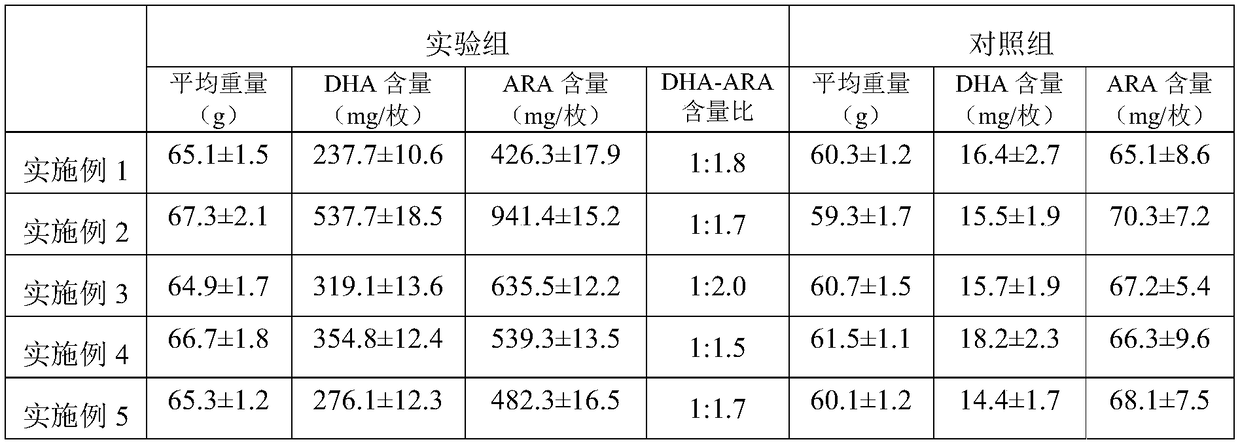

Nutrition enhancer for producing DHA-ARA eggs applicable to infants and young children and application thereof

ActiveCN109392831APromotes Neurological and Visual DevelopmentReduce financial burdenAnimal feeding stuffAccessory food factorsNutritionSocial significance

The invention provides a nutrition enhancer for producing DHA-ARA eggs applicable to infants and young children, and provides a method for preparing a nutrition-enhanced chicken feed by adopting the nutrition enhancer and producing the DHA-ARA eggs applicable to infants and young children by adopting the nutrition-enhanced chicken feed. The nutrition enhancer is composed of the following components by weight: 10 to 24 parts by weight of a DHA microalgae dry powder, 28 to 66 parts by weight of an ARA microalgae dry powder and 10 to 50 parts by weight of a Clostridium thermocellum dry powder. The nutrition enhancer provided by the invention solves the problem of incapability of simultaneously enriching DHA and ARA in eggs, fills the gap of the prior art, and has an important significance ondevelopment of chicken industry; meanwhile, the ratio of DHA to ARA reaches an optimal ratio of 1: 1.5 to 1: 2, so the nutrition enhancer provided by the invention realizes convenient and effective supplementation of DHA and ARA required for nerve and visual development of infants and young children, and has important social significance.

Owner:QINGDAO INST OF BIOENERGY & BIOPROCESS TECH CHINESE ACADEMY OF SCI +1

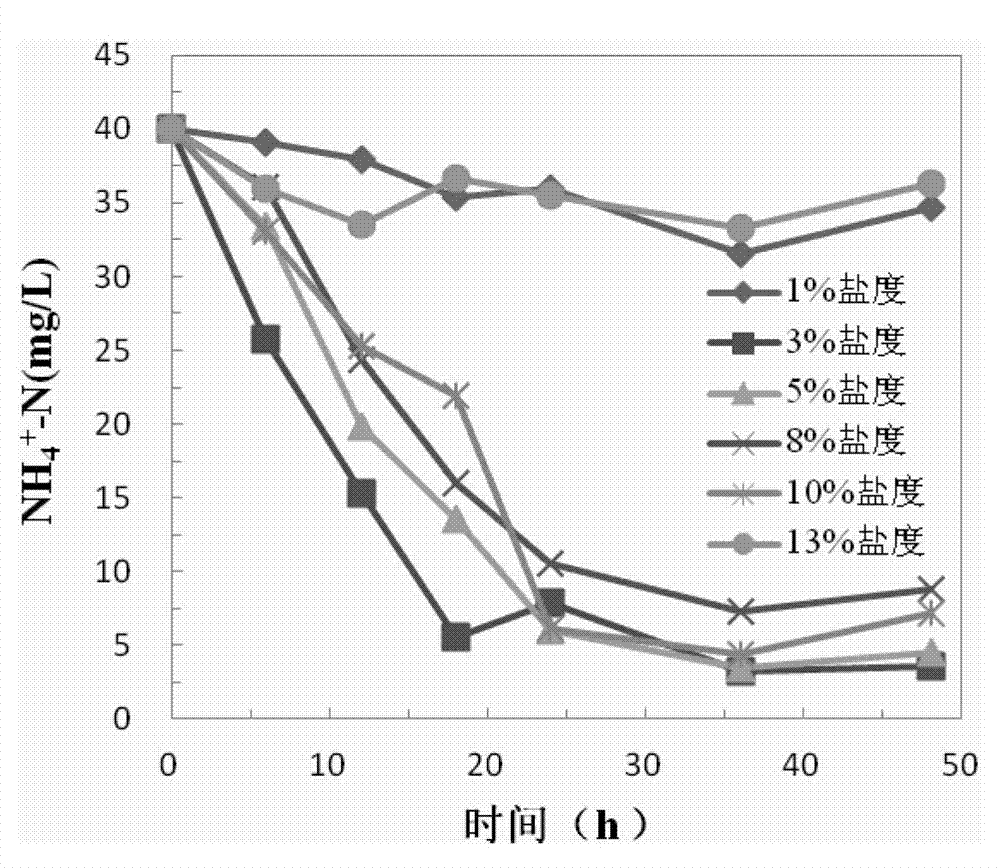

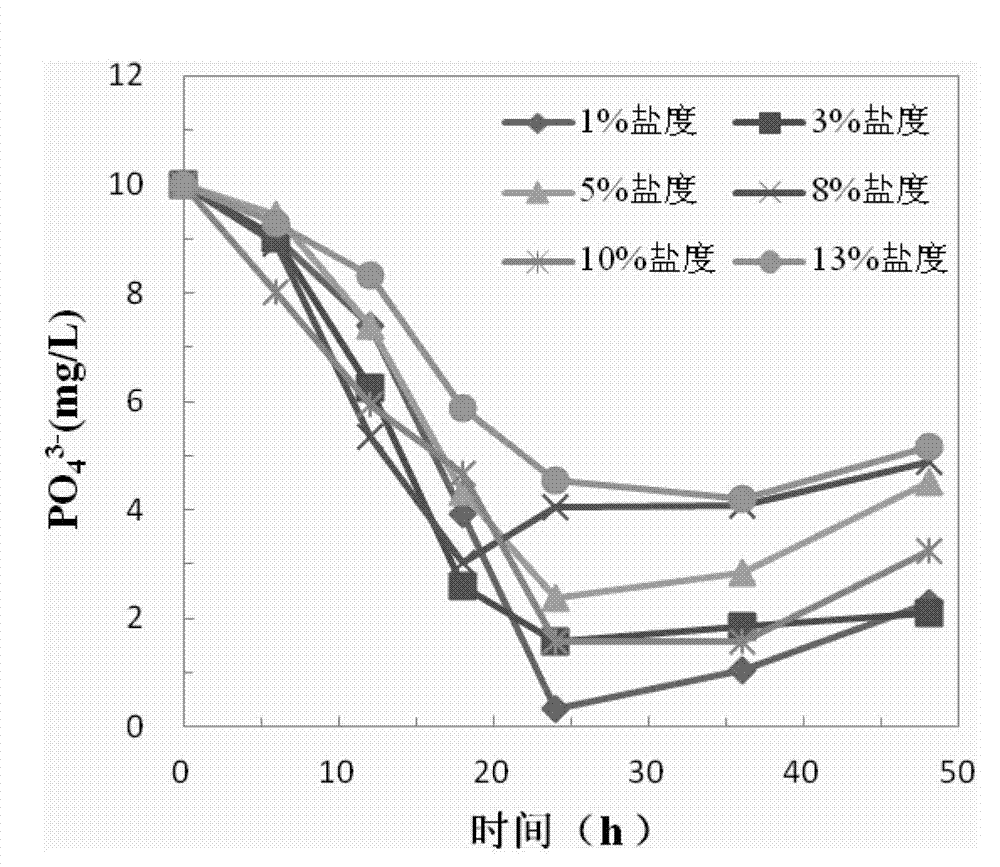

High-salt heterotrophic nitrification-aerobic denitrification dephosphorization brachybacterium and application of brachybacterium in wastewater treatment

ActiveCN103074285BStrong toleranceAvoid restrictionsTreatment using aerobic processesBacteriaEndurance capacityBrachybacterium species

The invention relates to high-salt heterotrophic nitrification-aerobic denitrification dephosphorization brachybacterium and an application of the brachybacterium in wastewater treatment. The brachybacterium has high endurance capacity to a high-salt environment, grows well under a high-salt condition, can metabolize by utilizing organic carbon as a sole carbon source and ammonia nitrogen as a sole nitrogen source, directly converts ammonia nitrogen into a gas product through the heterotrophic nitrification-aerobic denitrification action, and achieves denitrification; and the brachybacterium can also take nitrate nitrogen as a sole nitrogen source, converts nitrate nitrogen into a gas product through the aerobic denitrification action, and can take inorganic phosphorus in under an aerobic condition to convert into a self-component so as to remove phosphorus from sewage. The brachybacterium is applicable to high-salt wastewater treatment, can achieve synchronous removal of nitrogen and phosphorus under a single aerobic condition, is conducive to effectively achieving biological decarbonization, dephosphorization and denitrification under the high-salt condition, and has a wide application prospect.

Owner:PEKING UNIV

Health-care food of iron zinc calcium tablets and production method thereof

ActiveCN101690590BAbsorption and utilization have no effectTo achieve the same complementary effectFood preparationDiseaseSucrose

The invention discloses a health-care food of iron zinc calcium tablets and a production method thereof. The iron zinc calcium tablets consist of chewable tablets, calcium carbonate, ferric pyrophosphate, zinc gluconate, lactose, sucrose, sorbitol, mannitol, maltodextrin, casein phosphopeptide, milk powder, fruit powder, citric acid, sodium citrate, magnesium stearate, silicon dioxide and other raw materials by parts by weight. The prepration method comprises the steps of preparing the raw materials by parts by weight, smashing, screening, weighing the raw materials, granulating, baking, mixing, tabletting and coating. The product has the effects of reinforcing spleen, promoting appetite, improving myocardial ischemia, supplementing blood and calcium, improving sleep and preventing iron deficiency anemia and other diseases, thereby being the health-care product which can not only strengthen the body, but also improve the immunity and the anti-disease ability of the human body.

Owner:NANNING FRESH LIFE BIOTECH

Biological nitrogen and phosphorus removal device

PendingCN106315854AAchieve reuseAddress competitionTreatment using aerobic processesWater contaminantsNitrogen removalSludge

The invention discloses a biological nitrogen and phosphorus removal device which comprises a nitration reaction unit, a sequencing batch biological reaction unit, a first middle pool, a second middle pool, a first water outlet pipeline, a water draining pipeline, a discharging pipeline, a water inlet pipeline, a third water outlet pipeline, a first air pipeline, a second air pipeline, a first air supply device and a second air supply device, wherein the first middle pool and the second middle pool are arranged between the nitration reaction unit and the sequencing batch biological reaction unit at an interval and are formed into a closed loop; the nitration reaction unit is communicated with the first middle pool through the first water outlet pipeline and the water inlet pipeline and is communicated with the second middle pool through the third water outlet pipeline; and the sequencing batch biological reaction unit is communicated with the first middle pool through the discharging pipeline and is communicated with the second middle pool through the water draining pipeline. The device can solve the contradiction of different sludge updating speeds required by biological nitrogen removal and phosphorus removal, can realize reusability of the carbon source in the nitrogen removal and phosphorus removal processes, and can increase the efficiency of treating sewage and wastewater.

Owner:ANHUI AGRICULTURAL UNIVERSITY

A kind of AGV traffic control system and control method

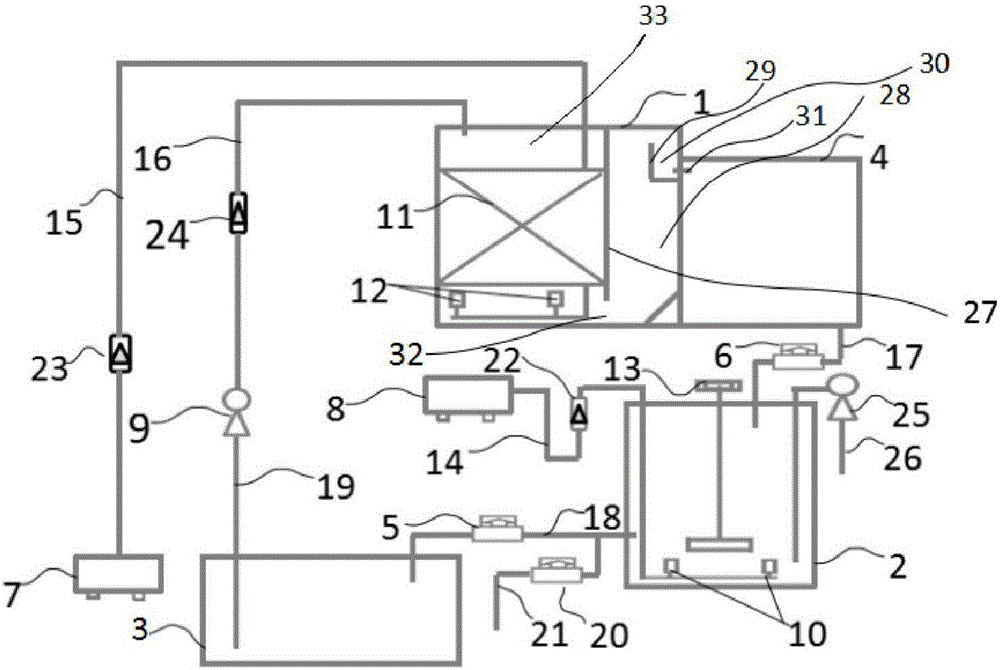

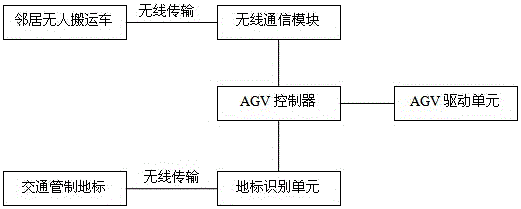

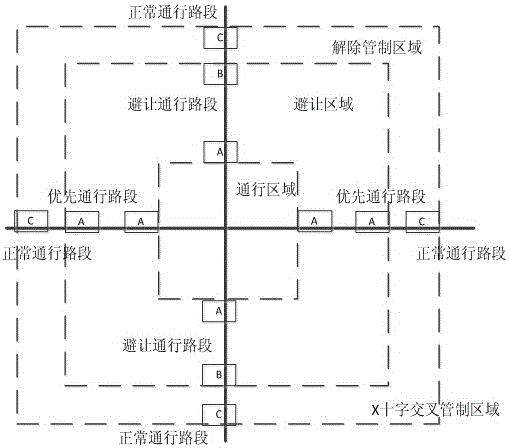

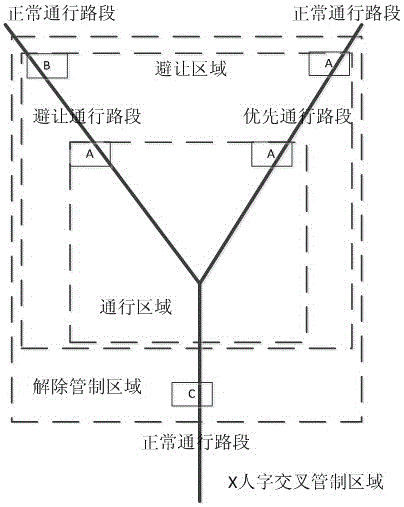

ActiveCN104331079BAddress competitionReduce the impact of autonomous traffic controlPosition/course control in two dimensionsRoad traffic controlControl system

The invention discloses an AGV traffic control system and a control method, and the system comprises a plurality of AGVs and navigation orbit, the system further comprises a plurality of traffic control landmarks, the traffic control landmark comprises A class landmark, B class landmark and C class landmark, the A class landmark is the priority passage landmark, B class landmark is avoiding control landmark, C class landmark is deregulation control landmark, the control landmark is formed in the traffic control region of the navigation orbit; the AGV comprises the landmark recognition unit, AGV controller and AGV drive unit, the landmark recognition unit receives the traffic control frame sent by the traffic control landmark, the output of the landmark recognition unit is connected to one input of the AGV controller, the output of the AGV controller is connected to the input of the AGV drive unit, the AGV controller gives the corresponding passage occupation right to the AGV according to the traffic control information. The system and the method can effectively solve the competition problem for the AGV while entering into the traffic control region; the impact to the AGV independent traffic control caused by the communication time delay can be reduced.

Owner:CHENGDU SIWI HIGH TECH IND GARDEN