Patents

Literature

88 results about "High performance system" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

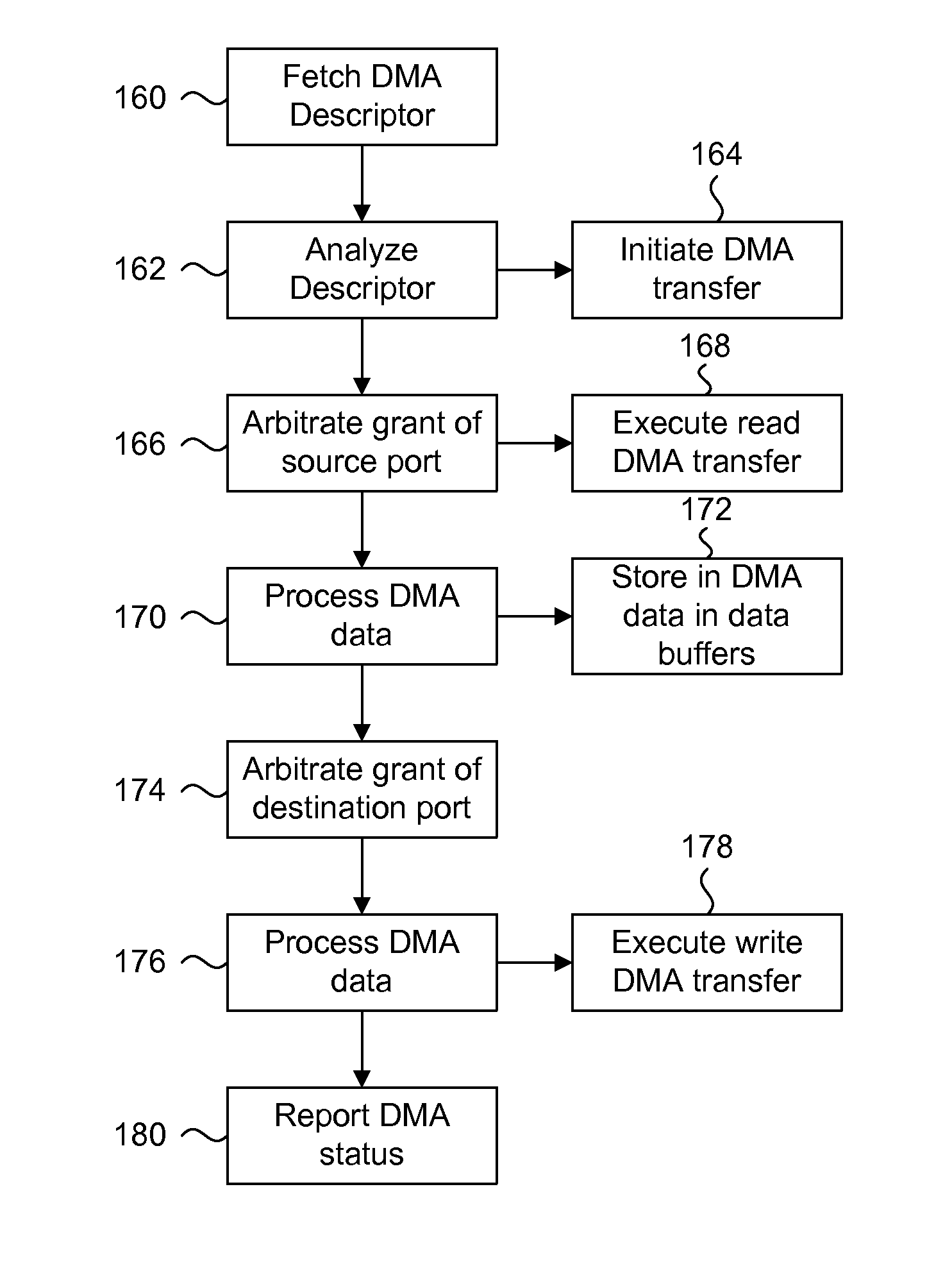

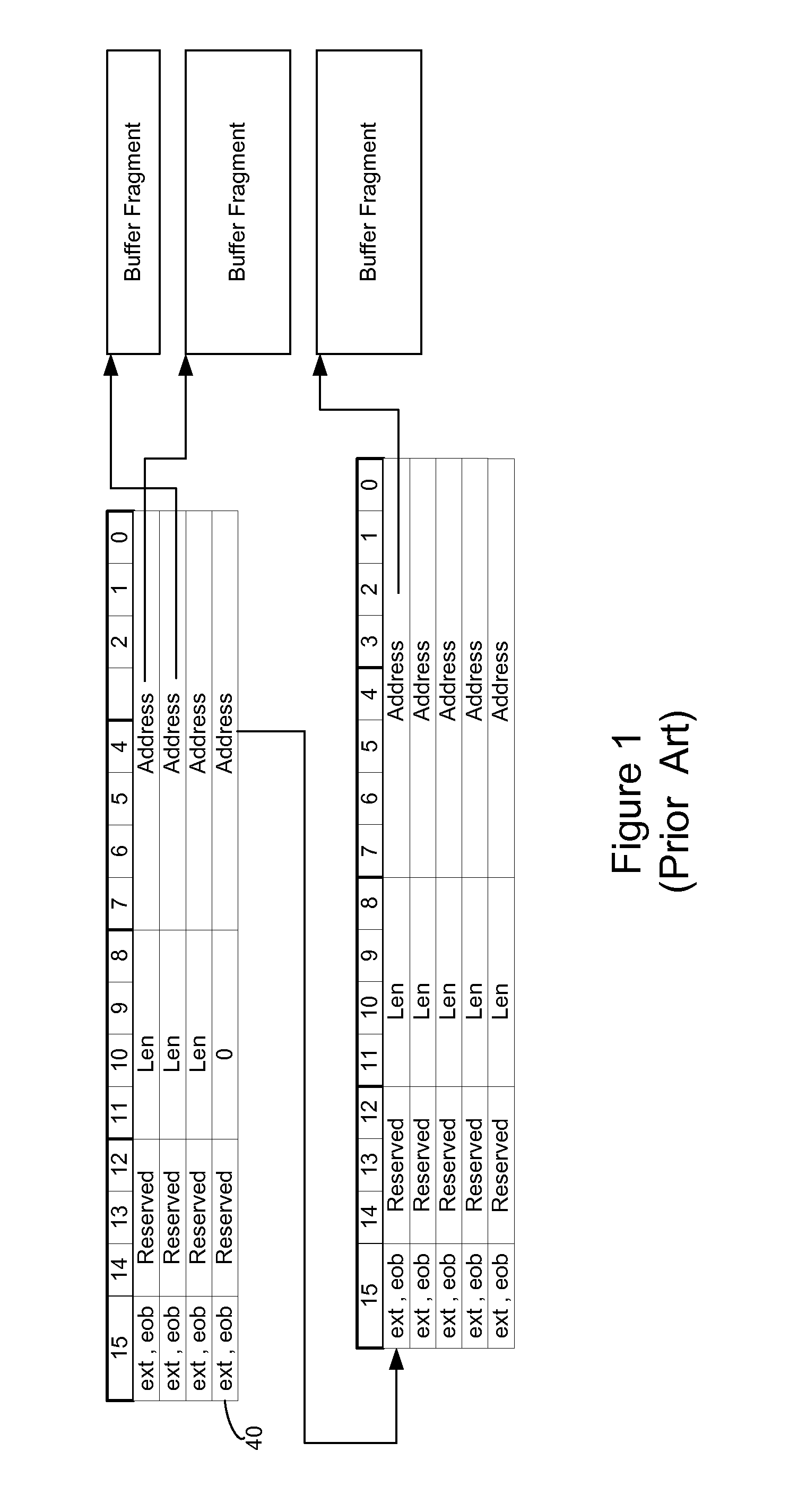

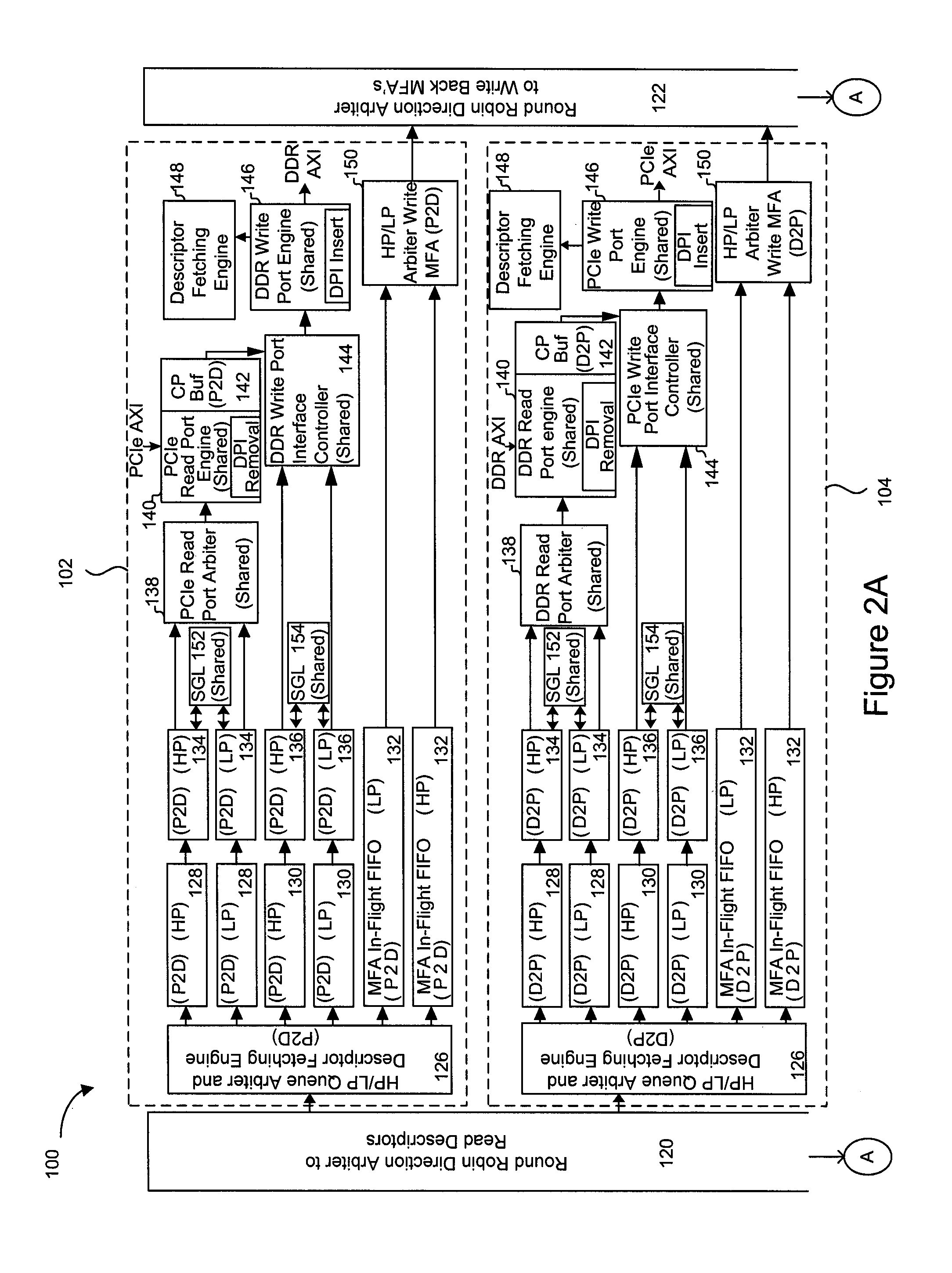

Logical address direct memory access with multiple concurrent physical ports and internal switching

A DMA engine is provided that is suitable for higher performance System On a Chip (SOC) devices that have multiple concurrent on-chip / off-chip memory spaces. The DMA engine operates either on logical addressing method or physical addressing method and provides random and sequential mapping function from logical address to physical address while supporting frequent context switching among a large number of logical address spaces. Embodiments of the present invention utilize per direction (source-destination) queuing and an internal switch to support non-blocking concurrent transfer of data on multiple directions. A caching technique can be incorporated to reduce the overhead of address translation.

Owner:MICROSEMI SOLUTIONS (US) INC

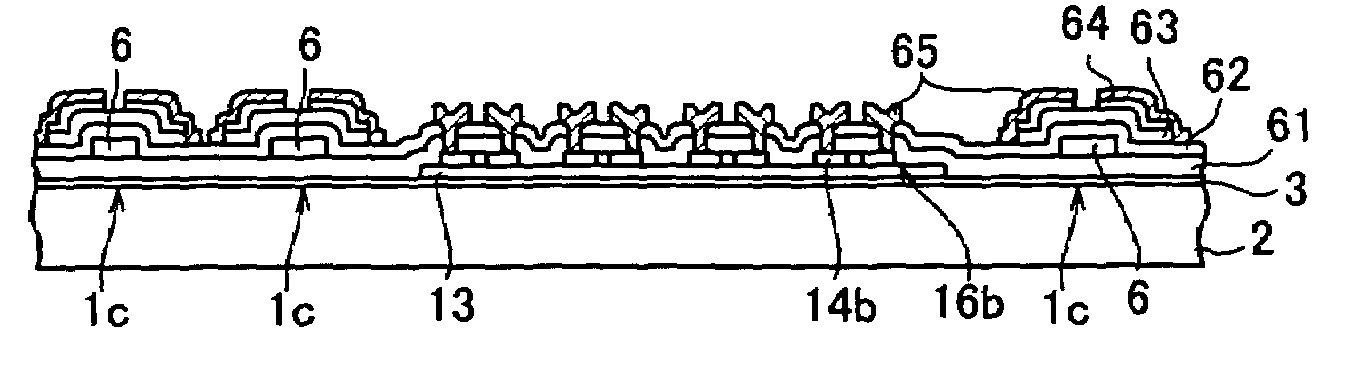

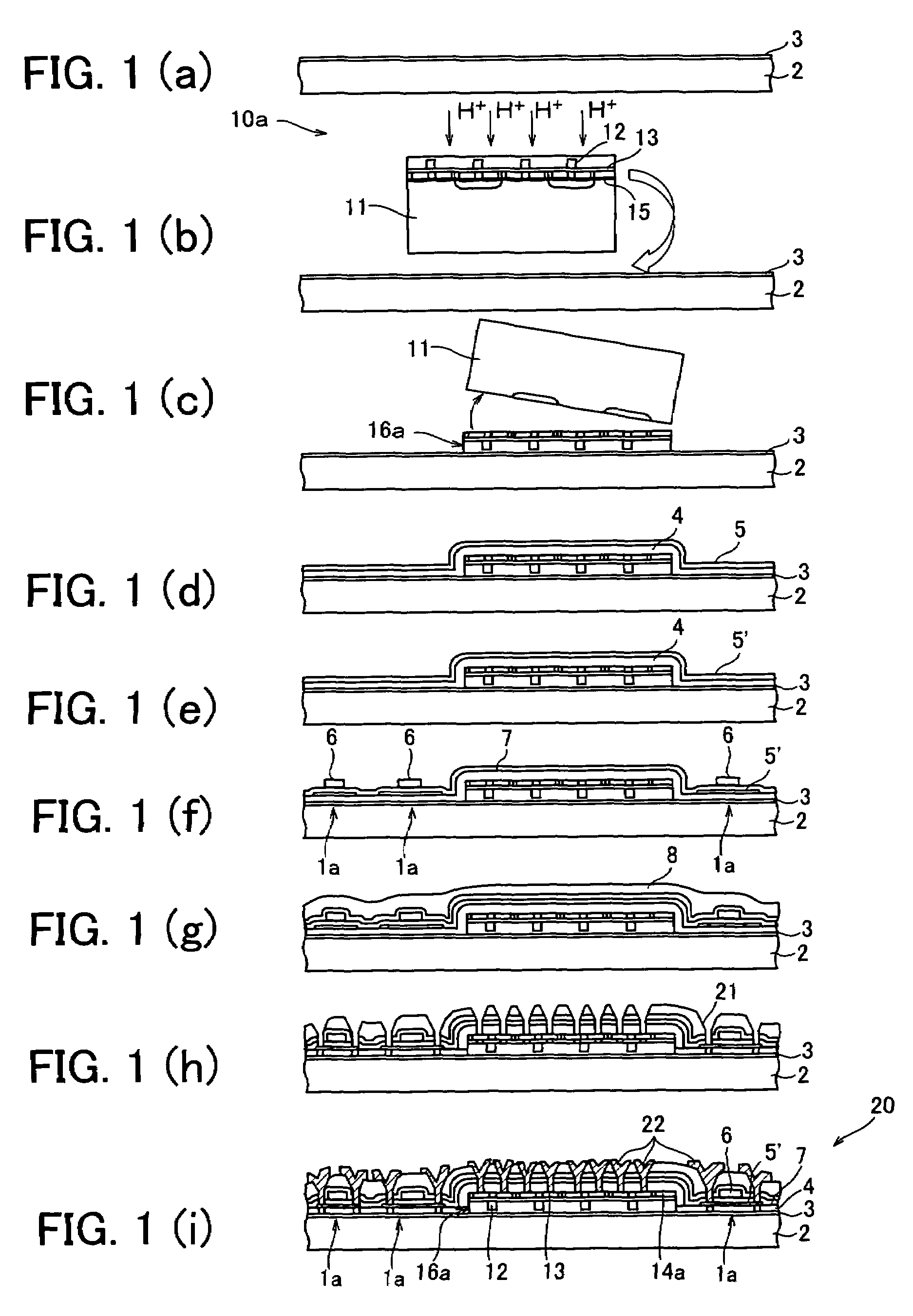

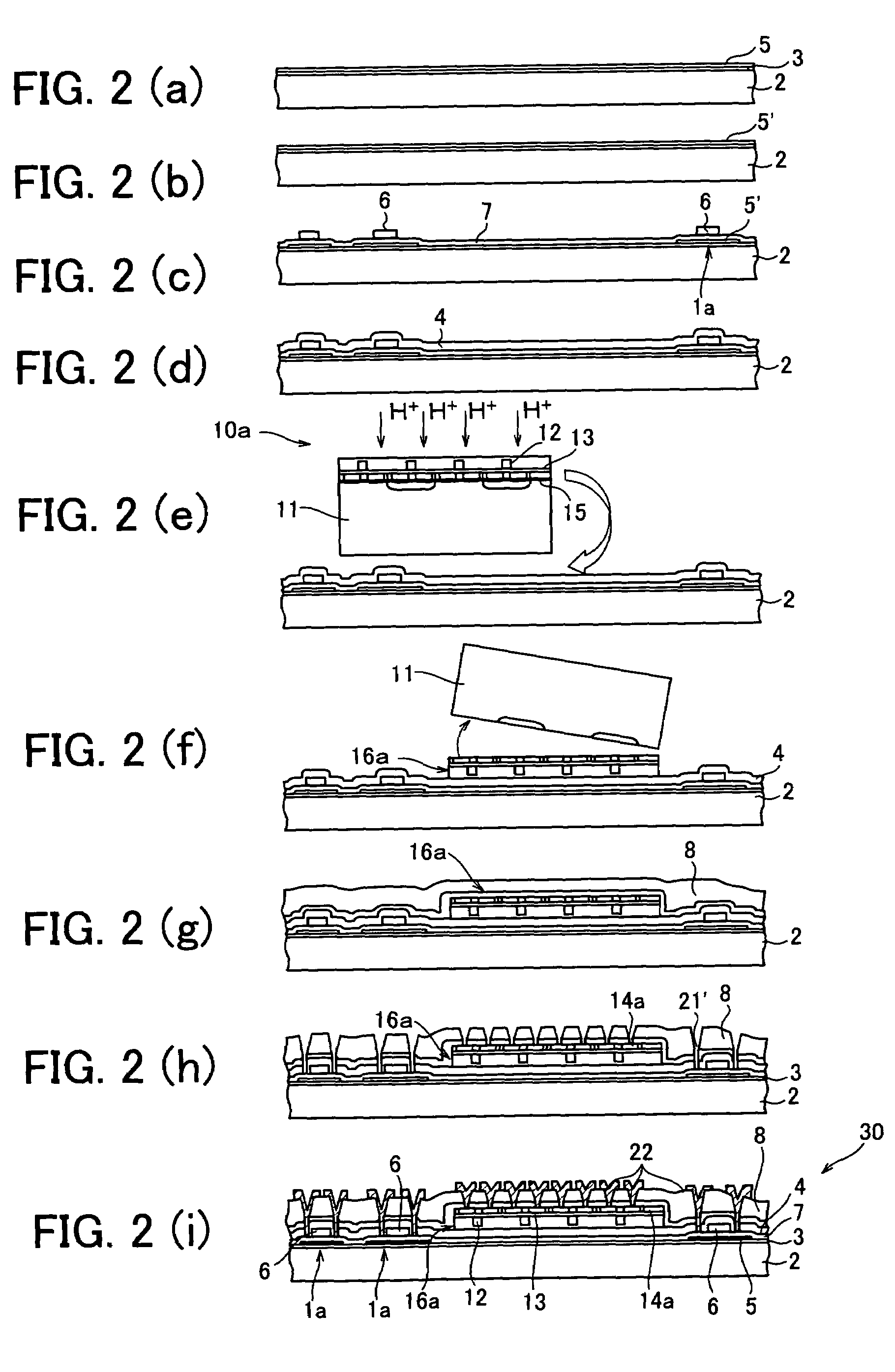

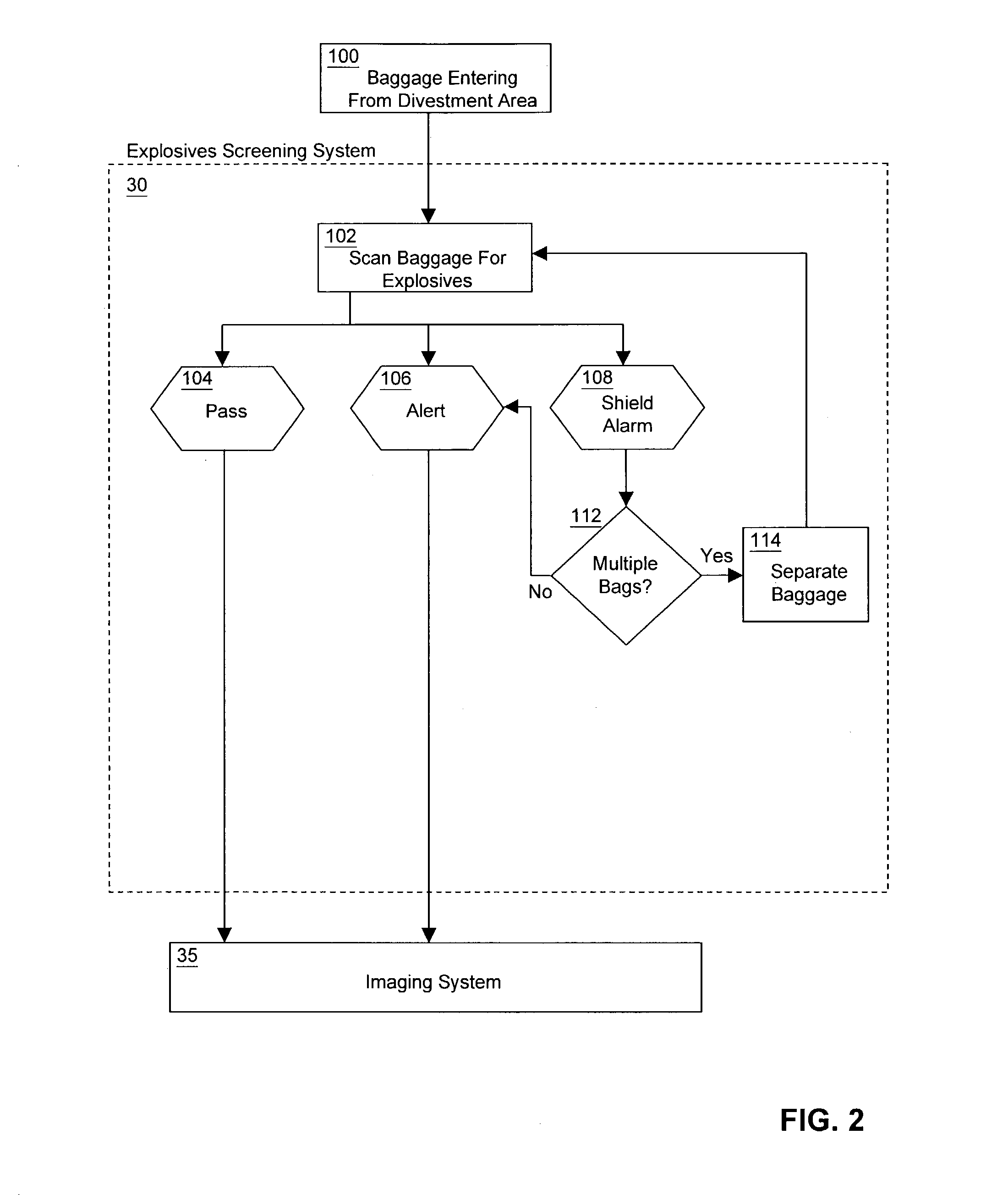

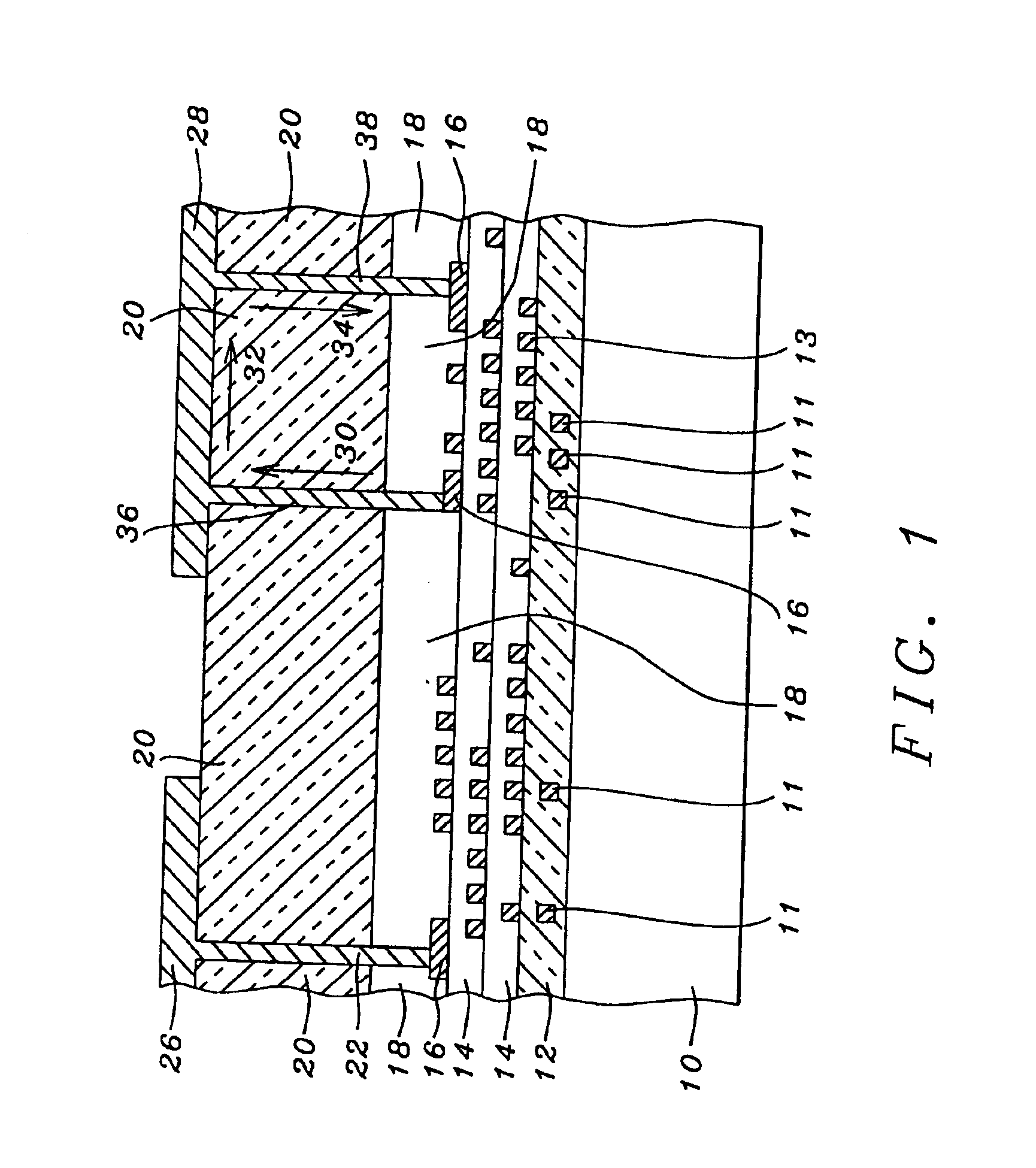

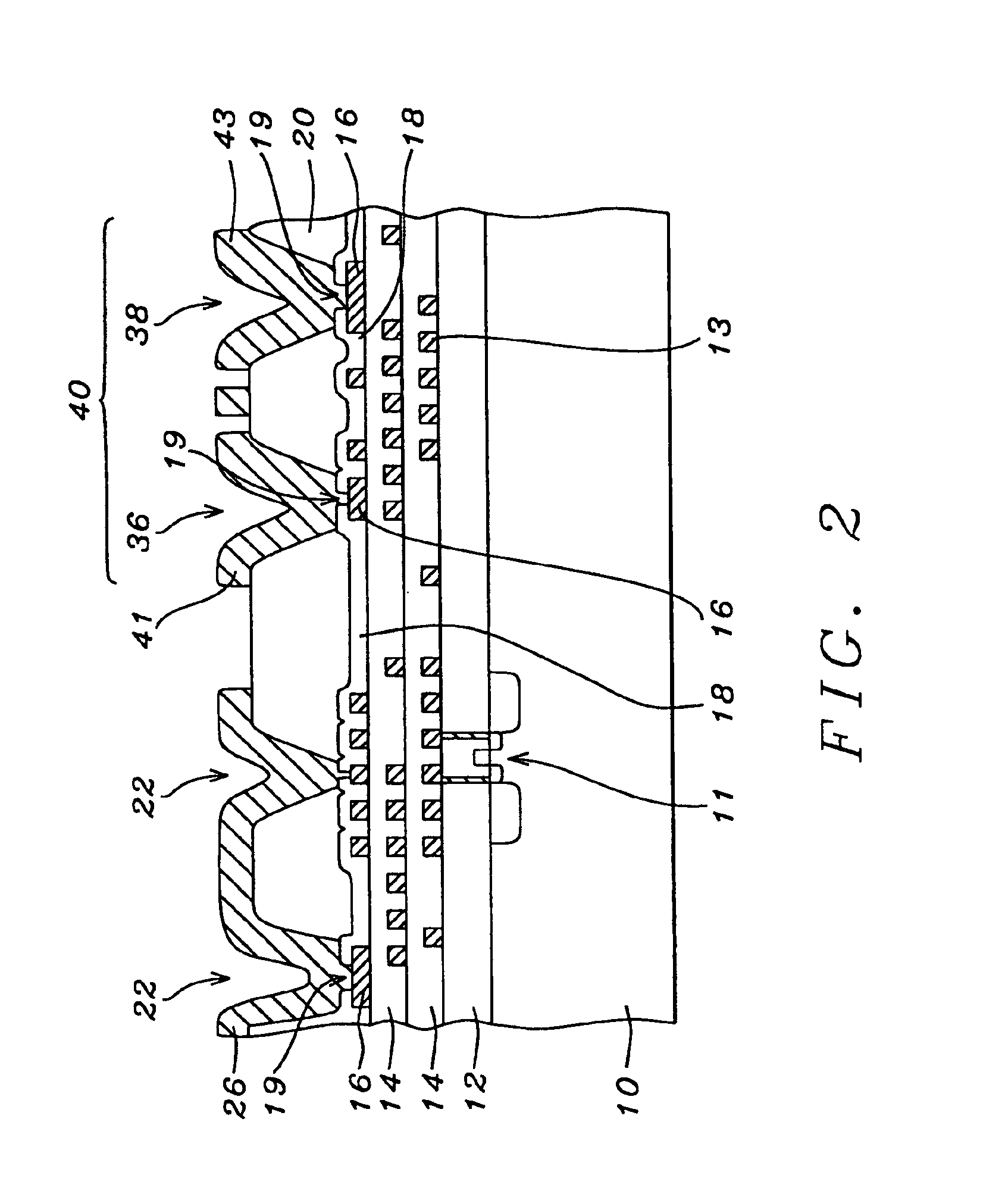

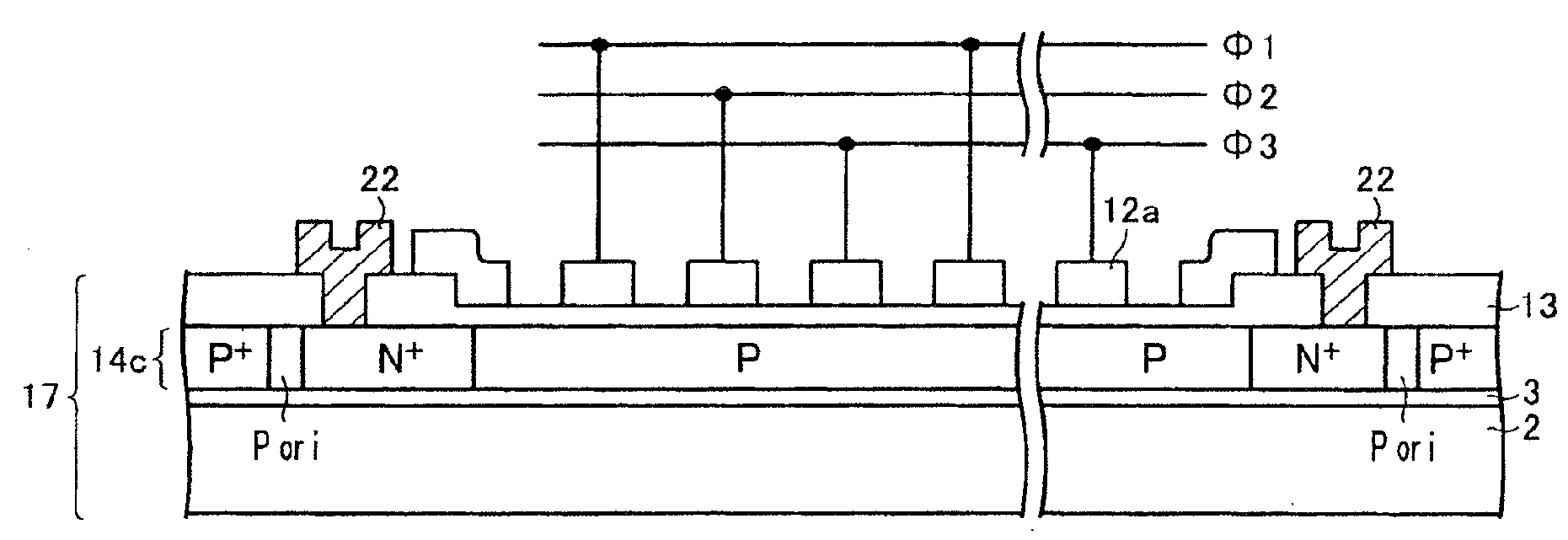

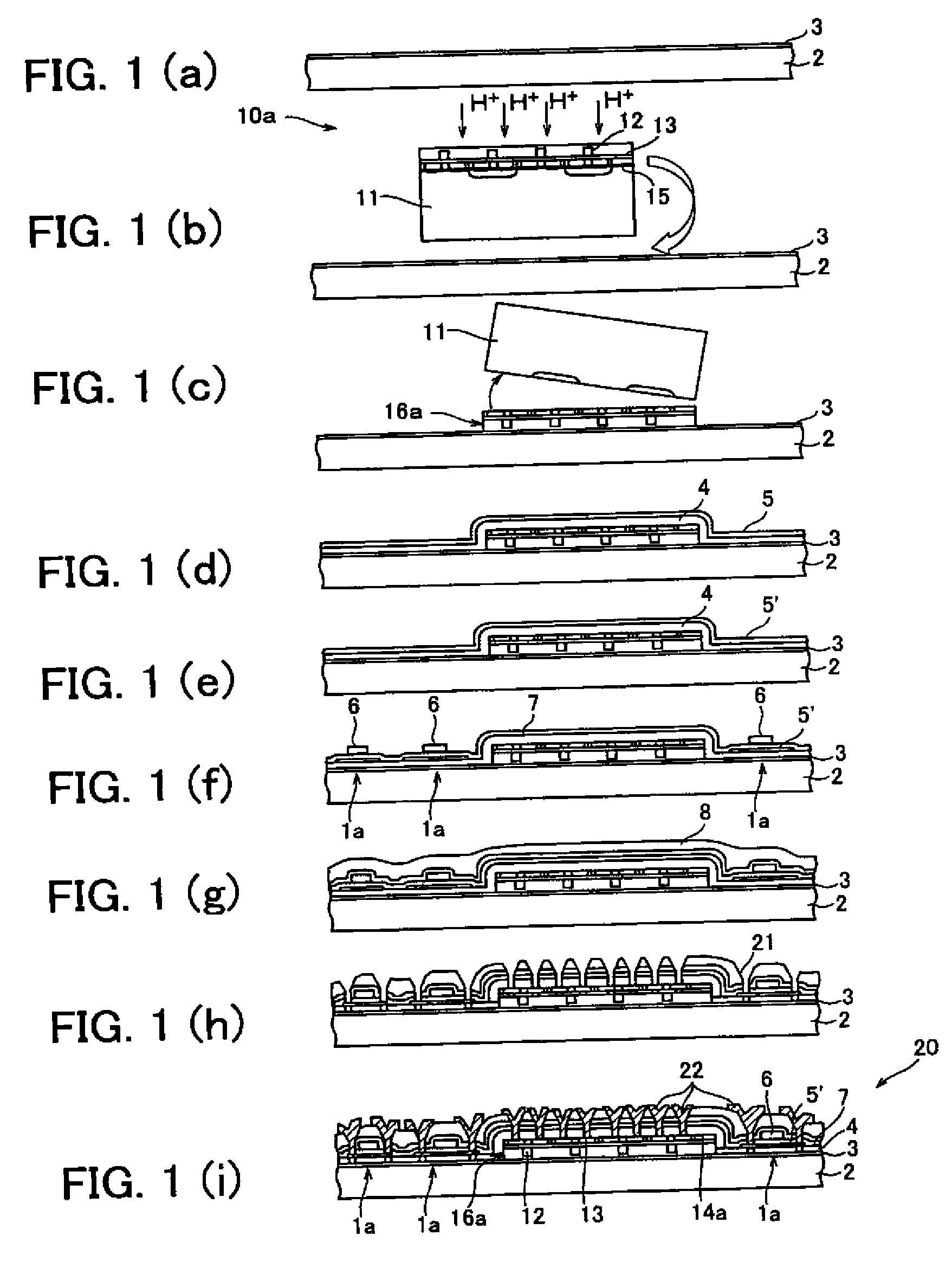

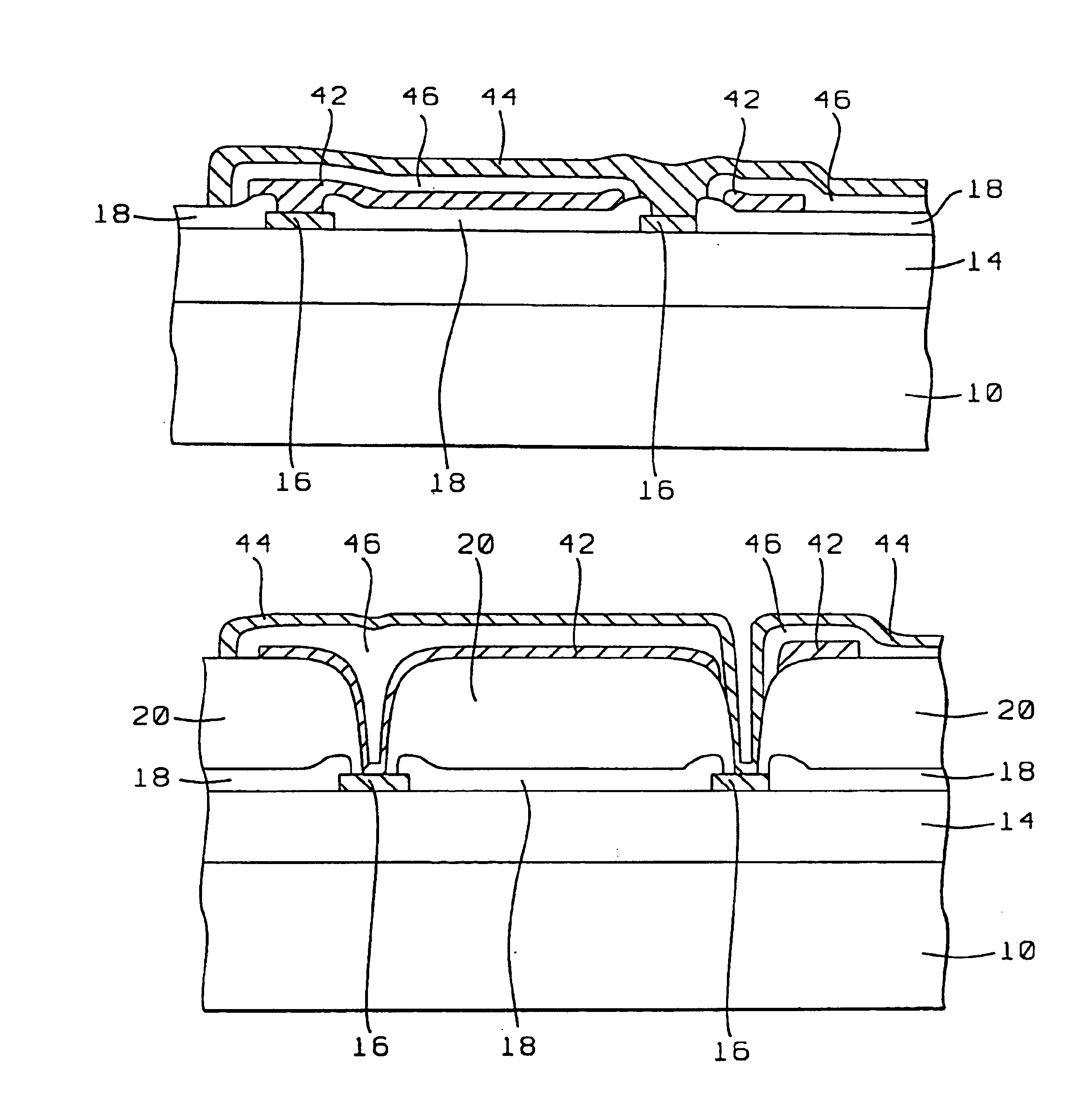

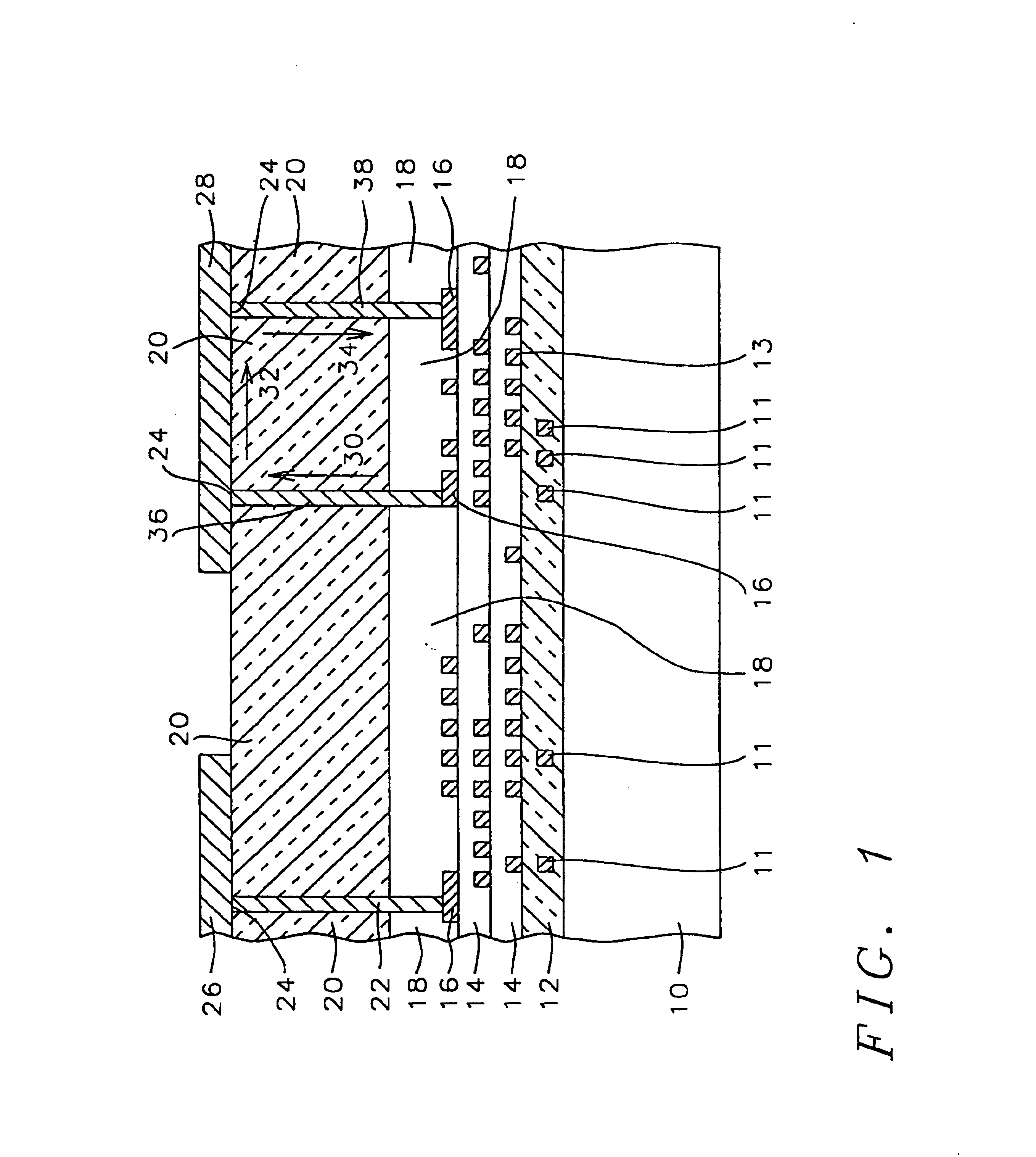

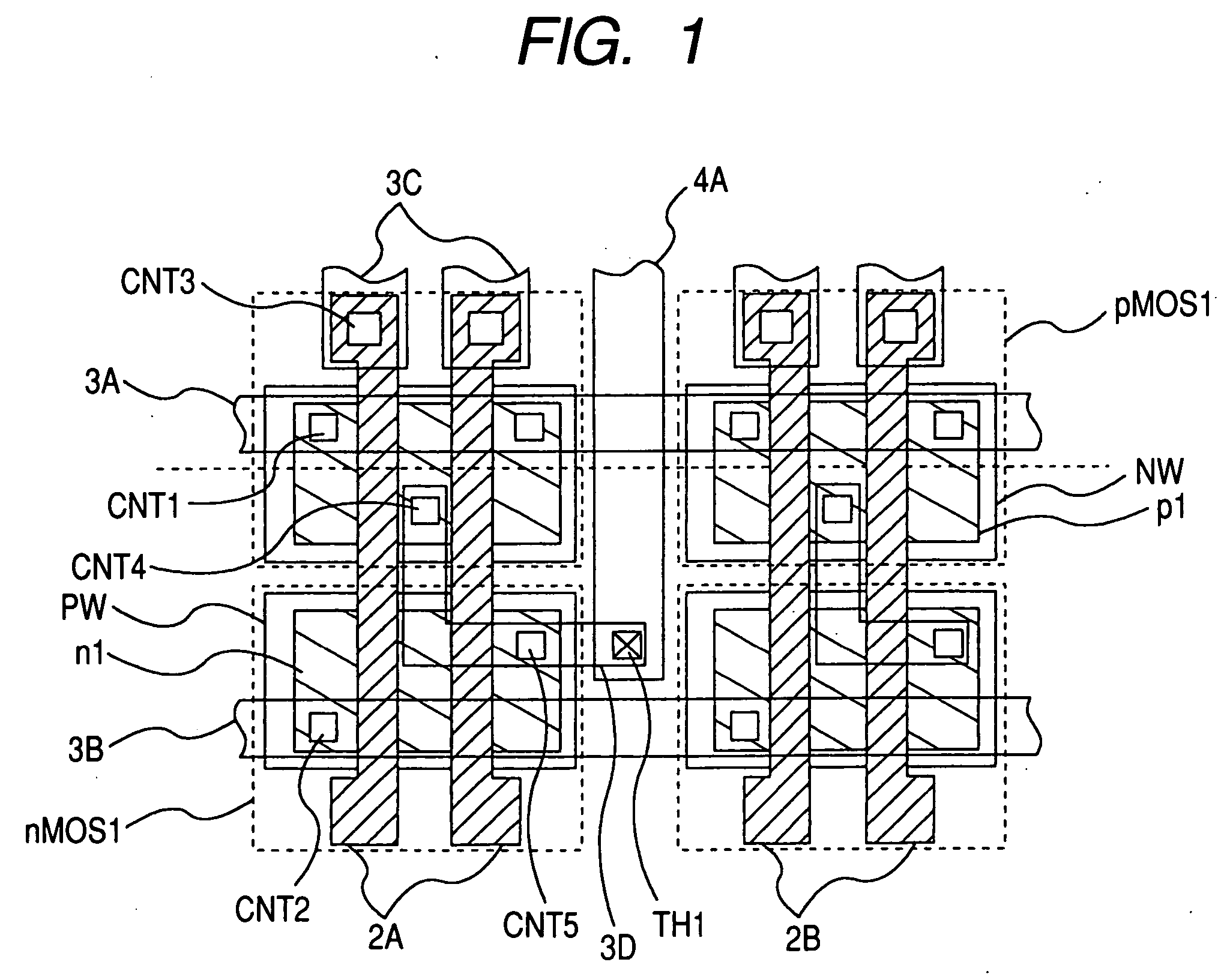

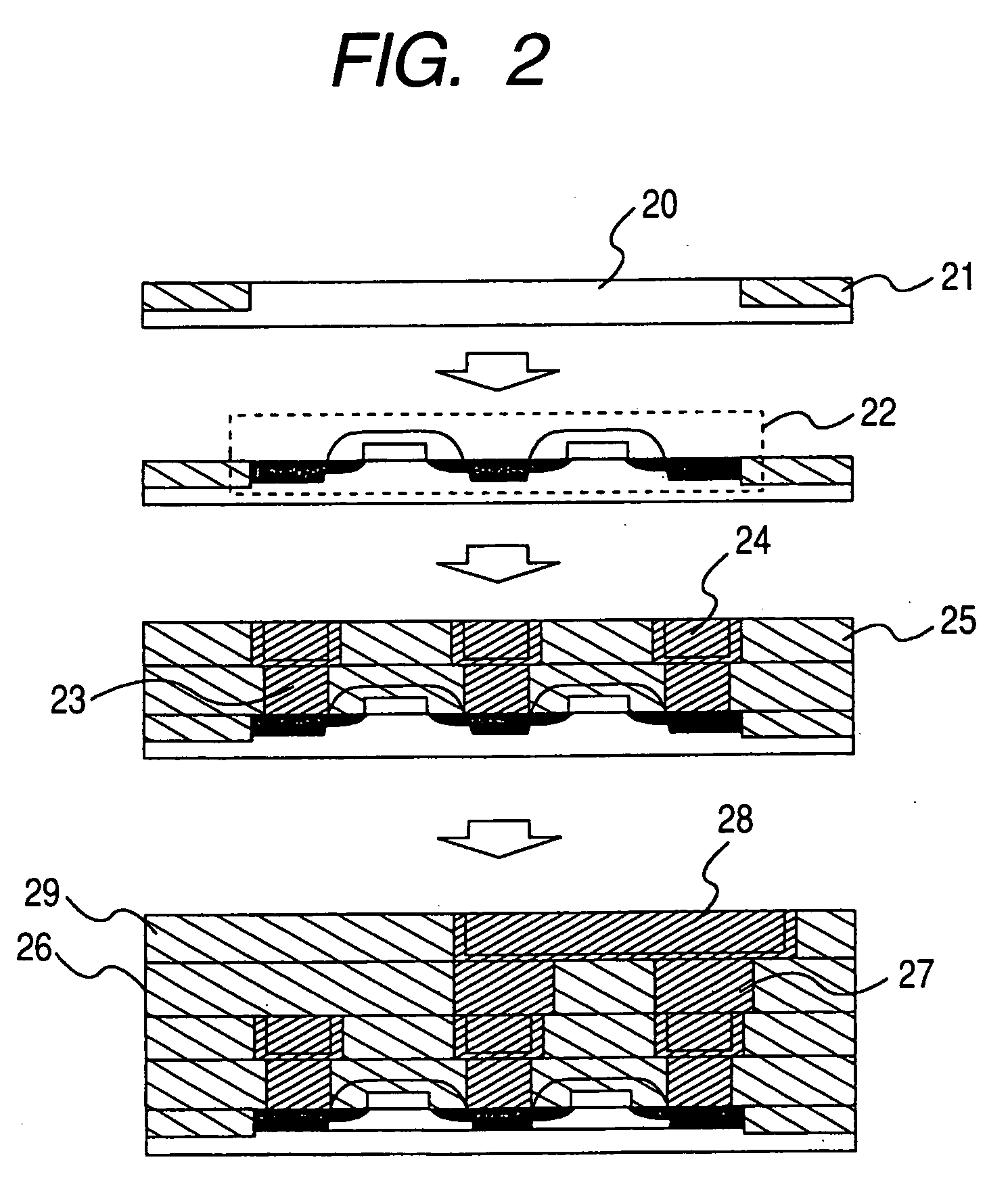

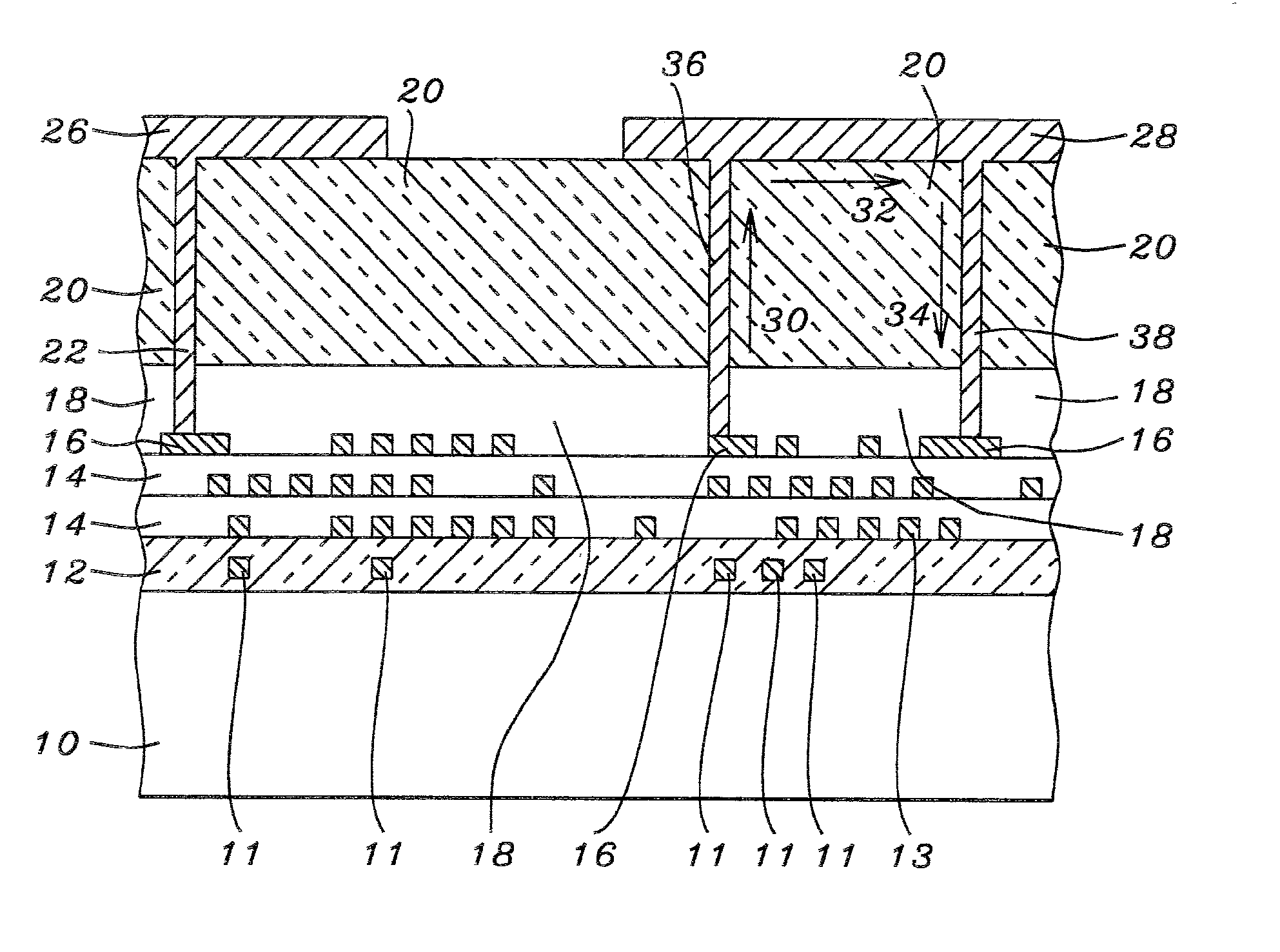

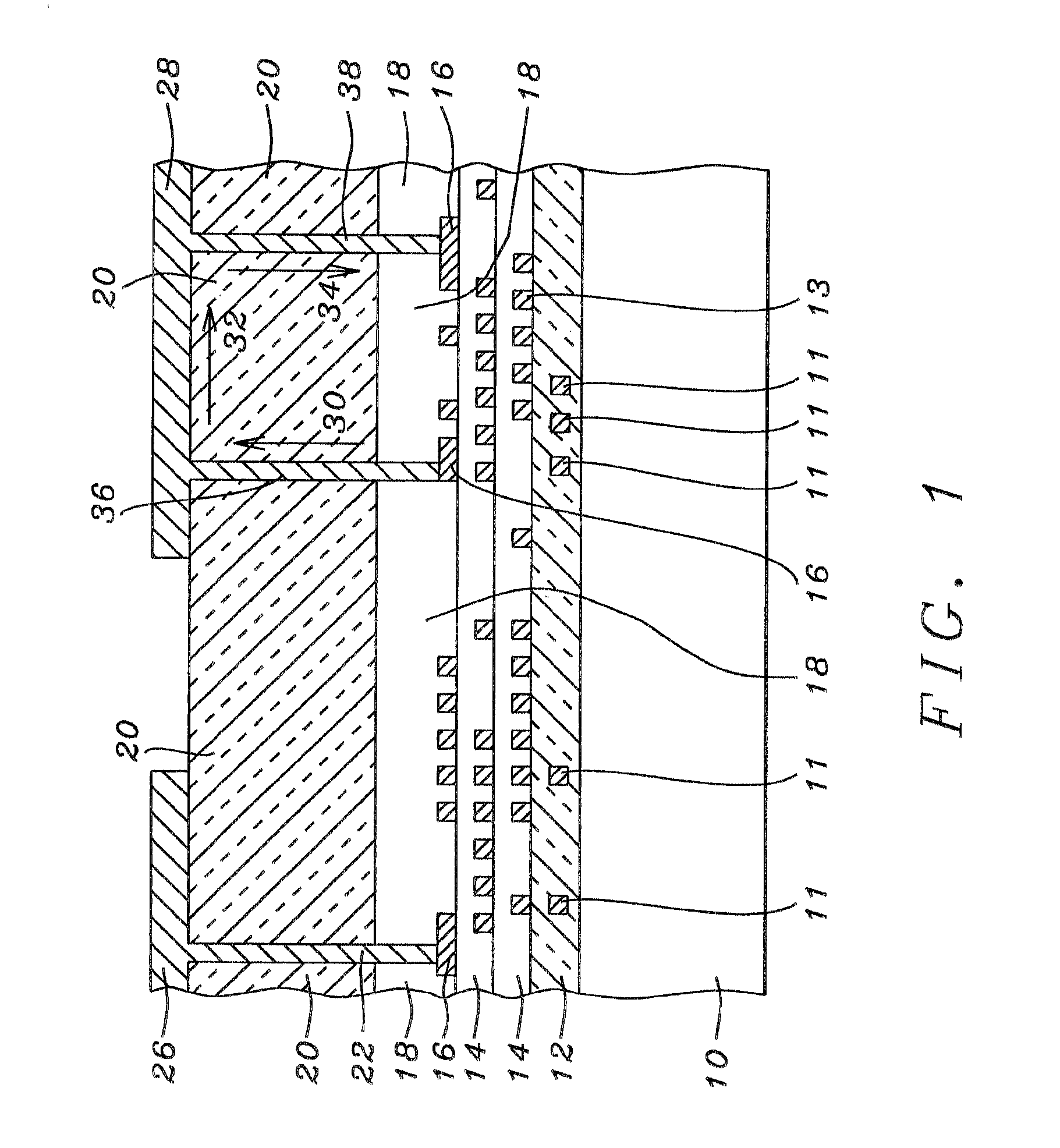

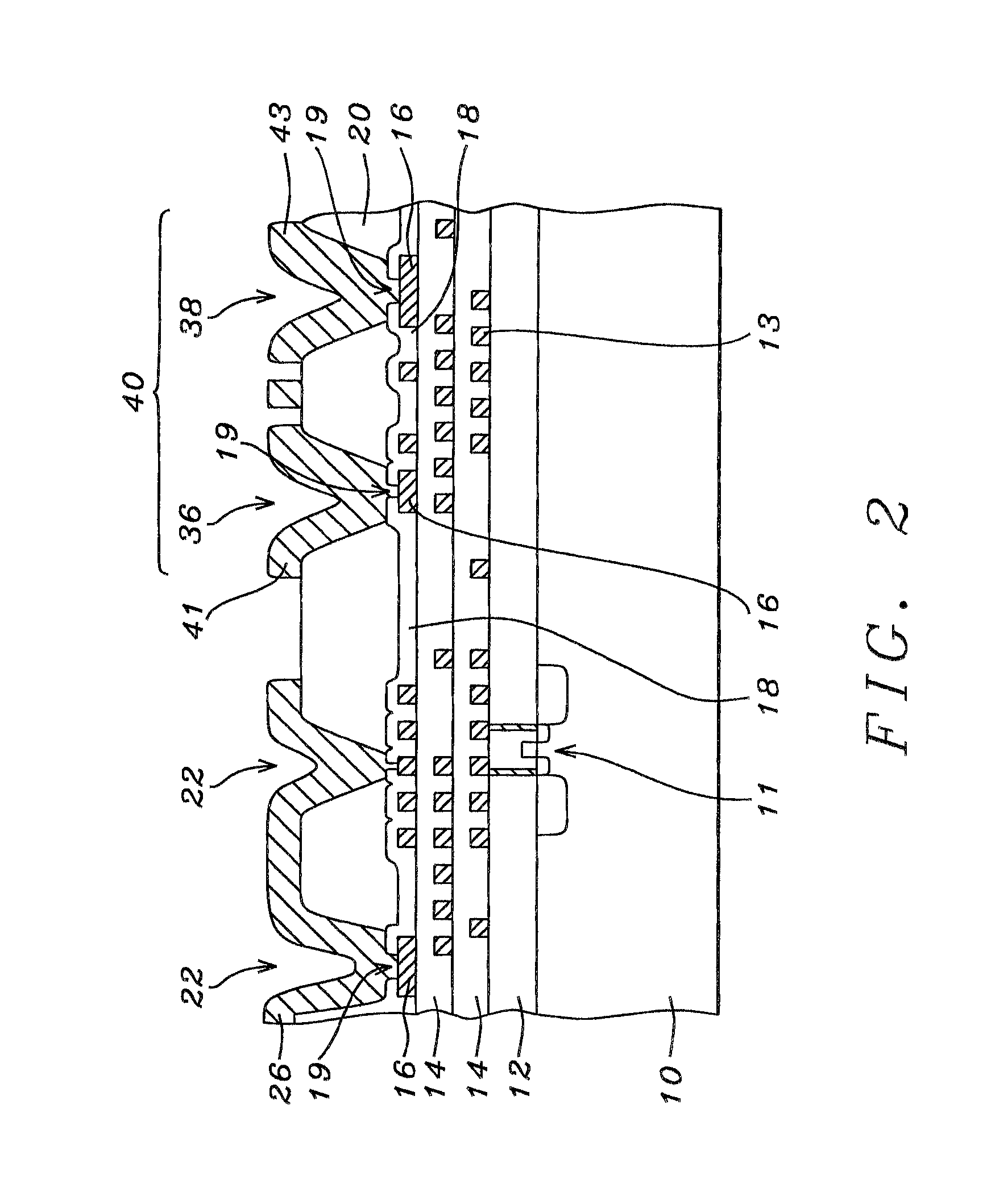

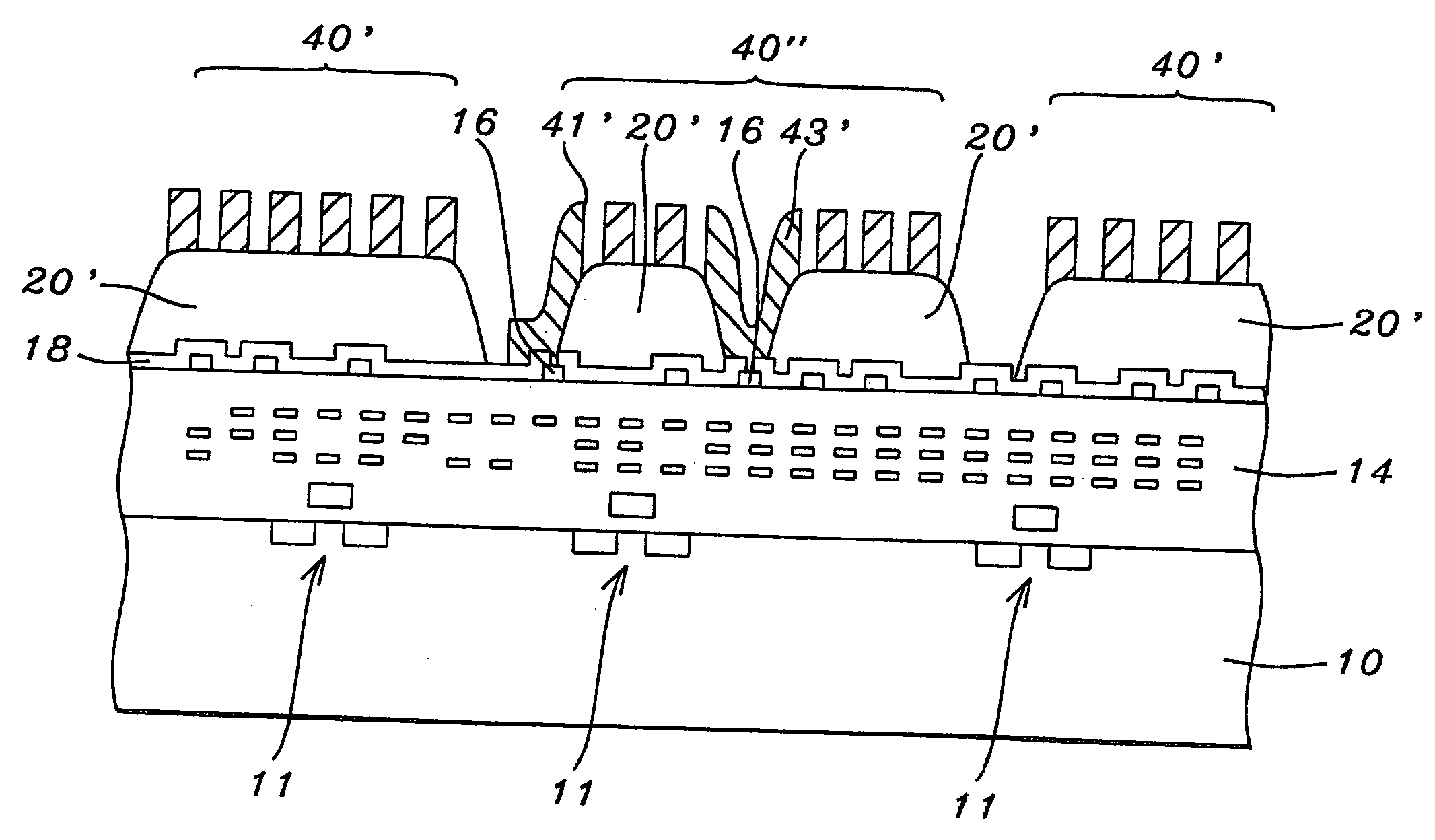

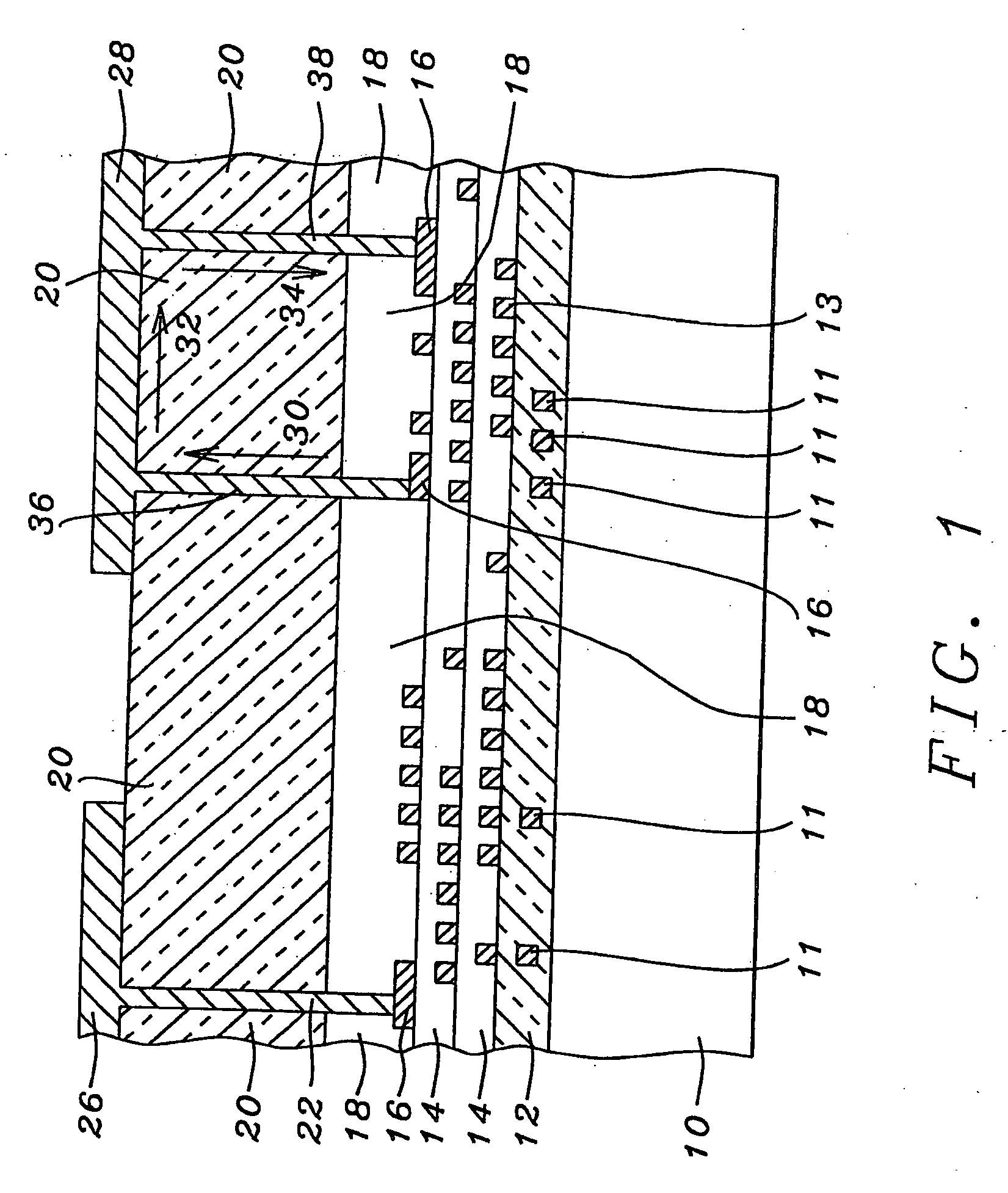

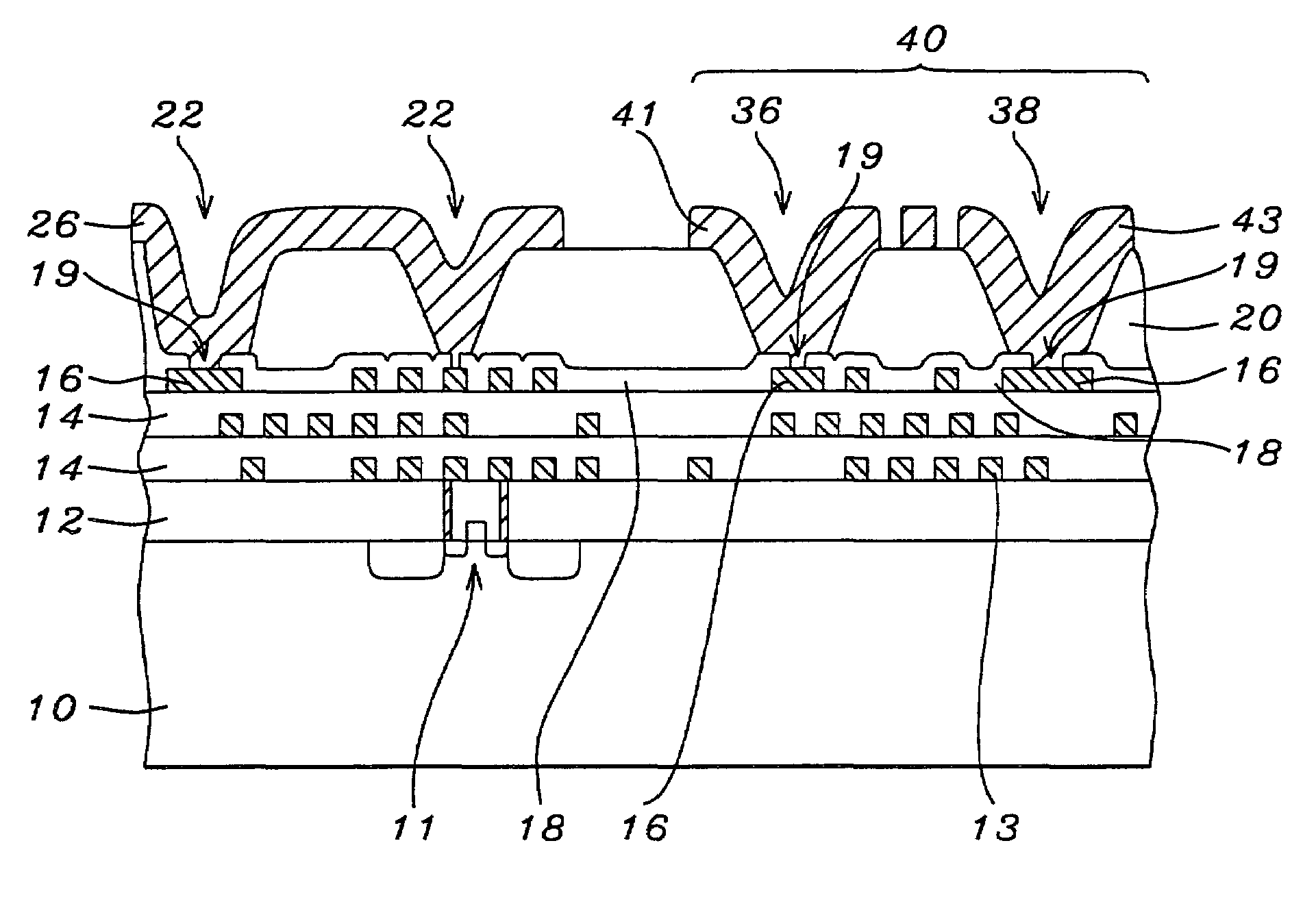

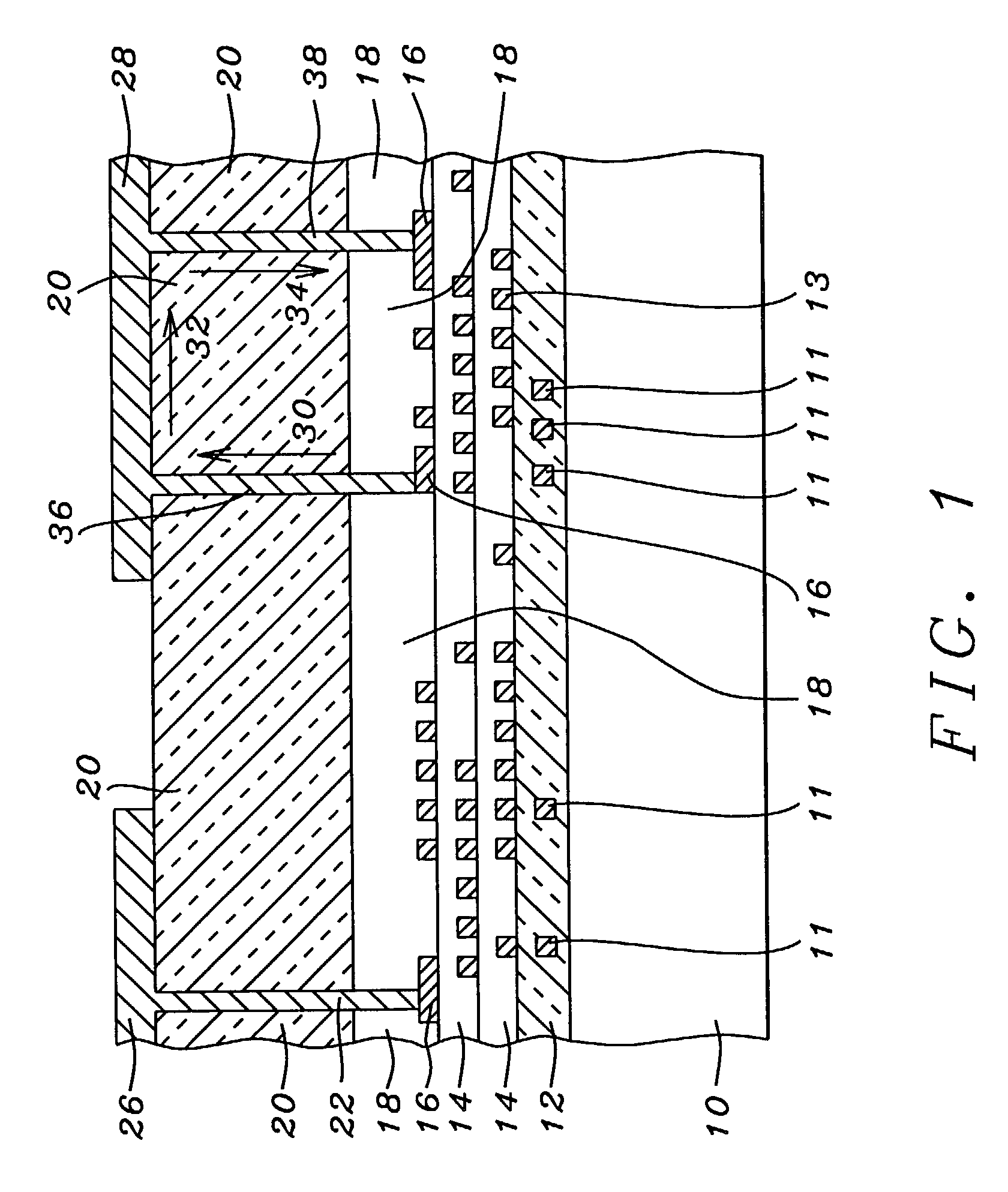

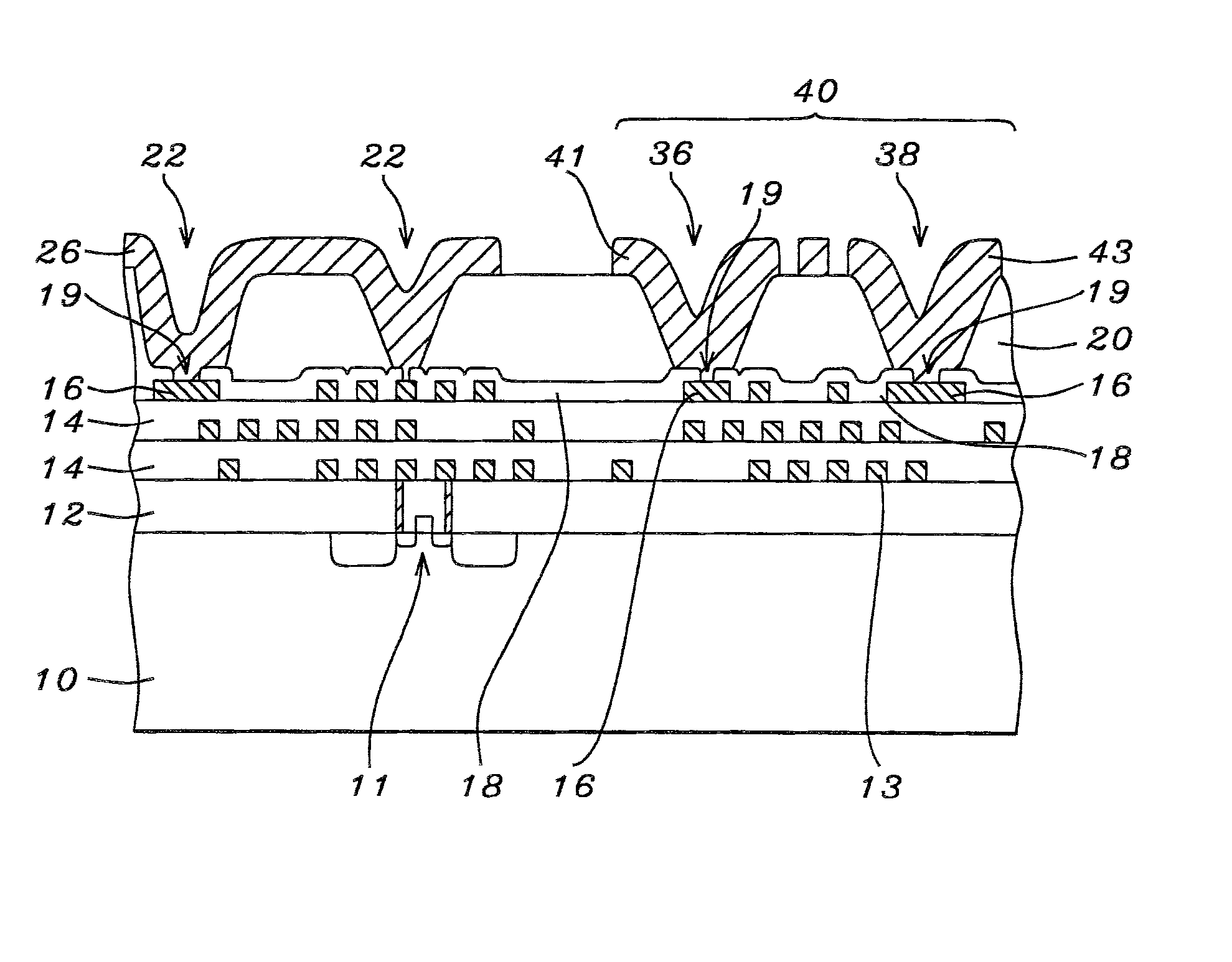

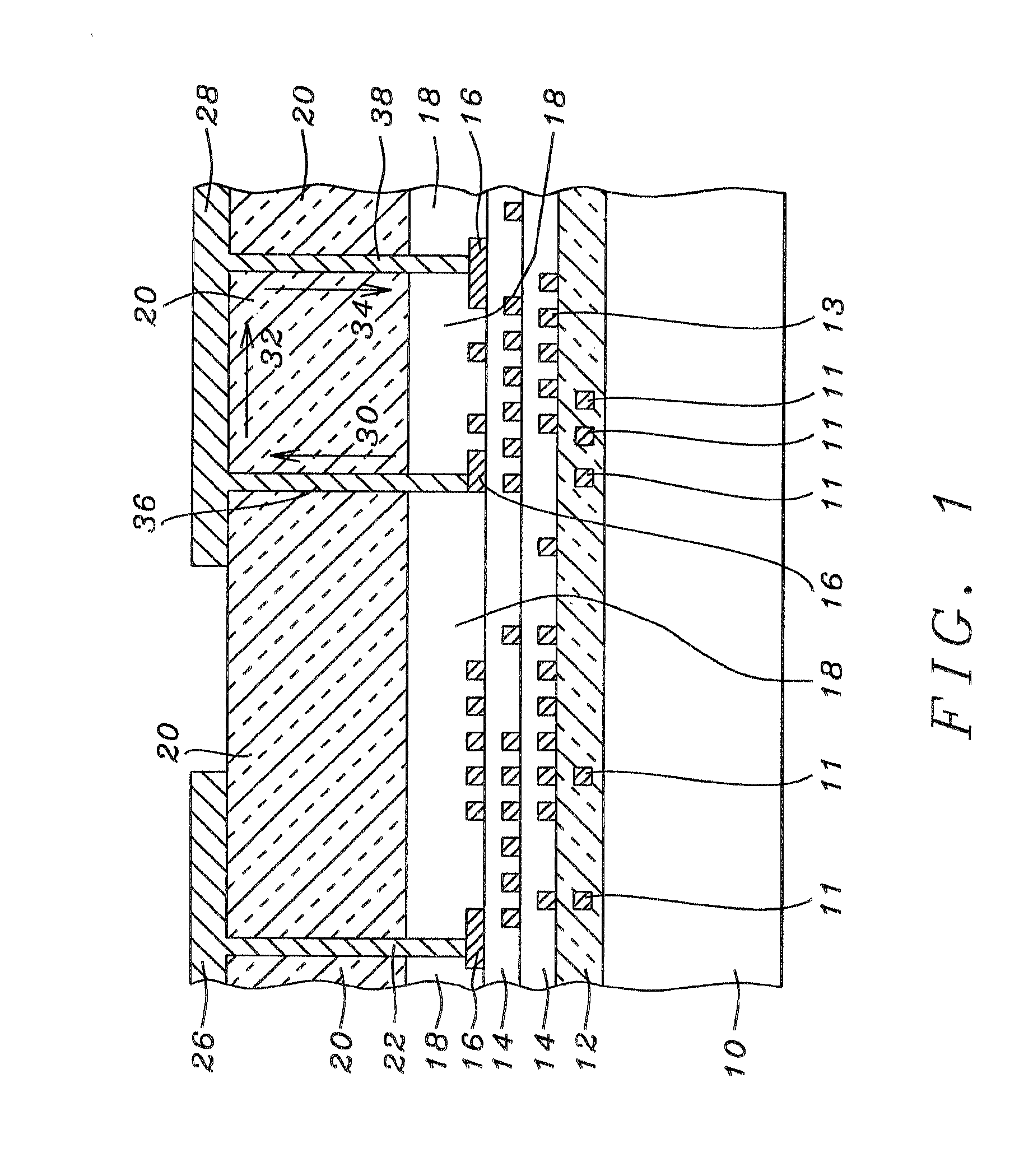

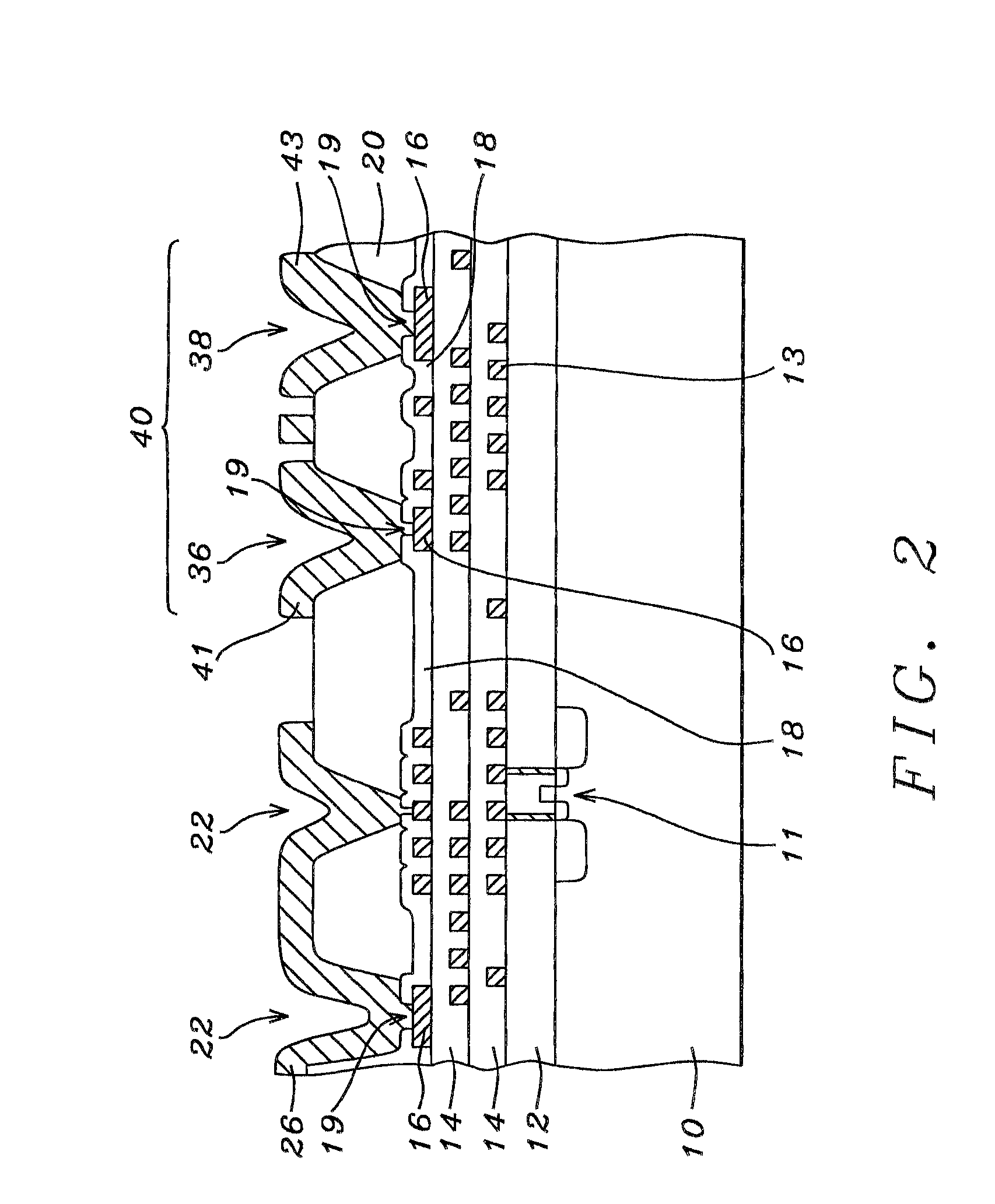

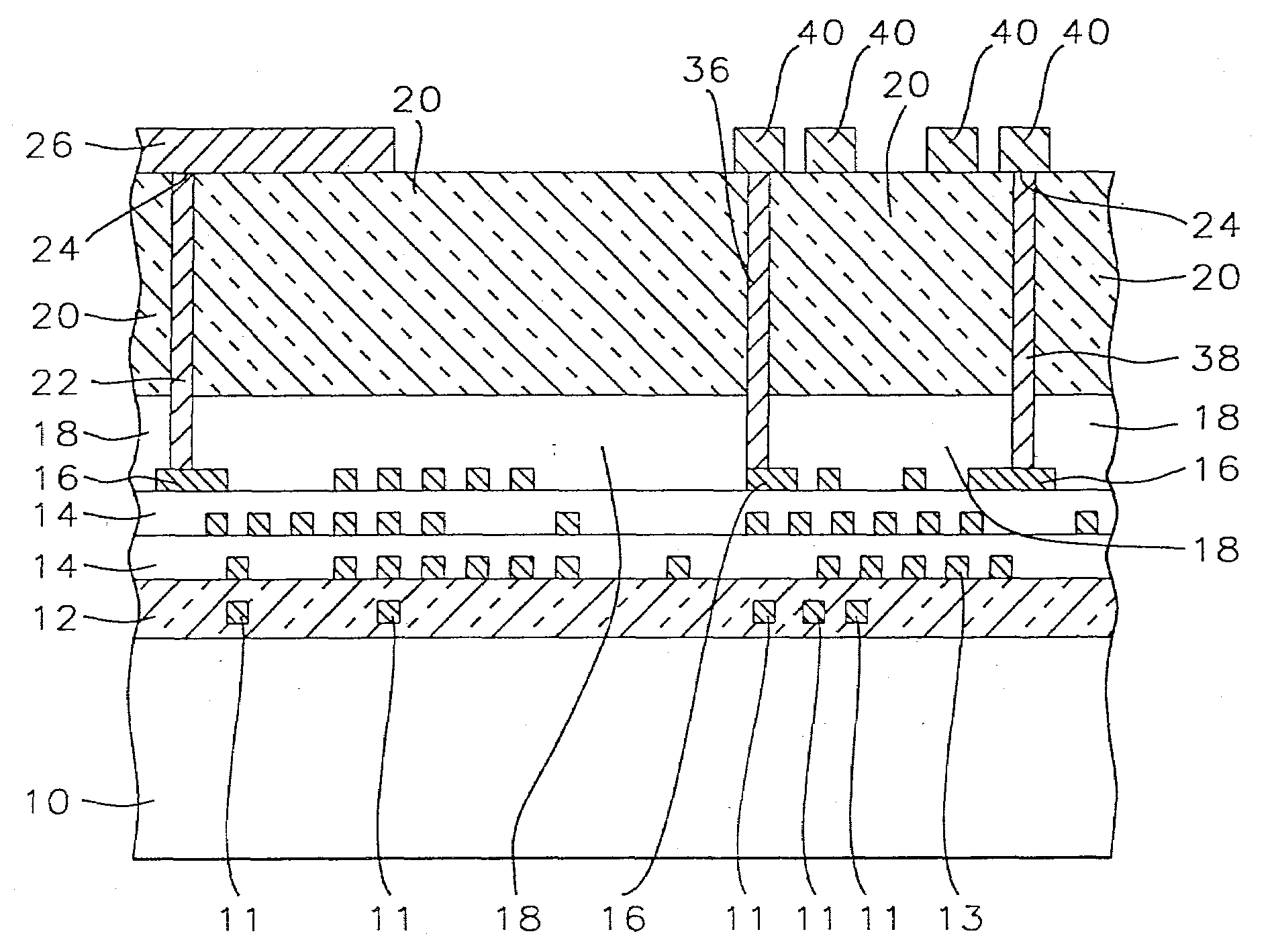

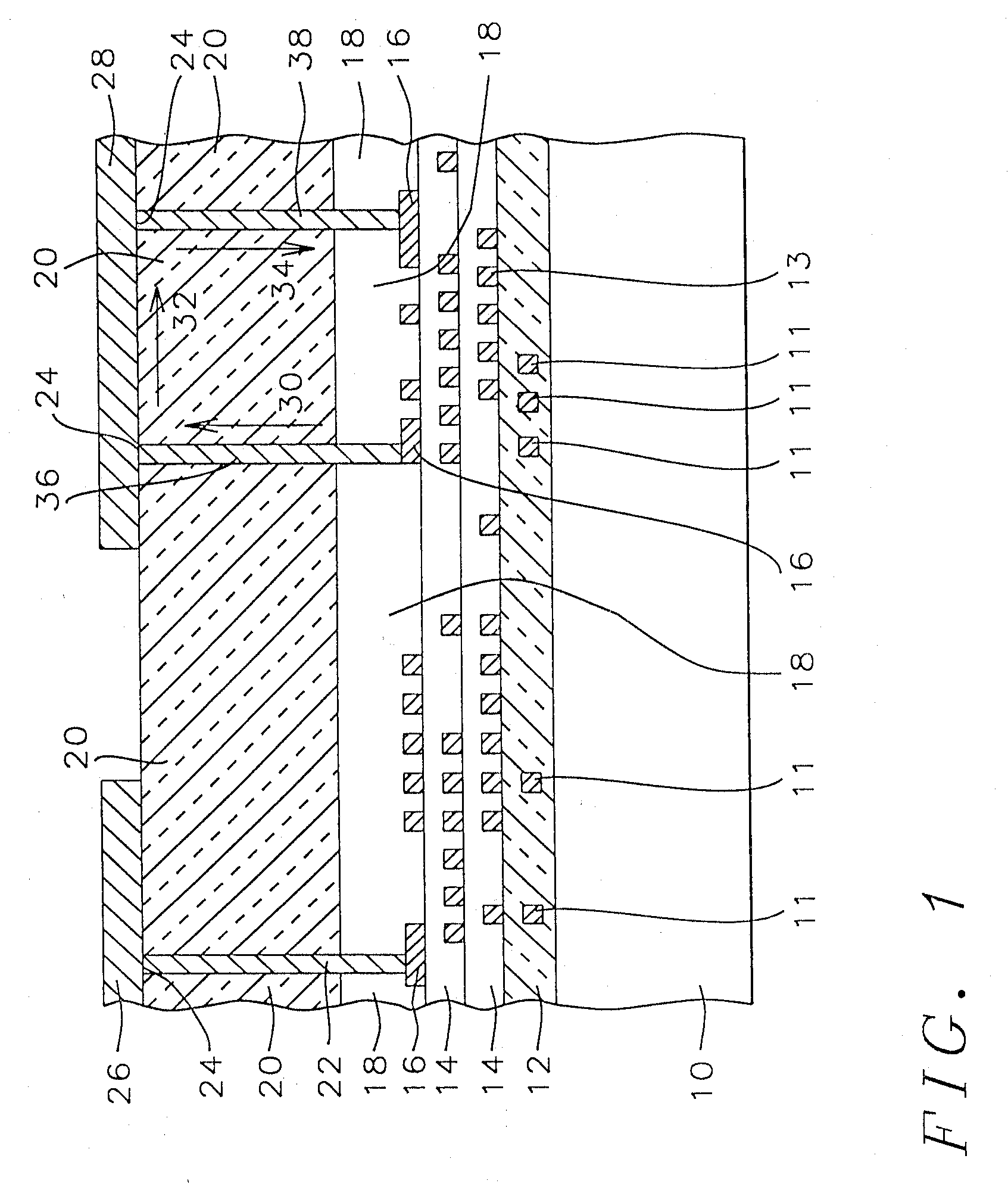

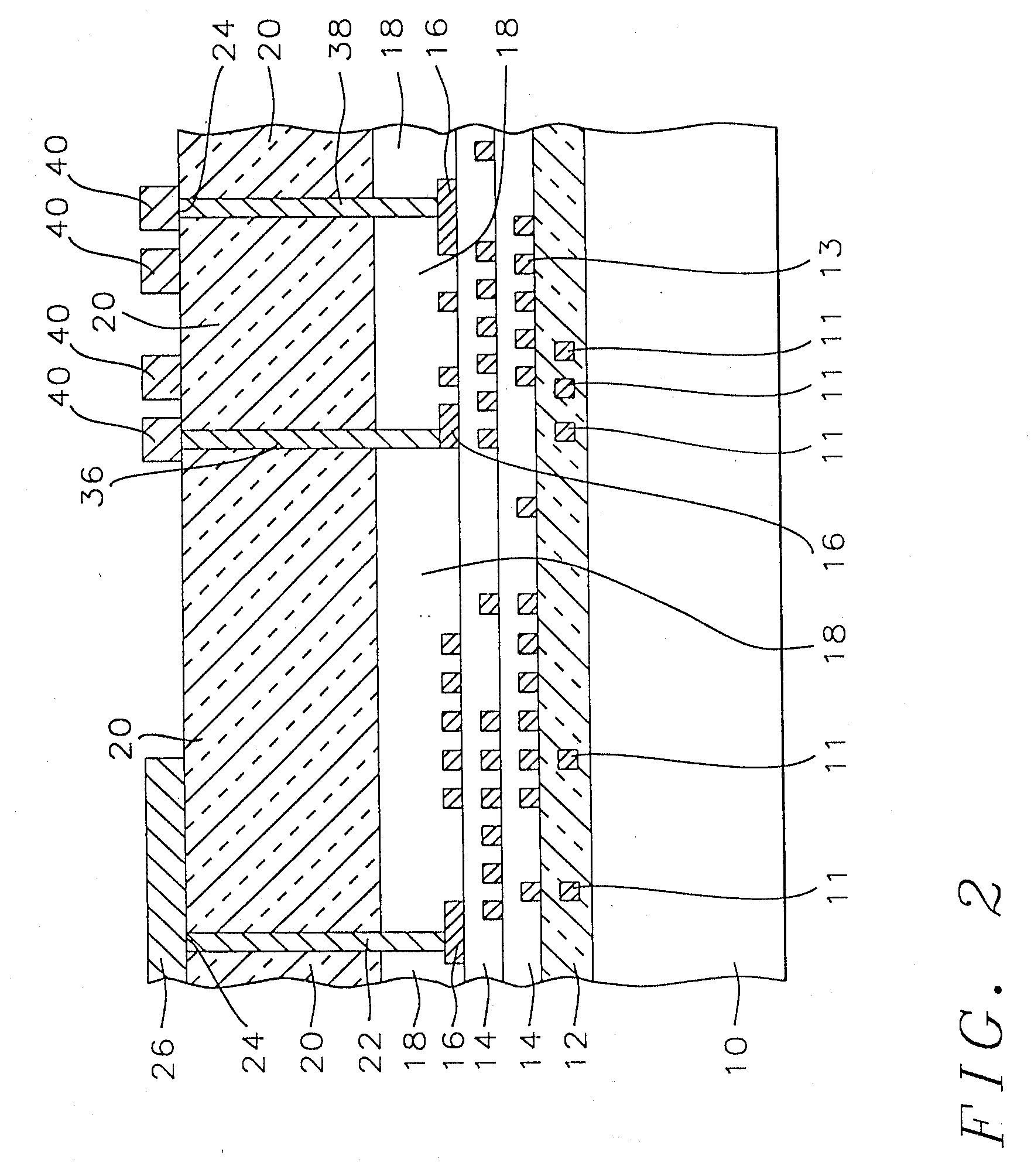

Single-crystal silicon substrate, SOI substrate, semiconductor device, display device, and manufacturing method of semiconductor device

InactiveUS7508034B2Well formedHigh bonding strengthTransistorSolid-state devicesDisplay deviceSoi substrate

A semiconductor device of the present invention is arranged in such a manner that a MOS non-single-crystal silicon thin-film transistor including a non-single-crystal silicon thin film made of polycrystalline silicon, a MOS single-crystal silicon thin-film transistor including a single-crystal silicon thin film, and a metal wiring are provided on an insulating substrate. With this arrangement, (i) a semiconductor device in which a non-single-crystal silicon thin film and a single-crystal silicon thin-film device are formed and high-performance systems are integrated, (ii) a method of manufacturing the semiconductor device, and (iii) a single-crystal silicon substrate for forming the single-crystal silicon thin-film device of the semiconductor device are obtained.

Owner:SHARP KK

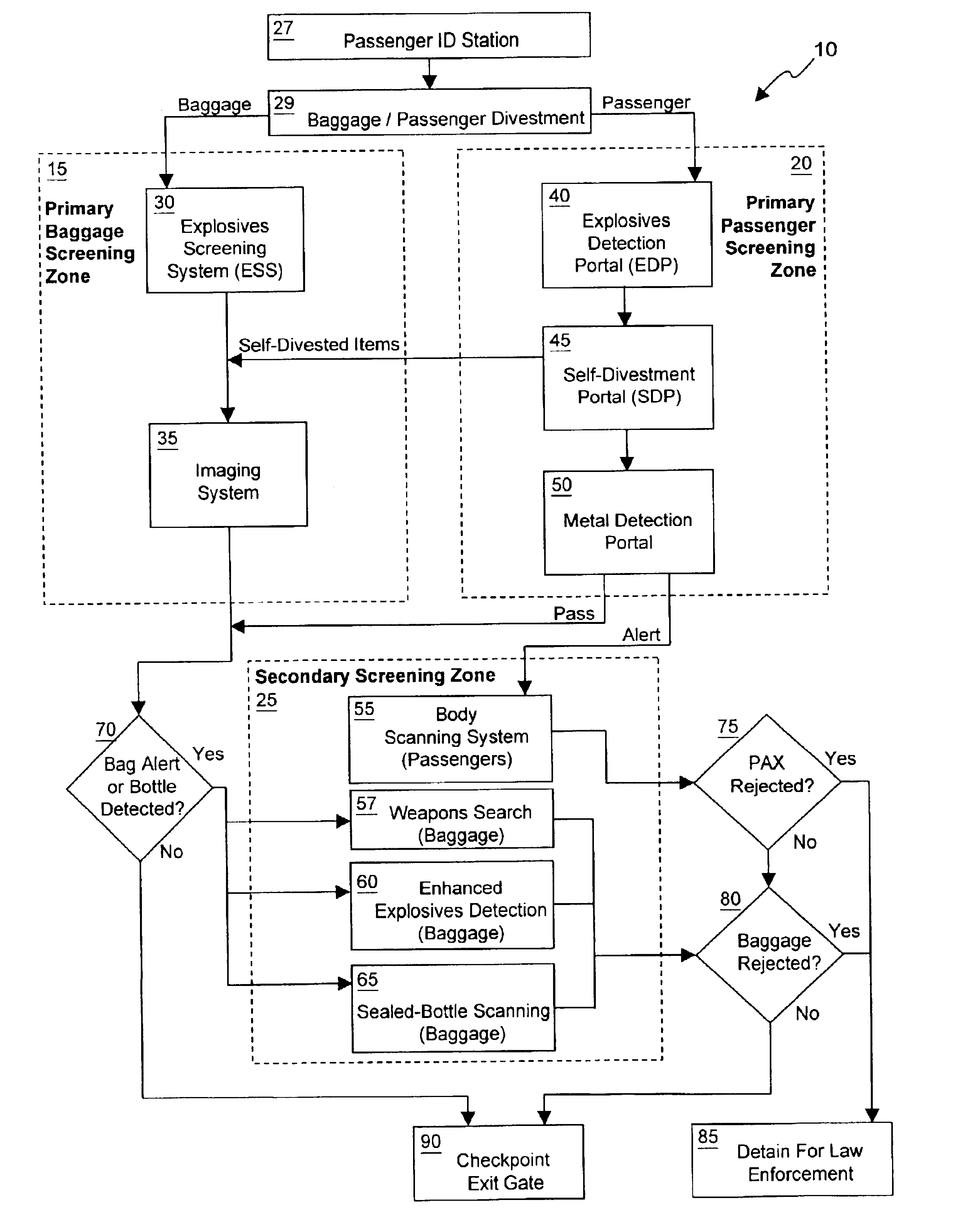

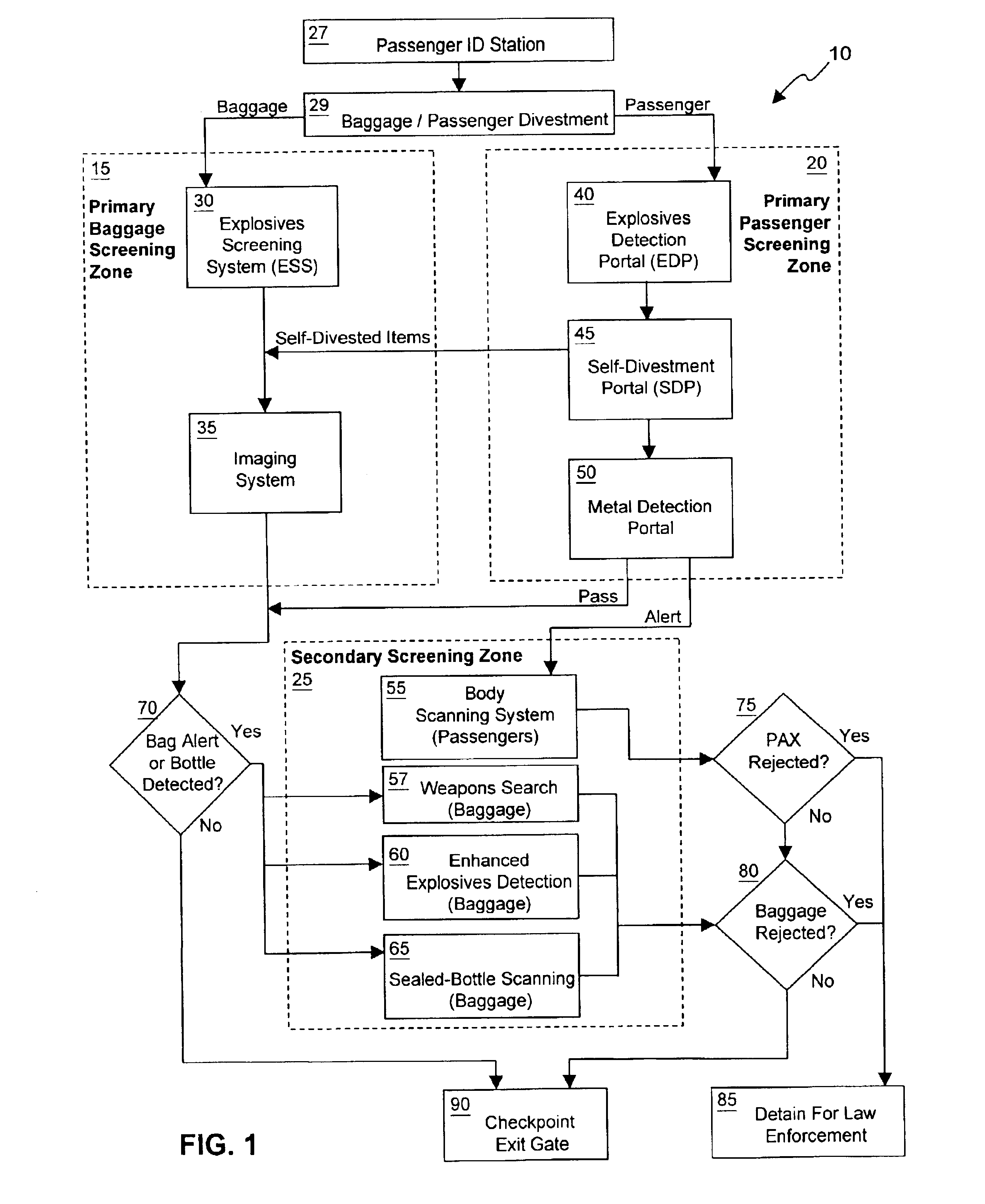

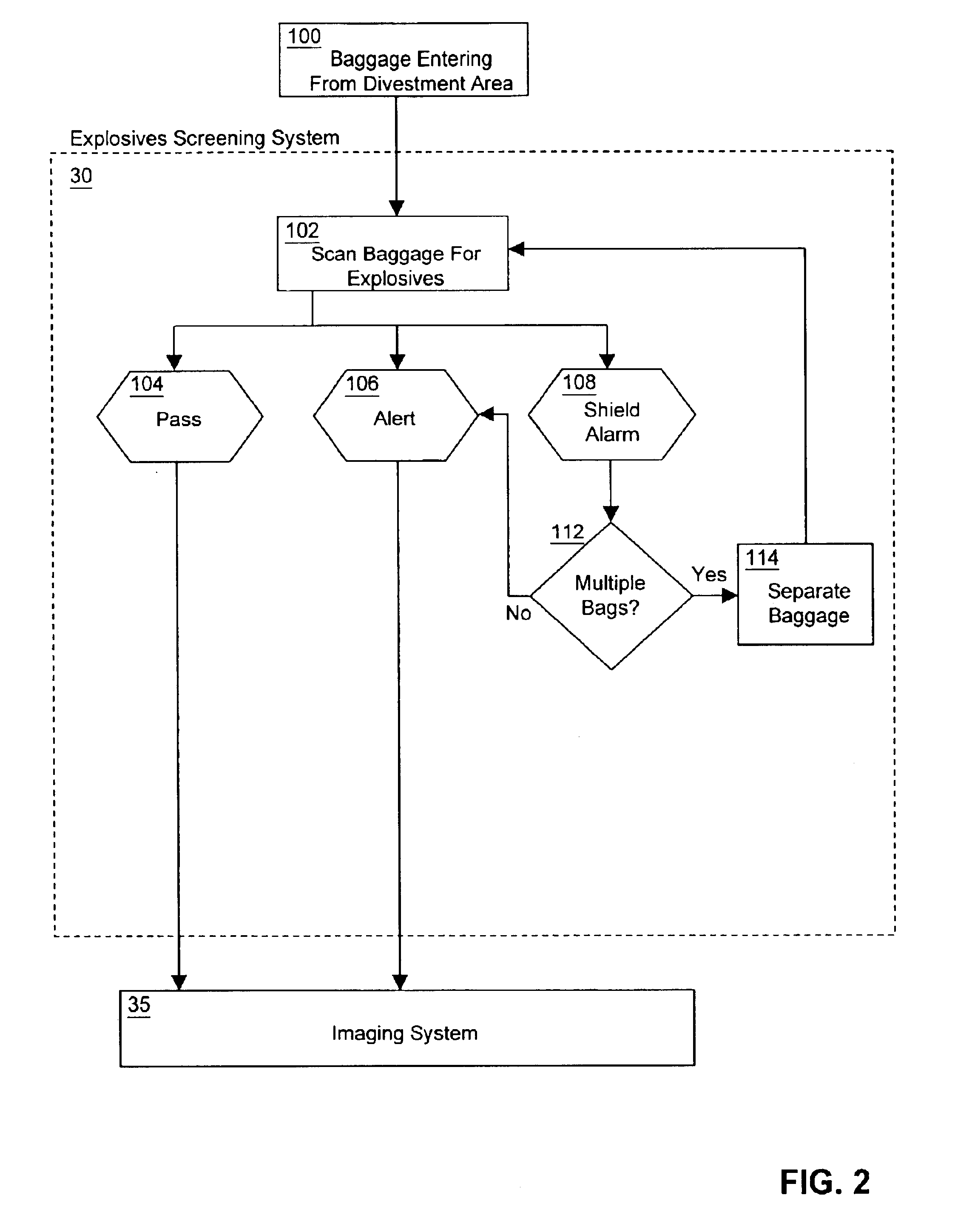

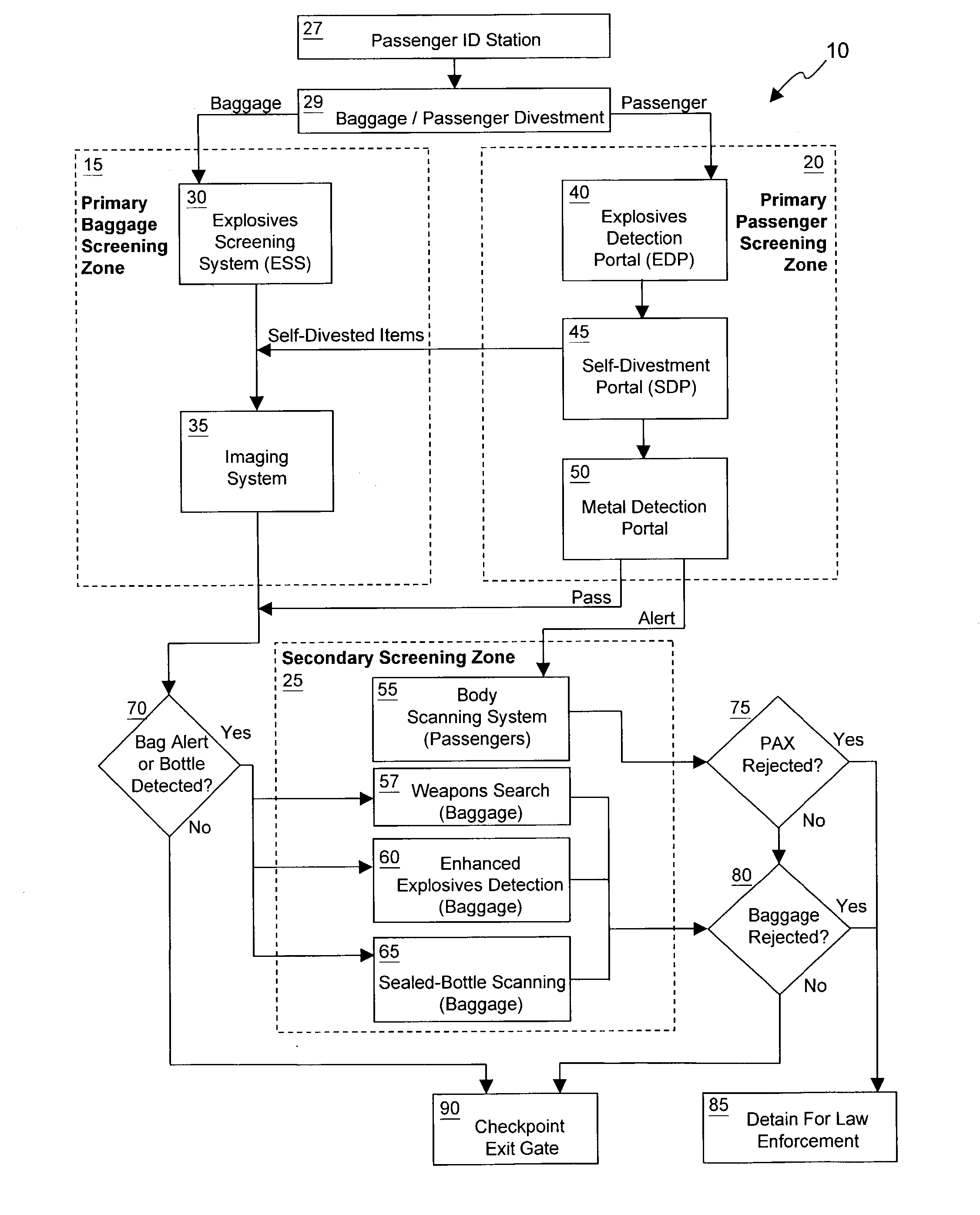

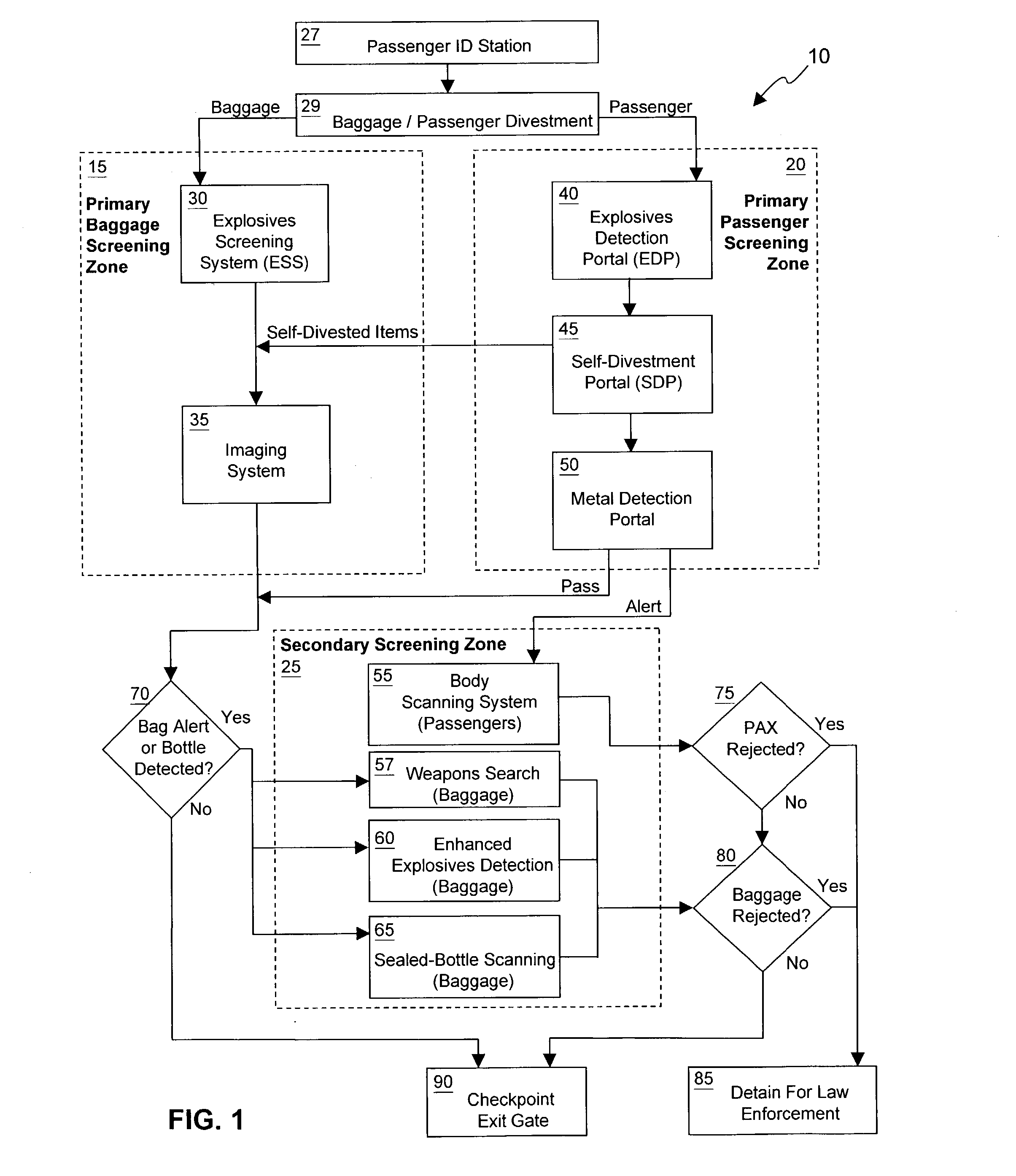

Combined systems user interface for centralized monitoring of a screening checkpoint for passengers and baggage

InactiveUS6952163B2Electric signal transmission systemsTicket-issuing apparatusScreening statusEngineering

A combined systems user interface (CUI) may be configured with an advanced technology screening checkpoint (ATSC), which is a passenger-friendly, high performance system for screening passengers and carry-on items to detect assembled bombs, bomb components, metallic and non-metallic weapons, and other contraband items. The CUI may include a baggage, passenger, and secondary screening status regions. The baggage screening status region displays screening information generated by an explosives screening system and a baggage imaging system, while the passenger screening status region displays screening information generated by an explosives detection portal and a metal detection portal. In some implementations, a secondary screening status region displays screening information generated by a body scanning system and an enhanced explosives screening system.

Owner:HUEY JOHN H

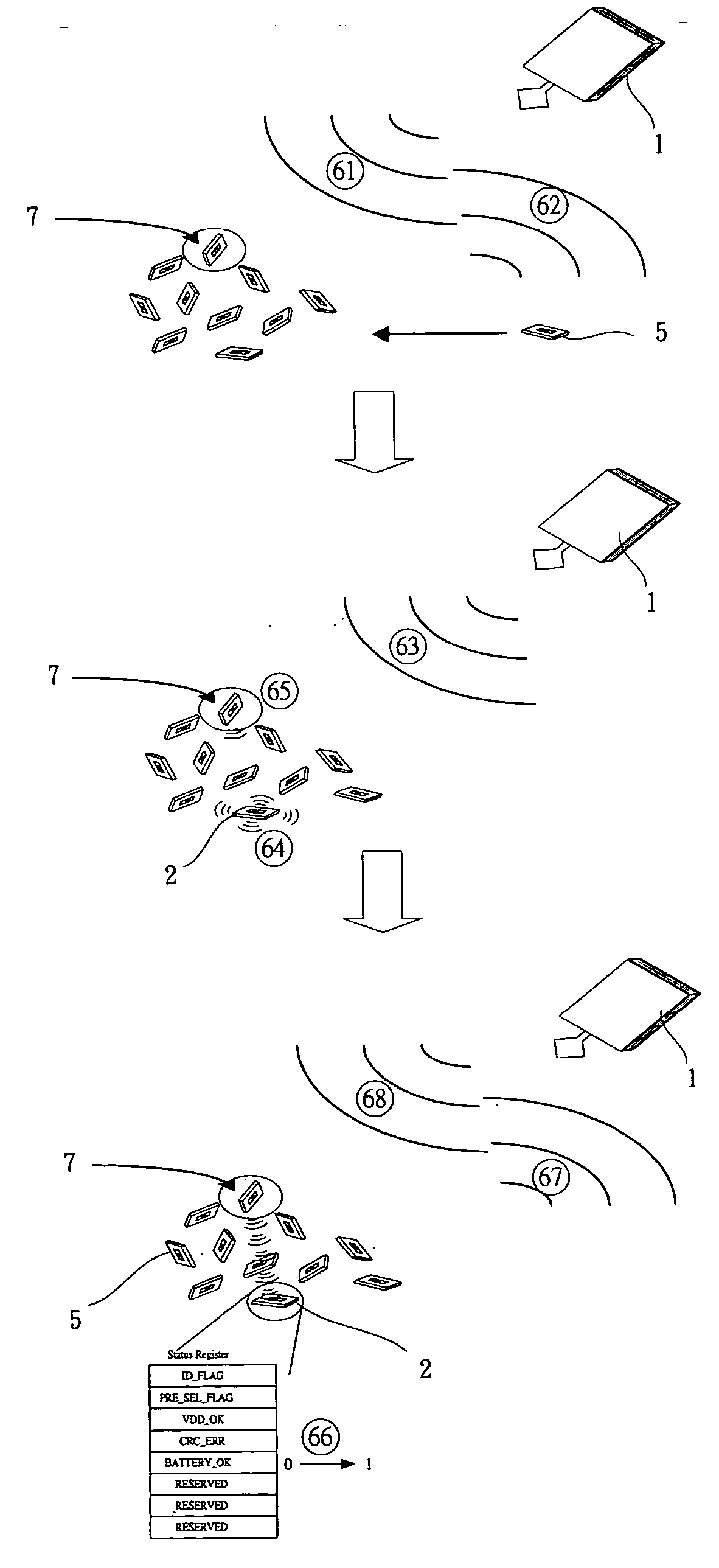

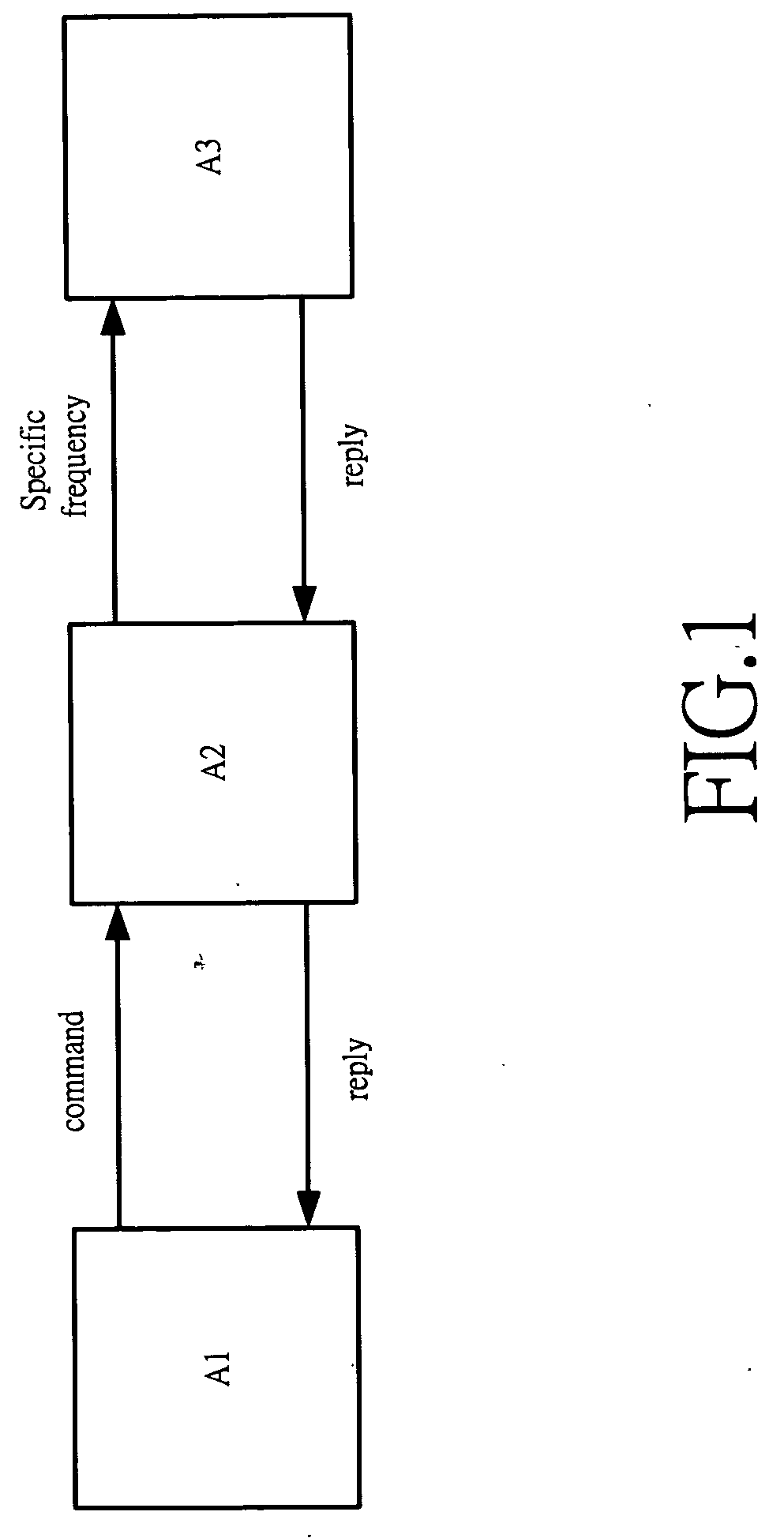

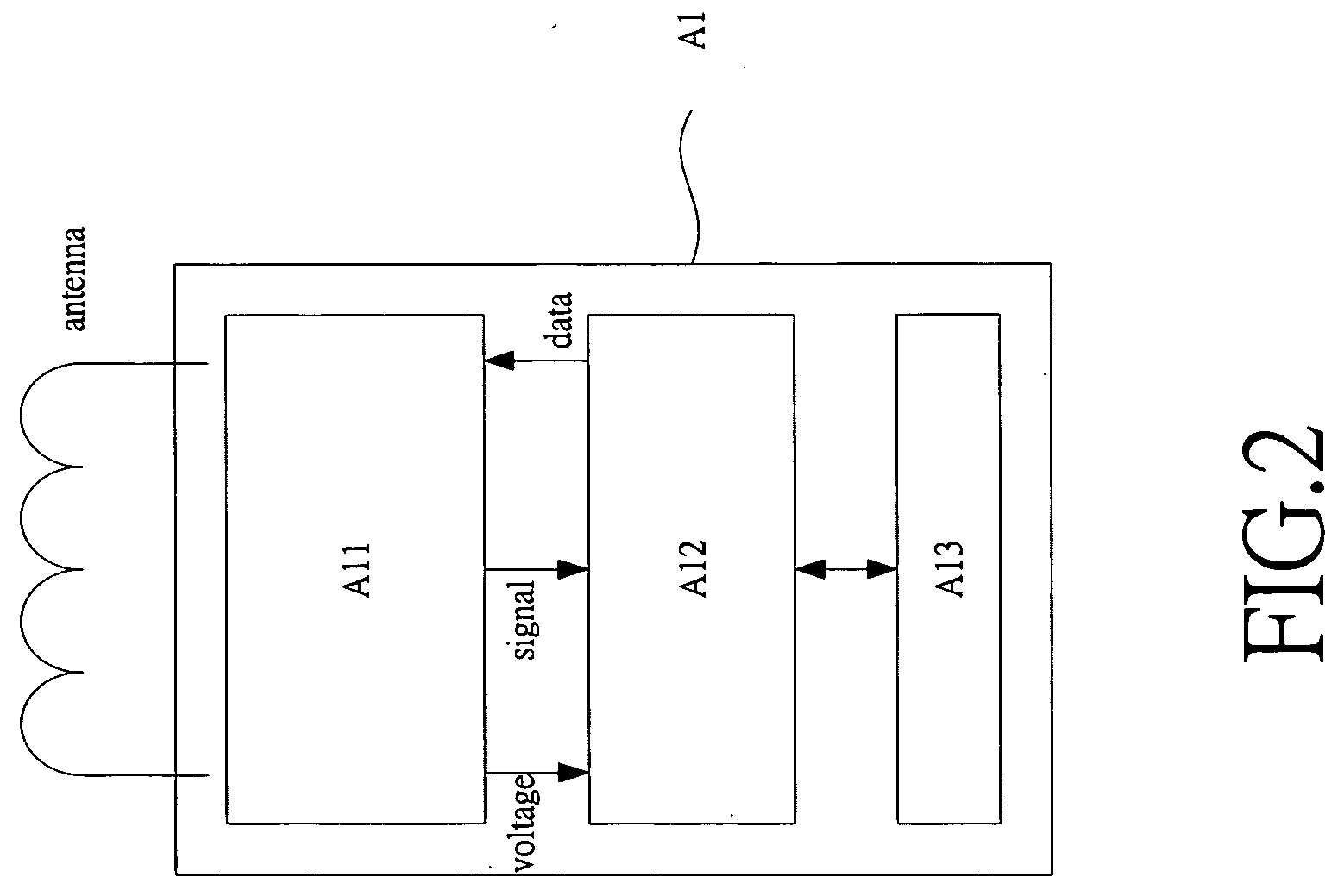

High performance RFID system and operating method thereof

InactiveUS20060114102A1Improve performanceMemory record carrier reading problemsSubscribers indirect connectionSemi activeTrunking

A high performance Radio Frequency Identification (RFID) system and the operating method thereof. The RFID system includes a reader, a plurality of passive tags, and at least one local reader to communicate with nearby passive tags and further forward results to the reader. A repeater tag or a semi-active tag can serve as a local reader. An operating method of the high performance RFID system, a repeater tag operating method, a semi-active tag electric power detecting method, and an operating method for searching for no electric power tags are further provided.

Owner:IND TECH RES INST

Combined systems user interface for centralized monitoring of a screening checkpoint for passengers and baggage

InactiveUS20050024199A1Improve performanceElectric signal transmission systemsTicket-issuing apparatusScreening statusEngineering

A combined systems user interface (CUI) may be configured with an advanced technology screening checkpoint (ATSC), which is a passenger-friendly, high performance system for screening passengers and carry-on items to detect assembled bombs, bomb components, metallic and non-metallic weapons, and other contraband items. The CUI may include a baggage, passenger, and secondary screening status regions. The baggage screening status region displays screening information generated by an explosives screening system and a baggage imaging system, while the passenger screening status region displays screening information generated by an explosives detection portal and a metal detection portal. In some implementations, a secondary screening status region displays screening information generated by a body scanning system and an enhanced explosives screening system.

Owner:HUEY JOHN H

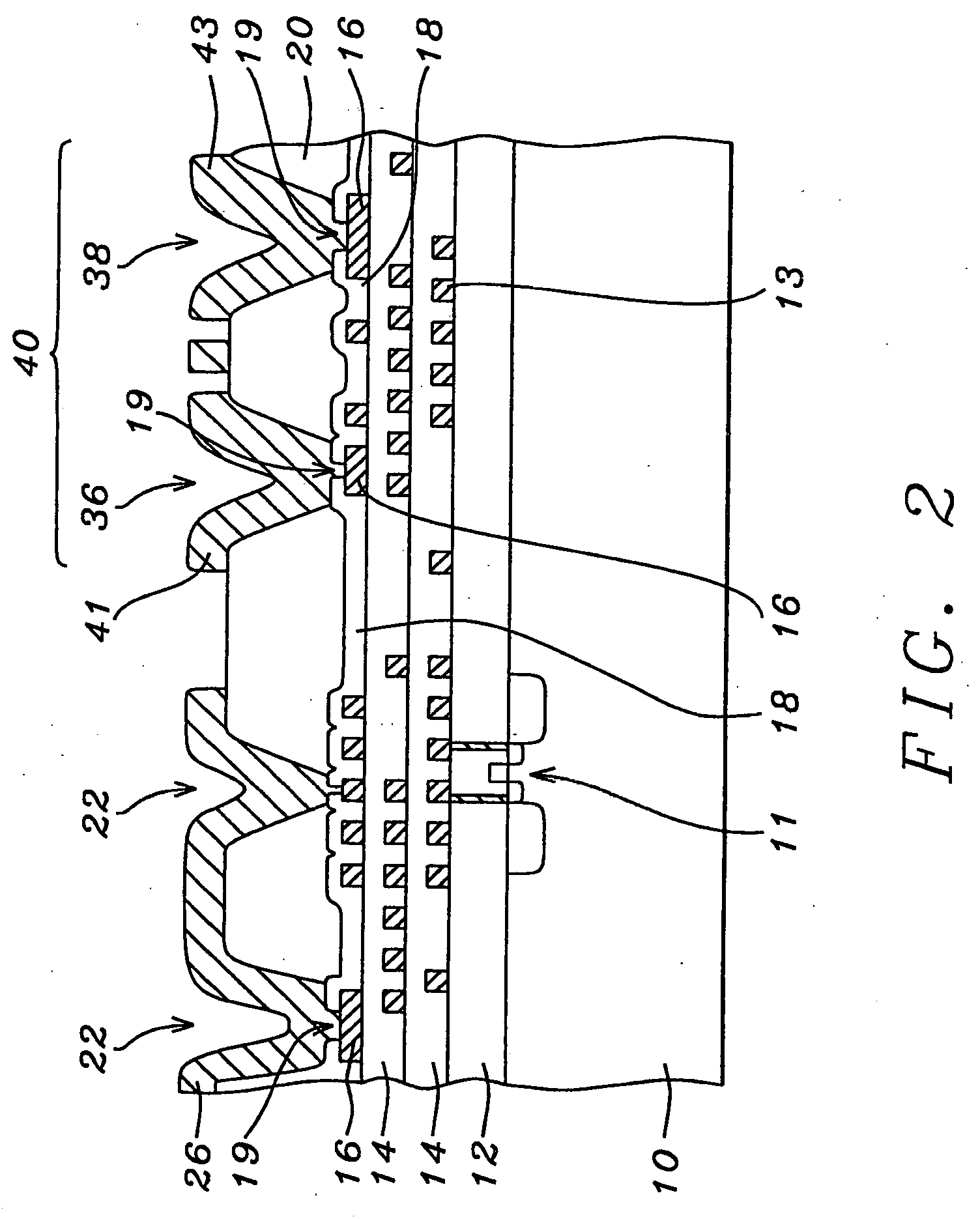

High performance system-on-chip discrete components using post passivation process

InactiveUS6869870B2Improve RF performanceIncreased frequency rangeTransistorSemiconductor/solid-state device detailsHigh performance systemMaterials science

A system and method for forming post passivation discrete components, is described. High quality discrete components are formed on a layer of passivation, or on a thick layer of polymer over a passivation layer.

Owner:QUALCOMM INC

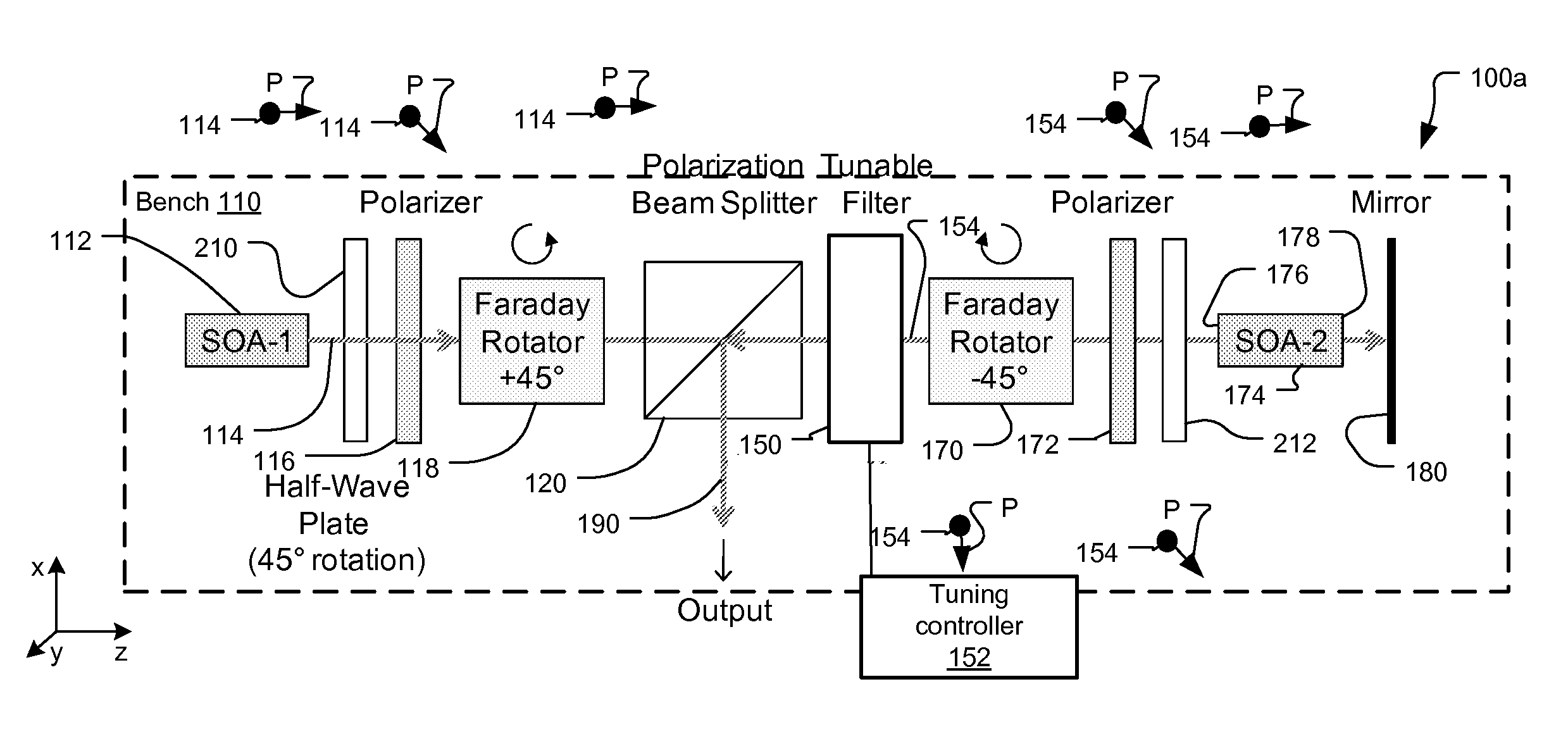

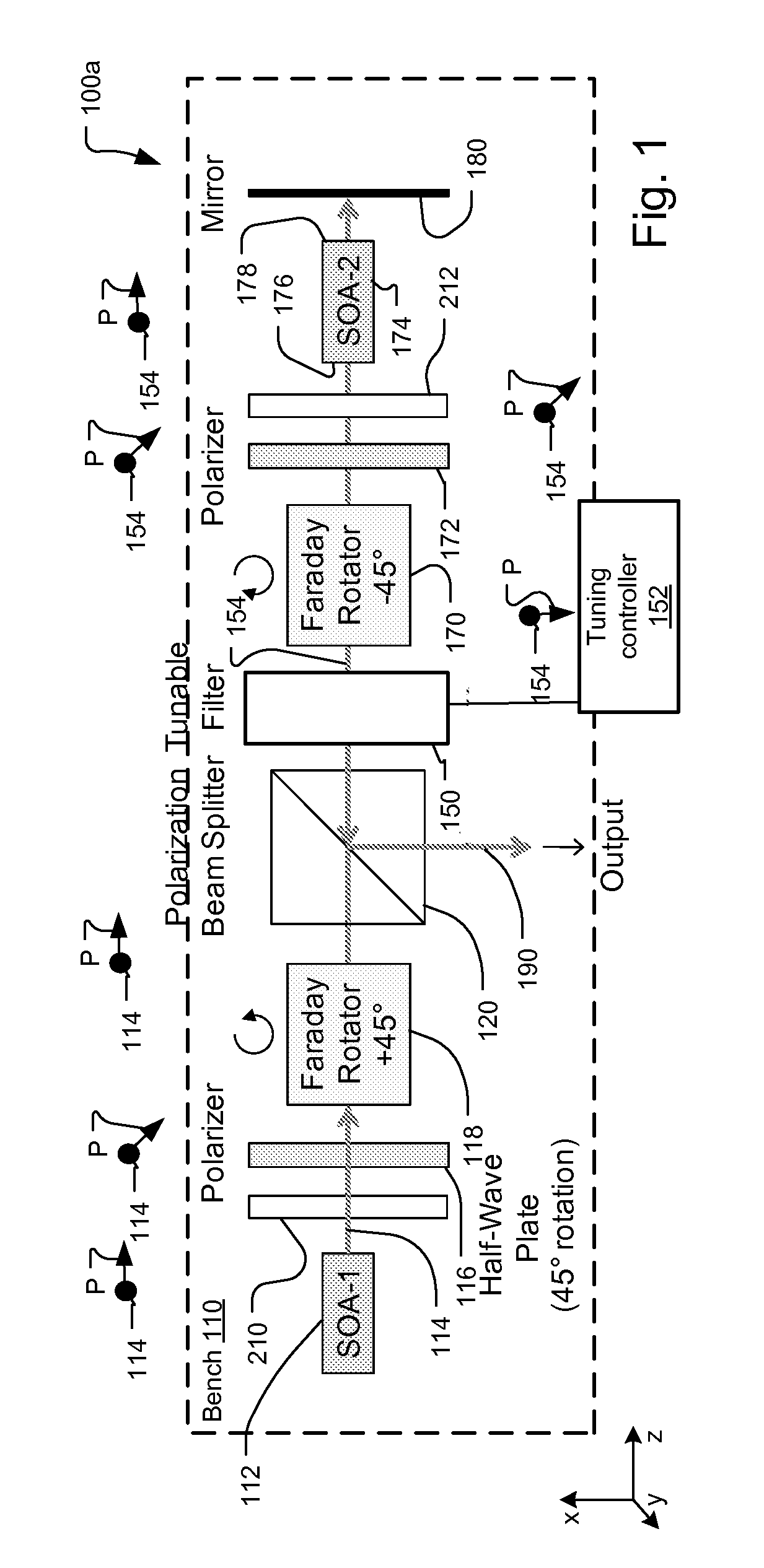

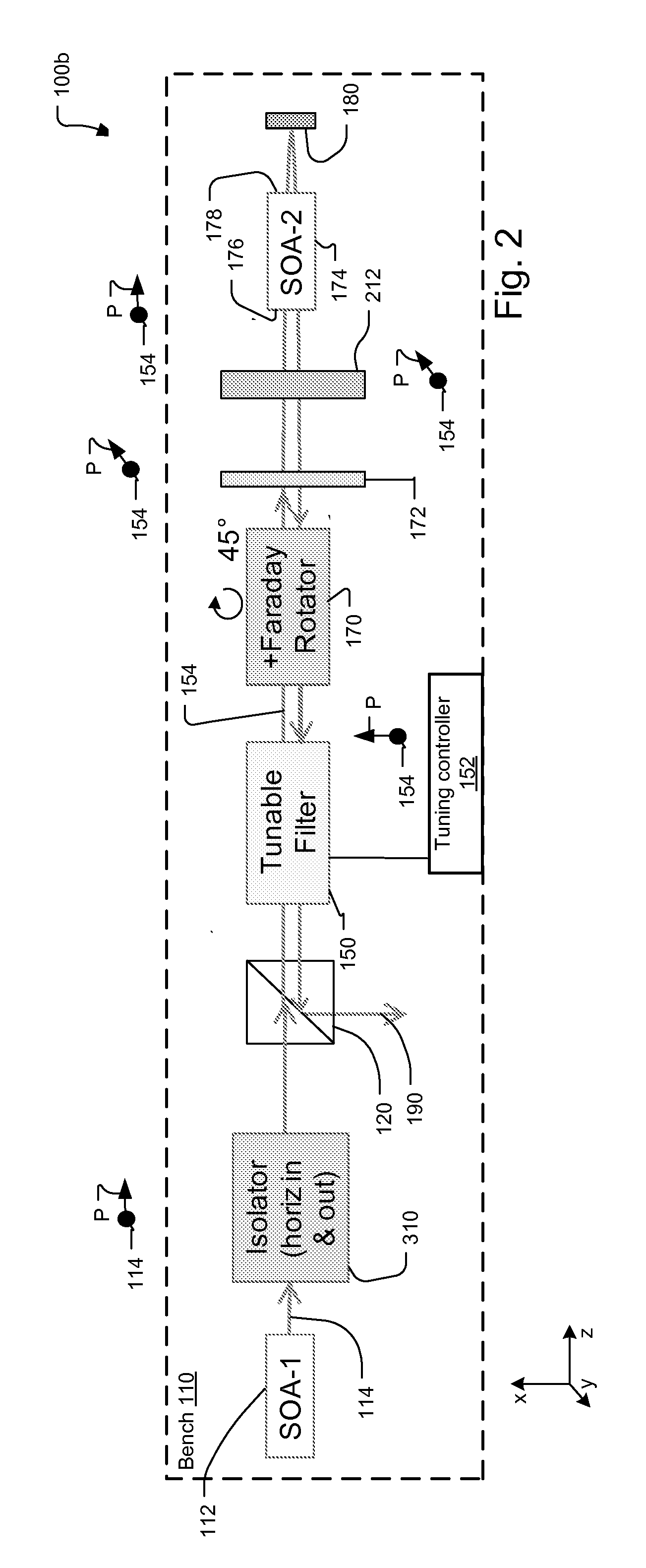

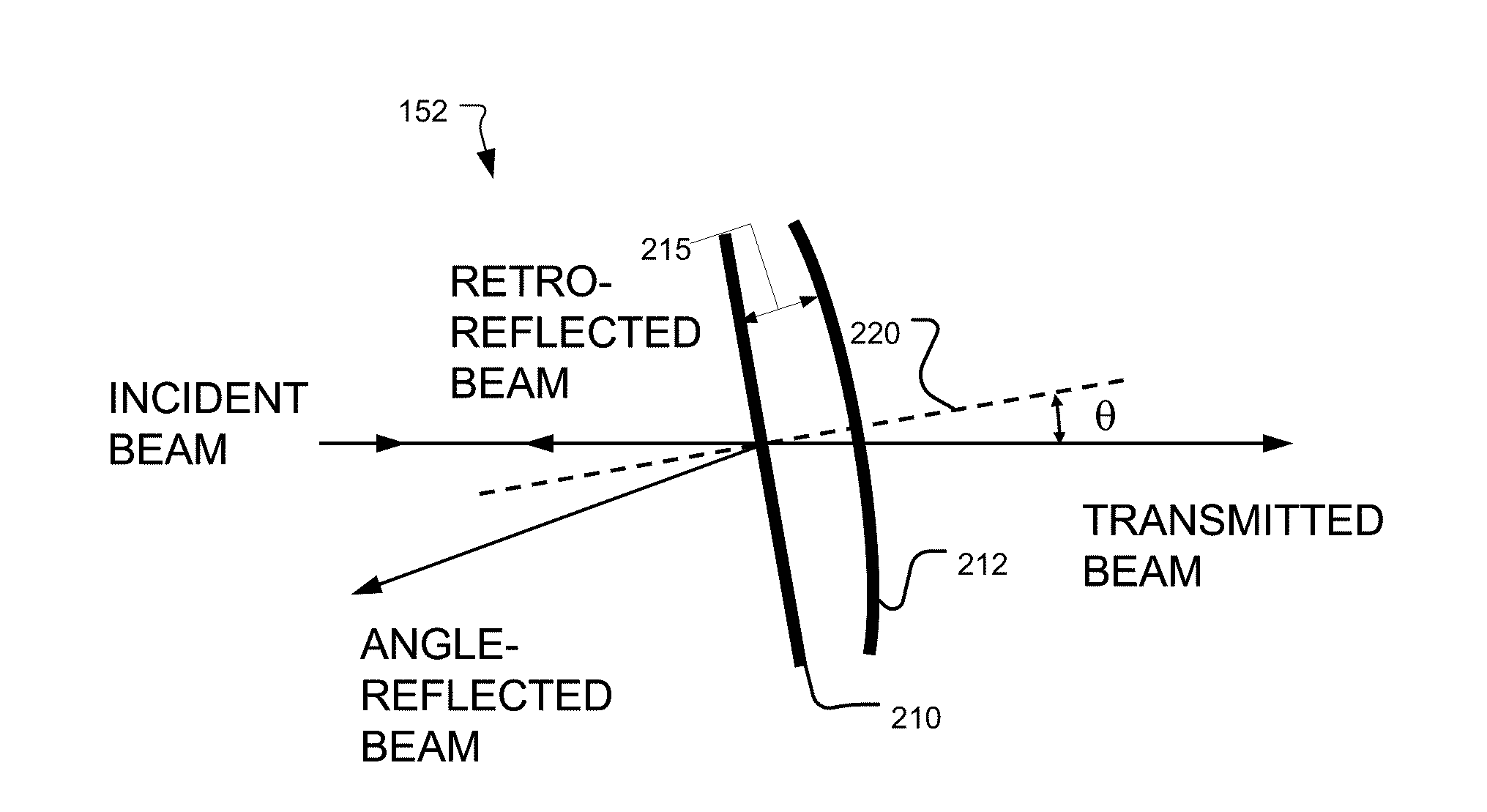

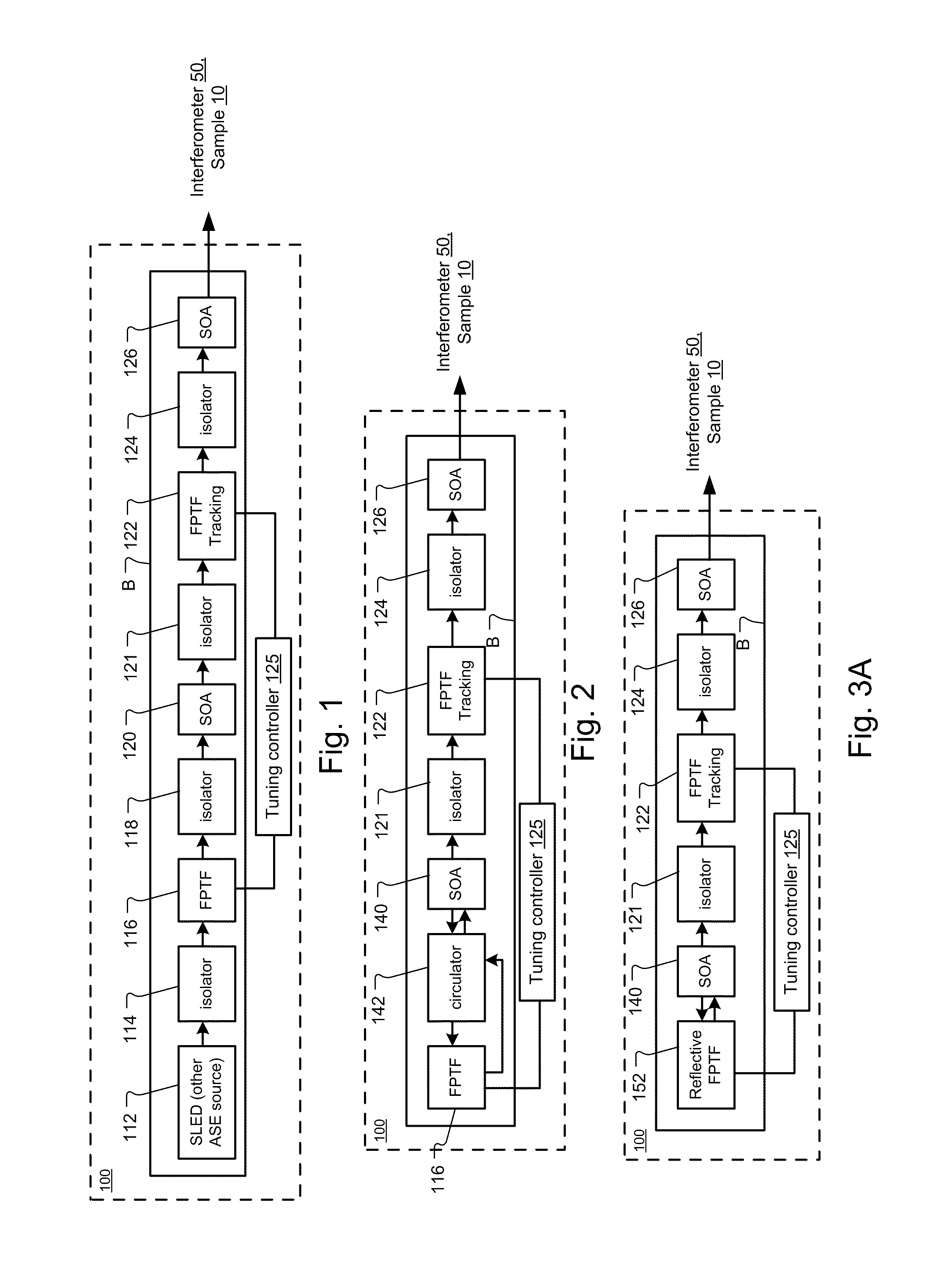

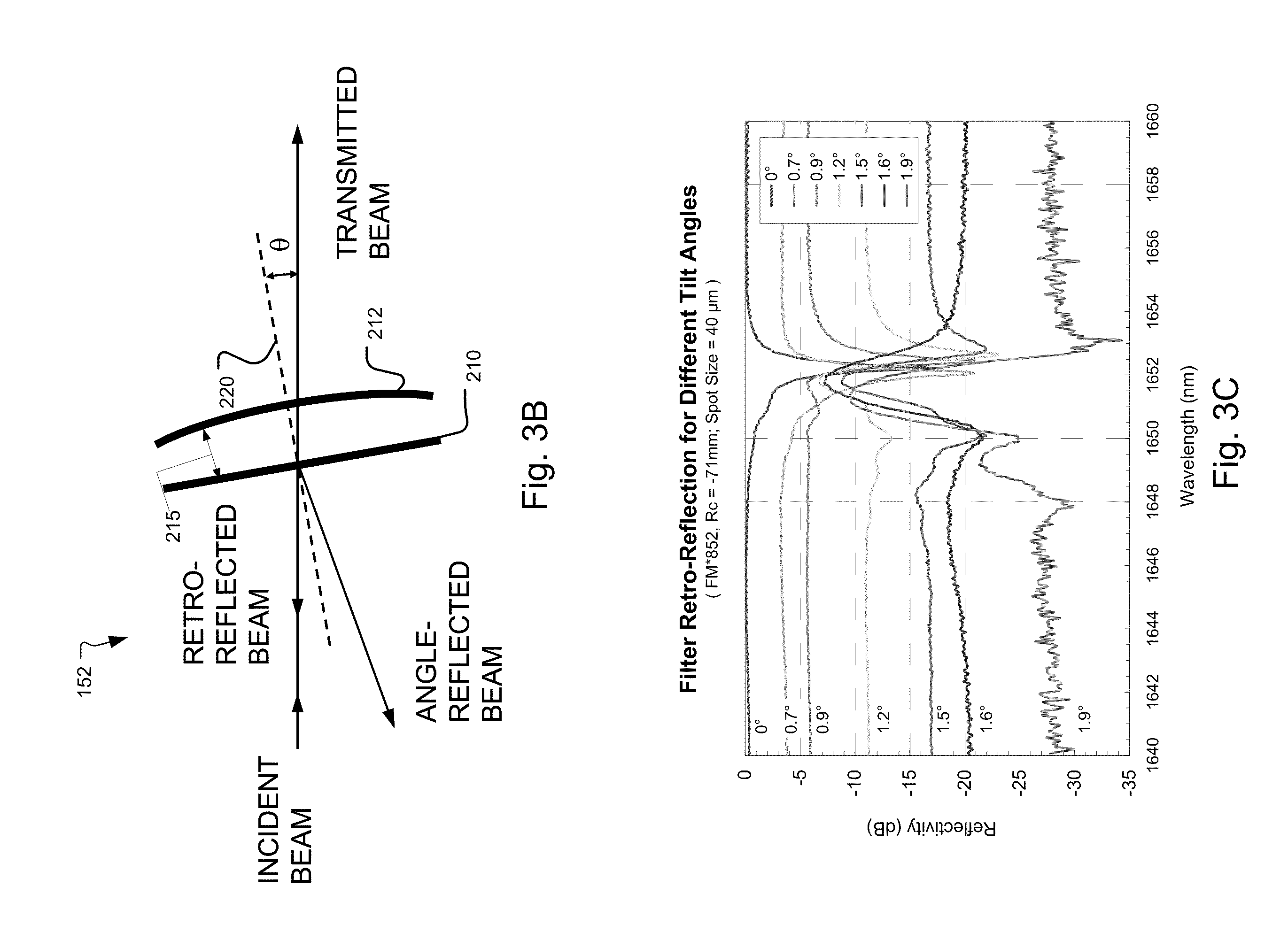

ASE Swept Source with Self-Tracking Filter for OCT Medical Imaging

InactiveUS20110051143A1Relax requirementsConvenient and accurateLaser detailsRadiation pyrometryFrequency spectrumOptoelectronics

An integrated swept wavelength tunable optical source uses a narrowband filtered broadband signal with an optical amplifier and self-tracking filter. This source comprises a micro optical bench, a source for generating broadband light, a tunable Fabry Perot filter, installed on the bench, for spectrally filtering the broadband light from the broadband source to generate a narrowband tunable signal, an amplifier, installed on the bench, for amplifying the tunable signal. The self-tracking arrangement is used where a single tunable filter both generates the narrowband signal and spectrally filters the amplified signal. In some examples, two-stage amplification is provided. The use of a single bench implementation yields a low cost high performance system. For example, polarization control between components is no longer necessary.

Owner:EXCELITAS TECH

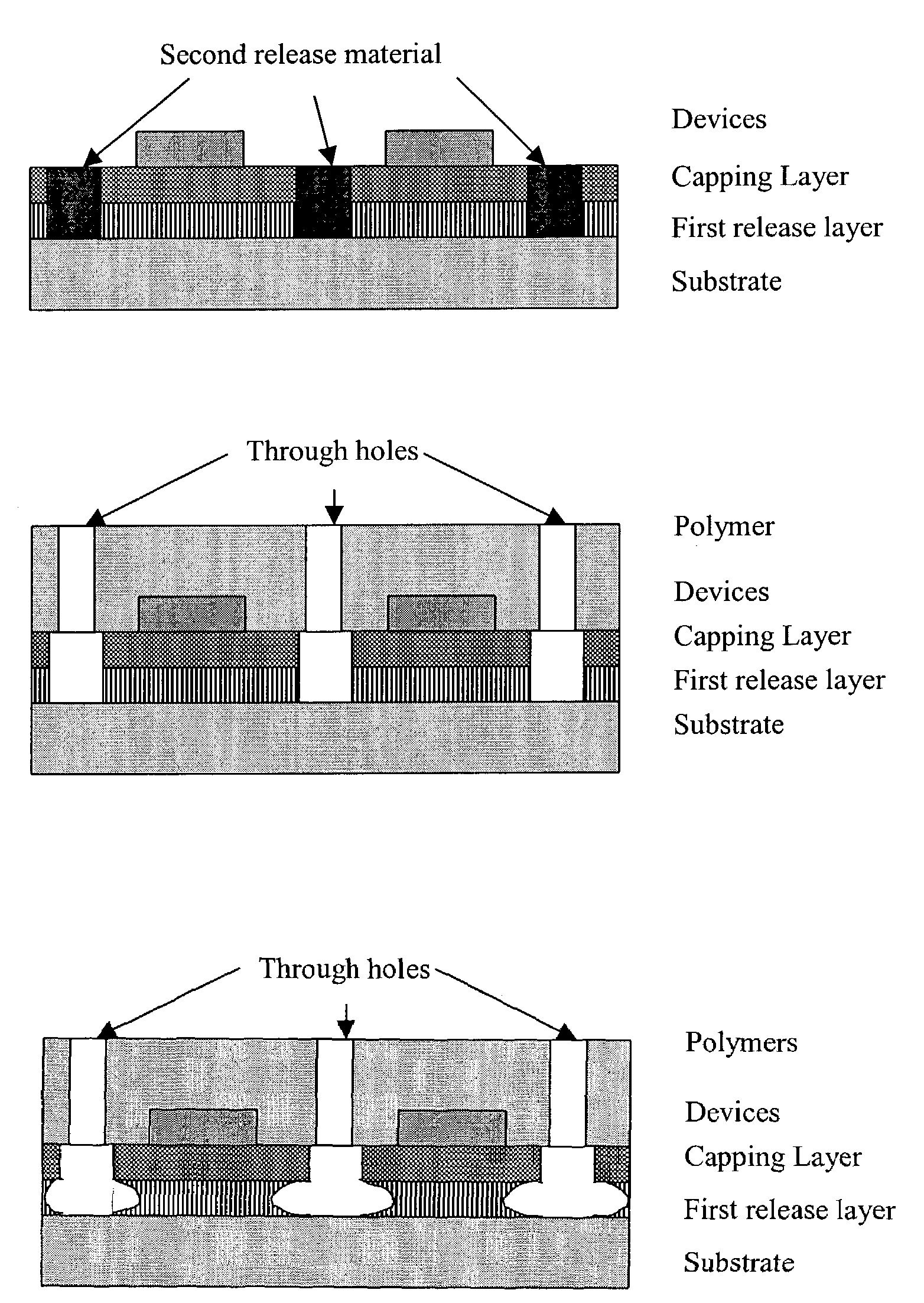

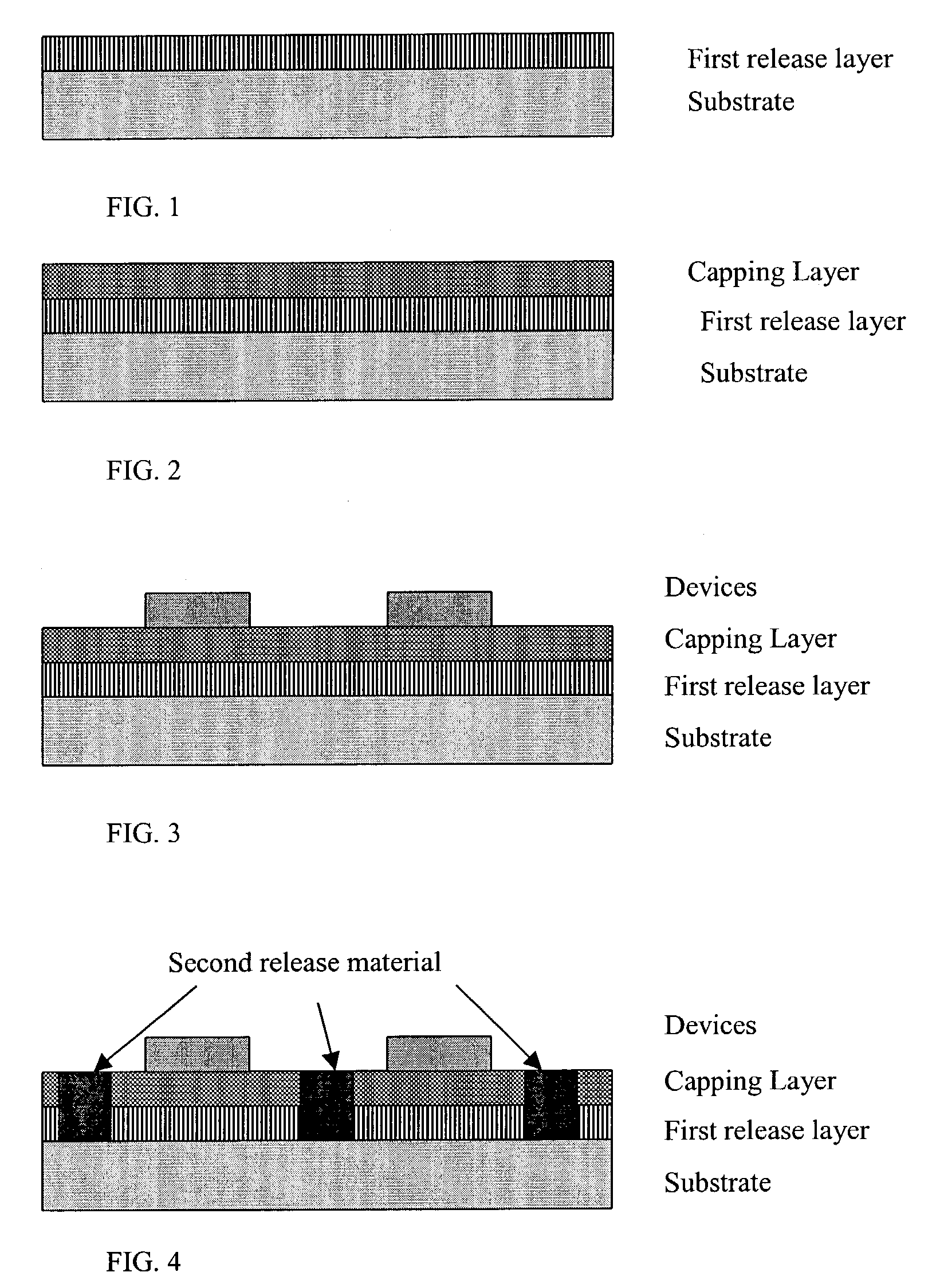

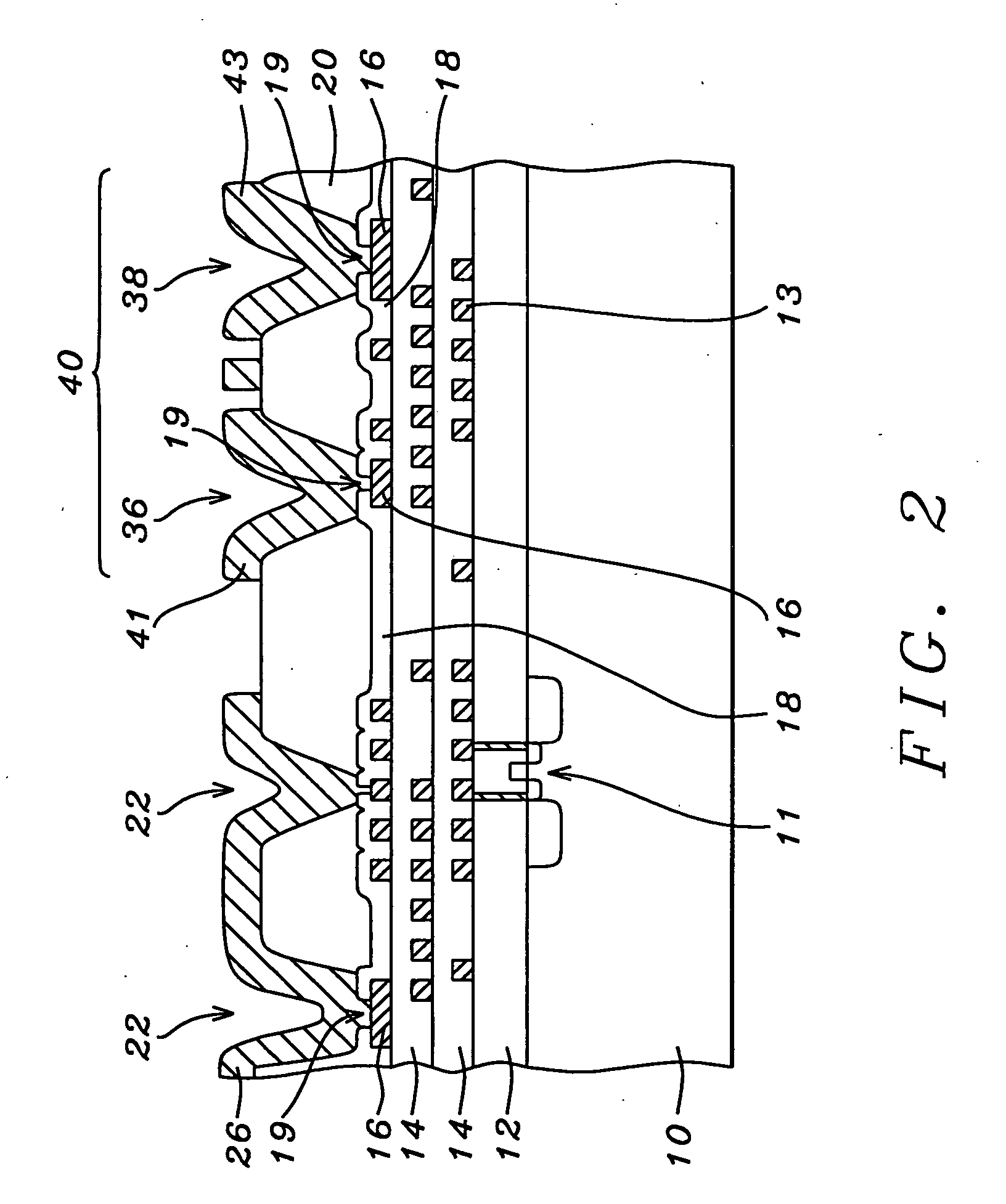

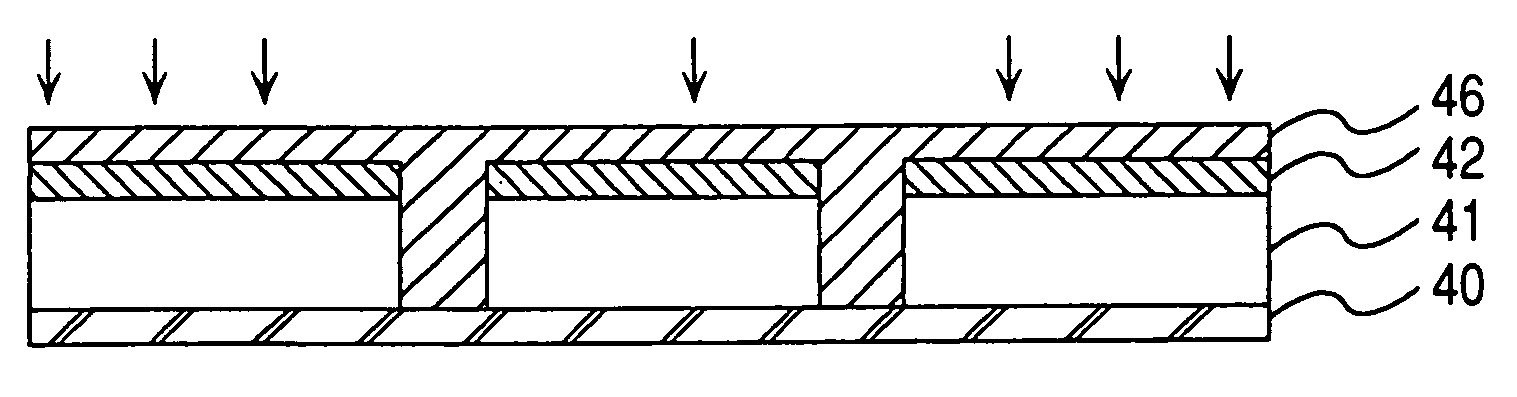

Use of sacrificial layers in the manufacture of high performance systems on tailored substrates

InactiveUS7309620B2Improve bindingFinal product manufactureSolid-state devicesChemical speciesEngineering

The invention relates to methods for preparing a removable system on a mother substrate. The method deposits a high surface to volume sacrificial layer on a mother substrate and stabilizes the sacrificial layer by a) removing volatile chemical species in and on the sacrificial layer and / or b) modifying the surface of the layer. The method coats over the sacrificial layer with a capping medium. A system is the fabricated on the capping medium. The method provides through holes to access the sacrificial layer. The method may also apply a top layer onto the system to form a covered system. The invention also includes the step of removing the sacrificial layer to release the system from the mother substrate. Methods of the invention also include selectively removing a portion of the system and capping layers to form void regions defining an array of islands composed of device, structure, or system and capping layer regions, and optionally filling the island-defining void region with a sacrificial material. In such methods the sacrificial material and the high surface to volume sacrificial layer are removed to release the system from the mother substrate. Methods of the invention also include applying a layer to the capping material side of the released system to form a configuration wherein the system is substantially within a bending-stress reduced neutral plane. The systems fabricated according to the invention may be placed on a wide variety of suitable substrates, including flexible substrates.

Owner:PENN STATE RES FOUND

Filtered ASE Swept Source for OCT Medical Imaging

InactiveUS20110051148A1Low costImprove performanceMaterial analysis by optical meansSpectrum generation using multiple reflectionFrequency spectrumOptical polarization

An integrated swept wavelength optical source uses a filtered ASE signal with an optical amplifier and tracking filter. This source comprises a micro optical bench, a source for generating broadband light, a first tunable Fabry Perot filter, installed on the bench, for spectrally filtering the broadband light from the broadband source to generate a narrowband tunable signal, an amplifier, installed on the bench, for amplifying the tunable signal, and a second tunable Fabry Perot filter, installed on the bench, for spectrally filtering the amplified tunable signal from the amplifier. A self-tracking arrangement is also possible where a single tunable filter both generates the narrowband signal and spectrally filters the amplified signal. In some examples, two-stage amplification is provided. The use of a single bench implementation yields a low cost high performance system. For example, polarization control between components is no longer necessary.

Owner:EXCELITAS TECH

Single-crystal silicon substrate, soi substrate, semiconductor device, display device, and manufacturing method of semiconductor device

InactiveUS20090095956A1Well formedHigh bonding strengthTransistorSemiconductor/solid-state device testing/measurementDisplay deviceSoi substrate

A semiconductor device of the present invention is arranged in such a manner that a MOS non-single-crystal silicon thin-film transistor including a non-single-crystal silicon thin film made of polycrystalline silicon, a MOS single-crystal silicon thin-film transistor including a single-crystal silicon thin film, and a metal wiring are provided on an insulating substrate. With this arrangement, (i) a semiconductor device in which a non-single-crystal silicon thin film and a single-crystal silicon thin-film device are formed and high-performance systems are integrated, (ii) a method of manufacturing the semiconductor device, and (iii) a single-crystal silicon substrate for forming the single-crystal silicon thin-film device of the semiconductor device are obtained.

Owner:TAKAFUJI YUTAKA +1

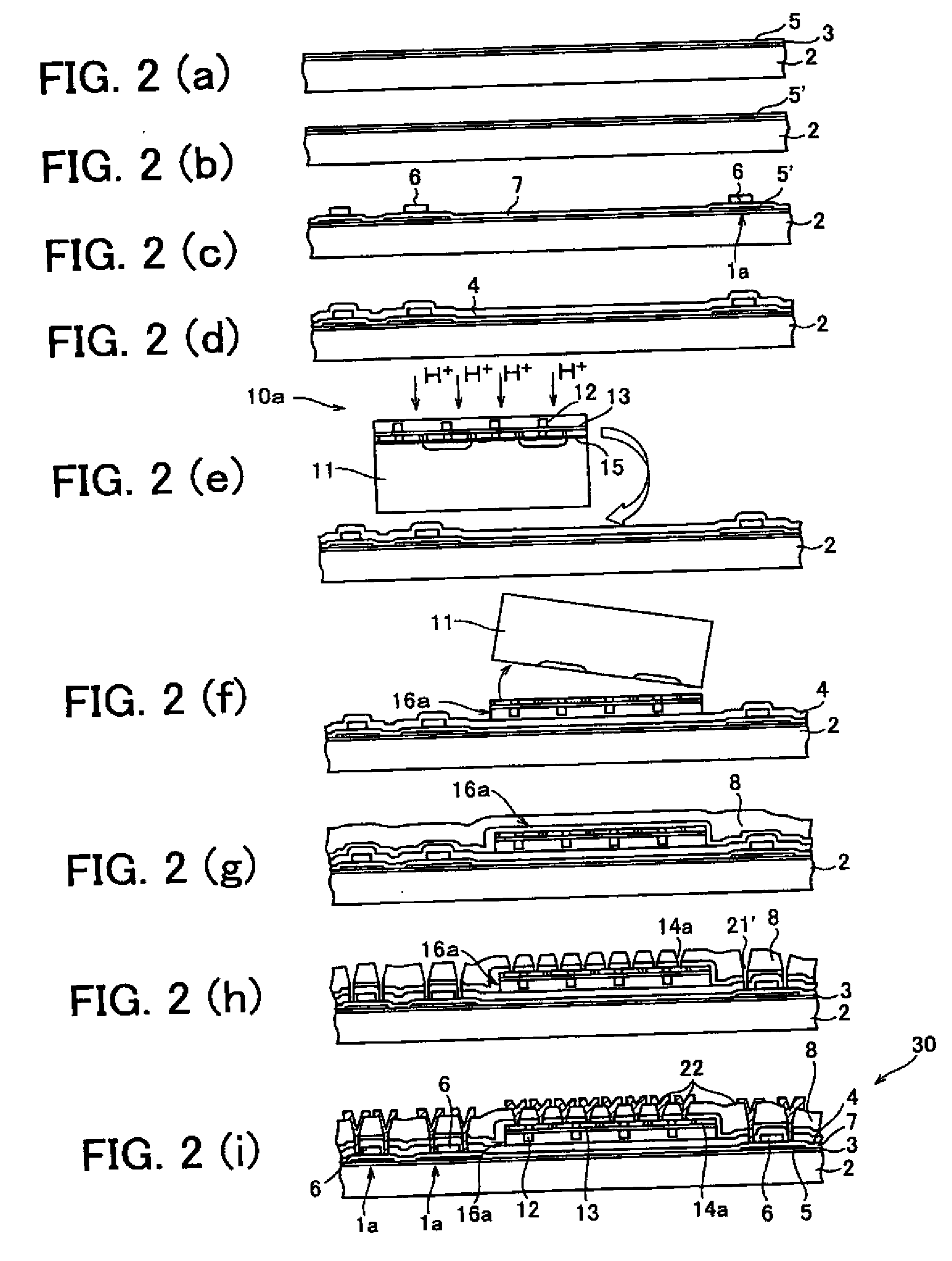

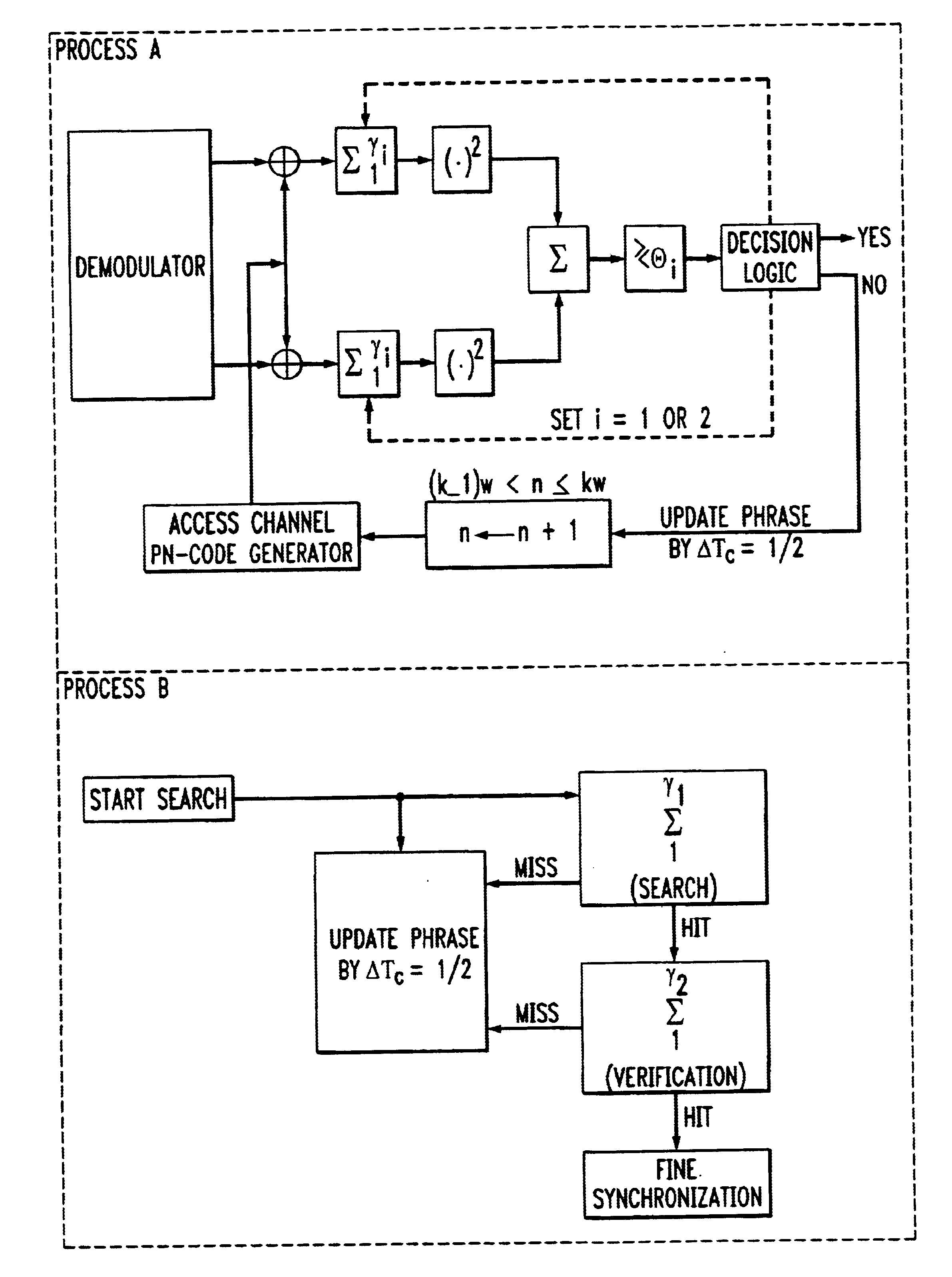

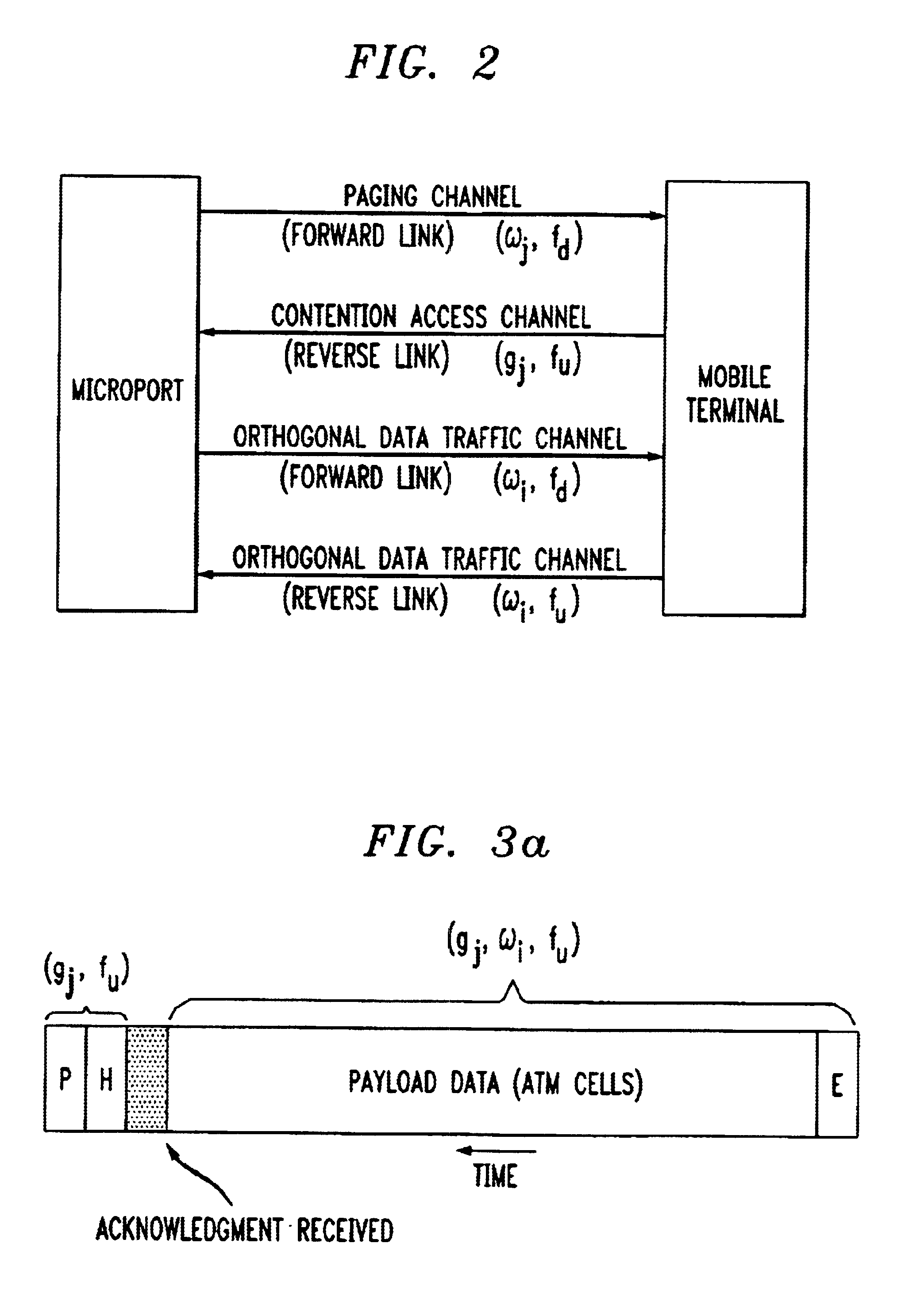

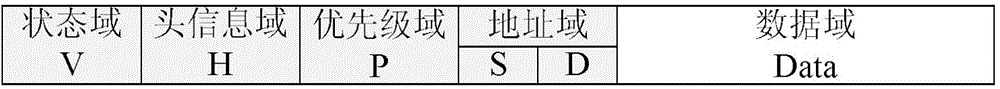

CDMA to packet-switching interface for code division switching in a terrestrial wireless system

InactiveUS6912211B2Reduce complexityReduce equipmentError prevention/detection by using return channelNetwork traffic/resource managementData signalFrequency extender

A low-cost, flexible, high performance system and method comprises a means for interfacing a code division wireless system to a fast packet-switched network for transmission over a core network to a destination terminal user via a destination access node and a destination access radio port. The method is for code division switching at an originating terminal, the originating terminal being located within a microport cell of a terrestrial wireless network at a given instant in time, where said network interfaces with an access radio port, and comprises the steps of spreading a transmission signal by a PN-code assigned to an intended receiving port, inserting an identifier of a few bits for identifying a user, spreading a payload data signal by an orthogonal code, spreading the orthogonal spread payload data signal by the PN-code associating the user with payload data, modulating the PN-code spread transmission signal and the twice-spread payload data signal, and forwarding the modulated PN-code spread transmission signal and the modulated twice-spread payload data signal to an access radio port. The code division switching system at an originating terminal is described, the originating terminal being located within a microport cell of a terrestrial wireless network at a given instant in time, where said network interfaces with an access radio port, comprises a first spreader for spreading a transmission signal by a PN-code assigned to an intended receiving port, a second spreader for spreading a payload data signal by an orthogonal code assigned to a receiving terminal user to which the payload data signal is directed, the payload data signal being further spread by the first spreader, a means for forwarding the PN-code spread transmission signal to an access radio port and a means for forwarding the twice-spread transmission signal to an access radio port.

Owner:AMERICAN TELEPHONE & TELEGRAPH CO

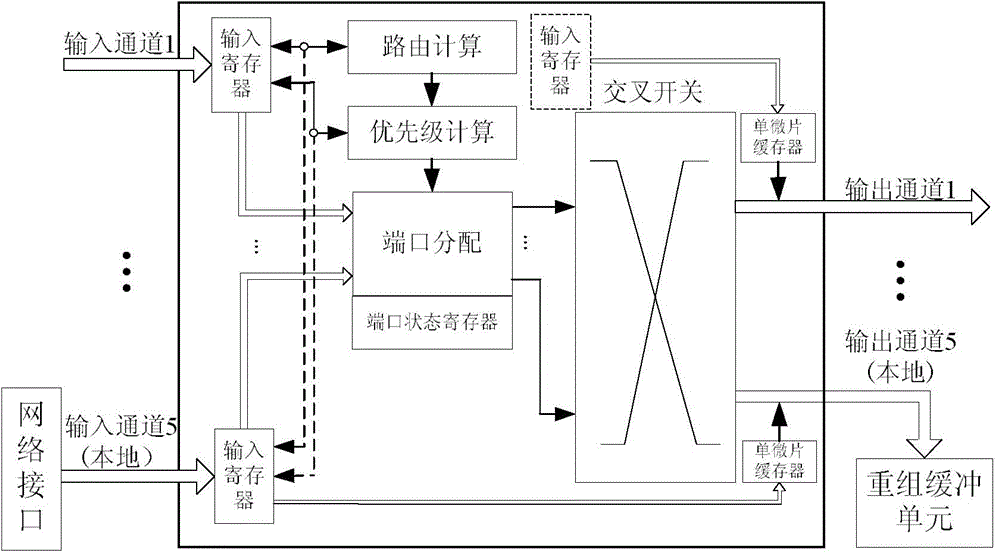

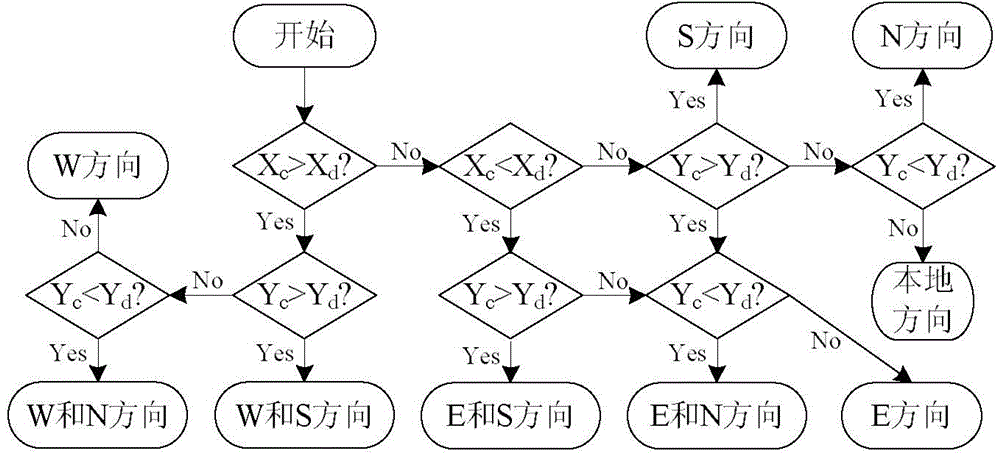

Network-on-chip router with low buffer area and routing method

The invention discloses a network-on-chip router with a low buffer area. The network-on-chip router comprises n input ports, n input registers, a routing computation module, a priority computation module, a port distribution module, a crossbar switch, p single microchip buffers and p output ports, wherein when microchips with high priority and secondary high priority compete for an effective output port, the port distribution module transmits the microchip with secondary high priority to the corresponding single micro-chip buffer according to a priority arbitration strategy, when other micro-chips with low priority compete for the port, a deflected output port is distributed; when the output port is idle, the microchip with secondary high priority is directly output to a lower routing node. According to the network-on-chip router, the area and the power consumption of a network-on-chip can be effectively reduced, meanwhile, the delay performance and the throughput performance are guaranteed, and the network-on-chip router with the low buffer area and the routing method are suitable for constructing a high-performance system on a chip.

Owner:CHINESE AERONAUTICAL RADIO ELECTRONICS RES INST

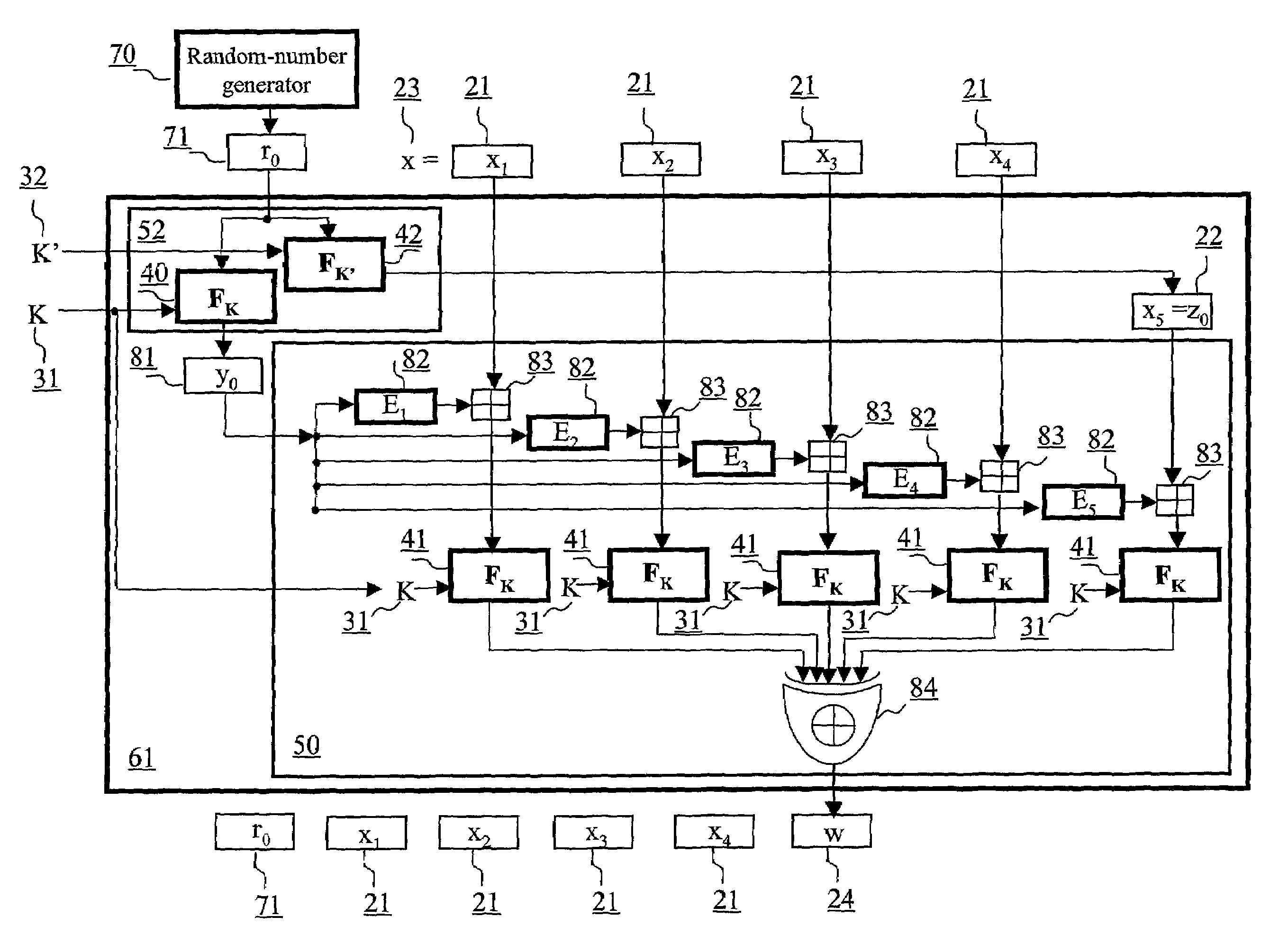

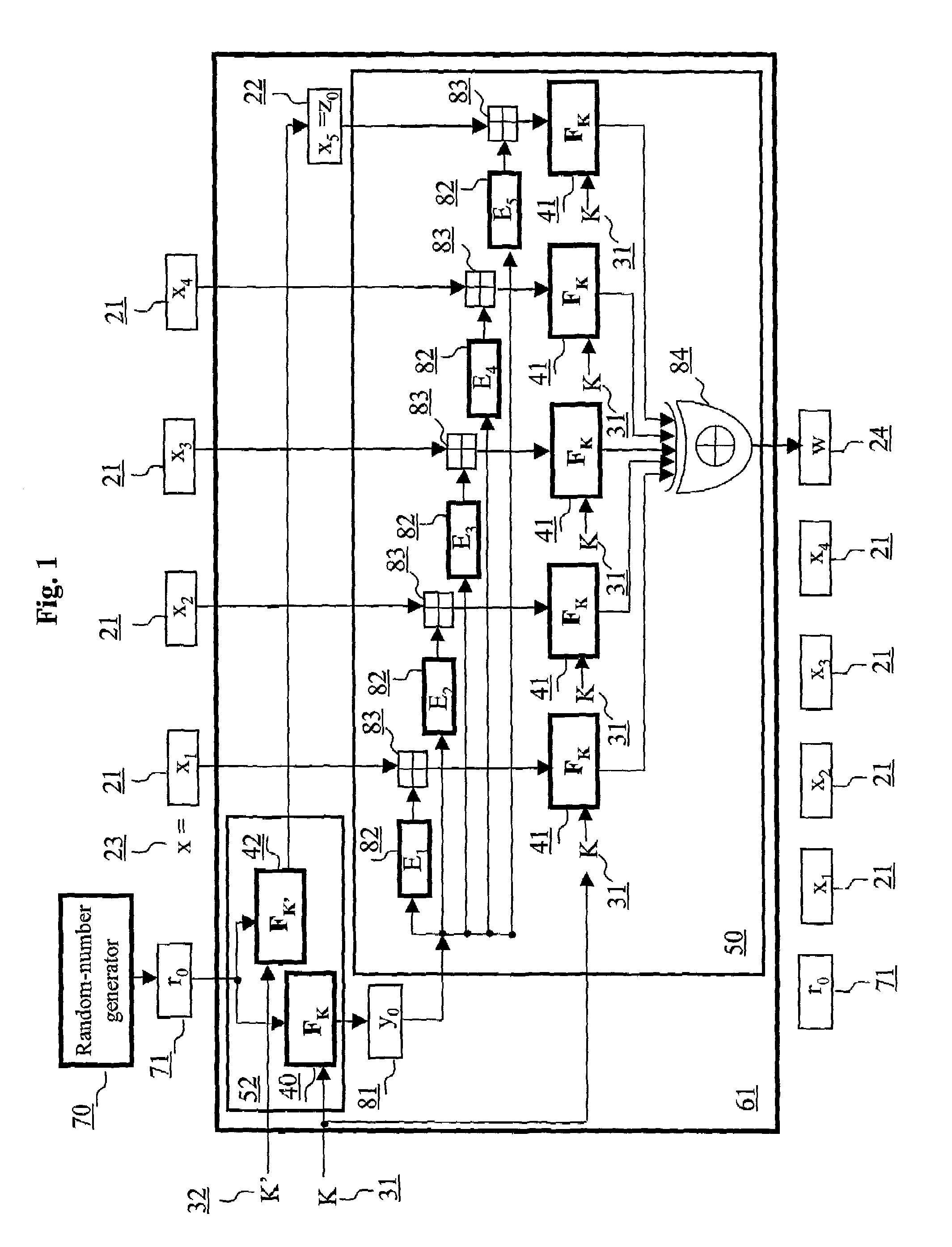

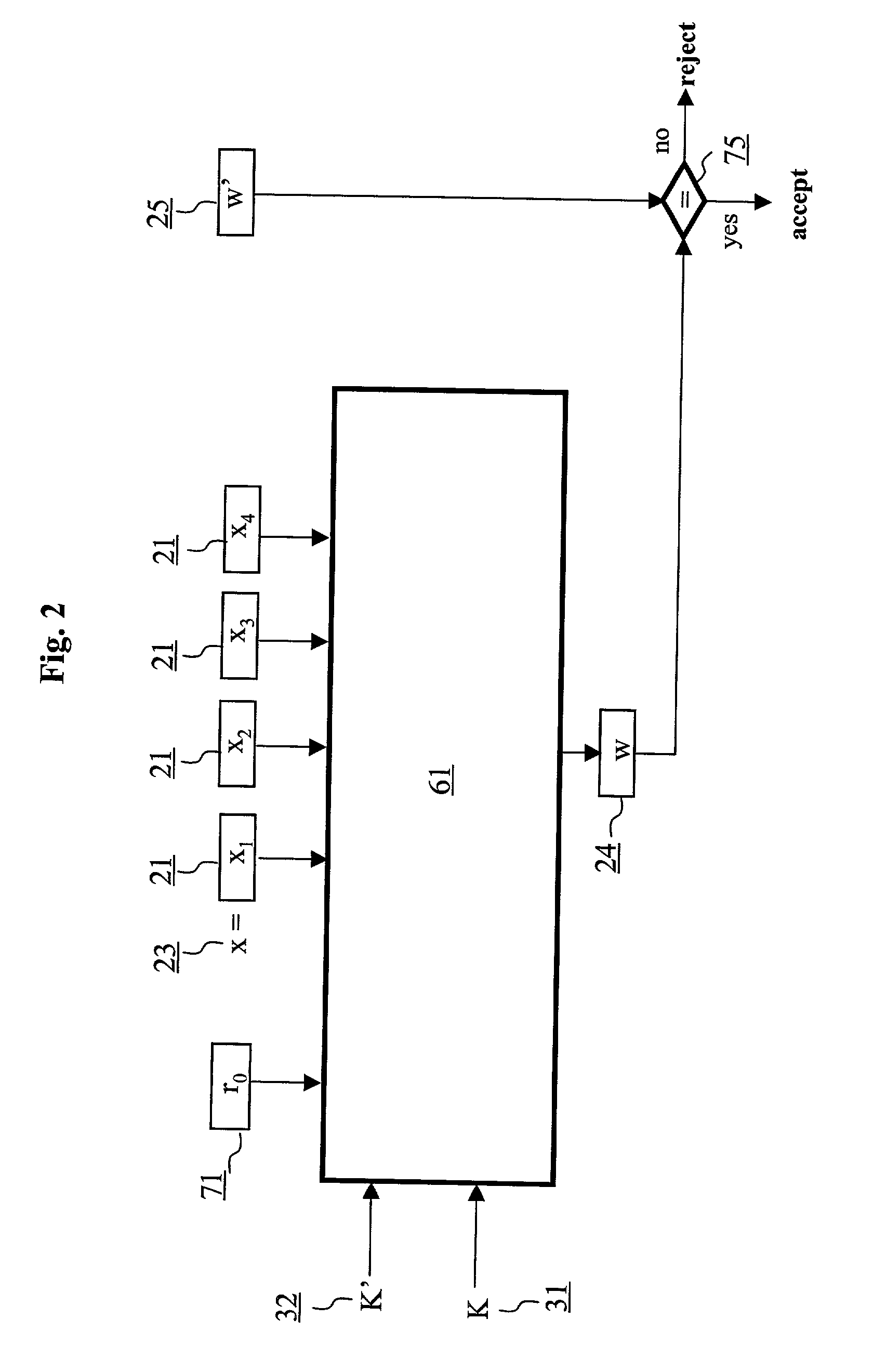

Authentication method and schemes for data integrity protection

ActiveUS7054445B2Public key for secure communicationUser identity/authority verificationComputer hardwareMessage length

An authentication method and schemes using a block cipher to protect data integrity (authenticity) during communication over insecure channels and during data storage on insecure media. The authentication method and schemes of this invention allow, in a further aspect, message and data signing and verification in parallel or pipelined manners, in addition to sequential operation, without requiring twice as many block enciphering operations as the number of input plaintext blocks. The present invention allows, in a yet further aspect, software and hardware implementations used in high-performance systems and networks where multiple processing units are available for block enciphering operations. In a yet further aspect, the authentication method and schemes of this invention allow incremental updates and out-of-order processing of authentication tags. In a yet further aspect, the authentication method and schemes of this invention are suitable for real-time applications where message length remains unknown until the entire message is received, and commencing message authentication cannot be deferred until the end of the message.

Owner:VDG

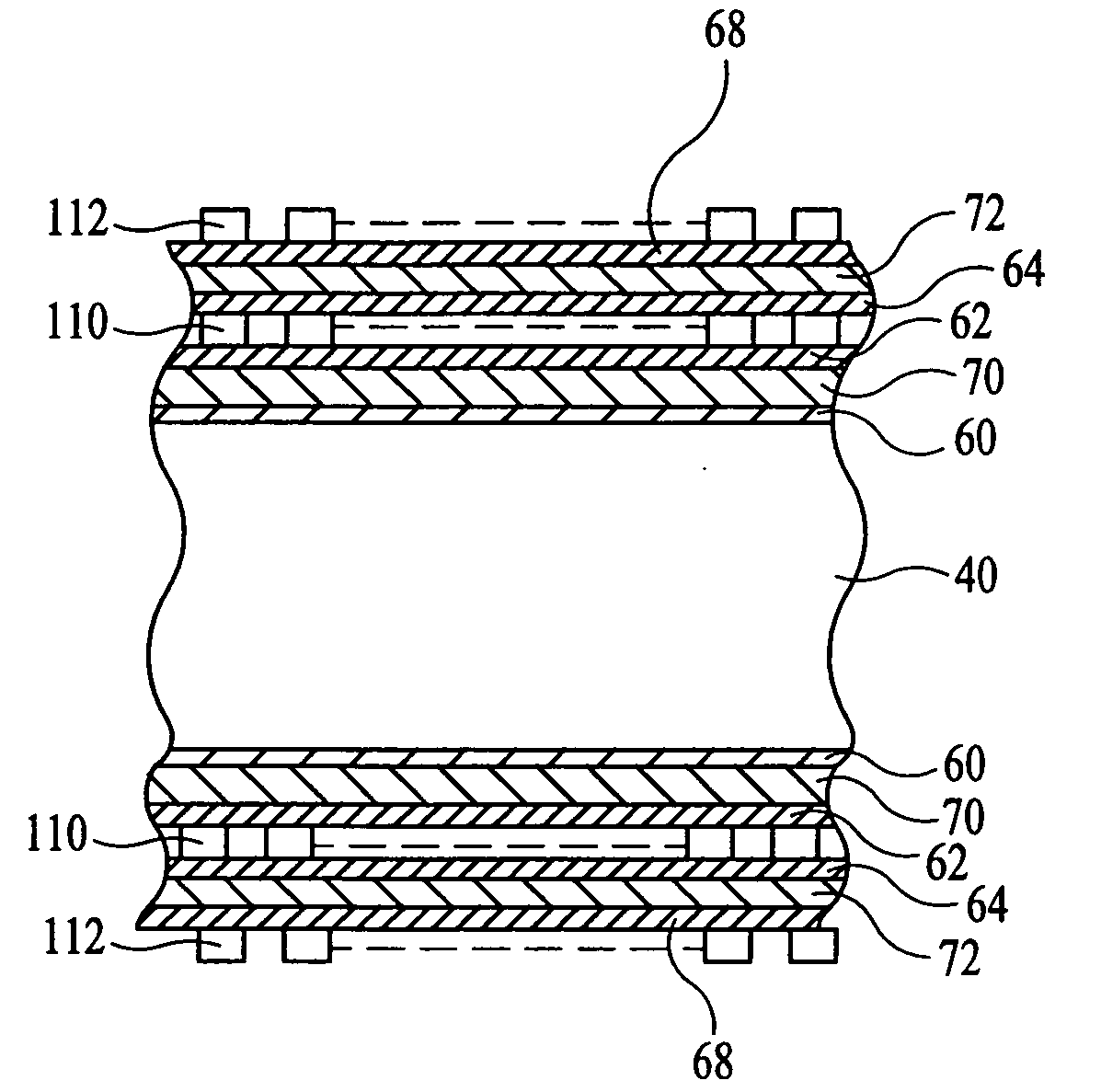

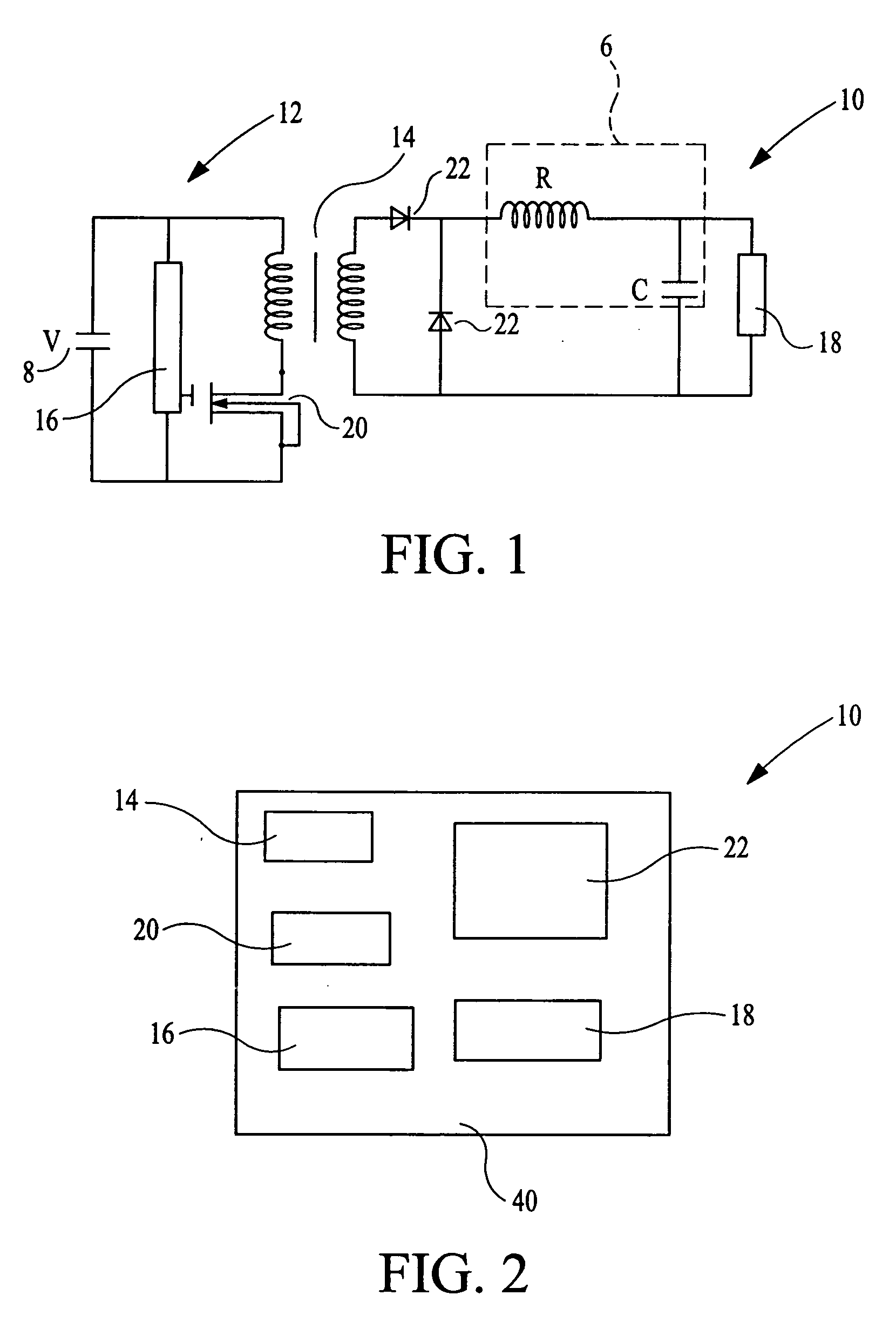

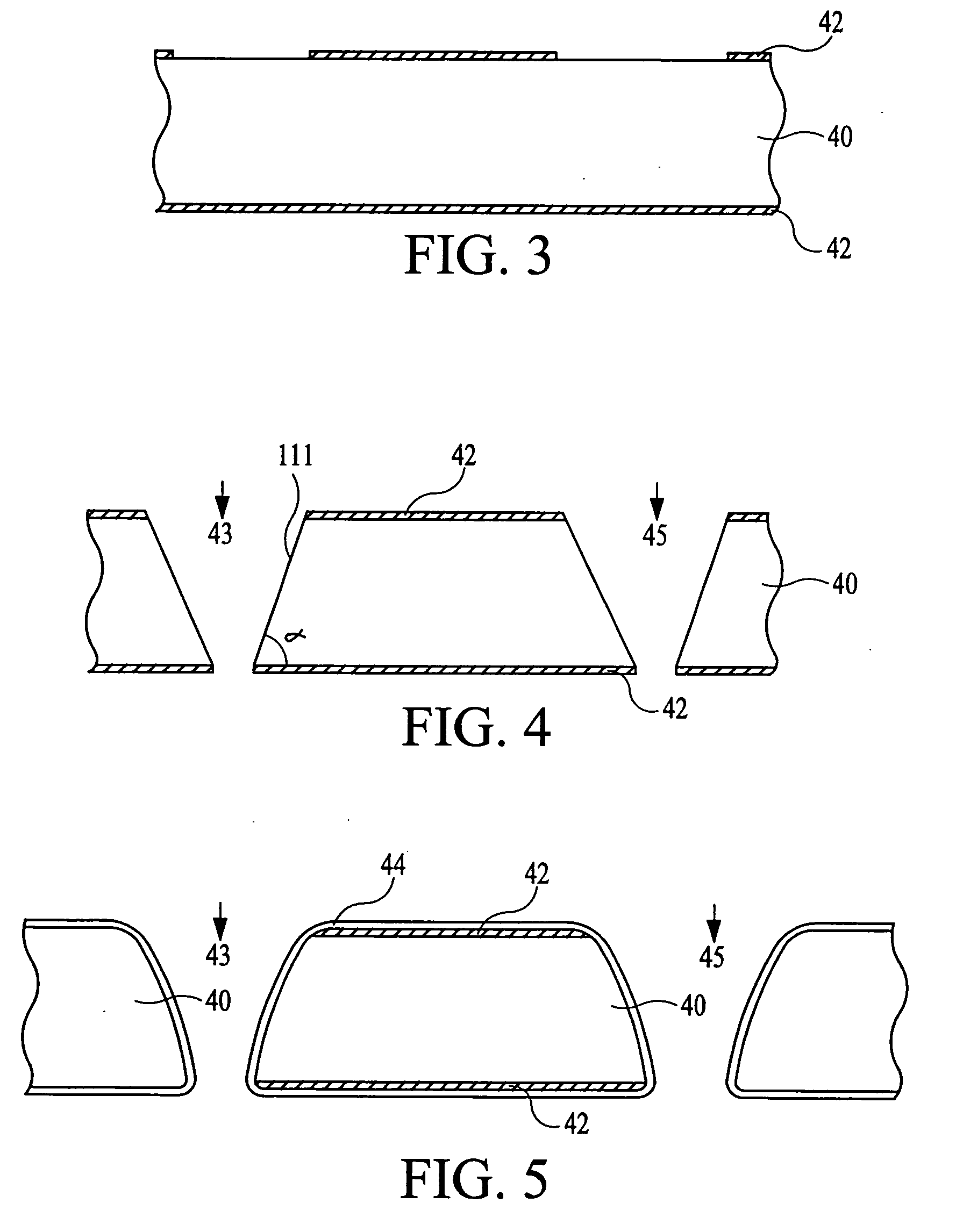

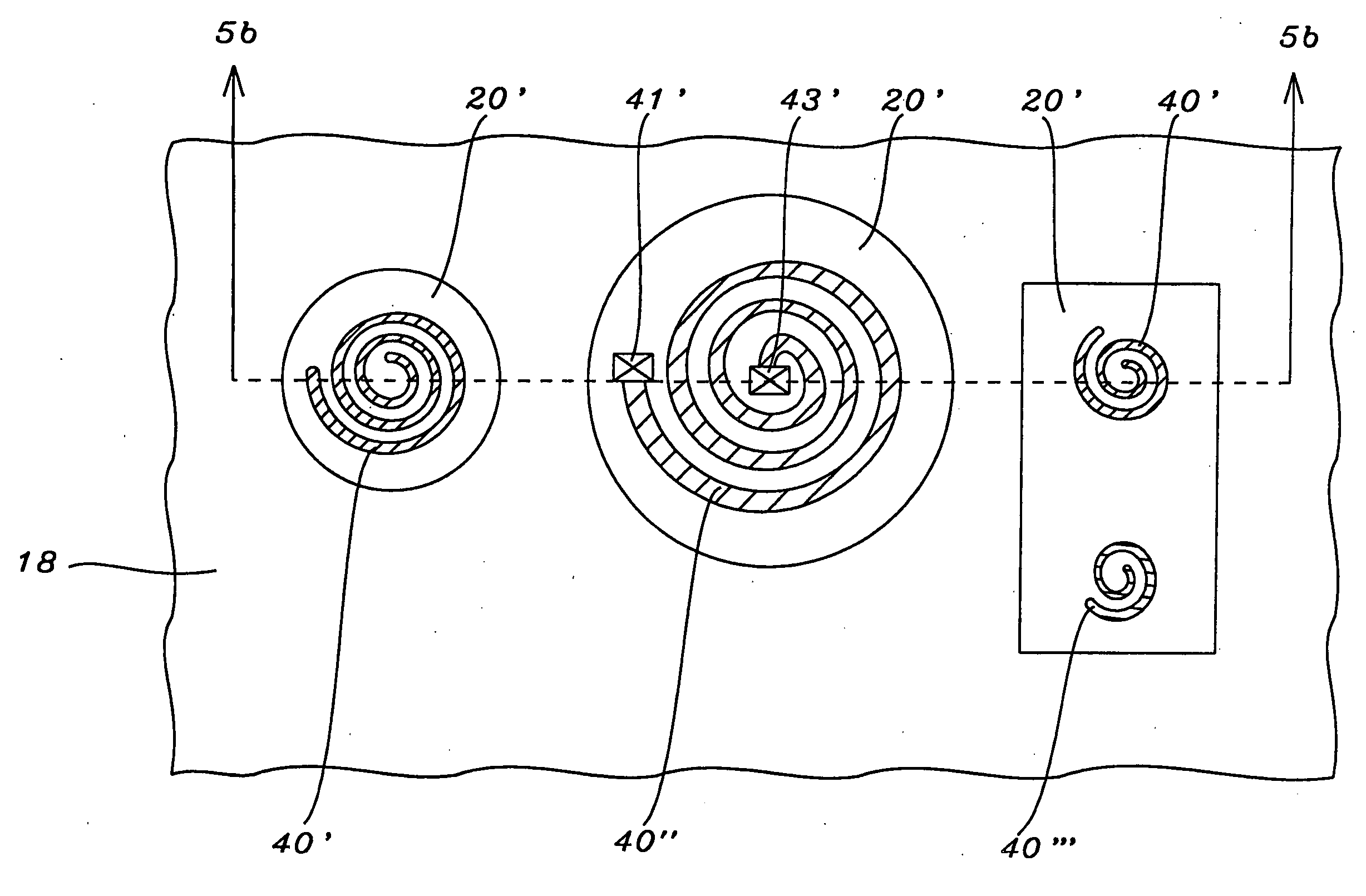

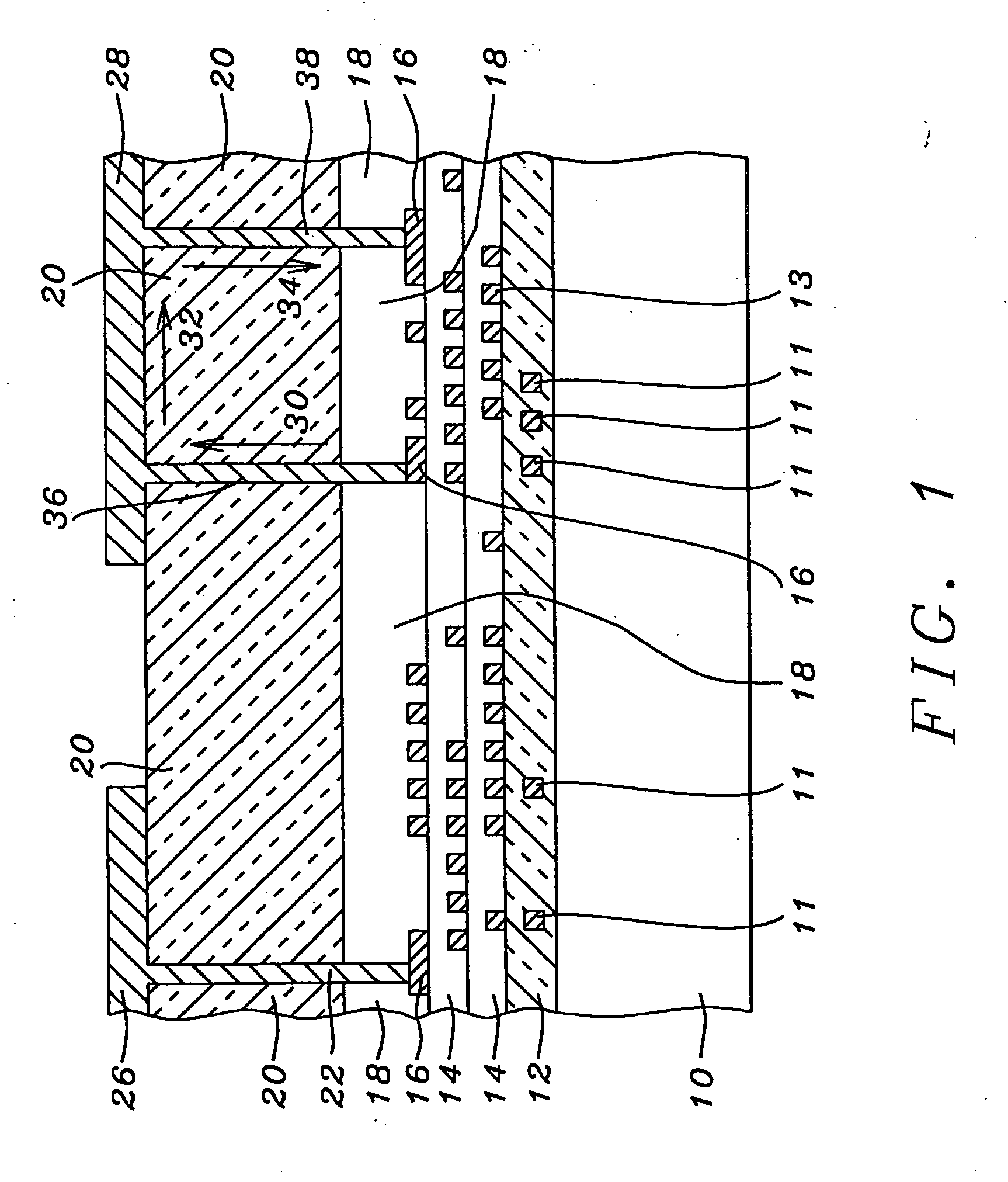

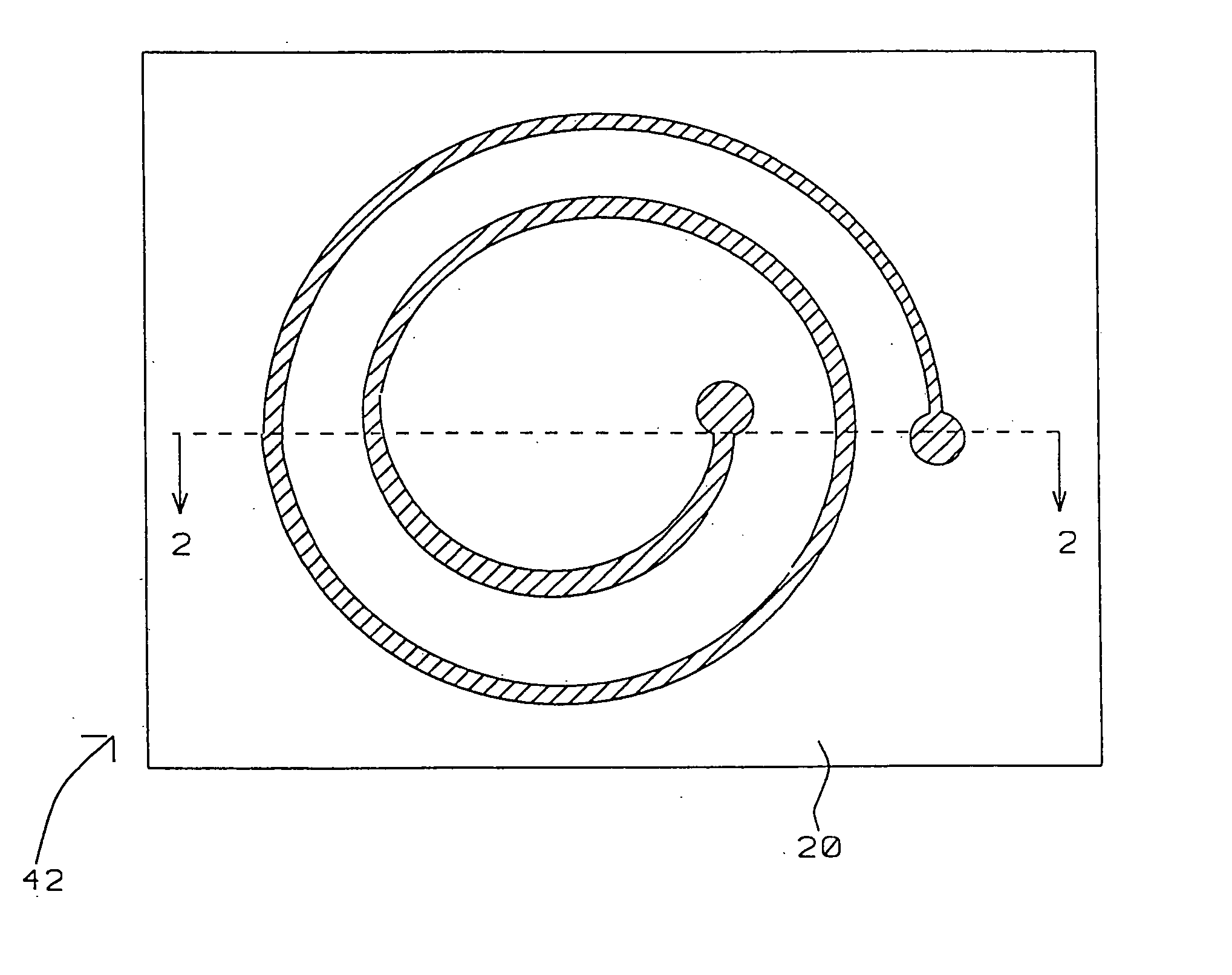

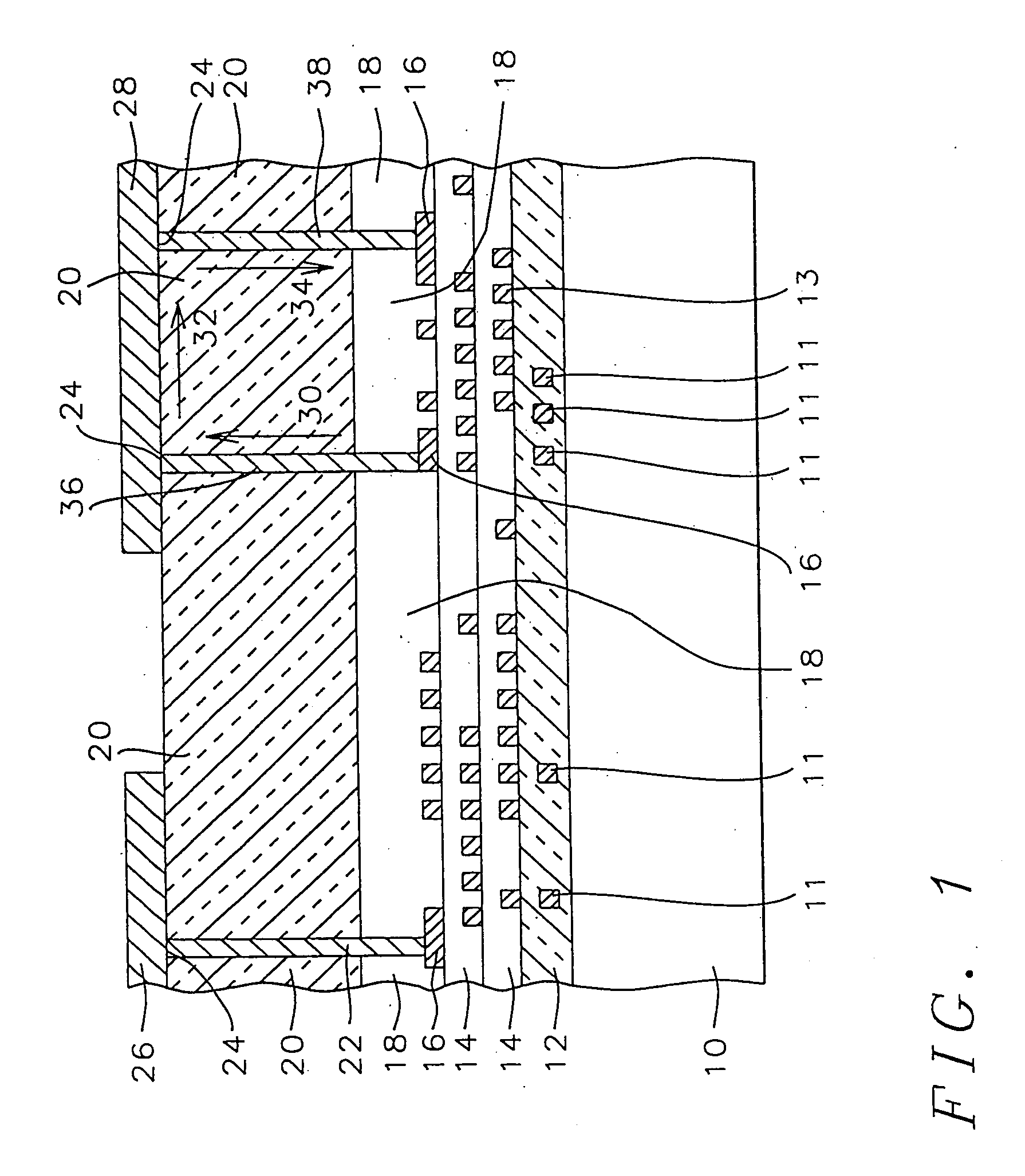

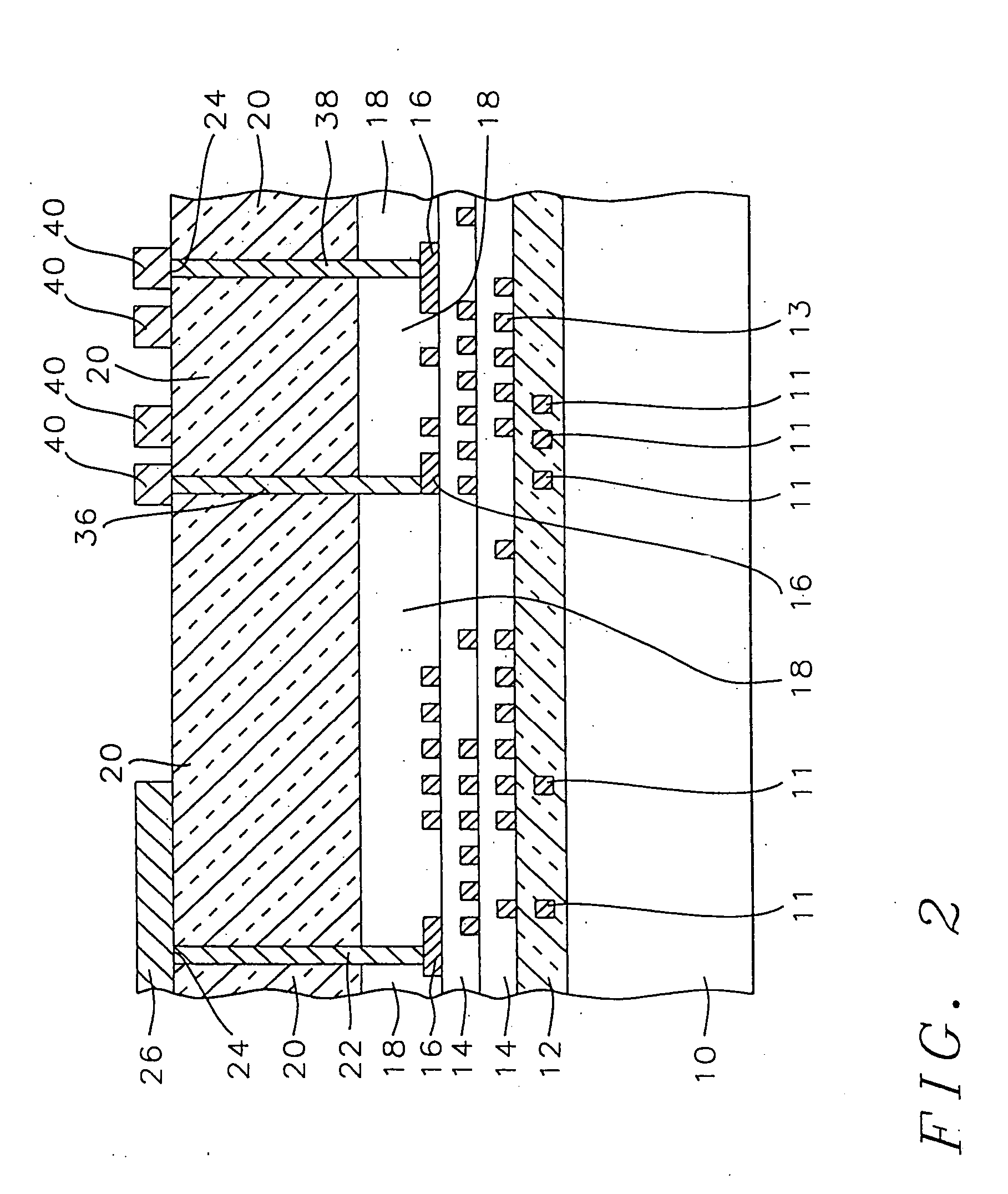

Microtransformer for system-on-chip power supply

InactiveUS20050105225A1High frequencyReduce lossSemiconductor/solid-state device detailsSolid-state devicesTransformerSilicon oxide

A microtransformer for a high-performance system-on-chip power supply is disclosed. Through-wafer openings in a substrate allow the primary and secondary wiring on both surfaces of the silicon substrate. An insulating silicon oxide layer is first deposited on all surfaces of the substrate. A magnetic film is further deposited on the silicon oxide layer followed by the application of another insulating layer. Coils are fabricated next by patterned deposition on both sides of the substrate and through the holes. The coils can be, e.g., single coils or primary or secondary coils of a transformer structure, with secondary having one or more output taps to supply different output voltages. For better flux closure, various magnetic layers and insulators can be deposited on top of the windings.

Owner:MICRON TECH INC

High performance system-on-chip inductor using post passivation process

InactiveUS20070108551A1Improve RF performanceIncreased frequency rangeSemiconductor/solid-state device detailsSolid-state devicesTransformerEngineering

A system and method for forming post passivation inductors, and related structures, is described. High quality electrical components, such as inductors and transformers, are formed on a layer of passivation, or on a thick layer of polymer over a passivation layer.

Owner:QUALCOMM INC

Capacitor for high performance system-on-chip using post passivation device

InactiveUS6897507B2Improve RF performanceIncreased frequency rangeTransistorSemiconductor/solid-state device detailsEngineeringInductor

The present invention extends the above referenced continuation-in-part application by in addition creating high quality electrical components, such as inductors, capacitors or resistors, on a layer of passivation or on the surface of a thick layer of polymer. In addition, the process of the invention provides a method for mounting discrete electrical components at a significant distance removed from the underlying silicon surface.

Owner:QUALCOMM INC

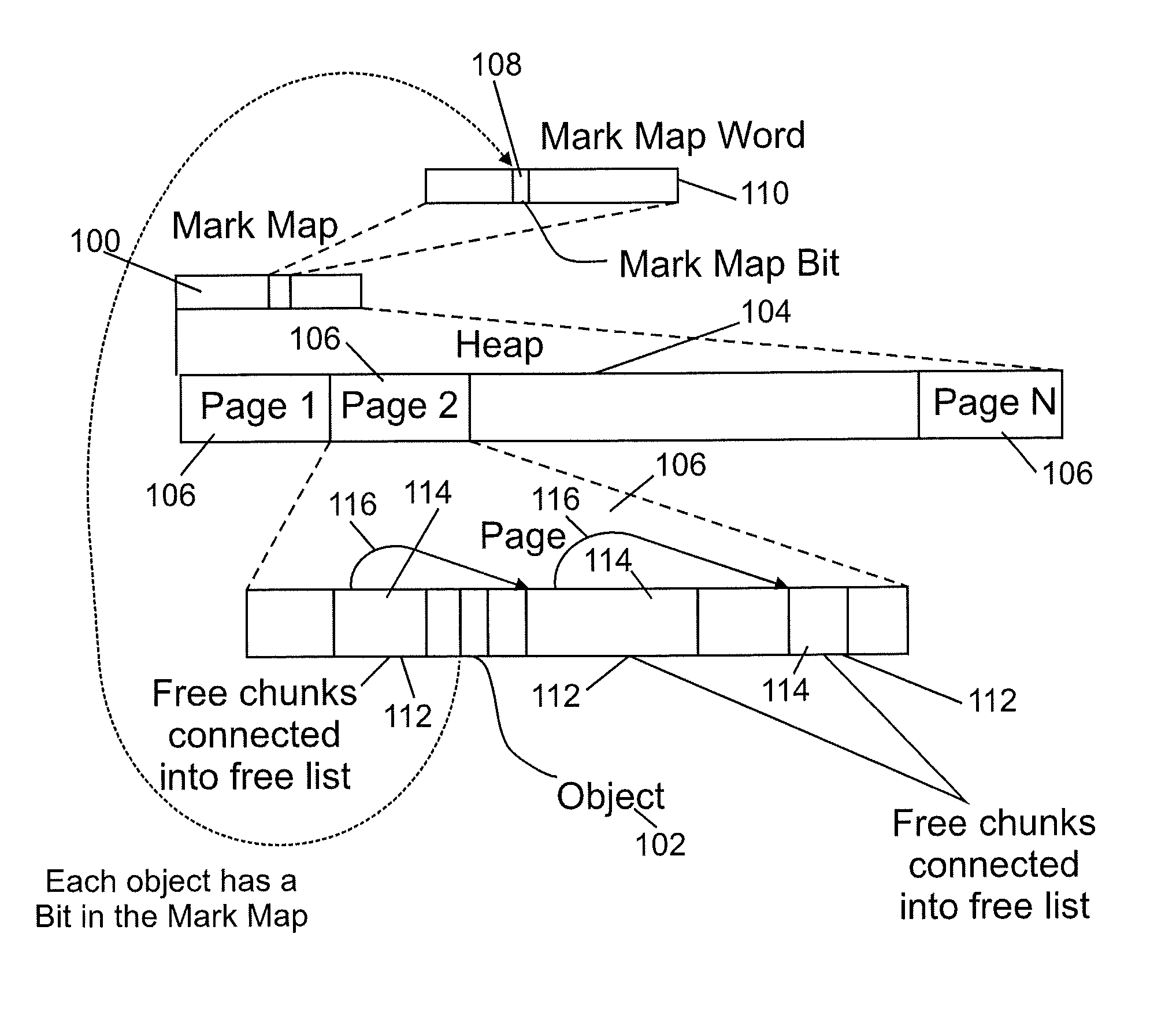

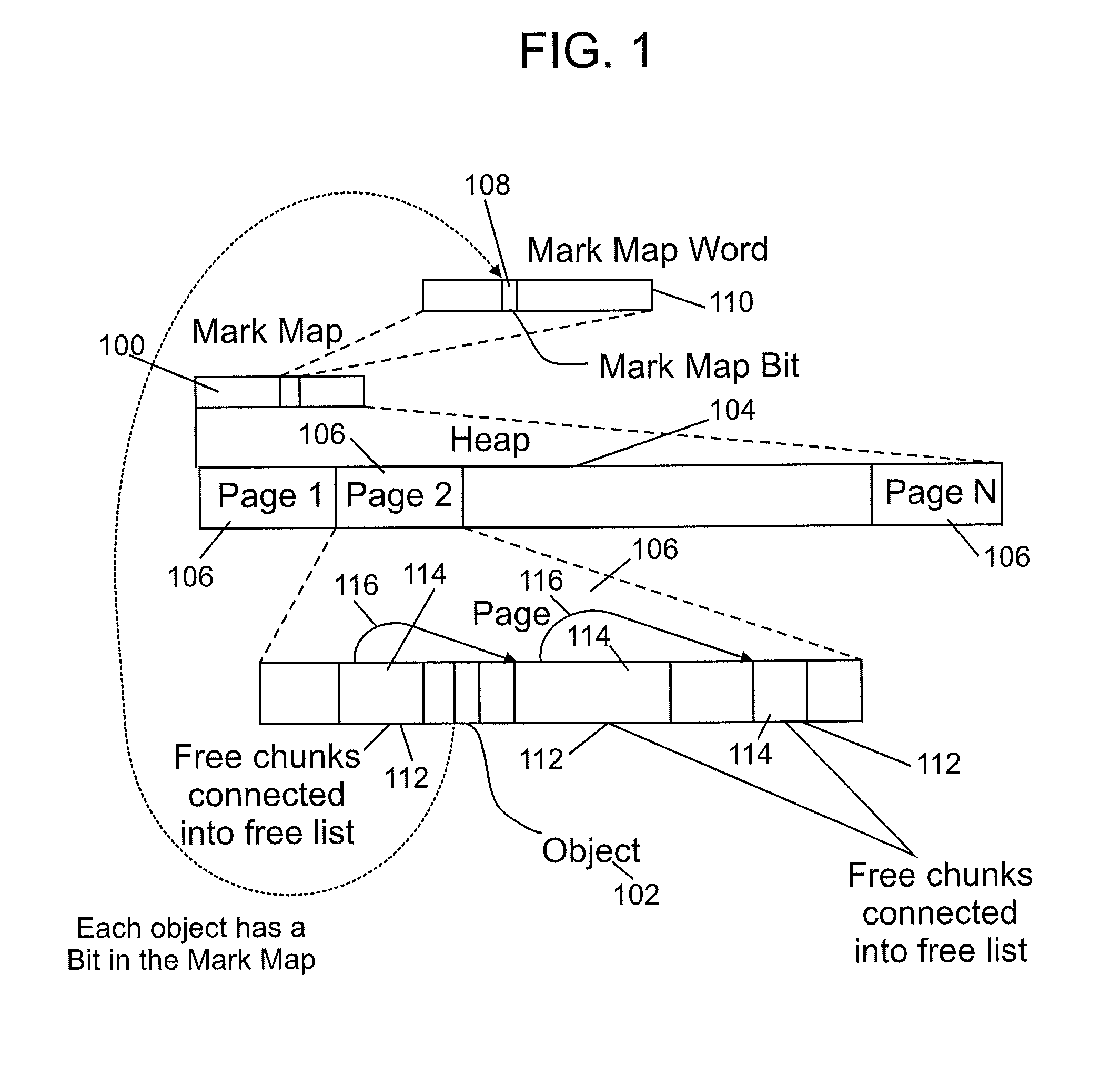

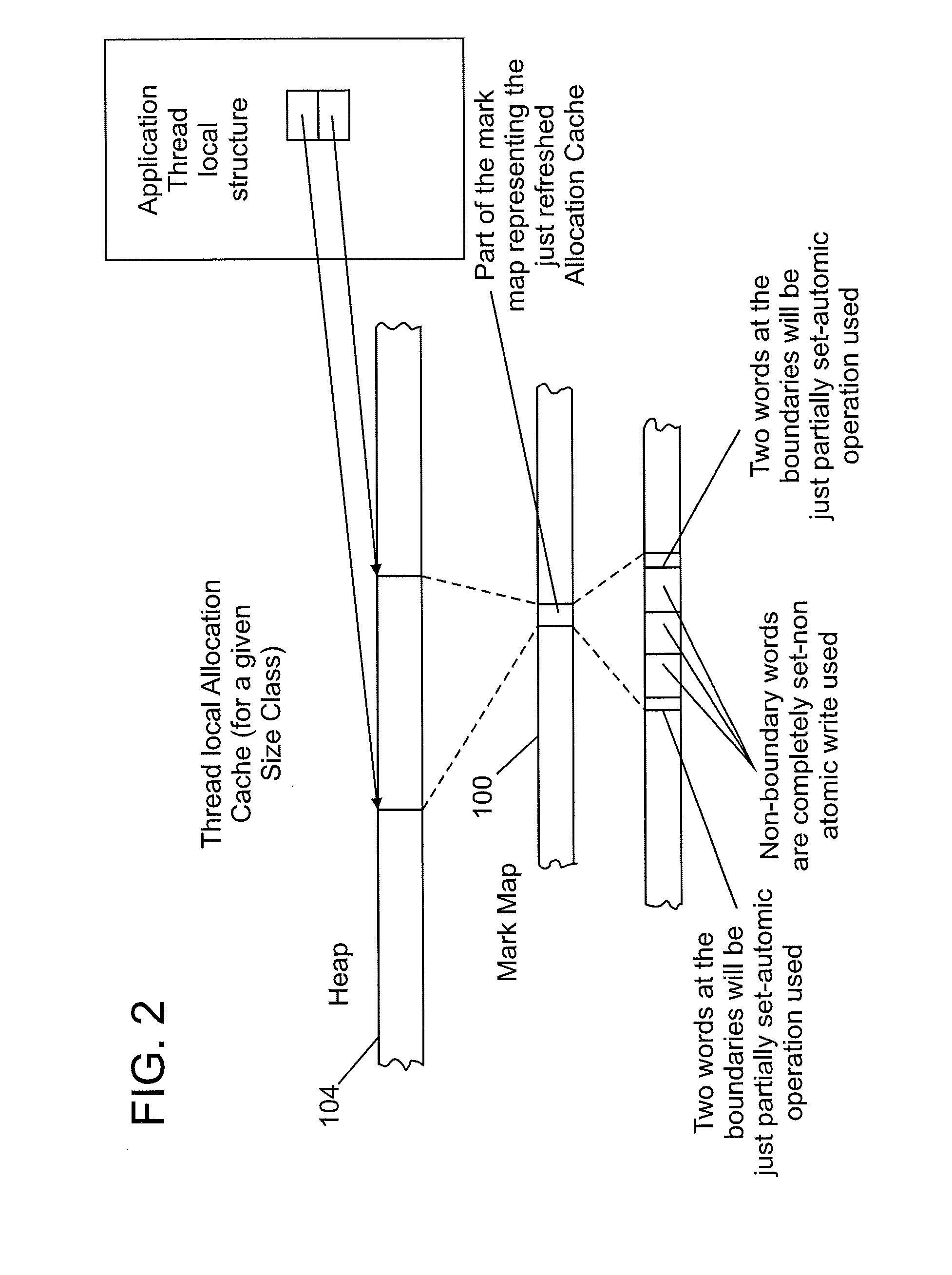

Allocation cache premarking for snap-shot-at-the-beginning concurrent mark-and-sweep collector

InactiveUS20100114997A1Effective supportHighly efficient allocating caching strategyMemory adressing/allocation/relocationSpecial data processing applicationsWaste collectionParallel computing

Tracking newly created objects during a garbage collection cycle includes marking newly allocated objects in the GC cycle during the allocation cache population phase. The goal is to take a high performance system for tracing live objects, such as the mark map, and combine the SATB with a cached allocation system for heap memory such that SATB representation is preserved. Embodiments combine both efficient support for an SATB model during a collection cycle and a highly optimized allocation path for heap objects in an allocation scheme (which may optionally be a size segregated class allocation scheme) that allows both mechanisms to co-exist effectively. Specifically, embodiments track newly created objects during a GC cycle such that they are kept alive during the trace phase while continuing to support a highly efficient allocating caching strategy.

Owner:IBM CORP +1

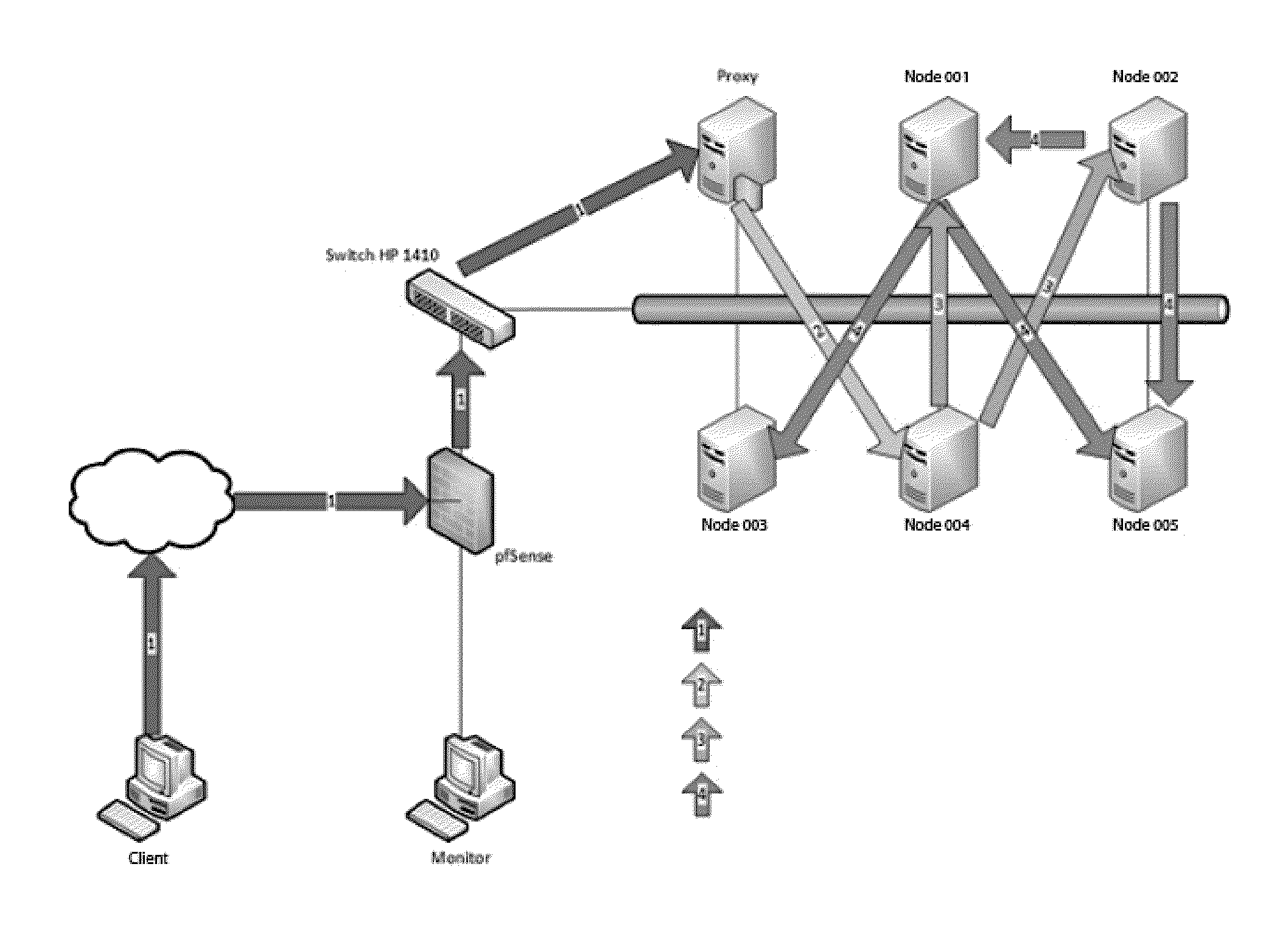

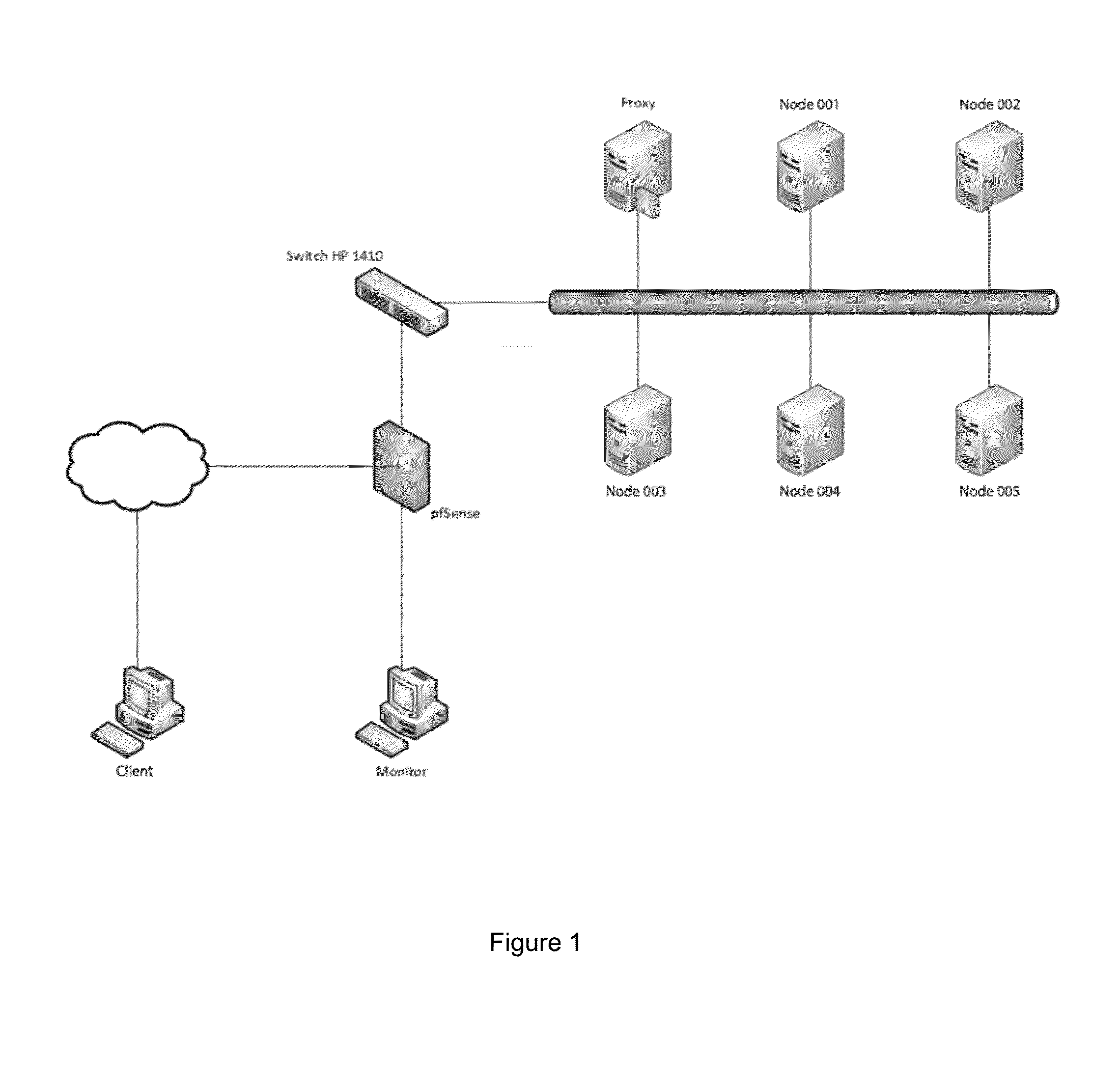

A High Performance System and Method for Data Processing and Storage, Based on Low Cost Components, Which Ensures the Integrity and Availability of the Data for the Administration of Same

InactiveUS20160266801A1Input/output to record carriersSpecial data processing applicationsData centerHigh performance system

The present invention refers to a high performance system and method for data processing and storage, based on low cost components, which ensures the integrity and availability of the data for the administration of same, for its application in data centres, hospitals, schools, industries, libraries, technological centres, etc.

Owner:FONDO DE INFORMACION Y DOCUMENTACION PARA LA IND INFOTEC

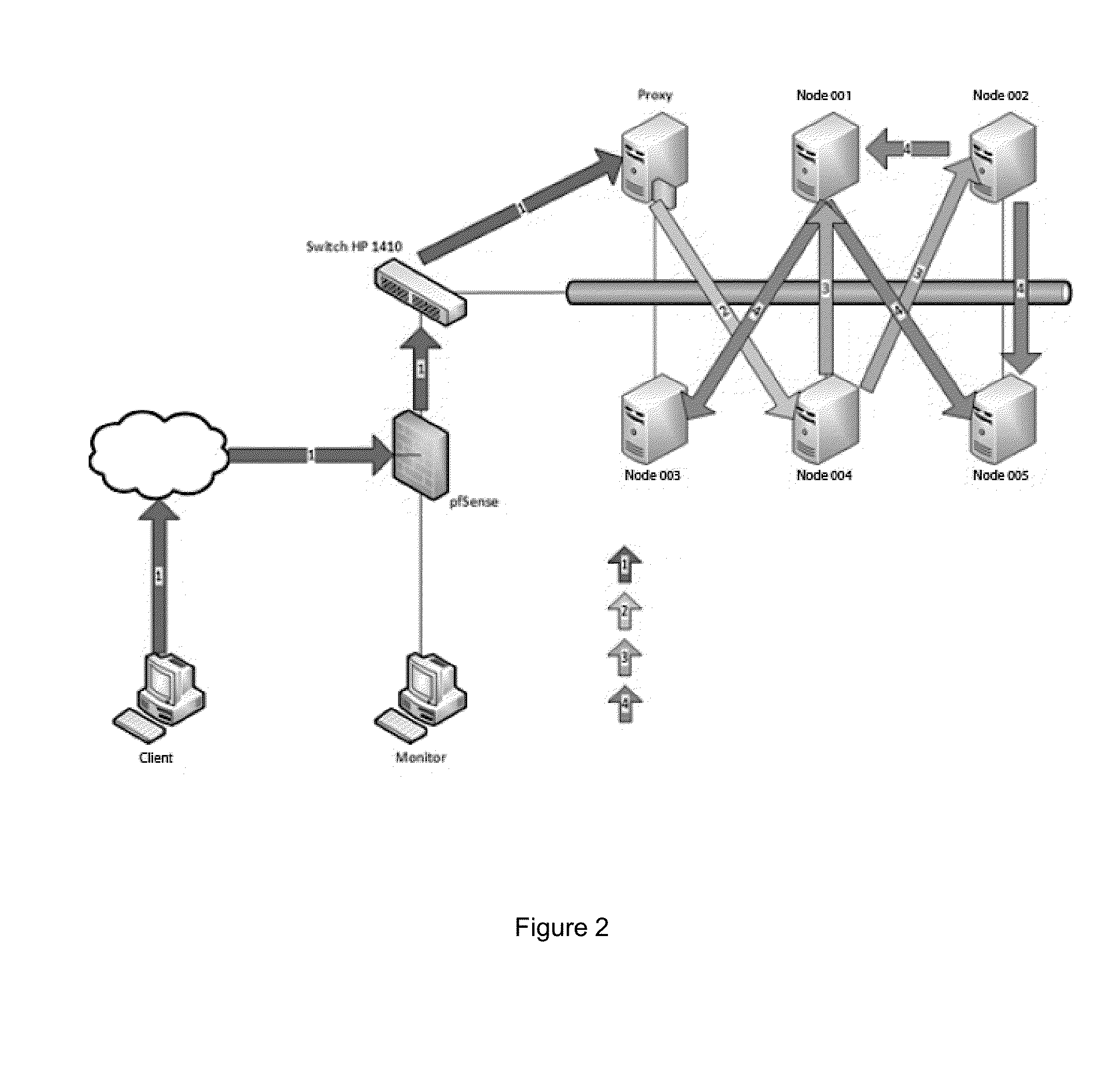

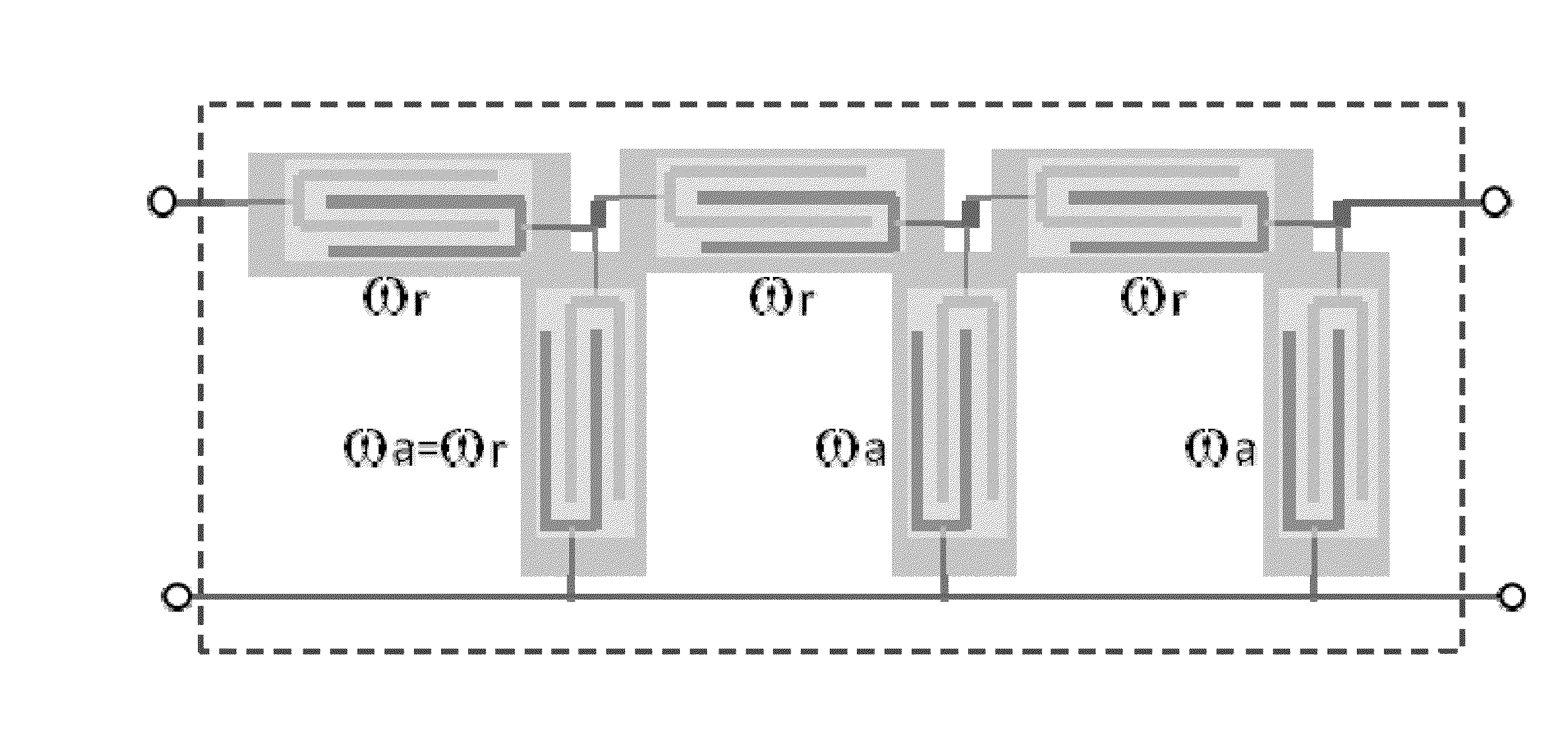

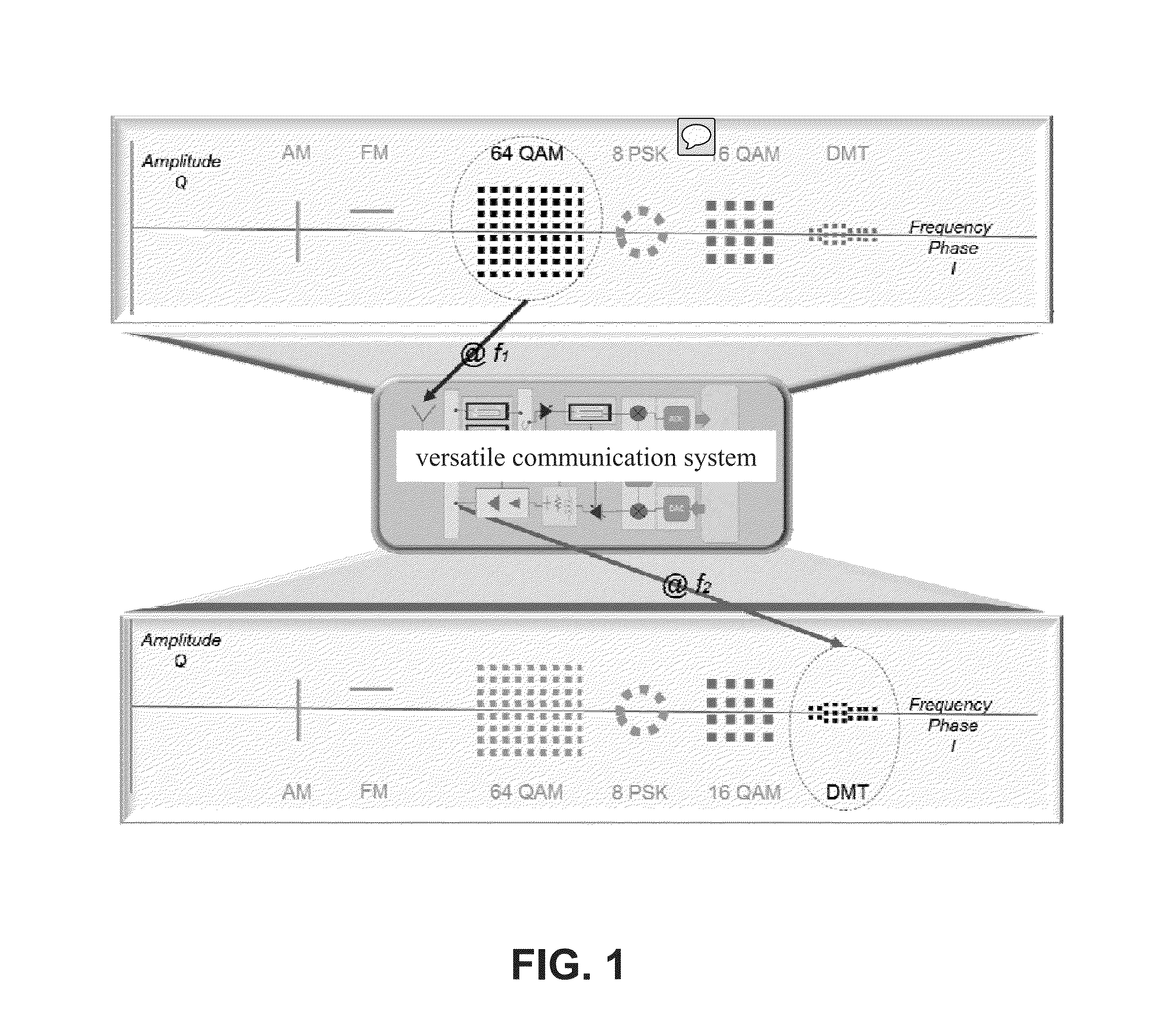

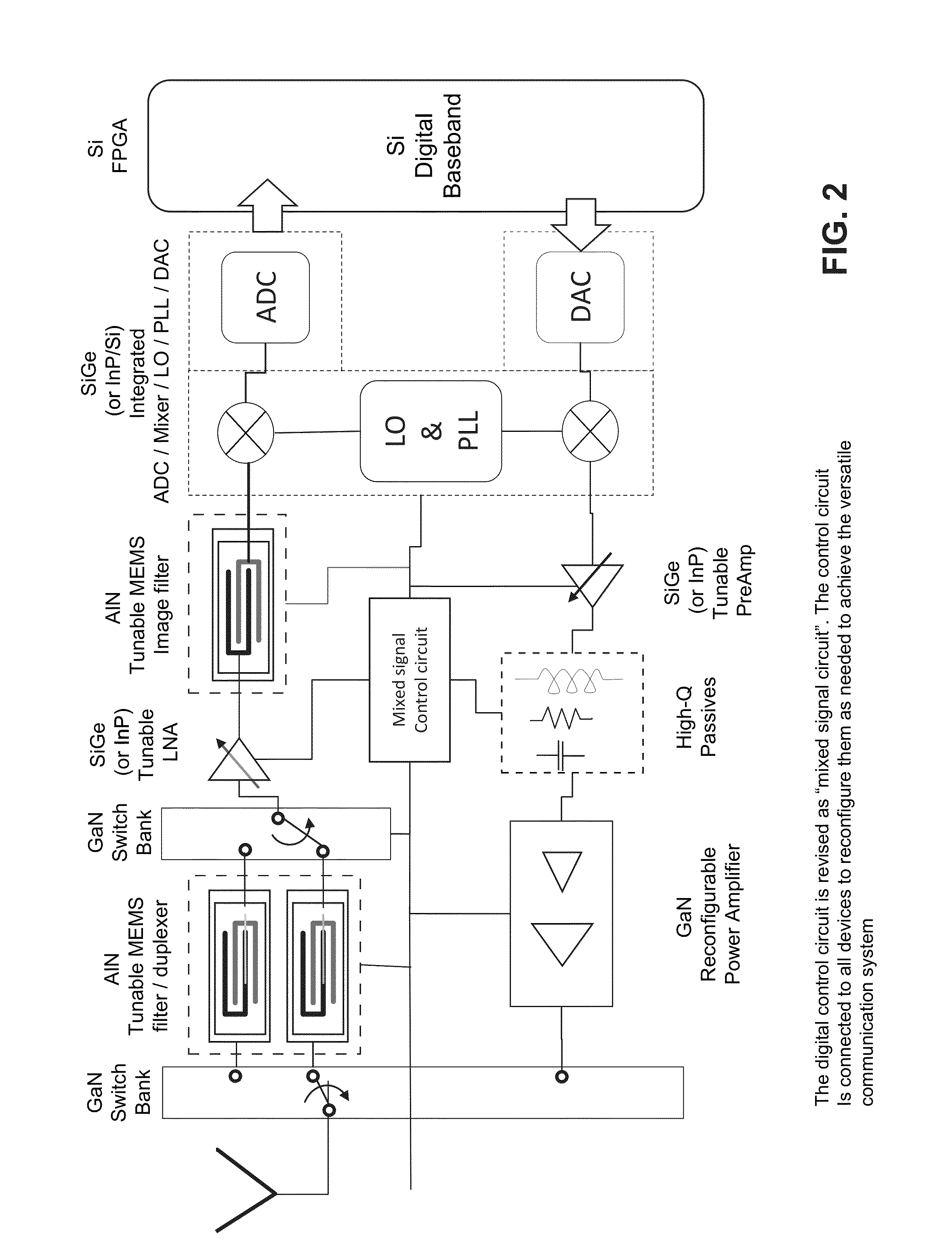

Versatile communication system and method of implementation using heterogeneous integration

ActiveUS20130344819A1Maximum flexibilityLow costImpedence networksSemiconductor/solid-state device detailsHeterojunctionPhotonics

A communication system front-end architecture and a method of fabricating same are disclosed in which a diverse set of semiconductor technologies and device types (including CMOS, SiGe CMOS, InP HBTs (heterojunction bipolar transistors), InP HEMTs (high electron mobility transistors), GaN HEMTs, SiC devices, any number from a diverse set of MEMS sensors and actuators, and potentially photonics) is merged onto a single silicon, or other material substrate to thereby enable the development of smaller, lighter, and higher performance systems.

Owner:FOR NAT RES INITIATIVES

Method for producing electronic device

ActiveUS20060105273A1Low costImprove performanceSolid-state devicesSemiconductor/solid-state device manufacturingResistSolubility

There is a problem in that when the demand accuracy with respect to a semiconductor pattern dimension comes close to a resist molecule size with miniaturization, the device performance is deteriorated due to edge roughness of a resist pattern to exert a bad influence on the system performance. The present invention overcomes the problem by the procedure in which super-molecules which are small in dimension as compared with the conventional polymers are used as main components, the reaction number required for the change of molecule solubility is made constant and as large as possible, and an acid generator is made clathrate or combinatory n super molecules to make an acid catalyst concentration large. As a result, it is possible to form a pattern of molecular accuracy with high productivity even with respect to the pattern dimension less than 50 nm, thereby realizing the high performance system.

Owner:RENESAS ELECTRONICS CORP

High performance system-on-chip inductor using post passivation process

InactiveUS20070182521A1Improve RF performanceIncreased frequency rangeSemiconductor/solid-state device detailsSolid-state devicesTransformerInductor

A system and method for forming post passivation inductors, and related structures, is described. High quality electrical components, such as inductors and transformers, are formed on a layer of passivation, or on a thick layer of polymer over a passivation layer.

Owner:QUALCOMM INC

High performance system-on-chip discrete components using post passivation process

InactiveUS20050170634A1Improve RF performanceIncreased frequency rangeTransistorSemiconductor/solid-state device detailsEngineeringHigh performance system

A system and method for forming post passivation discrete components, is described. High quality discrete components are formed on a layer of passivation, or on a thick layer of polymer over a passivation layer.

Owner:QUALCOMM INC

High performance system-on-chip using post passivation process

InactiveUS20050184358A1Improve RF performanceIncreased frequency rangeSemiconductor/solid-state device detailsSolid-state devicesInductorHigh performance system

The present invention extends the above referenced continuation-in-part application by in addition creating high quality electrical components, such as inductors, capacitors or resistors, on a layer of passivation or on the surface of a thick layer of polymer. In addition, the process of the invention provides a method for mounting discrete electrical components at a significant distance removed from the underlying silicon surface.

Owner:QUALCOMM INC

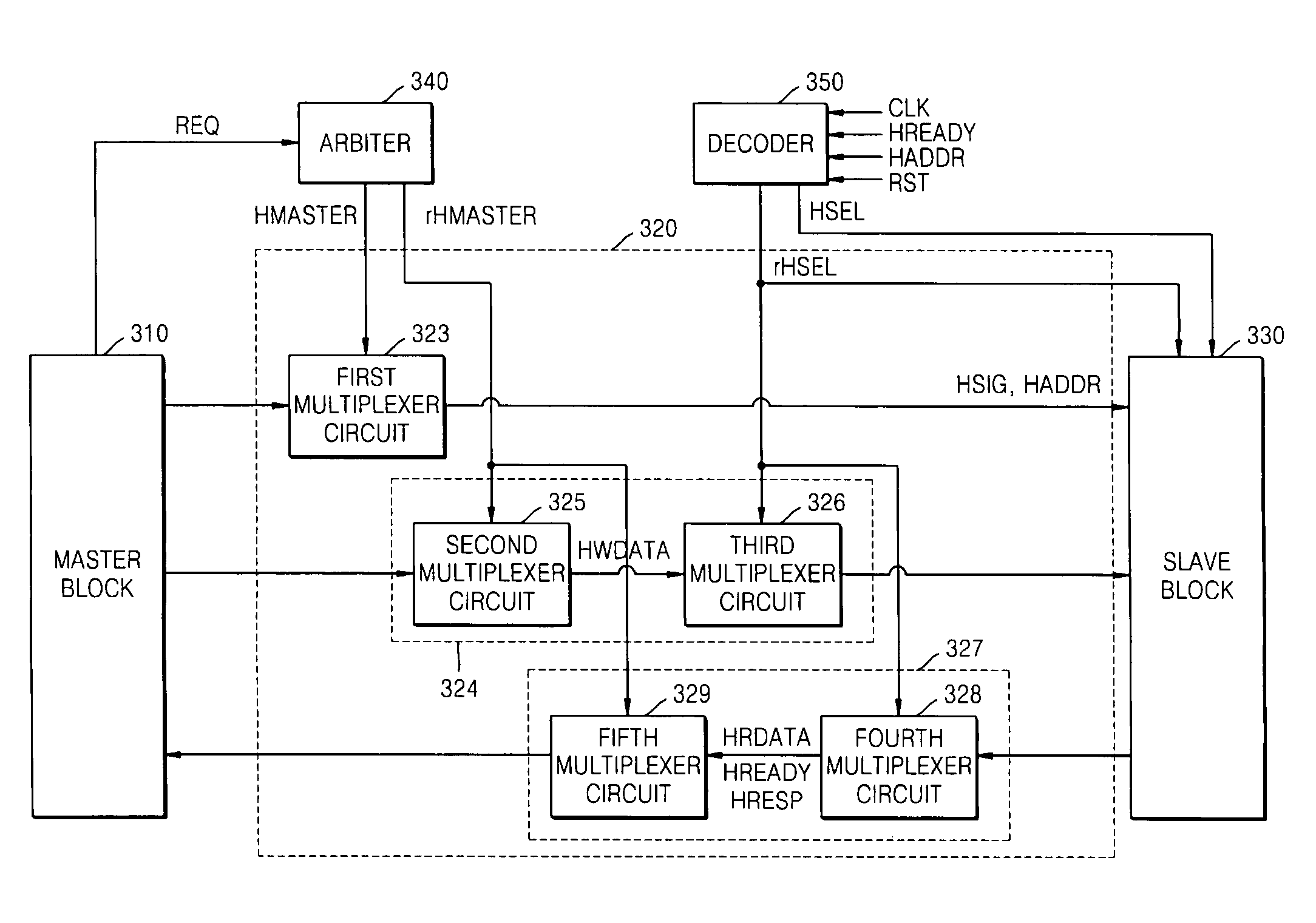

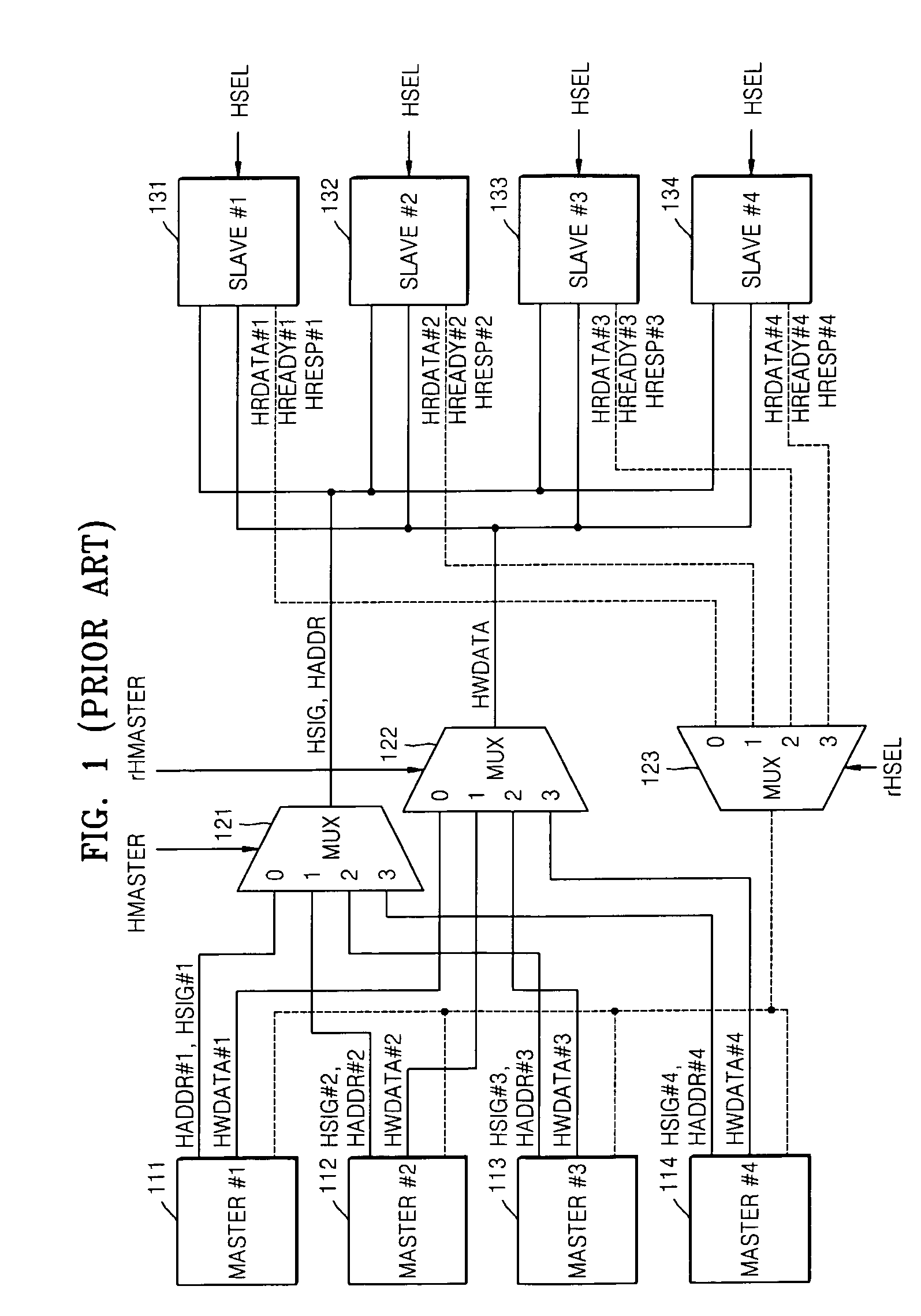

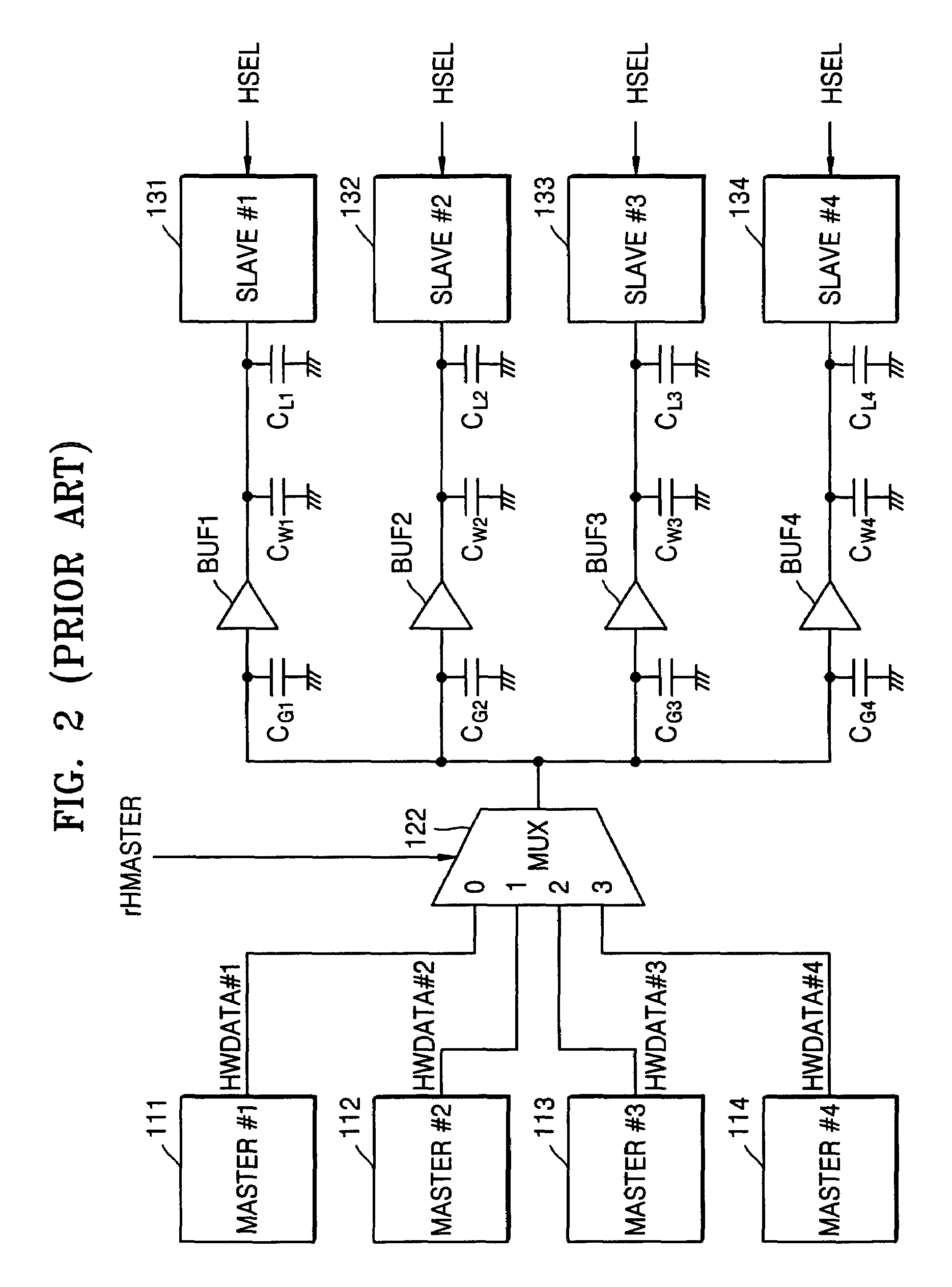

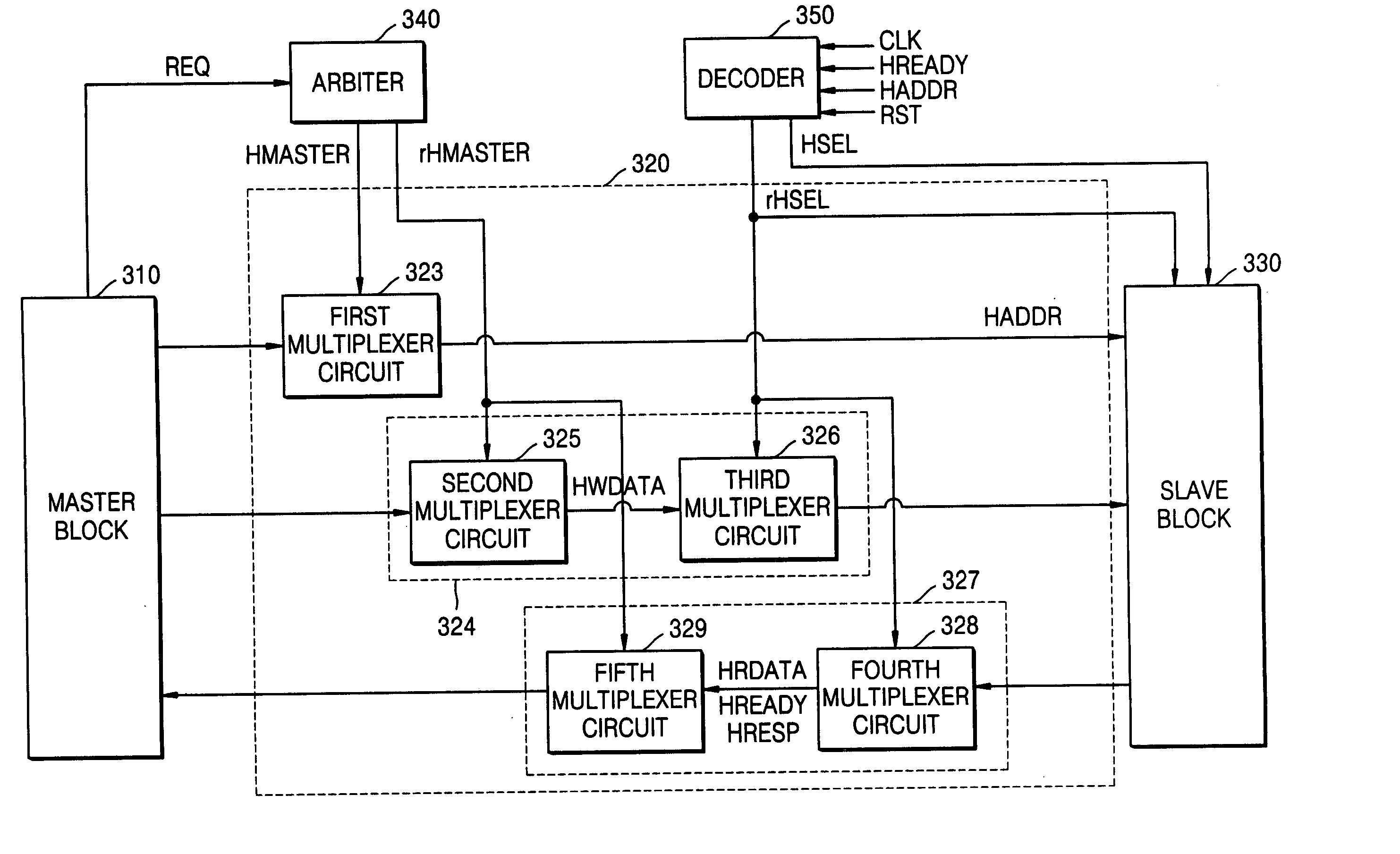

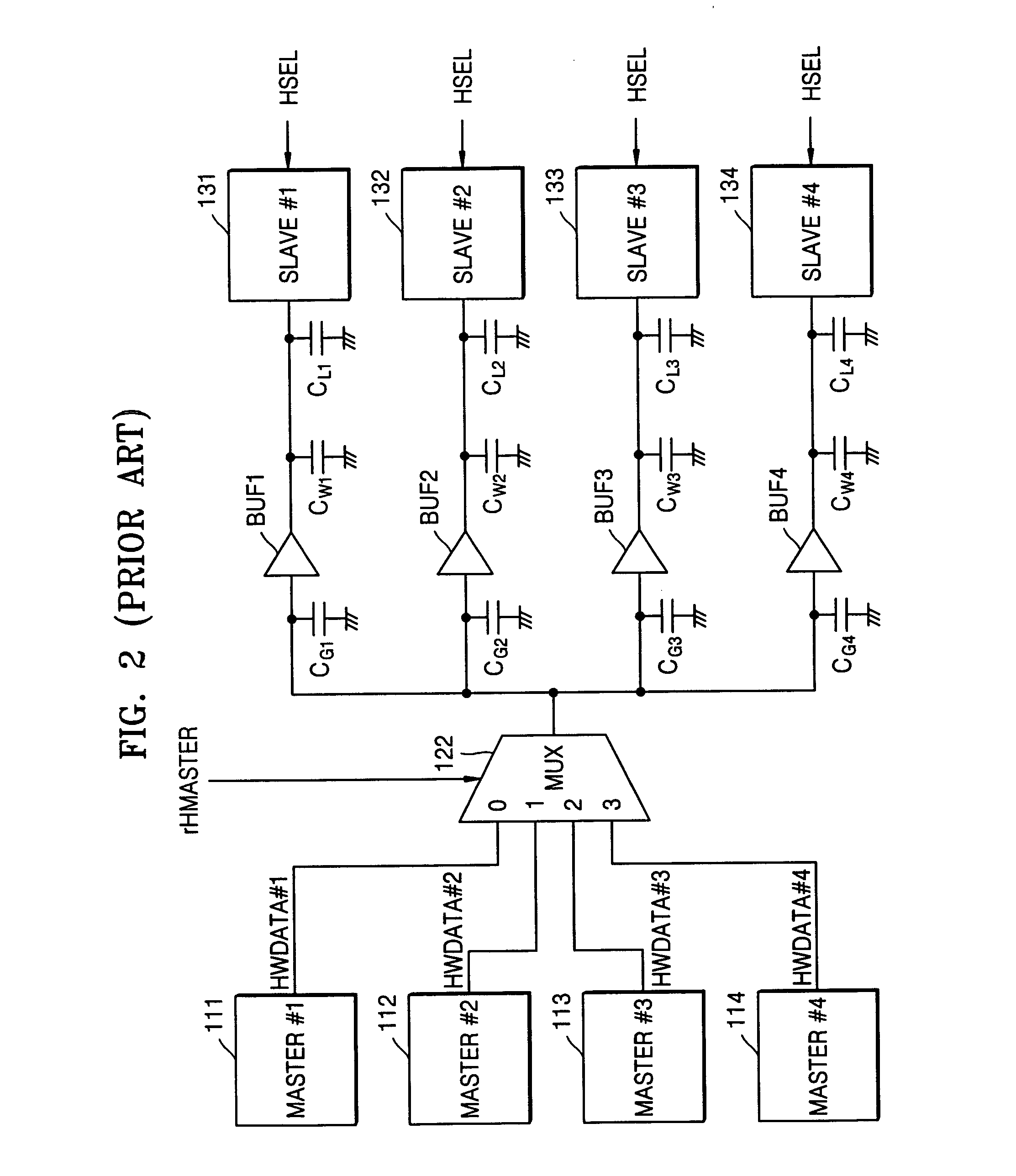

Advanced microcontroller bus architecture (AMBA) system with reduced power consumption and method of driving AMBA system

InactiveUS7234011B2Reduce power consumptionEnergy efficient ICTGeneral purpose stored program computerAdvanced Microcontroller Bus ArchitectureHigh performance system

In an advanced microcontroller bus architecture (AMBA) system with reduced power consumption, a signal transition is allowed to occur only in loads required for transferring bus signals by isolating loads on a bus signal transfer path requiring the signal transition from the other loads, so that the power consumption can be reduced in a bus architecture such as an advanced high-performance system bus (AHB).

Owner:SAMSUNG ELECTRONICS CO LTD

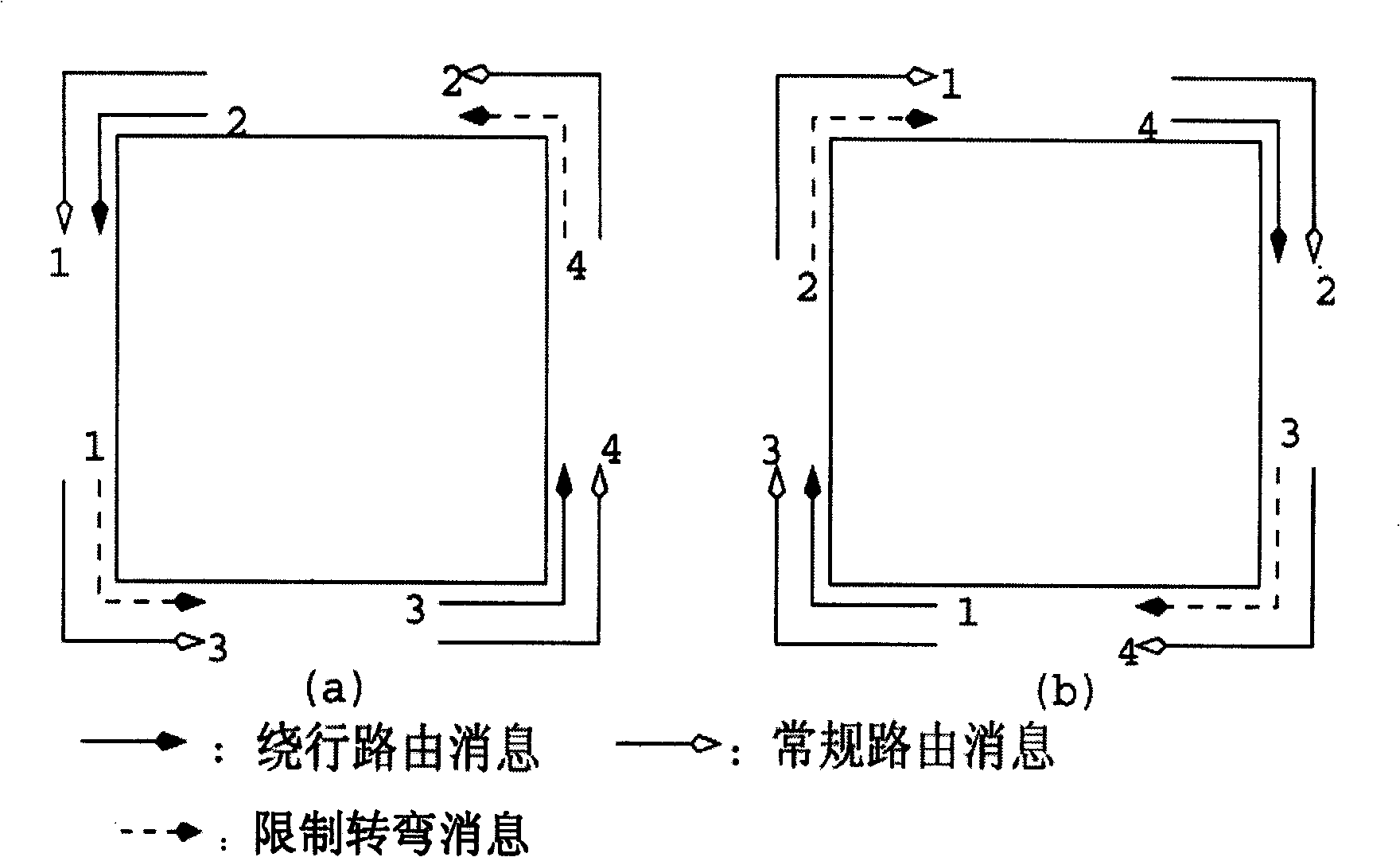

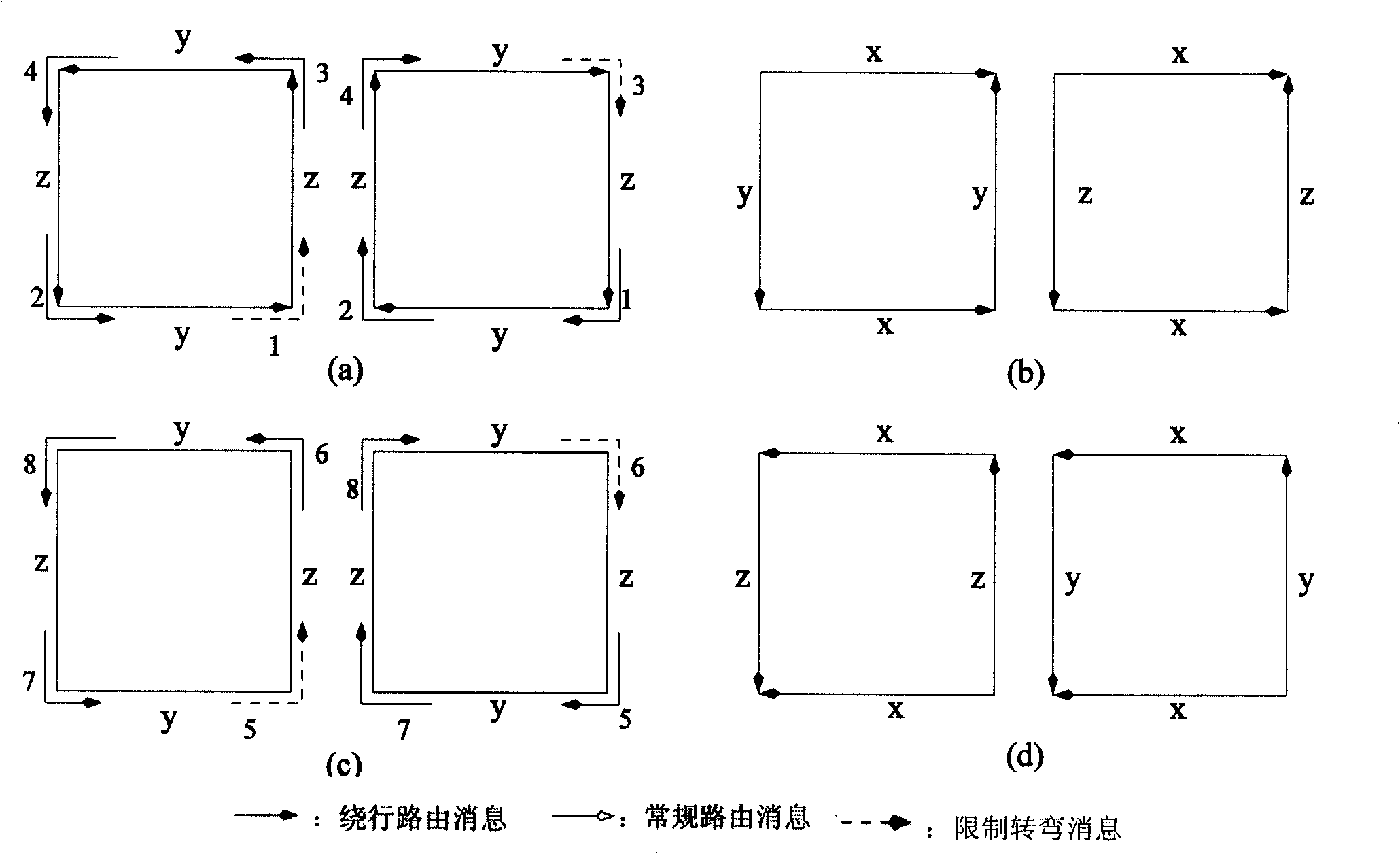

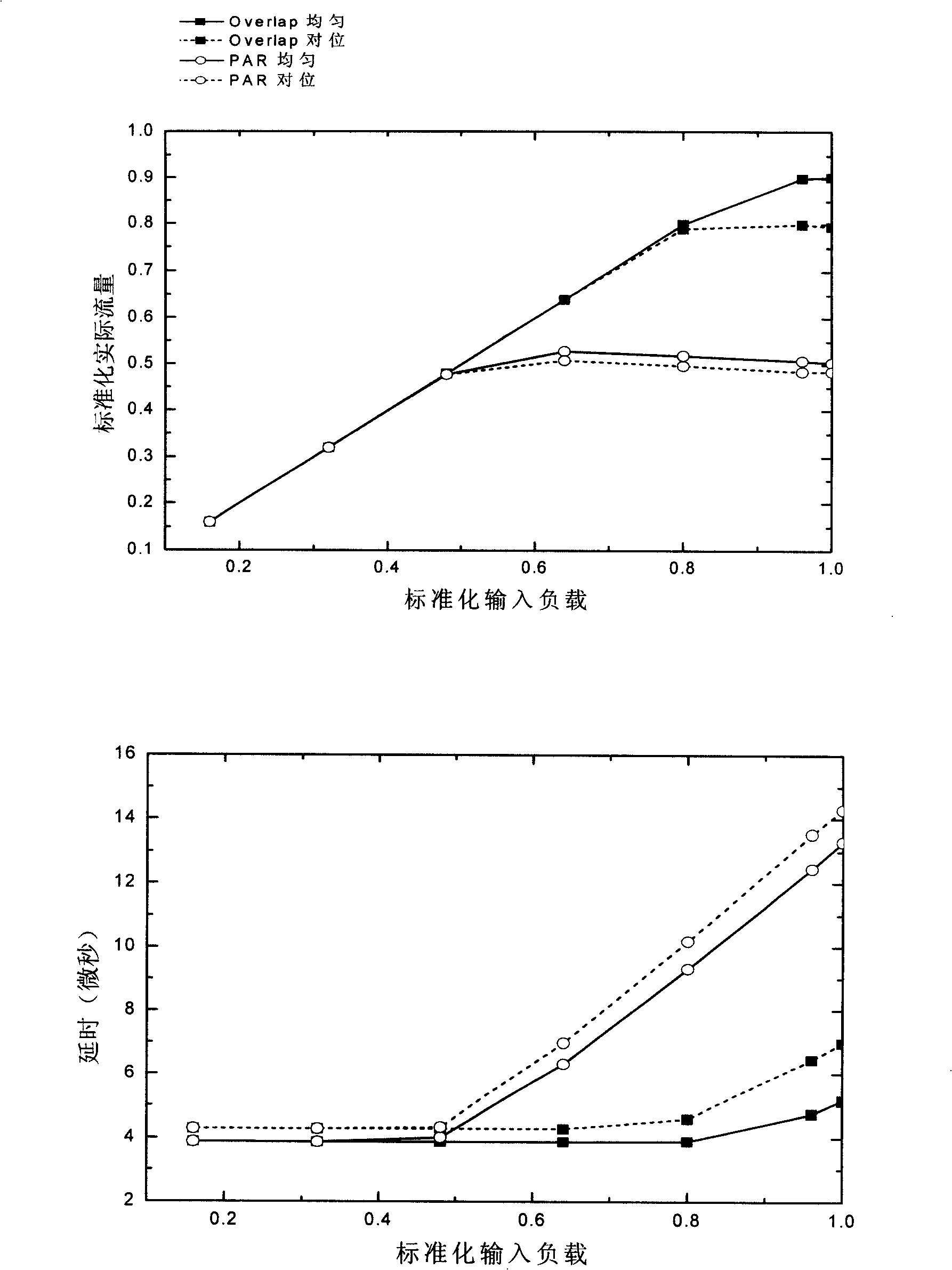

Routing method for avoiding dead lock in fault tolerance mesh based on channel overlapping

InactiveCN101262444AHigh trafficImprove transmission performanceData switching networksFault toleranceAdaptive routing

The invention provides a routing method for preventing a mesh network from deadlock based on channel overlapping, which pertains to routing error-tolerance technology of a distributed high performance system and is characterized in that: every physical channel is divided into two virtual channels and certain virtual channels are allowed to be shared by different virtual subnets; in a two-dimensional mesh network, c1- channels are applied along the direction of x and c1 channels are applied along the direction of y; in a three-dimensional mesh network, virtual subnets x+y+z* and x+y-z* share the c1 channels along the direction of z and virtual subnets x-y*z+ and x-y*z- share c2 channels along the direction of y, wherein, '+' and '-' represent positive direction and negative direction of information transmission, '*' represents either positive direction or negative direction, therefore, a non deadlock plane adaptive routing is finished; meanwhile, minimum networking part fault models are respectively built in all three-dimensional planes and safety information at all diagonal lines therein is utilized to fulfill the fault-tolerant routing method free from deadlock. Compared with the existing PAR and GOMEZ methods, the method of the invention improves transmission performance of the whole network when standard input load is increased.

Owner:TSINGHUA UNIV

High performance system-on-chip inductor using post passivation process

InactiveUS8178435B2Improve RF performanceIncreased frequency rangeTransistorSemiconductor/solid-state device detailsTransformerInductor

A system and method for forming post passivation inductors, and related structures, is described. High quality electrical components, such as inductors and transformers, are formed on a layer of passivation, or on a thick layer of polymer over a passivation layer.

Owner:QUALCOMM INC

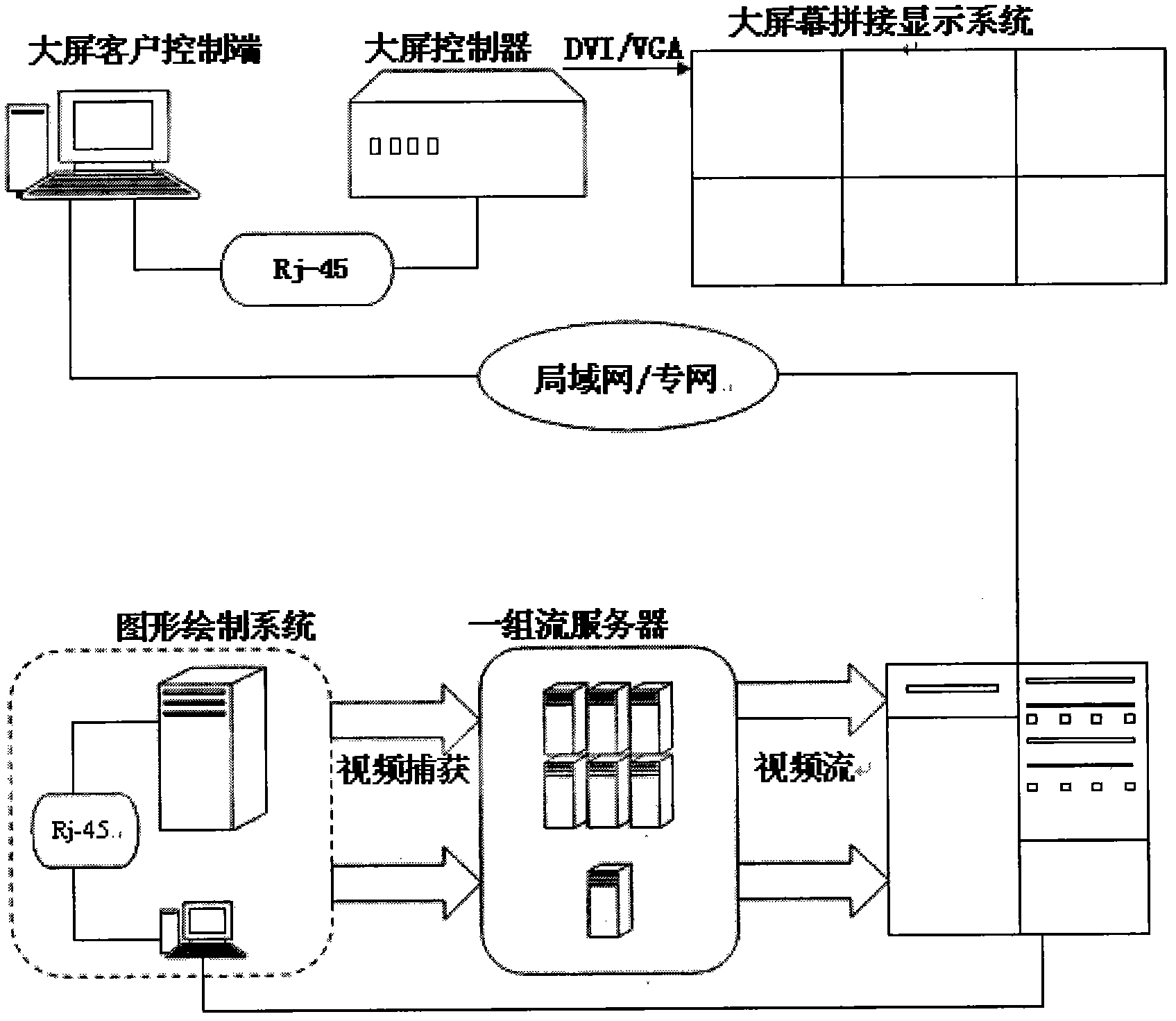

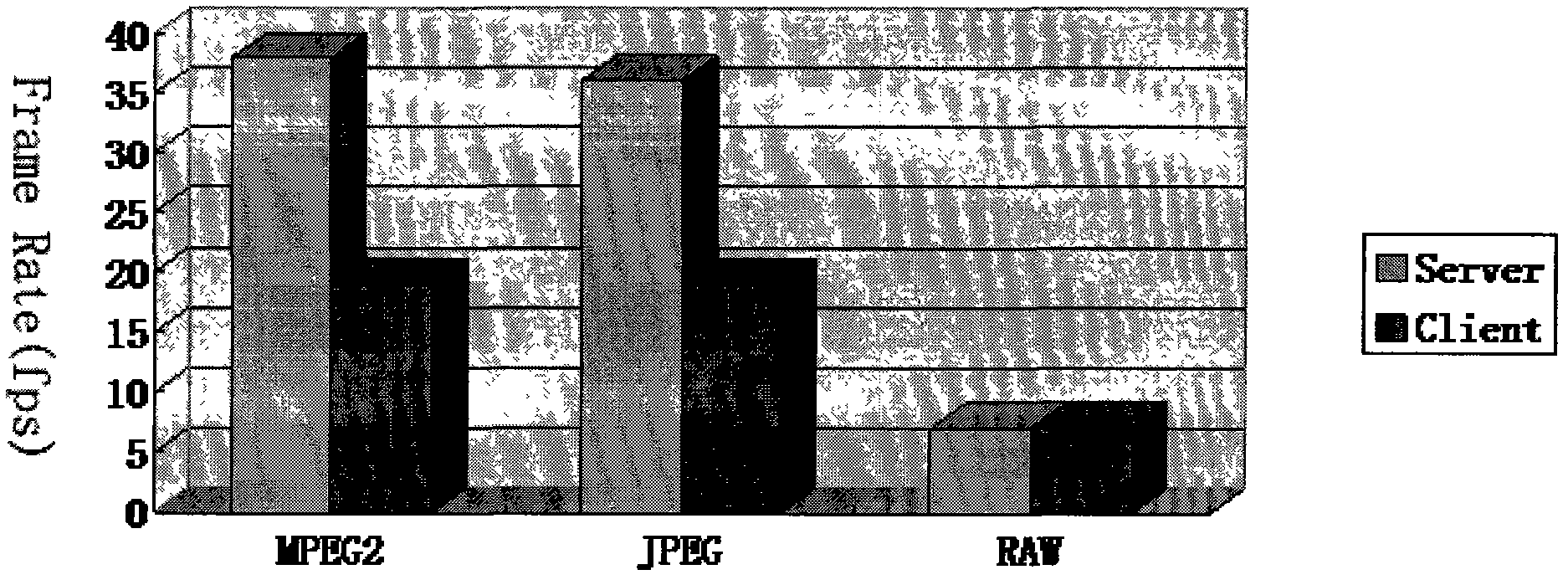

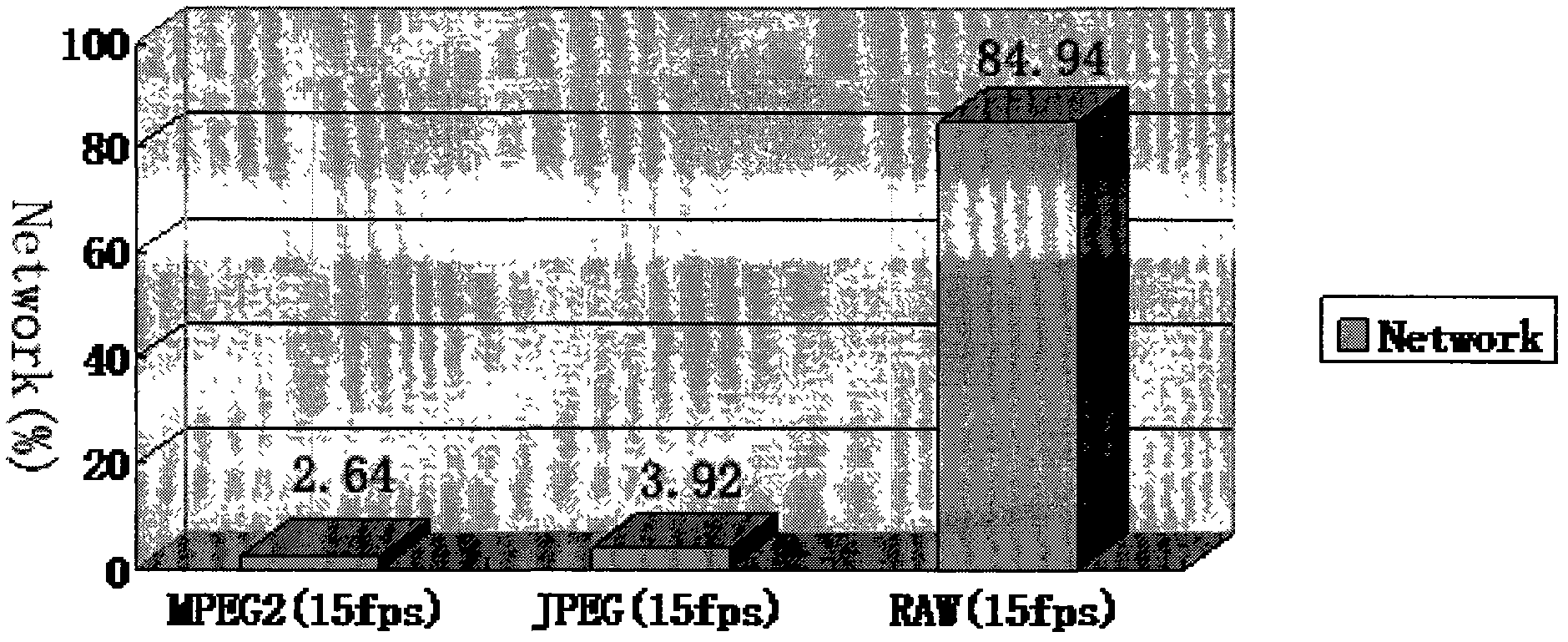

Interactive collaboration system based on large spliced screen and interactive collaboration method

InactiveCN102377745AImprove computing powerReduce bandwidth requirementsTelevision systemsTransmissionPrivate networkInformation resource

The invention relates to an interactive collaboration system based on a large spliced screen, which comprises a streaming server and a steam forwarding server, wherein the streaming server is used for capturing the multipath display output of a remote high-performance system and respectively compresses the captured signal into multiple pixel streams; the steam forwarding server is positioned on the rear end of the streaming server and is used for collecting the pixel streams from each streaming server, and then, the pixel streams are forwarded to a client side system by a local area network or a private network; the client side system comprises one large-screen control end and one set of large spliced screen display system, wherein the large-screen control end receives a bit stream from the stream forwarding server; and meanwhile, the large-screen control end sends a message, feedback information and an interaction command for regulating a visual pixel area to the stream forwarding server. The invention also provides an interactive collaboration method based on the system. The interactive collaboration system has the advantages that the interactive collaboration system not only can display local information resource but also can remotely access the remote high-performance system.

Owner:SHANGHAI GENIUS INFORMATION TECH

Advanced microcontroller bus architecture (AMBA) system with reduced power consumption and method of driving AMBA system

InactiveUS20050138253A1Reduce power consumptionEnergy efficient ICTGeneral purpose stored program computerAdvanced Microcontroller Bus ArchitectureHigh performance system

In an advanced microcontroller bus architecture (AMBA) system with reduced power consumption, a signal transition is allowed to occur only in loads required for transferring bus signals by isolating loads on a bus signal transfer path requiring the signal transition from the other loads, so that the power consumption can be reduced in a bus architecture such as an advanced high-performance system bus (AHB).

Owner:SAMSUNG ELECTRONICS CO LTD

High performance system-on-chip inductor using post passivation process

InactiveUS20070181970A1Improve RF performanceIncreased frequency rangeSemiconductor/solid-state device detailsSolid-state devicesTransformerInductor

A system and method for forming post passivation inductors, and related structures, is described. High quality electrical components, such as inductors and transformers, are formed on a layer of passivation, or on a thick layer of polymer over a passivation layer.

Owner:QUALCOMM INC

High performance system-on-chip using post passivation process

InactiveUS20090001511A1Improve RF performanceIncreased frequency rangeSemiconductor/solid-state device detailsSolid-state devicesInductorElectronic component

The present invention extends the above referenced continuation-in-part application by in addition creating high quality electrical components, such as inductors, capacitors or resistors, on a layer of passivation or on the surface of a thick layer of polymer. In addition, the process of the invention provides a method for mounting discrete electrical components at a significant distance removed from the underlying silicon surface.

Owner:QUALCOMM INC