Network-on-chip router with low buffer area and routing method

An on-chip network and router technology, applied in the field of on-chip network design, can solve problems such as low efficiency, increased delay, and inability to provide service quality assurance

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

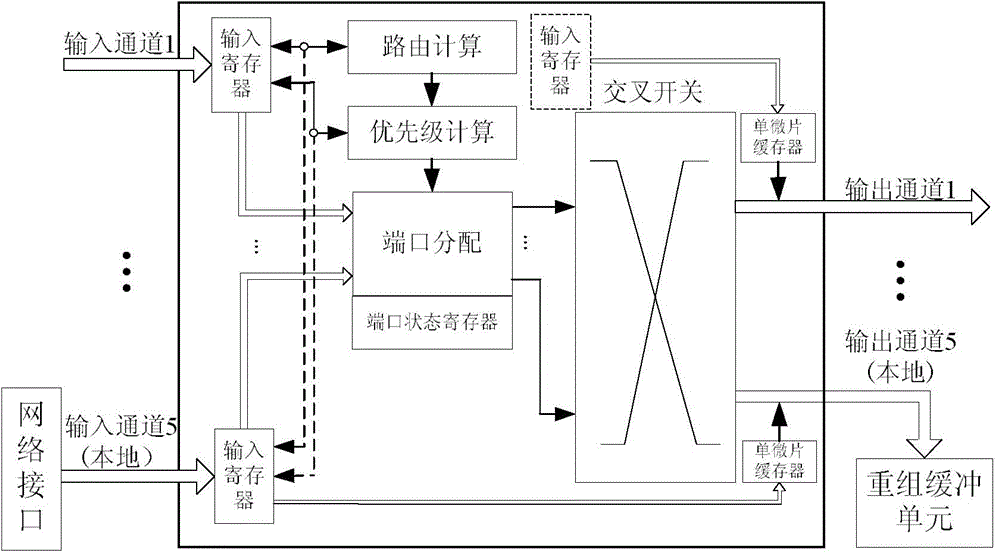

[0036] In order to more clearly introduce a low-buffer network-on-chip router and routing method proposed by the present invention, the following will be described in detail with reference to the accompanying drawings and specific examples.

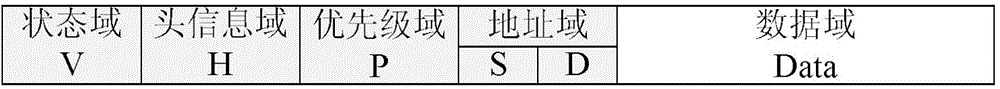

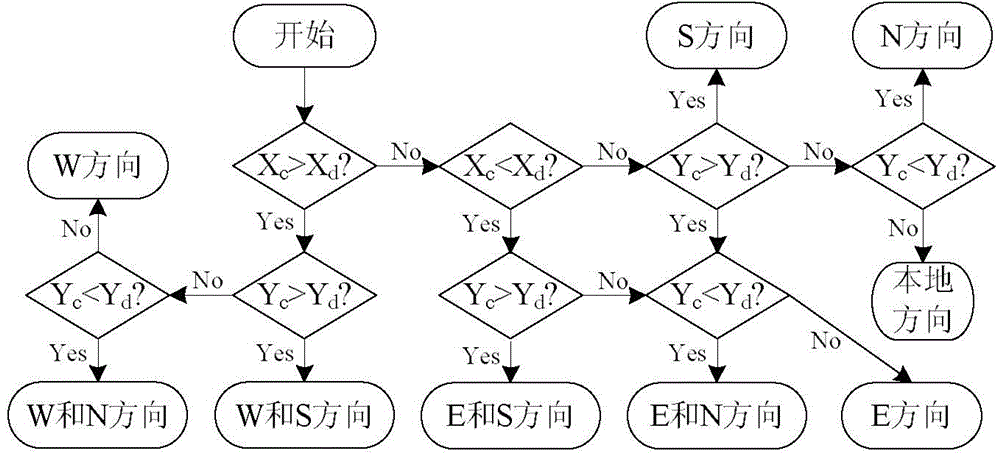

[0037] According to the low buffer on-chip network routing method described in the specification, the data flake frame format example it adopts is as follows: figure 1 shown. Each data micro-chip includes a valid state field V, a header information field H, a priority field P, an address field Addr and a data field Data. Each microchip is sent independently in the network. The microchips belonging to the same data packet arrive at the destination router through the same or different paths and are first sorted in the reassembly buffer of the network interface, and the sorted complete data packet is sent to the destination node. Taking the 4×4MESH network topology as an example, each packet contains 1 to 3 microchips, and the specific fram...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More