Patents

Literature

473 results about "Flag signals" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

Flag signals can mean any of various methods of using flags or pennants to send signals. Flags may have individual significance as signals, or two or more flags may be manipulated so that their relative positions convey symbols. Flag signals allowed communication at a distance before the invention of radio and are still used especially in connection with ships.

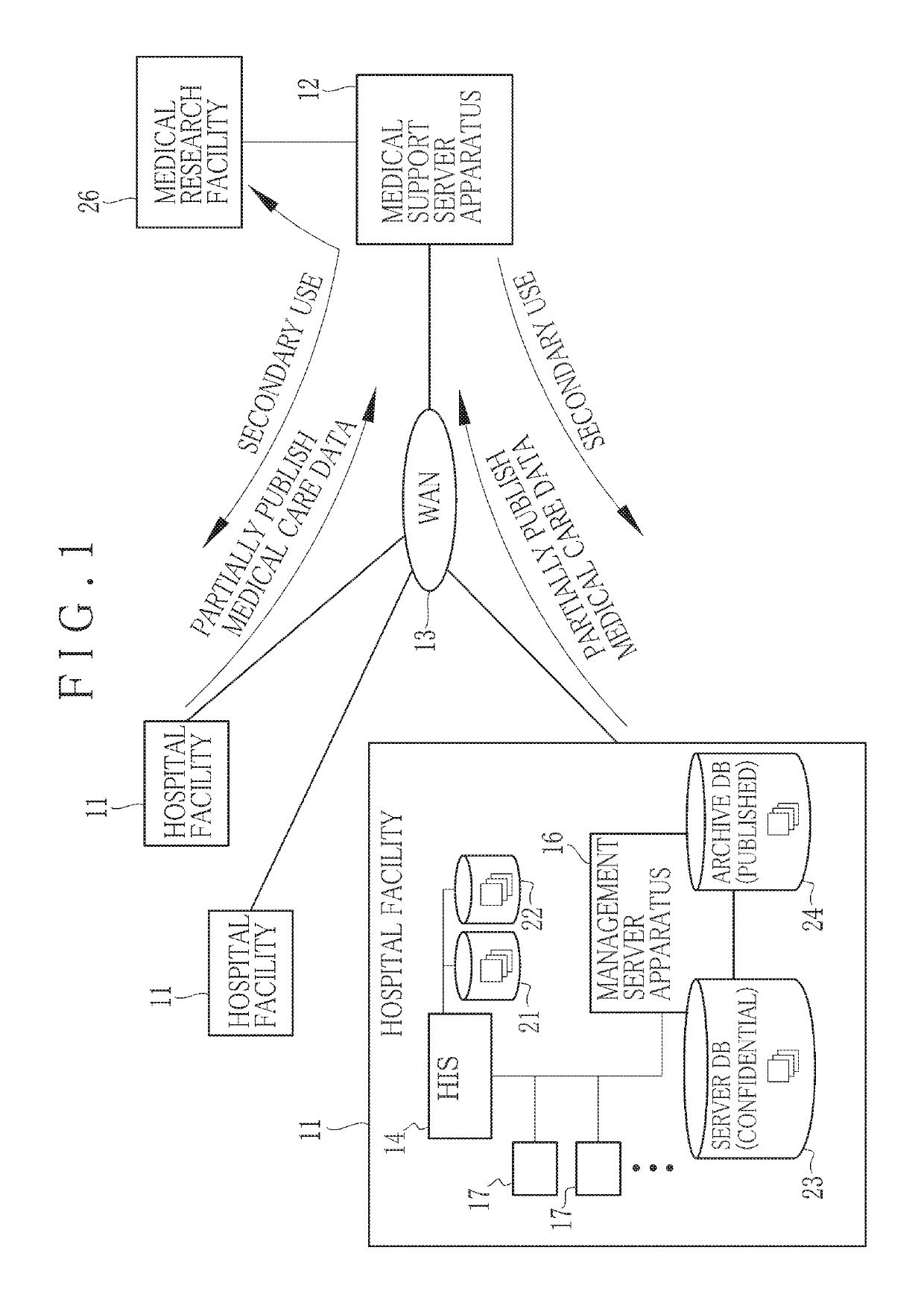

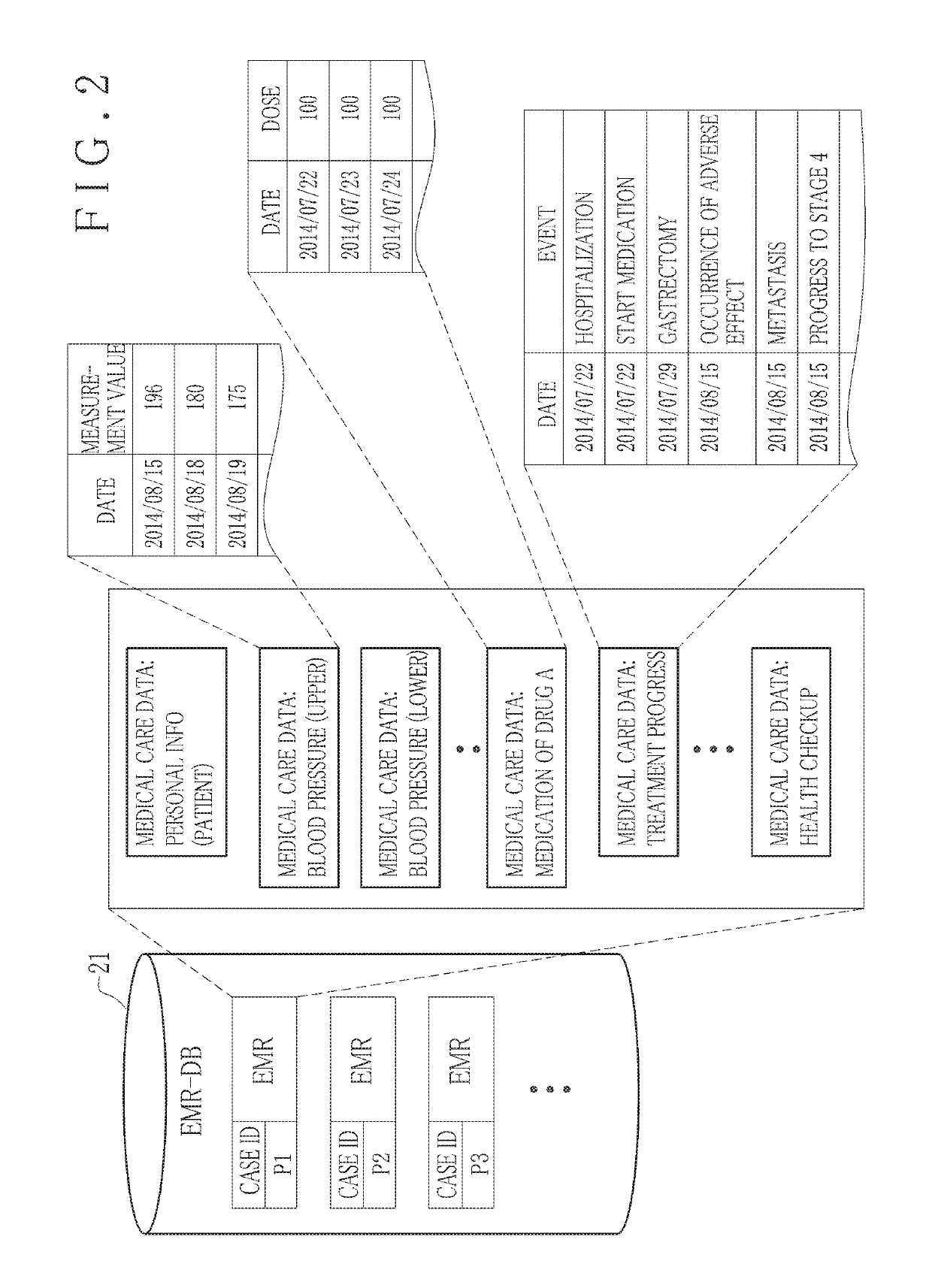

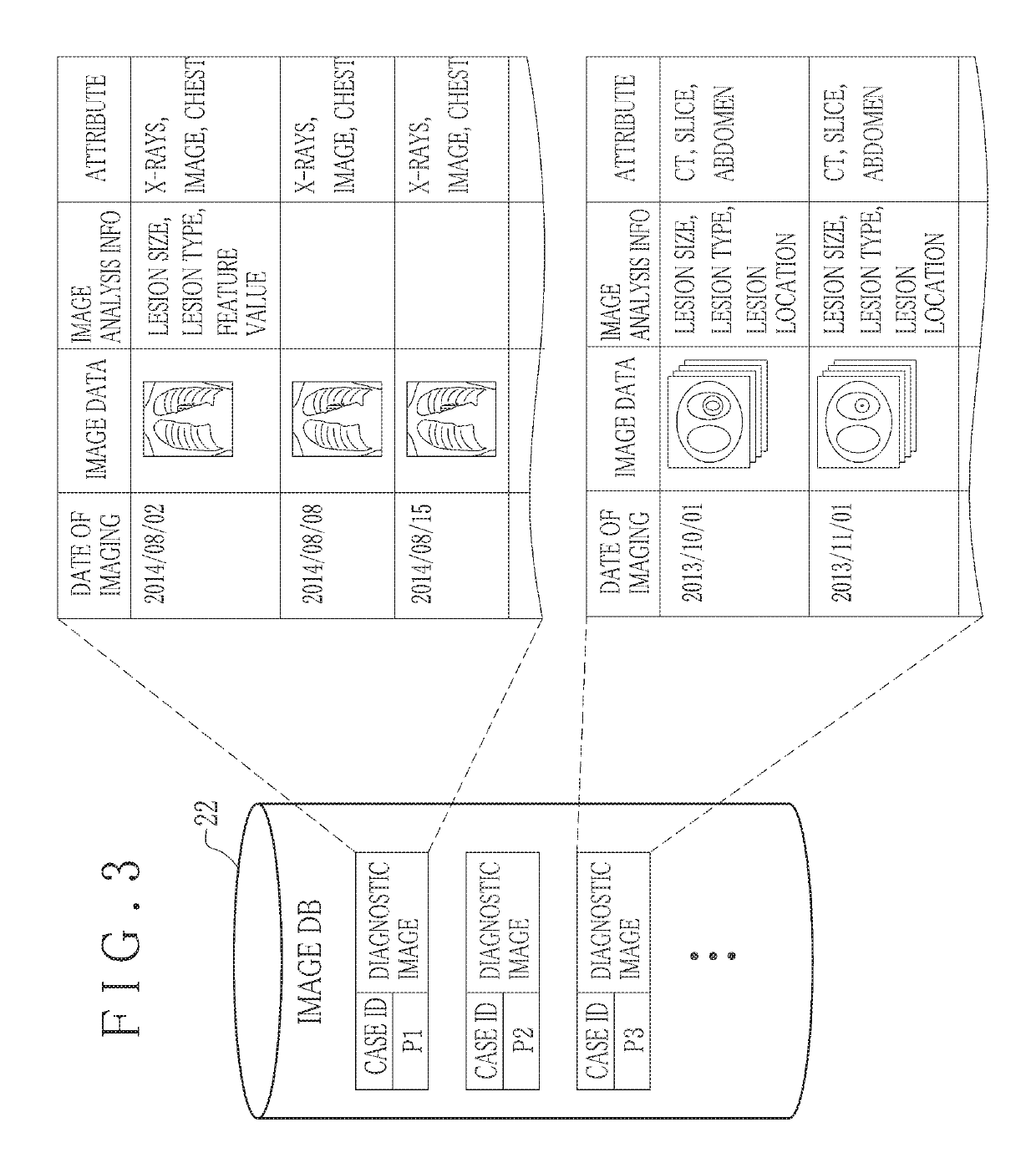

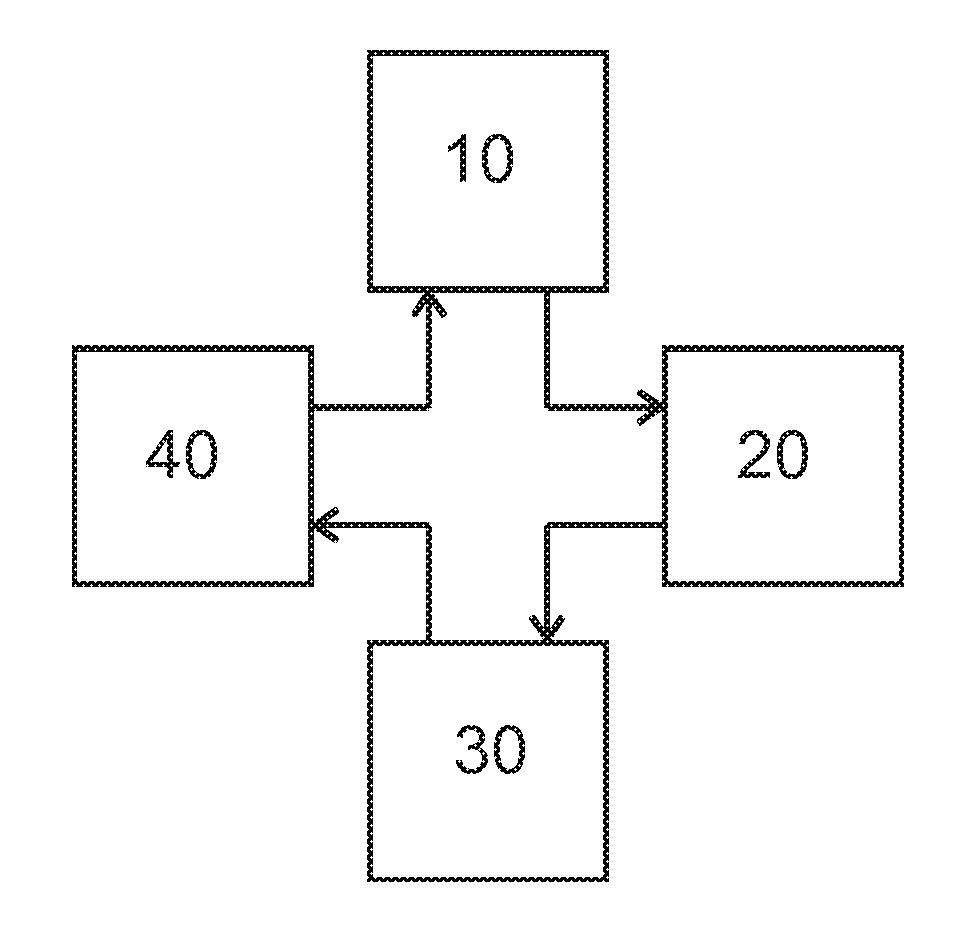

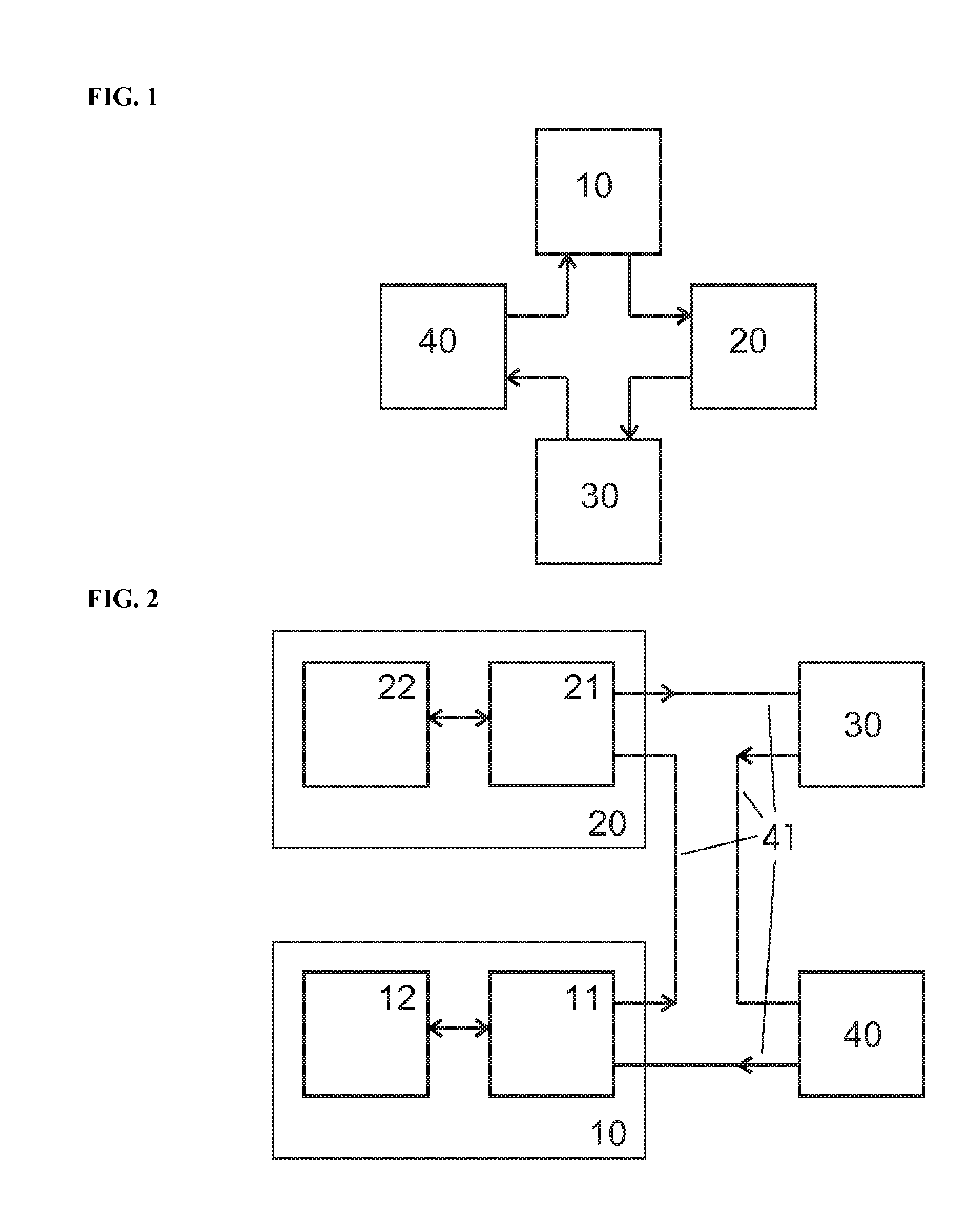

Information management apparatus and method for medical care data, and non-transitory computer readable medium

An information sharing apparatus (management apparatus) for medical care data of a patient body includes a data uploader for classifying the medical care data into confidential data for a primary use in medical care of the patient body, and published data published for a secondary use different from the primary use, to store the confidential data and the published data in a storage medium. A problem event detector monitors the confidential data being added or updated, to check occurrence of a problem event of clinical exacerbation of the patient body. An activation processor checks occurrence of a flag signal for activating relocation of the confidential data to the published data upon the occurrence of the problem event. A relocation unit filters the confidential data at least partially to produce published data upon occurrence of the flag signal after the occurrence of the problem event.

Owner:FUJIFILM CORP

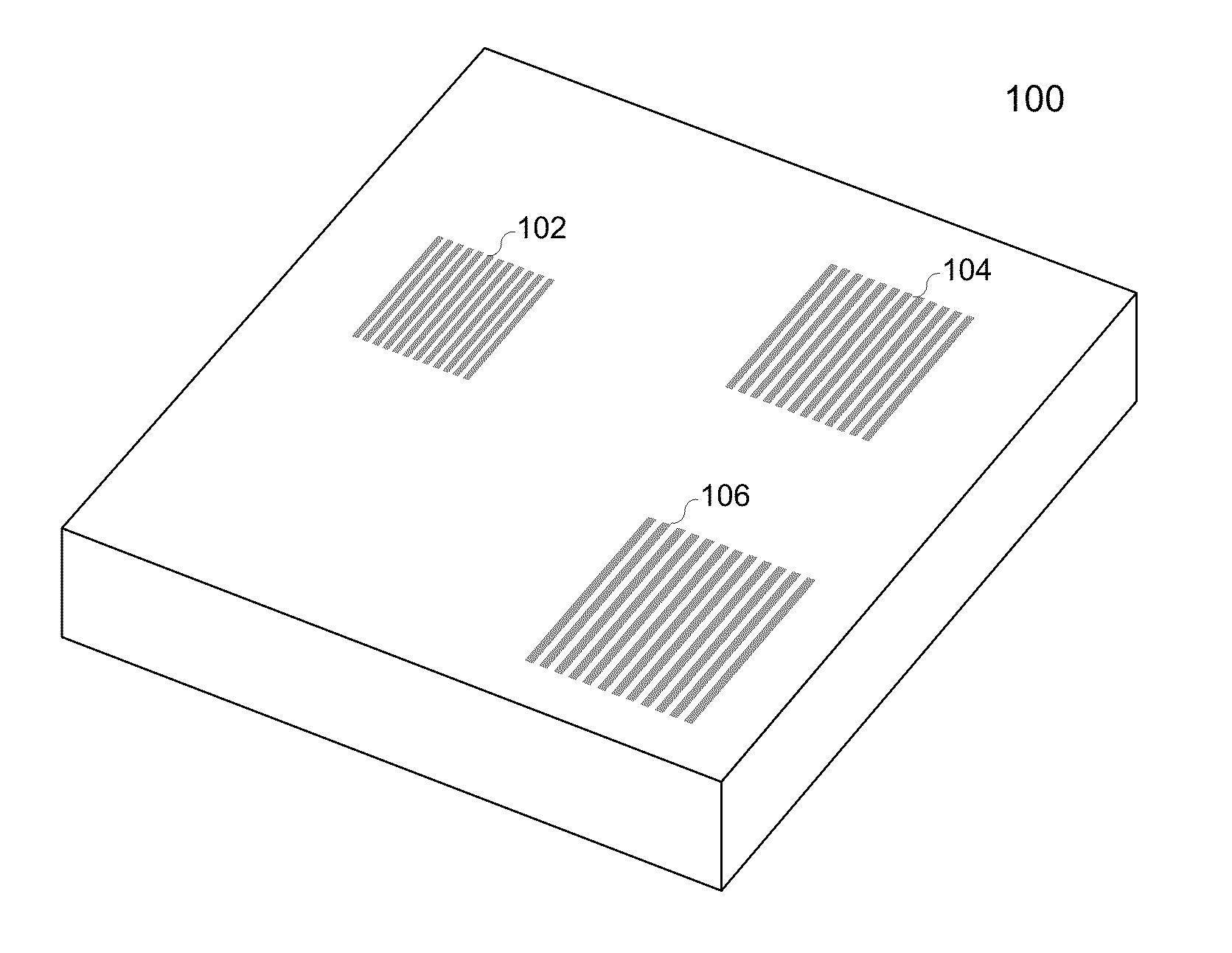

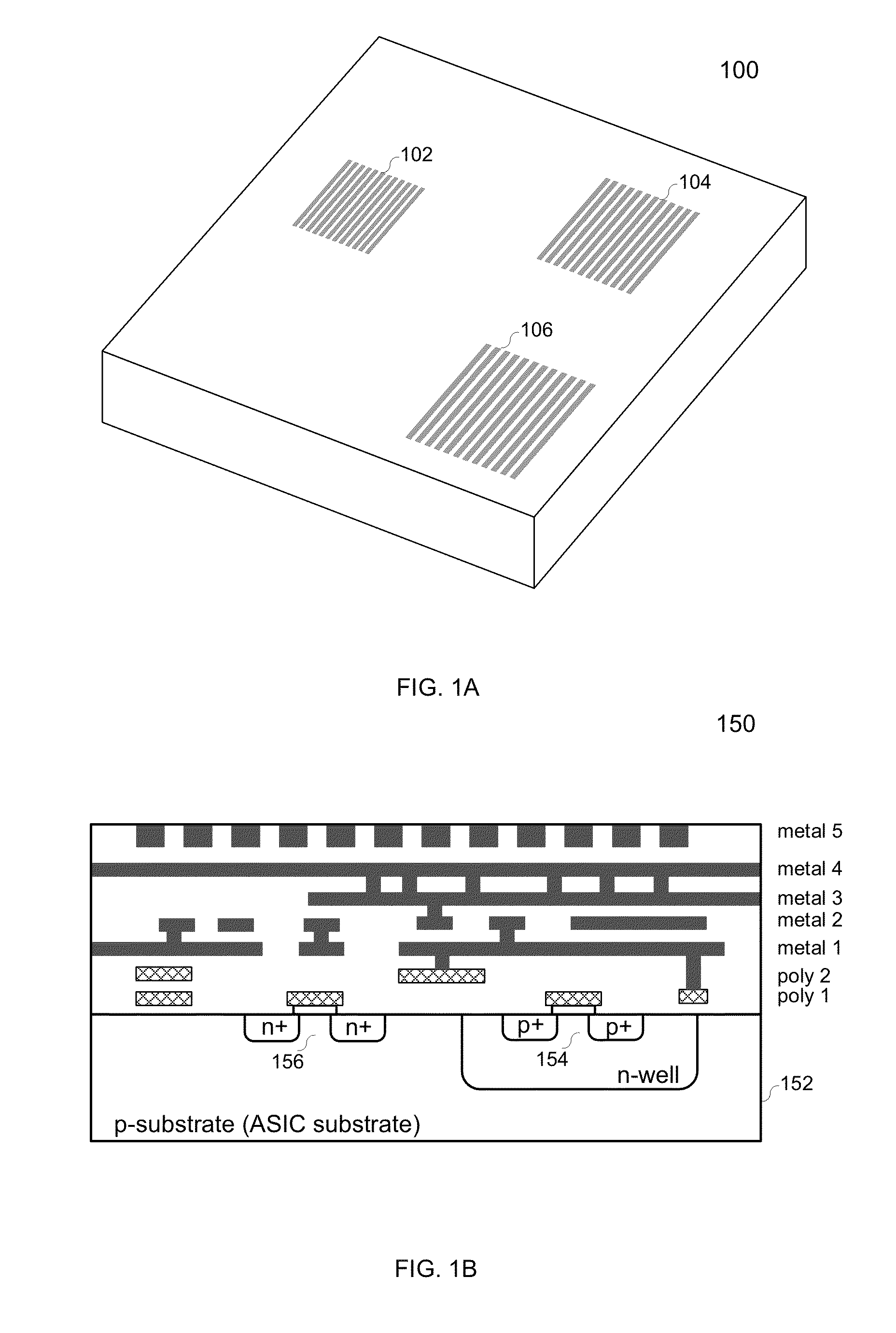

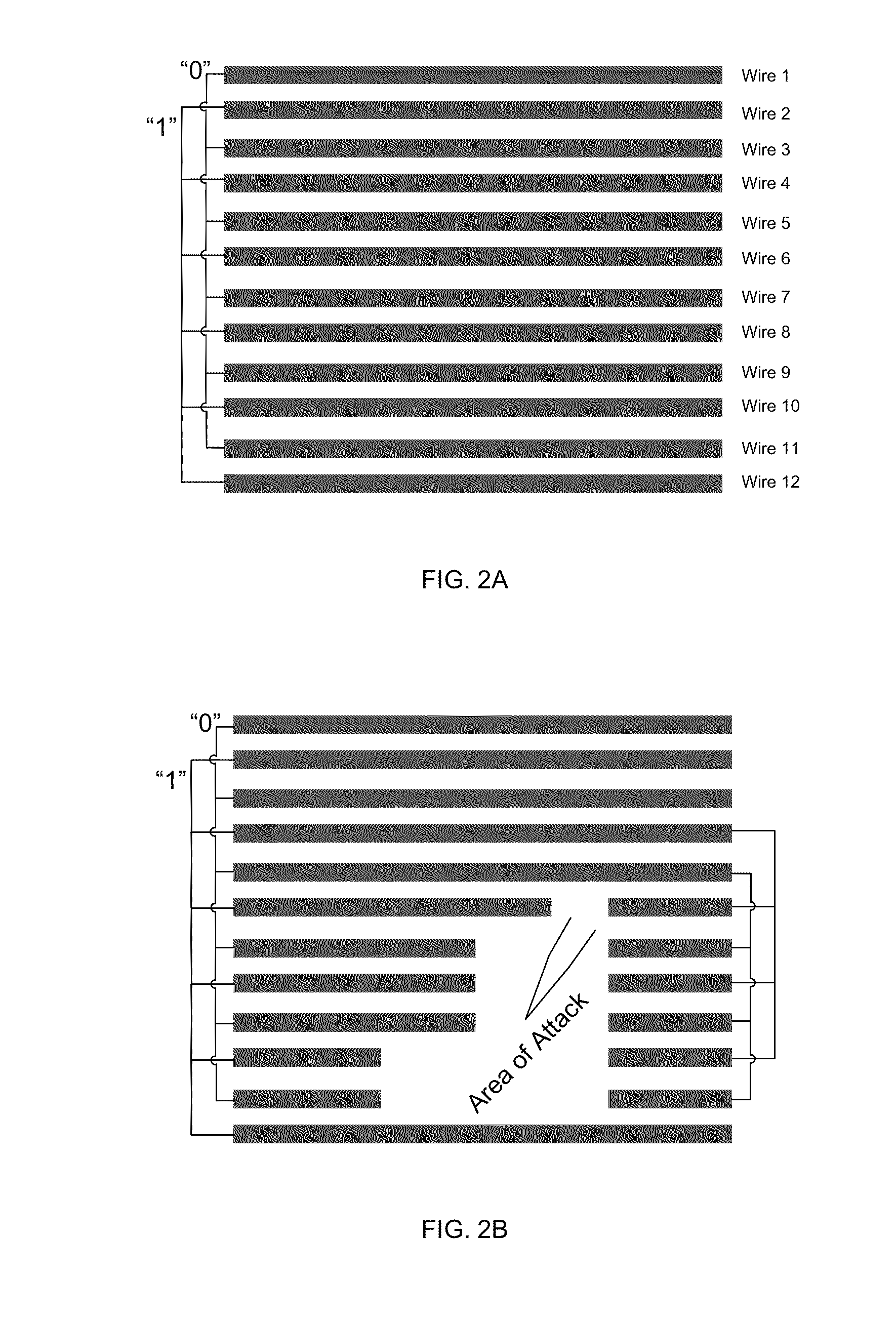

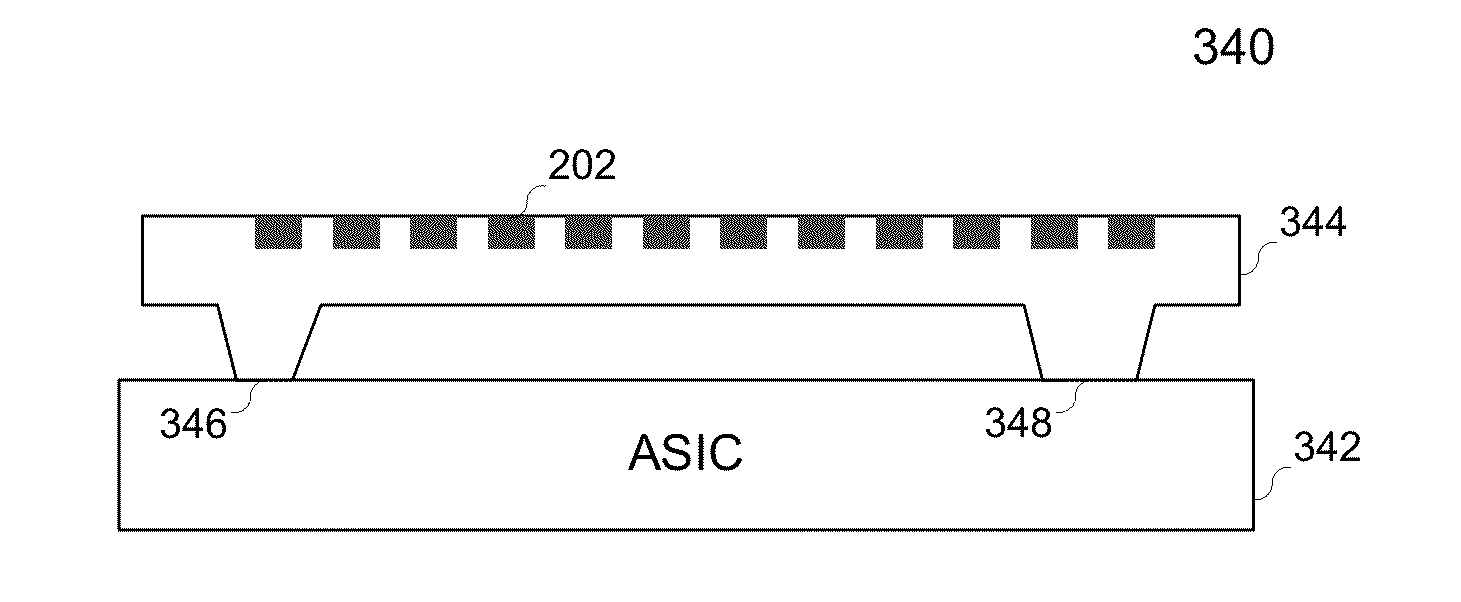

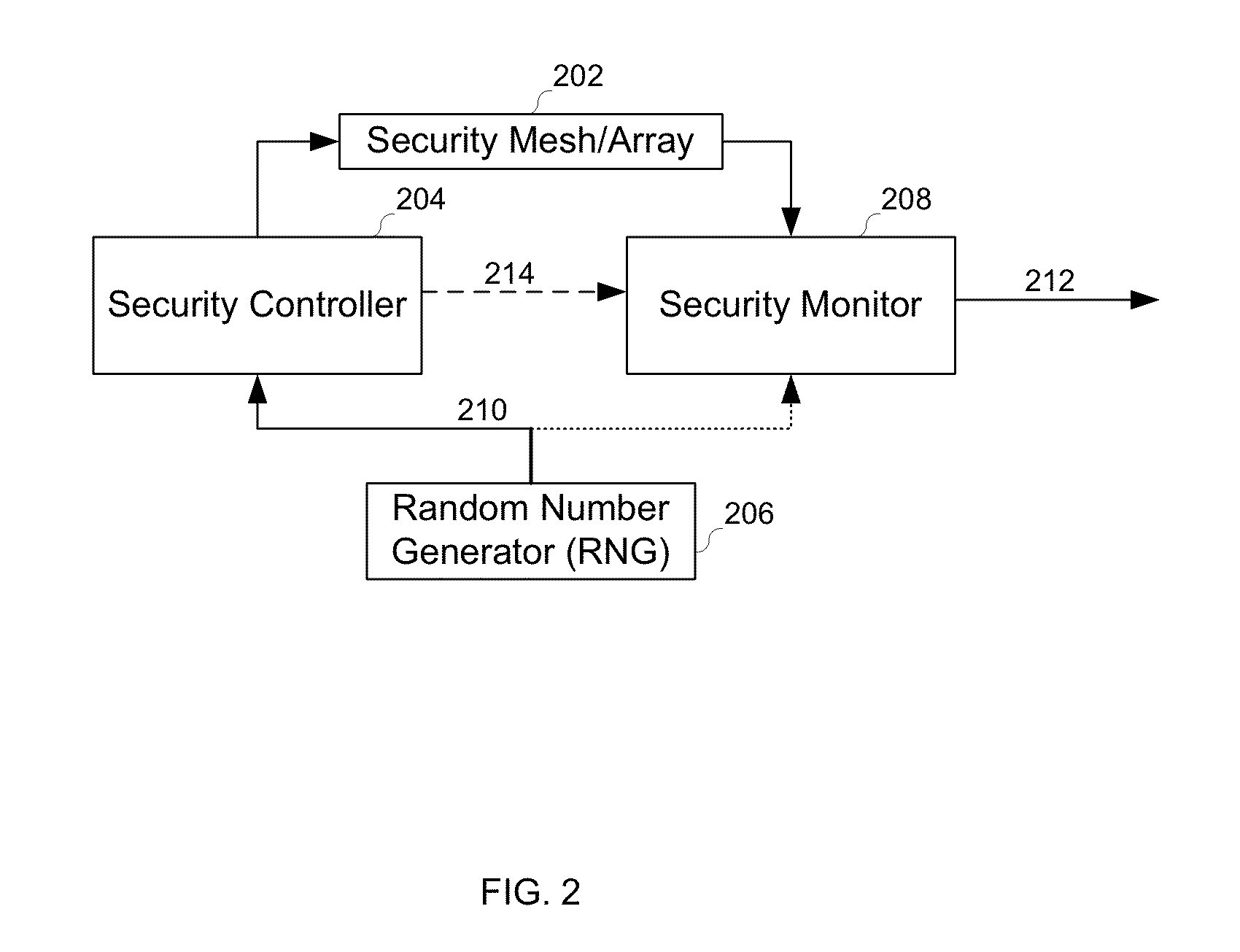

Tamper detection countermeasures to deter physical attack on a security asic

ActiveUS20130104252A1Error detection/correctionVolume/mass flow measurementCountermeasureNumber generator

Various embodiments of the present invention relates generally to an integrated circuit, and more particularly, to systems, devices and methods of incorporating a tamper detection countermeasure into a security ASIC to deter physical attacks. The tamper detection countermeasure architects an active mesh to cover a sensitive area in the security ASIC. A plurality of time-varying random numbers is generated by a random number generator (RNG), and the active mesh is driven and configured according to these random numbers. During tamper detection cycles, the active mesh is monitored with respect to the plurality of random numbers that is directly provided by the RNG. Upon a tampering attempt, a flag signal is generated and used to initialize subsequent anti-tampering actions. The active mesh may be controlled and monitored based on time-varying codes, and therefore, an adversary may not easily bypass the active mesh and attack the sensitive area.

Owner:MAXIM INTEGRATED PROD INC

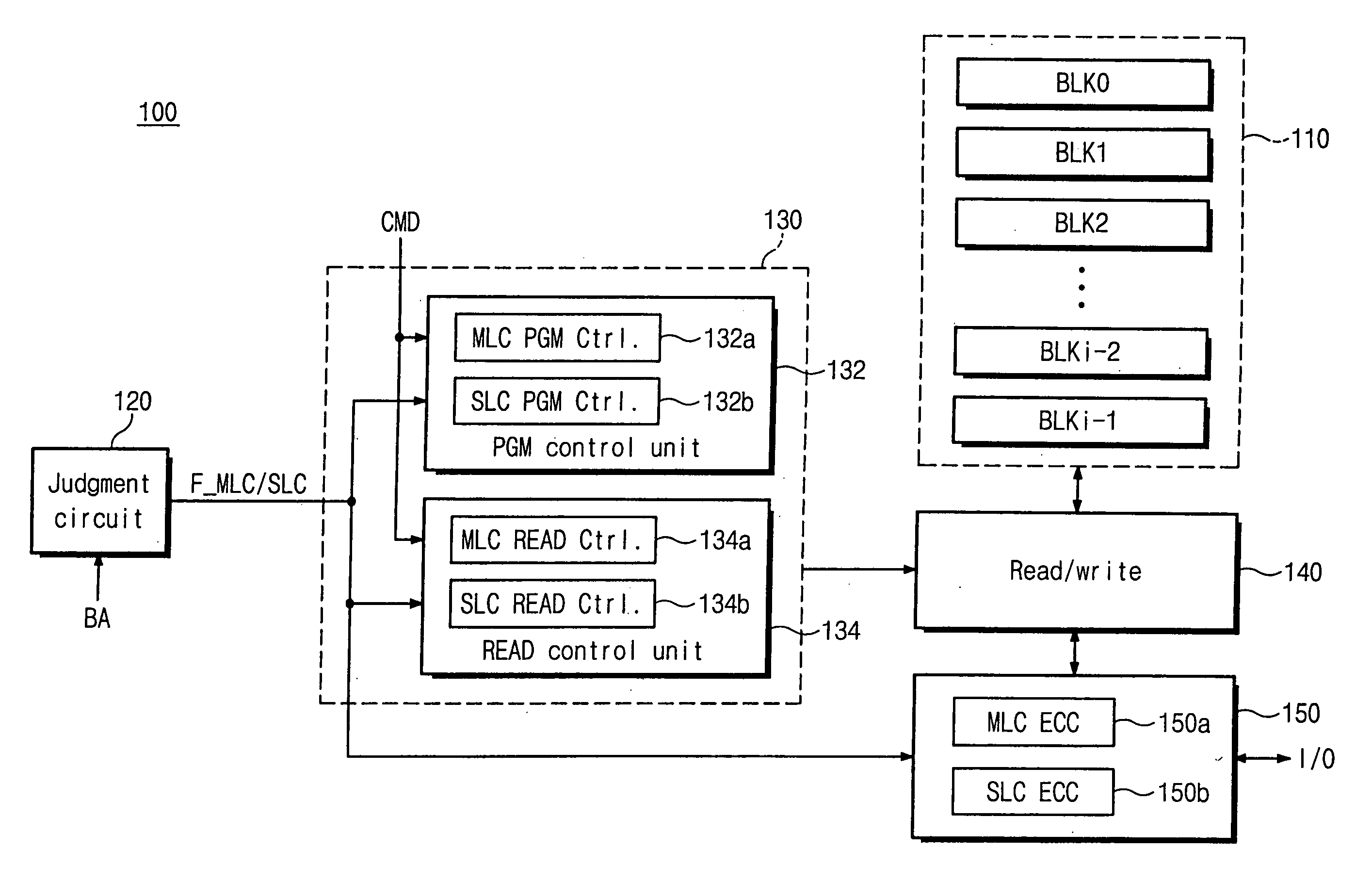

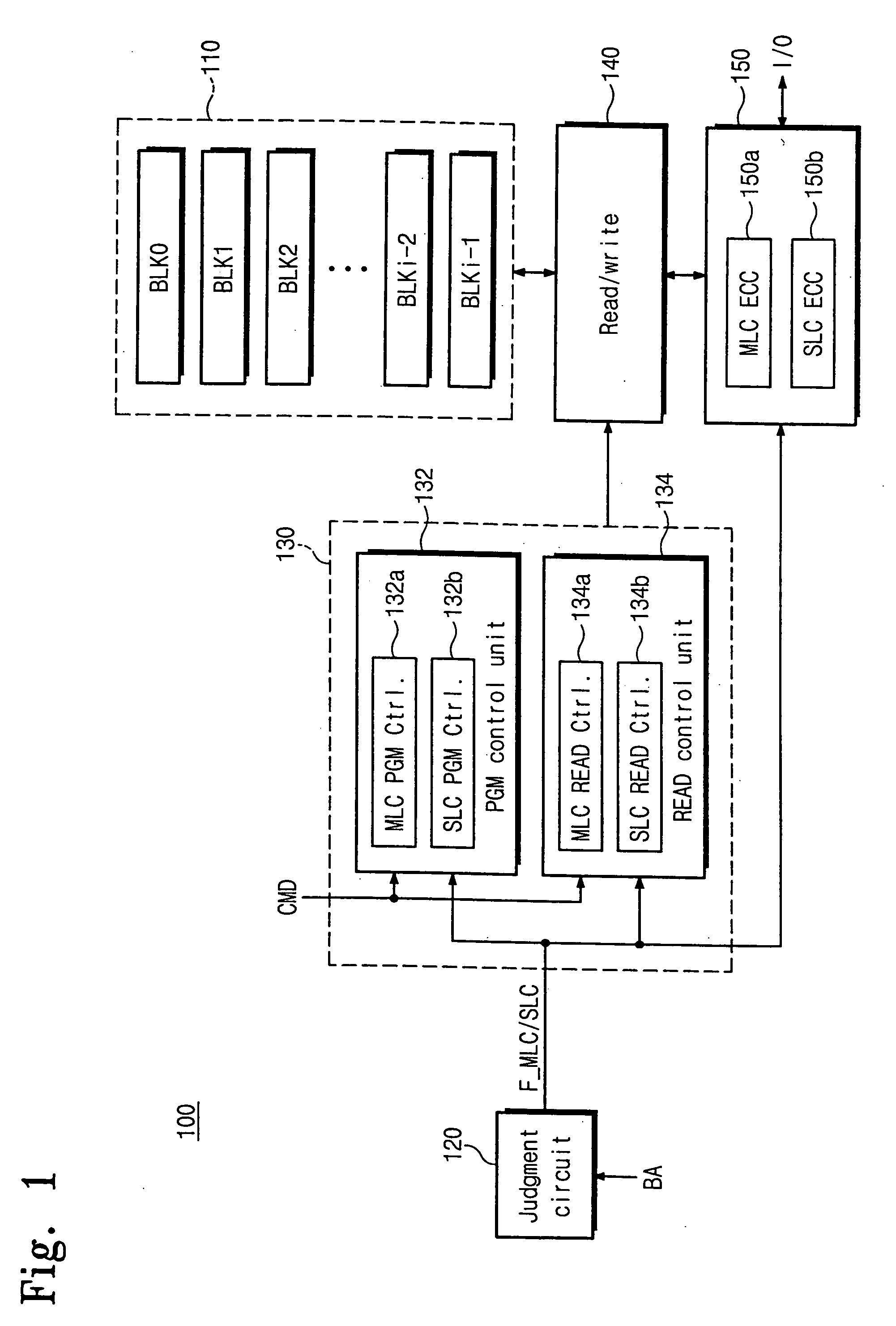

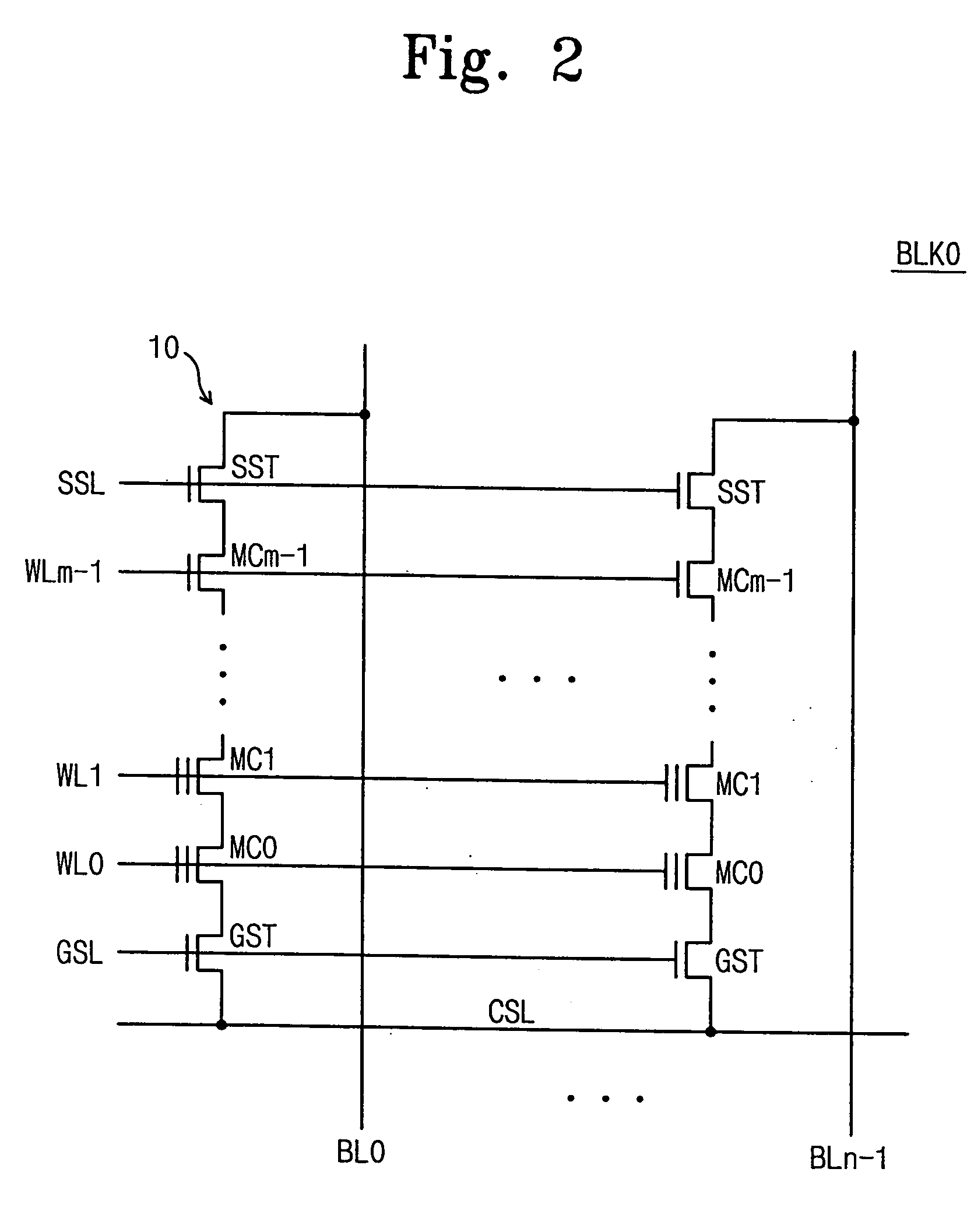

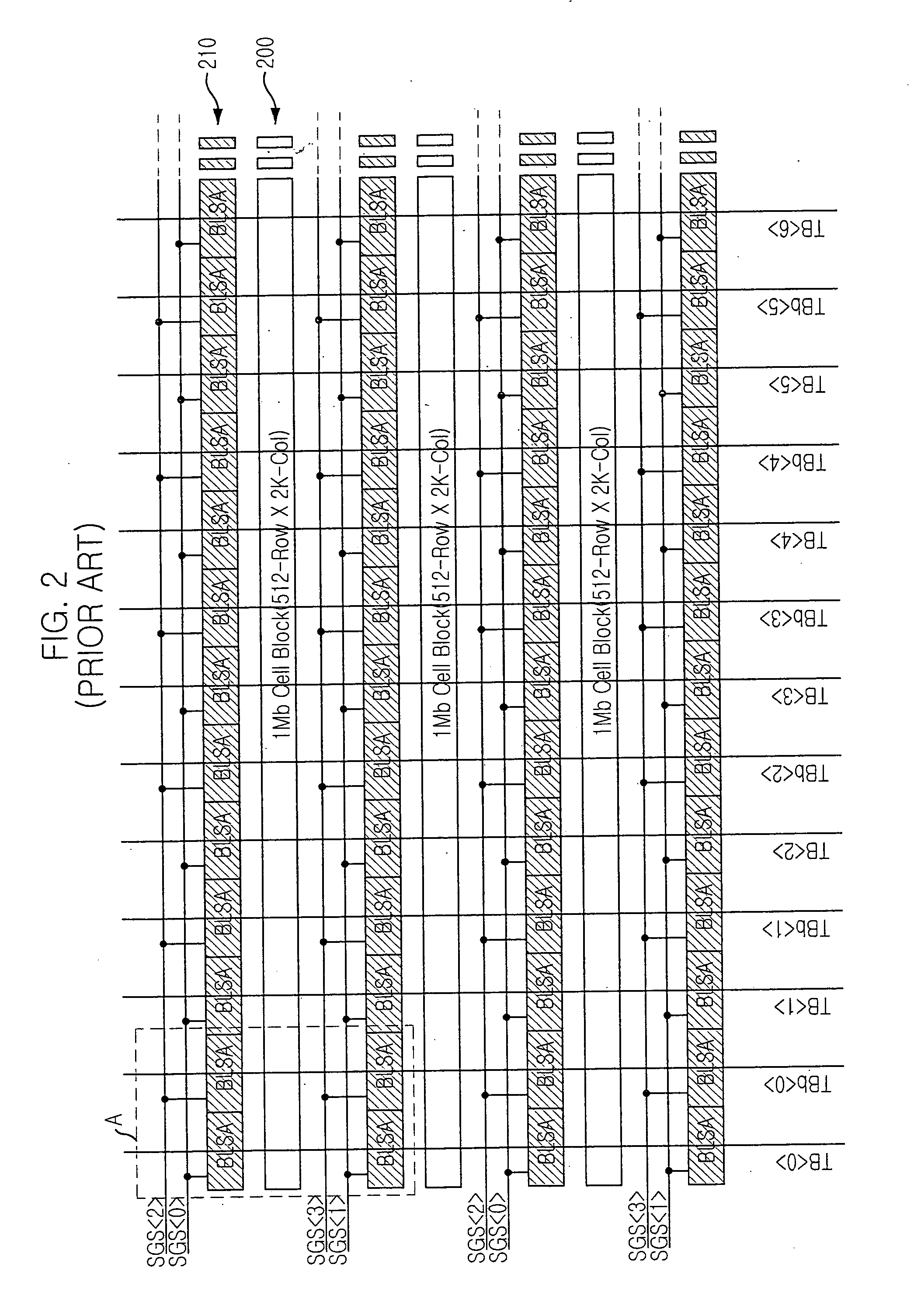

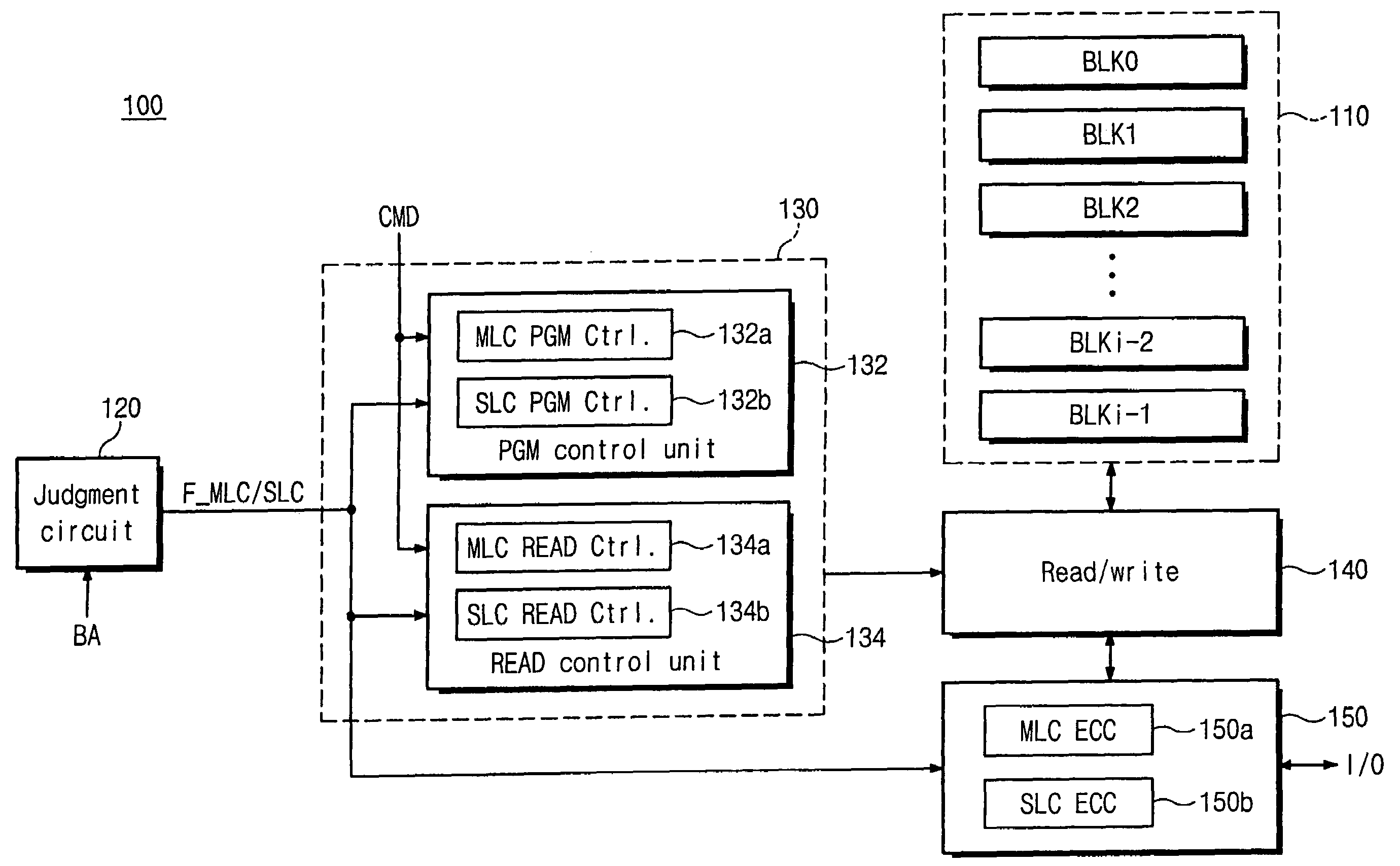

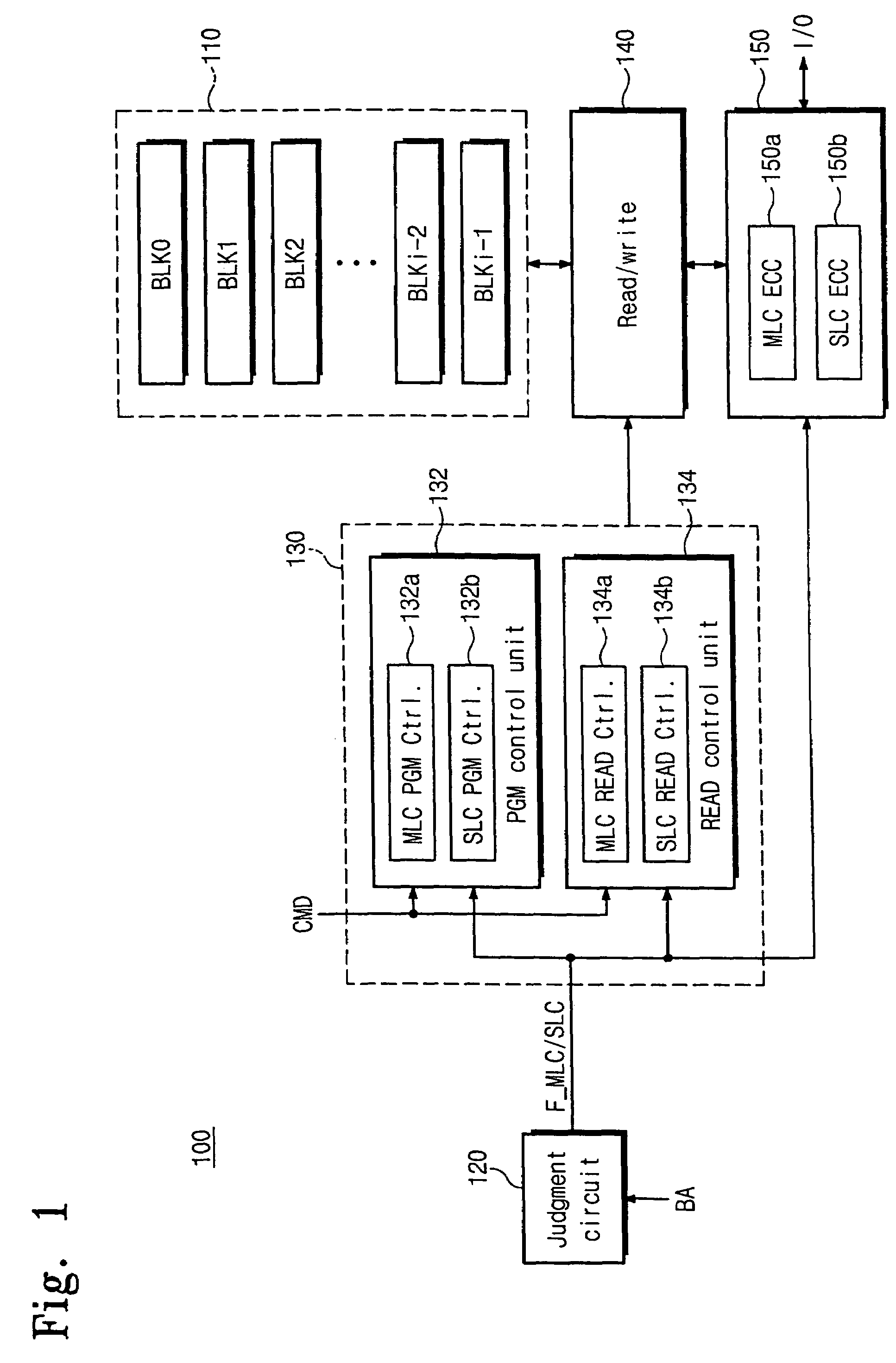

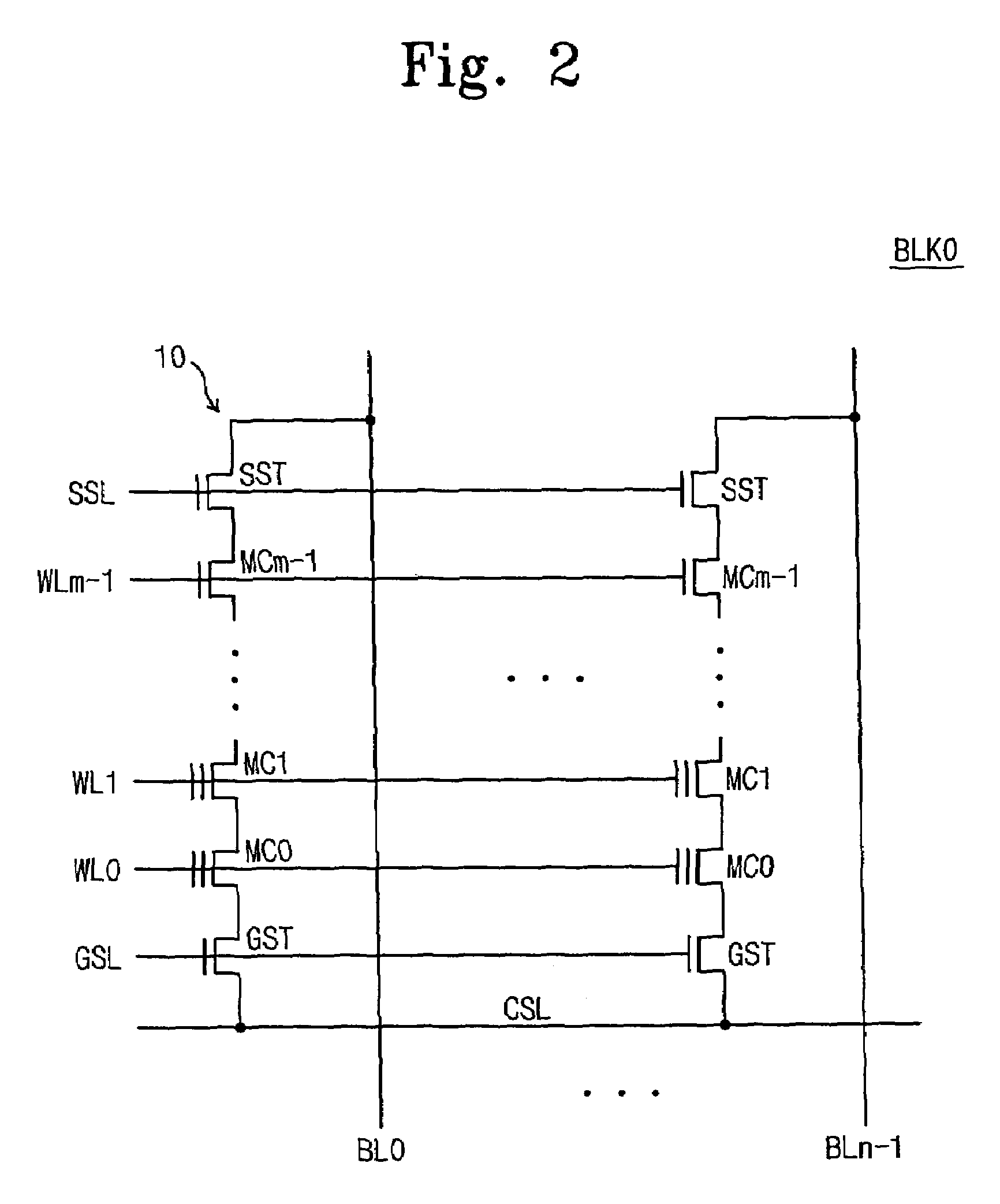

Flash memory device capable of storing multi-bit data and single-bit data

There is provided a flash memory device capable of manipulating multi-bit and single-bit data. The flash memory device can include a memory cell array with a plurality of memory blocks. The flash memory device can also include a judgment circuit for storing multi-bit / single-bit information indicating whether each of the memory blocks is a multi-bit memory block or not, determining whether or not a memory block of an inputted block address is a multi-bit memory block according to the stored multi-bit / single-bit information and outputting an appropriate flag signal. A read / write circuit for selectively performing multi-bit and single-bit read / program operations of the memory block corresponding to the block address is also included, as well as control logic for controlling the read / write circuit such that the read / write circuit can perform multi-bit or single-bit read / program operations based on the flag signal. An error checking and correction (ECC) circuit including a multi-bit ECC unit and a single-bit ECC unit for checking and correcting an error in a data of the read / write circuit can also be included.

Owner:SAMSUNG ELECTRONICS CO LTD

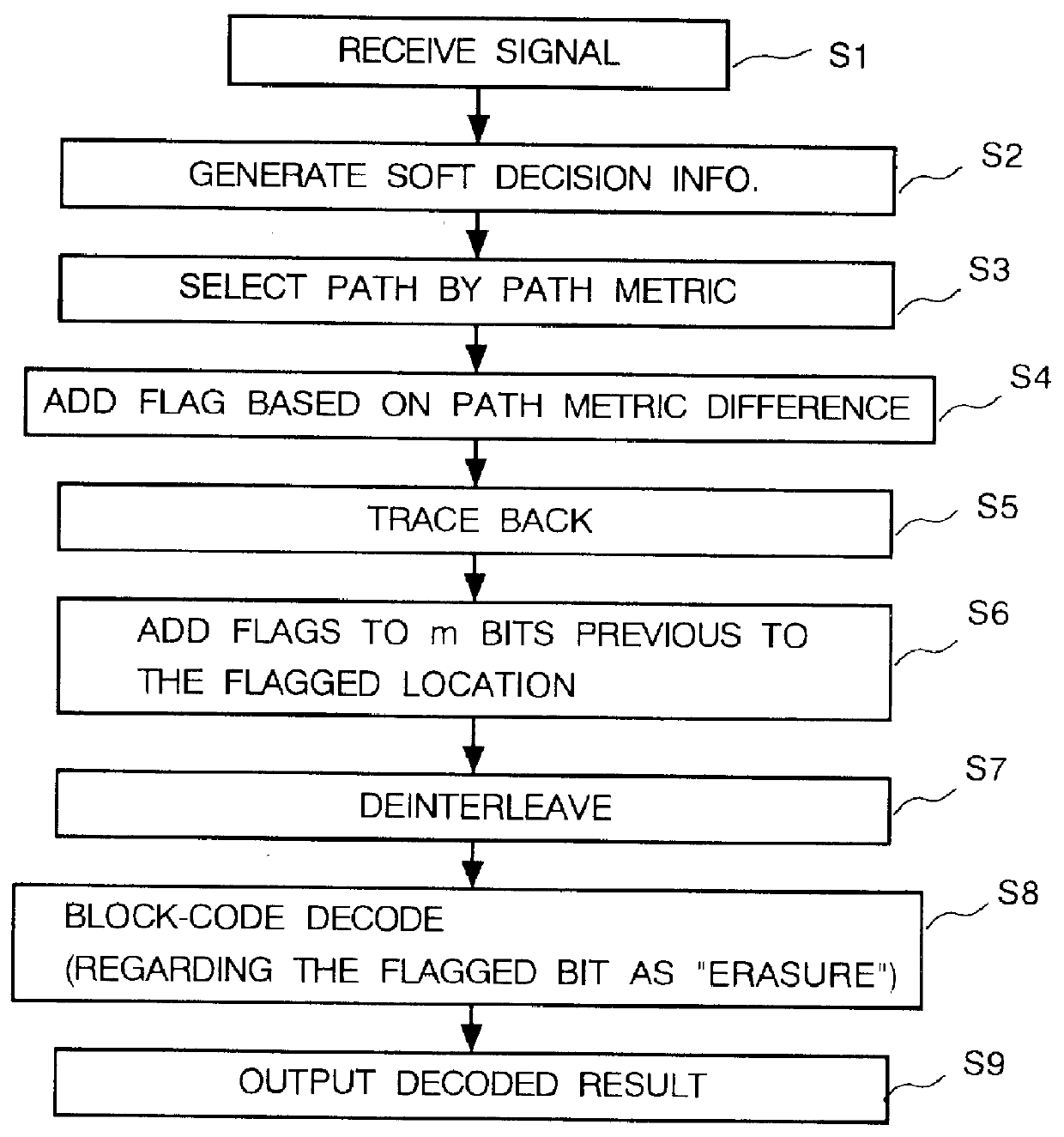

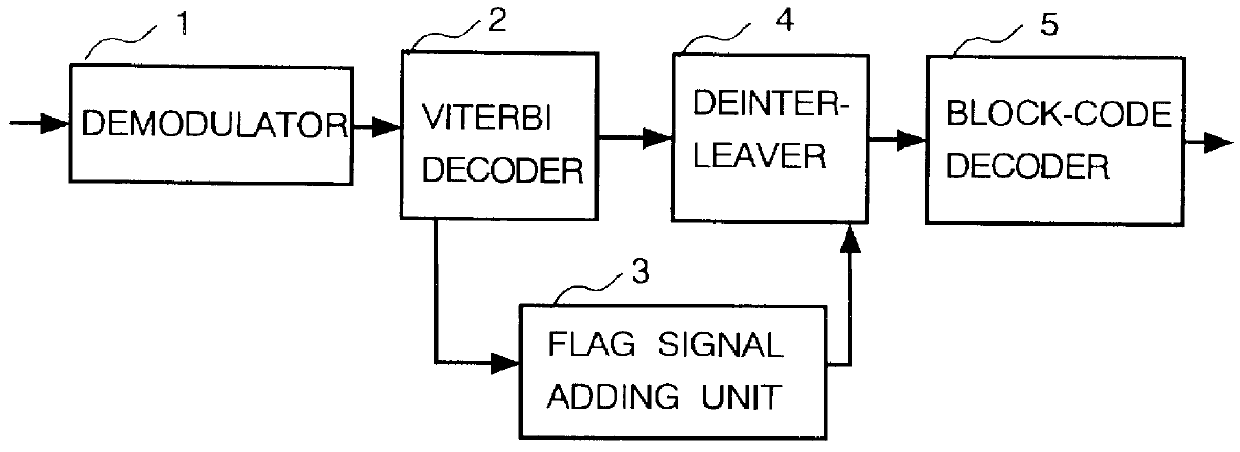

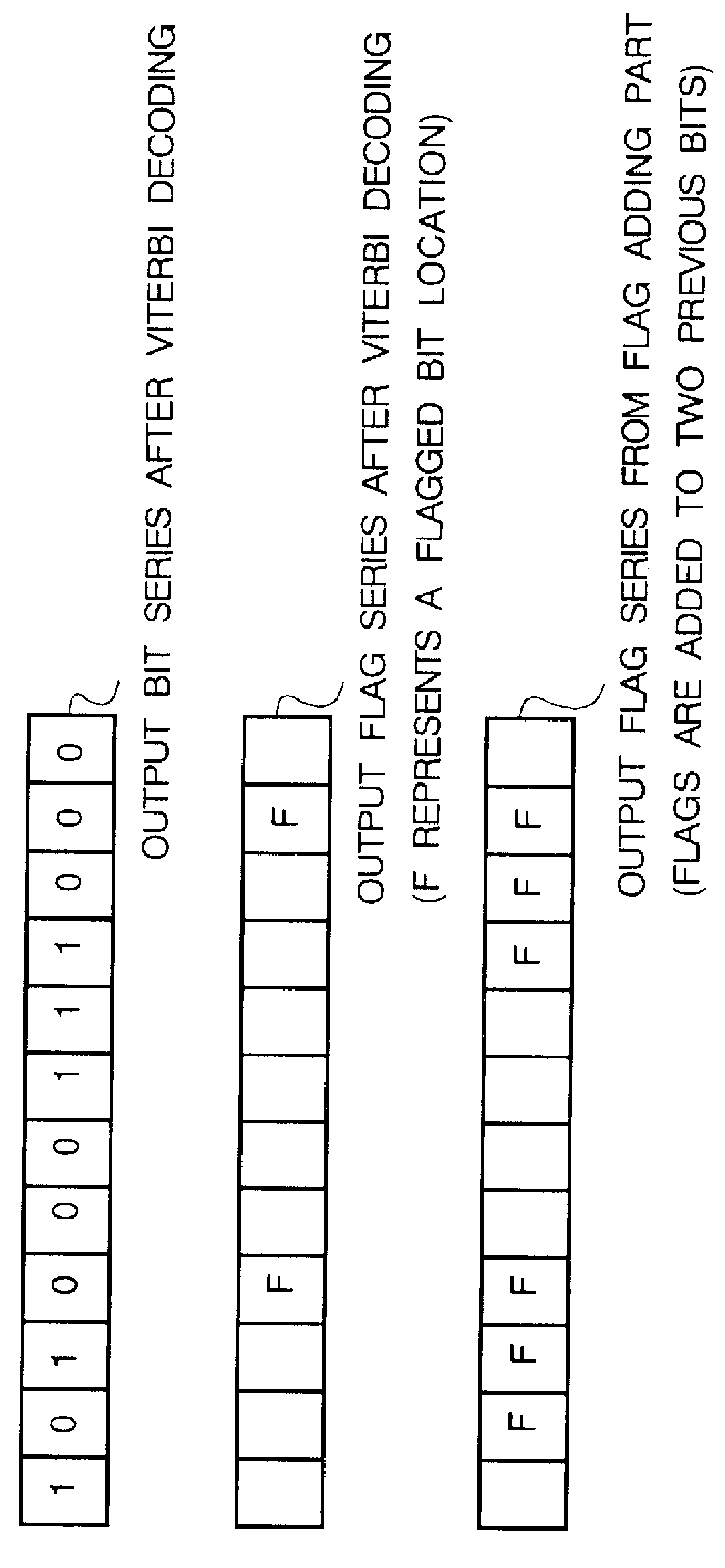

Error-correcting decoder continuously adding flag signals to locations preceding a first location at which a difference between path metrics is lower than the threshold

InactiveUS6108811AReduce probabilityIncrease capacityData representation error detection/correctionError preventionBlock codeError correcting

In an error-correcting decoder, in which an input digital signal including reliability information is decoded by using a Viterbi algorithm as a first decoding process and a final decoded result is obtained by block-code decoding as a second decoding process, a flag signal is added to a location where a value of reliability of path metric determined by the Viterbi algorithm is lower than a threshold, as an original flagged location. A flag signal adding unit continuously adds flag signals to locations, from the original flagged location to locations preceding the originally flagged location, after back tracing. The flagged locations are then regarded as erasure locations in the block-code decoding process.

Owner:MITSUBISHI ELECTRIC CORP

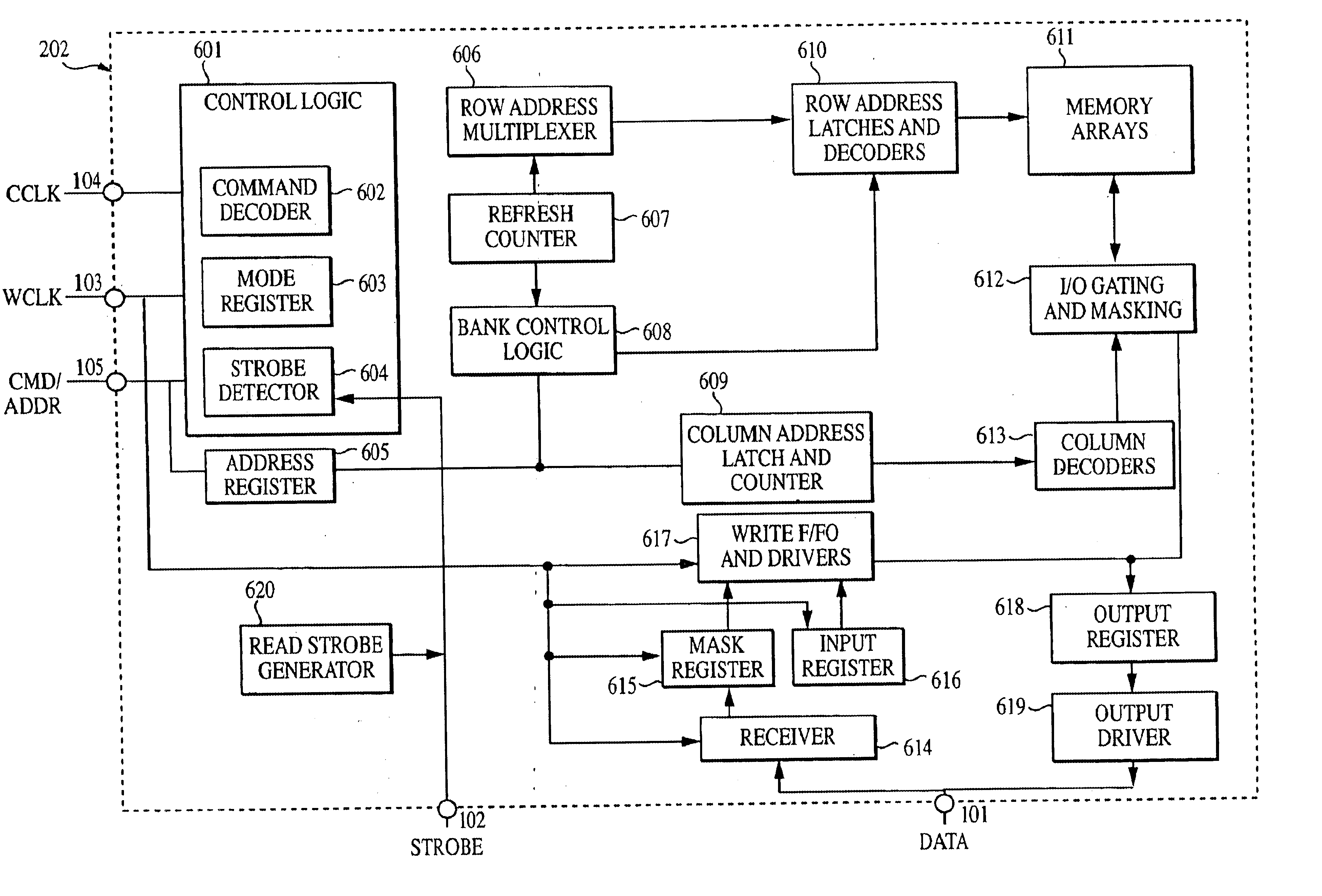

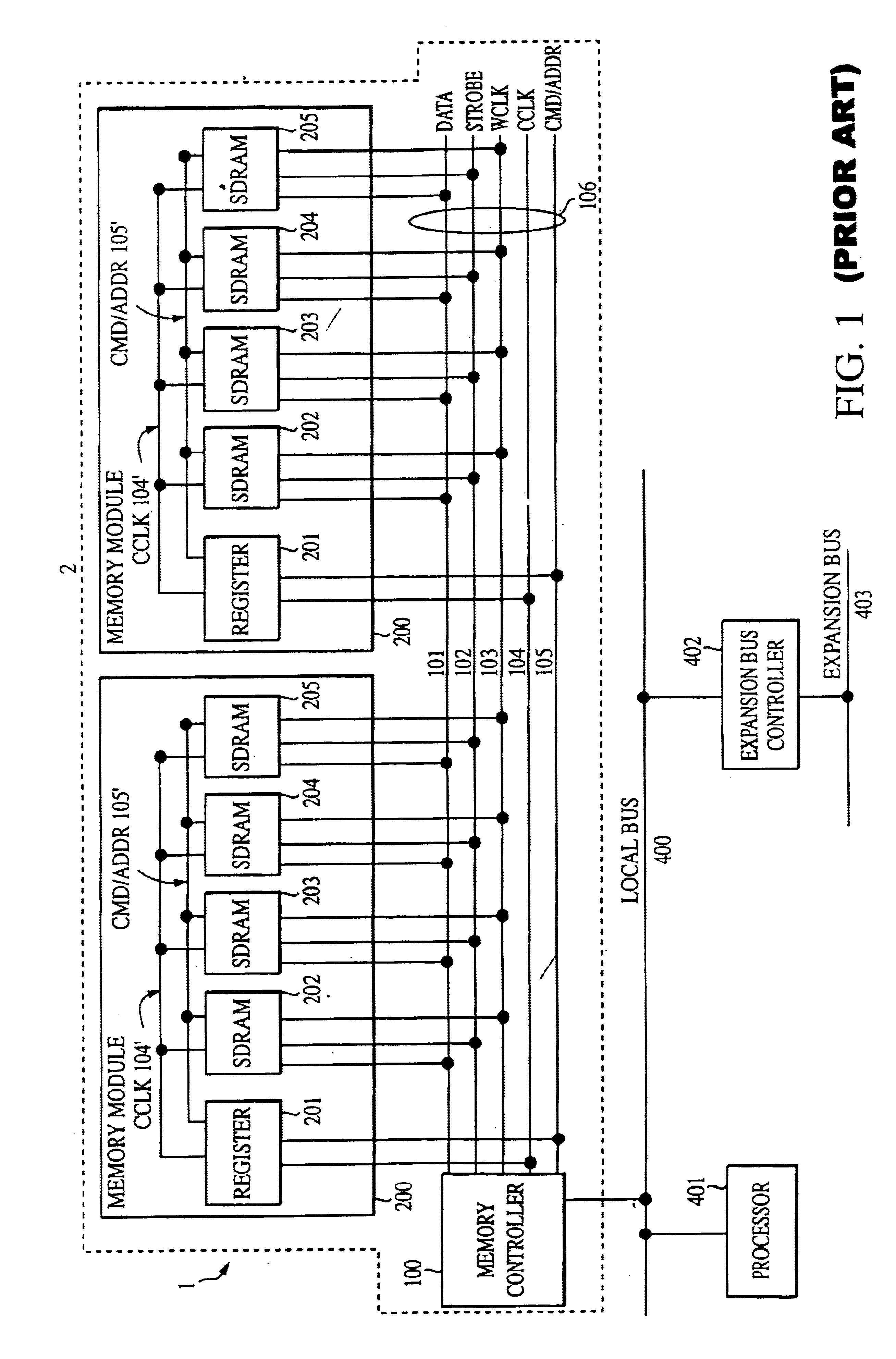

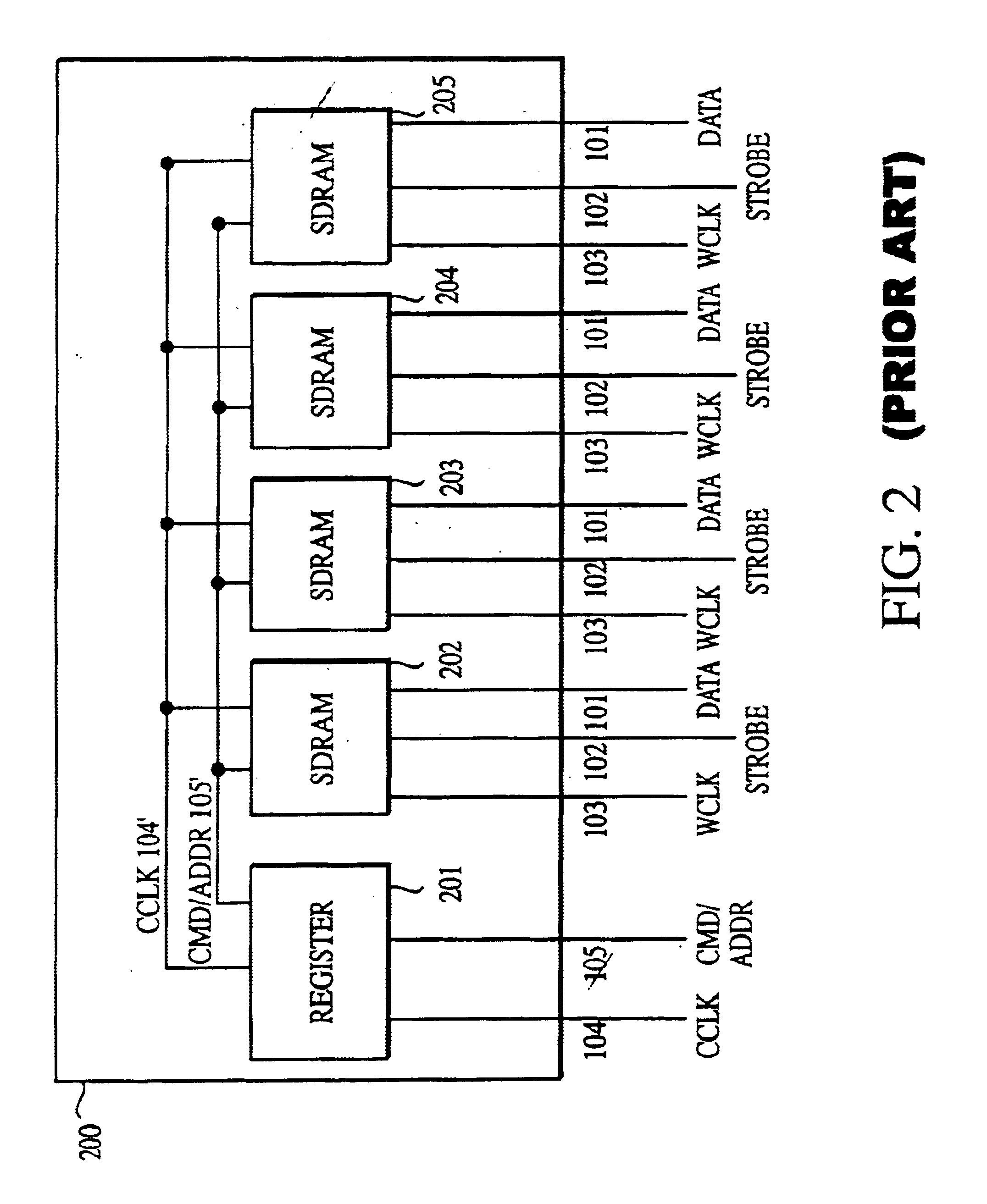

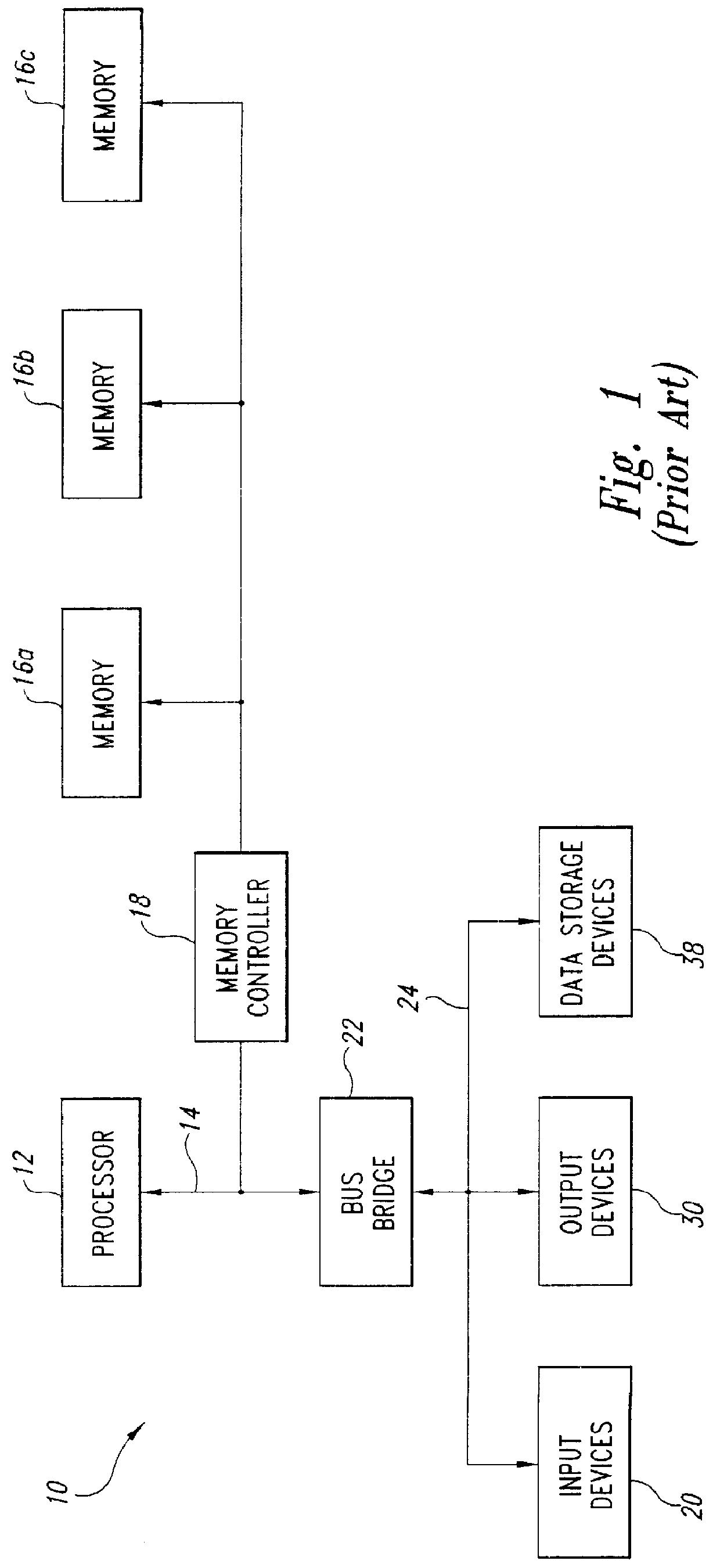

Synchronized write data on a high speed memory bus

InactiveUS6807613B1Memory adressing/allocation/relocationRead-only memoriesPhase shiftedHigh speed memory

Some synchronous semiconductor memory devices accept a command clock which is buffered and a write clock which is unbuffered. Write command are synchronized to the command clock while the associated write data is synchronized to the write clock. Due to the use of the buffer, an arbitrary phase shift can exist between the command and write clocks. The presence of the phase shift between the two clocks makes it difficult to determine when a memory device should accept write data associated a write command. A synchronous memory device in accordance with the present invention utilizes the unbuffered strobe signal which is normally tristated during writes as a flag to mark the start of write data. A preamble signal may be asserted on the strobe signal line prior to asserting the flag signal in order to simplify flag detection.

Owner:ROUND ROCK RES LLC

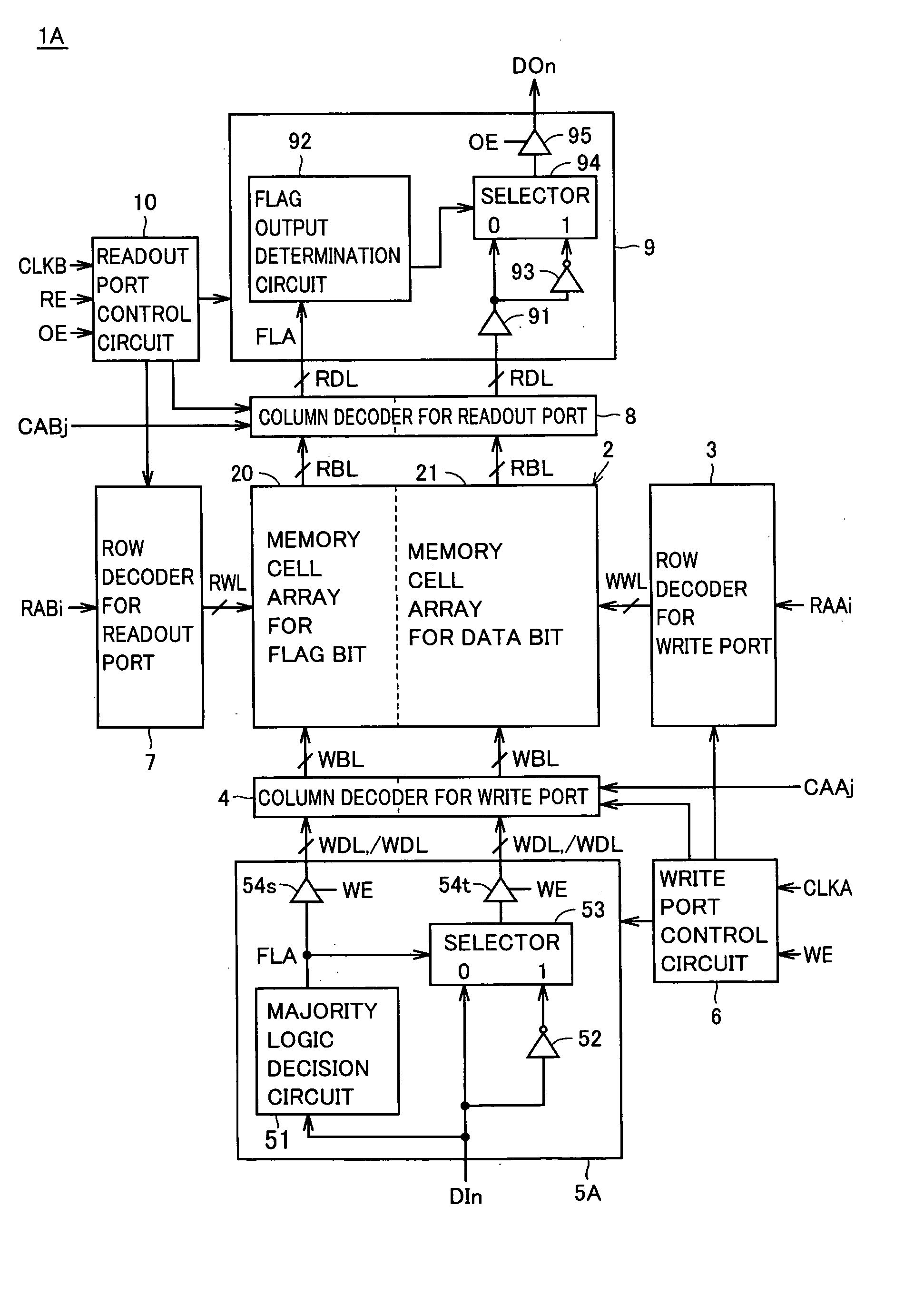

Semiconductor memory device capable of reducing power consumption during reading and standby

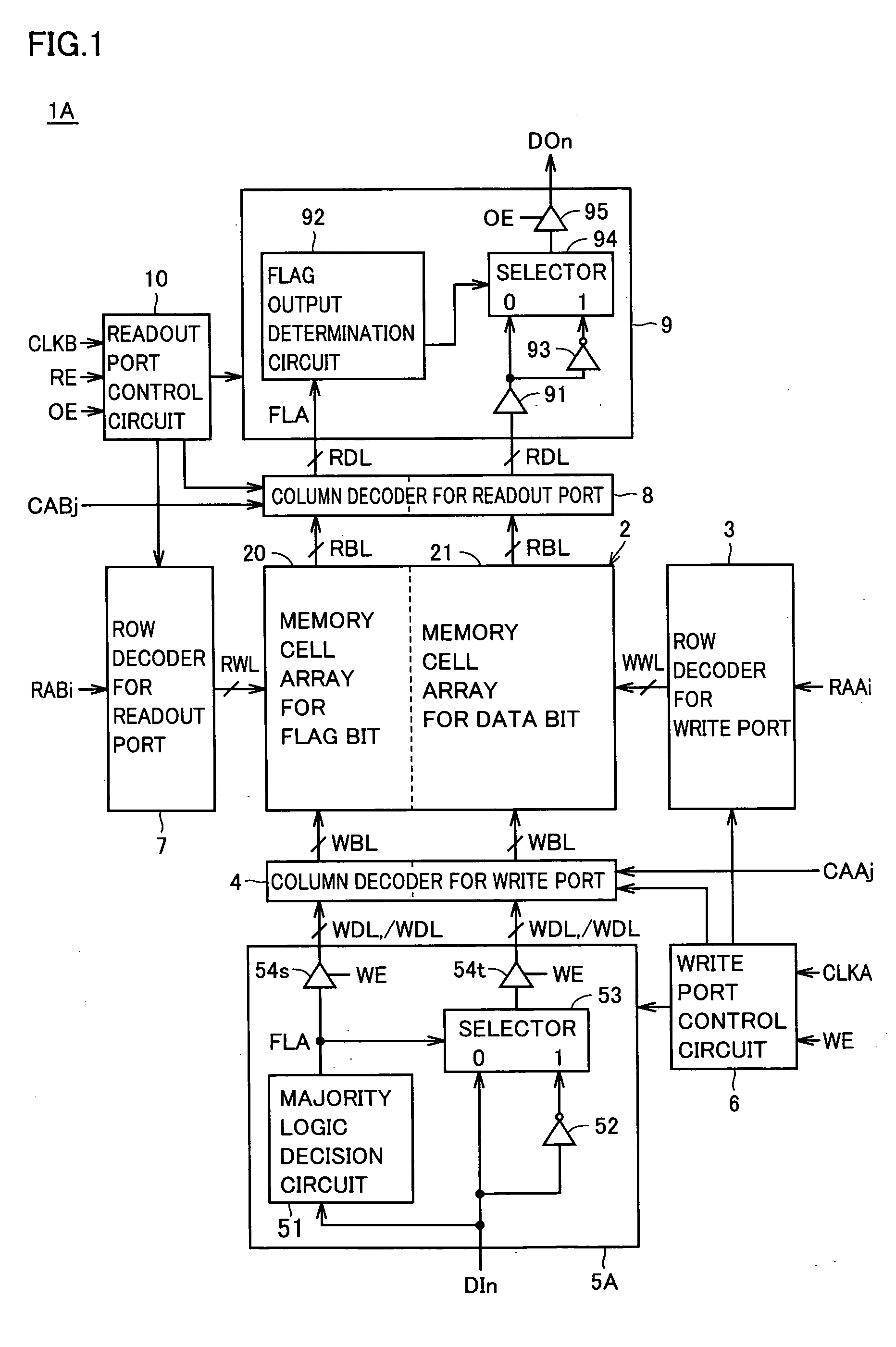

The input data at address 0 is “00000000”, including many “0”s. The data at address 0 is inverted to “11111111”. At the same time, flag information “1” indicative of inversion is written into the flag bit of the same address 0. The input data at address 3 also includes many “0”s. Therefore, the data of address 3 is inverted, and flag information “1” is written. The input data at addresses 1 and 2 includes more “1”s than “0”s. Therefore, the data is not inverted, and flag information “0” is written. With regards to the written data, only the data at an address whose flag signal is “1” is inverted again in a reading mode to be eventually read out as a data output signal.

Owner:RENESAS TECH CORP

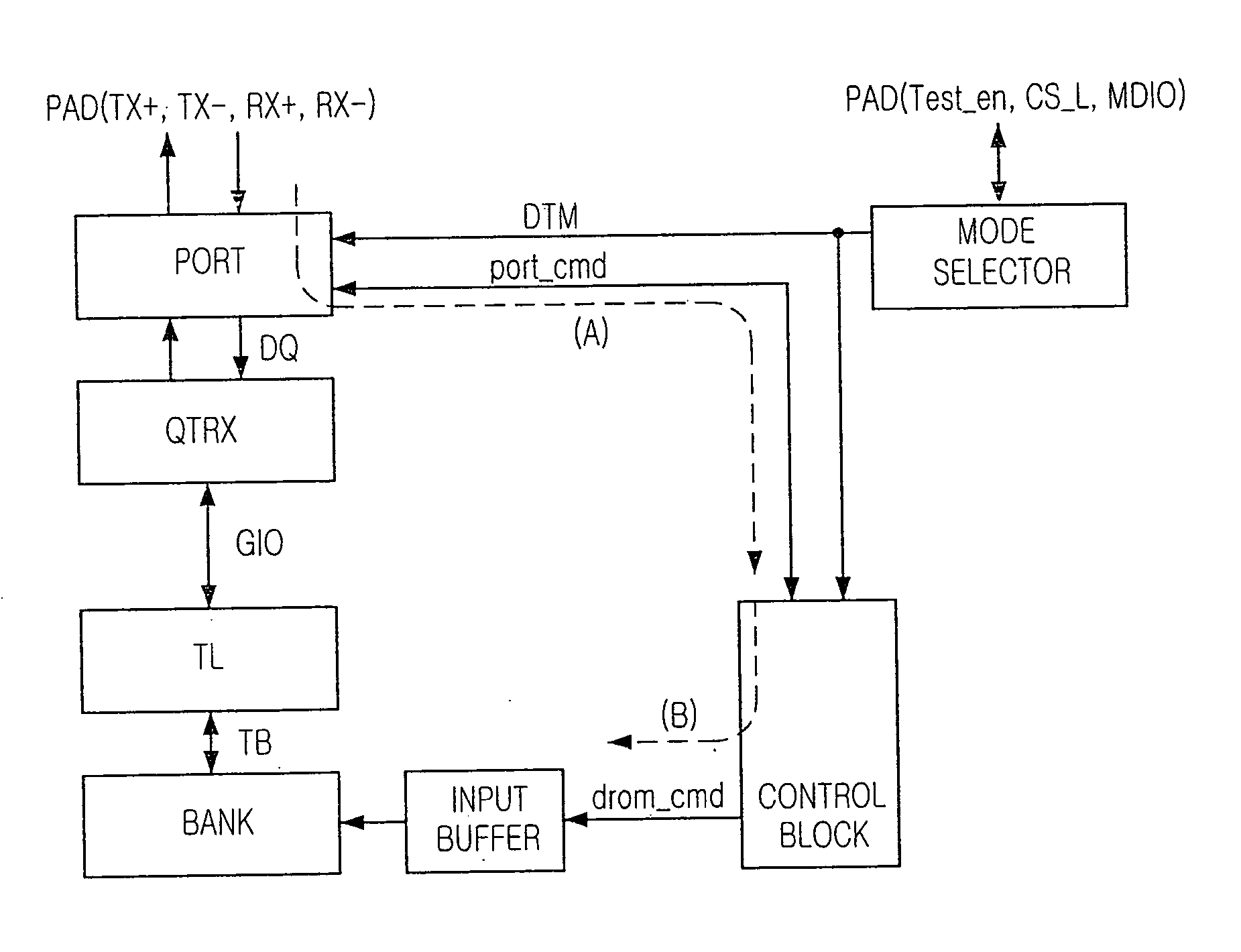

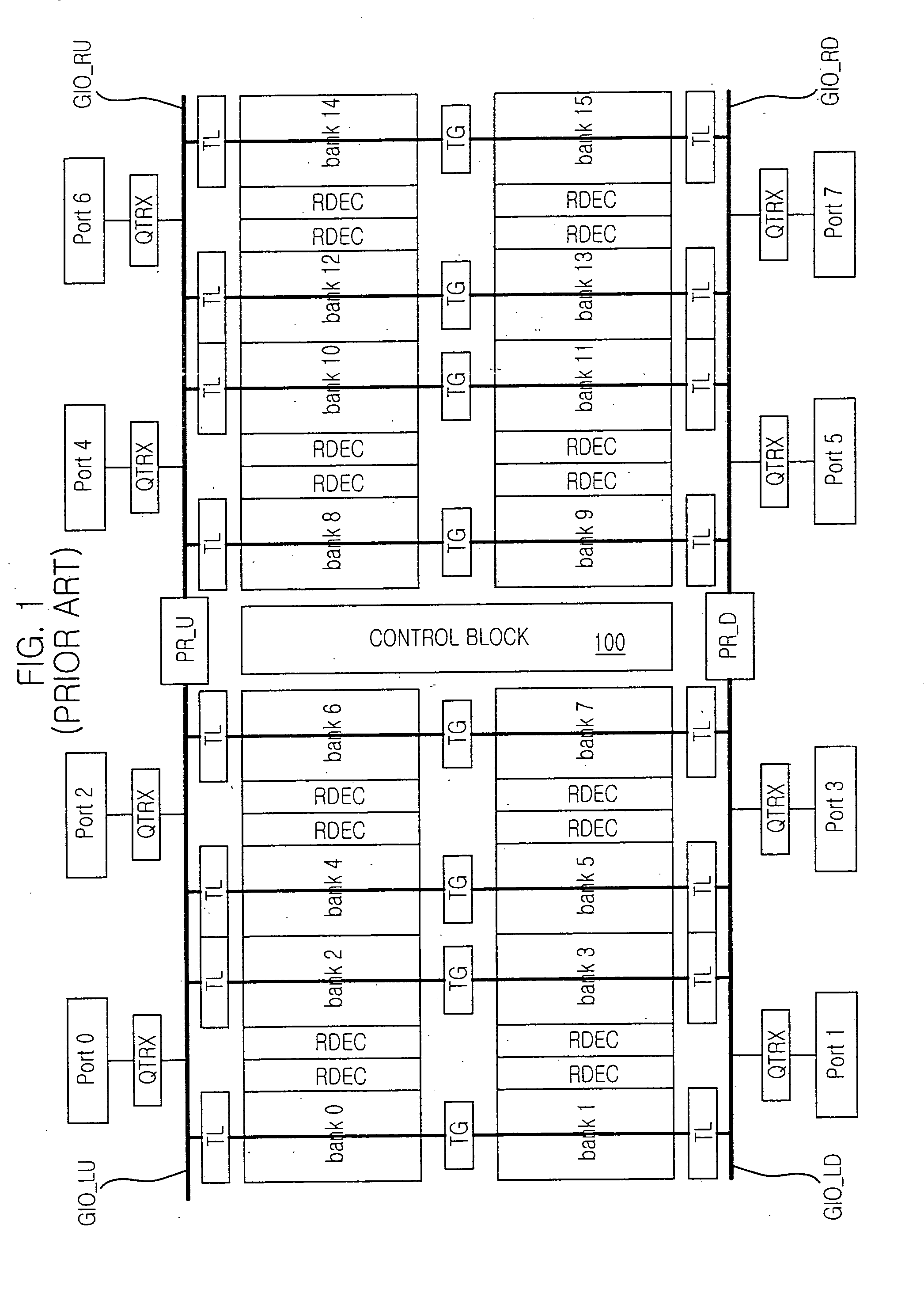

Multi-port memory device having serial I/O interface

There is provided a multi-port memory device having a serial I / O interface, which is capable of providing an operation test without any collision with an internal command / address generation path through a limited external pin. The multi-port memory device includes a plurality of ports supporting a serial I / O interface, and the plurality of ports includes a transmission pad and a reception pad. The multi-port memory device includes: a memory core; a control block for generating an internal command signal, an internal address and a control signal, which correspond to the command and are necessary for an operation of the memory core, using commands and addresses inputted to the plurality of ports in a packet form; and a mode selection block for combining signals applied to a plurality of mode selection pads and generating a test mode flag signal, in which I / O data assigned to the transmission pad and the reception pad in a test mode in response to the test mode flag signal are exchanged with the memory core through the ports. Also, the command, the address and the control signal assigned to the transmission pad and the reception pad in the test mode are bypassed at the control block and provided to the memory core.

Owner:SILICON IMAGE INC

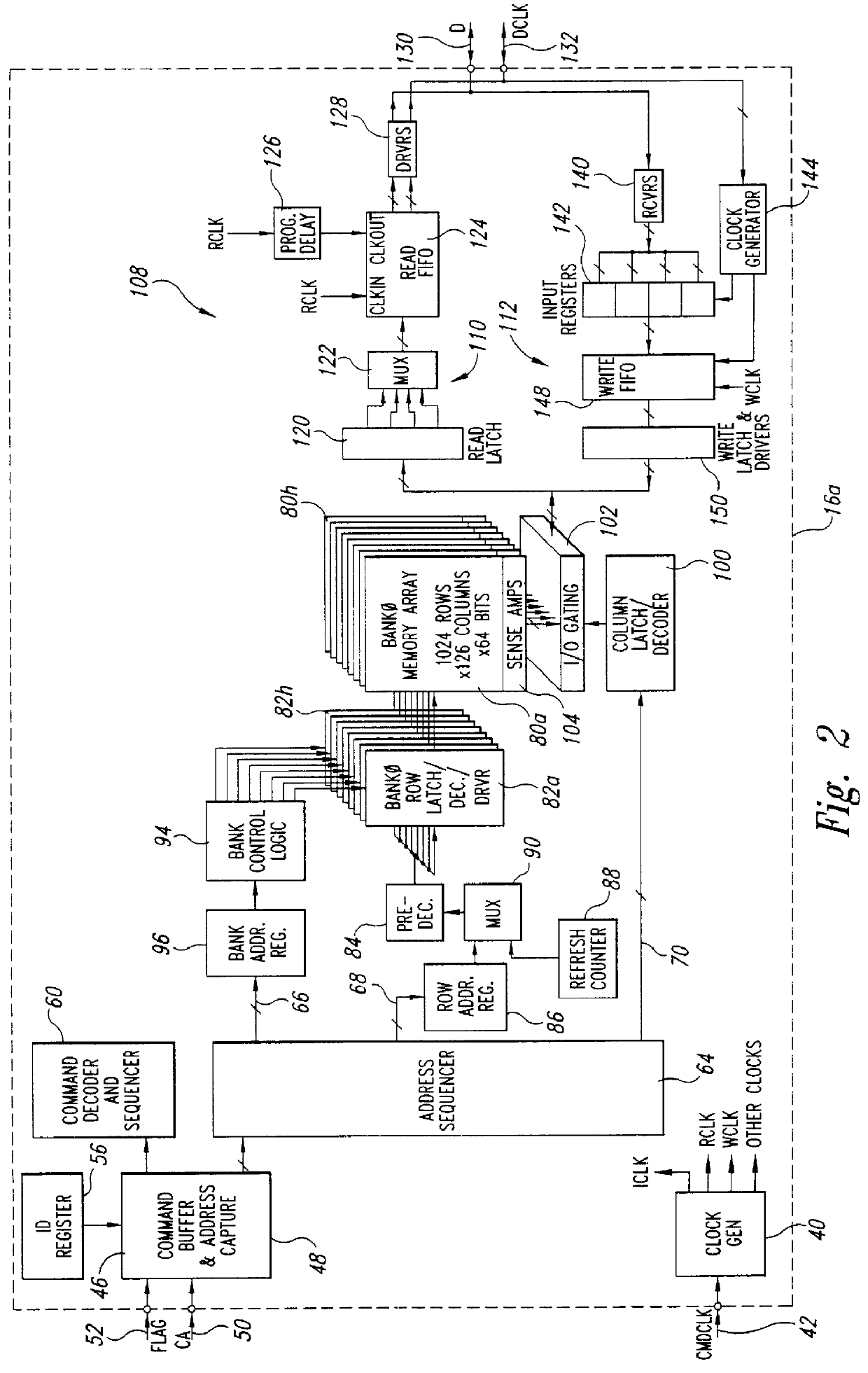

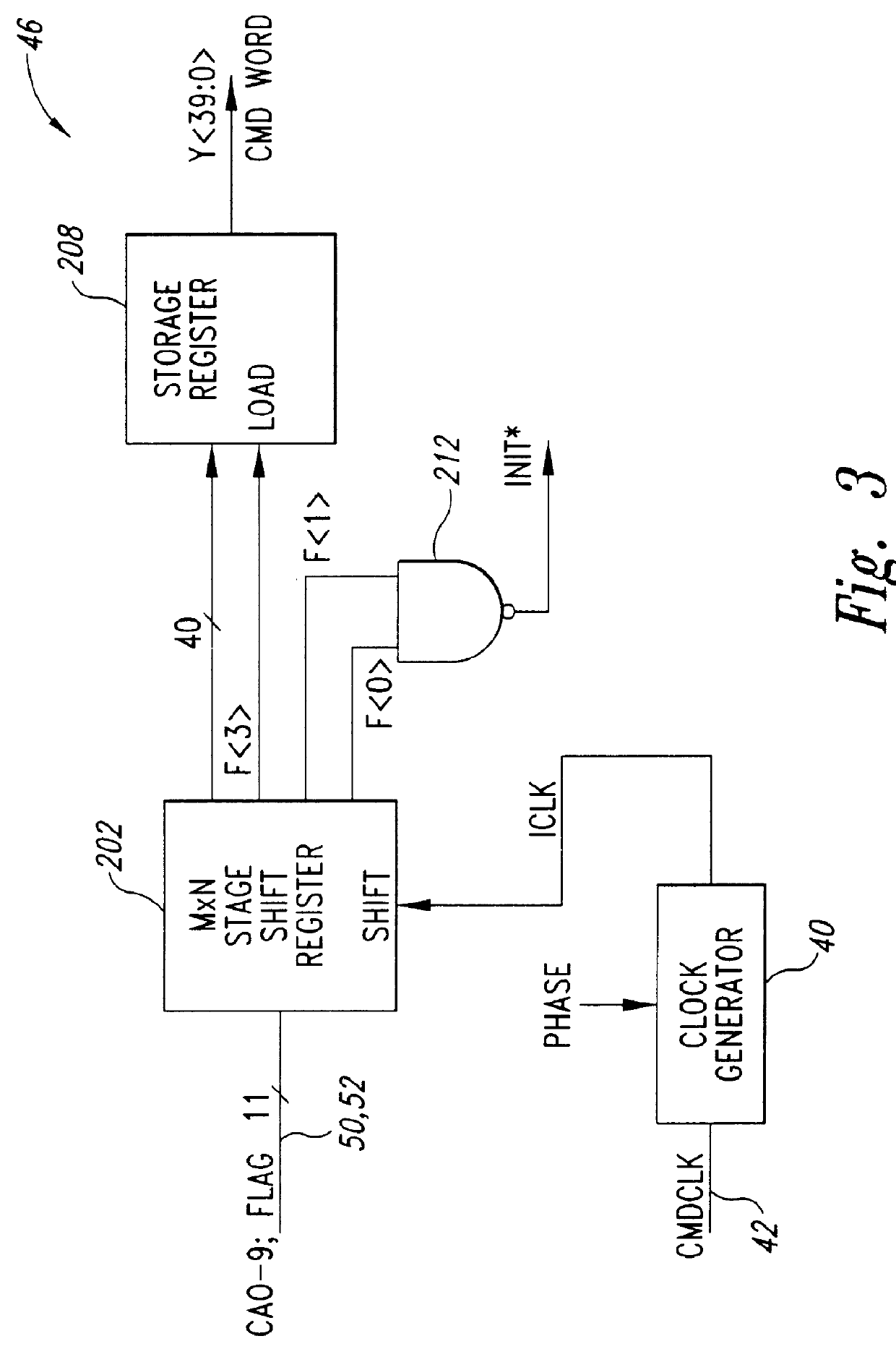

Method and apparatus for detecting an initialization signal and a command packet error in packetized dynamic random access memories

InactiveUS6167495AIncrease chanceMemory loss protectionError detection/correctionShift registerNAND gate

A system for detecting an initialization flag signal and distinguishing it from a normal flag signal having half the duration of the initialization flag signal. The initialization flag detection system may be included in the command buffer of a packetized DRAM that is used in a computer system. In one embodiment, the initialization flag detection system includes a pair of shift registers receiving the flag signal at their respective data inputs. One of the shift registers is clocked by a signal corresponding to an externally applied to command clock signal, while the other shift register is clocked by a quadrature clock signal. Together, the shift registers store a number of samples taken over a duration that is longer than the duration of the normal flag signal. The outputs of the shift registers are applied to a logic circuit, such as a NAND gate, that generates an initialization signal when all of the samples stored in the shift registers correspond to the logic levels of the flag signal. In another embodiment, the initialization flag detection system includes a plurality of latches receiving the flag signals at their data inputs. The latches are clocked by respective strobe signals corresponding to the command clock signal, but having phases that differ from each other. The outputs of the latches are applied to a logic circuit, such as a NAND) gate. Finally, in another embodiment of the invention, the bits of the command packet are sampled along with the flag signal and compared to the samples of the flag signal to detect when a command packet having a predetermined pattern does not correspond to a flag signal having a predetermined pattern.

Owner:MICRON TECH INC

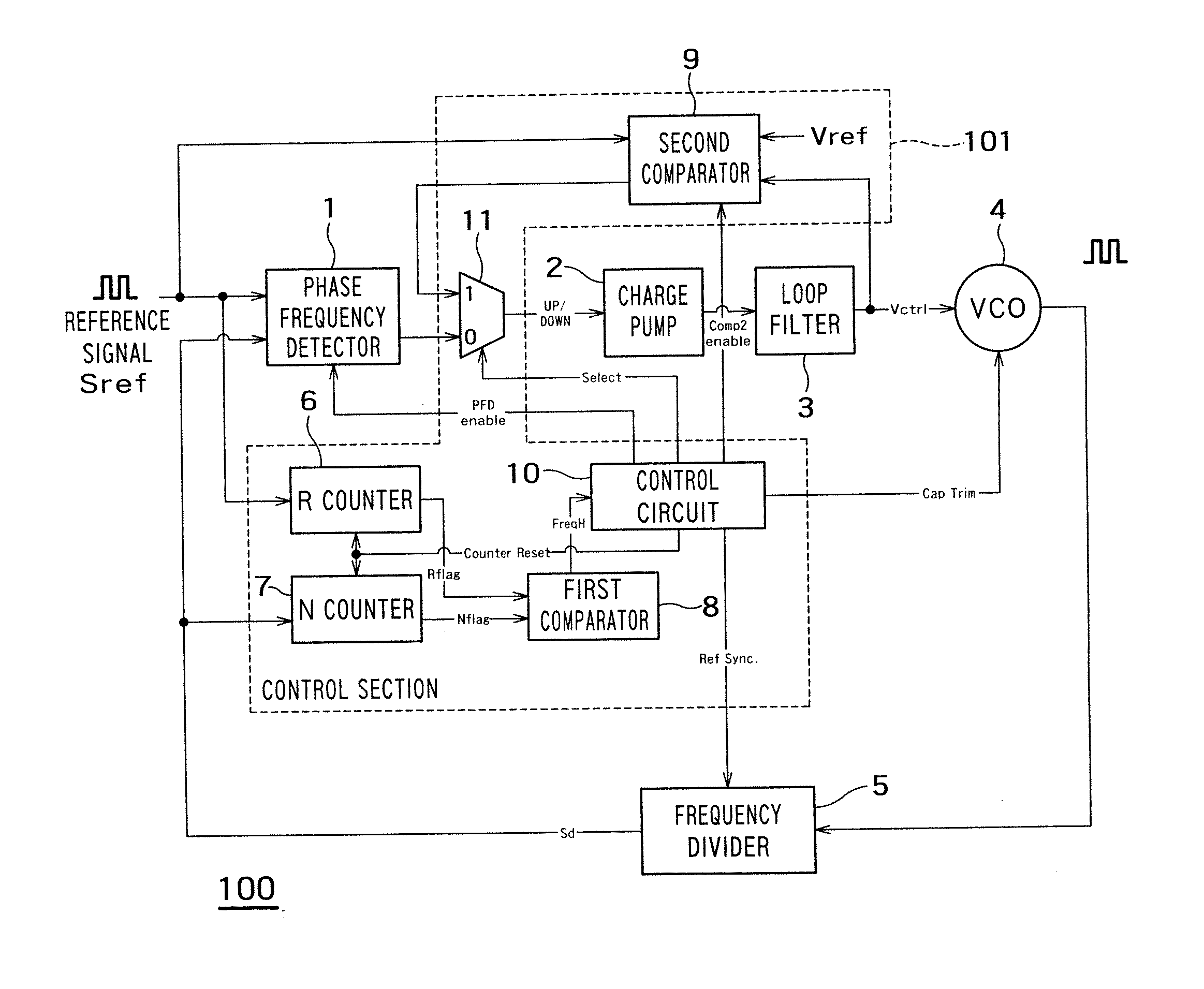

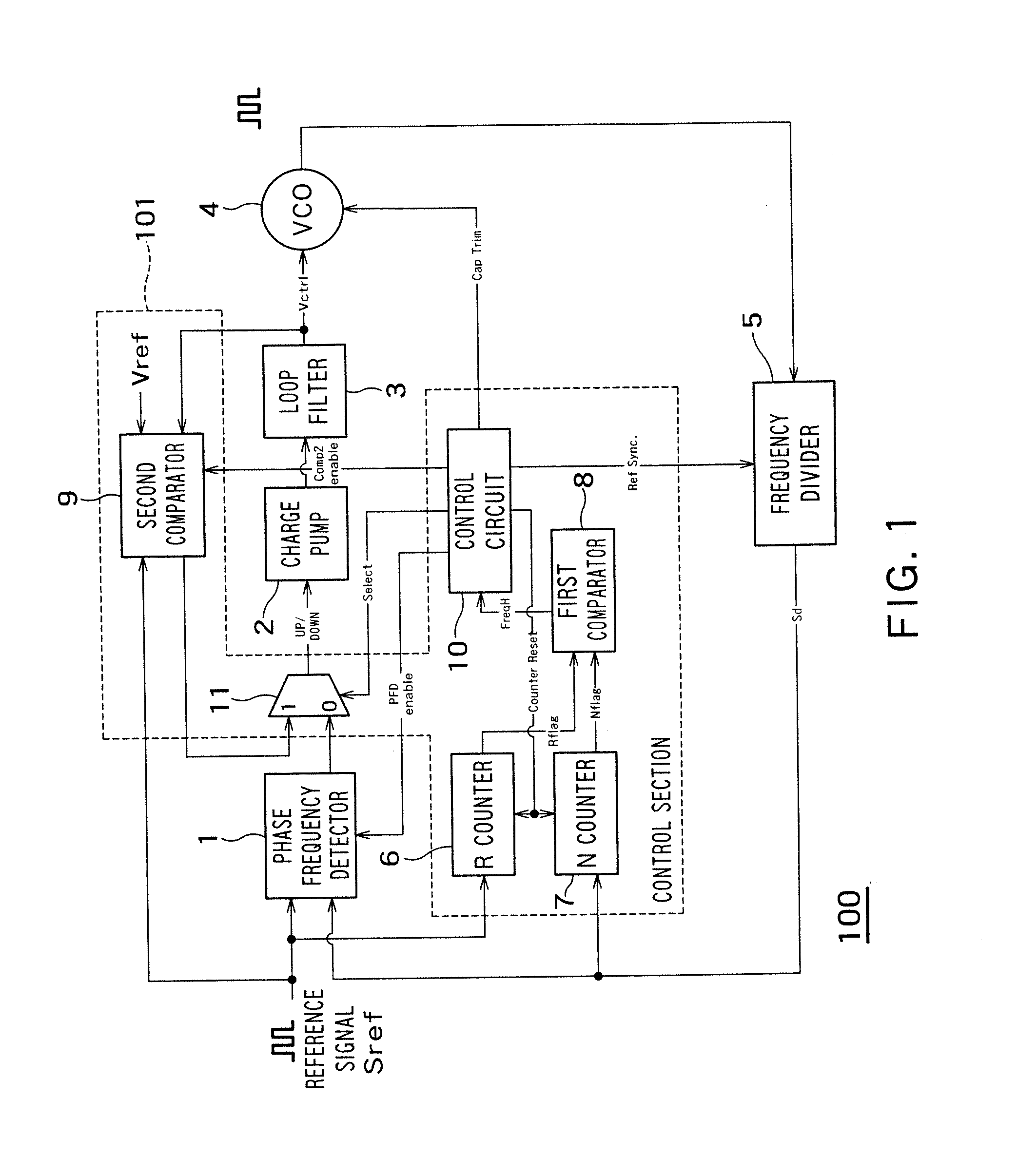

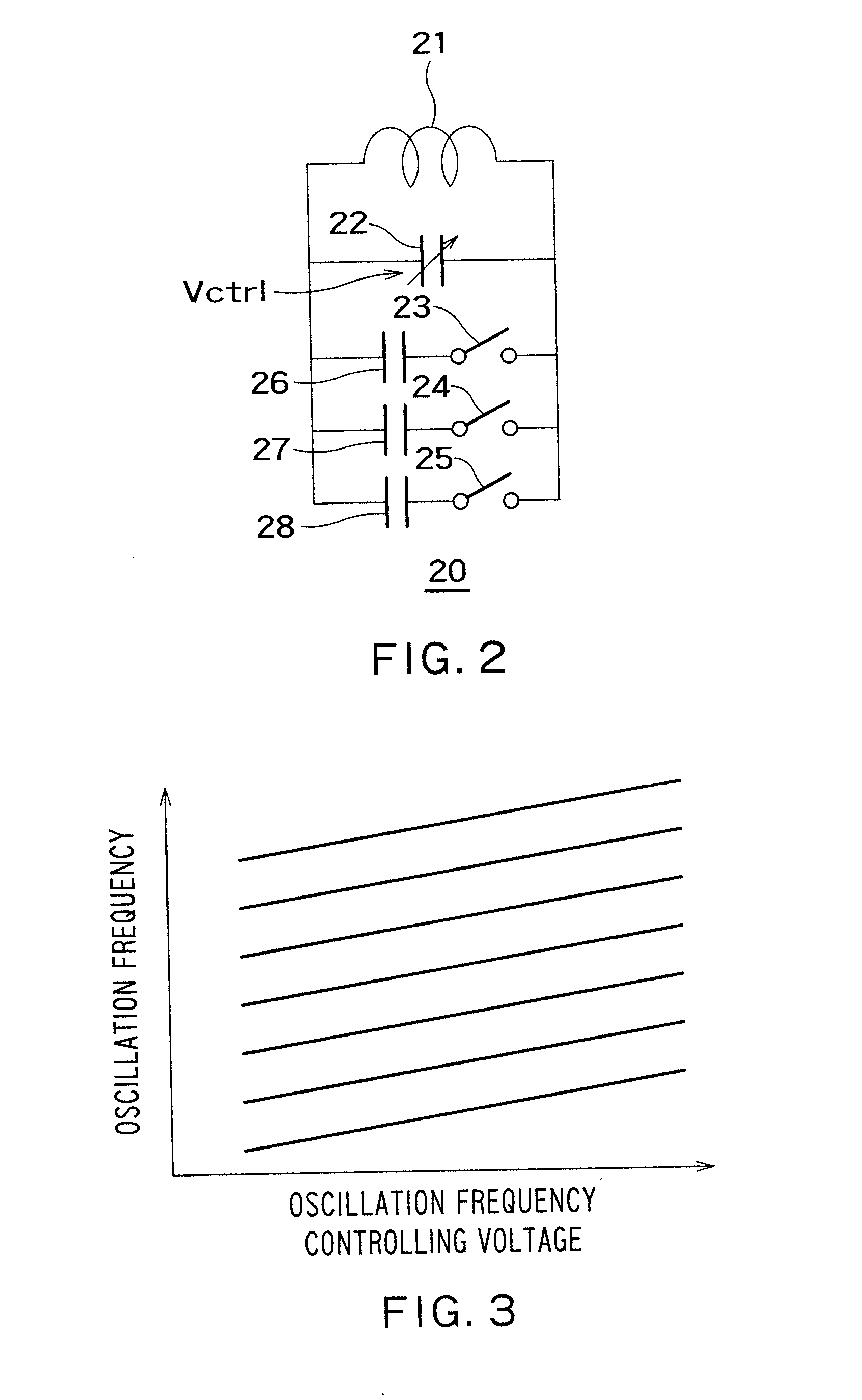

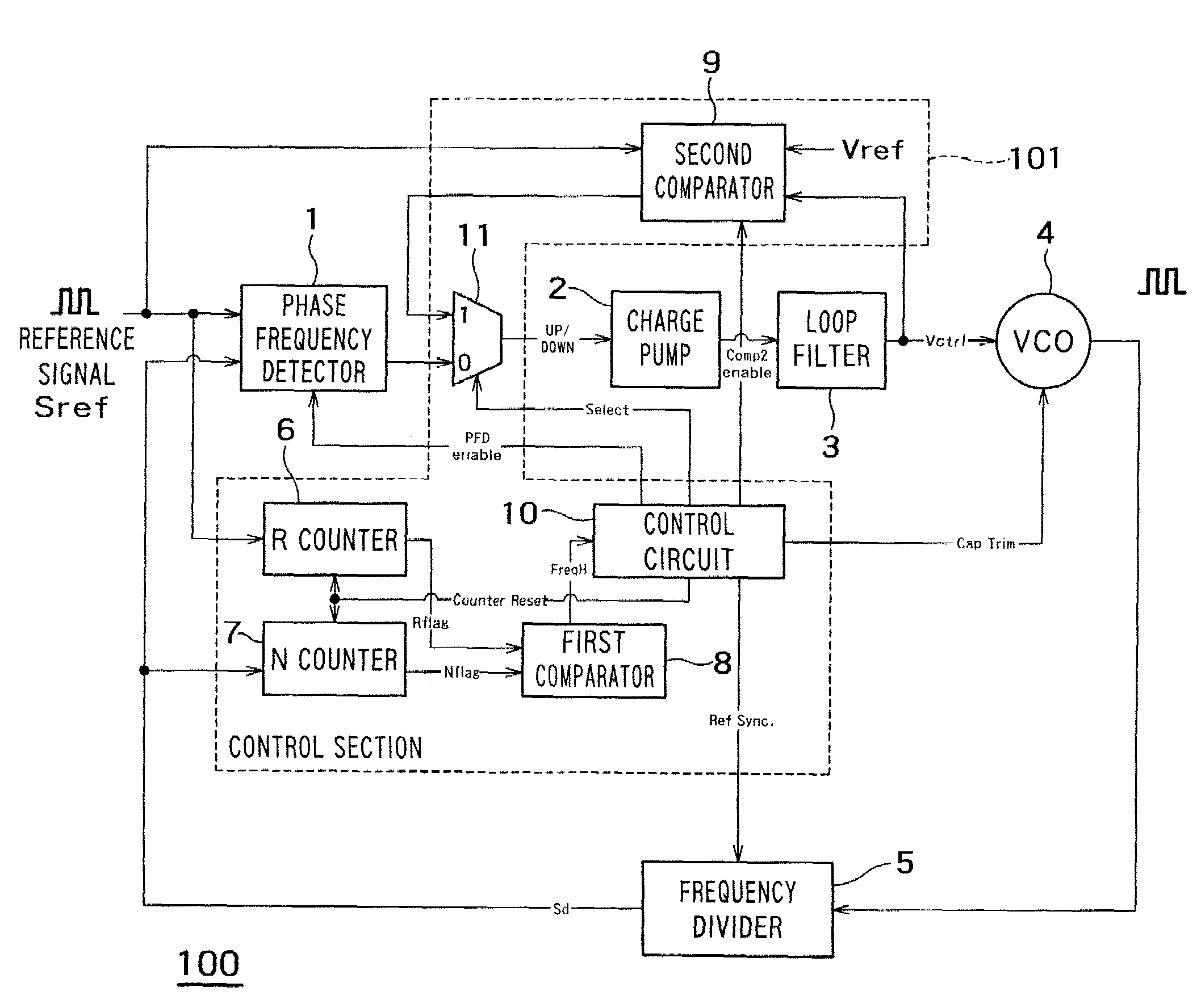

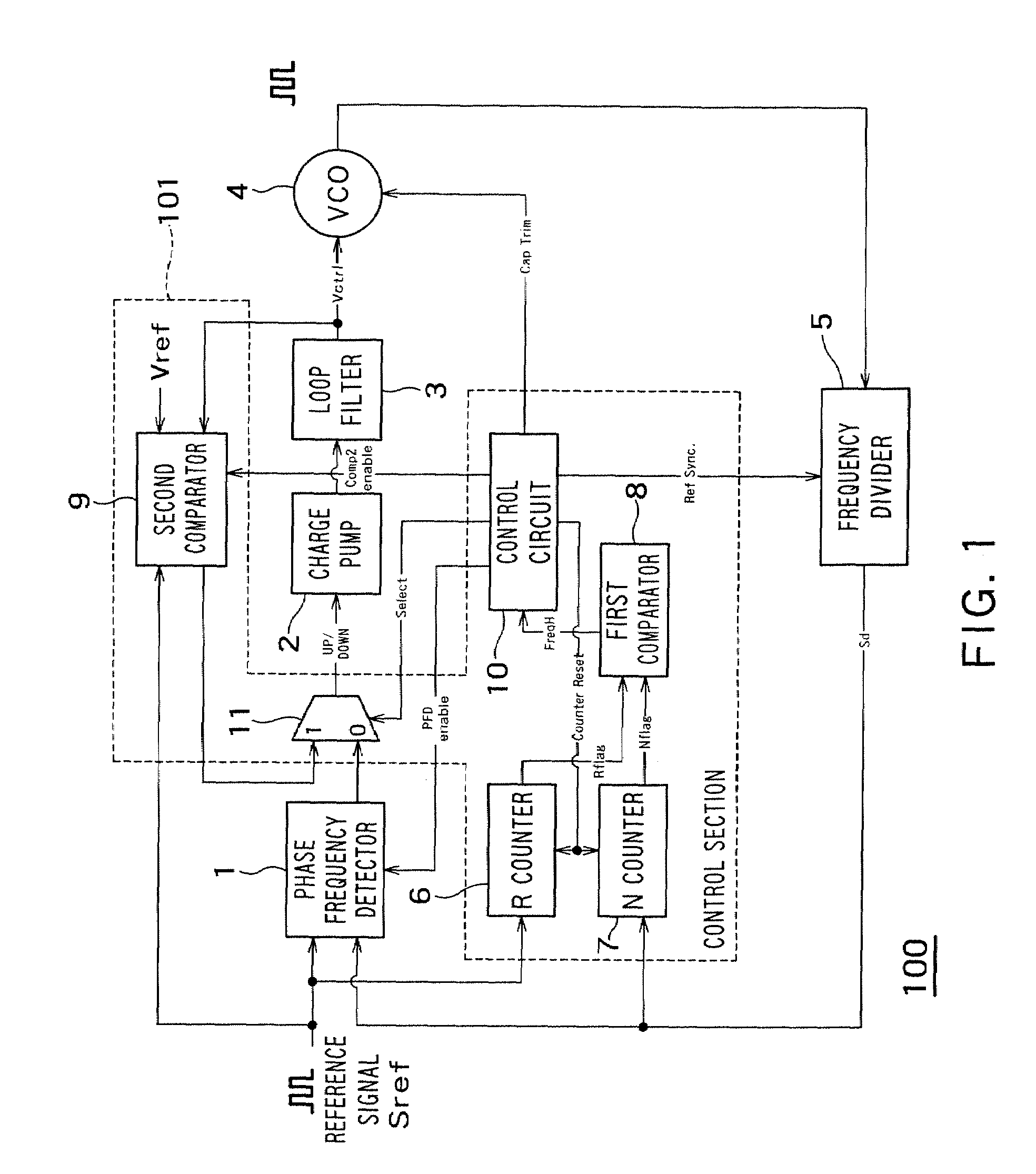

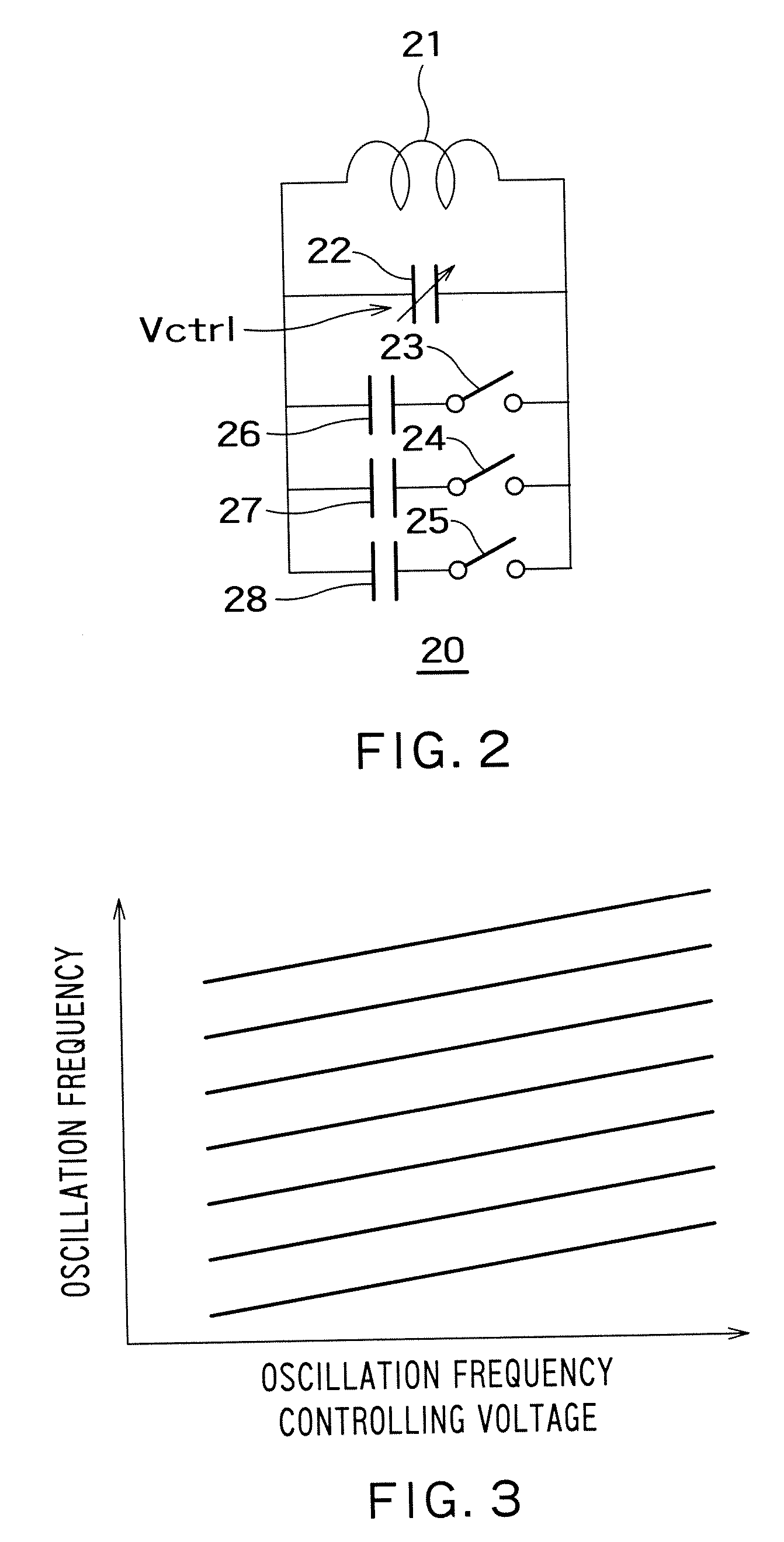

Controller for oscillator

An oscillator controller, has a phase frequency detector that compares a reference signal and a frequency-divided signal and outputs a phase difference signal; a charge pump that outputs a phase error signal according to the phase difference signal output from said phase frequency detector; a loop filter that filters the phase error signal output from said charge pump and outputs an oscillation frequency controlling voltage; a voltage-controlled oscillator that has an LC resonator having a coil, a variable capacitor connected to the opposite ends of the coil at the opposite ends thereof, and a capacitor connected in series with a switch between the opposite ends of said variable capacitor, the oscillation frequency of the voltage-controlled oscillator being controlled through adjustment of the capacitance value of said variable capacitor by said oscillation frequency controlling voltage; a frequency divider that divides the frequency of the output of said voltage-controlled oscillator and outputs said frequency-divided signal; a first counter that counts the number of waves of said reference signal to a desired number and outputs a first flag signal; a second counter that counts the number of waves of said frequency-divided signal to said desired number and outputs a second flag signal; a first comparator that compares said first flag signal and said second flag signal and outputs a frequency comparison signal; and a control circuit that controls said voltage-controlled oscillator, said first counter, said second counter and said frequency divider by outputting signals thereto.

Owner:KK TOSHIBA

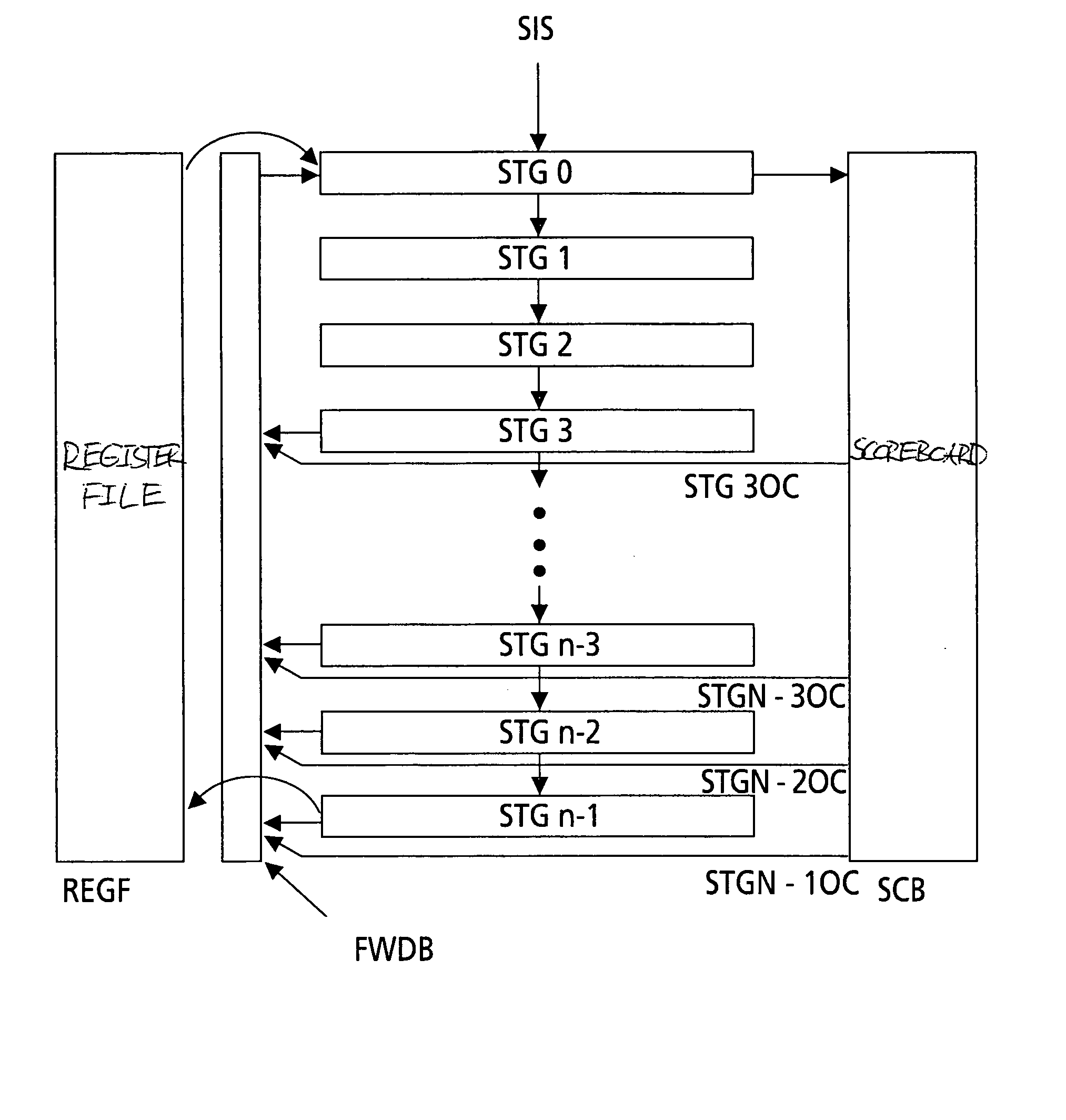

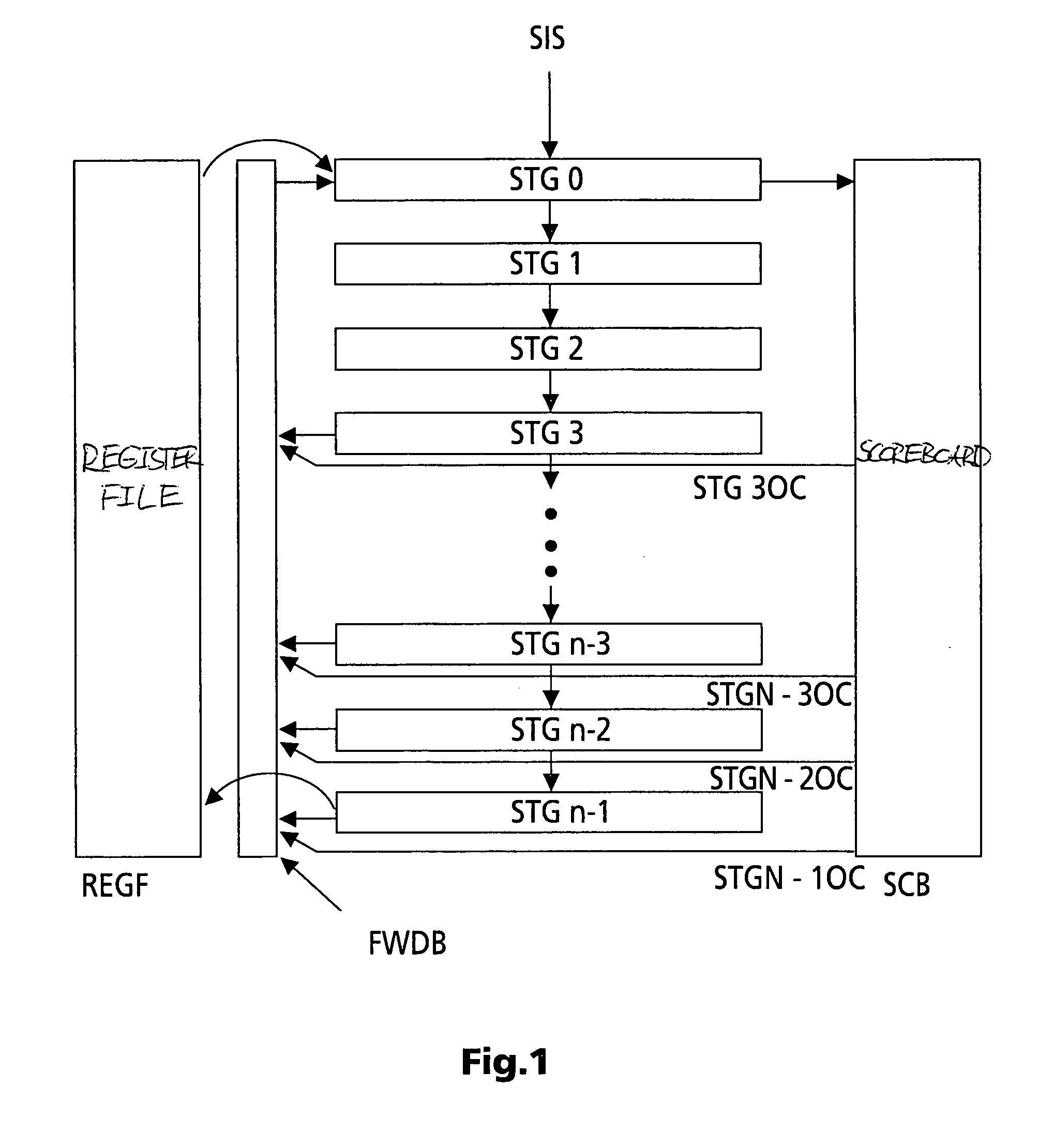

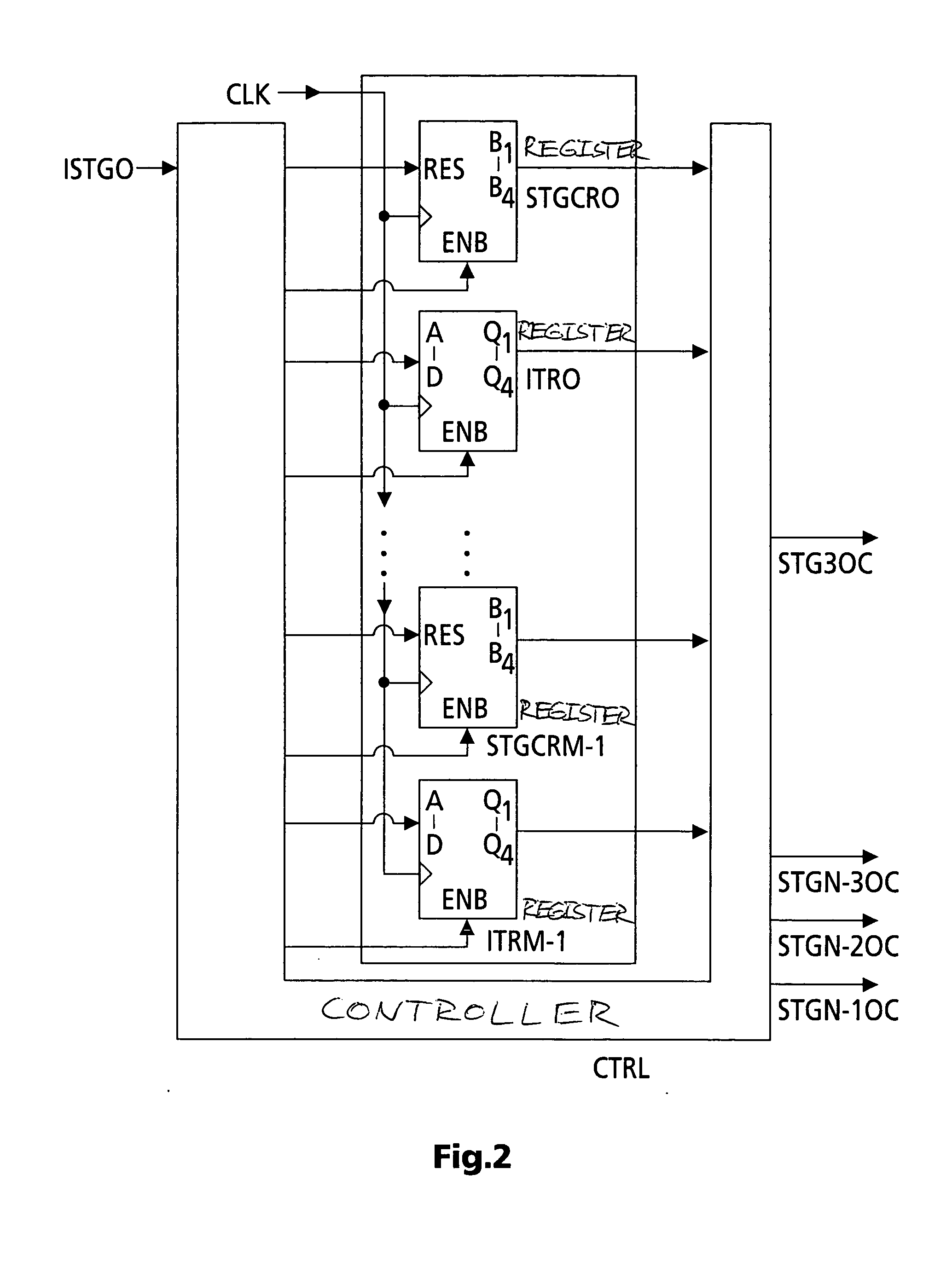

Method and apparatus for pipeline processing a chain of processing instructions

InactiveUS20050076189A1Improve reading efficiencyImprove efficiencyDigital computer detailsConcurrent instruction executionProcessing InstructionOperand

Processor instruction pipelines, which split the processing of individual instructions into several sub-stages and thus reduce the complexity of each stage while simultaneously increasing the clock speed, are typical features of RISC architectures. Operands required by the processing are read from a register file. Read-after-write access problems in the pipeline processing can be avoided by using a scoreboard that has an individual entry per address of the register file. Once an instruction enters the pipeline, a flag is set at the address of the destination address of this particular instruction. This flag signals that an instruction inside the pipeline wants to write its result to the respective register address. Hence the result is unavailable as long as the flag is set. It is cleared after the instruction process has successfully written the result into the register file. According to the invention, not only a single flag but the number of the pipeline stage, which currently carries the instruction that wants to write its result to a particular register file address, and the type of the respective instruction is stored in the corresponding scoreboard address for the particular instruction.

Owner:THOMSON LICENSING SA

Flash memory device capable of storing multi-bit data and single-big data

There is provided a flash memory device capable of manipulating multi-bit and single-bit data. The flash memory device can include a memory cell array with a plurality of memory blocks. The flash memory device can also include a judgment circuit for storing multi-bit / single-bit information indicating whether each of the memory blocks is a multi-bit memory block or not, determining whether or not a memory block of an inputted block address is a multi-bit memory block according to the stored multi-bit / single-bit information and outputting an appropriate flag signal. A read / write circuit for selectively performing multi-bit and single-bit read / program operations of the memory block corresponding to the block address is also included, as well as control logic for controlling the read / write circuit such that the read / write circuit can perform multi-bit or single-bit read / program operations based on the flag signal. An error checking and correction (ECC) circuit including a multi-bit ECC unit and a single-bit ECC unit for checking and correcting an error in a data of the read / write circuit can also be included.

Owner:SAMSUNG ELECTRONICS CO LTD

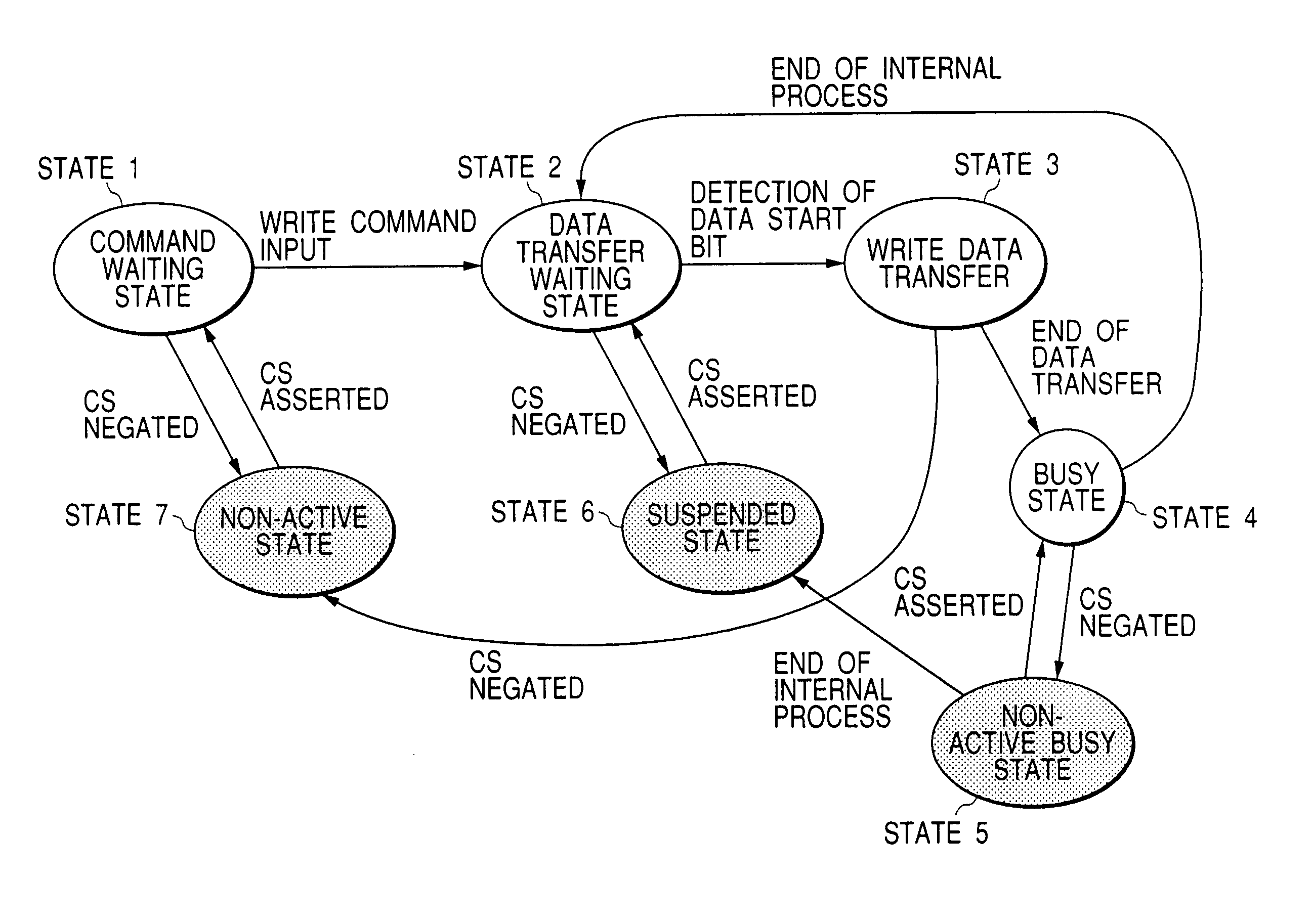

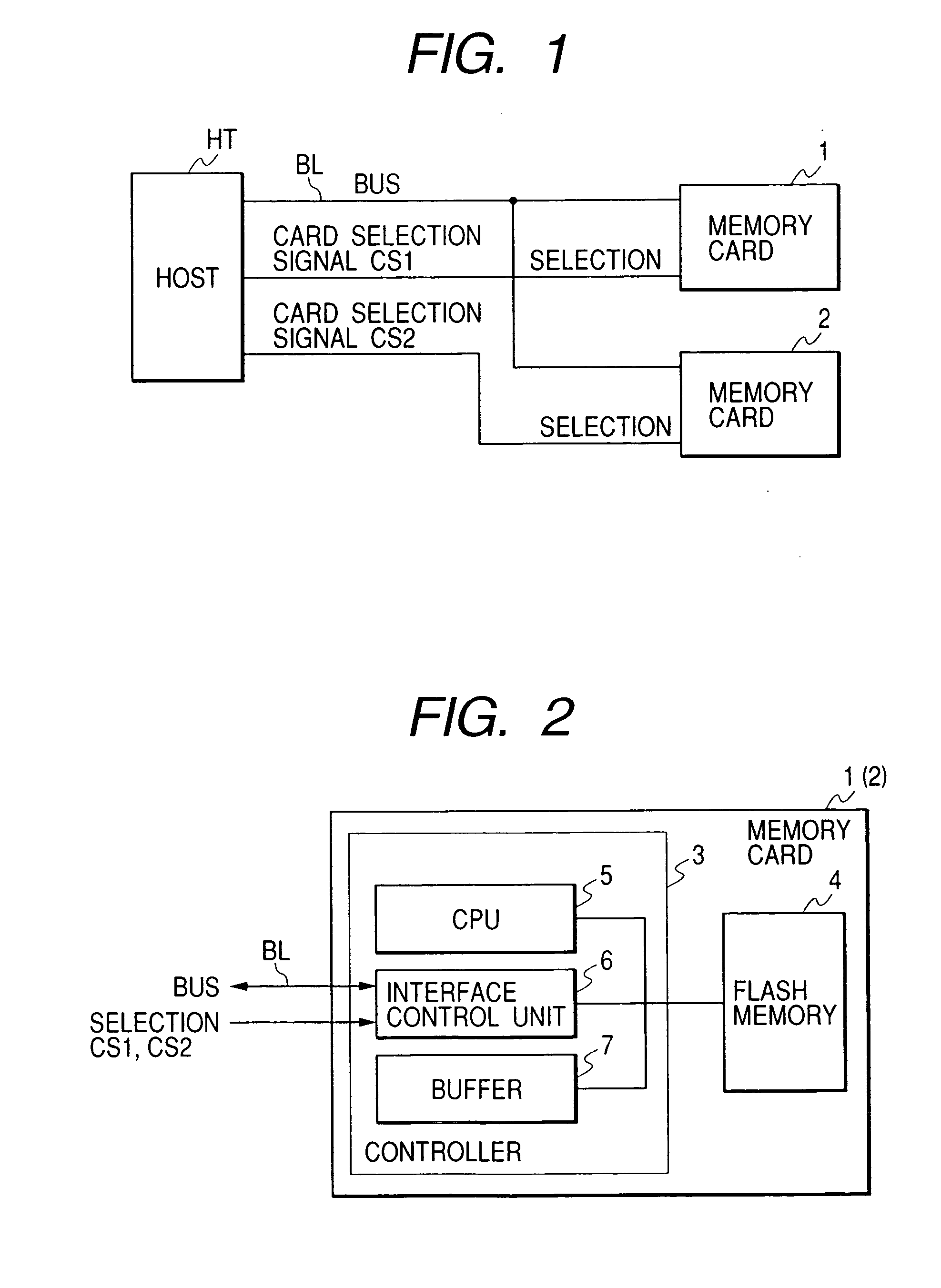

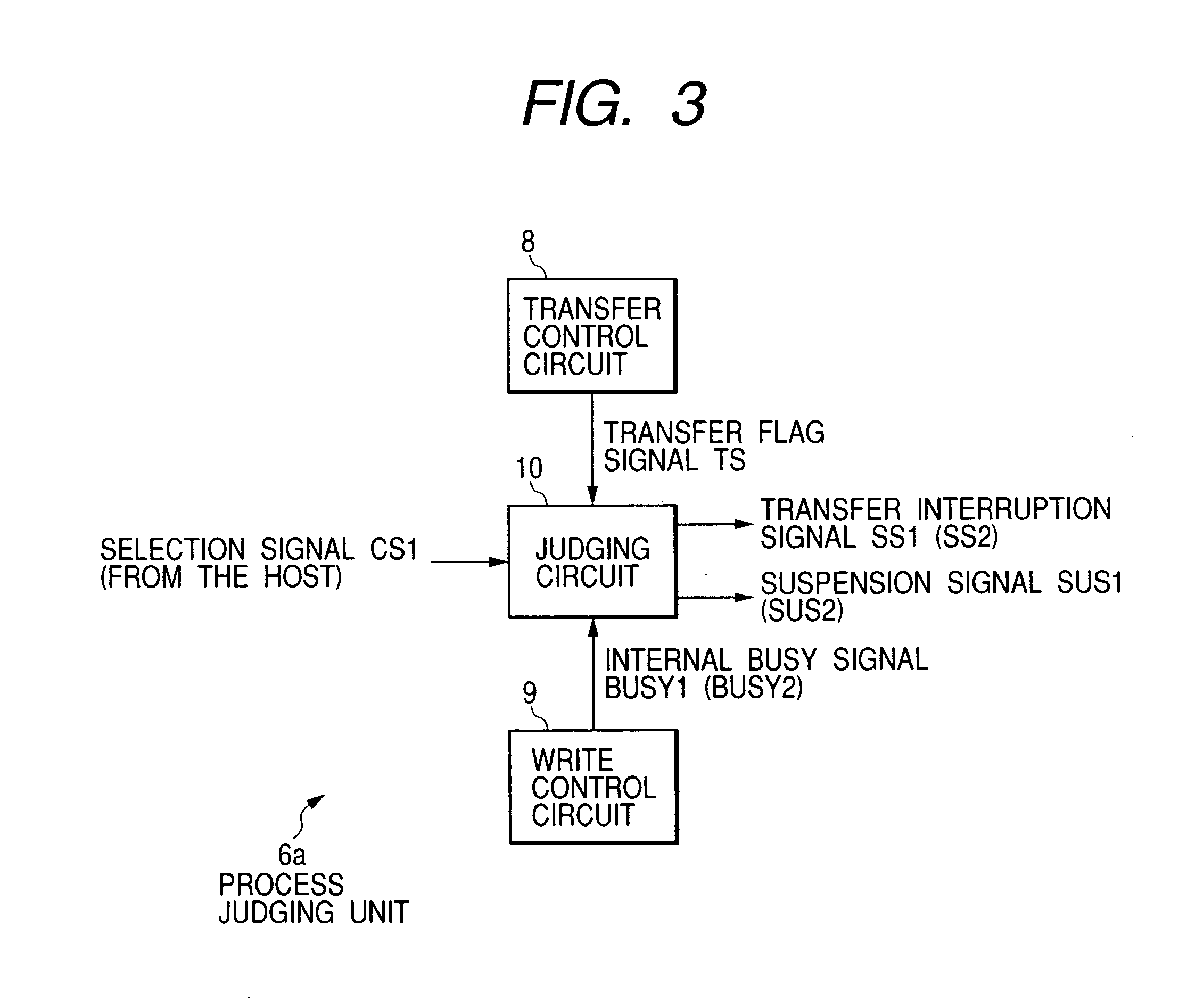

Non-volatile memory card and transfer interruption means

InactiveUS20070033334A1Easy to operateInput/output to record carriersRead-only memoriesTransfer procedureWait state

A memory card is provided with a transfer control circuit, a write control circuit and a judging circuit. The transfer control circuit outputs a transfer flag signal during the data transfer. The write control circuit outputs an internal busy signal during the data write operation. The judging circuit outputs a transfer interruption signal when a card selection signal of the host is negated during the input of the transfer flat signal and also outputs a suspension signal when the card selection signal is negated during the input of the internal busy signal. A CPU invalidates the data being transfer to interrupt the transfer process upon reception of the transfer interruption signal and completes, upon reception of the suspension signal, the process being executed and stays in the waiting condition. Consequently, even when the timing signal not conforming to the standards is transferred, the host can select the optimum processing operation from the internal processing conditions and thereby execute the selected operation.

Owner:RENESAS ELECTRONICS CORP

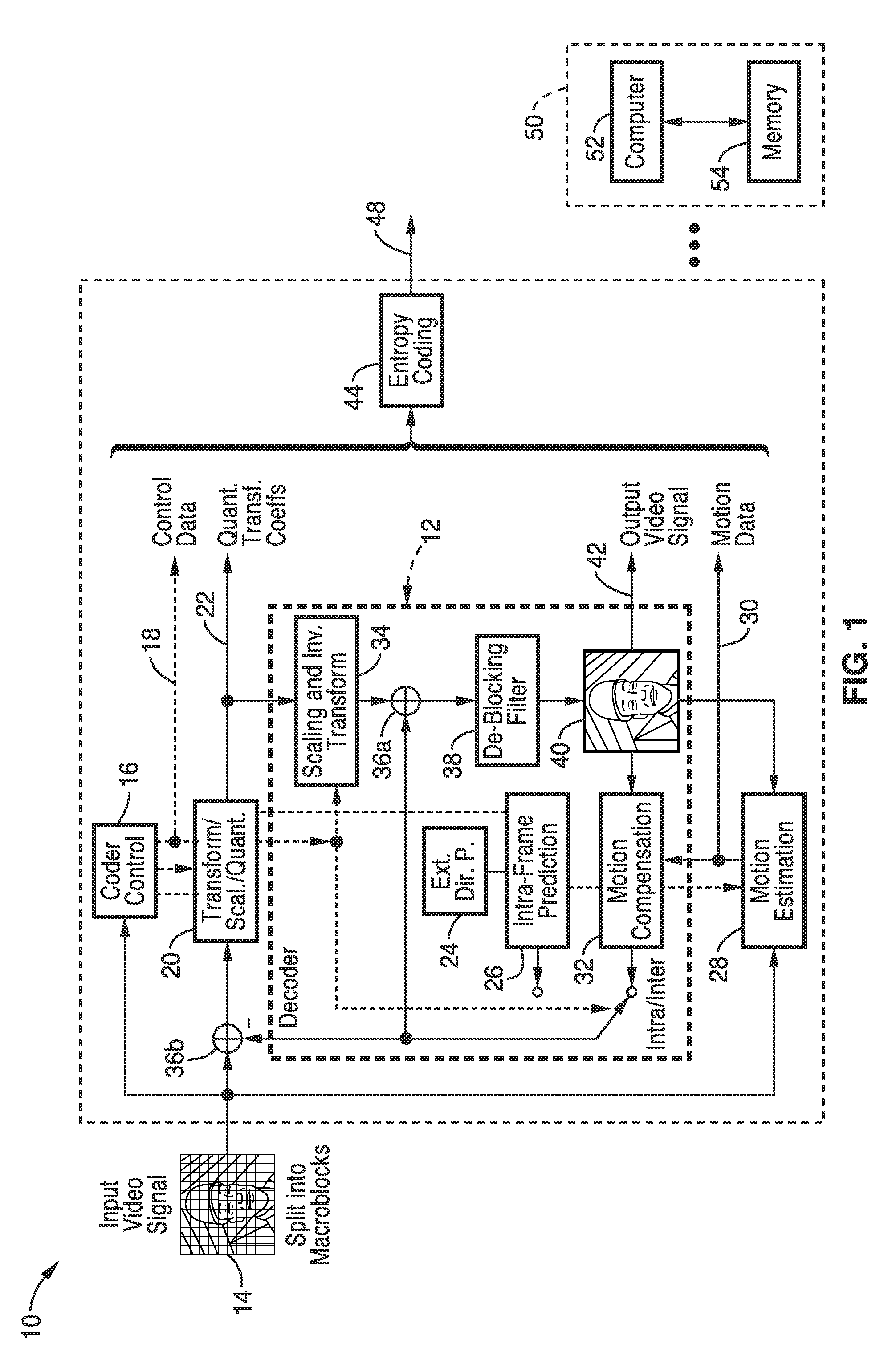

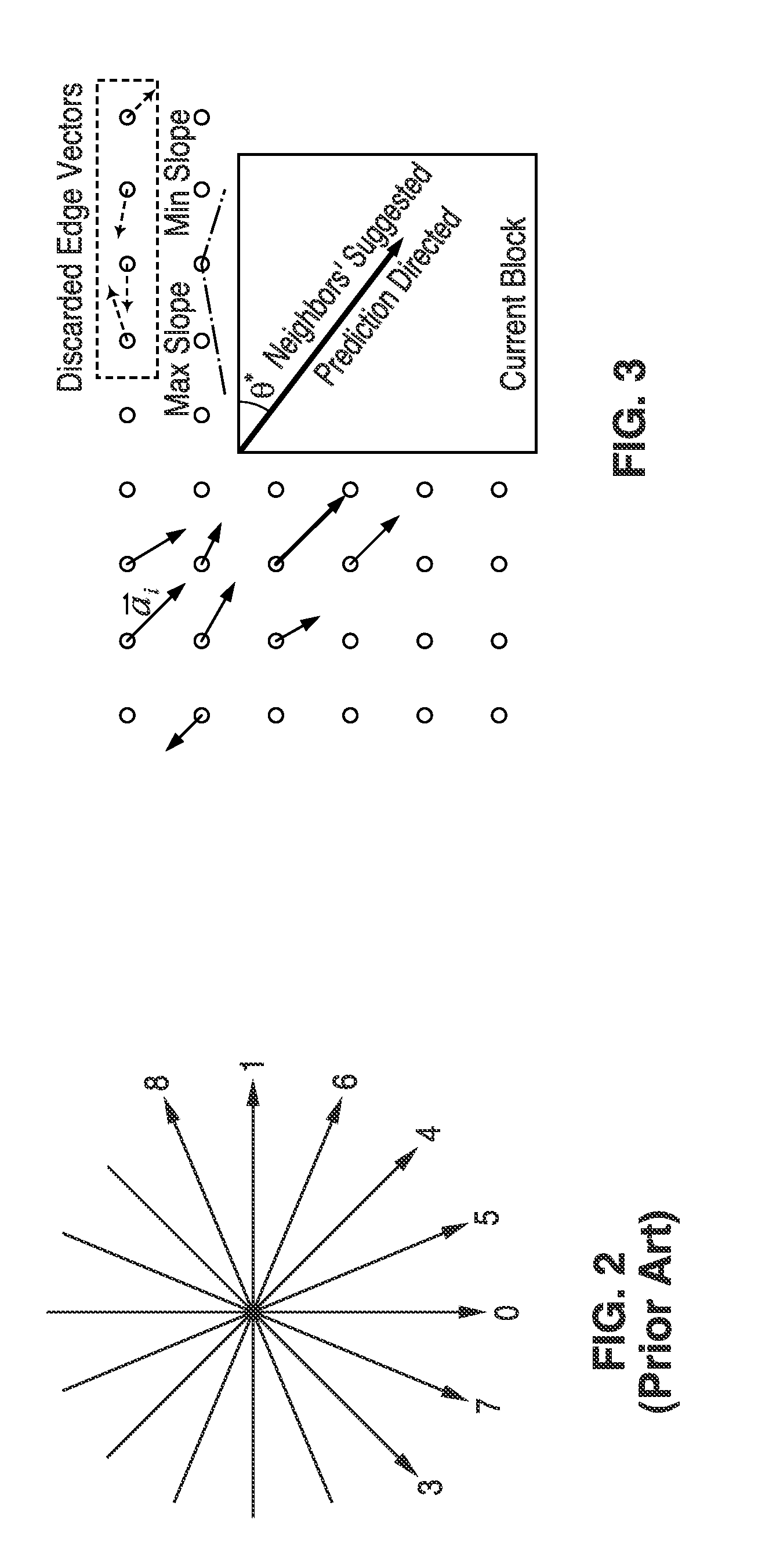

Context adaptive directional intra prediction

InactiveUS20110249739A1Enhanced directional predictionEnhanced direction predictionColor television with pulse code modulationColor television with bandwidth reductionFlag signalsSelf adaptive

Enhanced directional prediction apparatus and methods are taught which are based on edge-based adaptive directional estimation, for providing an improved prediction direction for intra prediction within a coding device. Image gradient vectors are obtained for pixels in the neighborhood of the current block, and edge directions determined. Candidate edge directions are processed to derive a dominant edge direction in response to defining an objective function as a summation of projections to a candidate direction and computing suggested direction of each neighboring pixel. The dominant edge direction may be utilized for the prediction direction, such as in response to a detection mode flag signaled to the decoder, or modified by an angular adjustment, which can be communicated to a decoder.

Owner:SONY CORP

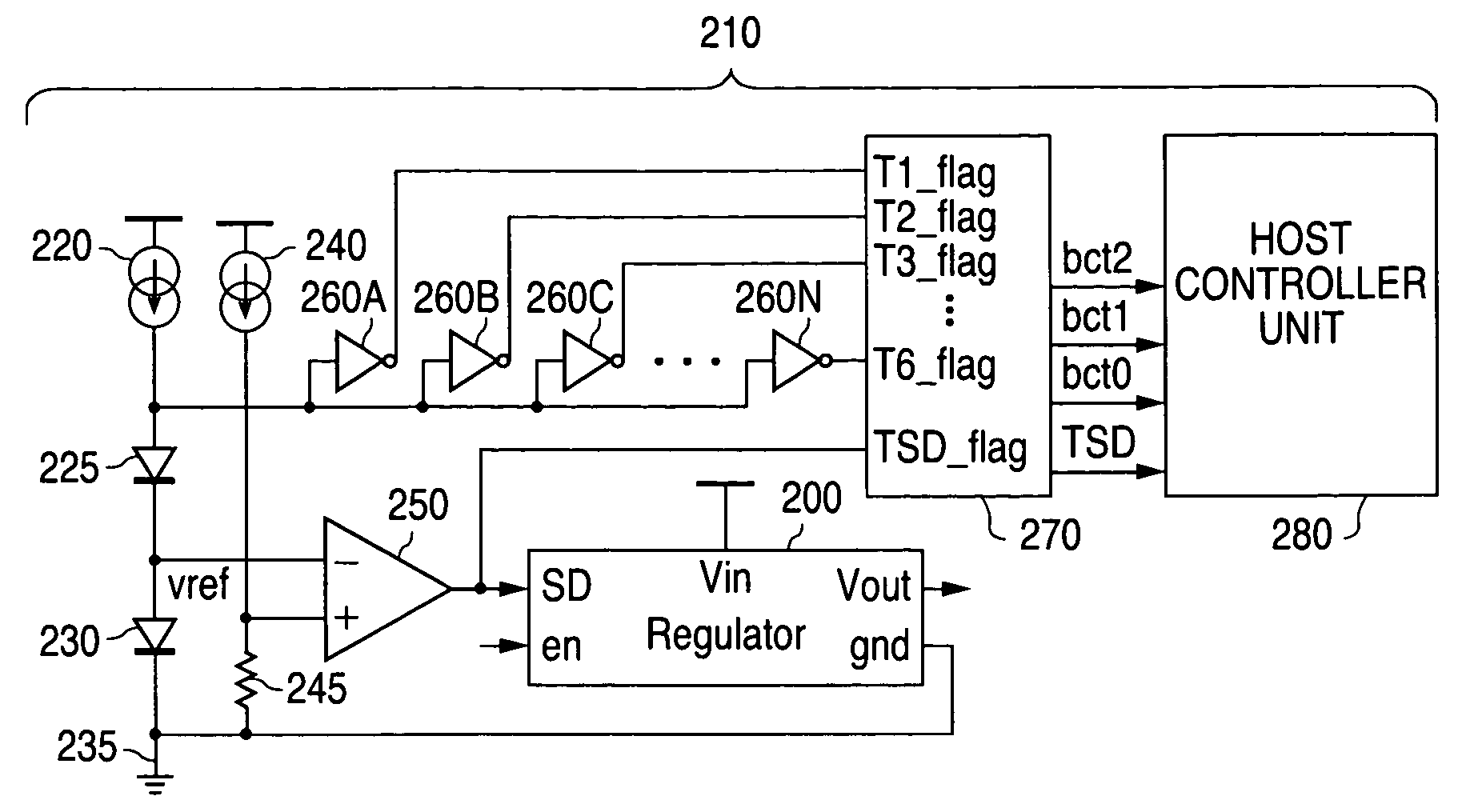

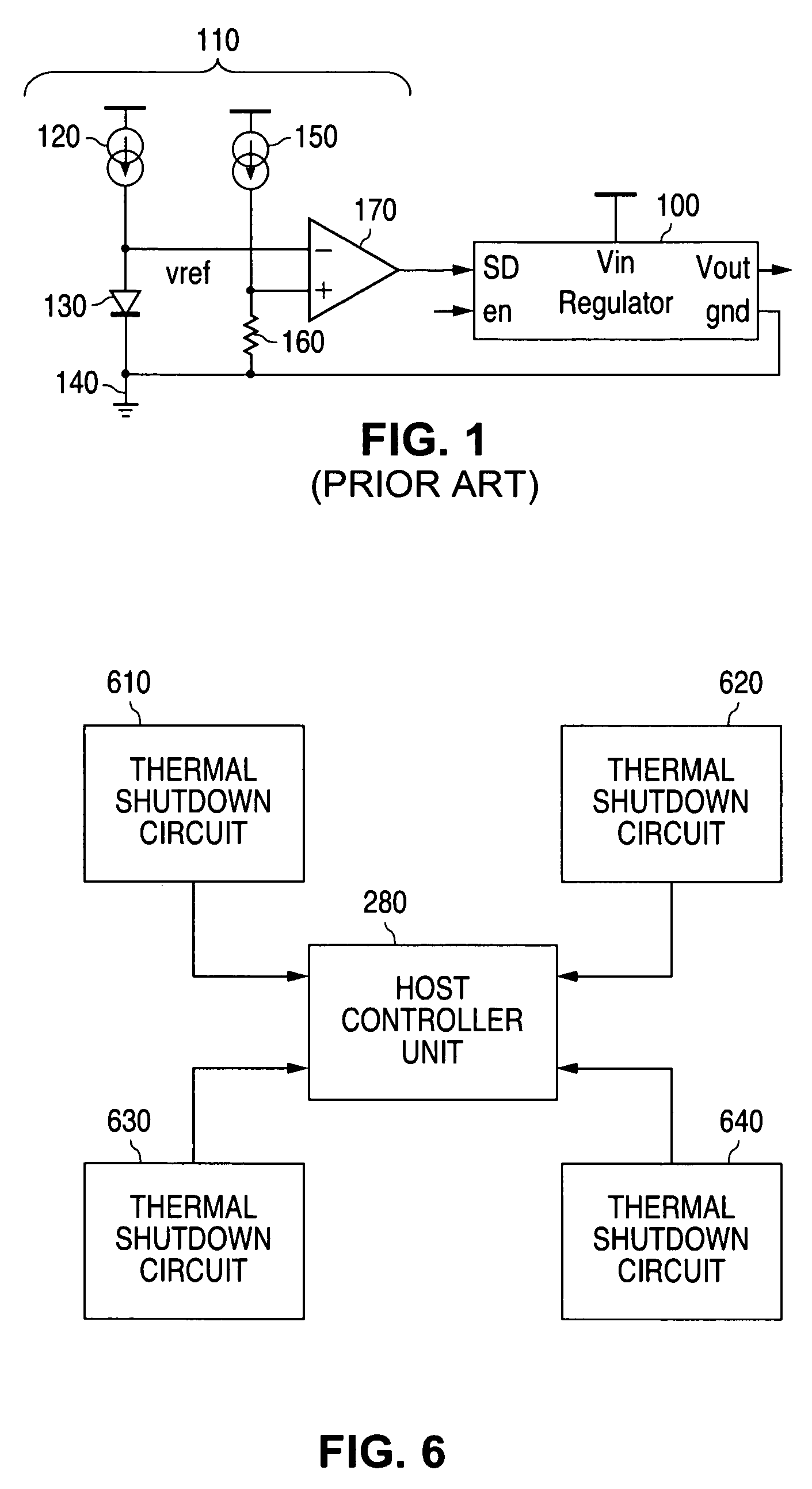

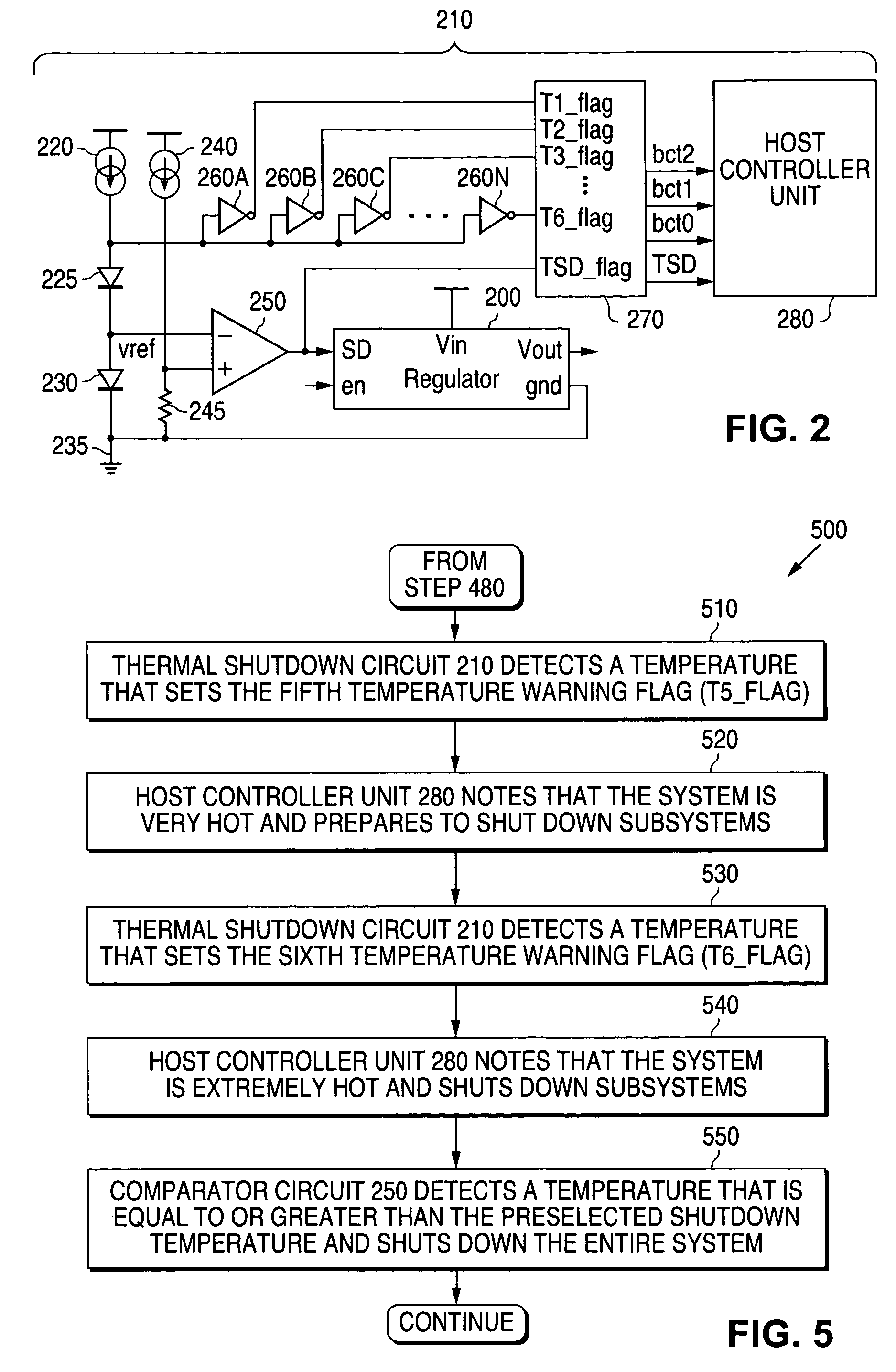

System and method for providing a thermal shutdown circuit with temperature warning flags

A system and method is disclosed that provides a thermal shutdown circuit that generates a plurality of temperature warning flag signals. Each temperature warning flag signal represents a different temperature. The thermal shutdown circuit comprises a plurality of inverter circuits in which each inverter circuit has a different temperature turn-on threshold. A temperature to binary code converter receives the temperature warning flag signals from the inverter circuits and generates a plurality of binary coded signals that represent a temperature that is detected by the thermal shutdown circuit. A host controller unit uses the temperature information from the binary coded signals to shut down subsystems in advance of an abrupt thermal shutdown of a system.

Owner:NAT SEMICON CORP

Semiconductor integrated circuit

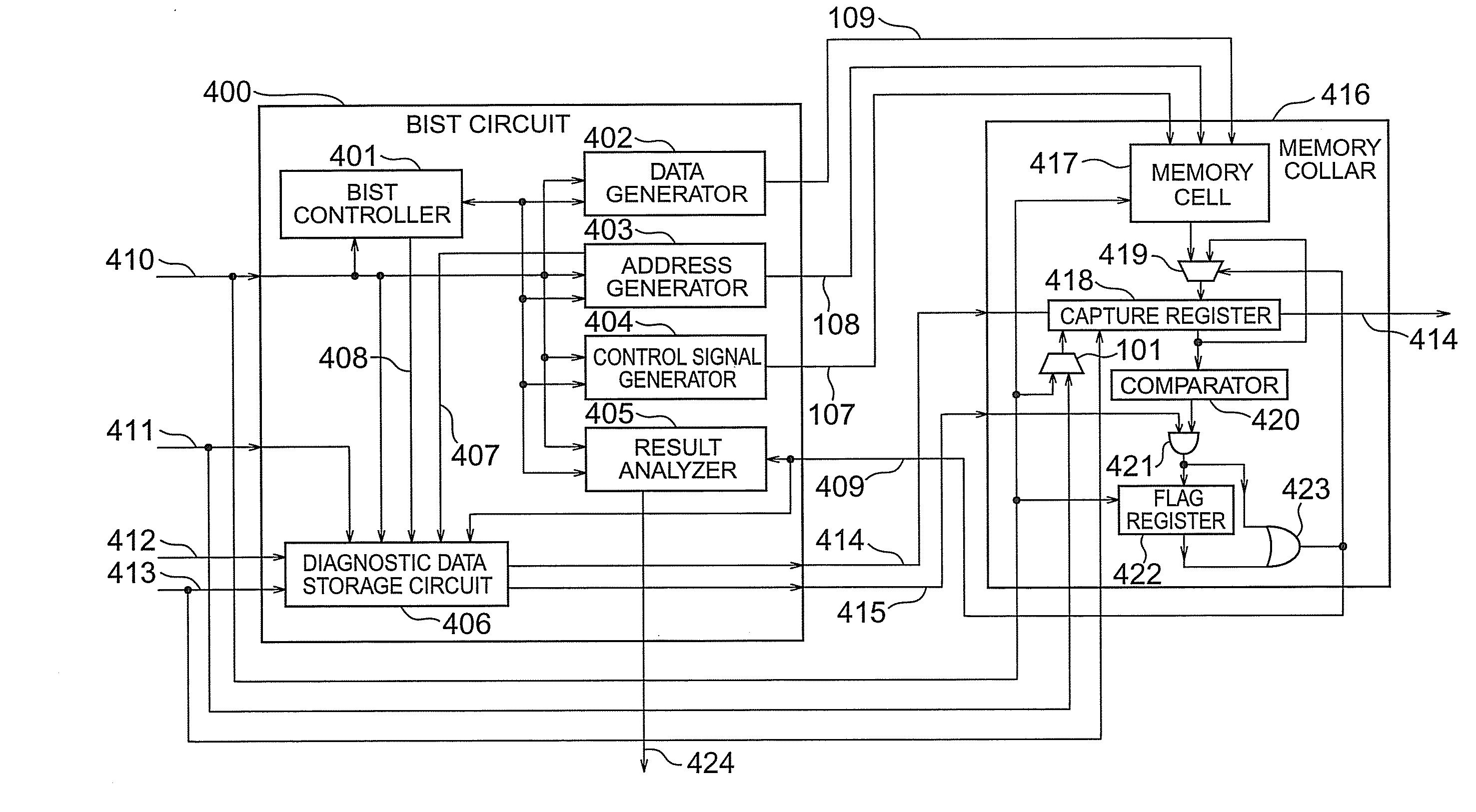

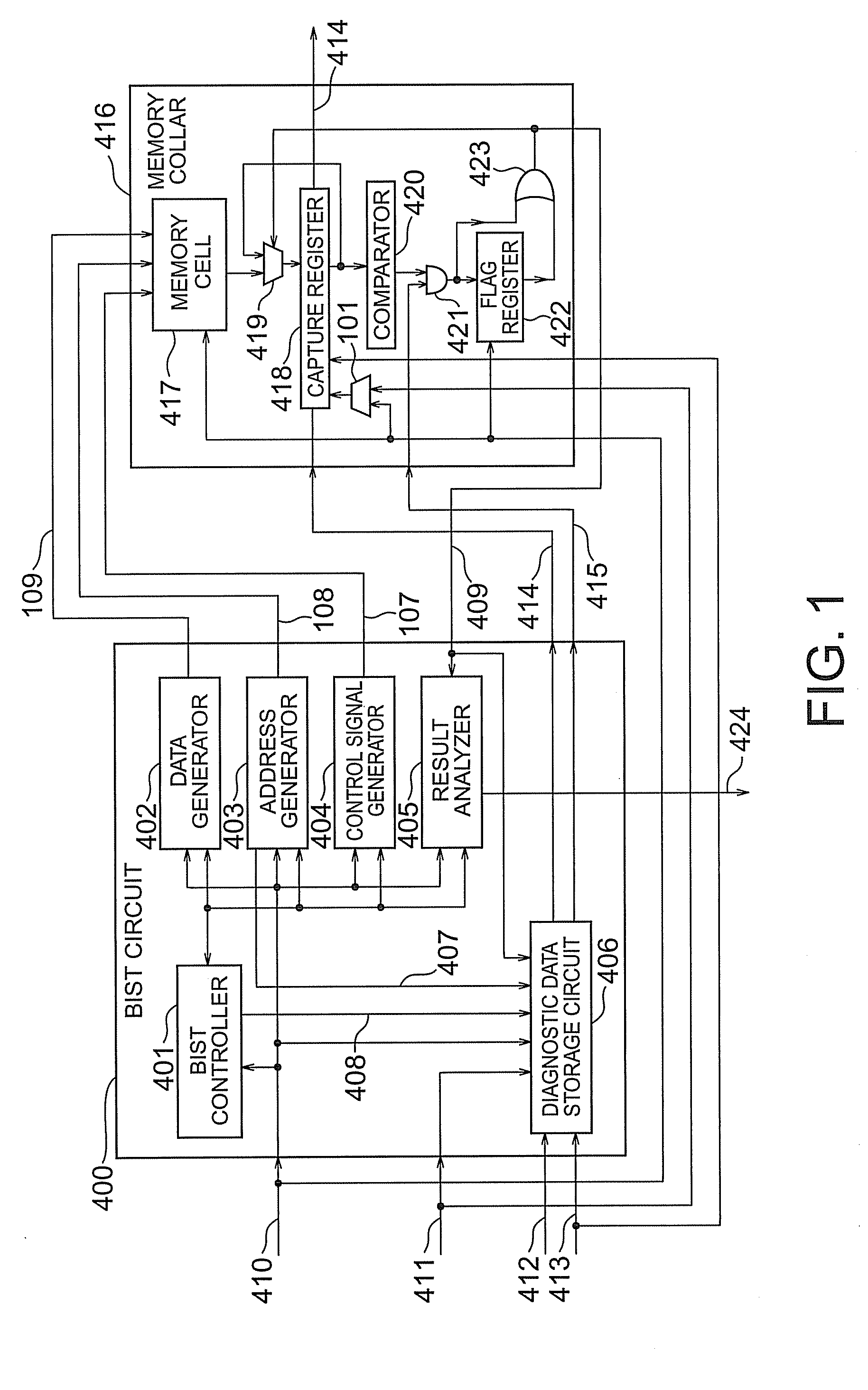

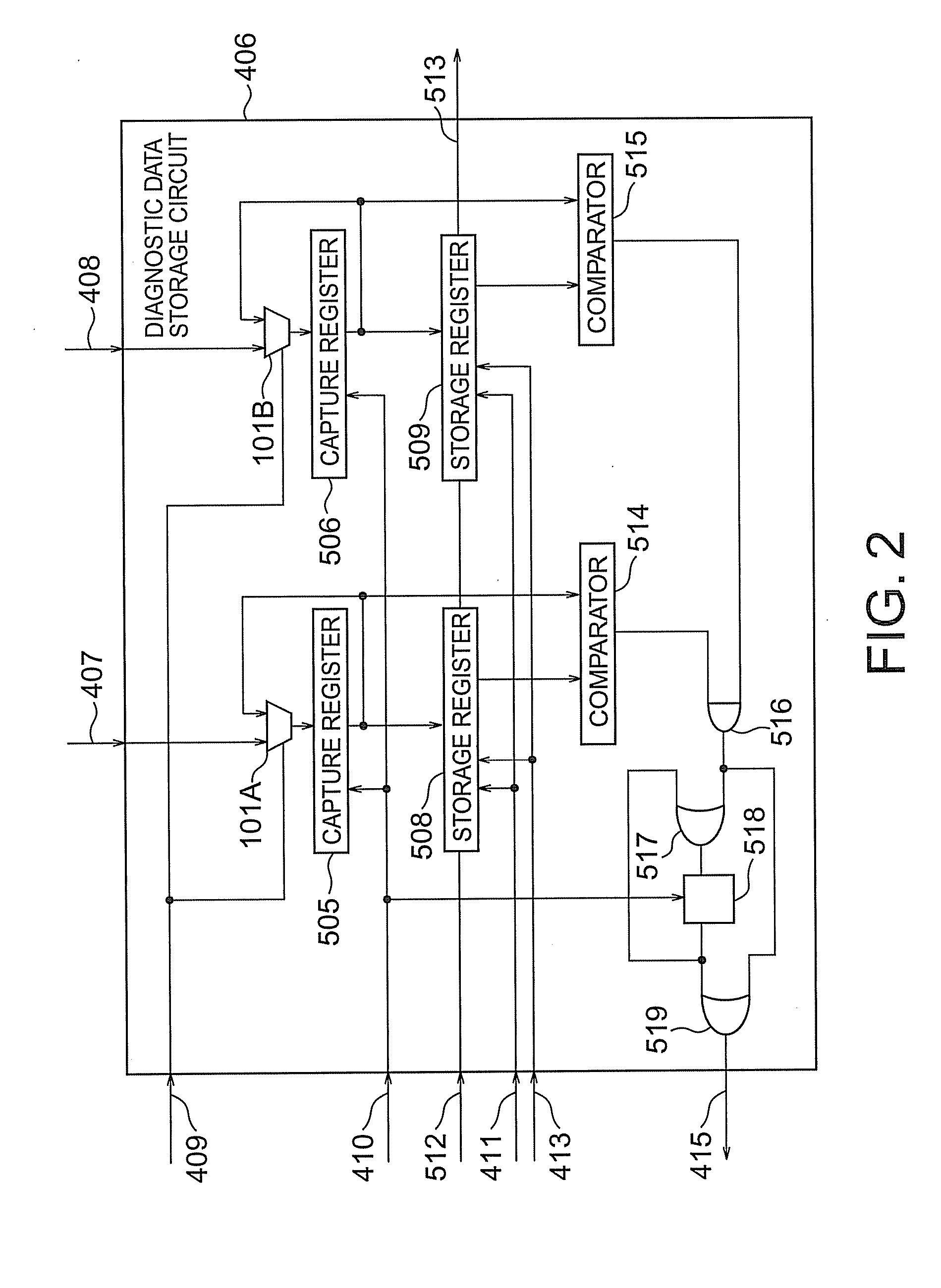

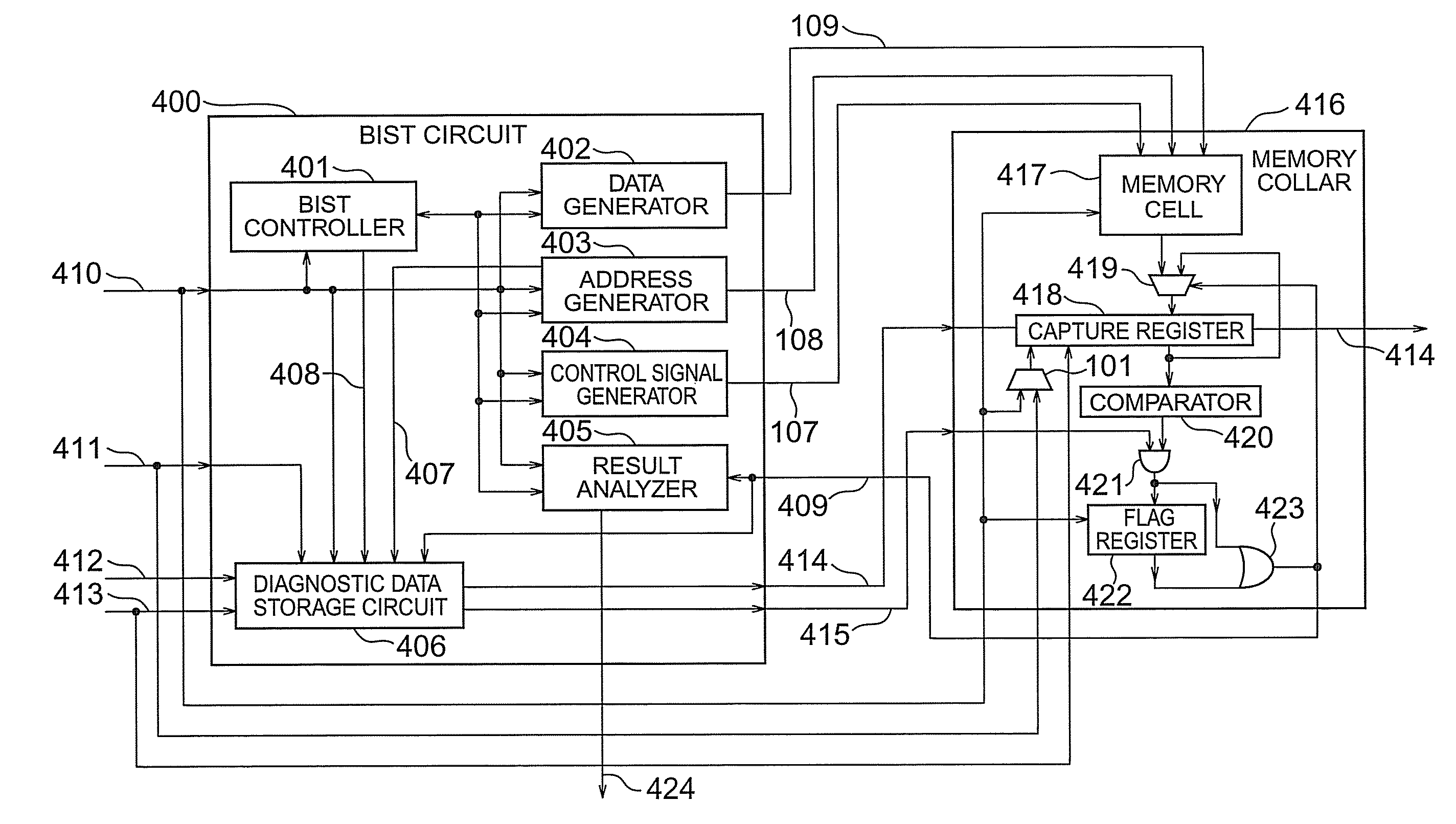

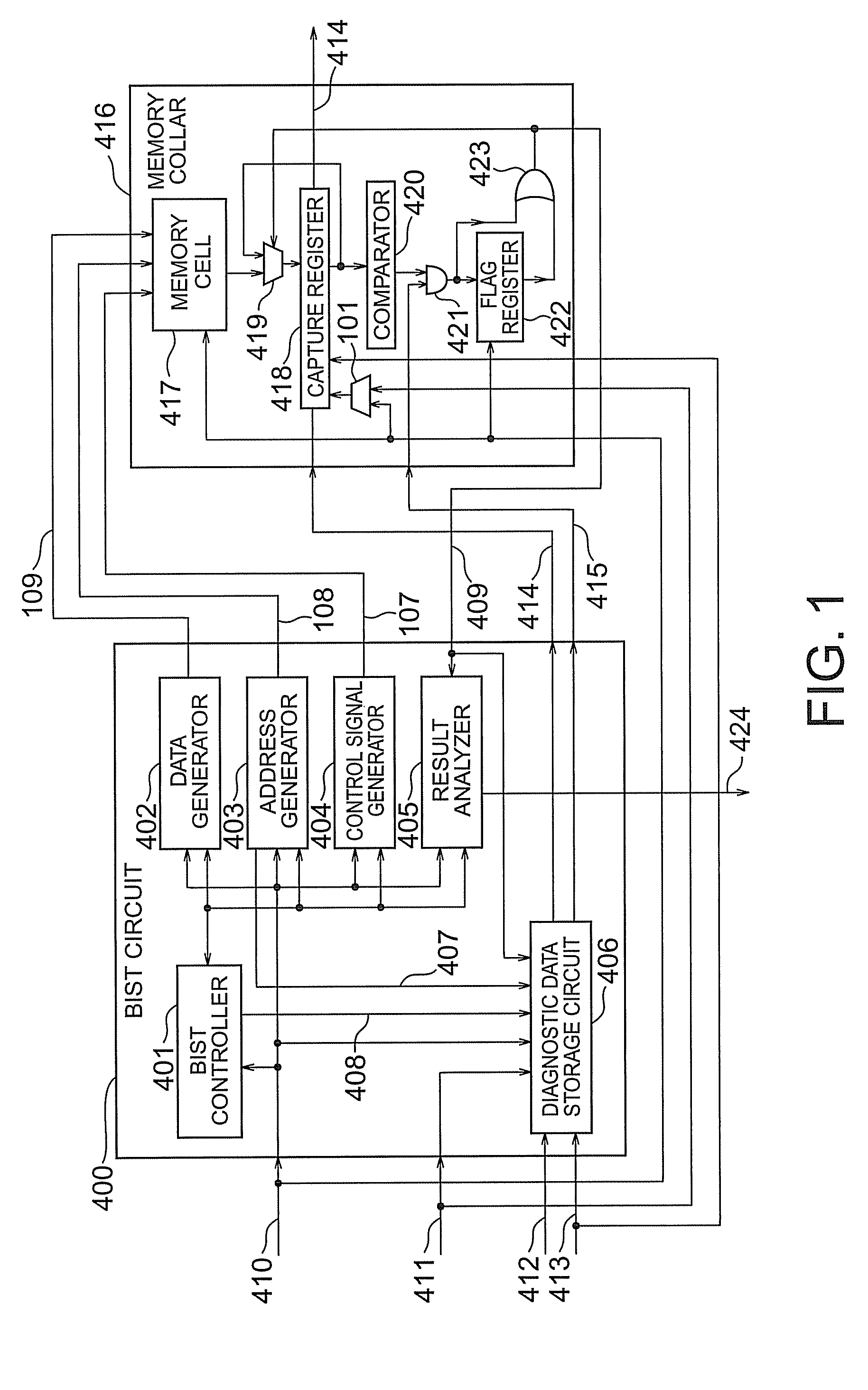

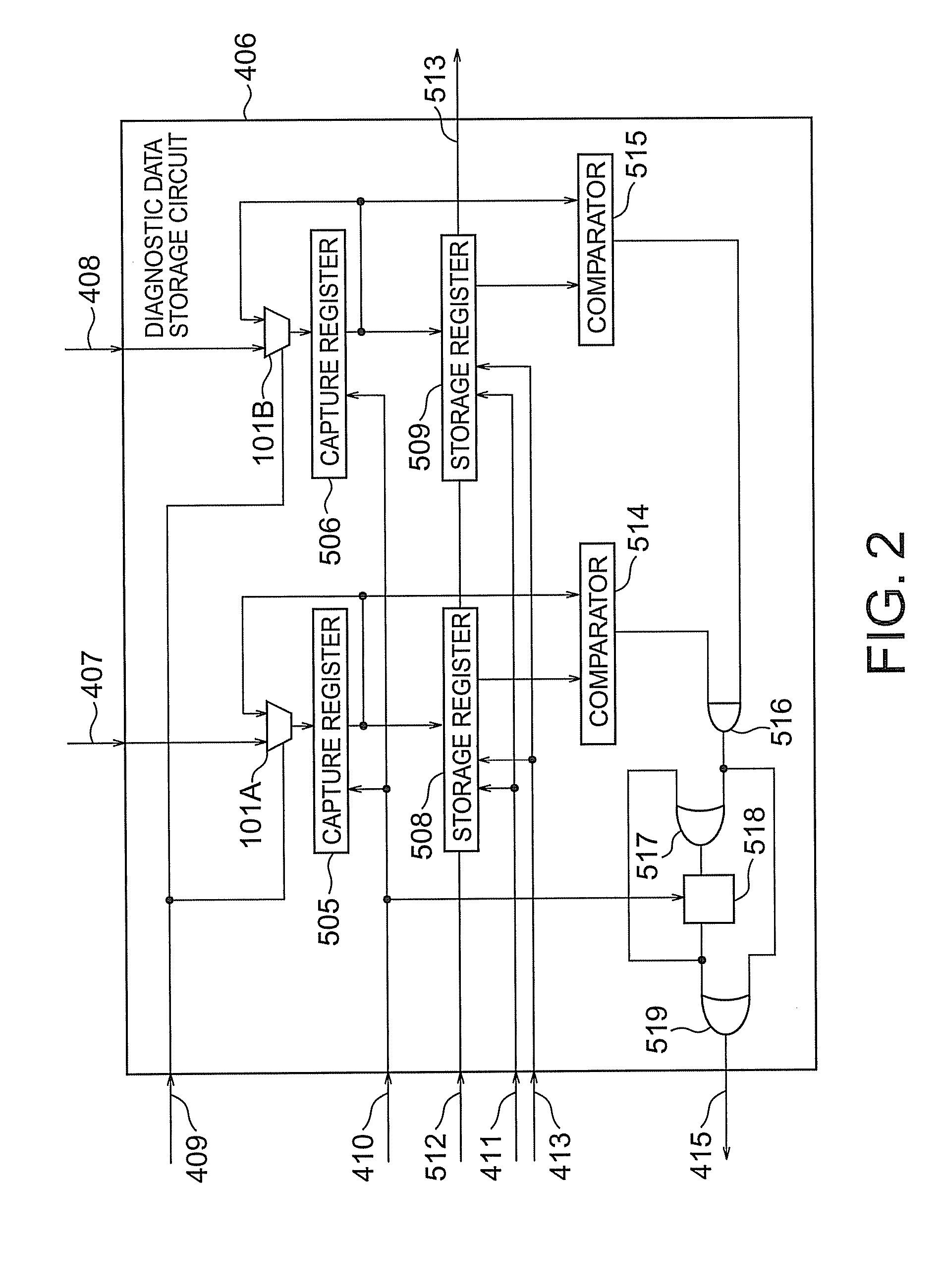

According to the present invention, there is provided a semiconductor integrated circuit having: a BIST circuit including, a data generator which generates and outputs write data to be supplied to a memory, an address generator which generates and outputs an address signal to be supplied to the memory, a control signal generator which generates and outputs a control signal for controlling the memory, a result analyzer which receives a flag signal, analyzes a result of a BIST, and outputs a BIST result signal, a BIST controller which controls operations of the data generator, the address generator, the control signal generator, and the result analyzer, and outputs a BIST state signal indicating a state of the BIST, and a diagnostic data storage circuit including a first capture register which captures and outputs, in accordance with a first clock, a latest address signal and the BIST state signal output from the BIST controller while no flag signal is supplied, and maintains outputs when the flag signal is supplied, a storage register which receive and stores the outputs from the first capture register in accordance with a second clock lower in speed than the first clock while no shift enable signal is supplied, thereby storing the address signal and the BIST signal corresponding to the supply timing of the flag signal, and outputs the stored contents outside by shifting them when the shift enable signal is supplied, and flag suppressing means for comparing the outputs from the first capture register with the stored contents of the storage register, and outputting a flag suppression signal, after the flag signal is supplied, until the latest address signal and the BIST state signal output from the first capture register match the address signal and the BIST control signal stored in the storage register; and a memory collar including, a memory cell which performs a write operation by receiving the write data, the address signal, and the control signal, and reads out and outputs the written data, in accordance with the first clock, a second capture register which captures latest data output from the memory cell while neither the shift enable signal nor the flag signal is supplied, maintains held contents when the flag signal is supplied, and outputs held contents outside by shifting the held contents when the shift enable signal is supplied, a comparator which compares the output from the second capture register with an expected value, and outputs a comparison result signal meaning failure detection if the output and the expected value do not match, and a flag register which outputs the flag signal on the basis of the comparison result signal while no flag suppression signal is supplied, and suppresses the output of the flag signal when the flag suppression signal is supplied

Owner:KK TOSHIBA

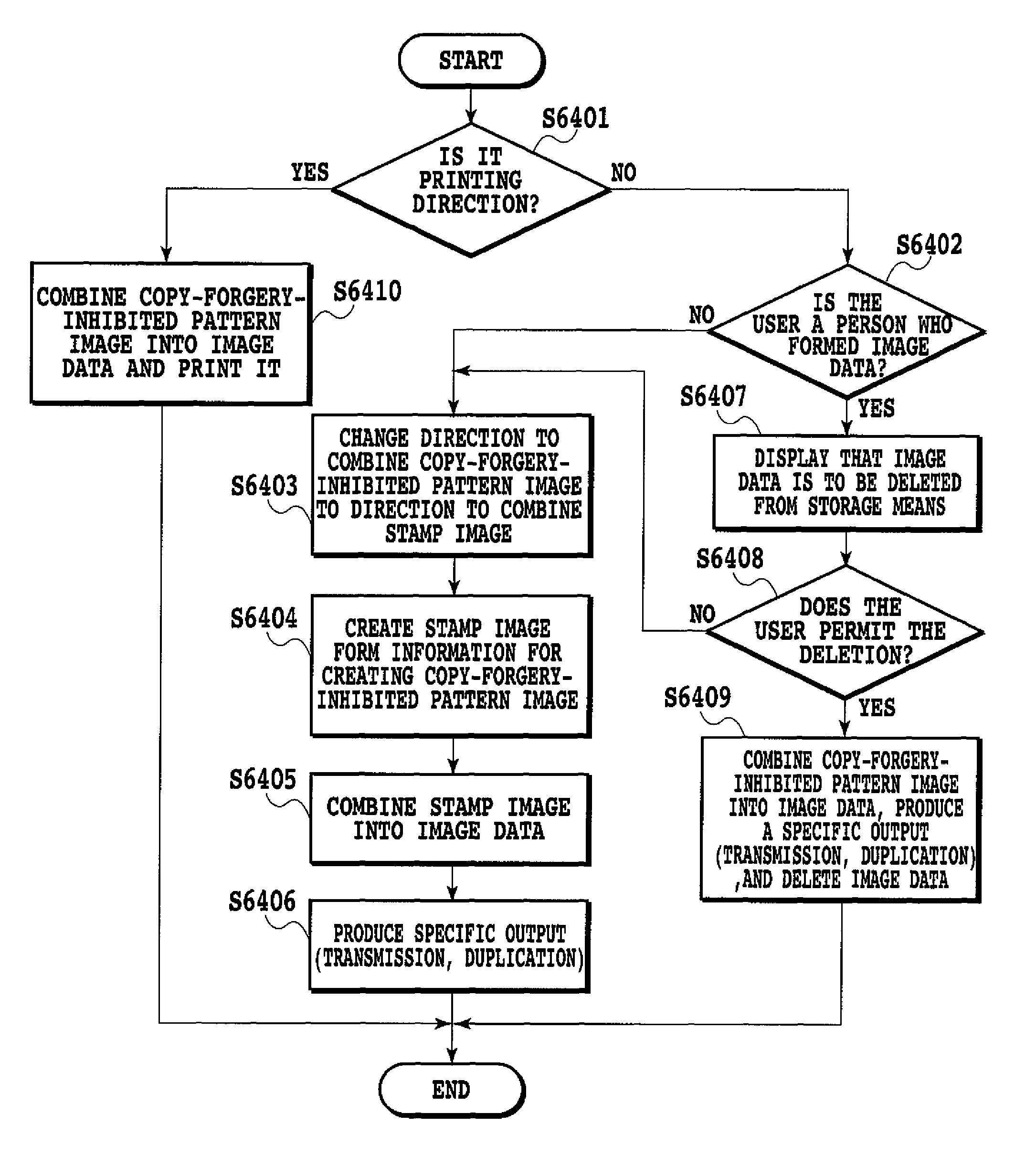

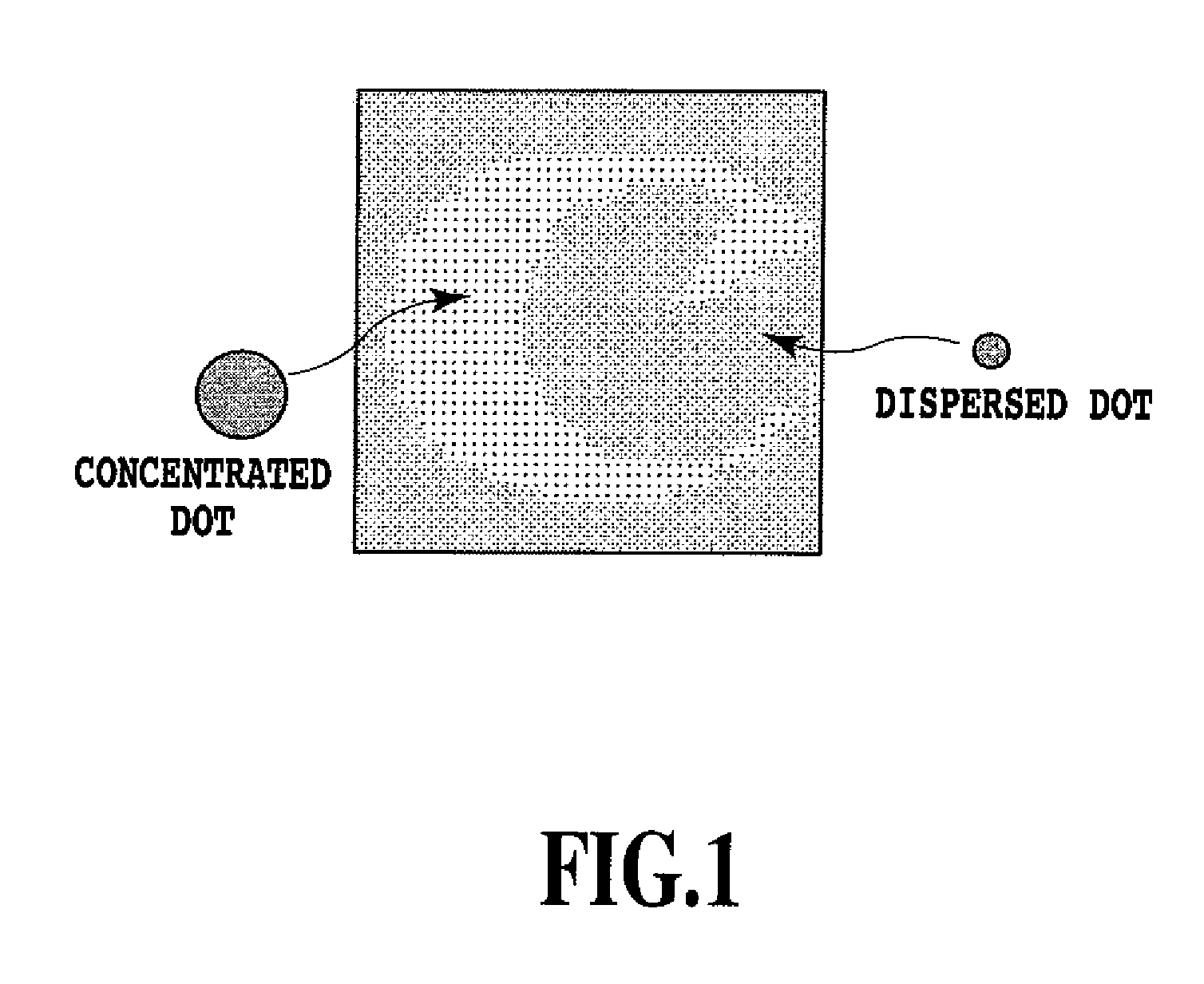

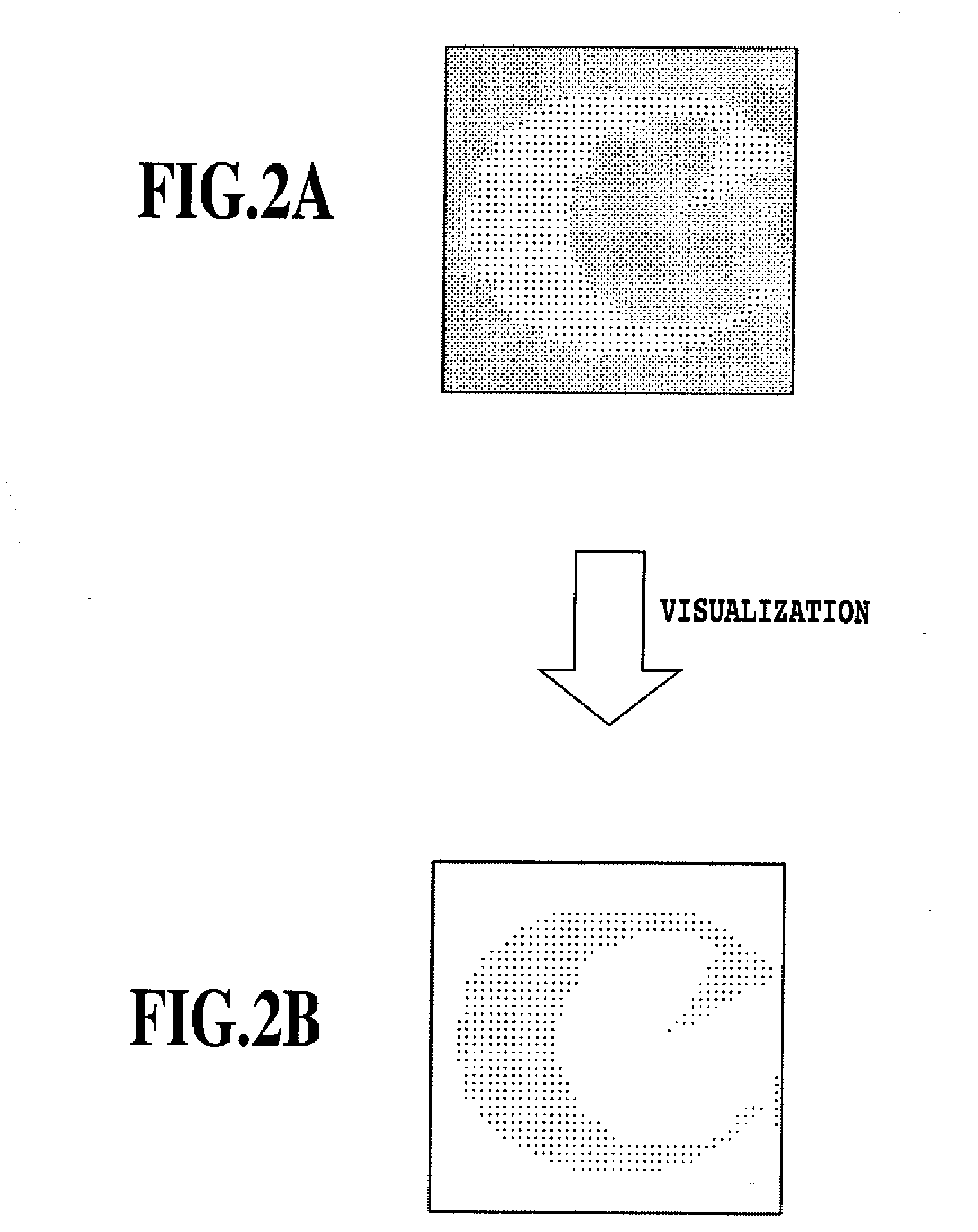

Copy-forgery-inhibited pattern or stamp image combined with image data based on user actions

InactiveUS7738143B2Improve securityHigh densityCharacter printing data arrangement from carrierError detection/correctionPattern recognitionHard disc drive

Owner:CANON KK

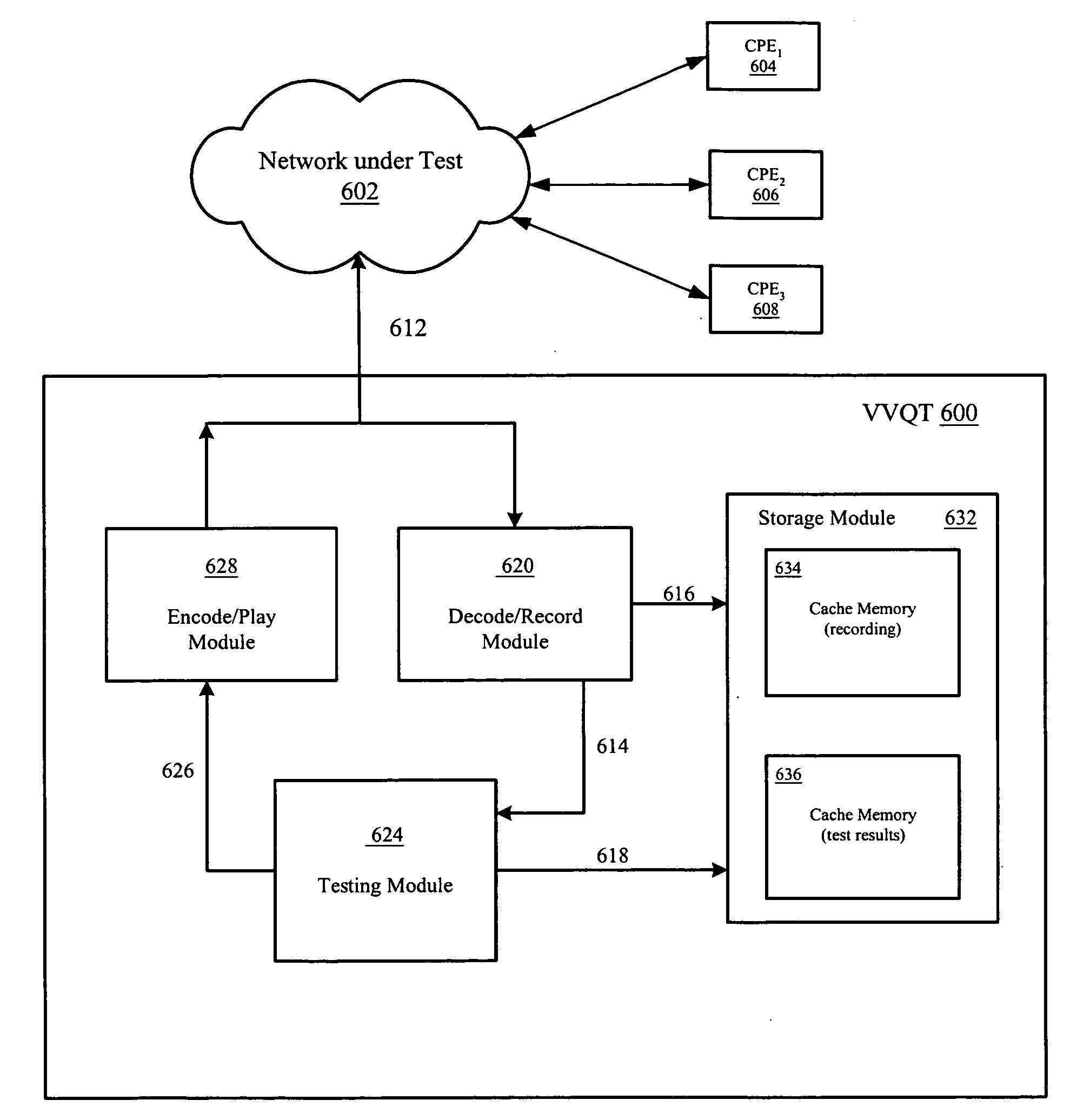

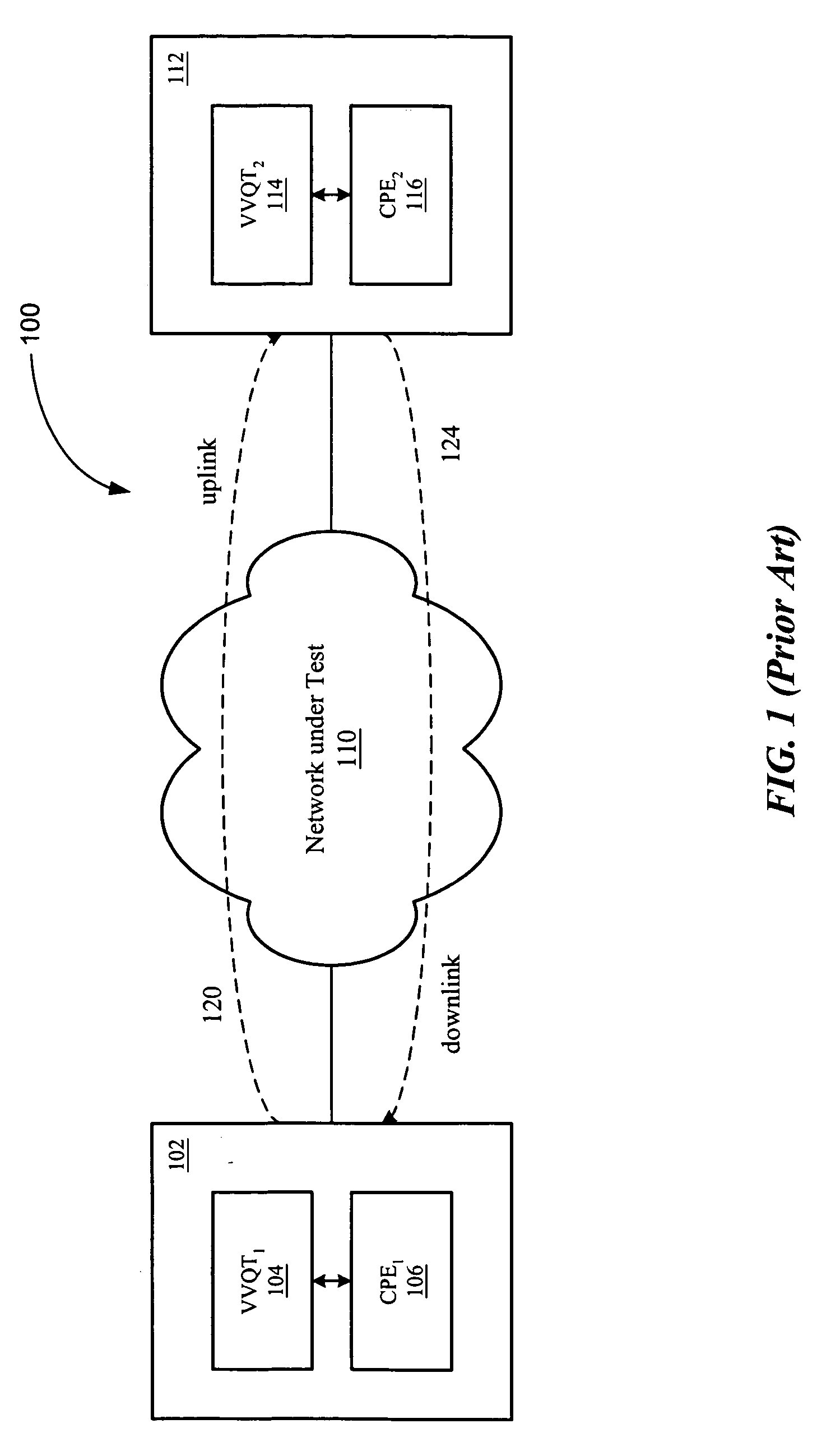

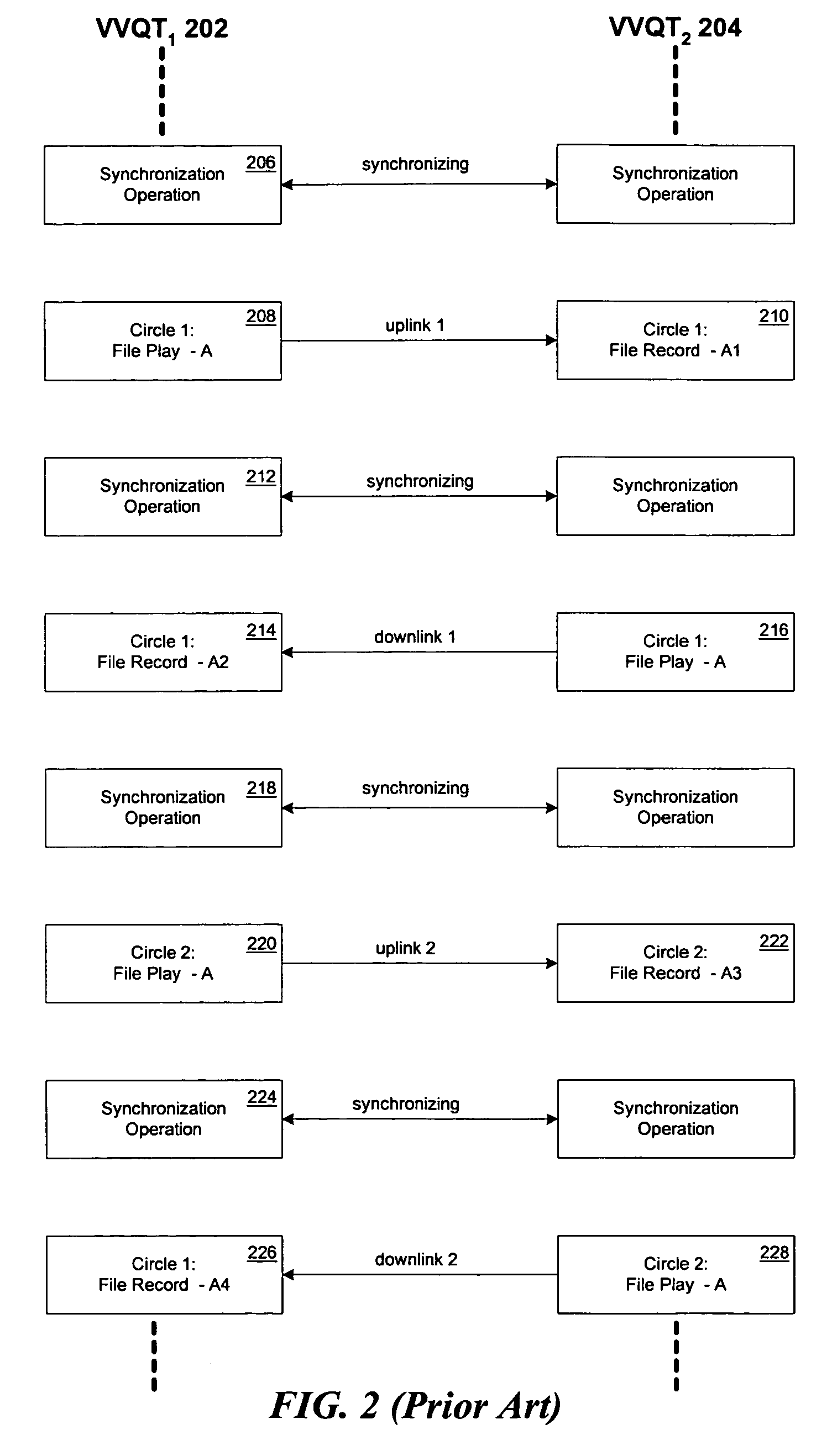

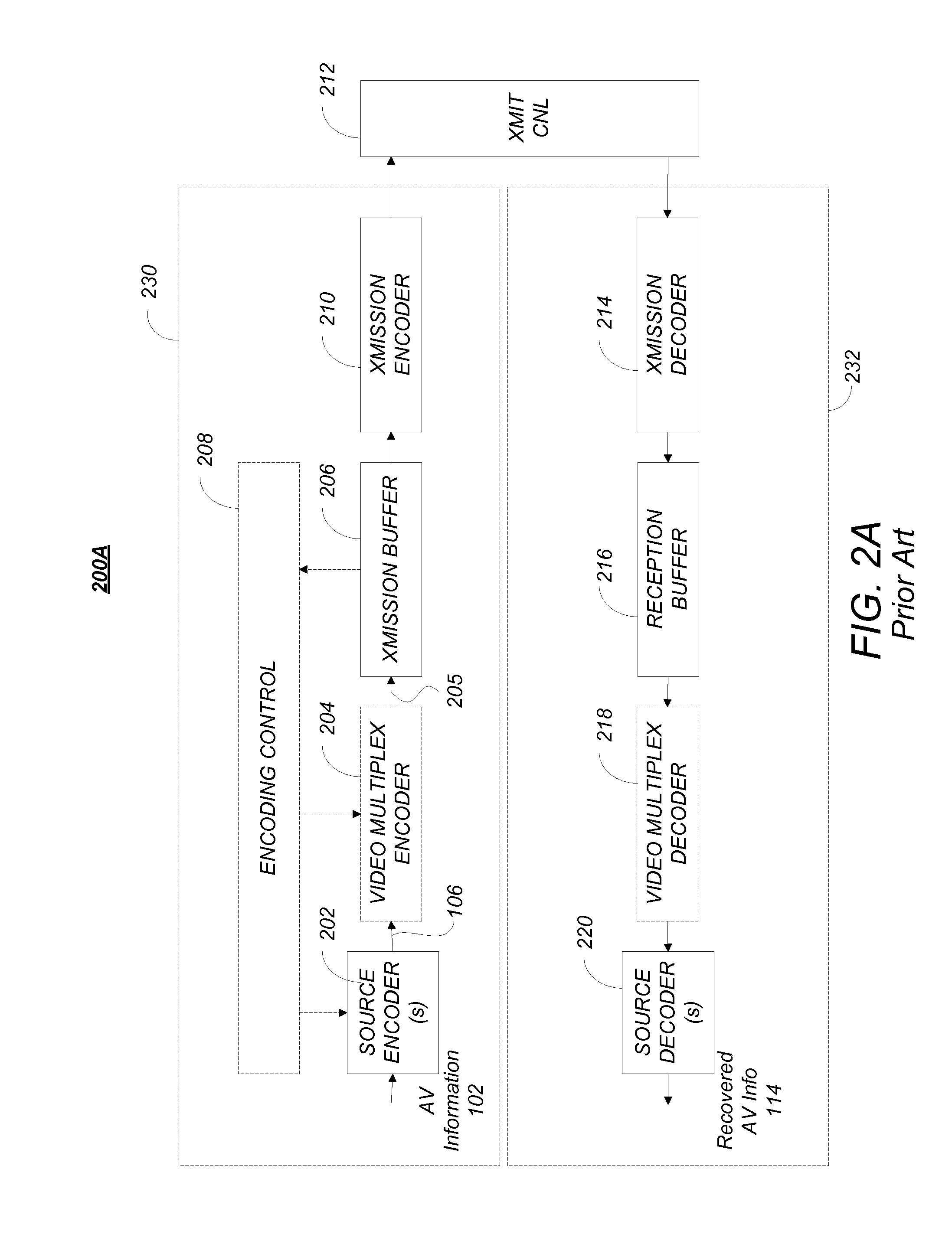

Bi-directional continuous voice and video quality testing system with TTMF tones

A continuous bi-directional file-play-record voice and video quality tester system (“CFPR-VVQT”) for measuring the quality of voice or video communication links from a customer premises equipment (“CPE”) through a Network under Test to a voice and video quality tester (“VVQT”). The start and end of a set of quality testing sample signals are determined by a start flag signal and an end flag signal, respectively, generated by the CFPR-VVQT. The flag signals may be triple tone modulation frequency (“TTMF”) tones. The CFPR-VVQT will measure the quality testing sample signals, determine a signal quality test result, and then transmit the test results back through Network under Test to the originating VVQT.

Owner:AGILENT TECH INC

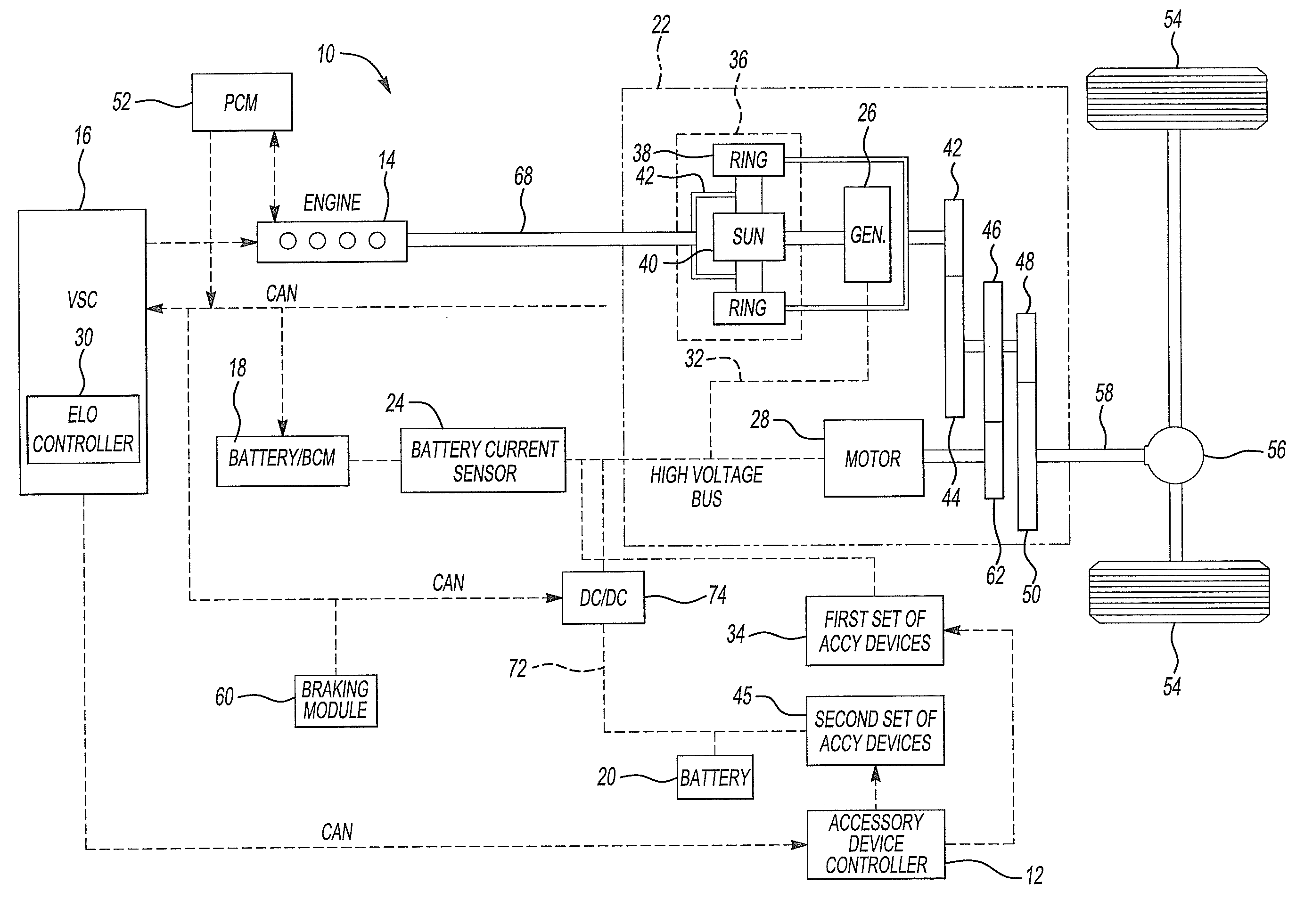

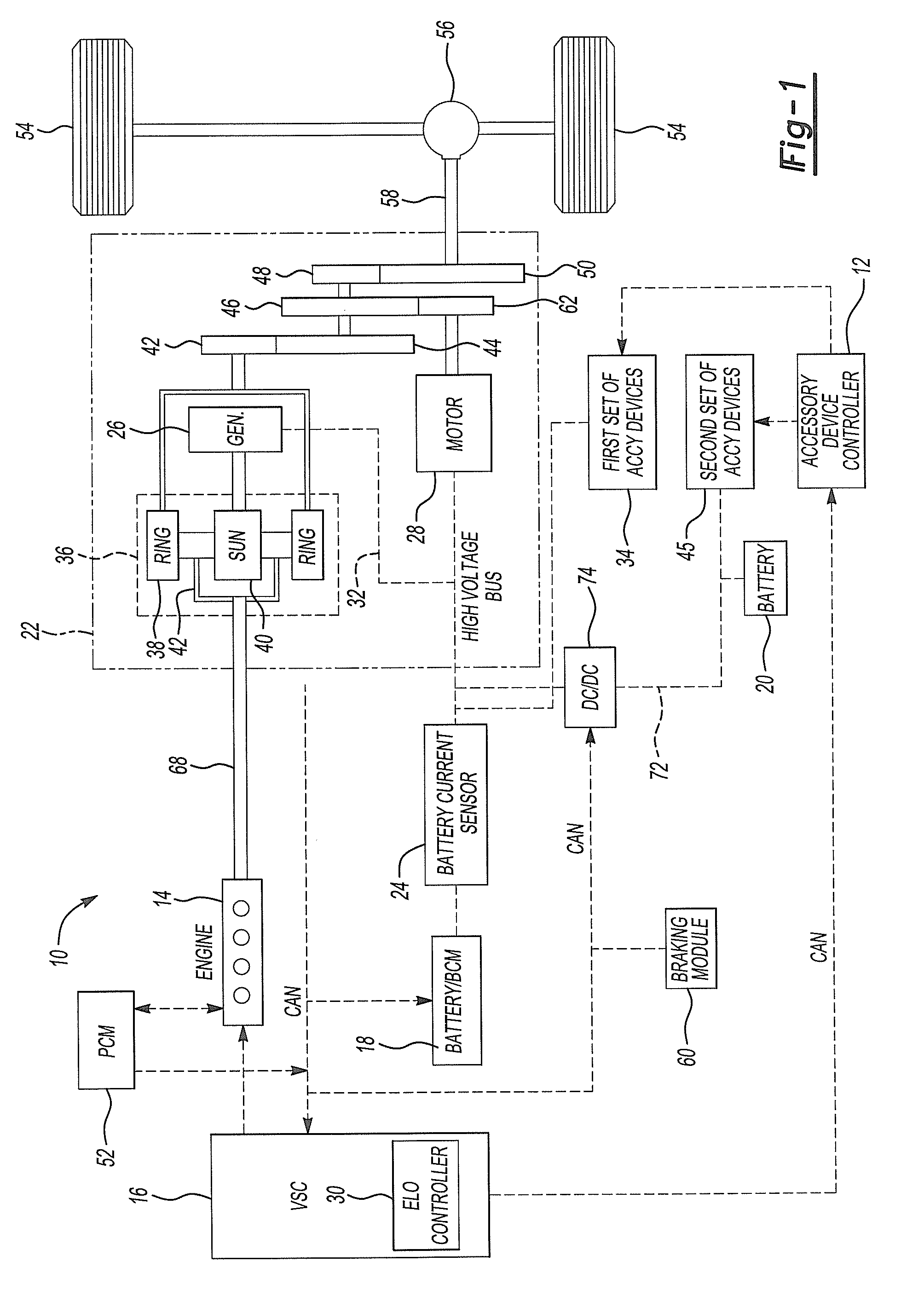

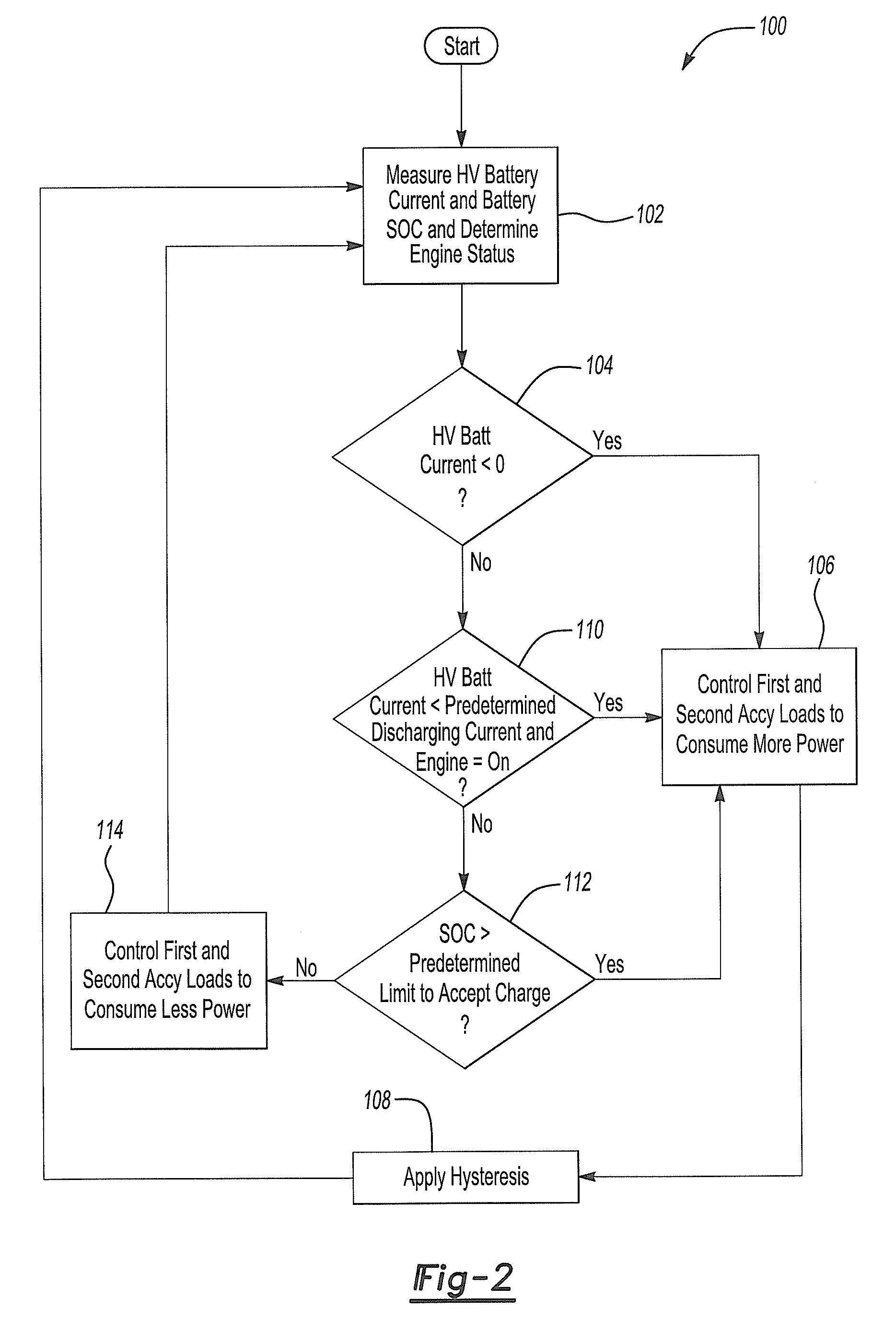

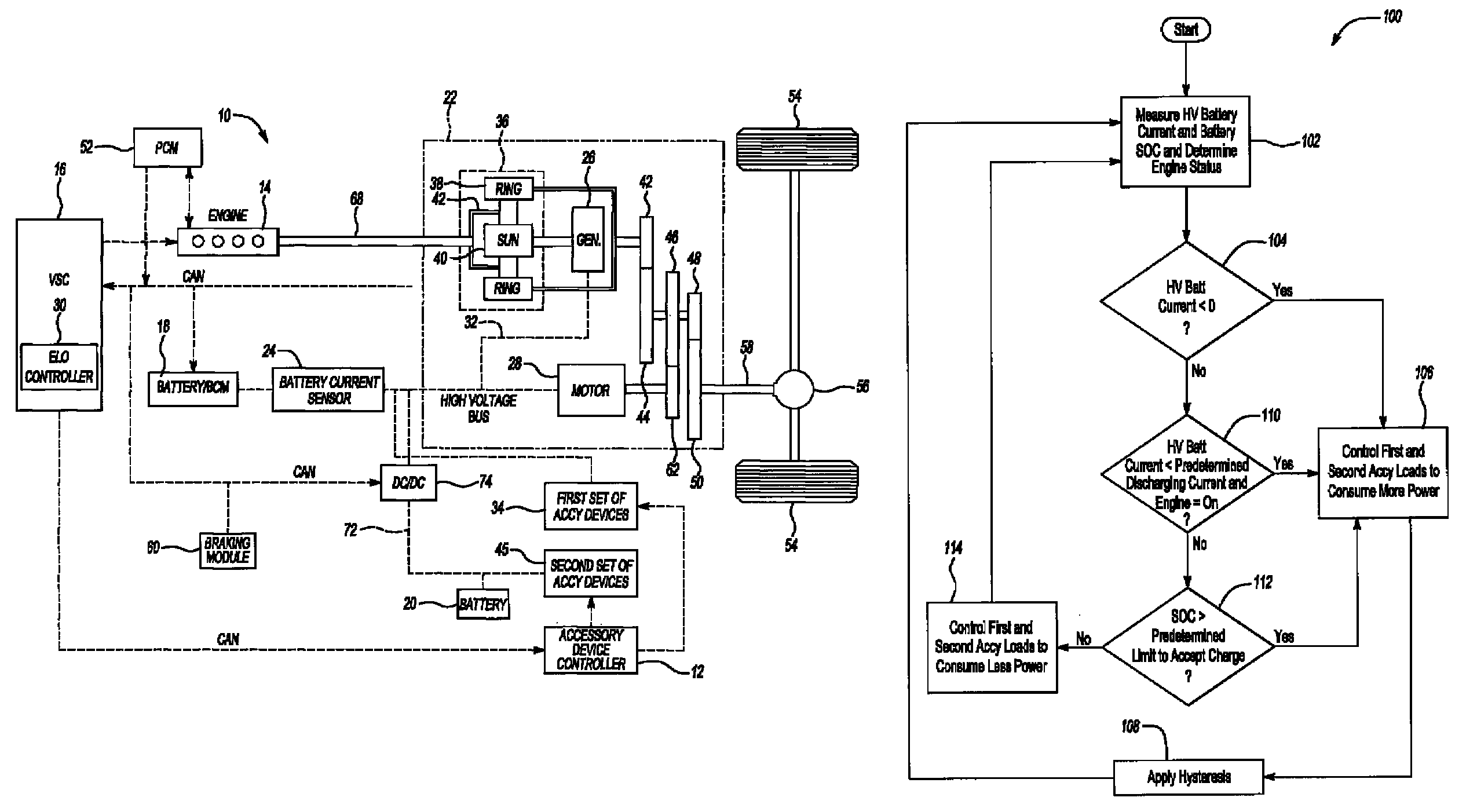

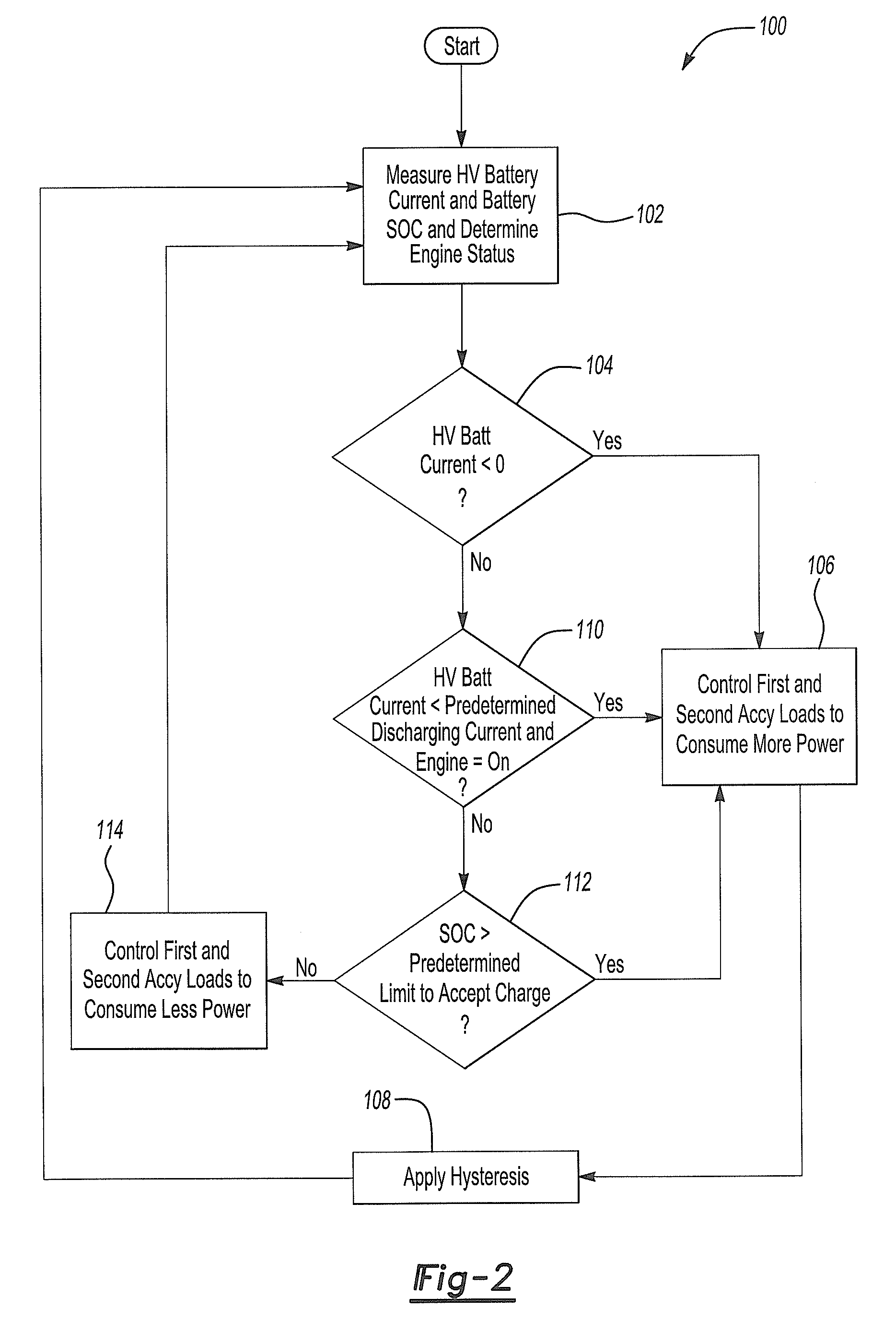

Method and apparatus to control electric power consumption

ActiveUS20080224663A1Increase powerControl power consumptionHybrid vehiclesCircuit monitoring/indicationCurrent sensorFlag signals

A system and method for controlling the electrical power consumption of an accessory device. A power transmission unit is adapted to generate electrical power. The system comprises a first controller, a current sensor and a second controller. The first controller is adapted to control the operation of the accessory device. The current sensor is configured to measure an amount of current being charged and discharged to and from the battery and generate a signal that corresponds to the measured amount of current charged and discharged to and from the battery. The second controller is configured to receive the signal from the current sensor and generate flag signal in response to detecting that current is being charged to the battery. The first controller is further adapted to control the accessory device to consume increased power from the electrical power generated by the power transmission unit in response to the flag signal.

Owner:FORD GLOBAL TECH LLC

Semiconductor integrated circuit having a (BIST) built-in self test circuit for fault diagnosing operation of a memory

According to the present invention, there is provided a semiconductor integrated circuit having: a BIST including a data generator, an address generator, a control signal generator, a result analyzer, a BIST controller, and a diagnostic data storage circuit including a first capture register which captures and outputs, in accordance with a first clock, a latest address signal and the BIST state signal output from said BIST controller while the flag signal is in as state that no fault is detected, and maintains outputs when the flag signal is in a state that a fault is detected. The semiconductor integrated circuit can further include a memory collar having a memory cell, a second capture register, a comparator, and a flag register. The semiconductor integrated circuit can perform a fault diagnosing operation of a memory by using a comparator type BIST circuit.

Owner:KK TOSHIBA

Oscillator controller incorporating a voltage-controlled oscillator that outputs an oscillation signal at a desired oscillation frequency

An oscillator controller has a phase frequency detector that compares a reference signal and a frequency-divided signal and outputs a phase difference signal; a charge pump; a loop filter that filters the phase error signal output from the charge pump and outputs an oscillation frequency controlling voltage; a voltage-controlled oscillator; a first counter that counts the number of waves of the reference signal to a desired number and outputs a first flag signal; a second counter that counts the number of waves of the frequency-divided signal to the desired number and outputs a second flag signal; a first comparator that compares the first flag signal and the second flag signal and outputs a frequency comparison signal; and a control circuit that controls the voltage-controlled oscillator, the first counter, the second counter and the frequency divider by outputting signals thereto.

Owner:KK TOSHIBA

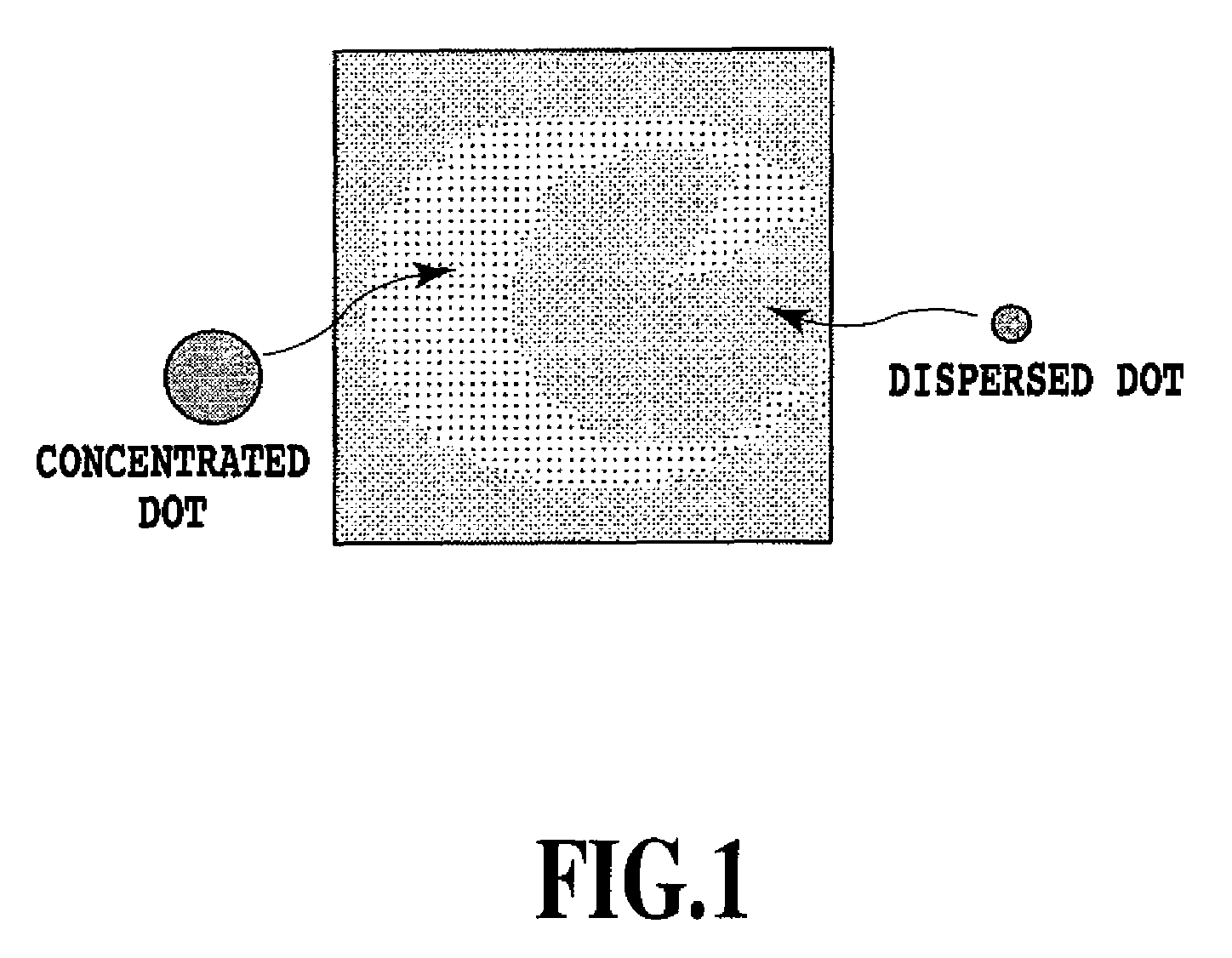

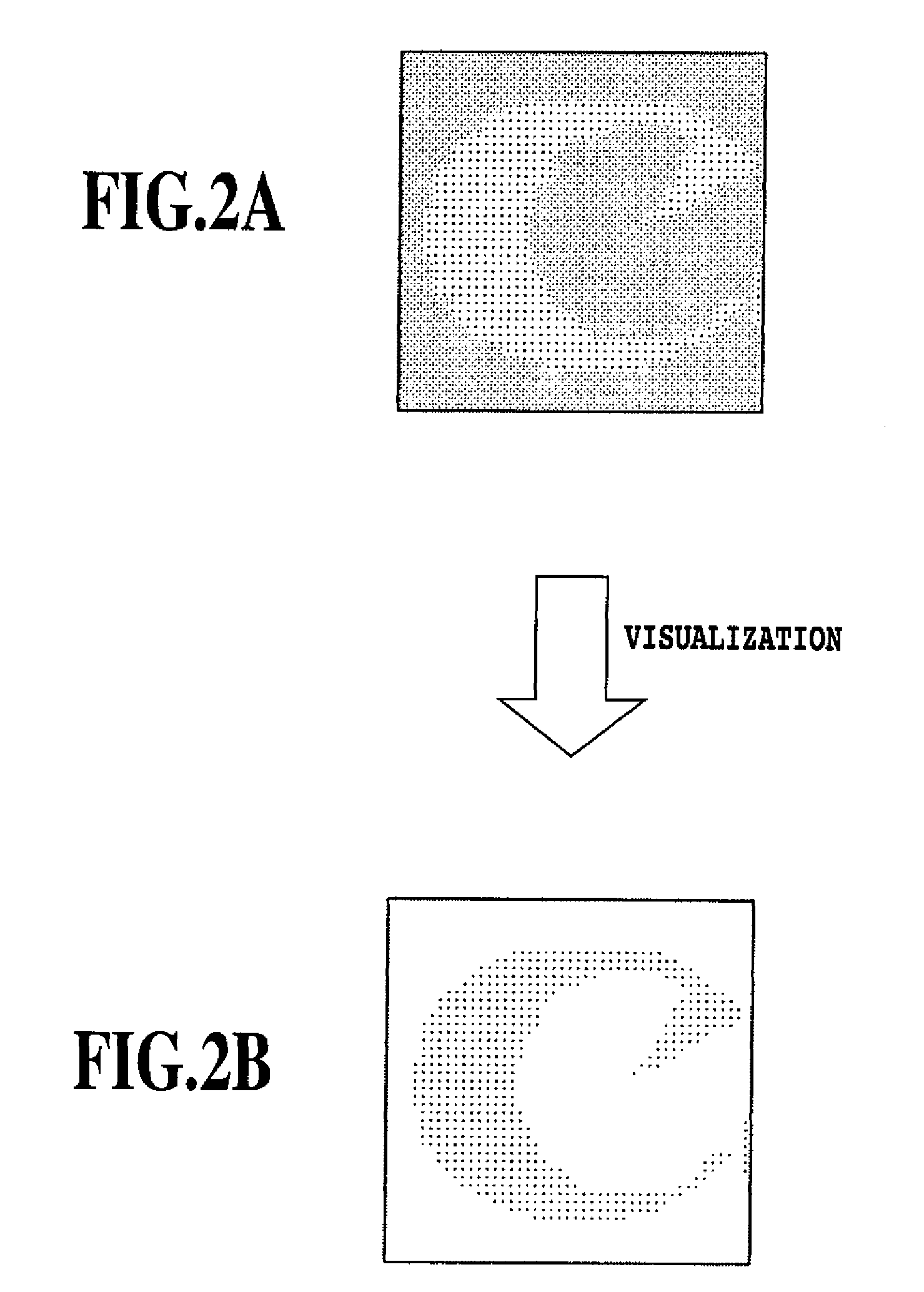

Image processing apparatus and image processing method

InactiveUS20070147929A1Improve securityHigh densityCharacter printing data arrangement from carrierError detection/correctionHard disc driveImaging processing

The image data with the copy-forgery-inhibited pattern image added and an image area flag signal stored in the hard disk drive are inputted into a thinning filter. A thinning circuit does not perform thinning processing on these pieces of data and outputs the inputted image, as it is. The filter performs processing so that an image of a copy-forgery-inhibited pattern background part may be deleted. A selector selects an image signal not passing through the filter for a latent mark of the copy-forgery-inhibited pattern whose image area flag is set as “Character,” and select an image signal subjected to the processing by the filter for a copy-forgery-inhibited pattern background part whose image area flag is set as “Photograph.” By doing so, it is possible to perform low pass processing on only the copy-forgery-inhibited pattern background part and perform processing of making a latent-mark part emerge.

Owner:CANON KK

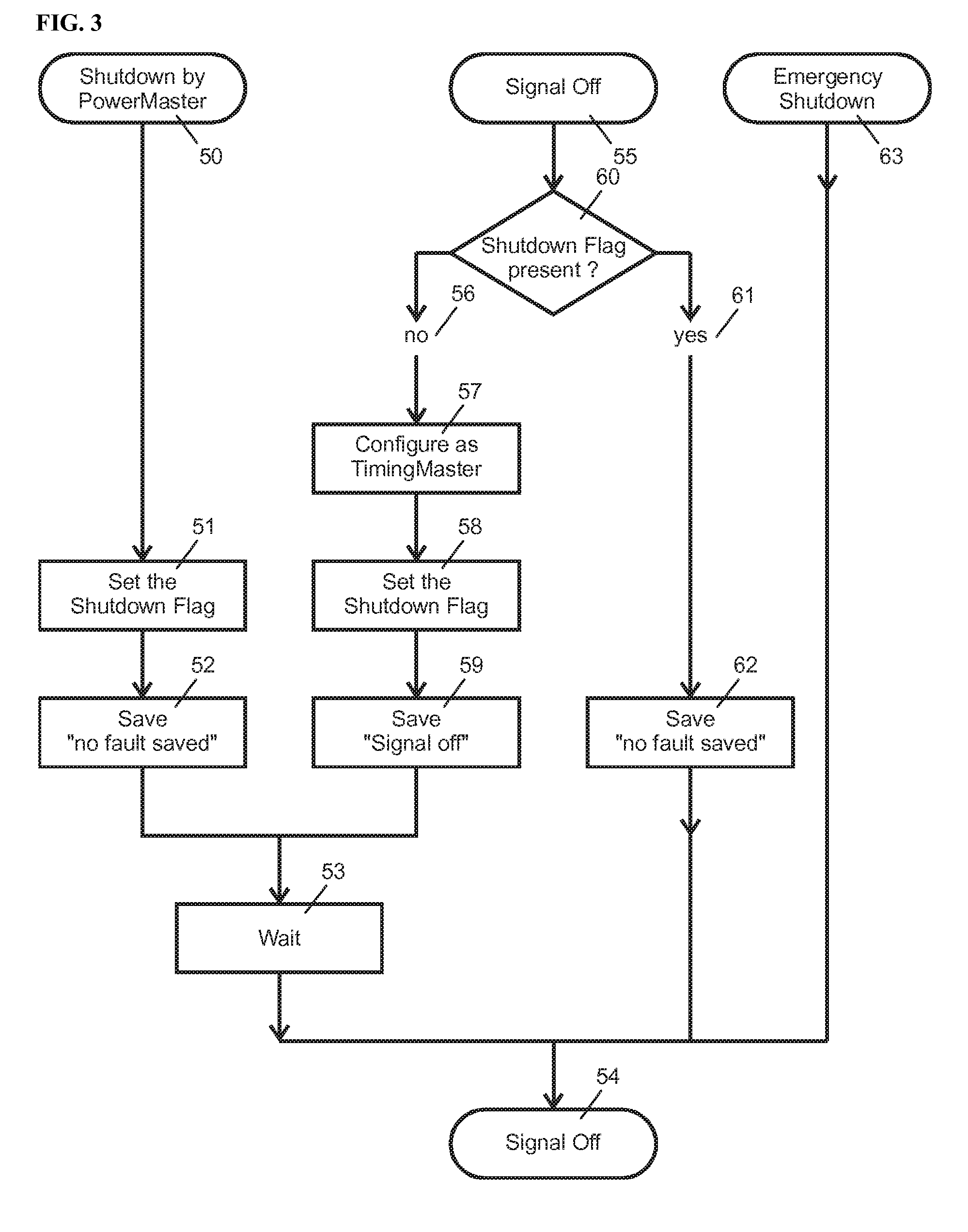

System and Method for Signal Failure Detection in a Ring Bus System

ActiveUS20100246408A1Error preventionFrequency-division multiplex detailsCommunications systemRing network

A communication system, network node, and communication port architecture are provided for transporting data across a ring network. If a network node detects a signal failure, the communication port of the network node configures itself as timing master and communicates a shutdown command to the other network nodes. In addition, the communication port sets an internal flag signaling this “signal off” event. All other network nodes, which receive the shutdown flag, do not set this internal status, and instead, save a status of “no fault saved.” Accordingly, it can be easily determined where the loss of signal occurred.

Owner:SMSC EURO

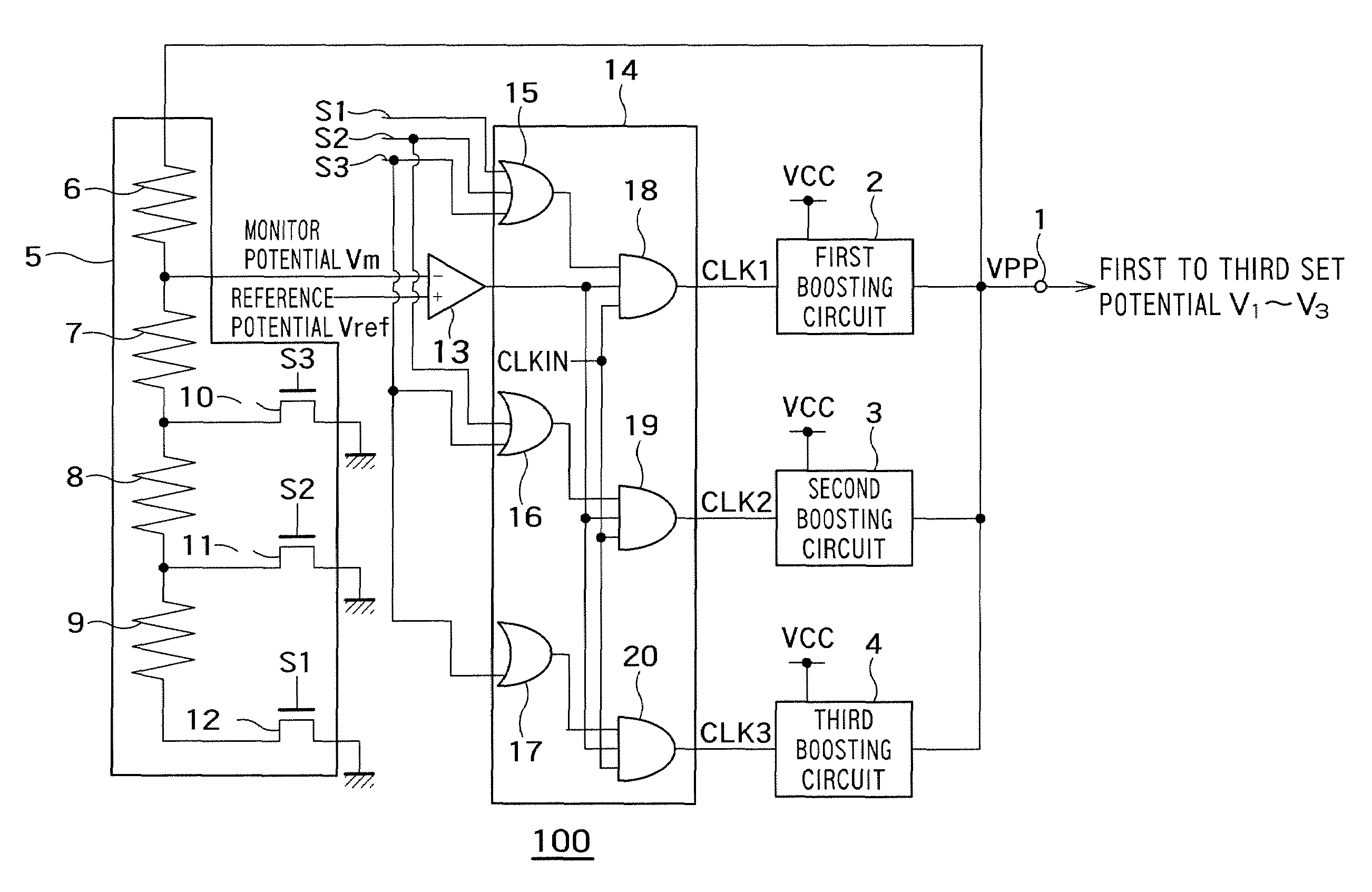

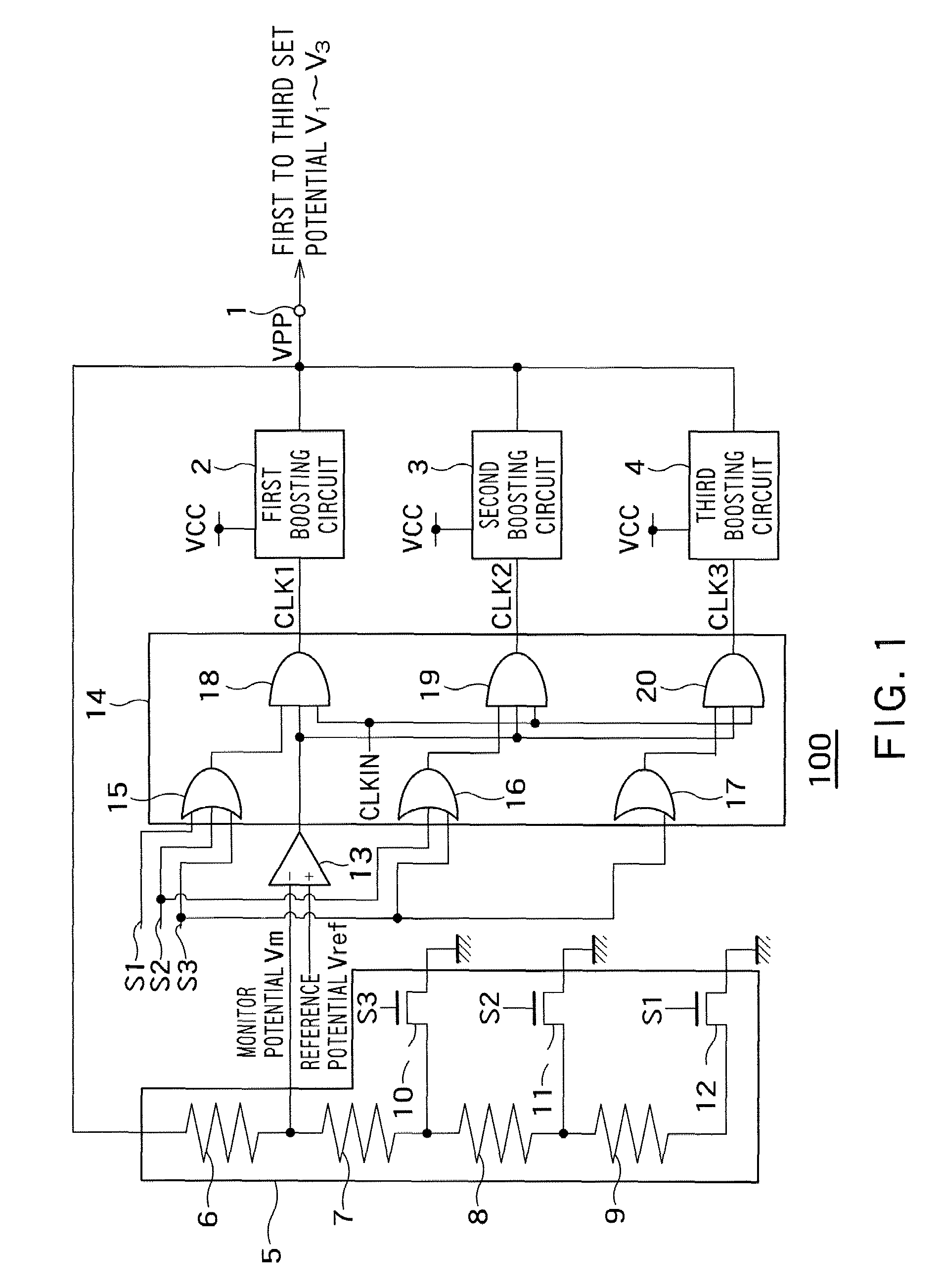

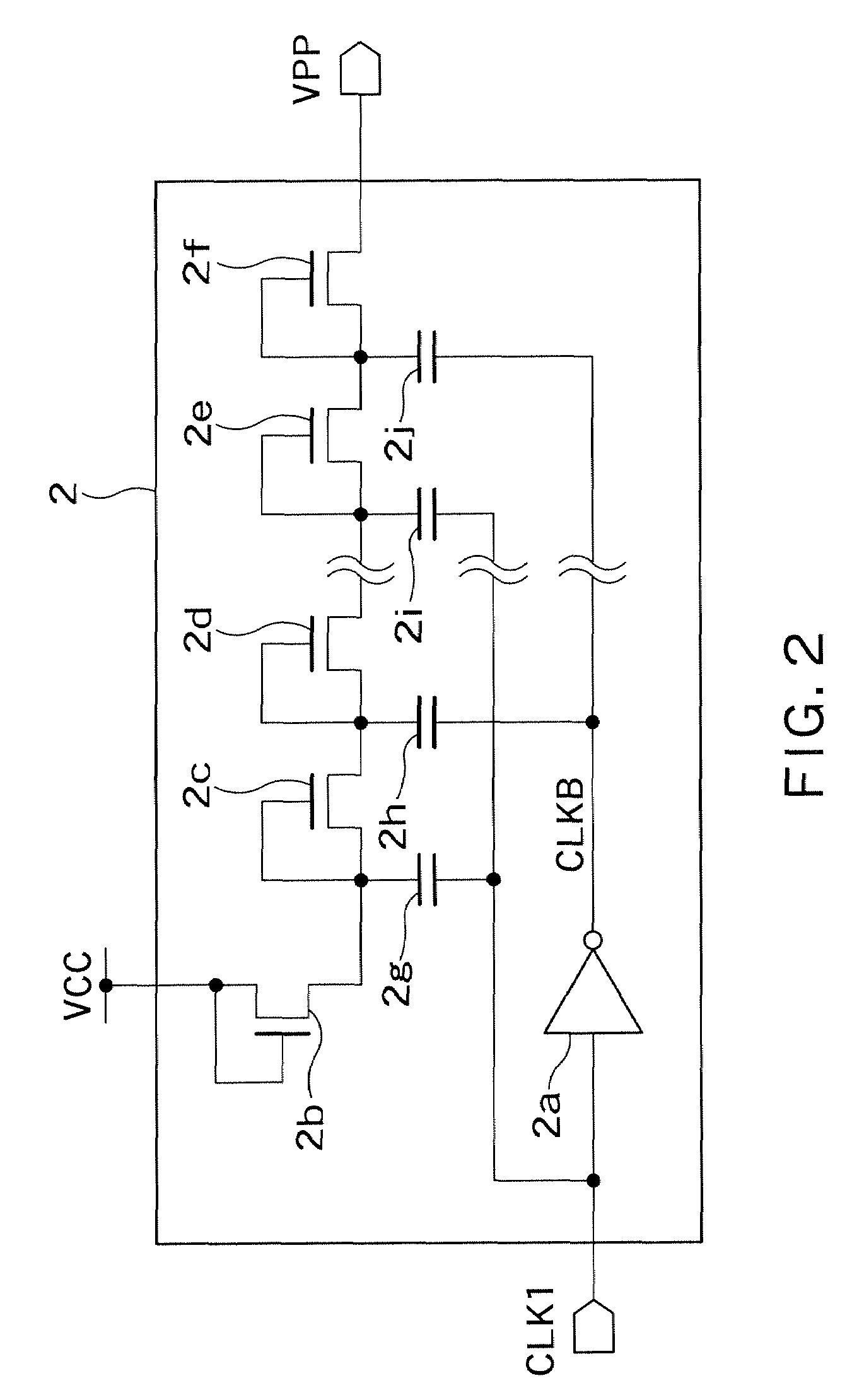

Power source circuit

A power source circuit adapted to output a first set potential which is set according to a first selection signal, or a second set potential which is set according to a second selection signal and higher than the first set potential, has an output terminal adapted to output the first set potential or the second set potential; a first boosting circuit adapted to boost a voltage supplied from a power source and to output the boosted voltage to the output terminal; a second boosting circuit adapted to boost the voltage supplied from the power source and to output the boosted voltage to the output terminal; a voltage dividing circuit adapted to output a monitor potential by dividing the output potential outputted from the output terminal according to the first selection signal, or to output a monitor potential by dividing the output potential and reducing a voltage dividing ratio of the monitor potential with respect to the output potential according to the second selection signal; a comparison amplifier adapted to compare the monitor potential with a reference potential, and to output a flag signal for activating the boosting circuit when the monitor potential is lower than the reference potential; and a logic circuit adapted to receive the flag signal from the comparison amplifier, and when receiving the first selection signal, to output a first clock signal for making the first boosting circuit perform the boosting operation, and adapted to receive the flag signal from the comparison amplifier, and when receiving the second selection signal, to output a second clock signal for making the second boosting circuit perform the boosting operation, together with the first clock signal.

Owner:KIOXIA CORP

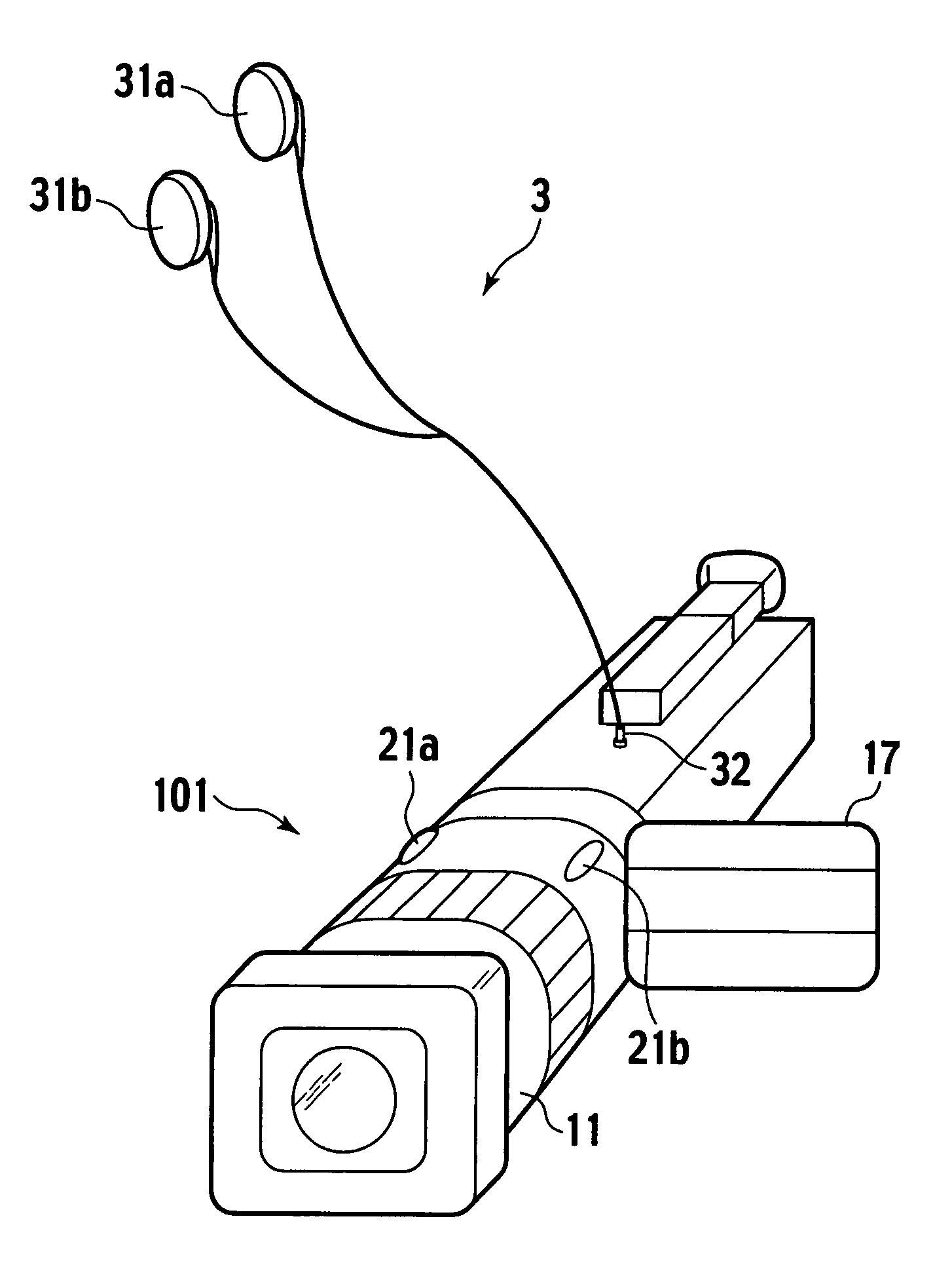

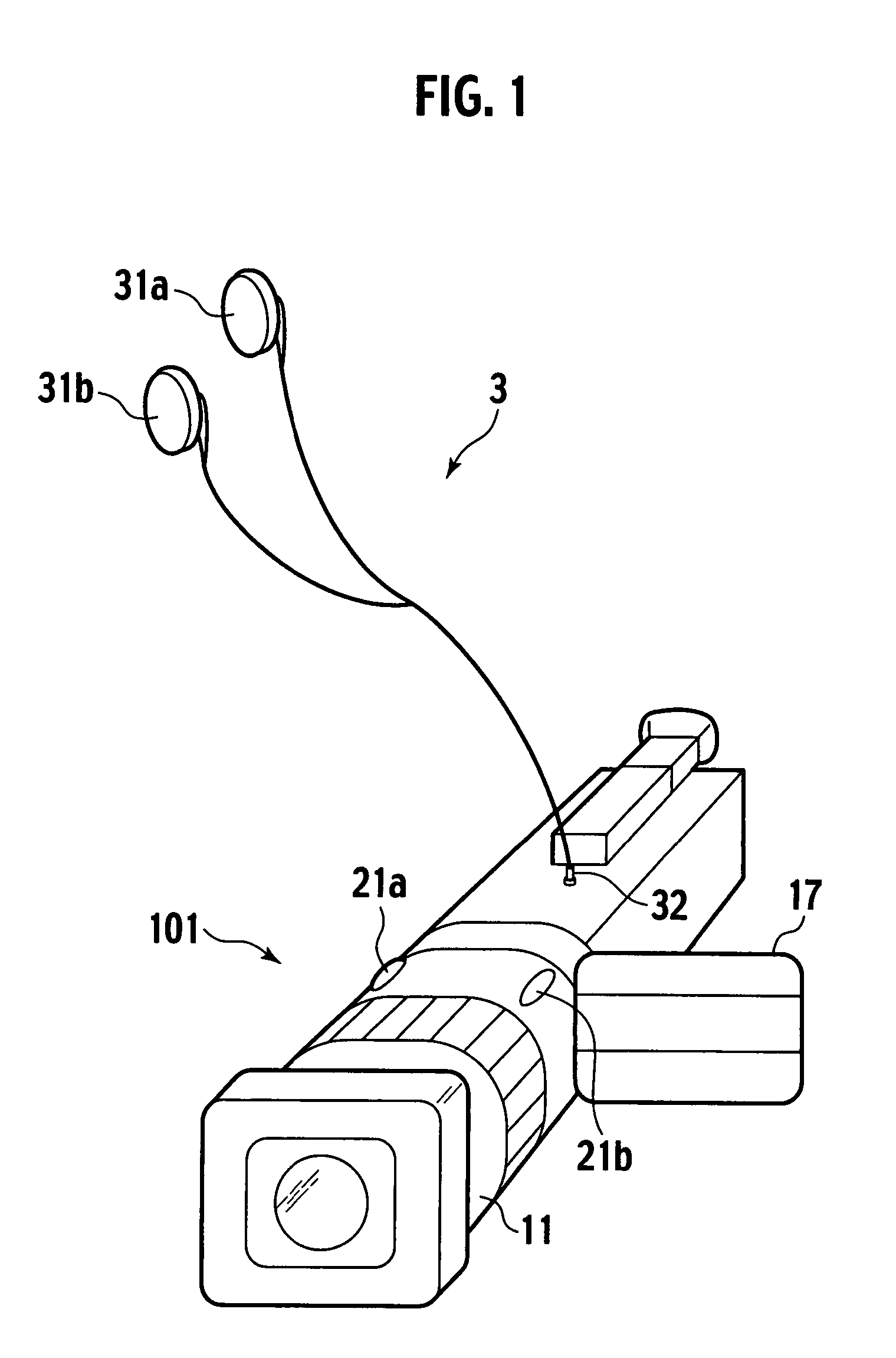

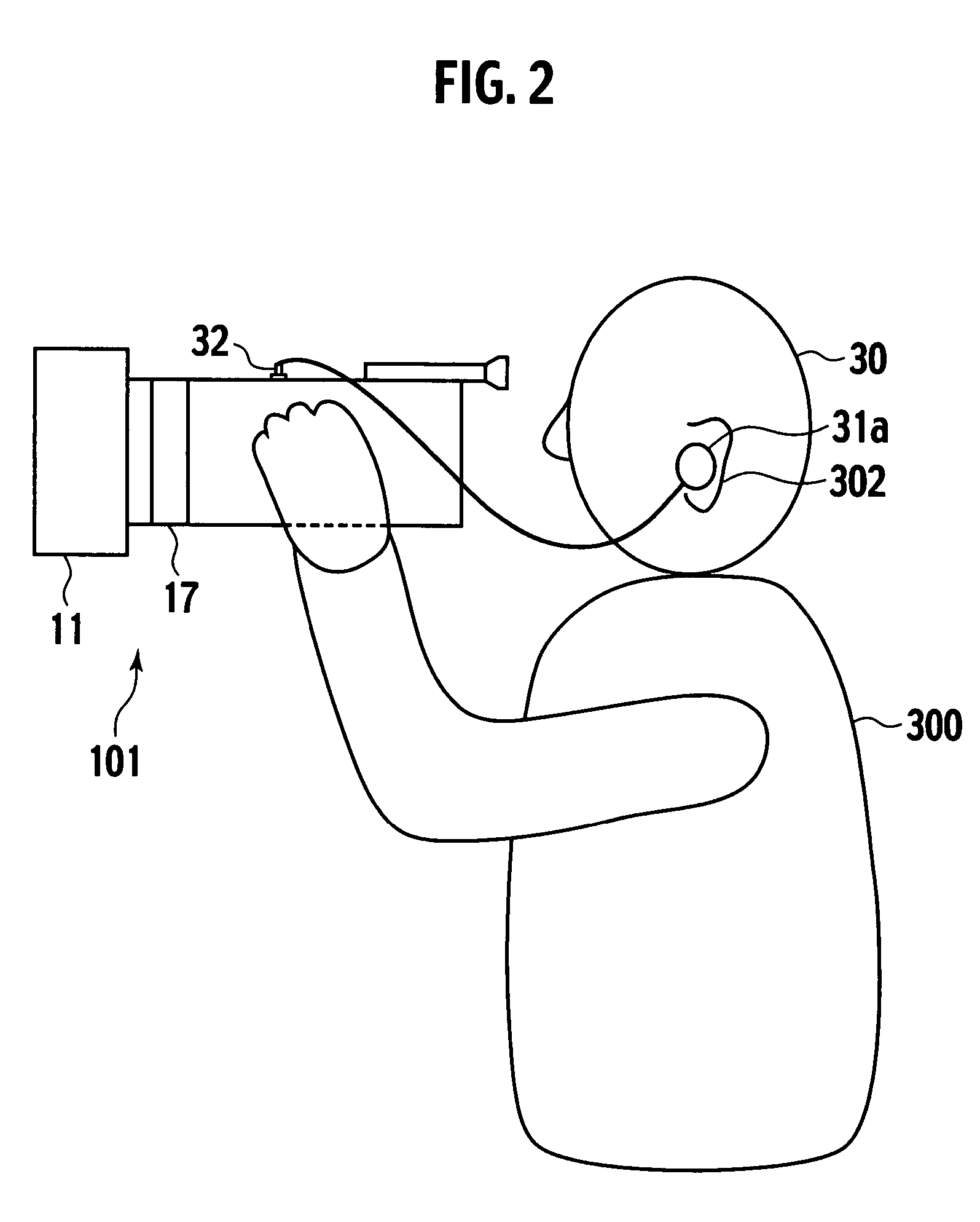

Video-audio recording apparatus and method, and video-audio reproducing apparatus and method

InactiveUS8045840B2Television system detailsSubstation/switching arrangement detailsFlag signalsComputer science

A video-audio recording and reproducing apparatus (101) has a built-in stereo microphone (21a, 21b) and an external microphone connection terminal (32). The external microphone connection terminal (32) is connected to a binaural microphone (3) to be attached to the ears of a photographer (300). When the binaural microphone (3) is used to collect ambient sounds, an audio signal to be recorded on a recording medium is switched from an audio signal from the built-in stereo microphone (21a, 21b) to a binaural audio signal from the binaural microphone (3). The photographer (300) puts the binaural microphone (3 (31a, 31b)) on his or her ears and collects ambient sounds around the photographer (300) including a sound emanating from an object. The object is photographed with a camera unit (11). The recording medium records the binaural audio signal, a photographed video signal, and a binaural flag signal.

Owner:JVC KENWOOD CORP

Systems and Methods for Detecting and Thwarting Unauthorized Access and Hostile Attacks on Secured Systems

ActiveUS20130055416A1Prevent unauthorized accessError detection/correctionSemiconductor/solid-state device detailsEngineeringNumber generator

Various embodiments of the present invention relates to systems, devices and methods of detecting tampering and preventing unauthorized access by incorporating programmability and randomness into a process of coupling, driving and sensing conductive wires that are arranged above sensitive areas in a secured system. Such a tampering detection system comprises a security mesh network, a random number generator, a security controller and a security monitor. The security mesh network includes a plurality of security elements made from the conductive wires. The security controller selects a subset of security elements, forms a security array, and generates a driving stimulus. The security monitor selects a SENSE node, monitors an output at the SENSE node, and generates a flag signal indicating the presence of a tampering attempt. Programmability and randomness are introduced to at least one of the system parameters including array configuration, driving stimulus, SENSE node, and detection mode via random numbers.

Owner:MAXIM INTEGRATED PROD INC

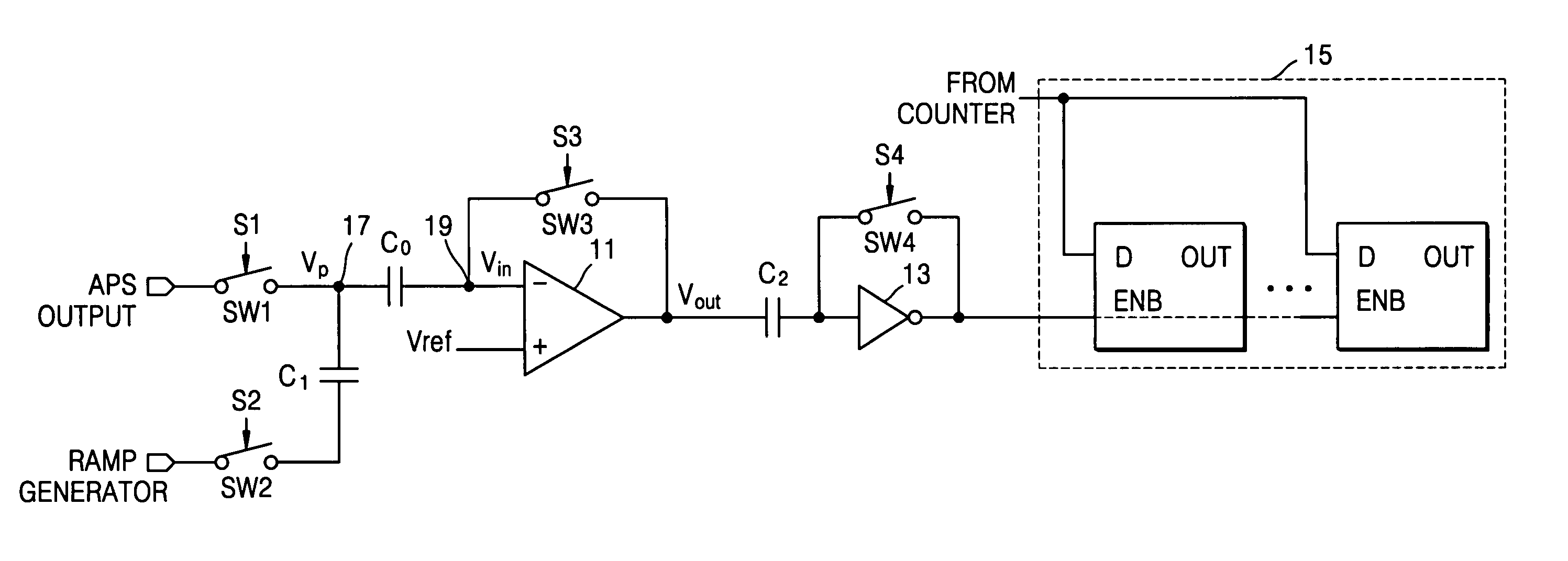

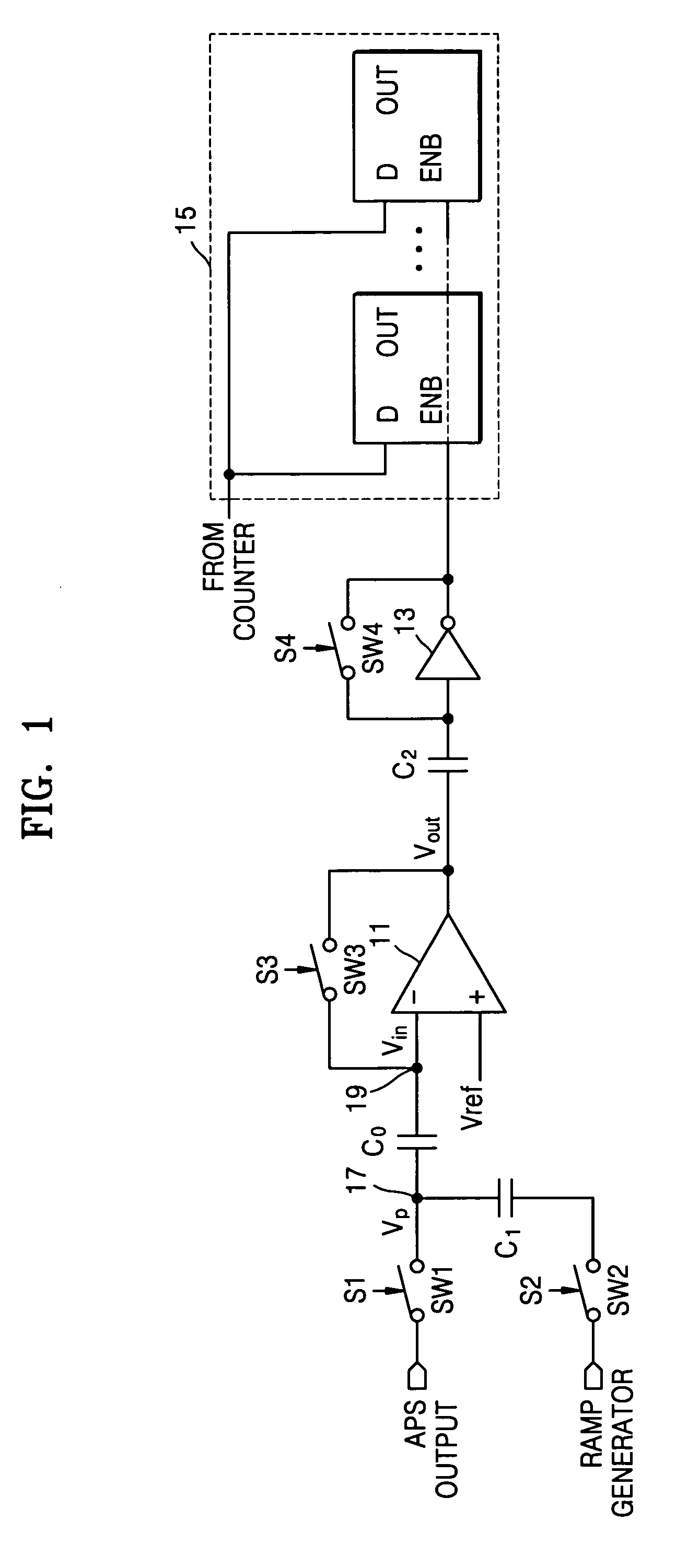

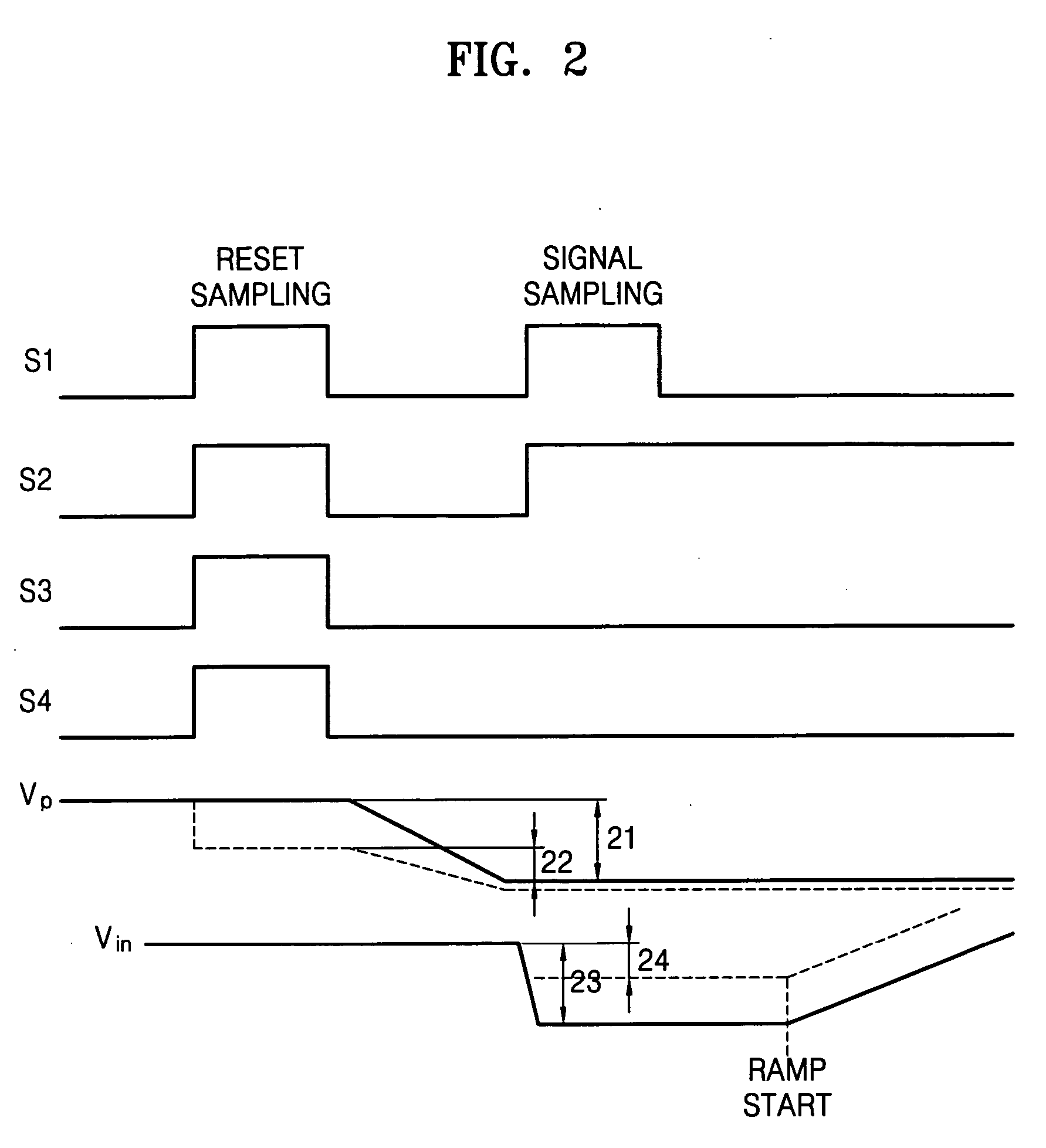

Column analog-to-digital converter of a CMOS image sensor for preventing a sun black effect

ActiveUS20060170803A1InhibitionTelevision system detailsElectric signal transmission systemsCMOSDigital data

A column analog-to-digital (ADC) circuit for preventing a sun black effect in a CMOS image sensor (CIS) is provided. The ADC circuit includes: a comparator having a signal voltage input port and a reference voltage input port, comparing a reset voltage output from one of a plurality of CIS pixels with a reference voltage in a reset sampling period, and outputting an overflow sensing signal when the reset voltage is lower than the reference voltage; and a digital converter converting the output of the comparator into digital data, wherein the digital converter comprises a first latch storing the overflow sensing signal and outputting a flag signal indicating an overflow in response to the overflow sensing signal in a signal sampling period, when the overflow sensing signal is output from the comparator in a first portion of the reset sampling period.

Owner:SAMSUNG ELECTRONICS CO LTD

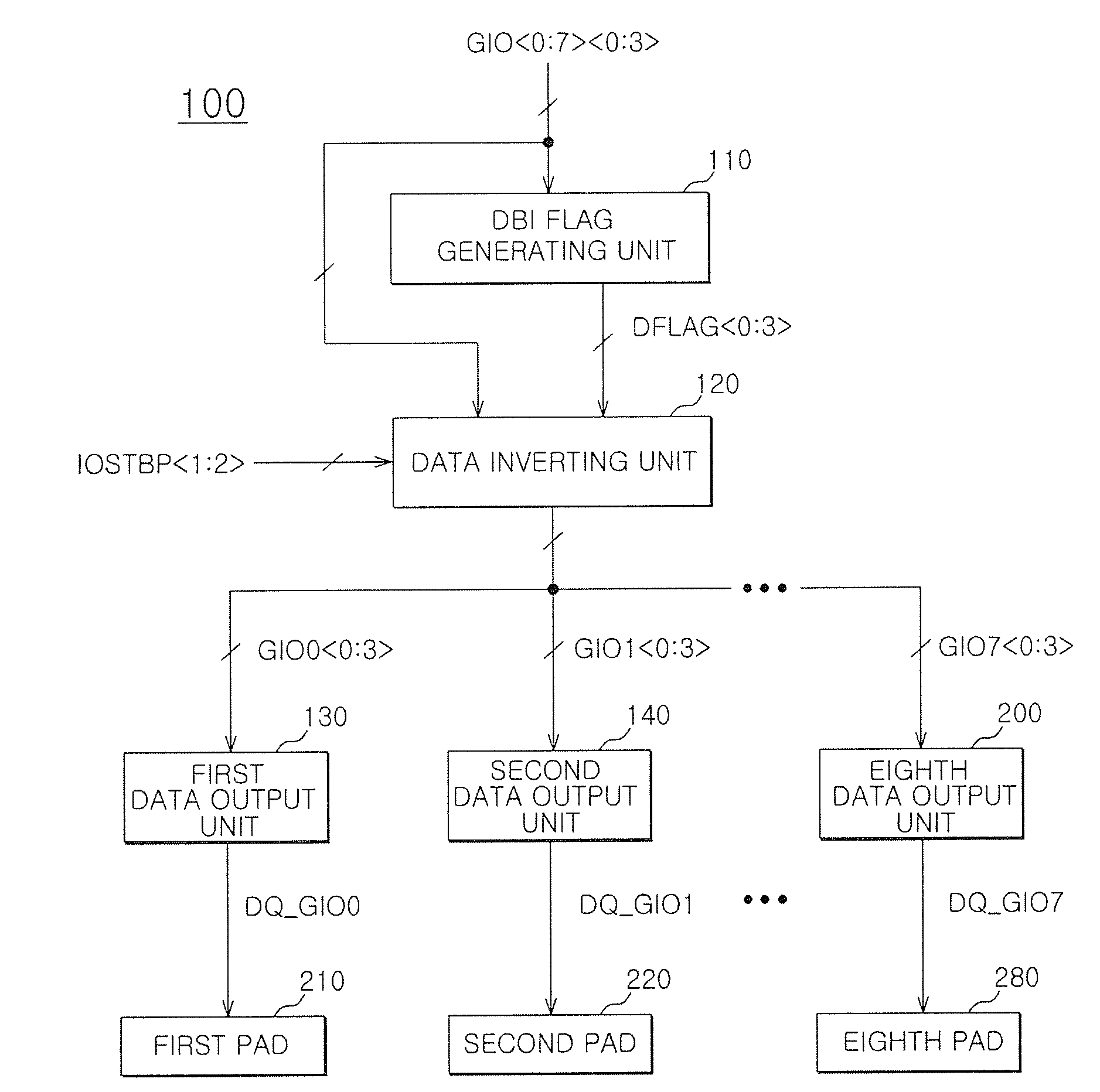

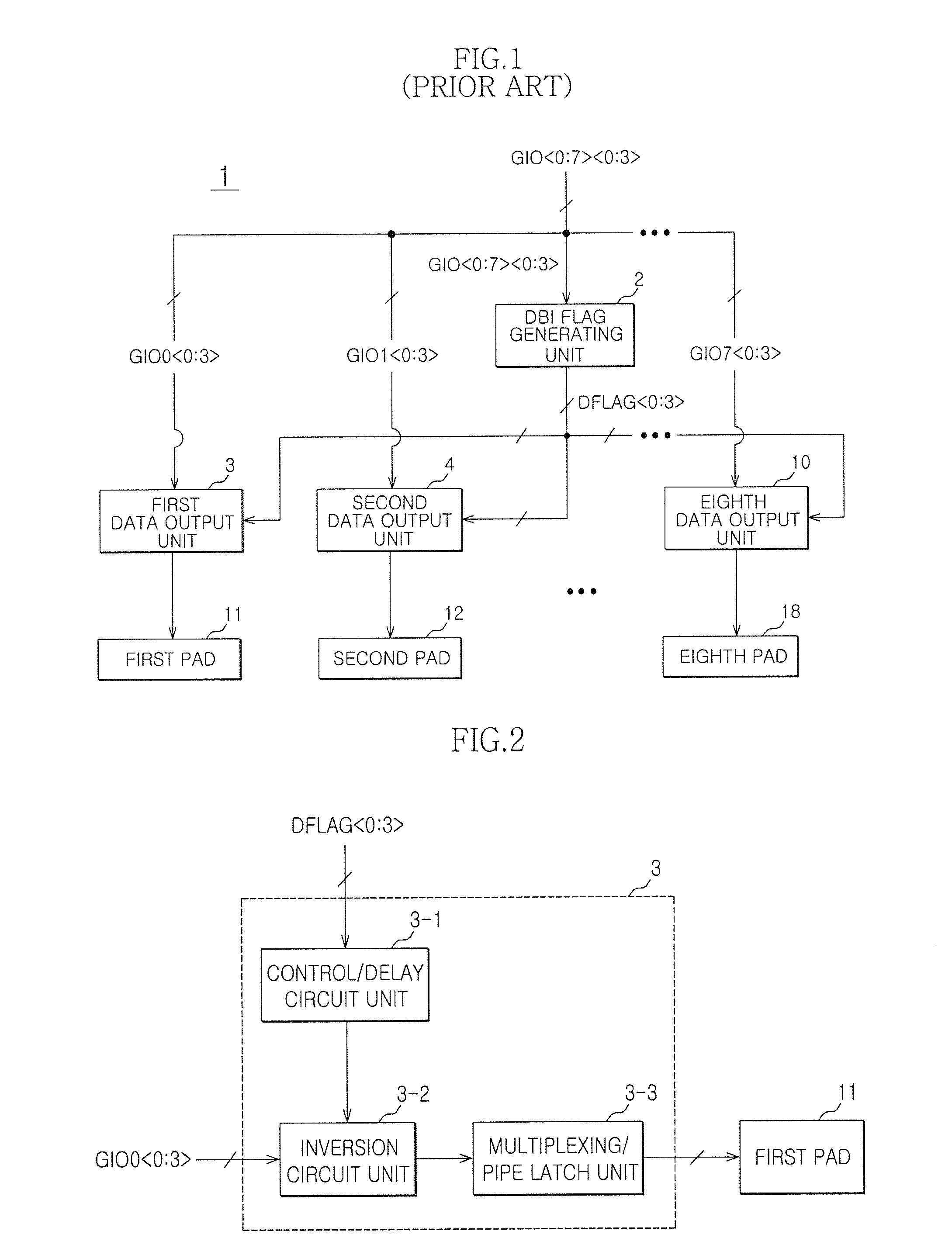

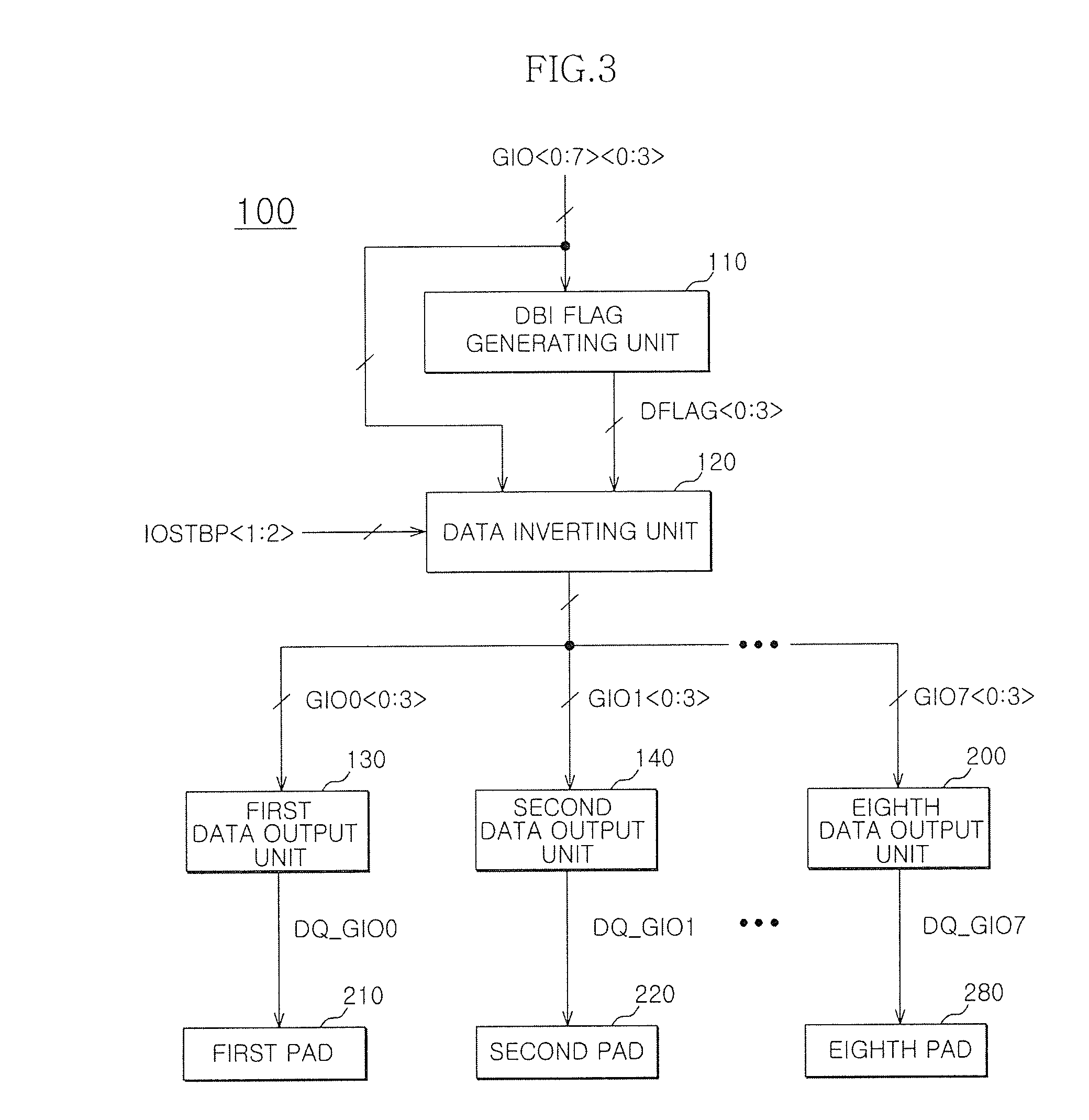

Semiconductor integrated circuit with data bus inversion function

A semiconductor integrated circuit includes a data bus inversion (DBI) flag generating unit to generate DBI flag signals using a plurality of output data sets, a data inverting unit to invert the plurality of output data sets according to the DBI flag signals and transmit the plurality of output data sets through global transmission lines, and a plurality of data output units to output the plurality of output data sets, which are transmitted through the global transmission lines by pads.

Owner:SK HYNIX INC

Method and apparatus to control electric power consumption

A system and method for controlling the electrical power consumption of an accessory device. A power transmission unit is adapted to generate electrical power. The system comprises a first controller, a current sensor and a second controller. The first controller is adapted to control the operation of the accessory device. The current sensor is configured to measure an amount of current being charged and discharged to and from the battery and generate a signal that corresponds to the measured amount of current charged and discharged to and from the battery. The second controller is configured to receive the signal from the current sensor and generate flag signal in response to detecting that current is being charged to the battery. The first controller is further adapted to control the accessory device to consume increased power from the electrical power generated by the power transmission unit in response to the flag signal.

Owner:FORD GLOBAL TECH LLC

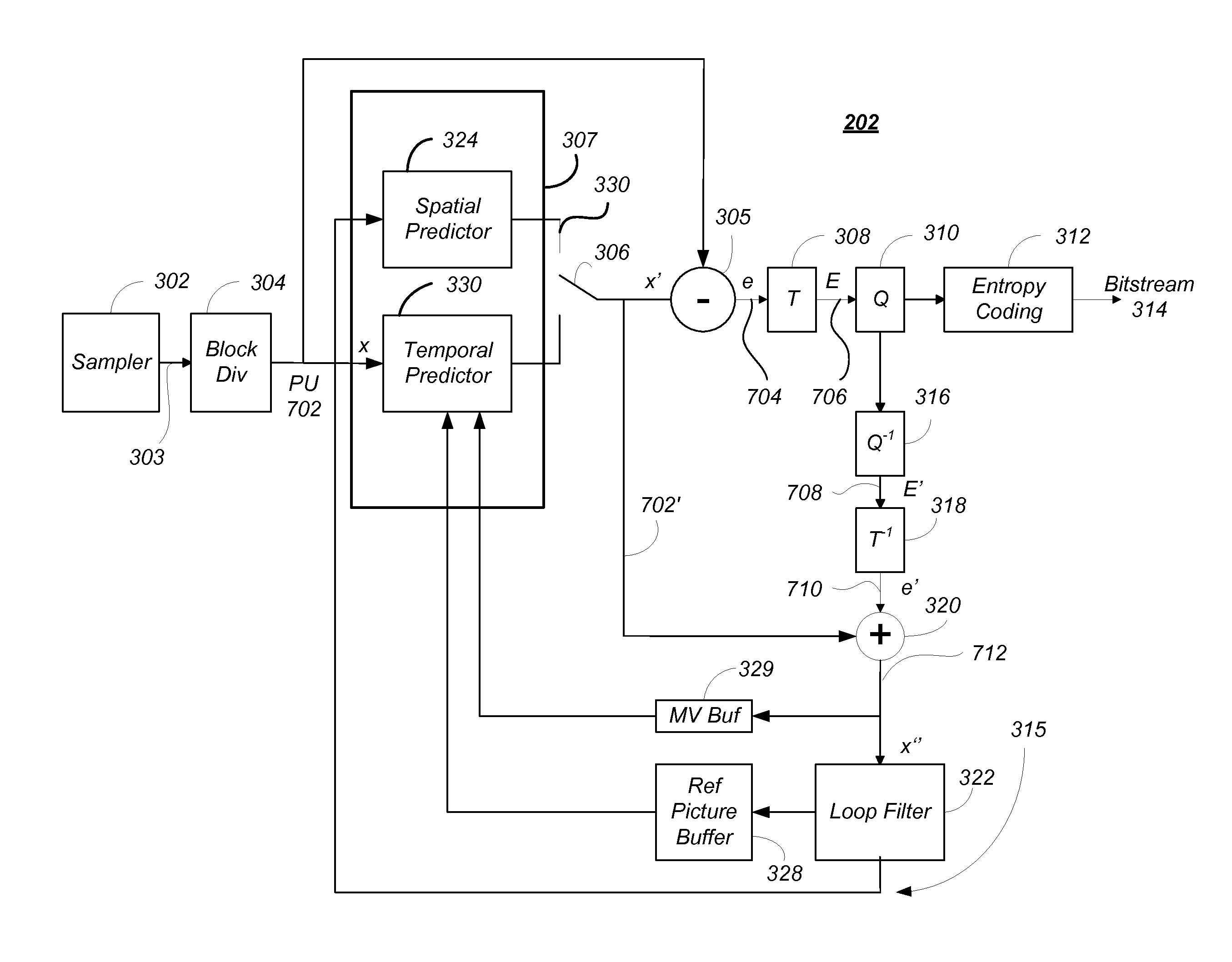

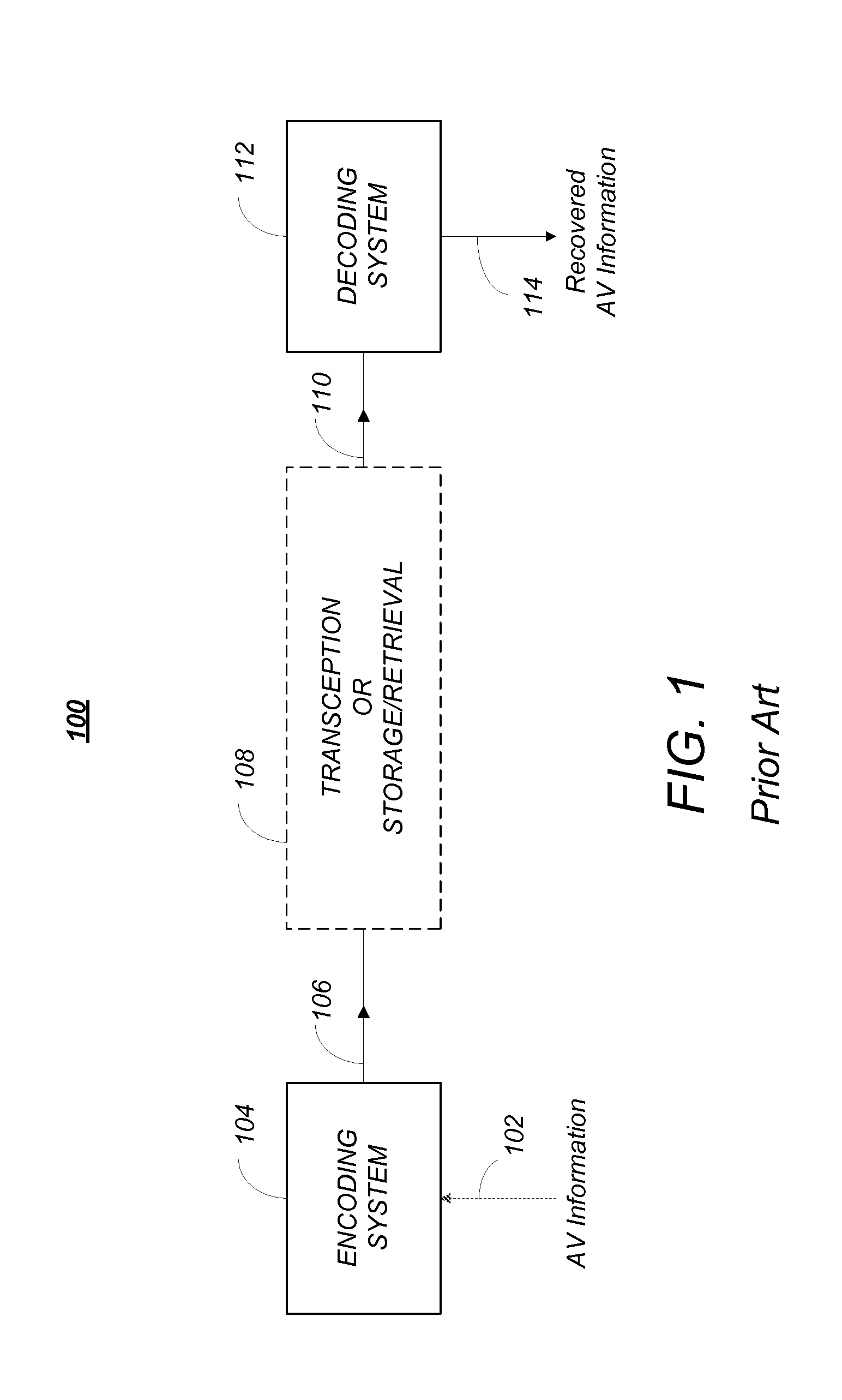

Modification of picture parameter set (PPS) for hevc extensions

InactiveUS20150195574A1Color television with pulse code modulationColor television with bandwidth reductionFlag signalsEmbedded system

A method, apparatus, article of manufacture, and a memory structure for signaling extension functions used in decoding a sequence comprising a plurality of pictures, each picture processed at least in part according to a picture parameter set is disclosed. In one embodiment, the method comprises reading a first extension flag signaling a first extension function in the processing of the sequence and determining if the first extension flag has a first value. Further, the method reads a second extension flag signaling a second extension function in the processing of the sequence and performs the second extension function according to the read second extension flag only if the first extension flag has a first value.

Owner:ARRIS ENTERPRISES LLC

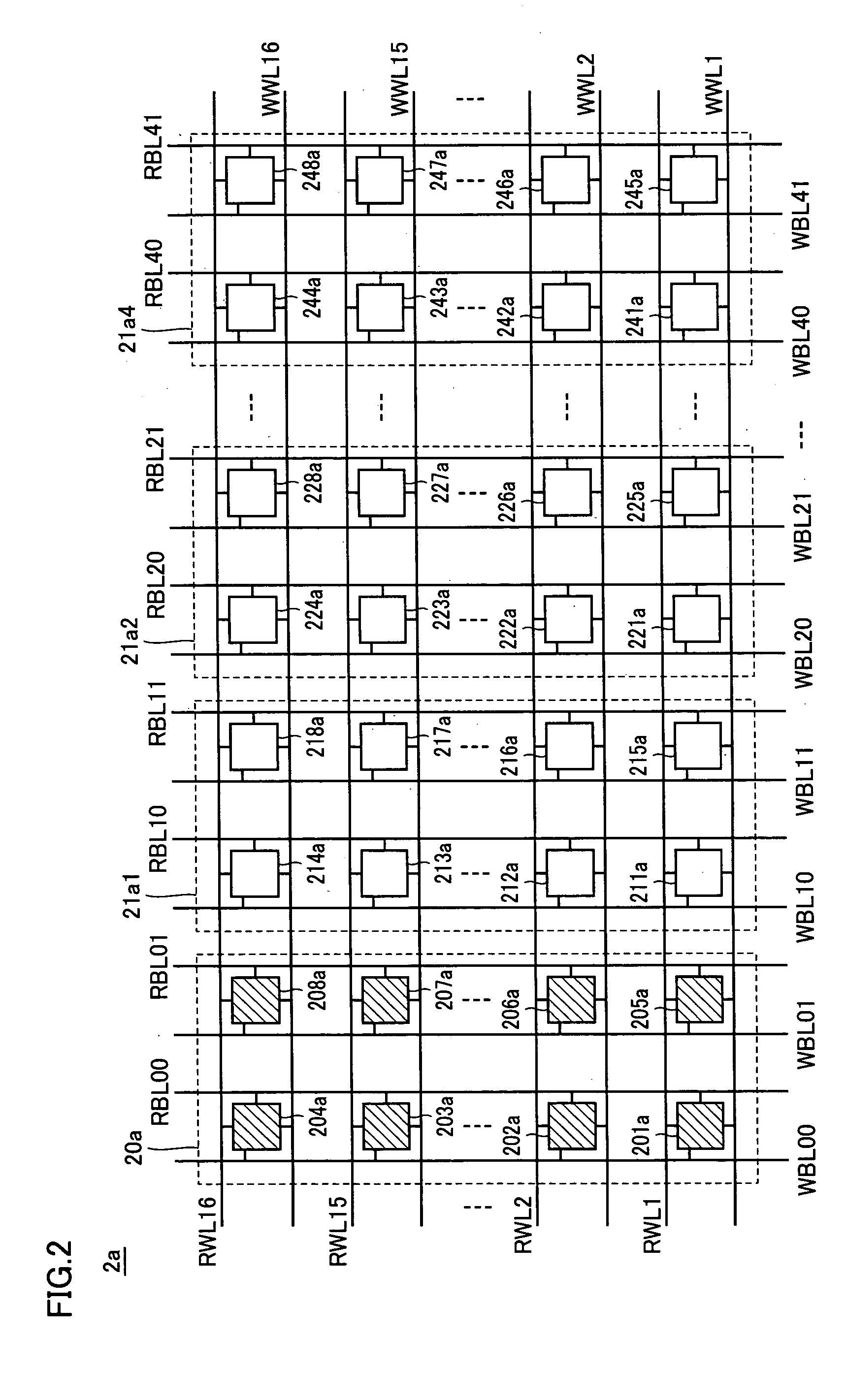

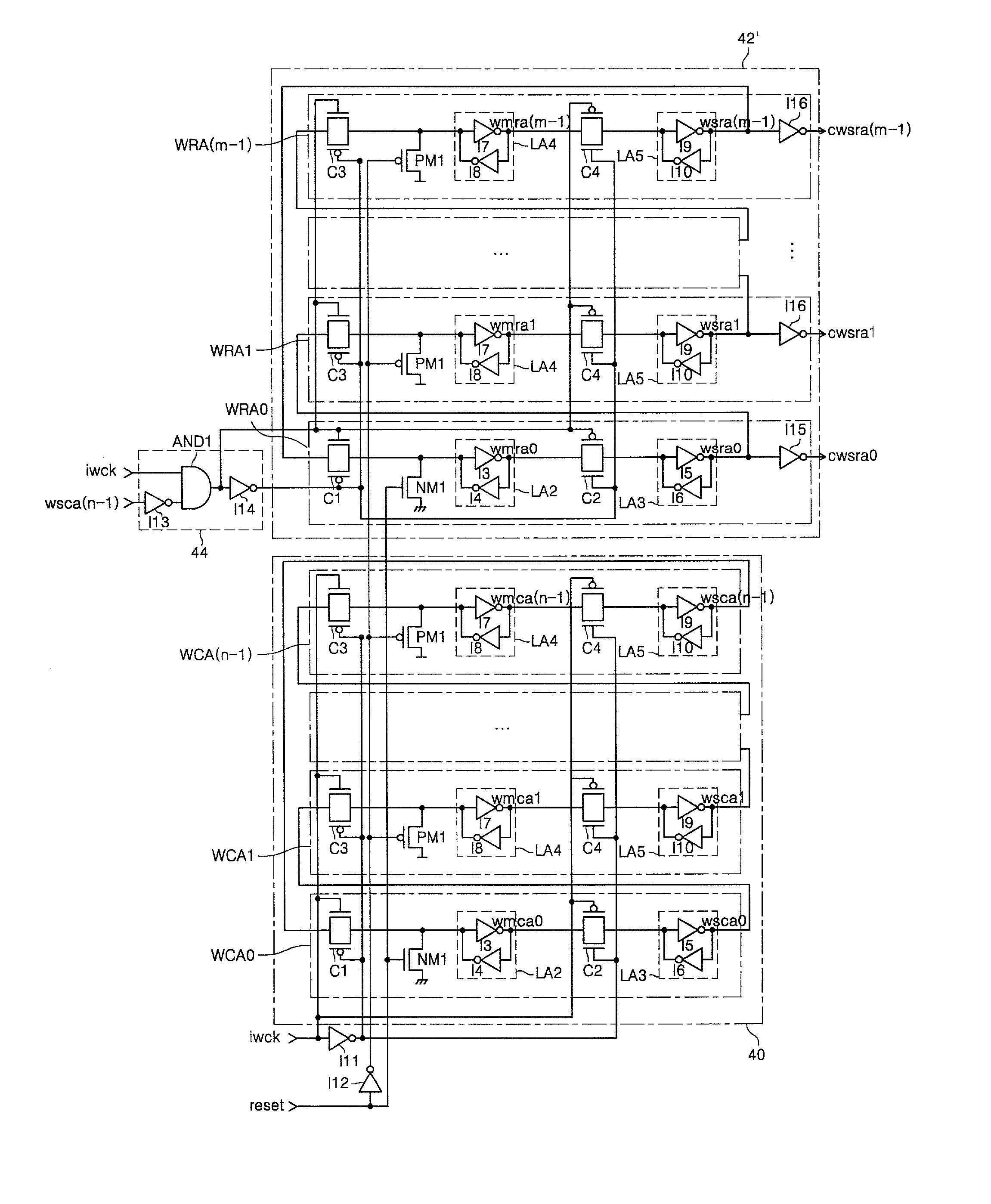

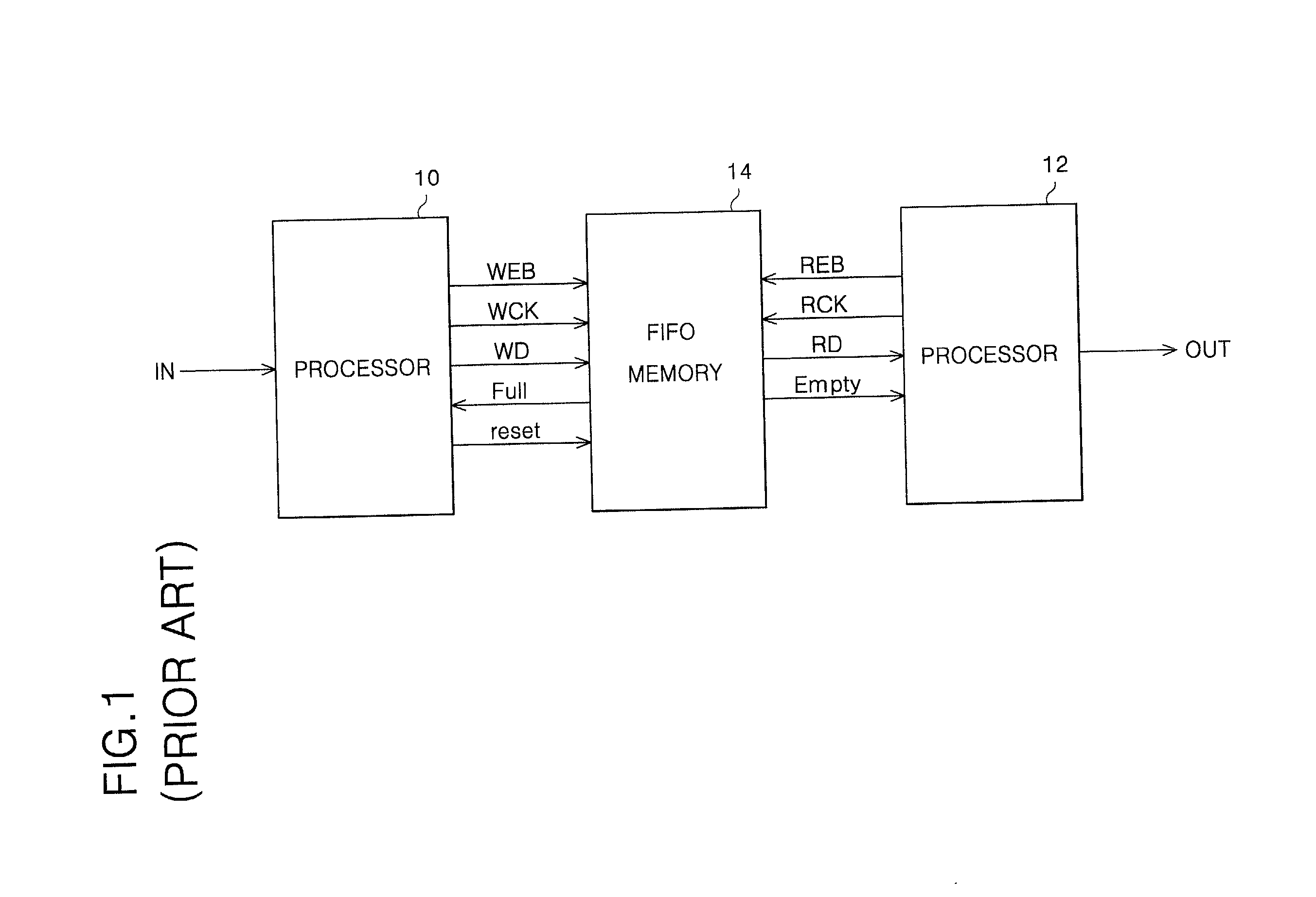

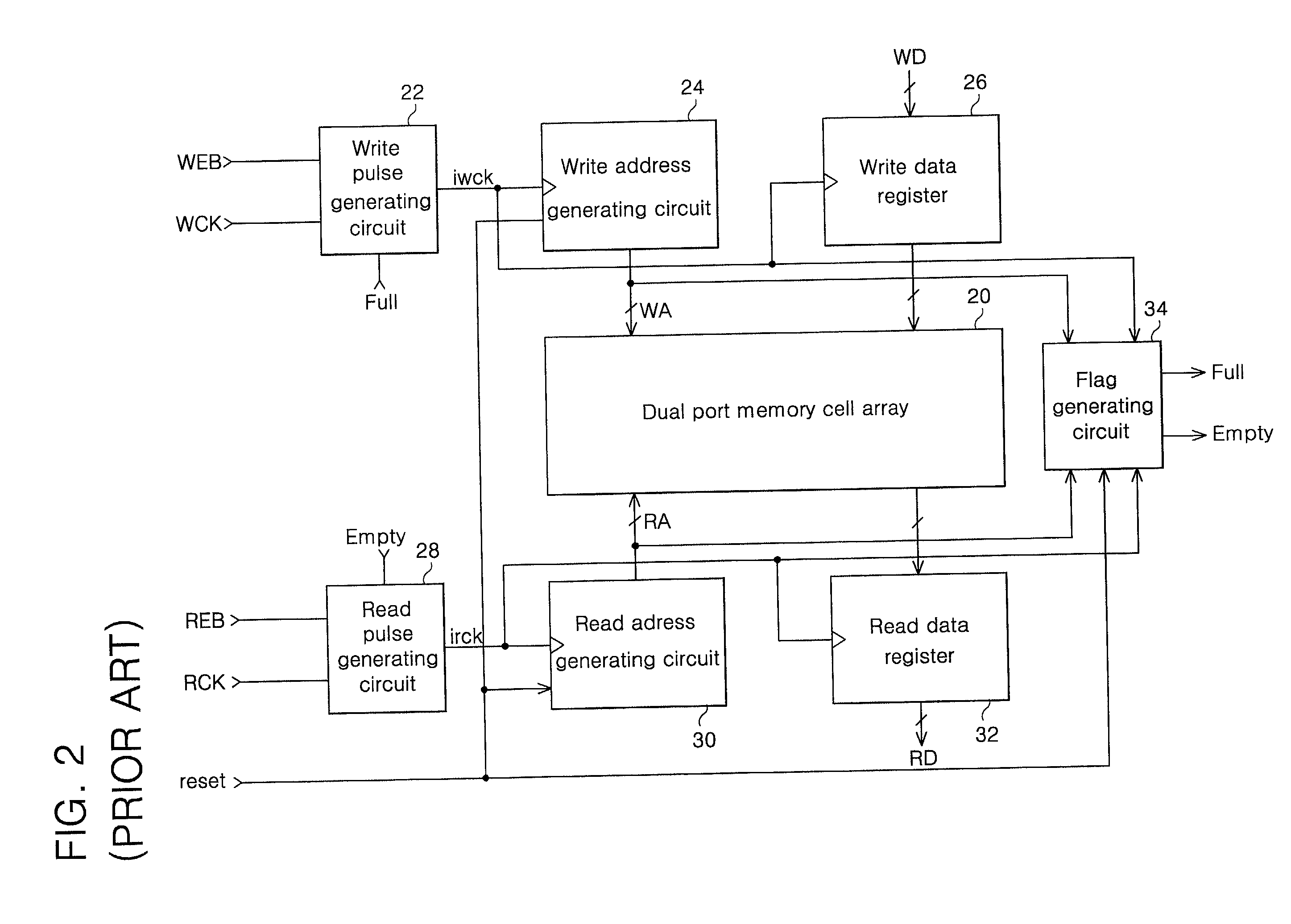

First-in first-out memory device and method of generating flag signal in the same

InactiveUS20020080672A1Memory adressing/allocation/relocationDigital storageFifo memoryComputer science

A FIFO memory device includes a write address generating means generating a write address in response to a write clock signal and a read address generating means generating a read address in response to a read clock signal. A memory cell array includes a plurality of memory cells arranged between a plurality of write and read word lines and a plurality of write and read bit lines, the memory cell array storing write data in response to the write address and outputting read data in response to the read address. A flag signal generating means compares a next write address with a current read address to generate a full flag signal in response to the write clock signal when the next write address and the current read address are equal, and compares a current write address with a next read address to generate an empty flag signal in response to the read clock signal when the current write address and the next read address are equal.

Owner:SAMSUNG ELECTRONICS CO LTD