Controllable test vector generator based on linear feedback shift register

A linear feedback shift and test vector technology, applied in static memory, instruments, etc., can solve the problems of high test power consumption, high hardware overhead, increased test time and power consumption, etc., and achieve low test cost and low hardware overhead. Effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment

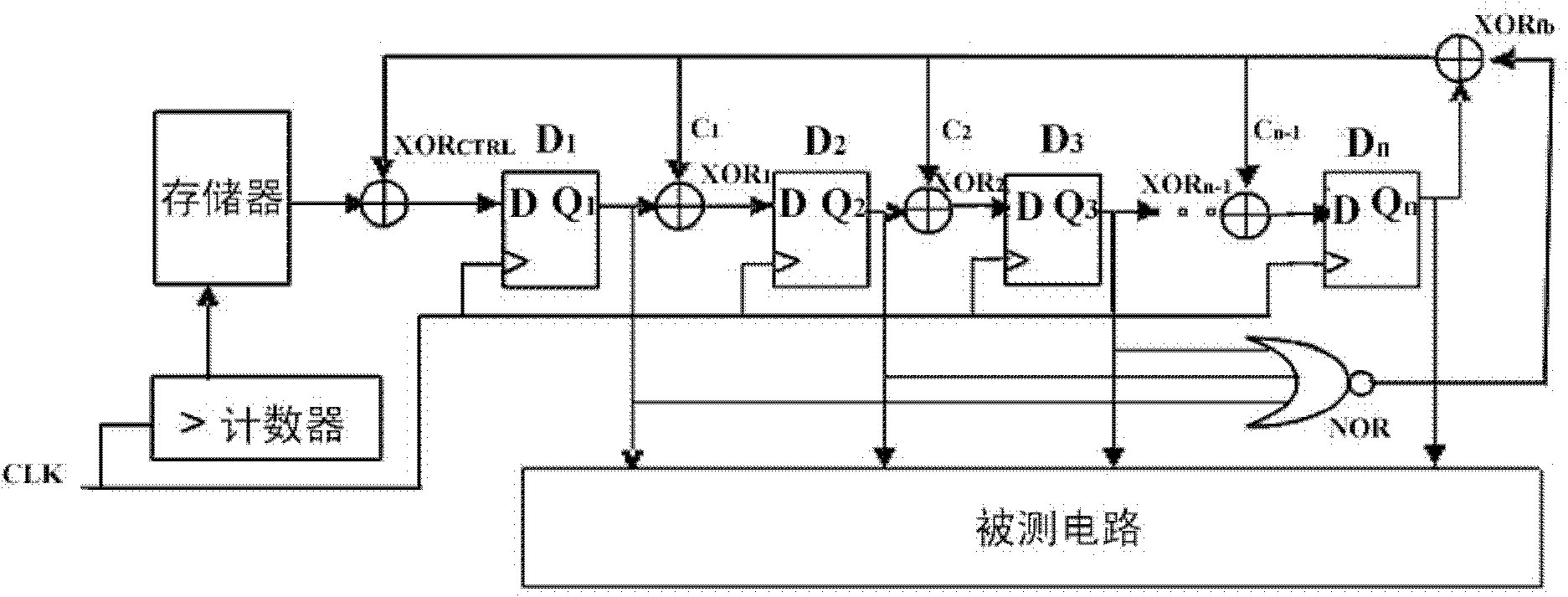

[0029] figure 1 It is a principle diagram of a specific implementation of the controllable test vector generator based on the linear feedback shift register of the present invention.

[0030] In this example, if figure 1 Shown, the present invention is based on the controllable test vector generator of linear feedback shift register, comprises:

[0031] One consists of n serially connected D flip-flops D 1~n XOR with n-1 XOR gates 1~n-1 The inner connection type linear feedback shift register formed;

[0032] An n-1-bit input NOR gate NOR and an exclusive OR gate XOR fb The feedback network formed, the n-1 input terminals of the NOR gate NOR are respectively connected to the D flip-flop D 1~n-1 The output Q 1~n-1 , XOR gate XOR fb The two input ends of the NOR gate are respectively connected to the output end of the NOR gate and the D flip-flop D n Output Q n;Exclusive OR gate XOR in the feedback network fb The output terminals of are respectively connected to n-1 ex...

example

[0077] In this example, the C17 circuit is taken as an example to illustrate the test vector generator of the present invention.

[0078] The main circuit of C17 is composed of 6 NAND gates with 5 input terminals. If the sequential test vector sequence of the maximum period is generated by the ergodic linear feedback shift register for testing, the ergodic linear feedback composed of 5 D flip-flops The shift register can achieve a fault coverage rate of 99.3%, with all "0" bits as the initial state, and its test vector set is shown in Table 1.

[0079]

[0080] Table 1

[0081] 00000

11001

11000

01001

01100

00001

00110

10001

00011

10000

[0082] Table 2

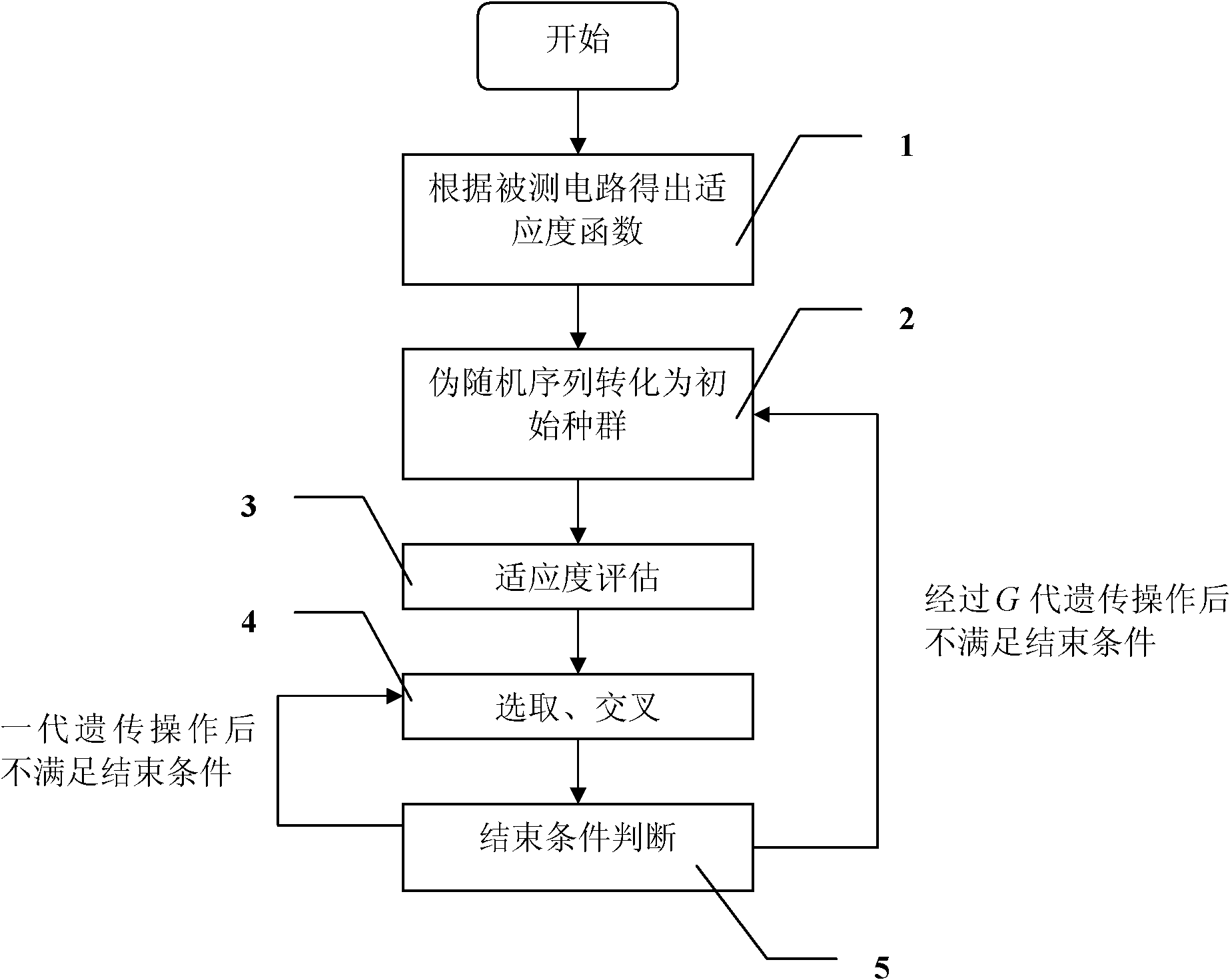

[0083] Under the same fault coverage requirement, the test vector generator of the present invention is used. First, according to the fault characteristics of the C17 reference circuit, the fitness function used by the genetic algorithm ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More