Patents

Literature

2434results about How to "Quick test" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

System, array and non-porous solid support comprising fixed or immobilized nucleic acids

InactiveUS7064197B1Easy to quantifyPromote repairSugar derivativesMicrobiological testing/measurementImmobilized Nucleic AcidsDouble strand

Nucleic acids are fixed or immobilized to non-porous solid supports (substrates), and include systems containing such supports and arrays with fixed or immobilized nucleic acids. These compositions are useful for nucleic acid analyses and a host of applications, including, for example, detection, mutational analysis and quantification. The non-porous solid supports can be transparent or translucent, and the surfaces can be treated with agents to fix or immobilize the nucleic acids. Such agents include, for example, amine providing compounds, epoxy compounds and acid solutions. The fixed or immobilized nucleic acids can be unlabeled, or labeled with at least one non-radioactive signaling moiety, such as the case when the nucleic acids are double-stranded.

Owner:ENZO BIOCHEM

Sensitive and rapid determination of antimicrobial susceptibility

ActiveUS20050048599A1Quick checkReduce sensitivityBioreactor/fermenter combinationsBiological substance pretreatmentsMicroorganismFiltration

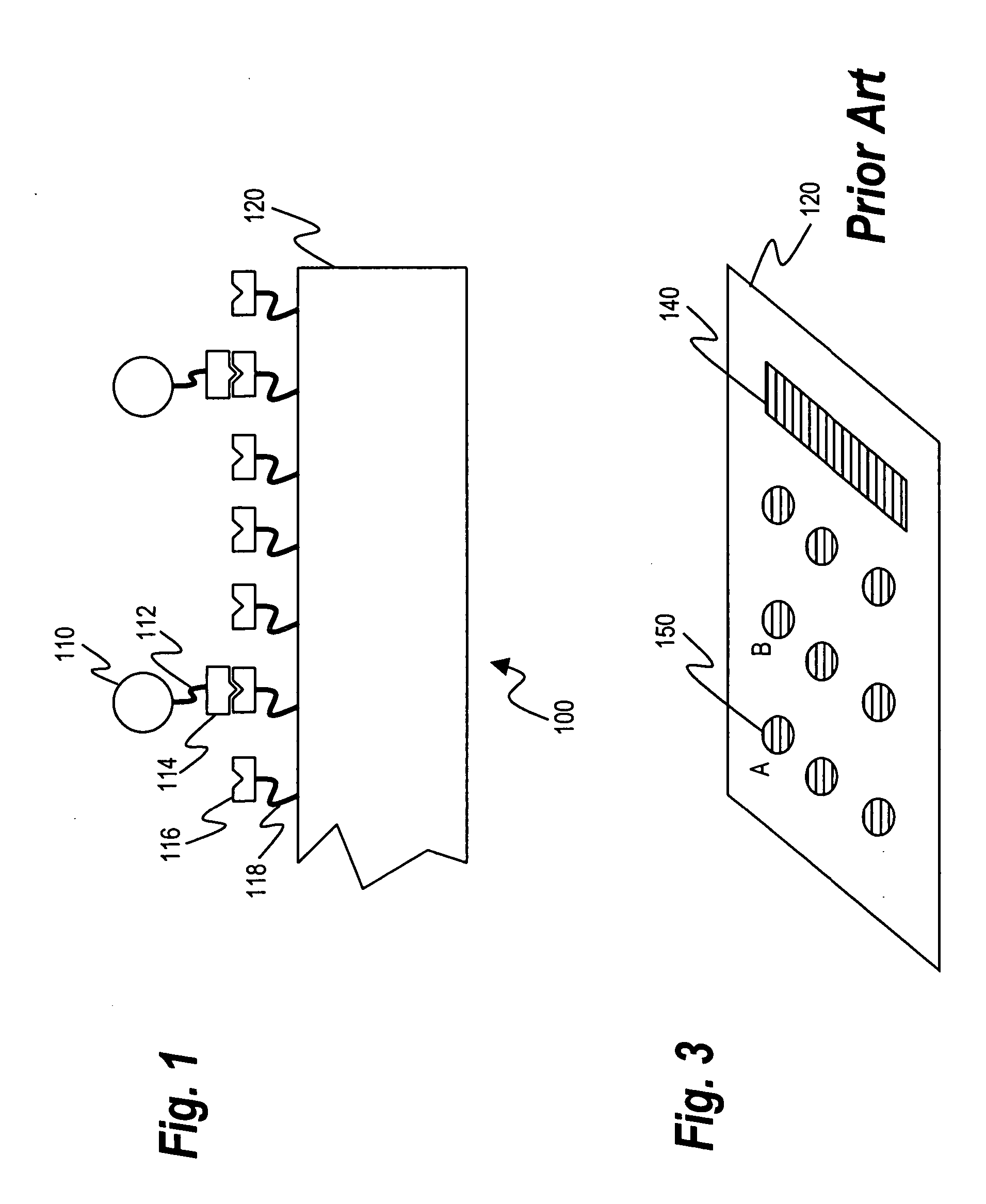

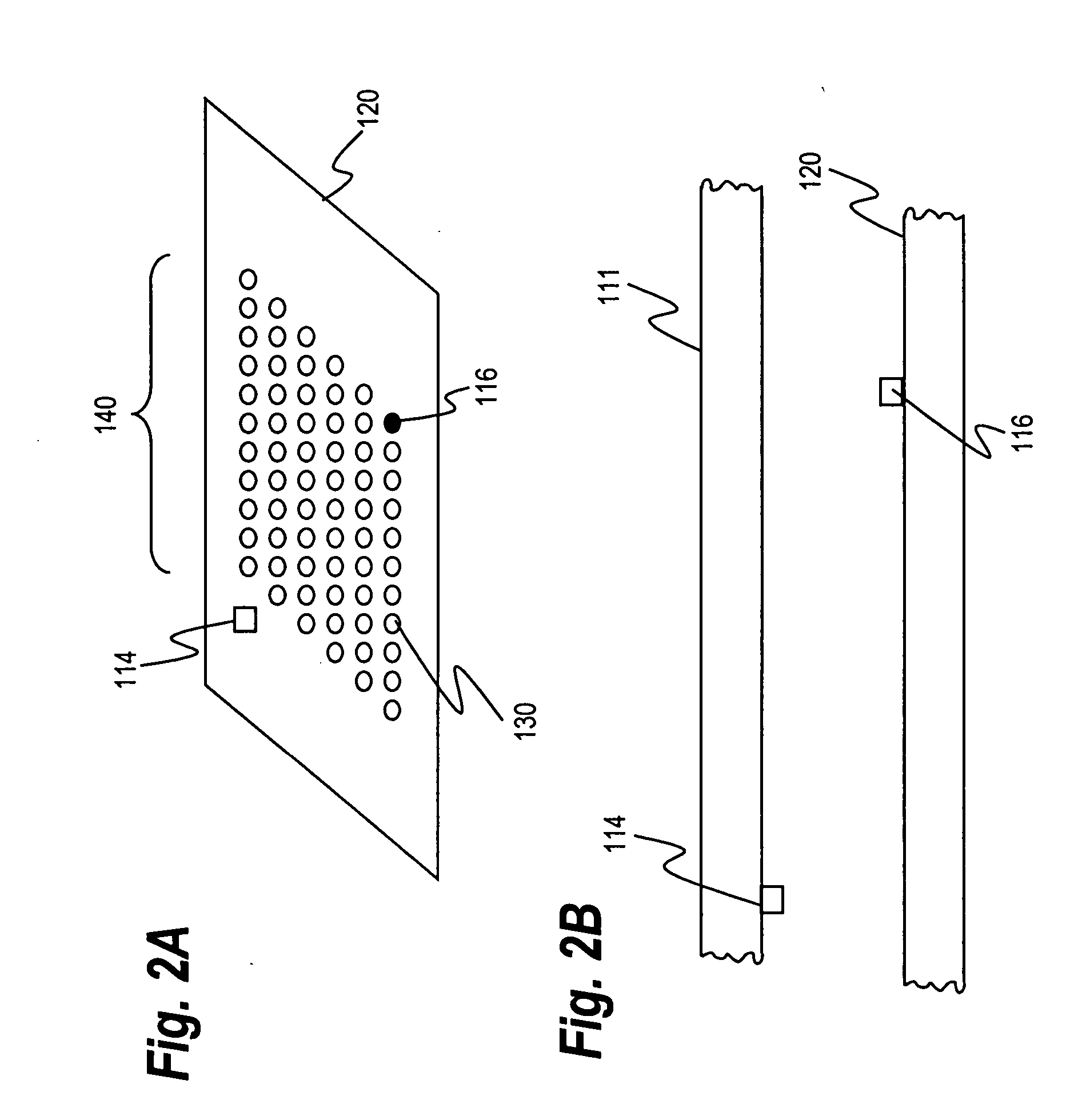

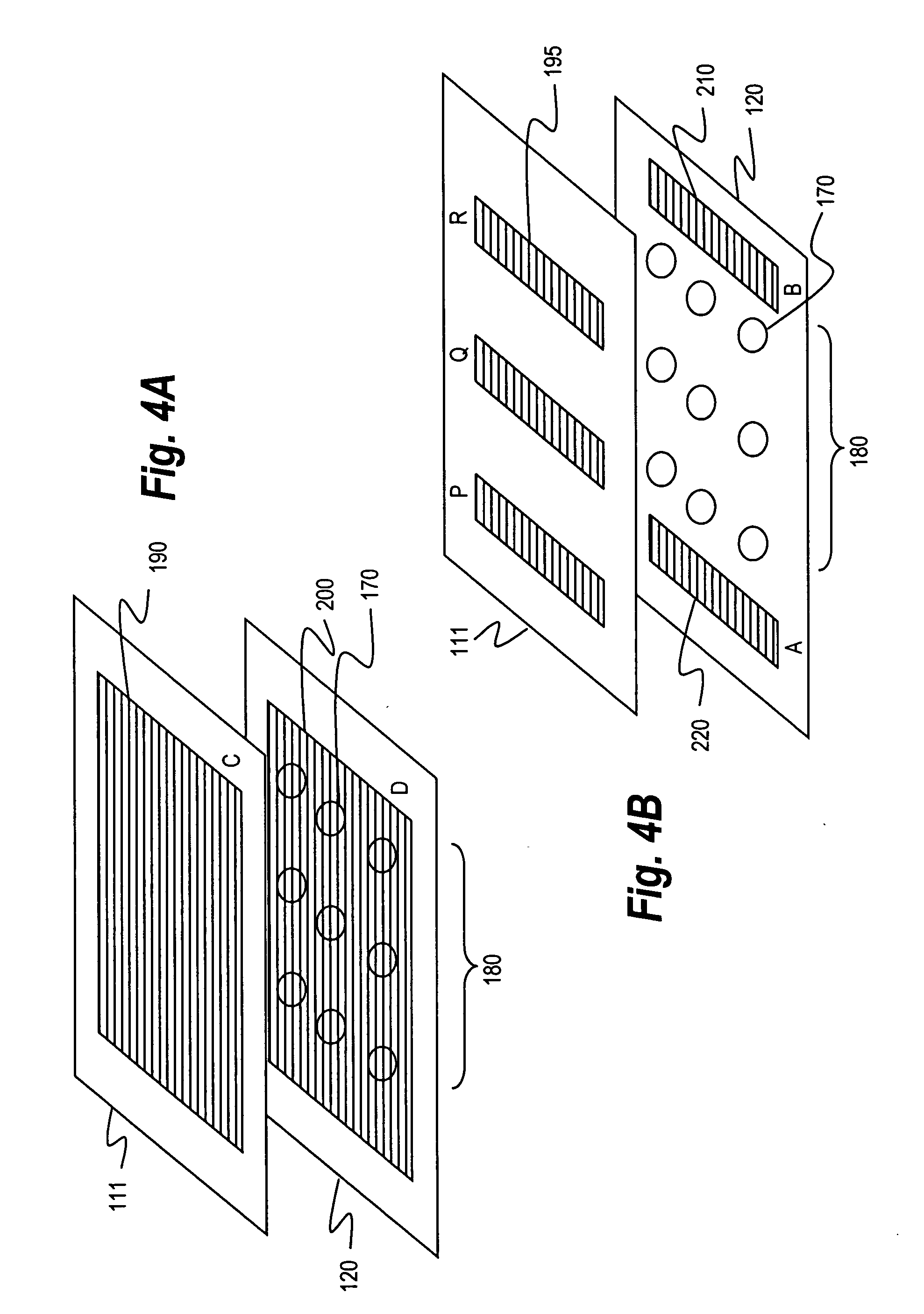

The present invention relates to moving microorganisms to a surface, where they are grown in the presence and absence of antimicrobials, and by monitoring the growth of the microorganisms over time in the two conditions, their susceptibility to the antimicrobials can be determined. The microorganisms can be moved to the surface through electrophoresis, centrifugation or filtration. When the movement involves electrophoresis, the presence of oxidizing and reducing reagents lowers the voltage at which electrophoretic force can be generated and allows a broader range of means by which the target can be detected. Monitoring can comprise optical detection, and most conveniently includes the detection of individual microorganisms. The microorganisms can be stained in order to give information about their response to antimicrobials.

Owner:ACCELERATED MEDICAL DIAGNOSTICS INC

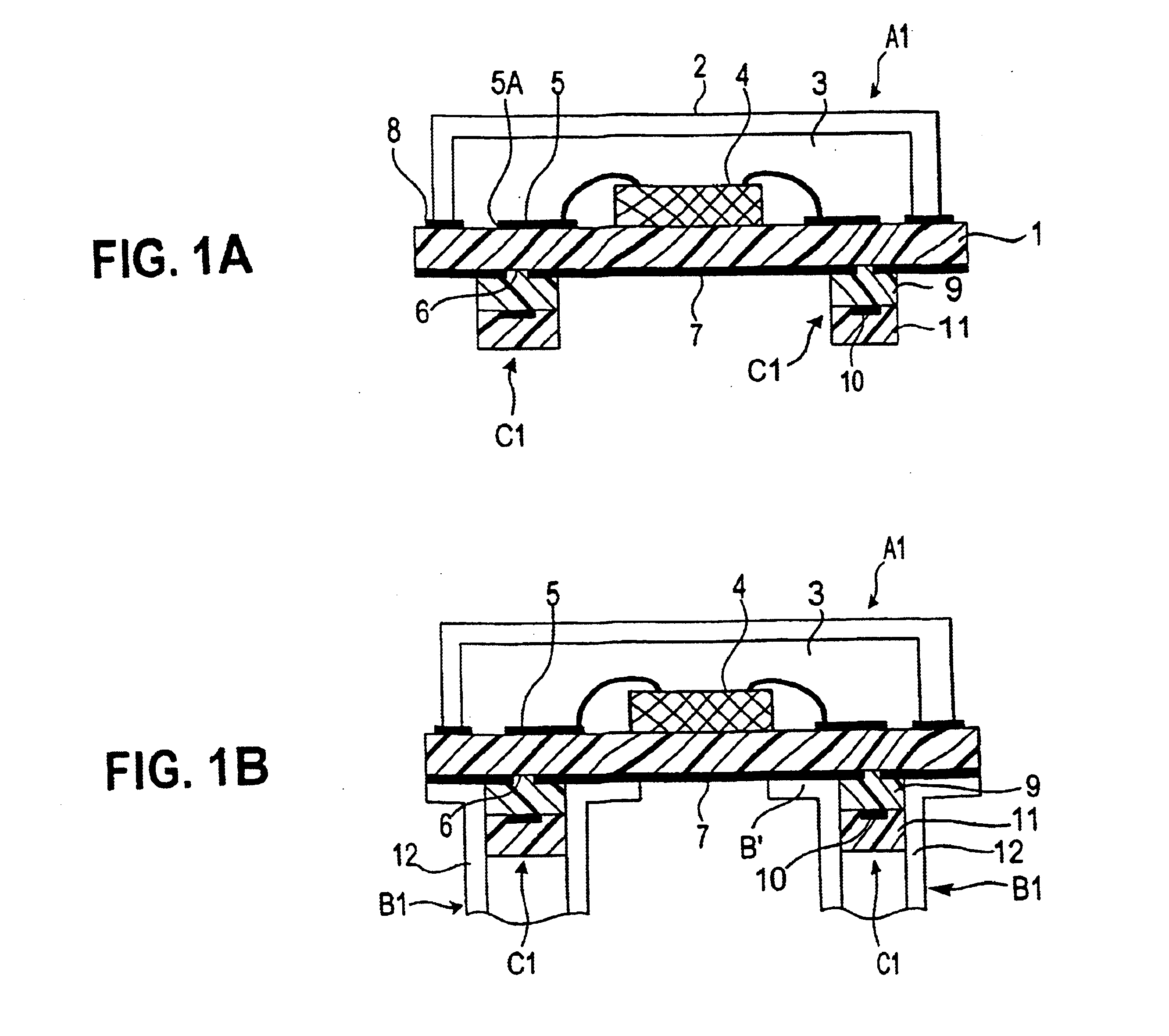

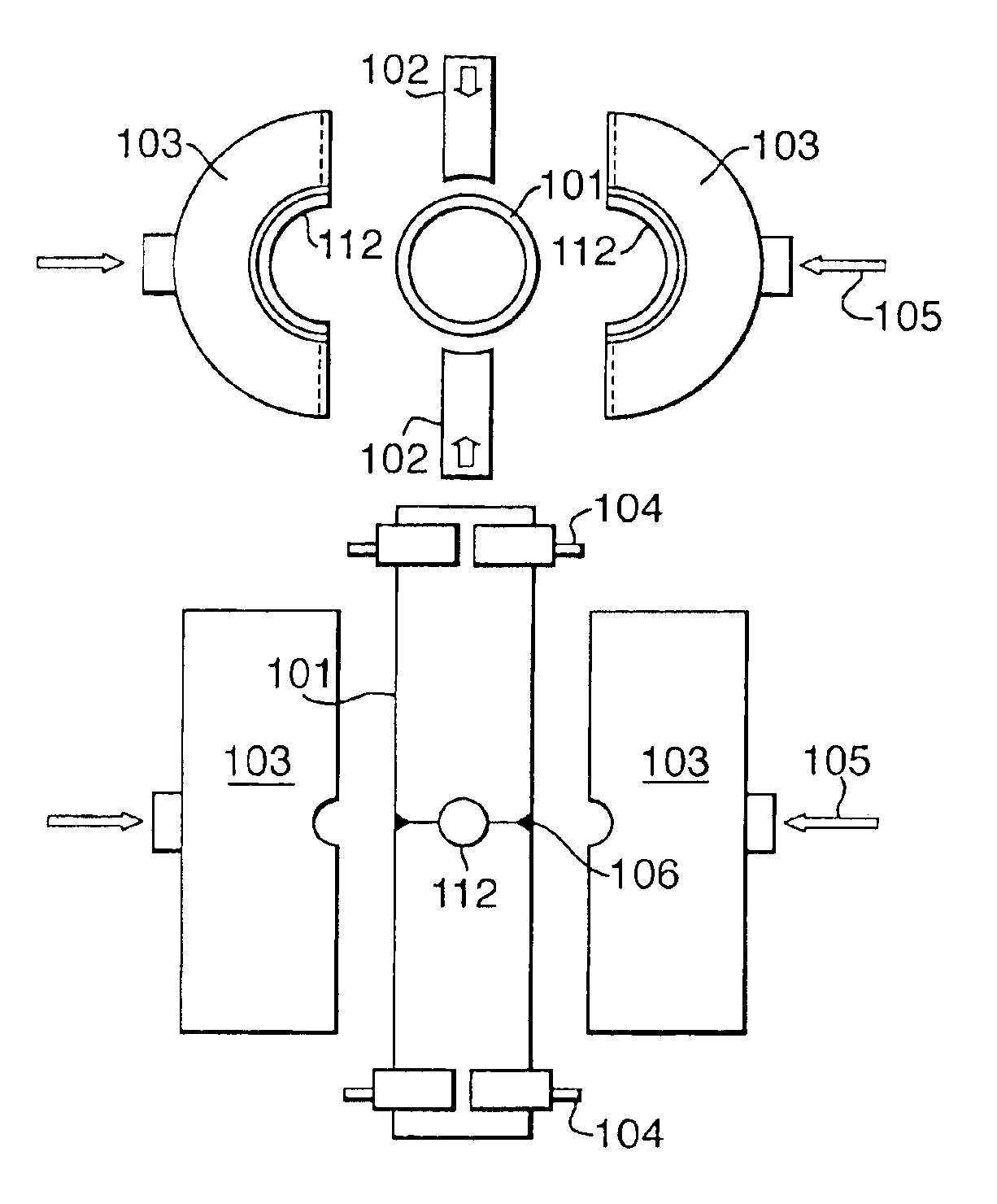

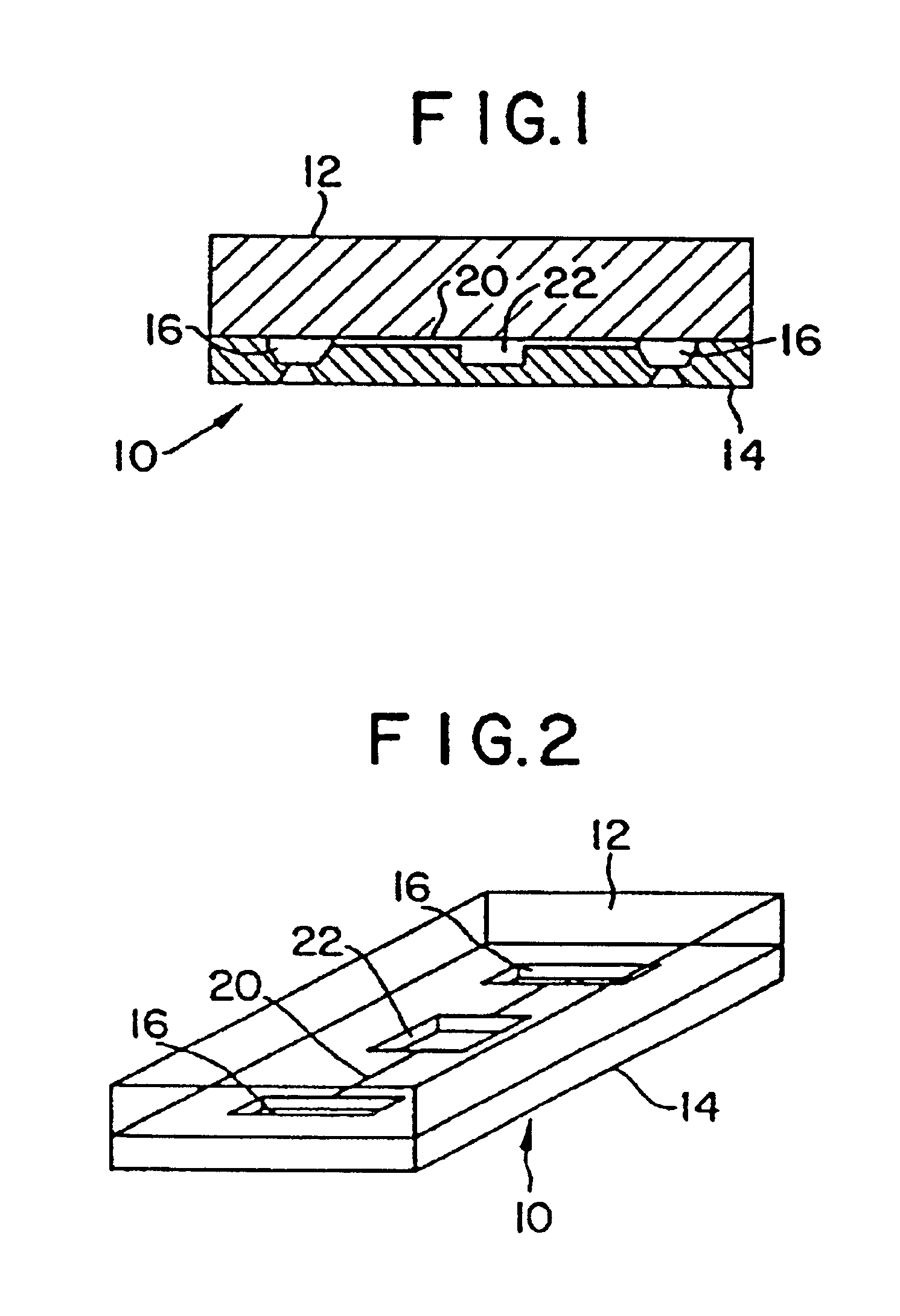

Multi-layered wiring board for slot coupling a transmission line to a waveguide

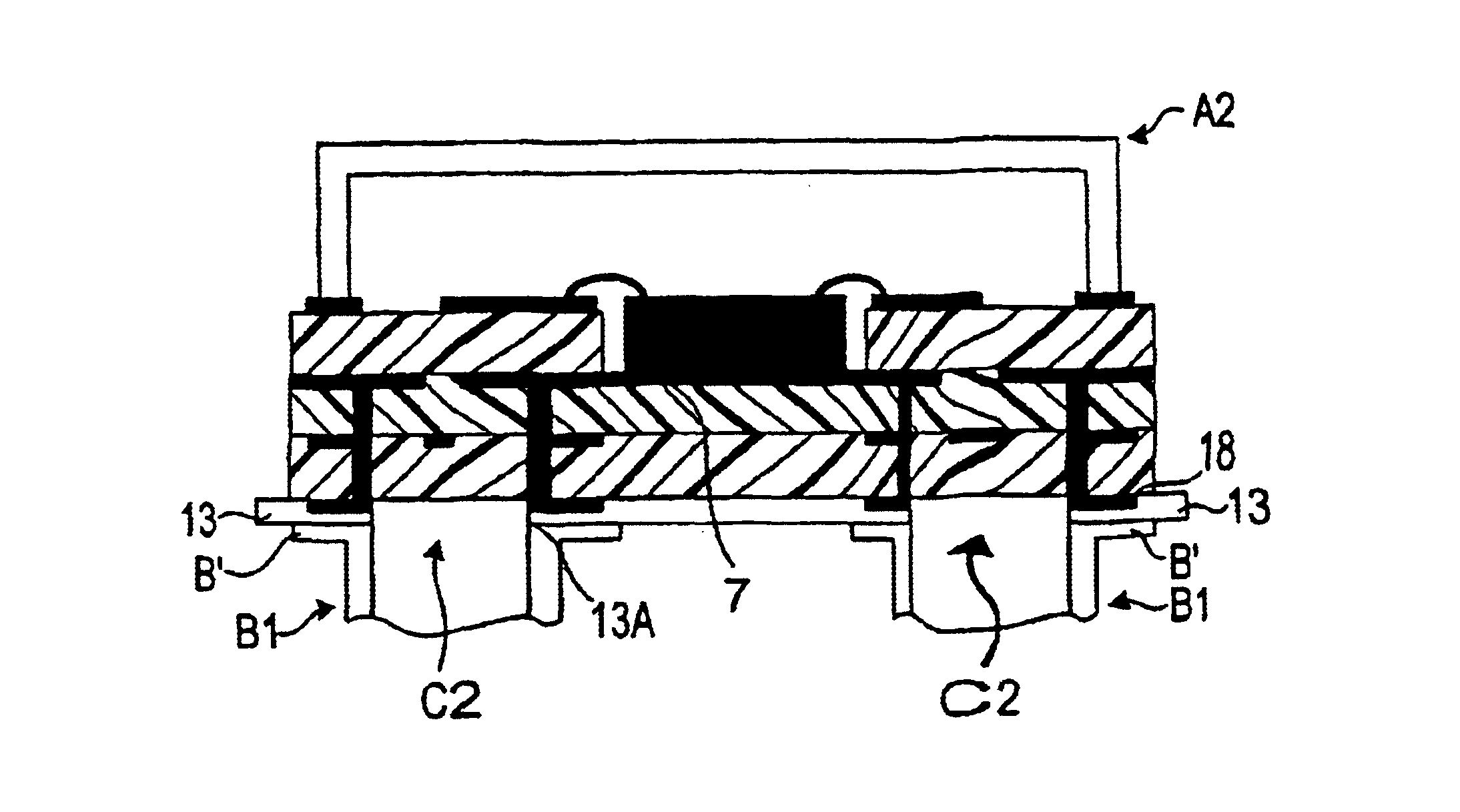

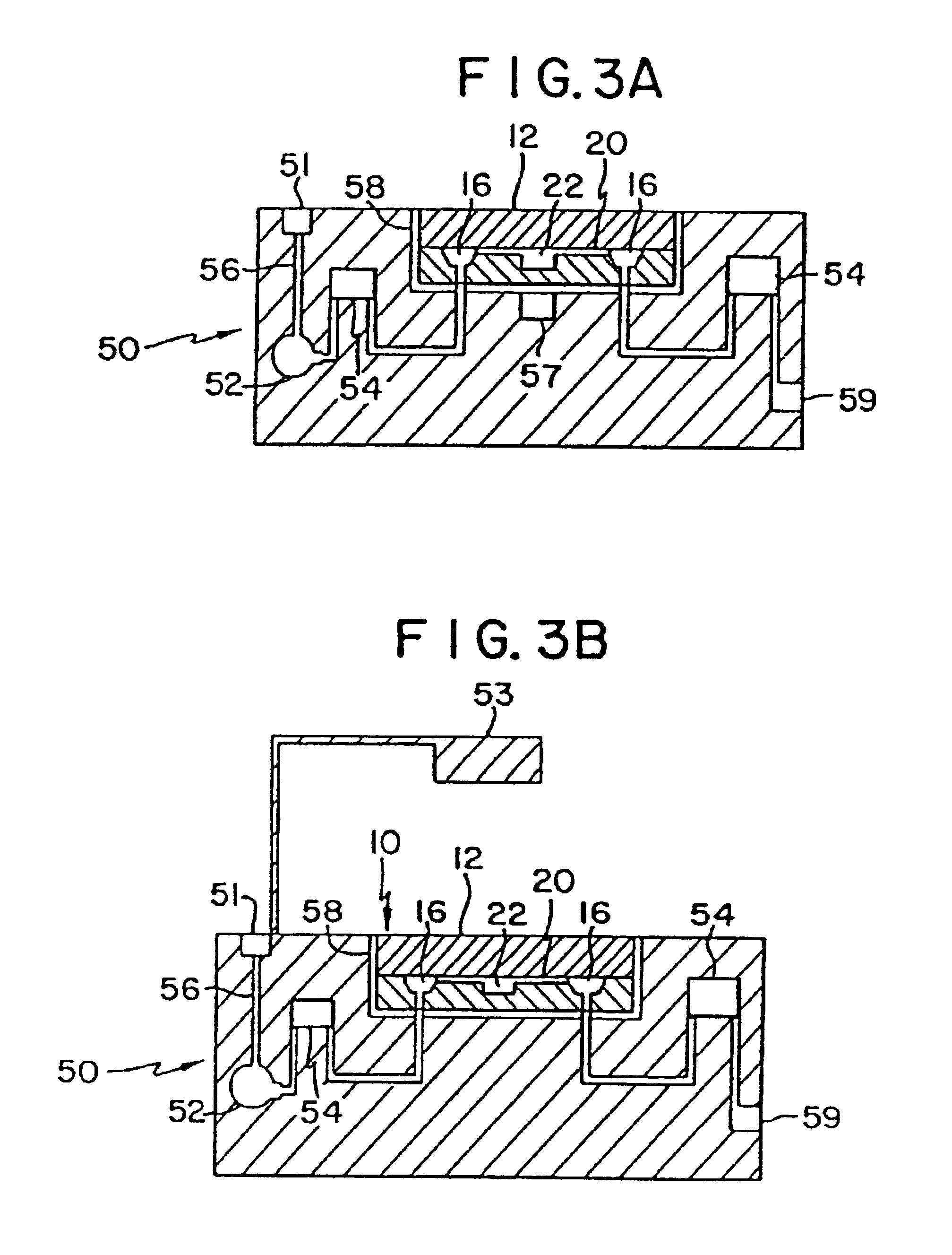

InactiveUS6870438B1Small signal lossSmall reflectionOne-port networksSemiconductor/solid-state device detailsElectrical conductorDielectric substrate

A wiring board includes a dielectric substrate, a signal transmission line formed on one surface of the dielectric substrate, a grounded layer formed on the other surface of the dielectric substrate, and a connection portion for connecting portion for connecting the signal transmission line to a waveguide, the connection portion being formed on the grounded layer. The grounded layer has a slot at a position opposed to an end of the signal transmission line. The connection portion includes a first dielectric portion disposed to cover the slot of the ground layer, a second dielectric portion laminated on the first dielectric portion, and a patch conductor provided at a position opposed to said slot on an interface between the first dielectric portion and the second dielectric portion. The wiring board enables the signals to be efficiently transmitted from the signal transmission line to the waveguide with a small loss and a small reflection.

Owner:KYOCERA CORP

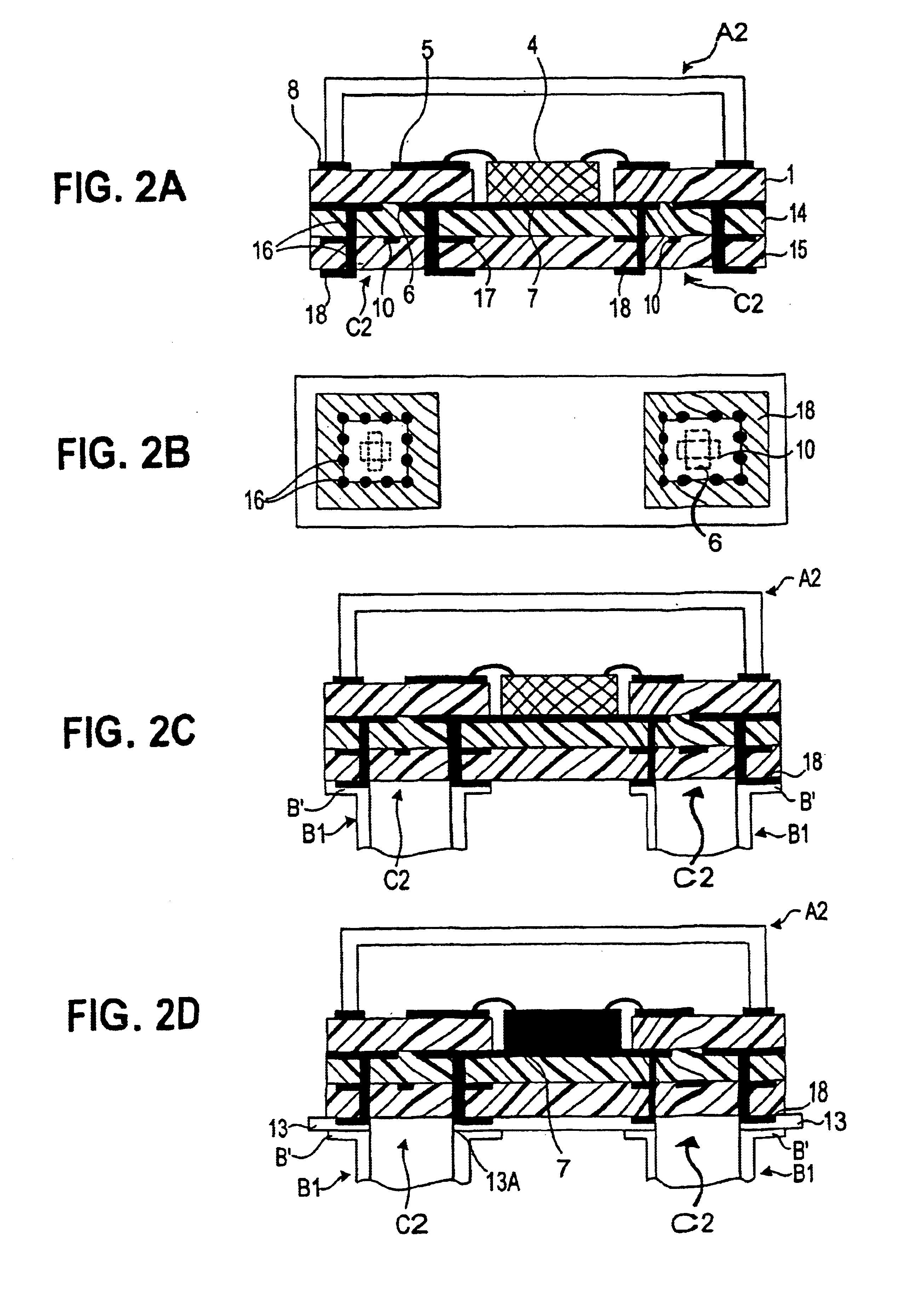

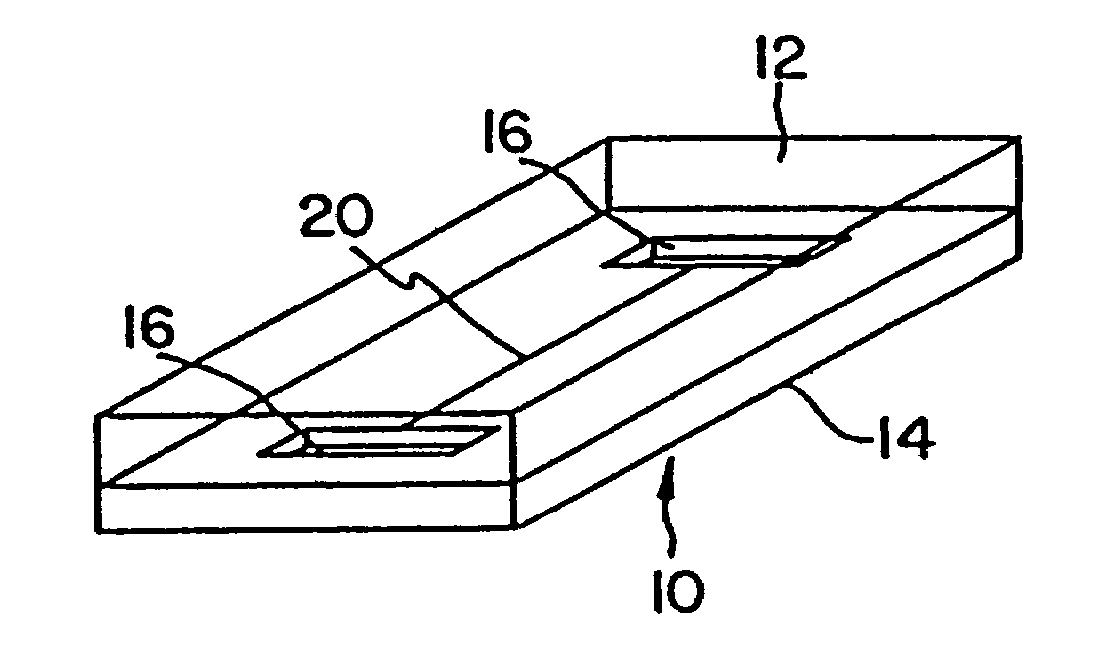

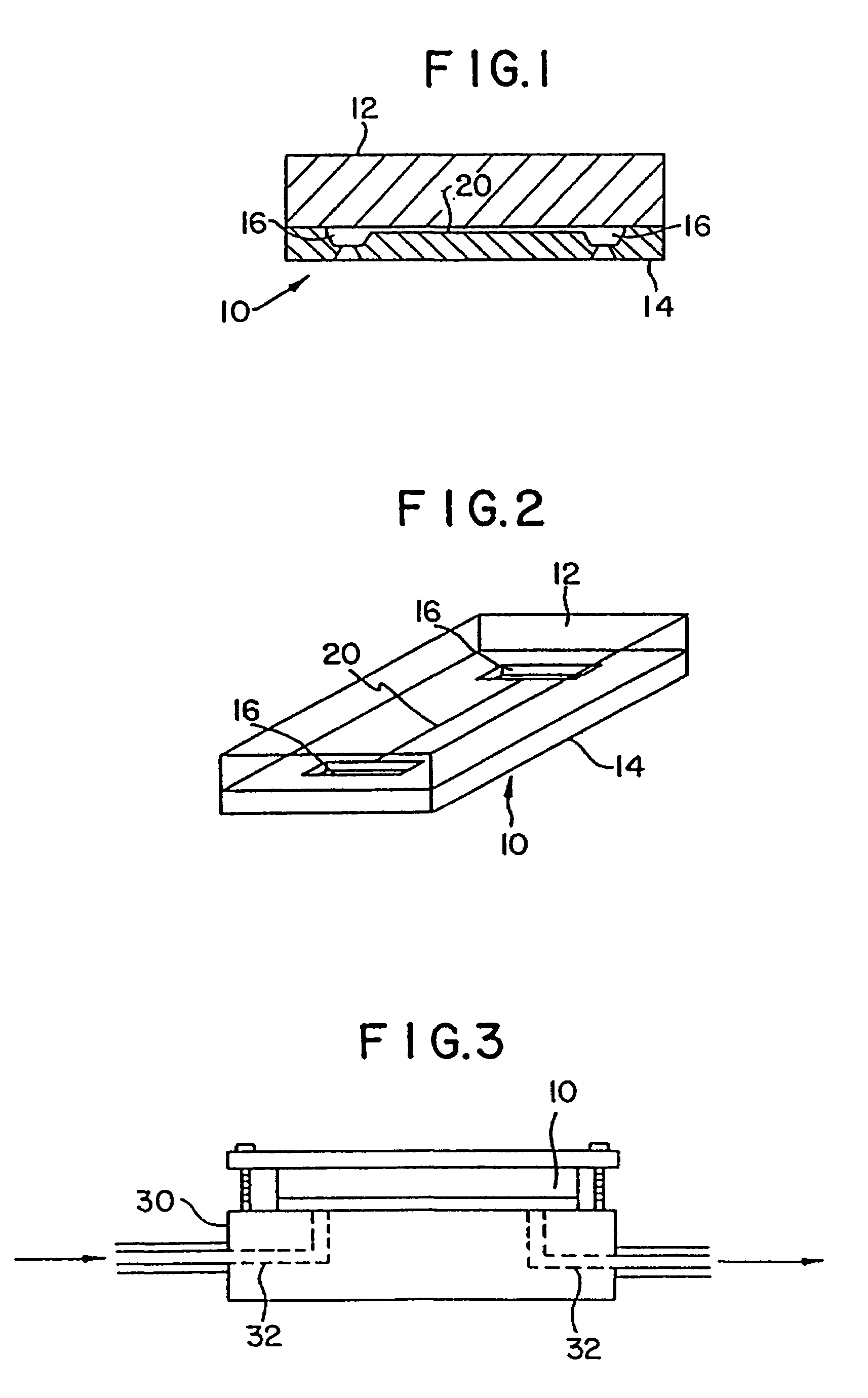

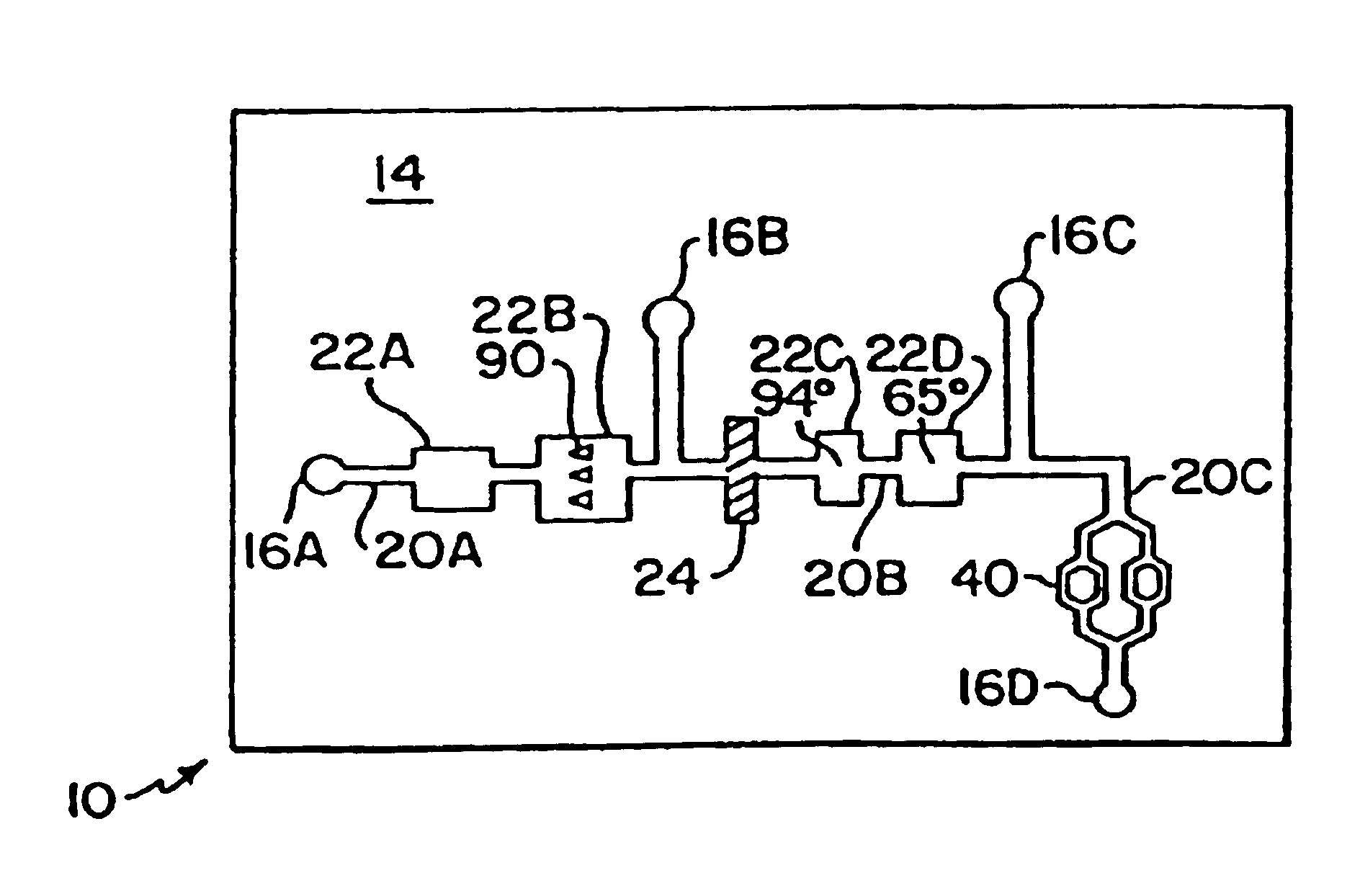

Device and method for the detection of an analyte utilizing mesoscale flow systems

InactiveUS7005292B2Quick testEasy to disinfectBioreactor/fermenter combinationsHeating or cooling apparatusAnalyteChemistry

Disclosed are devices for detecting the presence of a preselected analyte in a fluid sample. The devices comprise a substrate microfabricated to define a sample inlet port, and a mesoscale flow system that includes a sample flow channel extending from the inlet port. The mesoscale flow system further includes an analyte detection region in fluid communication with the flow channel comprised of a binding moiety for specifically binding the analyte. The detection region is constructed with a mesoscale dimension sufficiently small to enhance binding of the binding moiety and the analyte. The binding moiety may be immobilized in the detection region. The mesoscale detection systems of the invention may be used in a wide range of applications, including the detection of cells or macromolecules, or for monitoring reactions or cell culture growth.

Owner:THE TRUSTEES OF THE UNIV OF PENNSYLVANIA

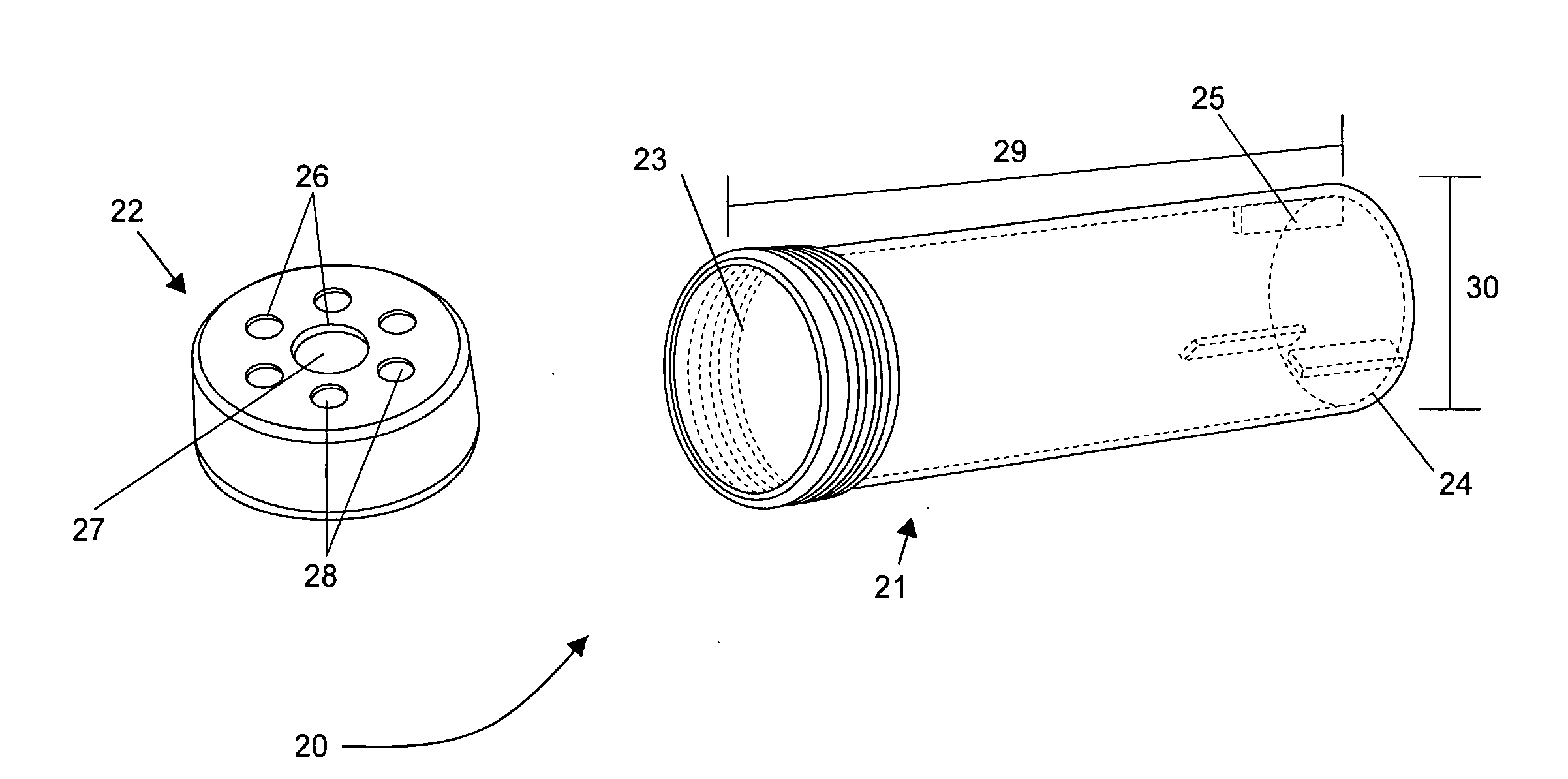

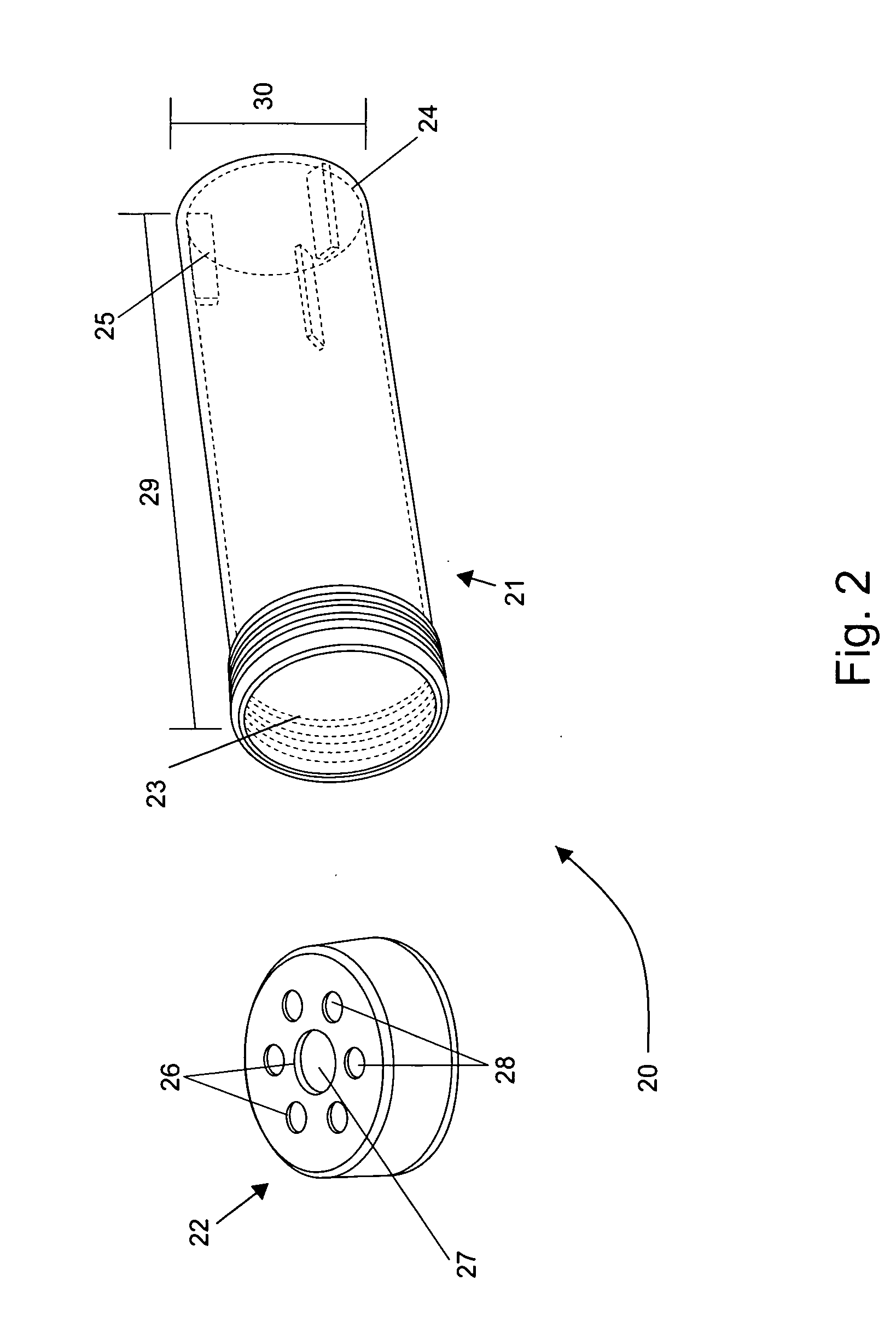

Disposable mini-bioreactor device and method

InactiveUS20090148941A1Quick testInhibition releaseBioreactor/fermenter combinationsCapsCulture cellGas exchange

This invention provides cylindrical cell culture tubes with a cap having both a septum and gas exchange membranes. The culture tubes can be used to inoculate media, culture cells, harvest cells and store cells in the same container with reduced risk of contamination, while facilitating automated handling.

Owner:OPTIMUM PROCESSING +1

Real-time wireless dynamic tire pressure sensor and energy harvesting system

ActiveUS20140070935A1Quick testImprove detection accuracyBatteries circuit arrangementsMaterial analysis using sonic/ultrasonic/infrasonic wavesAuditory radiationEnergy harvester

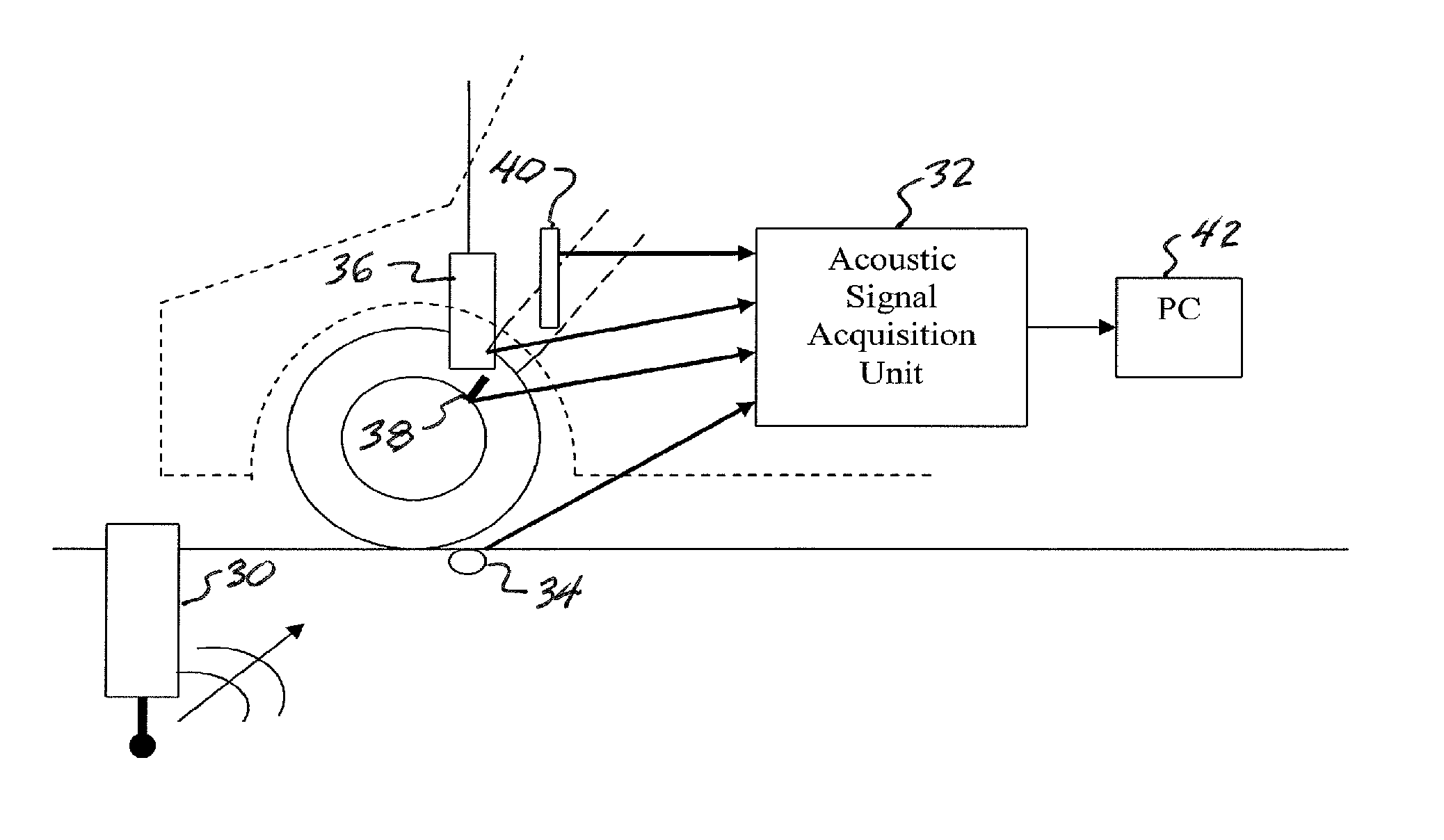

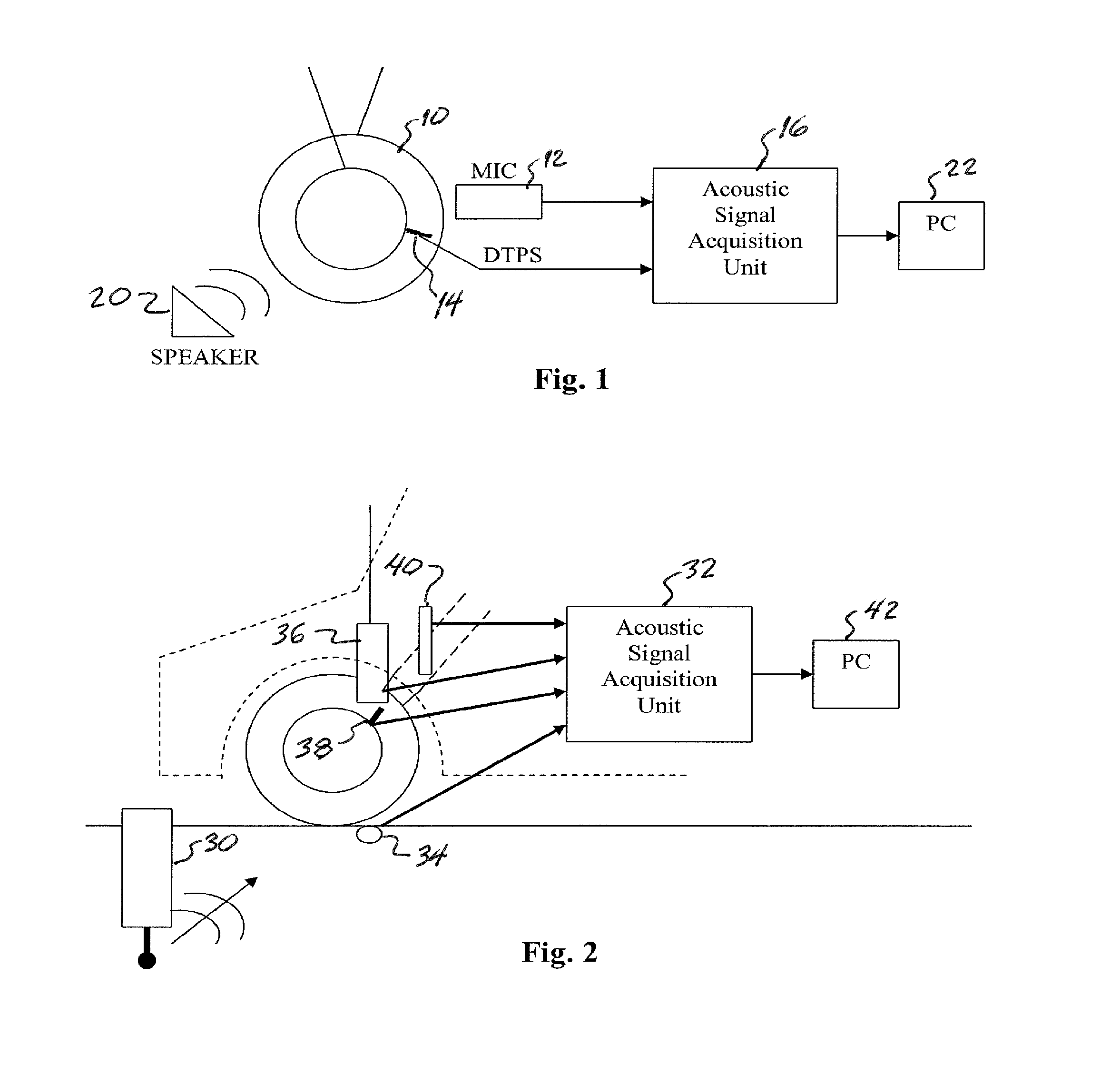

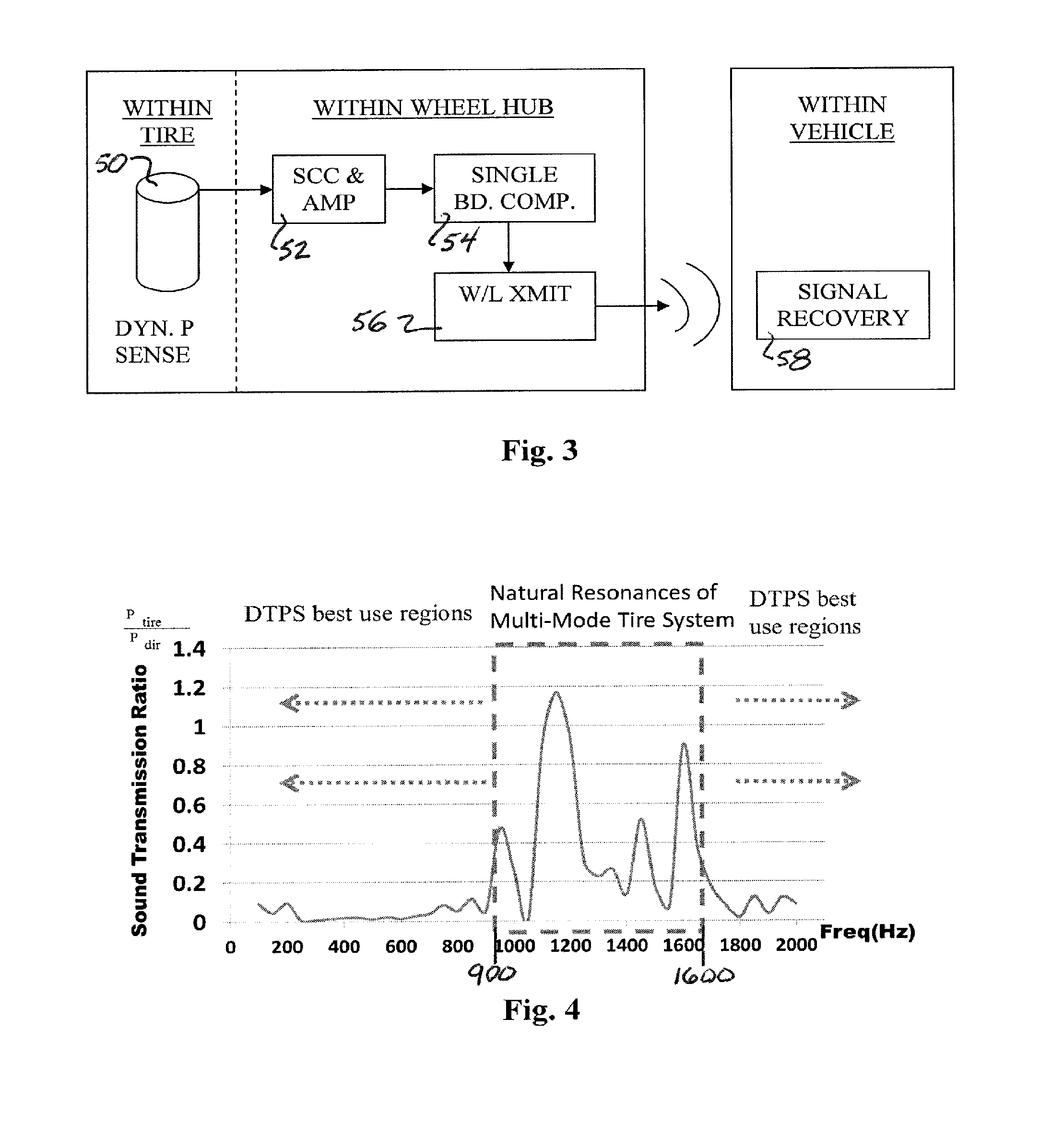

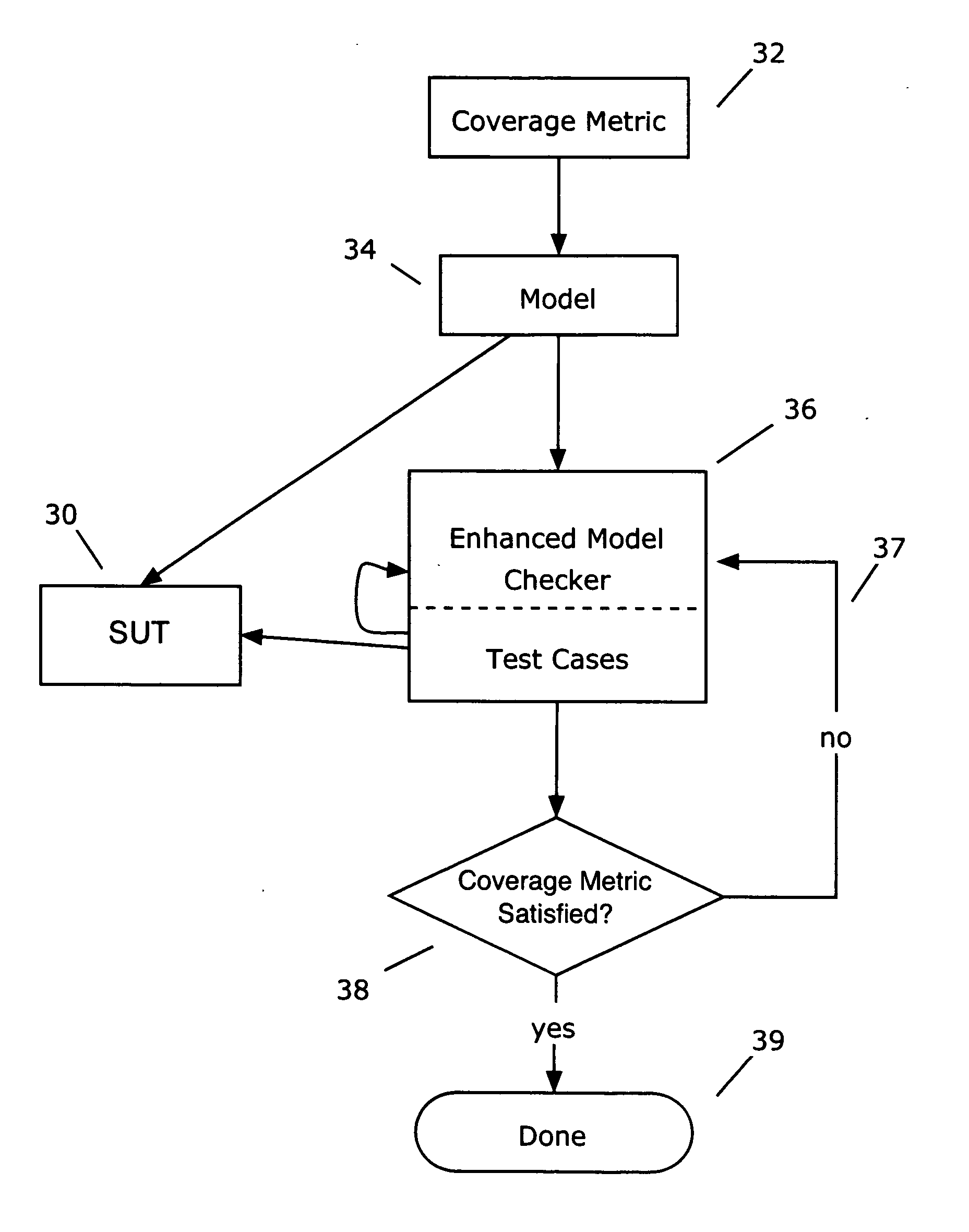

An instantaneous / real-time wireless dynamic tire pressure sensor (DTPS) for characterizing pavement qualities and for detecting surface and subsurface pavement defects under normal driving conditions. Signal processing provides quantitative assessment of surface conditions. DTPS includes a vehicle tire valve stem-mounted pressure sensor and wheel hub-mounted signal conditioning, amplification, and transmitting circuitry. A signal processing computer within the vehicle is wirelessly coupled to the hub-mounted circuitry. Tire pressure changes caused by ground vibration excitation from the interaction between the tire and pavement at normal driving speeds are detected. When acoustic radiation from a surface wave is significantly stronger than acoustic noise, subsurface information can be extracted. An energy harvester based on strong magnetostatic coupling between a high permeability core solenoid, fixed proximate a vehicle wheel, and a bias magnet array, fixedly mounted in conjunction with a dust shield, can provide power the DIPS.

Owner:NORTHEASTERN UNIV

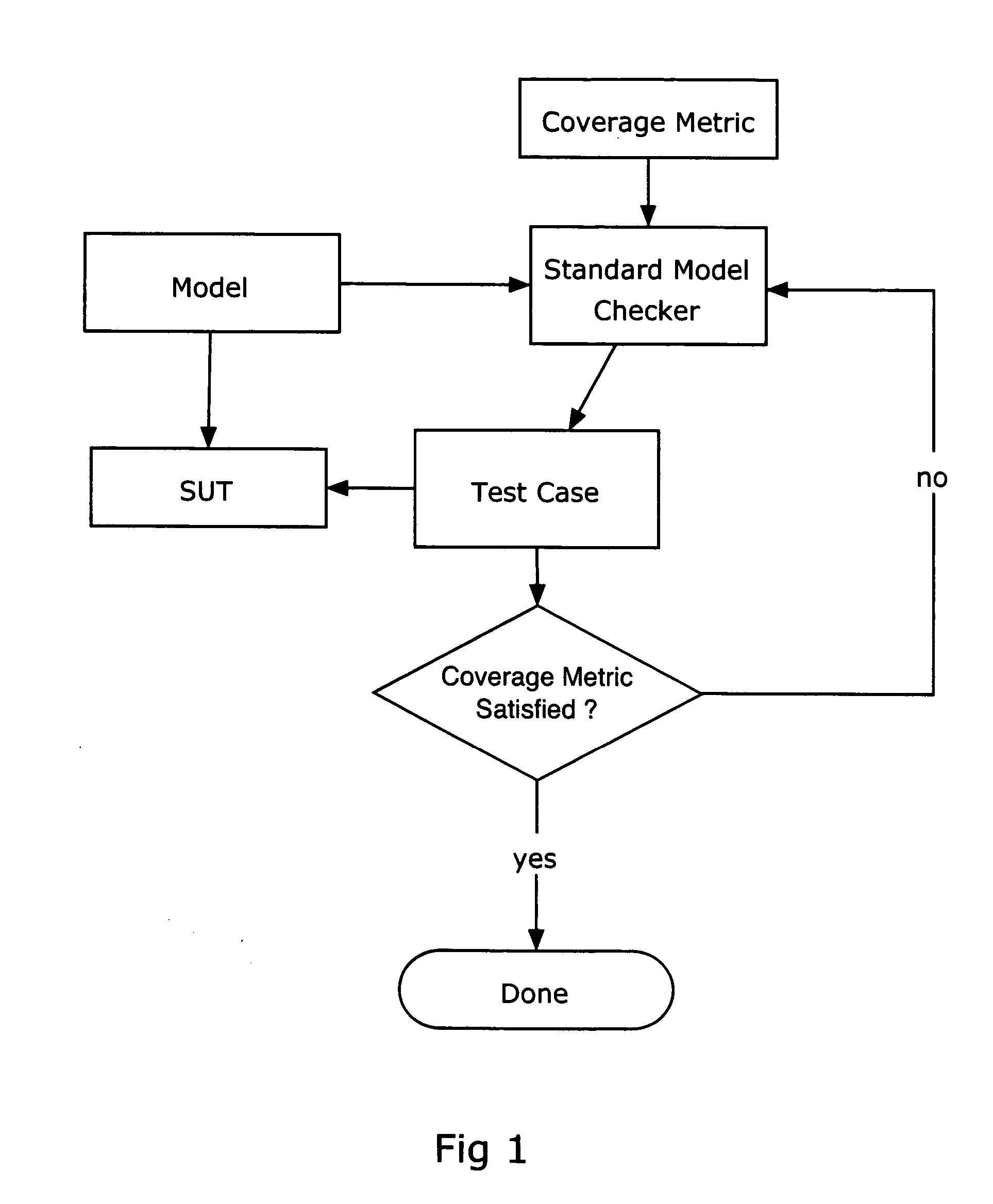

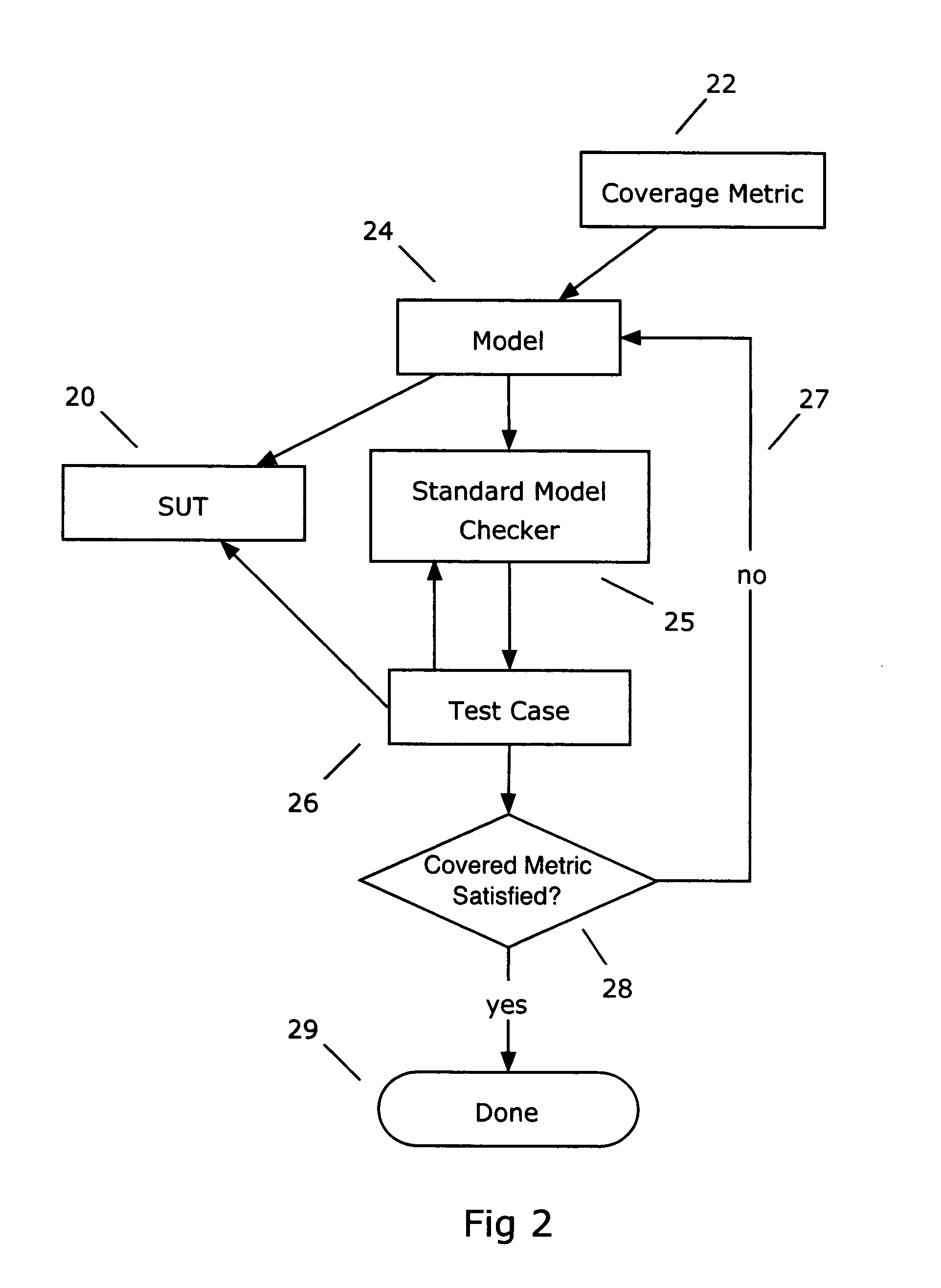

Formal methods for test case generation

ActiveUS20060010428A1Reduce development costsQuick testError detection/correctionComputation using non-denominational number representationSoftware systemFormal methods

The invention relates to the use of model checkers to generate efficient test sets for hardware and software systems. The method provides for extending existing tests to reach new coverage targets; searching *to* some or all of the uncovered targets in parallel; searching in parallel *from* some or all of the states reached in previous tests; and slicing the model relative to the current set of coverage targets. The invention provides efficient test case generation and test set formation. Deep regions of the state space can be reached within allotted time and memory. The approach has been applied to use of the model checkers of SRI's SAL system and to model-based designs developed in Stateflow. Stateflow models achieving complete state and transition coverage in a single test case are reported.

Owner:SRI INTERNATIONAL

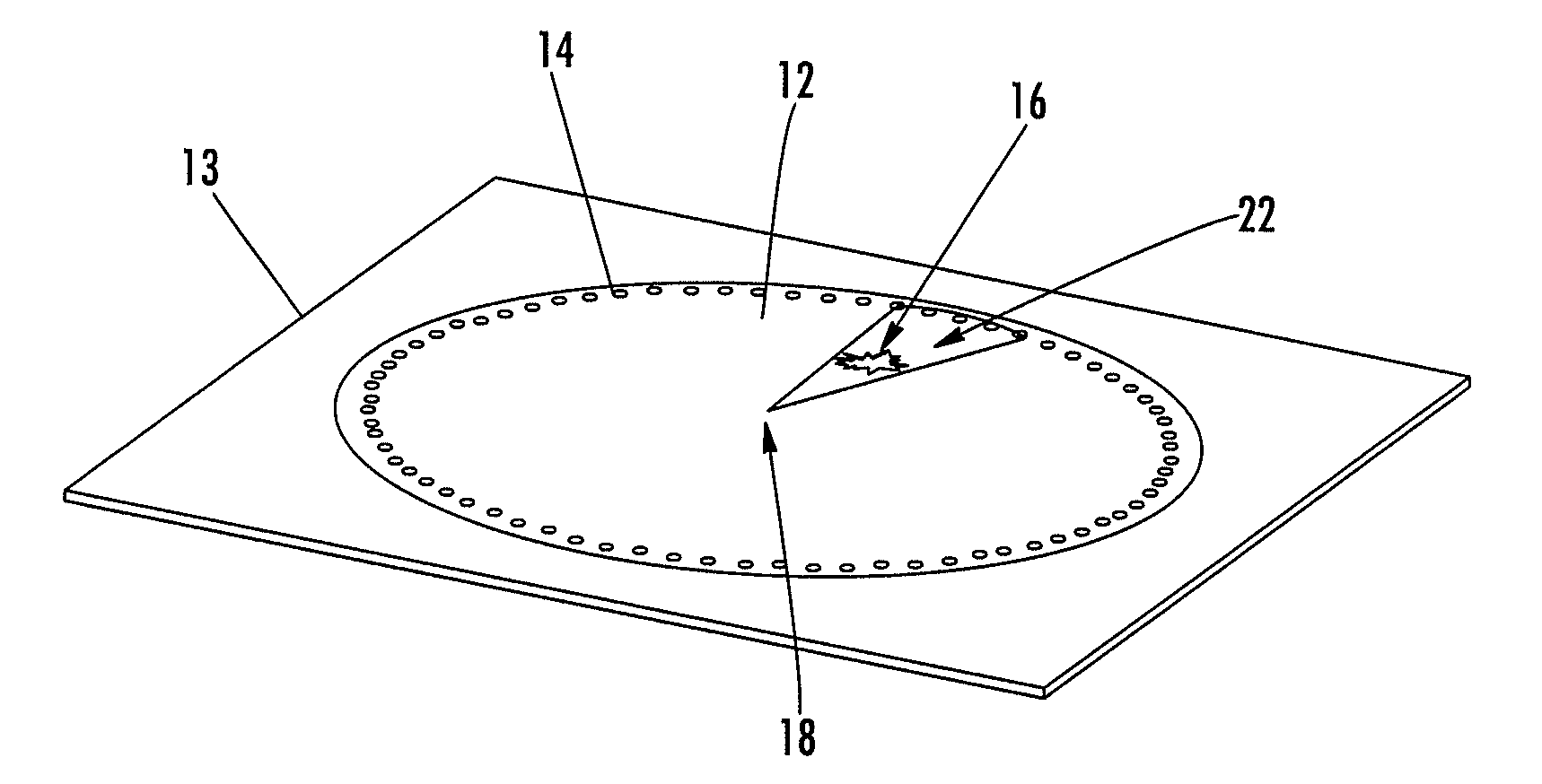

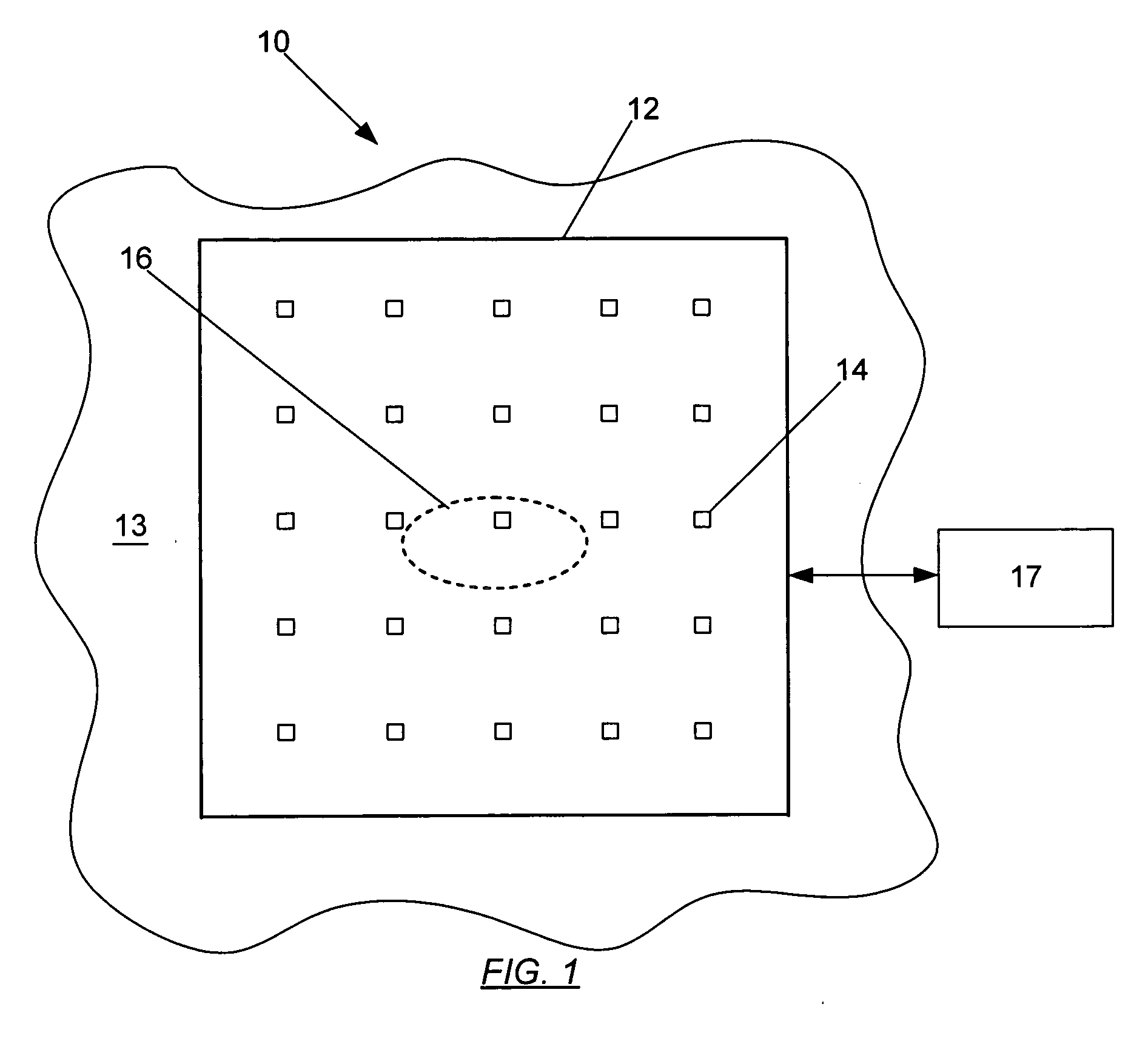

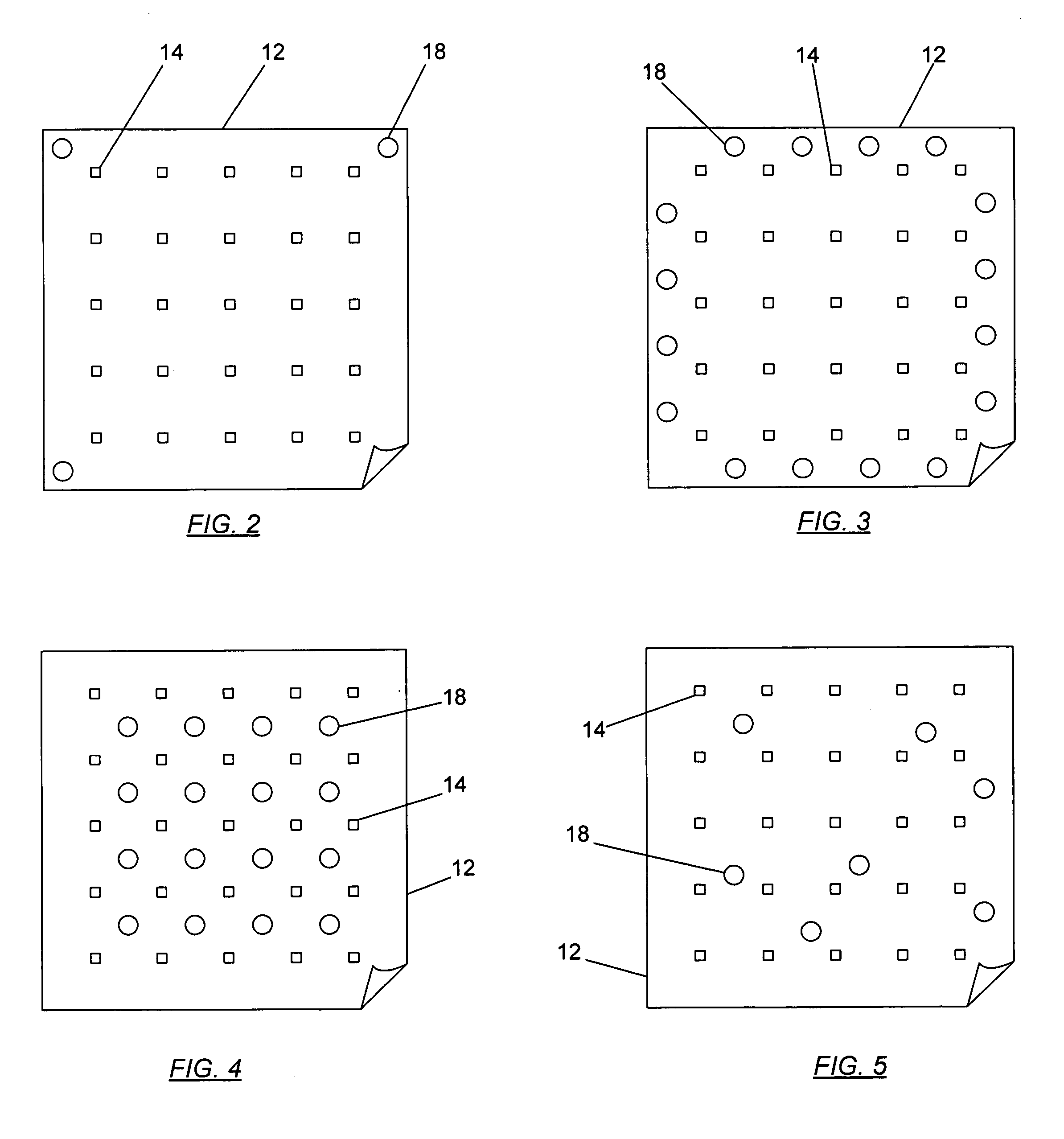

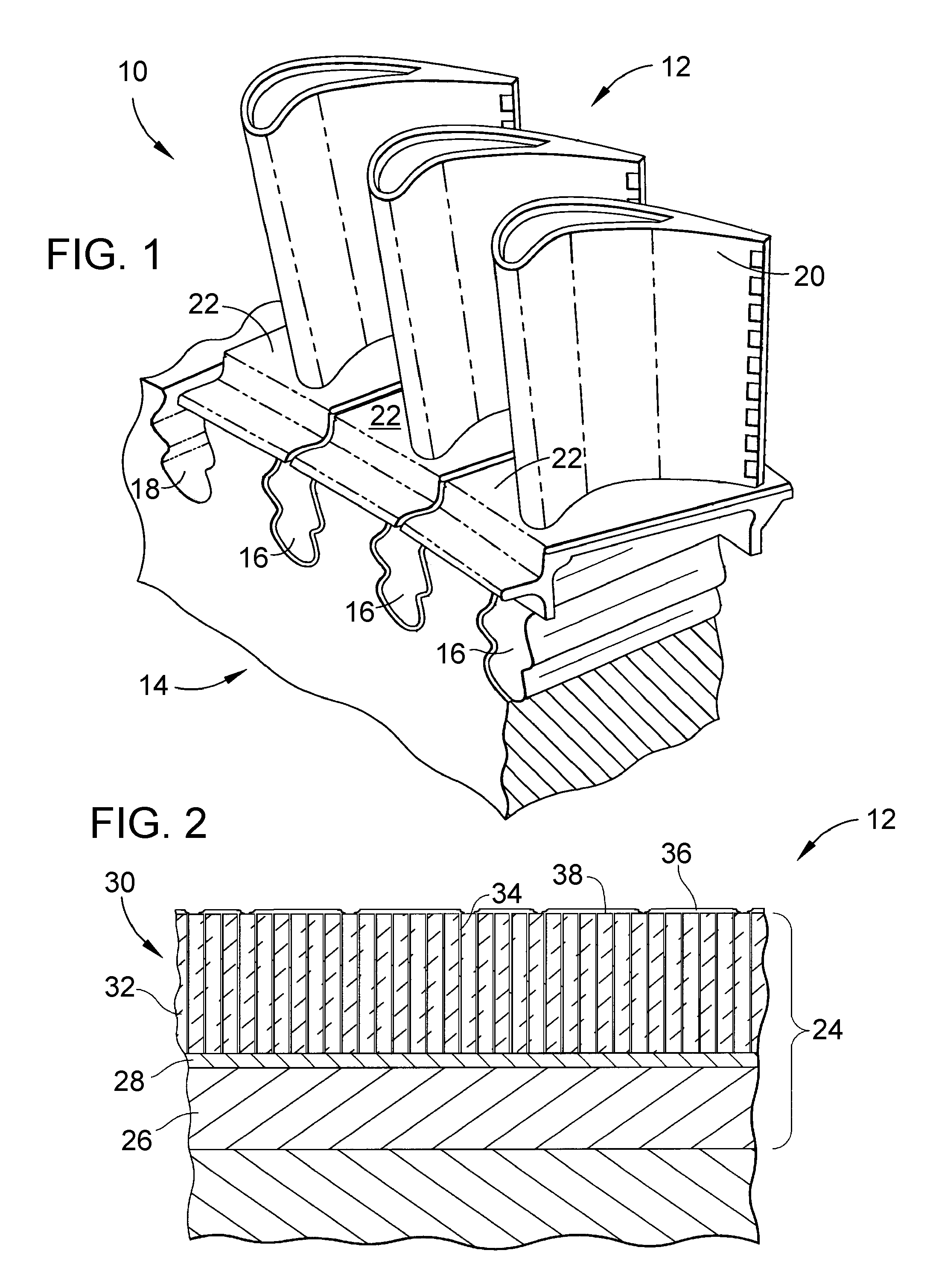

Smart repair patch and associated method

ActiveUS7398698B2Structure moreLow costAnalysing solids using sonic/ultrasonic/infrasonic wavesNuclear monitoringNon destructiveData acquisition

A system and method for identifying defects in a repair patch applied to a structure are provided. The system includes a sheet of material configured to be attached to the structure, and a mechanism operable to generate stress waves within and along the sheet of material. The system also includes a plurality of non-destructive sensors carried by the sheet of material. Each sensor is capable of detecting the stress waves. The system further includes a data acquisition system capable of communicating with the sensors such that the data acquisition system is also capable of generating information indicative of at least a portion of the sheet of material based on the data detected by the sensors.

Owner:THE BOEING CO

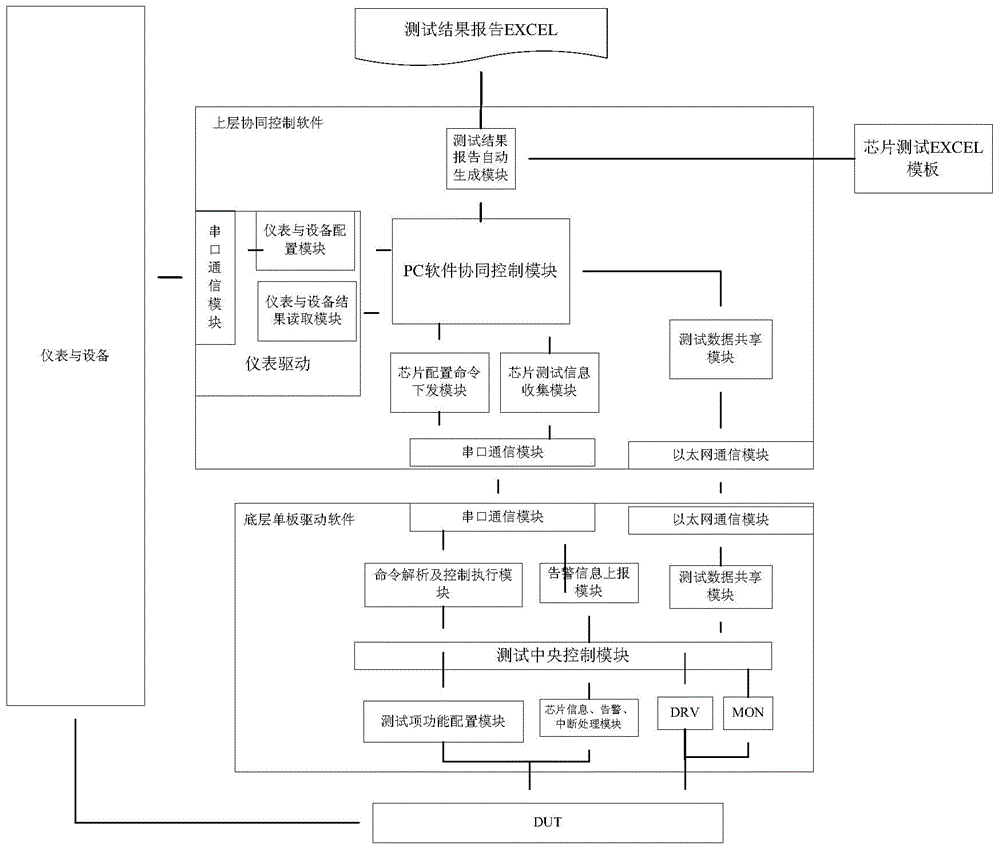

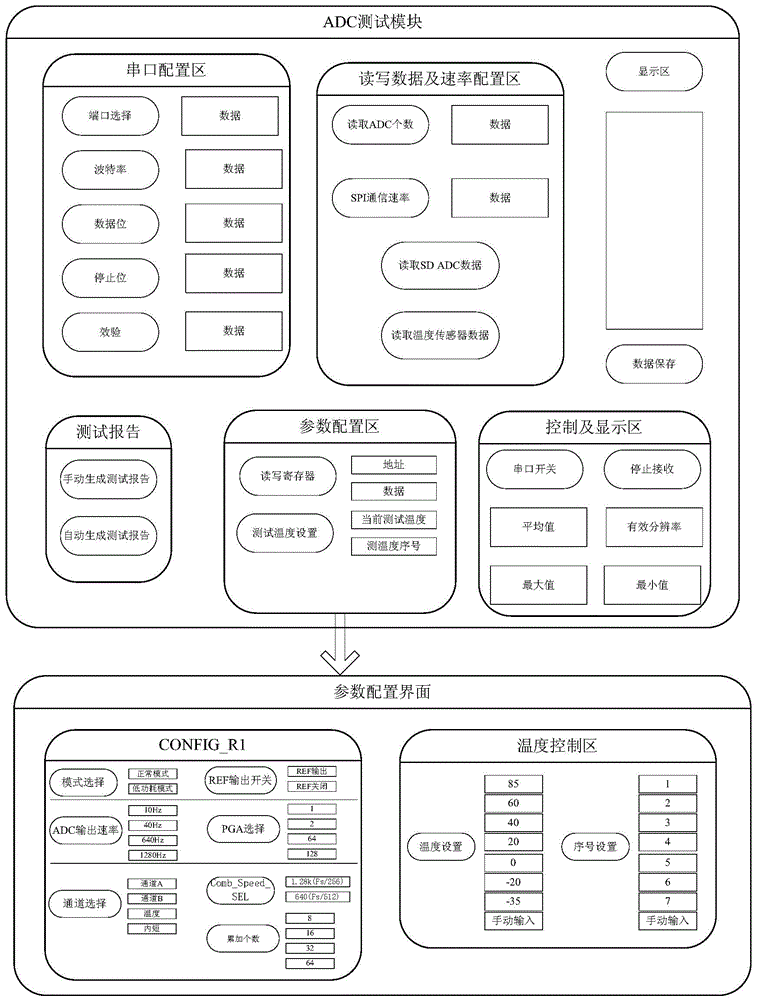

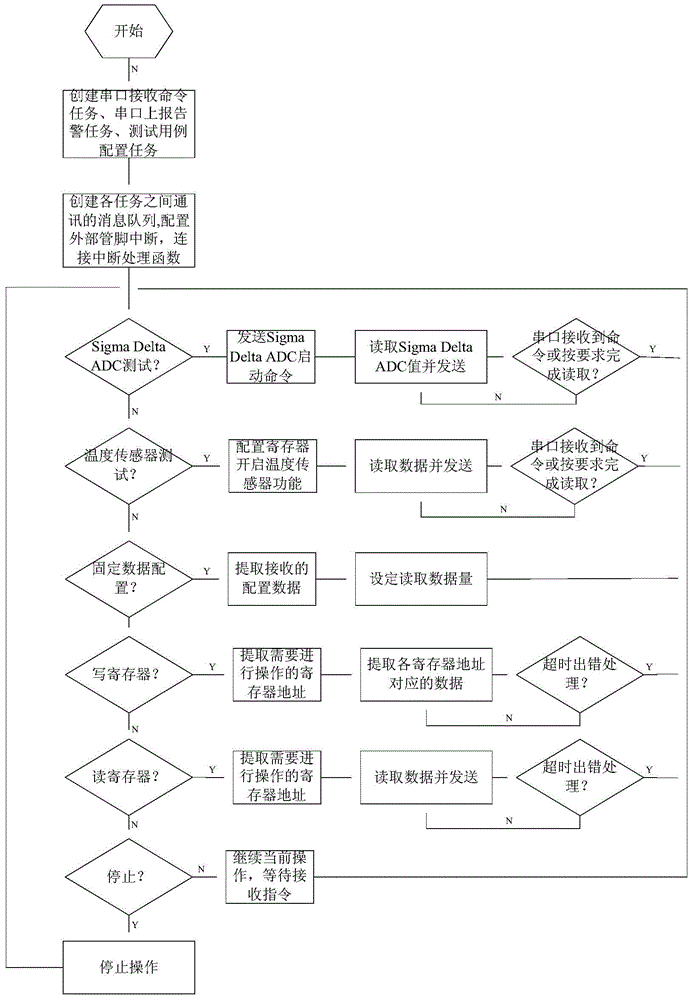

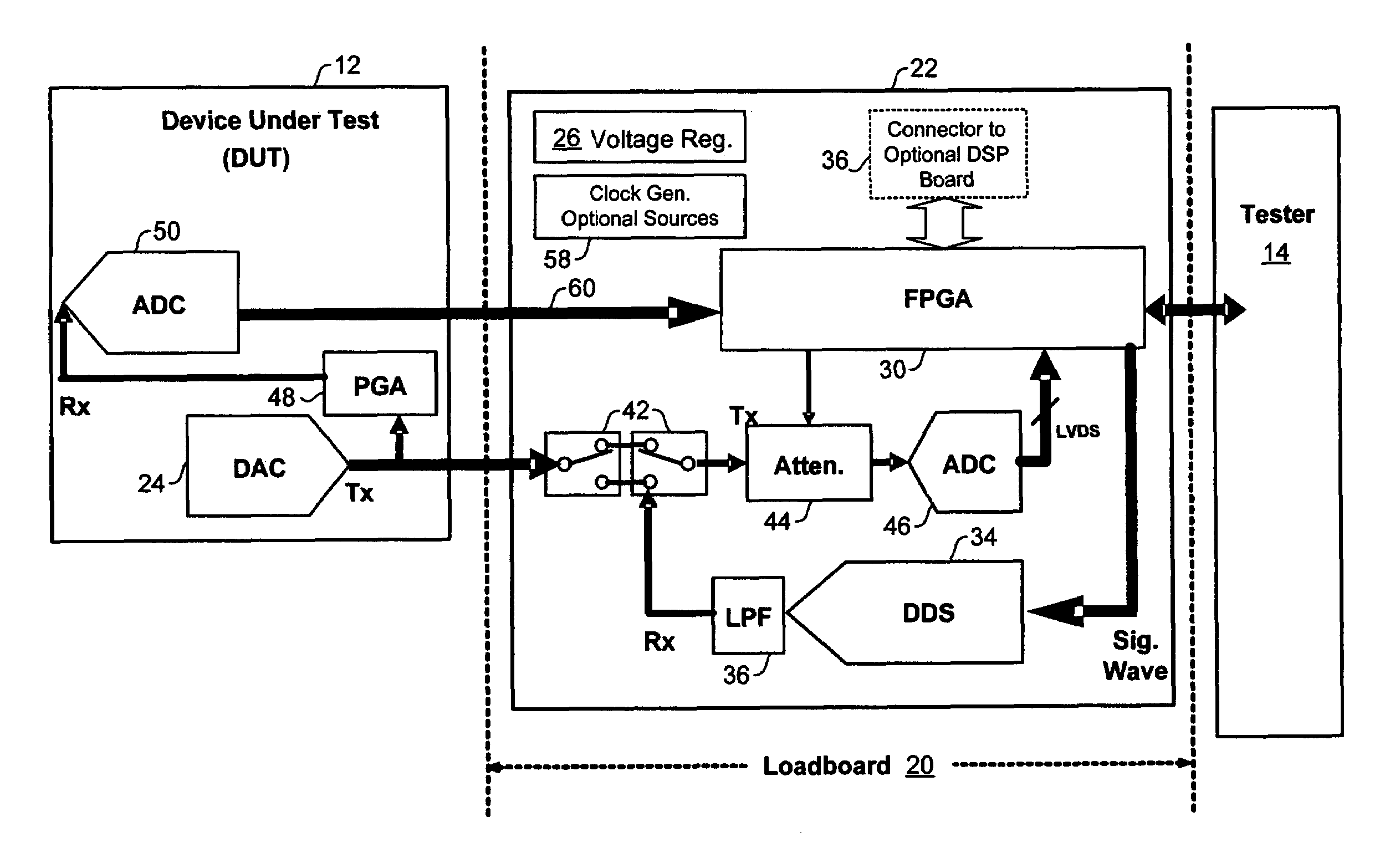

Automatic chip testing method

InactiveCN105004984AQuick testImplement automated testingElectronic circuit testingCommunication interfaceTest efficiency

The invention discloses a automatic chip testing method, which is characterized by comprising the steps that: the system is powered on, and initialization is completed; the configuration is carried out, a test thread needs to be started is determined according to chip types, and an instrument transceiving end is configured; a test command is generated, test items and test parameter setting in a chip integrated test case configuration file are read and analyzed, and a command frame is generated and transmitted to a single-board system through a communication interface; and the command is analyzed, and setting and testing steps are carried out. The automatic chip testing method can achieve the automatical test and data storage of chips, can be used for testing the chips quickly, is high in test efficiency, saves test time to a certain extent, can achieve the purposes of automatic configuration of a tested DUT chip, automatic configuration of instruments, automatic recovery of test results and automatic generation of test reports, automatic generation of test case reports and automatic switching of test cases through the development of an automatic chip testing platform.

Owner:CHIPSEA TECH SHENZHEN CO LTD

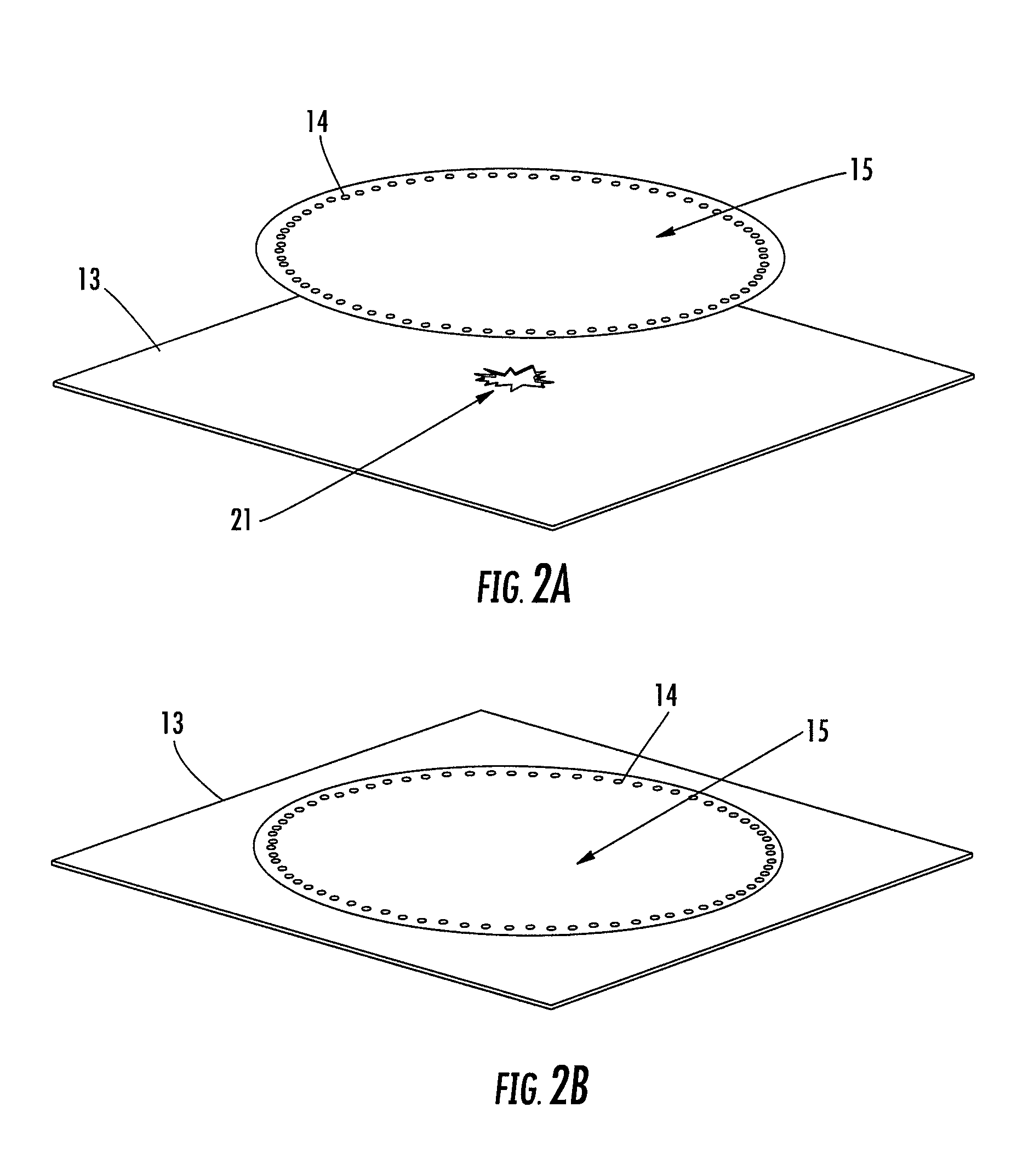

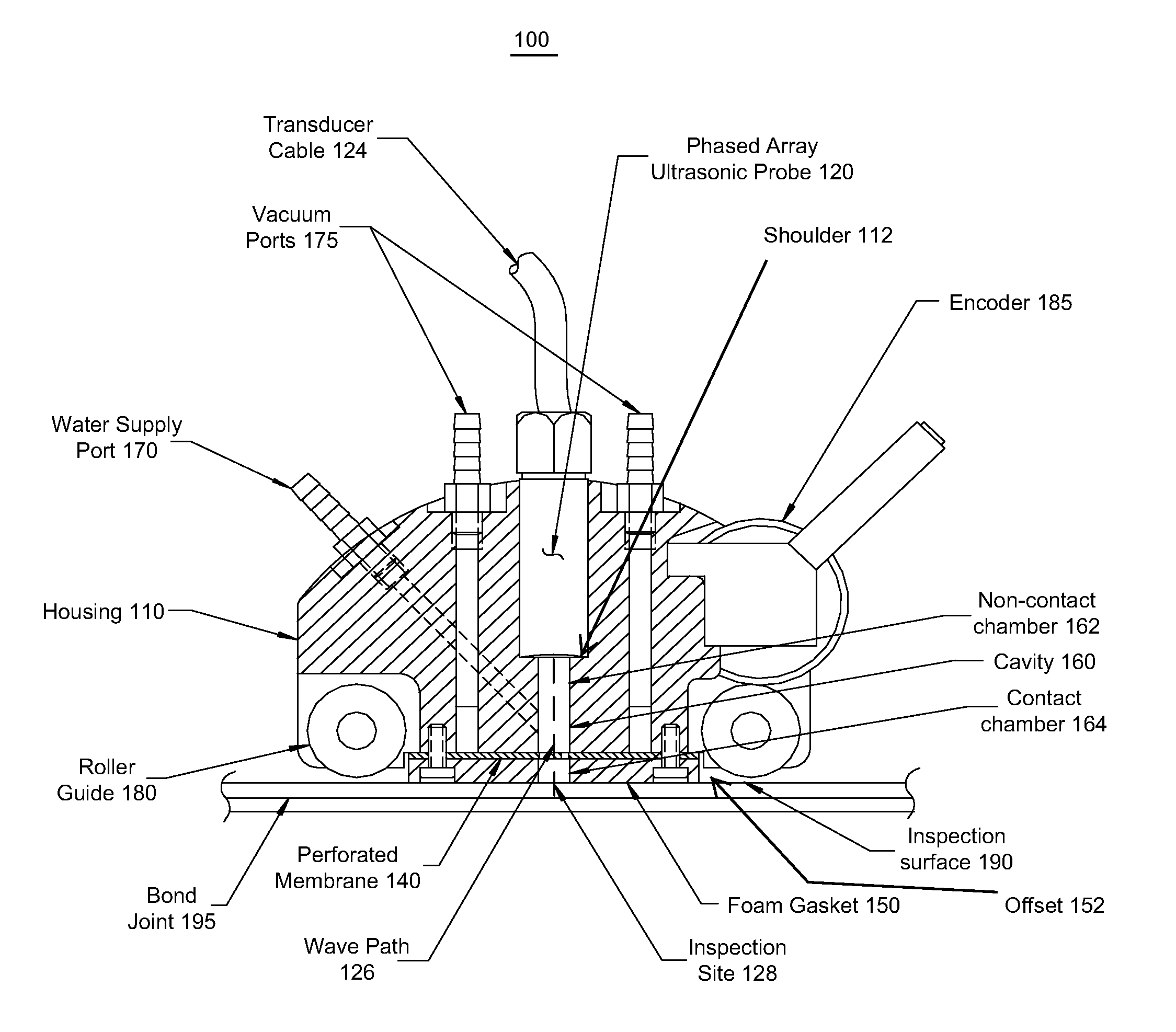

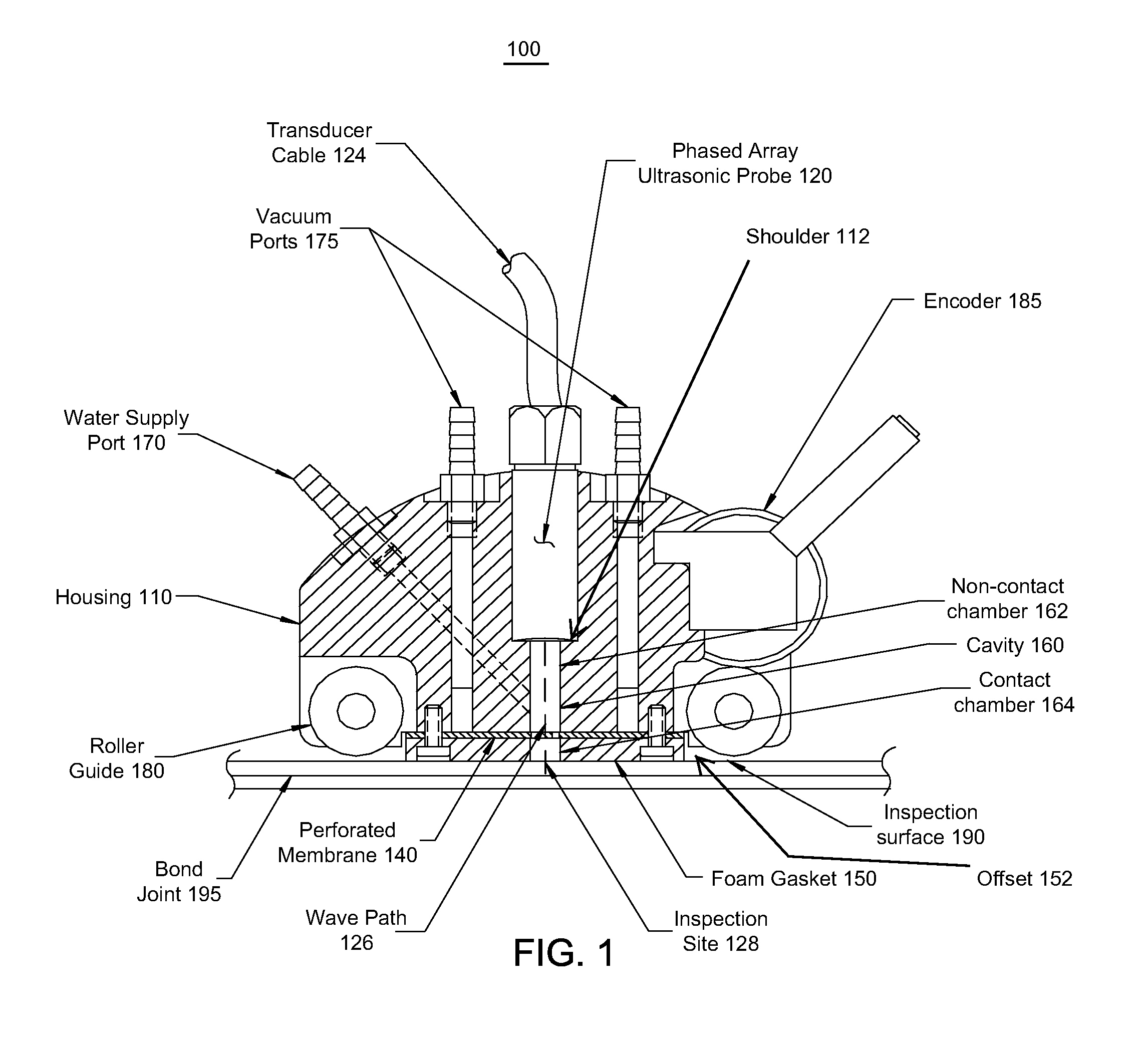

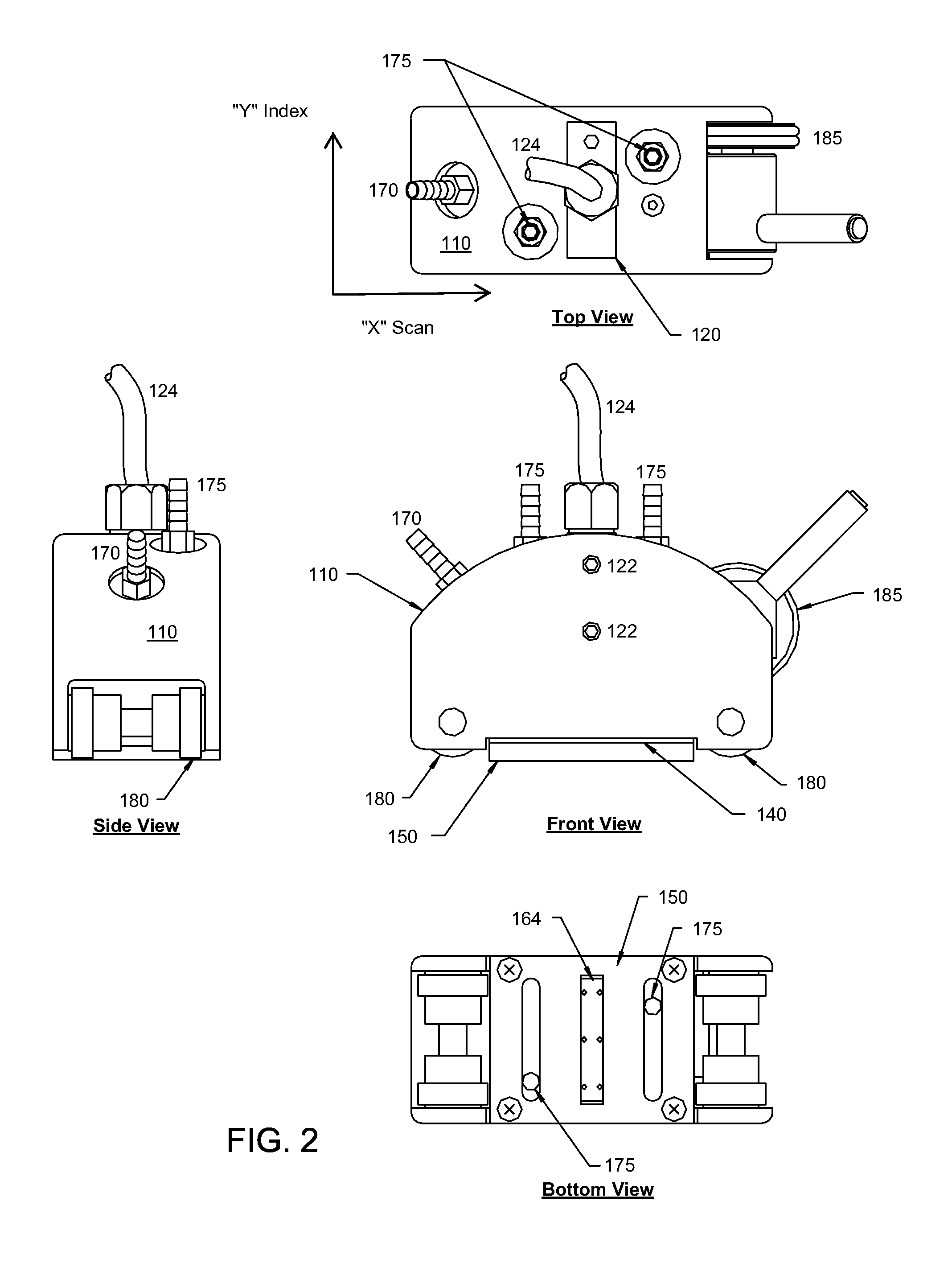

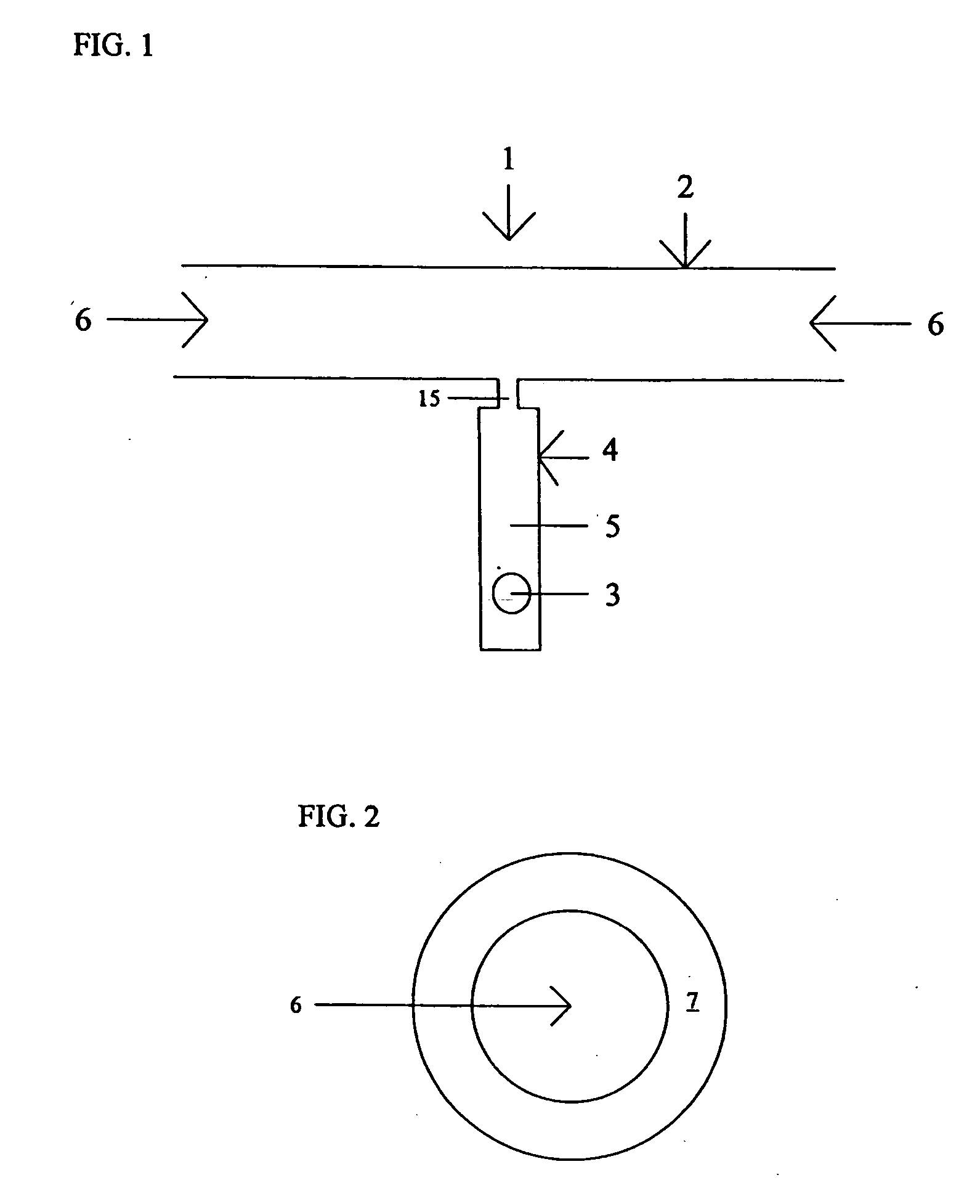

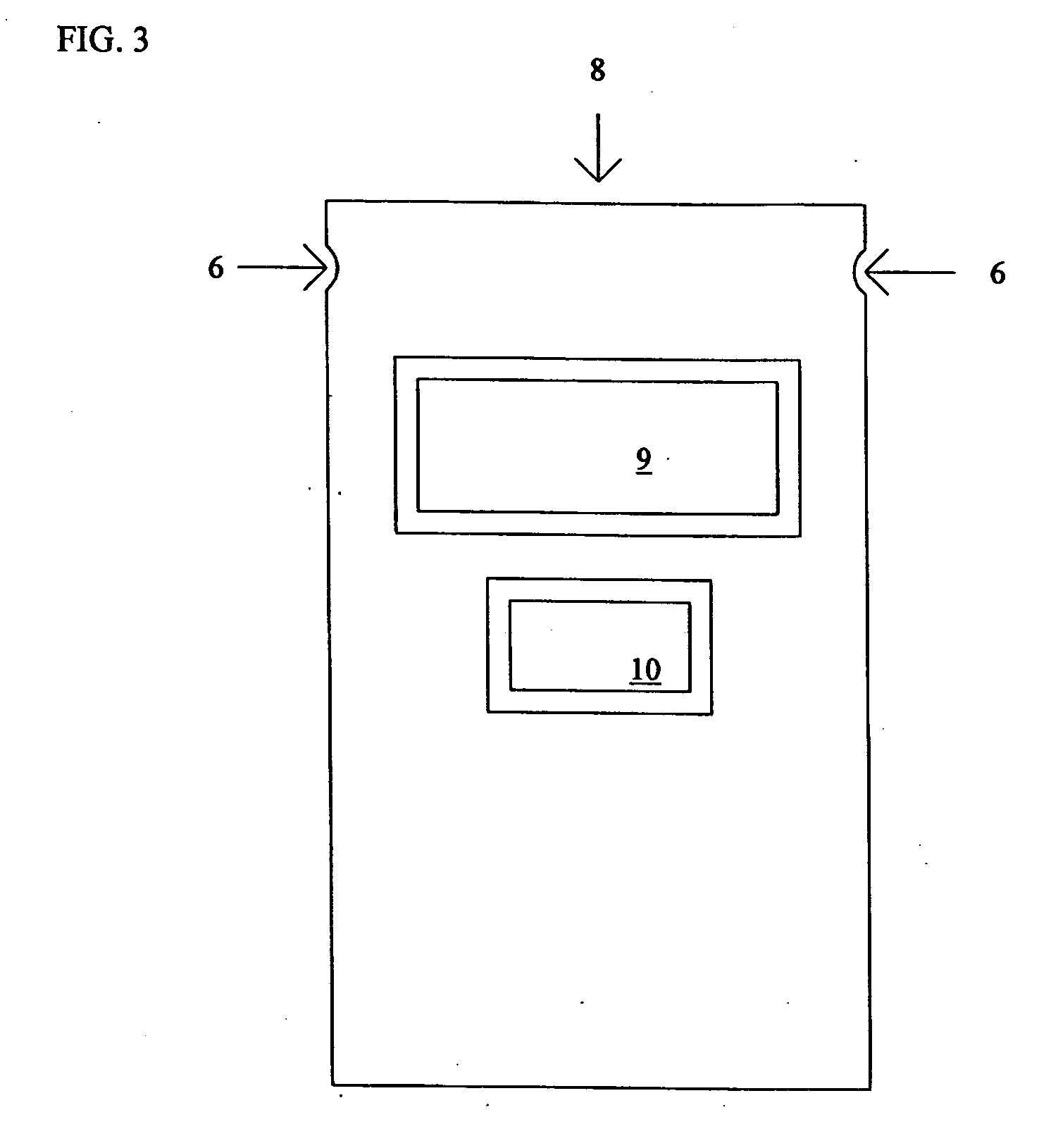

Ultrasonic probe deployment device for increased wave transmission and rapid area scan inspections

ActiveUS8087298B1Maximize effectivenessOvercome limitationsAnalysing solids using sonic/ultrasonic/infrasonic wavesWeather/light/corrosion resistanceEngineeringUltrasonic transmission

An ultrasonic probe deployment device in which an ultrasound-transmitting liquid forms the portion of the ultrasonic wave path in contact with the surface being inspected (i.e., the inspection surface). A seal constrains flow of the liquid, for example preventing the liquid from surging out and flooding the inspection surface. The seal is not rigid and conforms to variations in the shape and unevenness of the inspection surface, thus forming a seal (although possibly a leaky seal) around the liquid. The probe preferably is held in place to produce optimum ultrasonic focus on the area of interest. Use of encoders can facilitate the production of C-scan area maps of the material being inspected.

Owner:NAT TECH & ENG SOLUTIONS OF SANDIA LLC +1

Sensitive and rapid determination of antimicrobial susceptibility

ActiveUS7687239B2Quick checkReduce sensitivityBioreactor/fermenter combinationsBiological substance pretreatmentsFiltrationReducing agent

The present invention relates to moving microorganisms to a surface, where they are grown in the presence and absence of antimicrobials, and by monitoring the growth of the microorganisms over time in the two conditions, their susceptibility to the antimicrobials can be determined. The microorganisms can be moved to the surface through electrophoresis, centrifugation or filtration. When the movement involves electrophoresis, the presence of oxidizing and reducing reagents lowers the voltage at which electrophoretic force can be generated and allows a broader range of means by which the target can be detected. Monitoring can comprise optical detection, and most conveniently includes the detection of individual microorganisms. The microorganisms can be stained in order to give information about their response to antimicrobials.

Owner:ACCELERATED MEDICAL DIAGNOSTICS INC

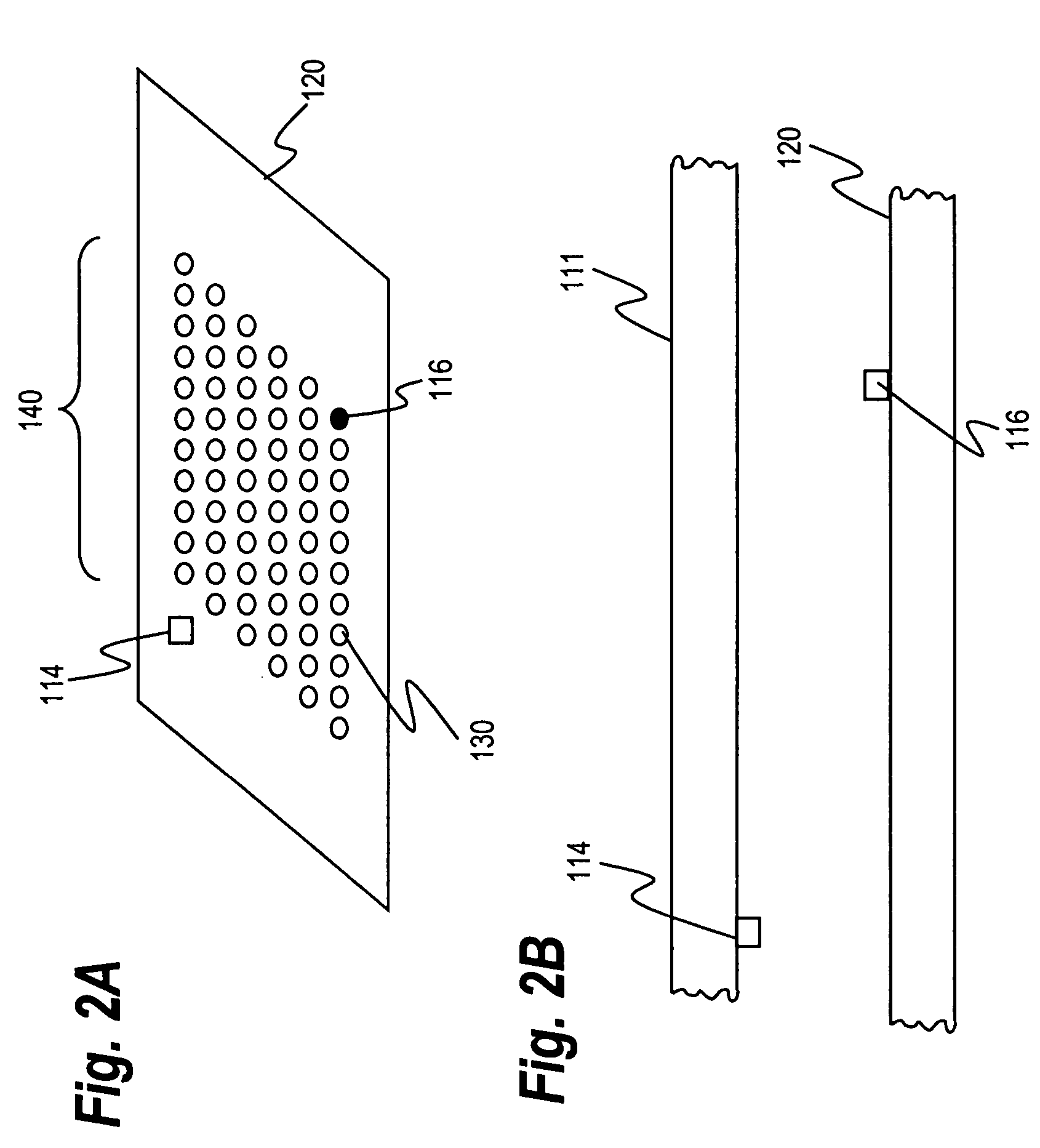

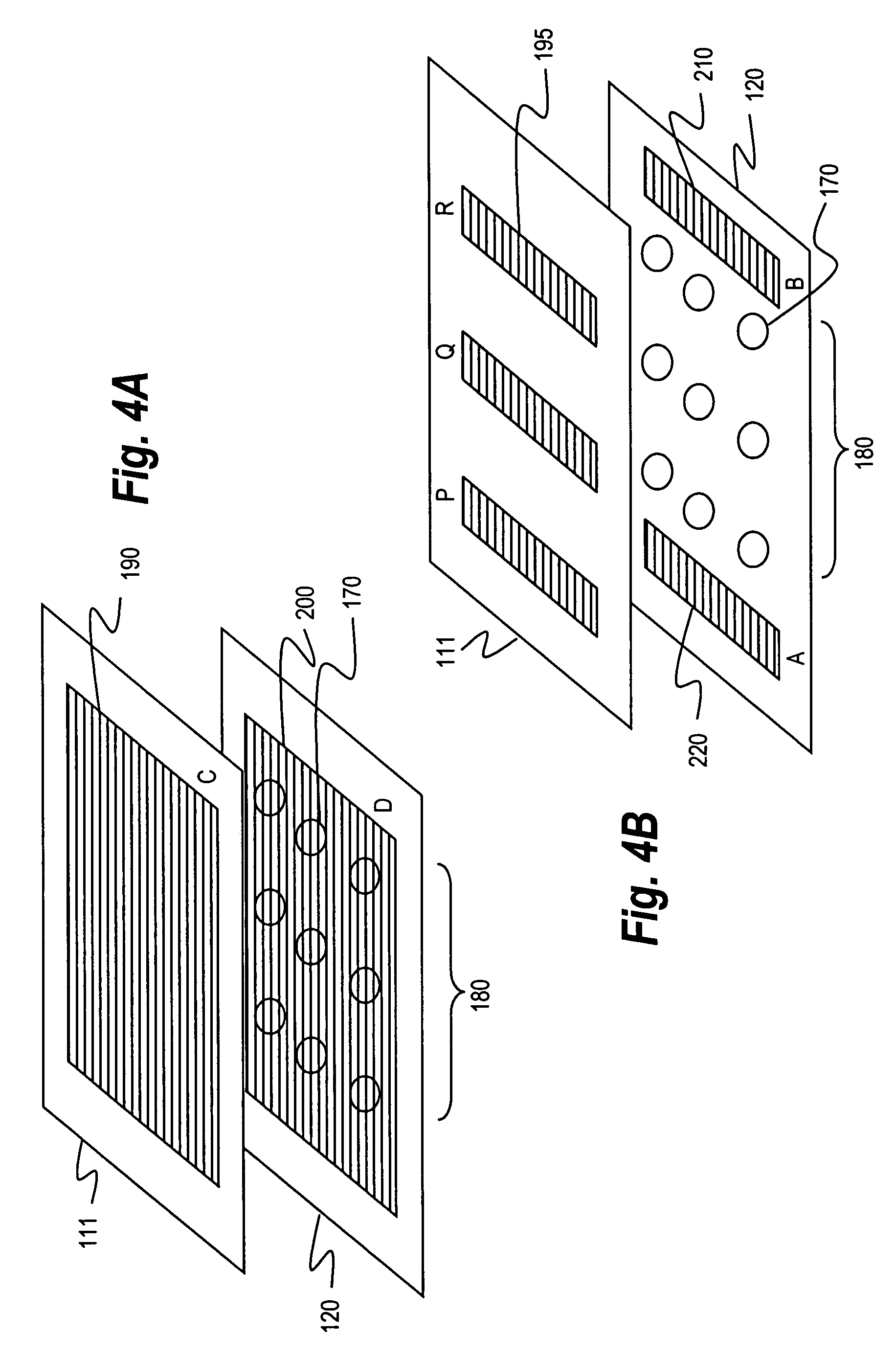

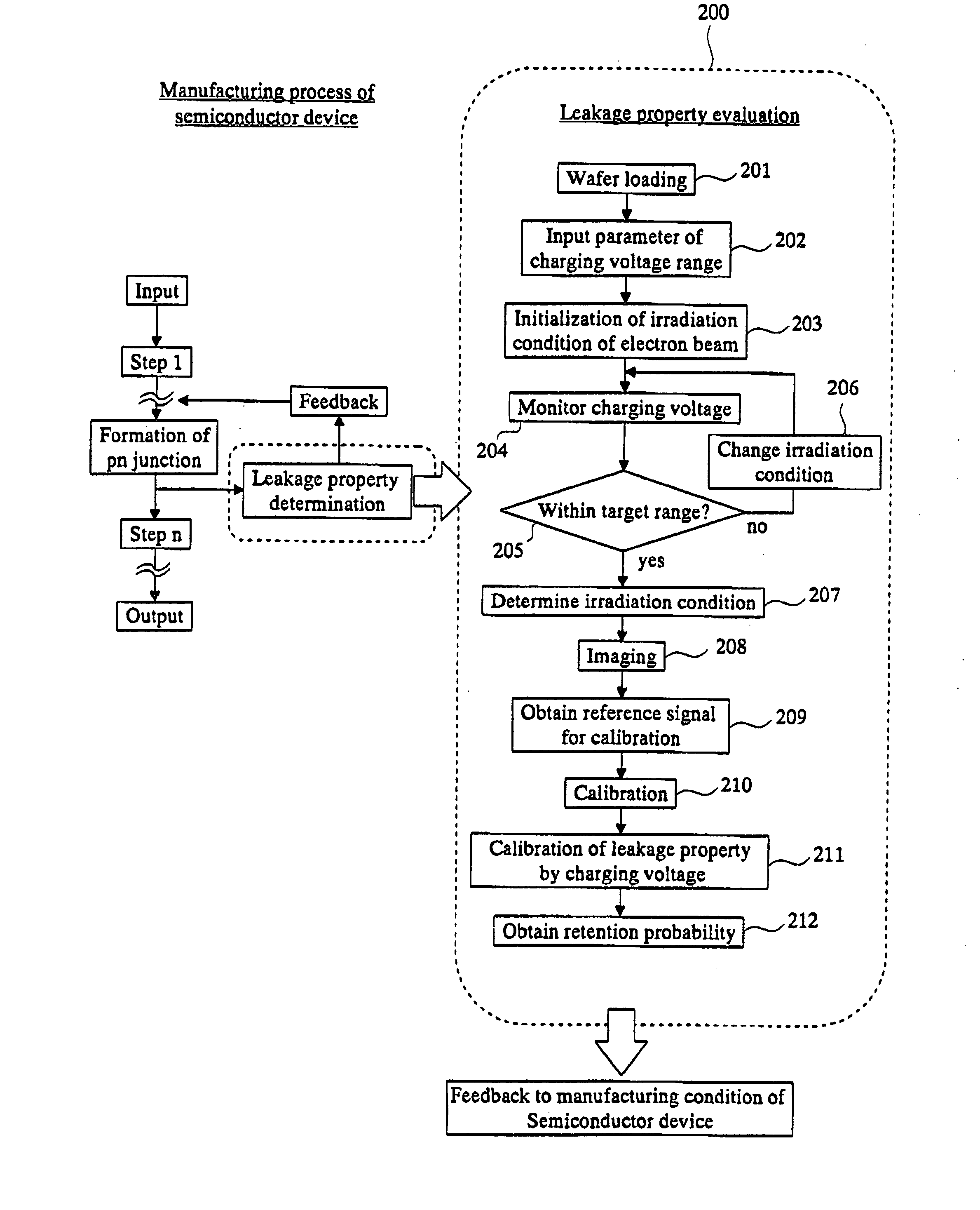

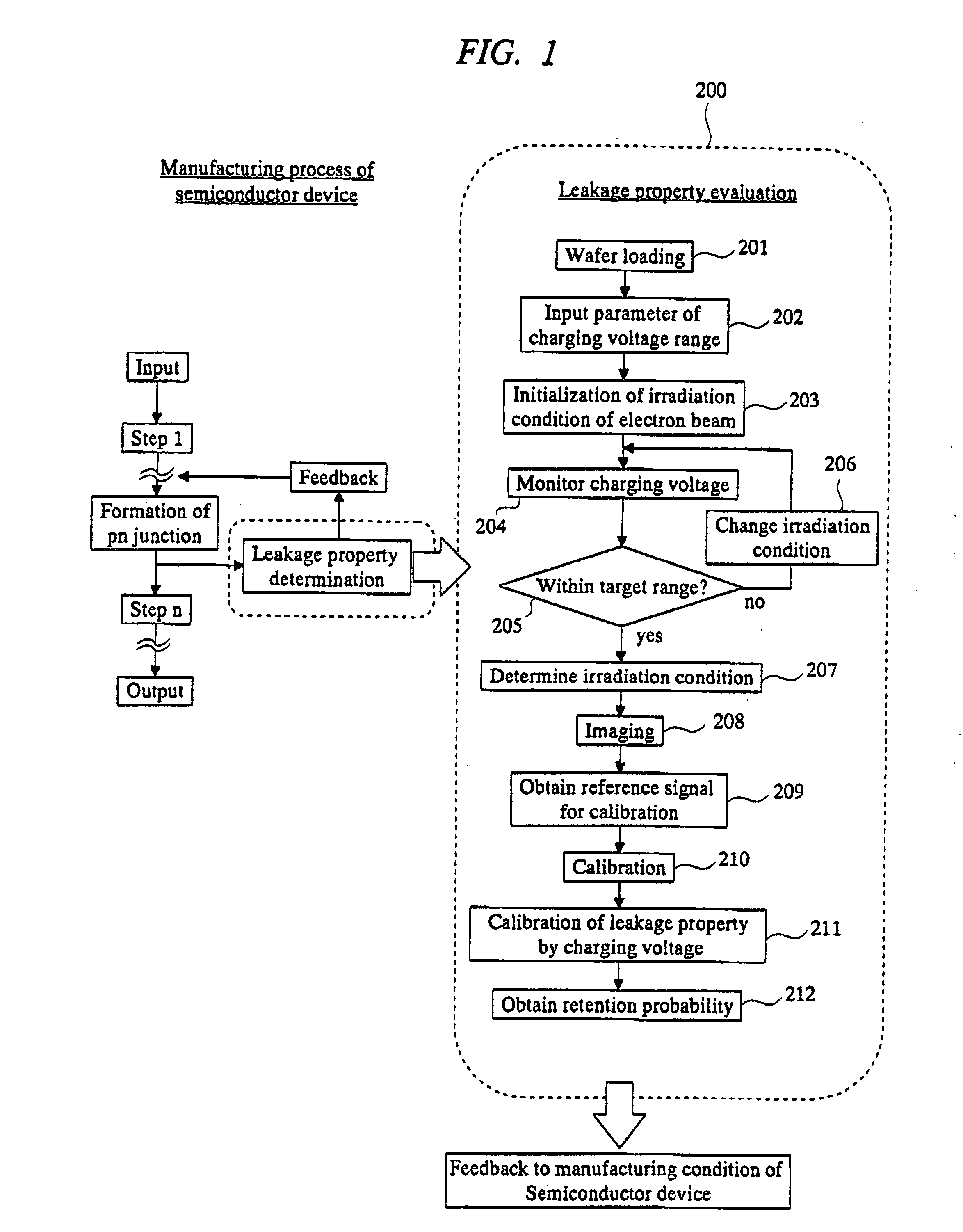

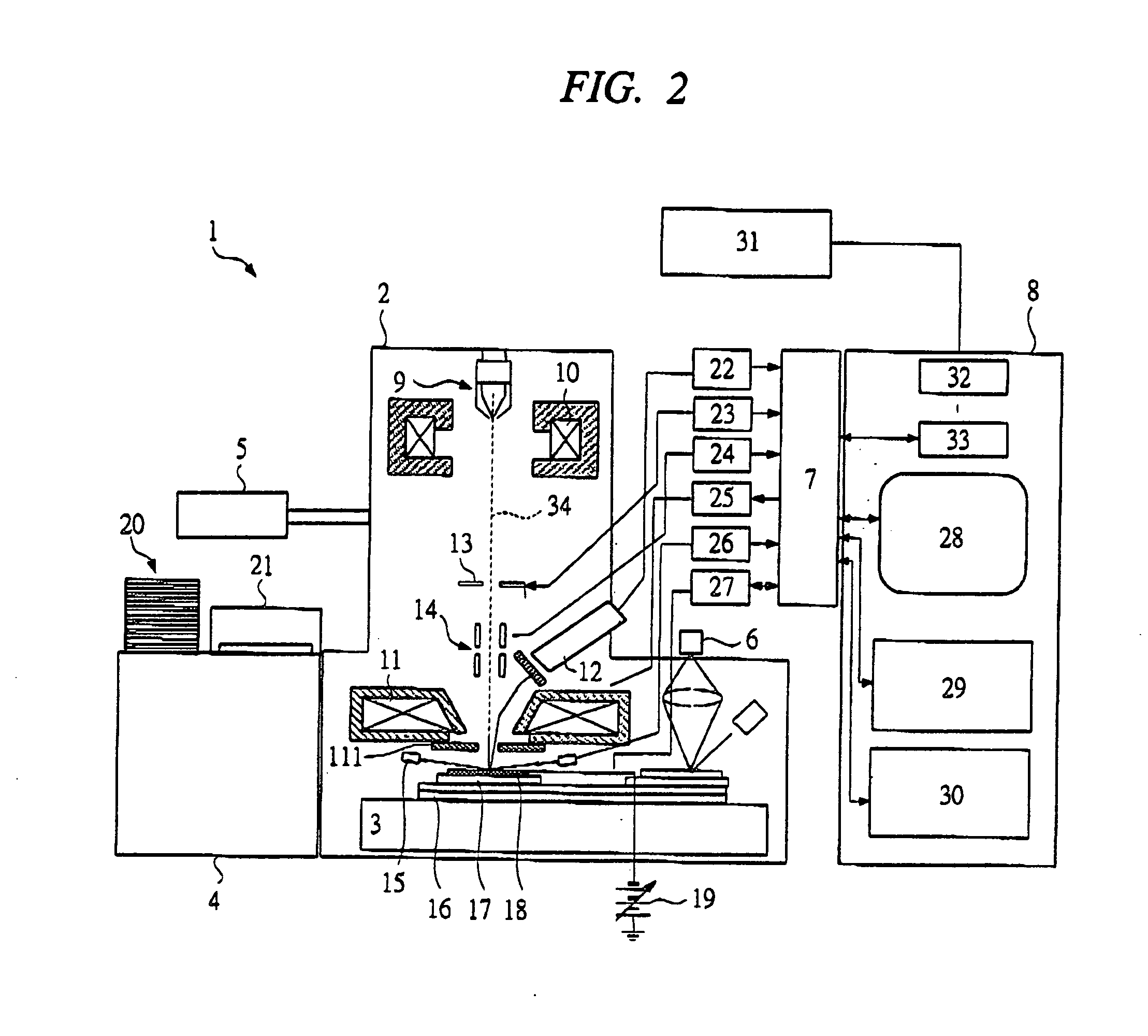

Evaluation method and manufacturing method of semiconductor device

InactiveUS20060022295A1Accurate measurementQuick measurementSemiconductor/solid-state device testing/measurementElectric discharge tubesDevice materialSecondary electrons

The electron beam is irradiated several times at predetermined intervals to the wafer surface on which the plugs are exposed in the course of the manufacturing process so that the pn junction is in the reverse bias state. Then, the irradiation conditions of the electron beam are changed while monitoring the charging voltage on the plug surface, and the secondary electron signals of the circuit pattern are obtained under the irradiation conditions that the charging is within a desired range, thereby evaluating the leakage property. Since the charging voltage of the pn junction is relaxed depending on the magnitude of the leakage current during the interval, the leakage property is evaluated based on the luminance signals of the voltage contrast image. By measuring the charging voltage and setting it within a desired range, the evaluation result reflects the state in the actual operation. Therefore, the accuracy is enhanced.

Owner:HITACHI LTD +1

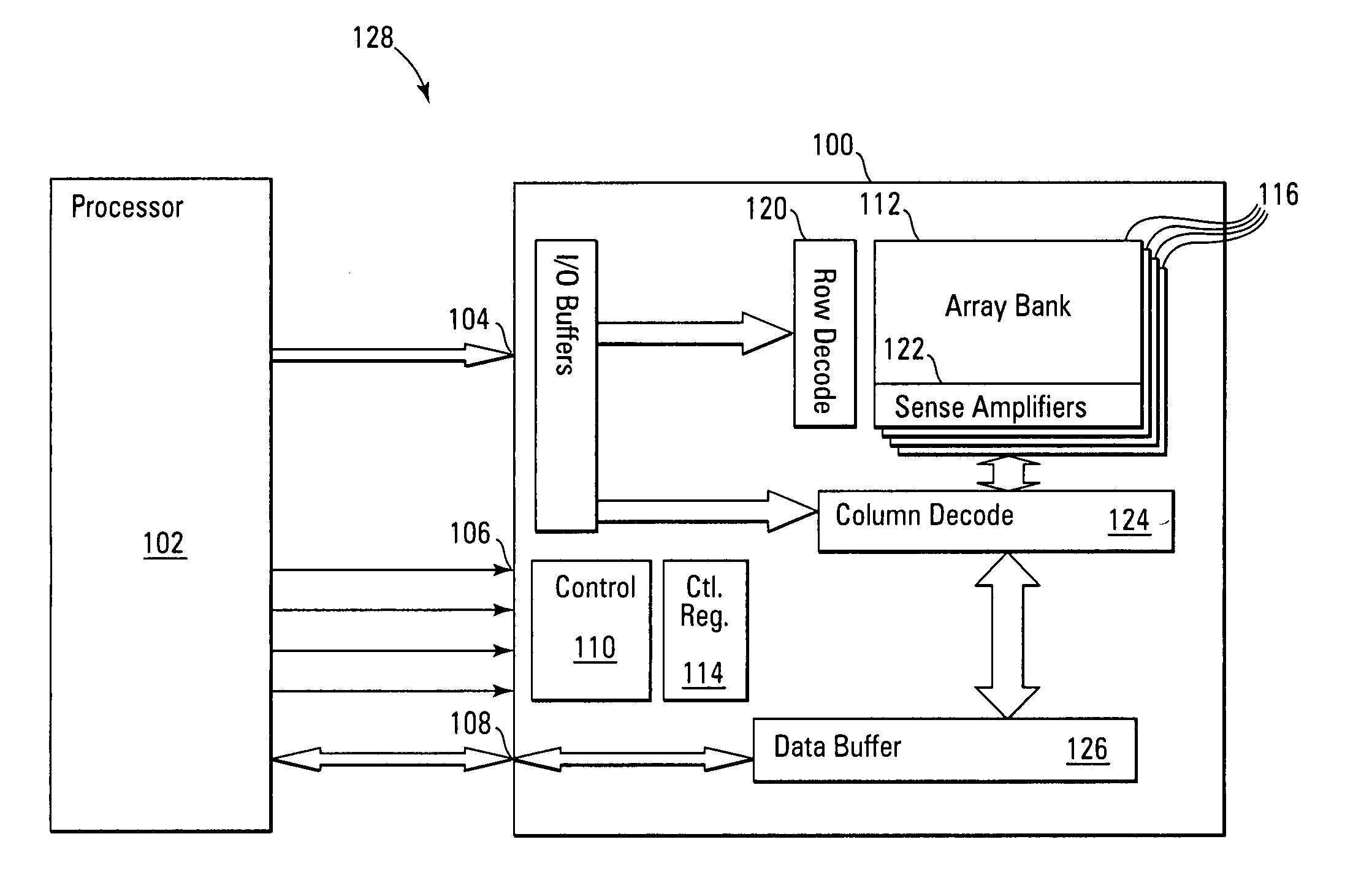

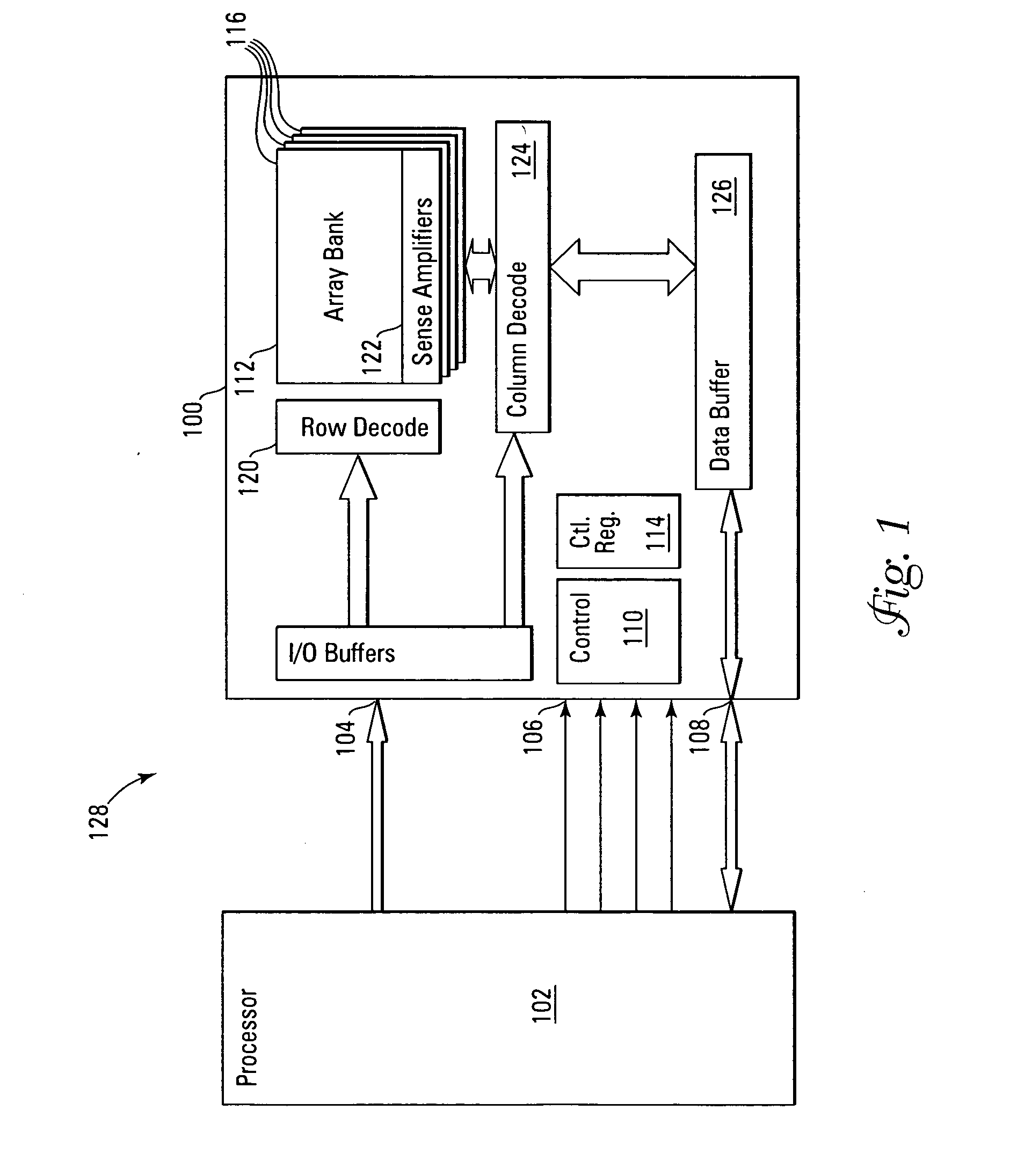

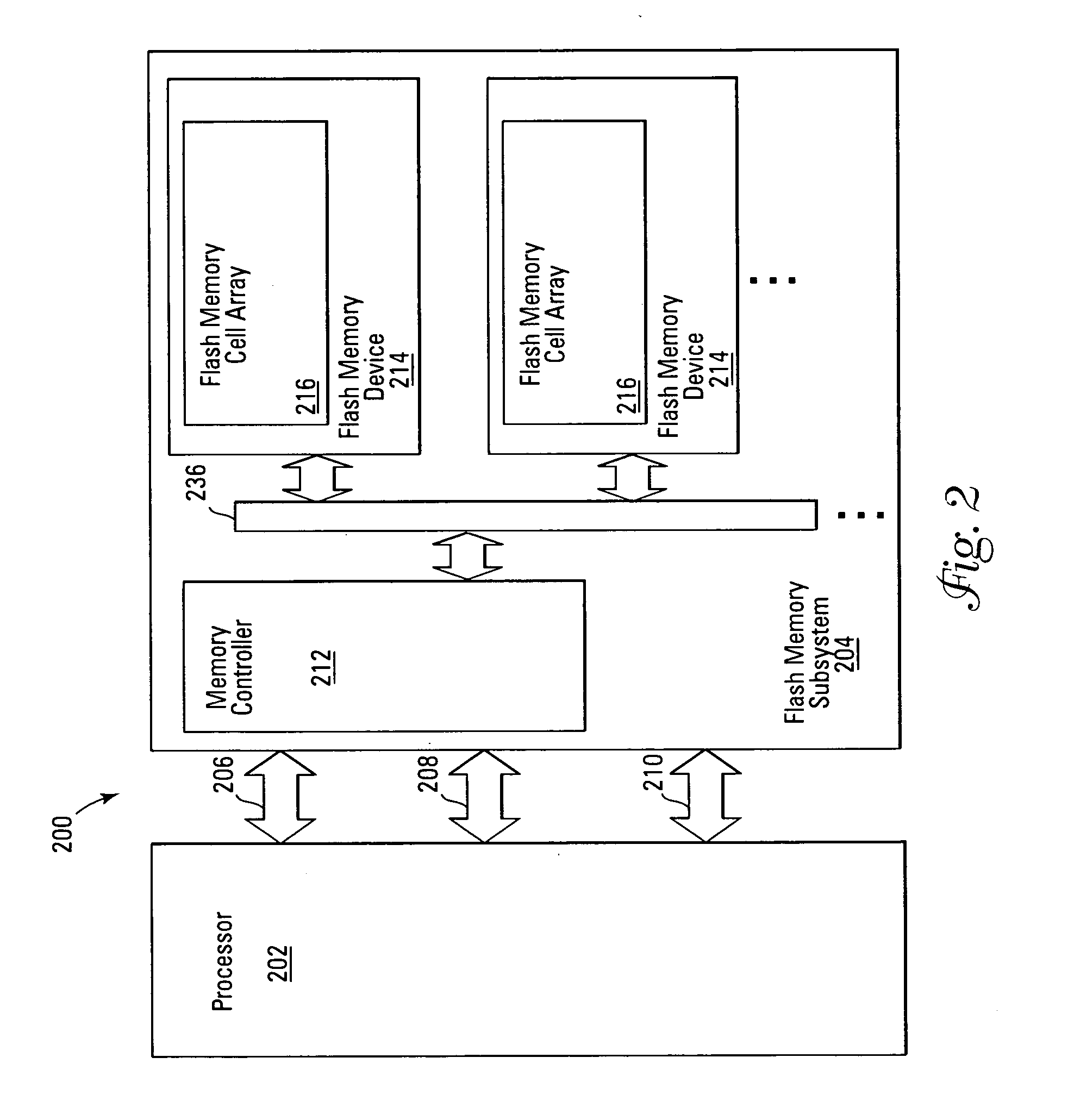

Method for testing flash memory power loss recovery

ActiveUS20050108491A1Quickly testSave time and resourceRead-only memoriesMemory systemsStorage cellRecovery cycle

Non-volatile memory device, driver, and method is described that utilizes write or erase cycle tracking to interrupt or stop a non-volatile memory programming or erase operation at a selected point to interrupt / stop execution or simulate power loss at a specific point. This ability allows for a deterministic and repeatable testing process of all write or erase cycles of a non-volatile command where the state of floating gate memory cells are changed in the non-volatile memory device. Additionally, this ability to utilize write or erase cycle tracking to interrupt or stop a non-volatile memory programming operation or erasing operation at any selected point enables simulation of power loss at each point in a selected operation that a non-volatile floating gate memory cell is programmed or erased, allowing for improved, deterministic testing of the power loss recovery cycle and faster code / design change verification.

Owner:MICRON TECH INC

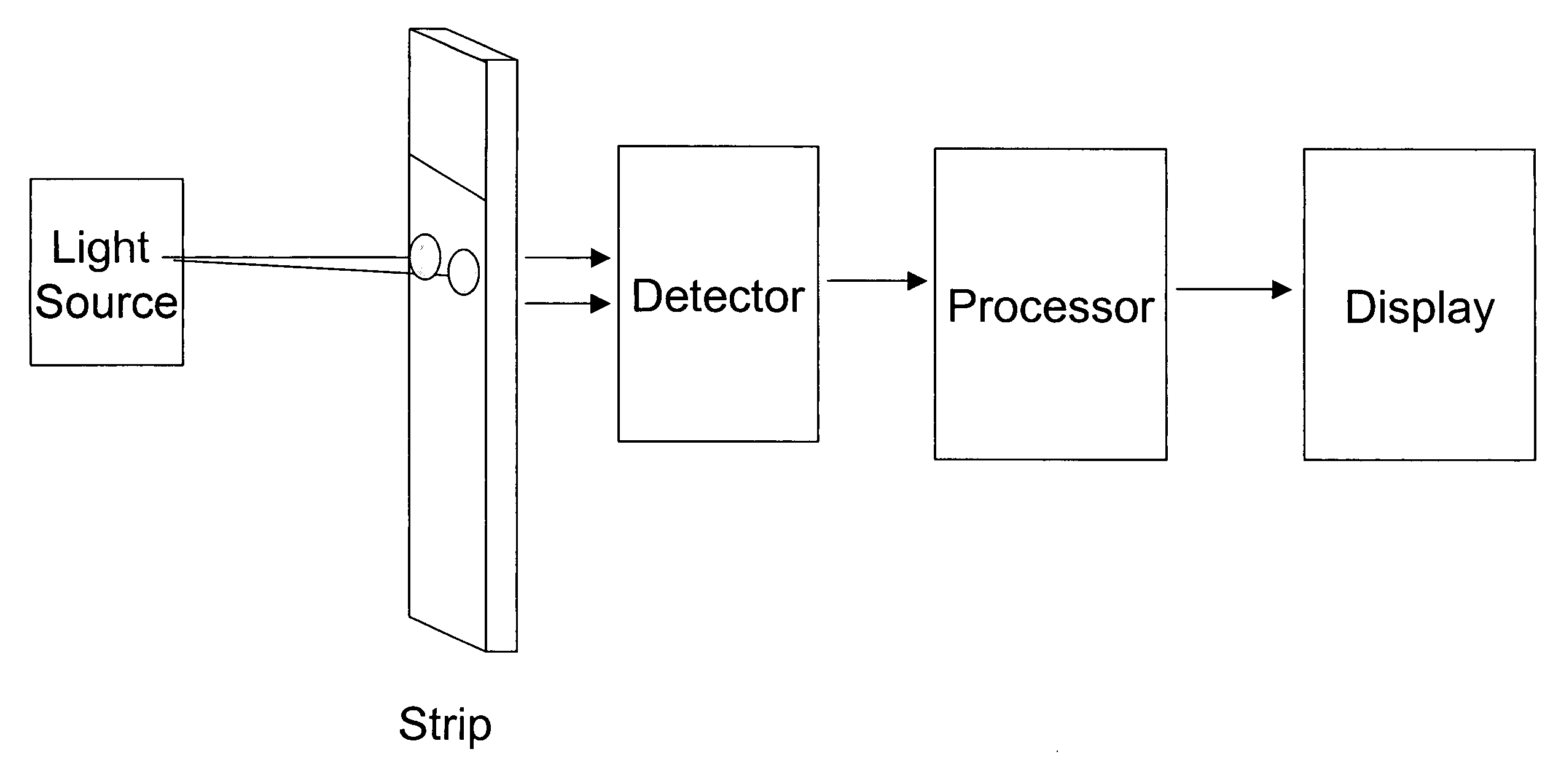

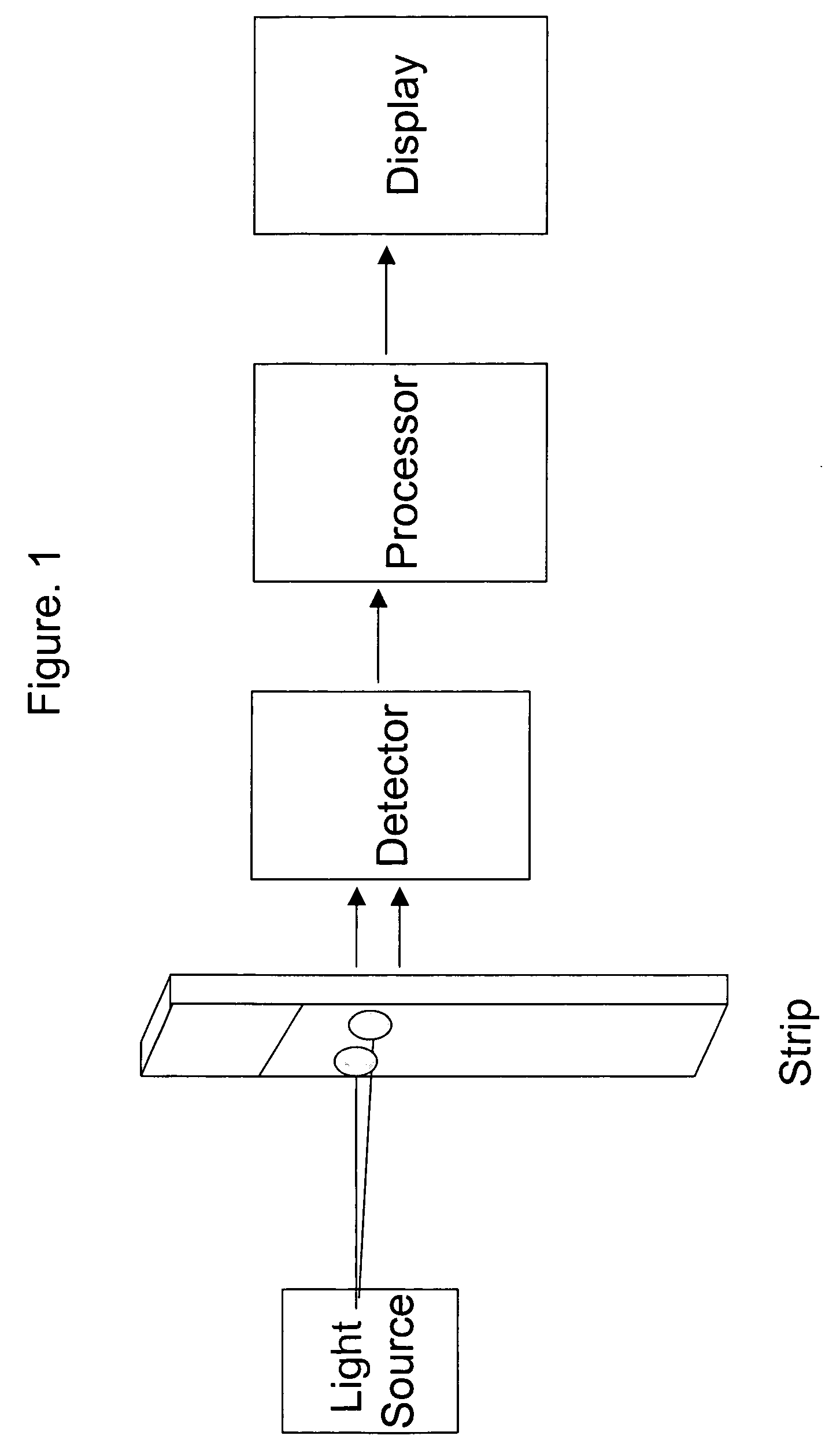

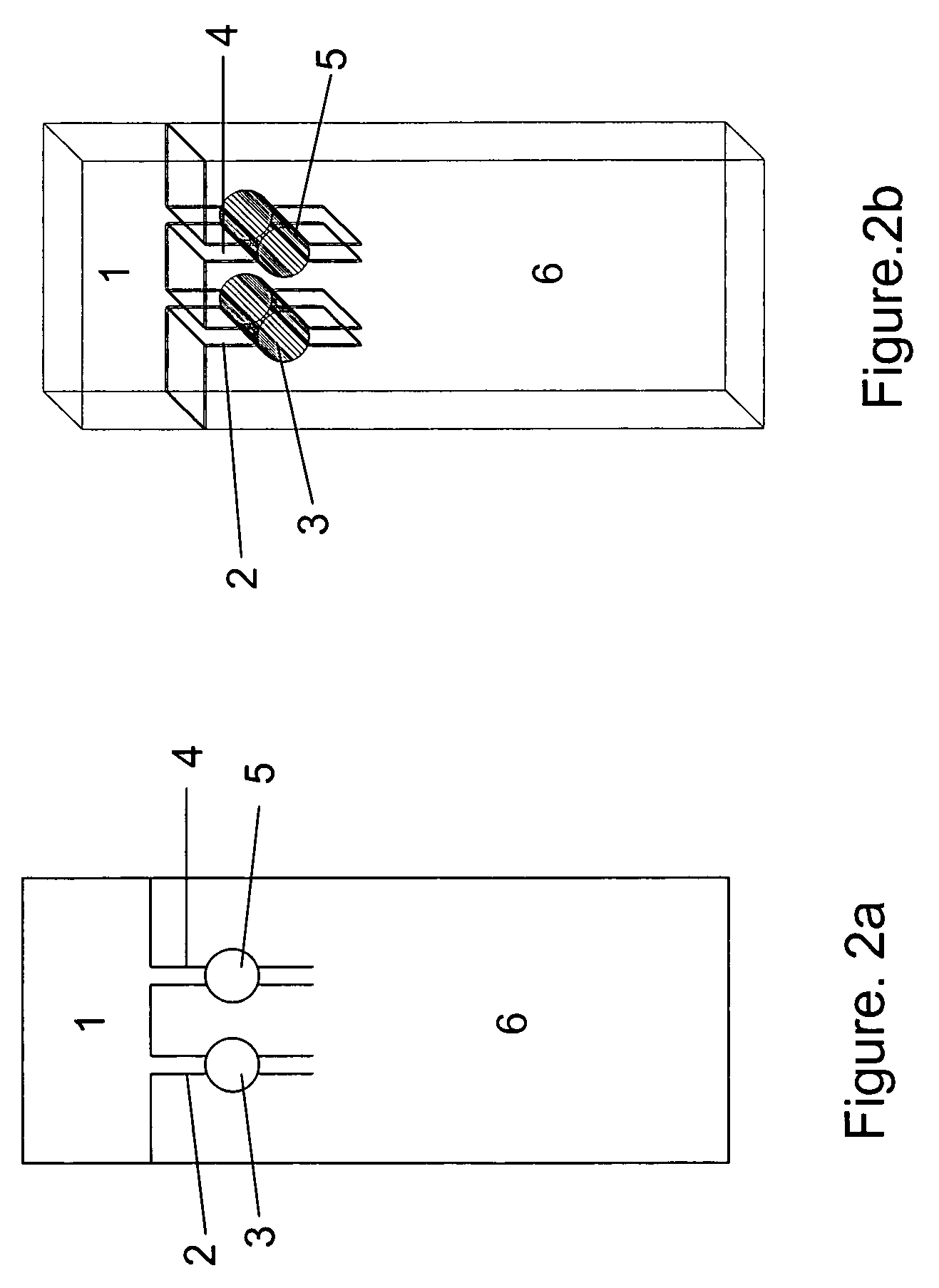

Combining transmittance detection and chromatographic strip techniques for quantification of analyte in biological fluids

InactiveUS7186566B2High sensitivityThe testing process is simpleBioreactor/fermenter combinationsBiological substance pretreatmentsAnalyteTransmittance

Owner:QIAN SUYUE

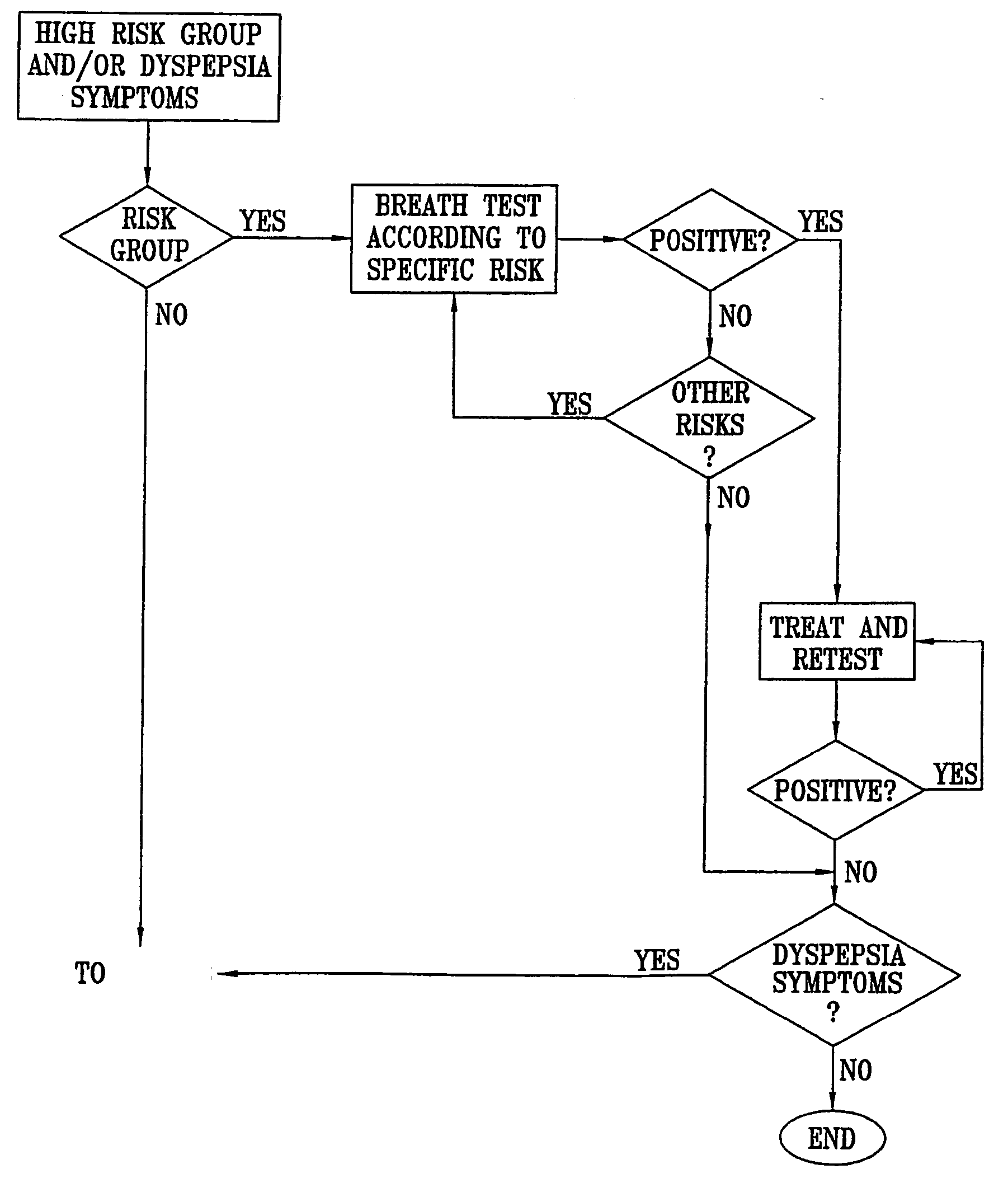

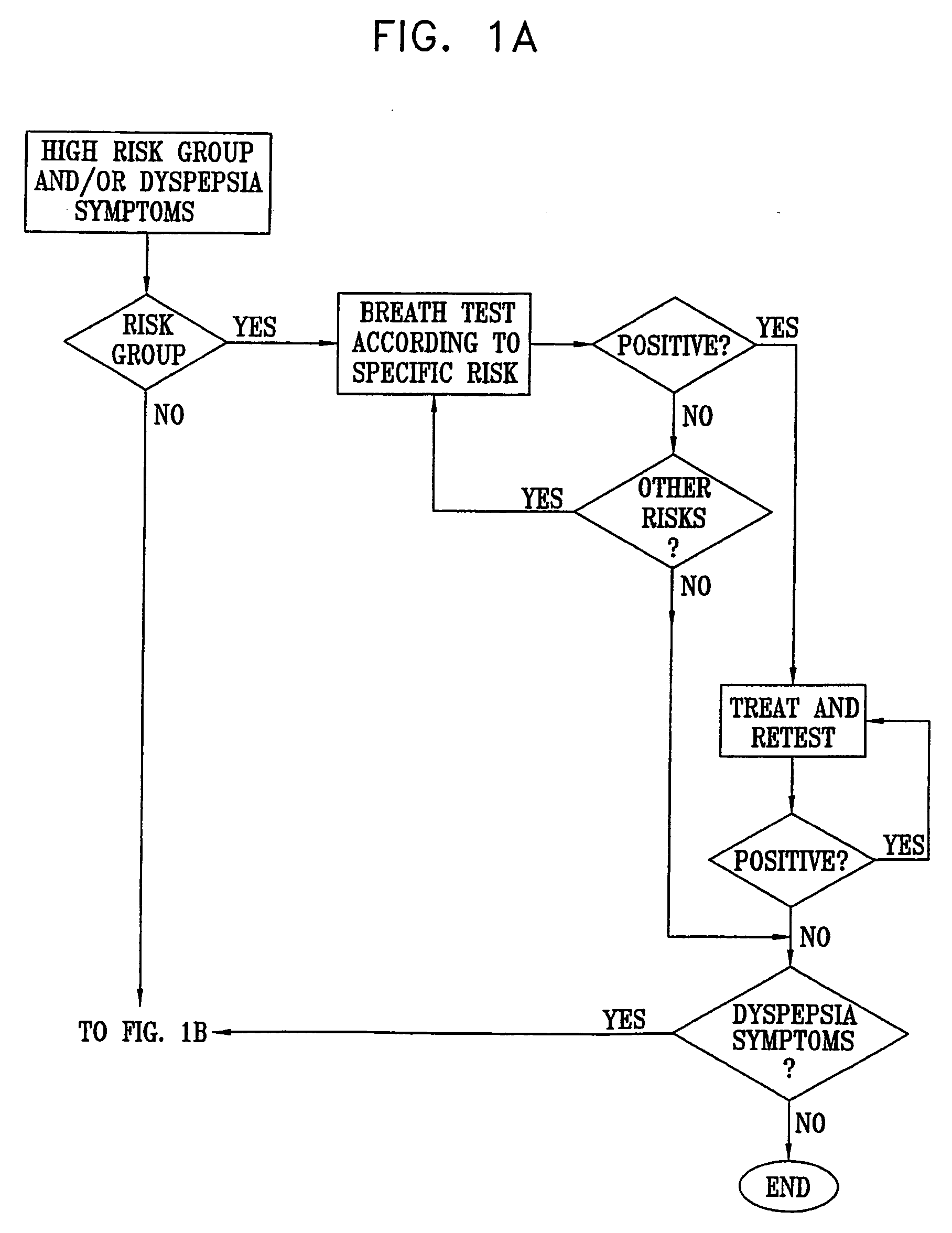

Management of gastro-intestinal disorders

InactiveUS20060074335A1Easily toleratedQuick testCompounds screening/testingPerson identificationDiseaseGastrointestinal dysfunction

The present invention relates to the field of methods and apparatus for the determination of various conditions of gastric and gastro-intestinal malfunction, especially those performed by means of breath tests.

Owner:EXALENZ BIOSCIENCE LTD

Methods of use of substrate having properties of keratinous tissue

ActiveUS20070288186A1Easy to produceEasy to storeComponent separationAnalogue computers for chemical processesZeta potentialCoated surface

Method of product evaluation comprising the steps of applying at least one substance to a surface of an artificial substrate to form a substance-coated surface, wherein the substrate surface demonstrates at least one physical property selected from the group consisting of a total surface energy of from about 15 mJ / m2 to about 50 mJ / m2, a polar component of the total surface energy of from about 0 mJ / m2 to about 15 mJ / m2, a zeta-potential at a pH of about 5.0 of from about −30 mV to about 30 mV, and combinations thereof, and performing at least one analysis of the substance-coated surface.

Owner:THE PROCTER & GAMBLE COMPANY

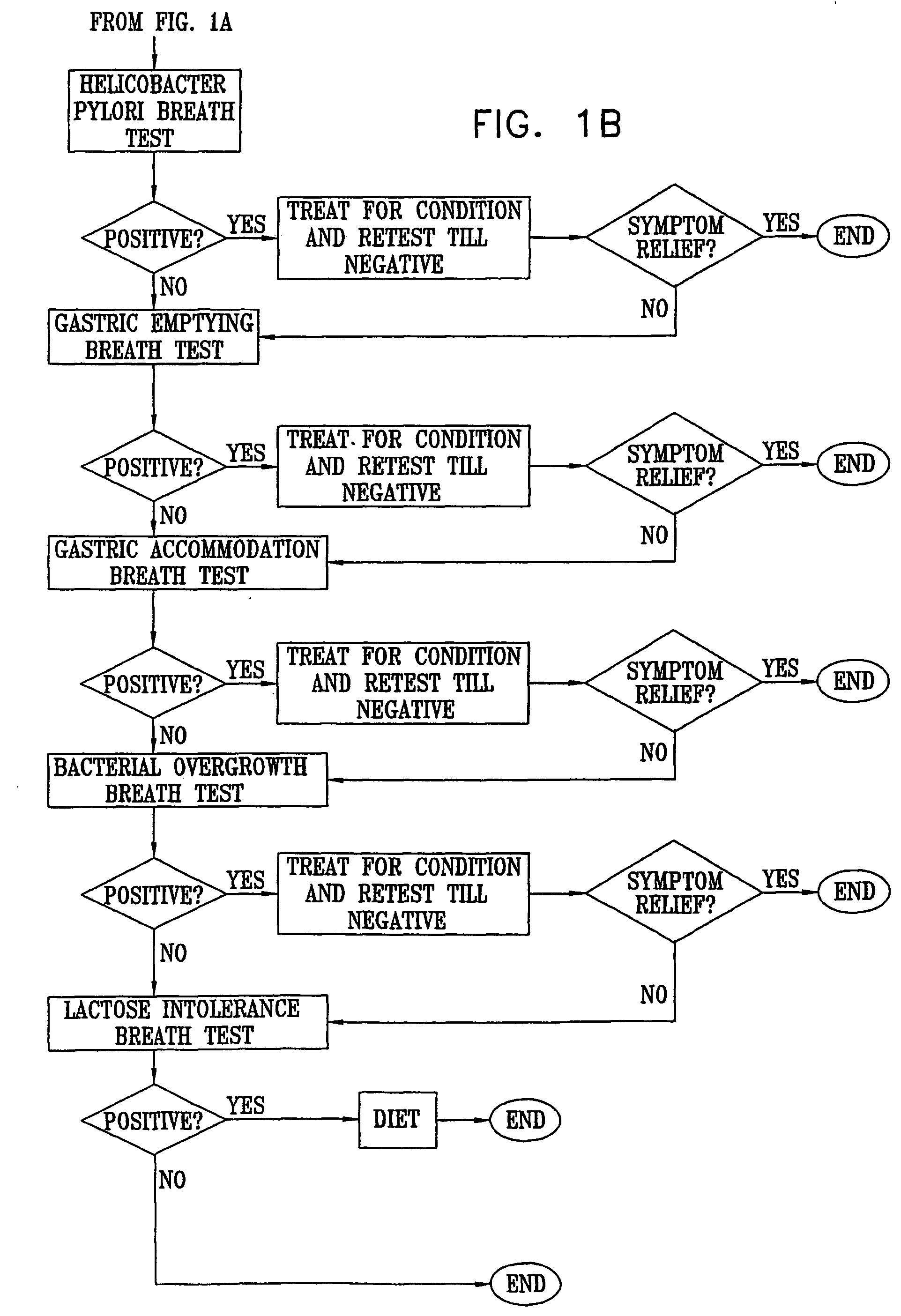

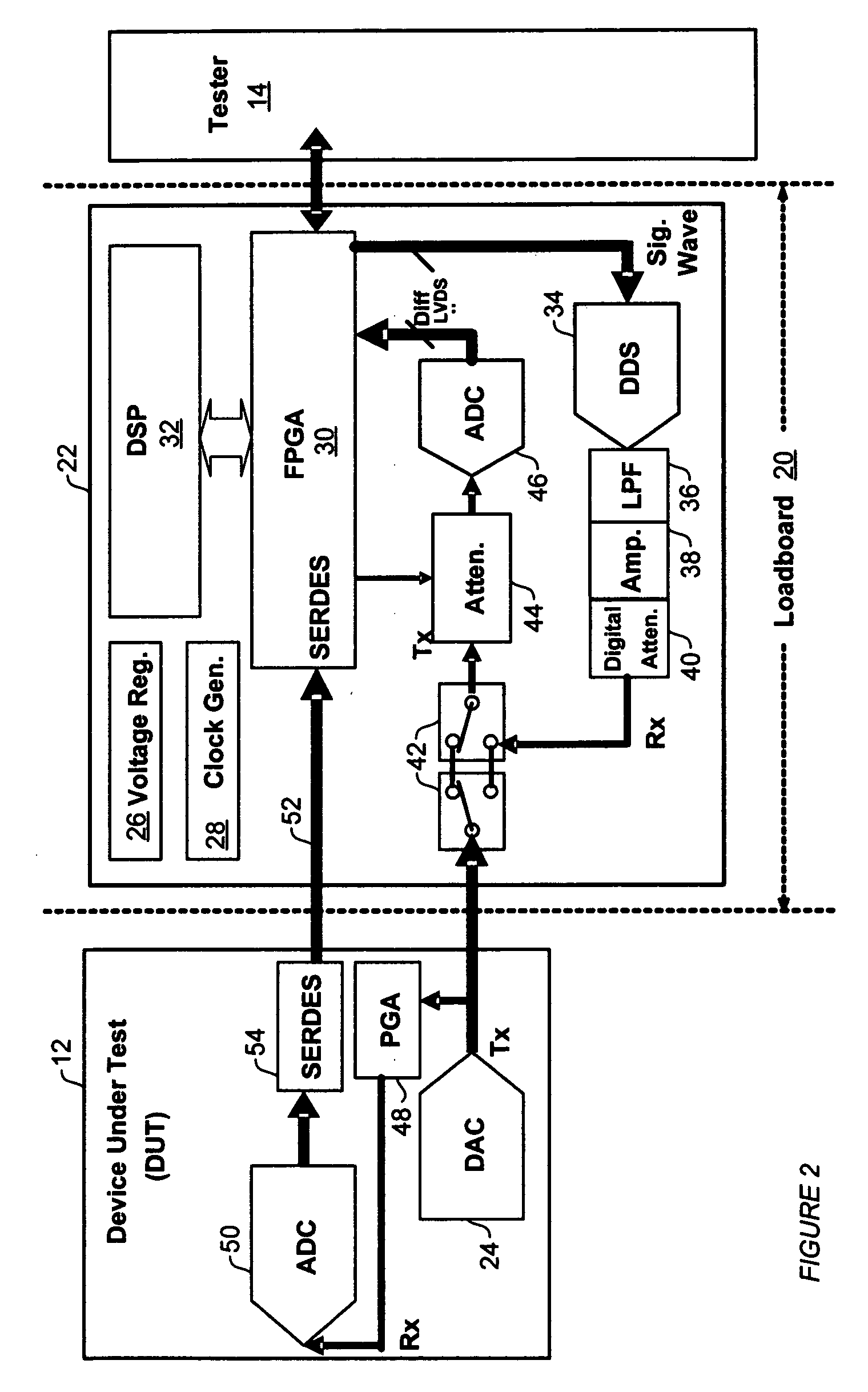

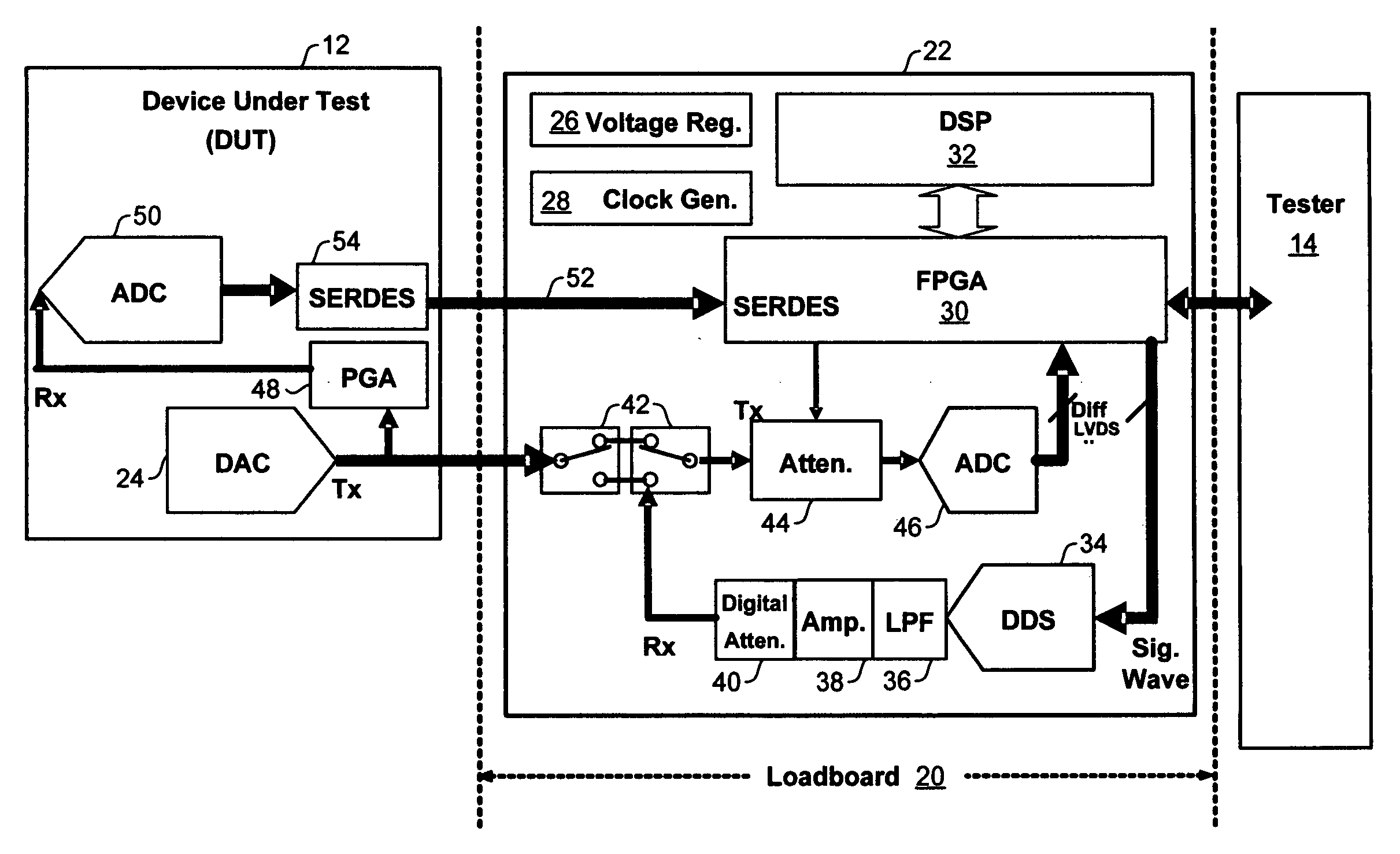

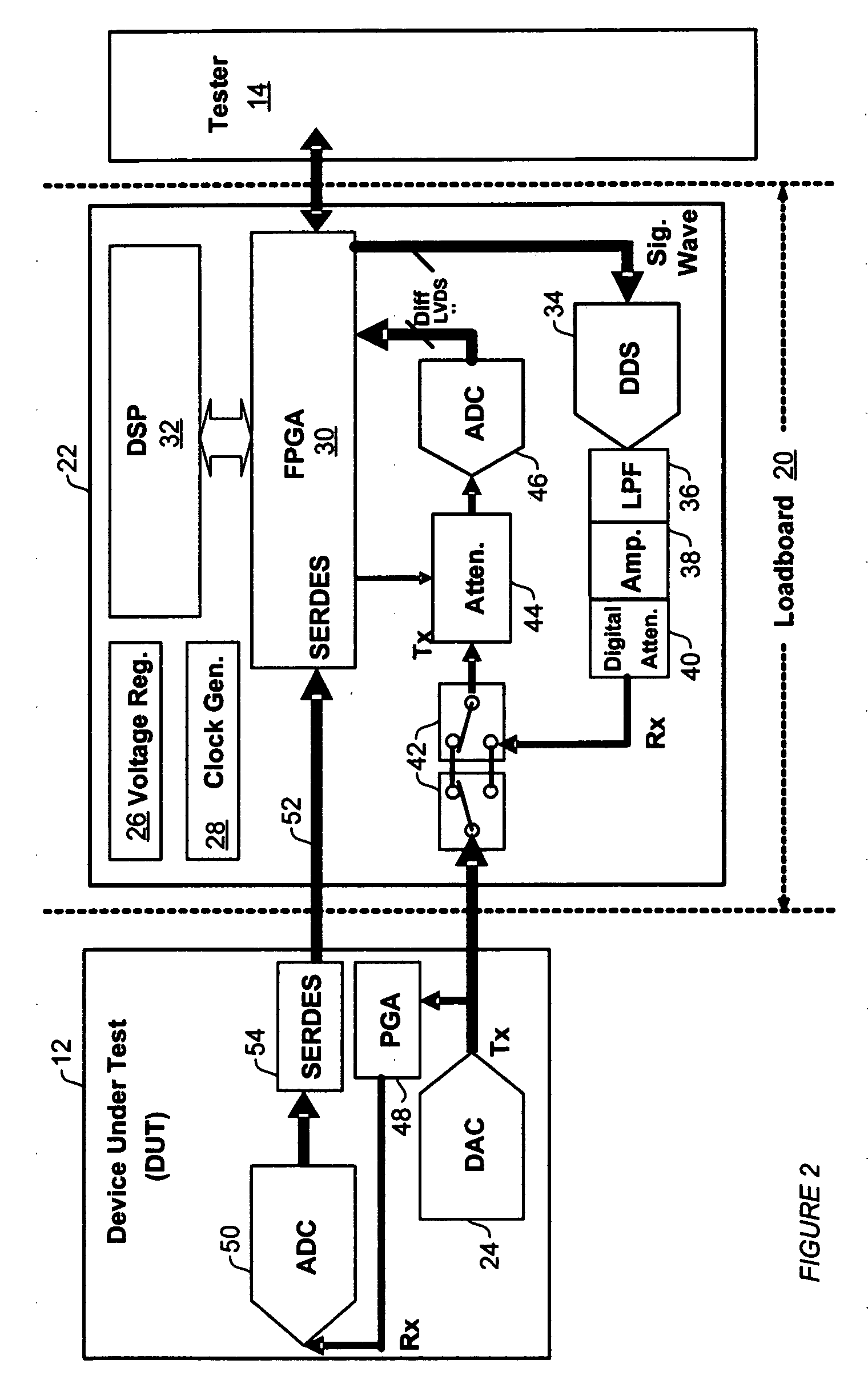

Analog built-in self-test module

ActiveUS7327153B2Quick testImprove efficiencyElectronic circuit testingError detection/correctionOn boardTester device

An analog BIST (Built-in Self-Test) module for a load board in a test system for testing Integrated Chips (IC) and other devices-under-test (DUTs). Components of the test module perform test setup, transmission of analog test signals to a DUT, capture of analog and digital test data from the DUT, and on-board analysis of the test data using DSPs without sending the test data to a tester. Modules may be add-on boards to load boards an contain one or more processors and multiple components to test DUTs in parallel, significantly decreasing test and analysis times of a test system such as a Very Low Cost Tester (VLCT).

Owner:TEXAS INSTR INC

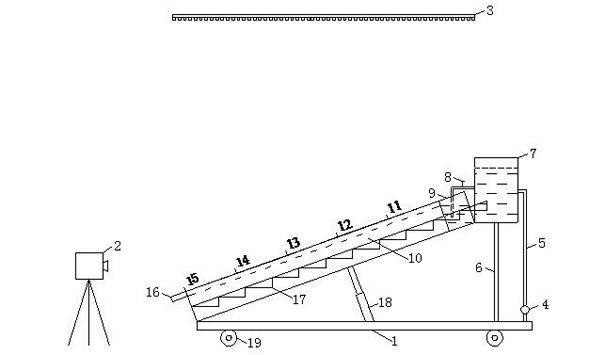

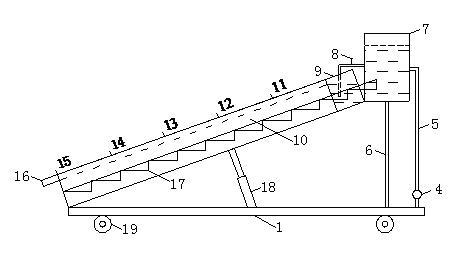

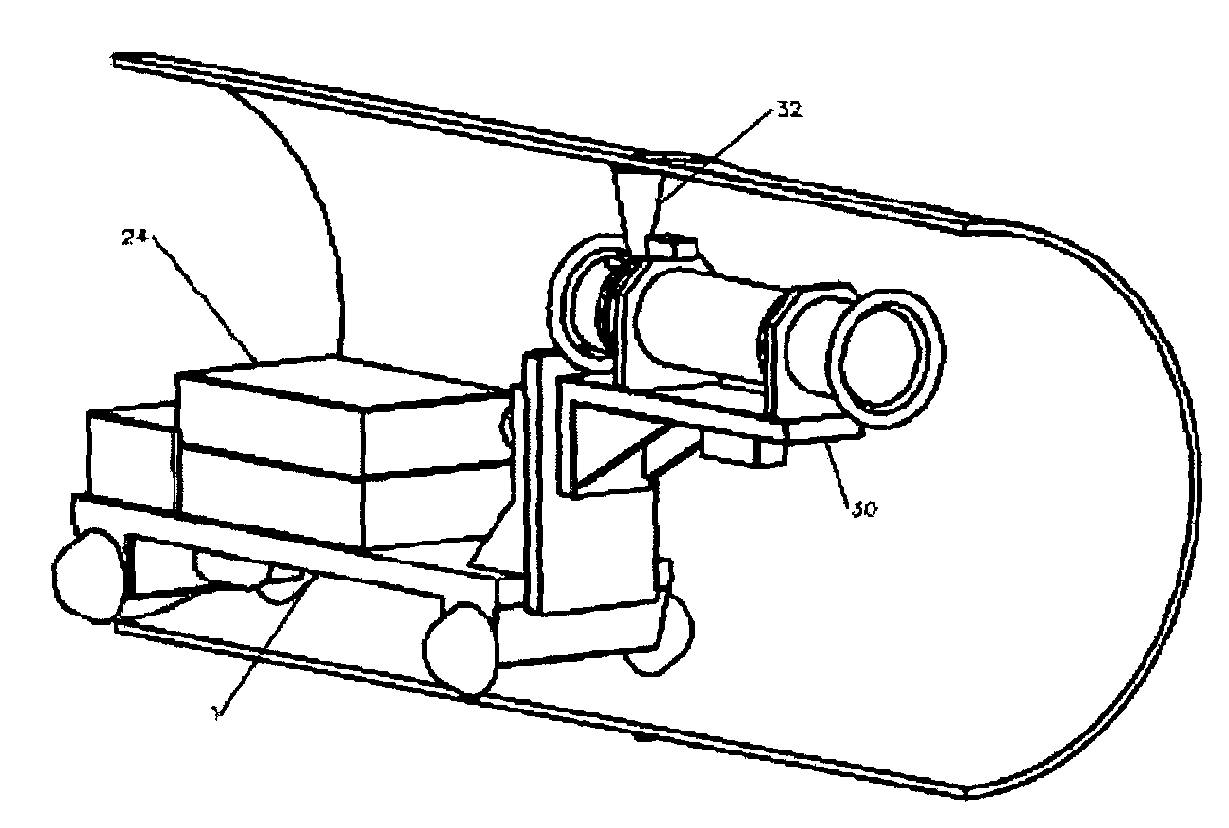

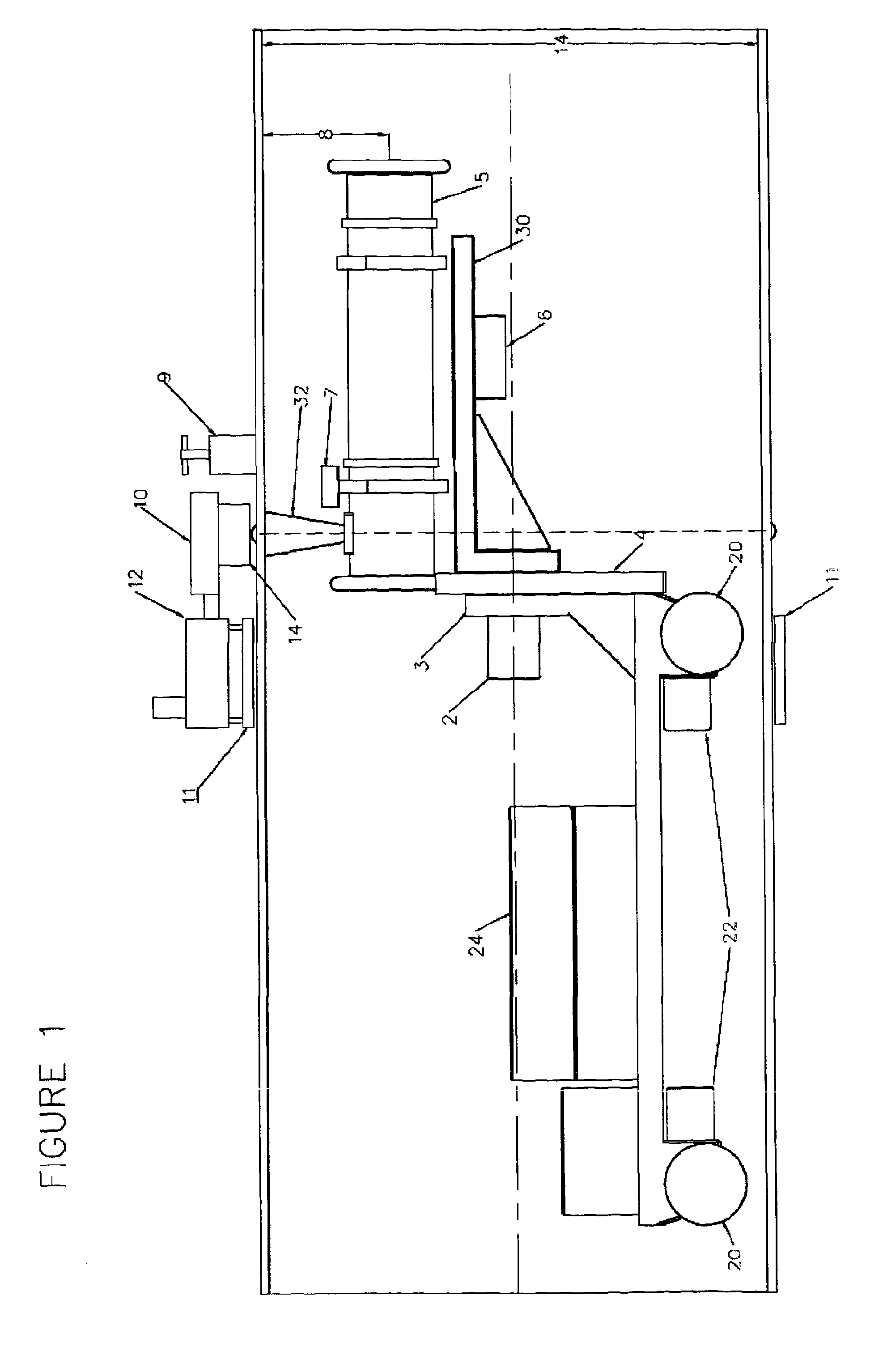

Fine simulation test device and fine simulation test method for slope water erosion

The invention discloses a fine simulation test device and a fine simulation test method for slope water erosion. The fine simulation test device comprises an underframe provided with trundles and a test soil groove connected with the underframe, the test soil groove is arranged above the underframe, one end of the test soil groove is hinged to one end of the underframe, and a water tank matched with the test soil groove is arranged at the other end of the test soil groove. A hydraulic rod is arranged between the test soil groove and the underframe, an equalization pond is arranged between thetest soil groove and the water tank, the equalization pond is communicated with the water tank through a water conveying pipe, the water conveying pipe and a water pump are arranged on one side of the water tank, a water discharging pipe is communicated with the lower portion of the water tank, a three-dimensional laser scanner is arranged in front of the test soil groove, a railfall device is arranged right above the test soil groove, and a flow collecting opening connected with the test soil groove is arranged at the end of the test soil groove hinged to the underframe. The fine simulation test device and the fine simulation test method for the slope water erosion have the advantages of being capable of controlling slope soil bulk density, vegetation types and cover degree manually, simulating soil water erosion conditions under different site conditions, and studying influences and response theories of all factors on soil water erosion under different underlying surface conditions.

Owner:YELLOW RIVER INST OF HYDRAULIC RES YELLOW RIVER CONSERVANCY COMMISSION

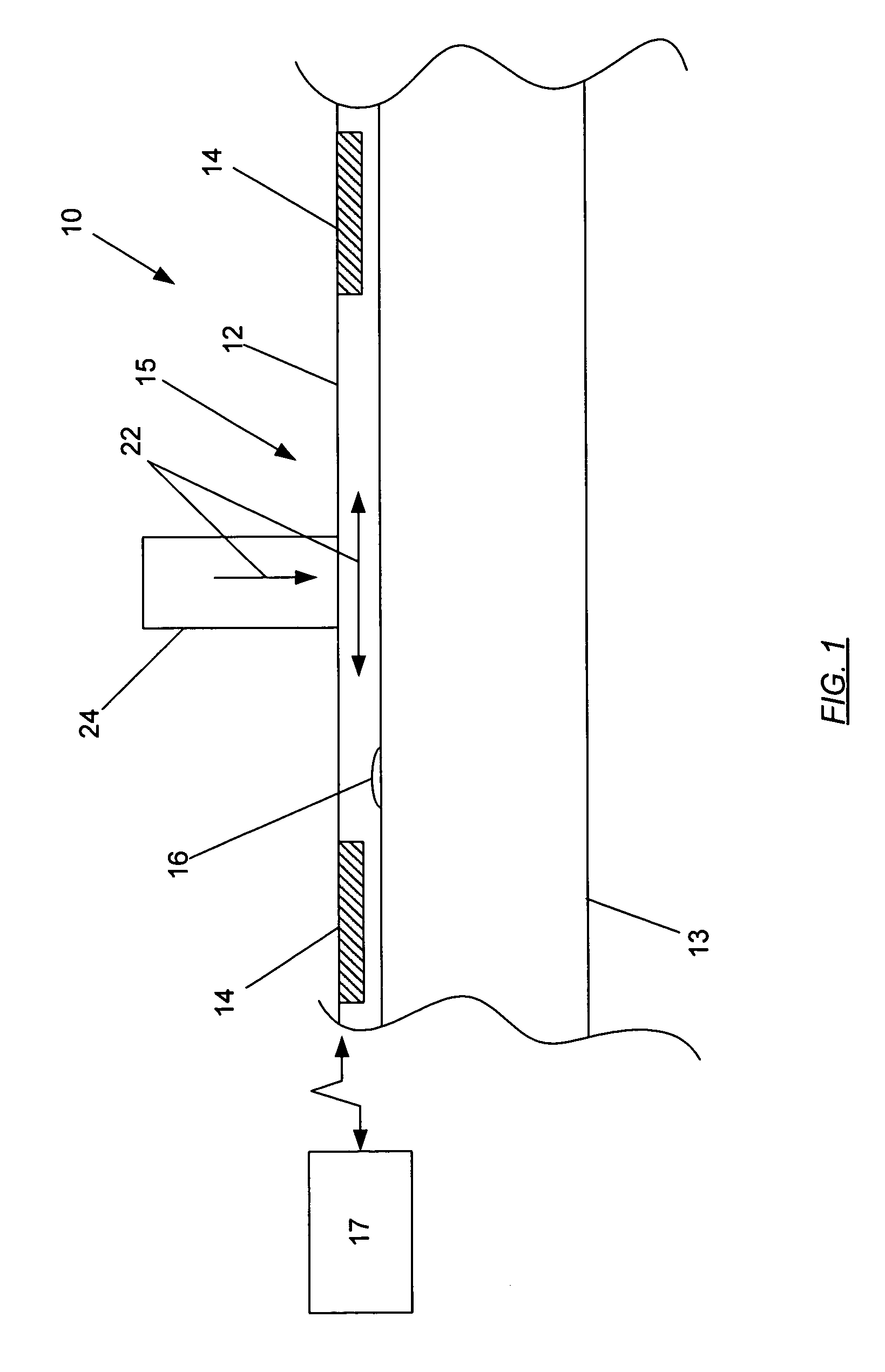

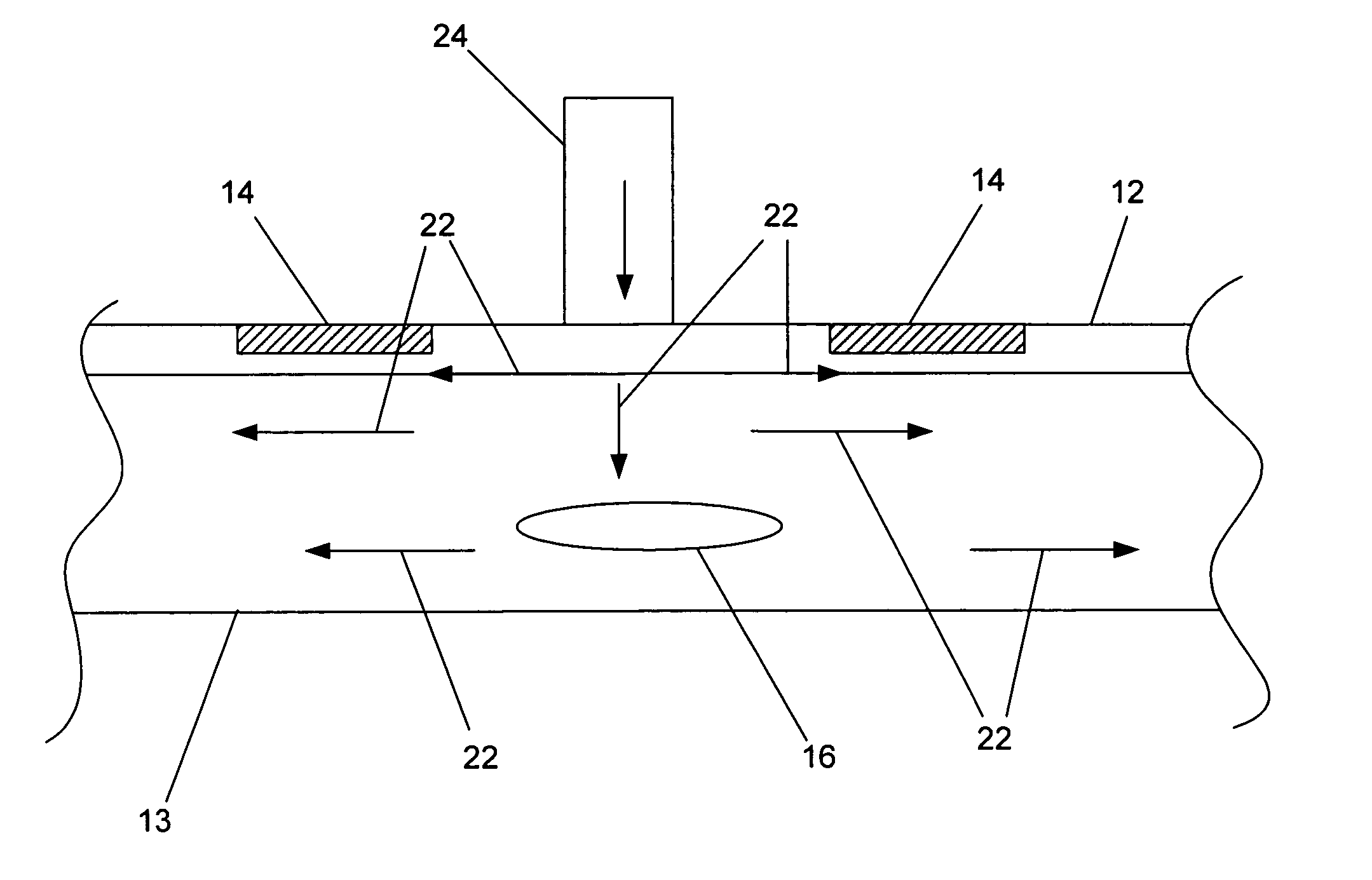

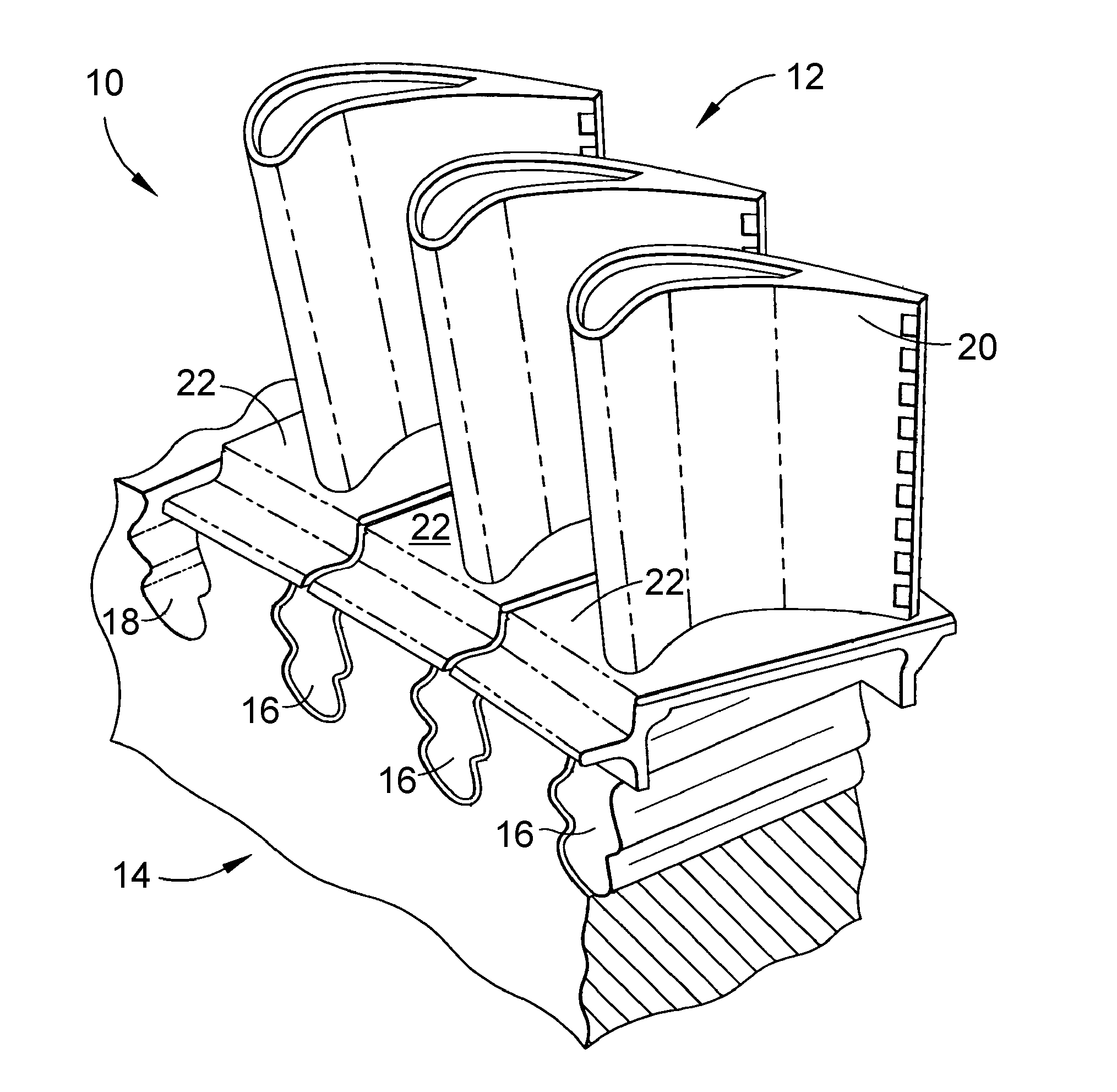

Non-destructive inspection system and associated method

ActiveUS20070017297A1Low costStructure moreAnalysing solids using sonic/ultrasonic/infrasonic wavesElasticity measurementNon destructiveProximate

An assembly, system, and method for identifying defects in a structure are provided. The assembly includes a structure of a metallic or composite material, and a flexible sheet of material positioned adjacent to the structure. The assembly also includes a plurality of non-destructive sensors secured to the flexible sheet, and a mechanism operable to impact the flexible sheet or proximate to the flexible sheet to generate stress waves within and along a surface of the structure. The system further provides a data acquisition system capable of communicating with the sensors such that the data acquisition system generates feedback indicative of at least a portion of the structure based on data from the stress waves acquired by the sensors.

Owner:THE BOEING CO

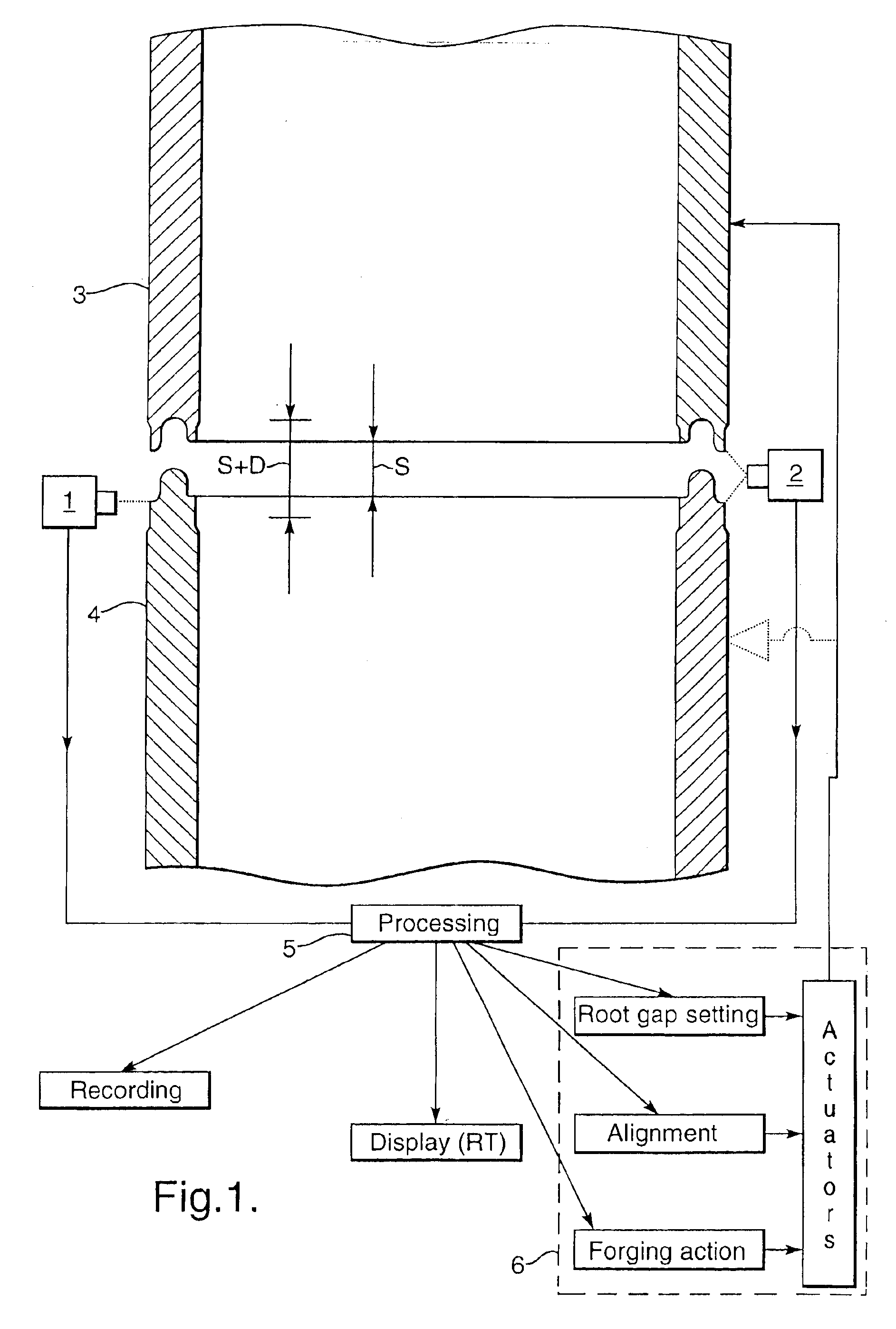

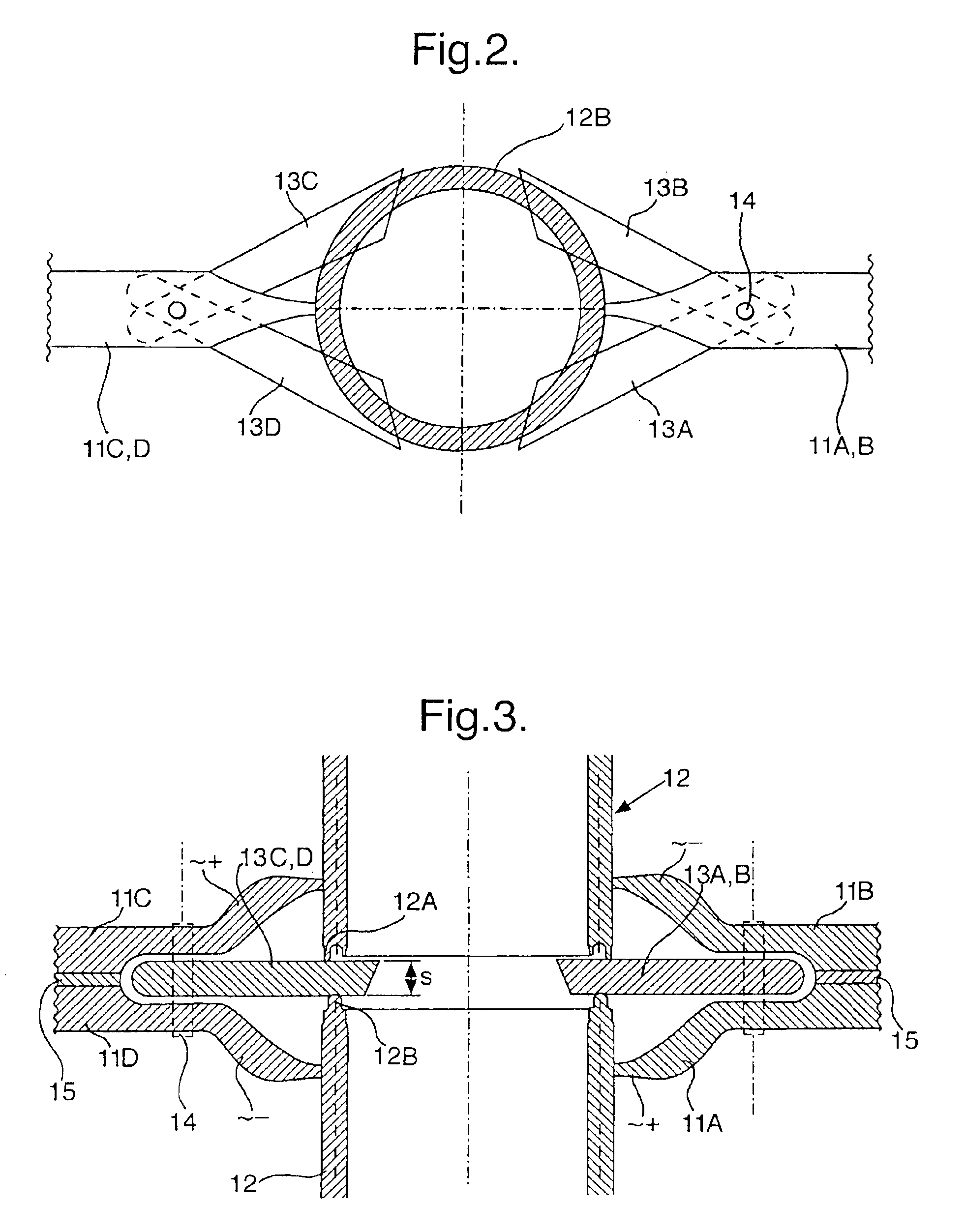

EMAT weld inspection

InactiveUS6896171B2Faster weld inspectionQuick testAnalysing solids using sonic/ultrasonic/infrasonic wavesMetal working apparatusEngineeringFixed position

A method for inspecting welds between welded tubular ends includes arranging a series electromagnetic acoustic transducer (EMAT) assemblies in circumferential direction adjacent to an inner and / or outer surface of at least one of the welded tubular ends and inducing the EMAT assemblies to transmit sequentially or simultaneously acoustic shear wave signals towards the weld and to detect the shear waves reflected by and / or passing through the weld while the EMAT assemblies are maintained in a substantially fixed position relative to the weld such that at least a substantial part of the weld is scanned by the EMAT assemblies instantly after the weld is made.

Owner:SHELL OIL CO

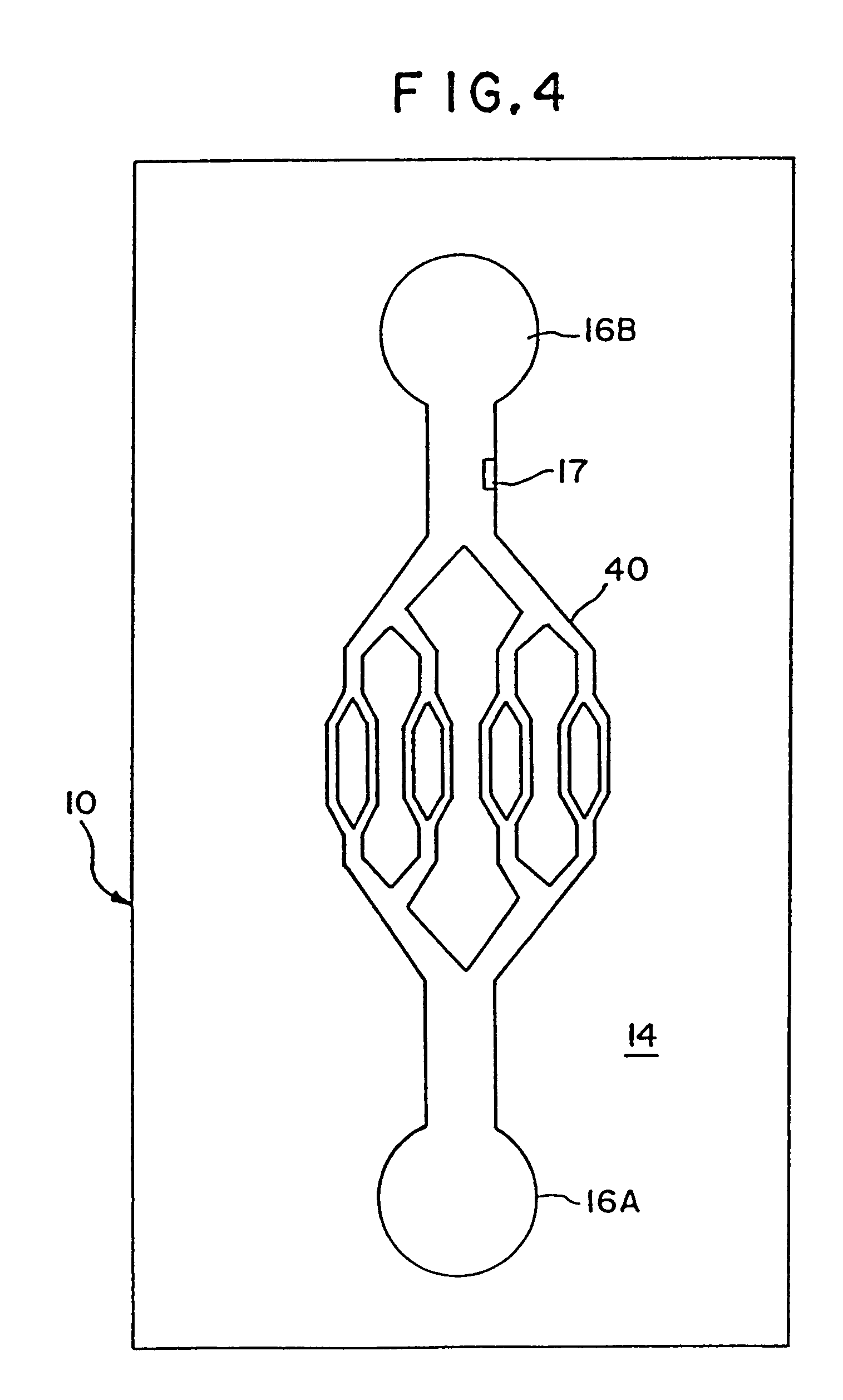

Mesoscale polynucleotide amplification device and method

InactiveUS6953676B1Quick testBioreactor/fermenter combinationsSequential/parallel process reactionsTemperature controlPolymerase L

Disclosed are devices for amplifying a preselected polynucleotide in a sample by conducting a polynucleotide polymerization reaction. The devices comprise a substrate microfabricated to define a sample inlet port and a mesoscale flow system, which extends from the inlet port. The mesoscale flow system includes a polynucleotide polymerization reaction chamber in fluid communication with the inlet port which is provided with reagents required for polymerization and amplification of a preselected polynucleotide. In one embodiment the devices may be utilized to implement a polymerase chain reaction (PCR) in the reaction chamber (PCR chamber). The PCR chamber is provided with the sample polynucleotide, polymerase, nucleoside triphosphates, primers and other reagents required for the polymerase chain reaction, and the device is provided with means for thermally controlling the temperature of the contents of the reaction chamber at a temperature controlled to dehybridize double stranded polynucleotide, to anneal the primers, and to polymerize and amplify the polynucleotide.

Owner:THE TRUSTEES OF THE UNIV OF PENNSYLVANIA

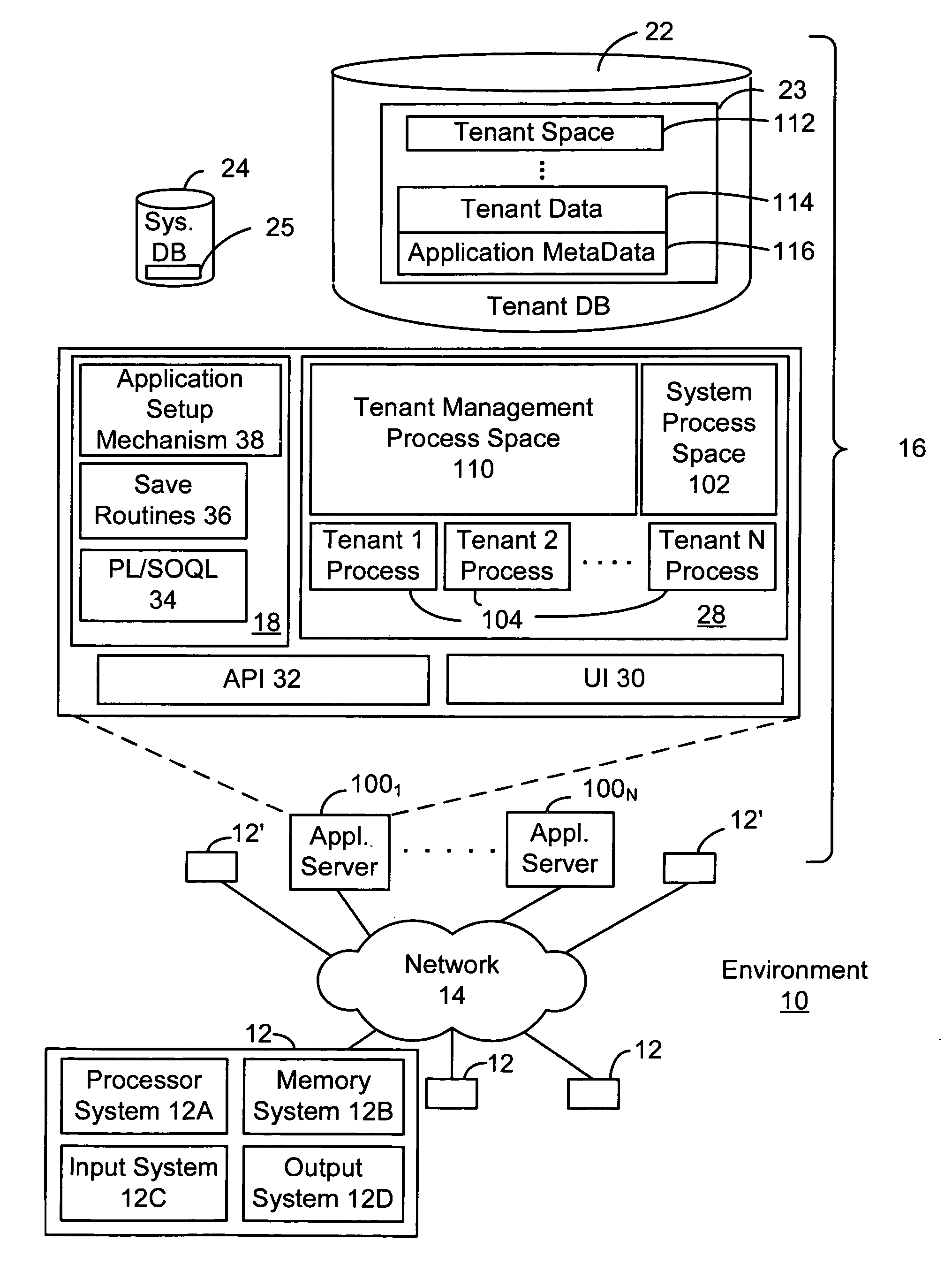

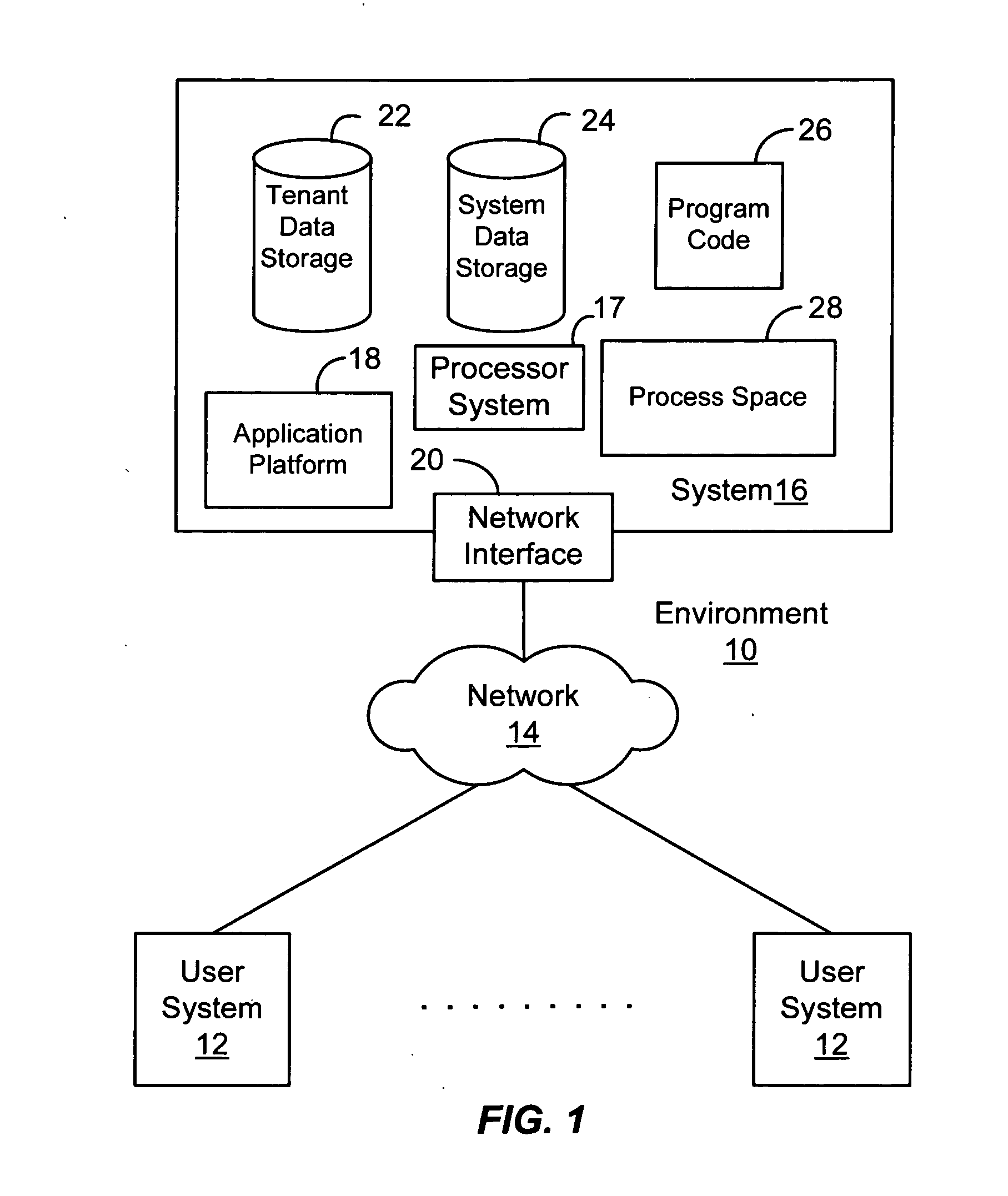

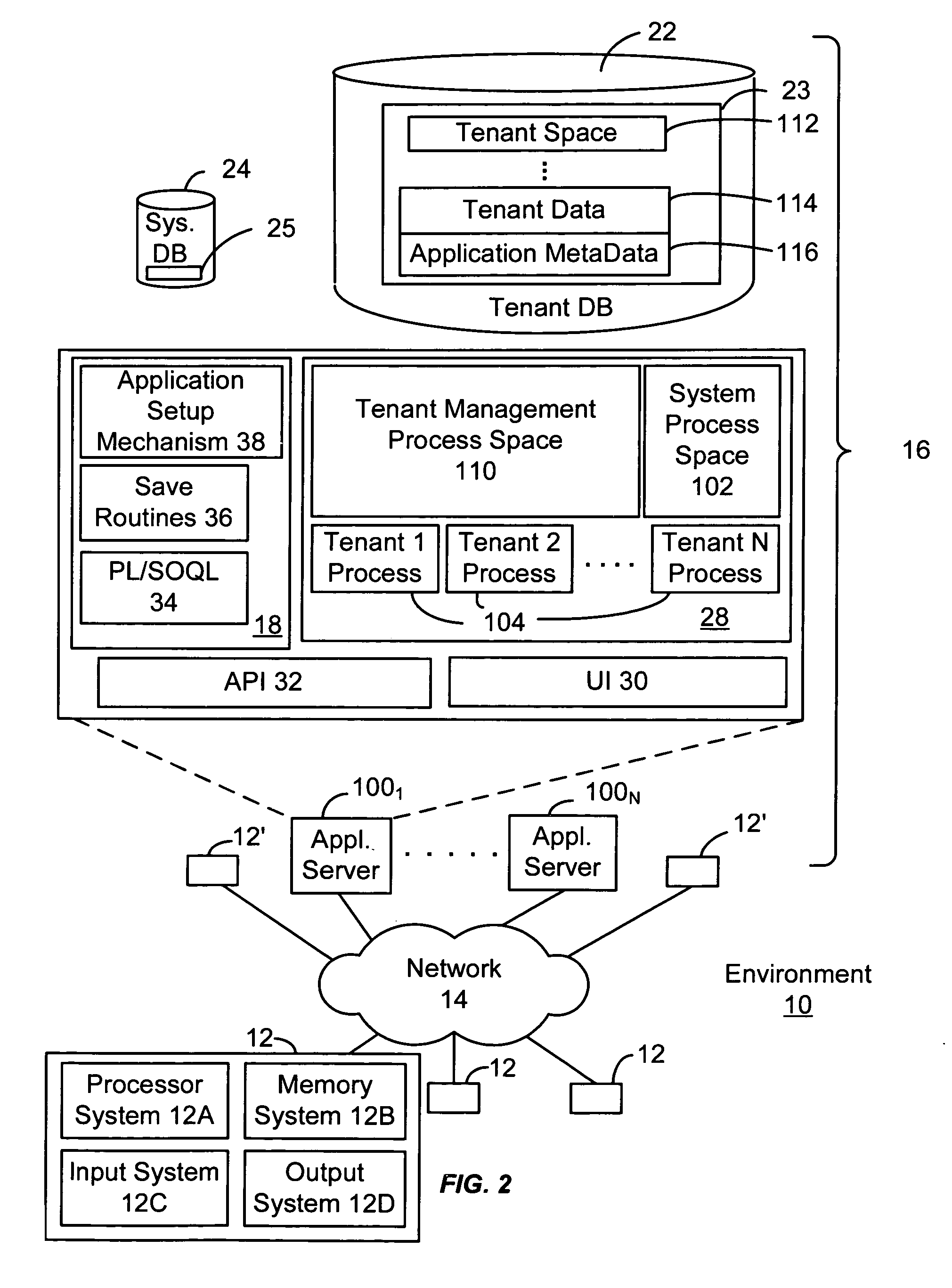

Method and system for automatically updating a software QA Test repository

ActiveUS20110246540A1Quickly testQuick testDigital data information retrievalError detection/correctionDocumentation procedureSoftware

In accordance with embodiments, there are provided mechanisms and methods for automatically updating a software QA test repository in a database system. These mechanisms and methods for automatically updating a QA test repository can enable embodiments to quickly and accurately update a test repository without requiring a user to repeatedly enter test case documentation data. These mechanisms and methods for automatically updating a QA test repository can also enable embodiments to extract plain language descriptions of test cases in the test repository. The ability of embodiments to automatically update the test repository and provide descriptions for the test cases stored in the test repository allows developers to efficiently update and share the contents of the test repository.

Owner:SALESFORCE COM INC

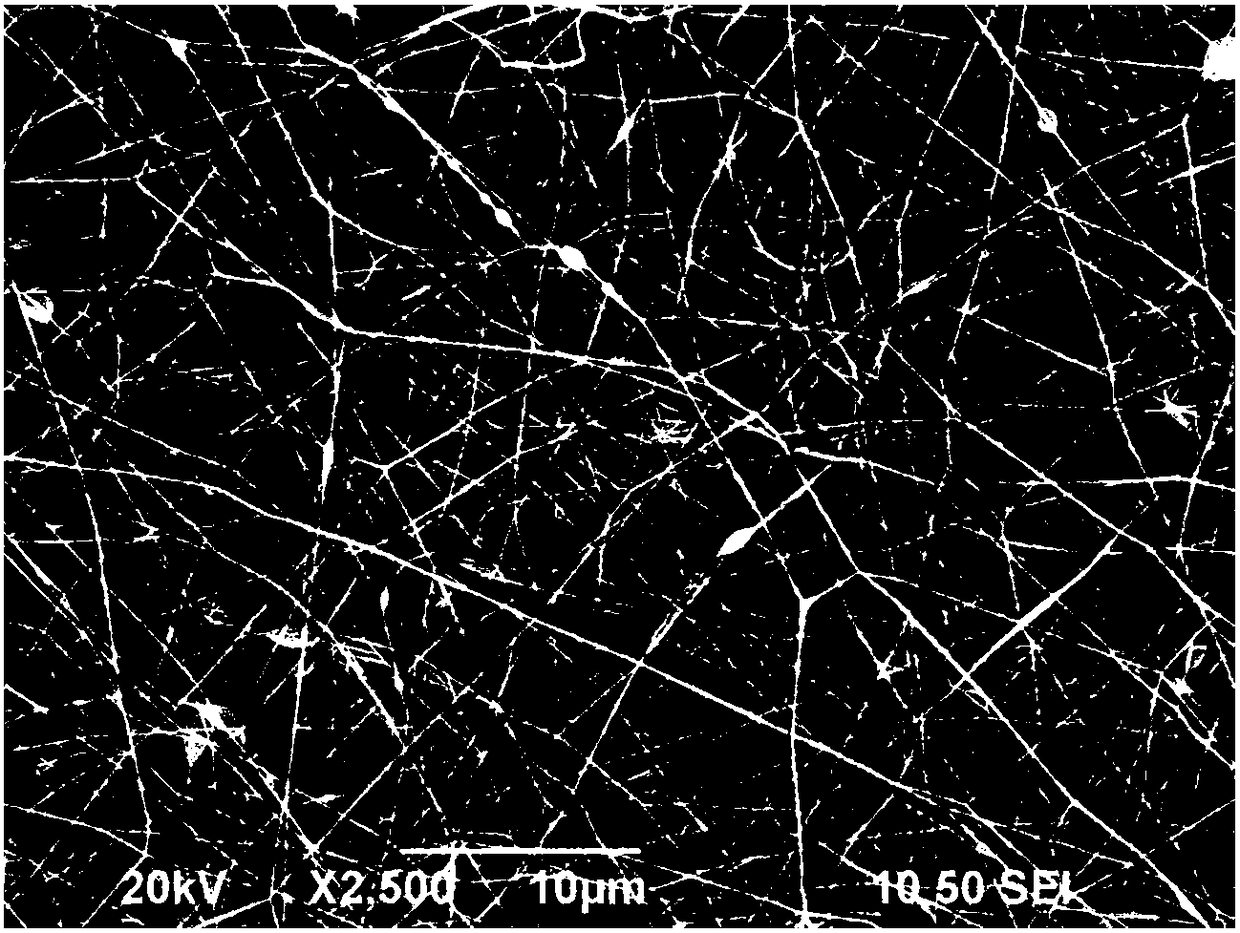

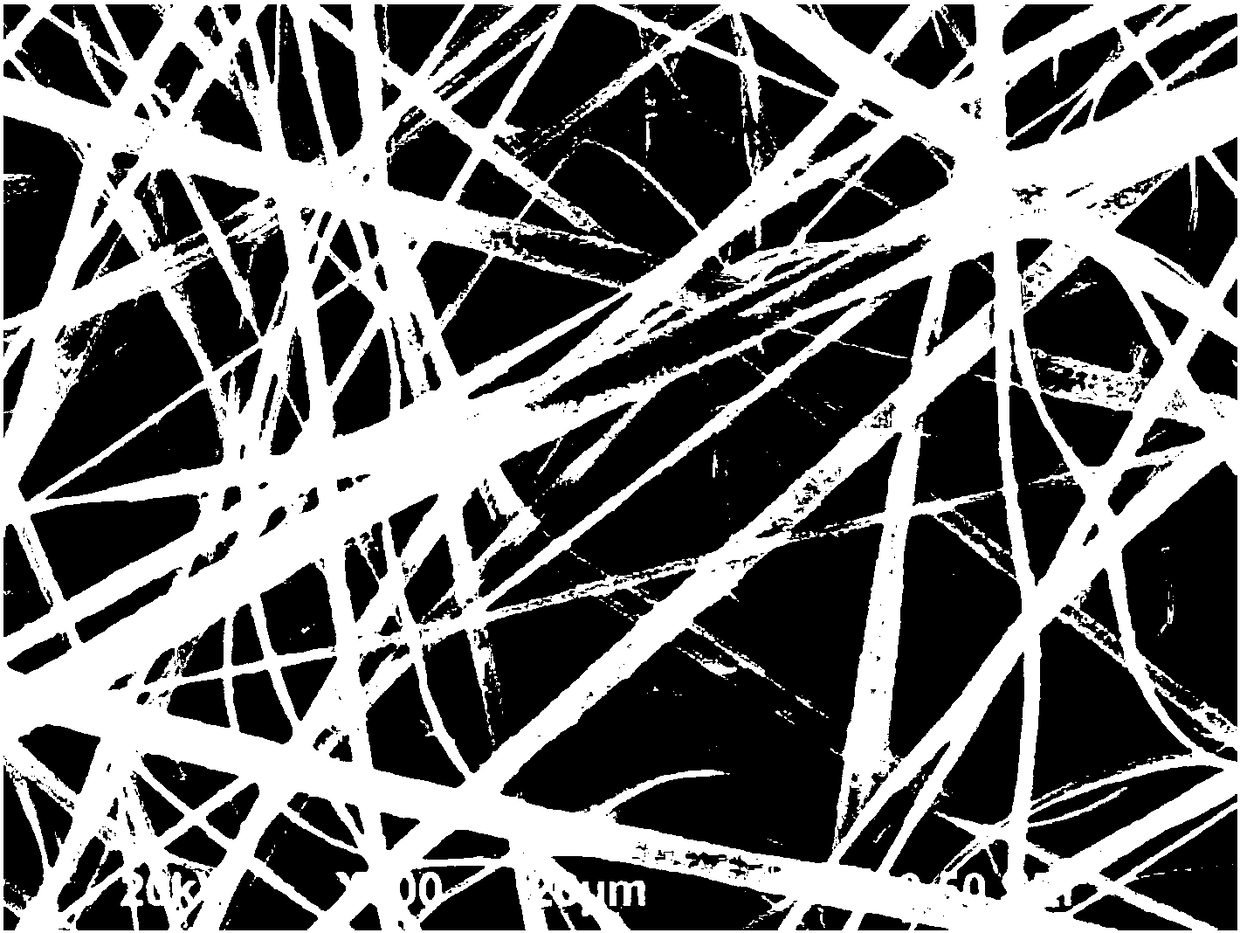

Preparation method and application of electrospinning nanofiber

PendingCN108866820AWith slow release functionPromote growthCosmetic preparationsCigar manufactureFiberFluorescence

The invention relates to a preparation method and application of electrospinning nanofiber. The preparation method is as follows: synthetic and / or natural polymer materials are dissolved in a volatilesolvent under normal temperature and normal pressure, functional substances are added, and nanofibers are obtained by electrospinning; the functional substances comprise, but are not limited to an odor substance, an organic fluorescent compound, a pigment, a temperature sensitive luminescent and color changing material, a cell growth factor, a hemostatic substance, one or a plurality of nutrientsincluding hyaluronic acid, collagen, and the like which promote skin growth. The nanofiber made by electrospinning has the special effects of sterilization, aromatic odor, fluorescent luminescence, multiple colors, temperature sensitive luminescence and color-changing, promoting wound healing, promoting inhibition and interfering with body function, maintaining skin cell vitality and the like. The method can be used in air purification, automotive air purification, fresh air systems, medical, beauty care, and other nanofiber products.

Owner:SHENZHEN RUXIANGJU TECHCAL DEV LTD

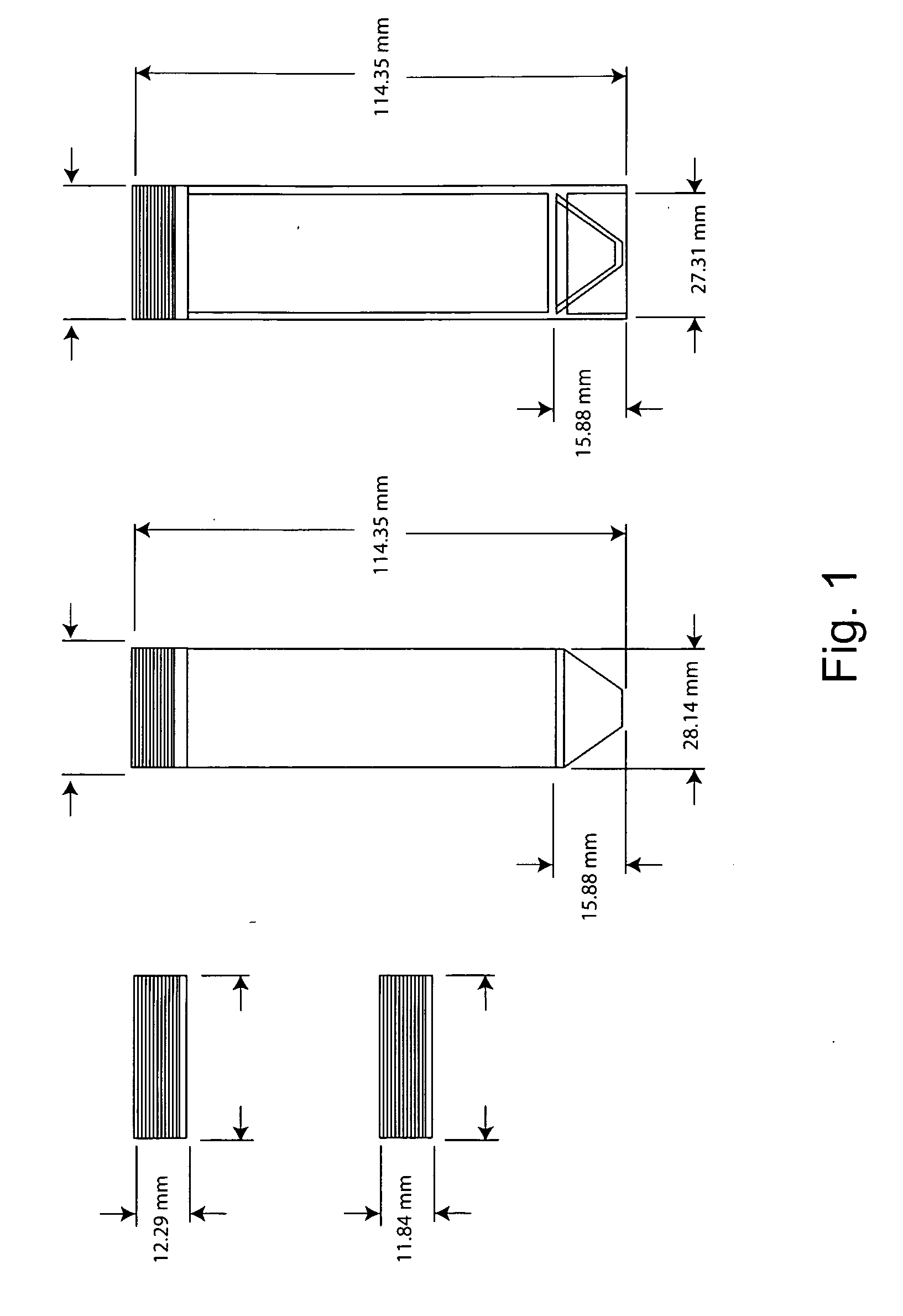

Self-purging, air-stabilizing, illuminated collection system for breath analysis

InactiveUS20070016092A1Accurate and immediate analysisOvercome deficienciesRespiratory organ evaluationSensorsCollection systemEngineering

A breath analysis system includes a dual-entry, illuminated breath collection tube that allows purging of ambient air while stabilizing the pressure and / or turbulence of exhaled breath. Circular illumination at either end of the collection tube acts as a visual prompt for proper use and for the reporting of test results. The collection tube may be placed along the width or length of a hand piece without adding size or bulk to the hand piece. The form factor utilization feature of the collection tube is suitable for adding breath alcohol measurement or other breath measurement capability to handheld products such as cell phones, PDAs, iPods®, MP3 players, GPS units, cigarette lighters, and police batons.

Owner:KHN SOLUTIONS

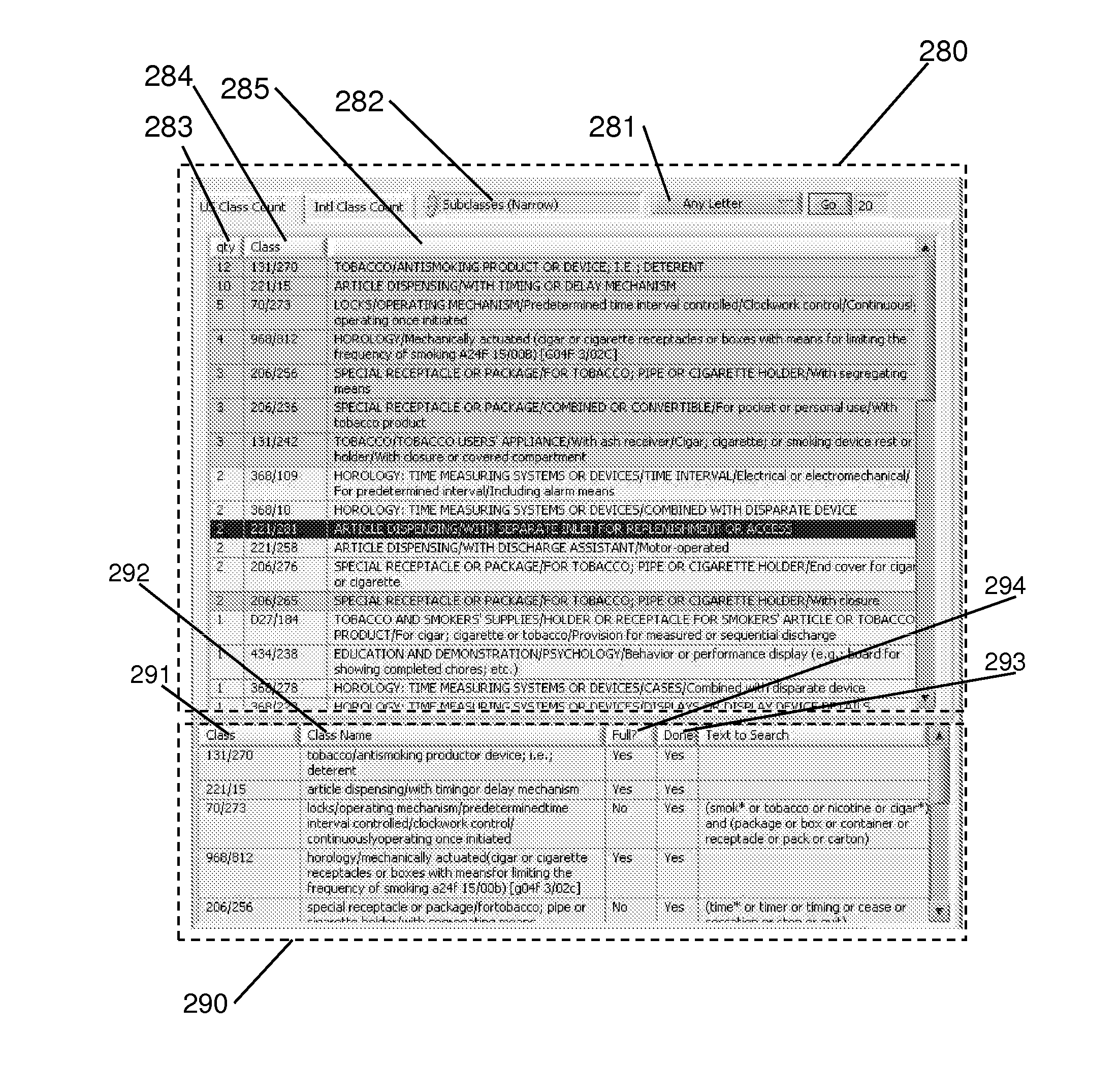

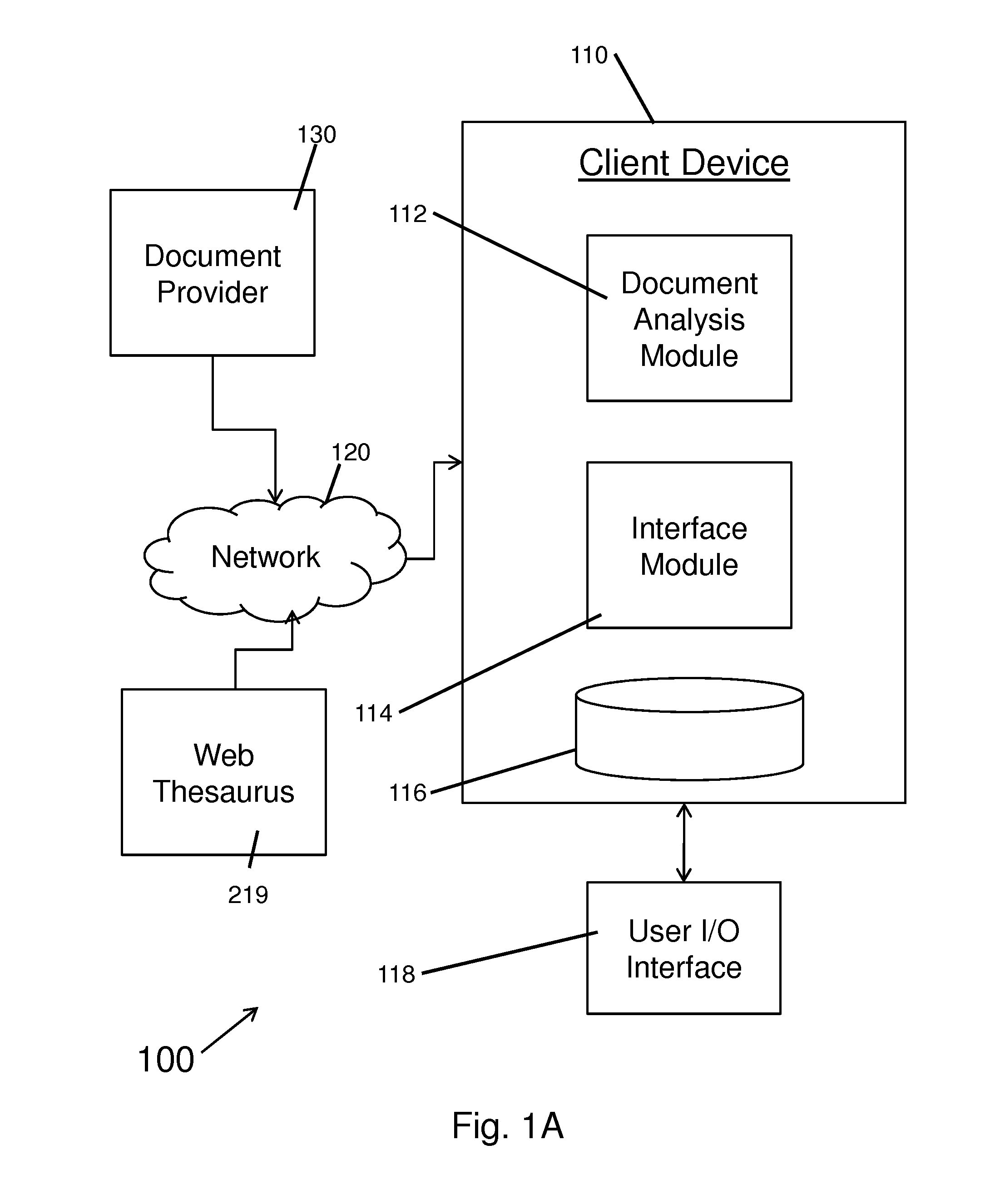

Method and system for document presentation and analysis

InactiveUS20120204104A1Rapid positioningQuickly assess relevance of a documentSpecial data processing applicationsText database clustering/classificationDocument analysisDocument preparation

A document analysis system receives multiple concepts along with multiple reference documents and generates sensory indicators that assist a researcher in assessing the relevance of each of the documents to the concepts. In one exemplary aspect, the document analysis system displays a table of keywords separated into blocks, each block of keywords corresponding to one of the concepts. Each block is colored according to the prevalence of any keyword within a given keyword group. The color of a block thus indicates the relative presence of a concept in the document. The document analysis system also determines a unique color for each block of keywords for highlighting in the text of the document. In this manner a researcher can quickly identify passages that contain multiple concepts. Additionally, the researcher is provided the ability to quickly locate reference characters, figure numbers and patent numbers in the document.

Owner:WALSH PATRICK SANDER

Imaging system with dynamic range maximization

ActiveUS20110064296A1Small rangeMaximize dynamic rangeMaterial analysis by optical meansCharacter and pattern recognitionComputer scienceImage system

A method of operating an instrument that is a macroscope, microscope, or slide scanner is provided where the instrument has a larger dynamic range for measurement than a dynamic range required in the final image of a specimen. In the method, data is measured from a specimen using the instrument, and the dynamic range of the measured data is contracted in the final image file during scanning.

Owner:HURON TECH INT

Analog built-in self-test module

ActiveUS20070096759A1Increase flexibilityFast analog final test analogElectronic circuit testingOn boardTester device

An analog BIST (Built-in Self-Test) module for a load board in a test system for testing Integrated Chips (IC) and other devices-under-test (DUTs). Components of the test module perform test setup, transmission of analog test signals to a DUT, capture of analog and digital test data from the DUT, and on-board analysis of the test data using DSPs without sending the test data to a tester. Modules may be add-on boards to load boards an contain one or more processors and multiple components to test DUTs in parallel, significantly decreasing test and analysis times of a test system such as a Very Low Cost Tester (VLCT).

Owner:TEXAS INSTR INC

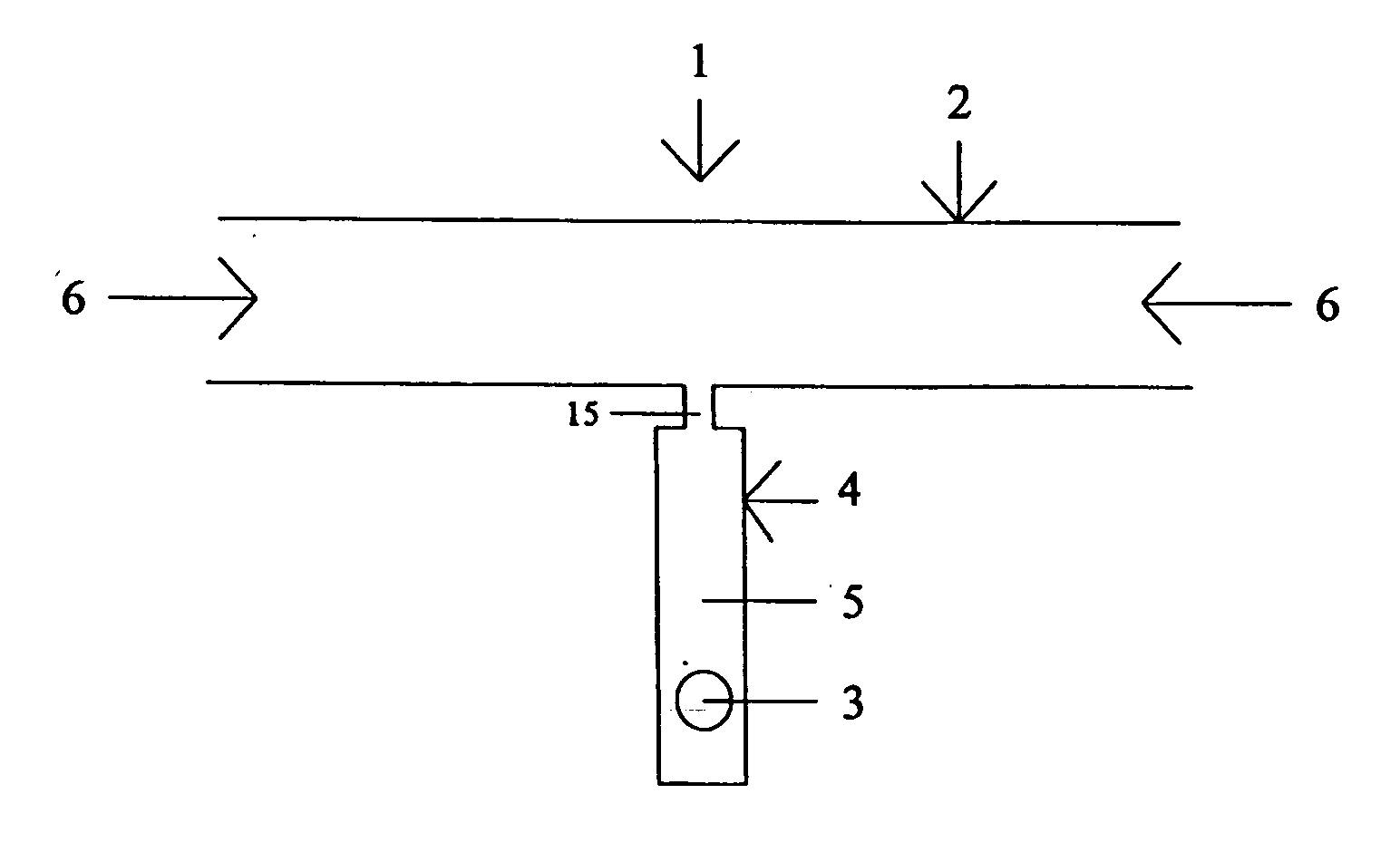

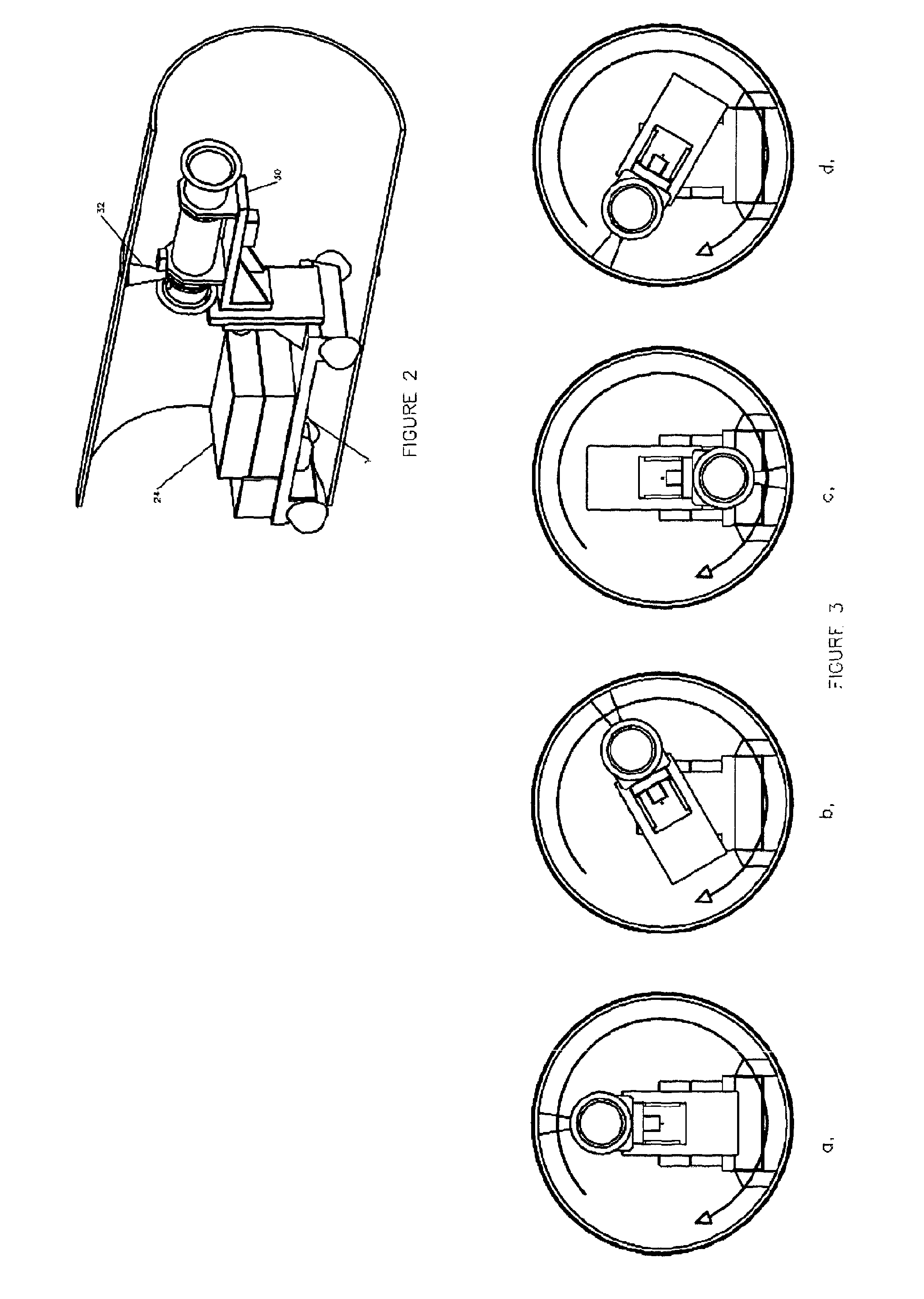

X-ray inspection apparatus for pipeline girth weld inspection

ActiveUS20120201348A1Shorten cycle timePerfect detection systemUsing wave/particle radiation meansMaterial analysis by transmitting radiationX-rayPhysics

An apparatus is provided for x-ray inspection of a pipeline girth weld. This comprises a directional x-ray source 5 which is insertable into a pipeline section and is rotatable within the pipeline. Means are provided to align the directional x-ray source with an external x-ray detector such that both may be rotated through 360 degrees substantially coaxially with the pipeline section. Means for sampling the data detected by the x-ray detector are provided so that it may be further analysed.

Owner:SHAWCOR LTD

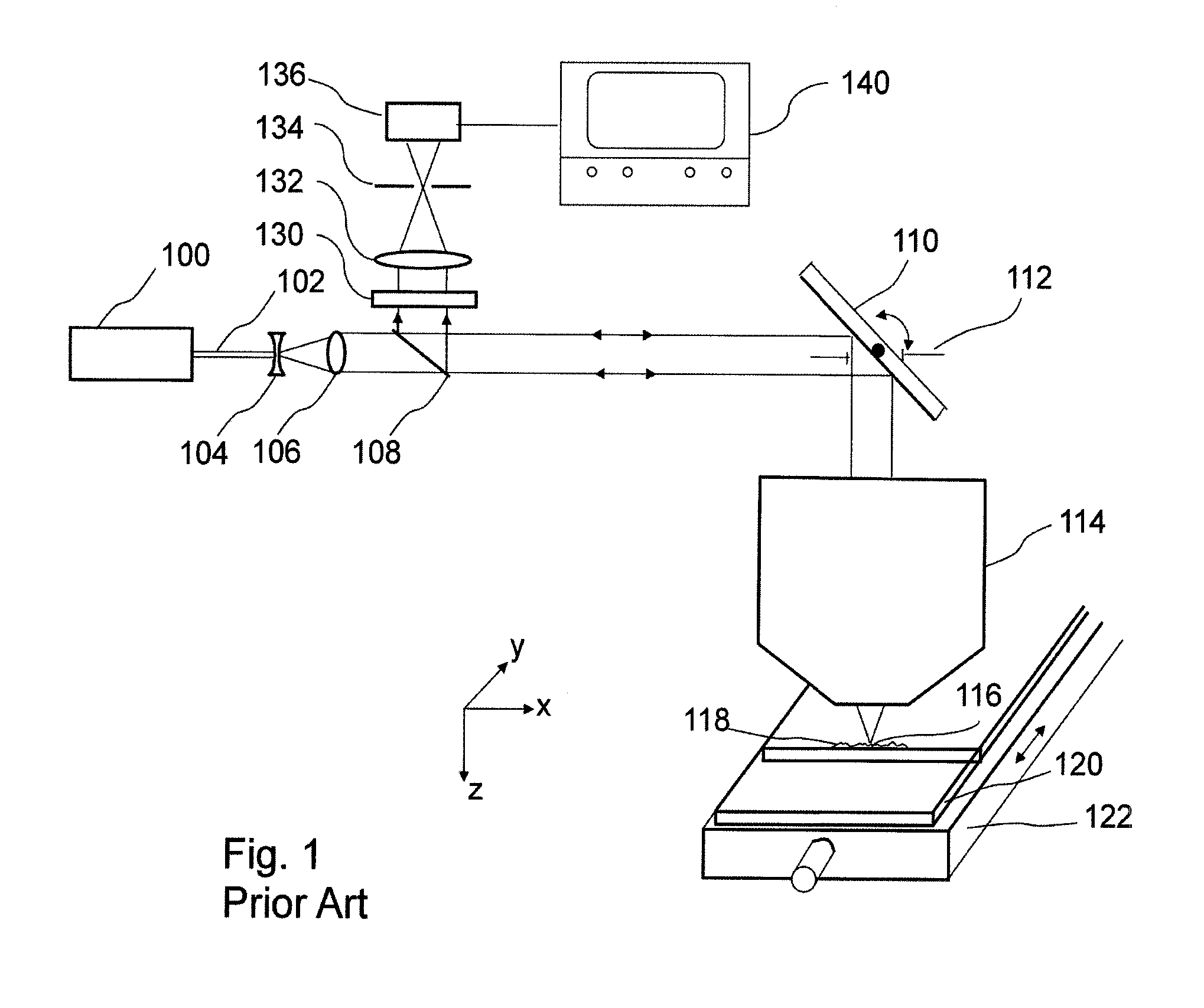

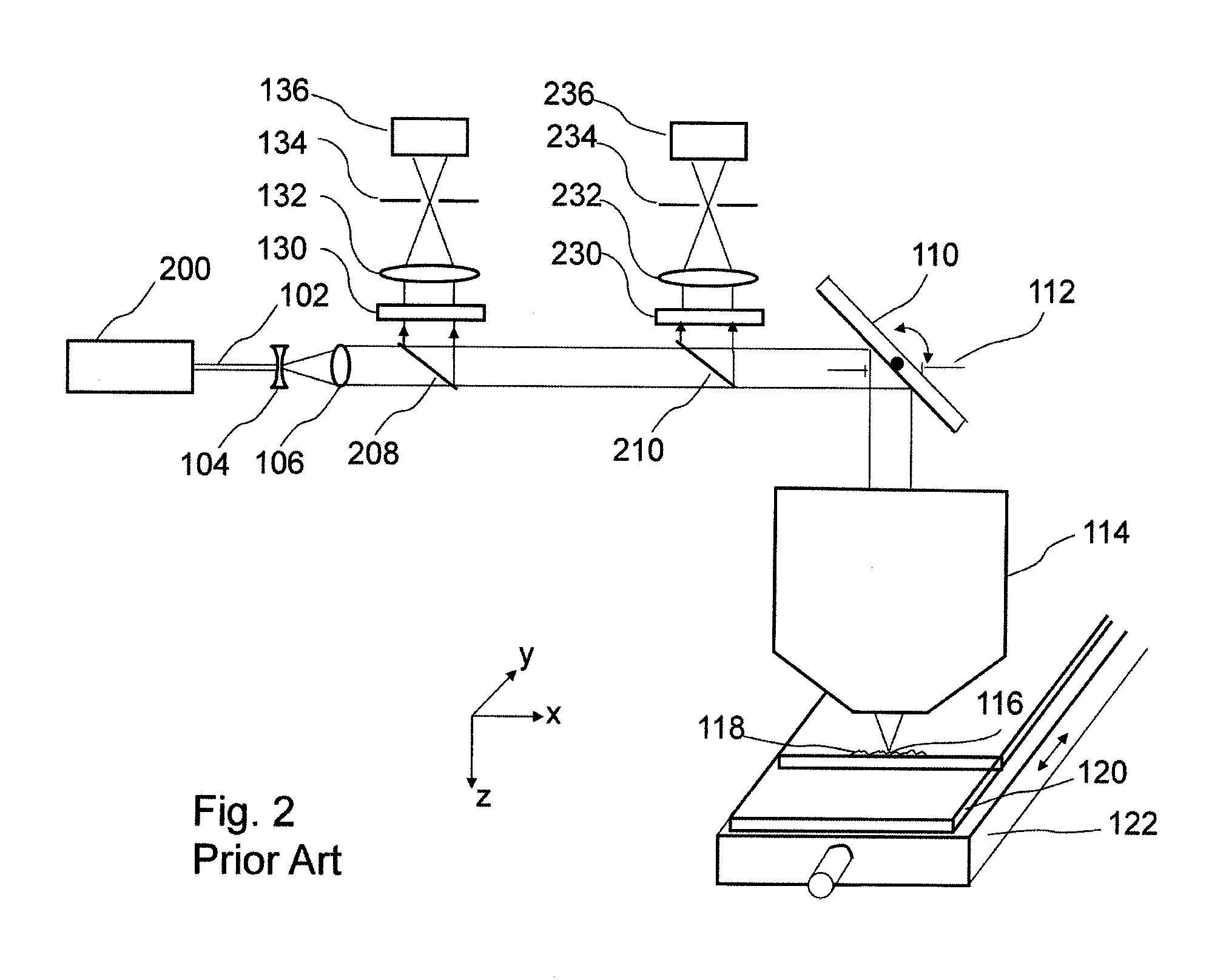

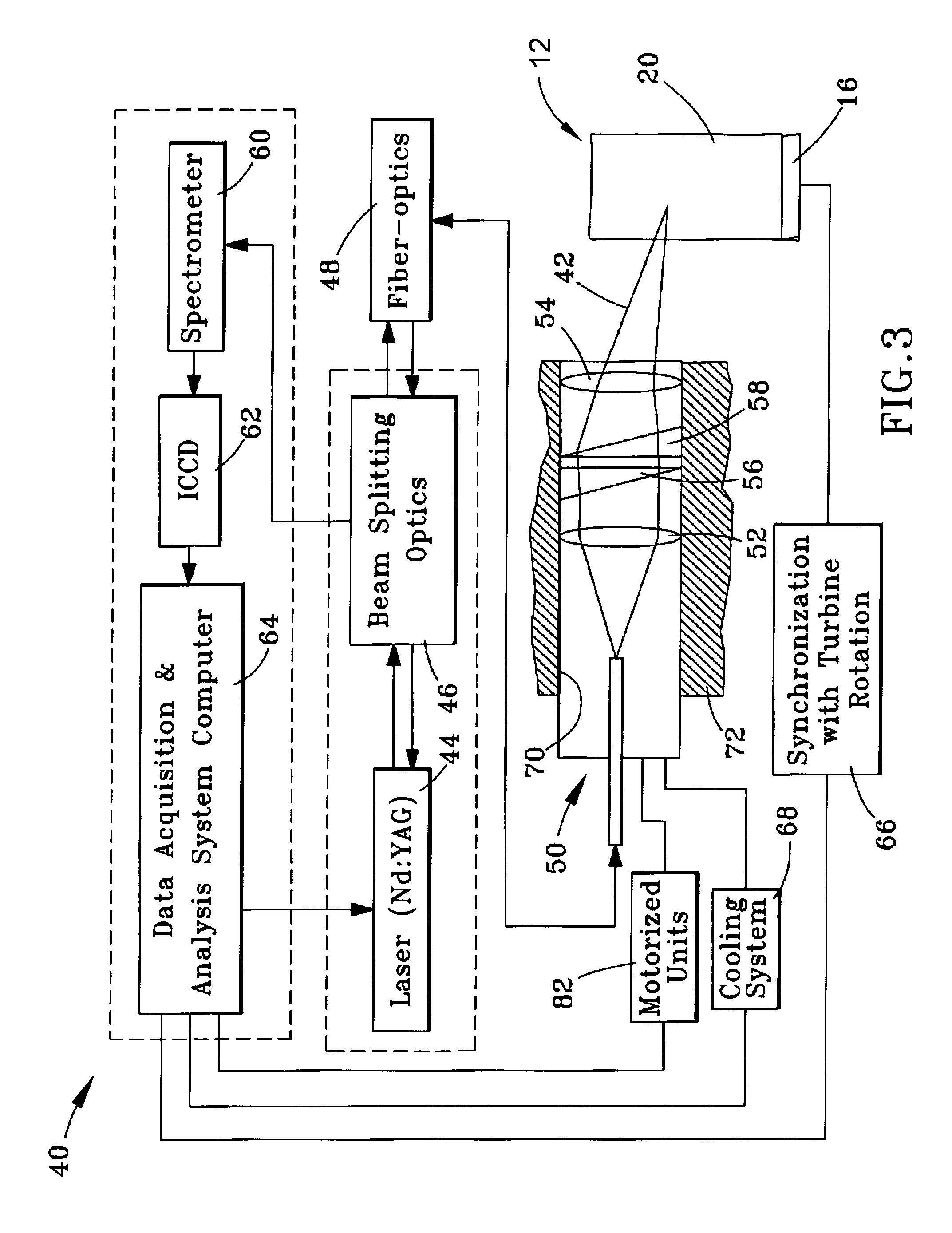

System and method for detecting and analyzing compositions

InactiveUS7535565B1Quick testRadiation pyrometrySpectrum investigationLaser beamsPlasma spectroscopy

A system and method for performing laser plasma spectroscopy on a surface of a component, particularly to detect, analyze, and determine the extent of deposit build up on turbomachine components protected by coatings that are susceptible to damage from infiltration of deposits. The system includes a laser energy source and a probe interconnected with the laser energy source to receive a laser beam therefrom and then direct the laser beam onto the surface of the component and scan an area of the surface while the component remains stationary. The probe is further configured to collect radiation emitted from a laser-induced plasma generated by the laser beam at the surface of the component. The system is further equipped to transmit the radiation from the probe and spectrally analyze the radiation.

Owner:GENERAL ELECTRIC CO

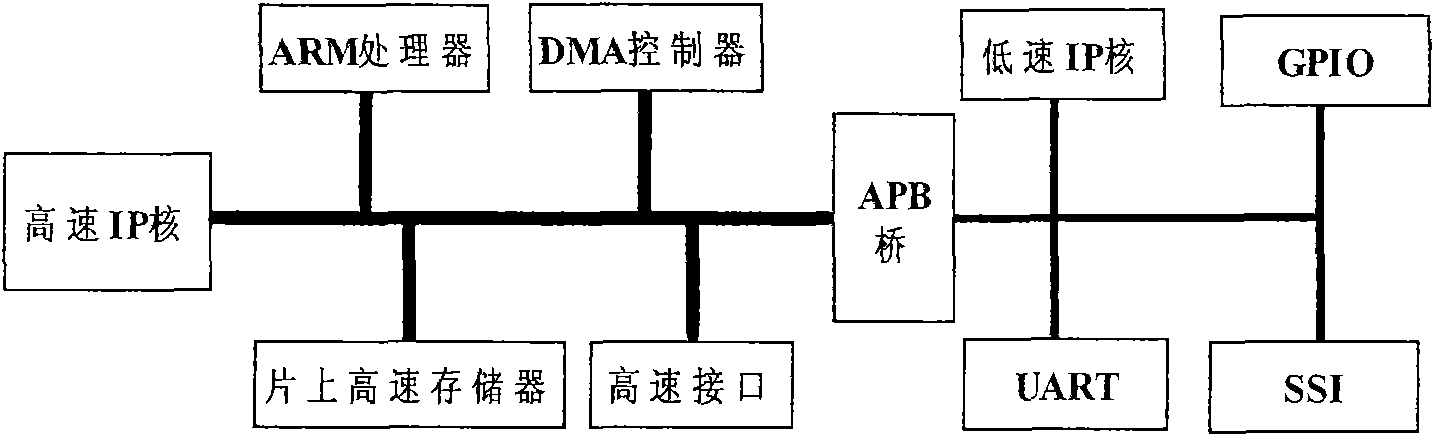

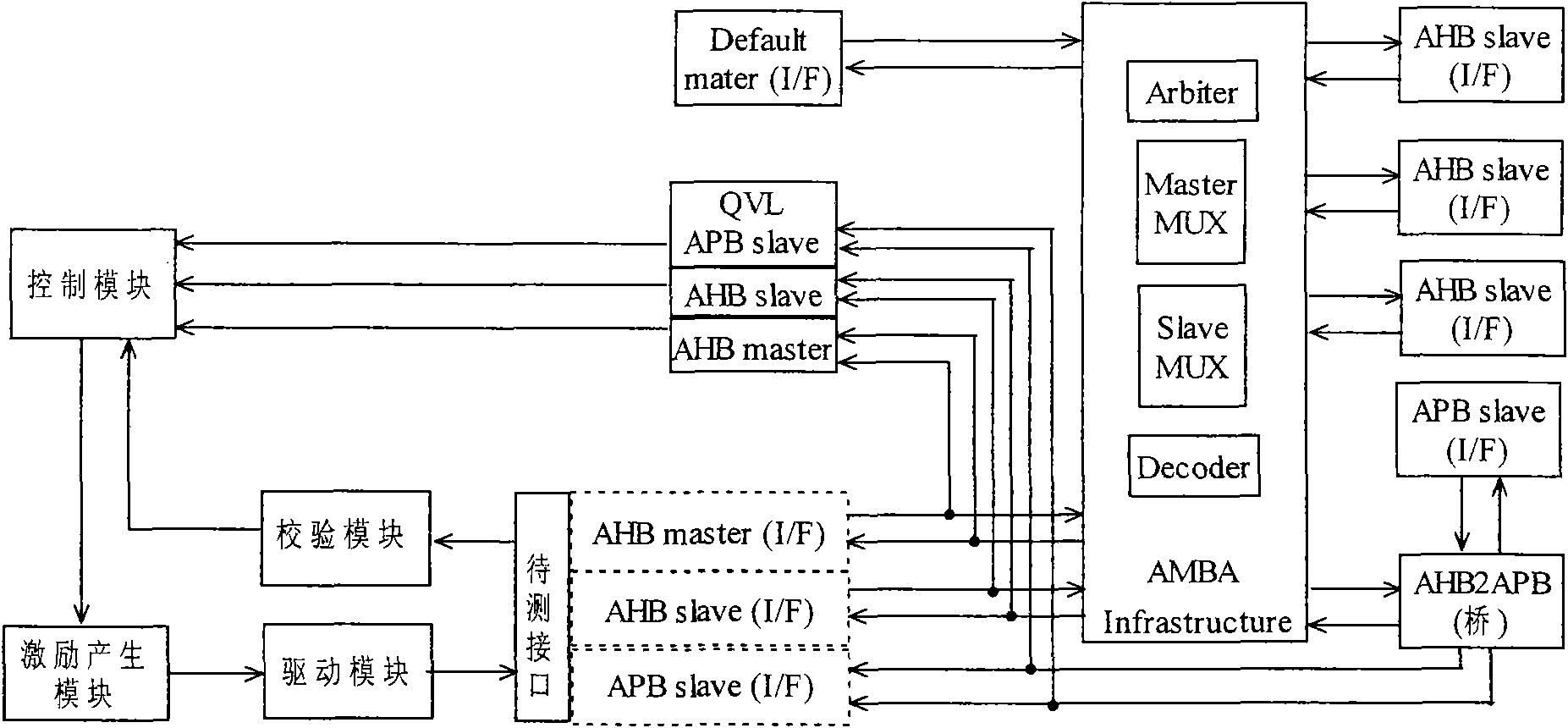

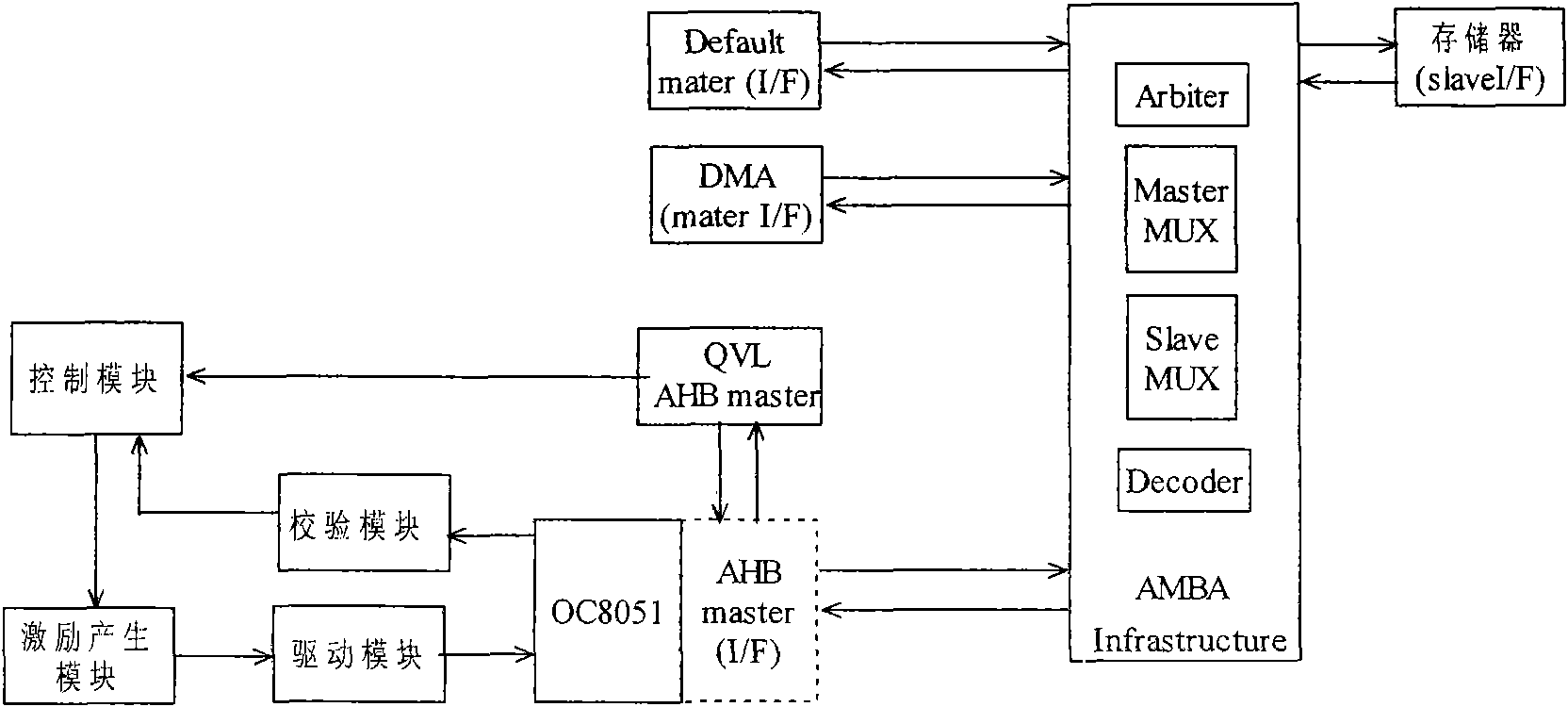

Universal method and platform for verifying compatibility between intellectual property (IP) core and advanced microcontroller bus architecture (AMBA) bus interface

InactiveCN102117238AImprove verification efficiencyImprove accuracyFunctional testingValidation methodsIntellectual property

The invention provides a universal platform of verifying compatibility between an intellectual property (IP) core and an advanced microcontroller bus architecture (AMBA) bus interface, which comprises a functional simulation tool, an AMBA bus infrastructure, a third-party verification IP core, a controller, a driver, a stimulus, a checker, an advanced peripheral bus (APB) bridge, an advanced high-performance bus (AHB) master interface, an AHB slave interface and an APB slave interface, wherein all the modules are connected to form an integrated coordinating verification environment by adopting a verification component and hierarchical packaging and interconnections ways provided by a SystemVerilog language and advanced verification methodology (AVM). The platform can verify the compatibility of different types of IP core interfaces, and the development time and cost of the verification platform and a verification method are reduced. The invention also provides the universal method for verifying the compatibility between the IP core and the AMBA bus interface. In the method, excitation is produced more normatively, scientifically and accurately, unnecessary iteration is reduced and the verification time is shortened.

Owner:SHANGHAI SILICON INTPROP EXCHANGE