Automatic chip testing method

A chip testing and chip technology, which is applied in the field of FPGA development and mutual cooperation to realize chip automatic testing, can solve the problems of increasing system reliability, stability, duplication of labor efficiency, and high testing efficiency, so as to save testing time, reduce personnel participation, The effect of high test efficiency

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0033] In order to make the object, technical solution and advantages of the present invention more clear, the present invention will be further described in detail below in conjunction with the accompanying drawings and embodiments. It should be understood that the specific embodiments described here are only used to explain the present invention, not to limit the present invention.

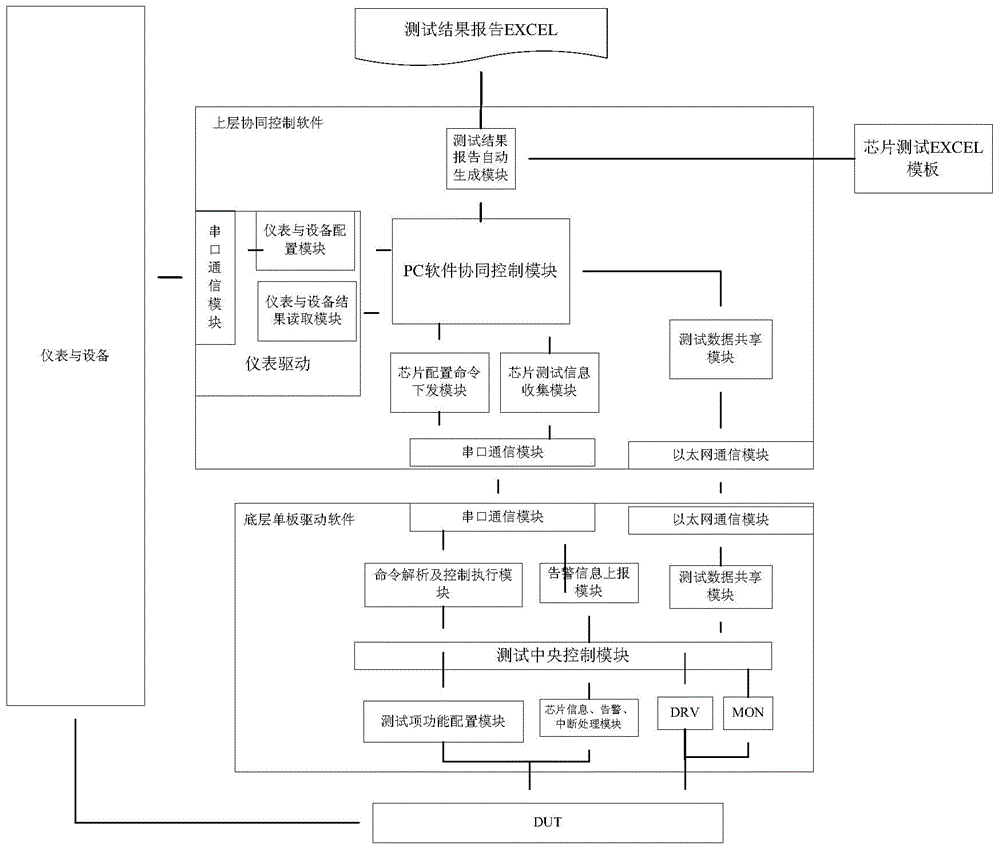

[0034] The hardware system composition of the automatic chip testing method realized by the present invention is divided into instrument and equipment drive part, PC, command analysis control execution information reporting and test item function configuration part, single board system, wherein the hardware is to utilize the existing hardware The facilities are completed, the following is a brief introduction as follows:

[0035] 1. Instrument and device driver, as attached figure 1 As shown, the main completion:

[0036] (1) Communication interface The communication module uses windows api to...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More