Universal method and platform for verifying compatibility between intellectual property (IP) core and advanced microcontroller bus architecture (AMBA) bus interface

A general verification method and technology of bus interface, applied in the field of general verification platform for compatibility between IP core and AMBA bus interface, can solve the problems of not considering generality, increase the development time and cost of verification platform, and reduce development time and cost. Improve verification efficiency and accuracy, and reduce the effect of iterations

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0055] In order to make the object, technical solution and advantages of the present invention clearer, the present invention will be further described in detail below in conjunction with the accompanying drawings.

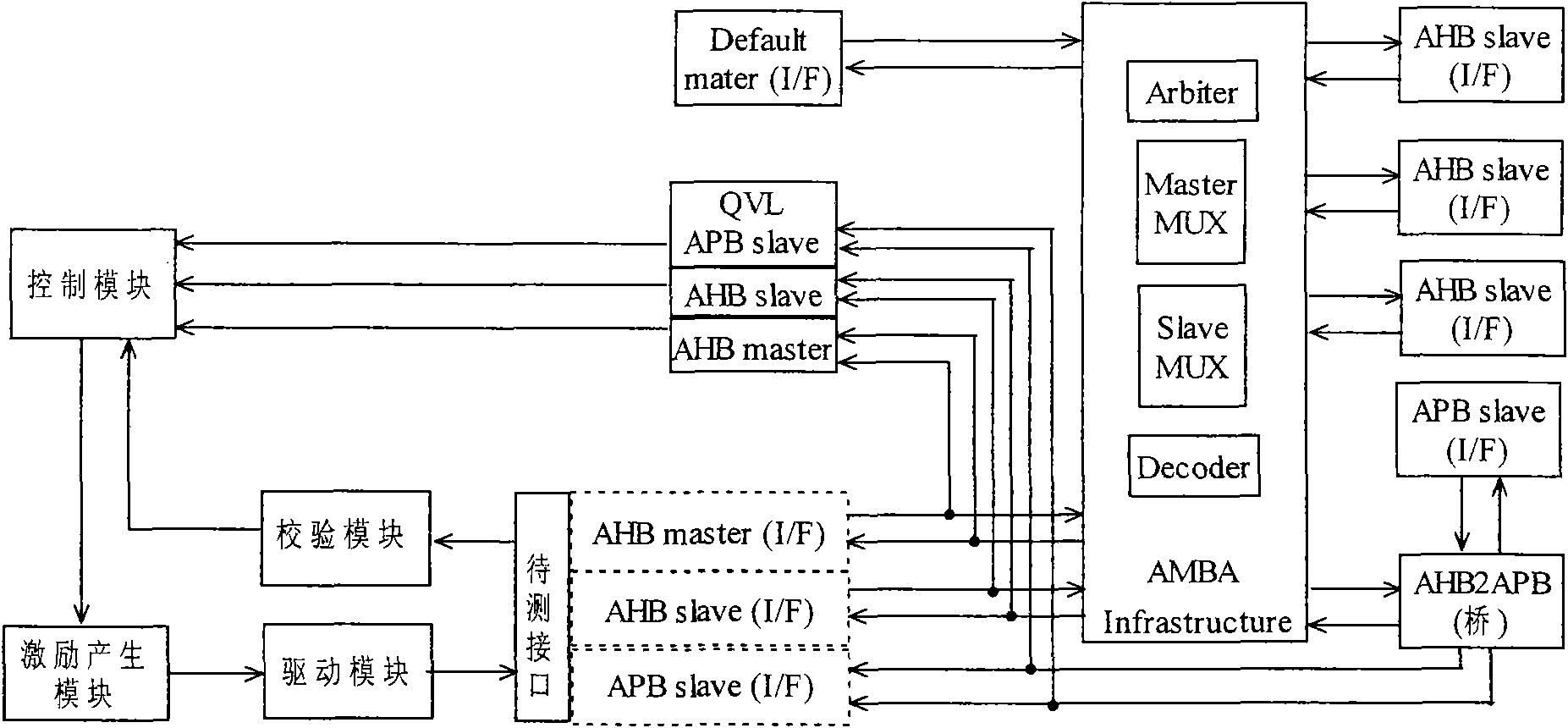

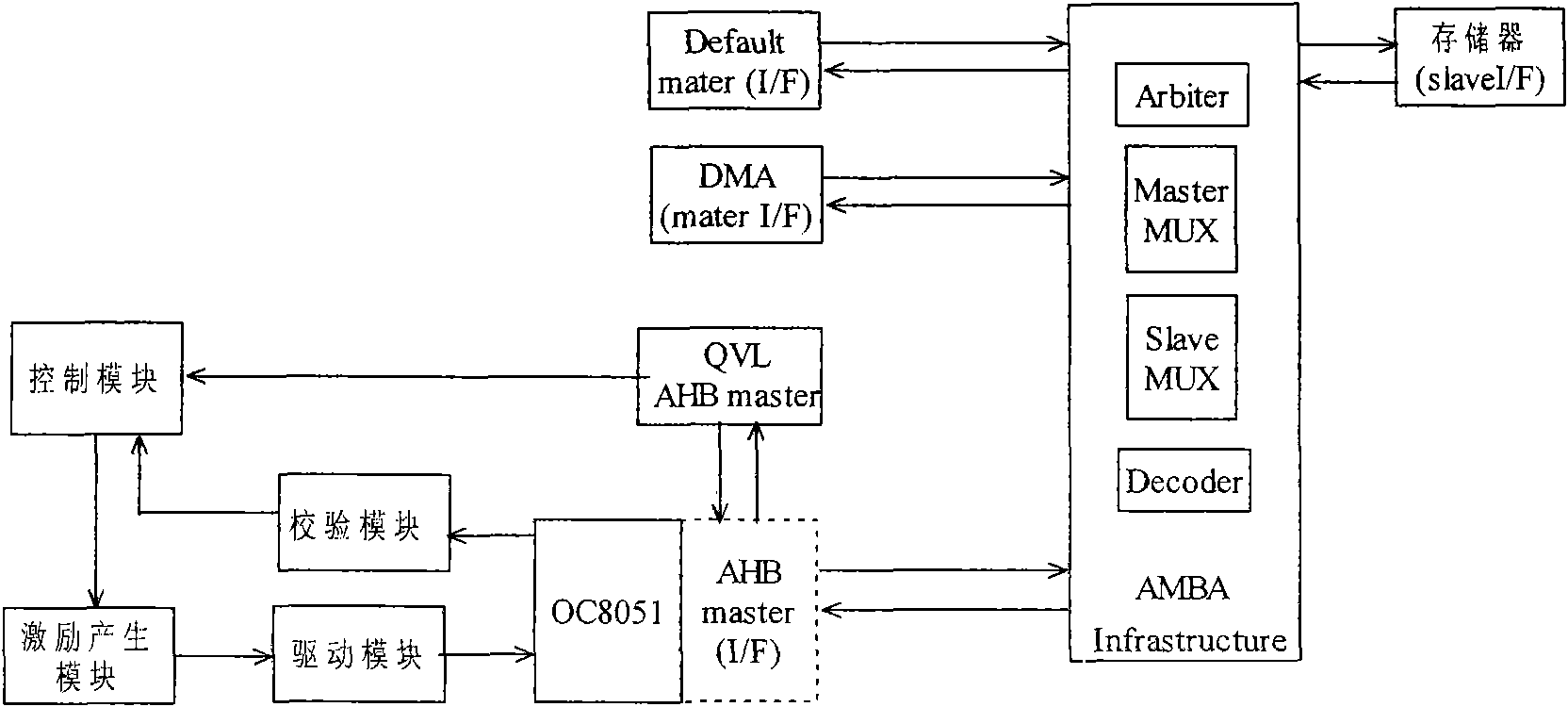

[0056] Such as figure 2 As shown, the universal verification platform of IP core and AMBA bus interface compatibility provided by the present invention includes functional simulation tool, AMBA bus underlying infrastructure, third party verification IP core, control module, driver module, incentive generation module, verification module, APB Bridge, AHB master interface, AHB slave interface and APB slave interface, the verification platform adopts the verification components provided by SystemVerilog language and AVM verification methodology and hierarchical packaging and interconnection to interconnect each module into an integrated coordinated verification environment; The verification platform adopts the verification components provided by the SystemVerilog la...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More