Patents

Literature

162 results about "Functional simulation" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

Functional simulation is the simplest form of simulation and models the functional behavior of an instruction set architecture (ISA). This means that instructions are simulated one at a time by taking input operands and by computing output values.

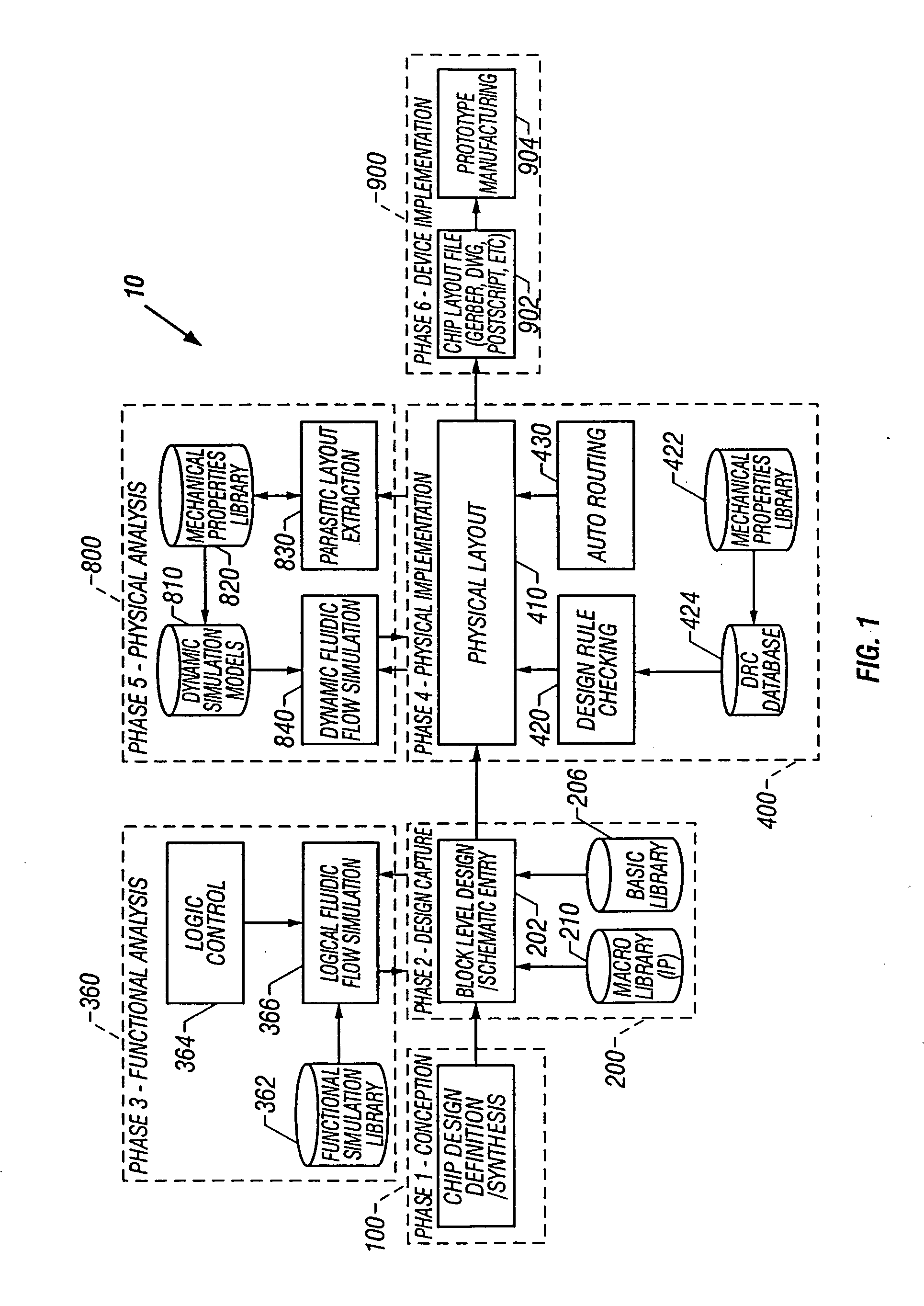

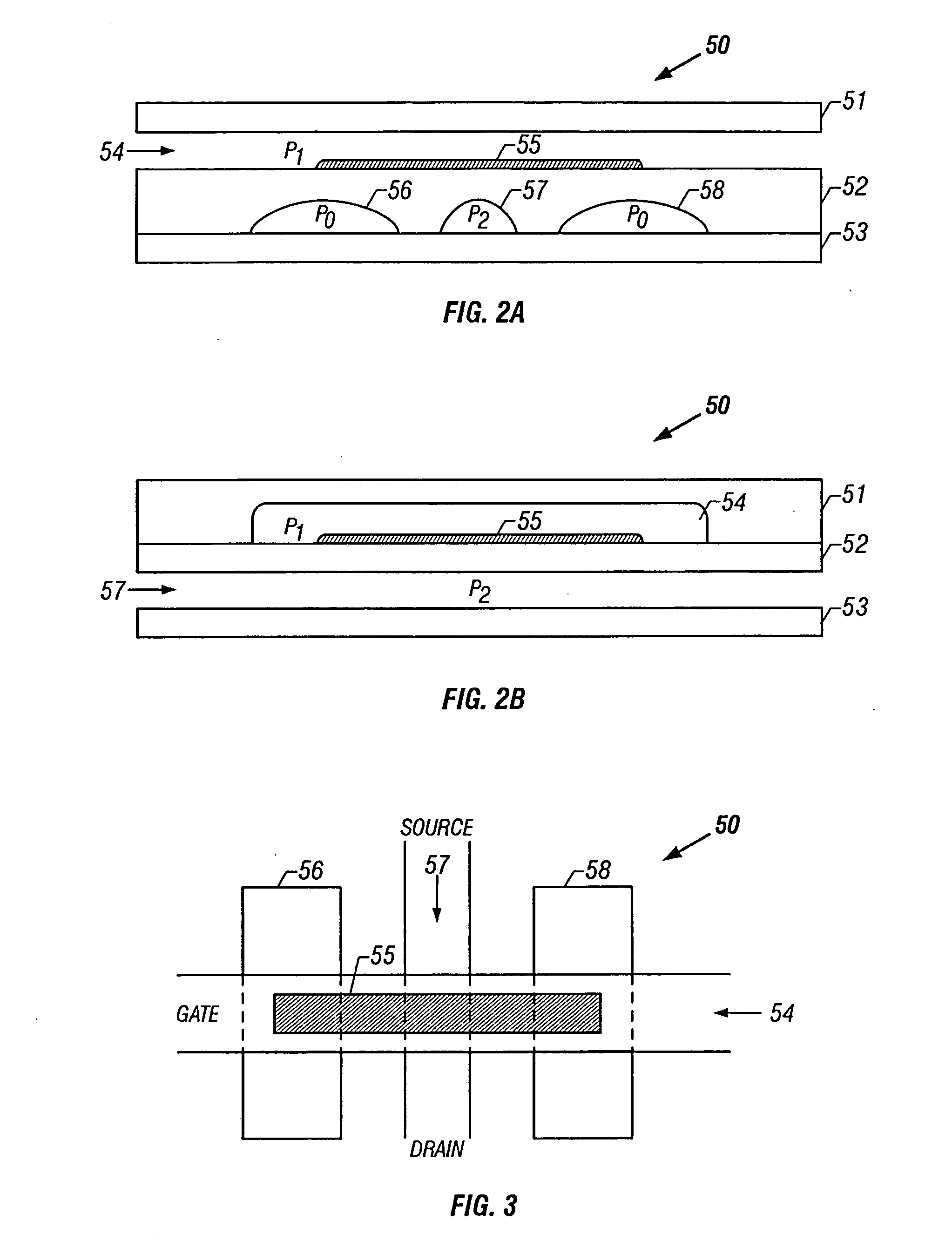

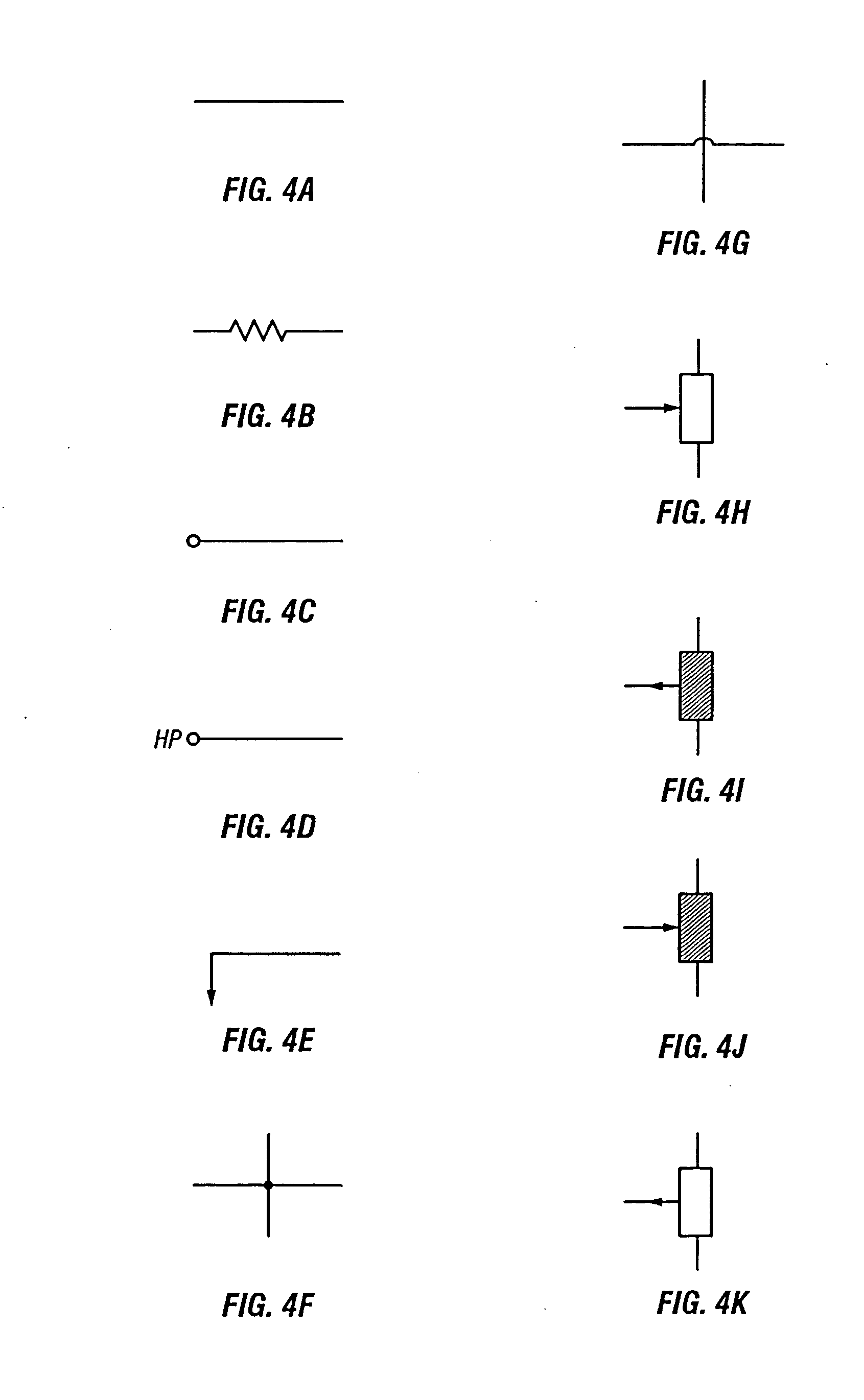

Microfluidic design automation method and system

InactiveUS20050065735A1Shorten the timeEasy placement and routingFixed microstructural devicesVolume/mass flow measurementComputer Aided DesignSystems design

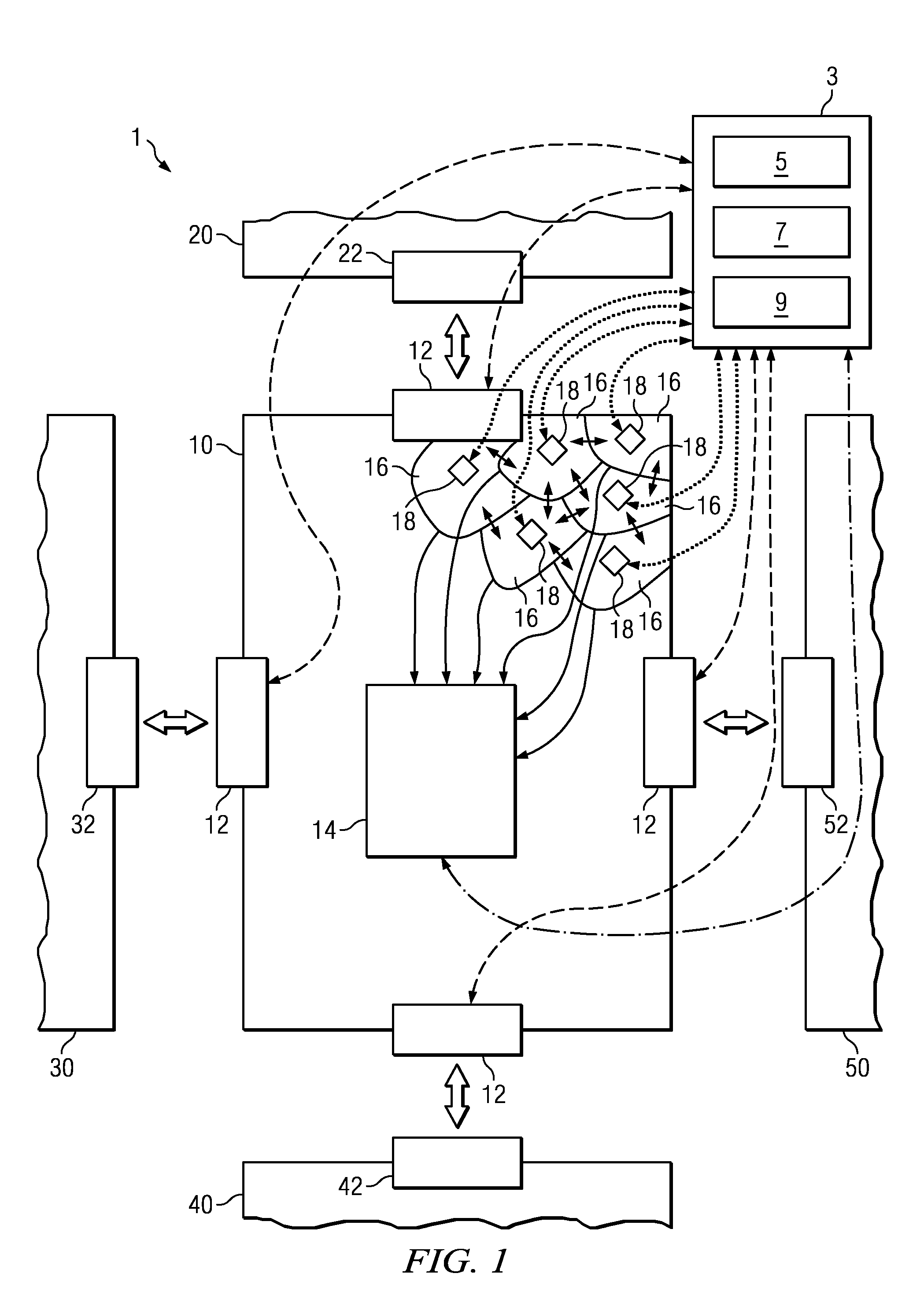

The present invention generally relates to microfluidics and more particularly to the design of customized microfluidic systems using a microfluidic computer aided design system. In one embodiment of the present invention a microfluidic circuit design method is provided. The method includes developing synthesizable computer code for a design. Next, a microfluidic circuit schematic, including a plurality of symbols for microfluidic components, is generated either interactively or using the synthesizable computer code. The microfluidic circuit schematic is then functionally simulated. The microfluidic components are placed and routed on a template to form a physical layout. Then the physical layout is physically simulated using dynamic simulation models of the microfluidic components; and the physical layout is written to a layout file.

Owner:FLUIDIGM CORP

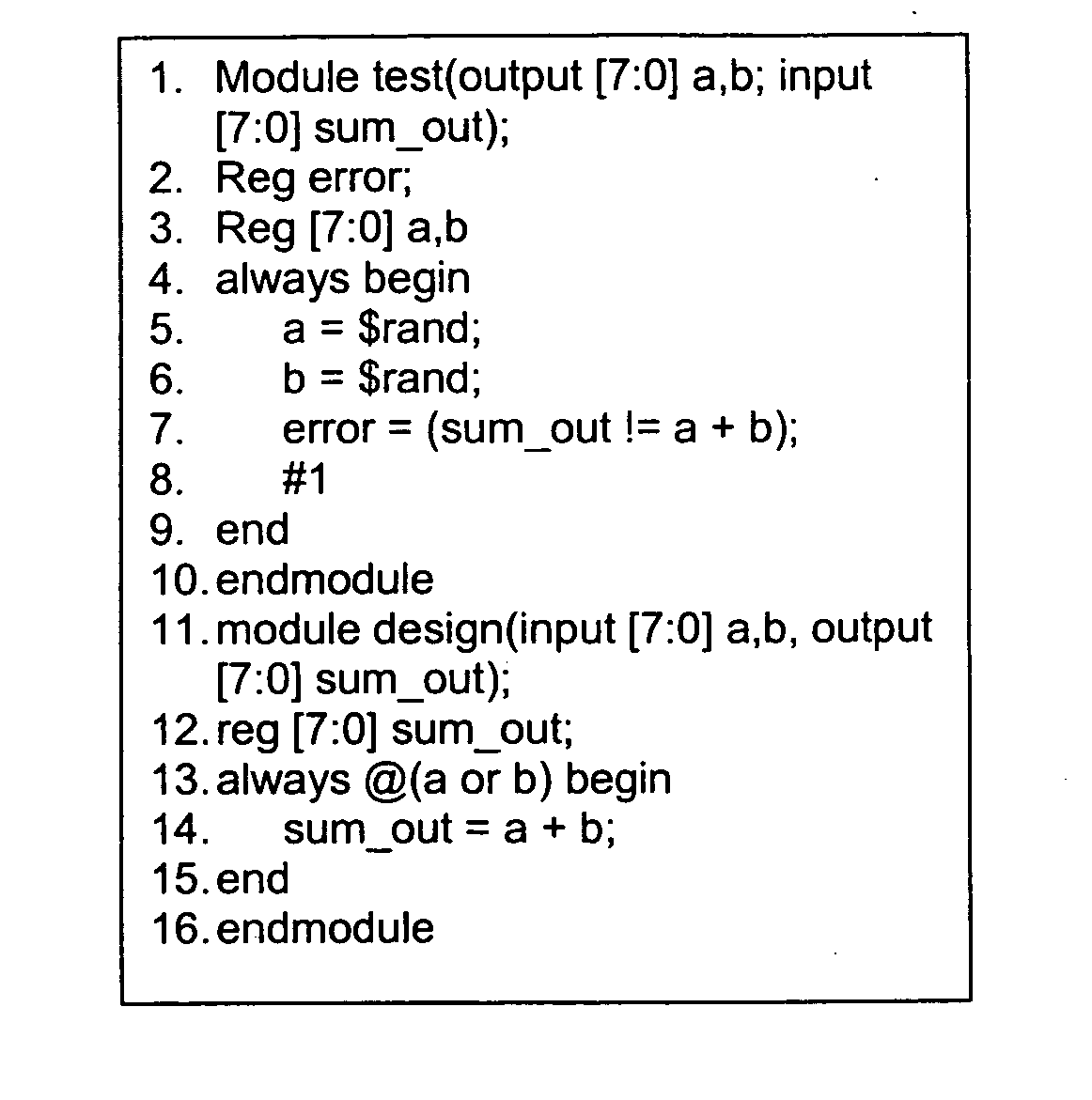

Methods and systems for improved integrated circuit functional simulation

InactiveUS20050091025A1Reduce in quantityElectrical apparatusComputer aided designSymbolic simulationBinary decision diagram

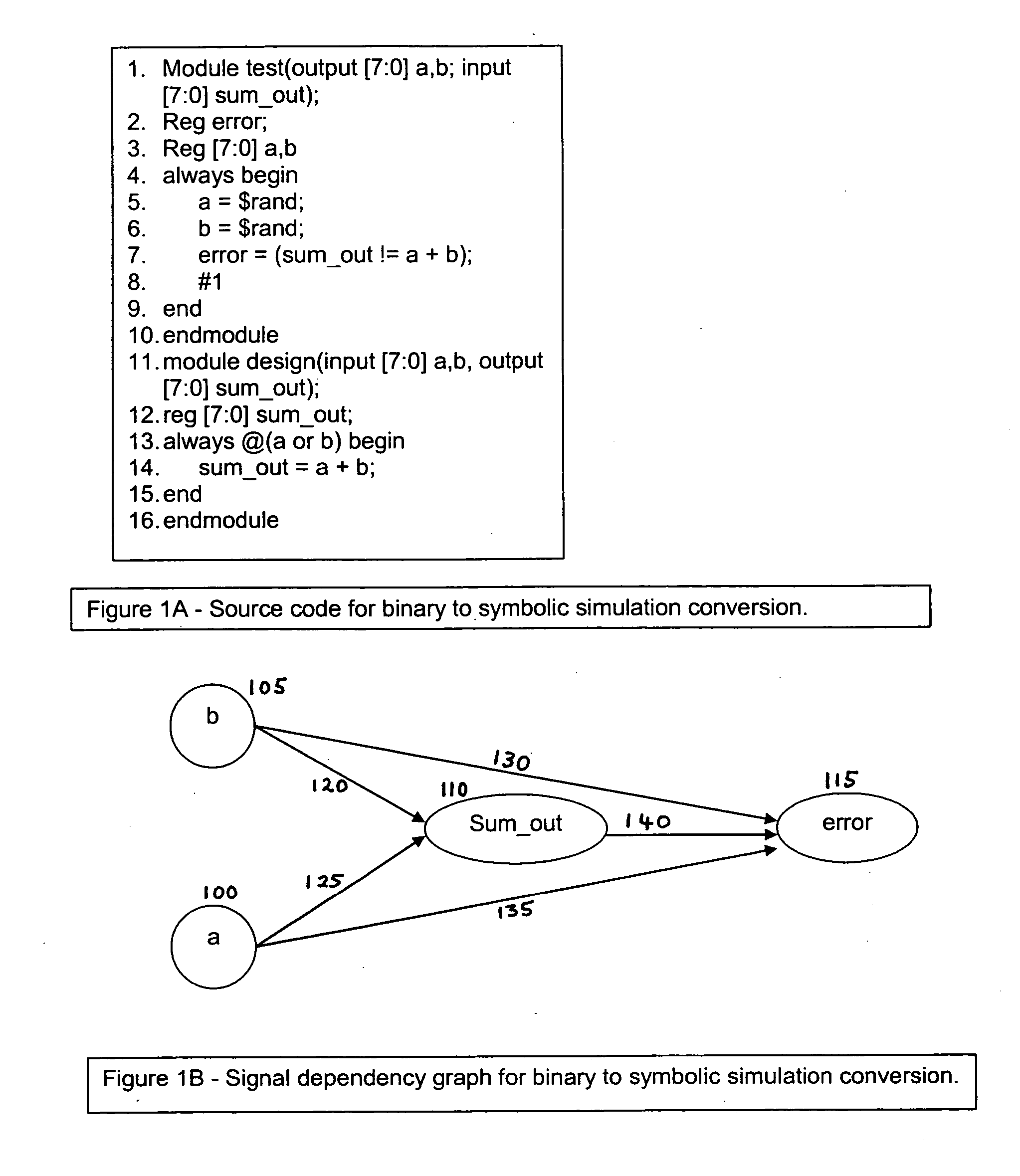

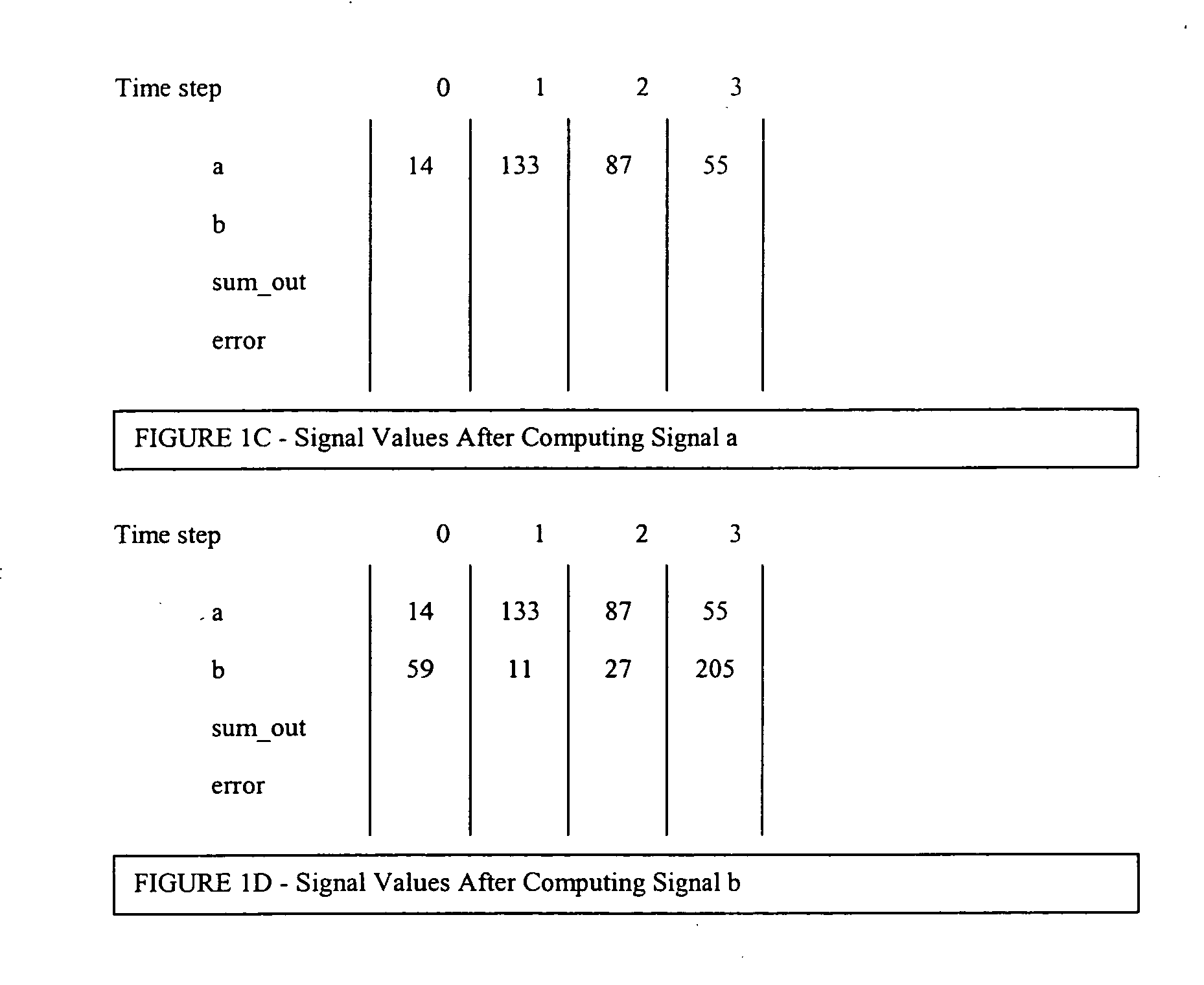

Methods and systems for performing symbolic simulation, including techniques for translating a conventional simulation into a symbolic simulation, for handling wait and delay states, and for performing temporally out-of-order simulations. Additional techniques for extracting a signal graph from an HDL representation of a device, for representing signal values as functions of time using binary decision diagrams, and for computing minimal signal sets for accurate simulation. Techniques and methods for improving waveform dumping, reducing the waveform database, and for combining out-of-order simulation or reduced time steps with conventional time-based simulation.

Owner:VENTURE LENDING & LEASING IV

Algorithmic electronic system level design platform

InactiveUS20070162268A1CAD circuit designSpecial data processing applicationsElement modelComputer architecture

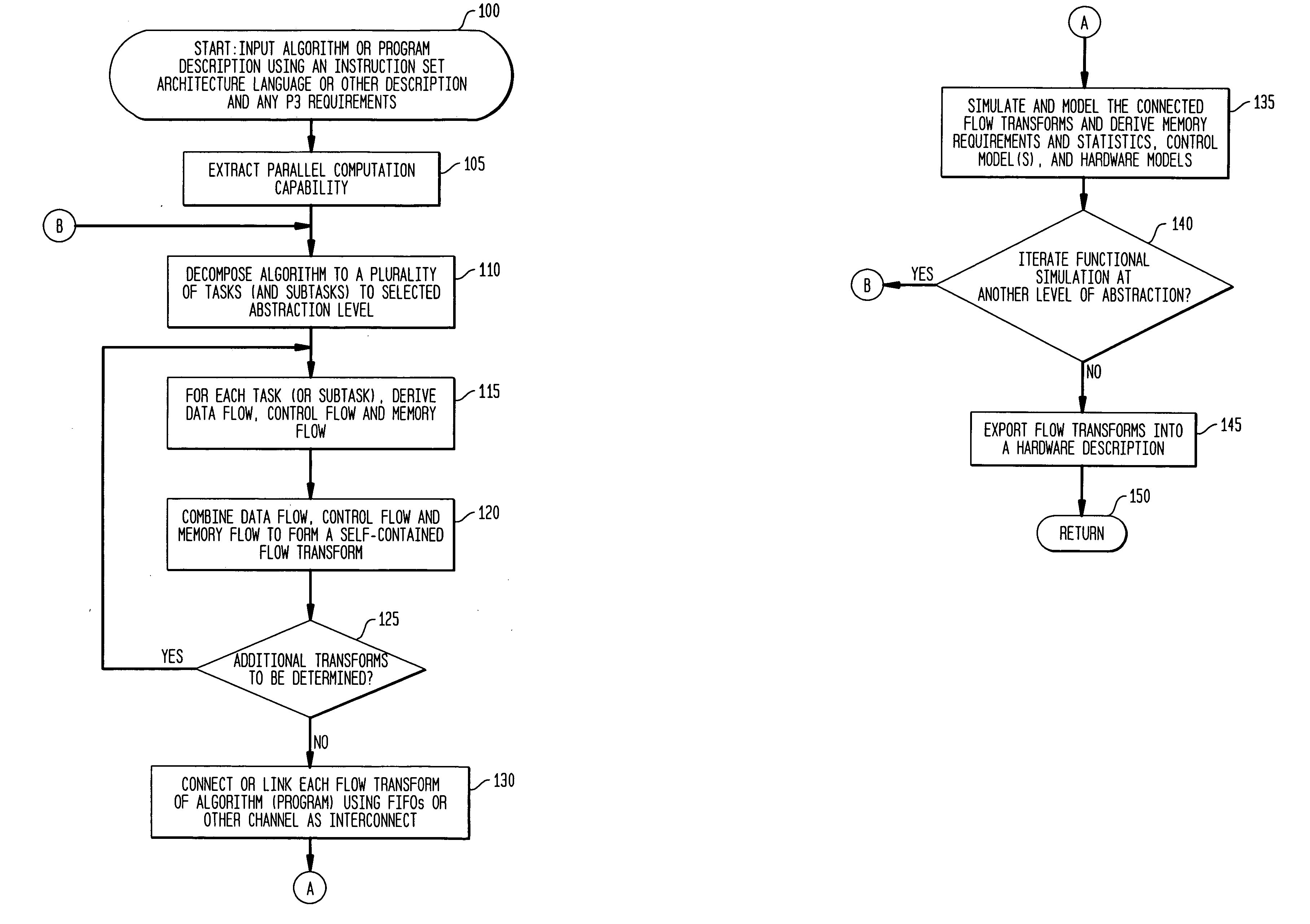

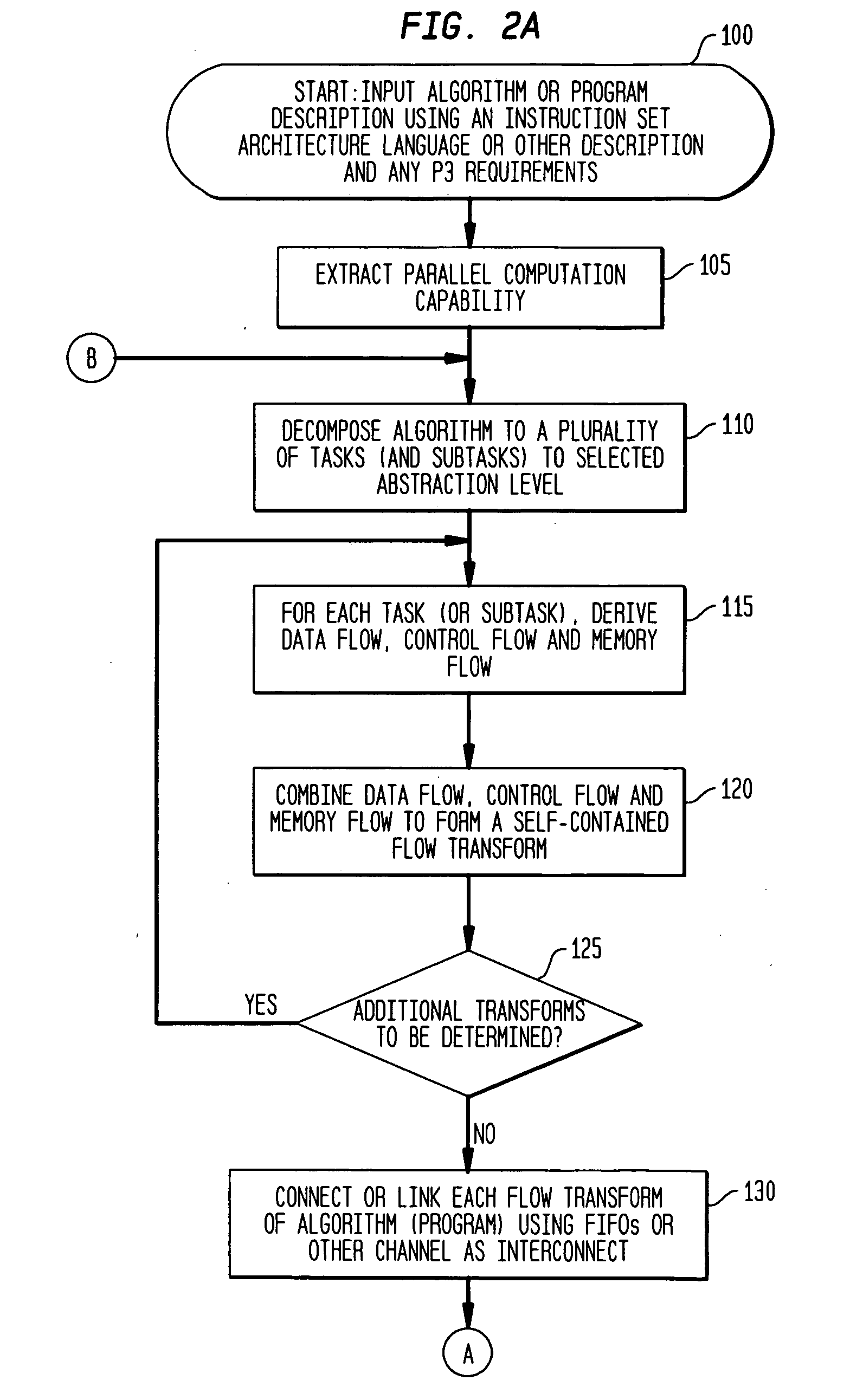

A computing system and method are provided for algorithmic electronic system level design. An exemplary system comprises a plurality of databases for storing a plurality of functional models, a plurality of computational element models, and a plurality of hardware definition representations. An application design processor is adapted to perform a first functional simulation of an algorithm using a plurality of computational element architecture definitions to generate a first selection of a plurality of computational elements and corresponding control code for an implementation of the algorithm. A control and memory modeling processor is adapted to generate a plurality of flow transforms from the algorithm and to convert the plurality of flow transforms into the plurality of plurality of computational element models. A system simulation processor is adapted to convert the plurality of computational element models into the plurality of hardware definition representations and to perform a second functional simulation of the algorithm using the plurality of computational element models corresponding to the first selection and the corresponding control code.

Owner:KOTA BHASKAR +3

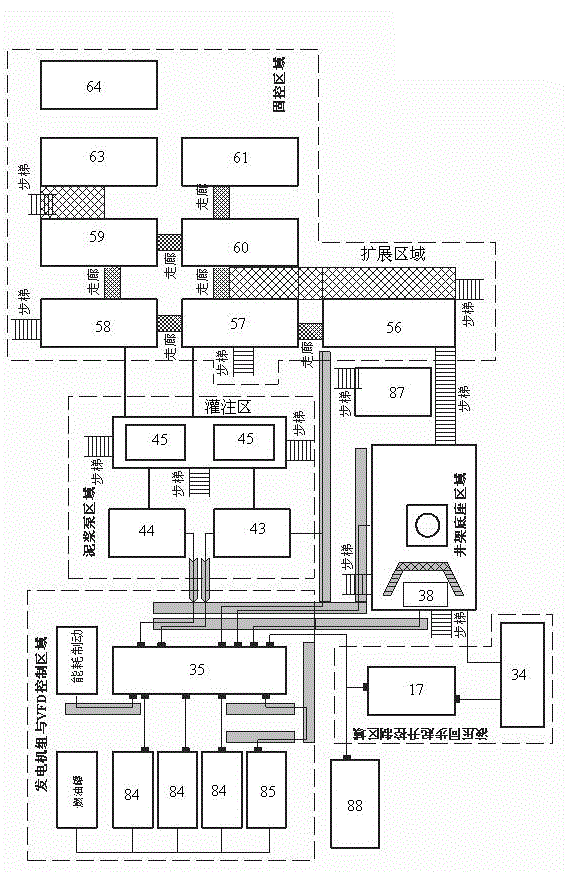

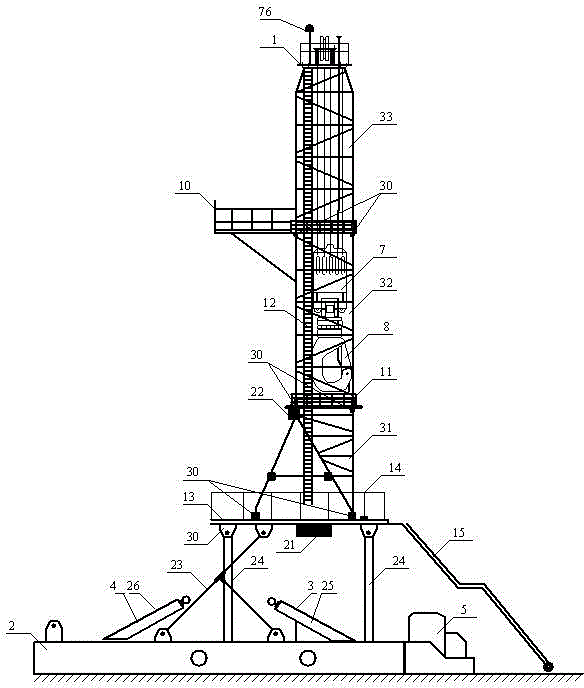

Tunnelling machine control system detection test platform

InactiveCN101211185AVersatileHigh degree of simulationSimulator controlElectric testing/monitoringMachine controlMathematical simulation

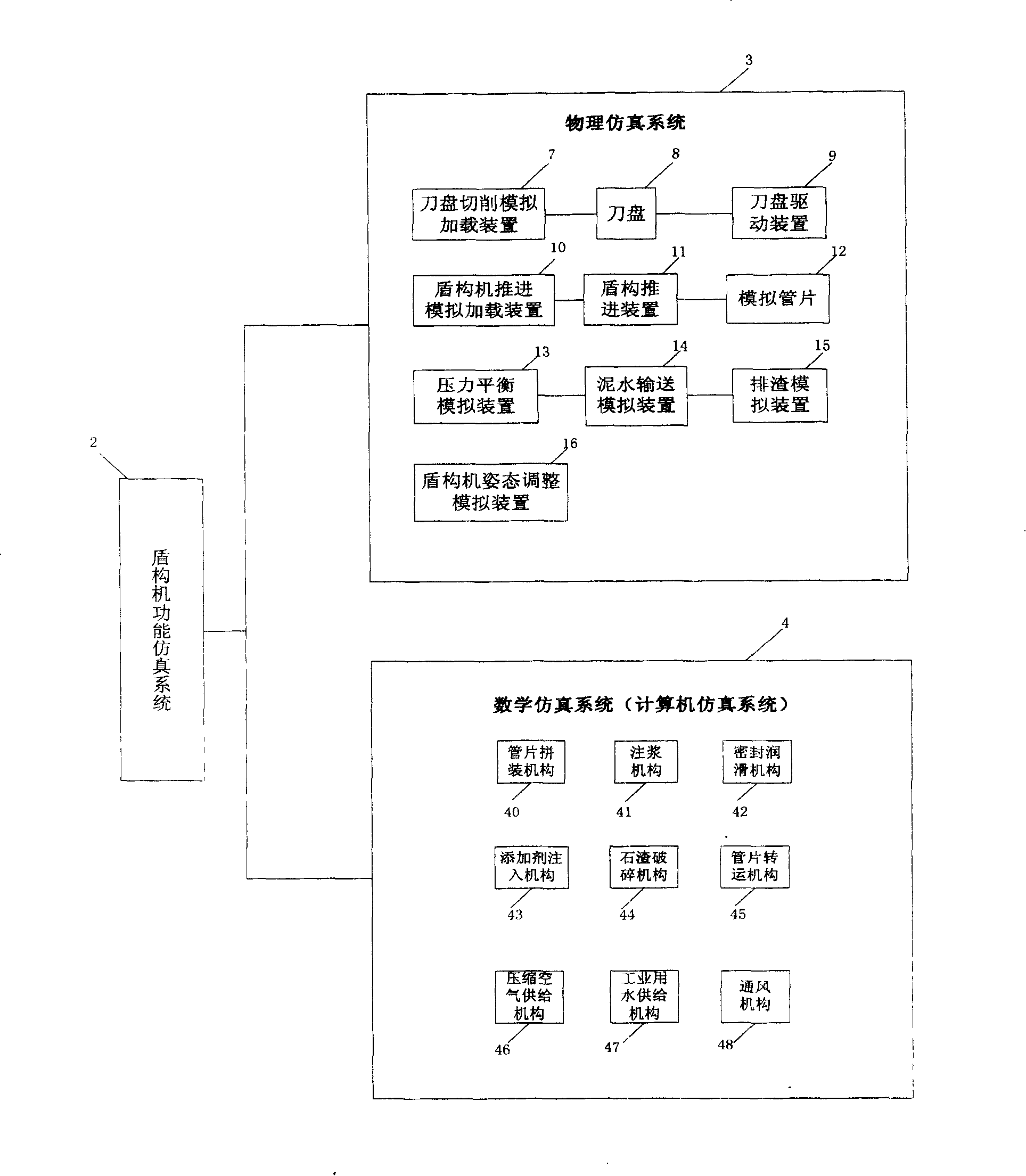

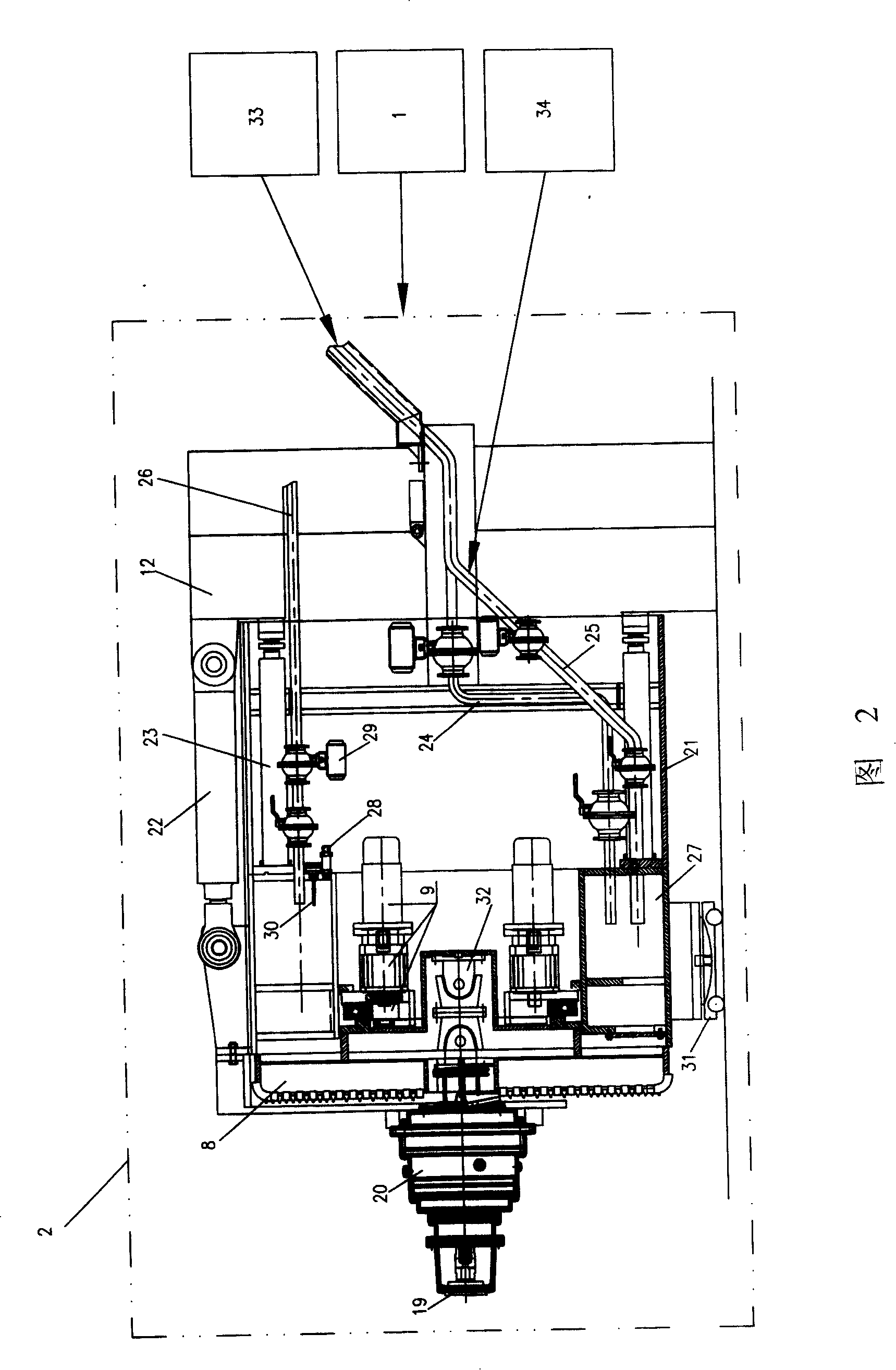

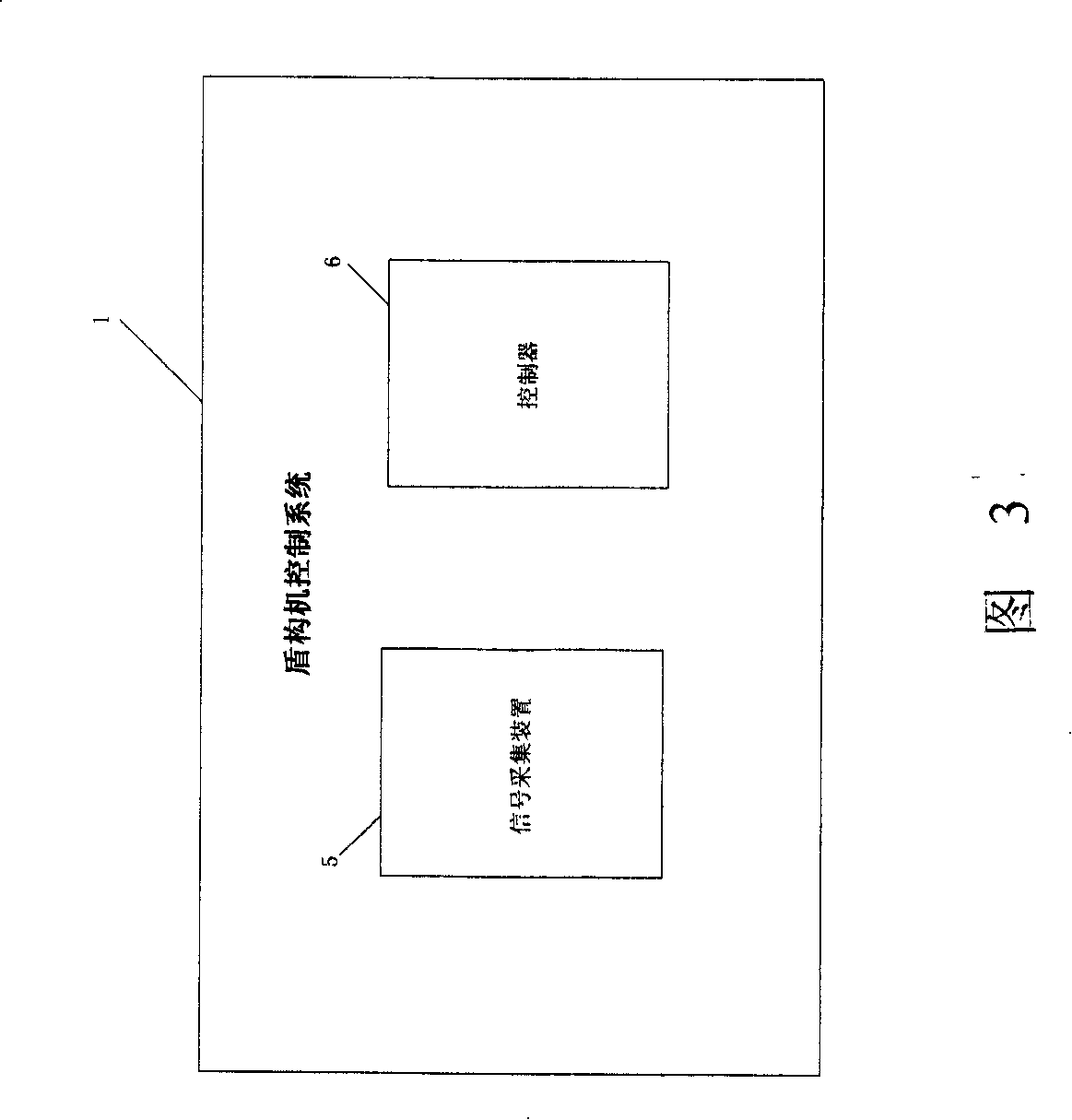

A test bench for testing a shield machine control system comprises a shield machine function simulation system and a sensing device arranged in the function simulation system, wherein the sensing device is communicated with the shield machine control system to be tested, and the function simulation system can be a physical simulation system, a mathematical simulation system or a combination of the physical simulation system and the mathematical simulation system. The test bench for testing the shield machine control system can completely simulate various functions of various types of shield machines, so as to test the correctness of the shield machine control system in design, assembly and debugging, avoid the risk arising from direct communication with the shield machine when the design of the control system is faulty, and shorten the circle of developing a new machine. Meanwhile, the invention is helpful for optimization and modification of the shield machine control system and remote fault diagnosis on the shield machine operated in a tunnel.

Owner:CHINA RAILWAY TUNNEL

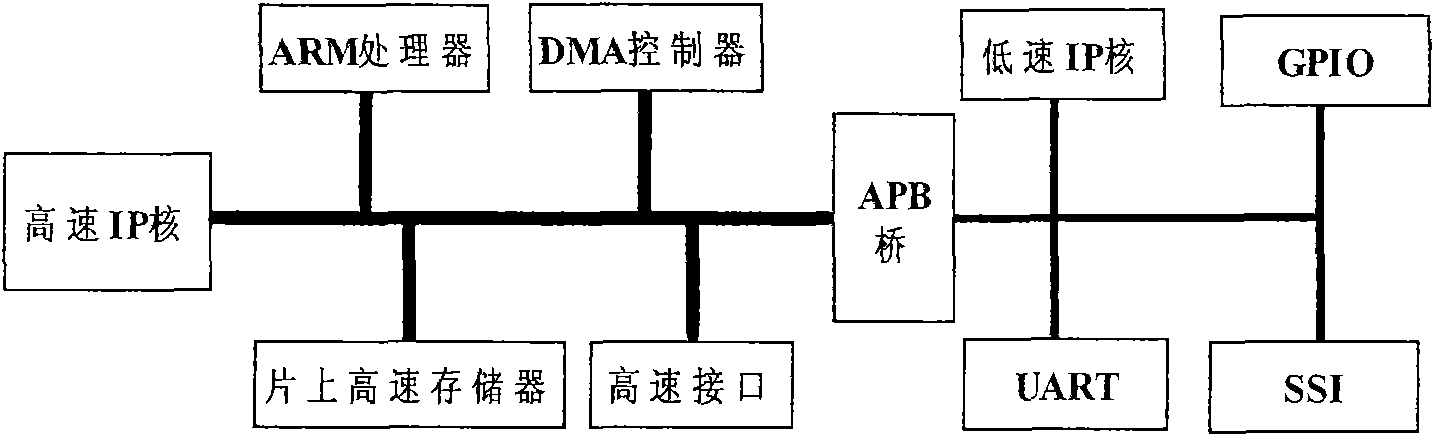

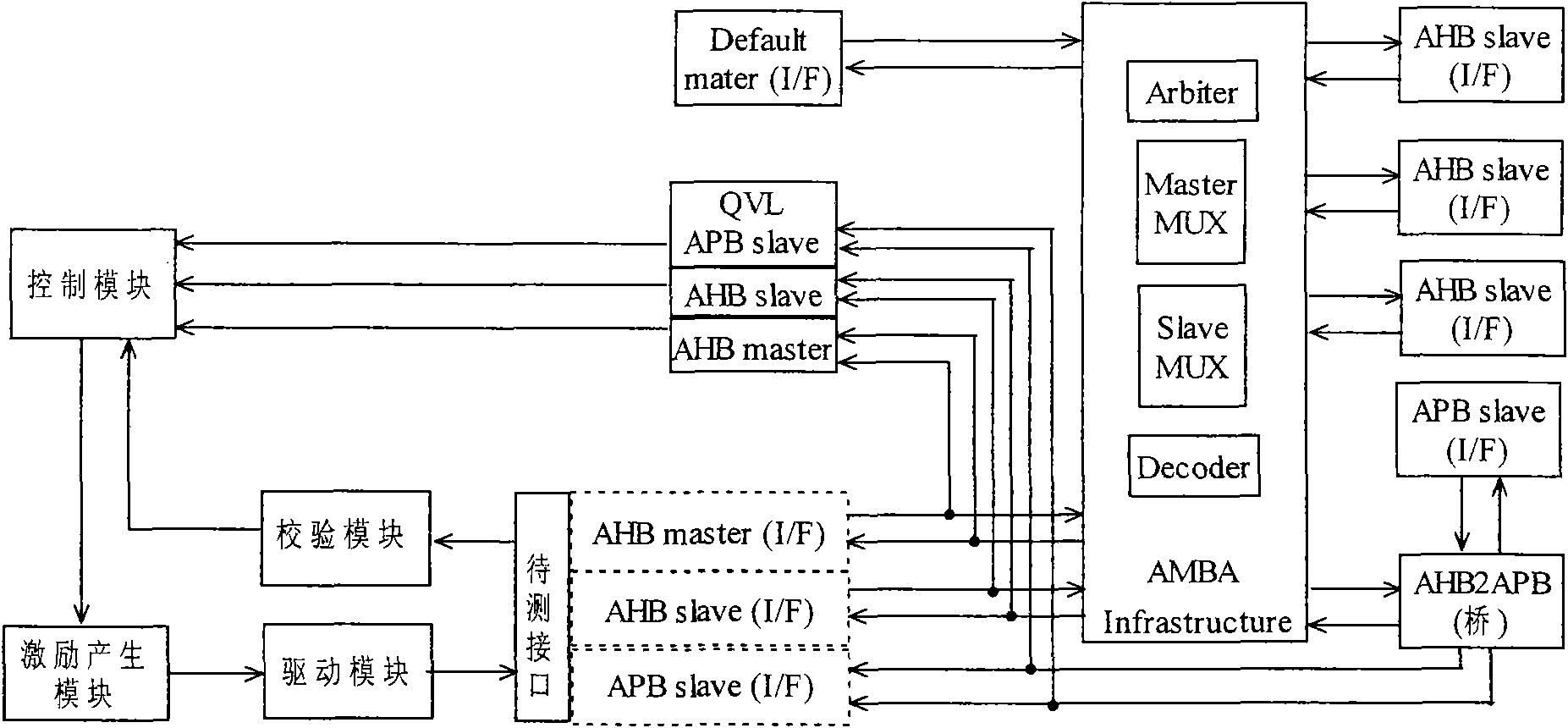

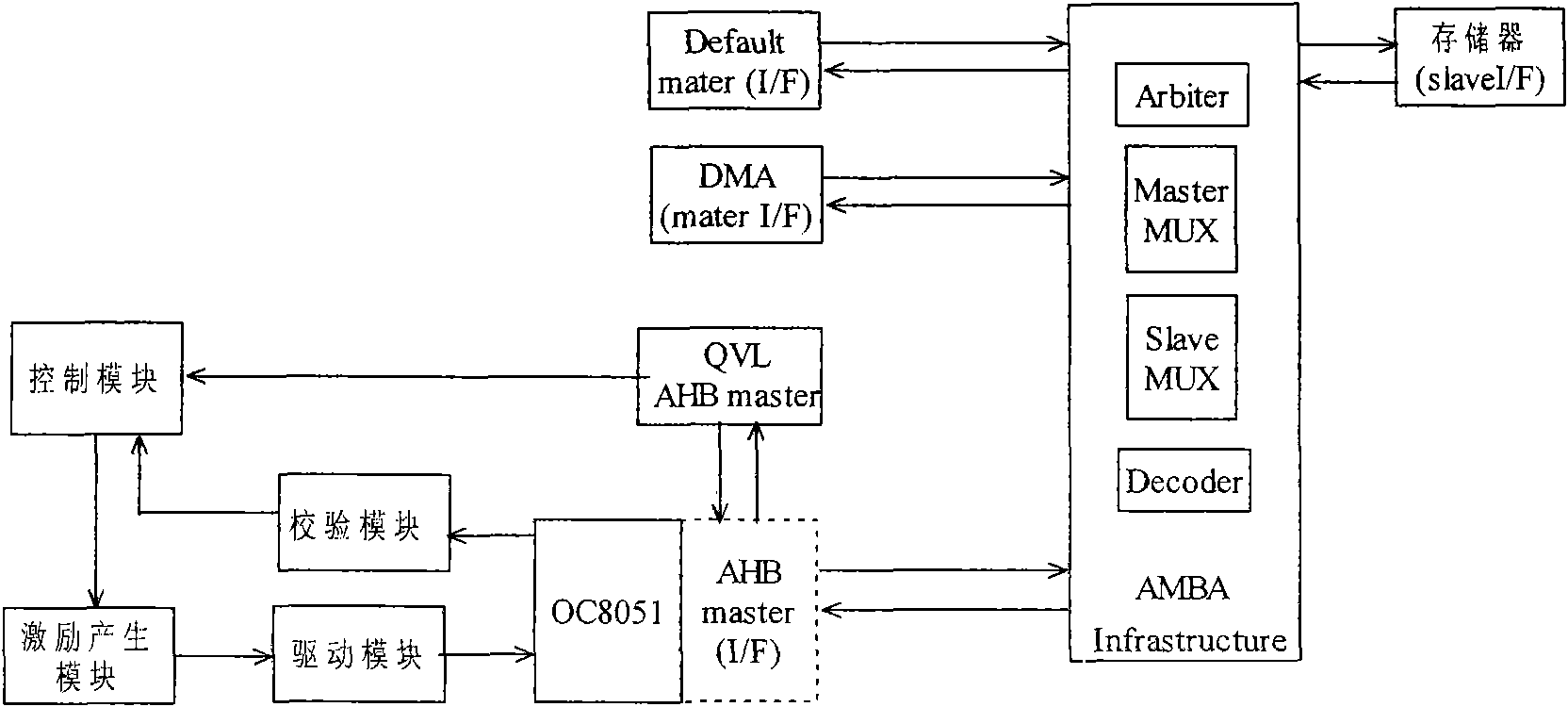

Universal method and platform for verifying compatibility between intellectual property (IP) core and advanced microcontroller bus architecture (AMBA) bus interface

InactiveCN102117238AImprove verification efficiencyImprove accuracyFunctional testingValidation methodsIntellectual property

The invention provides a universal platform of verifying compatibility between an intellectual property (IP) core and an advanced microcontroller bus architecture (AMBA) bus interface, which comprises a functional simulation tool, an AMBA bus infrastructure, a third-party verification IP core, a controller, a driver, a stimulus, a checker, an advanced peripheral bus (APB) bridge, an advanced high-performance bus (AHB) master interface, an AHB slave interface and an APB slave interface, wherein all the modules are connected to form an integrated coordinating verification environment by adopting a verification component and hierarchical packaging and interconnections ways provided by a SystemVerilog language and advanced verification methodology (AVM). The platform can verify the compatibility of different types of IP core interfaces, and the development time and cost of the verification platform and a verification method are reduced. The invention also provides the universal method for verifying the compatibility between the IP core and the AMBA bus interface. In the method, excitation is produced more normatively, scientifically and accurately, unnecessary iteration is reduced and the verification time is shortened.

Owner:SHANGHAI SILICON INTPROP EXCHANGE

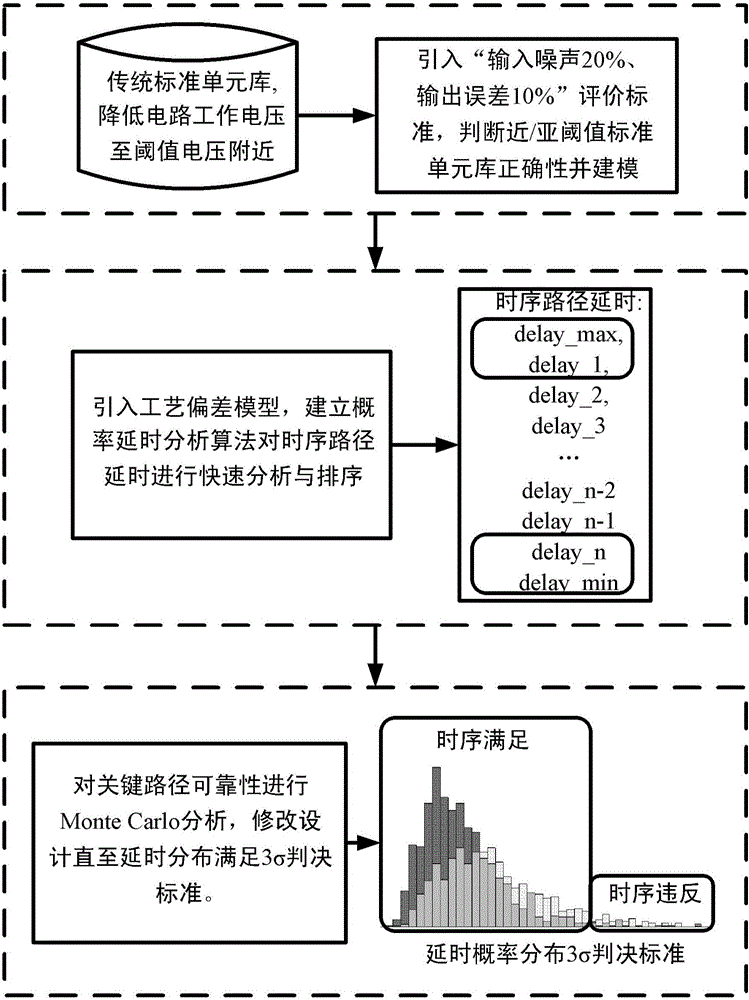

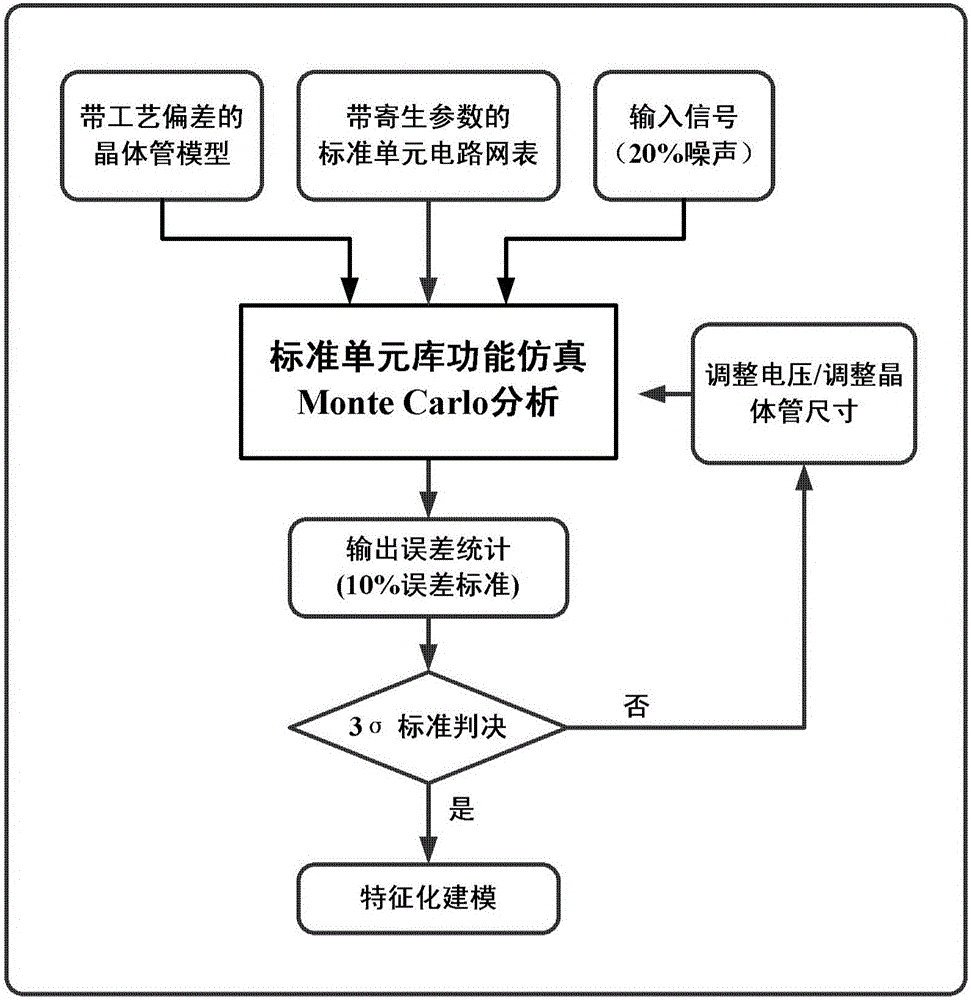

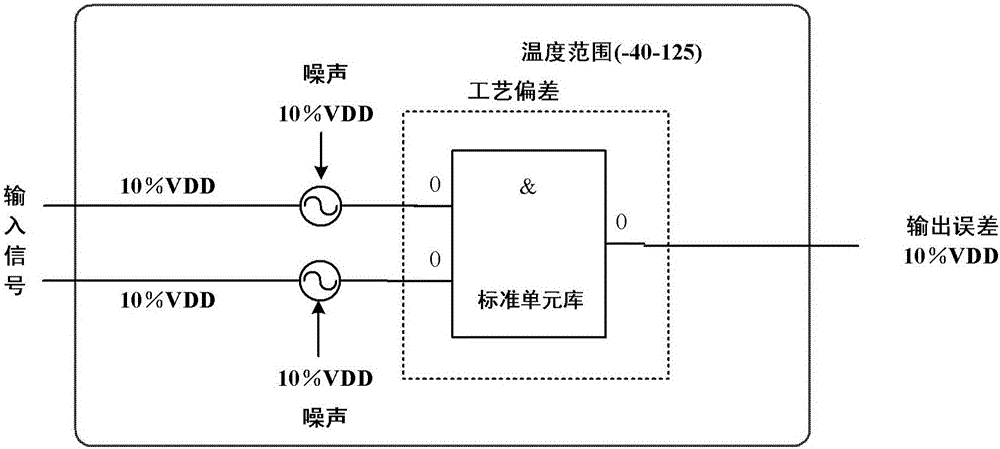

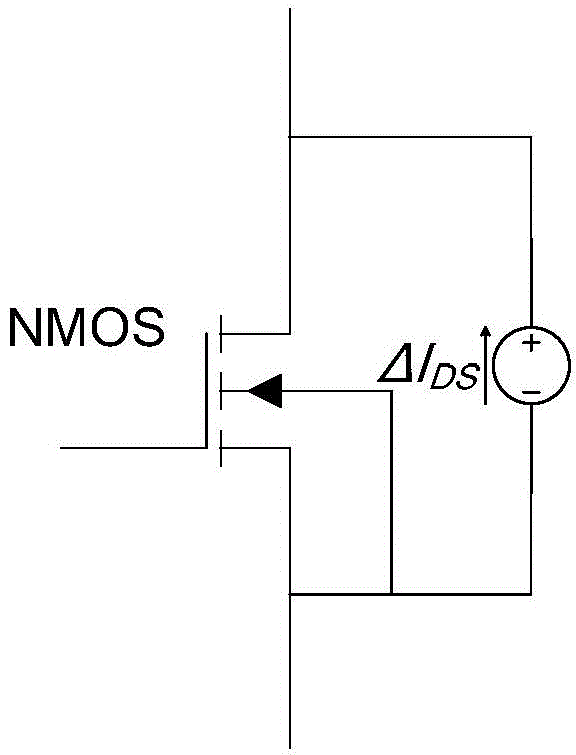

Statistics static state sequential analysis method applied to near/sub threshold digital circuit

ActiveCN106066919AResolve inaccuraciesSolve efficiency problemsSpecial data processing applicationsTime delaysSimulation

The invention discloses a statistics static state sequential analysis method applied to a near / sub threshold digital circuit; the method comprises the following steps: reducing the standard cell library work voltage to near the threshold-voltage, and carrying out function simulation and characterization modeling for a near / sub threshold standard cell library; using a probability time-delay analysis algorithm to fast parse and rank path time-delays; using a Monte Carlo parse strategy and 3 [sigma] decision standard to concisely parse a suspected path, thus further improving sequential reliability. The provided accurate, reliable and fast statistics static state sequential analysis method can solve near / sub threshold digital circuit sequential analysis reliability problems, fully considers technology deviation influences on the path sequence, thus solving the near / sub threshold digital circuit sequential analysis reliability problems; compared with a conventional static state sequential analysis method and a Hspice-based sequential simulation method, the statistics static state sequential analysis method has obvious advantages on sequential analysis accuracy and efficiency.

Owner:SOI MICRO CO LTD

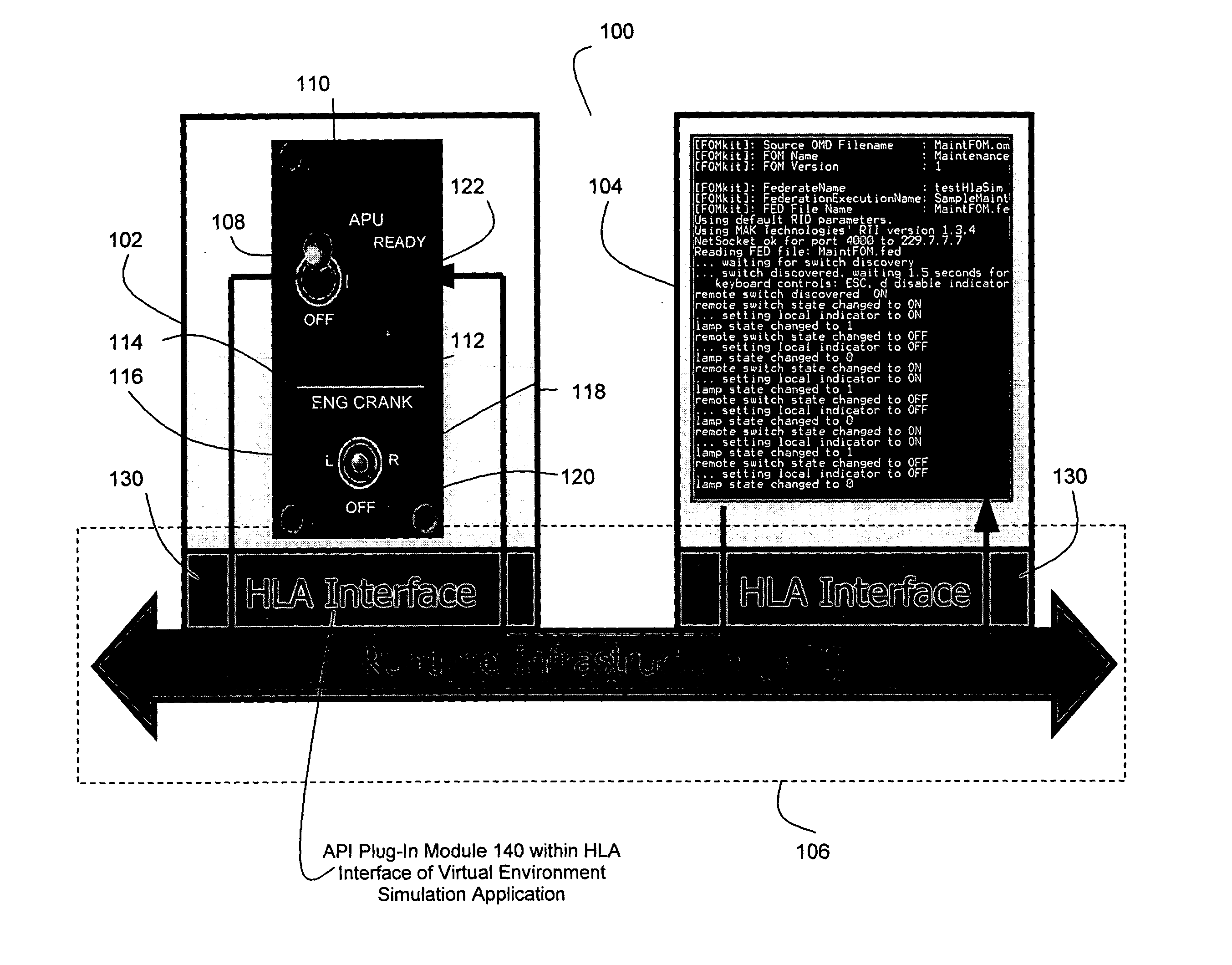

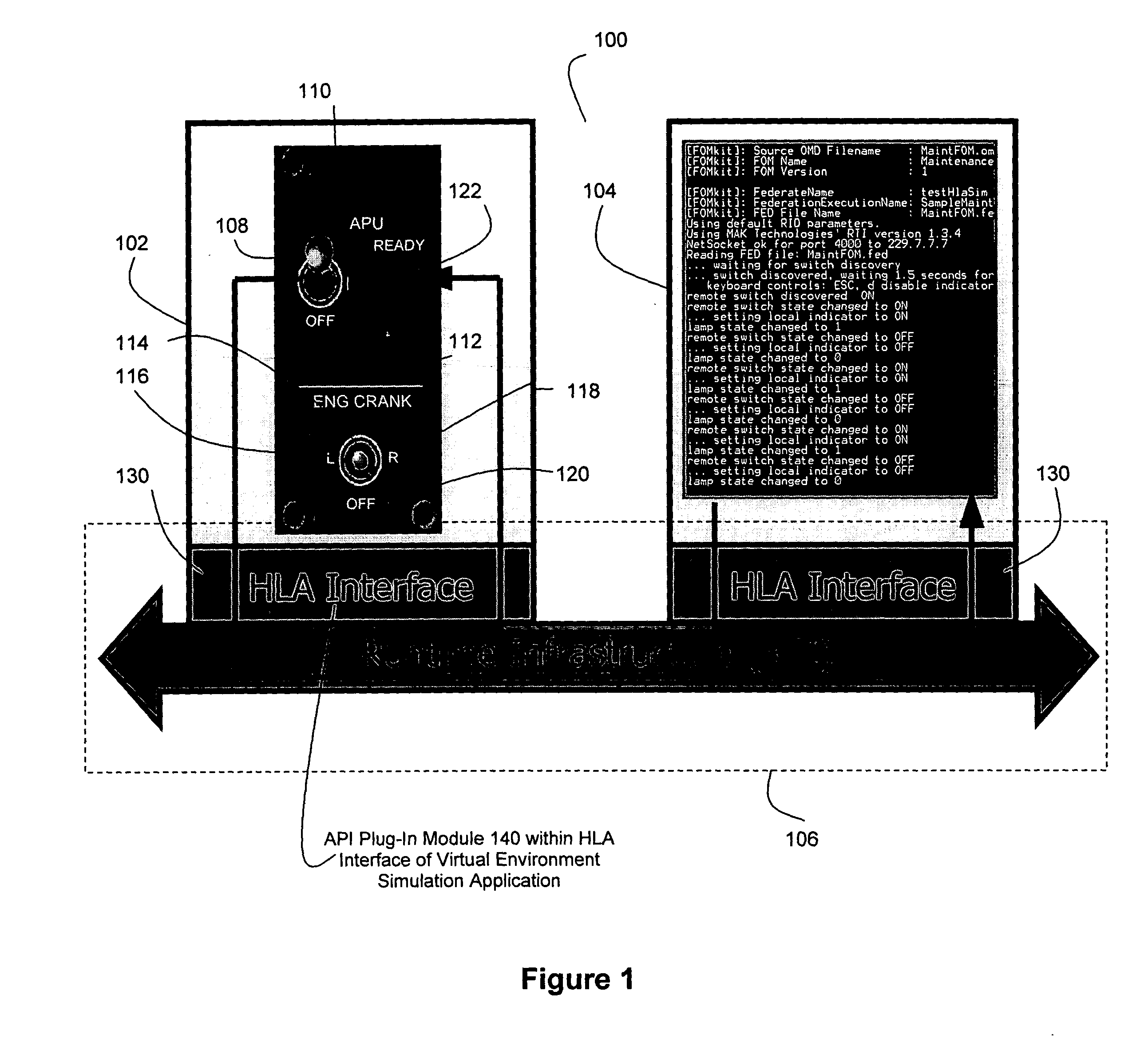

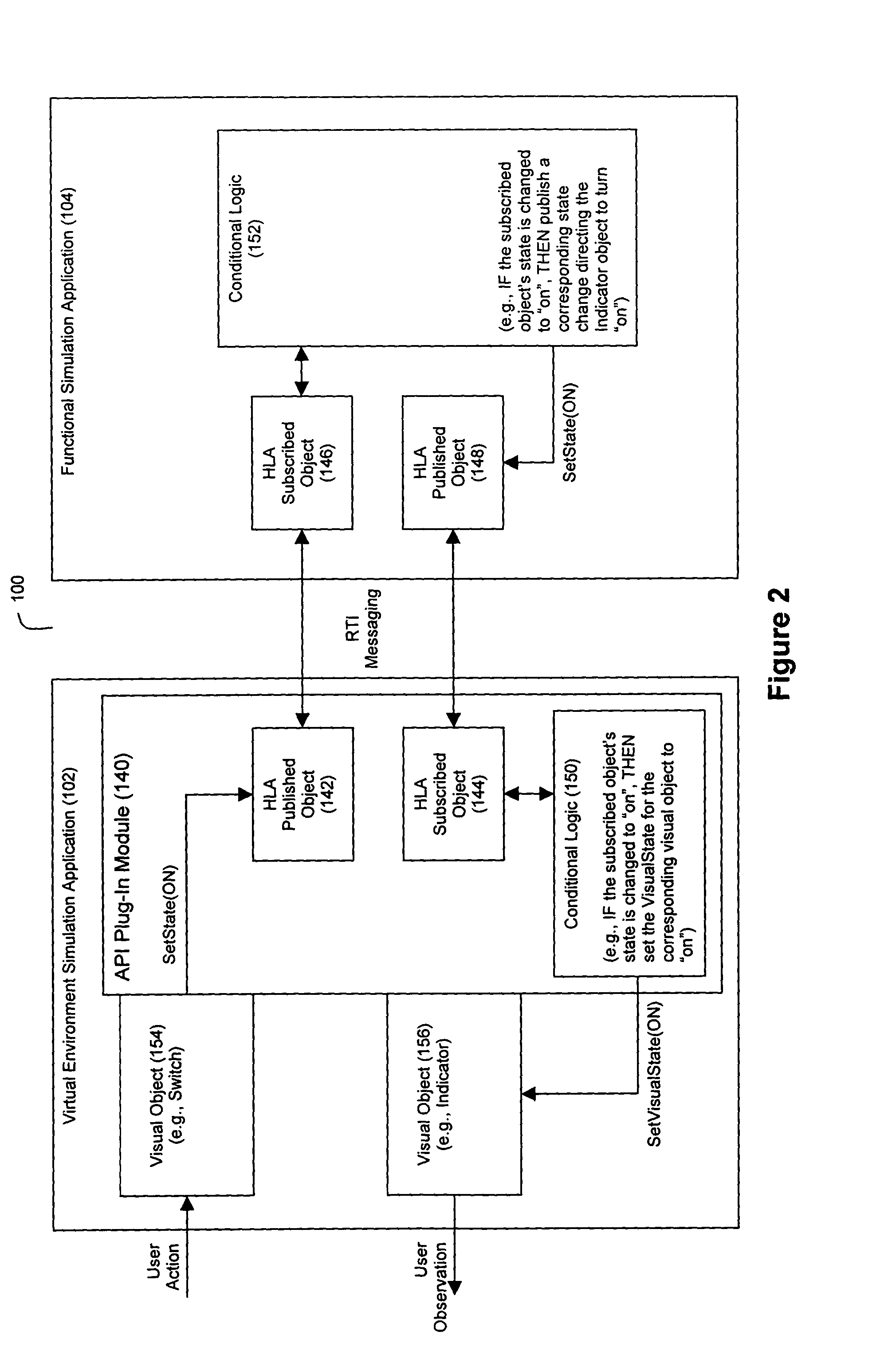

Method and apparatus for integrating virtual environments with functional simulations via HLA protocol

InactiveUS20050017977A1Low costIncrease flexibilityGeometric CADStatic indicating devicesGraphicsUser input

A method of simulating the behavior of a user-interactive environment, the method comprising: (a) running a virtual environment (VE) simulation application that (1) graphically depicts a VE, (2) receives input from a user that corresponds to a user interaction with the VE, and (3) provides graphical output to the user that corresponds to a condition of the VE; (b) running a functional simulation application that determines the condition for the VE at least in part based upon the user input; (c) communicating the user input received by the VE simulation application to the functional simulation application via a high level architecture (HLA) protocol; and (d) communicating the condition determined by the functional simulation application to the VE simulation application via the HLA protocol.

Owner:THE BOEING CO

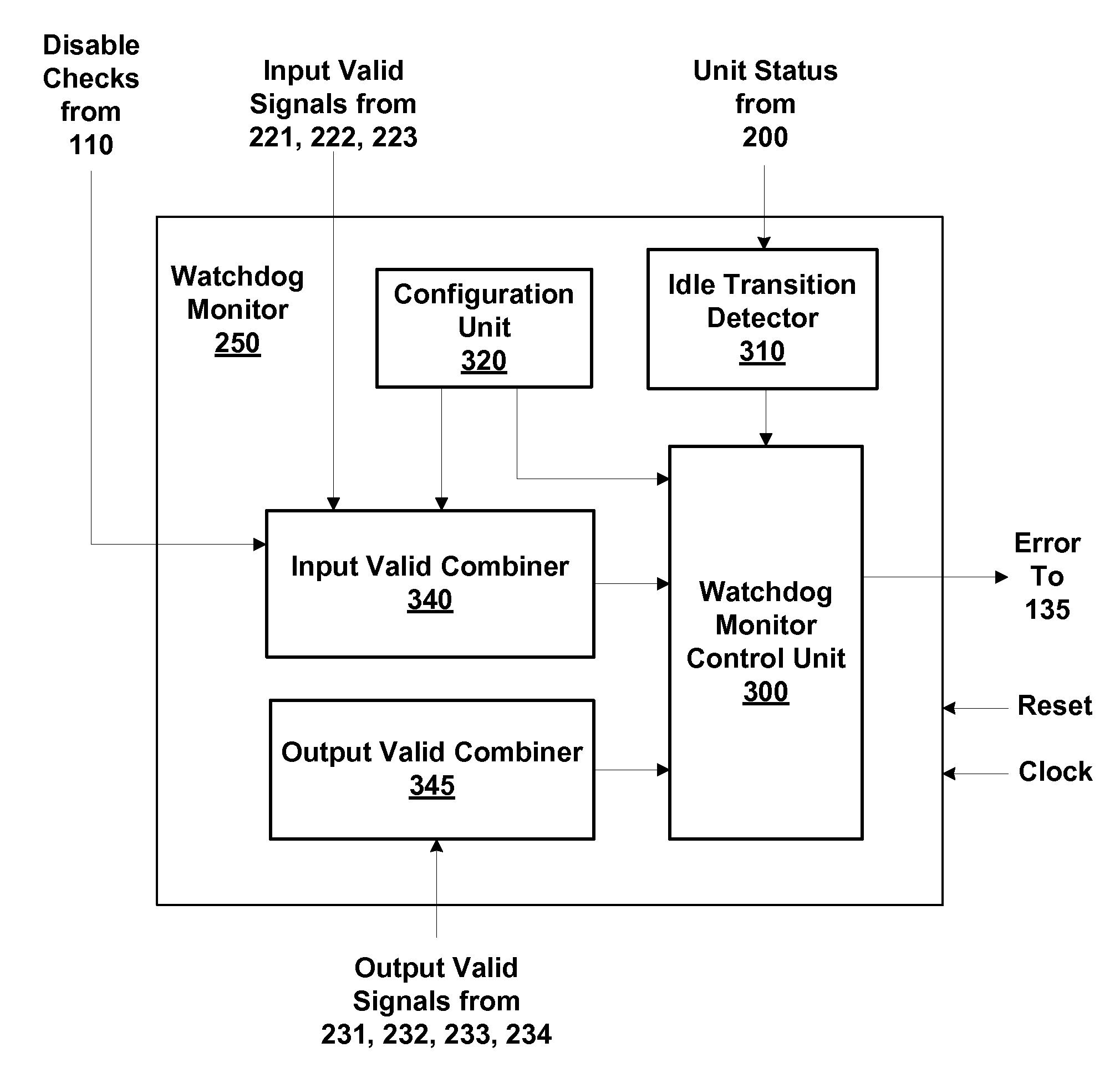

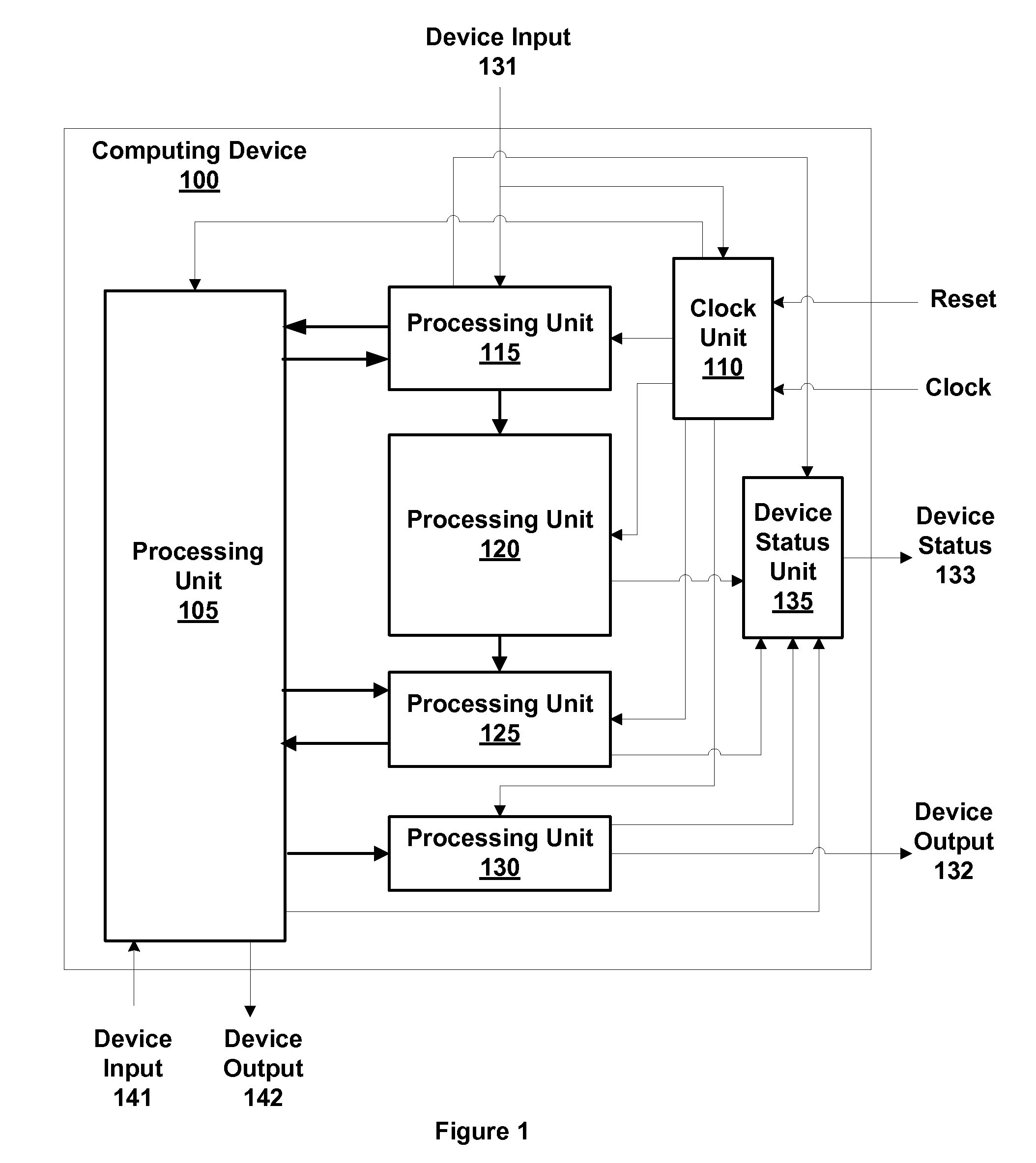

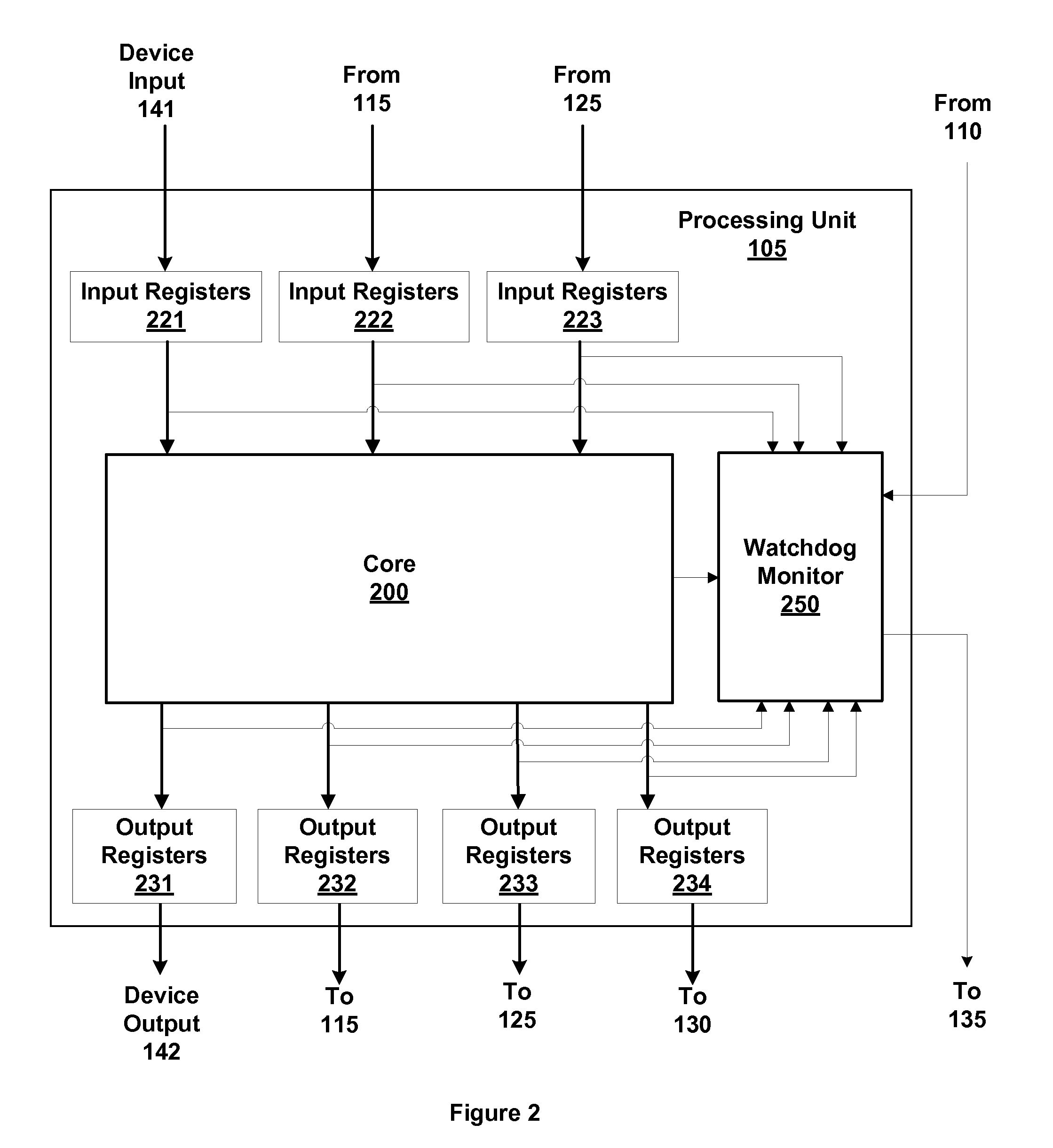

Watchdog monitoring for unit status reporting

ActiveUS7496788B1Digital data processing detailsError detection/correctionApplication-specific integrated circuitStatus report

Systems and methods for monitoring the accuracy of unit status reporting within an application specific integrated circuit device may be used reduce power consumption. Accurate status reporting of an idle state is needed to safely disable a clock signal for a unit in order to reduce the power needed by that unit. A watchdog monitor may be used during functional simulation and synthesized for formal verification, emulation, and functional device testing and debugging. The watchdog monitor may also be configured based on specific characteristics of the unit that it is monitoring.

Owner:NVIDIA CORP

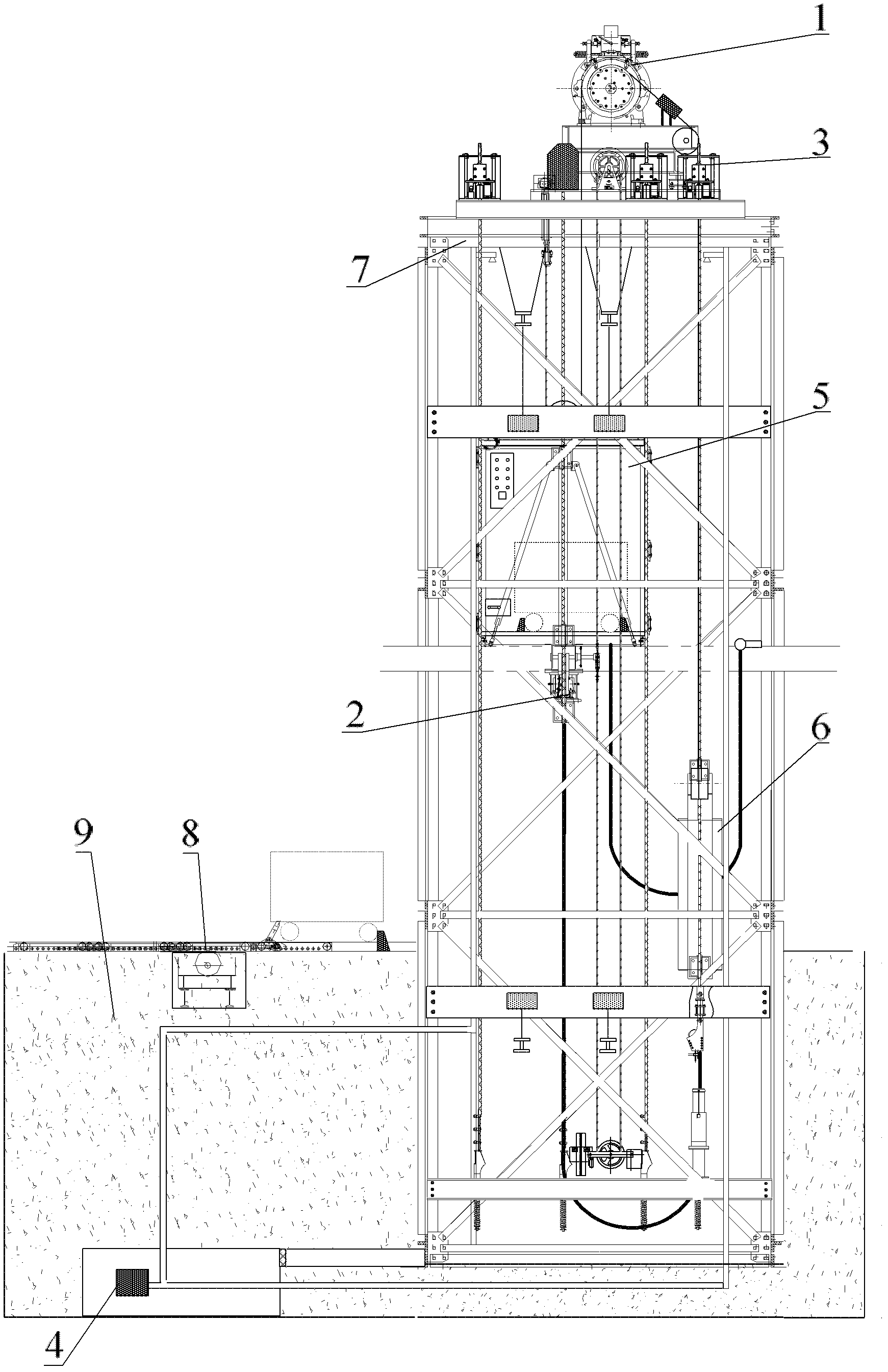

Multi-functional simulation experiment system for mining elevator

The invention relates to a multi-functional simulation experiment system for a mining elevator. The system comprises a head frame fixed on a concrete base, as well as an anti-explosion traction test system, a car protection test system, a flexible guide rail guide test system, a water-pouring simulation test system, a car and a counter weight which are arranged on the head frame. Hoisting rope tension dynamic regulating test, car over-speed or out of control protection test, car top reaching and bottom landing safety protection test, flexible guide rail tension dynamic balance test, car running stability test, tail rope hanging reliable test, car enduring water-pouring test for simulating hoistway water penetration and the like can be realized; and a safe and reliable multi-functional simulation experiment platform which has compact structure, is convenient to operate, is time-saving and labor-saving and can simulate the mine well environment is provided for lifting materials and personnel under a mine.

Owner:CHINA UNIV OF MINING & TECH +1

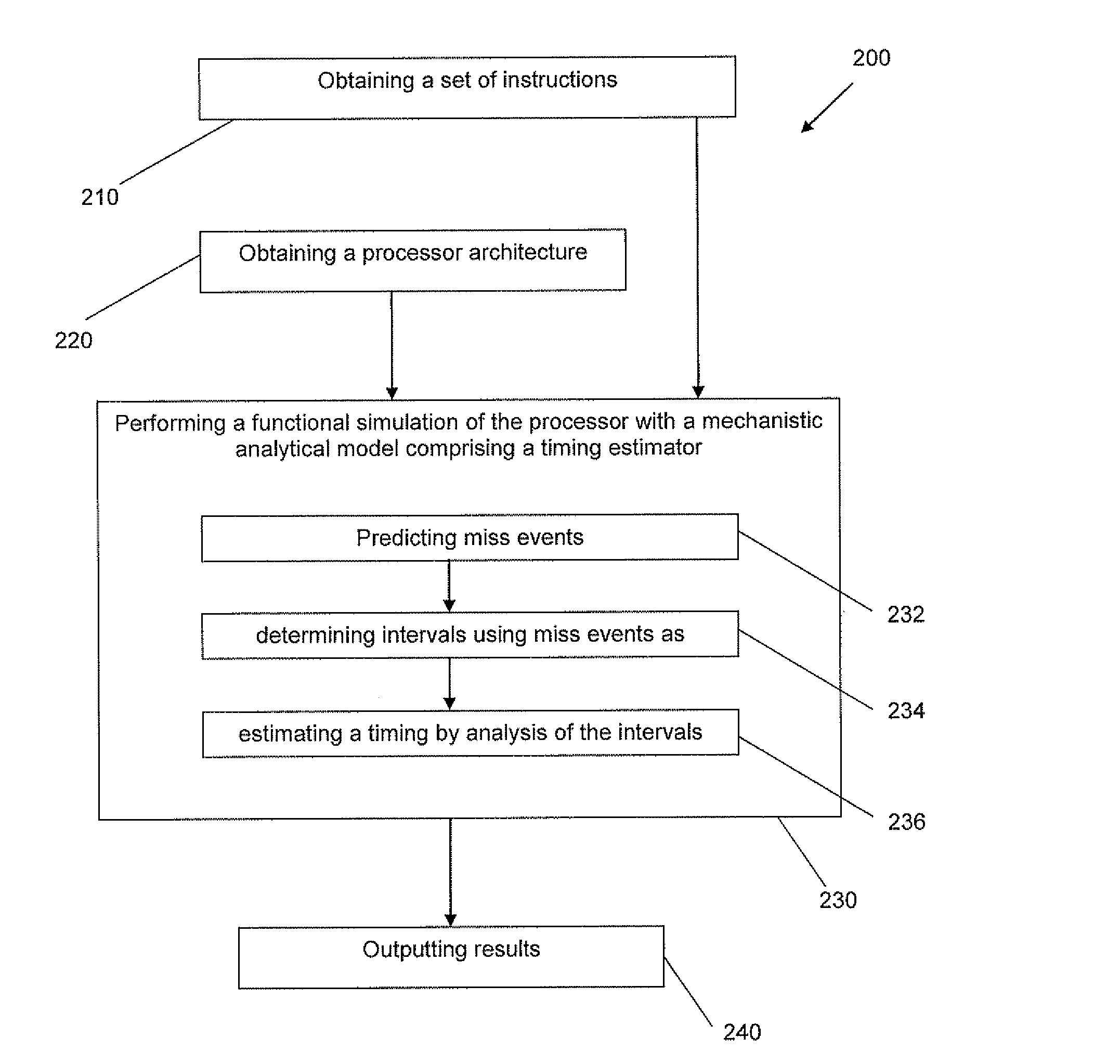

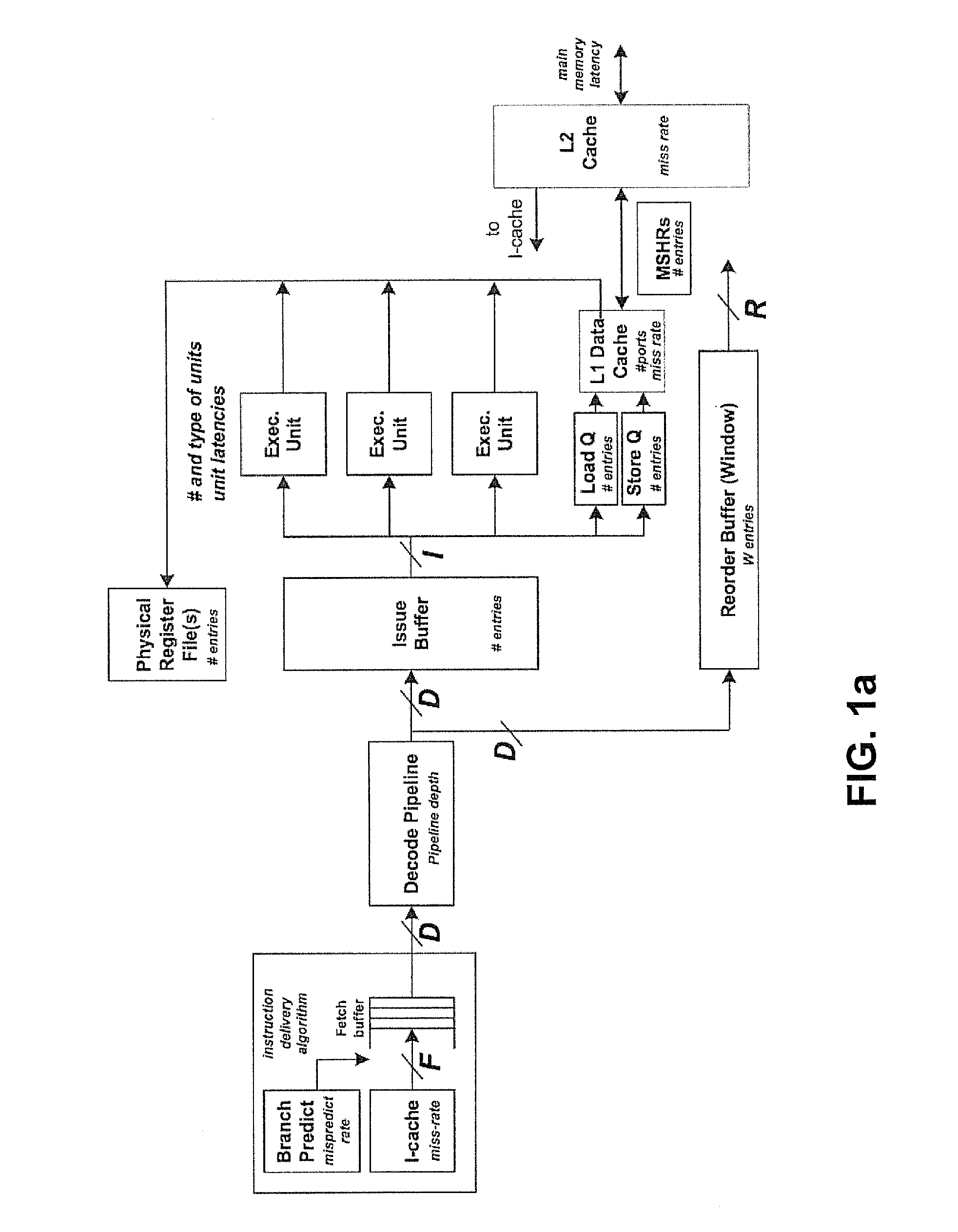

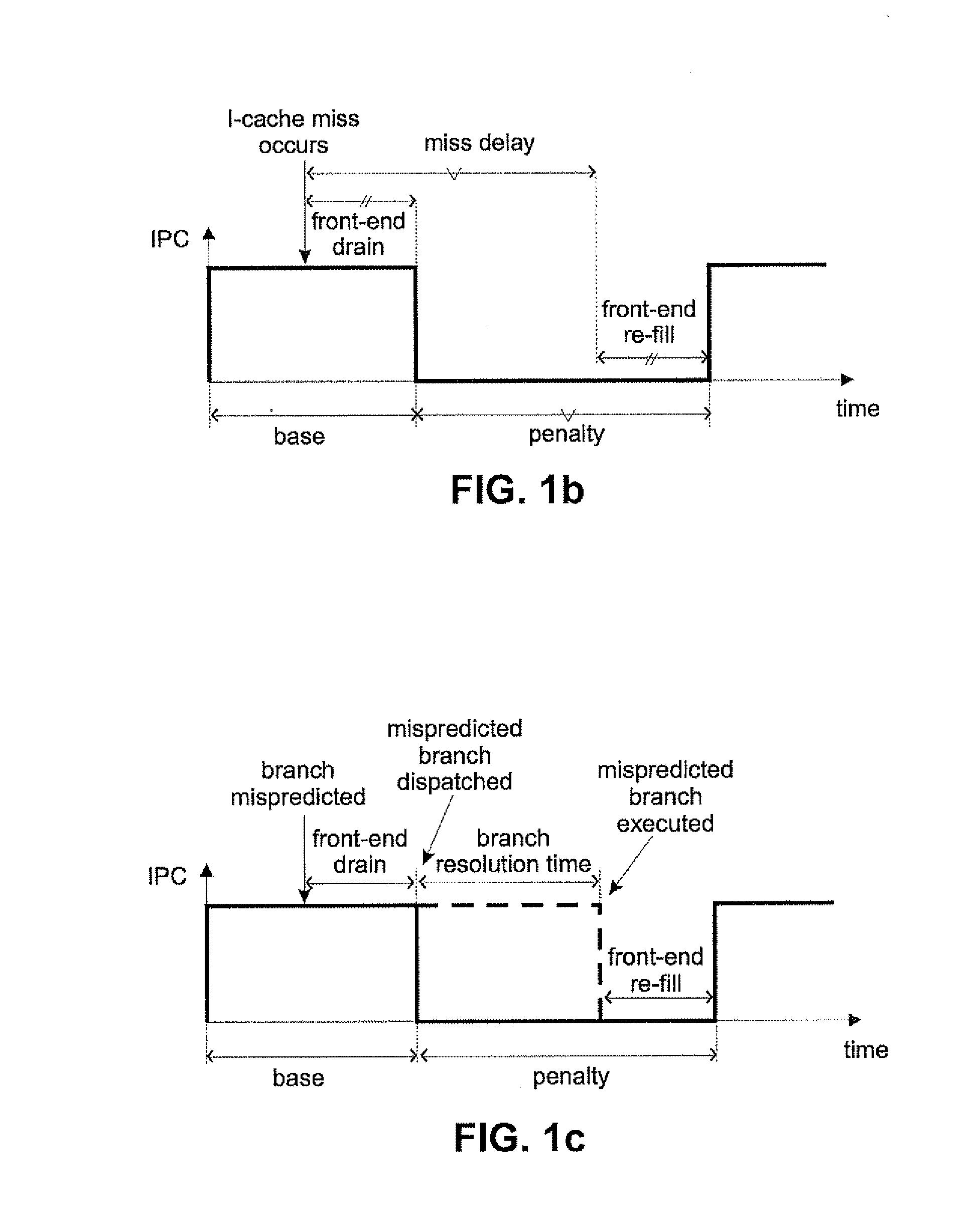

Methods and systems for simulating a processor

InactiveUS20110295587A1Accurate time informationEffective simulationError detection/correctionCAD circuit designAnalog processorParallel computing

A method is described for simulating a set of instructions to be executed on a processor. The method comprises performing a functional simulation of the processor over a number of simulation cycles. Performing the functional simulation of the processor thereby may comprise using an analytical model comprising a timing estimator and estimating during the functional simulation timing information of the processor.

Owner:UNIV GENT

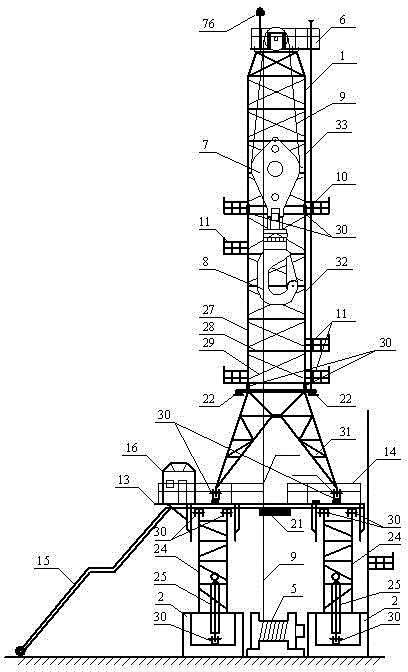

Simulating training system of intelligent well drilling device

ActiveCN103150957AEasy to operateAchieve runnabilityEducational modelsAutomatic controlHuman–machine interface

The invention discloses a simulating training system of an intelligent well drilling device. The simulating training system is characterized in that a well drilling machine is assorted with a derrick, a simulation system for simulating a hydraulic synchronous hoisting operation process, a dynamic operation simulation system of a drilling fluid circulating and solid control device, and an automatic operation control simulation system. According to the simulating training system disclosed by the invention, a dynamic effect of drilling equipment in field operation is truly and vividly represented, and a simulated hydraulic hoisting process of the derrick and a base, and function simulation, dynamic operation and simulated operation control of a drilling fluid circulating pump and the solid control device are focally represented; meanwhile, an automatic control technology and a wireless remote control technology are applied so that wireless remote control and local operation are completely compatible, and real operation and operation control of assorted devices and assorted equipment of the well drilling machine are realized; and furthermore, the same control function can be realized by touching the human-machine interface and current operation states and operation parameters of drilling equipment are displayed and the effect of simulating on-site construction work by the simulating training system of the well drilling device is achieved.

Owner:安徽立查信息科技有限公司

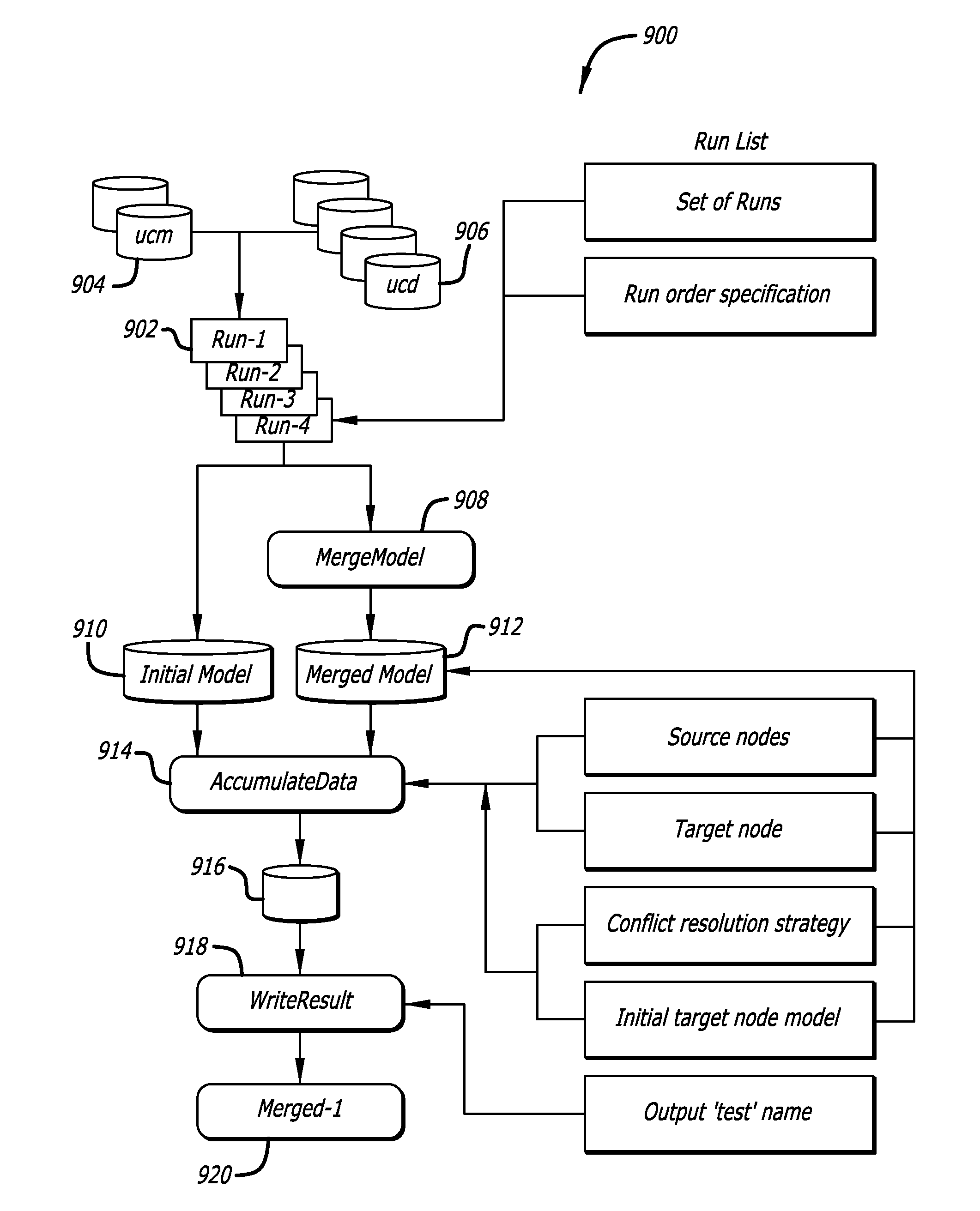

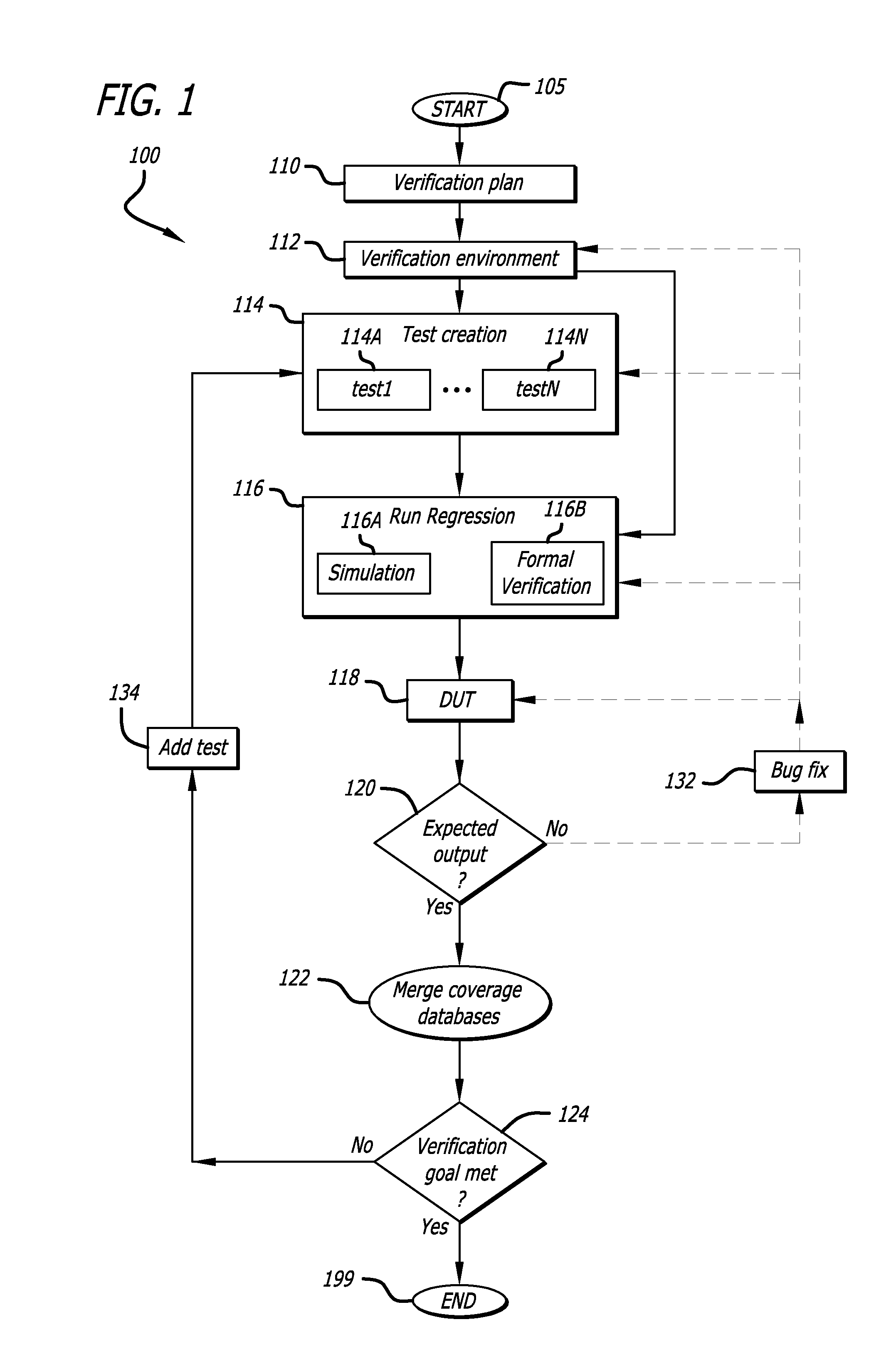

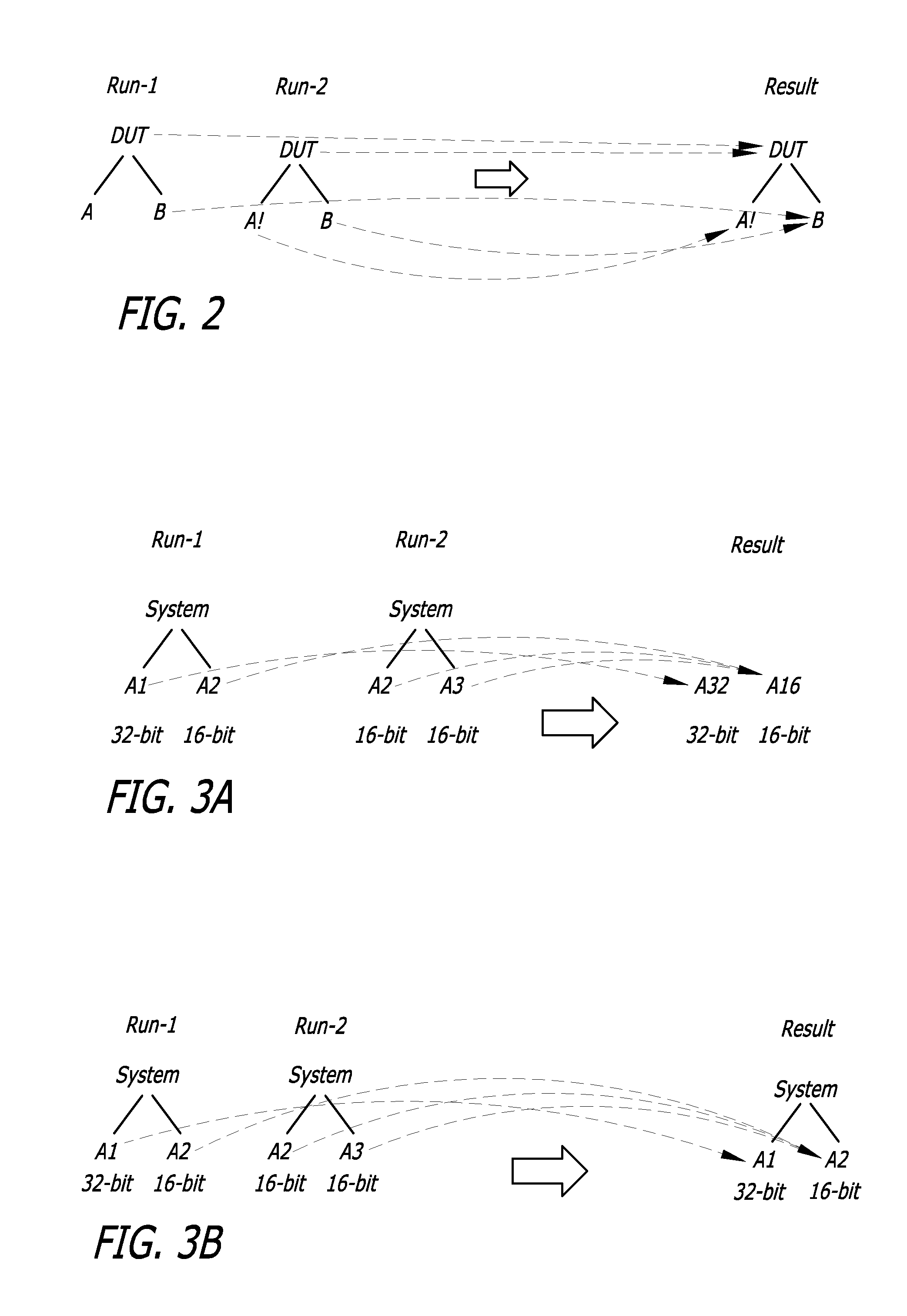

Configuration-based merging of coverage data results for functional verification of integrated circuits

In one embodiment of the invention, a method for verification of an integrated circuit design is disclosed. The method includes independently executing simulation runs in response to a plurality of coverage models to respectively generate a plurality of coverage data for a plurality of functional blocks within one or more integrated circuit designs; generating a target coverage model to selectively merge at least first coverage data associated with a first coverage model and second coverage data associated with a second coverage model; and in response to the target coverage model and the plurality of simulation runs, selectively projecting the plurality of coverage data into a merged coverage data result associated with the target coverage model. The method may further store the merged coverage data results into a storage device. The plurality of simulation runs may include at least one functional simulation run and at least one formal verification run.

Owner:CADENCE DESIGN SYST INC

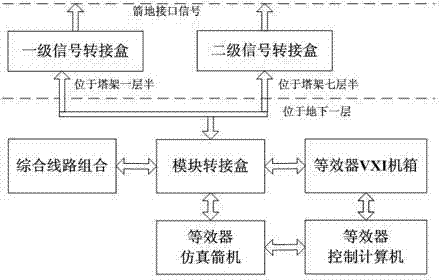

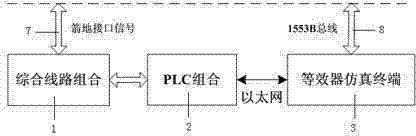

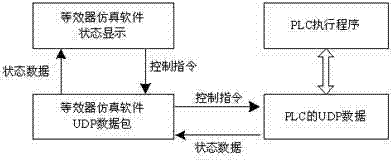

PLC and 1553B based portable equivalent device for carrier rocket test-launch control system

ActiveCN102809937AAbbreviated self-testStreamline recovery timeProgramme control in sequence/logic controllersSystem integrationProgrammable logic controller

The invention relates to a carrier rocket ground test-launch control system, and discloses a PLC (Programmable Logic Controller) and 1553B based portable equivalent device for a carrier rocket test-launch control system. The carrier rocket test-launch control system comprises a comprehensive circuit combination, a PLC combination and an equivalent device emulational terminal, wherein the comprehensive circuit combination is mainly used for isolating and conditioning a rocket-ground signal; the PLC combination is equipped with corresponding functional modules and used for completing functional simulation of an on-rocket power supply and distribution system and a time sequence system; and the equivalent device emulational terminal is mainly used for completing both communication simulation of a rocket-ground 1553B bus and monitoring control of the PLC. The PLC and 1553B based portable equivalent device solves the problems of a conventional equivalent device equipment system, such as complicated constitution, more intermediate adapter cables, poor portability and the like, and obtains the benefits of high system integration level, less adapter cables, good portability and the like.

Owner:SHANGHAI SPACEFLIGHT INST OF TT&C & TELECOMM

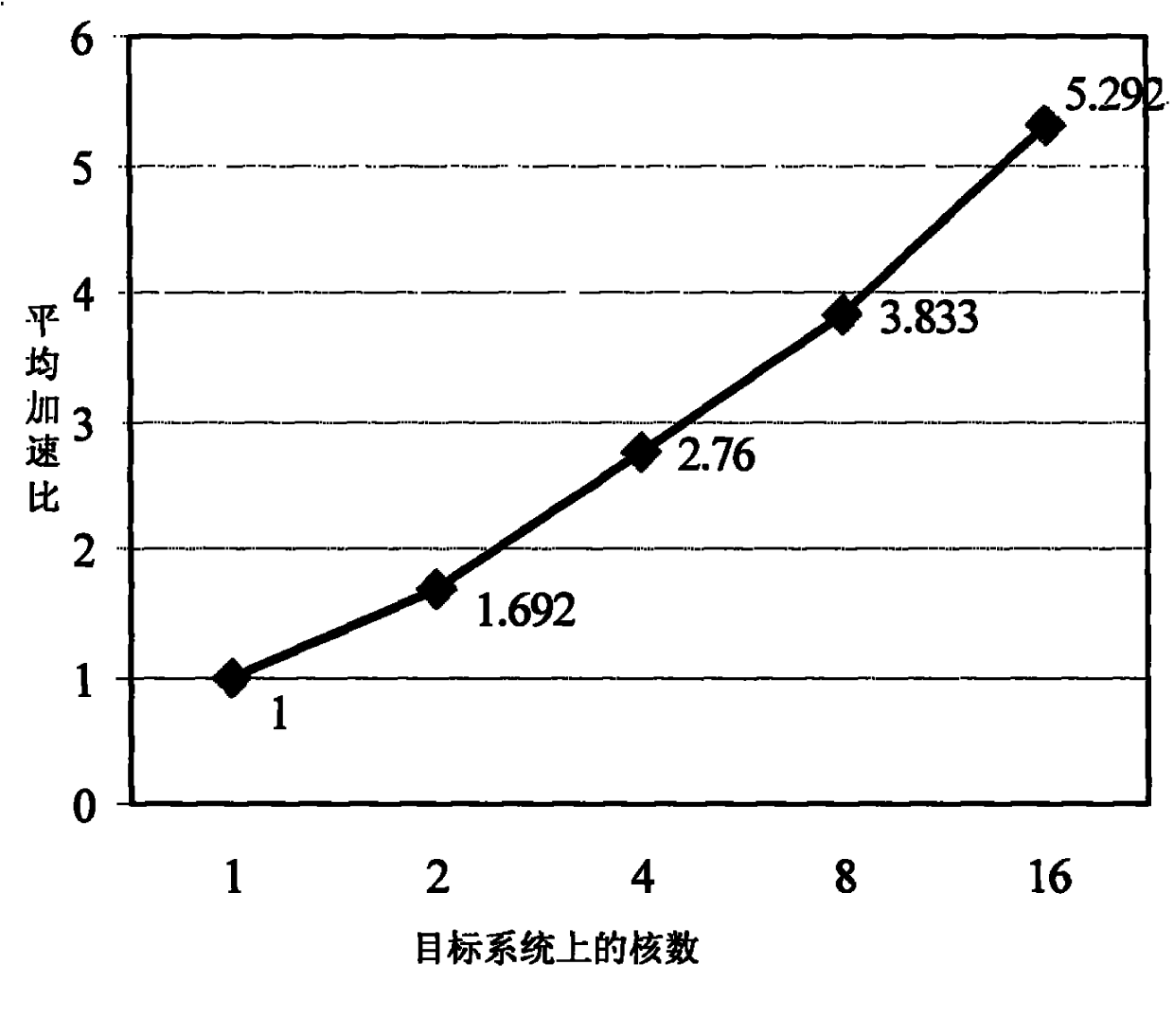

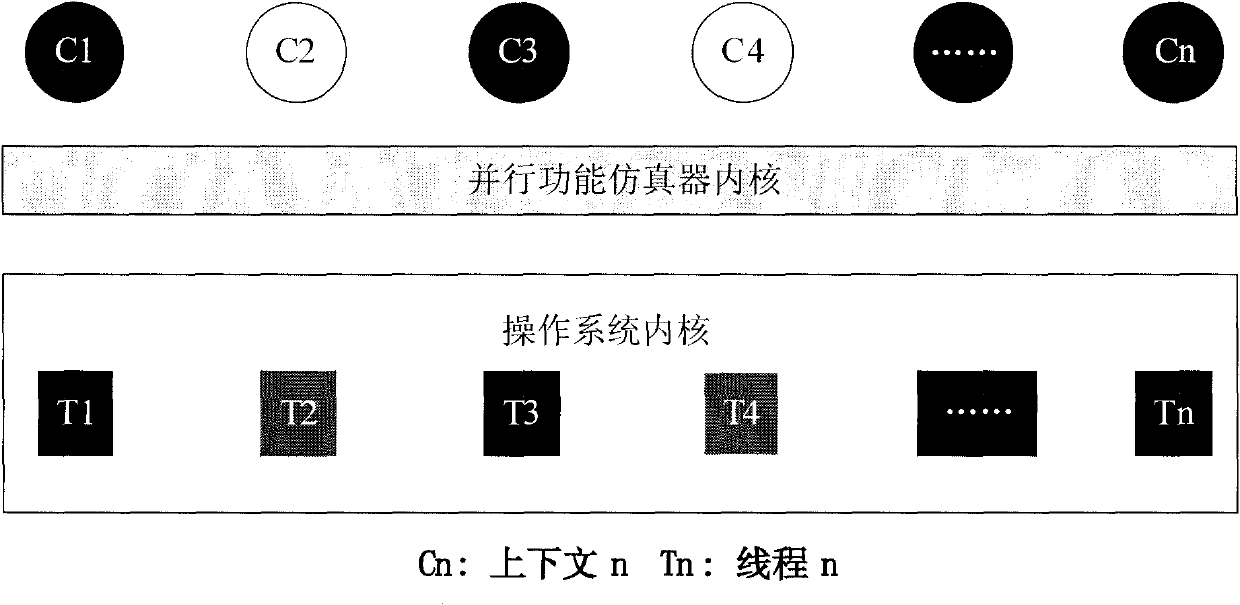

Parallel function simulation system for on-chip multi-core processor and method thereof

InactiveCN101777007AHigh speedupImprove performanceSoftware simulation/interpretation/emulationGoal systemWorkload

The invention discloses a parallel function simulation system for an on-chip multi-core processor and a method thereof. The system comprises a system input module and a system output module, and is characterized in that: a simulation kernel module is arranged between the system input module and the system output module; the simulation kernel module receives working load information run on a target system and provided by the system input module; and the simulation kernel module dynamically establishes a multithread according to the type of working load to perform the parallelization processingof simulation working load and outputs a result through the system output module. In the invention, the problem of performance reduction caused due to the increment of the cores of the target system in a serial function simulation technique is solved. The system of the invention has a higher speed-up ratio and relatively high overall performance.

Owner:SUZHOU INST FOR ADVANCED STUDY USTC

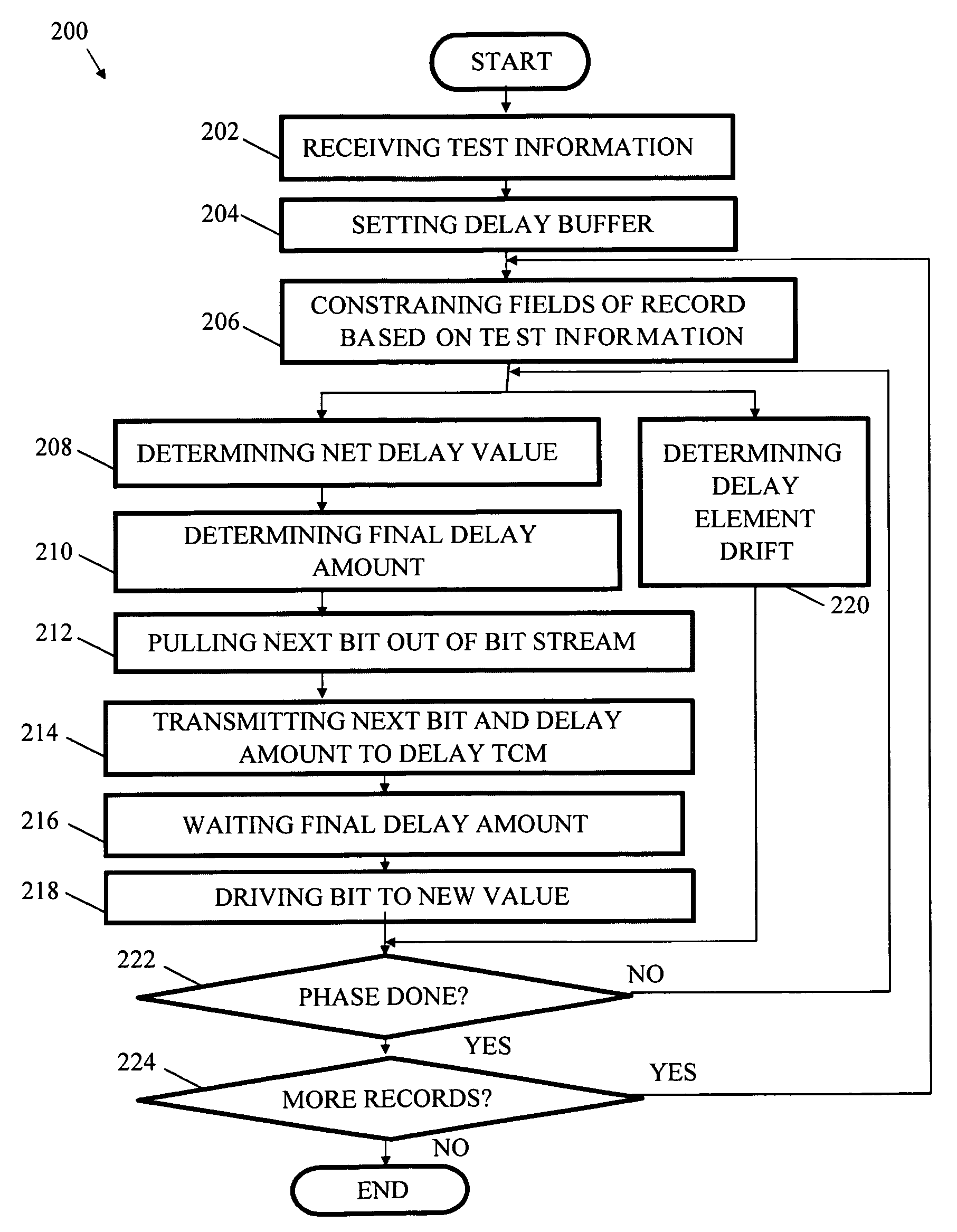

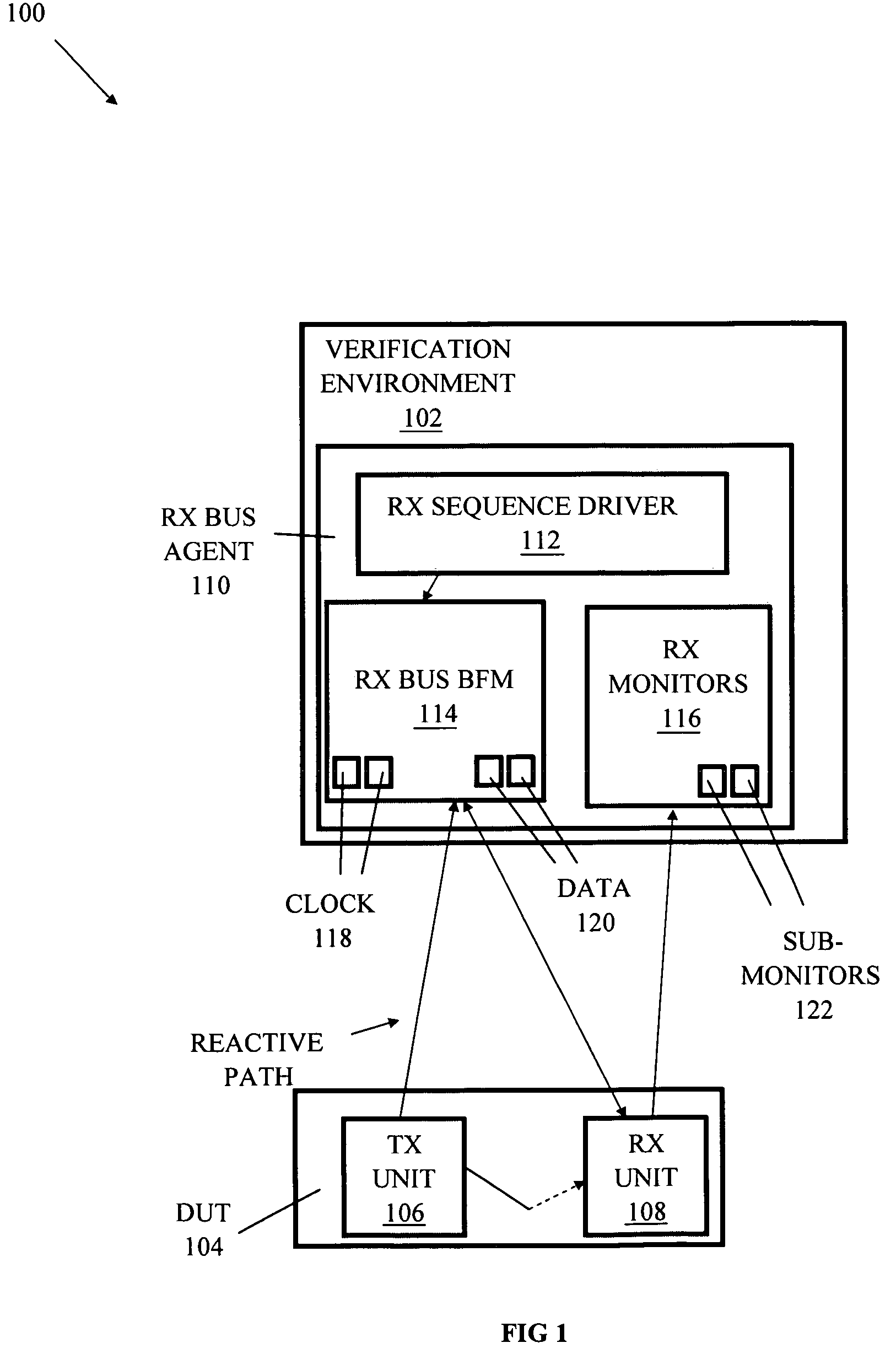

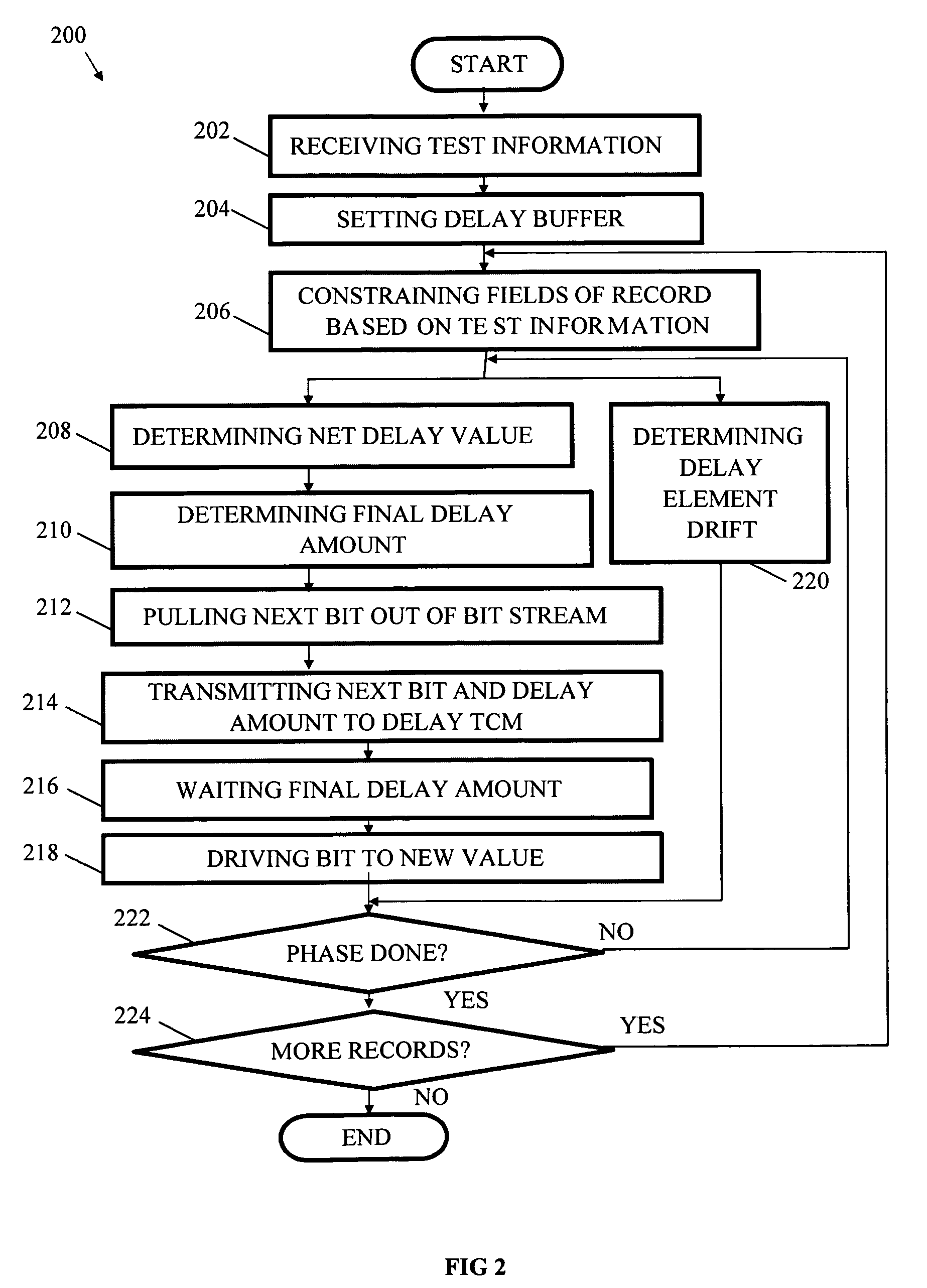

Methods, systems and media for functional simulation of noise and distortion on an I/O bus

ActiveUS7246332B2Analogue computers for electric apparatusCAD circuit designDuty cycle distortionVoltage reference

Methods, systems, and media for functional simulation of an I / O bus are disclosed. More particularly, a method of simulating distortion and noise parameters of an I / O bus is disclosed. Embodiments include constraining one or more fields of a record and determining delay amounts based on the resulting parameters, where the final delay amount includes a delay buffer and a net of delay amounts associated with the parameters. Embodiments may also include determining a value of a next bit to be sent to the I / O bus and, after waiting the delay amount, driving the bit on the bus to the next bit value. Parameters may include skew, jitter, duty cycle distortion, voltage reference distortion, and drift of any of these parameters. Further embodiments may include signaling the end of a phase in response to a phase done condition being satisfied.

Owner:GOOGLE LLC

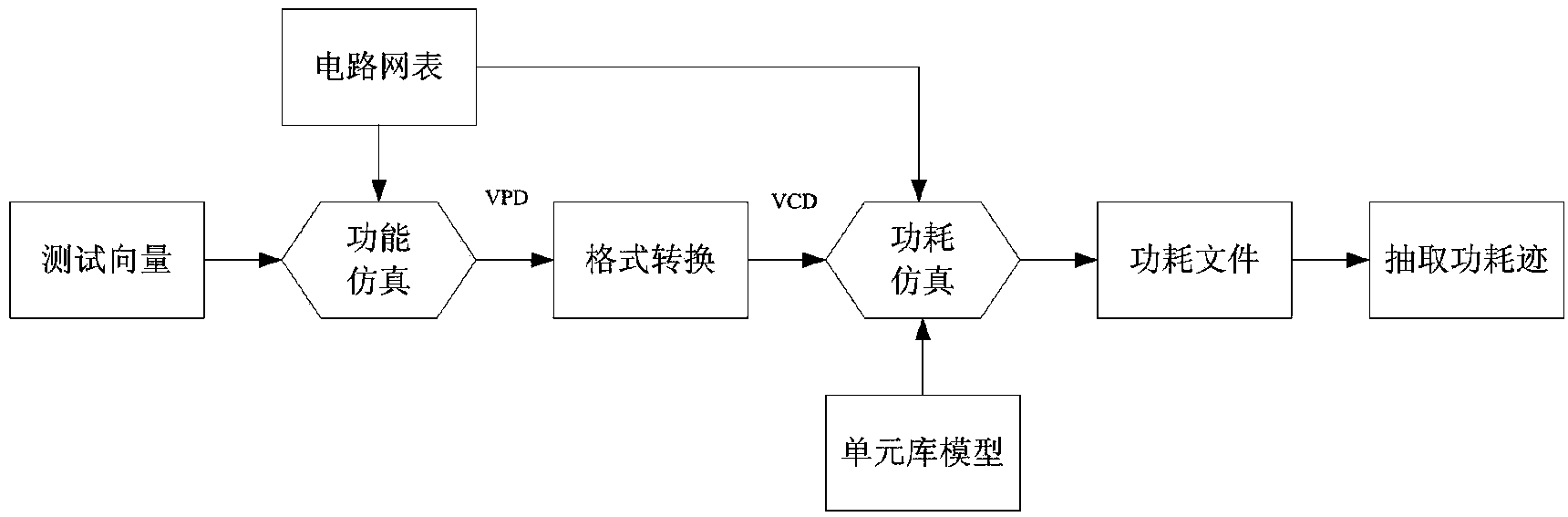

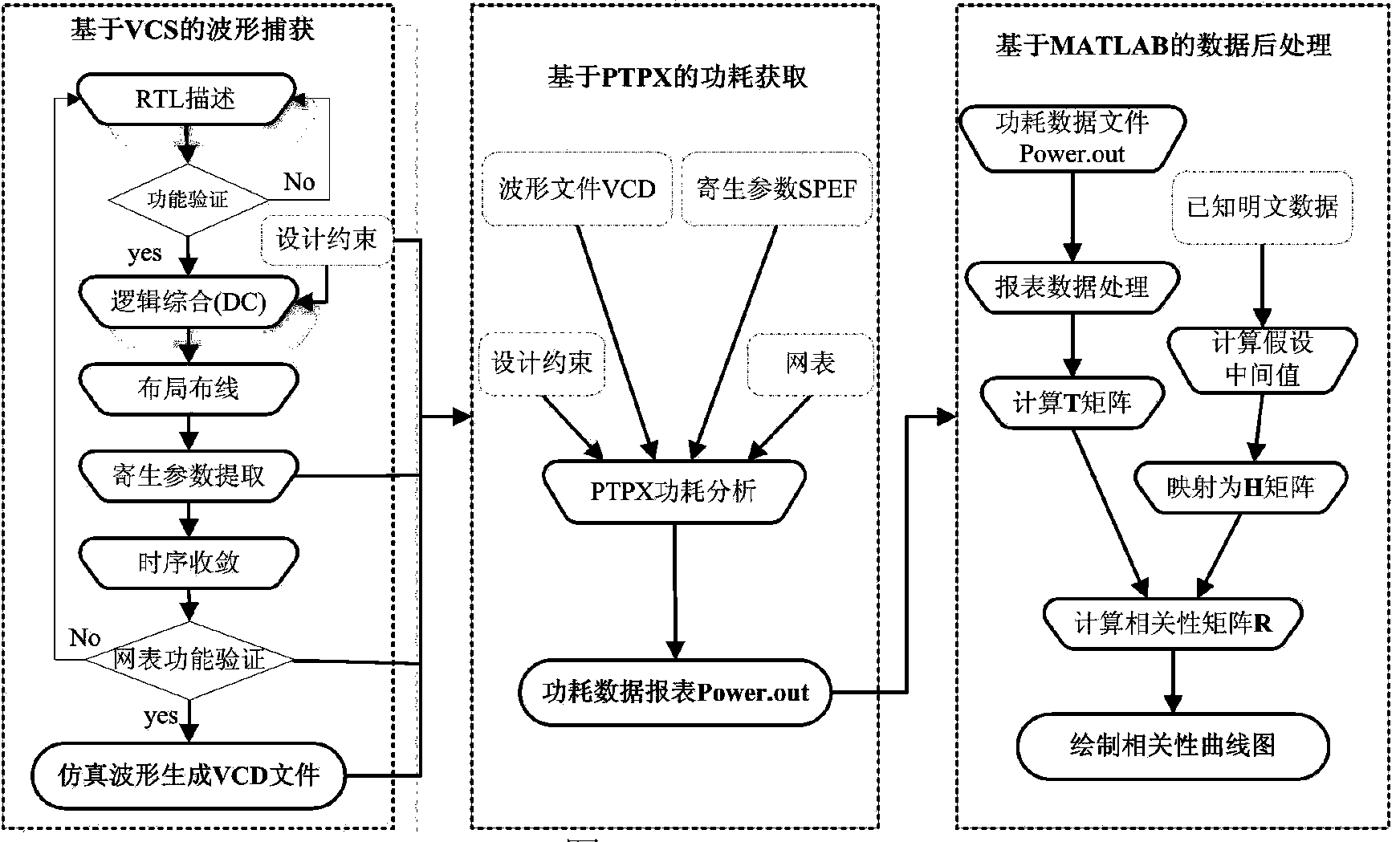

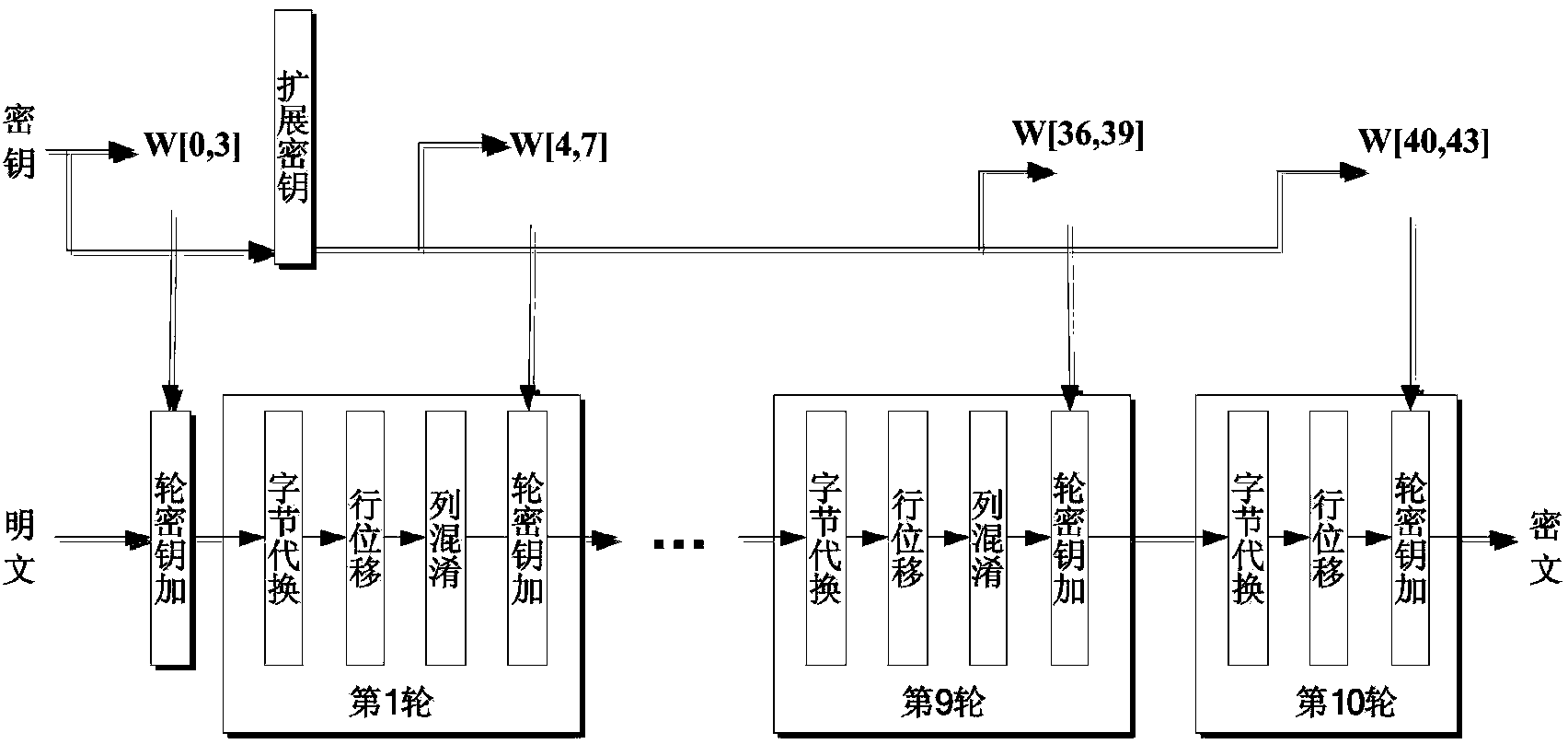

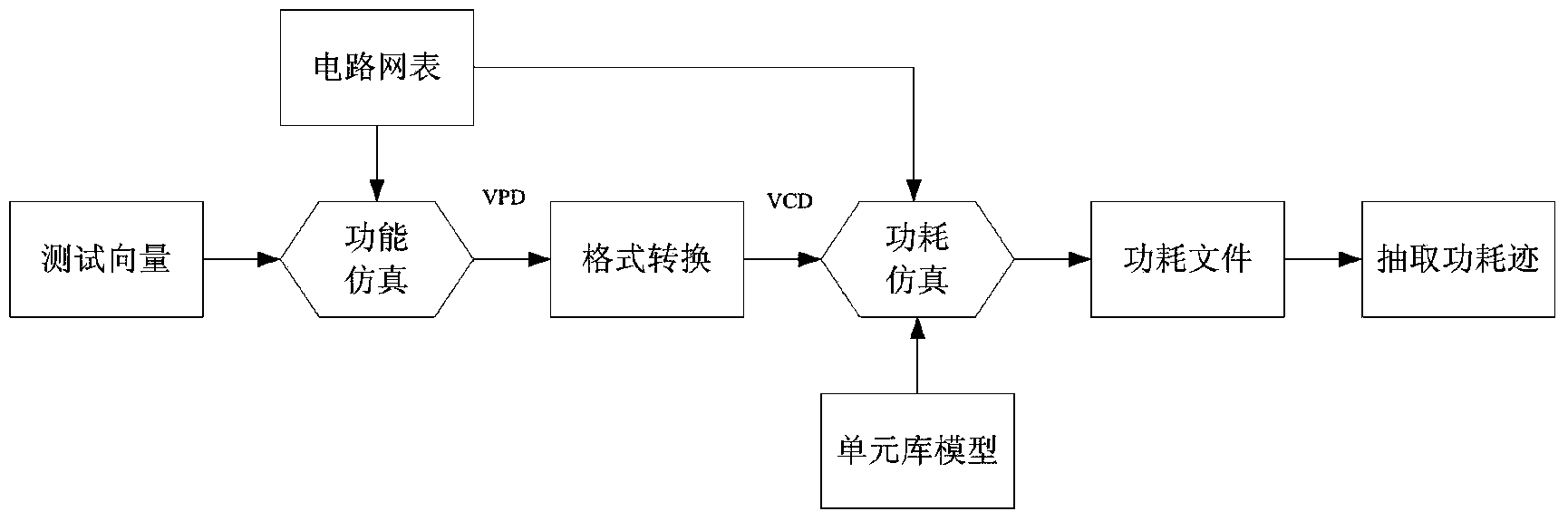

AES (advanced encryption standard) algorithm circuit oriented method for testing differential power attack

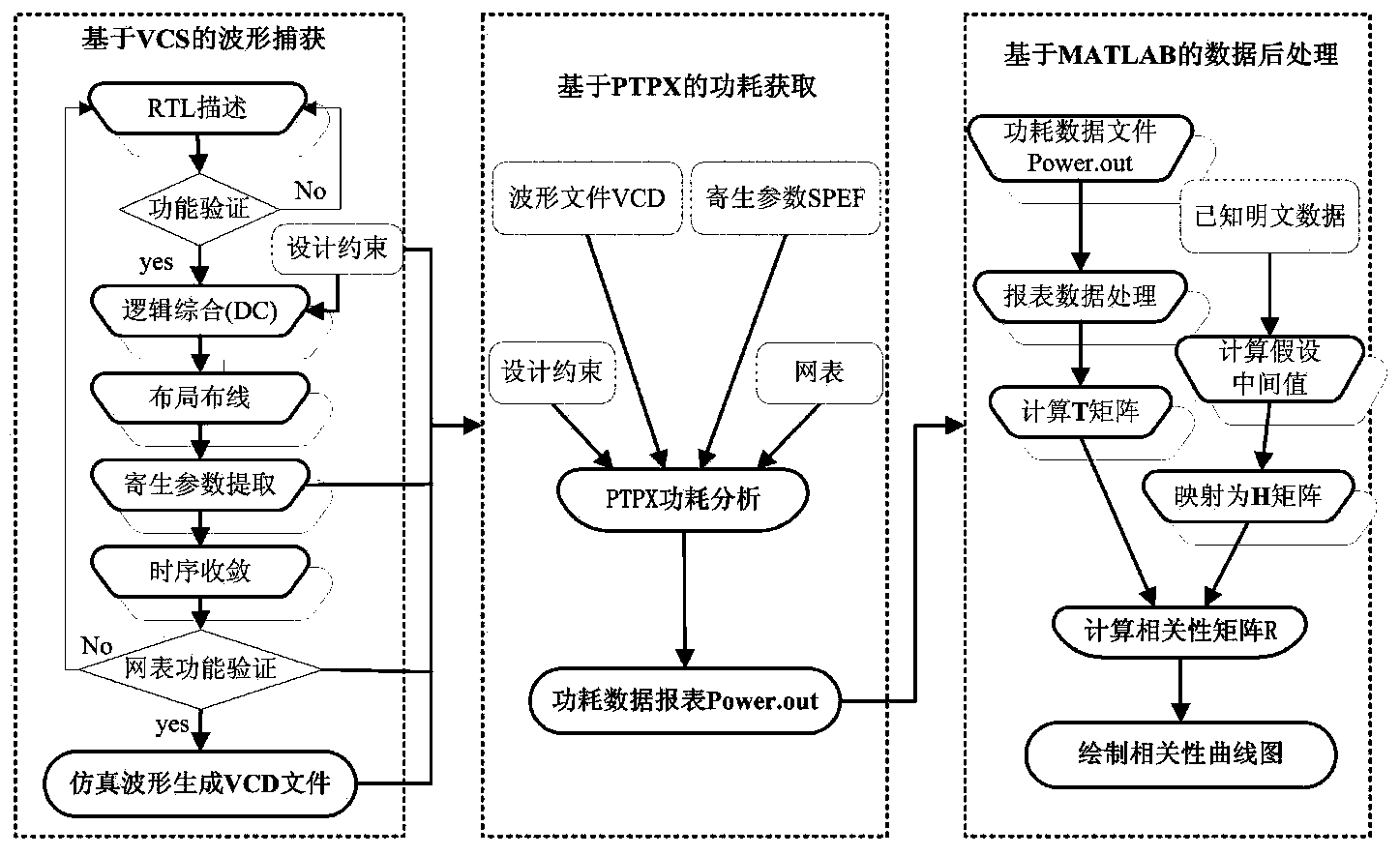

InactiveCN103530474ASolve the technical difficulties of power consumption attack testingReduce risk of redesignSpecial data processing applicationsCorrelation coefficientDesign stage

The invention discloses an AES (advanced encryption standard) algorithm circuit oriented method for testing differential power attack. An AES algorithm is a widely applied grouping symmetric cryptographic algorithm. The AES algorithm circuit oriented method is used for acquiring and processing power samples for tests for the differential power attack in a design stage of an AES cryptographic algorithm circuit and includes steps (1), carrying out functional simulation and acquiring power samples; (2), preprocessing the power samples; (3), acquiring hypothetical power samples; (4), computing correlation coefficients and analyzing attack results. The AES algorithm circuit oriented method has the advantages that only varied power points are sampled, so that large quantities of power sample data can be omitted, power attack computational complexity can be greatly reduced, the assess effectiveness and the speed are high, more importantly, the tests for the differential power attack can be carried out in the design stage of the circuit, the attack resistance of the cryptographic circuit can be assessed in advance, and tape-out risks of the AES circuit can be reduced.

Owner:SOUTHEAST UNIV

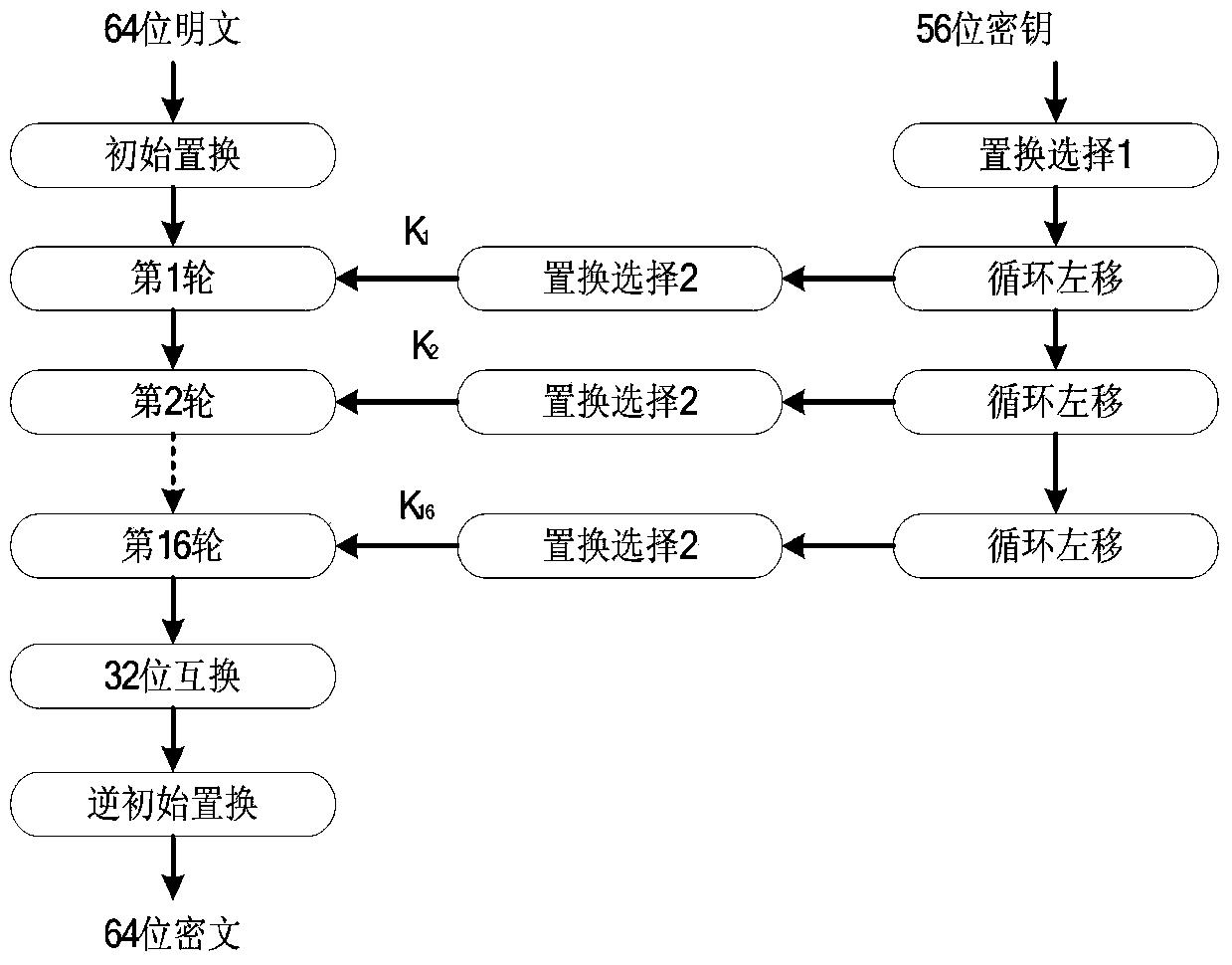

Differential power attack testing method for DES (data encryption standard) algorithm circuit

InactiveCN103532973ASolve the technical difficulties of power consumption attack testingReduce risk of redesignEncryption apparatus with shift registers/memoriesData switching networksCorrelation coefficientPassword

The invention discloses a differential power attack testing method for a DES algorithm circuit. A DES algorithm is a widely-applied grouping symmetric encryption algorithm. According to the method, a differential power attack test is performed on the DES algorithm circuit at a design stage, and the method comprises the steps as follows: (1), functional simulation and acquisition of a power consumption sample; (2), preprocessing of the power consumption sample; (3), acquisition of a hypothetical power consumption sample; and (4) calculation of correlation coefficients and analysis of attack results. According to the differential power attack testing method, only varying power consumption points are sampled, a large number of power consumption sample data are saved, the power attack calculation amount is reduced substantially, the method has the advantages of high evaluation efficiency and high speed, and above all, the power attack test can be performed at the circuit design stage, so that the anti-attack capability of a password circuit is evaluated in advance, and the redesign risk of the DES circuit after assembly line production of chips is reduced.

Owner:SOUTHEAST UNIV

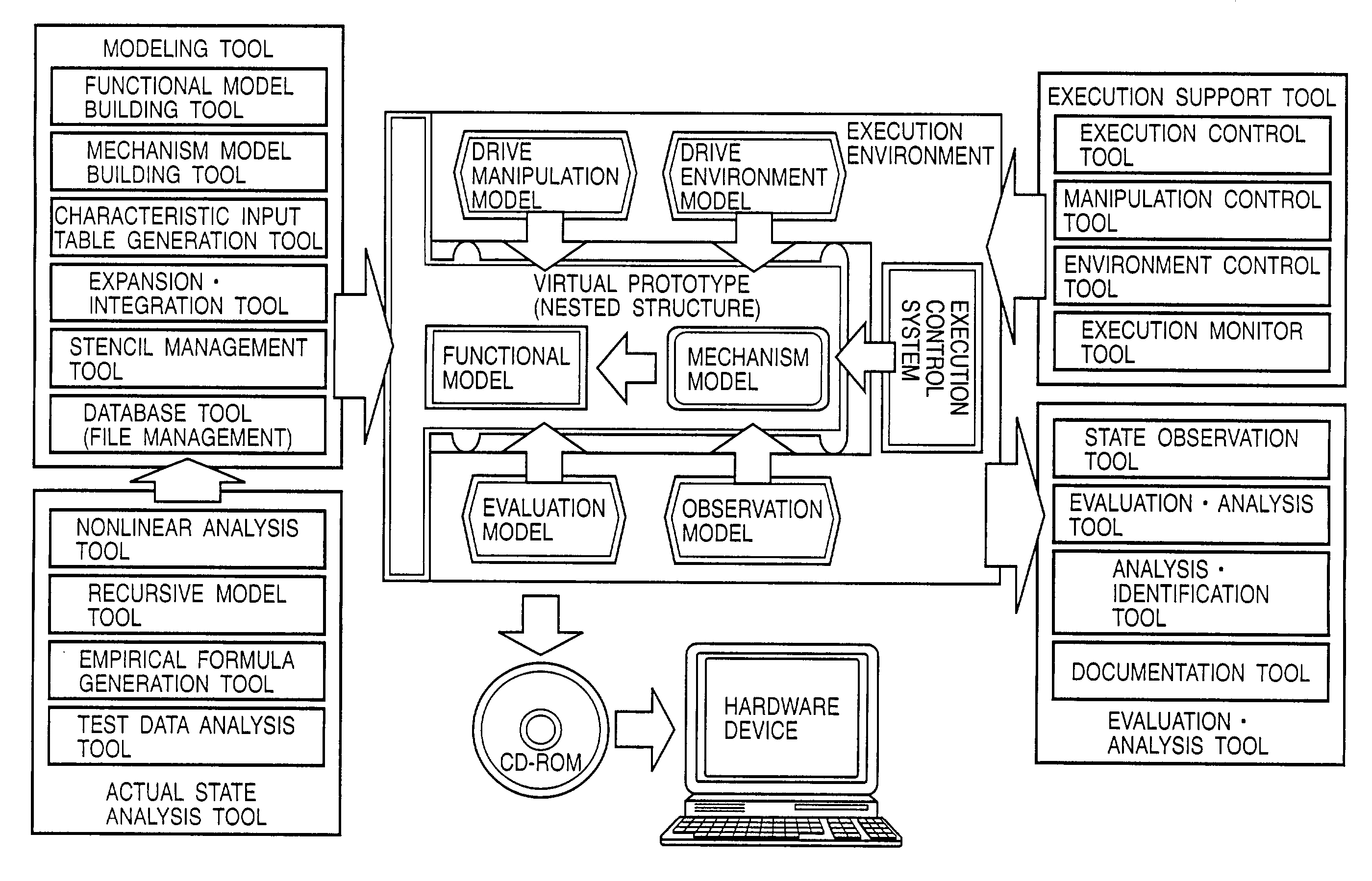

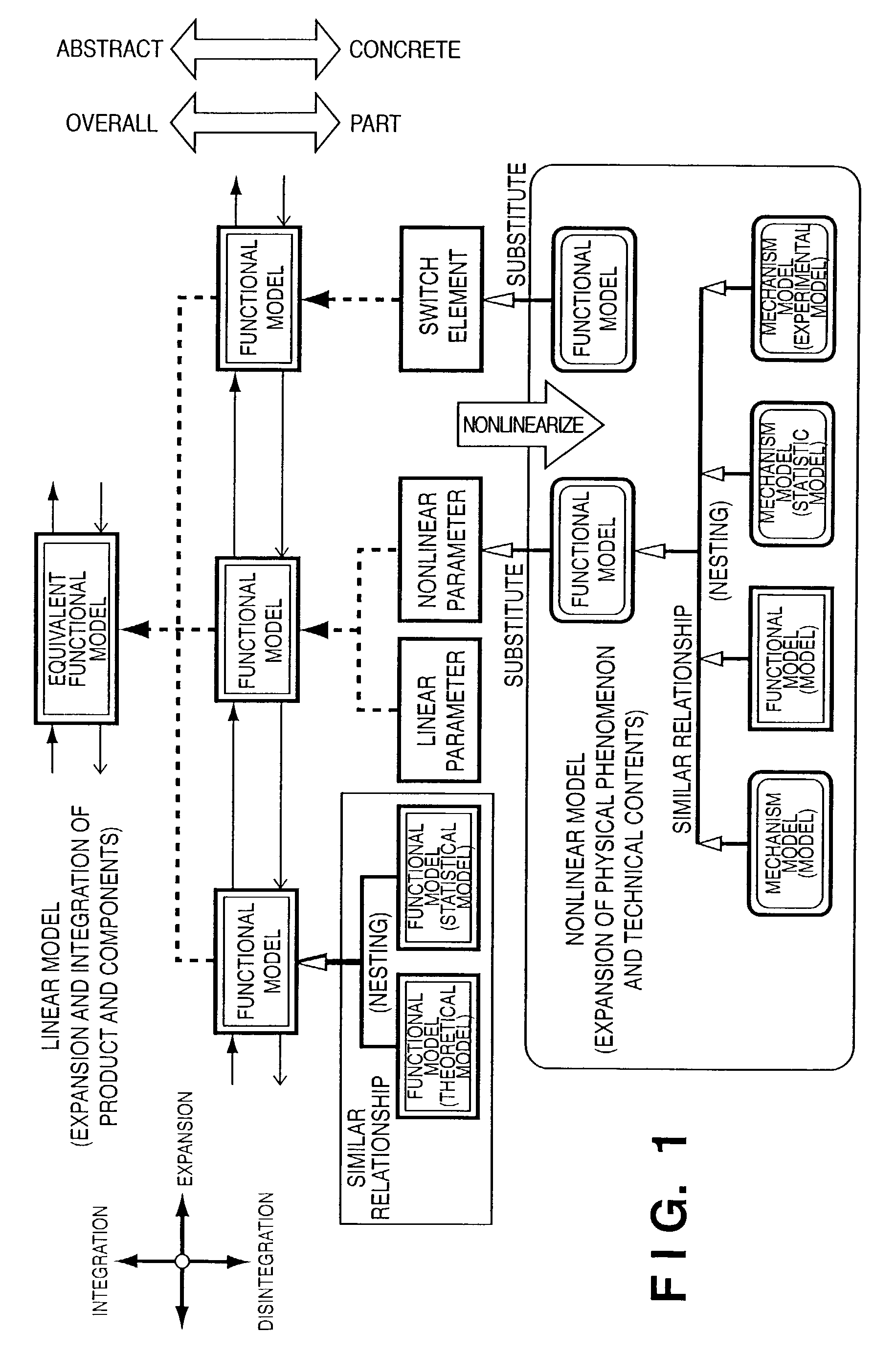

Simulation model creation method and system, and storage medium

InactiveUS7260510B2Processing volume can be minimizedHigh precisionData processing applicationsSimulator controlEngineeringPhysical system

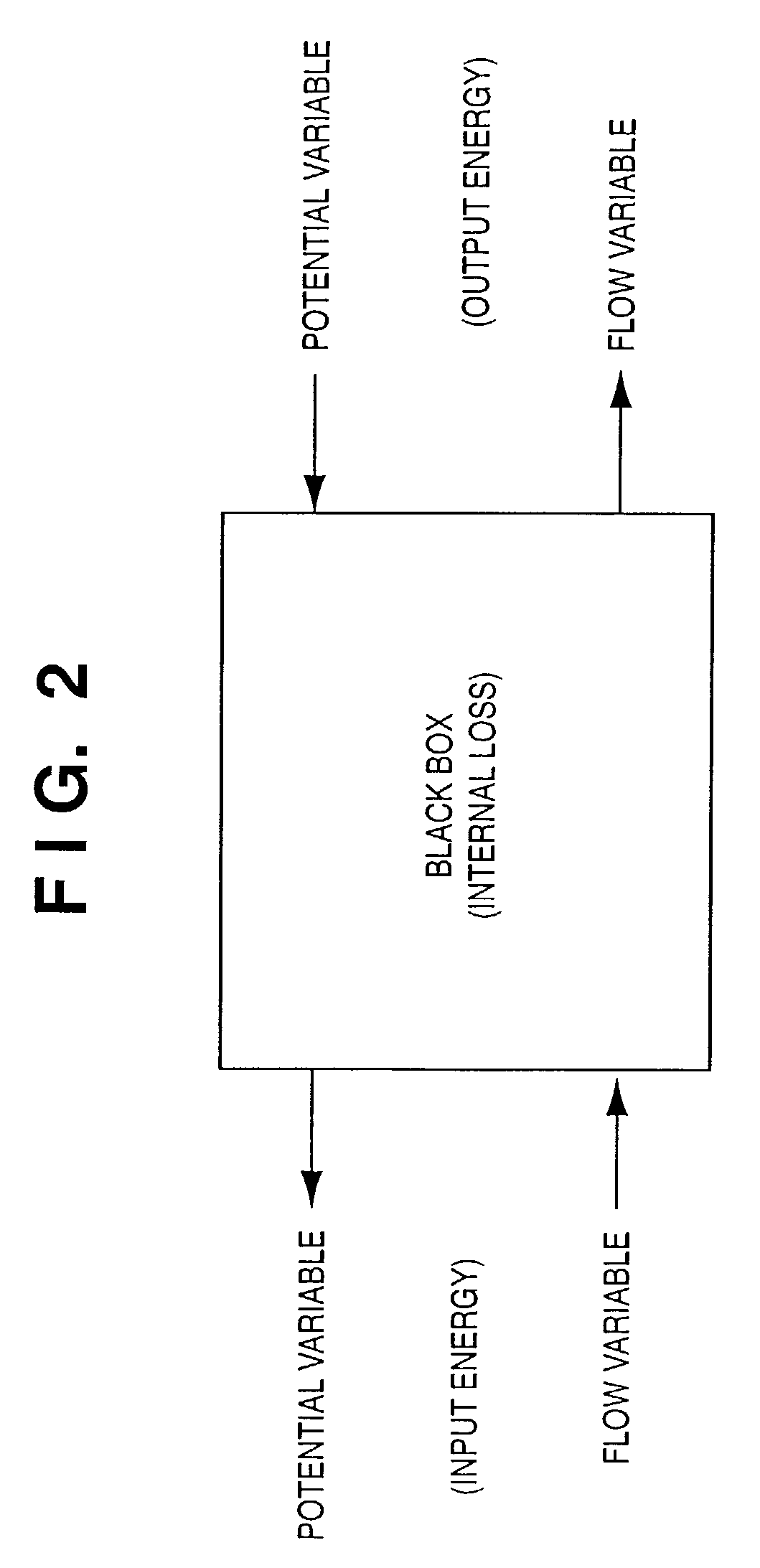

This invention systematically creates models that simulate operations from a component of a single function to a machine that combines many components and also to a system that combines a plurality of machines, which can be expressed by all physical systems such as an electric system and mechanical system, solid-state system and fluid system, and the like. The invention creates an overall function simulation model using a plurality of function simulation models which are independently provided for predetermined functions and are coupled via potential and flow variables. When respective function simulation models include linear characteristic elements A, B, C, E, F, and G and at least one function simulation model includes nonlinear characteristic elements X and Y, the nonlinear characteristic elements are separated from the linear characteristic elements by handling the nonlinear characteristics as functions in the function simulation model, the plurality of function simulation models are integrated as linear characteristic elements (integration process), and the nonlinear characteristic elements are linked to the functions in the integrated function simulation model (succession process).

Owner:MAZDA MOTOR CORP +1

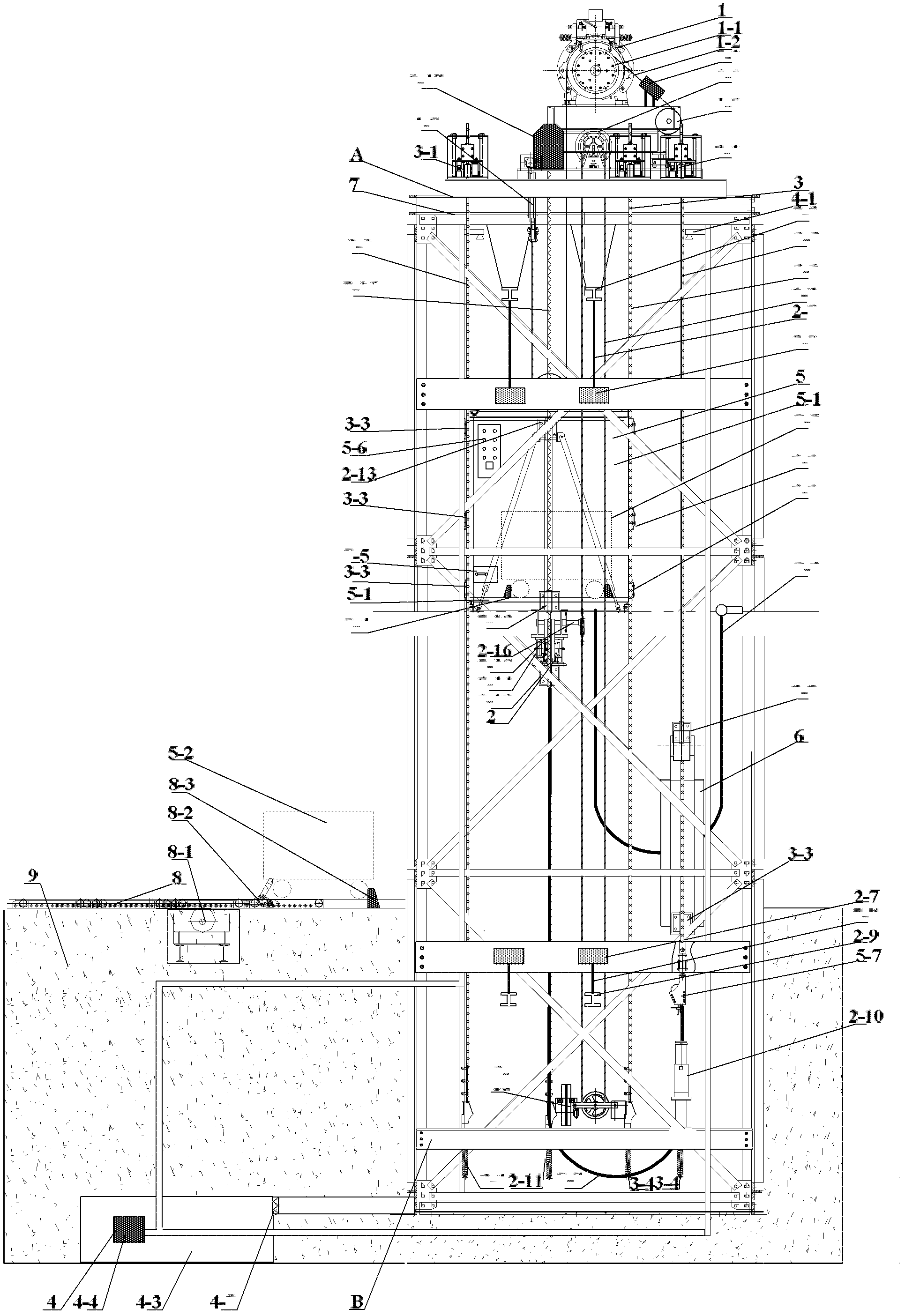

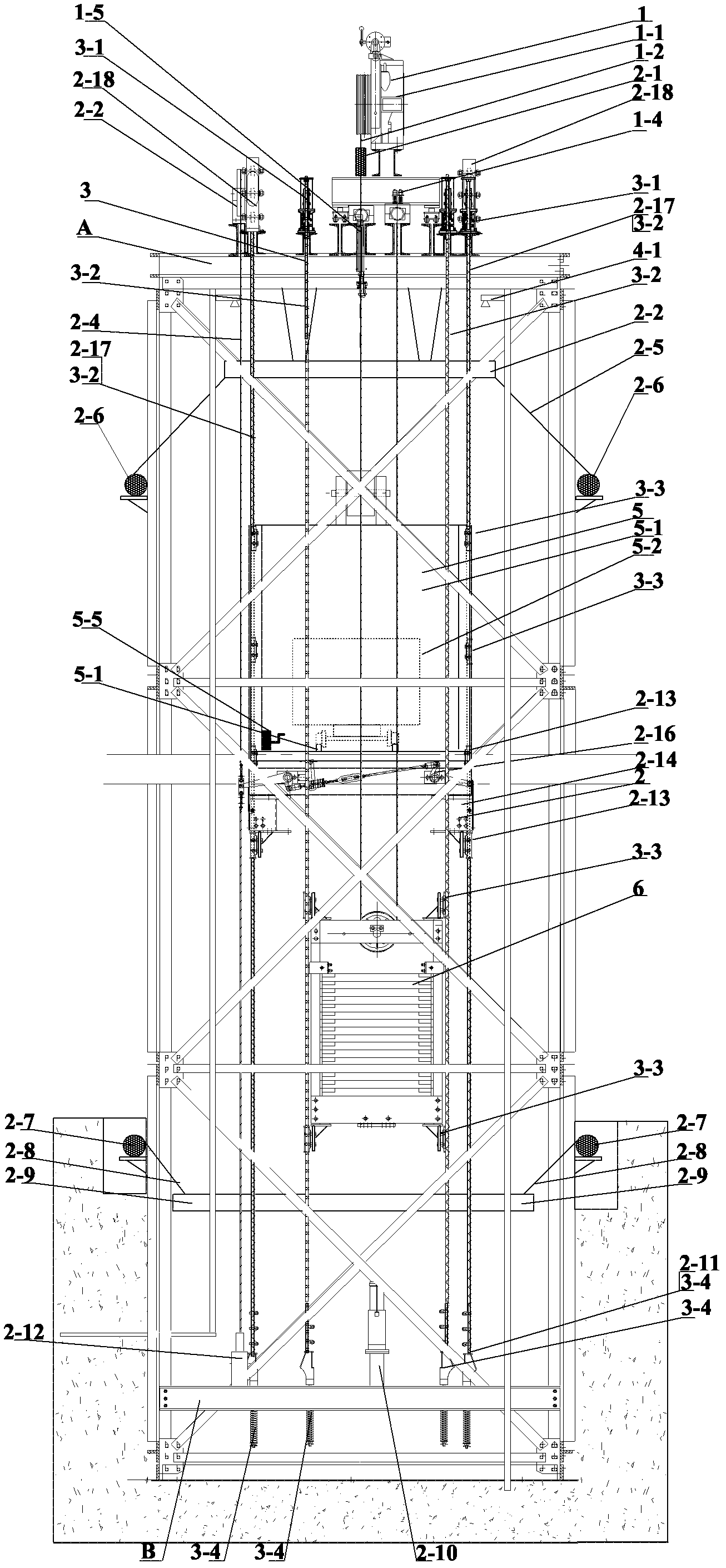

Ultra-deep mine hoisting system multi-functional simulation test platform and experimental method

InactiveCN105590535ACompact structureSmall footprintEducational modelsExperimental methodsControl system

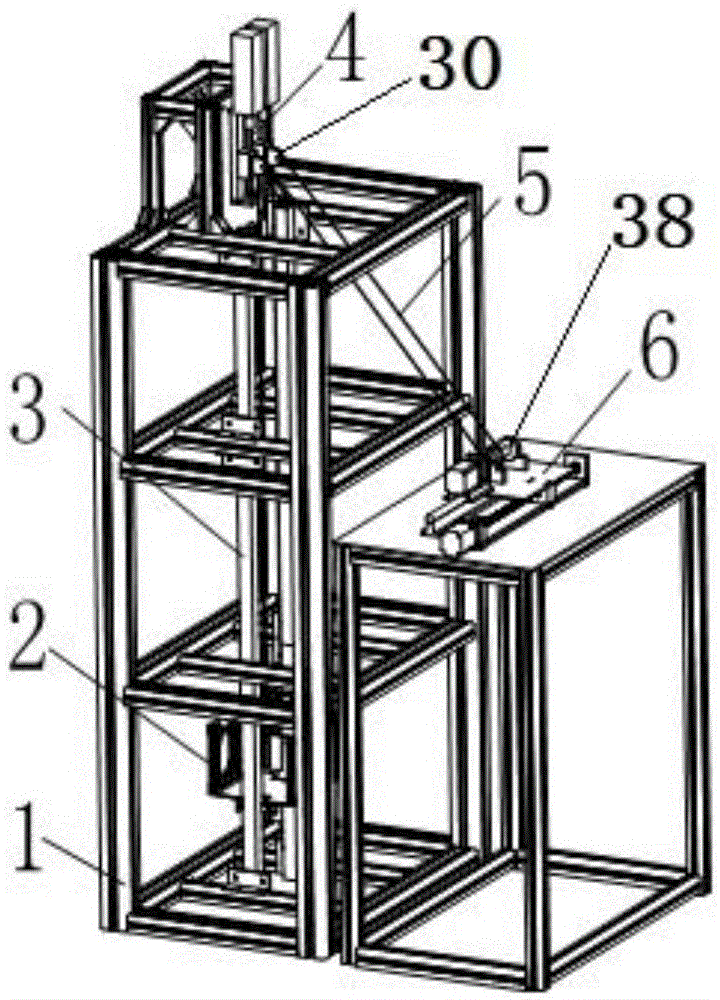

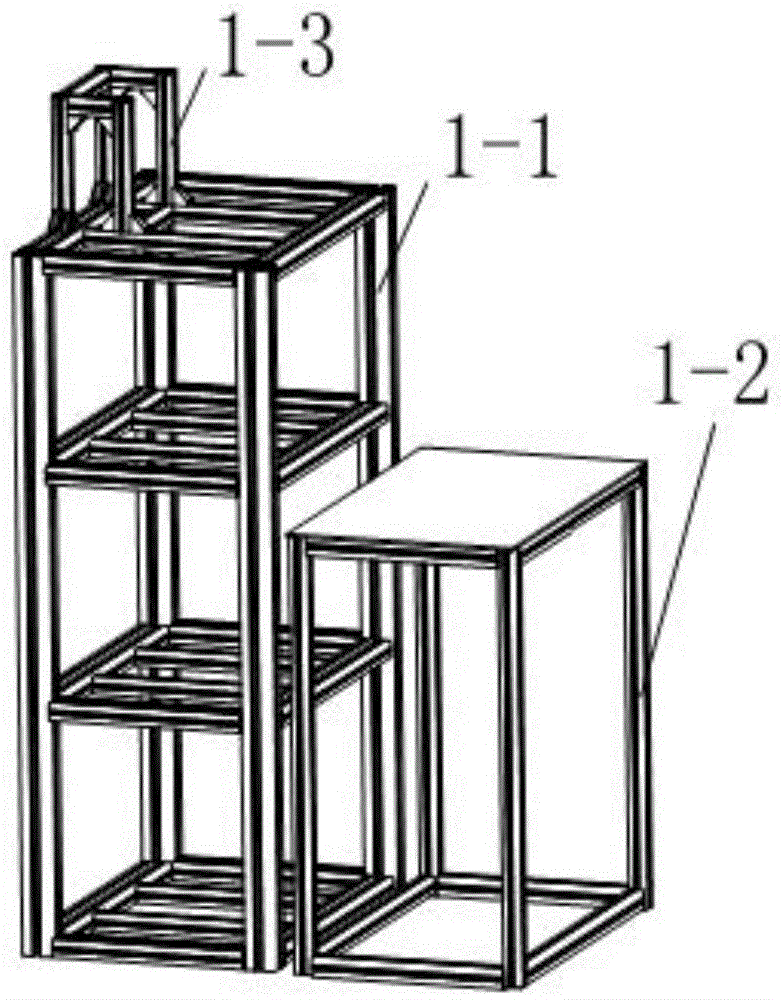

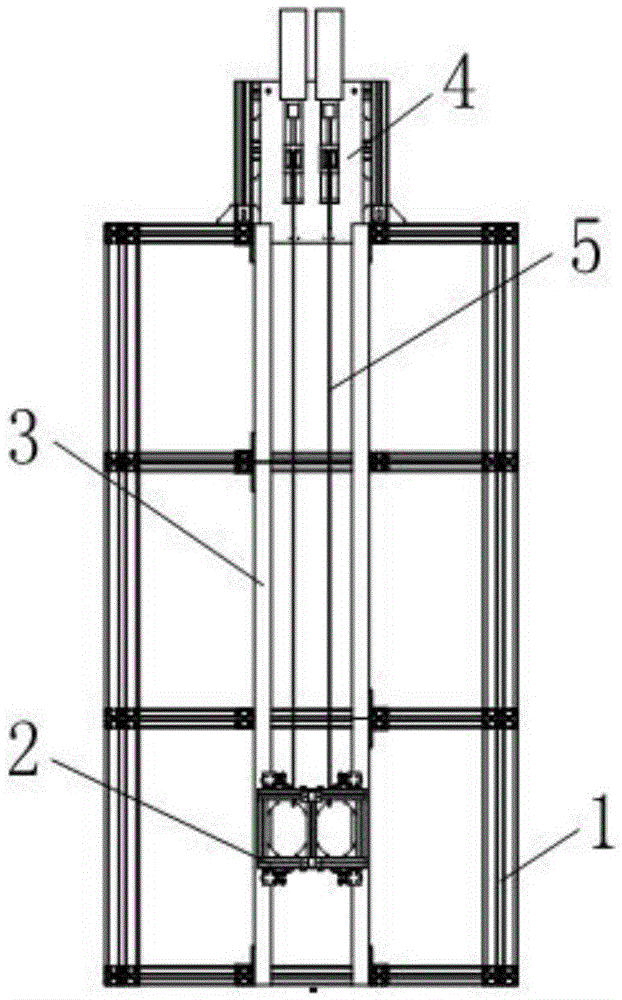

The present invention discloses an ultra-deep mine hoisting system multi-functional simulation test platform and an experimental method. The test platform comprises a frame which comprises a main frame, a sub frame, and a top layer frame. A driving device is installed on the sub frame. A rope adjustment device is arranged on the top layer frame. One end of a hoisting rope is wound on the reel of the driving device. One end of the hoisting rope passes through a rope adjustment device guide wheel and is connected to a hoisting container. A rectangular guide rail is installed on the main frame. The driving device drives the hoisting container through the hoisting rope to move up and down along the rectangular guide rail. When the guidance of the hoisting container by a flexible tank channel is simulated, a tension rope is installed on the main frame, the driving device drives the hoisting rope to drive the hoisting container to move up and down along the tension rope, two ends of the tension rope is provided with tension devices, and detection control systems are installed in the hoisting container, the rope adjustment device and the driving device. According to the ultra-deep mine hoisting system multi-functional simulation test platform and the experimental method, the ultra-deep mine hoisting equipment motion state in a real condition can be simulated, and the main performance parameters of hoisting equipment in a fault condition are obtained.

Owner:CHINA UNIV OF MINING & TECH

Simulation combined relay type stand-alone storage reliability assessment method

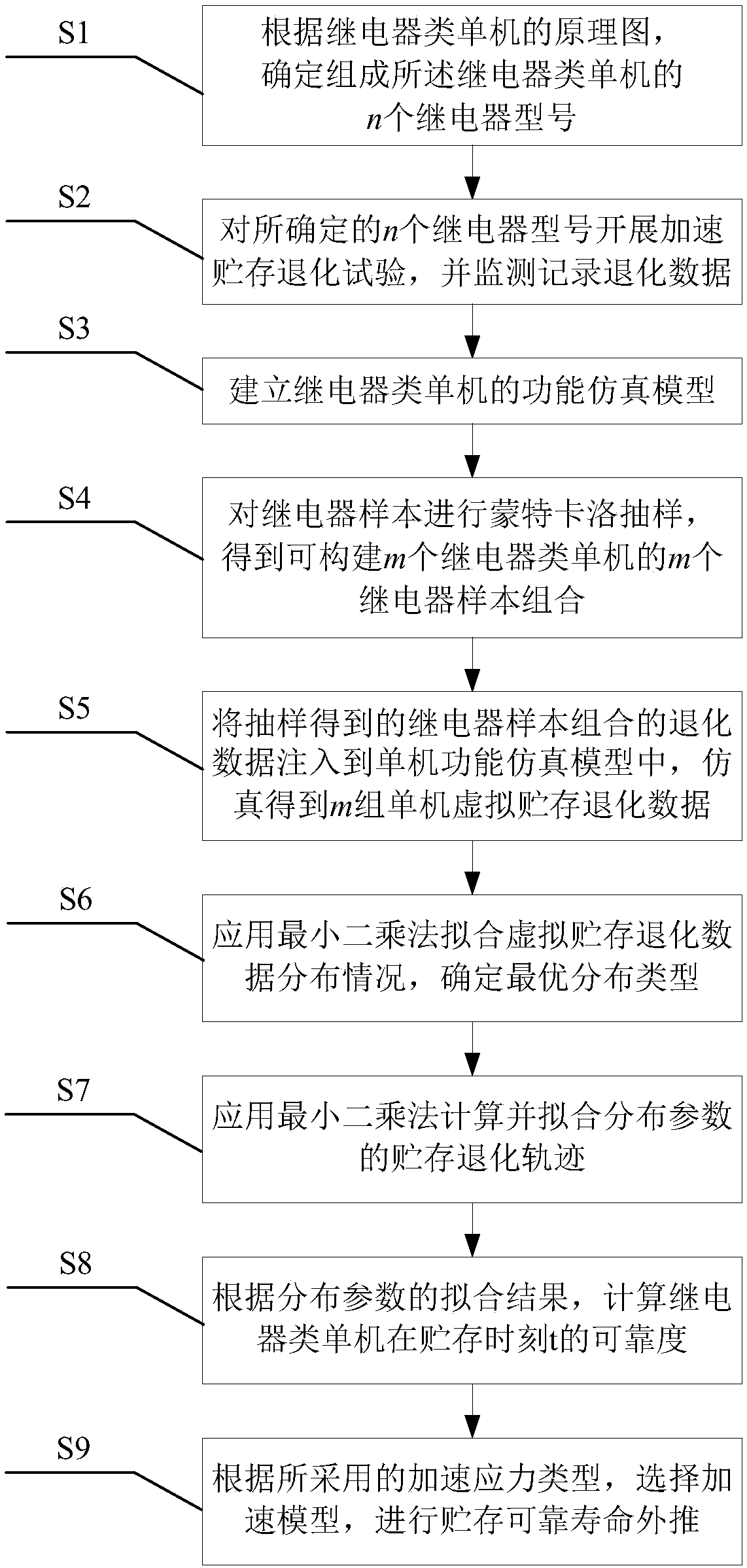

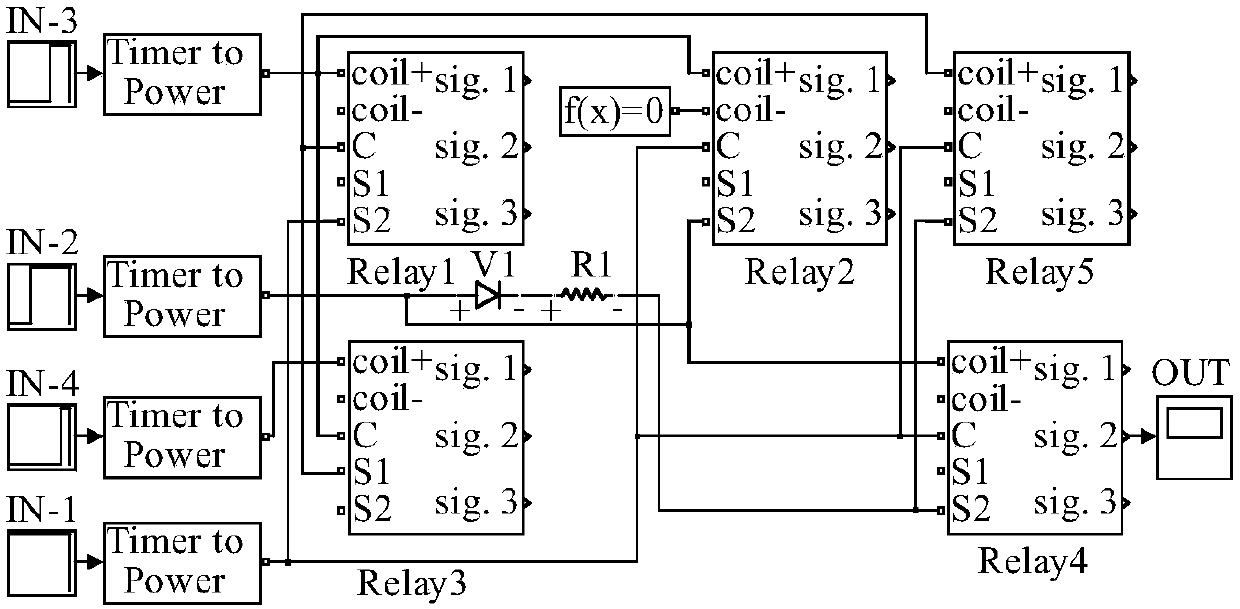

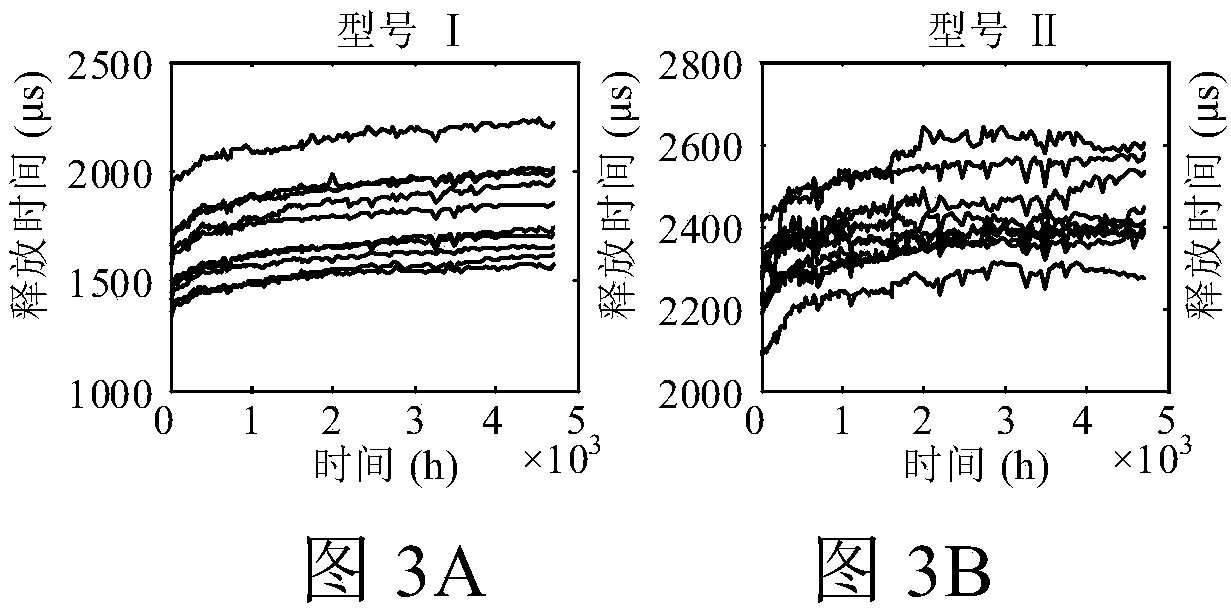

InactiveCN107729660ARealization of storage reliability assessmentRealize evaluationDesign optimisation/simulationSpecial data processing applicationsLife timeModel Number

The invention a simulation combined relay type stand-alone storage reliability assessment method. The method includes steps: determining models of n relays which form a relay type stand-alone according to a schematic diagram; subjecting the relays of different models to accelerated storage degradation testing, and monitoring and recording degradation data; establishing a functional simulation module of the relay type stand-alone; subjecting relay samples to Monte Carlo sampling to obtain m relay sample combinations for construction of m relay type stand-alones; performing relay type stand-alone functional simulation, and acquiring m groups of virtual storage degradation data; adopting a least square method for fitting virtual storage degradation data distribution to determine an optimal distribution type; fitting a storage degradation path of distribution parameters; according to a fitting result of the distribution parameters, calculating reliability of the relay type stand-alone at astorage moment t; according to an adopted acceleration stress type, selecting an acceleration model to perform storage life extrapolation. By adoption of the method, relay type stand-alone storage reliability indexes can be directly estimated in a design state.

Owner:HARBIN INST OF TECH

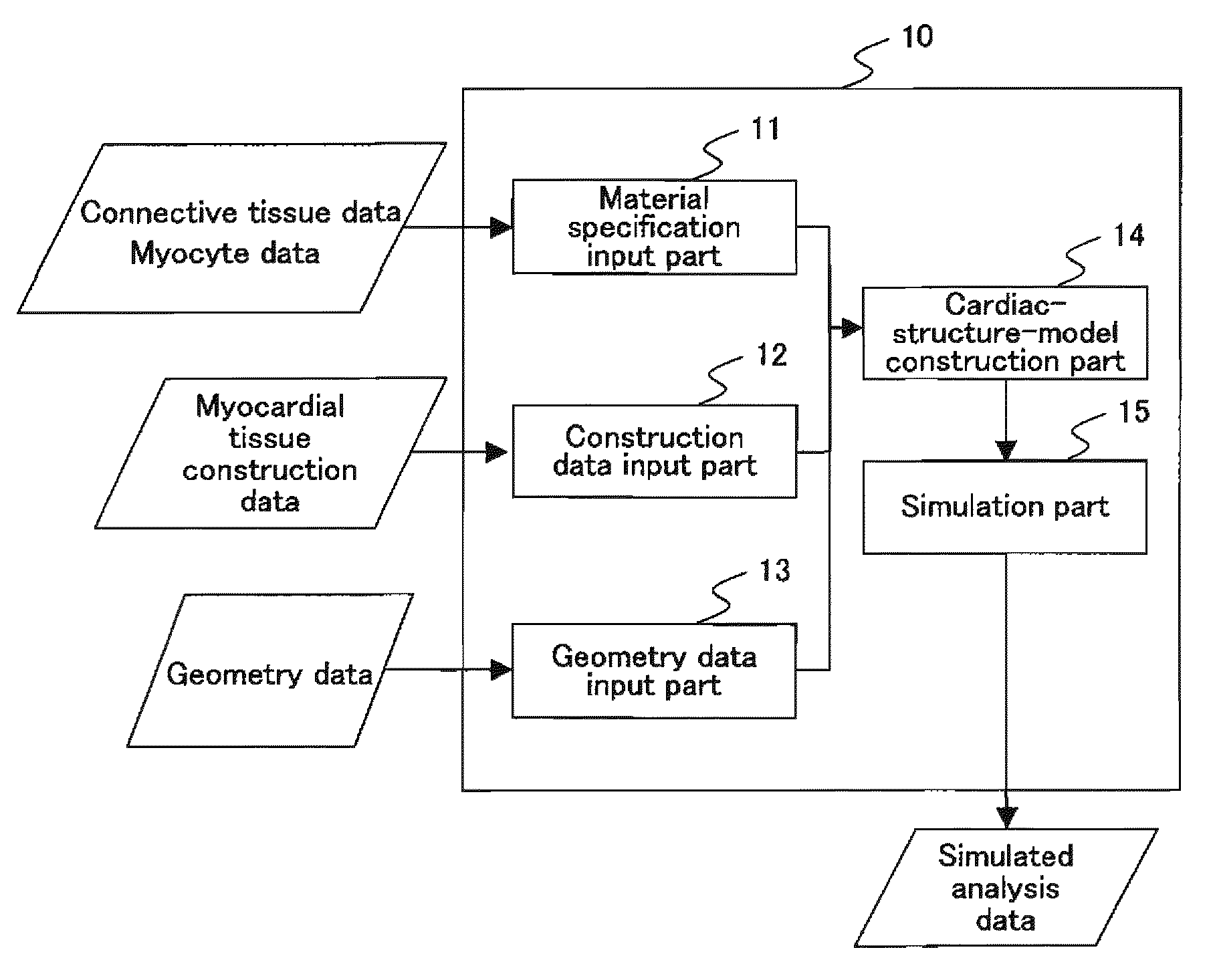

Simulation system of cardiac function, simulation method of cardiac function, simulation program of cardiac function, and composite material sheet

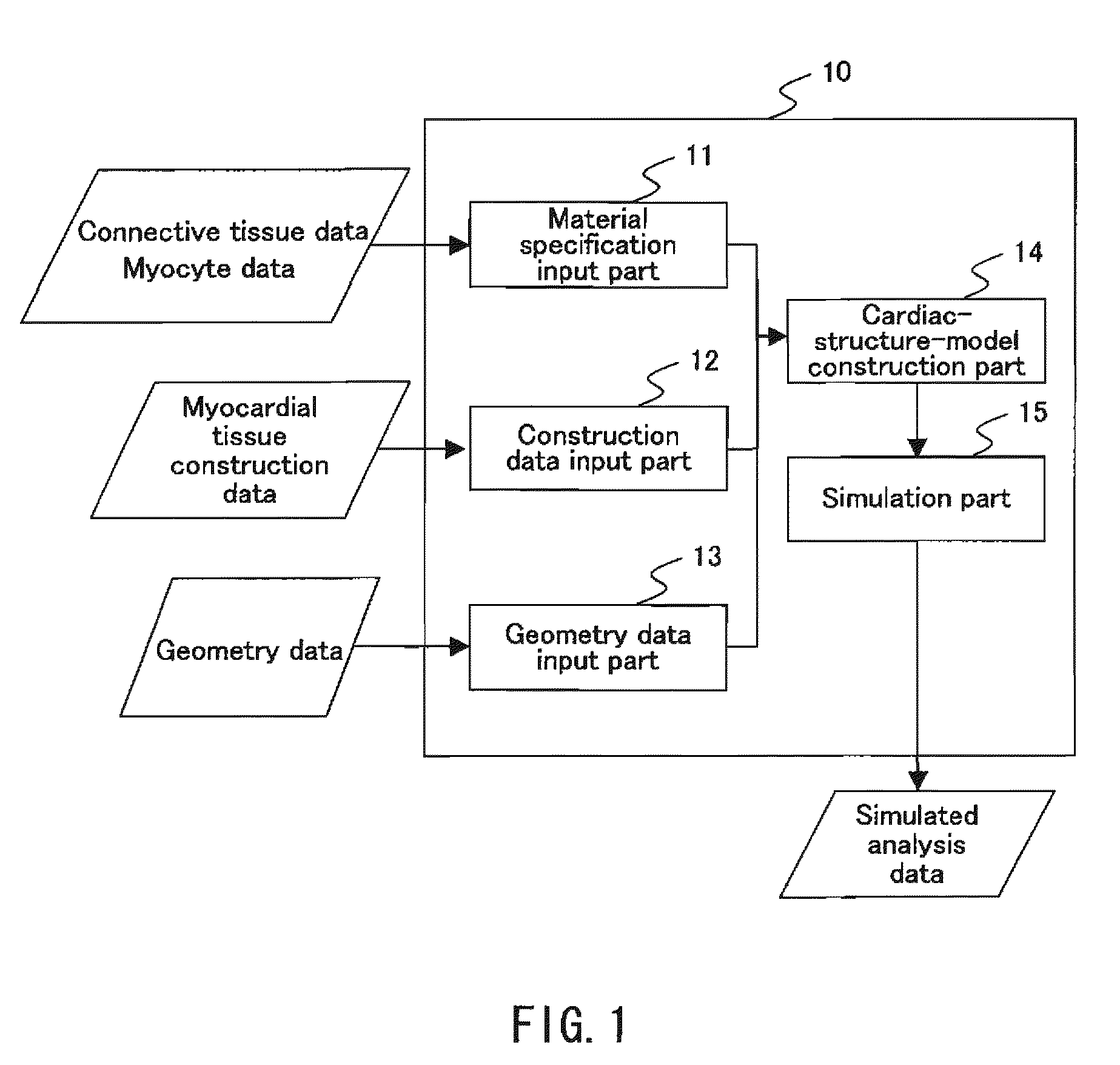

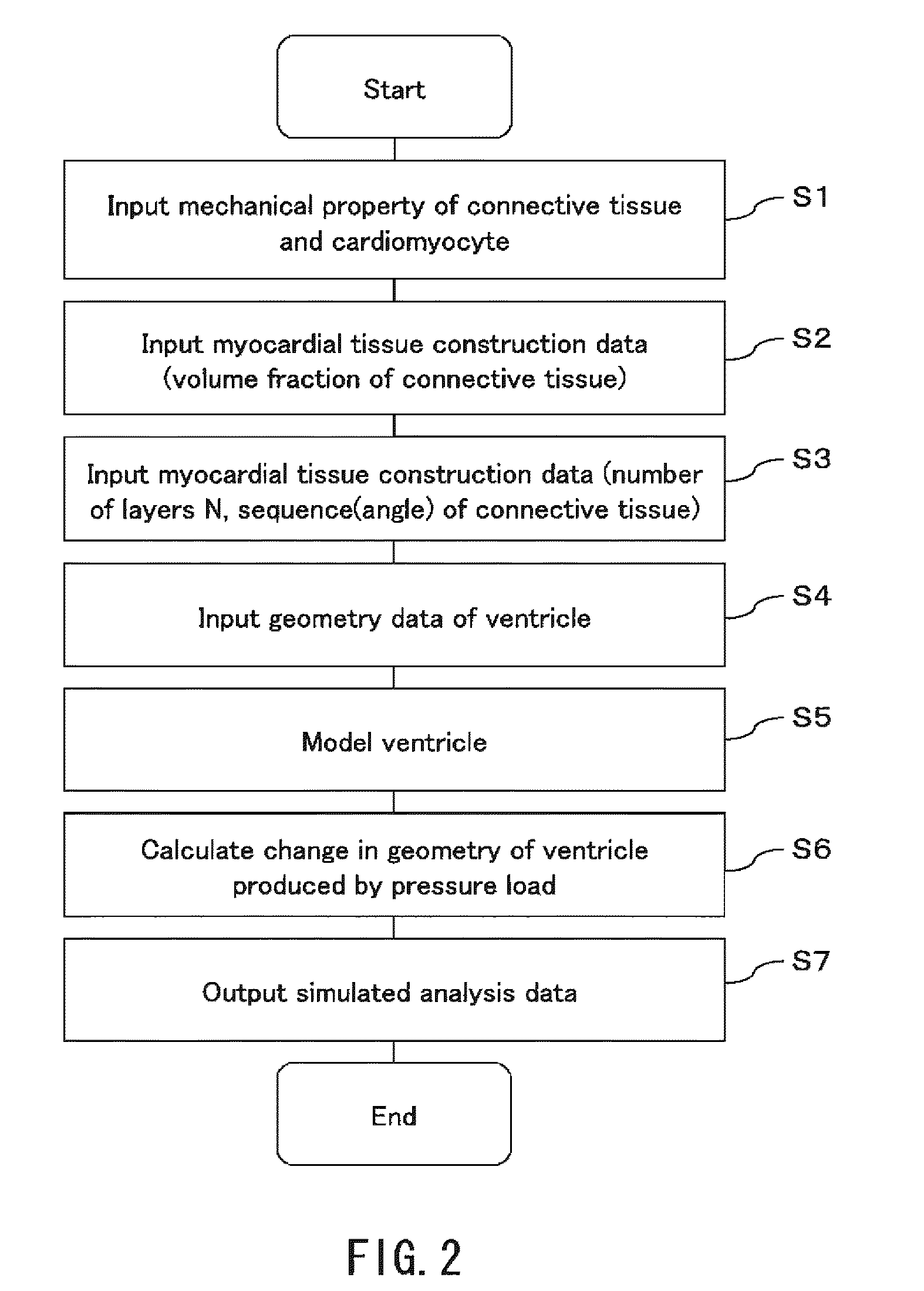

ActiveUS20100318326A1Simple designImprove impaired cardiac functionMedical simulationAnalogue computers for chemical processesFiberCardiac feature

To provide a simulation system of cardiac function utilizing a cardiac structure model which is generated based on an appropriate composite material view representing the myocardial tissue. A simulation system of cardiac function to predict a change in cardiac geometry using a cardiac structure model contains a material specification input part 11 to determine both connective tissue data and myocyte data, a geometry data input part 13 to input geometry data of three-dimensional geometry of a heart, and a cardiac-structure-model construction part 14 wherein a cardiac structure model assumes assembly of finite elements based on continuum data of three-dimensional geometry defined by geometry data and made of composite material containing matrix and reinforcement fiber, and possesses mechanical properties of reinforcement fiber reflecting mechanical properties of connective tissue data and mechanical properties of matrix reflecting mechanical properties of myocyte data. The simulation system also contains a simulation part 15 which predicts a change of geometry of the cardiac structure model produced by pressure load utilizing finite element method with computation.

Owner:YAMAMOTO SHOJI

Simulation/radio frequency integrated circuit design method based on SPICE software

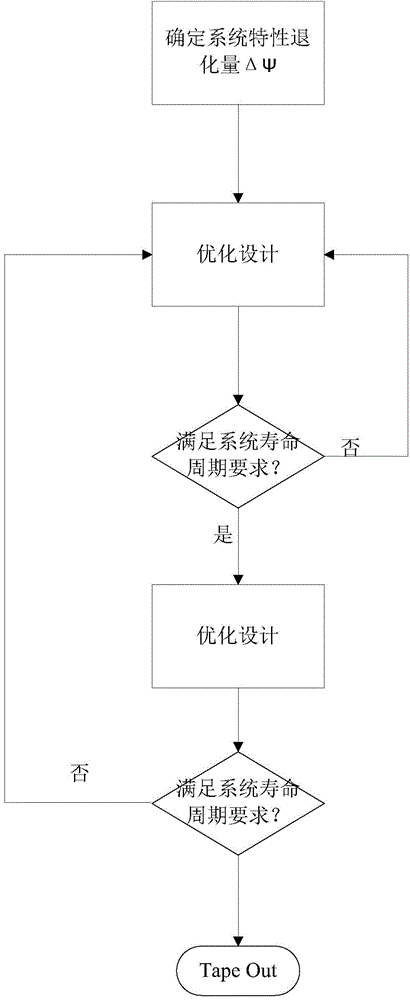

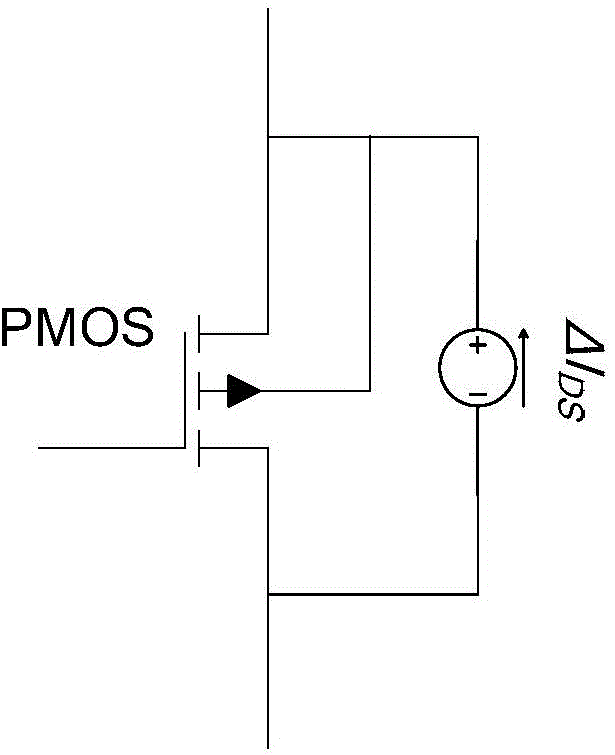

InactiveCN103955579ASolving synchronicitySpecial data processing applicationsSystem requirementsRadio frequency

The invention relates to a simulation / radio frequency integrated circuit design method based on SPICE software. The method comprises the following steps: (1) determining the demands of the circuit system characteristics on the reliability, and describing the amount of degeneration as a device characteristic function under the condition of the certain stress after some time; (2) adjusting the parameters of components, optimizing a circuit system, finding the key component with great effect on the circuit system characteristics and great effect by the stress, optimizing parameters of the key component, and lengthening the life cycle of the circuit system; (3) using the Monte Carlo simulation of the SPICE to carry out the model simulation on various technological parameters of the system; if the demands on the reliability are not accorded, returning to the step (2), and redesigning the key circuit to satisfy the demands of the system. The method greatly realizes the synchronism of the functional simulation and reliability simulation in the design stage, and the parameters affecting the life cycle are only required to be adjusted when the process is changed.

Owner:TIANJIN UNIV RENAI COLLEGE

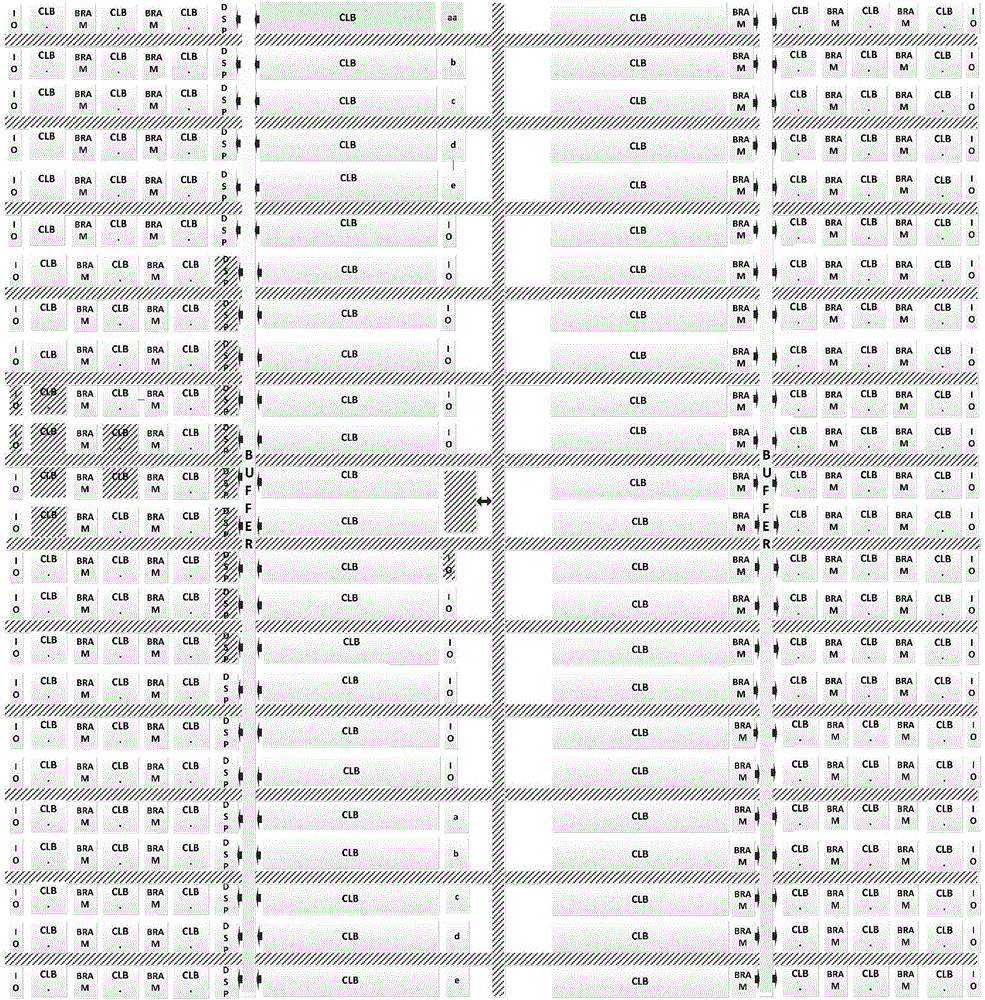

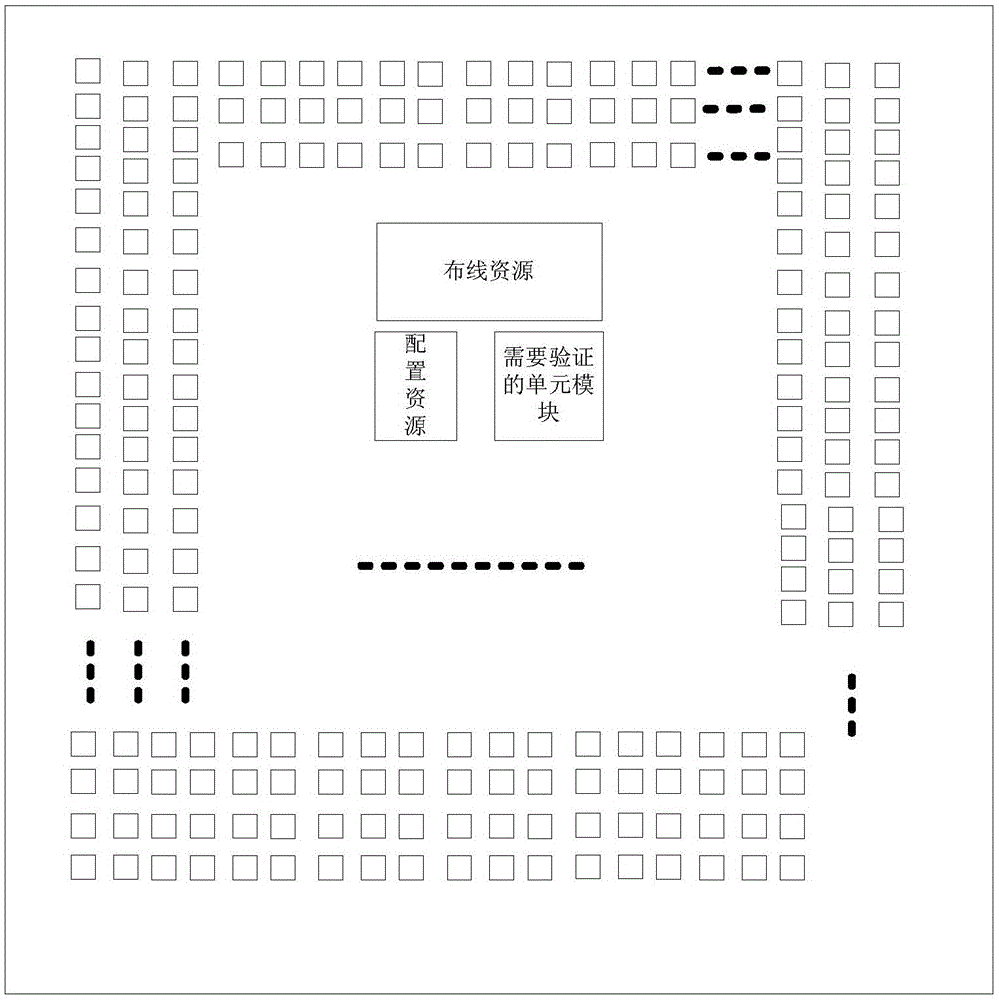

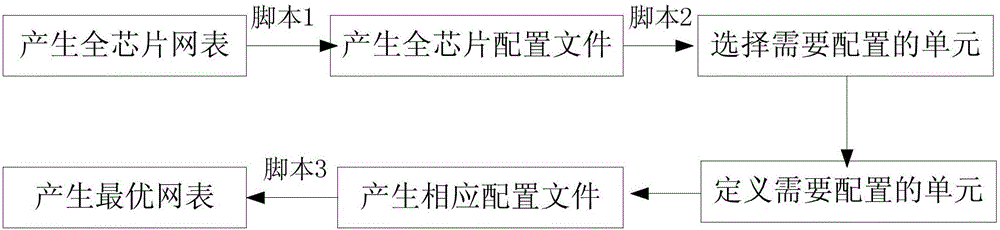

Generation method of optimal net list for functional simulation of large-capacity FPGA (Field Programmable Gate Array) circuit

ActiveCN106202761ARun fastIncrease coverageCAD circuit designSpecial data processing applicationsComputer architectureField-programmable gate array

The invention provides a generation method of an optimal net list for functional simulation of a large-capacity FPGA (Field Programmable Gate Array) circuit. The optimal net list can be dynamically generated according to resources utilized by the FPGA circuit. According to the method provided by the invention, all unit names and instantiation unit names of top-layer units in a full-chip net list need to be acquired and configuration files of the full-chip net list are obtained; then a corresponding full-chip net list is generated by matched FPGA software according to placement and routing resource distribution of the FPGA circuit, and module resources, routing resources and configuration resources of a used FPGA can be accurately positioned; finally, the configuration files of the needed resources are added into the full-chip net list and the optimal net list of all the resources used by the FPGA circuit is generated through script processing. According to the requirements of cases for validation, certain functions are pre-configured by utilizing the FPGA and the optimal net list is obtained by adopting the different configuration files. The generation method has a function of flexibly and dynamically configuring the net list and can save simulation resources; the operation speed and the validation efficiency of a simulator are improved and the coverage rate of a validation circuit is improved to the greatest extent.

Owner:WUXI ESIONTECH CO LTD

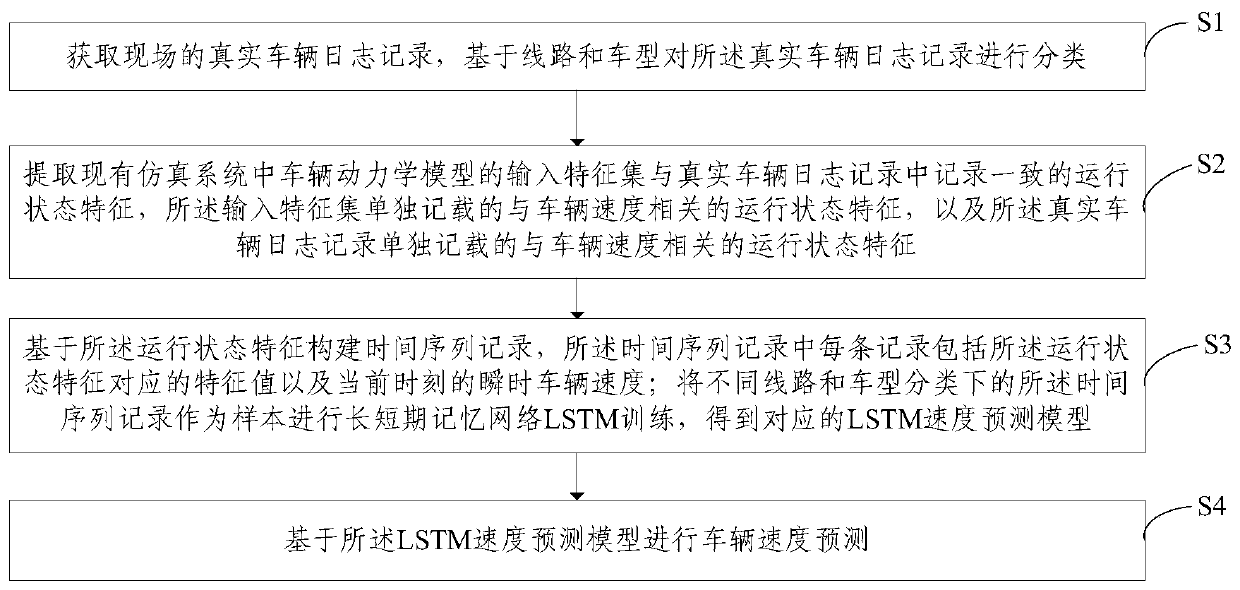

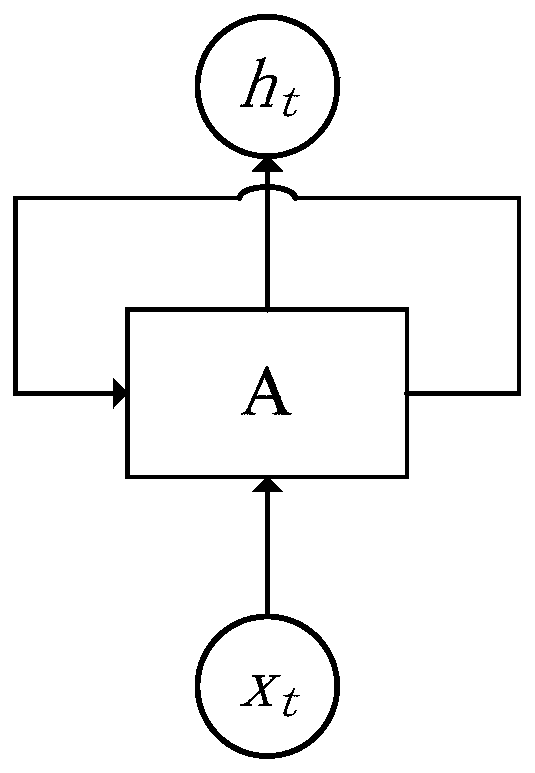

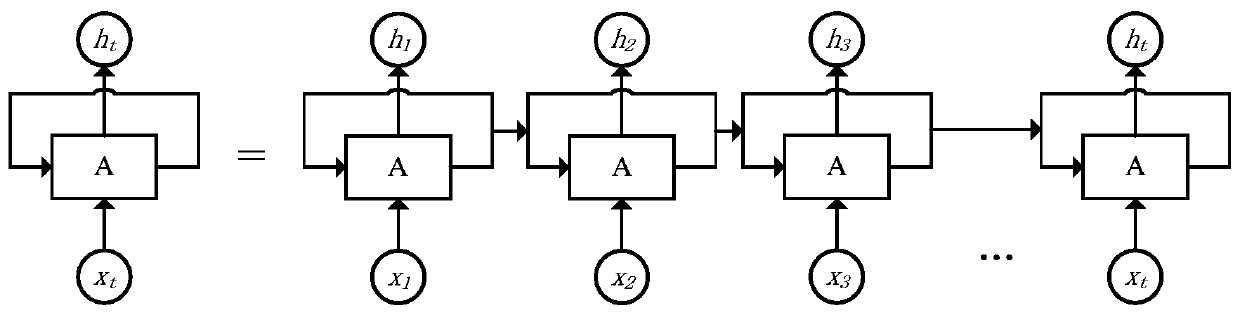

A simulation system vehicle dynamics model speed prediction method based on LSTM

ActiveCN109783843AFunction increaseInternal combustion piston enginesSustainable transportationVehicle dynamicsDynamic models

The embodiment of the invention provides a simulation system vehicle dynamics model speed prediction method based on LSTM. Based on actual train operation record data collected on site, the simulationvehicle dynamics model can better simulate the actual operation effect of the on-site vehicle in the full-function simulation test platform; a vehicle speed prediction model based on a time sequenceis trained based on the data source; a field real hidden mode can be contained in the model; wherein the hidden mode refers to some performance parameters of the vehicle; the hidden mode can be used for optimizing a vehicle dynamics model, such as increasing a function of a rain and snow mode, the application of the LSTM model enables factors which are difficult to adopt originally but have an important influence on actual operation speed output to pay attention to, and characteristics such as vehicle weight, actual line curvature and full load rate can be introduced into a simulation system;The problem that a traditional model does not introduce historical data into calculation is solved.

Owner:TRAFFIC CONTROL TECH CO LTD

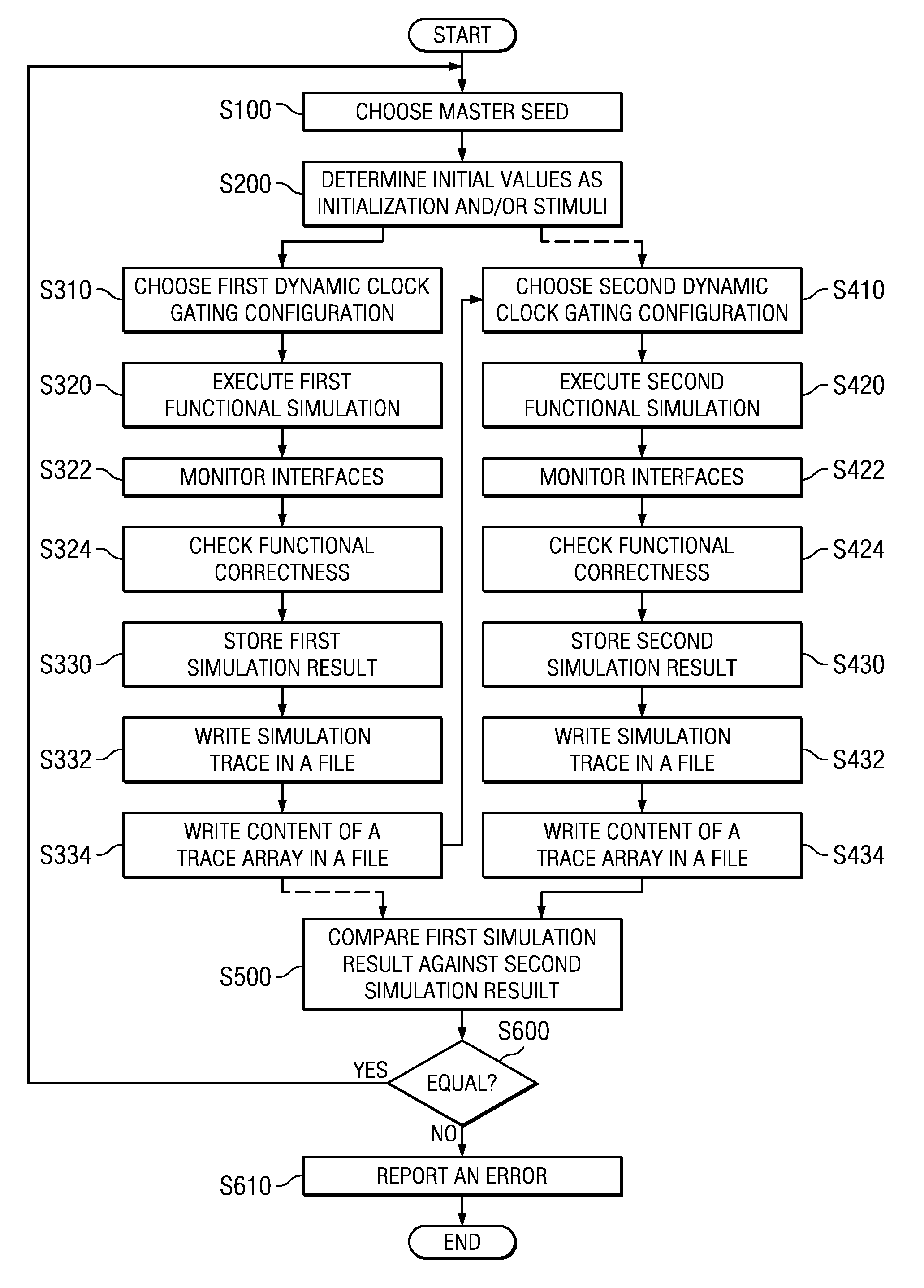

Method, System, Computer Program Product, and Data Processing Program for Verification of Logic Circuit Designs Using Dynamic Clock Gating

InactiveUS20110066988A1Guaranteed functionDetect changeDetecting faulty computer hardwareCAD circuit designComputer hardwareLogic circuit design

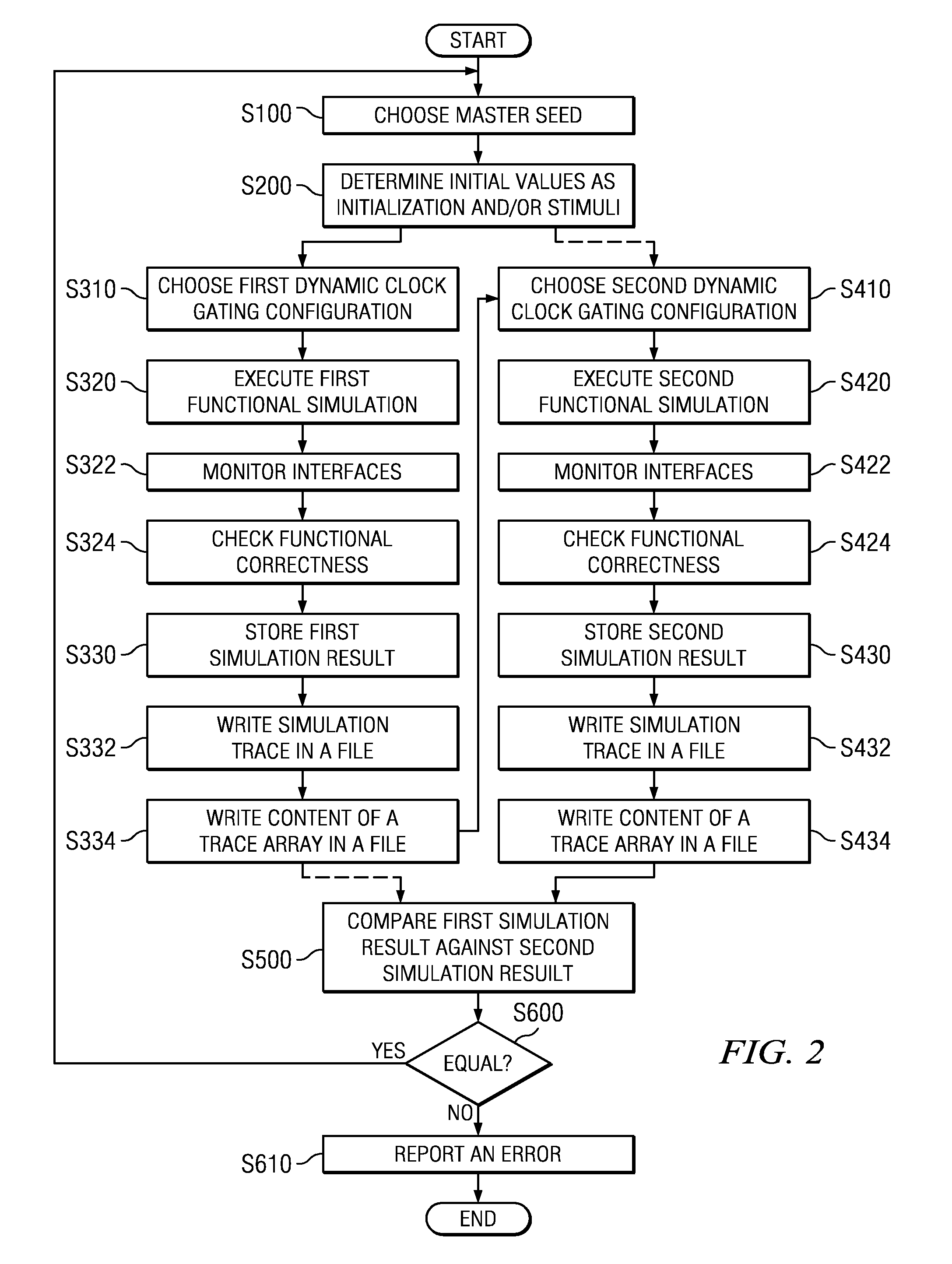

A method and system for verifying a logic circuit design using dynamic clock gating is disclosed. The method comprises choosing at least one master seed to determine initial values as initialization for said logic circuit and / or stimuli data for at least one interface of said logic circuit, choosing at least two different dynamic clock gating configurations for every chosen master seed, executing a functional simulation with said logic circuit for every chosen dynamic clock gating configuration by using said determined initialization and / or stimuli data based on a corresponding master seed, comparing simulation results of functional simulations against each other executed with said logic circuit for at least two different chosen dynamic clock gating configurations, and reporting an error if said at least two simulation results are not identical.

Owner:GLOBALFOUNDRIES INC

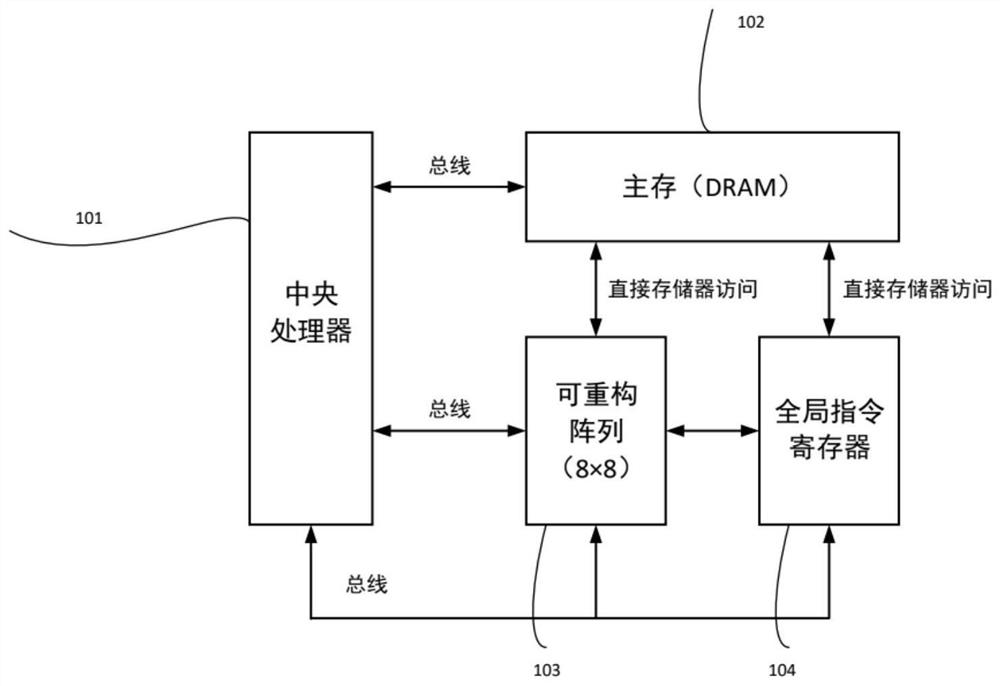

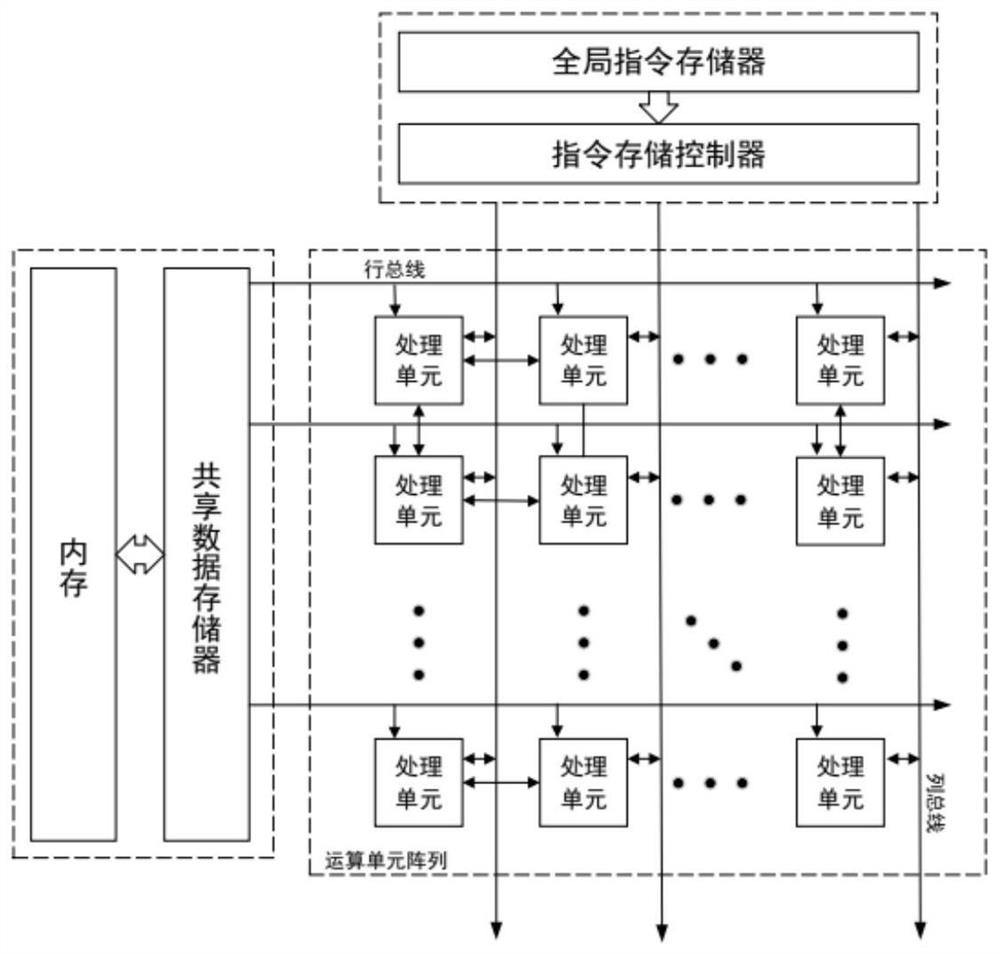

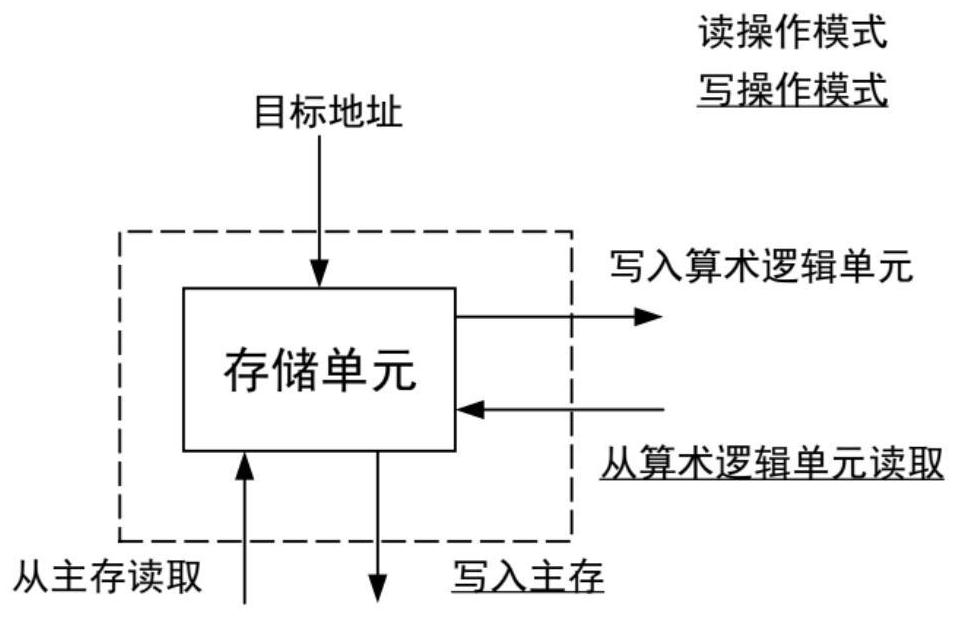

In-memory calculation method based on coarse-grained reconfigurable array

InactiveCN112463719AReduce physical distanceShorten the timeArchitecture with single central processing unitElectric digital data processingInstruction memoryComputer architecture

The invention relates to an in-memory processing system based on CGRA. The method is characterized by comprising a central processing unit, a main memory, a reconfigurable array and a global instruction register; a 3D stacking mode is adopted, each main memory block corresponds to a logic layer, and the logic layers and a memory chip are directly connected through the TSV technology; the processing unit of the reconfigurable array is configured as a storage unit or an arithmetic logic unit; the storage unit is used for exchanging data with the memory; and an arithmetic logic unit is used for performing calculating according to the register data, the nearby storage unit data and the configuration information. The in-memory processing system has the beneficial effects that the in-memory processing system has obvious performance advantages and wide application advantages, can realize the function simulation of the architecture under a simulation platform, is applied to a specific data intensive algorithm, adapts to more algorithm applications, and has higher flexibility; the reconfigurable array global instruction memories are all designed asymmetrically; and the transmission efficiency of the internal configuration data of the reconfigurable array is greatly improved.

Owner:SHANGHAI JIAO TONG UNIV

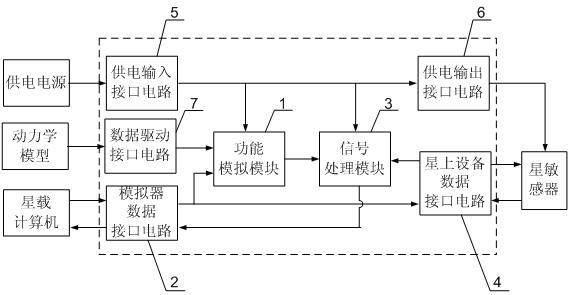

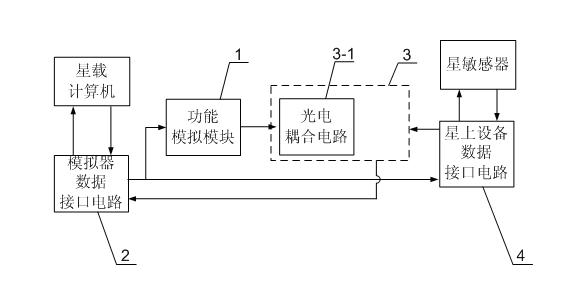

Electric simulator for star sensor

InactiveCN101937031ASimultaneous connectionSimple structural designElectrical testingElectricityControl system

The invention discloses an electric simulator for a star sensor, relates to an electric simulator for on-star equipment, and solves the problem that the conventional equipment or device cannot meet the requirement that the electric simulator of the star sensor and the star sensor are connected to a satellite test system simultaneously. The electric simulator comprises a functional simulation module, a simulator data interface circuit and a power supply input interface circuit, and also comprises a signal processing module, an on-star equipment data interface circuit and a power supply output interface circuit; an analog sensitive data signal output by the functional simulation module and a star sensitive data signal output by the on-star equipment data interface circuit are subjected to isolation synthesis processing in the signal processing module; the processed signal output end of the signal processing module is connected with the processed signal input end of the simulator data interface circuit; and the voltage output end of the power supply input interface circuit is connected with the voltage input end of the power supply output interface circuit. The electric simulator ensures that the electric simulator of the star sensor and the star sensor are connected to the satellite test system simultaneously, and is used for a satellite attitude control system or an entire star test.

Owner:HARBIN INST OF TECH

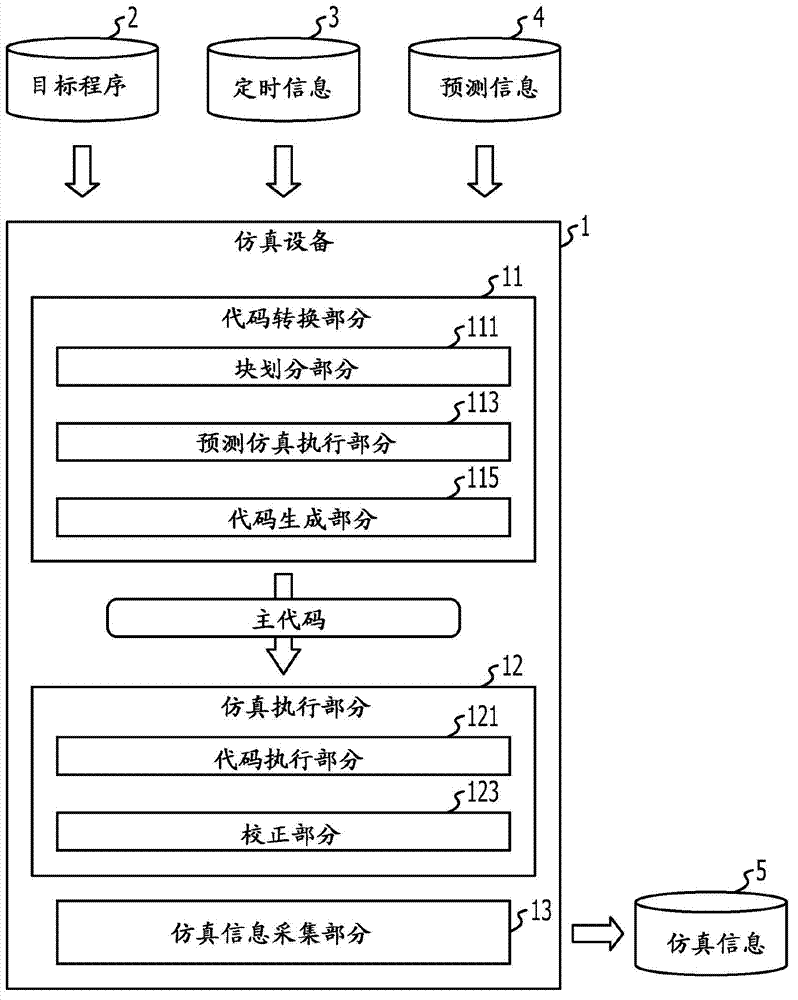

Simulation apparatus and simulation method

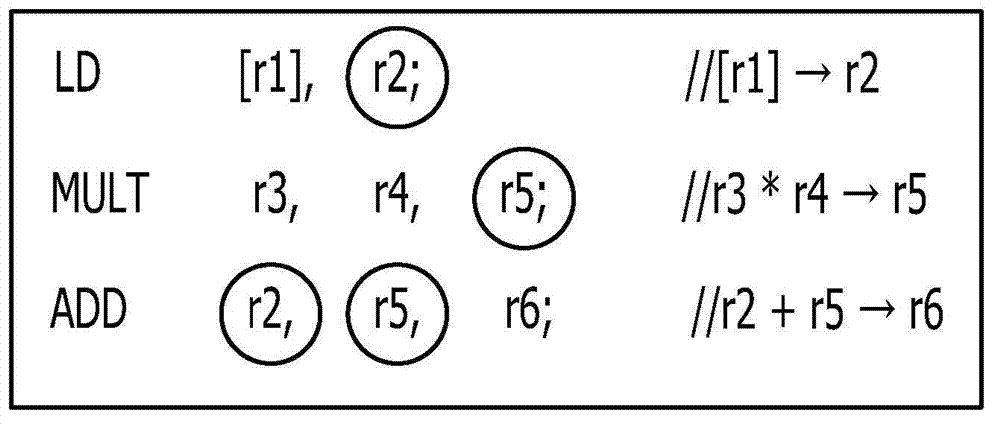

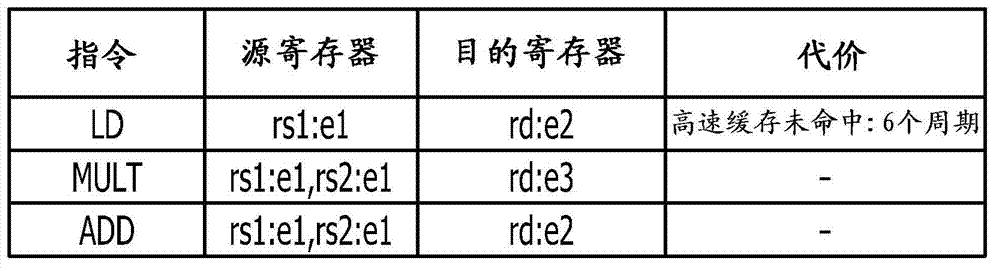

A simulation apparatus includes: operations of: dividing code of a program in a target processor into blocks,setting an execution result of an externally-dependant instruction depending on an external environment as a prediction result,carrying out function simulation based on the prediction result,calculating an execution time of the externally-dependant instruction according to instruction execution timing information and a function simulation result,generating host code which makes a host processor execute performance simulation based on the function simulation result: correcting the execution time of the externally-dependant instruction based on a delay time of the externally-dependent instruction and a execution time of an instruction executed before or after the externally-dependent function if an execution result of the externally-dependent function when the host processor executes the host code differs from the prediction result,and setting a corrected execution time of the external-dependent instruction as the execution time of the externally-dependant instruction.

Owner:FUJITSU LTD

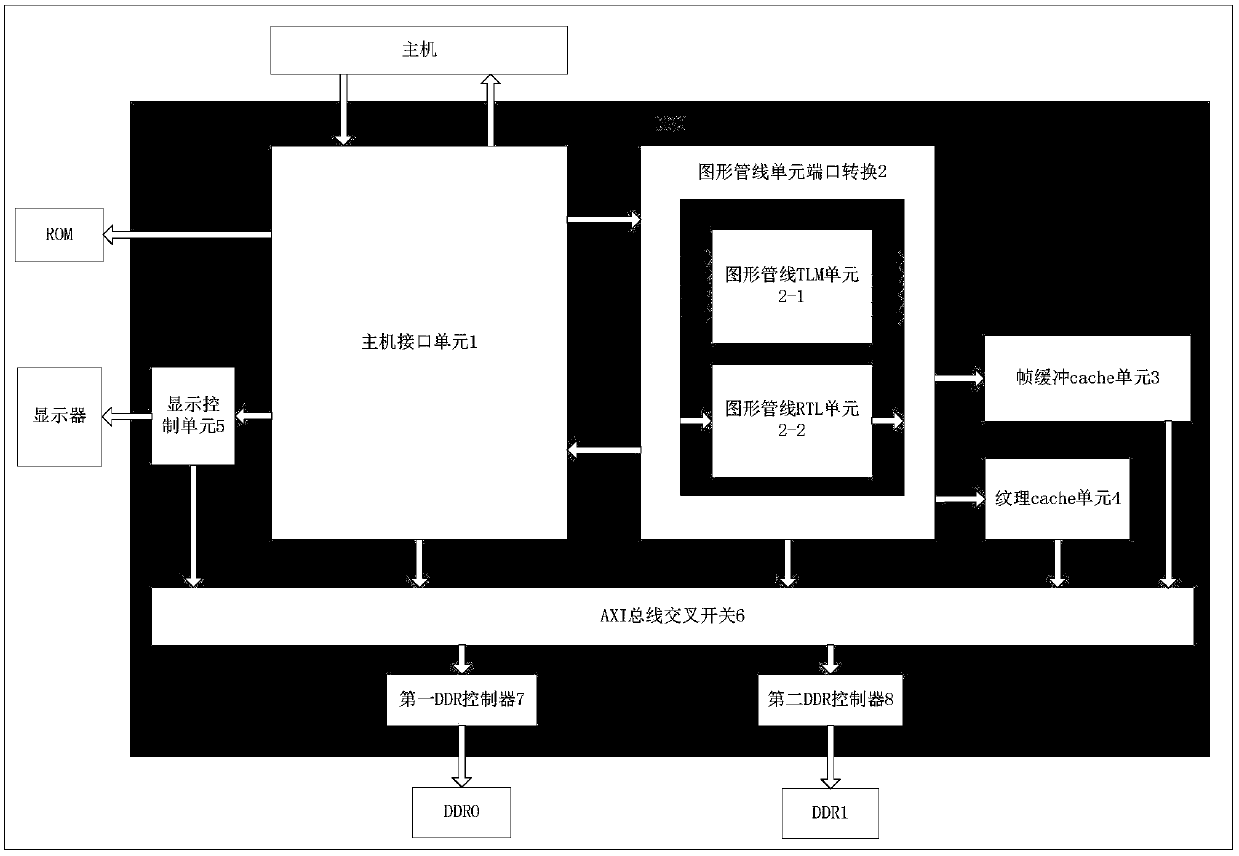

A GPU chip-oriented graphic pipeline unit performance verification method and a platform

The invention relates to the technical field of computer hardware verification, in particular to a GPU chip-oriented graphic pipeline unit performance verification method and a platform. According tothe method, a graphic processing unit (GPU) chip TLM virtual prototype platform based on SystemC is established (the virtual prototype verification platform comprises a host, an ROM, a display, DDR0,DDR1 and a GPU); a TLM transaction level port of a GPU graphic pipeline unit is converted into a hardware signal level port. By embedding the RTL code of the graphic pipeline unit into a TLM virtualprototype platform, and performing module-level and system-level function simulation on the RTL of the GPU to verify whether the RTL of the graphic pipeline unit meets the performance index of the corresponding model or not, whether the performance of the GPU graphic pipeline unit meets the requirement or not can be verified in advance before the FPGA stage, and the development and verification work of a GPU chip in the follow-up stage is accelerated.

Owner:XIAN AVIATION COMPUTING TECH RES INST OF AVIATION IND CORP OF CHINA

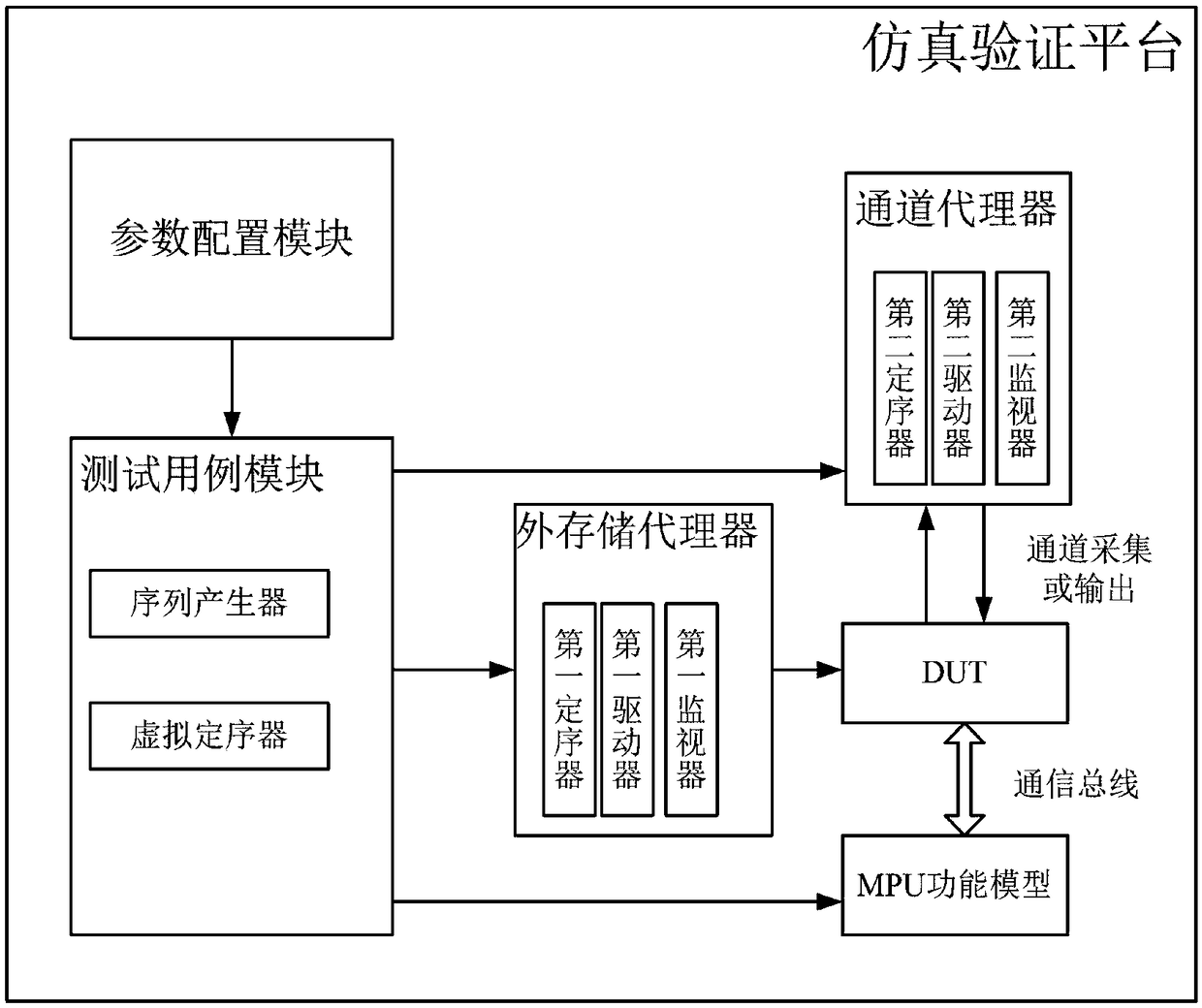

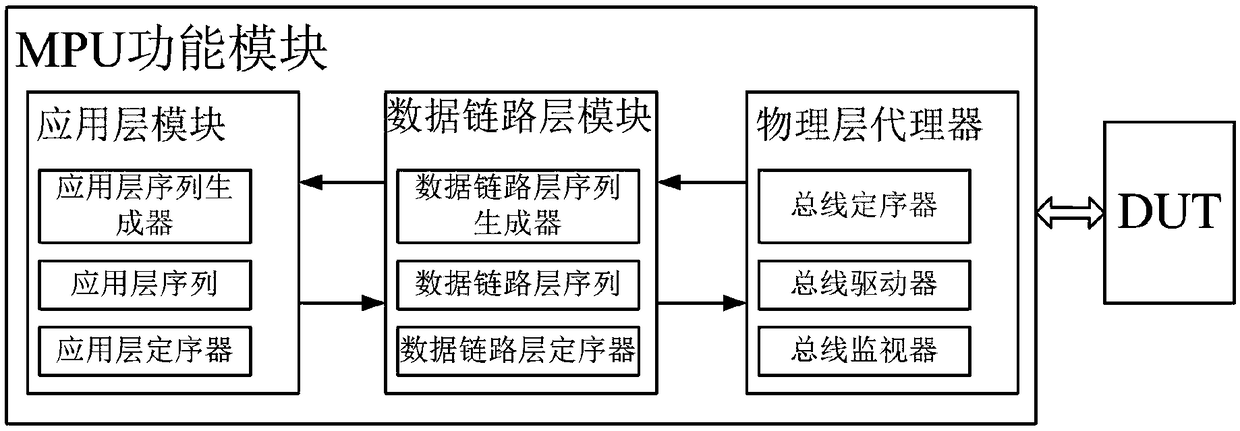

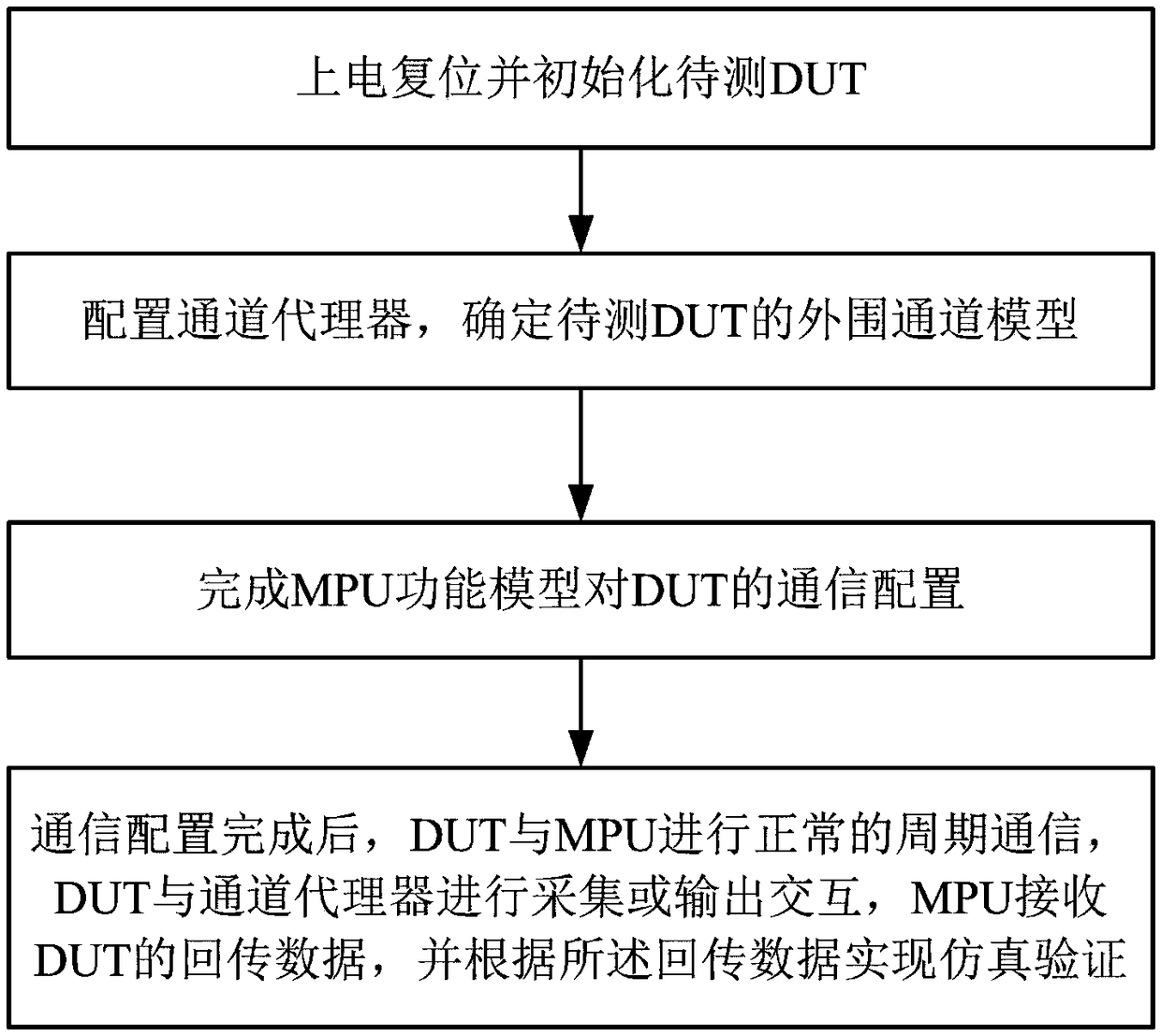

A reusable simulation verification platform and a simulation verification method

ActiveCN109472061AQuick buildEasy to reuseSoftware testing/debuggingSpecial data processing applicationsRegister allocationExternal storage

The invention relates to a reusable simulation verification platform and a simulation verification method, belonging to the technical field of FPGA product function simulation verification, which solves the problems of excessive manual intervention, large workload and low reusability of the verification platform in the existing directional test. Includes DUT and verification component. Verification component includes parameter configuration module, test case module, external storage agent, channel agent and MPU function model. Parameter configuration module is used to configure parameters of other verification components. The test case module is used for receiving the environmental parameters sent by the parameter configuration module and uniformly scheduling the excitation sequence of theexternal storage agent, the channel agent and the MPU function model. The external storage agent is used for storing register configuration data inside the DUT; The channel agent is used to simulatethe external channel of the DUT. The MPU functional model is used to interact with the DUT according to the test case model's test requirements. The simulation verification platform designed by the invention has the characteristics of reusability, easy expansion and the like.

Owner:CHINA TECHENERGY +1