In-memory calculation method based on coarse-grained reconfigurable array

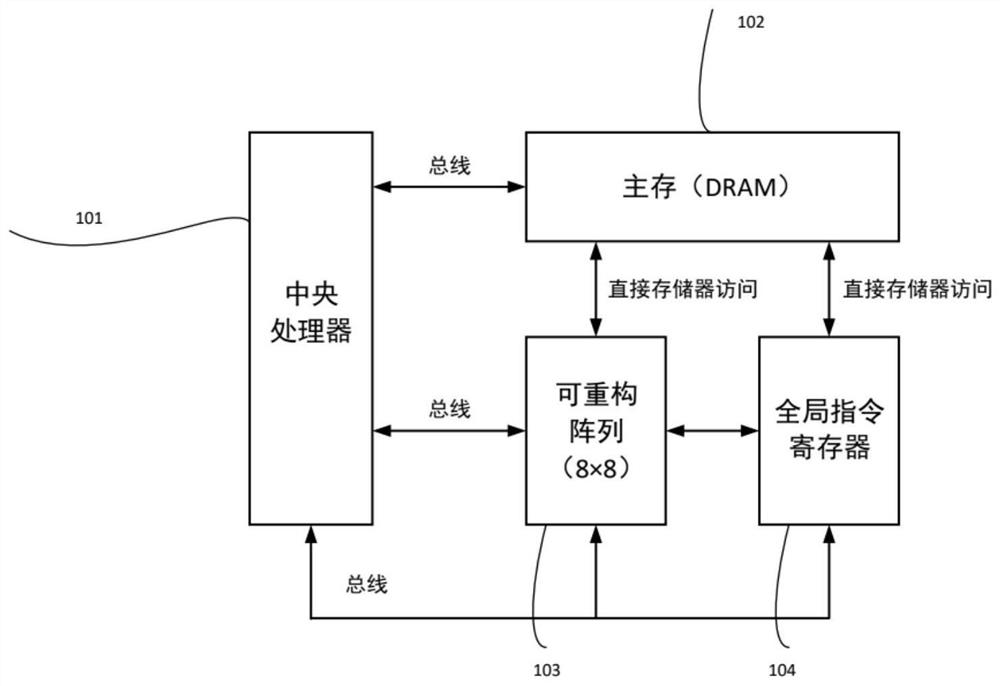

A coarse-grained, array technology, applied in the field of in-memory computing architecture design solutions based on coarse-grained reconfigurable arrays, which can solve non-in-memory processing accelerators with long transfer times, high performance and power consumption, and inflexible memory access. problem, to achieve obvious area and power consumption advantages, improve efficiency, and improve the effect of flexibility

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

specific Embodiment approach

[0095] The final system of the present invention is implemented in conjunction with C ++ and Python, and C ++ implements a specific structural configuration, Python provides parameter interface, but the present invention is not limited to C ++ and Python language. DETAILED DESCRIPTION

[0096] Step 1 Realize the simulation of CPU, DRAM, bus, etc. in C ++ and Python.

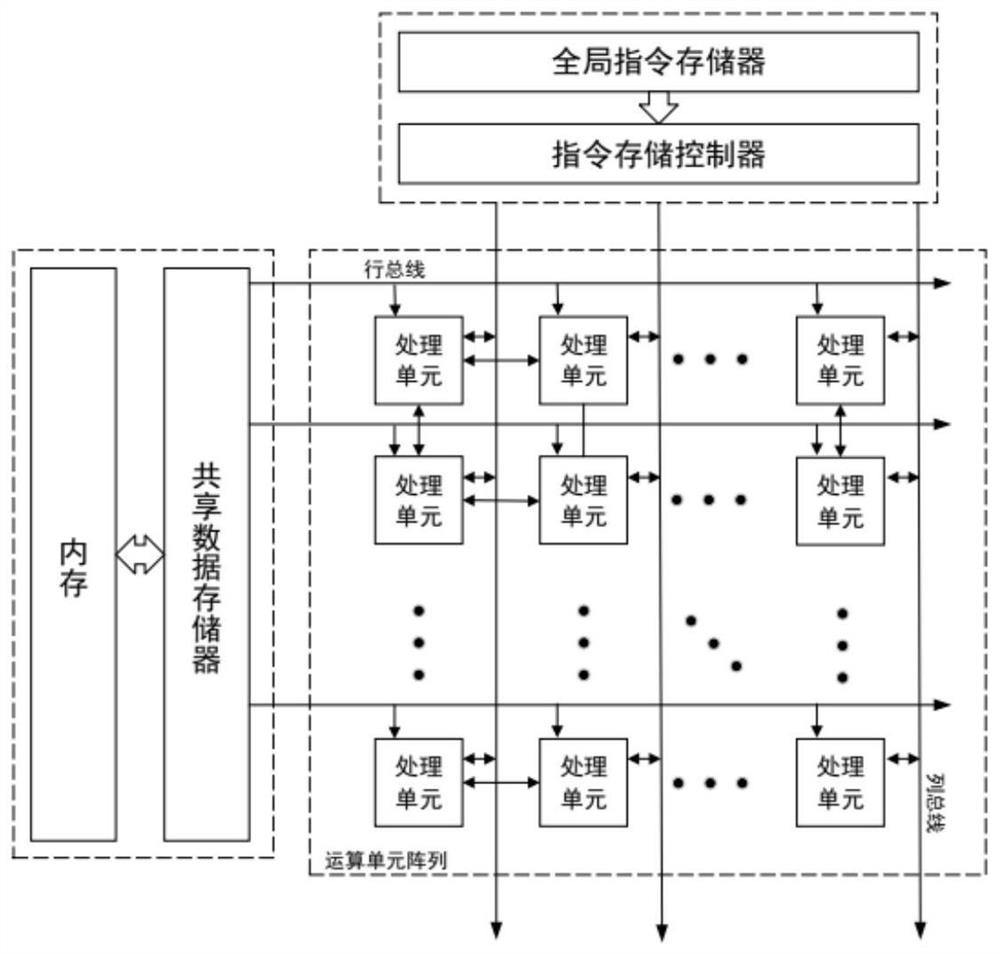

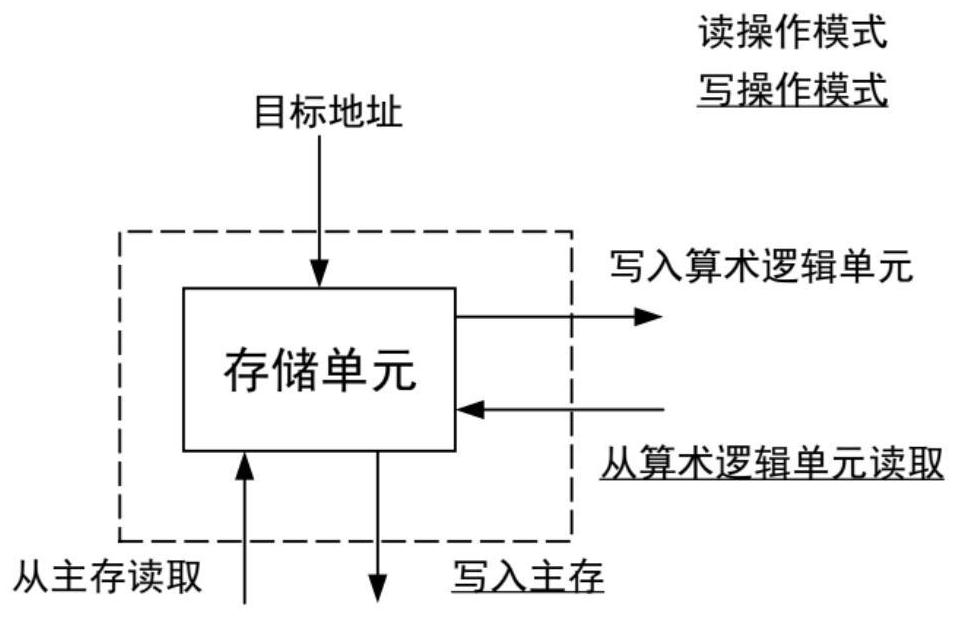

[0097] Step 2 image 3 Attach Figure 4 The solution achieves the processing unit of the reconstructed array.

[0098] Step 3 According to the attachment figure 2 Implement the PE combination as a reconfigurable array.

[0099] Step 4 follow Figure 5 The structure implements global instruction memory.

[0100] Step 5 follow Figure 7 The structure implementation instruction interconnection structure.

[0101] Step 6 follow figure 2 with Figure 6 The structure is directly connected to DRAM to design 3D stacking mode, and achieve near memory processing through Through Silicon VIA technology.

[0102] Step 7 follow f...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More