Patents

Literature

74 results about "SystemC" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

SystemC is a set of C++ classes and macros which provide an event-driven simulation interface (see also discrete event simulation). These facilities enable a designer to simulate concurrent processes, each described using plain C++ syntax. SystemC processes can communicate in a simulated real-time environment, using signals of all the datatypes offered by C++, some additional ones offered by the SystemC library, as well as user defined. In certain respects, SystemC deliberately mimics the hardware description languages VHDL and Verilog, but is more aptly described as a system-level modeling language.

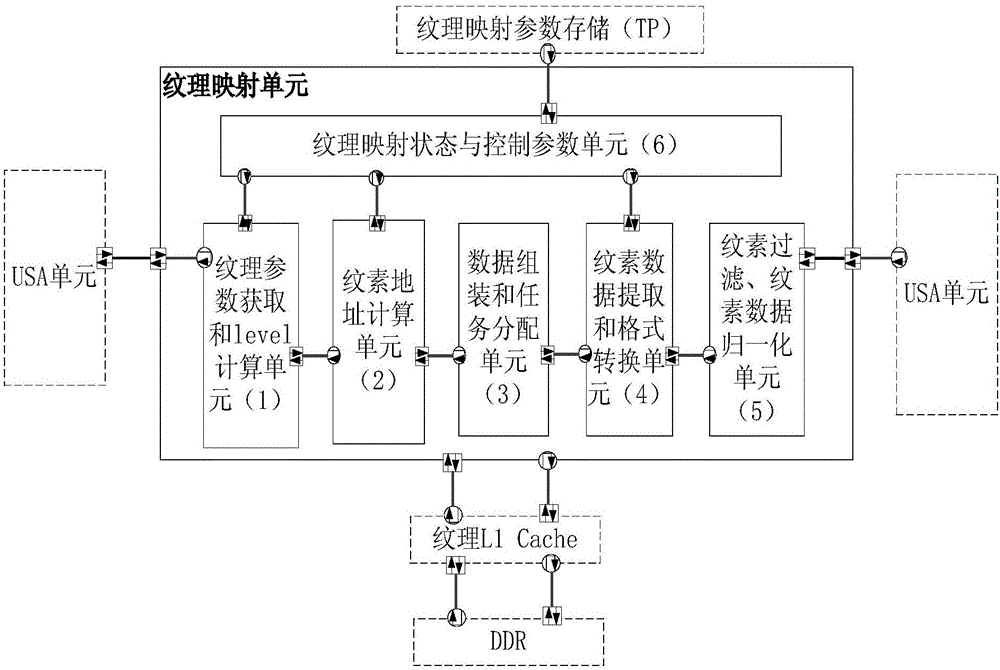

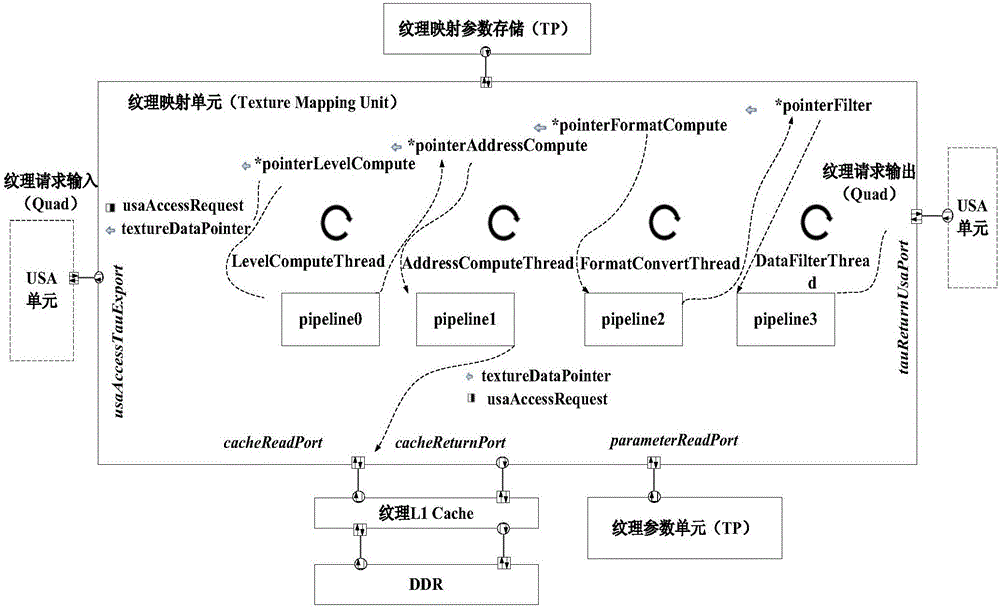

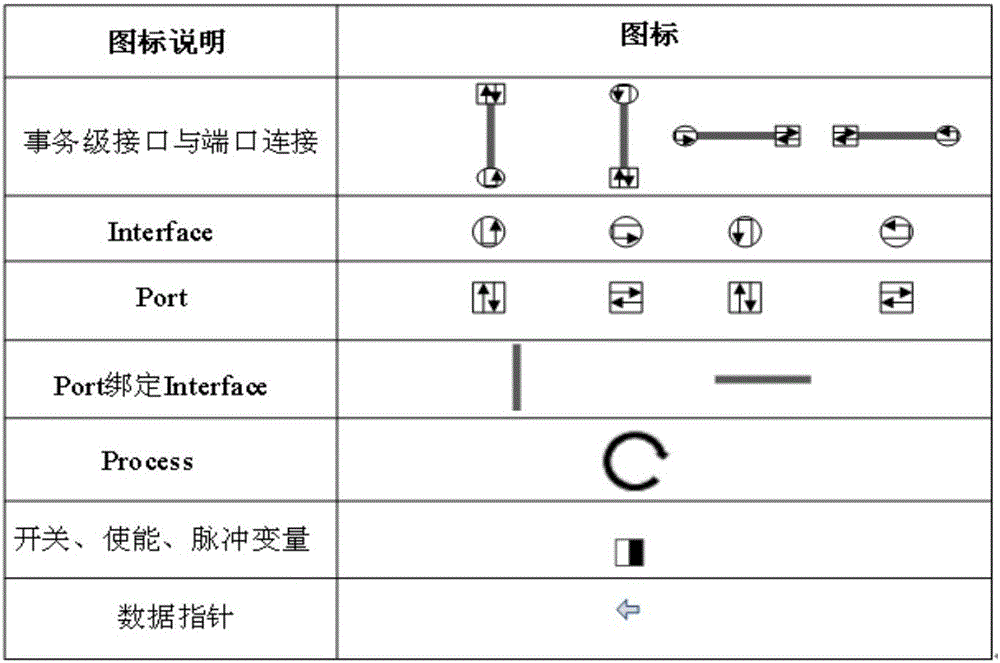

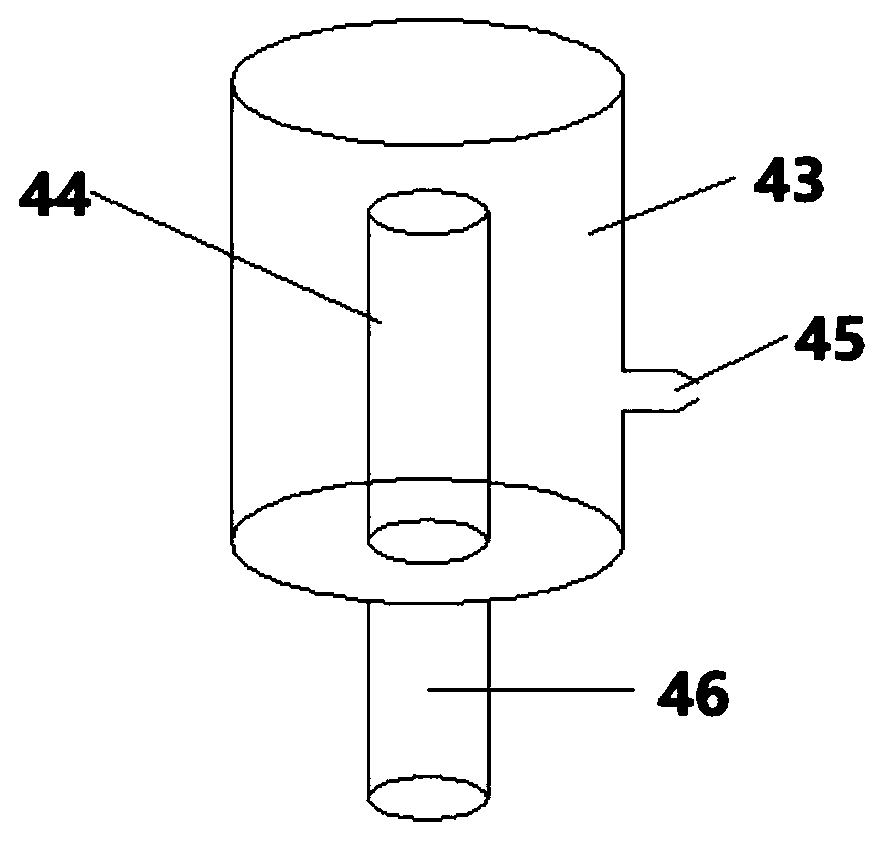

GPU multi-thread texture mapping SystemC modeling structure

ActiveCN106683171ARapid assessmentReduce volume and workloadProcessor architectures/configuration3D modellingGraphicsSystemC

The invention belongs to the field of computer graphics, and especially relates to a GPU multi-thread texture mapping SystemC modeling structure. The structure comprises a texture parameter obtaining and Level calculation unit (1), a texel address calculation unit (2), a data assembly and task distribution unit (3), a texel data extraction and format conversion unit (4), a texel filtering and texel data normalization unit (5) and a texture mapping state and control parameter unit (6). The structure can avoid the tedious circuit signal design, quickly evaluates the framework of a large-scale hardware system, is suitable for the early system-level design and development of a circuit, and provides an effective reference for the same type of products and functions.

Owner:XIAN AVIATION COMPUTING TECH RES INST OF AVIATION IND CORP OF CHINA

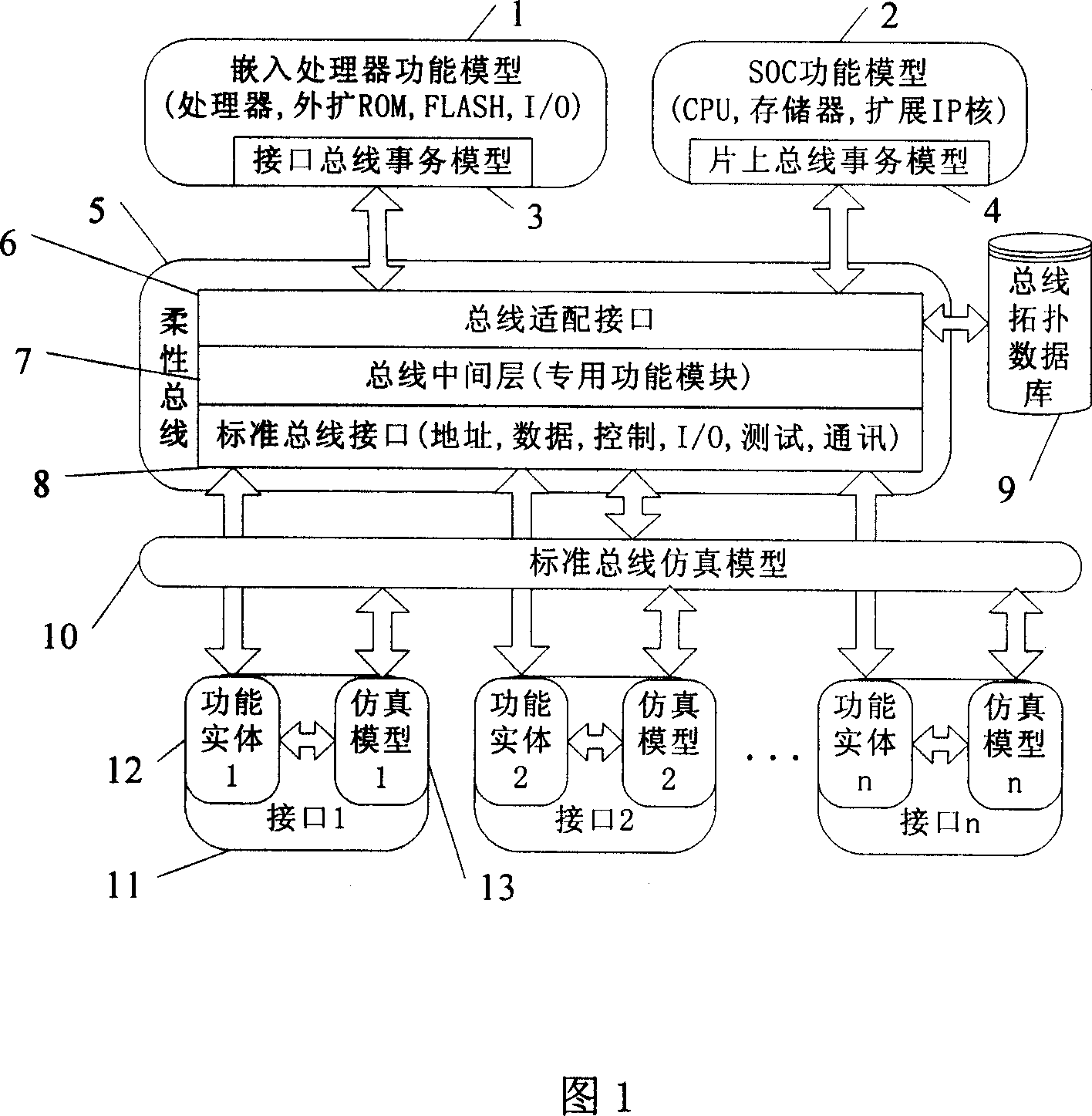

Bus model-based embedded system emulated platform

InactiveCN101059773ALarge simulation coverageHas hardware concurrencySoftware testing/debuggingSystemCSystems Modeling Language

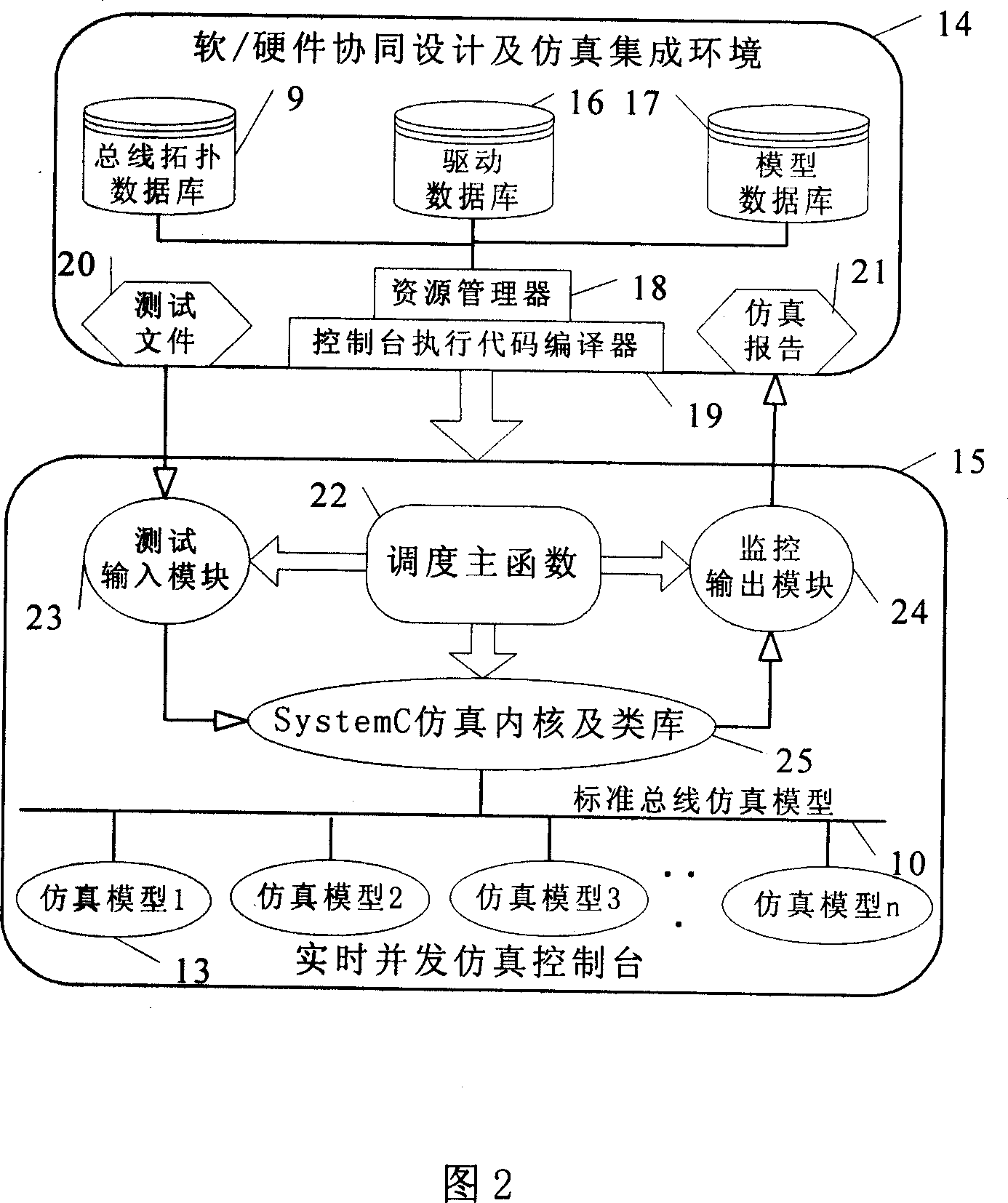

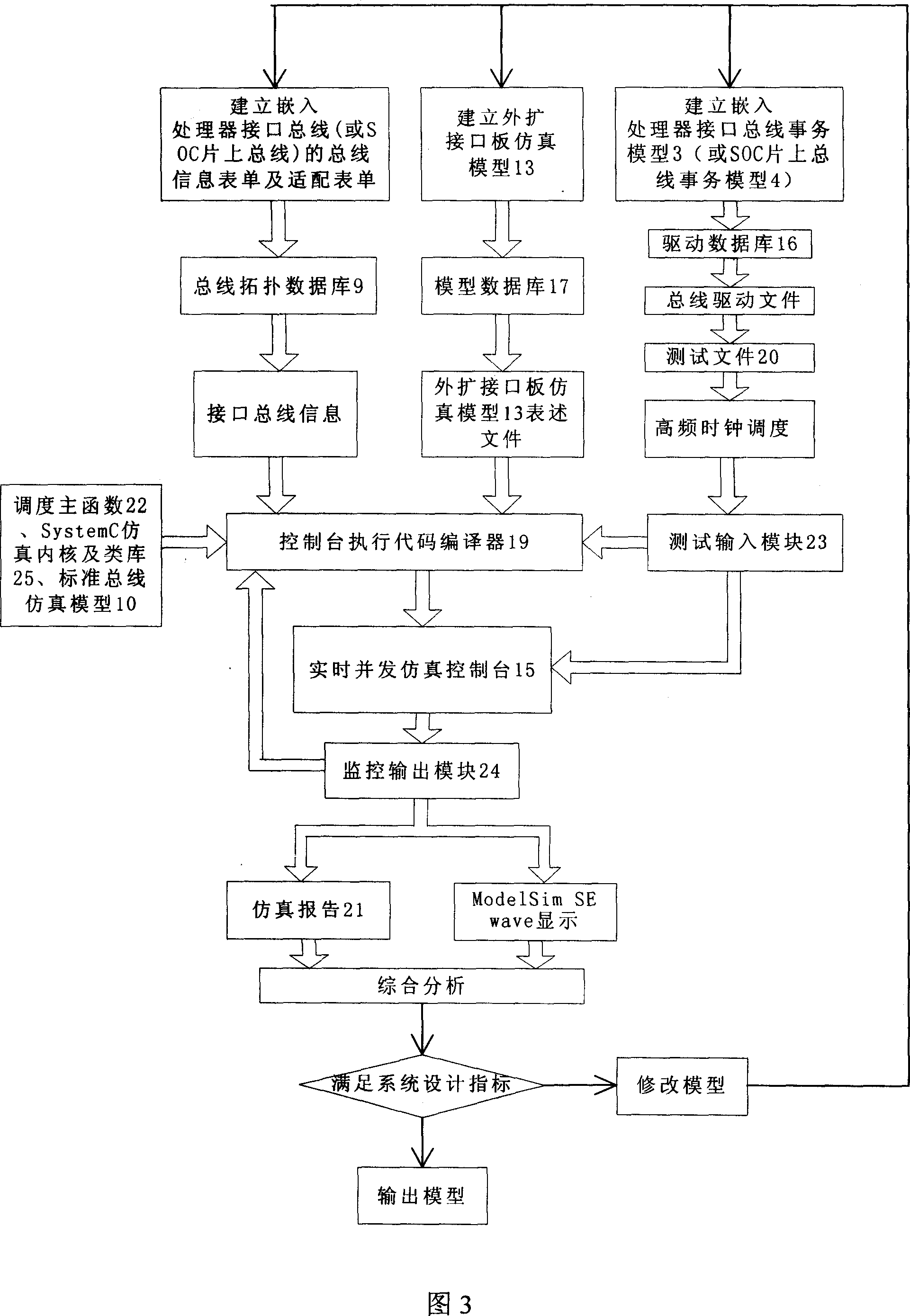

The invention relates to an embedded system simulate platform based on bus model, which leads in the embedded system flexible bus design theory, to realize the uniformity of various embedded system bottom structure, and use a system model language SystemC to build a processor host simulate model and an expansion interface board simulate model. The processor host simulate model comprises an embedded processor function model, an interface bus mission model or a SOC (on-chip system) function model, and an on-chip mission model. The invention uses software / hardware cooperate design and simulation integrated environment to realize the development of embedded system simulation model, and uses a real-time parallel simulation console to realize the parallel execution and detection of embedded system simulation model.

Owner:BEIHANG UNIV

RaceCheck: A Race Logic Ana,yzer Program for Digital Integrated Circuits

ActiveUS20060075367A1Reduce effortShorten the timeElectrical testingDesign optimisation/simulationTime informationSystemC

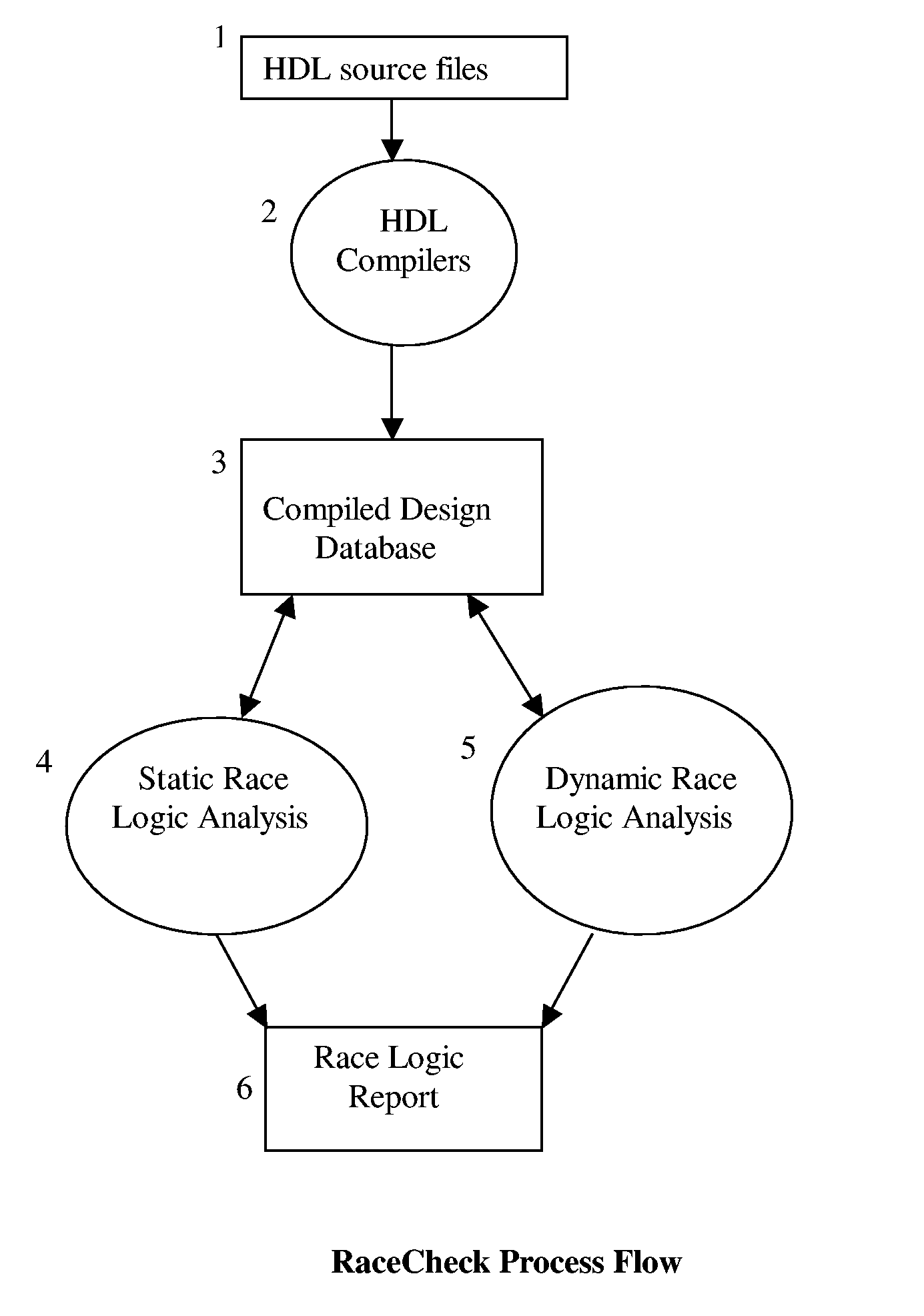

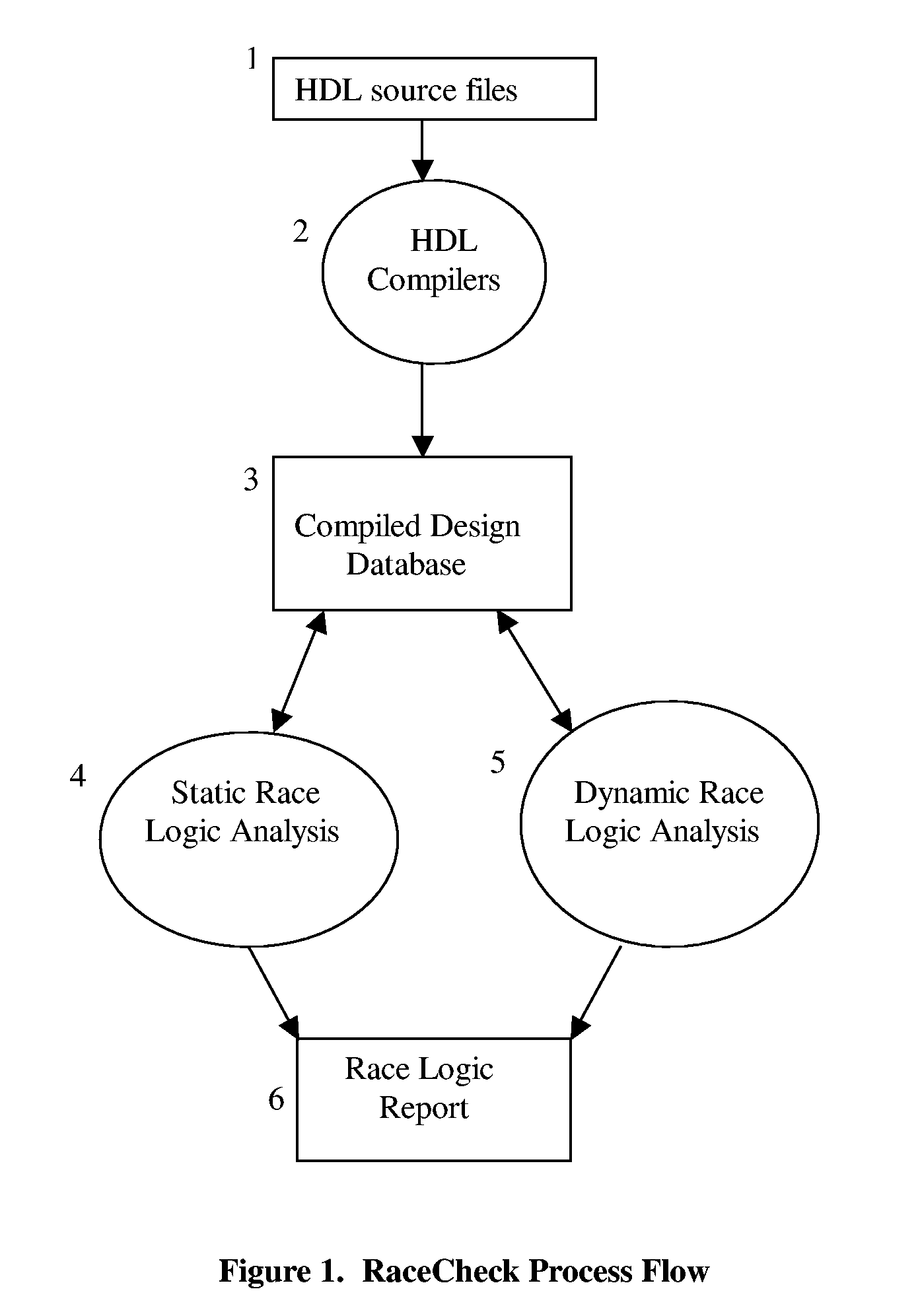

This invention describes a race logic audit program, RaceCheck, which is unique from the prior arts. Specifically, RaceCheck can perform both static and dynamic race logic analysis, and it works with a plurality of hardware description languages (HDL), which include but not limited to: VHDL, Verilog, SystemVerilog, and SystemC. Furthermore, RaceCheck makes use of both structural and timing information of IC designs, as well as binary-decision diagram (BDD) and automatic test pattern generation (ATPG) techniques to derive accurate race logic analysis results with few false violations. Finally, RaceCheck can detect concurrent invocation races of the $random system function, concurrent invocation races of user-defined tasks and functions, zero-delay combination loops, and RaceCheck's dynamic analysis engine uses a HDL simulation kernel to perform timing-accurate race logic analysis. All these aforementioned features are unique for the invention and have not been reported in any prior arts.

Owner:DYNETIX DESIGN SOLUTIONS

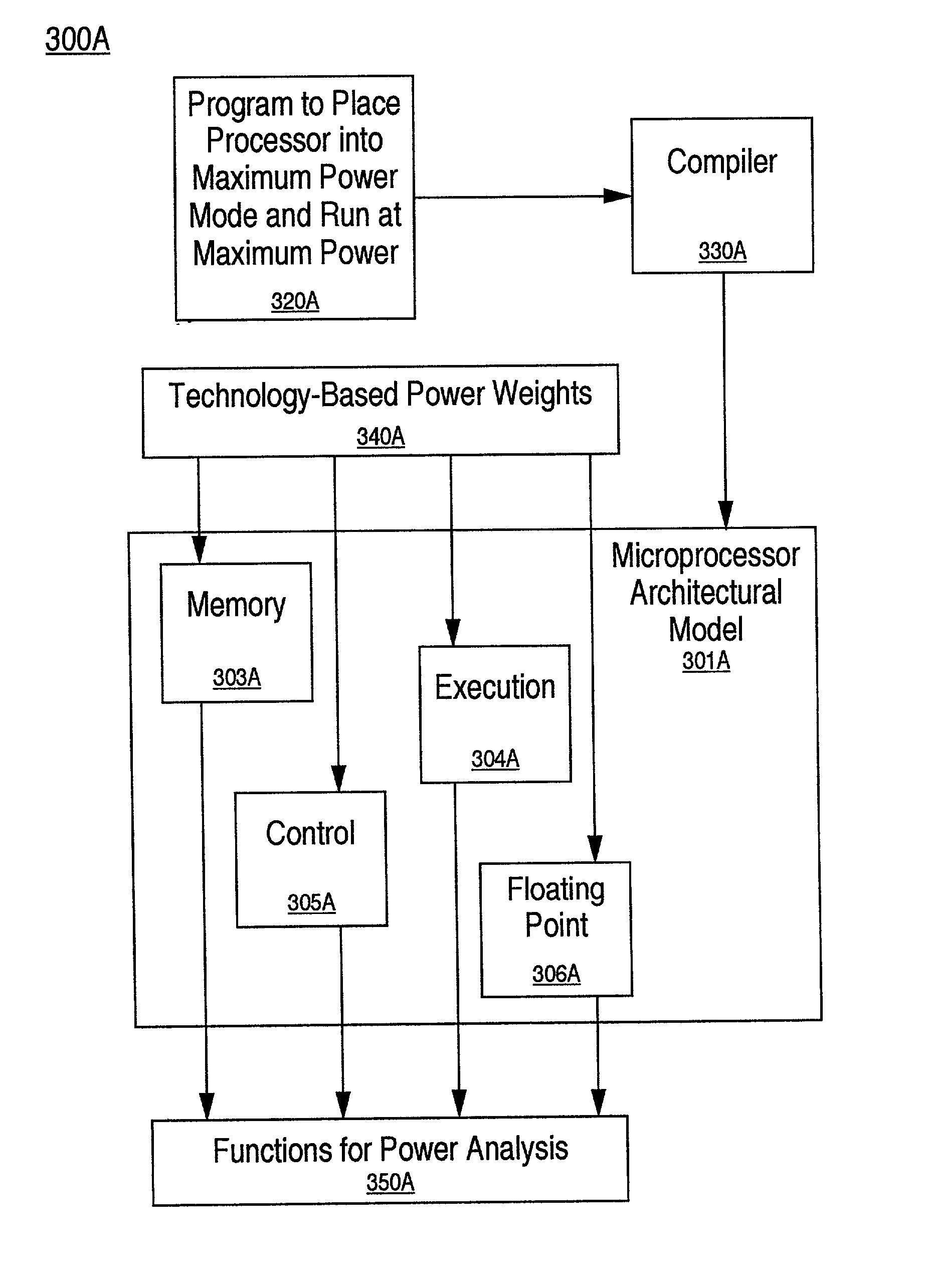

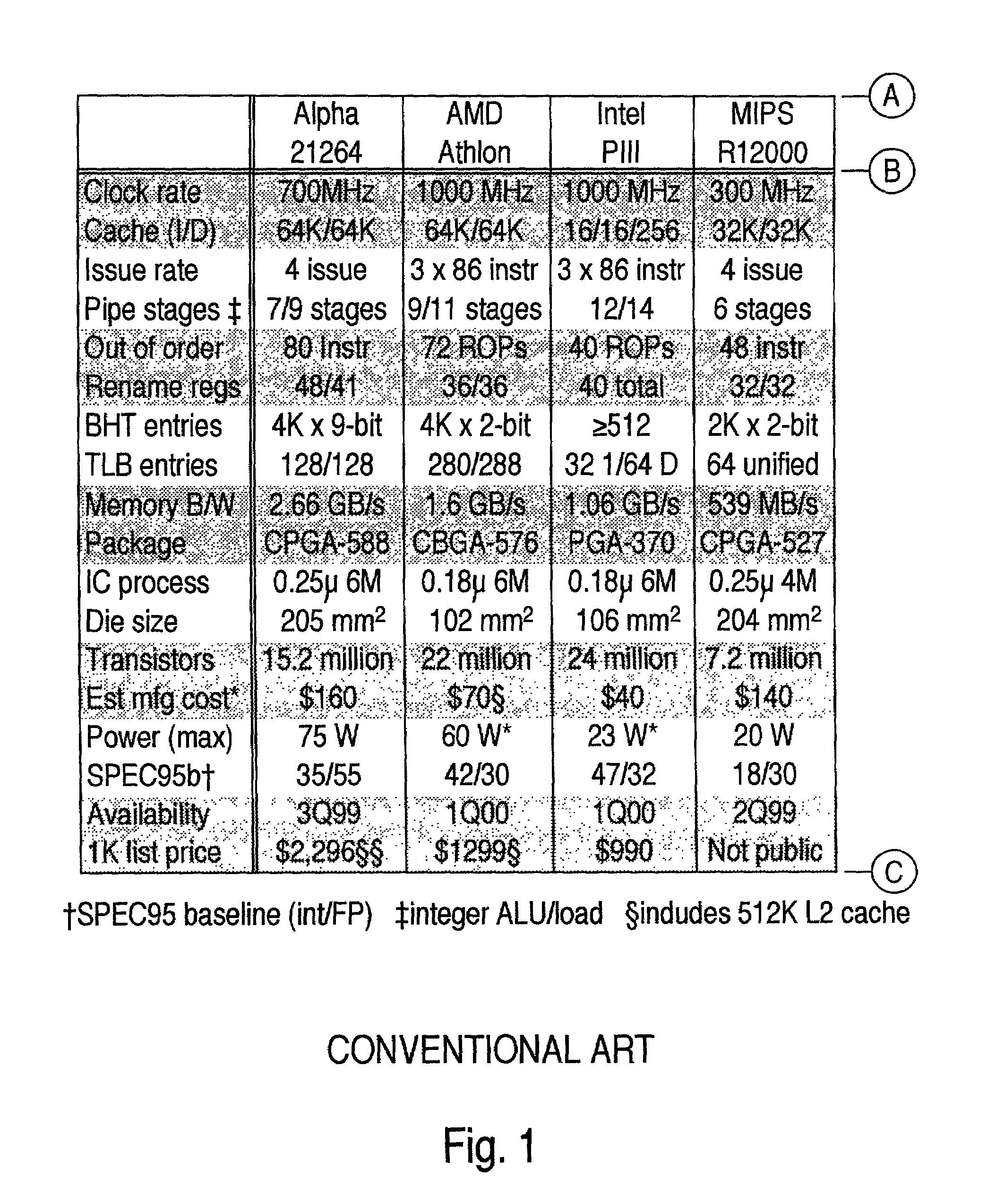

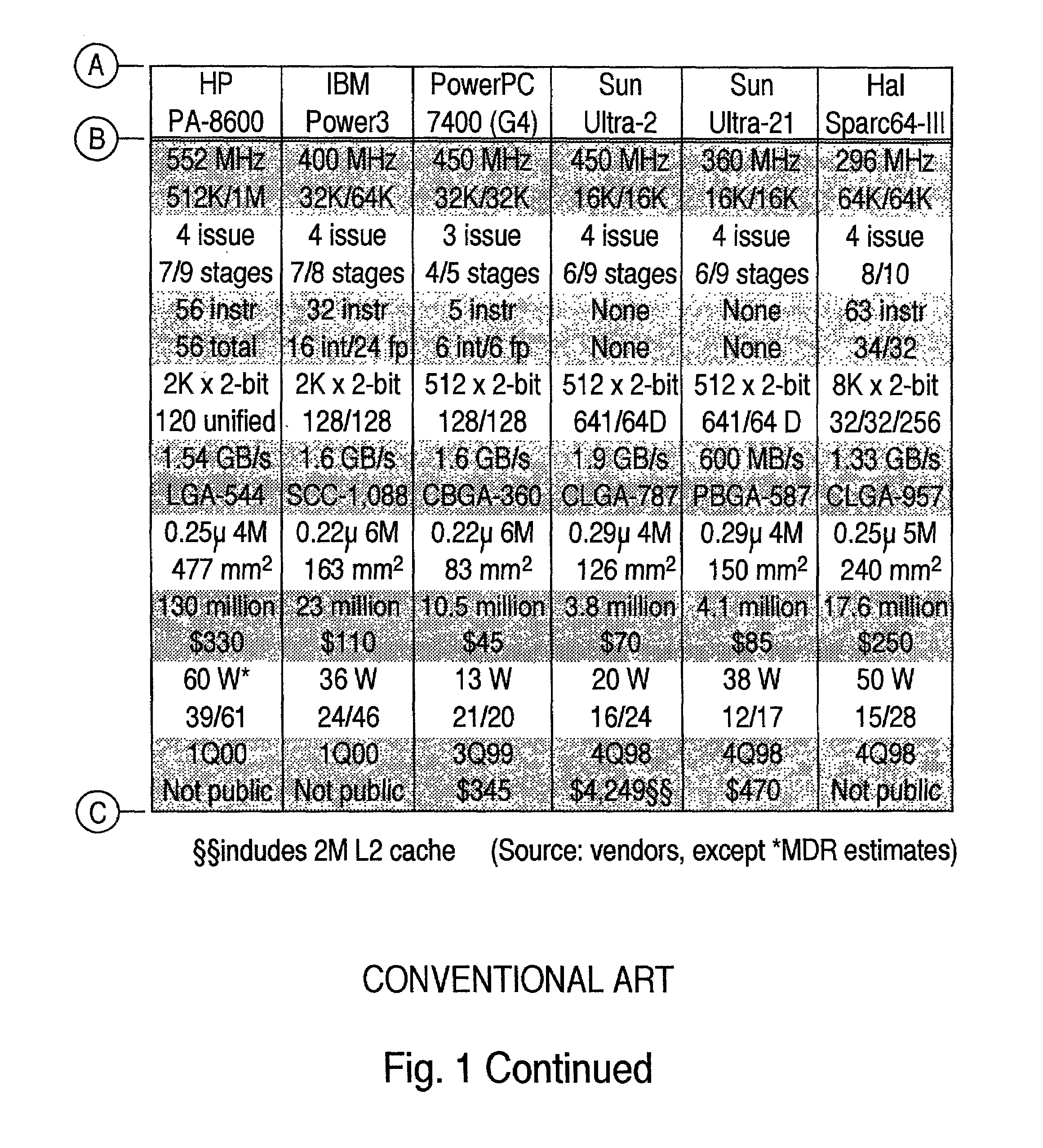

Method for deriving the benchmark program for estimating the maximum power consumed in a microprocessor

InactiveUS7003441B2Extensive analysisVolume/mass flow measurementAnalogue computers for electric apparatusSystemCInstruction stream

In one embodiment, for an electronic architecture with a functional constitution performing a number of functions characterized by separate stages performing subfunctions, a method of deriving a benchmark program for estimating the maximum power consumption by modeling a functional model of the architecture, compiling the benchmark program into a corresponding instruction stream, valuating power weights for each stage of each function of each constituent, inserting the power weights, running the model in a maximum power consumption mode, and summarizing power consumption. In one embodiment, the benchmark program is applied by specifying a design analysis to be performed, selecting a function, designating a stages performing that function, removing a set of instruction set architecture instructions corresponding the designated stage, emulating the constituent subfunction corresponding to the stages designated stage, and summarizing. In one embodiment, the model is written in SystemC. In one embodiment, a compiler used is a PERL script.

Owner:HEWLETT-PACKARD ENTERPRISE DEV LP

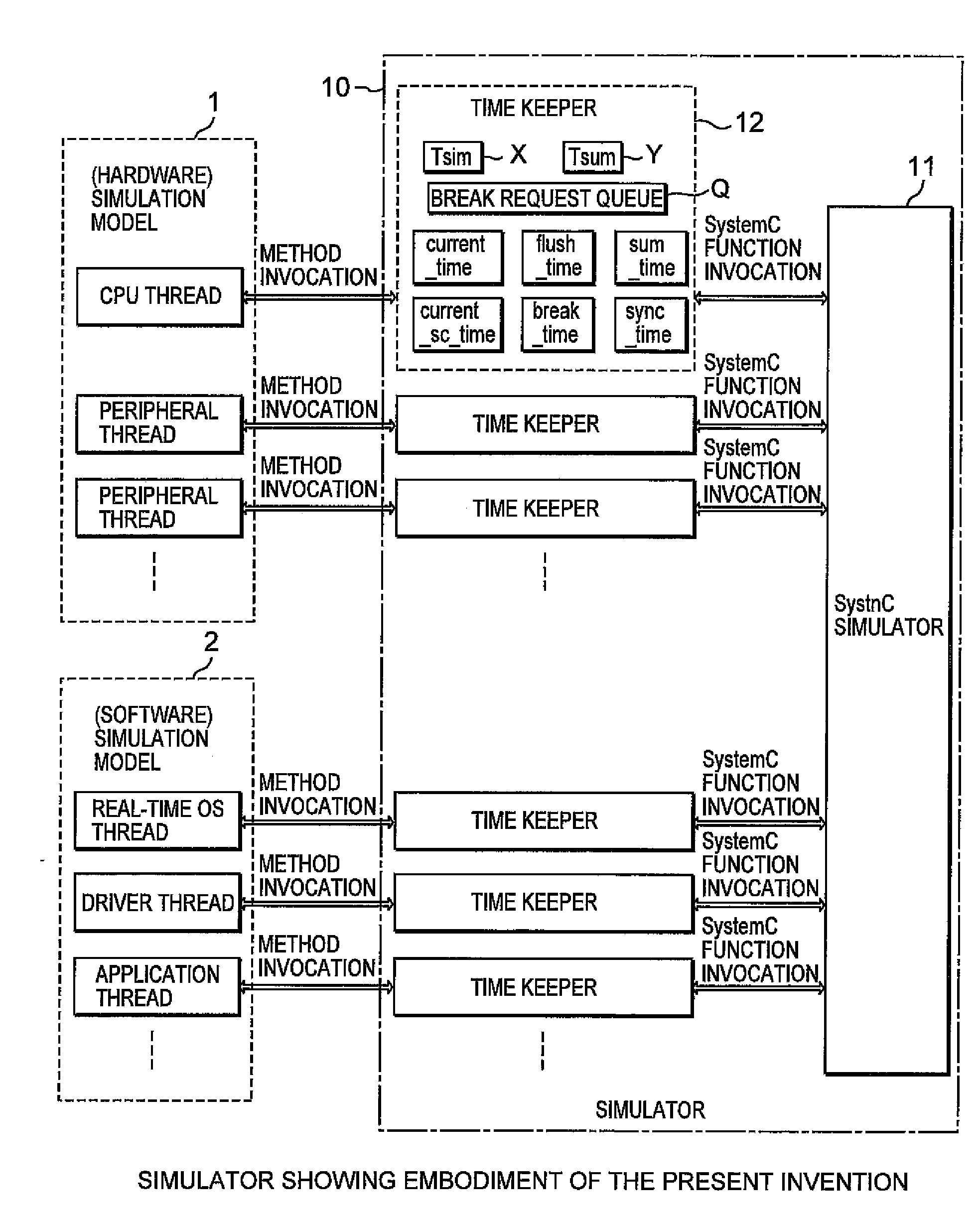

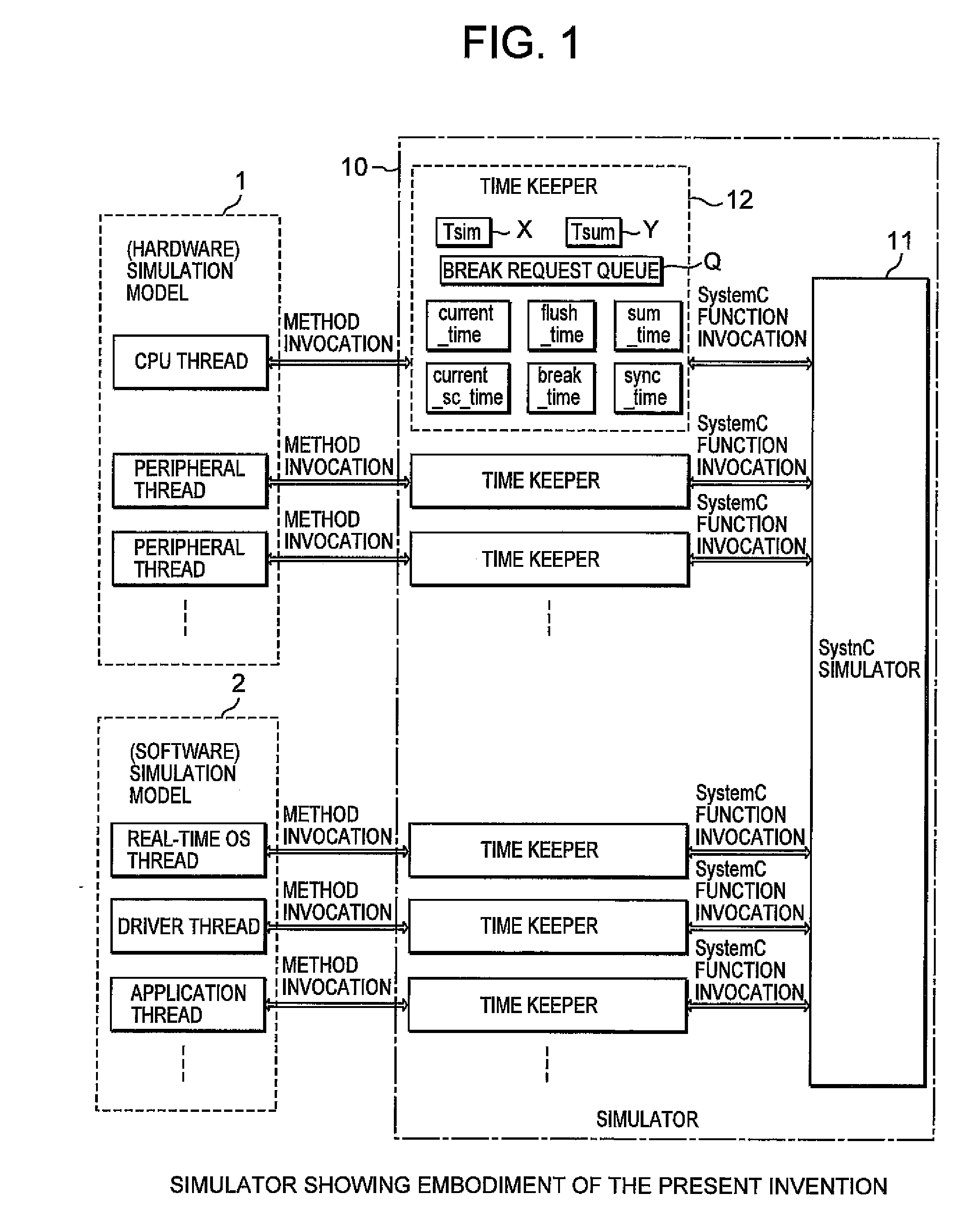

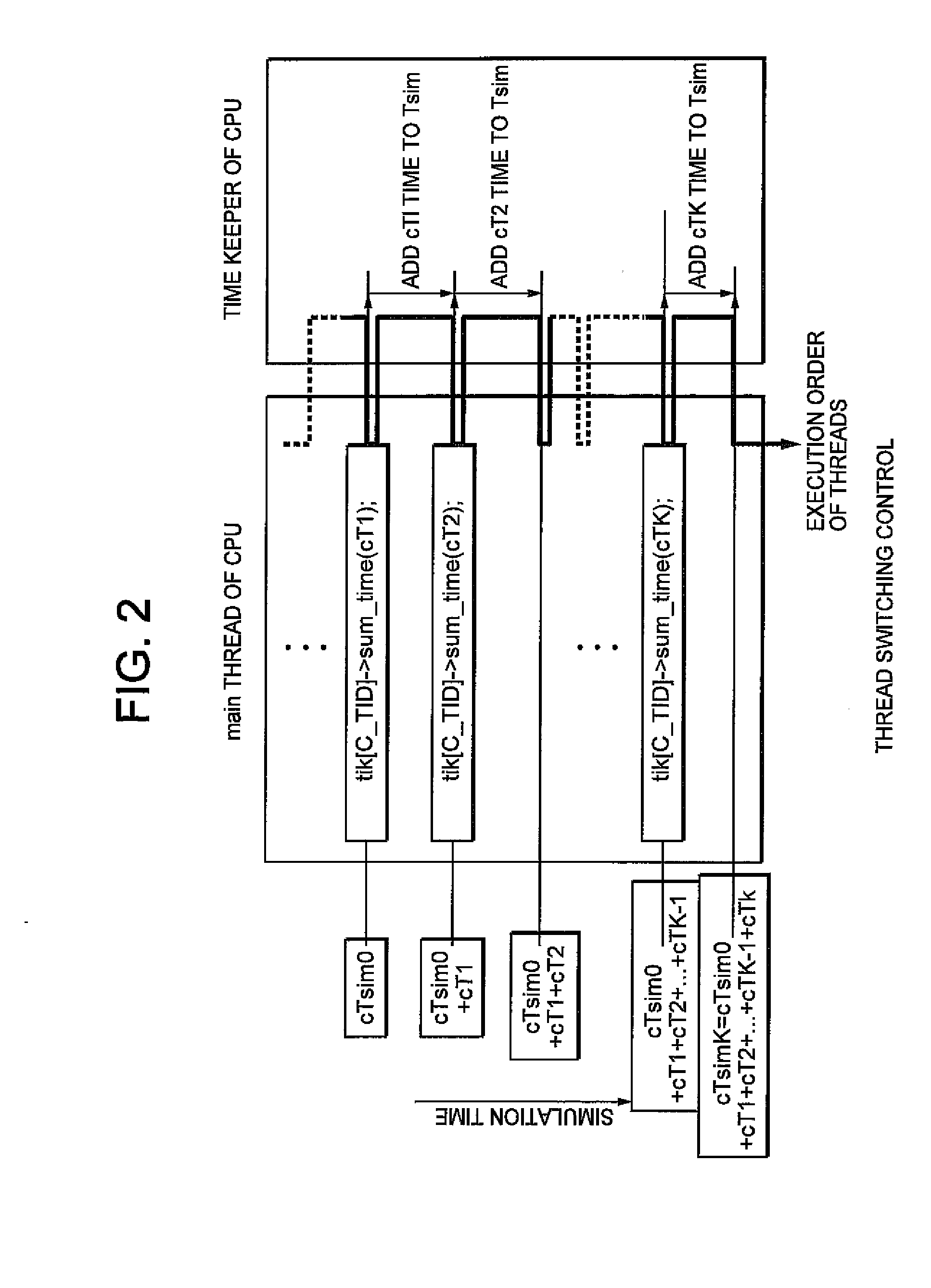

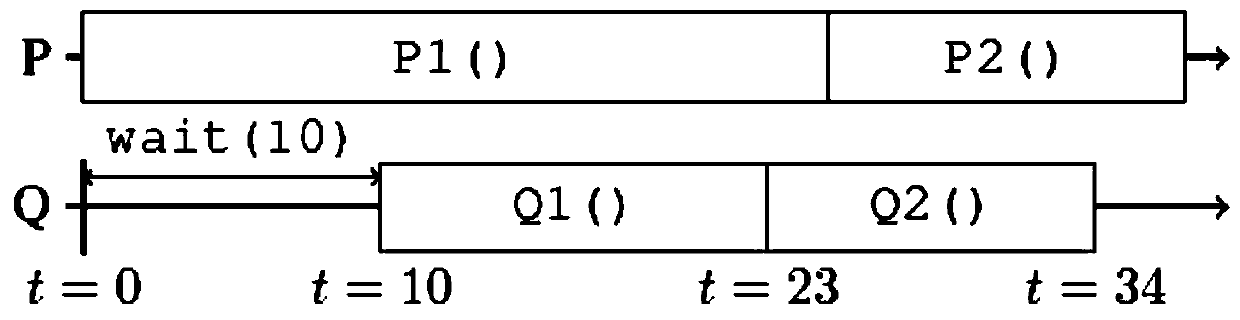

Hard/Soft Cooperative Verifying Simulator

InactiveUS20090222250A1Reduce overheadReduced simulation timeAnalogue computers for electric apparatusCAD circuit designSystemCParallel computing

The present invention provides a hard / soft cooperative verifying simulator based on a SystemC simulator, capable of reducing overhead of context switching control thereby to shorten processing time. Time keepers for controlling simulation times of a plurality of threads are provided corresponding to the threads generated as simulation models for hardware and software. Each of the time keepers has a variable which holds a simulation time for each thread, a variable which holds a summation time, and a break request queue which stores a break time and its corresponding break method therein. The time keeper manages both variables and the queue in response to six types of method invocations from the thread, and invokes a wait function of the SystemC simulator when necessary. It is thus possible to reduce the number of times that a wait function invocation is performed, and shorten the entire processing time.

Owner:LAPIS SEMICON CO LTD

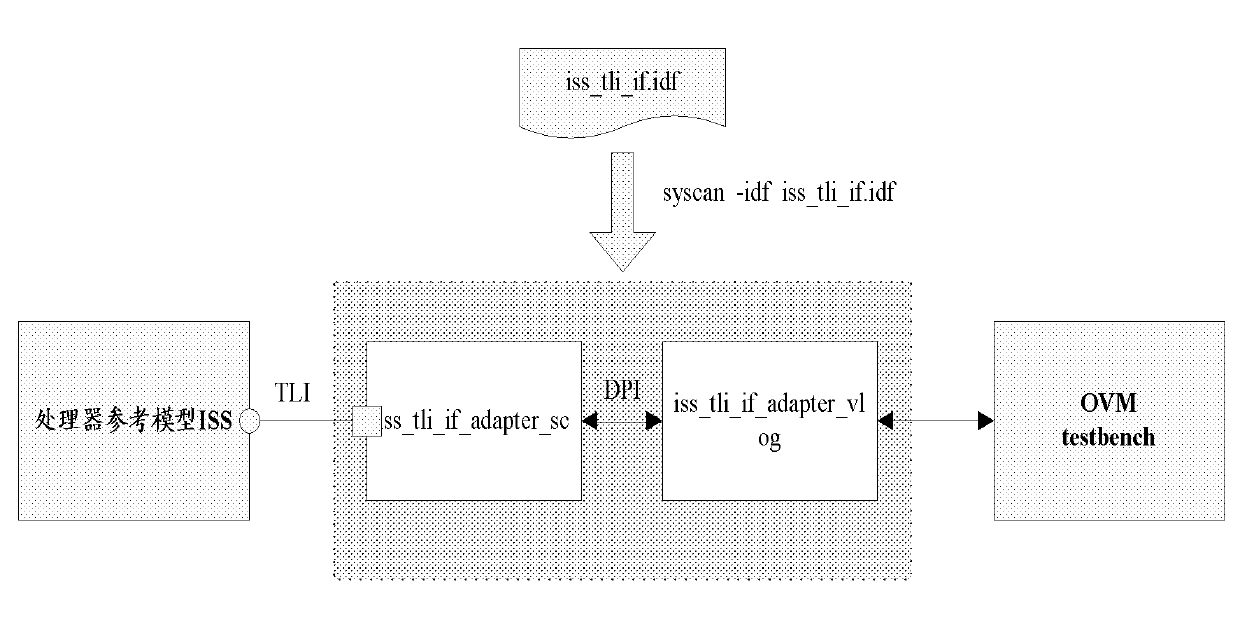

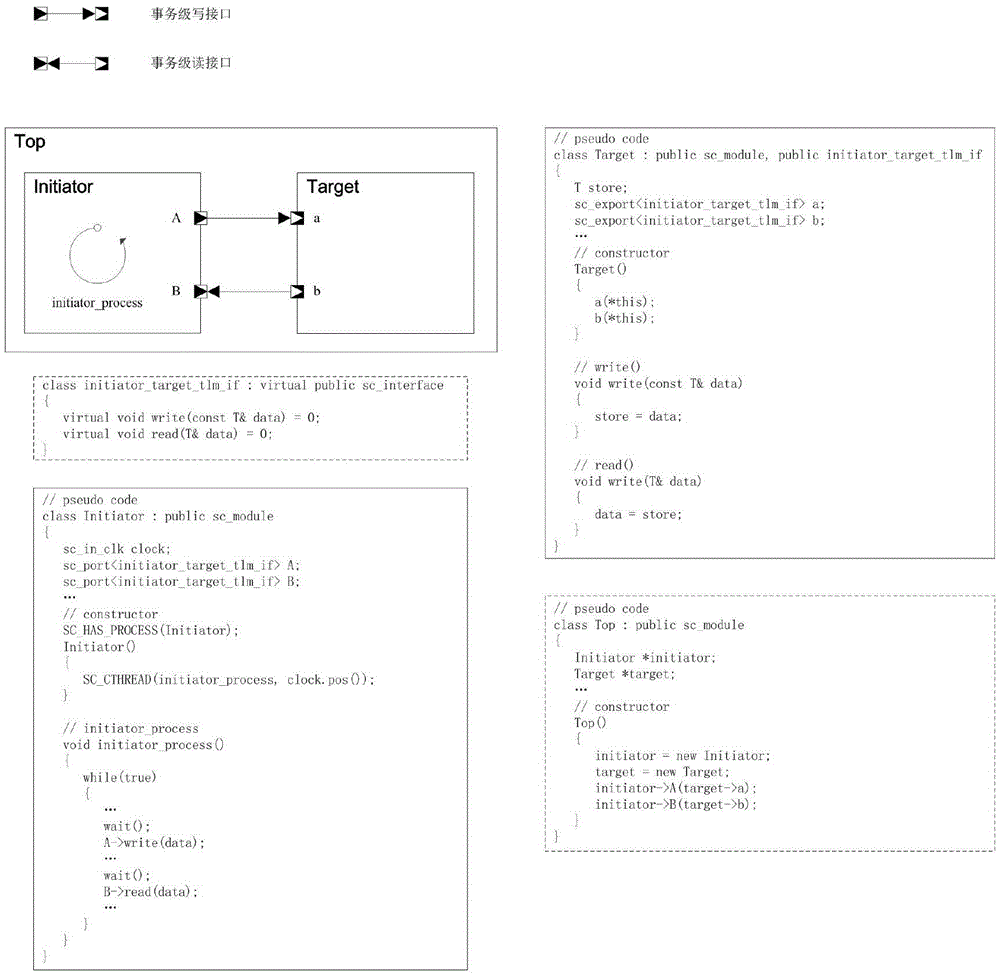

Communication interface method of processor reference model under multiple simulation and verification platforms

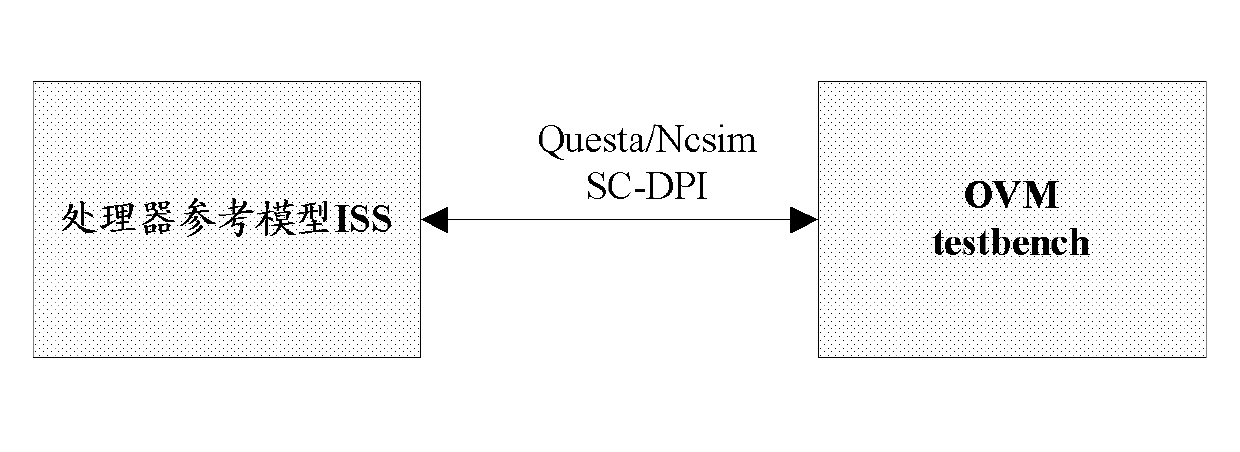

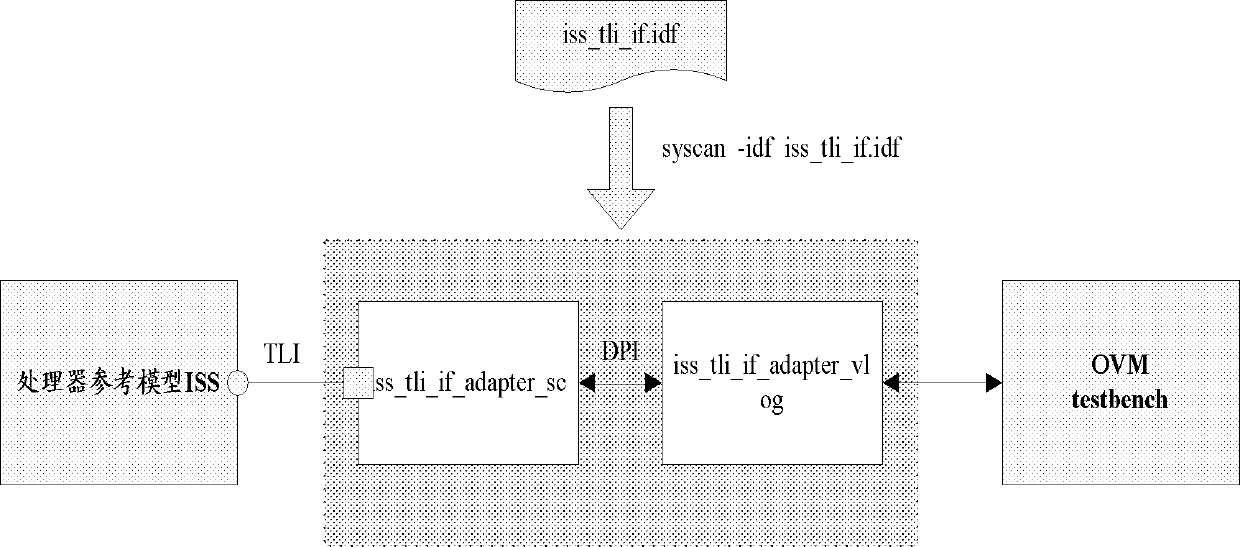

InactiveCN102567122AImprove efficiencyQuality improvementInterprogram communicationPerformance functionReference model

The invention relates to a communication interface method of a processor reference model under multiple simulation and verification platforms, wherein the communication interface method is used for realizing a blockable communication interface between the processor reference model and the verification platforms. The communication interface method comprises the steps of: under a VCS (Verilog Compiler Simulator) simulation and verification platform, defining a transaction-level communication interface according to an interface requirement of the processor reference model, fulfilling the function of a defined interface function to realize the interaction with the processor reference model, compiling an interface definition file and generating a corresponding SystemC / SystemVerilog adapter by using a VCS tool command, and exporting an interface performance function of a subsequent adapter to SystemVerilog by using a DPI (Direct Programming Interface); and under a Questa / Ncsim simulation platform, constructing a SystemC module, defining a member function, exporting a macro interface function embedded in a simulation tool to verilog, and importing the interface function by using an import sentence in the verilog.

Owner:北京国睿中数科技股份有限公司

Software and hardware synergic simulation verification platform and construction method thereof

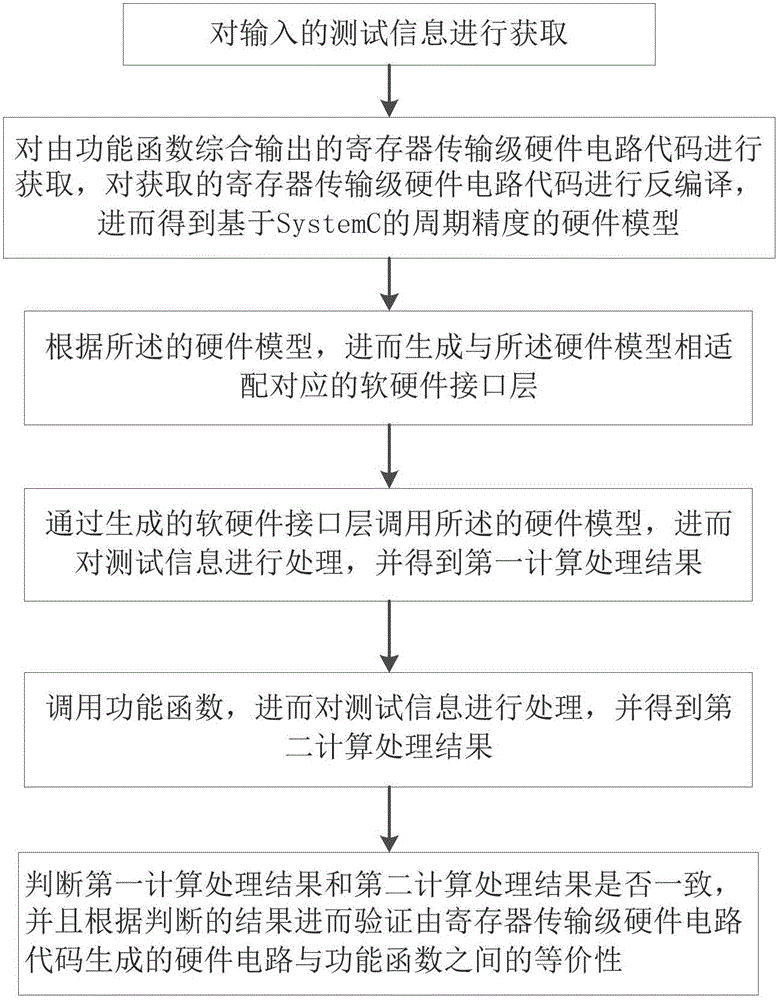

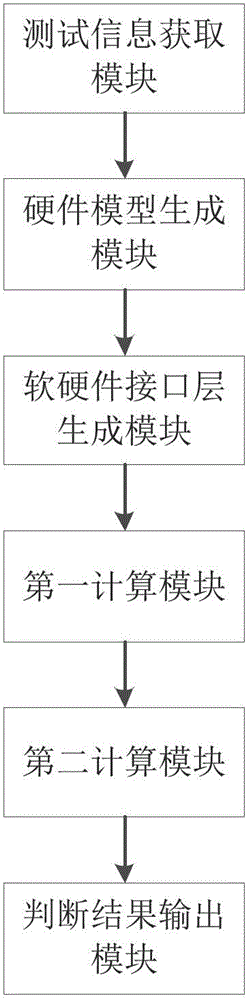

ActiveCN103150441AImprove the efficiency of equivalenceImprove simulation speedSpecial data processing applicationsPerformance functionSystemC

The invention discloses a software and hardware synergic simulation verification platform and a construction method thereof. The verification platform comprises a testing information acquisition module, a hardware model generation module, a software and hardware interface layer generation module, a first calculation module, a second calculation module and a judgment result output module. The method comprises the steps of obtaining a register transfer level hardware circuit code comprehensively output by a performance function, decompiling the obtained register transfer level hardware circuit code to obtain a hardware model based on SystemC cycle precision, generating a software and hardware interface layer, calling the hardware model through the generated software and hardware interface layer to process testing information, calling the performance function to process the testing information, and judging whether a first calculation processing result is the same as a second calculation processing result. The platform and the method improve simulation verification efficiency of high-level comprehensive design, and can check correctness of a high-level comprehensive tool. The platform and the method are widely applied to system level design.

Owner:SUN YAT SEN UNIV

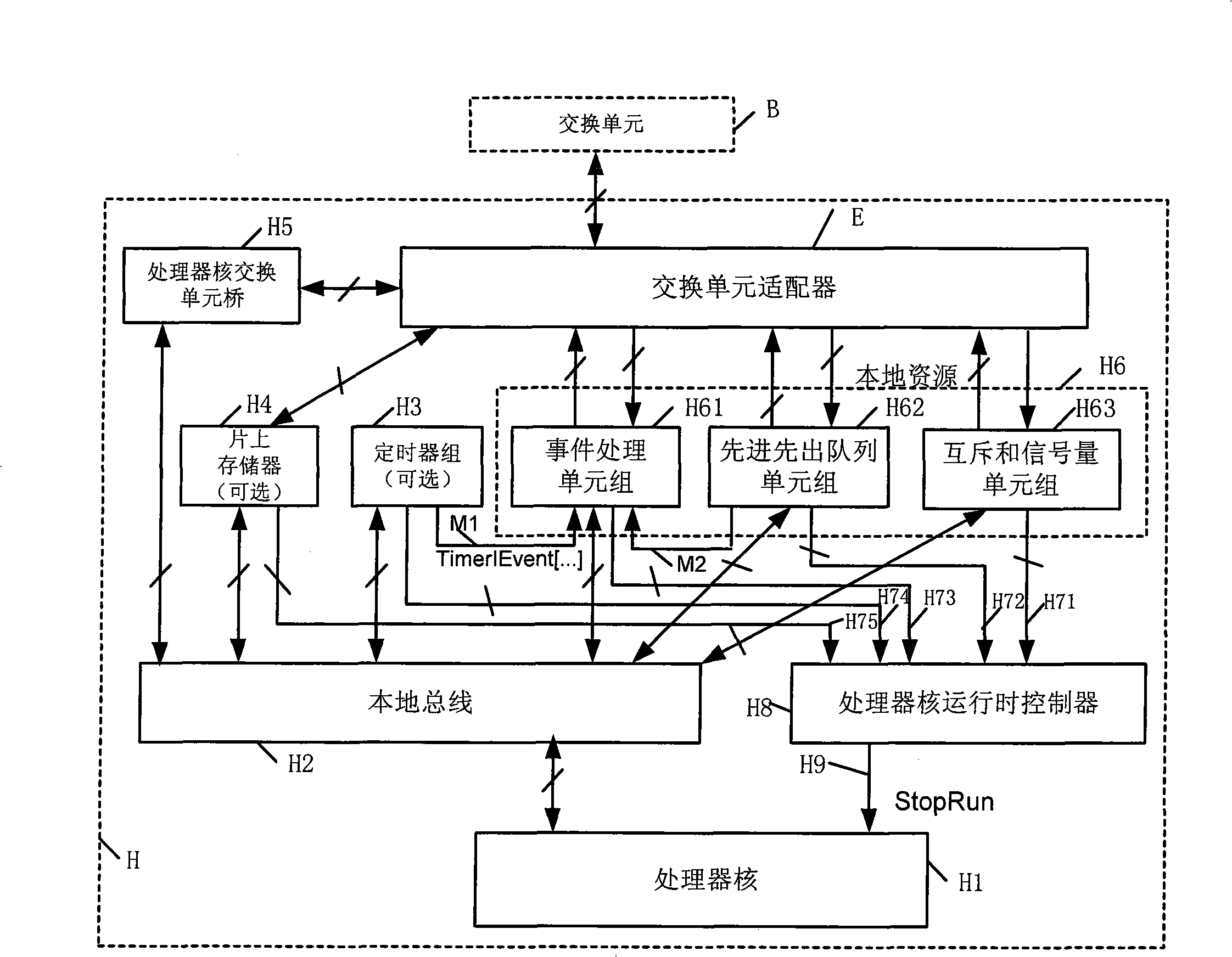

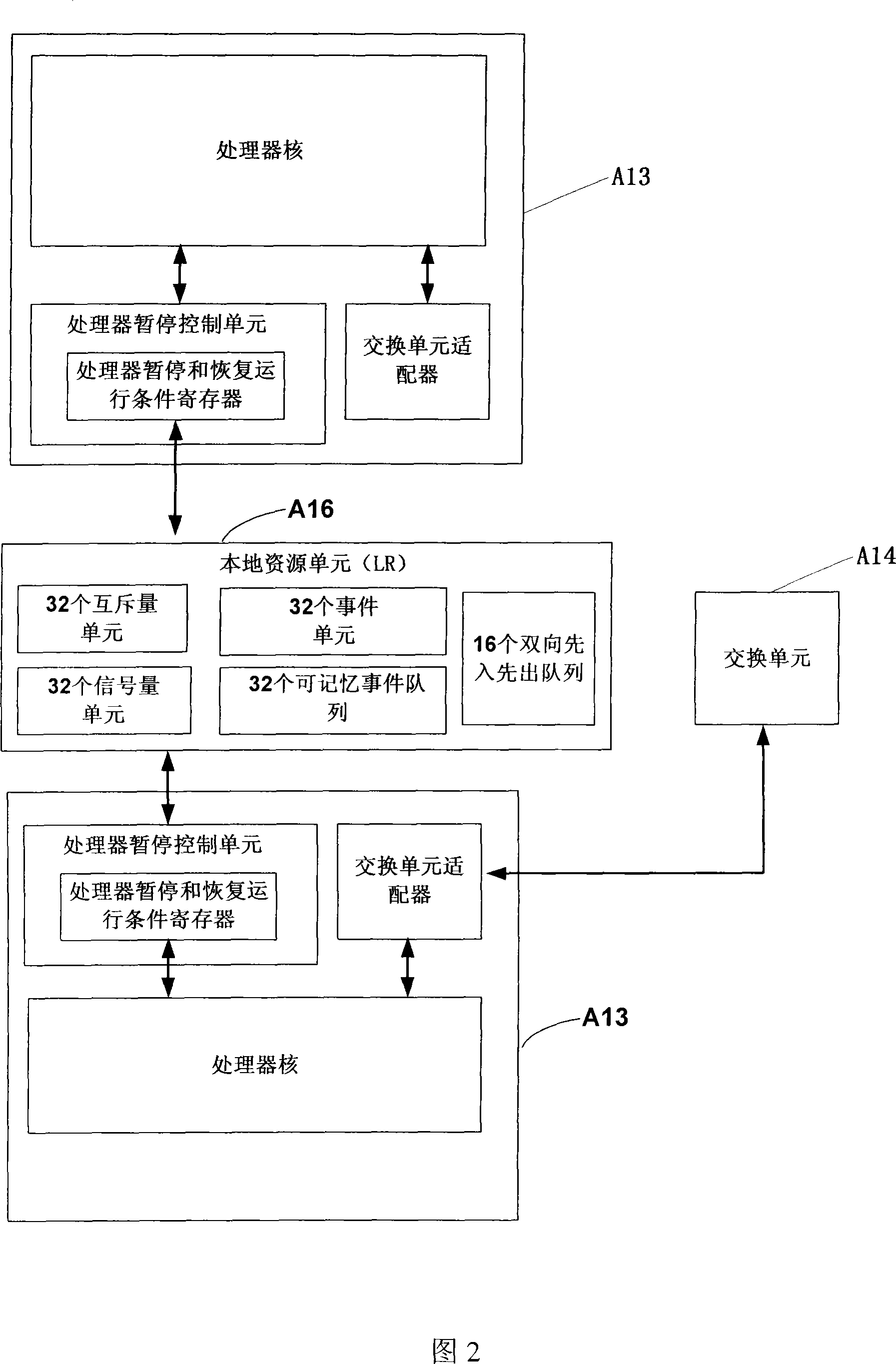

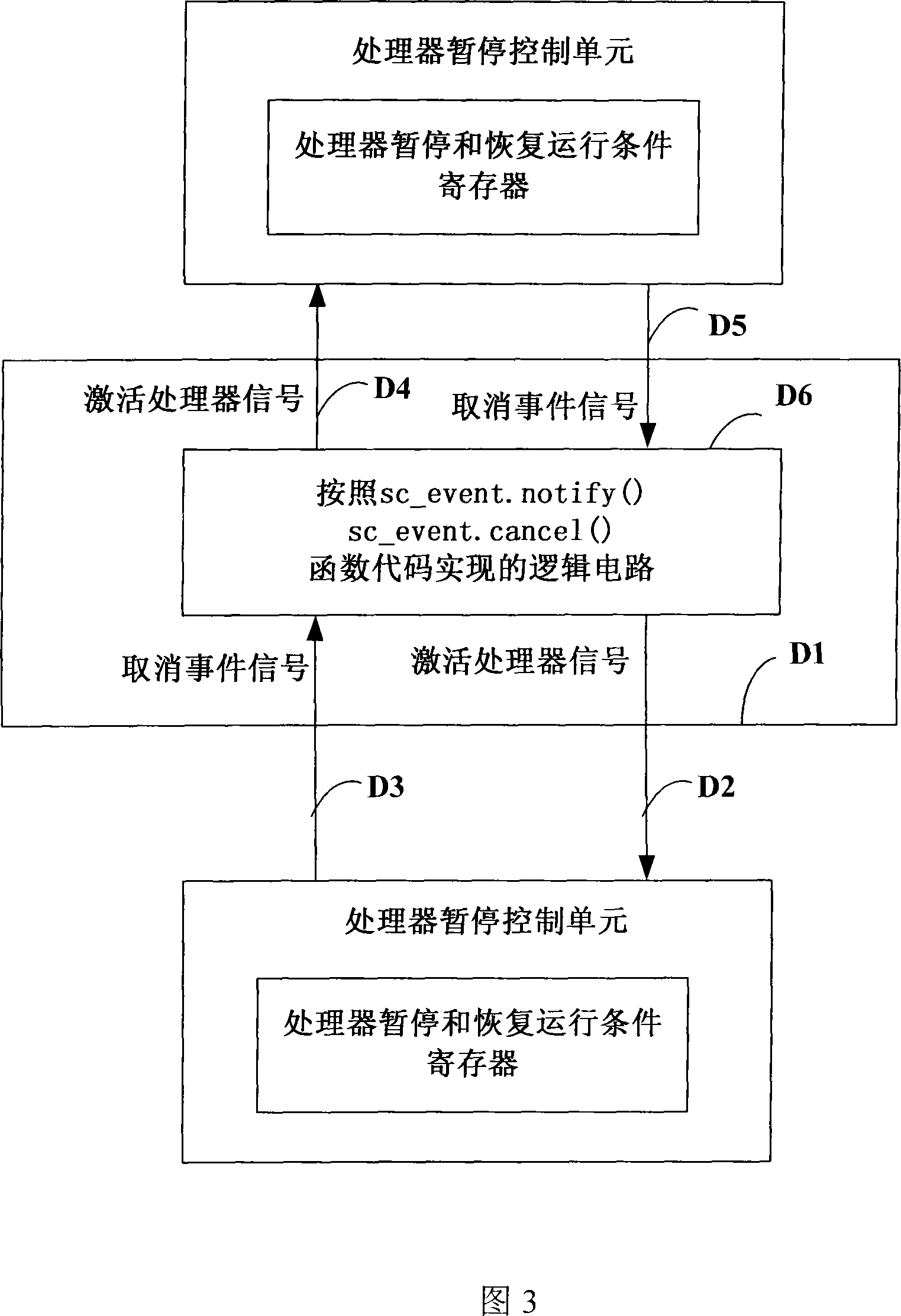

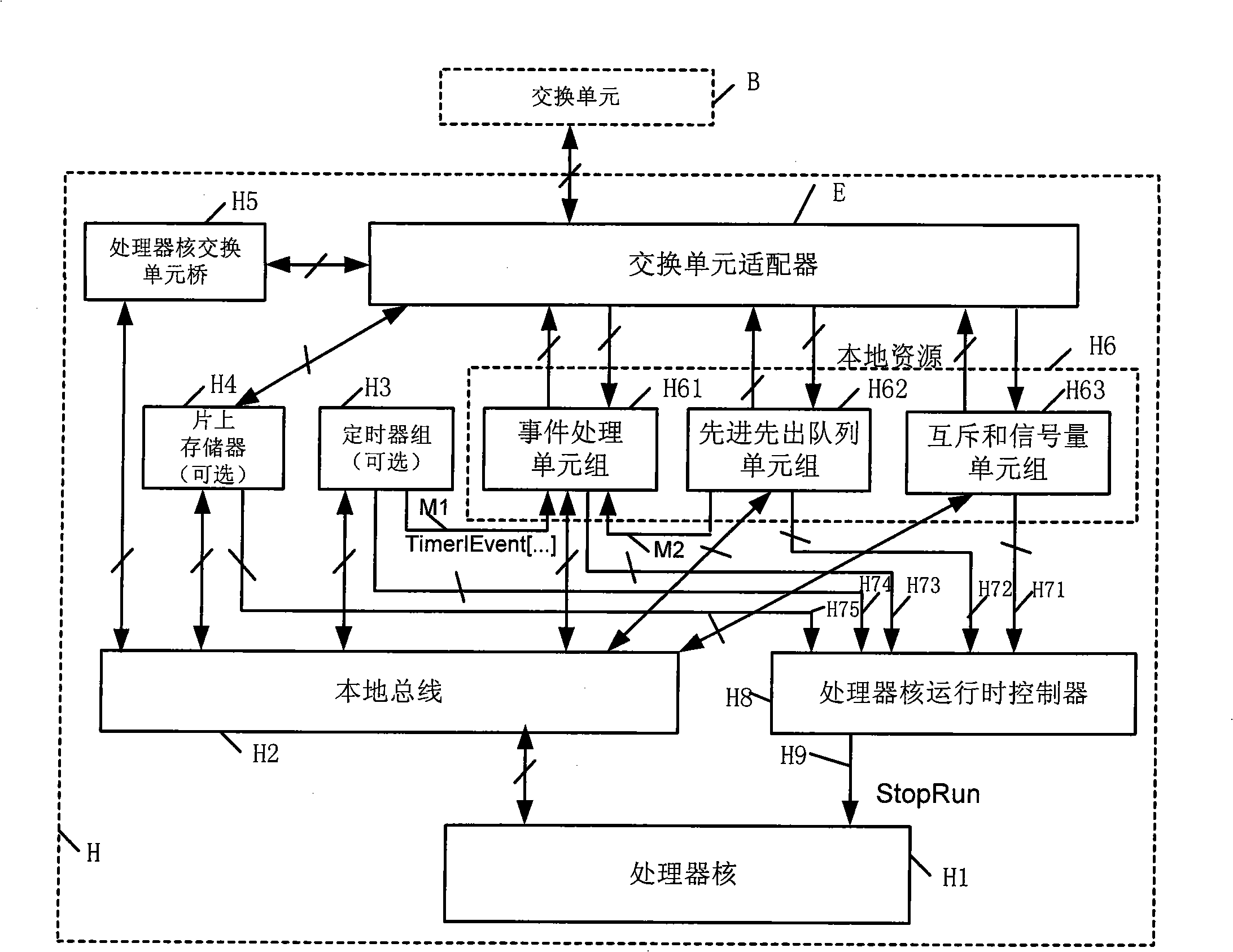

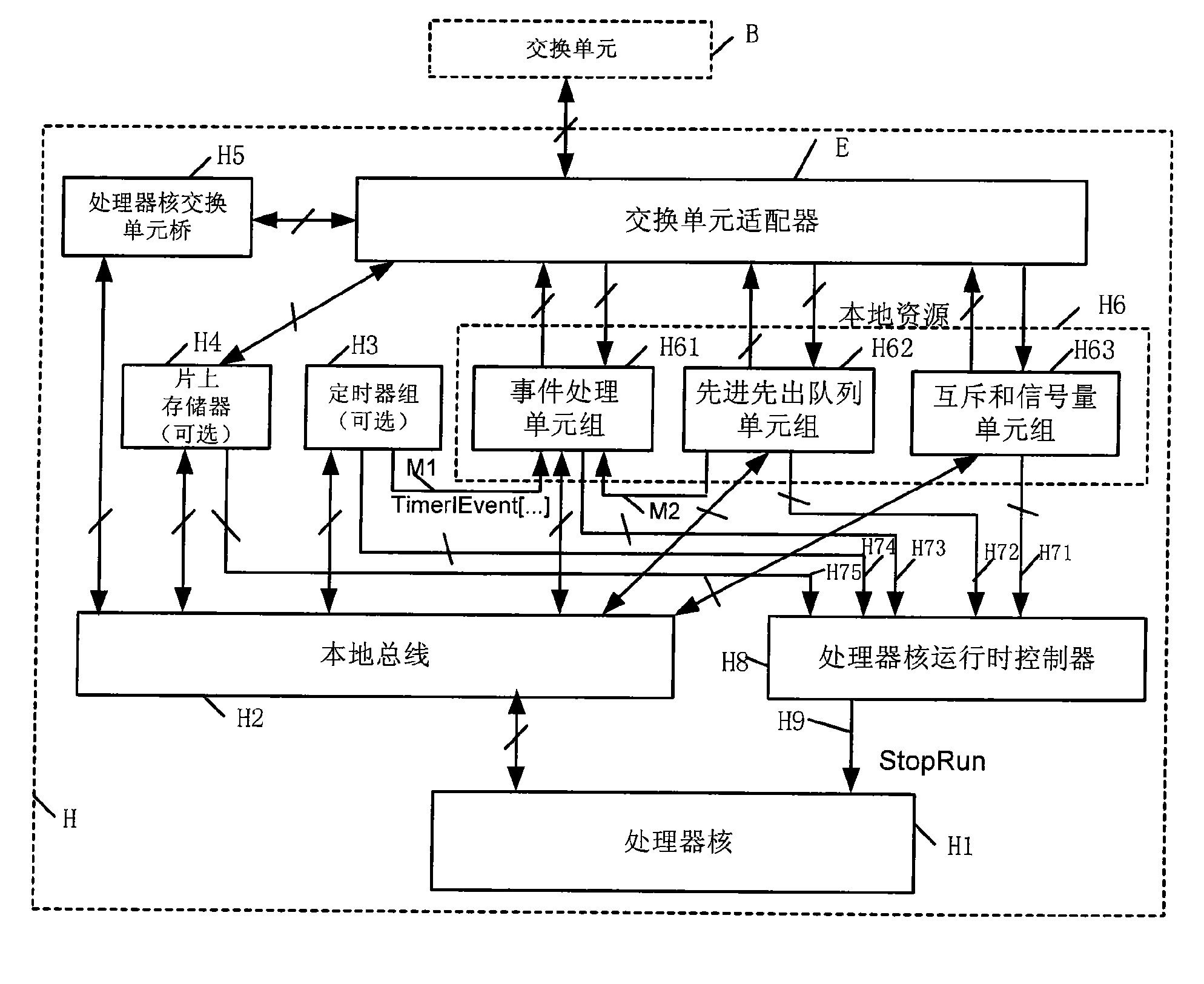

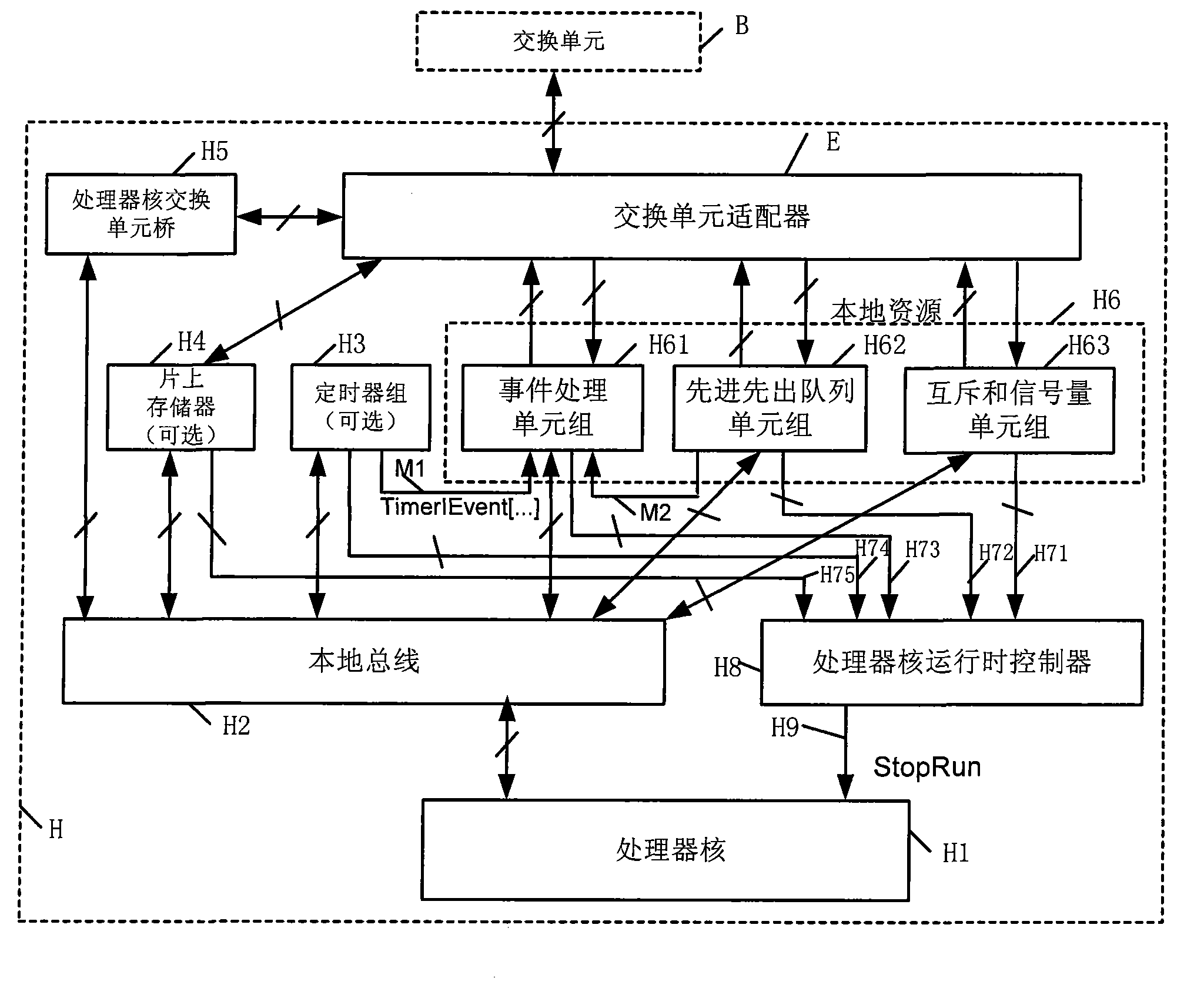

Event processing unit group of multi-core processor conforming to systemC grammar

ActiveCN101315648AMultiprogramming arrangementsSpecial data processing applicationsSystemCMapping algorithm

The invention discloses an event processing unit group of a multicore processor, which satisfies systemC grammar. The event processing unit group comprises various public functions of sc_event and sc_event_queue of the systemC grammar, various forms of wait (ellipsis) function, and a logic circuit for the realization of an SC_THREAD and SC_METHOD sensitive table, and is used for transmitting the signal to activate and suspend the processor and causing the mapping algorithm of a software developing tool to carry out combination to a plurality of the event processing unit groups of different processing units, thus realizing function defined by a plurality of sc_event or sc_event_queue grammar units, the function of the wait (ellipsis) function and the function of the SC_THREAD and SC_METHOD sensitive table. The event processing unit group supports a plurality of events in a single module and supports an event unit trigger event positioned in a processing unit, a plurality of the event units positioned in other processing units receive the notification message.

Owner:INST OF COMPUTING TECH CHINESE ACAD OF SCI

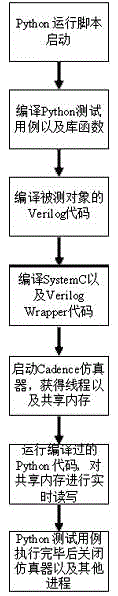

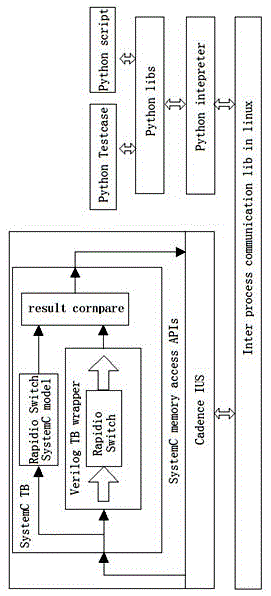

Python language based Rapidio switcher logic simulation verification platform and method

ActiveCN104965750AImprove writing efficiencyImprove reusabilitySoftware simulation/interpretation/emulationSystemCPython language

The present invention discloses a Python language based Rapidio switcher logic simulation verification platform and method. The verification platform comprises: a SystemC interface function for interpreting Python semantics, a DPI interface function used by SystemC to call SystemVerilog, and a test case and a running script realized by Python. According to the present invention, an interpreter between the Python language and the SystemC language is added, so that the Python language can directly control stimulus input of a logic simulator and compare responsive output and the test case programmed by using Python can be used directly in logic simulation and applied on a Rapidio switcher. By using the above environment, the programming efficiency and reusability of the test case can be greatly improved.

Owner:SHANDONG LANGCHAO YUNTOU INFORMATION TECH CO LTD

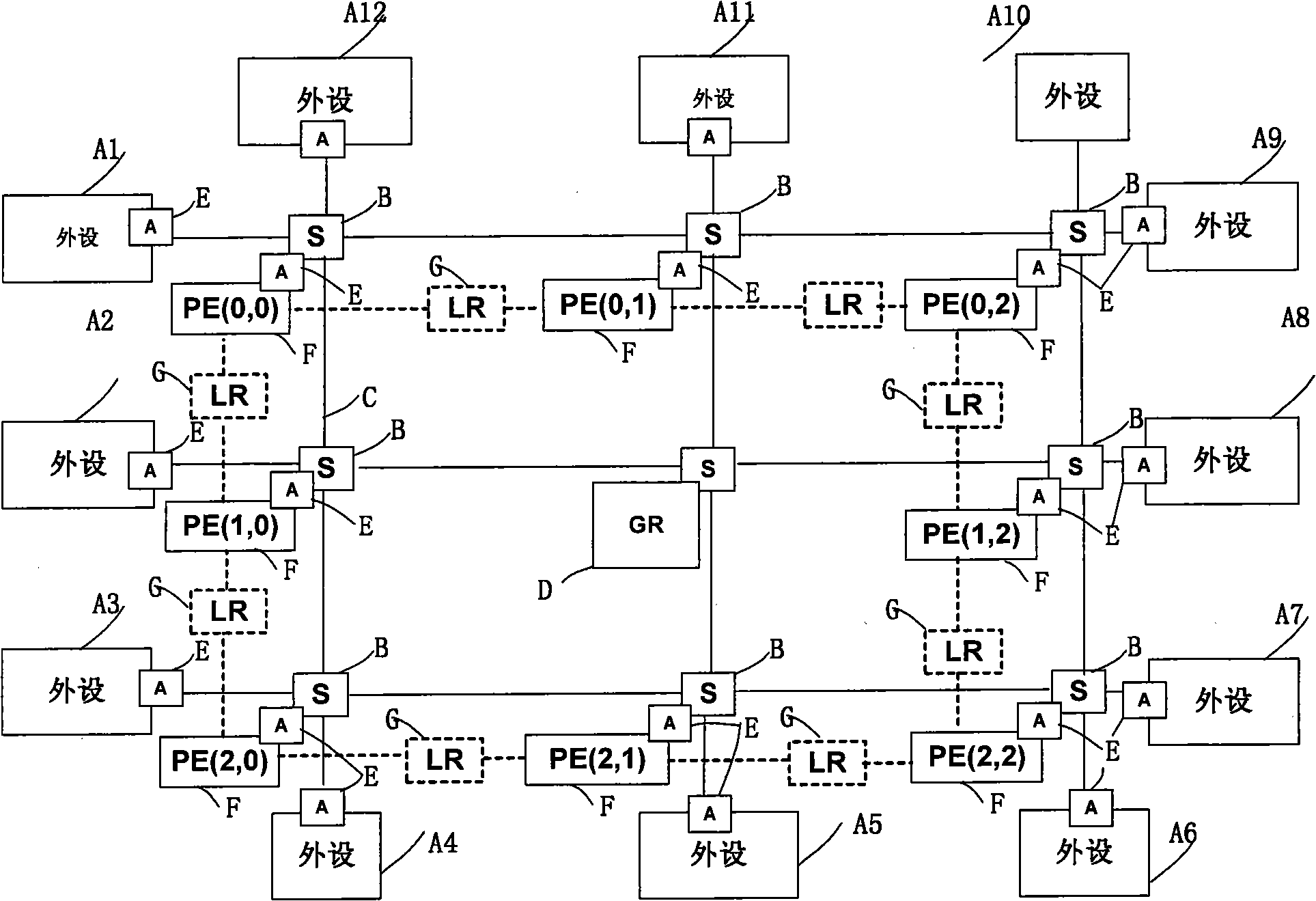

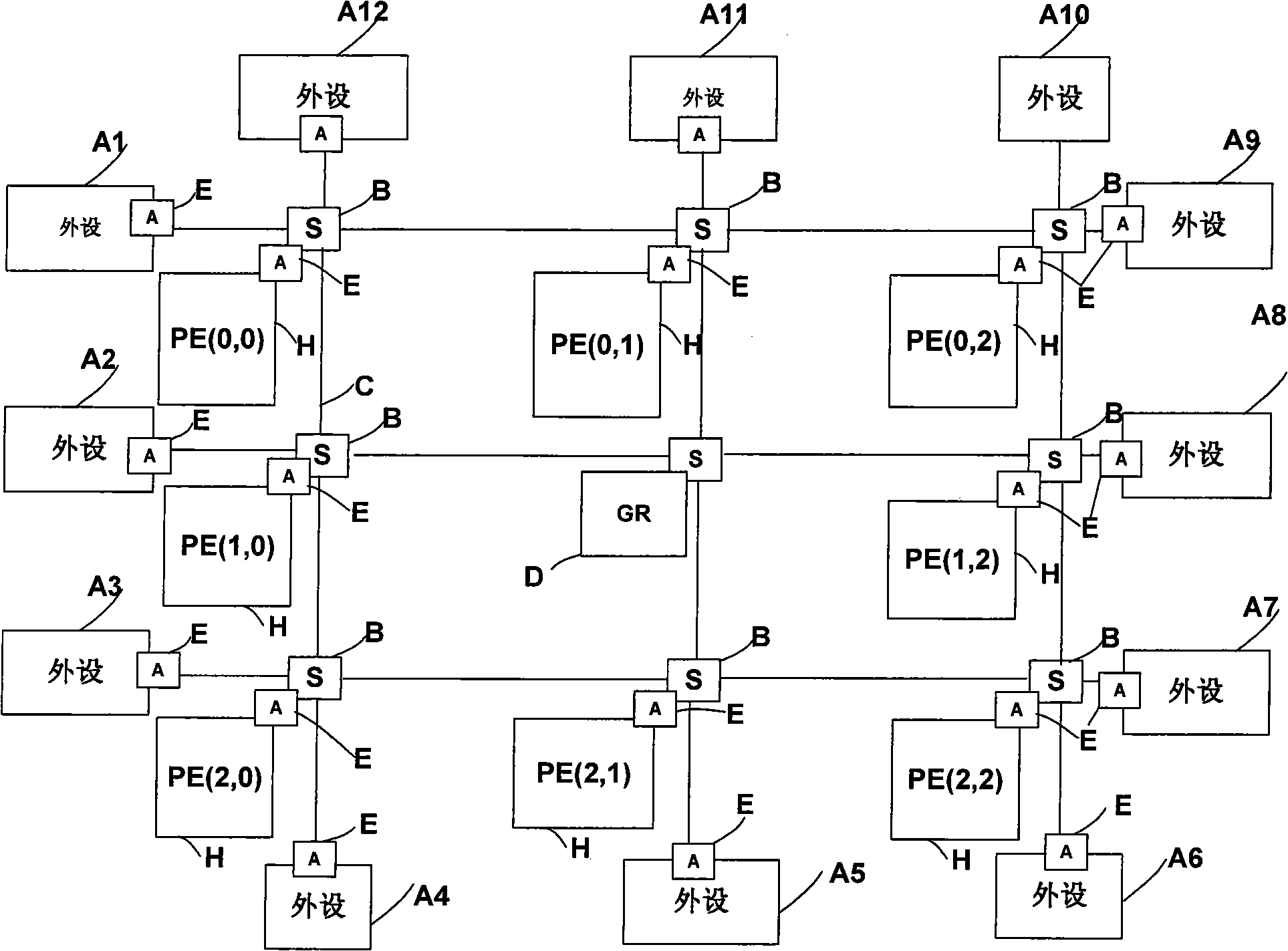

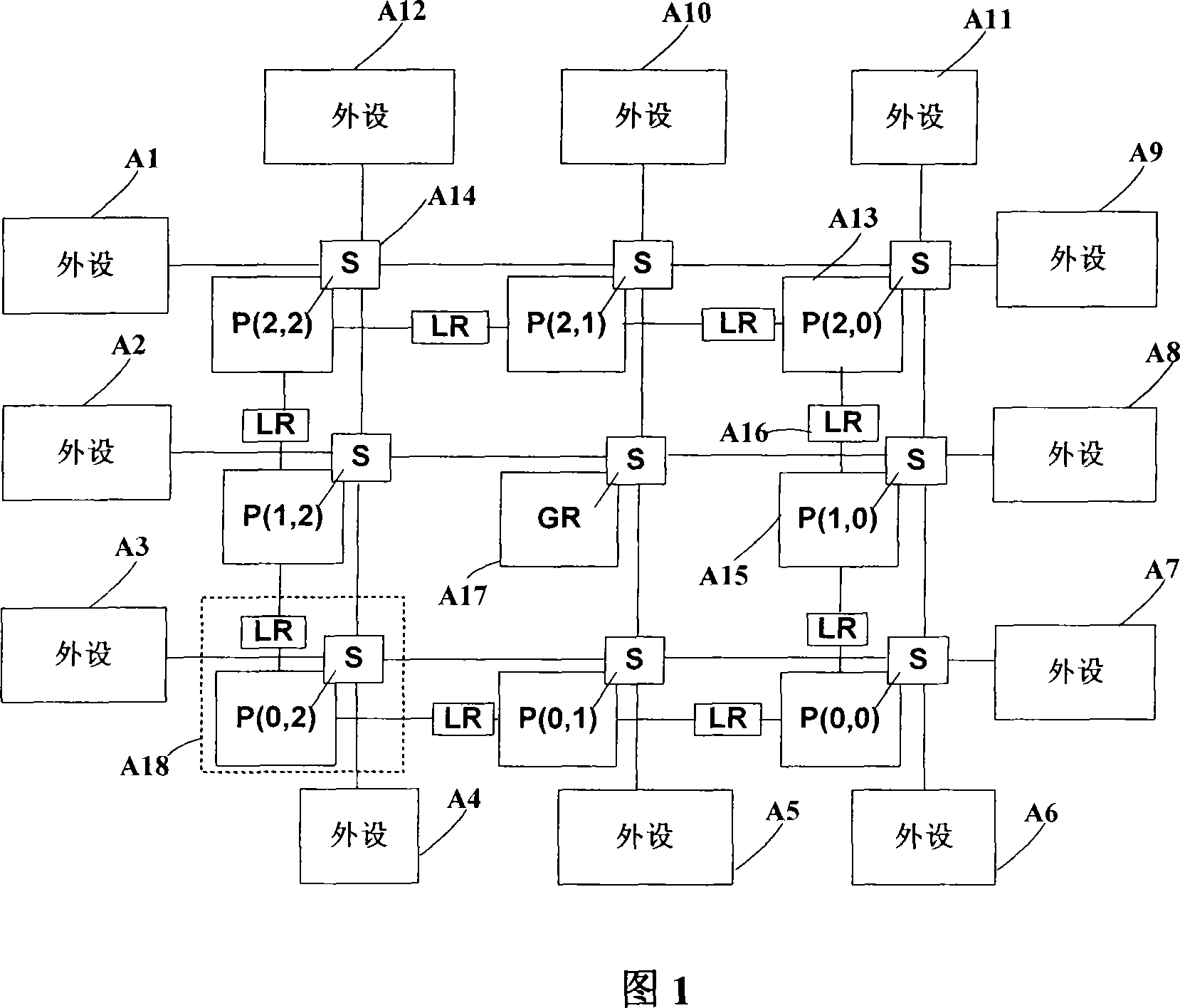

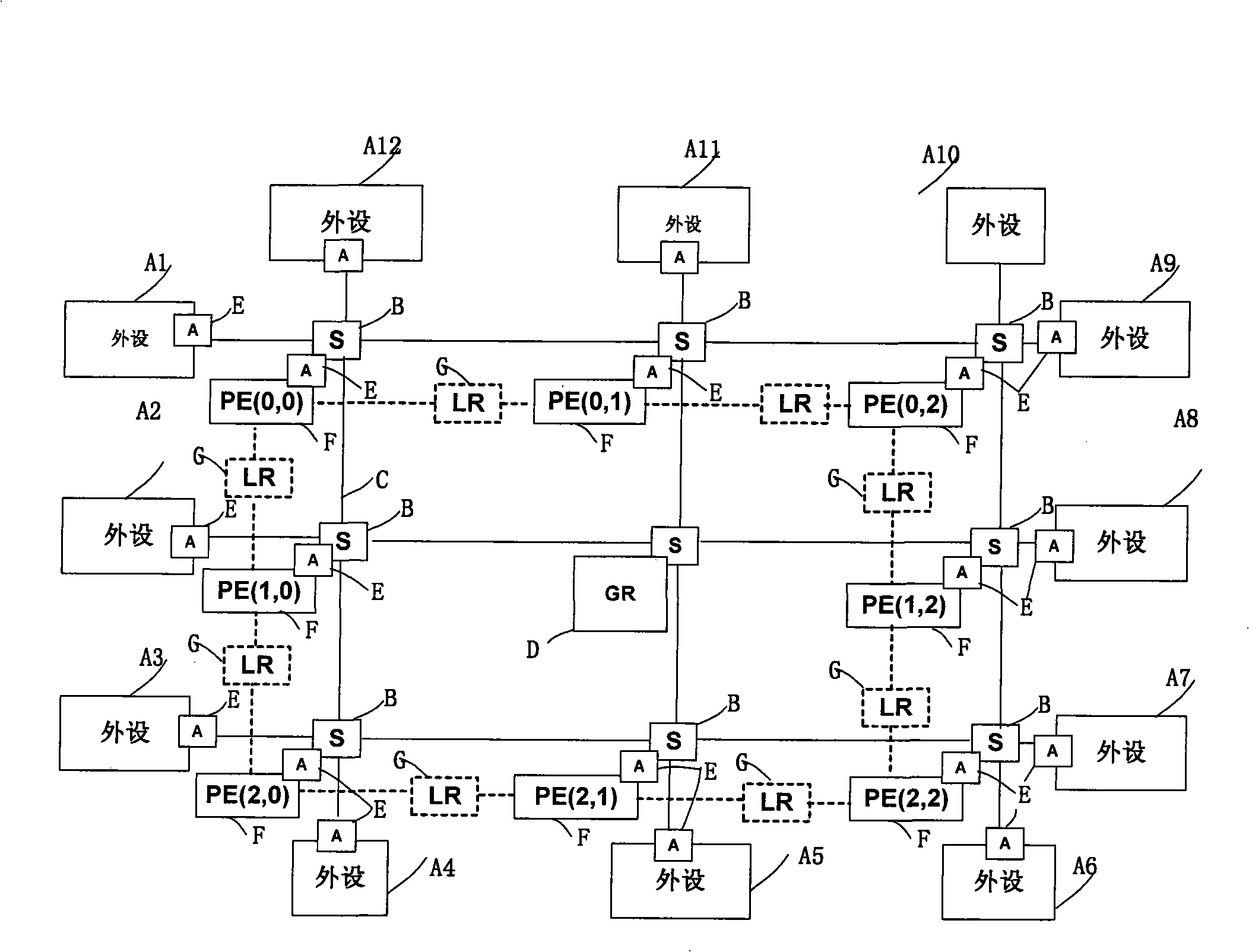

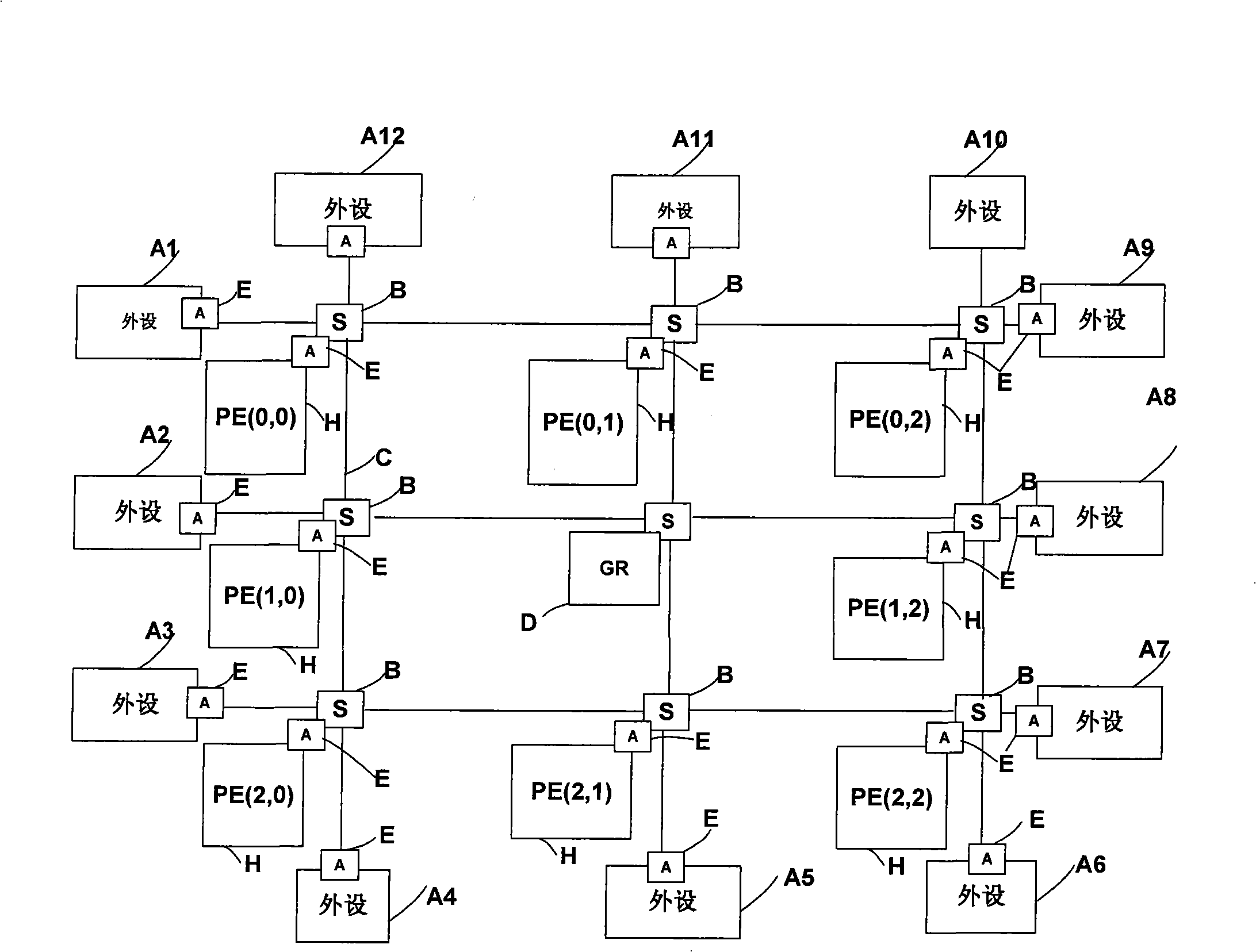

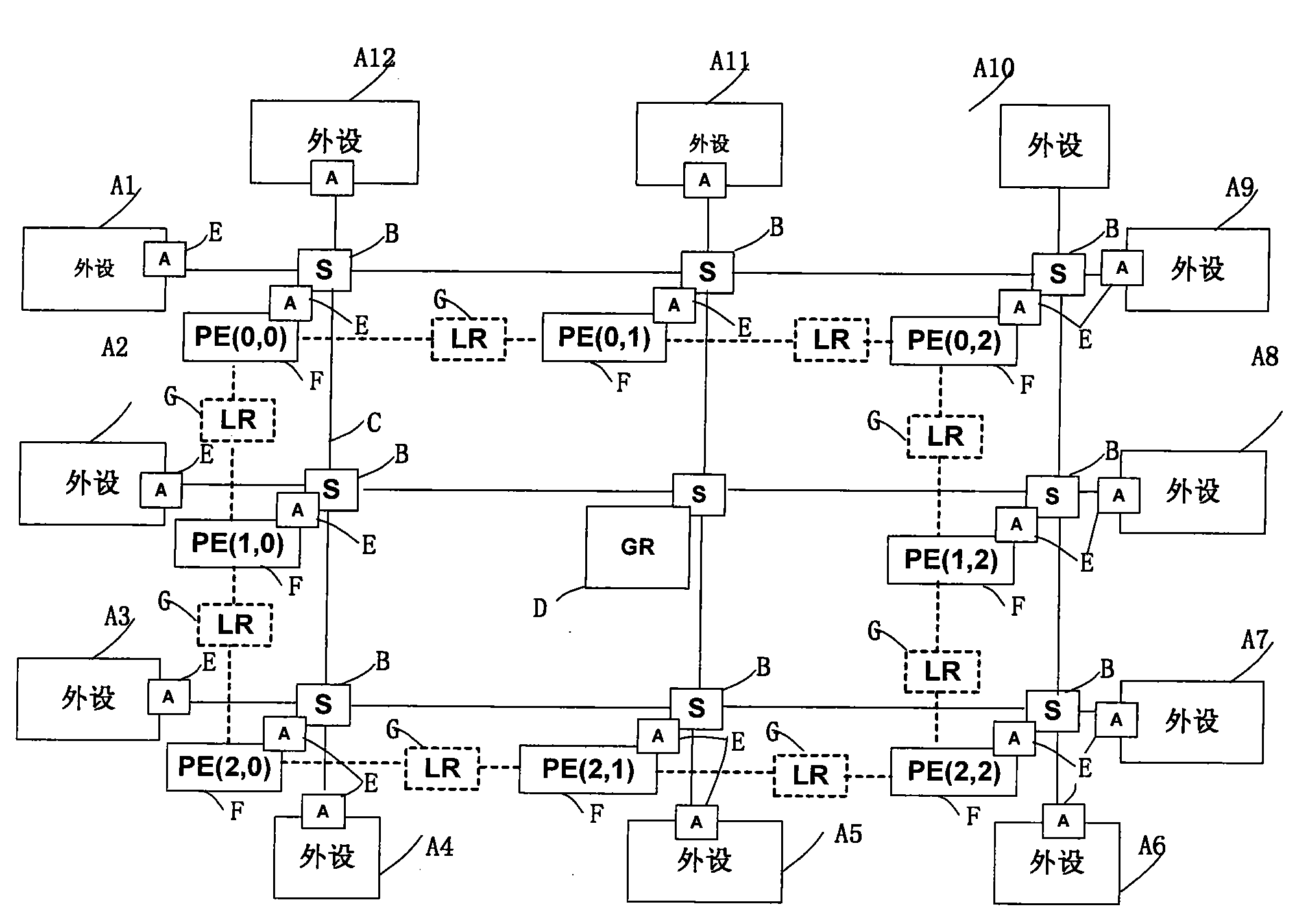

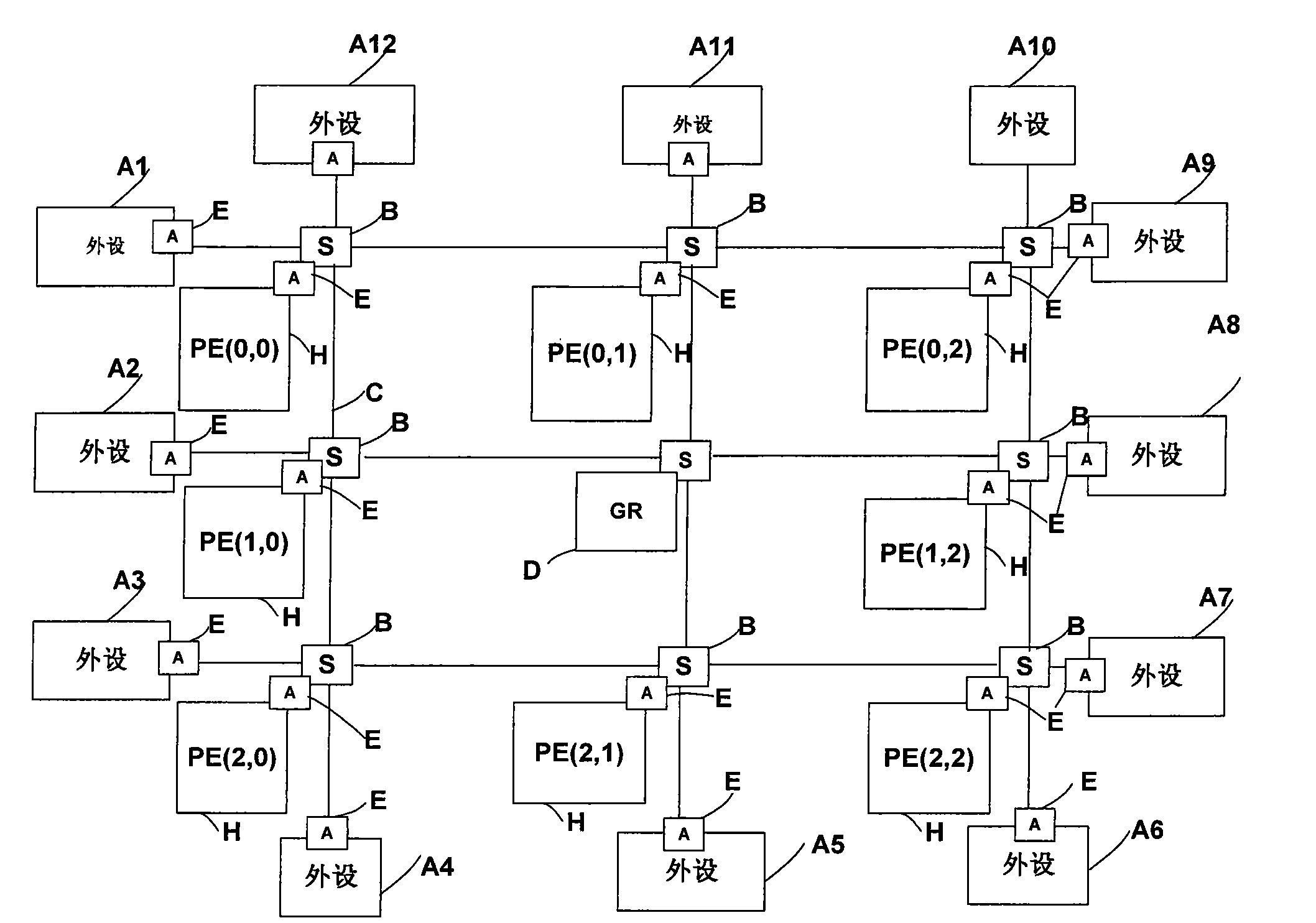

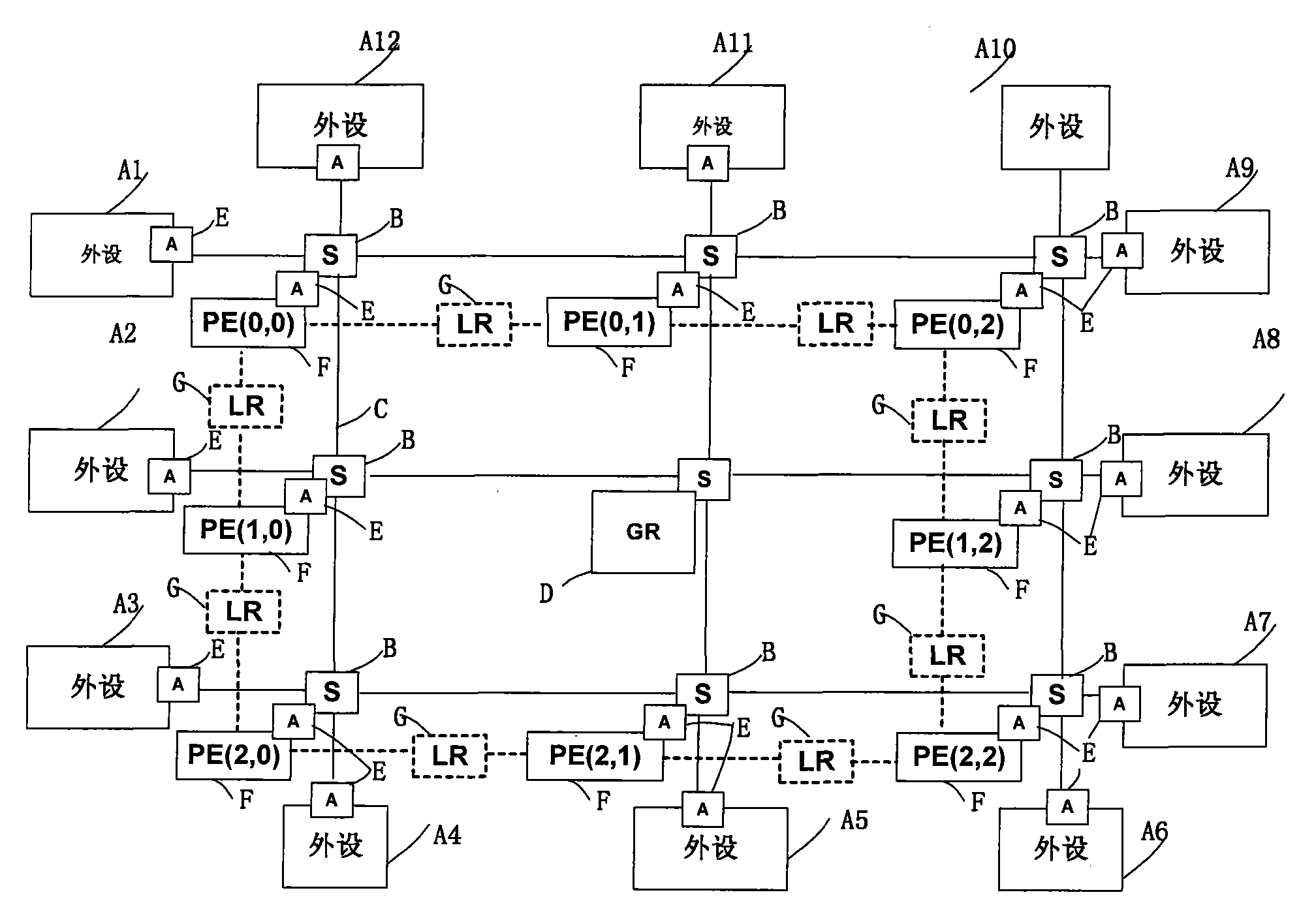

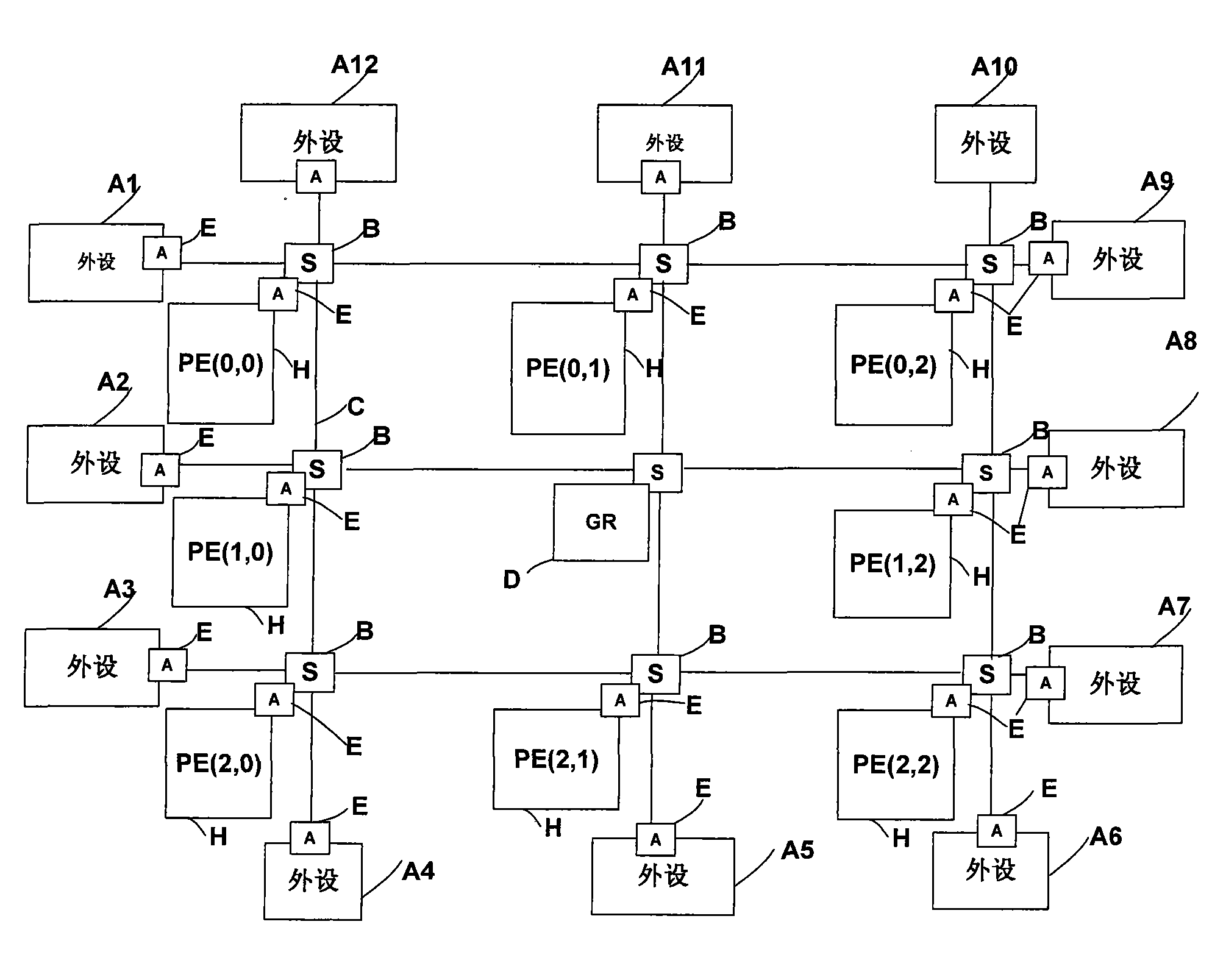

Multi-core processor meeting SystemC grammar request and method for acquiring performing code

ActiveCN101196826AReduce development difficultyProgram controlMemory systemsSystemCSystem development

The invention discloses a polynuclear processor satisfying SystemC grammatical requirements and a method of acquiring the related execution codes. The polynuclear processor comprises: an array formed by connection of a plurality of switching units for switching data, a plurality of processing units for data processing connected with the switching units; a local resource unit connected between adjacent processing units for synchronizing and data sharing between adjacent processing units, as well as at least one global resource unit connected with the switching unit for synchronizing and data sharing between all the processing units. The method comprises: step S1, translating SystemC software model into codes which can be coded by an instruction set complier of the processing unit; step S2, mapping the process in the software model on the processing unit, and mapping grammatical elements in the SystemC respectively on the local resource unit and the global resource unit. The invention can obviously lower the developing difficulty of the embedded type system.

Owner:INST OF COMPUTING TECH CHINESE ACAD OF SCI

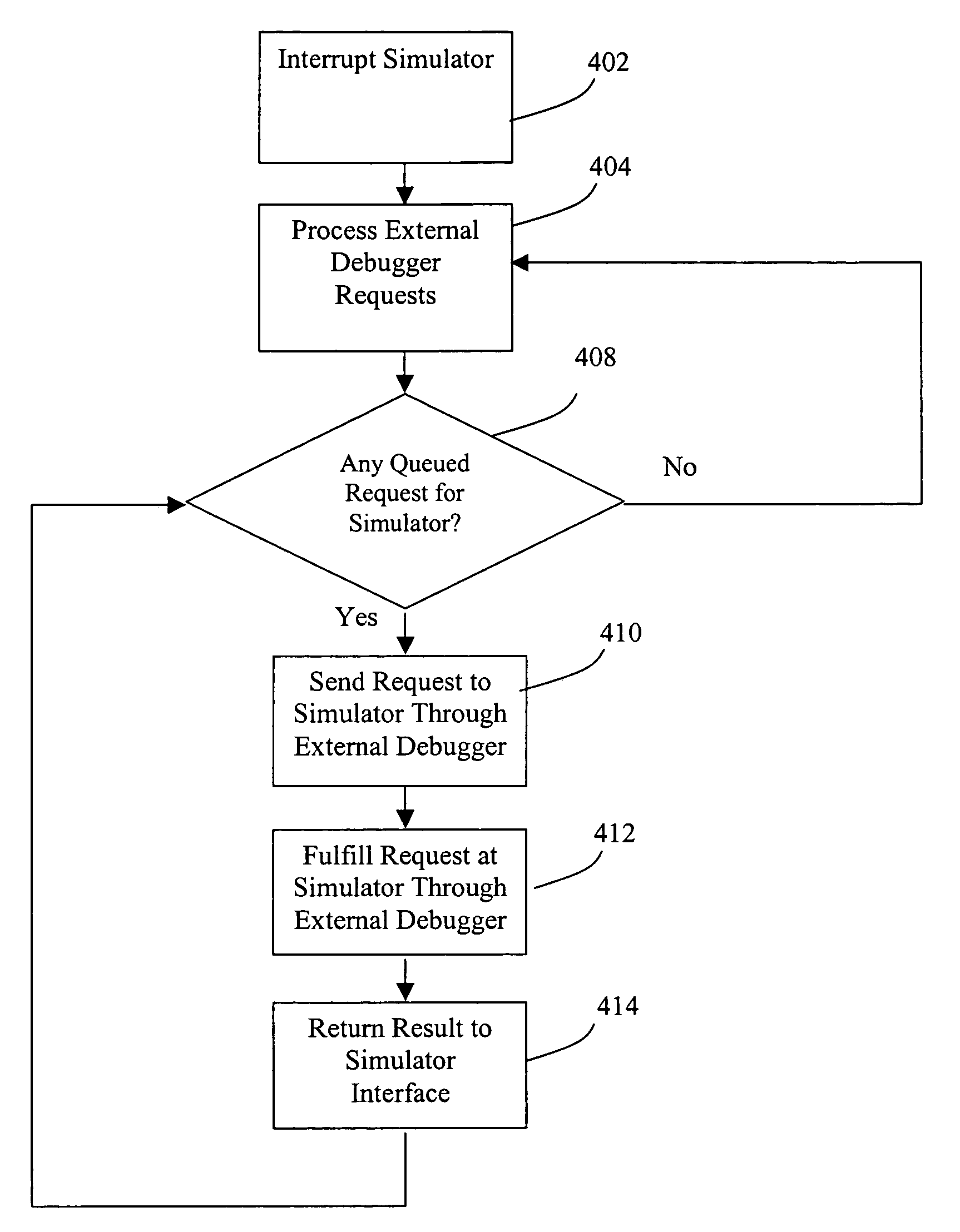

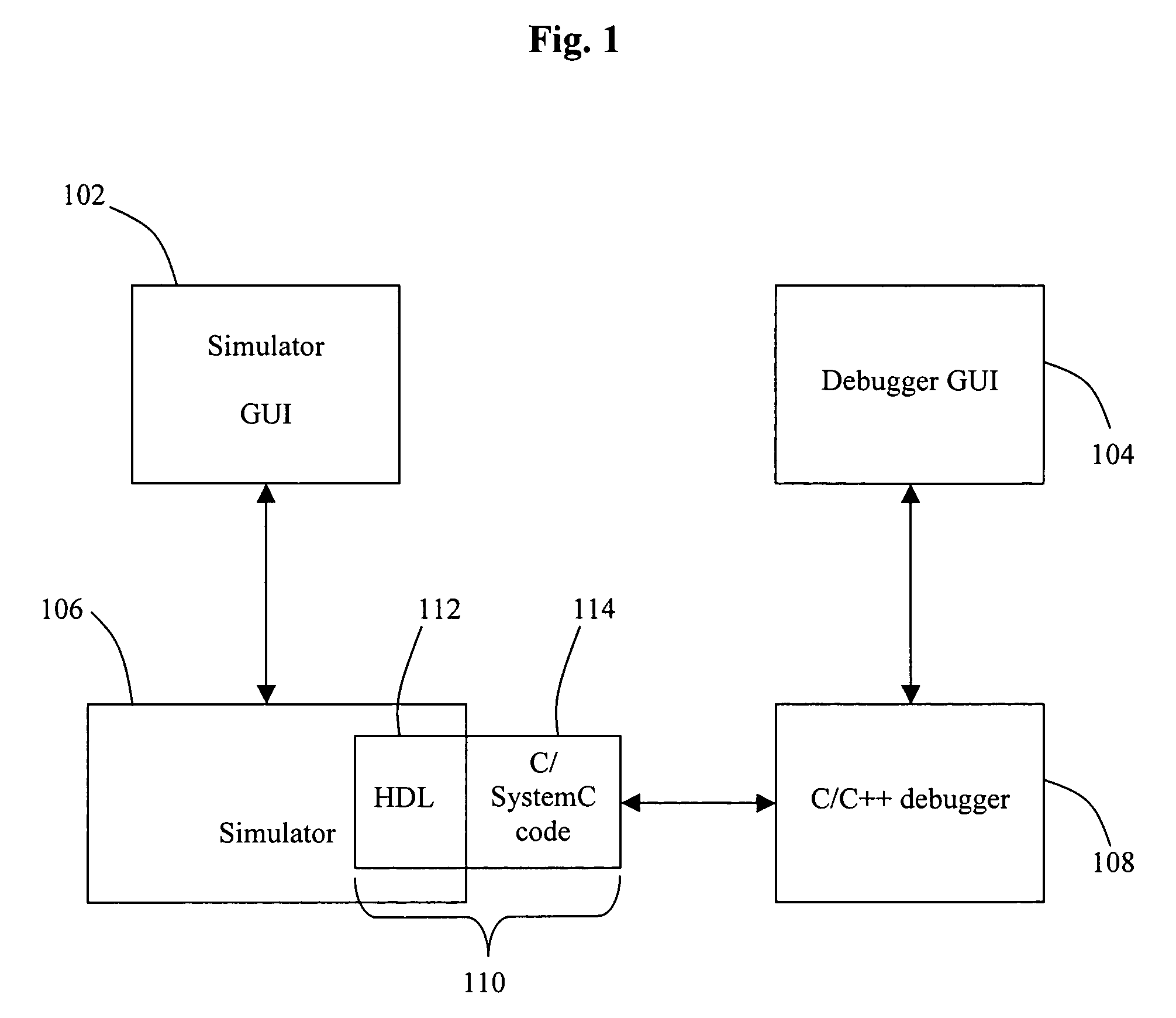

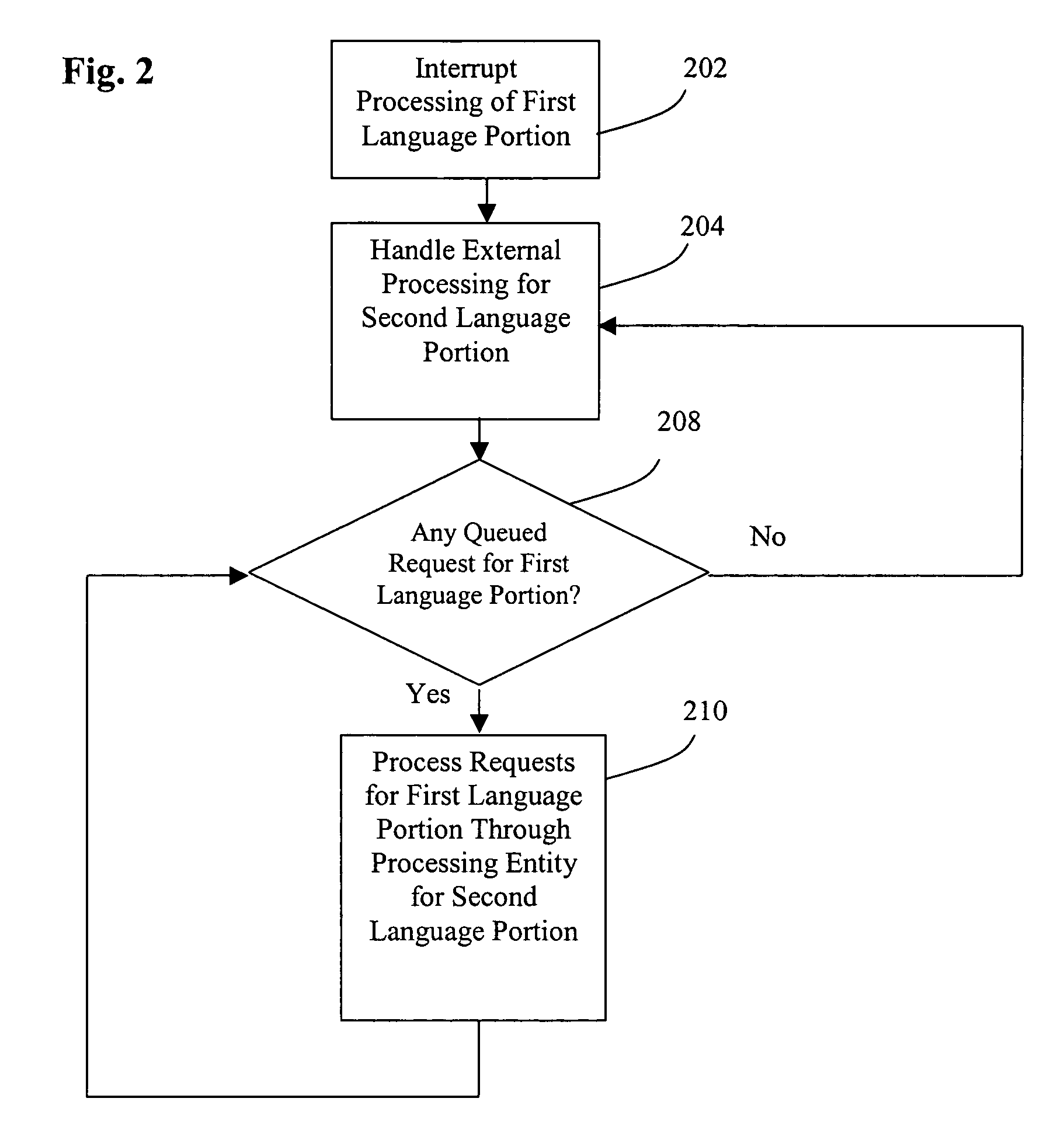

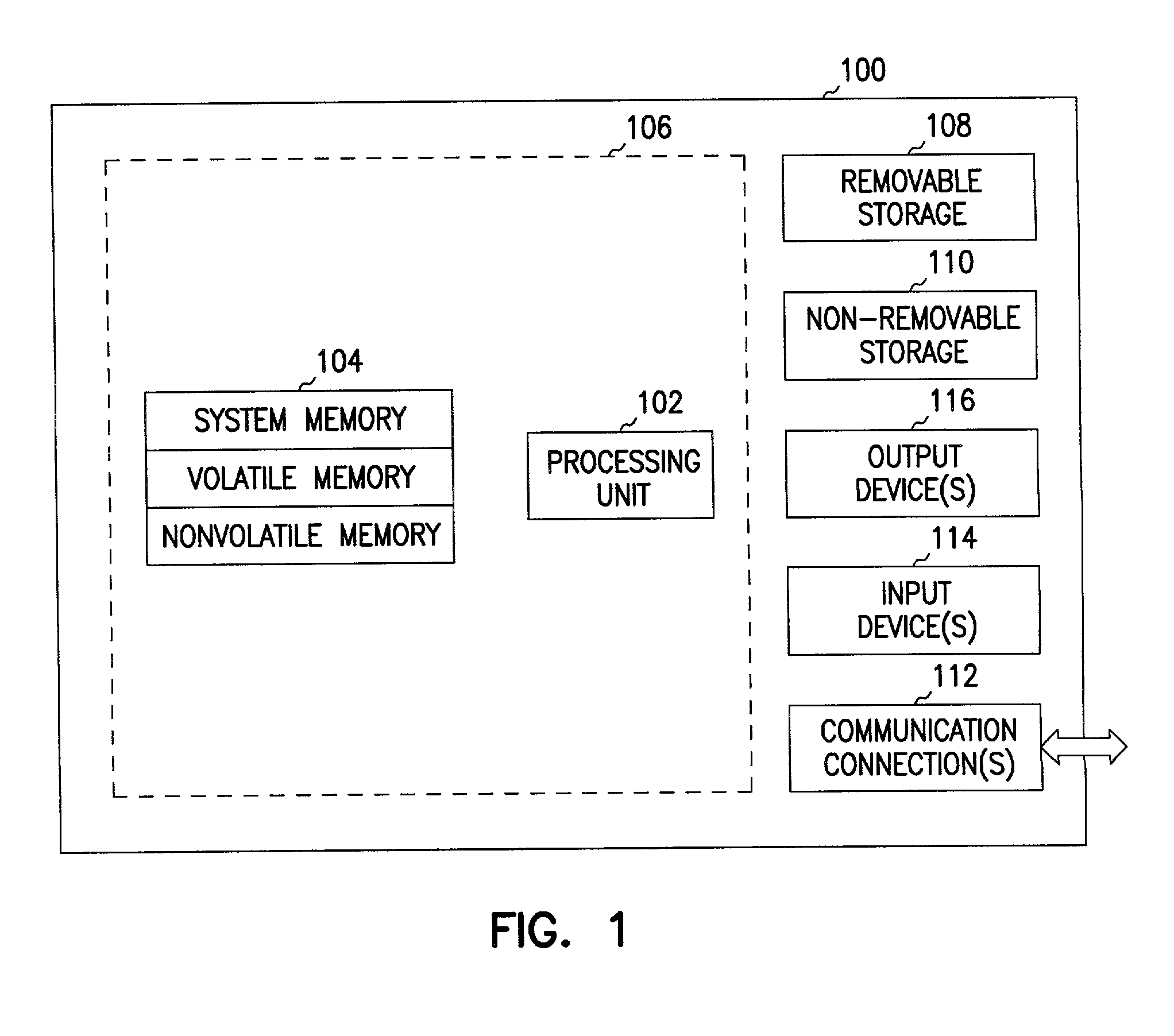

Mechanism and method for simultaneous processing and debugging of multiple programming languages

Disclosed is a method, mechanism, and computer usable medium for simultaneous processing or debugging of multiple programming languages. A particularly disclosed approach provides a method and mechanism for resolving the issue of simultaneous debugging of hardware represented by an HDL, e.g., Verilog or VHDL, and software, e.g., represented by C, C++, SystemC code. This approach overcomes the problem of the HDL portion of the design being inaccessible when C, C++ or SystemC code is debugged.

Owner:CADENCE DESIGN SYST INC

First-in first-out queue unit set of multi-core processor satisfying SystemC grammar

InactiveCN101329702AResource Sharing and SynchronizationSpecial data processing applicationsArchitecture with multiple processing unitsSystemCMapping algorithm

The invention provides a first-in-first-out cohort group which can meet systemC gramma. The cohort group comprises a plurality of first-in-first-out cohort units. The first-in-first-out cohort units output data, write an event signal and data and read the event signal for a corresponding event handling unit group, and comprise a logic circuit which is realized according to the function code of sc_fifo (name, size), sc_fifo(size), sc_fifo.read(), sc_fifo.nb_read(), sc_fifo.write(), sc_fifo.nb_write(), sc_fifo.num_available() and sc_fifo.num_free() of the systemC grammar. The logistic circuit allows the mapping algorithm of a software development tool to reset a plurality of first-in-first-out cohort units in different processing units, so as to jointly complete the function defined by sc_fifo grammar unit. The first-in-first-out cohort group supports the mapping from sc_fifo, a SystemC grammar unit, to chip internal resource, and allows the first-in-first-out cohort to be used for the resource sharing and synchronization among a plutlity of processing units, and between the processing unit and peripherals.

Owner:INST OF COMPUTING TECH CHINESE ACAD OF SCI

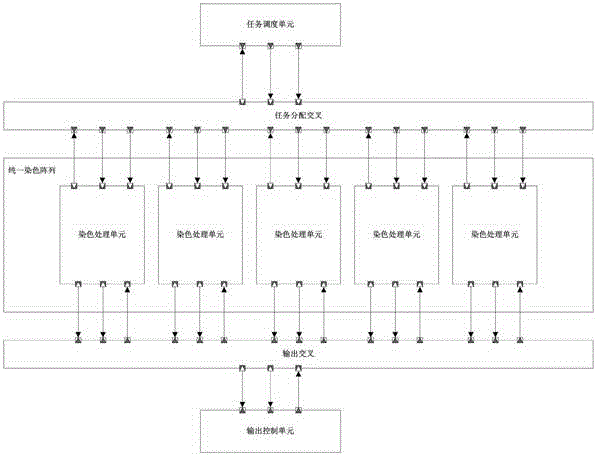

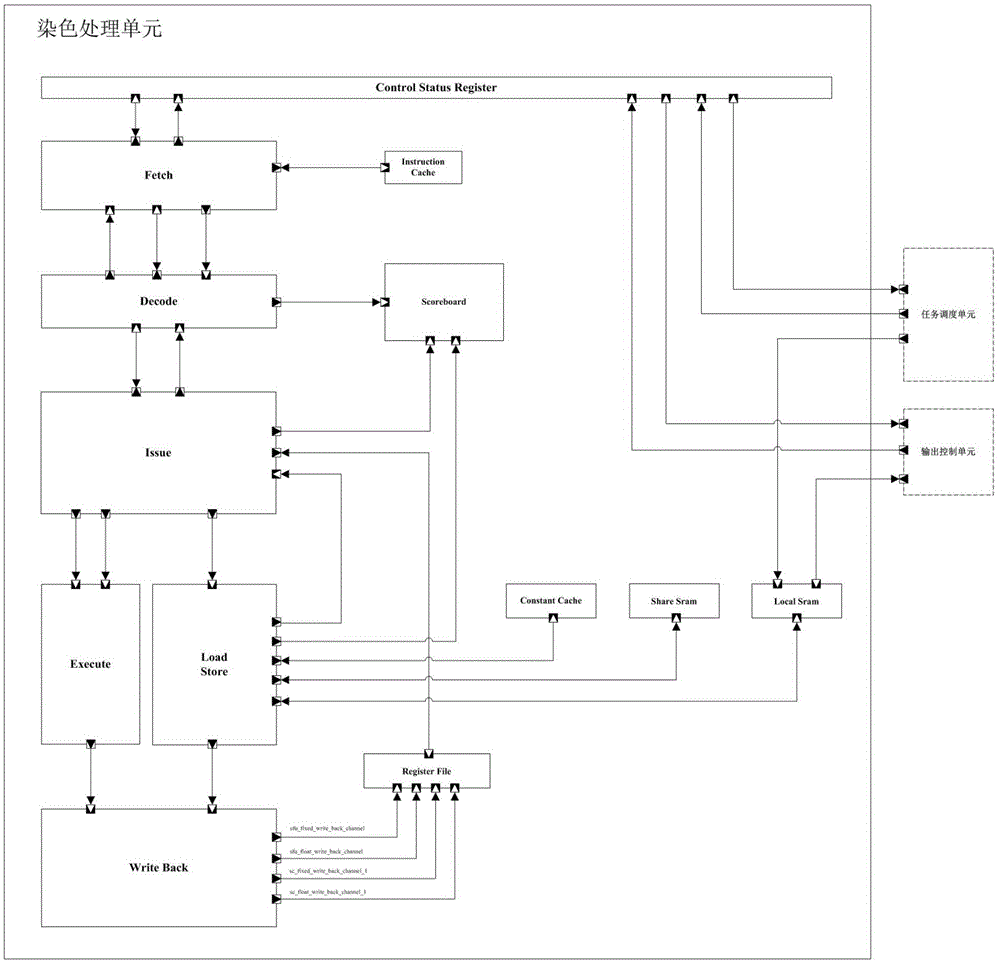

SystemC based unified stainer array TLM model with accurate cycle

The invention relates to a SystemC based unified stainer array TLM model with an accurate cycle. According to the model, a plurality of physically and logically independent dyeing treatment units are integrated in a unified stainer array; and the unified stainer array can be modeled only by modeling one dyeing treatment unit by adopting a SystemC language and then instantiating a model for five times.

Owner:XIAN AVIATION COMPUTING TECH RES INST OF AVIATION IND CORP OF CHINA

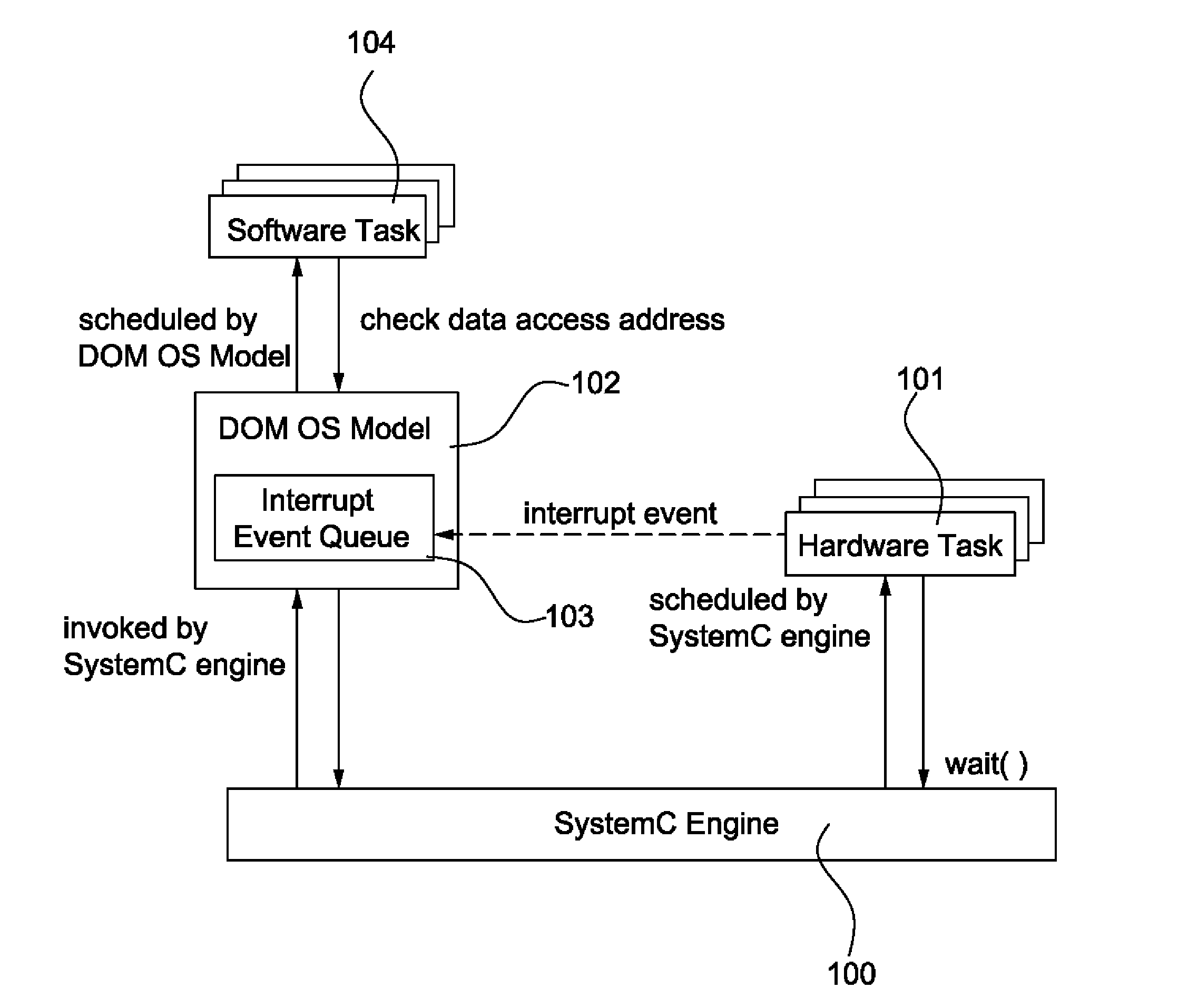

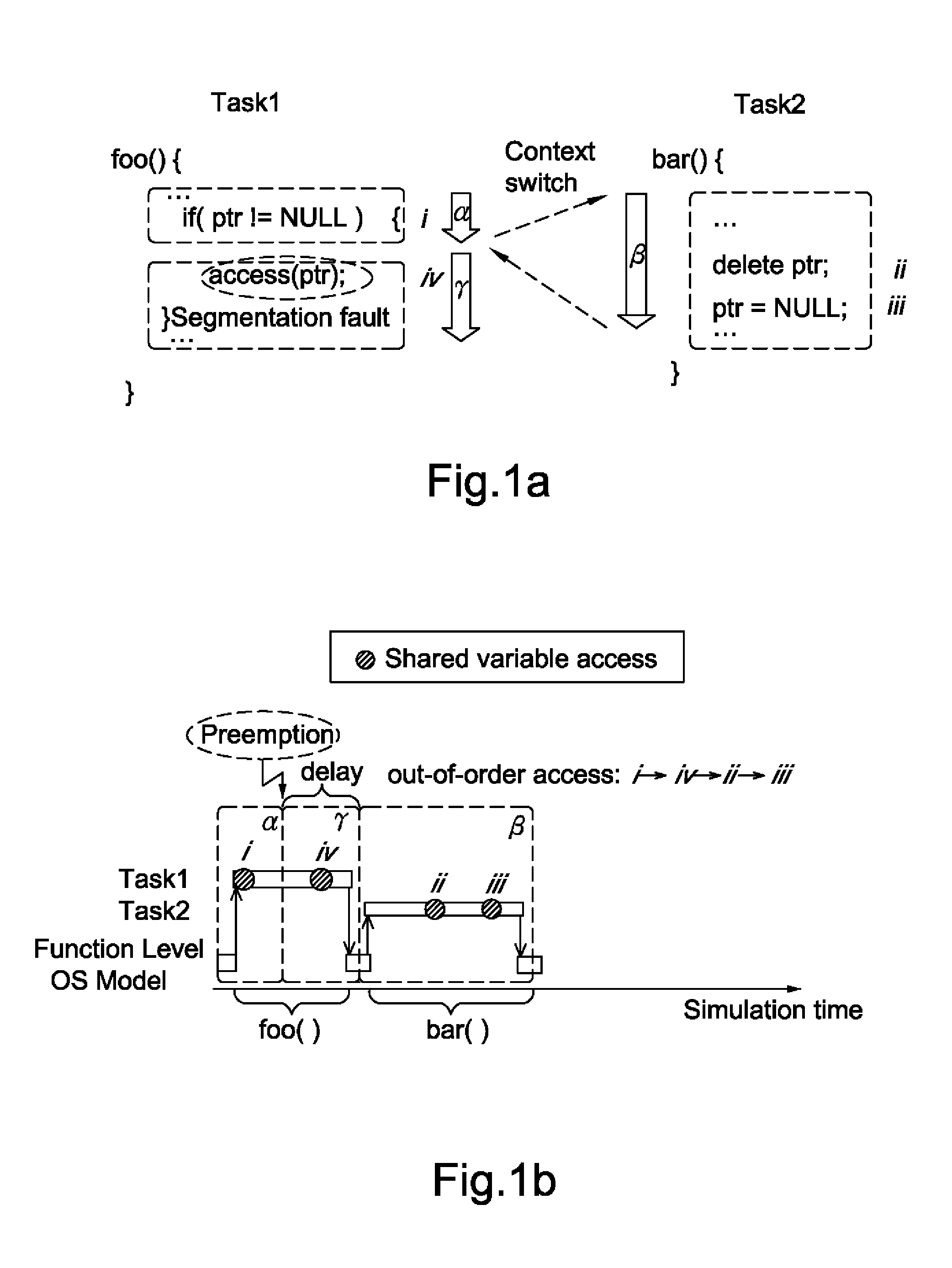

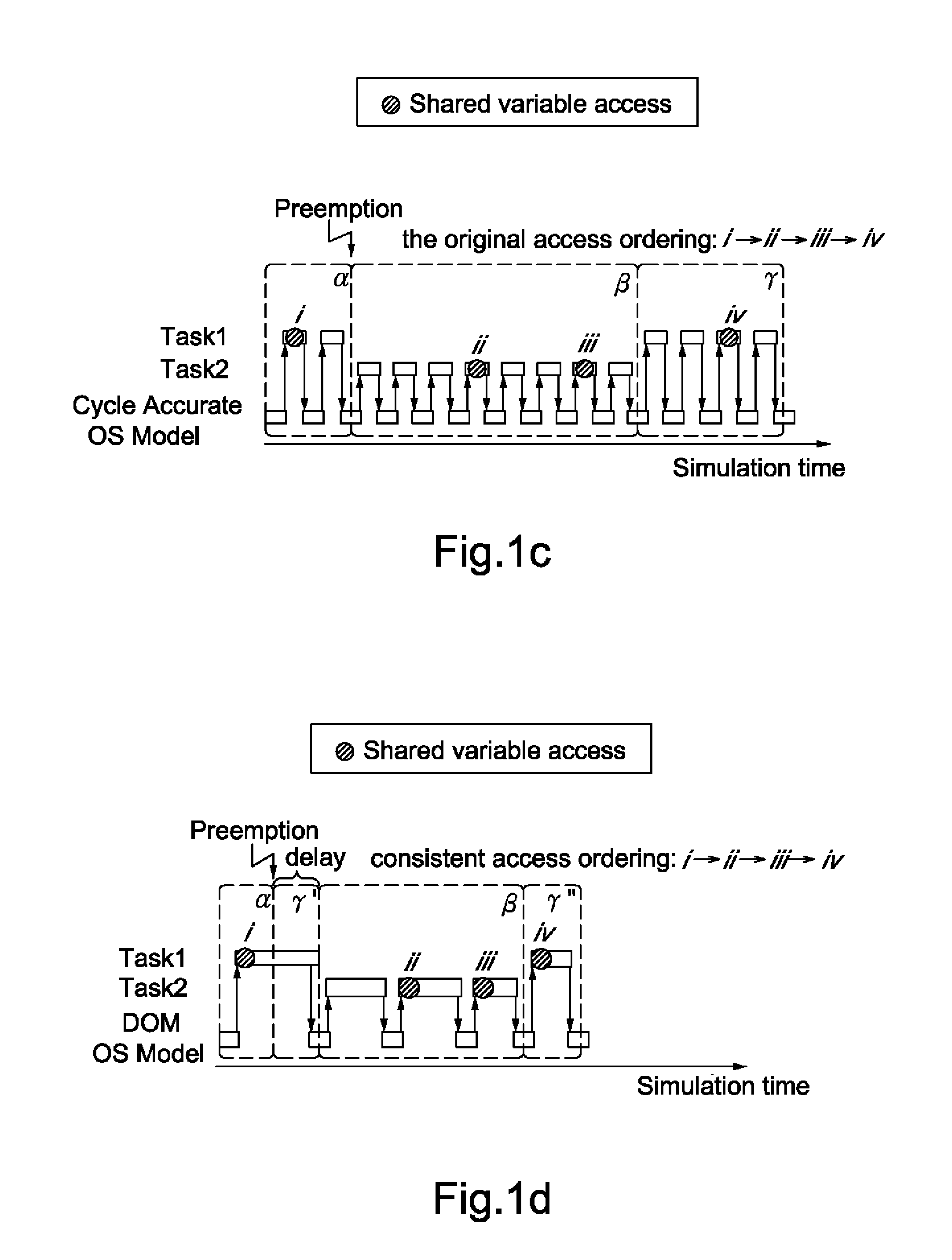

Data-dependency-Oriented Modeling Approach for Efficient Simulation of OS Preemptive Scheduling

InactiveUS20120197625A1Fast and accurate simulationReduce overheadCAD circuit designProgram controlSystemCSoftware

In the present disclosure, the DOM approach for the simulation of OS preemptive scheduling has presented and demonstrated. By maintaining the data-dependency between the software tasks, and guaranteeing the order of shared variable accesses, it can accurately simulate the preemption effect. Moreover, the proposed DOM OS model is implemented to enable preemptive scheduling in SystemC.

Owner:NATIONAL TSING HUA UNIVERSITY

Multi-core processor satisfying SystemC syntax

ActiveCN101634979AResource Sharing and SynchronizationProgram synchronisationSpecial data processing applicationsSystemCSyntax

The invention discloses a multi-core processor satisfying SystemC, which comprises an array formed by a plurality of exchanging units for exchanging data through connection, and a plurality of processing units connected with the exchanging units, used for processing data and comprising local resource units, wherein the processing units are connected to other processing units by an exchanging unit adapter and an exchanging unit array through the local resource units, and the local resource units comprise one or more of an event processing cell block of the SystemC, a first-in-first-out queue cell block of the SystemC and a mutual exclusion and semaphore cell block of the SystemC. Through the multi-core processor, the mapping supporting a SystemC syntax unit to resources in a chip is achieved so that the local resources can be applied to the resource sharing and the synchronization between any plurality of processing units and between the processing unites and peripherals.

Owner:INST OF COMPUTING TECH CHINESE ACAD OF SCI

Mutual exclusion and semaphore cell block of multi-core processor satisfying SystemC syntax

ActiveCN101635006ASupport sharingProgram synchronisationSpecial data processing applicationsSystemCMapping algorithm

The invention discloses a mutual exclusion and semaphore cell block of a multi-core processor satisfying SystemC syntax, which comprises a logic circuit achieved according to the function codes of sc_mutex (name), sc_mutex.lock(), sc_mutex.trylock(), sc_mutex.unlock(), sc_semaphore.wait(), sc_semaphore.trywait(), sc_semaphore.post(), sc_semaphore(init_value), sc_semaphore(name, init_value) of the SystemC syntax, wherein the logic circuit is used for sending signals for activating and pausing the processor to a controller at runtime of the processor cores, and allows a mapping algorithm of a software development tool to recombine a plurality of mutual exclusion and semaphore cells positioned at different processing units so as to finish the functions of an sc_mutex or sc_semaphore syntax unit defined by a SystemC language. By applying the mutual exclusion and semaphore cell block, local resources can be applied to the resource sharing and the synchronization between any plurality of processing units and between the processing unites and peripherals.

Owner:INST OF COMPUTING TECH CHINESE ACAD OF SCI

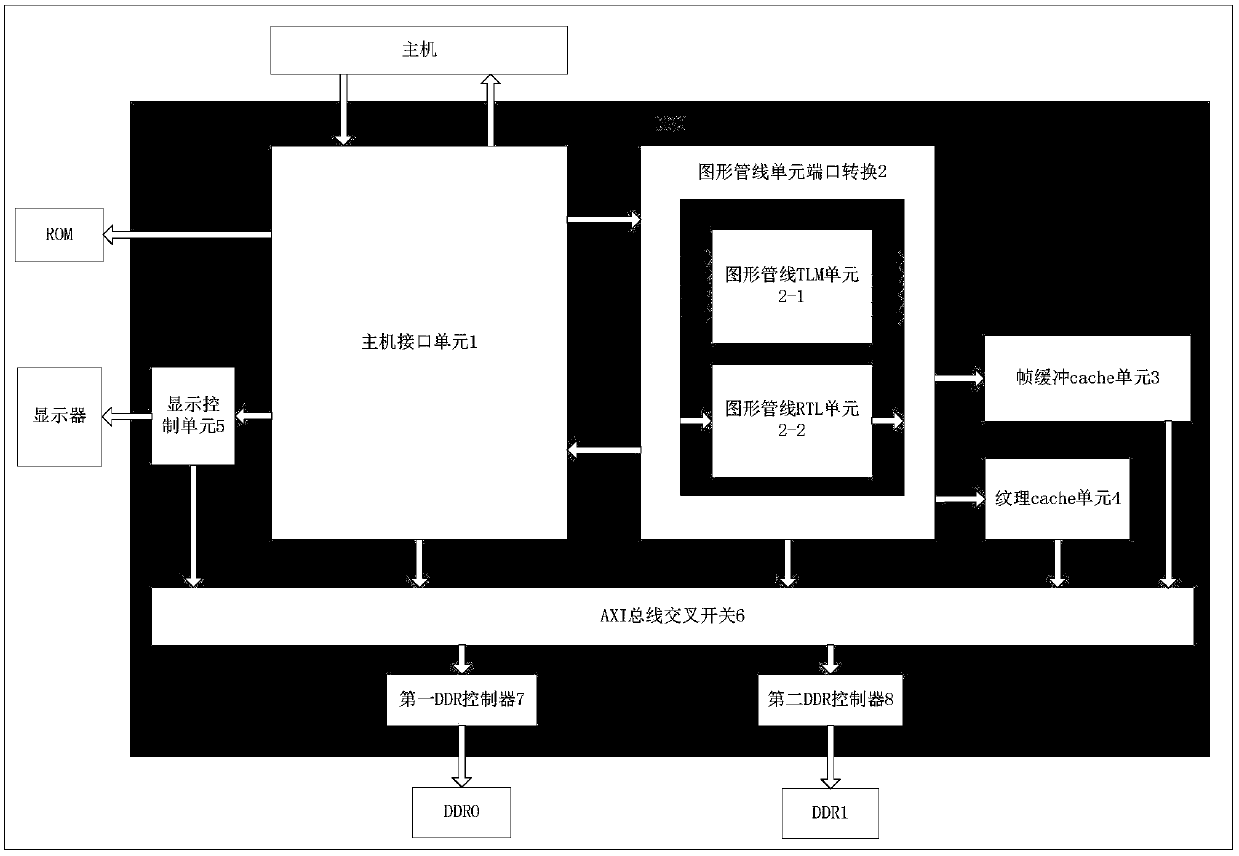

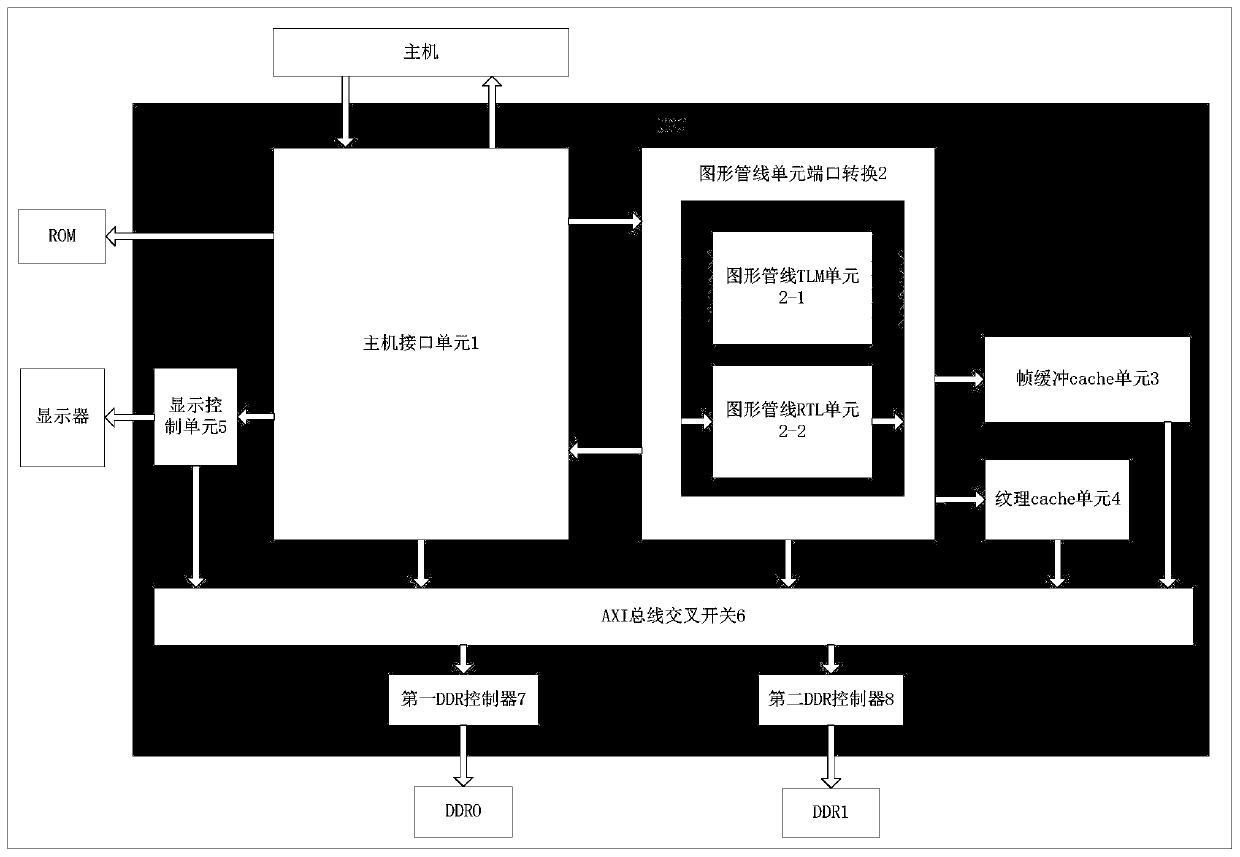

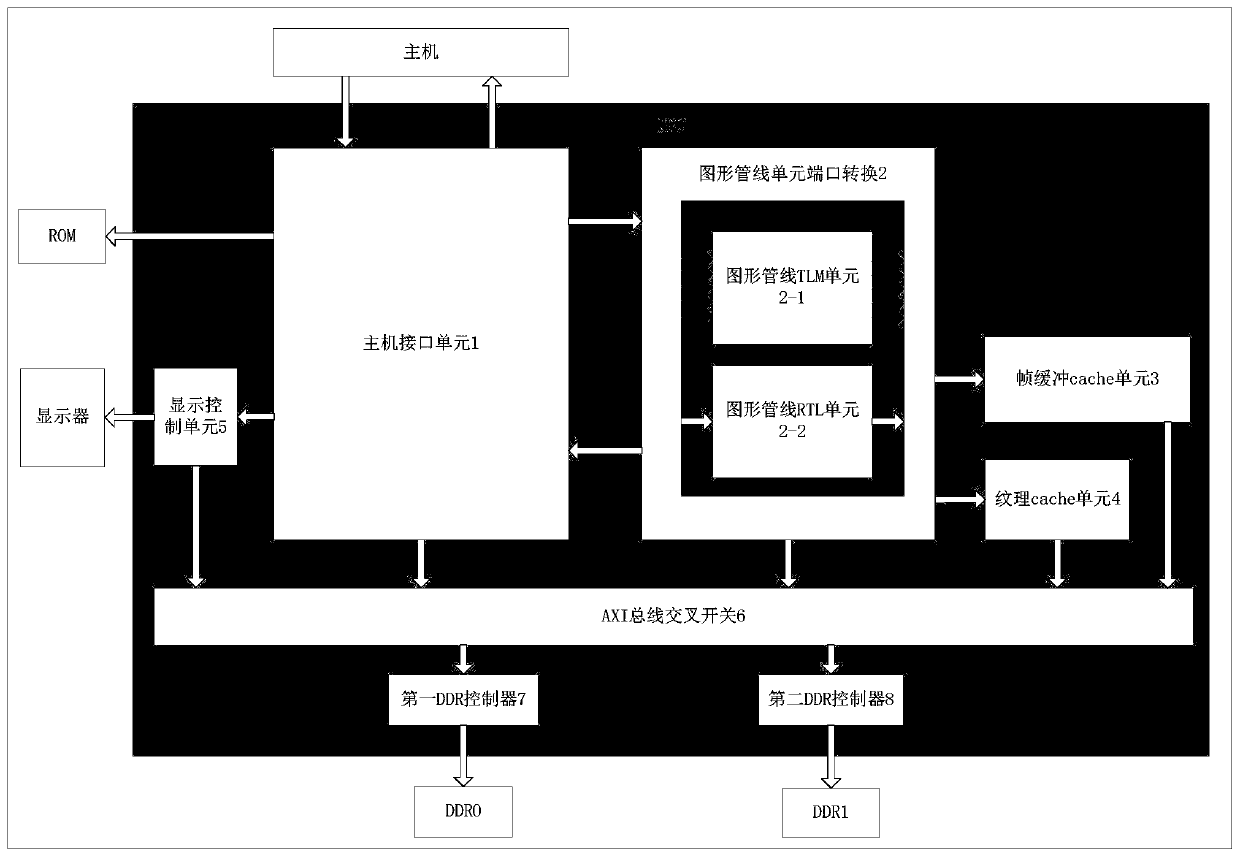

A GPU chip-oriented graphic pipeline unit performance verification method and a platform

The invention relates to the technical field of computer hardware verification, in particular to a GPU chip-oriented graphic pipeline unit performance verification method and a platform. According tothe method, a graphic processing unit (GPU) chip TLM virtual prototype platform based on SystemC is established (the virtual prototype verification platform comprises a host, an ROM, a display, DDR0,DDR1 and a GPU); a TLM transaction level port of a GPU graphic pipeline unit is converted into a hardware signal level port. By embedding the RTL code of the graphic pipeline unit into a TLM virtualprototype platform, and performing module-level and system-level function simulation on the RTL of the GPU to verify whether the RTL of the graphic pipeline unit meets the performance index of the corresponding model or not, whether the performance of the GPU graphic pipeline unit meets the requirement or not can be verified in advance before the FPGA stage, and the development and verification work of a GPU chip in the follow-up stage is accelerated.

Owner:XIAN AVIATION COMPUTING TECH RES INST OF AVIATION IND CORP OF CHINA

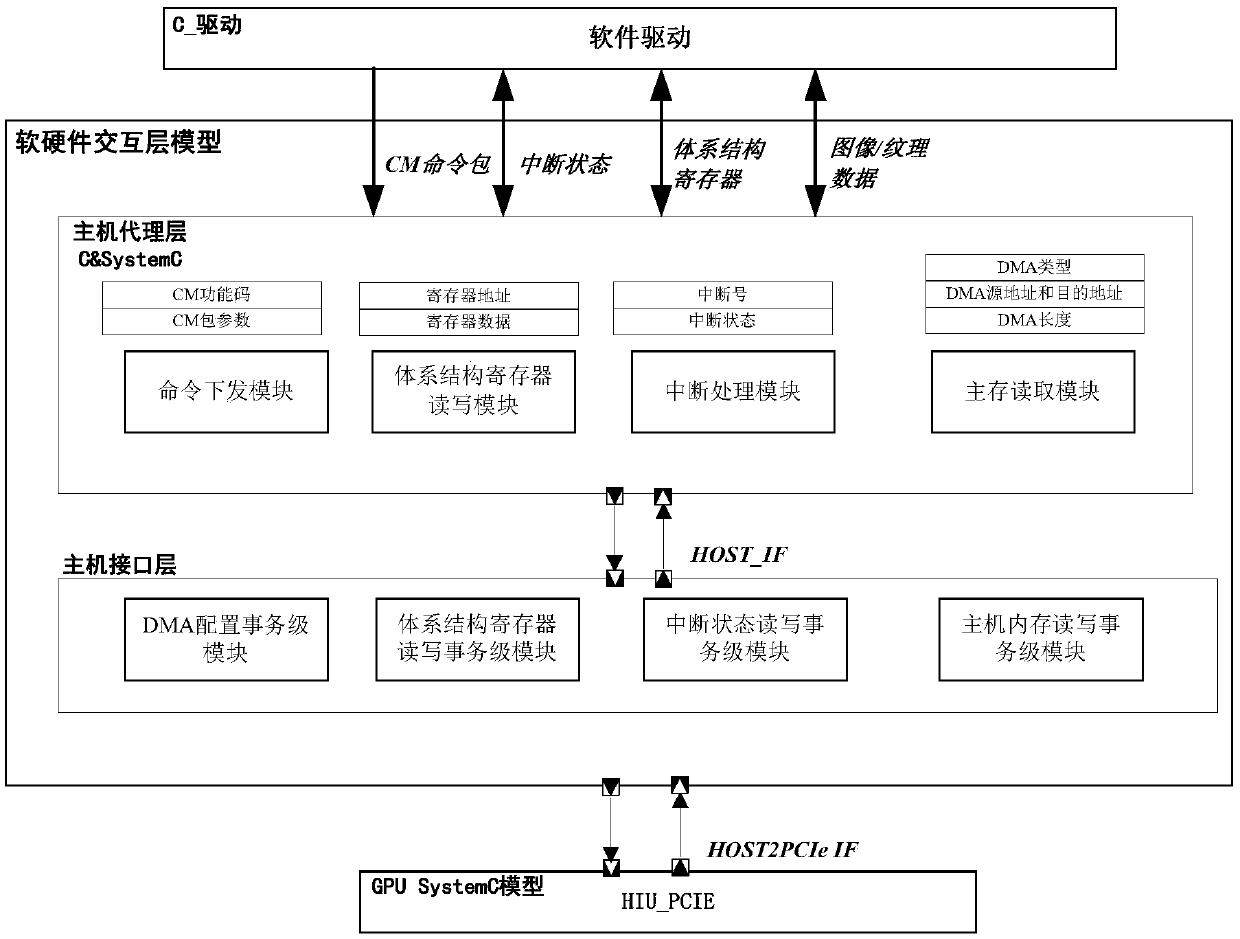

A GPU software and hardware interaction TLM system based on SystemC

ActiveCN109683877ASolving Interaction ProblemsResource allocationProgramming languages/paradigmsSystemCSoftware

The invention relates to the technical field of computer hardware modeling, in particular to a GPU software and hardware interaction TLM model based on SystemC. The GPU software and hardware interaction TLM model based on SystemC comprises a host agent layer model and a host interface layer model, wherein the host agent layer model provides an interaction path between a software driver and the host interface layer model; wherein the host interface layer model provides an interaction path between the host agent layer model and the GPU hardware TLM model, and the interaction content comprises issuing of an OpenGL CM command packet, reading and writing of an architecture register, interruption processing and image and texture data loading or acquisition. The GPU software and hardware model interaction method based on the TLM model is achieved, the problem of software drive and hardware model interaction in GPU modeling is solved, and RTL design development and verification are effectivelyfacilitated.

Owner:XIAN AVIATION COMPUTING TECH RES INST OF AVIATION IND CORP OF CHINA

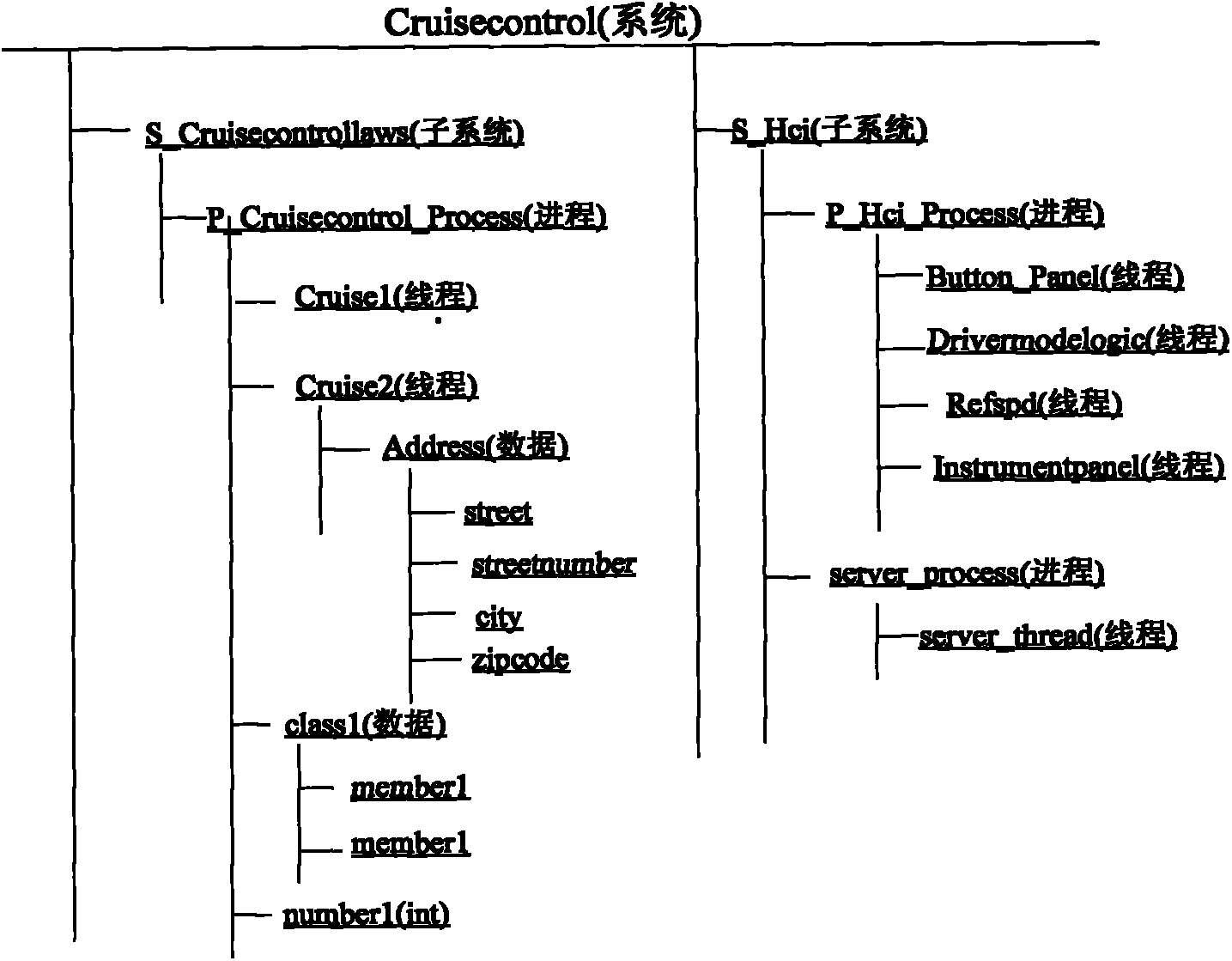

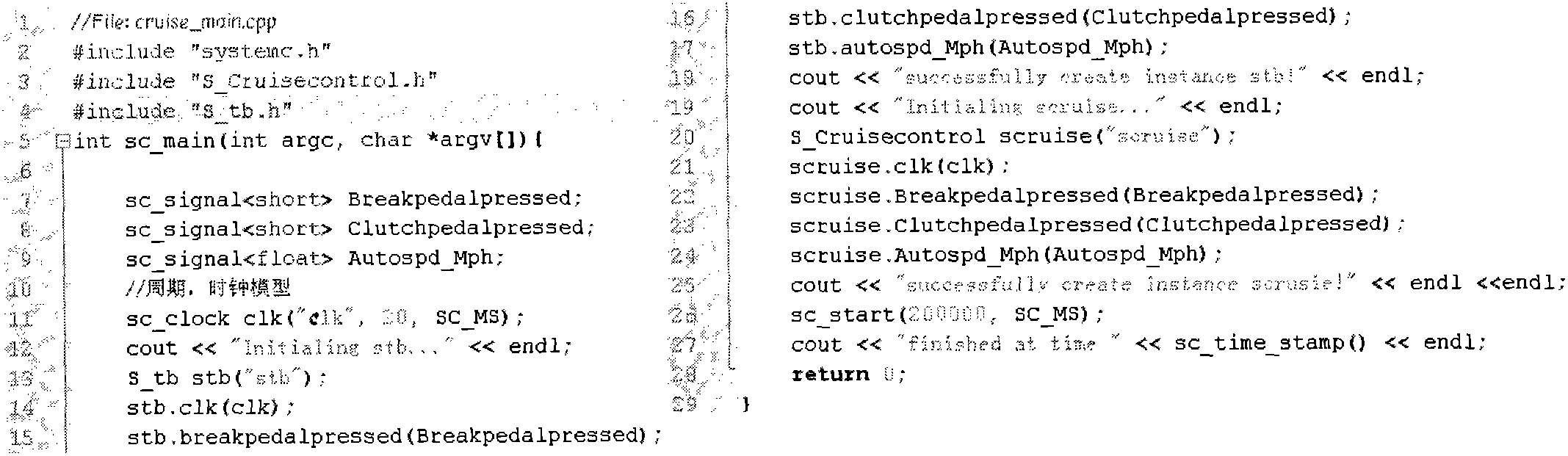

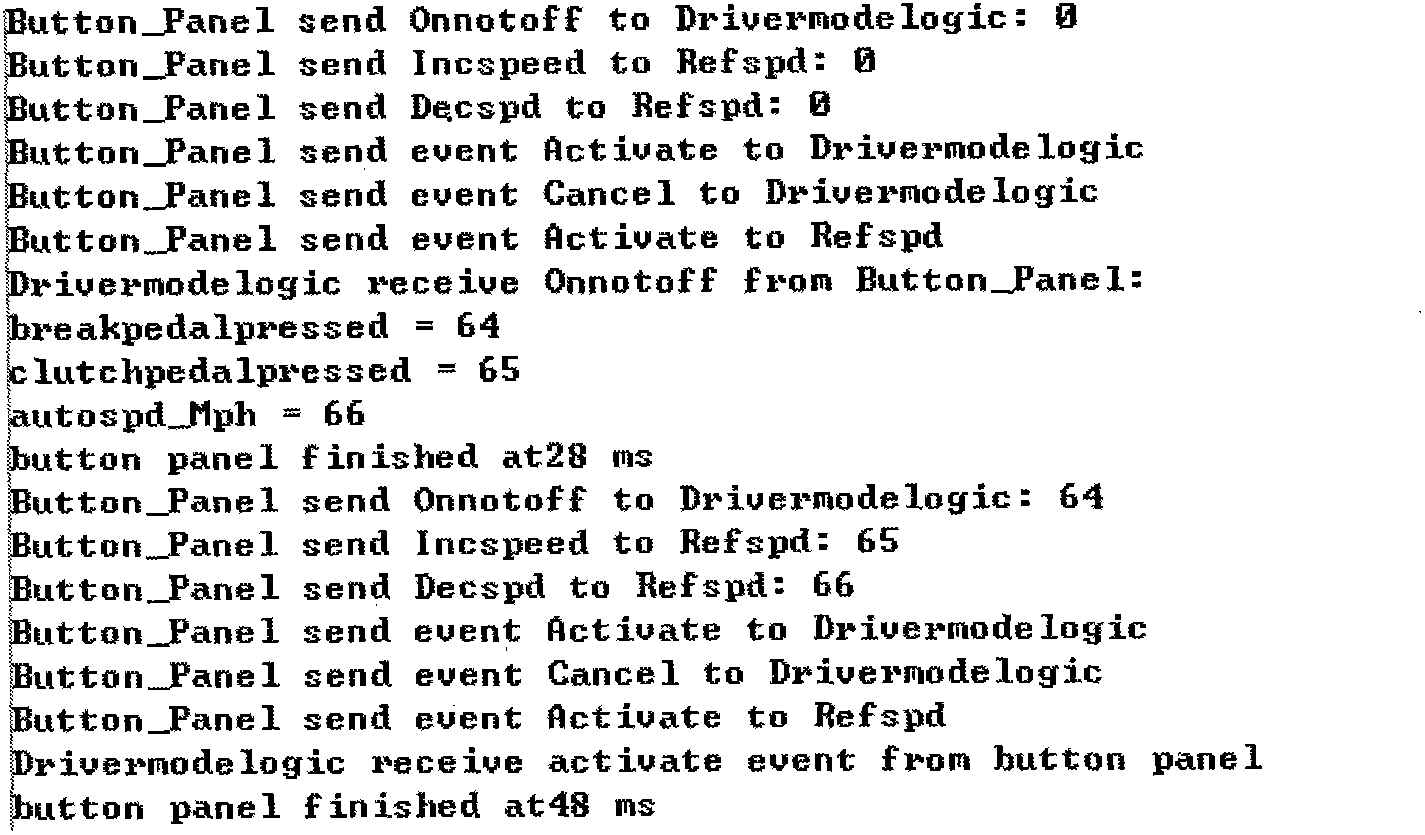

Method for generating simulation test example of AADL (Architecture Analysis and Design Language) software component model based on SystemC

InactiveCN102231132AQuality assuranceImprove reliabilitySoftware testing/debuggingInclusion relationSystemC

The invention provides a method for generating a simulation test example of an AADL (Architecture Analysis and Design Language) software component model based on SystemC. The method comprises the following steps of: firstly, providing a conversion technology for converting data components, ports and connections into a SystemC simulation test example; then, according to inclusion relations of the components, providing a conversion technology for converting each component into the SystemC simulation test example step by step from a bottom layer (sub-program) of a component tree to an intermediate layer (thread and progress) of the tree; and finally, providing a conversion technology of a sub-system and a system component. By means of the method disclosed by the invention, users can realize the simulations of the AADL software component based on the SystemC; the simulations include simulations of interactions, execution times and thread schedulings between software components and the like; the users can also combine the method disclosed by the invention with the simulation of an AADL execution platform component based on the SystemC; software and hardware can be subjected to cooperative simulation; in addition, according to a simulation result, a construction is iterated and a design model is refined so that problems existing in the design model is found out as soon as possible and the quality of the design model is ensured.

Owner:NORTHWESTERN POLYTECHNICAL UNIV

A GPU chip-oriented graphic pipeline unit function simulation method and platform

PendingCN109711003ASolve the problem that is not easy to buildConvenience to workSpecial data processing applicationsGraphicsSystemC

The invention relates to the technical field of computer hardware verification, in particular to a graphic pipeline unit function simulation method and platform for a graphic processing unit (GPU) chip. According to the method, a graphic processing unit (GPU) chip TLM virtual prototype platform based on SystemC is established (the virtual prototype verification platform comprises a host, an ROM, adisplay, DDR0, DDR1 and a GPU); a TLM transaction level port of a GPU graphic pipeline unit is converted into a hardware signal level port, an RTL code of the graphic pipeline unit is embedded into aTLM virtual prototype platform, and module level and system level function simulation is carried out on the RTL of the GPU. Therefore, the problem that the behaviors of the GPU module-level RTL simulation environment model and the GPU system-level RTL simulation environment model are not unified is solved through the TLM virtual prototype platform, the reusability of the simulation environment isimproved, and the development and verification work of the GPU chip RTL is accelerated.

Owner:XIAN AVIATION COMPUTING TECH RES INST OF AVIATION IND CORP OF CHINA

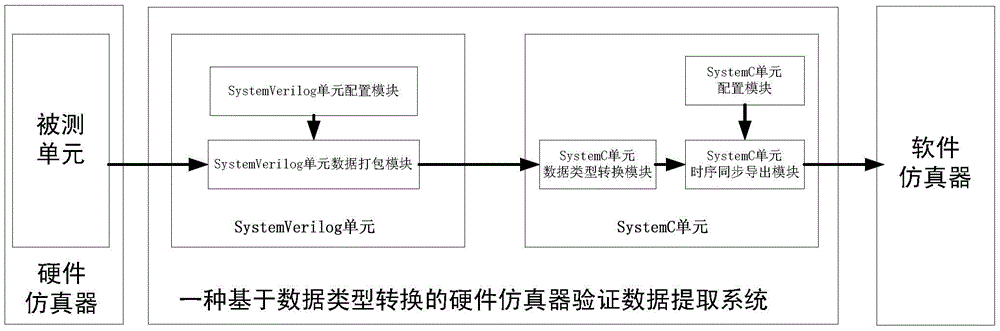

Data type conversion-based hardware simulator validation data extraction system

ActiveCN105653409ASimple structureEasy to implementFaulty hardware testing methodsSystemCData ingestion

The invention provides a data type conversion-based hardware simulator validation data extraction system. The system comprises a SystemVerilog unit and a SystemC unit, wherein the SystemVerilog is used for receiving input data sent from an external hardware simulator, checking the input data, packing the data into a data package and then sending the data package to the SystemC unit; and the SystemC unit is used for 6 data types defined in SystemVerilog into 6 data types defined in SystemVerilog according to a one-to-one corresponding manner, sending the data package to a software simulator according to the simulation precision of the software simulator, extracting the running result of a tested unit running on the hardware simulator with relatively high efficiency, and comparing the running result with a structure preset in the software simulator on a workstation so as to realize the determination of the running result of the tested unit. The method has the advantages of being flexible in data package, high in simulation speed and flexible in software simulator interface.

Owner:BEIJING MXTRONICS CORP +1

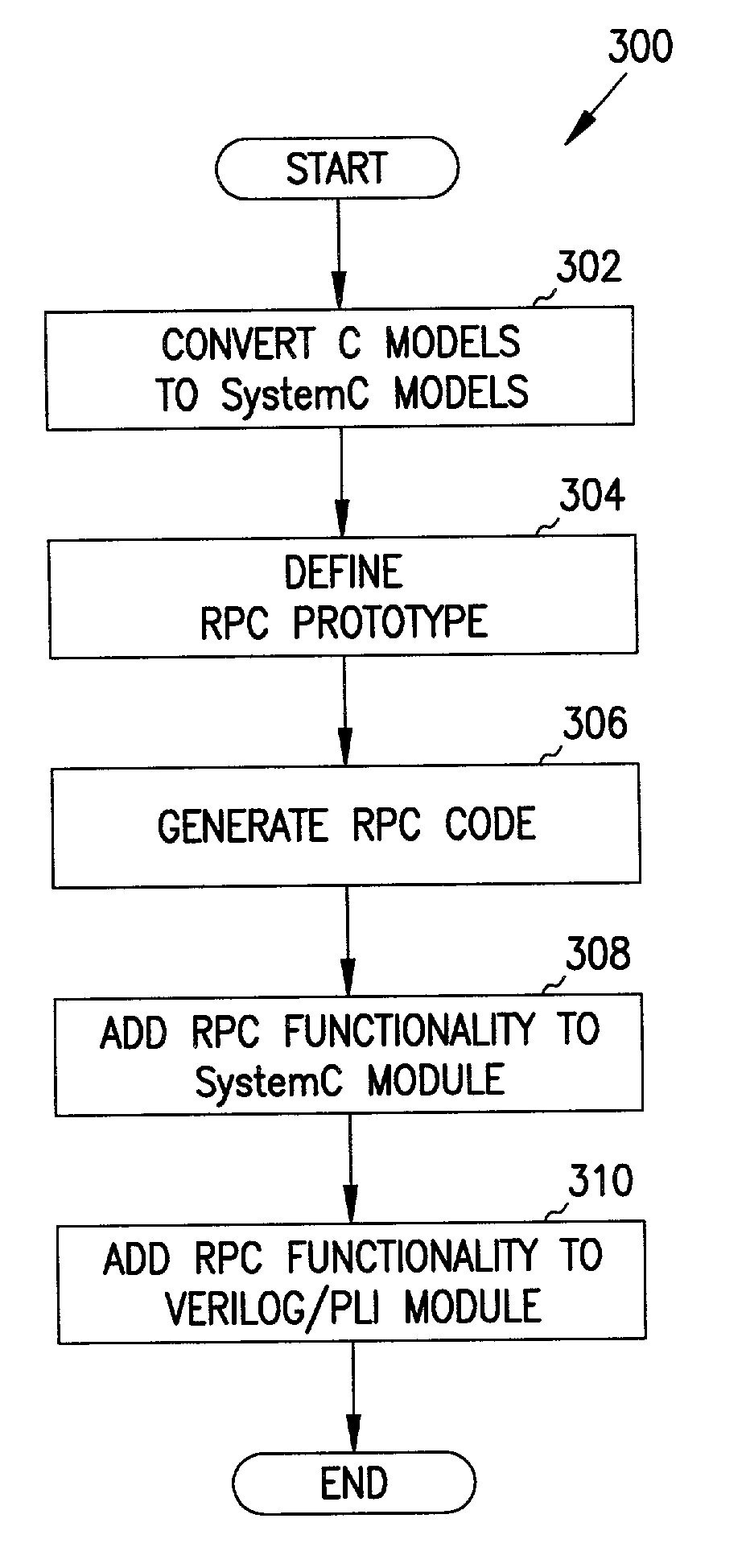

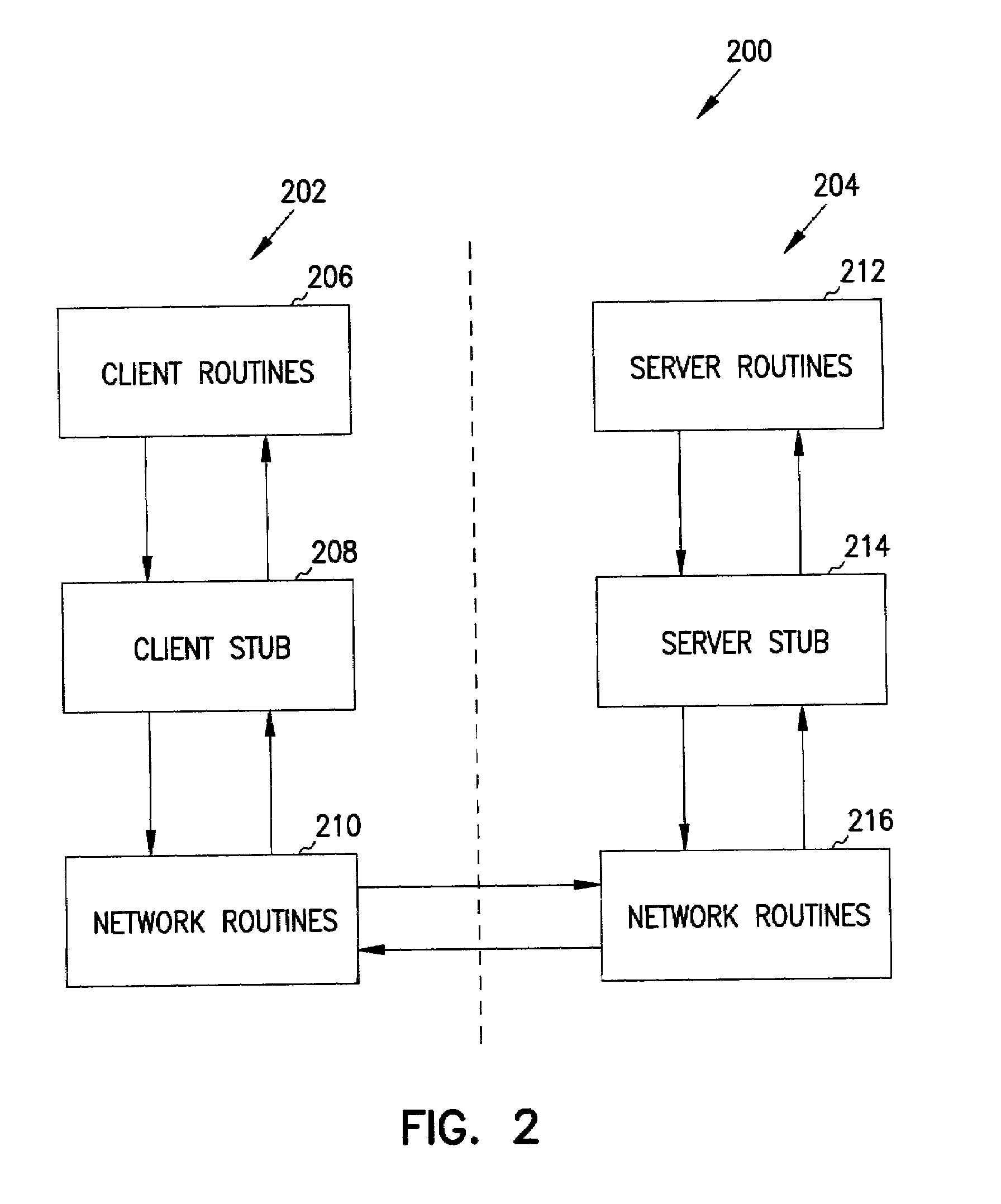

Co-simulation verilog/PLI and system C modules using remote procedure call

InactiveUS7117139B2Analogue computers for electric apparatusInterprogram communicationSystemCElectronic systems

A Verilog / PLI module that simulates behavior of an electronic system is co-simulated in a clock-accurate manner with a System C module that models the behavior of a component of the electronic system using a remote procedure call (RPC). Adding RPC functionality to the Verilog / PLI and System C modules facilitates exchanging parameters between the modules. The RPC is used to transfer process control to the SystemC module, after execution of which control is returned to the Verilog / PLI module. A return value is also returned to the Verilog / PLI module; this return value represents output signals associated with the System C module.

Owner:MICRON TECH INC

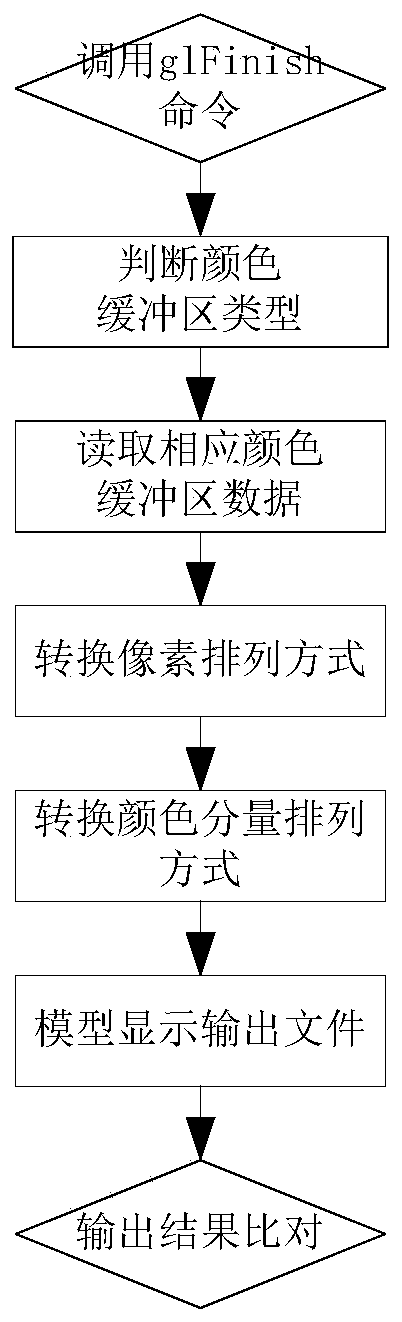

Graphic processor TLM model image output method based on SystemC

ActiveCN109753280AEffective design developmentValid verificationProcessor architectures/configurationCreation/generation of source codeSystemCGraphics

The invention relates to the technical field of computer hardware modeling, and especially relates to a graphic processor transaction level TLM model image output method based on SystemC. The graphicprocessor TLM model image output method comprises the steps of judging the type of a color buffer area, reading a corresponding color buffer area, converting a pixel arrangement mode, converting a pixel color component arrangement mode, creating an image file, writing converted color data into the file, comparing the converted color data with an output image and the like. The problem of quickly verifying the correctness of the GPU hardware model through picture display is solved, the design, development and verification of the GPU model are effectively facilitated, and powerful support is provided for RTL design, development and verification.

Owner:XIAN AVIATION COMPUTING TECH RES INST OF AVIATION IND CORP OF CHINA

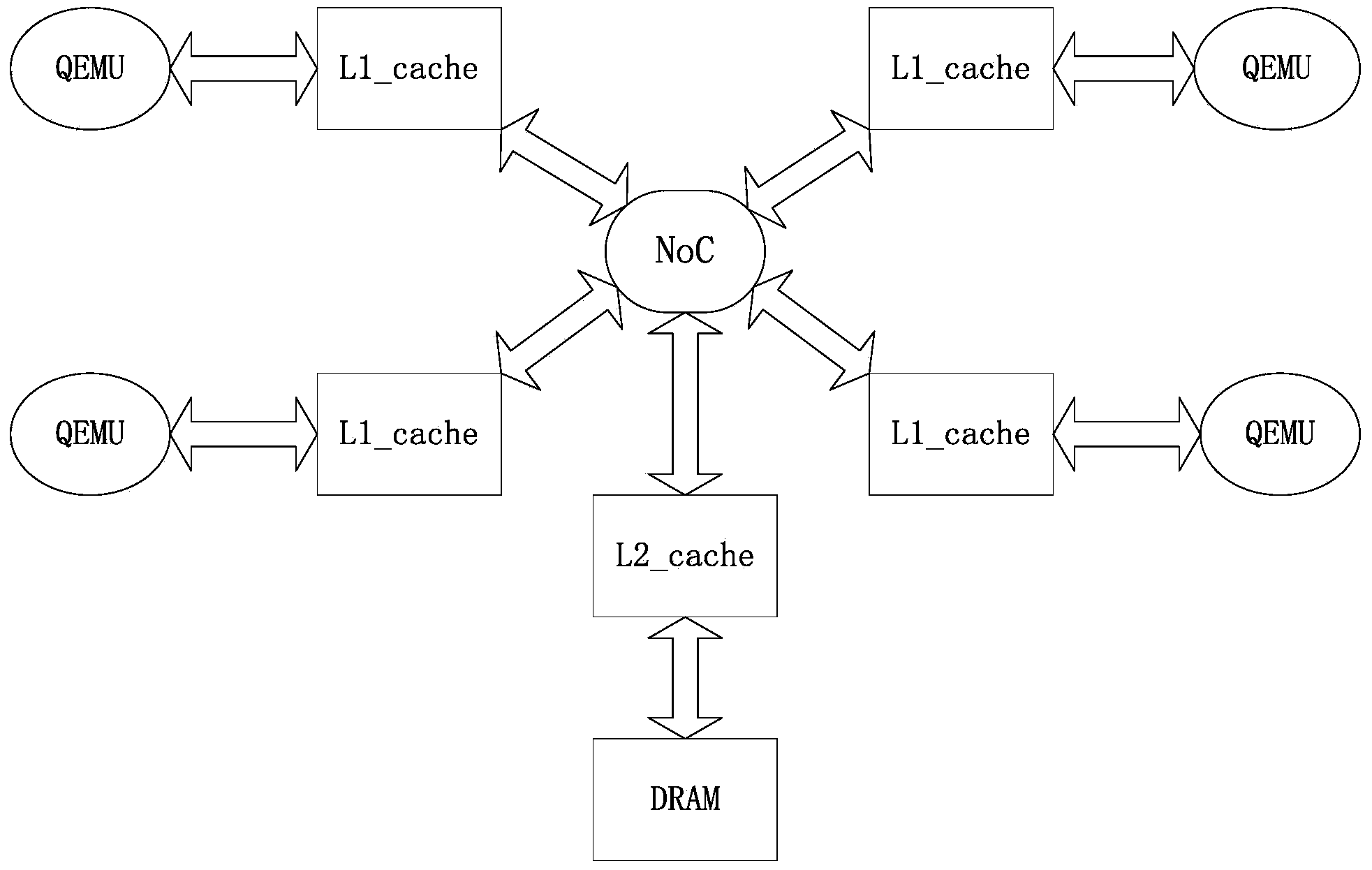

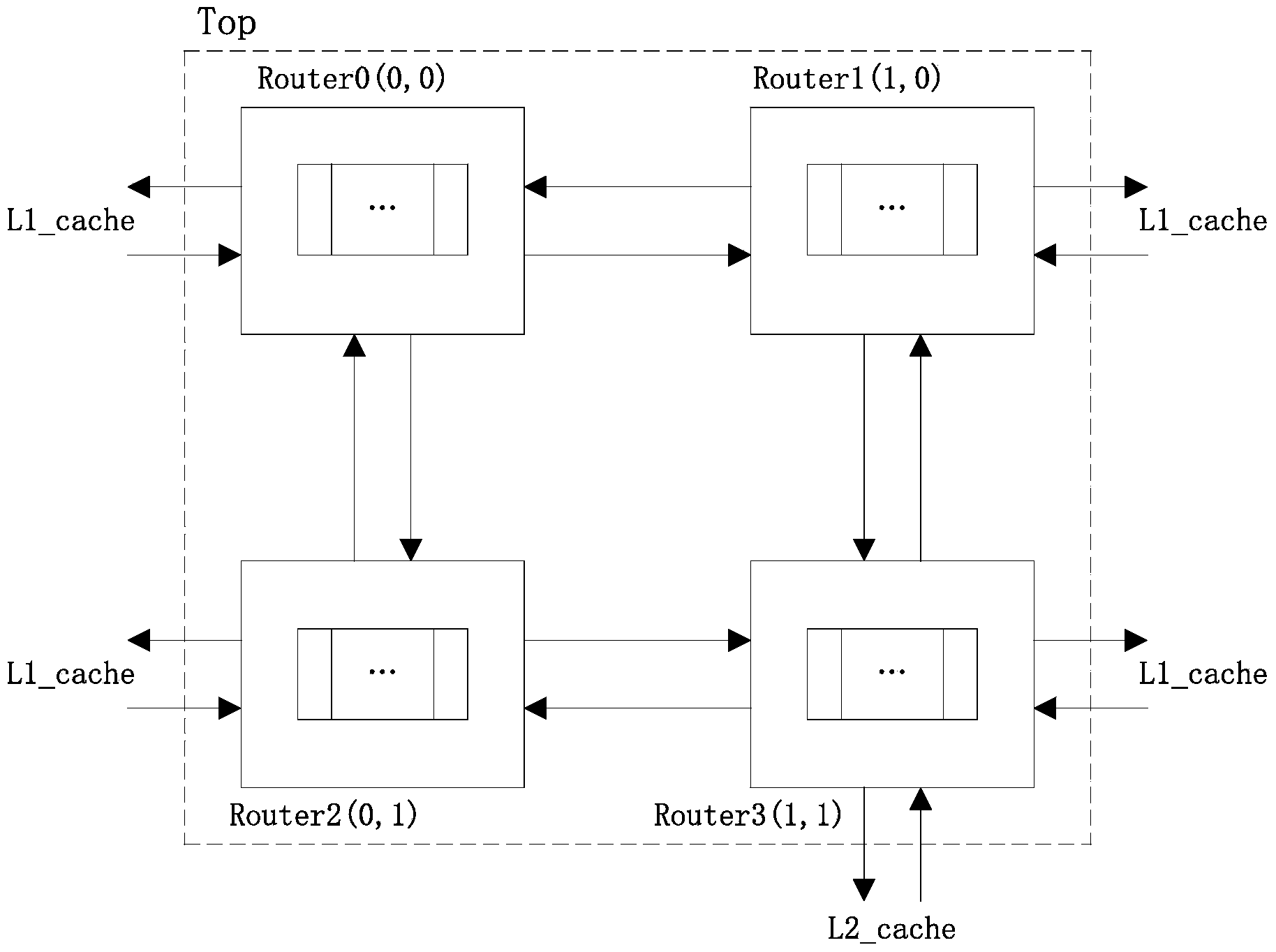

Multi-core memory system simulator on basis of network-on-chip interconnection

ActiveCN103914333ASpeed up developmentShort interconnectSoftware simulation/interpretation/emulationSystemCParallel computing

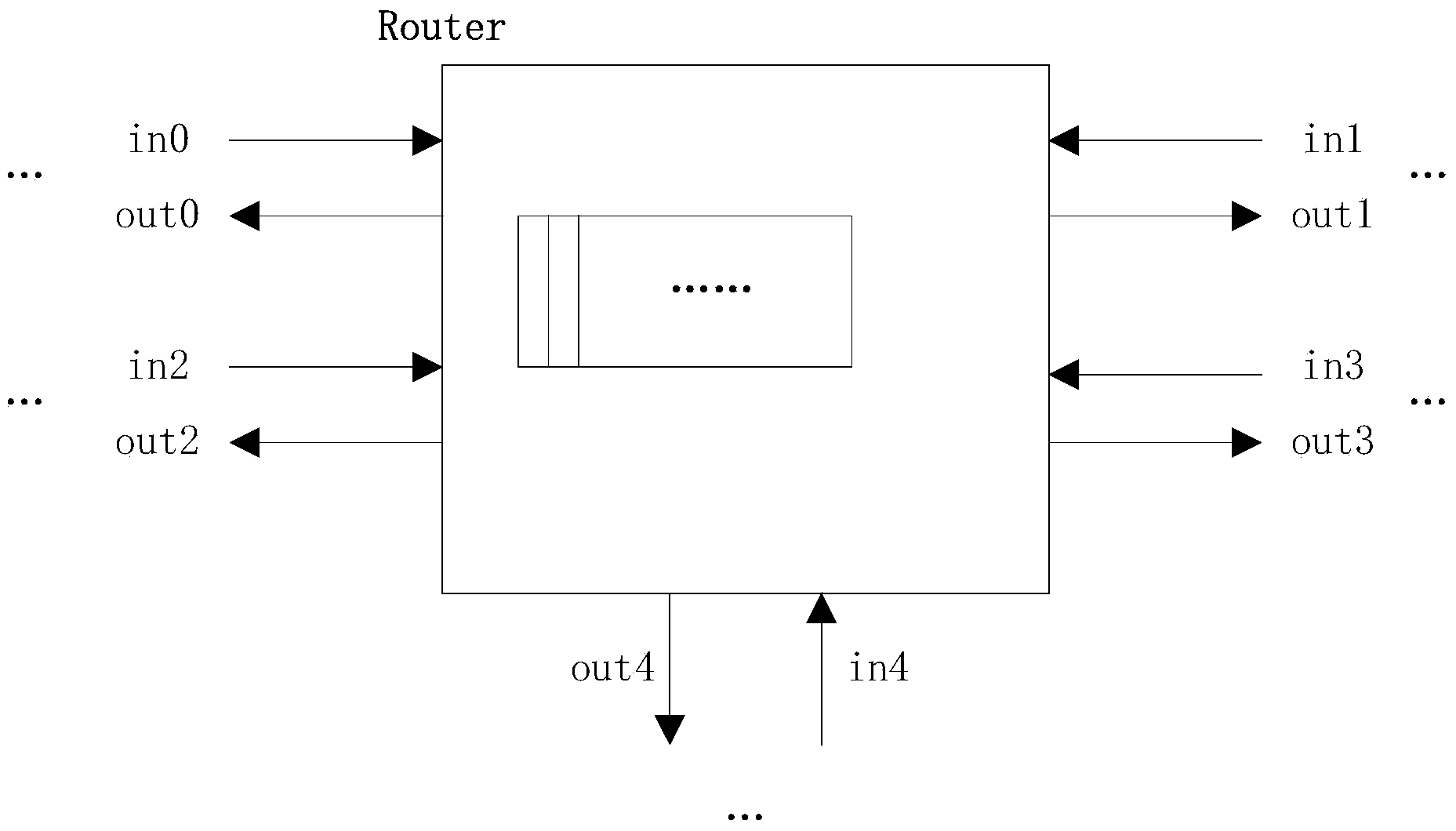

The invention discloses a multi-core memory system simulator on the basis of network-on-chip interconnection. The multi-core memory system simulator is characterized in that a core of SystemC is used as a driving core of the integral simulator, the multi-core memory system simulator comprises cache modules, a plurality of route modules and QEMU modules, the cache modules are used for simulating primary high-speed caches of cores of various processors, the route modules are used for simulating secondary high-speed caches of the cores of the various processors, and the QEMU modules are used for realizing functional simulation effects; the various route modules are interconnected with networks-on-chip which are formed by the secondary high-speed caches shared by the cores of the simulation processors, and each route module is provided with a group of signal lines connected with the corresponding cache modules; pkt (packet) messages which are transmitted by one cache module or one route module are distributed to another cache module or another route module. The multi-core memory system simulator has the advantages that system software of target systems can be developed by the aid of the simulator, the software and hardware can be simultaneously developed, and accordingly the system development speed can be increased.

Owner:SUZHOU INST FOR ADVANCED STUDY USTC

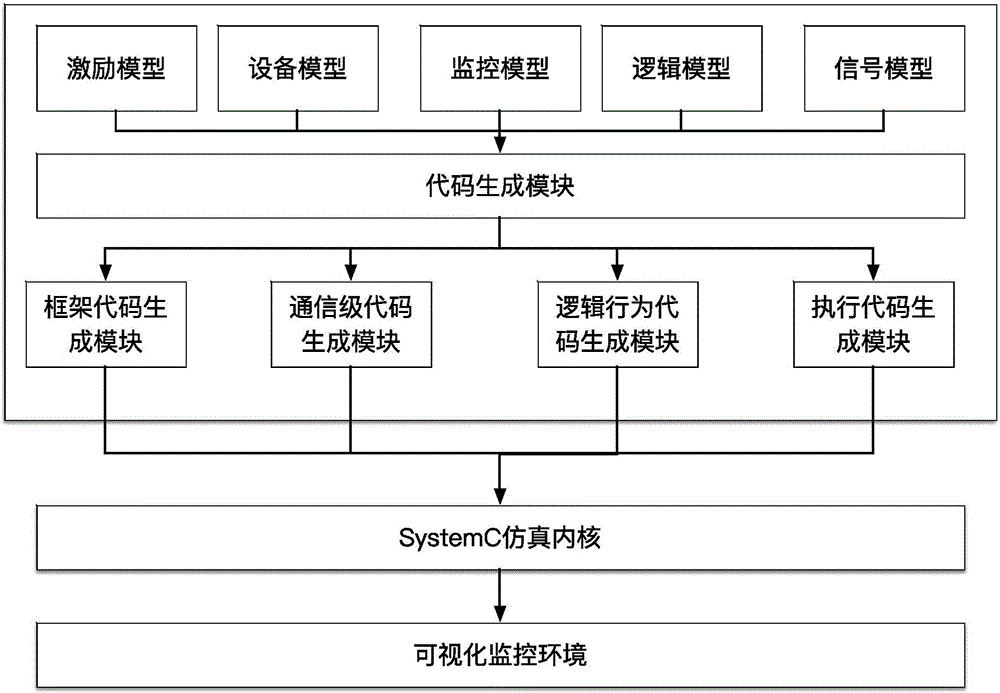

SystemC code generation system based on model

ActiveCN106354515ARealize automatic generationRealize Integrated Simulation VerificationSimulator controlProgramming languages/paradigmsSystemCElectronic systems

The invention discloses a SystemC code generation system based on a model and relates to the technical field of industrial electronic tools. With the adoption of the SystemC code generation system based on the model in the embodiment, automatic generation of model data SystemC codes can be realized through inheriting of behavior logic model data in Modelook, the logic model data is subjected to digital simulation verification directly, so that the economic cost is greatly reduced, and time is saved; besides, the logic model data is verified through hardware / software co-design language, and integrated simulation verification of hardware functions and software functions of an industrial electronic system is realized.

Owner:杭州杉石科技有限公司

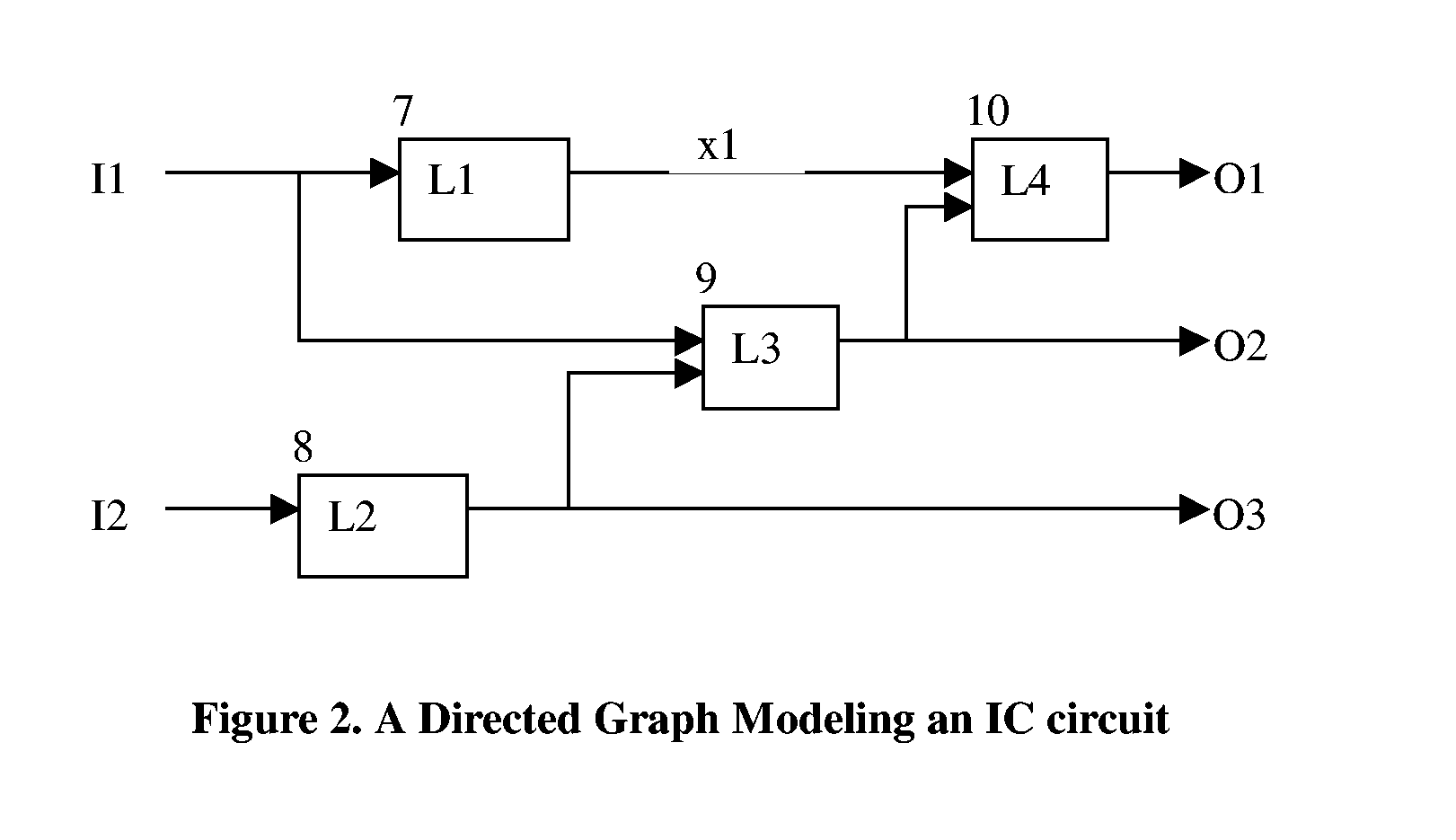

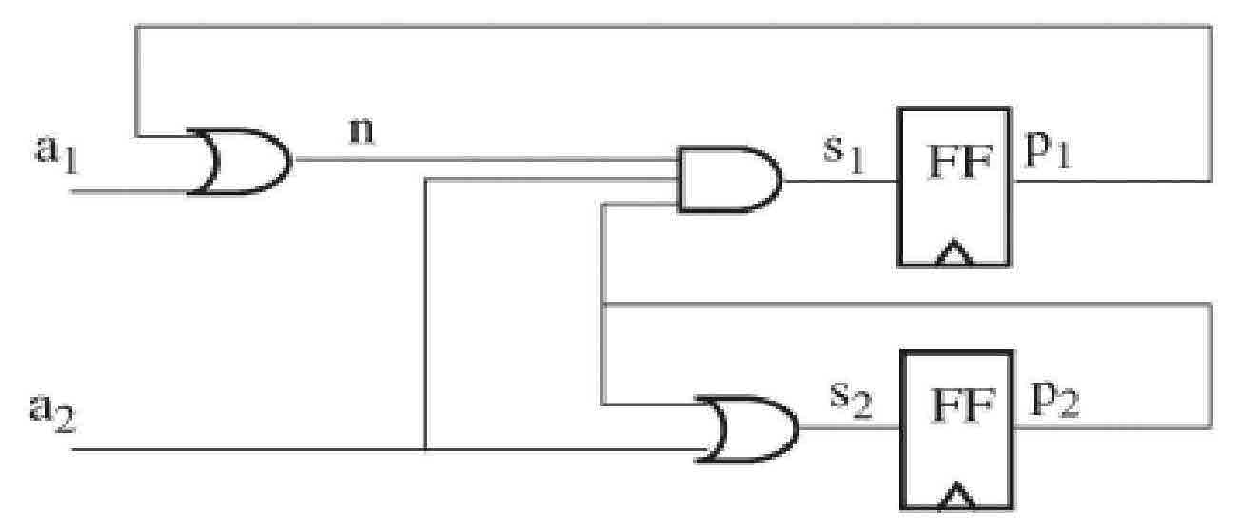

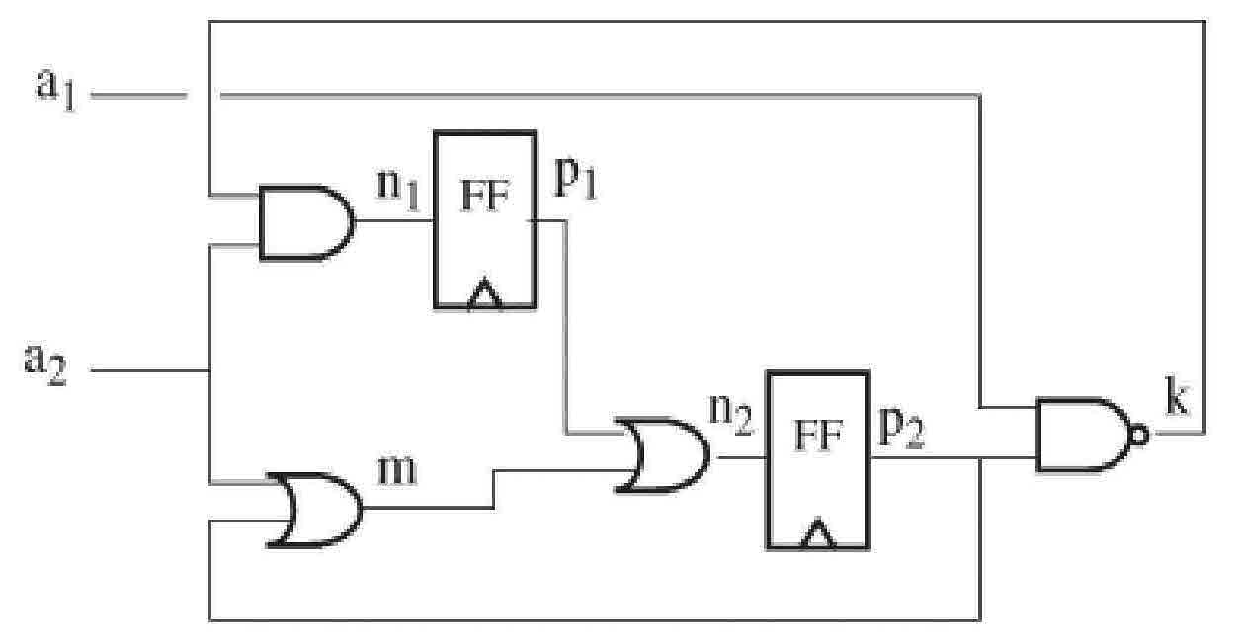

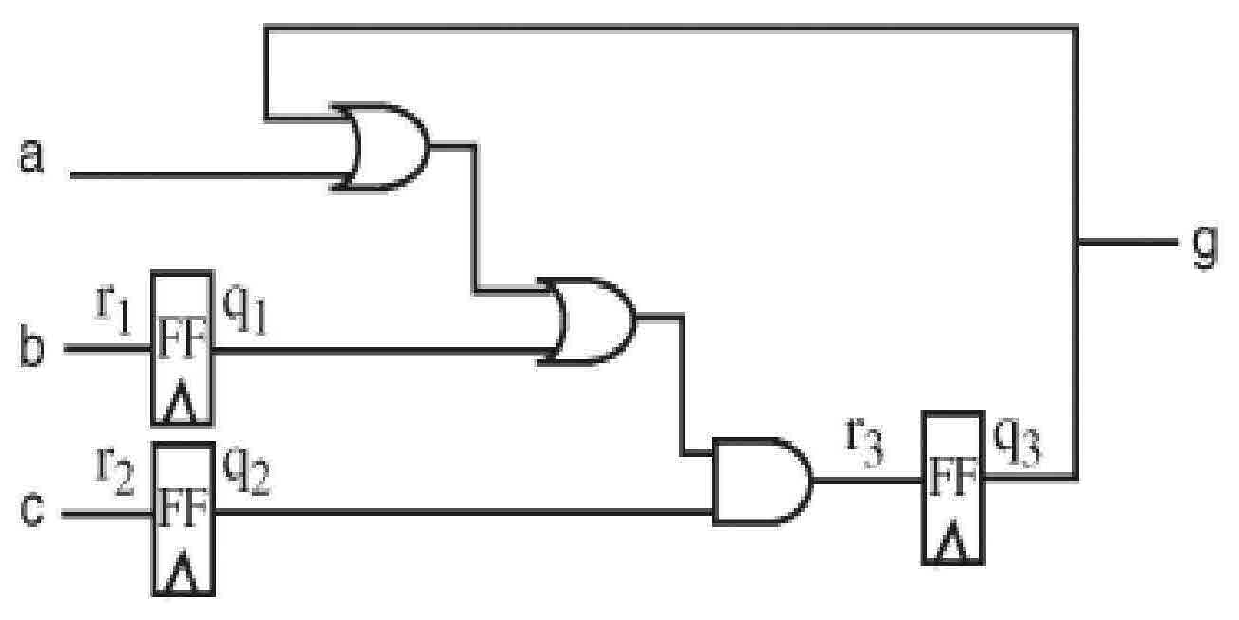

Topological structure analyzing method and state machine model extracting method of time sequence circuit

InactiveCN102567555AFormal analysis is goodAvoid complexitySpecial data processing applicationsDevice typeSystemC

The invention relates to a topological structure analyzing method and a state machine model extracting method of a time sequence circuit. The method is applicable to the time sequence circuit described according to SystemC and including a trigger and an elementary gate, wherein the trigger and the elementary gate are described by SystemC. Circuit information reflects a topological structure of a circuit and comprises trigger number and port information thereof, gate device type and port information thereof as well as primary input end number and information of a logic device connected with each lead. The method mainly comprises the following steps of: extracting circuit topological structure information; constructing a Boolean function of the circuit; showing the Boolean function of state transfer by using a binary decision diagram; initializing a time sequence circuit; and calculating the Boolean function of state transfer by using a constraint solver. According to the invention, by using a gate-level time sequence circuit state machine model extracting algorithm, the time sequence circuit state machine model can be very well obtained without need of applying any motivation to the design so that the complicatedness of realization is avoided.

Owner:北京国睿中数科技股份有限公司

Multi-thread optimization method and system for SystemC simulation scheduling core and medium

ActiveCN109783239AImprove scalabilityEasy to upgradeProgram initiation/switchingResource allocationSystemCExtensibility

The invention provides a multi-thread optimization method and system for a SystemC simulation scheduling core and a medium. The multi-thread optimization method comprises the steps of task separation,wherein a calculation task of SystemC simulation is stripped into threads of other operation systems except the operation system to which the calculation task belongs; a module communication step: injecting a callback function to realize communication between an external computing task and a SystemC thread; and a task synchronization step: realizing synchronization of a plurality of simulation tasks through decoupling in time and controlling duration time. Compared with the prior art, the current popular multi-processor equipment can be well and fully utilized, and the simulation efficiency is improved. The simulation synchronization is controlled through the minimum period simulation period, so that the simulation correctness is ensured. In addition, the callback function is used, so that the expandability of the simulation system is better, and the simulation system is more convenient to upgrade and maintain.

Owner:VISION MICROSYST SHANGHAI

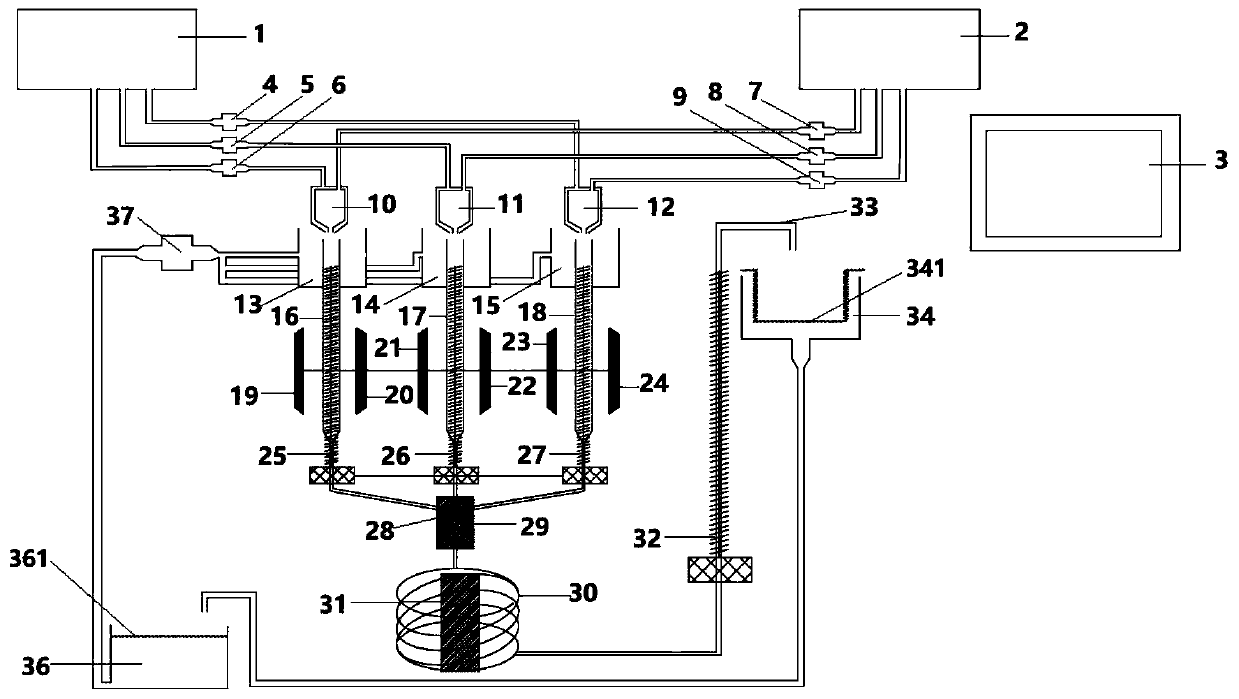

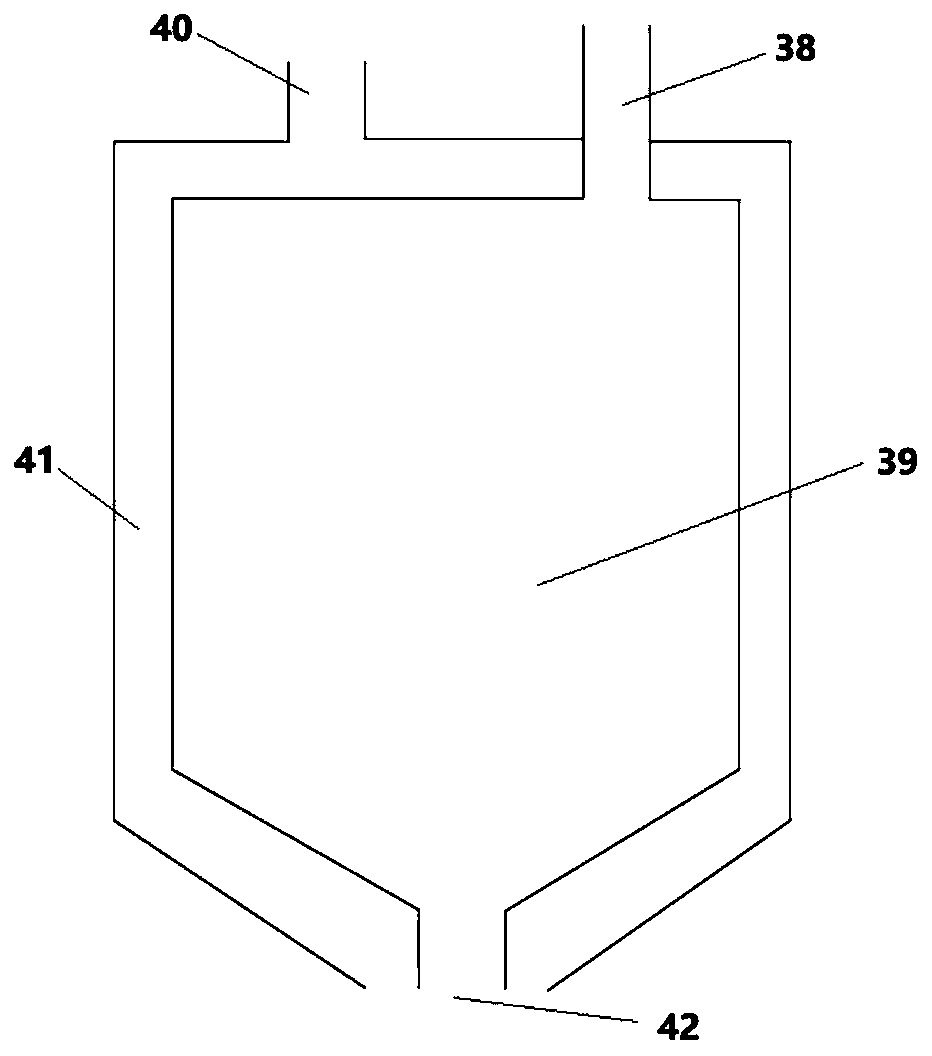

Multi-dripper UV photocuring water-based capsule production equipment

ActiveCN110338450AUniform curingEnsure controllabilityTobacco treatmentMicroballoon preparationWater basedSystemC

The invention relates to multi-dripper UV photocuring water-based capsule production equipment; the capsule production equipment comprises a feeding system A, a forming system B, a circulating systemC and a control system D; by using the multi-dripper UV photocuring water-based capsule production equipment disclosed by the invention, the consistency of the capsule materials is ensured from the source; meanwhile, equipment parts can be utilized to the maximum extent, the production efficiency is improved, the production cost is lowered, and the equipment is rapid, efficient, energy-saving andenvironment-friendly, and does not need to be subjected to excessive treatment in the later period, so that subsequent processing and transportation and storage can be conveniently carried out, and the UV light-cured water-based capsule capable of effectively storing contents for a long time can be obtained.

Owner:YUNNAN TOBACCO BIOLOGICAL TECH CO LTD +2

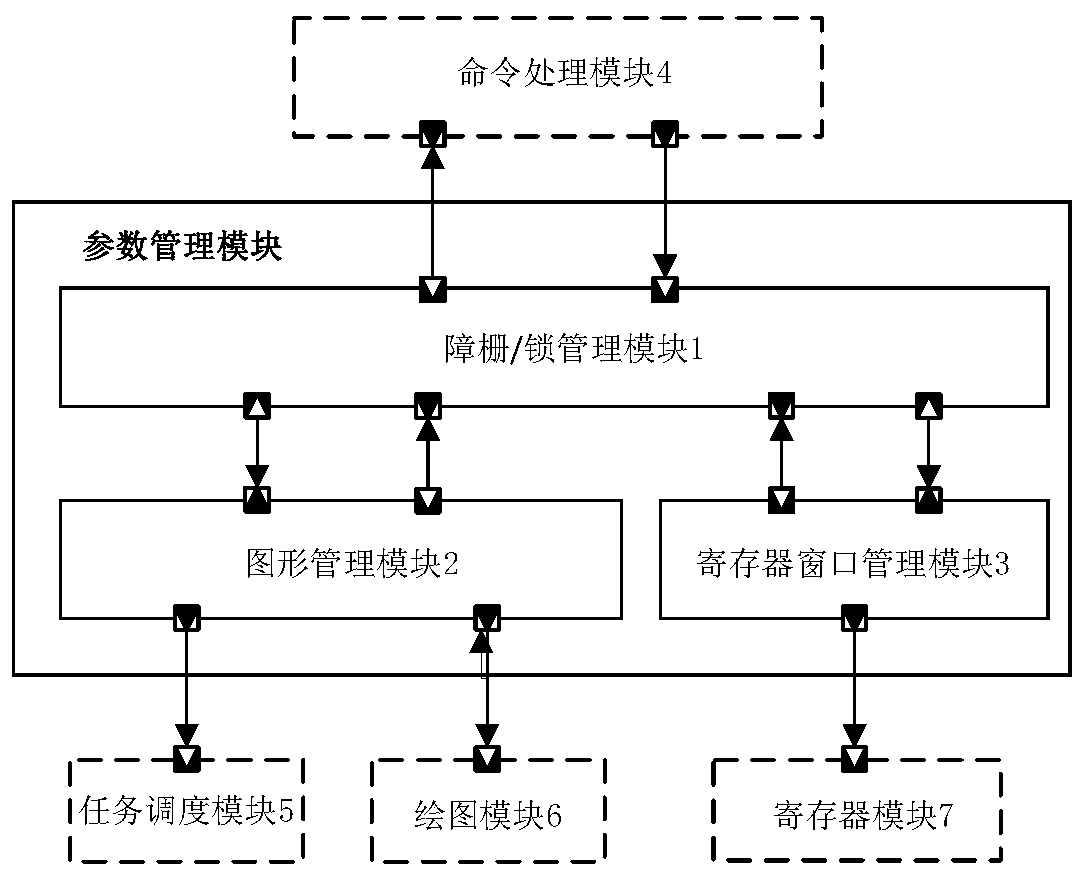

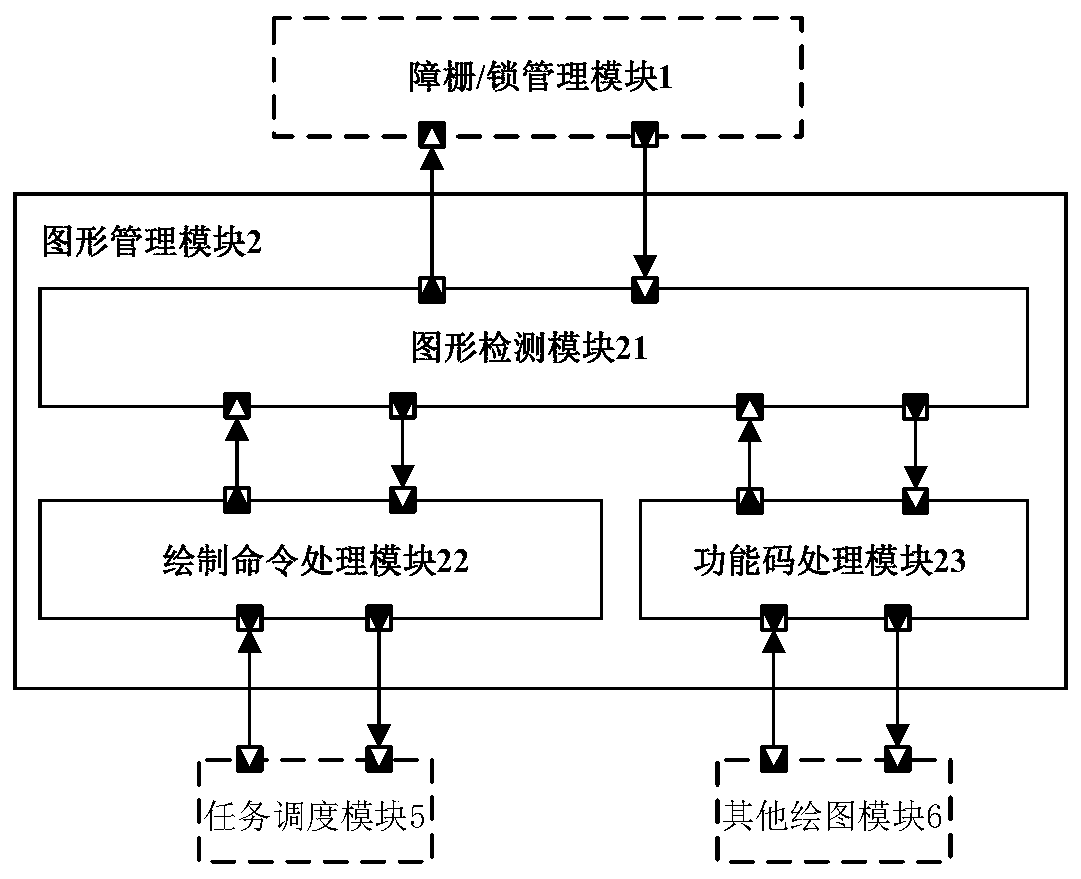

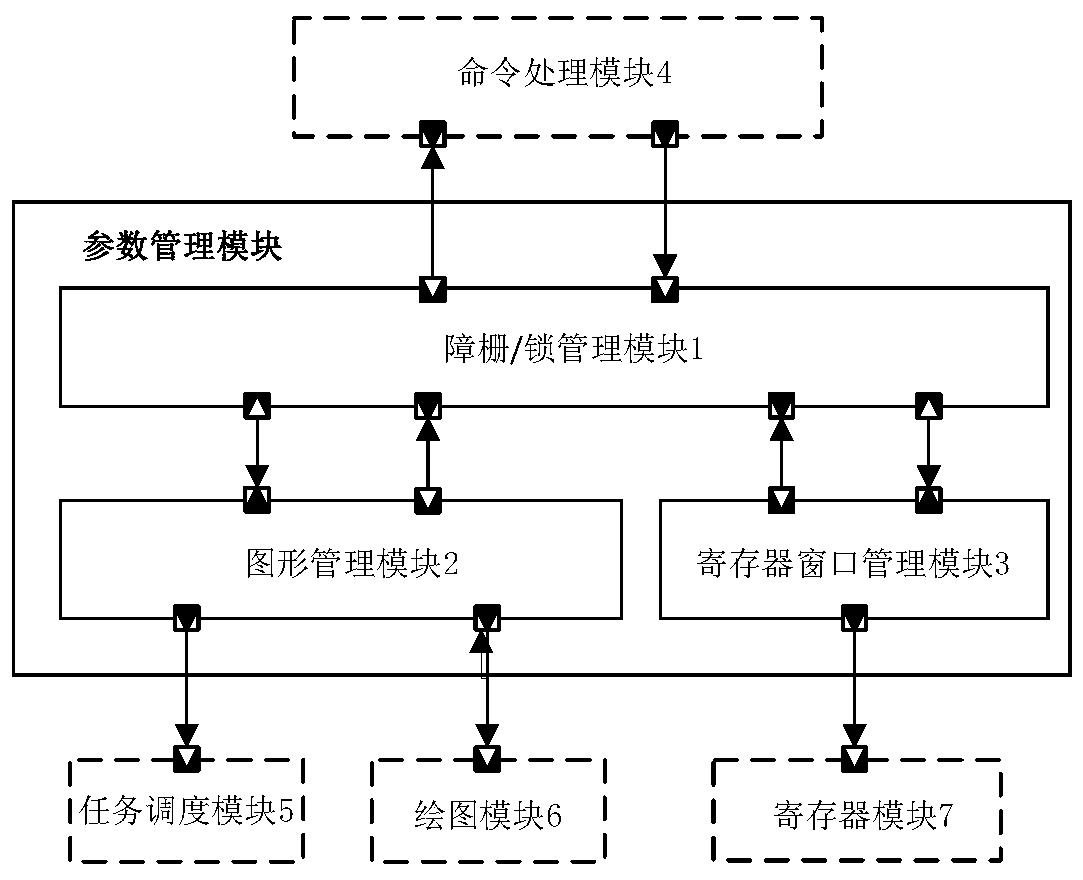

A GPU-oriented parameter management method based on SystemC

ActiveCN109840878ARealize distributionRealize managementMultiprogramming arrangementsProcessor architectures/configurationSystemCGraphics

The invention relates to the technical field of computer hardware modeling. The invention provides a GPU-oriented parameter management method based on SystemC. The method comprises the following steps: step 1, executing barrier / lock management, calculating a new barrier state according to the current barrier state and the FIFO state, when judging that the GraphRegLock is 0, outputting the GraphRegLock to a graphic management module (2) through a transaction-level interface, and executing the step 2, otherwise, outputting the GraphGrawLock to a register window management module (3) through thetransaction-level interface when the GraphGrawLock is 0 and the GraphFunction is 0, and executing the step 3; Step 2, executing graph drawing command parameter and function code parameter management;And step 3, executing read-write management of register parameters.

Owner:XIAN AVIATION COMPUTING TECH RES INST OF AVIATION IND CORP OF CHINA

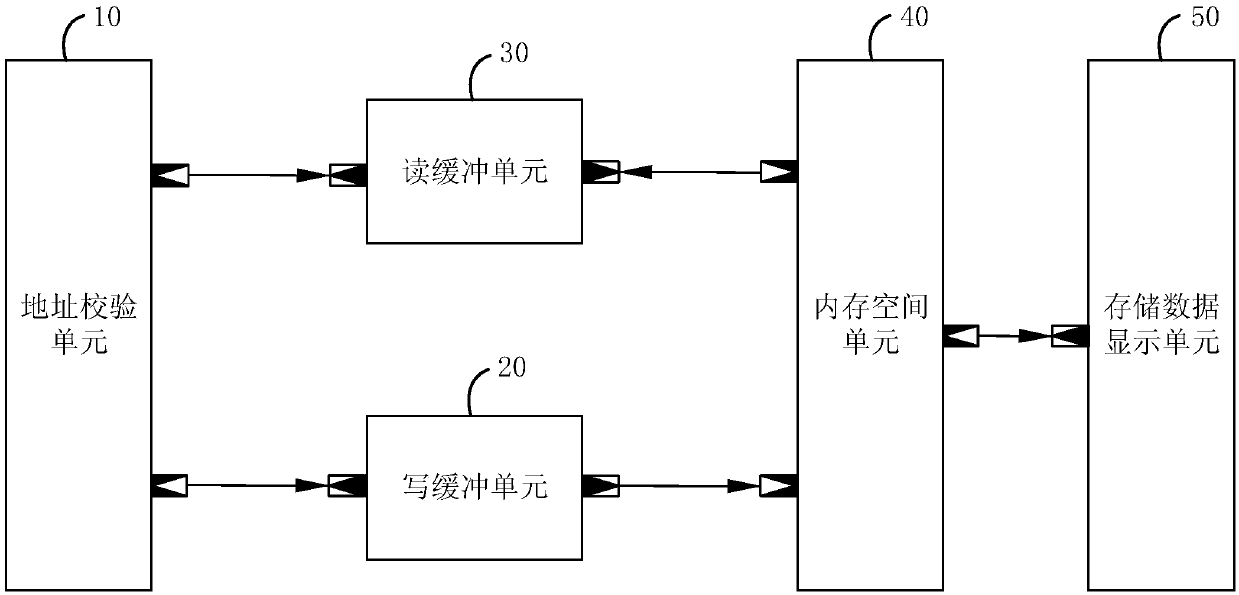

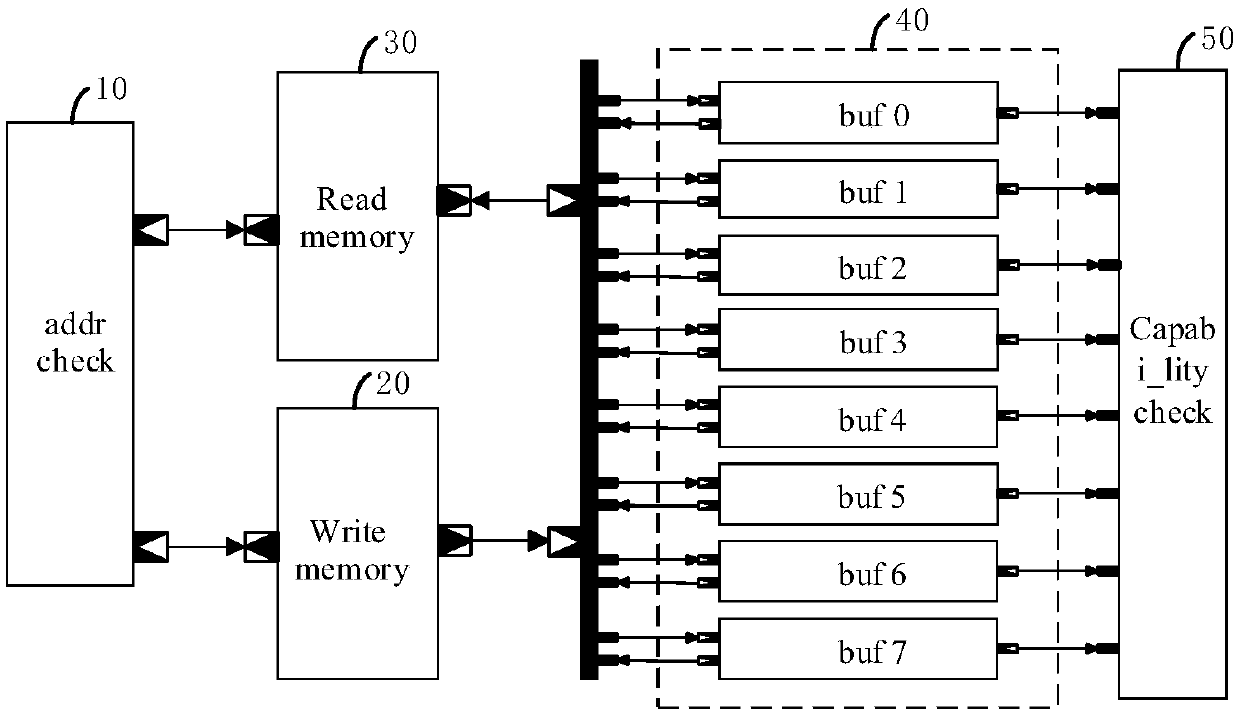

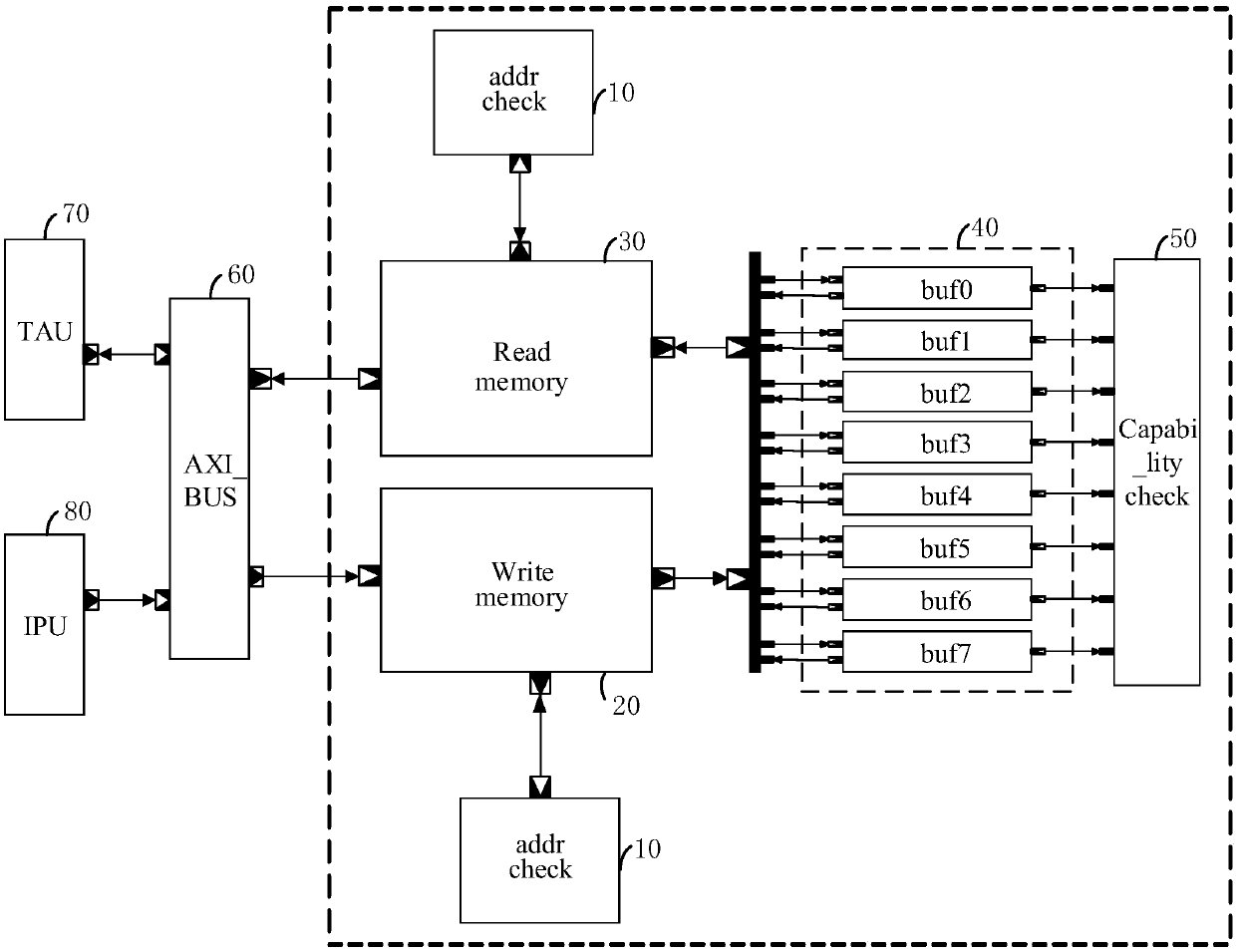

GPU-oriented texture buffer data storage TLM model based on SystemC and an implementation structure thereof

ActiveCN109614086AHigh speed storageImprove access speedHardware monitoringCreation/generation of source codeData displaySystemC

The invention relates to a GPU-oriented texture buffer data storage TLM model based on SystemC and an implementation structure thereof, and the TLM model comprises an address verification unit which is used for verifying the effectiveness of a texture data address, and generating and sending effective information when judging that the texture data address is effective; T. The write buffer area unit is used for writing the texture data into the memory space unit when effective information is received; T. The read buffer area unit is used for reading texture data from the memory space unit wheneffective information is received; T. The memory space unit is used for receiving the texture data written by the write buffer unit or providing the texture data for the read buffer unit; and the storage data display unit is used for displaying the texture data written by the write buffer unit and the size of the texture data read by the read buffer unit and carrying out performance evaluation. According to the hardware TLM model, a large amount of texture image buffer data can be stored at a high speed, and the access speed is increased.

Owner:西安翔腾微电子科技有限公司