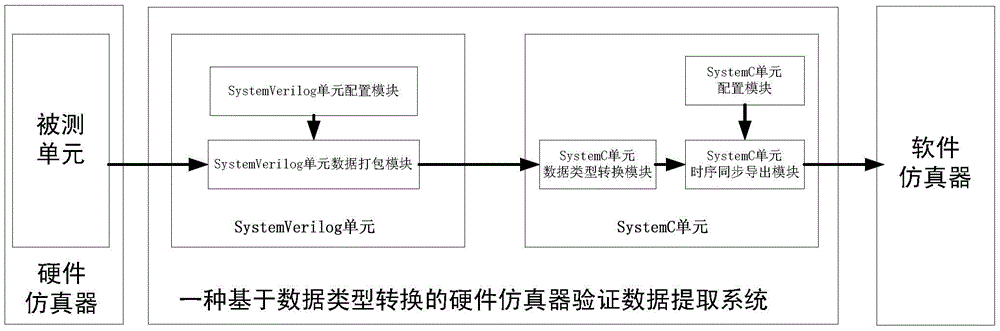

Data type conversion-based hardware simulator validation data extraction system

A hardware emulation, data type technology, applied in the detection of faulty computer hardware, faulty hardware testing methods, etc., can solve the problems of the progress of hardware emulator verification, the low efficiency of data extraction, and the impact of verification efficiency, etc. Simple, versatile, and fast

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment

[0034] When using a hardware emulator to verify the system chip with the AMBA bus as the internal interconnection bus, it is necessary to extract the data transmitted on the AMBA bus and compare it with the result set in the software emulator. Among them, the simulation accuracy of the AMBA bus in the unit under test is cycle-accurate, and the maximum length of one transmission is 8 words. The preset results in the software simulator are written in SystemC language, and the simulation accuracy of the software simulator is transaction-level accuracy, using 32-bit The wide transaction interface communicates with the system.

[0035] When using a hardware emulator verification data extraction system based on data type conversion described in the present invention to extract verification data, the SystemVerilog unit configuration module and the SystemC unit configuration module are firstly configured. For the SystemVerilog unit configuration module, the data volume threshold for r...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More