Topological structure analyzing method and state machine model extracting method of time sequence circuit

A technology of sequential circuits and topological structures, applied in electrical digital data processing, special data processing applications, instruments, etc., can solve problems such as complex simulation semantics, and achieve the effect of avoiding complexity and good formal analysis.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0025] Below in conjunction with accompanying drawing and specific embodiment the present invention is described in further detail:

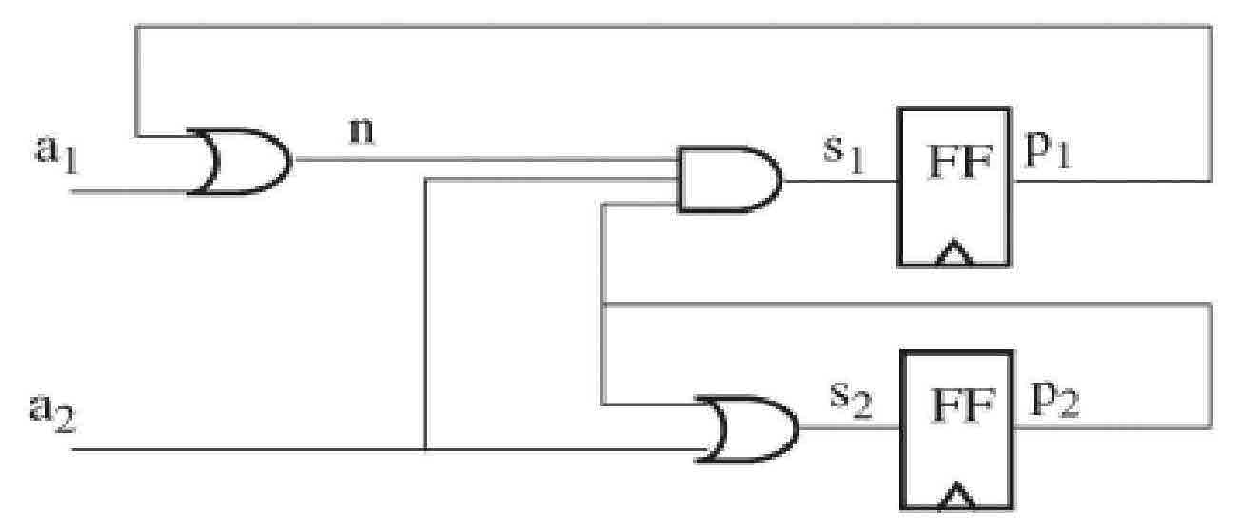

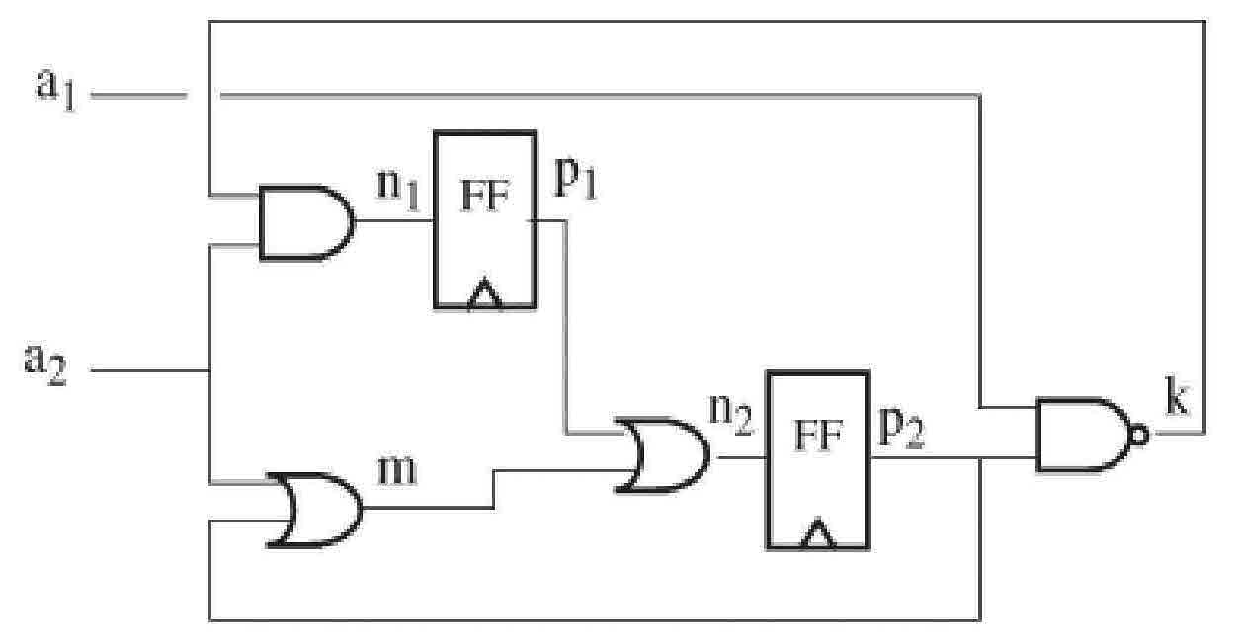

[0026] figure 1 It is a sequential gate-level circuit consisting of 2 flip-flops, two OR gates and a three-input AND gate. Now construct the bdd representation of the state transition function of the sequential circuit according to the above algorithm steps. The circuit information has been obtained by modifying the end_of_elaboration function during instantiation, and the names of the wires are all the names in the figure during instantiation, that is, a1, a2, s1, s2, p1, p2, n. Among them, the ports as the flip-flop ports are p1, s1, p2, s2, the ports as the primary input ports are a1, a2, and the middle wire has n. According to the above algorithm, the specific implementation process is as follows: figure 2 .

[0027] As an example, the following describes how to modify the end_of_elaboration function to obtain circuit port inter...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More