Patents

Literature

35results about How to "Short interconnect" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

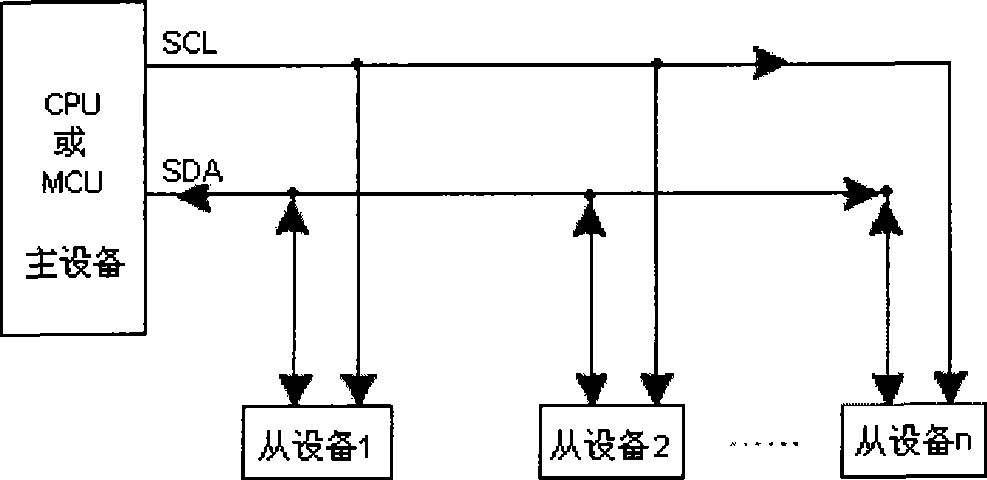

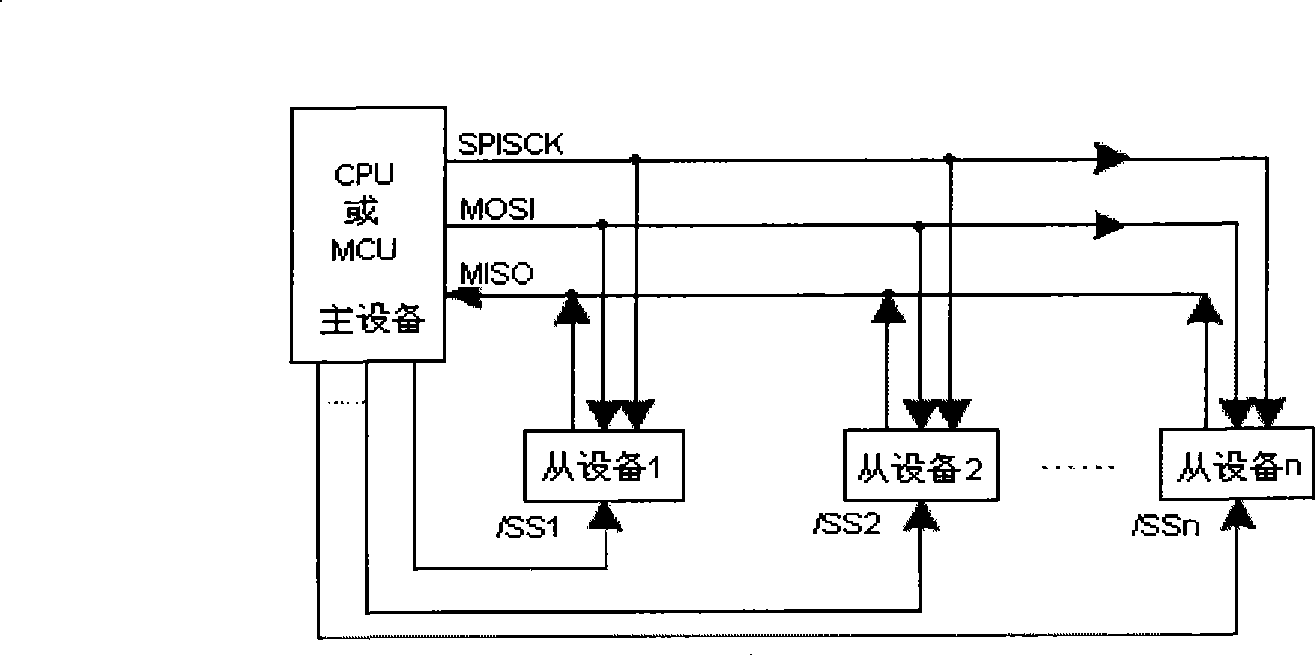

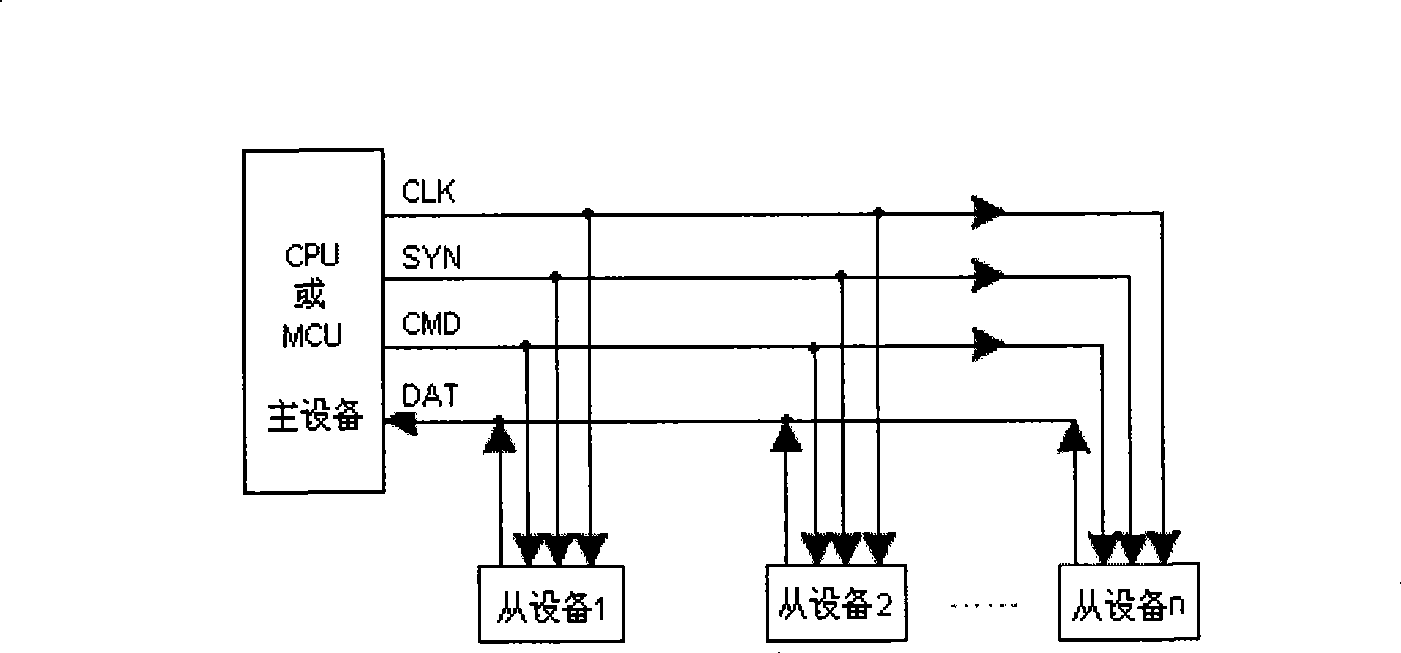

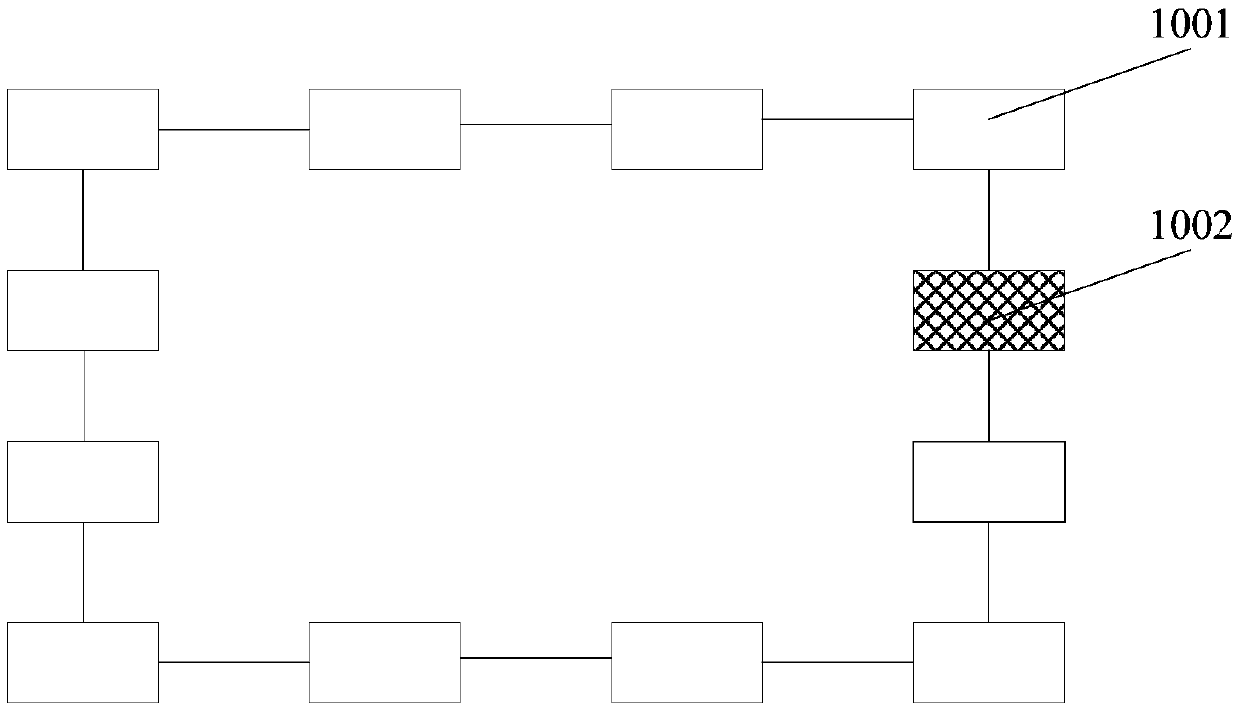

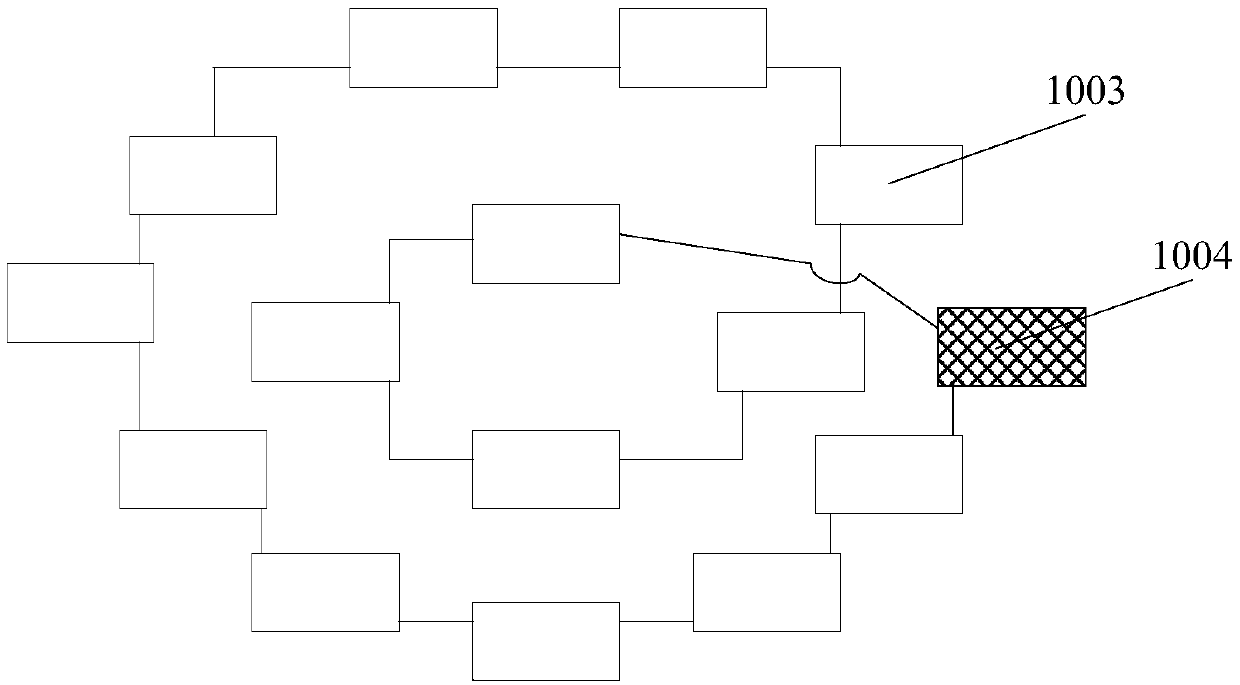

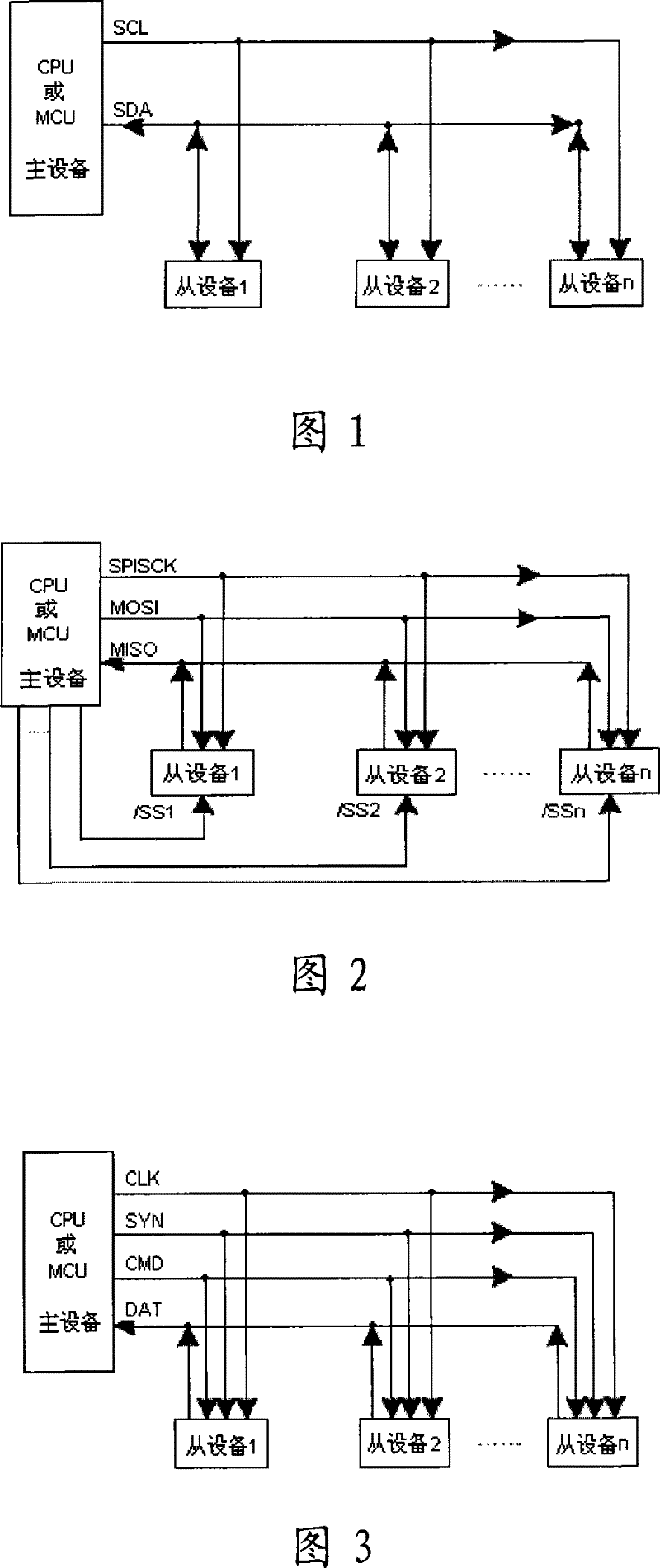

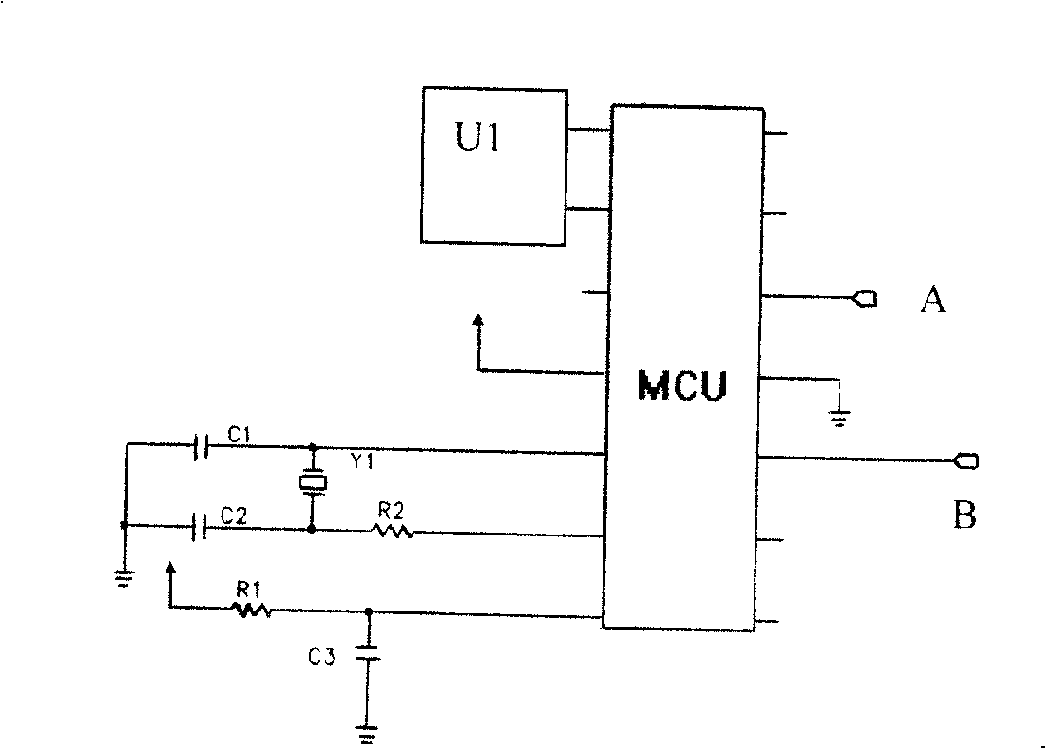

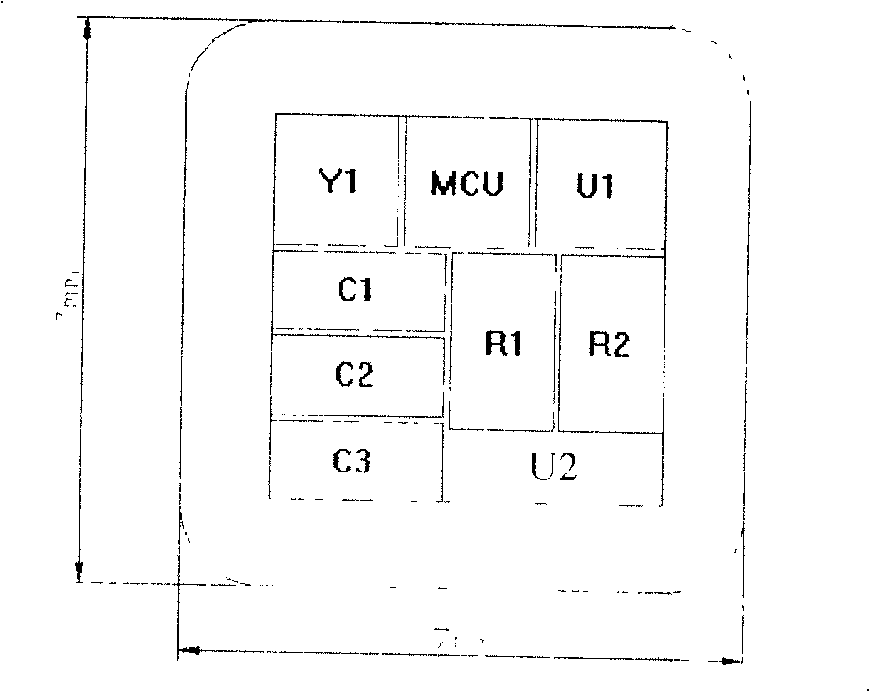

Serial communication method and apparatus

InactiveCN101399654AEasy to implementReduce logicSynchronising arrangementBus networksData signalEmbedded system

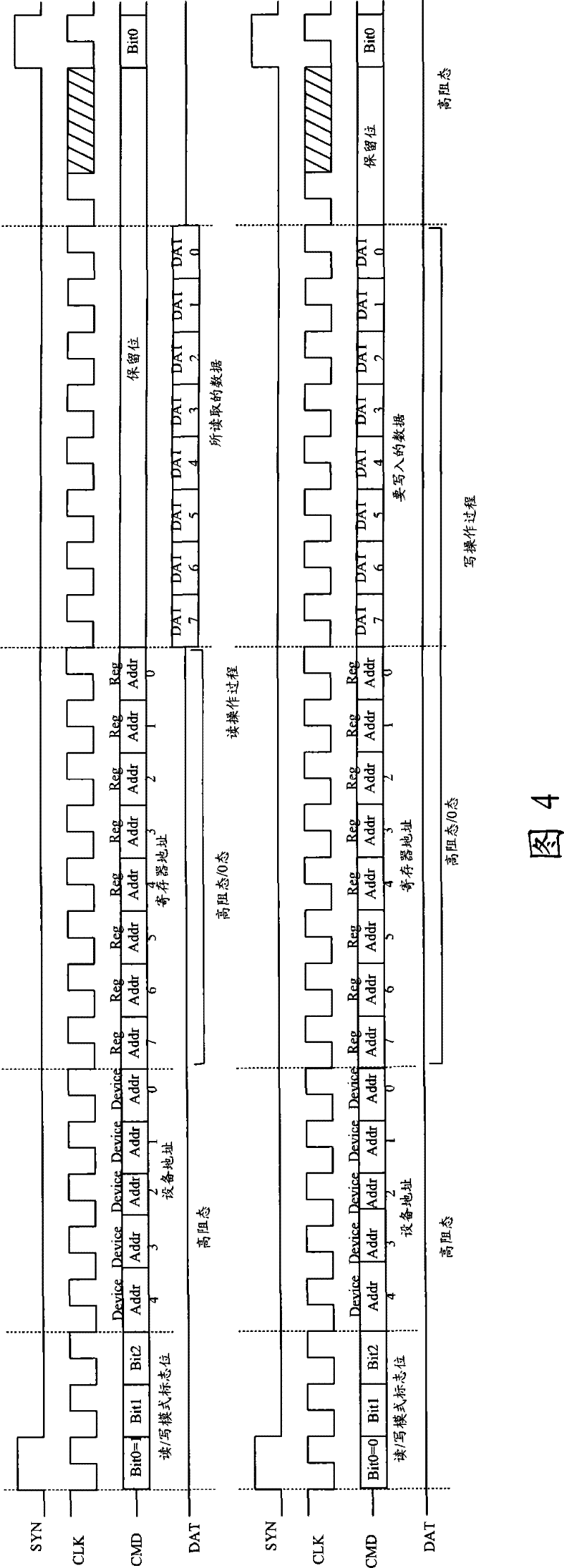

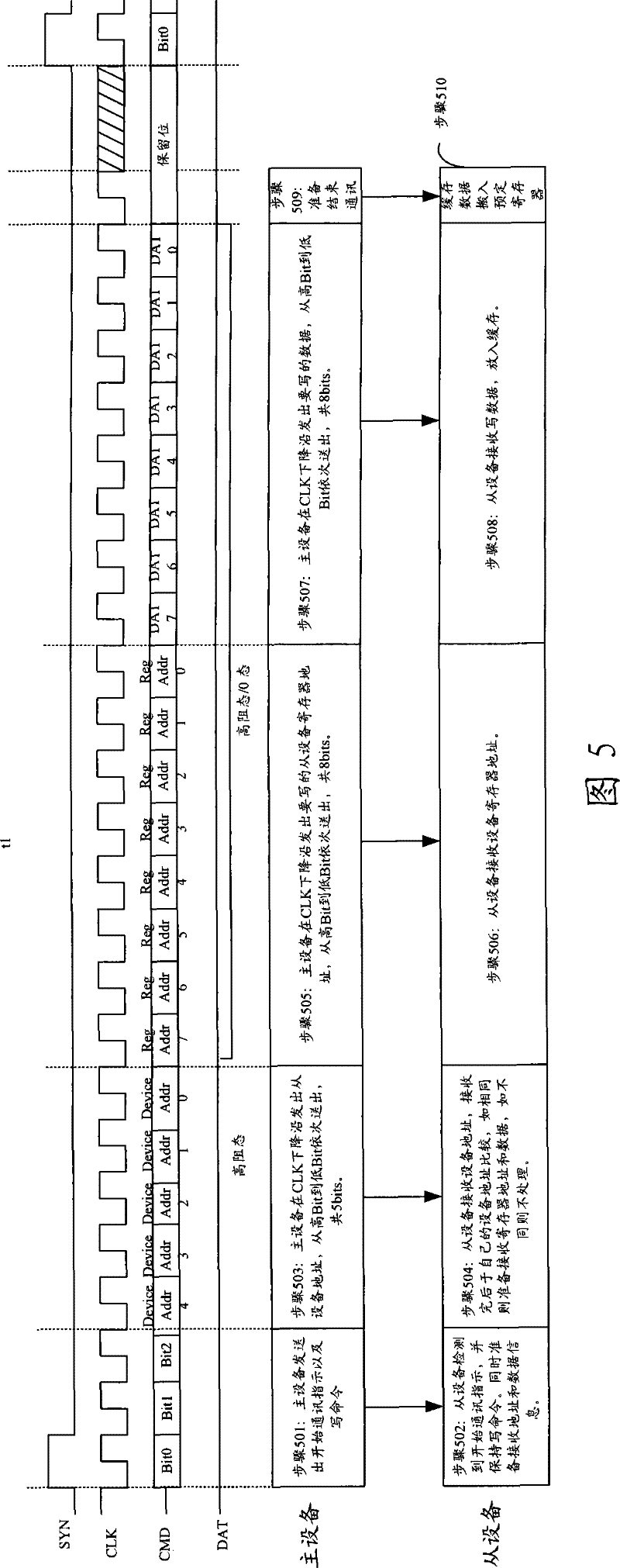

The invention discloses a method of serial communication, wherein, master equipment is connected with at least one slave equipment; the master equipment provides a communication clock signal (CLK) to the slave equipment by a clock signal wire, notifies the slave equipment to start reading / writing operation by a synchronous signal (SYN), and transmits a slave equipment address or a register address to the slave equipment by a downstream data signal (CMD); and the master equipment transmits downstream data to the slave equipment by the downstream data signal (CMD), or the slave equipmen transmits upstream data to the master equipment by an upstream data signal (DAT). The method of serial communication comprises a serial communication method of the master equipment, a serial communication method of the slave equipment and a serial communication method for interaction of the master equipment and the slave equipment. The invention also discloses the master equipment and the slave equipment. The proposal of the invention has the advantages of easy realization, pin resource conservation and cost reduction.

Owner:HUAWEI TECH CO LTD

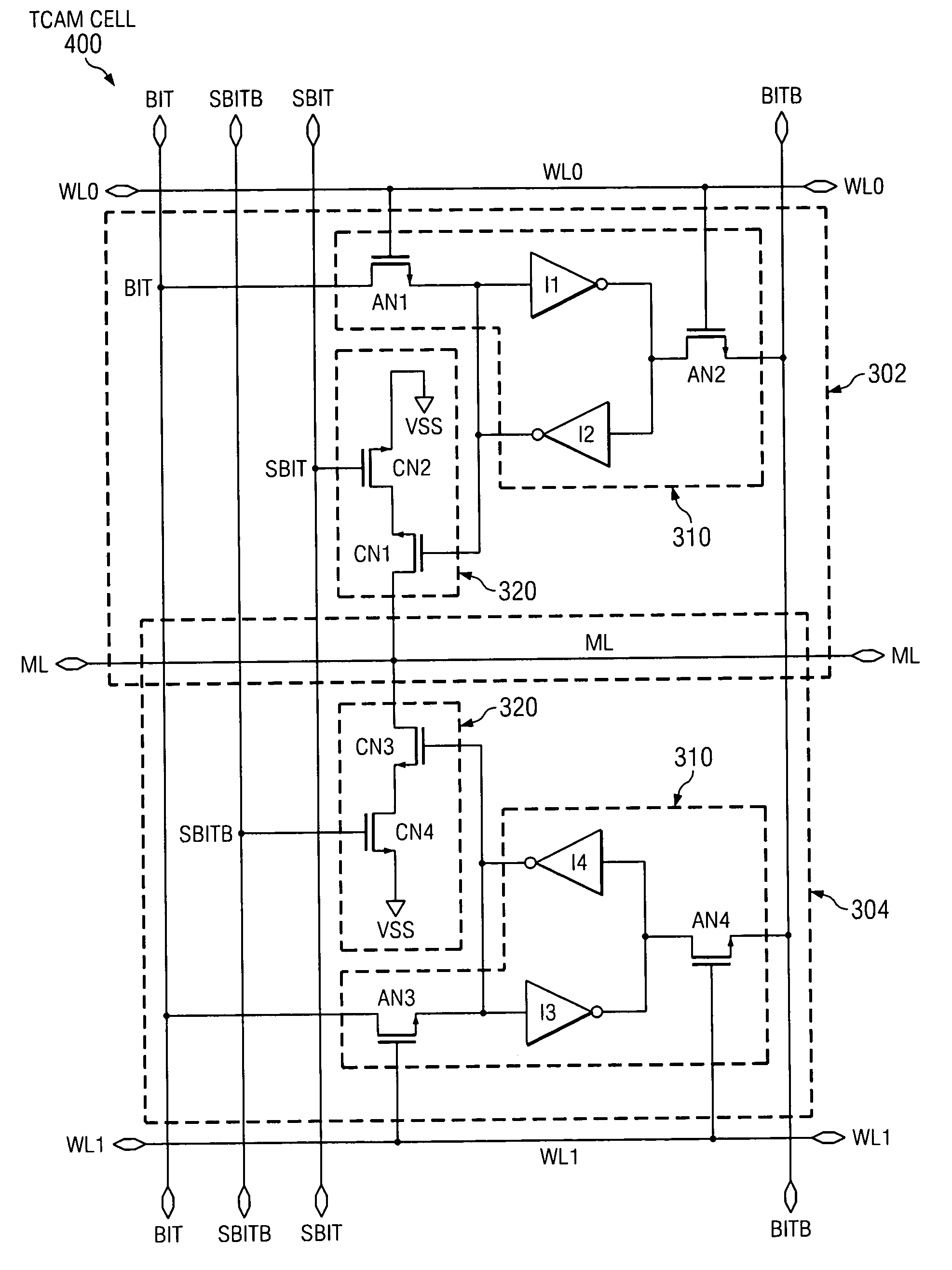

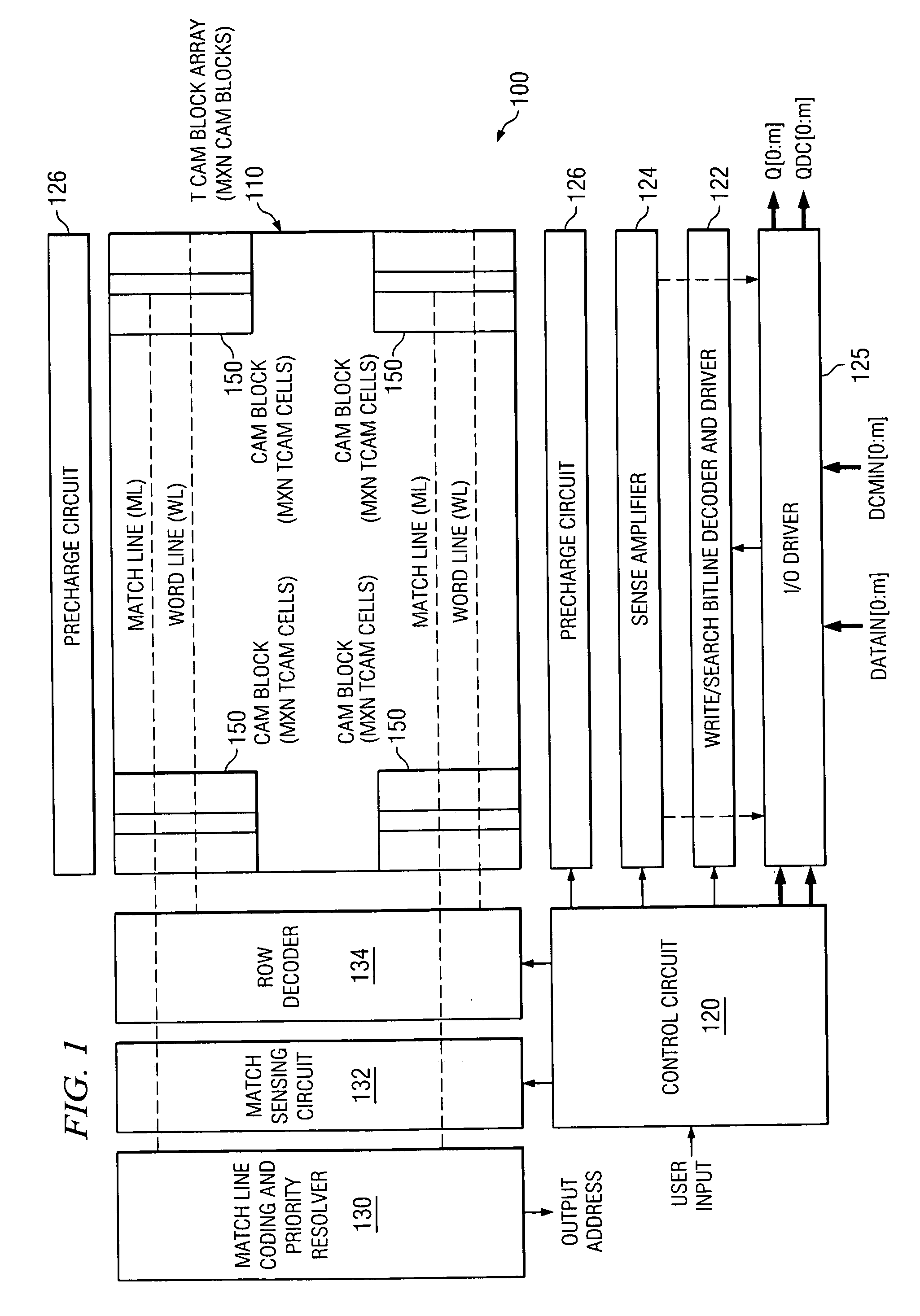

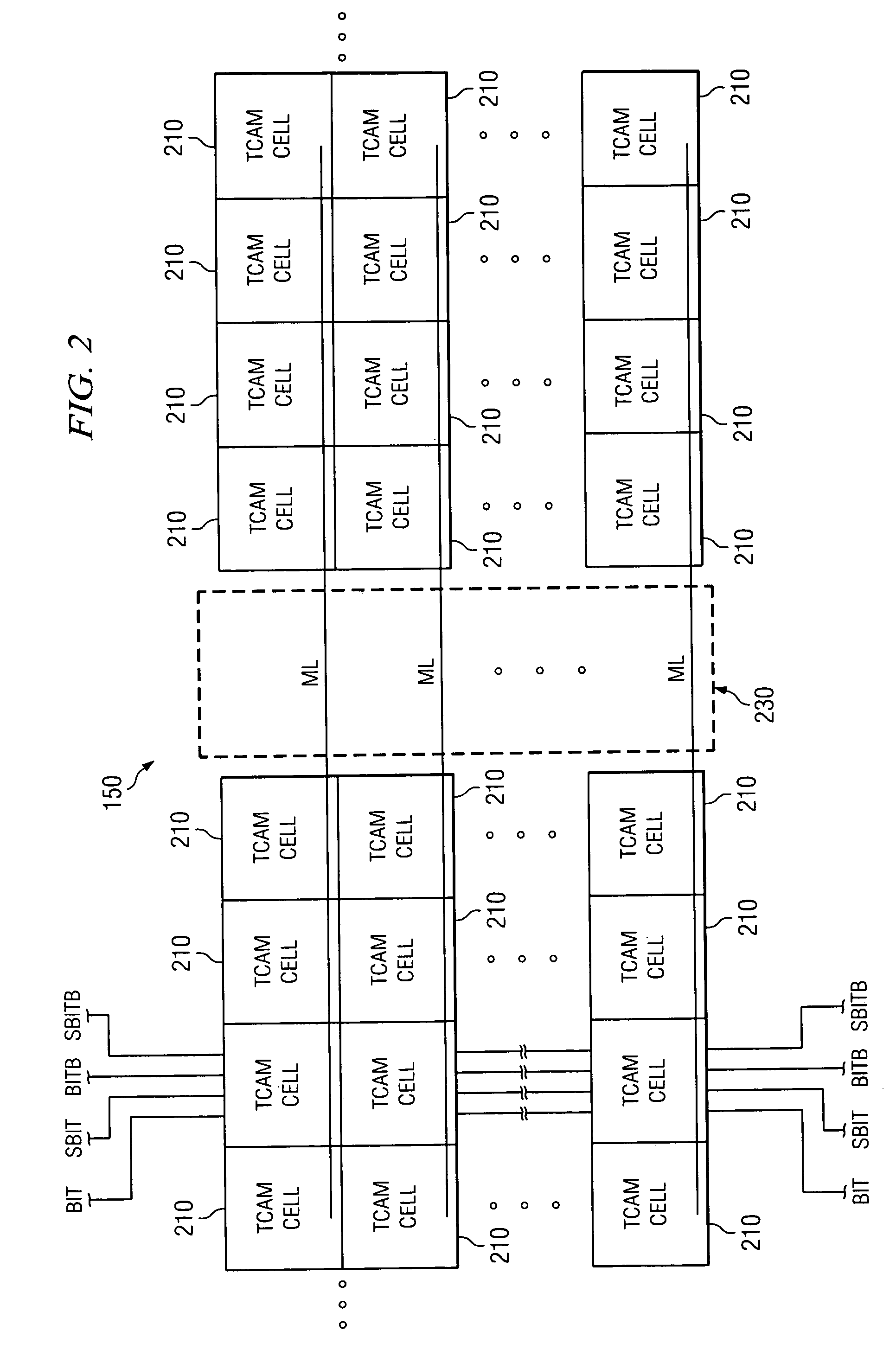

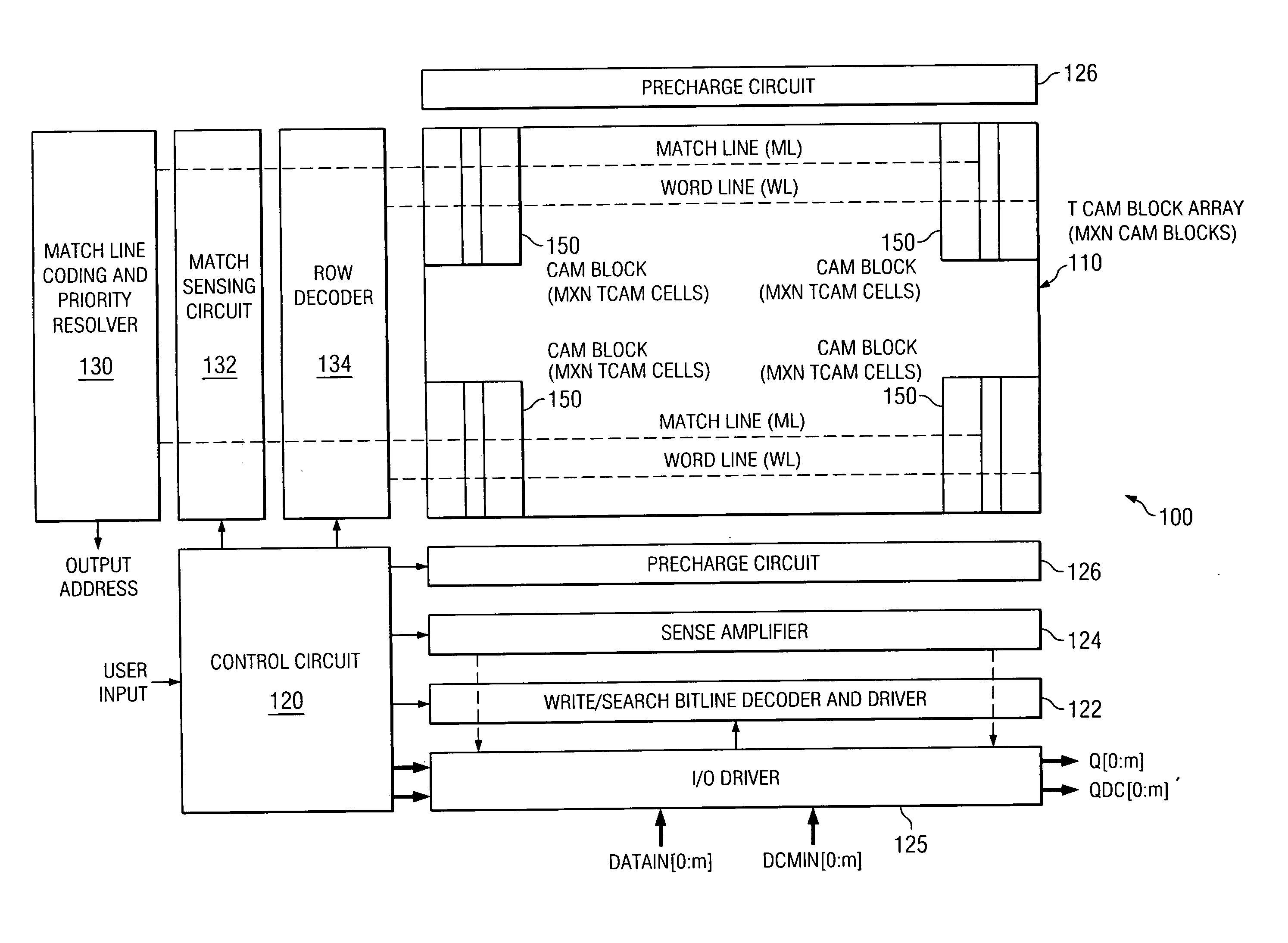

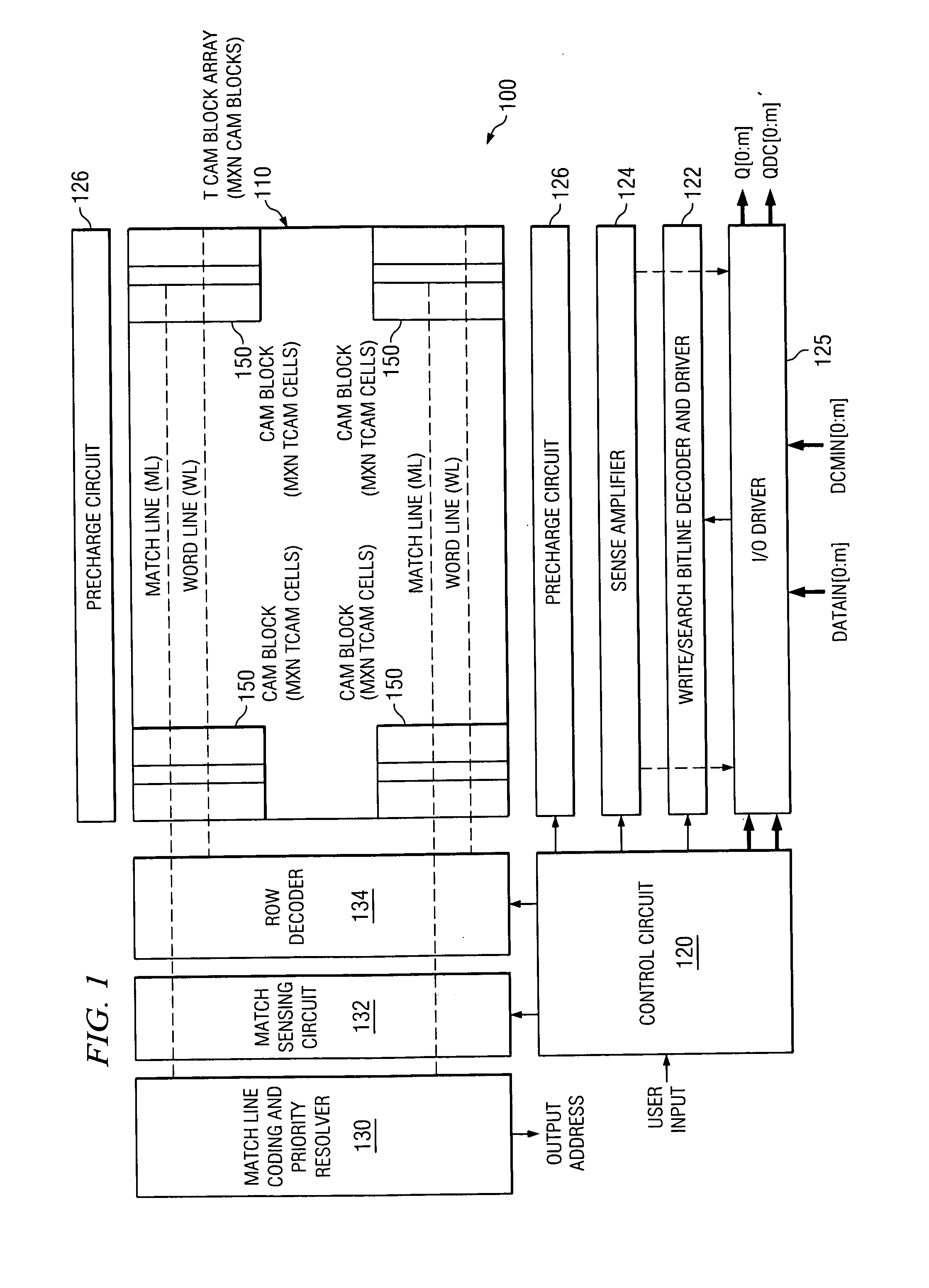

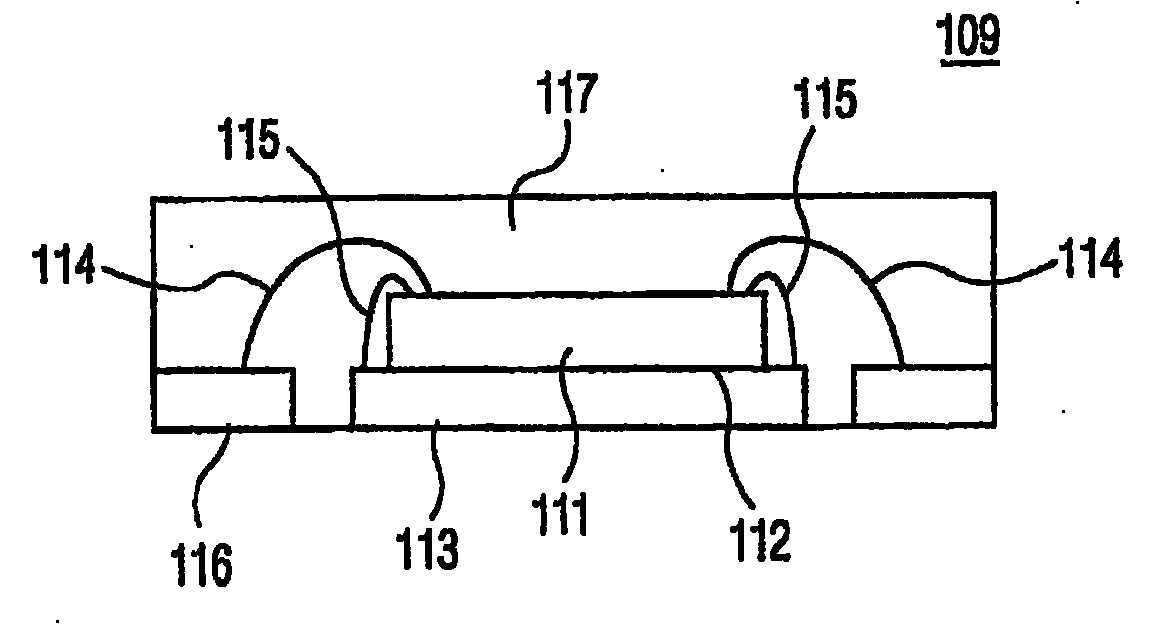

Area efficient stacked TCAM cell for fully parallel search

ActiveUS7259979B2No longer matchesReduce capacitanceSolid-state devicesDigital storageBit lineHemt circuits

An area efficient stacked TCAM cell for fully parallel search. The TCAM cell includes a top half circuit portion interconnected with a replicated bottom half circuit portion such that there is a shared match line between each of the half circuit portions. Each TCAM cell includes a pair of memory elements that is connected to a pair of associated compare circuits such that the interconnections between the memory elements and the compare circuits are substantially vertical in active MOS layers and substantially horizontal in metal layers. The memory elements and the compare circuits are connected such that they facilitate shorter interconnections and sharing of terminals at the boundary of adjacent cells. The resulting stacked TCAM cell provides shorter match lines, shared bit lines, and reduced silicon area to facilitate improved routing and performance.

Owner:TEXAS INSTR INC

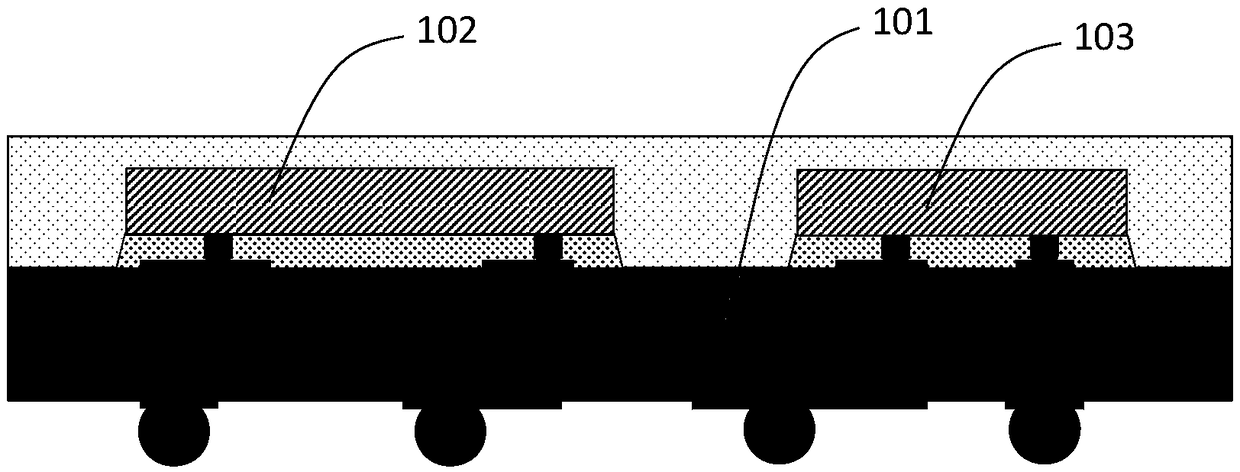

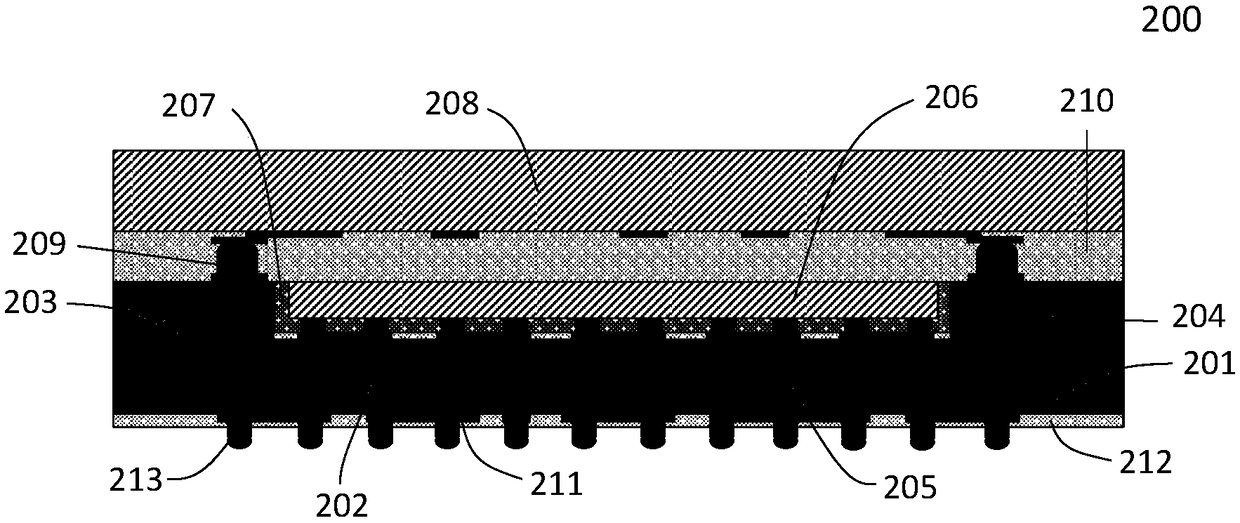

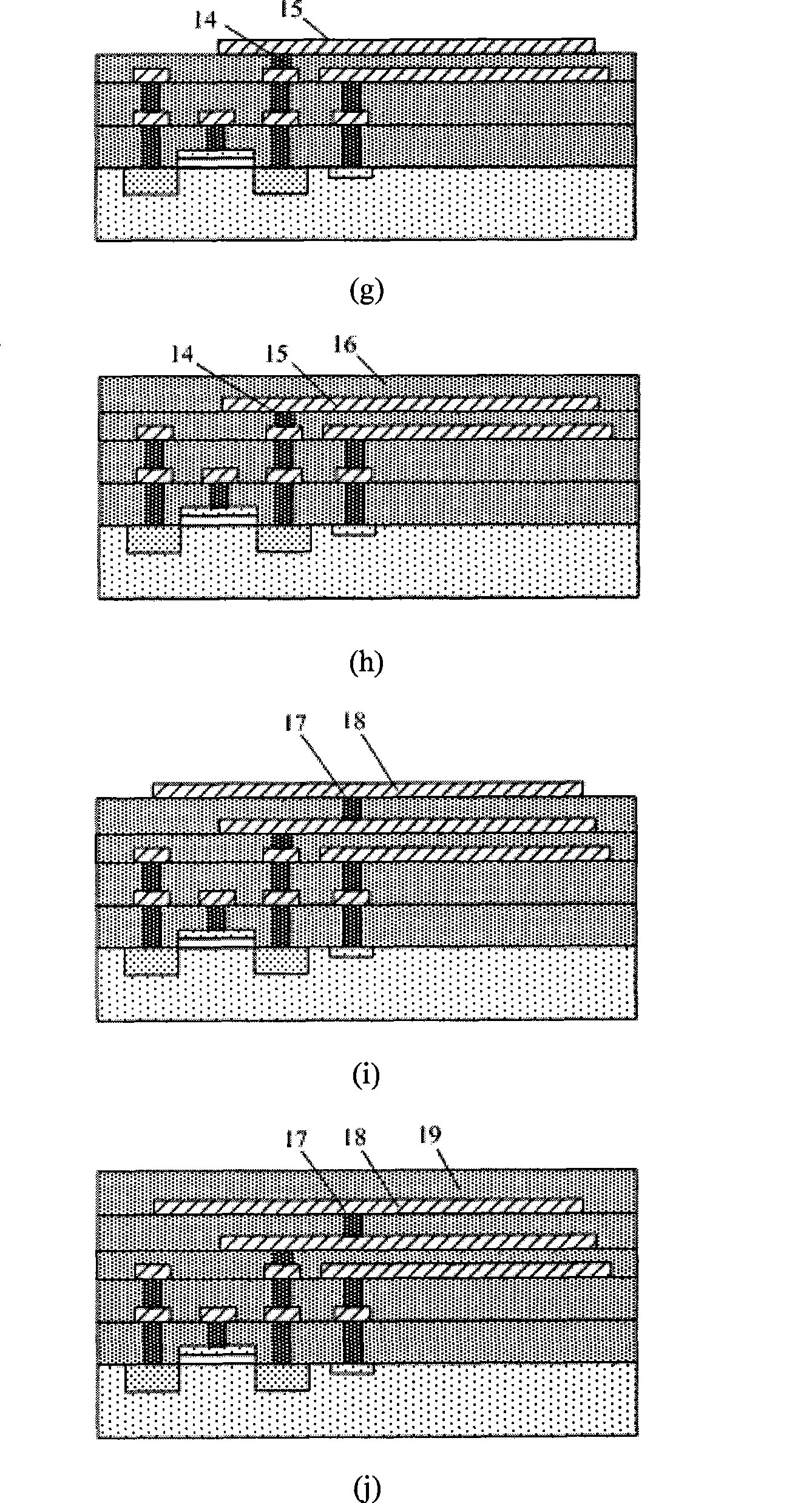

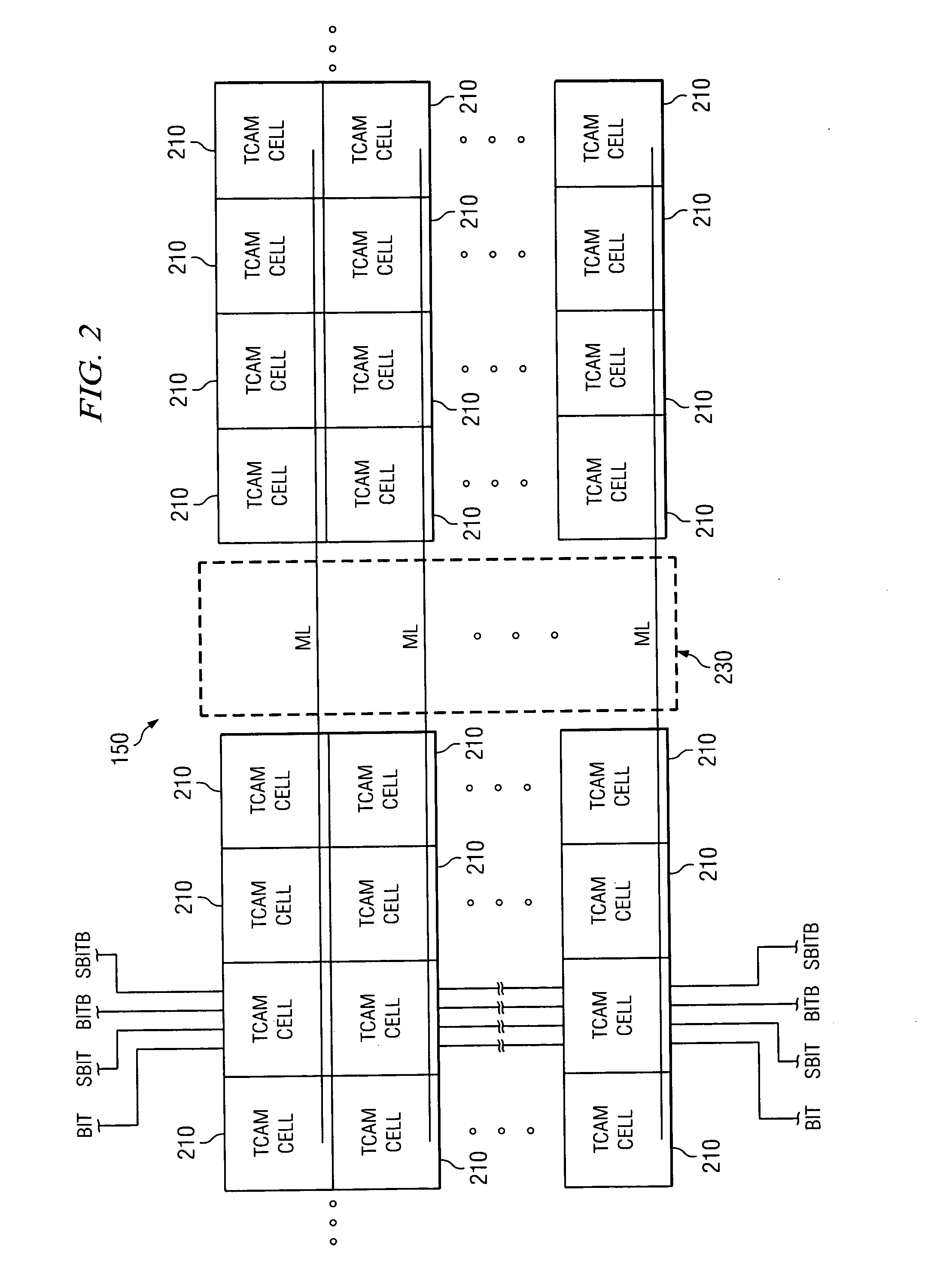

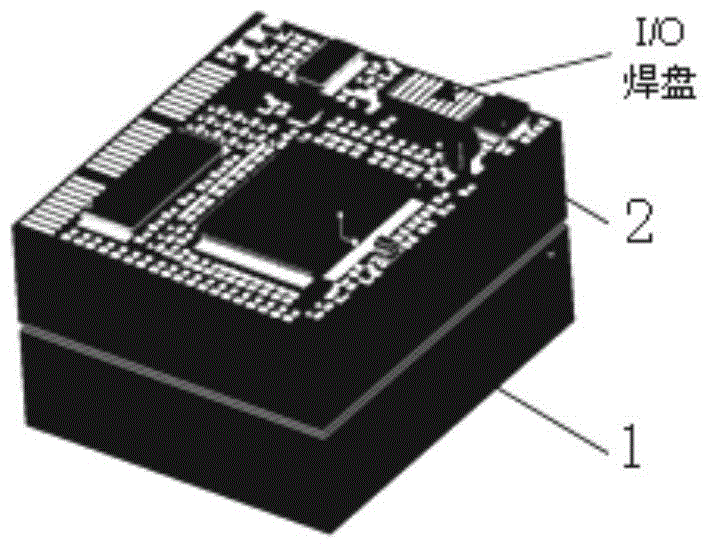

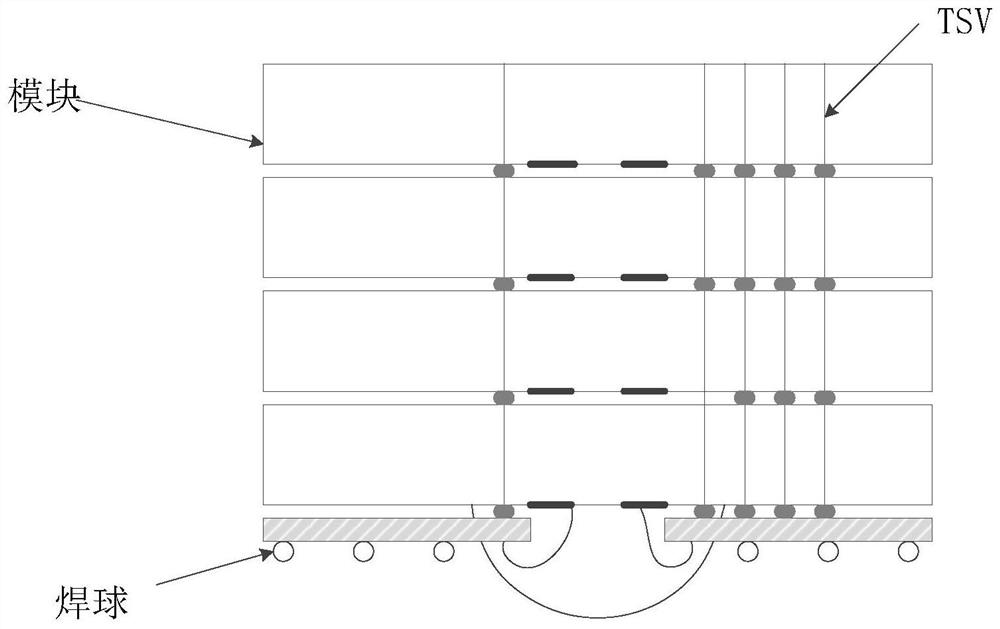

A 3D system integrate structure and a manufacturing method thereof

ActiveCN109003961AReduce depthImprove package integrationSemiconductor/solid-state device detailsSolid-state devicesEngineeringElectrical and Electronics engineering

The invention discloses a 3D system integration structure, comprising: an adapter board; A first silicon through hole arranged on the front face of the adapter board; A second silicon through hole arranged on the front face of the adapter board; A cavity arranged on the back surface of the adapter plate; A first relayout wiring layer and a pad arranged on a bottom surface of the cavity, the firstrelayout wiring layer and the pad being electrically connected with the first silicon via; A first chip disposed within the cavity, the first chip electrically connected to the first relayout wiring layer and the pad; A plastic filling layer arranged around the first chip and having a gap between the bottom and the adapter board; A second chip arranged on the back surface of the adapter board, thesecond chip being electrically connected to the second silicon through hole; A second relayout wiring layer disposed on a front face of the adapter board; And a welding structure provided on the front face of the adapter plate, the welding structure being electrically connected to the second relayout wiring layer.

Owner:NAT CENT FOR ADVANCED PACKAGING

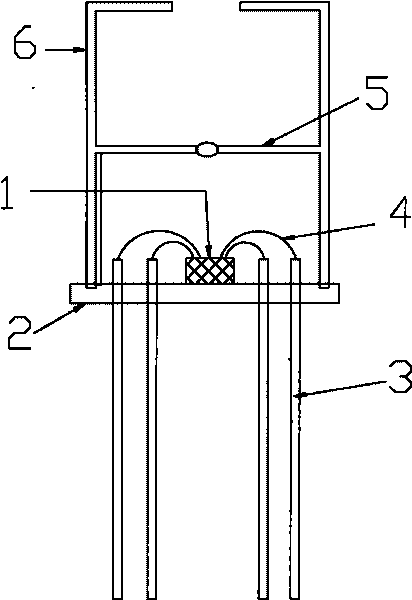

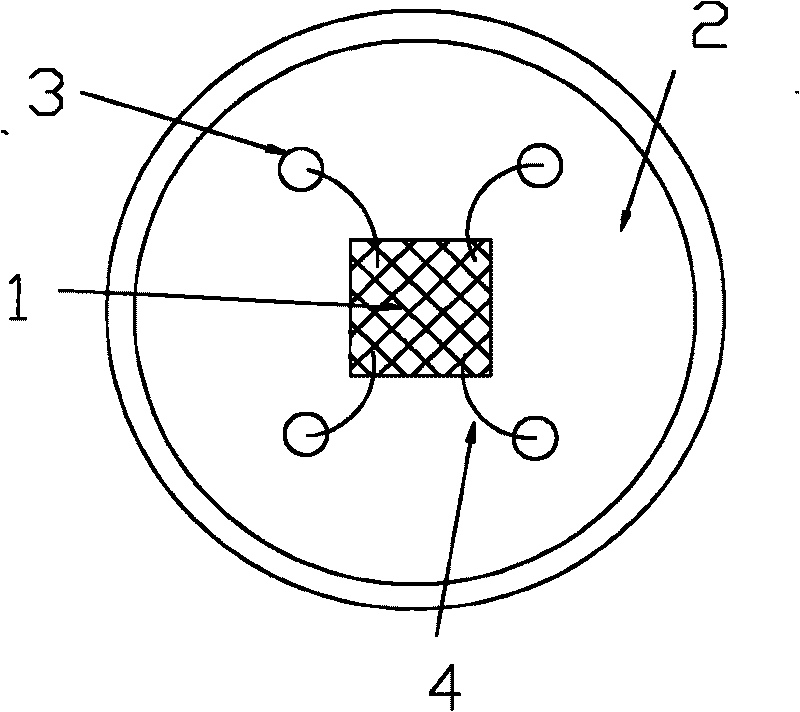

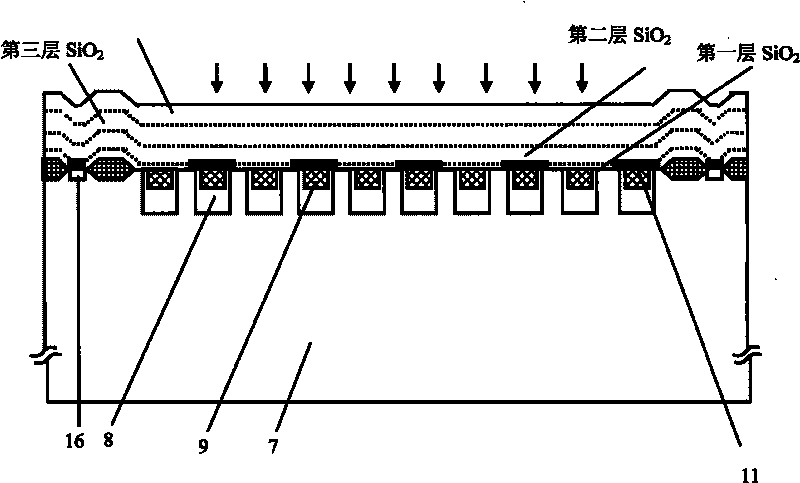

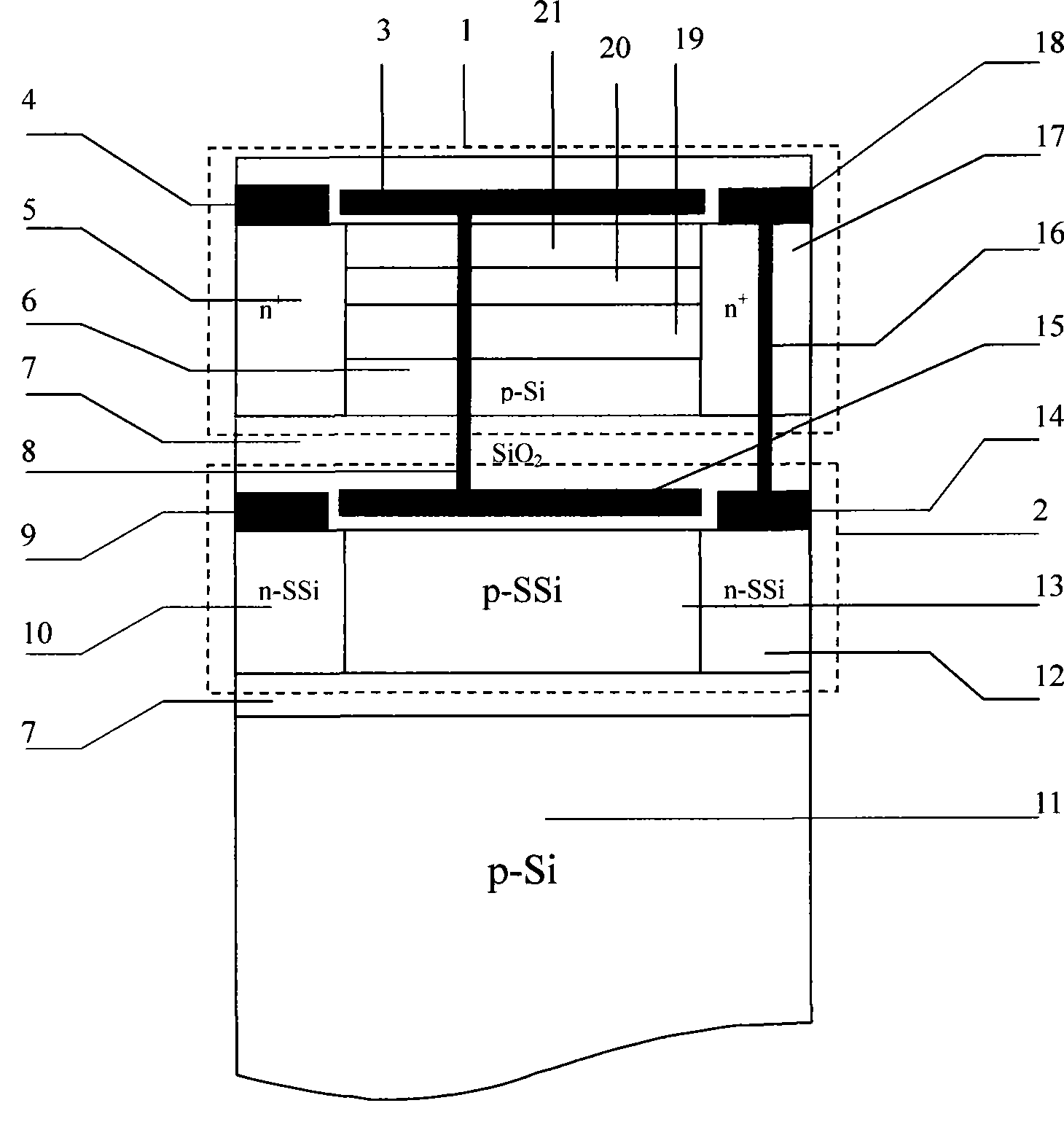

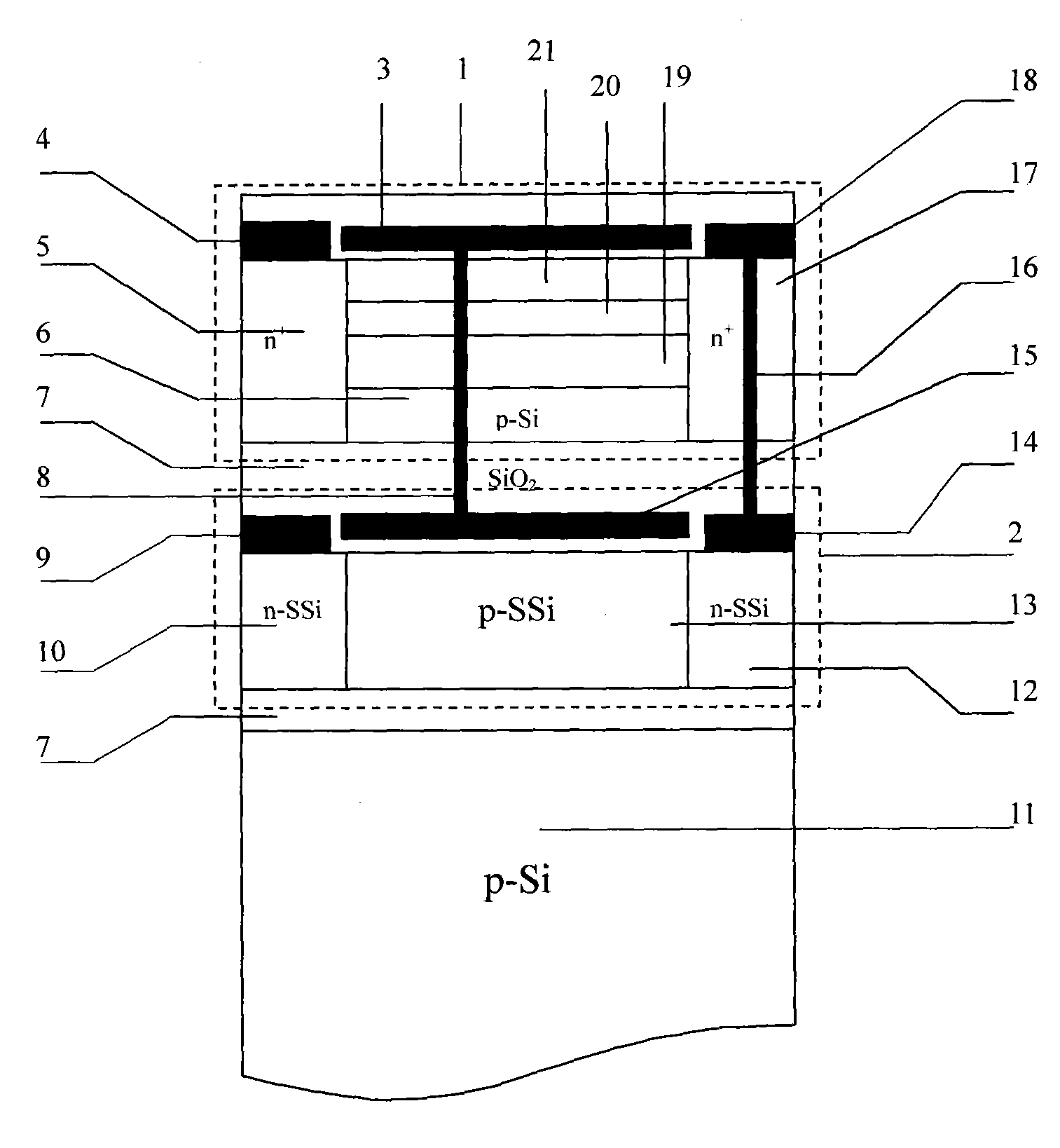

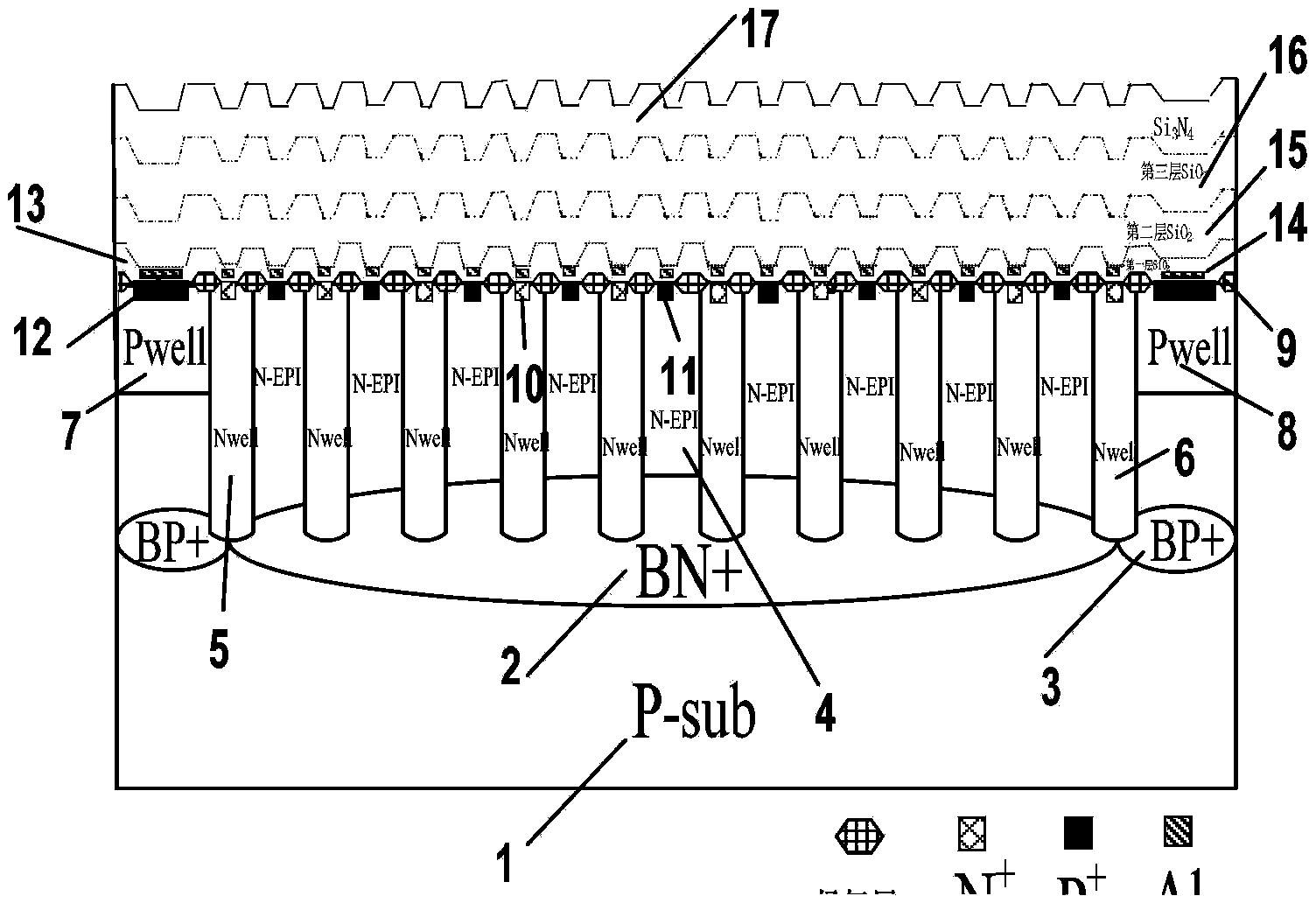

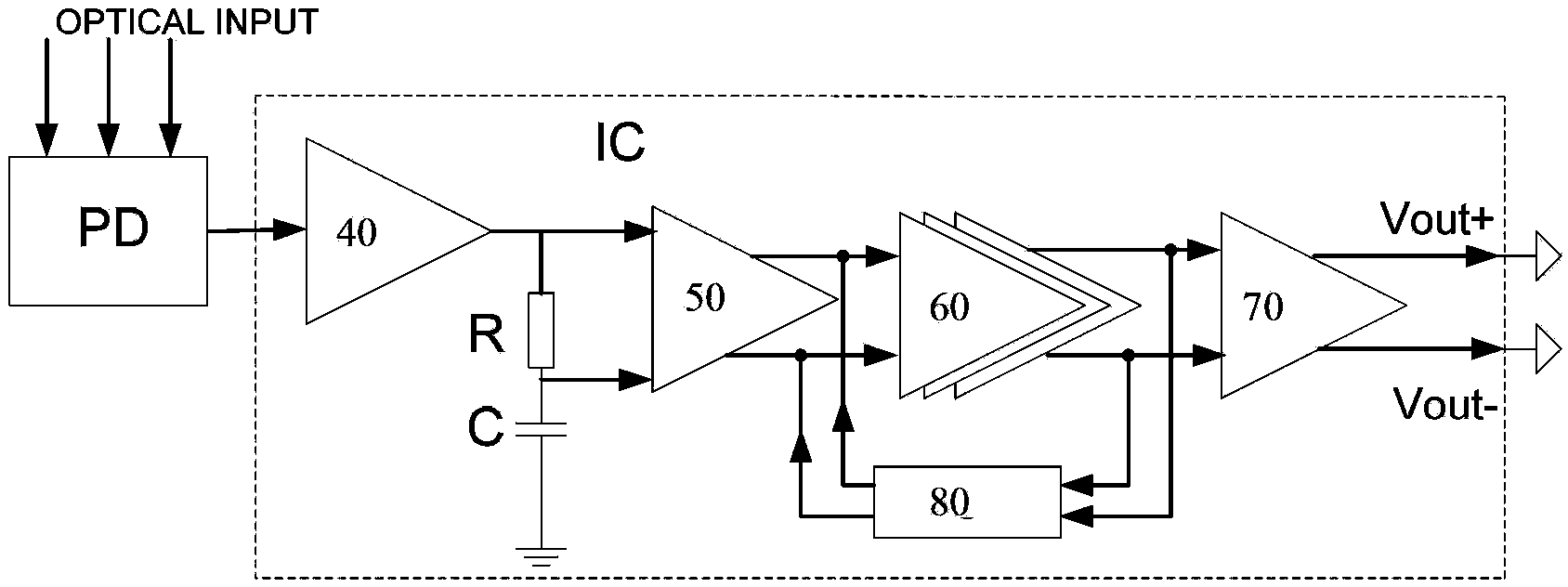

Optical receiving assembly for hundred trillion-grade 850nm optical communication and preparation method thereof

InactiveCN101718897ALower packaging costsImprove device performanceSemiconductor/solid-state device detailsSolid-state devicesOpto electronicDifferential amplifier

The invention relates to an optical receiving assembly for hundred trillion-grade 850nm optical communication and a preparation method thereof, and provides an optical receiving assembly for hundred trillion-grade 850nm optical communication, which is compatible with a commercial CMOS process and can replace the hybrid integration in the traditional 850nm optical transceiver and meet the transmission requirement, and a preparation method thereof. The optical receiving assembly is provided with a 850nm optoelectronic single integrated receiving chip, a pipe seat, a pipe cap, a pipe pin and an adapter, wherein the chip is provided with a prepositive amplifying circuit and an optoelectronic detector, and the prepositive amplifying circuit is provided with two mutual resistance type amplifying circuits, a three-grade differential amplifier, an output buffer circuit and a direct current negative feedback circuit. The optoelectronic detector is provided with a low doped P-shaped silicon substrate, a P pit, an N-shaped heavy doping silicon layer, a field oxide layer, an aluminum layer, three SiO2 insulating medium layers and a Si3N4 surface passivating layer from bottom to top in the longitudinal direction. The chip is attached to the pipe seat by a CMOS process; a welding disk of the chip is bonded with the pipe pin by a gold thread; and the pipe cap is covered to be encapsulated with the adapter according to the same shaft.

Owner:XIAMEN UNIV

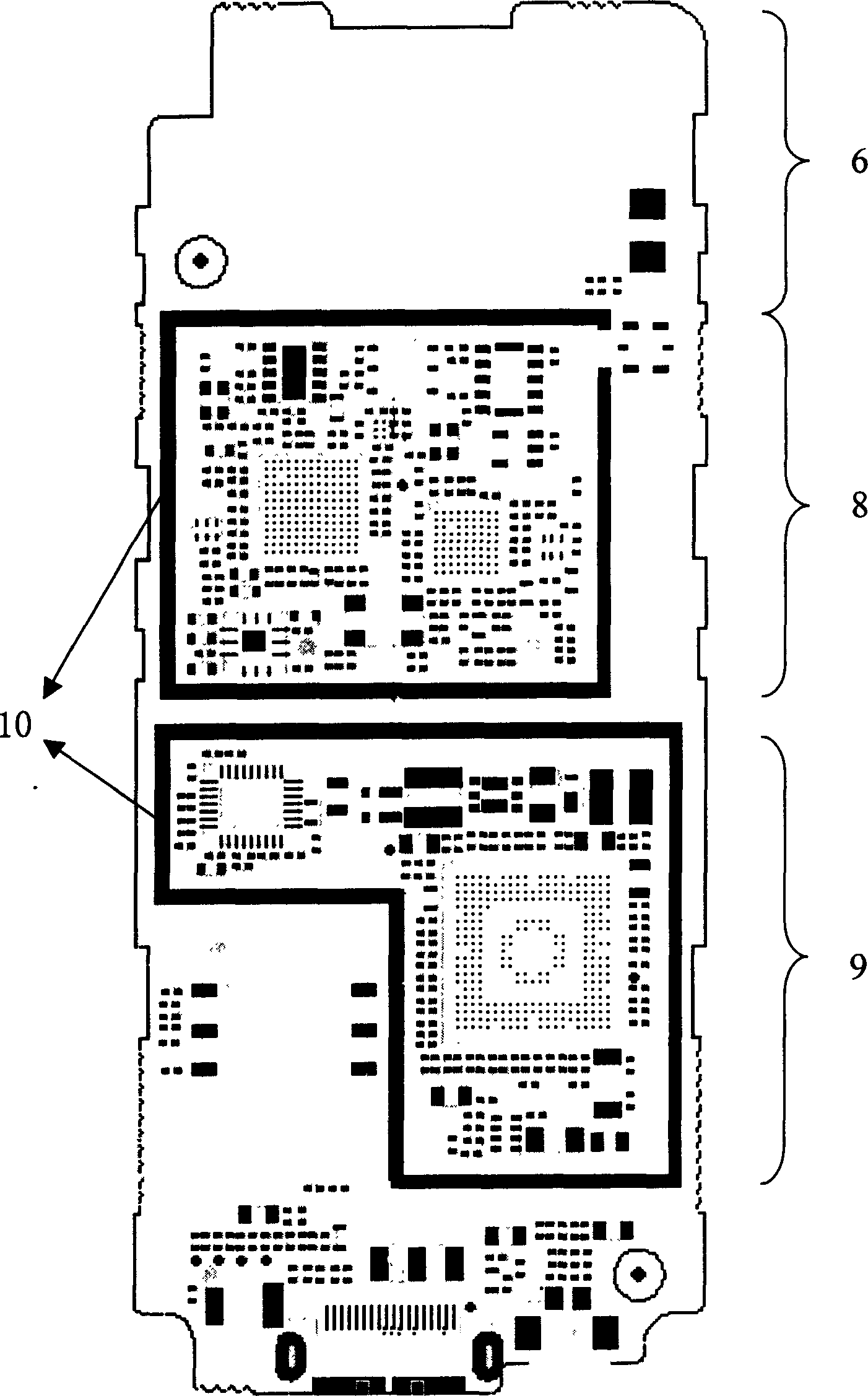

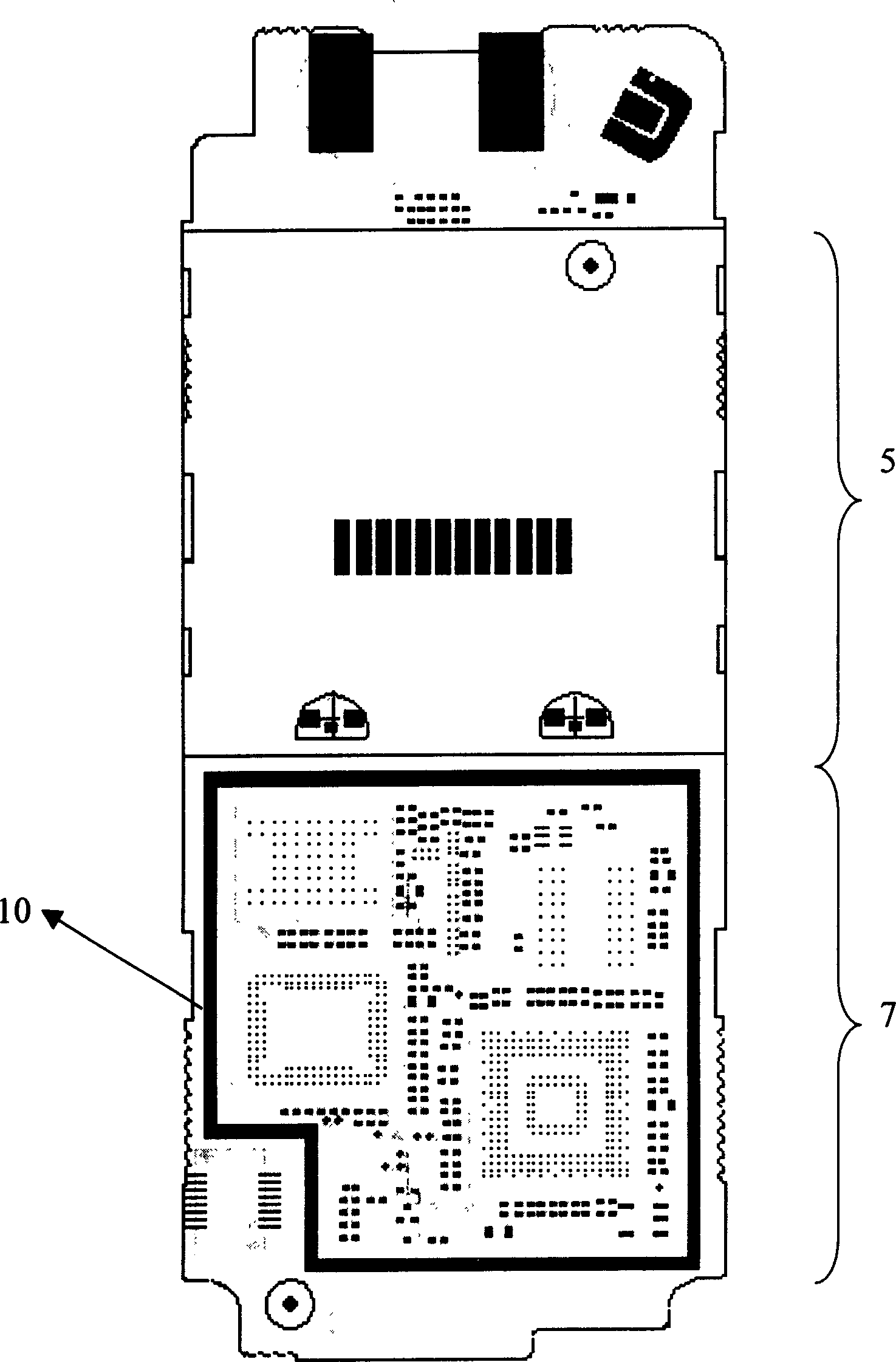

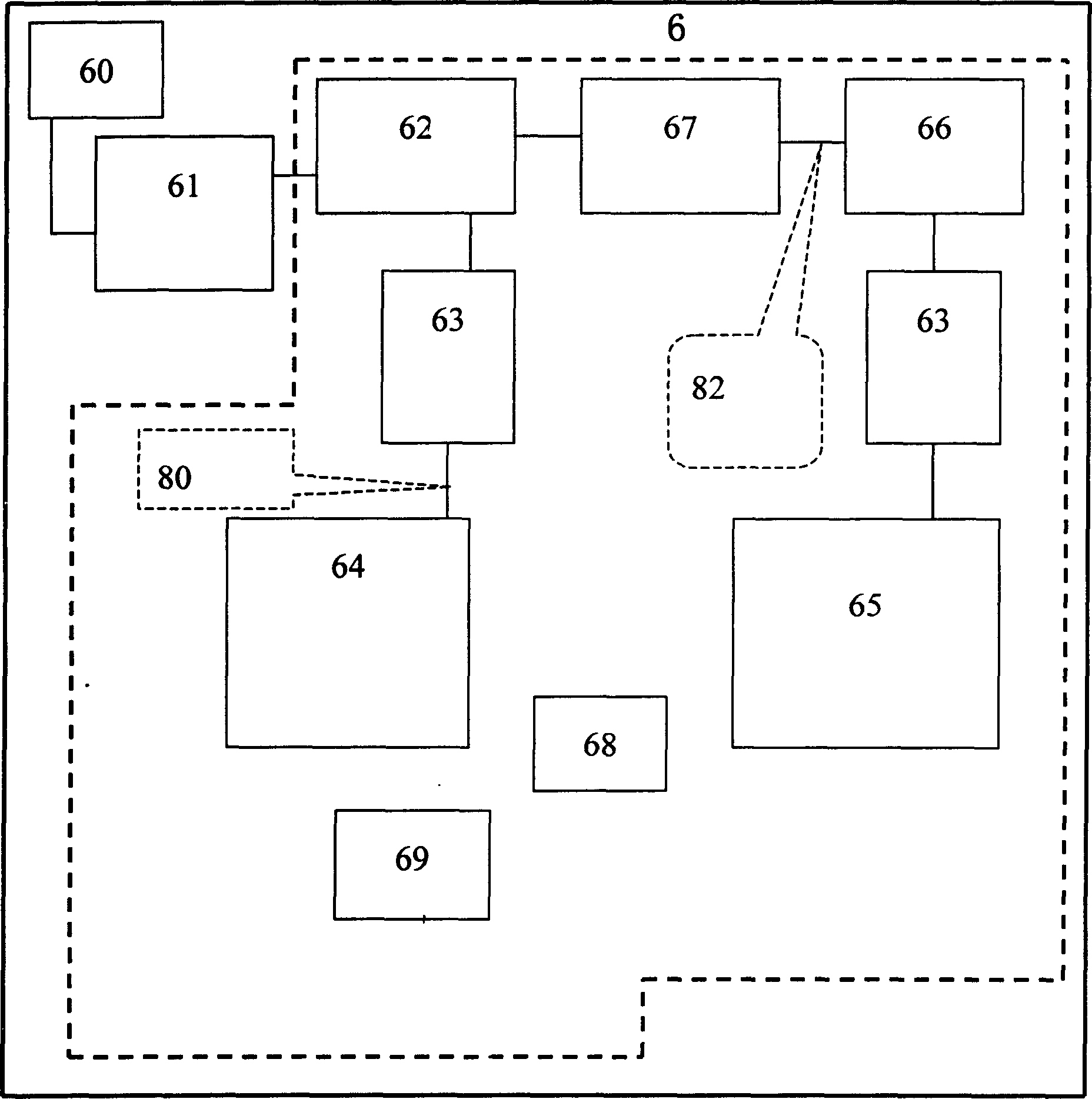

TD-SCDMA mobile phone circuit board for implementing eftective integral distribution

InactiveCN1658519AEffective layoutAvoid interferenceMagnetic/electric field screeningTransmissionTD-SCDMAMiniaturization

This invention discloses a TD-SCDMA mobile phone circuit board realizing effective and integrating distribution. It includes LCD screen module, the antenna, the digital baseband part, the radio frequency and stimulant baseband part. The relating circuit board has the upper and the lower layer, the lower layer includes the antenna on the upper part, and the antenna is internally set in the mobile phone, the middle part is the radio frequency part and the lower part is the stimulant baseband part. The upper layer mainly includes the LCD screen module of the upper part and the digital baseband part of the bottom. This invention realizes the effective distribution of TD-SCDMA mobile phone circuit board. In order to avoid the interfere between the modules, it uses the shielding can effectively isolate the radio frequency module, the stimulant baseband part and the digital baseband part and realizes the minimization of the product.

Owner:上海贝豪通讯电子有限公司

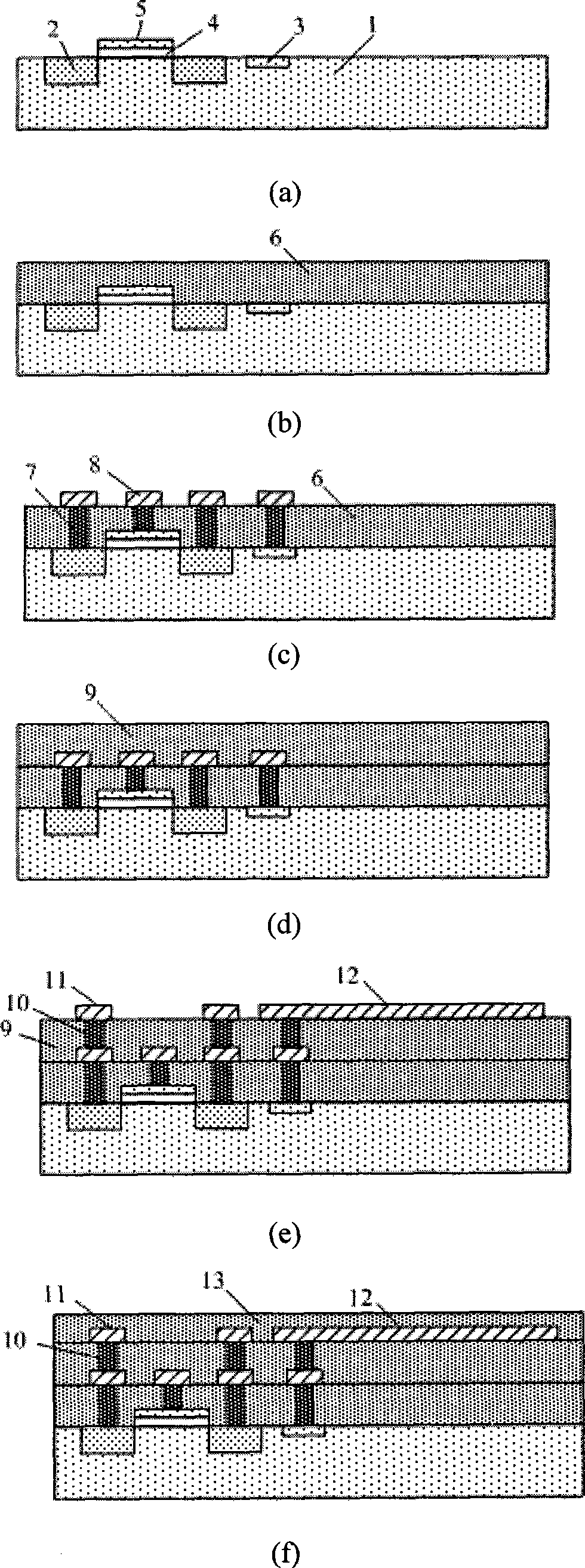

Monolithic integration method of grating light modulator and active matrix driving circuit

InactiveCN101393321AReduce chip power consumptionShort interconnectSemi-permeable membranesPiezoelectric/electrostrictive/magnetostrictive devicesCMOSOptical modulator

The invention provides a monolithic integration method for a grating optical modulator and an active matrix drive circuit, which is combined with the processing technique of monolithic integration of an MEMS device and a CMOS circuit, utilizes the CMOS circuit to process the active matrix drive circuit at first and then utilizes the low-temperature micromechanical manufacturing technique to obtain the MEMS grating optical modulator, so as to realize monolithic integration of the MEMS grating optical modulator which is formed by upper movable gratings supported on lower electrodes and the lower active matrix drive circuit. The grating optical modulator processed by the technique can project and display with high definition and high resolution.

Owner:CHONGQING UNIV

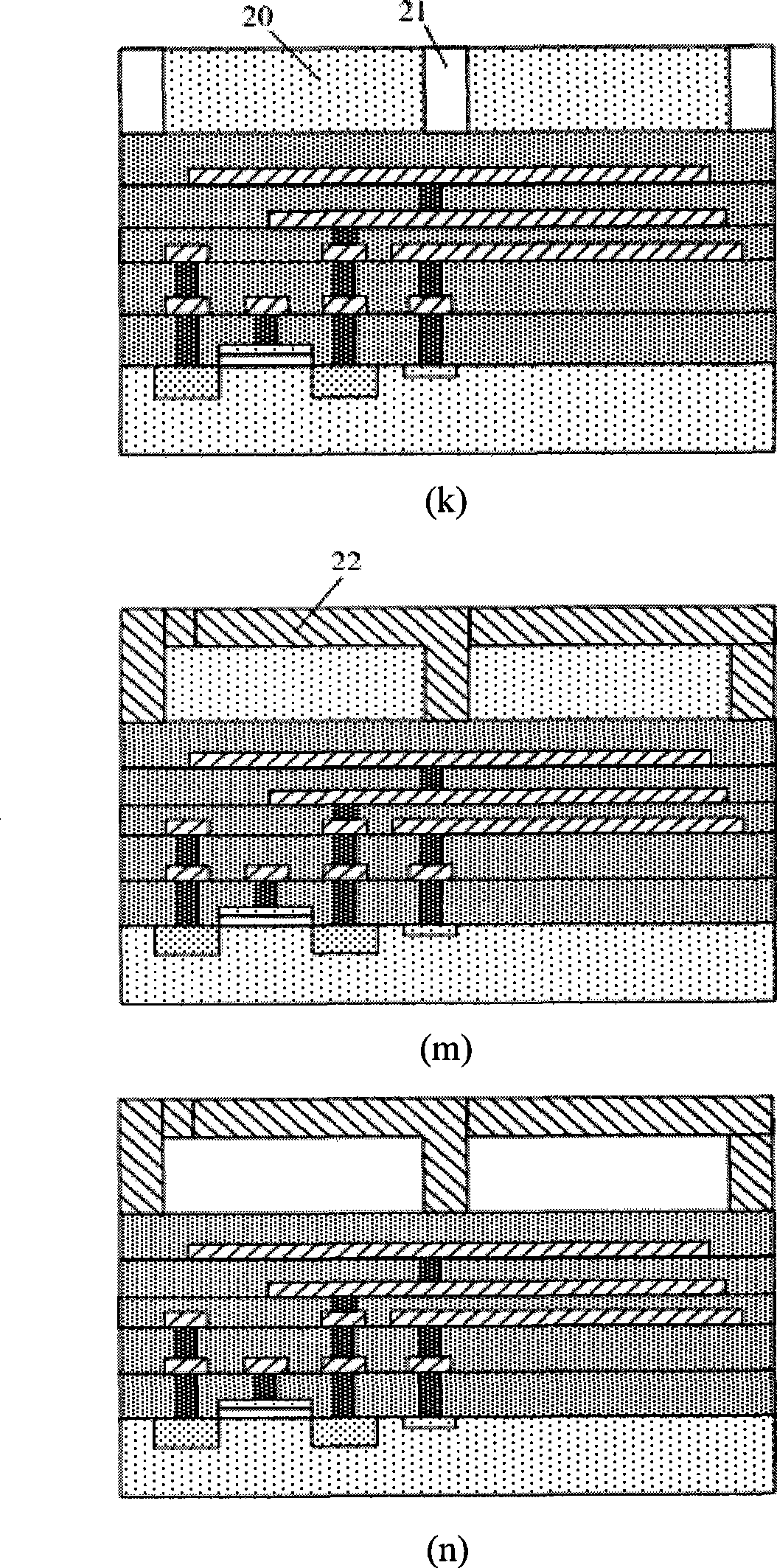

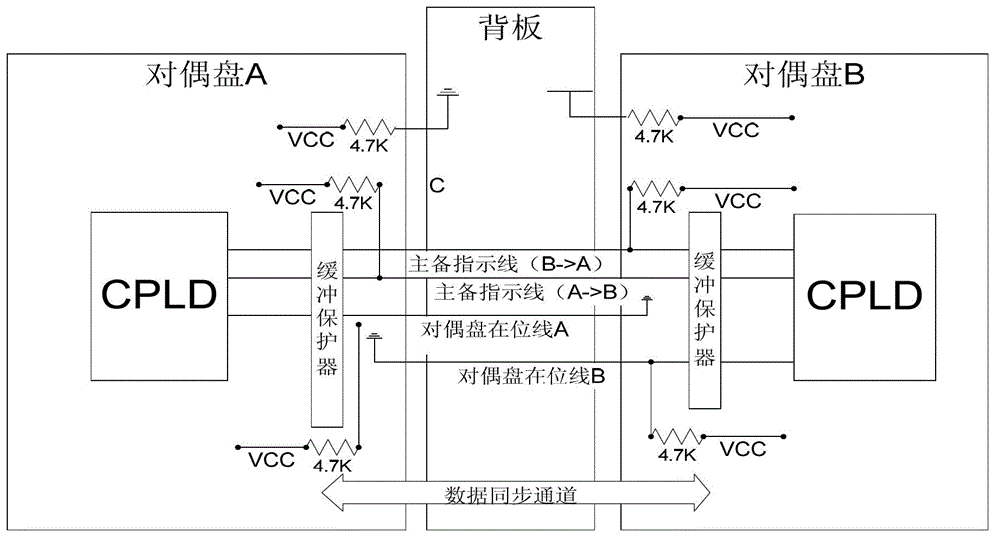

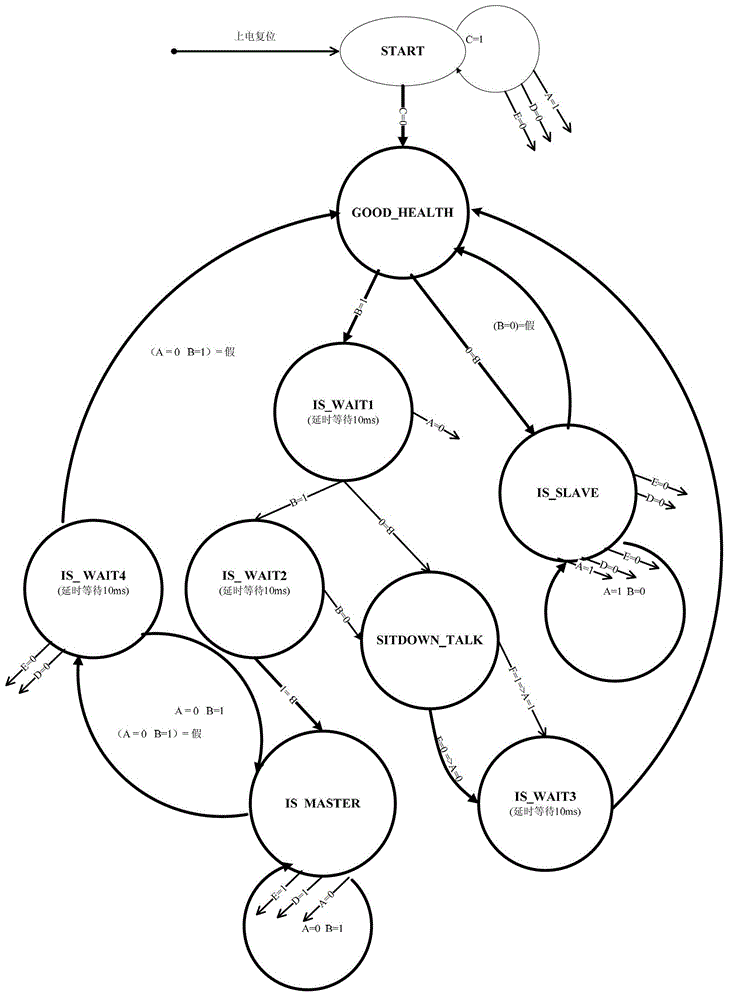

Method for switching master and slave redundancy protection of master control system of optical transmission equipment

ActiveCN102724013AShield operationReduce the number of tracesWavelength-division multiplex systemsData switching networksComplex programmable logic deviceSoftware

The invention relates to a method for switching master and slave redundancy protection of a master control system of optical transmission equipment. Two master control panels are divided into a dual panel A and a dual panel B according to master and slave redundancy protection, the dual panels A and B are respectively provided with a CPLD (complex programmable logic device); a switching control module is taken as a main body for completing master and slave switching function and is realized by a digital logic circuit, the logic circuit is compiled by a related compiler by adopting a hardware description language and then is downloaded into the CPLD; in the switching method, a standard interface for a back plate and a standard interface for software are defined, logic level agreement and slot position marker line setting of the logic circuit of the switching control module are defined; and a switching process is completely realized through auto-negotiation by the logic circuit in the CPLD. By adopting the switching method disclosed by the invention, a master and slave switching mechanism is completely realized by hardware, and fussy software operation is shielded; strict double-master exclusive ability is obtained; master and slave interconnection wires are reduced, and quantity of routings on the back plate is reduced; switching speed is faster; reliability is high; and one universal module can be packaged, thus being convenient for transplantation.

Owner:FENGHUO COMM SCI & TECH CO LTD

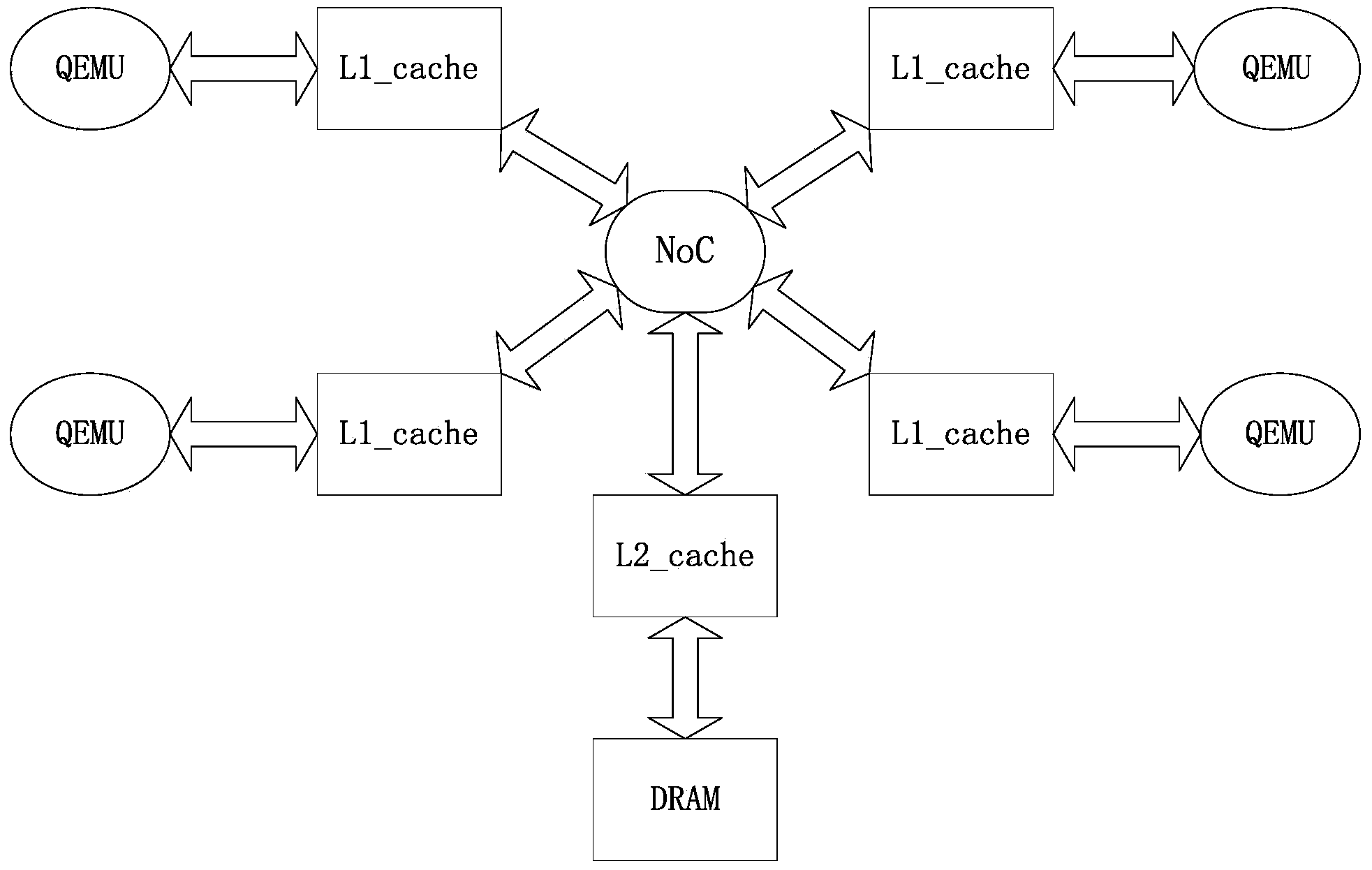

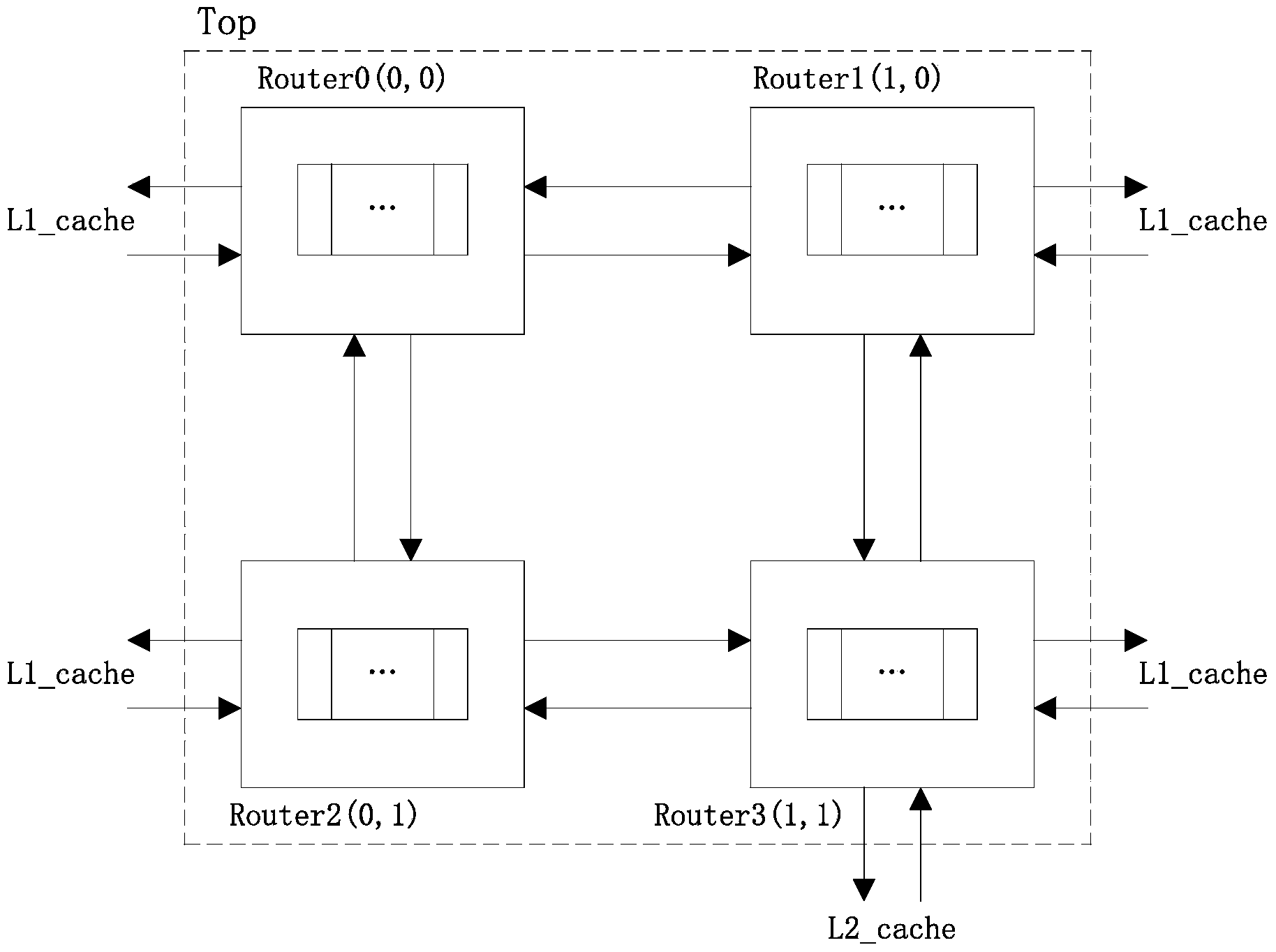

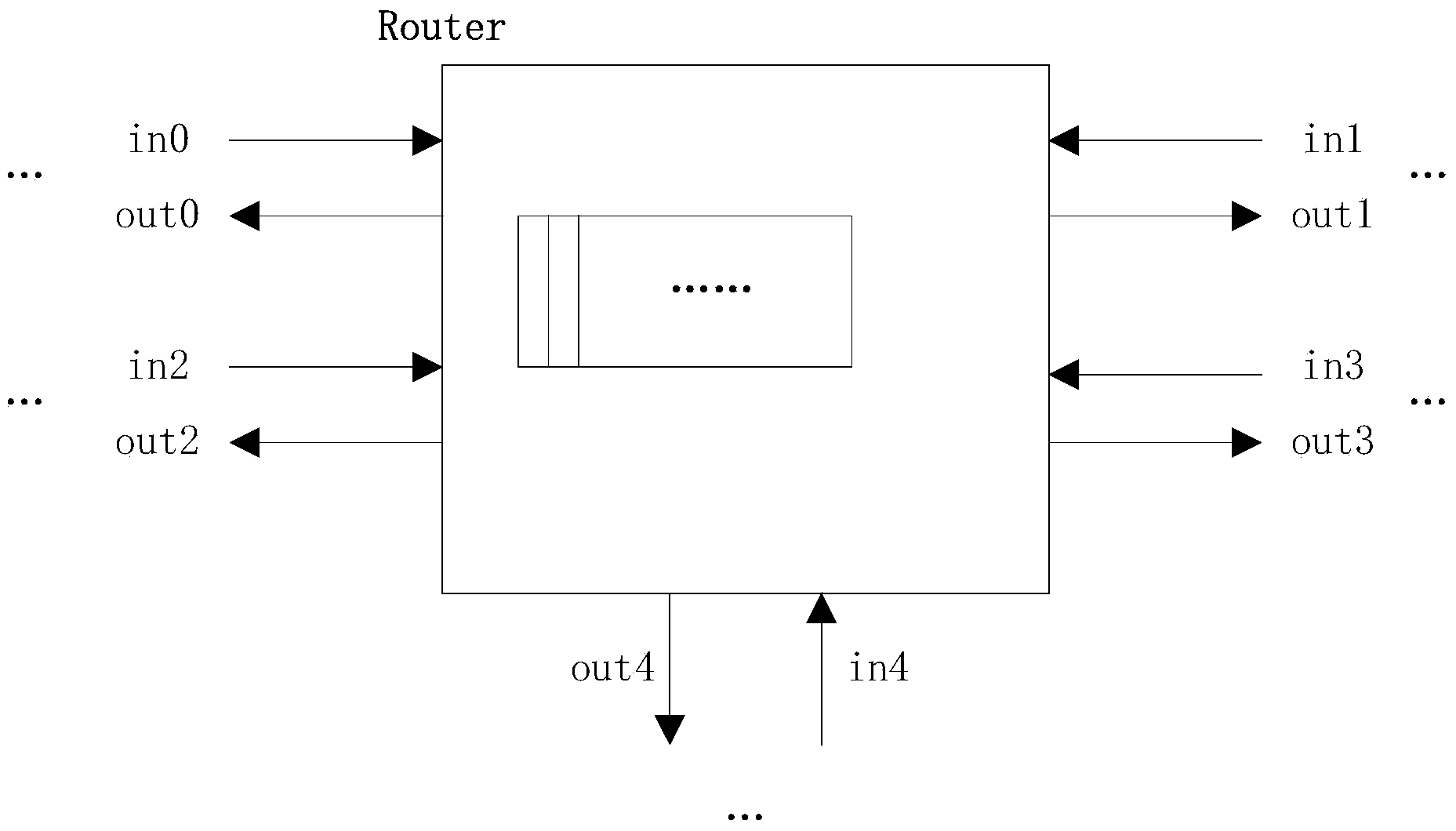

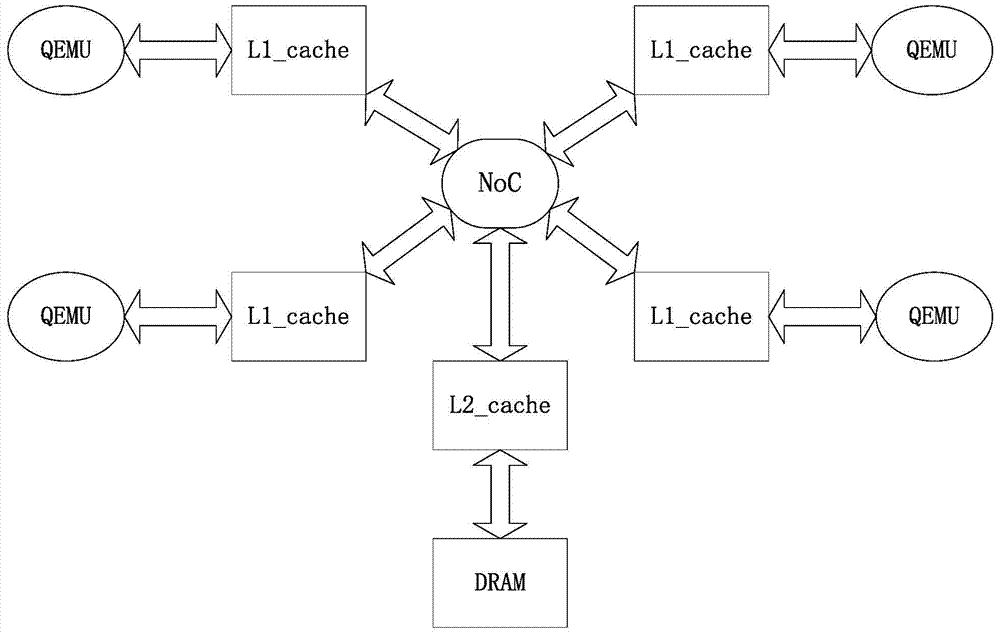

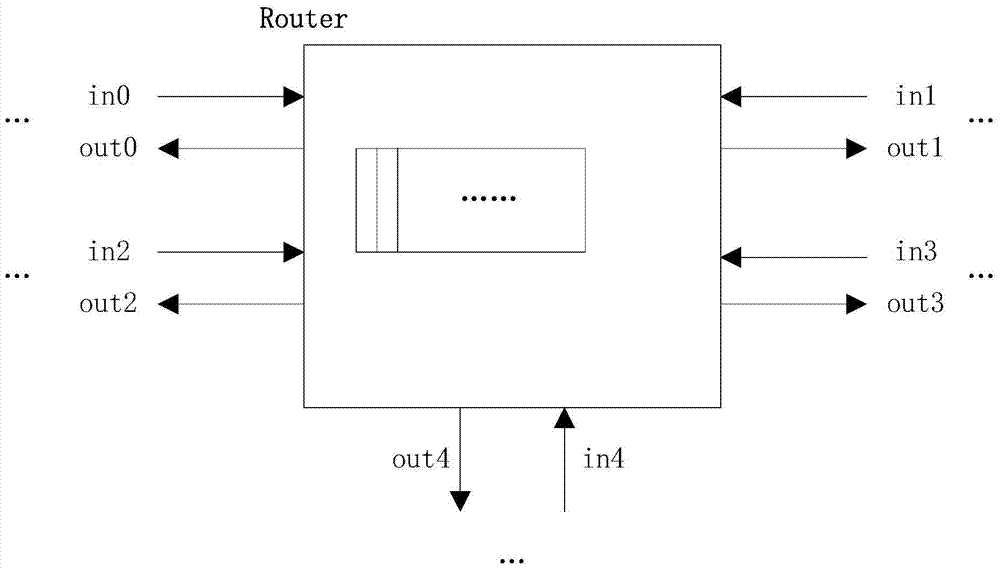

Multi-core memory system simulator on basis of network-on-chip interconnection

ActiveCN103914333ASpeed up developmentShort interconnectSoftware simulation/interpretation/emulationSystemCParallel computing

The invention discloses a multi-core memory system simulator on the basis of network-on-chip interconnection. The multi-core memory system simulator is characterized in that a core of SystemC is used as a driving core of the integral simulator, the multi-core memory system simulator comprises cache modules, a plurality of route modules and QEMU modules, the cache modules are used for simulating primary high-speed caches of cores of various processors, the route modules are used for simulating secondary high-speed caches of the cores of the various processors, and the QEMU modules are used for realizing functional simulation effects; the various route modules are interconnected with networks-on-chip which are formed by the secondary high-speed caches shared by the cores of the simulation processors, and each route module is provided with a group of signal lines connected with the corresponding cache modules; pkt (packet) messages which are transmitted by one cache module or one route module are distributed to another cache module or another route module. The multi-core memory system simulator has the advantages that system software of target systems can be developed by the aid of the simulator, the software and hardware can be simultaneously developed, and accordingly the system development speed can be increased.

Owner:SUZHOU INST FOR ADVANCED STUDY USTC

Area efficient stacked TCAM cell for fully parallel search

ActiveUS20070097723A1Reduce capacitanceShorter interconnectionSolid-state devicesDigital storageEngineeringHemt circuits

An area efficient stacked TCAM cell for fully parallel search. The TCAM cell includes a top half circuit portion interconnected with a replicated bottom half circuit portion such that there is a shared match line between each of the half circuit portions. Each TCAM cell includes a pair of memory elements that is connected to a pair of associated compare circuits such that the interconnections between the memory elements and the compare circuits are substantially vertical in active MOS layers and substantially horizontal in metal layers. The memory elements and the compare circuits are connected such that they facilitate shorter interconnections and sharing of terminals at the boundary of adjacent cells. The resulting stacked TCAM cell provides shorter match lines, shared bit lines, and reduced silicon area to facilitate improved routing and performance,

Owner:TEXAS INSTR INC

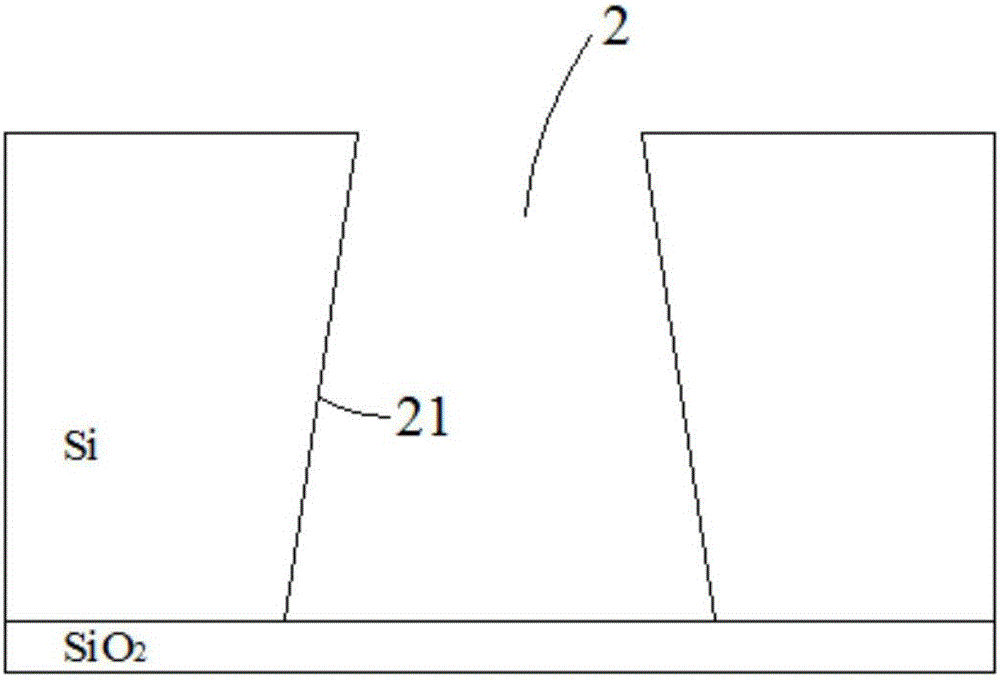

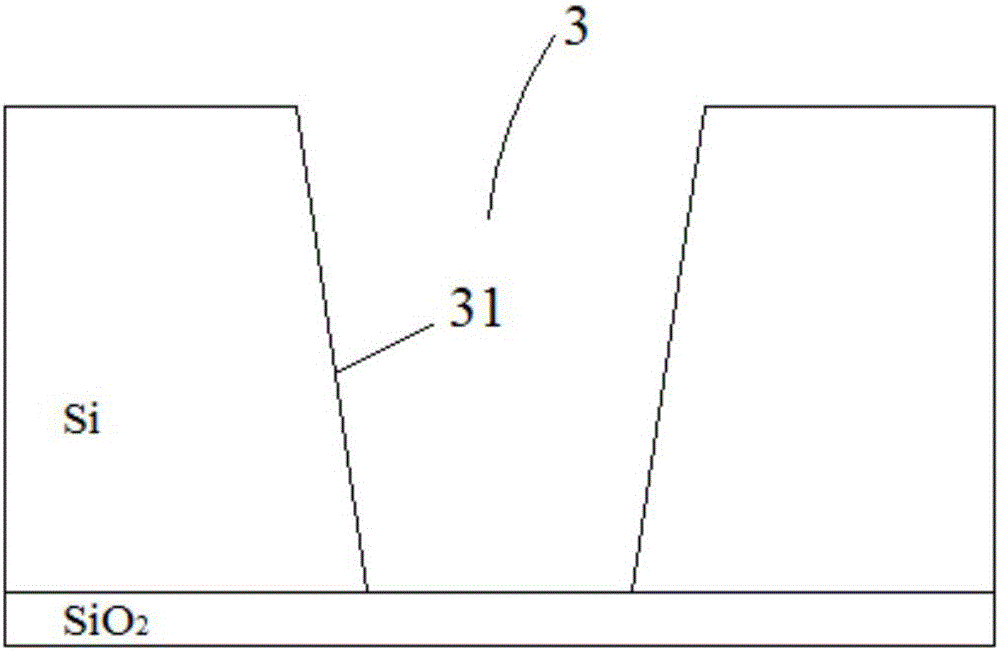

Substrate for micro electro mechanical system chip, micro electro mechanical system chip and preparation method thereof

InactiveCN106276770ASmall sizeHigh densitySemi-permeable membranesVolume/mass flow by thermal effectsMicromechanicsMaterials science

The invention relates to a substrate for a micro electro mechanical system chip, the micro electro mechanical system chip and a preparation method thereof, and belongs to the field of micromechanics. The substrate for the micro electro mechanical system chip comprises a substrate body and at least one cavity, wherein the substrate body has the upper surface and the lower surface; the at least one cavity is formed in the substrate body; each cavity comprises an upper sub cavity part and a lower sub cavity part in vertical arrangement; the upper sub cavity part and the lower sub cavity part are communicated; the upper sub cavity is formed by downwards extending from the upper surface of the substrate body; the shape and / or the dimension defined by the upper sub cavity part are / is different from the shape and / or the dimension defined by the lower sub cavity part; the positive projection area of the upper sub cavity part is greater than the positive projection area of the lower sub cavity part on the lower surface of the substrate body.

Owner:苏州工业园区纳米产业技术研究院有限公司

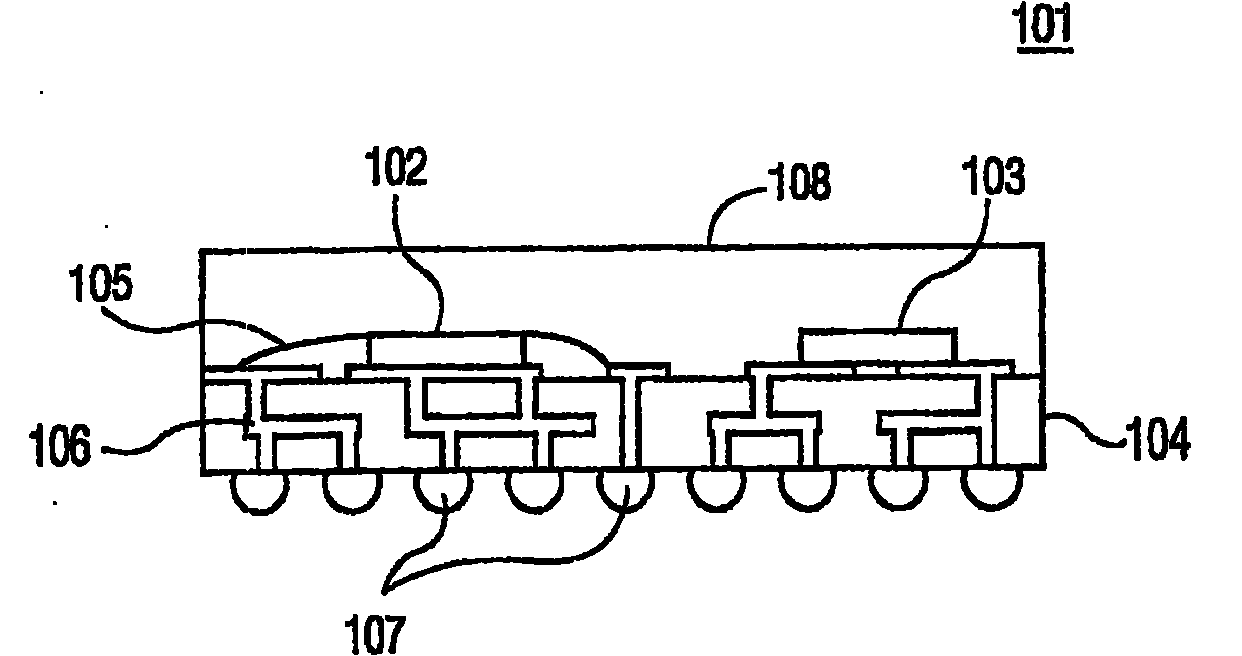

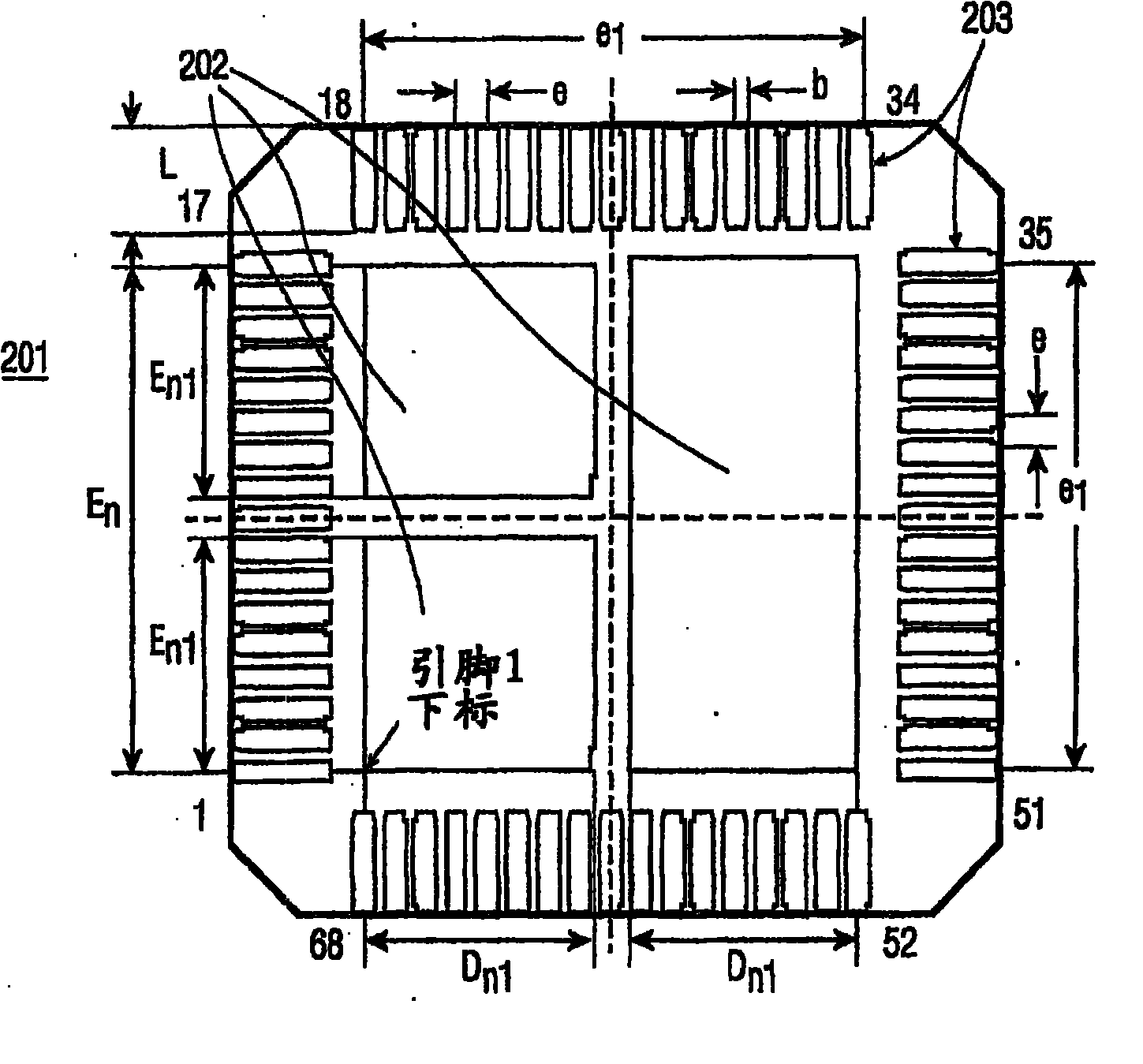

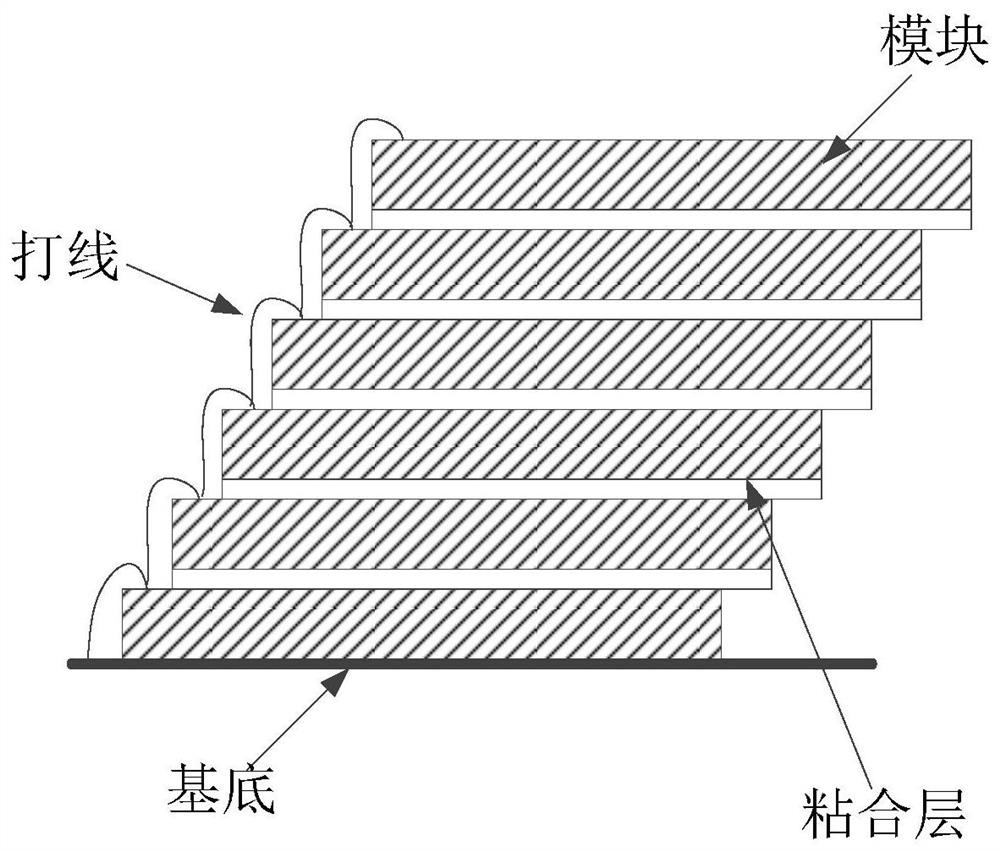

Bare chip building block packaging method

InactiveCN101000876AAchieving High Density PackagingShort interconnectSemiconductor/solid-state device manufacturingSquare arrayCapacitance

A modular-packaging method of bare chips includes collecting bare chips to be square array and filling waster chip at blank position, placing said array on base plate of at least 3-layer printed circuit board, cutting out square hole at middle of clamp plate and sheathing said clamp plate at external of square array, covering top plate then setting square array upside down to take off base plate, coating conductive glue at chip back then covering base plate and baking them to form a flat plate, using photo-resist to fill seams, finalizing metal connections and sticking on top plate.

Owner:徐中祐

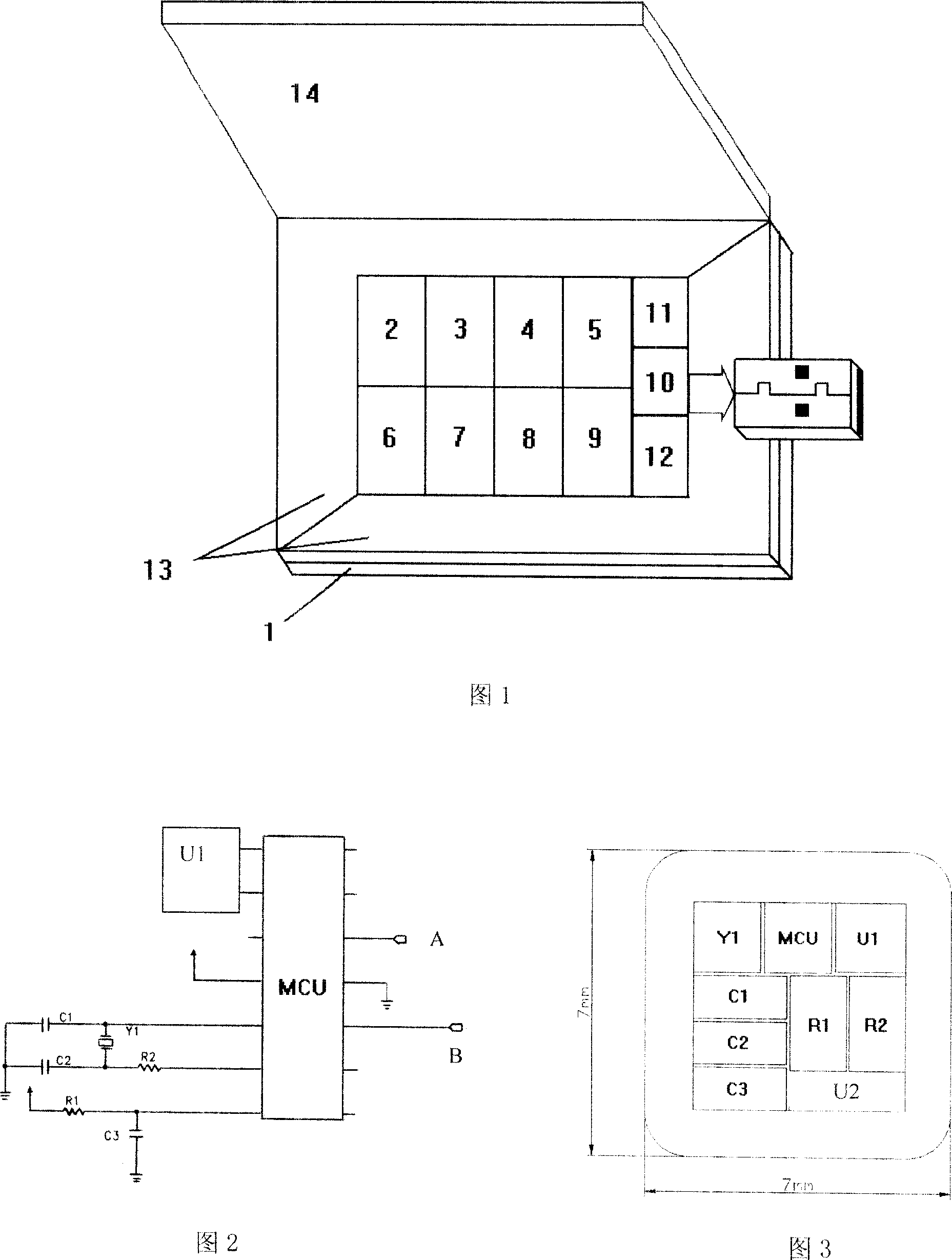

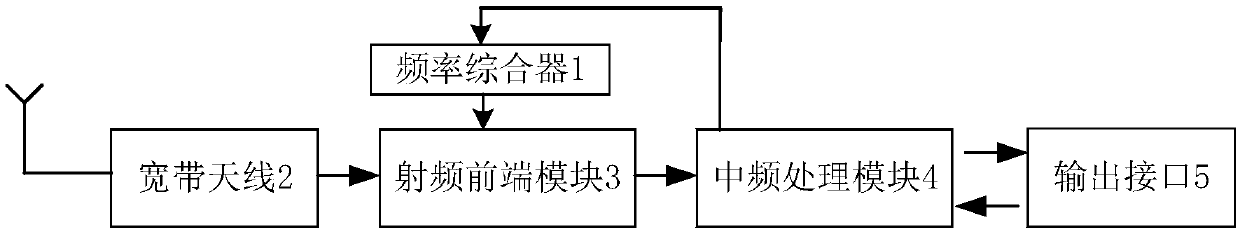

Miniaturization electromagnetic sensor

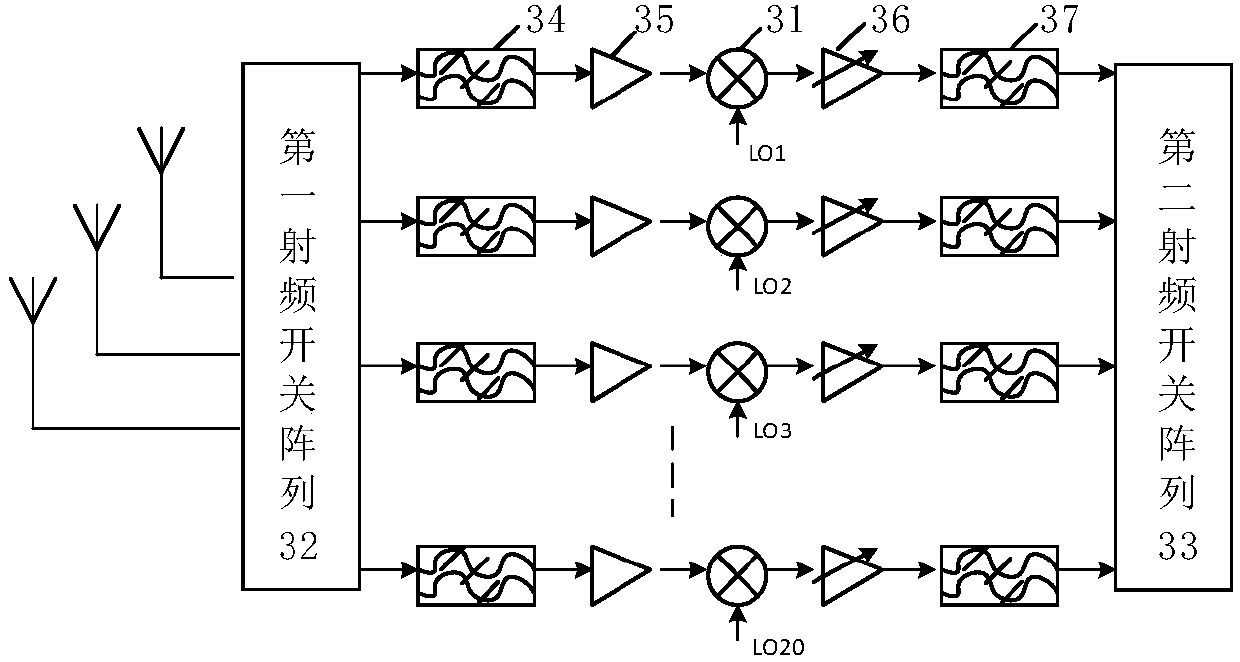

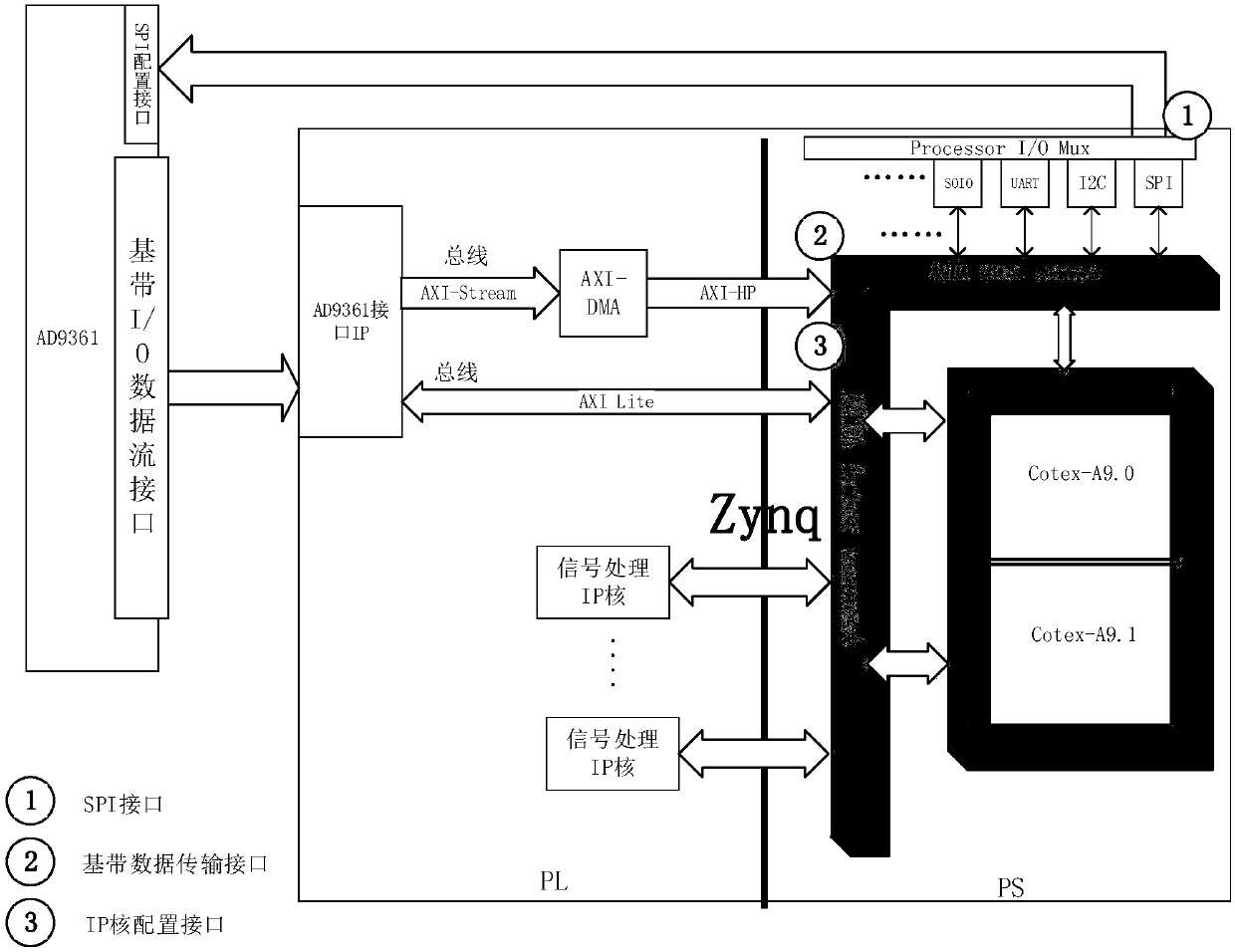

PendingCN108106640AReduce volumeIncrease in sizeTransmissionConverting sensor output electrically/magneticallyIntermediate frequencyComputer module

The invention relates to a miniaturization electromagnetic sensor comprising a frequency synthesizer, and a broadband antenna, a radio frequency front module, an intermediate frequency processing module and an output interface connected in order, wherein the broadband antenna is used for sensing space electromagnetic signals; the radio frequency front module comprises a radio frequency switch array and a plurality of radio frequency channels integrated on a same chip through a bonding technology; the radio frequency switch array respectively connects space electromagnetic signals of differentfrequencies into different radio frequency channels; a mixer is arranged in each radio frequency channel; the mixer can down-convert the space electromagnetic signal in the radio frequency channel into an intermediate frequency signal of a specific frequency; the intermediate frequency processing module can down-convert the intermediate frequency signal at the specific frequency into a base-band digital signal, thus outputting feature information of the space electromagnetic signals. A conventional electromagnetic signal measuring device is large in size, hard to move, and cannot realize filedelectromagnetic compatibility measurement and assessment for work equipment, especially aircraft equipment; the miniaturization electromagnetic sensor can solve said problems.

Owner:北京星航信通科技有限公司

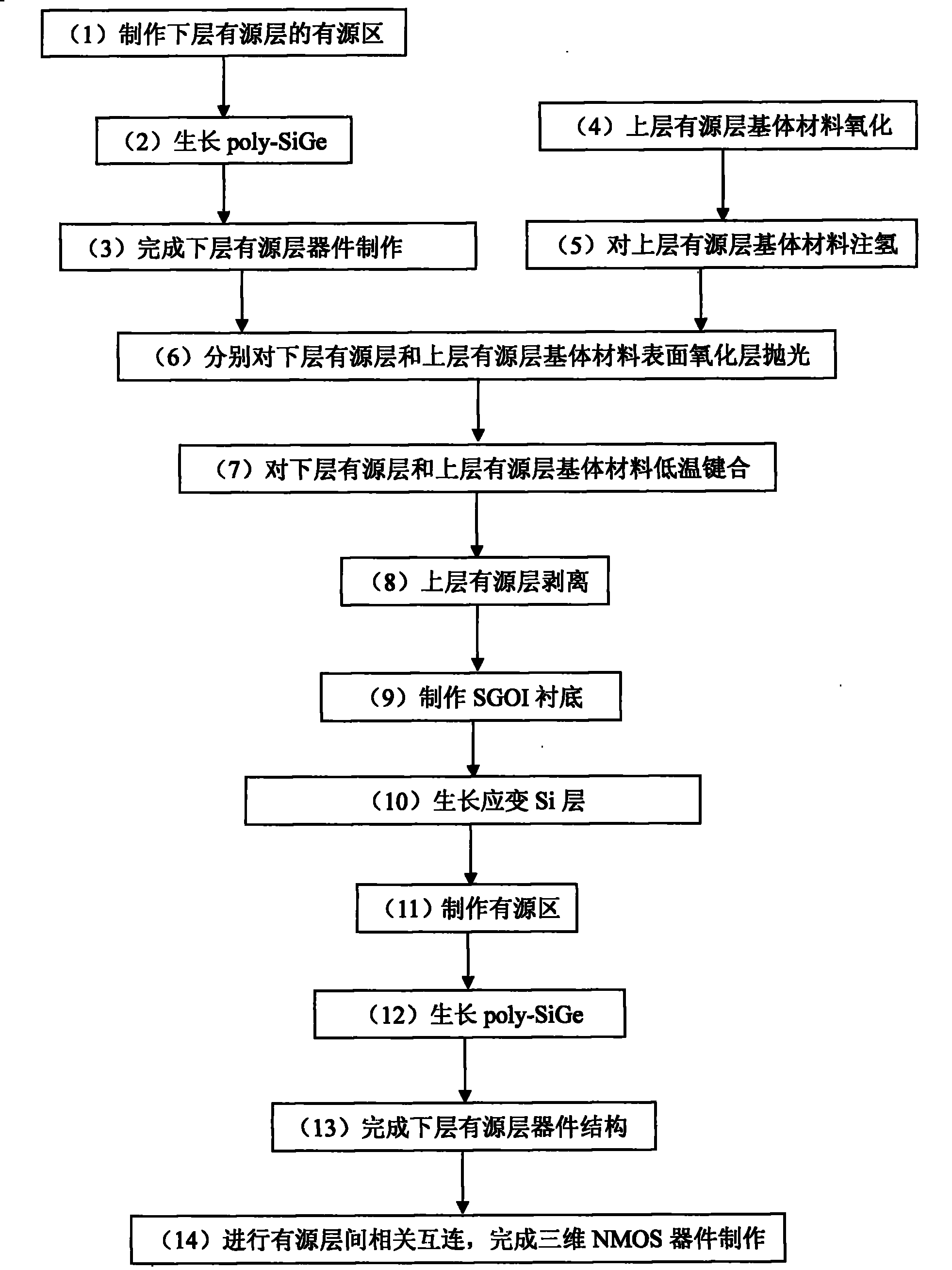

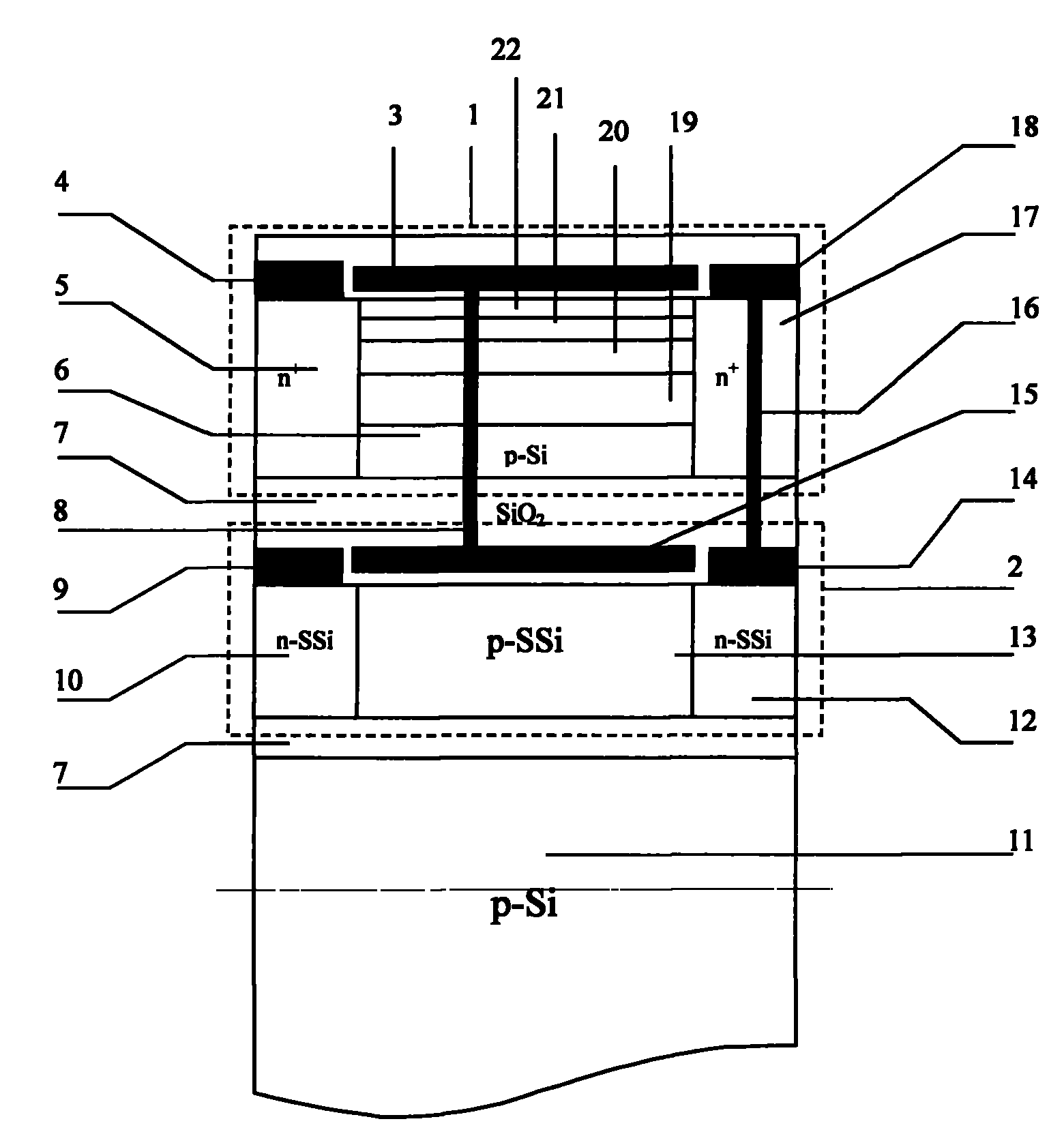

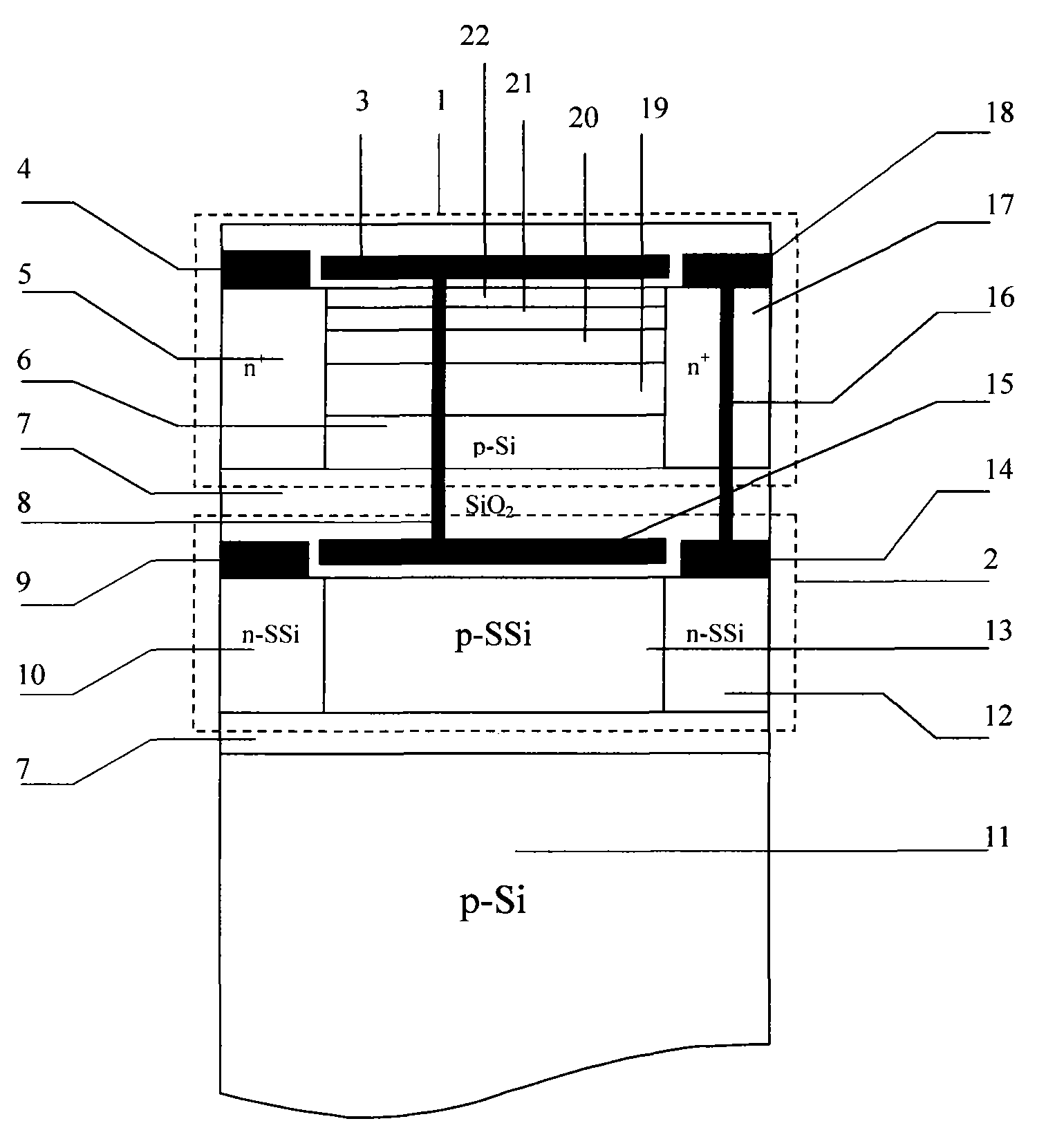

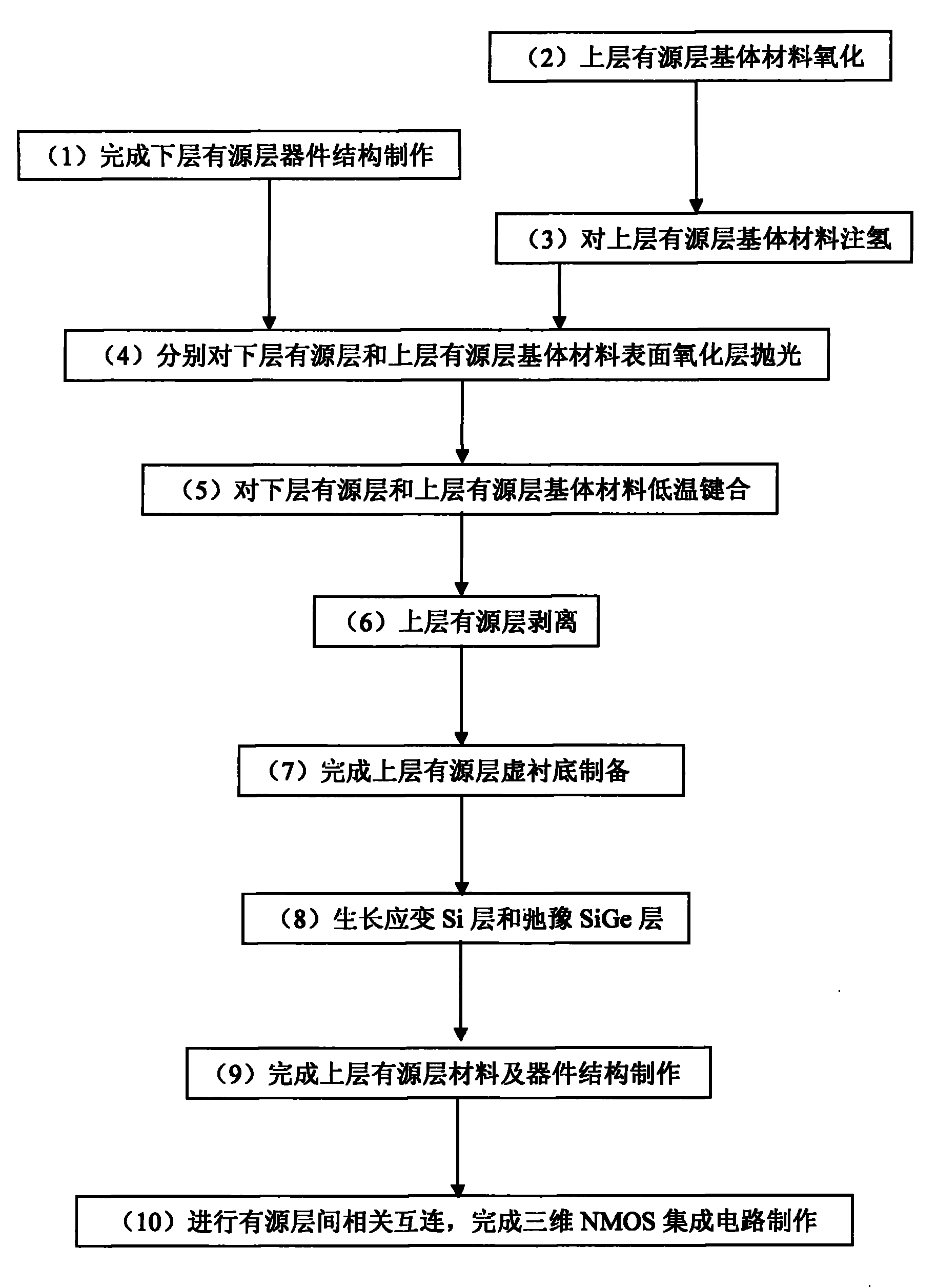

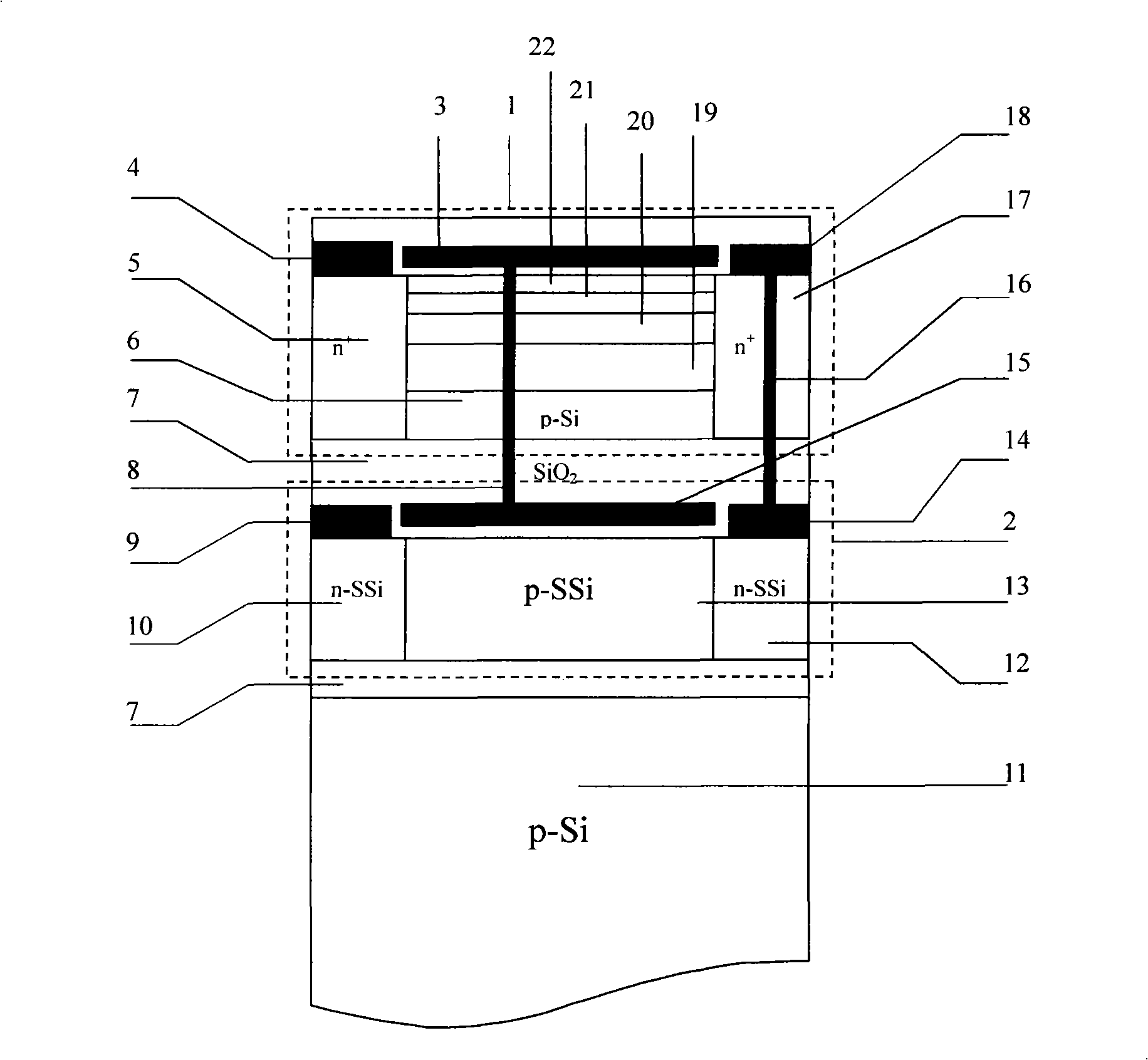

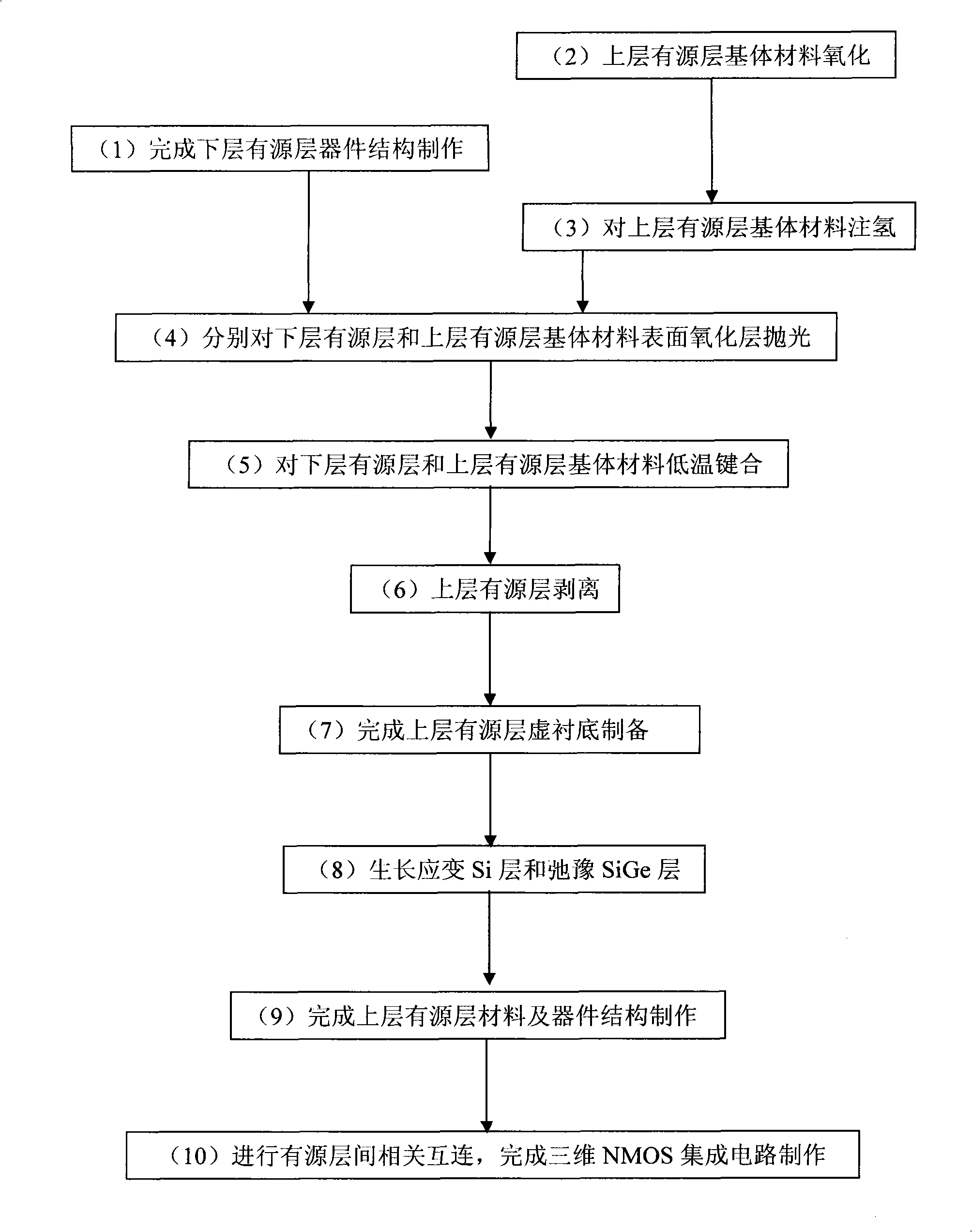

Three-dimensional strain NMOS integrated device and preparation method thereof

InactiveCN101409296BImprove performanceHigh speedSolid-state devicesSemiconductor/solid-state device manufacturing3d integrated circuitLow speed

The invention discloses a 3D strained NMOS integrated device and a manufacturing method thereof, relates to the technical field of microelectronics, and mainly solves the problem of low speed of the existing 3D integrated circuit. The proposal is that an SSOI substrate and an SGOI substrate are employed to construct two active layers of a new 3D integrated device; wherein, the lower active layer is the SSOI substrate and is made into strained Si NMOSFET with a poly-SiGe gate by utilizing the characteristic of high electron mobility of a strained Si material in the SSOI substrate; the upper active layer is the SGOI substrate on which a layer of strained Si grows and is made into strained Si surface channel NMOSFET with the poly-SiGe gate; the lower active layer and the upper active layer are connected by an interconnection line to form the 3D strained NMOS integrated device with a conducting channel of 65nm to 130nm. Compared with the existing 3D integrated devices, the 3D strained NMOS integrated device manufactured by the manufacturing method has the advantages of high speed and good performance, and can be applied to manufacturing large-scale and high-speed 3D CMOS integrated circuits.

Owner:XIDIAN UNIV

Folded-flex bondwire-less multichip power package

ActiveCN1711639BReduce noiseShort interconnectSemiconductor/solid-state device detailsSolid-state devicesThermal contactIntegrated circuit

A multichip wirebond-less integrated circuit and power die package is based on a folded single-layer flex circuit. The package is formed with metal-studbumped power dies and IC's flipchiped to a patterned flex substrate. Extensions of the flex substrate are folded and attached to the backside of the dies for electrical and / or thermal contact. I / O pins are along the periphery of the package for standard SMT mounting while heatspreaders are attached to both sides of the package for double-sided cooling.

Owner:INVENSAS CORP

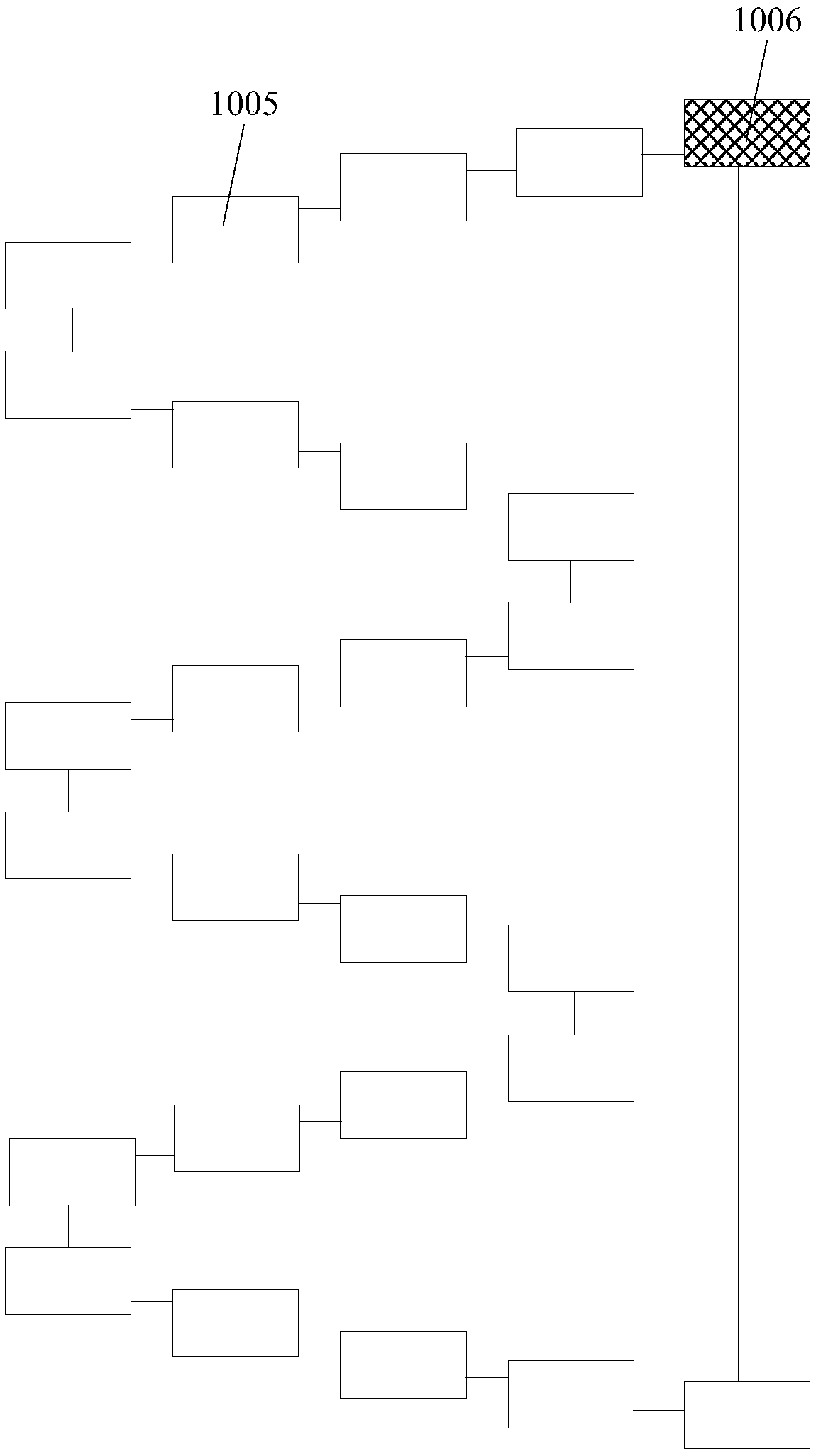

Standard cell test circuit layout and optimization method thereof, and standard cell test structure

The invention relates to a standard cell test circuit layout and an optimization method thereof, and a standard cell test structure. The standard unit test circuit layout comprises a first to-be-tested unit circuit, wherein the first to-be-tested unit circuit comprises a plurality of stages of first standard units, and a plurality of stages of first standard units are arranged into a Y1-row*X1-column array. The connection relation of a plurality of stages of first standard units is realized in a fishbone-shaped manner, so the circuit layout area is saved; secondly, accuracy of the delay characteristic of the actually tested first standard unit is improved, so performance of the standard unit test circuit layout is improved.

Owner:SEMICON MFG INT (SHANGHAI) CORP +1

Serial communication method and apparatus

InactiveCN101399654BEasy to implementReduce logicSynchronising arrangementBus networksProcessor registerData signal

The invention discloses a method of serial communication, wherein, master equipment is connected with a plurality of slave equipments; the master equipment provides a communication clock signal (CLK) to the slave equipment by a clock signal wire, notifies the slave equipment to start reading / writing operation by a synchronous signal (SYN), and transmits a slave equipment address or a register address to the slave equipment by a downstream data signal (CMD); and the master equipment transmits downstream data to the slave equipment by the downstream data signal (CMD), or the slave equipmen transmits upstream data to the master equipment by an upstream data signal (DAT). The method of serial communication comprises a serial communication method of the master equipment, a serial communication method of the slave equipment and a serial communication method for interaction of the master equipment and the slave equipment. The invention also discloses the master equipment and the slave equipment. The proposal of the invention has the advantages of easy realization, pin resource conservation and cost reduction.

Owner:HUAWEI TECH CO LTD

Three-axis structure and manufacturing process of micro inertial measurement unit based on ltcc process

ActiveCN104482938BReduce volumeReduce weightNavigation by speed/acceleration measurementsManufacturing technologyElectromagnetic interference

The invention discloses a low temperature co-fired ceramic (LTCC) technology micro inertial measurement unit (MIMU)-based three-axis structure and a manufacturing technology thereof. Circuit devices of X-axis, Y-axis, Z-axis and main control modules are respectively assembled to a LTCC substrate by SMT, the X-axis module and the Y-axis module are installed on a cavity base plate of the LTCC substrate of the Z-axis module in an orthogonal edge-on way so that a three-axis detection module is formed, and the main control module and the three-axis detection module are provided with BGA and are welded to form the three-axis MIMU assembly. The structure provided by the invention adopts a module design, has a small volume and light weight, and reduces size effect-caused adverse influences. Interconnection lines between devices are short so that transmission loss and crosstalk are reduced. The X-axis module and the Y-axis module are installed on a cavity base plate of the LTCC substrate of the Z-axis module in an orthogonal edge-on way so that X-Y-Z three-axis inertial 3D orthogonal detection is effectively realized. The structure is simple. The manufacturing technology has reliable processes and installation accuracy. A housing heat-radiation boss improves MIMU heat radiation performances and extraneous electromagnetic interference resistance.

Owner:EAST CHINA INST OF OPTOELECTRONICS INTEGRATEDDEVICE

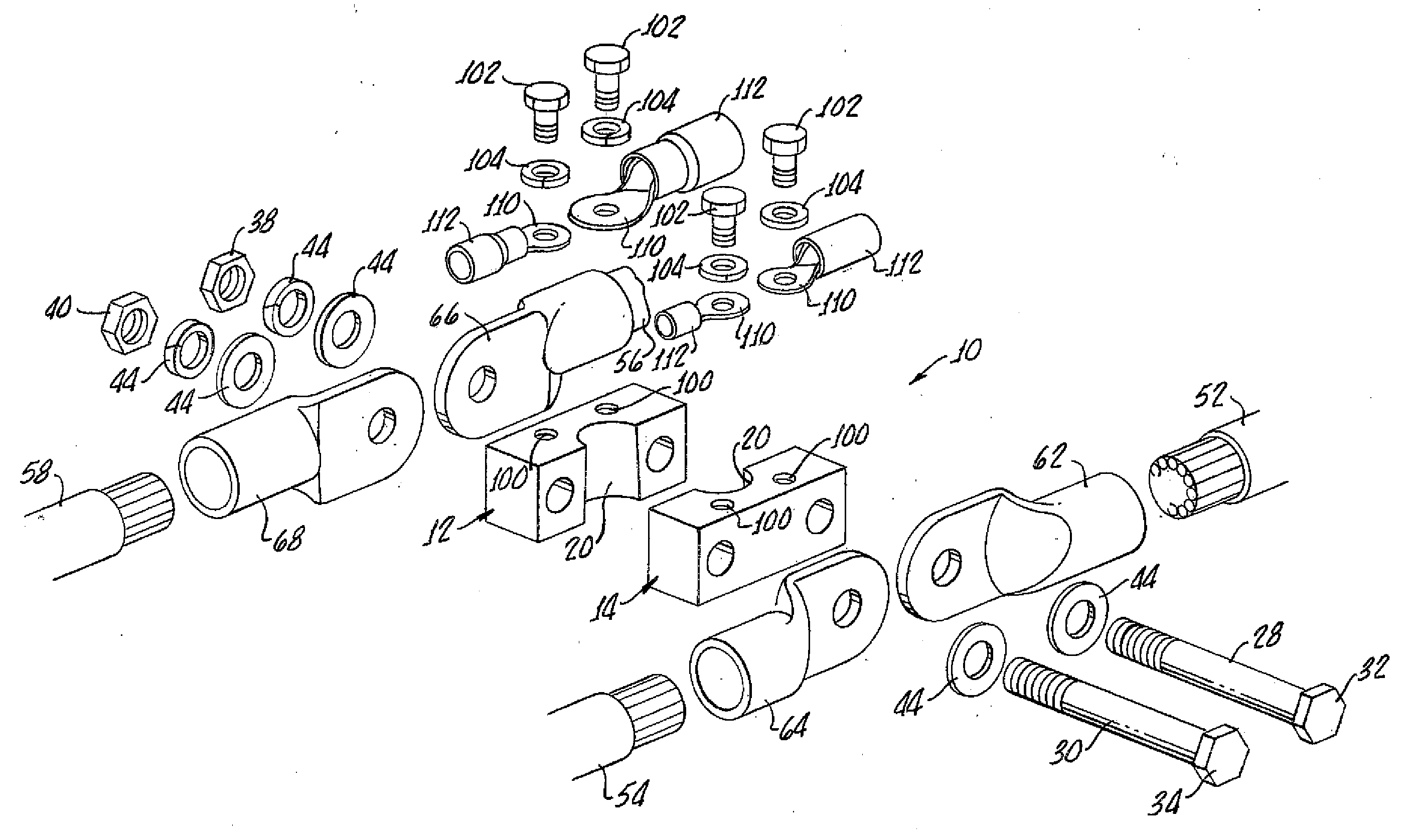

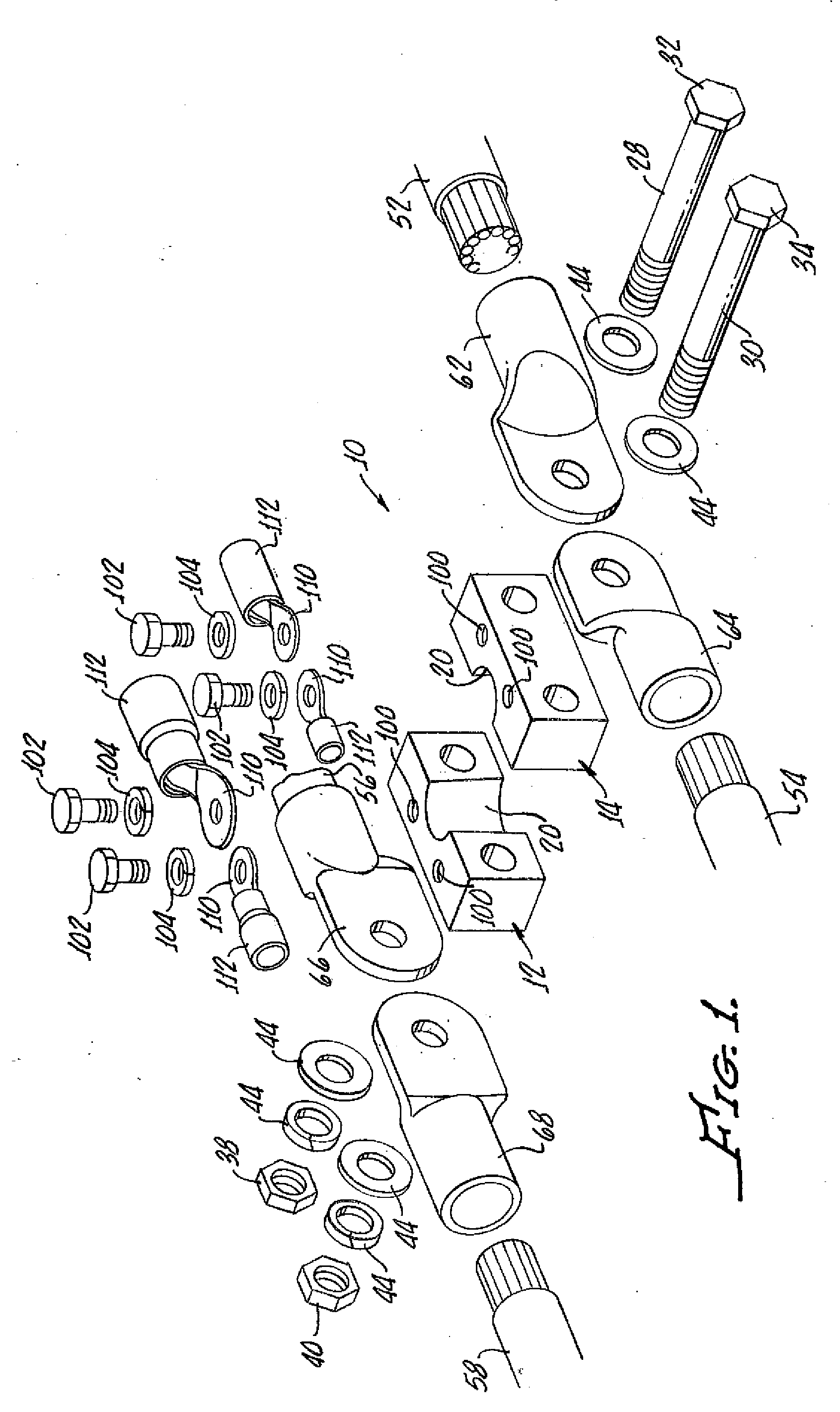

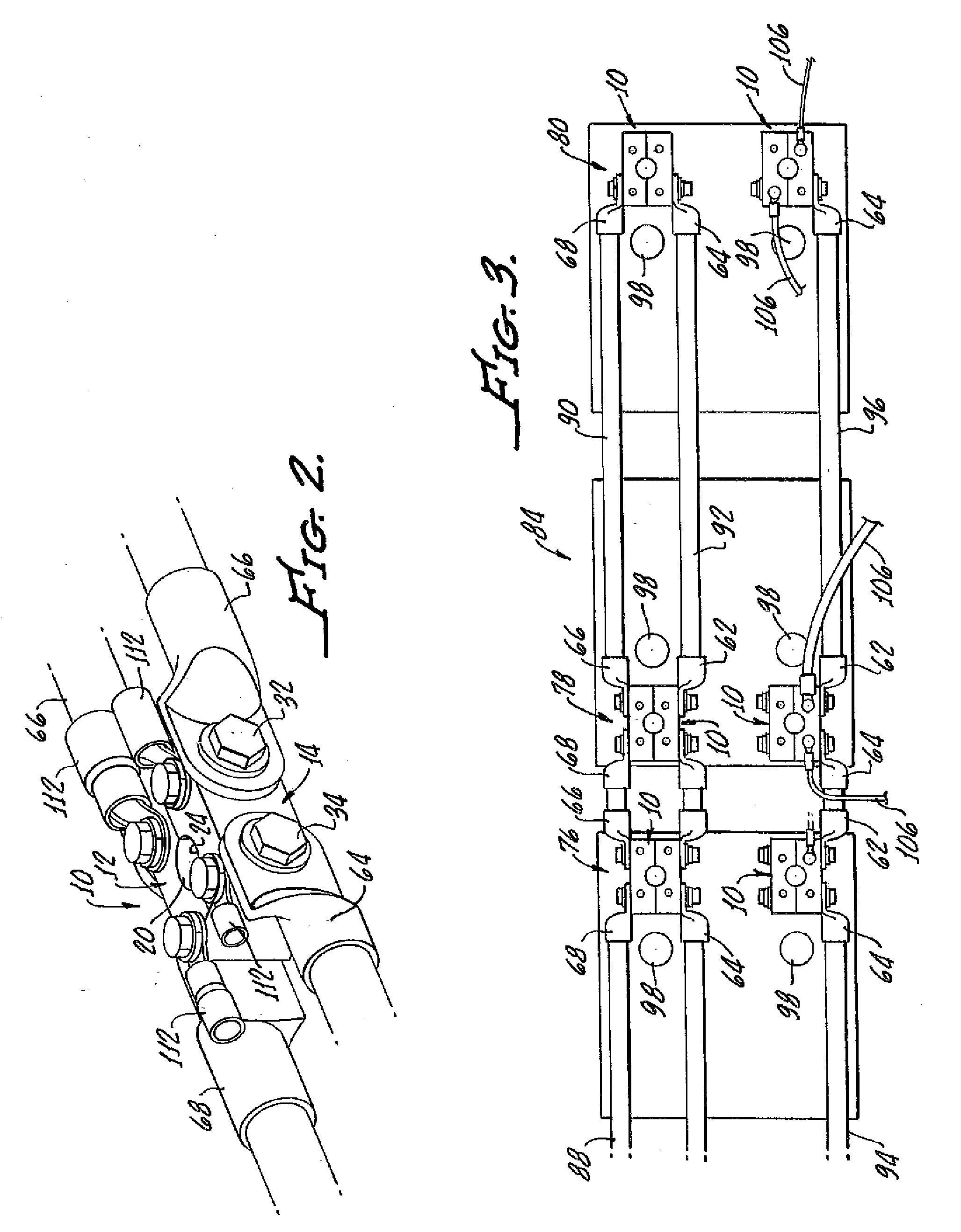

Battery post clamp

InactiveUS20100062661A1Loss of energy transferShort interconnectElectric connection structural associationsEngineeringCable harness

A battery post connector and harness in accordance with the present invention includes a pair of generally rectilinear jaws with each jaw having a peripheral notch sized and shaped to fit against a battery post. The jaws are abuttable with the notches facing one another to encompass the battery post. A pair of spaced apart bolts are provided with each bolt passing through the jaw transverse to the battery post and each bolt includes a head on one end thereof and a nut on the other end thereof for tightening jaws against the battery post. This enables the bolt to attach the cables to the jaws in a parallel relationship with respect to one another.

Owner:FELDMAN THOMAS H

Three-dimensional quantum well NMOS integrated component and preparation method thereof

InactiveCN101409297BImprove performanceHigh speedSolid-state devicesSemiconductor/solid-state device manufacturing3d integrated circuitLow speed

The invention discloses a 3D quantum well NMOS integrated device and a manufacturing method thereof, relates to the technical field of microelectronics, and mainly solves the problem of low speed of the existing 3D integrated circuits. The proposal is that an SSOI substrate and an SGOI substrate are respectively employed to construct two active layers of a new 3D integrated device; wherein, the lower active layer is the SSOI substrate and is made into strained Si NMOSFET by utilizing the characteristic of high electron mobility of a strained Si material in the SSOI substrate; the upper activelayer is the SGOI substrate on which a strained Si / relaxed SiGe double-layer structure grows and is made into strained Si quantum well channel NMOSFET; the lower active layer and the upper active layer are connected by an interconnection line to form the 3D quantum well NMOS integrated device with a conducting channel of 65nm to 130nm. Compared with the existing 3D integrated devices, the 3D quantum well NMOS integrated device manufactured by the manufacturing method has the advantages of high speed and good performance, and can be applied to manufacturing large-scale and high-speed 3D CMOS integrated circuits.

Owner:XIDIAN UNIV

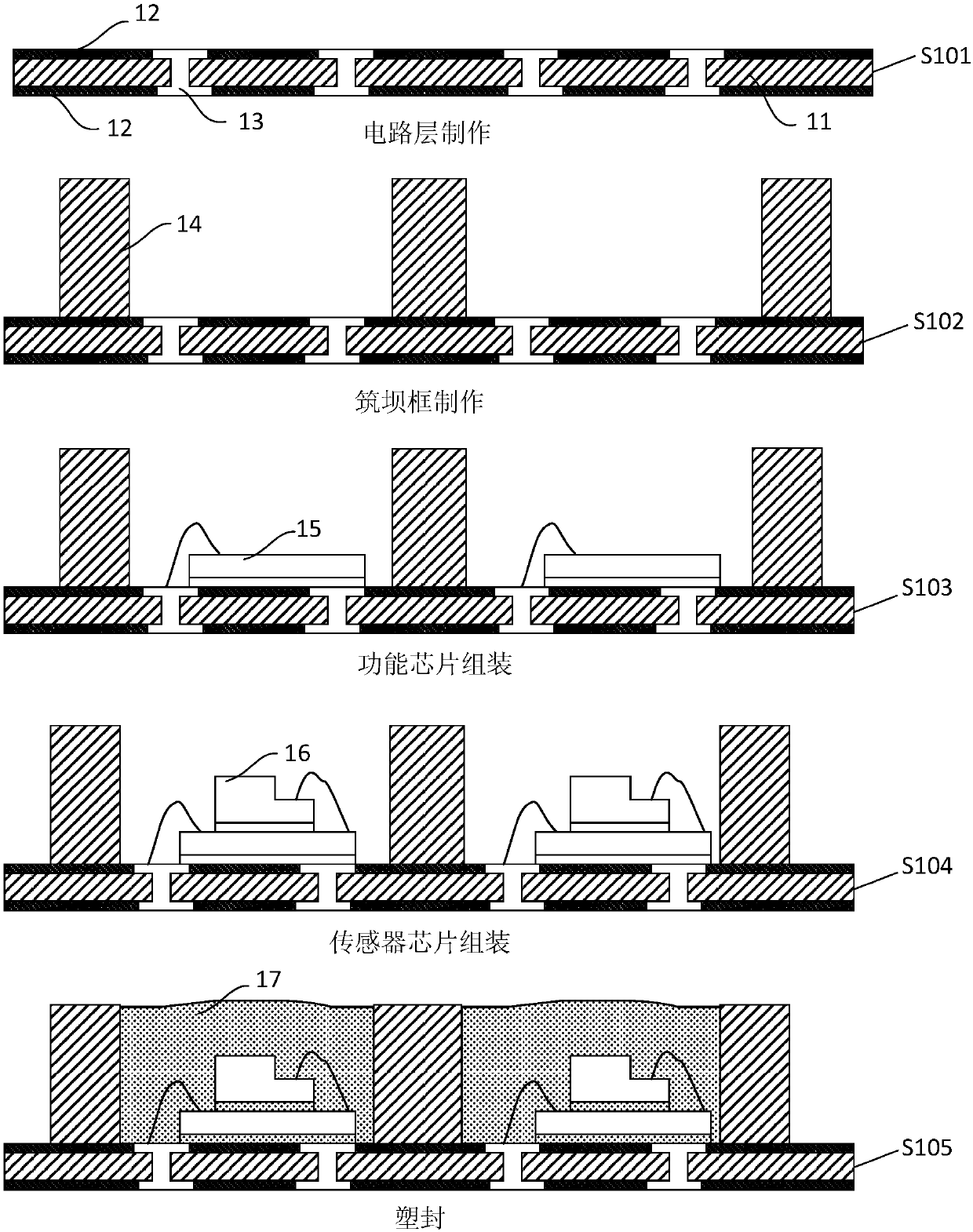

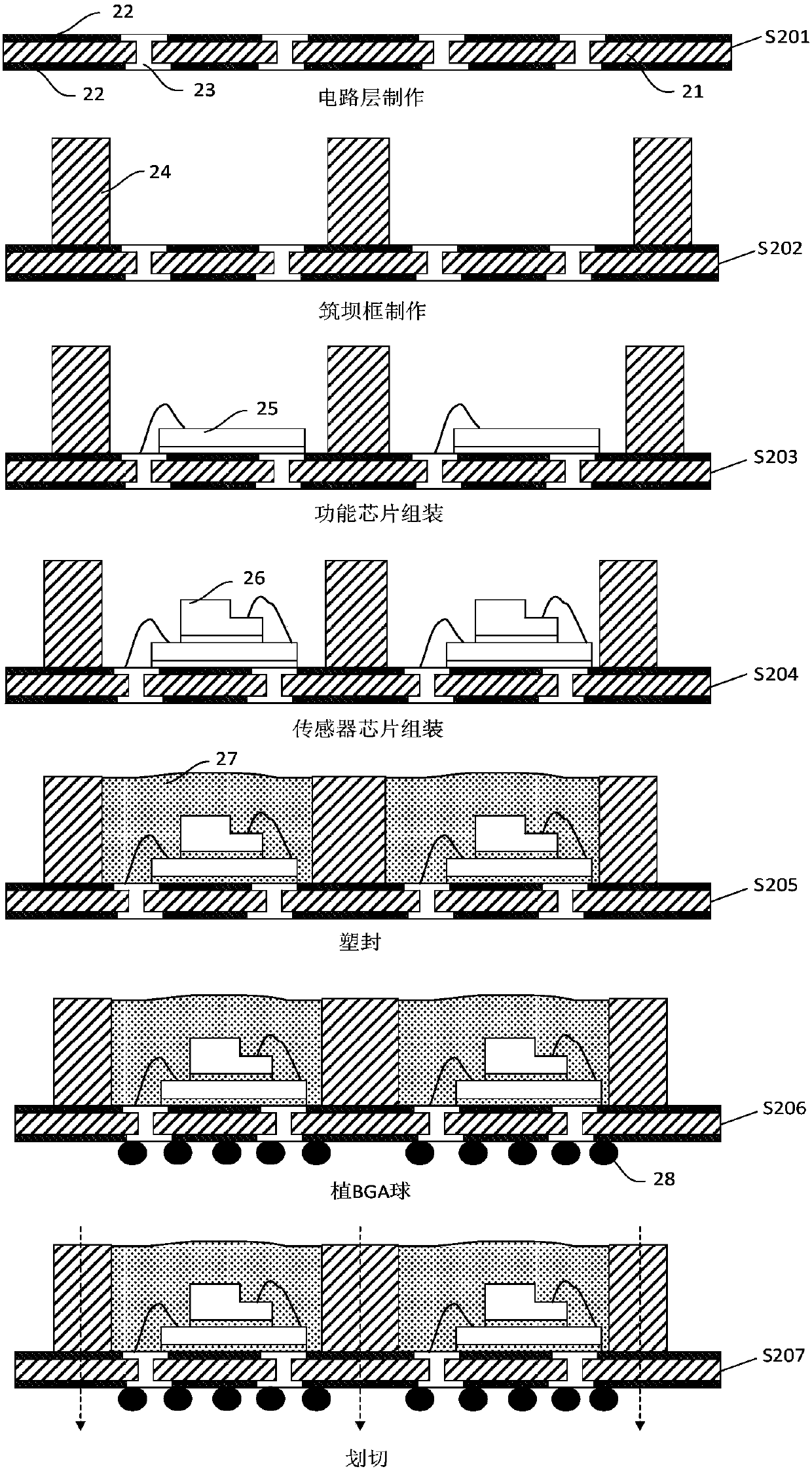

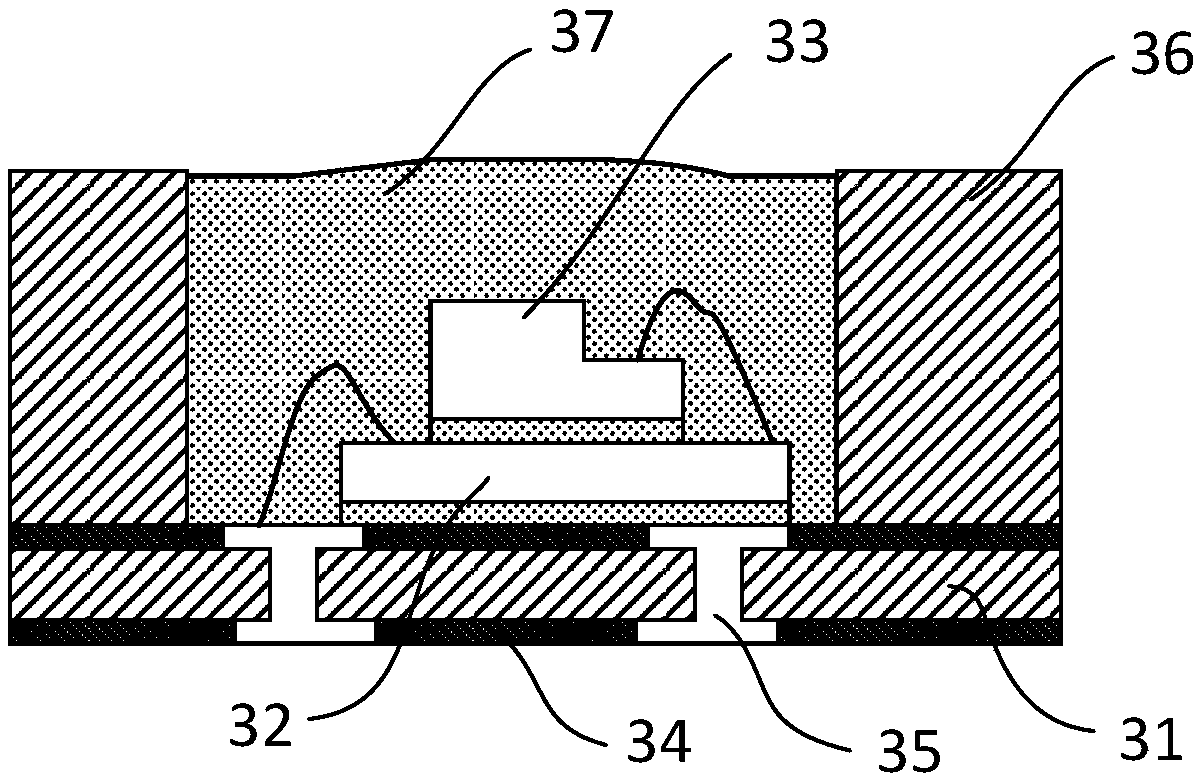

Sensor microsystem package method and sensor microsystem

PendingCN109950236AHigh precisionShort interconnectTelevision system detailsPiezoelectric/electrostriction/magnetostriction machinesWork performanceSilica gel

The present invention discloses a sensor microsystem and a package method thereof. The method comprises the steps of: respectively manufacturing circuit layers covering a substrate at the front surface and the back surface of the substrate, and manufacturing metal through holes penetrating the substrate and electrically connected with the circuit layers at the back surface of the substrate; manufacturing a plurality of damming frames configured to fix a functional chip and a sensor chip on the circuit layer at the front surface of the substrate; assembling and electrically and mutually connecting the back surface of the functional chip and the top portions of the circuit layers between every two damming frames, wherein the functional chip comprises a processor chip or a controller chip; assembling and mutually connecting the back surface of the sensor chip and the front surface of the functional chip; filling the position between every two damming frames with flexible glue or silica gel covering the functional chip and the sensor chip to obtain a sensor microsystem wafer comprising the functional chip and the sensor chip. According to the invention, the sensor microsystem-level package is achieved, the working performance is high, the stress is low, and the universality is high.

Owner:北京万应科技有限公司

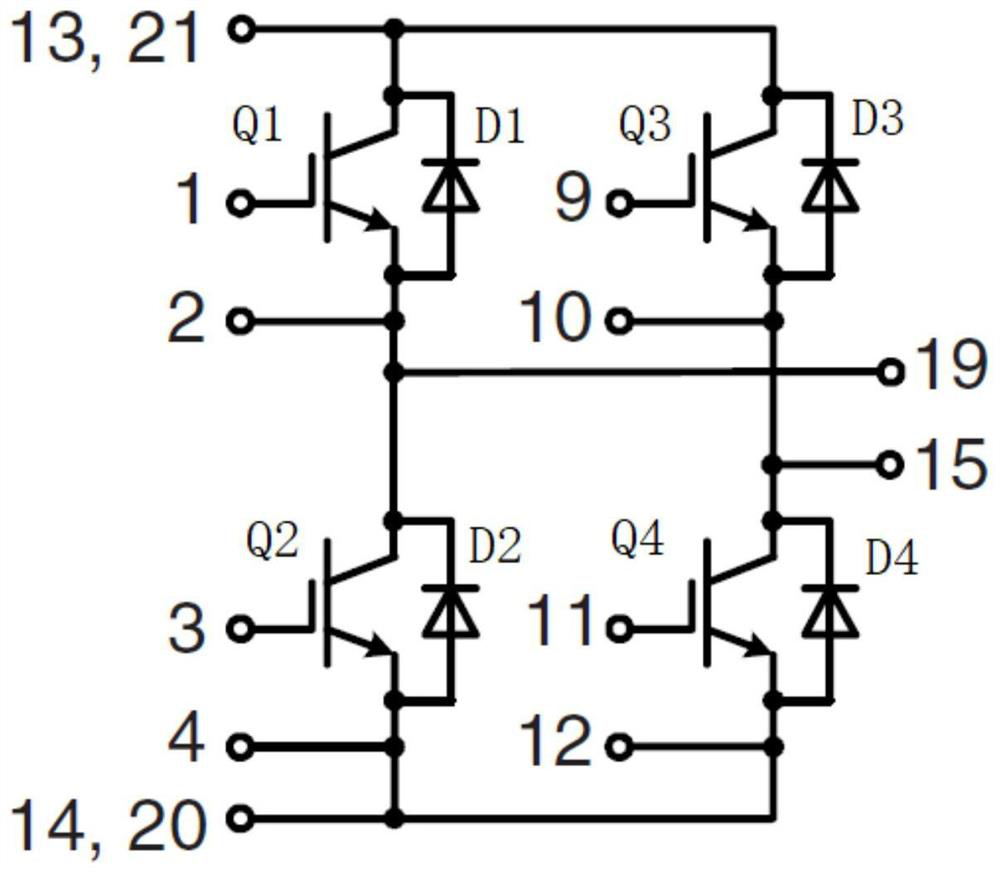

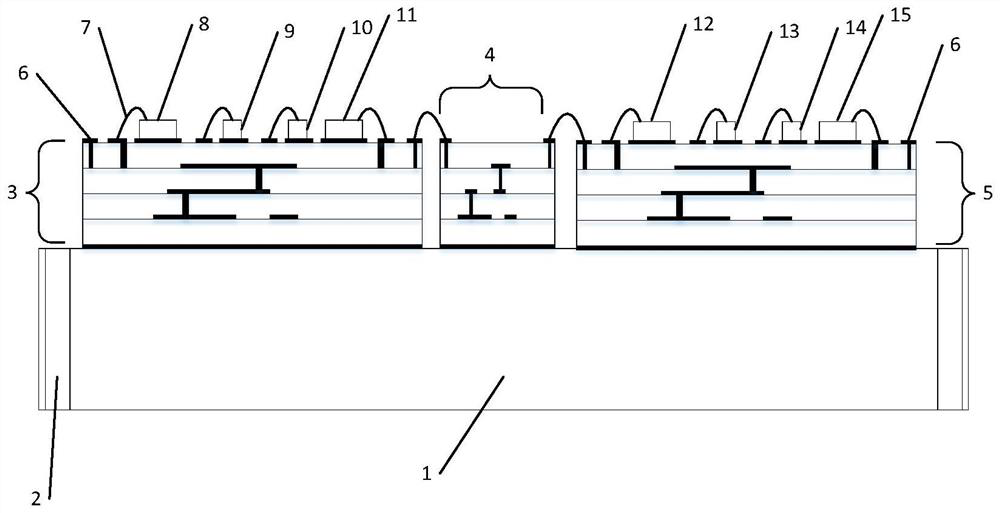

High-integration high-reliability IGBT power module and manufacturing method thereof

PendingCN113707643AImprove assembly densityShort interconnectSemiconductor/solid-state device detailsSolid-state devicesBackplaneH bridge

The invention discloses a high-integration and high-reliability IGBT power module and a manufacturing method thereof. The high-integration and high-reliability IGBT power module comprises a metal bottom plate, metal bottom plate fixing holes, a multilayer wiring ceramic left half bridge substrate, a multilayer wiring ceramic switching substrate, a multilayer wiring ceramic right half bridge substrate, module pins, bonding wires, four IGBT chips and four diode chips which form an H bridge circuit structure. Process technologies such as mounting and bonding of a metal bottom plate, a multilayer ceramic substrate and a bare chip, metal fixed connection and the like are comprehensively adopted, a multilayer wiring ceramic left half bridge substrate, a multilayer wiring ceramic switching substrate and a multilayer wiring ceramic right half bridge substrate are mounted and welded on the metal bottom plate, and four IGBT chips and four diode chips are mounted and welded on corresponding substrates according to a design layout. The problems that an existing IGBT module is poor in high voltage resistance, low in assembly density, complex in heat dissipation measure and low in reliability are solved. The module is widely applied to the packaging process of semiconductor power devices.

Owner:CHINA ZHENHUA GRP YONGGUANG ELECTRONICS CO LTD STATE OWNED NO 873 FACTORY

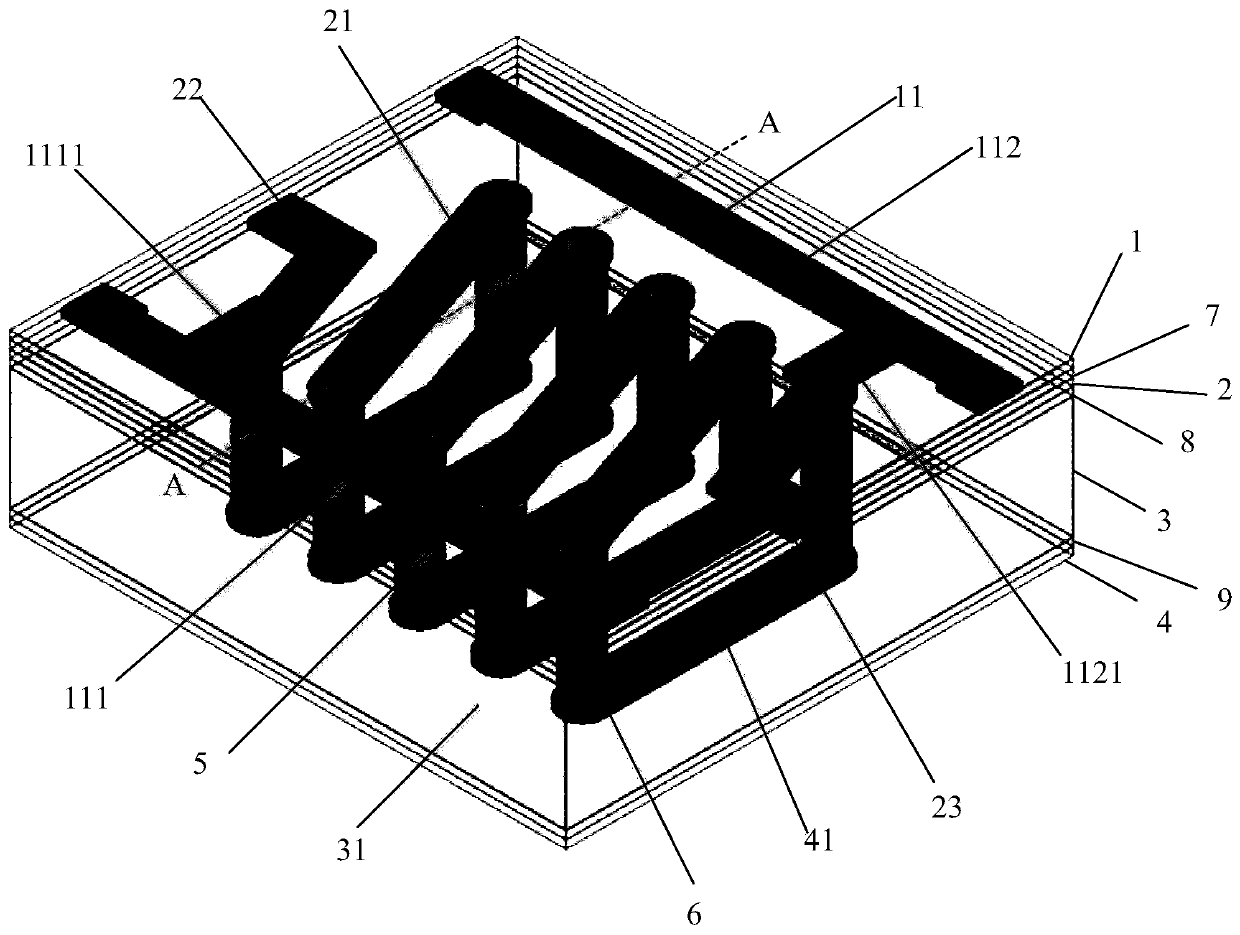

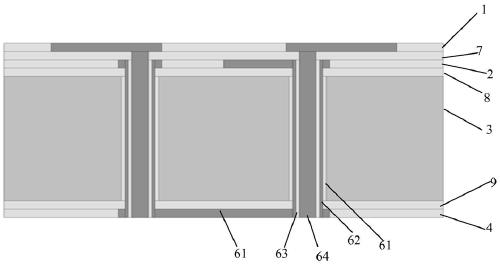

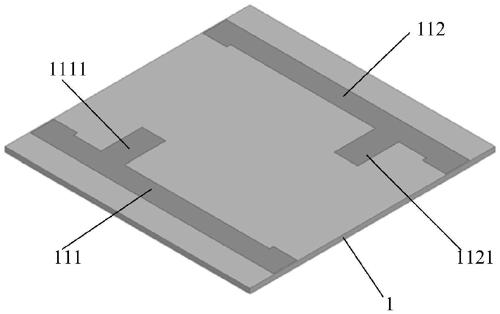

A Configurable Three-dimensional Microwave Filter Based on Coaxial Through-Silicon Vias

ActiveCN109950230BCompact structureImprove utilization efficiencySemiconductor/solid-state device detailsSolid-state devicesCapacitanceSpiral inductor

The invention relates to a configurable three-dimensional microwave filter based on coaxial silicon through holes. The configurable three-dimensional microwave filter comprises a ground layer, a firstinterconnect layer, a silicon through hole capacitor layer and a second interconnect layer in order from top to bottom, wherein a plurality of first connecting members are disposed on the first interconnect layer; a plurality of second connecting members are disposed on the second interconnect layer; the ground layer includes a ground lead-out terminal which is selectively grounded; the silicon through hole capacitor layer includes a substrate and a plurality of silicon through hole structures penetrating through the substrate; the plurality of silicon through hole structures are successivelyconnected end to end through the plurality of first connecting members and the plurality of second connecting members to form a three-dimensional spiral inductor. The configurable three-dimensional microwave filter is compact in structure, high in utilization efficiency, low in chip area, and integrated, avoids introduction of additional loss, is short in interconnect line, low in parasitic parameter and low in off-chip coupling.

Owner:XIDIAN UNIV

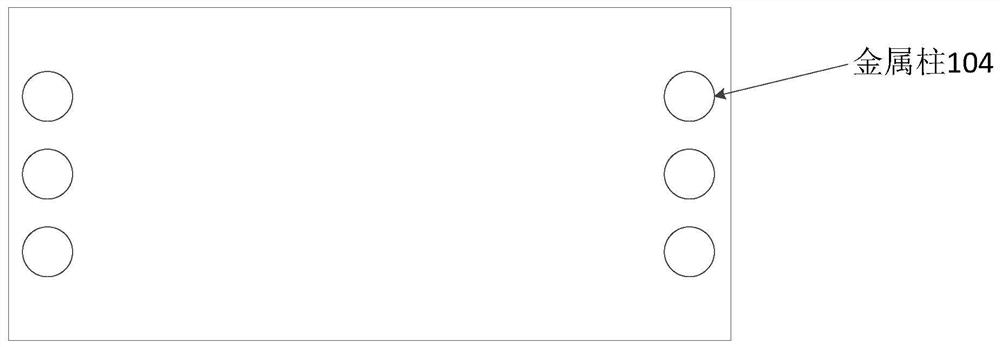

Memory structure and manufacturing method thereof

InactiveCN111834315AAchieve large capacityAchieve expansionSemiconductor/solid-state device detailsSolid-state devicesElectrical connectionEngineering

The invention discloses a memory structure and a manufacturing method thereof. The memory structure comprises a plurality of storage units with the same structure; each storage unit comprises a storage module, a plastic package layer covers the storage module, a connecting piece is arranged at the bottom of the storage module, a metal column is arranged on the side edge of the storage module, andthe connecting piece extends to the side edge of the storage module and is electrically connected with the metal column; the plurality of storage units with the same structure are stacked, and the storage units positioned at the lower part are electrically connected with the connecting pieces of the storage units positioned at the upper part through the metal column. According to the invention, the capacity of the memory is expanded by stacking the memory modules, external leads are not needed, the interference among the leads is avoided, the manufacturing of the high-capacity memory is realized without a complex packaging process, complex chip assembly equipment is not needed, the packaging process is simple, and the cost is low.

Owner:NAT CENT FOR ADVANCED PACKAGING

Three-dimensional quantum well NMOS integrated component and preparation method thereof

InactiveCN101409297AImprove performanceHigh speedSolid-state devicesSemiconductor/solid-state device manufacturing3d integrated circuitLow speed

The invention discloses a 3D quantum well NMOS integrated device and a manufacturing method thereof, relates to the technical field of microelectronics, and mainly solves the problem of low speed of the existing 3D integrated circuits. The proposal is that an SSOI substrate and an SGOI substrate are respectively employed to construct two active layers of a new 3D integrated device; wherein, the lower active layer is the SSOI substrate and is made into strained Si NMOSFET by utilizing the characteristic of high electron mobility of a strained Si material in the SSOI substrate; the upper active layer is the SGOI substrate on which a strained Si / relaxed SiGe double-layer structure grows and is made into strained Si quantum well channel NMOSFET; the lower active layer and the upper active layer are connected by an interconnection line to form the 3D quantum well NMOS integrated device with a conducting channel of 65nm to 130nm. Compared with the existing 3D integrated devices, the 3D quantum well NMOS integrated device manufactured by the manufacturing method has the advantages of high speed and good performance, and can be applied to manufacturing large-scale and high-speed 3D CMOS integrated circuits.

Owner:XIDIAN UNIV

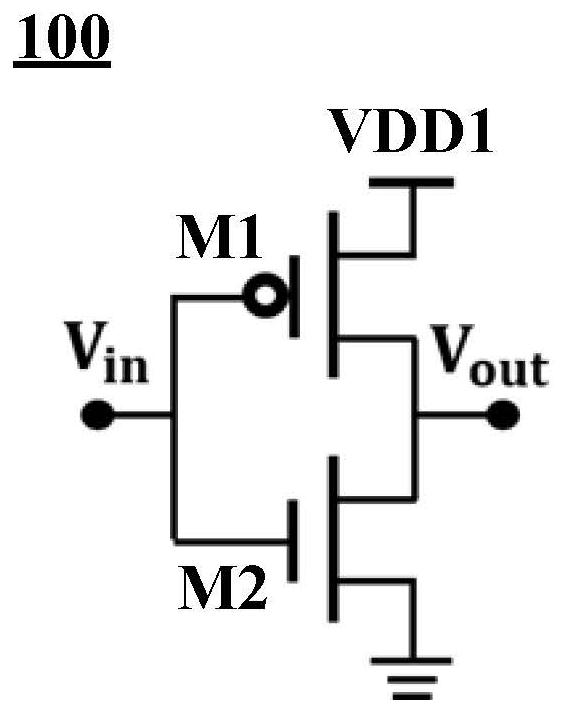

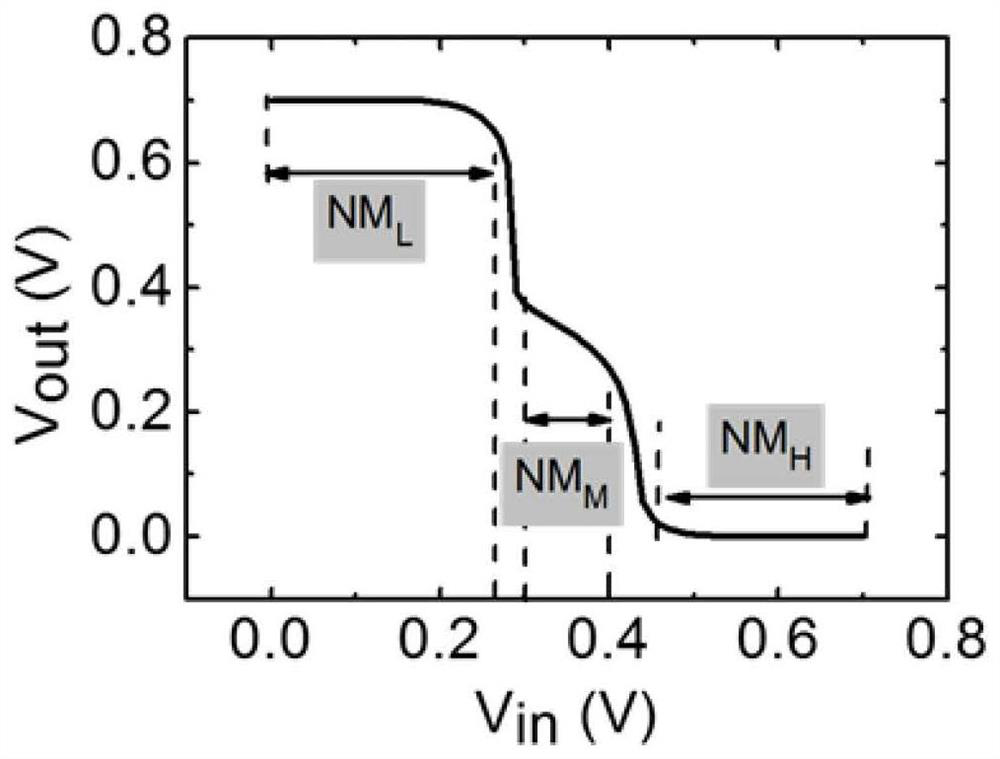

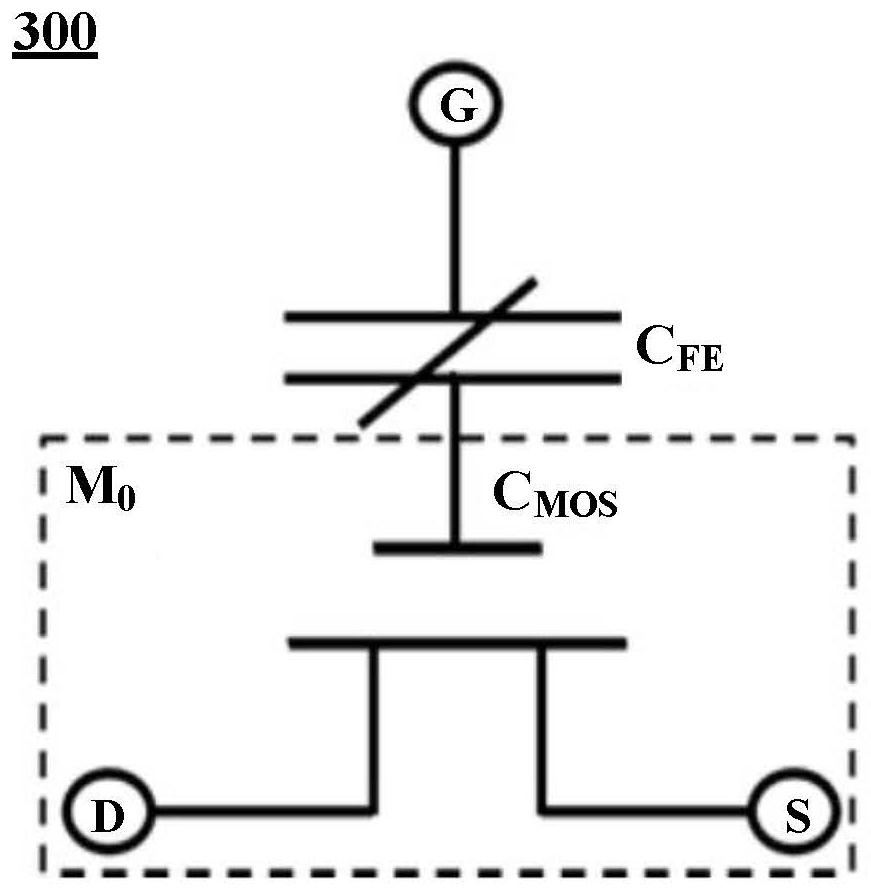

Inverter and memory device

The invention discloses an inverter and a memory device. The inverter includes negative capacitance transistors connected in series and configured to receive a first input level representing a logic value 1, a second input level representing a logic value 1 / 2, and a third input level representing a logic value 0, respectively, a first output level representing a logic value 0, a second output level representing a logic value 1 / 2, and a third output level representing a logic value 1 are output.

Owner:INST OF MICROELECTRONICS CHINESE ACAD OF SCI

Emulator of Multi-core Memory System Based on On-Chip Network Interconnection

ActiveCN103914333BSpeed up developmentShort interconnectSoftware simulation/interpretation/emulationSystemCParallel computing

Owner:SUZHOU INST FOR ADVANCED STUDY USTC

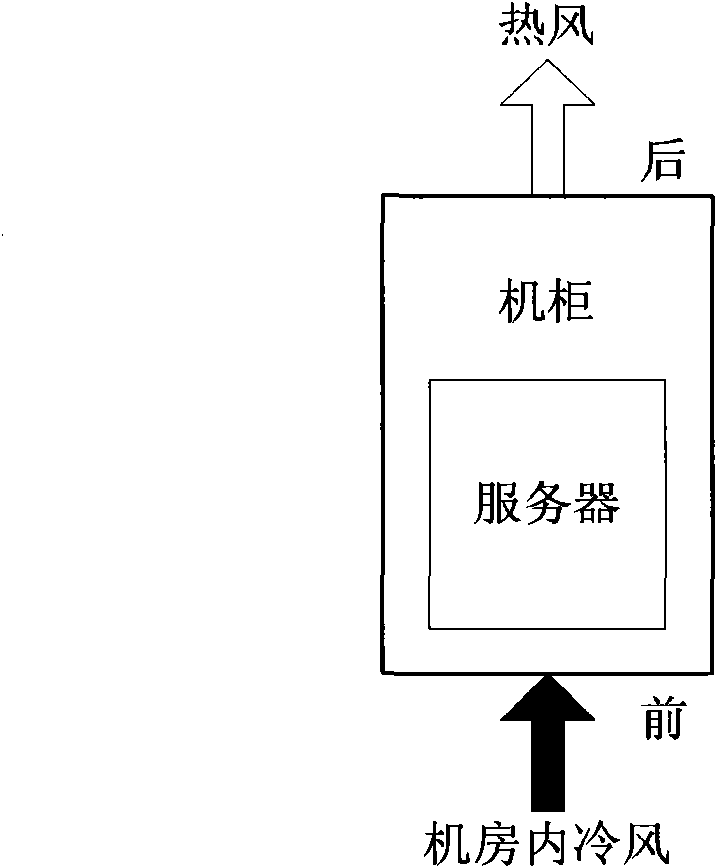

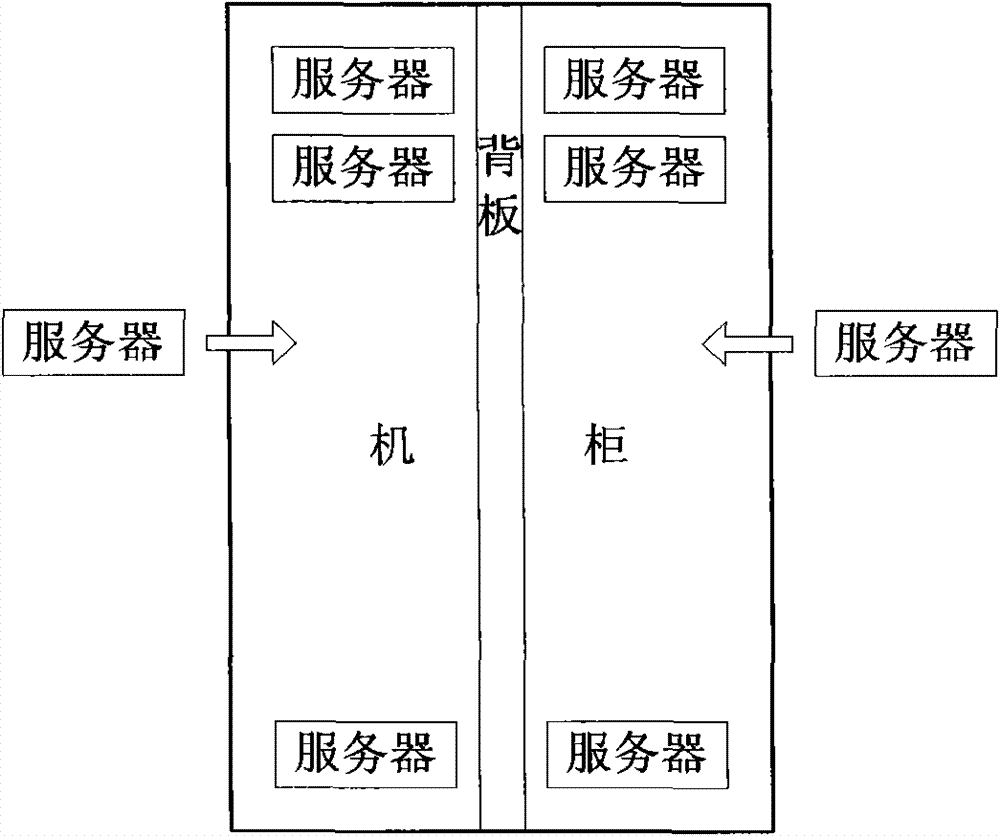

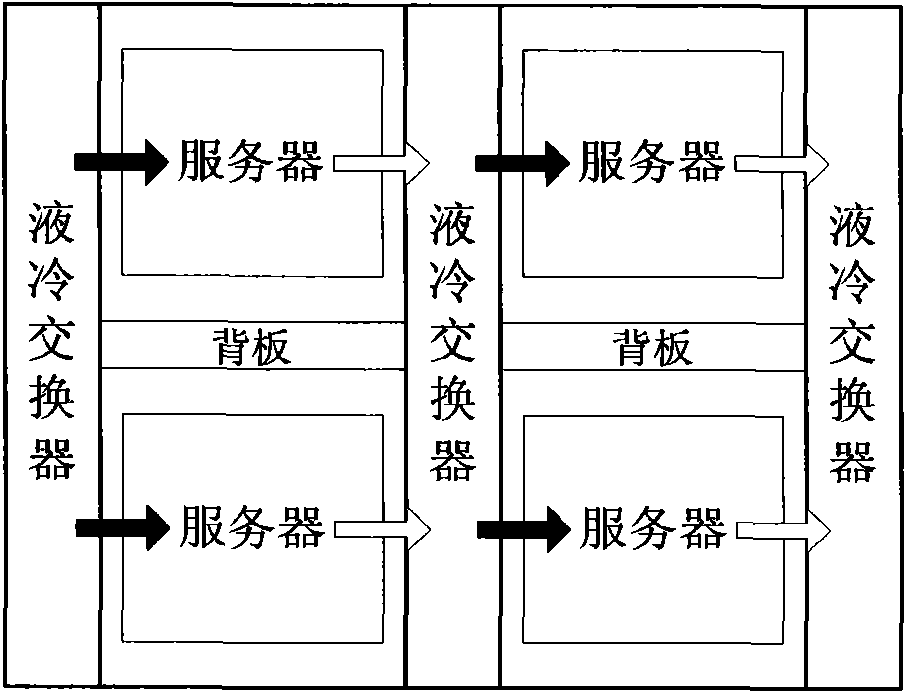

Machine cabinet, machine cabinet radiating system and movable data center

ActiveCN102339108BHigh densityImprove cooling efficiencyDigital data processing detailsCooling/ventilation/heating modificationsData centerEngineering

The invention provides a machine cabinet, a machine cabinet radiating system and a data center. The machine cabinet radiating system comprises at least one machine cabinet in which a plurality of operable computation systems are installed and a first liquid cooling exchanger, wherein the machine cabinet comprises a back plate which is vertical to the top surface and the bottom surface of the machine cabinet and is parallel to the front surface and the rear surface of the cabinet; the back plate is used for partitioning the machine cabinet into a front space and a rear space which mean a firstspace and a second space respectively; both the left side surface and the right side surface of the machine cabinet are provided with a vent hole; the vent holes are used for air inflow or air outflow; and the first liquid cooling exchanger is positioned on the left side or the right side of a first machine cabinet in the machine cabinet in which the plurality of operable computation systems are installed and is used for feeding cooled airflow into the vent holes of the first machine cabinet. By the machine cabinet, the machine cabinet radiating system and the data center, the radiating efficiency can be improved.

Owner:LENOVO (BEIJING) LTD

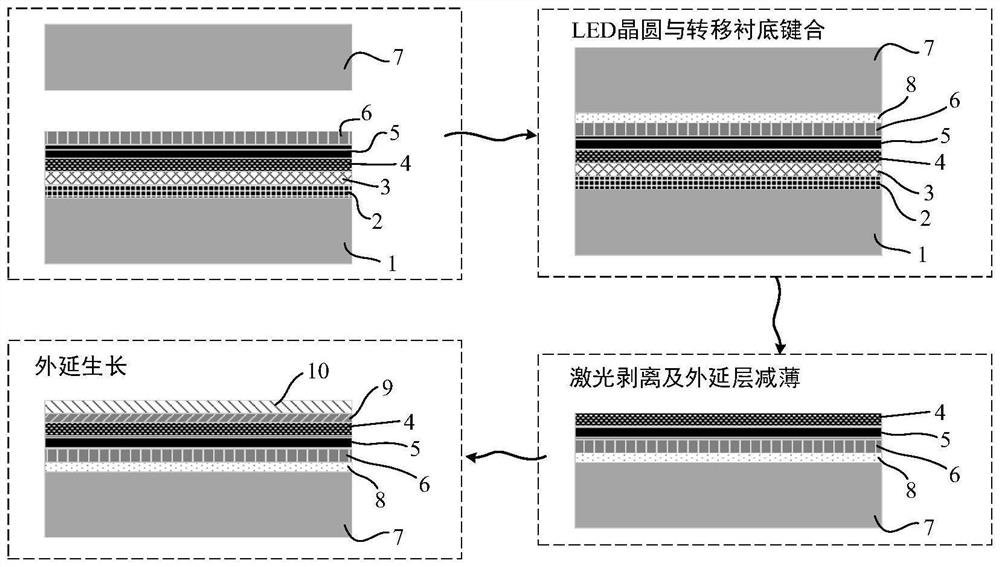

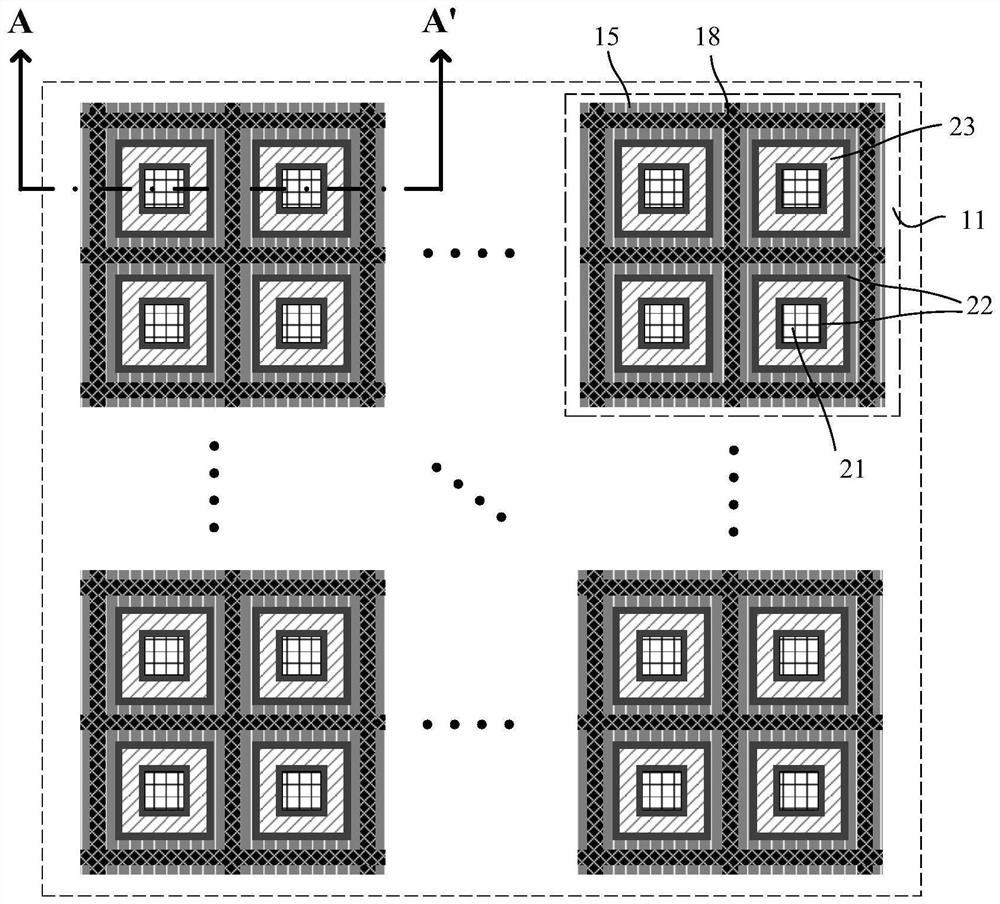

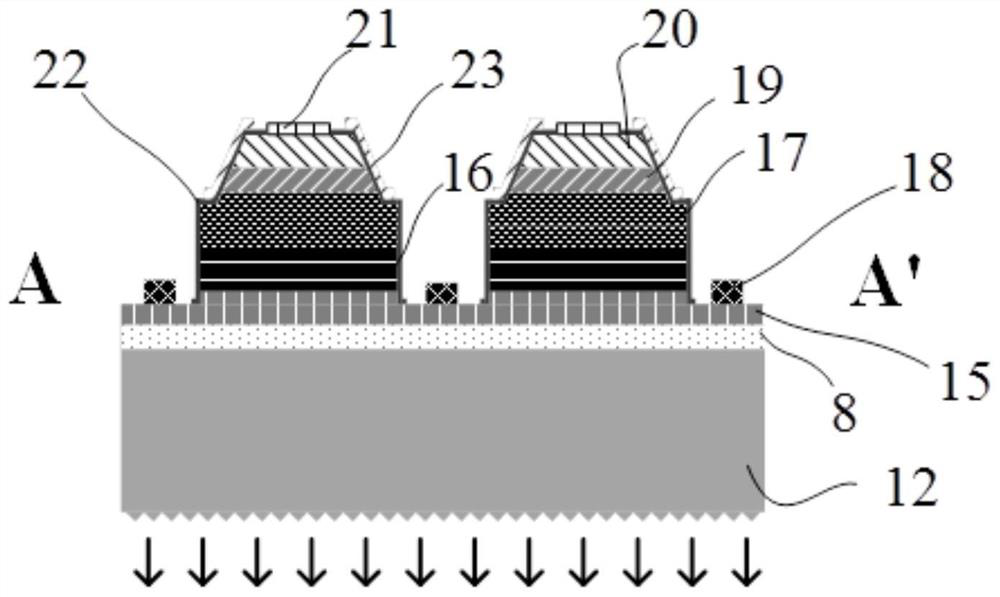

Photoelectric integrated device and preparation method

PendingCN114582911AReduce manufacturing costReduce volumeSolid-state devicesSemiconductor/solid-state device manufacturingMOSFETEngineering

The invention discloses a photoelectric integrated device and a manufacturing method thereof, and the device comprises a plurality of basic units which are arranged in order, and each basic unit comprises a multi-quantum well MicroLED and a vertical structure GaN MOSFET; the top layer of the sapphire substrate is provided with a bonding dielectric layer, and the bottom layer of the sapphire substrate is a light emitting surface of the device; the multi-quantum well Micro LED is arranged on the top layer of the bonding dielectric layer; the GaN MOSFET with the vertical structure is arranged above the multi-quantum well Micro LED, and a drain region of the GaN MOSFET with the vertical structure is connected in series with an N region of the multi-quantum well Micro LED through a shared diode N-GaN structure layer; the light-emitting device and the driving electronic device are manufactured on the same chip, batch manufacturing can be achieved through an existing GaN process platform, the production cost is reduced, and the light-emitting device and the driving electronic device have the remarkable advantages of being small in size, high in speed and high in reliability. The GaN MOSFET adopts a novel vertical structure design, so that the channel length of a driving transistor can be greatly shortened, and the GaN MOSFET has important significance in improving the performance and the integration level of an integrated device.

Owner:NANJING UNIV OF POSTS & TELECOMM

Bare chip building block packaging method

InactiveCN100452331CAchieving High Density PackagingShort interconnectSemiconductor/solid-state device manufacturingSquare arrayCapacitance

A modular-packaging method of bare chips includes collecting bare chips to be square array and filling waster chip at blank position, placing said array on base plate of at least 3-layer printed circuit board, cutting out square hole at middle of clamp plate and sheathing said clamp plate at external of square array, covering top plate then setting square array upside down to take off base plate, coating conductive glue at chip back then covering base plate and baking them to form a flat plate, using photo-resist to fill seams, finalizing metal connections and sticking on top plate.

Owner:徐中祐

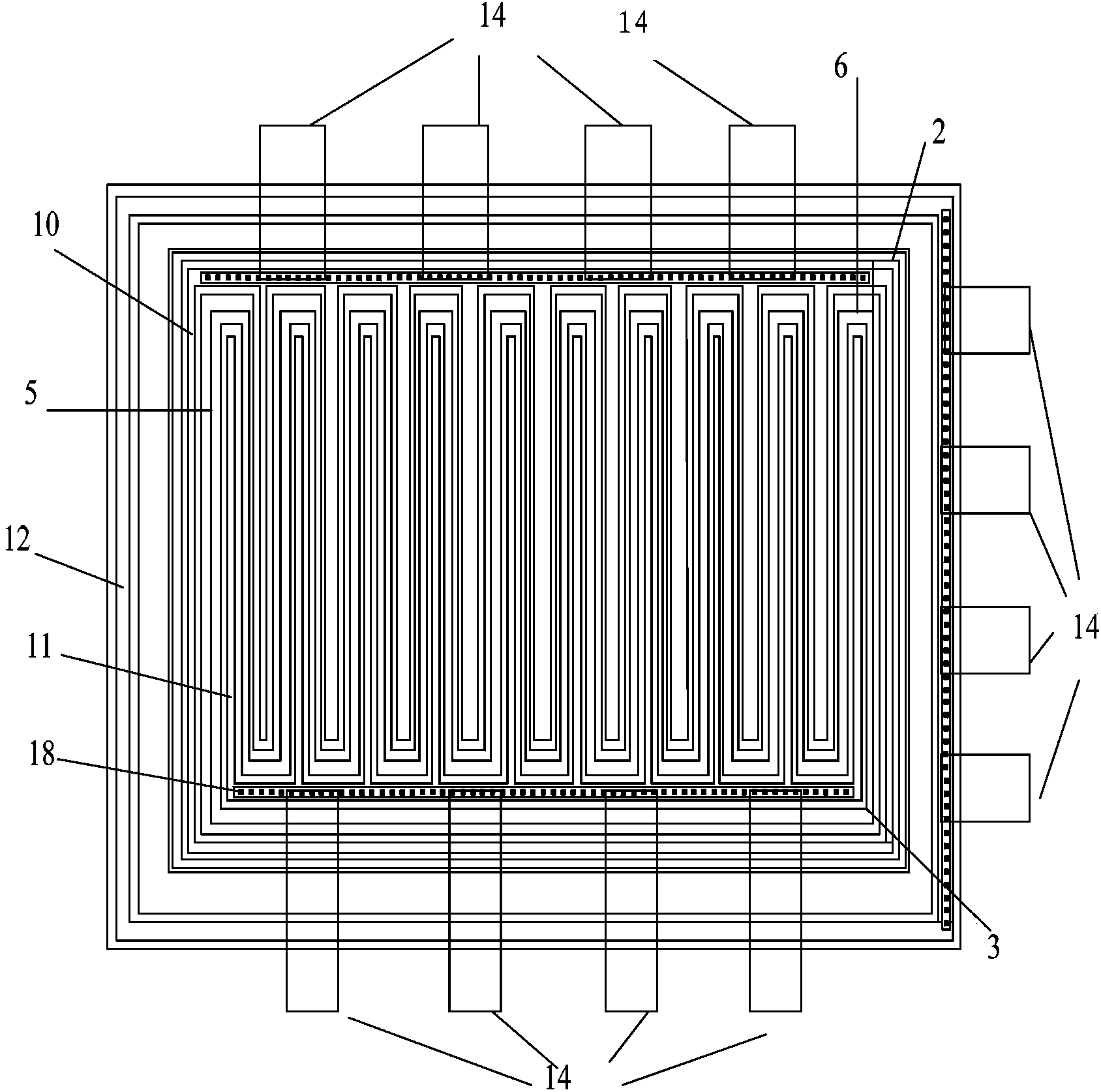

Silicon-based uniwafer photoelectricity integrated receiving chip for plastic optical fiber communication

ActiveCN102856324BShort interconnectImprove performanceSolid-state devicesFibre transmissionPhotovoltaic detectorsEngineering

The invention discloses a silicon-based uniwafer photoelectricity integrated receiving chip for plastic optical fiber communication, and relates to a silicon-based uniwafer photoelectricity integrated circuit. The chip is a uniwafer photoelectricity integrated receiving chip with the wavelength of 650 + / - 17.8nm for the plastic optical fiber communication; and a photoelectricity probe chip and a preposed amplifying integrated circuit chip in a light receiving module with the wavelength of 650 + / - 17.8nm for the conventional plastic optical fiber communication can be replaced by the chip, so that the uniwafer photoelectricity integration of the photoelectricity probe and the preposed amplifying integrated circuit with the wavelength of 650 + / - 17.8nm is realized; a requirement on 100Mbps transmission velocity for the plastic optical communication can be met; and the chip can be used for the light receiving end with the wavelength of 650 + / - 17.8nm for the plastic optical fiber communication; and moreover, the chip can be prepared by a 0.5-micron standard binary-coded decimal (BCD).

Owner:XIAMEN UNIV