Standard cell test circuit layout and optimization method thereof, and standard cell test structure

A standard unit and test circuit technology, applied in the direction of measuring electricity, measuring electrical variables, and electronic circuit testing, etc., can solve problems such as performance needs to be improved, and achieve the effect of saving area, improving performance, and improving accuracy

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0025] As mentioned in the background, the performance of the standard unit test structure in the prior art needs to be improved.

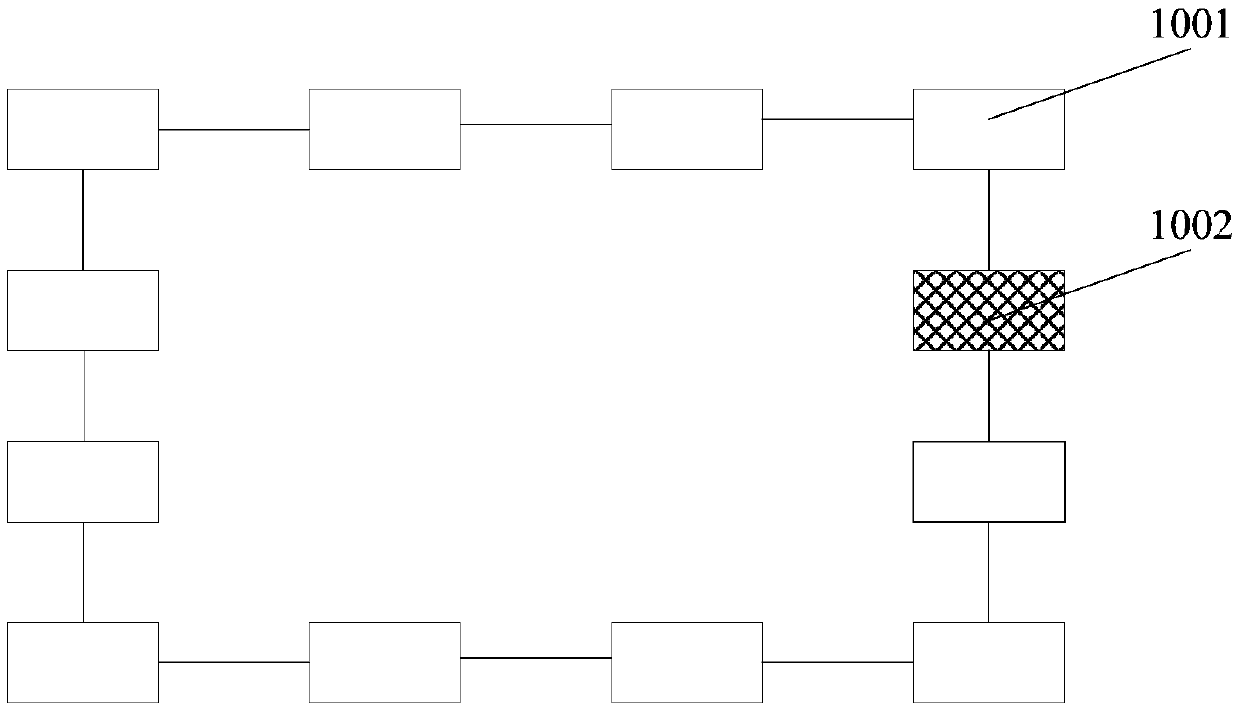

[0026] A standard unit test circuit layout, refer to figure 1 , including: a unit circuit to be tested; the unit circuit to be tested includes: an N-level standard unit 1001, the first-level standard unit 1001 to the N-th level standard unit 1001 are connected end to end; The first-level standard unit 1001 is connected to the Nth-level standard unit 1001, and the layout shape of the vibration-generating unit 1002 and the N-level standard unit 1001 forms a single ring.

[0027] figure 1 The placement of several standard units 1001 is simple and easy to control. But along with the quantity requirement of several standard units 1001 is more and more, promptly under the situation that the requirement to the test stage number of standard unit 1001 increases, make the length of described single-row ring too long, and the inside of described single-row...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More