Bare chip building block packaging method

A packaging method and bare chip technology, which is applied in the direction of electrical components, semiconductor/solid-state device manufacturing, circuits, etc., can solve the problems of large volume, complex process, low pass rate and production efficiency, etc., to simplify the process, reduce packaging costs, The effect of reducing the area

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

[0039] Embodiment 1: a video storage card with a USB interface.

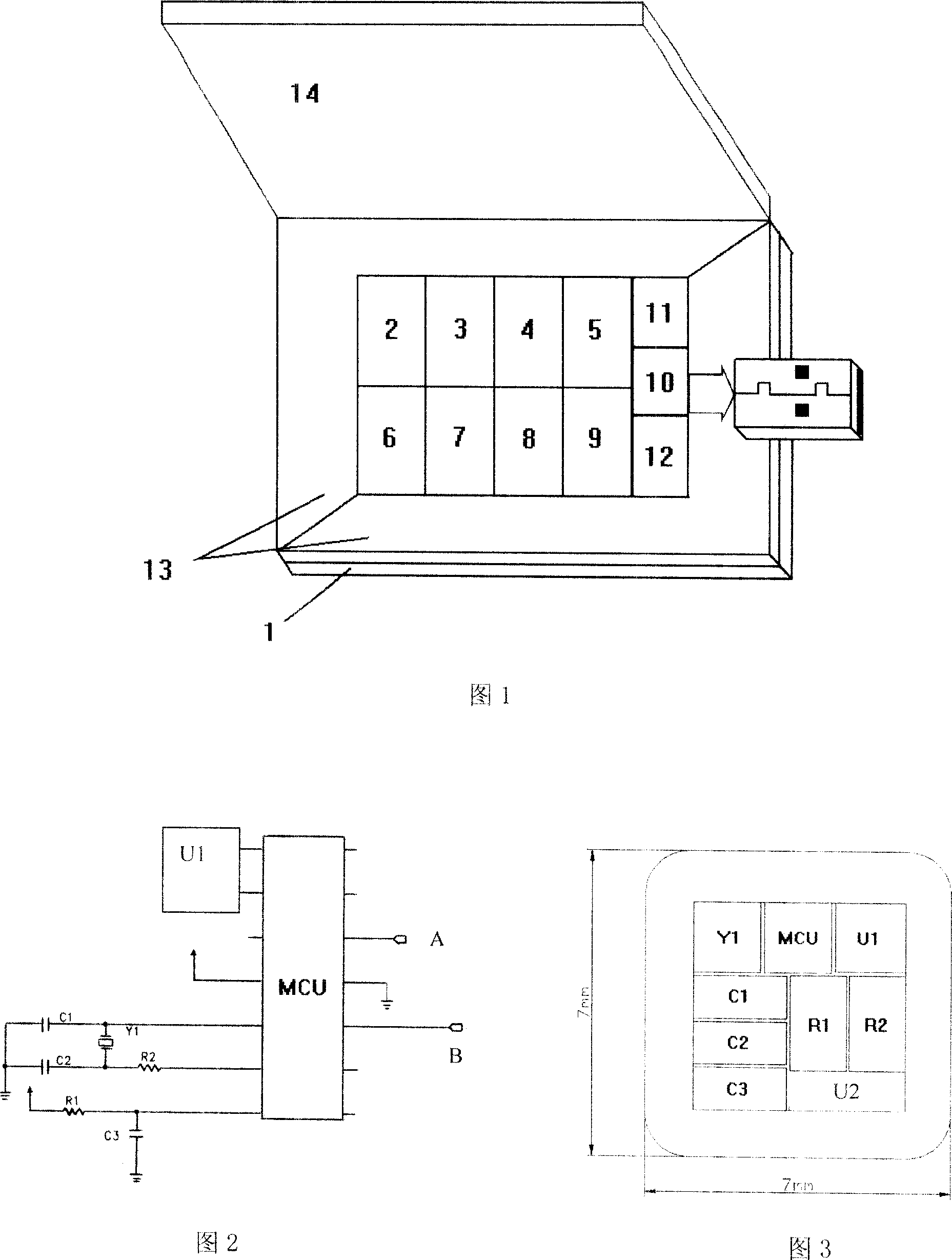

[0040] The card includes a USB interface chip, a microcontroller chip and eight 512M×8 FLASH memories. Movies can be downloaded from the network through the USB interface and the computer, and stored in the FLASH memory on the card. Then insert the card into a portable MP4 video player and watch it on the go. Adopt the manufacturing process of the present invention as follows (referring to Fig. 1):

[0041] 1) Assemble eight 512M×8 FLASH memory bare chips 2-9, a USB interface control chip 10, and a microcontroller chip 11 into a rectangular matrix as shown in Figure 1, and the blank space without chips is filled with waste Sheet 12, filling waste sheet 12 is filled with waste chips of the same shape, size and thickness as the blank in the blank space without chips to form a square matrix of rectangular silicon chips filled with the same thickness and packed tightly, and placed in a multi-layer printed circuit ...

Embodiment 2

[0048] Embodiment 2: Human heart timing monitor (see Fig. 2 and Fig. 3).

[0049] In order to monitor the heart conditions of patients with coronary heart disease under different activities, patients need to carry complex 24-hour heart monitors, which brings inconvenience to patients when dressing and bathing. The micro-control chip MCU, quartz crystal oscillator Y1, sheet resistors (R1 and R2), sheet capacitors (C1, C2, and C3) and pressure sensor chip U1 required for accurate timing monitoring are made into miniature sheets by adopting the present invention. The 17mm×34mm timing monitoring board produced by the technology is reduced to a micro-sheet with an area of 7mm×7mm and a thickness of 1mm, which can be attached to the chest or placed under the skin all year round. Once the patient has symptoms such as myocardial infarction, an alarm signal can be automatically sent. Adopt the manufacture process of the present invention as follows:

[0050] 1) Microcontroller bare...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More