Patents

Literature

3730 results about "Integrated circuit packaging" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

In electronics manufacturing, integrated circuit packaging is the final stage of semiconductor device fabrication, in which the block of semiconductor material is encapsulated in a supporting case that prevents physical damage and corrosion. The case, known as a "package", supports the electrical contacts which connect the device to a circuit board.

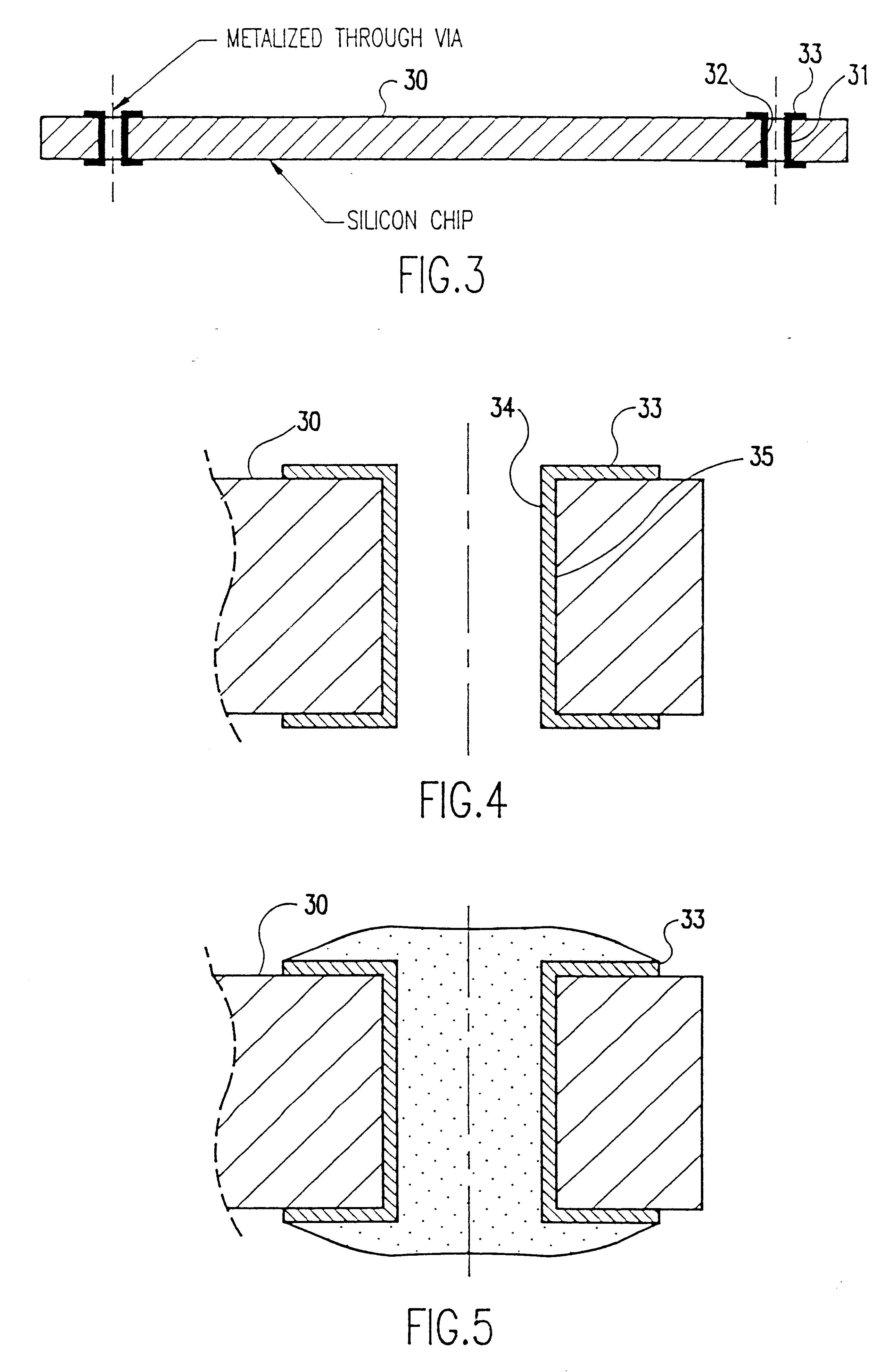

High density integrated circuit packaging with chip stacking and via interconnections

InactiveUS6236115B1Reduced connection exposureLarge capacitySemiconductor/solid-state device detailsSolid-state devicesEngineeringThermal expansion

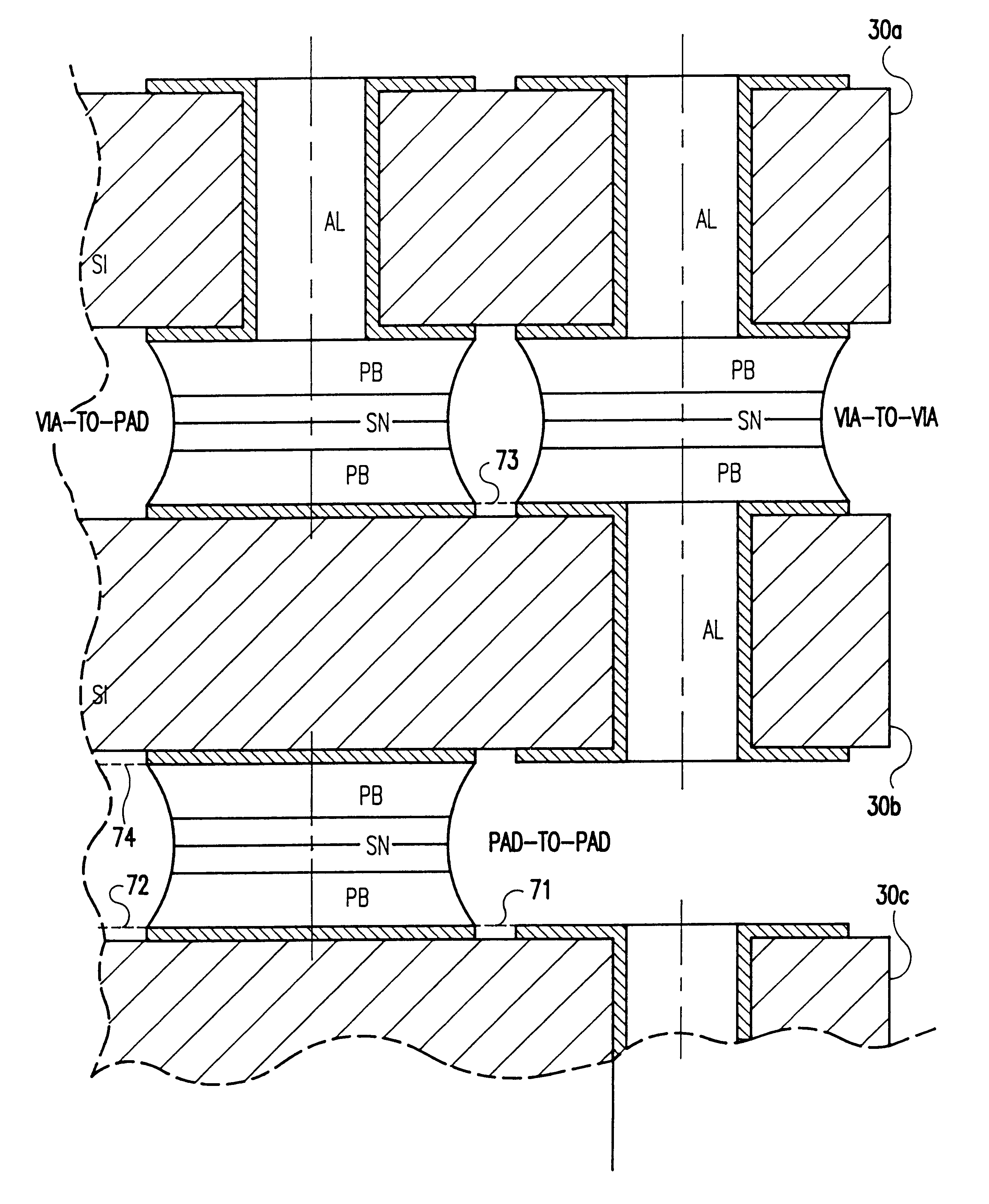

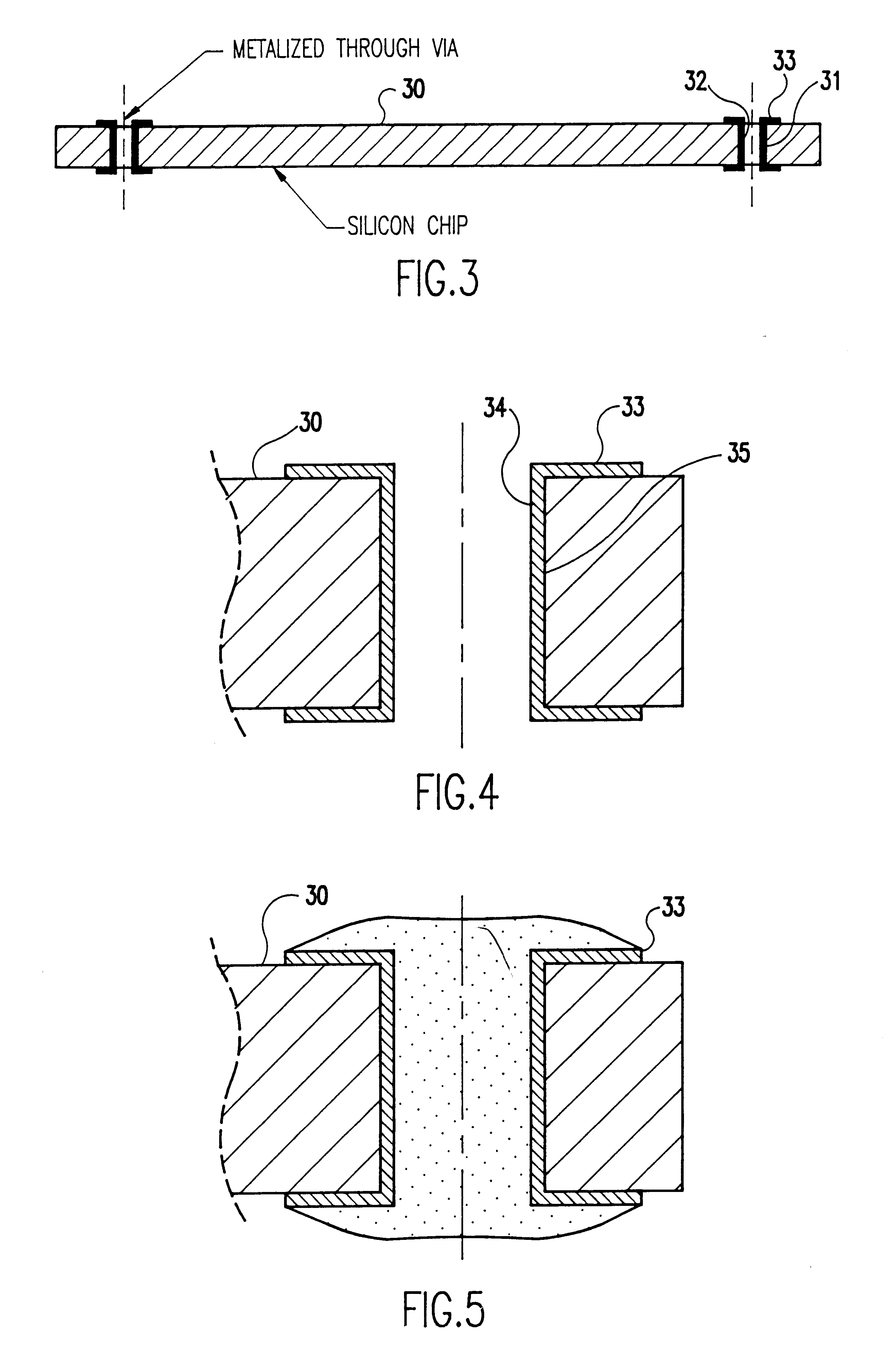

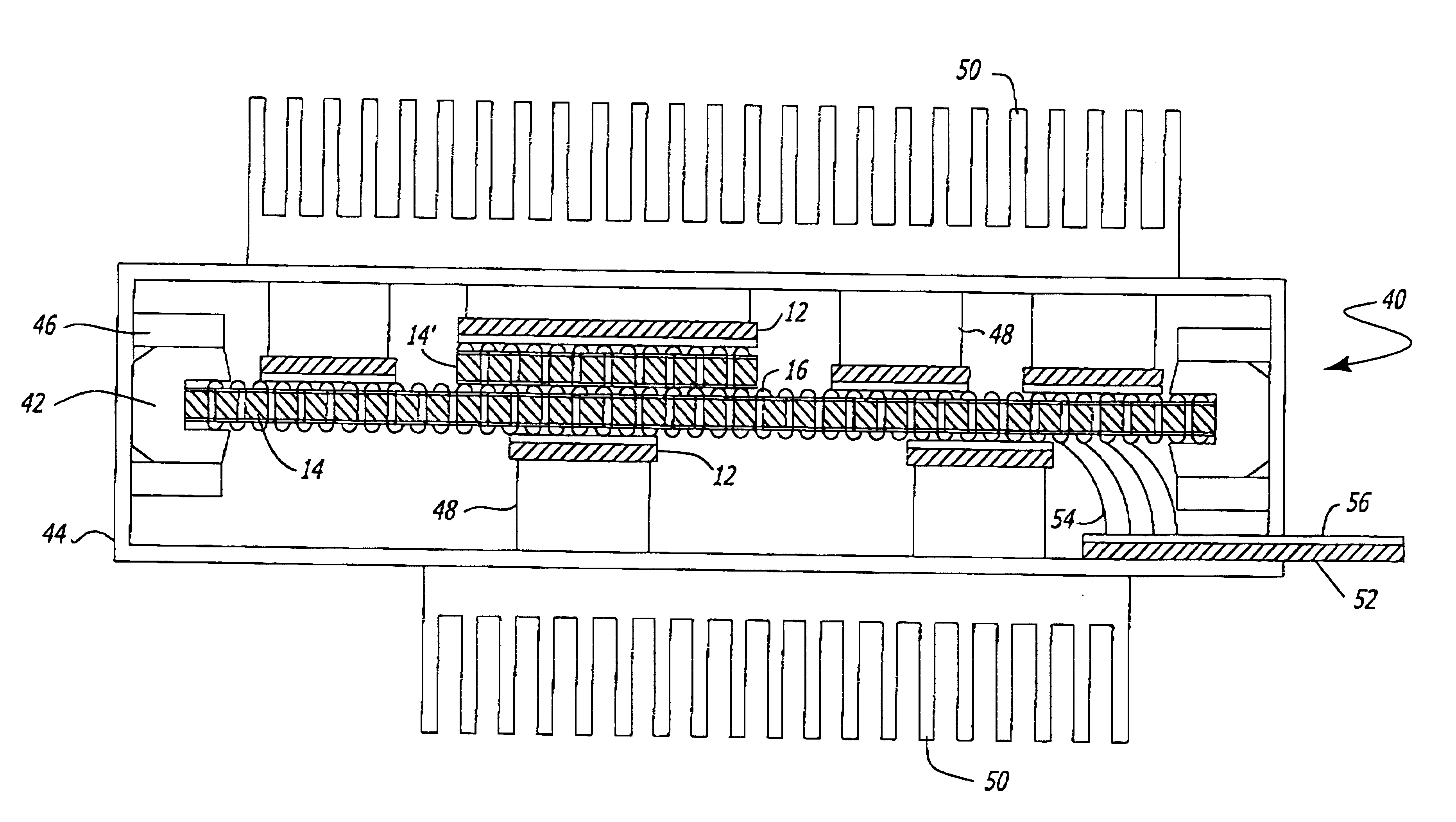

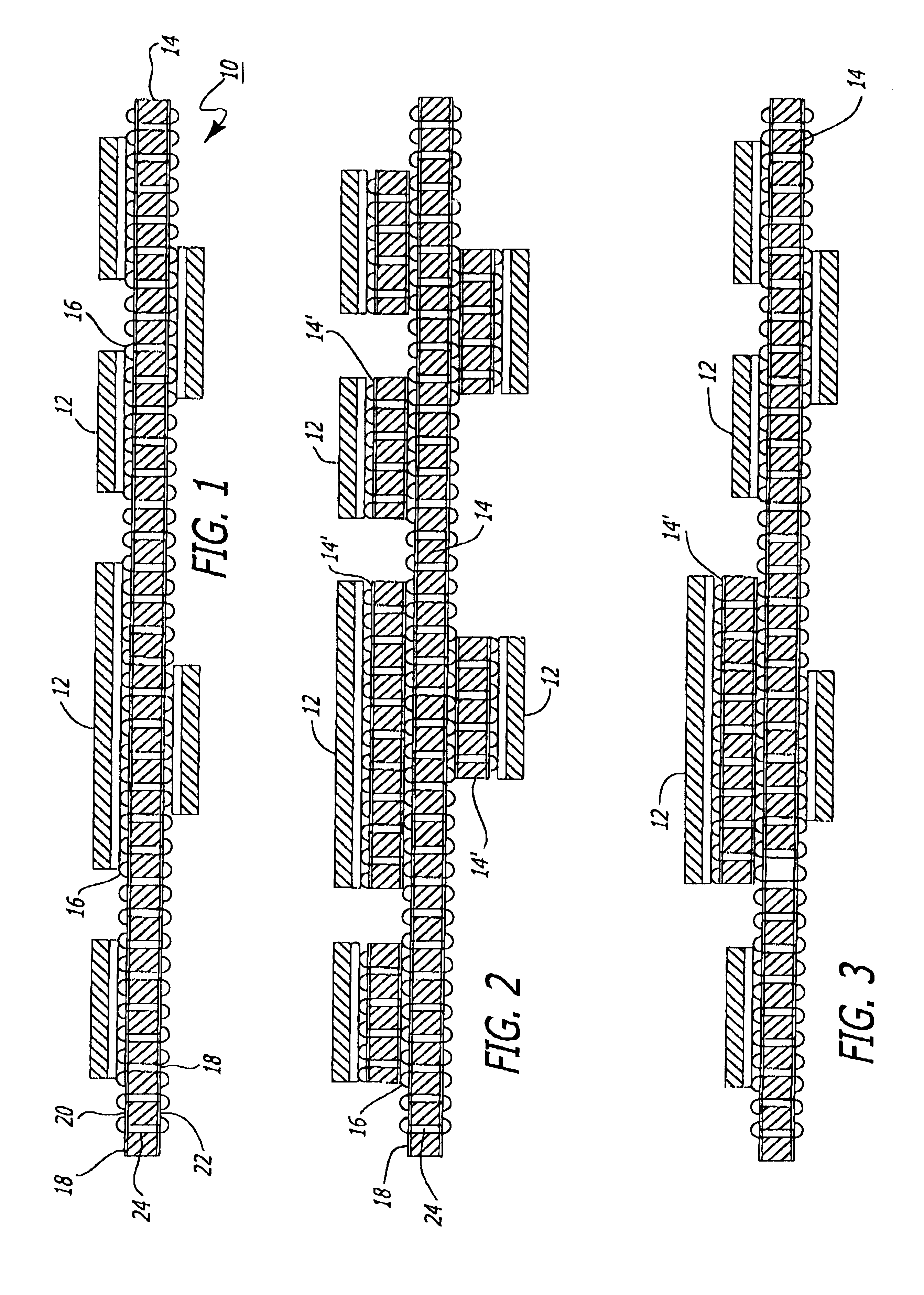

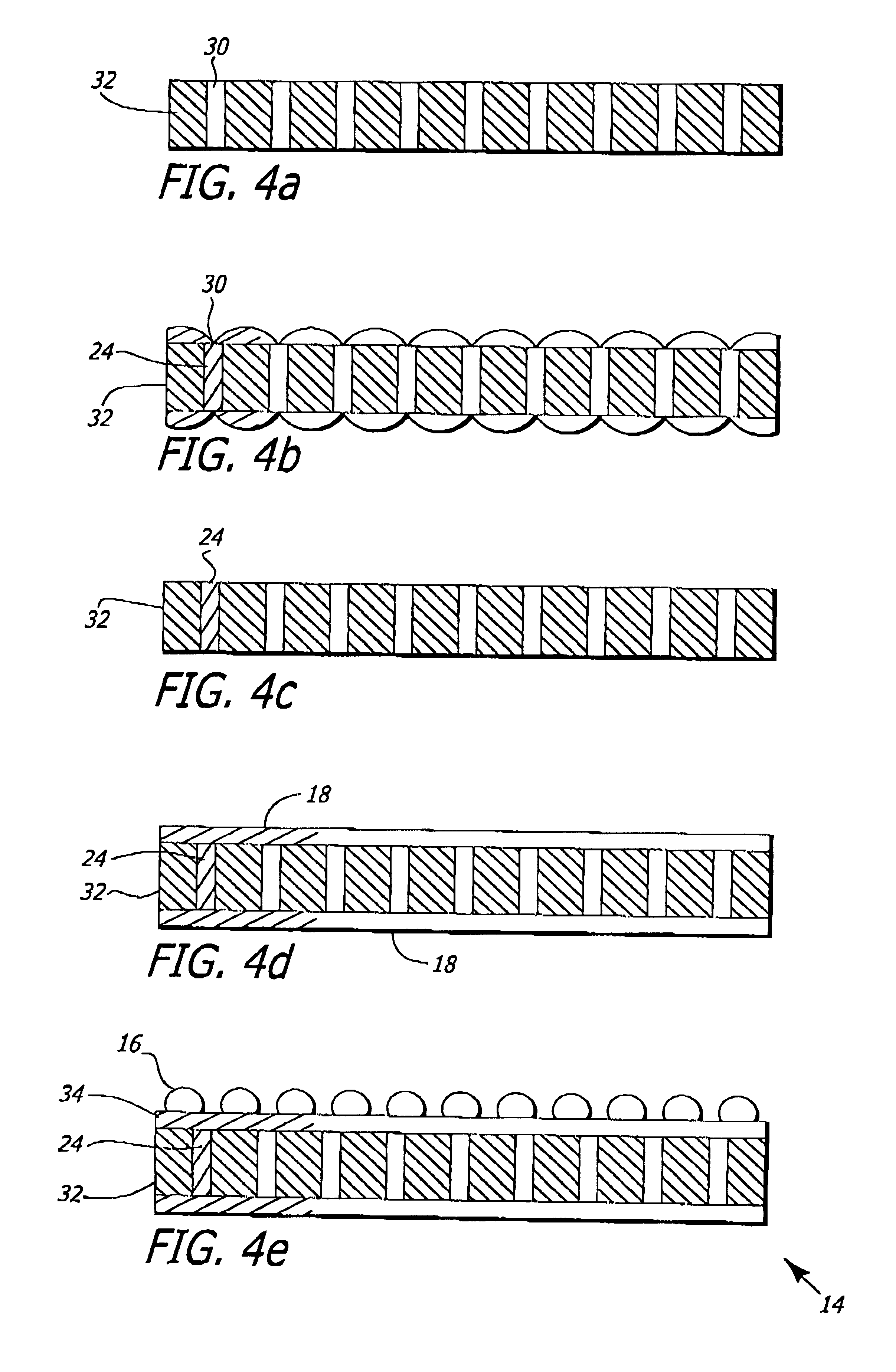

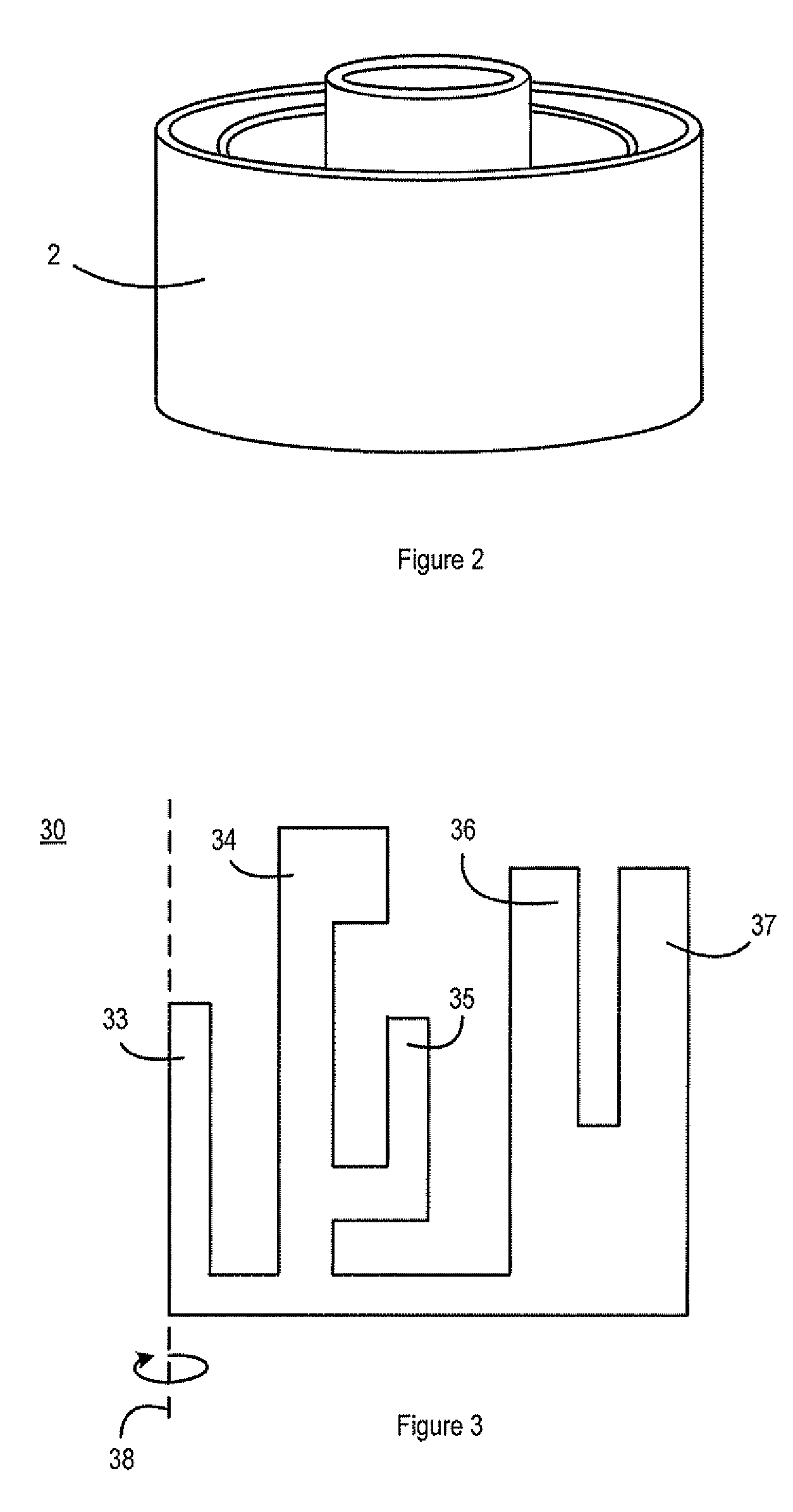

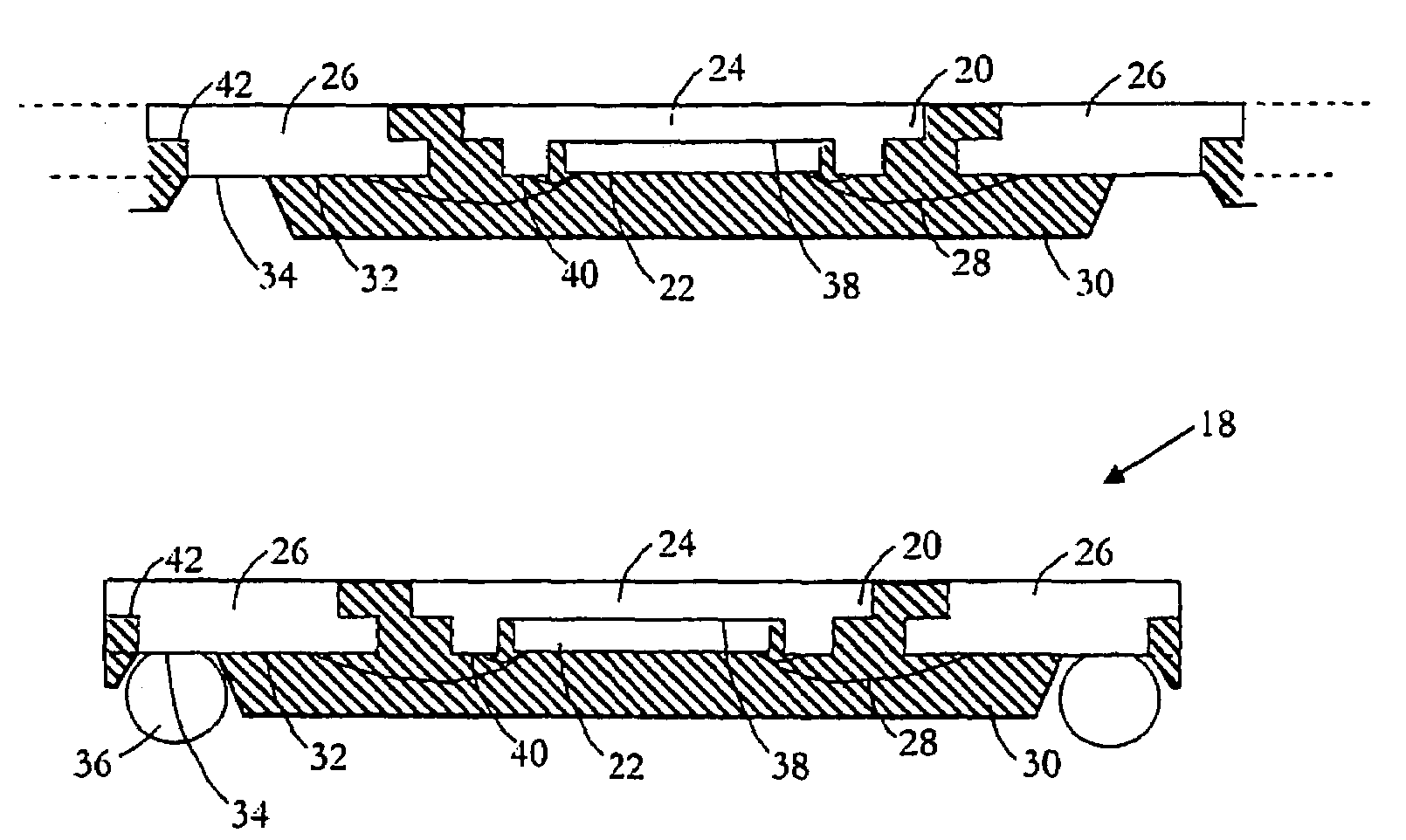

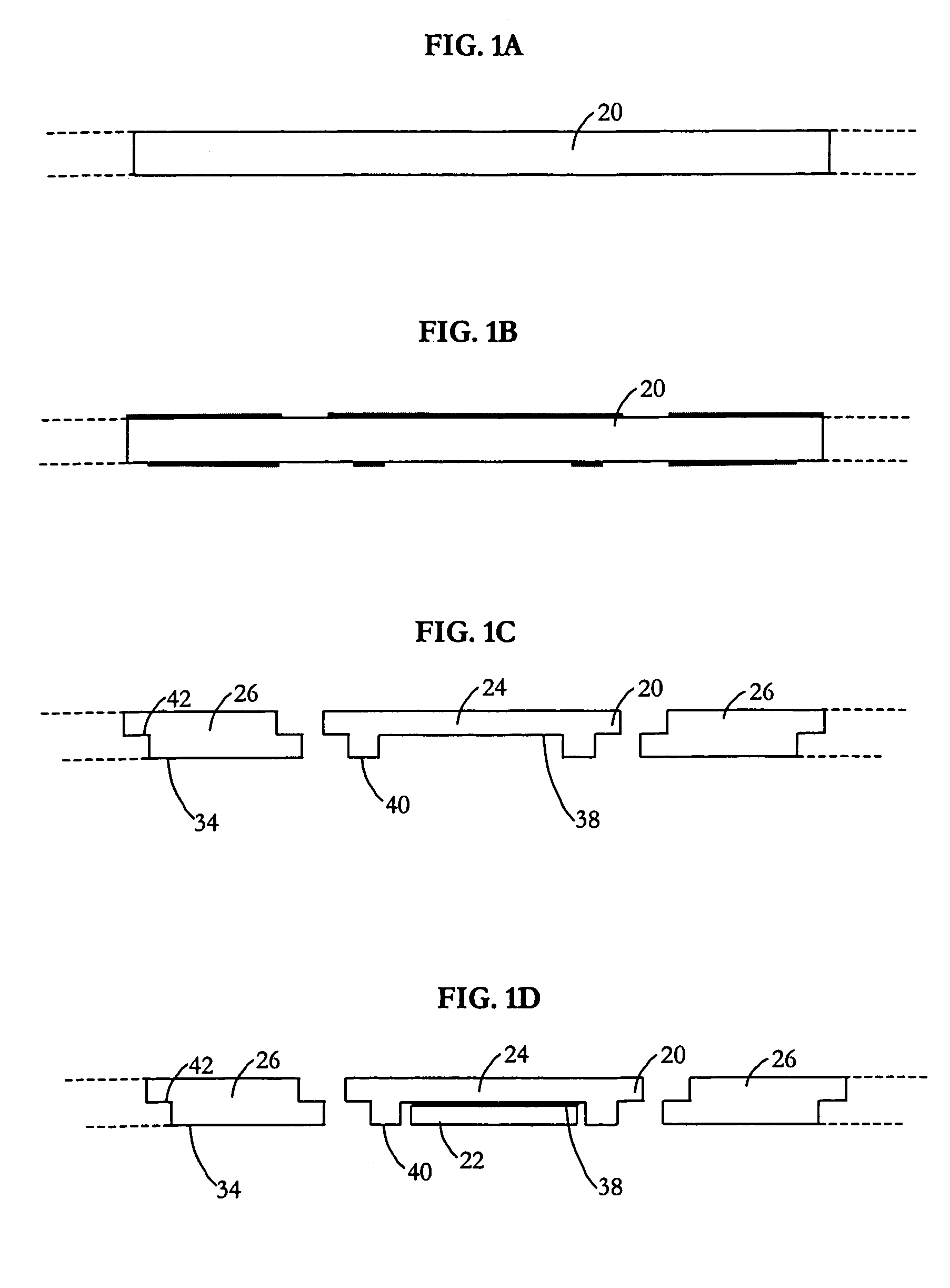

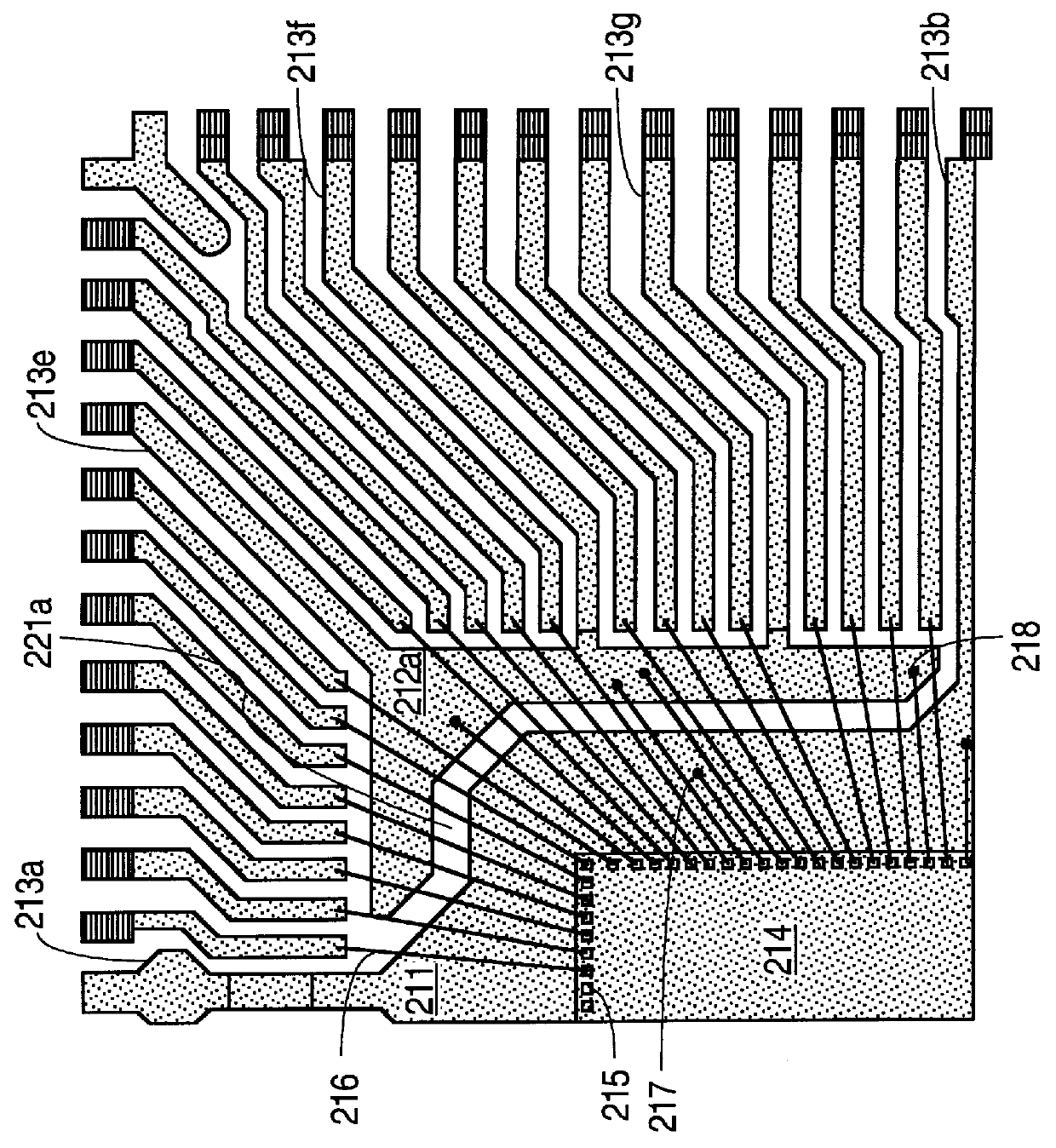

Chip stacks with decreased conductor length and improved noise immunity are formed by laser drilling of individual chips, such as memory chips, preferably near but within the periphery thereof, and forming conductors therethrough, preferably by metallization or filling with conductive paste which may be stabilized by transient liquid phase (TLP) processes and preferably with or during metallization of conductive pads, possibly including connector patterns on both sides of at least some of the chips in the stack. At least some of the chips in the stack then have electrical and mechanical connections made therebetween, preferably with electroplated solder preforms consistent with TLP processes. The connections may be contained by a layer of resilient material surrounding the connections and which may be formed in-situ. High density circuit packages thus obtained may be mounted on a carrier by surface mount techniques or separable connectors such as a plug and socket arrangement. The carrier may be of the same material as the chip stacks to match coefficients of thermal expansion. High-density circuit packages may also be in the form of removable memory modules in generally planar or prism shaped form similar to a pen or as a thermal conduction module.

Owner:INT BUSINESS MASCH CORP

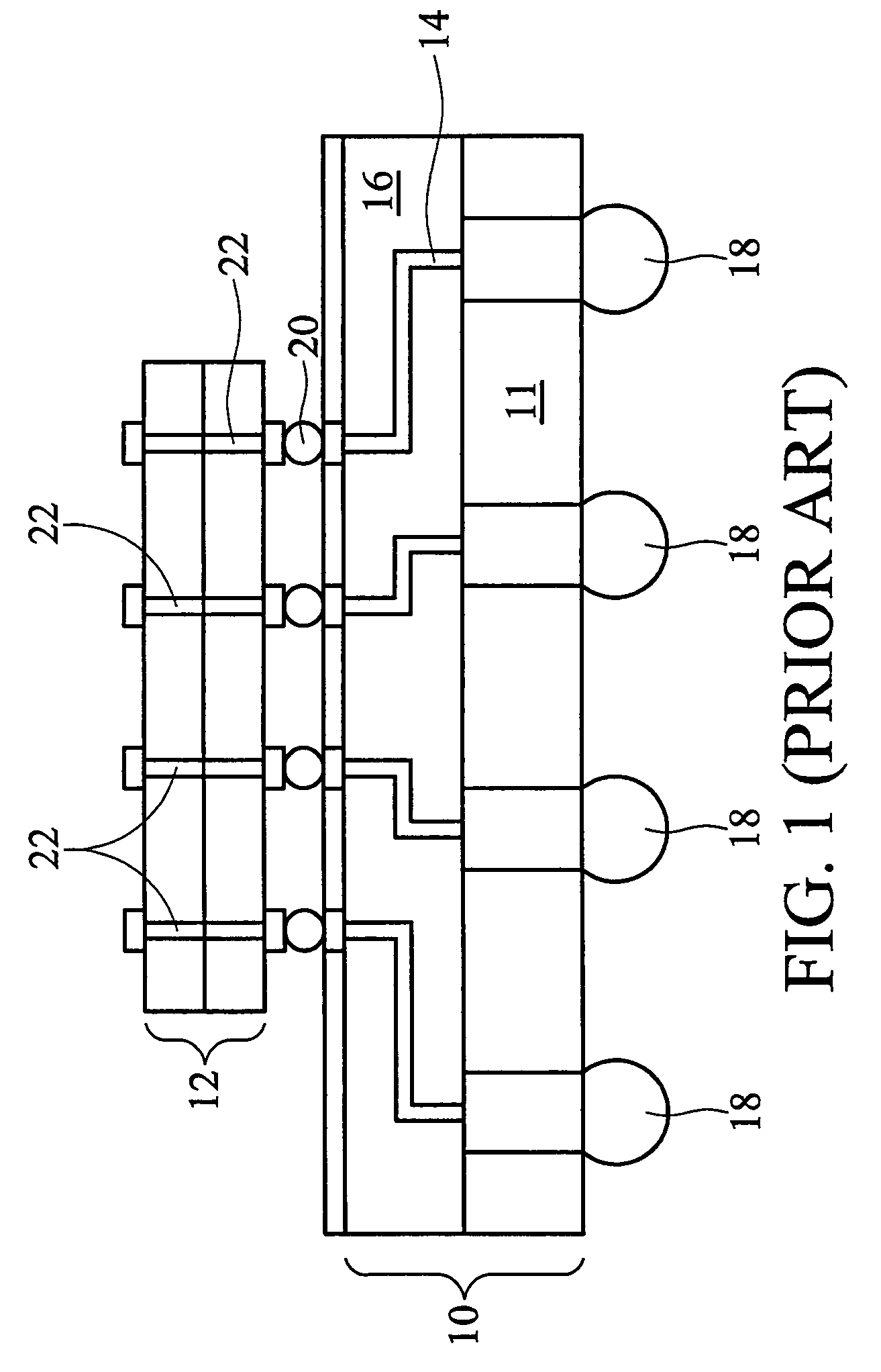

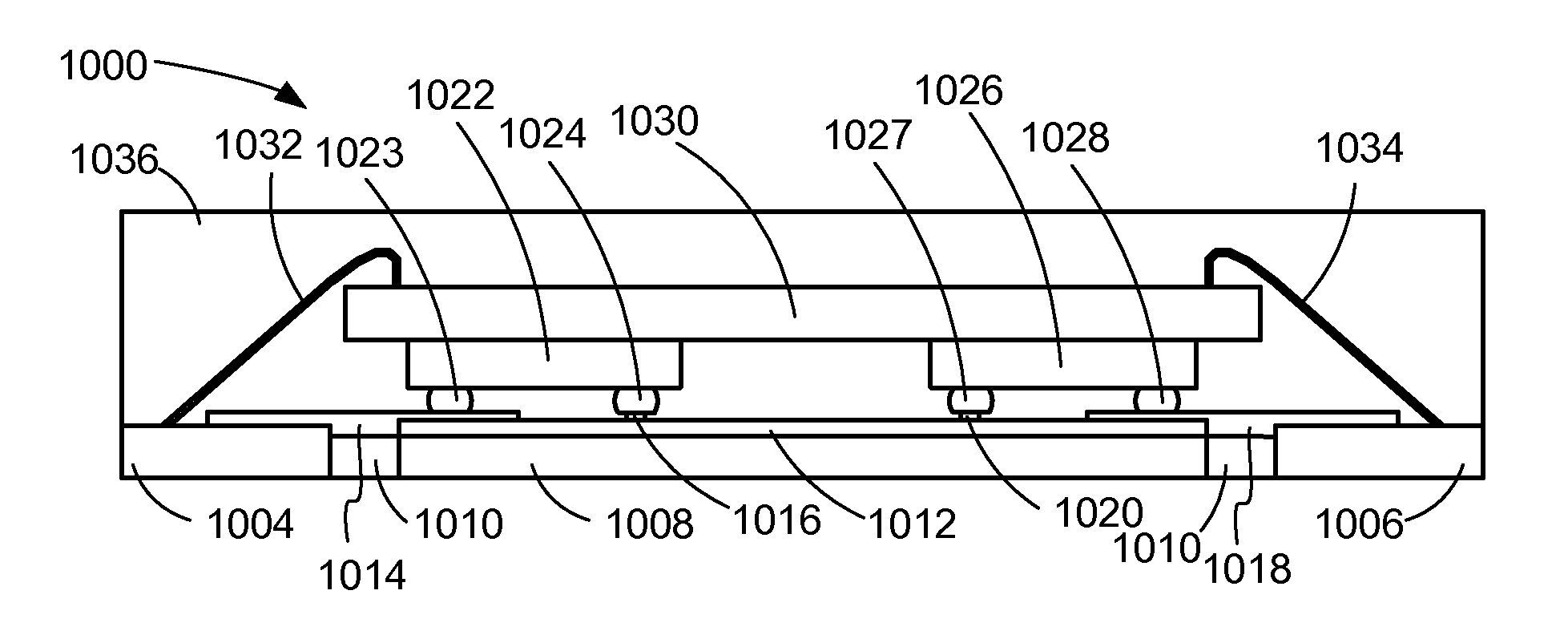

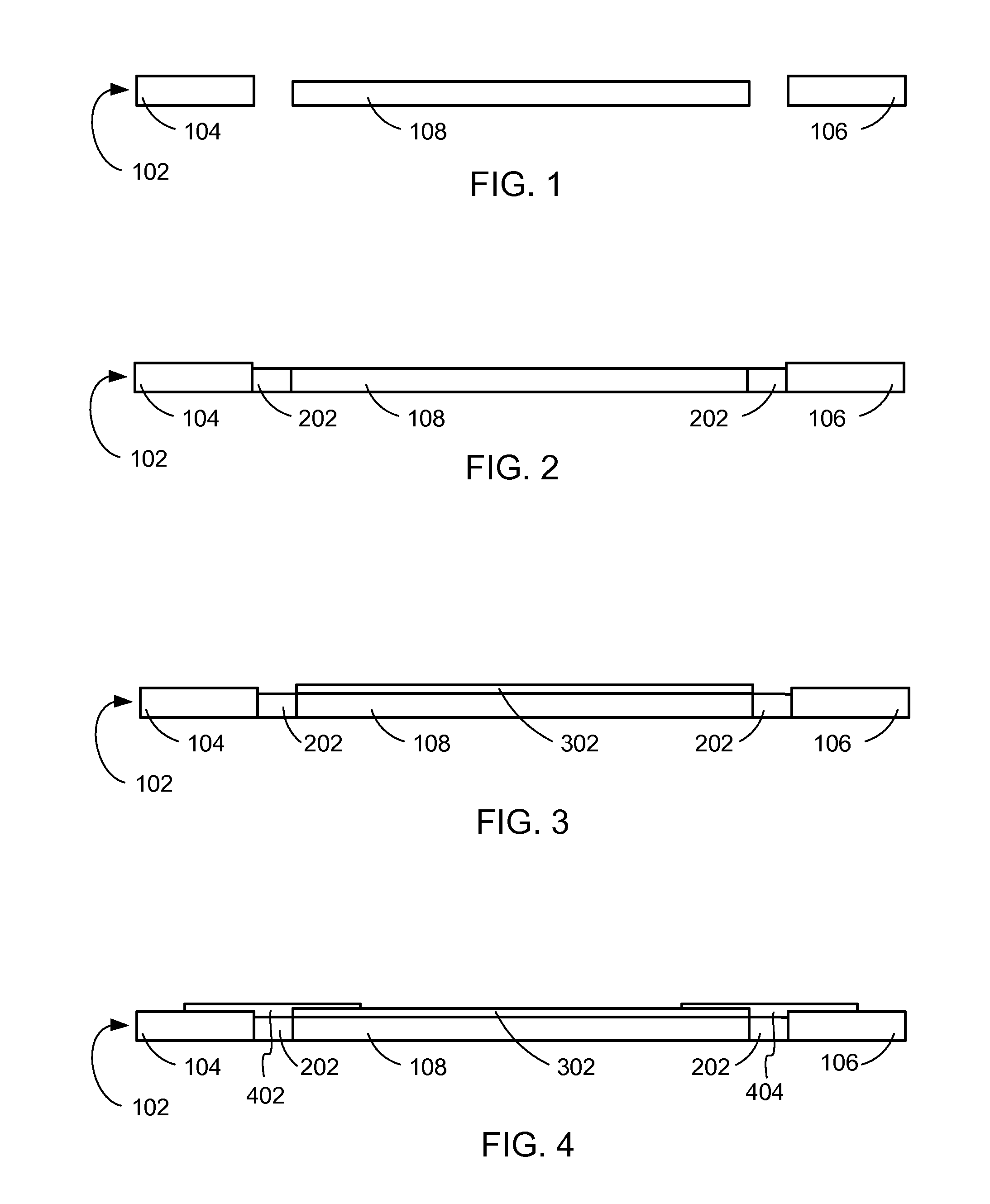

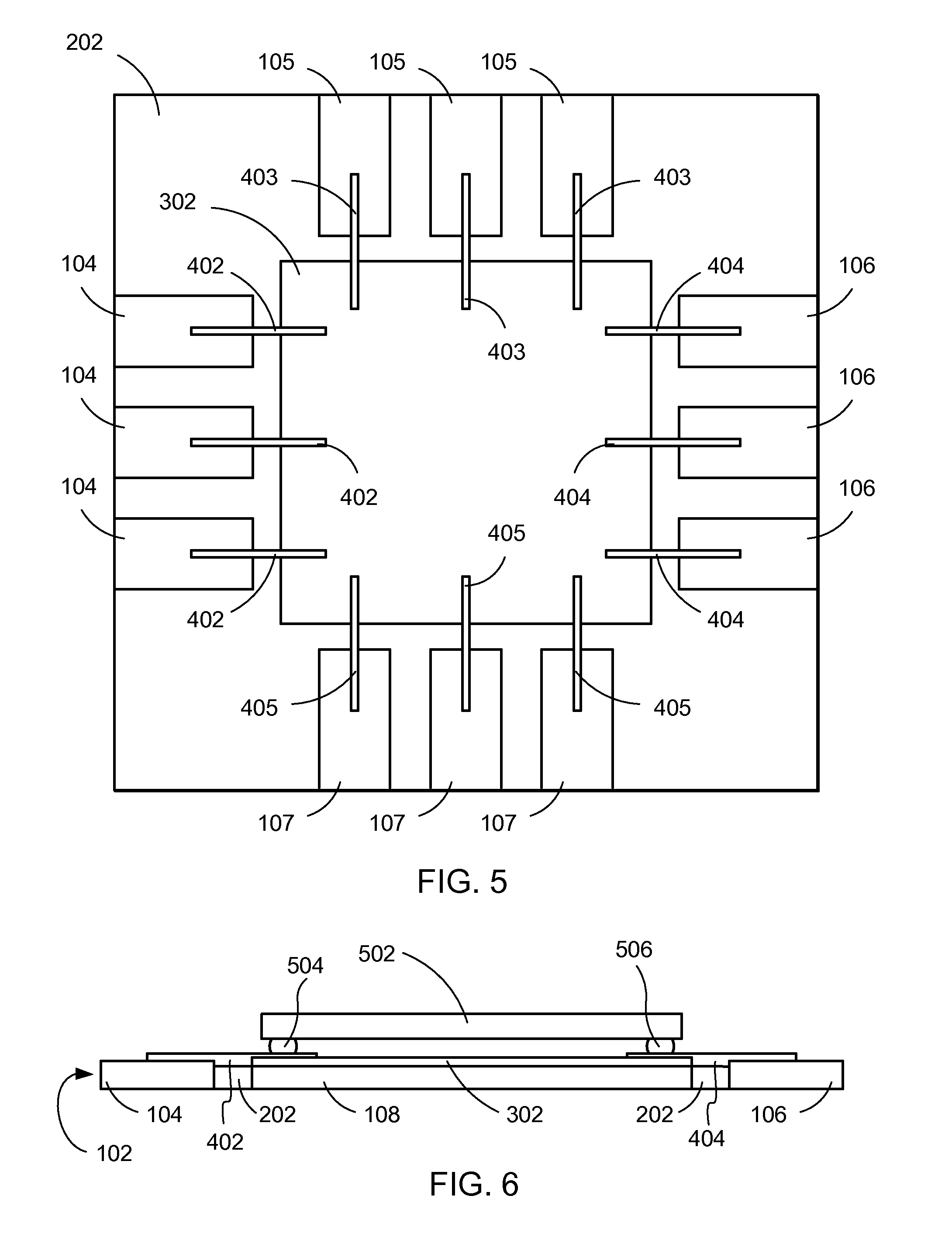

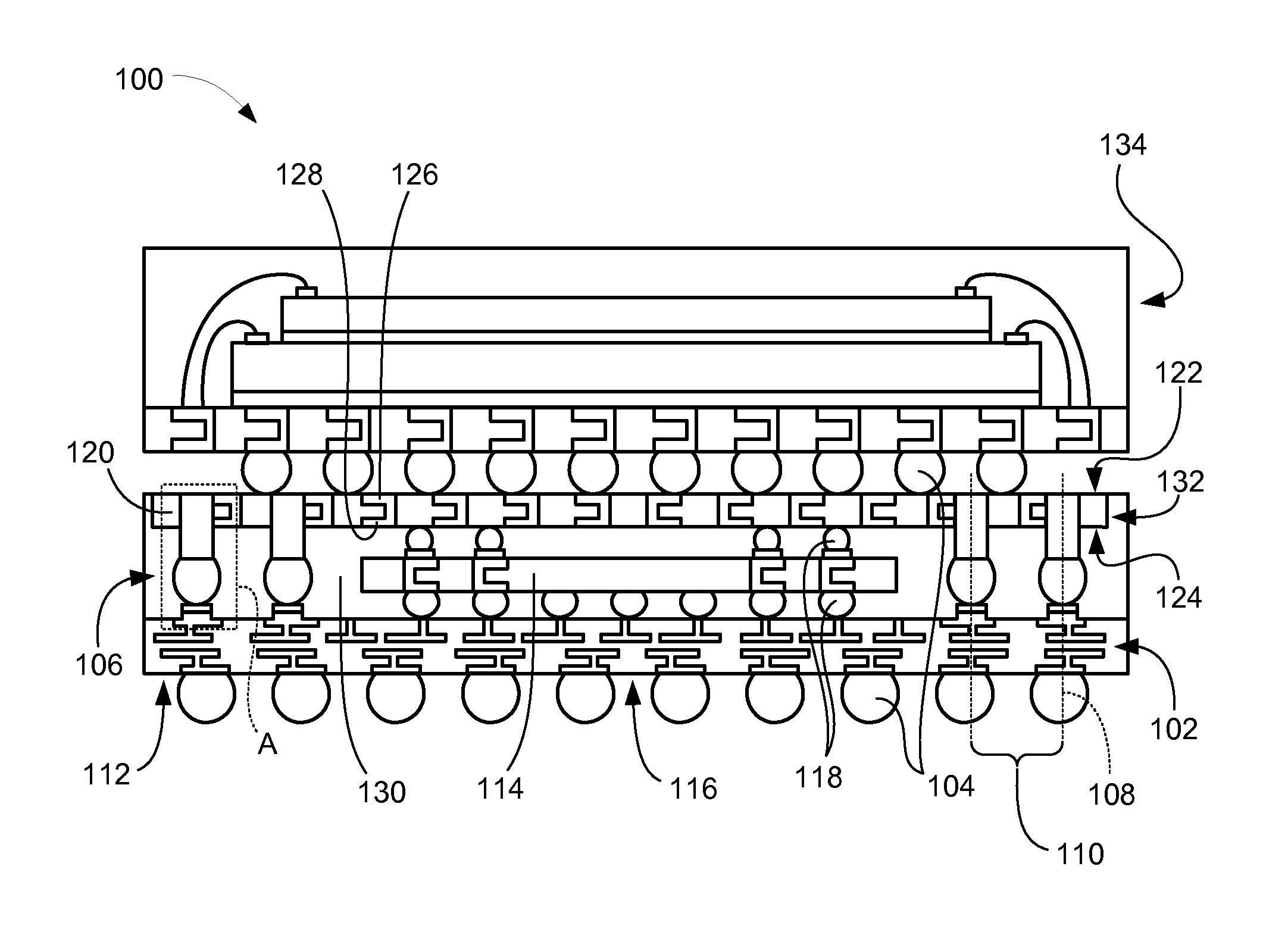

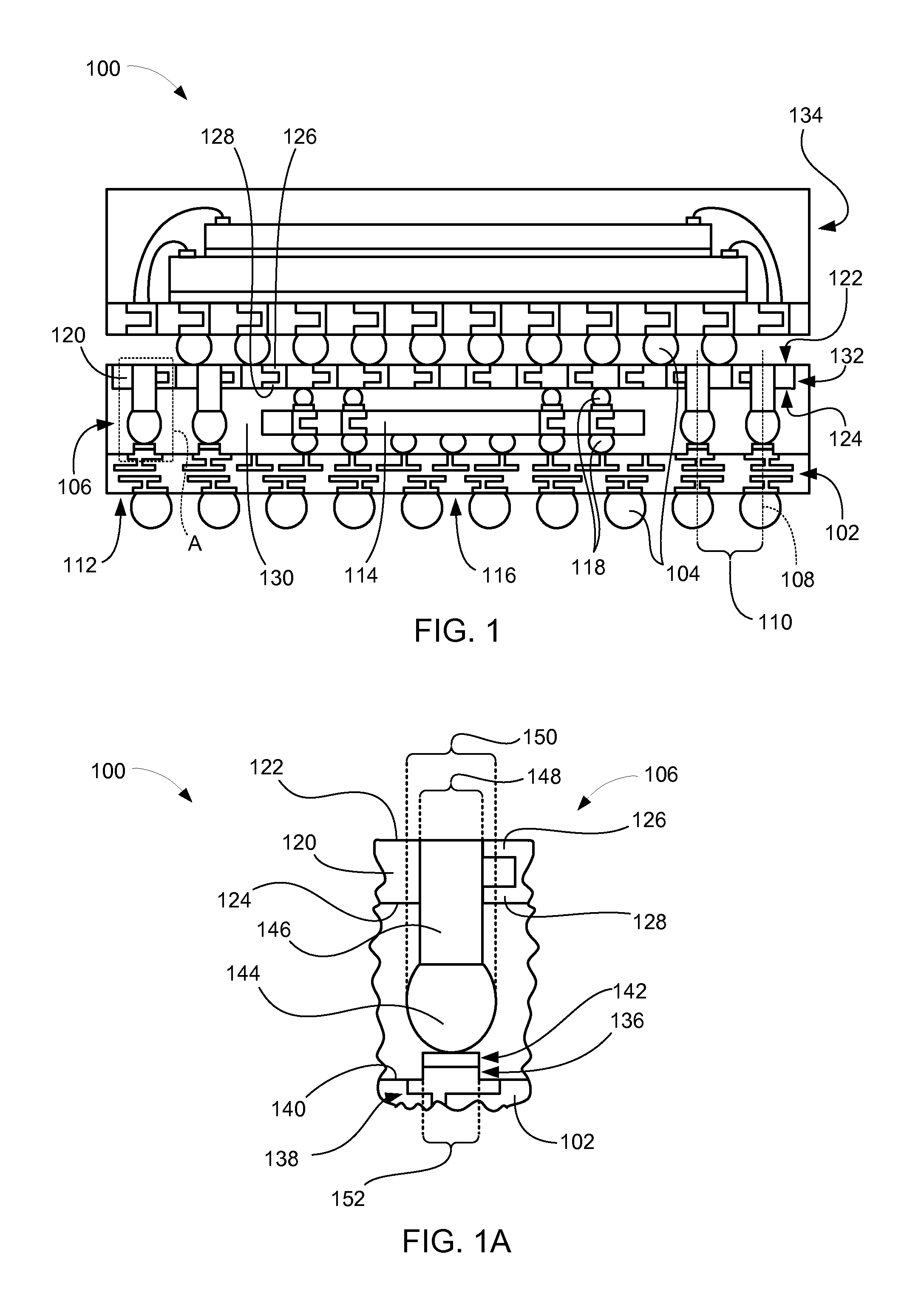

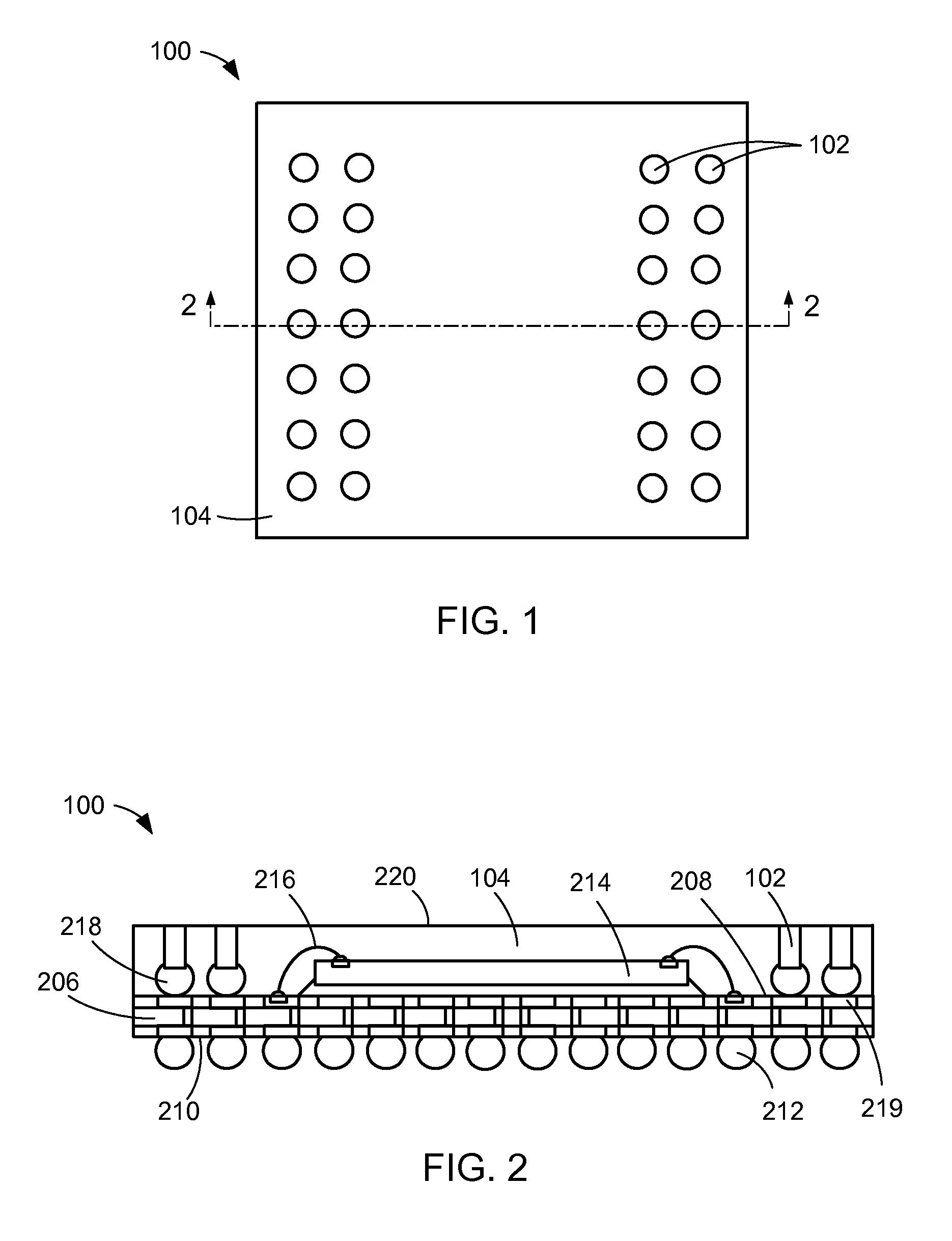

Integrated circuit (IC) package stacking and IC packages formed by same

ActiveUS20070290376A1Semiconductor/solid-state device detailsSolid-state devicesContact padSolder ball

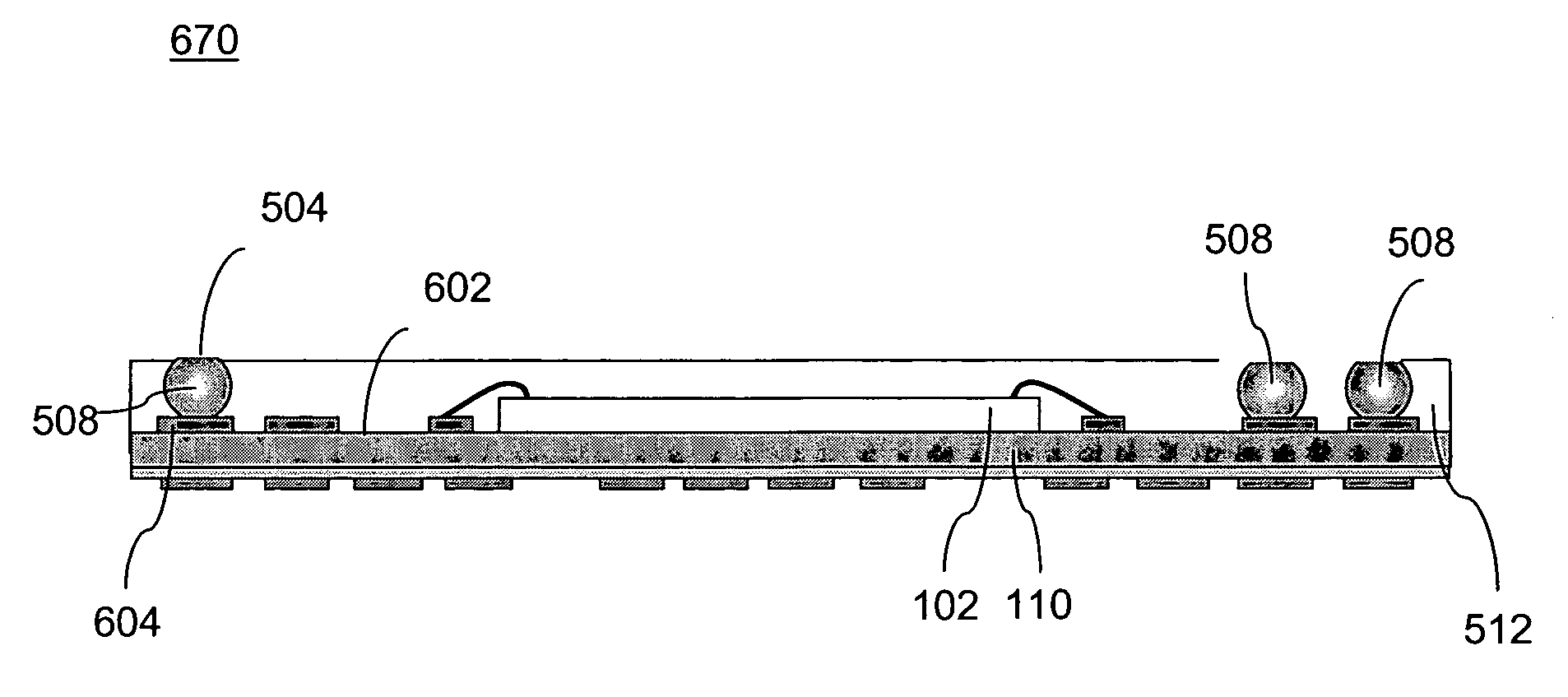

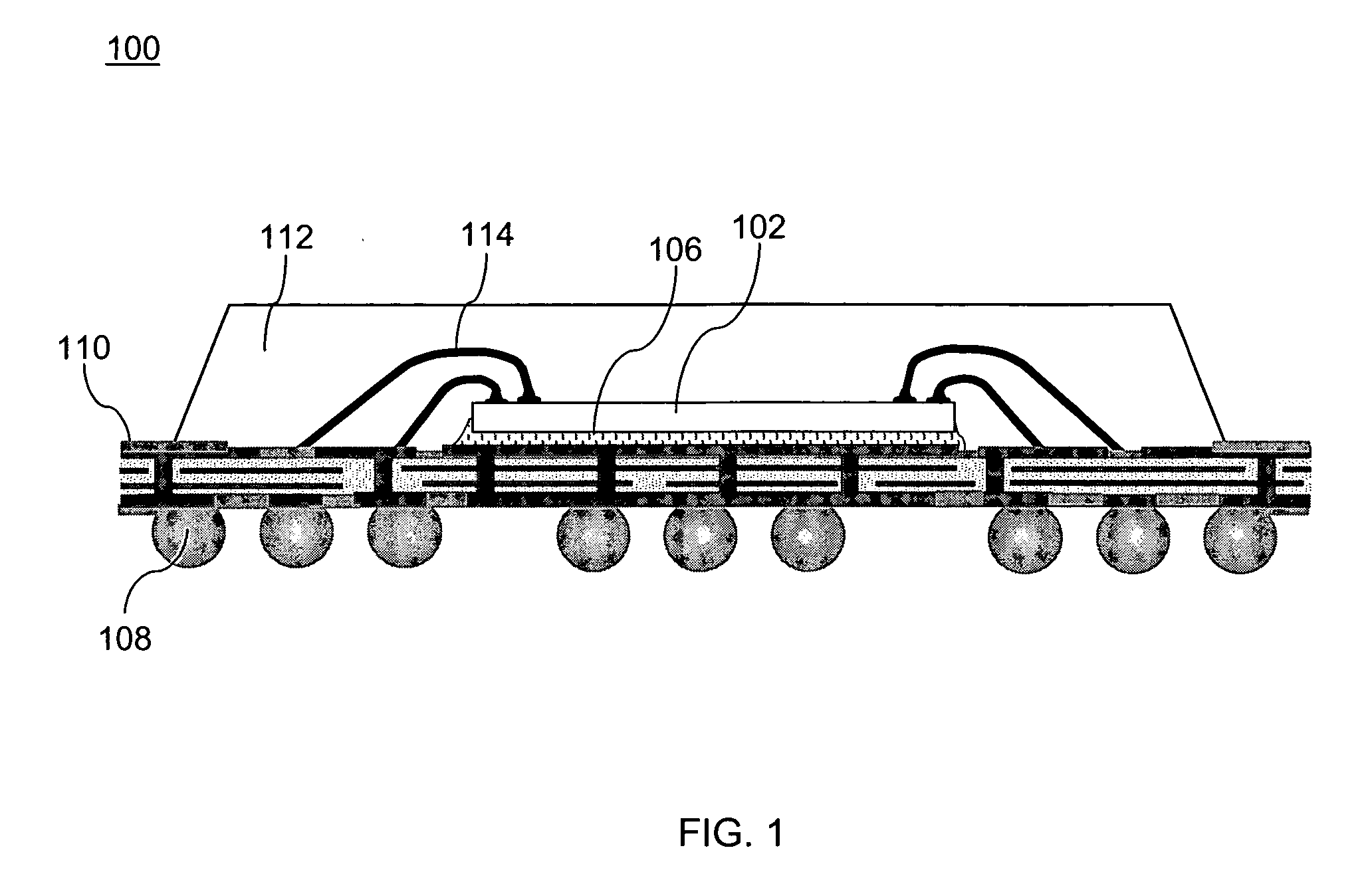

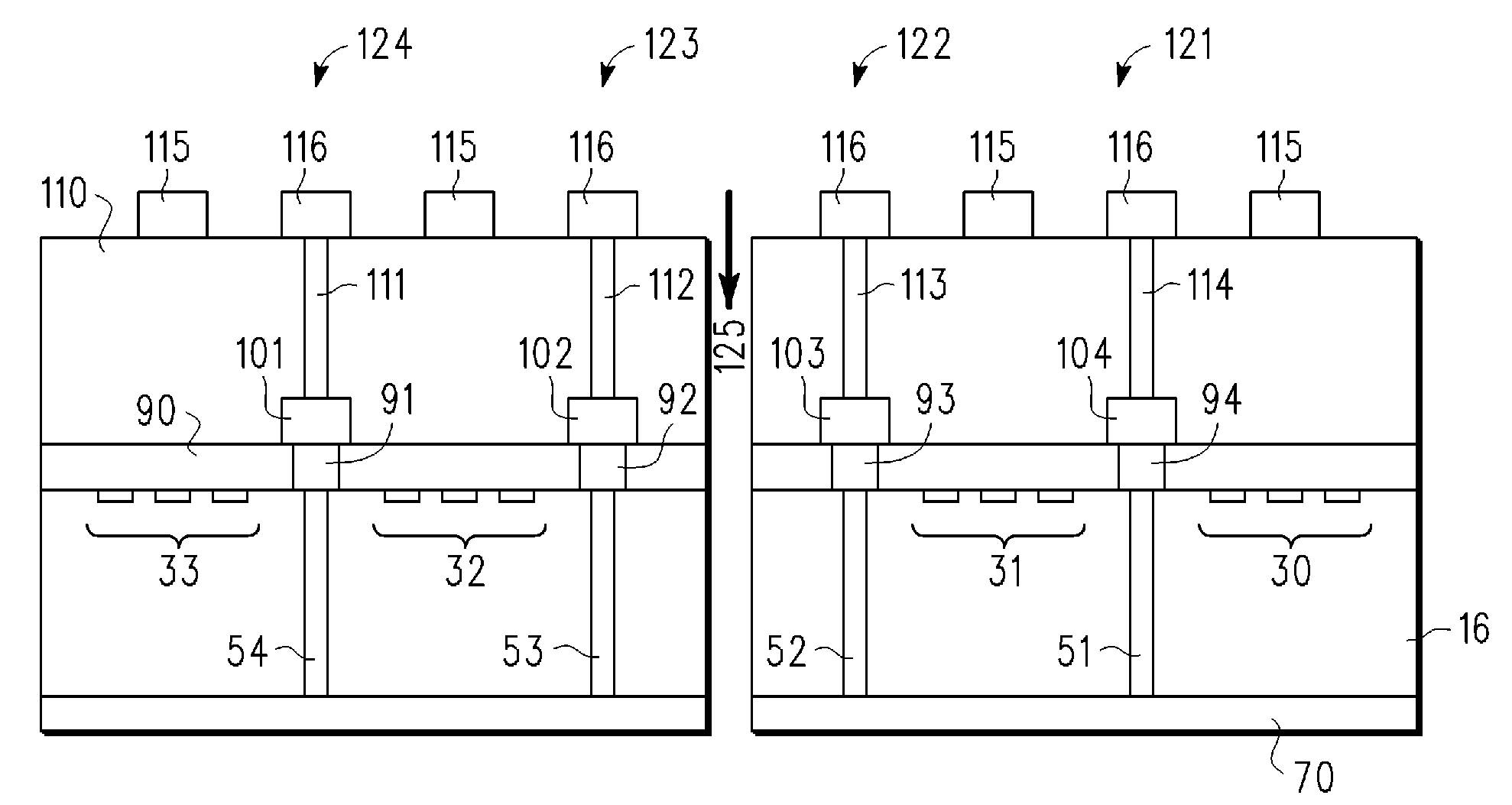

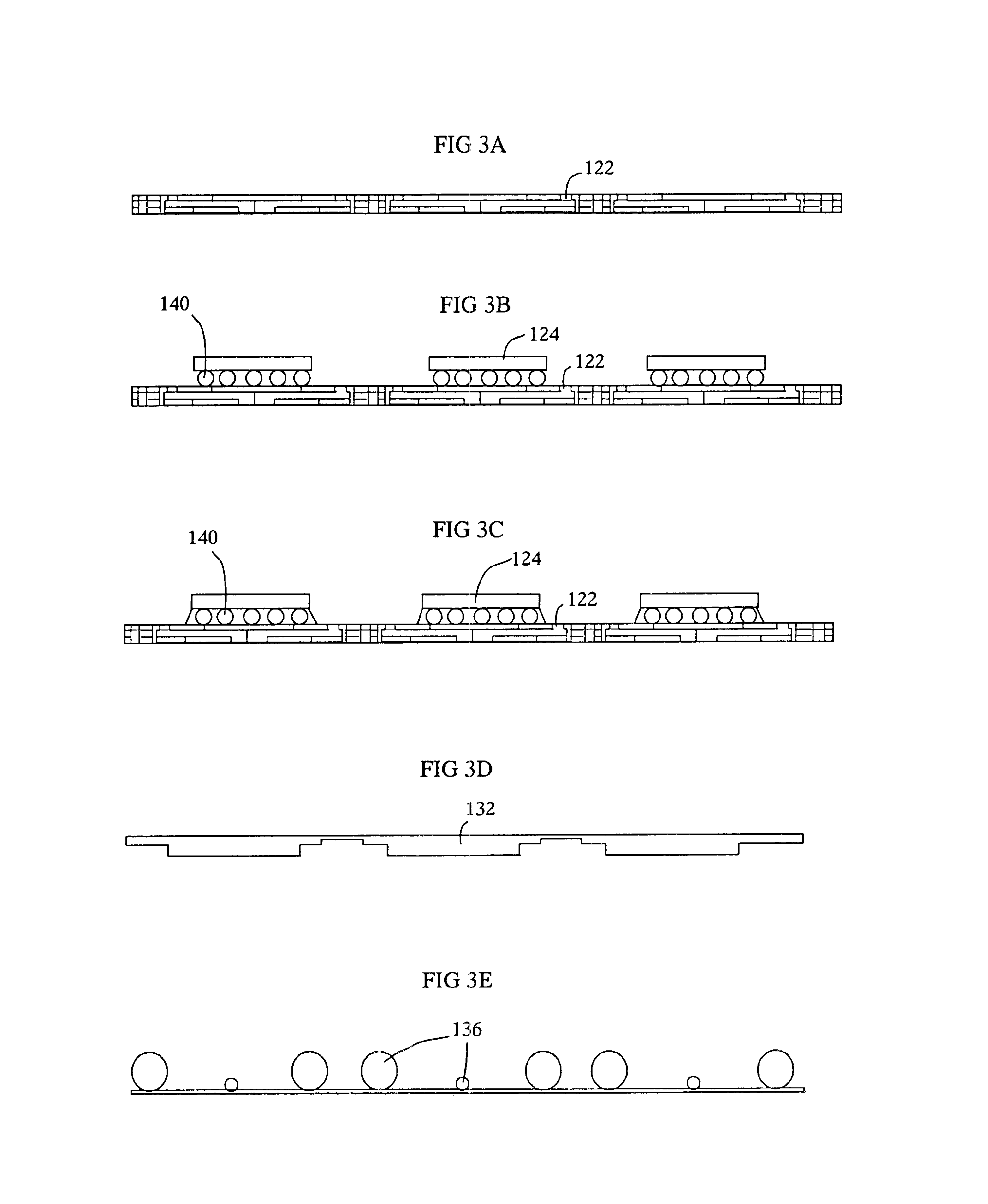

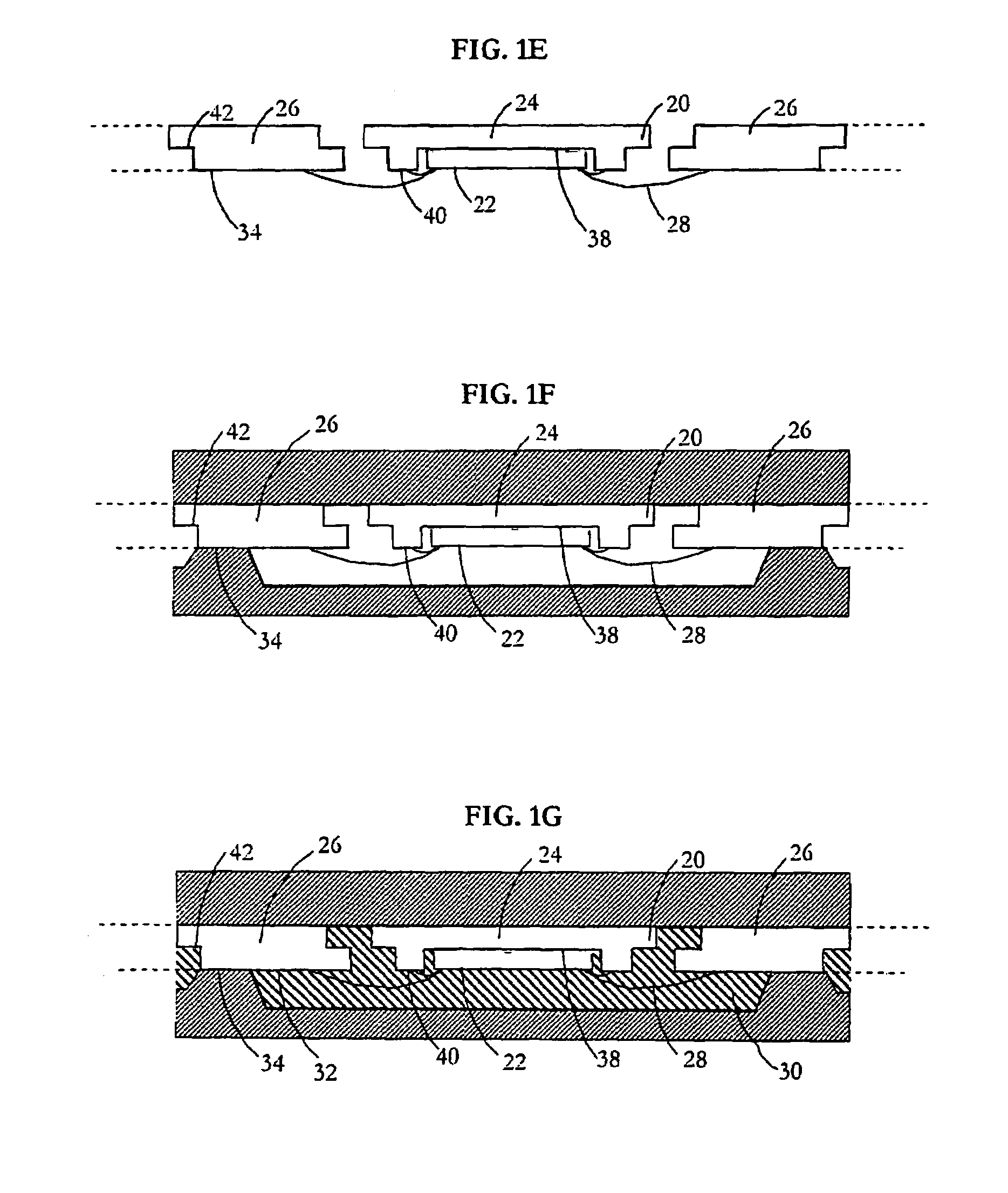

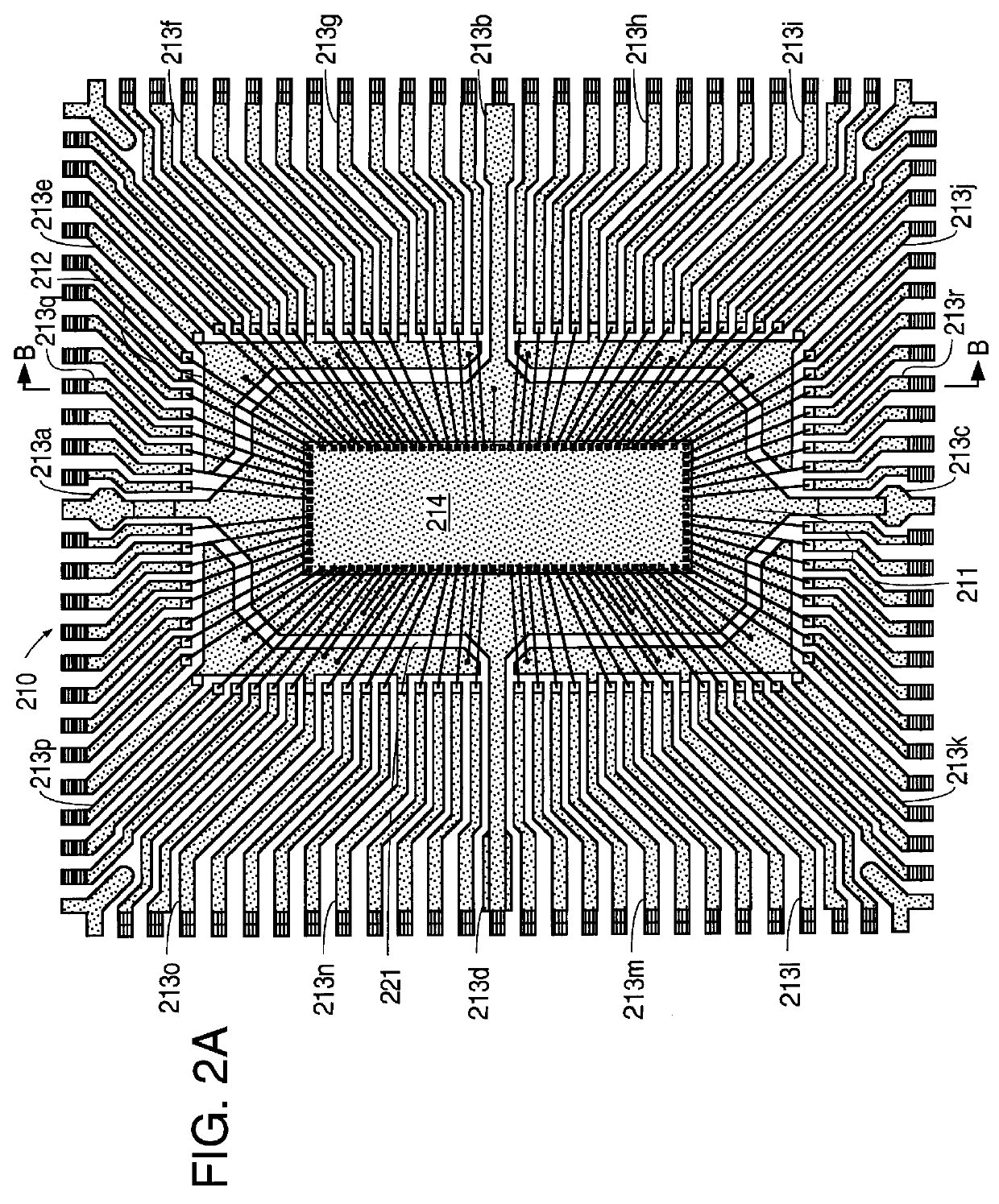

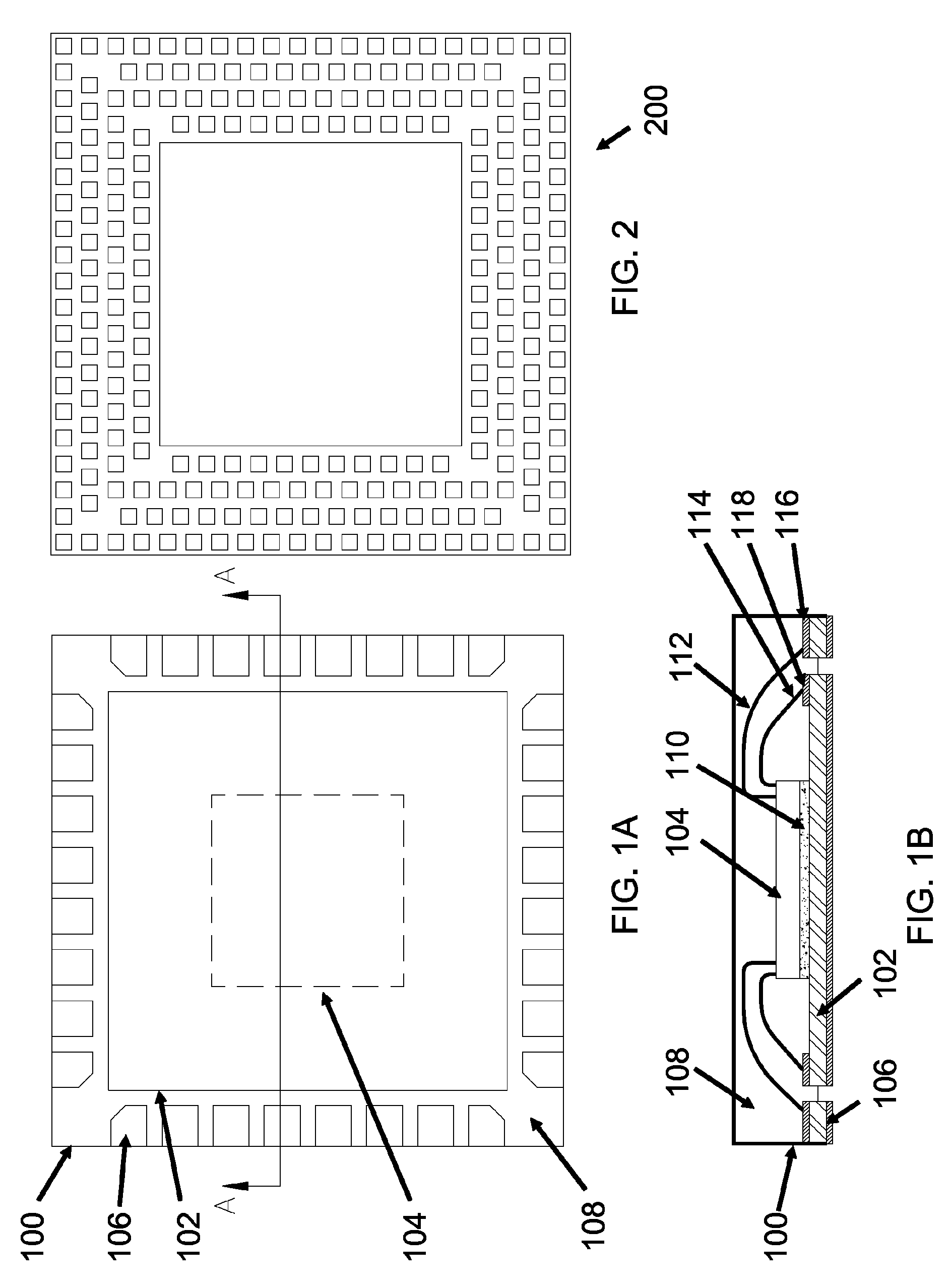

Methods, systems, and apparatuses for integrated circuit (IC) package vertical interconnection are described herein. In an aspect of the invention, an IC package includes an IC die with contact pads. The IC package also includes interconnect members which are coupled to the die at the contact pads. An encapsulating material encapsulates the IC die and the interconnect members such that a contact surface of each interconnect member is accessible at a surface of the encapsulating material. A second IC package is coupled to the first IC package through the plurality of interconnect members of the first IC package. In an example, solder balls attached to a bottom of the second IC package are coupled to the contact surfaces of the interconnect members to couple the first IC package and the second IC package.

Owner:AVAGO TECH INT SALES PTE LTD

High density integrated circuit packaging with chip stacking and via interconnections

InactiveUS6187678B1Reduced connection exposureLarge capacitySemiconductor/solid-state device detailsSolid-state devicesThermal expansionPrism

Chip stacks with decreased conductor length and improved noise immunity are formed by laser drilling of individual chips, such as memory chips, preferably near but within the periphery thereof, and forming conductors therethrough, preferably by metallization or filling with conductive paste which may be stabilized by transient liquid phase (TLP) processes and preferably with or during metallization of conductive pads, possibly including connector patterns on both sides of at least some of the chips in the stack. At least some of the chips in the stack then have electrical and mechanical connections made therebetween, preferably with electroplated solder preforms consistent with TLP processes. The connections may be contained by a layer of resilient material surrounding the connections and which may be formed in-situ. High density circuit packages thus obtained may be mounted on a carrier by surface mount techniques or separable connectors such as a plug and socket arrangement. The carrier may be of the same material as the chip stacks to match coefficients of thermal expansion. High-density circuit packages may also be in the form of removable memory modules in generally planar or prism shaped form similar to a pen or as a thermal conduction module.

Owner:IBM CORP

Silicon interposer and multi-chip-module (MCM) with through substrate vias

InactiveUS6562653B1Semiconductor/solid-state device detailsSolid-state devicesSilicon interposerEngineering

An integrated circuit package which includes an integrated circuit that is connected to a silicon substrate. The silicon substrate may have a via. The package may further include a solder bump that is attached to both the integrated circuit and the silicon subtstrate. The silicon substrate has a coefficient of thermal expansion that matches the coefficient of thermal expansion of the integrated circuit.

Owner:INTEL CORP

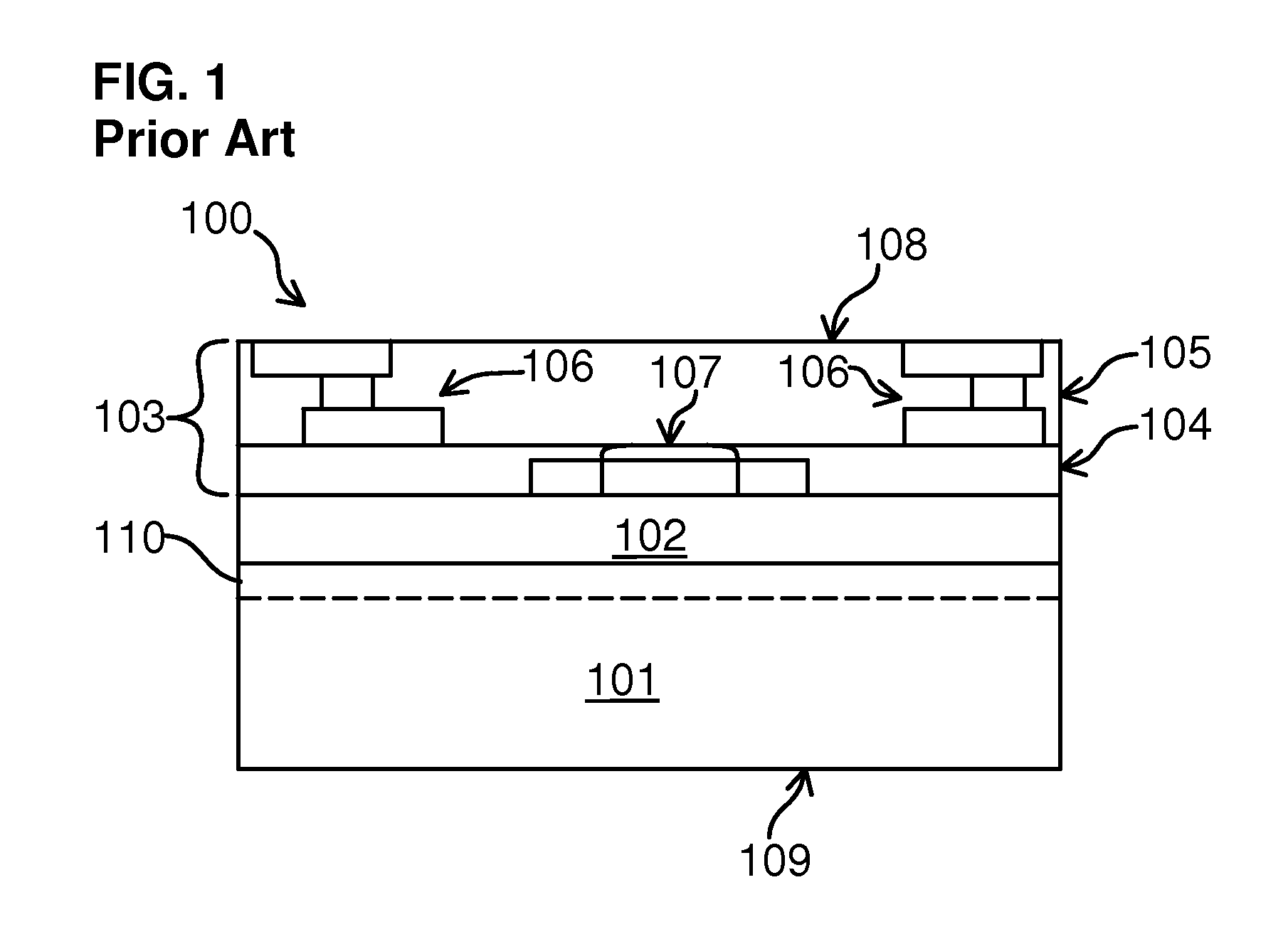

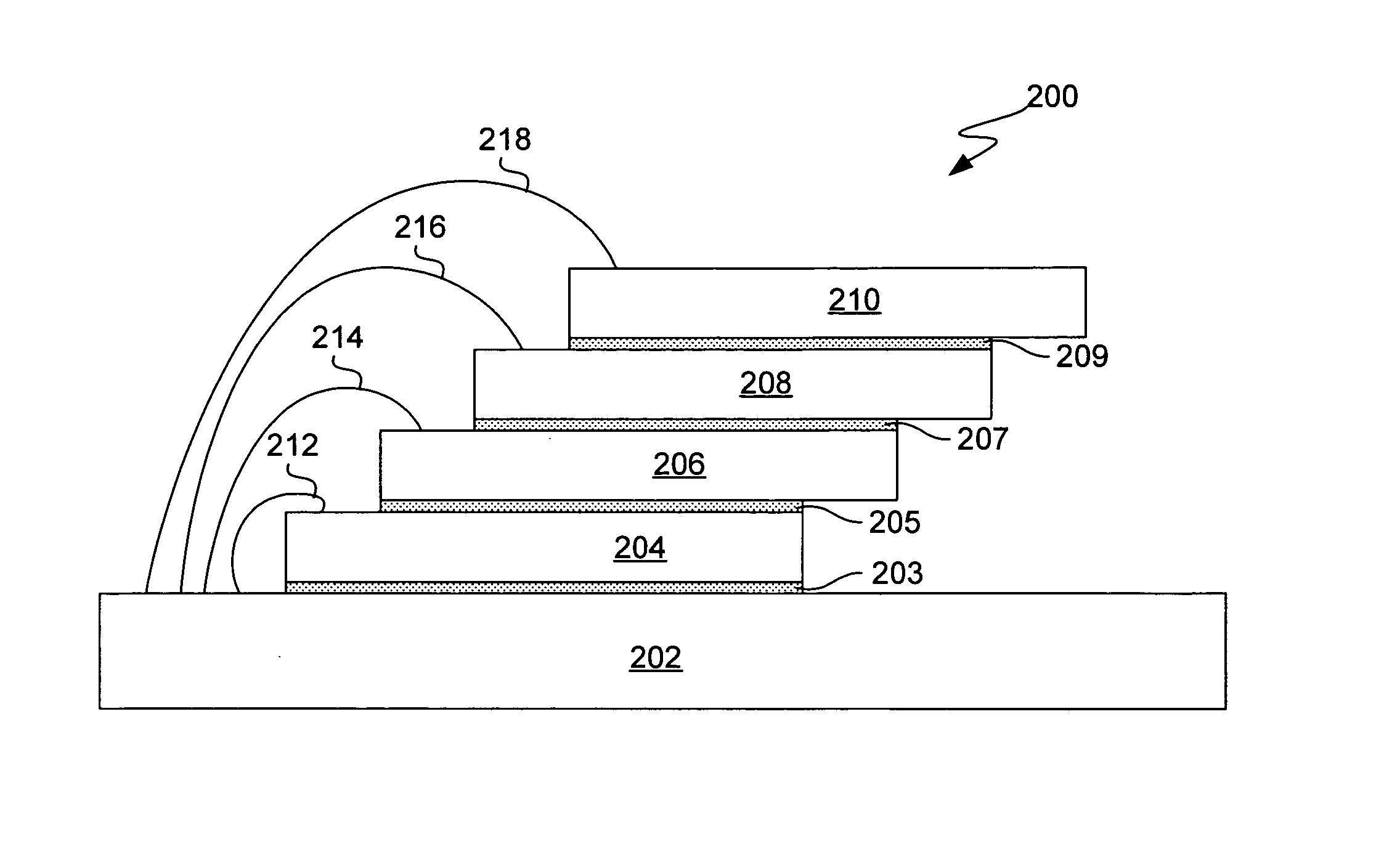

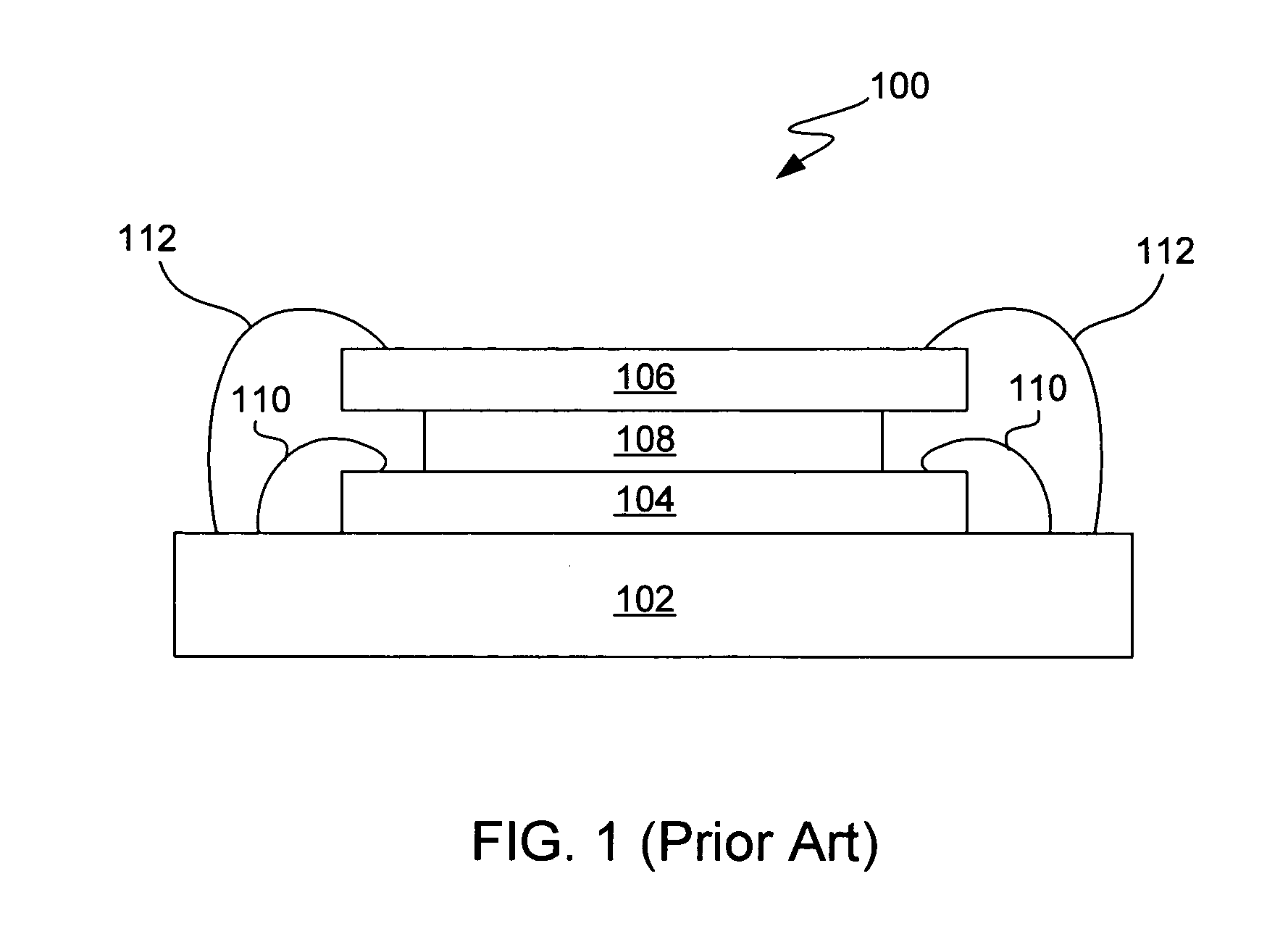

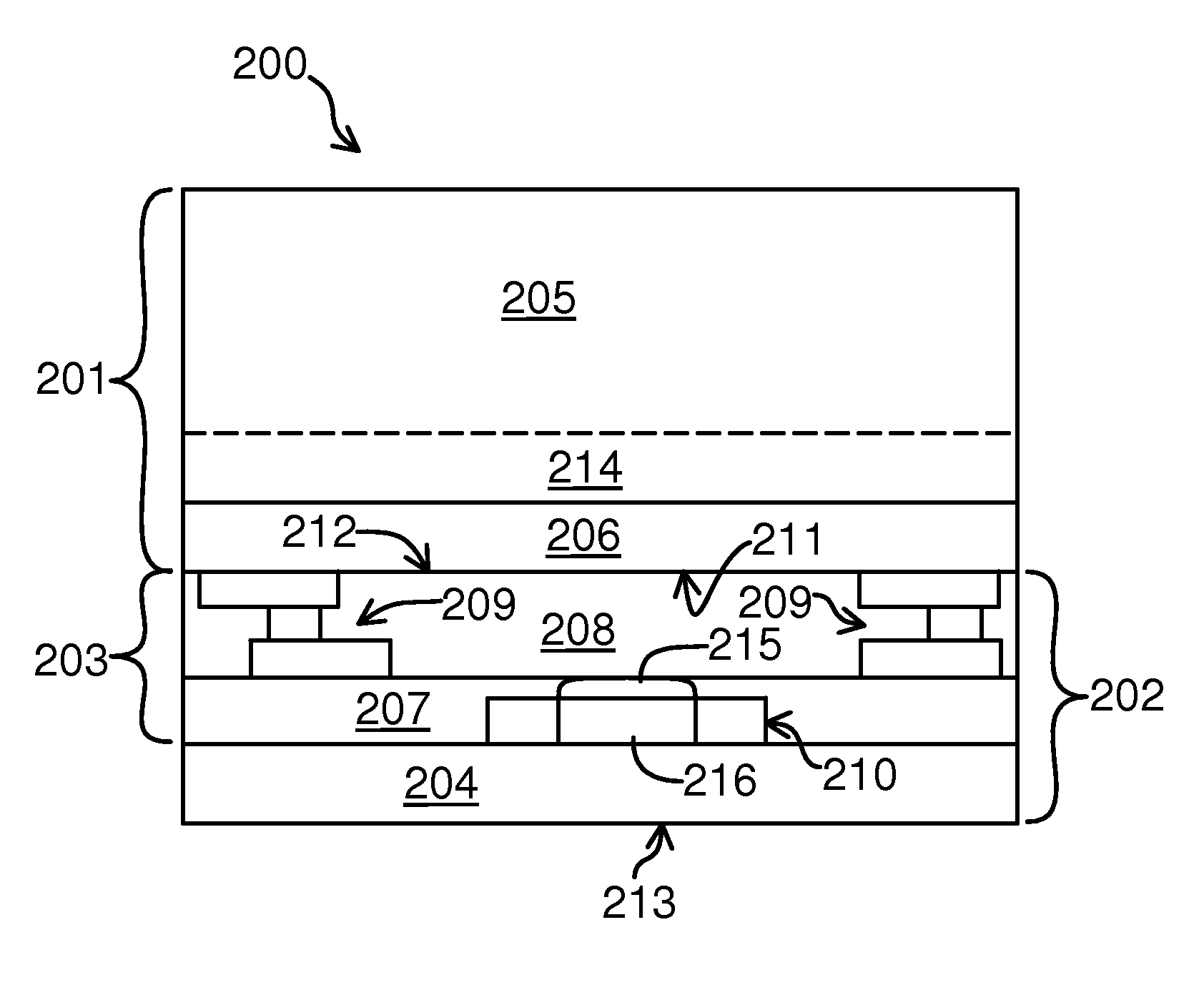

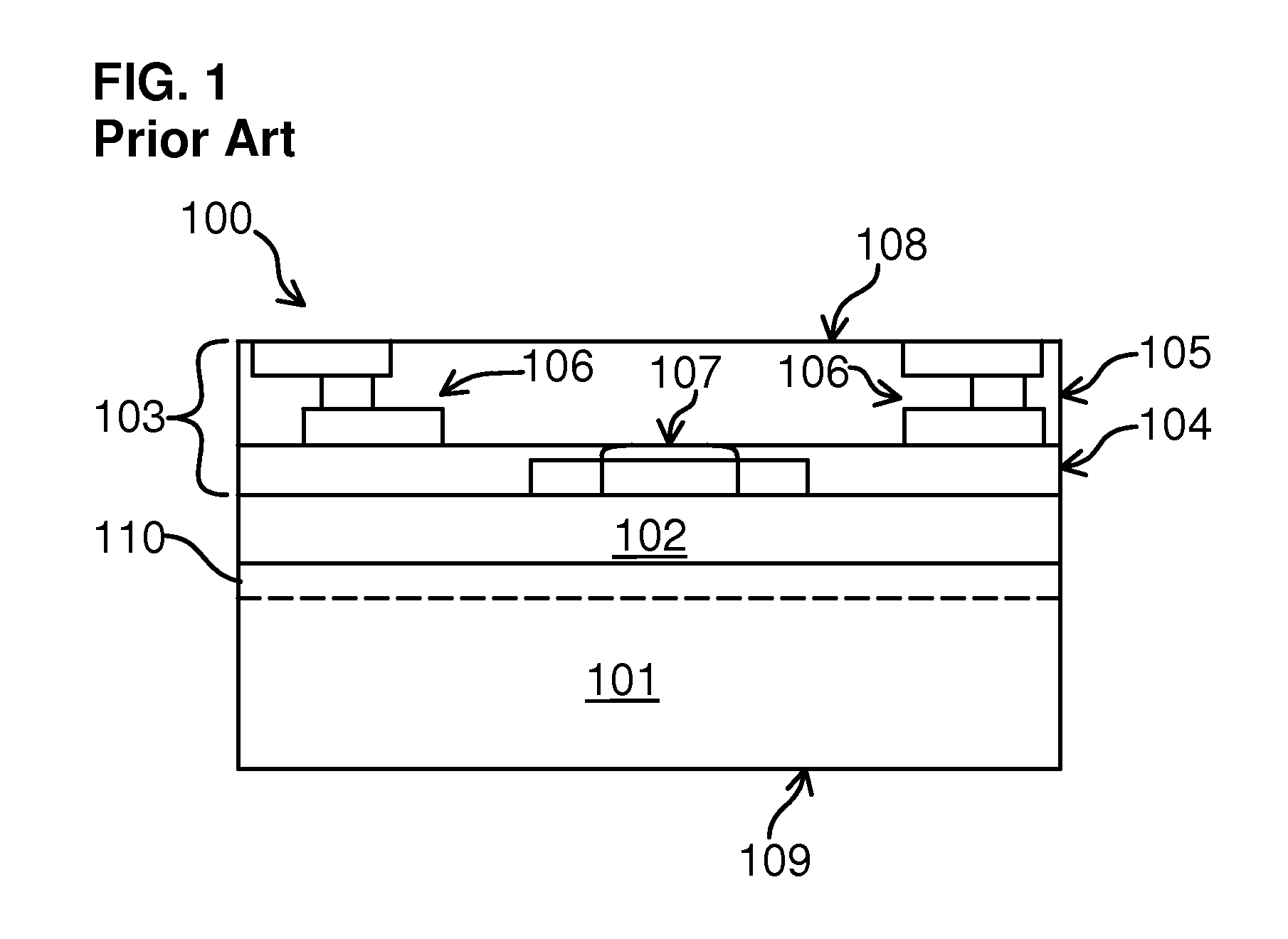

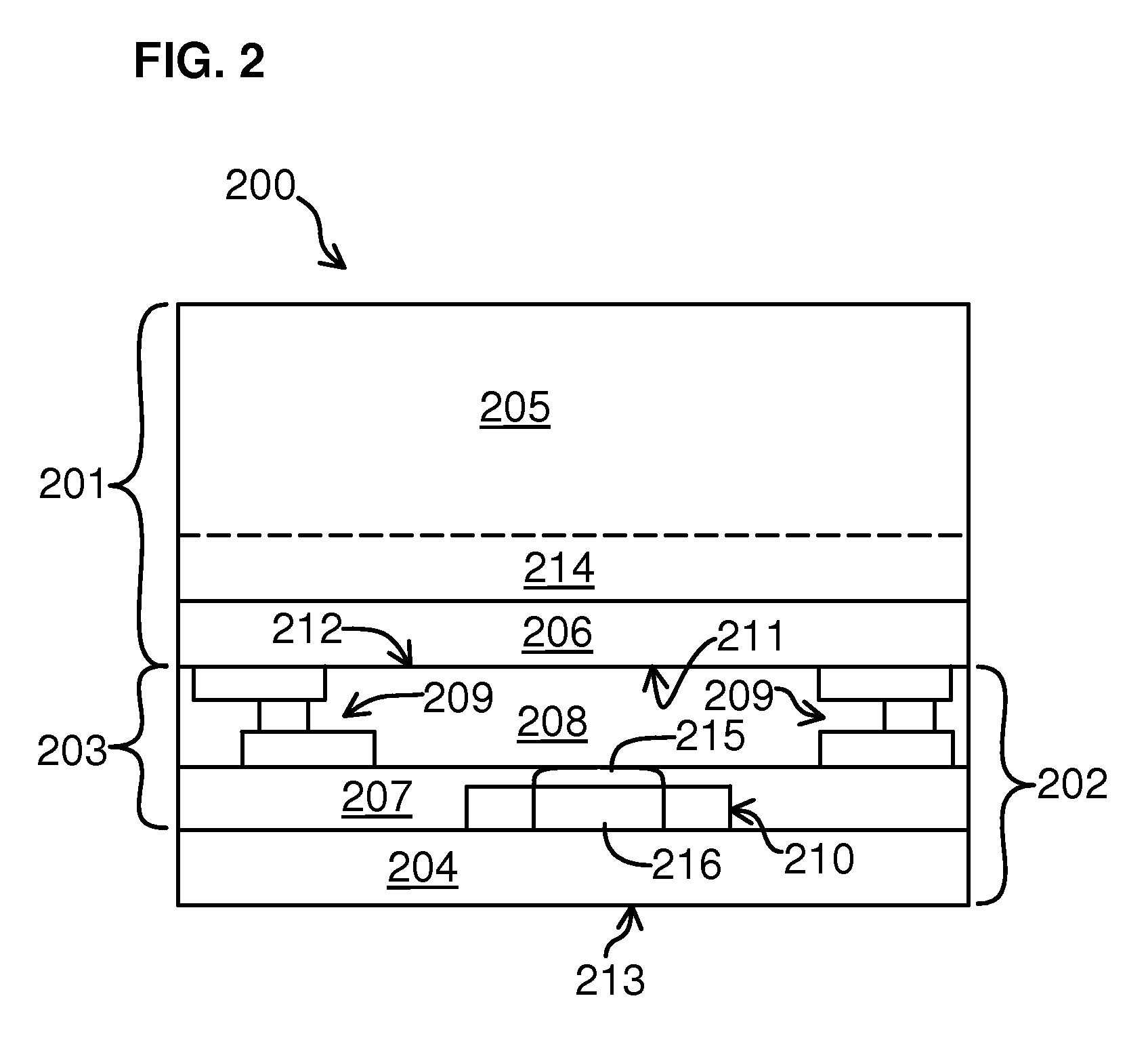

Trap Rich Layer for Semiconductor Devices

ActiveUS20120161310A1Semiconductor/solid-state device detailsSolid-state devicesMetal interconnectActive layer

An integrated circuit chip is formed with an active layer and a trap rich layer. The active layer is formed with an active device layer and a metal interconnect layer. The trap rich layer is formed above the active layer. In some embodiments, the active layer is included in a semiconductor wafer, and the trap rich layer is included in a handle wafer.

Owner:QUALCOMM INC

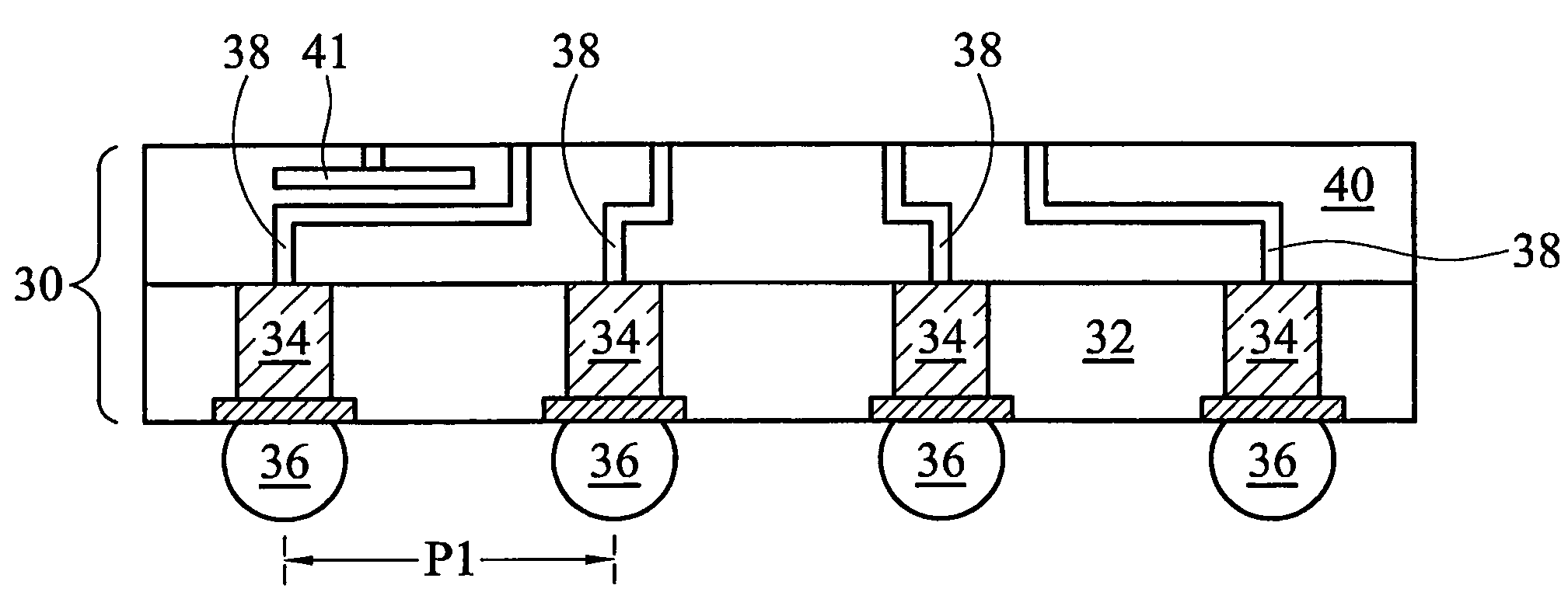

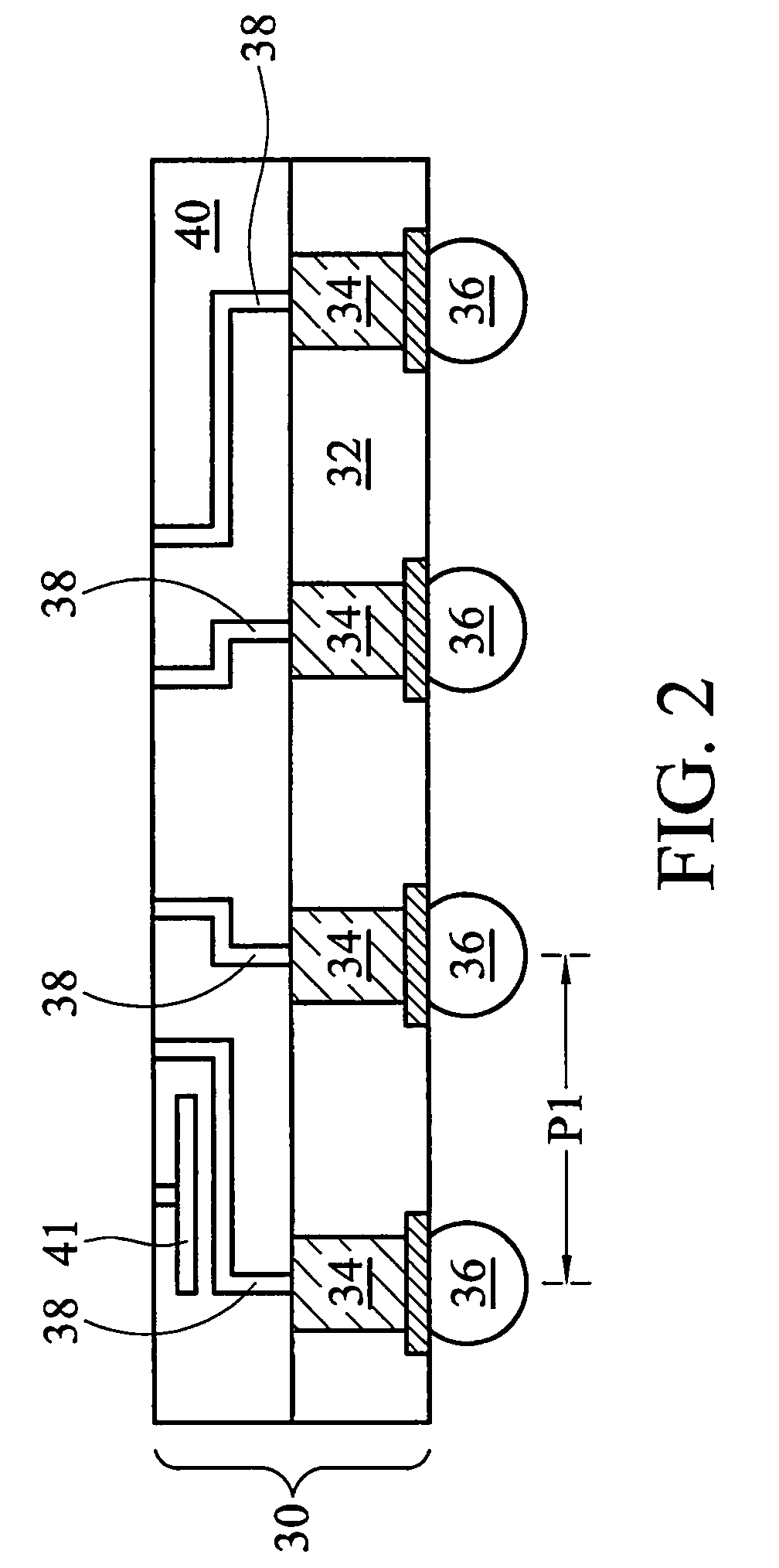

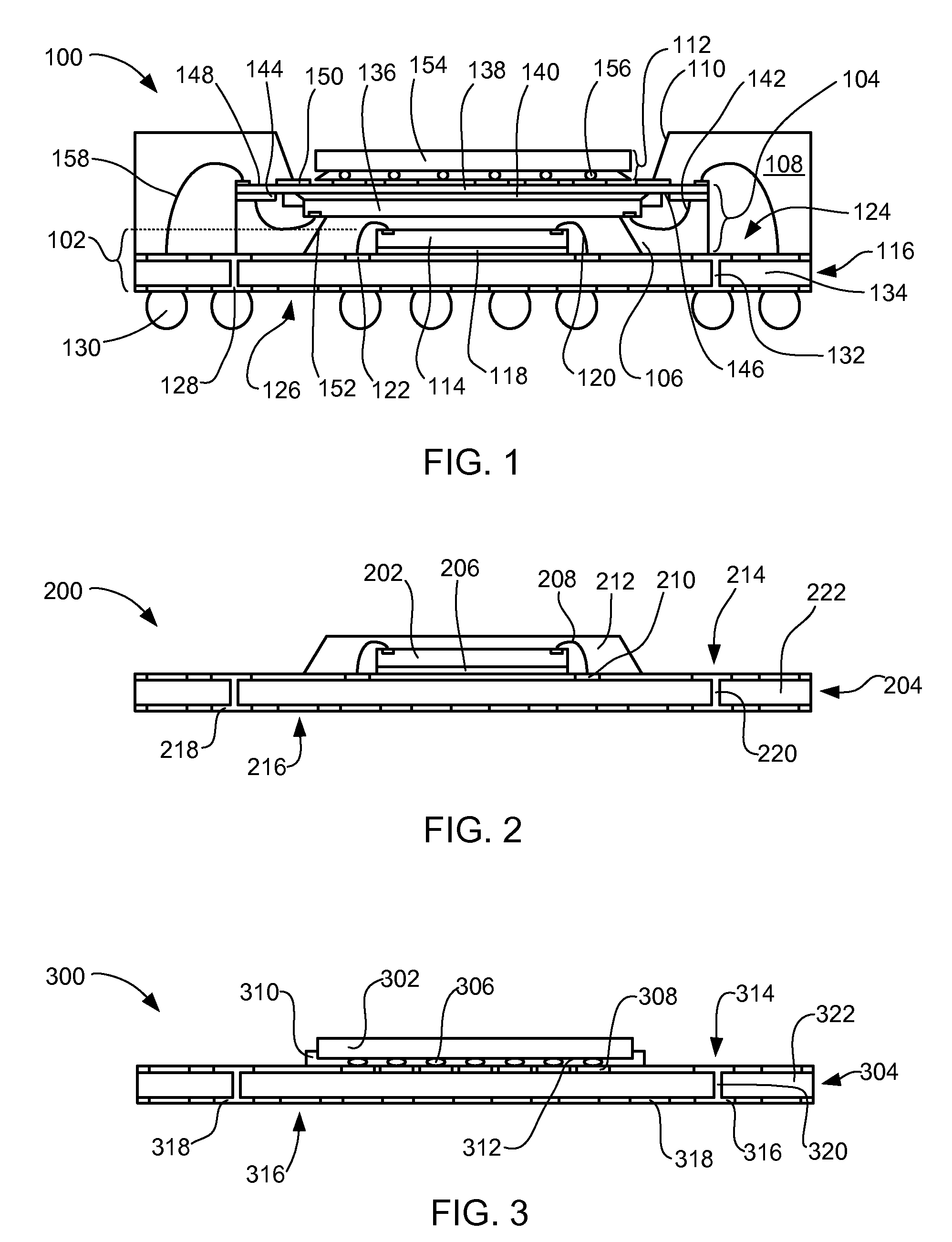

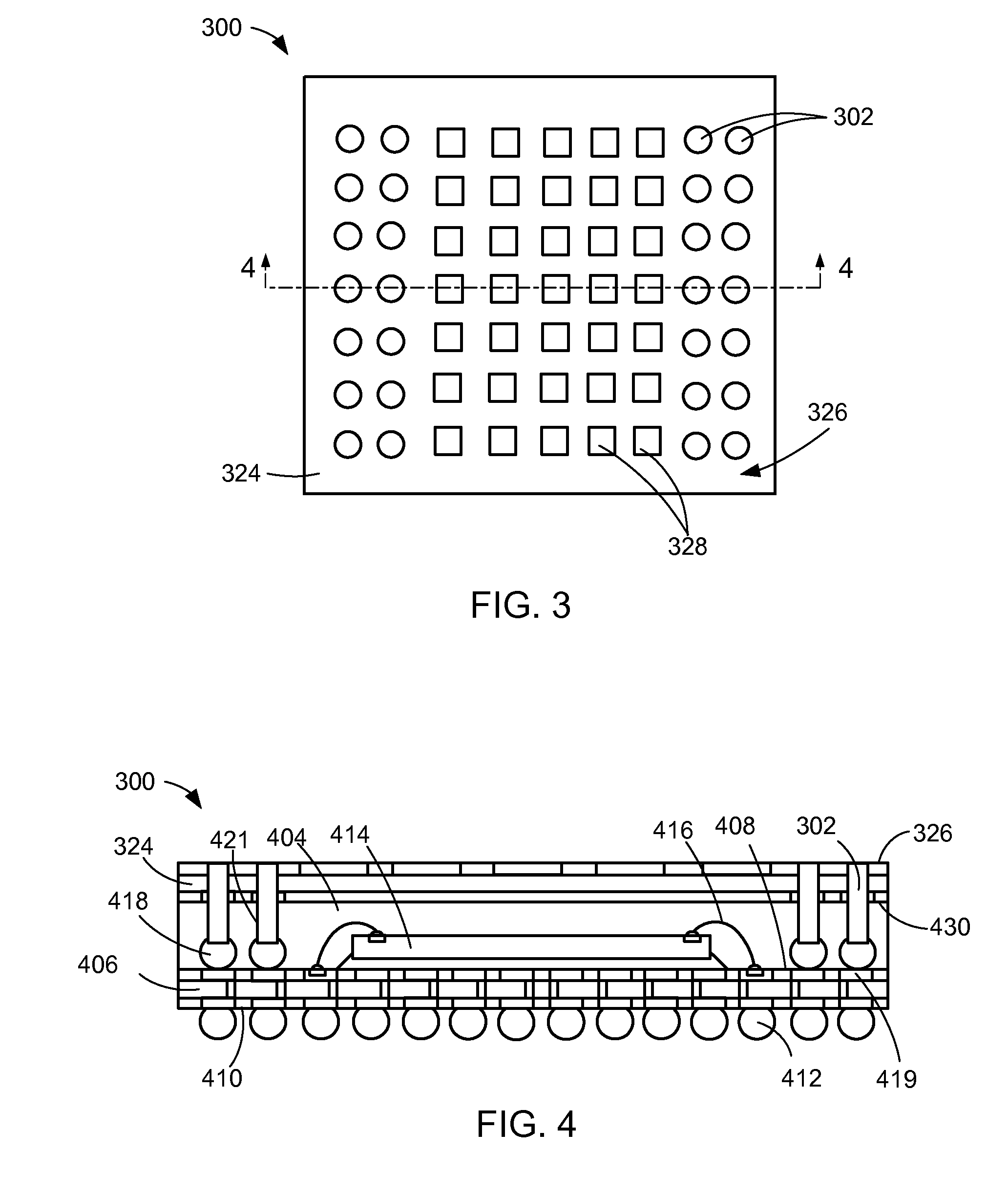

Interconnect structure and formation for package stacking of molded plastic area array package

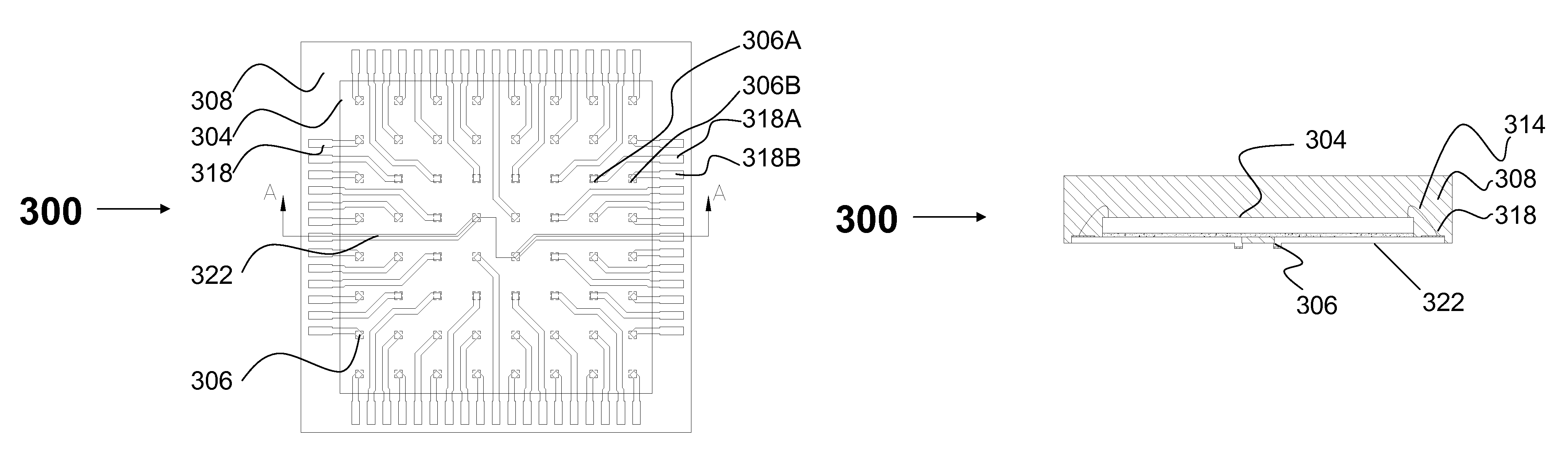

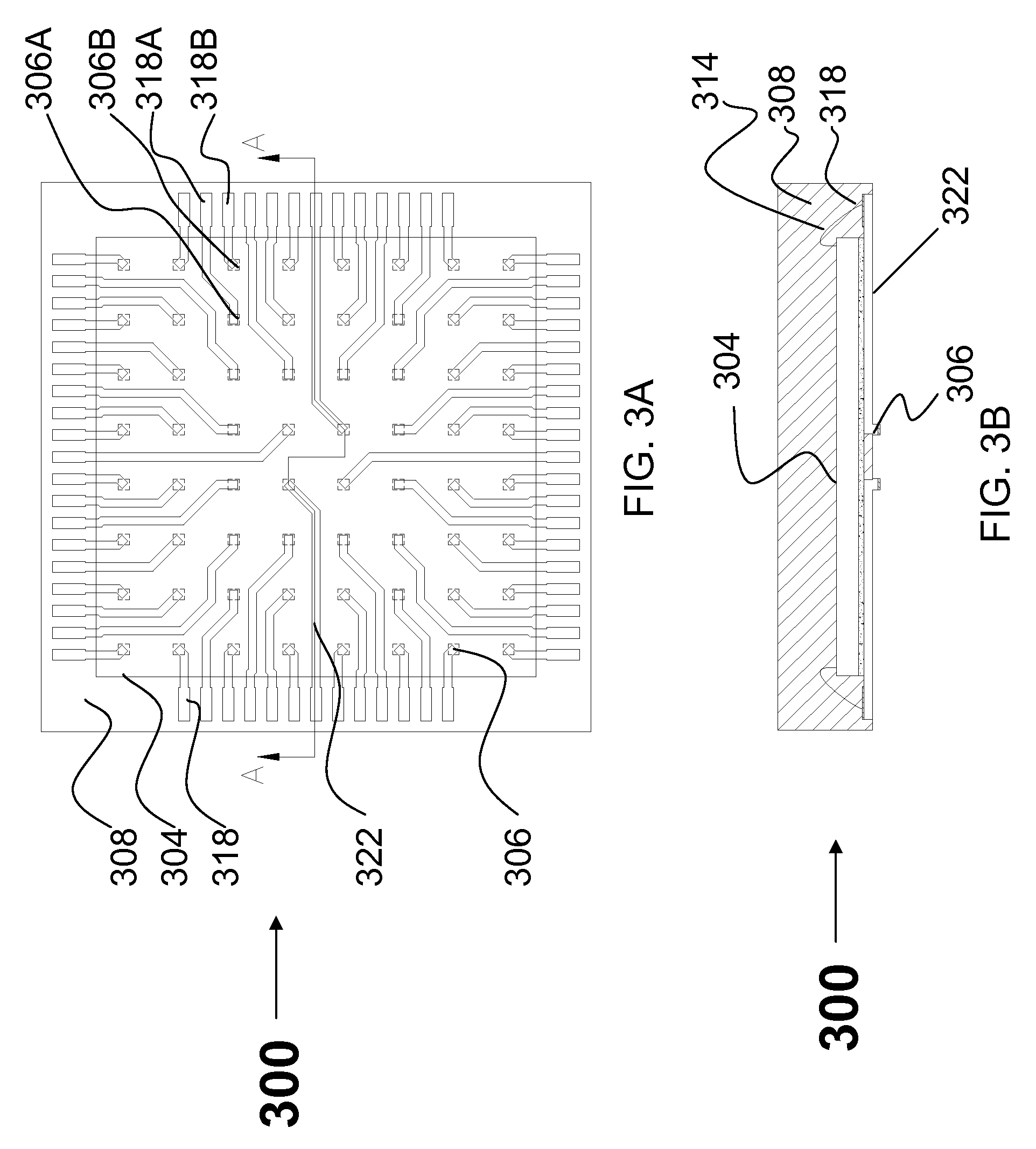

ActiveUS20070273049A1Semiconductor/solid-state device detailsSolid-state devicesContact padShell molding

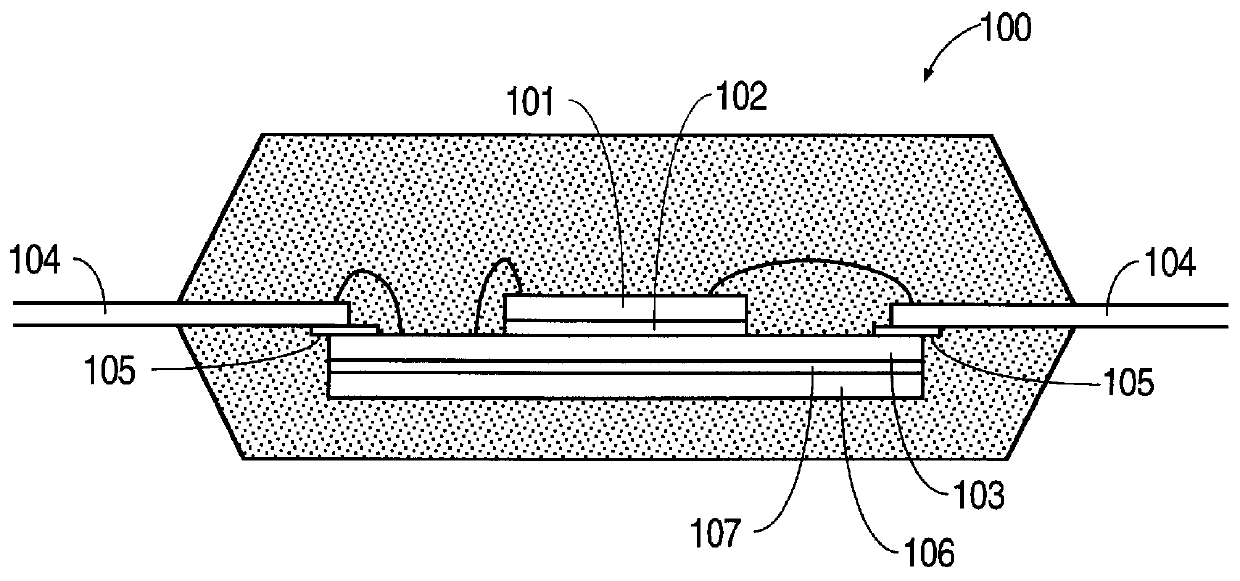

Apparatuses, methods, and systems for improved integrated circuit packages are described. An integrated circuit (IC) package includes a substrate having opposing first and second surfaces, an IC die, a plurality of conductive elements, and an encapsulating material. The substrate has a plurality of contact pads on the first surface that are electrically coupled to a plurality of electrically conductive features on the second surface. The plurality of conductive elements is formed on the first surface of the substrate. The IC die is located on the first surface of the substrate. The encapsulating material encapsulates the IC die and a portion of each element of the plurality of conductive elements.

Owner:AVAGO TECH WIRELESS IP SINGAPORE PTE

Low-cost and ultra-fine integrated circuit packaging technique

ActiveUS7576435B2Improved feasibility of formingReduce bondingSemiconductor/solid-state device detailsSolid-state devicesInterposerSemiconductor chip

A semiconductor package structure and the methods for forming the same are provided. The semiconductor package structure includes an interposer; a first plurality of bonding pads on a side of the interposer; a semiconductor chip; and a second plurality of bonding pads on a side of the semiconductor chip. The first and the second plurality of bonding pads are bonded through metal-to-metal bonds.

Owner:ADVANCED MFG INNOVATIONS INC

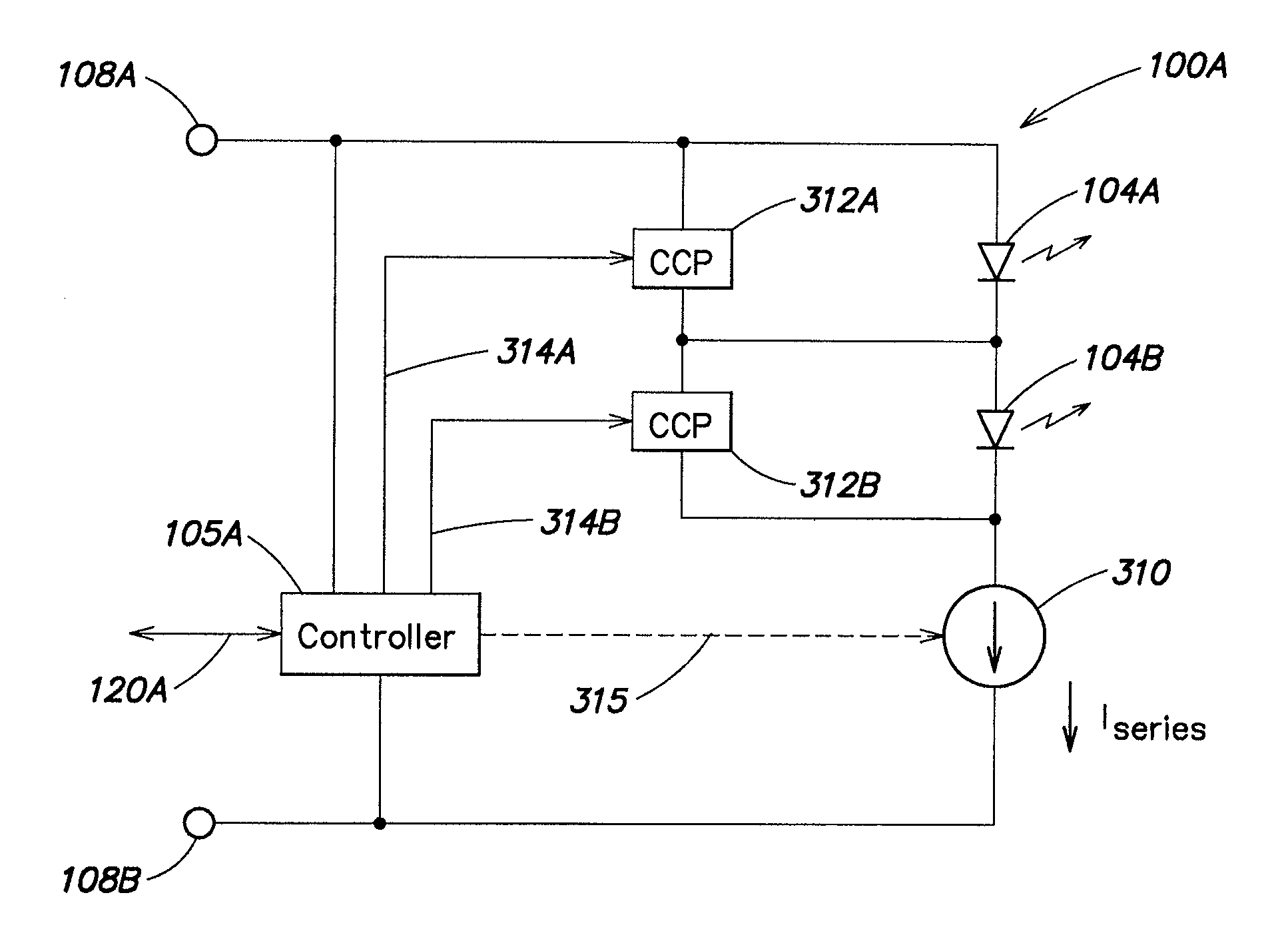

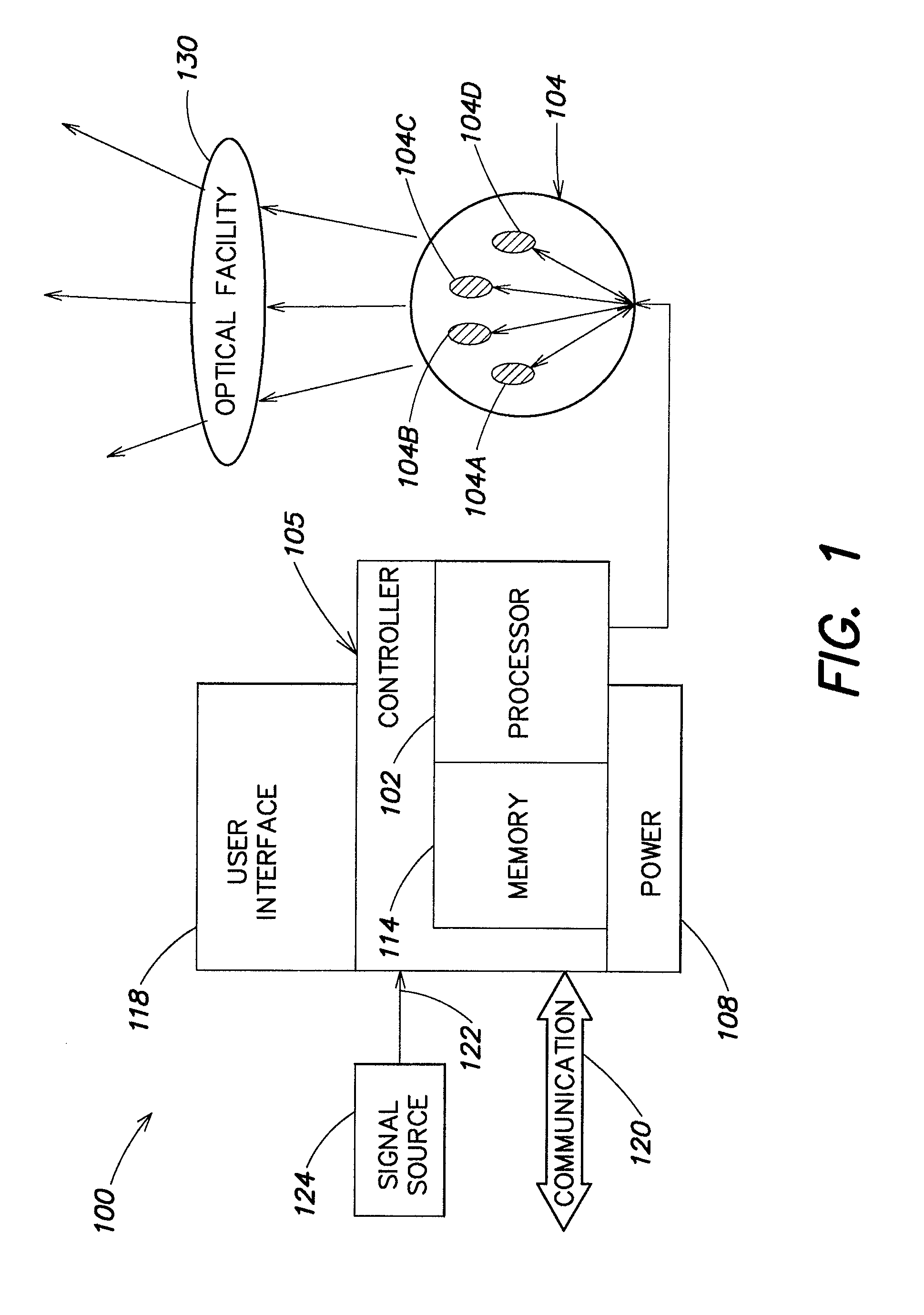

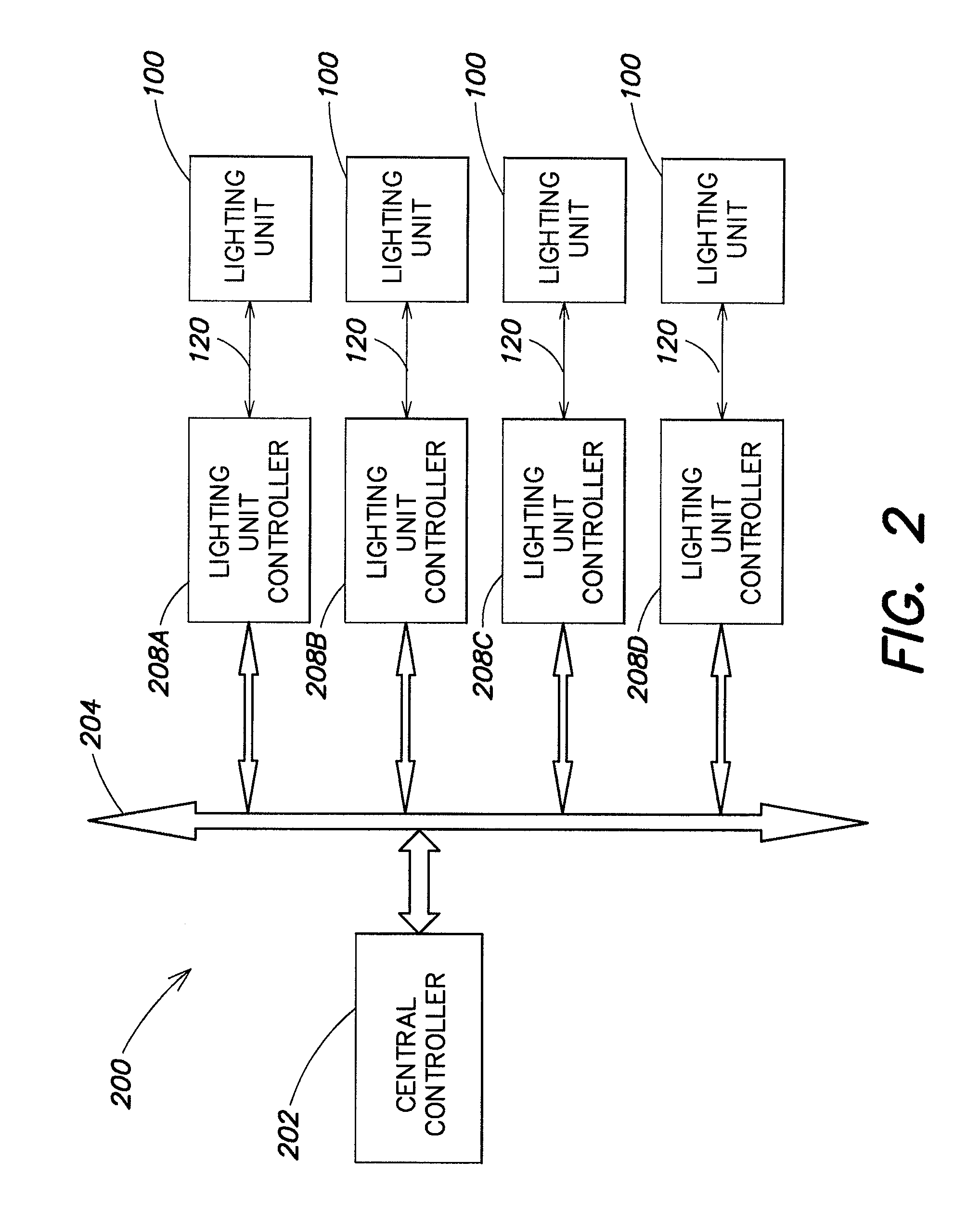

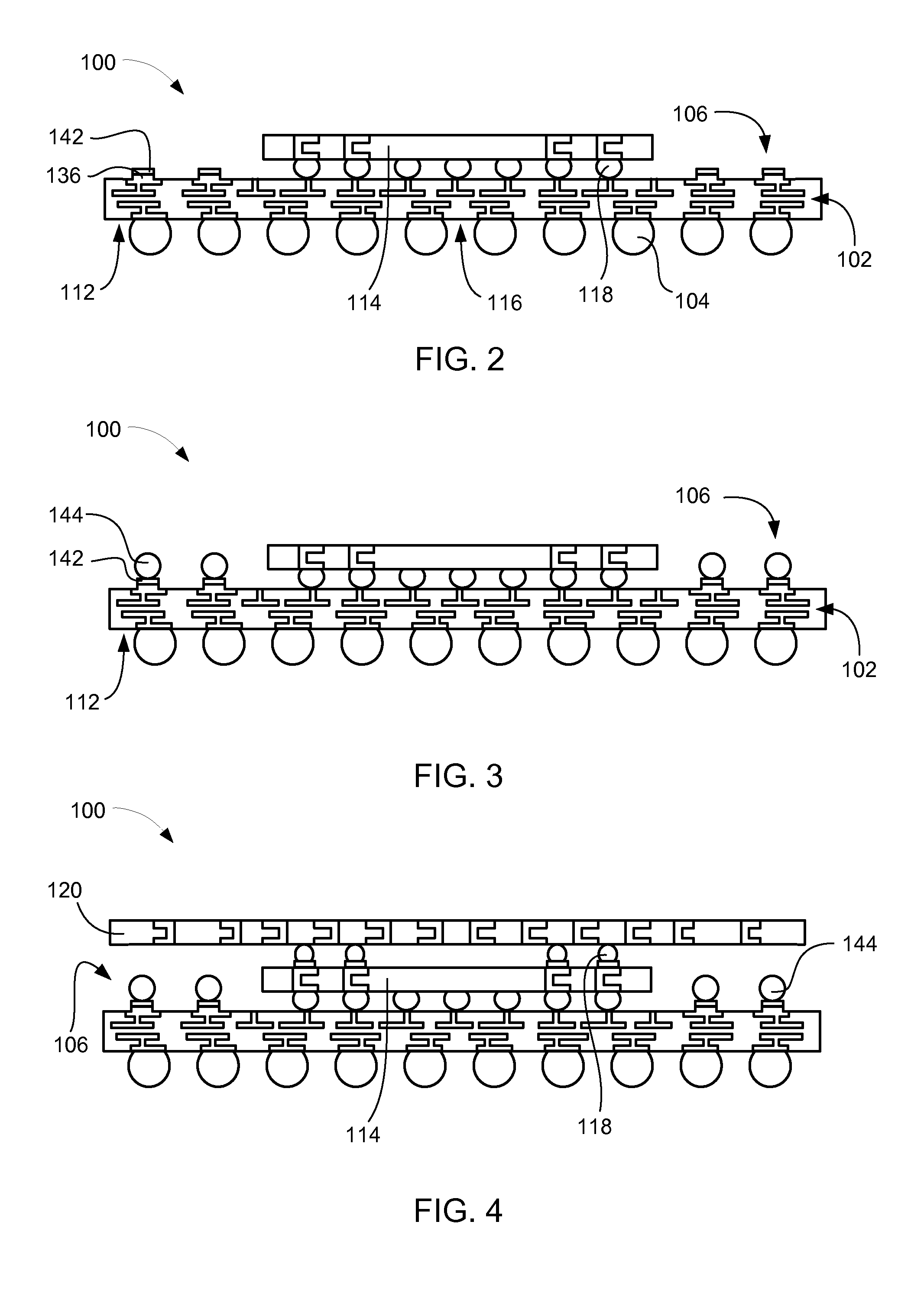

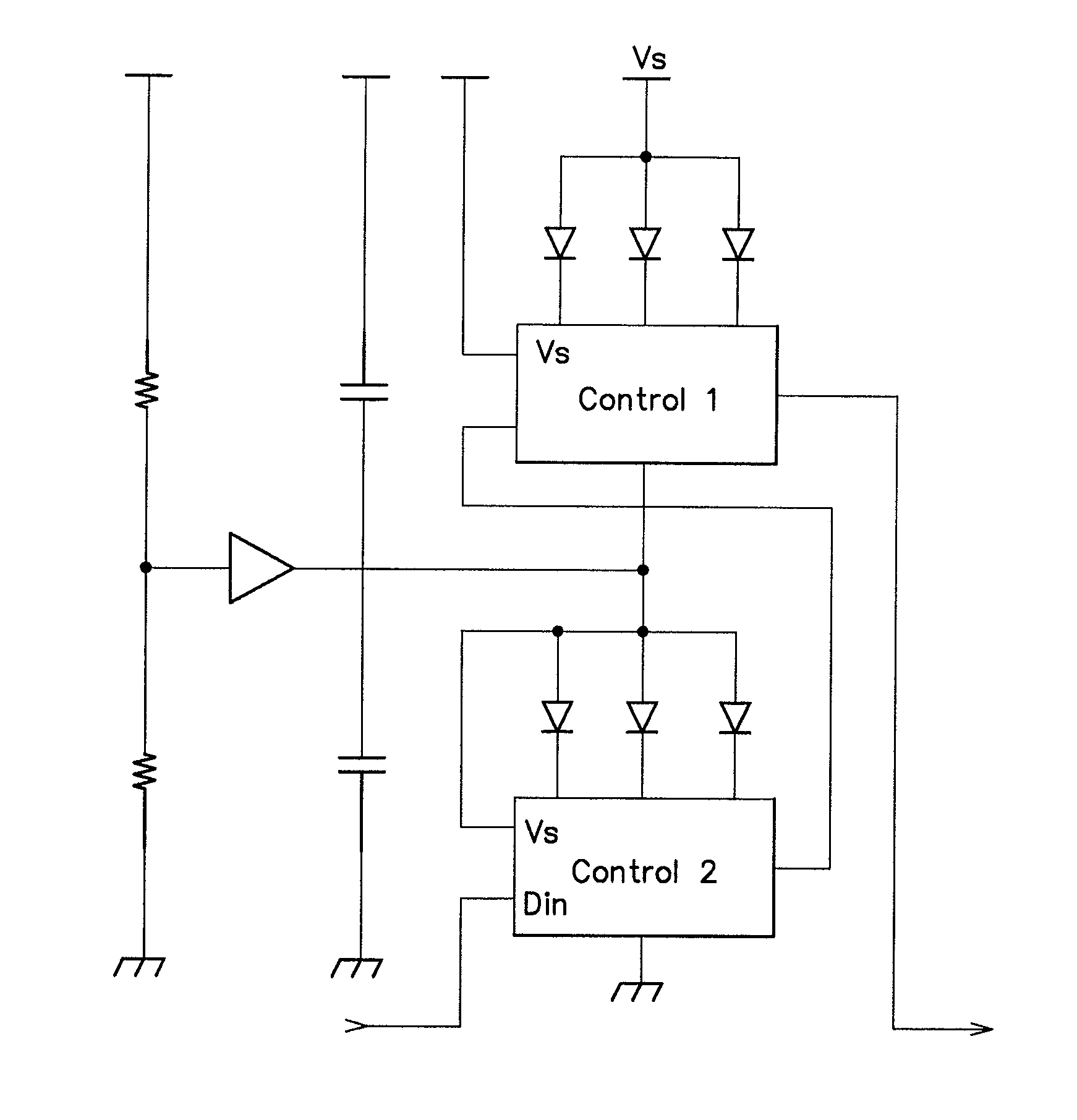

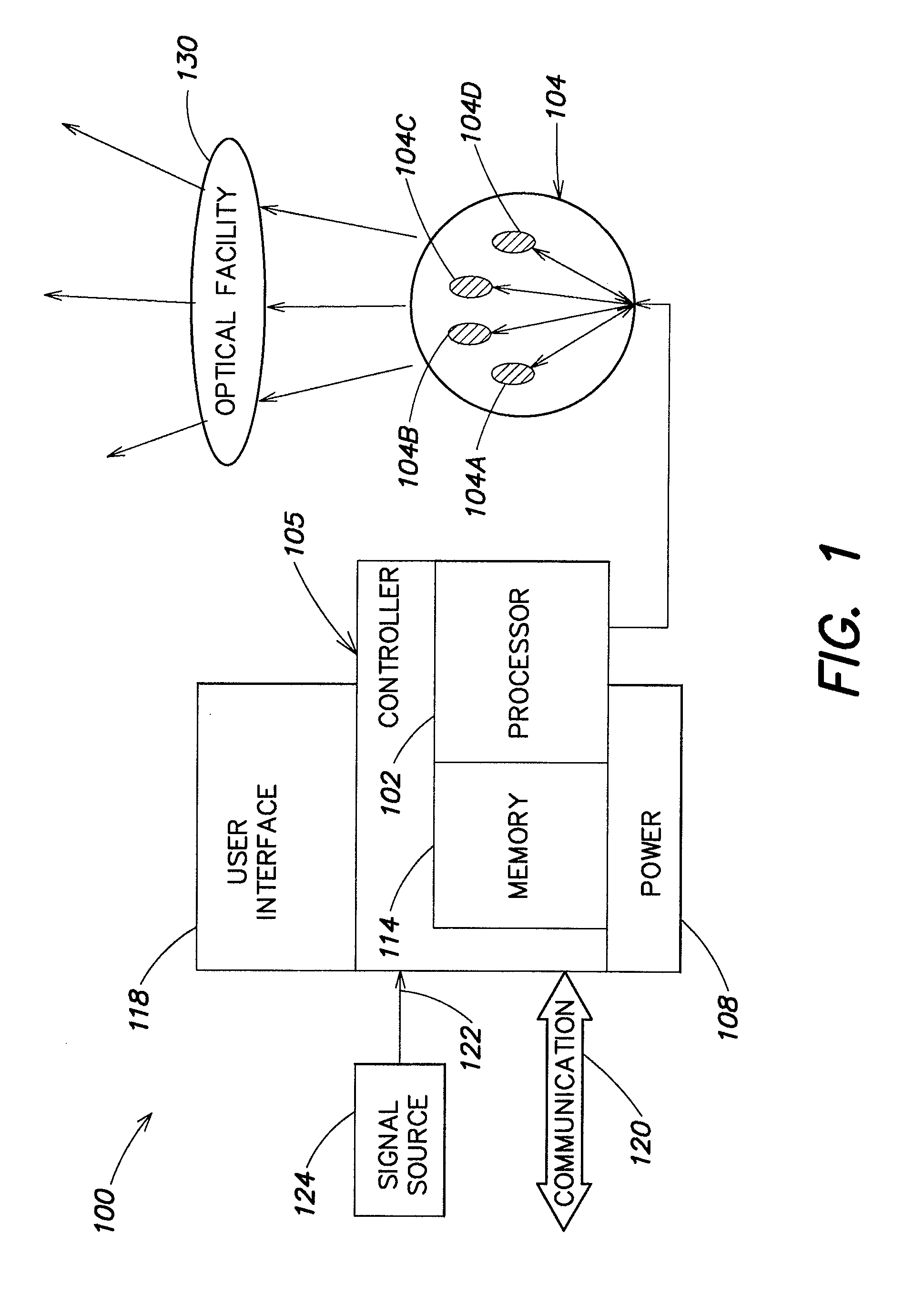

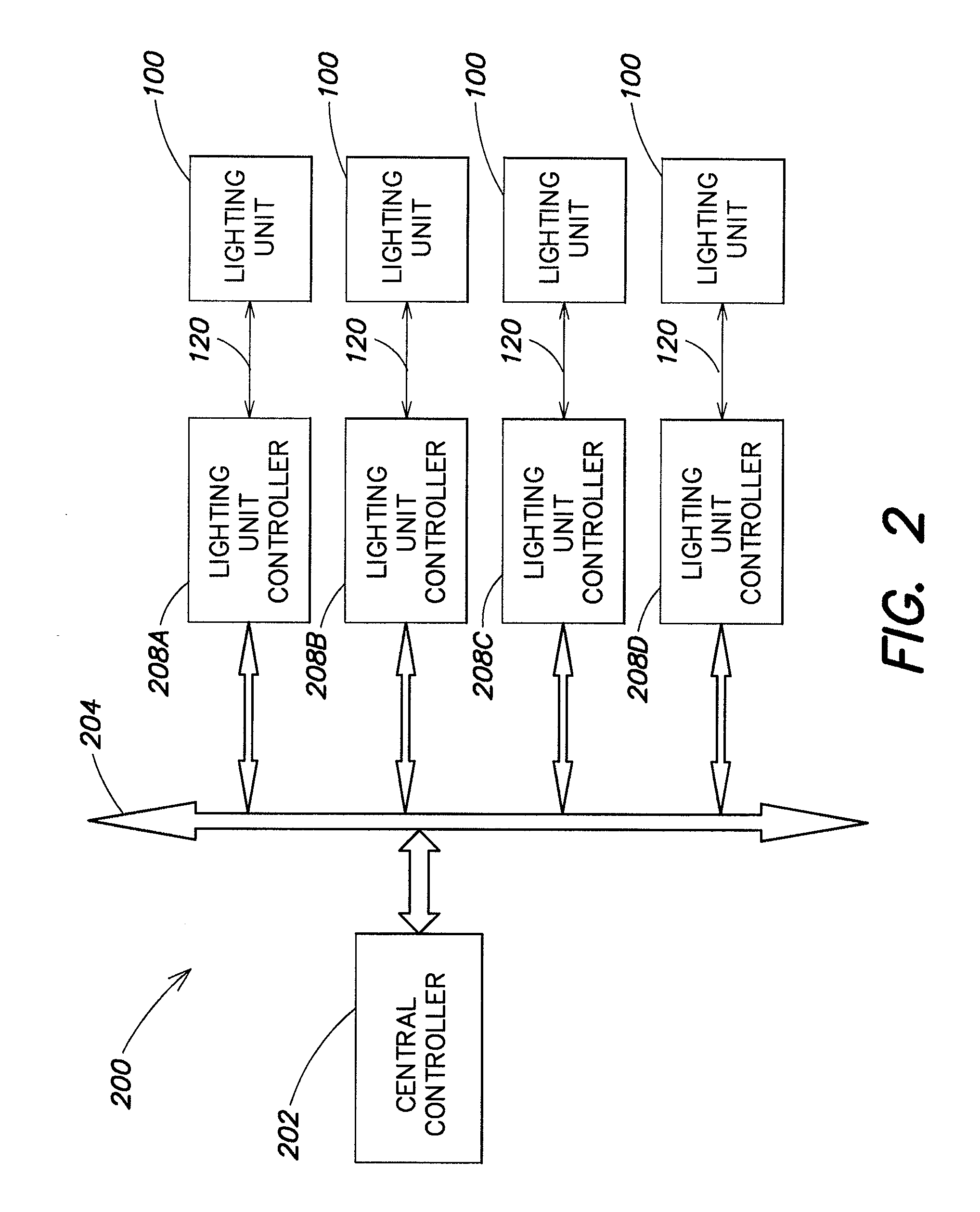

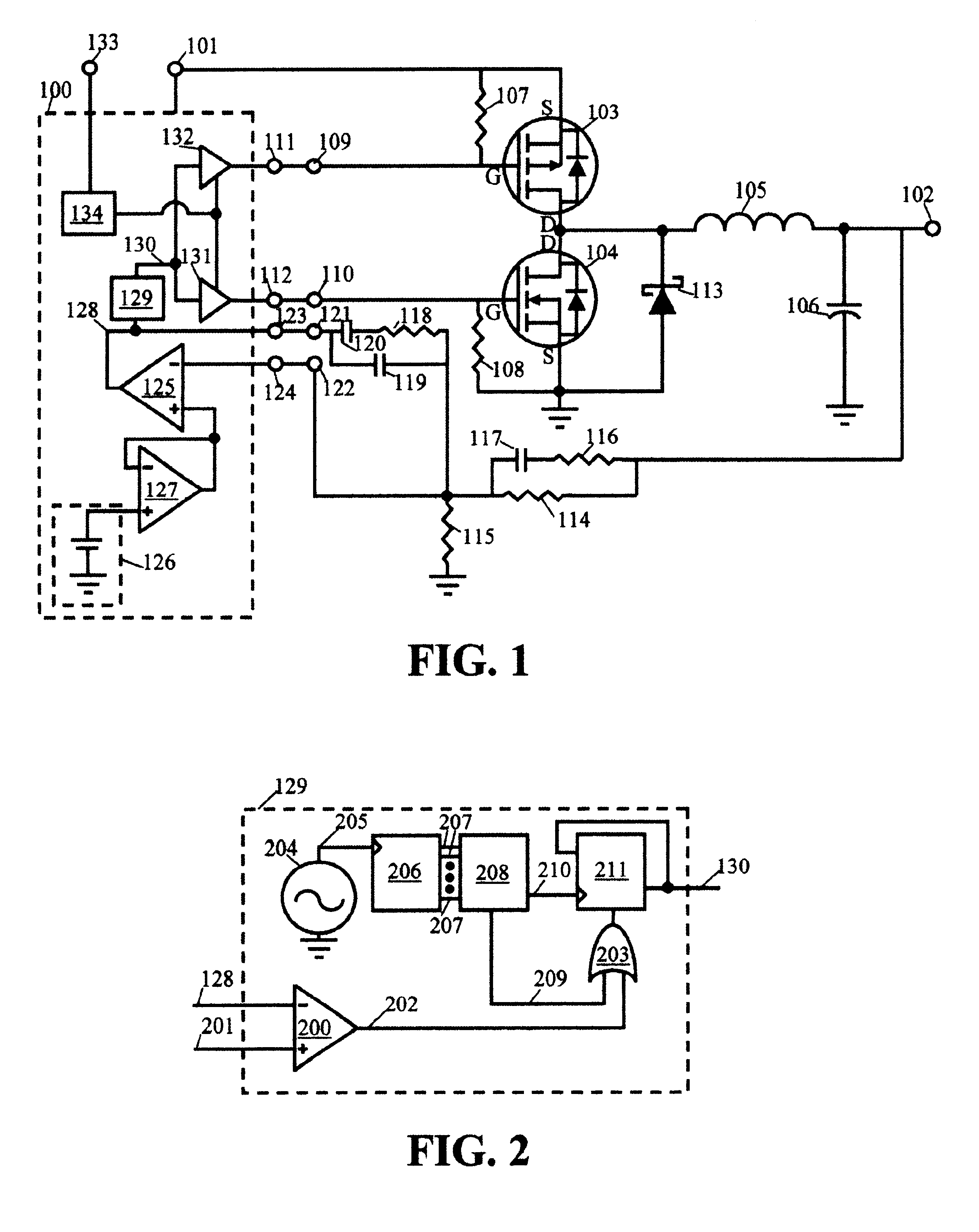

Methods and apparatus for controlling series-connected LEDs

ActiveUS7781979B2Increase volumeElectrical apparatusElectroluminescent light sourcesEffect lightElectrical current

Methods and apparatus for controlling series-connected LEDs. Two or more LEDs are connected in series between a first node and a second node, wherein a series current flows between the nodes when an operating voltage is applied across the nodes. One or more controllable current paths are connected in parallel with at least a first LED for at least partially diverting the series current around at least the first LED. A controller monitors at least one parameter representative of the operating voltage, determines a maximum number of the series-connected LEDs that can be energized by the operating voltage, and controls the controllable current path(s) so as to increase an amount of the series current that is diverted around at least the first LED when the maximum number is less than a total number of all of the LEDs connected in series. In one example, the foregoing may be implemented as an integrated circuit package to provide a lighting apparatus suitable for automotive applications.

Owner:SIGNIFY NORTH AMERICA CORP

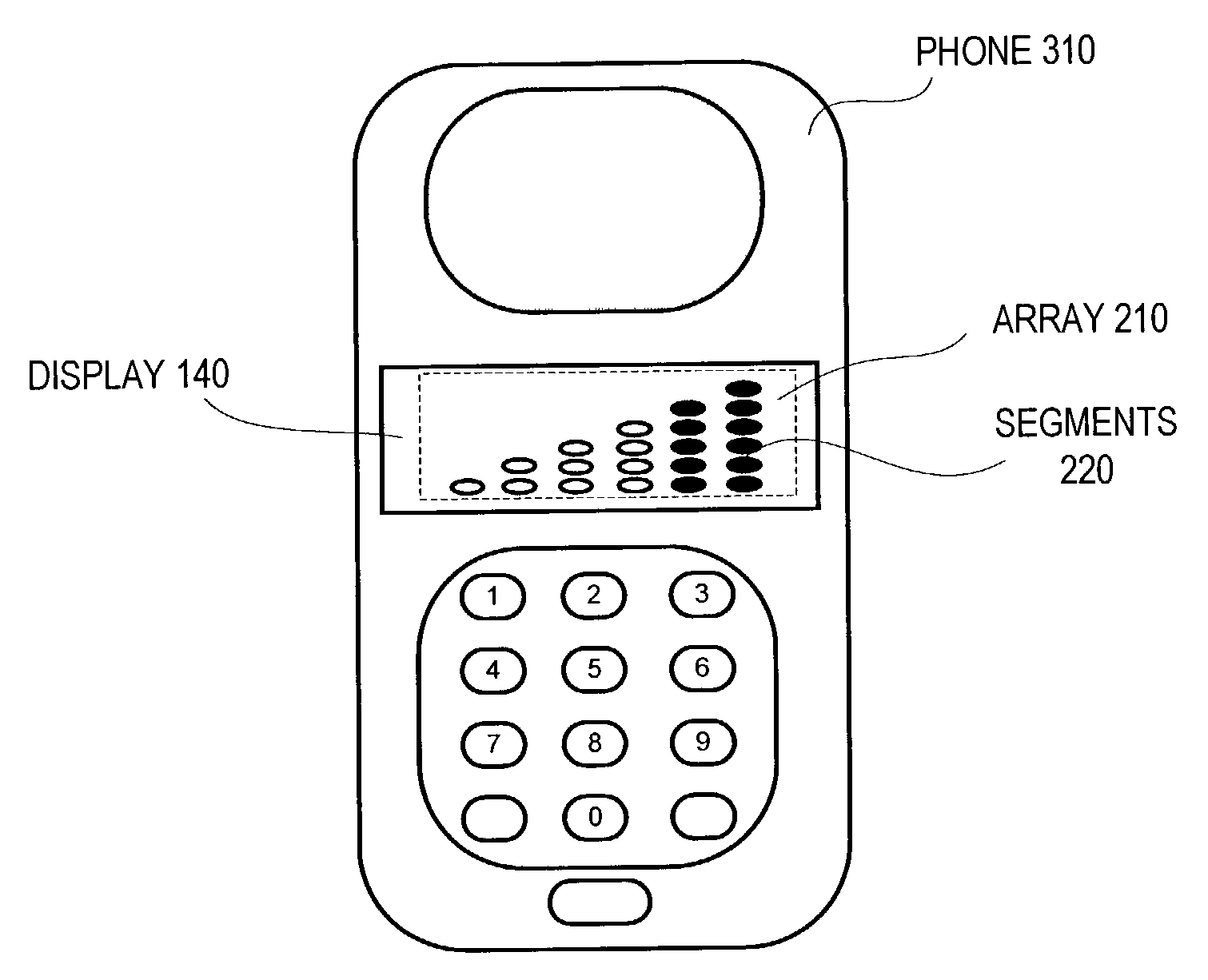

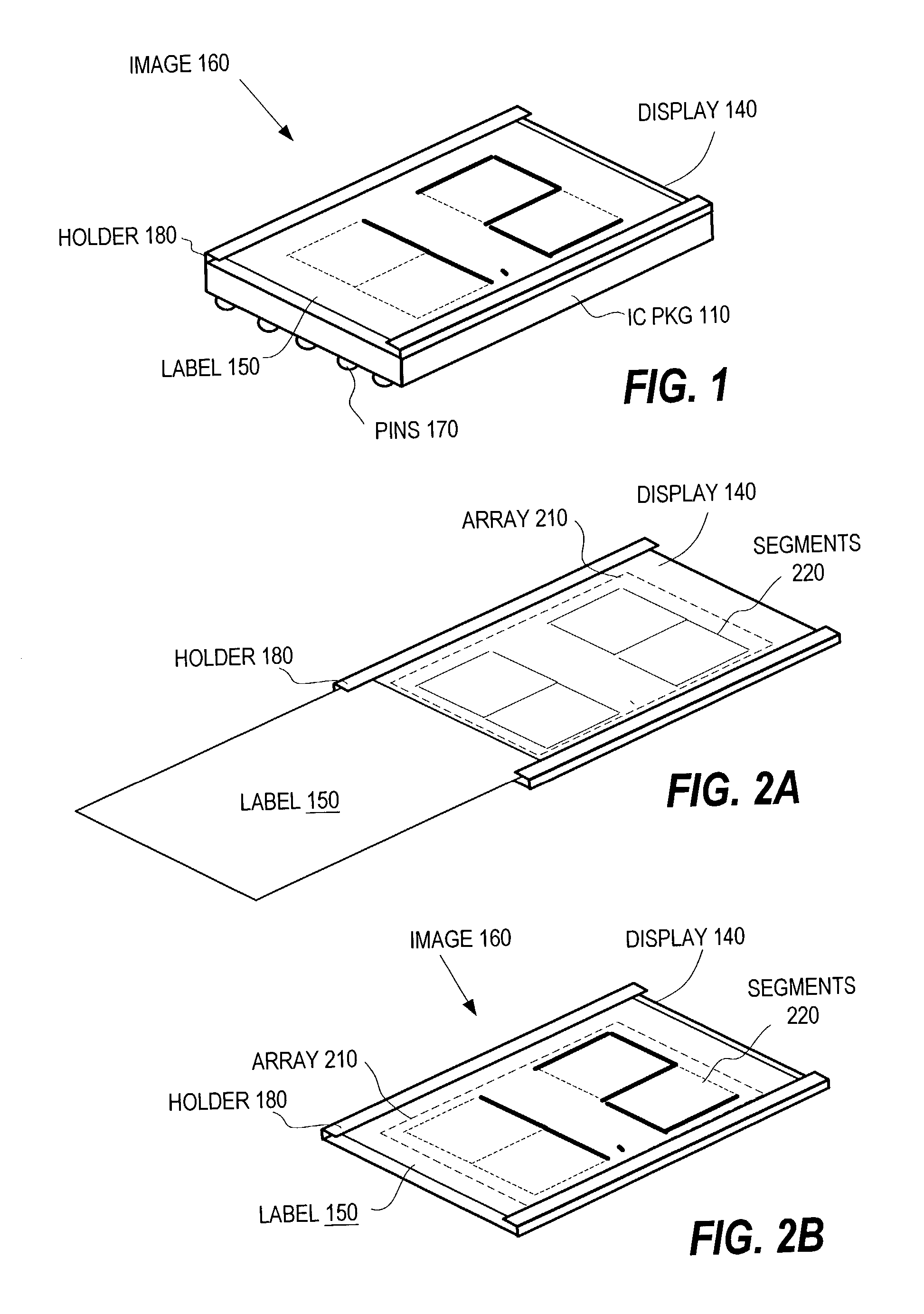

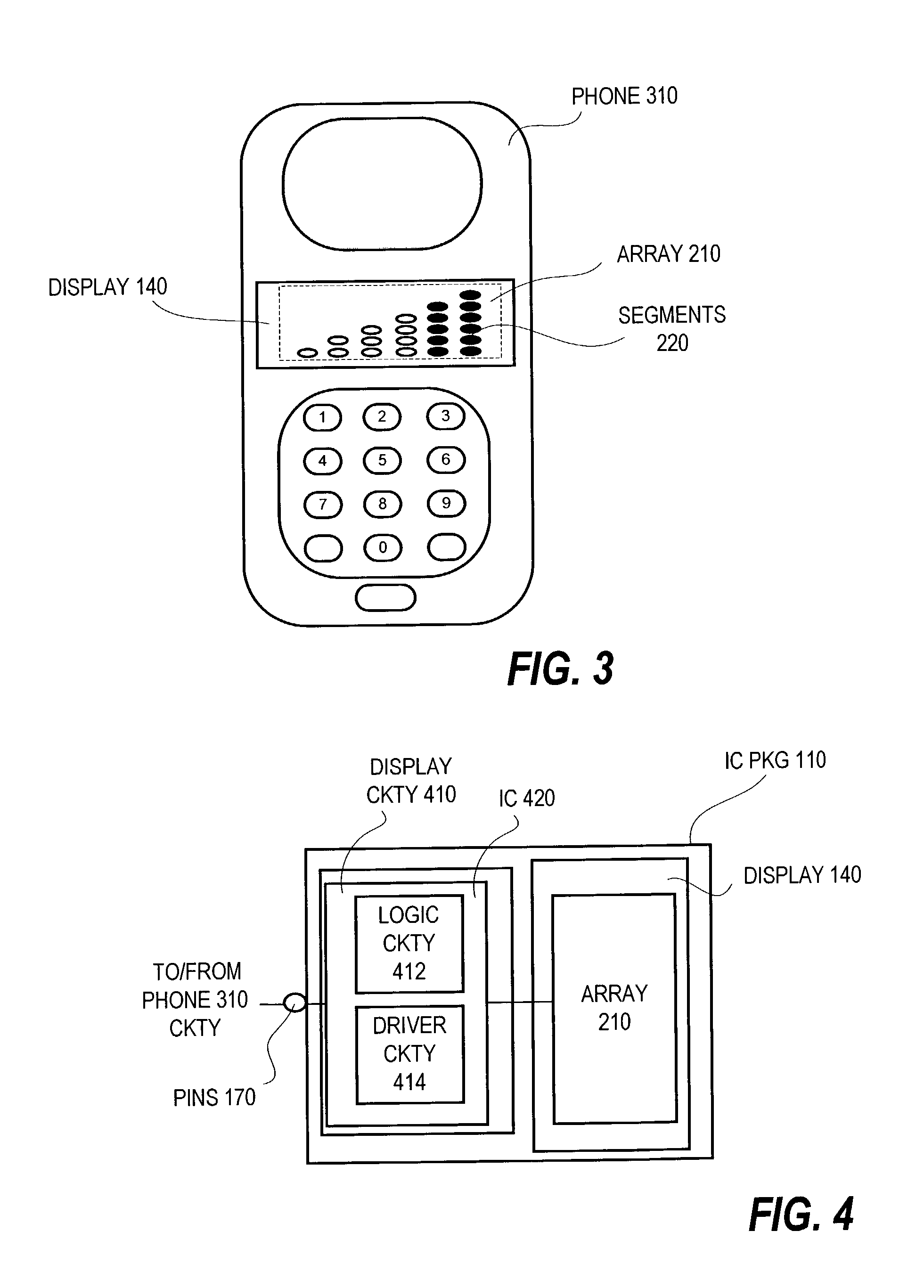

Method and apparatus for non-volatile display of information for an electronic device

In one form of the invention, an apparatus for visually displaying a non-volatile message includes an integrated circuit having first circuitry. The apparatus also includes a package for the integrated circuit and a display affixed to the integrated circuit package. The first circuitry is coupled to the display and operable to be coupled to an electronic device by pins of the integrated circuit package and to write a non-volatile, visual image via the display responsive to receiving a message from the electronic device.

Owner:IBM CORP

Thermal improvement for hotspots on dies in integrated circuit packages

ActiveUS20070290322A1Semiconductor/solid-state device testing/measurementSemiconductor/solid-state device detailsContact padEngineering

Methods and apparatuses for improved integrated circuit (IC) packages are described herein. In an aspect, an IC device package includes an IC die having a contact pad, where the contact pad is located on a hotspot of the IC die. The hotspot is thermally coupled to a thermal interconnect member. In an aspect, the package is encapsulated in a mold compound. In a further aspect, a heat spreader is attached to the mold compound, and is thermally coupled to the thermal interconnect member. In another aspect, a thermal interconnect member thermally is coupled between the heat spreader and the substrate.

Owner:AVAGO TECH INT SALES PTE LTD

Integrated circuit packaging system with flipchip leadframe and method of manufacture thereof

An integrated circuit packaging system and method of manufacture thereof includes: leads and a paddle; a first encapsulant molded between the leads and the paddle, the first encapsulant thinner than the leads; a non-conductive layer over the paddle; and conductive traces directly on the leads, the first encapsulant, and the non-conductive layer.

Owner:STATS CHIPPAC LTD

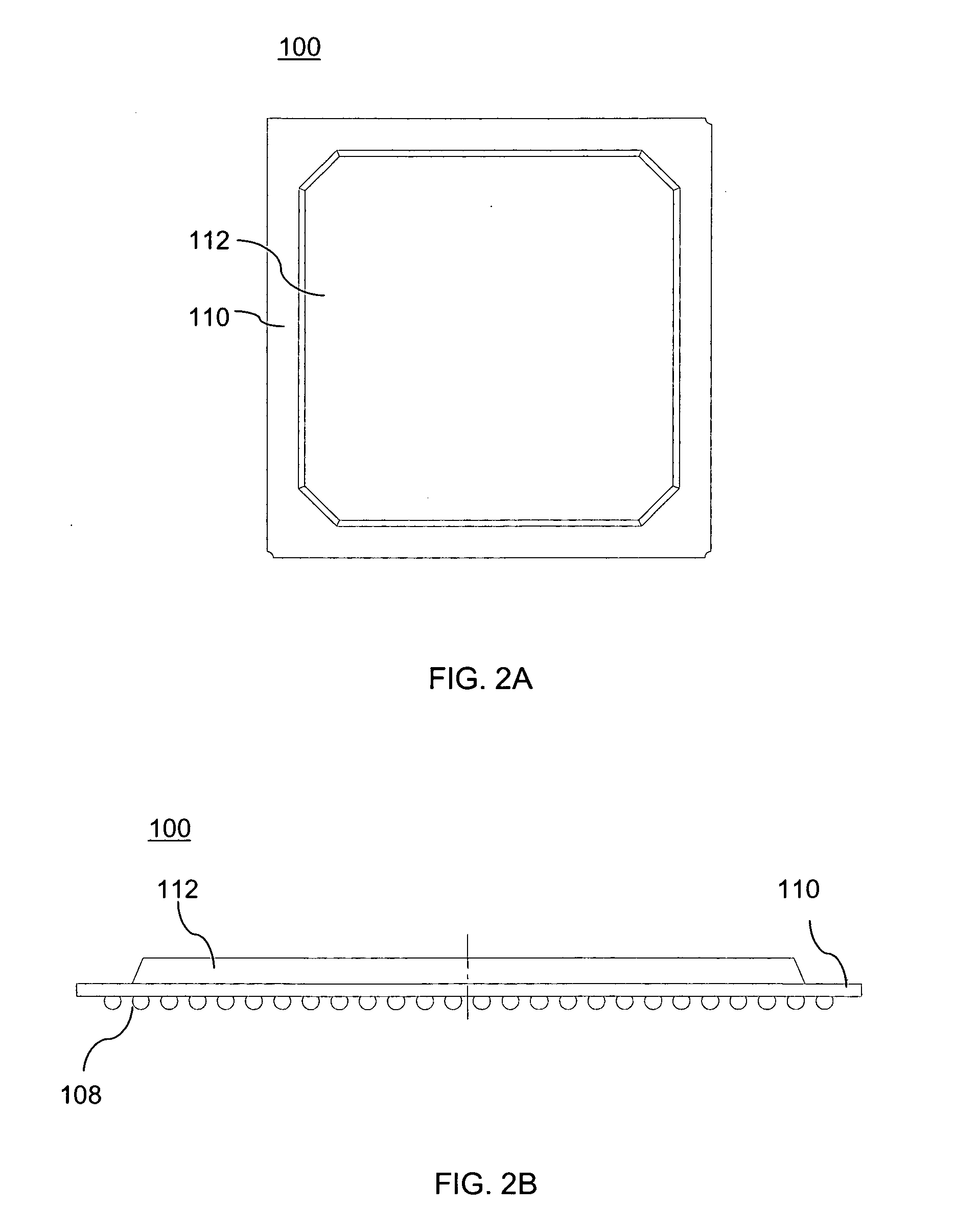

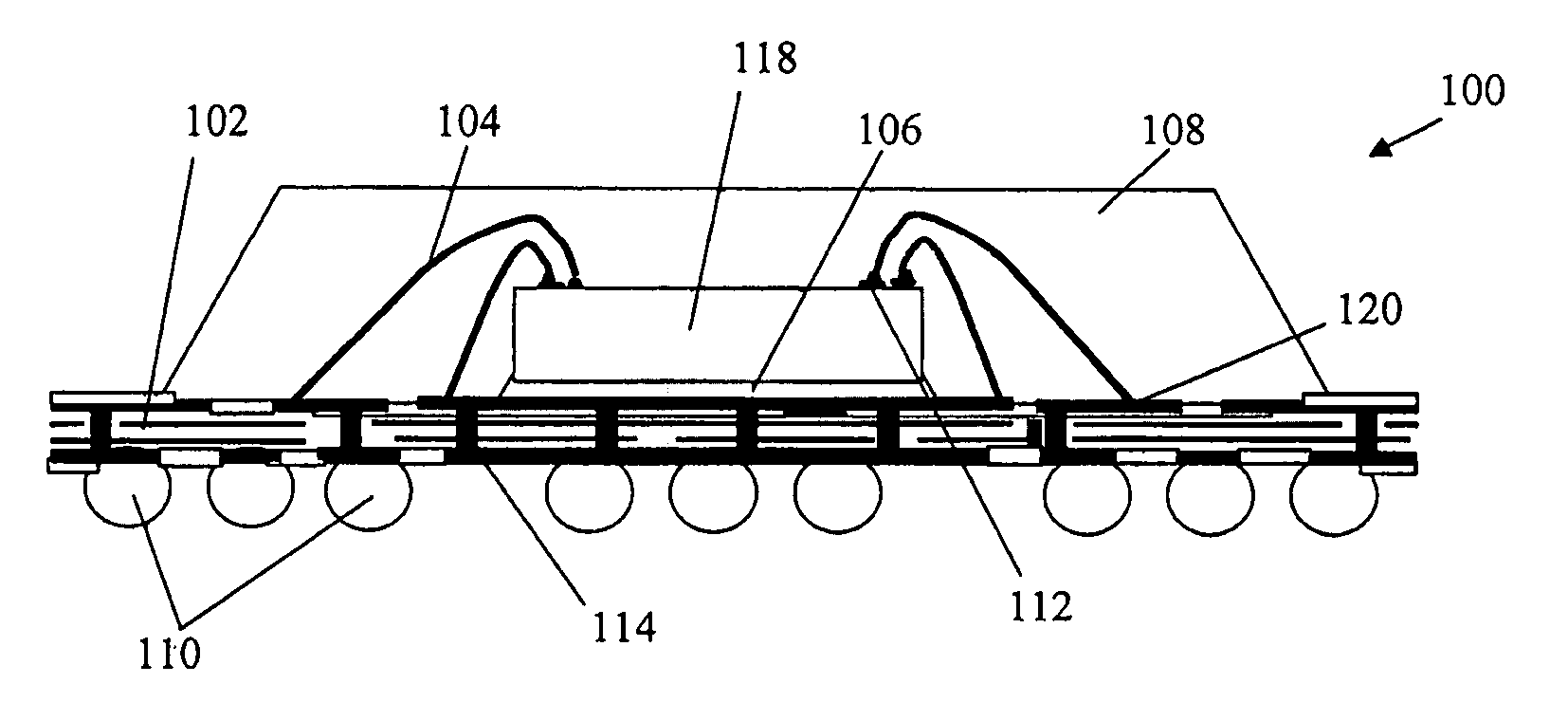

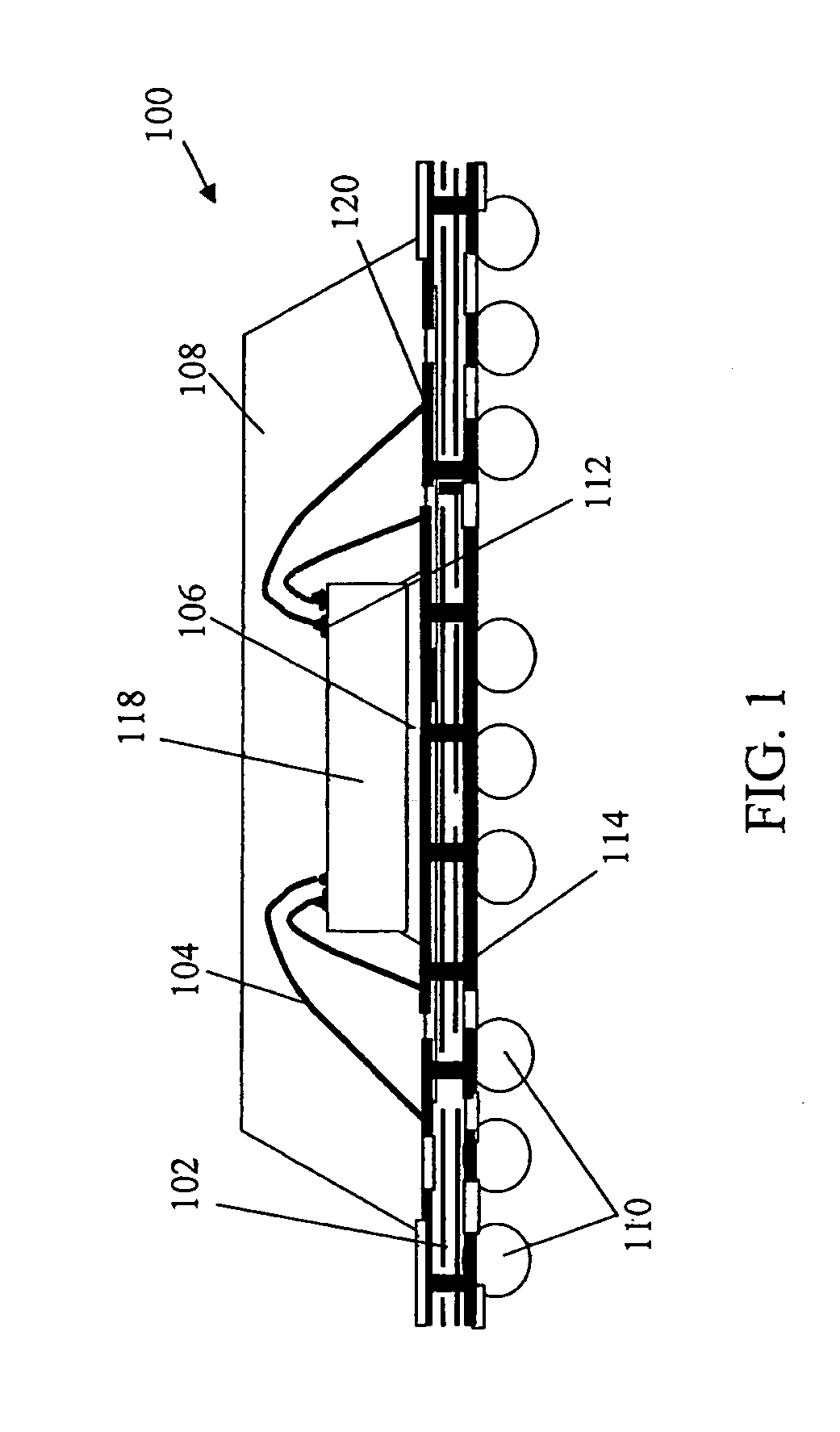

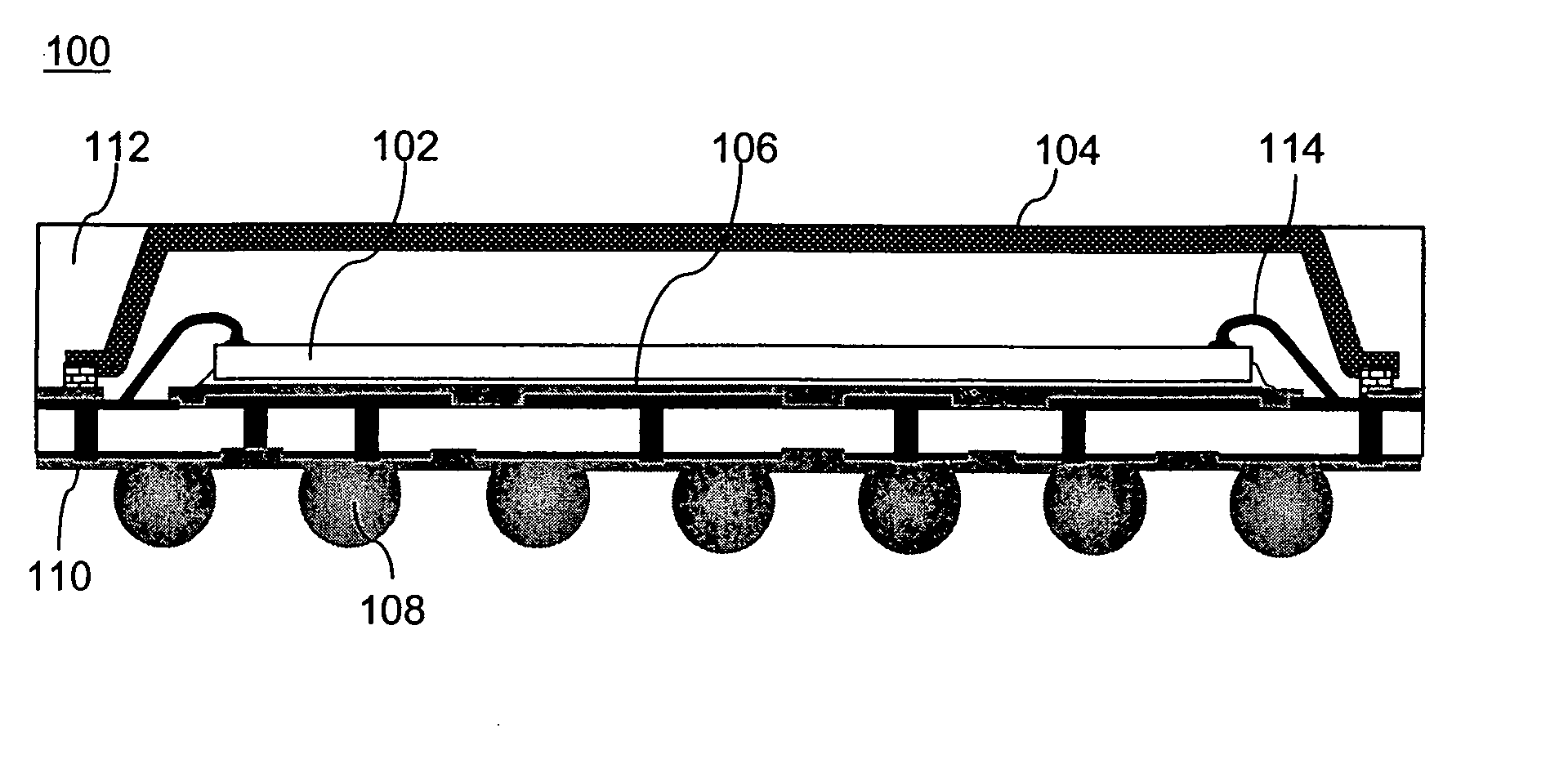

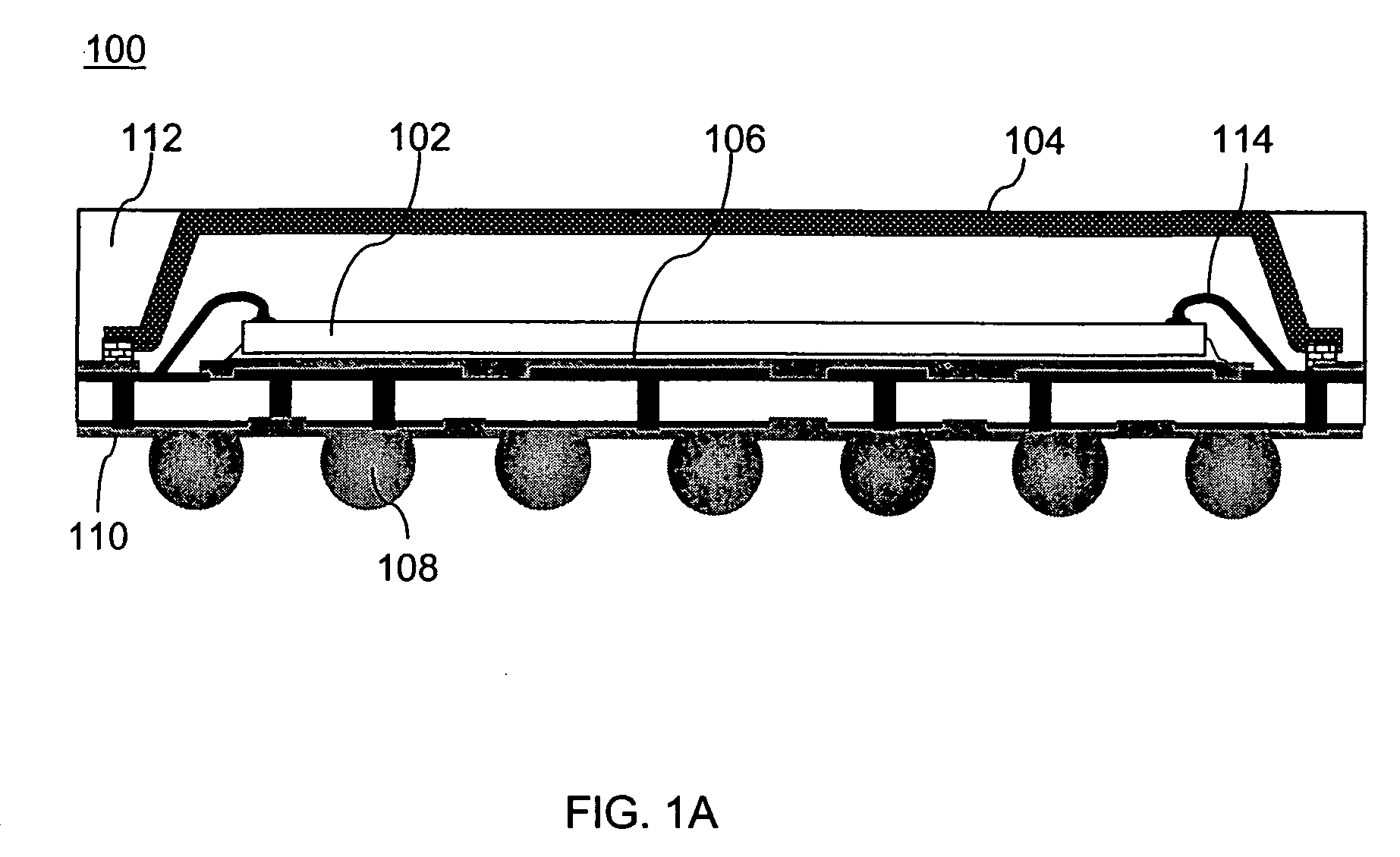

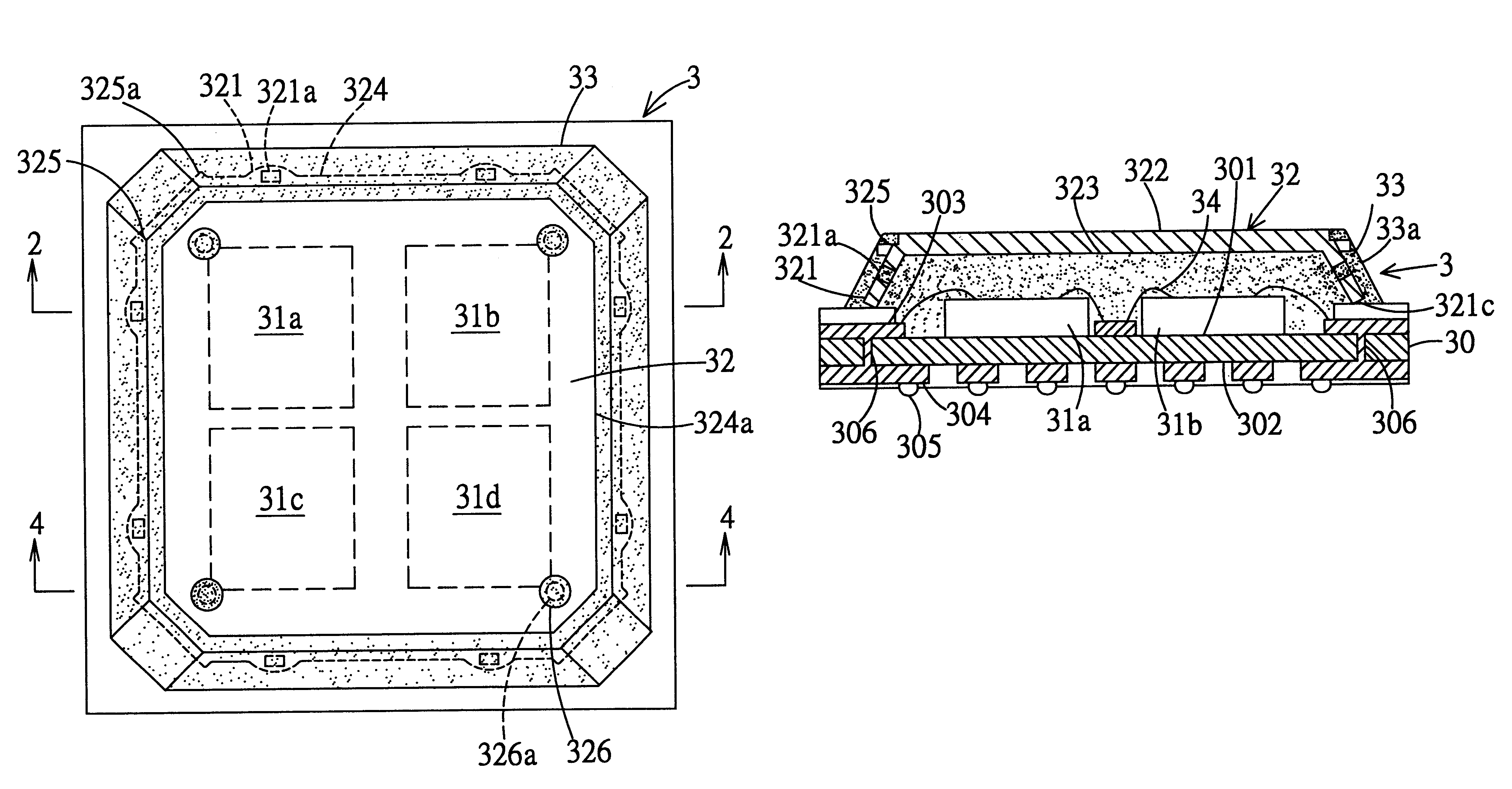

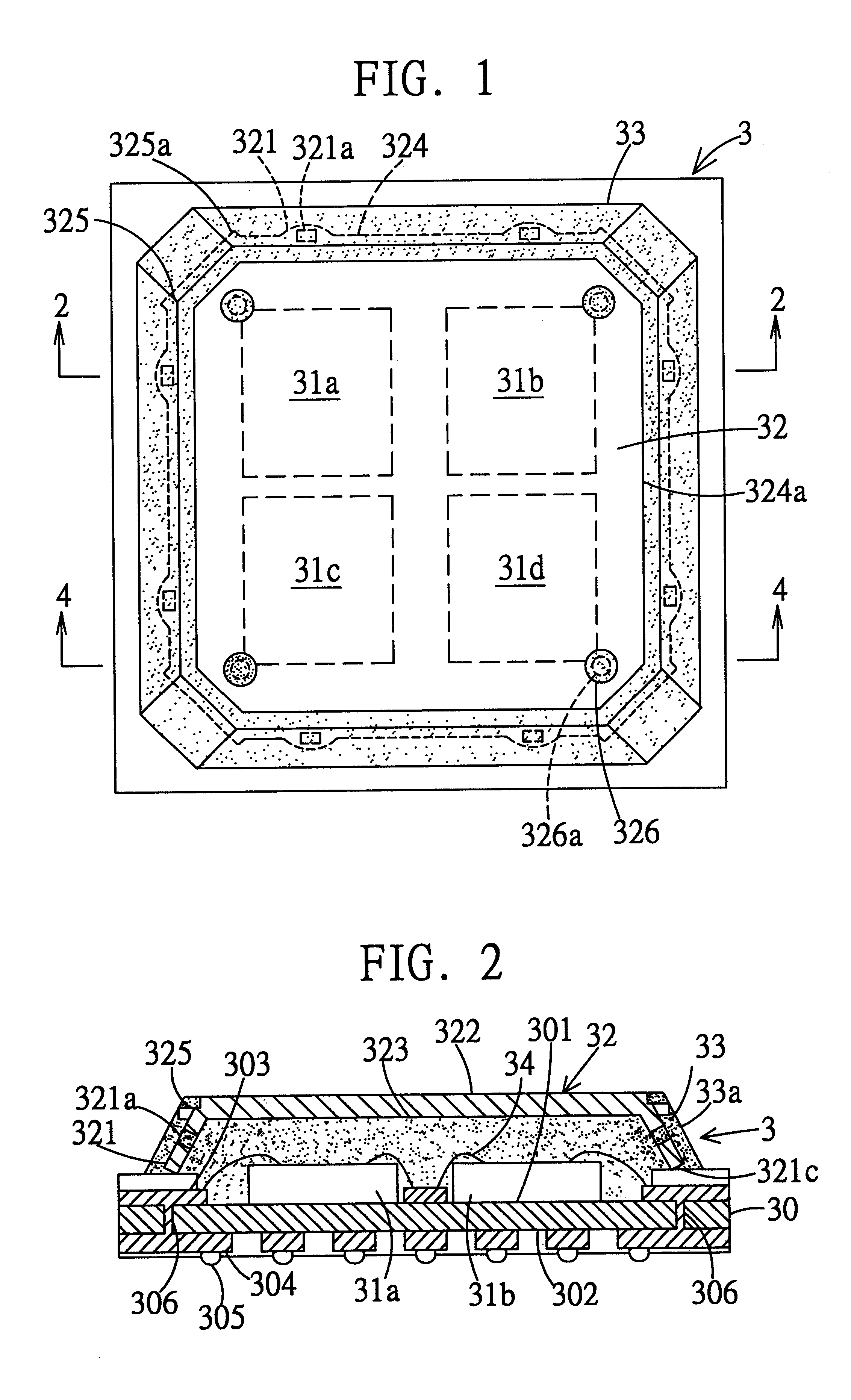

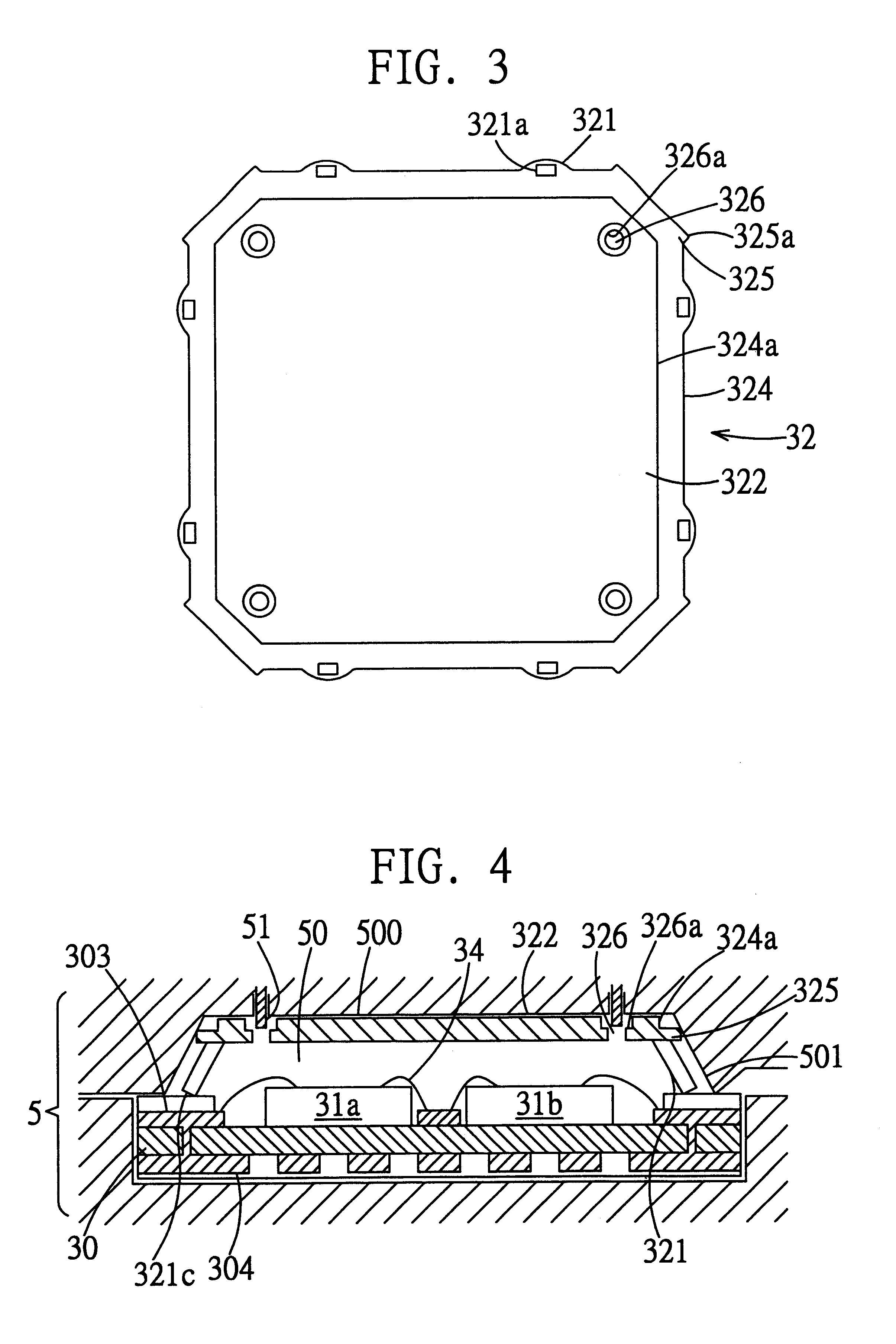

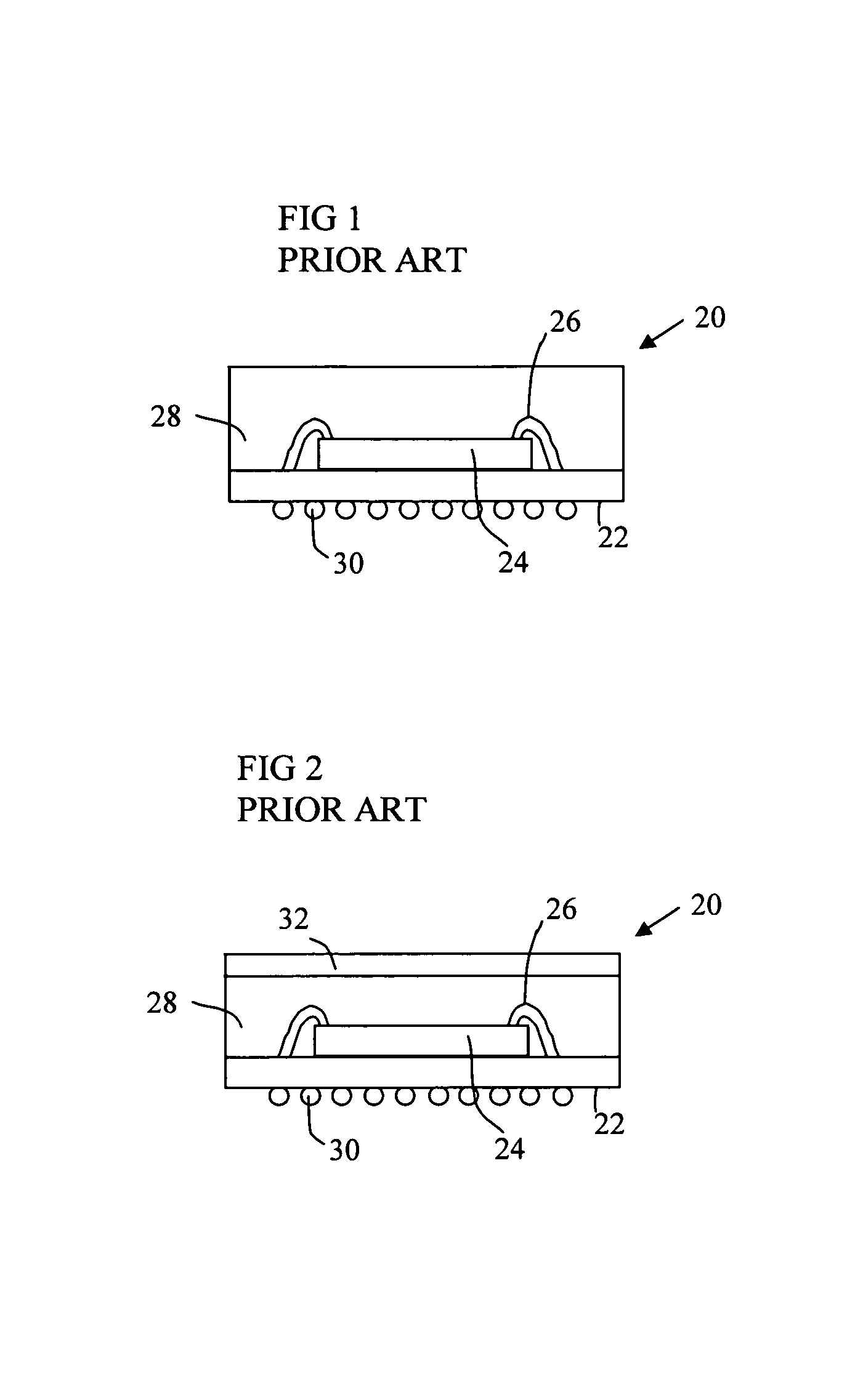

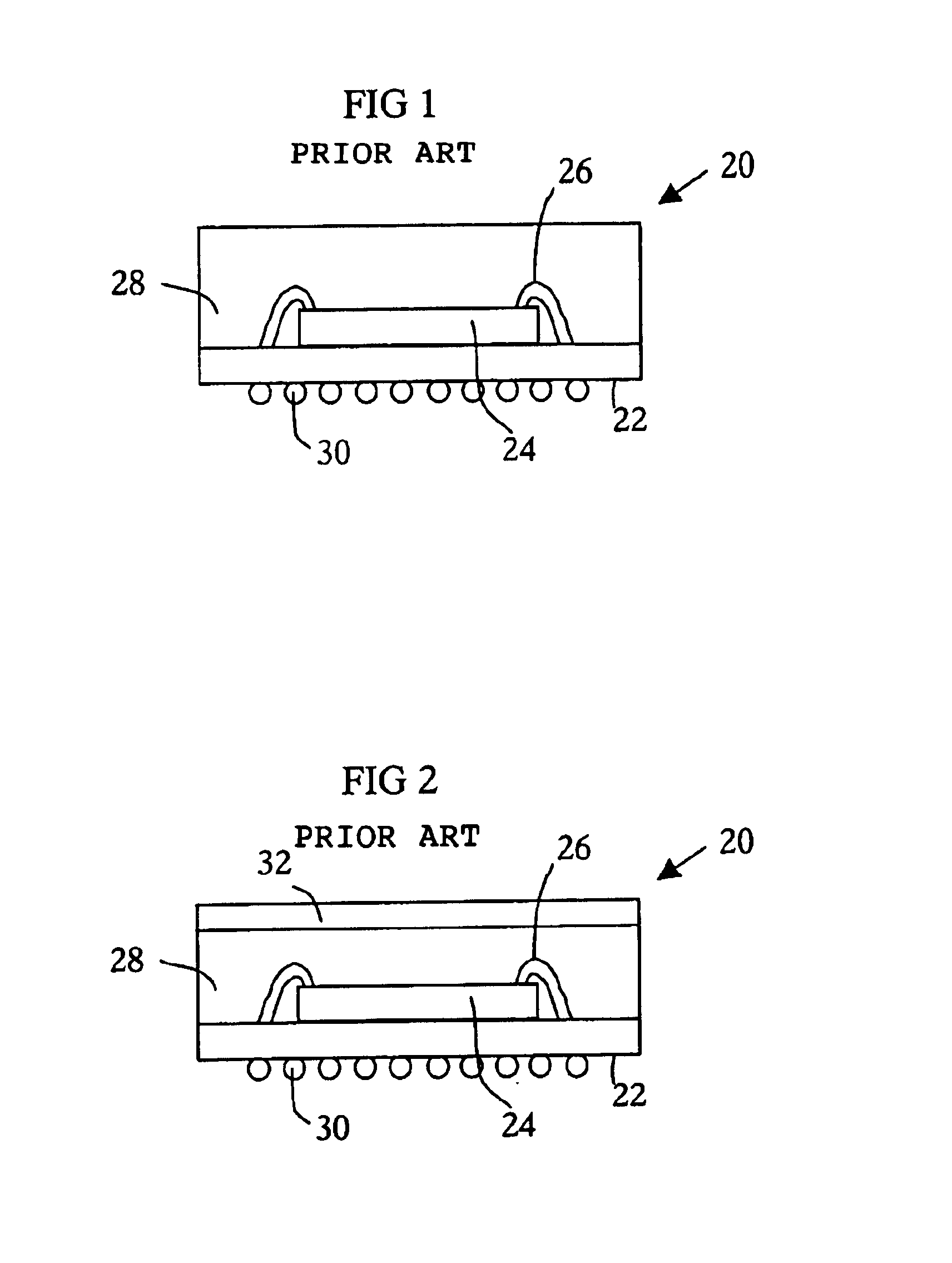

Semiconductor package having a heat sink with an exposed surface

InactiveUS6246115B1Precise positioningAvoid flashSemiconductor/solid-state device detailsSolid-state devicesAdhesiveSemiconductor package

An integrated circuit package with a fully-exposed heat sink is provided. The integrated circuit package includes a substrate having a first side being formed with first conductive traces and a second side being formed with second conductive traces. At least one chip is mounted on the substrate and electrically connected to the first conductive traces. A plurality of solder balls are provided at the terminal ends of the second conductive traces to allow external connection of the chip. The fully-exposed heat sink is mounted on the substrate. The heat sink is formed with a plurality of supportive legs arranged in such a manner as to allow a bottom surface of the heat sink to be separated from the chip and a top surface of the heat sink to be tightly attached to a cavity in a mold used to form an encapsulant for enclosing the chip. A plurality of positioning tongues are formed on the heat sink for securing the heat sink in position when performing a molding process for forming the encapsulant. With this integrated circuit package, no jig is required in the assembly of the integrated circuit package. Moreover, since there is no need to use adhesives to adhere the supportive legs onto the substrate, the integrated circuit package would not suffer from delamination as in the case of the prior art. The fully-exposed heat sink allows an increased heat-dissipating efficient as compared to the prior art.

Owner:SILICONWARE PRECISION IND CO LTD

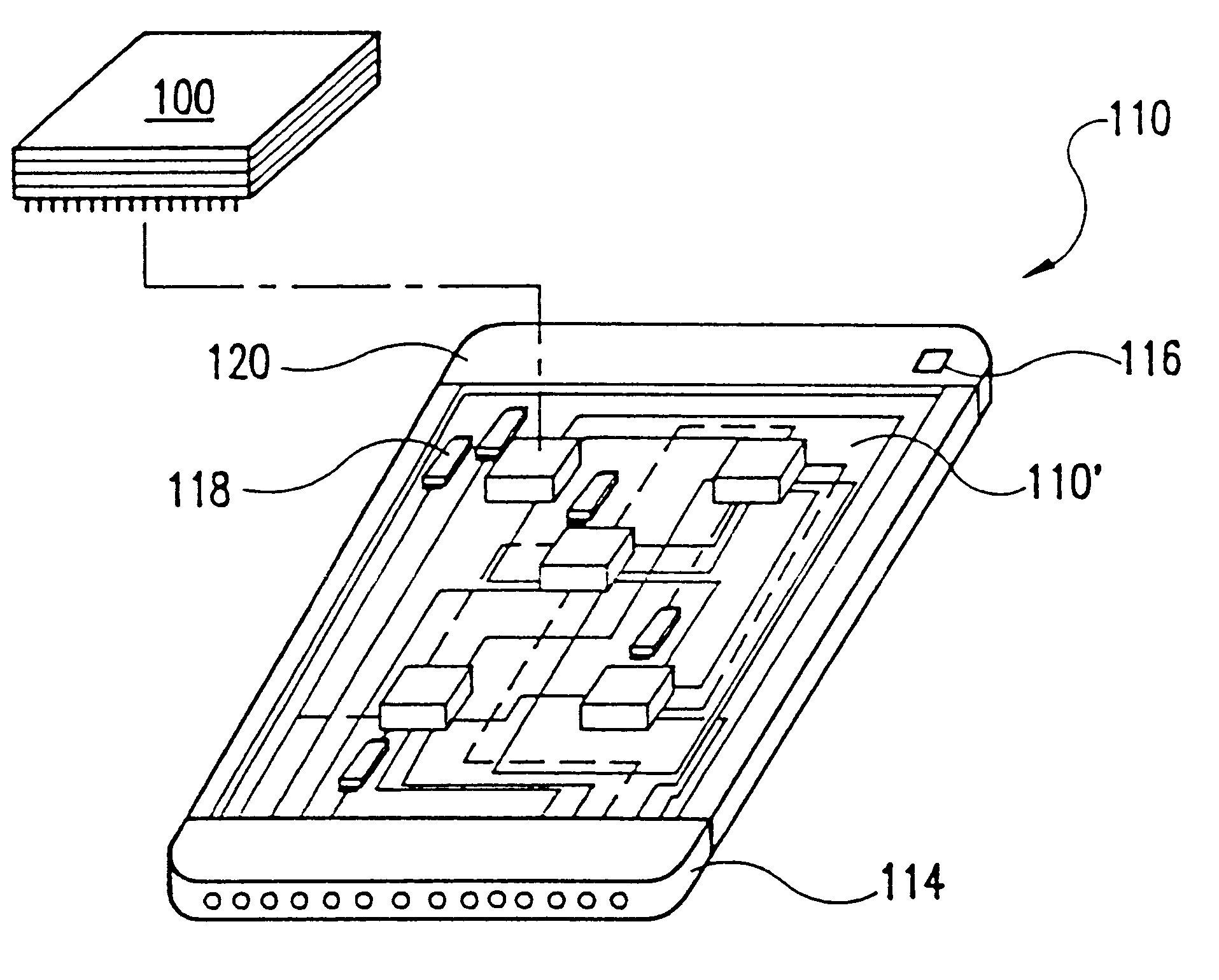

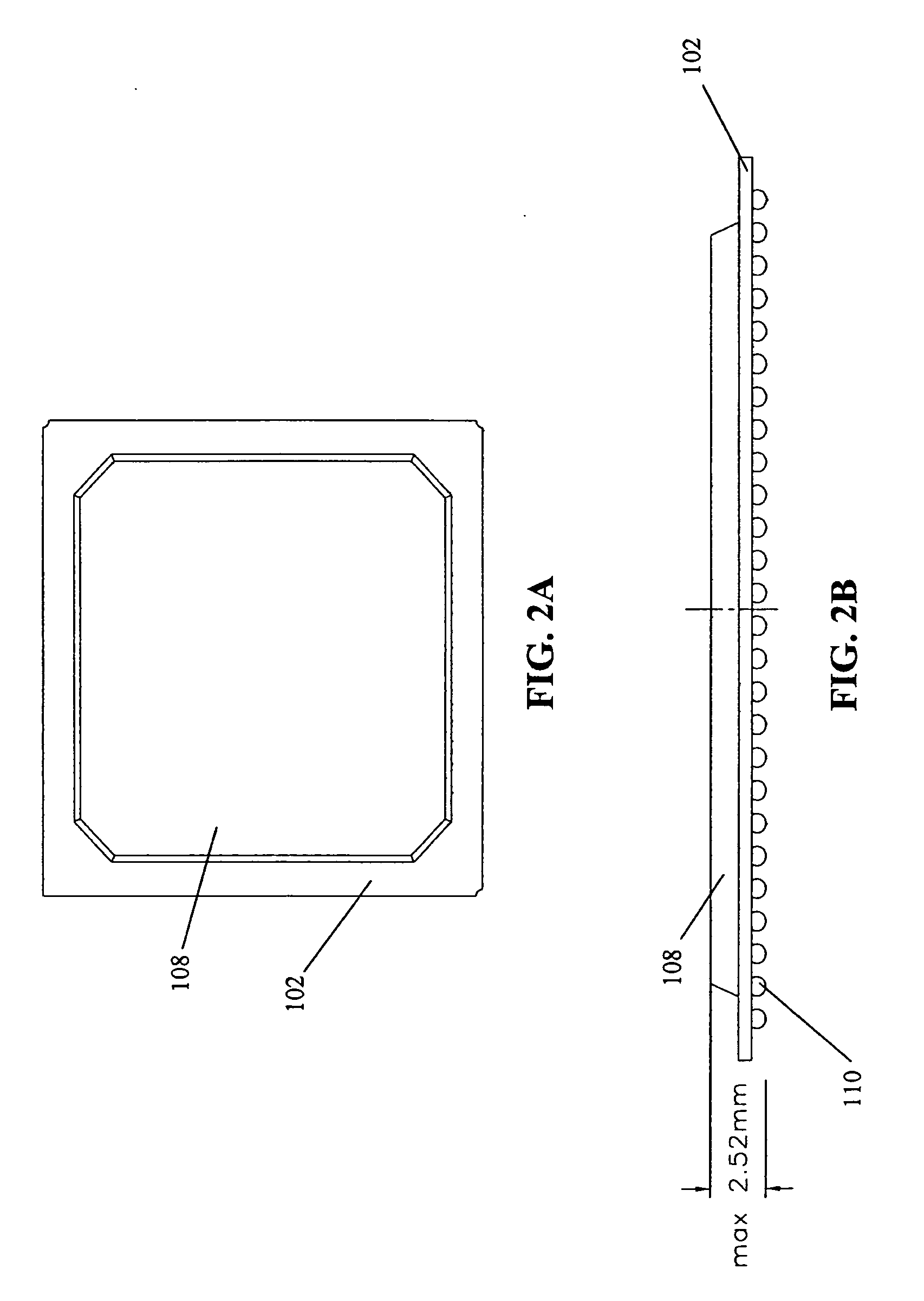

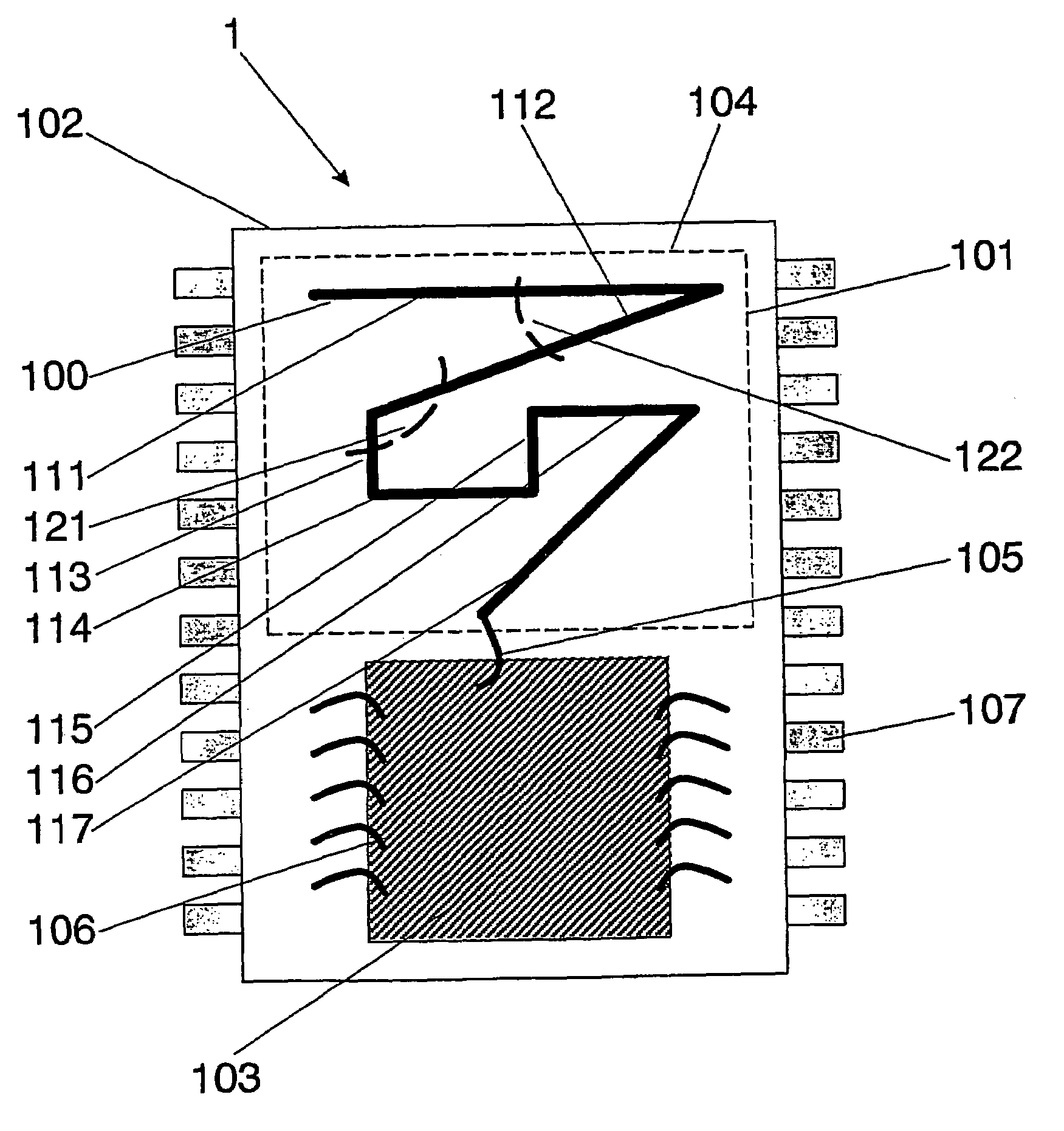

Integrated circuit package including miniature antenna

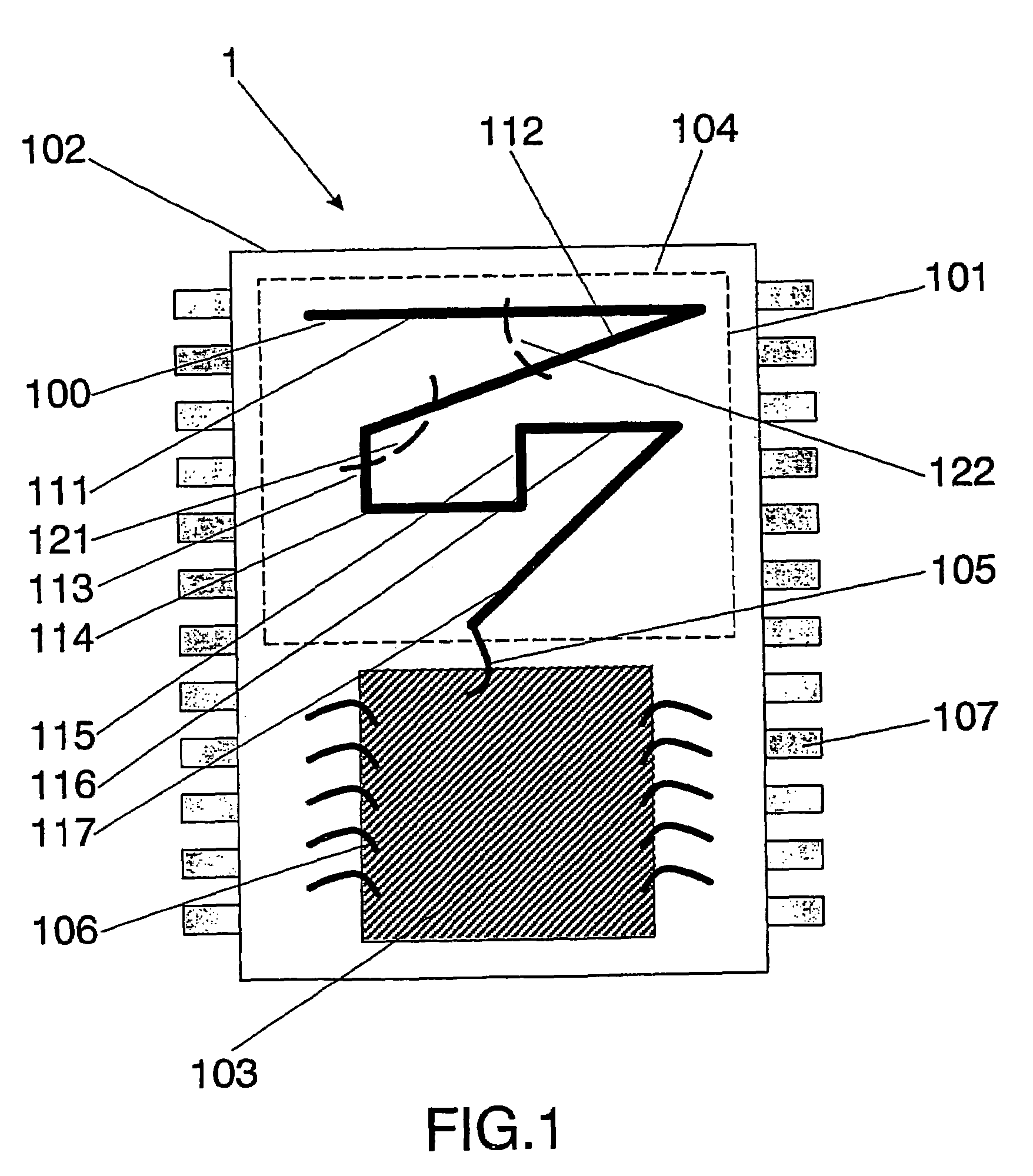

InactiveUS7095372B2Minimize coiling effectEfficient integrationResonant long antennasSimultaneous aerial operationsSemiconductor chipEngineering

The present invention relates to an integrated circuit package comprising at least one substrate, each substrate including at least one layer, at least one semiconductor die, at least one terminal, and an antenna located in the integrated circuit package, but not on said at least one semiconductor die. The conducting pattern comprises a curve having at least five sections or segments, at least three of the sections or segments being shorter than one-tenth of the longest free-space operating wavelength of the antenna, each of the five sections or segments forming a pair of angles with each adjacent segment or section, wherein the smaller angle of each of the four pairs of angles between sections or segments is less than 180° (i.e., no pair of sections or segments define a longer straight segment), wherein at least two of the angles are less than 115°, wherein at least two of the angles are not equal, and wherein the curve fits inside a rectangular area the longest edge of which is shorter than one-fifth of the longest free-space operating wavelength of the antenna.

Owner:FRACTUS

Antenna arrangement

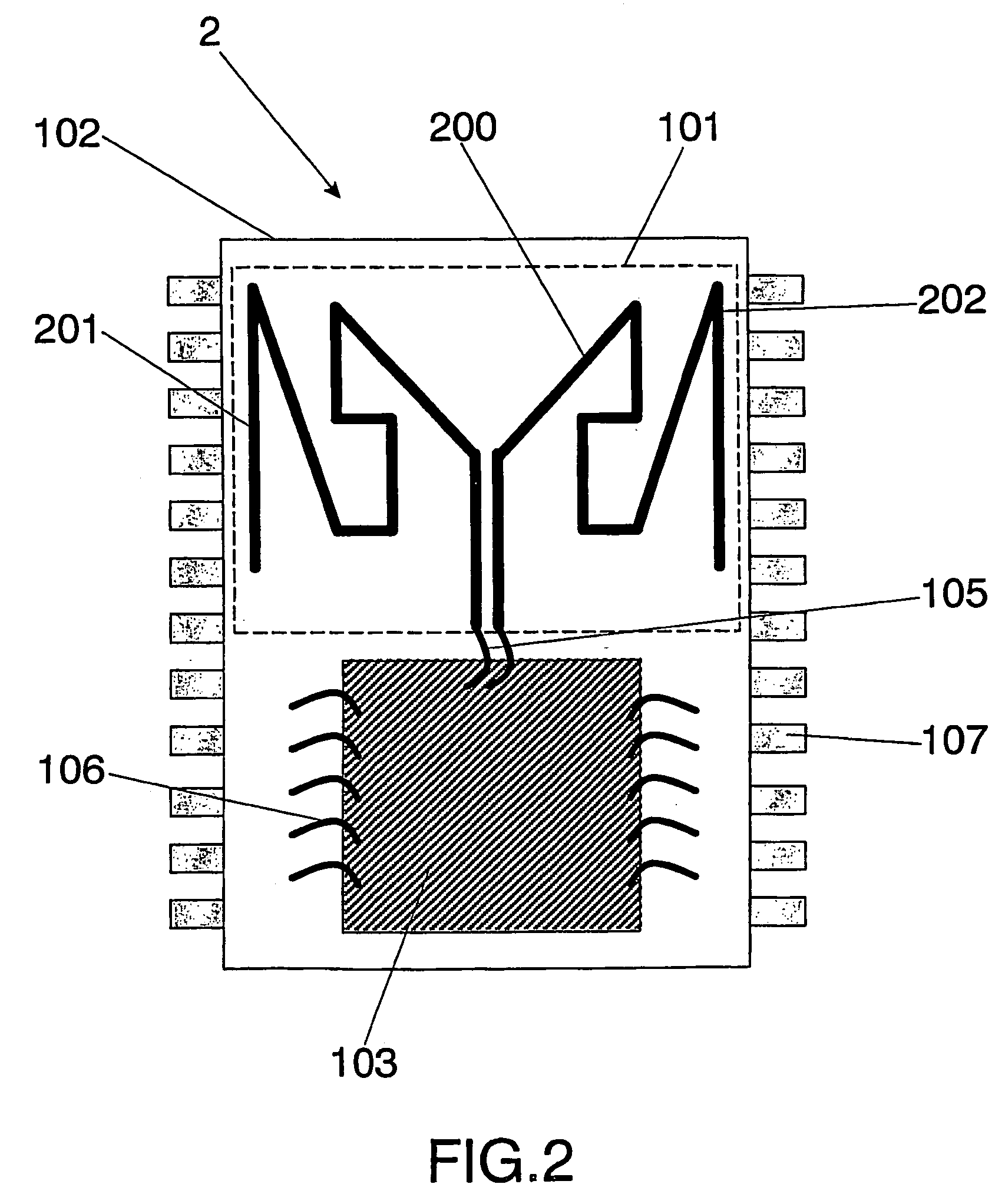

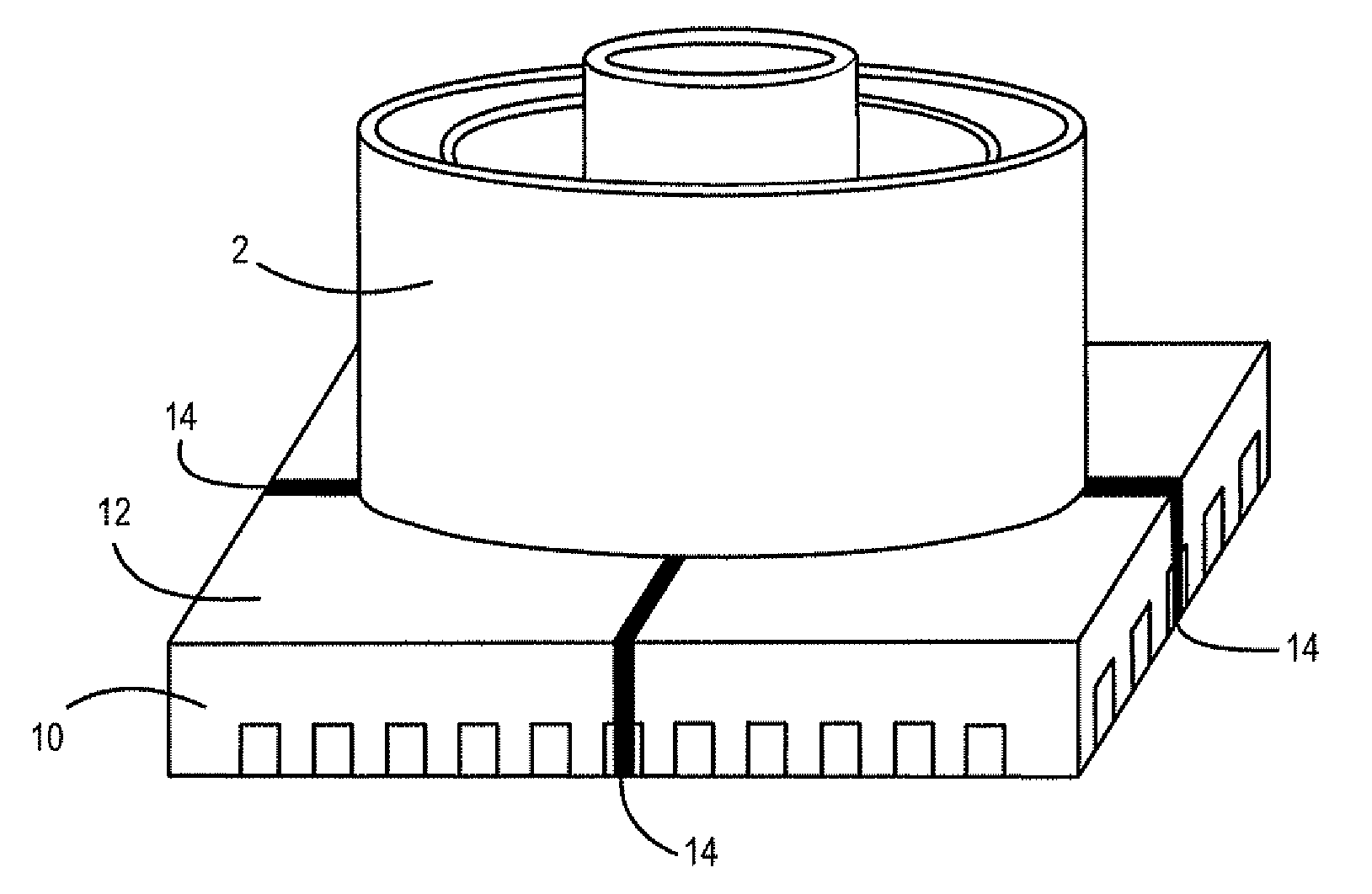

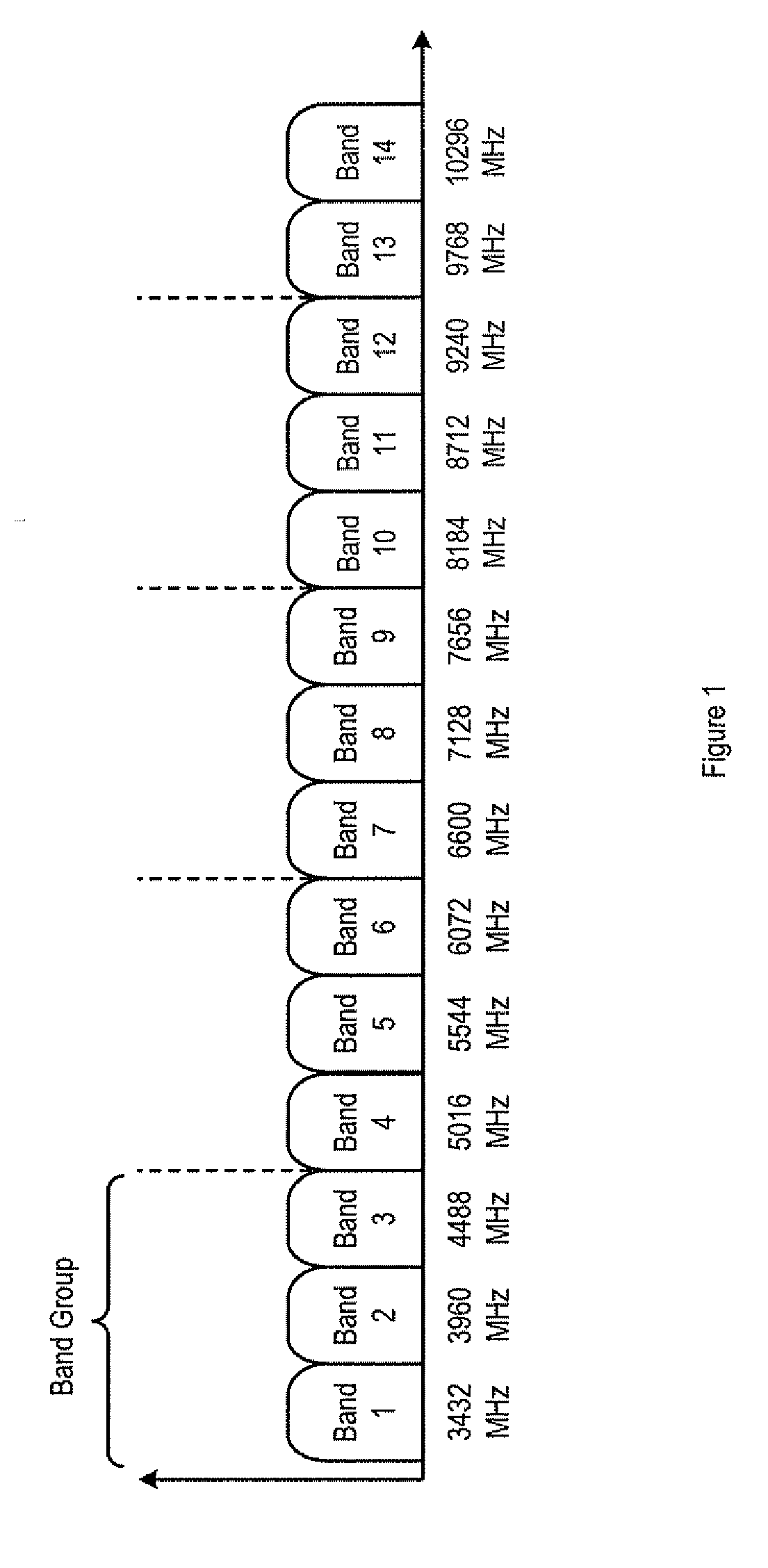

InactiveUS20080024376A1Small sizeSemiconductor/solid-state device detailsSolid-state devicesUltra-widebandElectricity

There is provided an antenna for use in an ultra-wideband device, wherein the antenna is used as an RF radiator and as a heat sink. There is also provided a device for use in an ultra wideband network, the device comprising a component, for example an integrated circuit package, that generates unwanted heat as part of its normal operation, the device further comprising an antenna as described above placed in thermal contact with the component. The antenna may be electrically connected to one or more pins of the component. Alternatively, the antenna may be capacitively connected to the component. There is also provided a heat sink for a wireless communications device, the heat sink being shaped such that it can operate as an antenna for radio frequencies.

Owner:ITI SCOTLAND

Electromagnetic shield formation for integrated circuit die package

InactiveUS20090075428A1Semiconductor/solid-state device detailsSolid-state devicesConductive materialsElectromagnetic shielding

Electromagnetic shielding for an integrated circuit packaged device. The method includes forming shielding structures by forming openings in an encapsulated structure. The openings are filled with conductive material that surrounds at least one die. The encapsulated structure may include a plurality of integrated circuit die. A layered redistribution structure is formed on one side of the encapsulated structure.

Owner:NORTH STAR INNOVATIONS

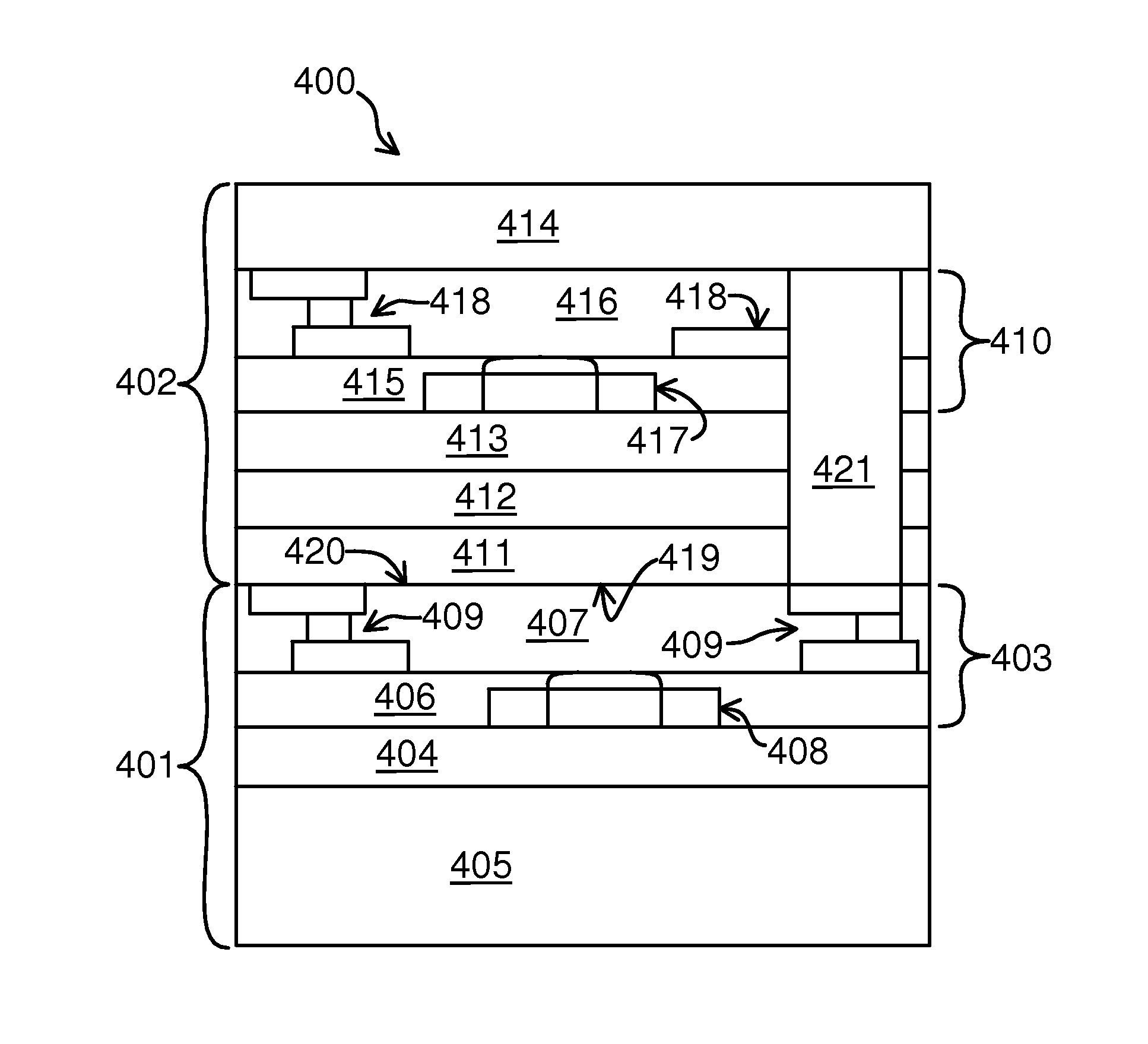

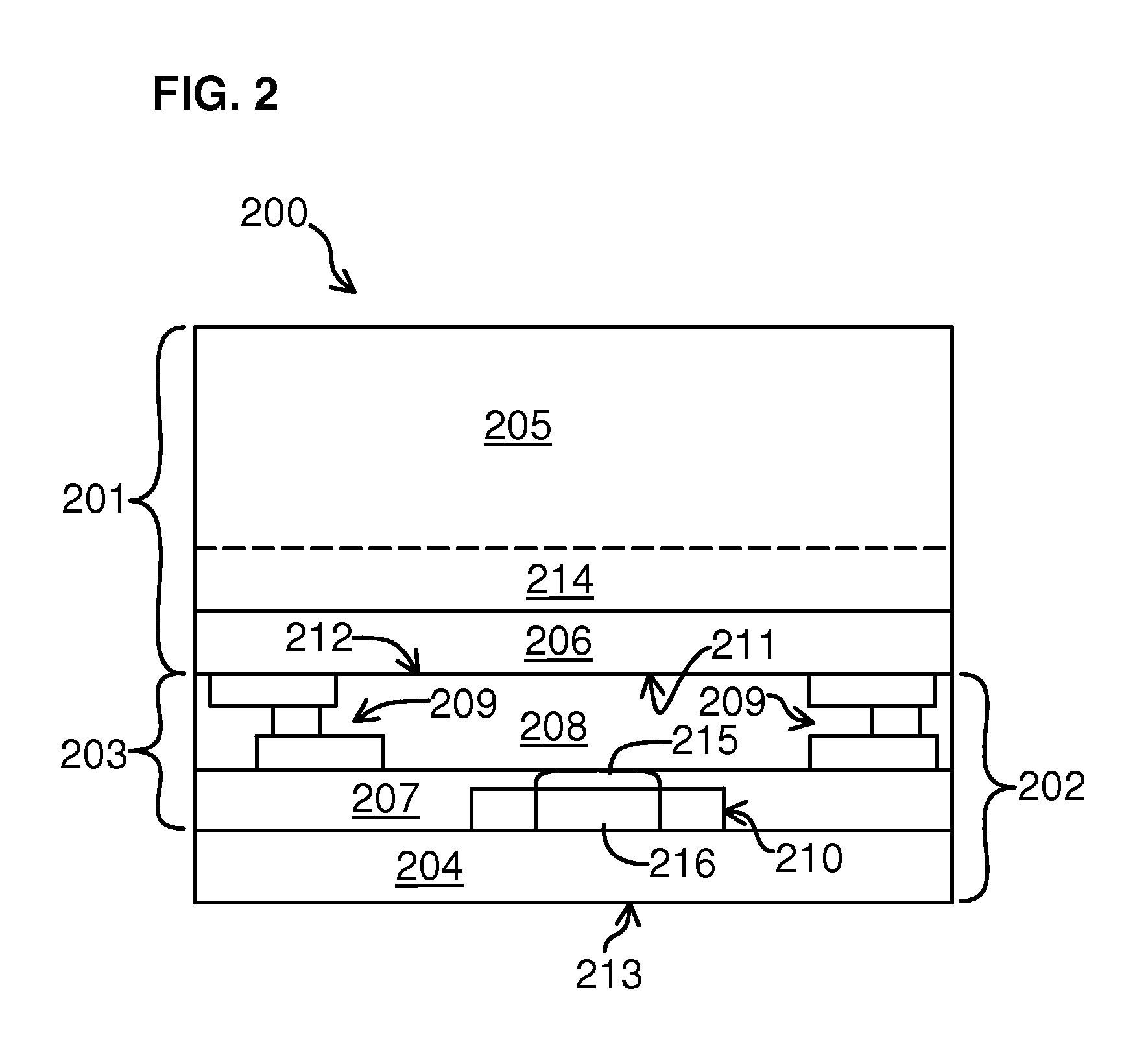

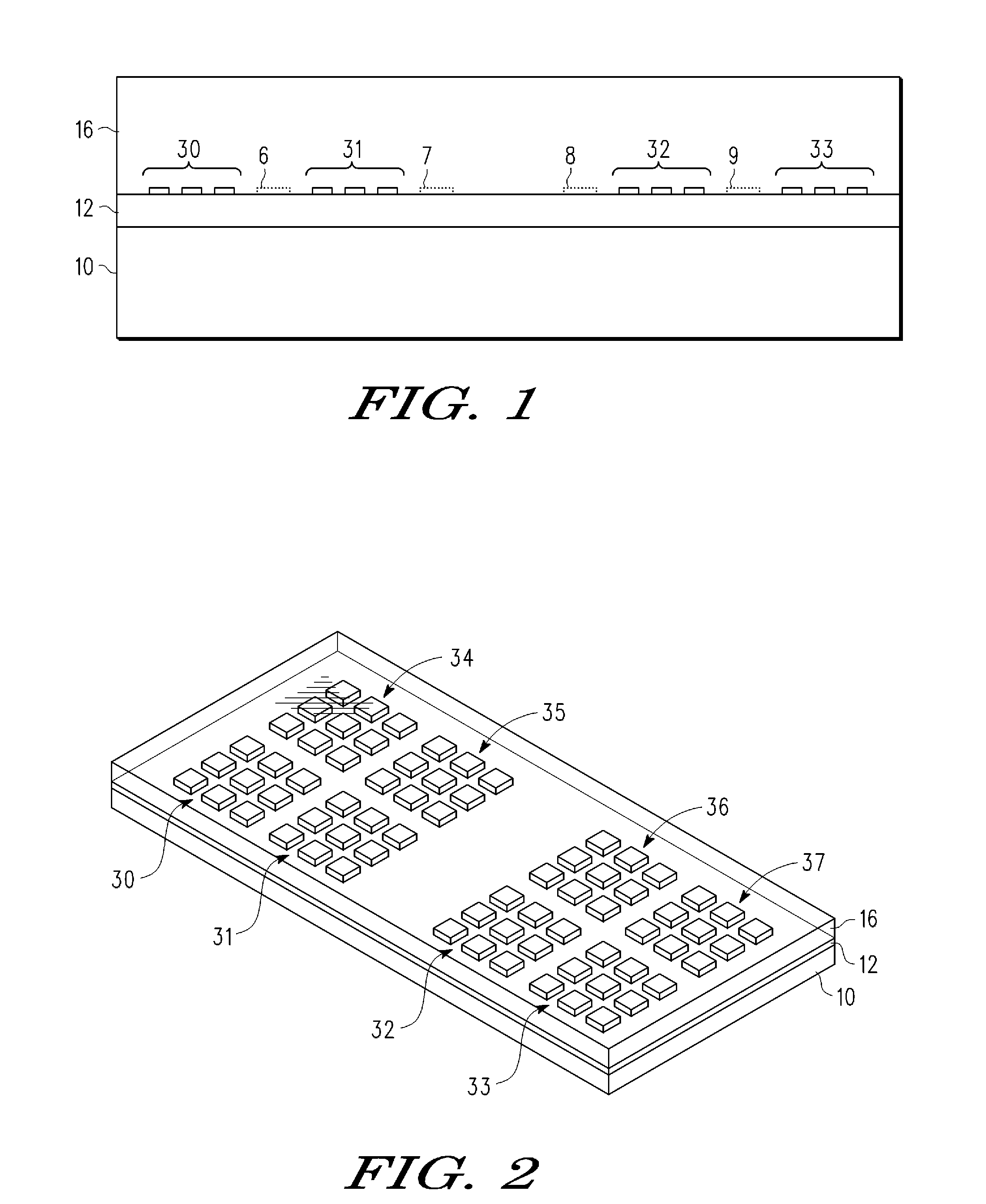

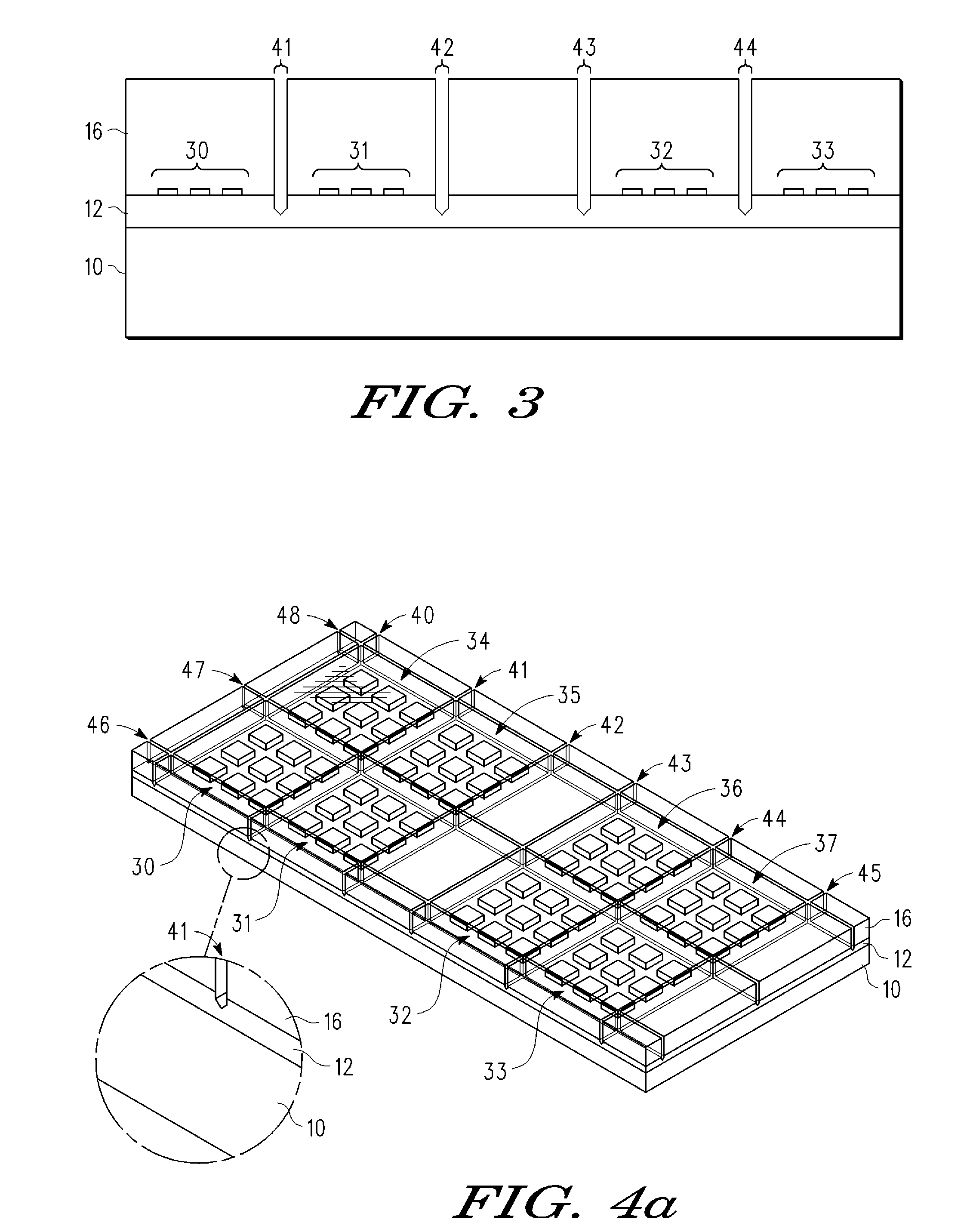

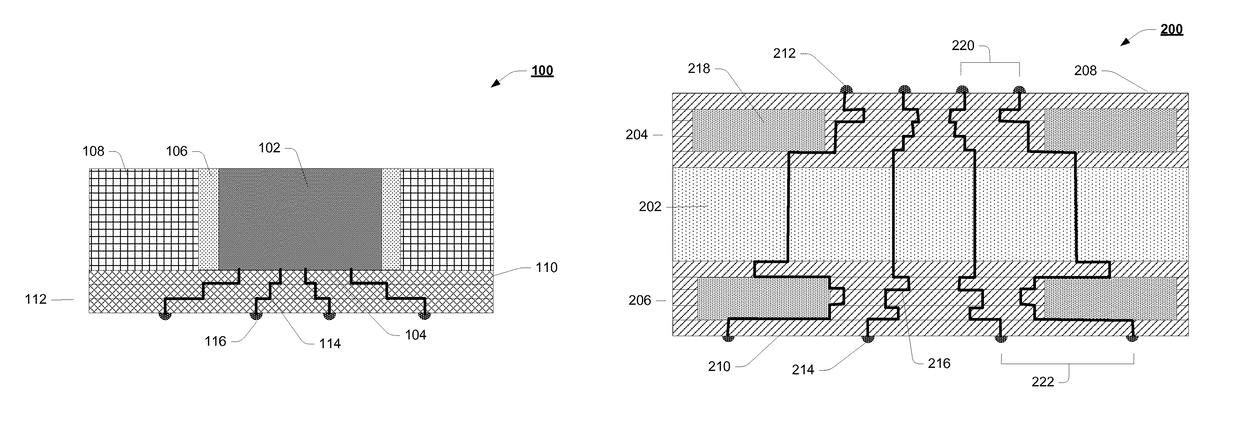

Integrated circuit packages including high density bump-less build up layers and a lesser density core or coreless substrate

In some embodiments, integrated circuit packages including high density bump-less build up layers and a lesser density core or coreless substrate are presented. In this regard, an apparatus is introduced having a first element including a microelectronic die having an active surface and at least one side, an encapsulation material adjacent said at least one microelectronic die side, wherein said encapsulation material includes at least one surface substantially planar to said microelectronic die active surface, a first dielectric material layer disposed on at least a portion of said microelectronic die active surface and said encapsulation material surface, a plurality of build-up layers disposed on said first dielectric material layer, and a plurality of conductive traces disposed on said first dielectric material layer and said build-up layers and in electrical contact with said microelectronic die active surface; and a second element coupled to the first element, the second element including a substrate having a plurality of dielectric material layers and conductive traces to conductively couple conductive contacts on a top surface with conductive contacts on a bottom surface, said conductive contacts on said top surface conductively coupled with said conductive traces of said first element. Other embodiments are also disclosed and claimed.

Owner:INTEL CORP

Integrated circuit package and method for fabricating same

ActiveUS7348663B1Reduce electrical impedanceImprove cooling effectSemiconductor/solid-state device detailsSolid-state devicesDielectricContact pad

A process for fabricating an integrated circuit package includes: selectively etching a first side of a substrate thereby providing etched regions of the substrate to partially define at least a plurality of contact pads; adding a dielectric material to the etched regions of the substrate; selectively etching a second side of the substrate to further define at least the plurality of contact pads and thereby provide a package base of at least the contact pads and the dielectric; mounting a semiconductor die to the package base and connecting the semiconductor die to the contact pads; fixing a lid to the package base to cover the semiconductor die in a cavity between the lid and the package base; and singulating to provide the integrated circuit package.

Owner:UTAC HEADQUARTERS PTE LTD

Process for fabricating an integrated circuit package

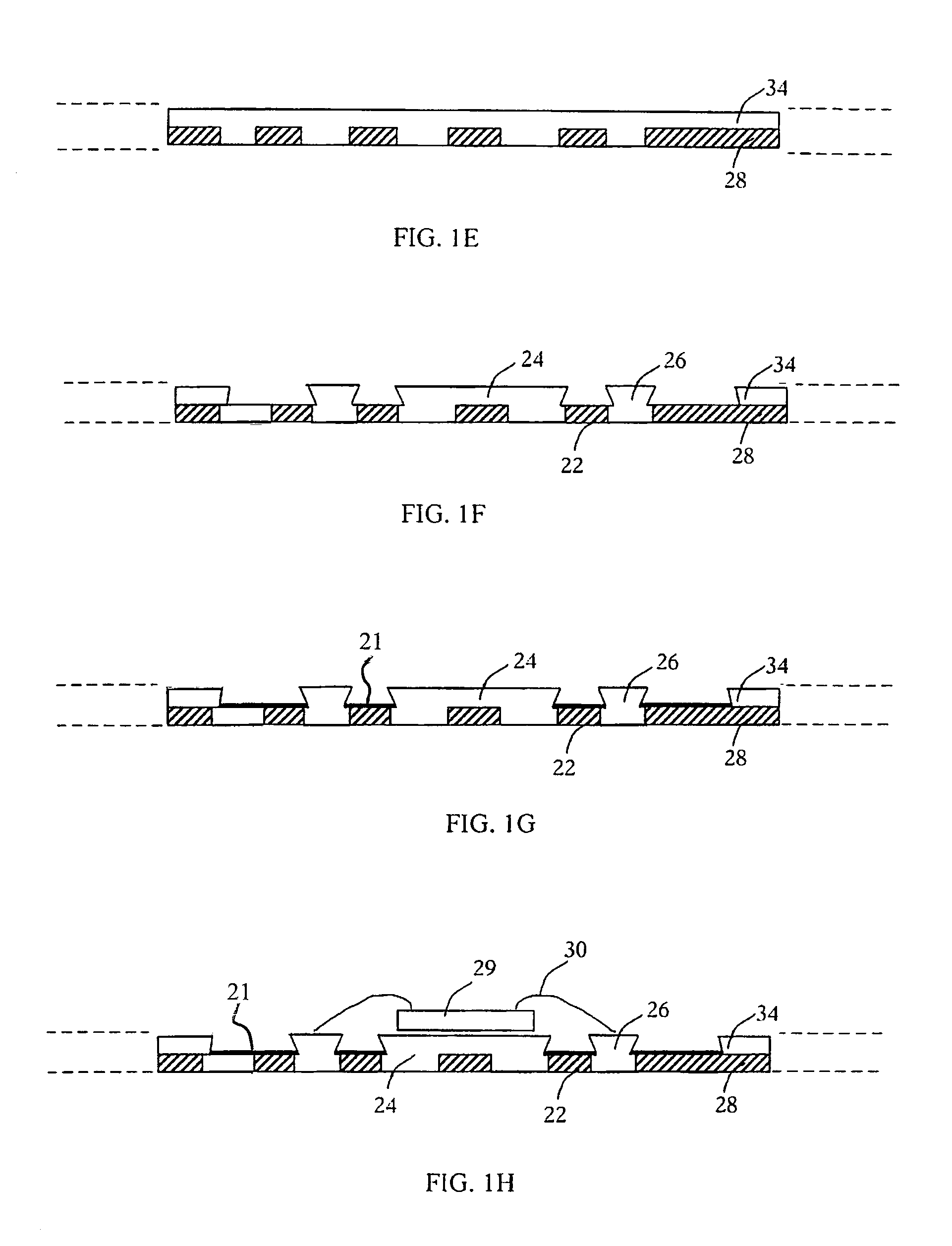

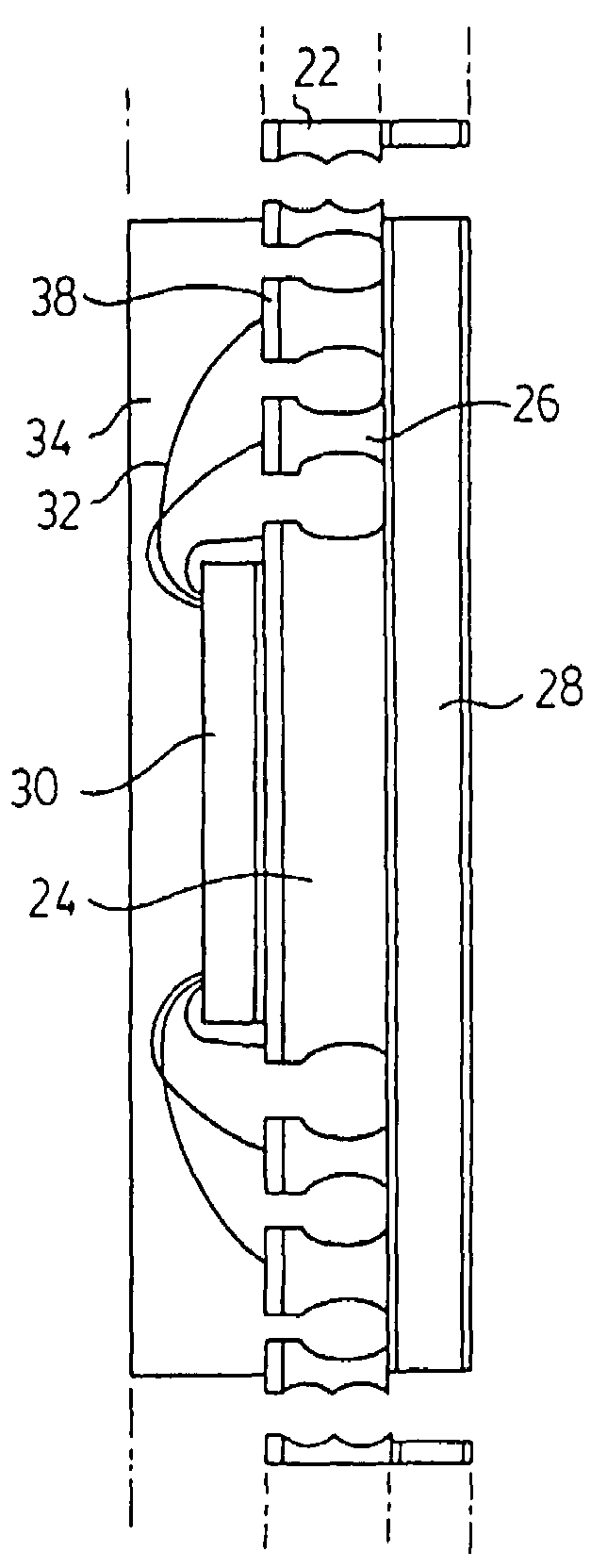

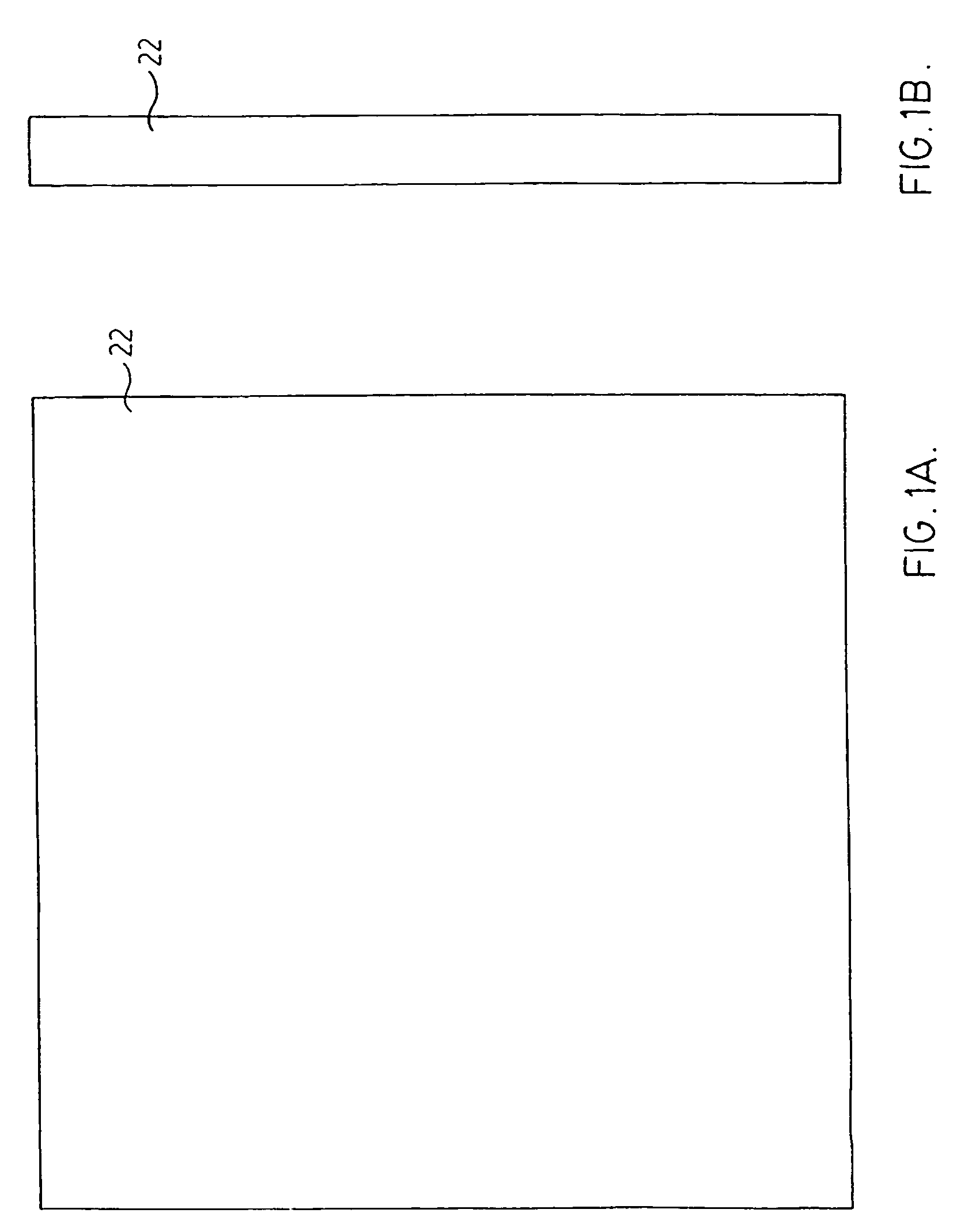

InactiveUS7247526B1Board mount reliabilityReduce manufacturing costSemiconductor/solid-state device detailsSolid-state devicesLead frameSemiconductor

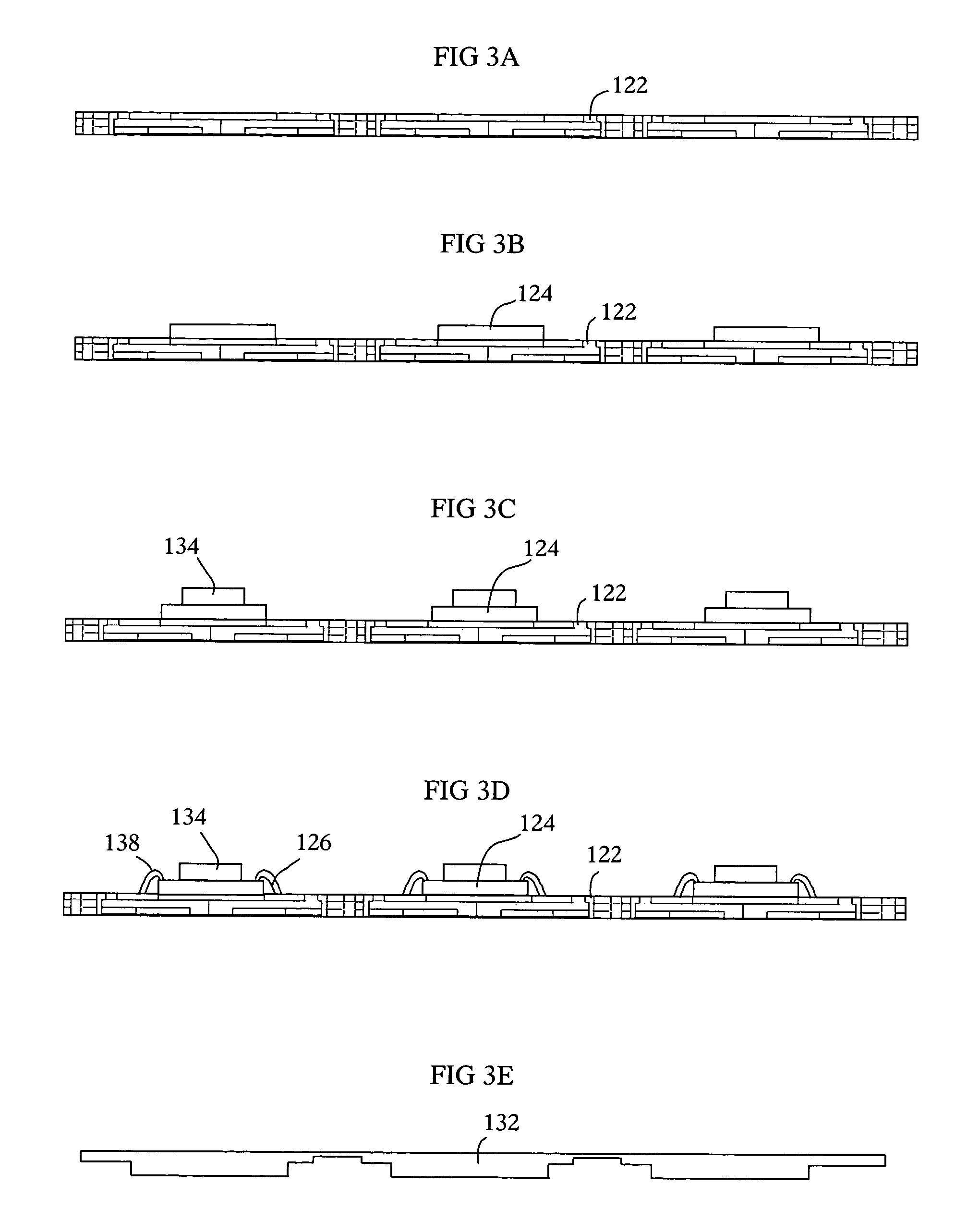

A process for fabricating an integrated circuit package. At least a first side of a leadframe strip is selectively etched to define portions of a die attach pad and at least one row of contacts adjacent the die attach pad. A carrier strip is laminated to the first side of the leadframe strip and a second side of the leadframe strip is selectively etched to thereby define a remainder of the die attach pad and the at least one row of contacts. A semiconductor die is mounted to the die attach pad, on the second side of the leadframe strip and the semiconductor die is wire bonded to ones of the contacts. The second side of the leadframe strip is encapsulating, including the semiconductor die and wire bonds, in a molding material. The carrier strip is removed from the leadframe strip and the integrated circuit package is singulated from a remainder of the leadframe strip.

Owner:UTAC HEADQUARTERS PTE LTD

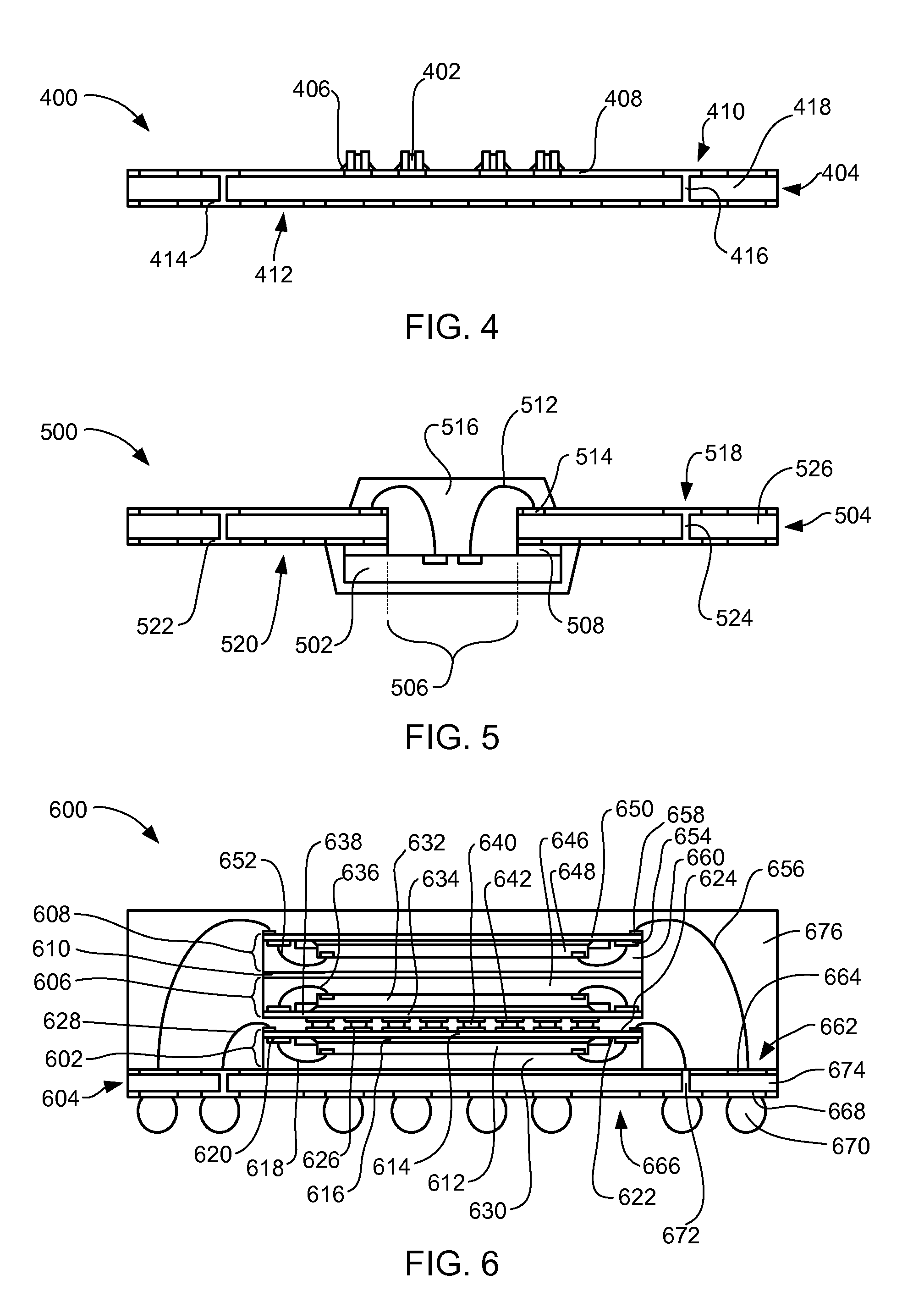

Integrated circuit packaging system with multipart conductive pillars and method of manufacture thereof

ActiveUS8217502B2Semiconductor/solid-state device detailsSolid-state devicesSemiconductor chipInterposer

A method of manufacture of an integrated circuit packaging system includes: providing a pillar ball; mounting an interposer having a first functional side and a second functional side over the pillar ball and a semiconductor chip; encapsulating the interposer, the pillar ball, and the semiconductor chip with an encapsulation; forming a via through the first functional side and the second functional side of the interposer, and through the encapsulation to expose a portion of the pillar ball; and filling the via with a pillar post.

Owner:STATS CHIPPAC LTD

Methods and apparatus for controlling series-connected leds

ActiveUS20080122376A1Increase volumeElectrical apparatusElectroluminescent light sourcesEngineeringOperating voltage

Methods and apparatus for controlling series-connected LEDs. Two or more LEDs are connected in series between a first node and a second node, wherein a series current flows between the nodes when an operating voltage is applied across the nodes. One or more controllable current paths are connected in parallel with at least a first LED for at least partially diverting the series current around at least the first LED. A controller monitors at least one parameter representative of the operating voltage, determines a maximum number of the series-connected LEDs that can be energized by the operating voltage, and controls the controllable current path(s) so as to increase an amount of the series current that is diverted around at least the first LED when the maximum number is less than a total number of all of the LEDs connected in series. In one example, the foregoing may be implemented as an integrated circuit package to provide a lighting apparatus suitable for automotive applications.

Owner:SIGNIFY NORTH AMERICA CORP

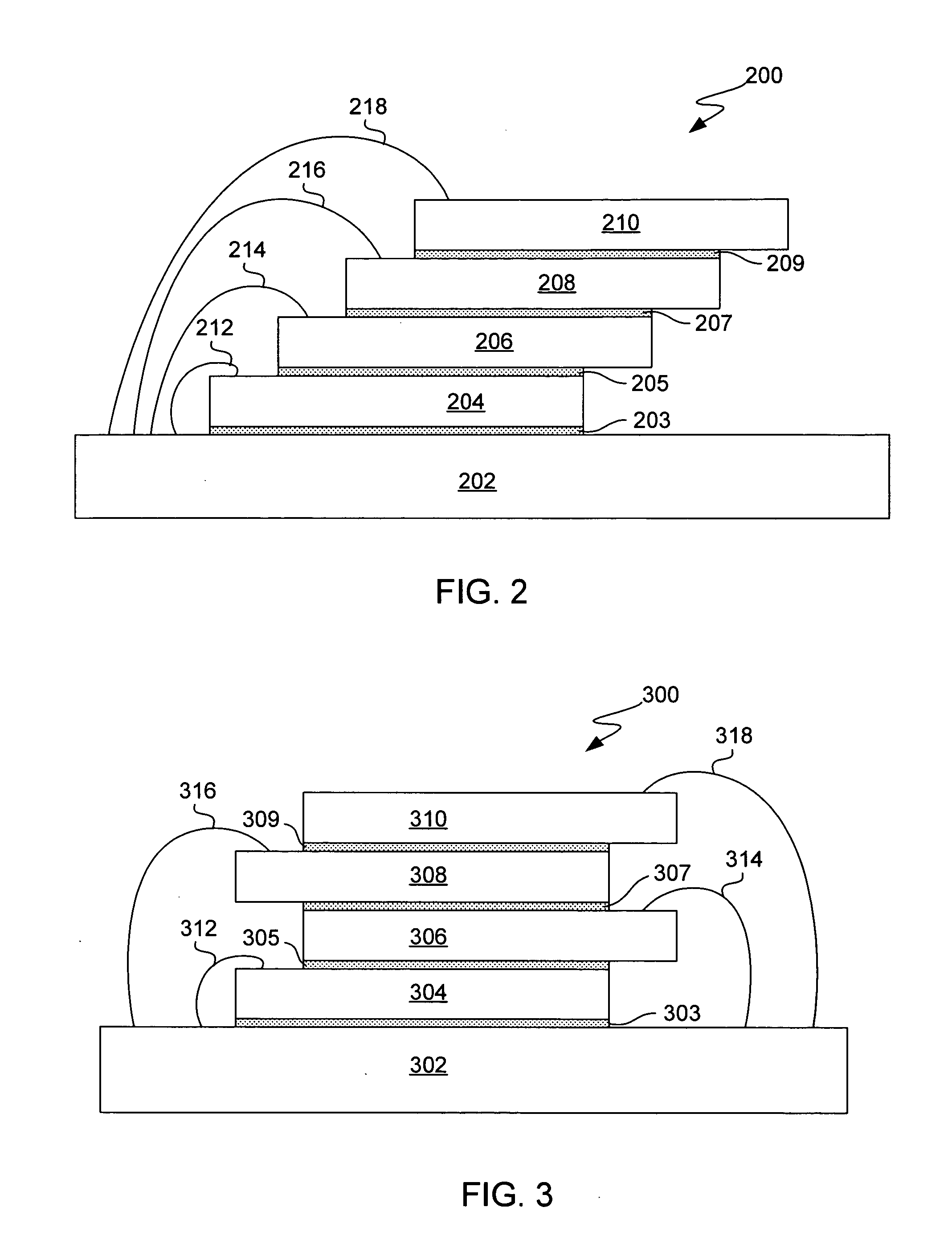

Integrated circuit package having stacked integrated circuits and method therefor

InactiveUS20060267173A1Great stacking densityReduce in quantitySemiconductor/solid-state device detailsSolid-state devicesElectrical connectionEngineering

Improved techniques for stacking integrated circuit dies within an integrated circuit package are disclosed. These improved techniques allow greater stacking density of integrated circuit dies within an integrated circuit package. Additionally, the improved stacking techniques permit conventional bonding techniques for electrical connection of the various integrated circuit dies to each other or to a substrate. These improved approaches are particularly useful for stacking same size (and often same function) integrated circuit dies within integrated circuit packages. One example of such an integrated circuit package is a non-volatile memory integrated circuit package that contains multiple, like-sized memory storage integrated circuit dies arranged in a stack.

Owner:SANDISK TECH LLC

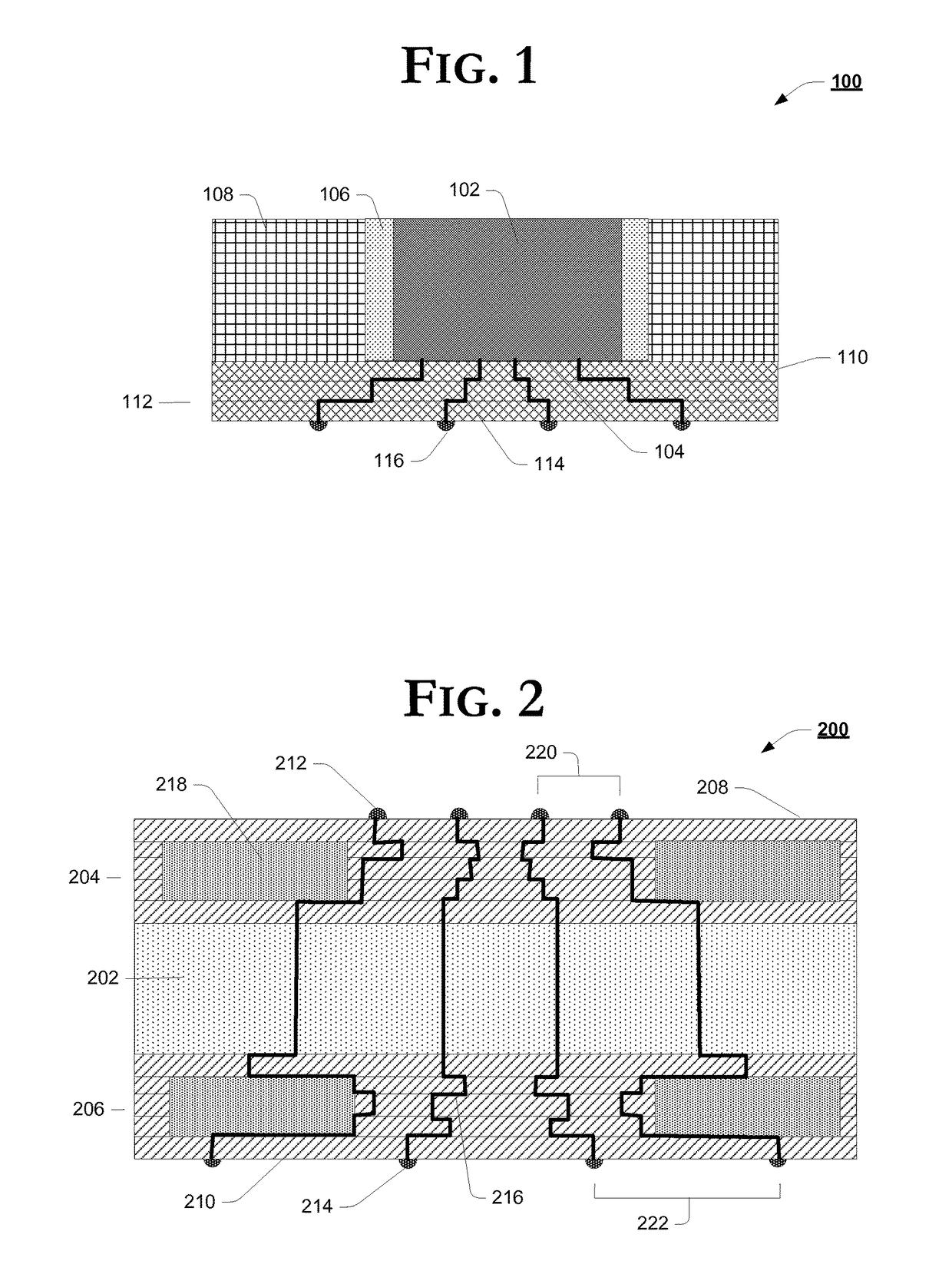

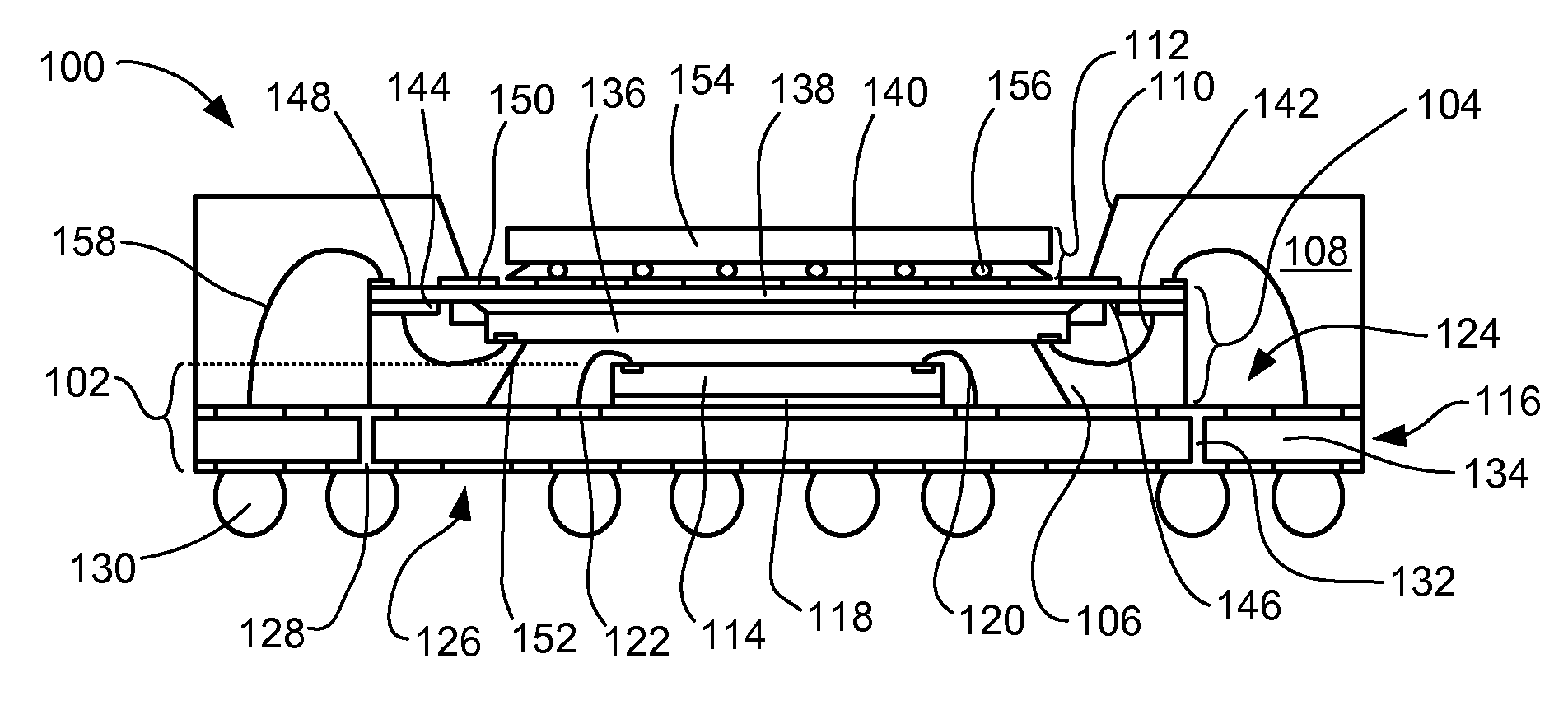

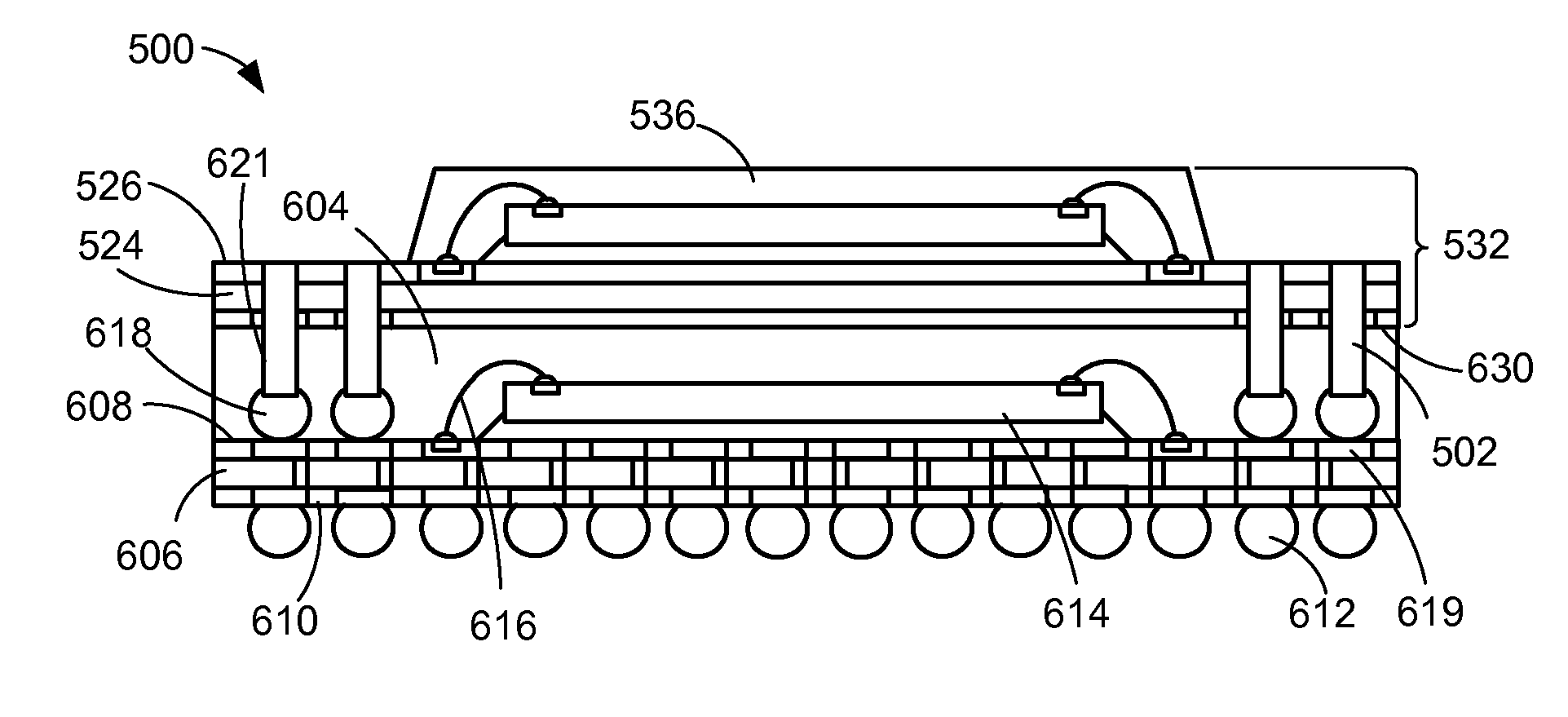

Integrated circuit package-in-package system

ActiveUS7288835B2Semiconductor/solid-state device detailsSolid-state devicesEngineeringIntegrated circuit packaging

An integrated circuit package-in-package system is provided forming a first integrated circuit package having a first interface, stacking a second integrated circuit package having a second interface above the first integrated circuit package, fitting the first interface and the second interface, and attaching a third integrated circuit package on the second integrated circuit package.

Owner:STATS CHIPPAC LTD

Integrated circuit packaging system with encapsulated via and method of manufacture thereof

ActiveUS20110068453A1Semiconductor/solid-state device detailsSolid-state devicesEngineeringIntegrated circuit packaging

A method of manufacture of an integrated circuit packaging system includes: providing a substrate; mounting an integrated circuit over the substrate; attaching a buffer interconnect to and over the substrate; forming an encapsulation over the substrate covering the buffer interconnect and the integrated circuit; and forming a via in the encapsulation and to the buffer interconnect.

Owner:STATS CHIPPAC LTD

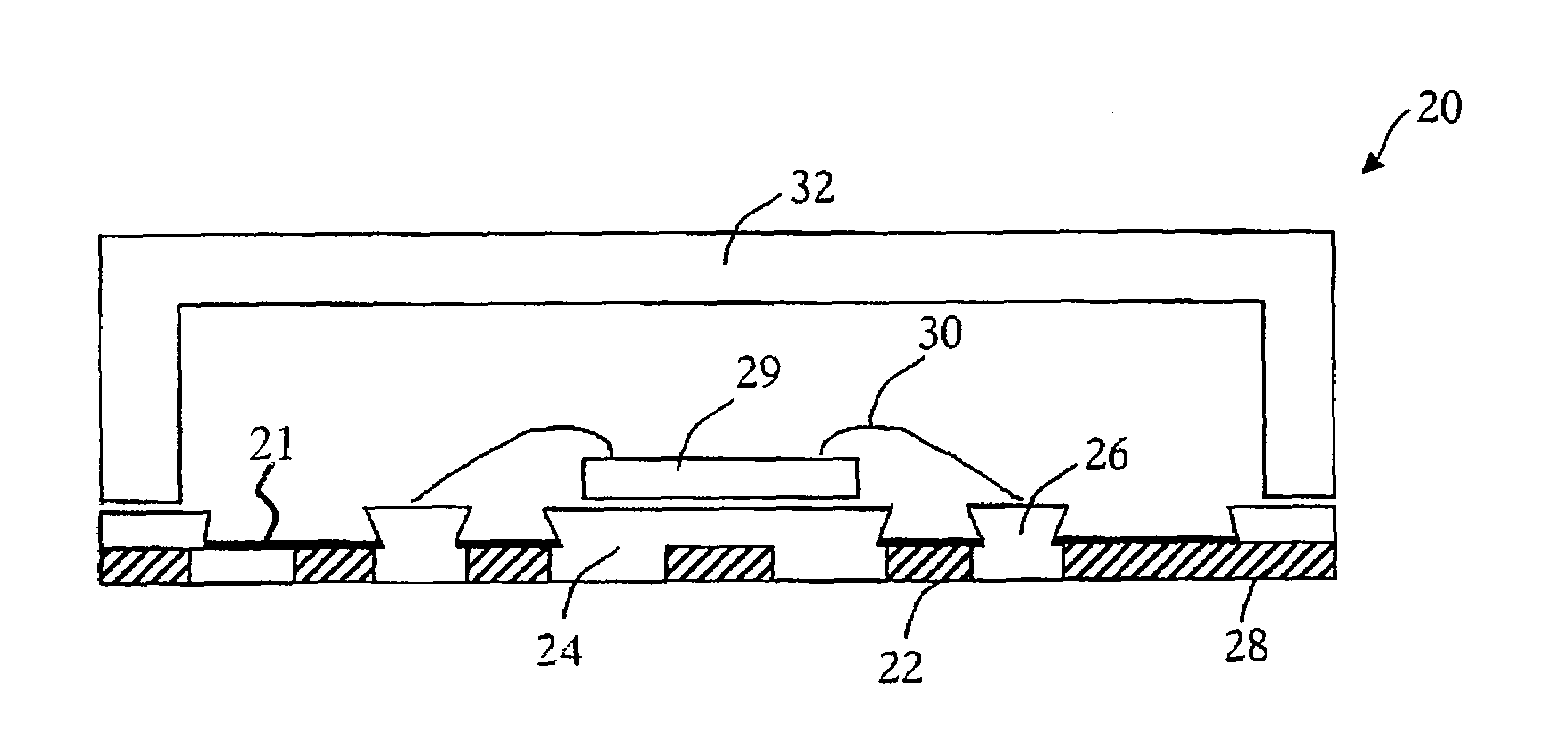

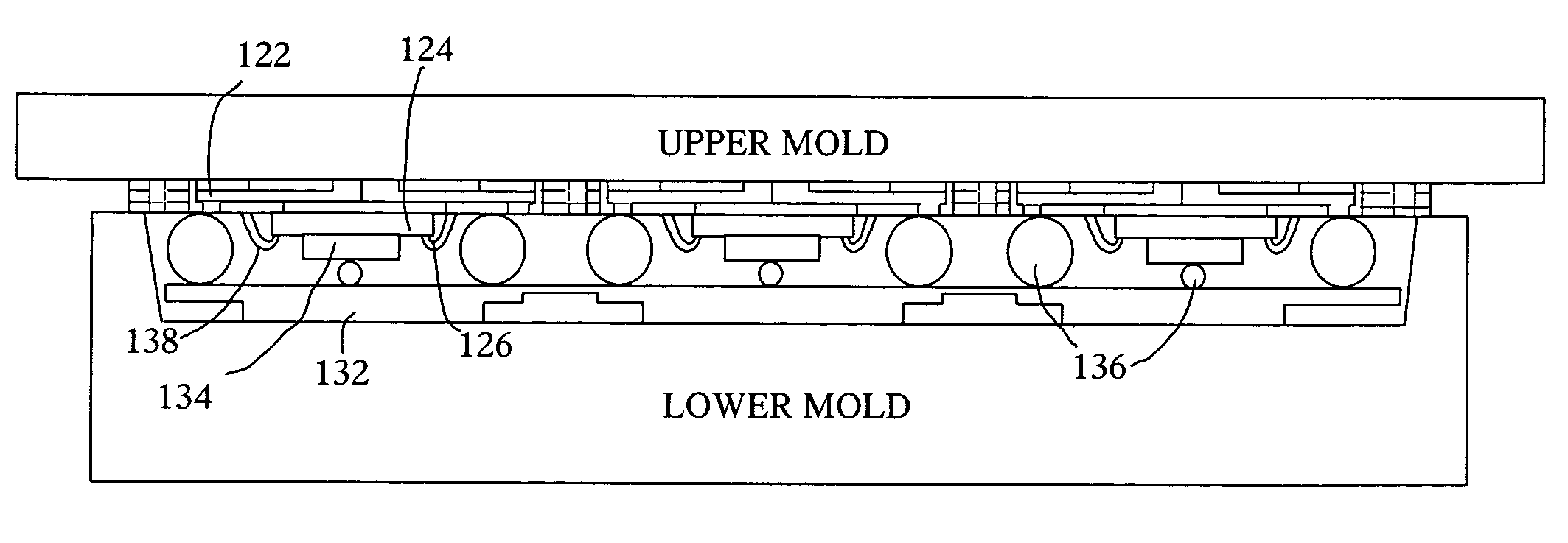

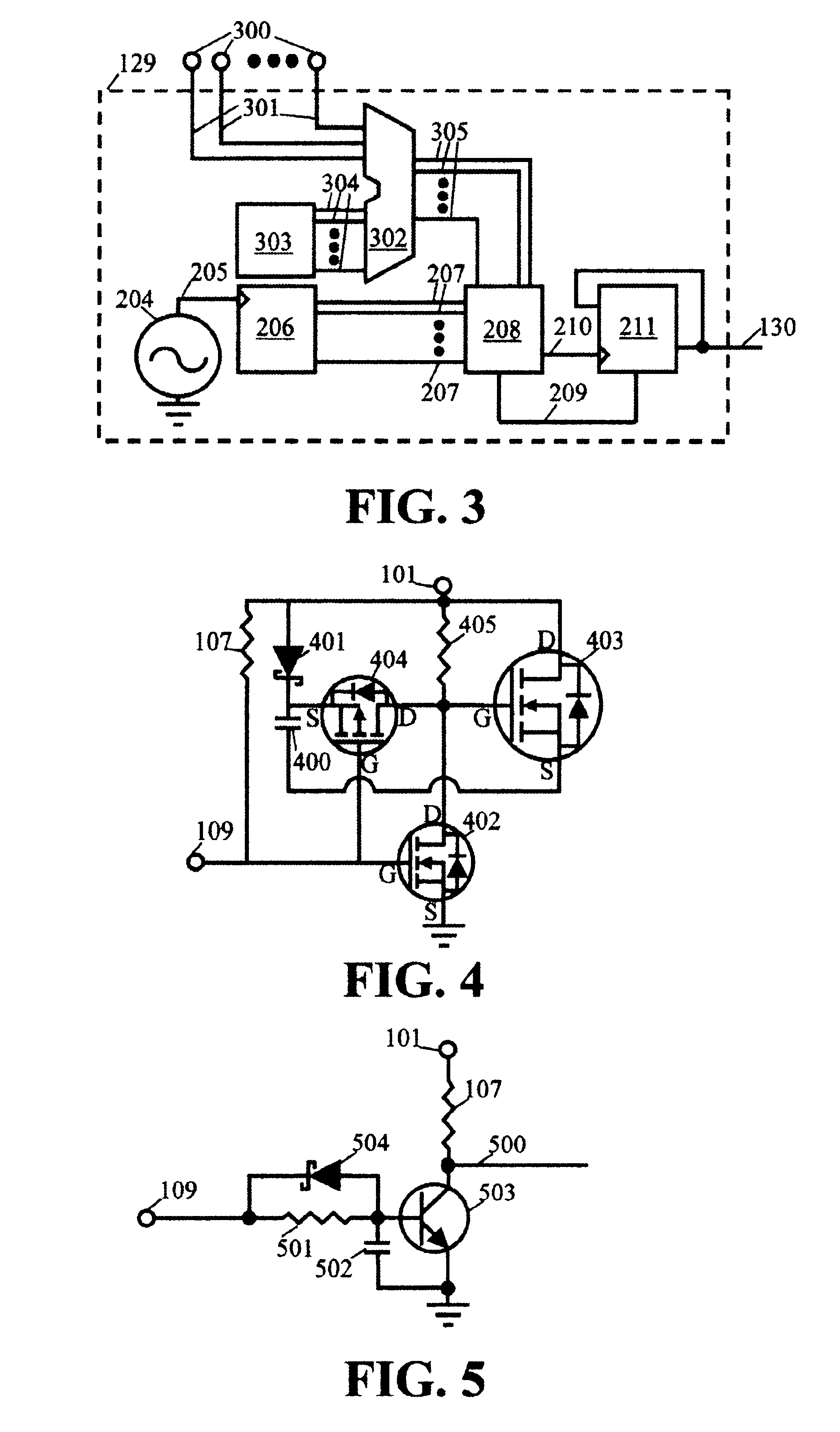

Ball grid array package and process for manufacturing same

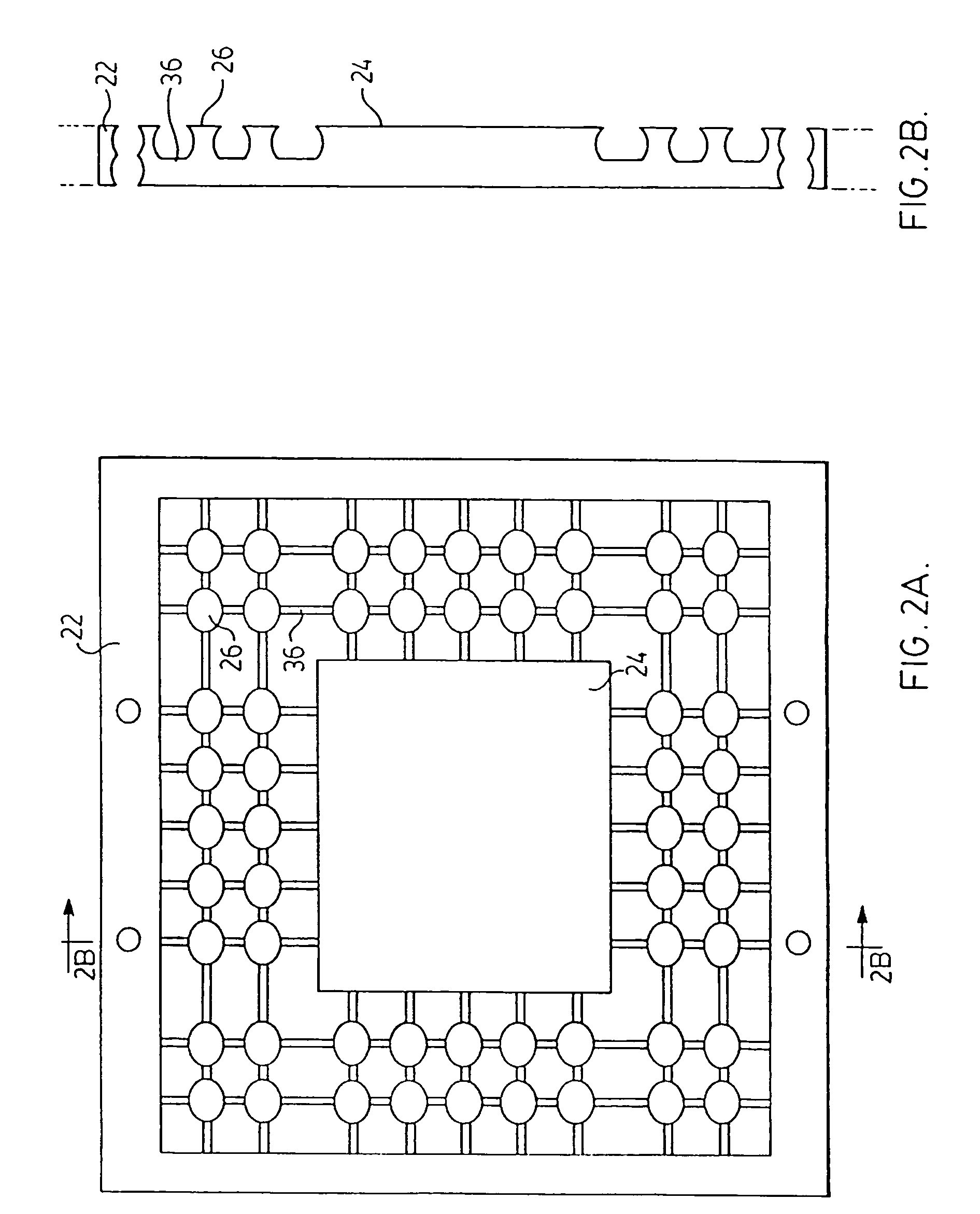

InactiveUS6987032B1Inhibiting mold flashReducing mold flashSemiconductor/solid-state device detailsSolid-state devicesBall grid arraySemiconductor

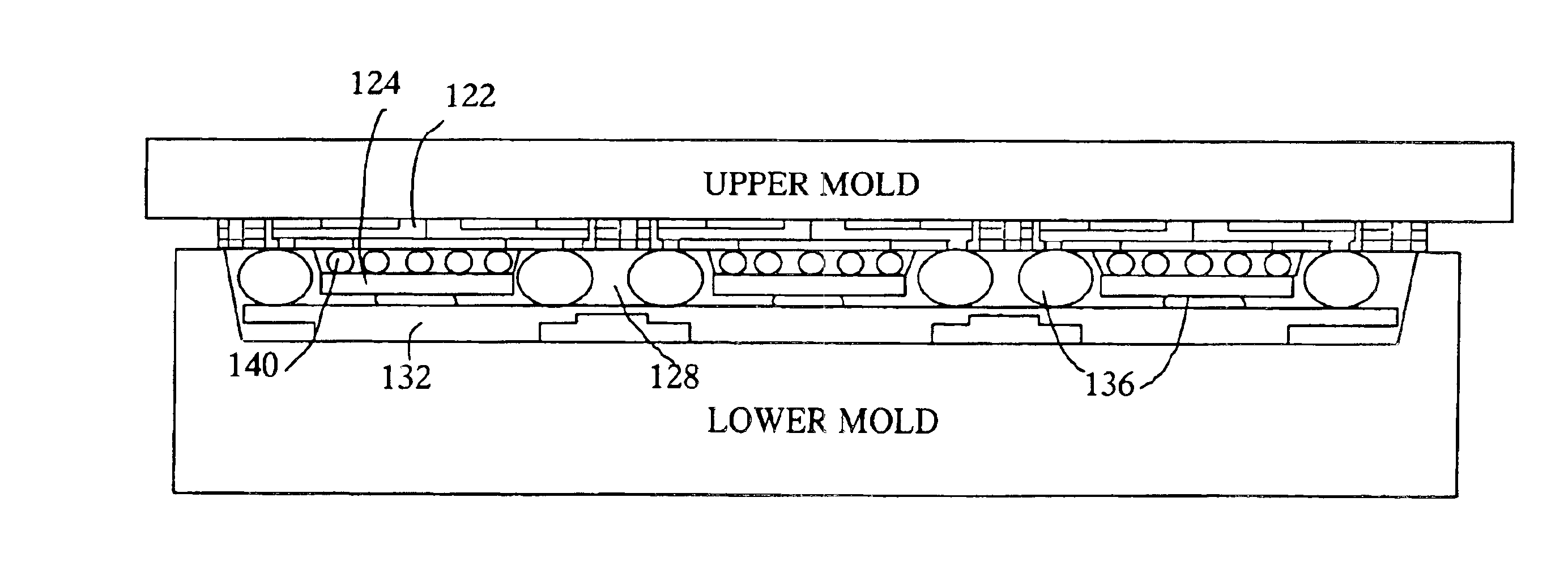

A ball grid array package is manufactured by mounting a semiconductor die to a first surface of a substrate and mounting a die adapter to the semiconductor die. The semiconductor die is wire bonded to ones of conductive traces of the substrate. A collapsible spacer is mounted to the substrate and the substrate is releasably clamped to an upper side of a mold cavity. A heat spreader and at least one collapsible spacer are placed in the mold cavity such that the collapsible spacer is disposed between the heat spreader and the substrate. A molding compound is molded in the mold, thereby molding the semiconductor die, the substrate, the wire bonds, the die adapter, the at least one collapsible spacer and the heat spreader into the molding compound to provide a molded package. A ball grid array is formed on a second surface of the substrate, bumps of the ball grid array being electrically connected to the conductive traces and the integrated circuit package is singulated.

Owner:UTAC HEADQUARTERS PTE LTD

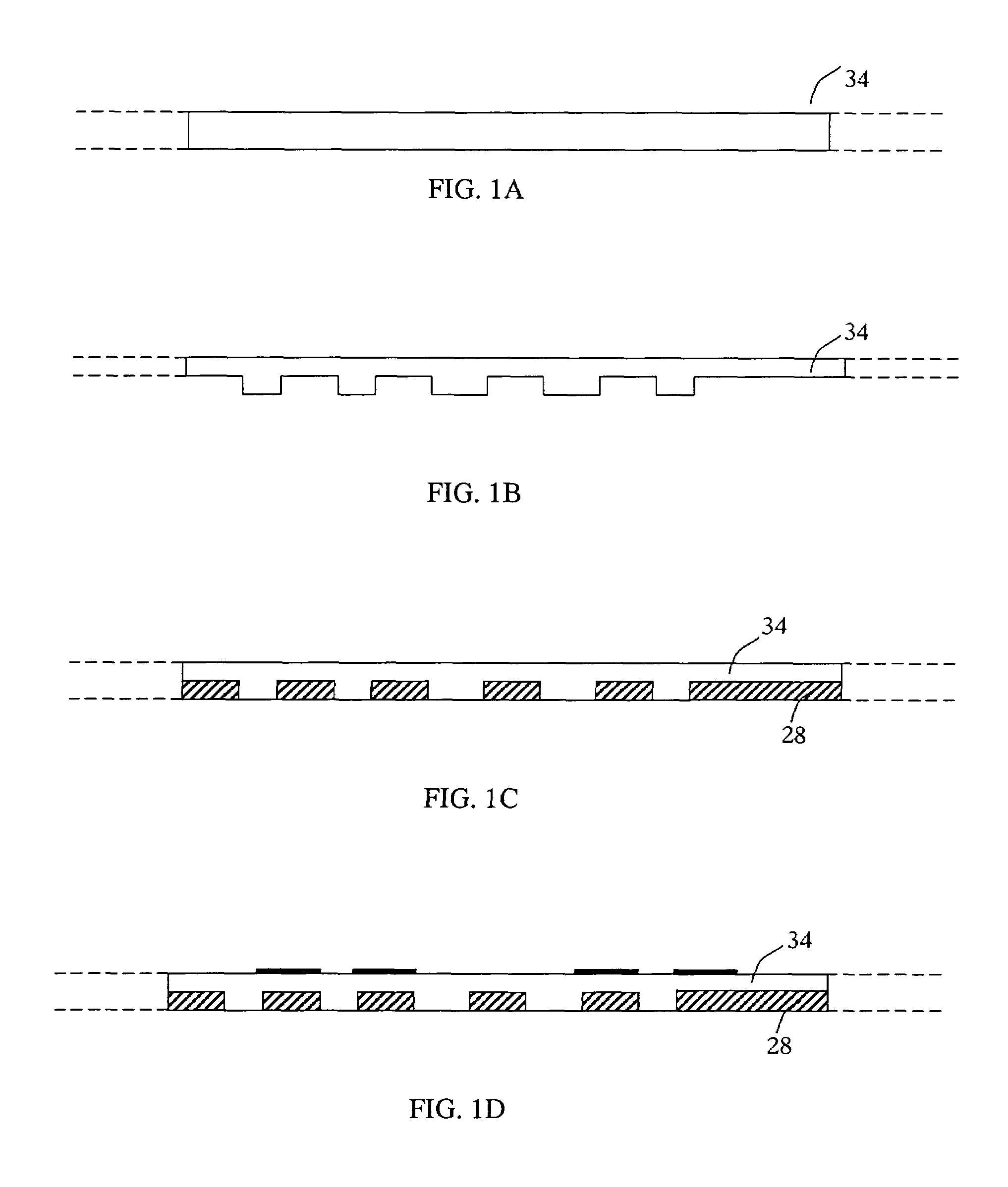

Ball grid array package and process for manufacturing same

InactiveUS6933176B1Inhibiting mold flashReducing mold flashSemiconductor/solid-state device detailsSolid-state devicesManufacturing technologyBall grid array

A ball grid array integrated circuit package is manufactured by mounting a semiconductor die, to a surface of a substrate such that bumps on the semiconductor die are electrically connected to conductive traces of the substrate. At least one collapsible spacer is mounted to at least one of a heat spreader, the semiconductor die and the substrate. The heat spreader is fixed to the at least one of the first surface of the substrate and the semiconductor die such that he at least one collapsible spacer is disposed therebetween. A ball grid array is formed on a second surface of the substrate, bumps of the ball grid array being electrically connected to the conductive traces and the integrated circuit package is singulated.

Owner:UTAC HEADQUARTERS PTE LTD

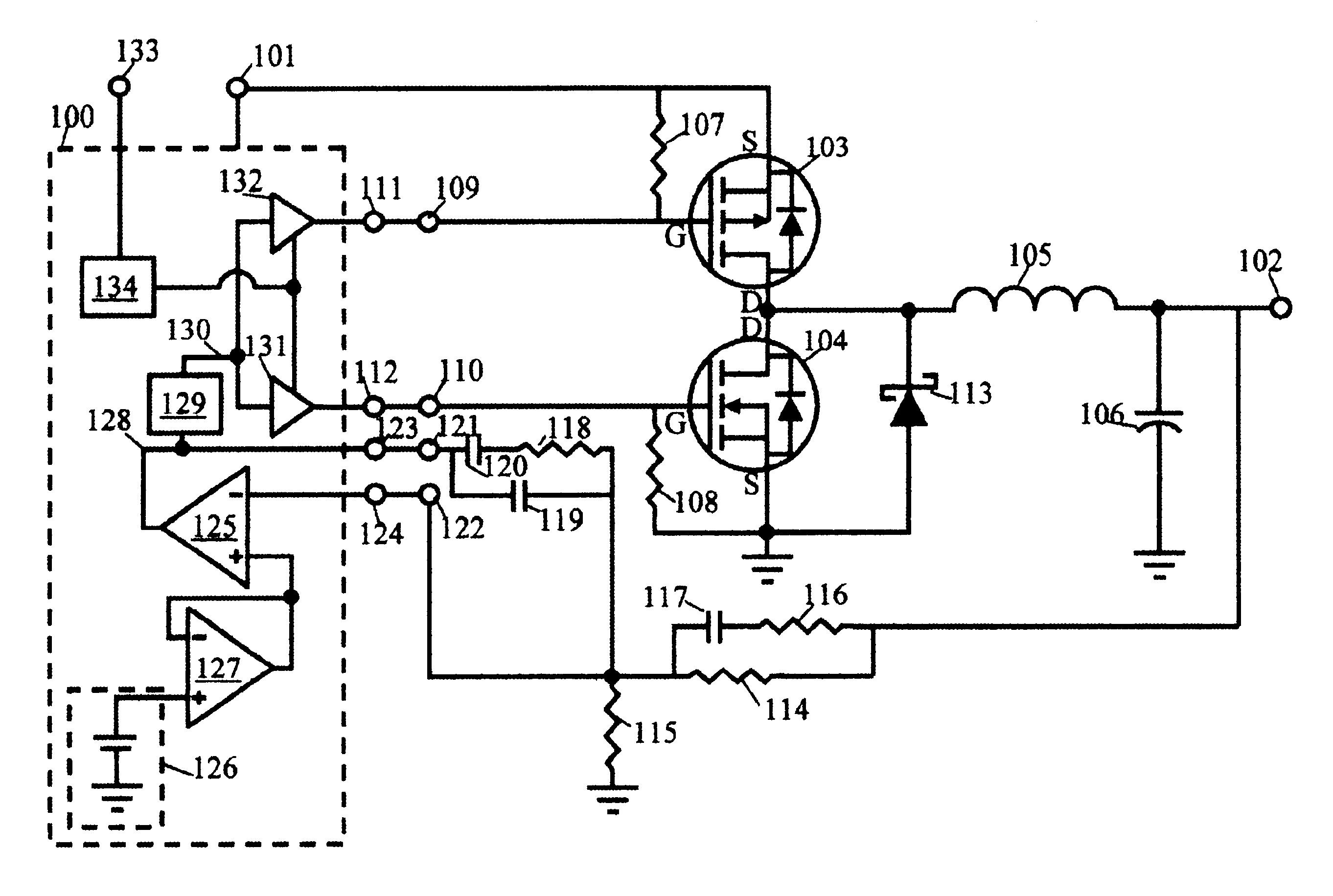

System and method for integrating a digital core with a switch mode power supply

InactiveUS6940189B2Improve powerMinimal costVolume/mass flow measurementSolid-state devicesVoltage converterPower switching

A digital core embodied within a semiconductor die that requires plural separate power supply voltage domains is situated within any of a variety of integrated circuit packaging technologies. Within the integrated circuit package including this semiconductor die also exists a switch mode DC-to-DC voltage converter, preferably a synchronous step-down regulator powering the entire integrated circuit from one supply voltage. The components contained within the integrated circuit package along with the semiconductor die include the switch mode power supply's power switching transistors, inductor core and windings, digital open-loop output voltage fixing circuitry, output capacitors and substrate for mounting said components when integrated within a packaging technology that does not already include a substrate.

Owner:CUFER ASSET LTD LLC

Trap rich layer for semiconductor devices

ActiveUS8466036B2Semiconductor/solid-state device detailsSolid-state devicesMetal interconnectActive layer

An integrated circuit chip is formed with an active layer and a trap rich layer. The active layer is formed with an active device layer and a metal interconnect layer. The trap rich layer is formed above the active layer. In some embodiments, the active layer is included in a semiconductor wafer, and the trap rich layer is included in a handle wafer.

Owner:QUALCOMM INC

Integrated circuit package and process for fabricating the same

ActiveUS7091581B1Improve thermal characteristicsReduce generationSemiconductor/solid-state device detailsSolid-state devicesContact padLead bonding

A process for fabricating an integrated circuit package includes: selectively etching a leadframe strip to define a die attach pad and at least one row of contact pads; mounting a semiconductor die to one side of the leadframe strip, on the die attach pad; wire bonding the semiconductor die to ones of the contact pads; releasably clamping the leadframe strip in a mold by releasably clamping the contact pads; molding in a molding compound to cover the semiconductor die, the wire bonds and a portion of the contact pads not covered by the clamping; releasing the leadframe strip from the mold; depositing a plurality of external contacts on the one side of the leadframe strip, on the contact pads, such that the external contacts protrude from the molding compound; and singulating to provide the integrated circuit package.

Owner:UTAC HEADQUARTERS PTE LTD

Leadframe with power and ground planes

InactiveUSRE36907E1Reduced effective inductanceReduce crosstalkSemiconductor/solid-state device detailsSolid-state devicesVoltage sourceLead frame

A leadframe for use in an integrated circuit package is described. The leadframe comprises a plurality of electrically conductive leads, a die attach pad, and an electrically conductive ring or rings formed generally around the circumference of the die attach pad and between the die attach pad and leads. In one embodiment, at least one of the leads is formed integrally with each ring. The die attach pad may also be formed integrally with one or more leads. In another embodiment, the ring or rings are formed so that they are electrically isolated from the die attach pad, and the die attach pad, leads, and ring or rings are all formed in substantially the same plane. In some embodiments, the ring or rings are broken into electrically isolated sections. Each of the ring sections (and die attach pad, if appropriate) may be electrically connected to a voltage source outside the integrated circuit package (e.g., a power supply or ground). The leadframe is formed from a single sheet of material by, for instance, stamping or etching. The leadframe may be used in either ceramic or plastic packages. The leadframe reduces switching noise and crosstalk, allows more flexibility in placement of power and / or ground bond pads on the die, and allows provision of ground and power planes in an integrated circuit package that is thinner than previous integrated circuit packages containing both ground and power planes.

Owner:INTEGRATED DEVICE TECH INC

Leadless integrated circuit package having electrically routed contacts

A leadless integrated circuit (IC) package comprising an IC chip mounted on a metal leadframe and a plurality of electrical contacts electrically coupled to the IC chip. The IC chip, the electrical contacts, and a portion of the metal leadframe are covered with an encapsulation compound, with portions of the electrical contacts exposed on a bottom surface of the encapsulation compound. The electrical contacts of the IC package having metal traces connecting bonding areas on a top surface thereof and contact areas on a bottom surface thereof, wherein at least some of the bonding areas are laterally disposed from the contact areas connected thereto.

Owner:KAIXIN INC