Patents

Literature

242results about How to "Improve thermal characteristics" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

Integrated circuit package and process for fabricating the same

ActiveUS7091581B1Improve thermal characteristicsReduce generationSemiconductor/solid-state device detailsSolid-state devicesContact padLead bonding

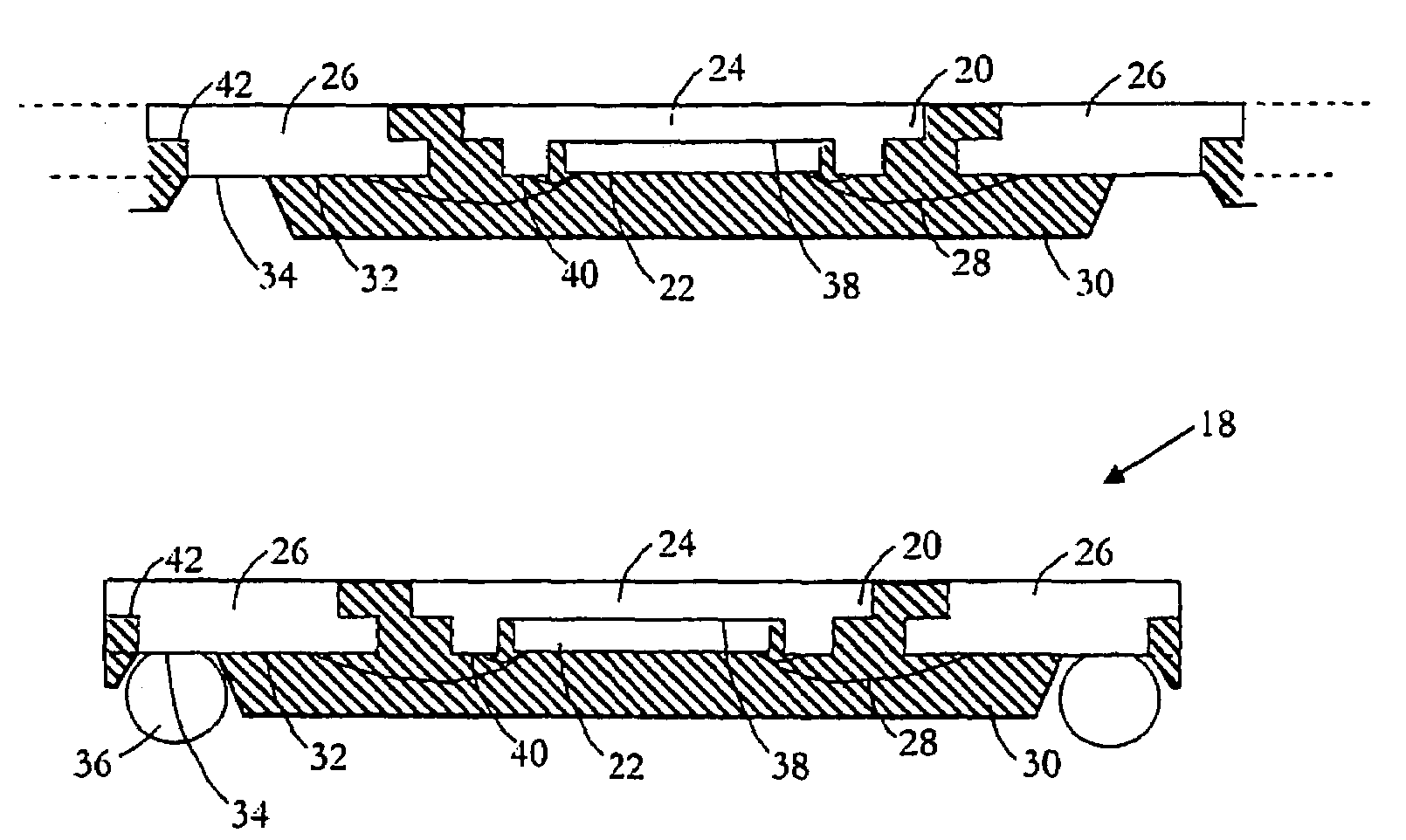

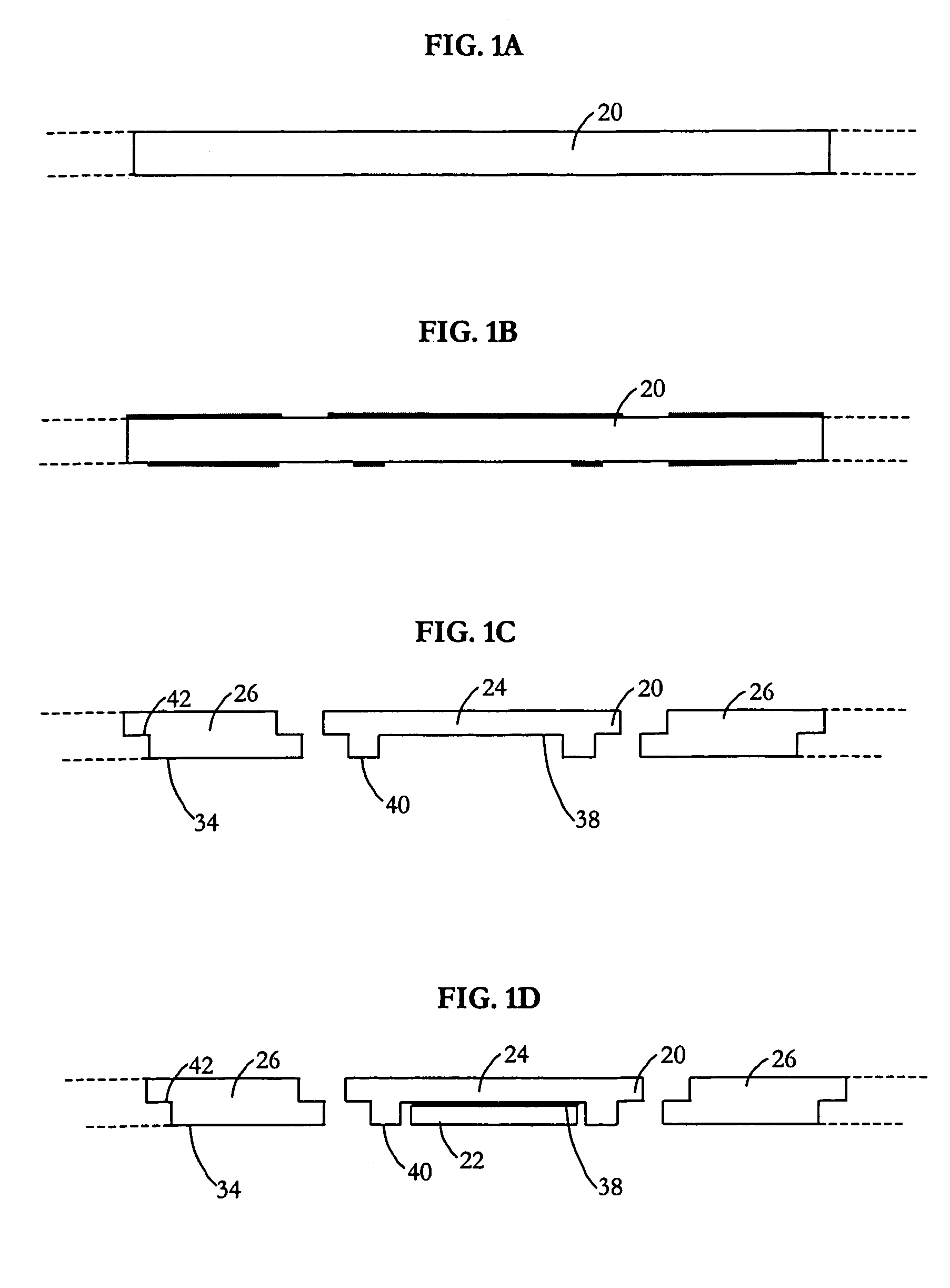

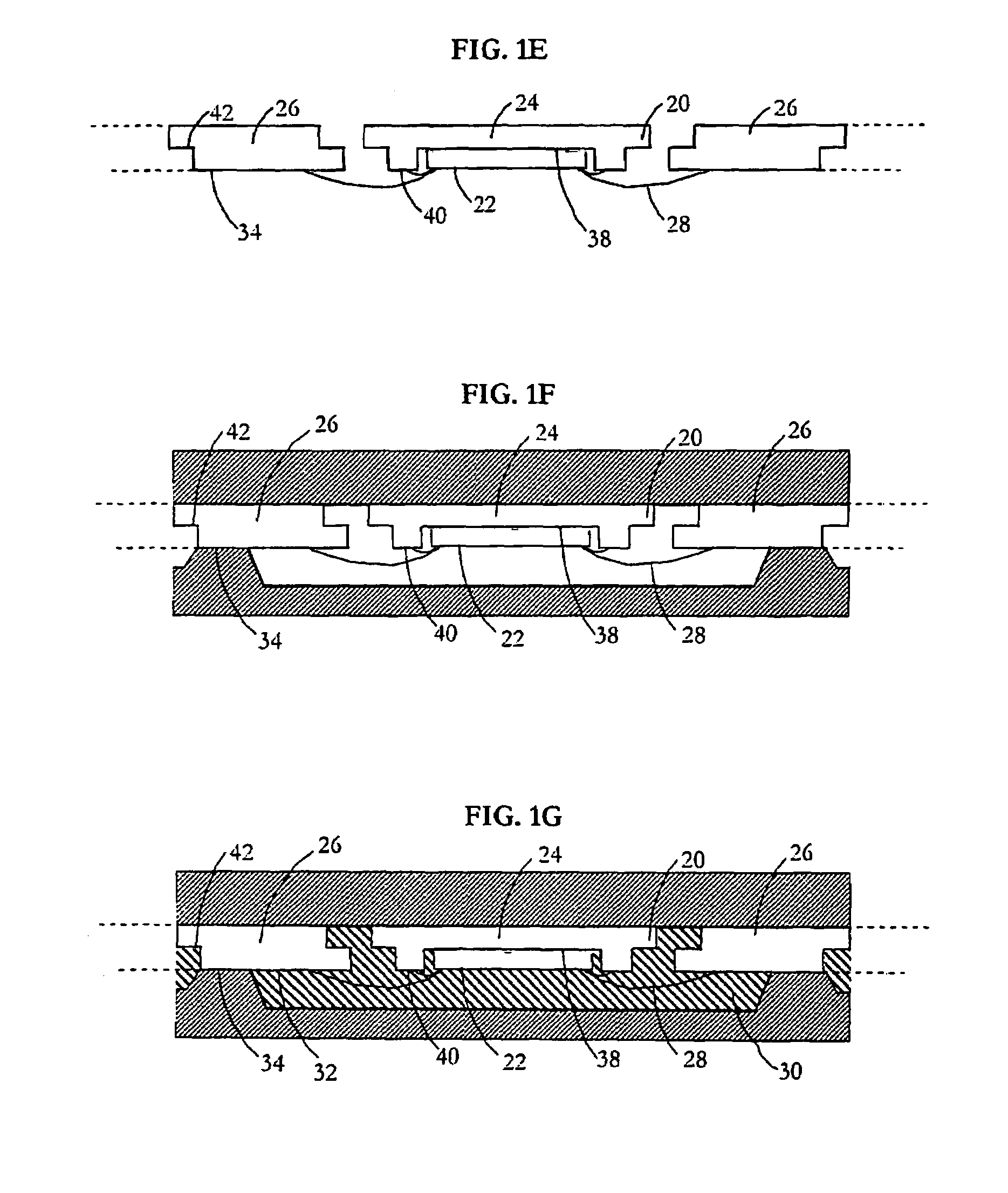

A process for fabricating an integrated circuit package includes: selectively etching a leadframe strip to define a die attach pad and at least one row of contact pads; mounting a semiconductor die to one side of the leadframe strip, on the die attach pad; wire bonding the semiconductor die to ones of the contact pads; releasably clamping the leadframe strip in a mold by releasably clamping the contact pads; molding in a molding compound to cover the semiconductor die, the wire bonds and a portion of the contact pads not covered by the clamping; releasing the leadframe strip from the mold; depositing a plurality of external contacts on the one side of the leadframe strip, on the contact pads, such that the external contacts protrude from the molding compound; and singulating to provide the integrated circuit package.

Owner:UTAC HEADQUARTERS PTE LTD

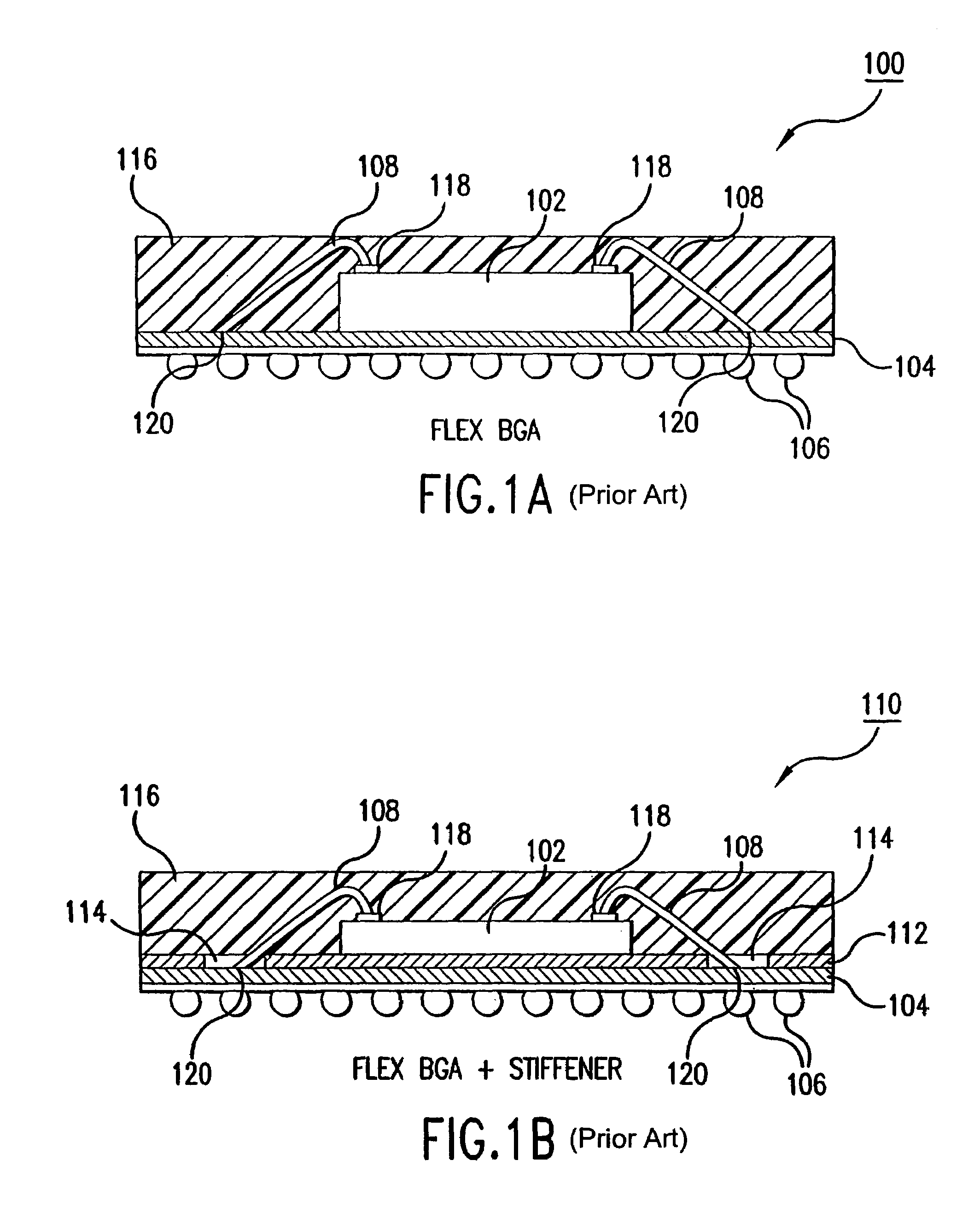

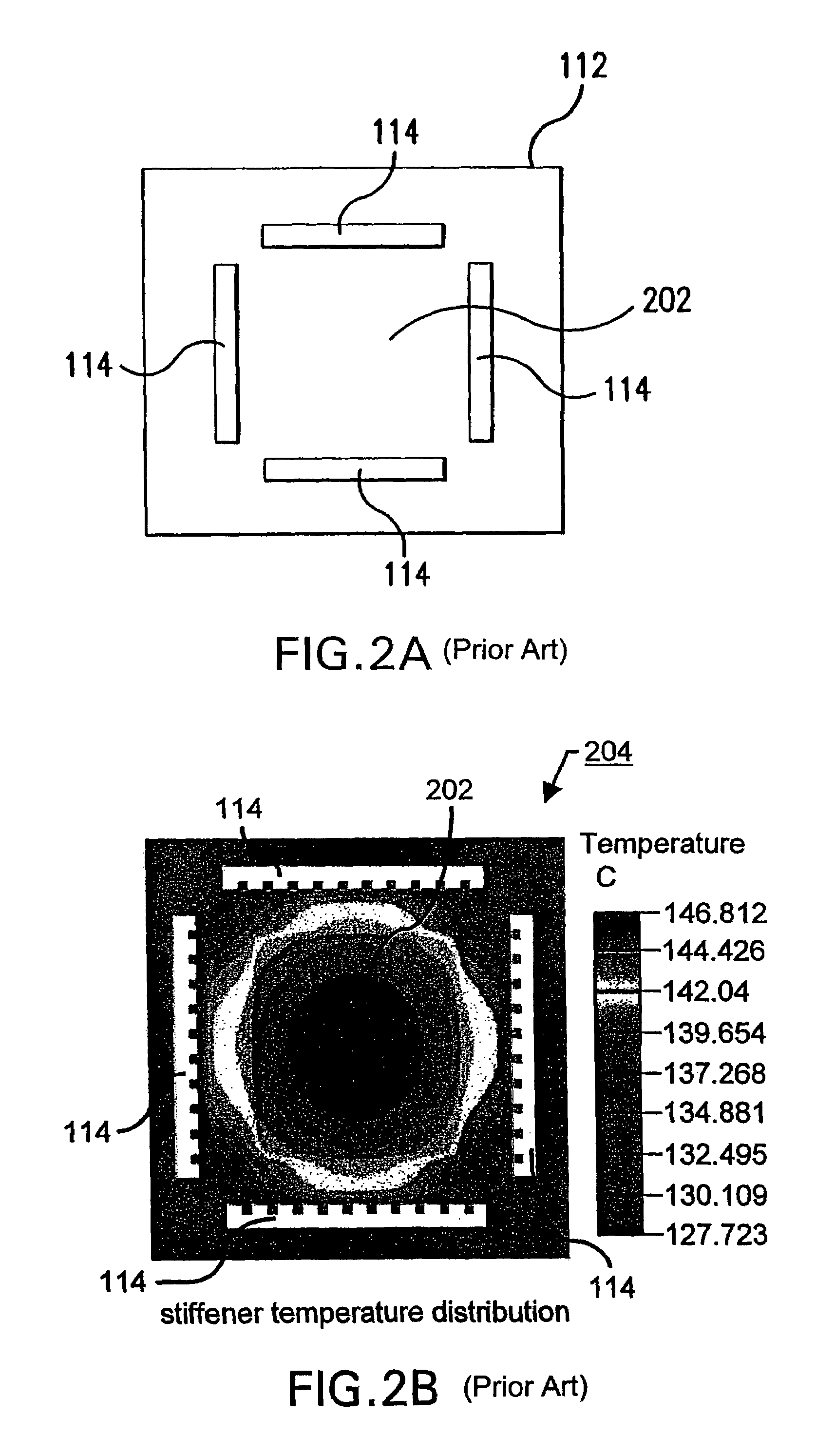

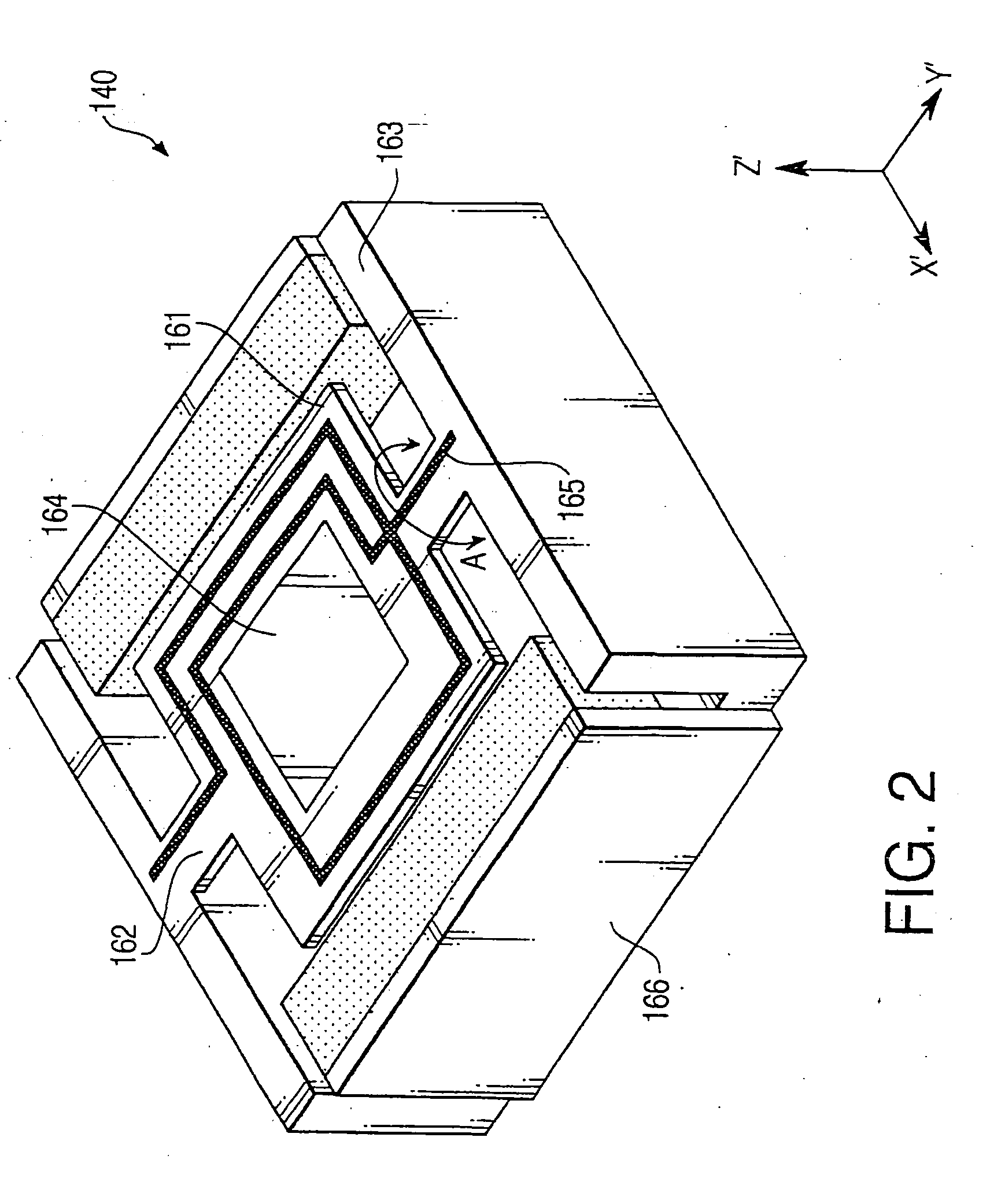

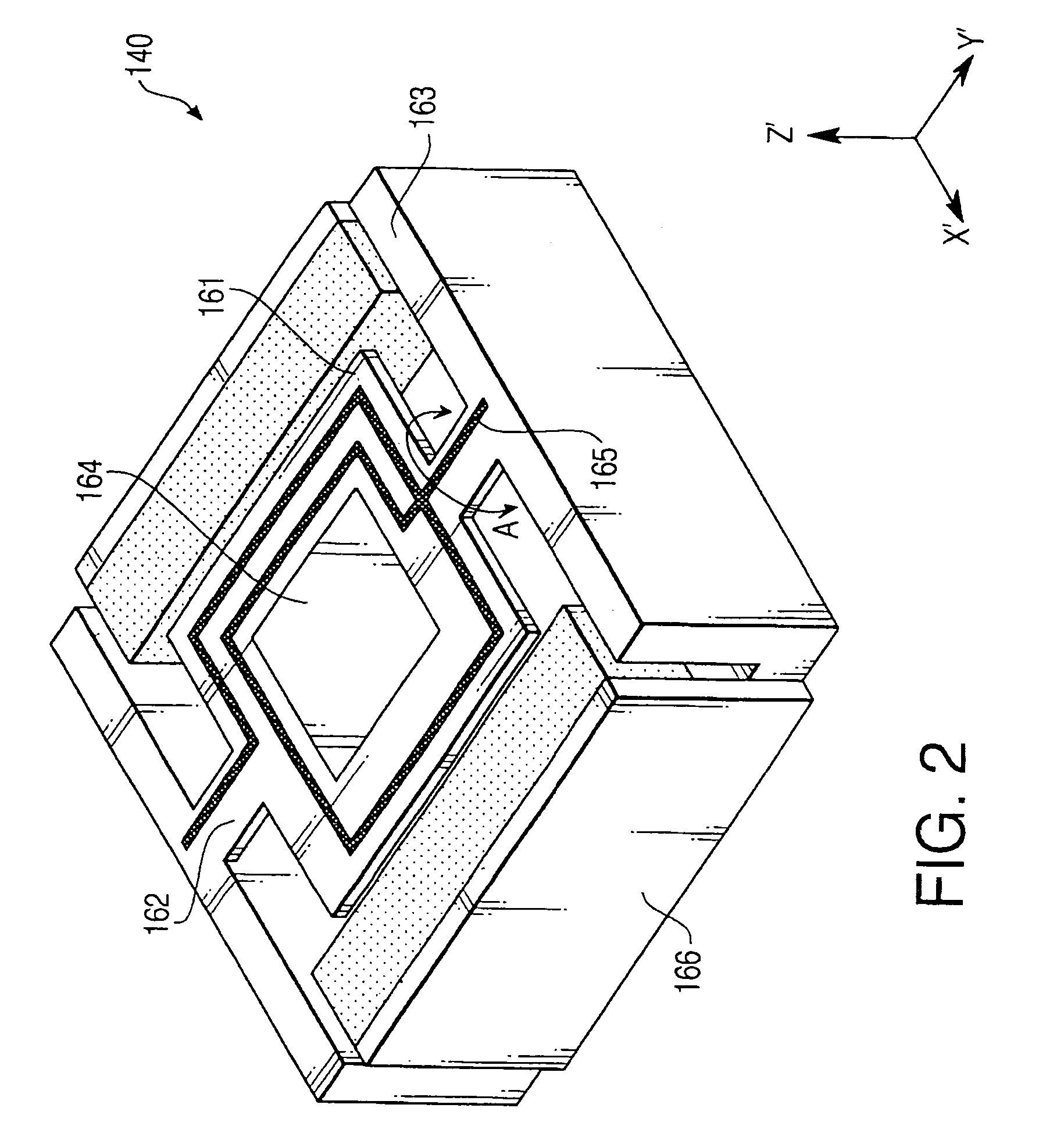

Ball grid array package enhanced with a thermal and electrical connector

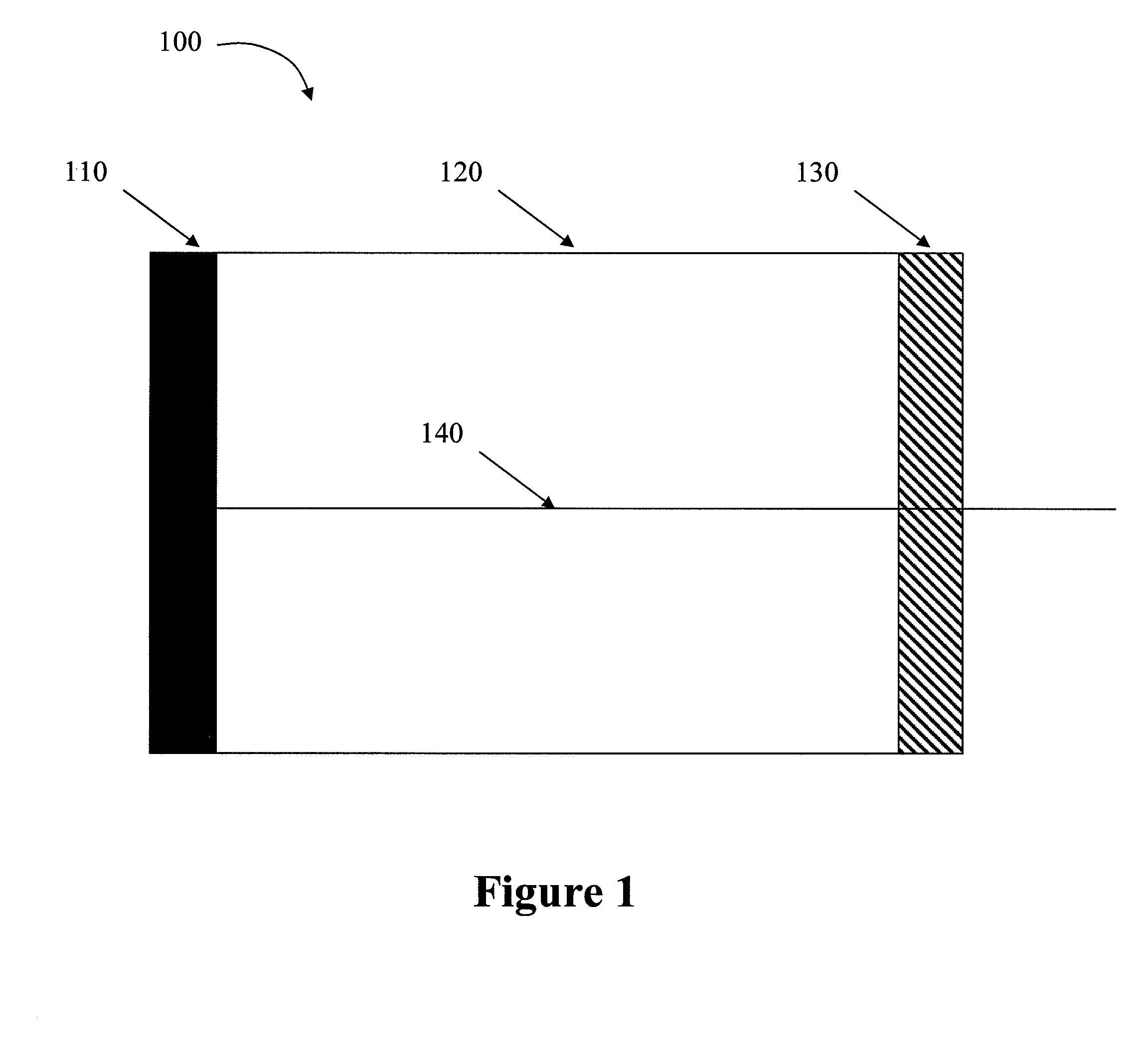

InactiveUS7161239B2Improve electricityImprove thermal characteristicsSemiconductor/solid-state device detailsSolid-state devicesElectrical connectorBall grid array

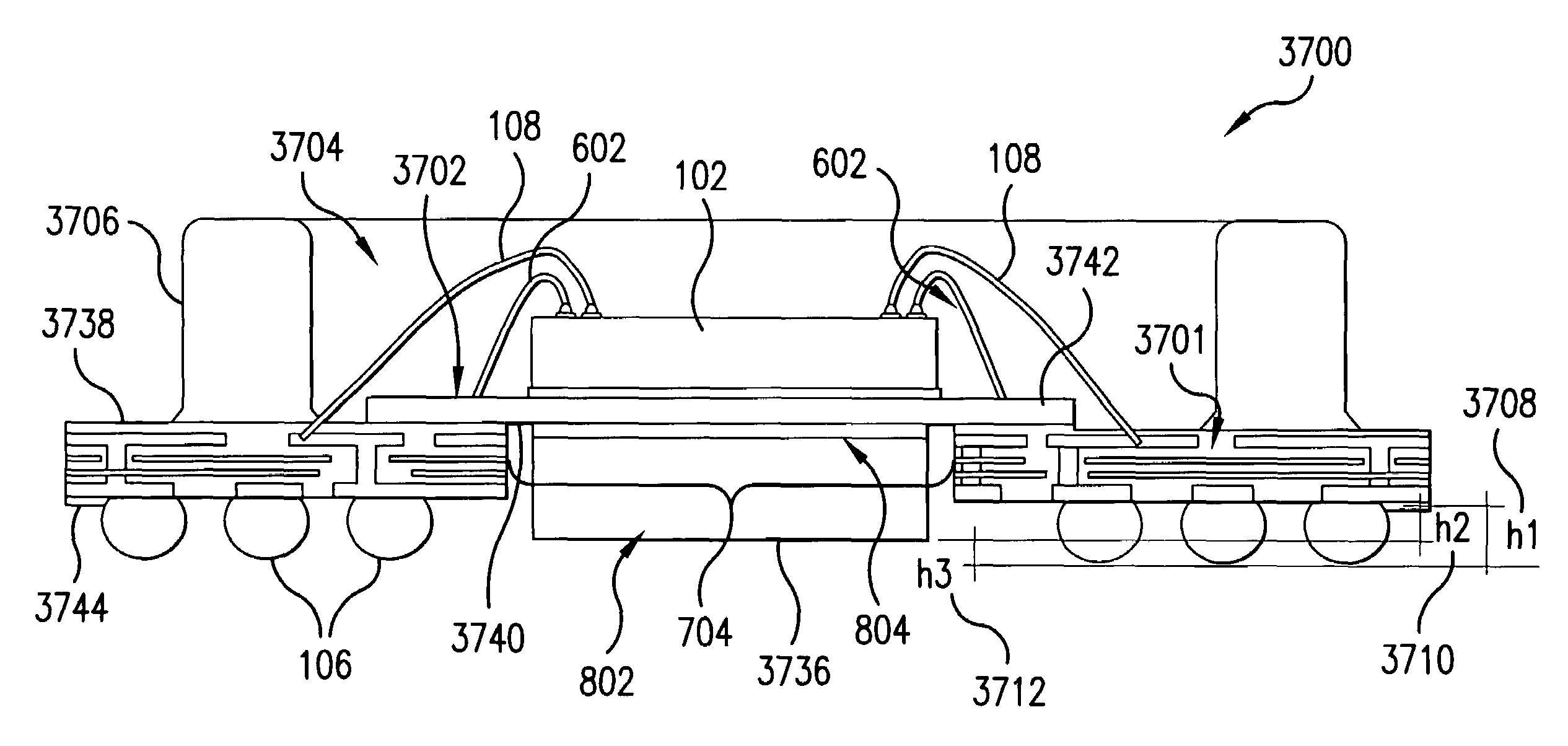

Electrically, mechanically, and thermally enhanced ball grid array (BGA) packages are described. A substrate has a surface, wherein the surface has an opening therein. A stiffener has a surface coupled to the surface of the substrate. An area of the surface of the stiffener can be greater than, equal to, or less than an area of the surface of the substrate. A thermal connector is coupled to the surface of the stiffener through the opening. A surface of the thermal connector is capable of attachment to a printed circuit board (PCB) when the BGA package is mounted to the PCB. The thermal connector can have a height such that the thermal connector extends into a cavity formed in a surface of the PCB when the BGA package is mounted to the PCB. Alternatively, the stiffener and thermal connector may be combined into a single piece stiffener, wherein the stiffener has a protruding portion. The protruding portion extends through the opening when the stiffener is coupled to the substrate, and is capable of attachment to the PCB.

Owner:AVAGO TECH INT SALES PTE LTD

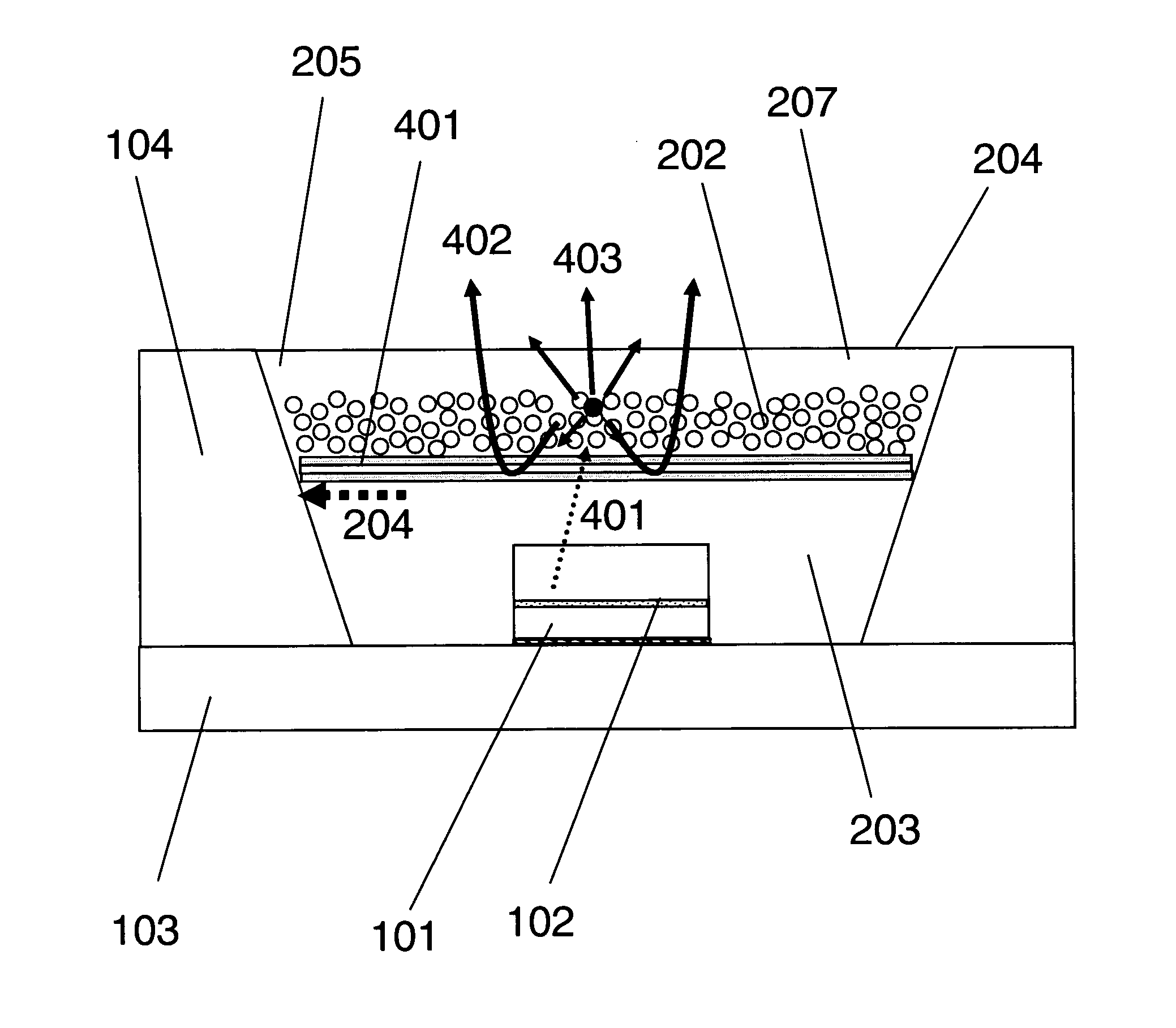

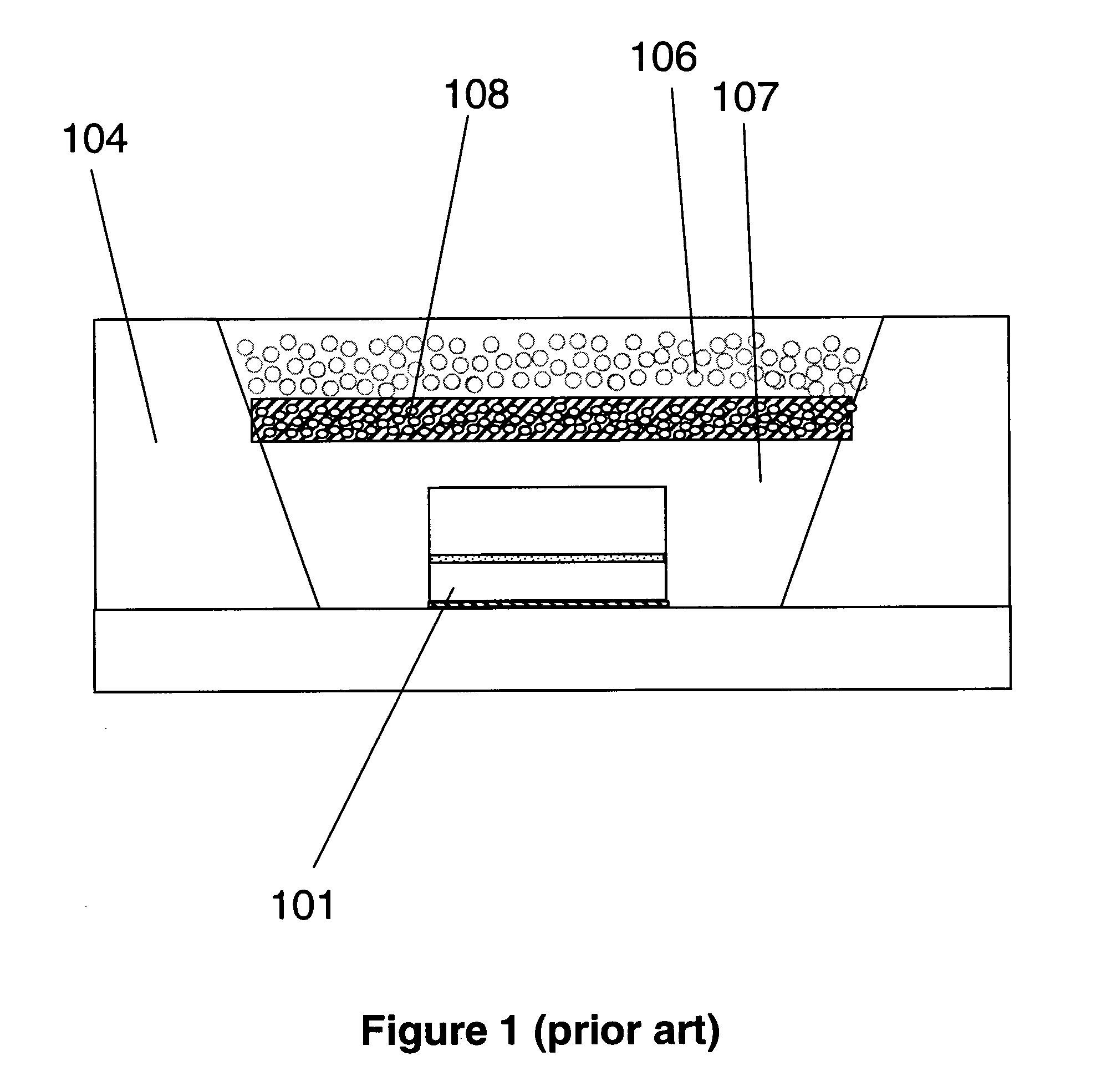

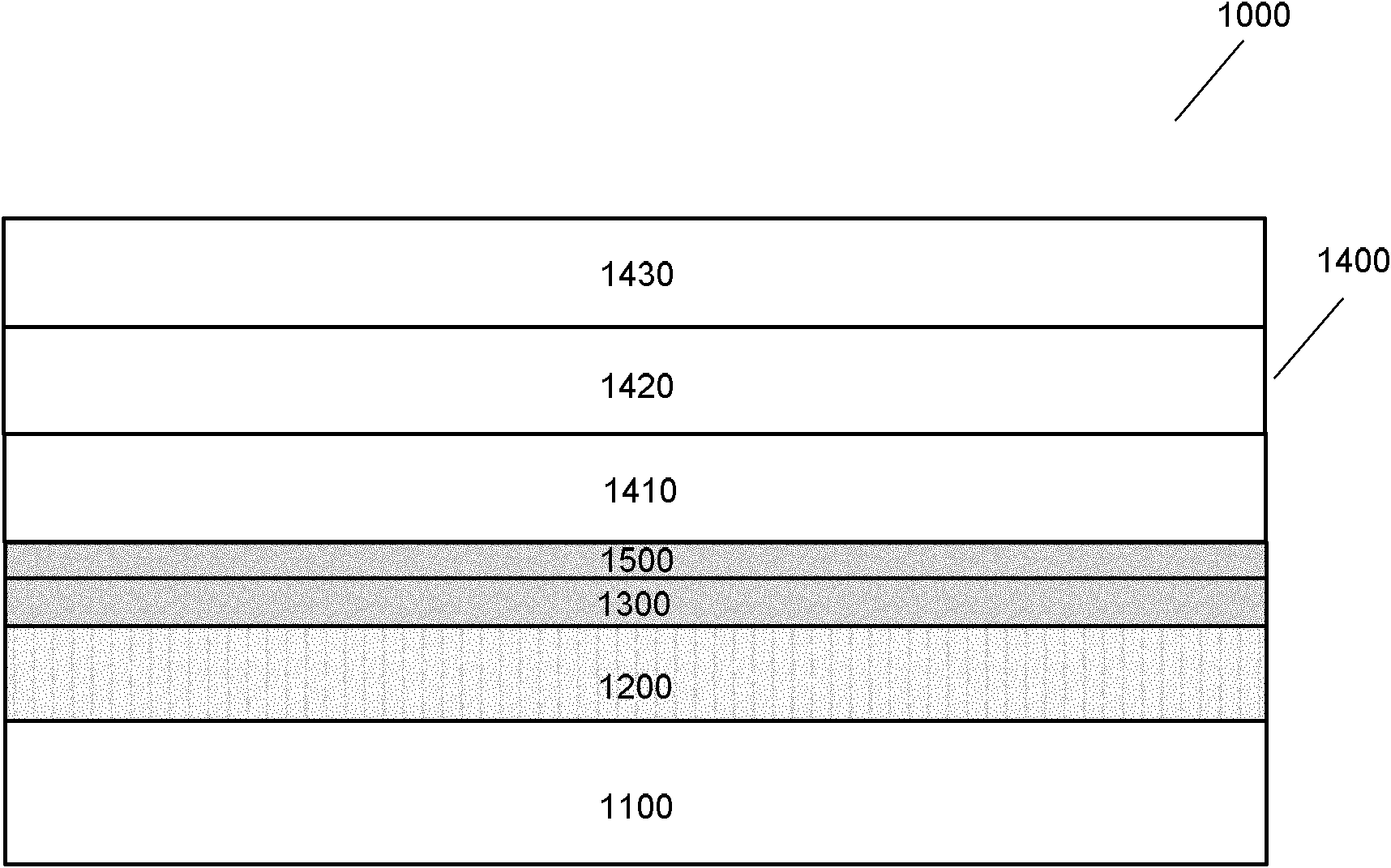

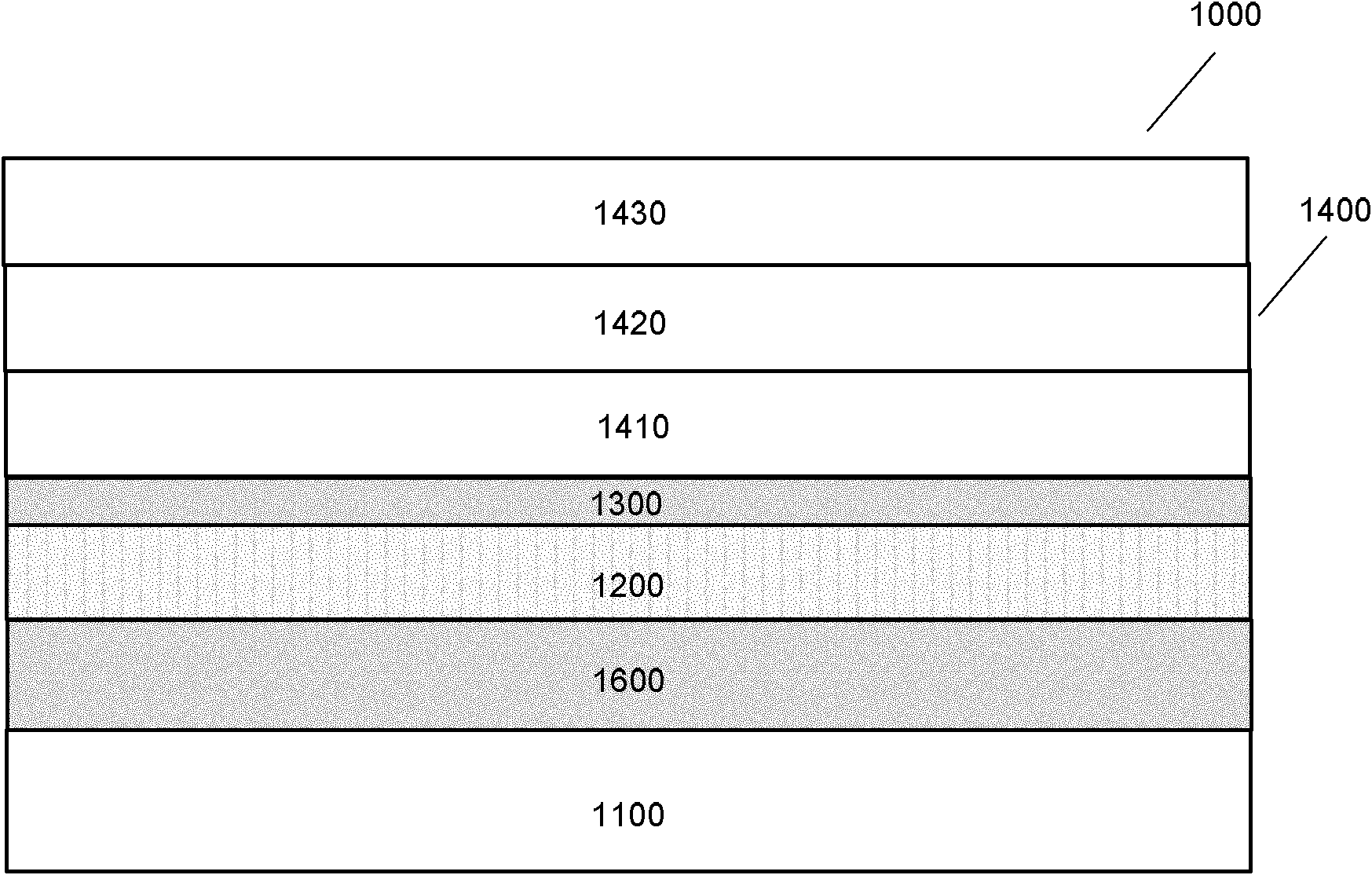

Light emitting module with optically-transparent thermally-conductive element

ActiveUS20110001157A1Extended service lifeThe process is compact and efficientSolid-state devicesSemiconductor/solid-state device manufacturingLength waveInorganic materials

A light emitting module with improved optical functionality and reduced thermal resistance is described, which comprises a light emitting device (LED), a wavelength converting (WC) element and an inorganic optically-transmissive thermally-conductive (OTTC) element. The WC element is capable of absorbing light generated from the LED at a specific wavelength and re-emitting light having a different wavelength. The re-emitted light and any unabsorbed light exits through at least one surface of the module. The OTTC is in physical contact with the WC element and at least partially located in the optical path of the light. The OTTC comprises one or more layers of inorganic material having a thermal conductivity greater than that of the WC element. As such, a compact unitary integrated module is provided with excellent thermal characteristics, which may be further enhanced when the OTTC provides a thermal barrier for vertical heat propagation through the module but not lateral propagation.

Owner:LUMILEDS HLDG BV

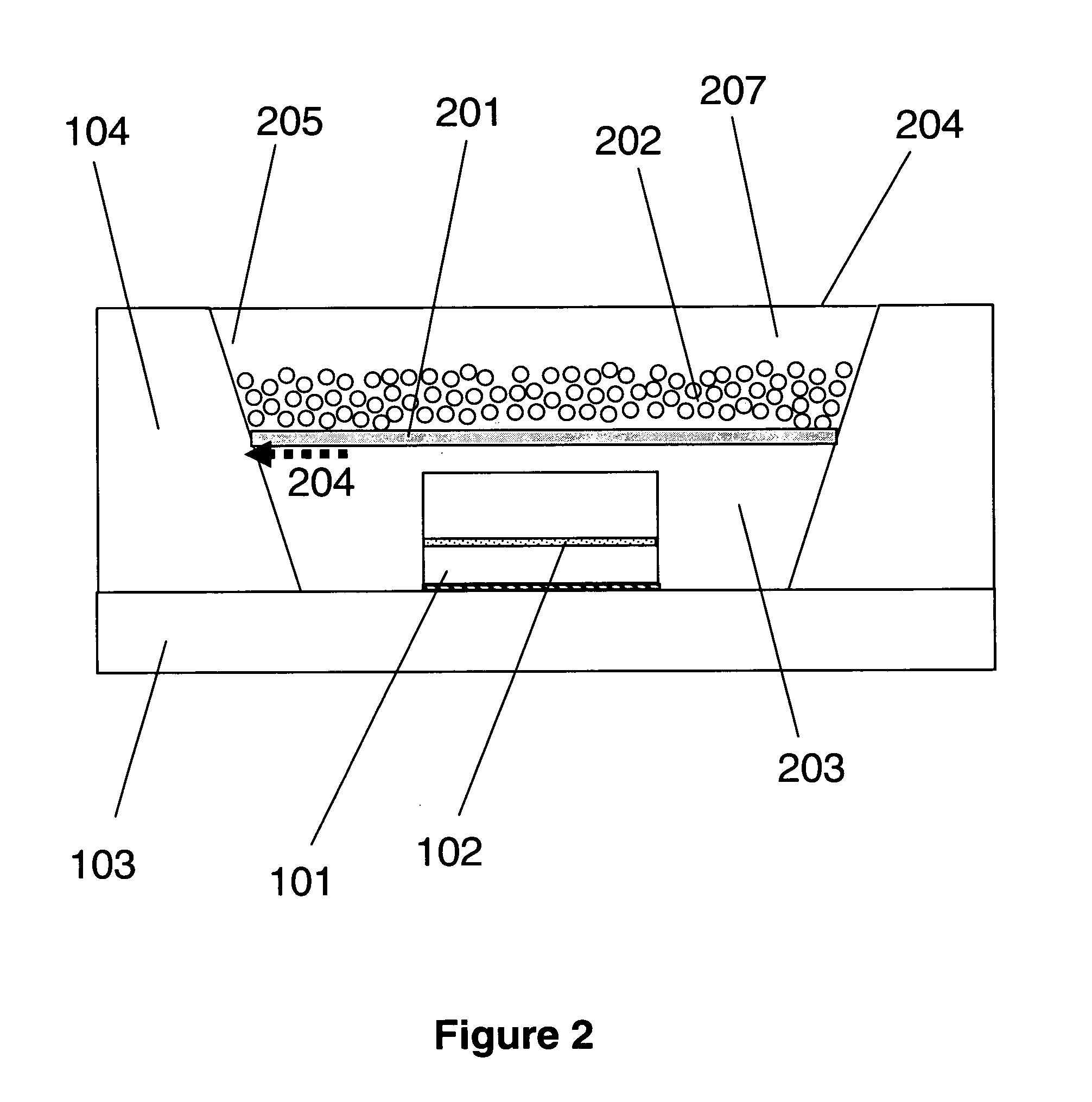

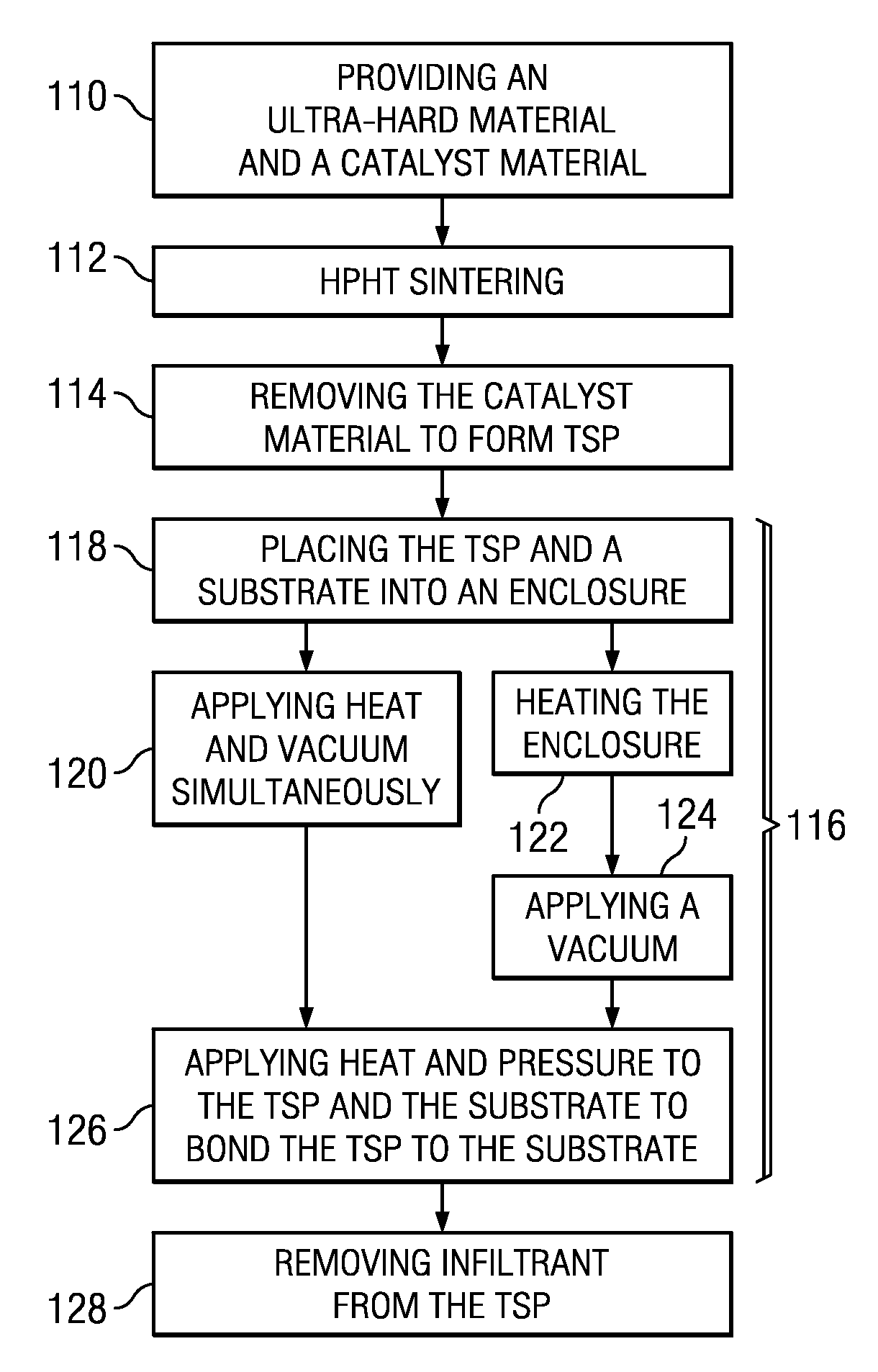

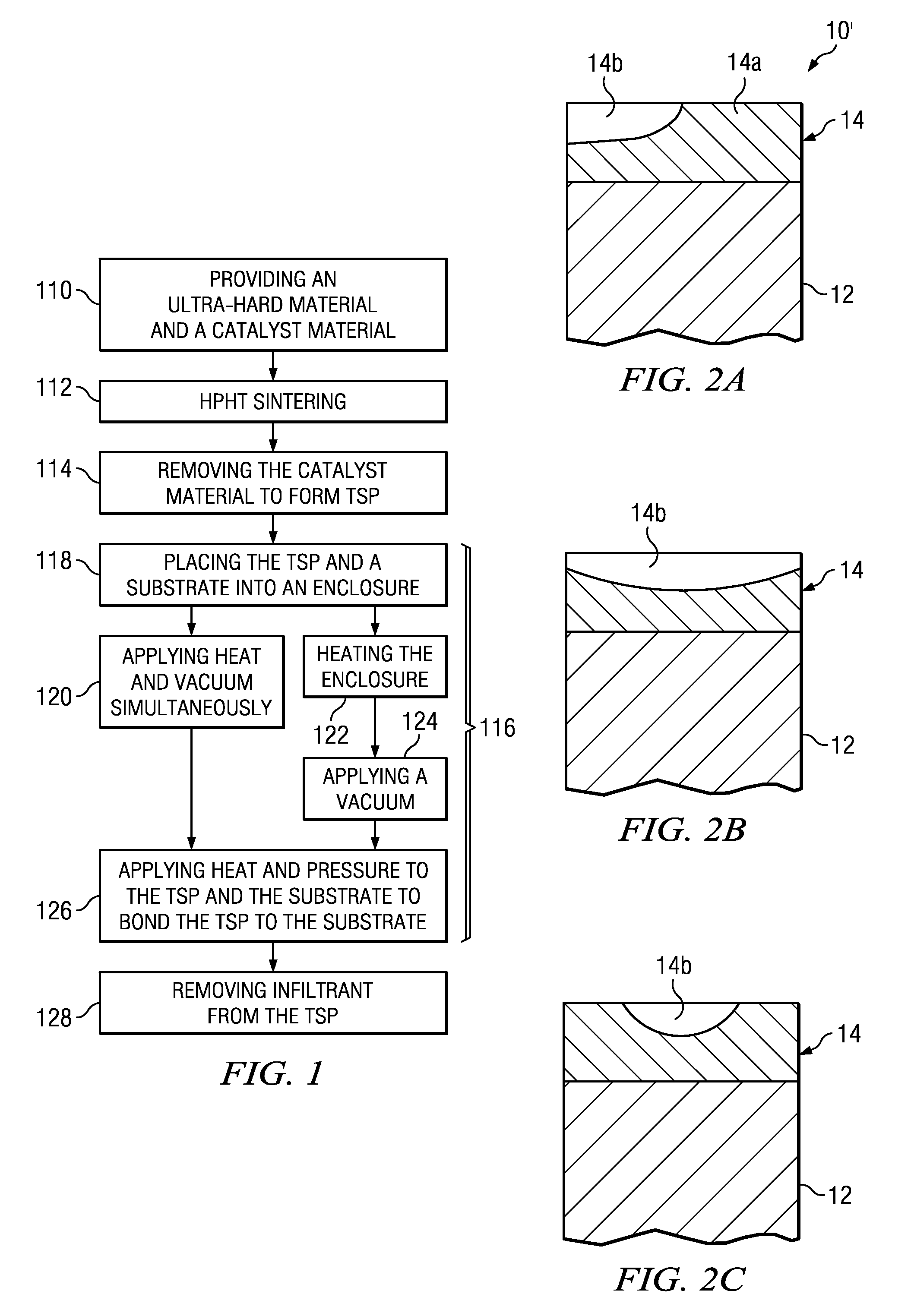

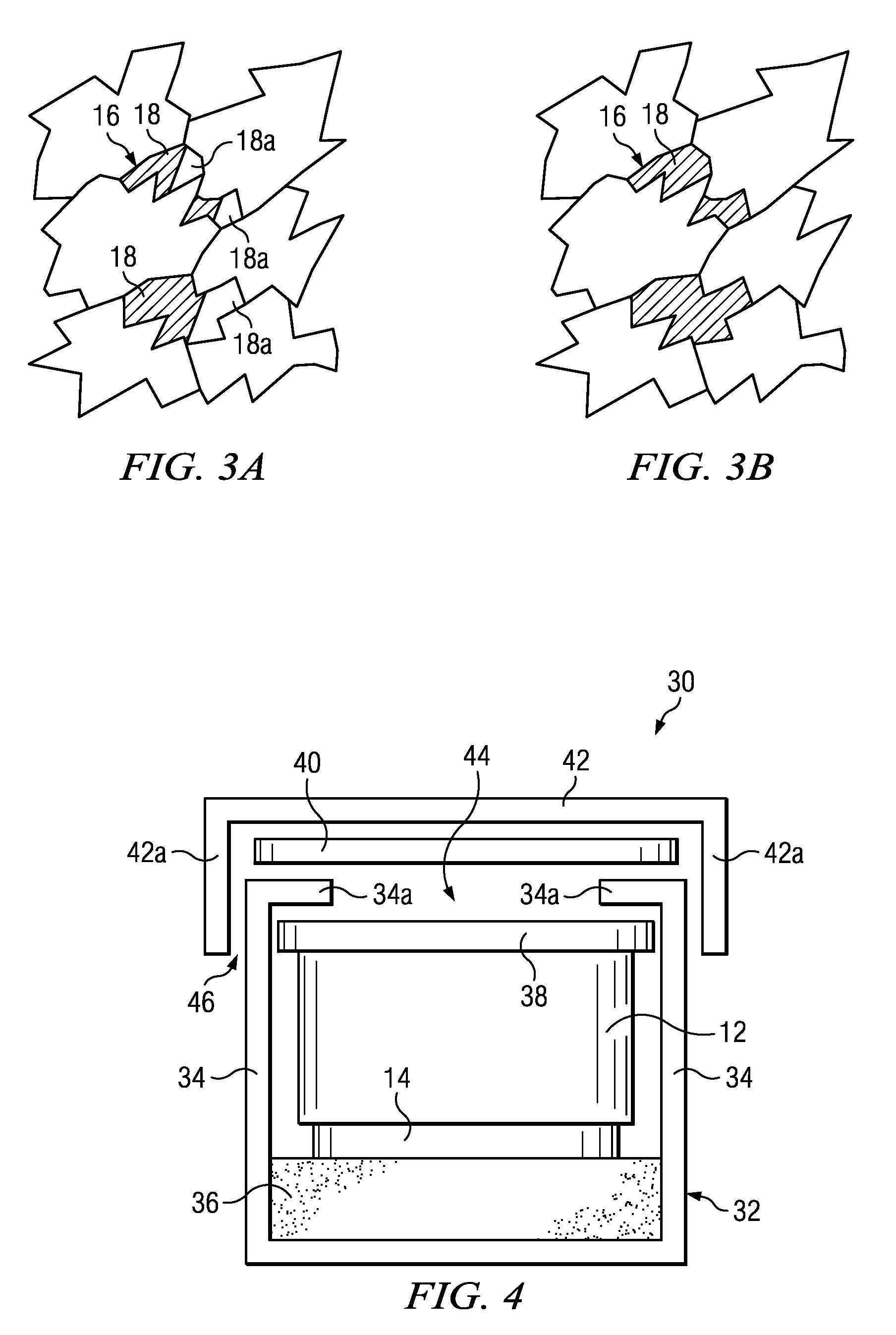

Method of forming a thermally stable diamond cutting element

InactiveUS20110030283A1Improve thermal characteristicsReduce thermal stressPressurized chemical processOther chemical processesDiamond cuttingDiamond crystal

In one aspect, a vacuum-sealed can is used during the bonding process to improve the properties of an infiltrated TSP cutting element. In one embodiment, ultra hard diamond crystals and a catalyst material are sintered to form a polycrystalline diamond material (PCD). This PCD material is leached to remove the catalyst, forming a thermally stable product (TSP). The TSP material and a substrate are placed into an enclosure such as a can assembly, heated, and subjected to a vacuum in order to remove gas, moisture and other residuals that can inhibit infiltration of the infiltrant into the TSP layer. The can assembly is then subjected to high temperature, high pressure bonding to bond the TSP material to the substrate. During bonding, material from the substrate infiltrates the TSP layer.

Owner:SMITH INT INC

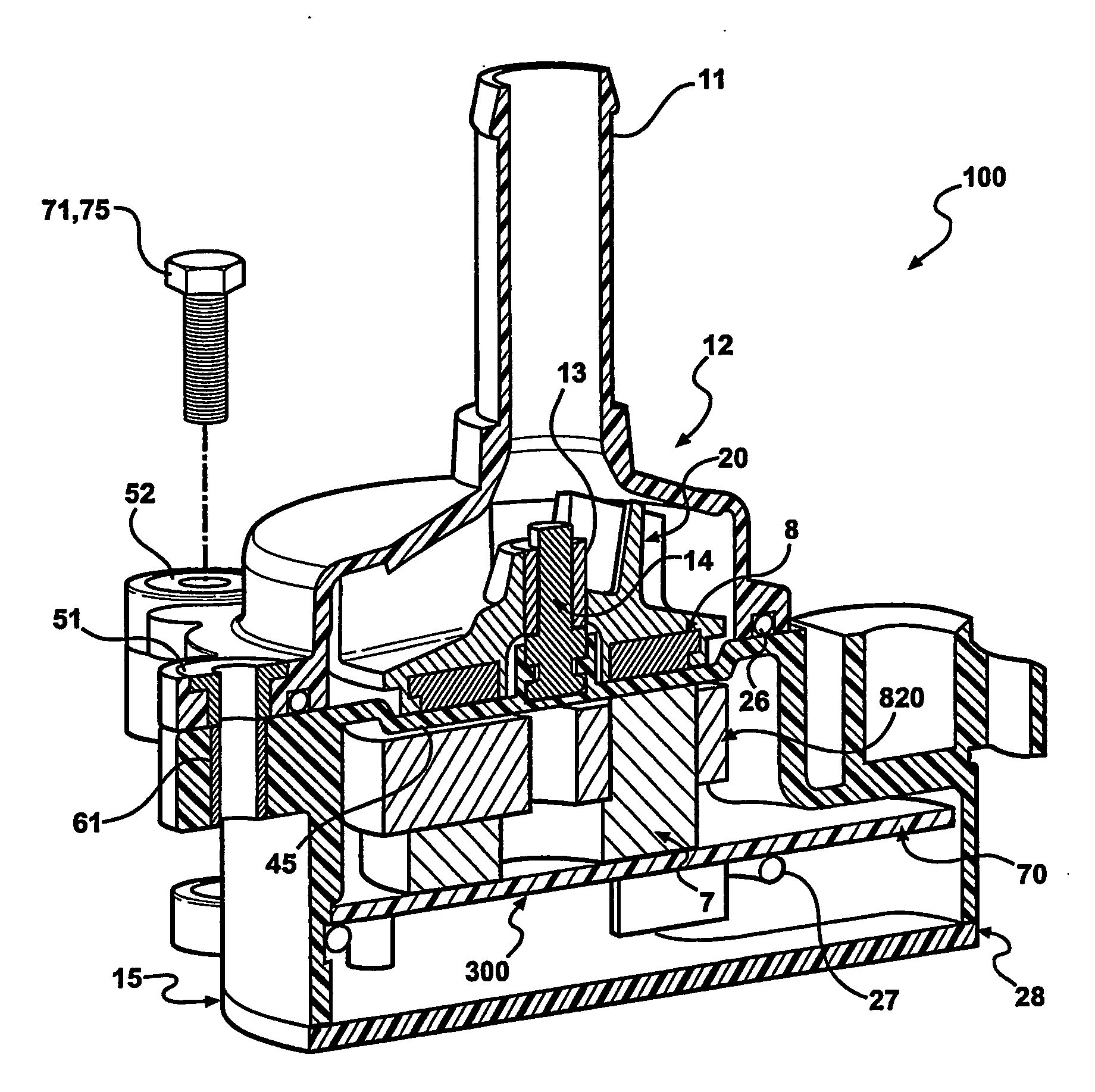

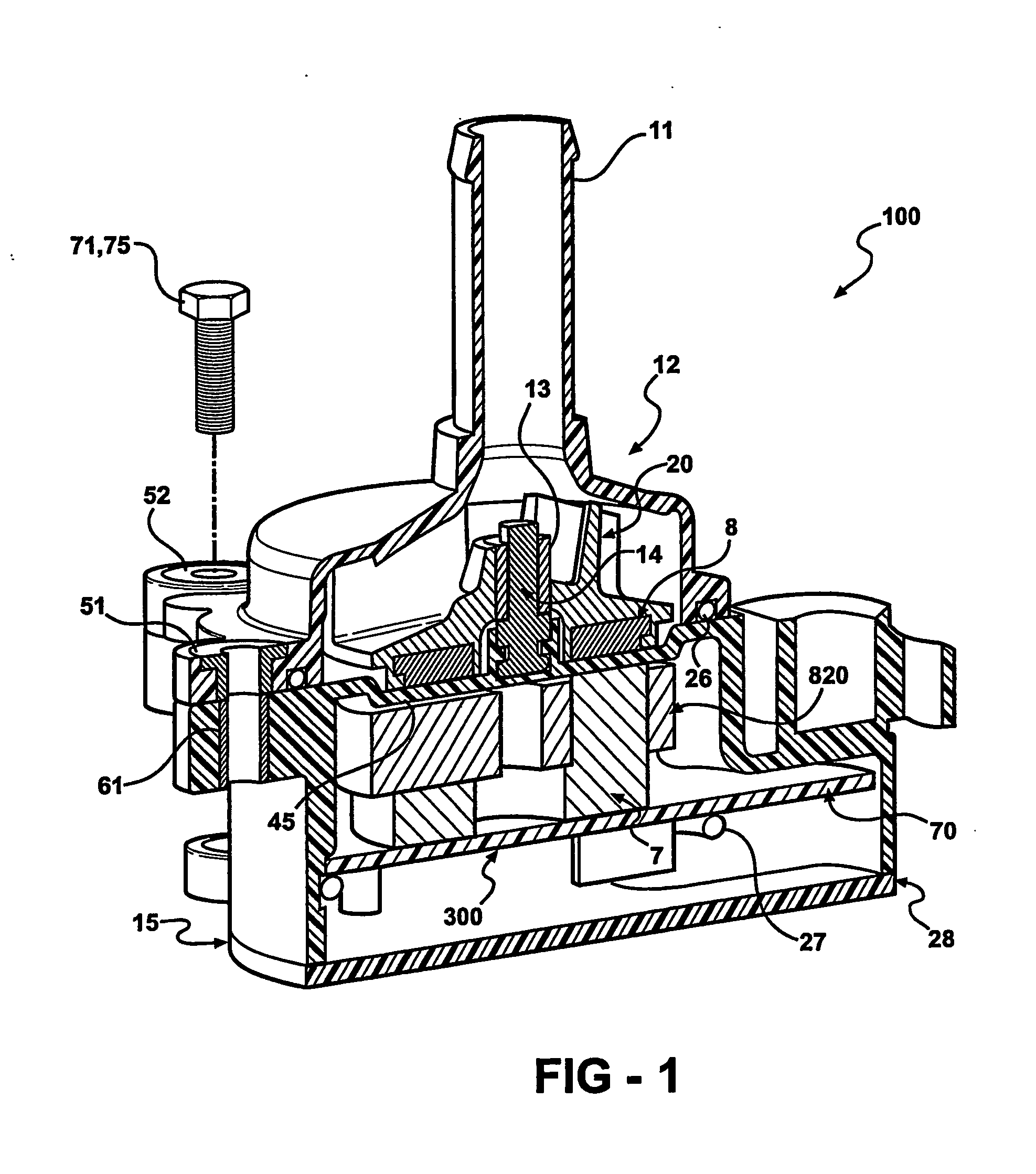

Electric fluid pump

InactiveUS20060245956A1Reduce numberGreat efficiencyPiston pumpsMechanical energy handlingImpellerStator

An electric fluid pump includes an upper housing having a fluid inlet and outlet. An impeller is seated within the upper housing for pumping fluid between the inlet and the outlet. The impeller includes at least one magnet secured thereto. A lower housing mates with the upper housing. The lower housing has an upper wall for closing the upper housing and a shaft extending from the upper wall for rotatably supporting the impeller. A stator is seated within the lower housing and spaced from the impeller by the upper wall. The stator includes a plurality of pillars supporting a winding of coils for producing a magnetic field to energize the magnet and rotate the impeller, and a plurality of top plates covering each of the coils and spaced apart by a predetermined gap for maintaining the magnetic field between the stator and the impeller. An end cap closes the stator within the lower housing.

Owner:TESMA INT INC

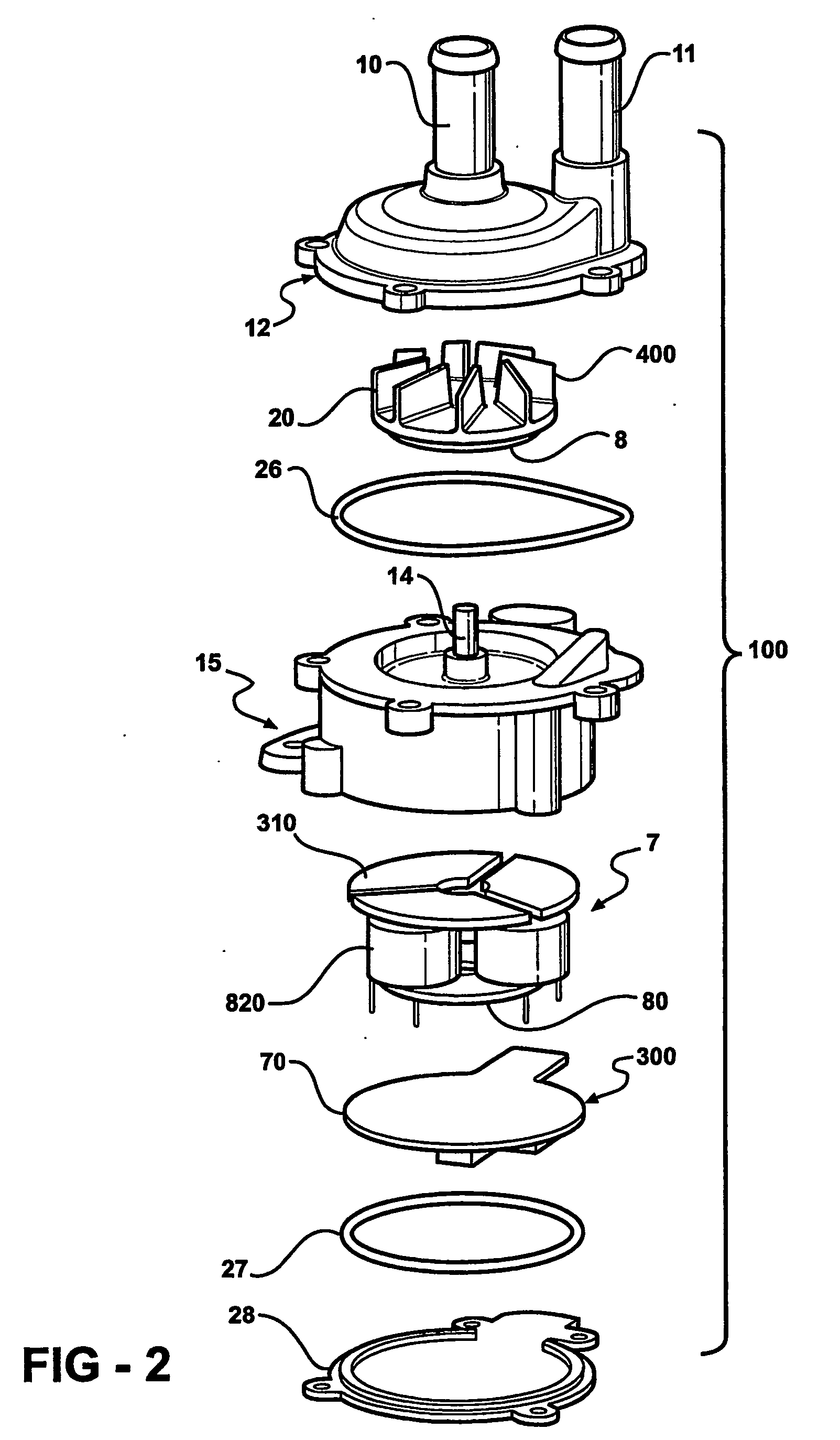

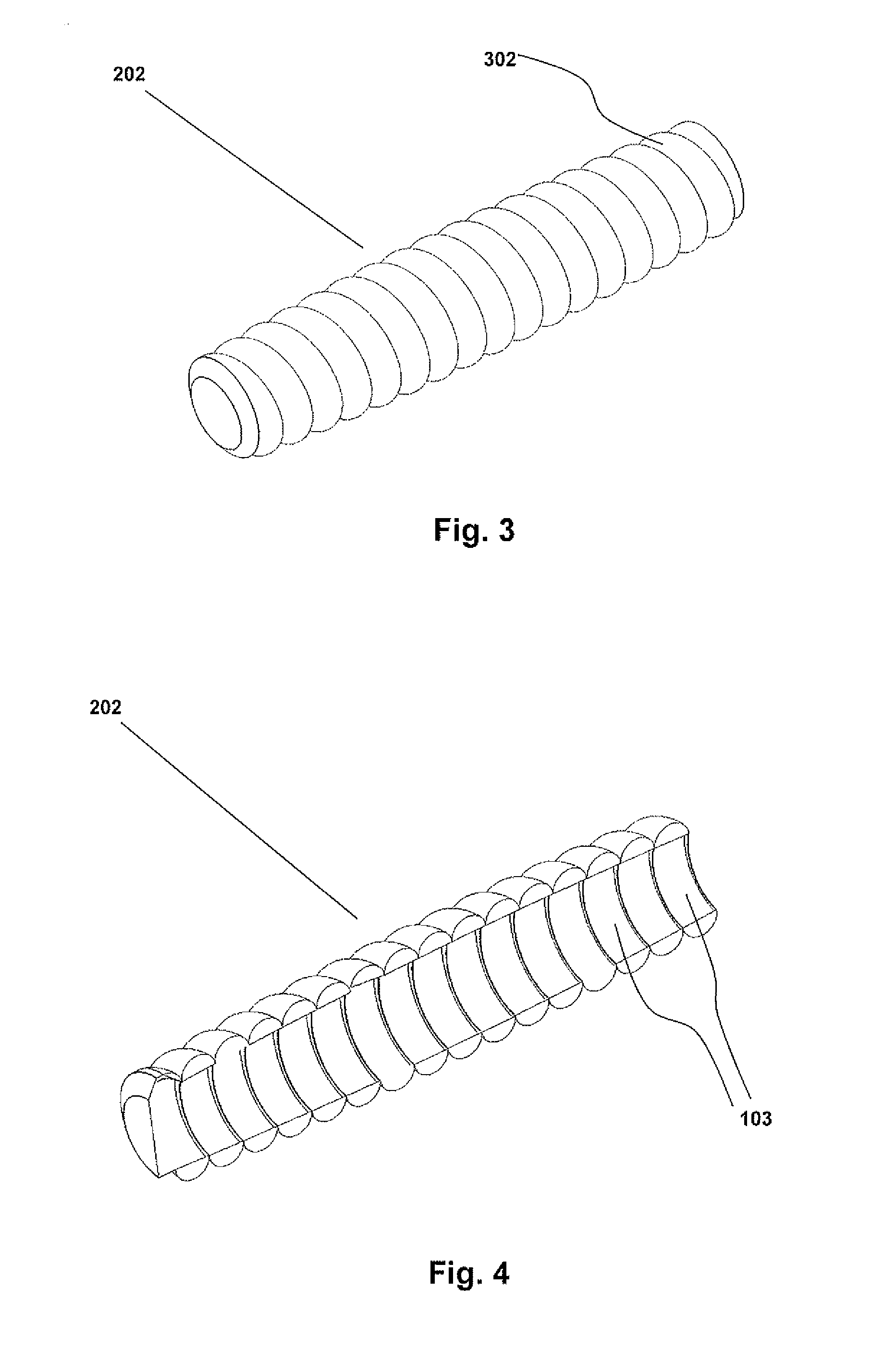

Fiber laser coil form and related manufacturing techniques

InactiveUS20090296746A1Good thermal contactHeat dissipationLaser using scattering effectsFilament handlingOptoelectronicsThermal contact

A fiber laser thermal coil form and related manufacturing techniques that are substantially suitable for automation. The fiber laser thermal coil form including a thermally conductive substrate to support a fiber placed thereon and to dissipate a heat of the fiber, and a fiber guide groove defined in a surface of the substrate to guide the fiber and dimensioned to partially enclose the fiber and to enhance a thermal contact of the fiber and the substrate.

Owner:MORGAN RES CORP

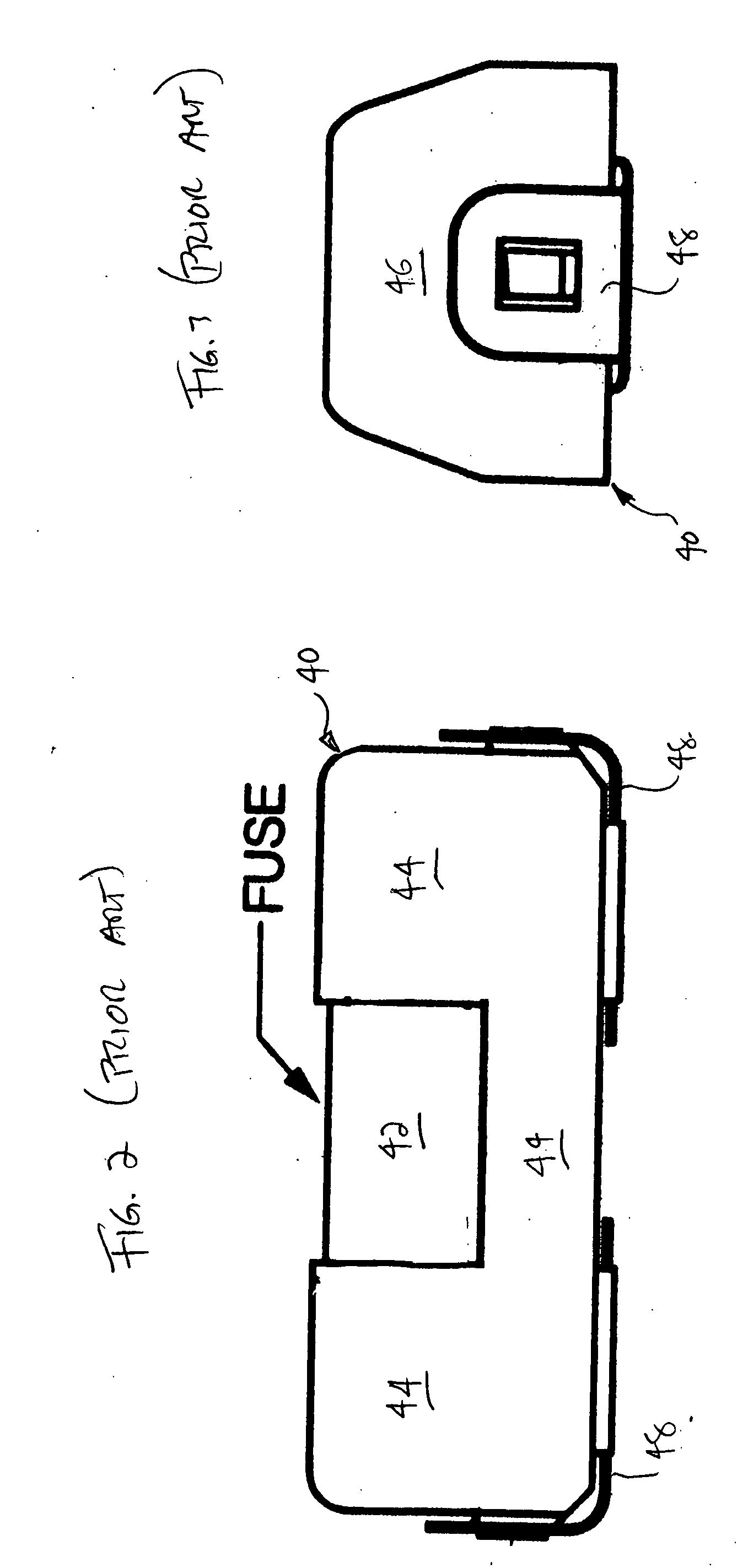

Thermally decoupling fuse holder and assembly

ActiveUS20060197647A1Easy to optimizeImprove thermal characteristicsIncorrect coupling preventionFinal product manufactureEngineeringMechanical engineering

Owner:LITTELFUSE INC

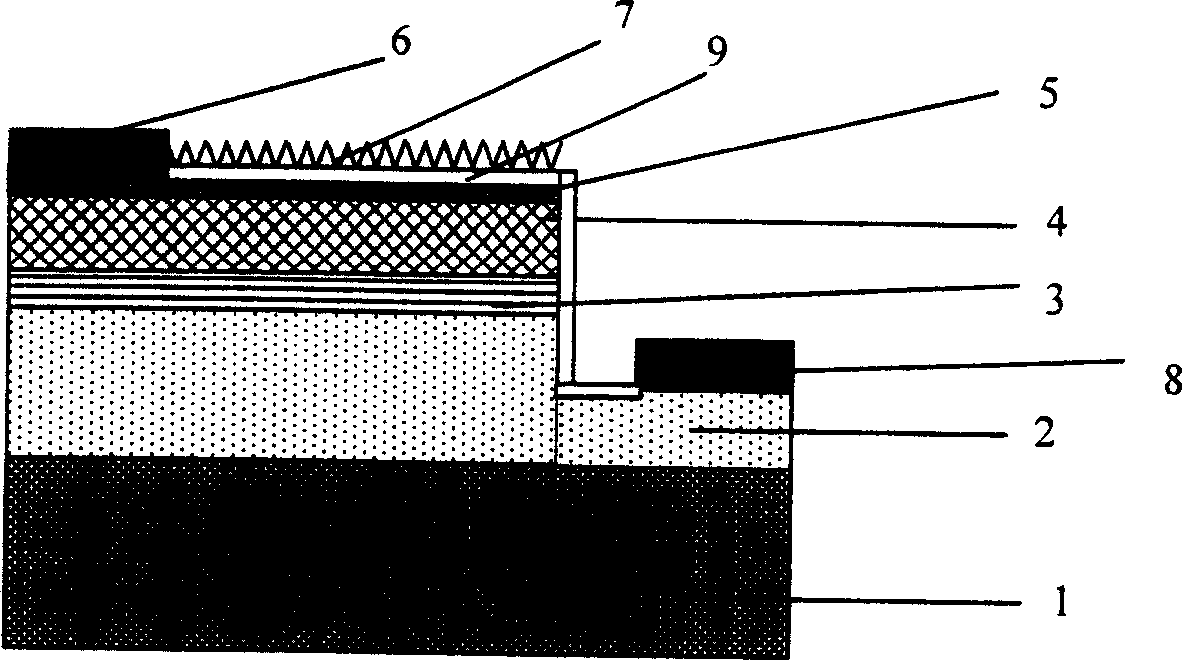

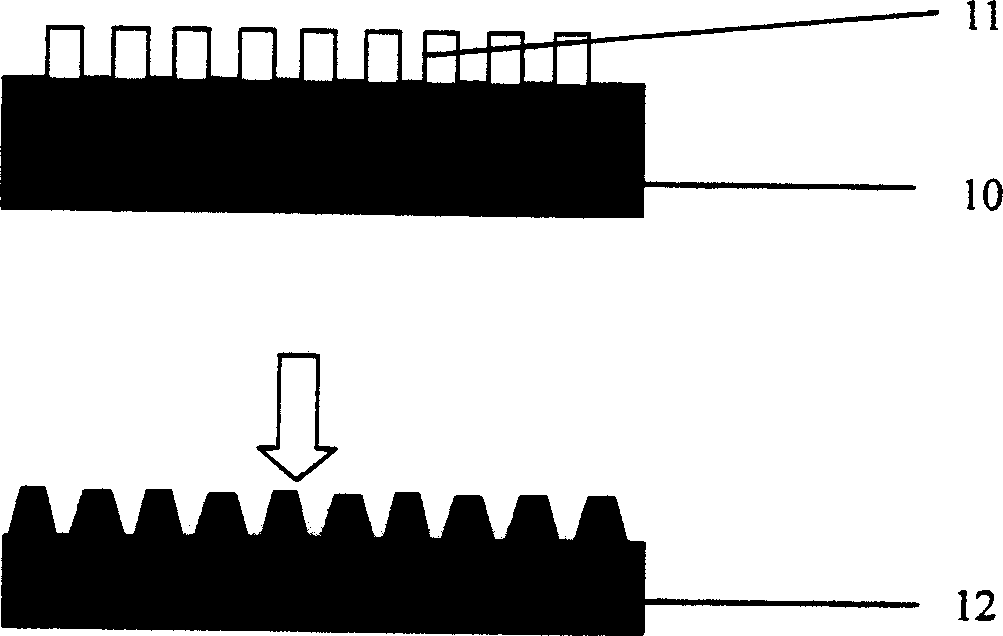

High-luminance chip of luminescent tube in GaN base, and preparation method

InactiveCN1874012AImprove thermal characteristicsImprovement and conductivityLaser detailsSolid-state devicesPhotonic crystal structureLead structure

The technical scheme discloses high brightness LED structure with graphic surface and microstructure. Using Nano pressing technique prepares each graphic film from organic material on luminous surface of LED so as to form microstructure on LED surface in favor of transgression of emitting light from active region, for example micrographics with structure or coarsening, and photon crystal structure. Introducing the said micrographics on surface makes interfacial area of light emergence medium increase. The increased surface presents great lot small areas unordered arranged. Emergence of light from active region and interface of medium is at random in a certain extent. The invention improves directions of emergence light, increases probability of emergence so as to raise light extraction efficiency and external quantum efficiency of LED.

Owner:PEKING UNIV

Cathode active material for lithium secondary batteries with high safety and method of preparing for the same and lithium secondary batteries comprising the same

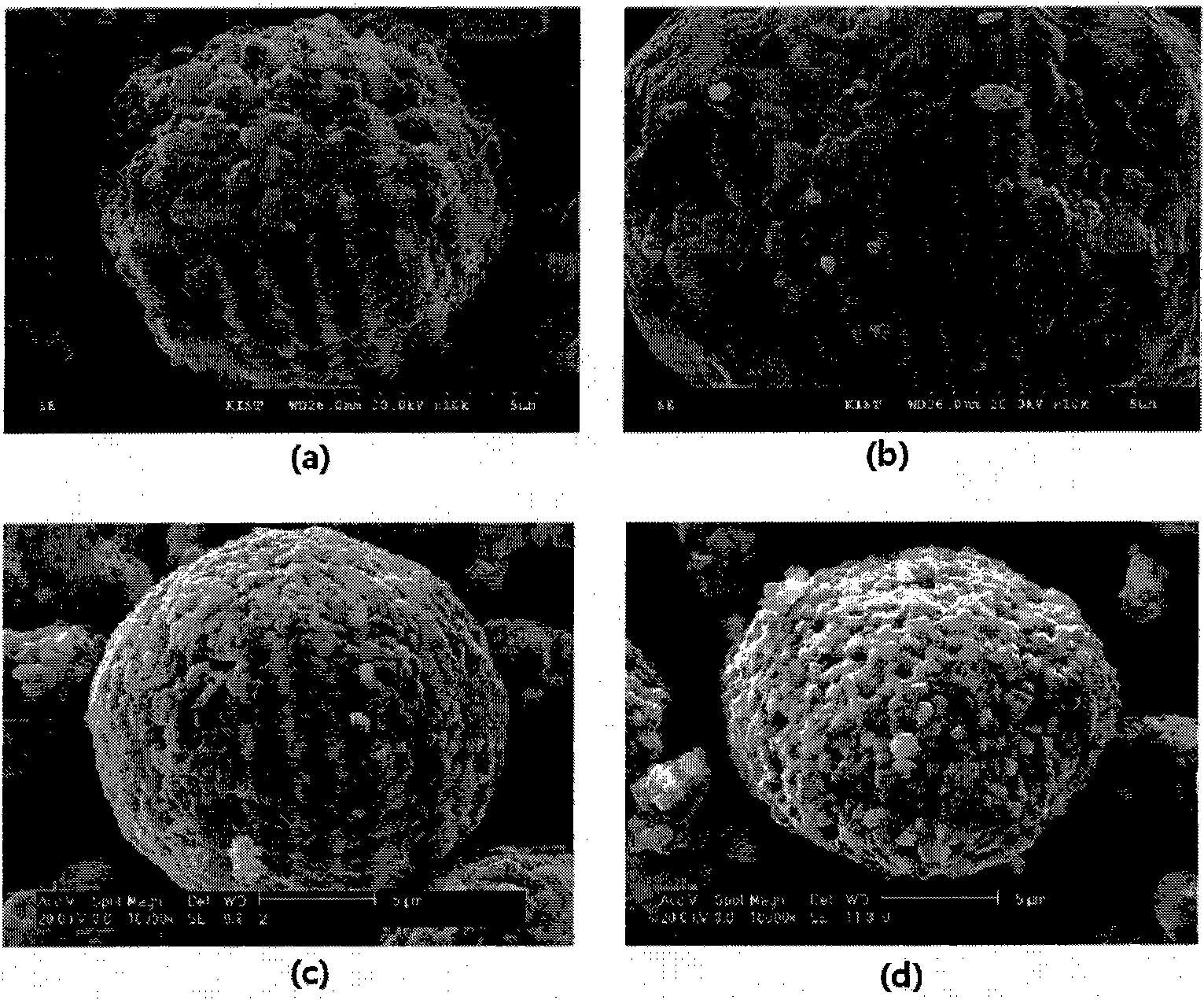

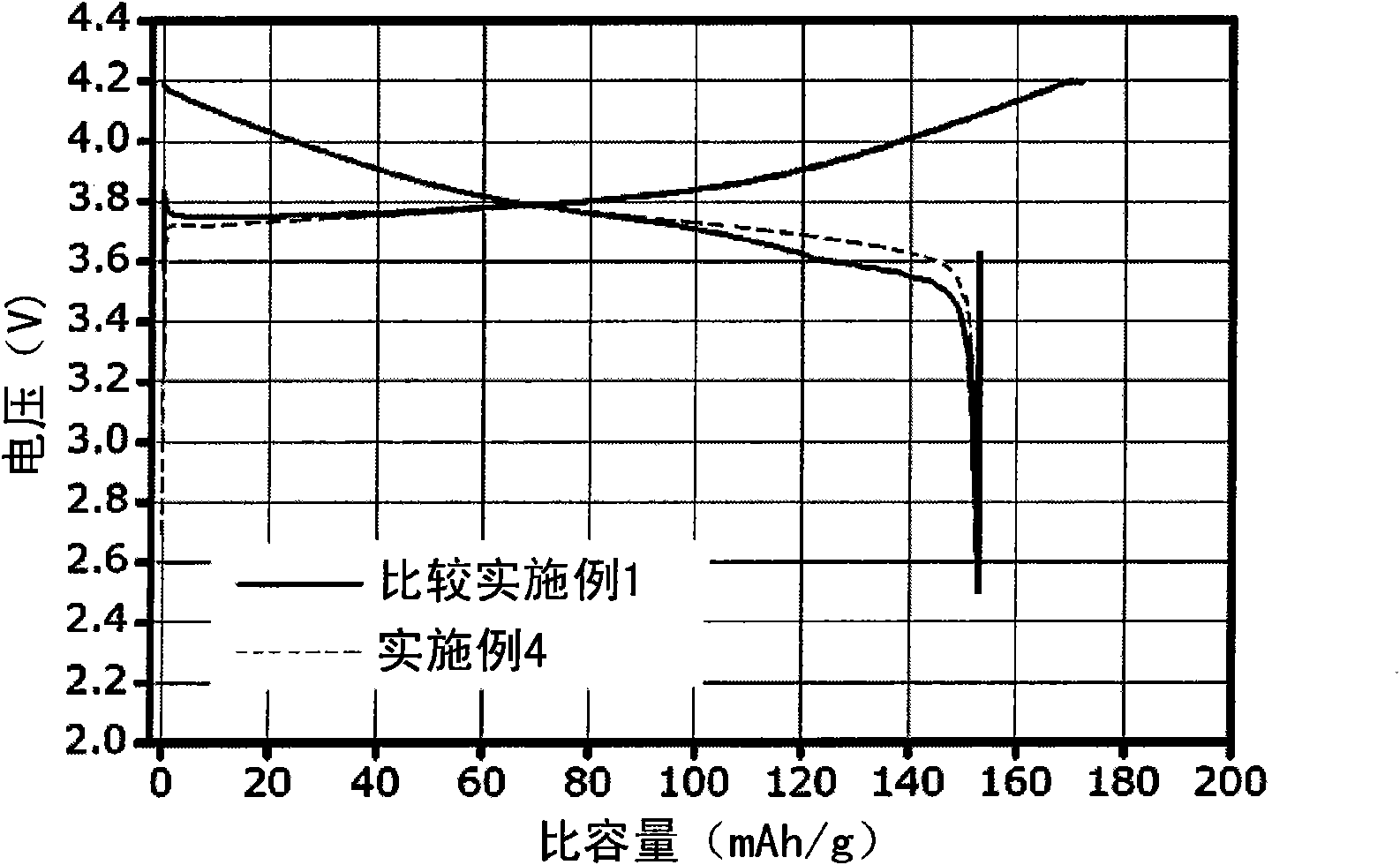

ActiveCN101884126AHigh yieldGood reproducibilityAlkaline earth titanatesMaterial nanotechnologyBarium titanateLithium metal

A cathode active material for a lithium secondary battery includes a lithium metal oxide secondary particle core formed by agglomerating lithium metal oxide primary particles; and a shell formed by coating the secondary particle core with barium titanate and metal oxide. This cathode active material allows making a lithium secondary battery having improved safety, particularly in thermal stability and overcharging characteristics.

Owner:SOLE SOLAR TECH KOREA CO LTD

Method for producing sheet type thermosensitive resistor

InactiveCN101067981ASimplify the manufacturing processEasy to operateNegative temperature coefficient thermistorsResistor manufactureThermal resistorProtection layer

This invention discloses a manufacturing method for slice thermal resistors, which prints a back electrode on the back of a marked slot side of an insulated ceramic chip, prints a face electrode on the slot side, then prints a thermal resisting layer and a protection layer with a thick film silk screen, which can reduce the processing time of slice thermal resistors effectively.

Owner:GUANGDONG FENGHUA ADVANCED TECH HLDG +1

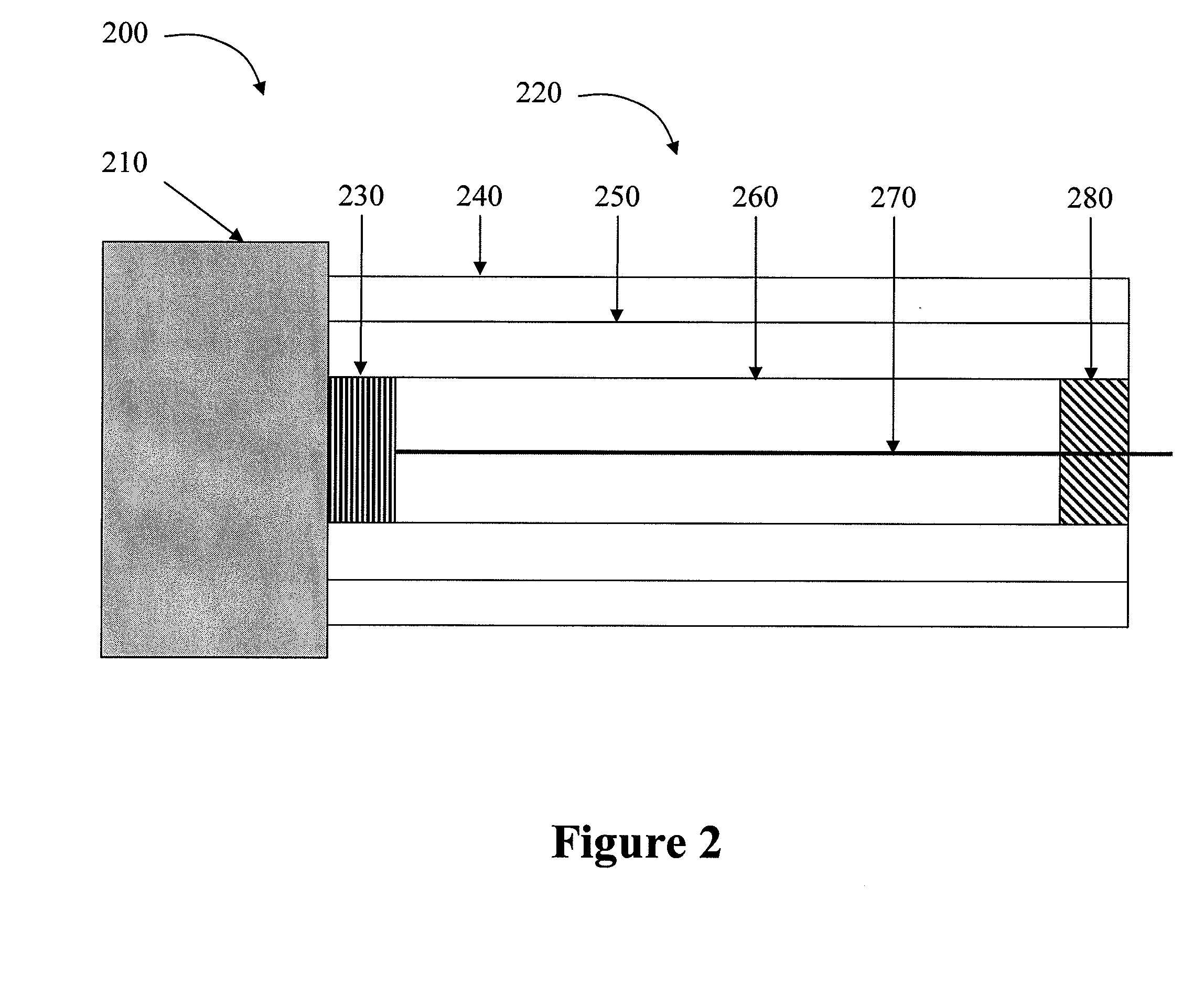

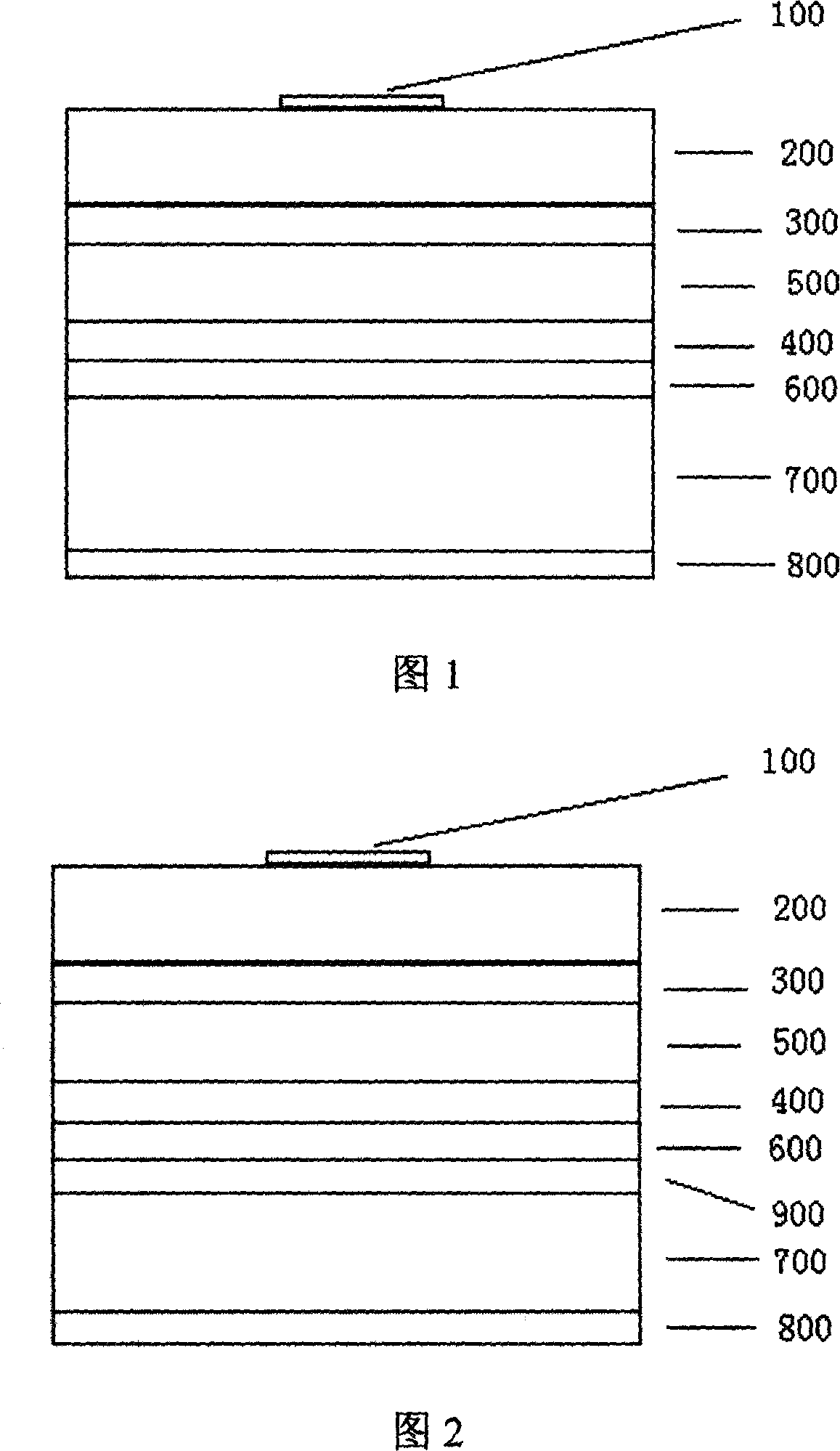

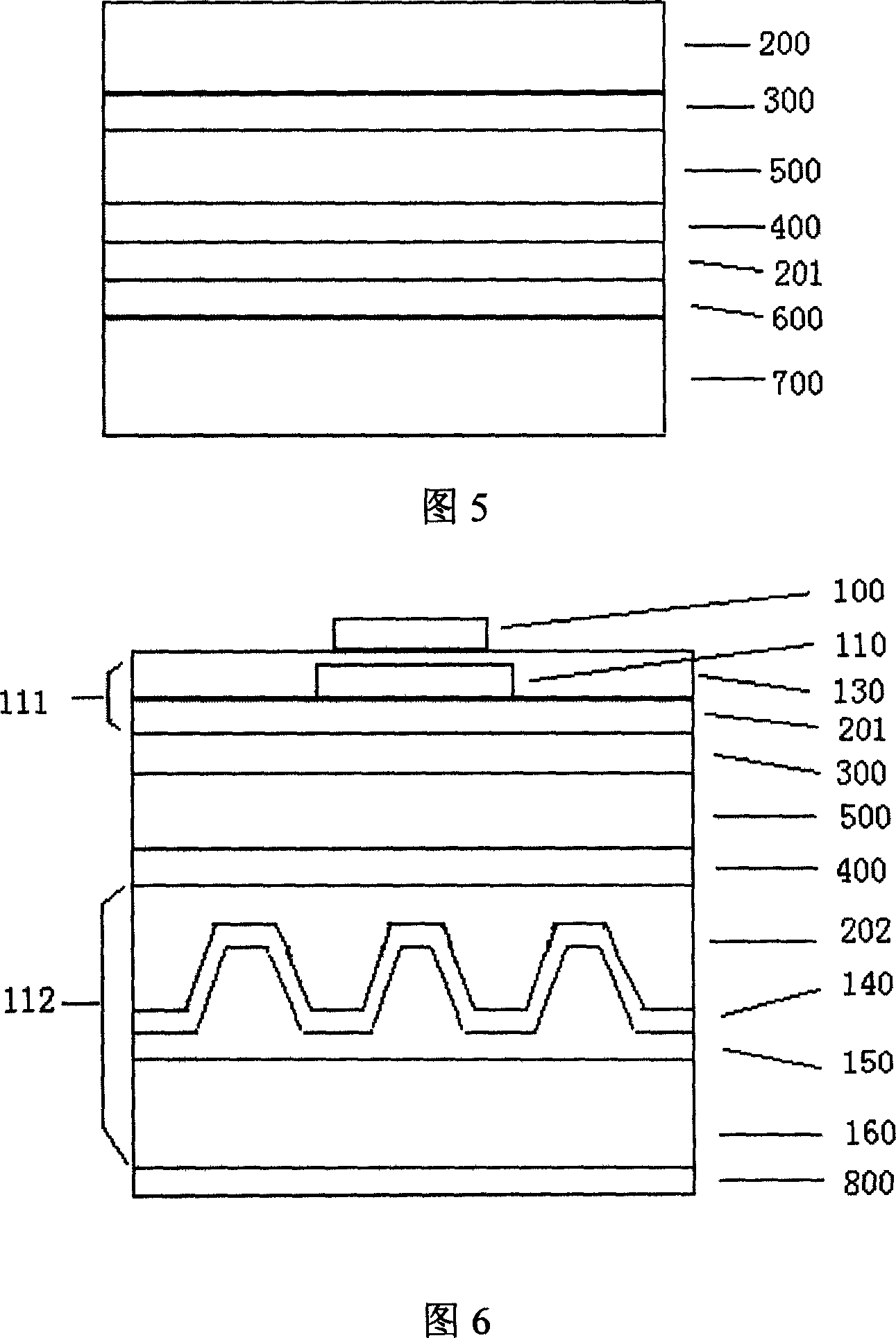

Current-transfer enhanced window layer and LED with the high reflection graph shift substrate structure

InactiveCN101009353AImprove thermal characteristicsIncrease productionSemiconductor devicesLower limitSource area

The LBD of current transmission reflection reducing window layer and high reflecting graph transfer underlay configuration belongs to field of semiconductor photoelectron technique. It includes upper electrode (100), current transmission reflection reducing window layer (111) which comprises conducting reflection reducing light layer (130), current barrier layer (110) and current expansion layer (201), upper limit layer (300), source area (500), lower limit layer (400), graphic current expansion layer (202), conducting high glisten layer (140), conducting linkage layer (150) and transfer underlay (160) or rack constructed by the upper current expansion layer (200), conducting linkage layer (150), conducting high glisten layer (140) and graphic transfer underlay (161), lower electrode (800). The invention increases the current expansion and light output, and can increase the light efficiency greatly, it can realize the high efficiency, high brightness LED lightening; the heat property and reliability are high.

Owner:BEIJING TIMESLED TECH CO LTD

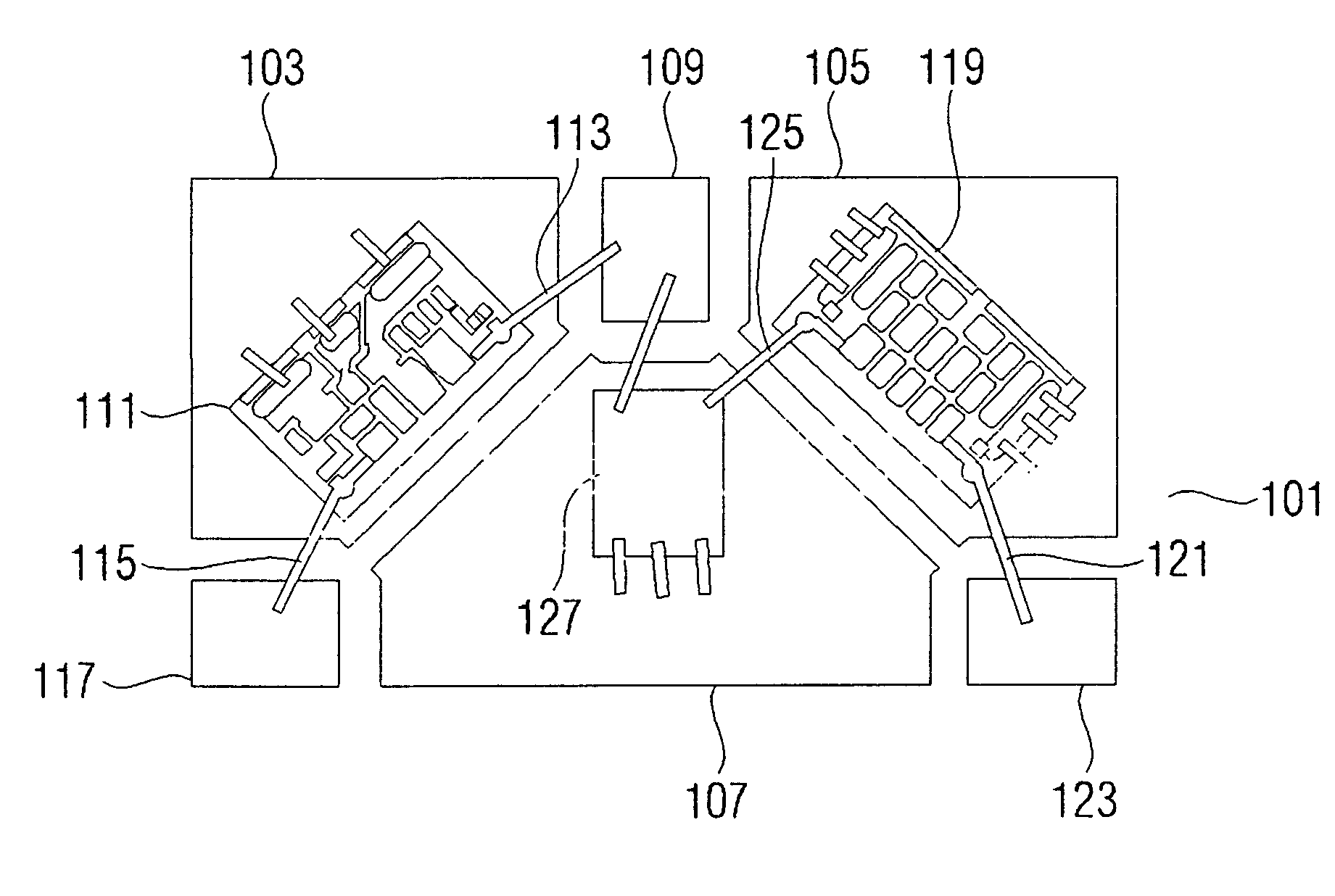

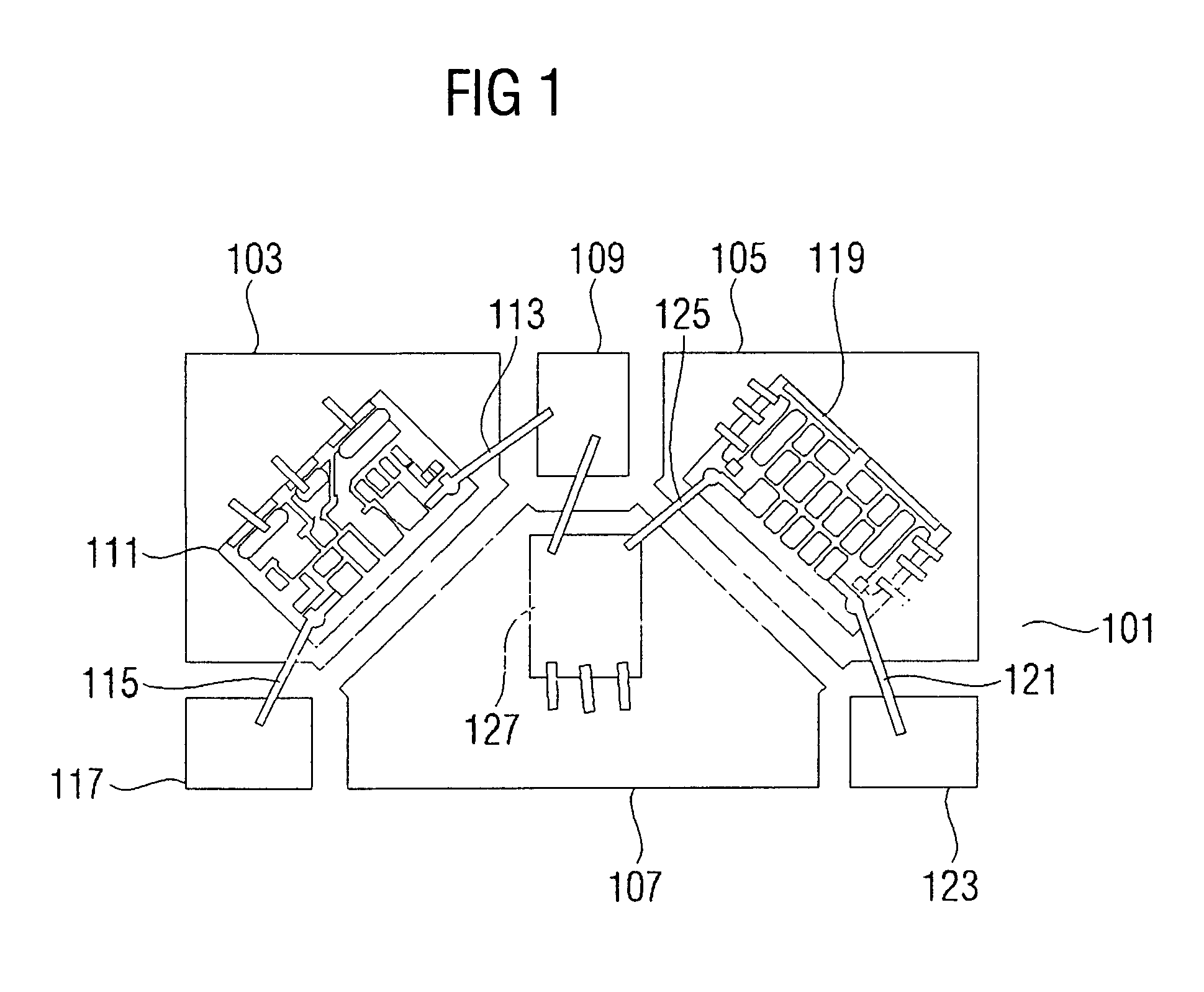

Transmit/receive filter and method for manufacturing same

InactiveUS20050207481A1Small sizeImprove thermal characteristicsImpedence networksWaveguide type devicesEngineeringFilter bank

A transmit / receive filter includes a substrate, an antenna terminal, a transmit filter assembly arranged on a first substrate portion, an output of the transmit filter assembly being connected to the antenna terminal, a receive filter assembly arranged on a second substrate portion, and a discrete phase shifter arranged on a third substrate portion, the discrete phase shifter being formed of discrete circuit elements and an input of the receive filter assembly being connected to the antenna terminal via the discrete phase shifter, the discrete phase shifter being formed to set a predetermined phase relation to decouple the receive filter assembly from the transmit filter assembly.

Owner:INFINEON TECH AG

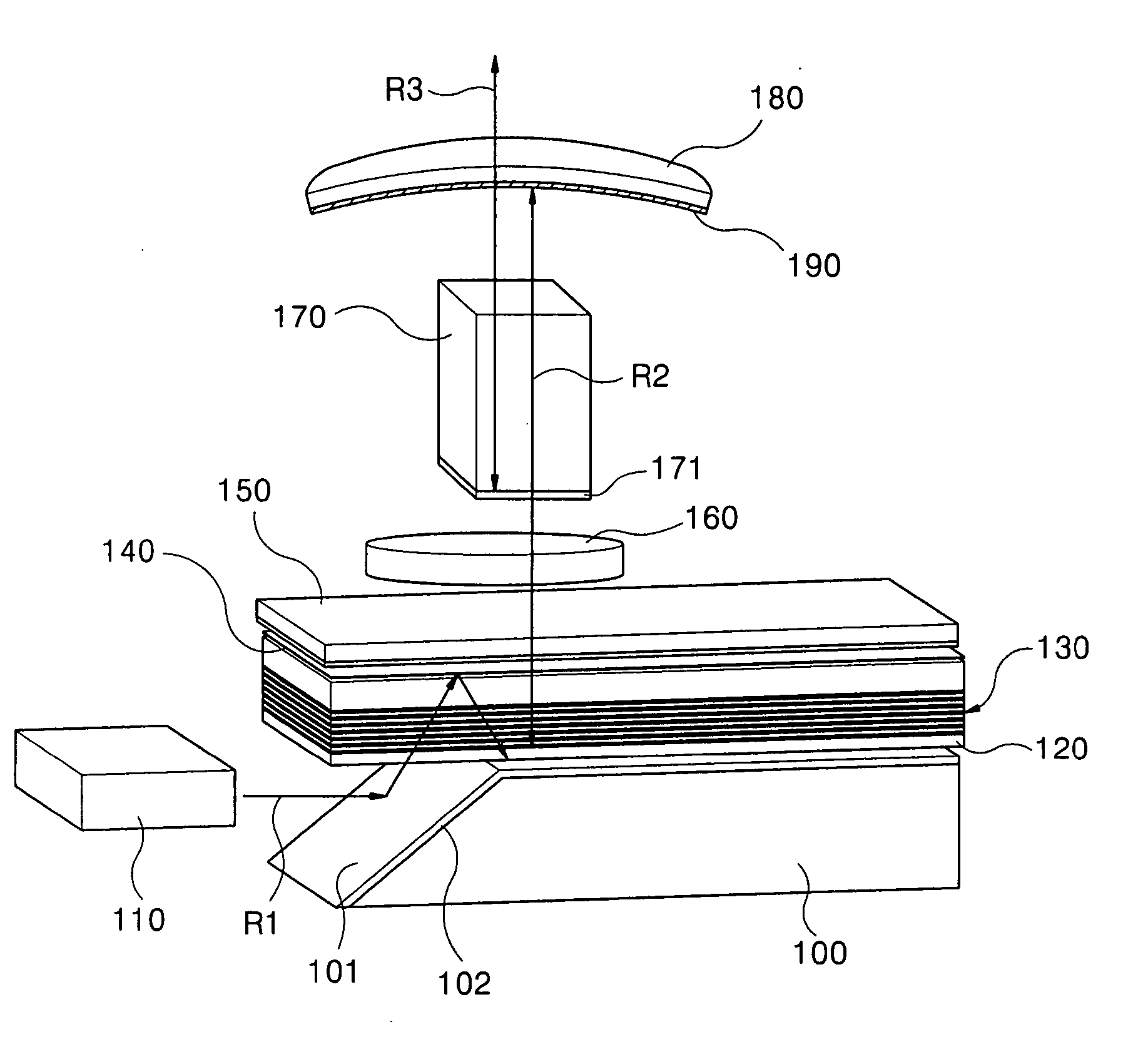

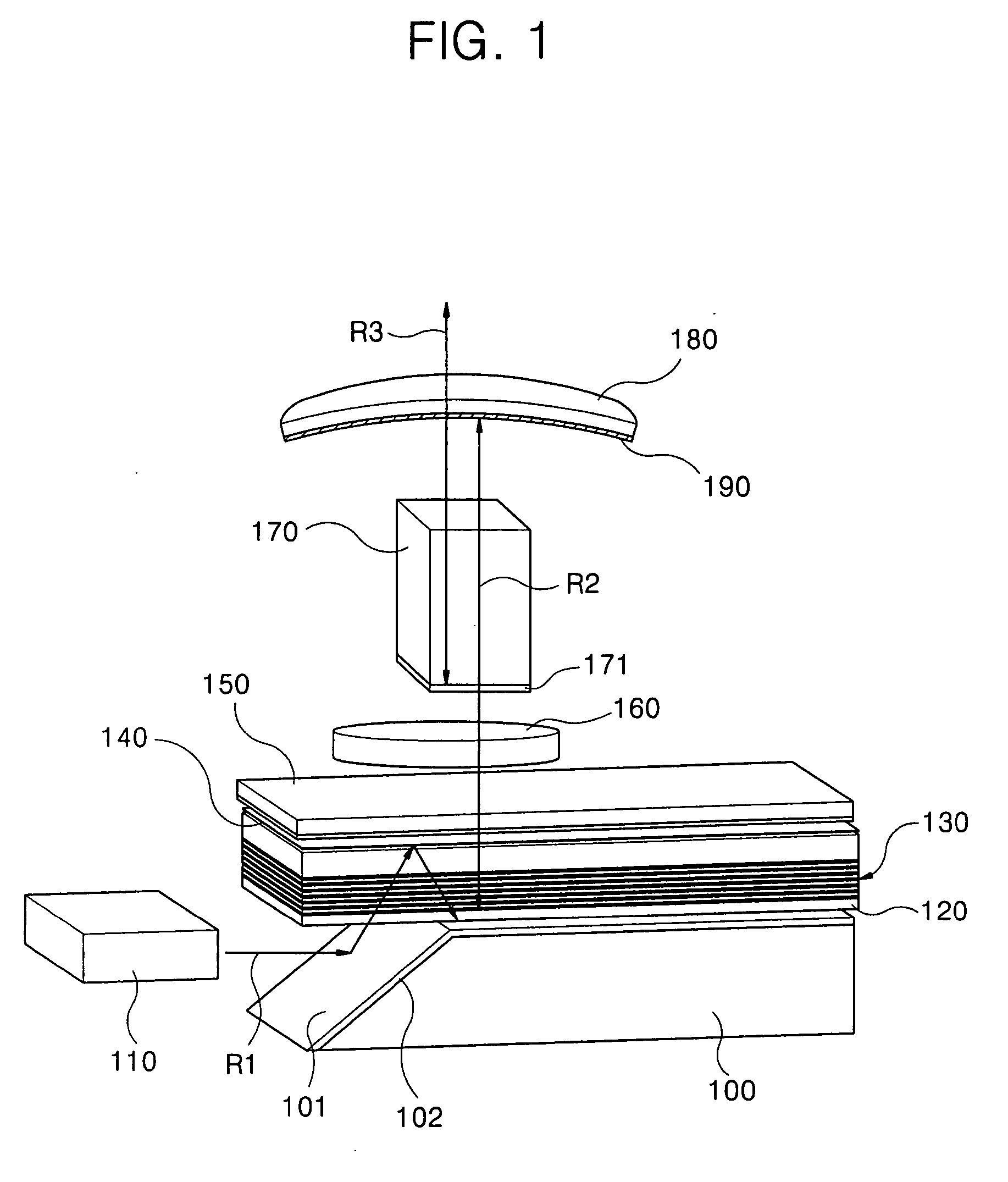

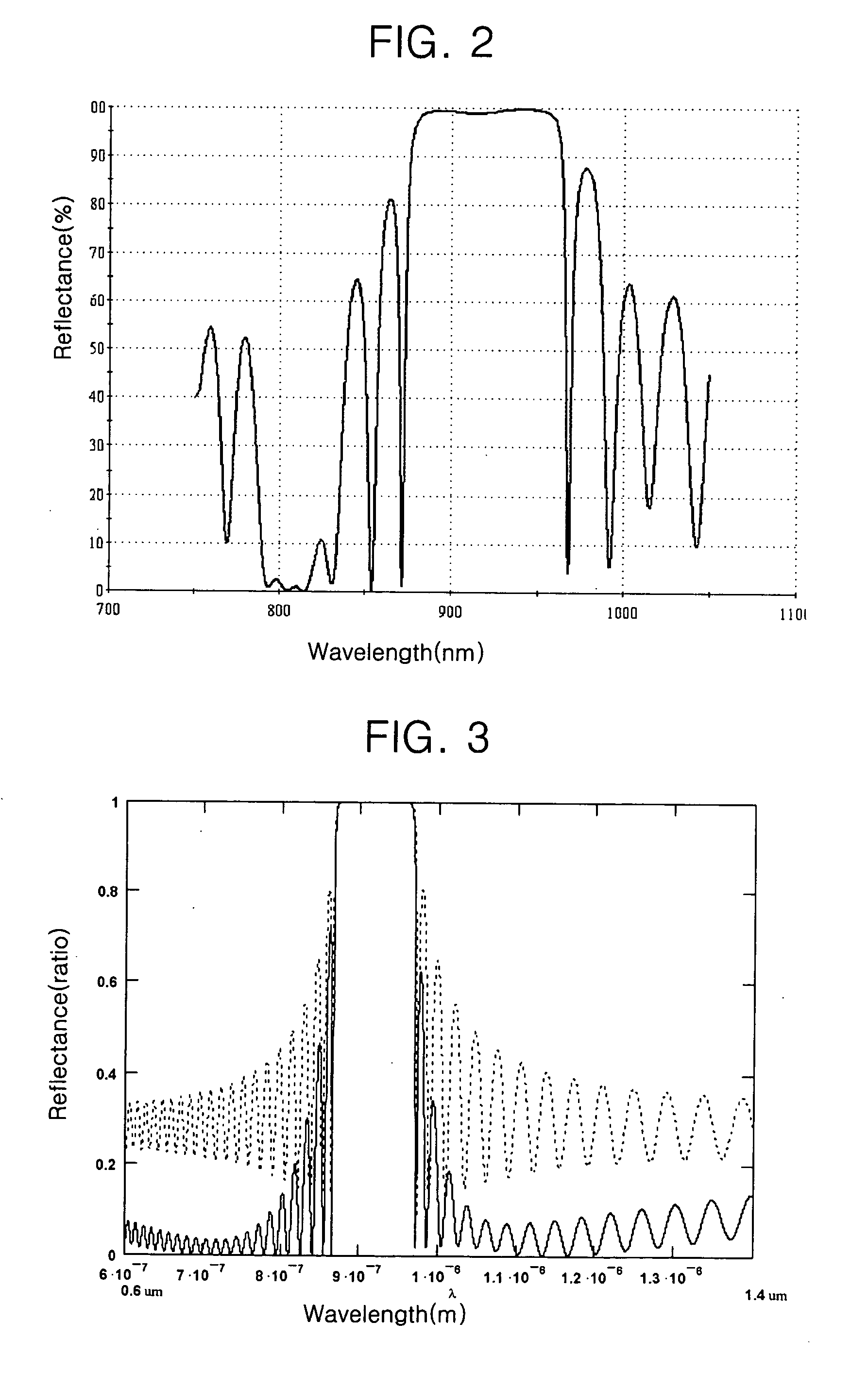

Optically pumped semiconductor laser

InactiveUS20070014325A1Structure miniaturizationLow threshold pumping powerOptical resonator shape and constructionNanoopticsOptical pumpingHarmonic

An optically pumped semiconductor laser and an optical pumping method are disclosed. The optically pumped semiconductor laser includes first and second reflective bodies forming a resonant region therebetween, a gain medium disposed between the first and second reflective bodies; and a light source for applying a source light to the resonant region in a lateral direction with regard to the gain medium for generating a basic wavelength. The laser further comprising an output mirror and a nonlinear crystal disposed between the output mirror and the second reflective body to generate a predetermined wavelength as a second harmonic of the basic wavelength.

Owner:SAMSUNG ELECTRONICS CO LTD

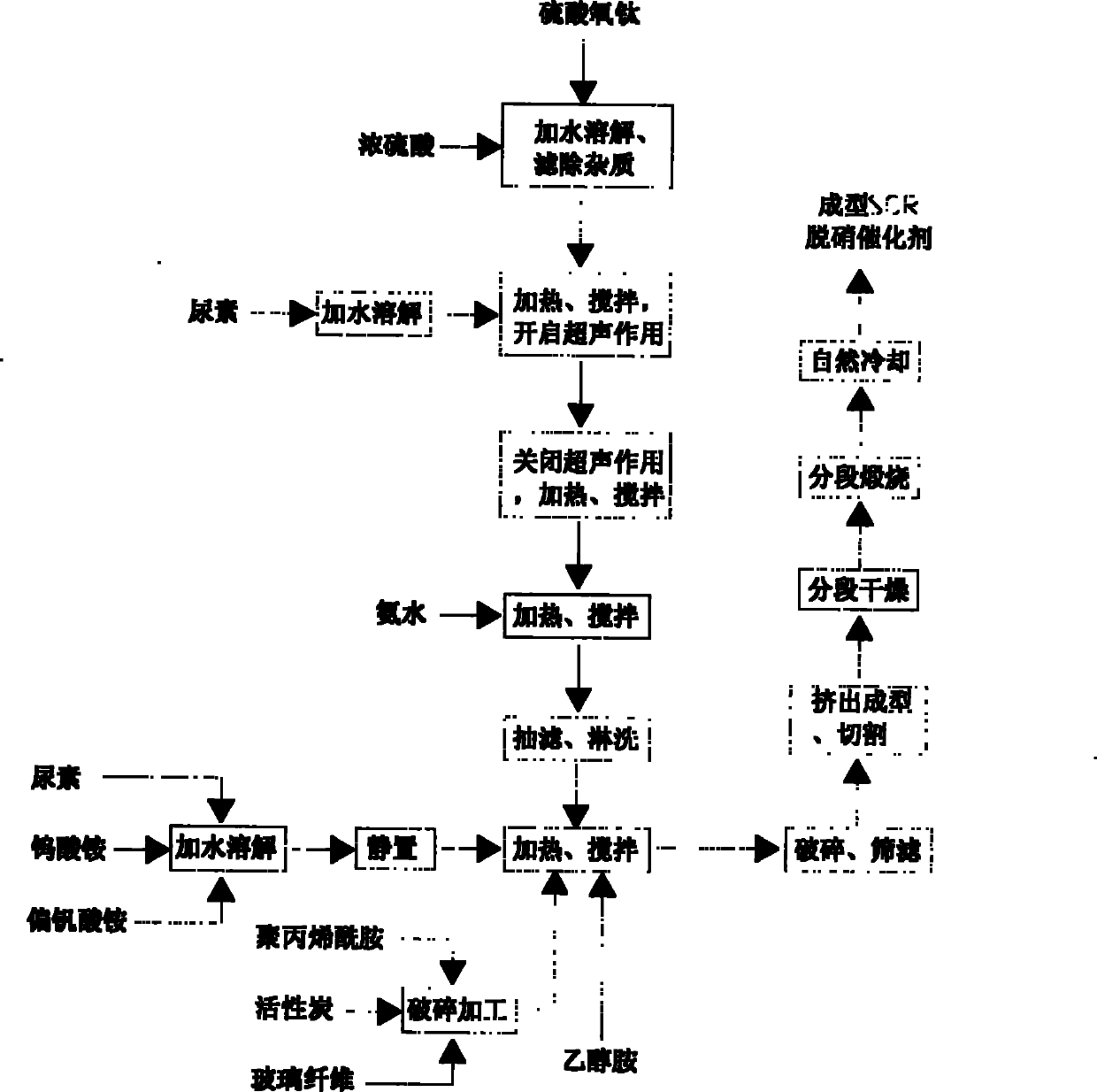

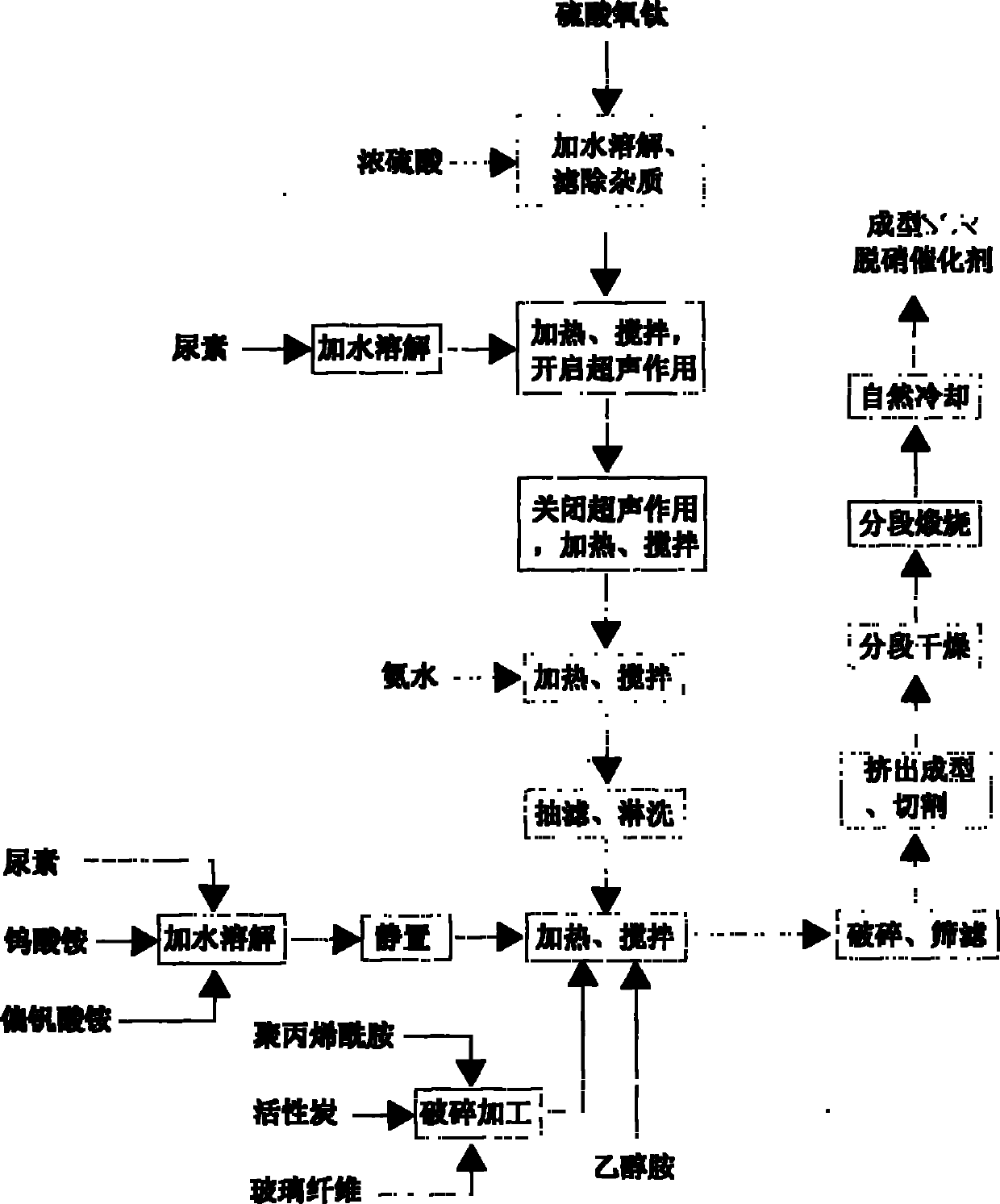

Method for preparing formed selective catalytic reduction denitration catalyst by using ultrasonic mixing sedimentation method

InactiveCN101791549ASmall particle sizeGood dispersionDispersed particle separationCatalyst activation/preparationTungstateAmmonium metavanadate

The invention discloses a method for preparing a formed selective catalytic reduction (SCR) denitration catalyst by using an ultrasonic mixing sedimentation method, comprising the following steps of: preparing metatitanic acid as a dipping carrier by using the processes of uniform sedimentation and direct sedimentation sequentially and being assisted by an ultrasonic strengthened reaction process by taking industry titanyl sulfate as a raw material; then mixing with an ammonium metavanadate-ammonium tungstate-oxalate solution, a flocculating agent comprising polyacrylamide and glass fibre, a structure promoter, and the like, and stirring to finish the processes of active component dipping and loading and plastic pasty master batch preparation synchronously. The prepared master batch is processed by a vacuum-extruder after finely crushed to obtain a formed catalyst green body, and finally the preparation process of the formed SCR denitration catalyst is finished through drying and sintering operations. Compared with the traditional preparation process of the SCR denitration catalyst, the method has simple and clear process and high production efficiency, and the raw materials for preparing the carrier of the catalyst have wide sources and low cost, thereby lowering the production cost to a certain extent.

Owner:SOUTHEAST UNIV

Method for preparing copper base composite material by chemical precipitation method to obtain composite powder

The process of preparing copper base composite material with composite powder prepared through chemical precipitation includes the following steps: dropping ammonium bicarbonate into mother liquid comprising copper sulfate and aluminum ammonium sulfate at 25-30 deg.c to obtain settled NH4Al(OH)2CO3-Cu2(OH)2CO3 sol, ageing for 8 hr and centrifuging to obtain NH4Al(OH)2CO3 -Cu2(OH)2CO3 gel, washing the gel with anhydrous alcohol, centrifuging to eliminate alcohol and stoving and grinding at 50deg.c to obtain NH4Al(OH)2CO3-Cu2(OH)2CO3 precursor, igniting the precursor at 1100-1200 deg.c to obtain composite Al2O3-CuO powder, reducing the composite Al2O3-CuO powder in reducing methanol or hydrogen atmosphere at 350 deg.c for 0.5-1 hr to obtain composite Al2O3-Cu powder; cold pressing the composite Al2O3-Cu powder at 100 kN pressure to form blank, and final at 800-850 deg.c. The present invention has precisely controlled Al2O3 content for required wear resistance and conductivity.

Owner:HUAIYIN INSTITUTE OF TECHNOLOGY

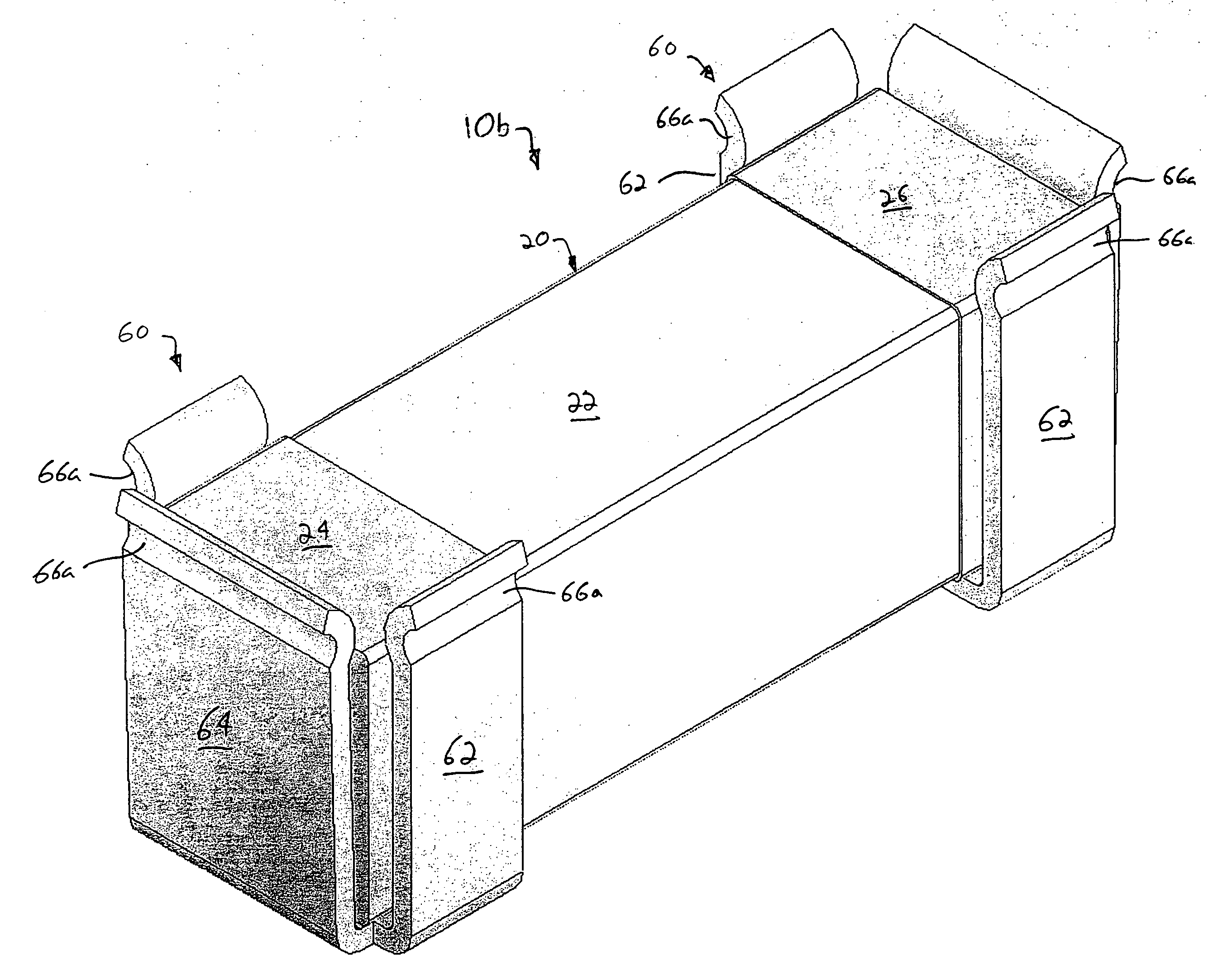

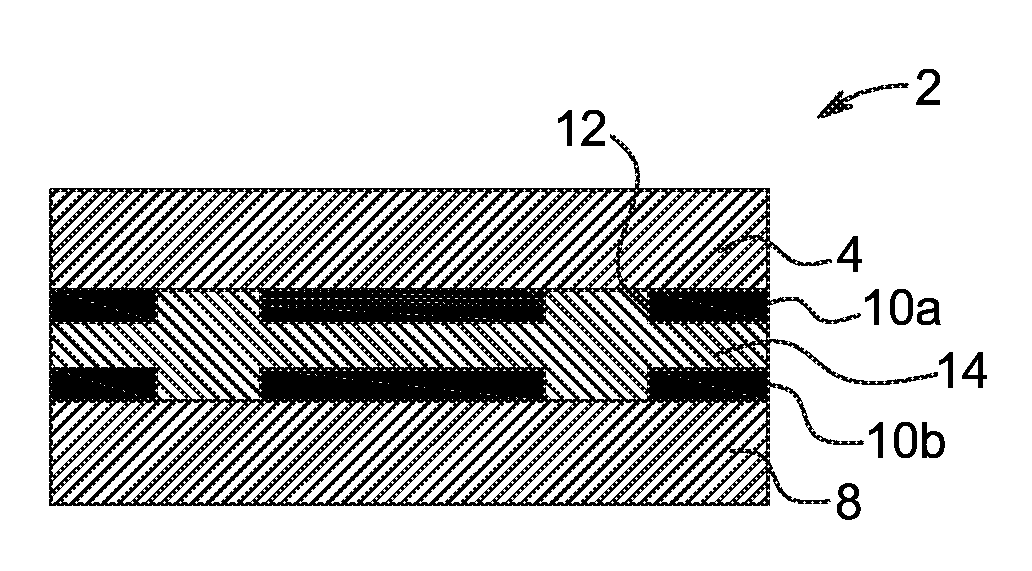

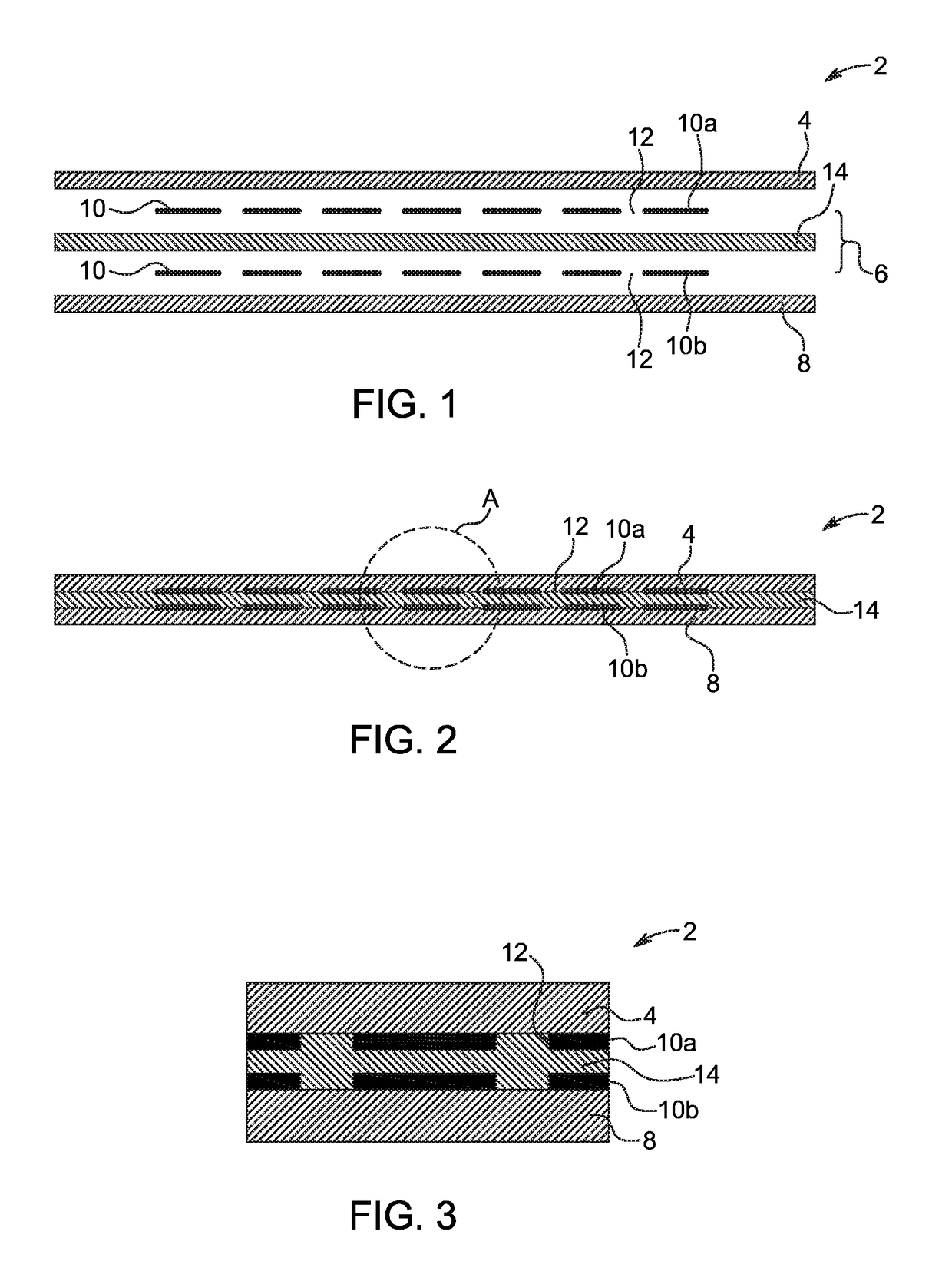

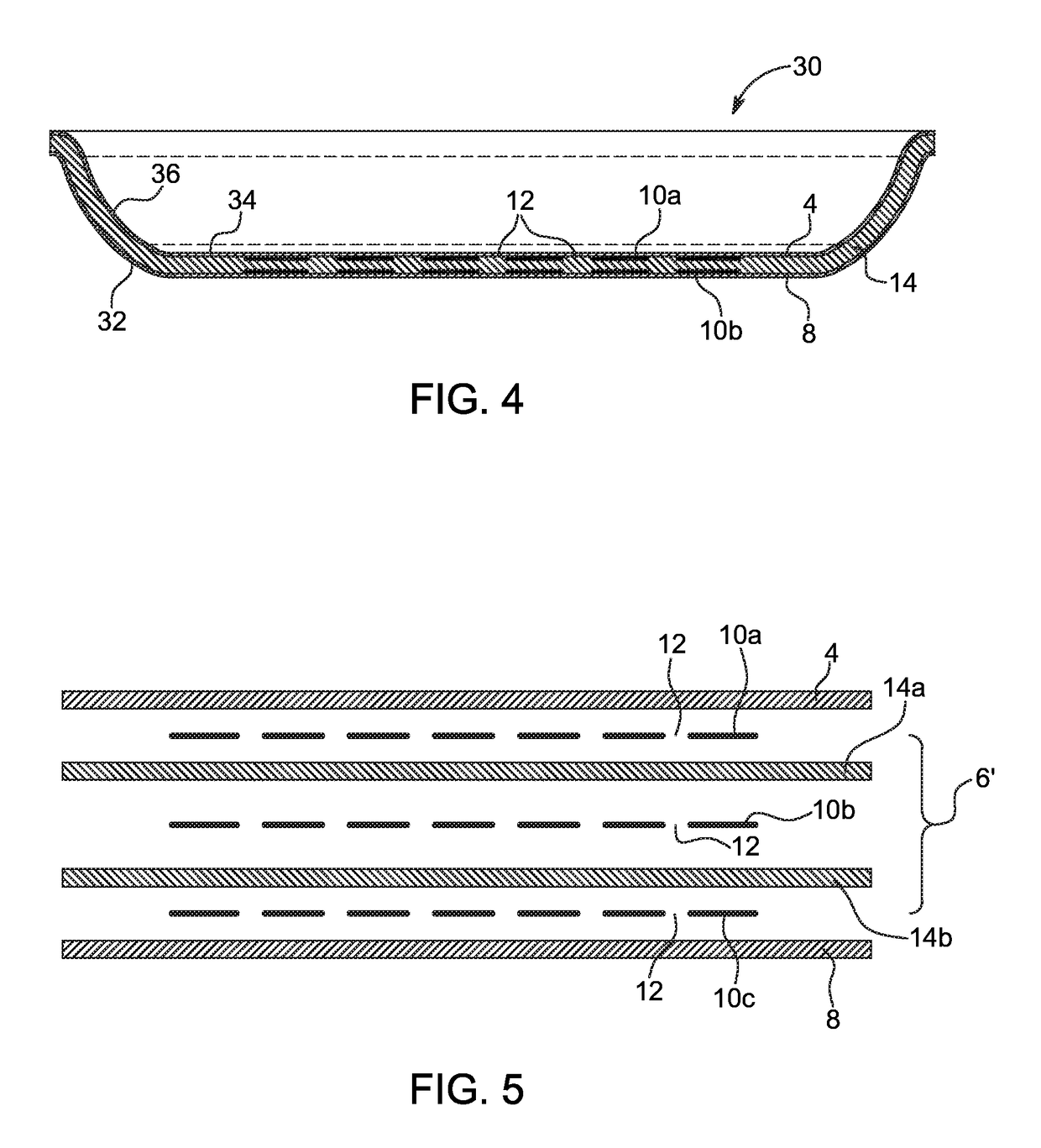

Cooking Utensil Having A Graphite Core

ActiveUS20170157895A1Reduce weightImprove thermal characteristicsCooking-vessel materialsTransportation and packagingGraphiteMaterials science

Provided is an article of cookware and a method of making the same. The cookware has a multi-layer bonded composite wall structure having an inner metal layer and an outer metal layer, and a core layer between the inner layer and the outer layer. The core layer has at least two perforated graphite plates, each plate having a plurality of spaced-apart holes formed therethrough, and at least one intermediate metal element disposed between the at least two perforated graphite plates and extending through the plurality of spaced-apart holes of each of the at least two perforated graphite plates. The at least one intermediate metal element is metallurgically bonded to the inner layer and the outer layer at least through the plurality of spaced-apart holes.

Owner:CLAD METALS

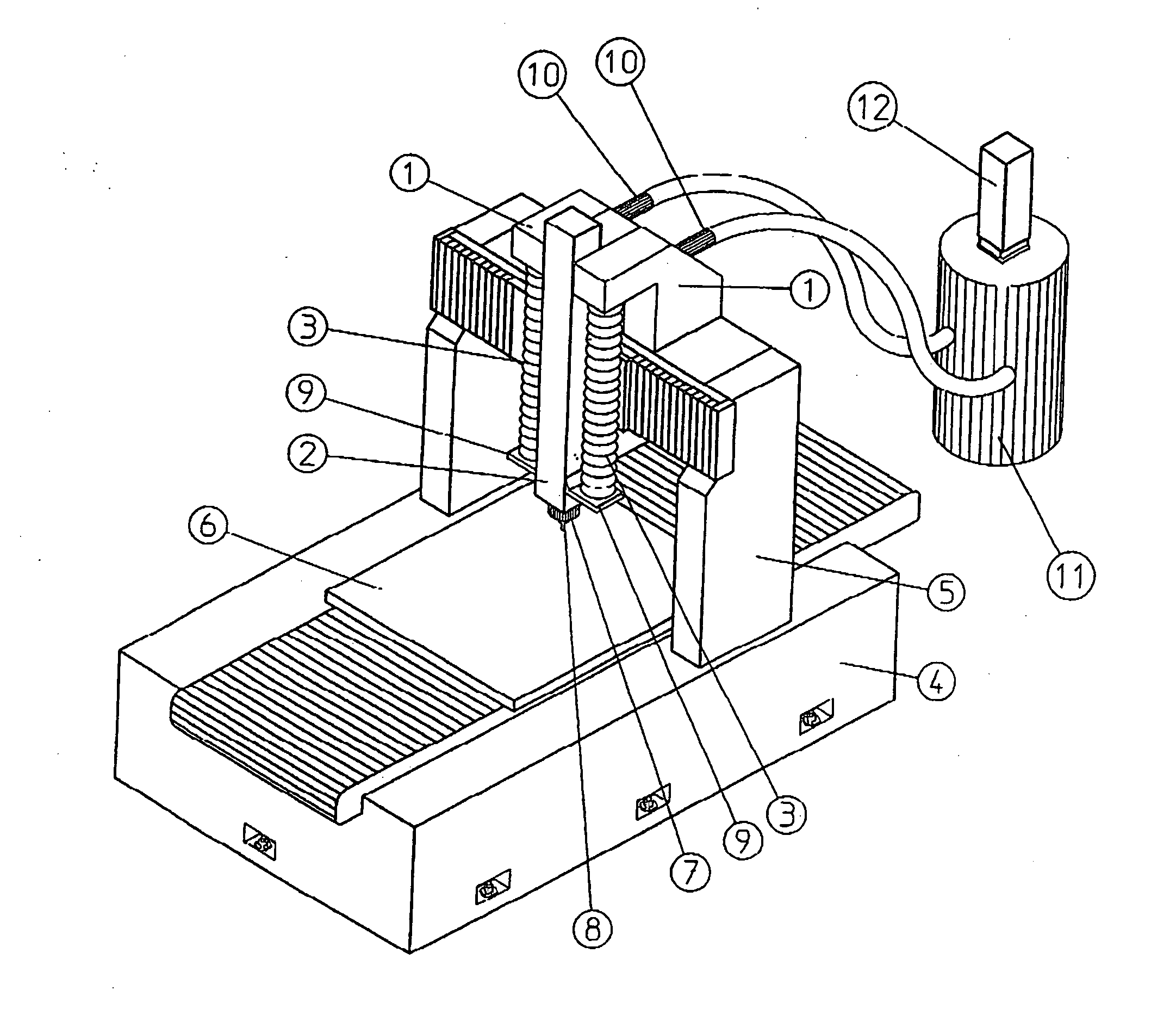

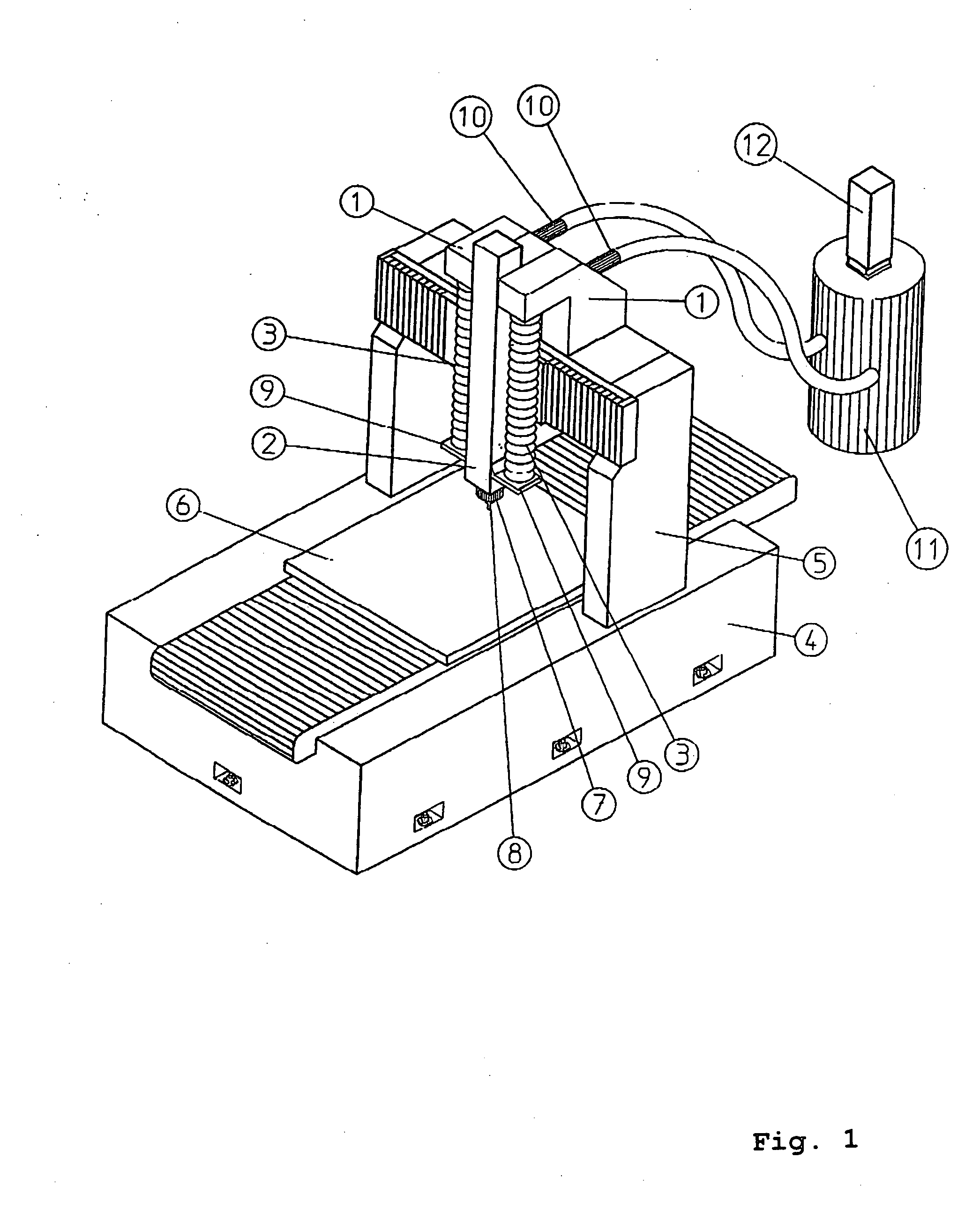

Weight-compensating device

ActiveUS20050158134A1Improve thermal characteristicsControl precisionPlaning/slotting machinesMilling machinesEngineeringVariable length

The present invention relates to a weight compensating device comprising a carrier and a component which is supported on the carrier and is displaceable particularly in vertical direction by means of a drive, characterized in that the carrier and the component have arranged thereinbetween at least one negative pressure body of a variable length which is connected to a negative pressure source for compensating the weight acting on the component.

Owner:P&L GMBH & CO KG

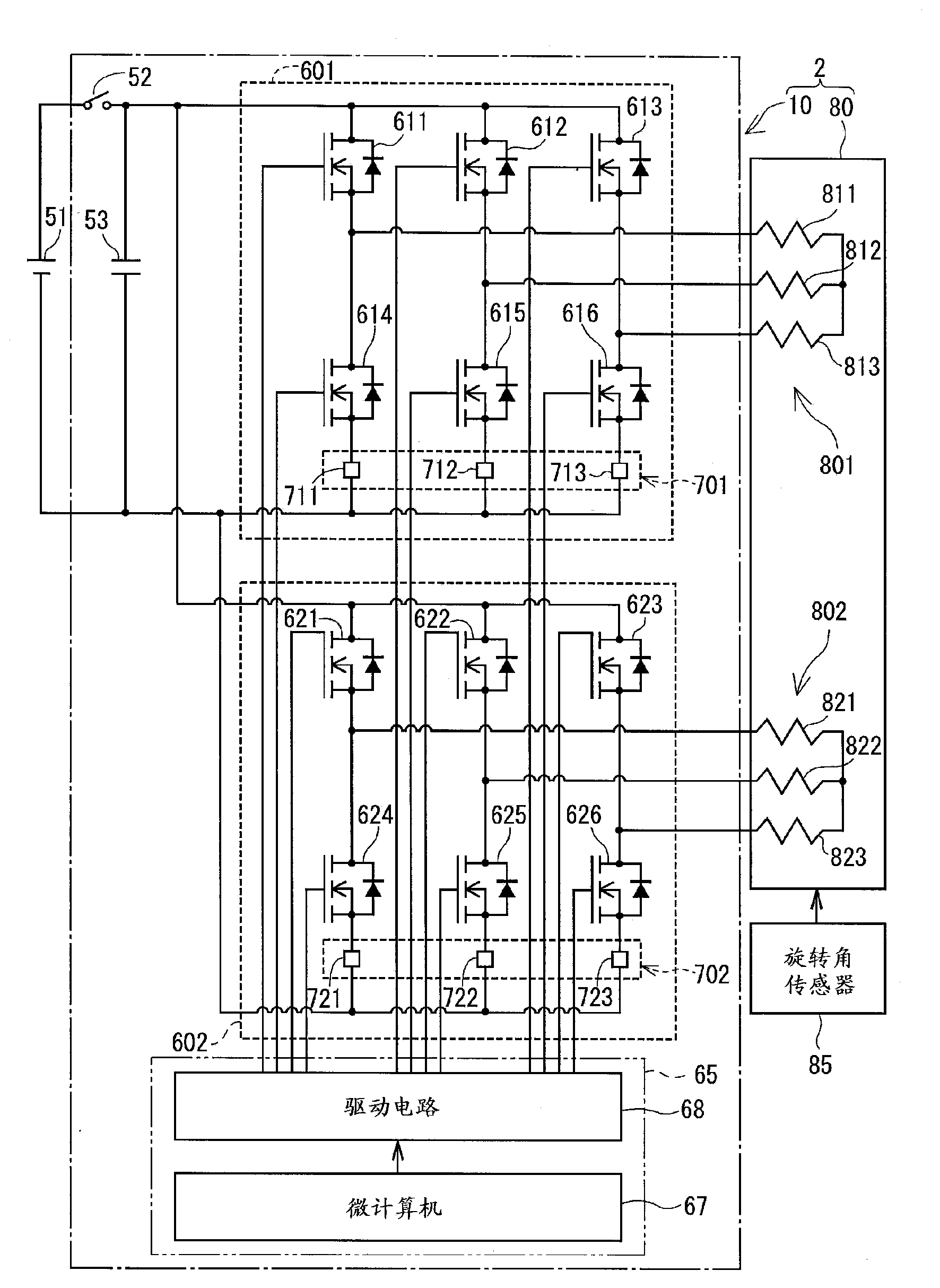

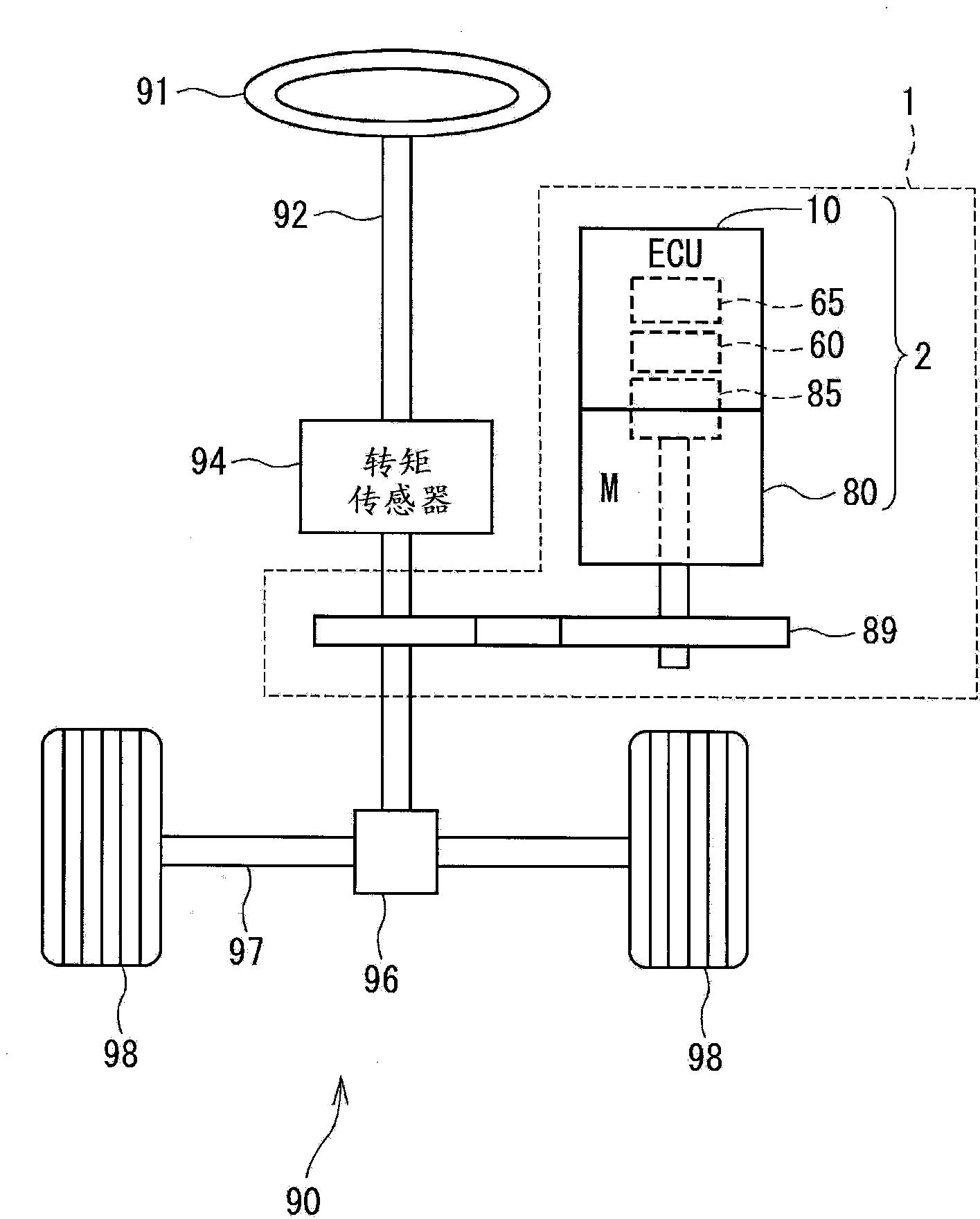

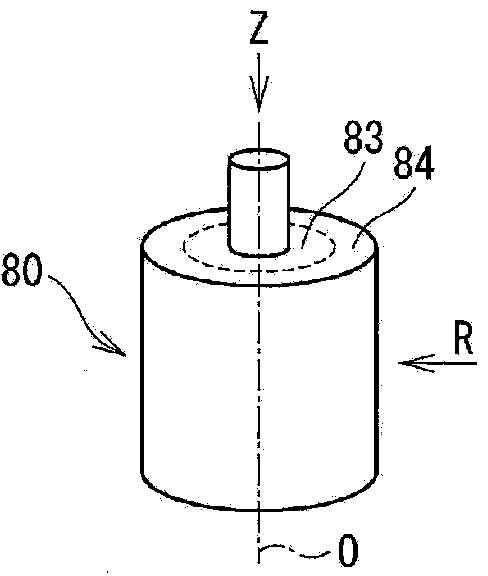

Control device for a three-phase rotating machine

ActiveCN103378790AReduce the soundReduce/or vibrationTorque ripple controlVector control systemsThree-phaseAlternating current

In a control device for a three-phase rotating machine with first and second winding sets, a current feedback computing section includes a current sum controller and a current difference controller. The current sum controller multiplies, by a sum gain, an error between a sum of current command values for alternating currents output from first and second inverters and a sum of sensed current values and computes a sum of voltage command values. The current difference controller multiplies, by a difference gain, an error between a difference of the current command values and a difference between the sensed current values, and computes a difference of voltage command values. In a variable-responsiveness mode, a gain ratio between the sum gain and the difference gain is varied according to a reference frequency such that the current sum controller and the current different controller are different in responsiveness.

Owner:DENSO CORP

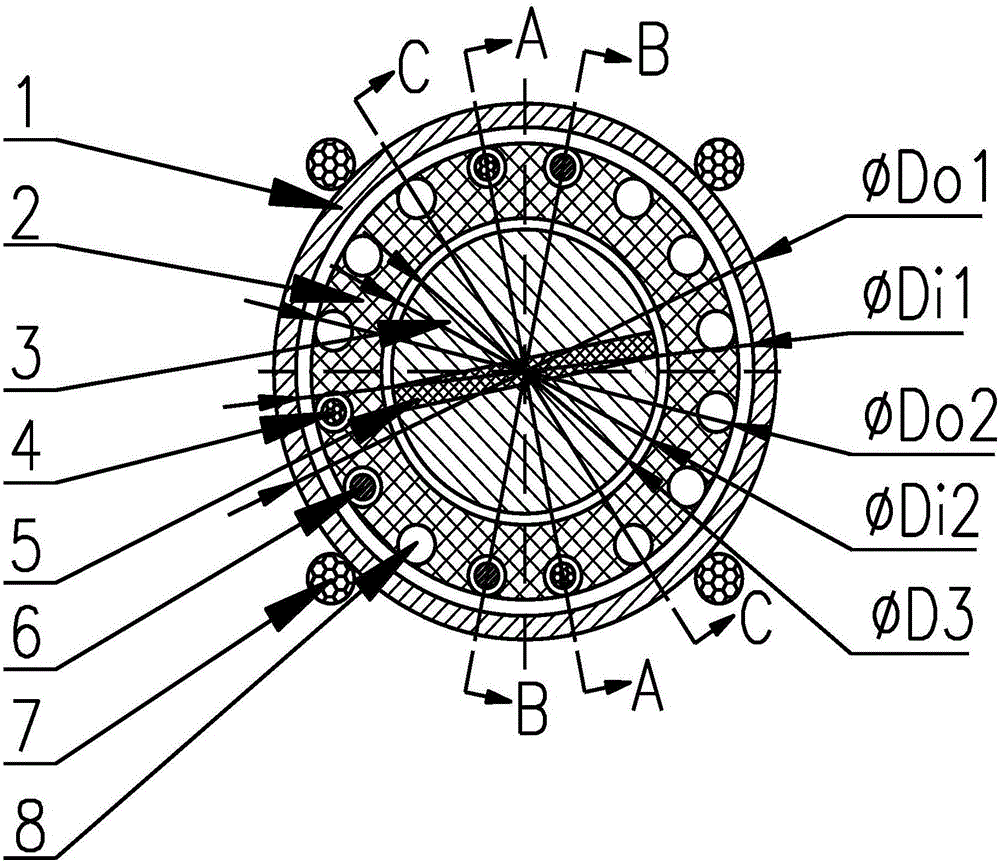

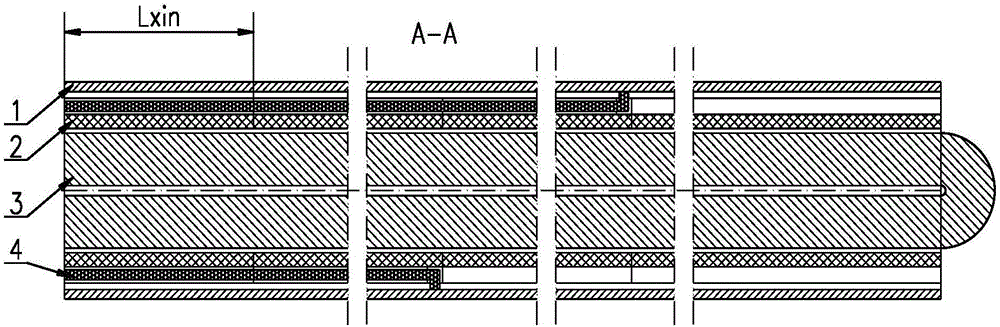

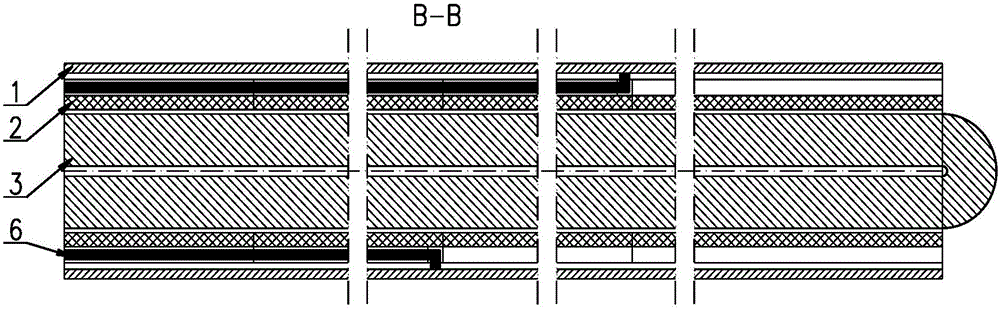

Nuclear reactor fuel rod simulating electric heating device and assembly process

ActiveCN106328226ASimulate Thermal PropertiesAccurate and controllable electric heating powerNuclear energy generationNuclear monitoringPressurized water reactorThermocouple Wire

The invention discloses a nuclear reactor fuel rod simulating electric heating device and an assembly process. The device comprises a simulation jacket and simulation fuel element pellets, each simulation fuel element pellet is provided with 16 through holes axially extending along the simulation fuel element pellet, thermocouple wire anodes are mounted in part of the through holes, thermocouple wire cathodes are mounted in part of the through holes, and inert gas is stored in the rest through holes. Electric heating rods are mounted in an inner cavity of each simulation fuel element pellet, and a plurality of external wall temperature thermocouples are mounted on the outer side of the simulation jacket. The electric heating device is used for laboratory simulation of nuclear reactor fuel rods to carry out high-temperature degradation and reflooding behavioral experiments of fuel rods for pressurized water reactors under severe accident conditions. A working medium is an aqueous medium, a steam medium or an inert gas medium, a working pressure is 5MPa, a long-term working temperature is 1800 DEG C, and a short-term working temperature is 2400 DEG C.

Owner:NUCLEAR POWER INSTITUTE OF CHINA

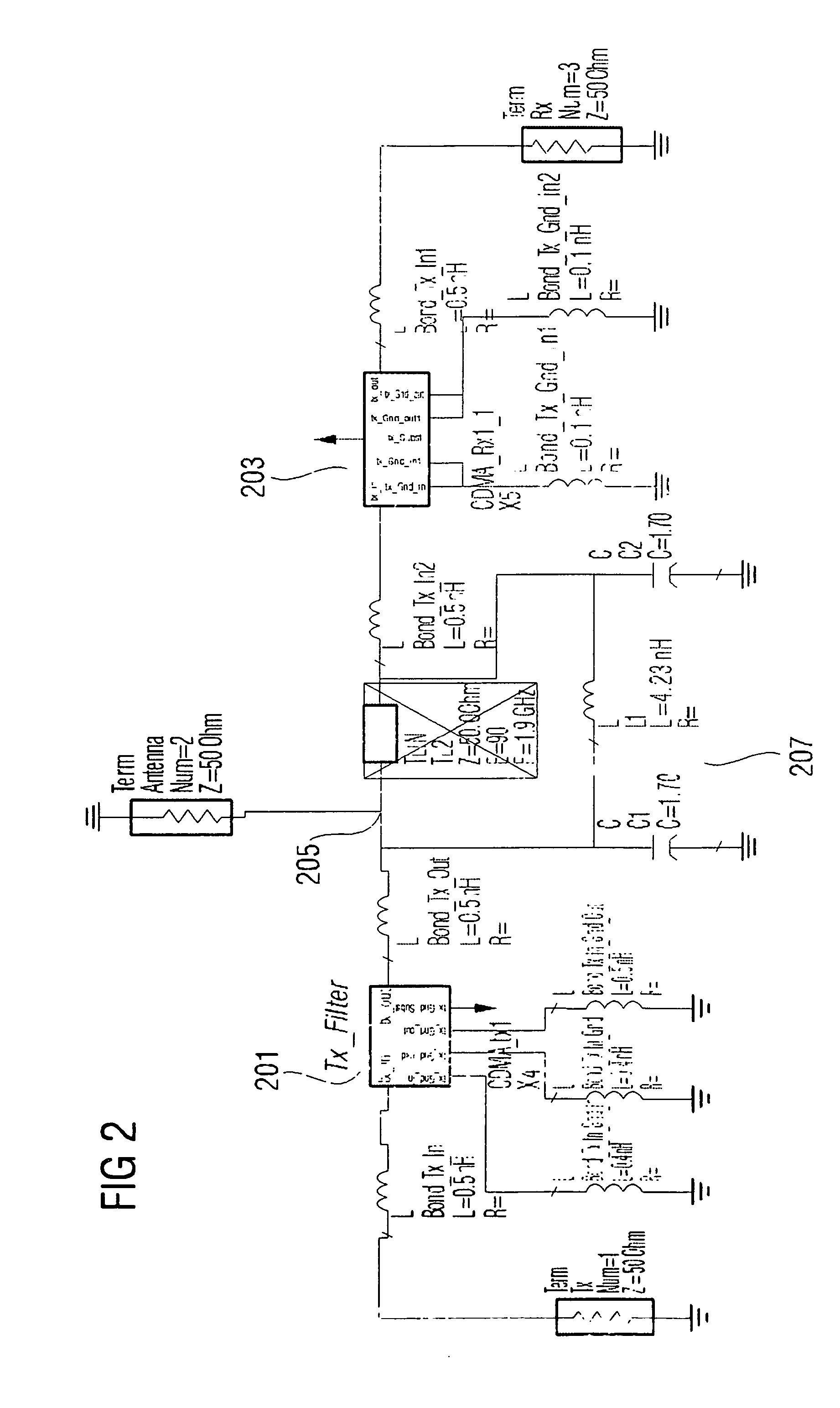

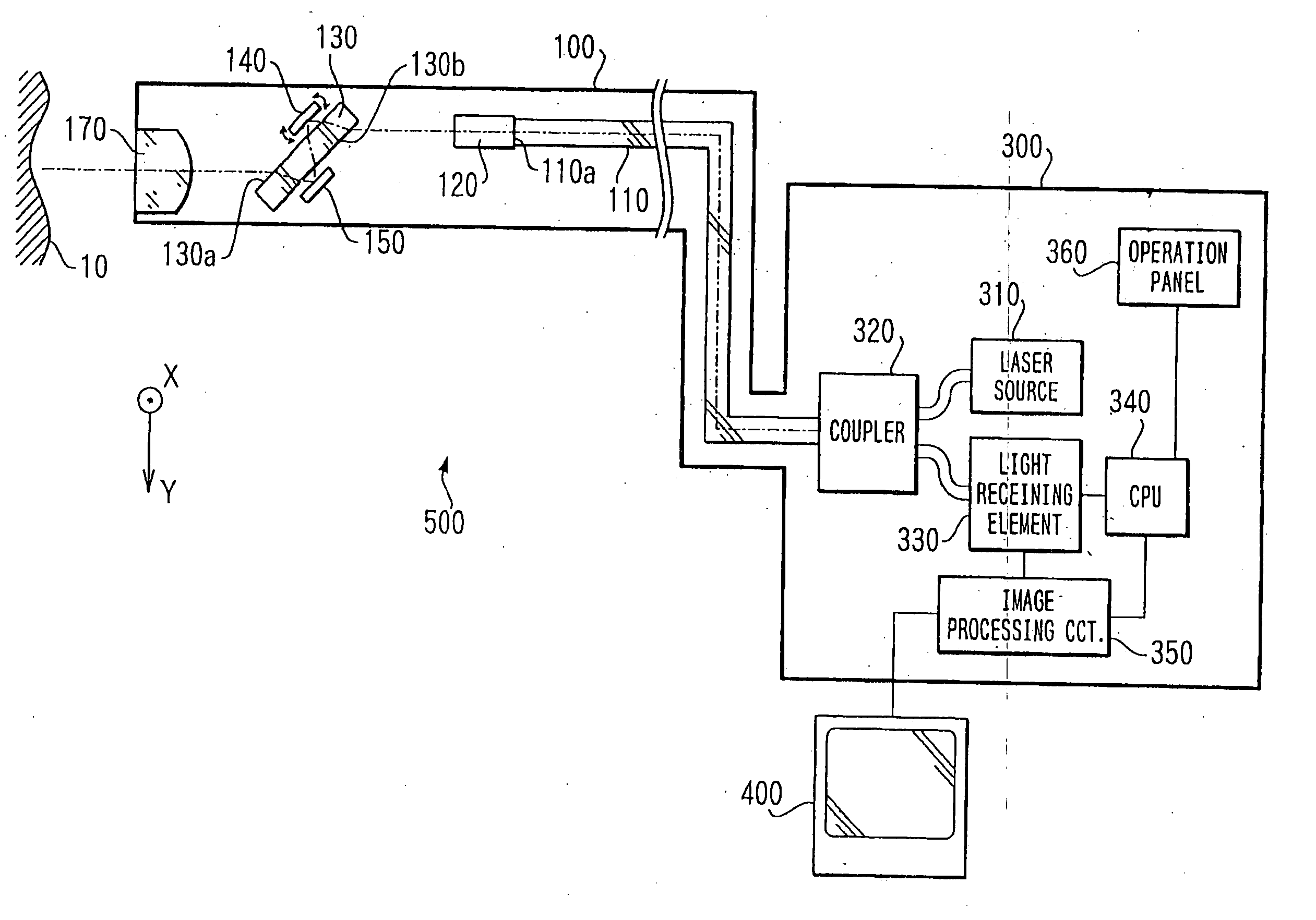

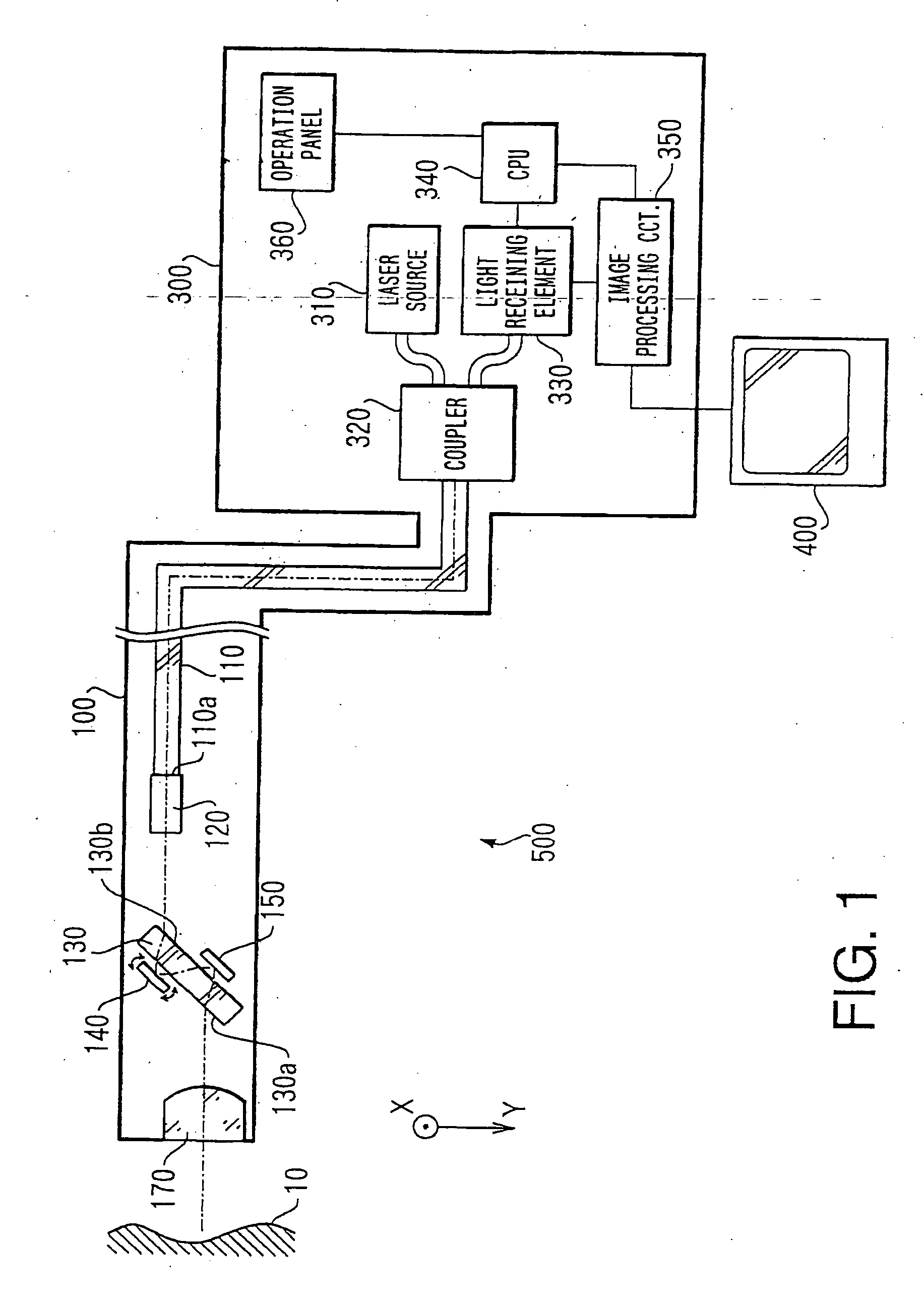

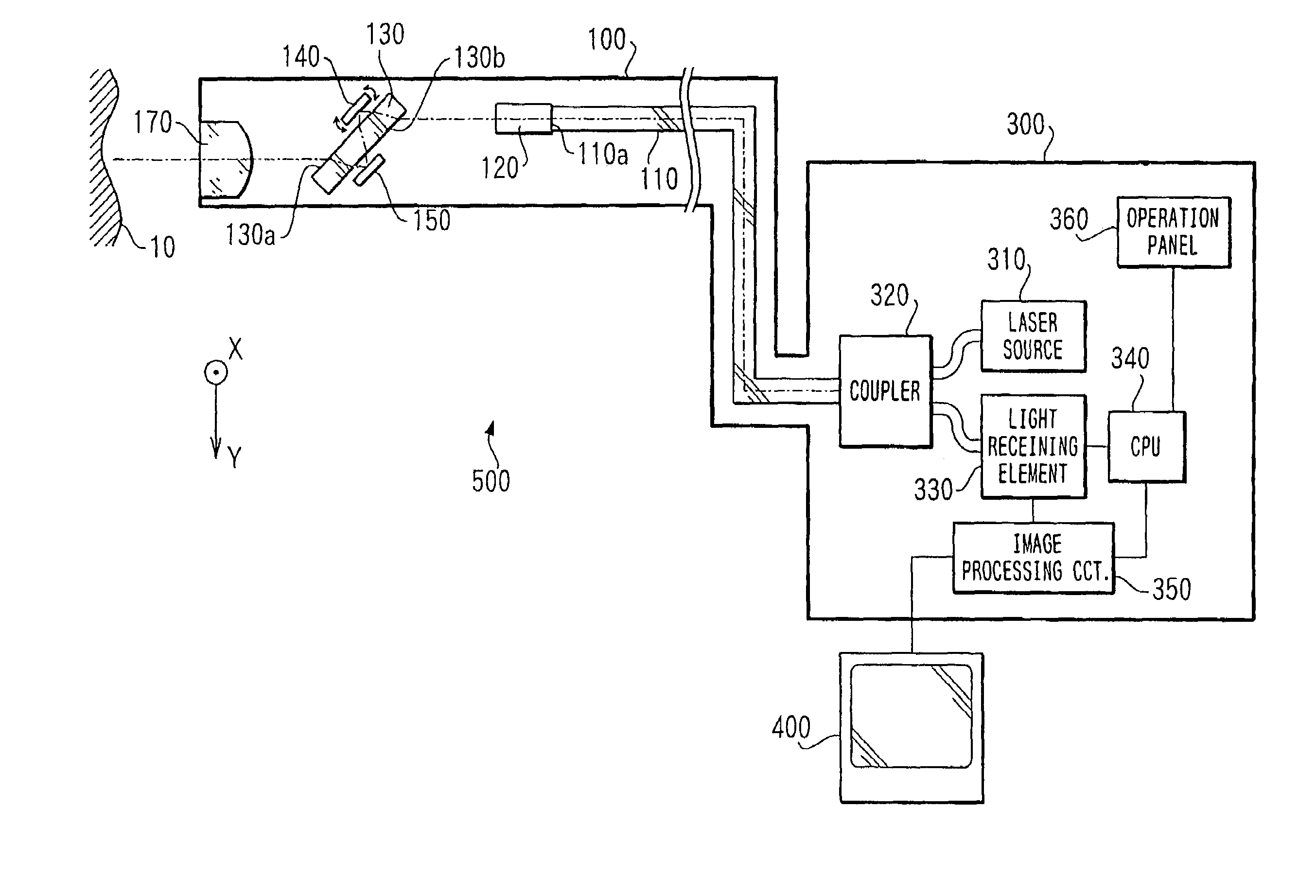

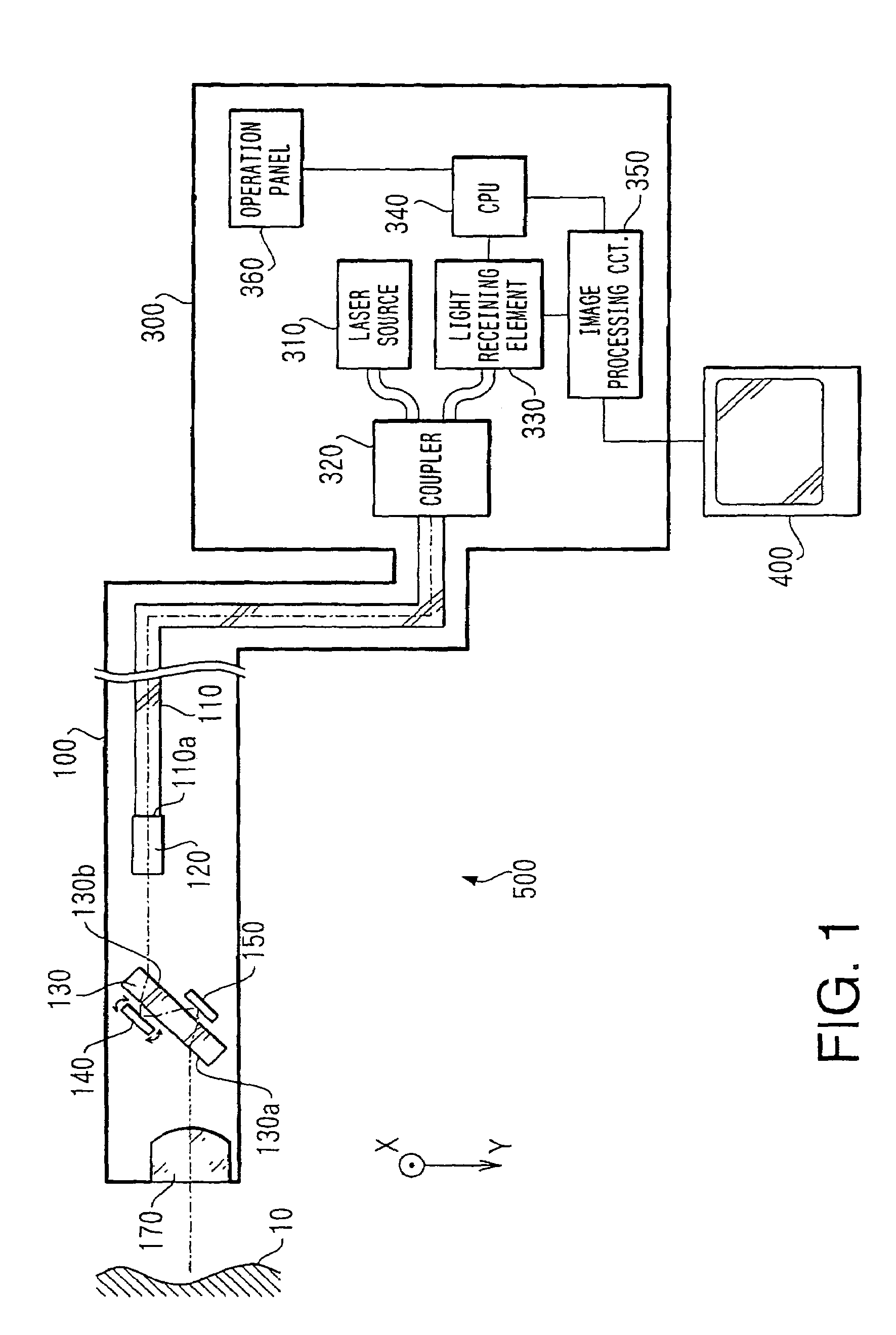

Confocal probe and endoscope device

InactiveUS20060167344A1Small diameterImprove thermal characteristicsSurgeryEndoscopesLight beamScanning mirror

A confocal probe unit is provided with a scanning type confocal probe, which includes at least one scanning mirror, and a transparent substrate on which the at least one scanning mirror is mounted. The transparent substrate is inserted in an optical path of the confocal probe such that a light beam proceeding along the optical path is deflected by the scanning mirror.

Owner:ASAHI KOGAKU KOGYO KK

SOI (silicon on insulator) LIGBT (lateral insulated gate bipolar transistor) device unit with p buried layer and longitudinal channel

ActiveCN102157550AReduce adverse effectsImprove vertical pressure resistanceSemiconductor devicesMetal electrodesConductivity modulation

The invention relates to an SOI (silicon on insulator) LIGBT (lateral insulated gate bipolar transistor) device unit with a p buried layer and a longitudinal channel. The existing products restrict the improvement of the device structures and the electrical properties. The device unit comprises a p-type semiconductor substrate, a buried oxide layer and a p buried layer region in sequence, wherein a metal gate, an n-type heavily doped polysilicon gate, a gate oxide layer and an n-type lightly doped drift region are arranged at the top of the p buried layer region side by side in sequence; a first p-type well region and an n-type buffer region are respectively embedded at the two sides at the top of the n-type lightly doped drift region; an n-type cathode region and a first p well ohmic contact region are embedded at the top of the first p-type well region; a second p-type well region and an anode short-circuit point region are embedded at the top of the n-type buffer region; a second p well ohmic contact region is embedded at the top of the second p-type well region; and a first field oxide layer, a second field oxide layer, an anode metal electrode and a cathode metal electrode are arranged at the top of the device unit. The device unit has the beneficial effects of reducing the spreading resistance, improving the conductivity modulation effect of the drift region, reducing the on-state power consumption and obviously improving the thermal property of the device.

Owner:SERVICE CENT OF COMMLIZATION OF RES FINDINGS HAIAN COUNTY

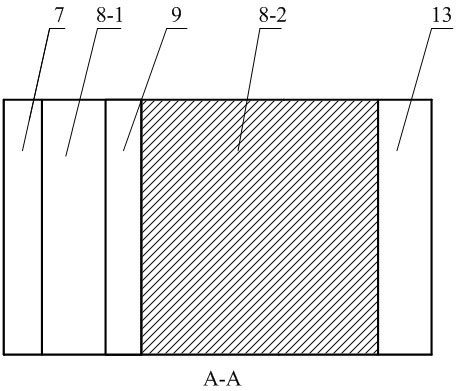

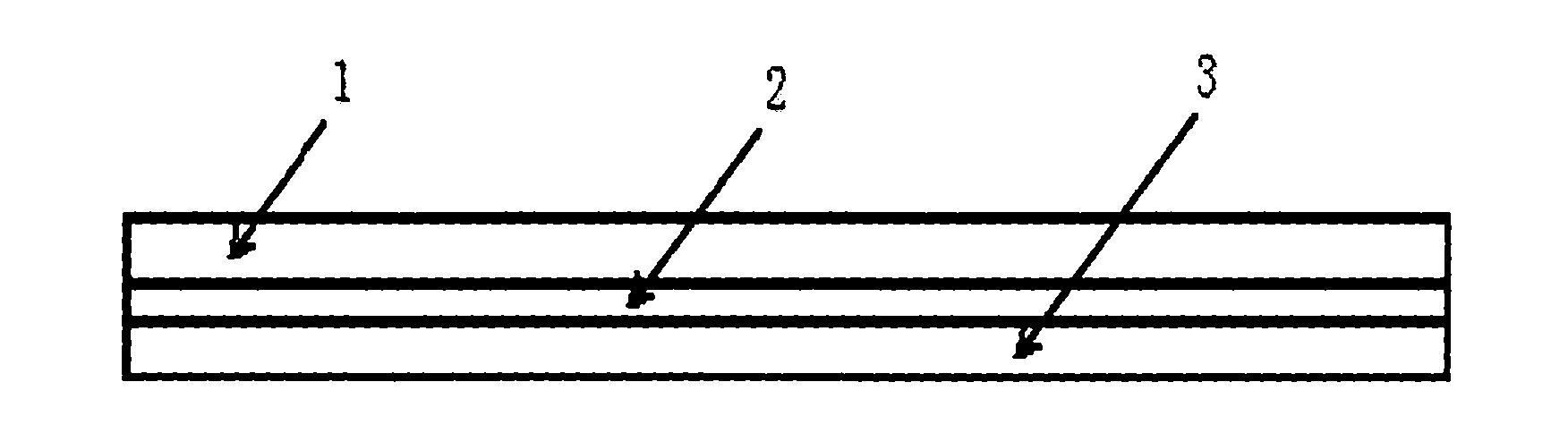

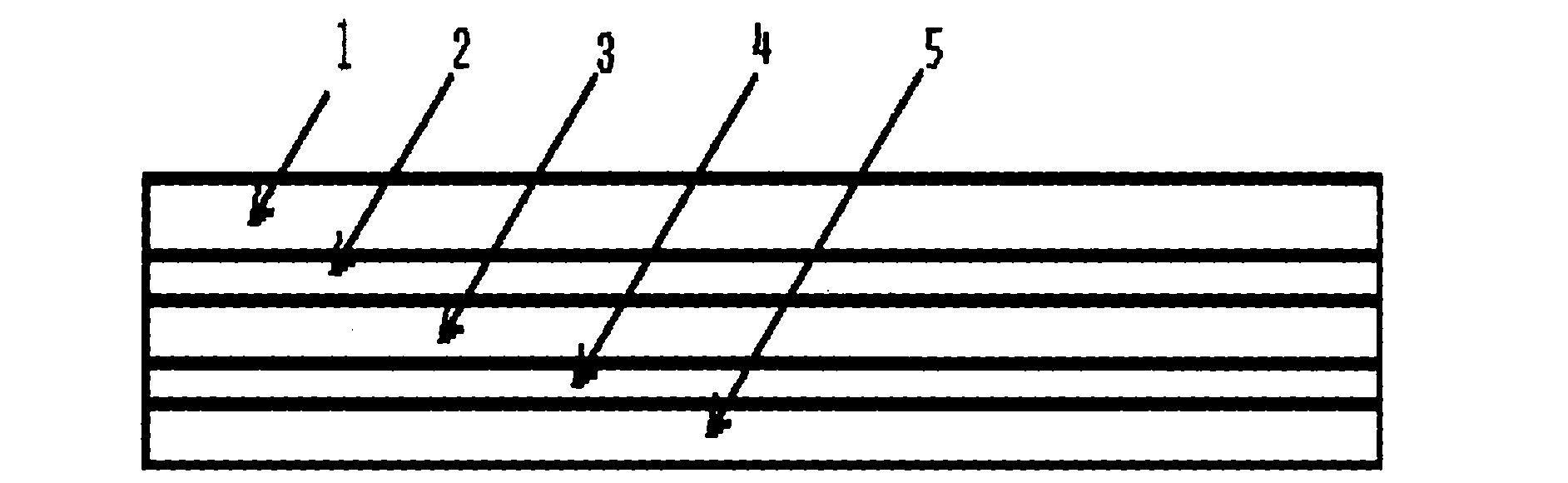

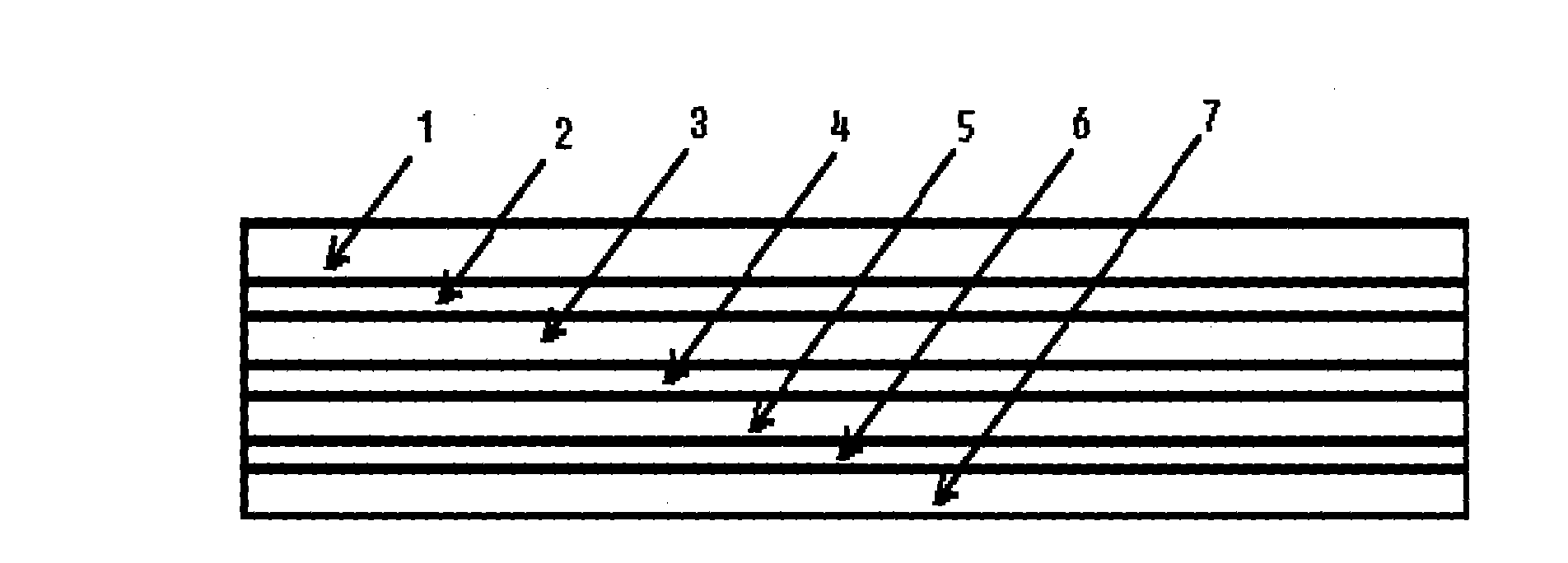

High temperature resistant electrical soft composite material and manufacturing method thereof

ActiveCN101877259AMeet technical requirements for performanceImprove heat resistancePolyureas/polyurethane adhesivesSynthetic resin layered productsTransformerAdhesive

The invention discloses a high temperature resistant electrical soft composite material and a manufacturing method thereof. The invention is characterized in that: the high temperature resistant electrical soft composite material is a two-, three- or four-layer high temperature resistant electrical soft composite material comprised of a thin film layer, an adhesive layer and a synthetic fiber paper layer; the adhesive layer is prepared by mixing 115 to 230 weight parts of hydroxy-terminated prepolymer, 30 to 83 weight parts of multifunction isocyanate prepolymer, 70 weight parts of polyglycerol-modified ureido-ene resin, 150 to 300 weight parts of solvent; after an adhesive is applied on a thin film or synthetic fiber paper, the thin film or synthetic fiber paper is delivered to a drying channel to pass through an area, an area II at and an area II at 50 to 120 DEG C respectively and at a vehicle speed of 2 to 20 m / min to remove the solvent; then the thin film or synthetic fiber paper is cooled first to room temperature and then to 80 DEG C and is combined with the synthetic fiber paper or the thin film by hot rolling; the combined product is wounded and heated to 140 DEG C from room temperature for aging for 8 to 72 hours; and thus, the product is obtained. The product of the invention, which has high performance, can be used for motor element insulation, inter-winding insulation, gasket insulation and air-immersed transformer interlayer insulation.

Owner:四川东材新材料有限责任公司

Konjak-red jujube sugar-free soft sweet and preparation method thereof

A preparation method of konjak-red jujube sugar-free soft sweet comprises the steps of preparing red jujube juice, preparing mixed gel fluid of konjak glucomannan, boiling, condensing and molding, and cutting and drying. The preparation method of the konjak-red jujube sugar-free soft sweet is simple, convenient to obtain materials and low in cost. By using the principle of the generation of hot reversible gel through a synergistic action of konjak glucomannan and carrageenan under an acid condition and fully combining the gel property of konjak glucomannan and the nutritive value of red jujube, the invention overcomes the defects of poor mechanical performance and irregular shaping appearance of common soft sweets, improves thermal property and mechanical property of products and enhancestoughness of products by physically mixing konjak glucomannan and carrageenan. The prepared soft sweet has special color of red jujube and is rich in nutrition, fresh and delicious, and convenient tocarry.

Owner:FUJIAN AGRI & FORESTRY UNIV

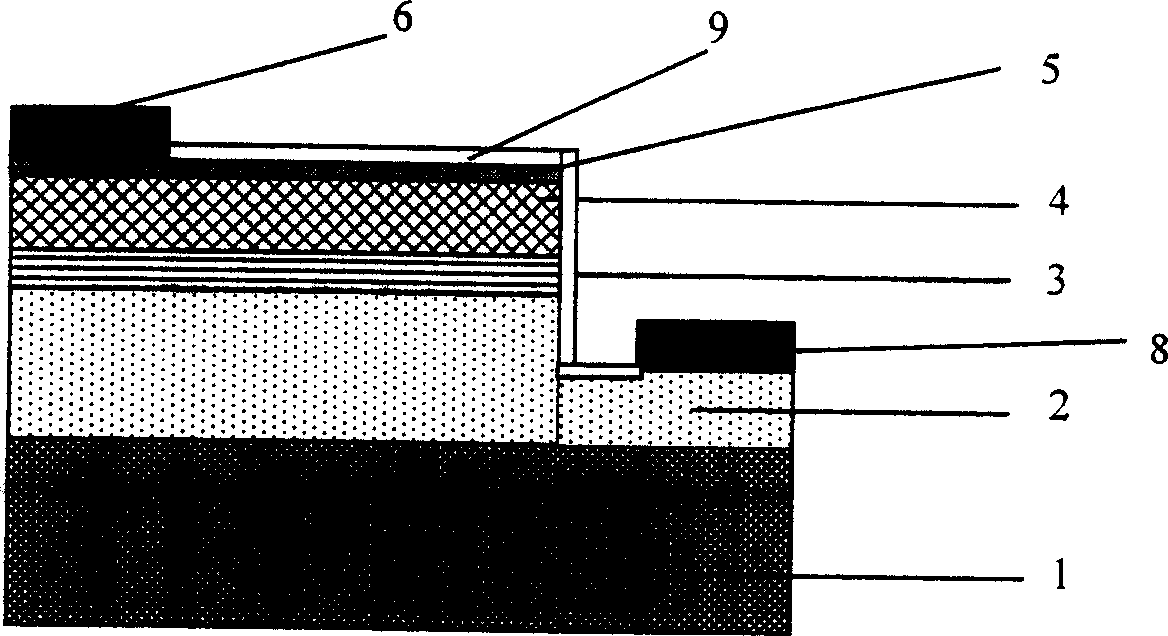

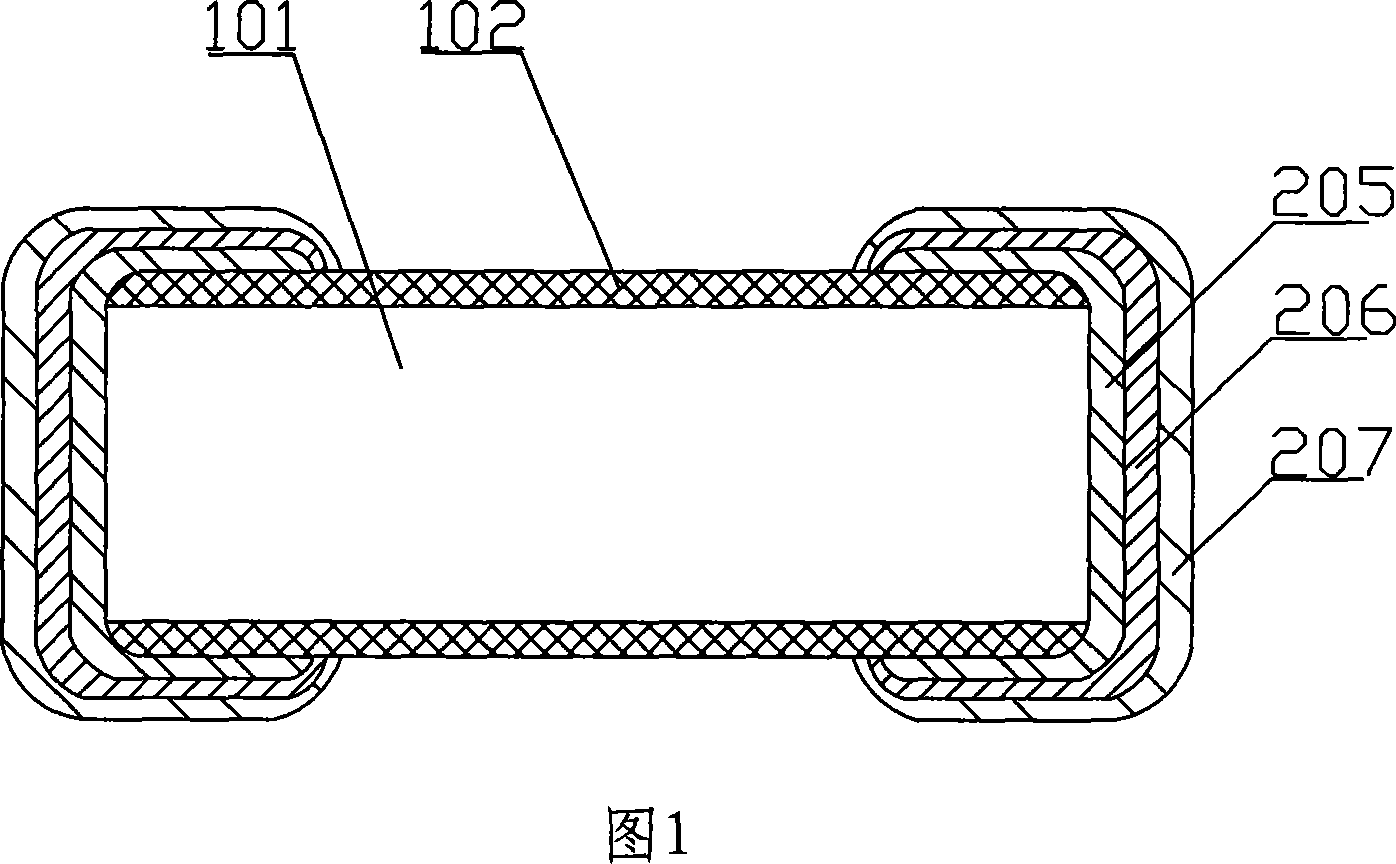

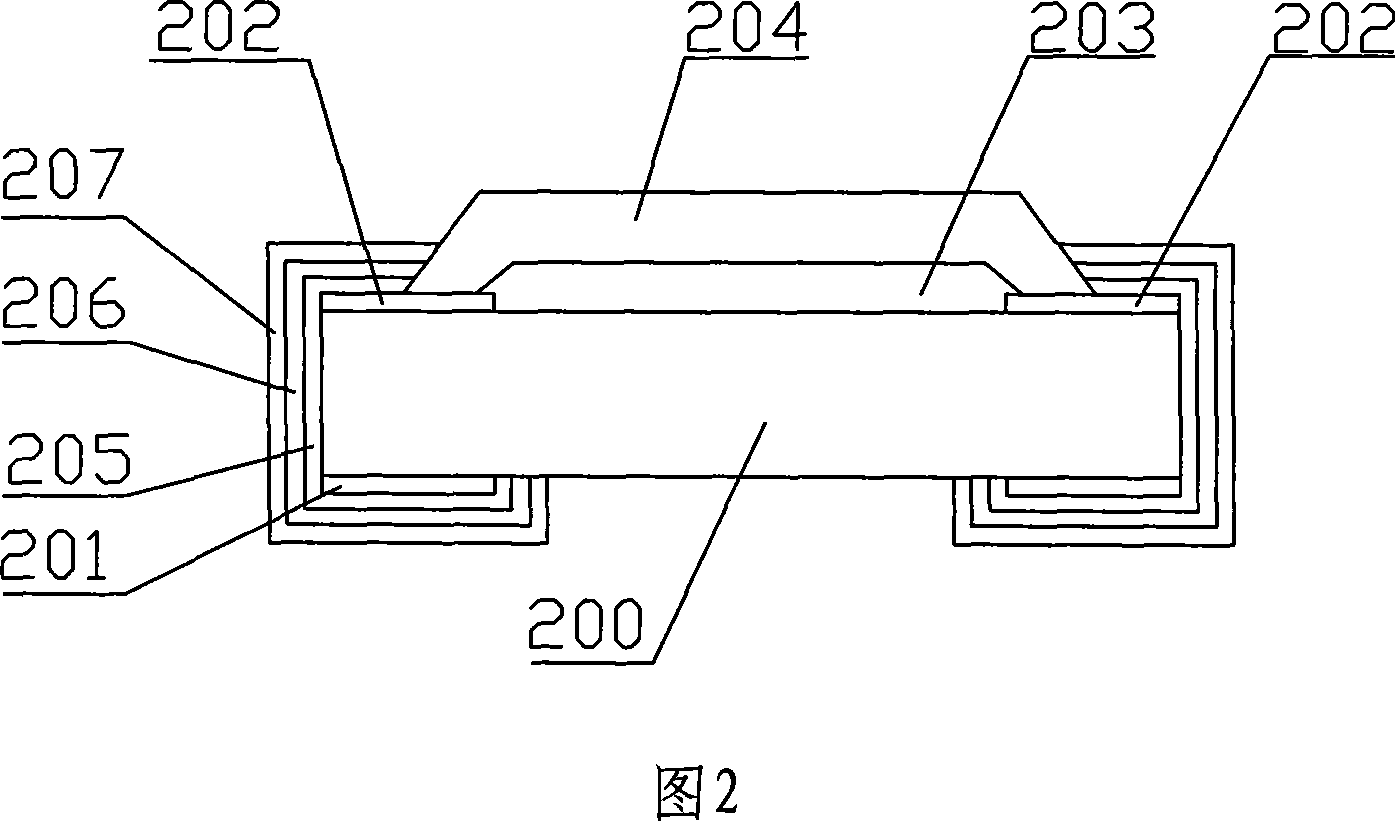

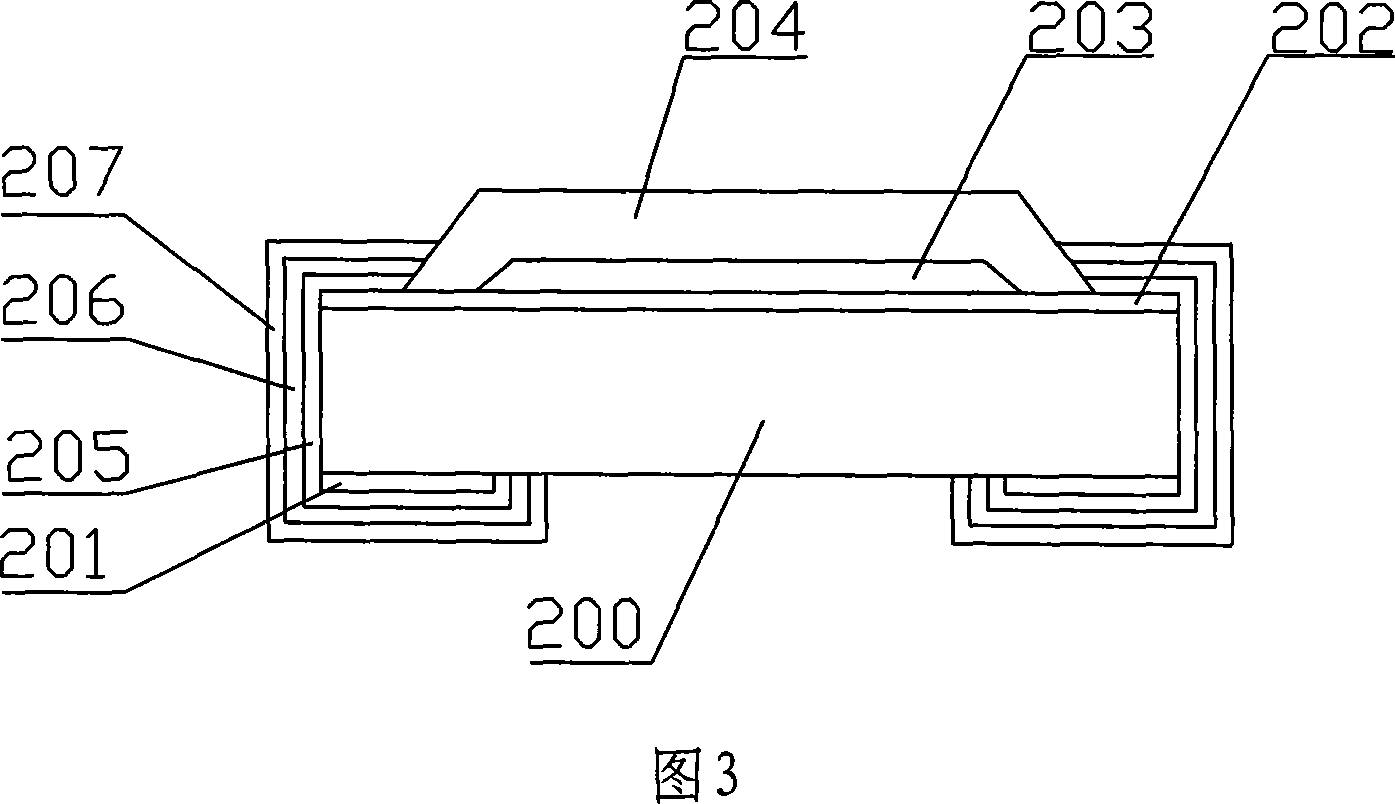

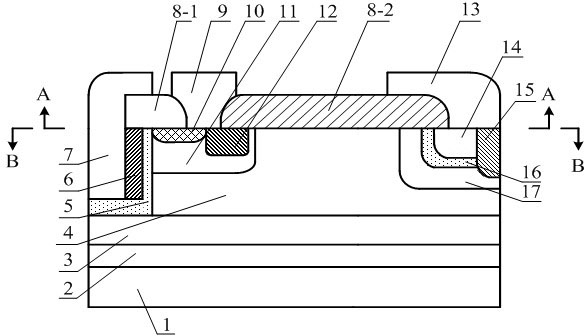

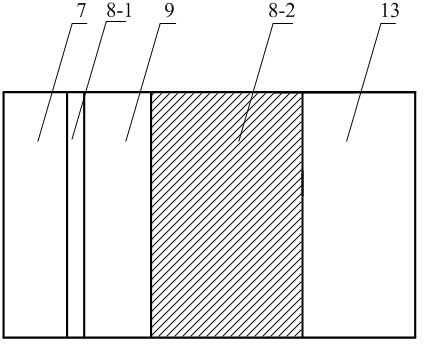

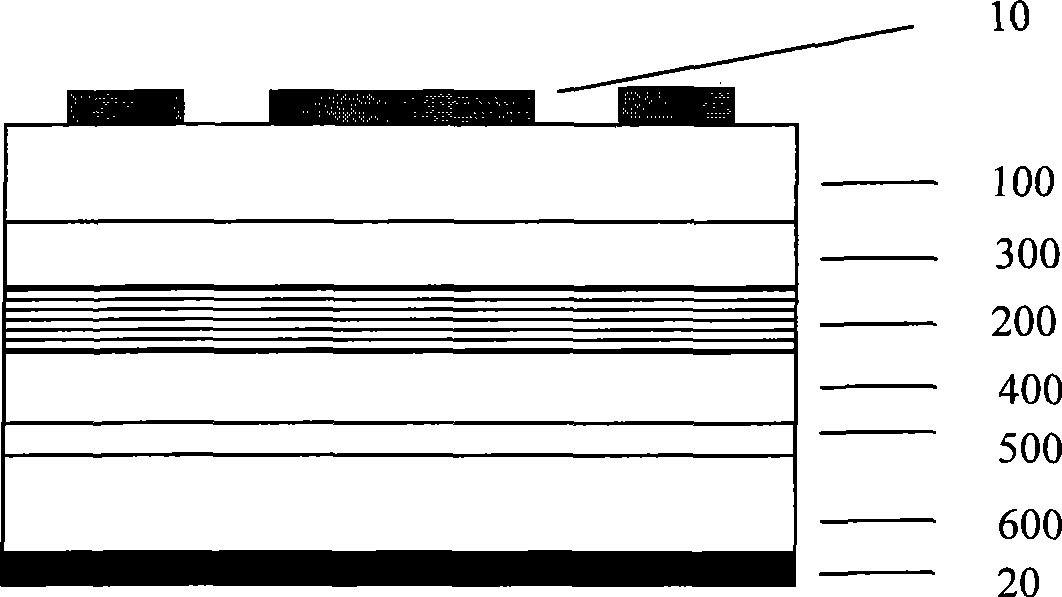

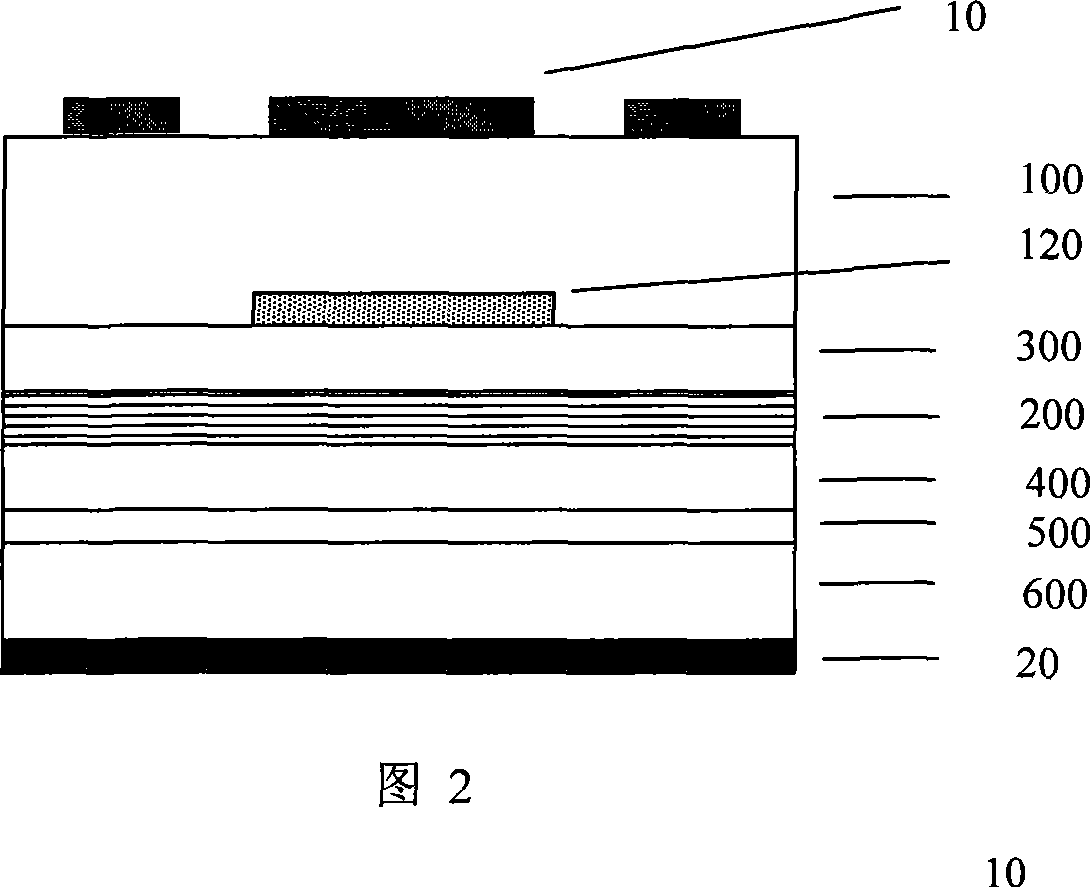

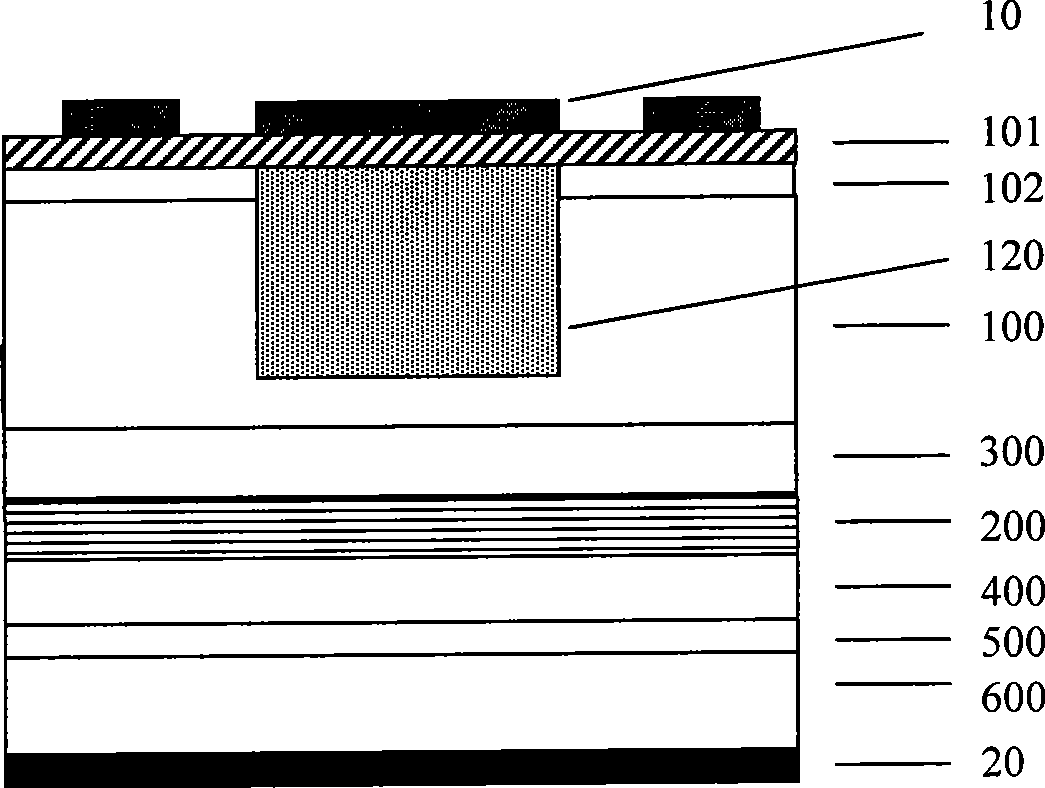

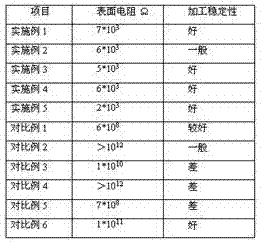

Distribution of current blocking layer, LED corresponding to the upper electrode and preparation thereof

InactiveCN101388431AImprove light extraction efficiencyHigh luminous intensitySemiconductor devicesLower limitLuminous intensity

The invention relates to the distribution of a current barrier layer, a light-emitting diode which is corresponding to an upper electrode and a process for preparation, belonging to the technical field of semiconductor photoelectrons. The structure comprises an upper electrode (10), a current spreading layer (100), an upper limiting layer (300), an active region (200), a lower limiting layer (400), a buffer layer (500), an under-layer (600) and a lower electrode (20), and further comprises a current barrier layer (120) located on the right lower portion of the upper electrode, wherein the distribution of the current barrier layer is corresponding to the upper electrode, a conductive light anti-reflection layer (101) is arranged between the upper electrode and the current spreading layer inside the conductive light anti-reflection layer or the current spreading layer or the upper limiting layer or the active region, or inside adjacent two layers, three layers or four layers, wherein the current barrier layer is realized through the post techniques. The current barrier layer corresponding to the upper electrode nearly completely avoids light and heat loss generated by idle current, thereby increasing the light extraction efficiency of the LED, and increasing the light emitting intensity, and the structure reduces the generation of heat, which is especially suitable for the preparation of large-power LEDs.

Owner:沈光地

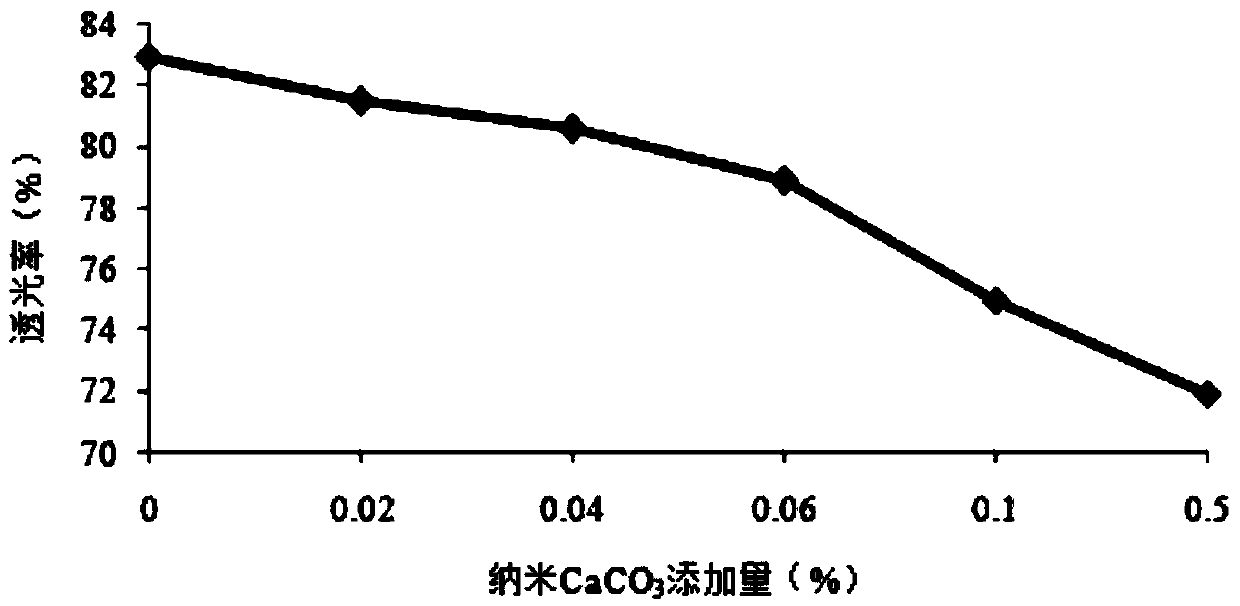

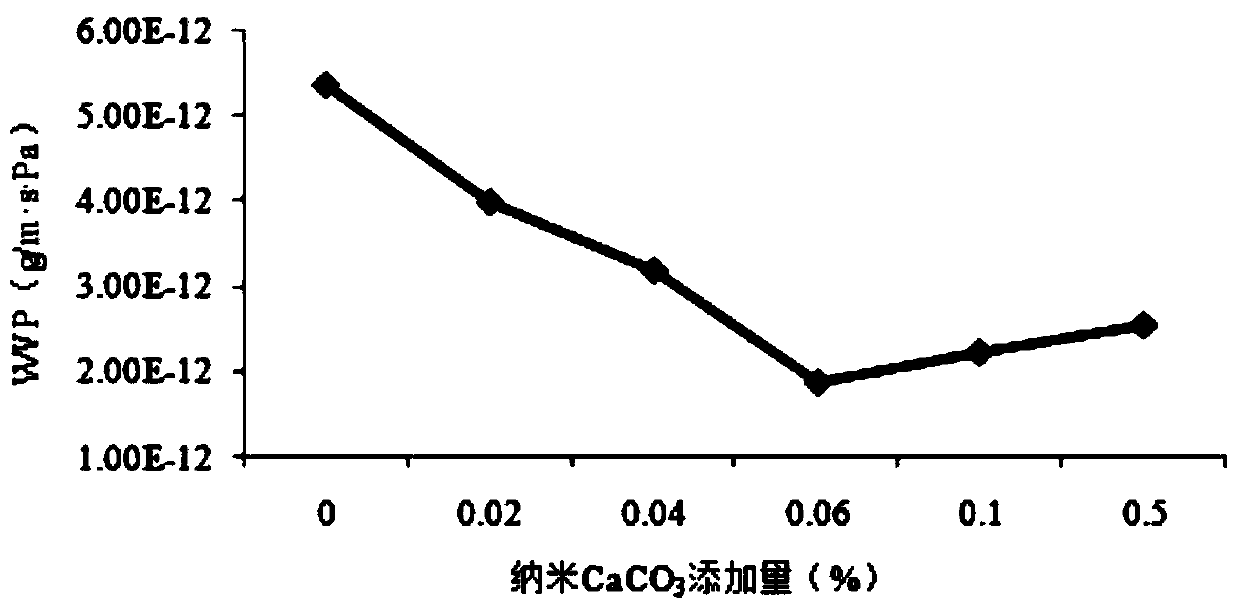

Corn starch composite membrane as well as preparation method and applications thereof

ActiveCN104194064AReduce light transmittanceLow moisture permeabilityFlexible coversWrappersWaxy cornNanoparticle

The invention discloses a corn starch composite membrane as well as a preparation method and applications thereof. The corn starch composite membrane comprises corn starch, glycerol and an enhancer, wherein the enhancer is nano CaCO3, waxy corn starch nanoparticles or chitosan, the mass ratio of the corn starch to glycerol is equal to (6.5-8.0):(1.5-3.0), when the enhancer is nano CaCO3 and waxy corn starch nanoparticles, the masses of the enhancer / corn starch are respectively 0.02-0.5, and 1-25; when the enhancer is nano CaCO3 or chitosan, the mass ratio of nano CaCO3 and corn starch is 0.06, and the mass ratio of chitosan and corn starch is 10-50; the size of the nano CaCO3 ranges from 30nm to 50nm; and the size of the waxy corn starch nanoparticles is 70-120nm. The mechanical performance of the composite membrane is obviously improved; the light transmittance and moisture penetrability of the membrane can be reduced; the thermal characteristic is better; the thermal stability of the composite membrane is higher than that of the corn starch membrane; and the corn starch and the nano CaCO3 particles have better compatibility.

Owner:QINGDAO AGRI UNIV

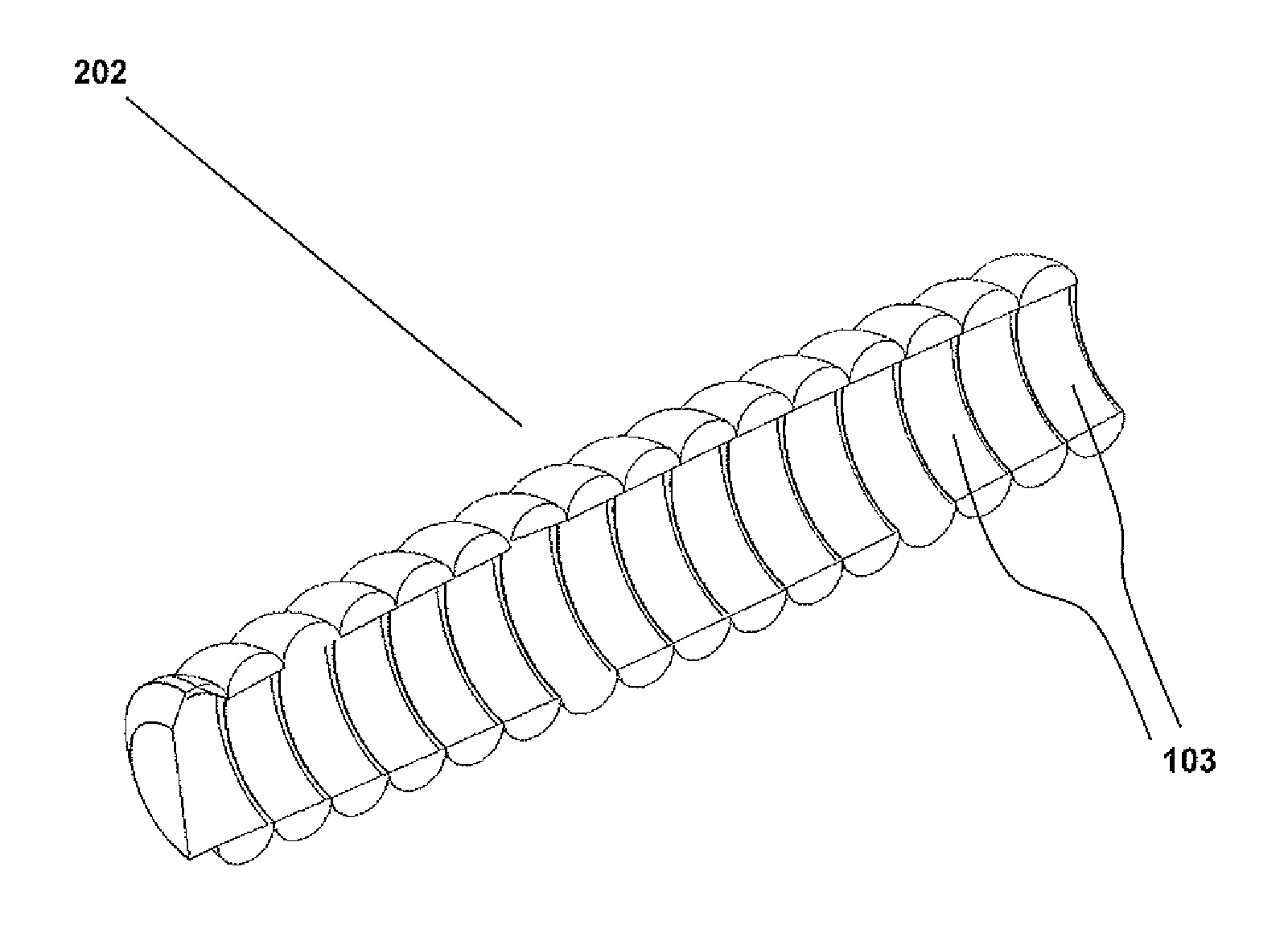

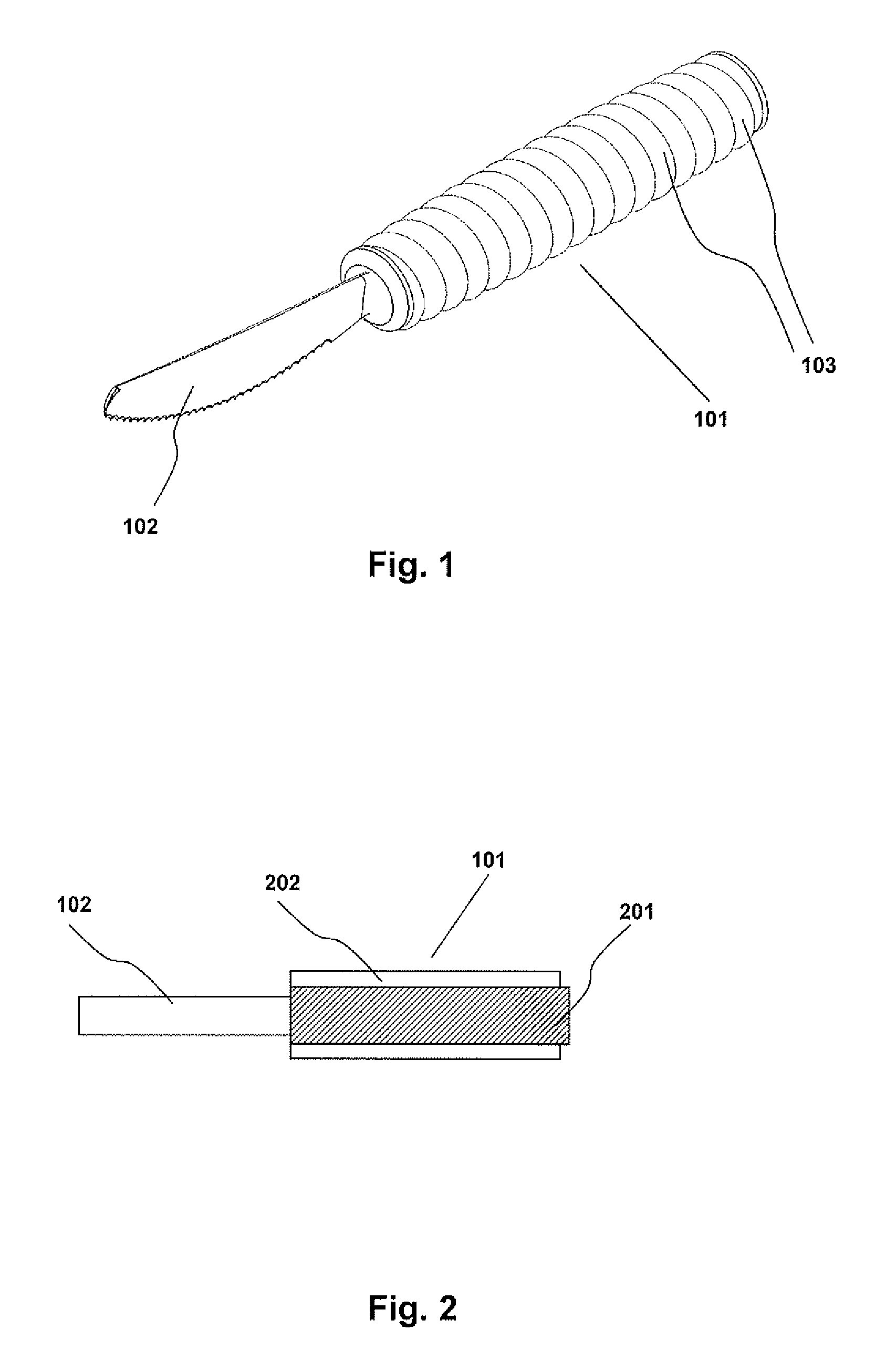

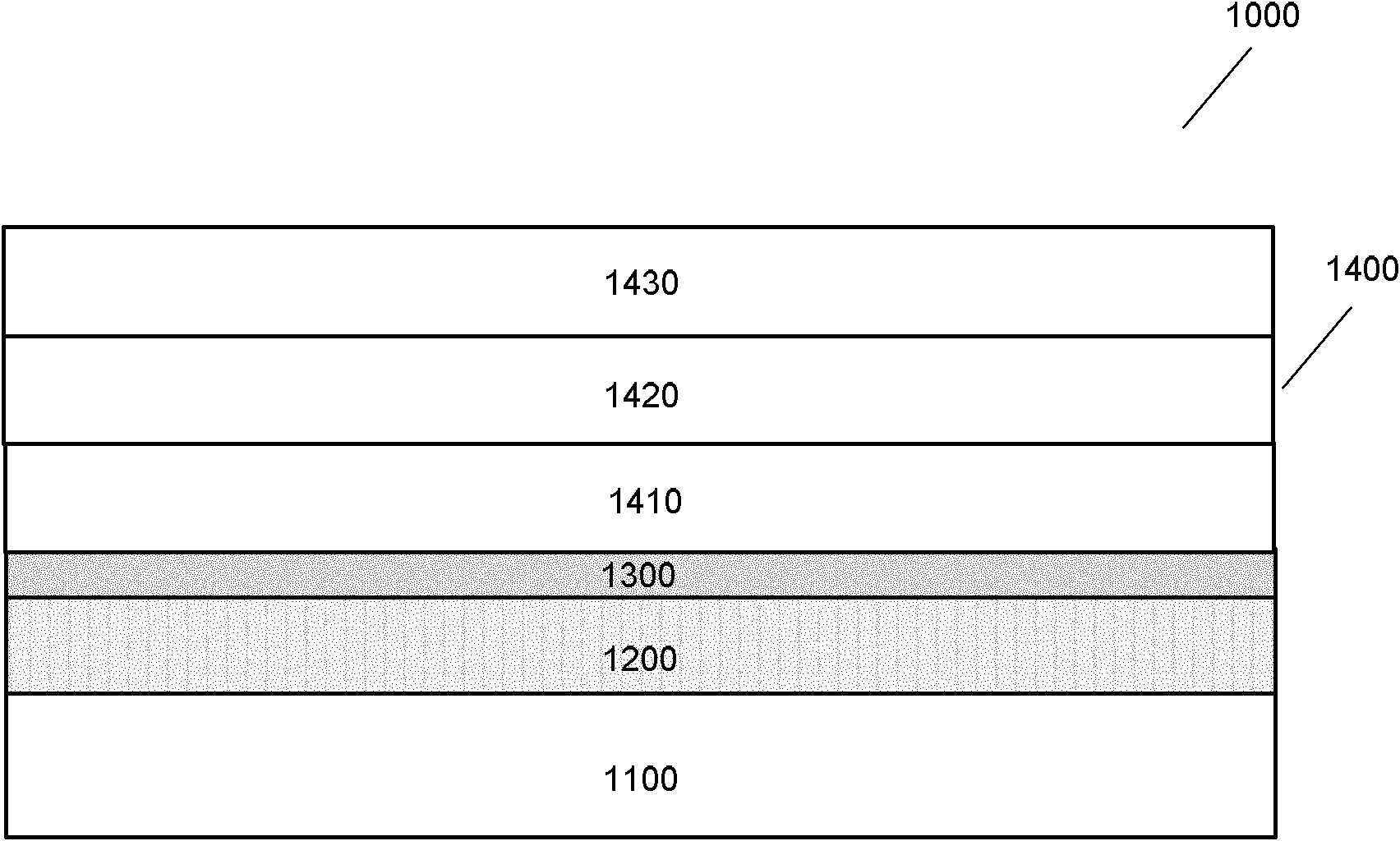

Grip enhancer

InactiveUS20120260463A1Easy to handleComfortable gripTravelling carriersHoldersWorking temperatureEngineering

A coil of elastic material can be wrapped around the handle of a utensil to thereby provide an enhanced grip. An ideal material for this application is a food grade or medical grade silicone rubber because this material is relatively inert both chemically and biologically. Other advantageous properties include a wide range of working temperatures and the availability of a variety of grades, colors, and firmness. Material of different grades can be combined to provide rigidity to the coil shape while also providing a compliant surface. Texturing of the inner and / or outer coil surfaces can also provide for better handholds and for a more positive contact between the grip enhancer and the utensil handle.

Owner:HINES STEVE

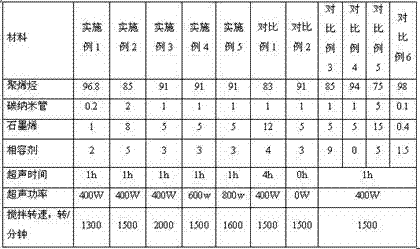

Polyolefin-based conductive master batch based on carbon nano tube and graphene compounded system and preparation method thereof

The invention provides a polyolefin-based conductive master batch based on a carbon nano tube and graphene compounded system and a preparation method thereof. The preparation method comprises the following steps: firstly respectively uniformly dispersing carbon nano tubes and graphene into a volatile inert solvent, respectively treating for 1 hour by virtue of an ultrasonic treatment device, thenstirring the treated dispersion liquid with raw materials in a high-speed stirring machine in proportion, then mixing with a compatilizer in a certain ratio at room temperature, and then carrying outmelt extrusion by virtue of a twin screw, so that the conductive master batch is prepared. The prepared composite material has excellent conductivity, is easy to add and can be widely applied to the fields of injection molding, extrusion and modification.

Owner:上海统慧科技发展有限公司

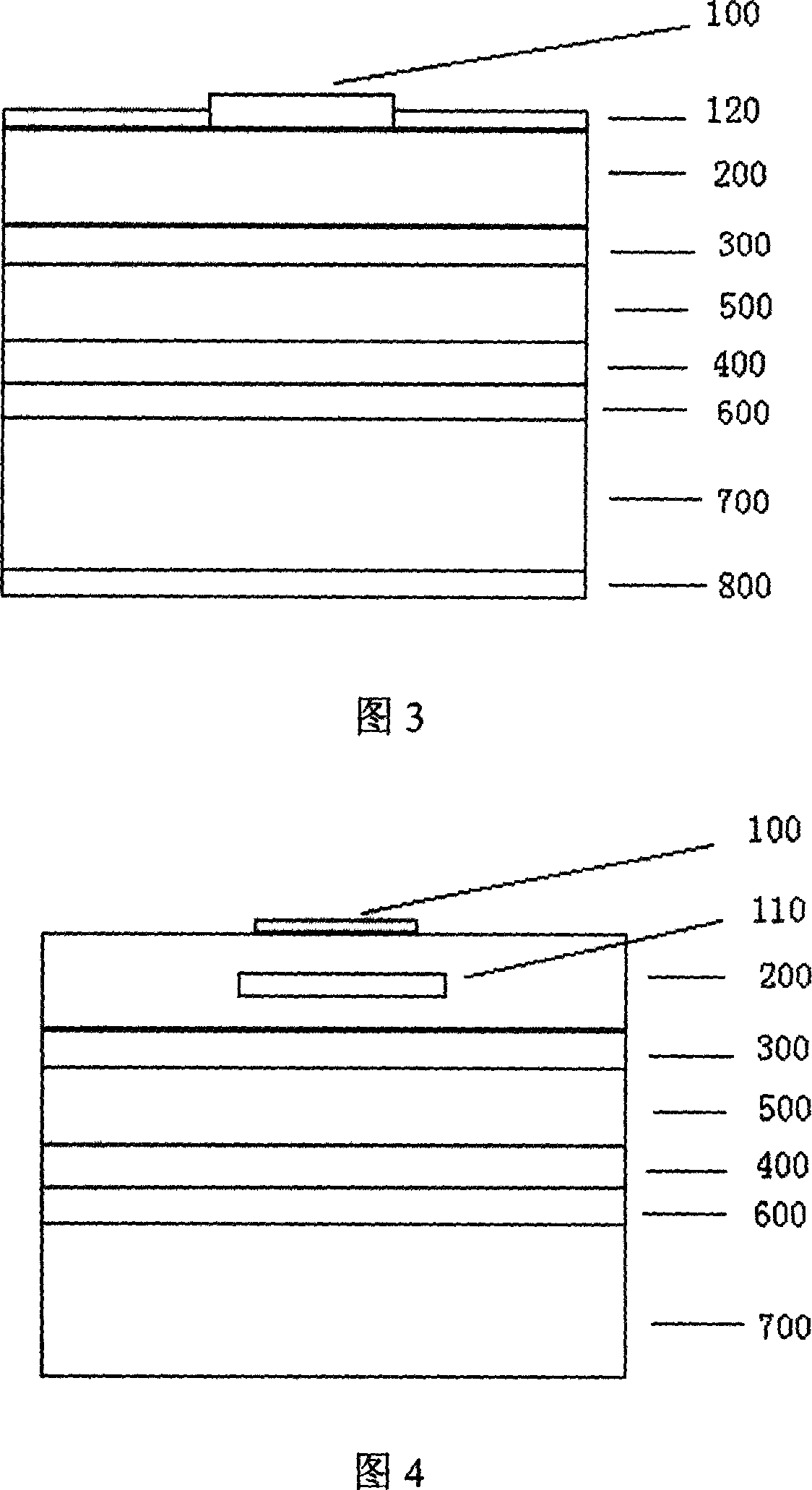

LED (light-emitting diode) epitaxial wafer, LED structure and formation method of LED structure

InactiveCN102122691AGuaranteed integrityControl releaseFrom chemically reactive gasesSemiconductor devicesLarge sizeLead structure

The invention provides an LED (light-emitting diode) epitaxial wafer which comprises a substrate, a first porous structure layer formed on the top layer of the substrate, a second porous structure layer formed on the first porous structure layer and an LED structure layer formed on the second porous structure layer, wherein the porosity and aperture of the second porous structure layer are smaller than those of the first porous structure layer, and the LED structure layer at least comprises a first-type semiconductor layer, a luminous layer and a second-type semiconductor layer. An LED structure which has the characteristics of large porosity and great thermal mismatch between an epitaxy on porous silicon and a Si (silicon) material is adopted, thereby enabling a weak porous silicon layer to deform partially, releasing thermal mismatch stress, ensuring the integrity of the epitaxial LED structure, forming the large-size epitaxial LED structure, and improving the quality of an epitaxial crystal of the LED structure layer through the second porous structure layer.

Owner:王楚雯 +1

Confocal probe having scanning mirrors mounted to a transparent substrate in an optical path of the probe

InactiveUS7252634B2Small diameterImprove thermal characteristicsSurgeryEndoscopesLight beamScanning mirror

A confocal probe unit is provided with a scanning type confocal probe, which includes at least one scanning mirror, and a transparent substrate on which the at least one scanning mirror is mounted. The transparent substrate is inserted in an optical path of the confocal probe such that a light beam proceeding along the optical path is deflected by the scanning mirror.

Owner:HOYA CORP

Preparation method for vanadium phosphorus oxide catalyst used in selective oxidation of hydrocarbon

ActiveCN105381809AImprove thermal characteristicsImprove catalytic performanceOrganic chemistryPhysical/chemical process catalystsPhosphoric acidMaleic anhydride

The present invention relates to a vanadium phosphorus oxide catalyst, and mainly solves the problem that the catalytic performance of a catalyst in the prior art in preparing maleic anhydride by selective oxidation of a hydrocarbon is poor. For well solving the aforementioned technical problem, according to the technical scheme of the present invention, a preparation method of the vanadium phosphorus oxide catalyst comprises the following steps of: 1) mixing tungsten carbide powder with a phosphoric acid solution, raising the temperature of the mixture to 50-100 DEG C and enabling the mixture to react for 1-10 hours, and carrying out filtering and drying to obtain tungsten-carbide subjected to phosphate processing; 2) after mixing a vanadium compound, and the tungsten-carbide subjected to phosphate processing with an organic solvent, carrying out stirring and slowly adding 85wt%-110wt% of phosphoric acid, and performing heating reflux for 8-32 hours; 3) filtering and washing the obtained catalyst precursor solution after cooling, and carrying out drying at 100-150 DEG C to obtain a catalyst precursor; and 4) obtaining an active catalyst by performing calcination activation on the catalyst precursor. The prepared catalyst can be used in the industrial production of maleic anhydride.

Owner:CHINA PETROLEUM & CHEM CORP +1