Patents

Literature

90 results about "Silicon interposer" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

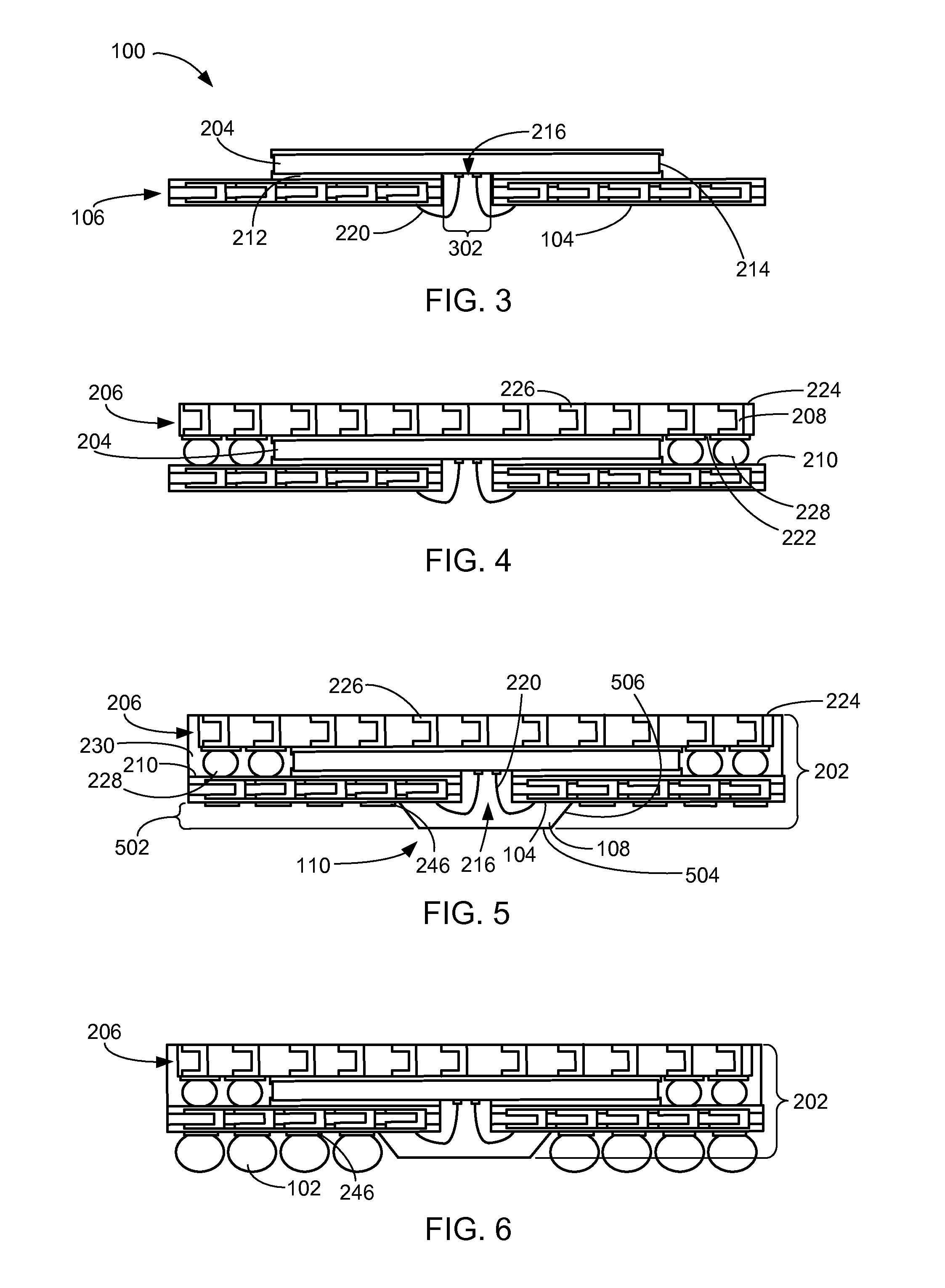

Silicon interposer and multi-chip-module (MCM) with through substrate vias

InactiveUS6562653B1Semiconductor/solid-state device detailsSolid-state devicesSilicon interposerEngineering

An integrated circuit package which includes an integrated circuit that is connected to a silicon substrate. The silicon substrate may have a via. The package may further include a solder bump that is attached to both the integrated circuit and the silicon subtstrate. The silicon substrate has a coefficient of thermal expansion that matches the coefficient of thermal expansion of the integrated circuit.

Owner:INTEL CORP

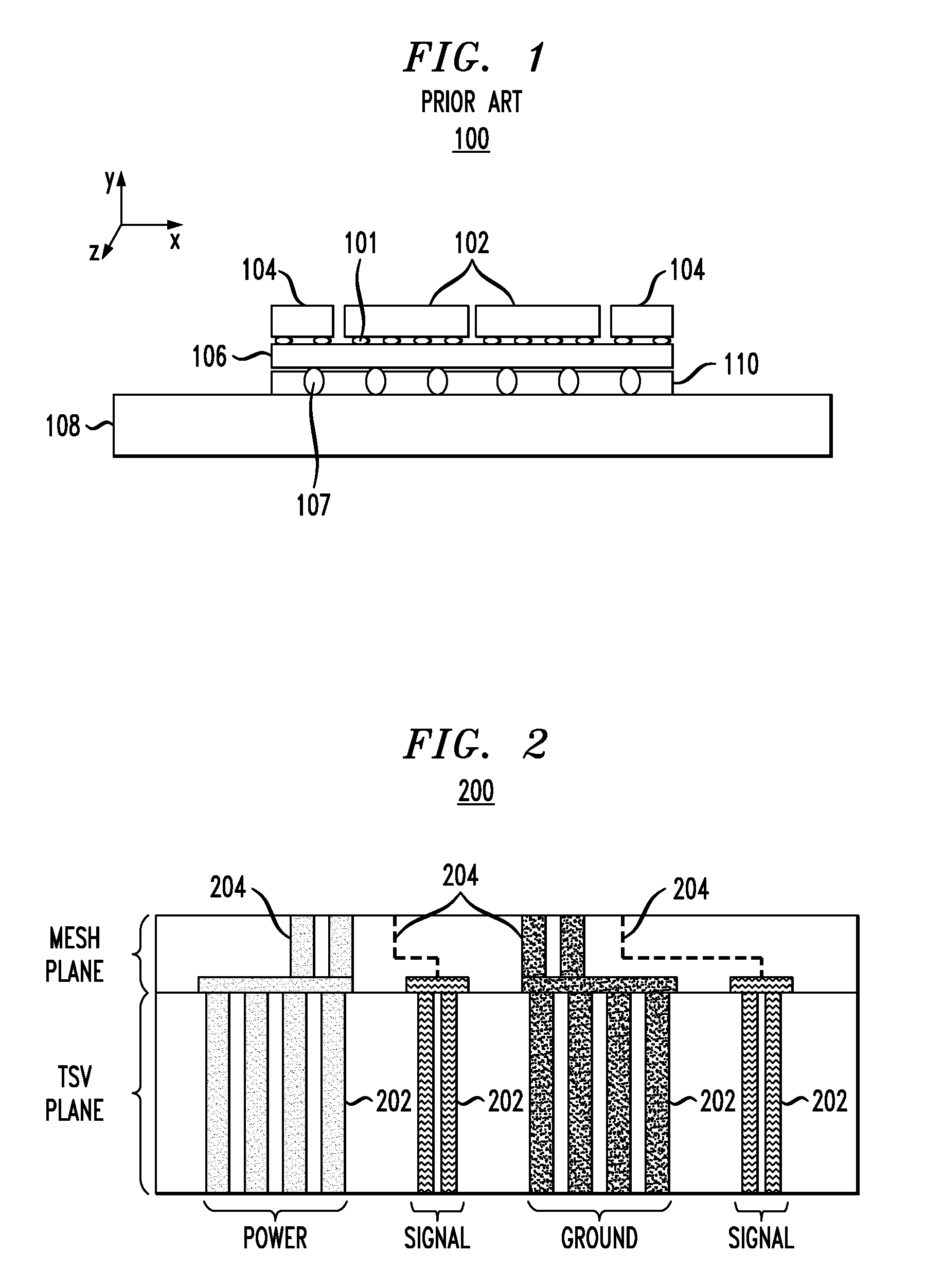

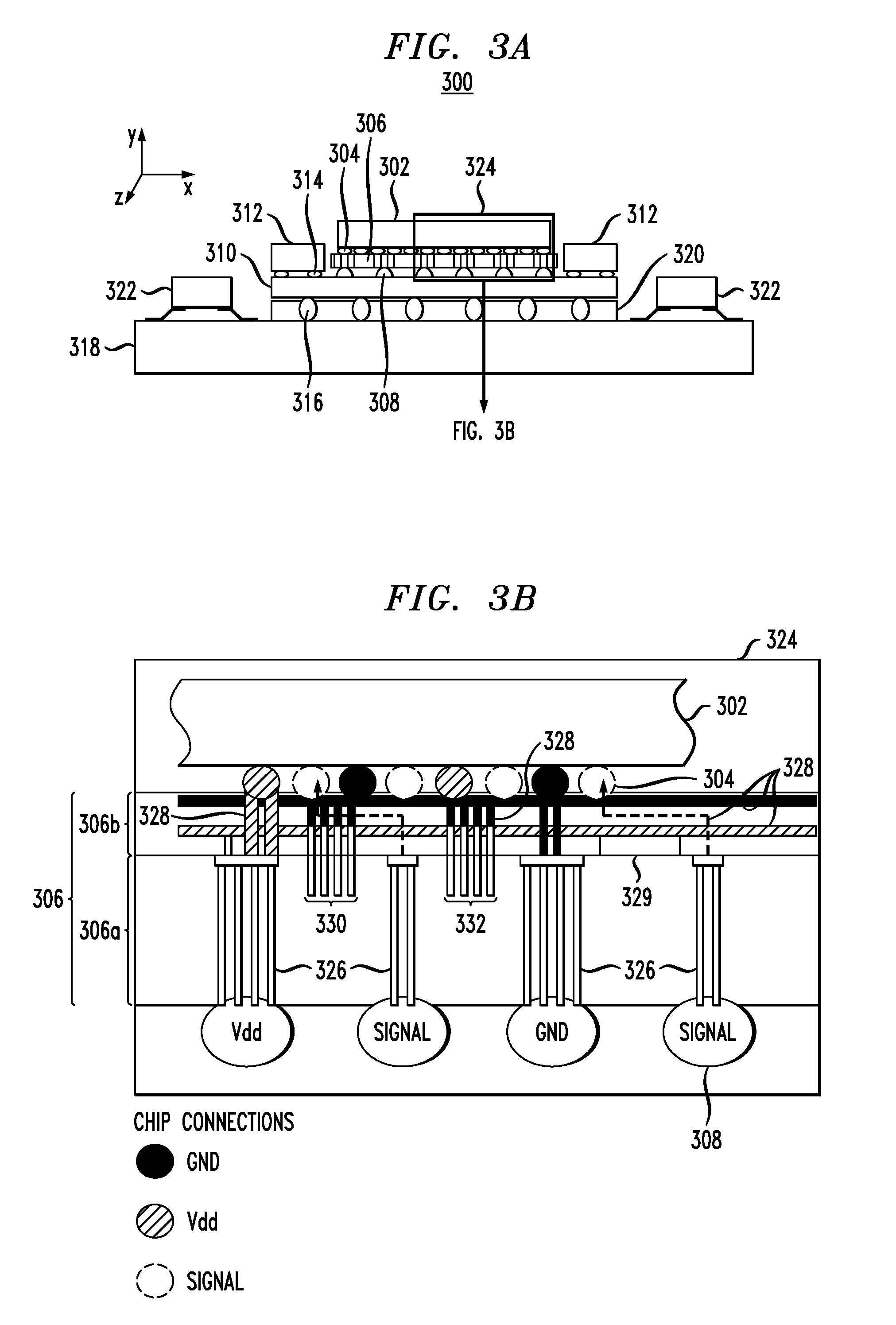

Three-Dimensional Silicon Interposer for Low Voltage Low Power Systems

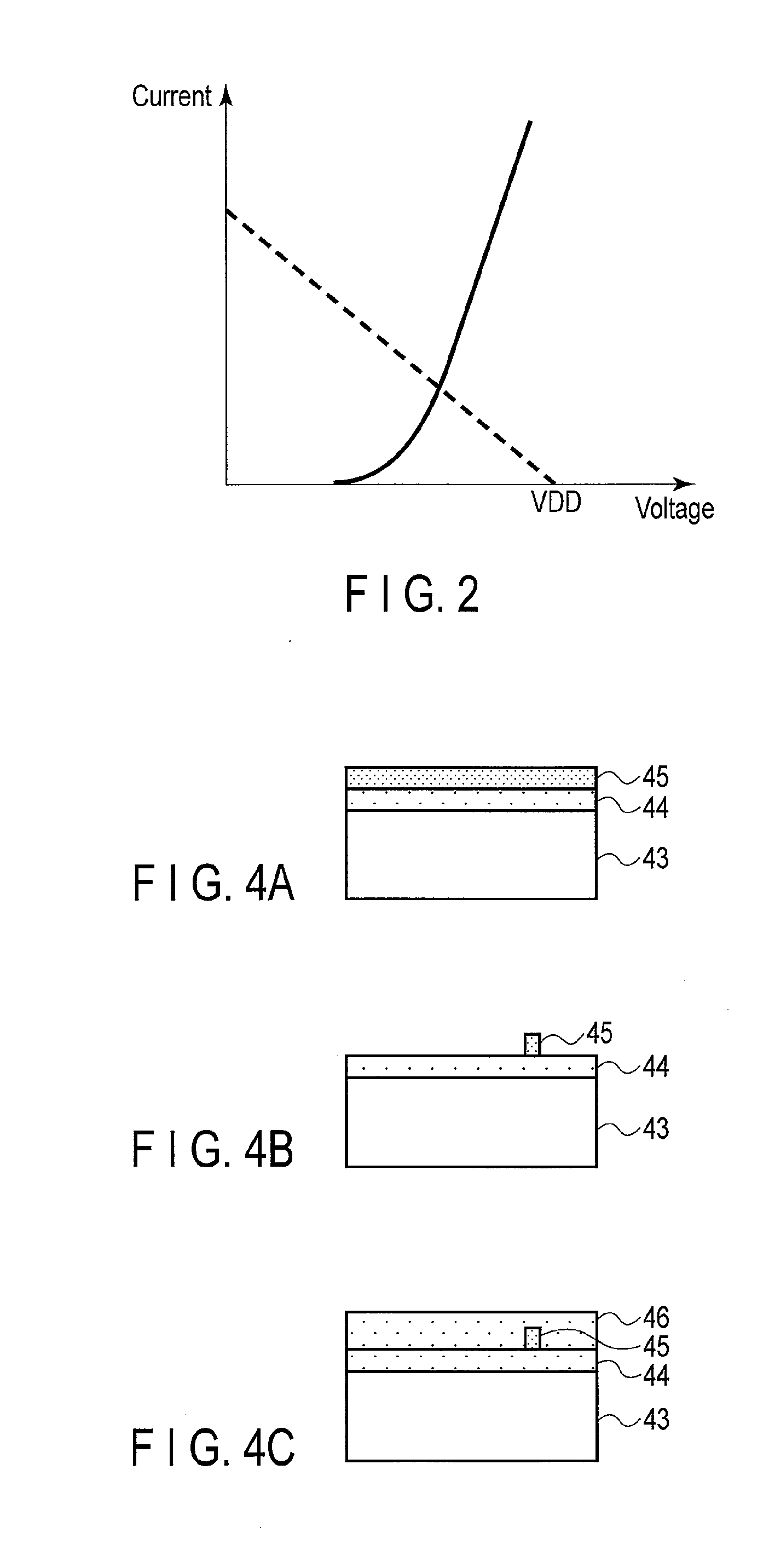

ActiveUS20110042795A1Reduce voltageLow power operationSemiconductor/solid-state device detailsSolid-state devicesSilicon interposerLow voltage

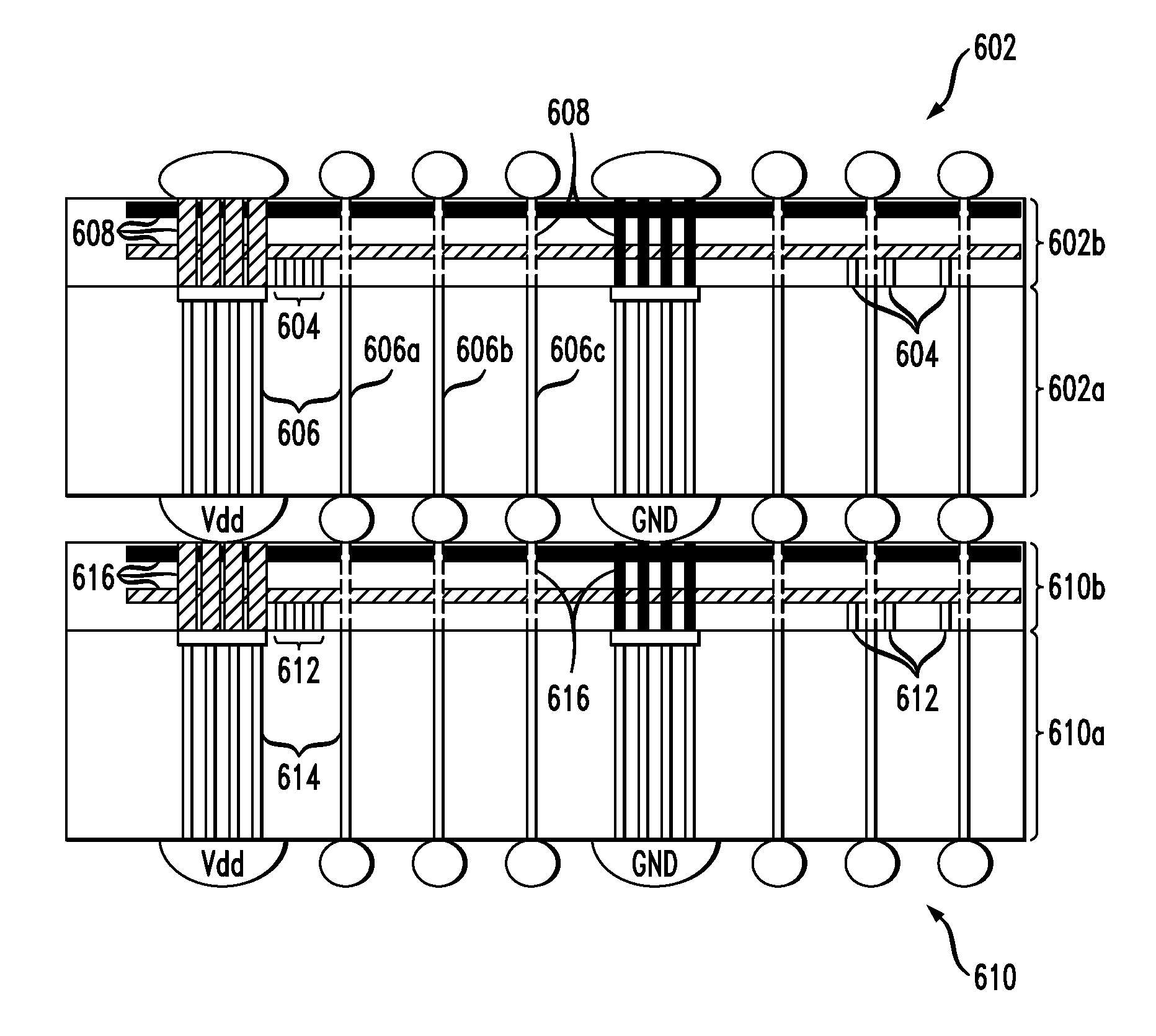

Scalable silicon (Si) interposer configurations that support low voltage, low power operations are provided. In one aspect, a Si interposer is provided which includes a plurality of through-silicon vias (TSVs) within a first plane thereof adapted to serve as power, ground and signal interconnections throughout the first plane such that the TSVs that serve as the power and ground interconnections are greater in number and / or size than the TSVs that serve as the signal interconnections; and a plurality of lines within a second plane of the interposer in contact with one or more of the TSVs in the first plane, the second plane being adjacent to the first plane, adapted to serve as power, ground and signal interconnections throughout the second plane such that the lines that serve as the power and the ground interconnections are greater in number and / or size than the lines that serve as the signal interconnections.

Owner:IBM CORP

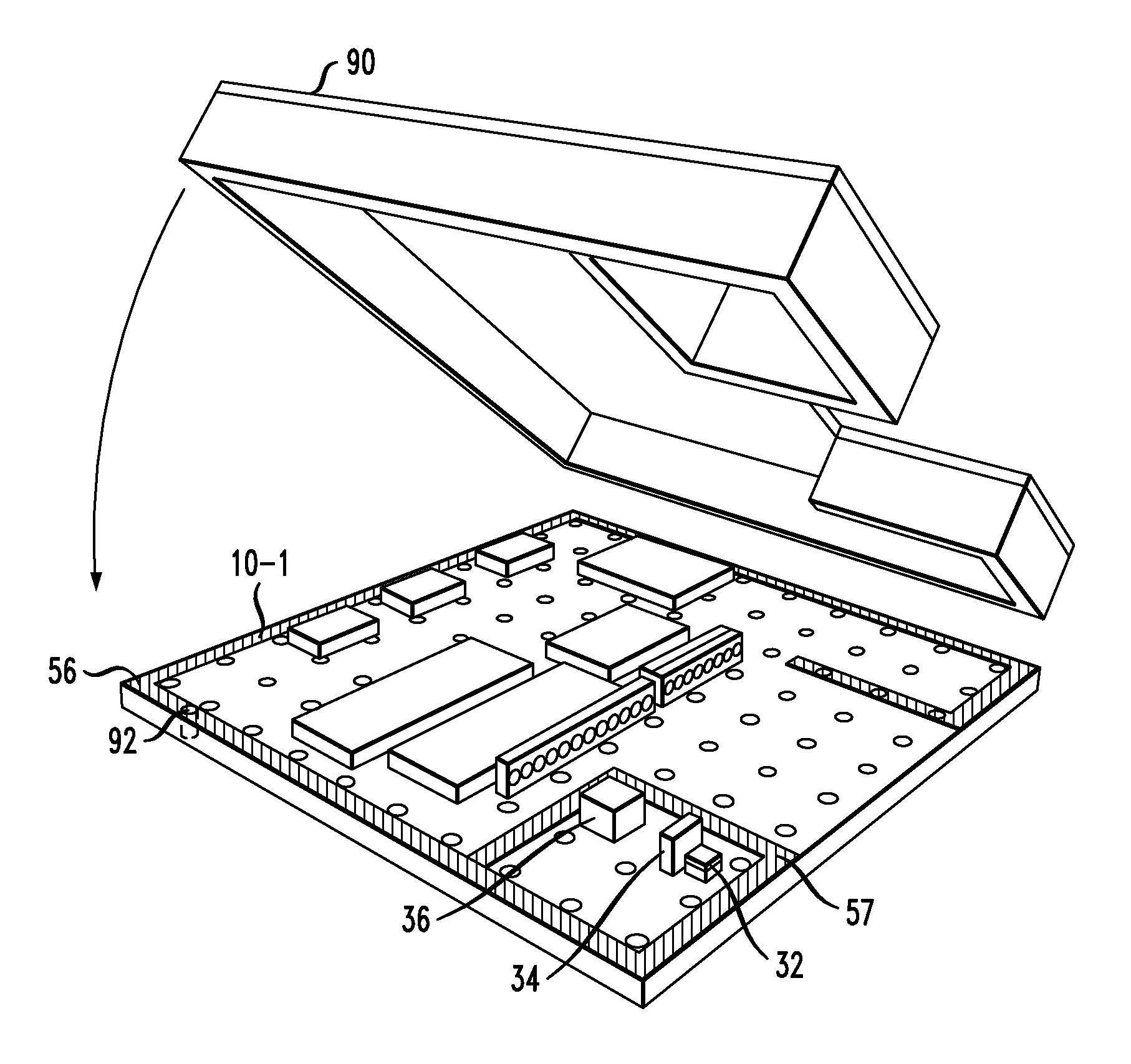

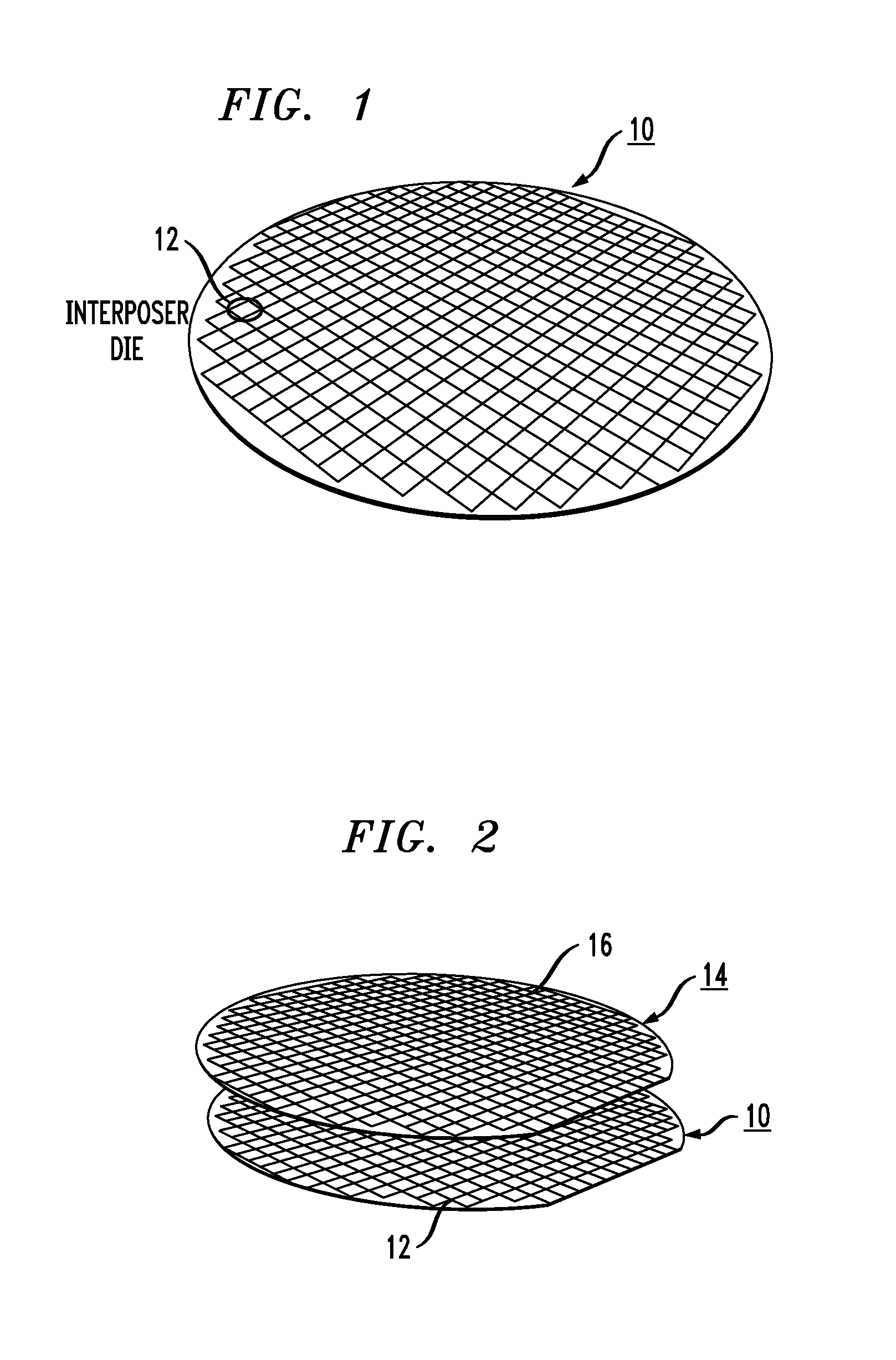

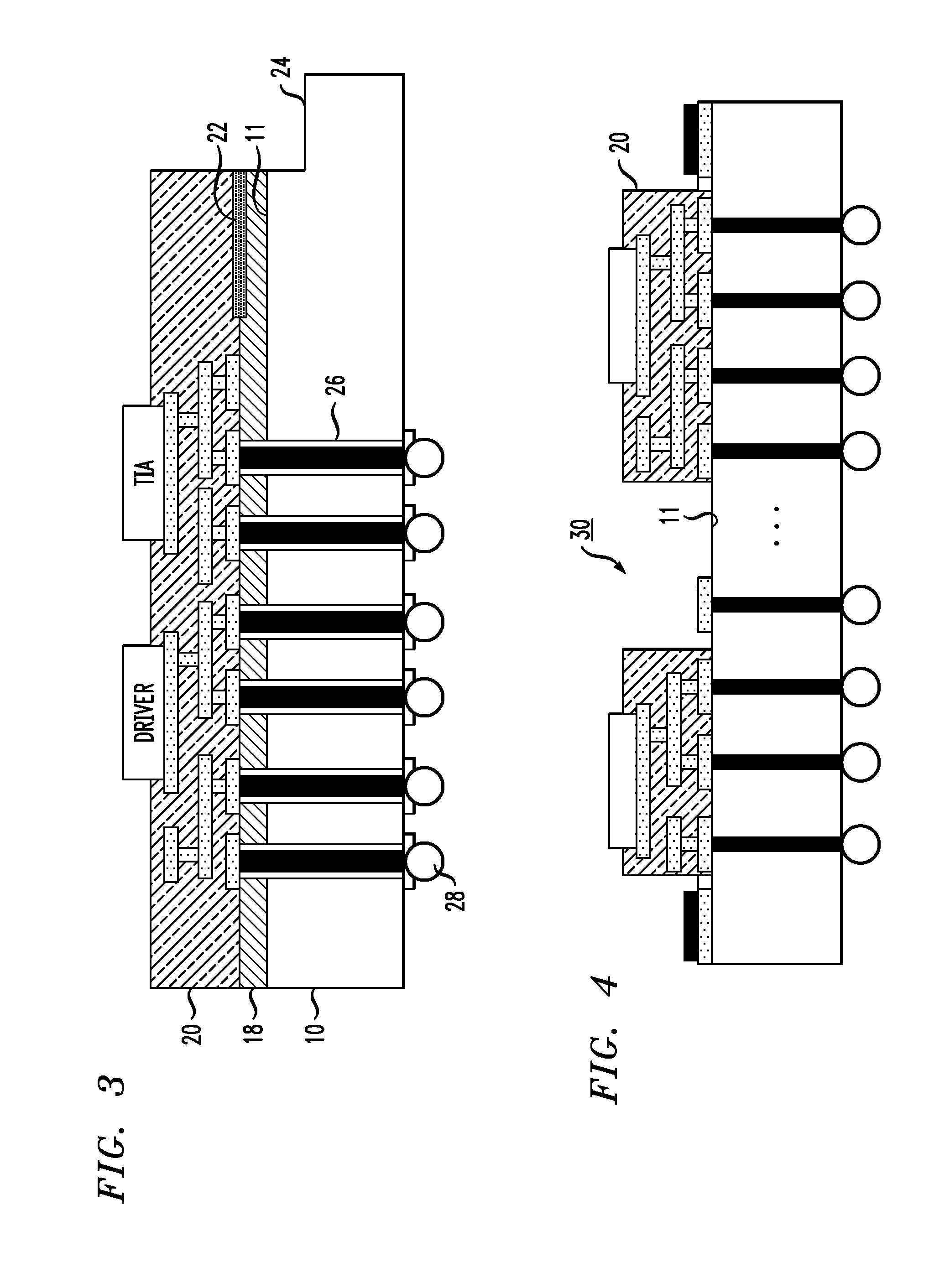

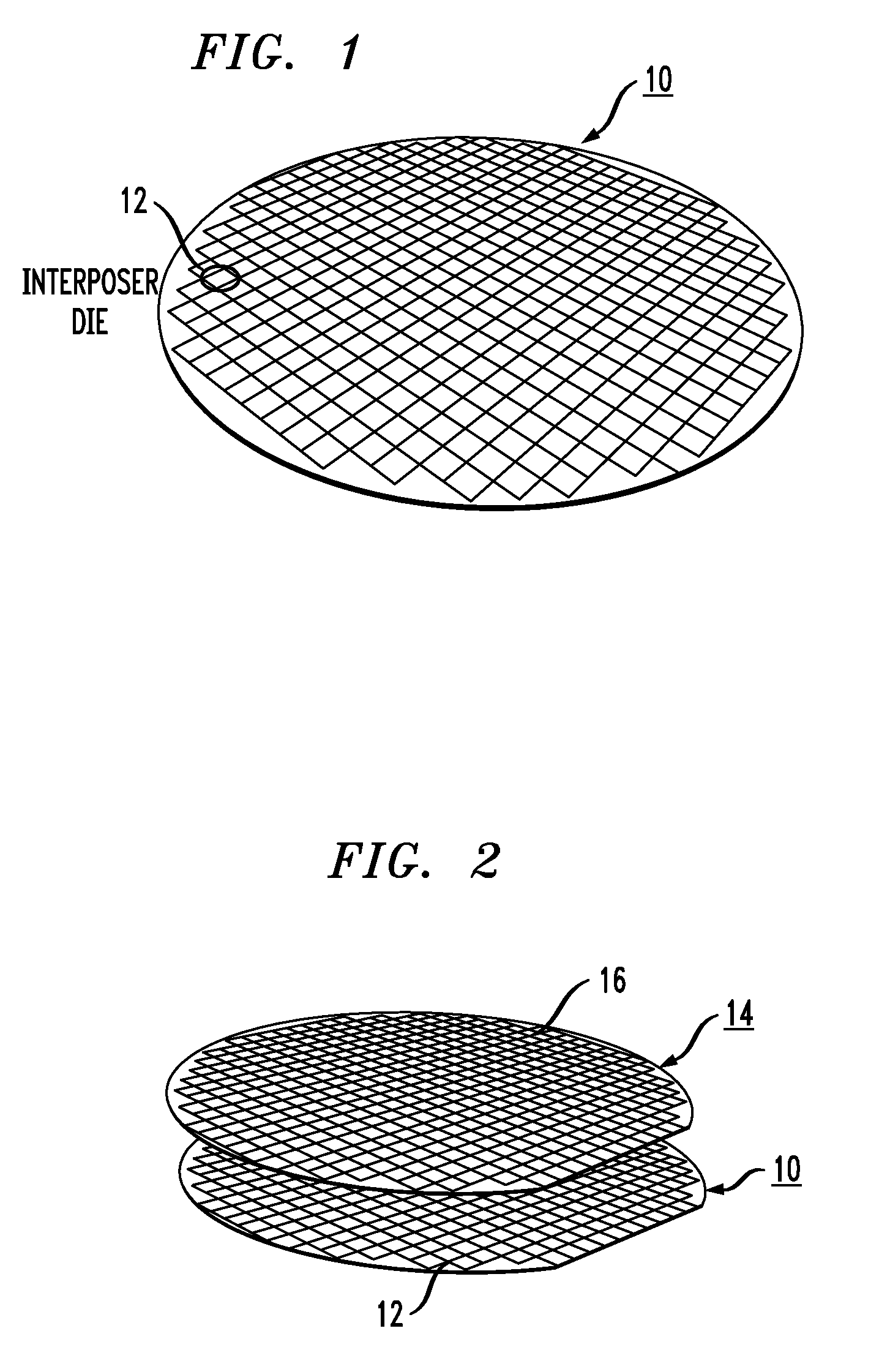

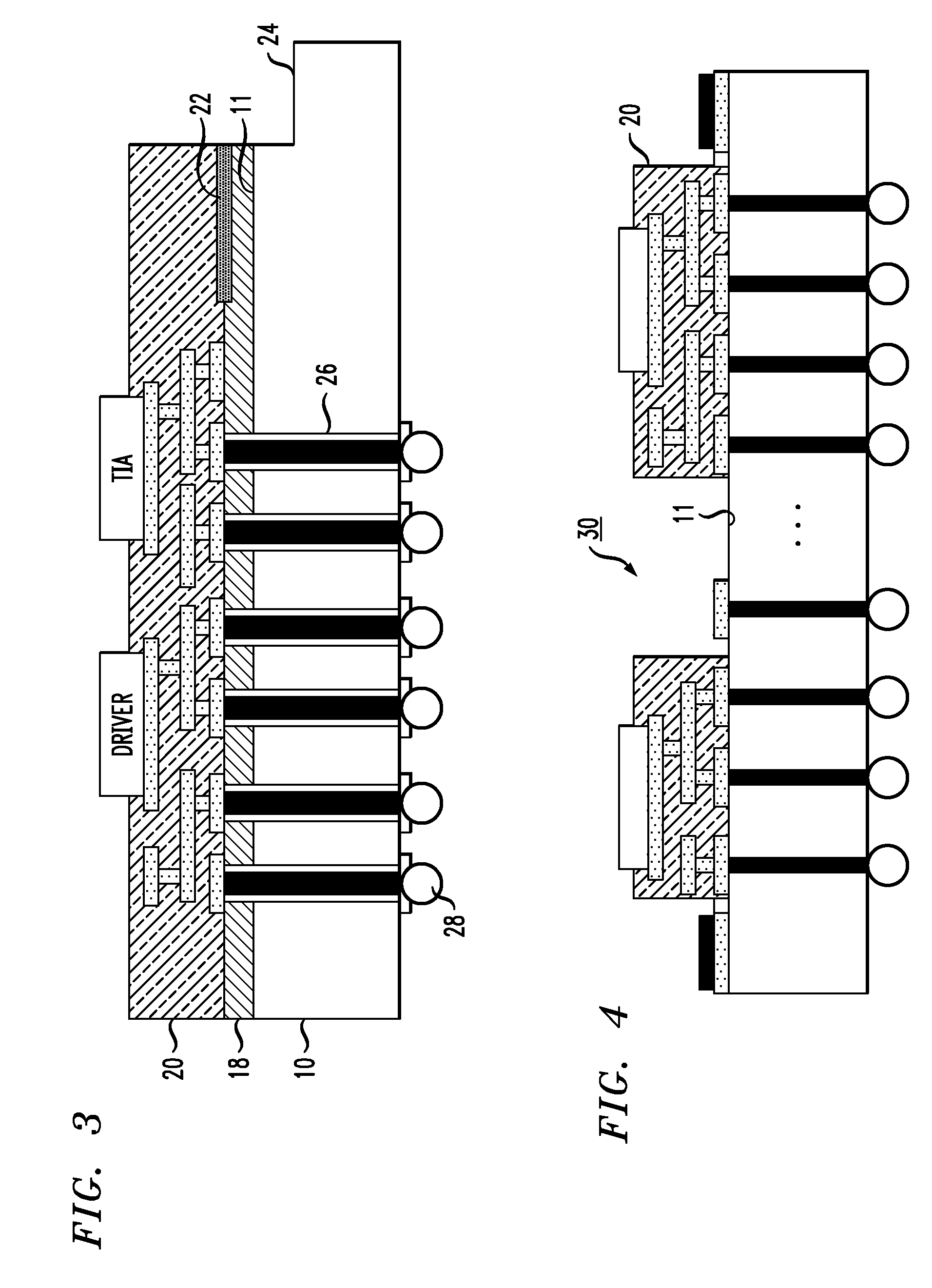

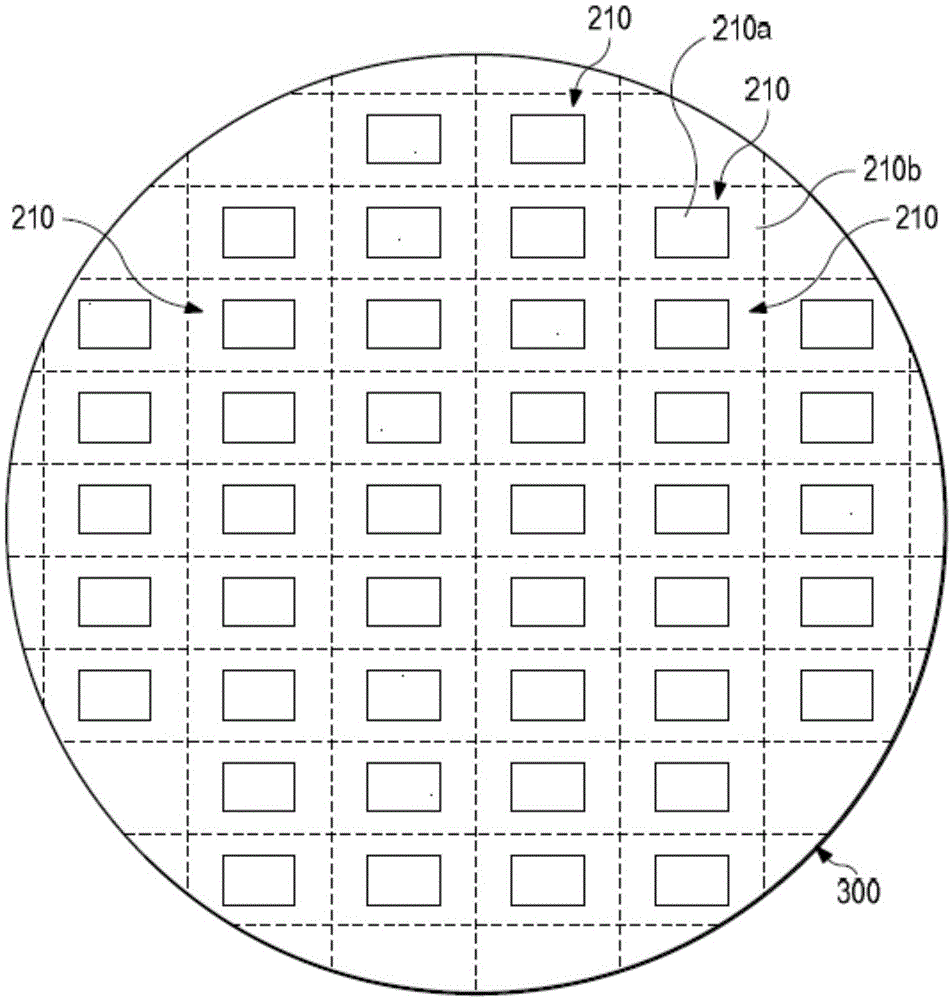

Wafer Scale Packaging Platform For Transceivers

InactiveUS20120280344A1Accurate placementSolid-state devicesOptical light guidesSilicon interposerTransceiver

A wafer scale implementation of an opto-electronic transceiver assembly process utilizes a silicon wafer as an optical reference plane and platform upon which all necessary optical and electronic components are simultaneously assembled for a plurality of separate transceiver modules. In particular, a silicon wafer is utilized as a “platform” (interposer) upon which all of the components for a multiple number of transceiver modules are mounted or integrated, with the top surface of the silicon interposer used as a reference plane for defining the optical signal path between separate optical components. Indeed, by using a single silicon wafer as the platform for a large number of separate transceiver modules, one is able to use a wafer scale assembly process, as well as optical alignment and testing of these modules.

Owner:CISCO TECH INC

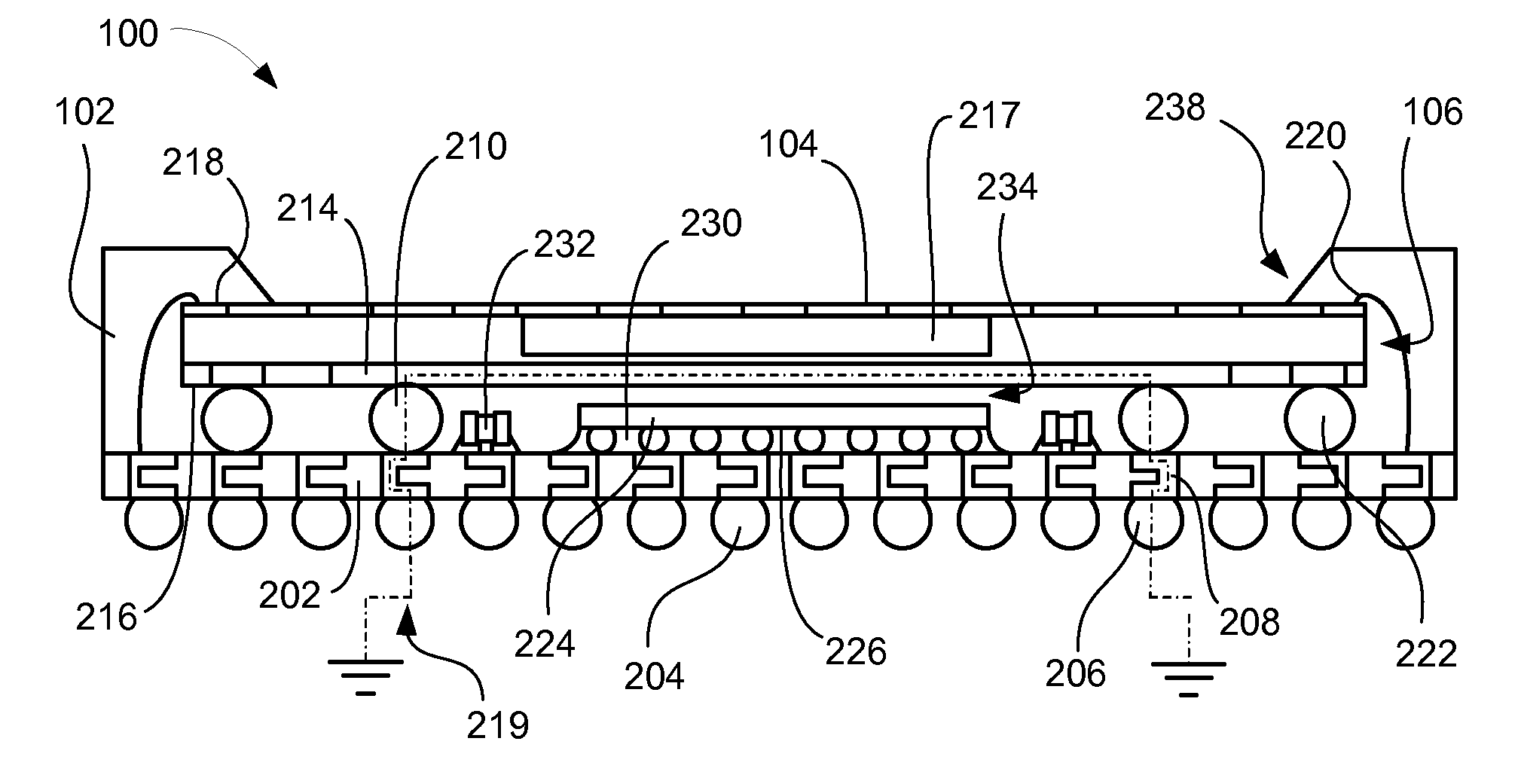

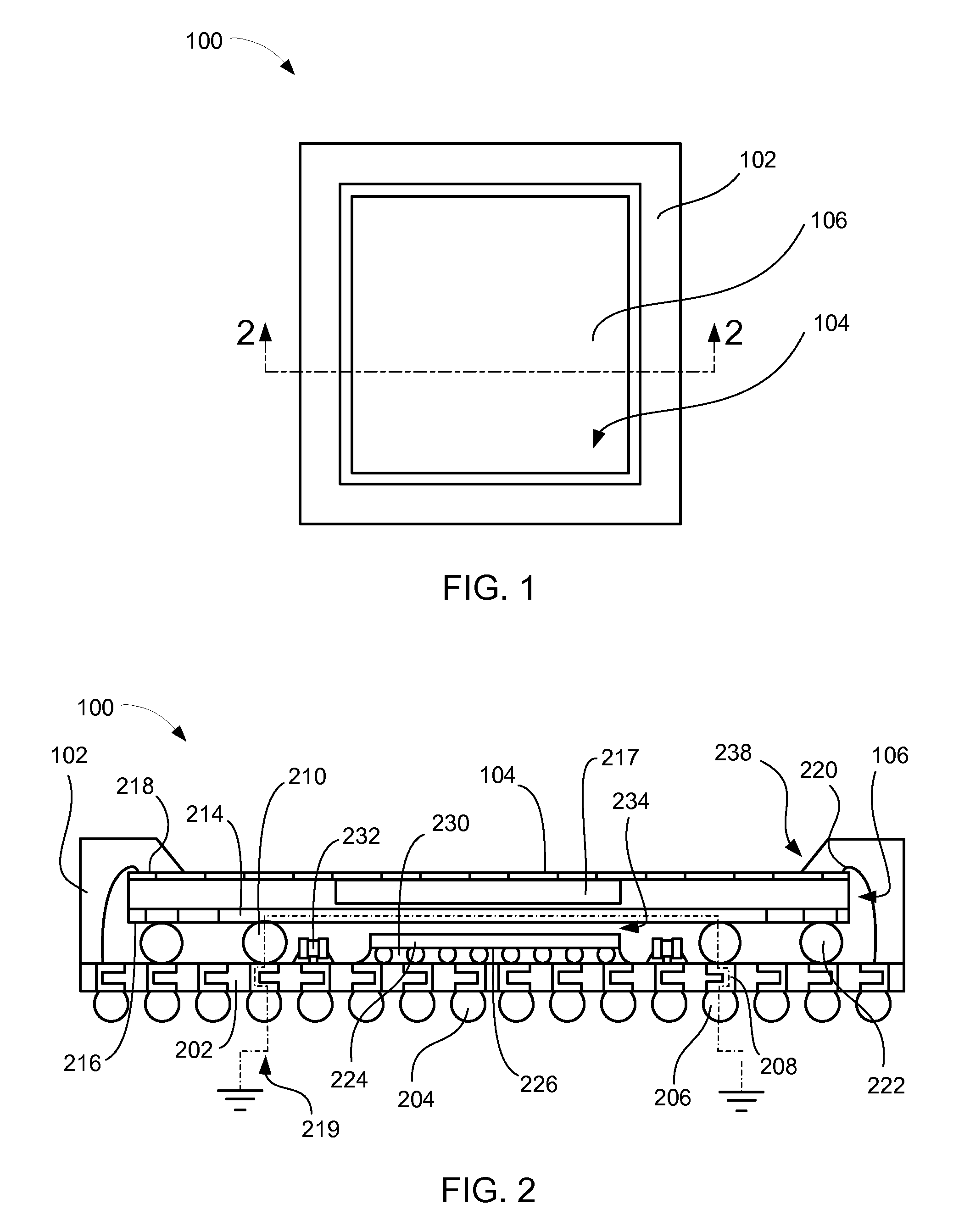

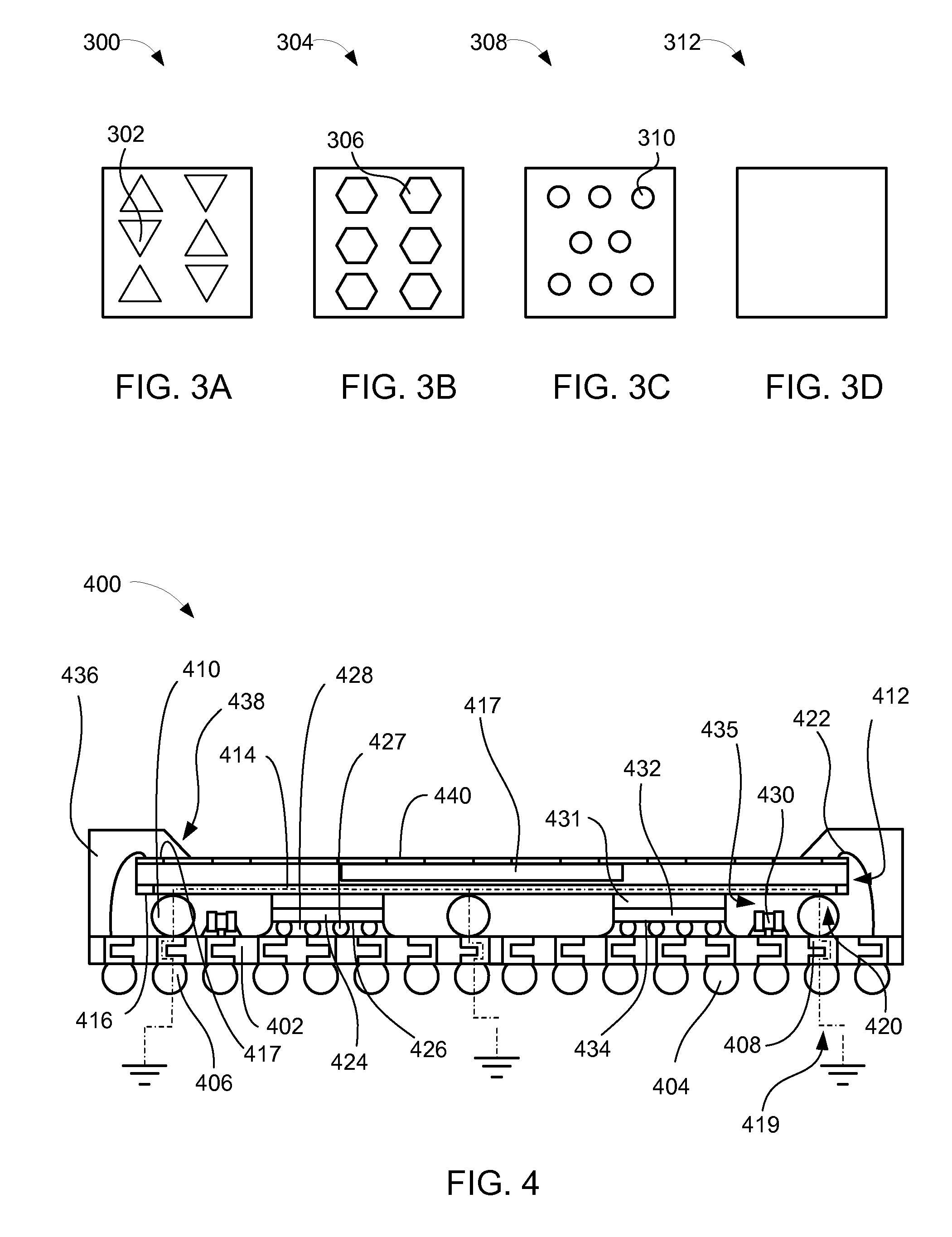

Integrated circuit packaging system with an integral-interposer-structure and method of manufacture thereof

InactiveUS20100244223A1Semiconductor/solid-state device detailsSolid-state devicesSilicon interposerIntegrated circuit packaging

A method of manufacture of an integrated circuit packaging system includes: providing a substrate having a shielding channel through a substrate first side and a substrate second side; mounting a first shielding interconnect to the shielding channel; mounting an integrated circuit over the substrate and adjacent to the first shielding interconnect; attaching a silicon interposer, having an integral-conductive-shield and a via, to the first shielding interconnect with the integral-conductive-shield over the integrated circuit; grounding the shielding channel at the substrate second side; and forming an encapsulation over the substrate covering the integrated circuit and the first shielding interconnect.

Owner:STATS CHIPPAC LTD

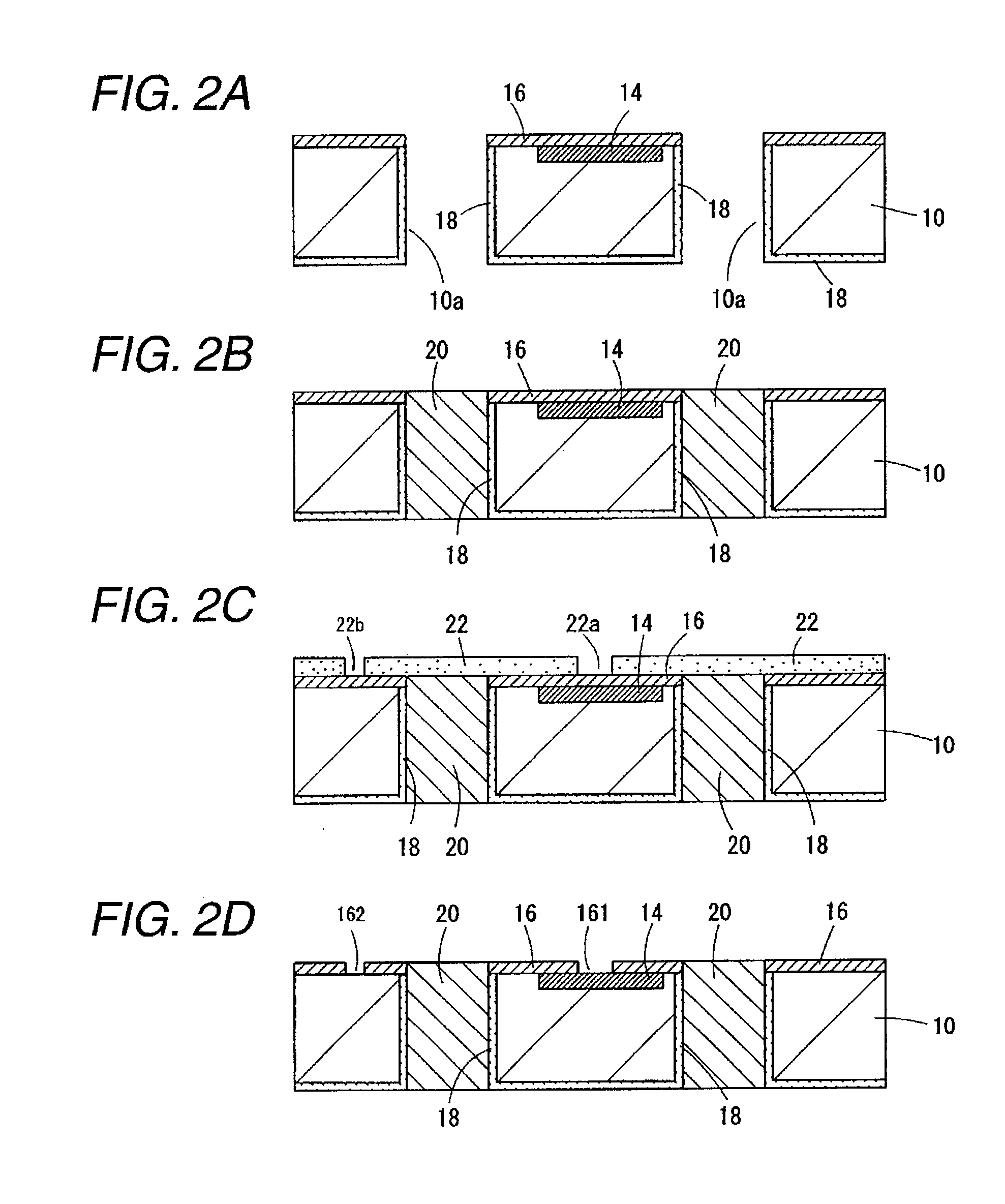

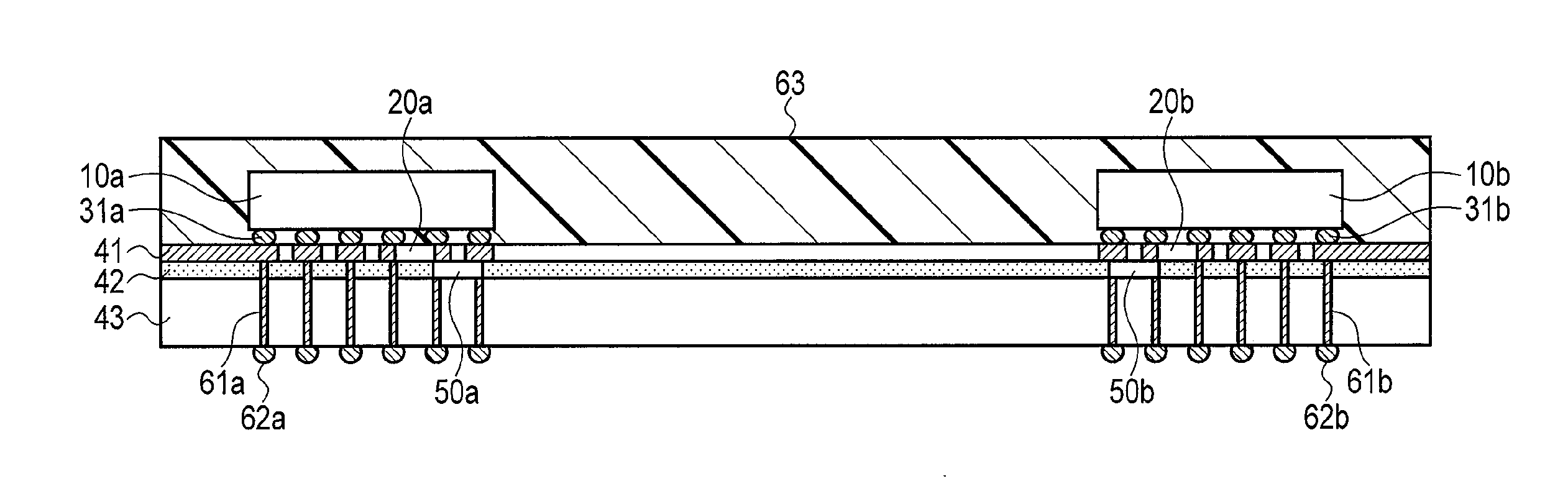

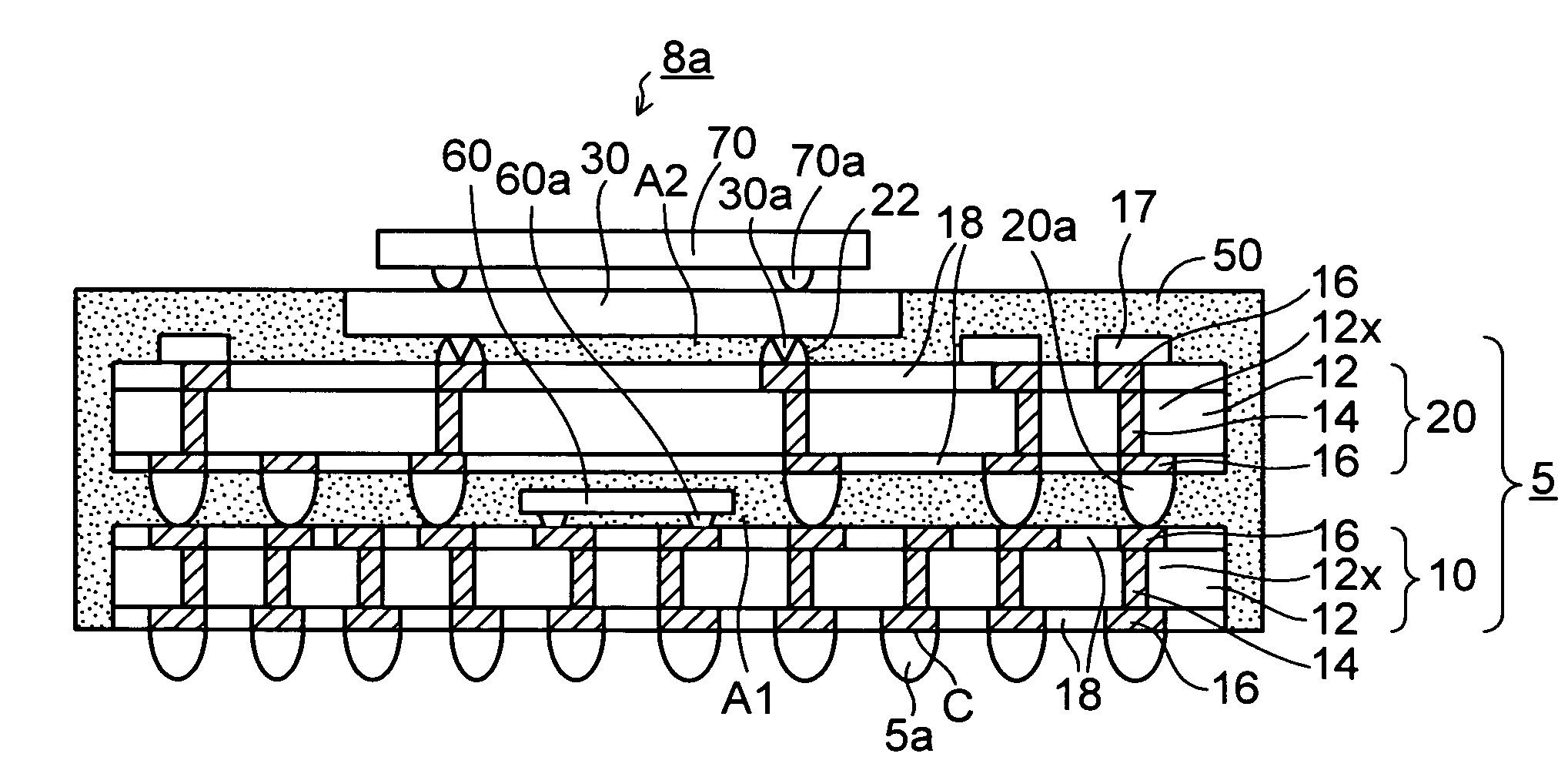

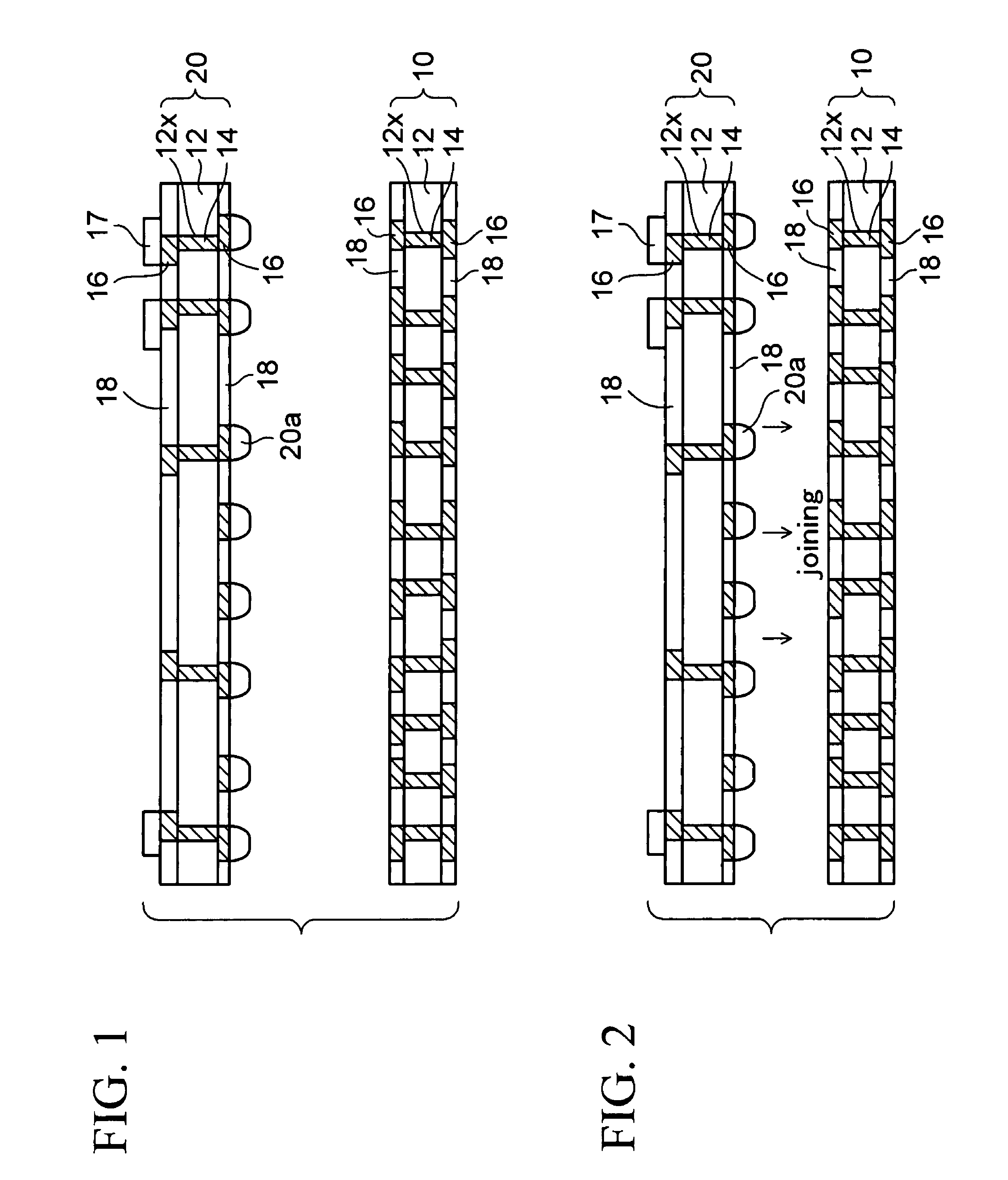

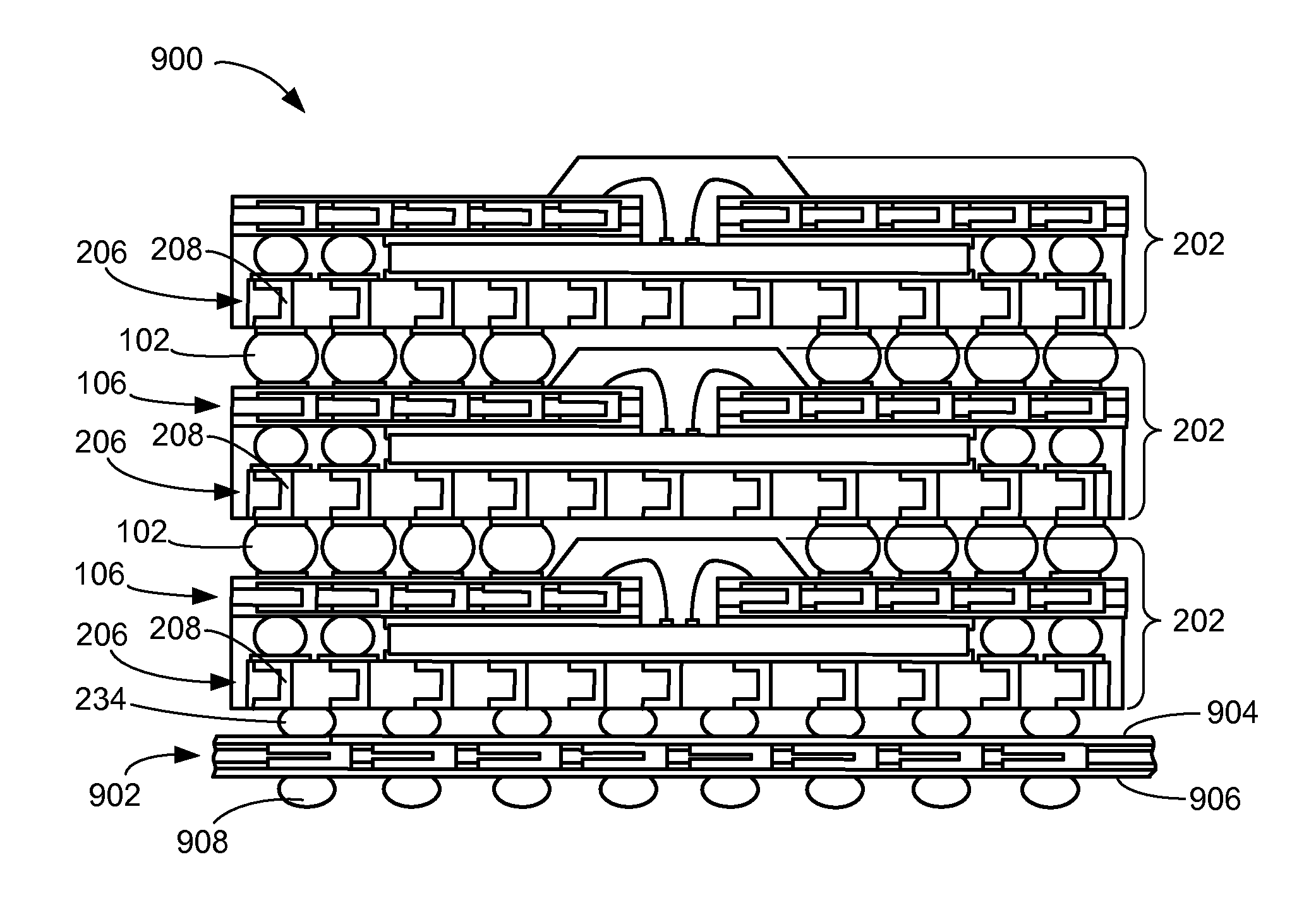

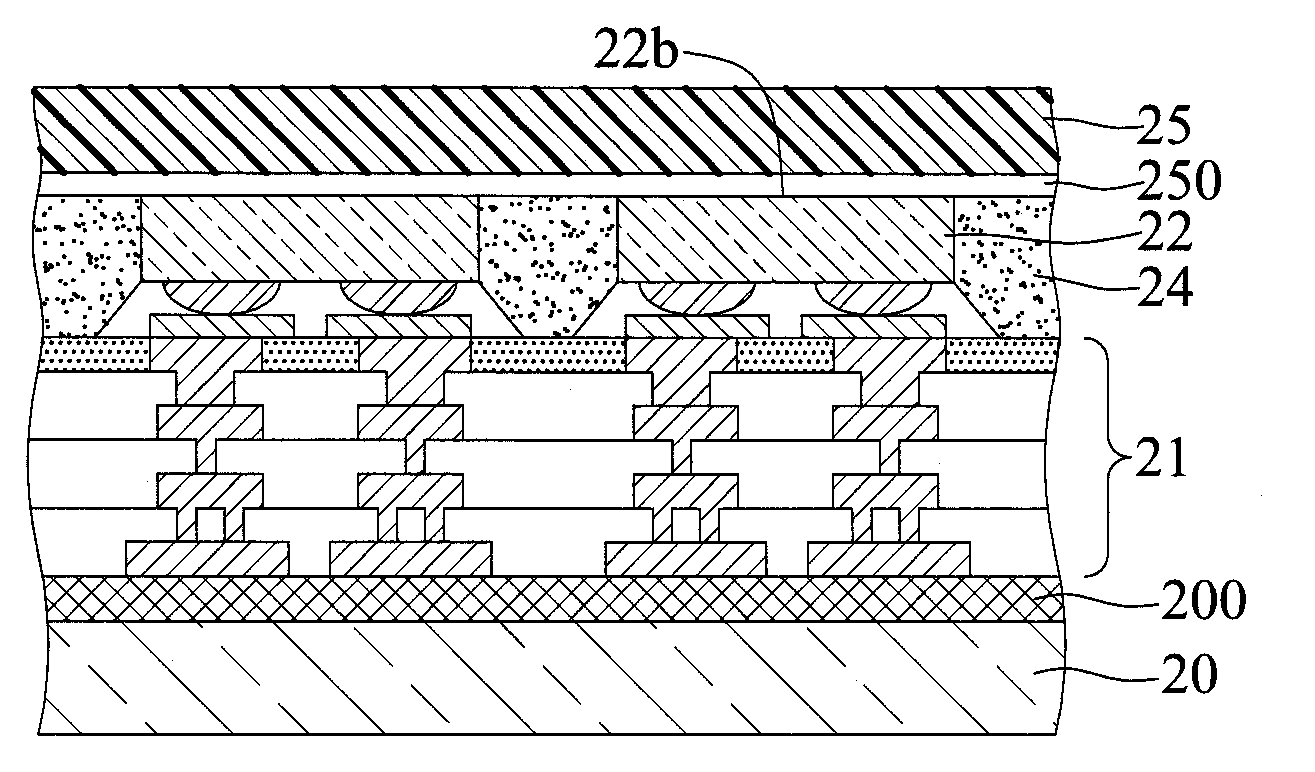

Wiring substrate, manufacturing method thereof, and semiconductor device

ActiveUS20080155820A1Easy to manufactureReliable fillingPrinted circuit assemblingSemiconductor/solid-state device detailsSilicon interposerElectrical connection

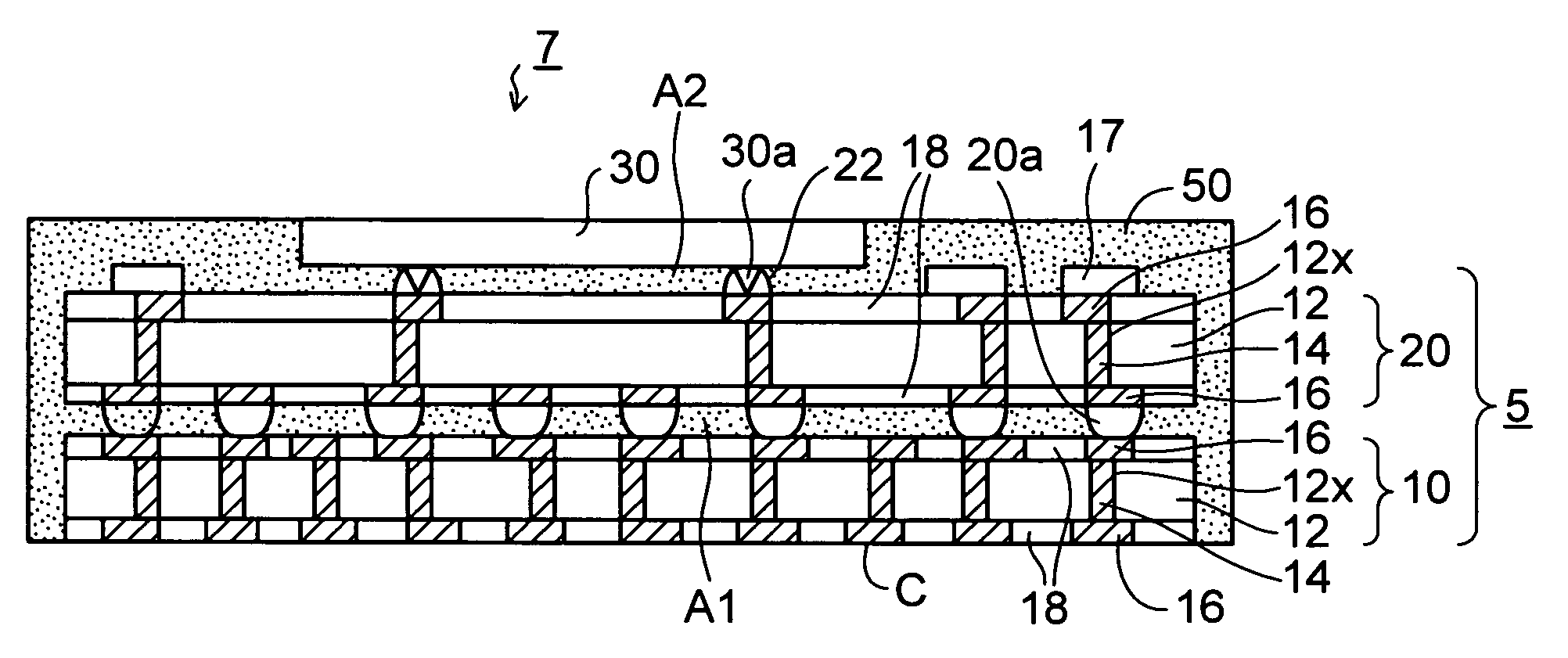

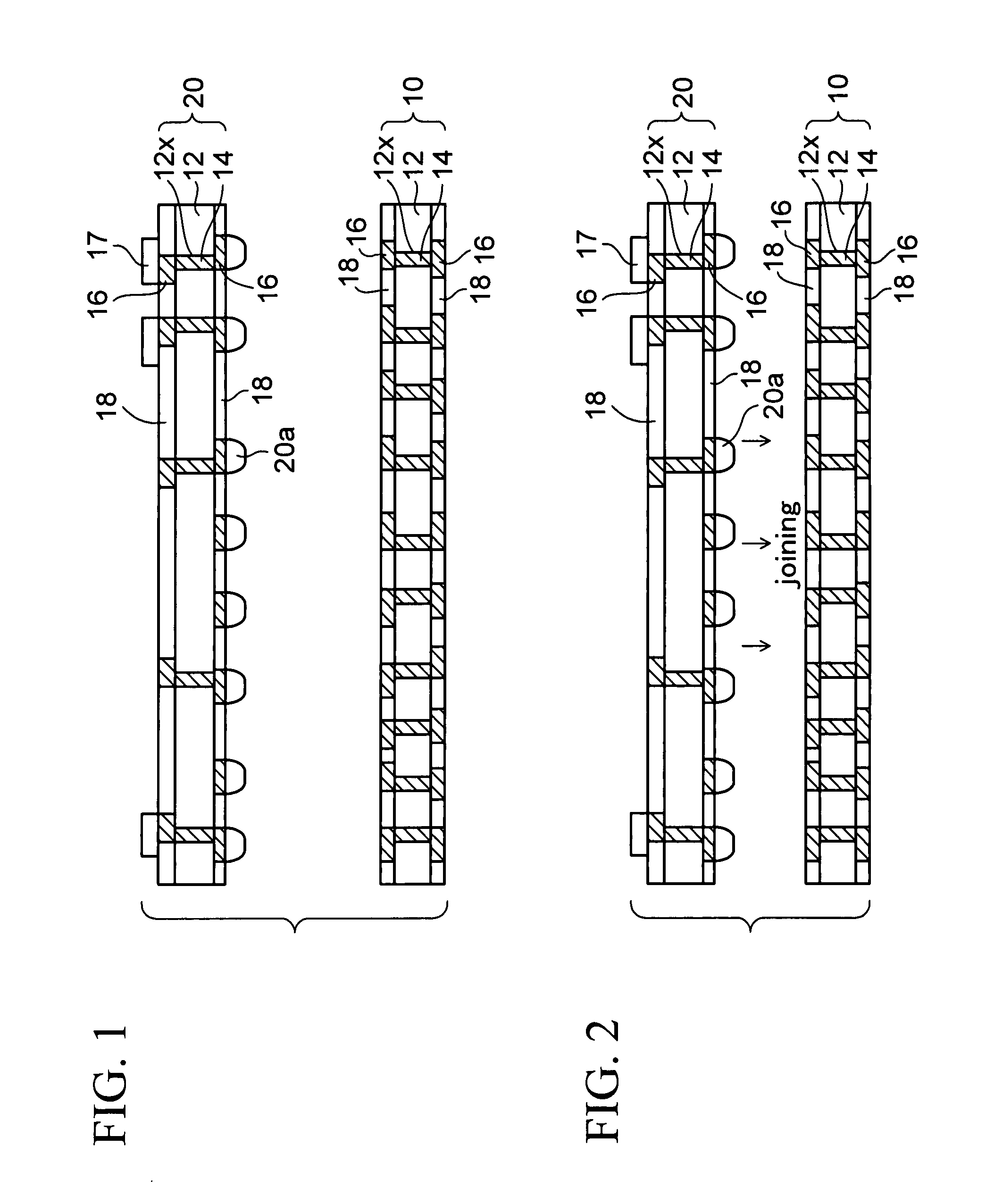

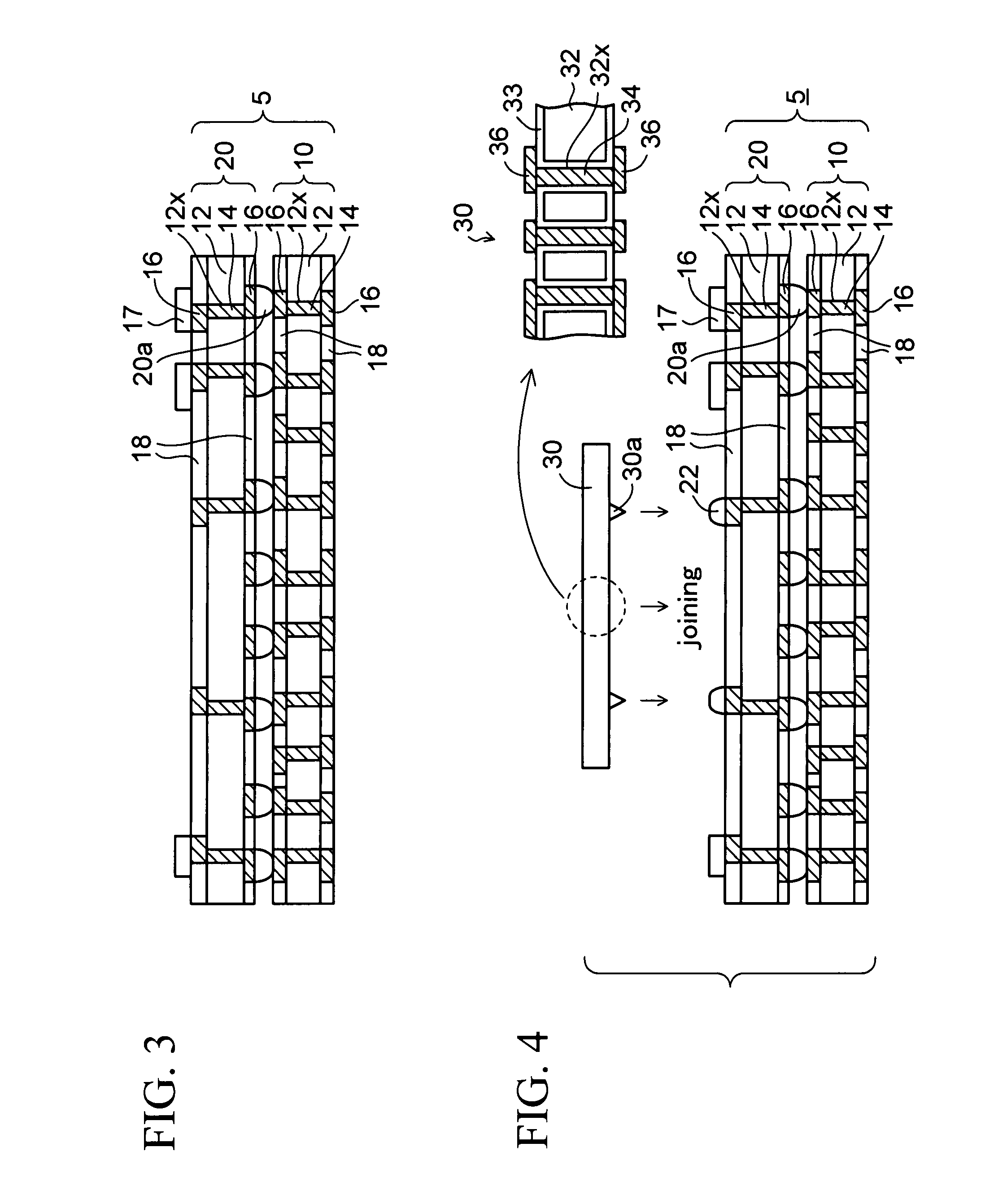

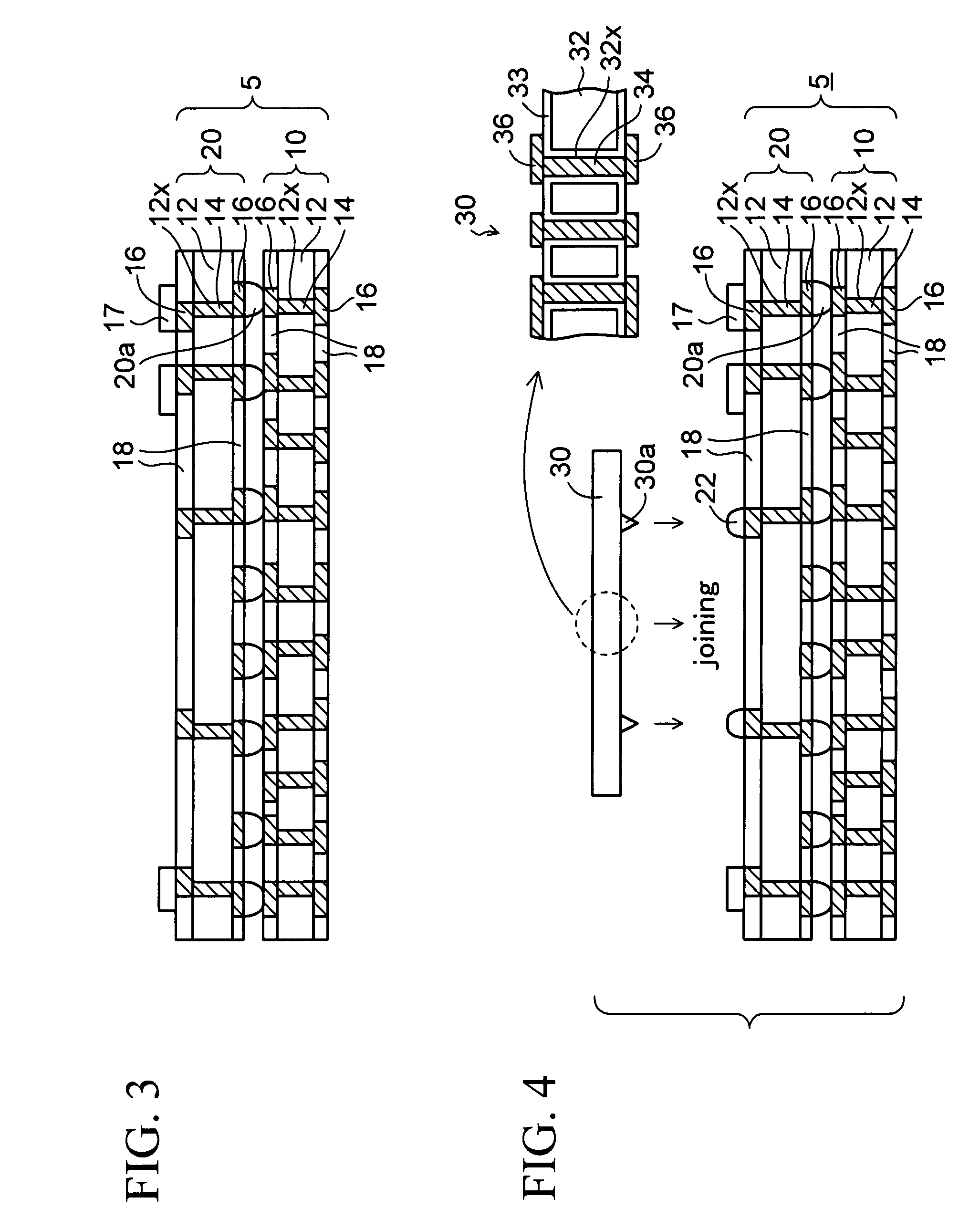

In a wiring substrate according to the present invention, a base wiring board is constructed by stacking a plurality of unit wiring boards each having wiring patterns which enable an electrical connection between upper and lower sides, in a state that the plurality of unit wiring boards are connected to each other via a connection terminal, and a silicon interposer is stacked on the base wiring board via a connection terminal, and a resin portion is filled in a gap between the plurality of unit wiring boards as well as a gap between the base wiring board and the silicon interposer, and a resin portion serves as a substrate which integrates the base wiring board and the silicon interposer.

Owner:SHINKO ELECTRIC IND CO LTD

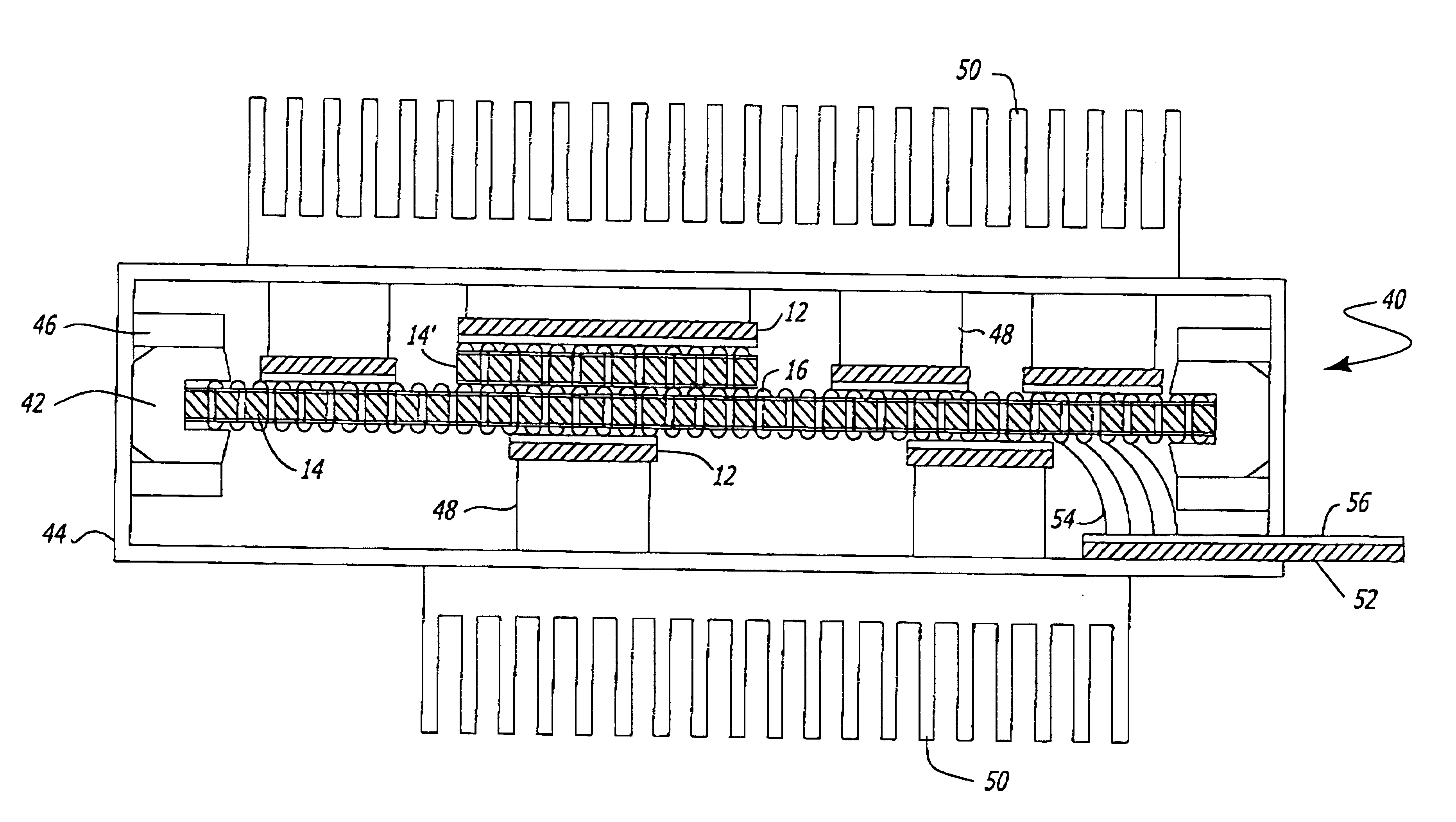

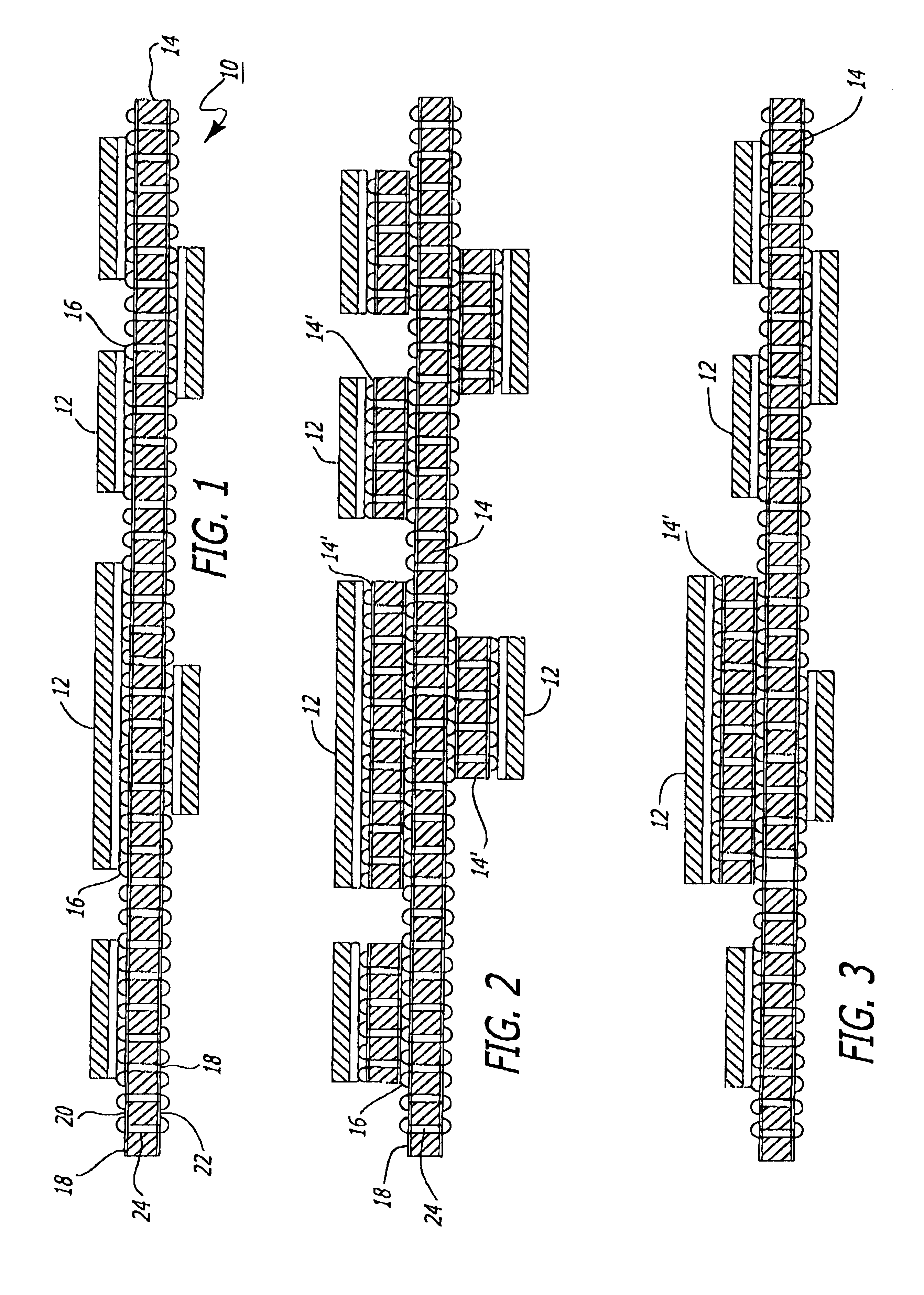

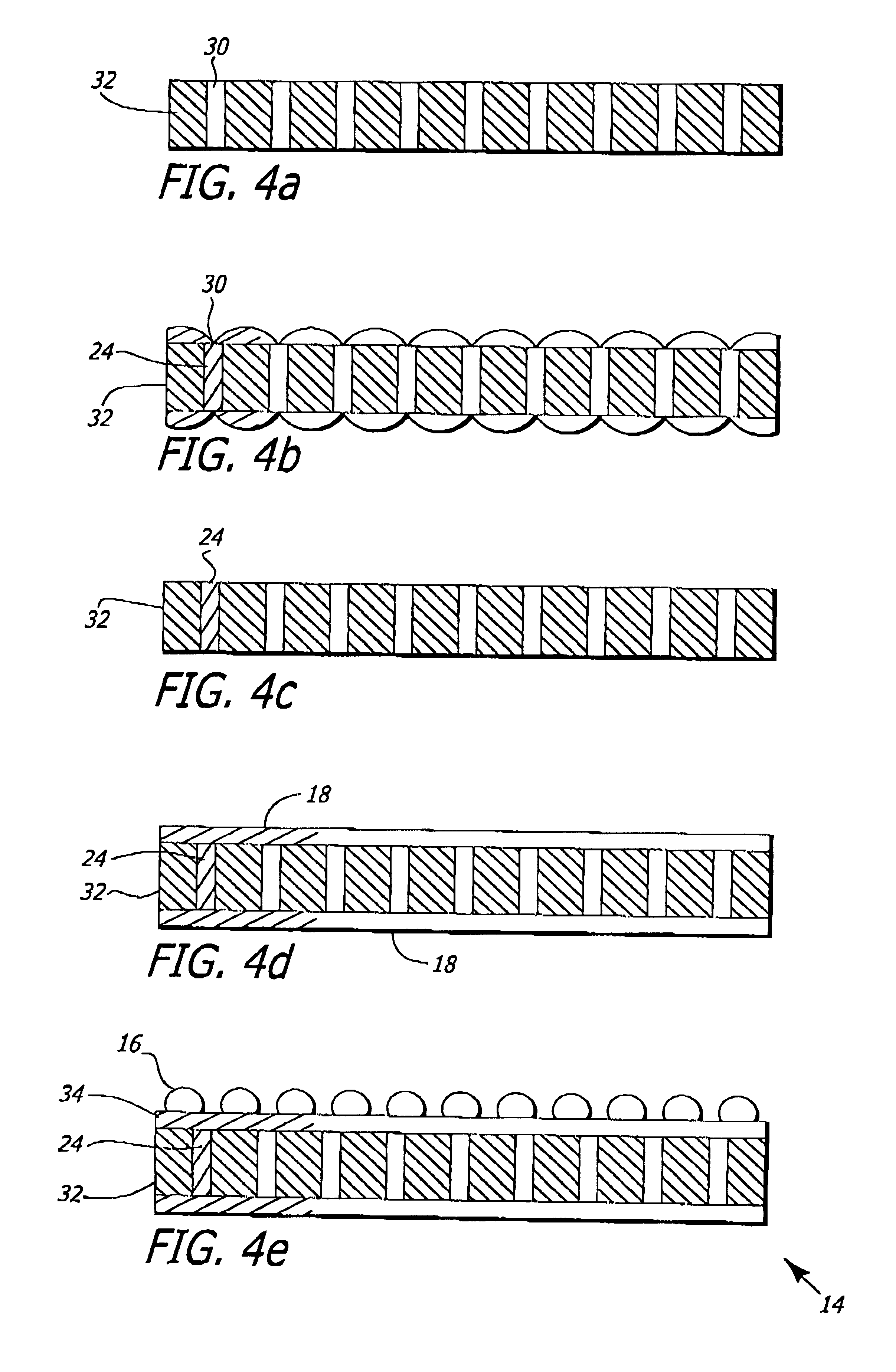

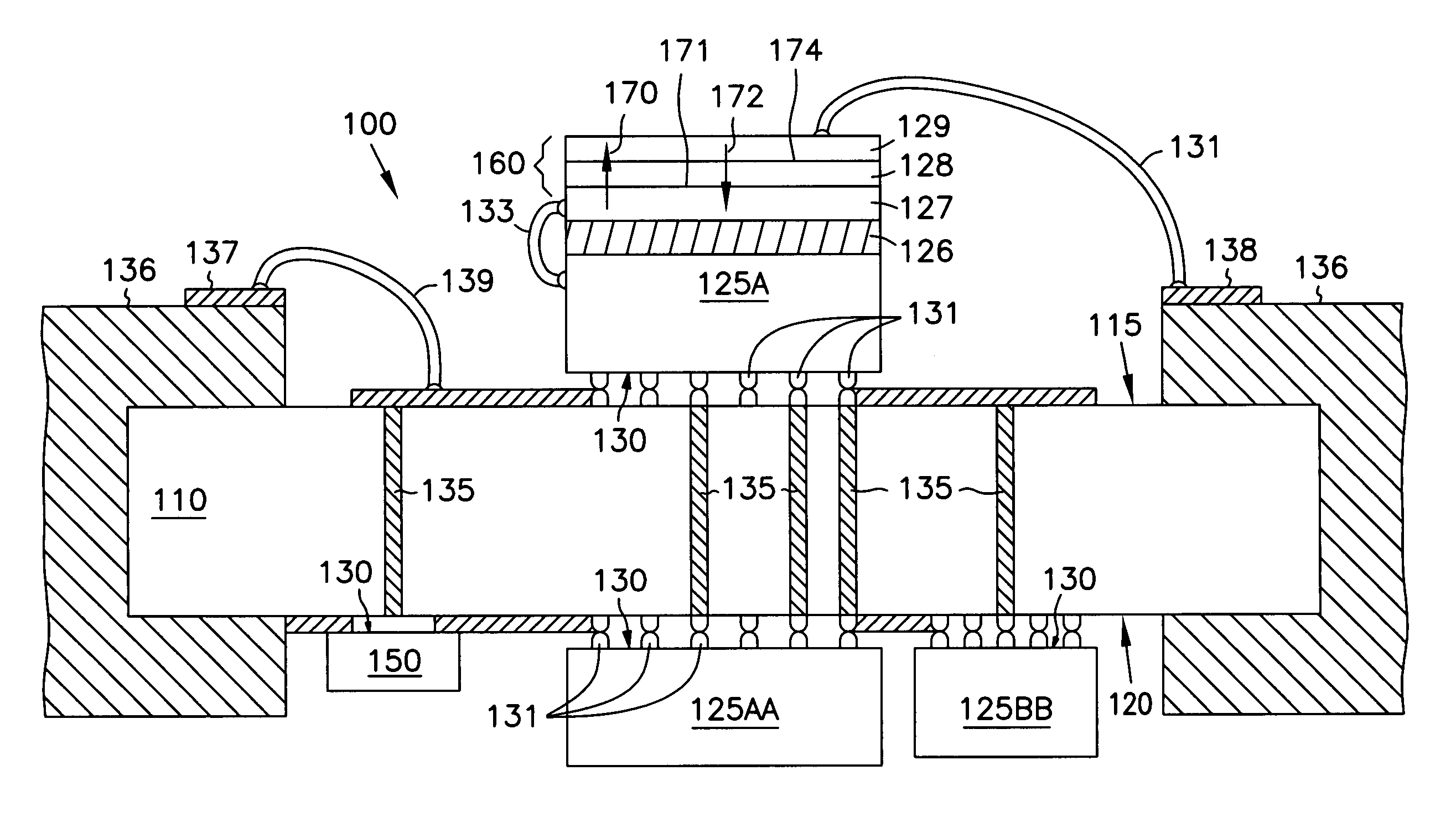

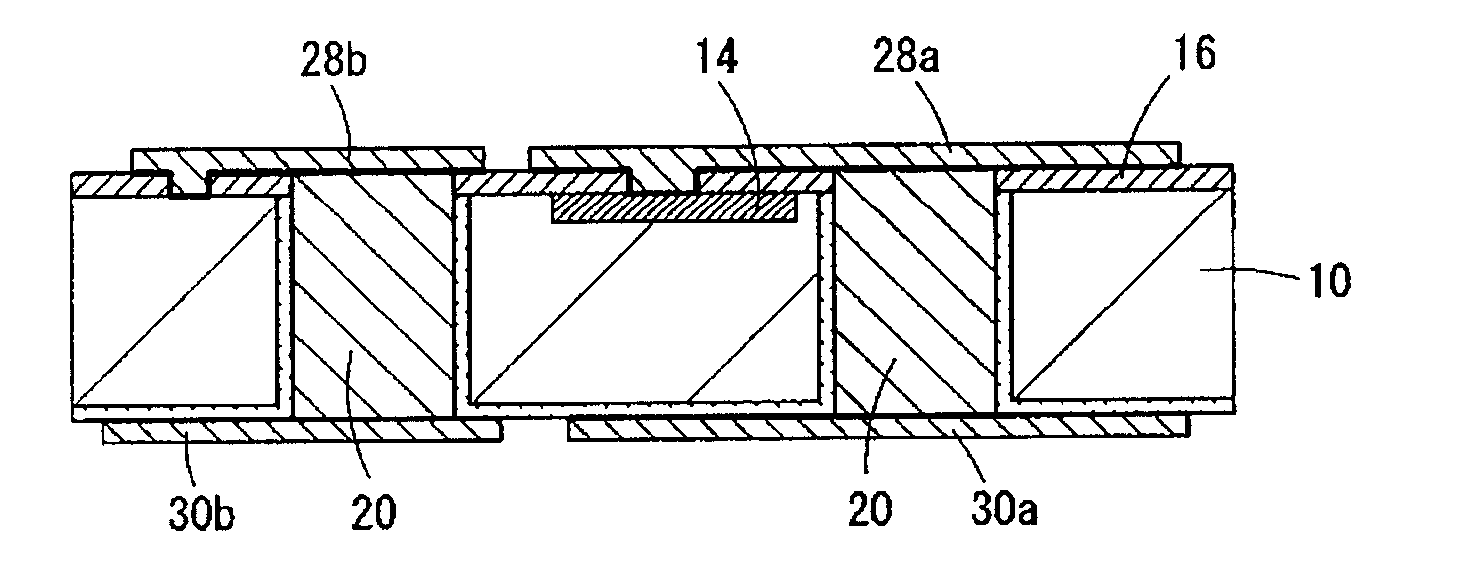

Compact system module with built-in thermoelectric cooling

InactiveUS20060128059A1Improve cooling effectComponent with highSemiconductor/solid-state device detailsSolid-state devicesCMOSMemory chip

An improved integrated circuit package for providing built-in heating or cooling to a semiconductor chip is provided. The improved integrated circuit package provides increased operational bandwidth between different circuit devices, e.g. logic and memory chips. The improved integrated circuit package does not require changes in current CMOS processing techniques. The structure includes the use of a silicon interposer. The silicon interposer can consist of recycled rejected wafers from the front-end semiconductor processing. Micro-machined vias are formed through the silicon interposer. The micro-machined vias include electrical contacts which couple various integrated circuit devices located on the opposing surfaces of the silicon interposer. The packaging includes a Peltier element.

Owner:MICRON TECH INC

Three-dimensional silicon interposer for low voltage low power systems

ActiveUS8344512B2Semiconductor/solid-state device detailsSolid-state devicesSilicon interposerLow voltage

Scalable silicon (Si) interposer configurations that support low voltage, low power operations are provided. In one aspect, a Si interposer is provided which includes a plurality of through-silicon vias (TSVs) within a first plane thereof adapted to serve as power, ground and signal interconnections throughout the first plane such that the TSVs that serve as the power and ground interconnections are greater in number and / or size than the TSVs that serve as the signal interconnections; and a plurality of lines within a second plane of the interposer in contact with one or more of the TSVs in the first plane, the second plane being adjacent to the first plane, adapted to serve as power, ground and signal interconnections throughout the second plane such that the lines that serve as the power and the ground interconnections are greater in number and / or size than the lines that serve as the signal interconnections.

Owner:INT BUSINESS MASCH CORP

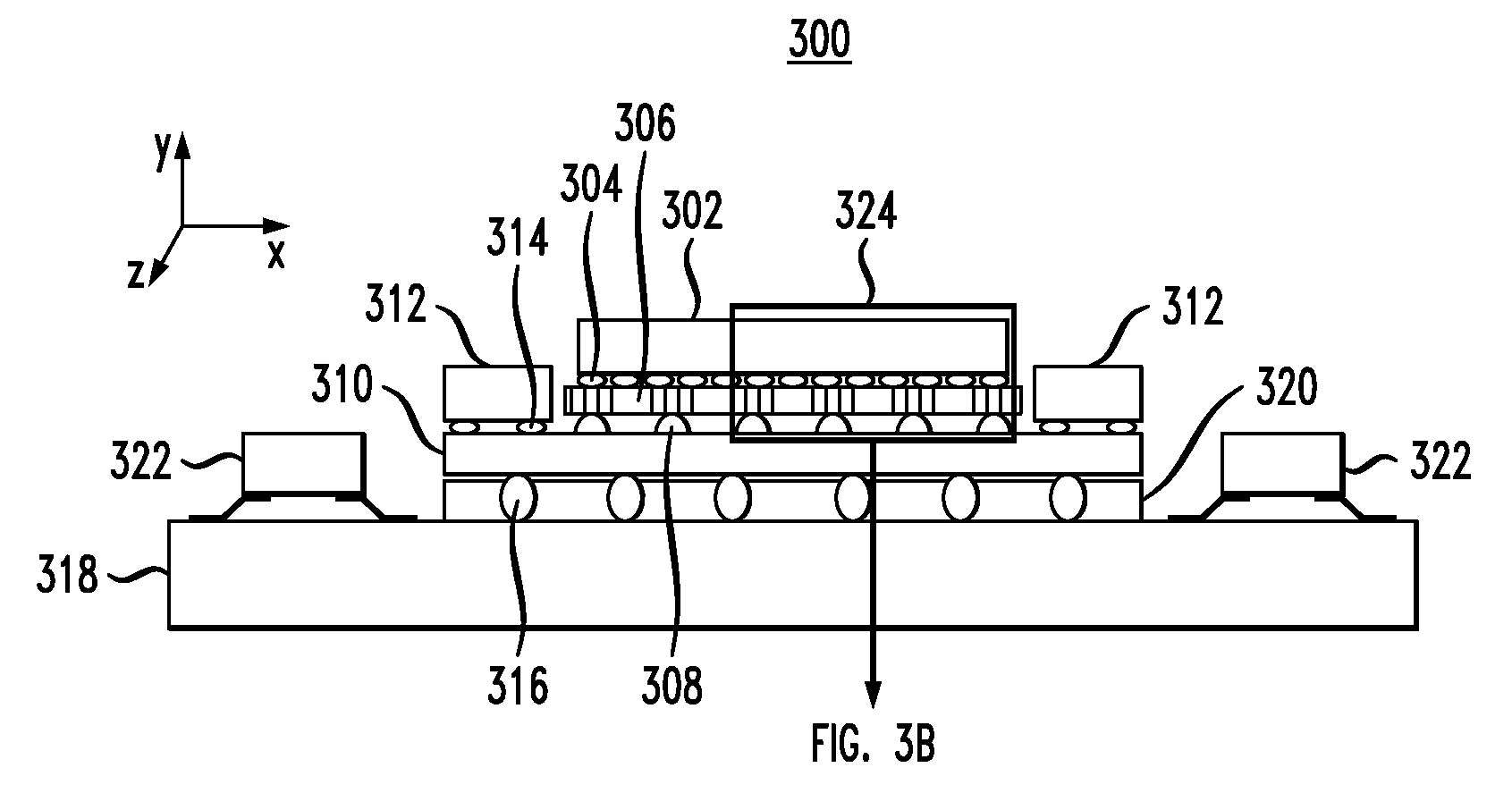

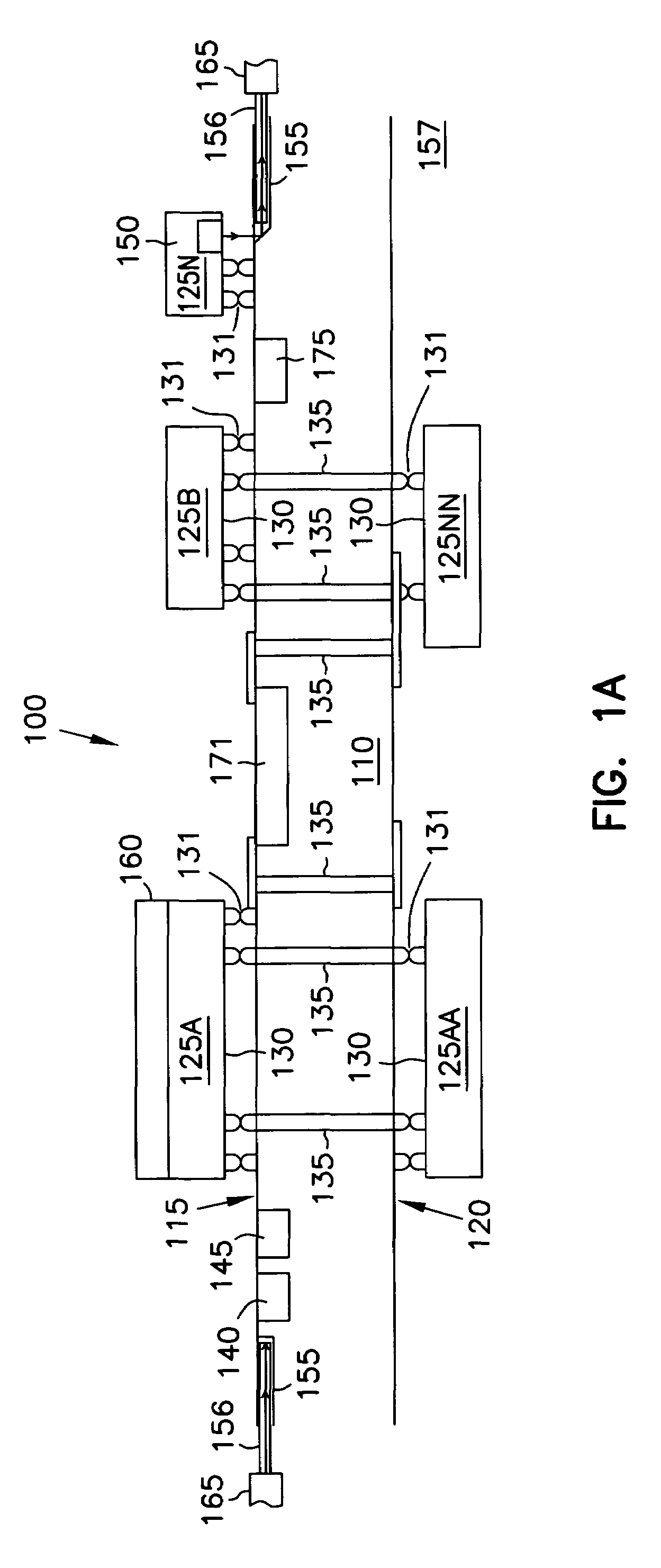

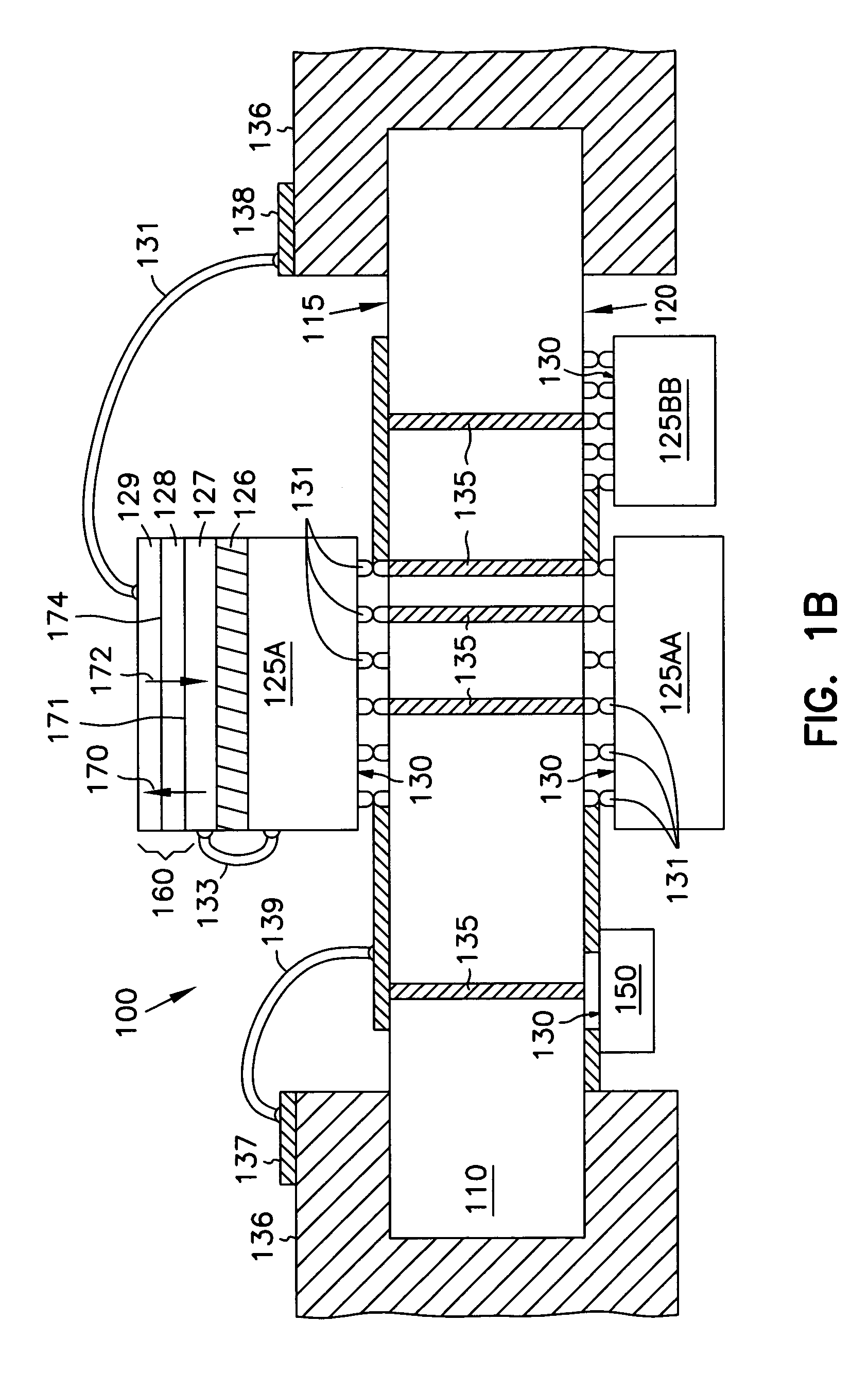

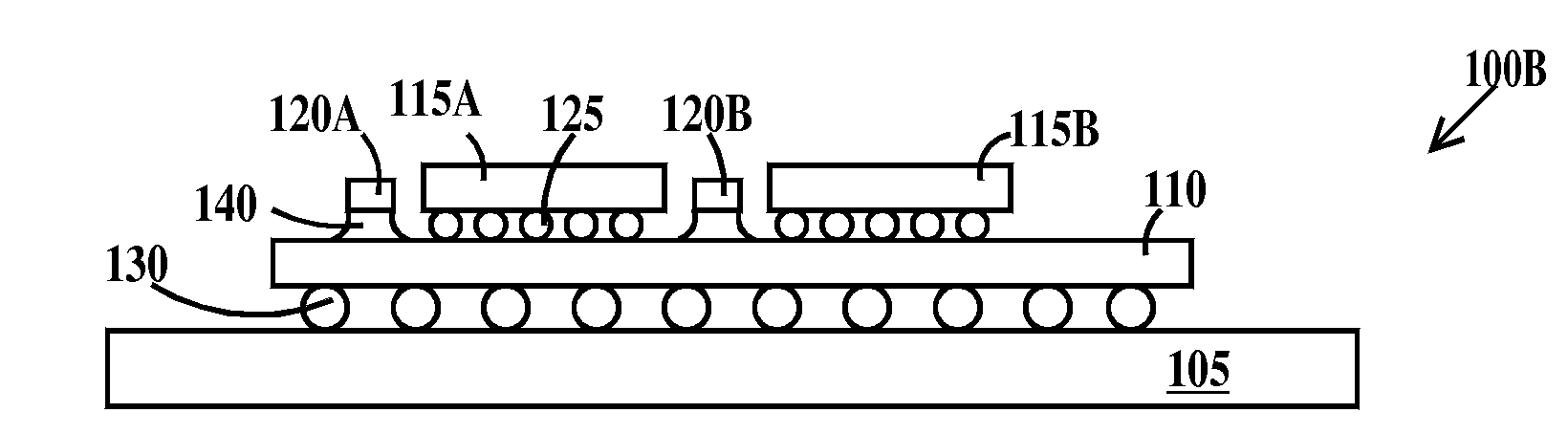

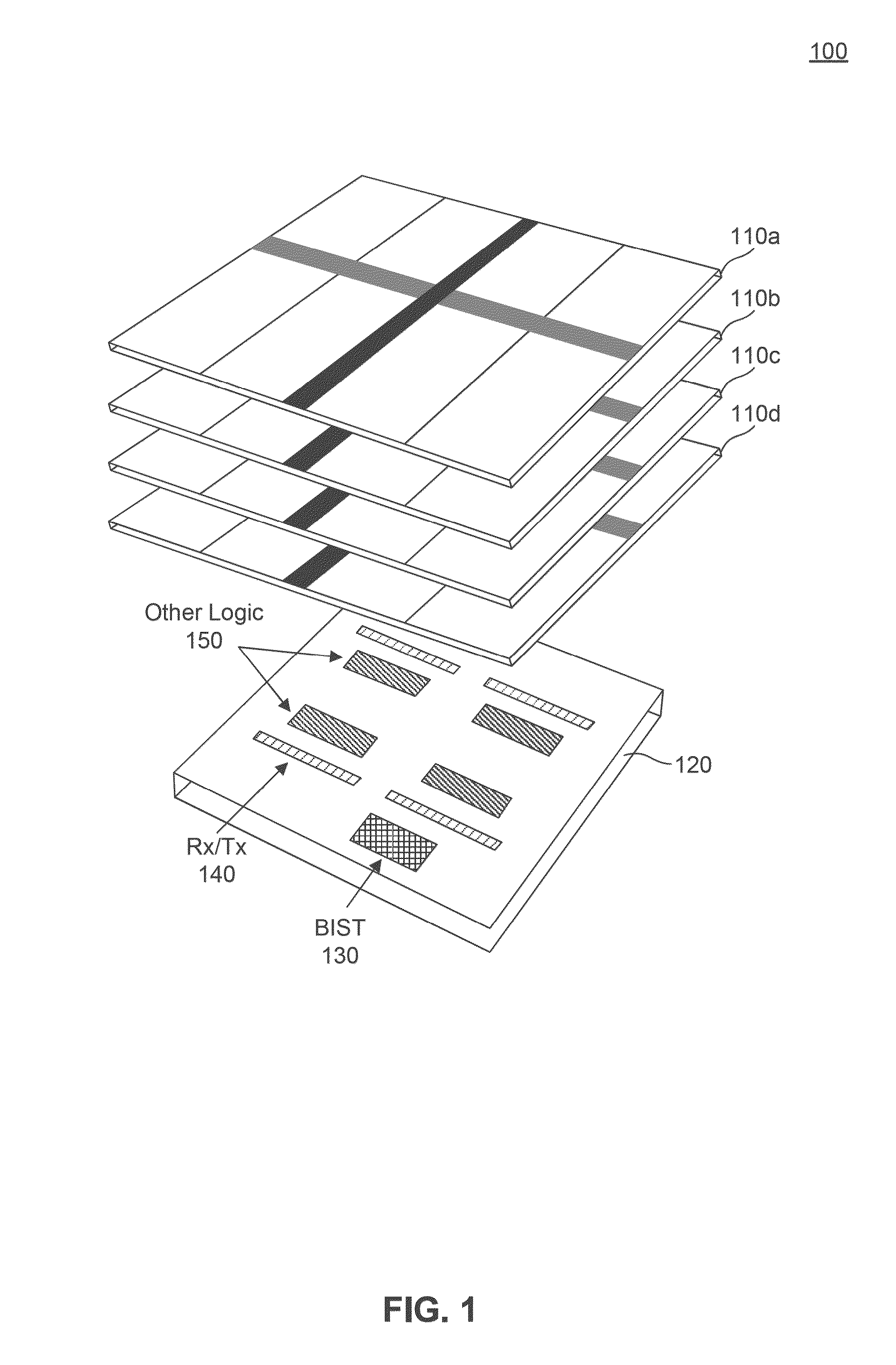

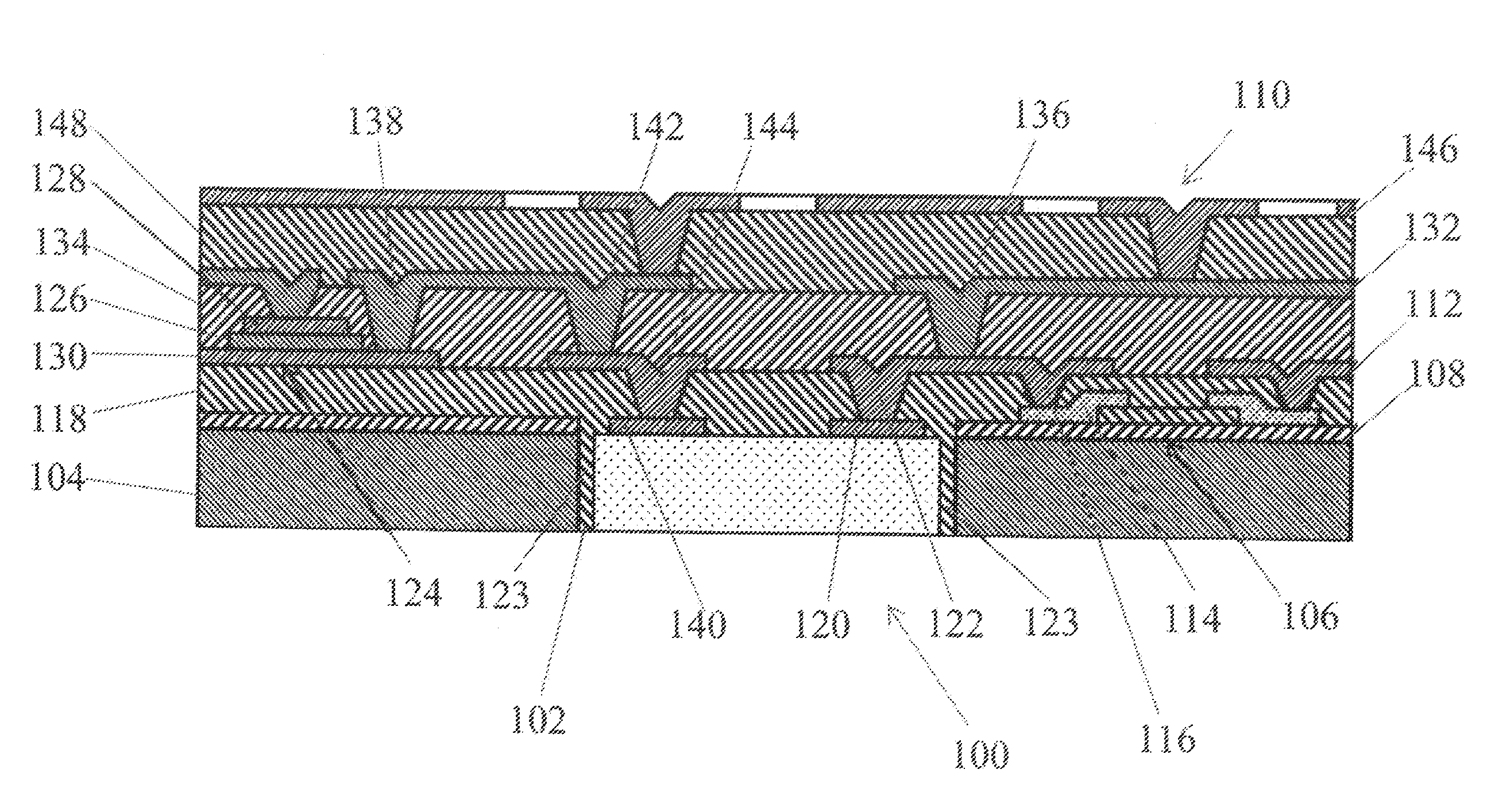

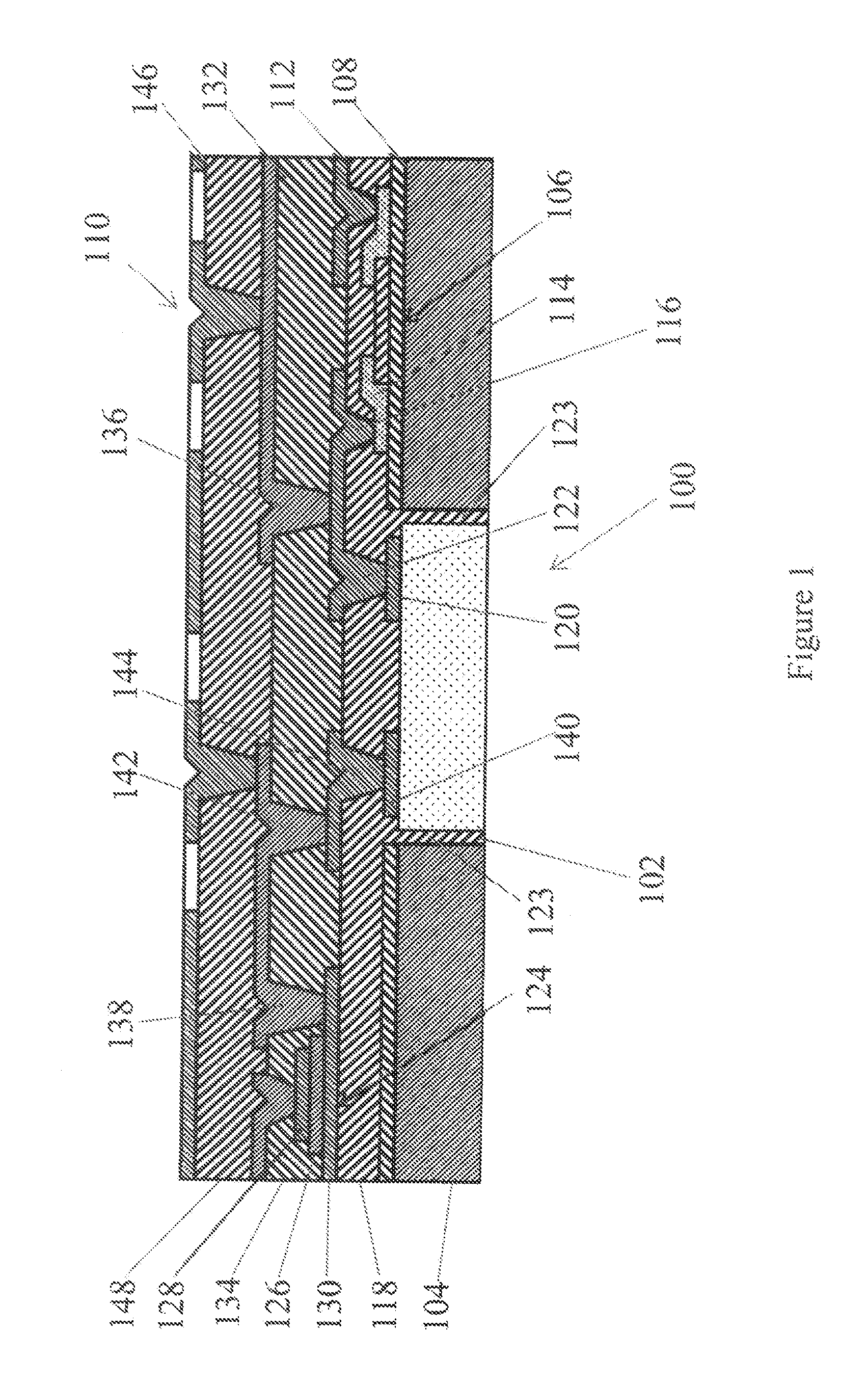

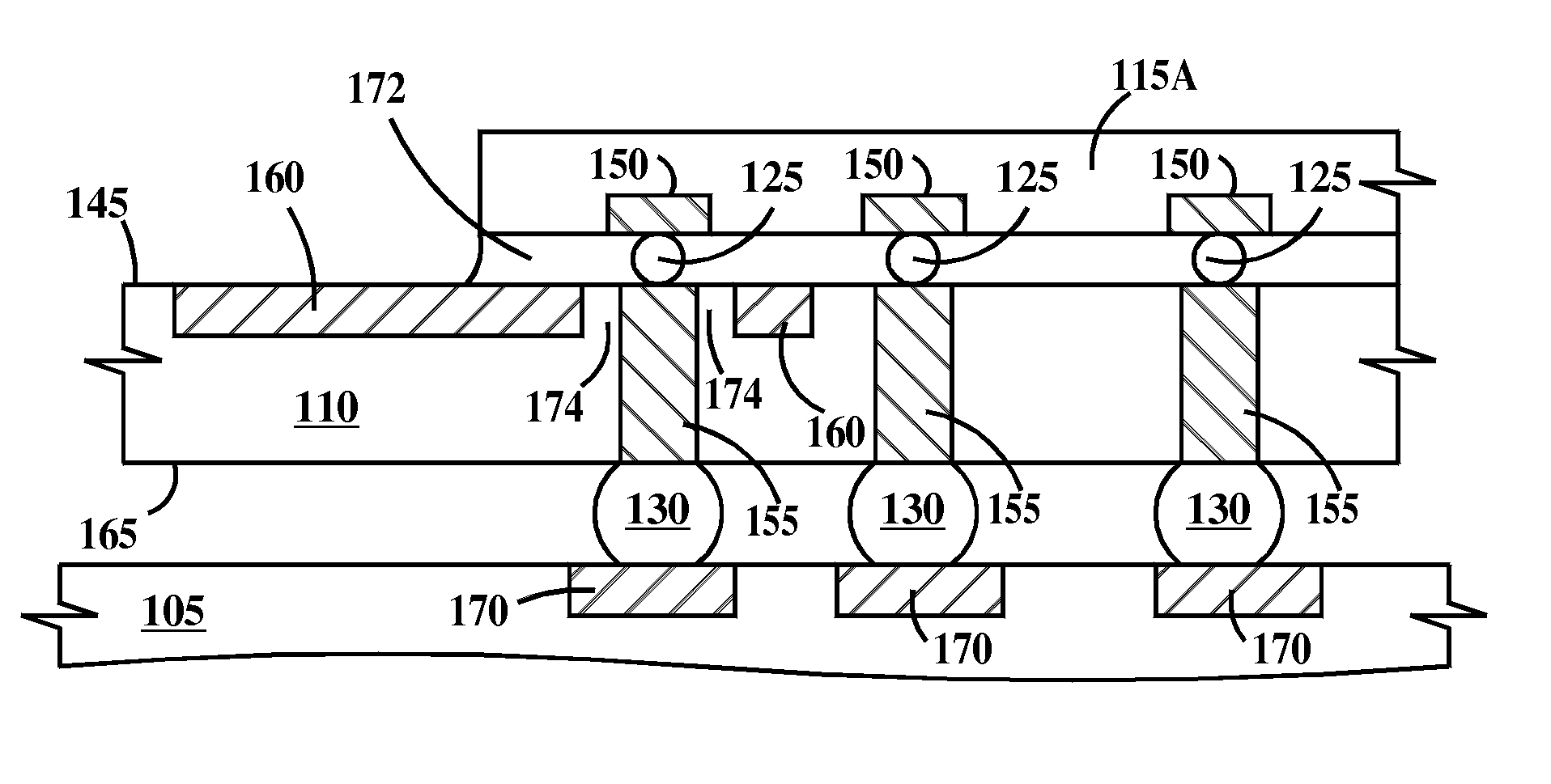

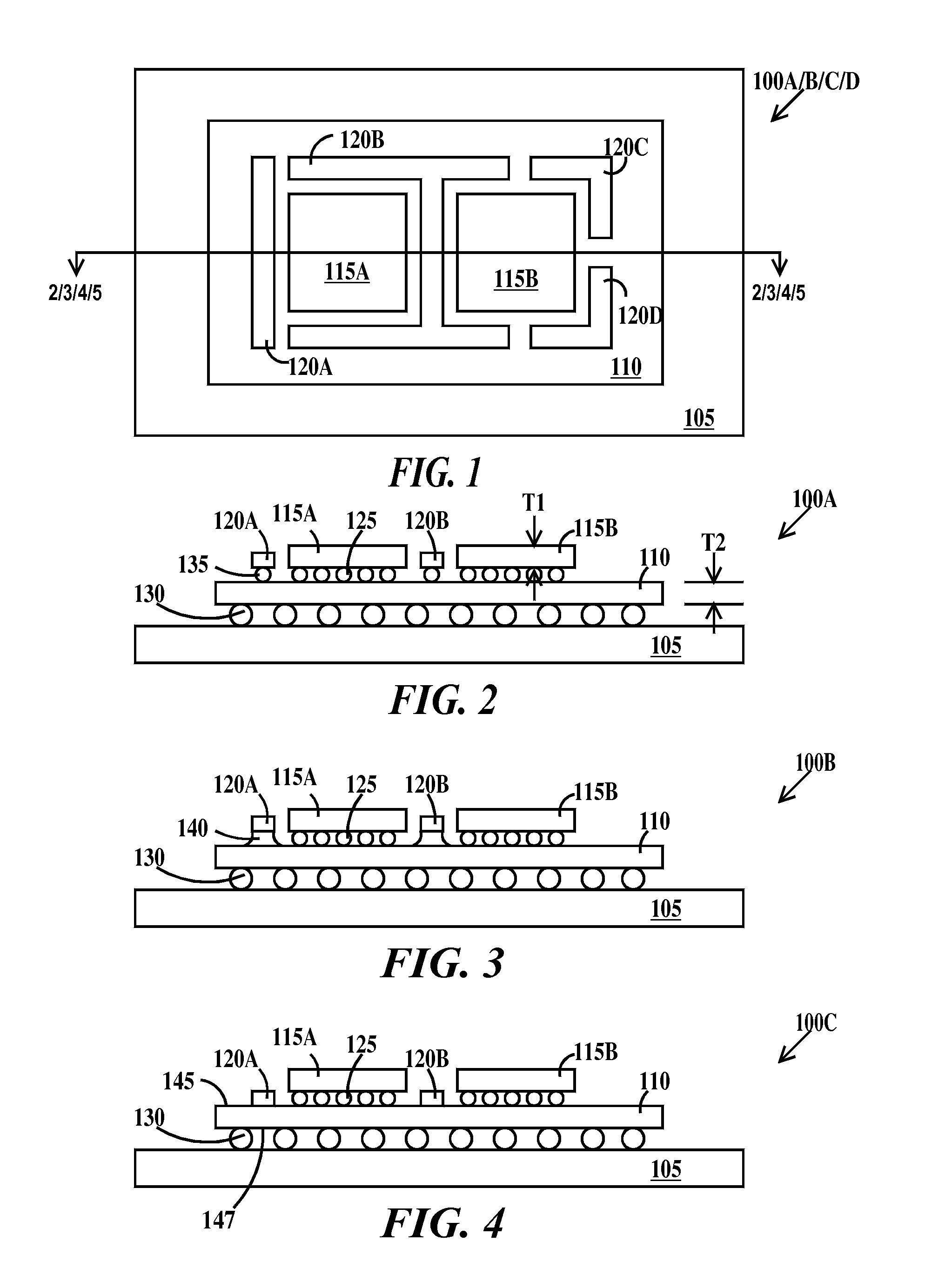

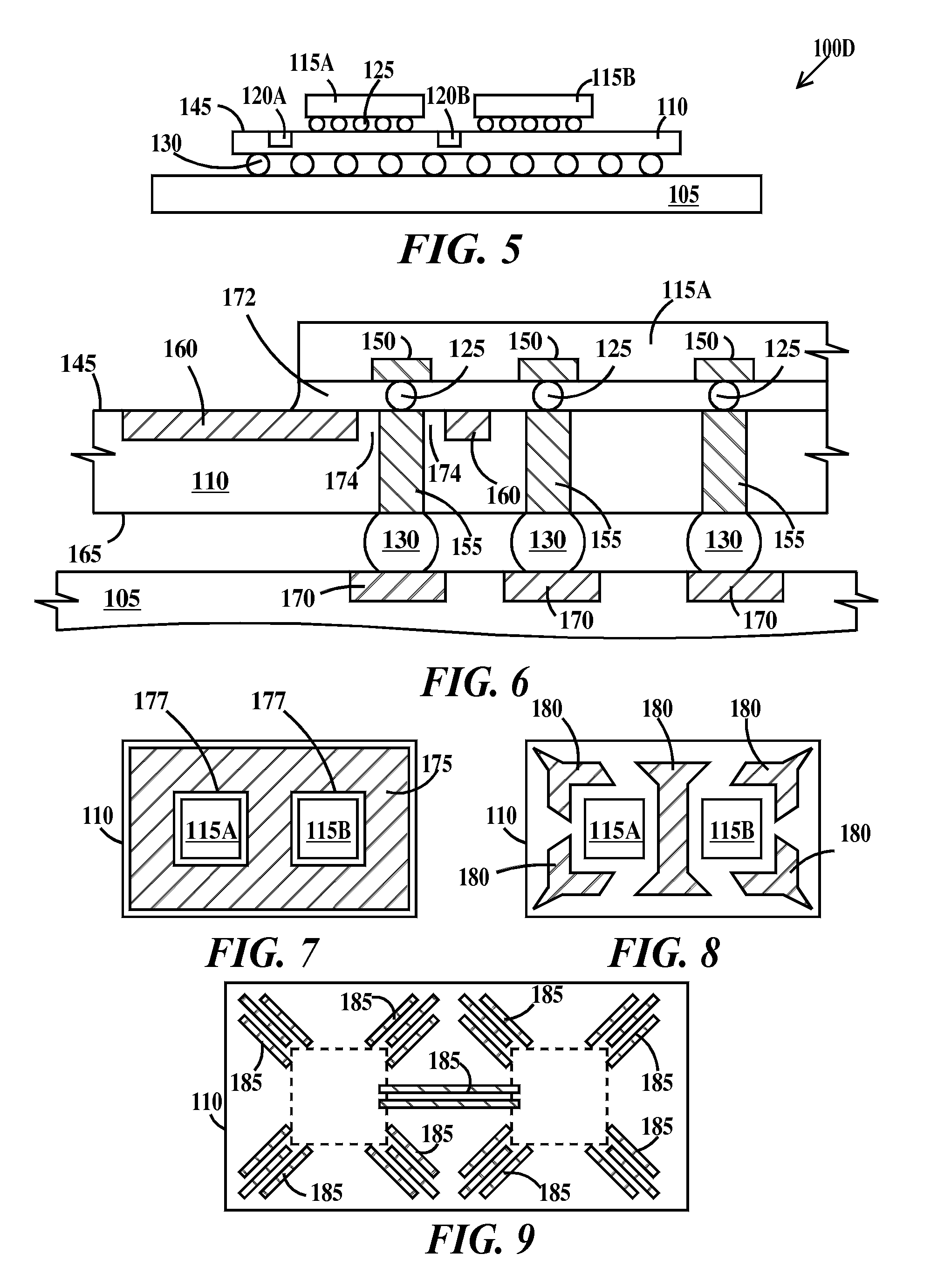

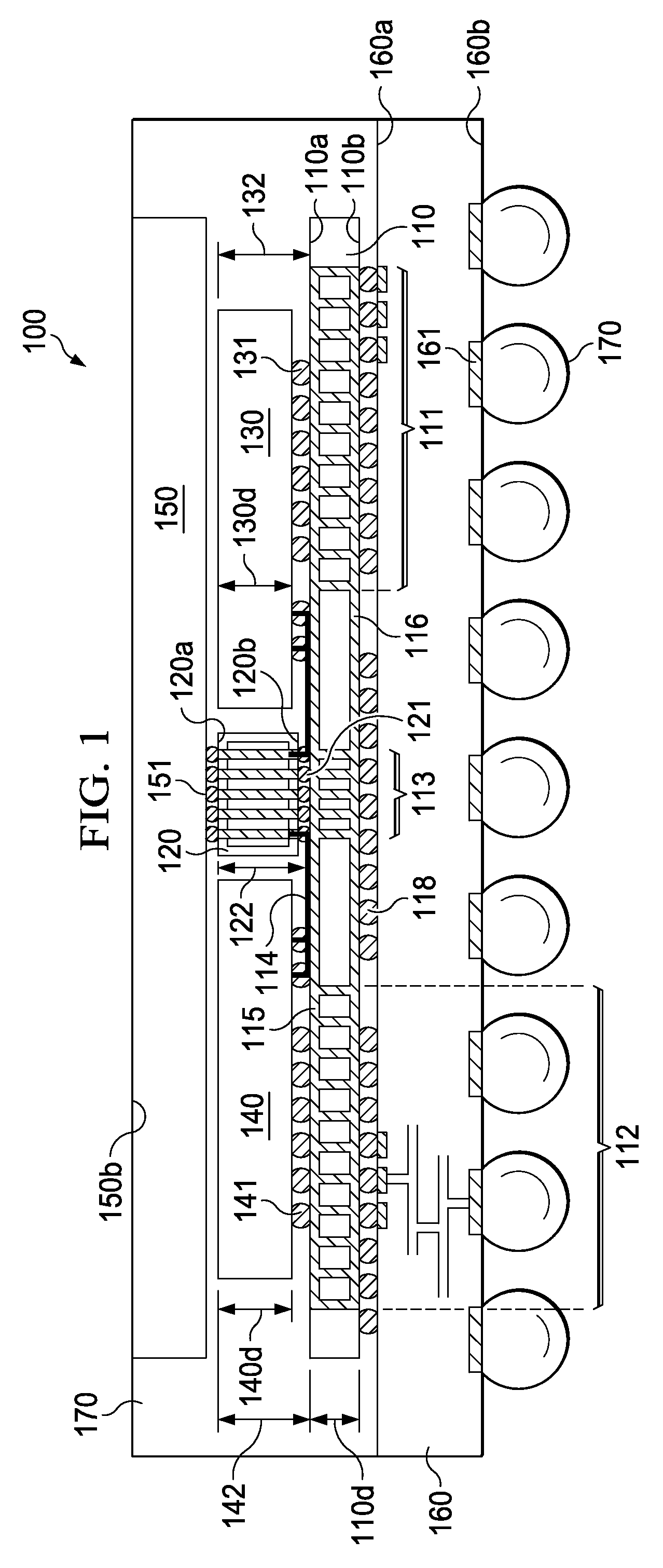

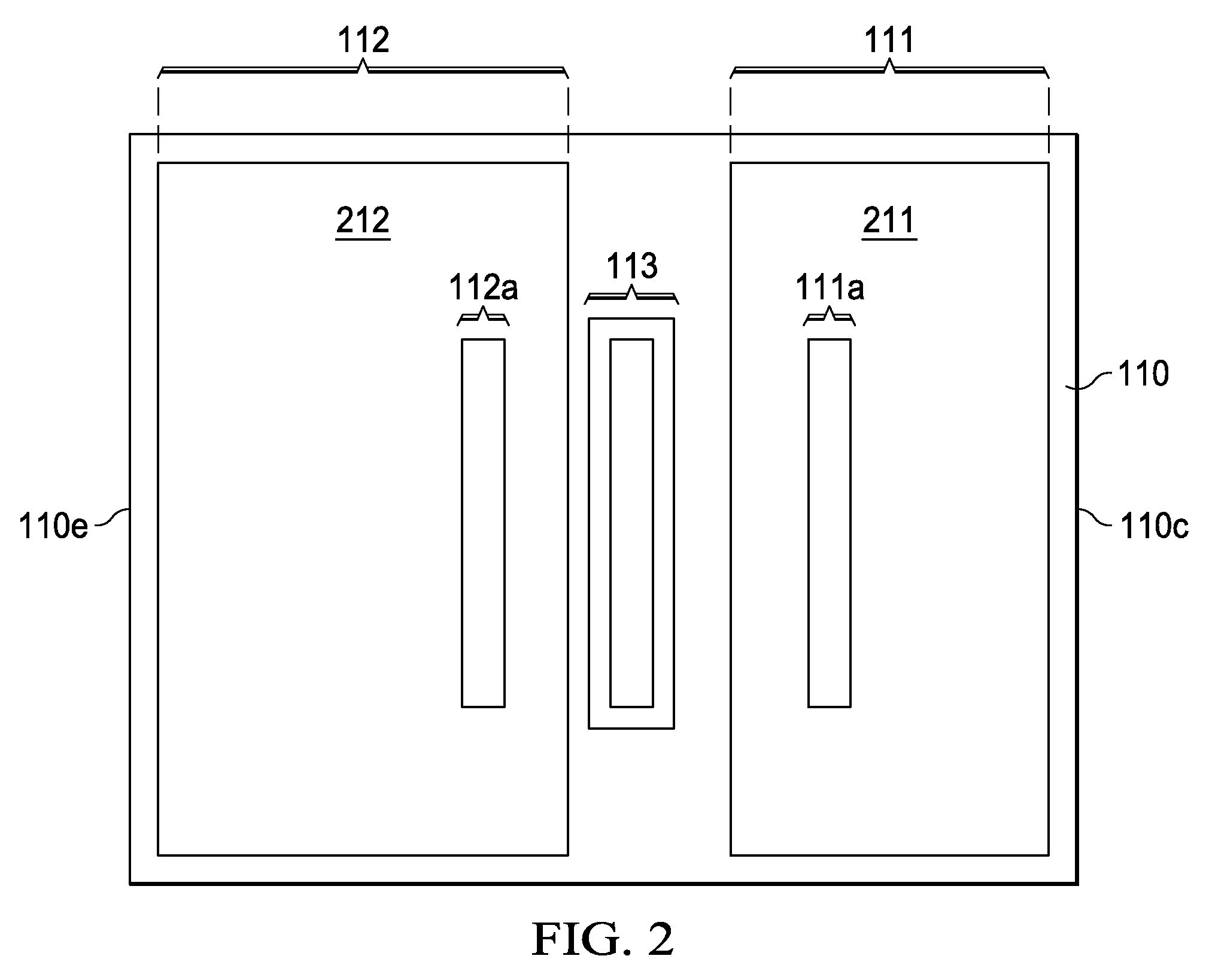

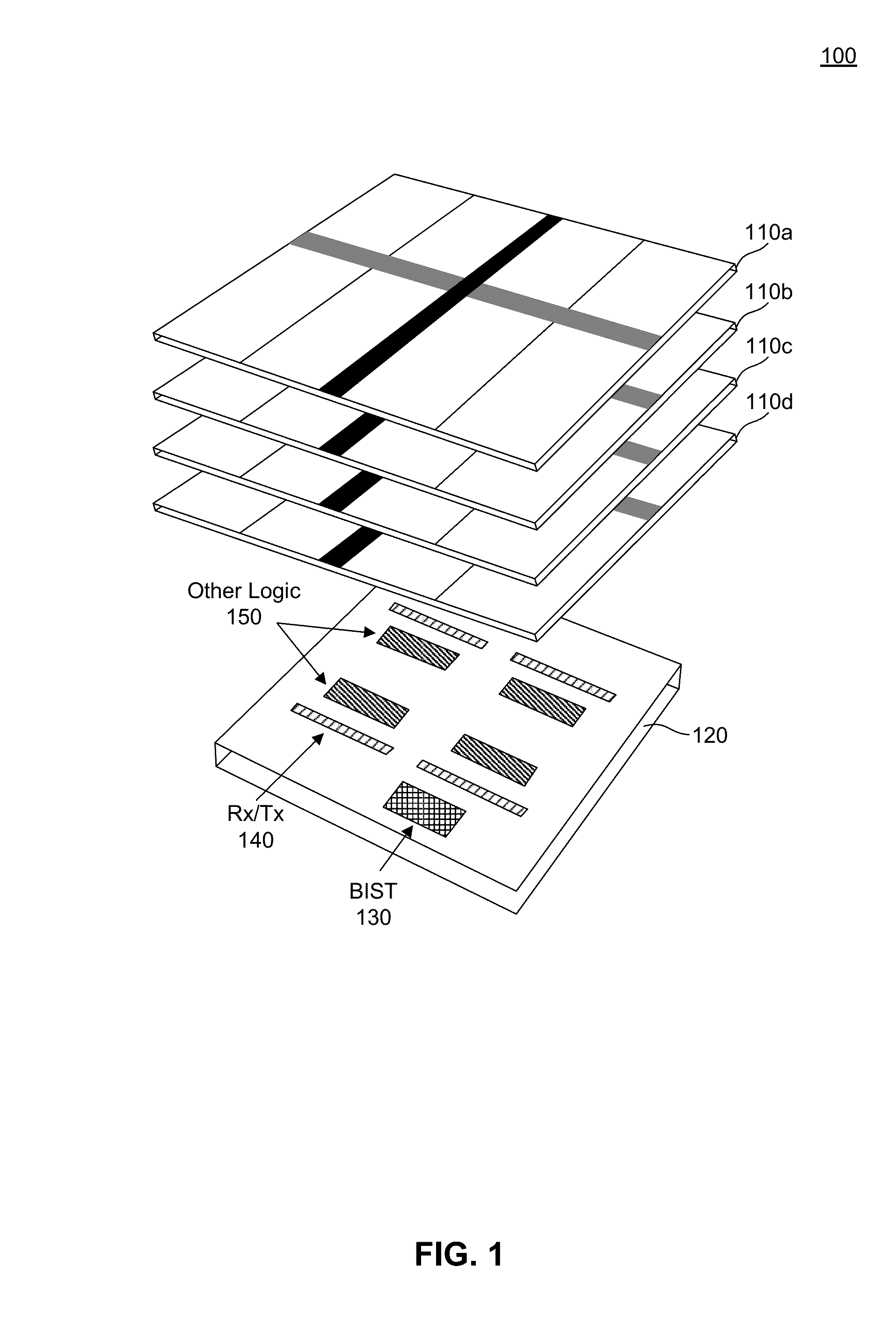

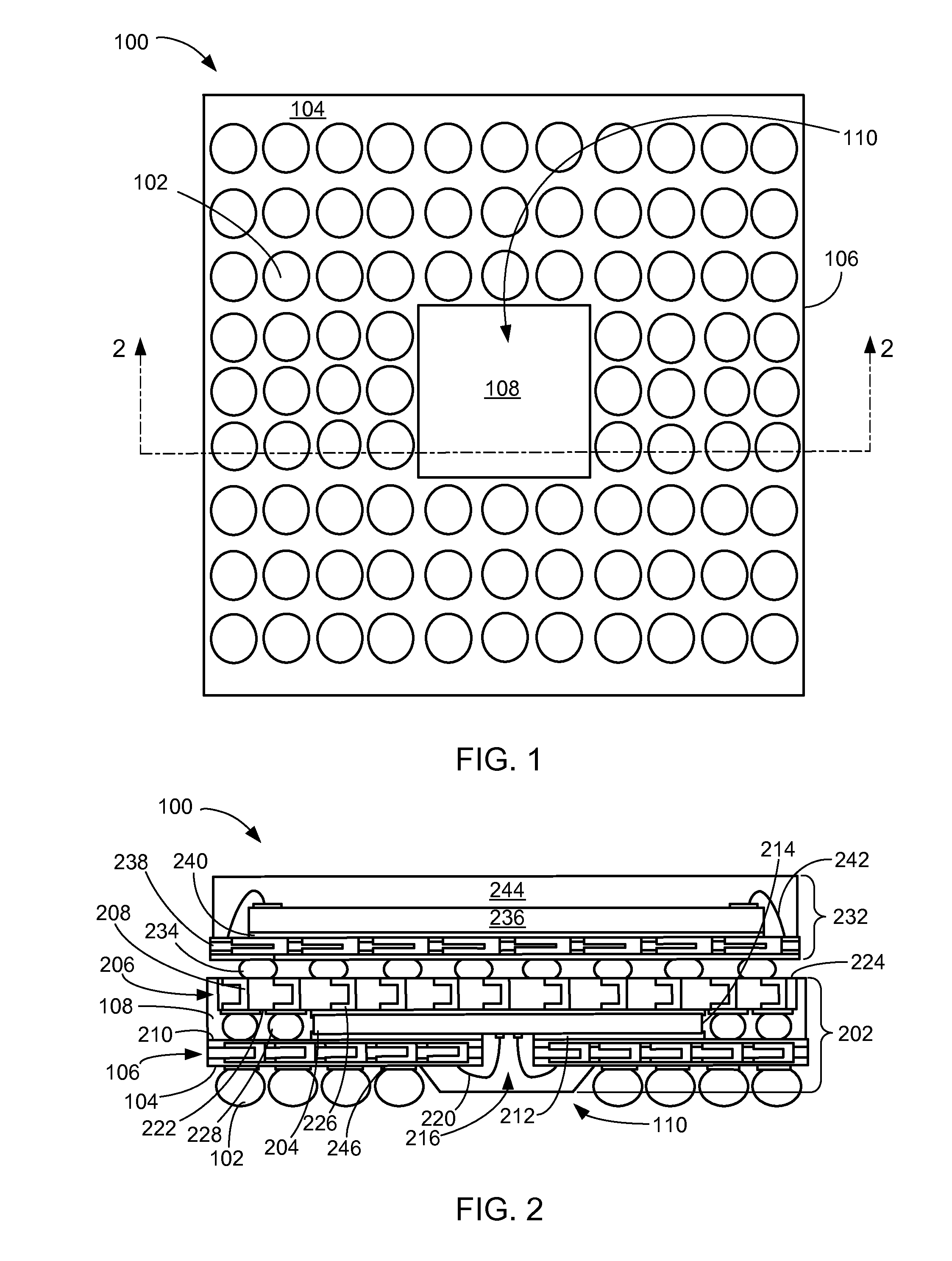

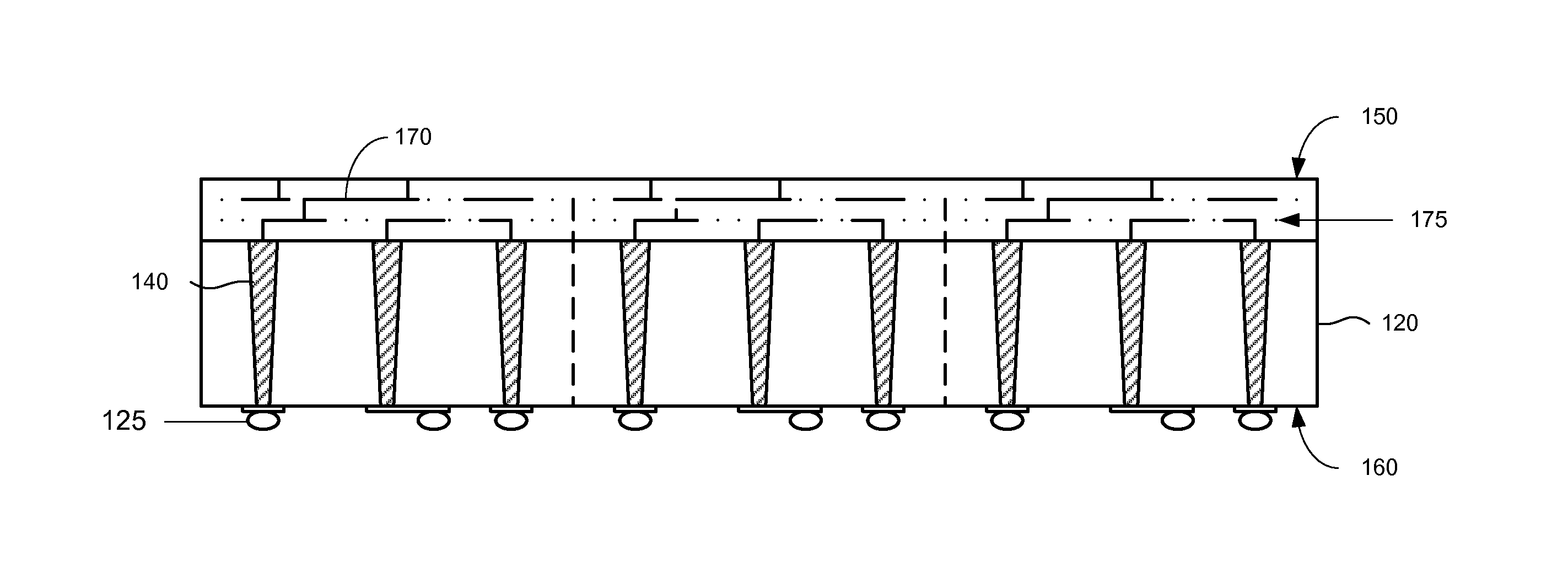

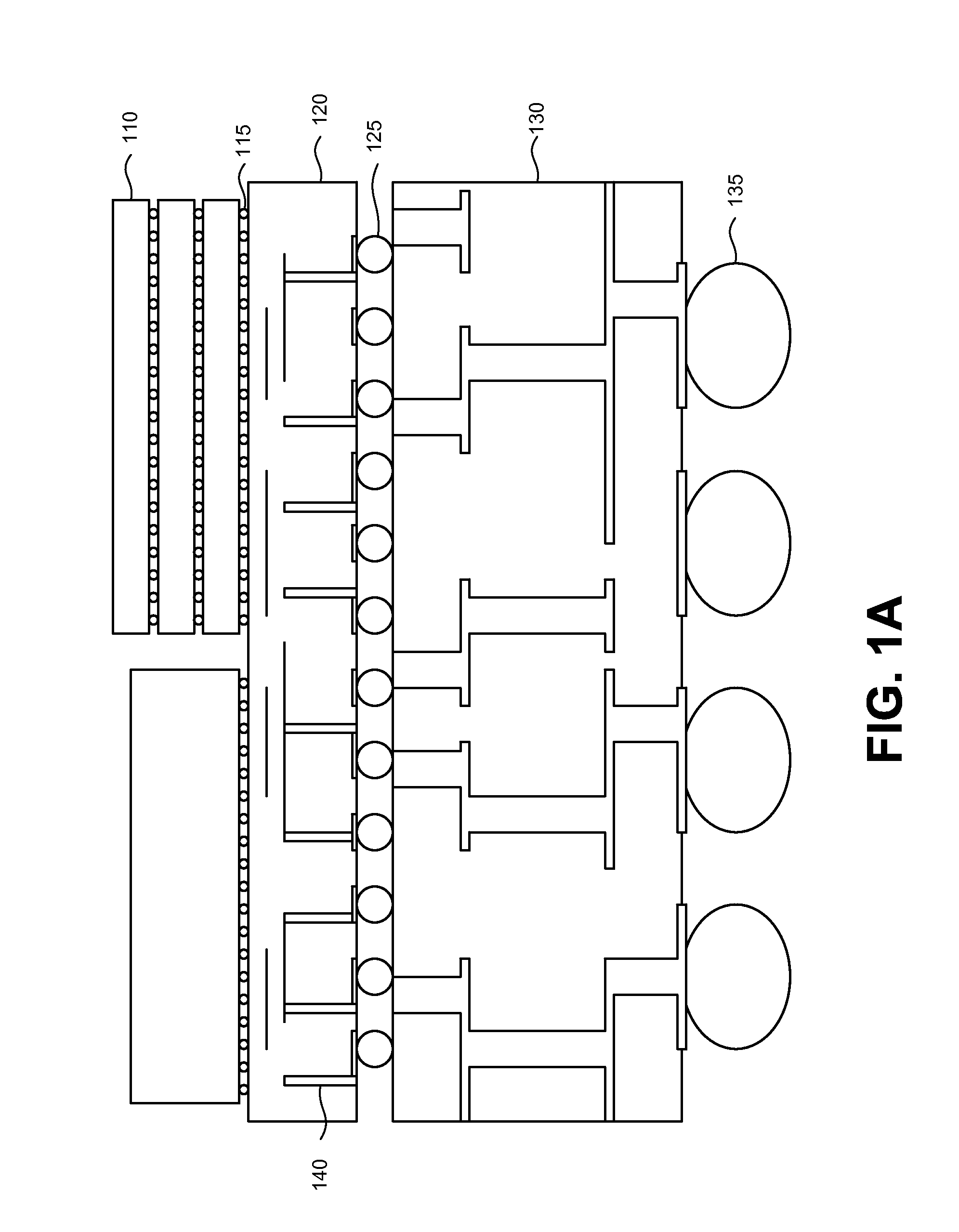

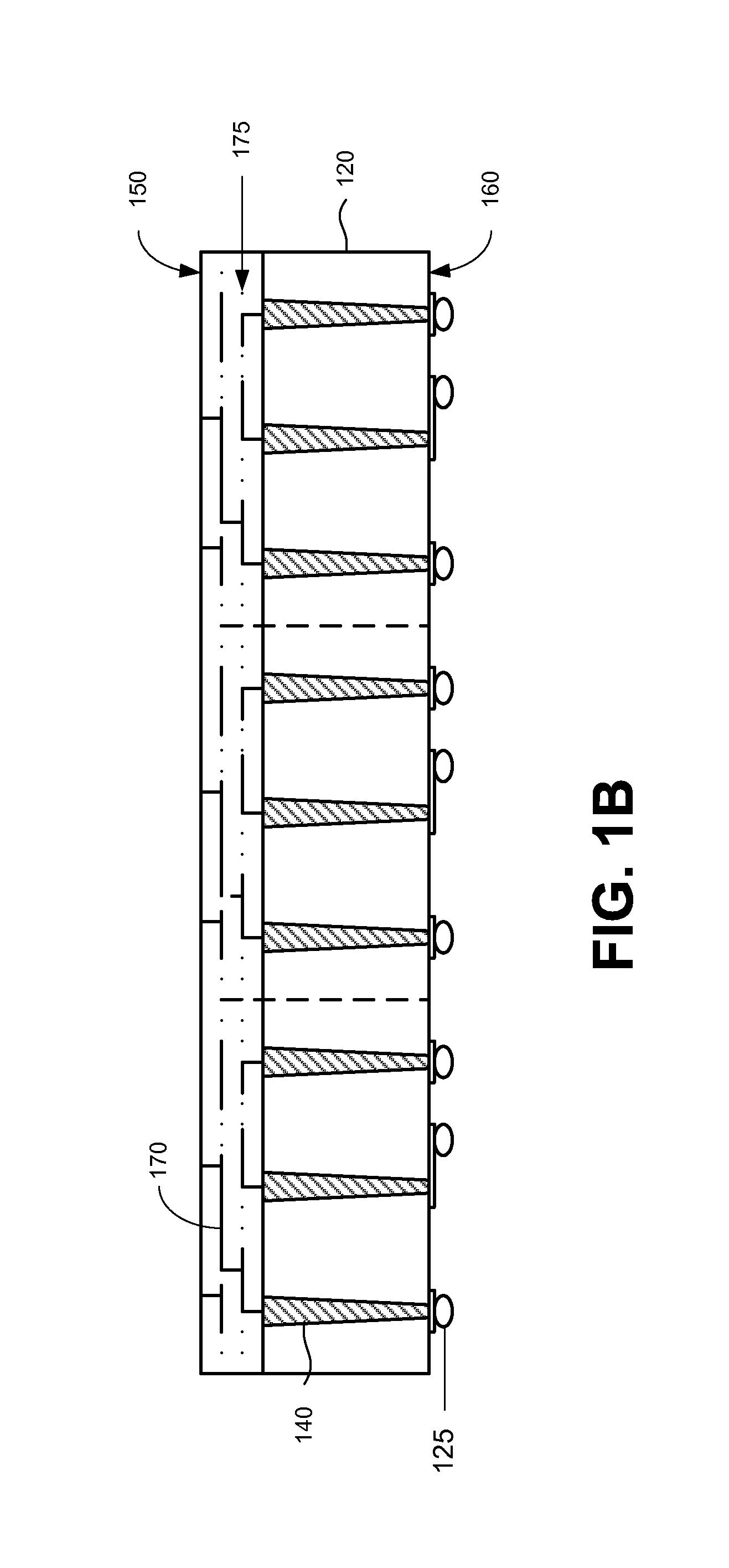

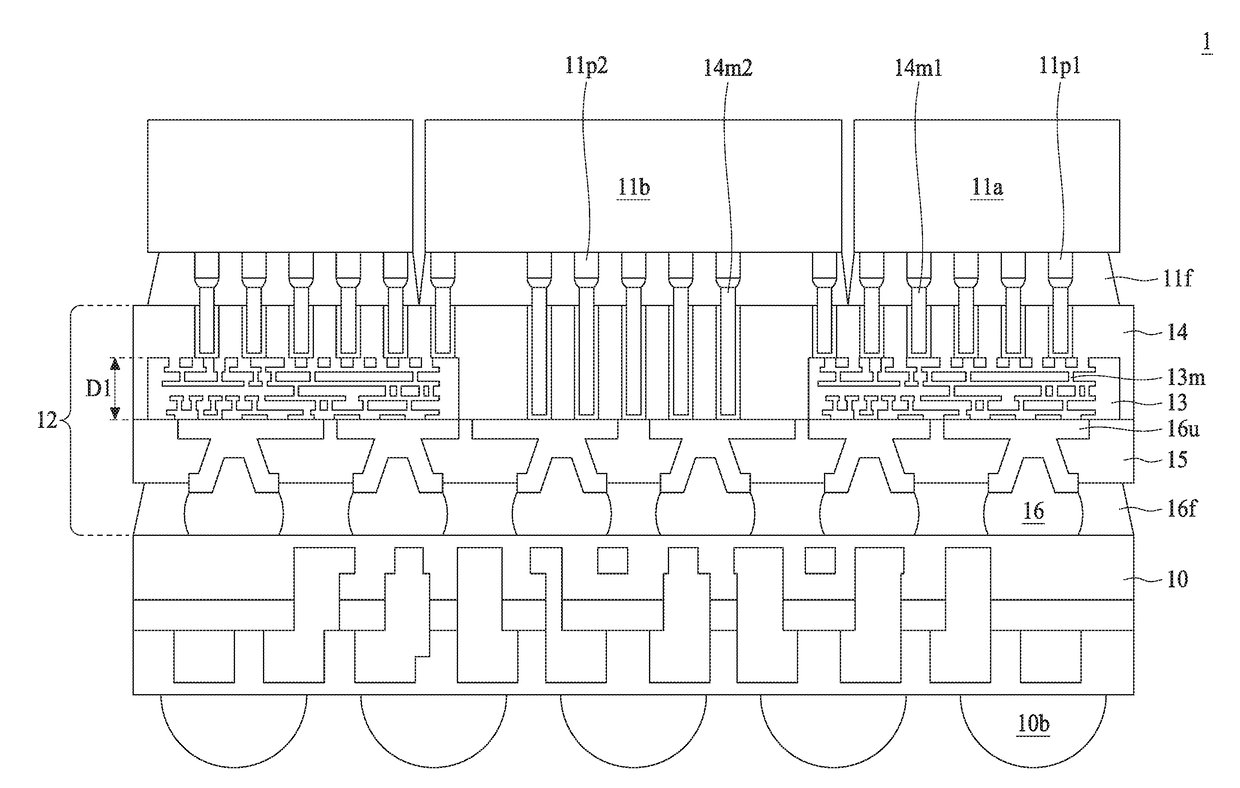

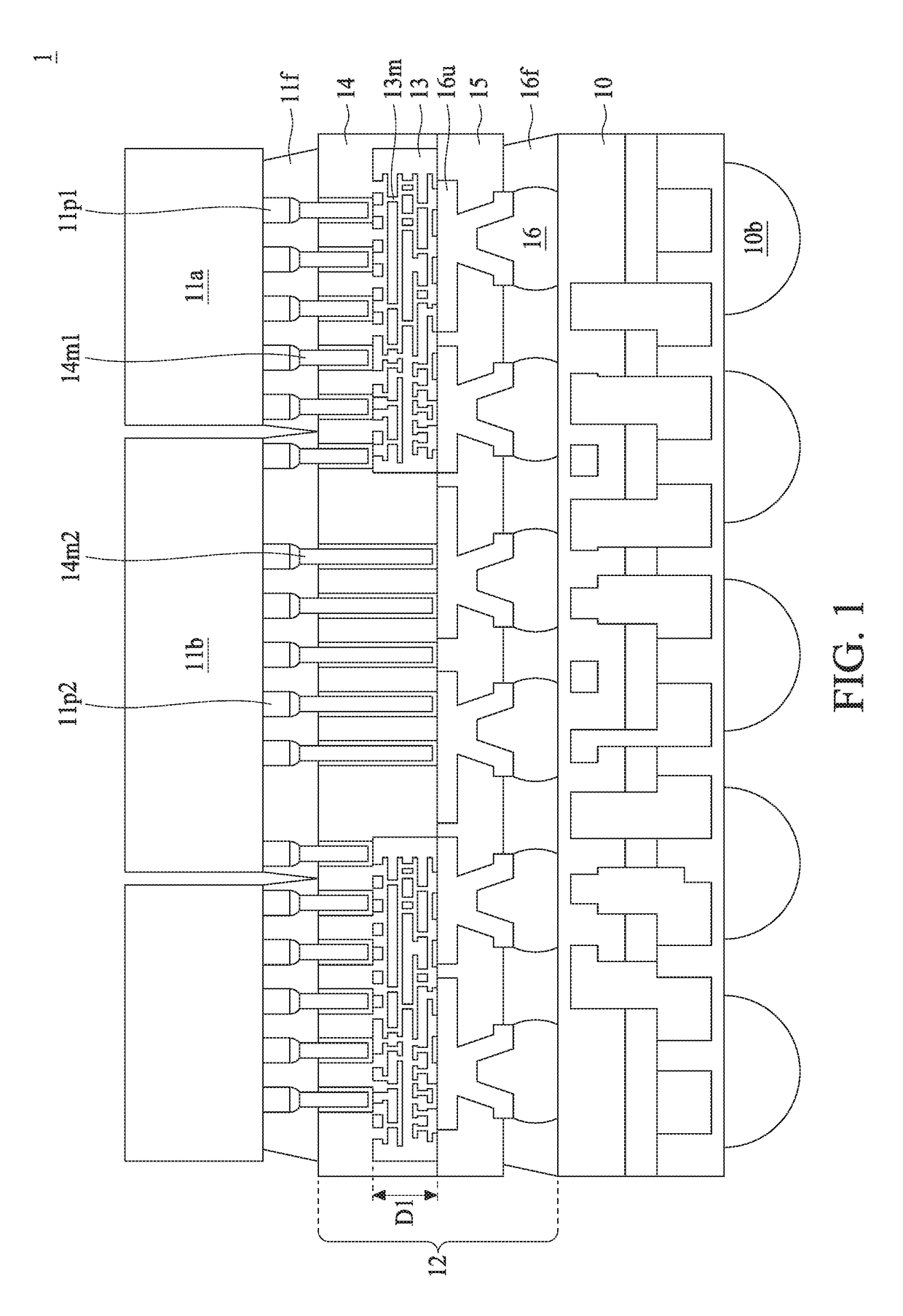

3D Semiconductor Interposer for Heterogeneous Integration of Standard Memory and Split-Architecture Processor

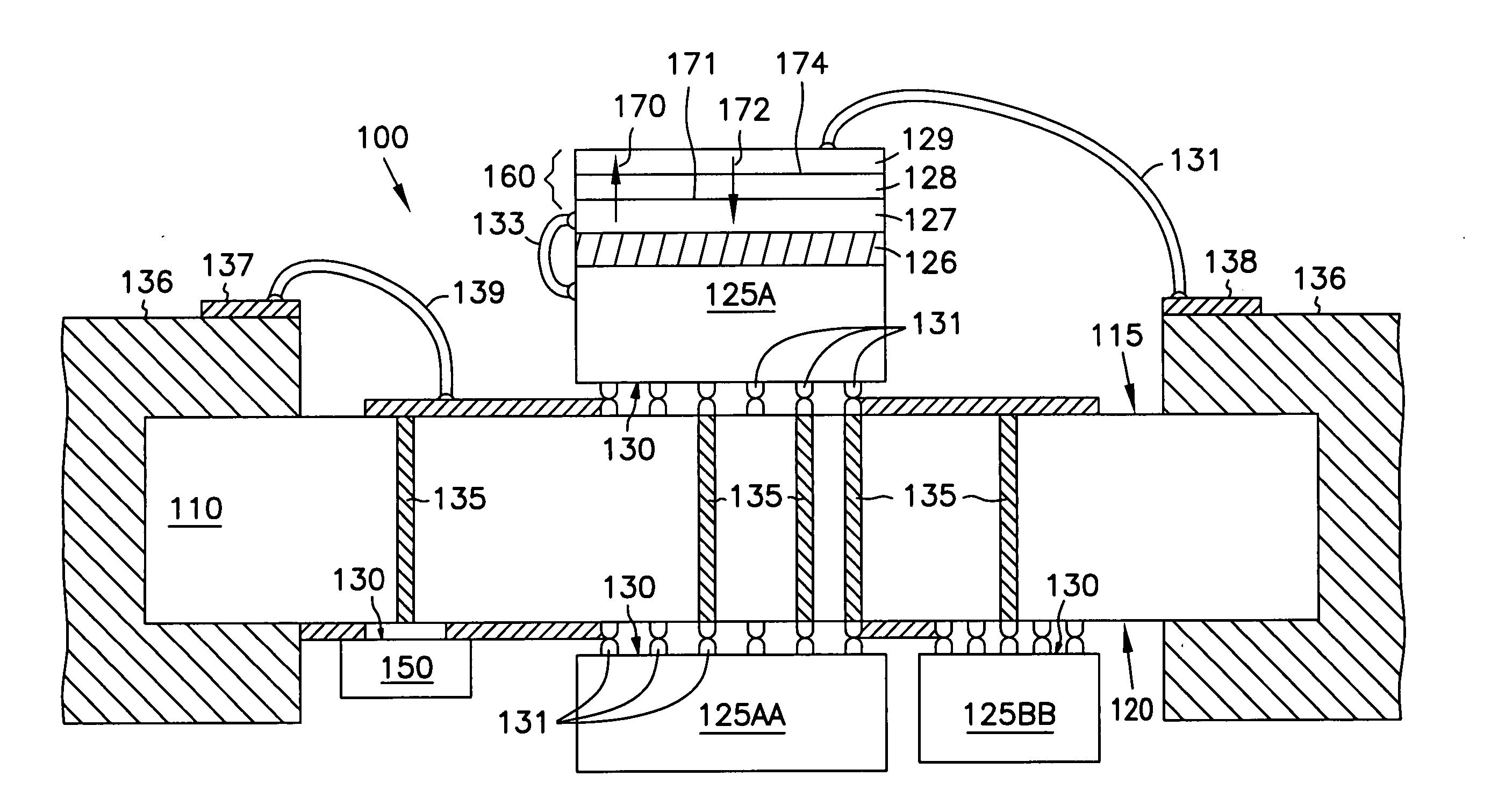

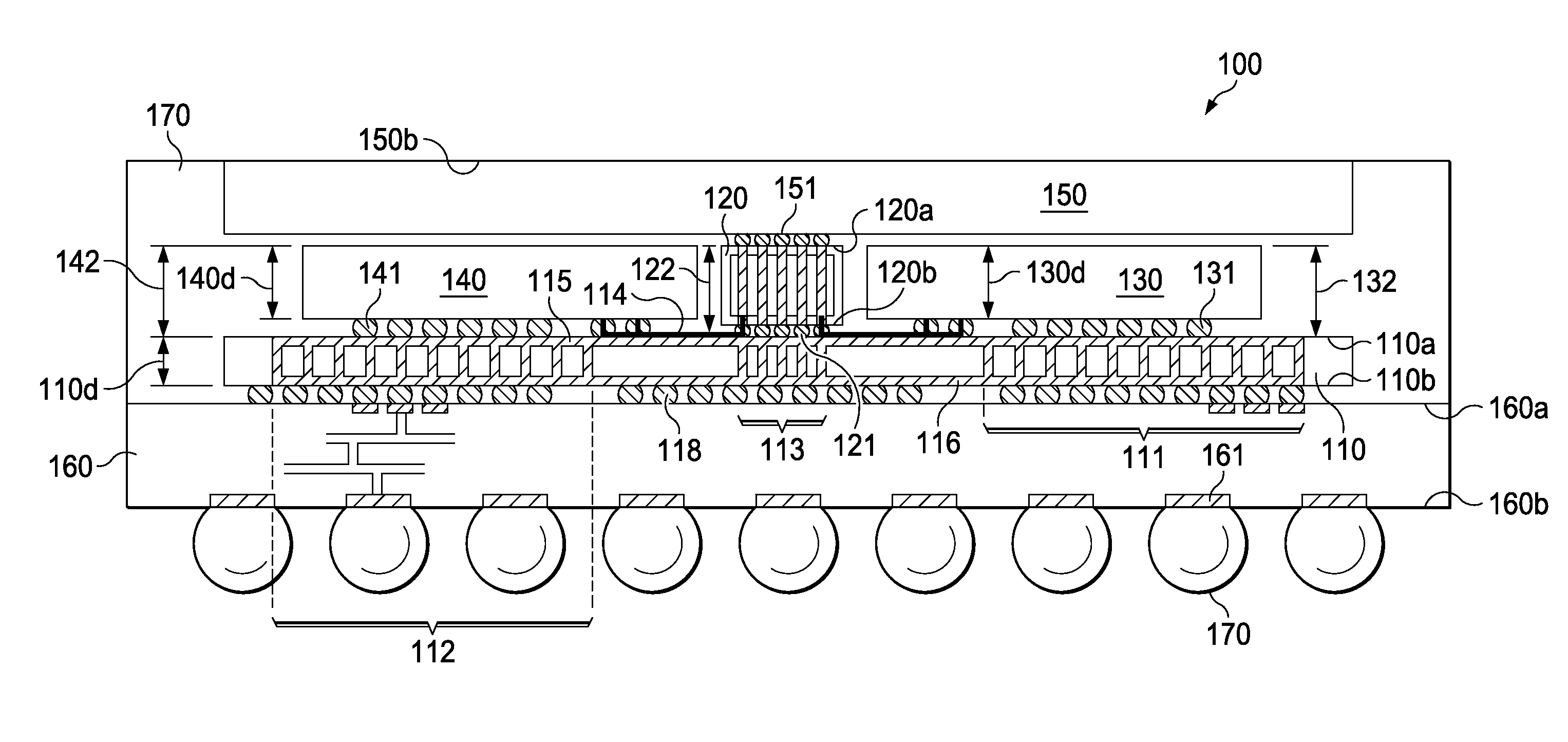

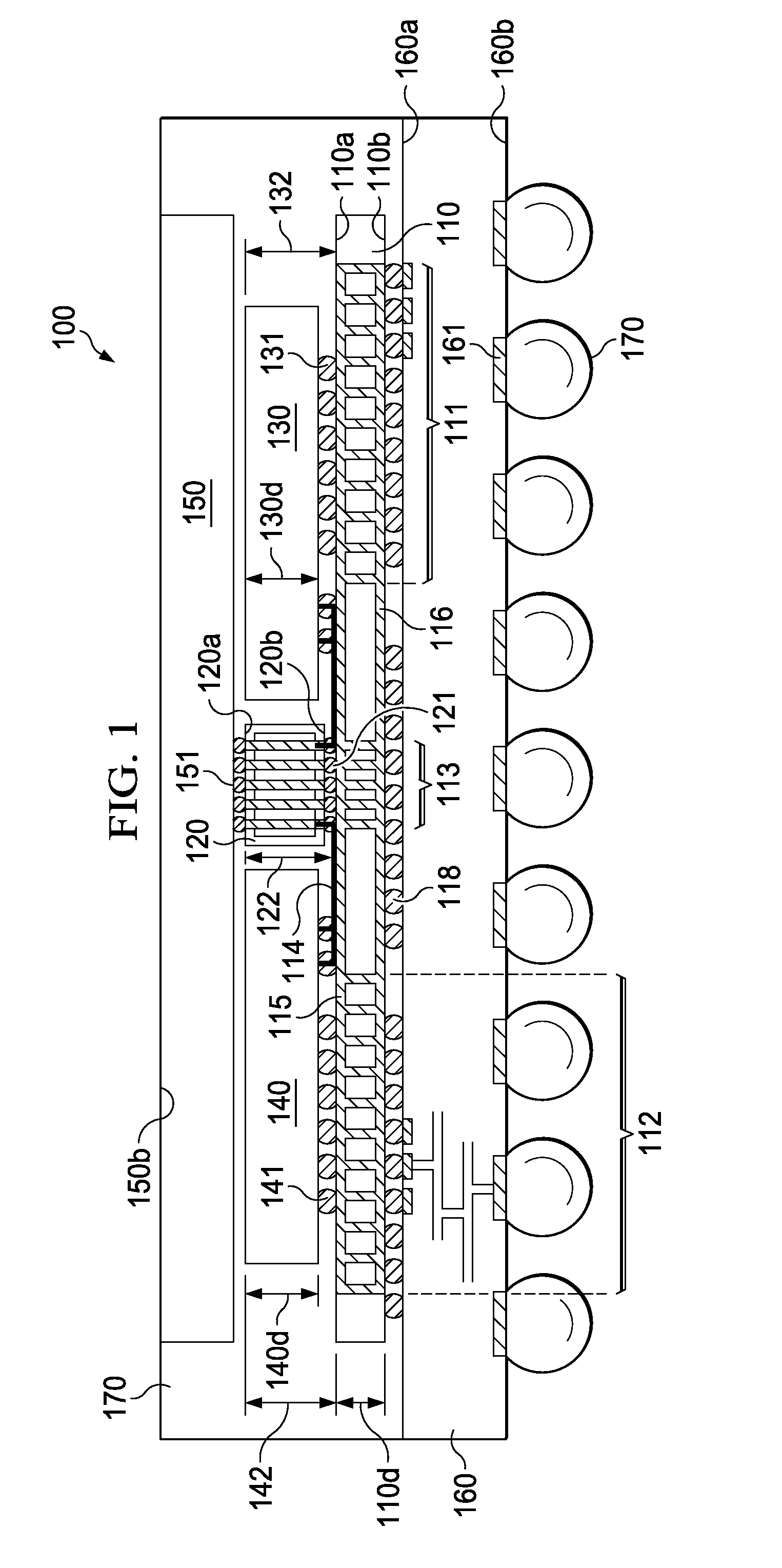

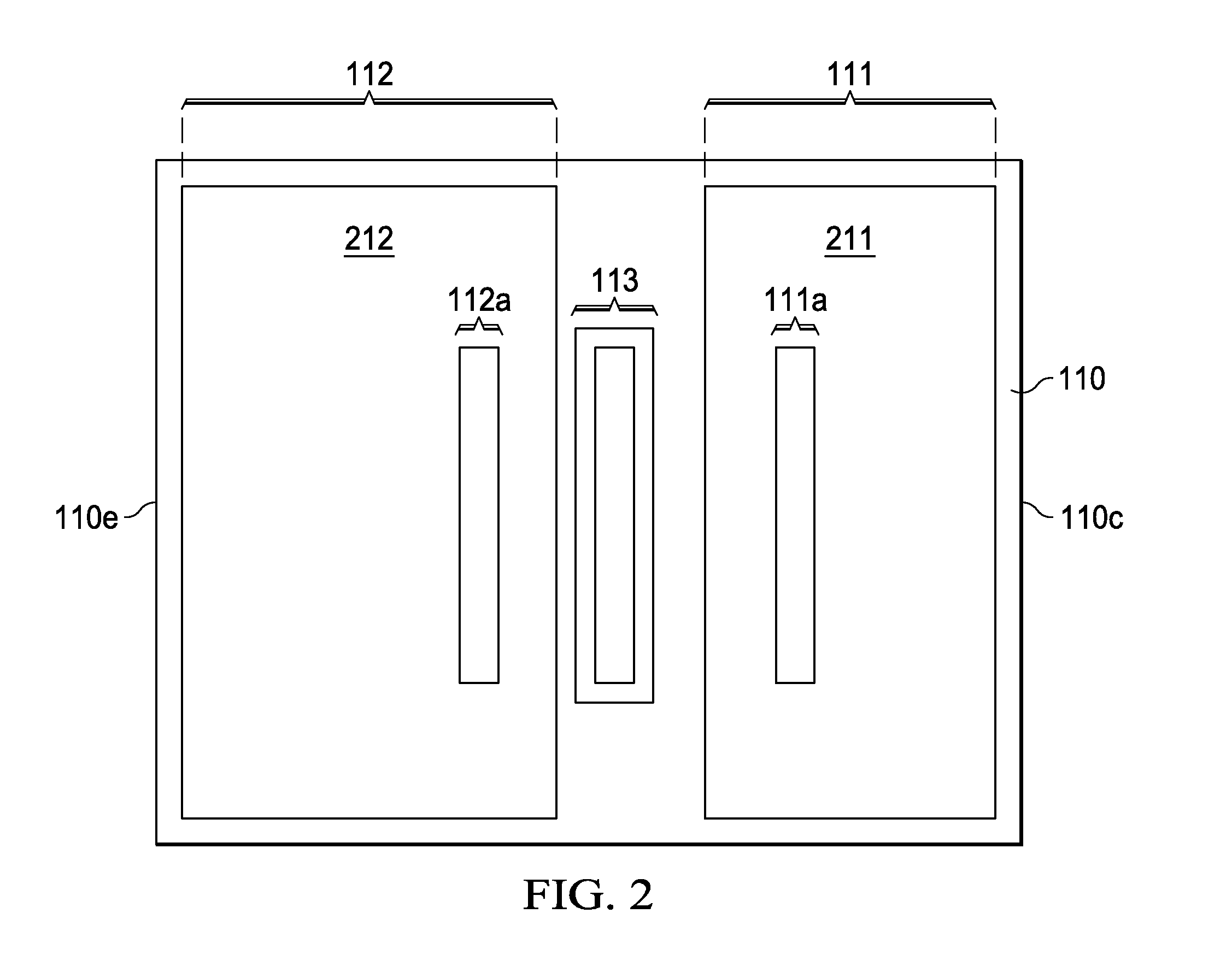

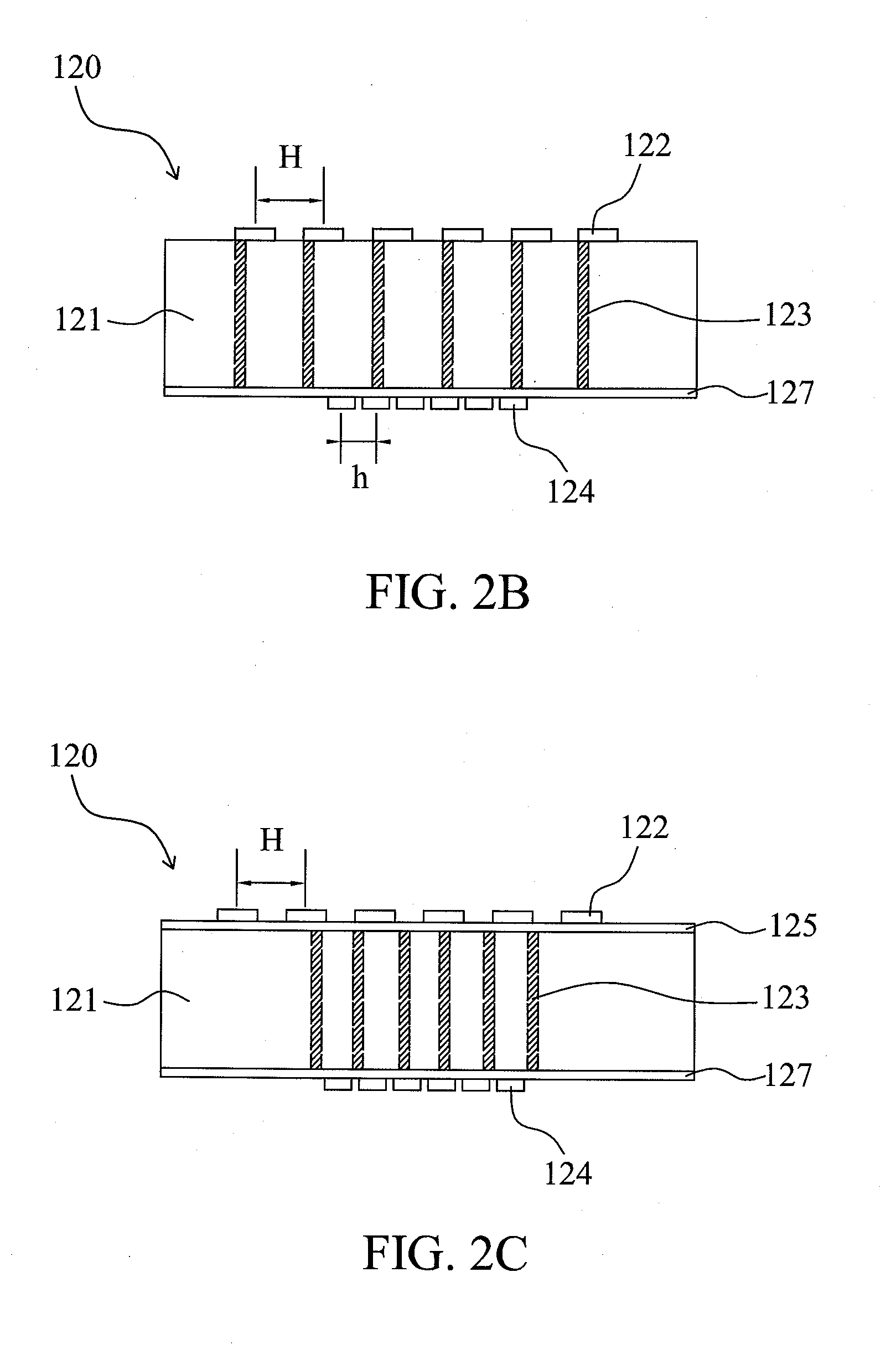

ActiveUS20140159247A1Minimizing needed board real estateImprove equipment reliabilityCooking-vessel materialsSemiconductor/solid-state device detailsSilicon interposerMemory chip

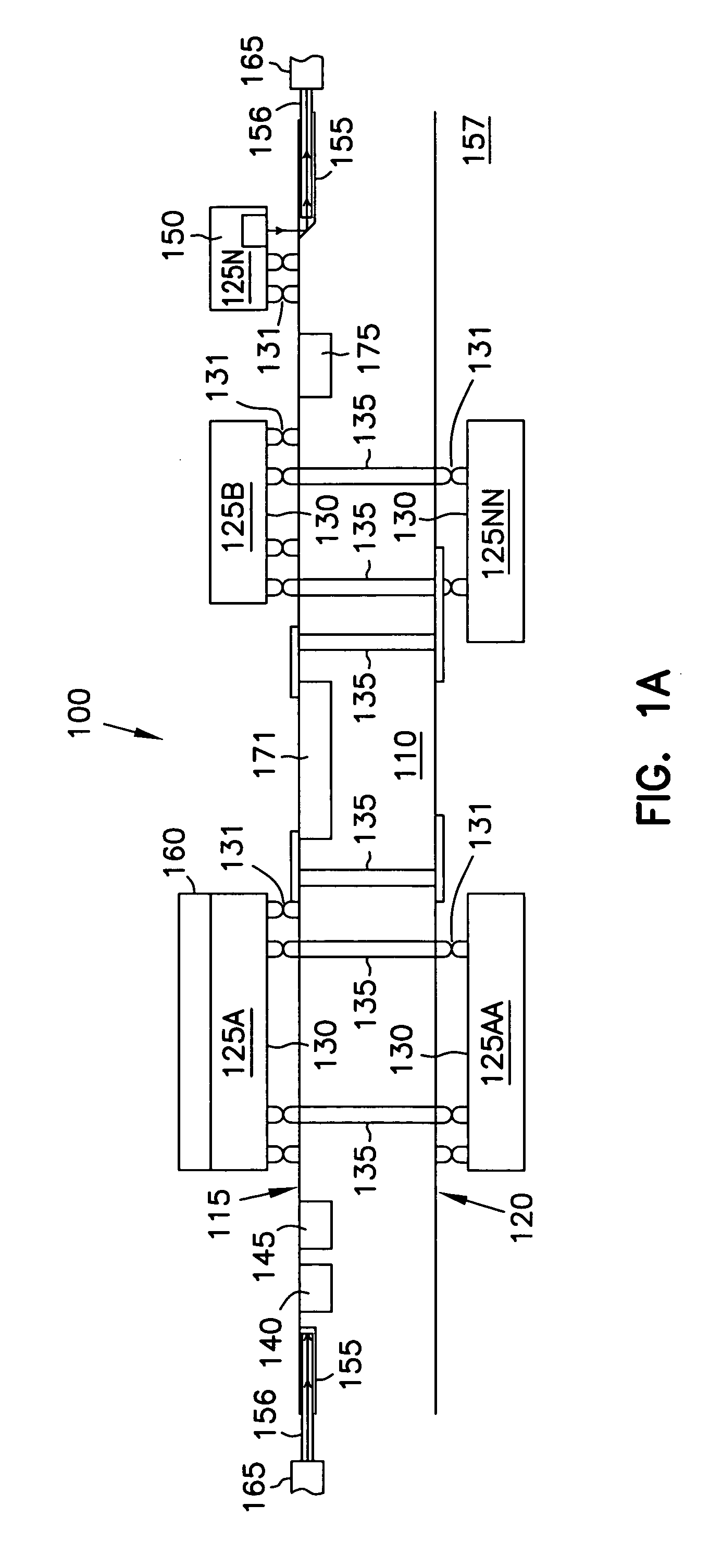

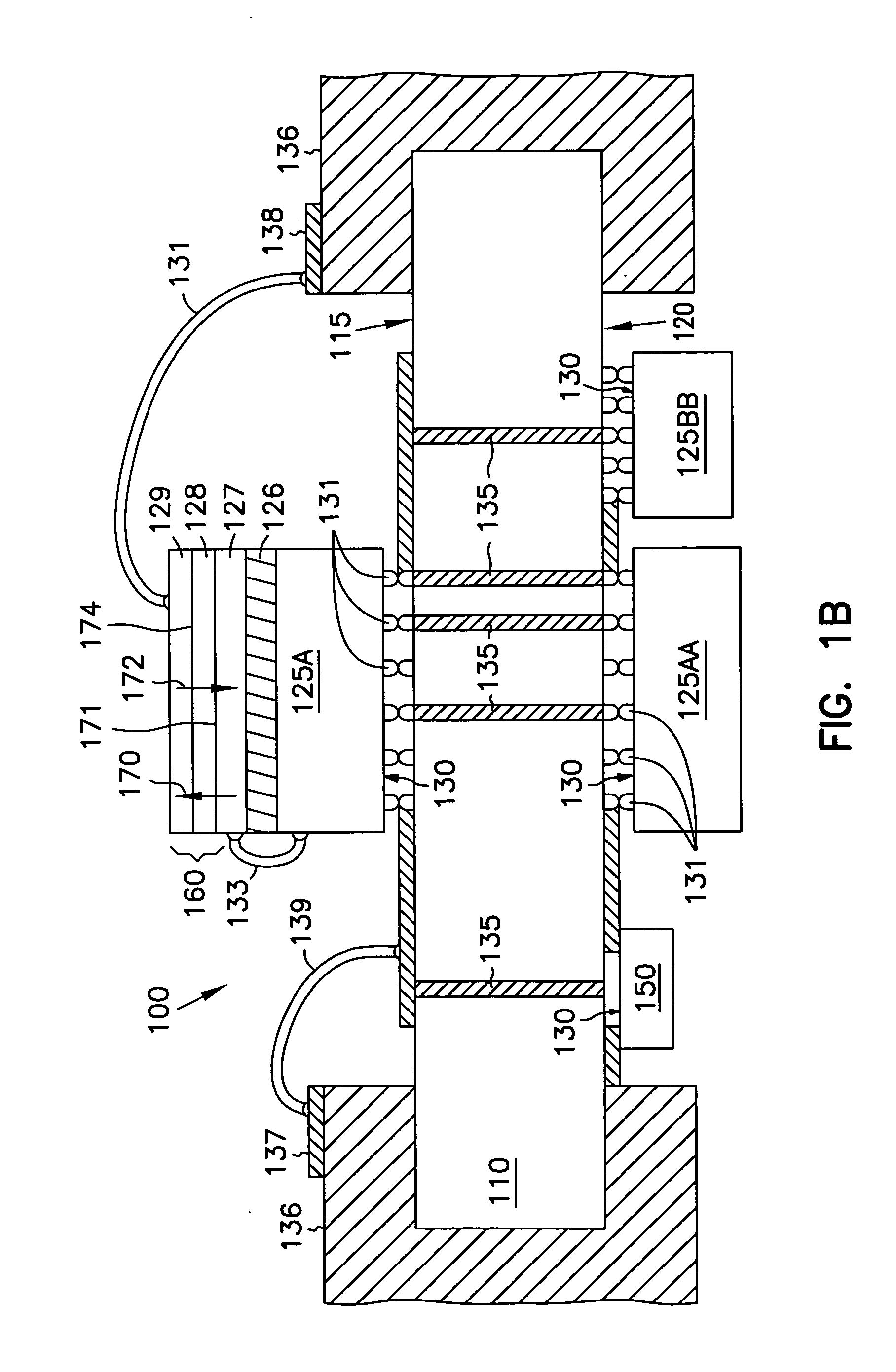

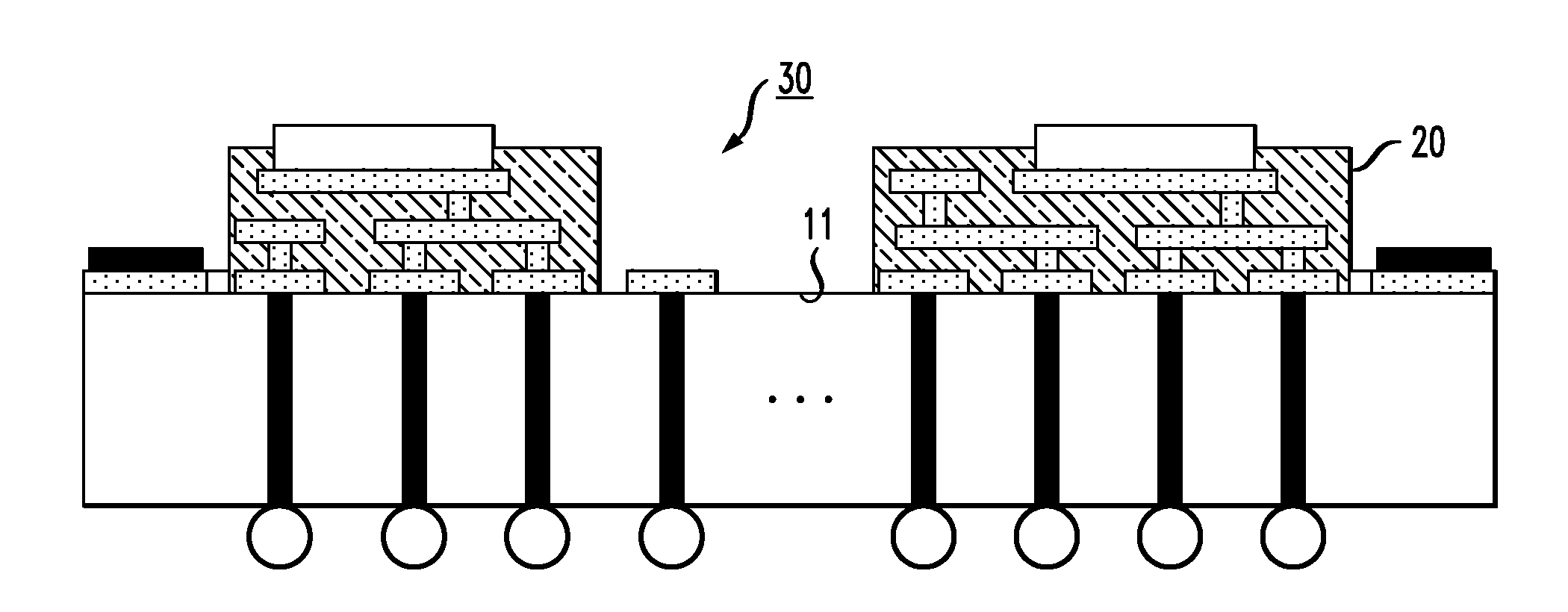

A standard memory chip (150) is vertically assembled with two processor chips (130, 140) of split architecture by means of a small silicon interposer (120) stacked onto a large silicon interposer (110); both interposers include through-silicon vias (TSVs), while the chips are free of TSVs. The TSVs of small interposer (120) connect to the memory chip (150) and to the bottom interposer (110). Symmetrically positioned relative to interposer (120), and connected to it by short signal traces, chips (130, 140) are attached to the TSVs of interposer 110, which in turn is attached to a substrate (160) with supply connections.

Owner:TEXAS INSTR INC

Compact system module with built-in thermoelectric cooling

InactiveUS7022553B2Increased operating bandwidthImprove cooling effectSemiconductor/solid-state device detailsSolid-state devicesMemory chipSilicon interposer

An improved integrated circuit package for providing built-in heating or cooling to a semiconductor chip is provided. The improved integrated circuit package provides increased operational bandwidth between different circuit devices, e.g. logic and memory chips. The improved integrated circuit package does not require changes in current CMOS processing techniques. The structure includes the use of a silicon interposer. The silicon interposer can consist of recycled rejected wafers from the front-end semiconductor processing. Micro-machined vias are formed through the silicon interposer. The micro-machined vias include electrical contacts which couple various integrated circuit devices located on the opposing surfaces of the silicon interposer. The packaging includes a Peltier element.

Owner:MICRON TECH INC

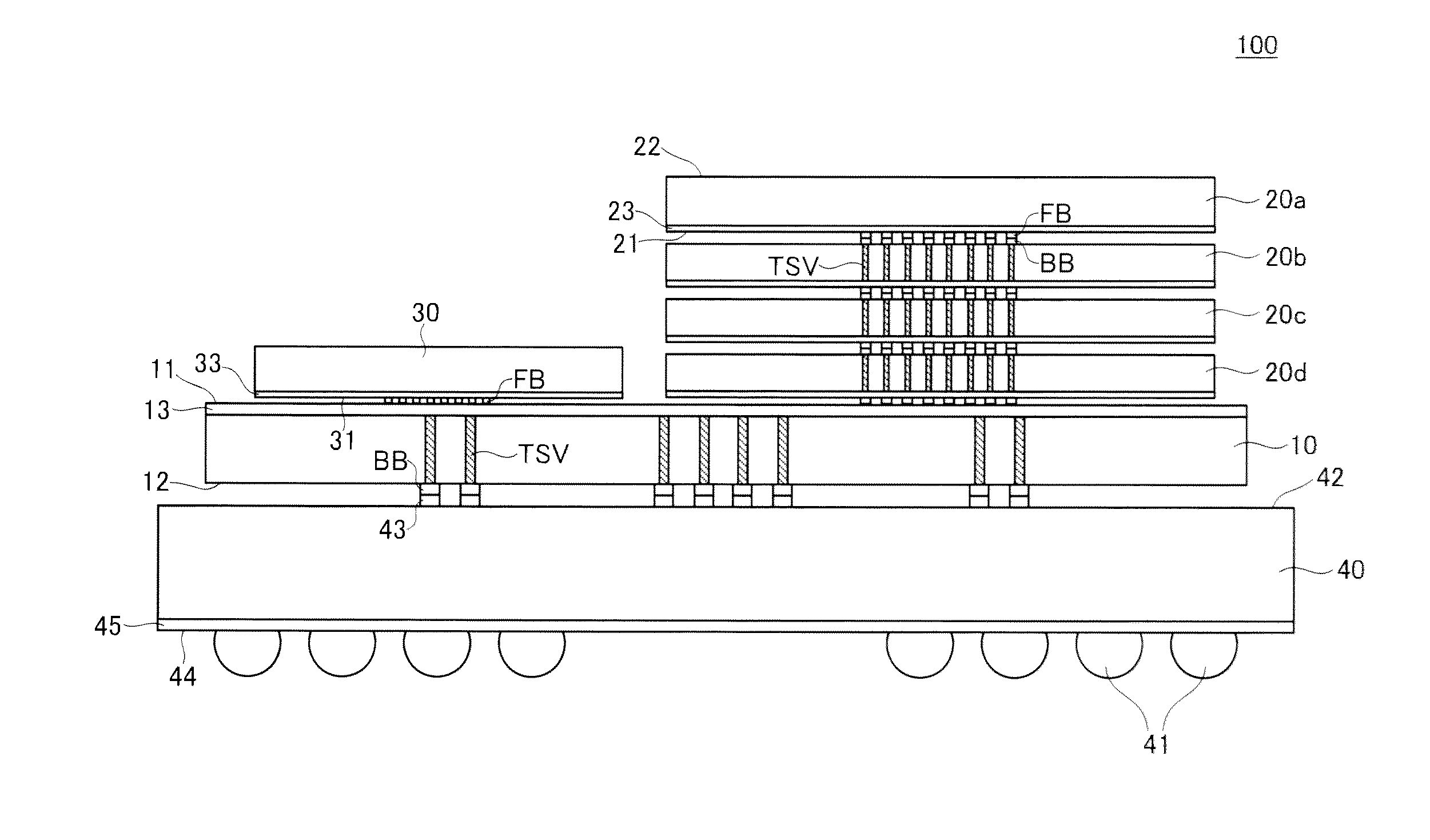

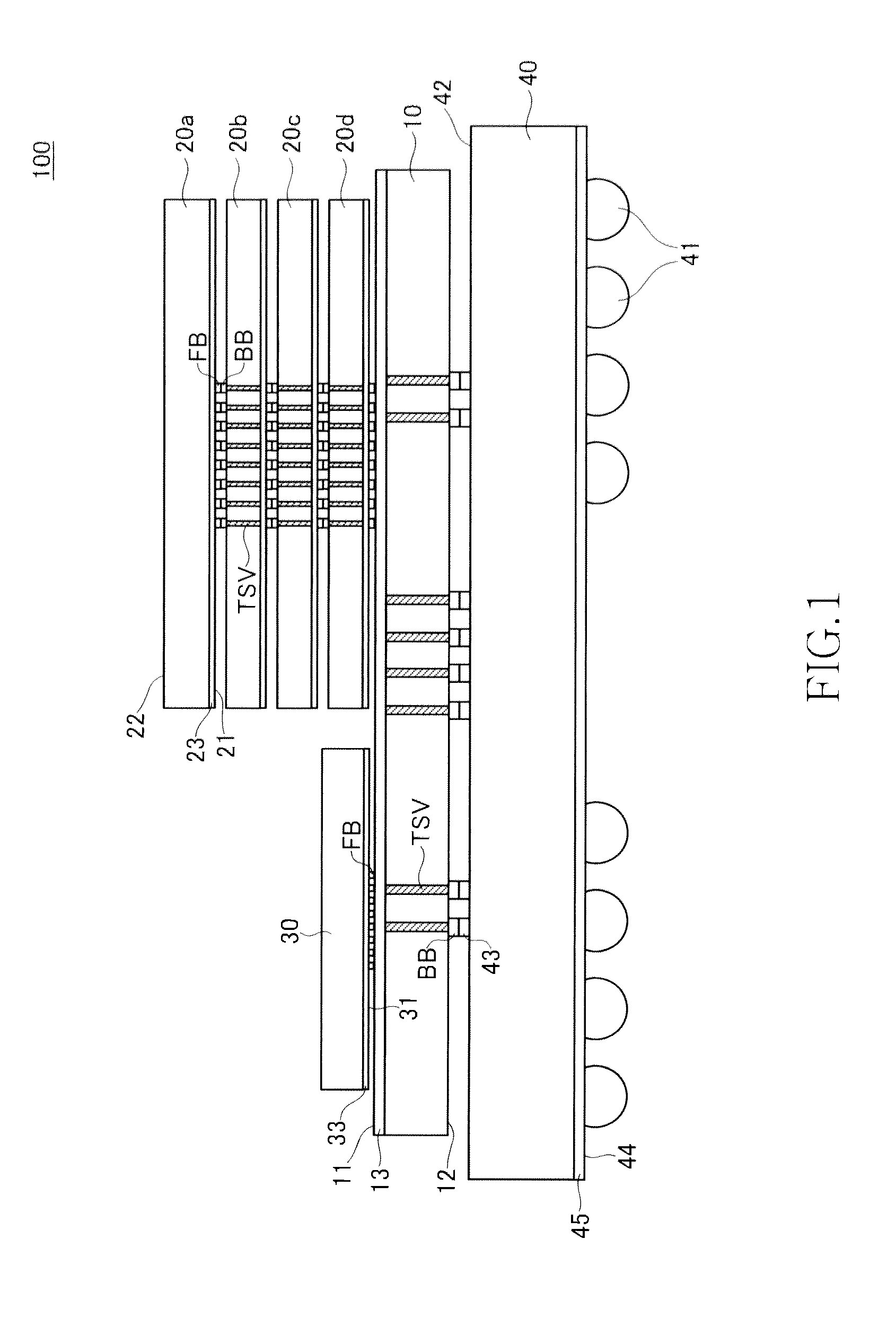

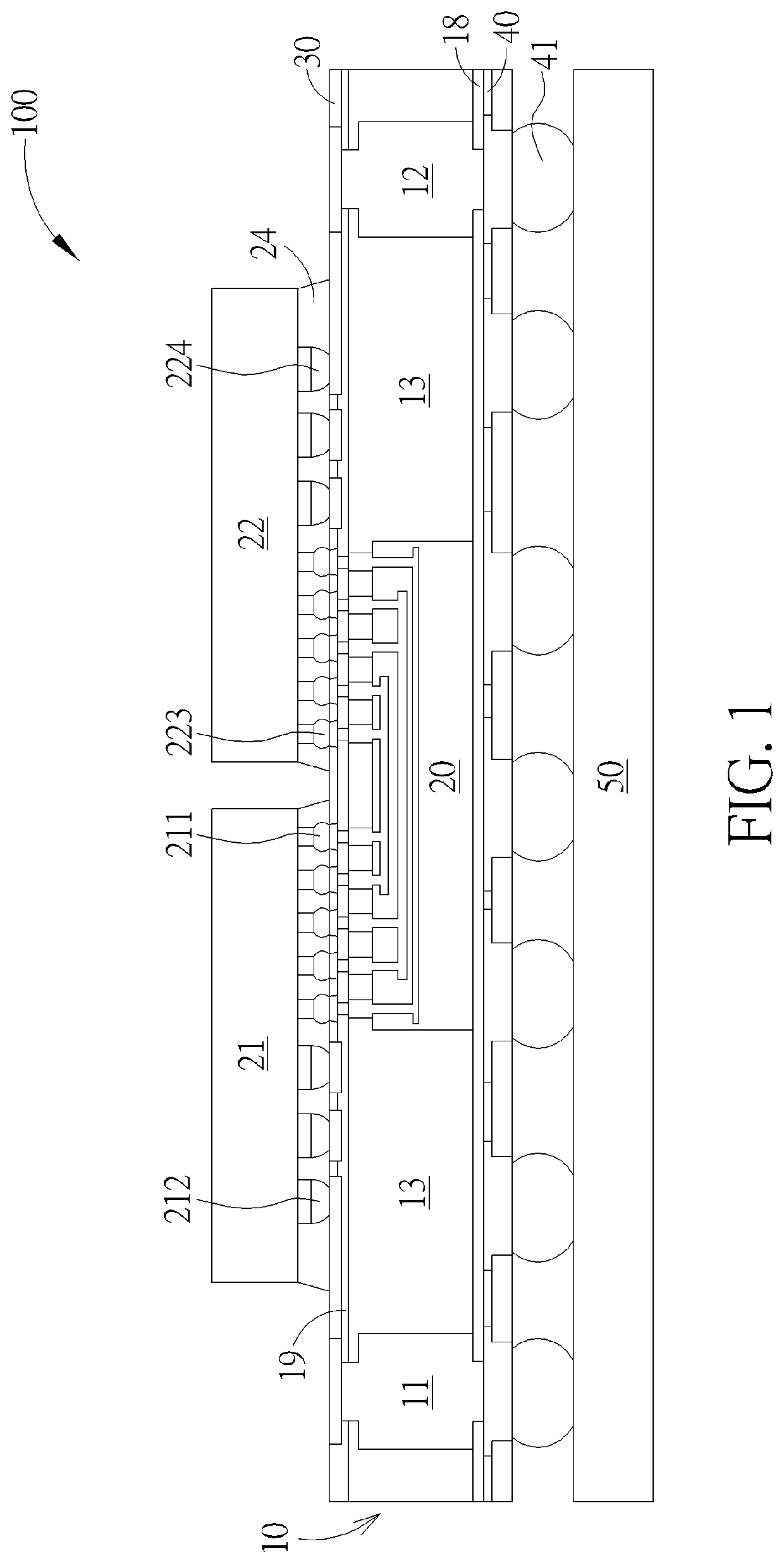

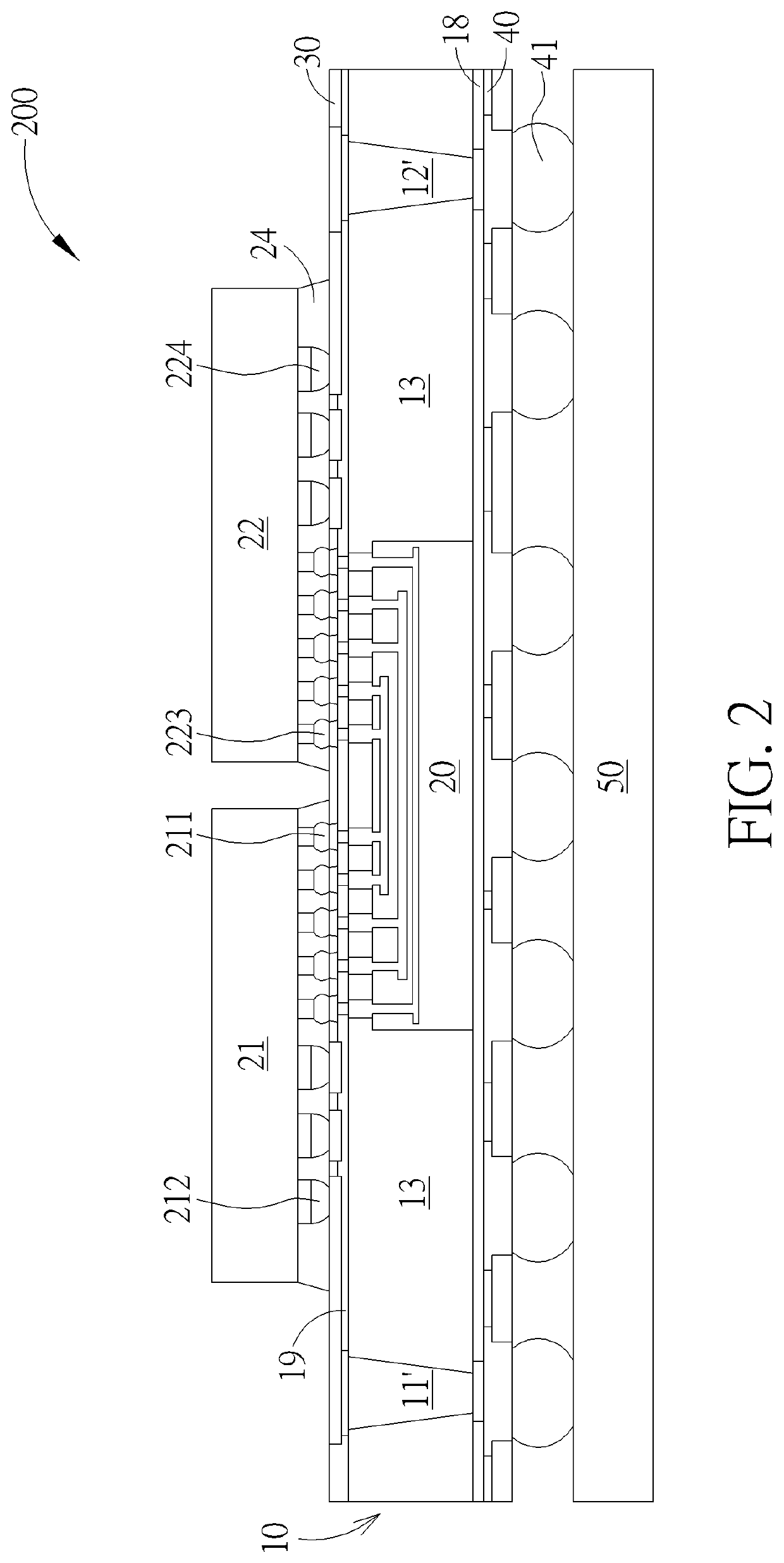

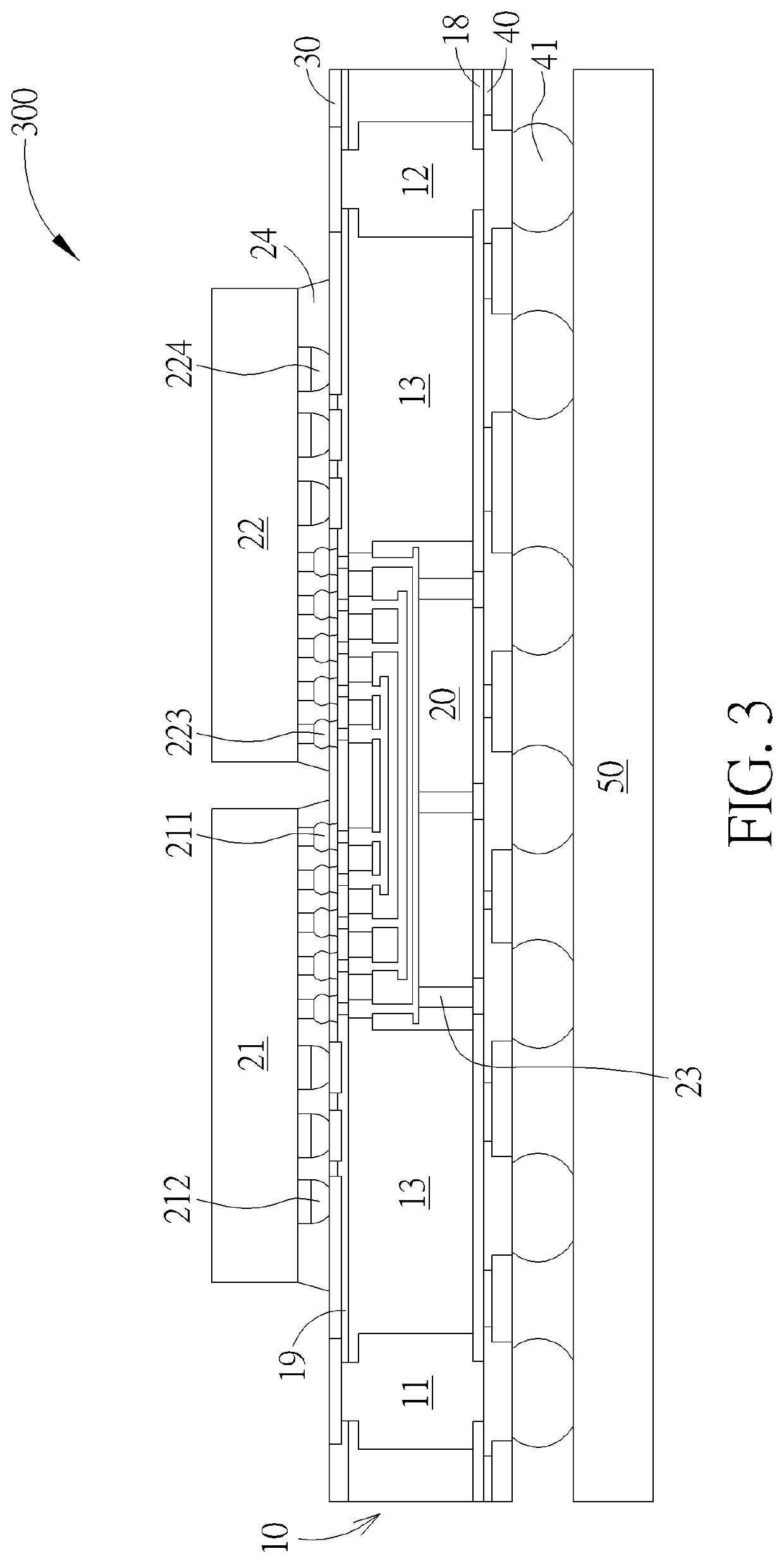

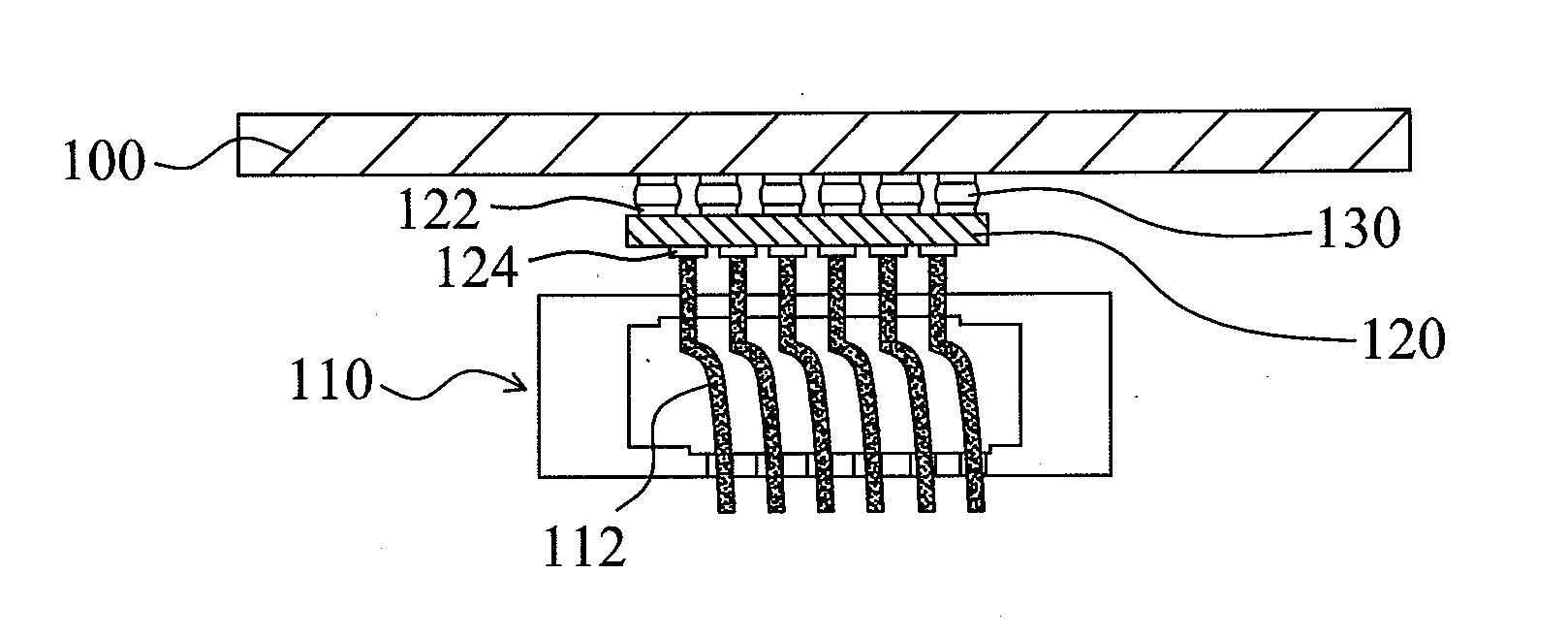

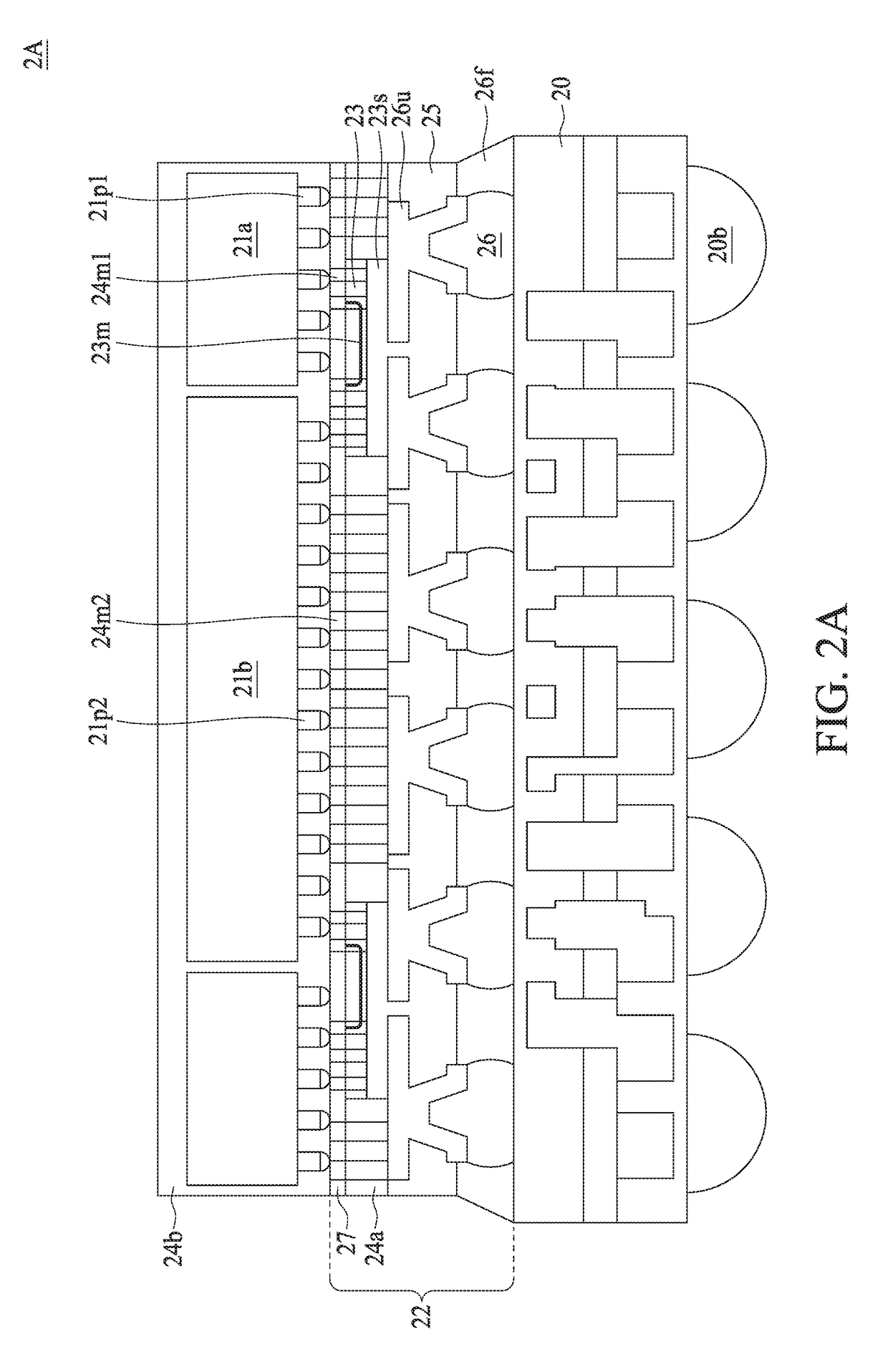

Semiconductor device having silicon interposer on which semiconductor chip is mounted

ActiveUS20140001639A1Semiconductor/solid-state device detailsSolid-state devicesSilicon interposerSemiconductor chip

Disclosed herein is a device that includes a silicon interposer having wiring lines on first and second wiring layers. The wiring lines includes first, second and third wiring lines provided on the first wiring layer and a fourth wiring line provided on the second wiring layer. The third wiring line is arranged between the first and second wiring lines on the first wiring layer. The fourth wiring line is overlapped with the third wiring line. Each of the first, second and fourth wiring lines conveys a power supply potential to first and second semiconductor chips mounted on the silicon interposer, and the third wiring line conveys a first signal communicated between the first and second semiconductor chips.

Owner:LONGITUDE LICENSING LTD

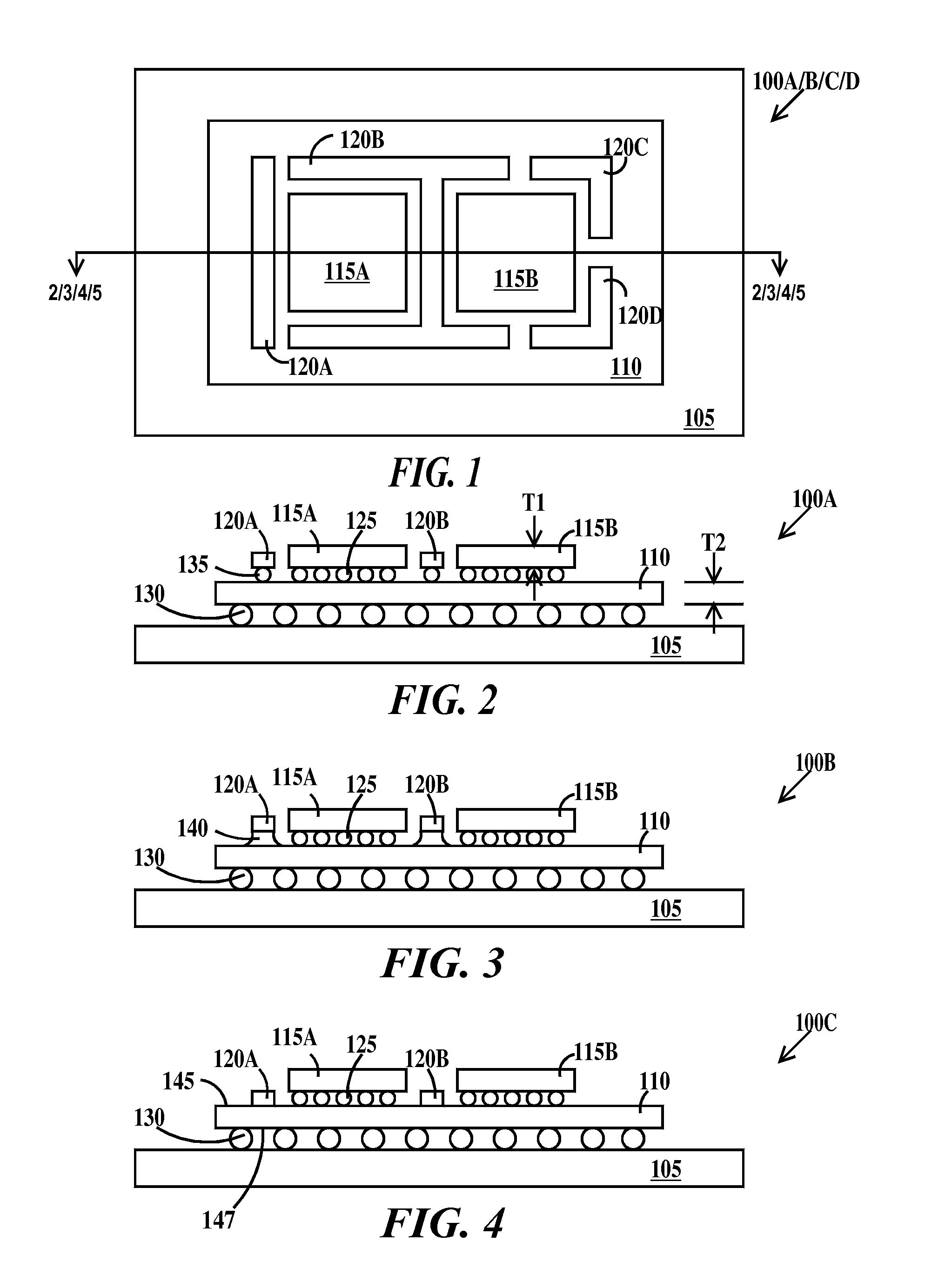

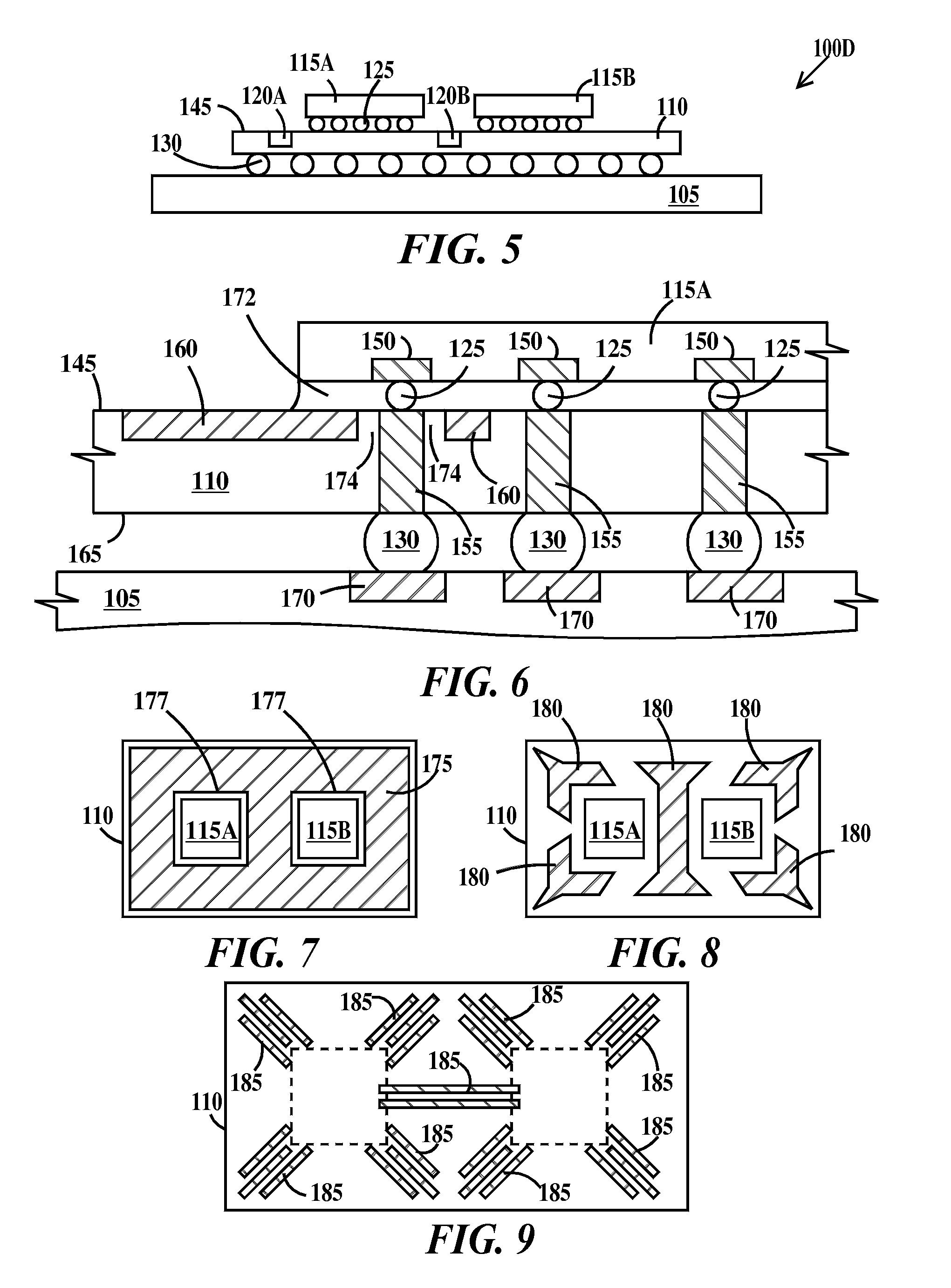

Stress relief structures for silicon interposers

ActiveUS20090079071A1Semiconductor/solid-state device detailsPrinted circuit aspectsSilicon interposerEngineering

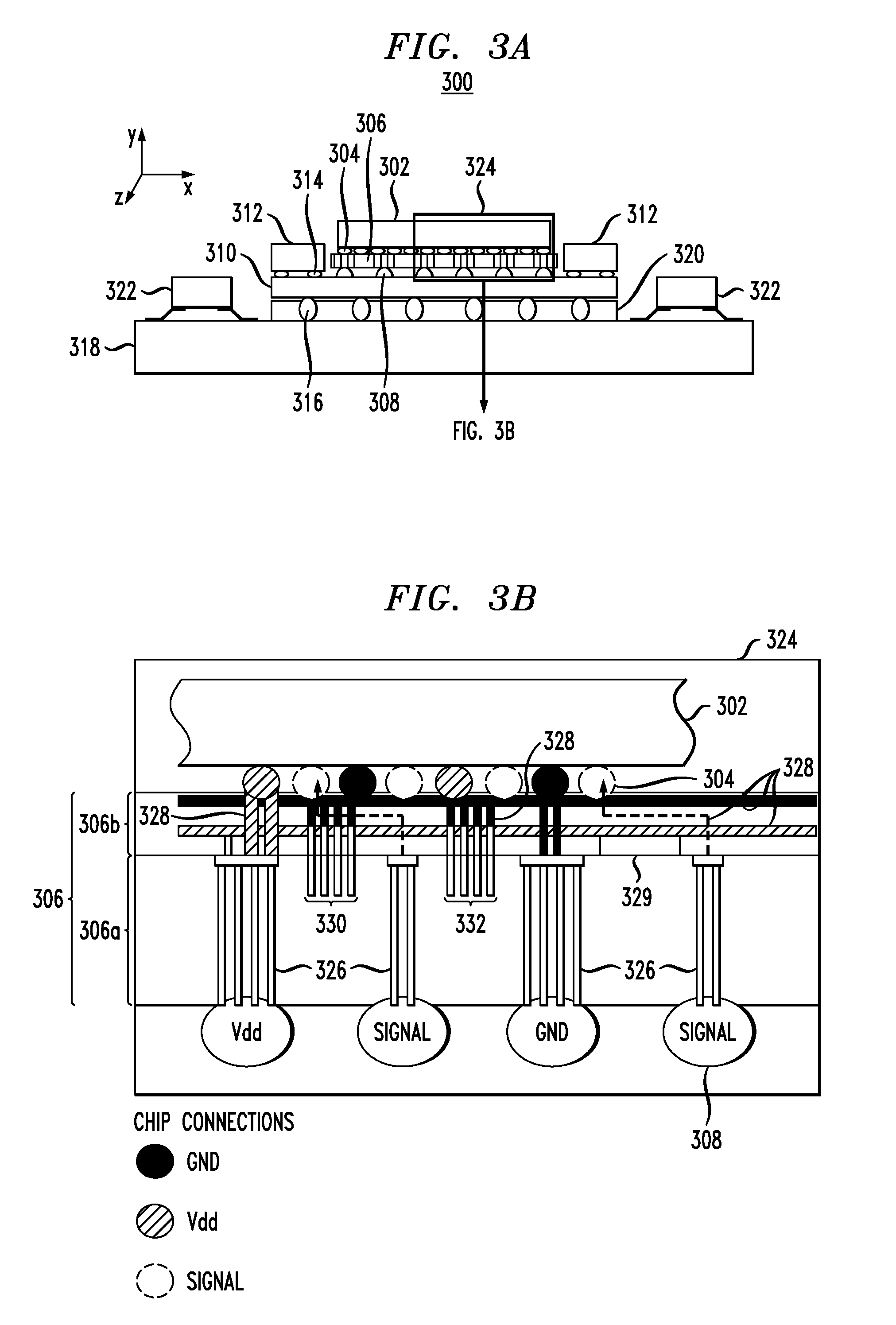

An electronic device and method of making the device. The device includes: a carrier; a silicon interposer connected to a top surface of the carrier, the interposer having wires extending from a top surface of the interposer, through the interposer, to a bottom surface of the interposer, the wires at the bottom surface of the interposer electrically connected to wires in a top surface of the carrier; an integrated circuit chip connected to the top surface of the interposer, wires at a surface of the integrated circuit chip electrically connected to the wires in the top surface of the interposer; and a stress relief structure attached to the interposer, the stress relief structure either (i) not electrically connected to the wires of the interposer or integrated circuit chip or (ii) electrically connected to ground by wires of the interposer or wires of the integrated circuit chip.

Owner:GLOBALFOUNDRIES US INC

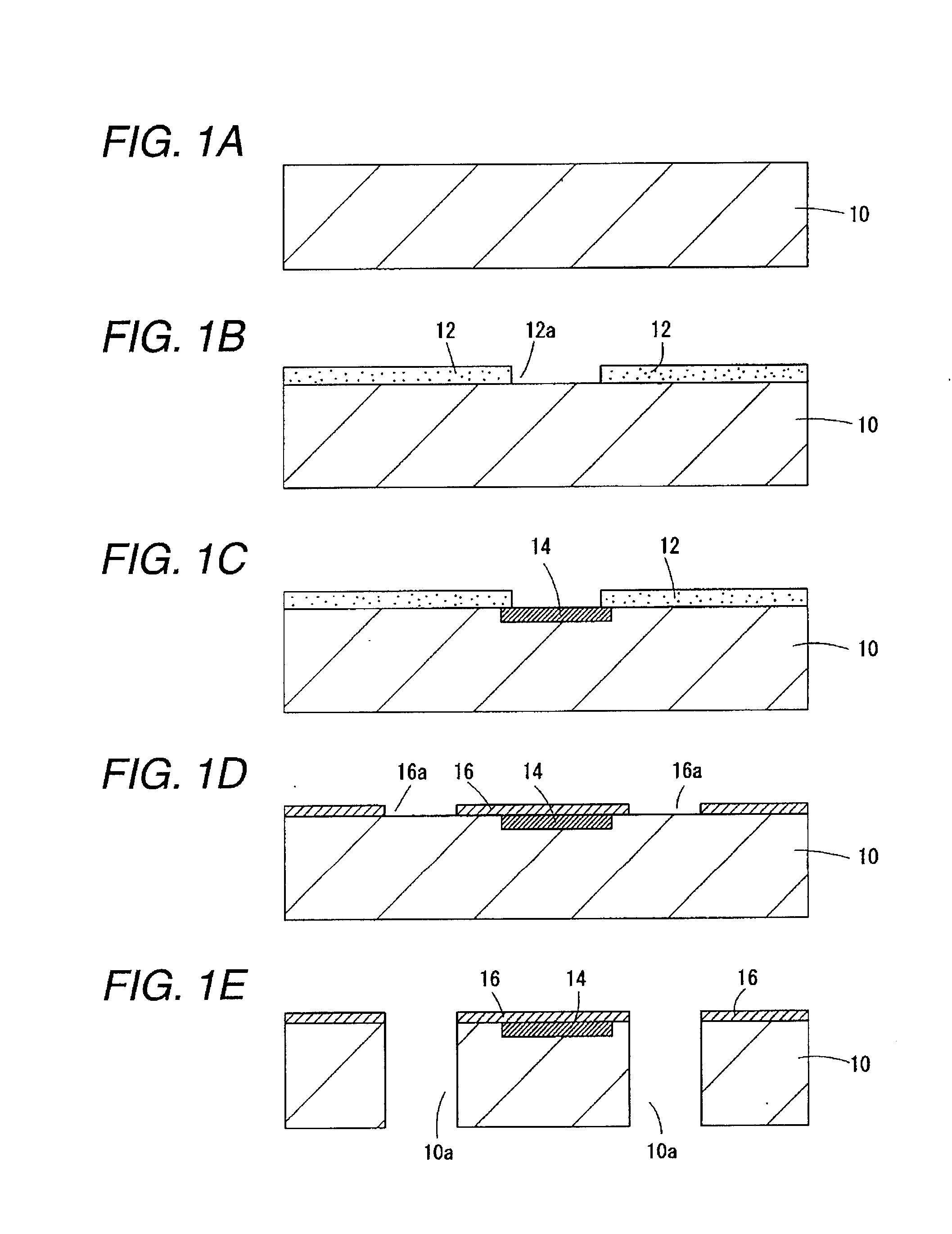

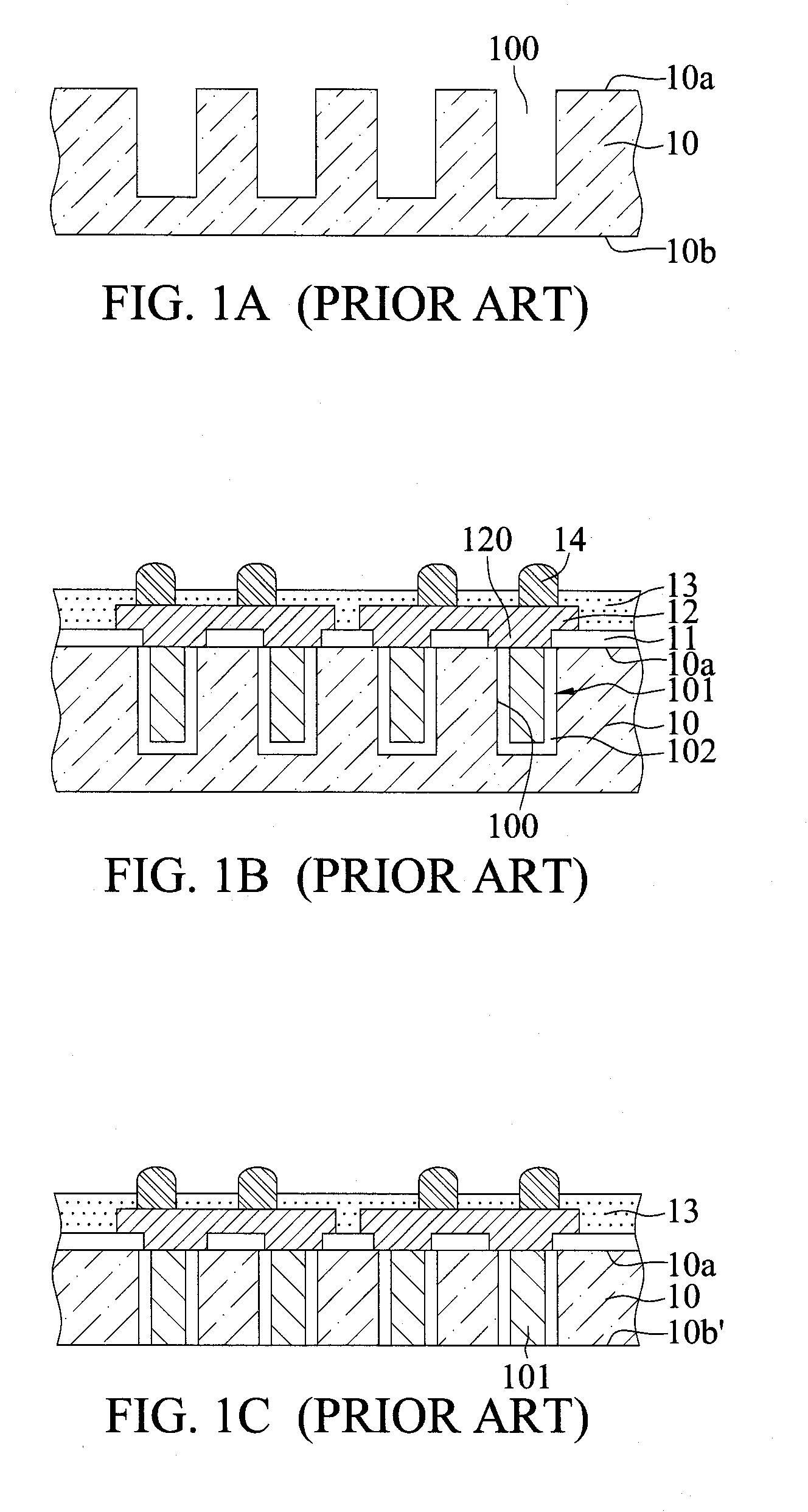

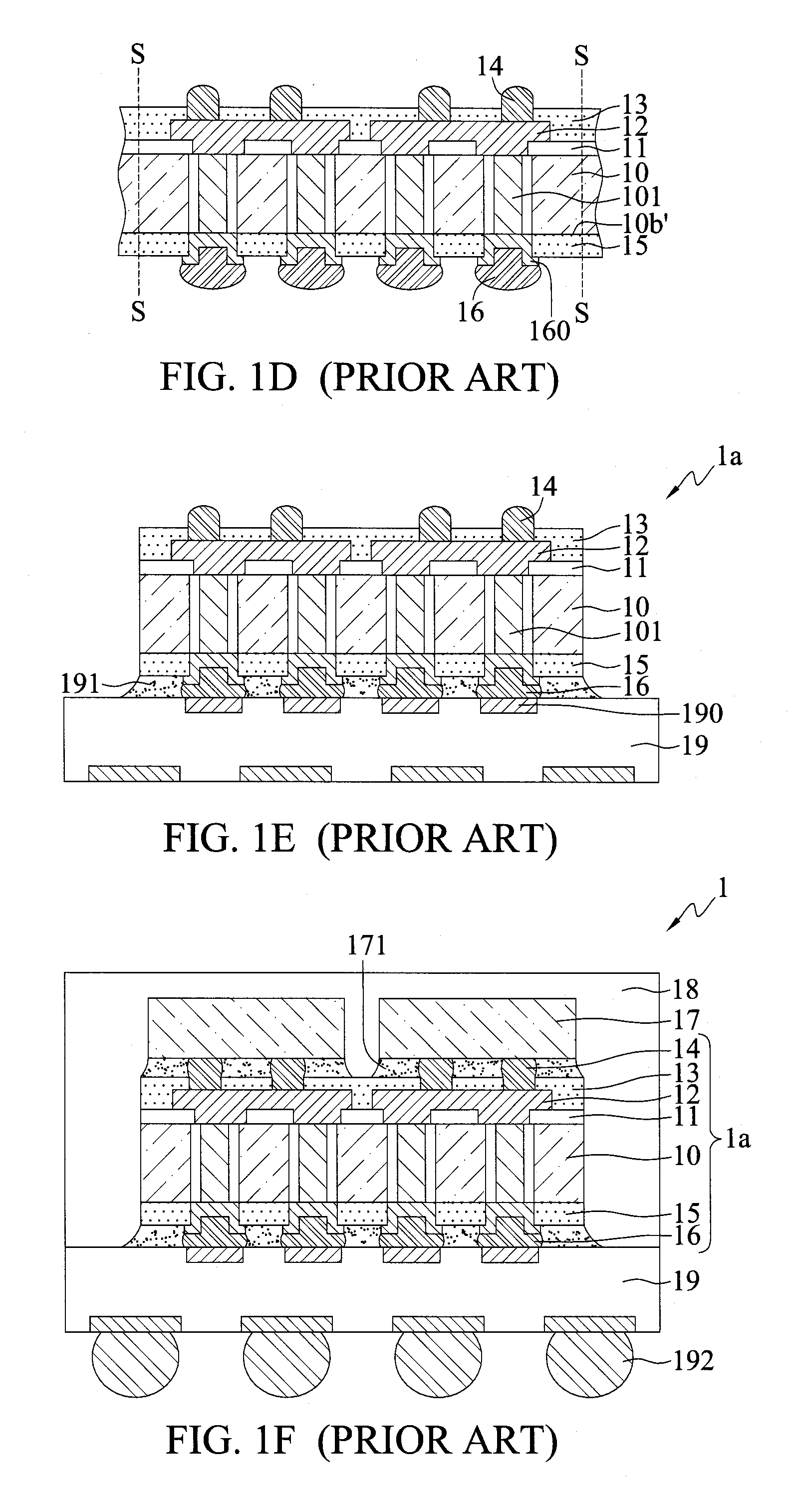

Silicon interposer and method for manufacturing the same

ActiveUS20090283914A1Semiconductor/solid-state device detailsSolid-state devicesSilicon interposerMaterials science

A method for manufacturing a silicon interposer, includes a step of forming a protection film on a surface, on which an element portion is formed, of a silicon wafer, a step of forming open holes according to planar arrangements of through holes which pass through the silicon wafer in a thickness direction, a step of forming the through holes by etching the silicon wafer using the protection film as a mask, a step of forming an oxide film on inner wall surfaces of the through holes by a thermal oxidation, a step of forming a contact hole, which is in communication with the element portion, in the protection film, and a step of forming wirings on both surfaces of the silicon wafer. In the step of forming the wirings, one of the wirings is formed to be connected electrically to the element portion via a contact portion formed in the contact hole.

Owner:SHINKO ELECTRIC IND CO LTD

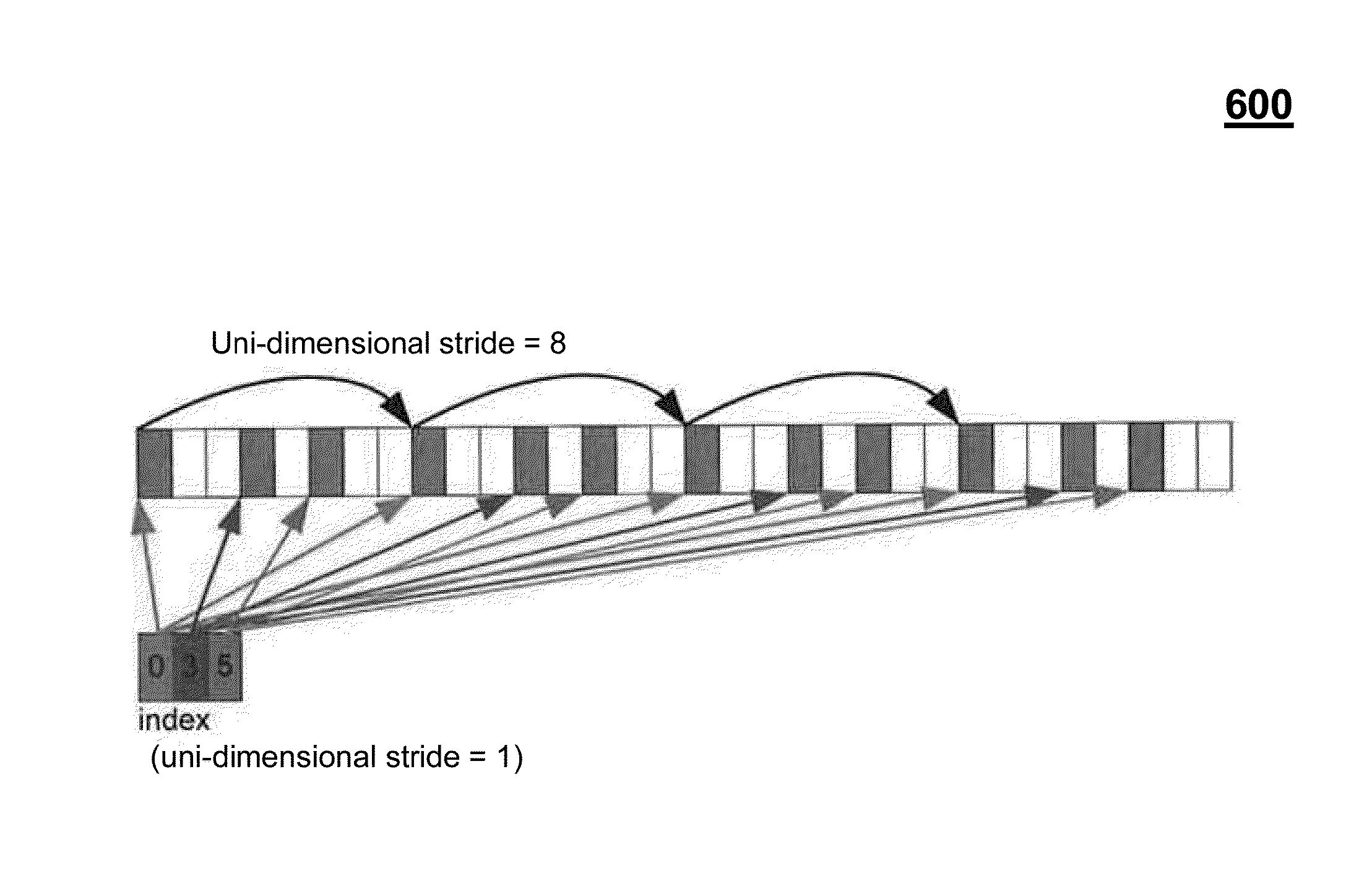

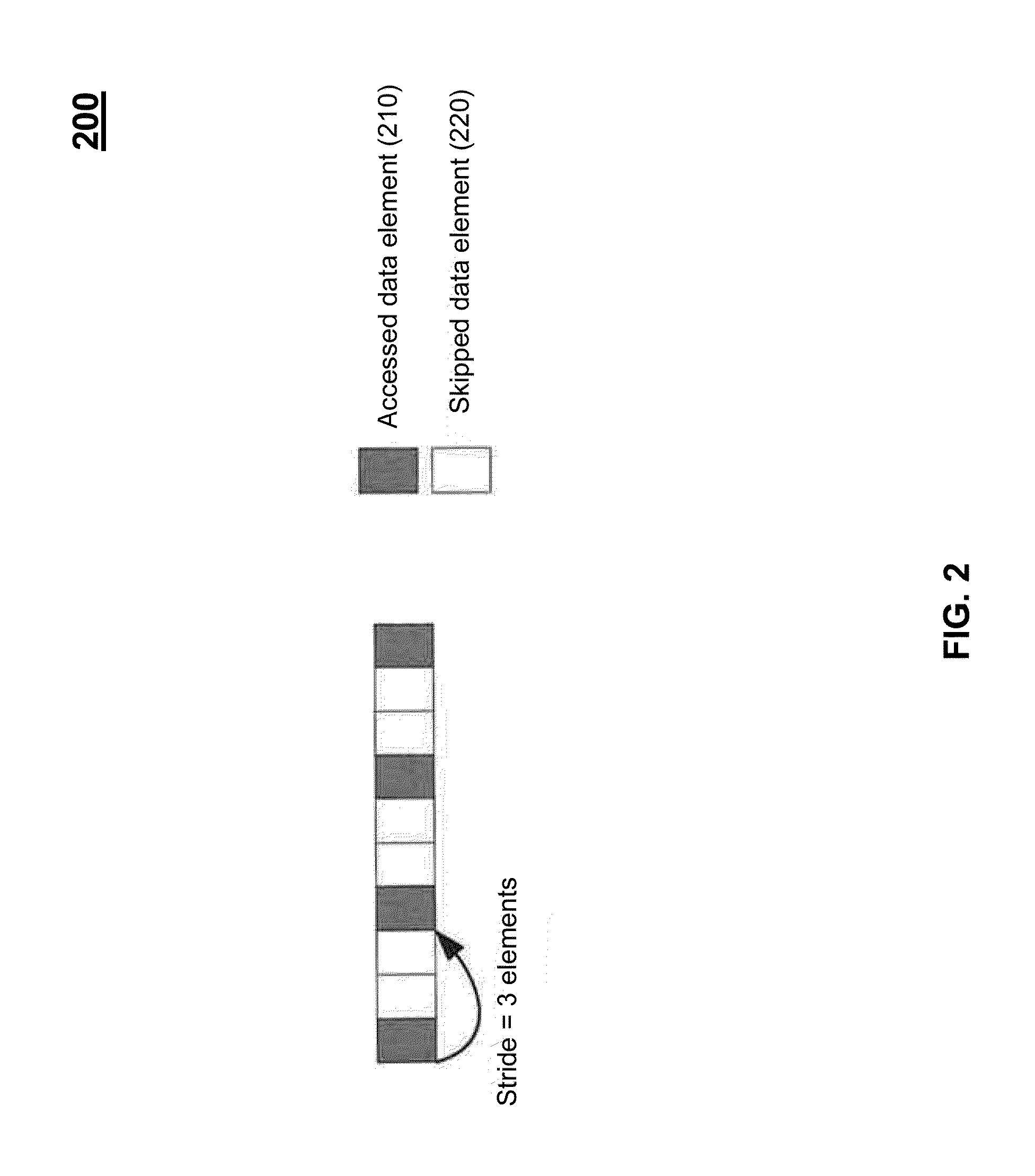

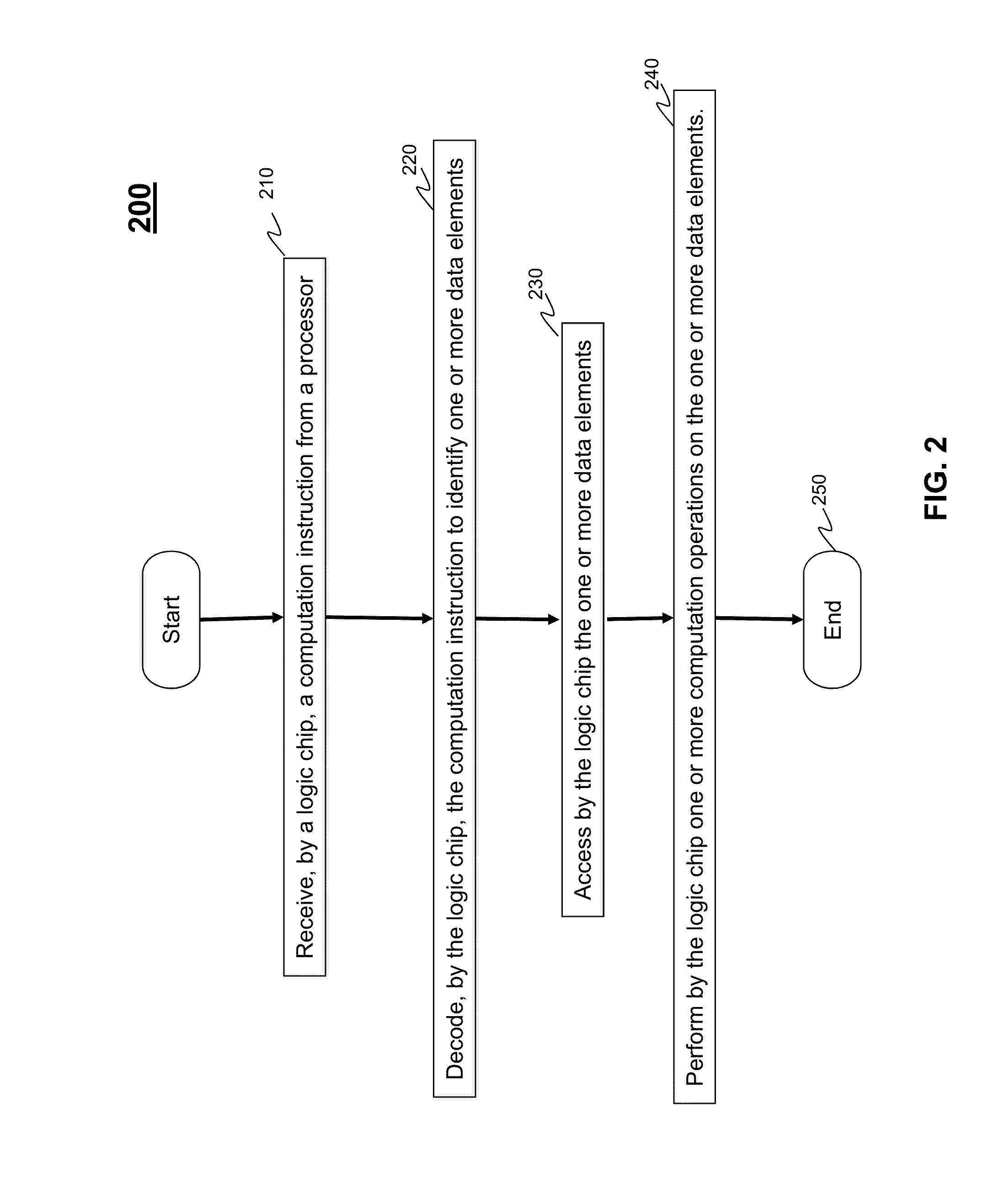

Compound Memory Operations in a Logic Layer of a Stacked Memory

InactiveUS20140181427A1Lower performance requirementsReduce energy overheadDigital computer detailsProgram controlSilicon interposerVisibility

Some die-stacked memories will contain a logic layer in addition to one or more layers of DRAM (or other memory technology). This logic layer may be a discrete logic die or logic on a silicon interposer associated with a stack of memory dies. Additional circuitry / functionality is placed on the logic layer to implement functionality to perform various data movement and address calculation operations. This functionality would allow compound memory operations—a single request communicated to the memory that characterizes the accesses and movement of many data items. This eliminates the performance and power overheads associated with communicating address and control information on a fine-grain, per-data-item basis from a host processor (or other device) to the memory. This approach also provides better visibility of macro-level memory access patterns to the memory system and may enable additional optimizations in scheduling memory accesses.

Owner:ADVANCED MICRO DEVICES INC

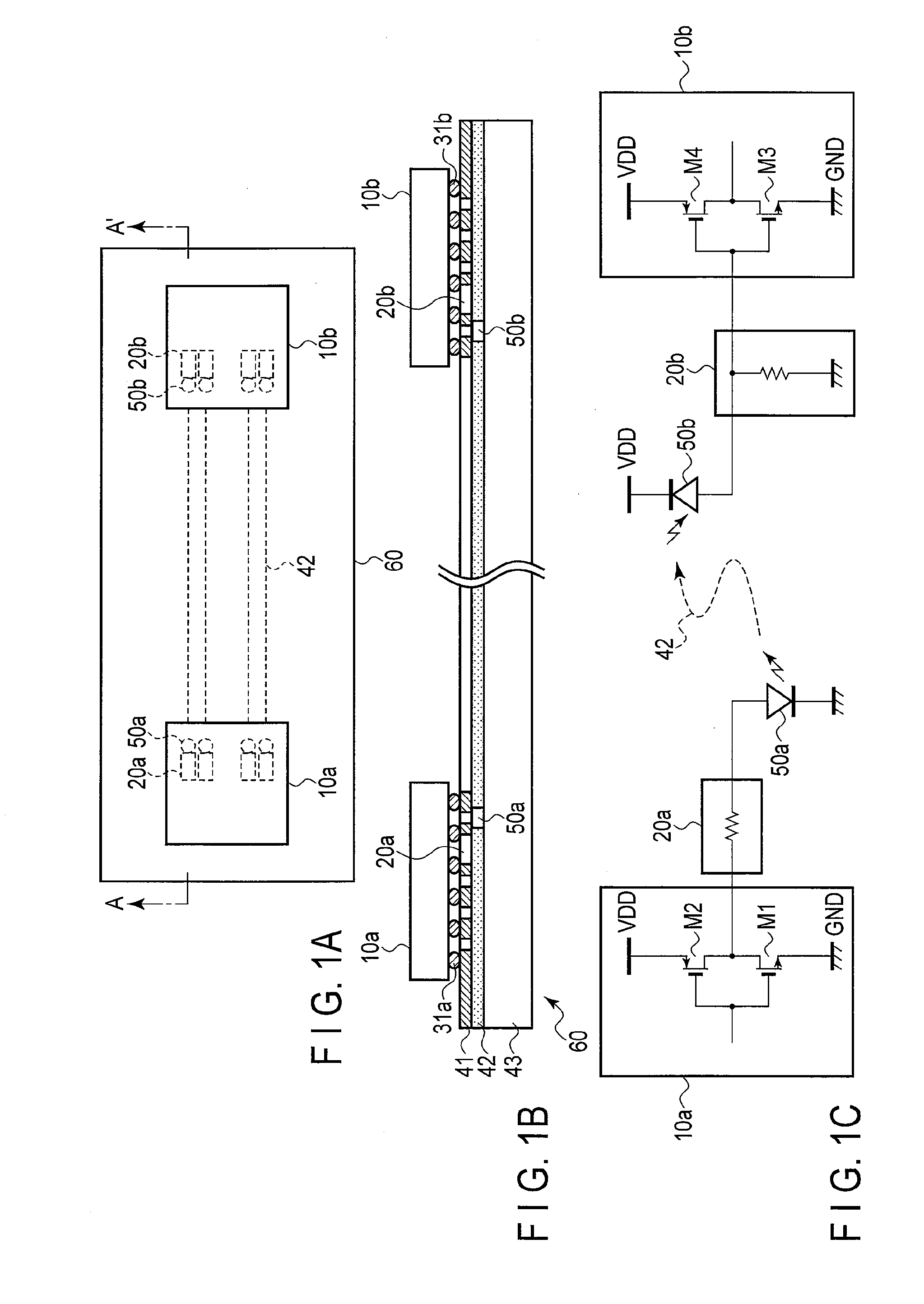

Optoelectronic integrated package module

According to one embodiment, there is provided an optoelectronic integrated package module including a silicon interposer that has an electrical interconnection and an optical waveguide, and formed on a silicon substrate, an optical semiconductor element formed in the silicon interposer, and electrically connected to the electrical interconnection and optically coupled to the optical waveguide, an electrical circuit element formed in the silicon interposer, and electrically connected to the optical semiconductor element, and a semiconductor integrated circuit chip mounted on the silicon interposer, and electrically connected to the electrical circuit element. The semiconductor integrated circuit chip transmits an electrical signal to the optical semiconductor element via the electrical circuit element or receives an electrical signal from the optical semiconductor element via the electrical circuit element.

Owner:KK TOSHIBA

Interposer Based Monolithic Microwave Integrate Circuit (iMMIC)

InactiveUS20110089531A1Semiconductor/solid-state device detailsSolid-state devicesSilicon interposerEngineering

A system is disclosed for IC fabrication, including seating an integrated circuit (“IC”) having at least one contact into a recess of a silicon interposer substrate, applying an insulator in liquid form to fill portions of the recess not otherwise occupied by the IC and to cover a top surface of the IC and the silicon interposer substrate, introducing the insulator to a ramped environmental temperature, holding the environmental temperature at a reflow temperature to reflow the insulator and ramping down the environmental temperature to cure the insulator.

Owner:TELEDYNE SCI & IMAGING

Stress relief structures for silicon interposers

ActiveUS7763965B2Semiconductor/solid-state device detailsPrinted circuit aspectsSilicon interposerElectrical connection

An electronic device and method of making the device. The device includes: a carrier; a silicon interposer connected to a top surface of the carrier, the interposer having wires extending from a top surface of the interposer, through the interposer, to a bottom surface of the interposer, the wires at the bottom surface of the interposer electrically connected to wires in a top surface of the carrier; an integrated circuit chip connected to the top surface of the interposer, wires at a surface of the integrated circuit chip electrically connected to the wires in the top surface of the interposer; and a stress relief structure attached to the interposer, the stress relief structure either (i) not electrically connected to the wires of the interposer or integrated circuit chip or (ii) electrically connected to ground by wires of the interposer or wires of the integrated circuit chip.

Owner:GLOBALFOUNDRIES U S INC

3D semiconductor interposer for heterogeneous integration of standard memory and split-architecture processor

ActiveUS8957525B2Minimization requirementsRelieve stressSemiconductor/solid-state device detailsSolid-state devicesMemory chipSilicon interposer

A standard memory chip (150) is vertically assembled with two processor chips (130, 140) of split architecture by means of a small silicon interposer (120) stacked onto a large silicon interposer (110); both interposers include through-silicon vias (TSVs), while the chips are free of TSVs. The TSVs of small interposer (120) connect to the memory chip (150) and to the bottom interposer (110). Symmetrically positioned relative to interposer (120), and connected to it by short signal traces, chips (130, 140) are attached to the TSVs of interposer 110, which in turn is attached to a substrate (160) with supply connections.

Owner:TEXAS INSTR INC

Wiring substrate, manufacturing method thereof, and semiconductor device

ActiveUS7901986B2Reduce manufacturing costHigh yieldPrinted circuit assemblingSemiconductor/solid-state device detailsSilicon interposerElectrical connection

In a wiring substrate according to the present invention, a base wiring board is constructed by stacking a plurality of unit wiring boards each having wiring patterns which enable an electrical connection between upper and lower sides, in a state that the plurality of unit wiring boards are connected to each other via a connection terminal, and a silicon interposer is stacked on the base wiring board via a connection terminal, and a resin portion is filled in a gap between the plurality of unit wiring boards as well as a gap between the base wiring board and the silicon interposer, and a resin portion serves as a substrate which integrates the base wiring board and the silicon interposer.

Owner:SHINKO ELECTRIC IND CO LTD

Chip package structure using silicon interposer as interconnection bridge

ActiveUS20210074645A1Easy to integrateImproves signal/consumption performanceSemiconductor/solid-state device detailsSolid-state devicesSilicon interposerEngineering physics

A chip package structure using silicon interposer as interconnection bridge lifts multi-dies above the fan-out molding package embedded with premade Si interposer interconnection bridge under the multi-die space. The interconnection bridge connects the multi-dies through fine pitch high I / O interconnection. A first RDL and a second RDL are further disposed on top side and bottom side of the fan-out molding package, further providing connection for the multi-dies to a substrate via the connection routing inside the fan-out molding package.

Owner:POWERTECH TECHNOLOGY

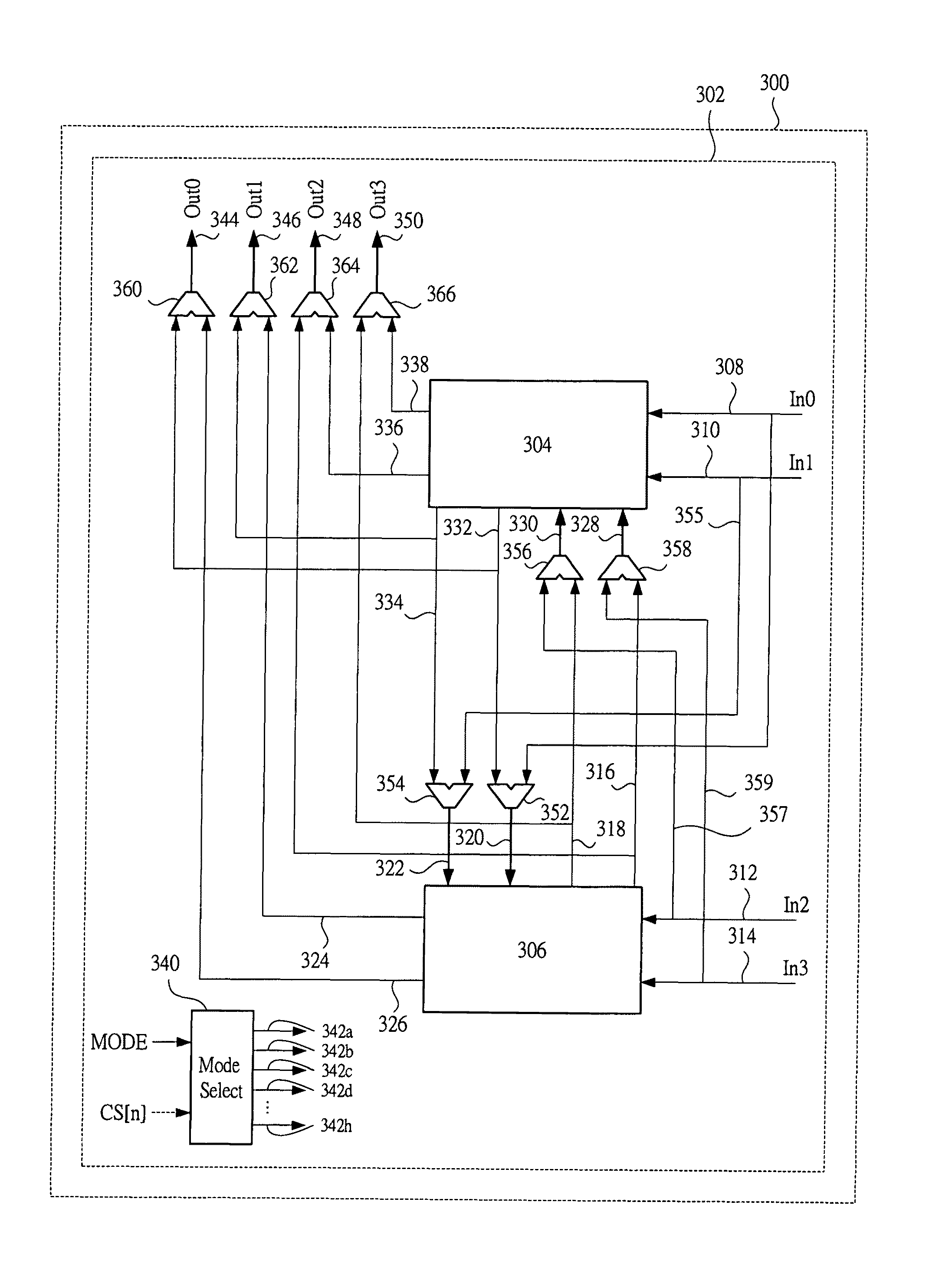

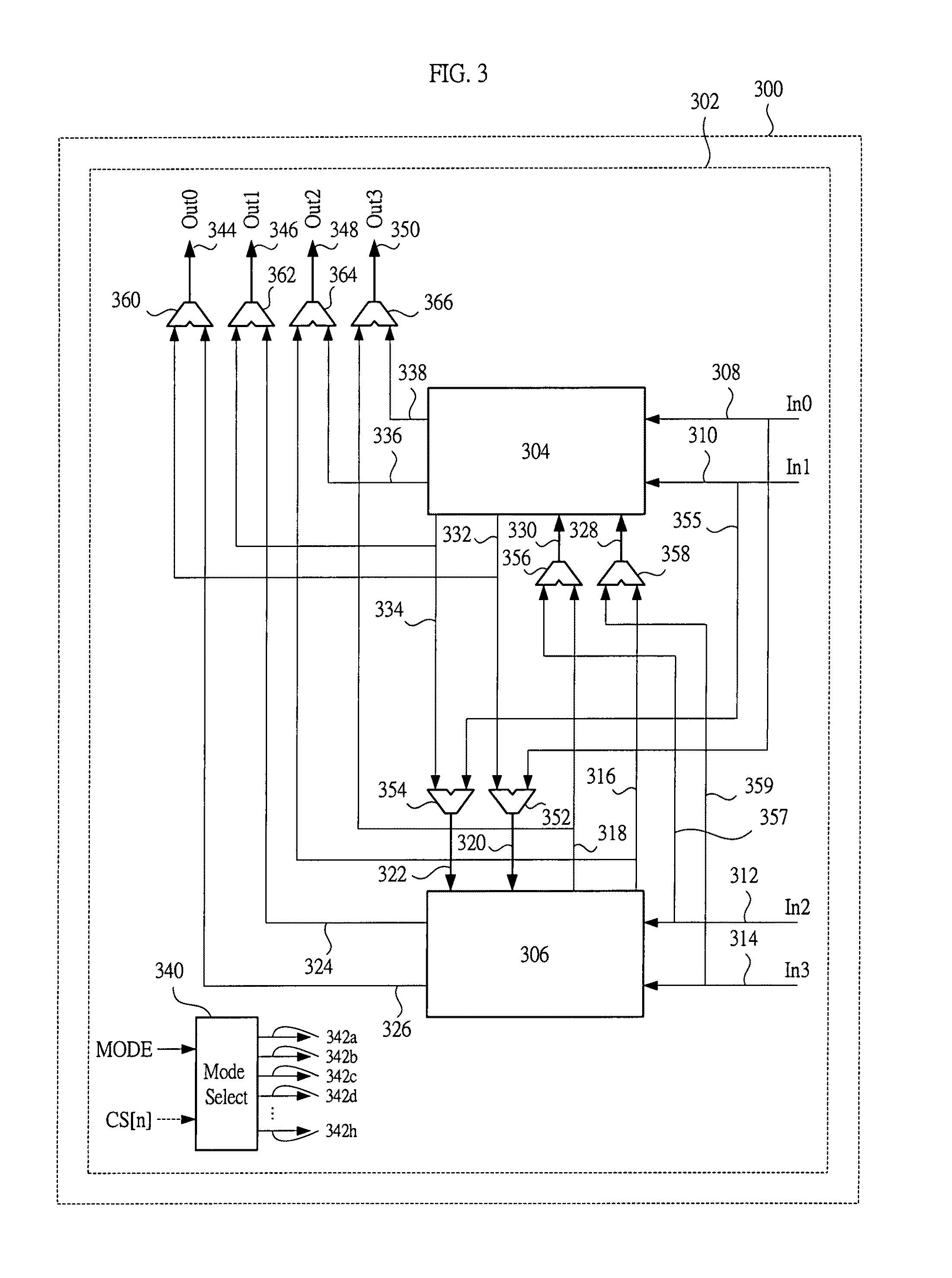

Method and device for scan chain management of dies reused in a multi-chip package

InactiveUS7945827B1Electronic circuit testingInput/output processes for data processingSilicon interposerManufacturing technology

An apparatus and method for economical testing of dies in a multichip module. Internal I / O pins on a die are logically connected to external I / O pins of the multichip module through the use of a silicon interposer on which the dies are attached. Multiplexers on the interposer can select between the external pins of the multichip module and the internal pins of the dies. The silicon interposer can be economically manufactured using manufacturing technology having relatively a large feature size, such as is found in a relatively mature IC fabrication plant. Further, use of the present invention allows multichip modules to be tested for faults without the necessity of redesigning test circuitry or adding additional pins to the package.

Owner:MARVELL INT TECH

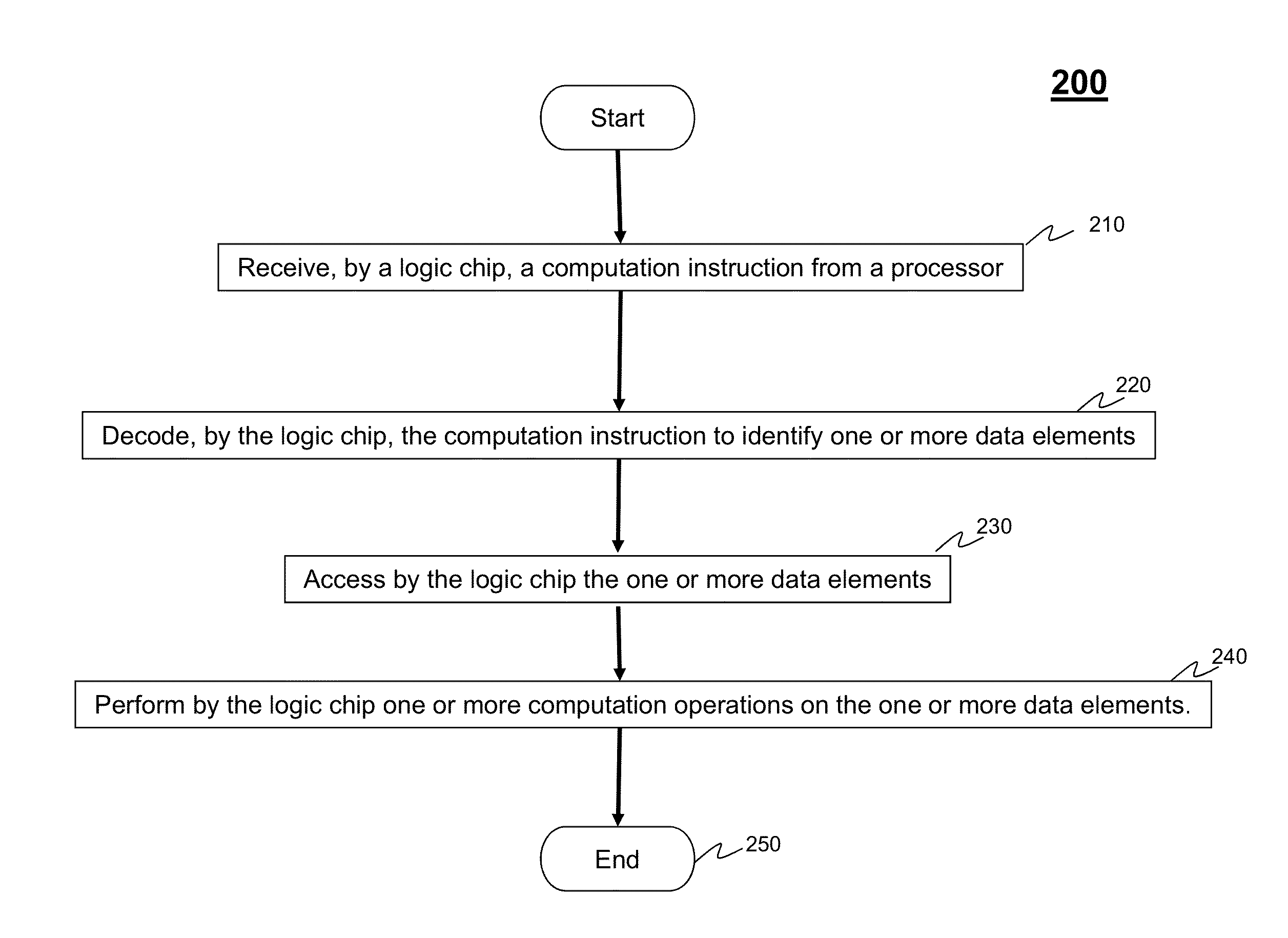

Computation Memory Operations in a Logic Layer of a Stacked Memory

ActiveUS20140181483A1Improve performance efficiencyImprove power efficiencyDigital computer detailsEnergy efficient computingSilicon interposerMaster processor

Some die-stacked memories will contain a logic layer in addition to one or more layers of DRAM (or other memory technology). This logic layer may be a discrete logic die or logic on a silicon interposer associated with a stack of memory dies. Additional circuitry / functionality is placed on the logic layer to implement functionality to perform various computation operations. This functionality would be desired where performing the operations locally near the memory devices would allow increased performance and / or power efficiency by avoiding transmission of data across the interface to the host processor.

Owner:ADVANCED MICRO DEVICES INC

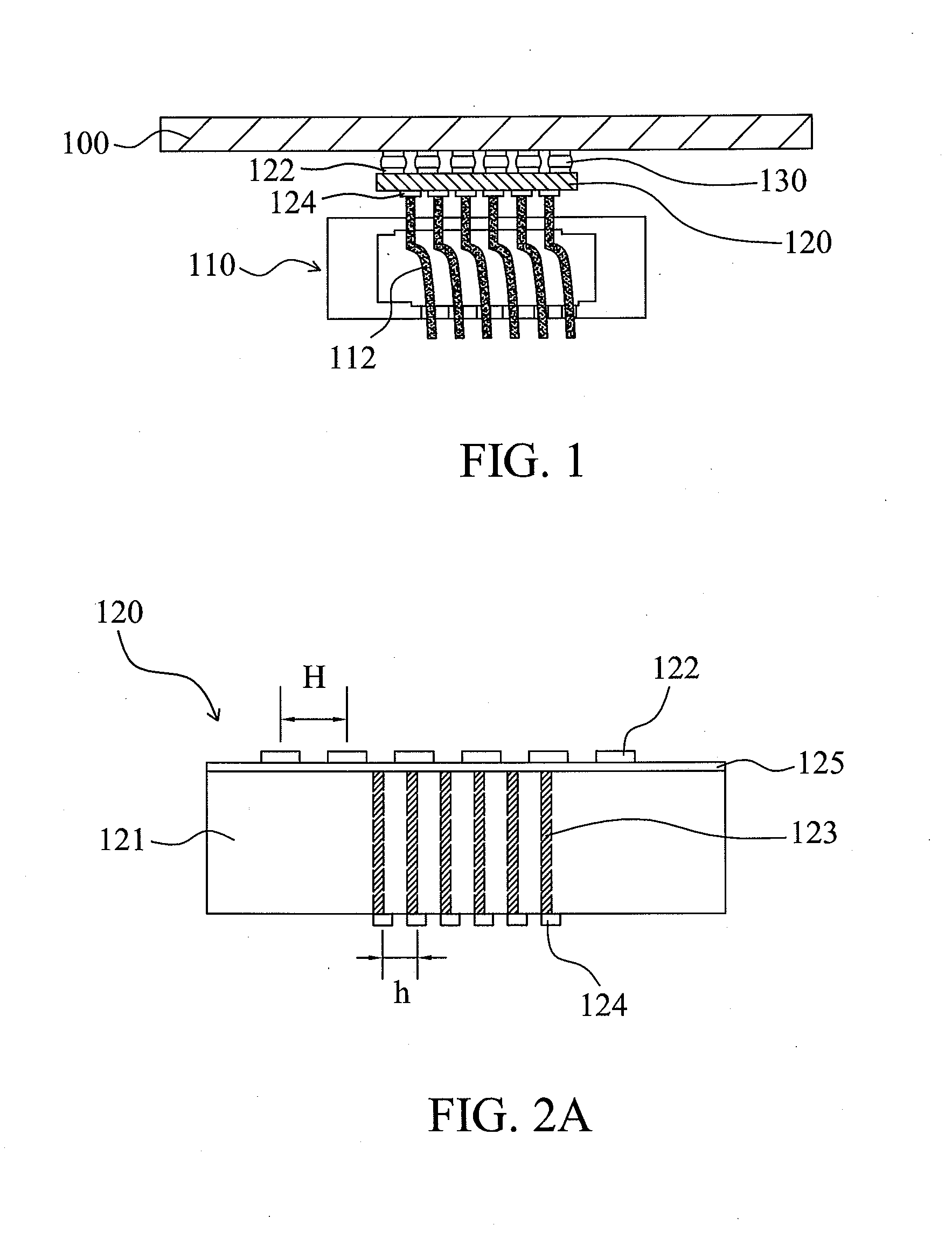

Probe card for circuit-testing

ActiveUS20140091827A1Reduce spacingElectrical measurement instrument detailsElectrical testingSilicon interposerProbe card

A probe card for circuit-testing comprising a testing PCB, a probe head, and a silicon interposer substrate is provided. The probe head has a plurality of probes provided with a fine pitch arrangement and held inside. The silicon interposer substrate is used for conveying signals between said probes and said test PCB. The interconnection of said silicon interposer substrate is formed by utilizing the through-silicon via process. A plurality of upper terminals and a plurality of lower terminals are respectively array-arranged on the top surface and the bottom surface of said silicon interposer substrate. The pitch between the upper terminals is larger than the pitch between the lower terminals and the pitch between adjacent lower terminals is equal to the fine pitch of the arrangement of probes.

Owner:HERMES EPITEK

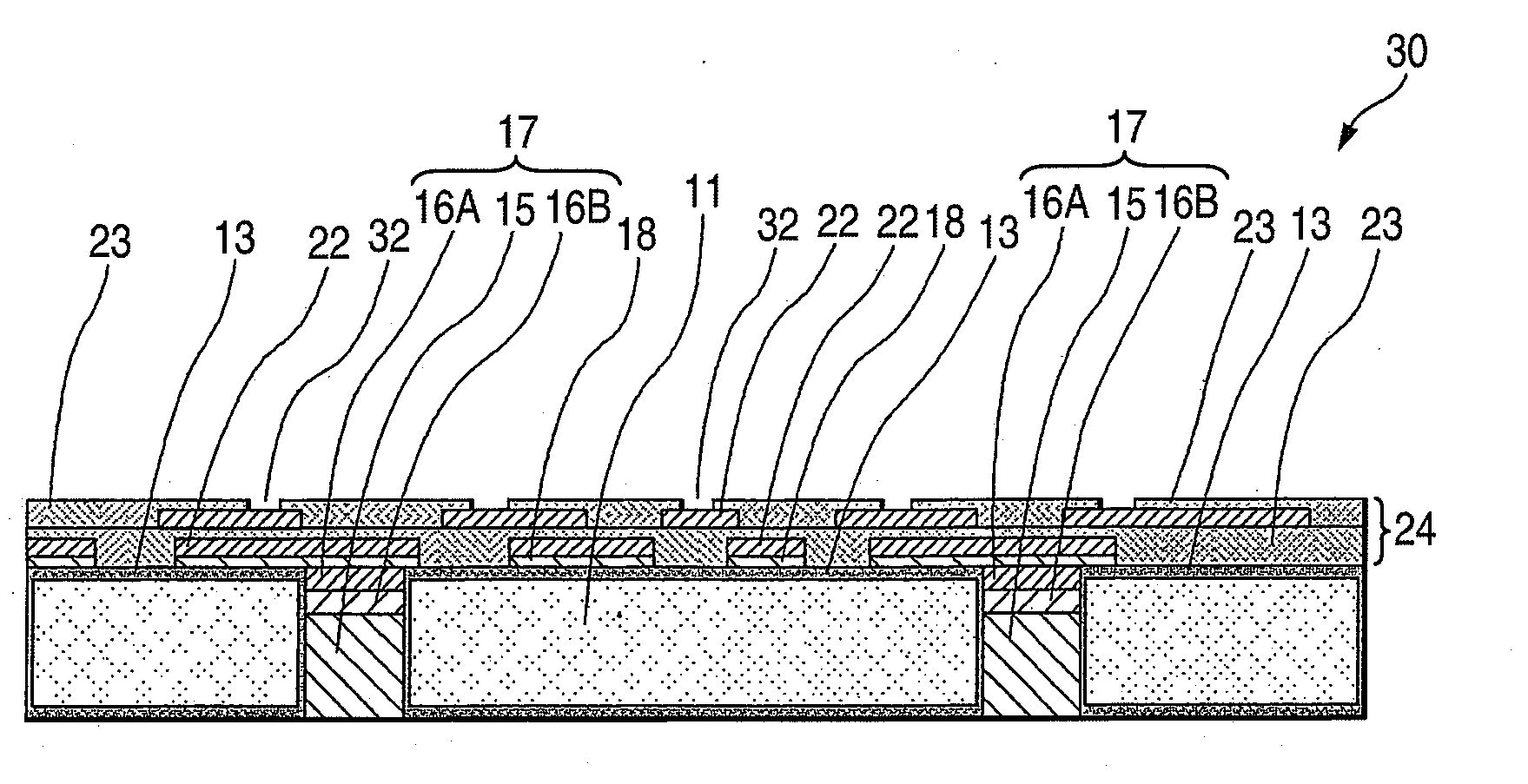

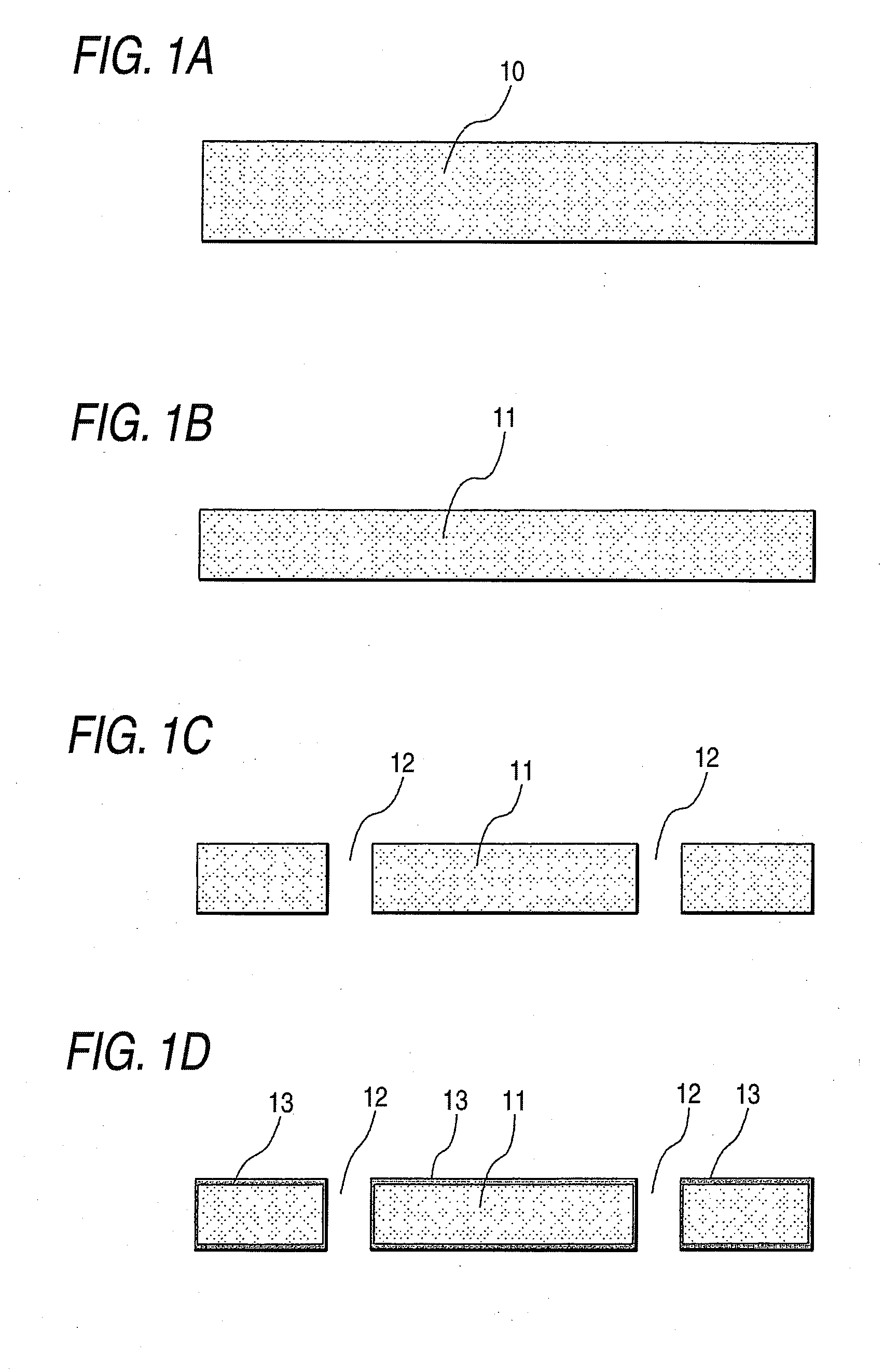

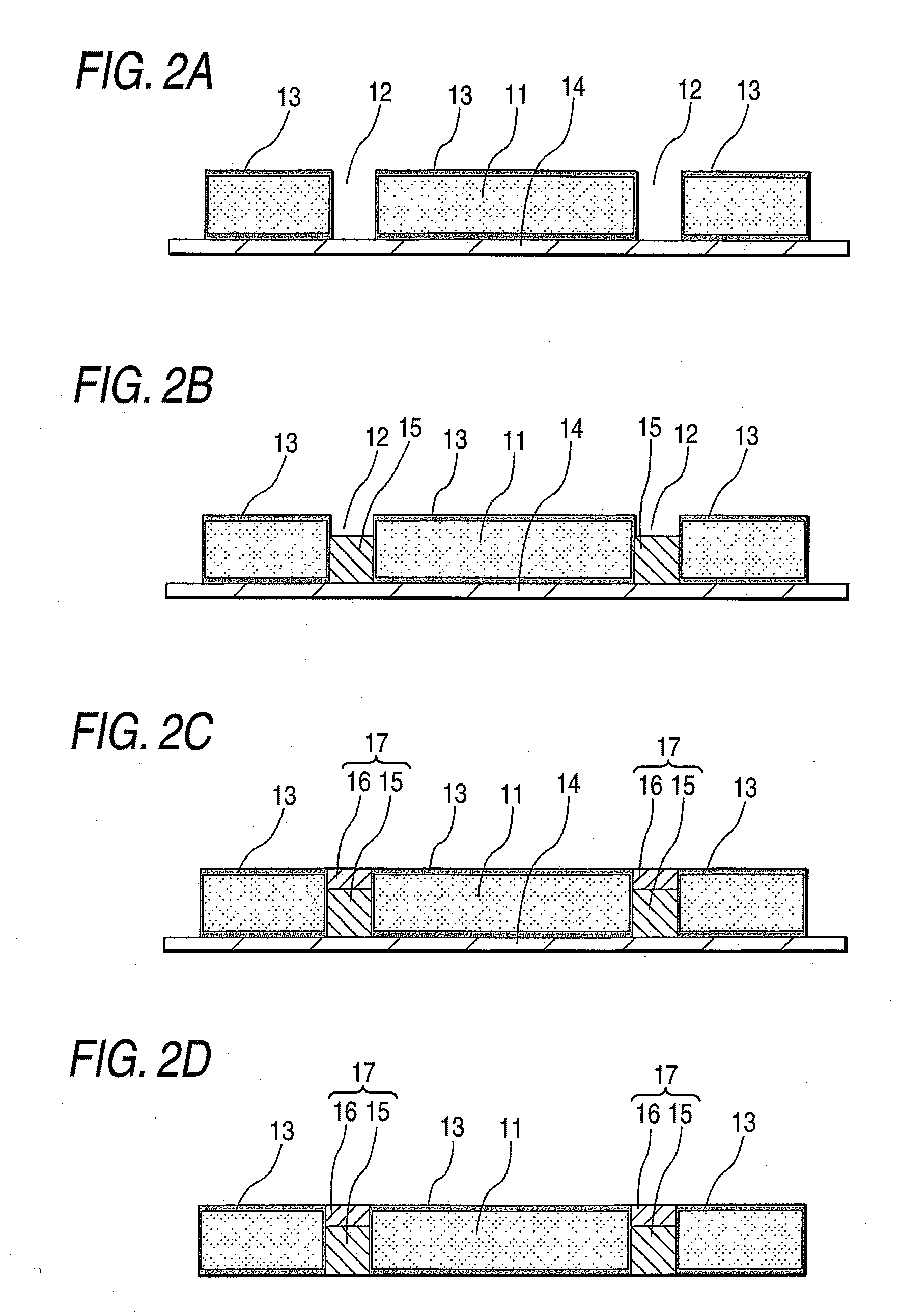

Silicon interposer and semiconductor device package and semiconductor device incorporating the same

InactiveUS20090121344A1Relieve stressSemiconductor/solid-state device detailsSolid-state devicesSilicon interposerSemiconductor package

A silicon interposer 30 being held between a wiring board 40 and a semiconductor element 60 to electrically connect the wiring board 40 to the semiconductor element 60, wherein through-hole electrodes 17 for electrically connecting the wiring board 40 to the semiconductor element 60 are each formed of a base section and a buffer section, and the buffer section is formed of a conductive material having an elastic coefficient lower than that of the conductive material of the base section, and a semiconductor device package 50 and a semiconductor device 70 incorporating the silicon interposer 30.

Owner:SHINKO ELECTRIC IND CO LTD

Interconnection and package method on basis of TSV (through silicon via) chips

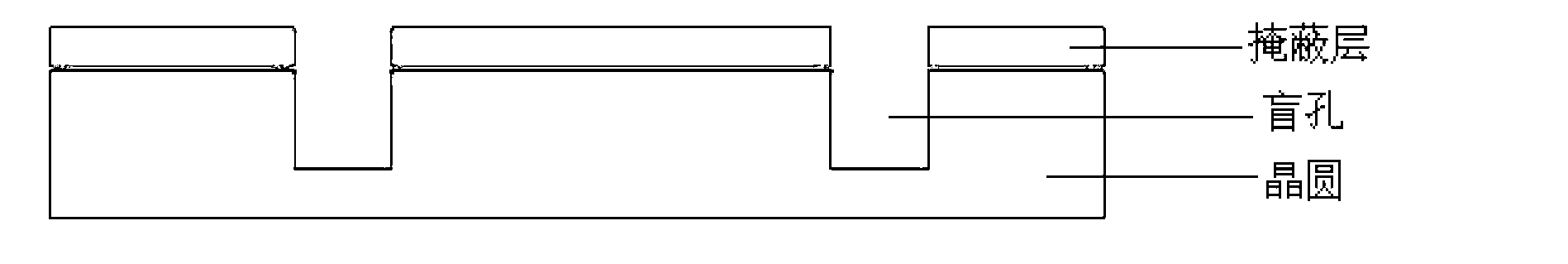

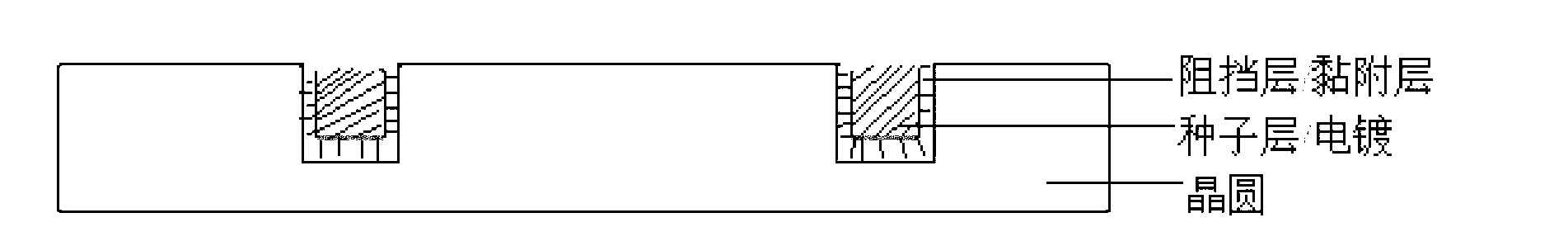

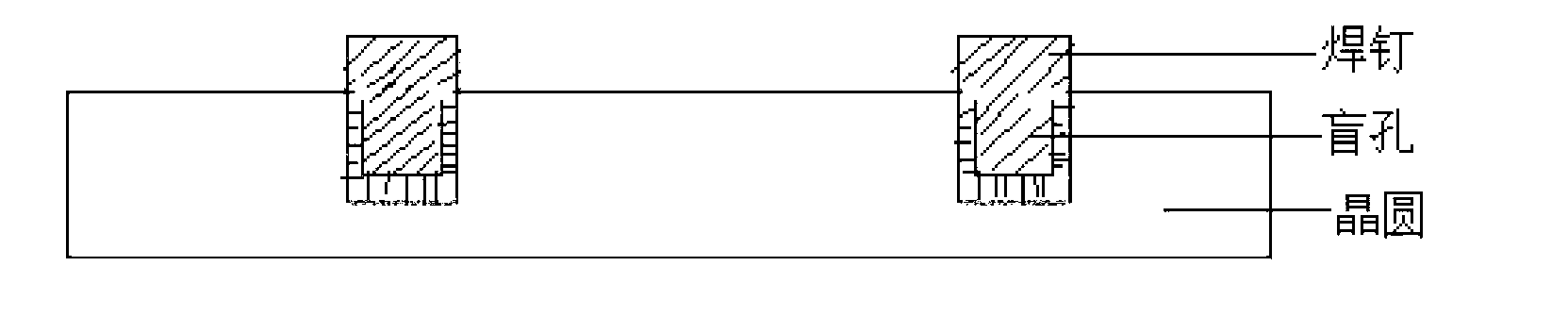

ActiveCN103295926AAchieving Sealed ProtectionImprove reliabilitySolid-state devicesSemiconductor/solid-state device manufacturingSilicon interposerEngineering

The invention discloses an interconnection and package method on the basis of TSV (through silicon via) chips. By the aid of silicon interposers, interconnection of multi-layer laminated chips with narrow salient points and narrow spacing is changed into interconnection with large salient points and large spacing, and accordingly, subsequent installation process is achieved. By means of padding-bottom among the chips, between the chips and the interposers, and between the interposers and a substrate, multi-layer chip structure and the substrate structure are fixed onto the substrate. By means of package, seal protection of the TSV unpacked chips is realized and reliability of devices is improved.

Owner:NO 771 INST OF NO 9 RES INST CHINA AEROSPACE SCI & TECH

Wafer scale packaging platform for transceivers

InactiveUS8803269B2Accurate placementSemiconductor/solid-state device detailsSolid-state devicesSilicon interposerTransceiver

A wafer scale implementation of an opto-electronic transceiver assembly process utilizes a silicon wafer as an optical reference plane and platform upon which all necessary optical and electronic components are simultaneously assembled for a plurality of separate transceiver modules. In particular, a silicon wafer is utilized as a “platform” (interposer) upon which all of the components for a multiple number of transceiver modules are mounted or integrated, with the top surface of the silicon interposer used as a reference plane for defining the optical signal path between separate optical components. Indeed, by using a single silicon wafer as the platform for a large number of separate transceiver modules, one is able to use a wafer scale assembly process, as well as optical alignment and testing of these modules.

Owner:CISCO TECH INC

Integrated circuit packaging system with stackable package and method of manufacture thereof

ActiveUS20110127662A1Semiconductor/solid-state device detailsSolid-state devicesSilicon interposerSealant

A method of manufacture of an integrated circuit packaging system includes: providing a package base having an inward base side and an outward base side; mounting a device over the inward base side and connected to the outward base side; connecting a silicon interposer having a through silicon via to the device and having an external side facing away from the device; and applying an encapsulant around the device, over the package base, and over the silicon interposer with the external side substantially exposed, the encapsulant having a protrusion over the outward base side.

Owner:STATS CHIPPAC LTD

Electronic package and fabrication method thereof

ActiveUS20160329267A1Eliminate needReduce package thicknessSemiconductor/solid-state device detailsSolid-state devicesSilicon interposerEngineering

An electronic package is provided, which includes: a circuit structure having opposite first and second sides; at least an electronic element disposed on the first side of the circuit structure; an encapsulant formed on the first side of the circuit structure for encapsulating the electronic element; a dielectric layer formed on portions of the second side of the circuit structure; and a metal structure formed on the dielectric layer and the circuit structure. The metal structure has a first metal layer bonded to the circuit structure and a second metal layer formed on the first metal layer and the dielectric layer. Therefore, by replacing a conventional silicon interposer with the circuit structure, the invention eliminates the need to fabricate through silicon vias so as to greatly reduce the fabrication difficulty and cost. The invention further provides a method for fabricating the electronic package.

Owner:SILICONWARE PRECISION IND CO LTD

Parallel Signal Via Structure

ActiveUS20140346678A1Reduce the differenceOvercome limitationsSemiconductor/solid-state device detailsSolid-state devicesSilicon interposerEngineering

A silicon interposer with redundant thru-silicon vias. The silicon interposer includes a first trace structure on a first side of the interposer and a second trace structure on a second side of the interposer. The silicon interposer also includes at least two redundant thru-silicon vias connecting the first trace structure to the second trace structure.

Owner:TESSERA ADVANCED TECH

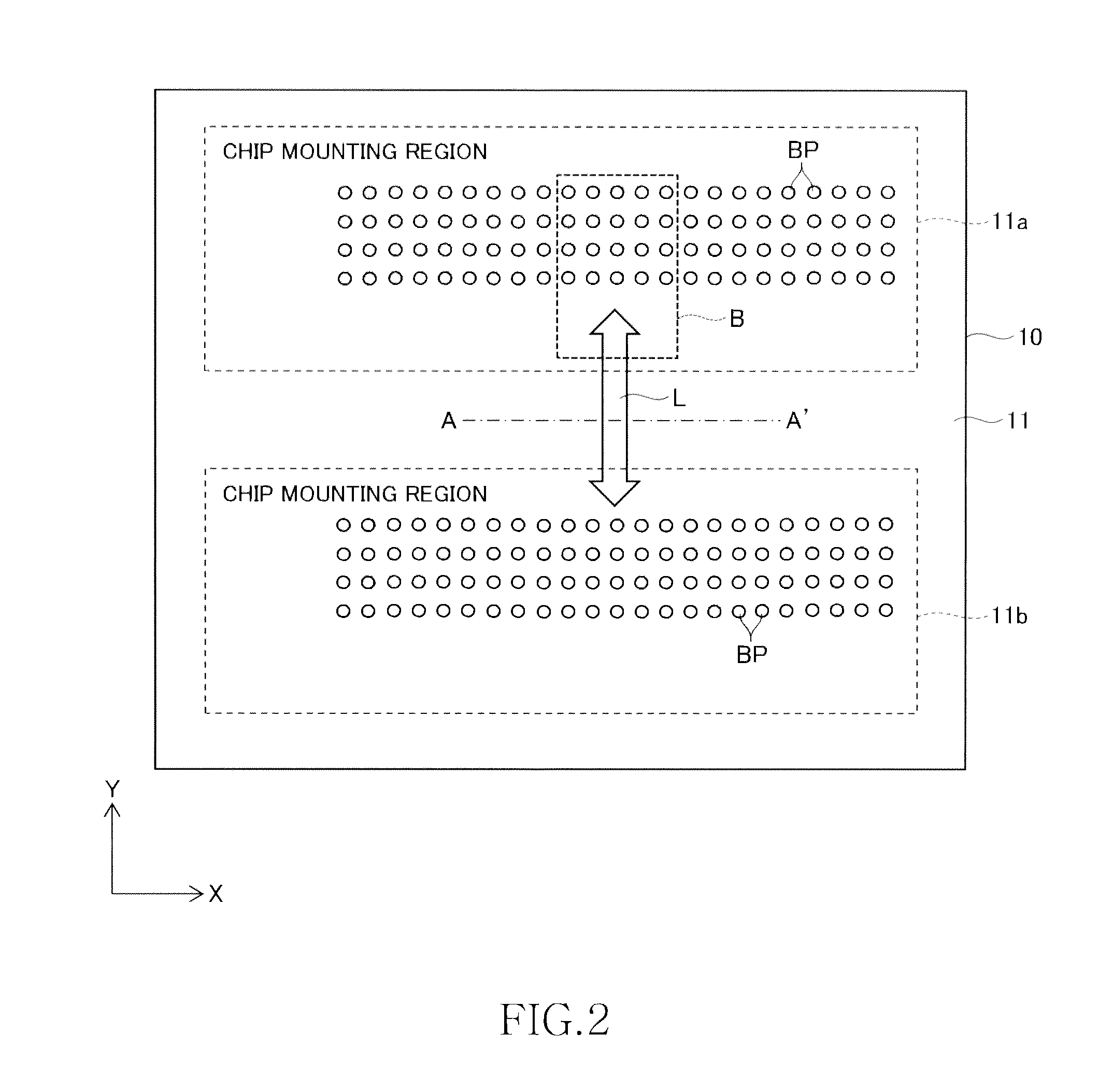

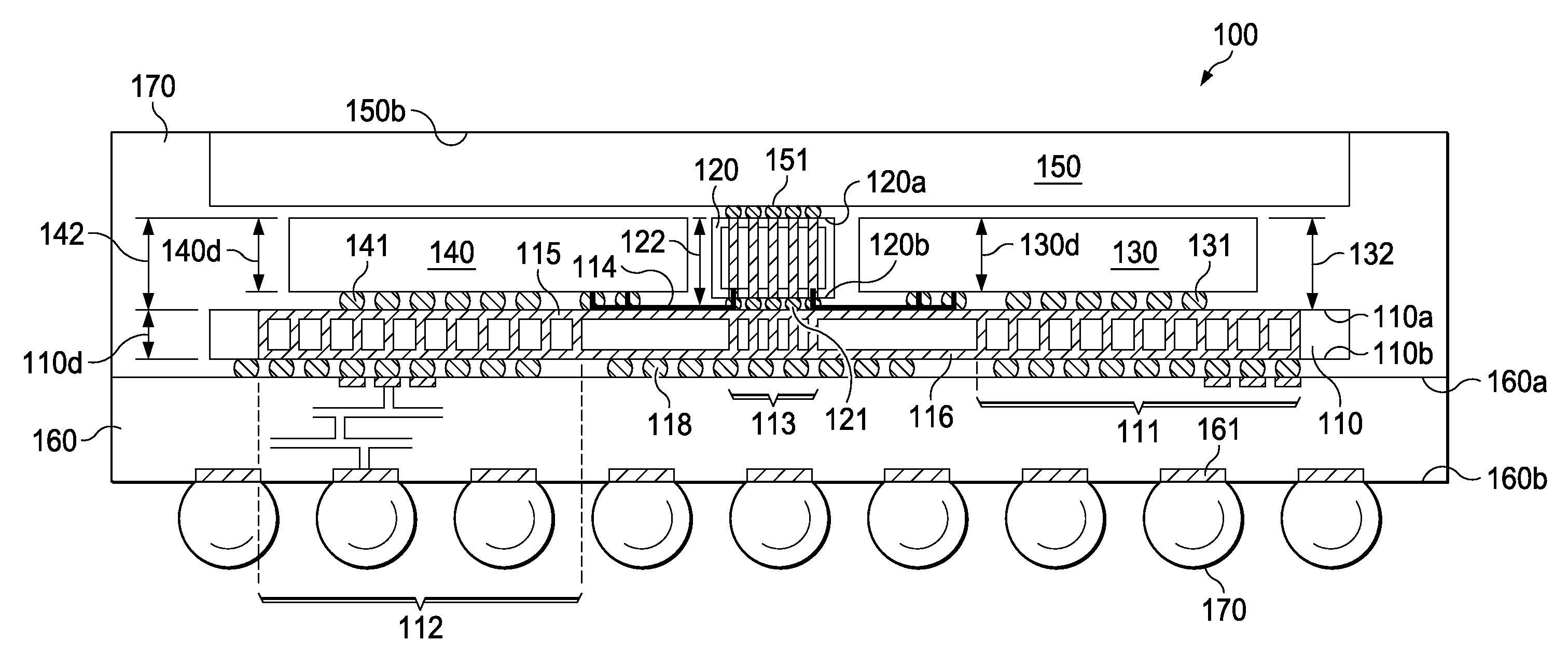

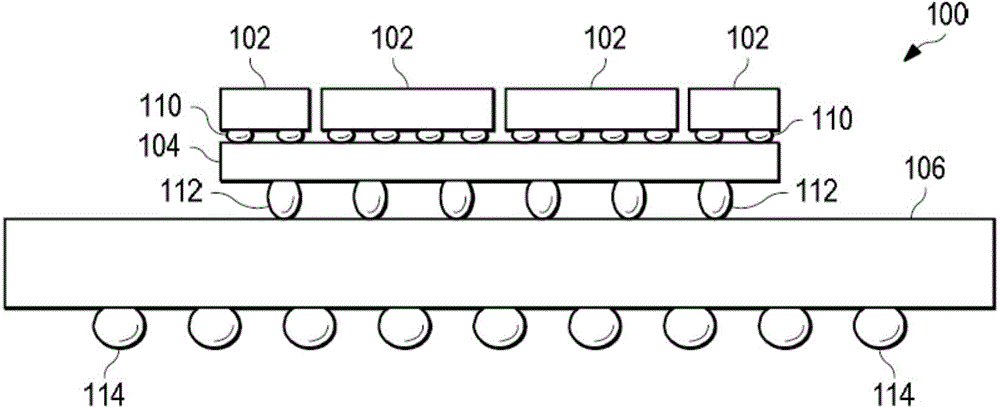

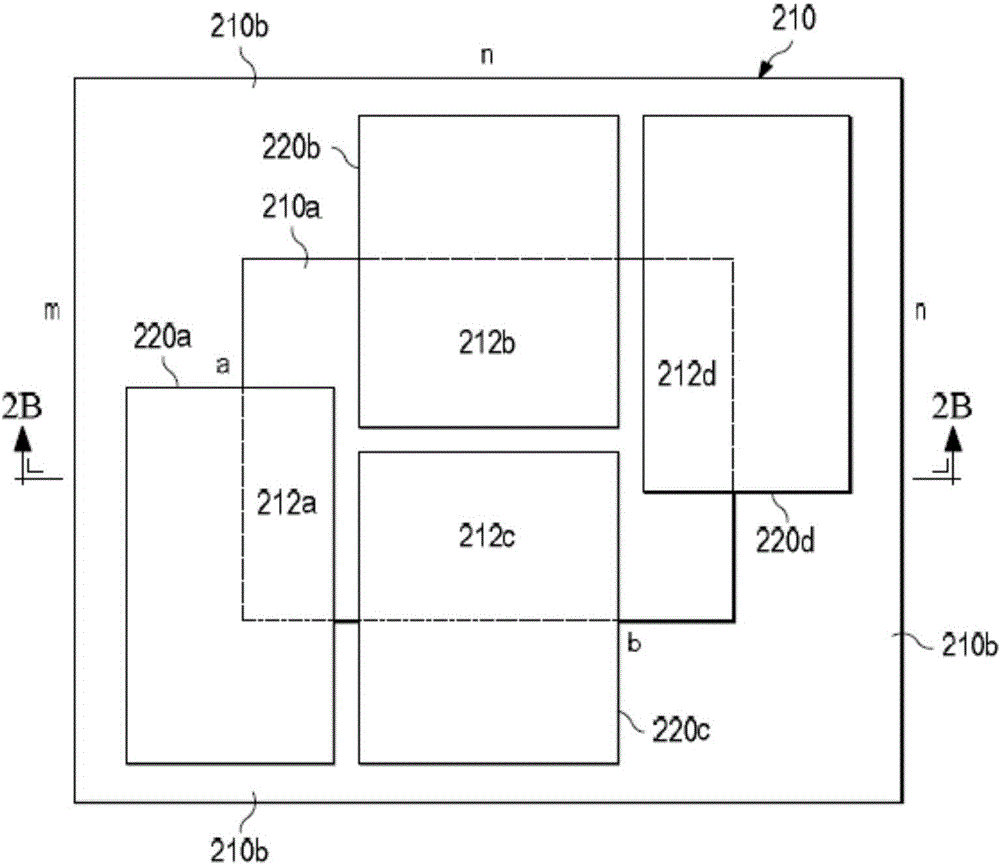

Large sized silicon interposers overcoming the reticle area limitations

ActiveCN104350595ASemiconductor/solid-state device detailsSolid-state devicesSilicon interposerDie (integrated circuit)

A multi-die integrated circuit assembly includes an interposer substrate larger than the typical reticle size used in fabricating the "active area" in which the through-silicon vias (TSVs) and interconnect conductors are formed in the interposer. At the same time, each of the dies has its external power / ground and I / O signal line connections concentrated into a smaller area of the die. The dies are disposed or mounted on the interposer such that these smaller areas (with the power / ground / IO connections) overlap with the active area of the interposer. In this configuration, a plurality of dies having a combined area substantially greater than the active area of the interposer can be mounted on the interposer (and take advantage of the active area for interconnections).

Owner:HUAWEI TECH CO LTD

Semiconductor package device and method of manufacturing the same

ActiveUS20180337130A1Semiconductor/solid-state device detailsSolid-state devicesSilicon interposerSemiconductor package

A semiconductor package device includes a first interconnection structure, a non-silicon interposer and a first die. The first interconnection structure has a first pitch. The non-silicon interposer surrounds the first interconnection structure. The non-silicon interposer includes a second interconnection structure having a second pitch. The second pitch is larger than the first pitch. The first die is above the first interconnection structure and is electrically connected to the first interconnection structure.

Owner:ADVANCED SEMICON ENG INC