Patents

Literature

447 results about "Multi-chip module" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

A multi-chip module (MCM) is generically an electronic assembly (such as a package with a number of conductor terminals or "pins") where multiple integrated circuits (ICs or "chips"), semiconductor dies and/or other discrete components are integrated, usually onto a unifying substrate, so that in use it can be treated as if it were a larger IC. Other terms, such as "hybrid" or "hybrid integrated circuit", also refer to MCMs. The individual ICs that make up an MCM are known as Chiplets. Intel and AMD are using MCMs to improve performance and reduce costs, as splitting a large monolithic IC into smaller chiplets allows for more ICs per wafer, and improved yield, as smaller dies have a reduced risk of getting destroyed by dust particles during semiconductor fabrication. Each chiplet is physically smaller than a conventional monolithic IC die, (A monolithic IC is an IC package contining a single IC). An example of MCMs in use for mainstream CPUs is AMD's Zen 2 design.

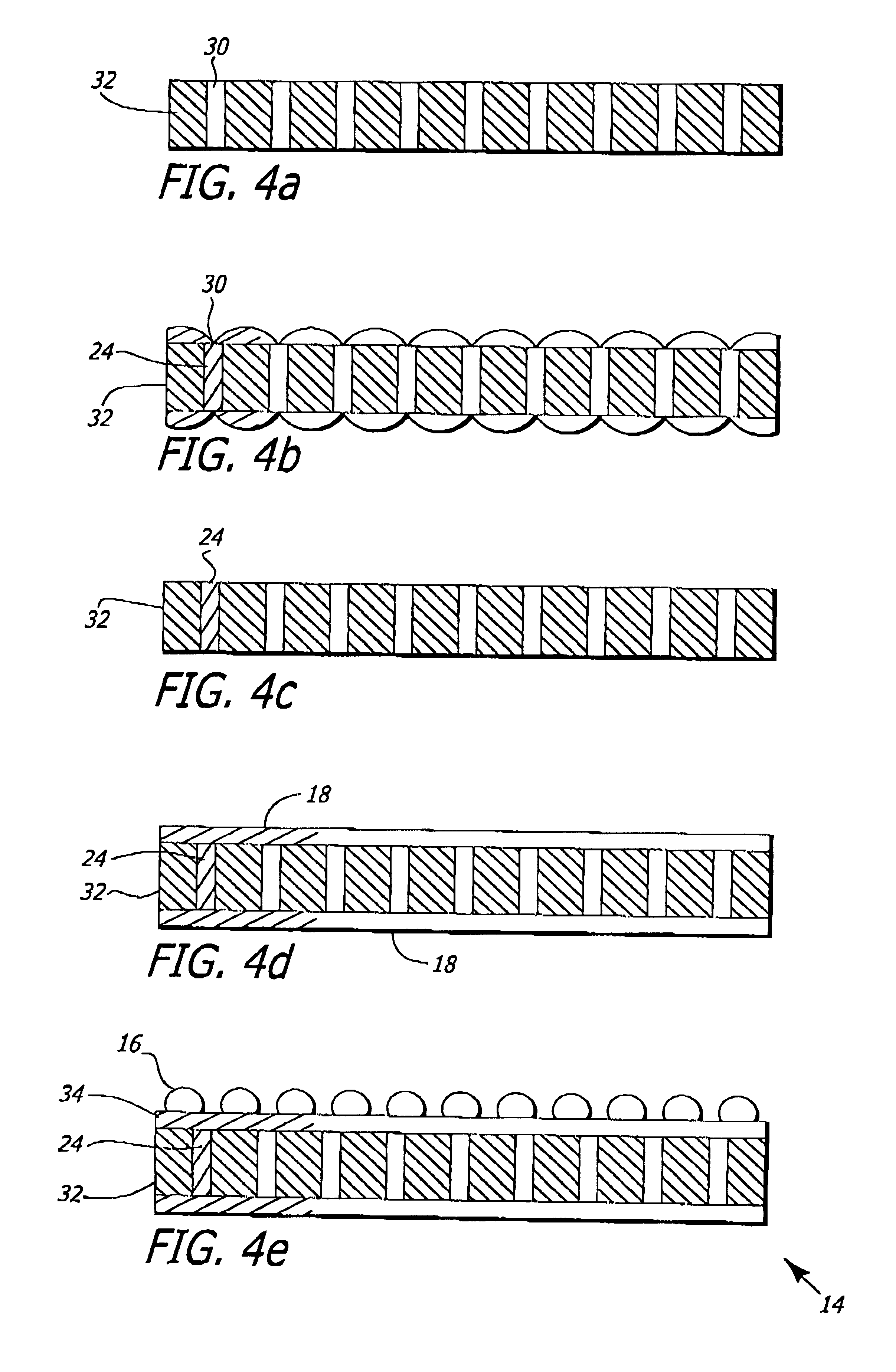

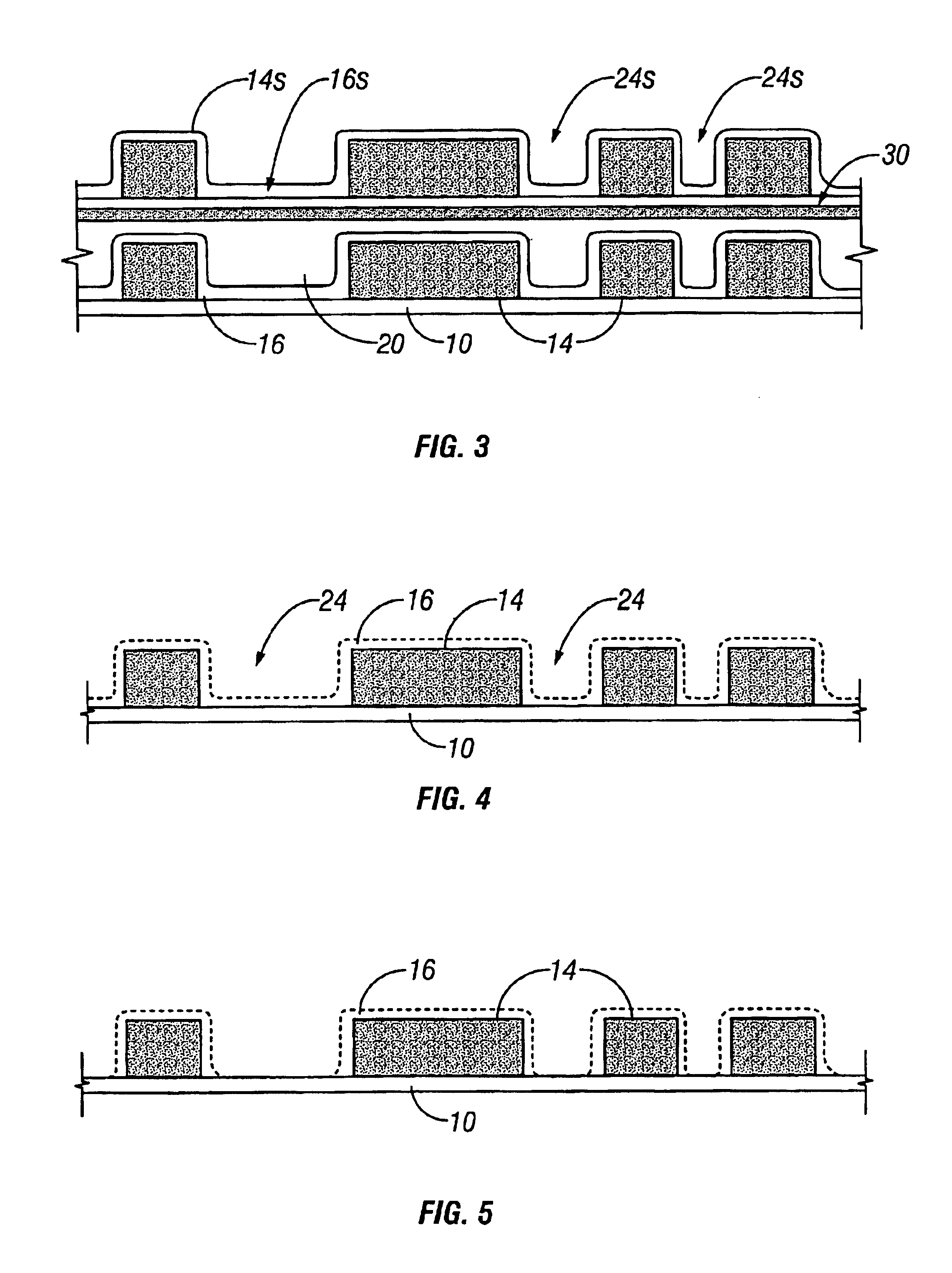

High reliability multlayer circuit substrates and methods for their formation

InactiveUS20040061234A1Semiconductor/solid-state device detailsPrinted circuit aspectsElectrical conductorOptoelectronics

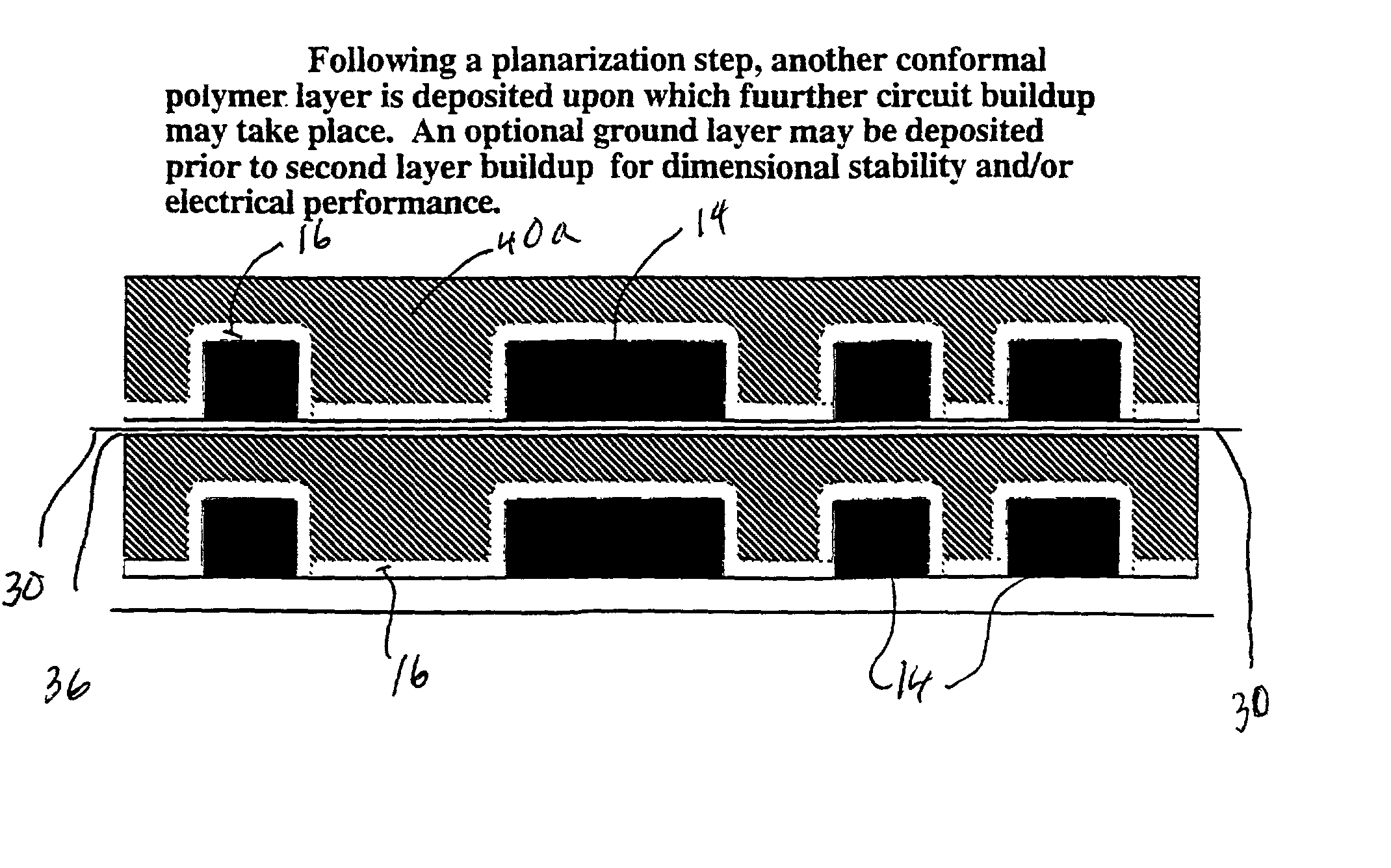

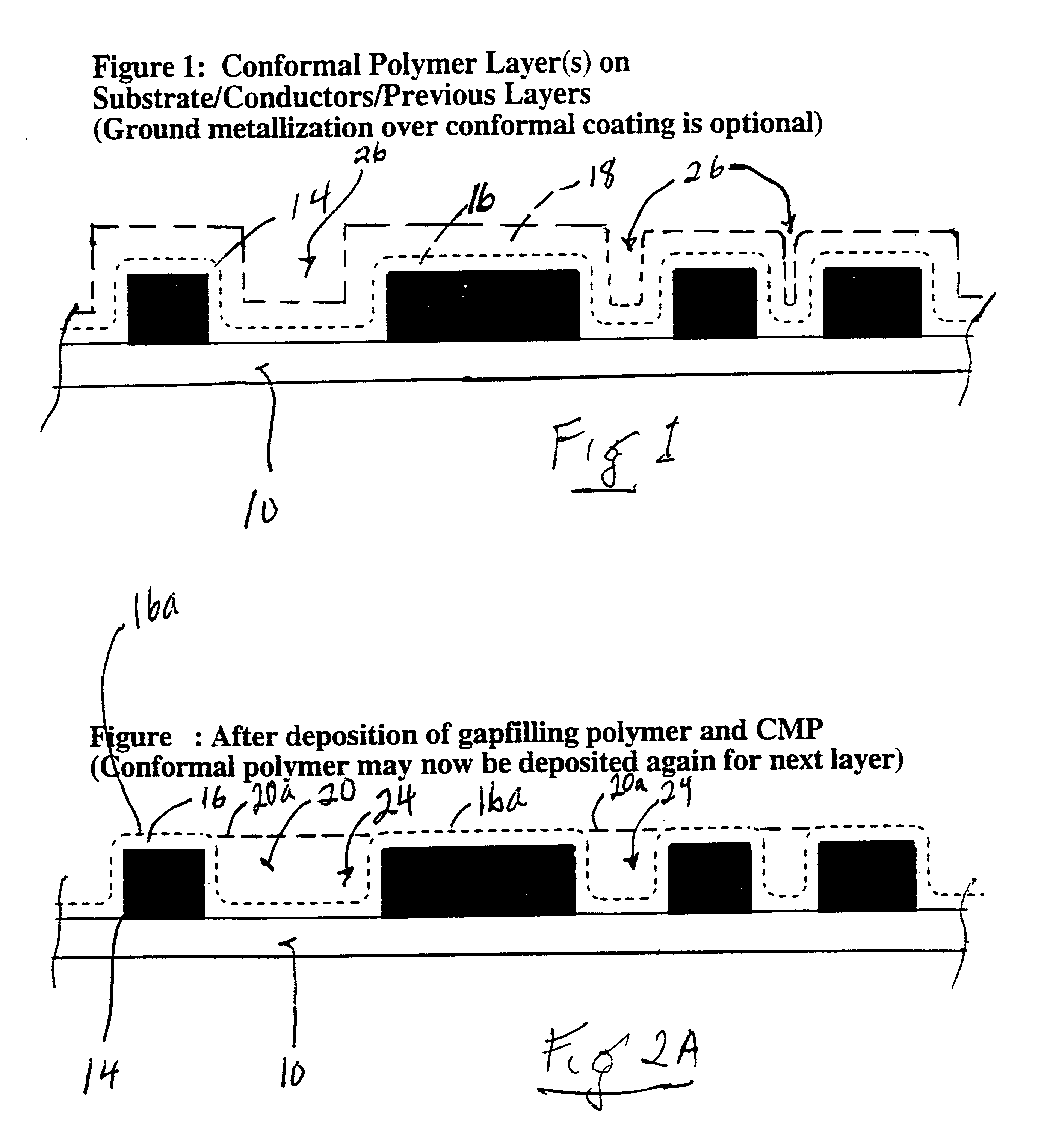

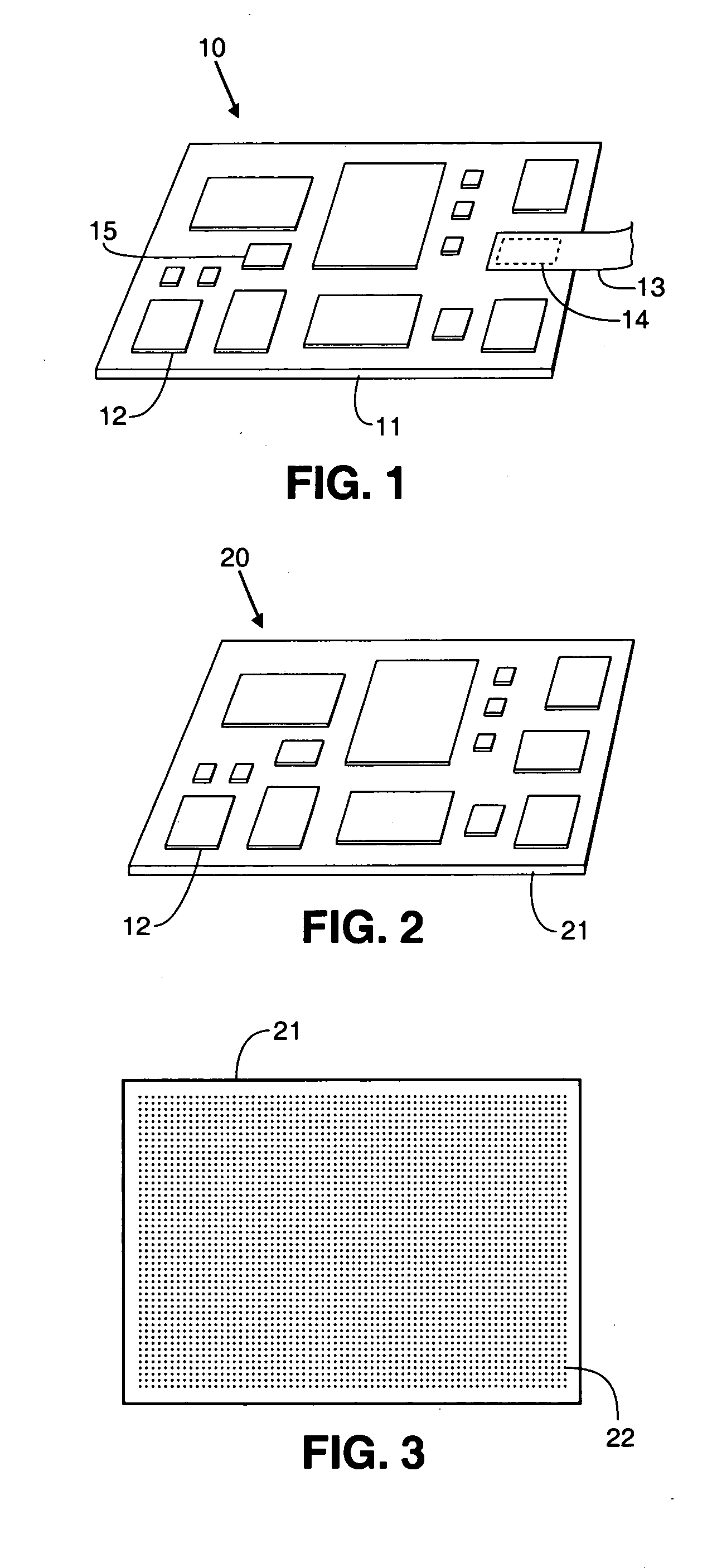

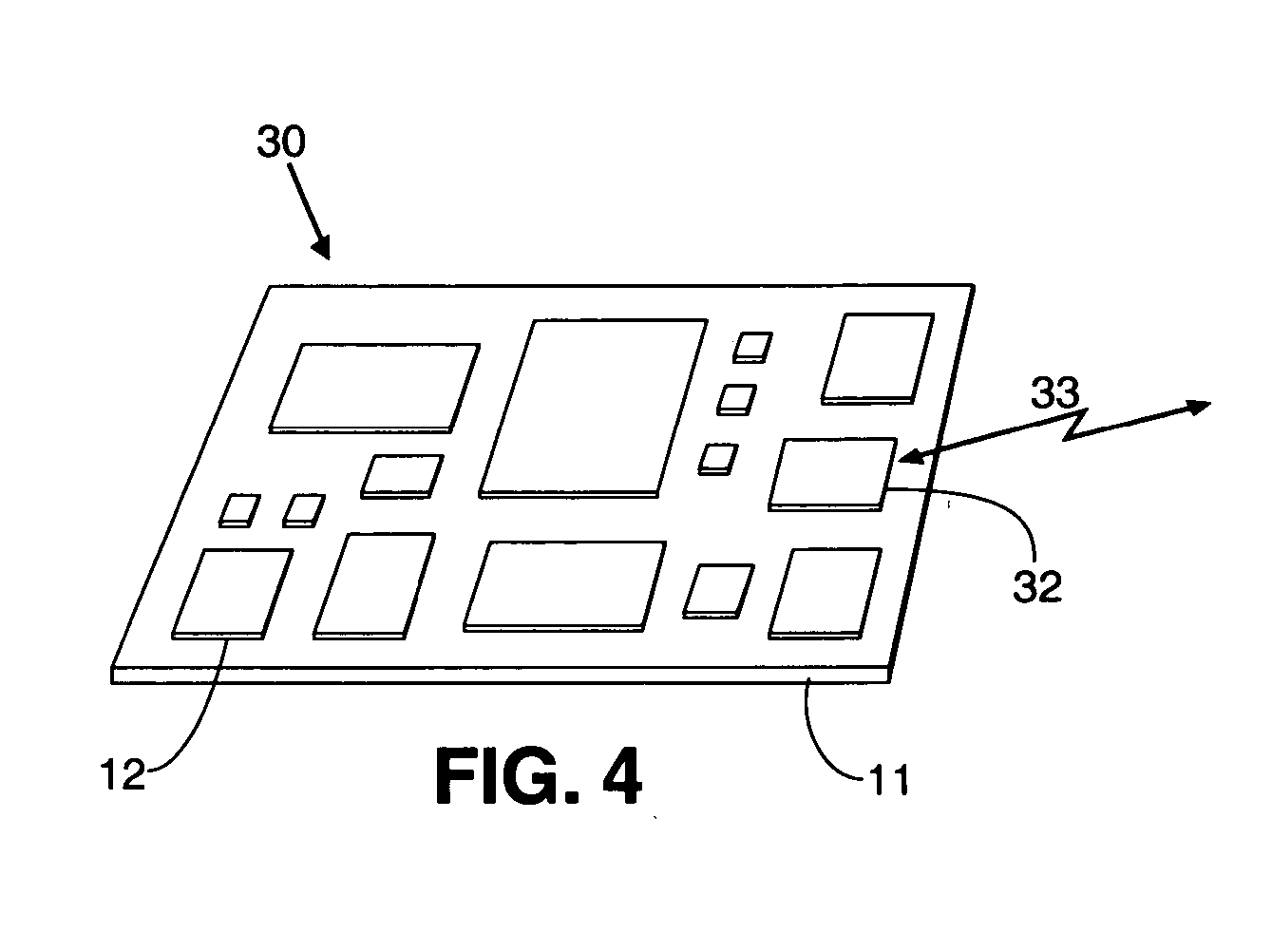

A multilayer circuit substrate for multi-chip modules or hybrid circuits includes a dielectric base substrate, conductors formed on the base substrate and a vacuum deposited dielectric thin film formed over the conductors and the base substrate. The vacuum deposited dielectric thin film is patterned using sacrificial structures formed by shadow mask techniques. Substrates formed in this manner enable significant increases in interconnect density and significant reduction of over-all substrate thickness.

Owner:MEDTRONIC MIMIMED INC

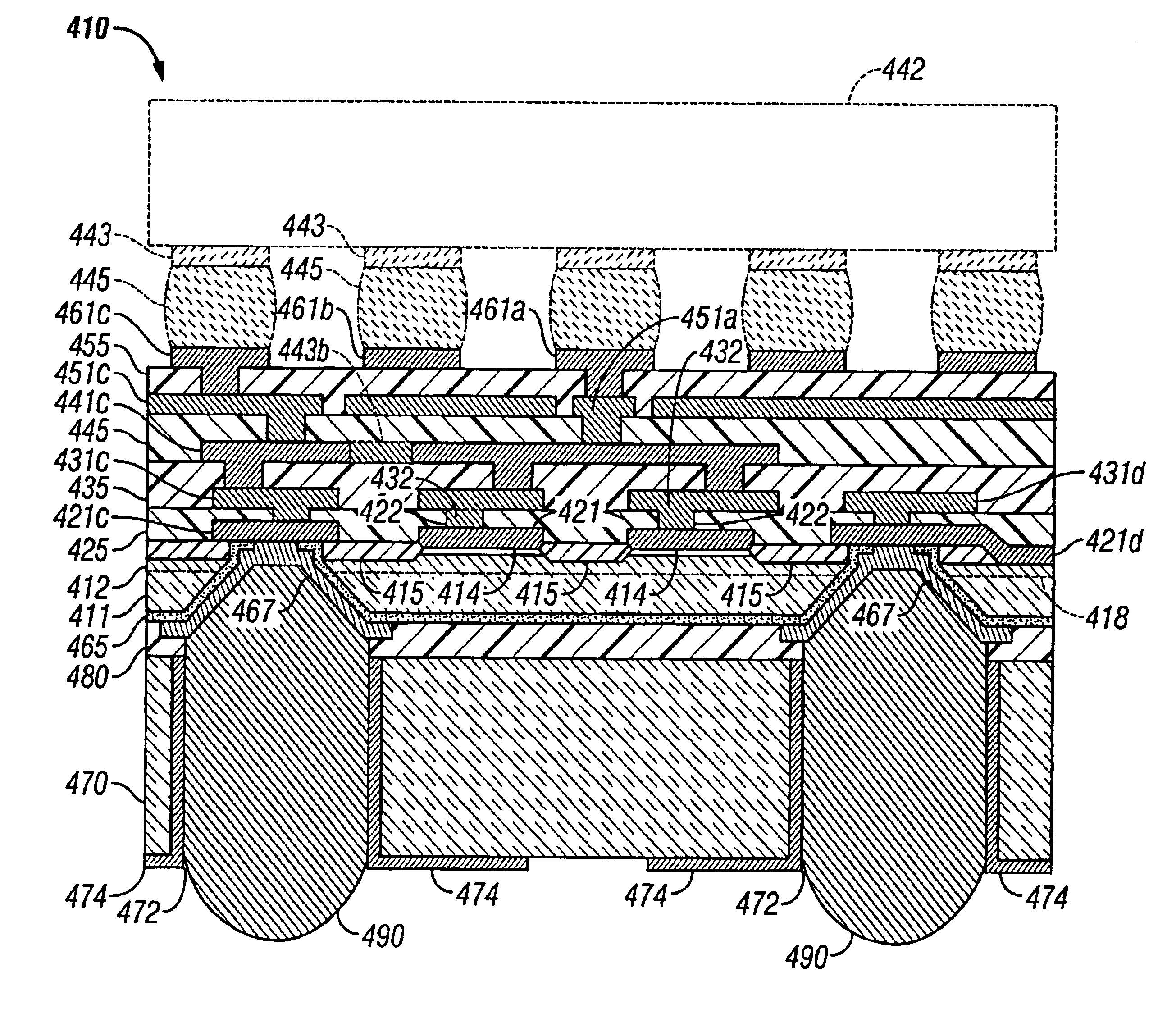

Silicon interposer and multi-chip-module (MCM) with through substrate vias

InactiveUS6562653B1Semiconductor/solid-state device detailsSolid-state devicesSilicon interposerEngineering

An integrated circuit package which includes an integrated circuit that is connected to a silicon substrate. The silicon substrate may have a via. The package may further include a solder bump that is attached to both the integrated circuit and the silicon subtstrate. The silicon substrate has a coefficient of thermal expansion that matches the coefficient of thermal expansion of the integrated circuit.

Owner:INTEL CORP

Robust lidar sensor for broad weather, shock and vibration conditions

InactiveUS20160047901A1Optical rangefindersElectromagnetic wave reradiationLaser transmitterVibration control

An apparatus and method are used for real-time wide-field-of-view ranging with a time-of-flight lidar sensor having one or a plurality of laser emitters and one or a plurality of photodetectors. When a plurarity of laser emitters are used, they are preferably copackaged or are in the form of an integrated multi-emitter chip or emitting multi-chip module in a single package, and when a plurarity of photoreceivers are used, they are preferably copackaged or are in the form of an integrated multi-photoreceiver chip or photoreceiving multi-chip module in a single package. Furthermore, the apparatus comprises any combination of (a) no moving external parts in contact with the environment, (b) wireless energy and data transfer between the static and the moving parts of the lidar, and (c) protective body, sealant and / or damage-resistant tamper-resistant theft-resistant cage.

Owner:QUANERGY SYST

Hybrid Transactional Memory System (HybridTM) and Method

InactiveUS20110119452A1Simple/cost-effective hardware designAdd supportNon-redundant fault processingMemory systemsOperational systemHandling system

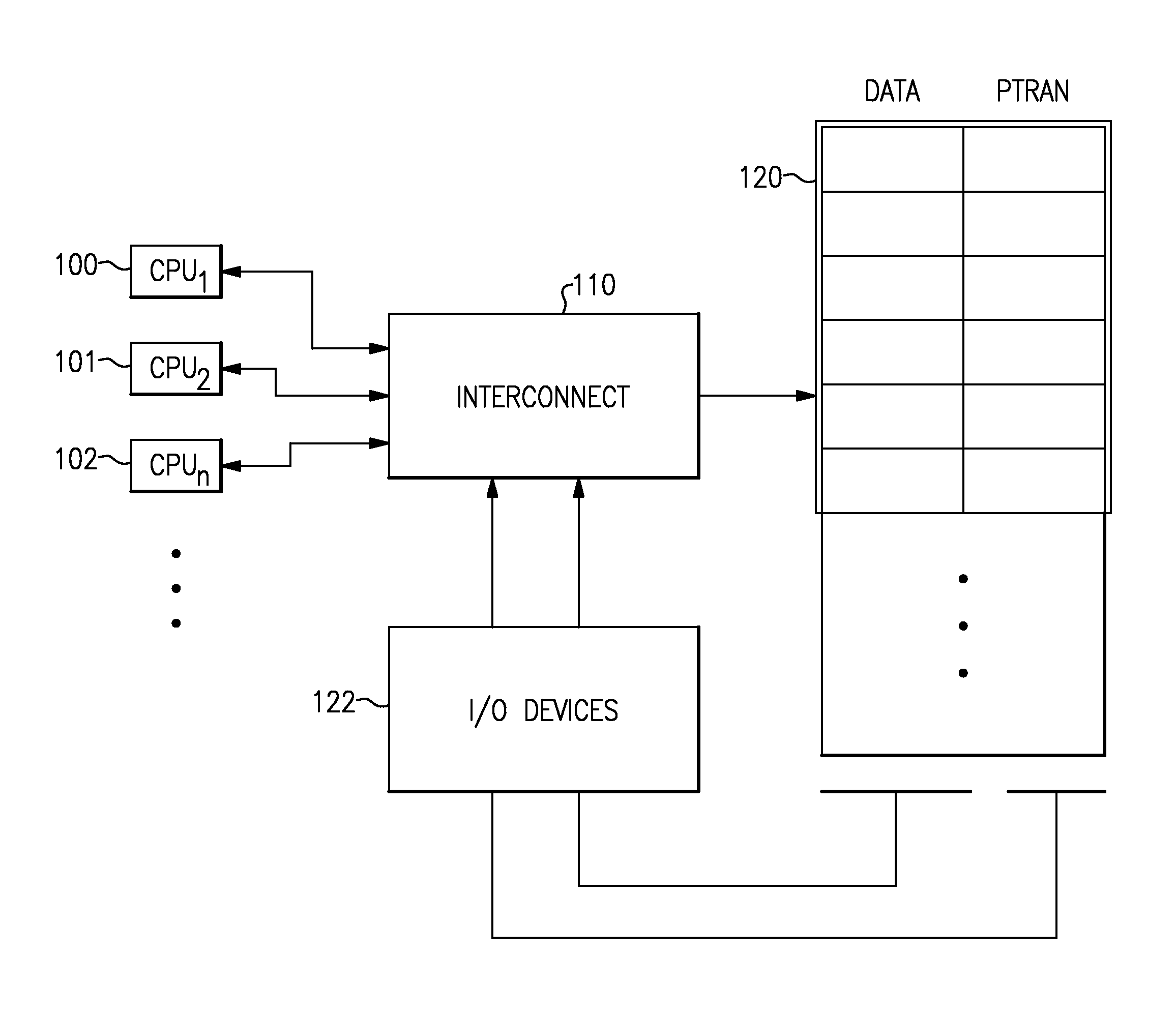

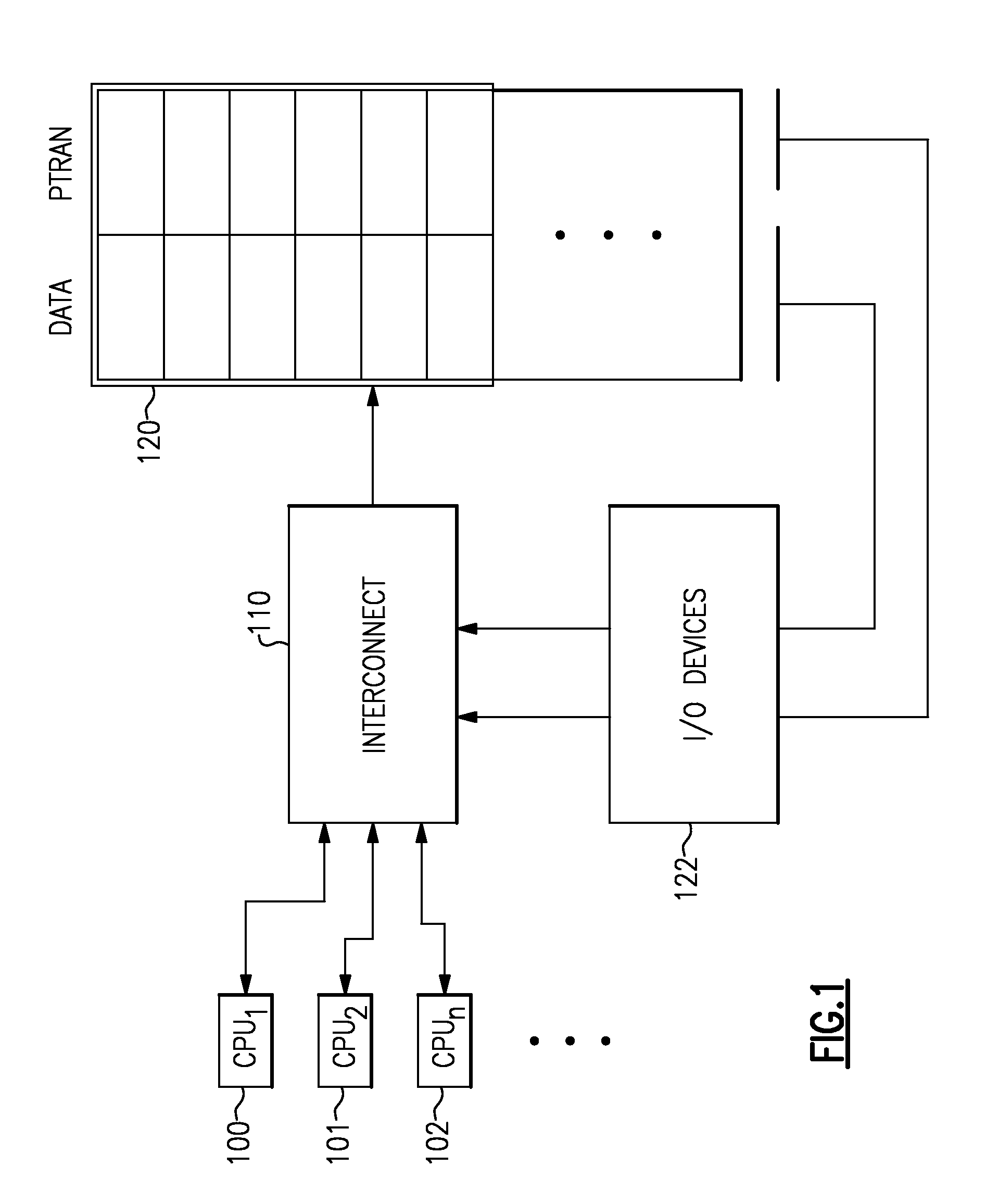

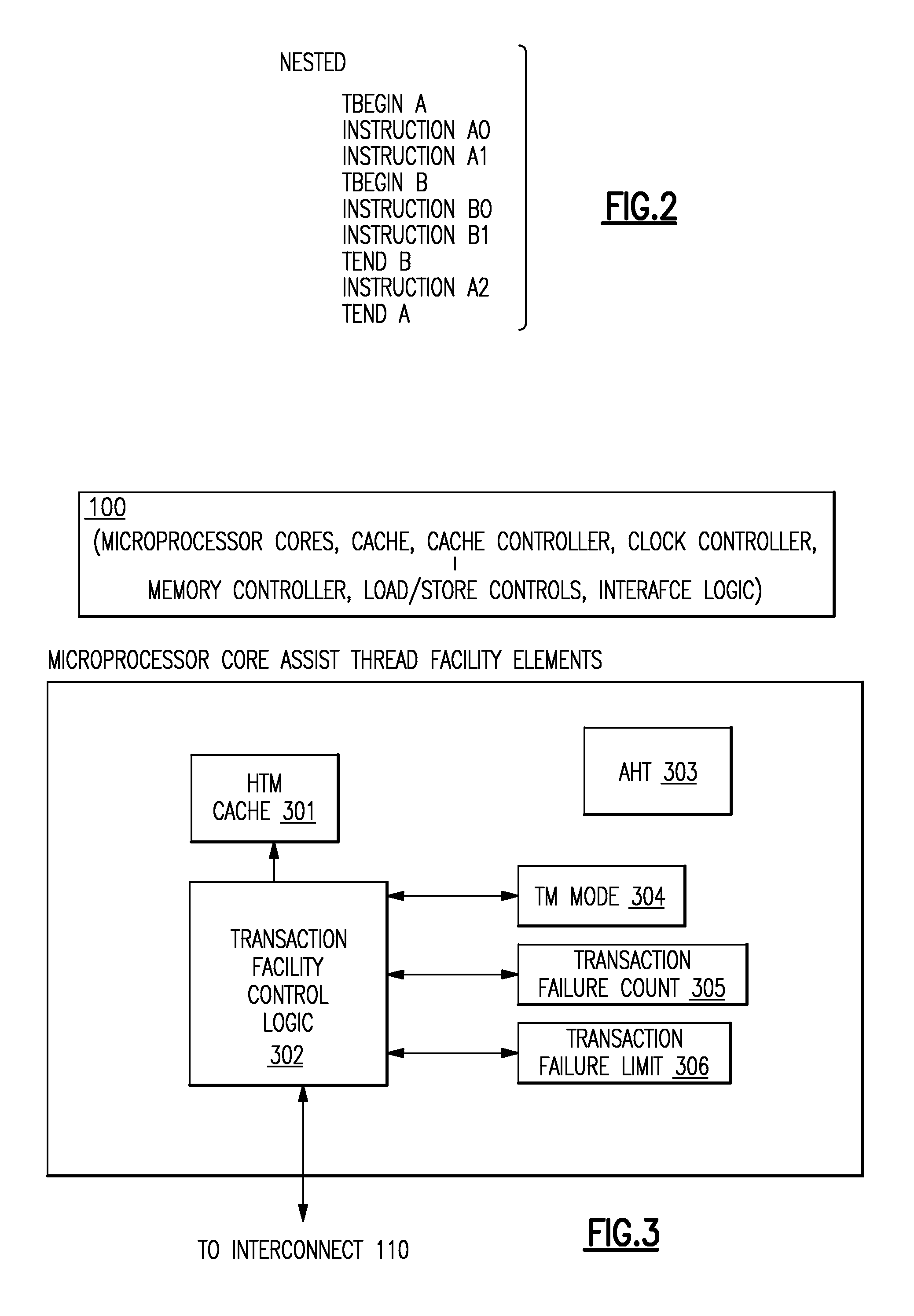

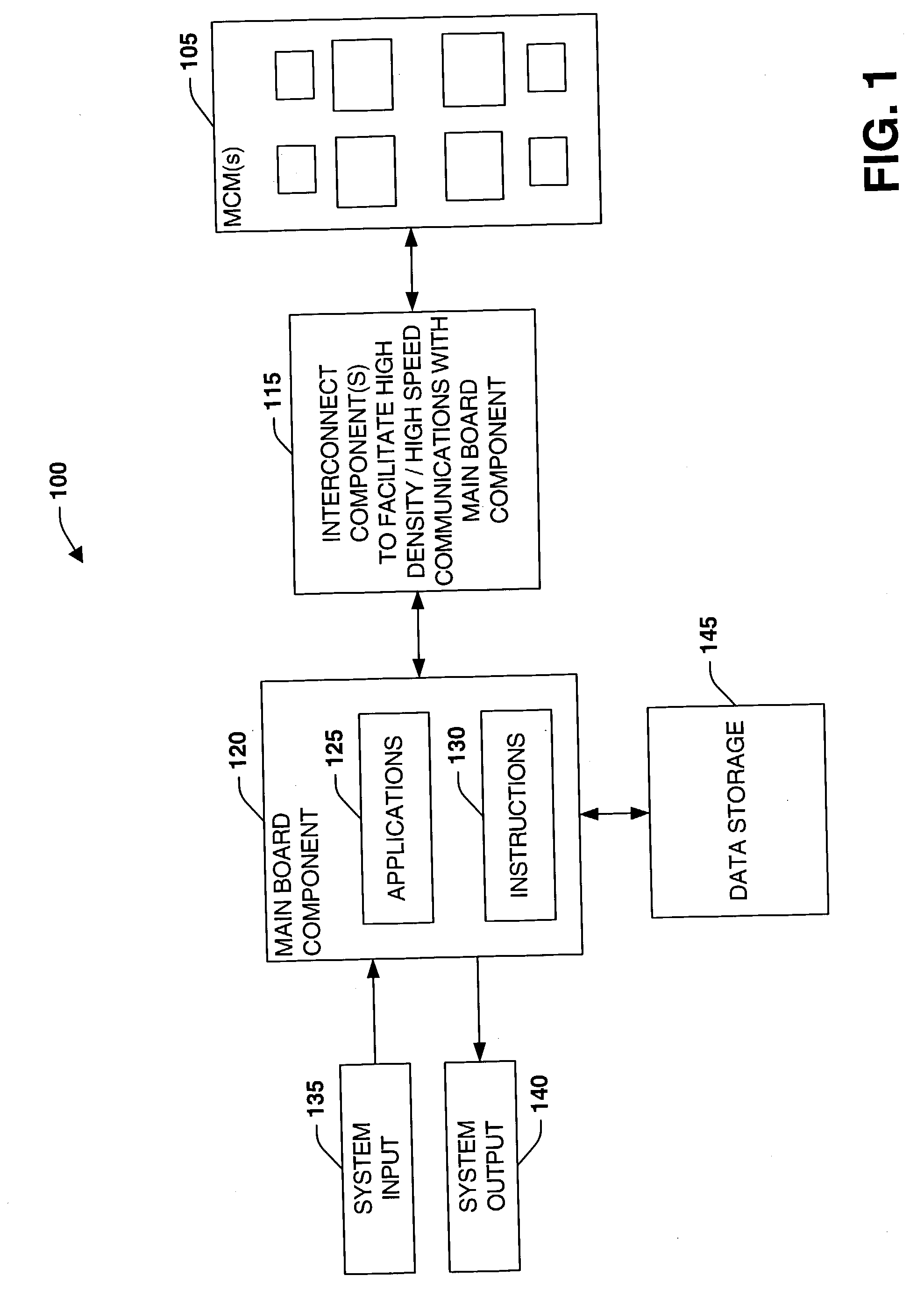

A computer processing system having memory and processing facilities for processing data with a computer program is a Hybrid Transactional Memory multiprocessor system with modules 1 . . . n coupled to a system physical memory array, I / O devices via a high speed interconnection element. A CPU is integrated as in a multi-chip module with microprocessors which contain or are coupled in the CPU module to an assist thread facility, as well as a memory controller, cache controllers, cache memory, and other components which form part of the CPU which connects to the high speed interconnect which functions under the architecture and operating system to interconnect elements of the computer system with physical memory, various 1 / 0, devices and the other CPUs of the system. The current hybrid transactional memory elements support for a transactional memory system that has a simple / cost effective hardware design that can deal with limited hardware resources, yet one which has a transactional facility control logic providing for a back up assist thread that can still allow transactions to reference existing libraries and allows programmers to include calls to existing software libraries inside of their transactions, and which will not make a user code use a second lock based solution.

Owner:IBM CORP

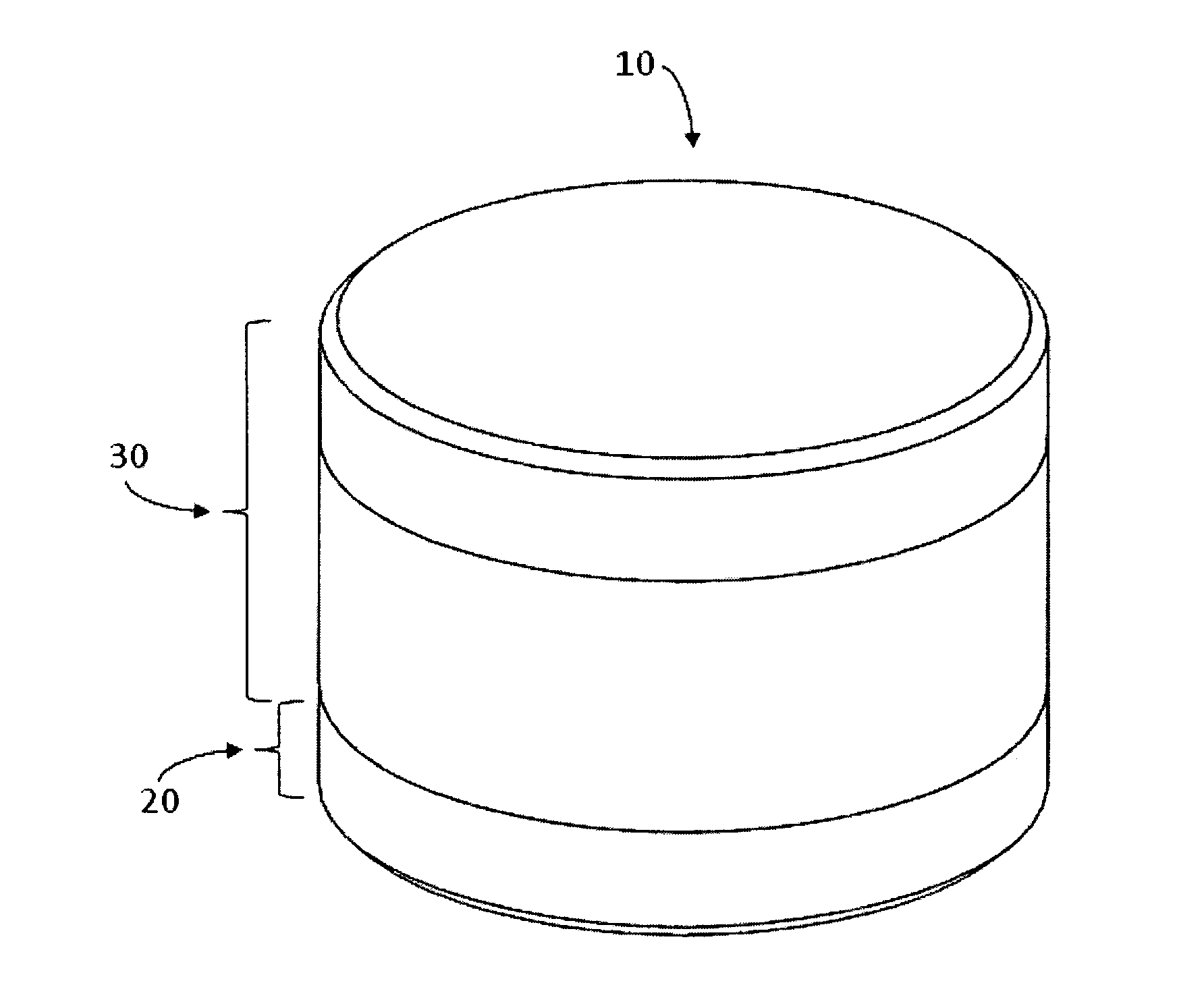

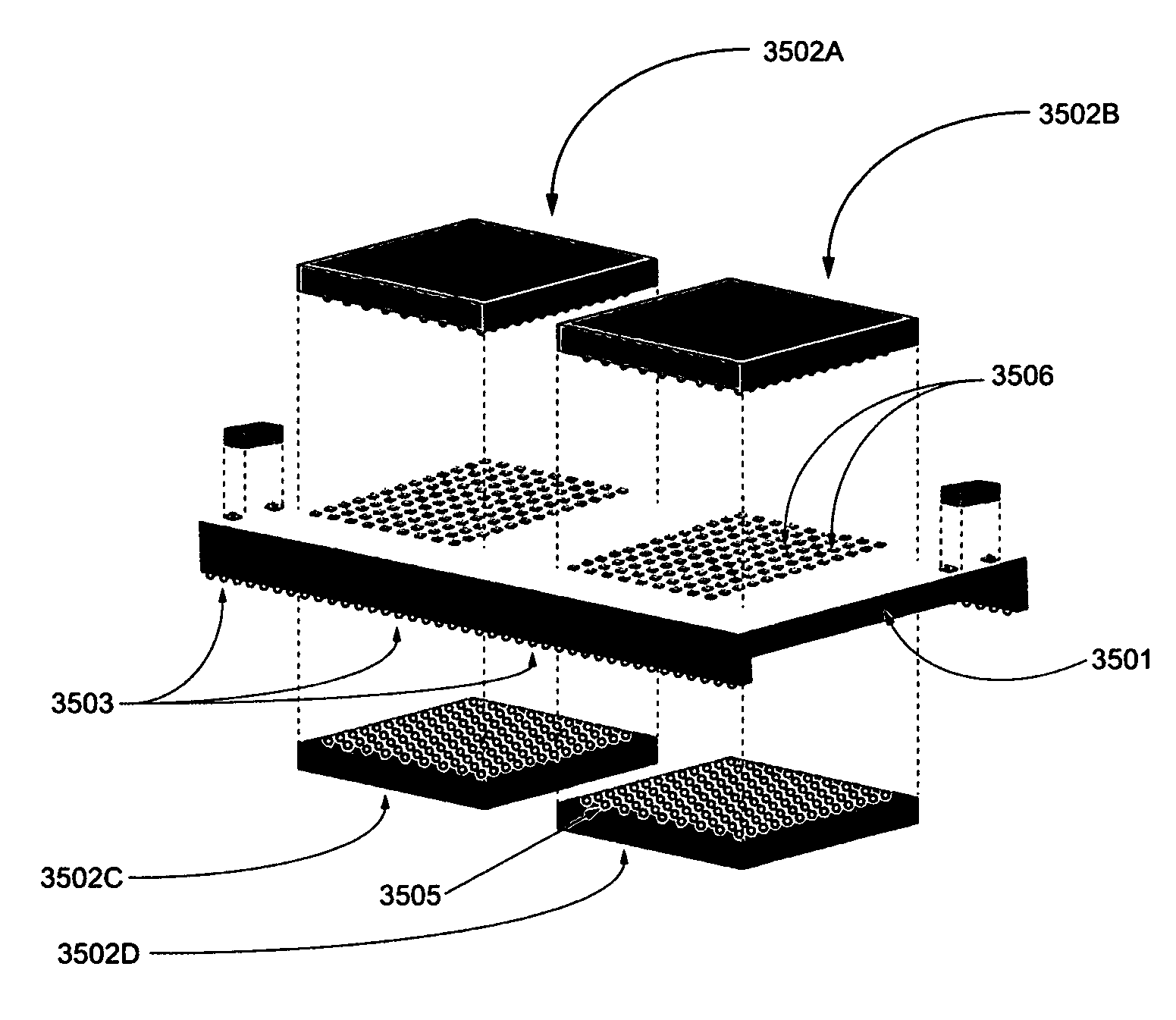

Apparatus for stacking semiconductor chips

InactiveUSRE36916E1Low profileHigh densitySemiconductor/solid-state device detailsSolid-state devicesMemory chipSurface mounting

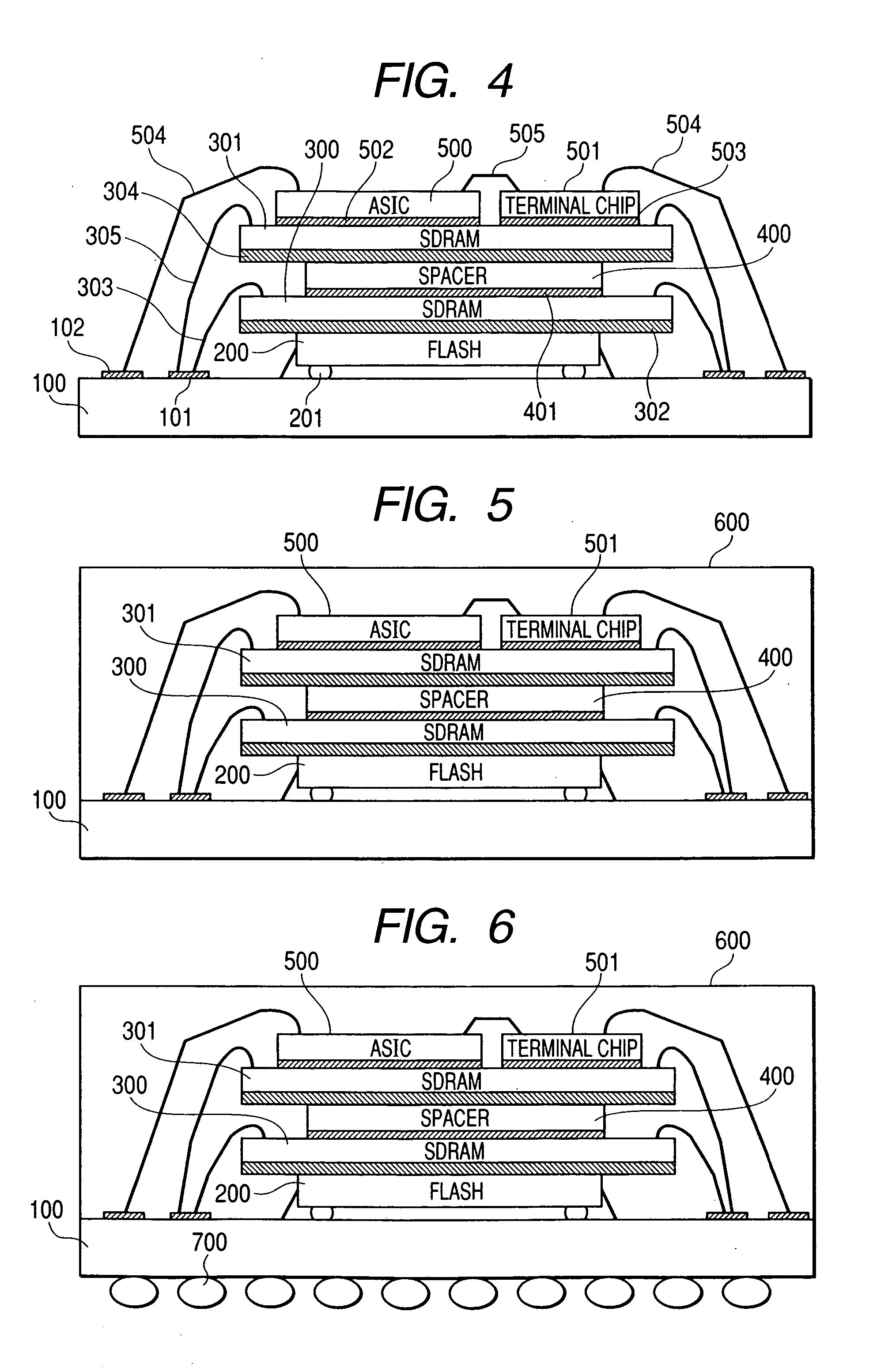

A multi-chip memory module comprises multiple standard, surface-mount-type memory chips stacked on top of each other, and a pair of printed circuit boards mounted on opposite sides of the memory chips to electrically interconnect the memory chips. Each printed circuit board has vias that are positioned to form multiple rows, with each row of vias used to connect the printed circuit board to a respective memory chip. The vias falling along the bottom-most row of each printed circuit board are also exposed and are used to surface mount the multi-chip module to pads of a memory board.

Owner:HGST TECH SANTA ANA

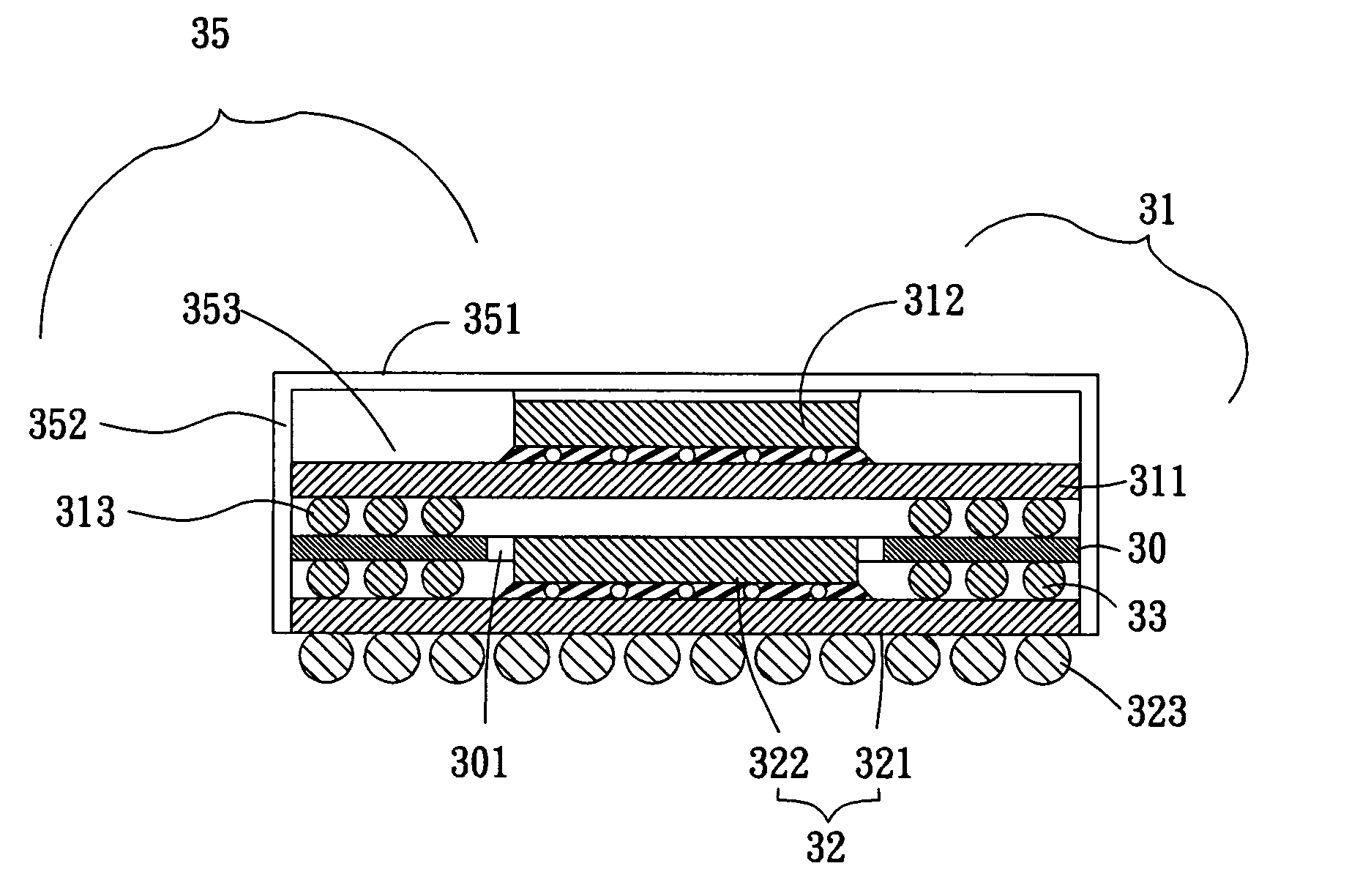

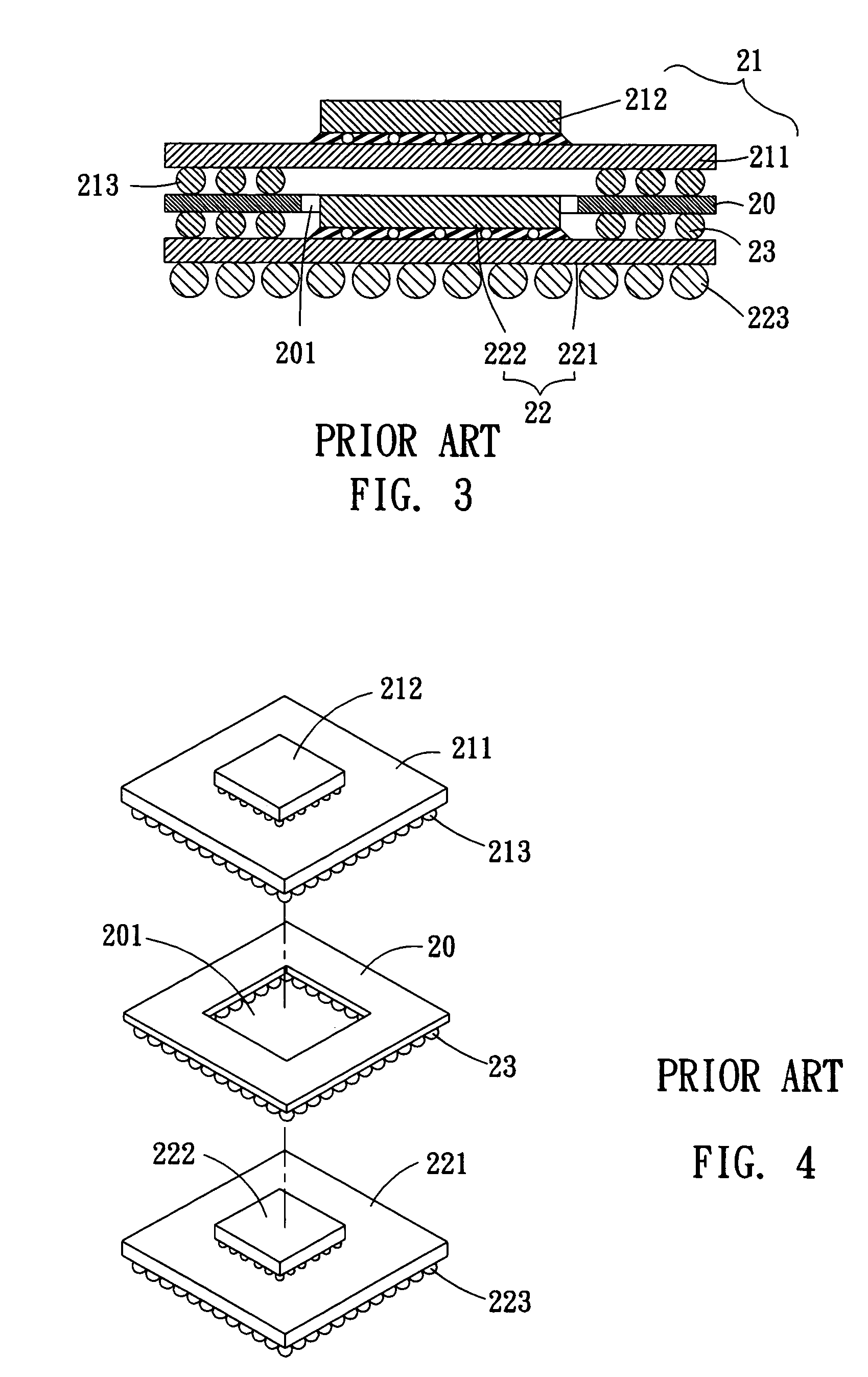

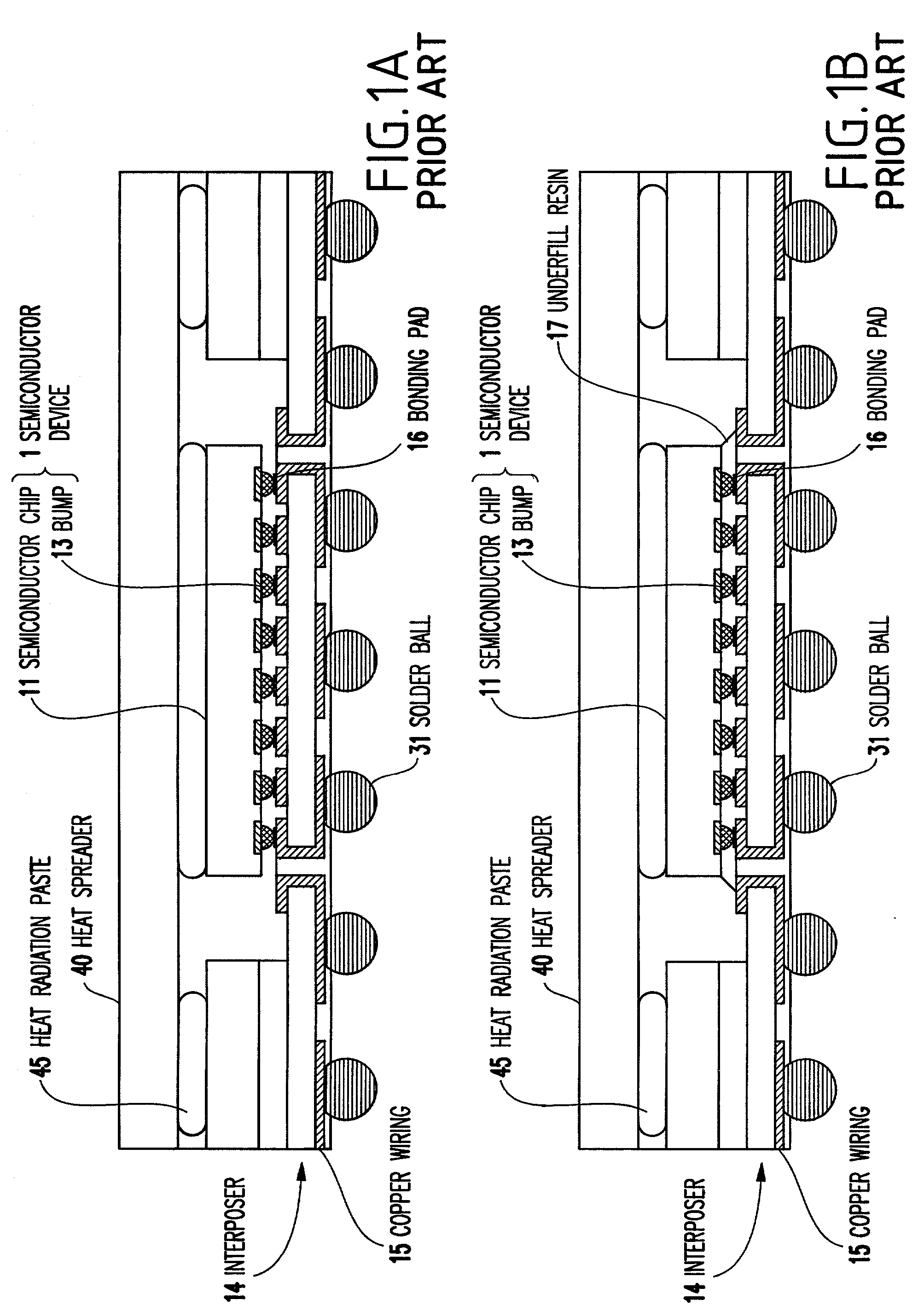

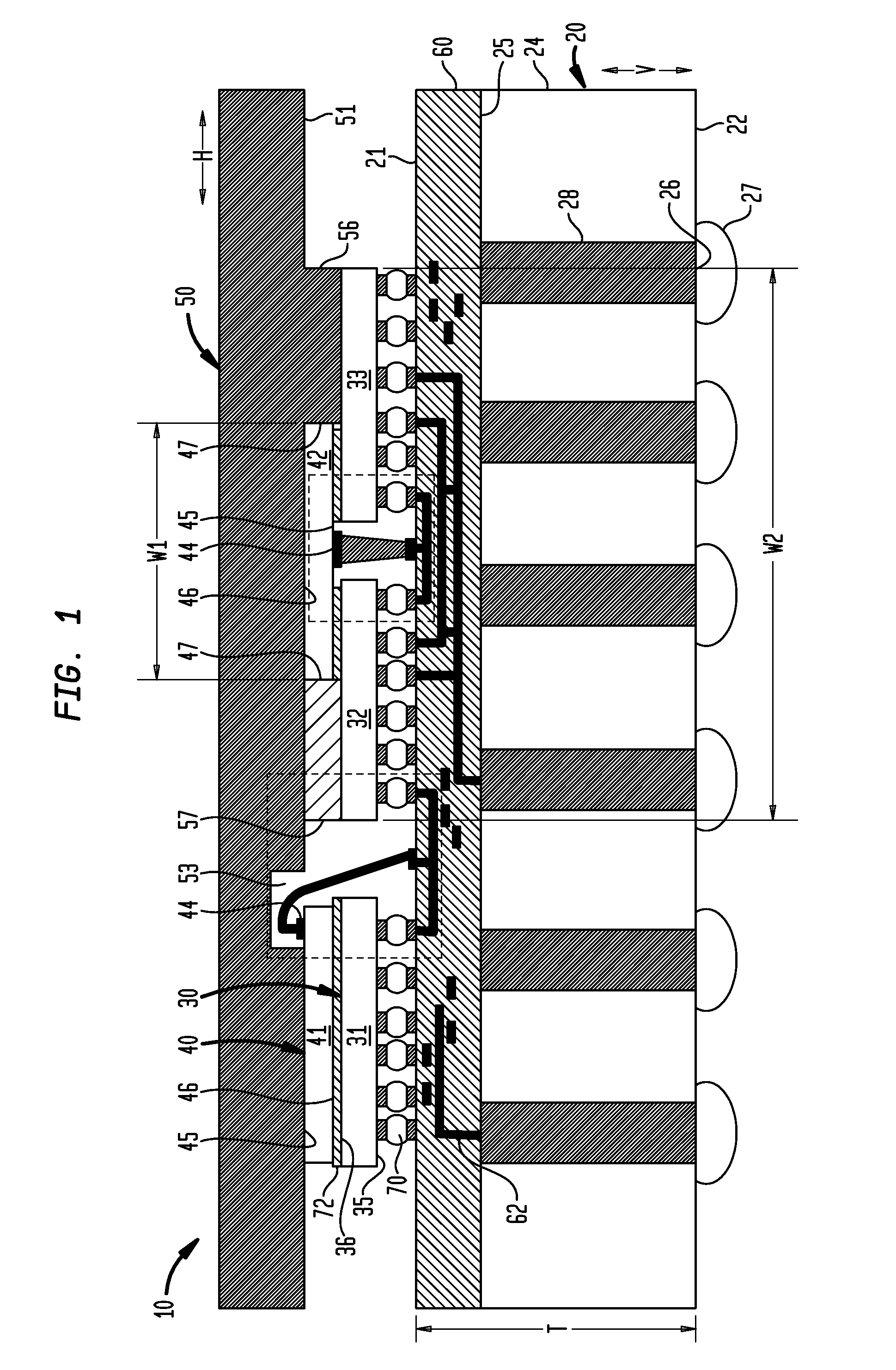

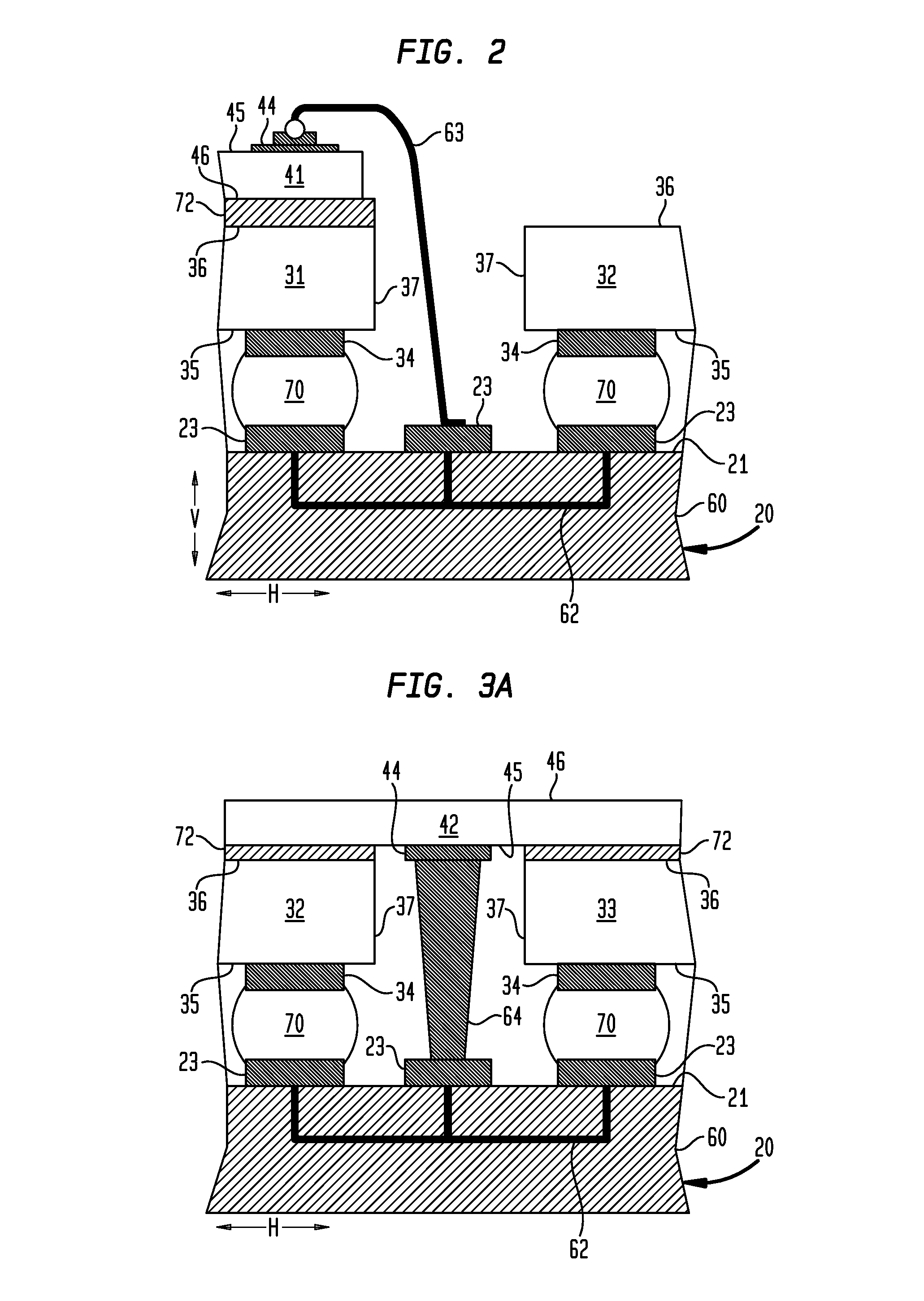

Thermal enhance MCM package and manufacturing method thereof

ActiveUS7002805B2Simple manufacturing processReliable electrical connectionSemiconductor/solid-state device detailsSolid-state devicesEngineeringDislocation

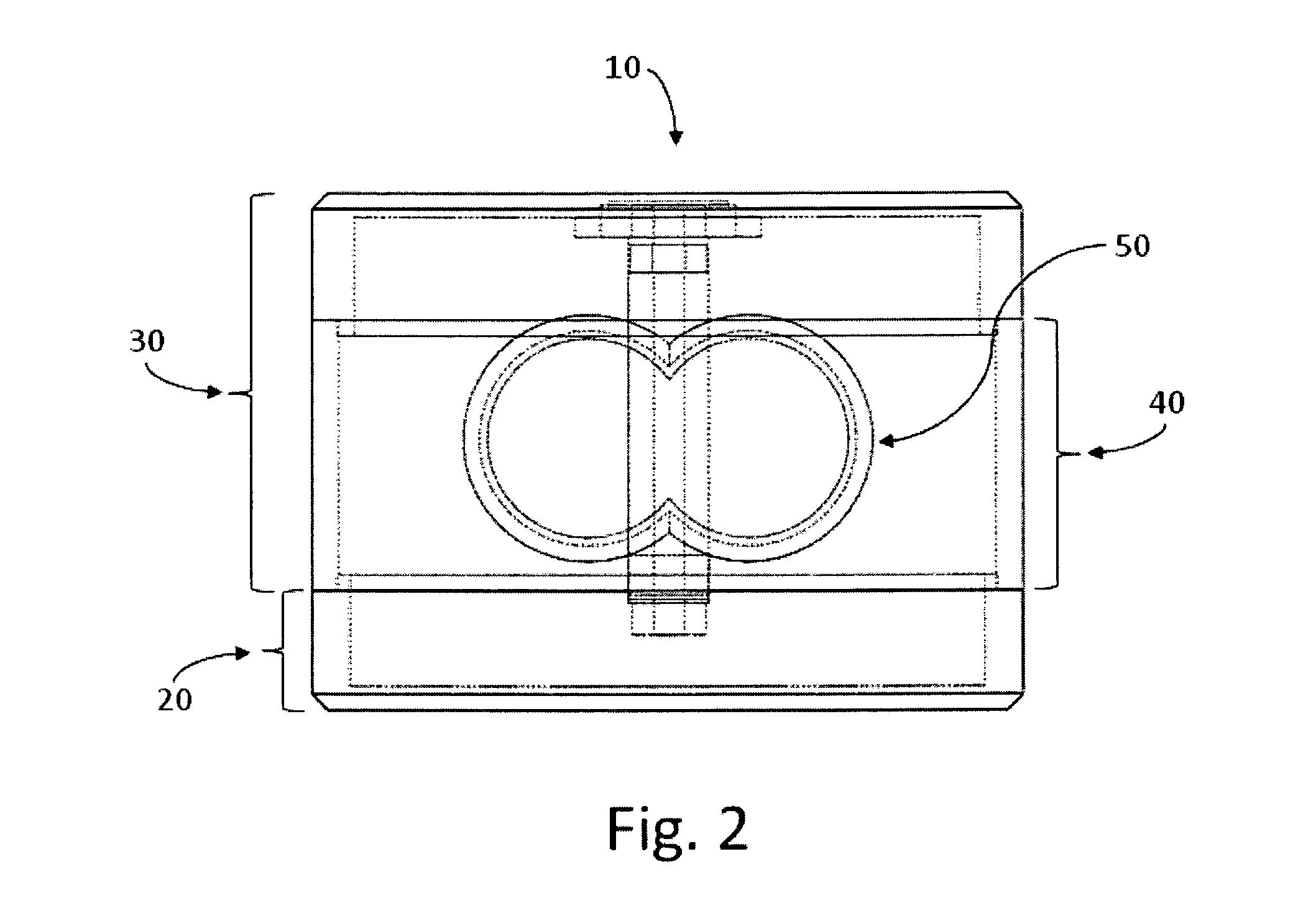

A thermal enhance multi-chips module (MCM) package mainly comprises a first package, a first carrier, a second package, a second carrier, an intermediate substrate and a cap-like heat spreader. The intermediate substrate has an opening. The first carrier and the second carrier are electrically connected to the first package and the second package respectively. The second package is accommodated in the opening and electrically connected to the first package via the first carrier, the second carrier and the intermediate carrier. The cap-like heat spreader has a supporting portion and an alignment portion wherein the supporting portion is connected to the alignment portion to define a cavity. The cavity not only accommodates the first package, the first carrier, the second package, the second carrier and the intermediate substrate but also provides alignment mechanism by the supporting portion and the alignment portion to prevent the dislocation after all the components of the thermal enhance MCM package are connected with each other. Furthermore, the first carrier has a first side and the second carrier has a second side. The first side and the second side both have grounding portions, for example recessed portions and metal layers, for providing a ground shielding of the first package and the second package against the outside. In addition, the grounding portions also provide thermal paths to increase the ability of the heat dissipation. Besides, a method for manufacturing the thermal enhance MCM package is provided.

Owner:ADVANCED SEMICON ENG INC

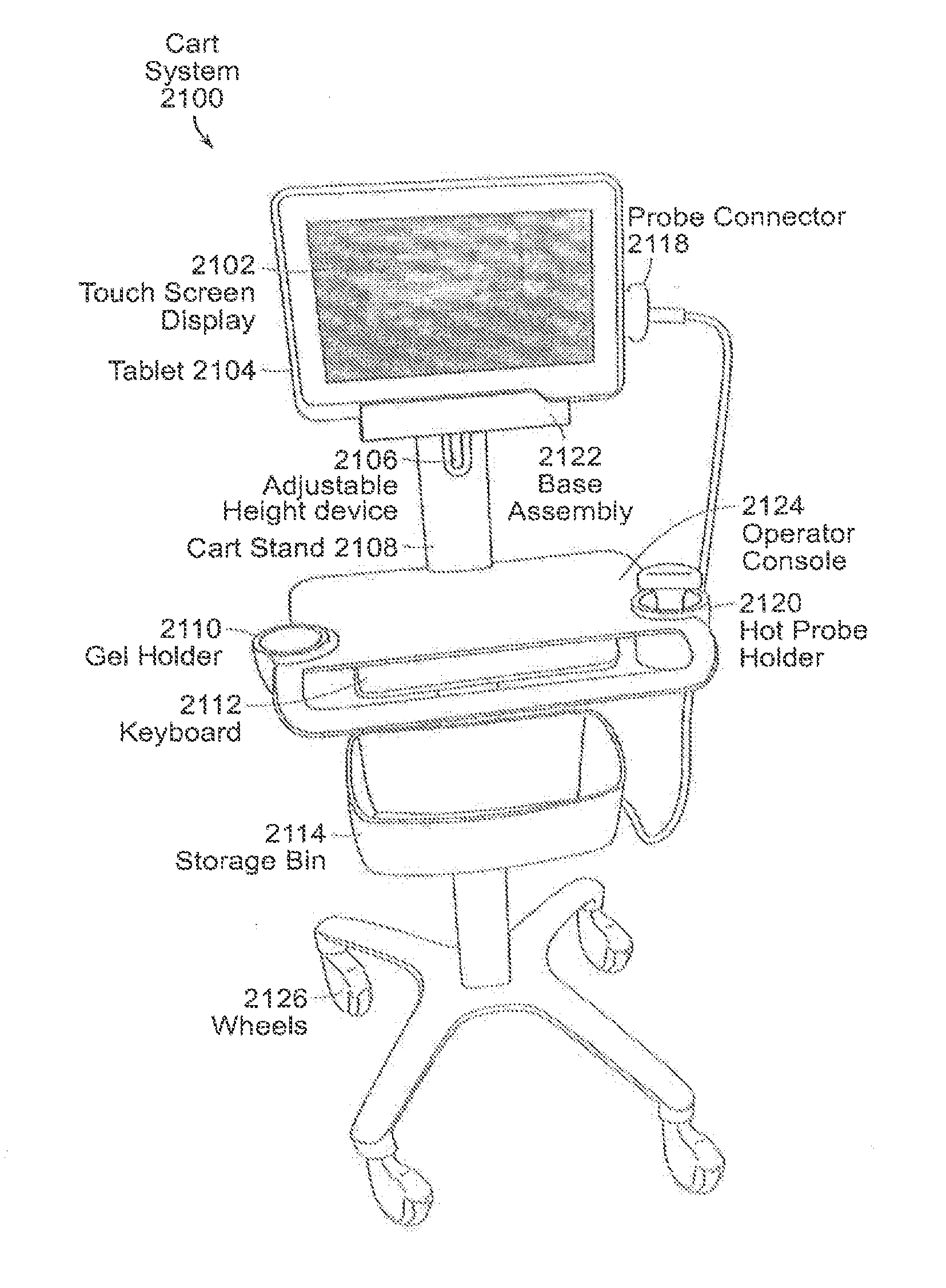

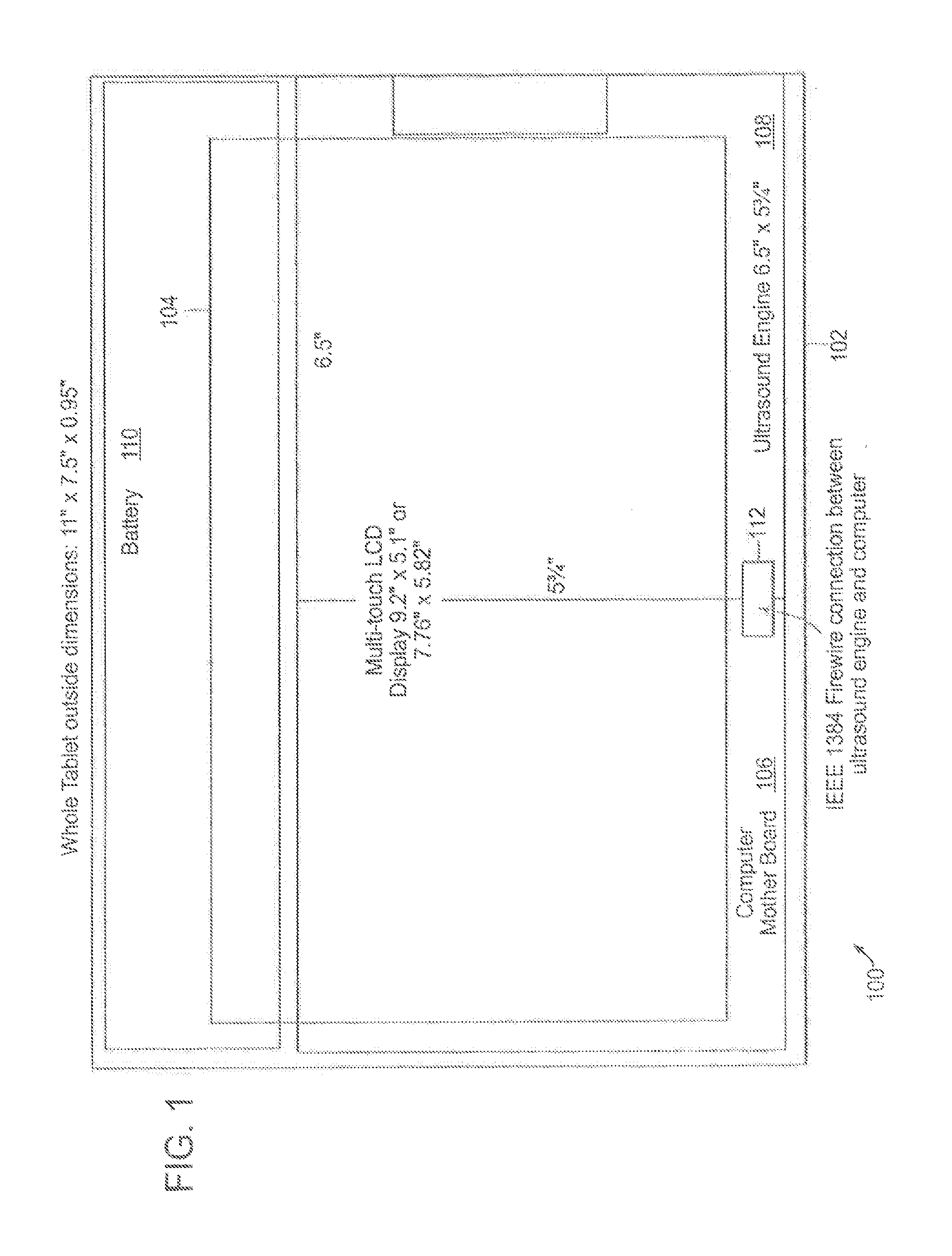

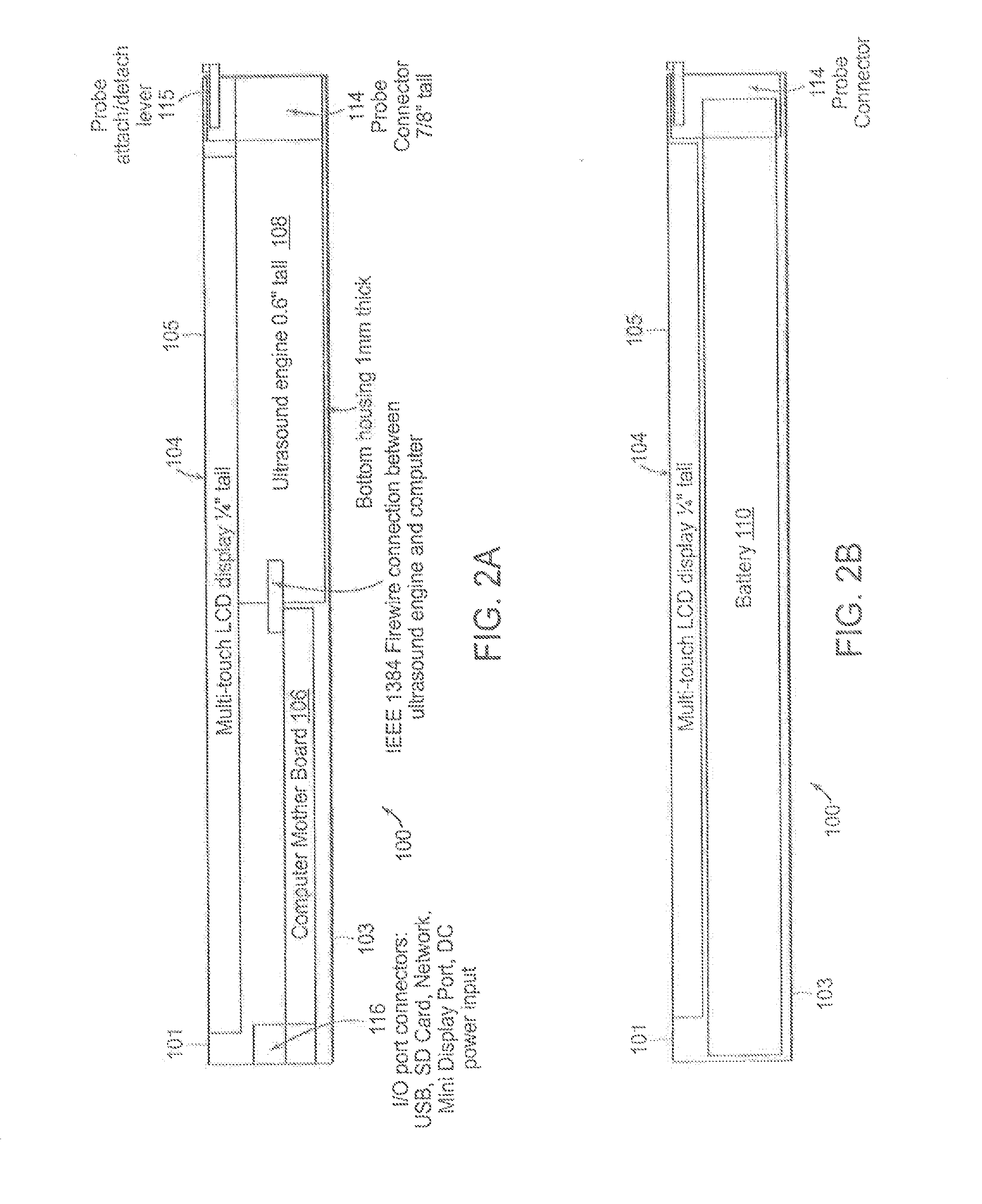

Tablet ultrasound system

ActiveUS20140121524A1Minimize packaging sizeMinimized footprintSolid-state devicesTomographyUltrasonographySonification

Exemplary embodiments provide systems and methods for portable medical ultrasound imaging. Preferred embodiments utilize a tablet touchscreen display operative to control imaging and display operations without the need for using traditional keyboards or controls. Certain embodiments provide ultrasound imaging system in which the scan head includes a beamformer circuit that performs far field sub array beamforming or includes a sparse array selecting circuit that actuates selected elements. Exemplary embodiments also provide an ultrasound engine circuit board including one or more multi-chip modules, and a portable medical ultrasound imaging system including an ultrasound engine circuit board with one or more multi-chip modules. Exemplary embodiments also provide methods for using a hierarchical two-stage or three-stage beamforming system, three dimensional ultrasound images which can be generated in real-time.

Owner:TERATECH CORP

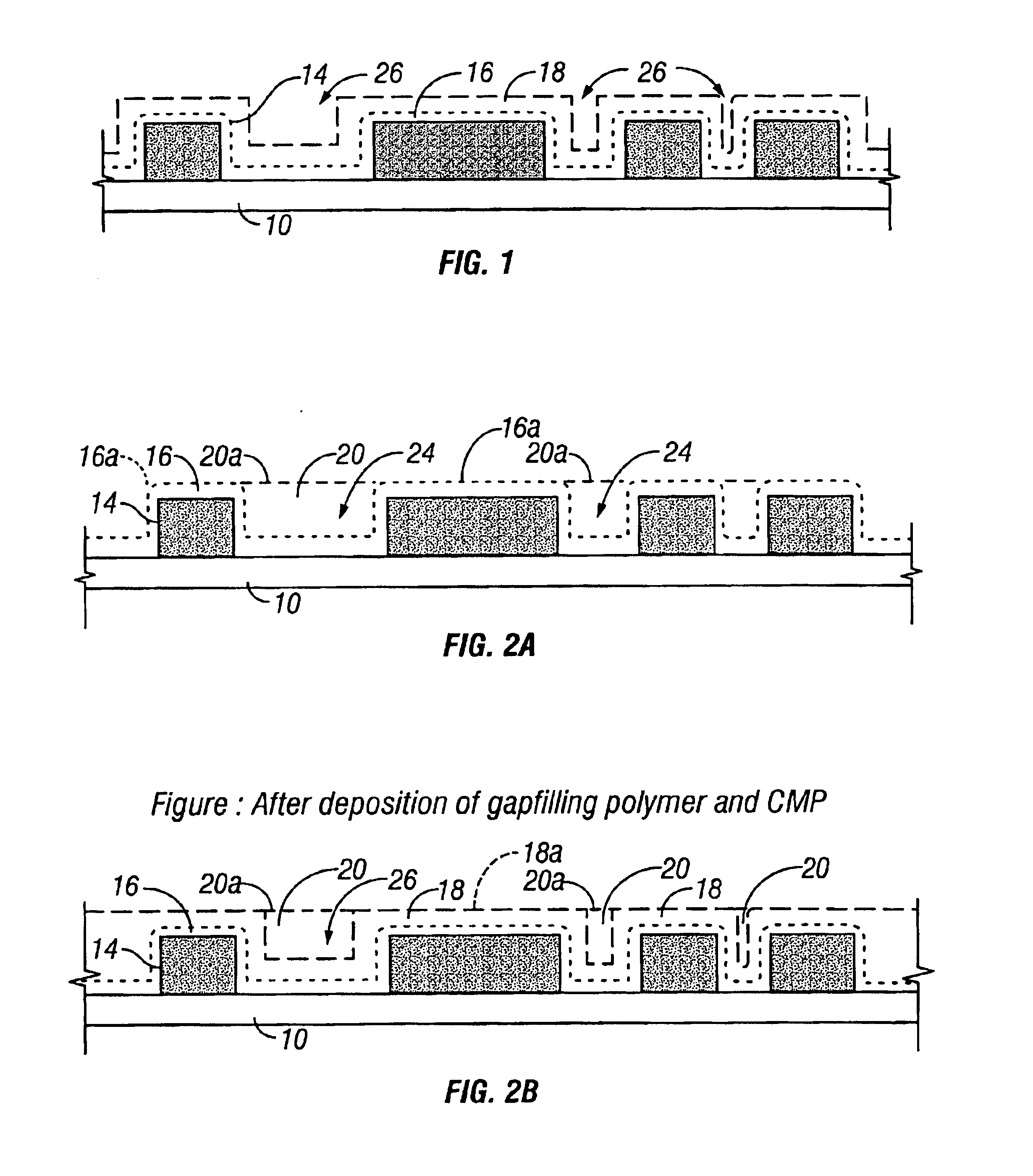

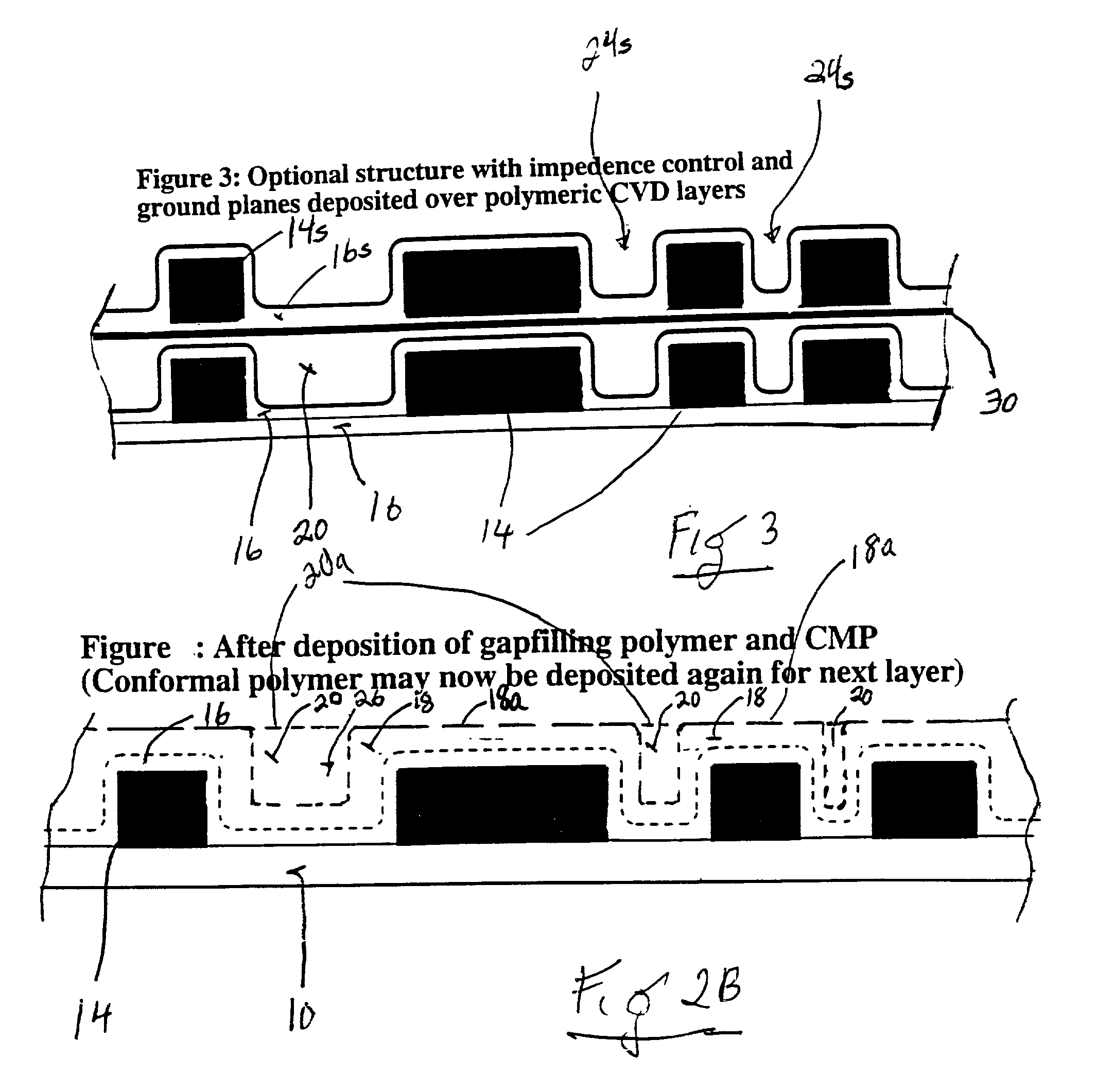

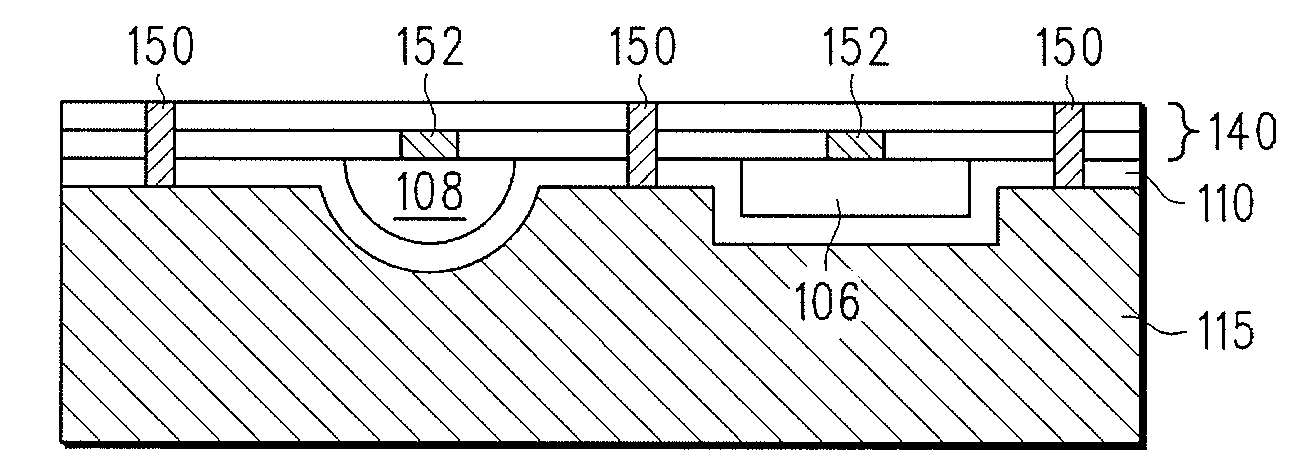

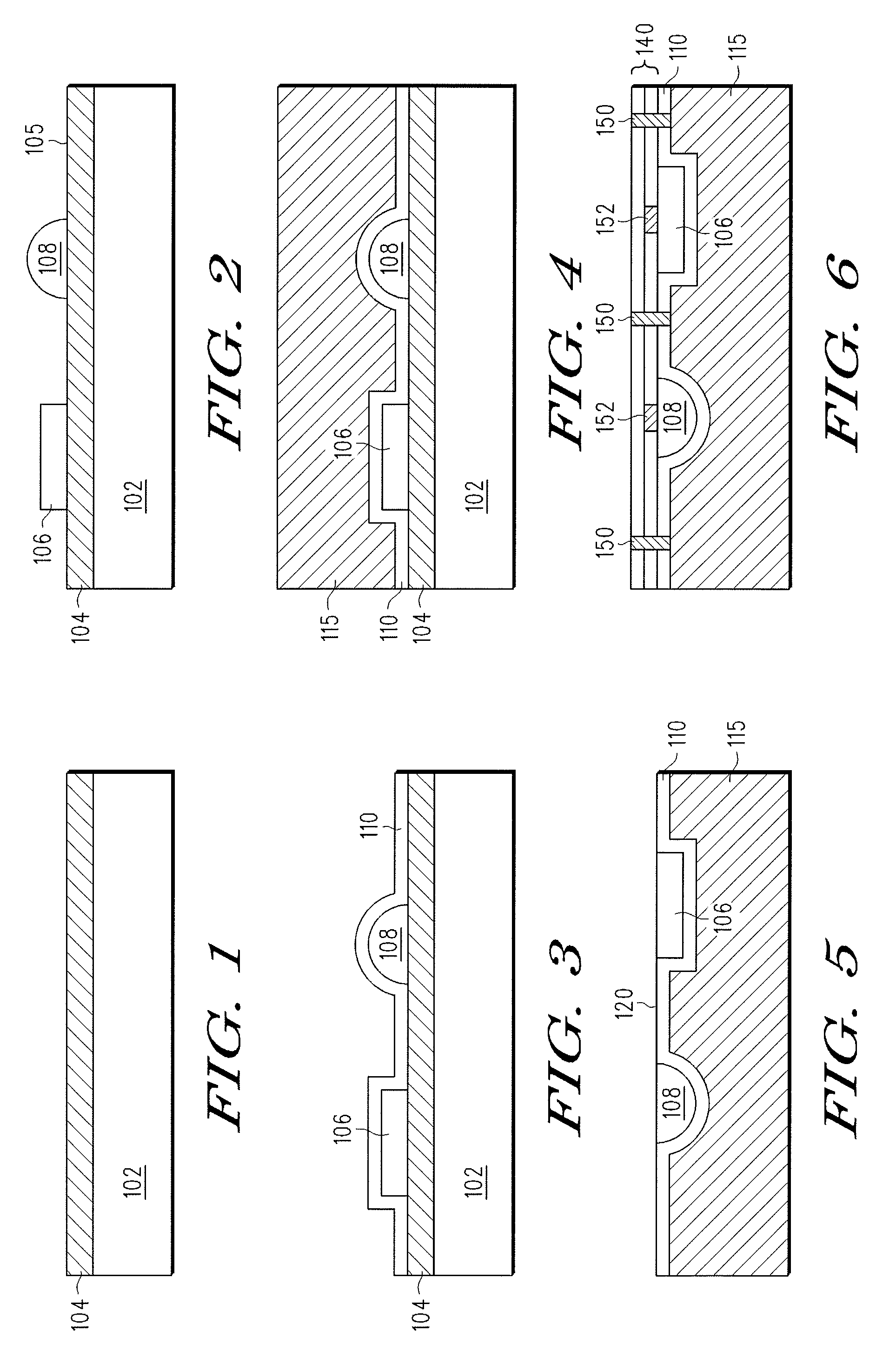

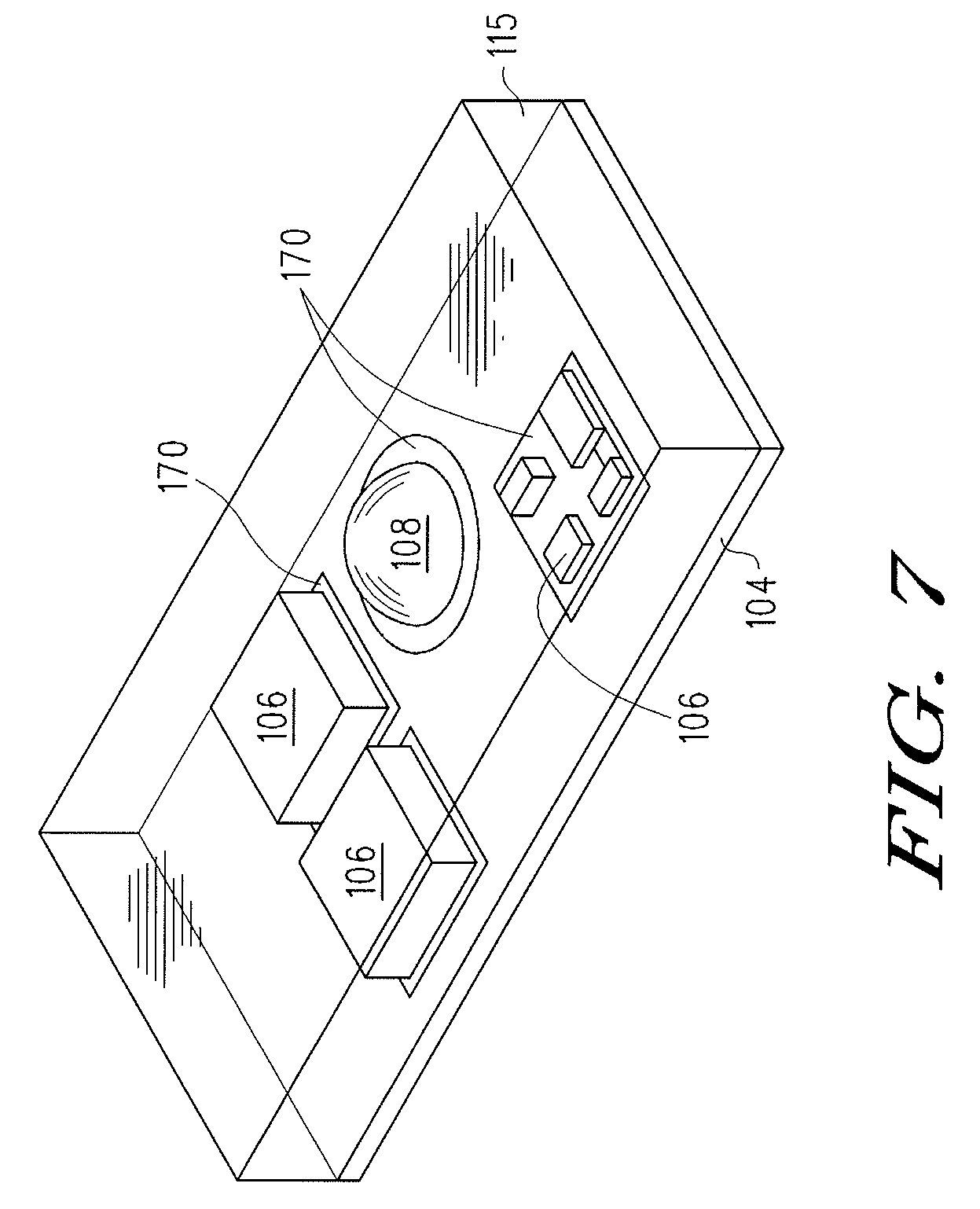

Multi-chip module and method for forming and method for deplating defective capacitors

A method for deplating defective capacitors comprising forming a plurality of capacitors on a semiconductor substrate, forming a plurality of metal contacts on the plurality of capacitors, and depositing a layer of photoresist on the semiconductor substrate. The photoresist layer is patterned so that the plurality of metal contacts are exposed, which are then contacted with an electrically conductive solution. The metal contacts, which are disposed over defective capacitors, are subsequently deplated. A method for forming a multi-chip module comprising forming a thin-film polymeric interconnect structure having a pair of sides, one of which is disposed on a silicon substrate having active or passive devices and the other of which has a computer chip mounted thereon. A multi-chip module formed by the method.

Owner:FUJITSU LTD

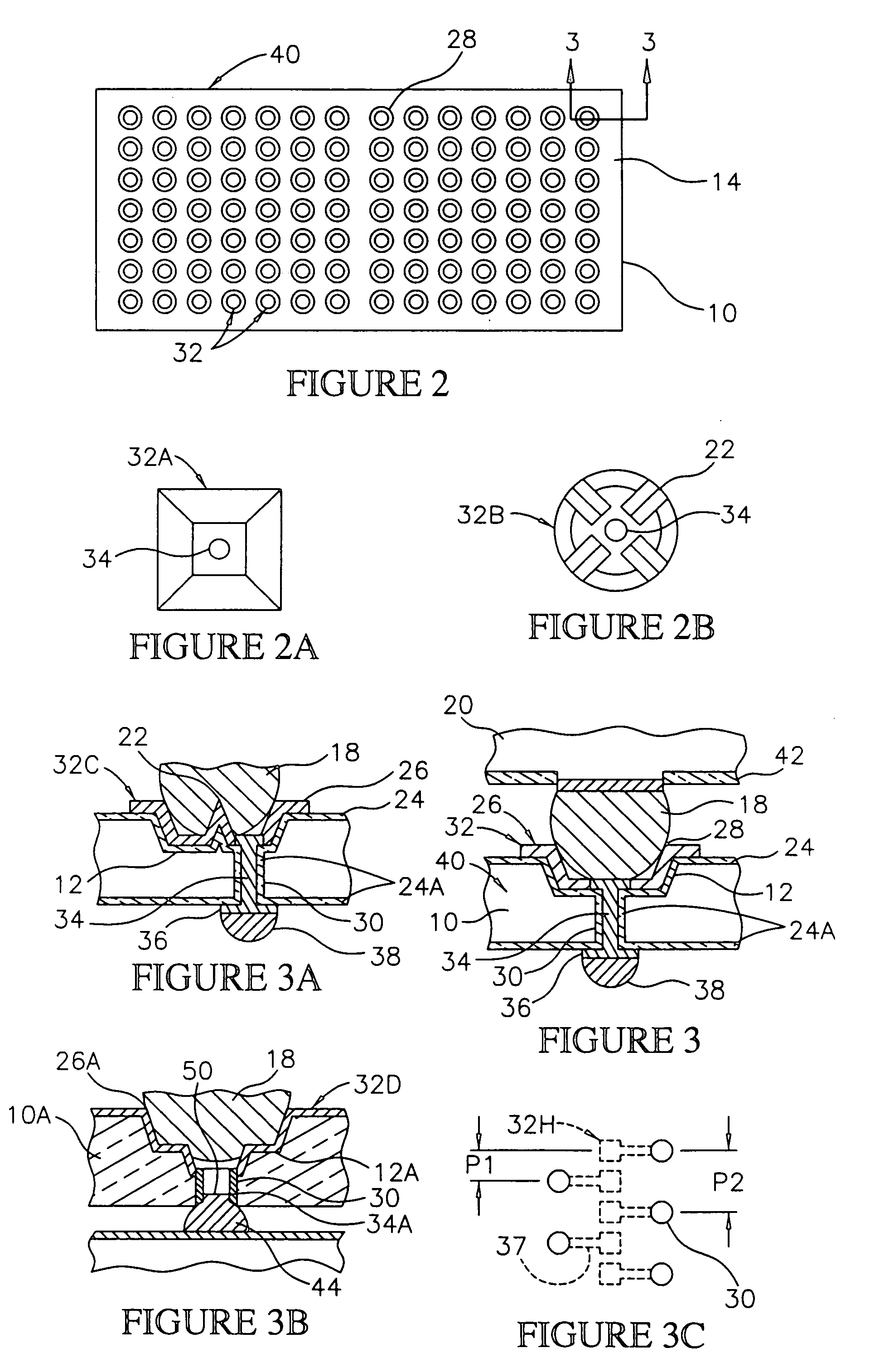

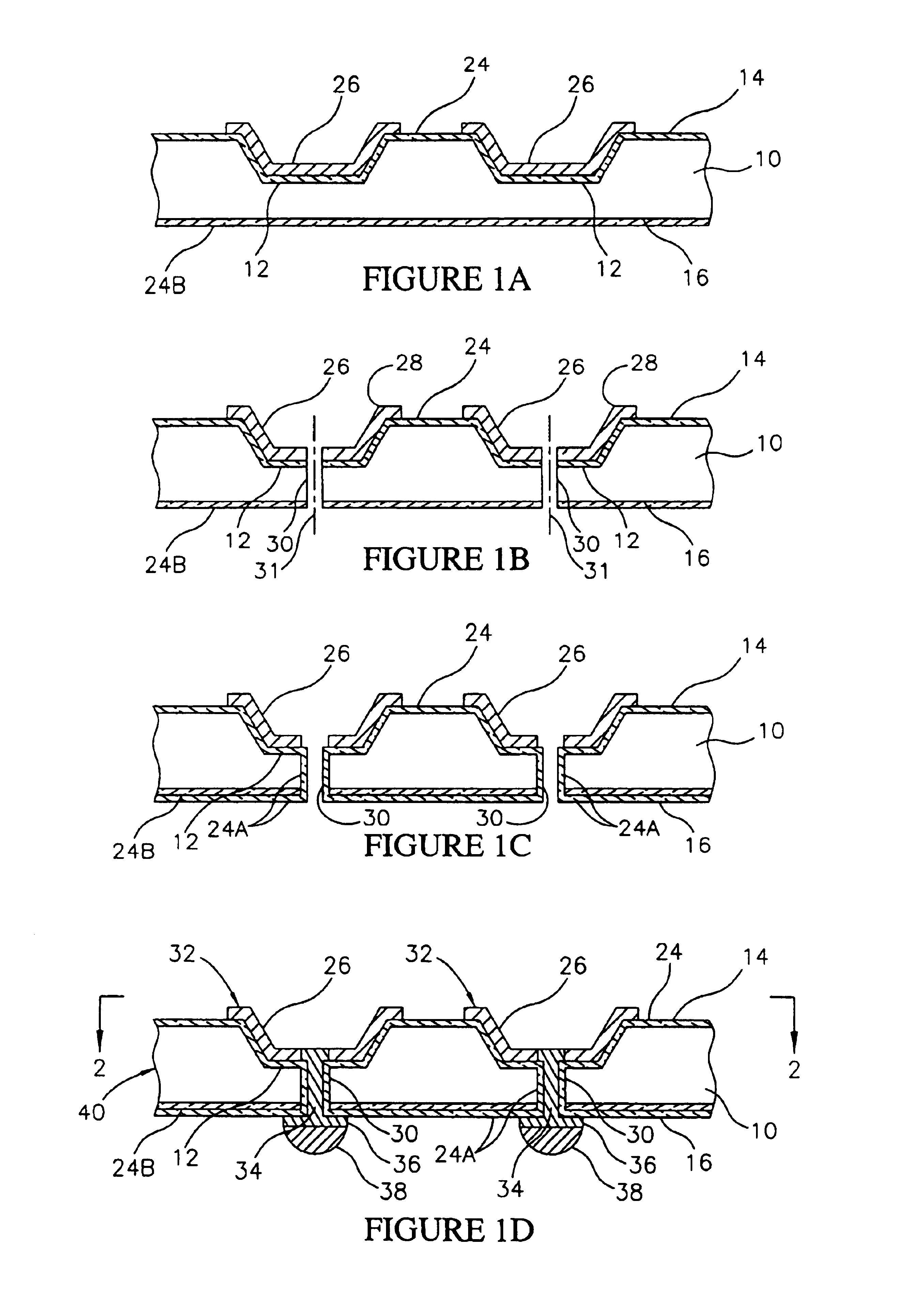

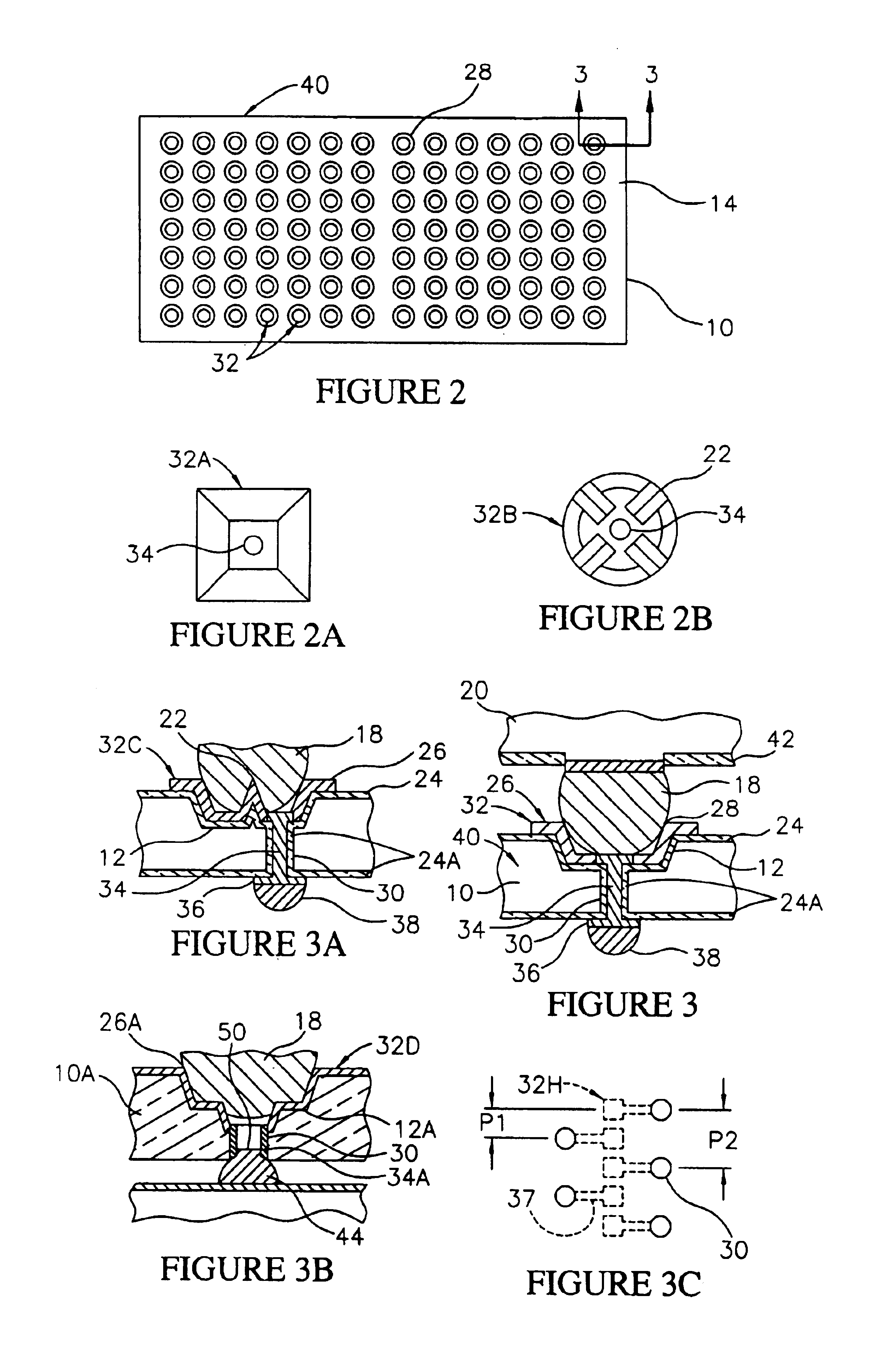

Method for fabricating semiconductor components by forming conductive members using solder

InactiveUS6998344B2Semiconductor/solid-state device detailsPrinted circuit aspectsConductive polymerConductive materials

An interconnect for semiconductor components such as dice, wafers and chip scale packages is provided. The interconnect includes a substrate, and patterns of contacts formed on a face side of the substrate adapted to electrically engage external contacts (e.g., bond pads, solder bumps) on the components. The interconnect also includes insulated conductive members through the substrate, which provide direct electrical paths from the interconnect contacts to a backside of the substrate. The conductive members can be formed by laser machining openings in the substrate, and then filling the openings with a conductive material (e.g., metal, conductive polymer). The conductive members can also include pads with contact balls, configured for electrical interface with a test apparatus, such as test carrier or wafer handler. The interconnect can be used to construct test systems for testing semiconductor components, or to construct chip scale packages and multi chip modules.

Owner:ROUND ROCK RES LLC

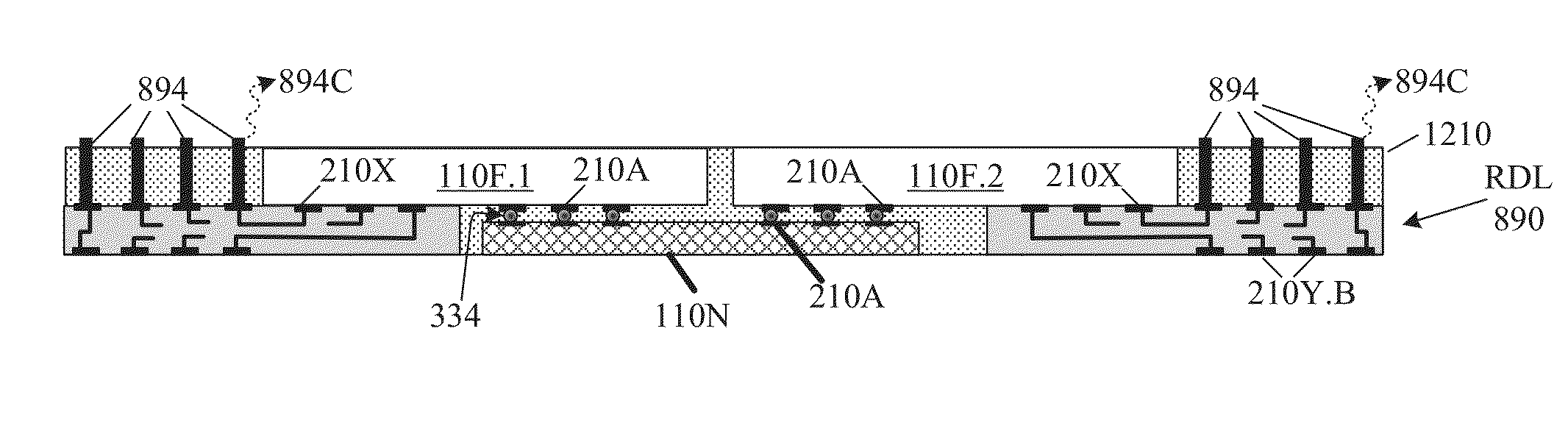

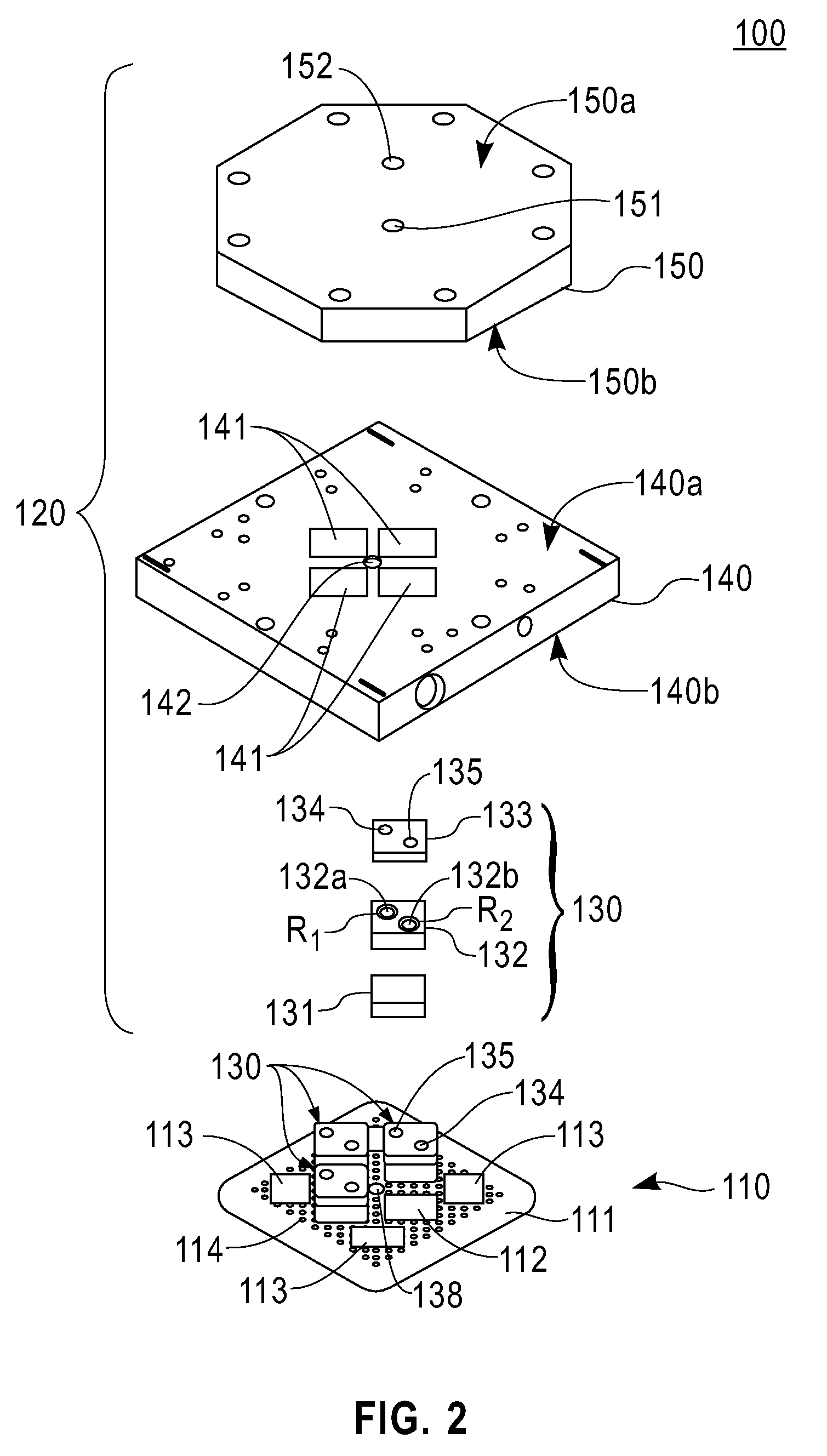

Multichip modules and methods of fabrication

ActiveUS20160071818A1Low costEasy to makeDecorative surface effectsSemiconductor/solid-state device detailsLow speedEngineering

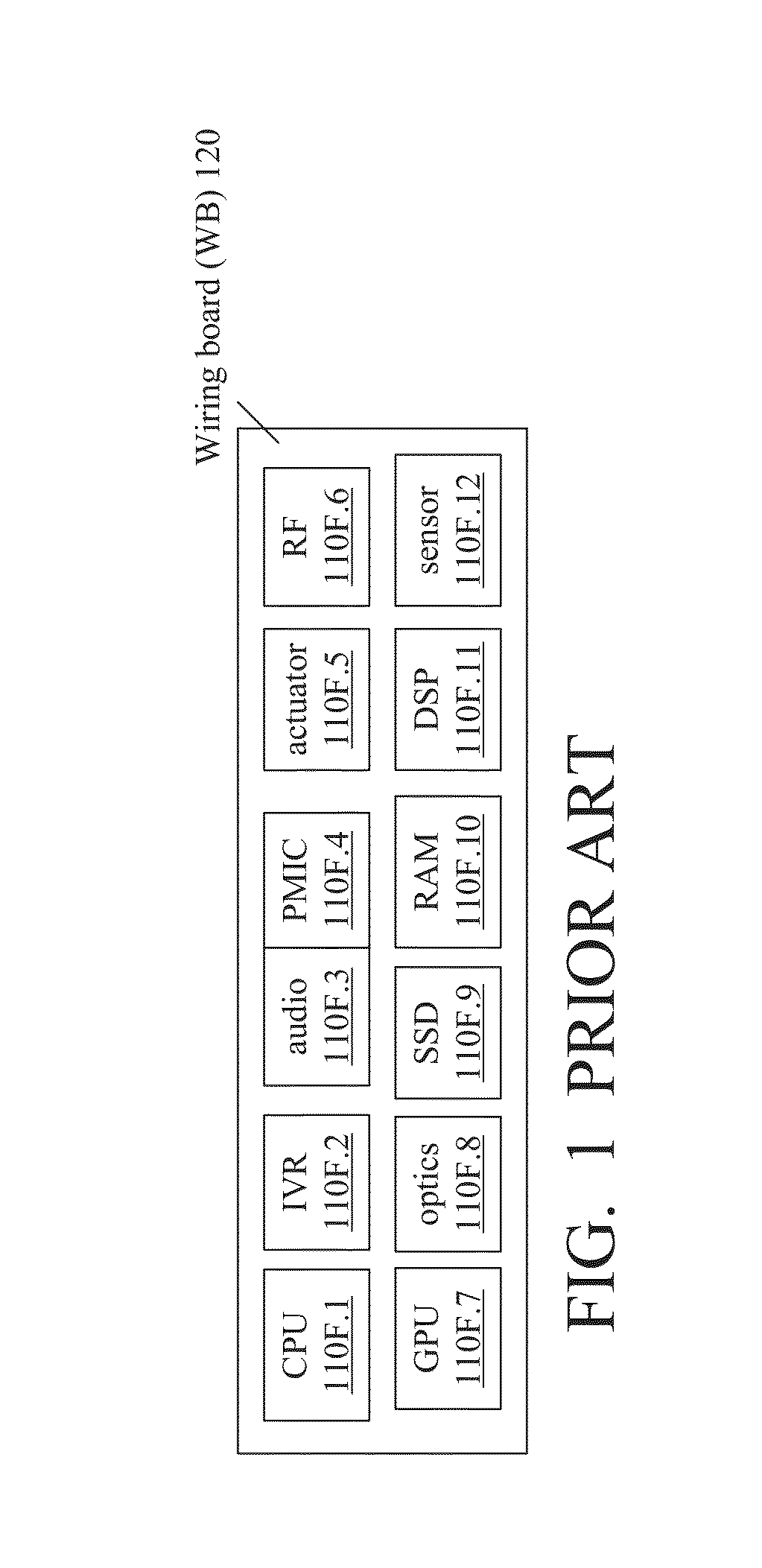

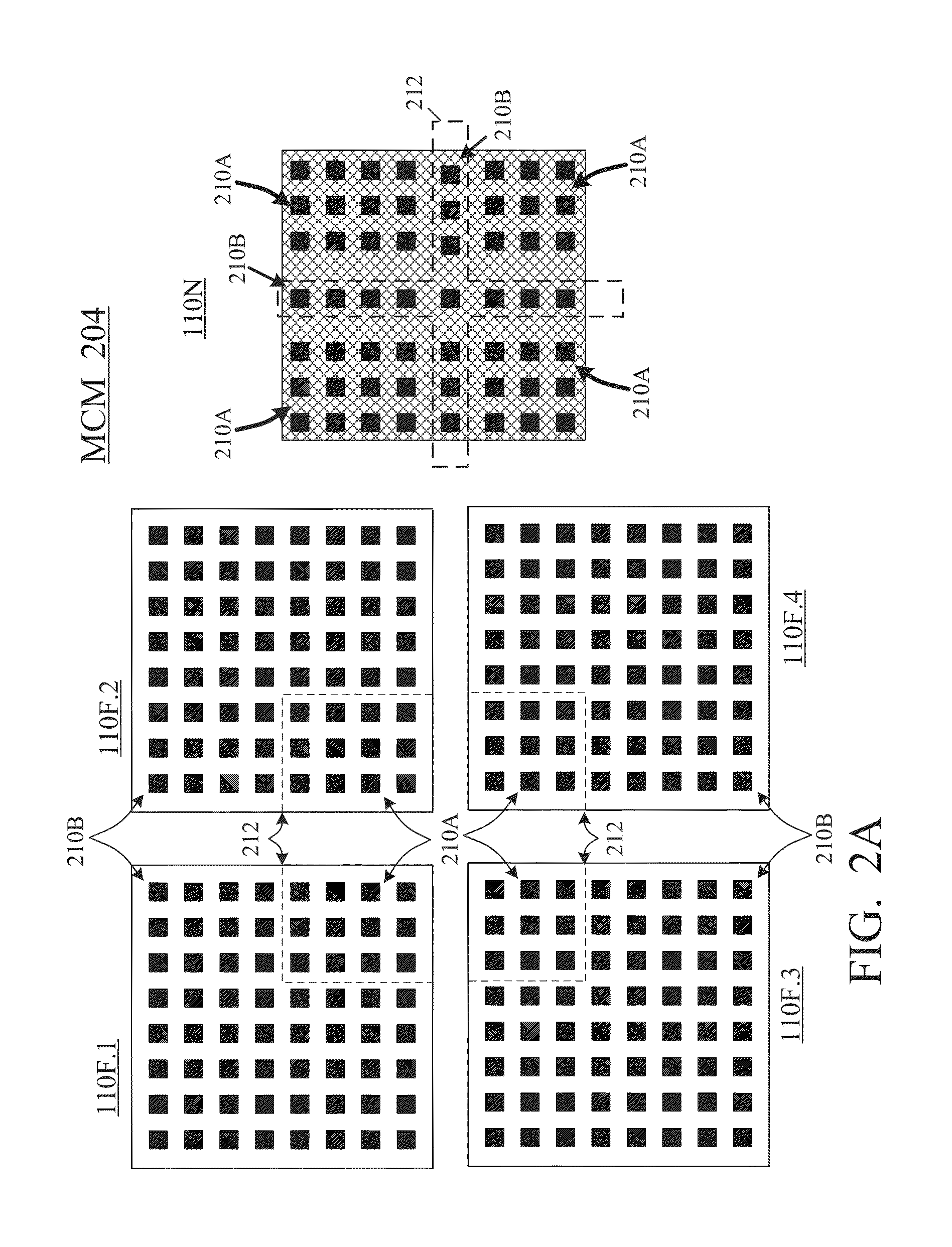

In a multi-chip module (MCM), a “super” chip (110N) is attached to multiple “plain” chips (110F′“super” and “plain” chips can be any chips). The super chip is positioned above the wiring board (WB) but below at least some of plain chips (110F). The plain chips overlap the super chip. Further, the plain chips' low speed IOs can be connected to the WB by long direct connections such as bond wires (e.g. BVAs) or solder stacks; such connections can be placed side by side with the super chip. Such connections can be long, so the super chip is not required to be thin. Also, if through-substrate vias (TSVs) are omitted, the manufacturing yield is high and the manufacturing cost is low. Other structures are provided that combine the short and long direct connections to obtain desired physical and electrical properties.

Owner:INVENSAS LLC

Multi-chip module and method for forming and method for deplating defective capacitors

A method for deplating defective capacitors comprising forming a plurality of capacitors on a semiconductor substrate, forming a plurality of metal contacts on the plurality of capacitors, and depositing a layer of photoresist on the semiconductor substrate. The photoresist layer is patterned so that the plurality of metal contacts are exposed, which are then contacted with an electrically conductive solution. The metal contacts, which are disposed over defective capacitors, are subsequently deplated. A method for forming a multi-chip module comprising forming a thin-film polymeric interconnect structure having a pair of sides, one of which is disposed on a silicon substrate having active or passive devices and the other of which has a computer chip mounted thereon. A multi-chip module formed by the method.

Owner:FUJITSU LTD

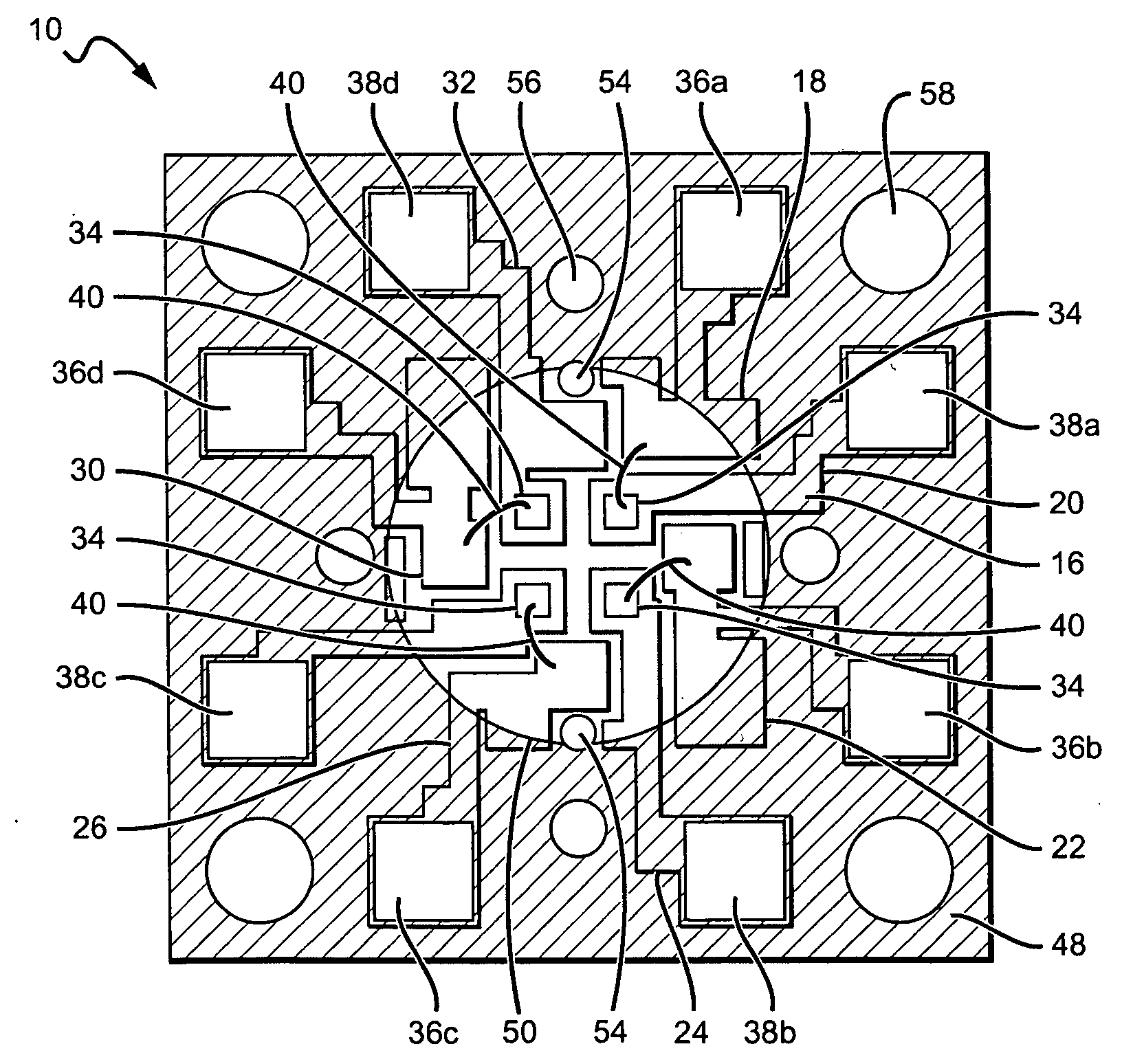

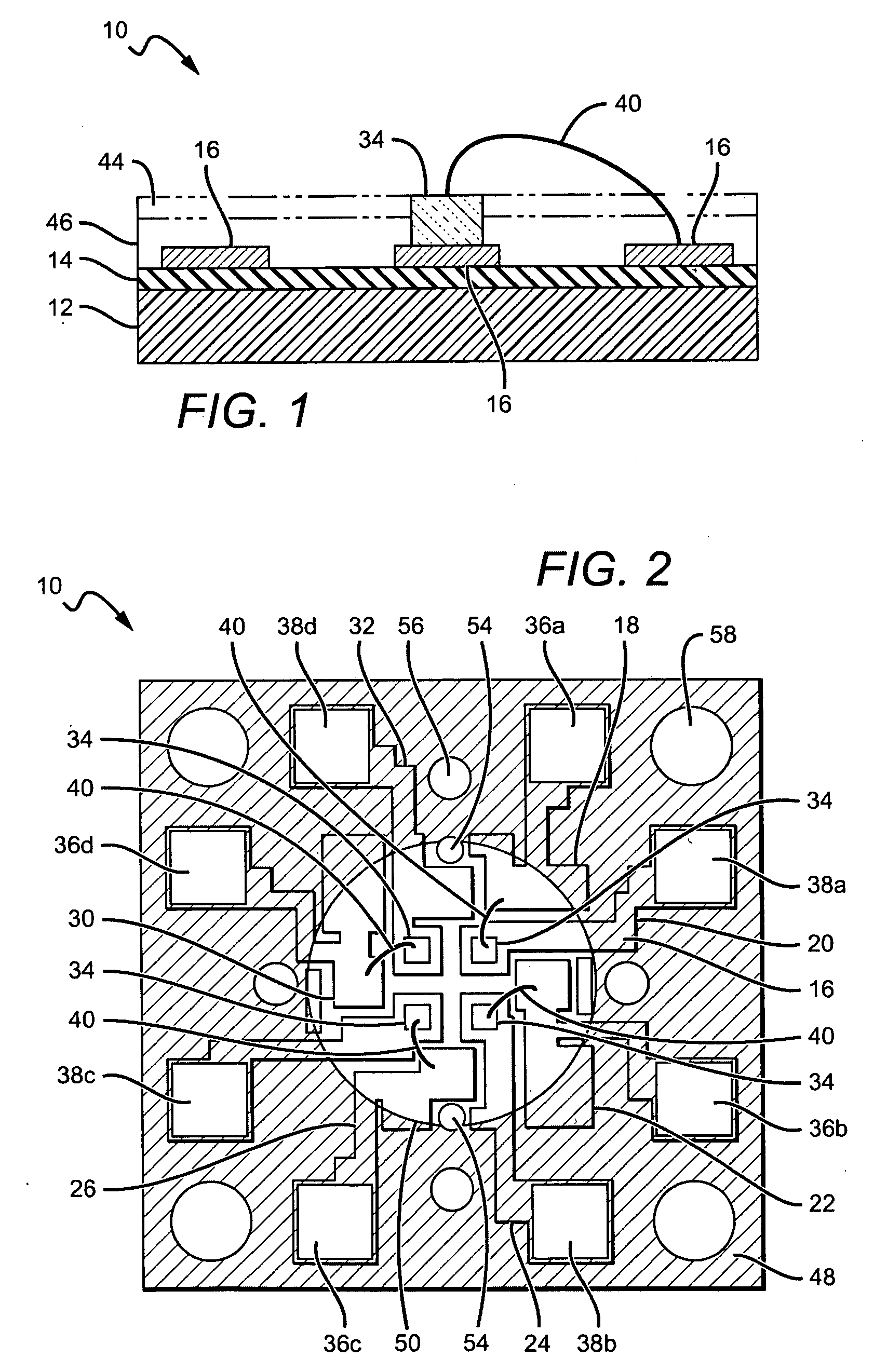

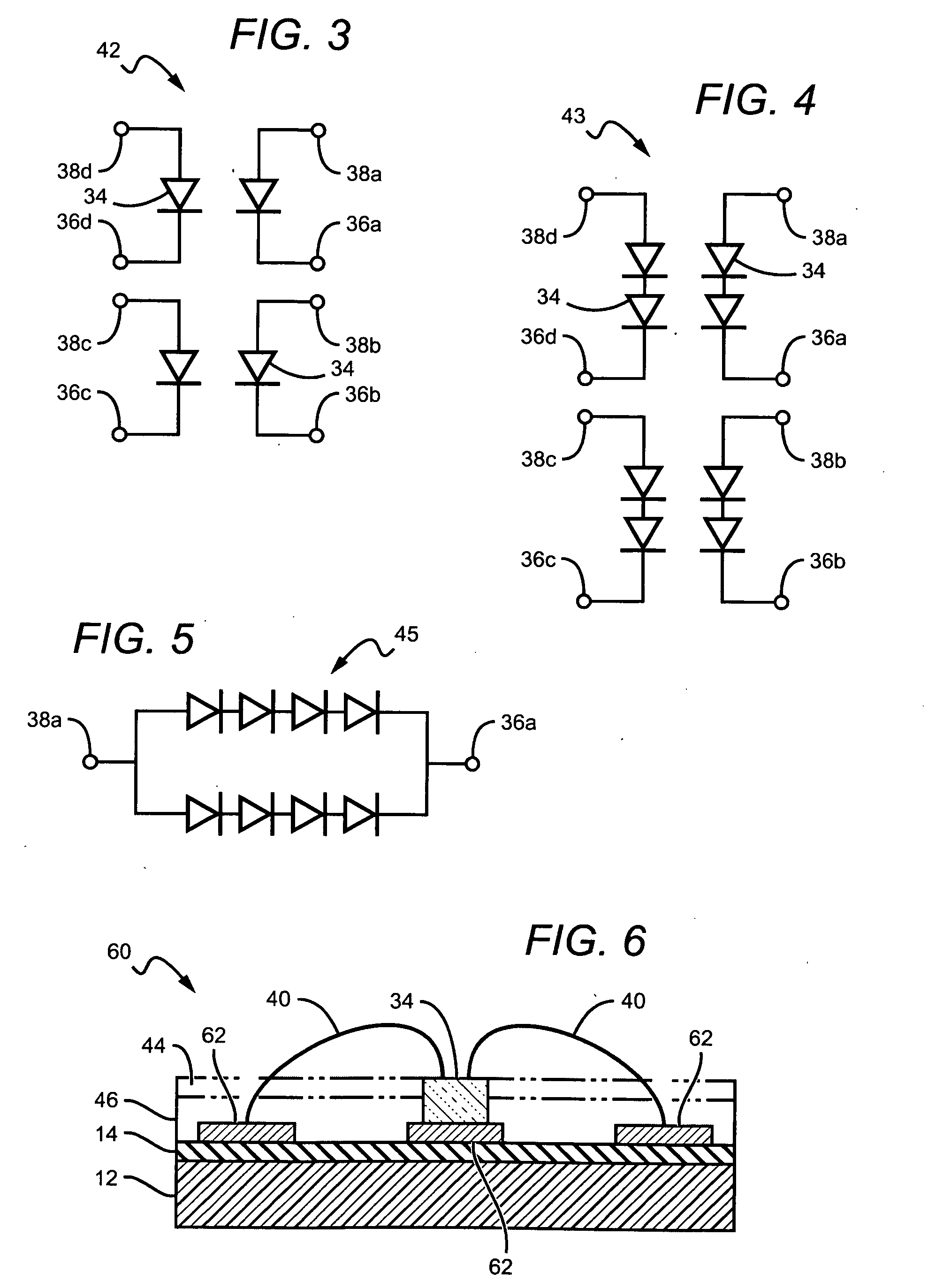

Multi-chip light emitting diode modules

ActiveUS20100117099A1Increased luminous flux outputImprove cooling effectLight absorption dielectricsSemiconductor/solid-state device detailsLuminous fluxReflective layer

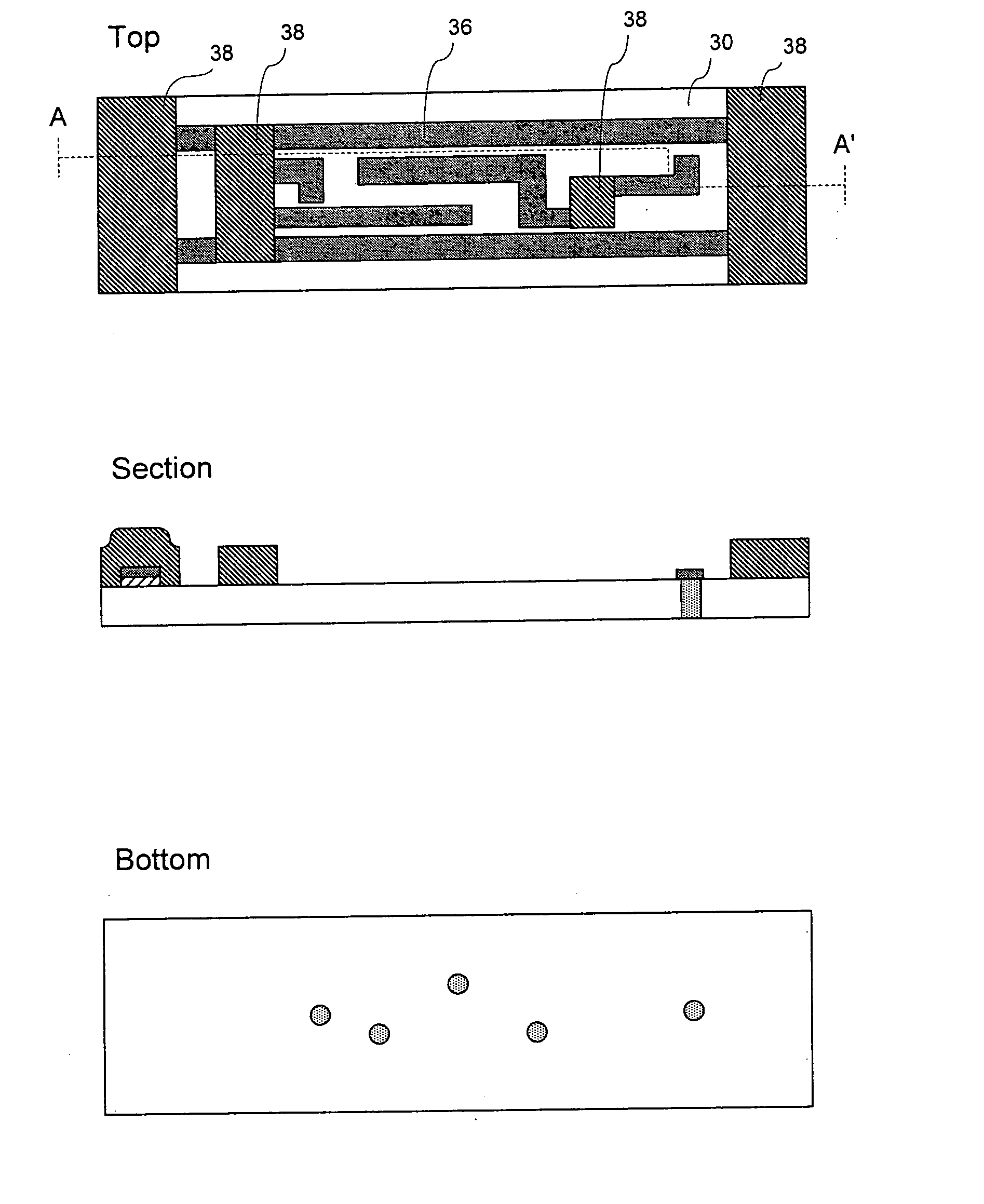

A multi-chip lighting module is disclosed for maximizing luminous flux output and thermal management. In one embodiment, a multi-chip module device comprises a substantially thermally dissipative substrate with a dark insulating layer deposited on a surface of the substrate. A plurality of light emitting devices is also provided. An electrically conductive layer is applied to a surface of the substrate, with the conductive layer comprising a plurality of chip carrier parts each having a surface for carrying at least one of the light emitting devices. Each light emitting device has a first and a second electrical terminal. A reflective layer is also provided that at least partially covers the conductive layer.

Owner:CREELED INC

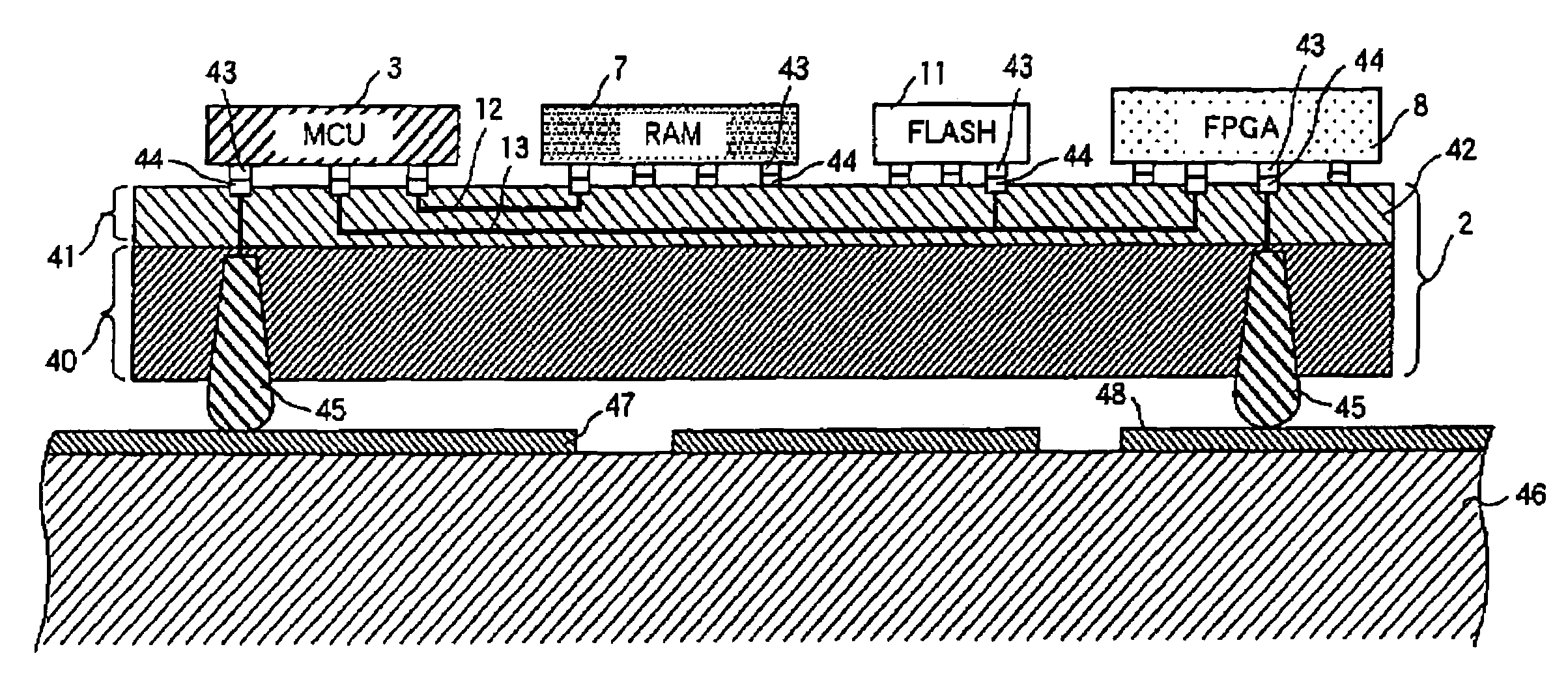

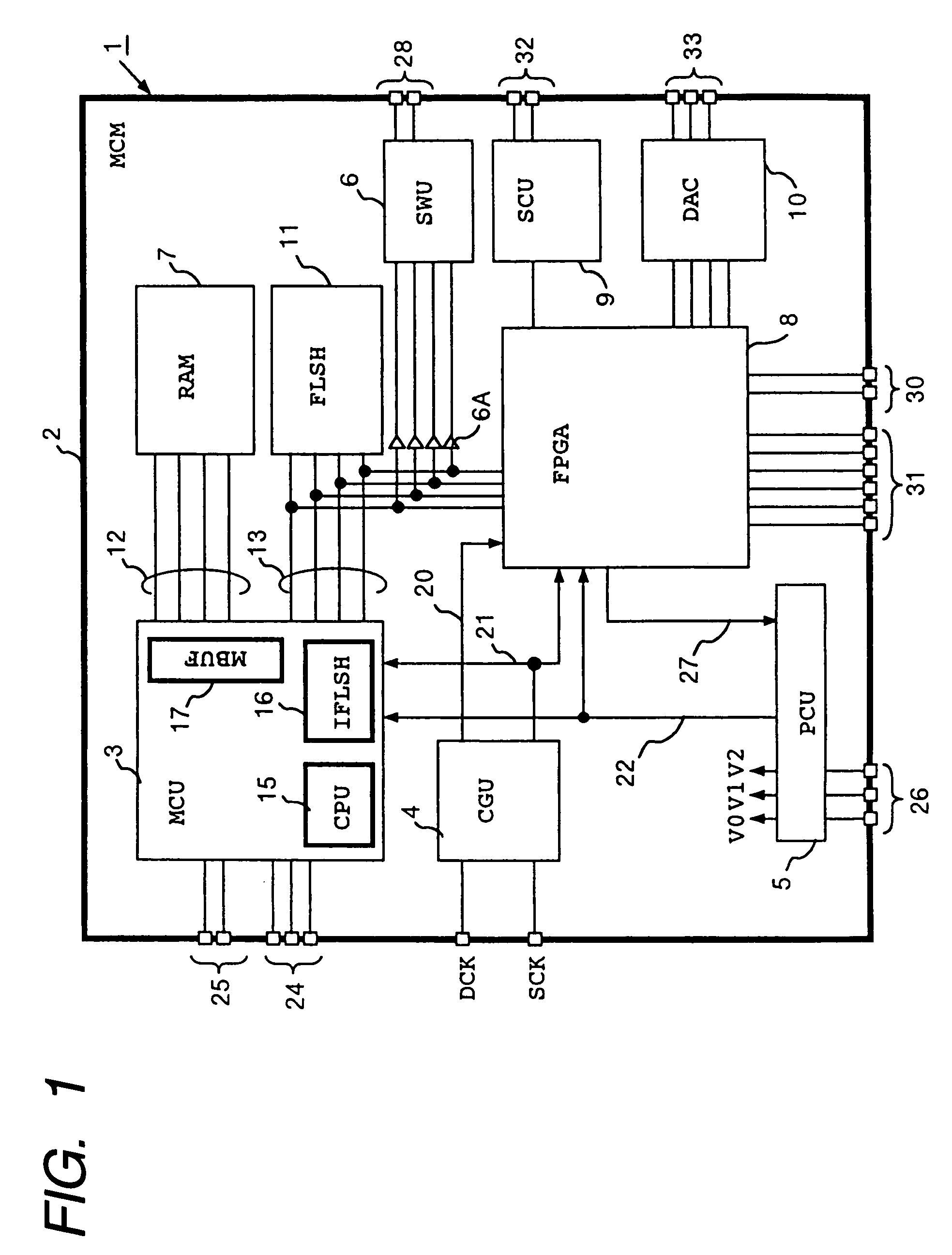

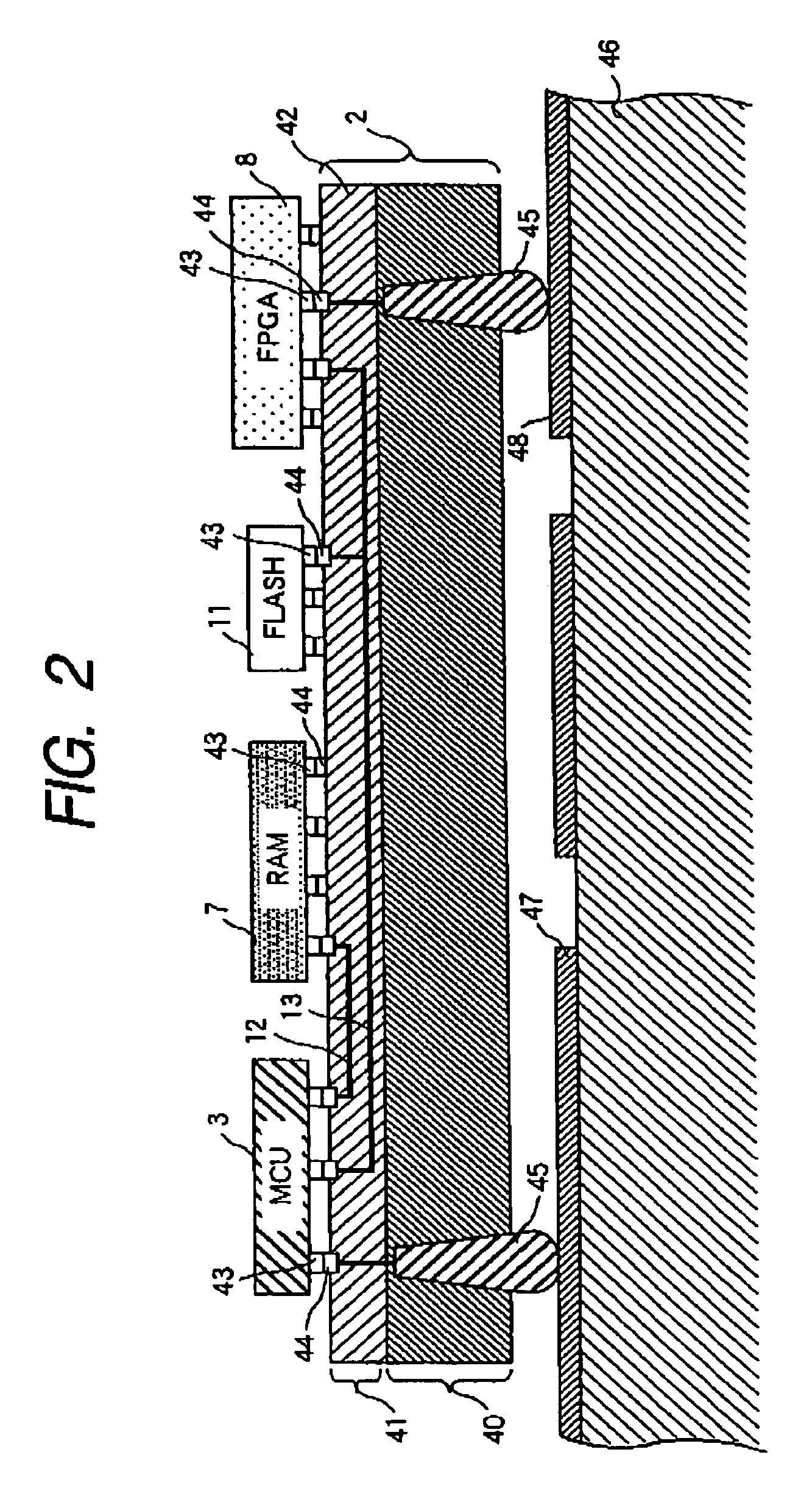

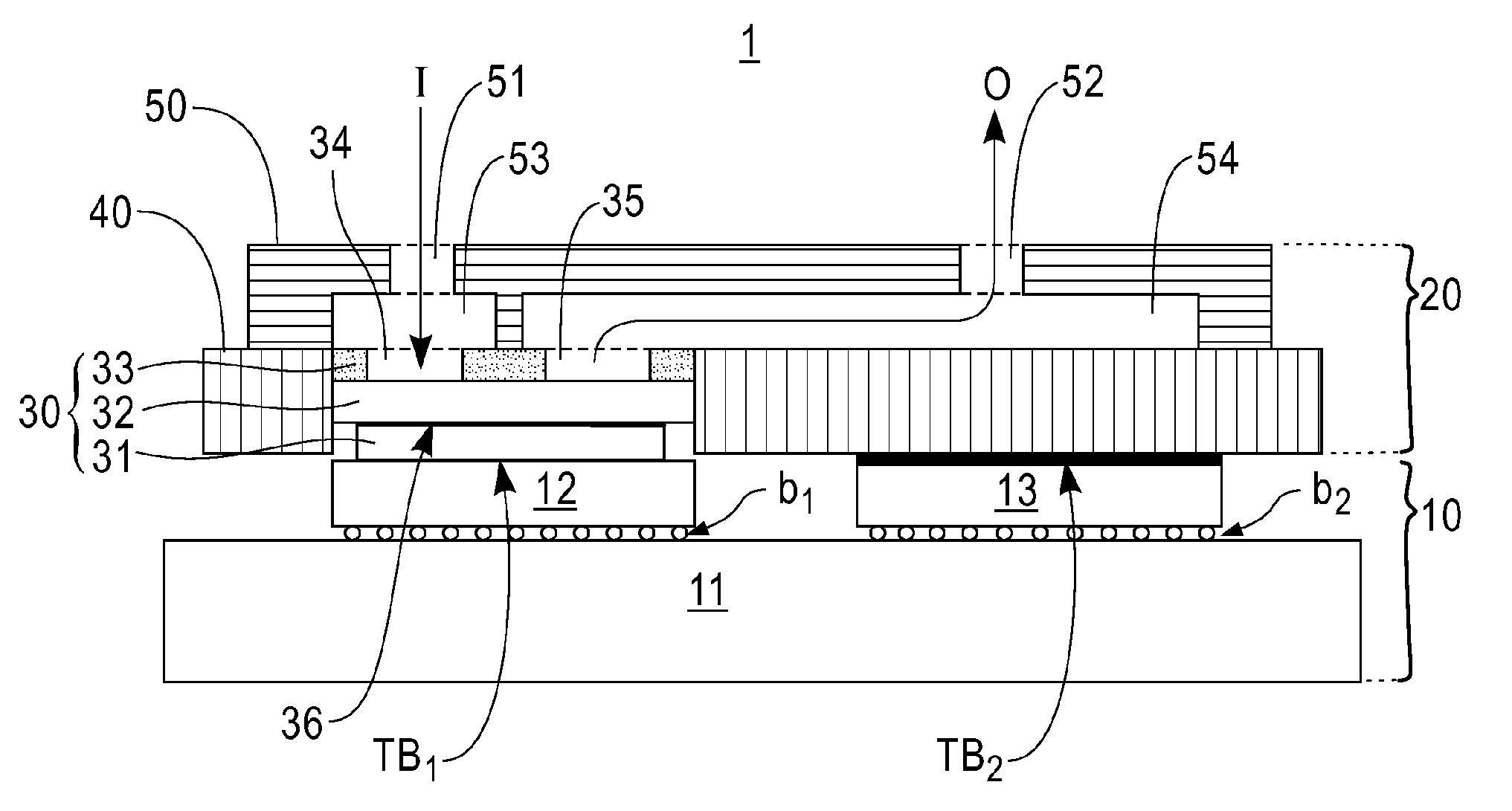

Electronic circuit device

InactiveUS7091598B2Easy to debugLow costError detection/correctionSemiconductor/solid-state device detailsStatic random-access memoryBase function

An electronic circuit device has a high-density mount board, on which are disposed a microcomputer, a random access memory, a programmable device which is a variable logic circuit represented by FPGA, and an electrically-rewritable nonvolatile memory which can store the operation program of the microcomputer. The high-density mount board has external mounting pins on the bottom surface so as to be mounted on a mother board in the same manner as a system on-chip multi-chip module. With an intended logic function being set on the programmable device, a hardware-based function to be realized by the electronic circuit device is simulated. With an operation program being written to the nonvolatile memory, a software-based function to be realized is simulated. Consequently, the device facilitates the debugging at early stages of system development, configures a prototype system, and contributes to the time reduction throughout the system development, prototype fabrication and large-scale production.

Owner:RENESAS TECH CORP

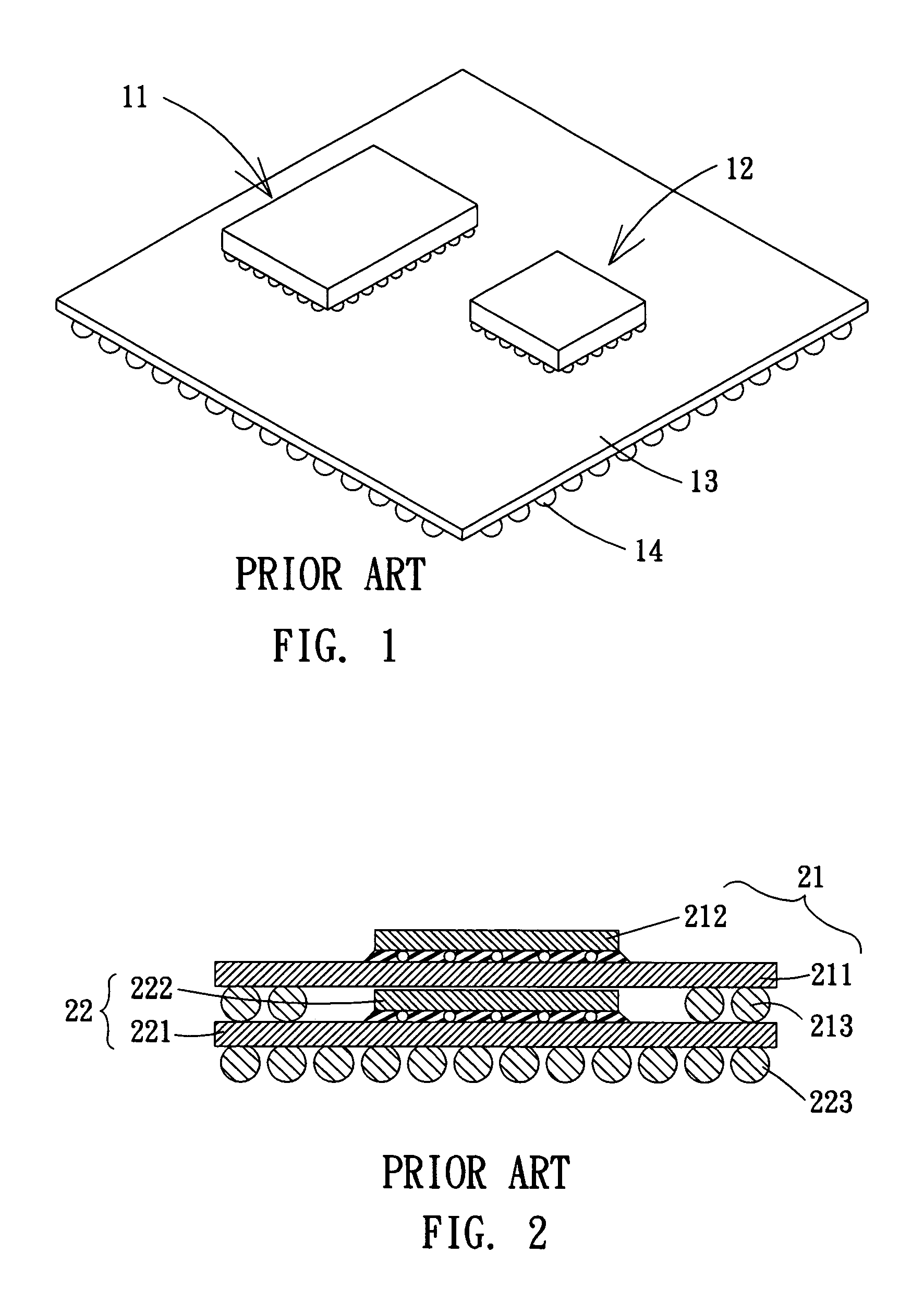

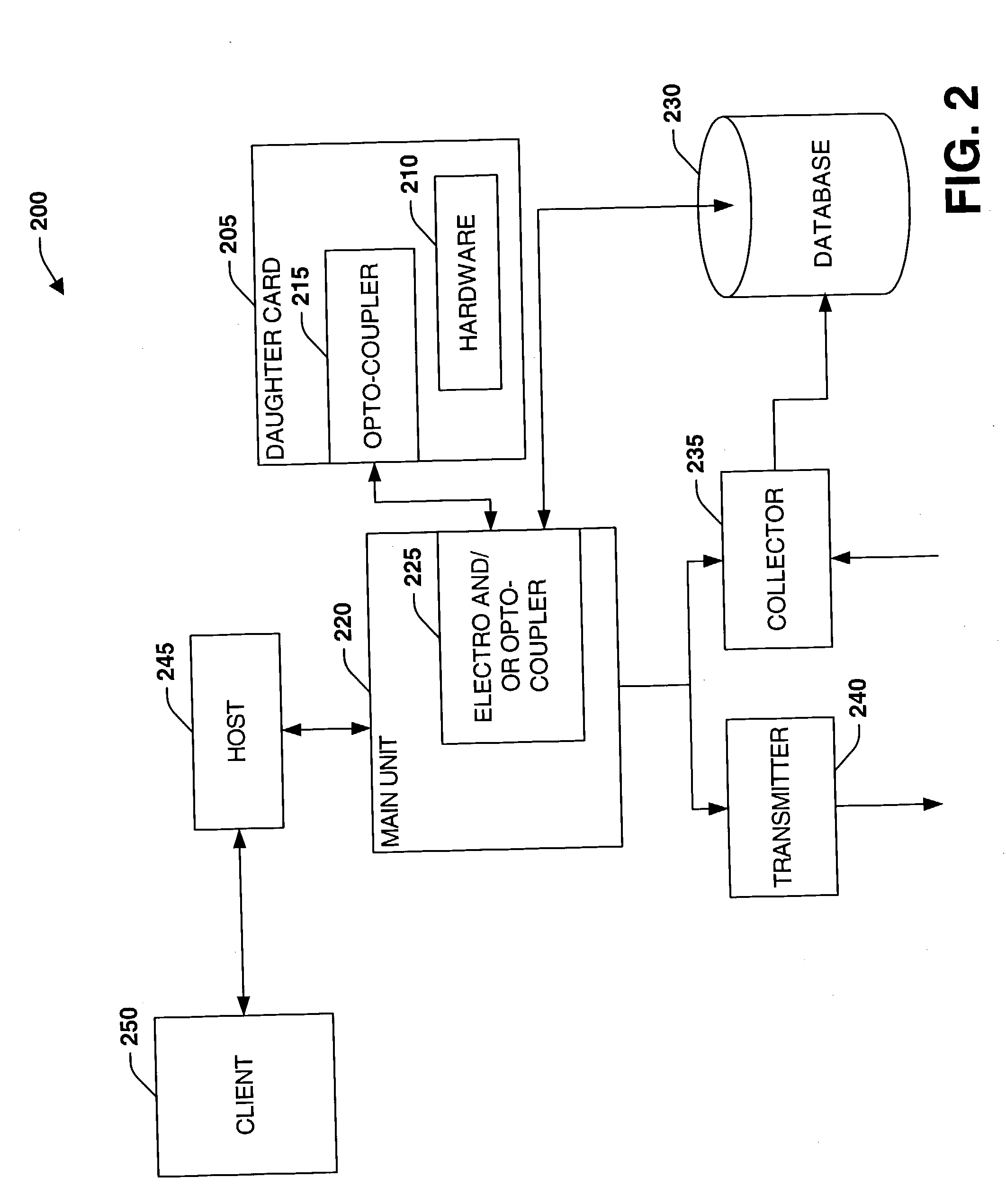

Compact low cost plastic MCM to PCB

InactiveUS20040190274A1Mitigate electrical signal problem and costLow costPrinted circuit aspectsSolid-state devicesElectricityHigh density

The present invention relates to a system and methodology to reduce size, weight and cost, improve data processing rates and serviceability, and accommodate higher I / O multi-chip modules (MCMs) for printed circuit board (PCB) assemblies employed in the electronics industry. This is accomplished by selecting low cost, pre-assembled, plastic chip type MCMs for constructing a daughter card where the daughter card material can accommodate high density lines and spaces. Optical interconnects are employed between the daughter card and the motherboard to provide a high speed interface that is substantially not effected by contaminates or limitations associated with electrical lead wires and solder bonds. The result is a high performance card that meets current and projected future demands in signal processing.

Owner:NORTHROP GRUMAN CORP

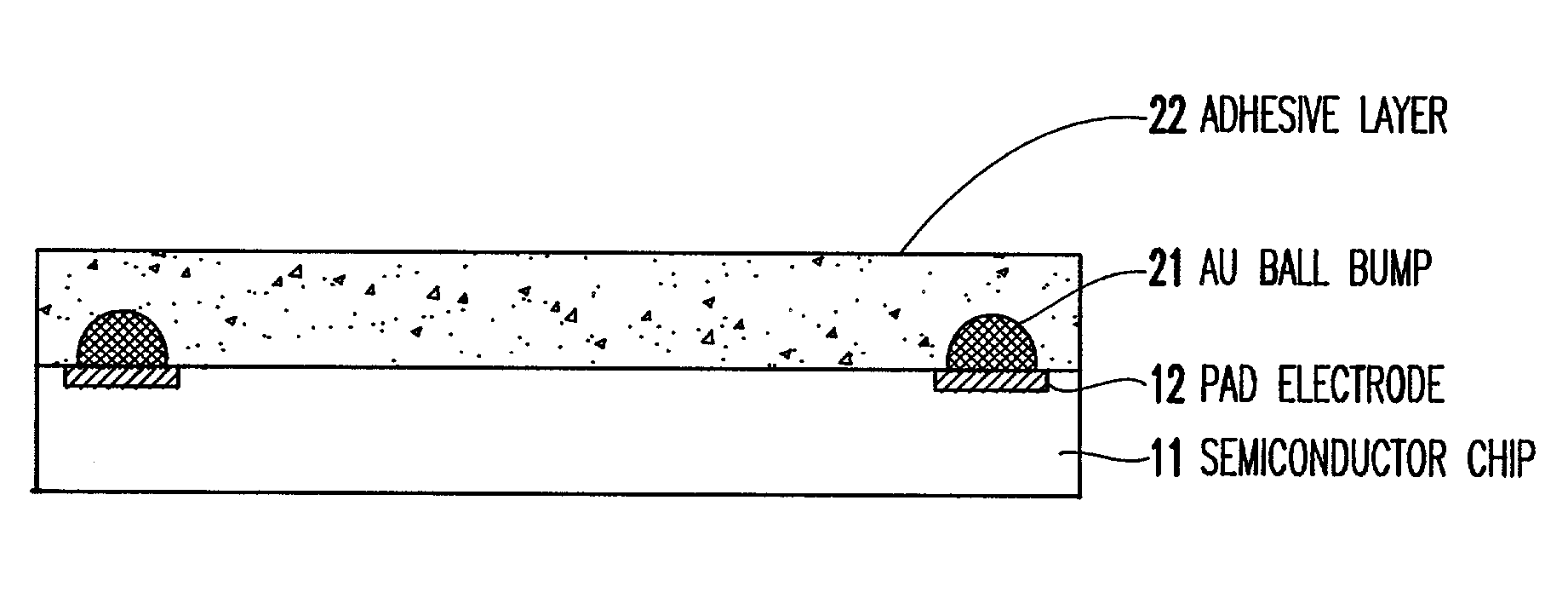

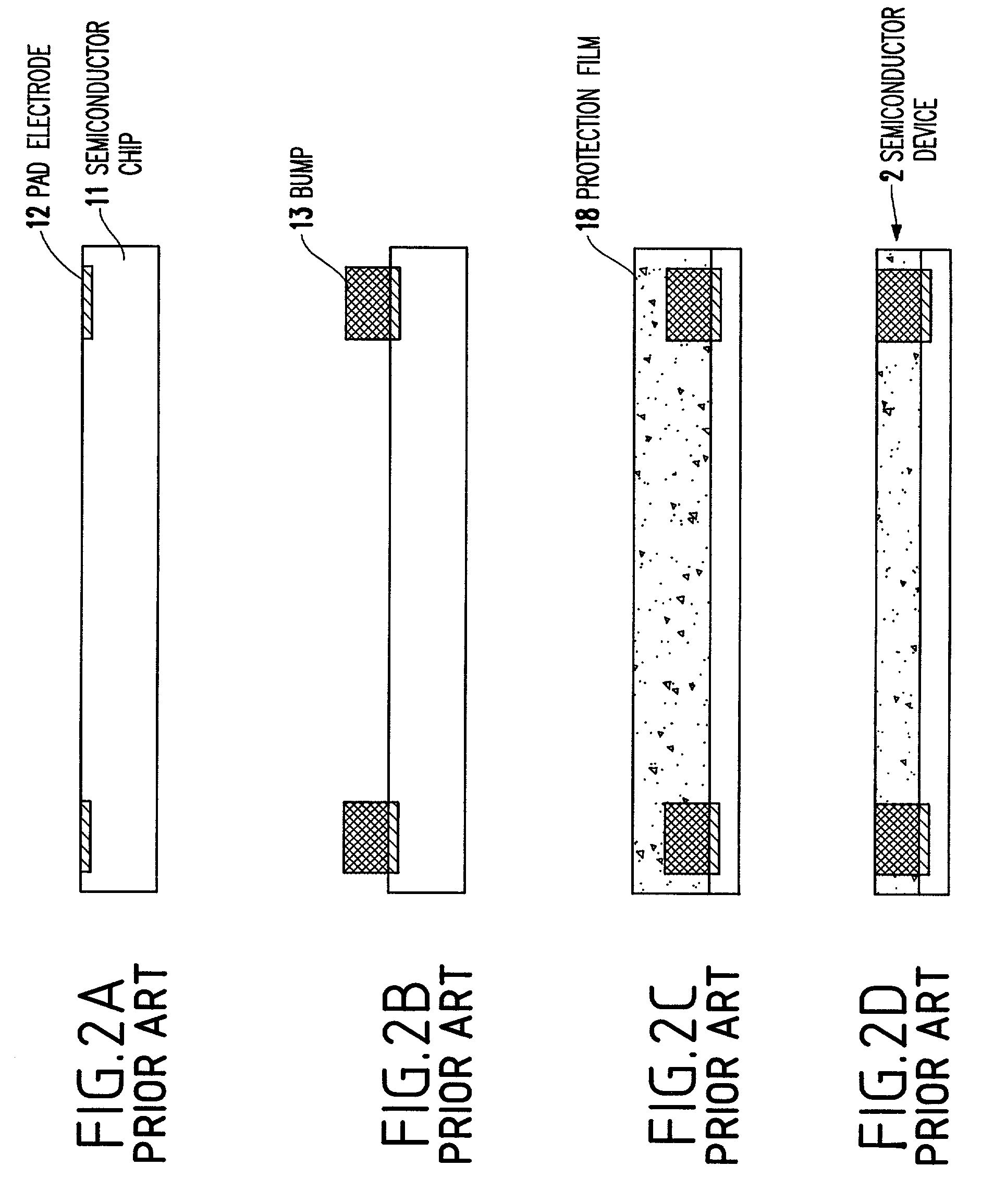

Semiconductor device and manufacturing method of the same

InactiveUS20020132463A1Semiconductor/solid-state device detailsSolid-state devicesDevice materialElectrical connection

Semiconductor device 3 comprises semiconductor chip 11, Au ball bumps 21 formed on pad electrodes 12 with a stud bump method, and thermoplastic adhesive layer 22 provided on the surface of semiconductor chip 11 on which pad electrodes 12 are formed, in which the tops of Au ball bumps 21 project from the surface of adhesive layer 22. Reliable bonding can be realized by forming the bumps for electrical connection and the adhesive resin having an adhesion function on the semiconductor chip. In addition, the present invention provides a method of bonding a copper foil to a semiconductor wafer to form a wiring pattern, a multi chip module in which electrical connection is established by bumps bonded to each other through an adhesive layer, and the like.

Owner:NEC ELECTRONICS CORP

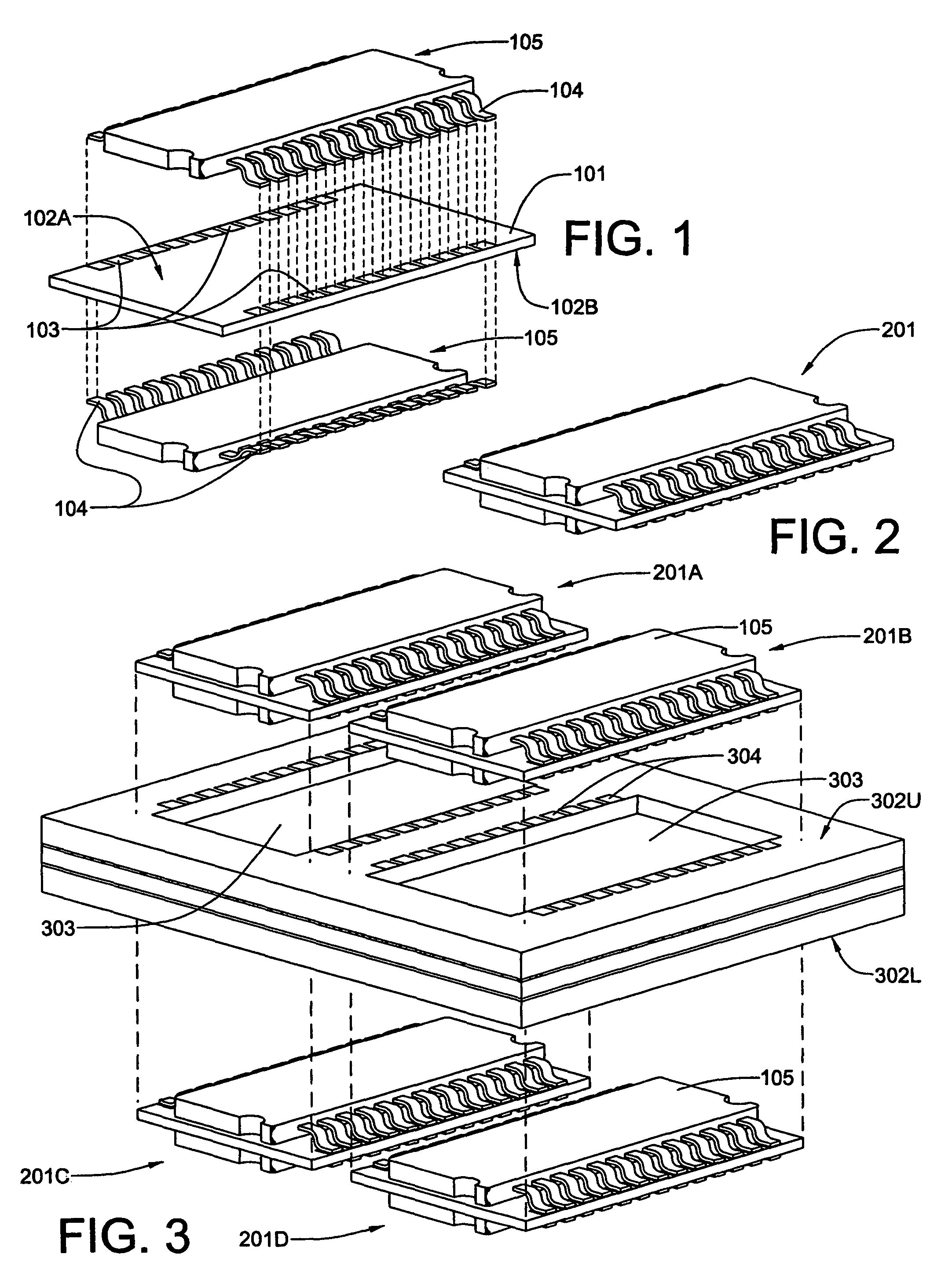

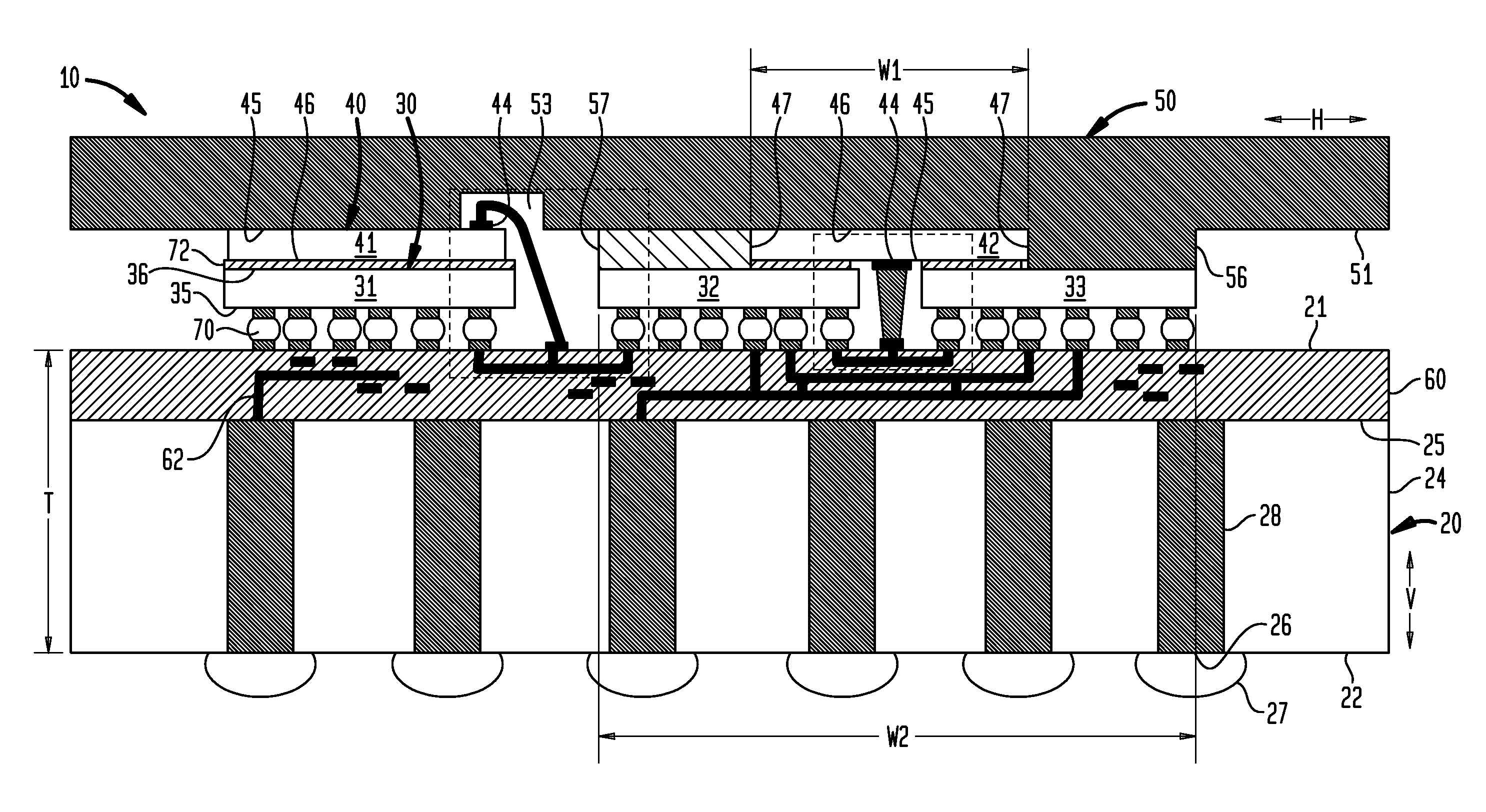

Carrier-based electronic module

InactiveUS7405471B2Increase memory densityEfficient use ofPrinted circuit assemblingSemiconductor/solid-state device detailsElectricityContact pad

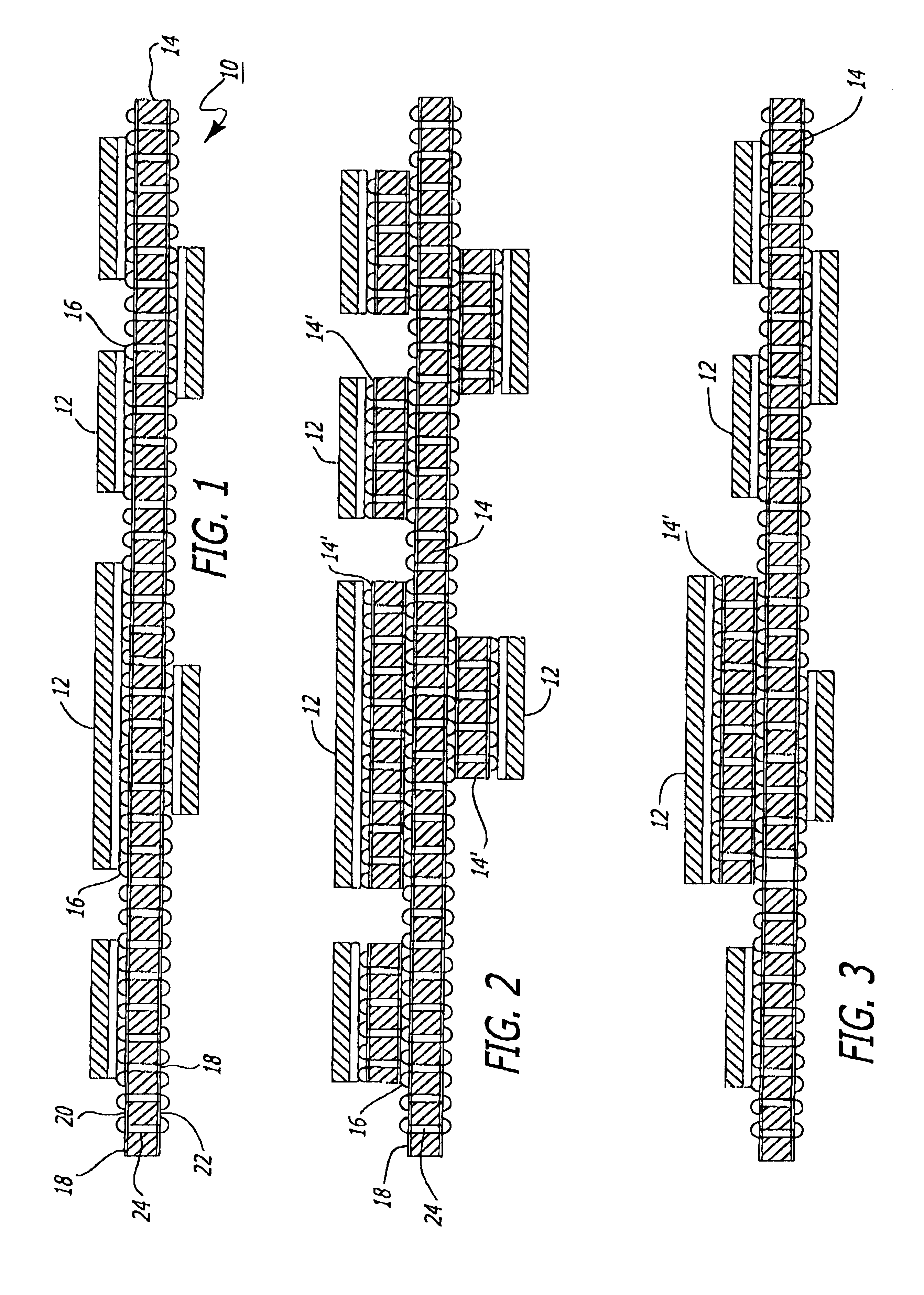

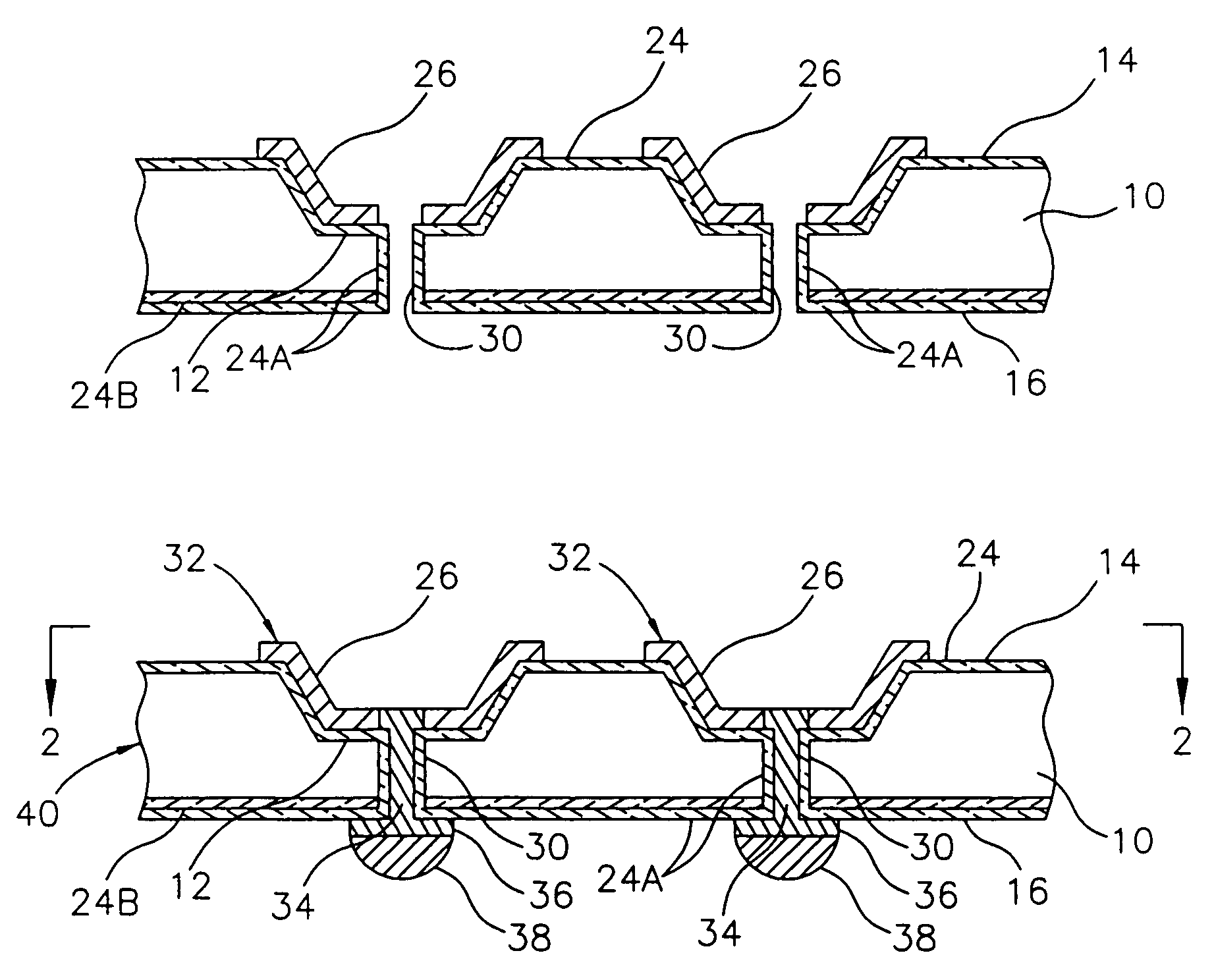

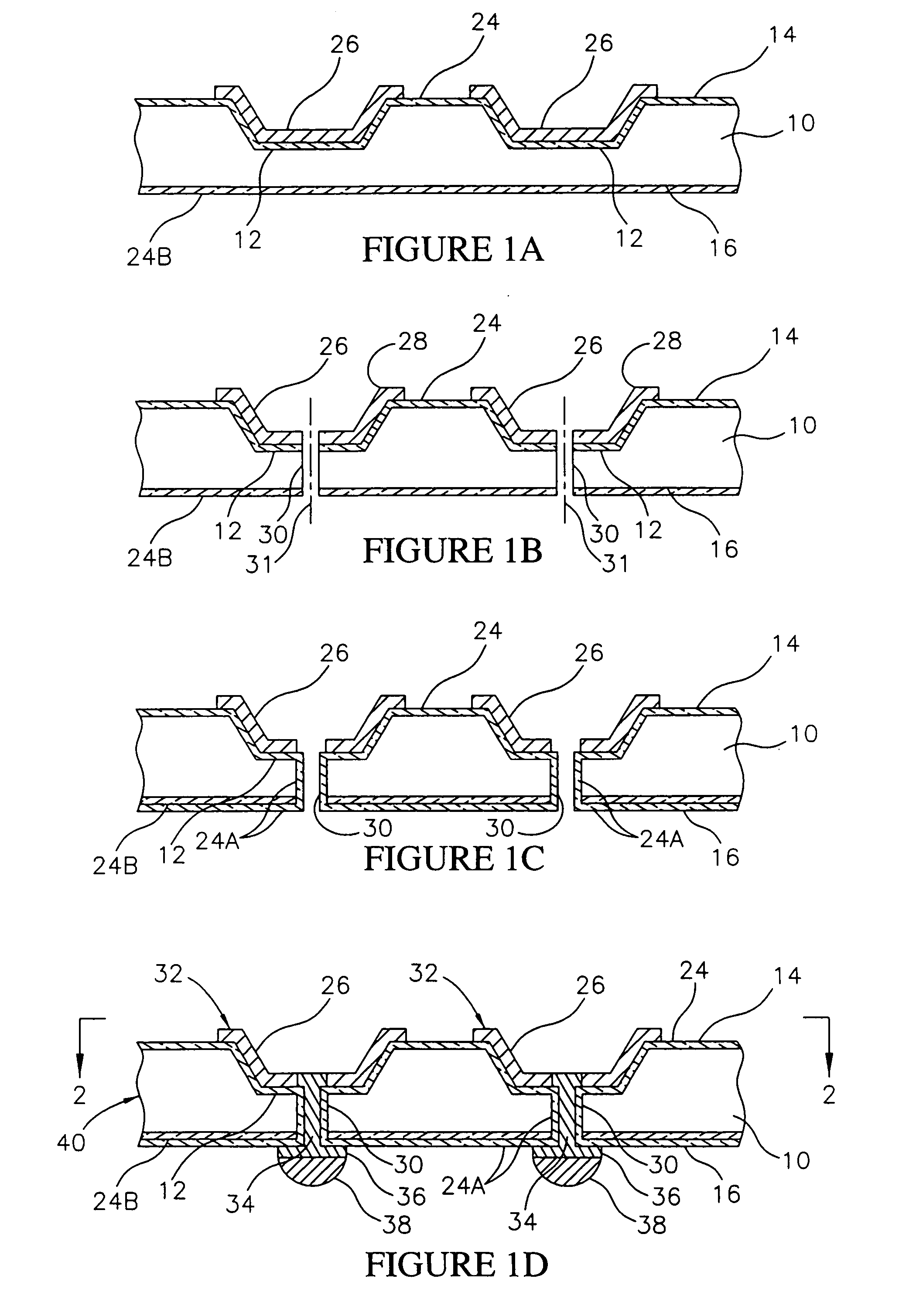

An improved multi-chip module includes a circuit board having an array of electrical interconnection pads to which are mounted a plurality of IC package units. Each IC package unit includes multiple IC packages, which are mounted on opposite sides of a package carrier. The package units may be mounted on one or both sides of the circuit board. A variety of package carriers are used to create a number of different modules. One type of package carrier has a pair of major planar surfaces. Each planar surface incorporates electrical contact pads. At least one IC package is surface mounted on each major planar surface, by interconnecting the connection elements, or leads, of the package with the contact pads on the planar surface, to form the IC package unit. Another type of package carrier substrate has a multiple recesses for back-to-back surface mounting of the IC packages. The package also includes in various versions heat sinks.

Owner:LEGACY ELECTRONICS INC

Methods and apparatus for EMI shielding in multi-chip modules

InactiveUS7648858B2Cross-talk/noise/interference reductionSemiconductor/solid-state device detailsEngineeringElectronic component

Owner:TAIWAN SEMICON MFG CO LTD

Multi-chip module with stacked face-down connected dies

ActiveUS8841765B2Semiconductor/solid-state device detailsPrinted circuit aspectsMemory chipElectrical and Electronics engineering

A microelectronic assembly can include a substrate having first and second surfaces, at least two logic chips overlying the first surface, and a memory chip having a front surface with contacts thereon, the front surface of the memory chip confronting a rear surface of each logic chip. The substrate can have conductive structure thereon and terminals exposed at the second surface for connection with a component. Signal contacts of each logic chip can be directly electrically connected to signal contacts of the other logic chips through the conductive structure of the substrate for transfer of signals between the logic chips. The logic chips can be adapted to simultaneously execute a set of instructions of a given thread of a process. The contacts of the memory chip can be directly electrically connected to the signal contacts of at least one of the logic chips through the conductive structure of the substrate.

Owner:TESSERA INC

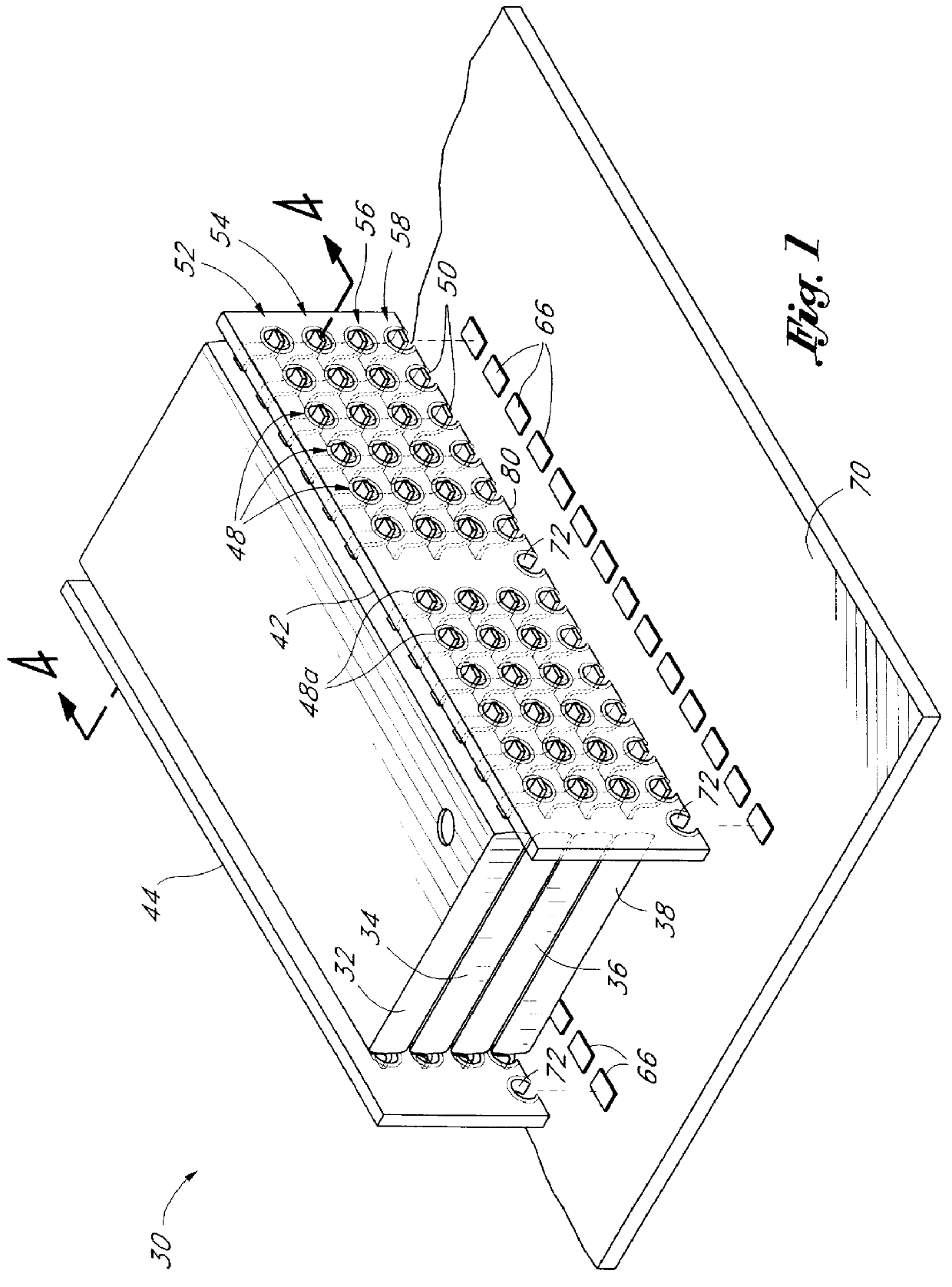

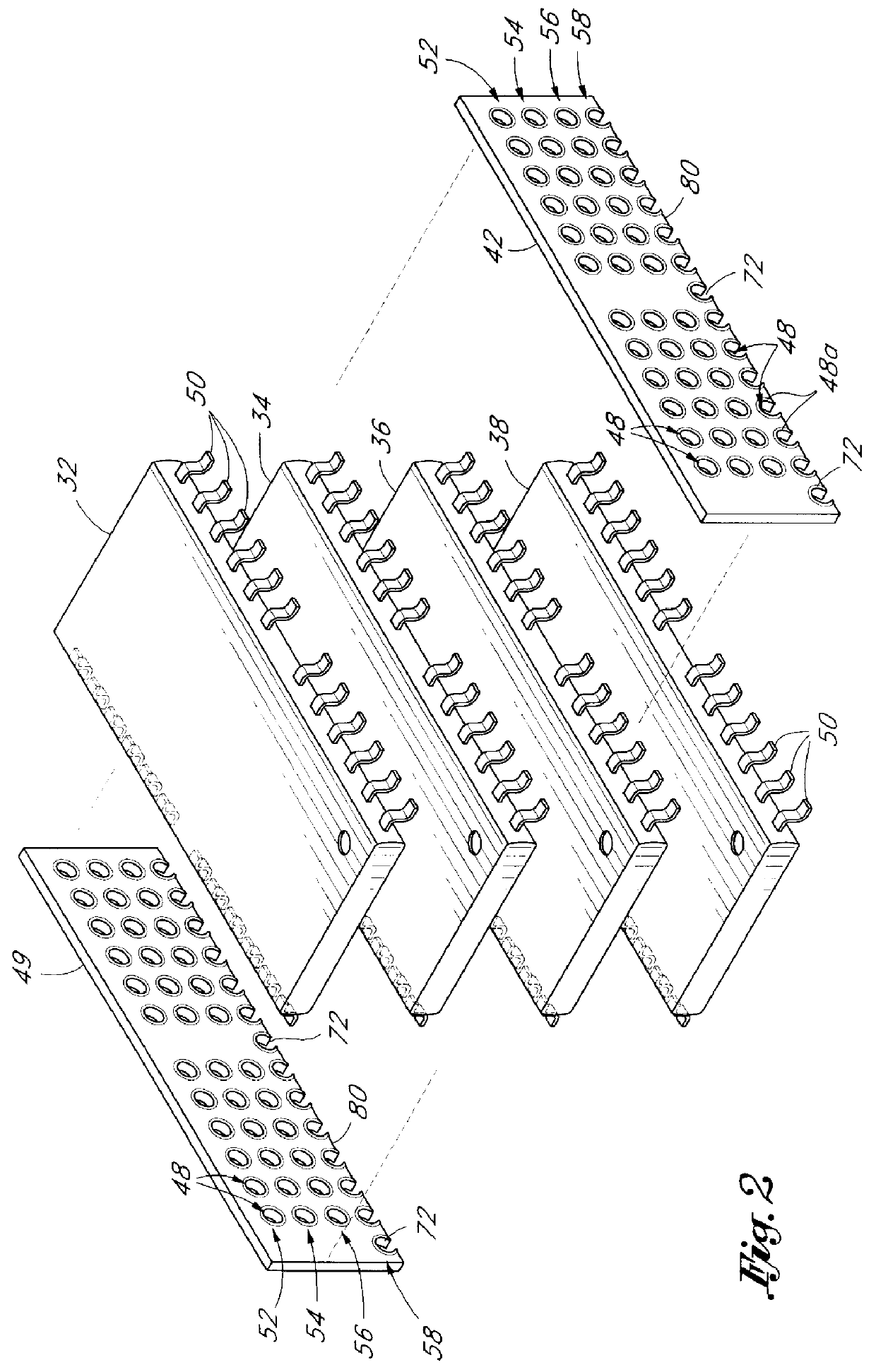

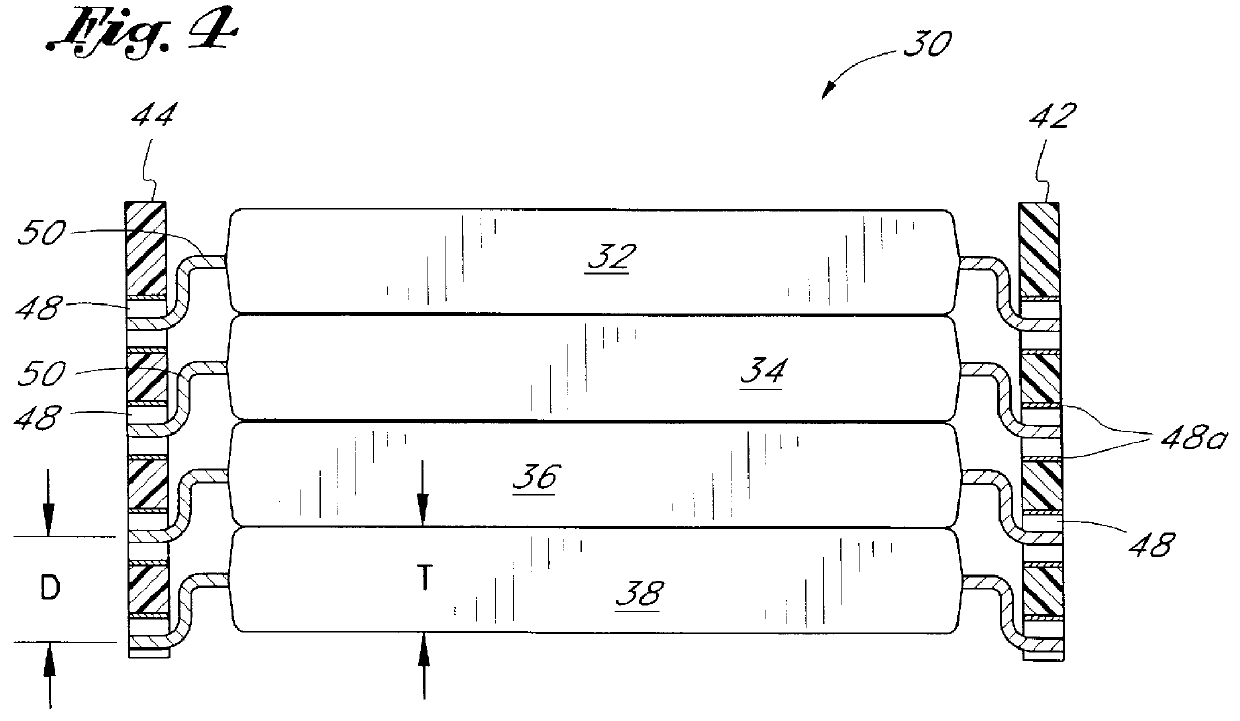

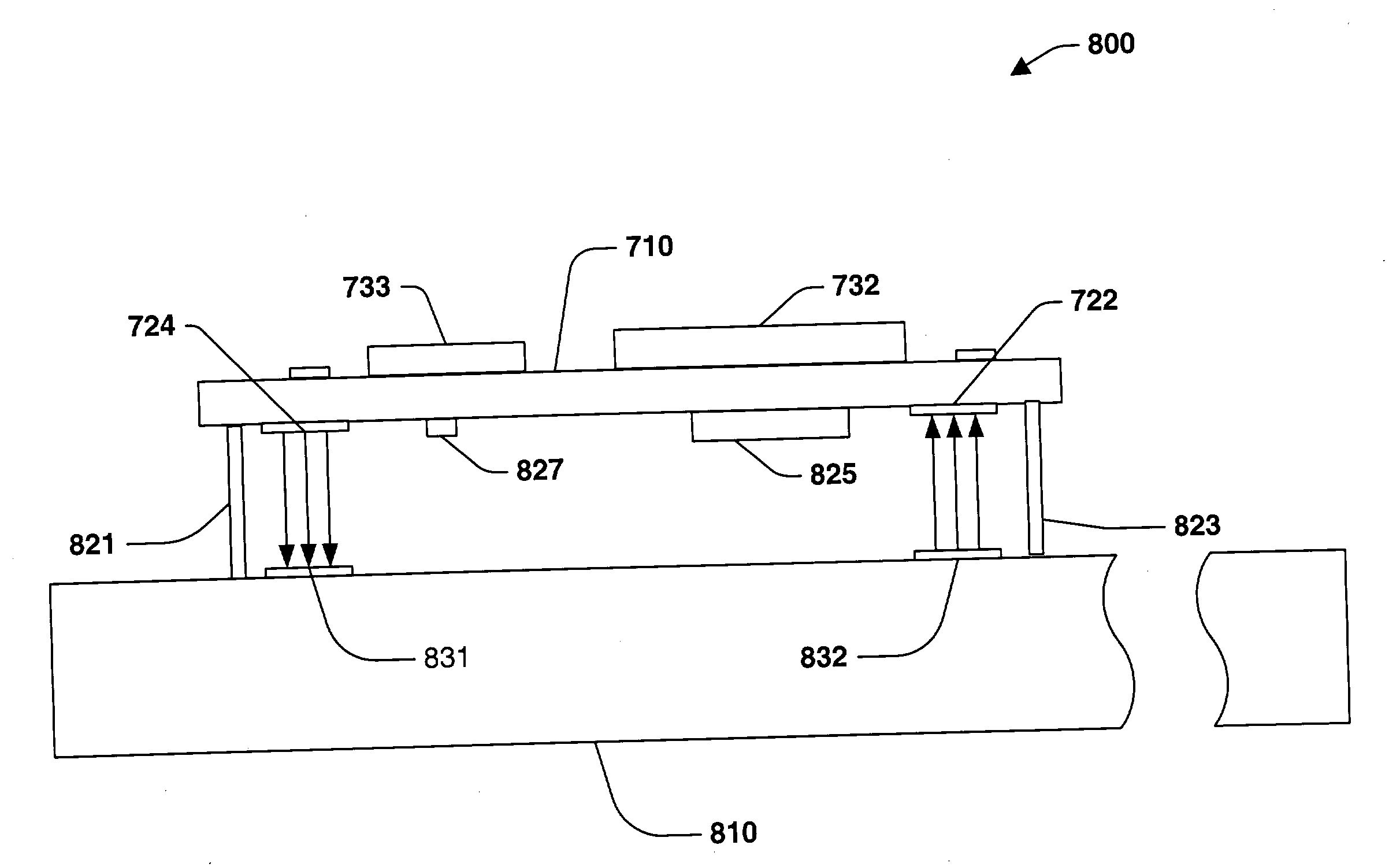

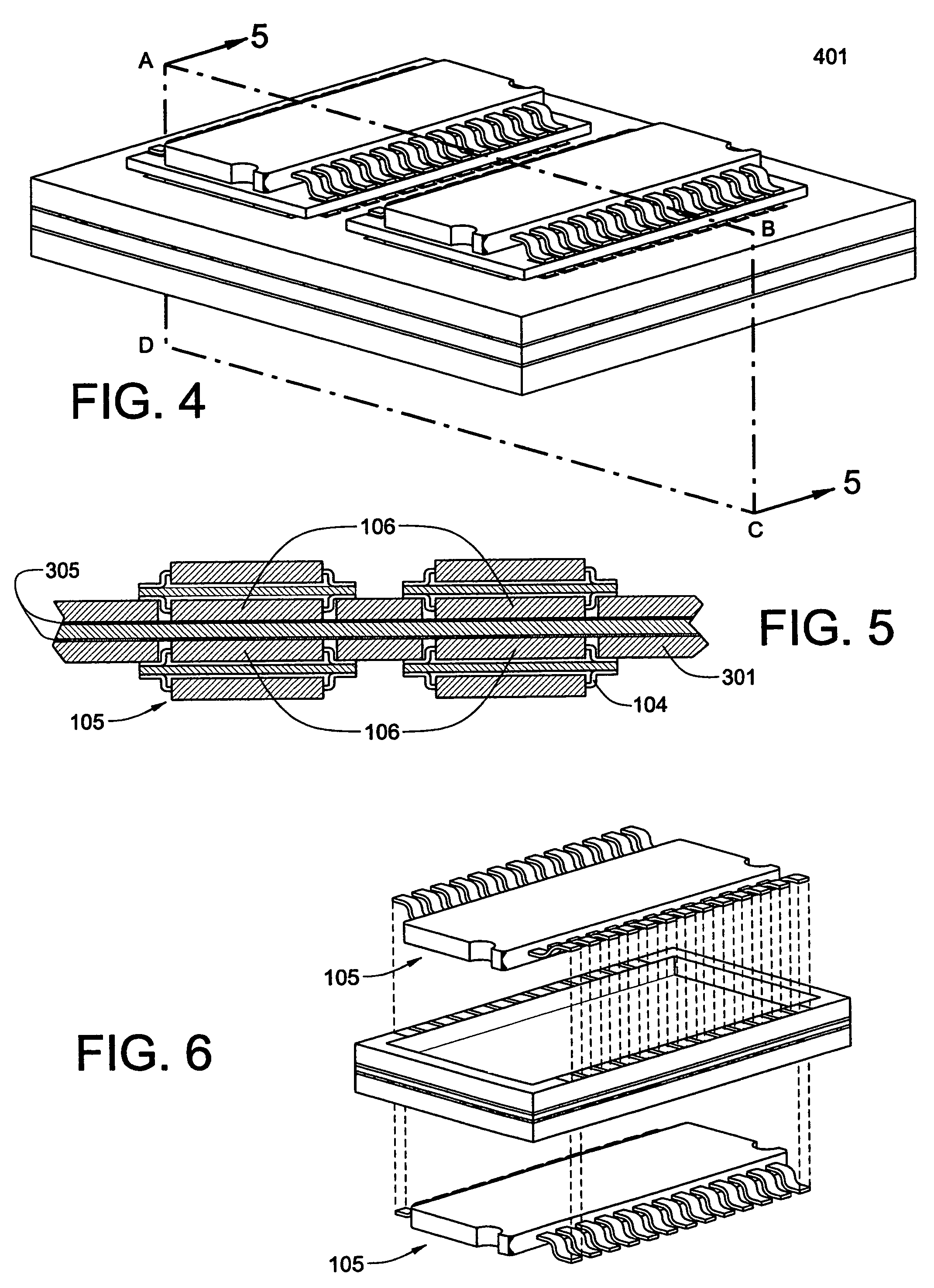

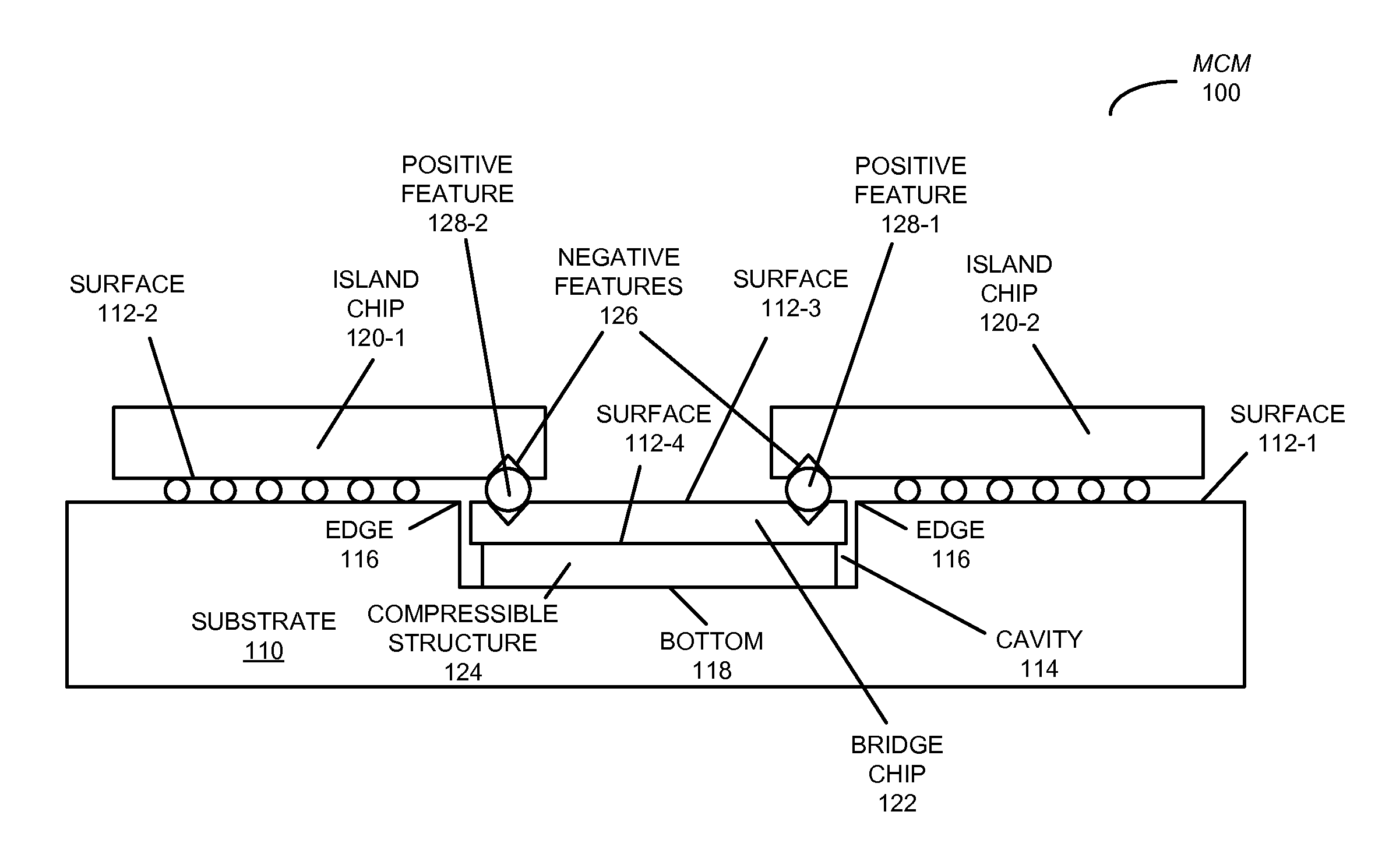

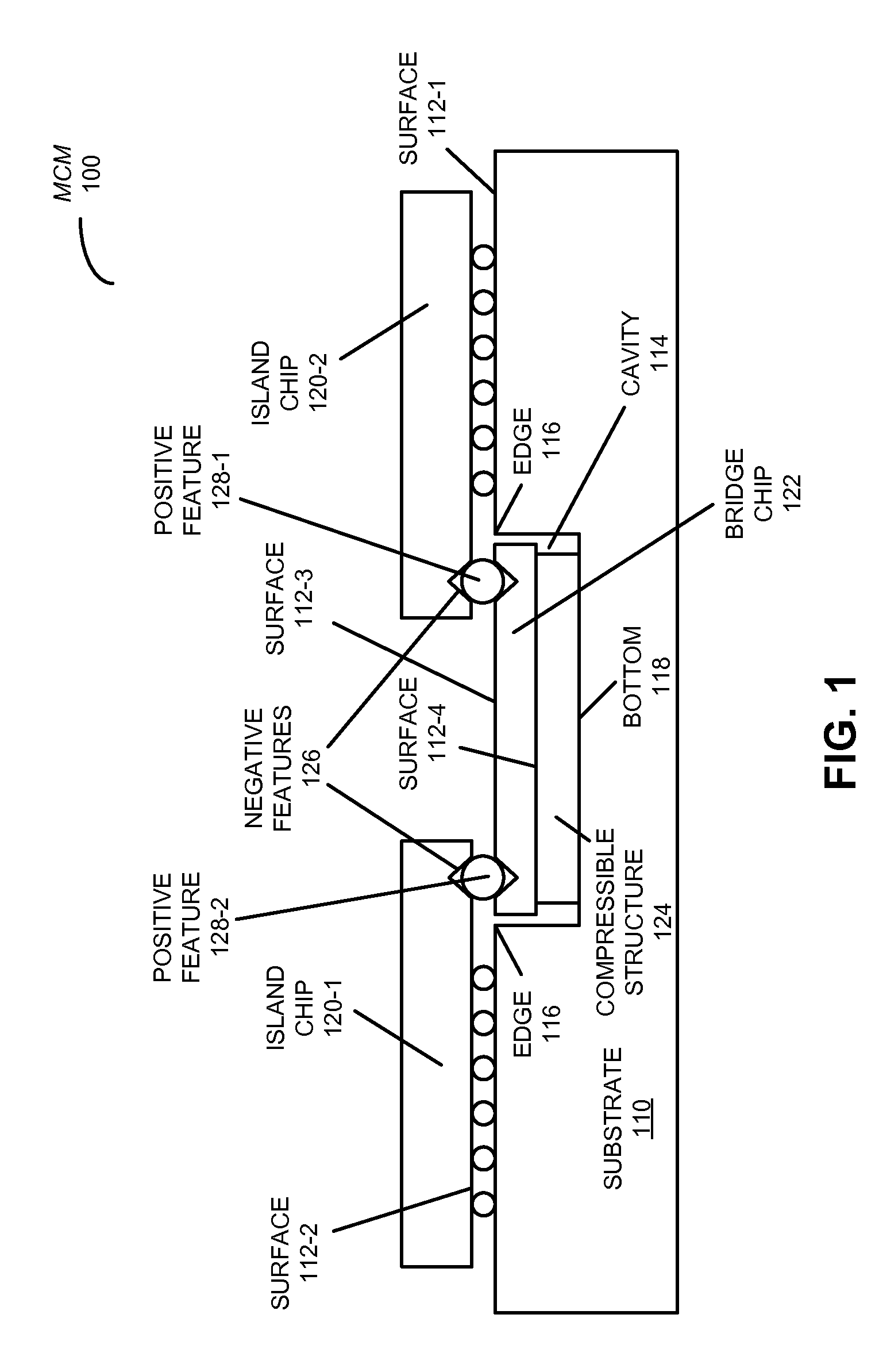

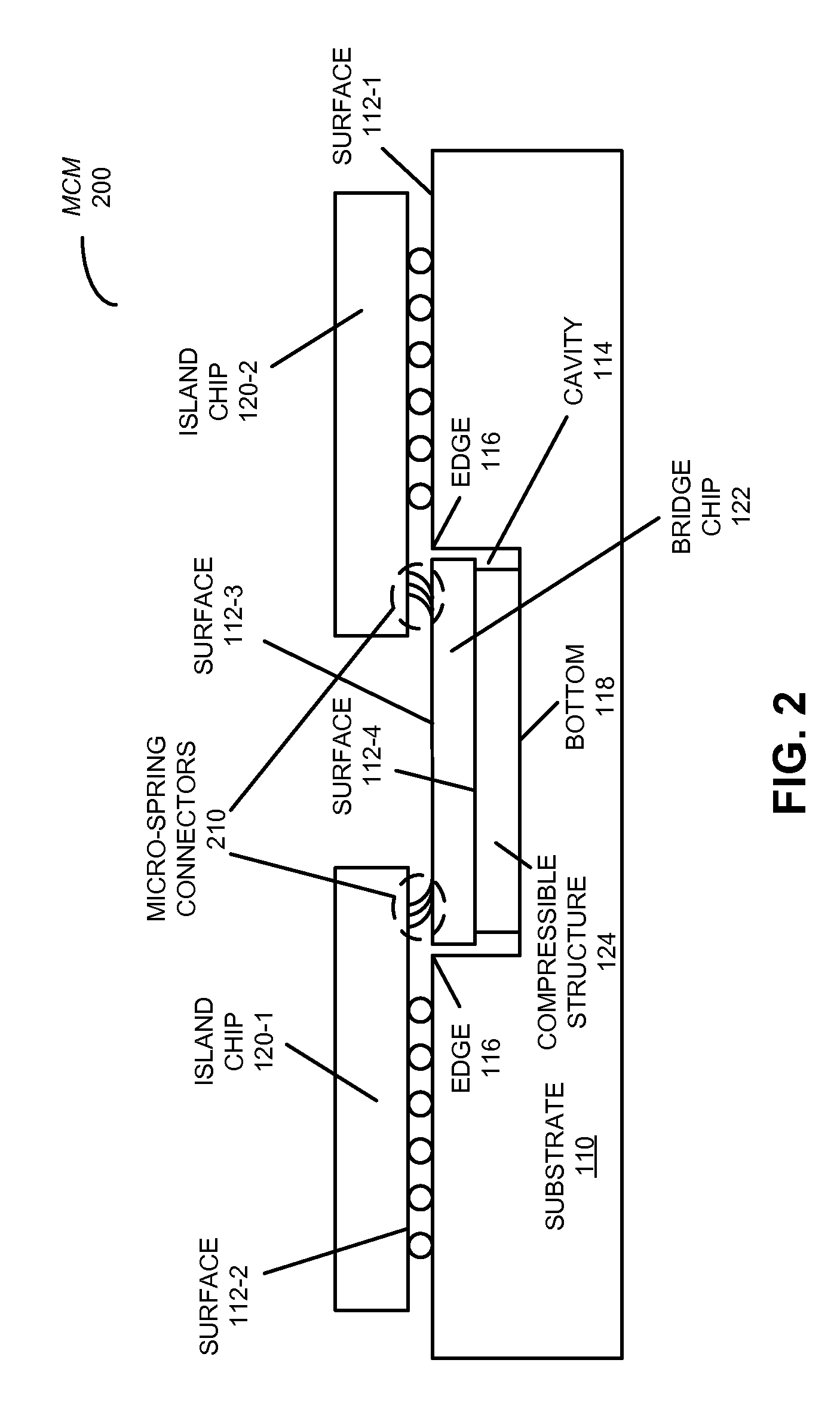

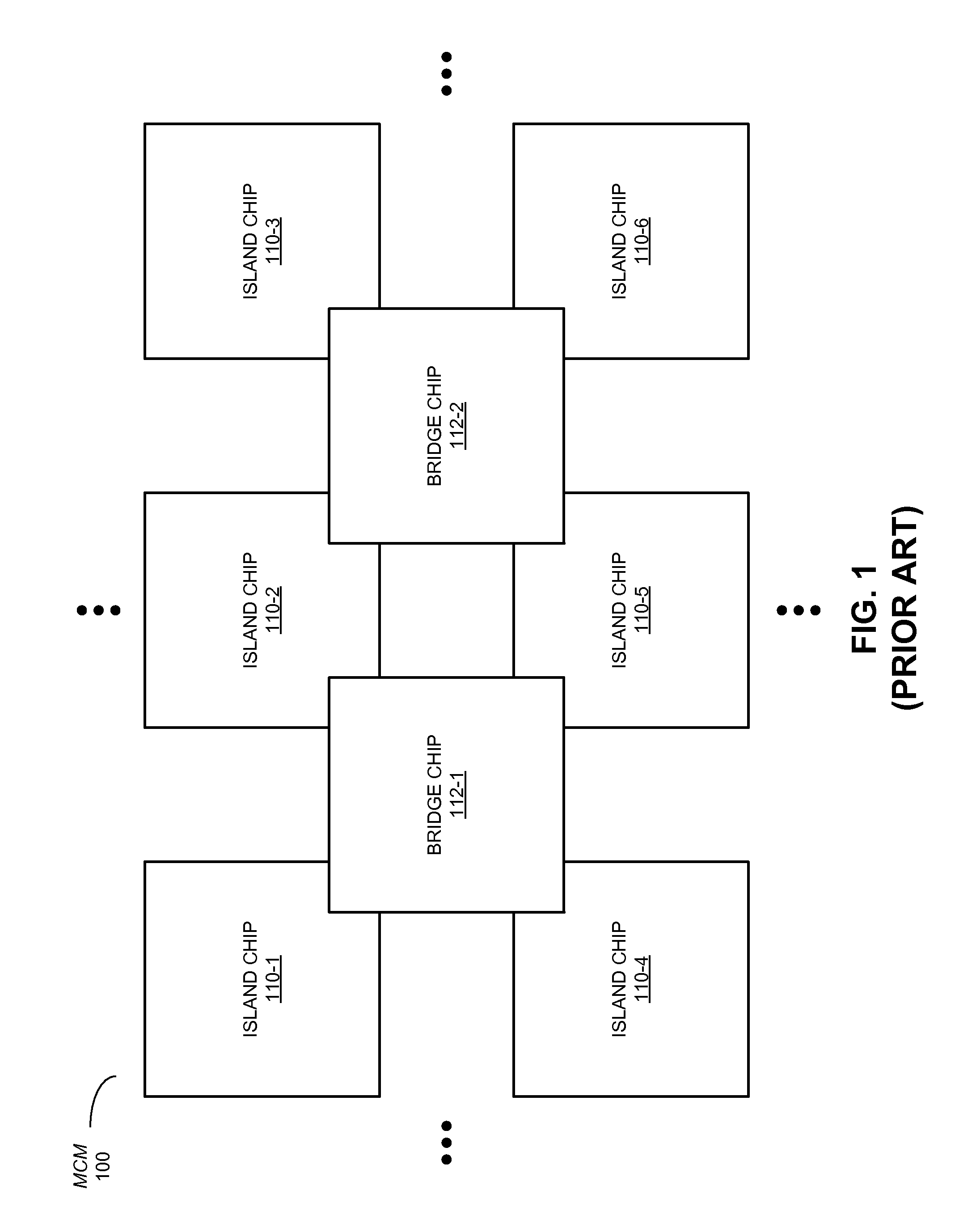

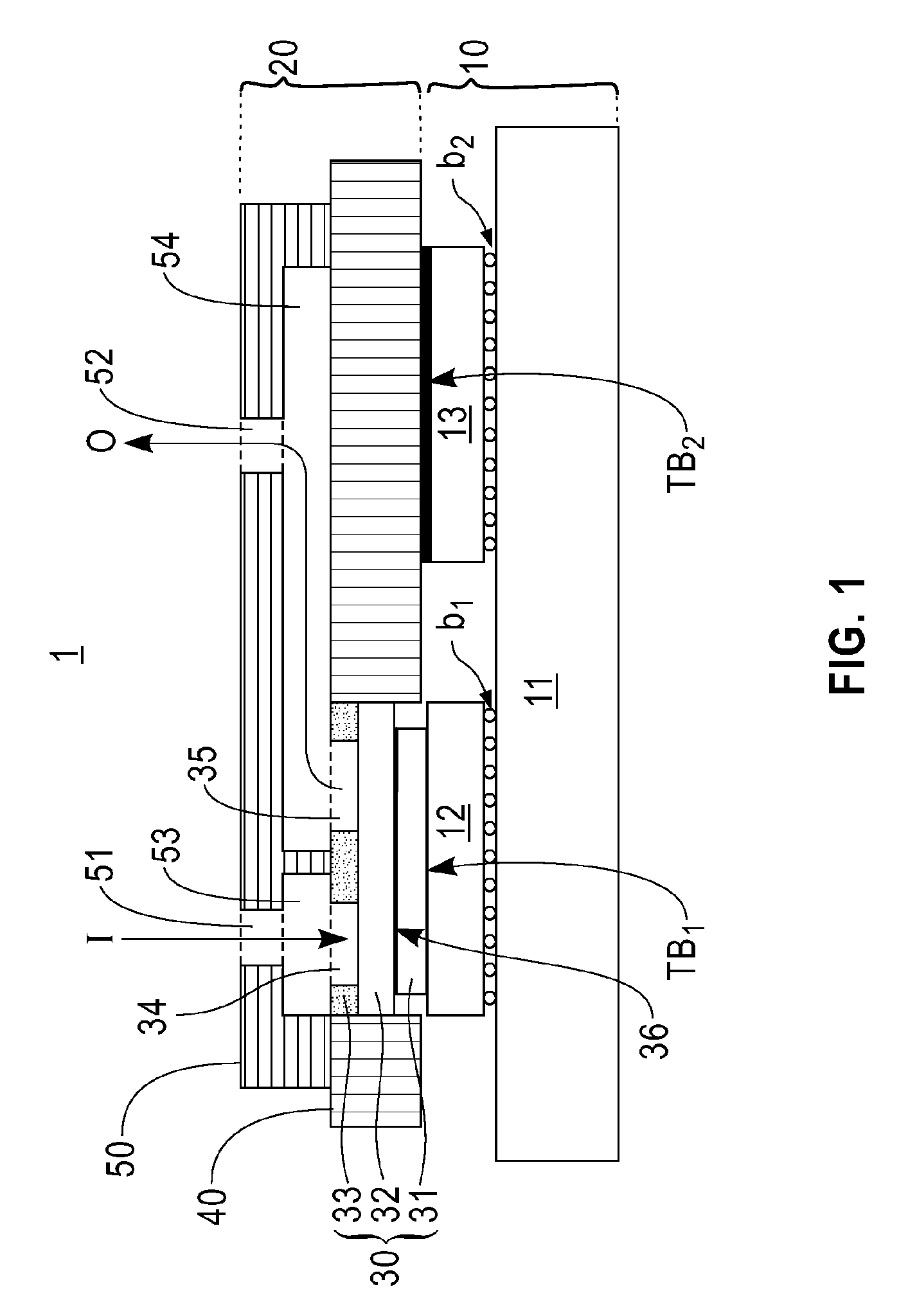

Maintaining alignment in a multi-chip module using a compressible structure

ActiveUS8742576B2Electrically conductive connectionsSemiconductor/solid-state device detailsEngineeringCompressed structure

An MCM includes a two-dimensional array of facing chips, including island chips and bridge chips that communicate with each other using overlapping connectors. In order to maintain the relative vertical spacing of these connectors, compressible structures are in cavities in a substrate, which house the bridge chips, provide a compressive force on back surfaces of the bridge chips. These compressible structures include a compliant material with shape and volume compression. In this way, the MCM may ensure that facing surfaces of the island chips and the bridge chips, as well as connectors on these surfaces, are approximately coplanar without bending the bridge chips.

Owner:ORACLE INT CORP

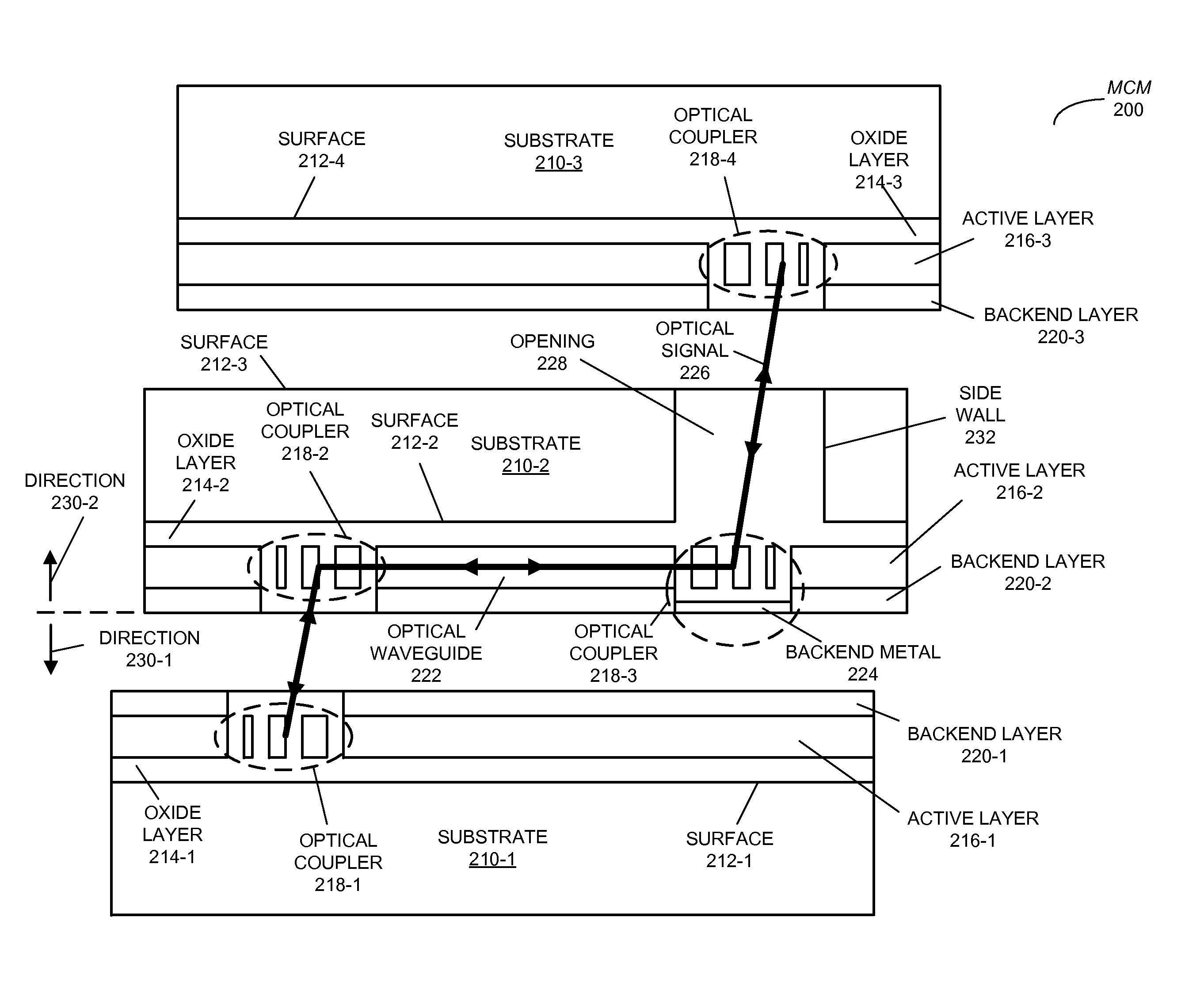

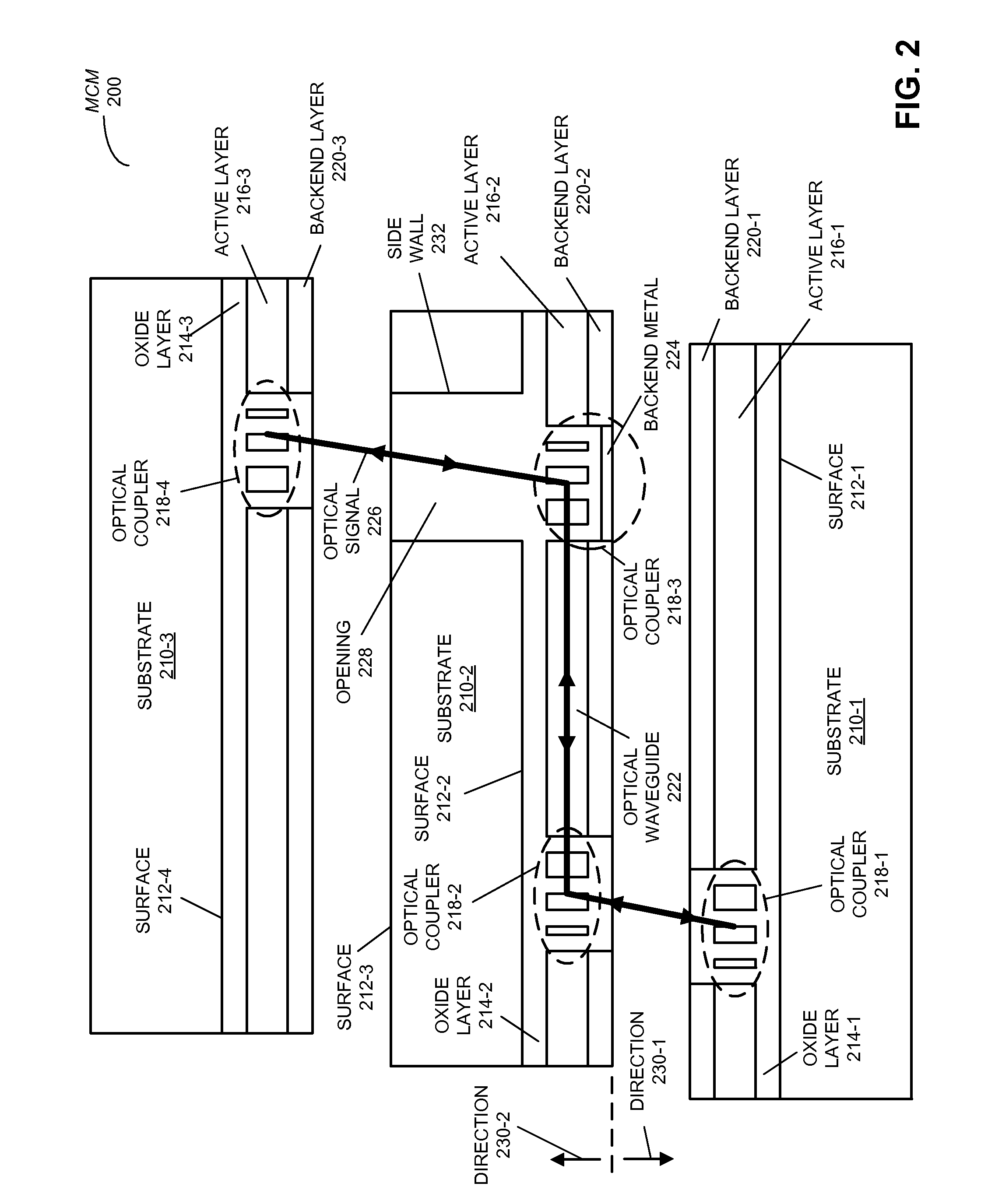

Three-dimensional macro-chip including optical interconnects

ActiveUS8267583B2Reduce expensesShorten the timeLinear bearingsCoupling light guidesOptical couplingWaveguide

A multi-chip module (MCM), which includes a three-dimensional (3D) stack of chips that are coupled using optical interconnects, is described. In this MCM, disposed on a first surface of a middle chip in the 3D stack, there are: a first optical coupler, an optical waveguide, which is coupled to the first optical coupler, and a second optical coupler, which is coupled to the optical waveguide. The first optical coupler redirects an optical signal from the optical waveguide to a first direction (which is not in the plane of the first surface), or from the first direction to the optical waveguide. Moreover, the second optical coupler redirects the optical signal from the optical waveguide to a second direction (which is not in the plane of the first surface), or from the second direction to the optical waveguide. Note that an optical path associated with the second direction passes through an opening in a substrate in the middle chip.

Owner:ORACLE INT CORP

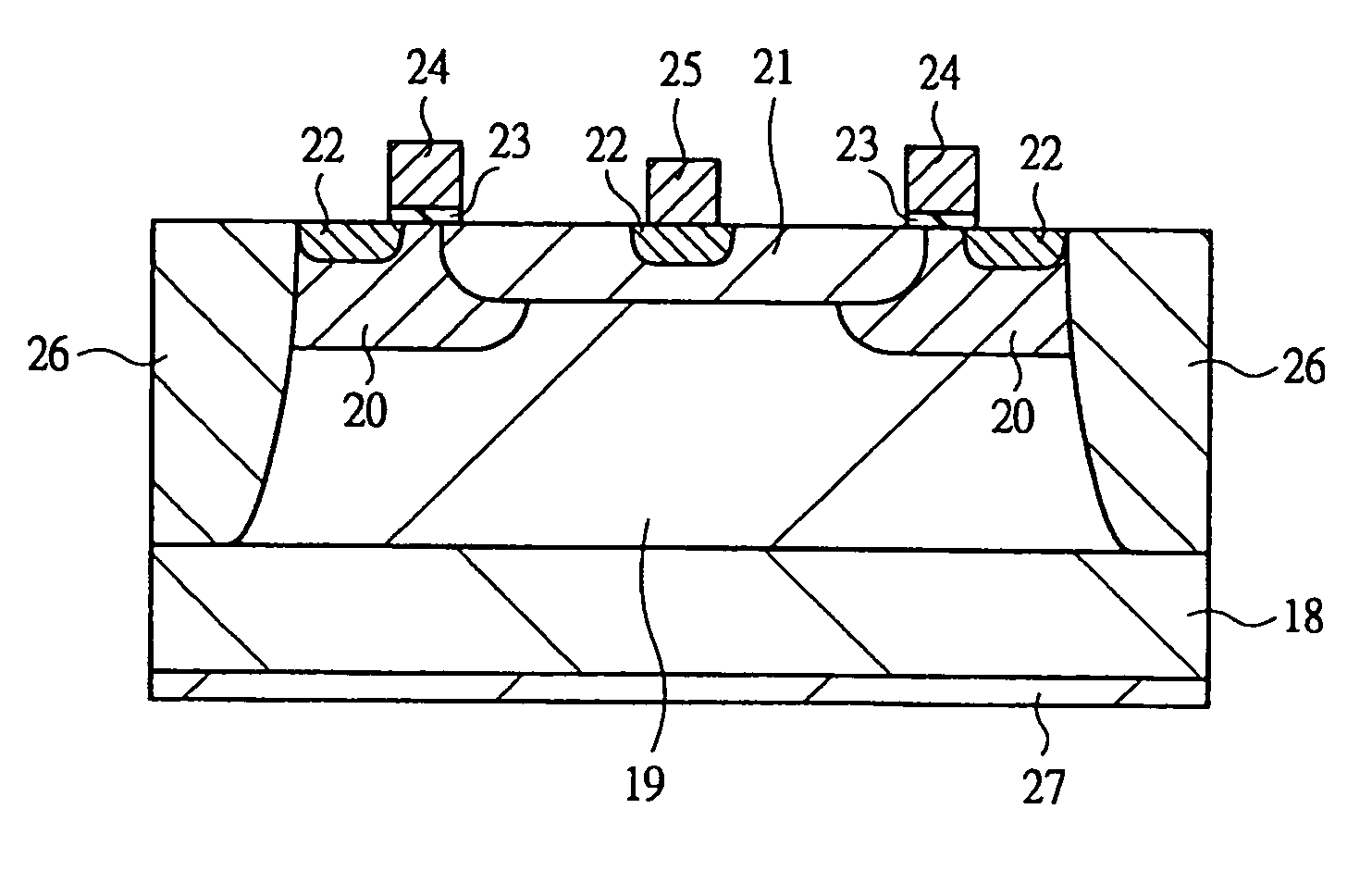

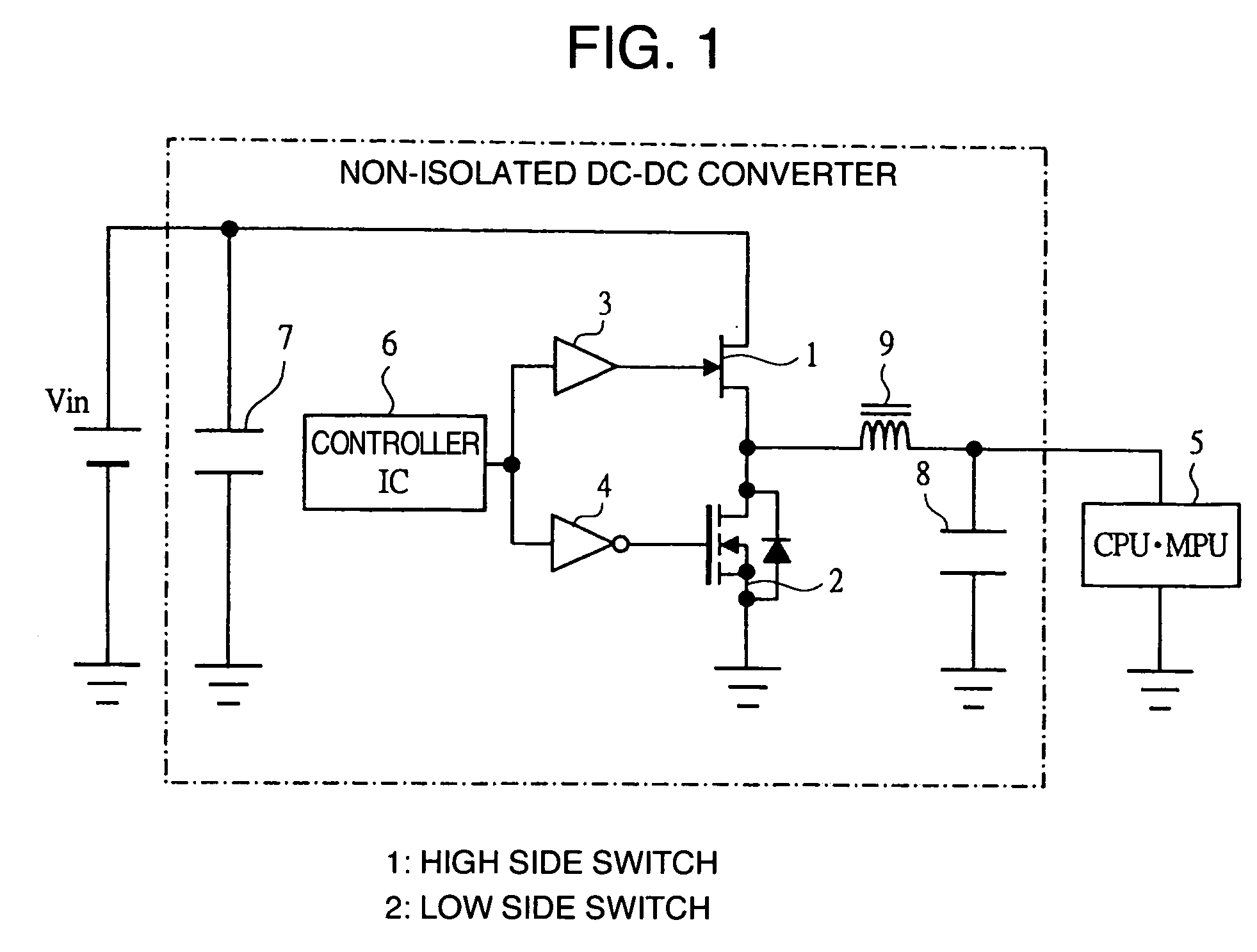

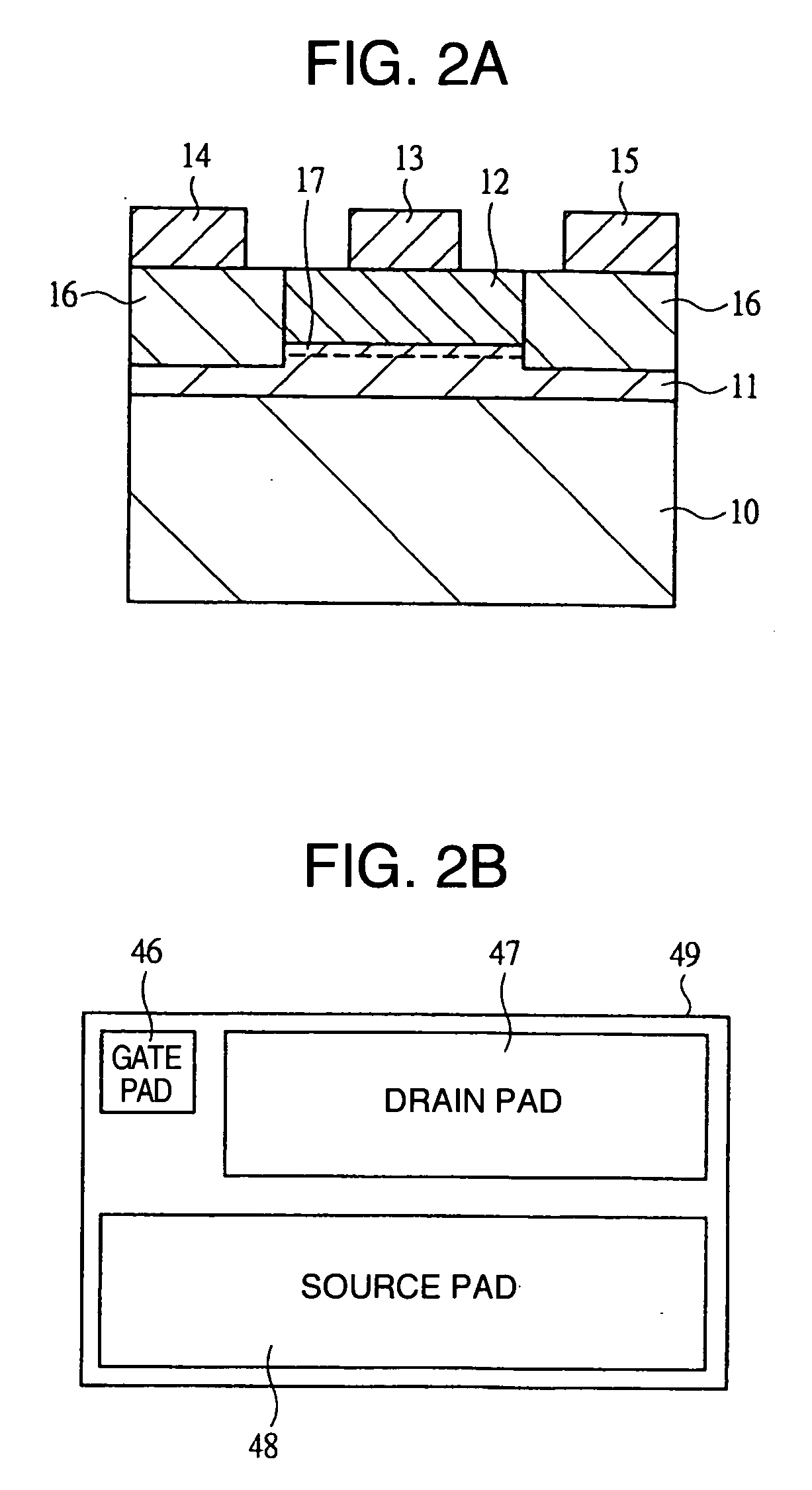

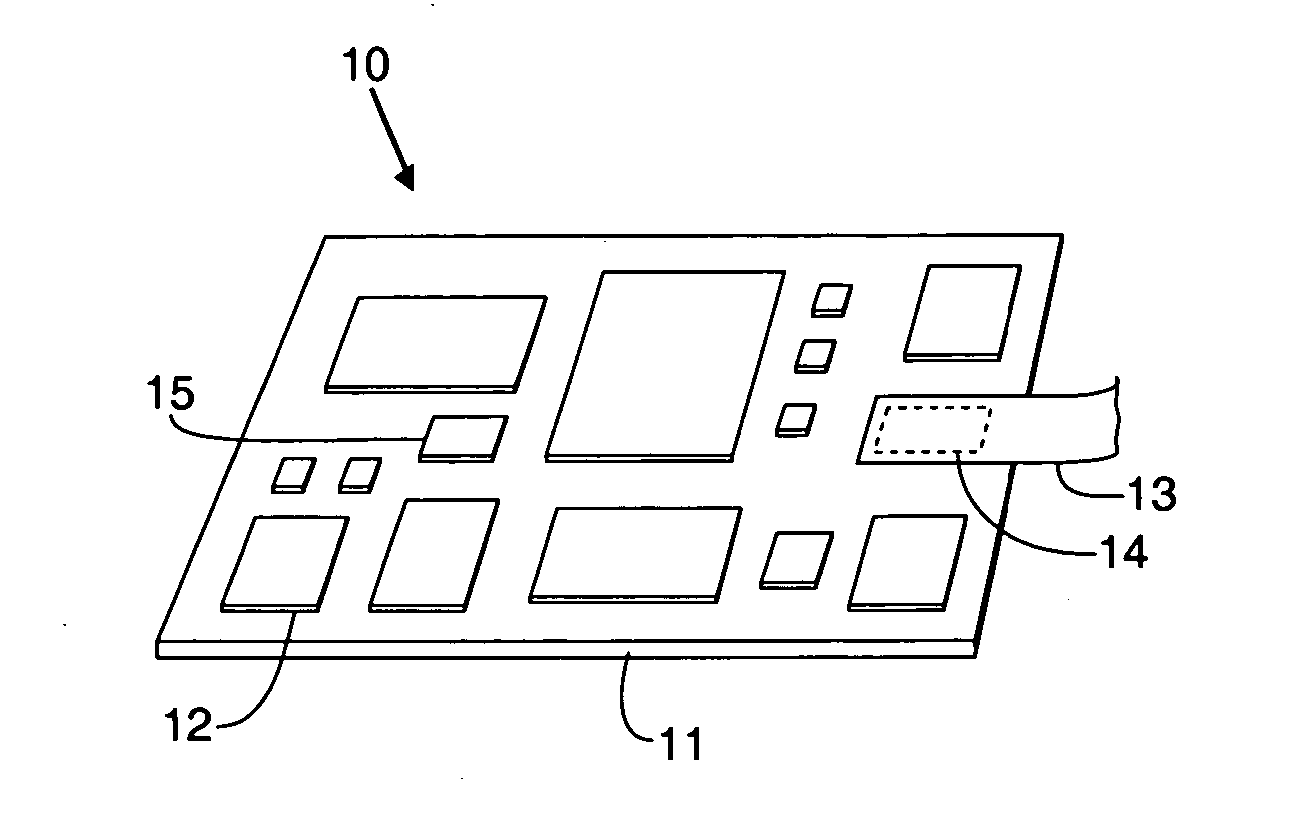

Power supply, multi chip module, system in package and non-isolated DC-DC converter

InactiveUS20060175627A1Reduce capacityLower on-resistanceEfficient power electronics conversionSemiconductor/solid-state device detailsDc dc converterComputer module

A power supply includes a non-isolated DC-DC converter for use in a power source system having a high side switch and a low side switch, in which HEMT or HFET or gallium nitride device with low capacity and low on-resistance is used for the high side switch and a vertical power MOSFET of silicon device with low on-resistance is used for the low side switch.

Owner:RENESAS TECH CORP

Copper-faced modules, imprinted copper circuits, and their application to supercomputers

InactiveUS20050040513A1Avoid mechanical failureReduce thermal strainInsulating substrate metal adhesion improvementSemiconductor/solid-state device detailsSupercomputerElectronic systems

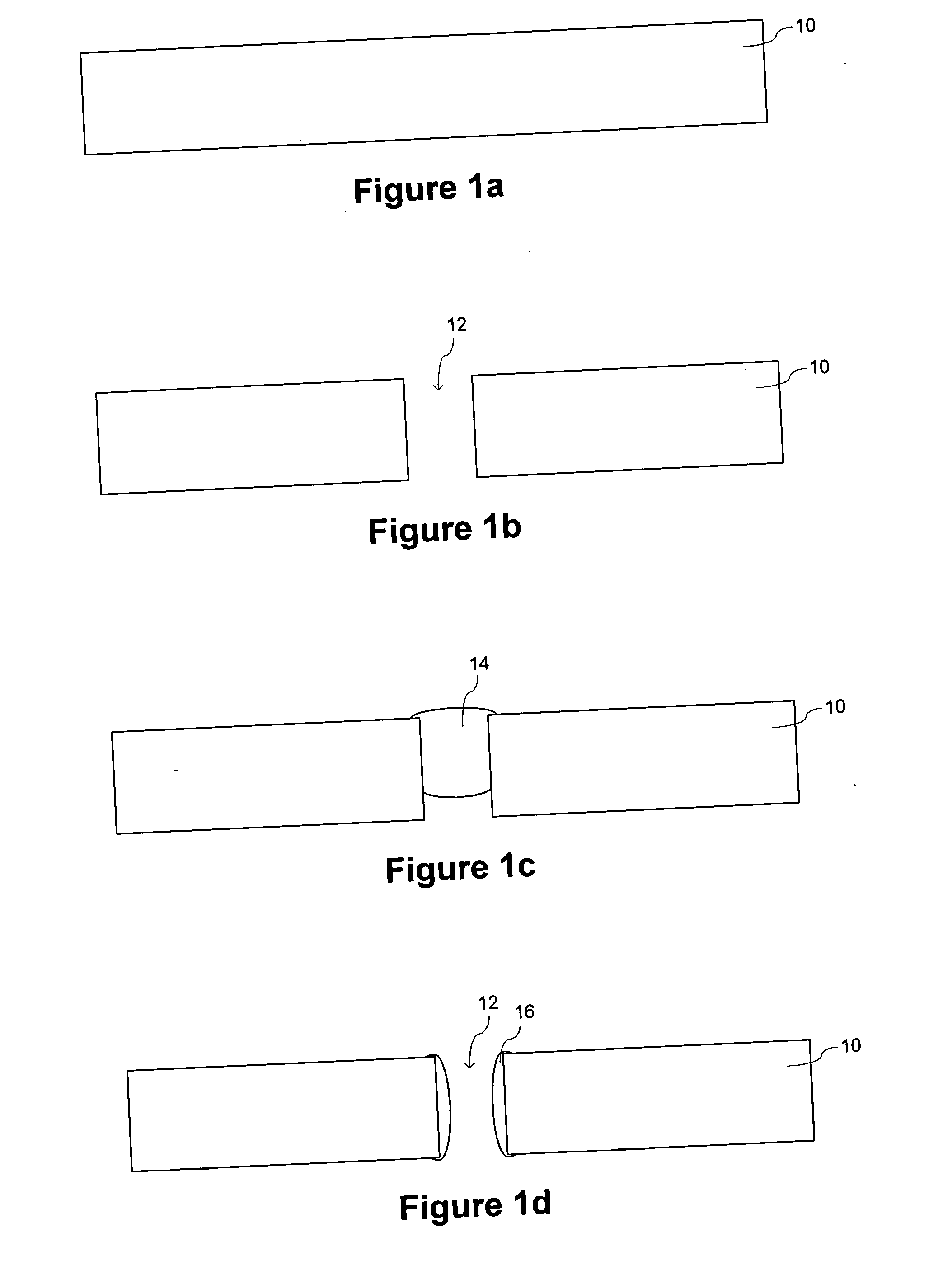

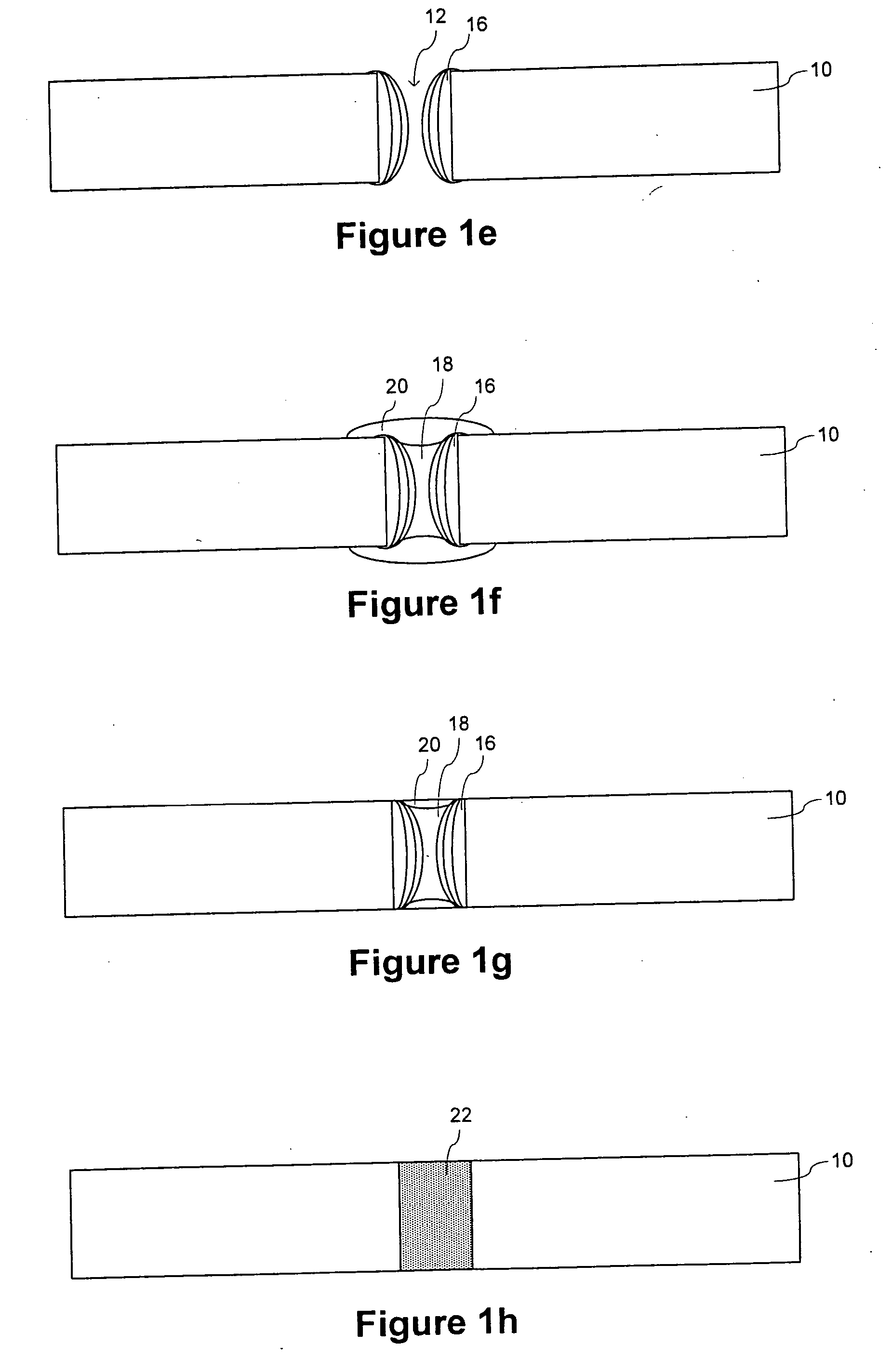

A method for fabricating copper-faced electronic modules is described. These modules are mechanically robust, thermally accessible for cooling purposes, and capable of supporting high power circuits, including operation at 10 GHz and above. An imprinting method is described for patterning the copper layers of the interconnection circuit, including a variation of the imprinting method to create a special assembly layer having wells filled with solder. The flip chip assembly method comprising stud bumps inserted into wells enables unlimited rework of defective chips. The methods can be applied to multi chip modules that may be connected to other electronic systems or subsystems using feeds through the copper substrate, using a new type of module access cable, or by wireless means. The top copper plate can be replaced with a chamber containing circulating cooling fluid for aggressive cooling that may be required for servers and supercomputers. Application of these methods to create a liquid cooled supercomputer is described.

Owner:SALMON TECH

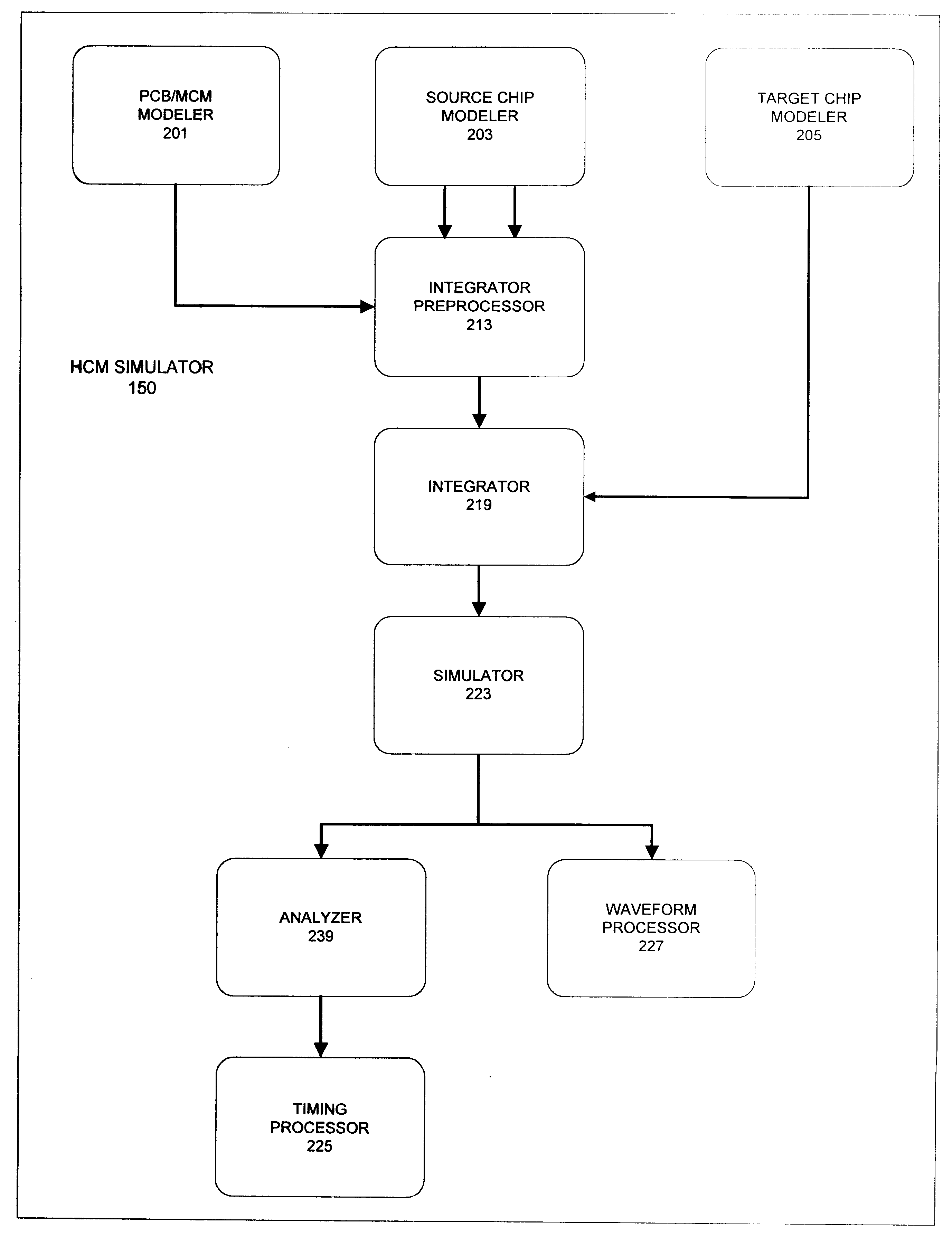

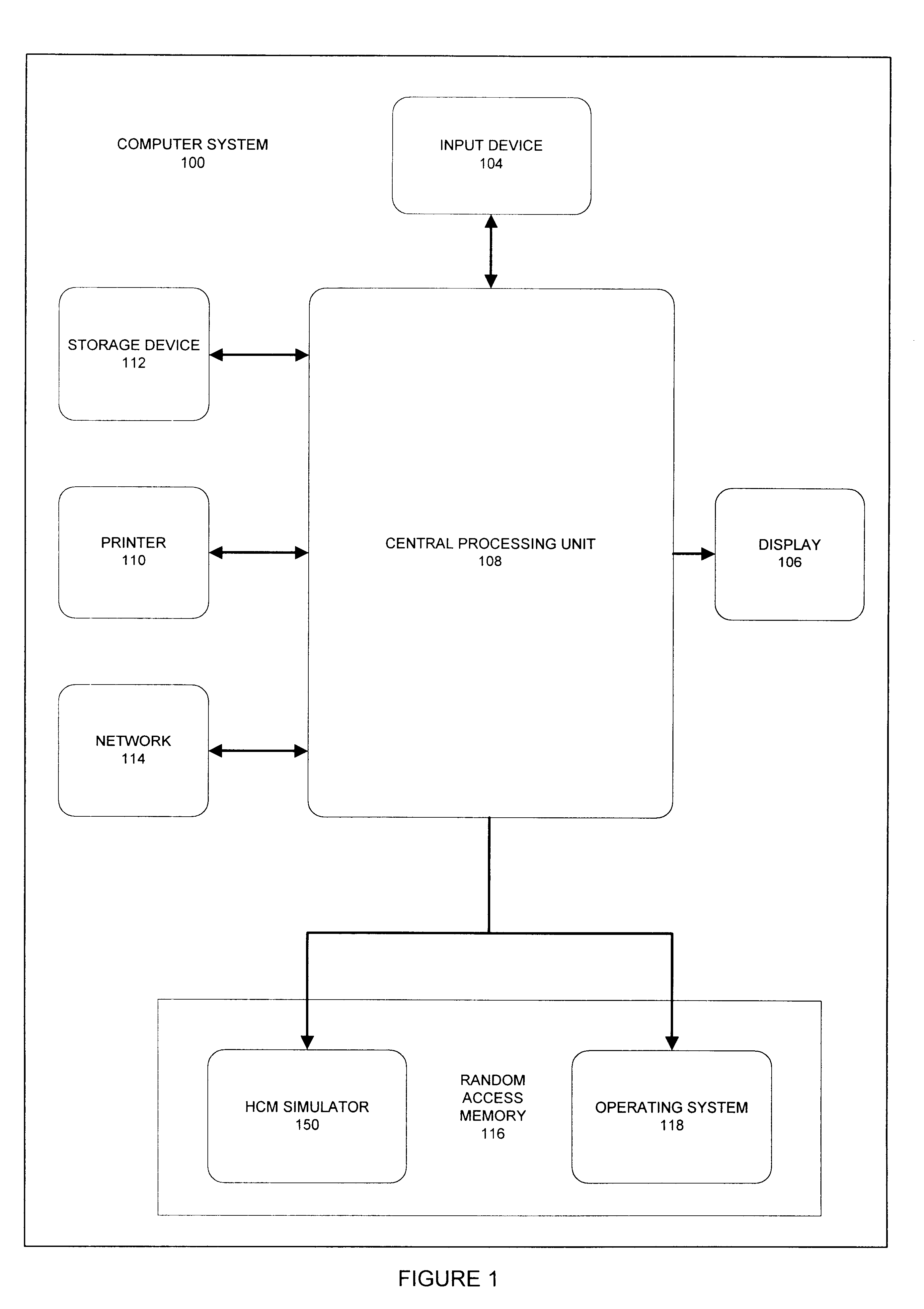

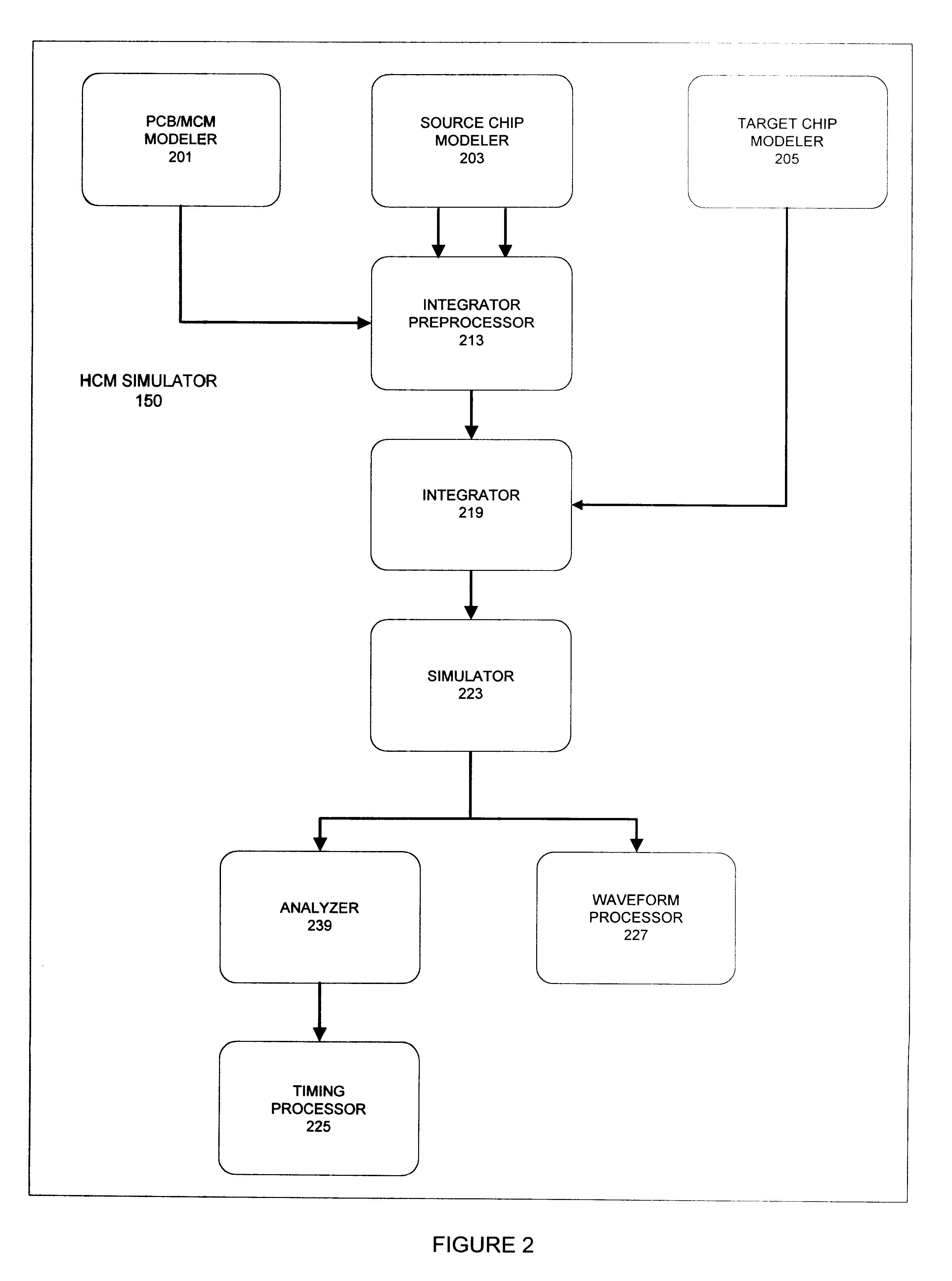

Hybrid circuit model simulator for accurate timing and noise analysis

InactiveUS6212490B1Easily realizedAccurate representationDetecting faulty computer hardwareComputer aided designCircuit modelsPrinted circuit board

A system and method for analyzing timing and noise effects in a hybrid circuit which contains a plurality of electrical components. The timing and noise effects for the hybrid circuit are generated by simulating electrical conditions within a hybrid circuit model. The hybrid circuit model is constructed by creating and integrating analog and behavioral models from the plurality of electrical components. The timing and noise effects remain accurate even at high printed circuit board / multi-chip module clock speeds, thereby ensuring that a user is able to construct an optimal design for any one of the plurality of electrical components.

Owner:ALTERA CORP

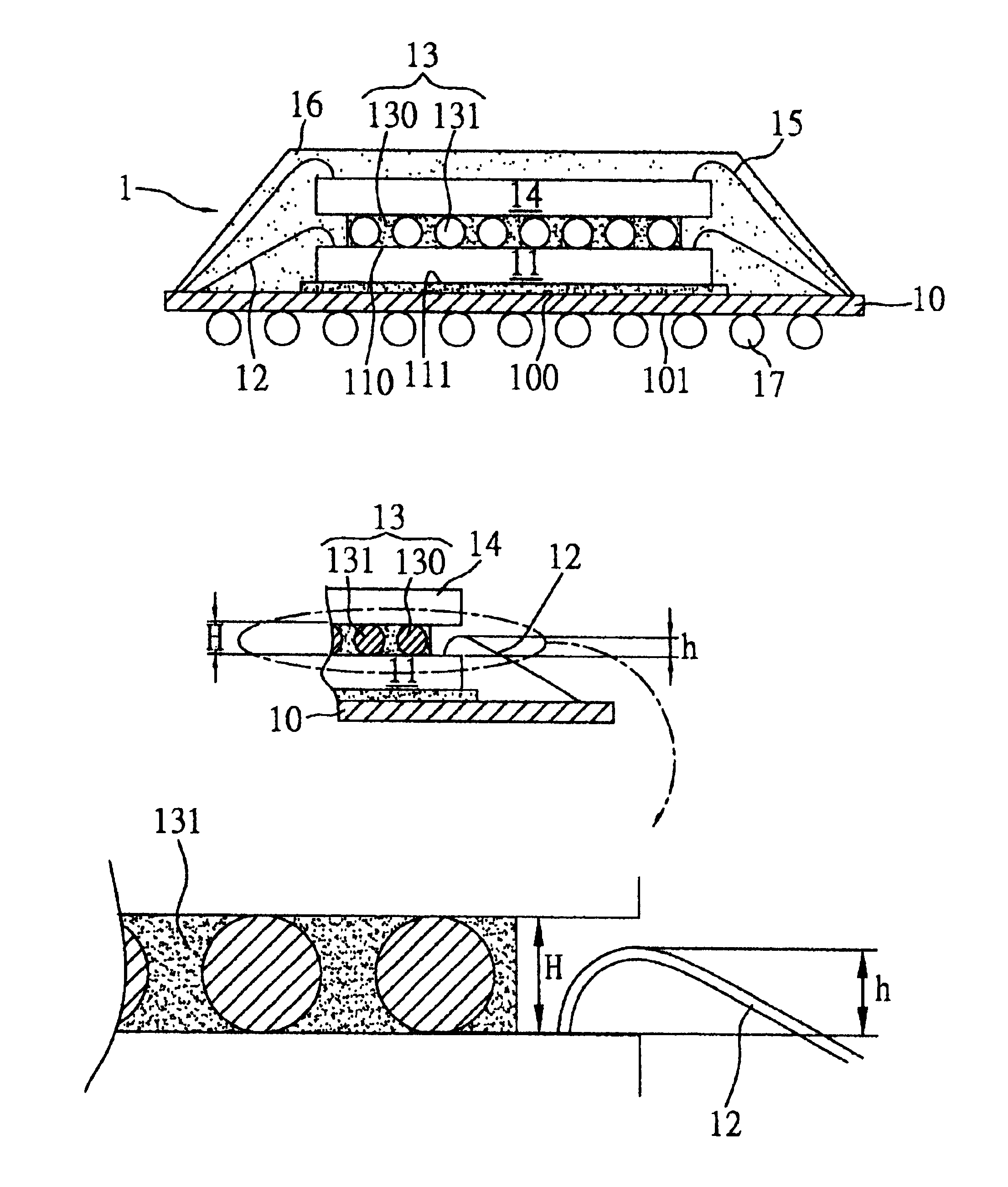

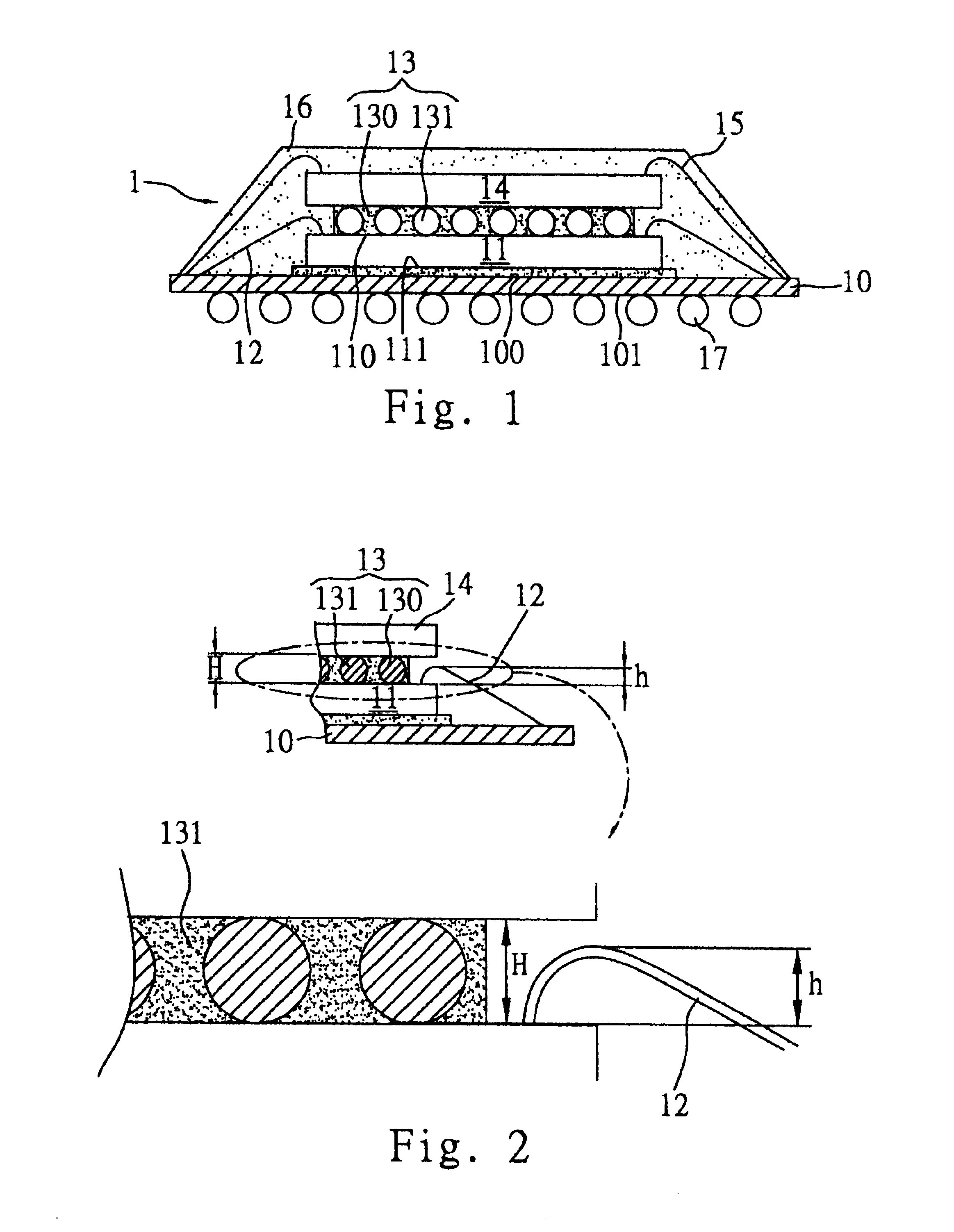

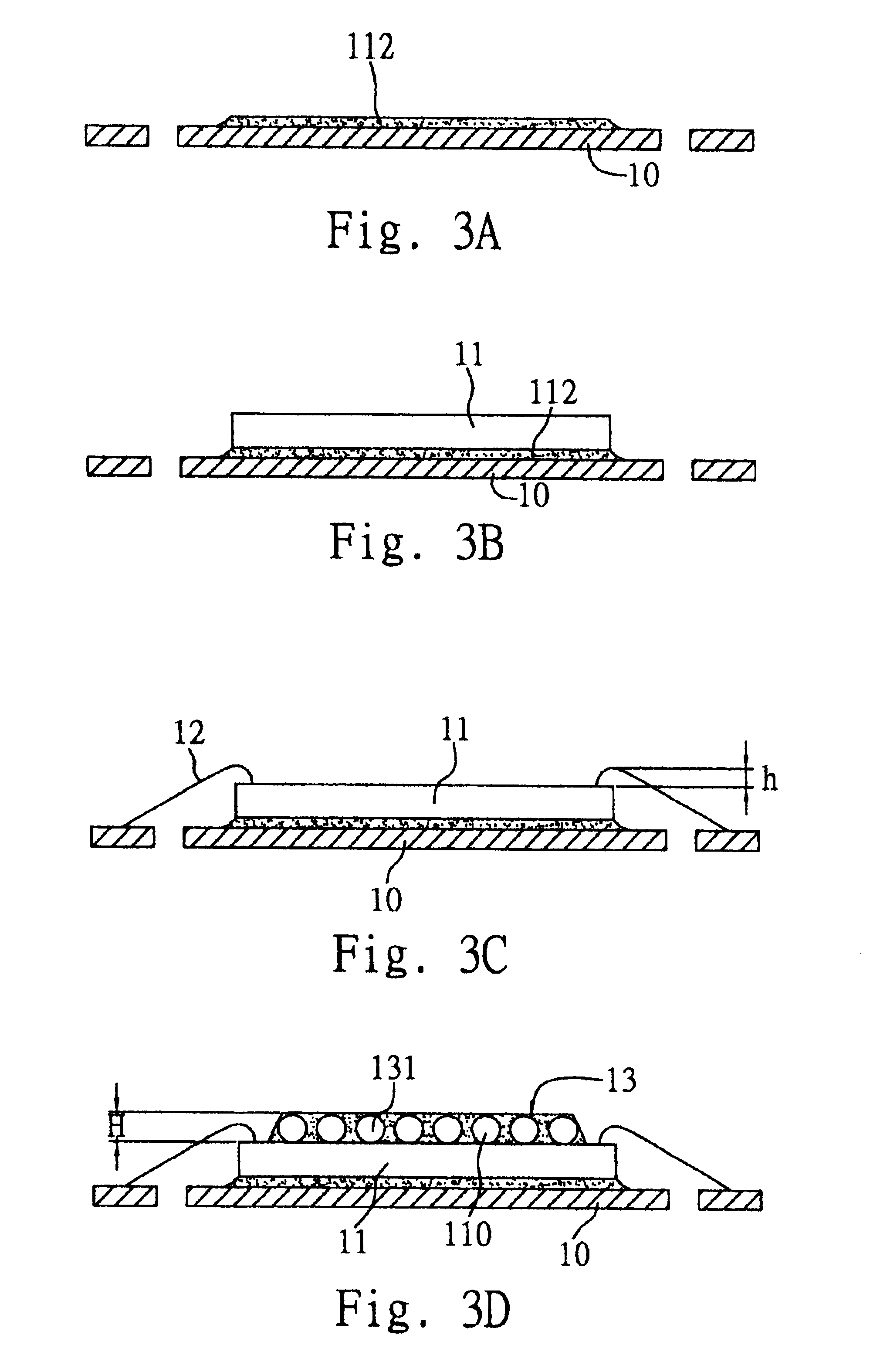

Multichip module

InactiveUS6919627B2Simplifies and reduces timeIncrease productionSemiconductor/solid-state device detailsSolid-state devicesAdhesiveSemiconductor chip

A multi-chip module is proposed, which is designed to pack two or more semi-conductor chips in a stacked manner over a chip carrier in a single package. The multi-chip module is characterized by the use of adhesive with fillers to allow the topmost chip (i.e. the second chip) superimposed to the bottommost chip (i.e. the first chip) after the first chip electrically connected to the chip carrier. The thickness of the adhesive layer depends on the diameter of the fillers higher than loop height of the bonding wires that is positioned above the active surface of the first chip to prevent the bonding wires connected to the first chip to come in contact with the overlaid chip.

Owner:SILICONWARE PRECISION IND CO LTD

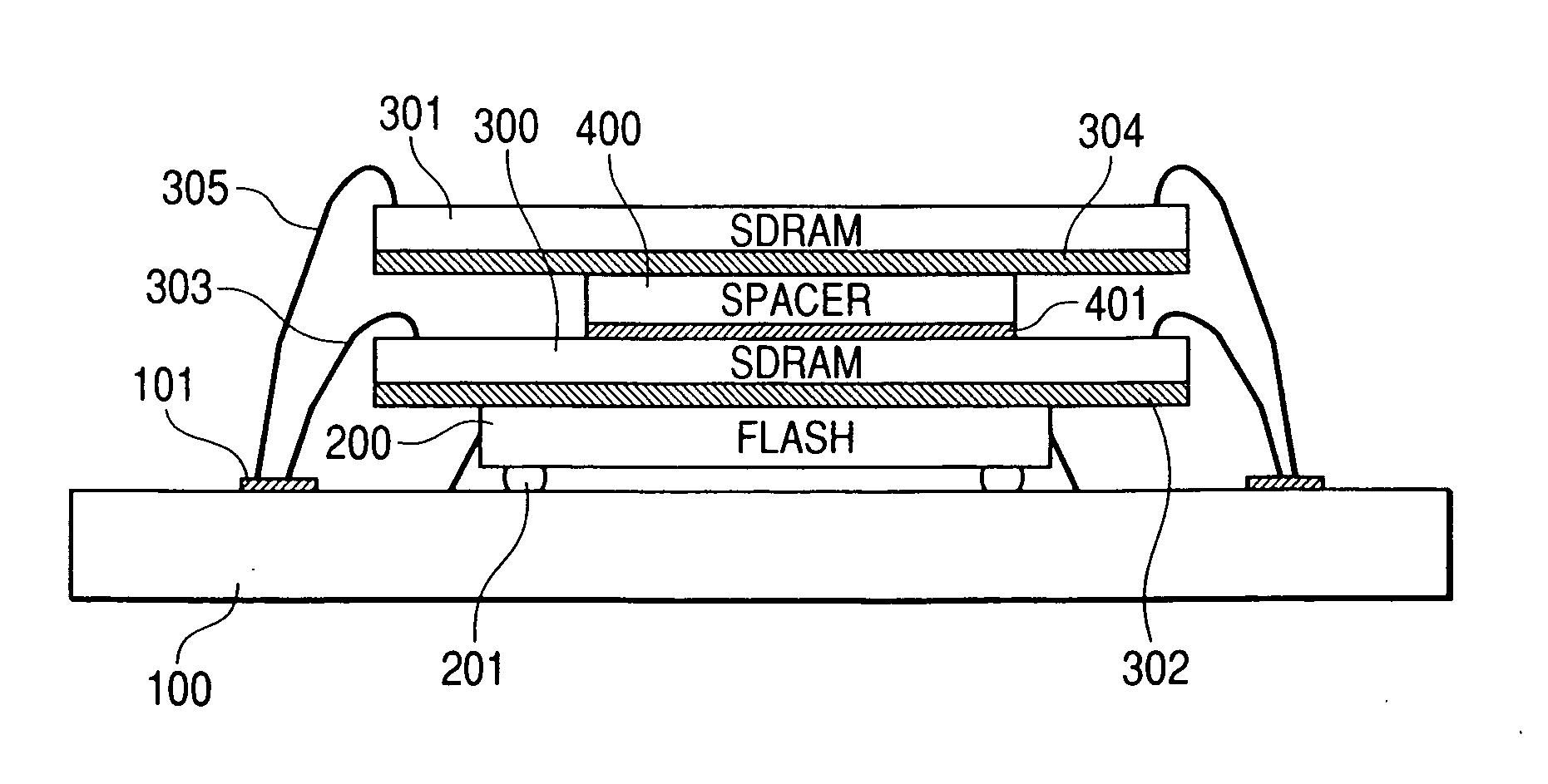

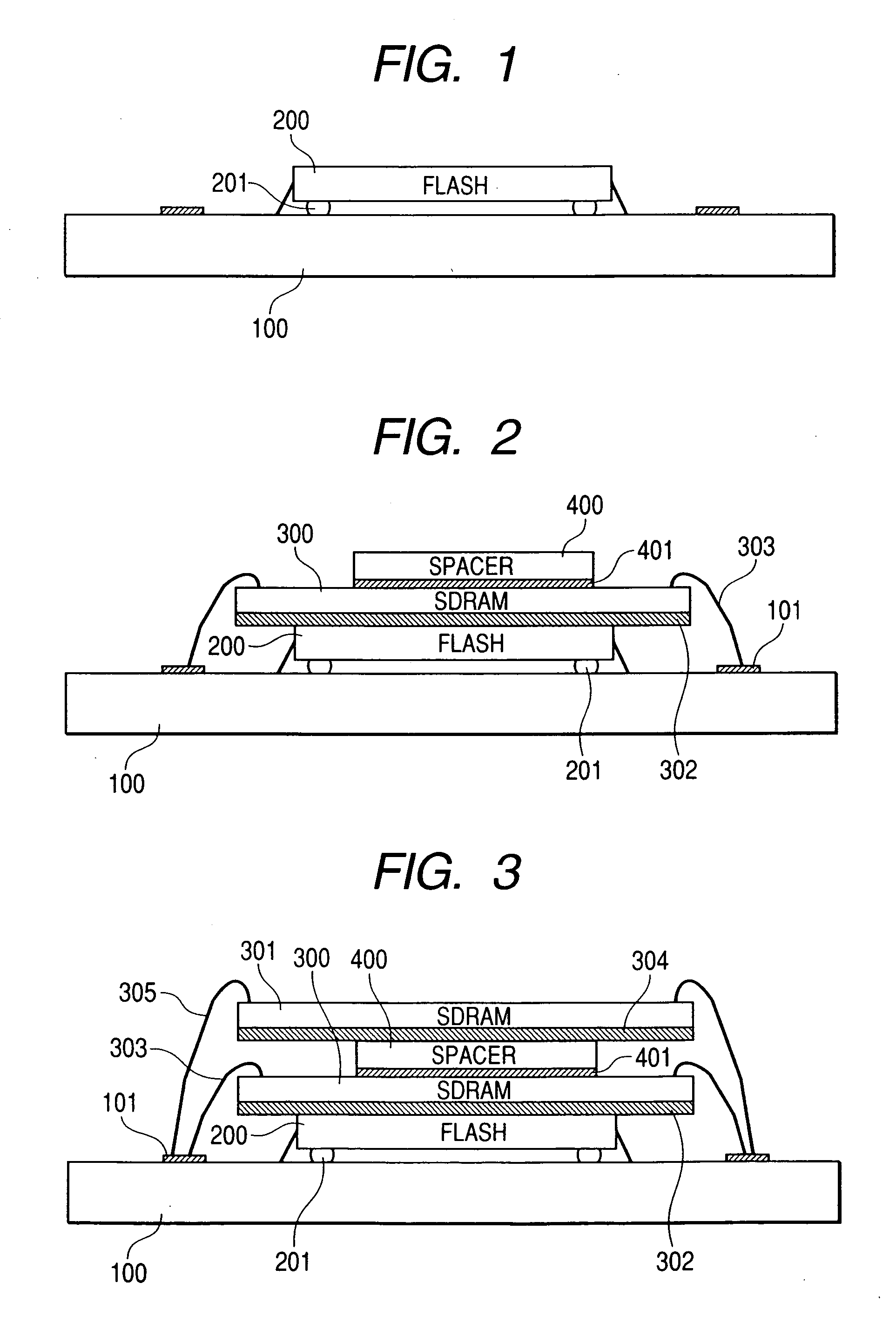

Multi-chip module

ActiveUS20050104183A1Small sizeShorten wiring distanceSemiconductor/solid-state device detailsSolid-state devicesSemiconductor chipEngineering

Disclosed here is a multi-chip module enhanced in performance and reduced in size. A second semiconductor chip having bonding pads at the periphery of its surface is mounted over a first semiconductor chip laid out over a surface of a substrate back to back and a spacer is provided at a portion of the second semiconductor chip surface except for a predetermined area that includes the portion where the bonding pads are formed while a third semiconductor chip is mounted over the spacer, the third semiconductor having the same circuit function as the second semiconductor chip and oriented similarly to the second semiconductor chip. The bonding pads of the second and third semiconductor chips are connected to their corresponding electrodes formed over the substrate through bonding wires respectively, then the first to third semiconductor chips and the bonding wires provided over the substrate are all sealed by a sealing agent.

Owner:RENESAS ELECTRONICS CORP

Semiconductor package having interconnect with conductive members

InactiveUS6952054B2Facilitate electrical interfaceSemiconductor/solid-state device detailsPrinted circuit aspectsConductive polymerSemiconductor package

An interconnect for semiconductor components such as dice, wafers and chip scale packages is provided. The interconnect includes a substrate, and patterns of contacts formed on a face side of the substrate adapted to electrically engage external contacts (e.g., bond pads, solder bumps) on the components. The interconnect also includes insulated conductive members through the substrate, which provide direct electrical paths from the interconnect contacts to a backside of the substrate. The conductive members can be formed by laser machining openings in the substrate, and then filling the openings with a conductive material (e.g., metal, conductive polymer). The conductive members can also include pads with contact balls, configured for electrical interface with a test apparatus, such as test carrier or wafer handler. The interconnect can be used to construct test systems for testing semiconductor components, or to construct chip scale packages and multi chip modules.

Owner:ROUND ROCK RES LLC

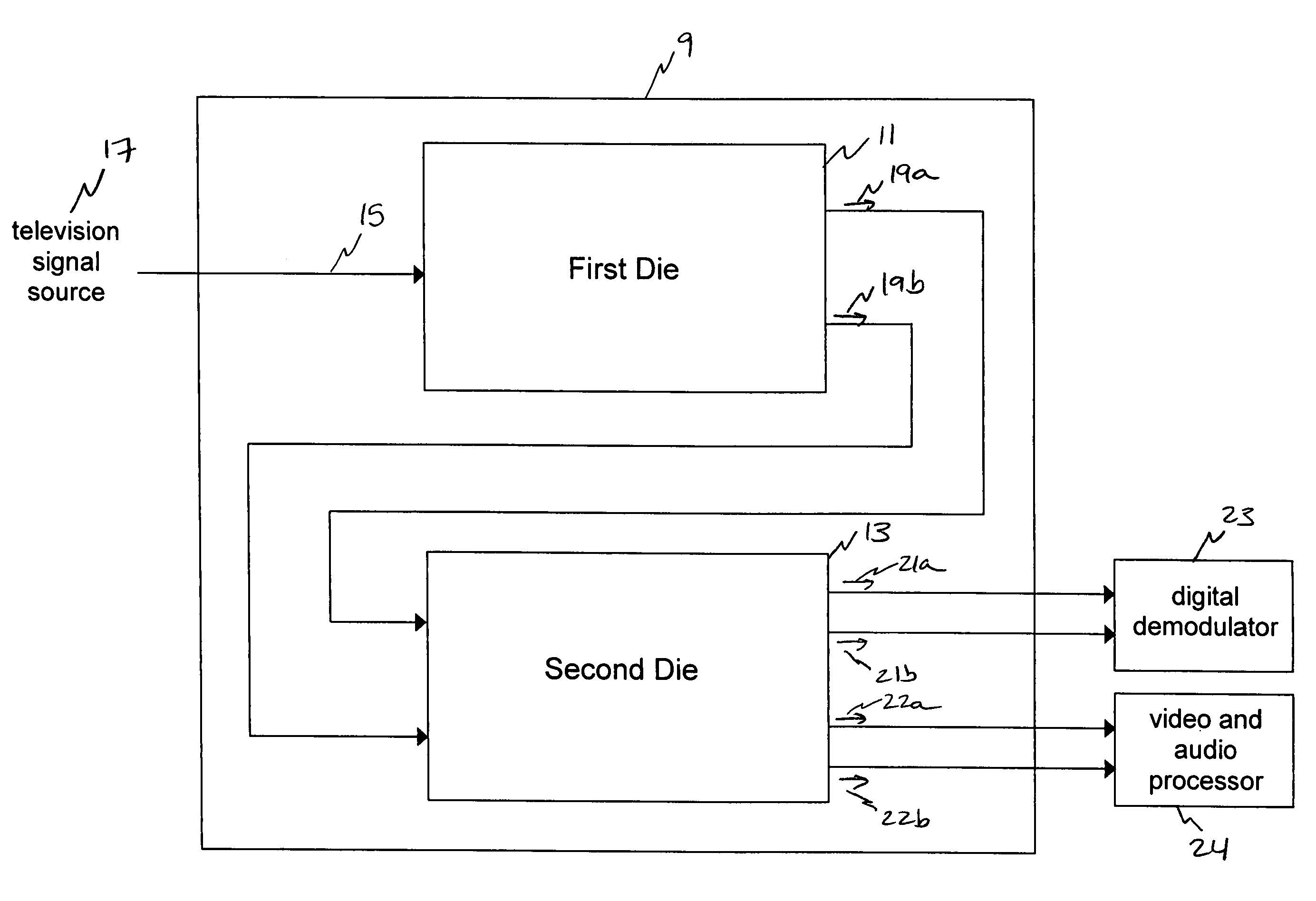

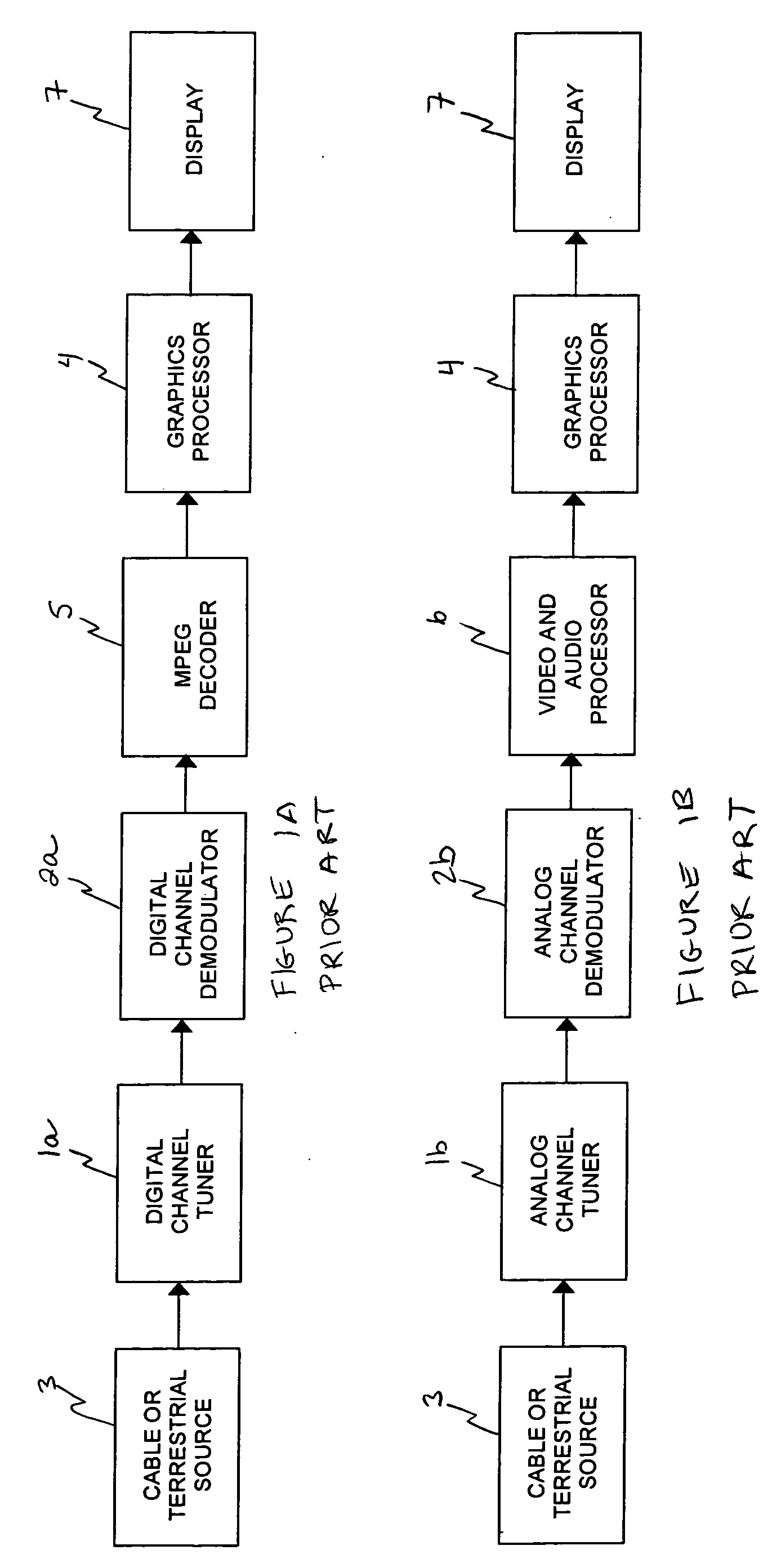

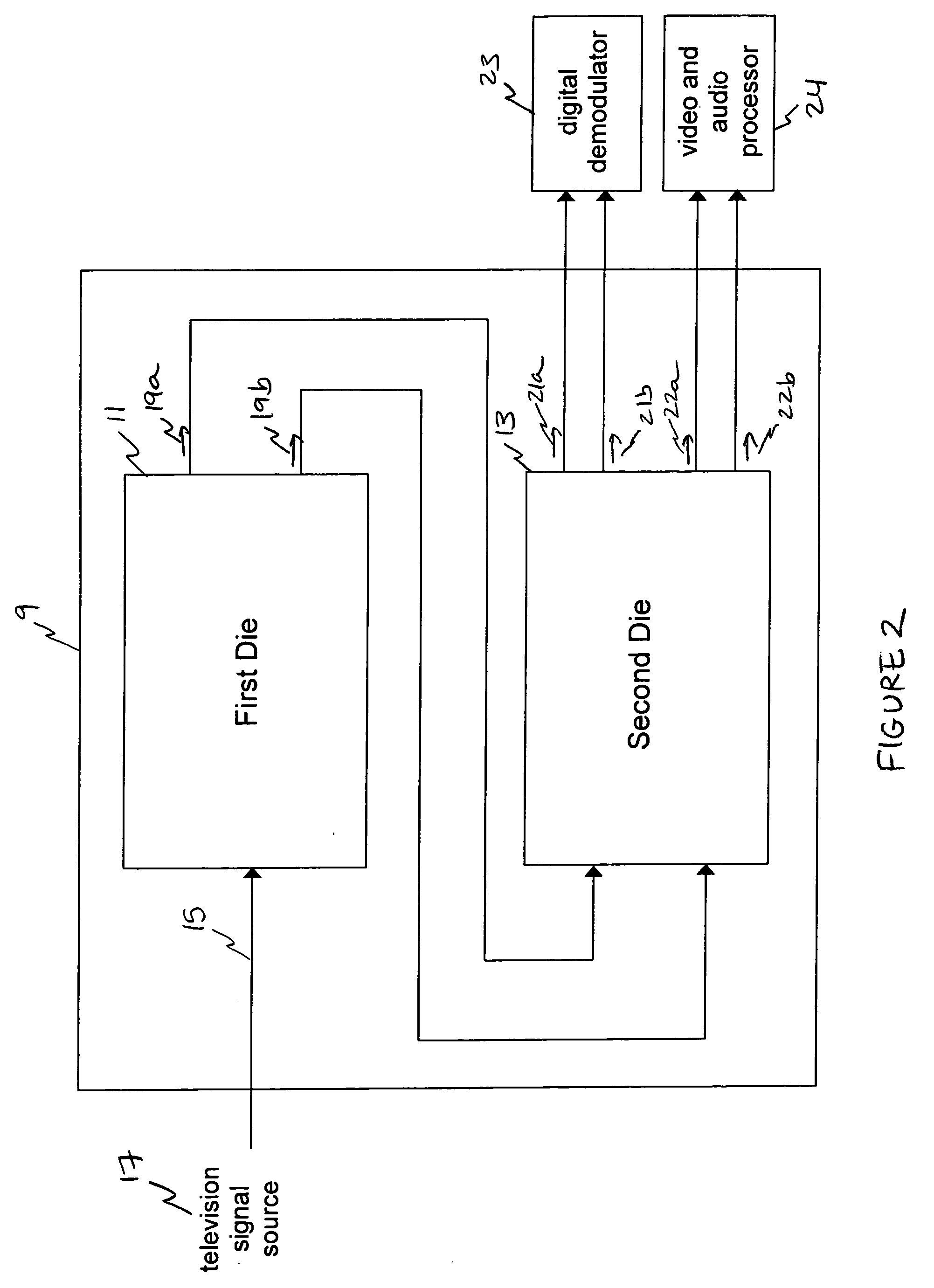

Methods and apparatus for tuning signals

ActiveUS20050259186A1Television system detailsTelevision system scanning detailsAnalog signalSignal source

Methods and apparatus for tuning are disclosed. One embodiment of the invention is directed to a tuner formed on a substrate. The tuner comprises a first die that receives an analog input signal and processes the analog input signal using analog processing circuitry to form analog output signals, and a second die that receives the analog output signals, converts the analog output signals to digital signals, and processes the digital signals to form output signals. Another embodiment of the invention is directed to a multi-chip module comprising a tuner adapted to process television signals of a plurality of types and of a plurality of standards to form output signals. A further embodiment of the invention is directed to a method that comprises receiving an analog signal from a signal source, filtering the analog signal to remove a portion of the analog signal, converting the analog signal to quadrature analog signals, converting the quadrature analog signals to digital signals, and filtering the digital signals to substantially isolate a channel of interest.

Owner:ANALOG DEVICES INC

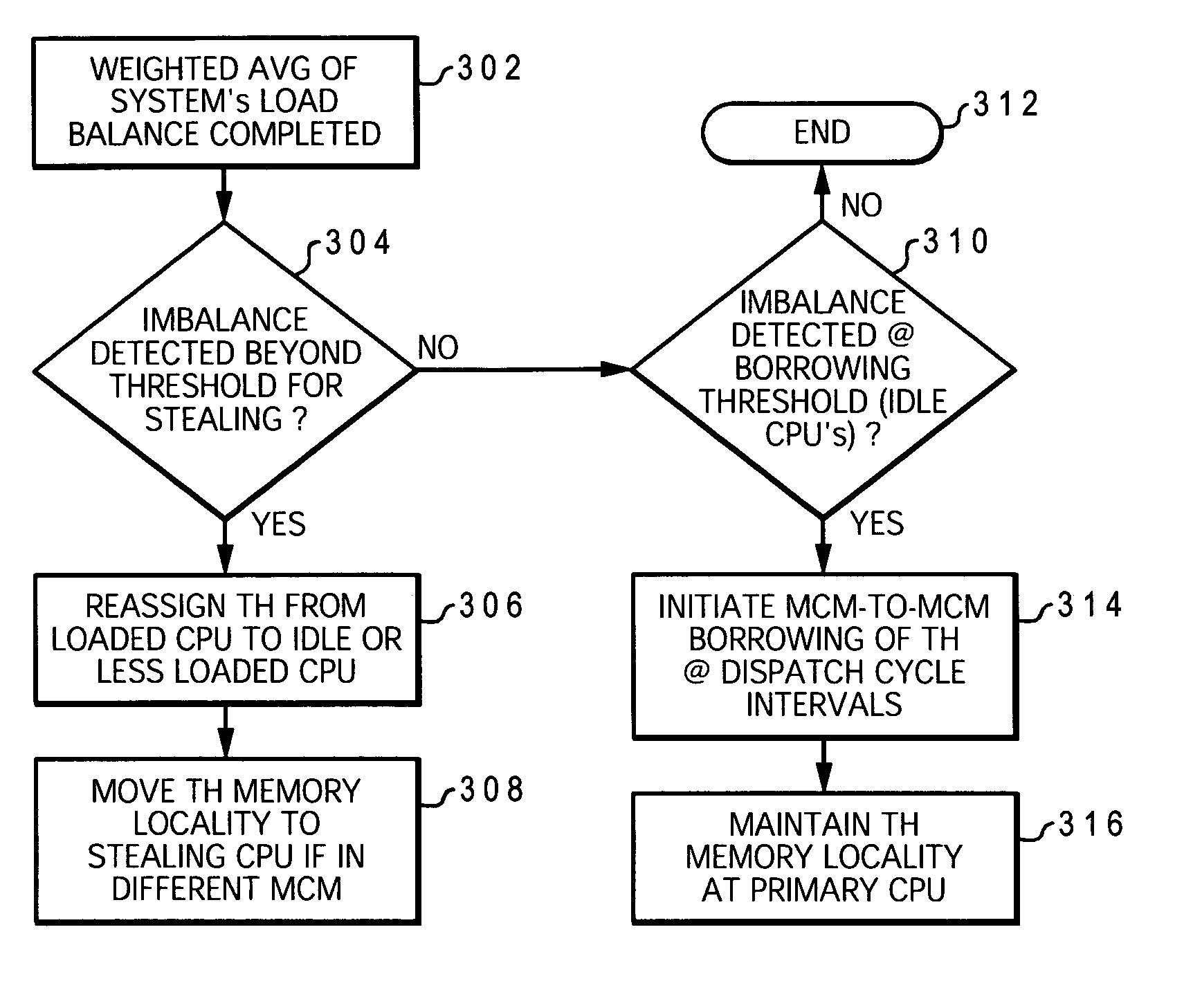

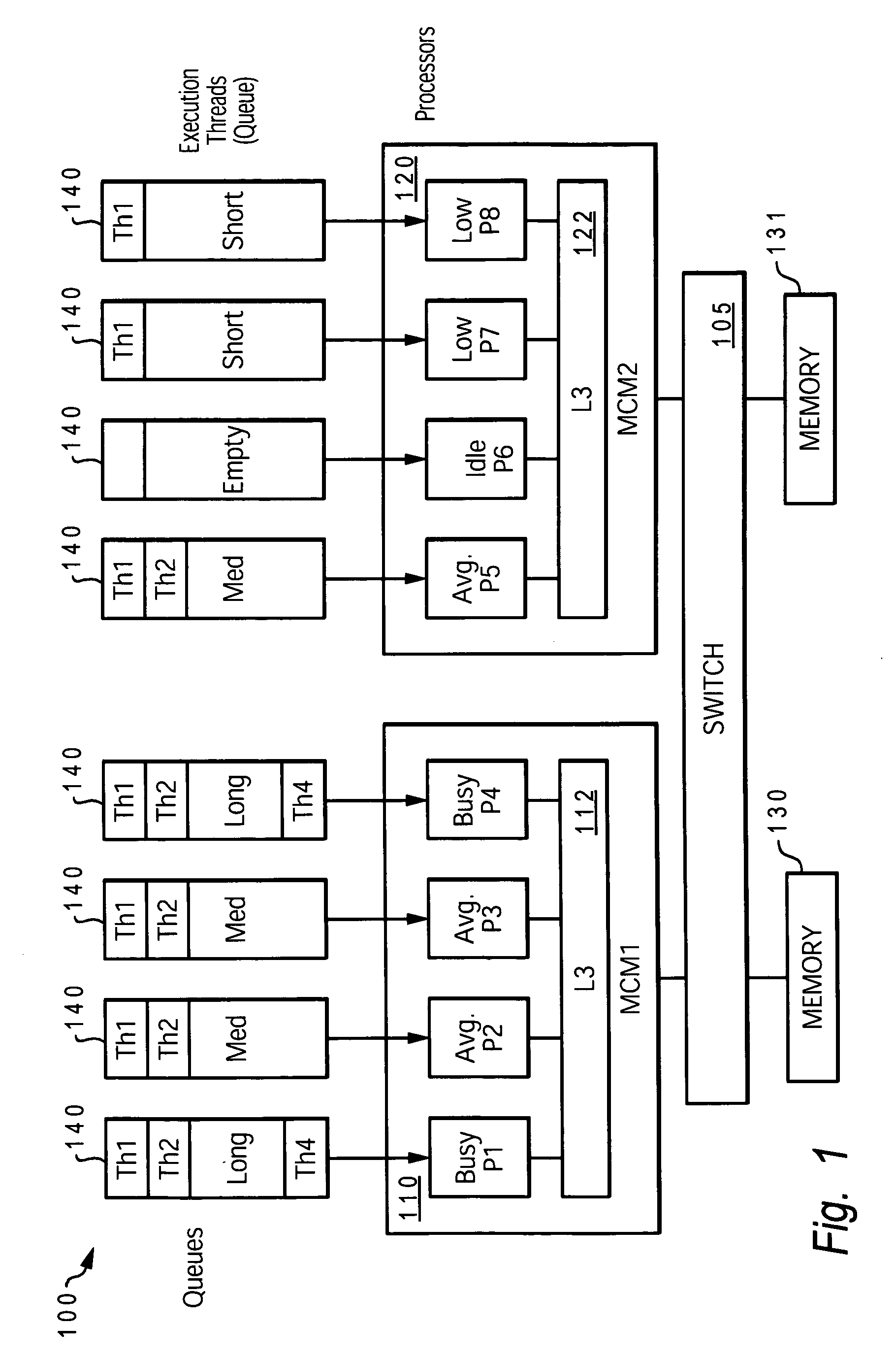

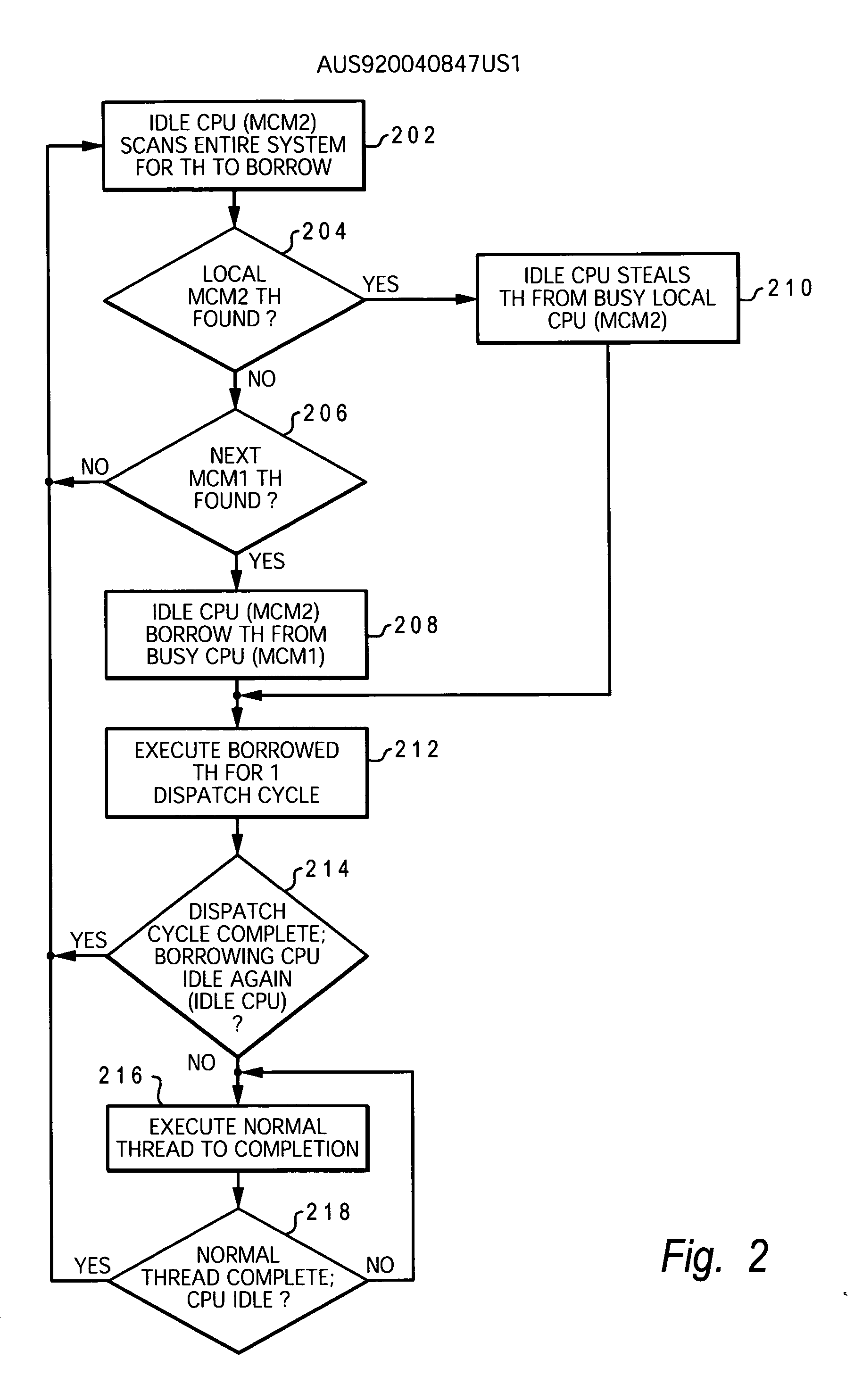

Borrowing threads as a form of load balancing in a multiprocessor data processing system

InactiveUS20060123423A1Efficient load balancingReduce executionMultiprogramming arrangementsMemory systemsLoad SheddingData processing system

A method and system in a multiprocessor data processing system (MDPS) that enable efficient load balancing between a first processor with idle processor cycles in a first MCM (multi-chip module) and a second busy processor in a second MCM, without significant degradation to the thread's execution efficiency when allocated to the idle processor cycles. A load balancing algorithm is provided that supports both stealing and borrowing of threads across MCMs. An idle processor is allowed to “borrow” a thread from a busy processor in another memory domain (i.e., across MCMs). The thread is borrowed for a single dispatch cycle at a time. When the dispatch cycle is completed, the thread is released back to its parent processor. No change in the memory allocation of the borrowed thread occurs during the dispatch cycle.

Owner:IBM CORP

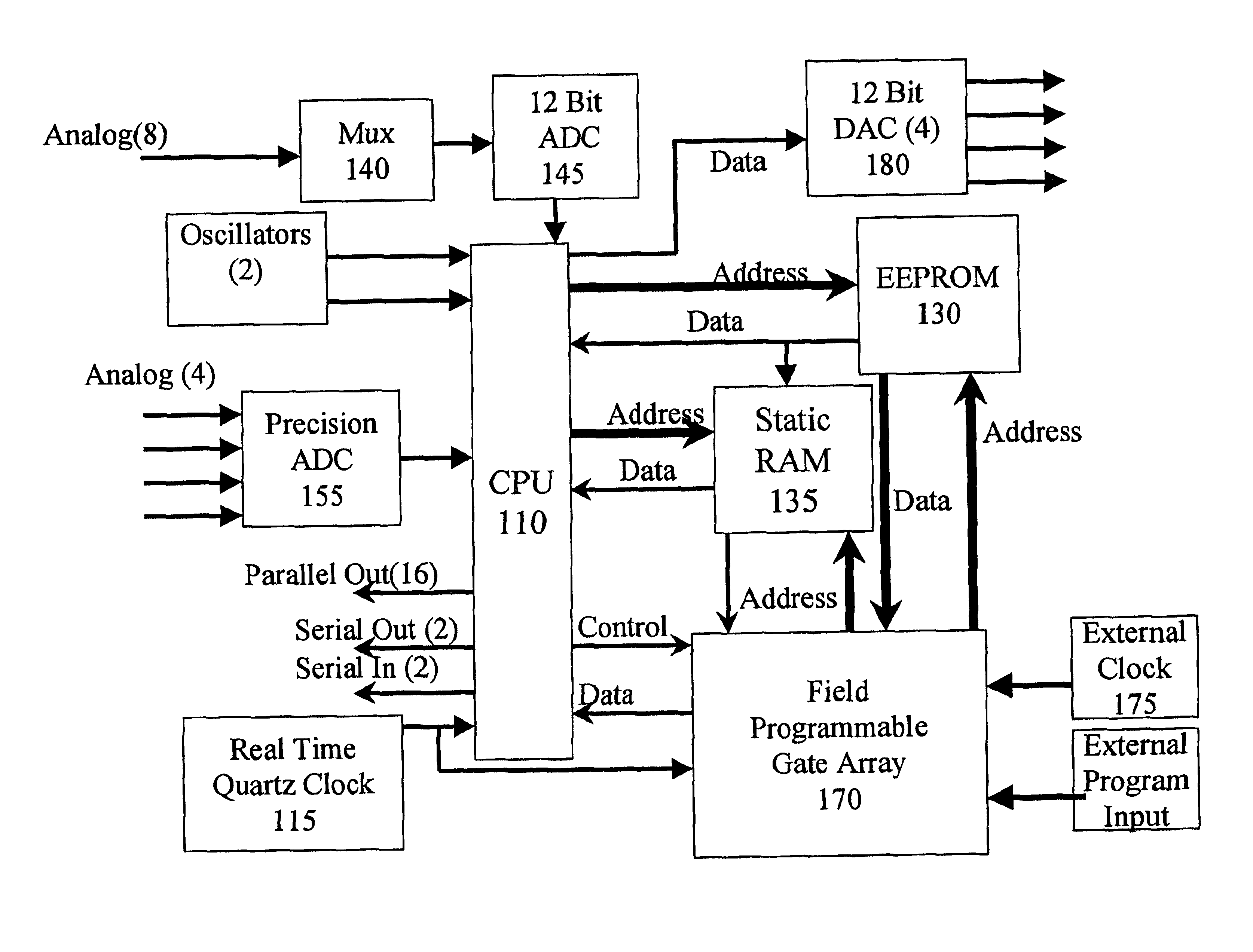

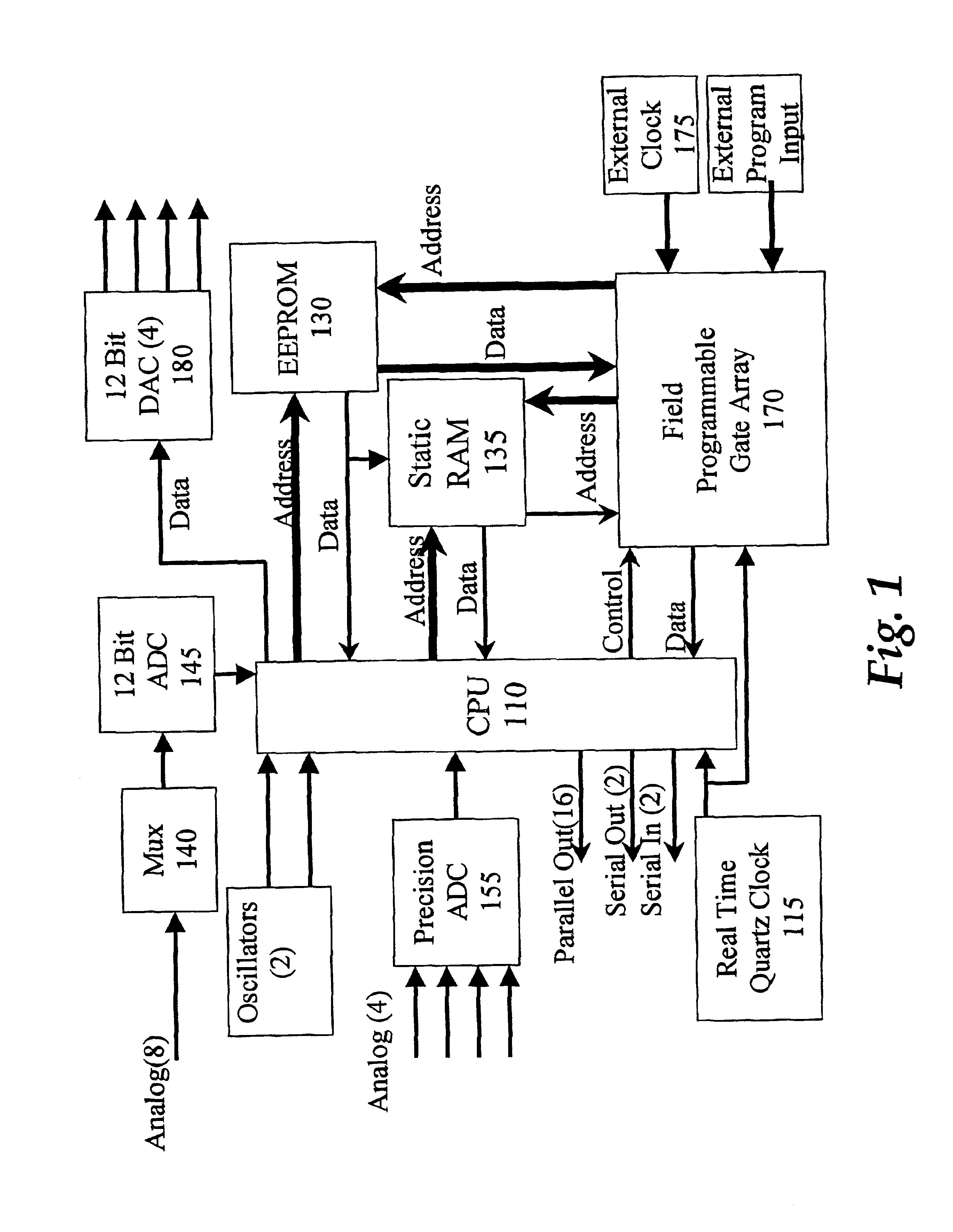

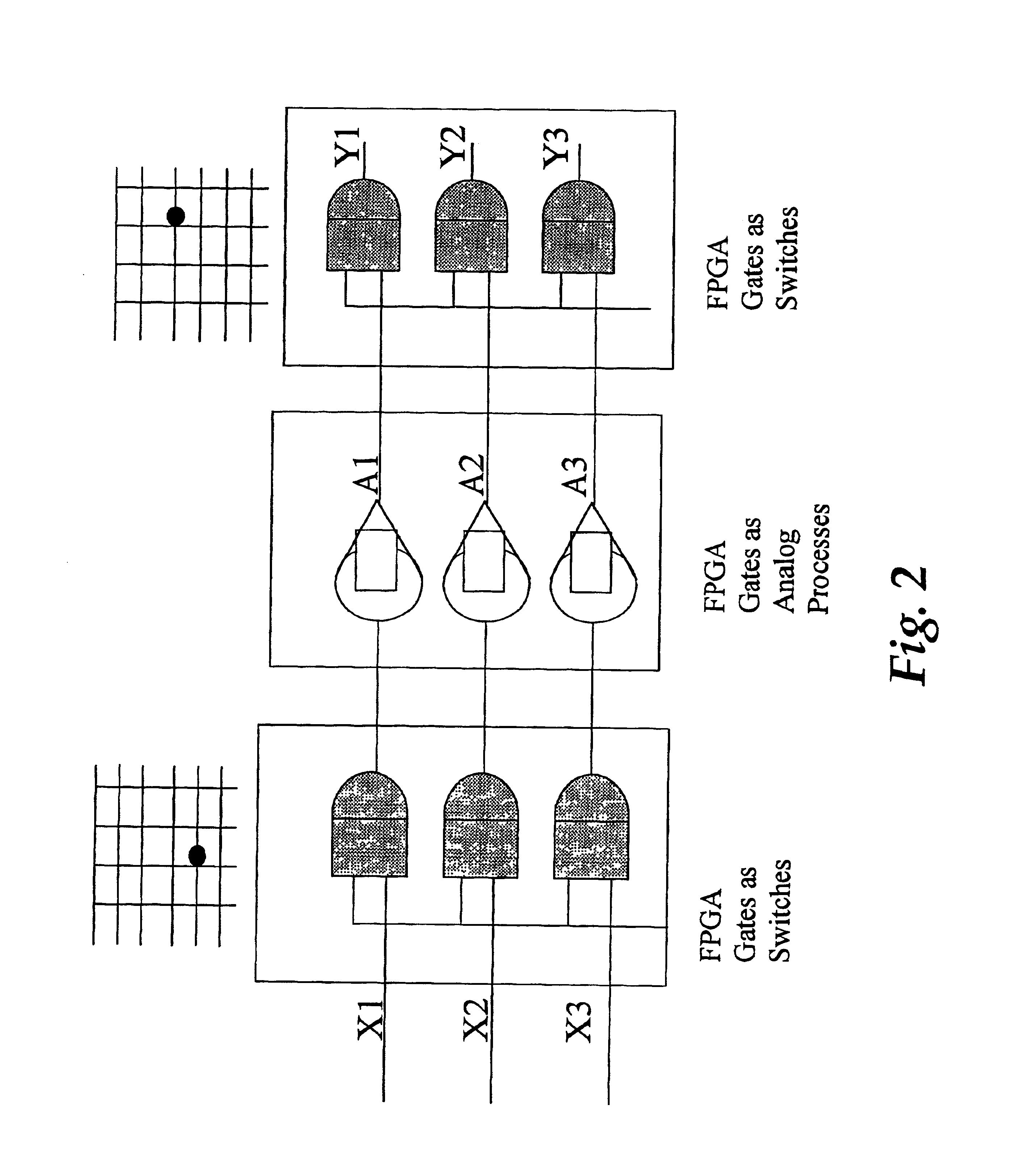

Multi-chip module smart controller

ActiveUS6938177B1Less complexConvenient power managementElectronic switchingGenerating/distributing signalsComputer moduleOperational capabilities

A multi-chip module instrument controller having various interface and operational capabilities. The controller incorporate a microprocessor and both volatile and non-volatile memories. The controller includes variable analog-to-digital conversion bit depths, with higher bit depths for some applications. Additionally, the controller includes a separately controllable field programmable gate array that acts as a parallel processor with internal or separate external clock. The FPGA preferably includes more than thirty thousand gates (30,000) and adds a freely re-configurable and separately programmable multi-purpose digital system that can run independent of the microprocessor.

Owner:BLEMEL TECH

Apparatus and methods for high-performance liquid cooling of multiple chips with disparate cooling requirements

InactiveUS7808781B2Effective heat conductionMinimizes mechanical stressDigital data processing detailsSemiconductor/solid-state device detailsComputer moduleEngineering

Apparatus and methods are provided for packaging multi-chip modules with liquid cooling modules designed to provide different thermal resistances for effectively conducting heat from various chips with disparate cooling requirements while minimizing mechanical stresses in thermal bonds due to thermal excursions.

Owner:INT BUSINESS MASCH CORP