Semiconductor device and manufacturing method of the same

a technology of semiconductor devices and manufacturing methods, applied in semiconductor devices, semiconductor/solid-state device details, electrical apparatus, etc., can solve the problems of insufficient reliability, prior art, and inability to ensure sufficient reliability for bonding to such interposers

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

embodiment 1

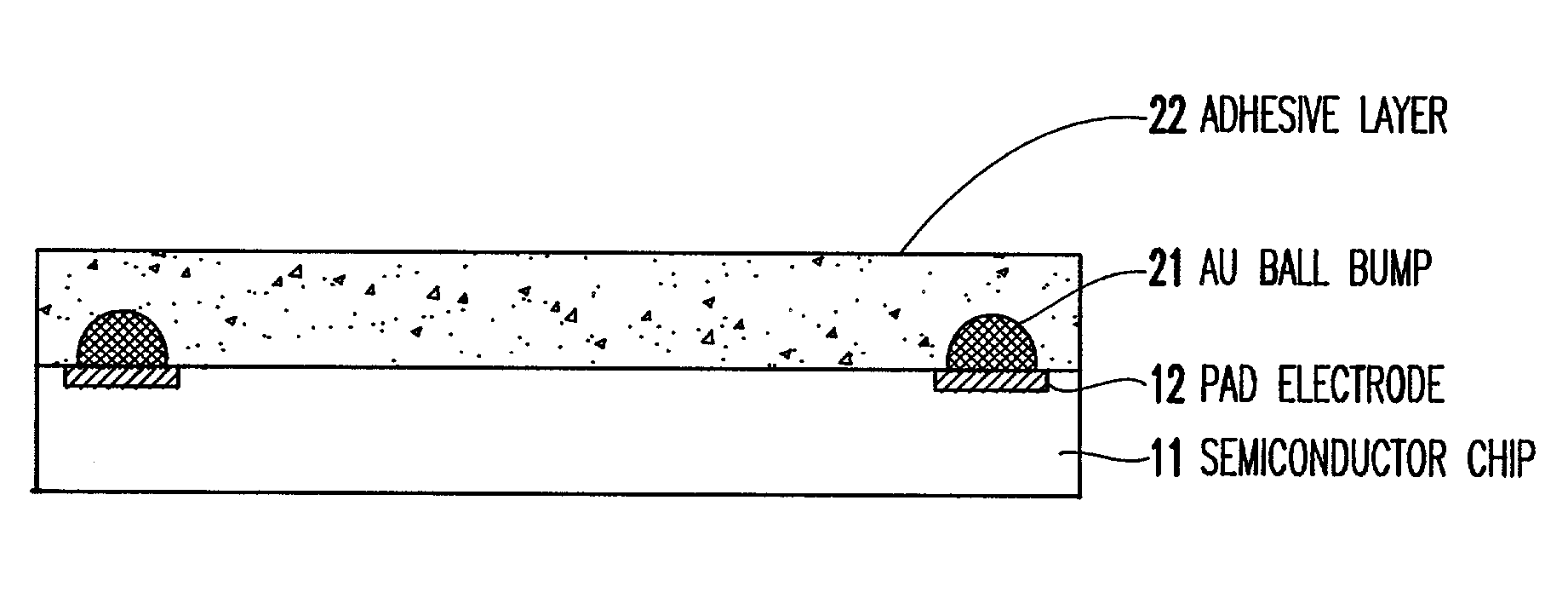

[0183] As shown in FIG. 4(d), semiconductor device 3 (HDP: High Density Package) of Embodiment 1 comprises semiconductor chip 11, Au ball bumps 21 provided on pad electrodes 12 with a stud bump method, and thermoplastic adhesive layer 22 disposed on the surface of semiconductor chip 11 on which pad electrodes 12 are formed such that the tops of Au ball bumps 21 project from the surface of adhesive layer 22.

[0184] While adhesive layer 22 is formed of a thermoplastic adhesive in consideration of replacement of a defective item after adhesion, a thermosetting adhesive may be used instead of the thermoplastic adhesive if such replacement is not required.

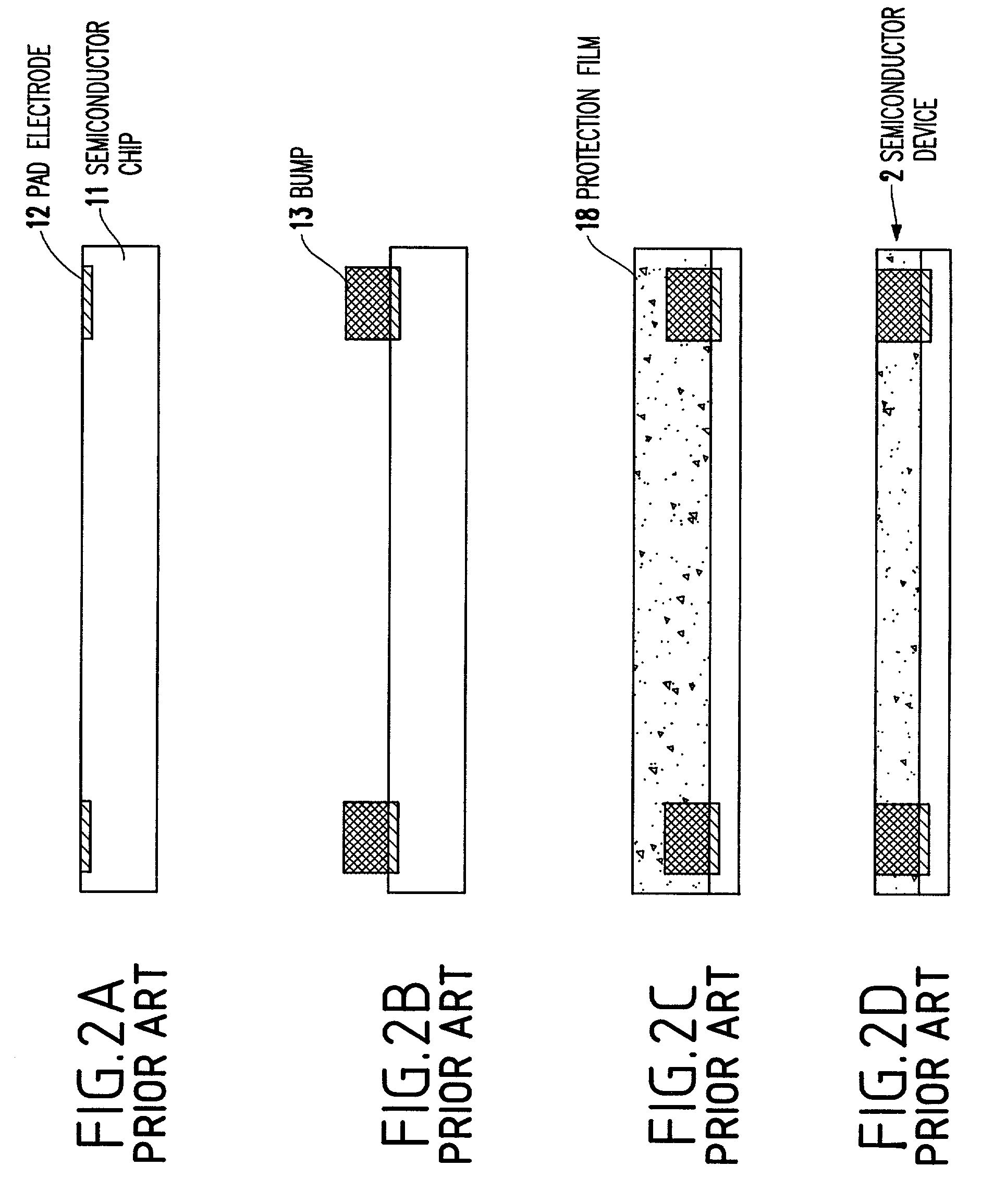

[0185] Semiconductor device 3 is manufactured as follows. FIGS. 4(a) to (d) are enlarged views showing one particular semiconductor chip 11 formed in semiconductor wafer 20.

[0186] After a predetermined number of semiconductor chips 11 are manufactured in semiconductor wafer 20, Au ball bumps 21 are provided on pad electrodes 12 of each s...

embodiment 2

[0190] Next, a semiconductor device and a manufacturing method thereof according to Embodiment 2 of the present invention are described with reference to FIG. 5(a). FIG. 5(a) is a cross section showing the semiconductor device of Embodiment 2 of the present invention.

[0191] The semiconductor device shown in FIG. 5(a) is a semiconductor device (BGA type semiconductor package) in which semiconductor device 3 is bonded to wiring tape 23 as an interposer through thermocompression bonding and resin molding is performed. For manufacturing, semiconductor wafer 20 (see FIG. 4) is first cut for division into individual semiconductor devices 3.

[0192] Next, one, or two or more semiconductor devices 3 are mounted on one wiring tape 23, and heating and pressing are performed to establish adhesion to wiring tape 23 with adhesive layer 22 and electrical connection to copper wiring 24 on wiring tape 23 with Au ball bumps 21. Such adhesion and connection may be performed as follows.

[0193] Wiring tap...

embodiment 3

[0203] Next, a semiconductor device and a manufacturing method thereof according to Embodiment 3 of the present invention are described with reference to FIG. 5(b). FIG. 5(b) is a cross section showing the semiconductor device of Embodiment 3 of the present invention.

[0204] The semiconductor device shown in FIG. 5(b) comprises semiconductor chip 11, adhesive layer 22 as a protection resin layer provided on the surface on which pad electrodes 12 are formed, Au ball bums 21 formed on pad electrodes 12 and exposed at the surface of adhesive layer 22, and wiring tape 23 adhered to the surface of adhesive layer 22 through cured flux 28 and serving as an interposer for electrical connection to Au ball bumps 21. The semiconductor device is a semiconductor device (BGA type semiconductor package) manufactured by bonding semiconductor device 3 to wiring tape 23 with thermocompression bonding and performing resin molding.

[0205] For manufacture, semiconductor wafer 20 (see FIG. 4) is first cut ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More