Apparatus for stacking semiconductor chips

a technology of semiconductor chips and apparatus, applied in the direction of electrical apparatus construction details, solid-state devices, basic electric elements, etc., can solve the problems of many techniques not using surface mount technology, a number of defects, etc., and achieve the effect of increasing the density of memory chips and increasing the density of components

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Benefits of technology

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

In accordance with one embodiment of the present invention, one multi-chip memory module design is described herein. In order to fully specify this

preferred design, various embodiment-specific details are set forth, such as the number of memory chips in the module, the layouts of the printed circuit boards of the module, and the capacity, number of data bits and pin-outs of the memory chips. It should be understood, however, that these details are provided only to illustrate this single preferred embodiment, and are not intended to limit the scope of the present invention.

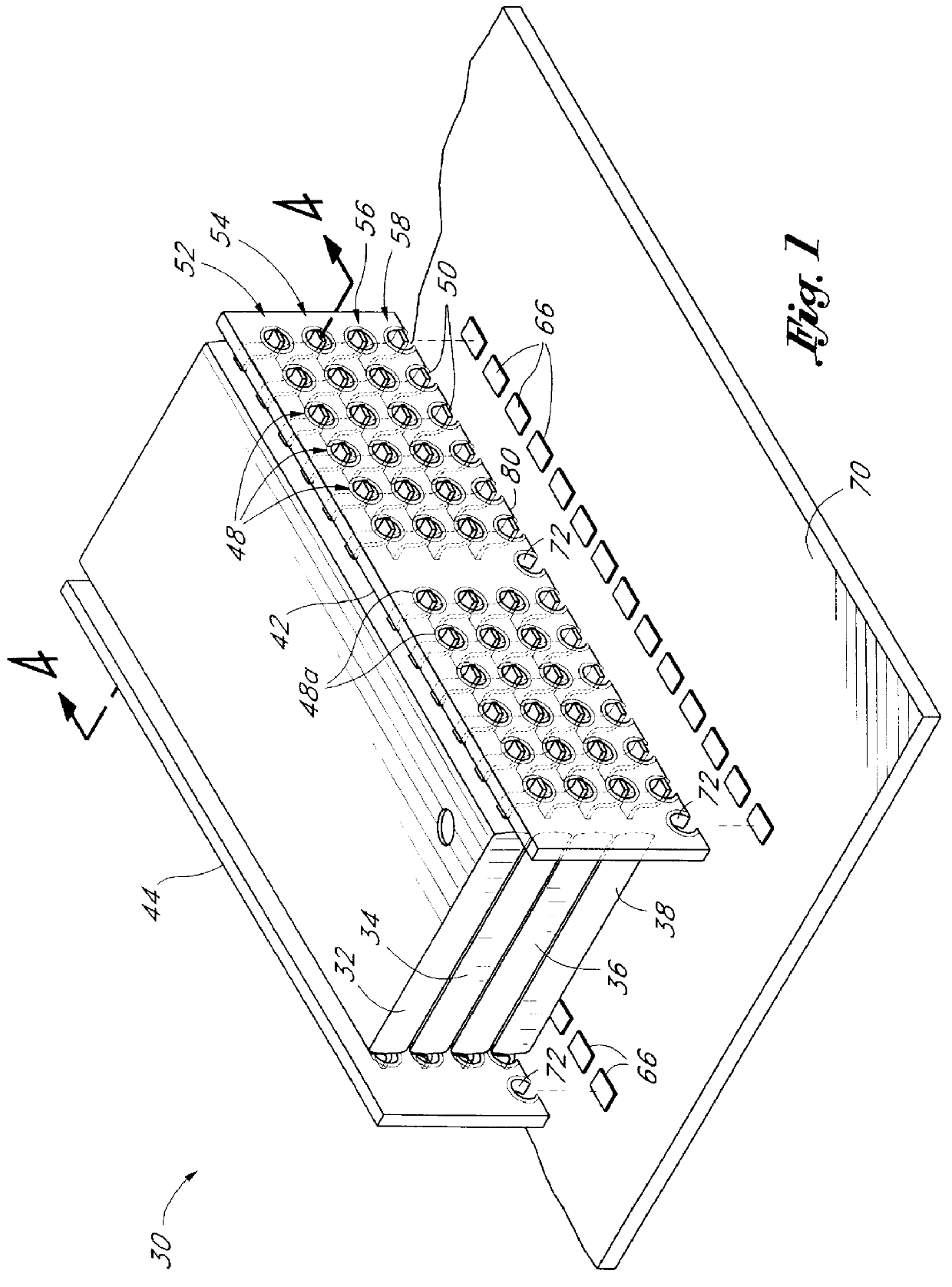

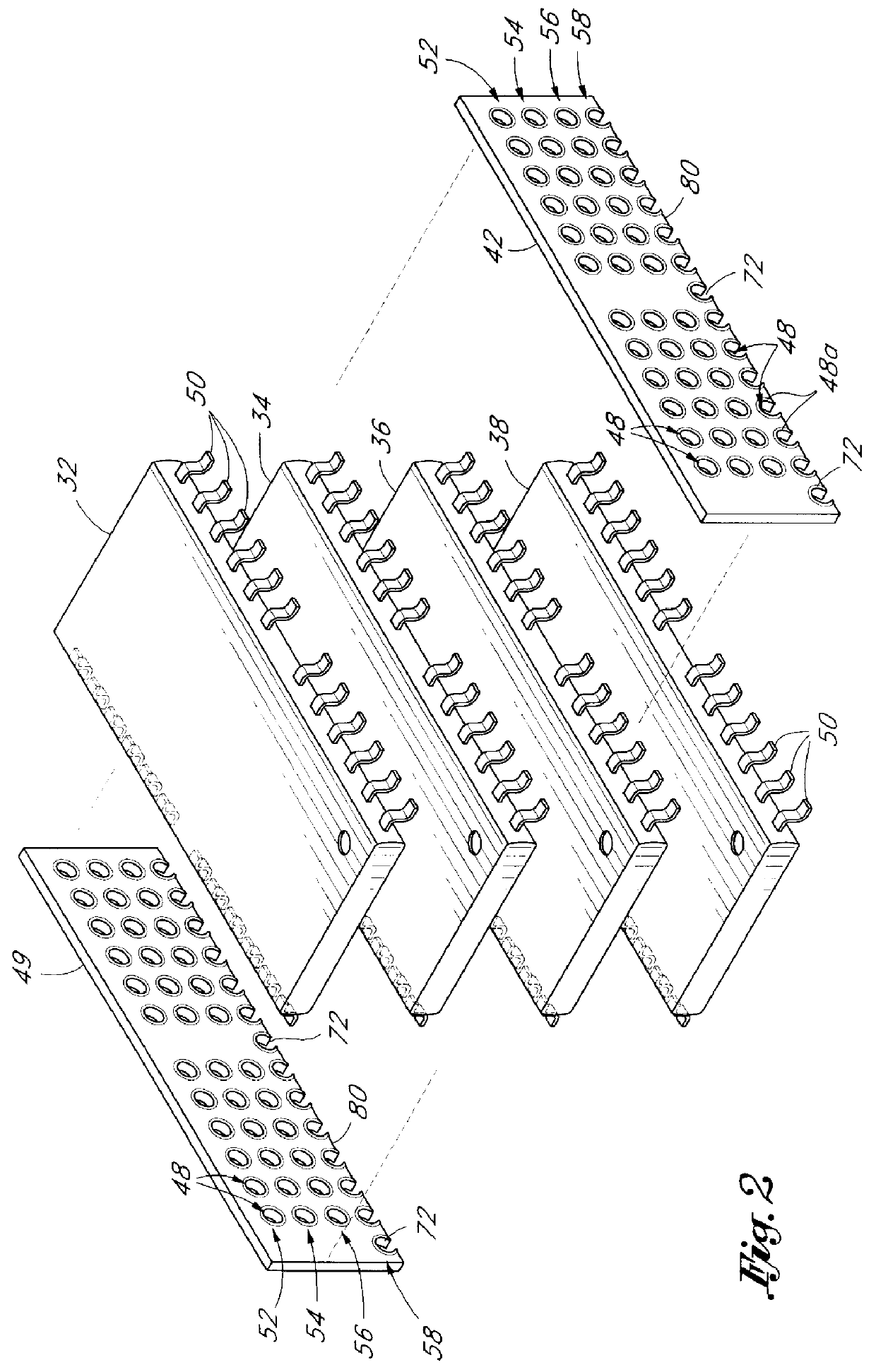

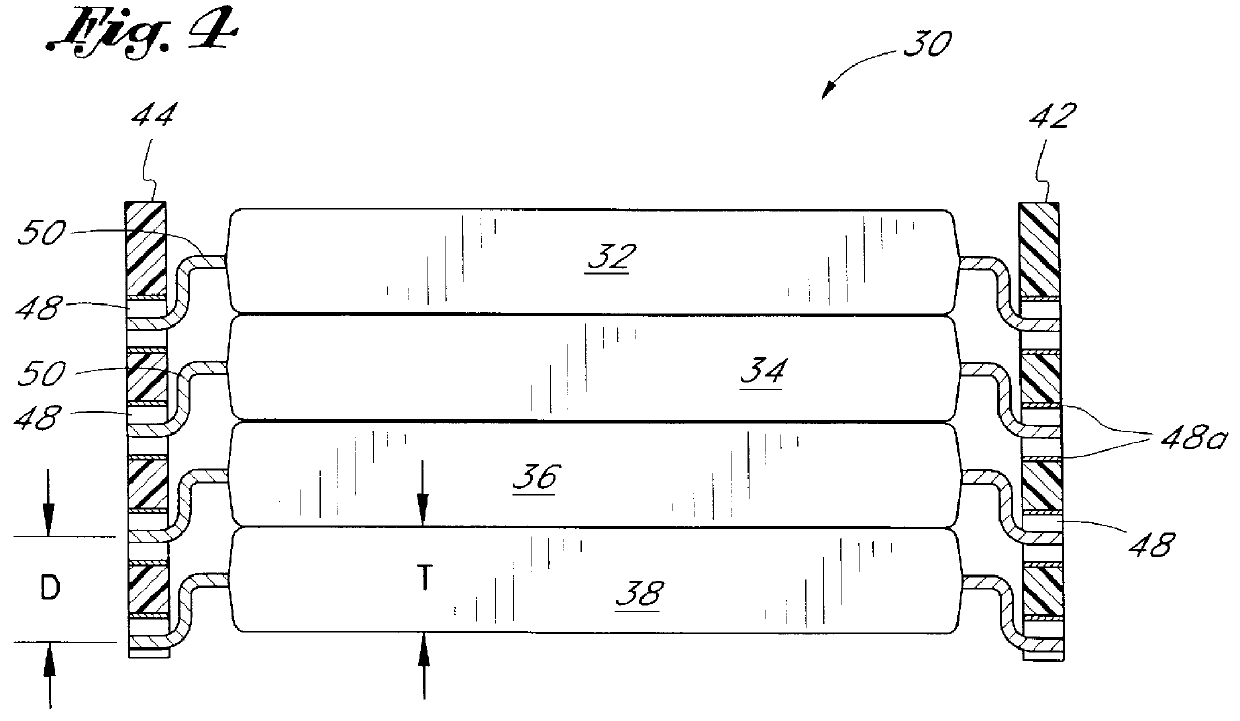

With reference to FIGS. 1-4, a 28-terminal multi-chip memory module 30 (hereinafter "multi-chip module") comprises four functionally-identical, vertically-stacked memory chips 32, 34, 36, 38. The memory chips 32-38 are conventional 24-pin surface mount TSOP ("thin small outline package") chips, available from Toshiba, Mitsubishi, and the like. Each memory chip 32-38 has a capacity of 16M.times.1-bit.

The vertically-...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More