Interconnection and package method on basis of TSV (through silicon via) chips

A packaging method and chip technology, applied in the manufacturing of electrical components, electric solid-state devices, semiconductor/solid-state devices, etc., can solve the problem of unguaranteed device reliability, and achieve the effect of improving device reliability and preventing low reliability.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

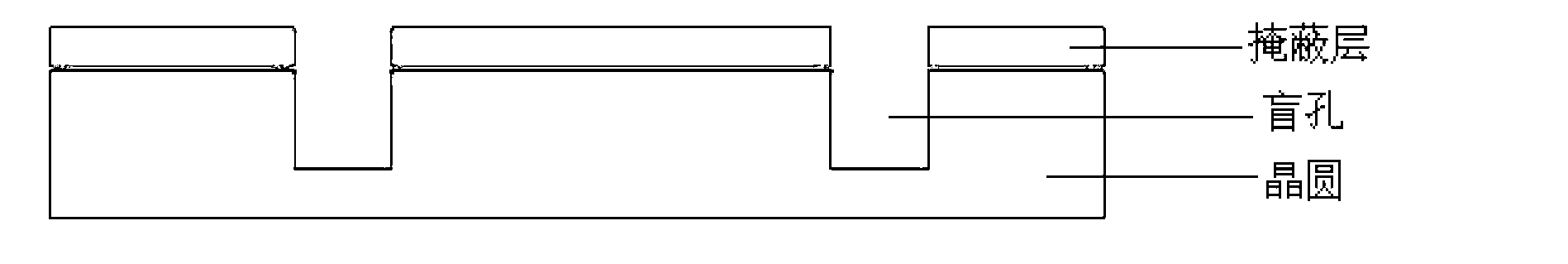

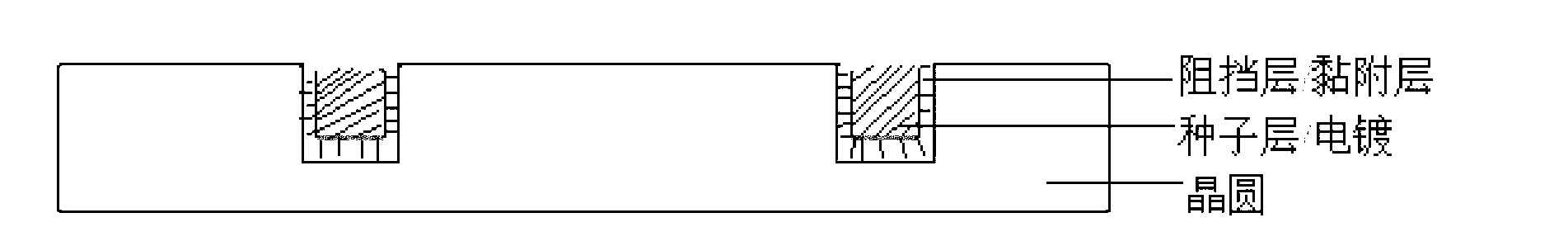

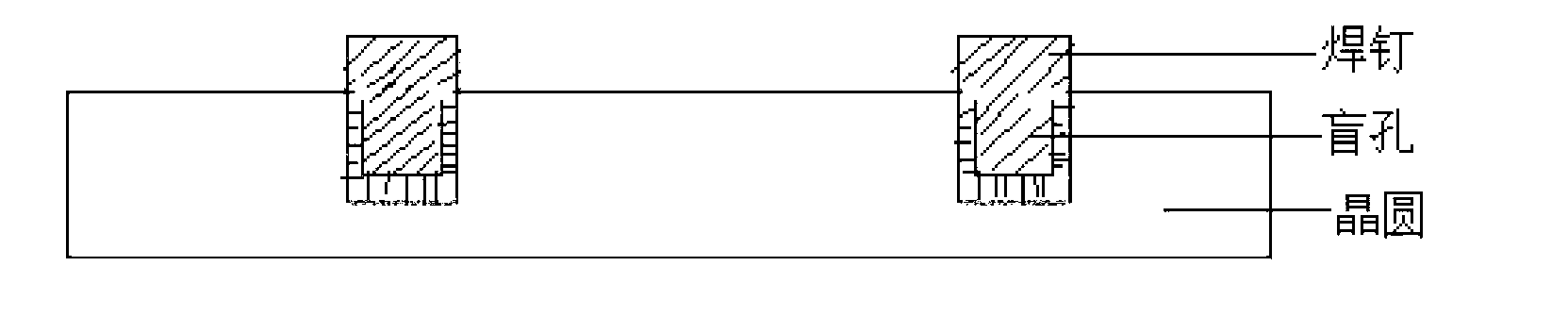

[0047] Specific embodiments of the present invention will be described in detail below in conjunction with the accompanying drawings. It should be noted that the specific embodiments discussed below are only specific embodiments in a specific environment, and do not limit the scope of the present invention.

[0048] A method for interconnecting and packaging based on TSV chips, comprising the following steps:

[0049] 1) Stack and bond multiple TSV chips with through holes to obtain stacked TSV chips;

[0050] 2) Interconnect the stacked multi-layer TSV chips with the interposer board with bumps to obtain the interposer board stack structure;

[0051] 3) Using flip-chip welding technology to interconnect the laminated structure of the adapter board with the substrate to obtain a laminated module;

[0052] 4) Carry out underfill protection between the chip and the chip, between the chip and the interposer, between the interposer and the substrate, and obtain an underfill prot...

PUM

| Property | Measurement | Unit |

|---|---|---|

| Diameter | aaaaa | aaaaa |

| Height | aaaaa | aaaaa |

| Thickness | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More