Large sized silicon interposers overcoming the reticle area limitations

An interposer and intermediary technology, applied in the field of interconnection, can solve the problems of increasing cost, reducing output, and not being easy to manufacture.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

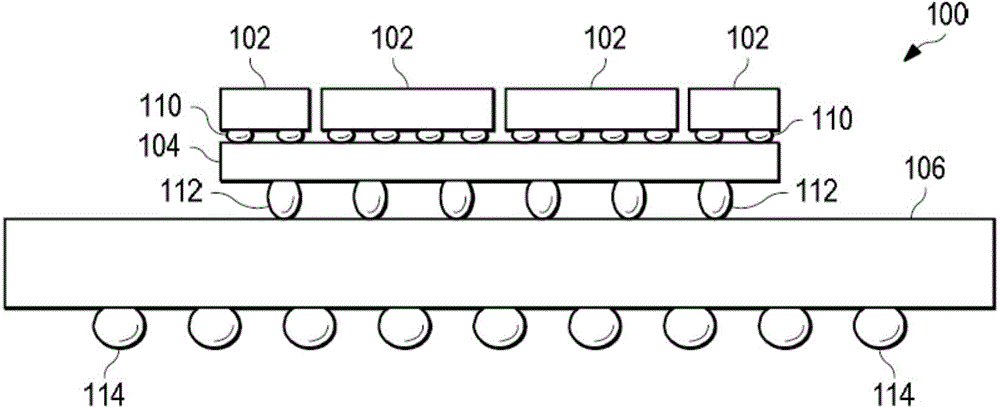

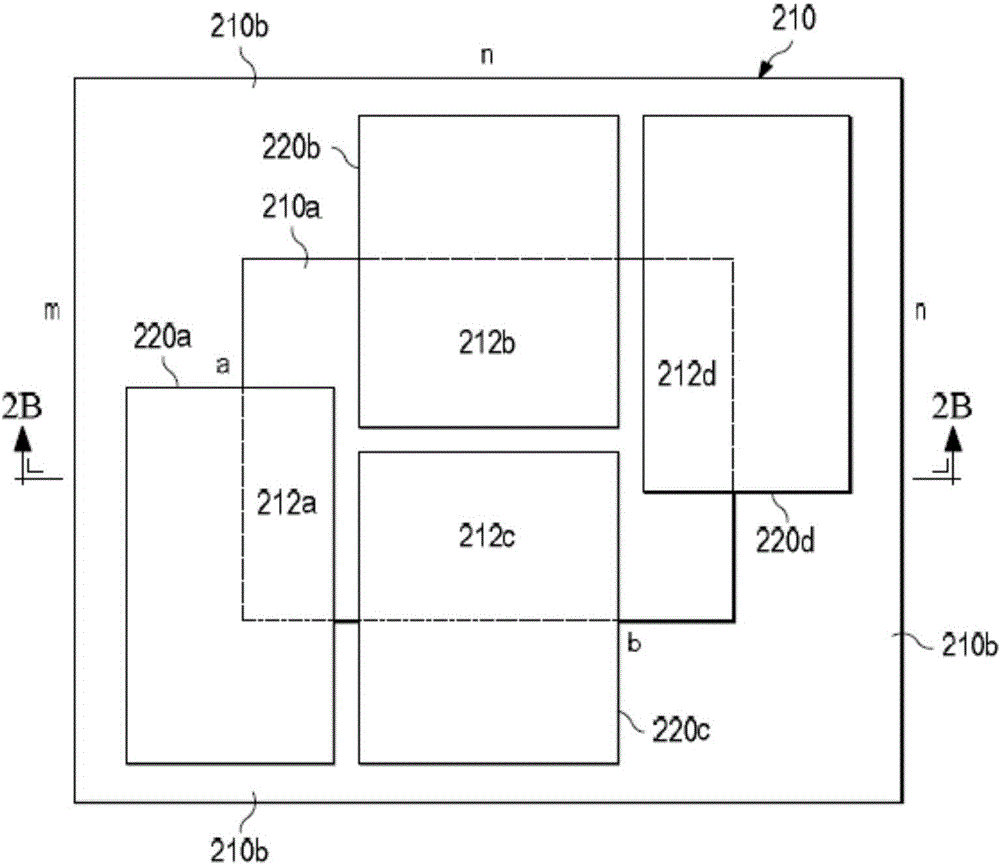

[0016] In general, the present invention describes and teaches the design and construction of a new 2.5D IC package assembly that enables The package size is larger overall. As shown in FIG. 1 , existing technology is limited by dies mounted on a silicon interposer whose total area is less than the area of the silicon interposer. Therefore, if the die is large, its composability with other dies to 2.5D IC package components is limited. By aligning only portions of multiple dies over the "active area," larger dies and / or greater numbers of dies can be combined and assembled into a single package.

[0017] For the purposes of this patent document, the term "active area" in a silicon interposer refers to areas where TSVs and other interconnecting conductors (such as power, ground, and other area formed for the photomask).

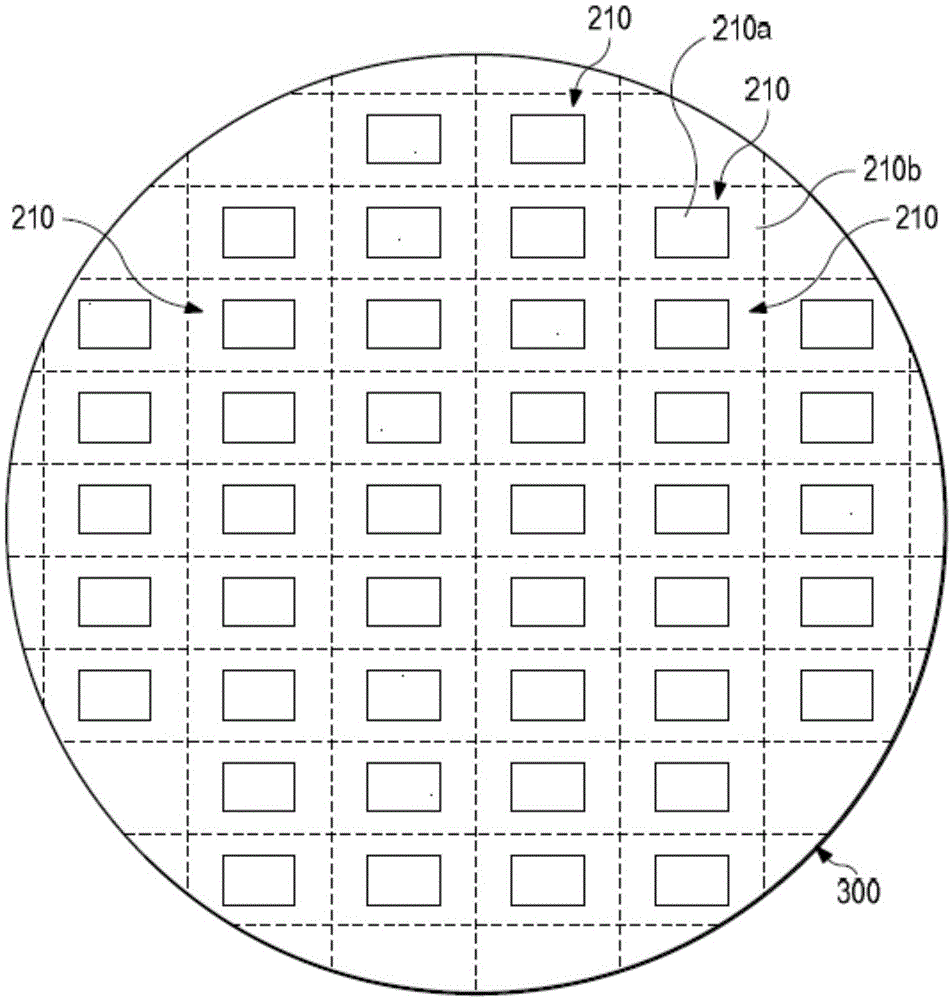

[0018] Figure 2A and Figure 2B Top and cross-sectional views, respectively, of an example multi-die integrated circuit package 200 according to the pr...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More