Patents

Literature

548 results about "Die (integrated circuit)" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

A die, in the context of integrated circuits, is a small block of semiconducting material on which a given functional circuit is fabricated. Typically, integrated circuits are produced in large batches on a single wafer of electronic-grade silicon (EGS) or other semiconductor (such as GaAs) through processes such as photolithography. The wafer is cut (diced) into many pieces, each containing one copy of the circuit. Each of these pieces is called a die.

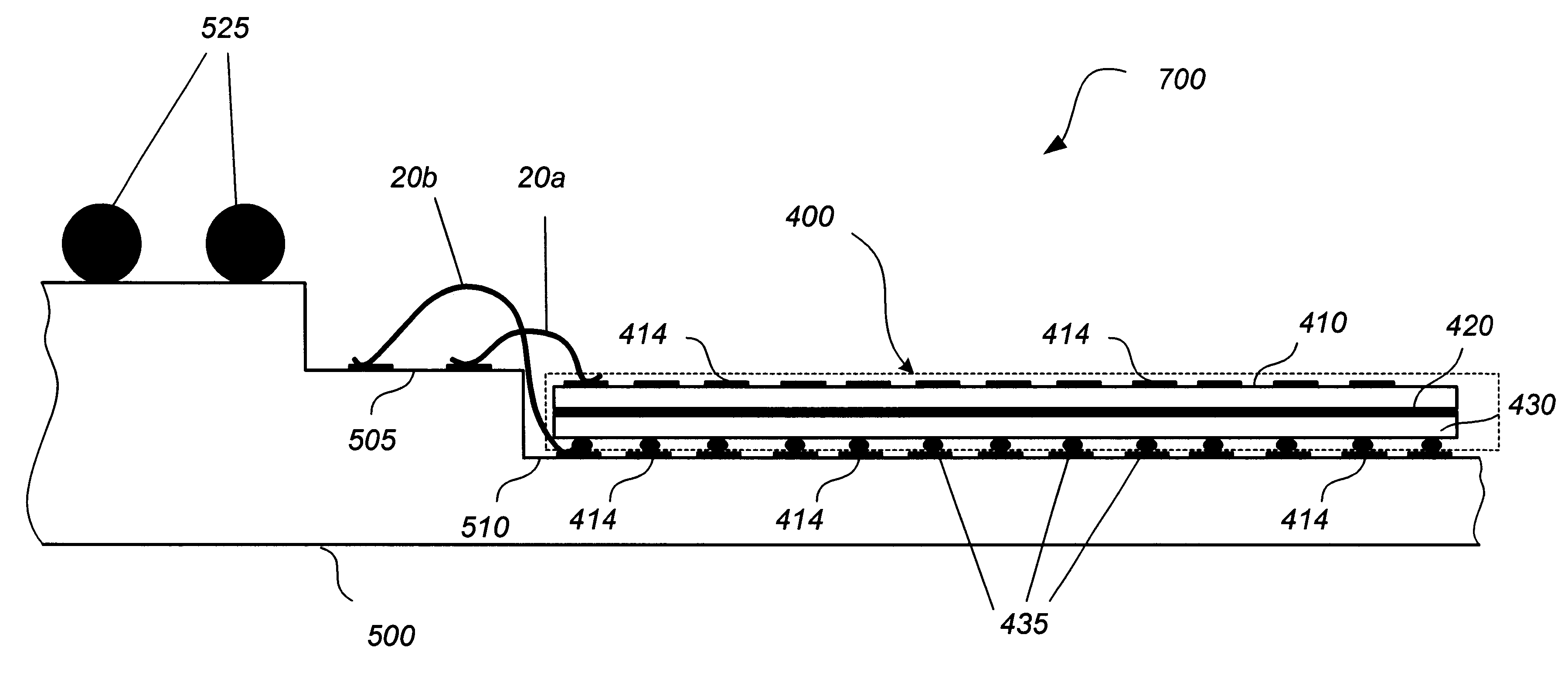

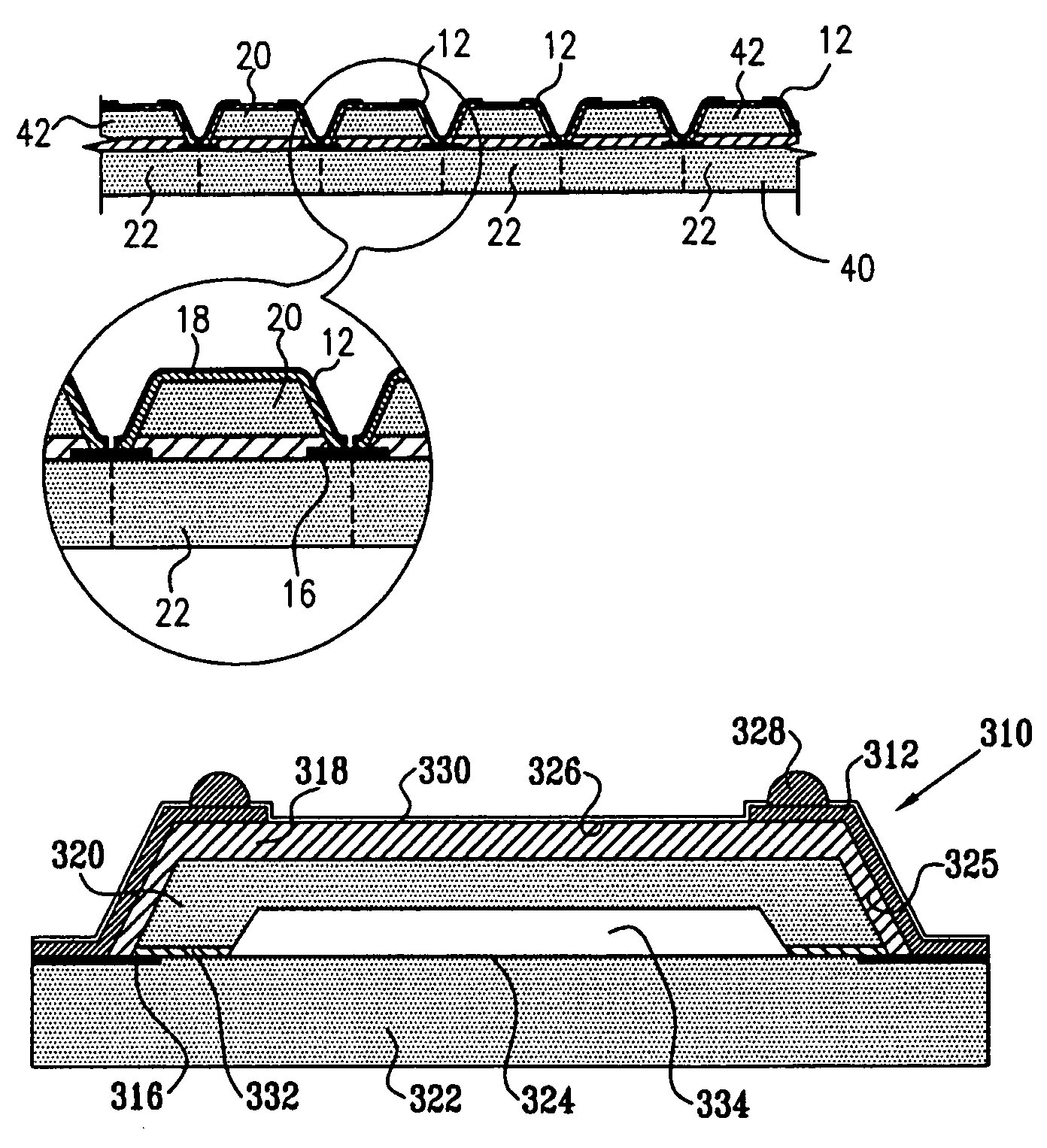

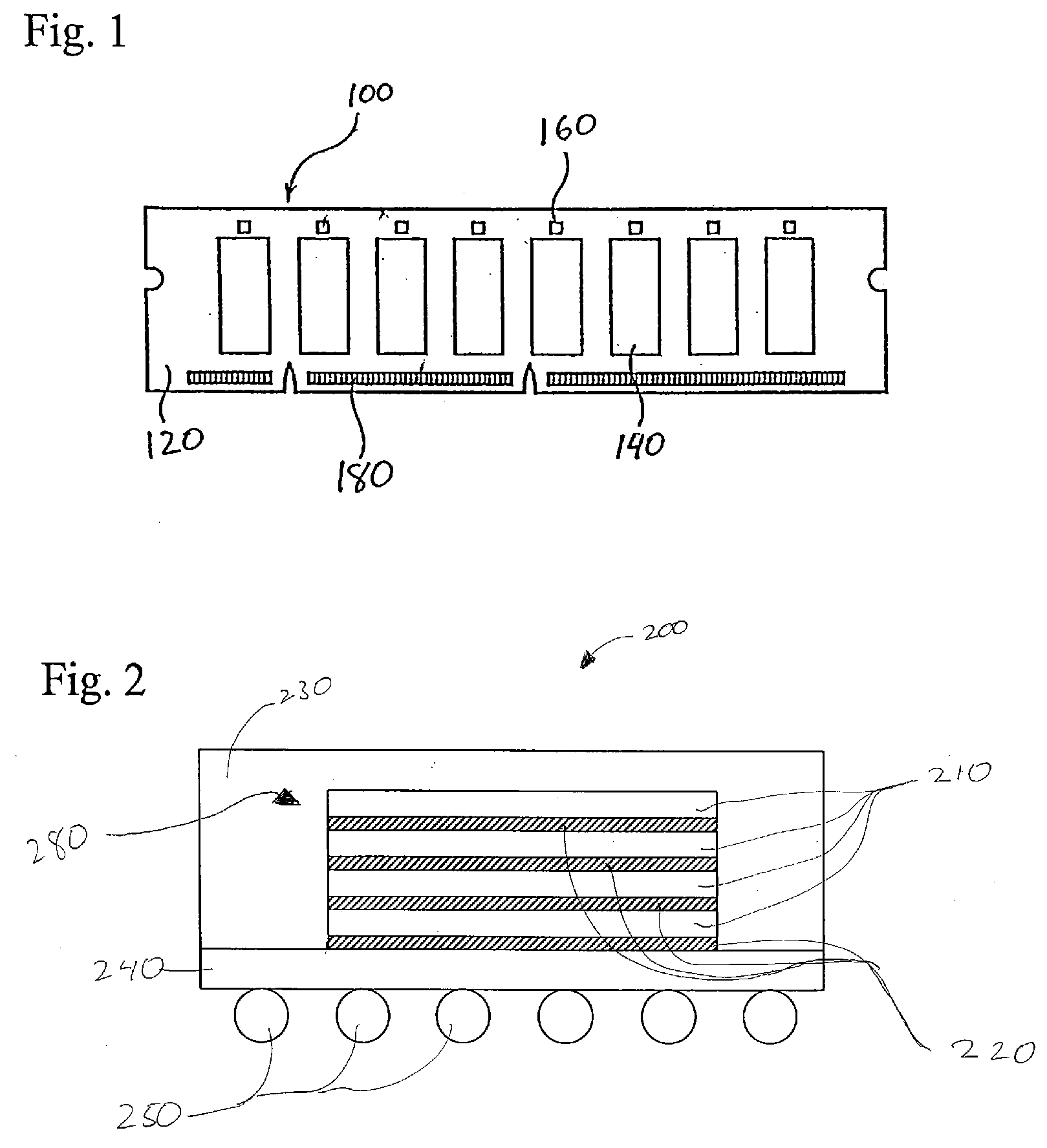

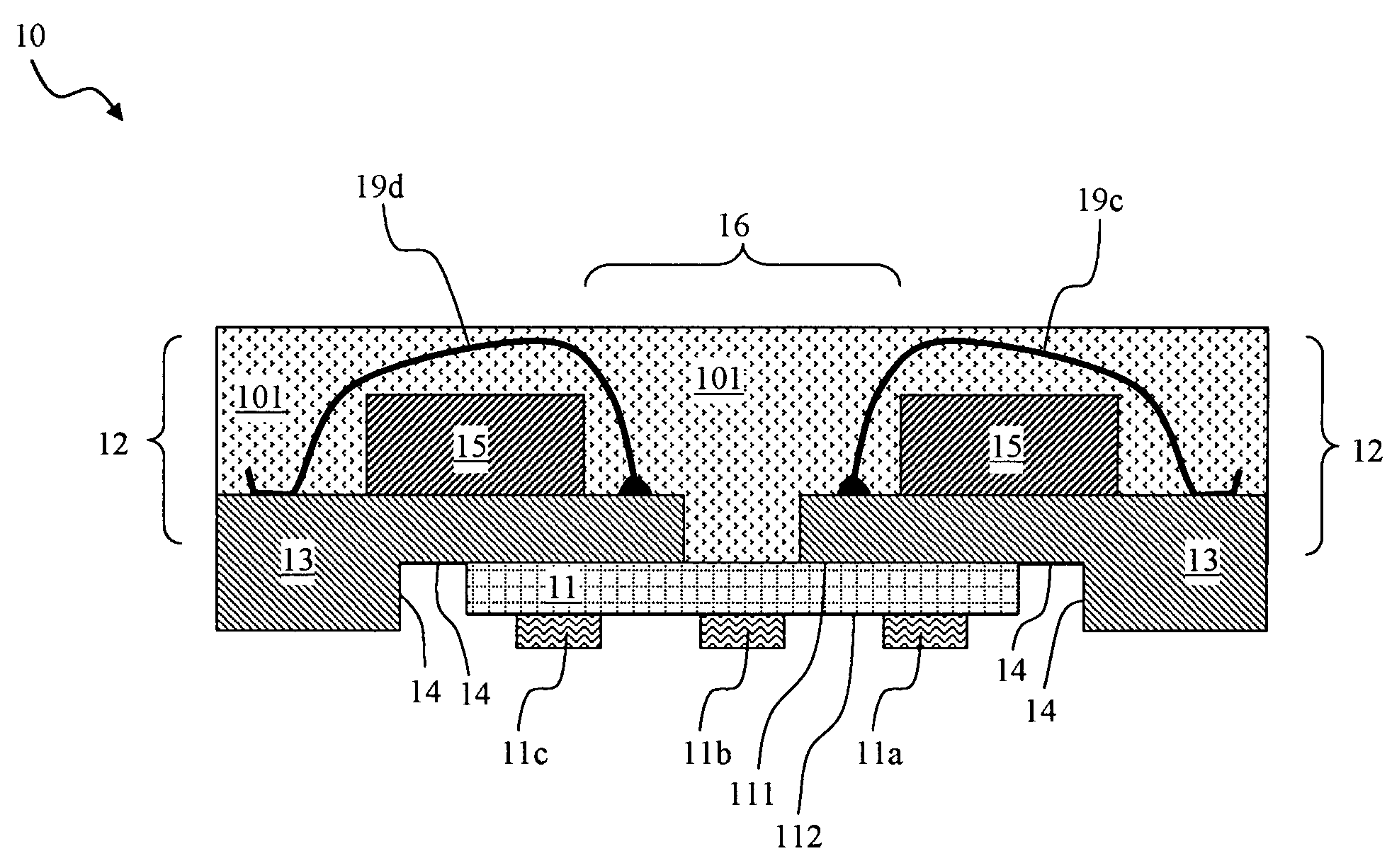

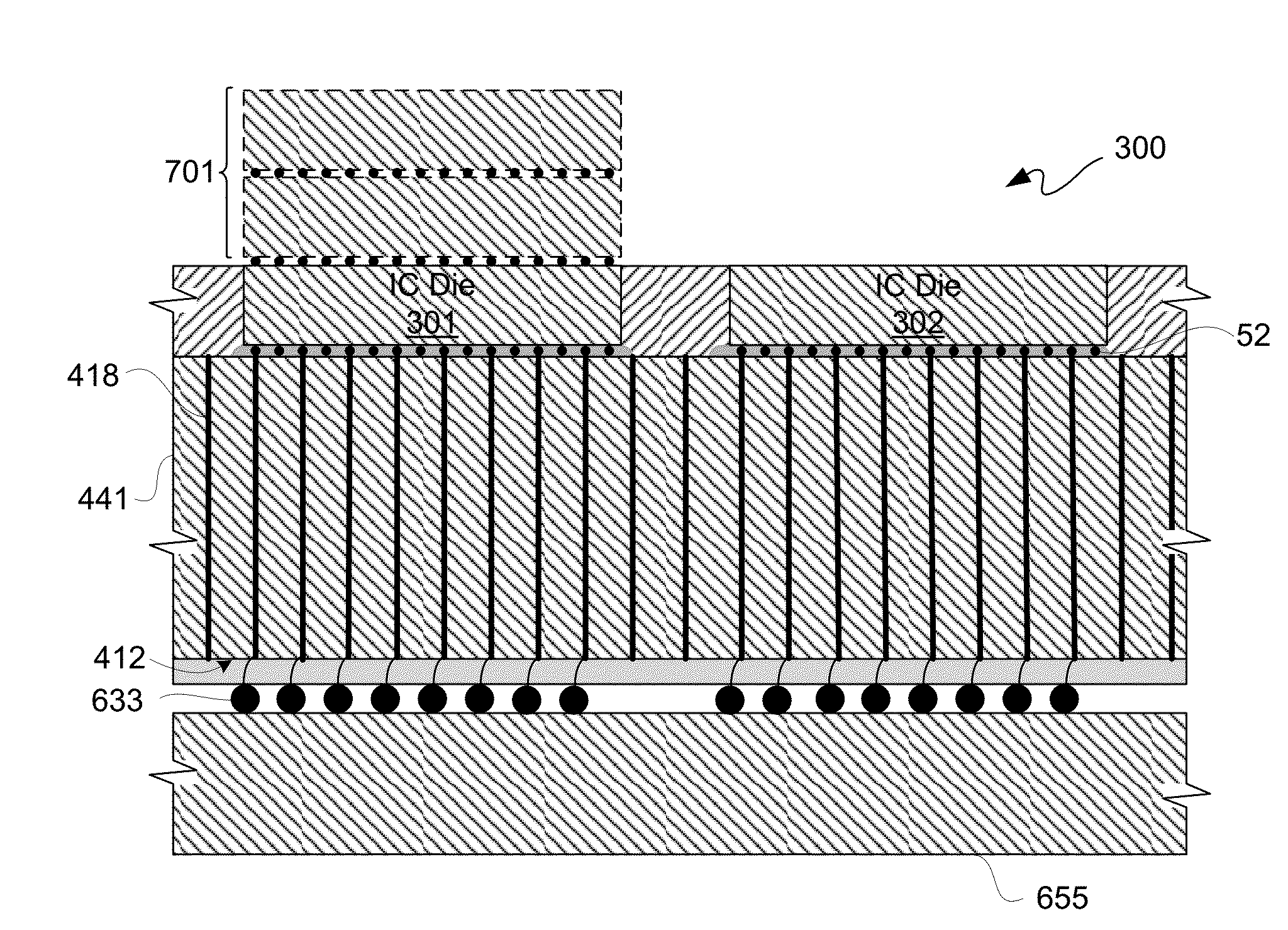

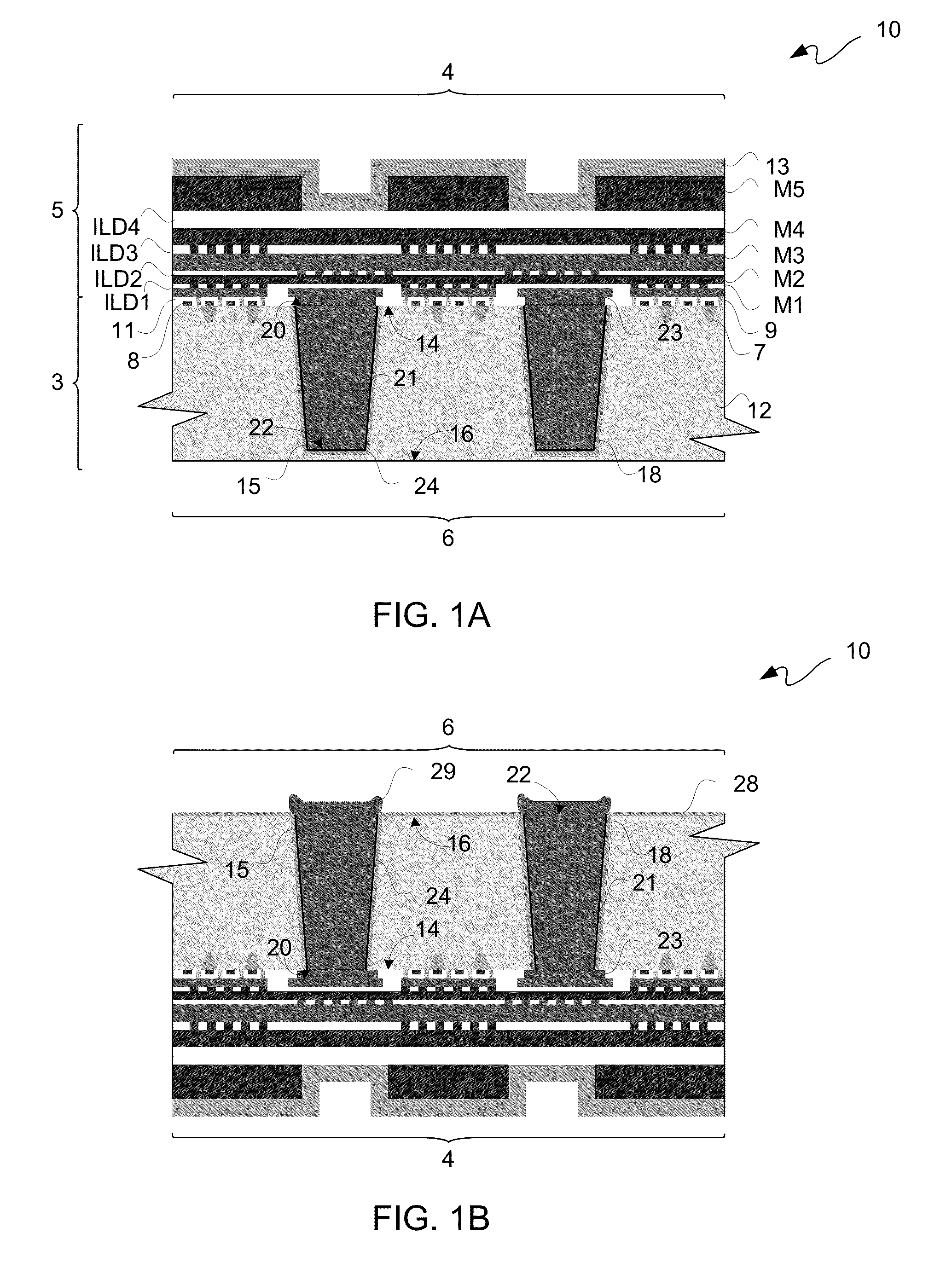

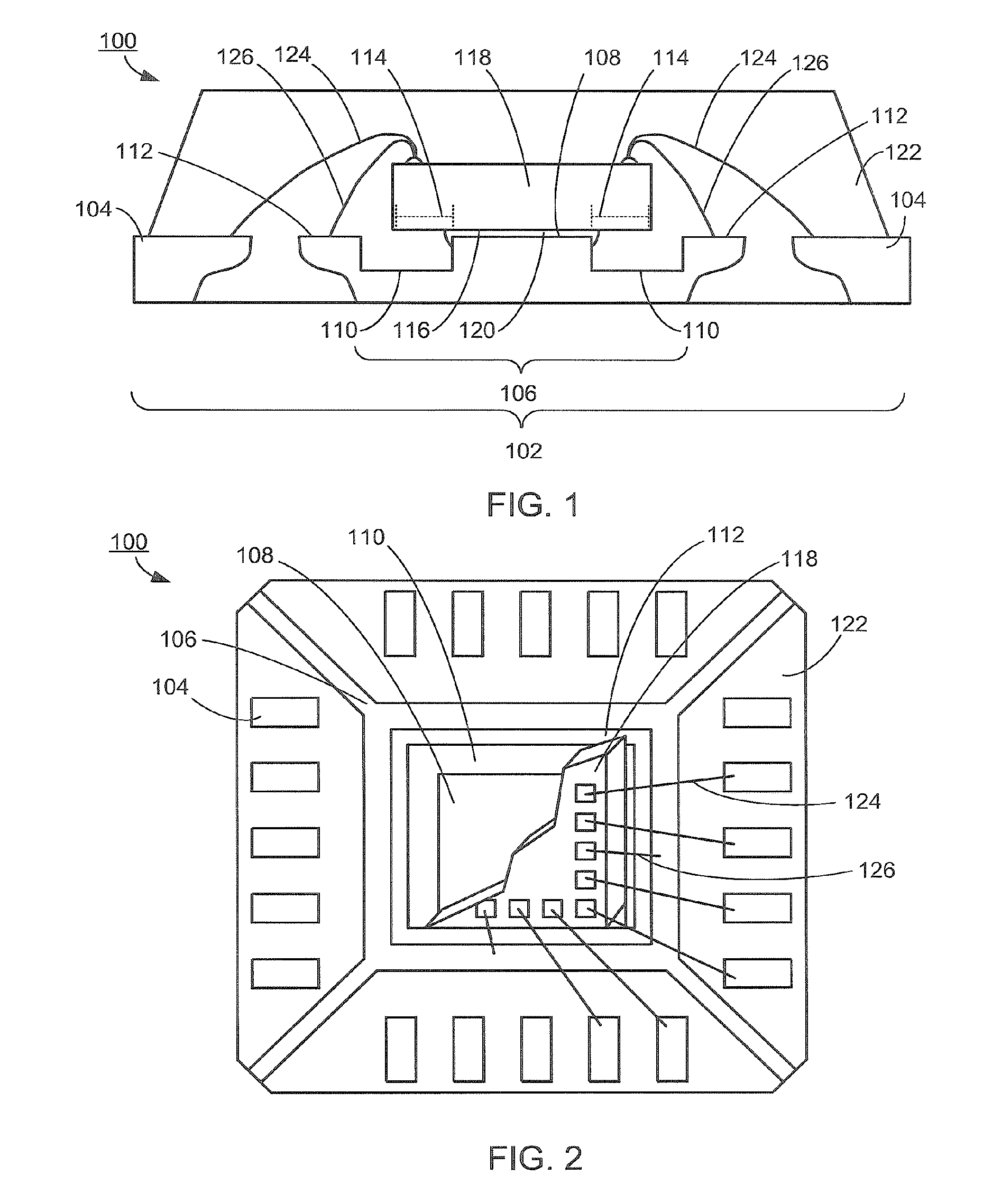

Integrated circuit (IC) package stacking and IC packages formed by same

ActiveUS20070290376A1Semiconductor/solid-state device detailsSolid-state devicesContact padSolder ball

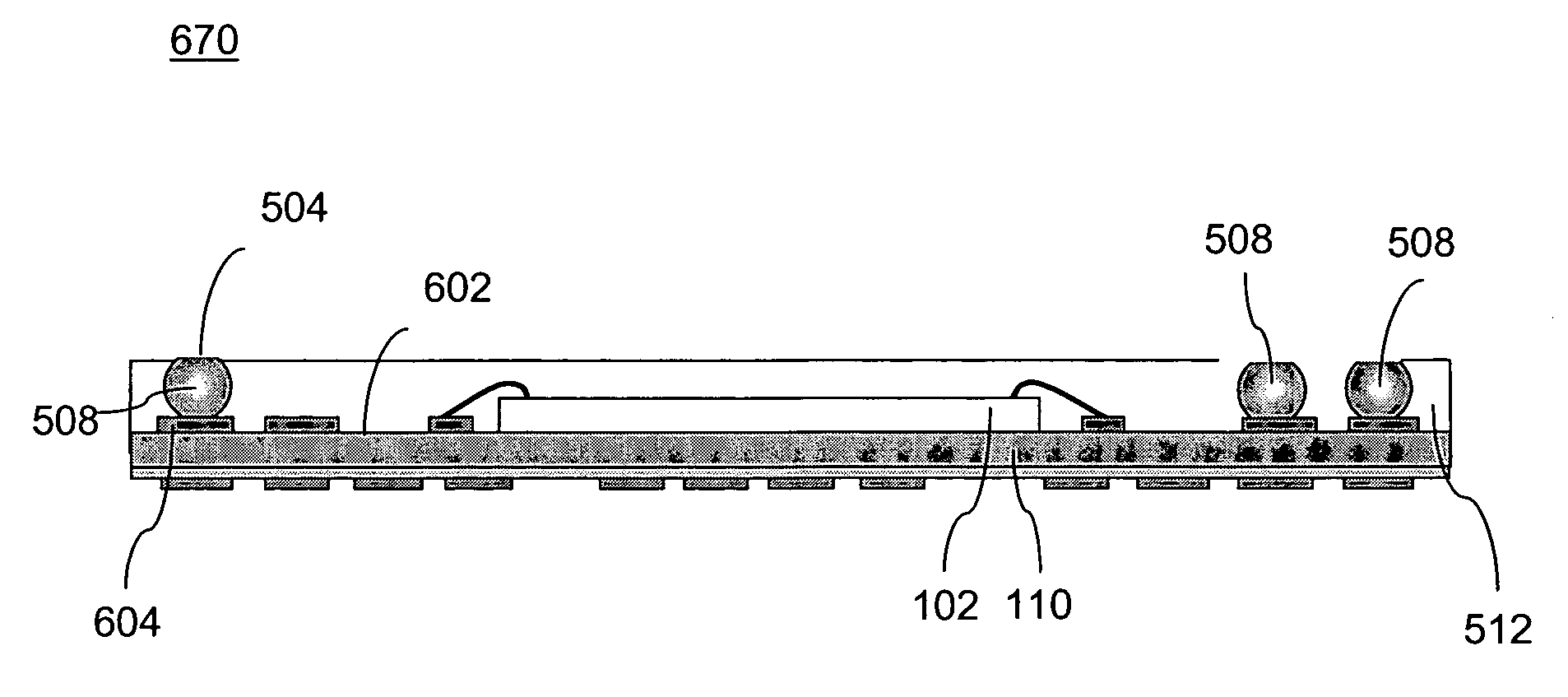

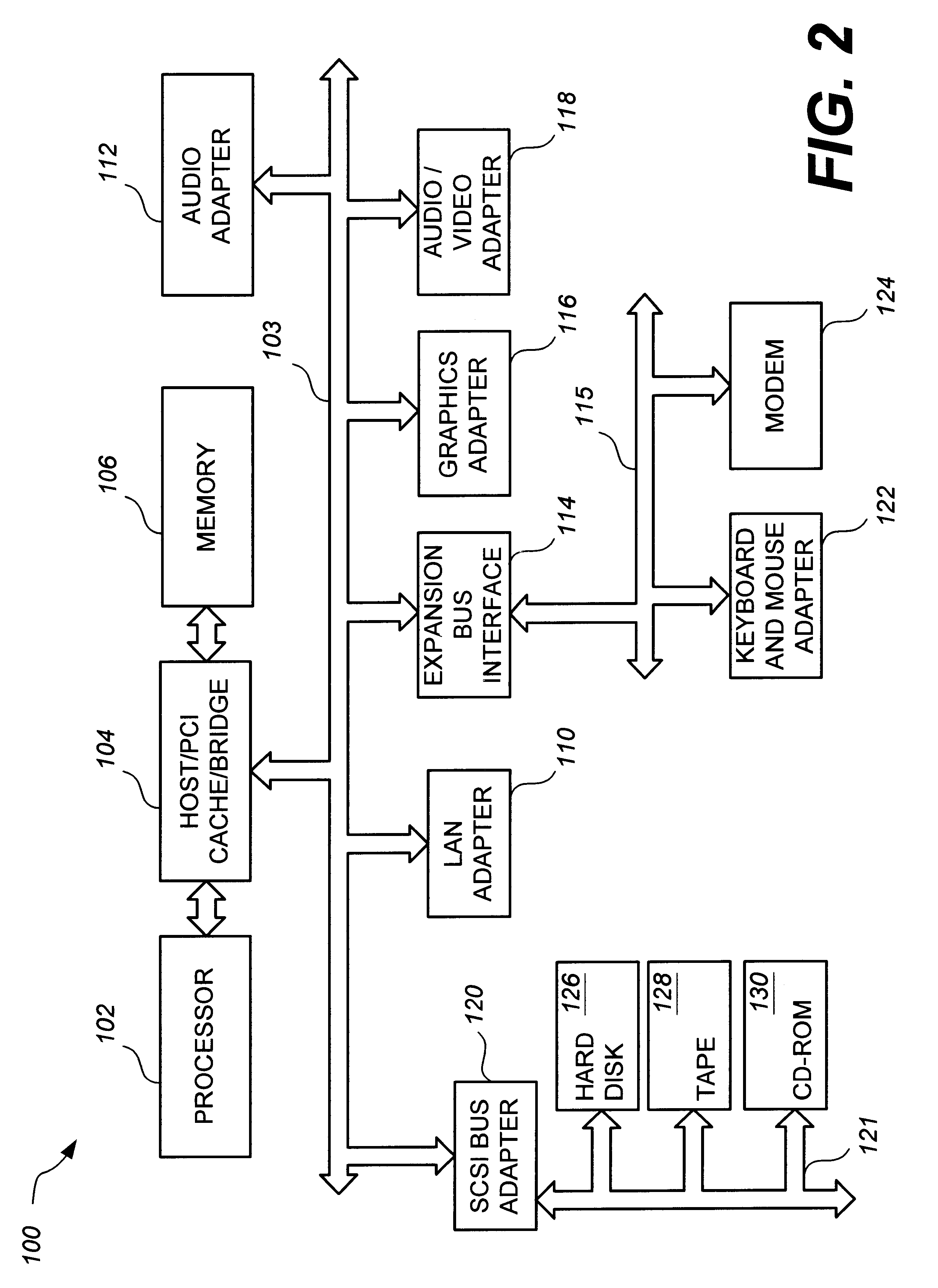

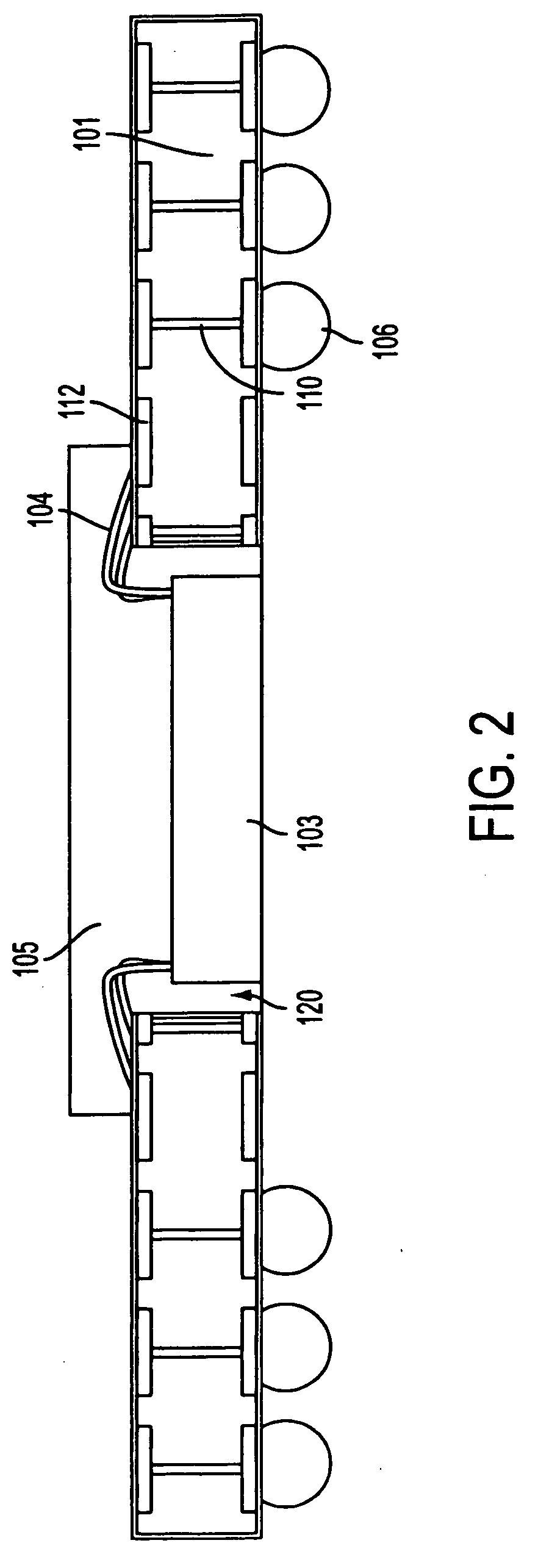

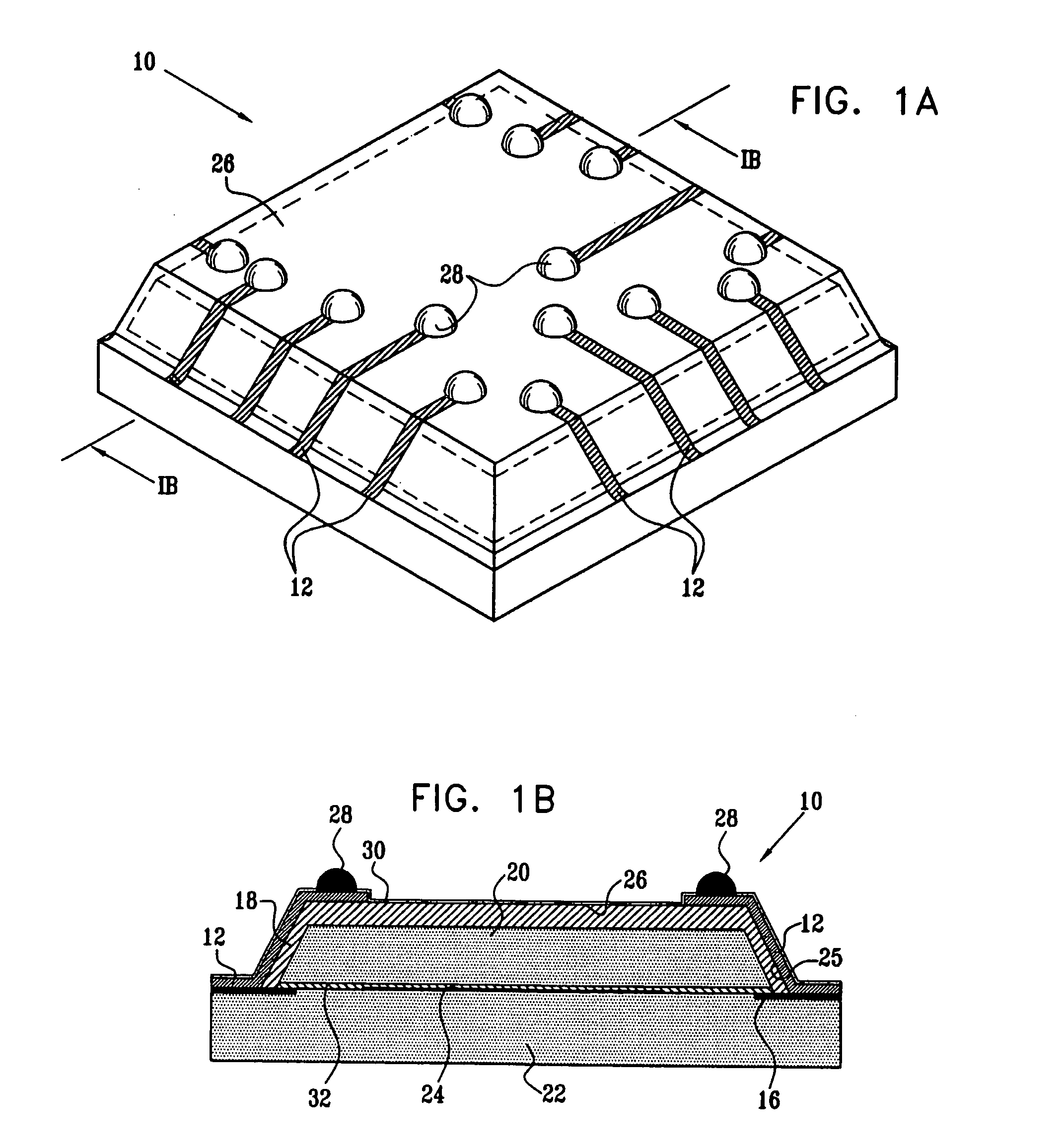

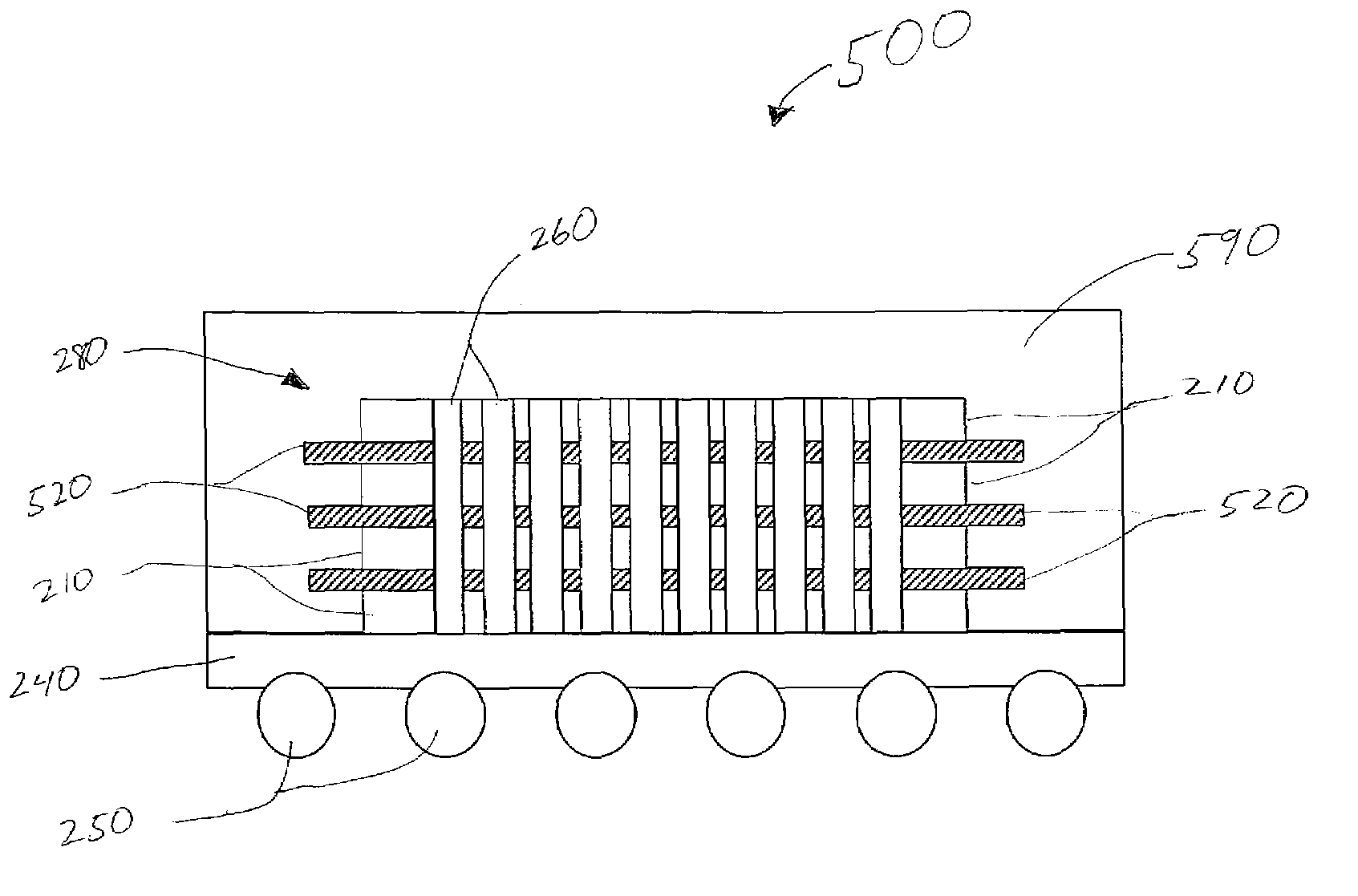

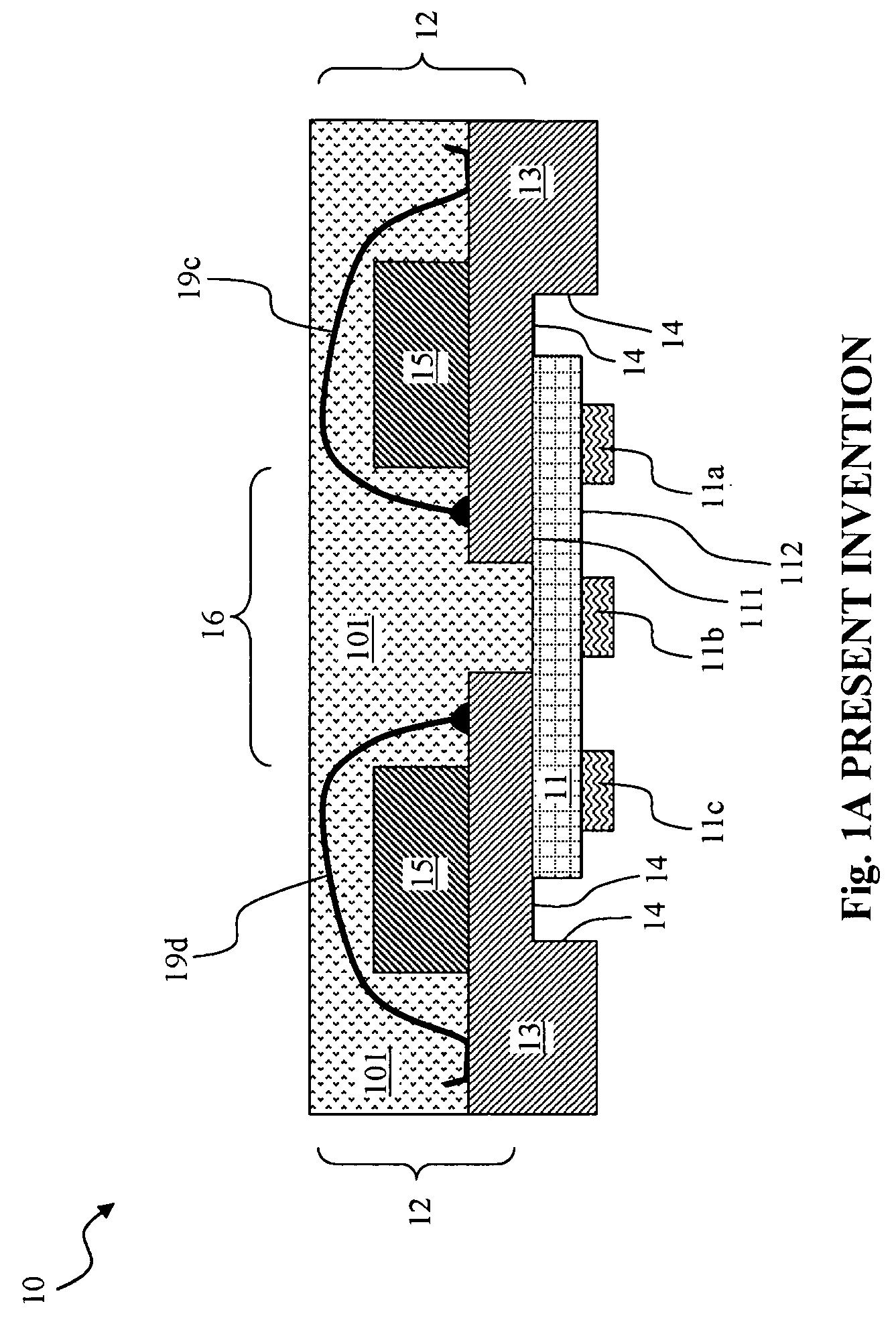

Methods, systems, and apparatuses for integrated circuit (IC) package vertical interconnection are described herein. In an aspect of the invention, an IC package includes an IC die with contact pads. The IC package also includes interconnect members which are coupled to the die at the contact pads. An encapsulating material encapsulates the IC die and the interconnect members such that a contact surface of each interconnect member is accessible at a surface of the encapsulating material. A second IC package is coupled to the first IC package through the plurality of interconnect members of the first IC package. In an example, solder balls attached to a bottom of the second IC package are coupled to the contact surfaces of the interconnect members to couple the first IC package and the second IC package.

Owner:AVAGO TECH INT SALES PTE LTD

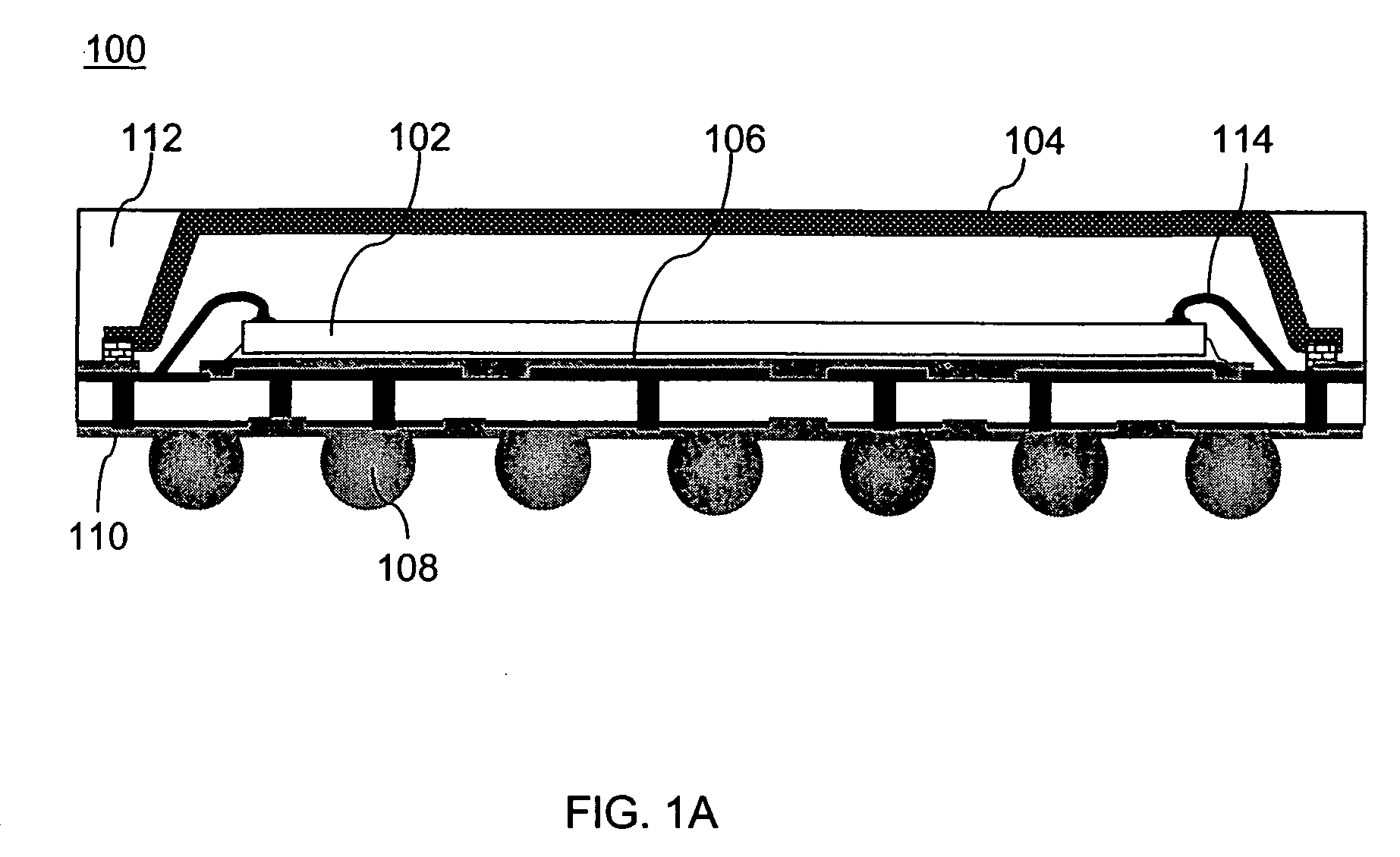

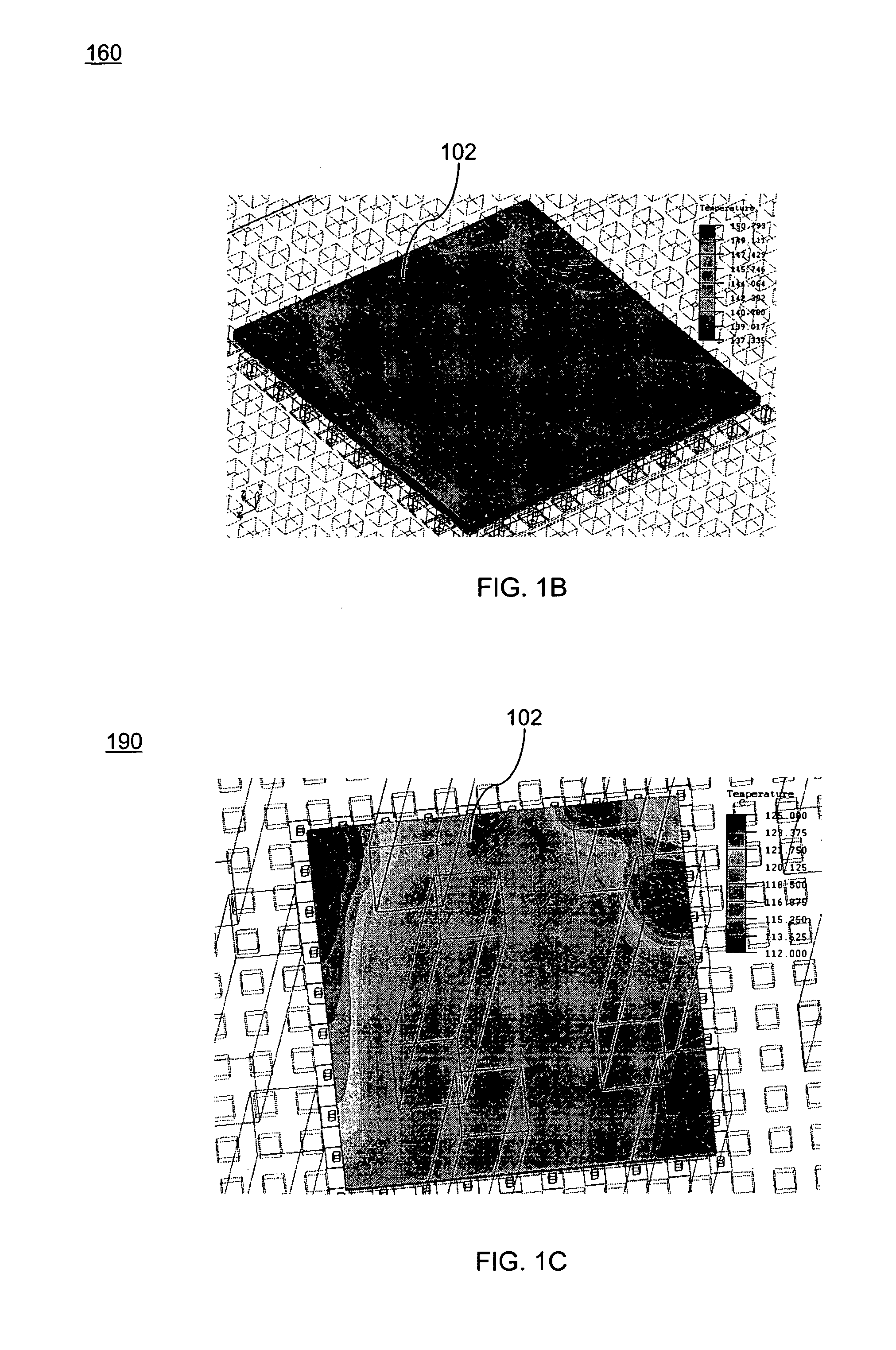

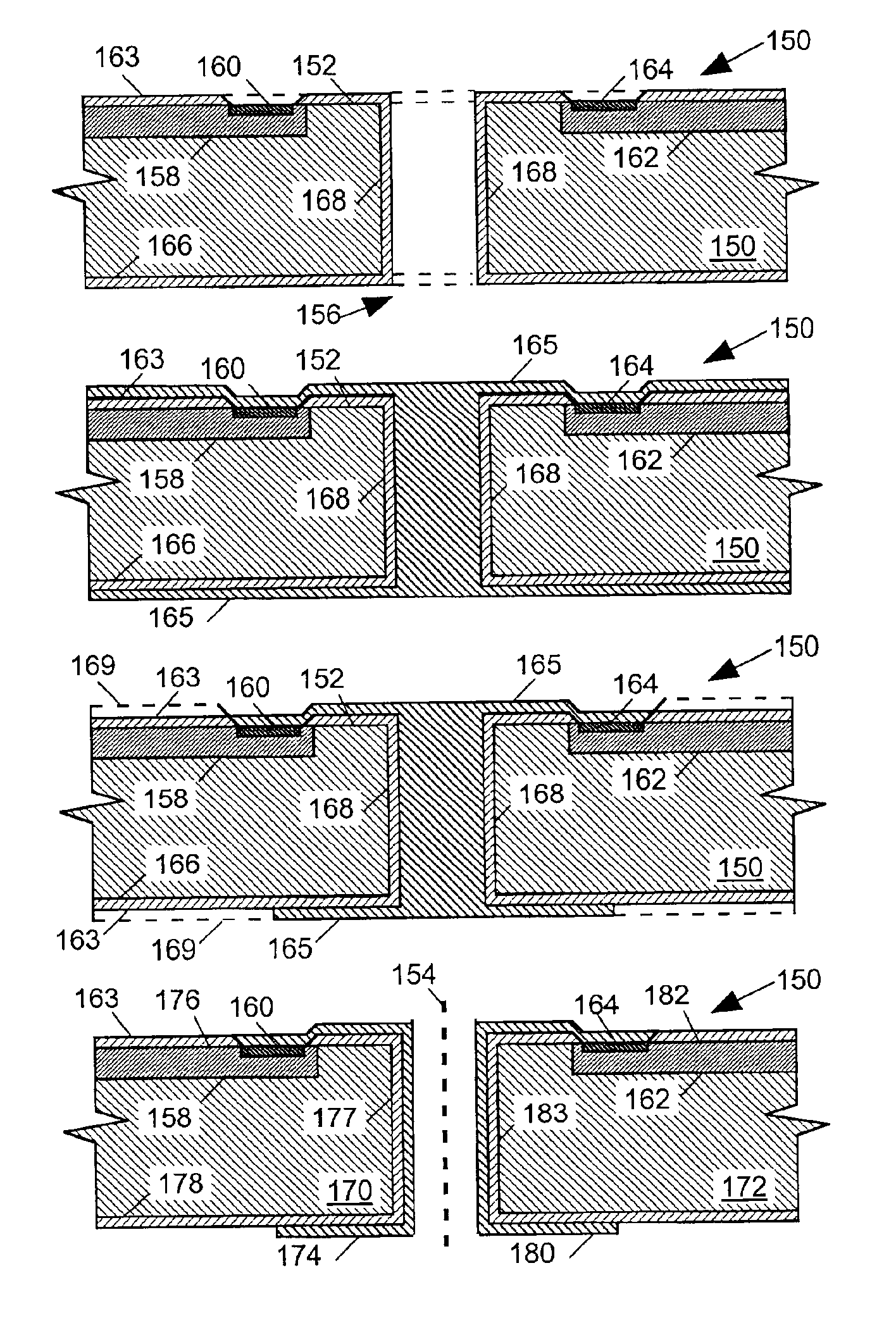

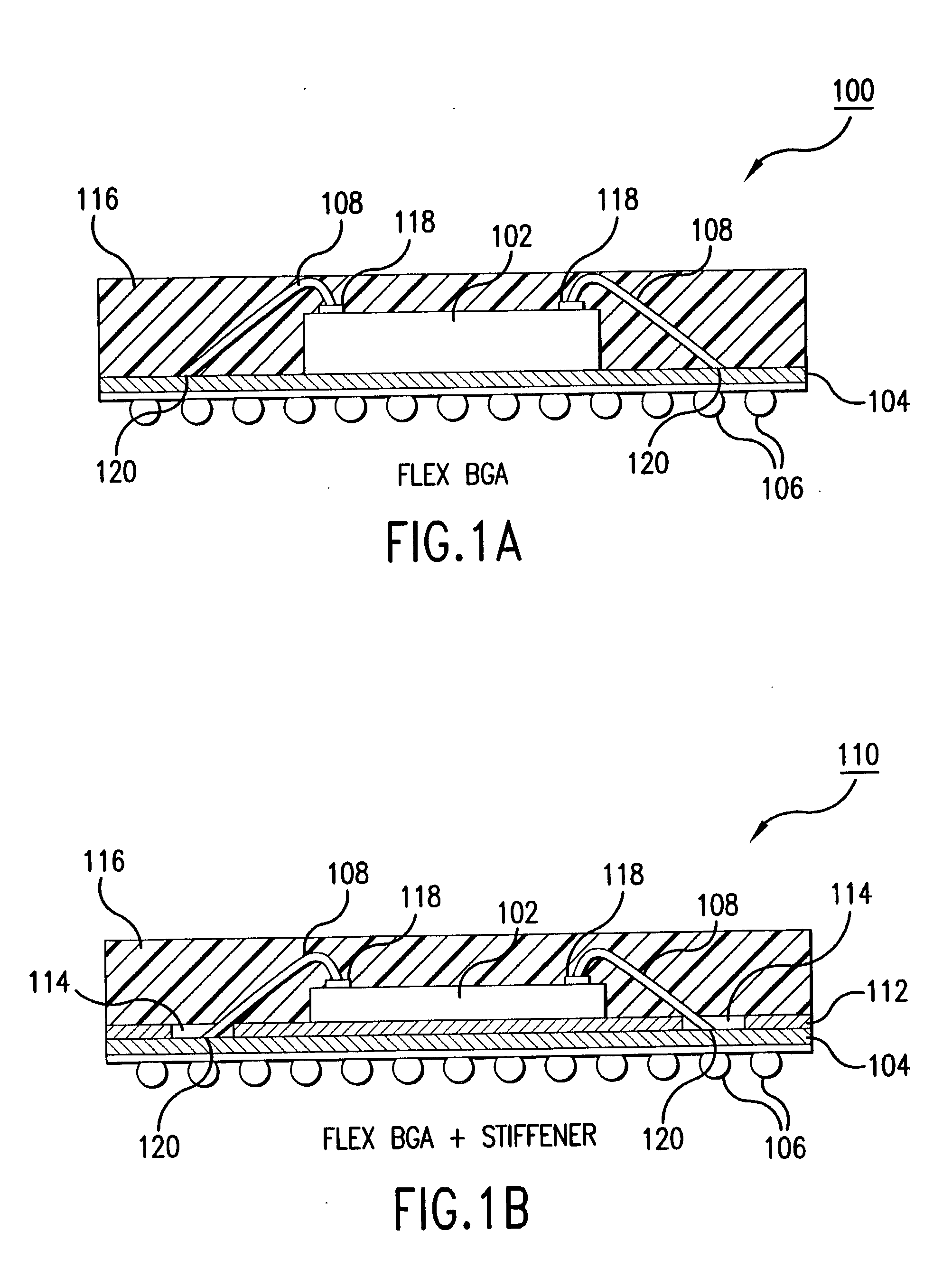

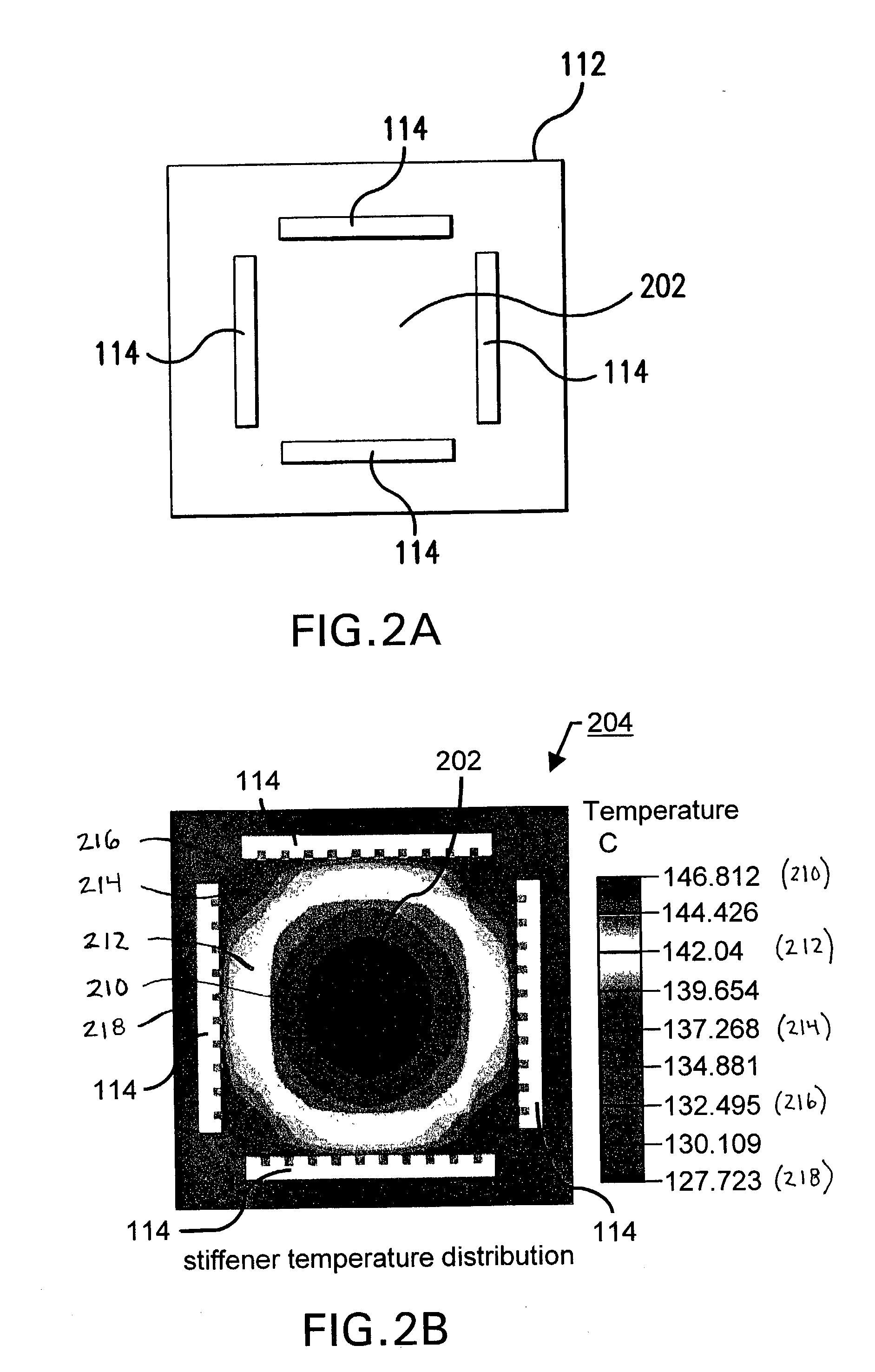

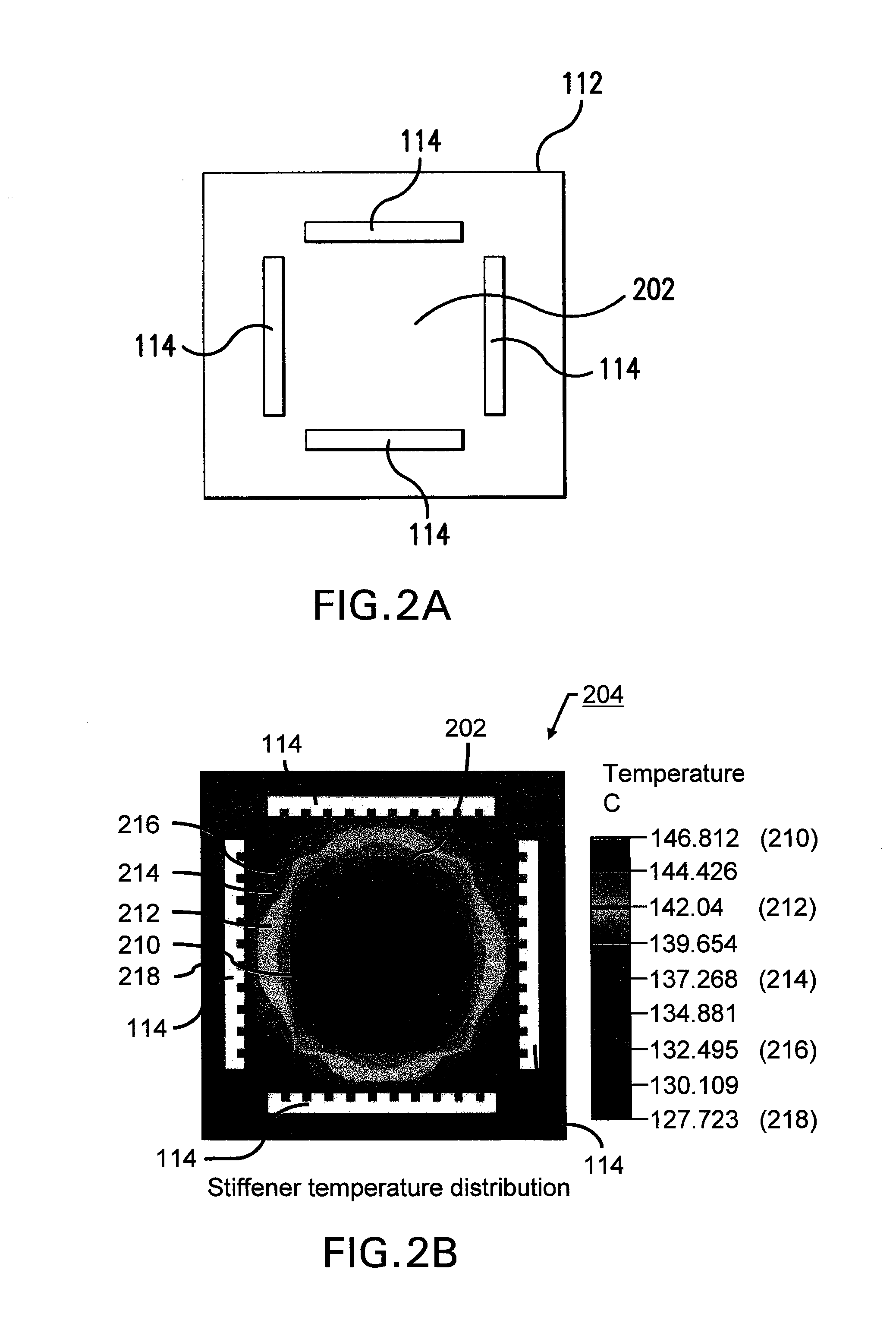

Thermal improvement for hotspots on dies in integrated circuit packages

ActiveUS20070290322A1Semiconductor/solid-state device testing/measurementSemiconductor/solid-state device detailsContact padEngineering

Methods and apparatuses for improved integrated circuit (IC) packages are described herein. In an aspect, an IC device package includes an IC die having a contact pad, where the contact pad is located on a hotspot of the IC die. The hotspot is thermally coupled to a thermal interconnect member. In an aspect, the package is encapsulated in a mold compound. In a further aspect, a heat spreader is attached to the mold compound, and is thermally coupled to the thermal interconnect member. In another aspect, a thermal interconnect member thermally is coupled between the heat spreader and the substrate.

Owner:AVAGO TECH INT SALES PTE LTD

Method for fabricating an IC interconnect system including an in-street integrated circuit wafer via

InactiveUS6910268B2Inexpensively formedSemiconductor/solid-state device detailsSolid-state devicesEngineeringConductive materials

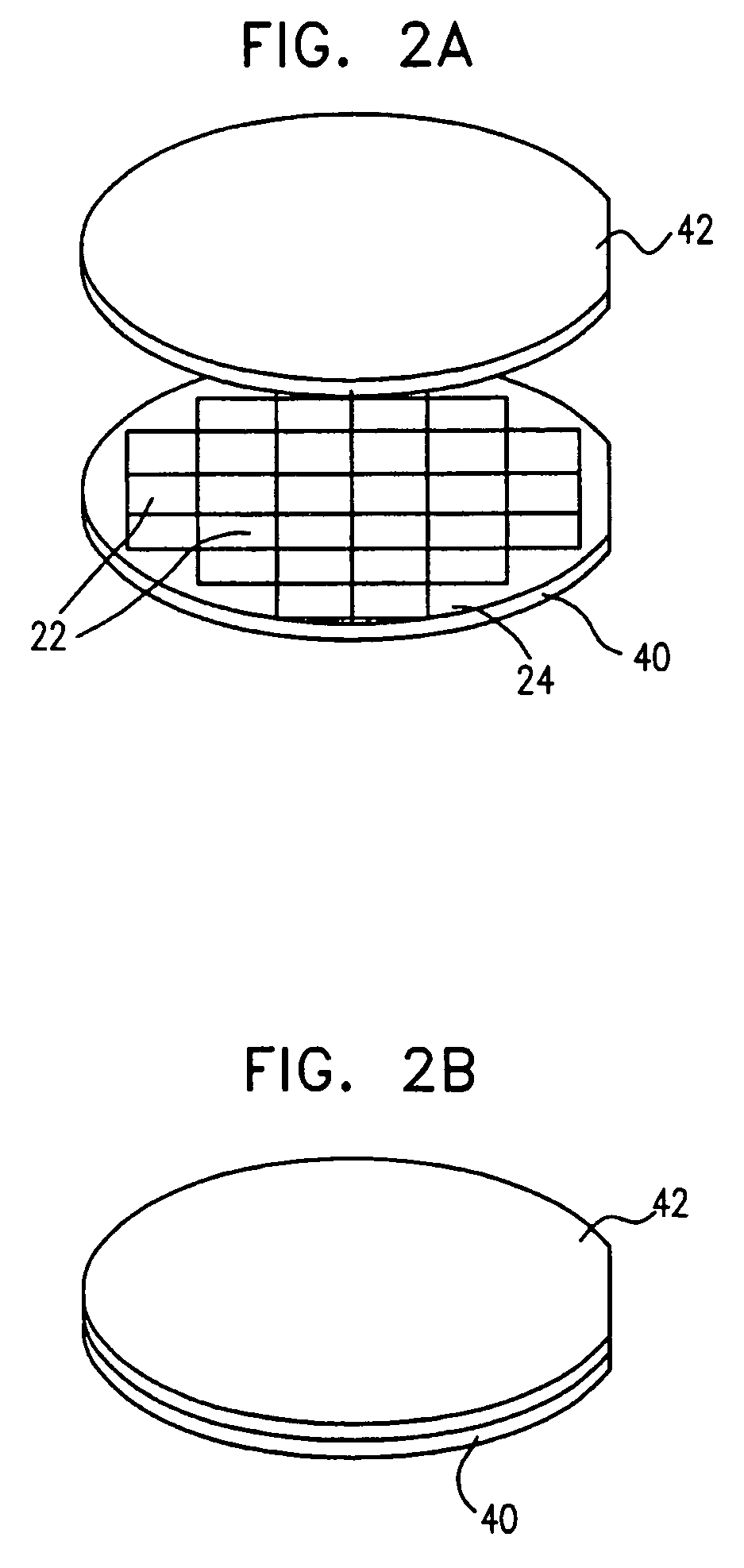

Vertical holes are created in streets separating individual integrated circuit (IC) dies formed on a semiconductor wafer, the holes spanning saw-lines along which the wafer is to be later cut to separate the IC die from one another to form individual IC chips. The holes are then filled with conductive material. After the wafer is cut along the saw-lines, portions of the conductive material on opposing sides of the saw-lines remain on peripheral edges of the IC chip to form signal paths between the upper and lower surfaces of the IC chips.

Owner:FORMFACTOR INC

Packaged integrated circuit devices with through-body conductive vias, and methods of making same

A device is disclosed which includes at least one integrated circuit die, at least a portion of which is positioned in a body of encapsulant material, and at least one conductive via extending through the body of encapsulant material.

Owner:MICRON TECH INC

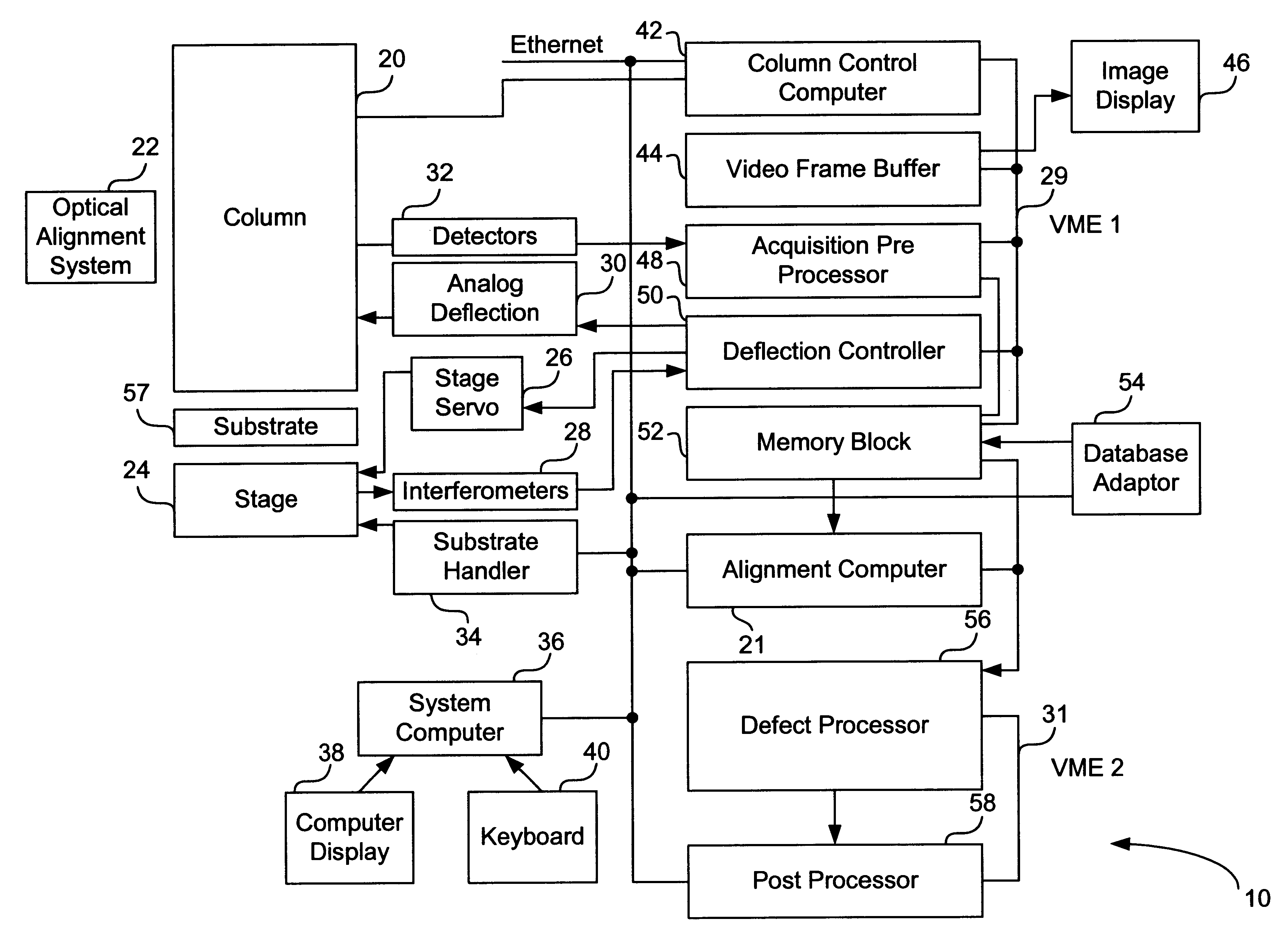

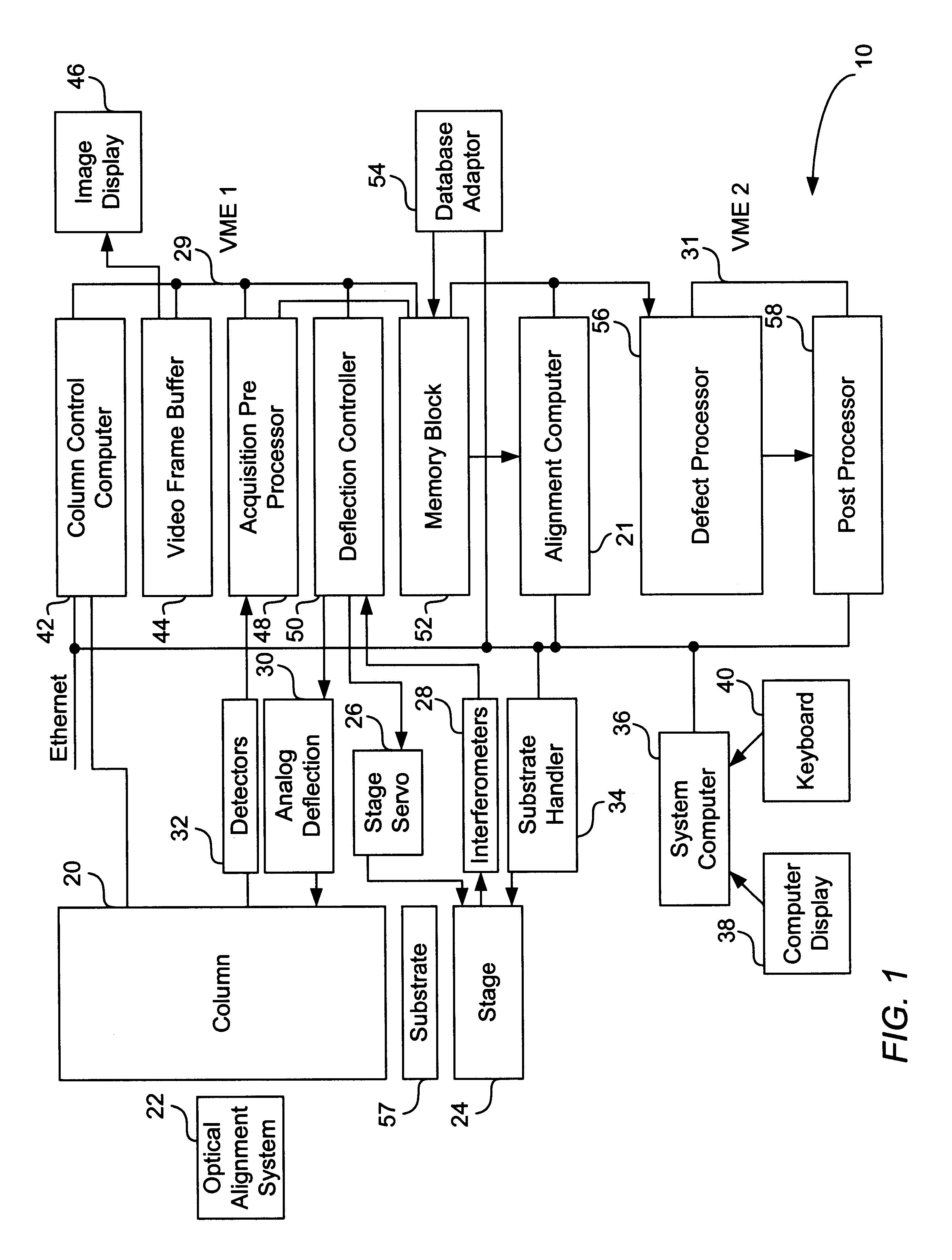

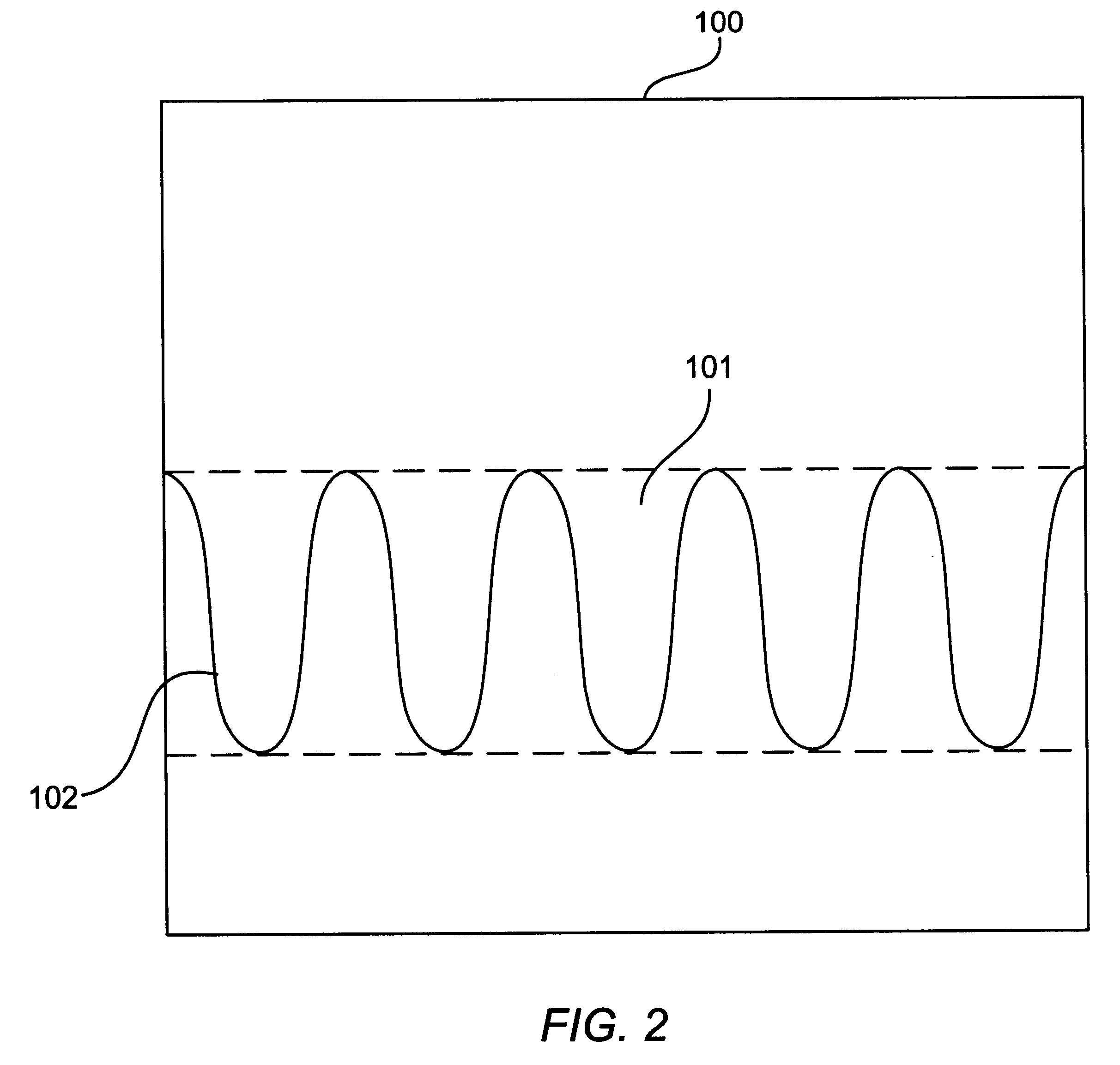

Continuous movement scans of test structures on semiconductor integrated circuits

InactiveUS6524873B1Reduce pressureSemiconductor/solid-state device testing/measurementElectric discharge tubesElectricityEngineering

Disclosed is, a method for detecting electrical defects on test structures of a semiconductor die. The semiconductor die includes a plurality of electrically-isolated test structures and a plurality of non-electrically-isolated test structures. Voltages are established for the plurality of electrically-isolated test structures. These voltages are different than the voltages of the plurality of non-electrically-isolated test structures. A region of the semiconductor die is continuously inspected in a first direction thereby obtaining voltage contrast data indicative of whether there are defective test structures. The voltage contrast data is analyzed to determine whether there are one or more defective test structures.

Owner:KLA CORP

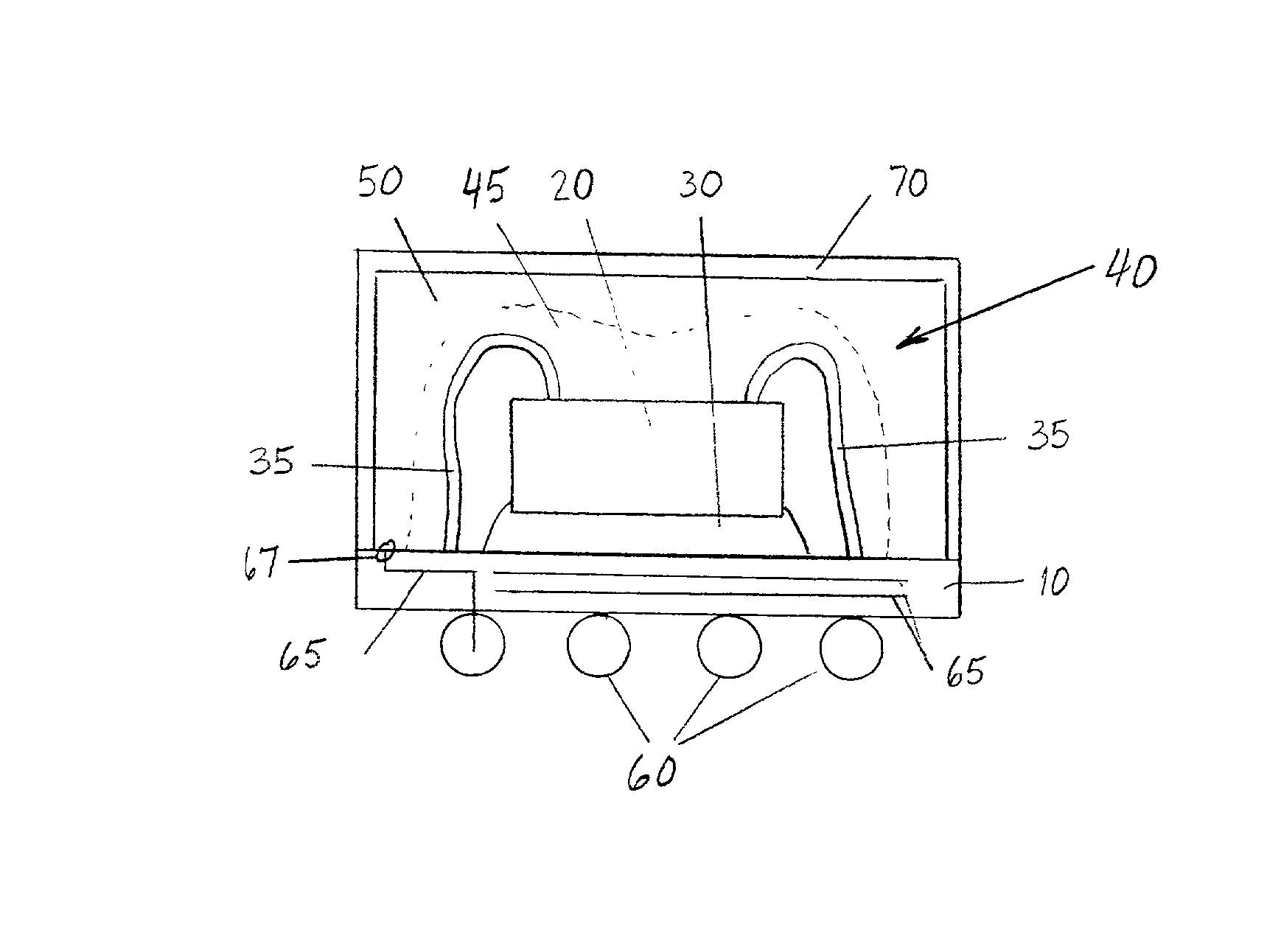

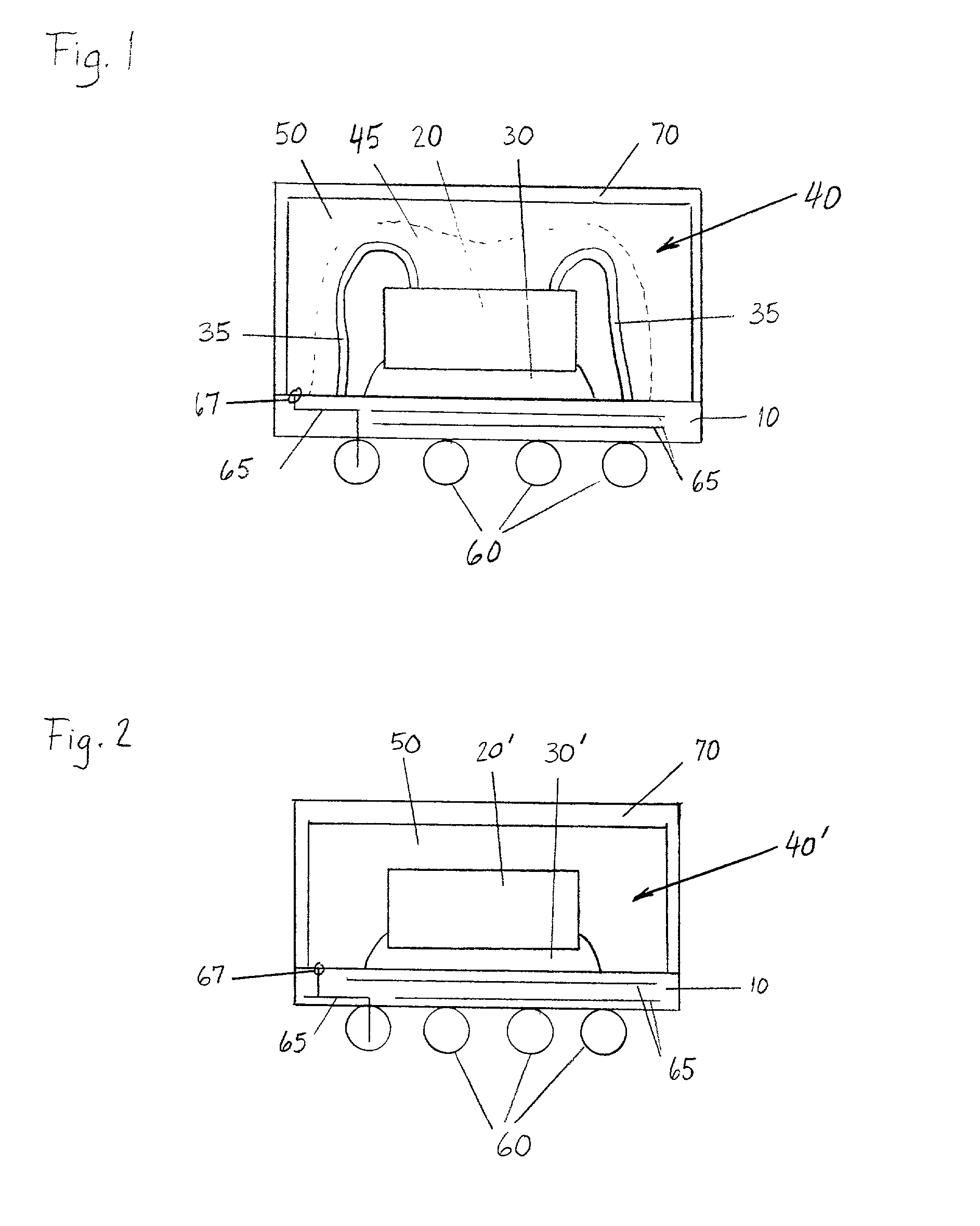

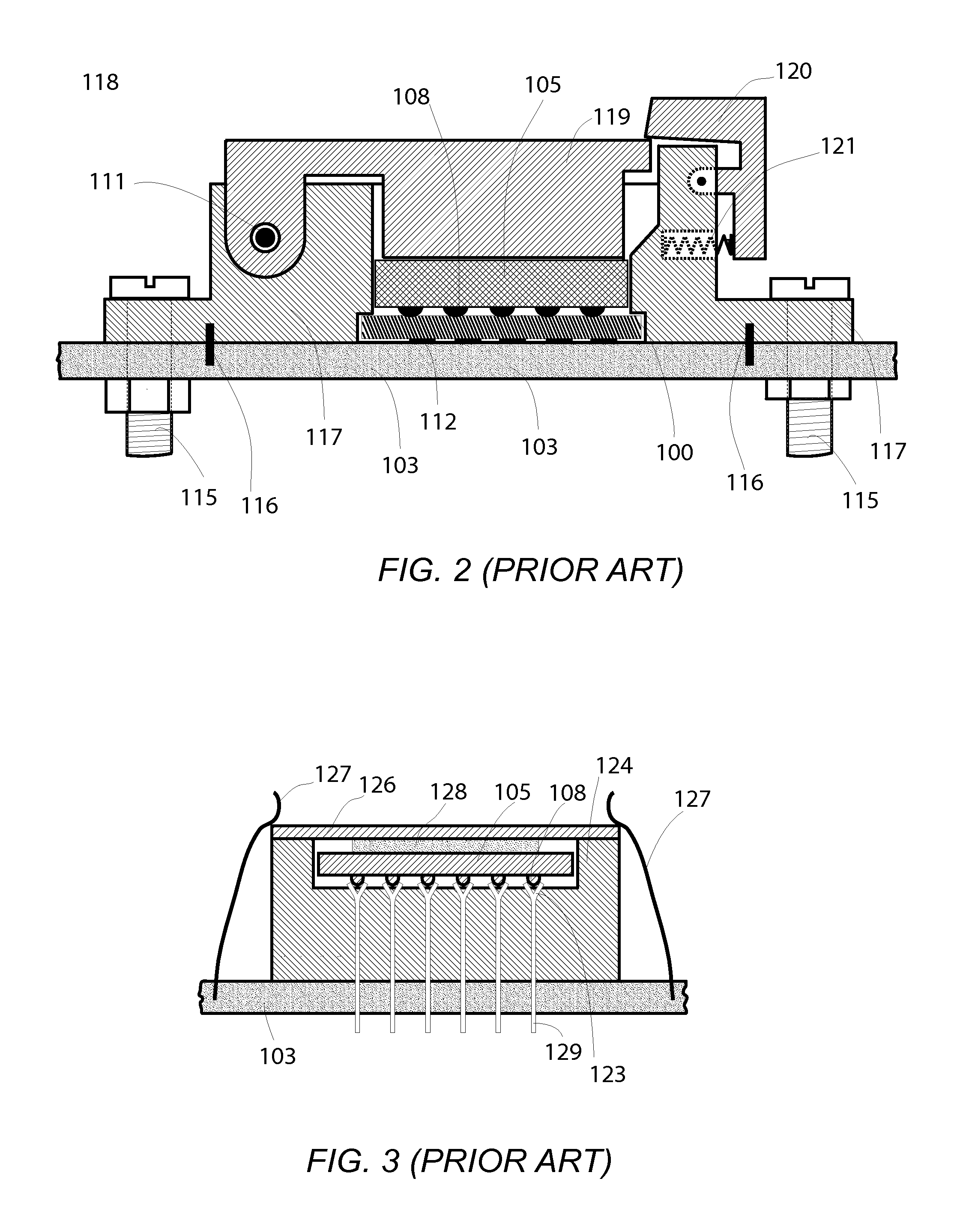

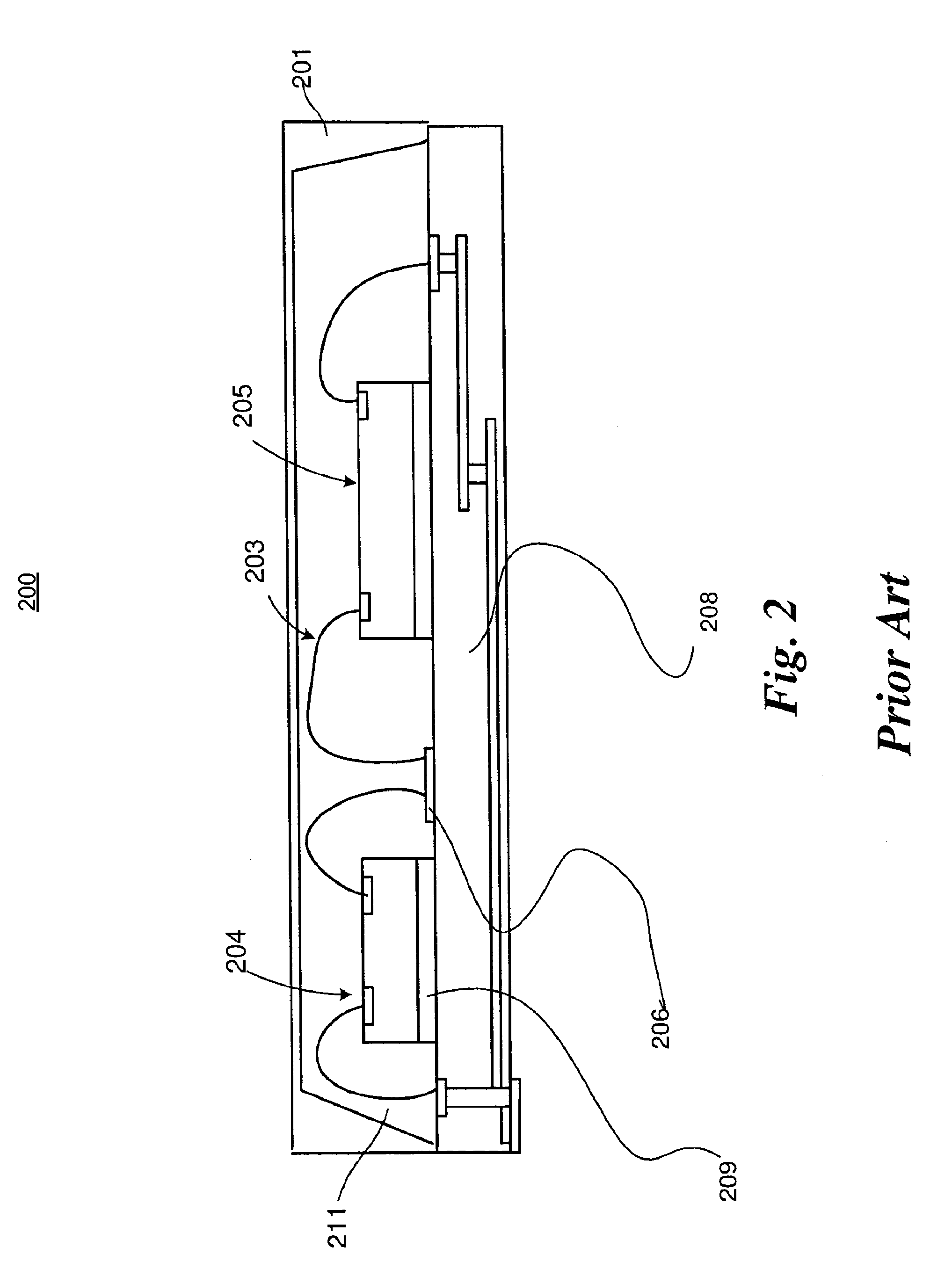

Low voltage drop and high thermal perfor mance ball grid array package

InactiveUS20030179549A1Optimized heat conduction pathImprove the environmentSemiconductor/solid-state device detailsSolid-state devicesContact padIntegrated circuit

An apparatus and method for a low voltage drop and thermally enhanced integrated circuit (IC) package are described. A substantially planar substrate having a plurality of contact pads on a first surface is electrically connected through the substrate to a plurality of solder ball pads on a second surface of the substrate. An IC die having a first surface is mounted to the first surface of the substrate. The IC die has a plurality of I / O pads electrically connected to the plurality of contact pads on the first surface of the substrate. A heat sink assembly is coupled to a second surface of the IC die and to a first contact pad on the first surface of the substrate to provide a thermal path from the IC die to the first surface of the substrate. The heat sink assembly can also provide an electrical path from the IC die to the first surface of the substrate. The heat sink assembly may have one or two heat sink elements to provide thermal and / or electrical connectivity between the IC die and the substrate.

Owner:AVAGO TECH INT SALES PTE LTD

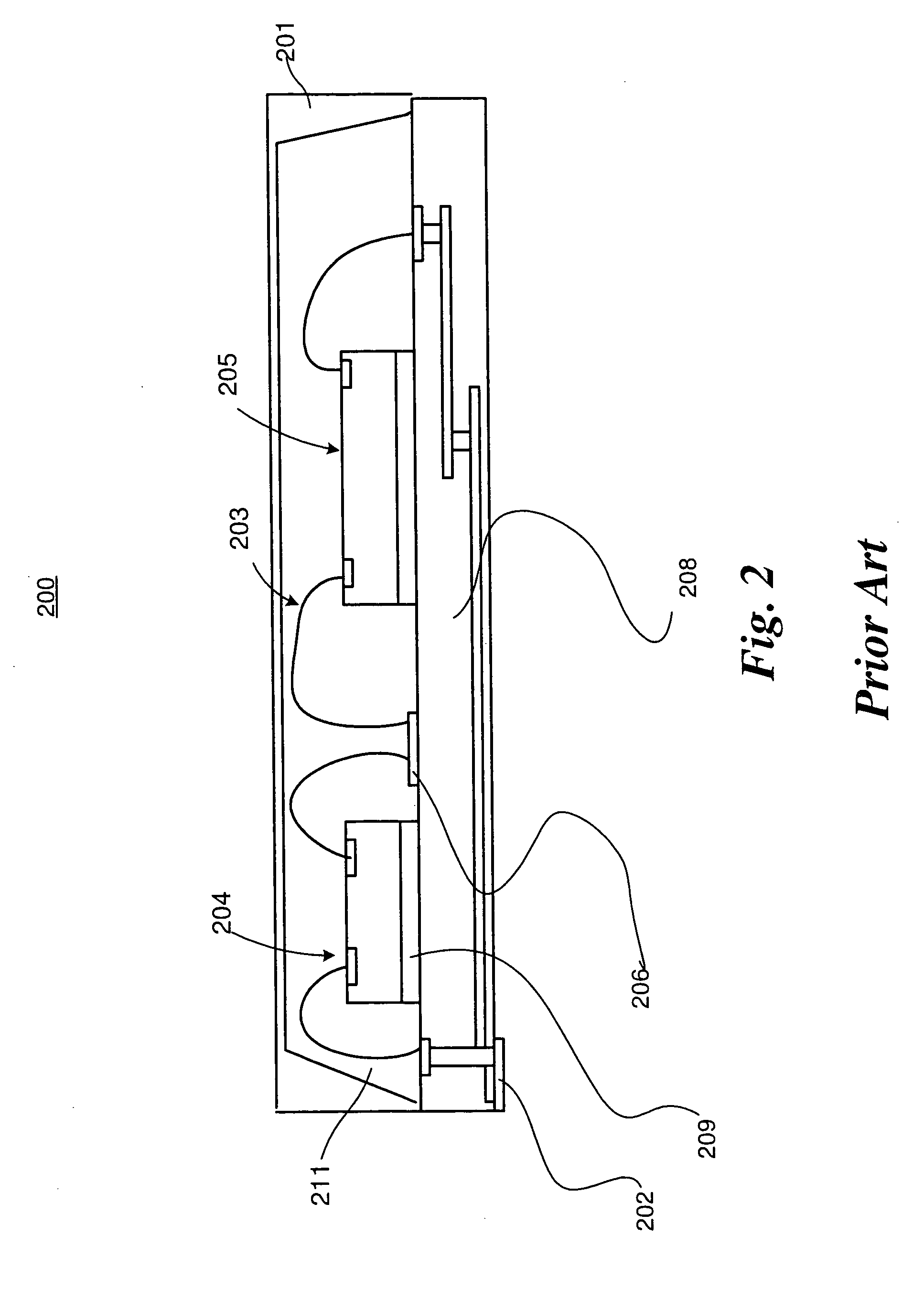

Assembly and method for constructing a multi-die integrated circuit

InactiveUS6404648B1Semiconductor/solid-state device detailsCircuit arrangements on support structuresDie (integrated circuit)Engineering

A multi-die integrated circuit (IC) assembly and method for constructing the same are disclosed. Briefly described, the IC assembly can be constructed with a semiconductor die, a layer of die-attach material, and a flip-chip die. The semiconductor die may contain circuit elements disposed across a top surface of the die. The flip-chip die may be oriented such that circuit elements are disposed across a bottom surface of the flip-chip die. The die-attach material may contact and bond the non-circuit element surfaces of the semiconductor die an the flip-chip die (i.e., the bottom surface of the semiconductor die and the top surface of the flip-chip die). This configuration permits the close arrangements of input / output circuit drivers along the entire perimeter of each of the dies. A method for constructing the multi-die IC assembly is also presented. The method can be broadly summarized by the following steps: arranging a semiconductor die such that circuit components are found on the upper surface of the die; arranging a flip-chip such that circuit components are found on the lower surface of the flip-chip; and introducing a layer of die-attach material such that it contacts and bonds the lower surface of the semiconductor die and the upper surface of the flip-chip.

Owner:HEWLETT PACKARD DEV CO LP

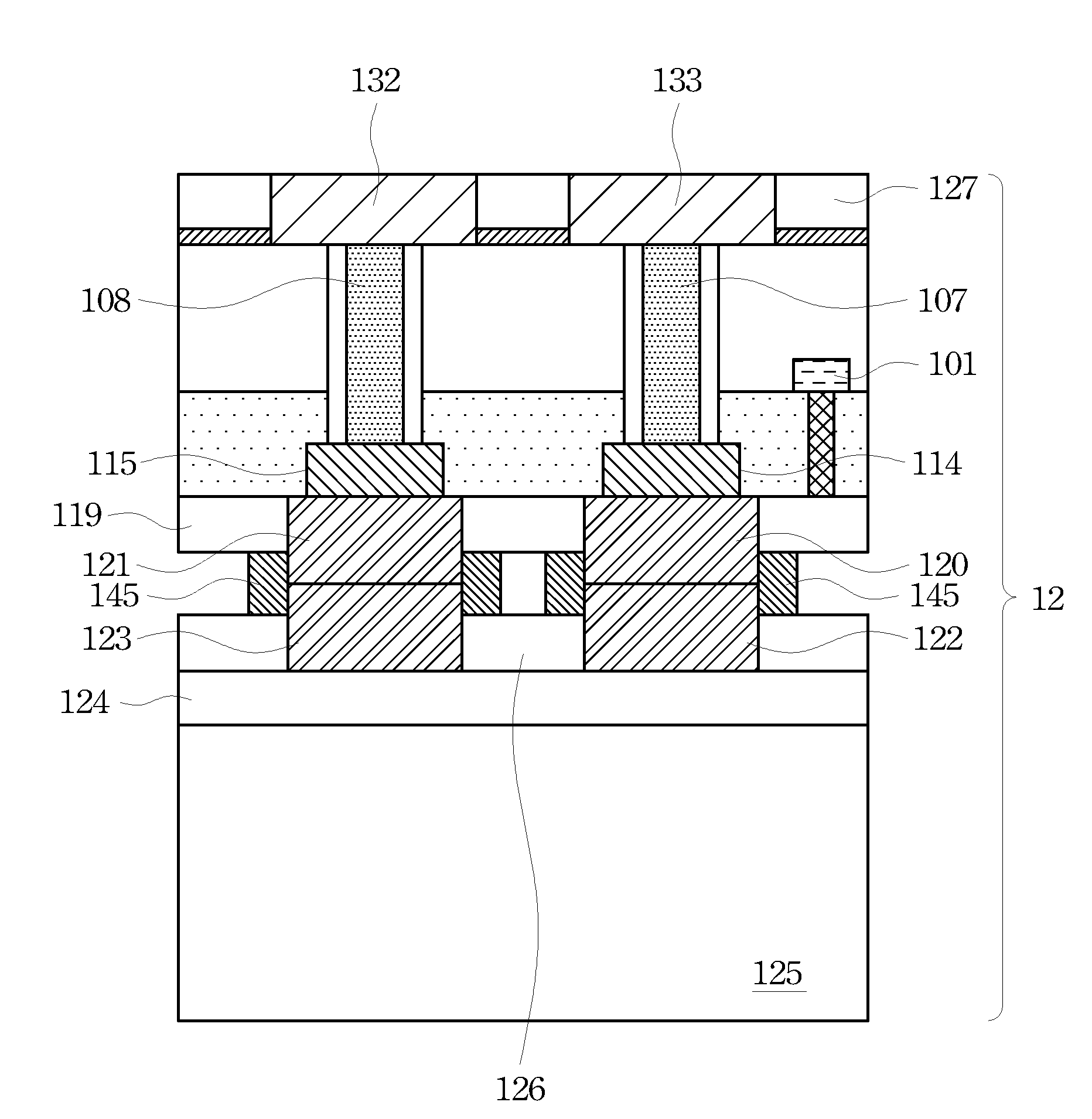

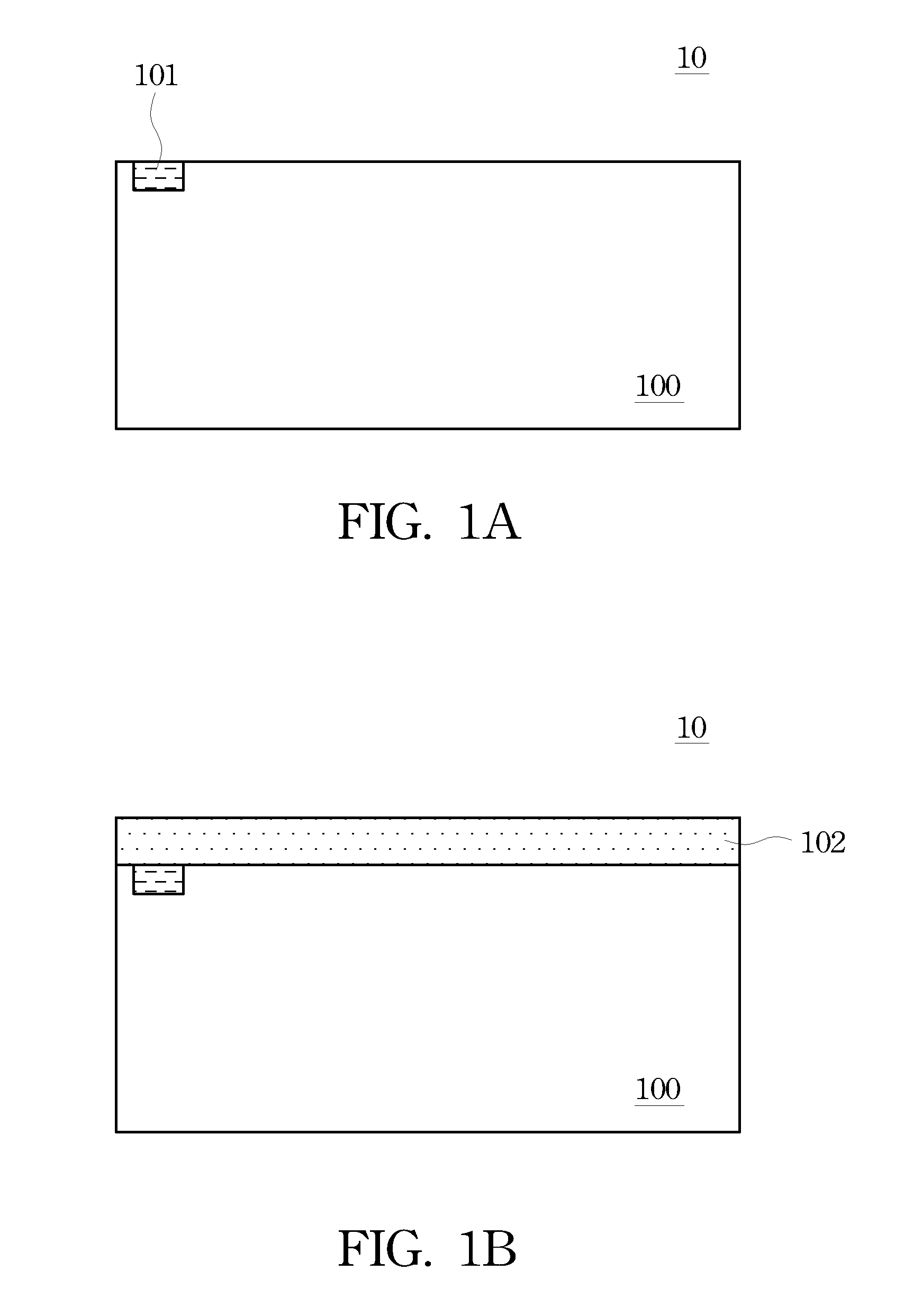

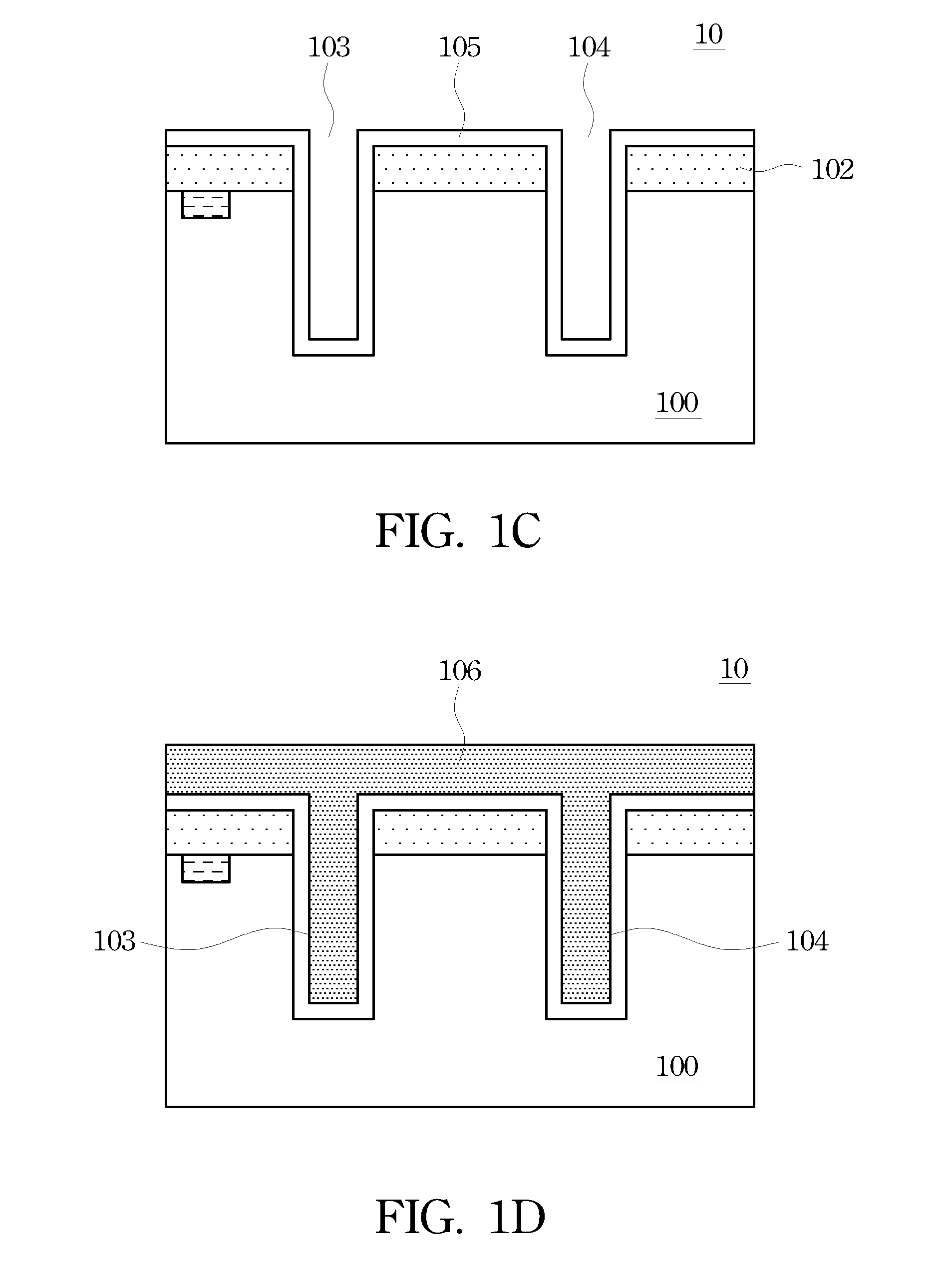

Integrated circuit package

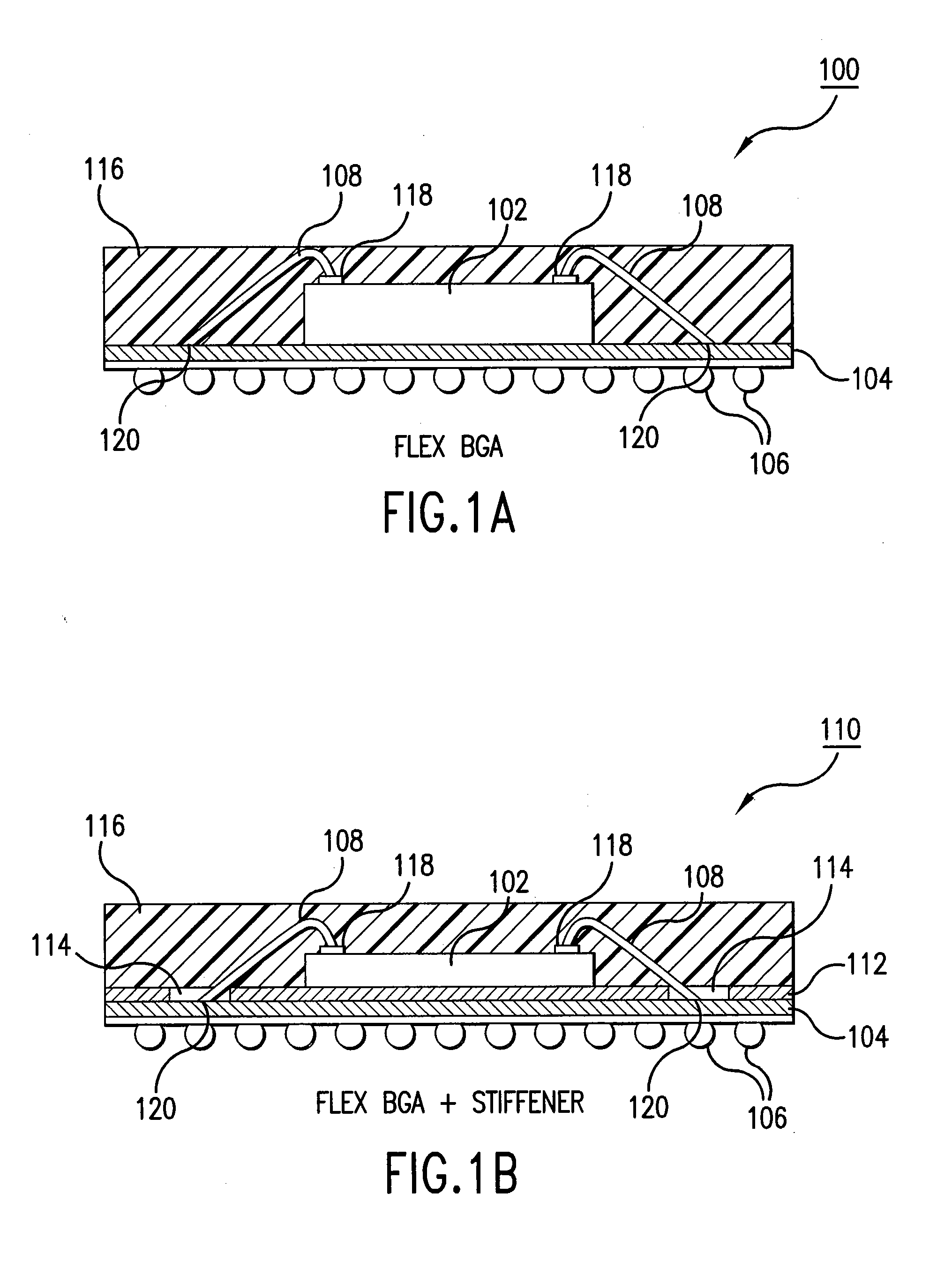

InactiveUS20050077613A1Semiconductor/solid-state device detailsSolid-state devicesElectrical connectionEngineering

In one aspect, the present invention features a method of manufacturing an integrated circuit package including providing a substrate having a first surface, a second surface opposite the first surface, a cavity through the substrate between the first and second surfaces and a conductive via extending through the substrate and electrically connecting the first surface of the substrate with the second surface of the substrate, applying a strip to the second surface of the substrate, mounting a semiconductor die on the strip, at least a portion of the semiconductor die being disposed inside the cavity, encapsulating in a molding material at least a portion of the first surface of the substrate, and removing the strip from the substrate. In another aspect, the invention features an integrated circuit package including a substrate having a first surface, a second surface opposite the first surface, a cavity through the substrate between the first and second surfaces and a conductive via extending through the substrate and electrically connecting the first surface of the substrate with the second surface of the substrate, a semiconductor die electrically coupled with the conductive via, at least a portion of the semiconductor die being disposed inside the cavity of the substrate, an encapsulant material encapsulating a portion of the semiconductor die such that at least a portion of a surface of the semiconductor die is exposed.

Owner:ASAT CO LTD

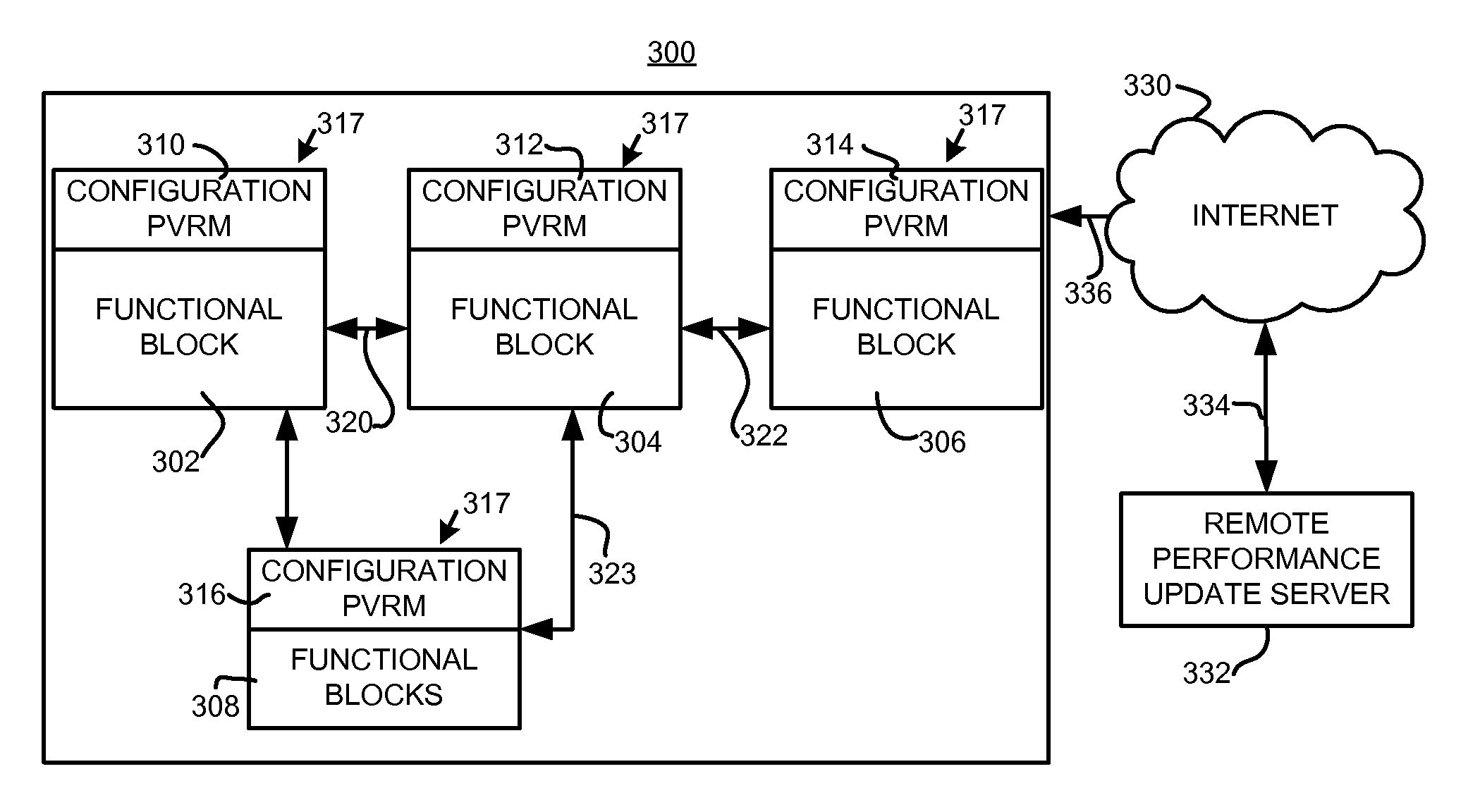

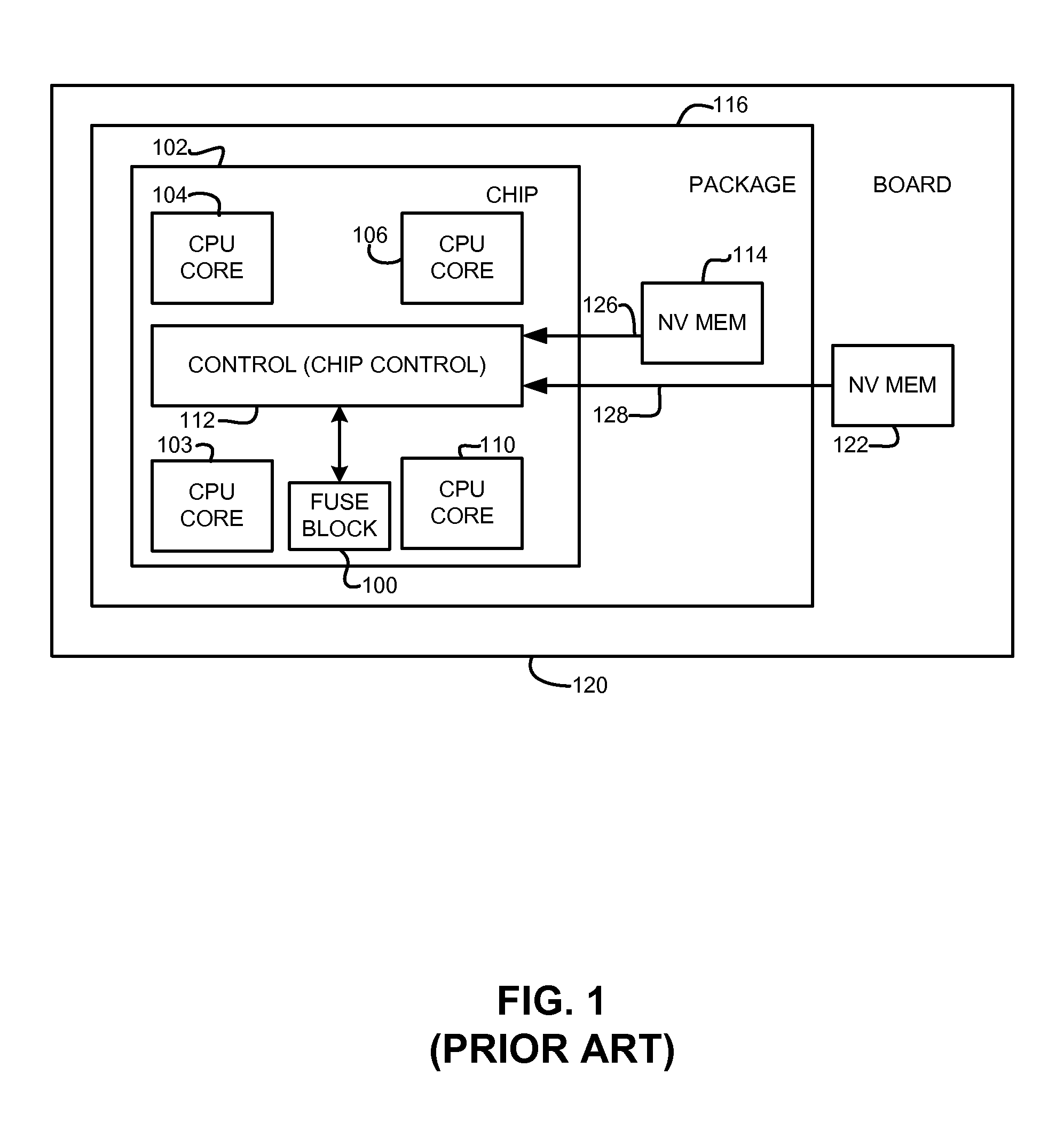

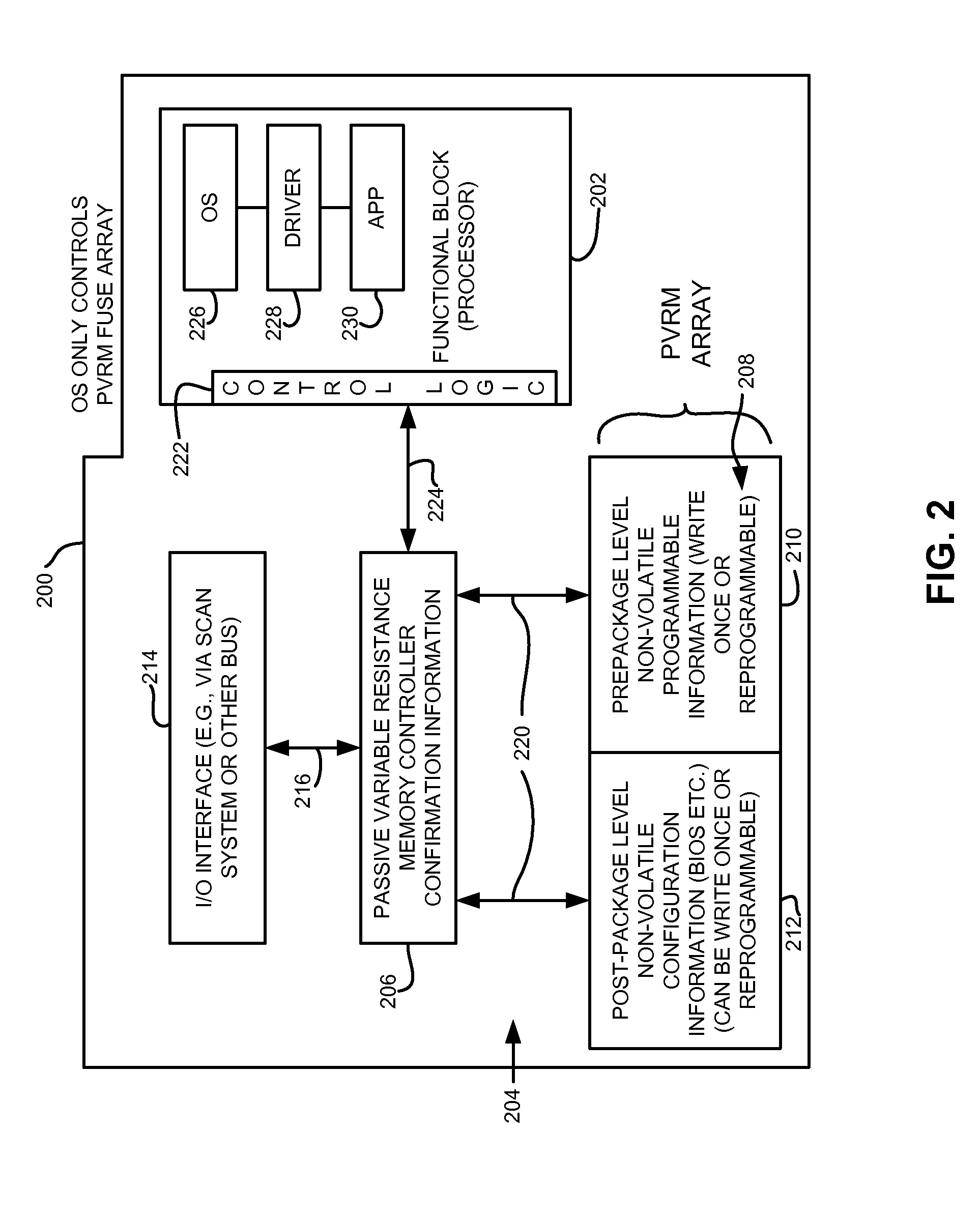

Integrated circuit with on-die distributed programmable passive variable resistance fuse array and method of making same

InactiveUS20130070514A1Solid-state devicesSemiconductor/solid-state device manufacturingElectrical resistance and conductanceEngineering

An integrated circuit employs a plurality of functional blocks, such as but not limited to, processors (e.g., cores), and an on-die distributed programmable passive variable resistance memory array configured to provide configuration information for each of the plurality of functional blocks. A corresponding sub-portion of the on-die distributed programmable passive variable resistance memory array is fabricated in layers above each respective plurality of functional blocks. The on-die distributed programmable passive variable resistance memory array is used as either non-volatile prepackage configuration information store, or a non-volatile post-package configuration information store that may allow dynamic changing of hardware configuration of the functional blocks both during normal operation and prior to die packaging. A method for making the same is also disclosed.

Owner:ADVANCED MICRO DEVICES INC

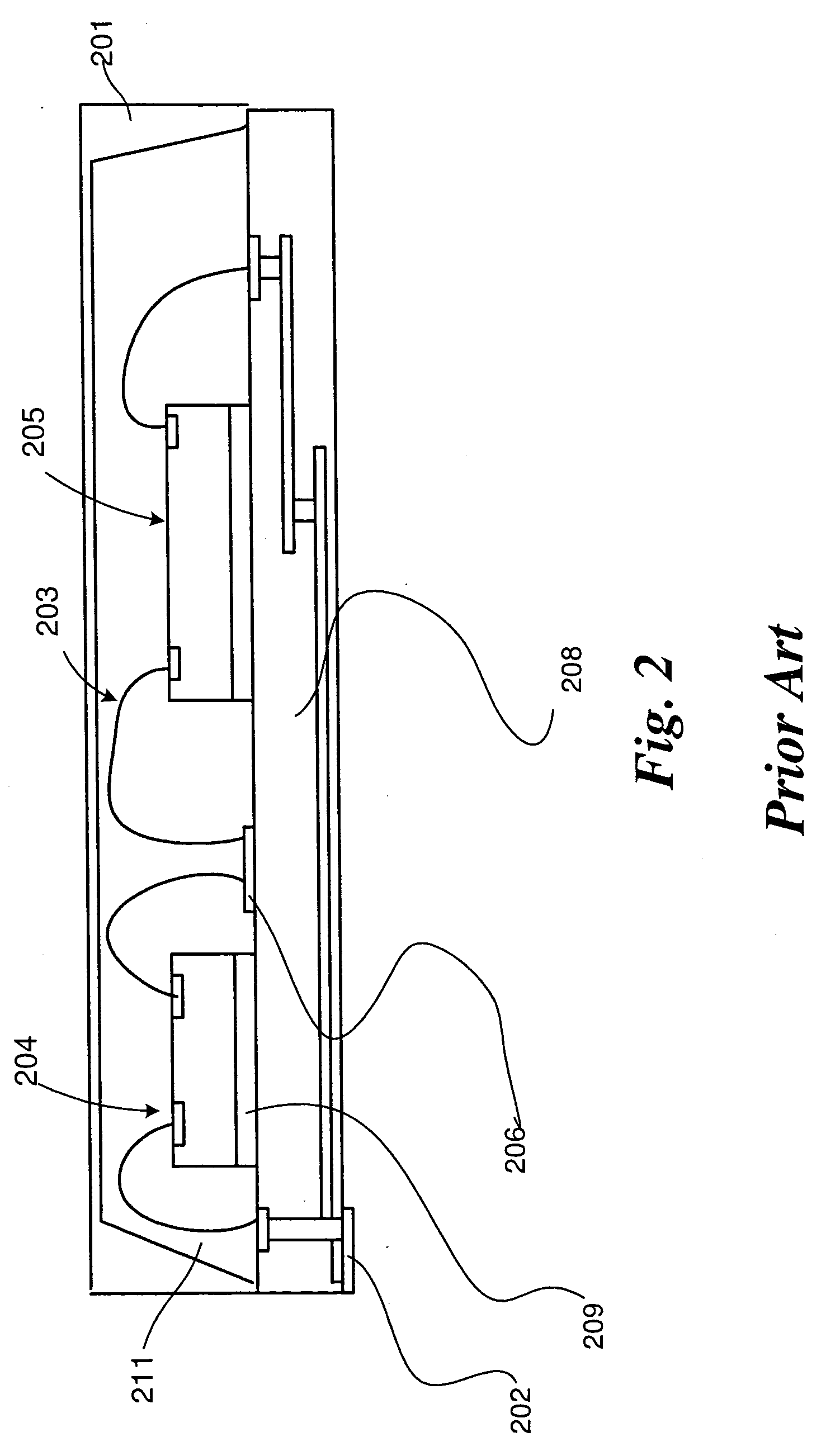

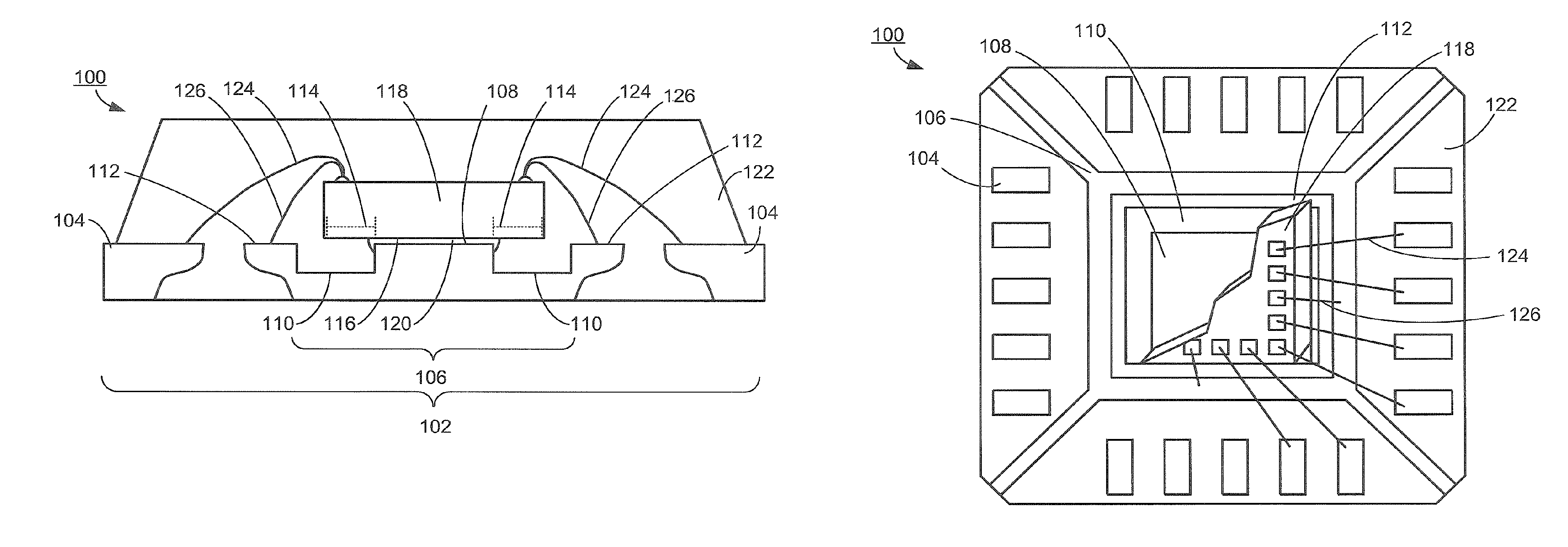

Methods and apparatus for packaging integrated circuit devices

InactiveUS7265440B2Semiconductor/solid-state device detailsSolid-state devicesEdge surfaceHemt circuits

An integrally packaged integrated circuit device including an integrated circuit die including a crystalline substrate having first and second generally planar surfaces and edge surfaces and an active surface formed on the first generally planar surface, at least one chip scale packaging layer formed over the active surface and at least one electrical contact formed over the at least one chip scale packaging layer, the at least one electrical contact being connected to circuitry on the active surface by at least one pad formed on the first generally planar surface.

Owner:TESSERA TECH HUNGARY KFT +1

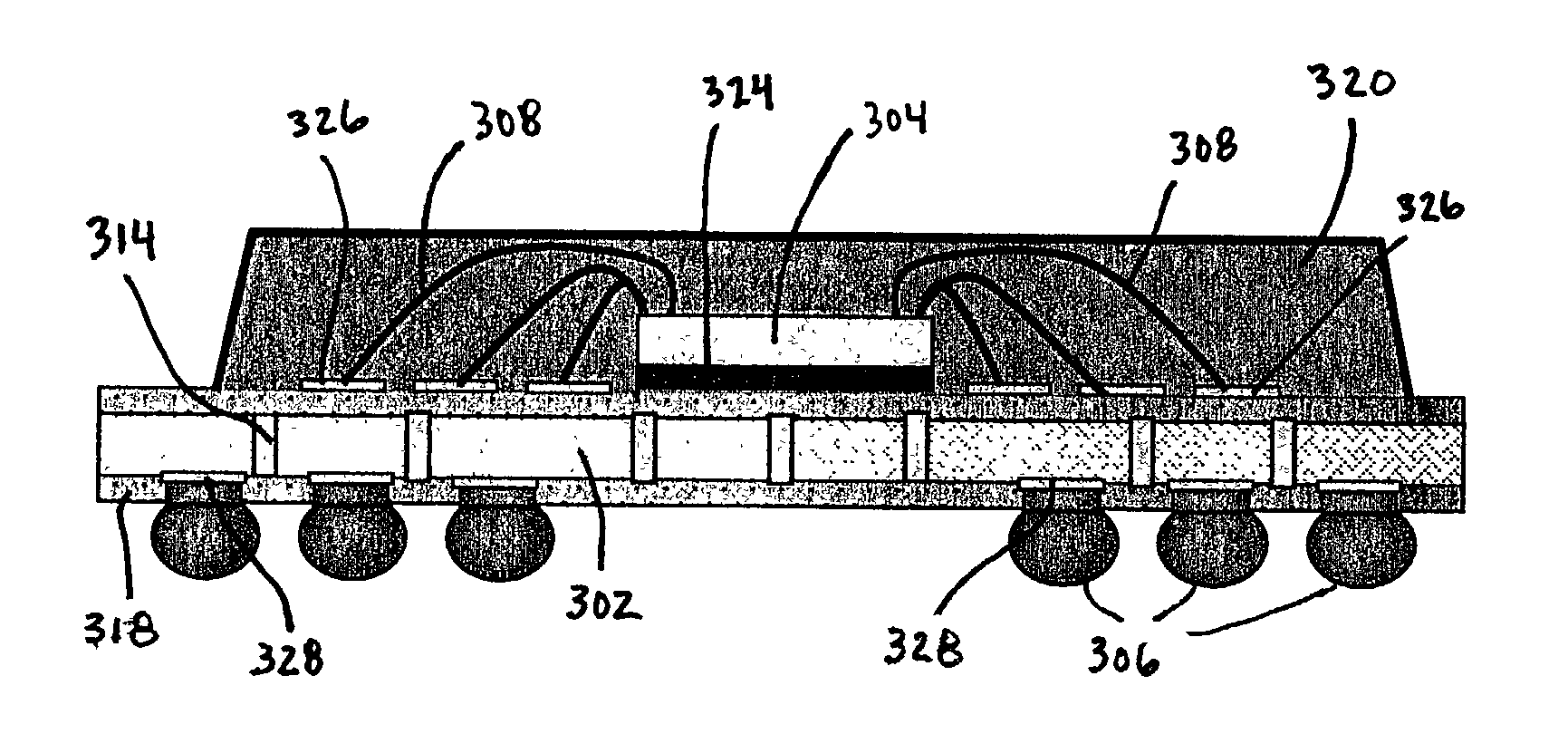

Low Voltage Drop and High Thermal Performance Ball Grid Array Package

InactiveUS20070108598A1Fast heat conductionEnhanced thermal and electrical connectionSemiconductor/solid-state device detailsSolid-state devicesContact padLow voltage

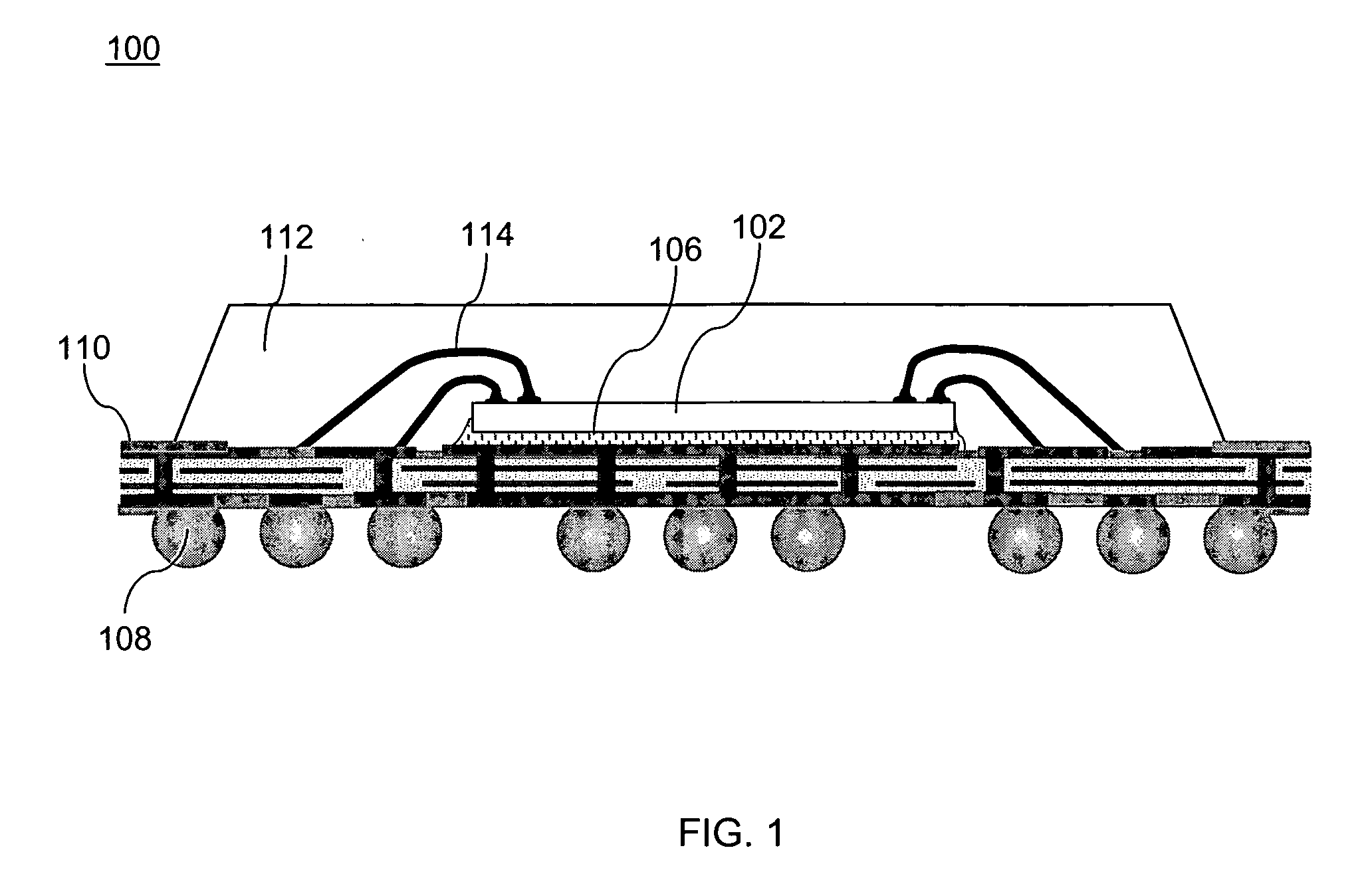

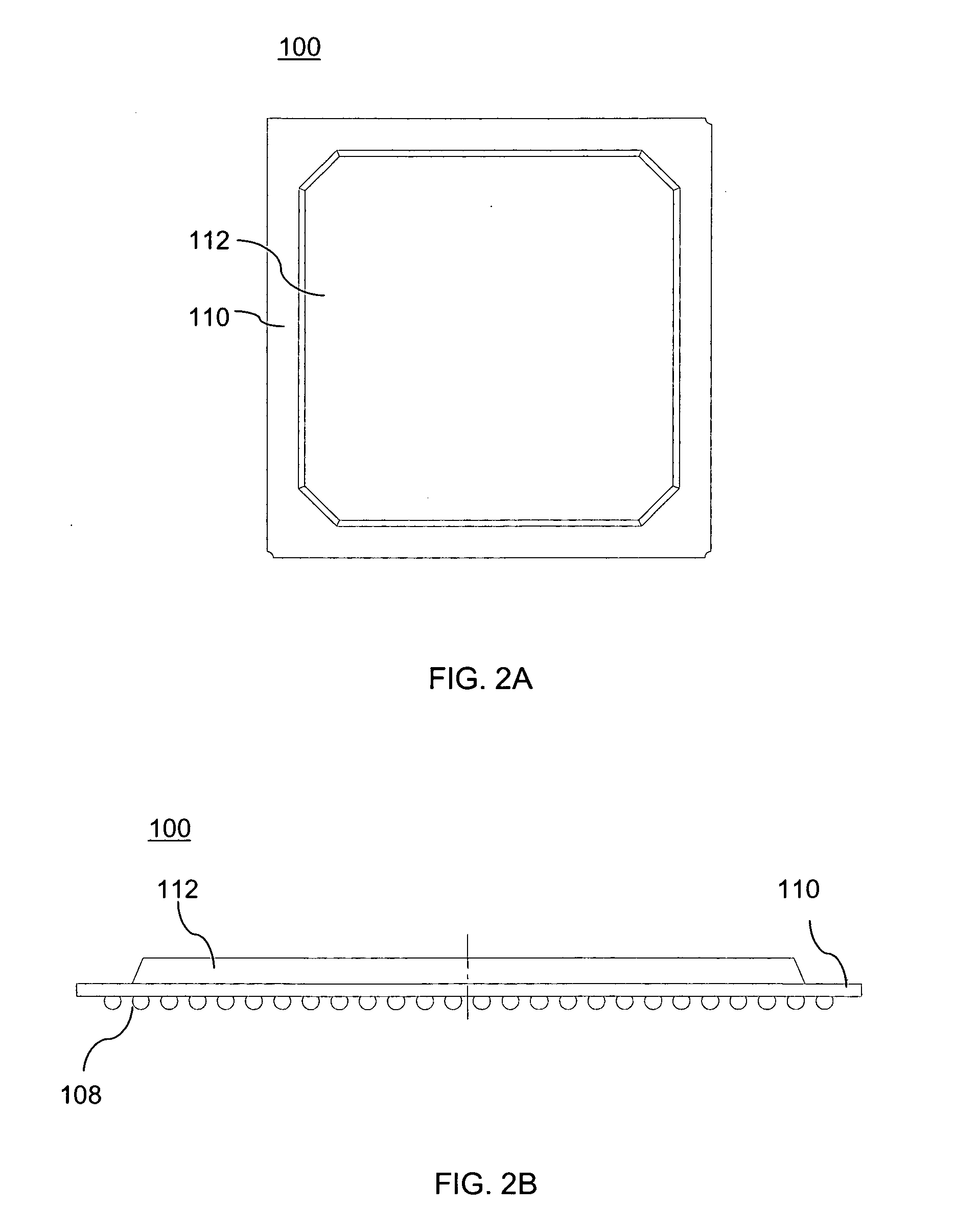

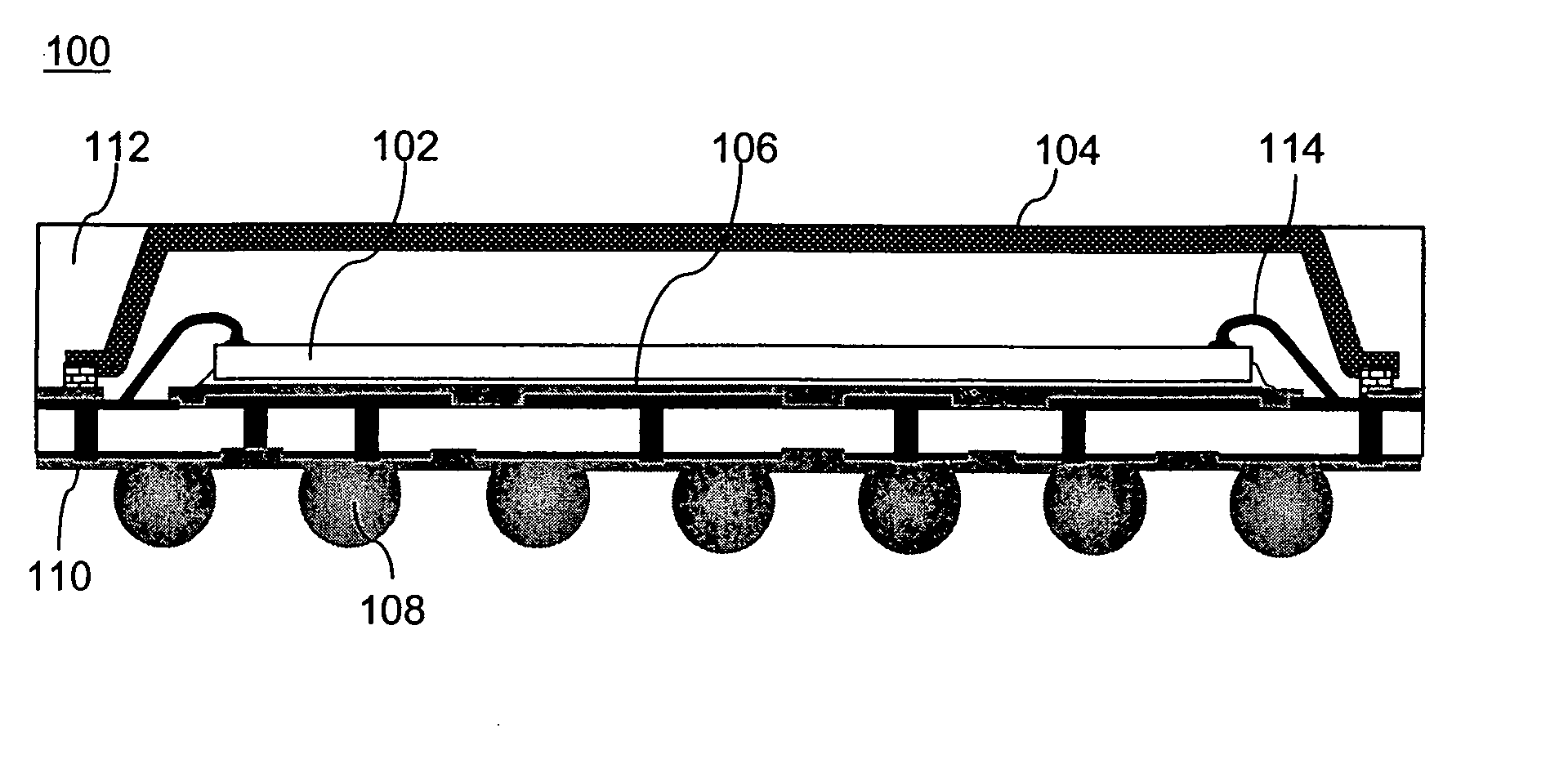

An apparatus and method for a low voltage drop and thermally enhanced integrated circuit (IC) package are described. A substantially planar substrate having a plurality of contact pads on a first surface is electrically connected through the substrate to a plurality of solder ball pads on a second surface of the substrate. An IC die having a first surface is mounted to the first surface of the substrate. The IC die has a plurality of I / O pads electrically connected to the plurality of contact pads on the first surface of the substrate. A heat sink assembly is coupled to a second surface of the IC die and to a first contact pad on the first surface of the substrate to provide a thermal path from the IC die to the first surface of the substrate. The heat sink assembly can also provide an electrical path from the IC die to the first surface of the substrate. The heat sink assembly may have one or two heat sink elements to provide thermal and / or electrical connectivity between the IC die and the substrate.

Owner:AVAGO TECH WIRELESS IP SINGAPORE PTE

Protection for Bonding Pads and Methods of Formation

ActiveUS20090224371A1Semiconductor/solid-state device detailsSolid-state devicesEngineeringWafer bonding

The formation of bonding pad protective layer over exposed bonding pad materials between stacked integrated circuit (IC) dies or wafers is described in preferred embodiments in which the bonding pad protective layer is formed in the integrated process of forming wafer bonding pads. The bonding pad protective layer prevents the exposed bonding pad materials from oxidation and corrosion in open-air or other harsh environments. By providing a bonding pad protective layer on exposed bonding pad materials, significant product reliability improvement is expected on ICs having a three-dimensional “stacked-die” configuration.

Owner:TAIWAN SEMICON MFG CO LTD

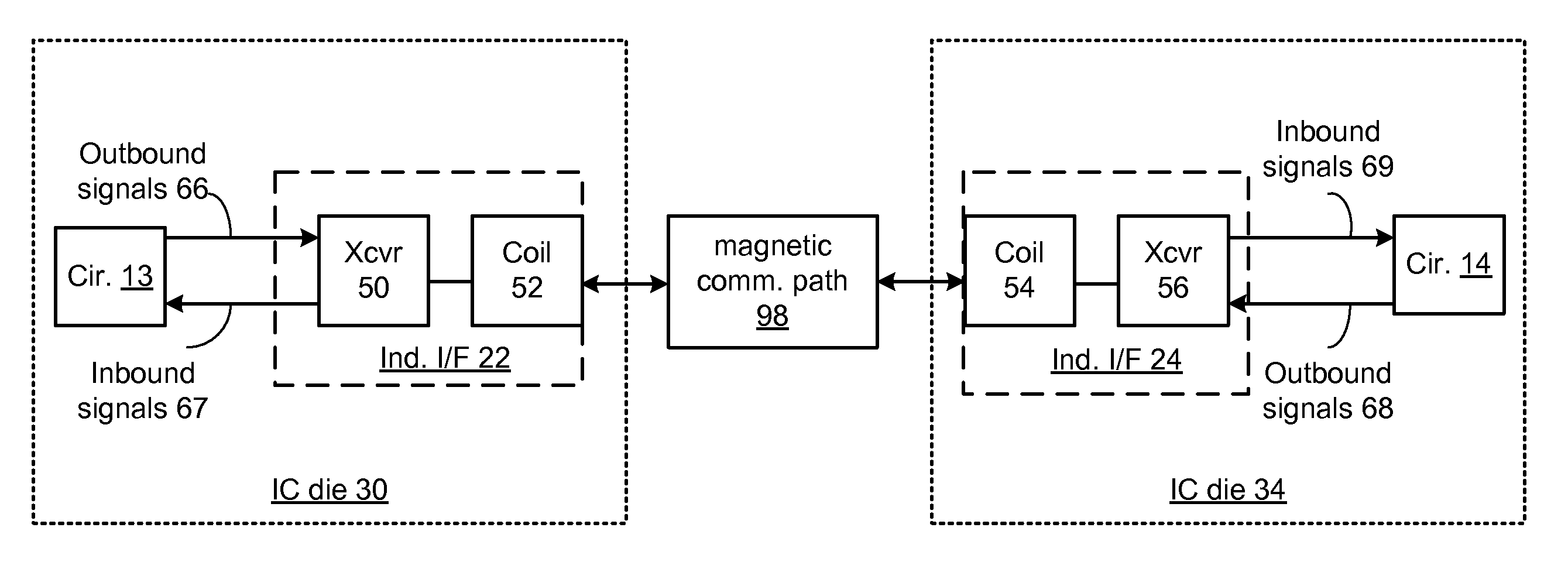

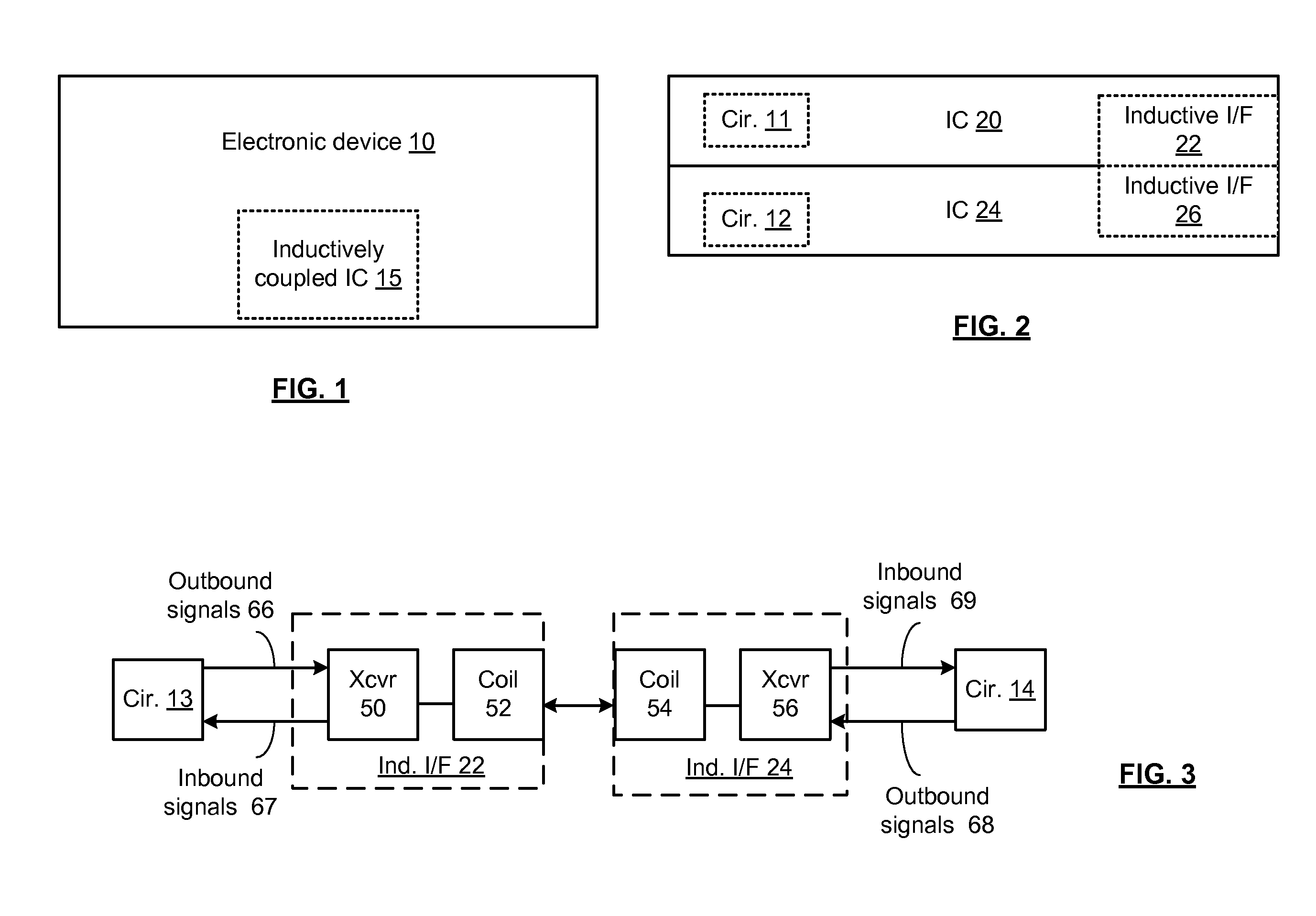

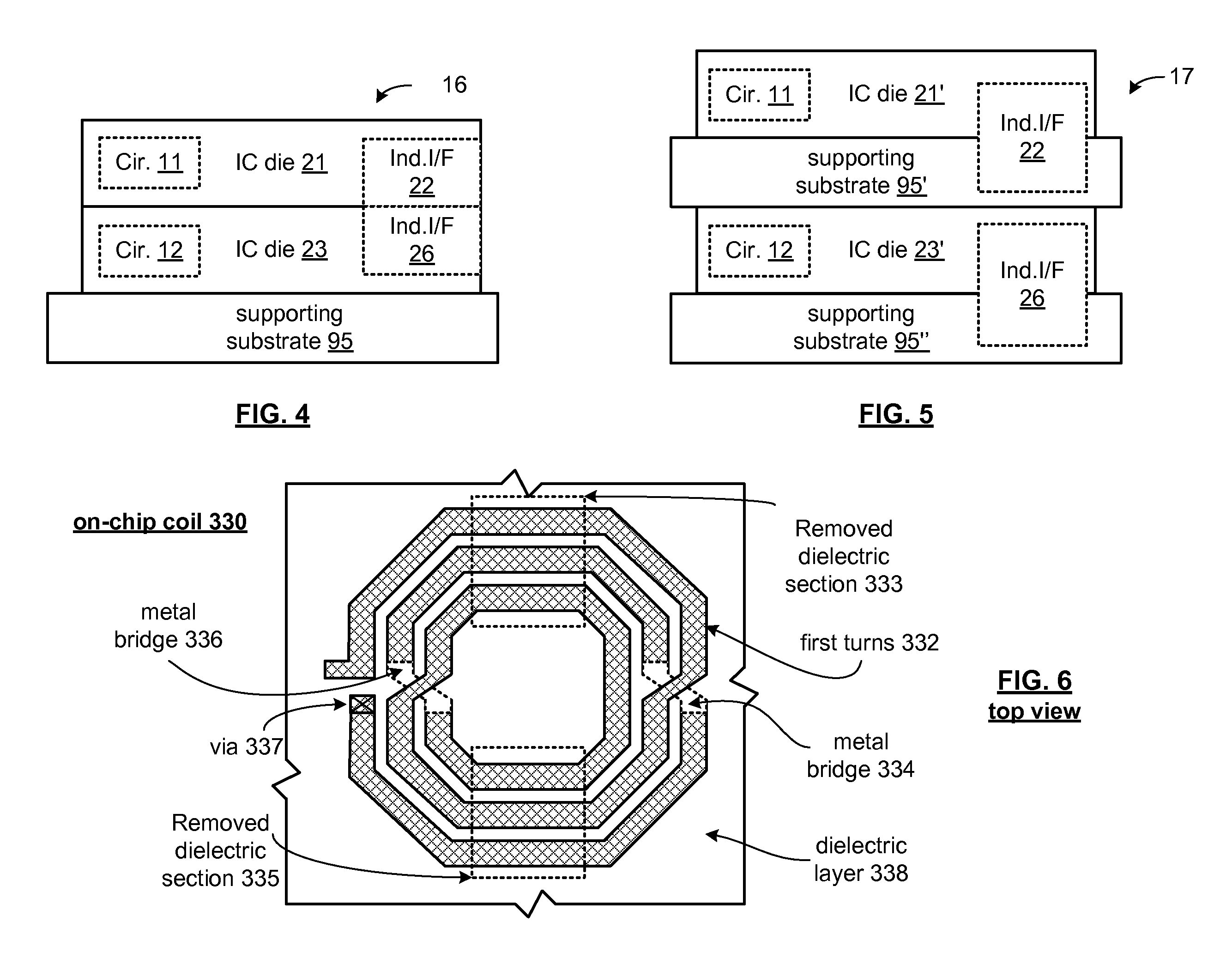

Inductively coupled integrated circuit with multiple access protocol and methods for use therewith

A circuit includes a plurality of integrated circuit dies having a corresponding plurality of circuits and a corresponding plurality of inductive interfaces. A substrate is coupled to support the plurality of integrated circuit dies, the substrate including a magnetic communication path aligned with the plurality of inductive interfaces, to magnetically communicate signals between the plurality of circuits via the plurality of inductive interfaces in accordance with a multi access protocol.

Owner:AVAGO TECH WIRELESS IP SINGAPORE PTE

Integrated circuit package with a heat dissipation device and a method of making the same

InactiveUS20080042261A1Dissipate generated heat spikeImprove electrical reliabilitySemiconductor/solid-state device detailsSolid-state devicesHeat conductingEngineering

Integrated circuit assembly including a die stack assembly having a heat dissipation device thermally coupled to a lateral of surface the die stack assembly. The die stack assembly includes a plurality integrated circuits placed on each other. In another embodiment a heat dissipation device comprising an encapsulant is thermally coupled to and surrounds a die stack assembly that includes a plurality of integrated circuits placed on each other. At least one heat conducting intermediate layer between integrated circuits is thermally coupled to the heat dissipation device.

Owner:POLARIS INNOVATIONS

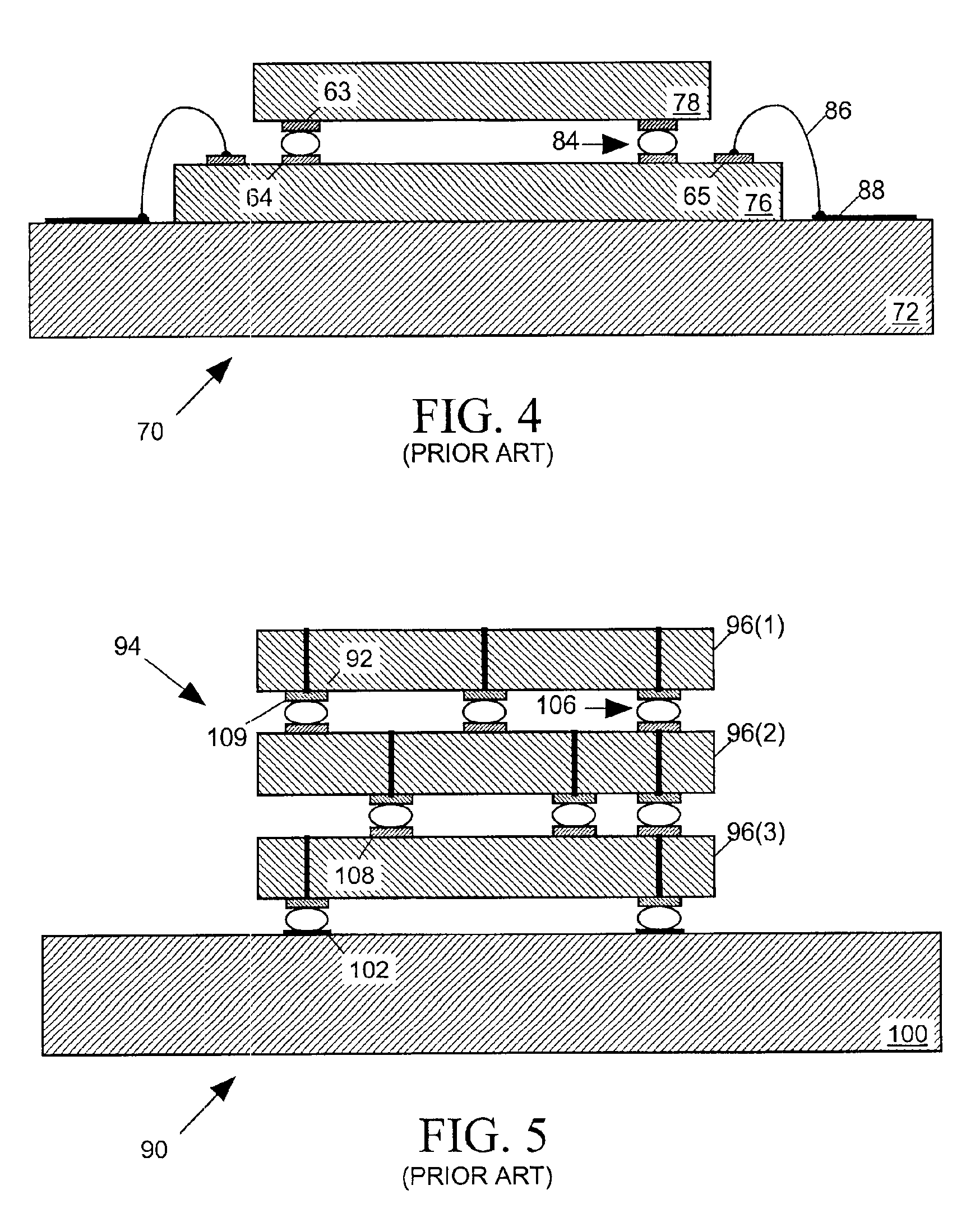

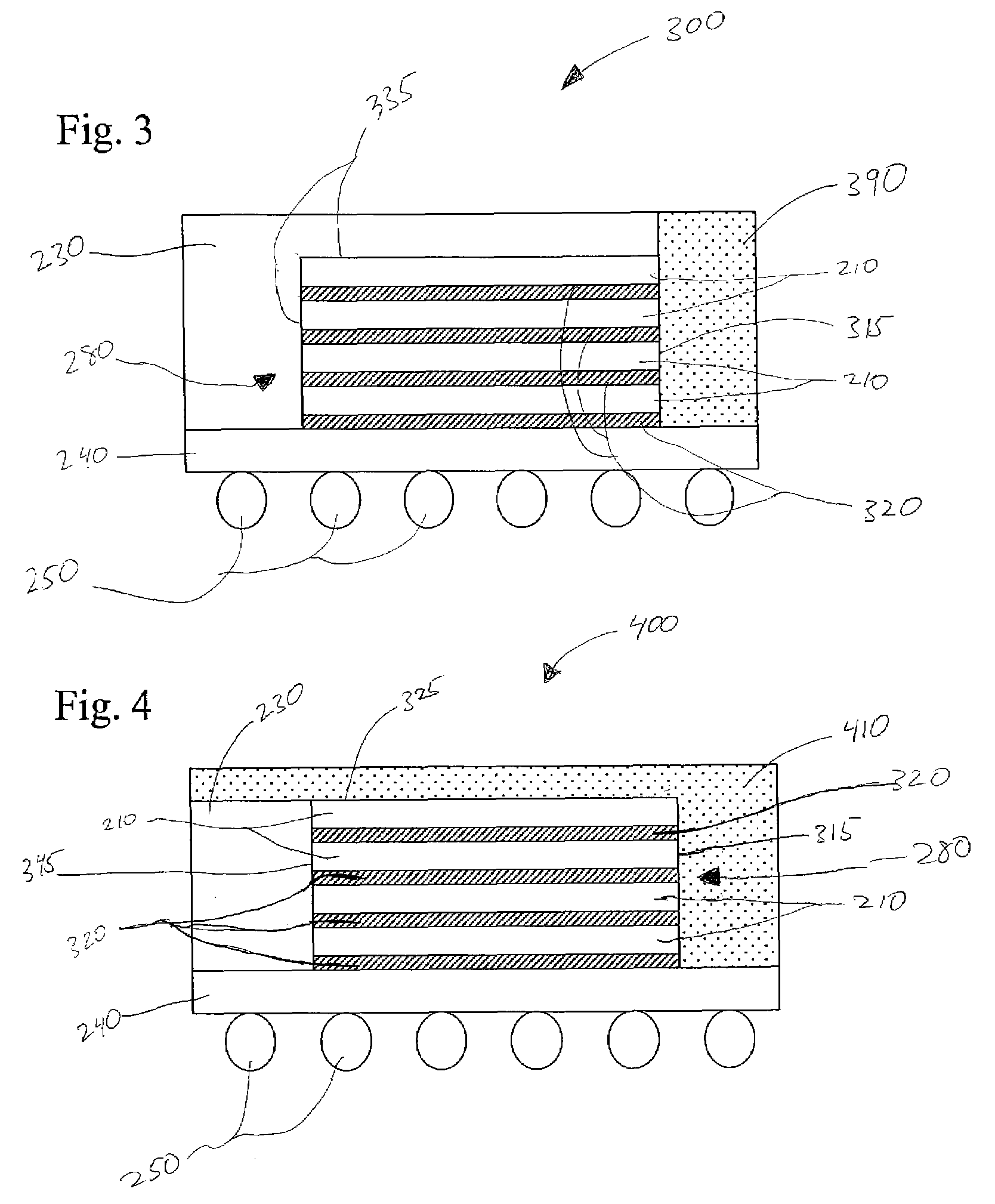

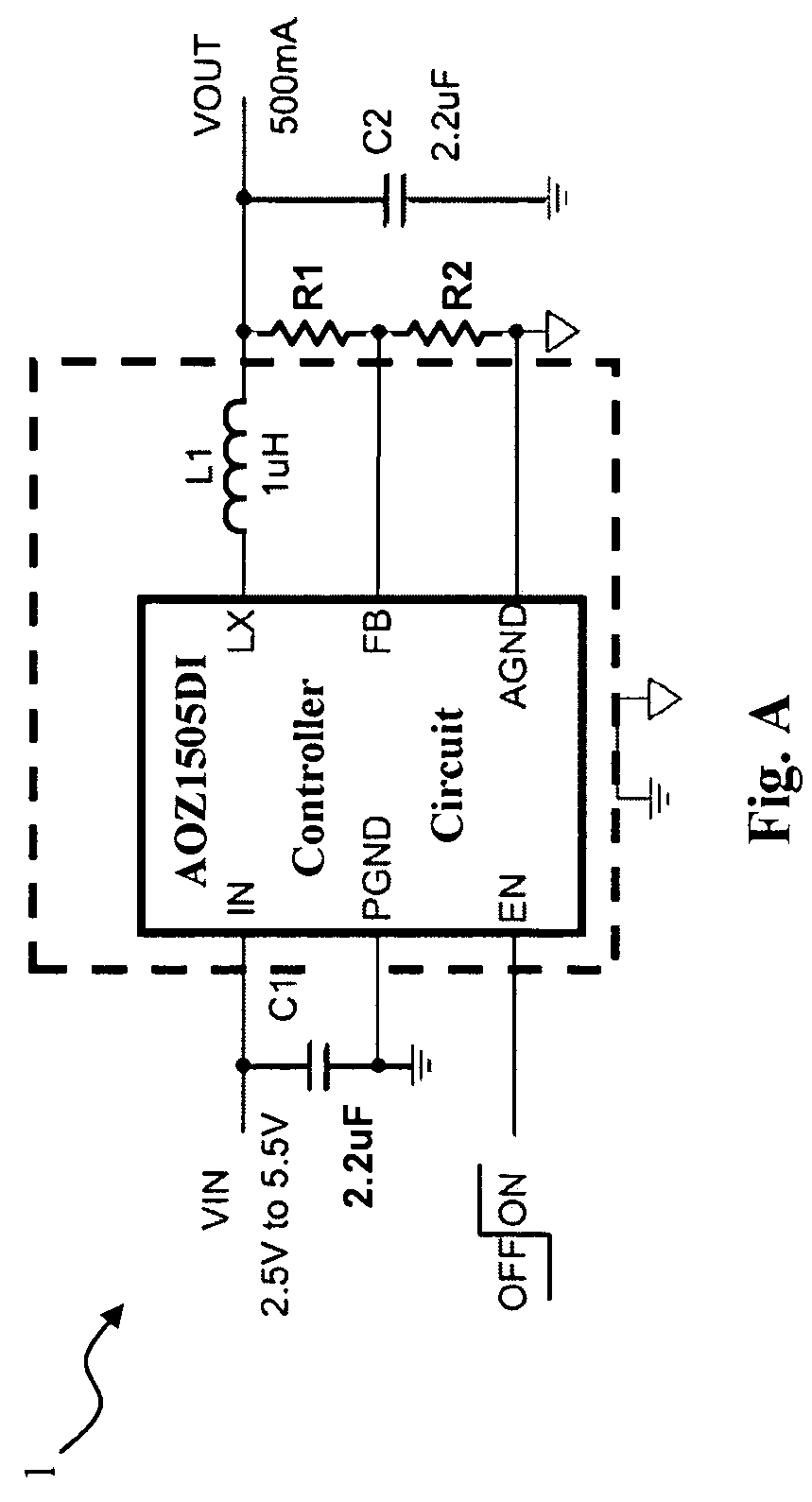

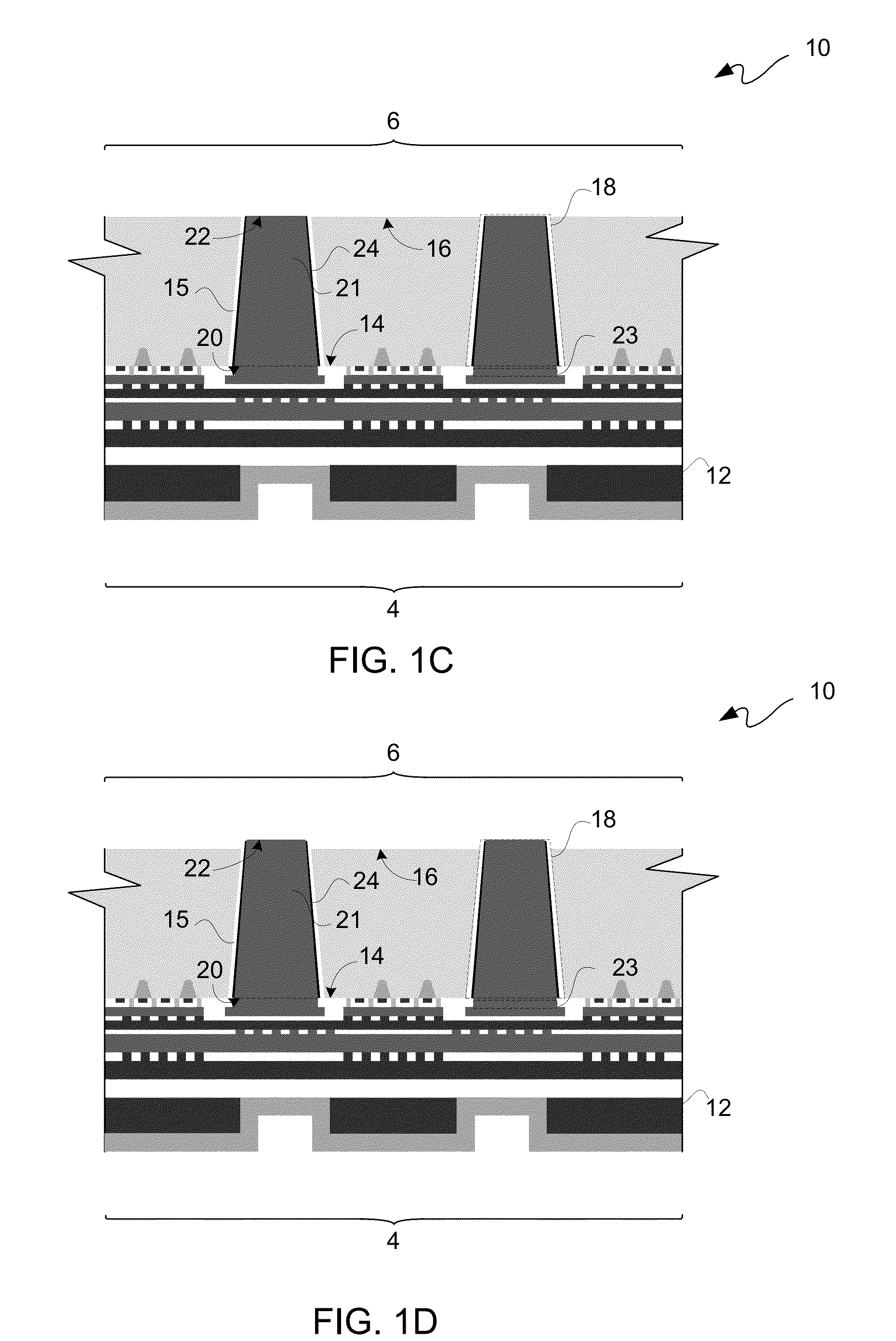

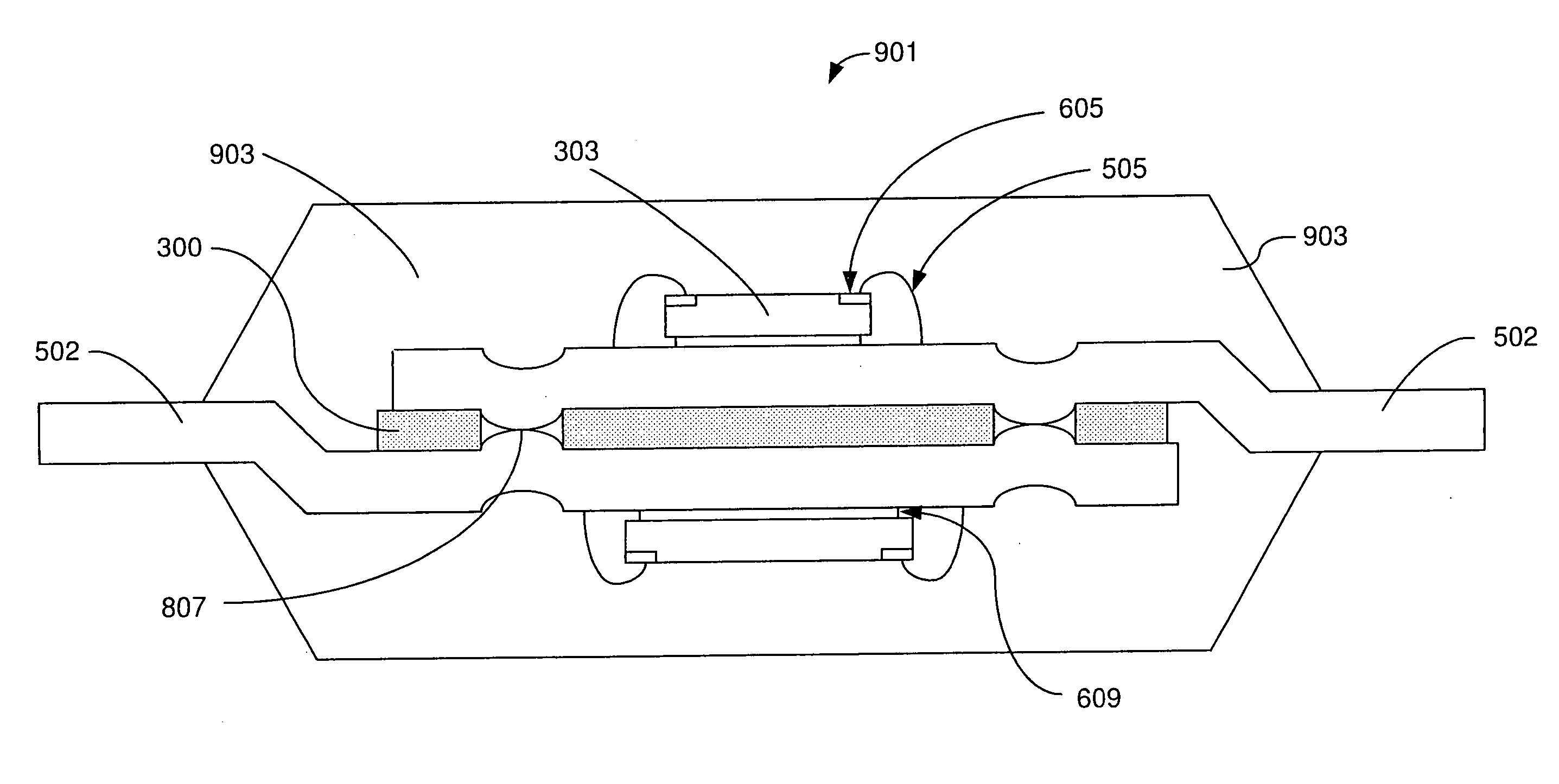

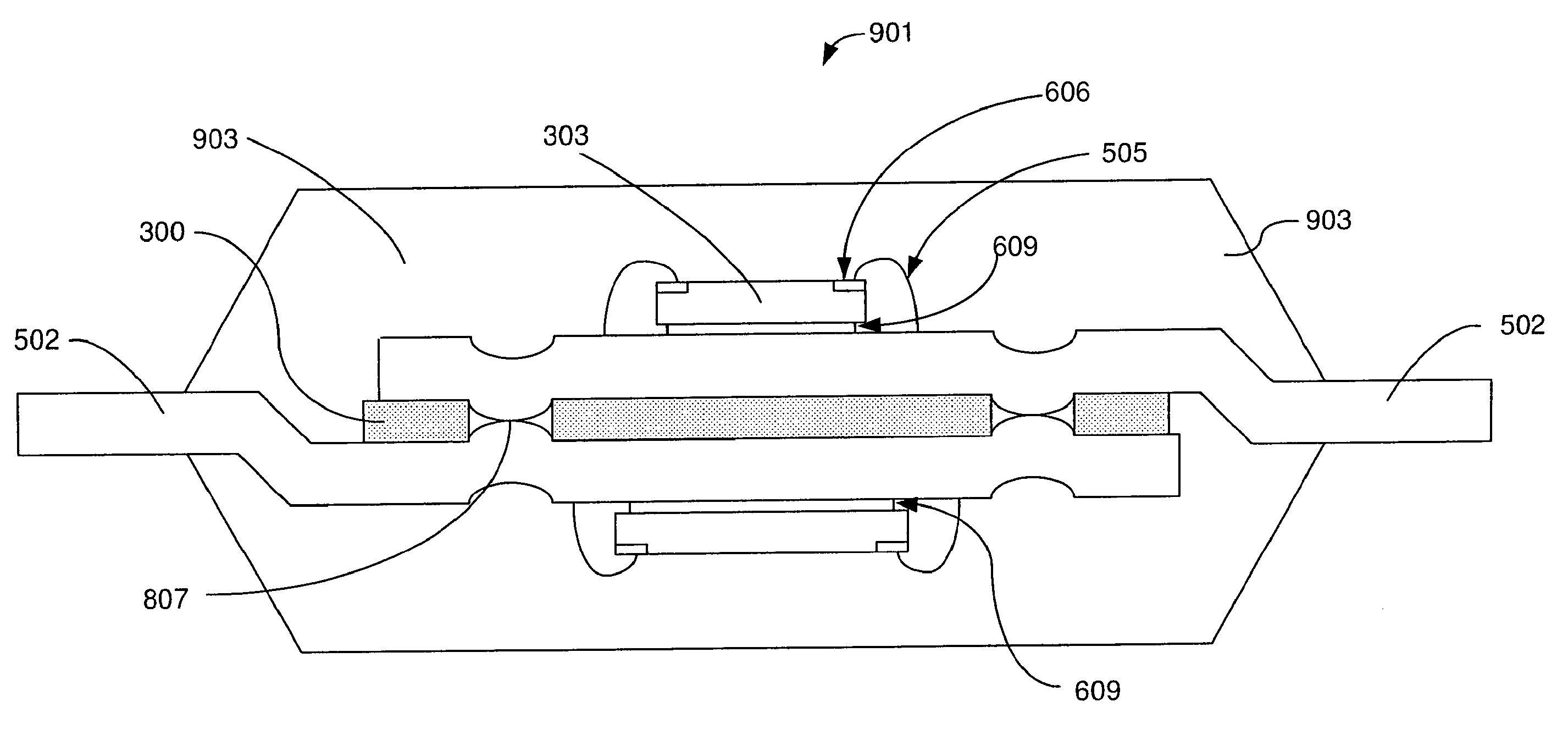

Compact power semiconductor package and method with stacked inductor and integrated circuit die

ActiveUS7868431B2Increase ratingsSemiconductor/solid-state device detailsSolid-state devicesSemiconductor packageEngineering

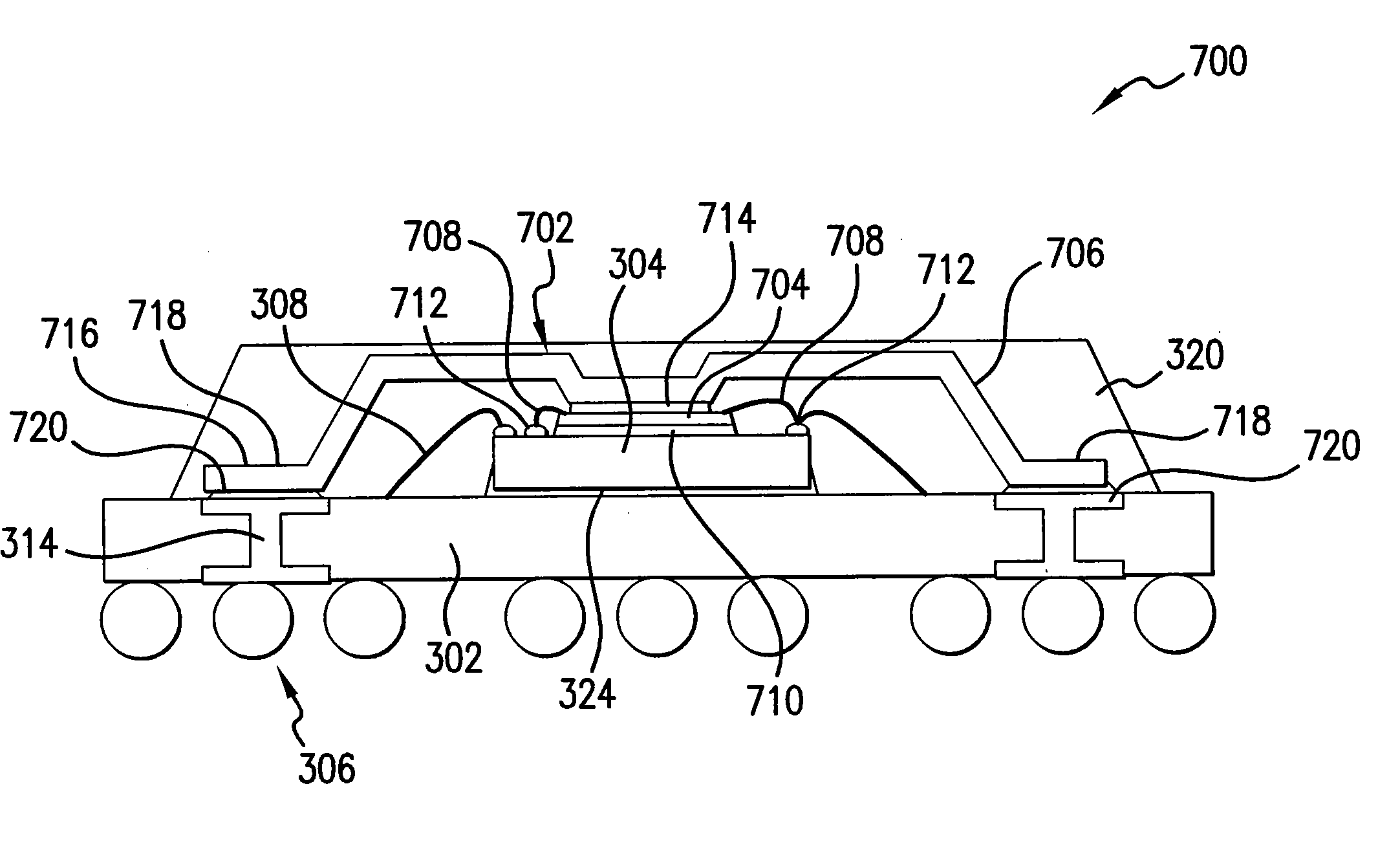

A power semiconductor package is disclosed with high inductance rating while exhibiting a reduced foot print. It has a bonded stack of power IC die at bottom, a power inductor at top and a circuit substrate, made of leadframe or printed circuit board, in the middle. The power inductor has a inductor core of closed magnetic loop. The circuit substrate has a first number of bottom half-coil forming conductive elements beneath the inductor core. A second number of top half-coil forming conductive elements, made of bond wires, three dimensionally formed interconnection plates or upper leadframe leads, are located atop the inductor core with both ends of each element connected to respective bottom half-coil forming conductive elements to jointly form an inductive coil enclosing the inductor core. A top encapsulant protectively encases the inductor core, the top half-coil forming conductive elements, the bottom half-coil forming conductive elements and the circuit substrate.

Owner:ALPHA & OMEGA SEMICON INC

Transformer-based multi-band RF front-end architecture

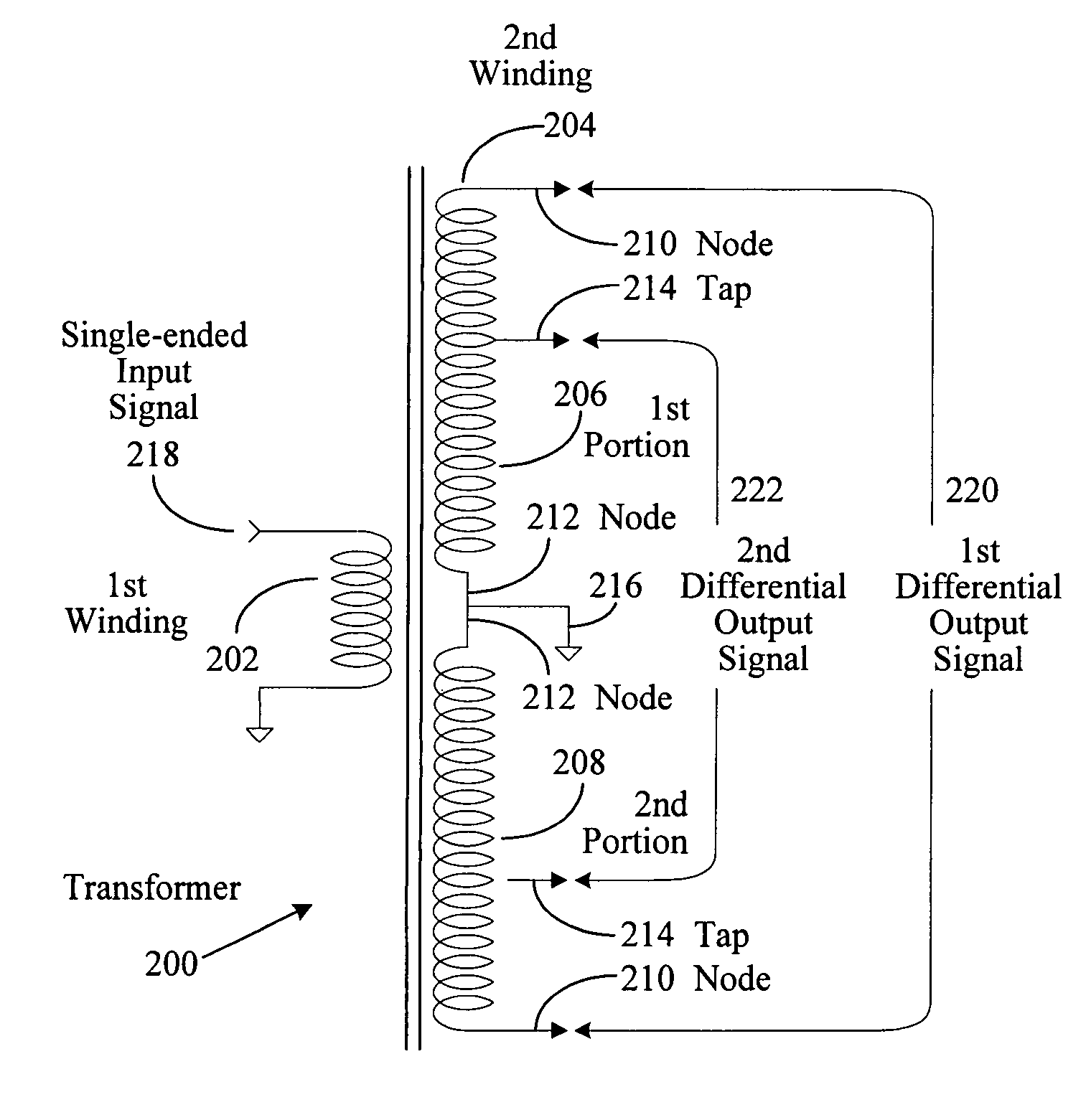

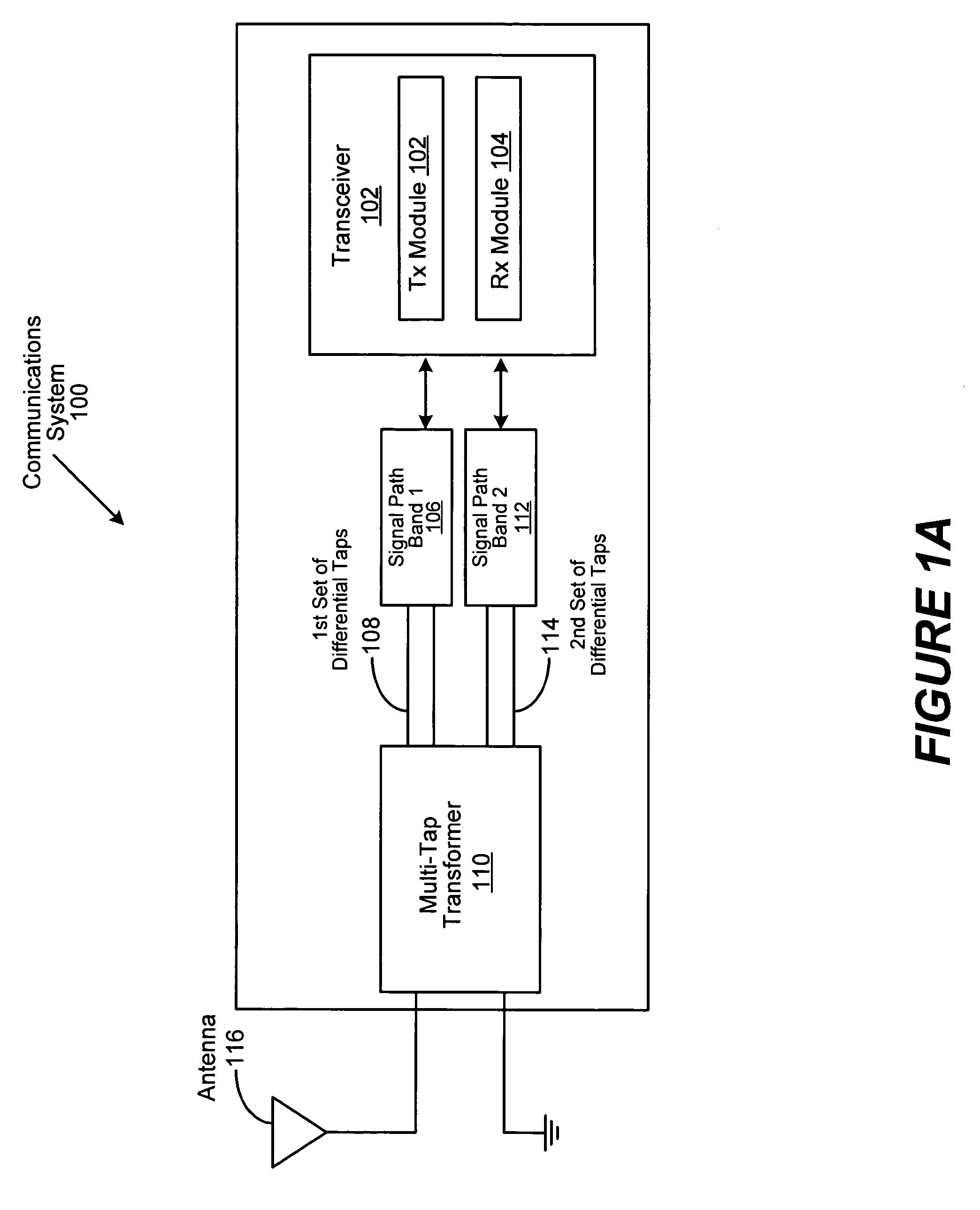

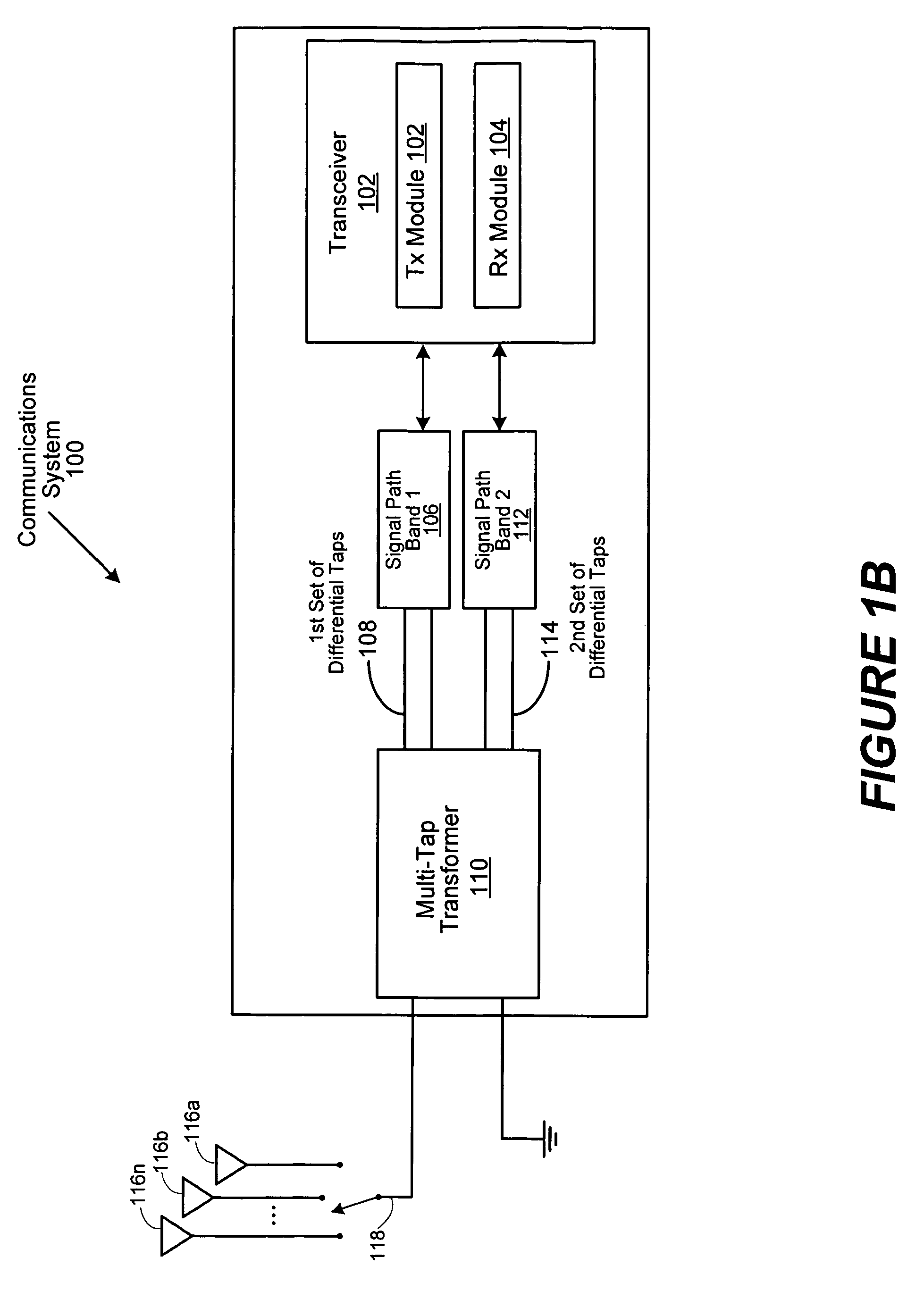

InactiveUS7526256B2Reduce area requirementsOne-port networksDc level restoring means or bias distort correctionMulti bandTransformer

Owner:AVAGO TECH INT SALES PTE LTD

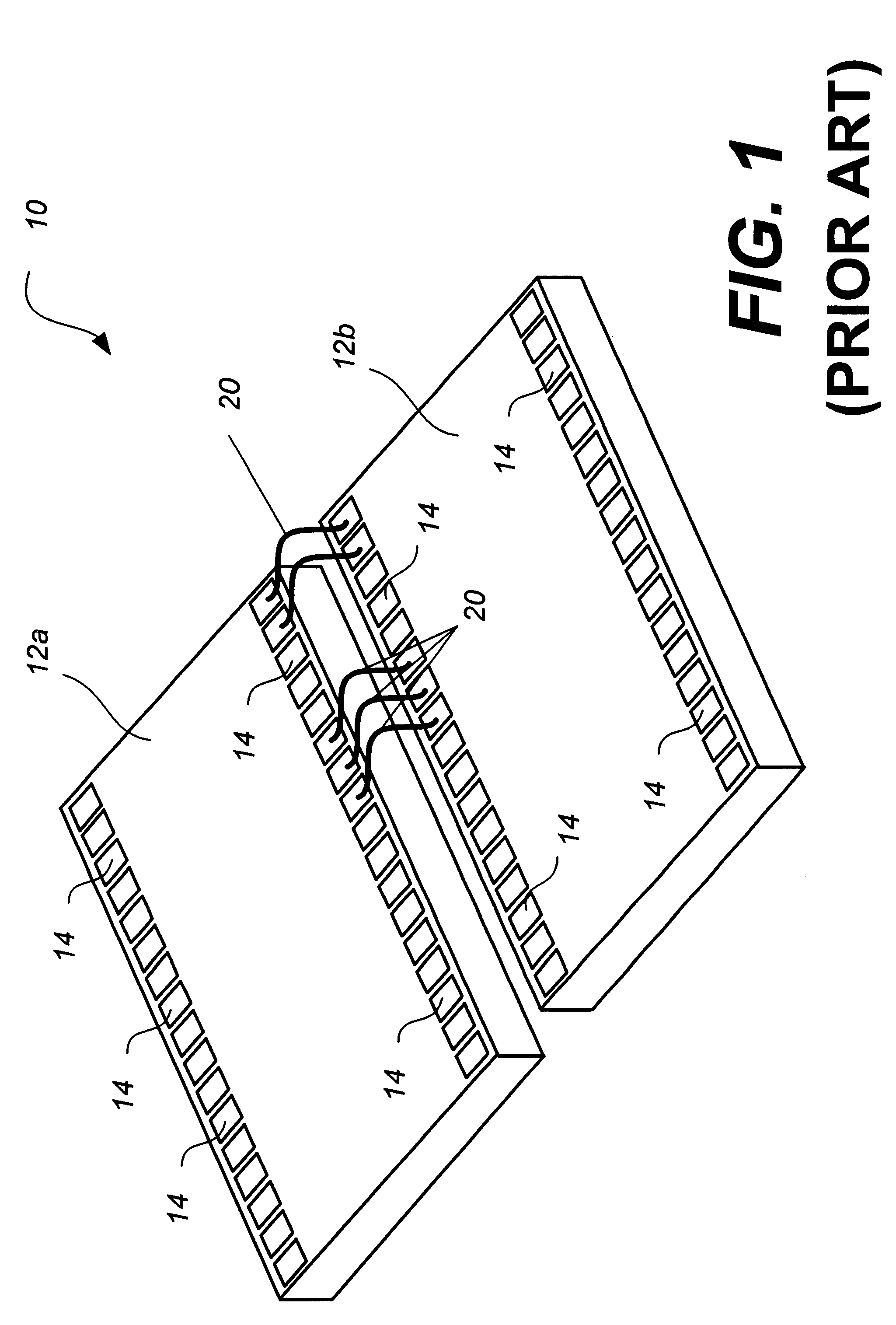

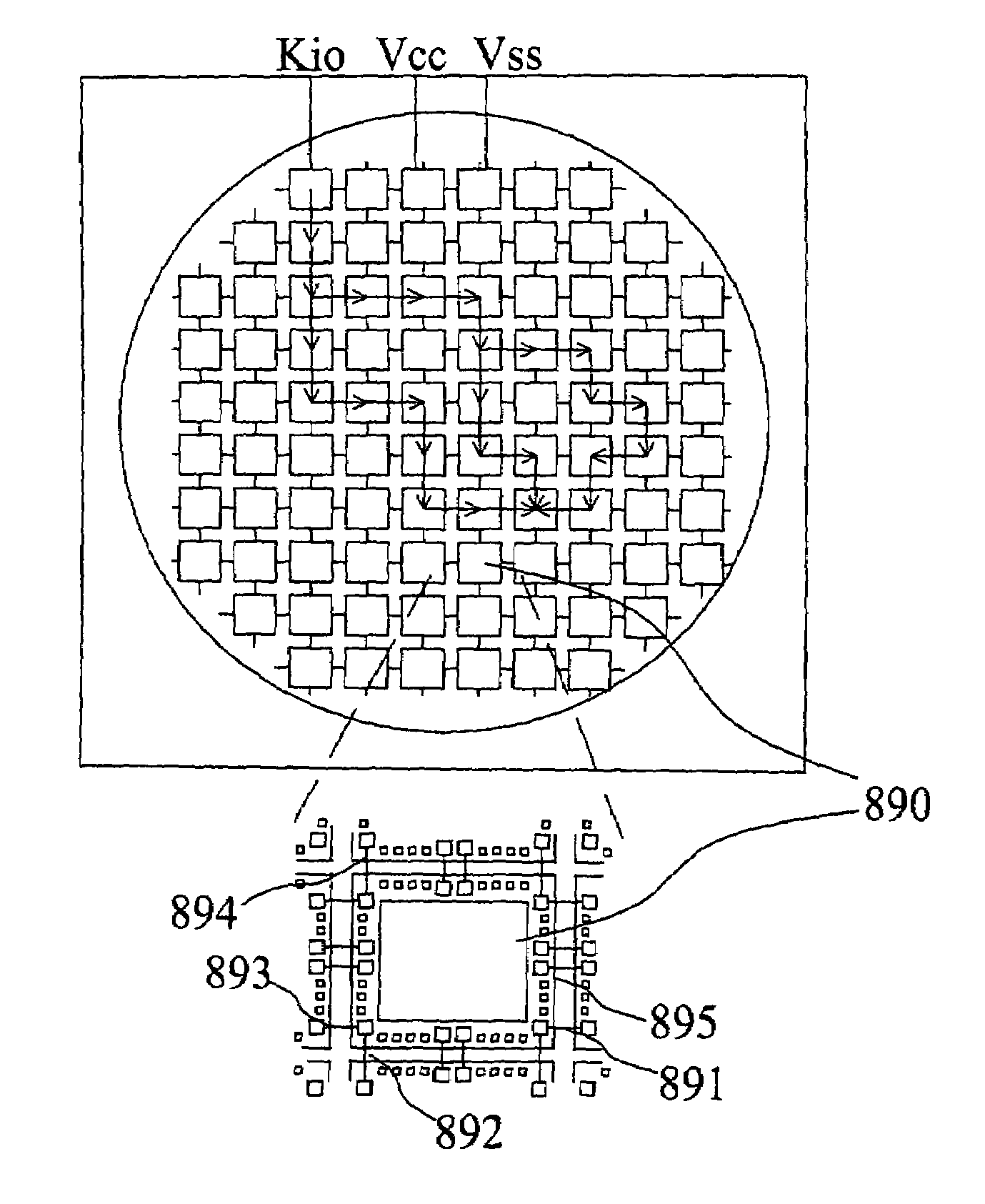

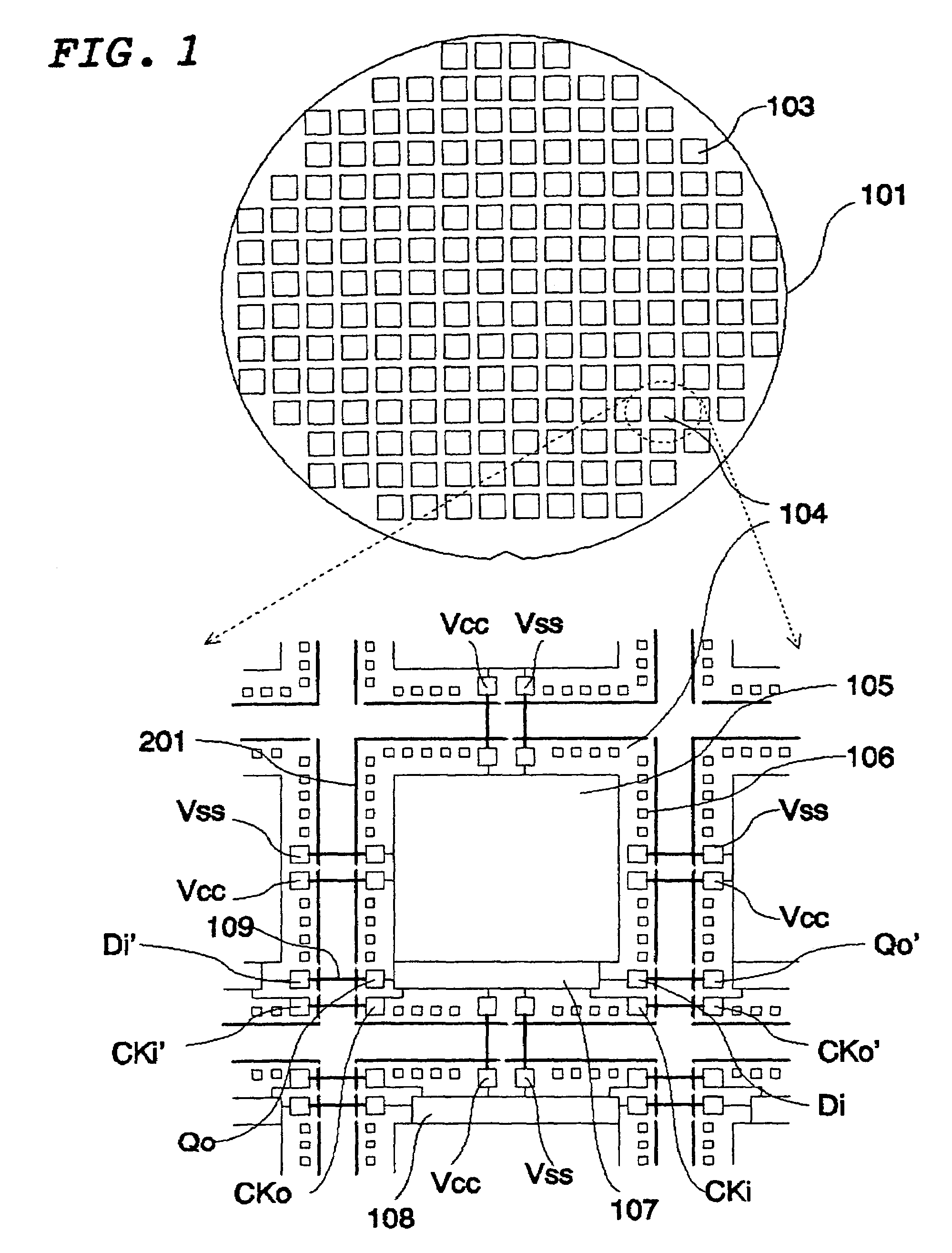

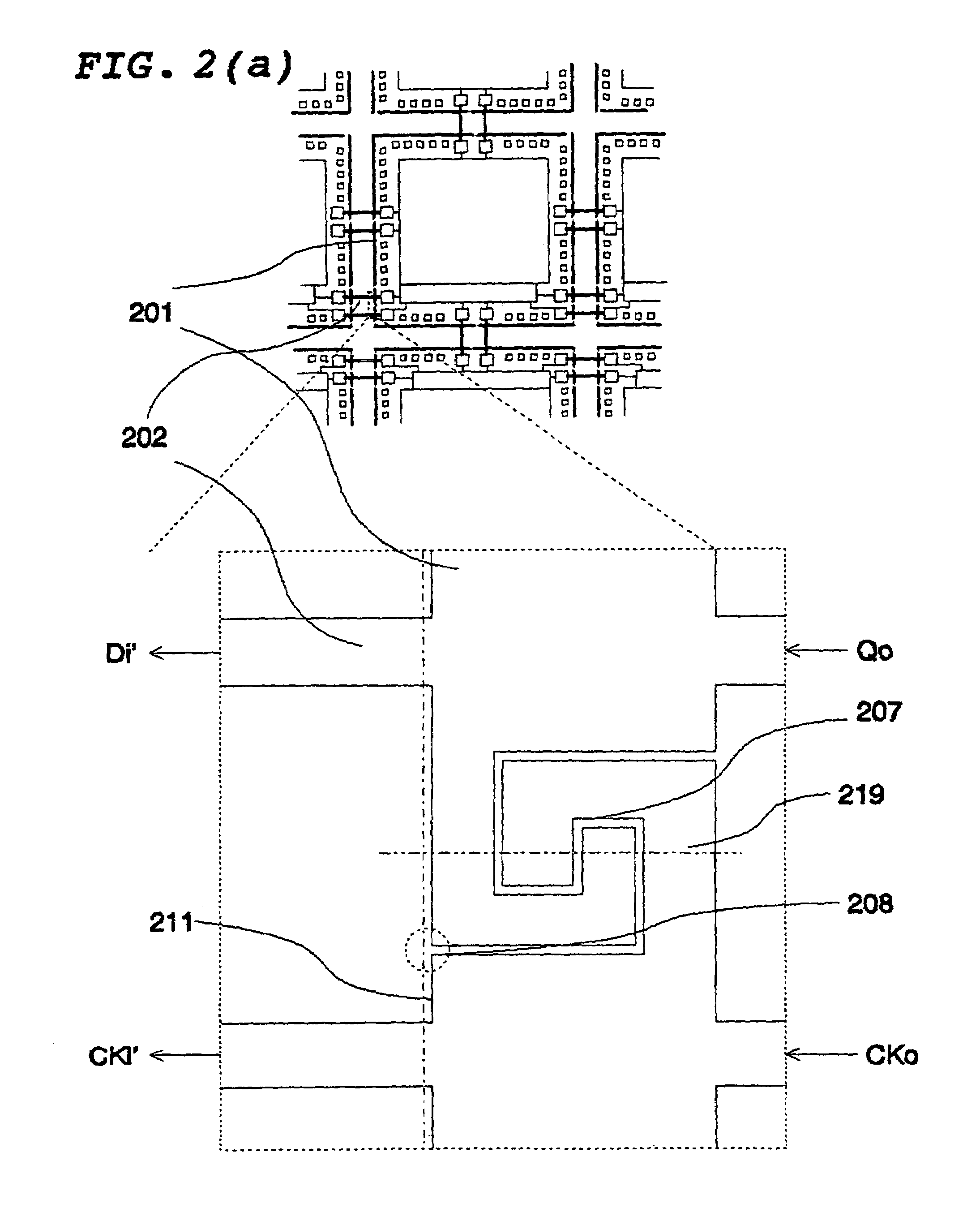

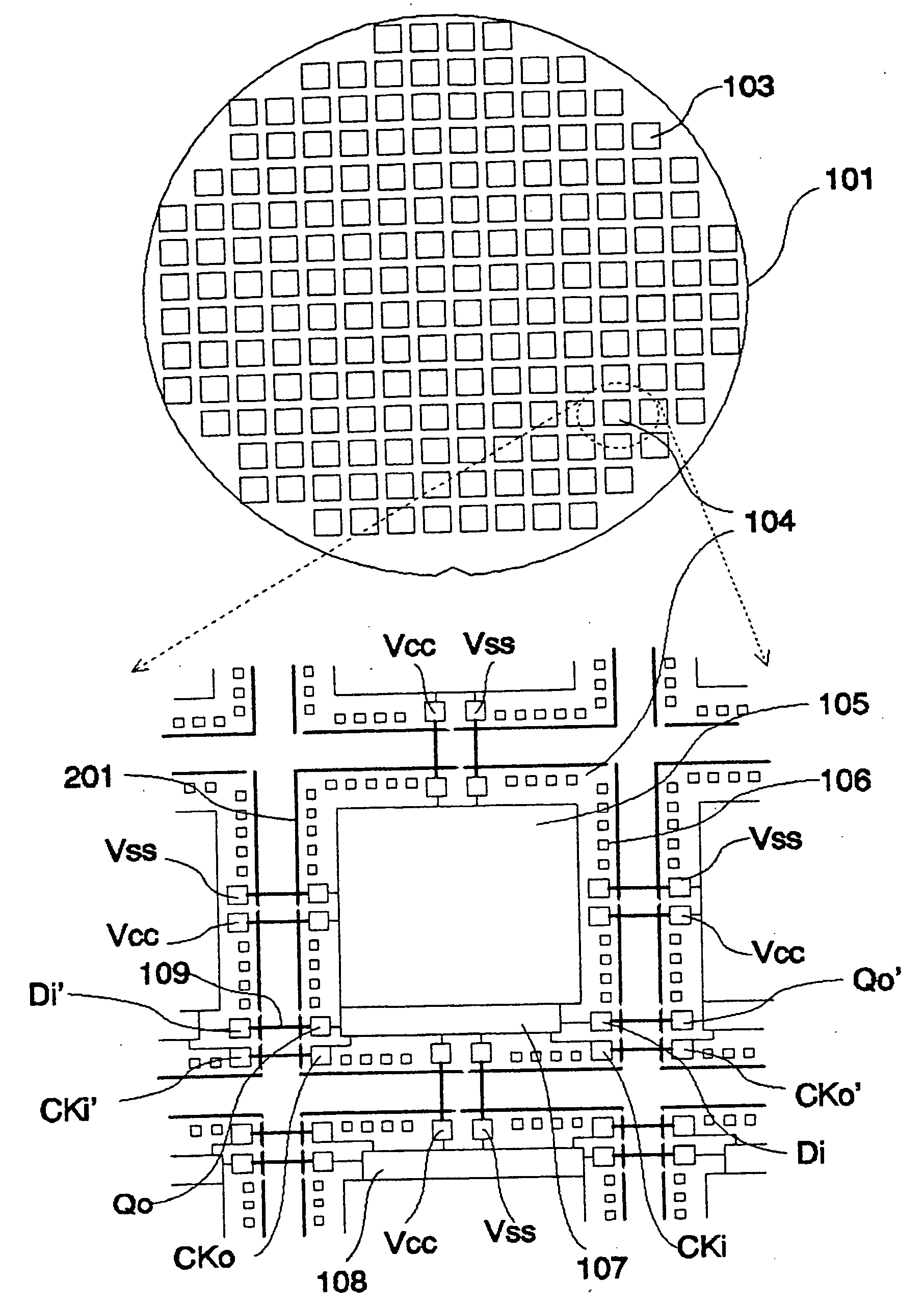

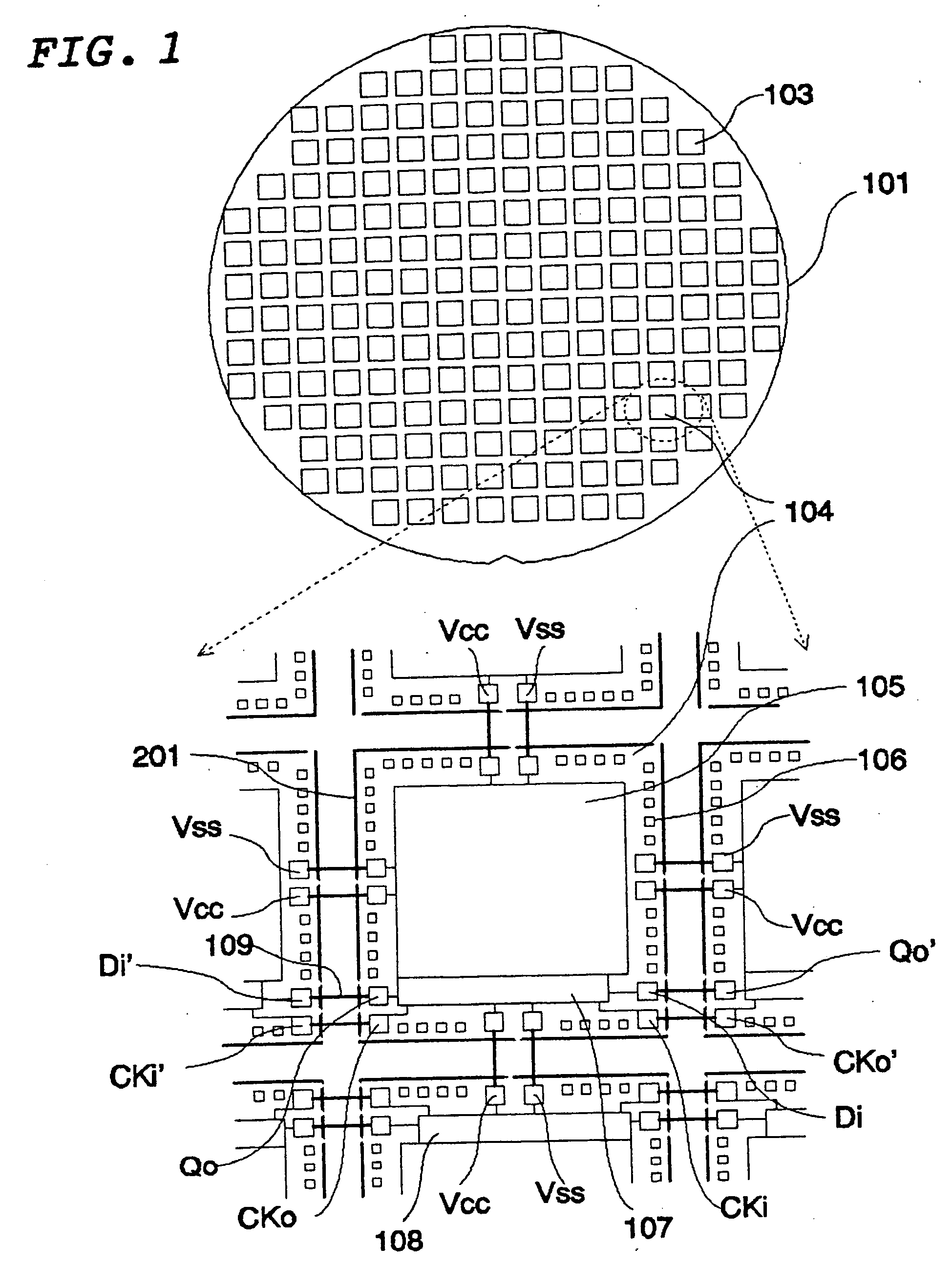

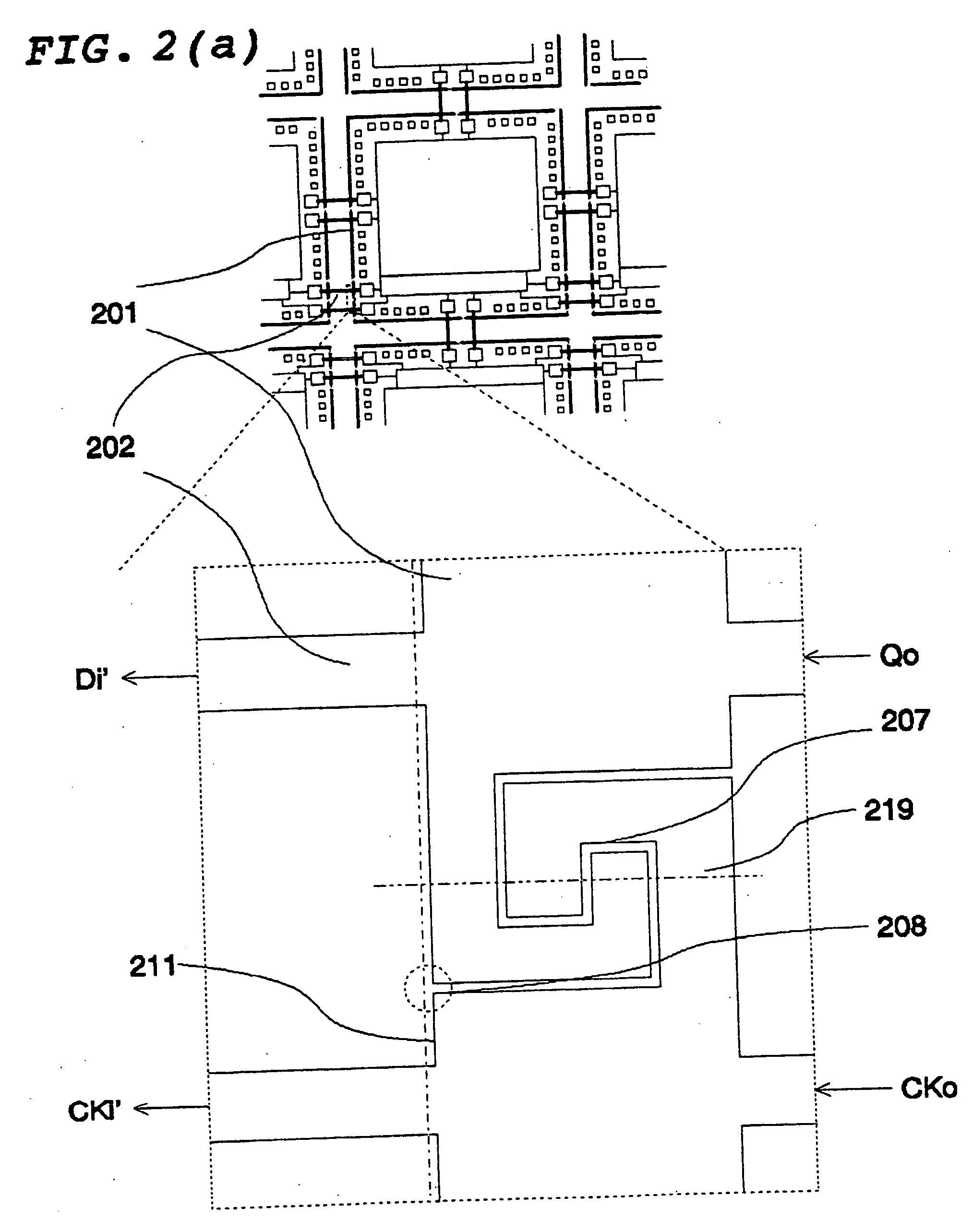

Inter-dice signal transfer methods for integrated circuits

InactiveUS7161175B2Good yieldEffectiveSemiconductor/solid-state device testing/measurementElectronic circuit testingDie (integrated circuit)Integrated circuit layout

The present invention discloses novel methods to transfer data between a plurality of integrated circuit dice on a semiconductor wafer. Each individual die contains internal circuits to control data transfer to nearby dice. Wafer level data transfer is achieved by a series of inter-dice data transfers. It is therefore possible to use a small number of small area metal lines to support wafer level parallel processing activities. External connections are provided by a small number of bonding pads on each wafer. The load on each external bounding pad is by far lower than that of prior art wafer level connections. These inter-dice data transfer mechanism also can be programmed to avoid defective circuitry. This invention has been used to support wafer level functional tests and wafer level burn-in tests. A Testing system of the present invention can test thousands of dice in parallel using simple testing equipment. Testing costs for integrated circuits are therefore reduced dramatically. The present application also makes it possible to build large area IC containing multiple dice. Extremely powerful products are realized using parallel processing capability of such multiple die integrated circuits.

Owner:ALPHA & OMEGA SEMICON LTD

Stacked die integrated circuit

ActiveUS20150270209A1Semiconductor/solid-state device detailsSolid-state devicesRedistribution layerDie (integrated circuit)

An apparatus relates generally to an integrated circuit package. In such an apparatus, a package substrate has a first plurality of via structures extending from a lower surface of the package substrate to an upper surface of the package substrate. An die has a second plurality of via structures extending to a lower surface of the die. The lower surface of the die faces the upper surface of the package substrate in the integrated circuit package. The package substrate does not include a redistribution layer. The die and the package substrate are coupled to one another.

Owner:INVENSAS CORP

Integrated EMC shield for integrated circuits and multiple chip modules

InactiveUS20030002271A1Printed circuit assemblingMagnetic/electric field screeningTransfer moldingSemiconductor package

A semiconductor package has a die connected to a substrate with a transfer molding applied over the die. The transfer molding includes an electrically conductive material for forming an electromagnetic compatibility shield as an integral part thereof.

Owner:NOKIA CORP

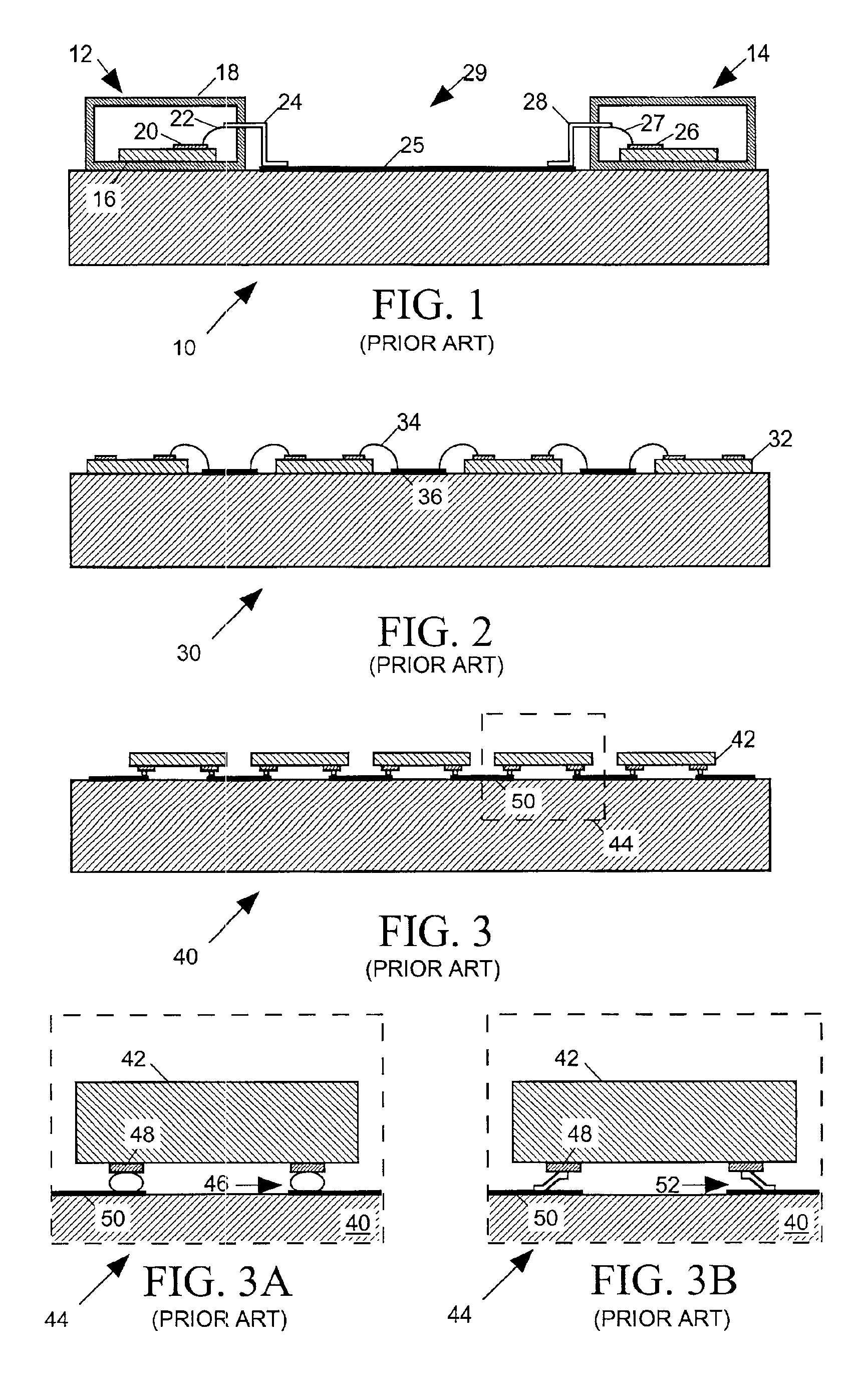

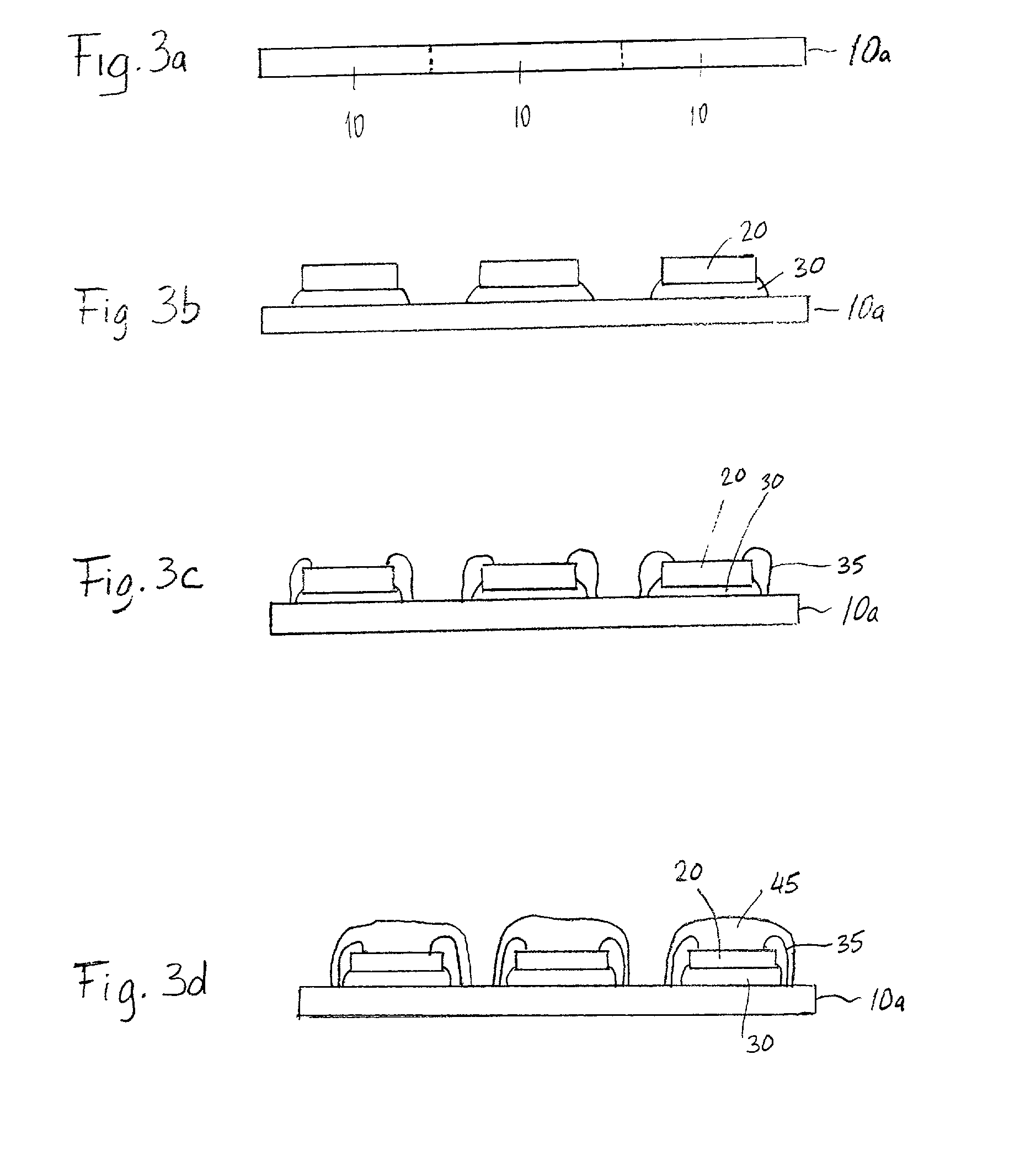

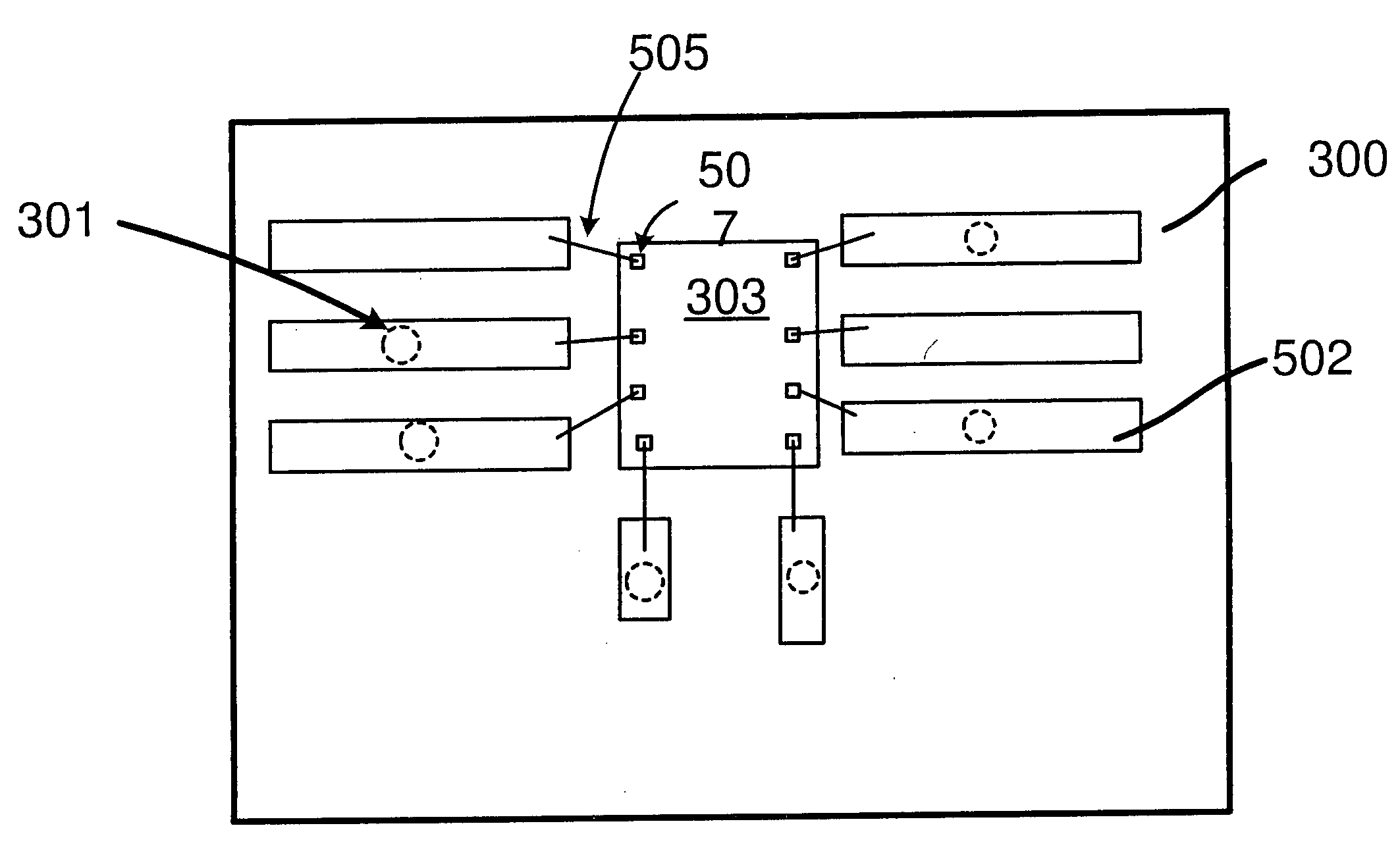

Methods for a multiple die integrated circuit package

ActiveUS20070096284A1Semiconductor/solid-state device detailsSolid-state devicesElectrical connectionEngineering

Methods for a multiple die package for integrated circuits are disclosed. An insulator layer is provided and one or more vias are formed within it. The insulator may be provided without vias, and vias formed later. At least one integrated circuit is provided and electrically coupled to at least one lead of a first leadframe overlying one surface of the insulator. At least one second integrated circuit is provided and electrically coupled to a second leadframe overlying a second surface of the insulator. Electrical connections between the two leadframes and the first and second integrated circuits are made through the insulator at selected locations, by coupling at least one lead of the first and second leadframes one to another. The leads of the first and second leadframe may be physically coupled by a welding process within vias in the insulator. A method for a removable storage card is also described.

Owner:SANDISK TECH LLC

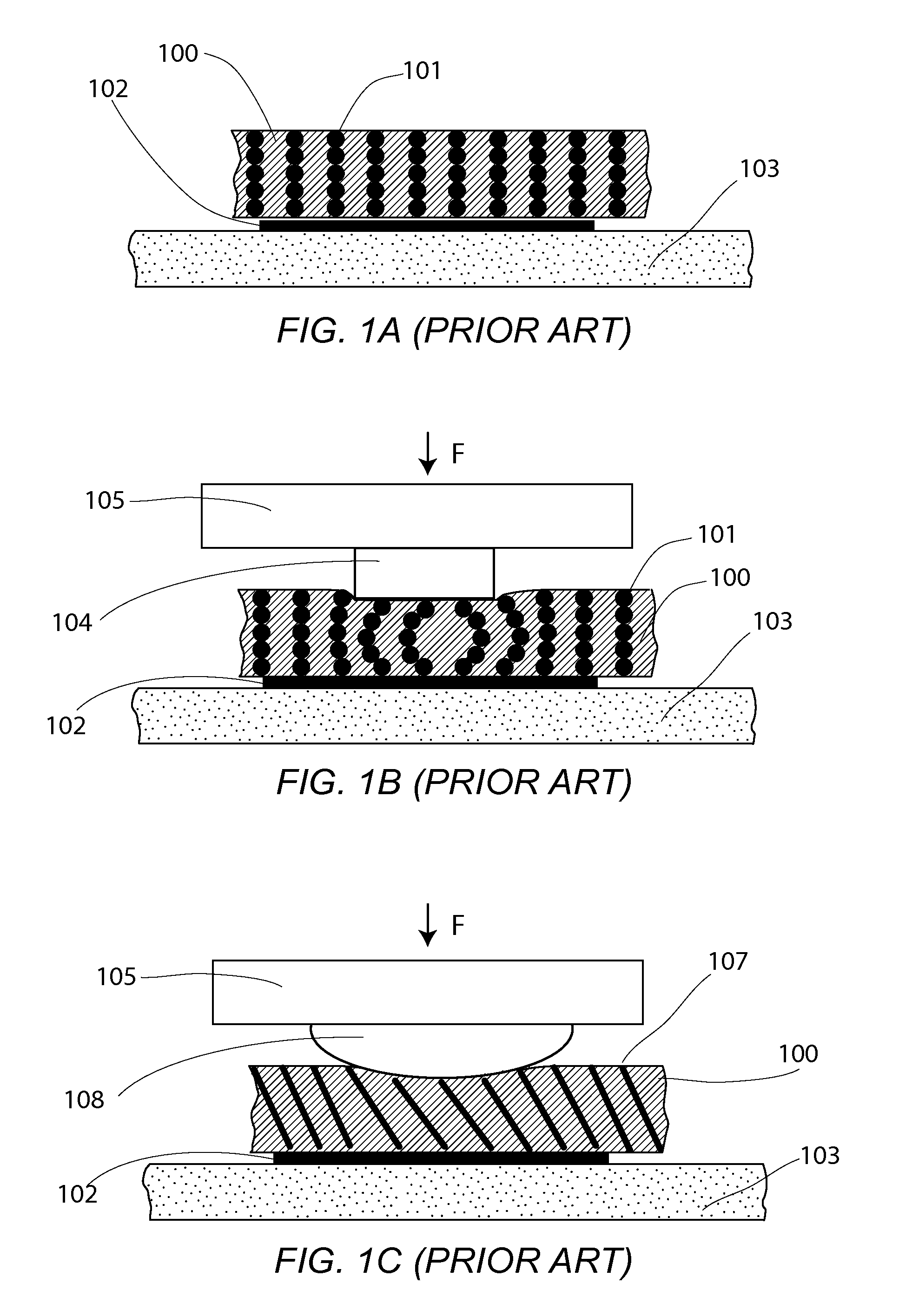

Die attachment with reduced adhesive bleed-out

InactiveUS6734569B2Reducing contamination and staining of substrate surfaceIncrease expensesSemiconductor/solid-state device detailsSolid-state devicesAdhesiveLead bonding

Owner:INT BUSINESS MASCH CORP

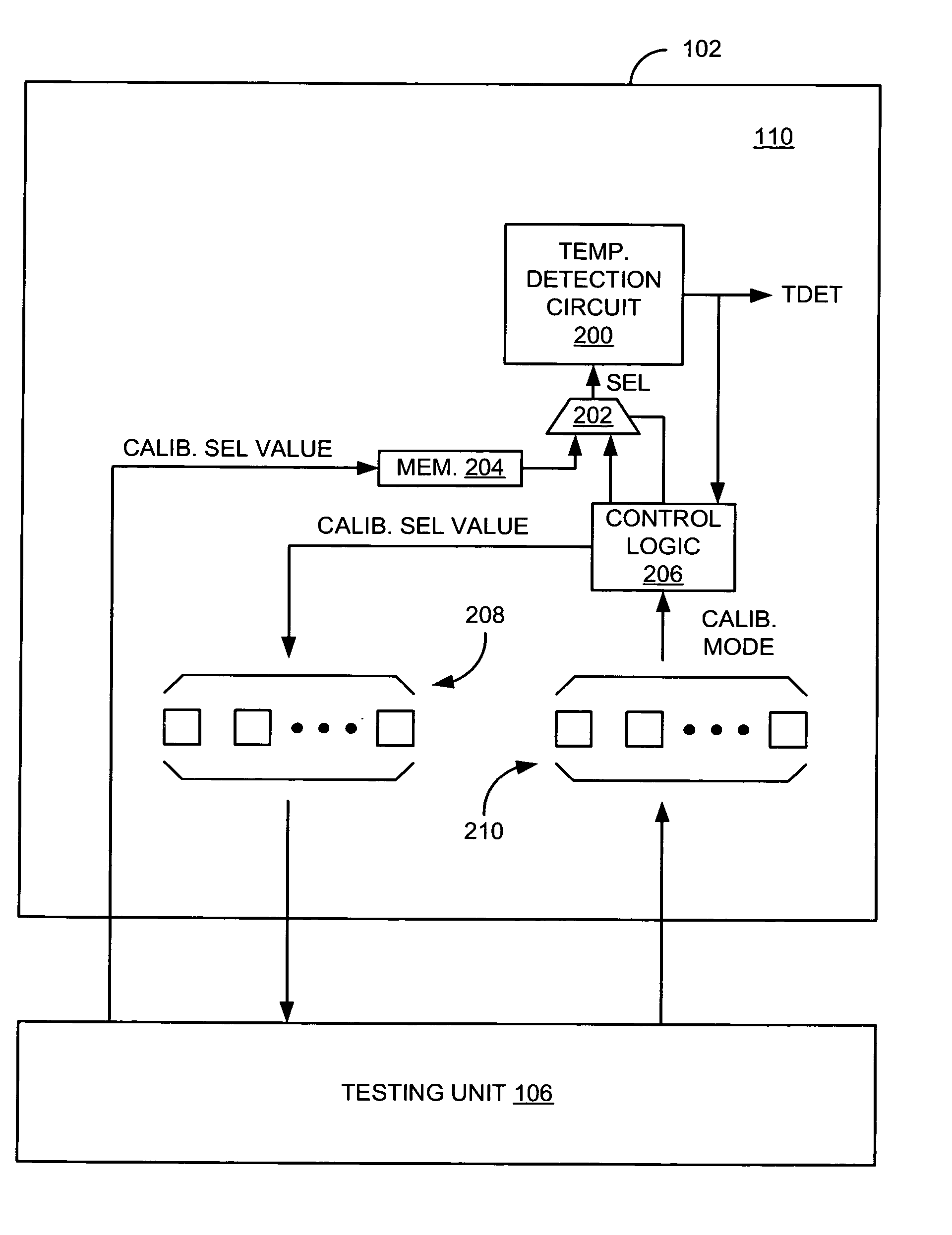

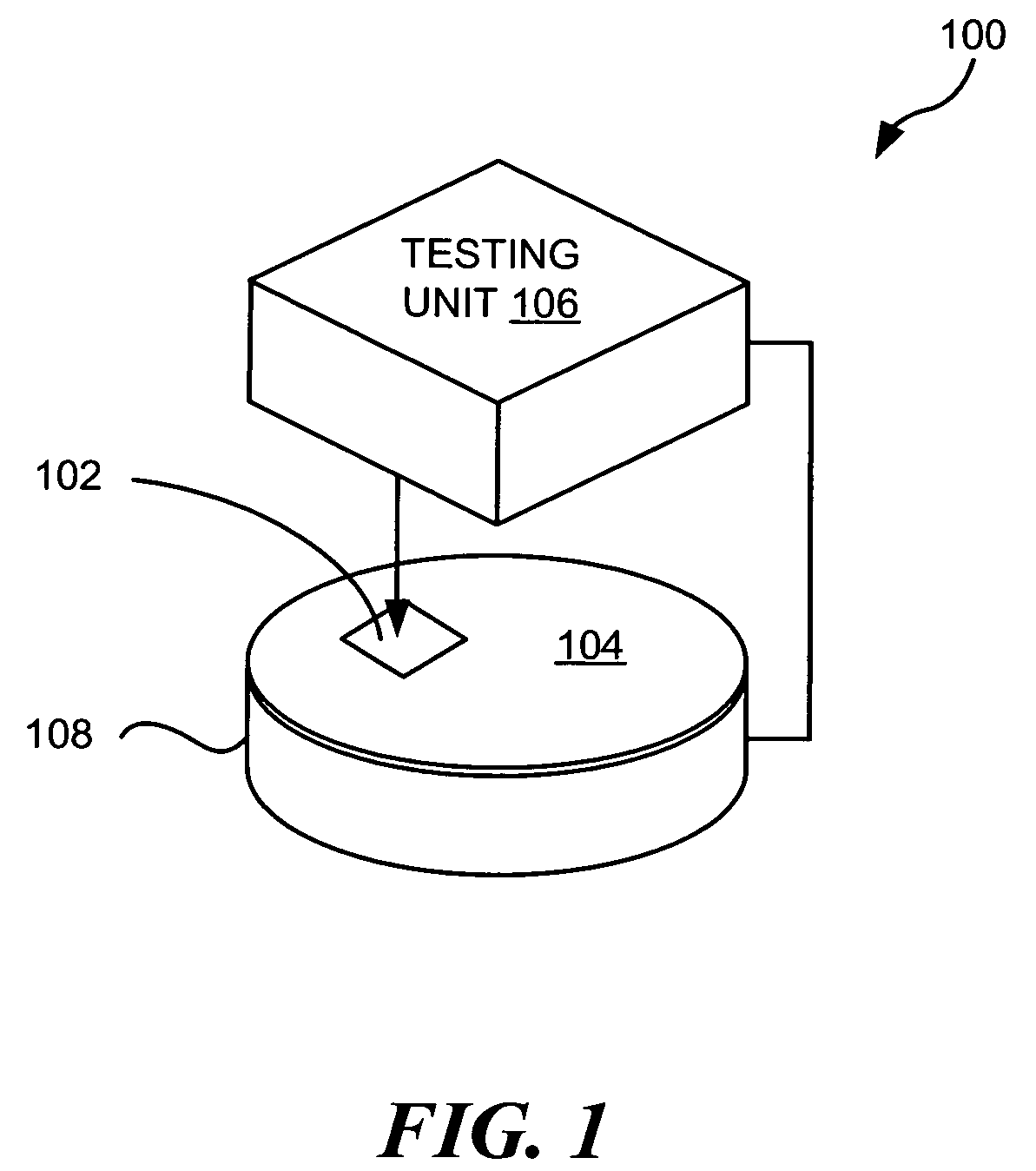

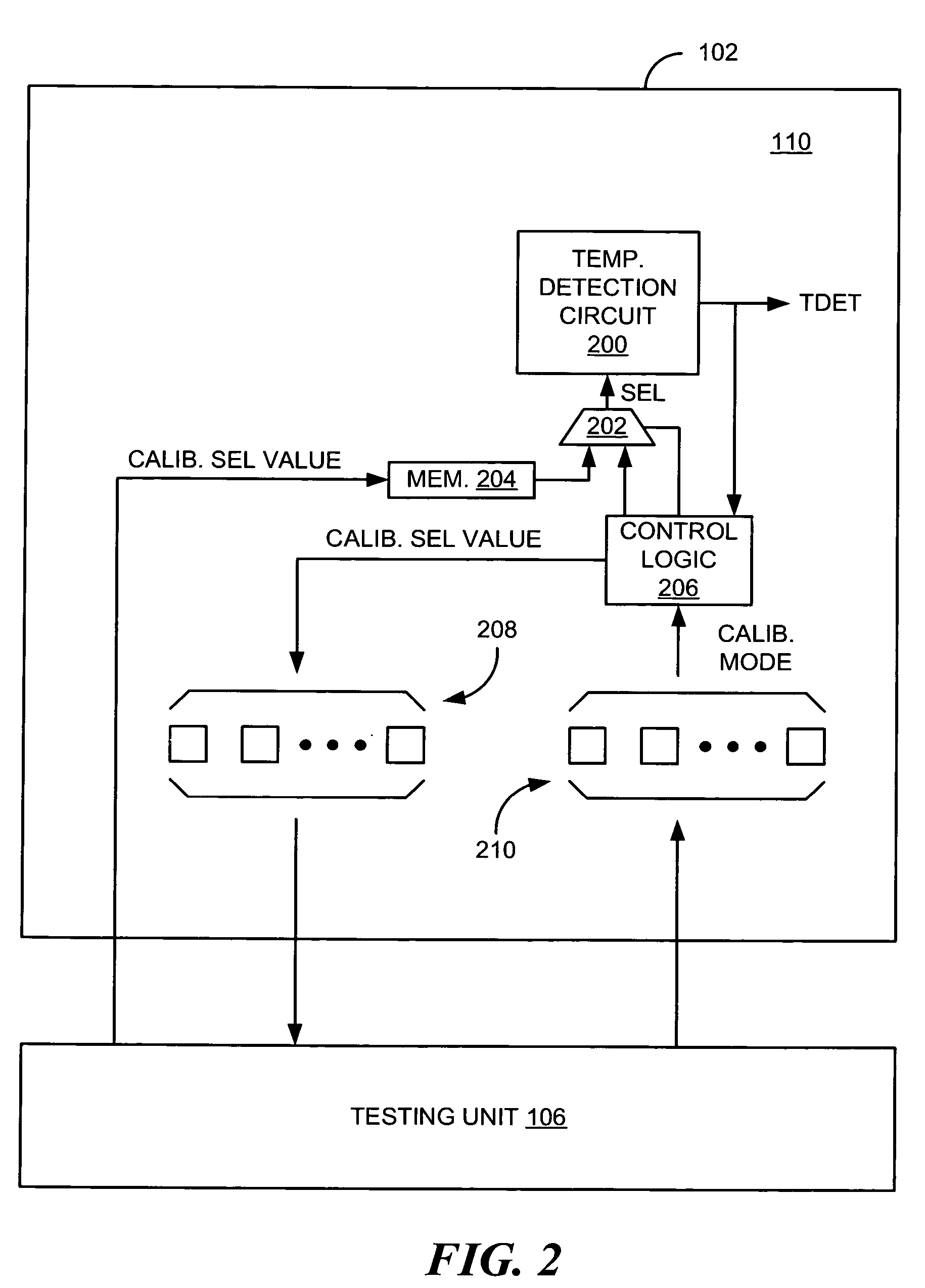

Integrated circuit die including a temperature detection circuit, and system and methods for calibrating the temperature detection circuit

An integrated circuit die is disclosed including a temperature detection circuit and a memory configured to store calibration data. The temperature detection circuit is operatively coupled to the memory, and receives an input signal. The temperature detection circuit is configured to produce an output signal dependent upon the input signal and indicative of whether a temperature of the integrated circuit die is greater than a selected temperature. During a normal operating mode of the integrated circuit die the input signal comprises the calibration data. A system and methods for calibrating the temperature detection circuit are also described.

Owner:TOSHIBA AMERICA ELECTRONICS COMPONENTS +2

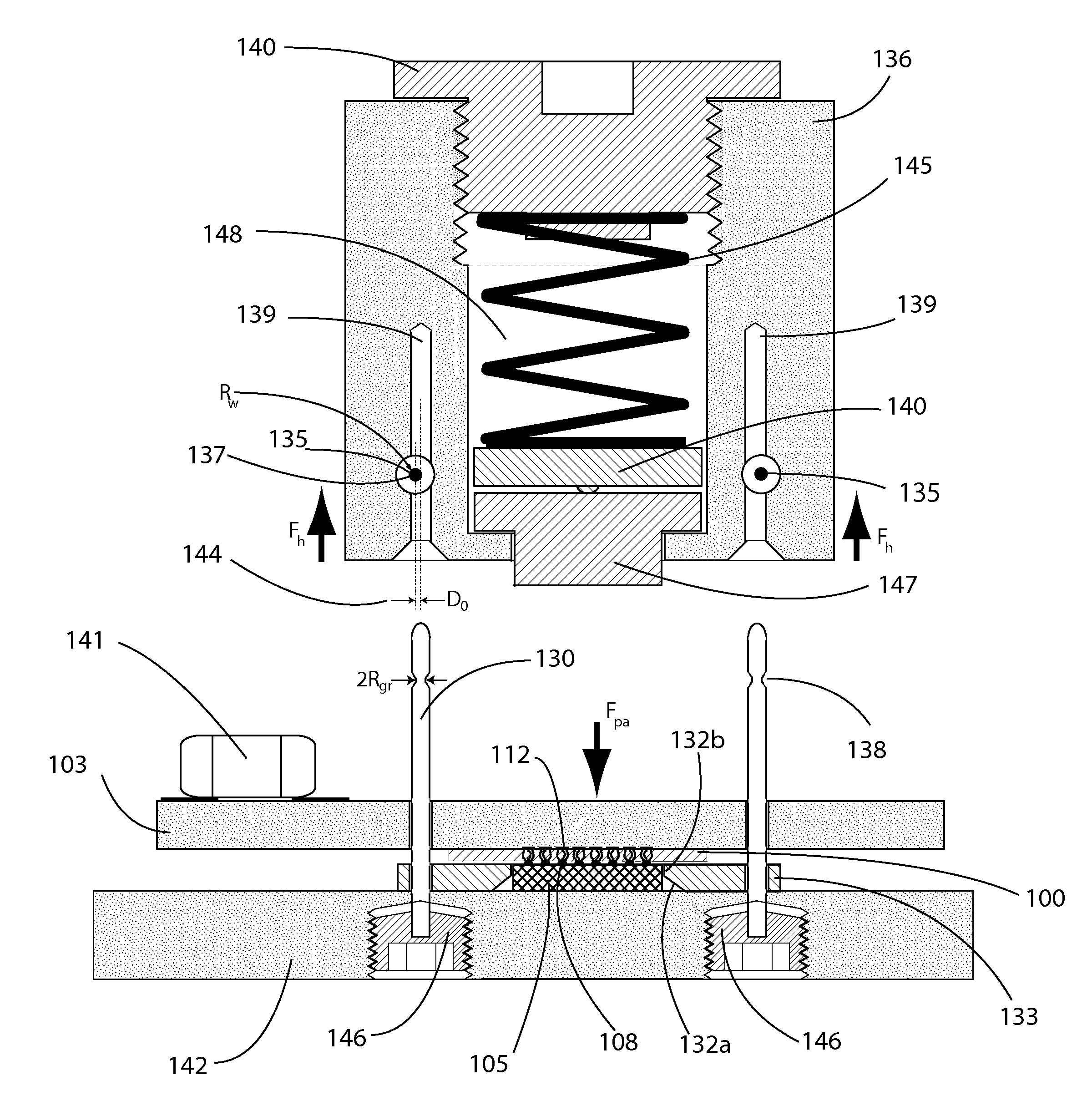

Method and apparatus for positioning and contacting singulated semiconductor dies

InactiveUS8044673B1Reduced parasitic inductiveReduce capacityElectrical measurement instrument detailsIndividual semiconductor device testingSemiconductorIntegrated circuit

A re-configurable test socket system and test socket architecture are described involving a combination of particular micro elements and re-useable macro elements that can be reused and reconfigured for testing a wide variety of different semiconductor and integrated circuit (IC) DUT packages having different shapes, sizes, and terminal configurations.

Owner:BURGYAN LAJOS

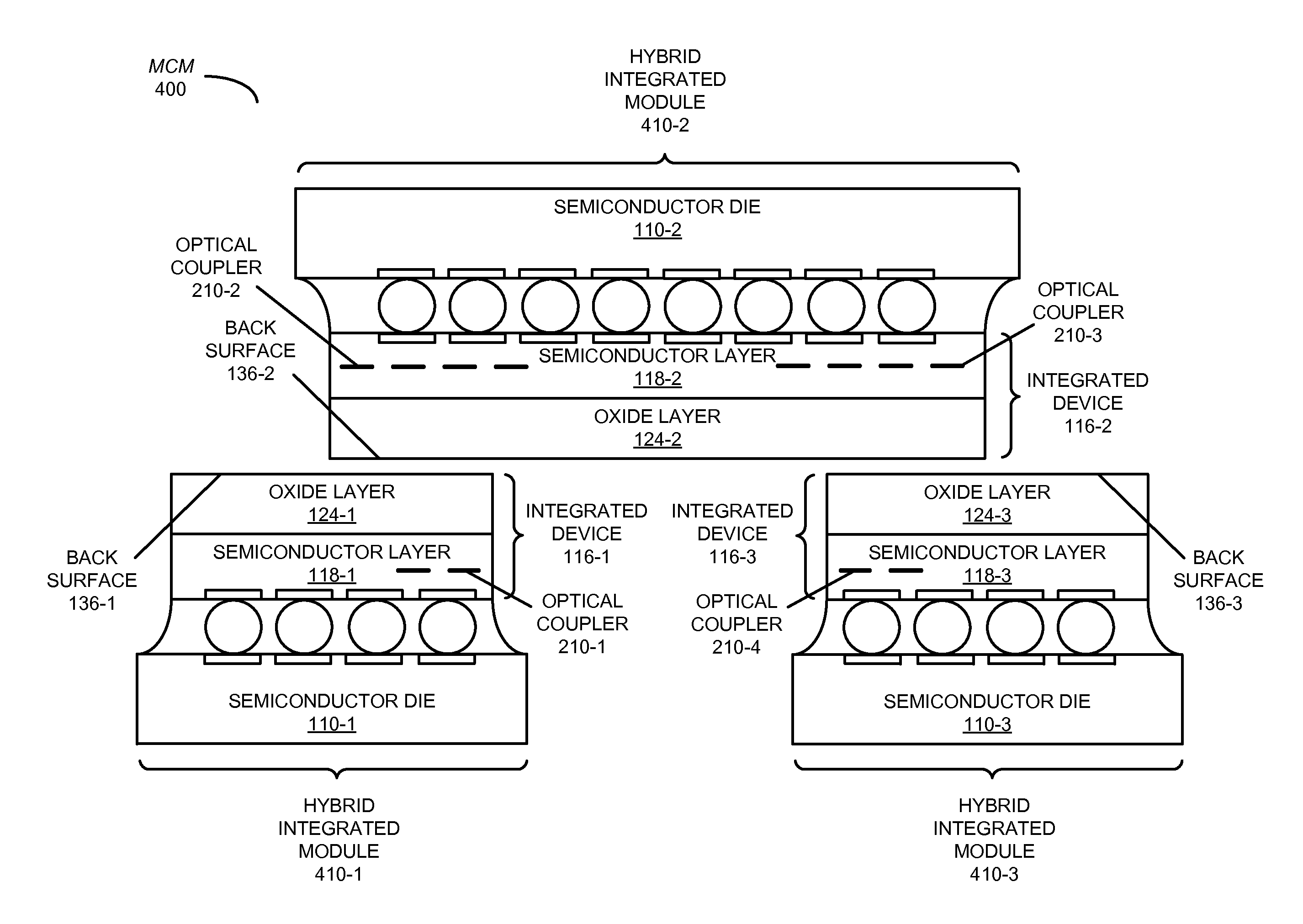

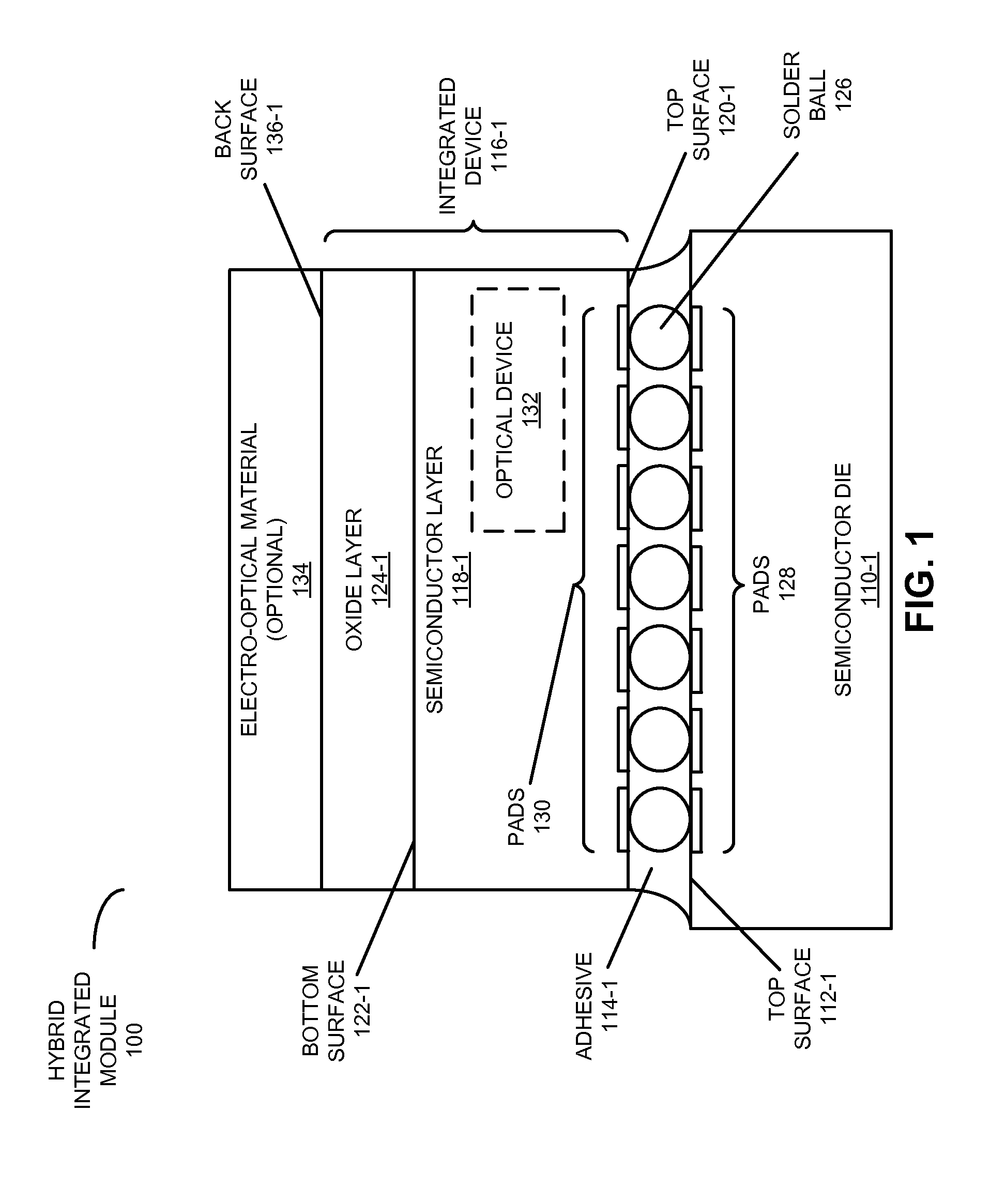

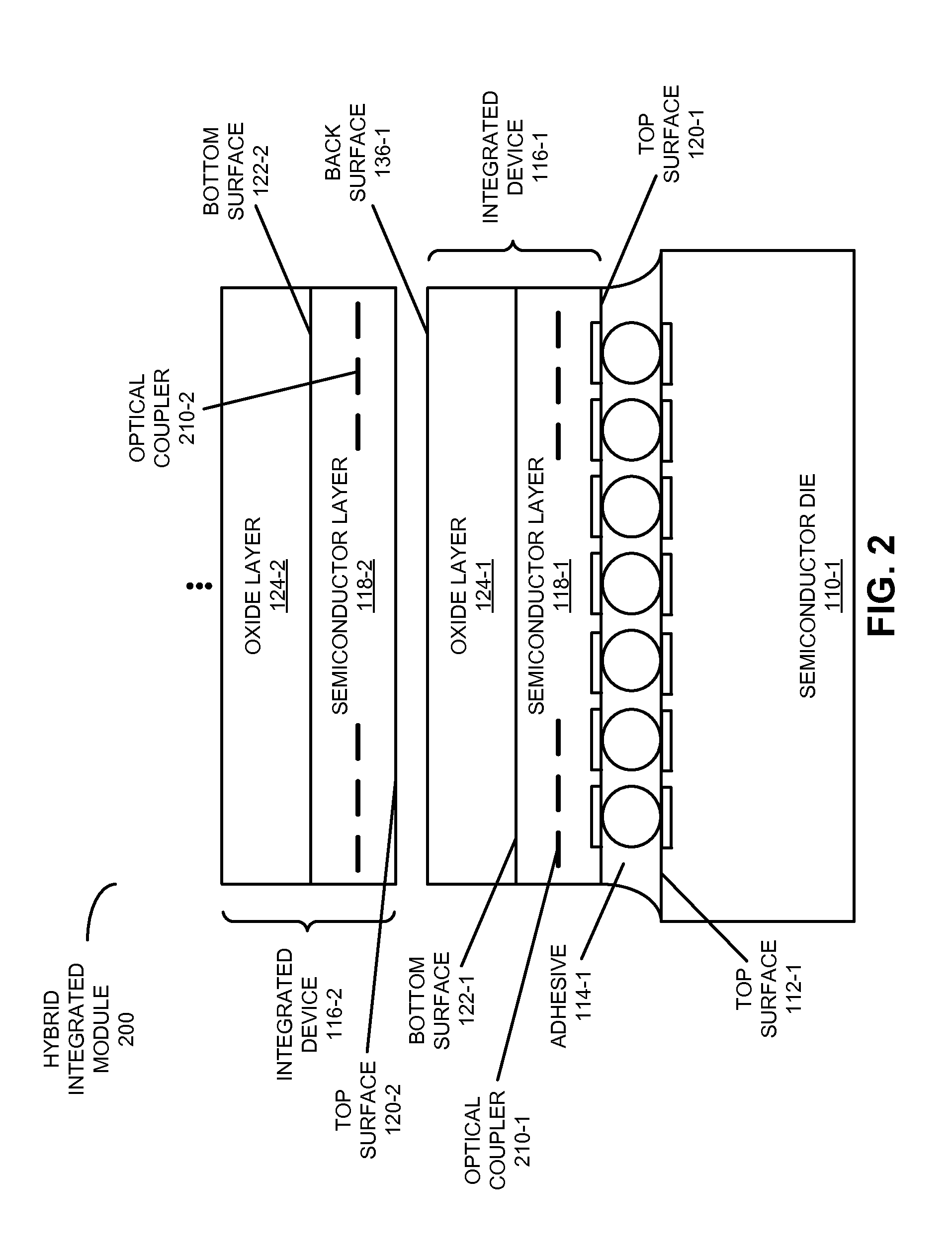

Hybrid substrateless device with enhanced tuning efficiency

ActiveUS20130037905A1Improve device performanceEasy to operateSemiconductor/solid-state device detailsSolid-state devicesWaferingEngineering

In a hybrid integrated module, a semiconductor die is mechanically coupled face-to-face to an integrated device in which the substrate has been removed. For example, the integrated circuit may include an optical device fabricated on a silicon-on-insulator (SOI) wafer in which the backside silicon handler has been completely removed, thereby facilitating improved device performance and highly efficient thermal tuning of the operating wavelength of the optical device. Moreover, the semiconductor die may be a VLSI chip that provides power, and serves as a mechanical handler and / or an electrical driver. The thermal tuning efficiency of the substrateless optical device may be enhanced by over 100× relative to an optical device with an intact substrate, and by 5× relative to an optical device in which the substrate has only been removed in proximity to the optical device.

Owner:ORACLE INT CORP

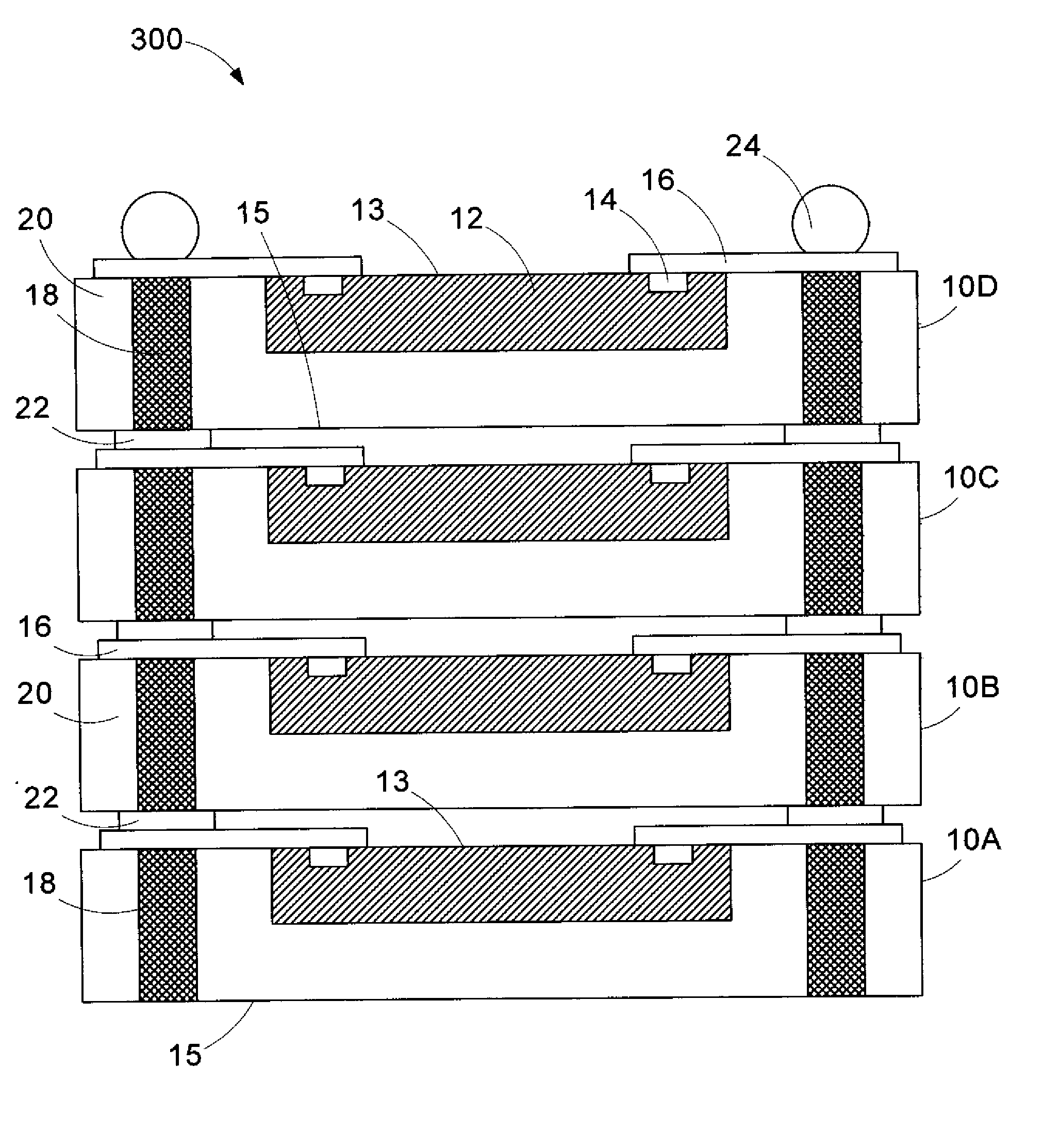

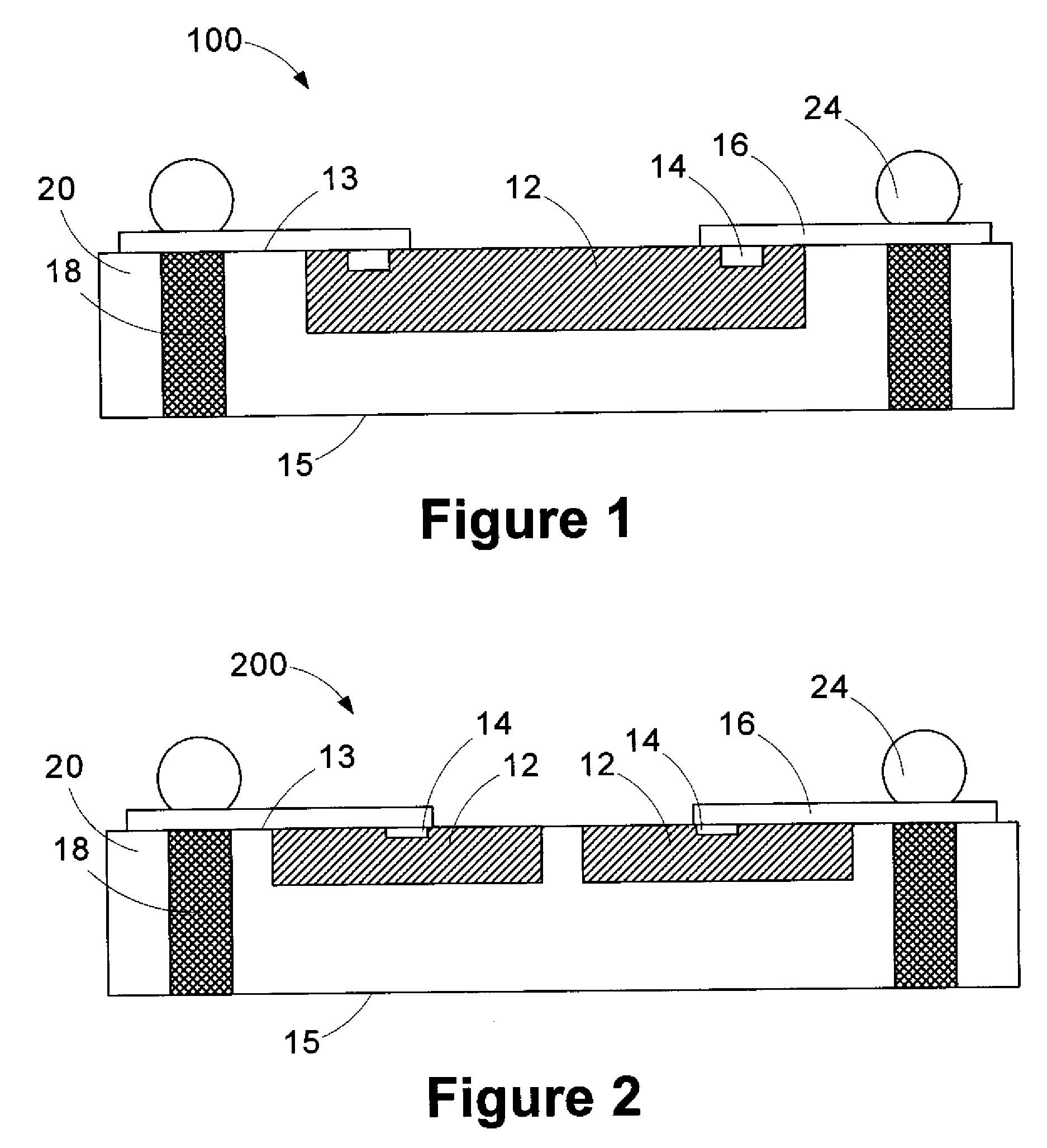

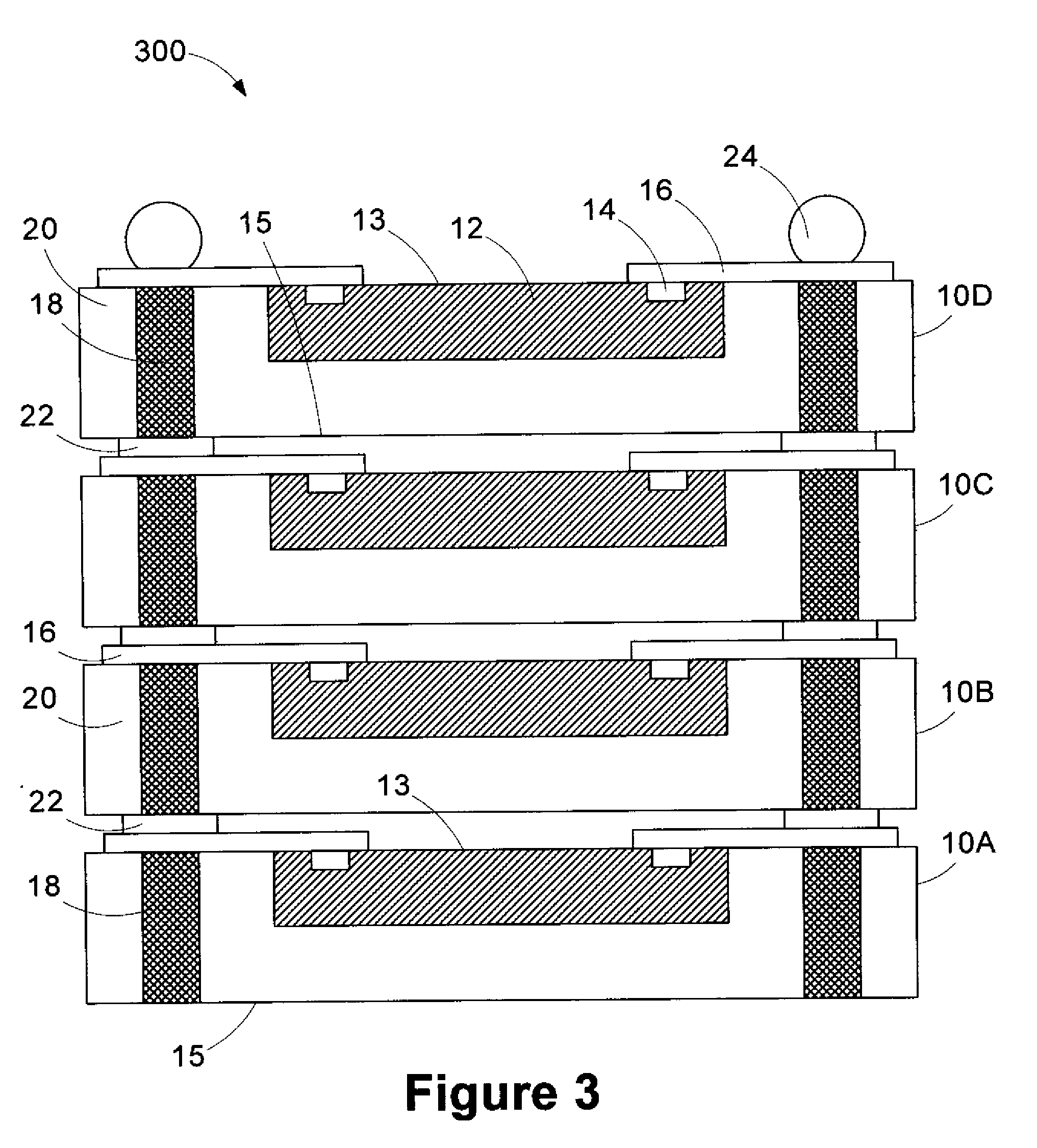

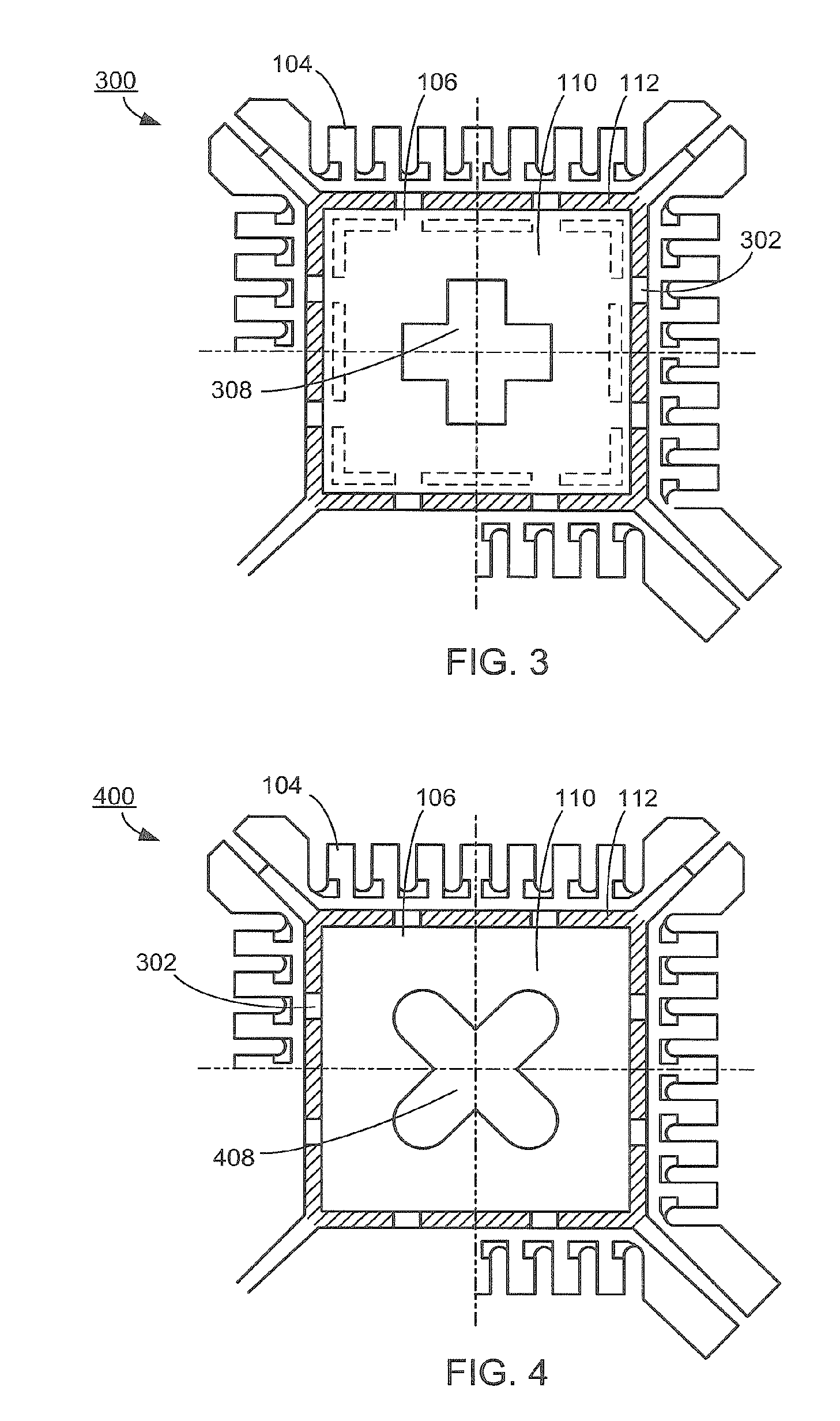

Multiple die integrated circuit package

ActiveUS20070096265A1Easy to useSemiconductor/solid-state device detailsSolid-state devicesElectrical connectionEngineering

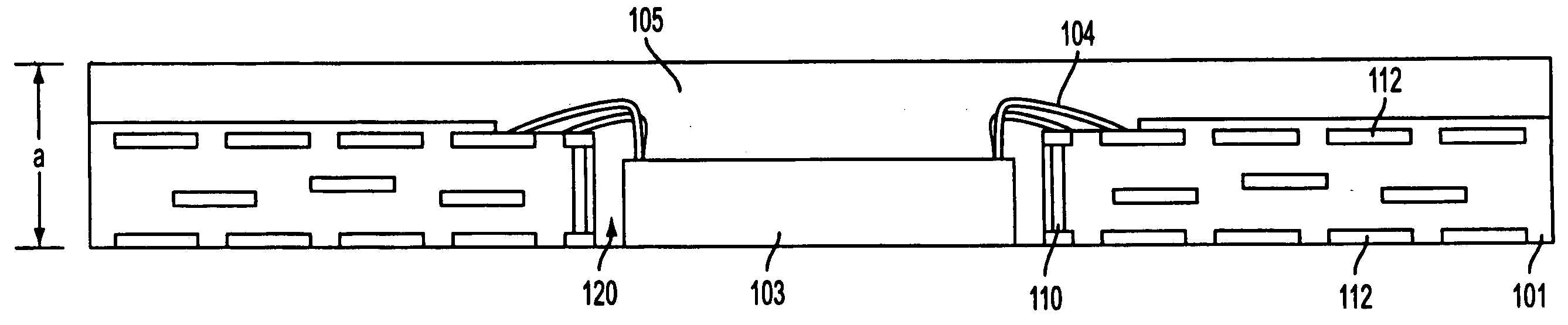

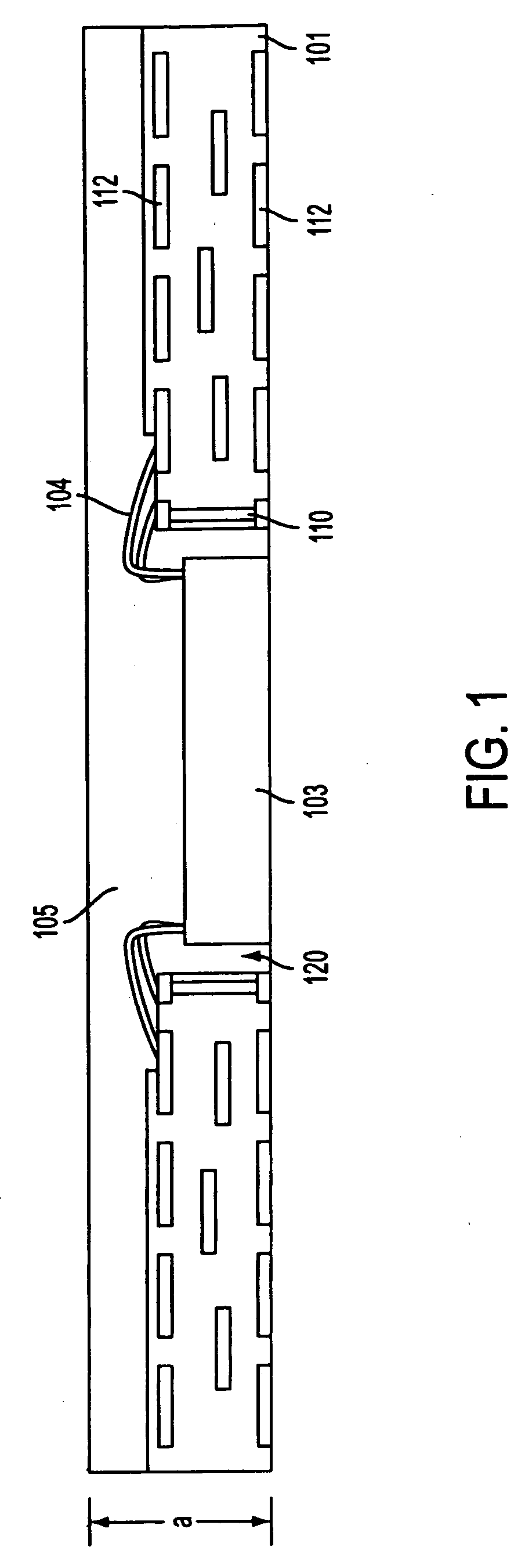

A multiple die package for integrated circuits is disclosed. An insulator layer is provided and one or more vias are formed within it. The insulator may be provided without vias, and vias formed later. At least one integrated circuit is provided and electrically coupled to at least one lead of a first leadframe overlying one surface of the insulator layer. At least one second integrated circuit is provided and electrically coupled to a second leadframe overlying a second surface of the insulator layer. Electrical connections between the two leadframes and the first and second integrated circuits are made through the insulator, at selected locations, by coupling at least one lead of the first and second leadframes one to another. The leads of the first and second leadframe may be physically coupled by a welding process within vias in the insulator. A removable storage card package is also described.

Owner:SANDISK TECH LLC

Integrated circuit package system with multi-surface die attach pad

ActiveUS20070075404A1Semiconductor/solid-state device detailsSolid-state devicesLead frameIntegrated circuit packaging

An integrated circuit package system is provided including an integrated circuit package system including an integrated circuit and a lead frame. The lead frame has a multi-surface die attach pad and the integrated circuit is mounted to the multi-surface die attach pad.

Owner:STATS CHIPPAC LTD

Inter-dice signal transfer methods for integrated circuits

InactiveUS20050151248A1Simple processReduce testing costsSemiconductor/solid-state device testing/measurementElectronic circuit testingFunctional testingControl data

The present invention discloses novel methods to transfer data between a plurality of integrated circuit dice on a semiconductor wafer. Each individual die contains internal circuits to control data transfer to nearby dice. Wafer level data transfer is achieved by a series of inter-dice data transfers. It is therefore possible to use a small number of small area metal lines to support wafer level parallel processing activities. External connections are provided by a small number of bonding pads on each wafer. The load on each external bounding pad is by far lower than that of prior art wafer level connections. These inter-dice data transfer mechanism also can be programmed to avoid defective circuitry. This invention has been used to support wafer level functional tests and wafer level burn-in tests. A Testing system of the present invention can test thousands of dice in parallel using simple testing equipment. Testing costs for integrated circuits are therefore reduced dramatically. The present application also makes it possible to build large area IC containing multiple dice. Extremely powerful products are realized using parallel processing capability of such multiple die integrated circuits.

Owner:ALPHA & OMEGA SEMICON LTD

Multiple die integrated circuit package

ActiveUS7511371B2Easy to useSemiconductor/solid-state device detailsSolid-state devicesElectrical connectionDie (integrated circuit)

A multiple die package for integrated circuits is disclosed. An insulator layer is provided and one or more vias are formed within it. The insulator may be provided without vias, and vias formed later. At least one integrated circuit is provided and electrically coupled to at least one lead of a first leadframe overlying one surface of the insulator layer. At least one second integrated circuit is provided and electrically coupled to a second leadframe overlying a second surface of the insulator layer. Electrical connections between the two leadframes and the first and second integrated circuits are made through the insulator, at selected locations, by coupling at least one lead of the first and second leadframes one to another. The leads of the first and second leadframe may be physically coupled by a welding process within vias in the insulator. A removable storage card package is also described.

Owner:SANDISK TECH LLC

Radio frequency data communications device

InactiveUS6947513B2Avoid switchingSolid-state devicesSemiconductor/solid-state device manufacturingCouplingDie (integrated circuit)

A radio frequency identification device comprises an integrated circuit including a receiver, a transmitter, and a microprocessor. The receiver and transmitter together define an active transponder. The integrated circuit is preferably a monolithic single die integrated circuit including the receiver, the transmitter, and the microprocessor. Because the device includes an active transponder, instead of a transponder which relies on magnetic coupling for power, the device has a much greater range.

Owner:ROUND ROCK RES LLC

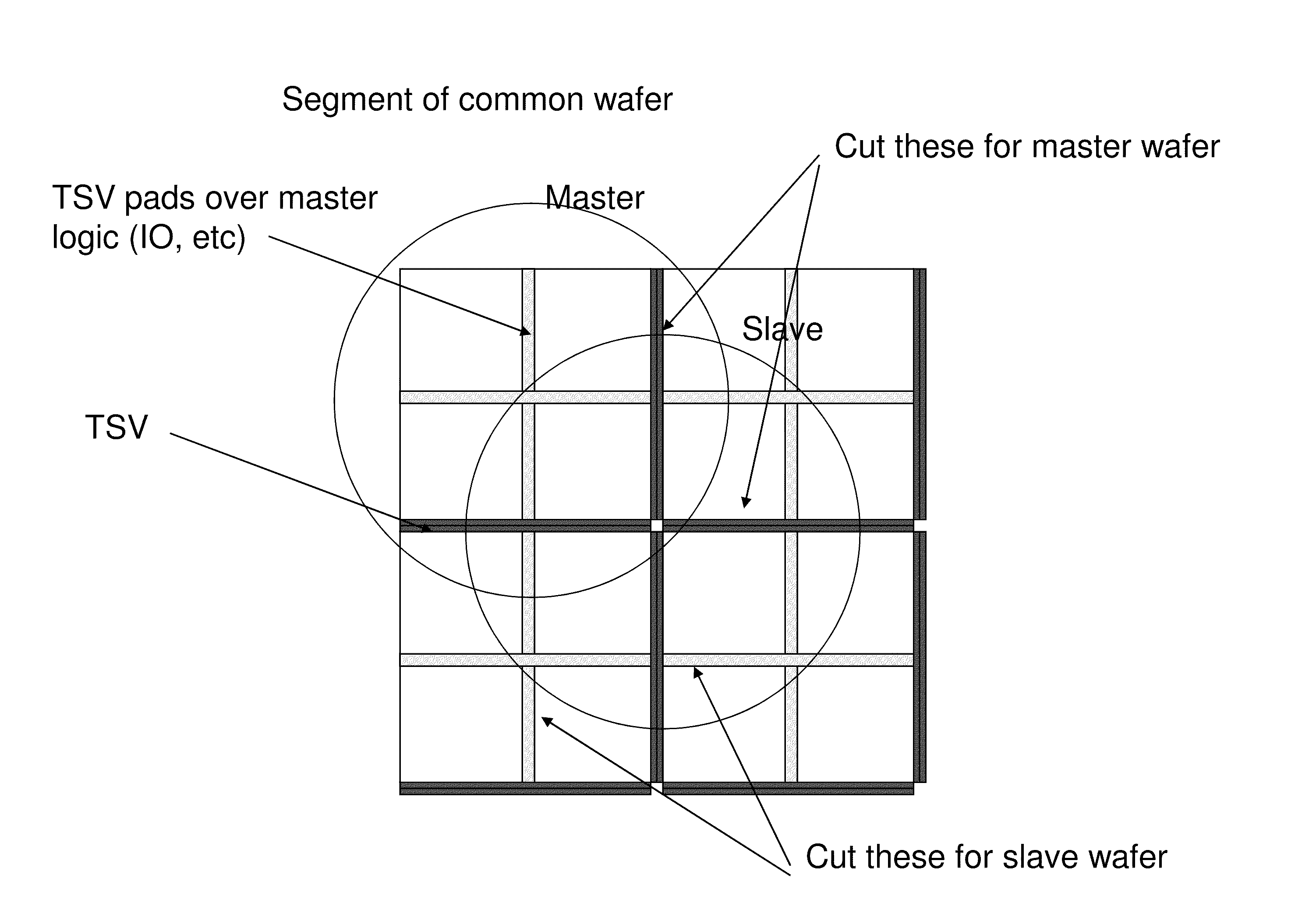

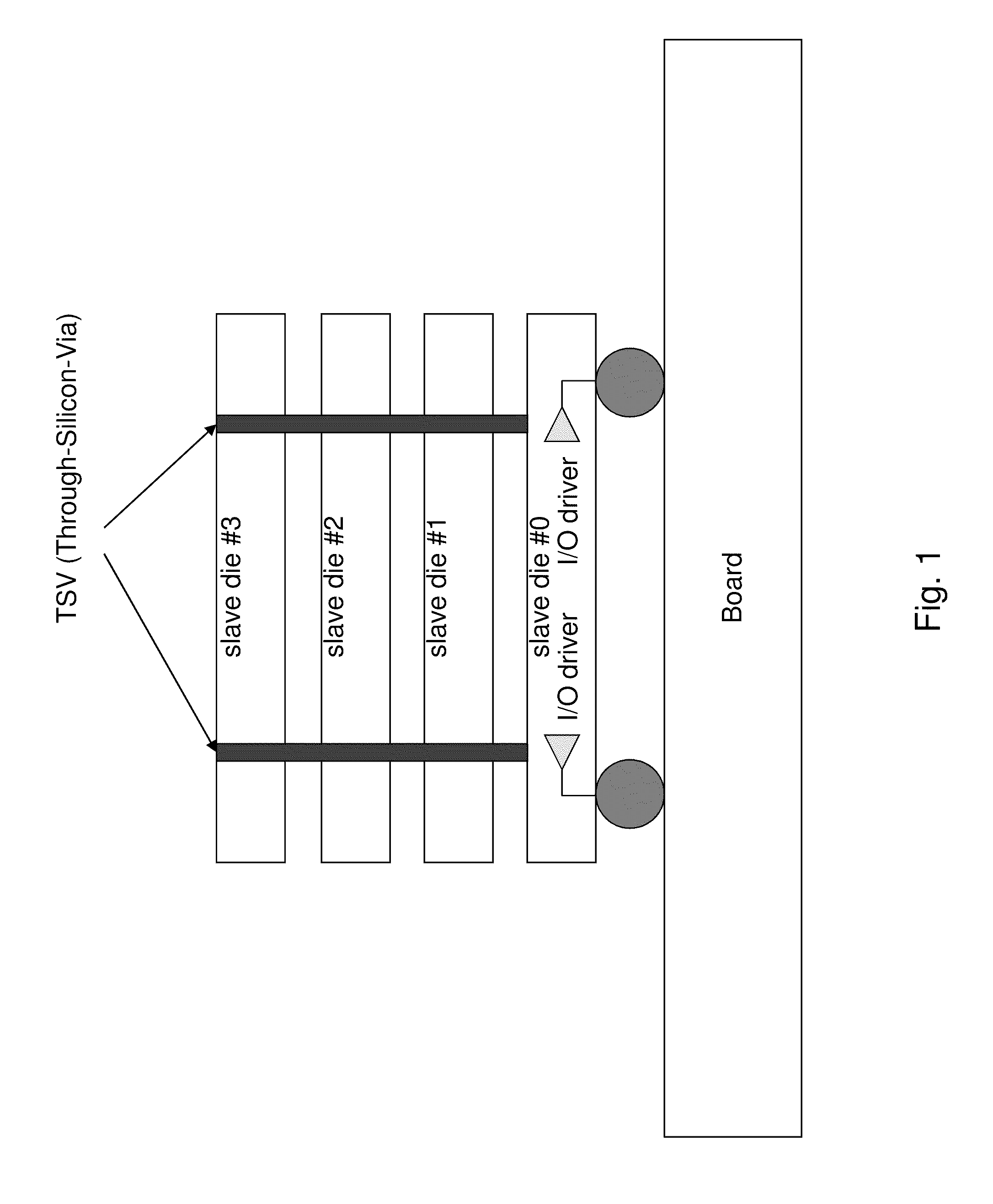

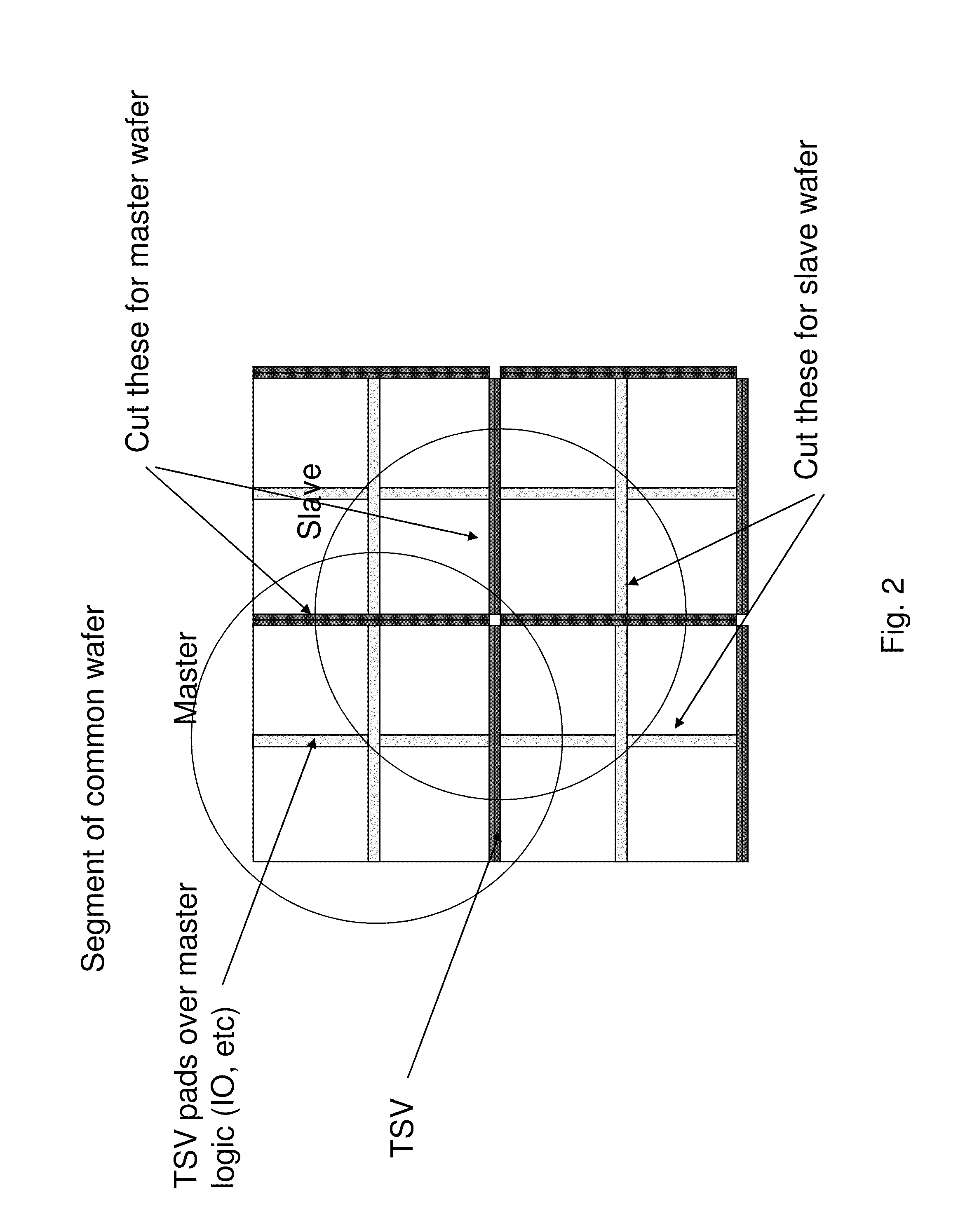

Computer system wafer integrating different dies in stacked master-slave structures

InactiveUS20110272788A1Reduce I/O loadEfficient preparationSolid-state devicesSemiconductor/solid-state device manufacturingEngineering3d integrated circuit

A stacked 3D integrated circuit structure is manufactured with a common image design for dies which allows diced master dies to cut from the common wafer and diced slave dies cut to be cut from a wafer which has the common image design. In an embodiment is stacked to form a wafer-to-wafer 3D stack before dicing. Master and slave elements which are used for only one kind of separated individual integrated circuit dies which are located along die edges and at die centers before dicing separation of individual integrated circuit chips. A master wafer is shifted ½ way across a die to make cutting along a kerf line effective to provide both master and slave dies. Multiple slaves can be stacked and coupled to a master die which acts as a bus master when attached to a bus to which only the master die is directly connected. The use of a common wafer design minimizes cost of manufacture of chips destined to be stacked as 3D integrated circuits.

Owner:GLOBALFOUNDRIES INC