Integrated circuit package

a technology of integrated circuits and circuit components, applied in the direction of semiconductor devices, semiconductor/solid-state device details, electrical equipment, etc., can solve the problem that the semiconductor device generates a great deal of heat during normal operation

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Benefits of technology

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0014] Various embodiments of the integrated circuit package and various examples of methods for manufacturing integrated circuit packages according to the present invention will now be described with reference to the drawings.

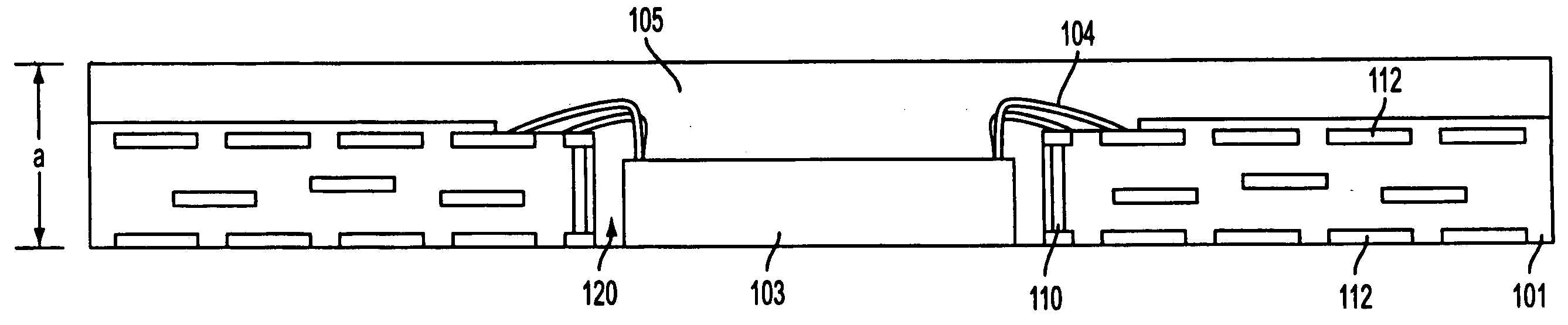

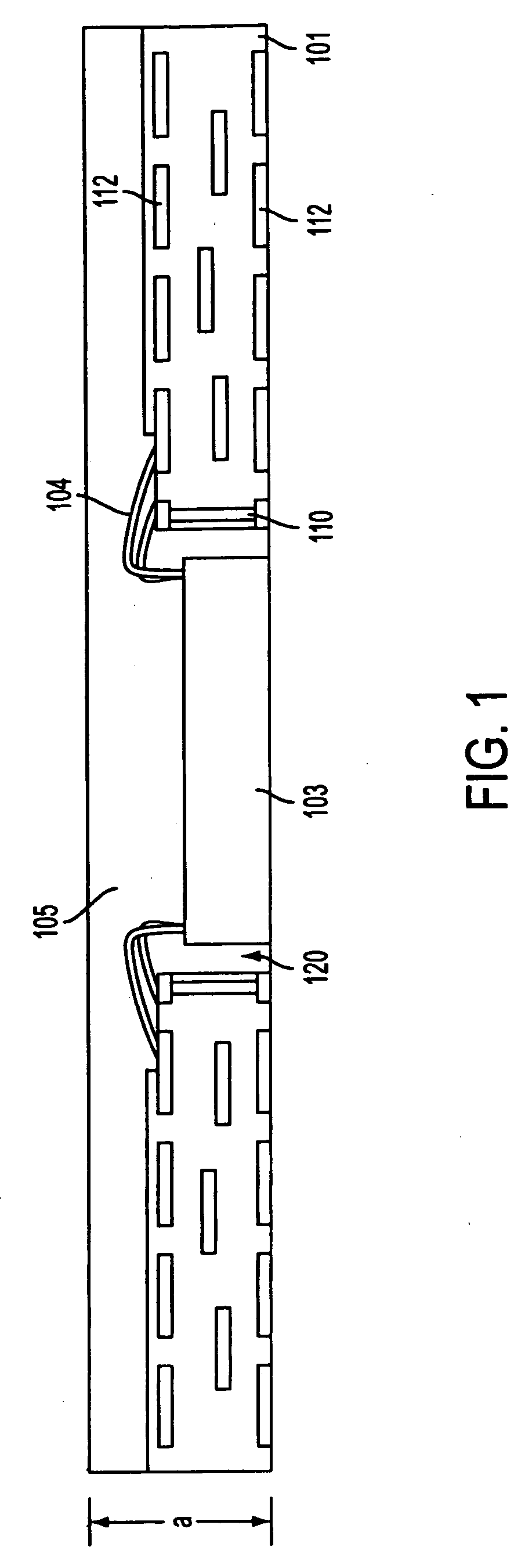

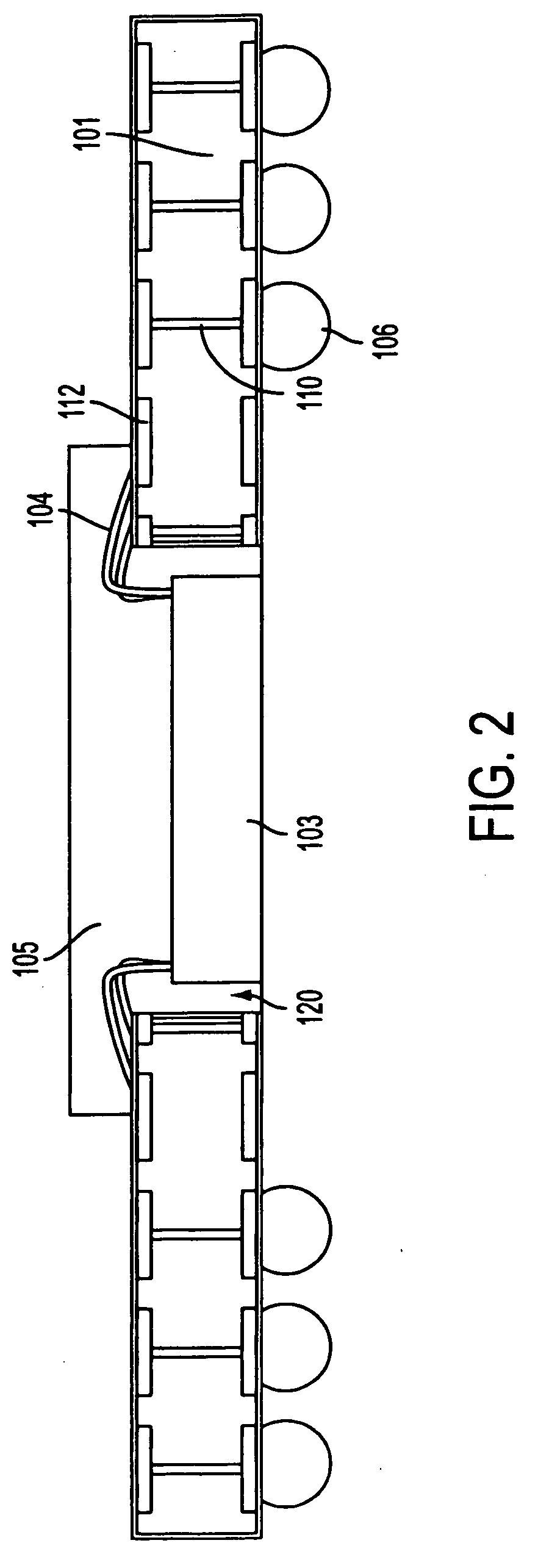

[0015]FIGS. 1 and 2 show certain components of integrated circuit packages according to embodiments of the present invention. The integrated circuit packages depicted in FIGS. 1 and 2 each generally include a substrate 101, a semiconductor die 103 and an encapsulant 105. The substrate 101 may be made of either a rigid material (e.g., BT, FR4, FR5 or ceramic) or a flexible material (e.g., polyimide), and may have circuit traces 112 onto which a semiconductor die 103 may be interconnected using, for example, wire bonding techniques or tape automated bonding. In the embodiment shown in FIG. 1, the package measures about 1.0 mm thick (shown as dimension “a” in FIG. 1) and about 35 mm wide (shown as dimension “b” in FIG. 3). The width dimension of certain other em...

PUM

| Property | Measurement | Unit |

|---|---|---|

| thick | aaaaa | aaaaa |

| thick | aaaaa | aaaaa |

| width | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More